Instruction set extension using operand bearing NOP instructions

an instruction set and operand technology, applied in the field of instruction sets, can solve the problems of limited number of ways to specify operands, difficulty in extending instruction sets, and difficulty in adding new functionality to existing instruction sets

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

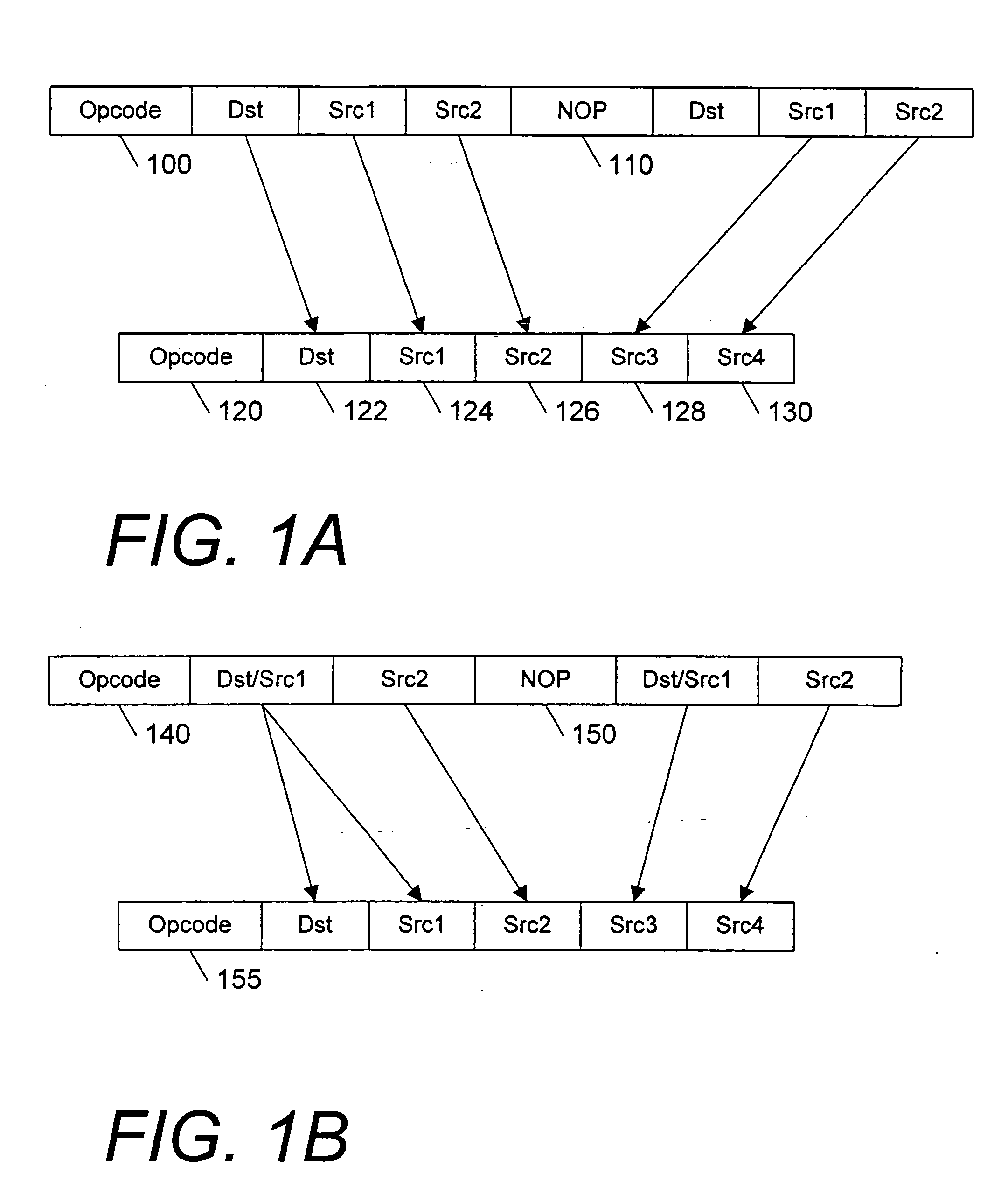

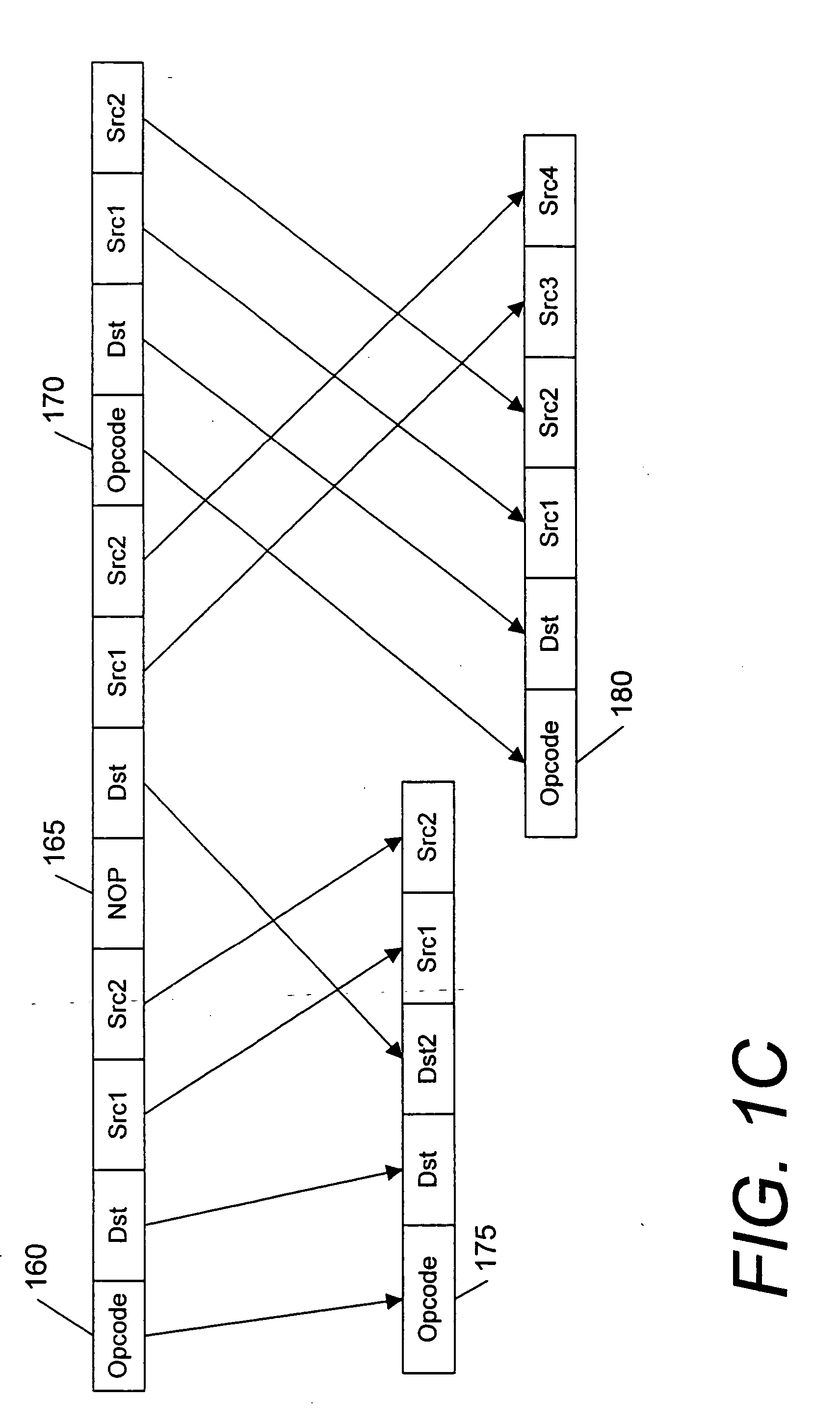

[0022] The following description provides instruction set extension using operand bearing instructions. In the following description, numerous specific details are set forth in order to provide a more thorough understanding of the present invention. It will be appreciated, however, by one skilled in the art that the invention may be practiced without such specific details. In other instances, control structures and gate level circuits have not been shown in detail in order not to obscure the invention. Those of ordinary skill in the art, with the included descriptions, will be able to implement appropriate logic circuits without undue experimentation. While one embodiment is directed to a microprocessor, the techniques described may more generally be applied to other types of electronic processing components that have instruction sets.

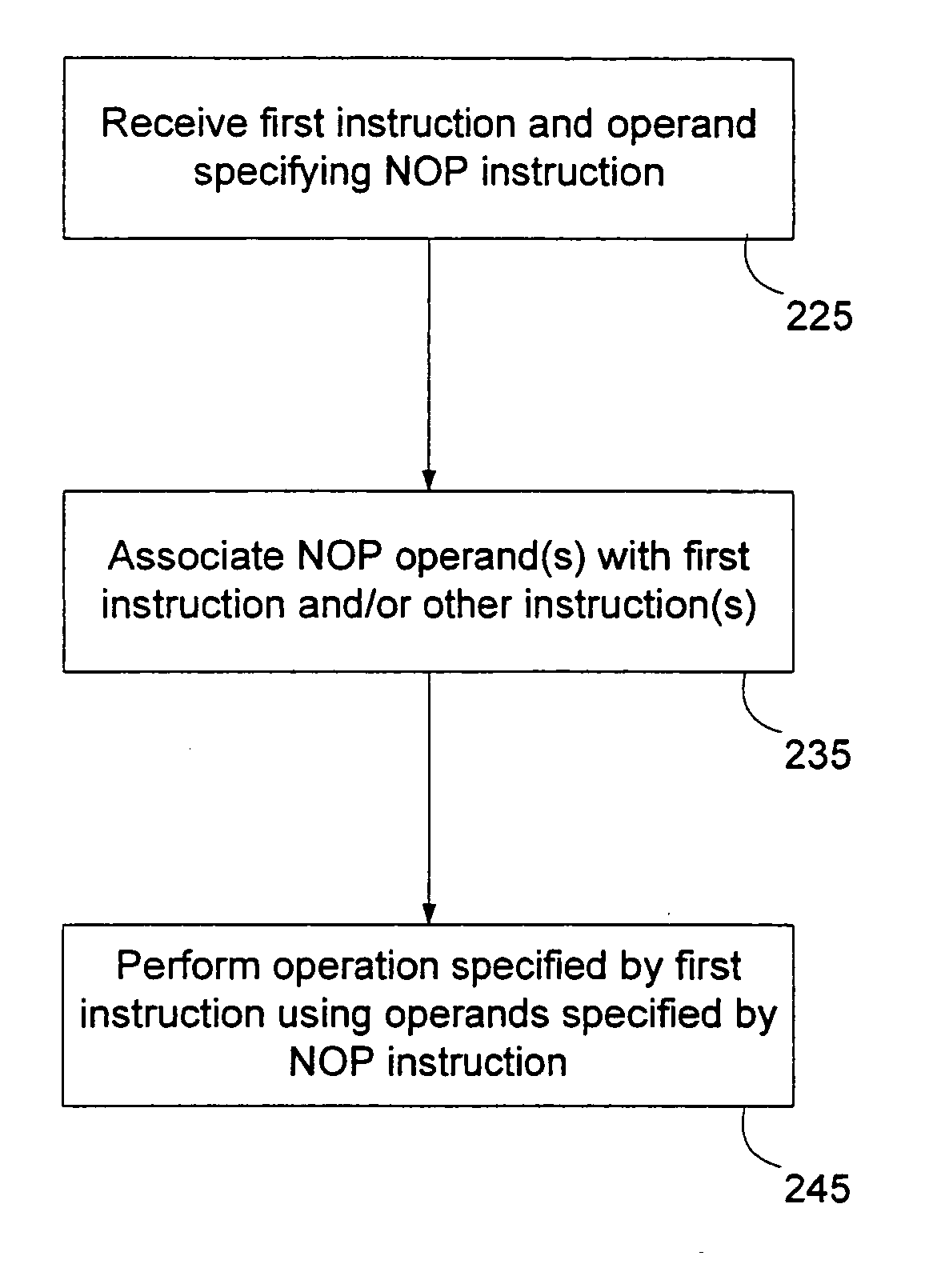

[0023] A NOP with operands is designed to carry operand information to other instructions preceding and / or following it. Those other instructions may...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More