Patents

Literature

72results about How to "Suppresses increase in code size" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

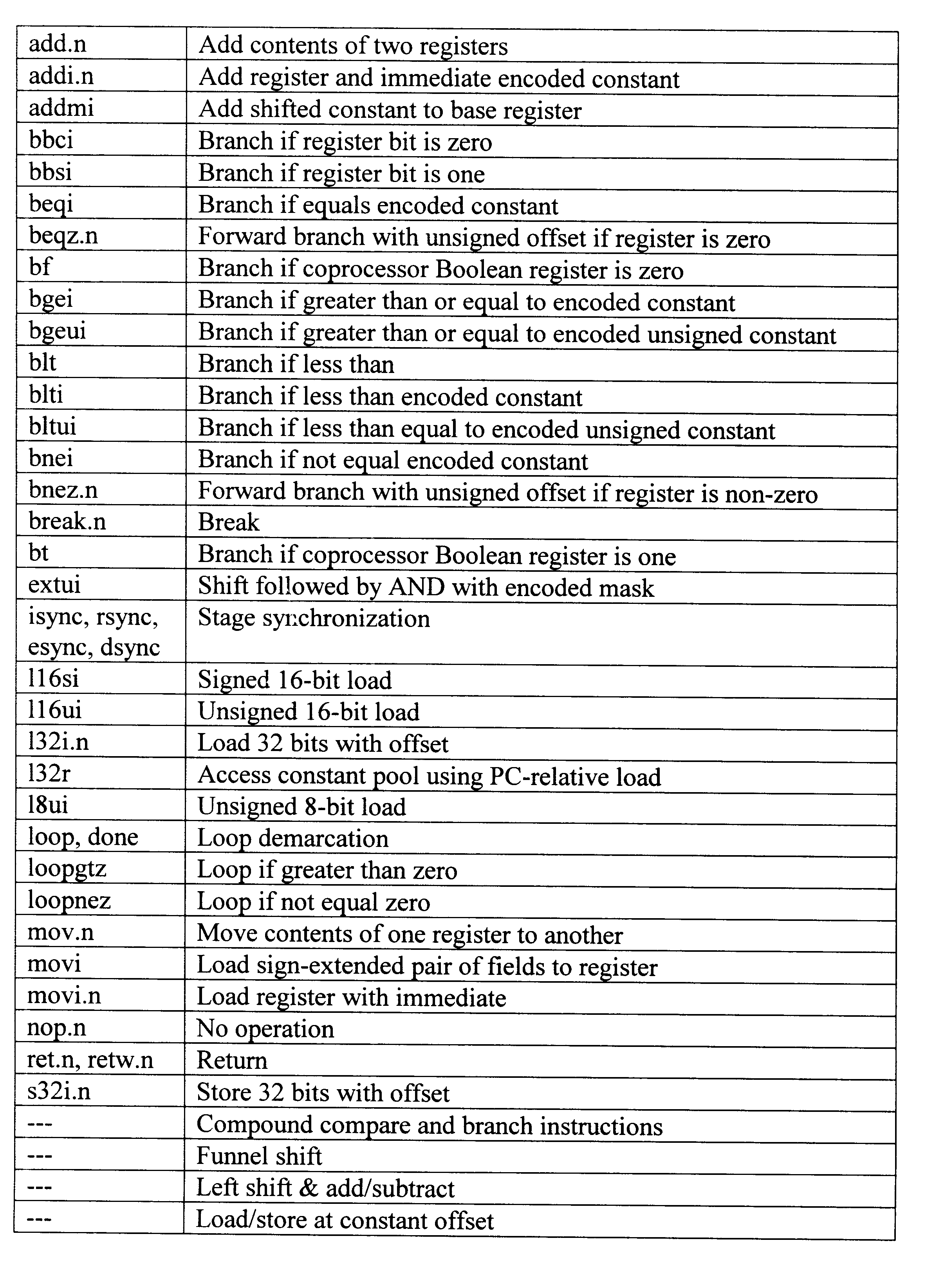

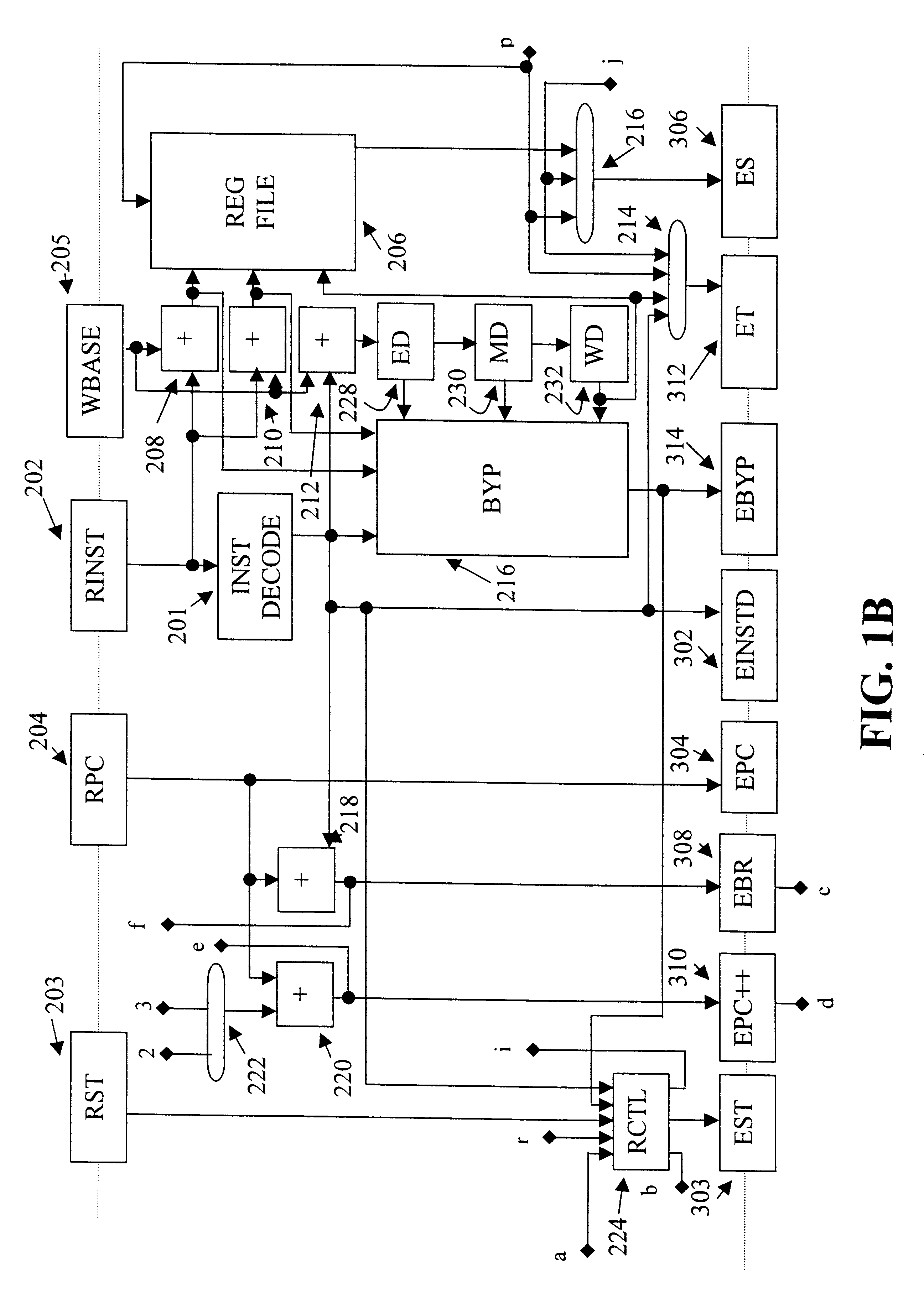

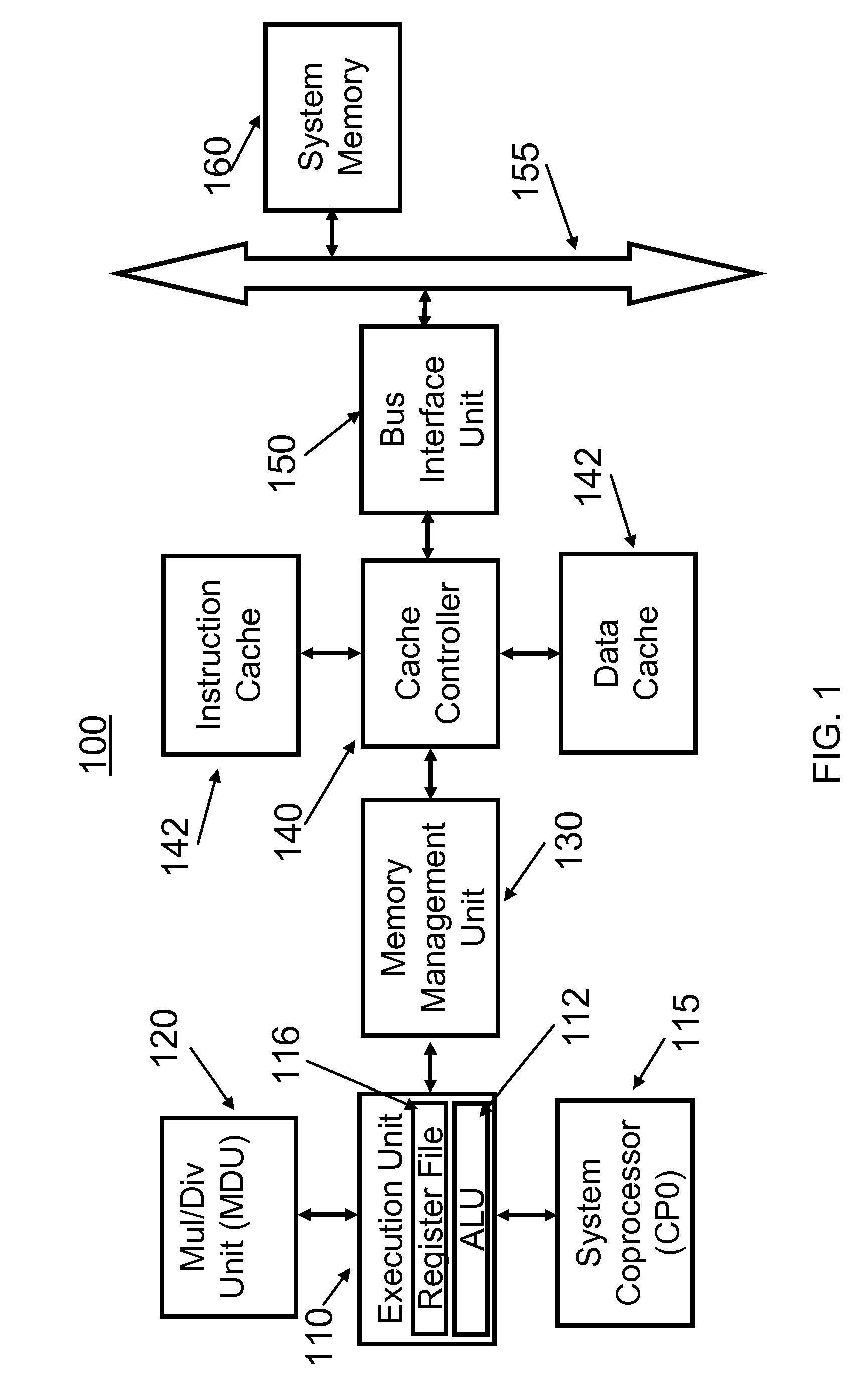

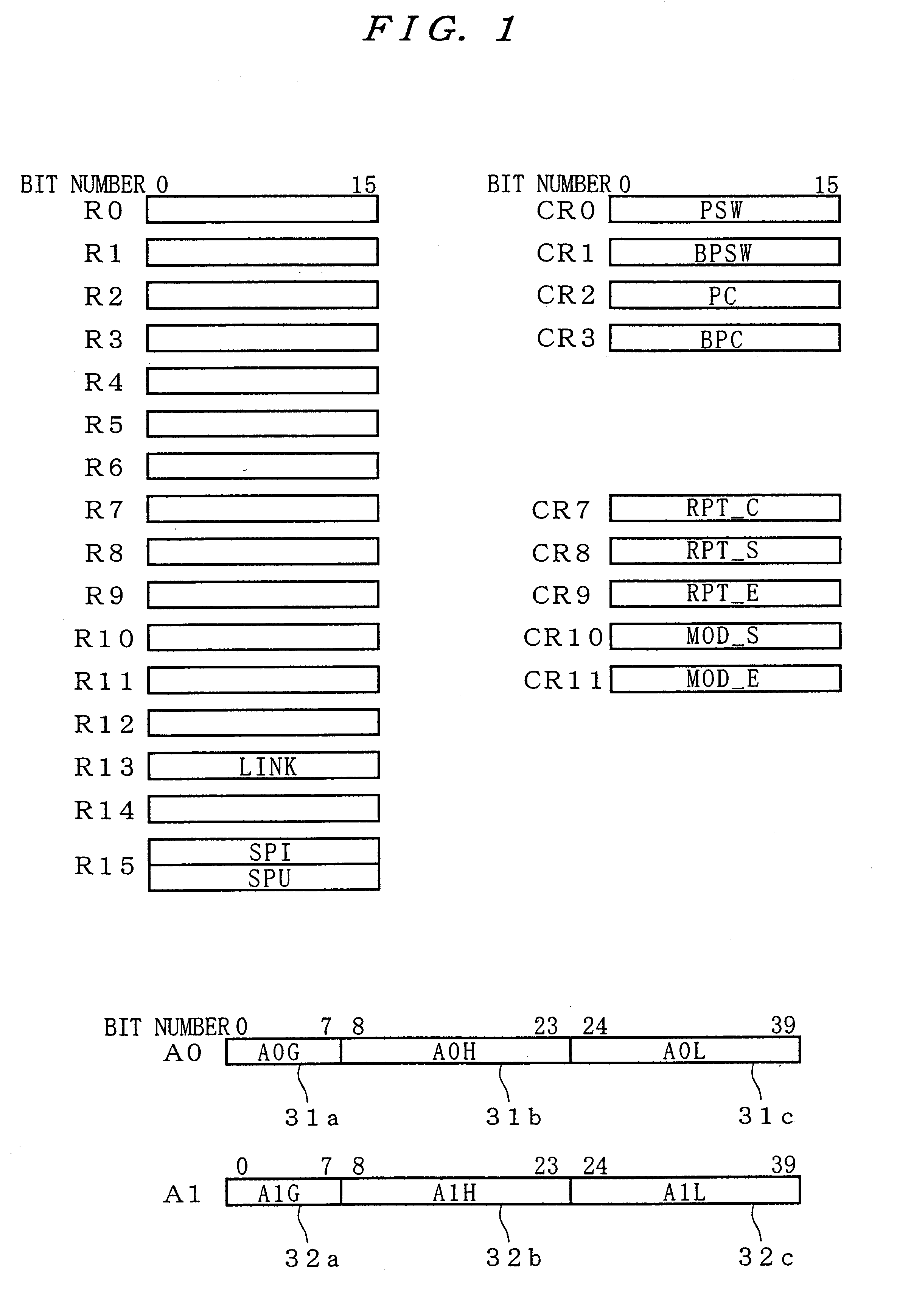

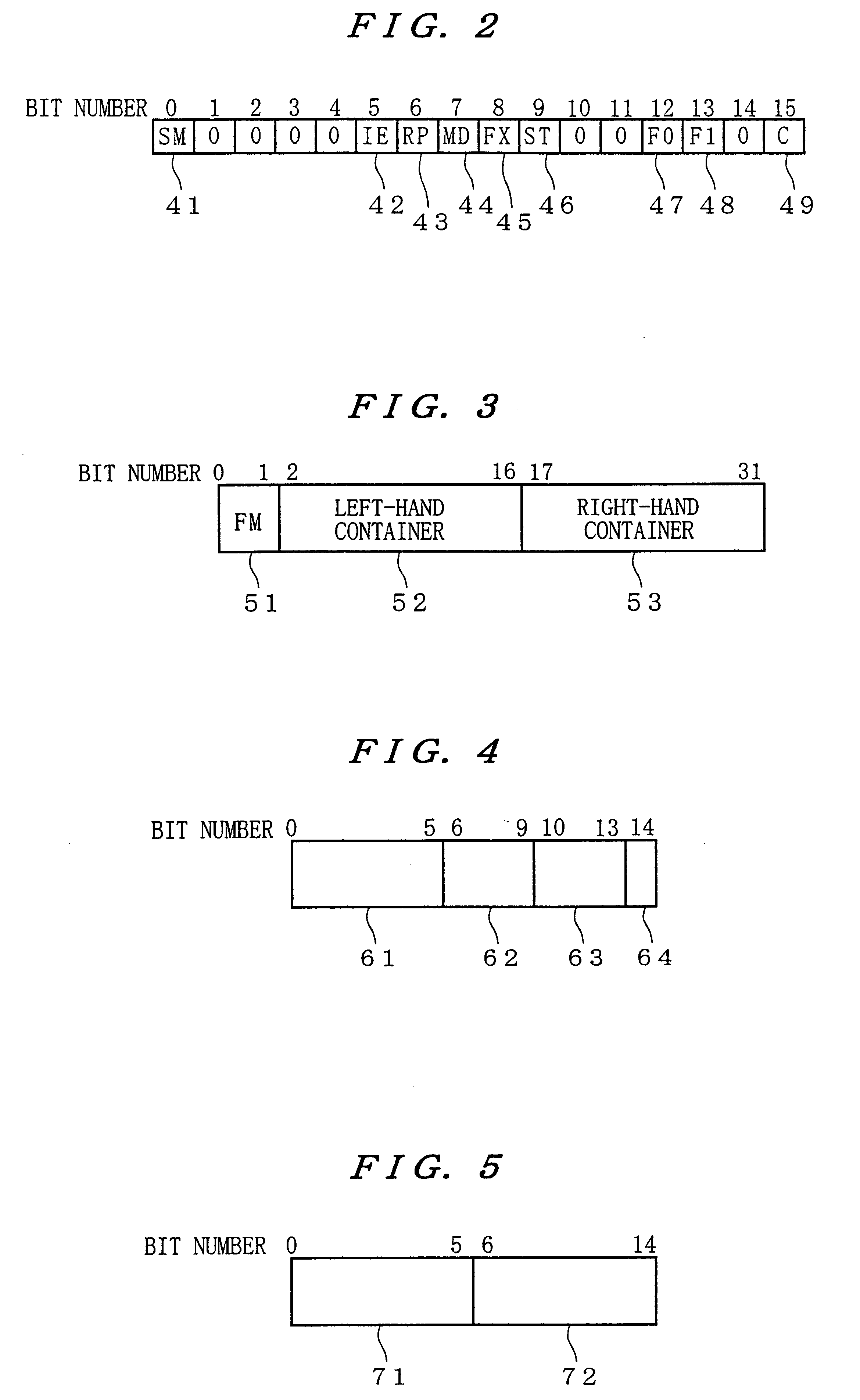

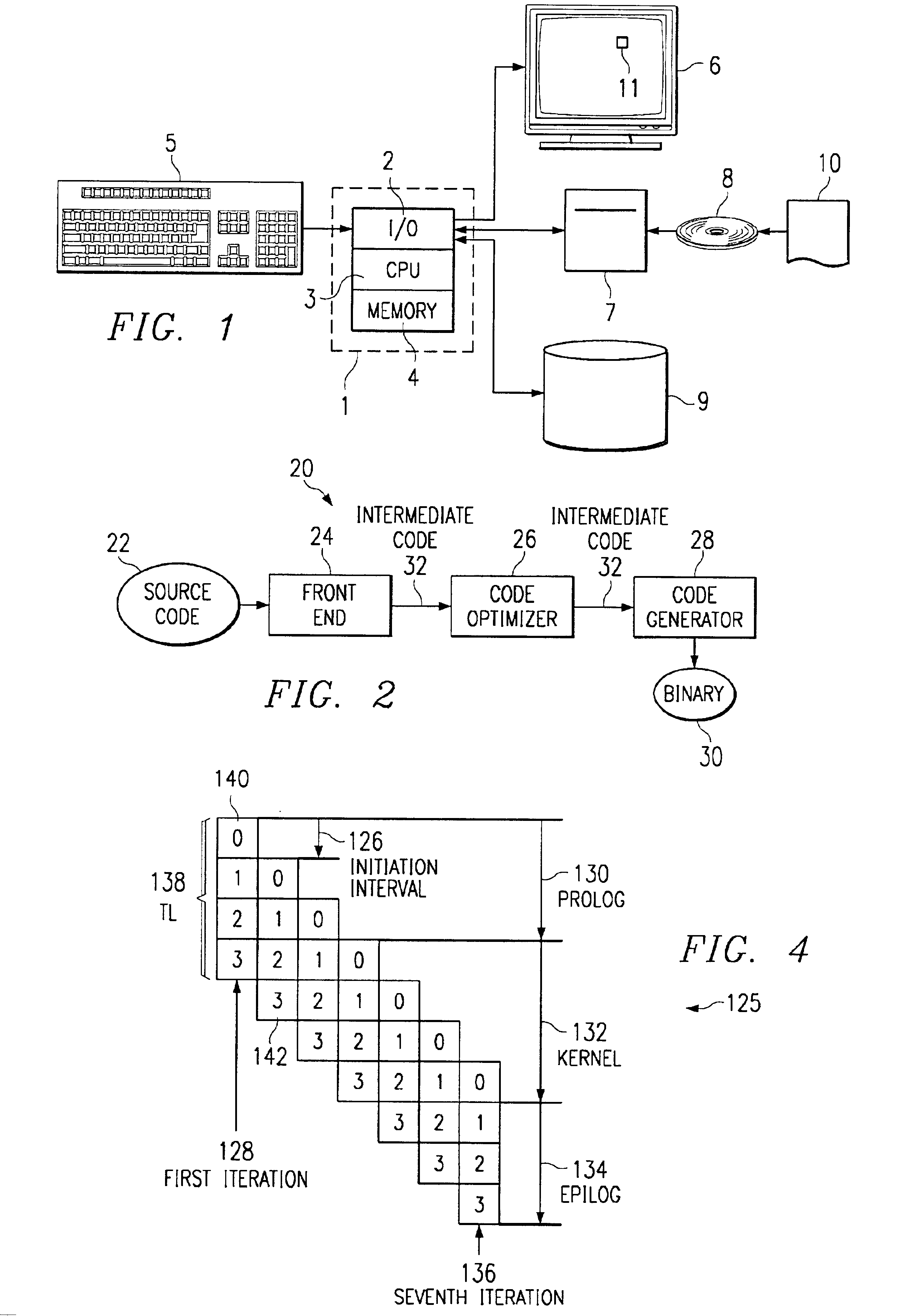

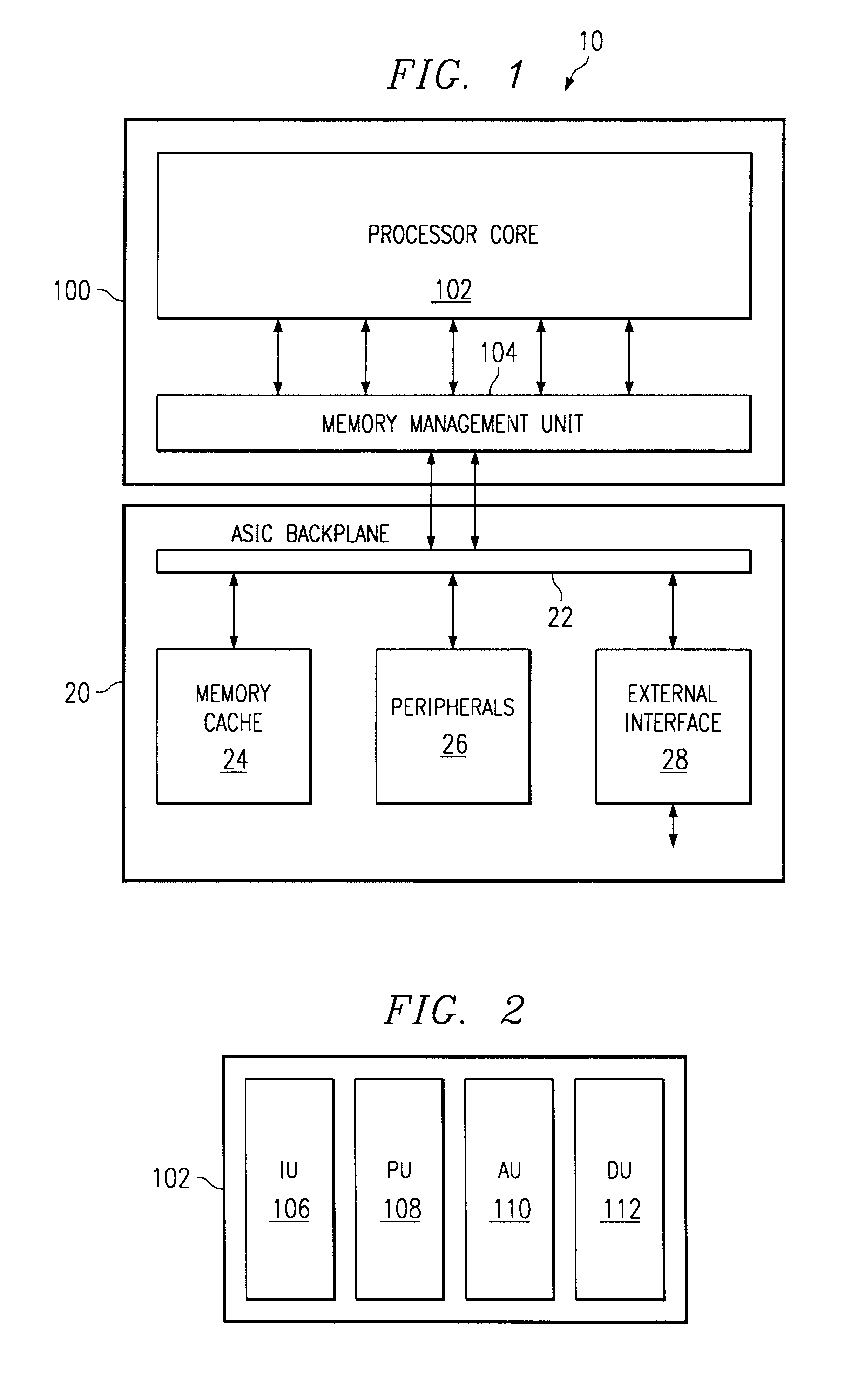

High data density RISC processor

InactiveUS6282633B1High densityIncrease in CPIInstruction analysisDigital computer detailsProgram instructionProcessor register

A RISC processor implements an instruction set which, in addition to optimizing a relationship between the number of instructions required for execution of a program, clock period and average number of clocks per instruction, also is designed to optimize the equation S=IS * BI, where S is the size of program instructions in bits, IS is the static number of instructions required to represent the program (not the number required by an execution) and BI is the average number of bits per instruction. Compared to conventional RISC architectures, this processor lowers both BI and IS with minimal increases in clock period and average number of clocks per instruction. The processor provides good code density in a fixed-length high-performance encoding based on RISC principles, including a general register with load / store architecture. Further, the processor implements a simple variable-length encoding that maintains high performance.

Owner:TENSILICA

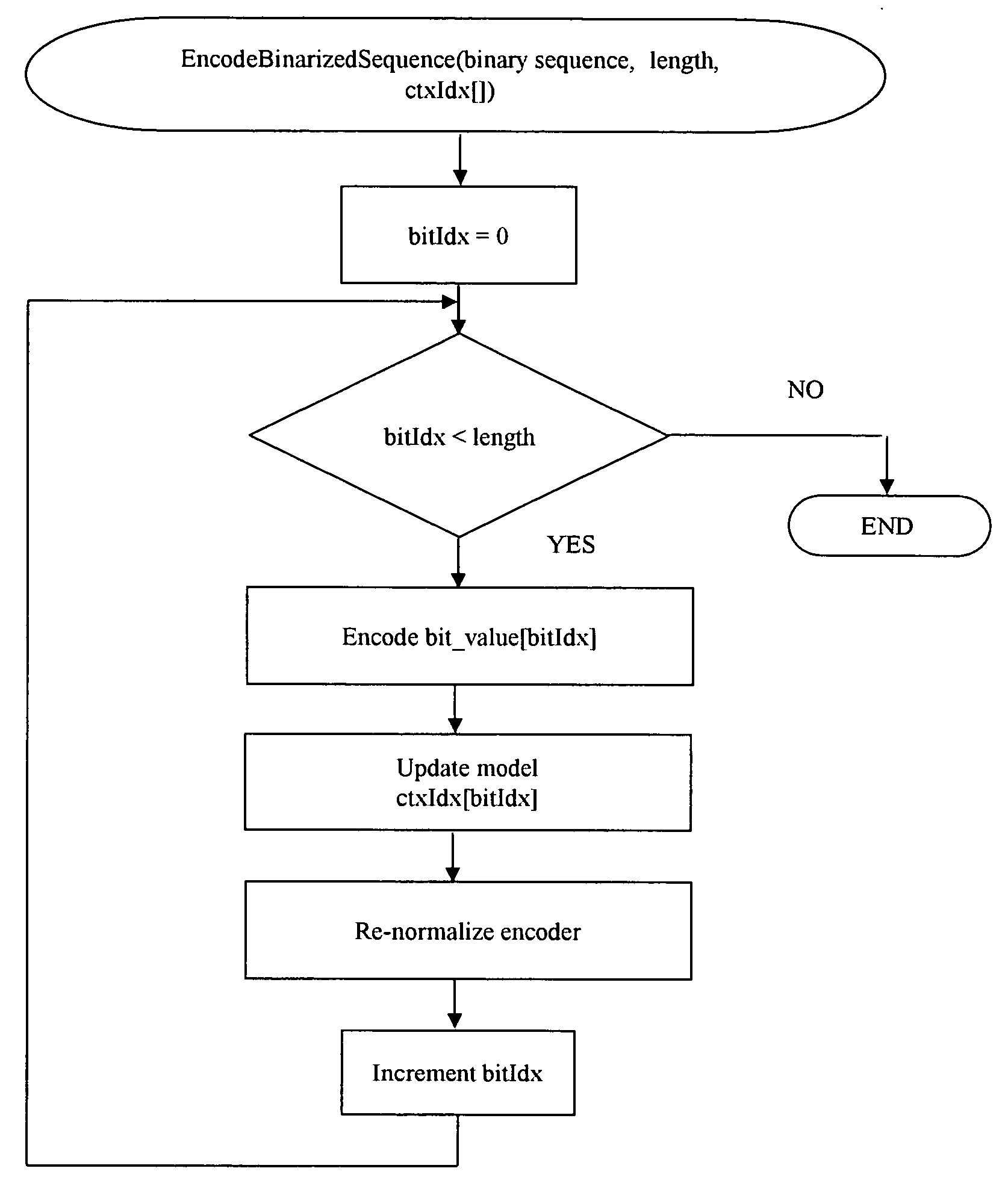

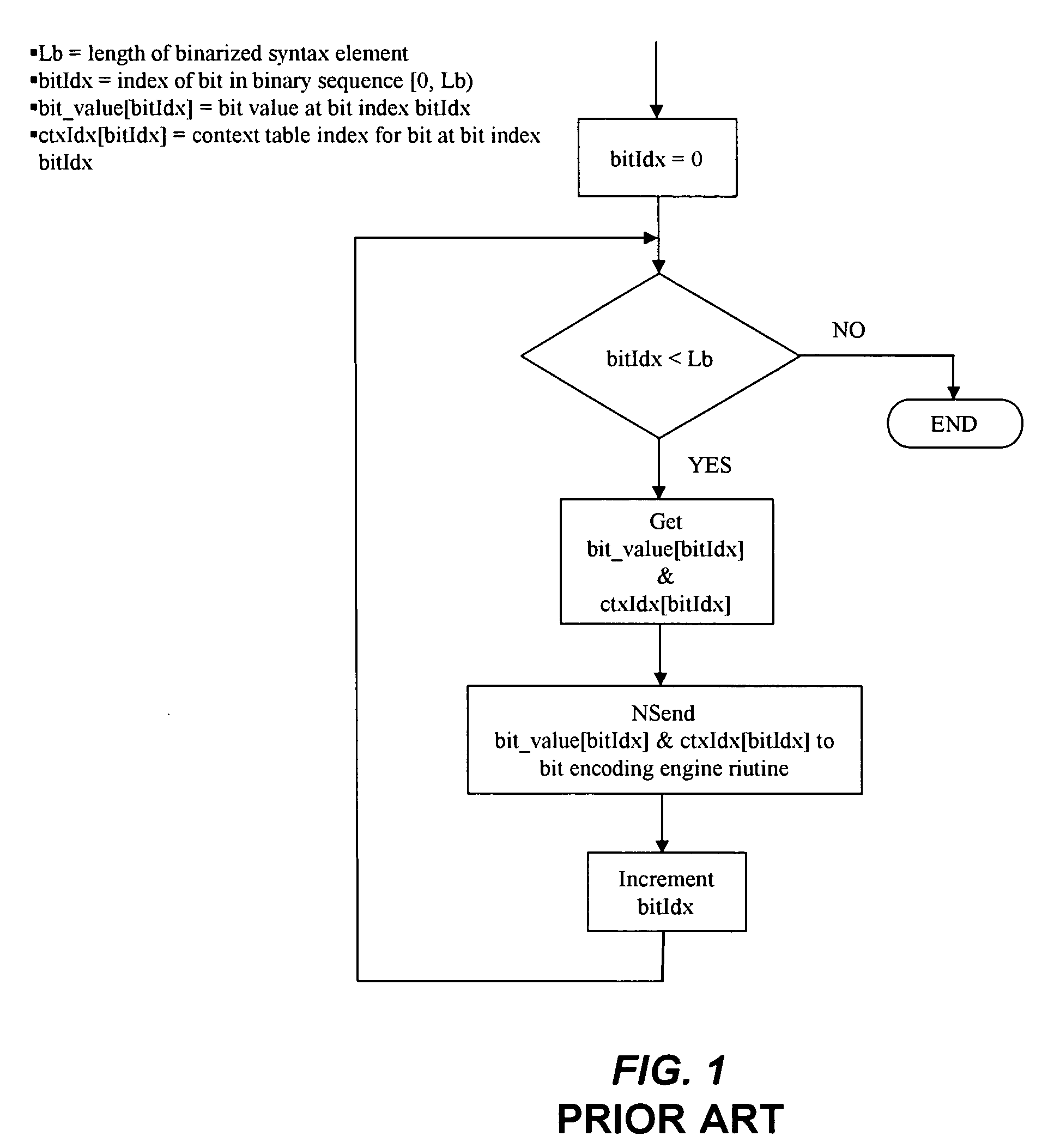

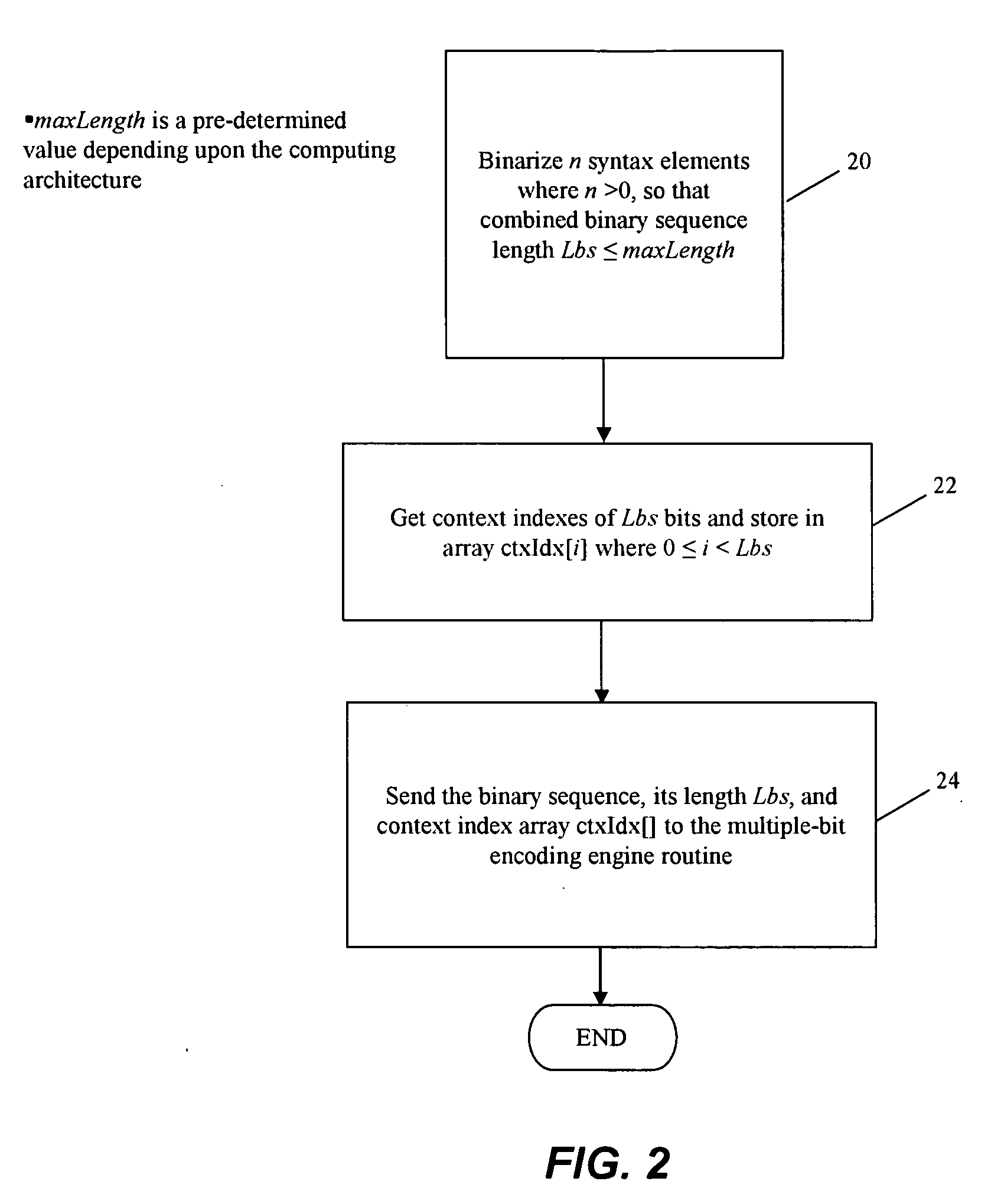

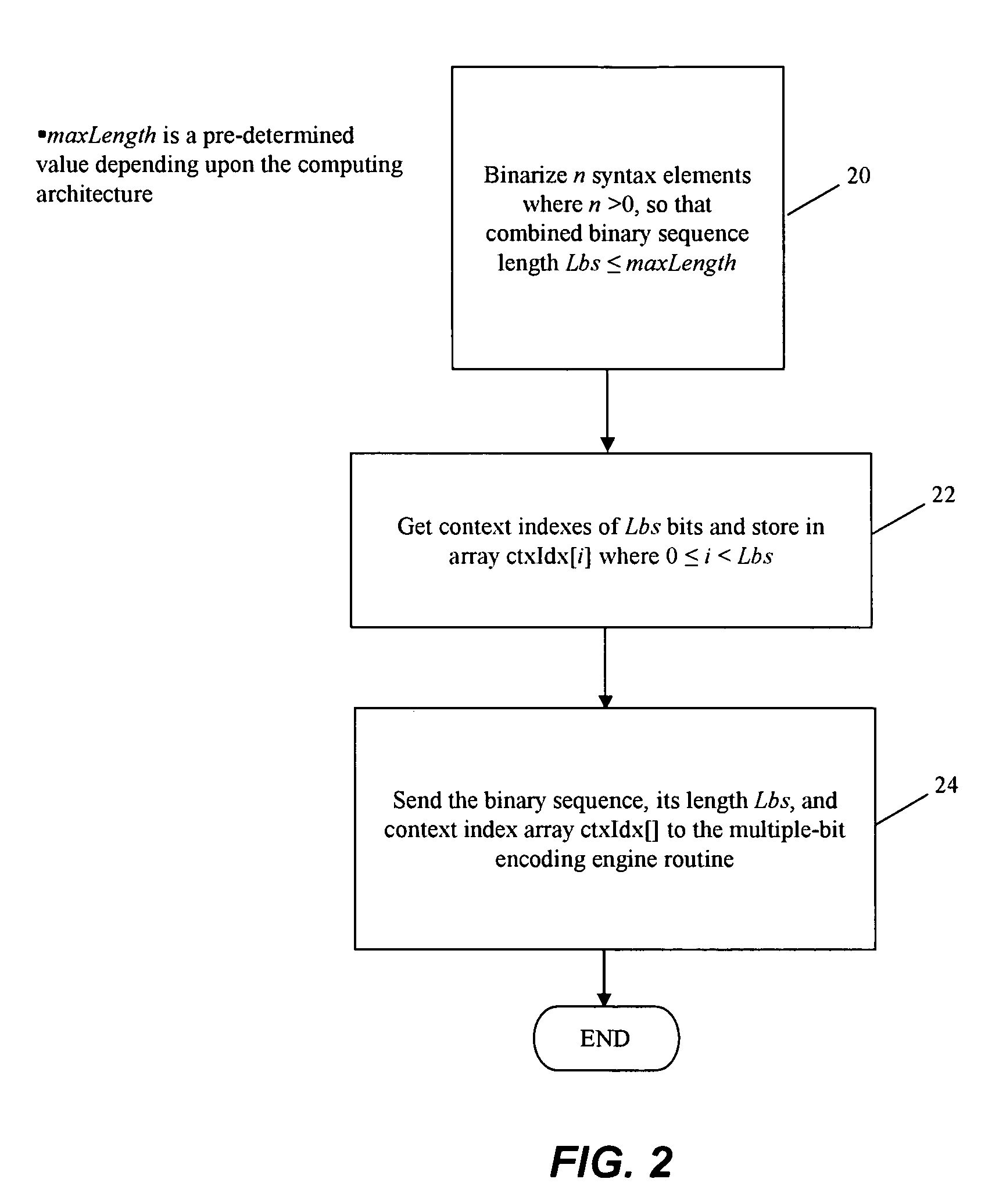

Method and system for fast context based adaptive binary arithmetic coding

InactiveUS20070040711A1Increasing instruction level parallelismReduces function call overheadCode conversionCharacter and pattern recognitionProcedure callsContext-adaptive variable-length coding

A method for efficient and fast implementation of context-based adaptive binary arithmetic encoding in H.264 / AVC video encoders is disclosed. The H.264 / AVC video standard supports two entropy coding mechanisms. These include Context Adaptive Binary Arithmetic Coding (CABAC) and Context Adaptive Variable Length Coding (CAVLC). The entropy coding efficiency of CABAC exceeds that of CAVLC by a clear margin. The method further provides techniques that make the implementation of CABAC on digital signal processors (DSPs) and other processing devices significantly faster. In one aspect, the method increases decoupling between the binarization process and the arithmetic encoding process from bit level to single or multiple syntax element(s) level. The binarized data is provided to the arithmetic encoding engine in bulk, thereby significantly reducing the overhead due to procedure calls. In another aspect, a CABAC arithmetic encoding engine format is provided which decreases data writing overhead and better exploits parallelism in the encoding process. This aspect is particularly advantageous to, for example, very long instruction word (VLIW) DSPs and media processors. In yet another aspect, the method discloses efficient CABAC binarization schemes for syntax elements.

Owner:STREAMING NETWORKS PVT

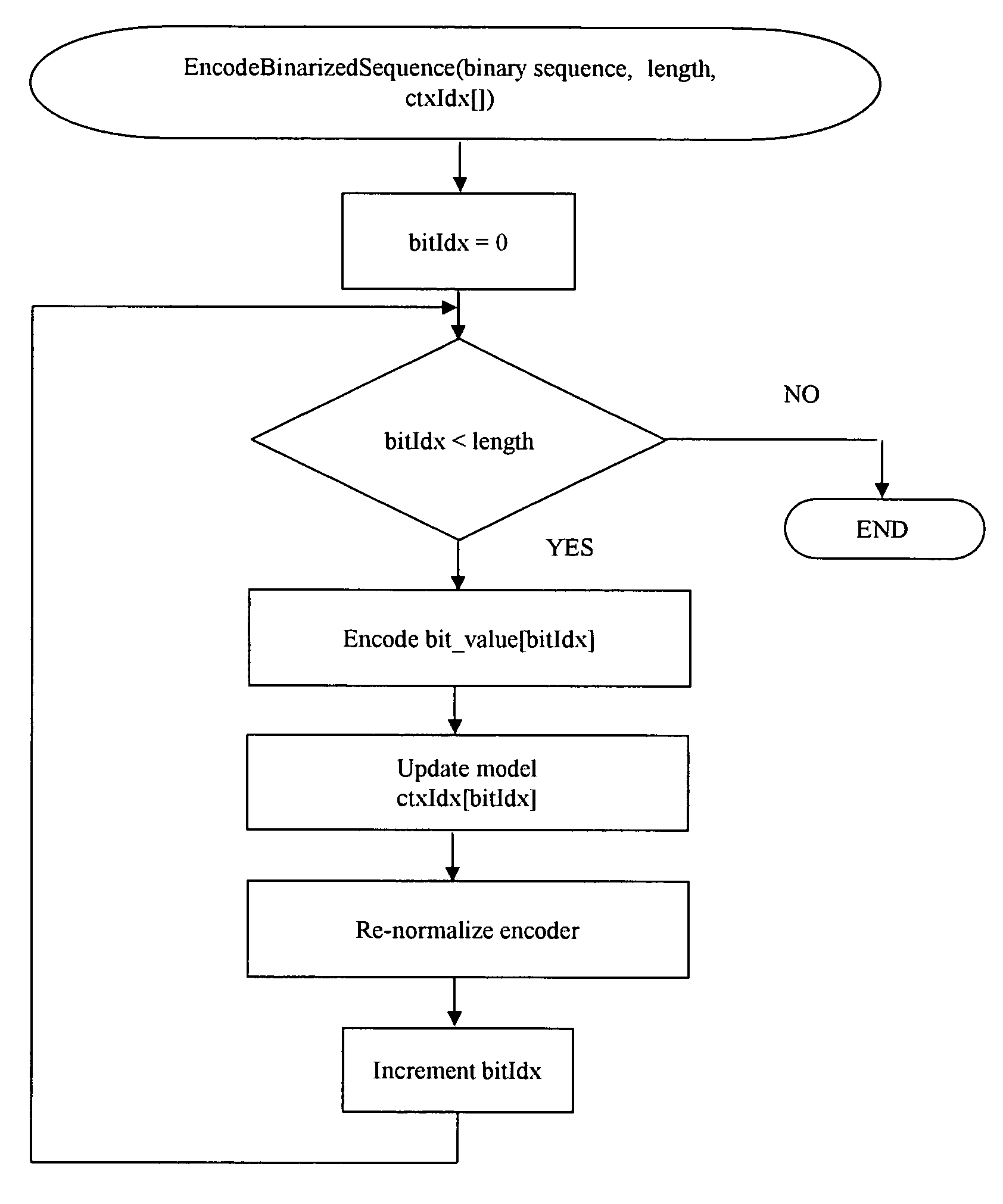

Method and system for fast context based adaptive binary arithmetic coding

InactiveUS7221296B2Improve the level ofReduce overheadCode conversionCharacter and pattern recognitionParallel computingFloating point

A method and processor for providing context-based adaptive binary arithmetic CABAC coding. Binarization is performed on one or more syntax elements to obtain a binary sequence. Data bits of the said binary sequence are provided to an arithmetic encoding unit in bulk. Binarization is performed on one or more syntax elements to generate exp Golomb code by converting mapped syntax-element values to corresponding floating point type values. Re-normalization of CABAC encoding is performed by restructuring the re-normalization into two processing units including an arithmetic encoding unit and a bit writing unit. The bit writing unit is configured to format signal bits into a multiple-bit sequence, and write multiple bits simultaneously during an execution of a bit writing loop.

Owner:STREAMING NETWORKS PVT

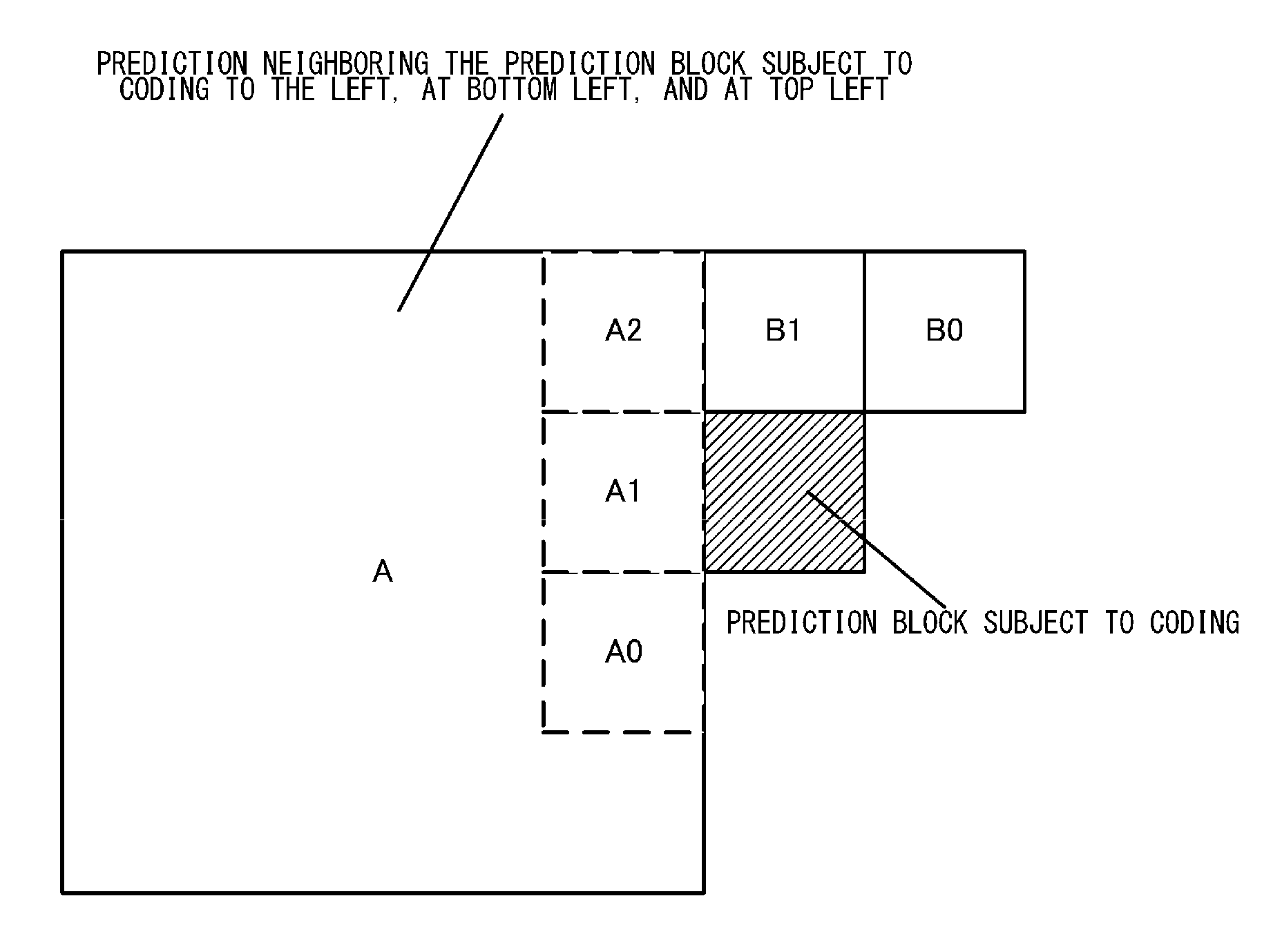

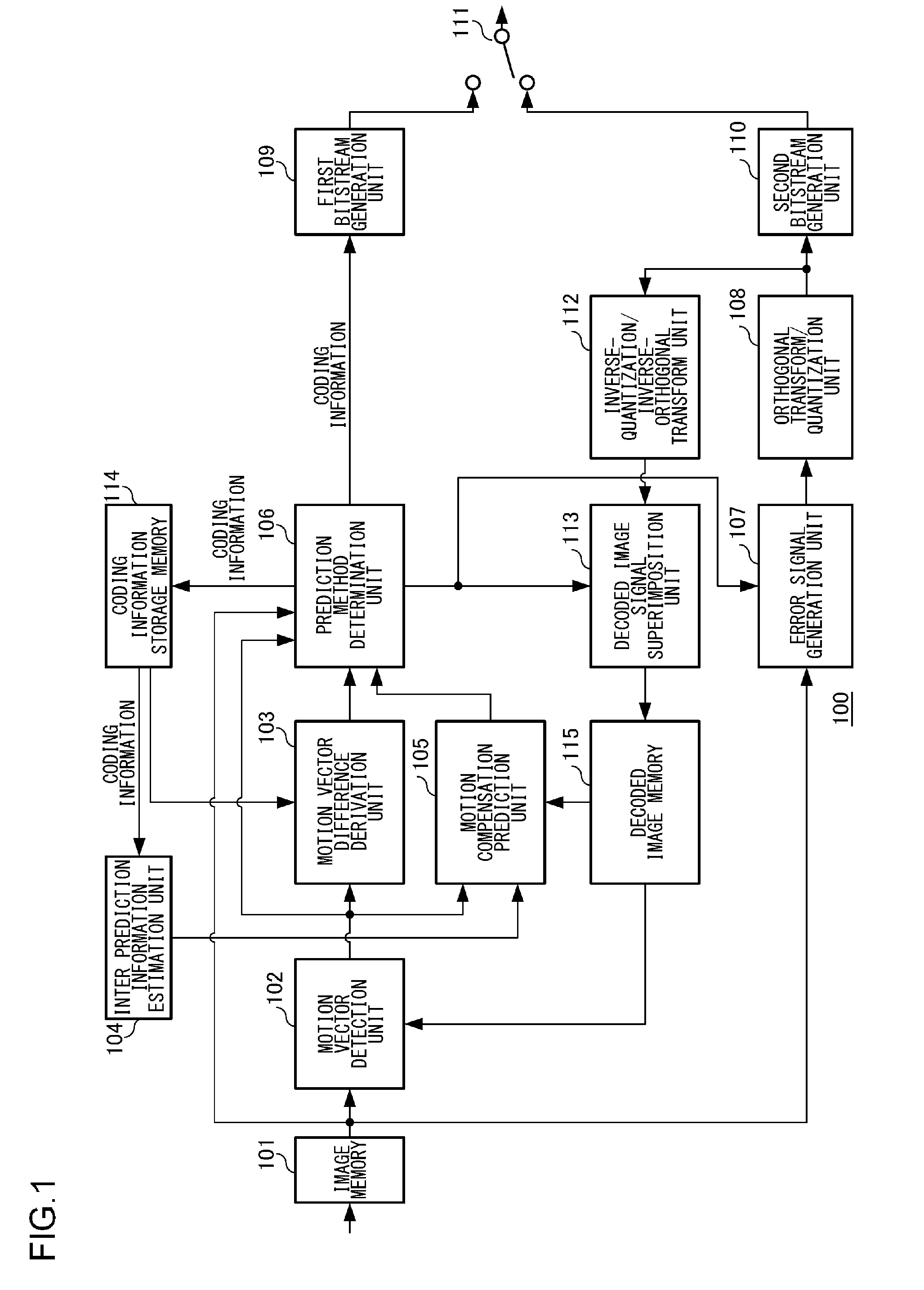

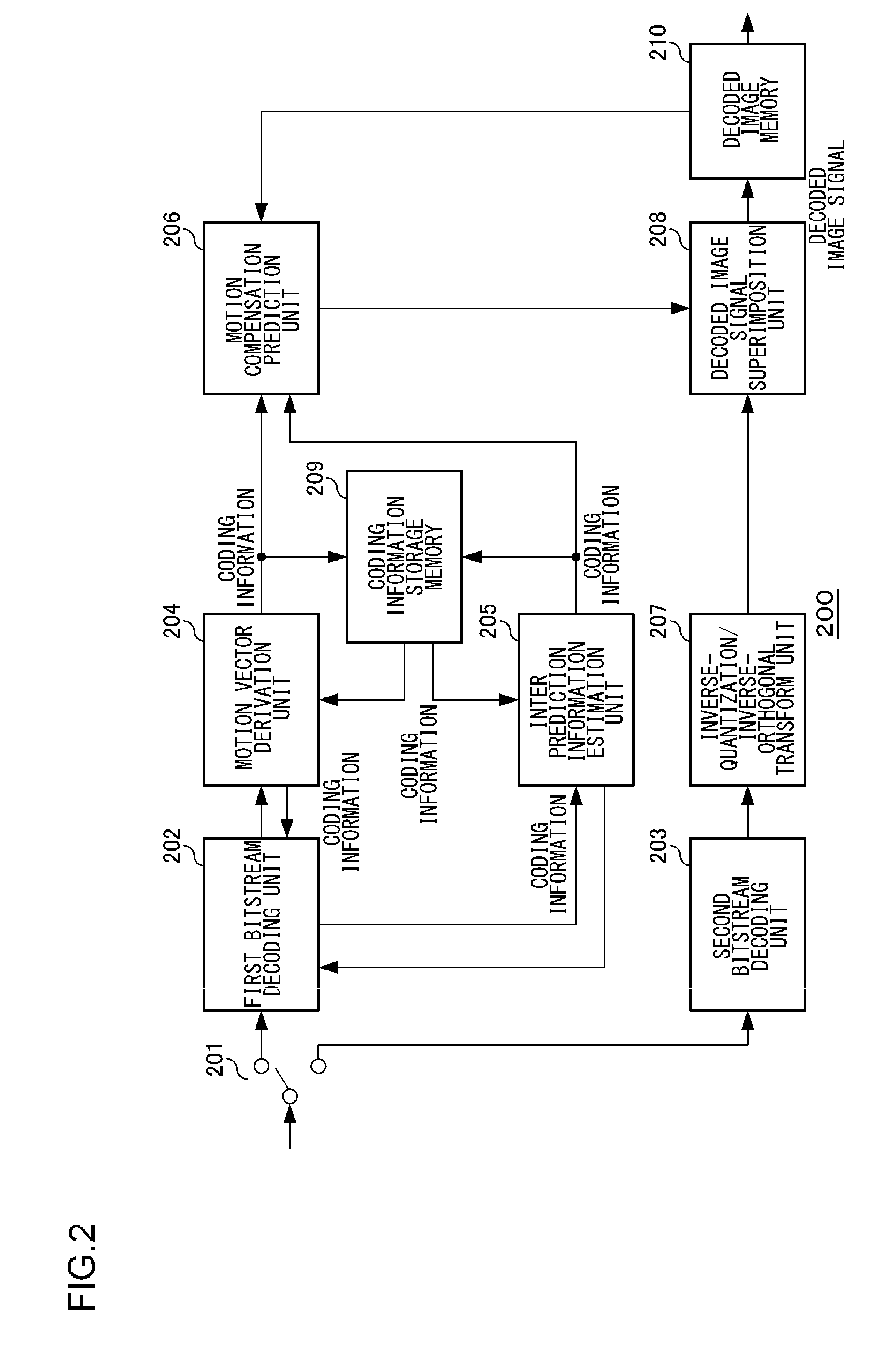

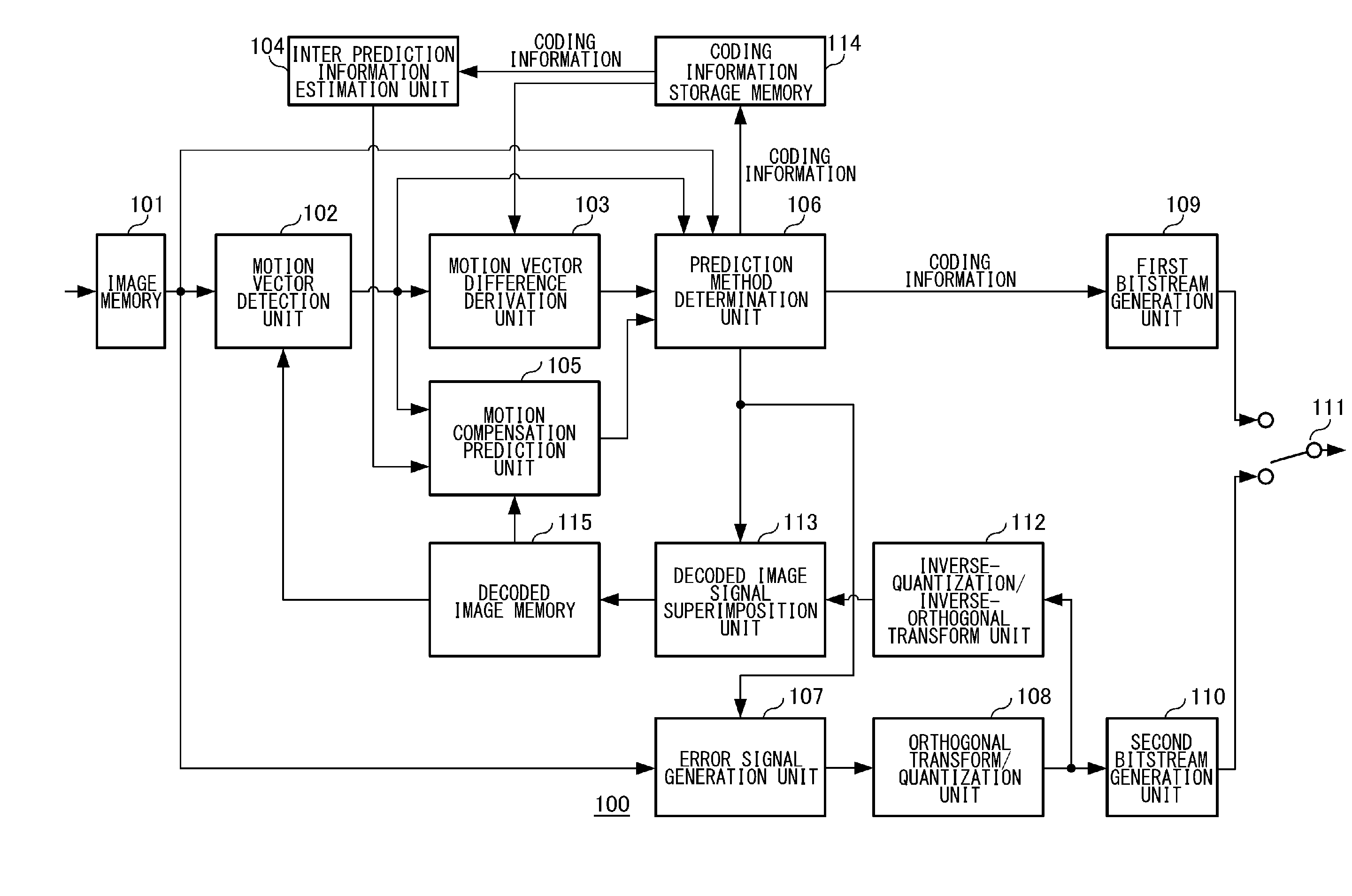

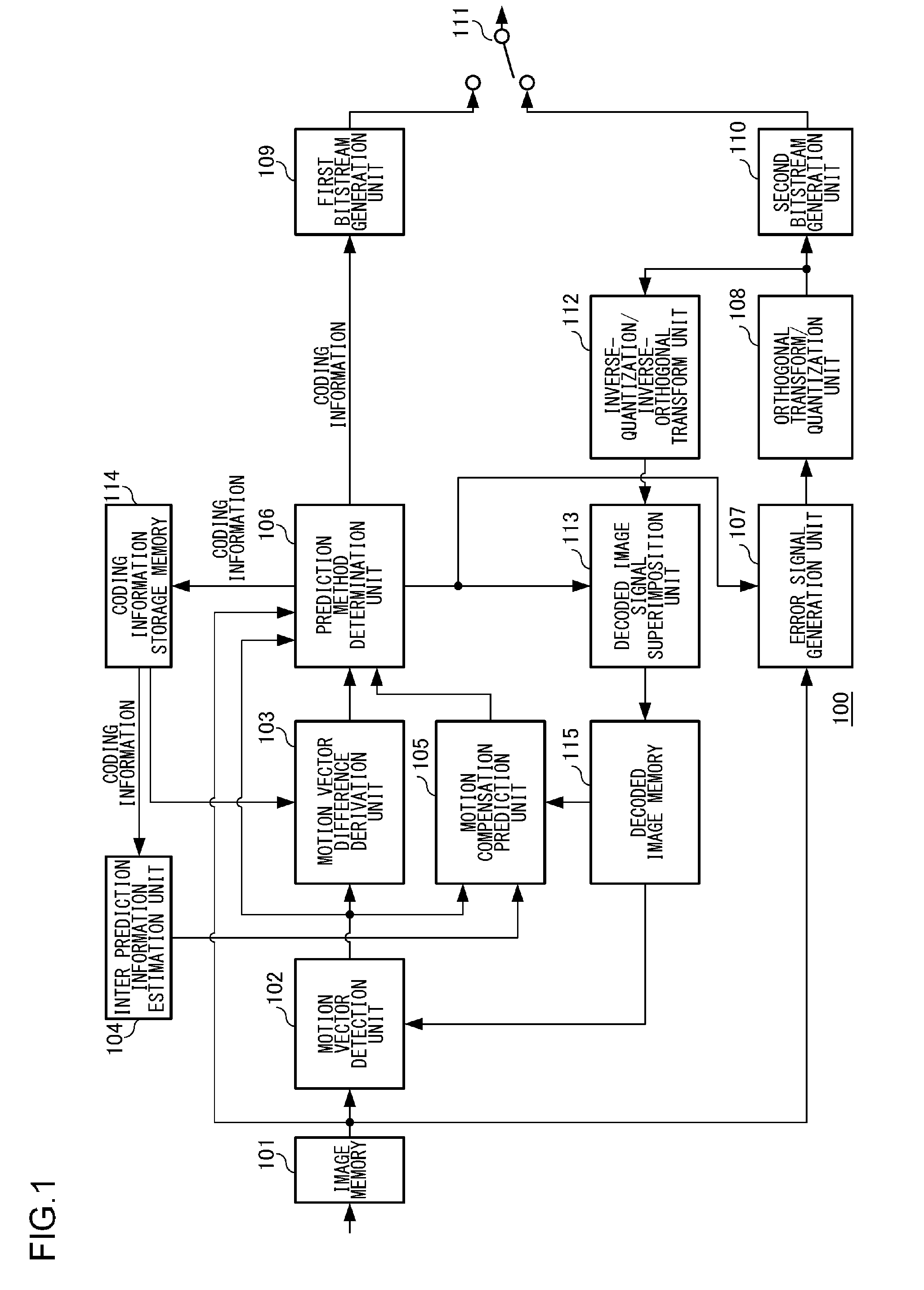

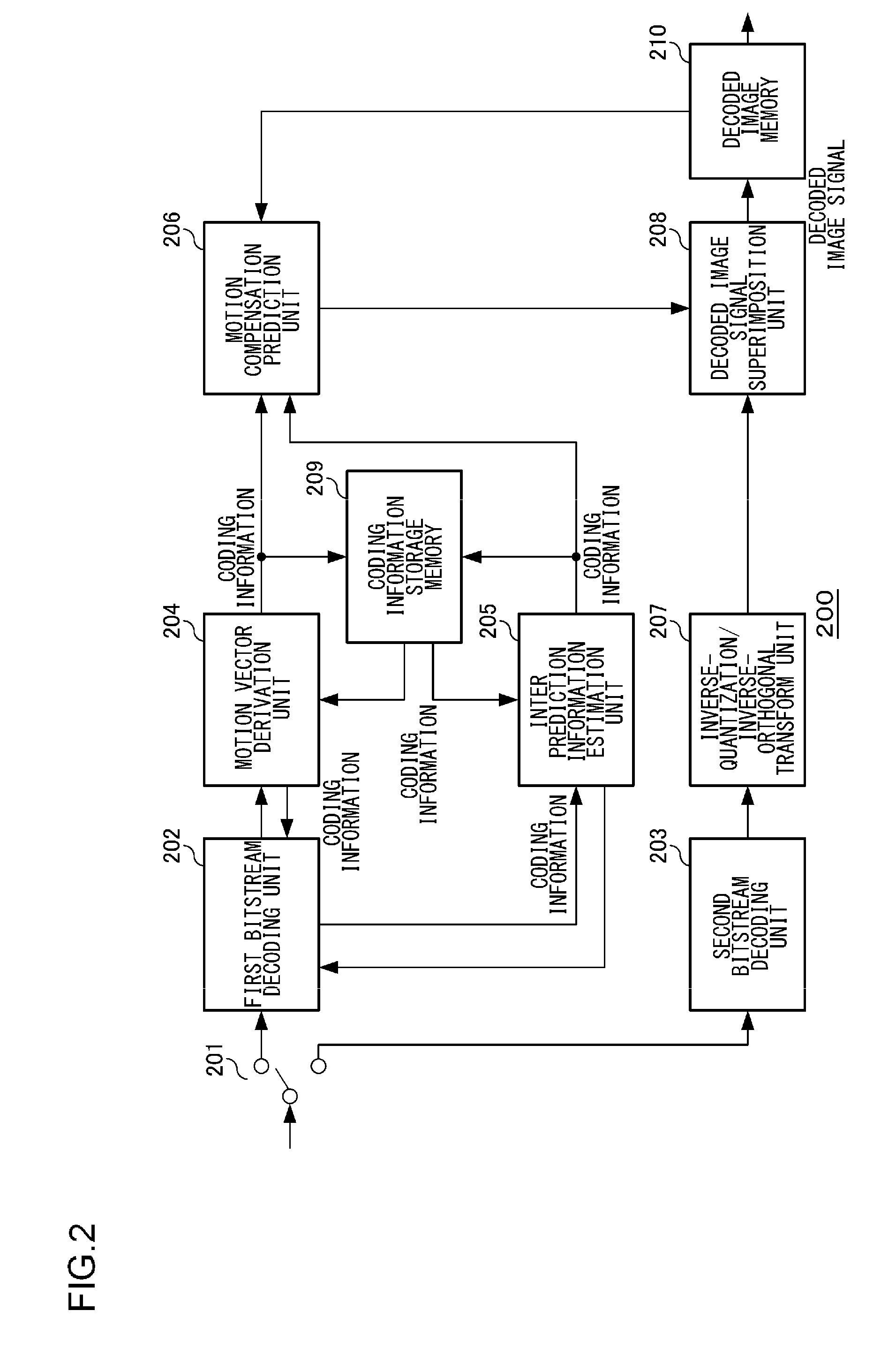

Moving picture coding apparatus, moving picture coding method, and moving picture coding program, and moving picture decoding apparatus, moving picture decoding method, and moving picture decoding program

ActiveUS20140153647A1Suppresses increase in code sizeImprove coding efficiencyColor television with pulse code modulationColor television with bandwidth reductionDecoding methodsMotion vector

A motion vector predictor candidate generation unit derives a plurality of motion vector predictor candidates by prediction from first coded prediction blocks neighboring a prediction block subject to coding within the same picture as the prediction block subject to coding, or from a second coded prediction block located at the same position as or in the neighborhood of the prediction block subject to coding in a picture different from that of the prediction block subject to coding, and adds the derived motion vector predictor candidates in a motion vector predictor candidate. The motion vector predictor candidate generation unit determines, for the purpose of obtaining a predetermined number of motion vector predictor candidates, which of first coded prediction blocks provides the motion vector from which to derive the motion vector predictor candidate, organizing the blocks in the order of priority.

Owner:JVC KENWOOD CORP A CORP OF JAPAN

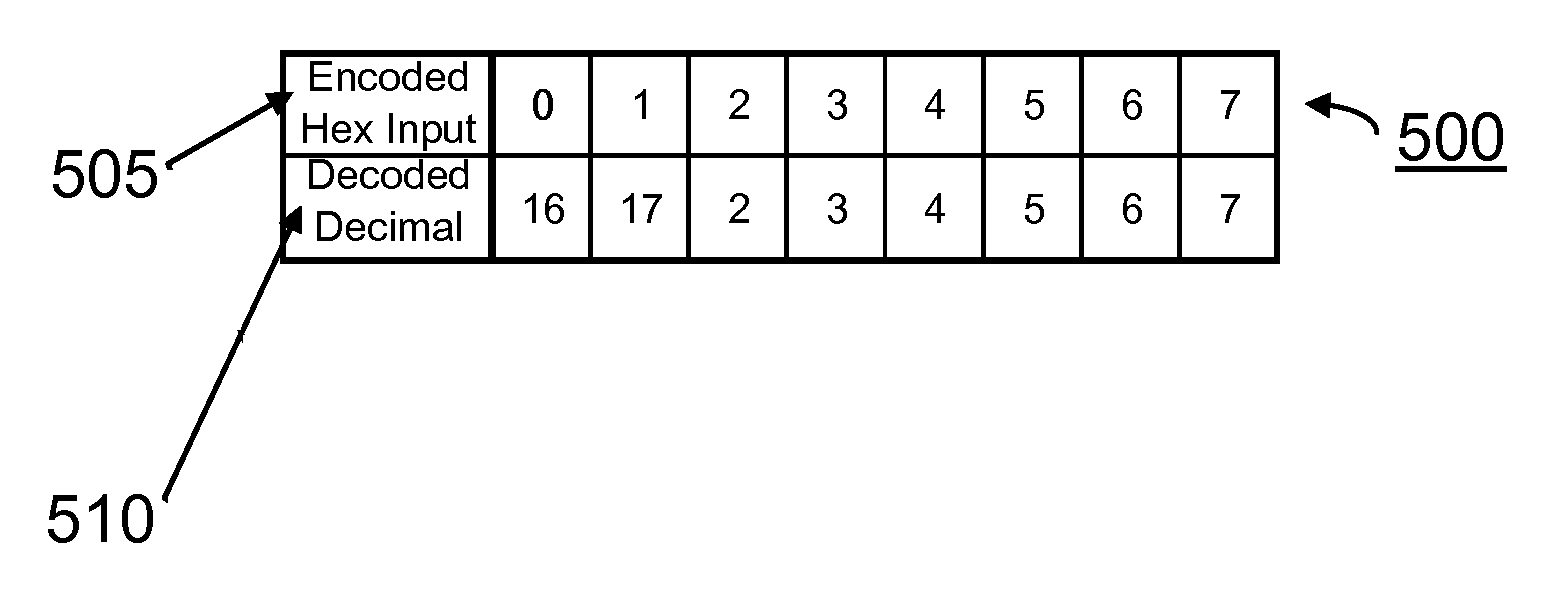

Variable register and immediate field encoding in an instruction set architecture

ActiveUS20100287359A1Suppresses increase in code sizeSpecific costInstruction analysisDigital computer detailsOperation modeApplication software

A method and apparatus provide means for compressing instruction code size. An Instruction Set Architecture (ISA) encodes instructions compact, usual or extended bit lengths. Commonly used instructions are encoded having both compact and usual bit lengths, with compact or usual bit length instructions chosen based on power, performance or code size requirements. Instructions of the ISA can be used in both privileged and non-privileged operating modes of a microprocessor. The instruction encodings can be used interchangeably in software applications. Instructions from the ISA may be executed on any programmable device enabled for the ISA, including a single instruction set architecture processor or a multi-instruction set architecture processor.

Owner:ARM FINANCE OVERSEAS LTD

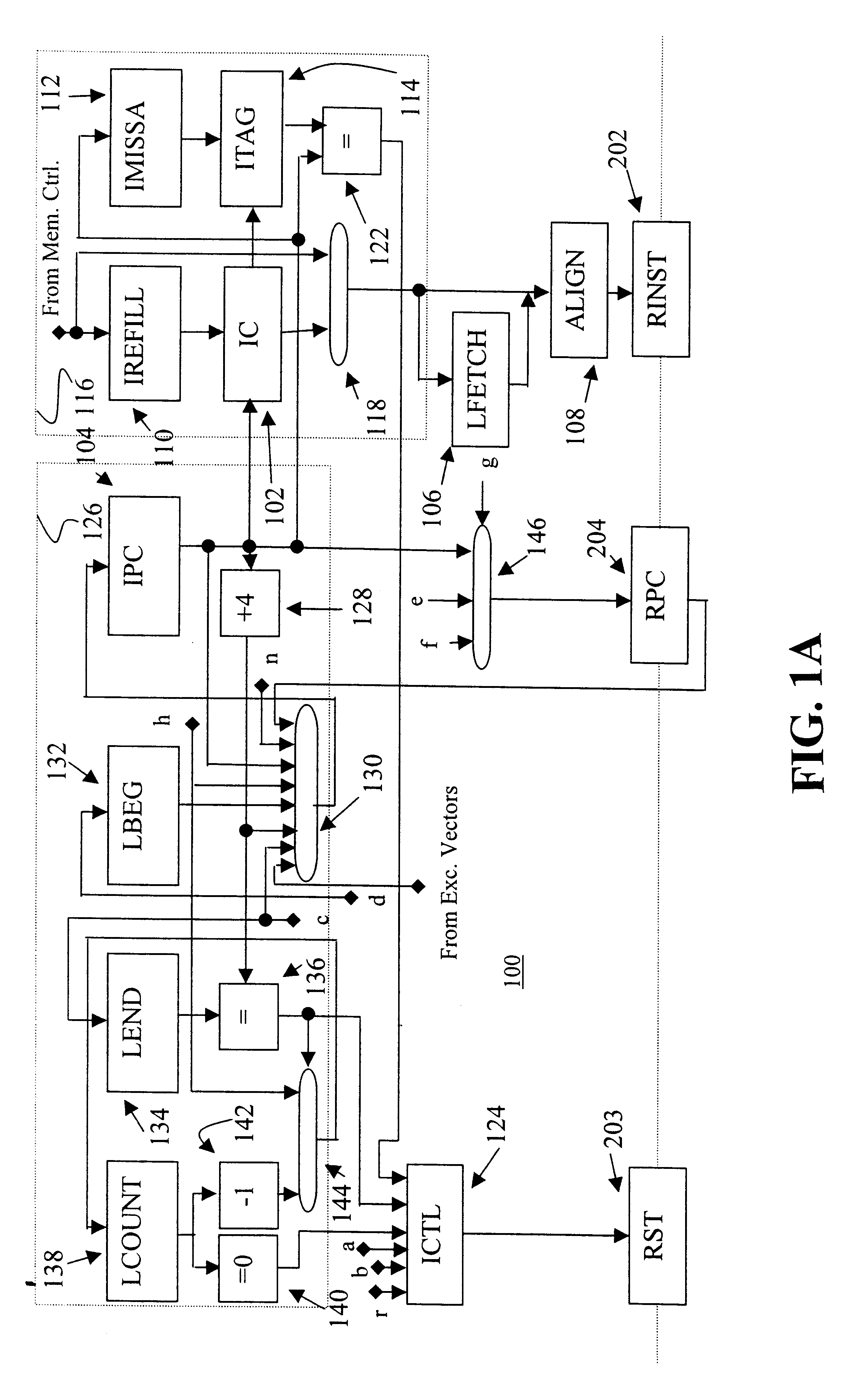

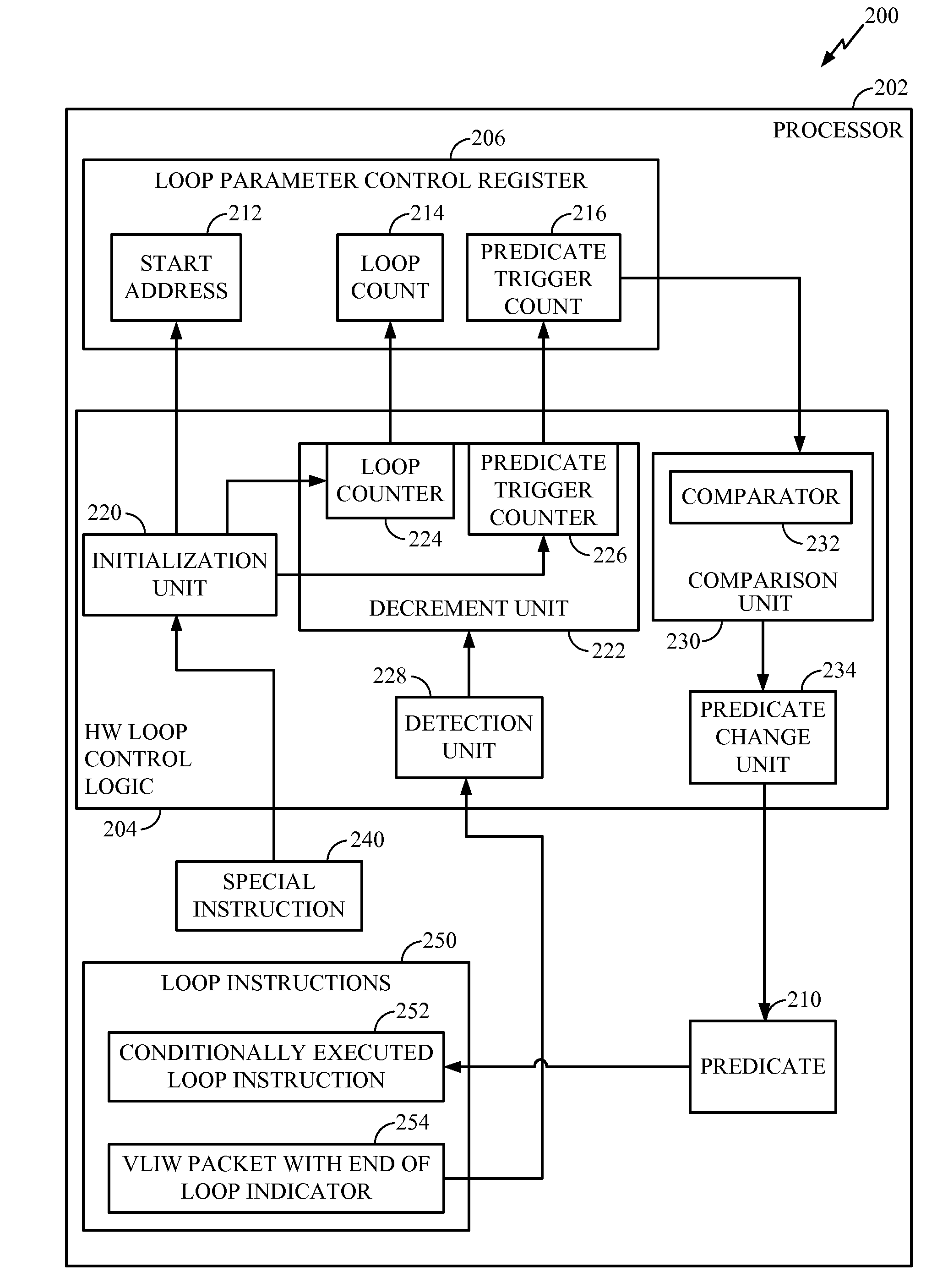

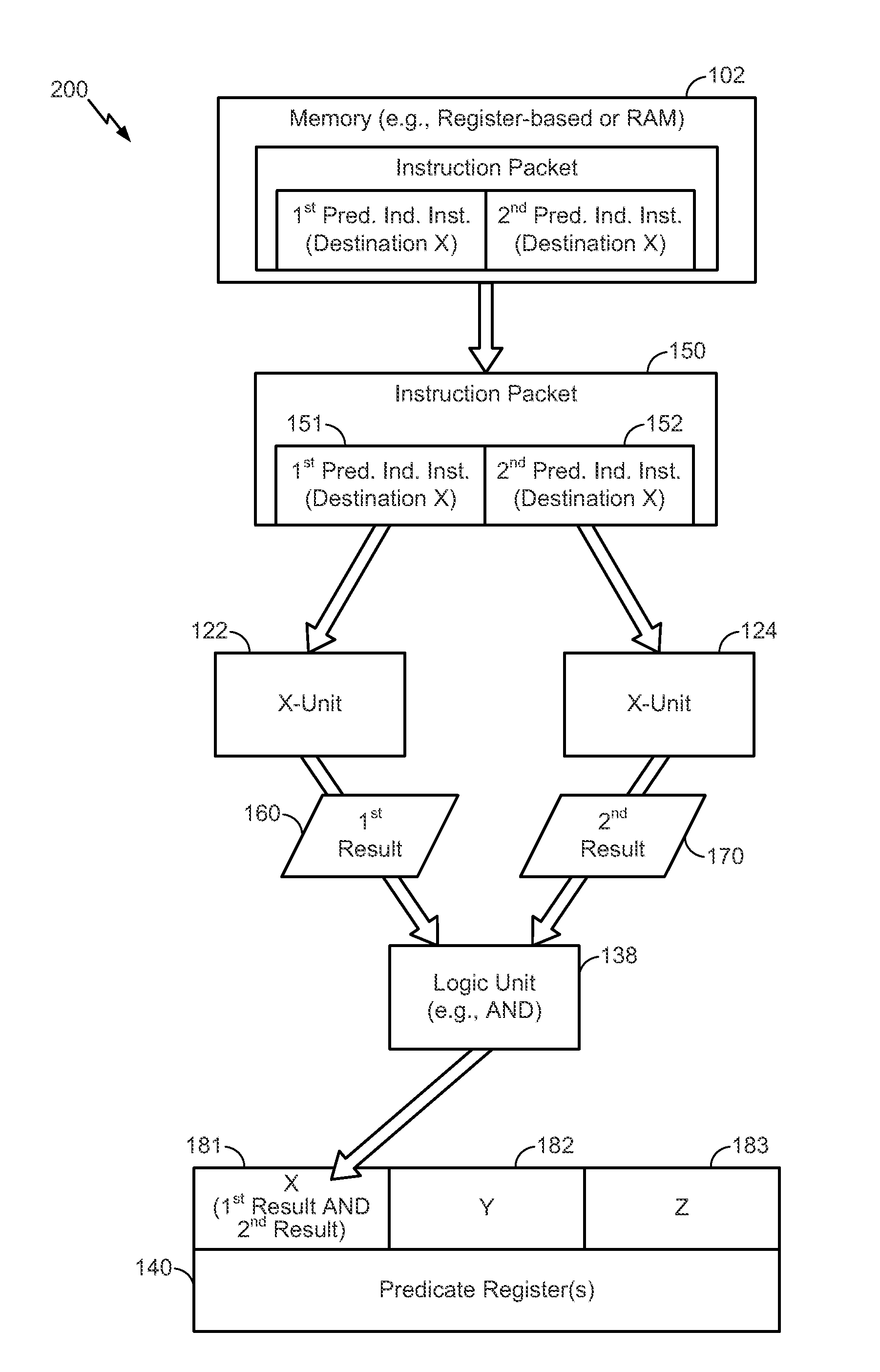

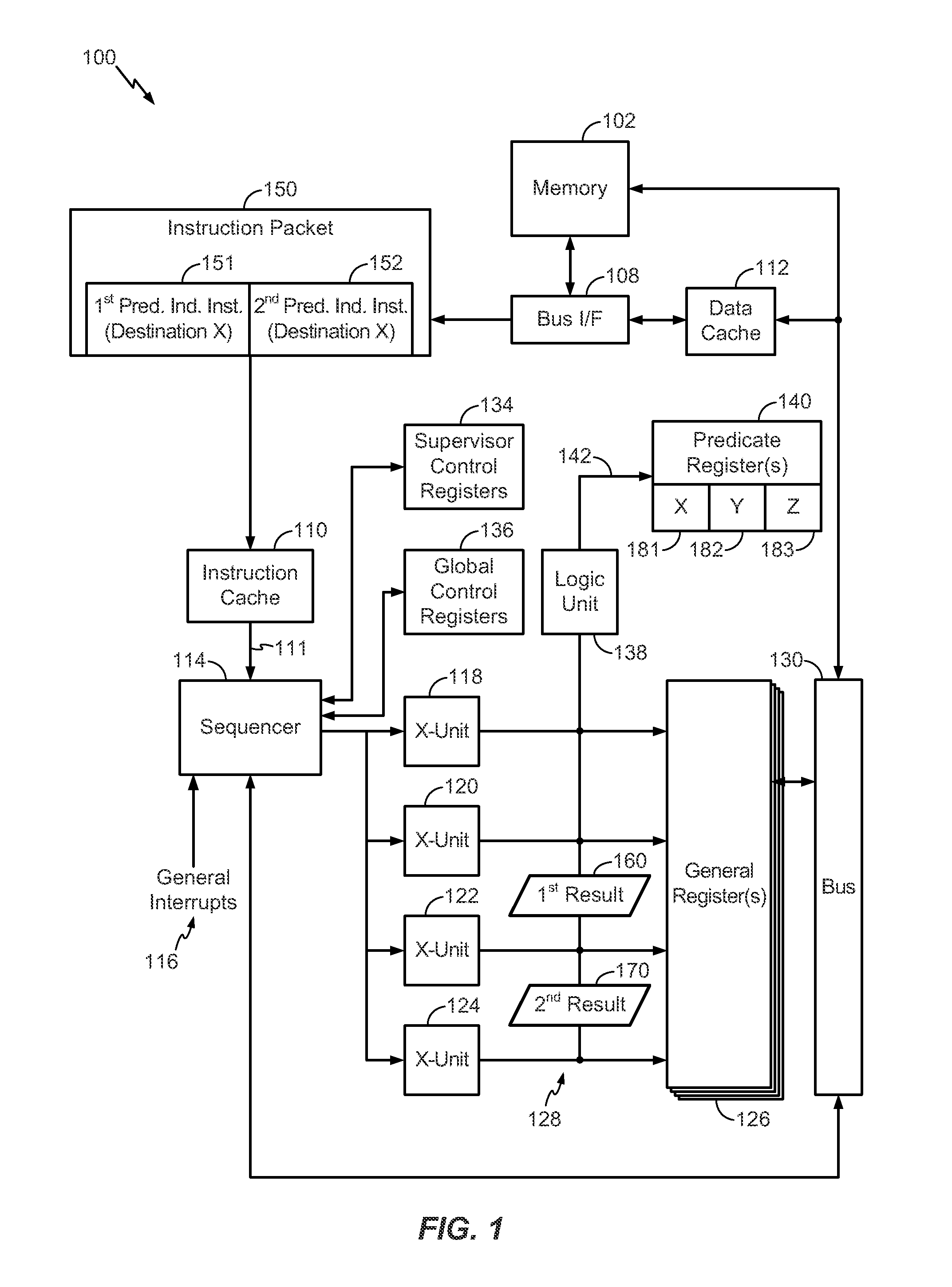

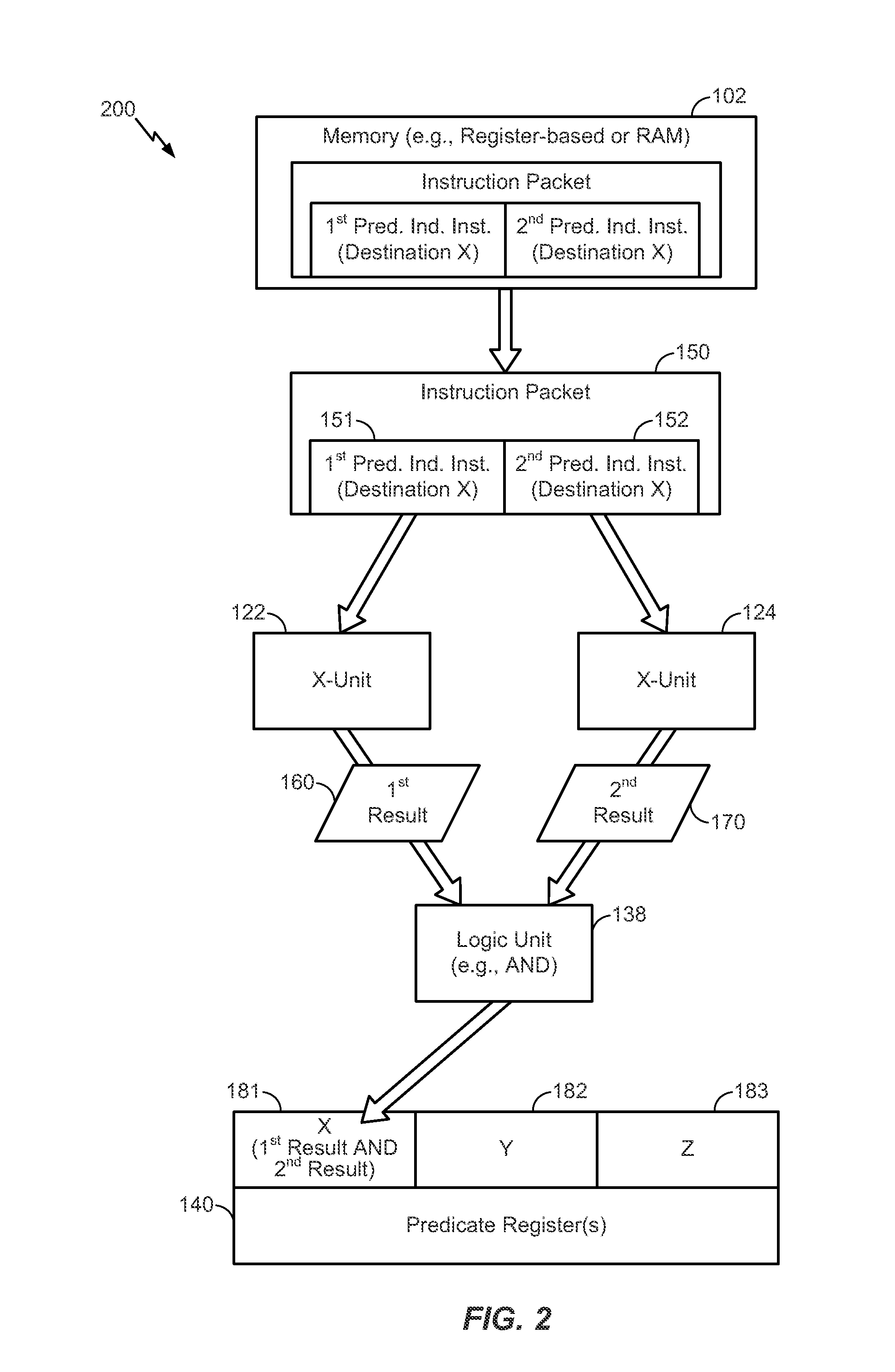

Loop Control System and Method

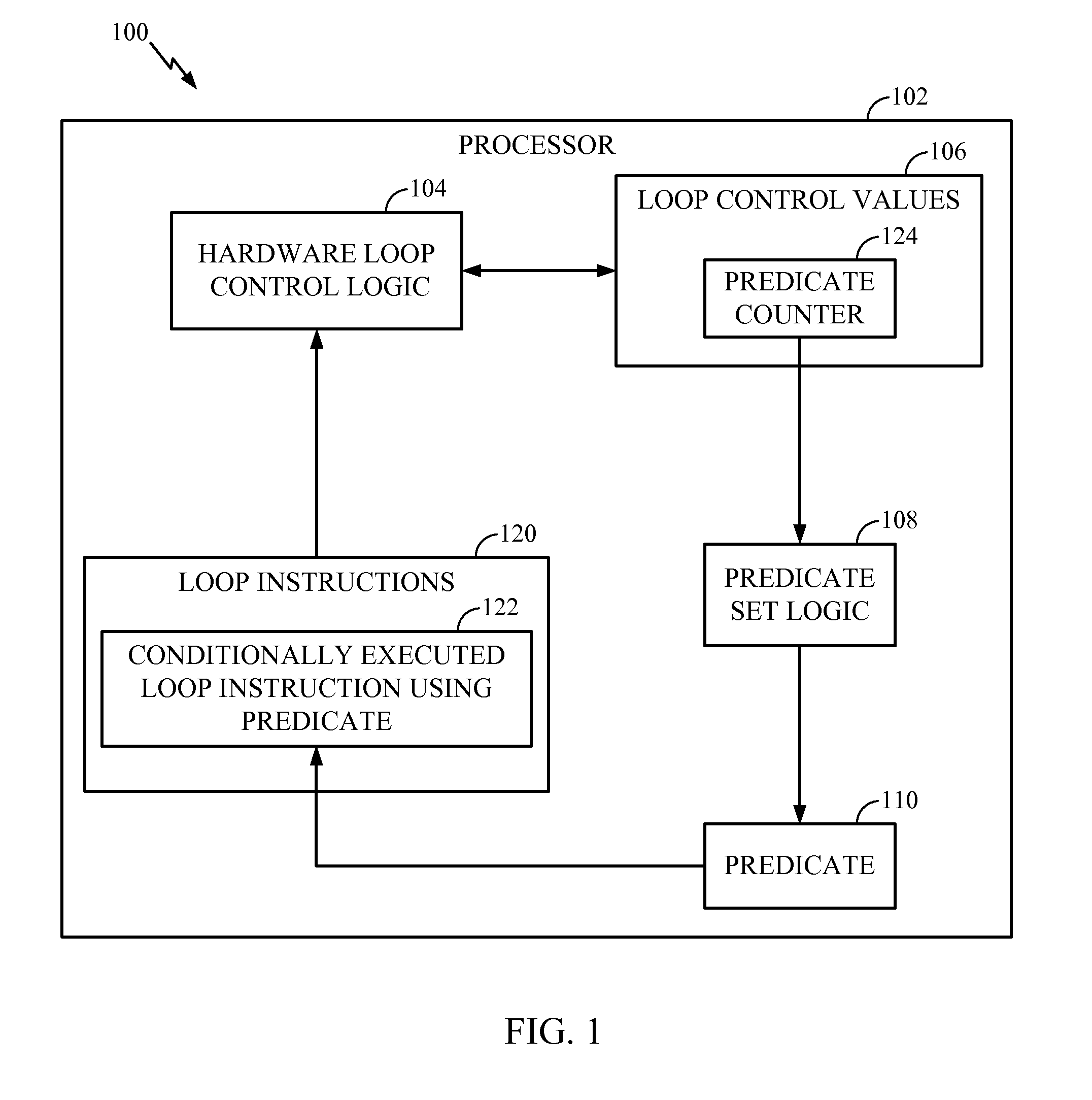

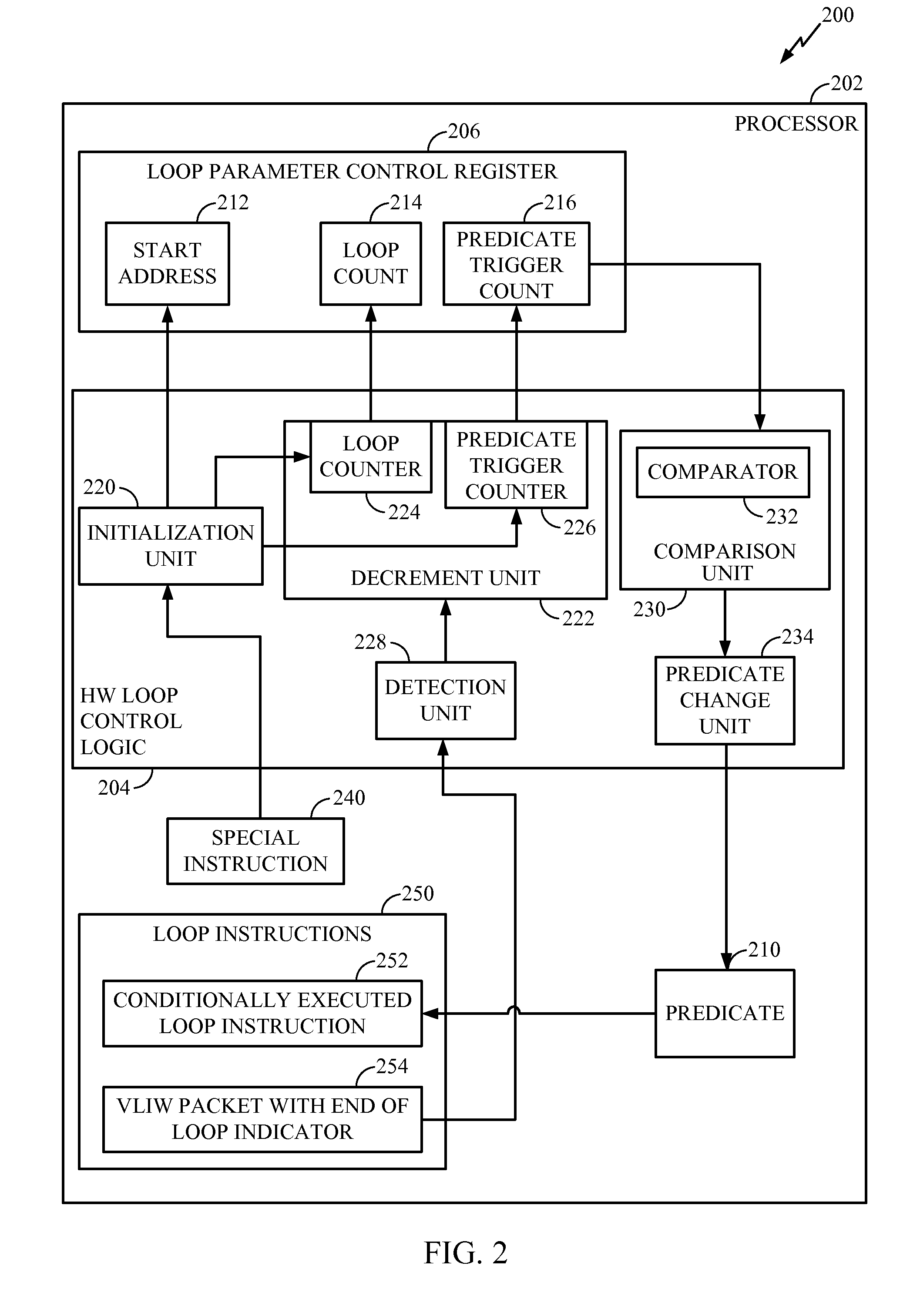

InactiveUS20090327674A1High speed machiningSuppresses increase in code sizeLink editingDigital computer detailsLoop controlControl system

Loop control systems and methods are disclosed. In a particular embodiment, a hardware loop control logic circuit includes a detection unit to detect an end of loop indicator of a program loop. The hardware loop control logic circuit also includes a decrement unit to decrement a loop count and to decrement a predicate trigger counter. The hardware loop control logic circuit further includes a comparison unit to compare the predicate trigger counter to a reference to determine when to set a predicate value.

Owner:QUALCOMM INC

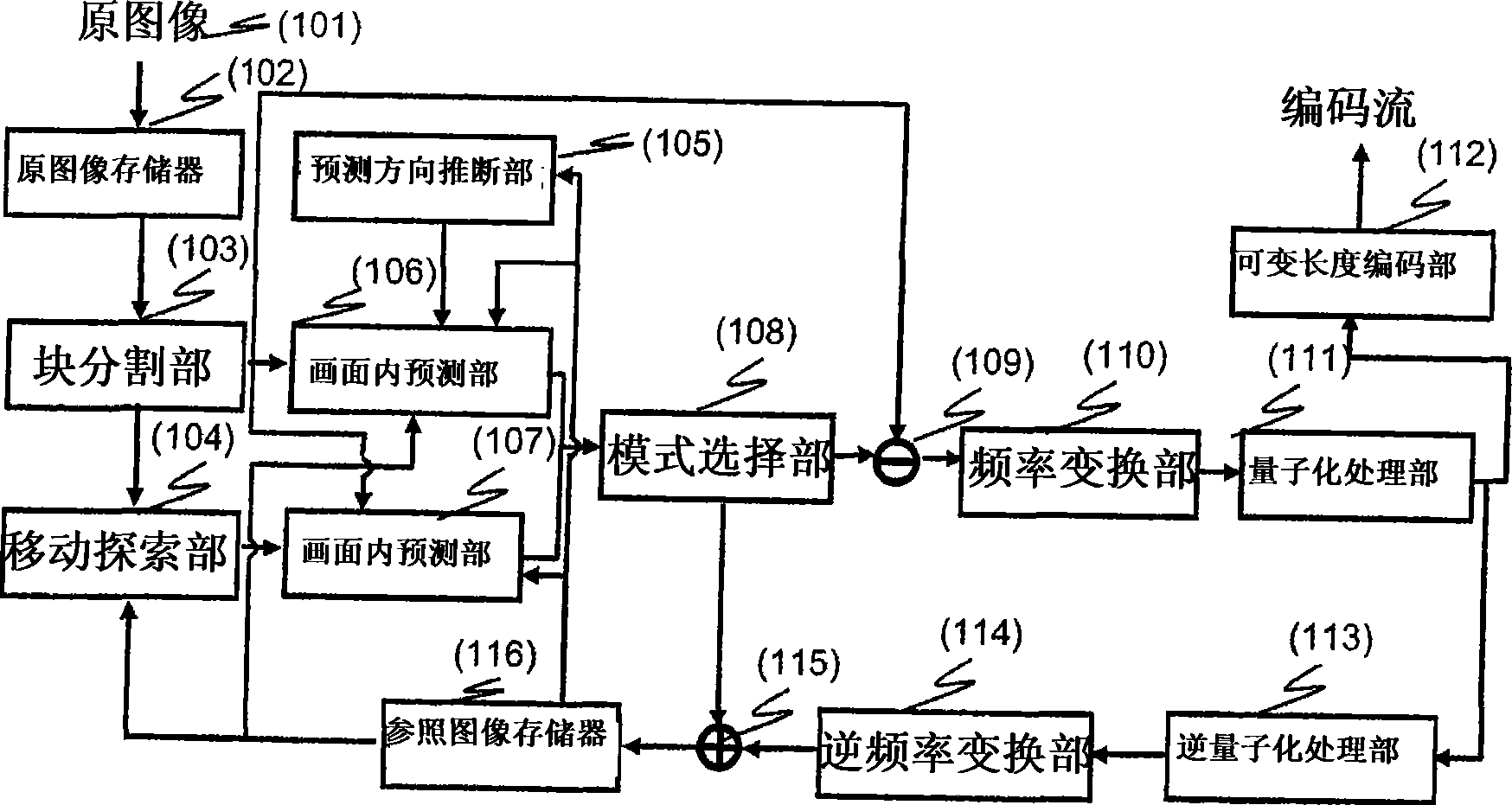

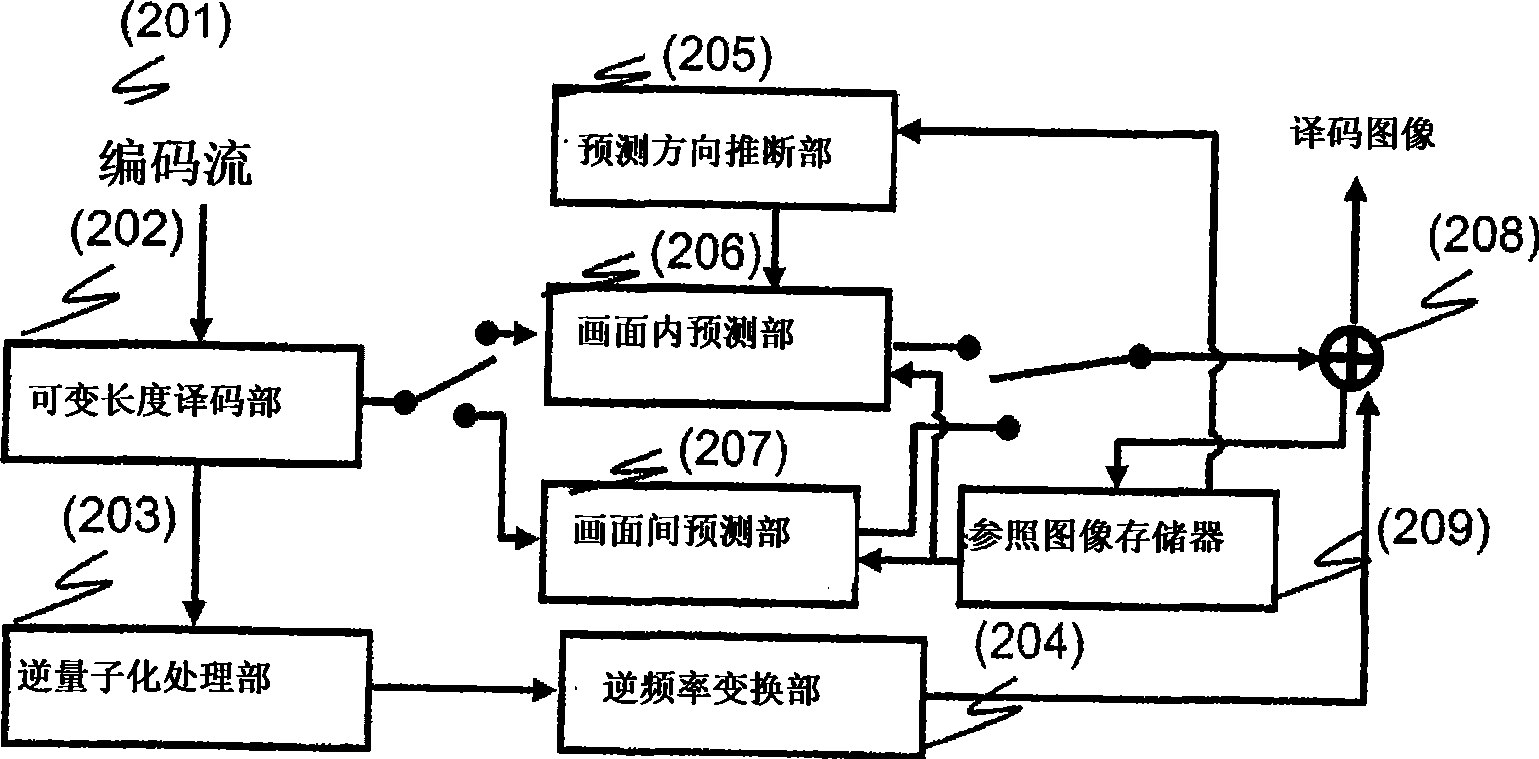

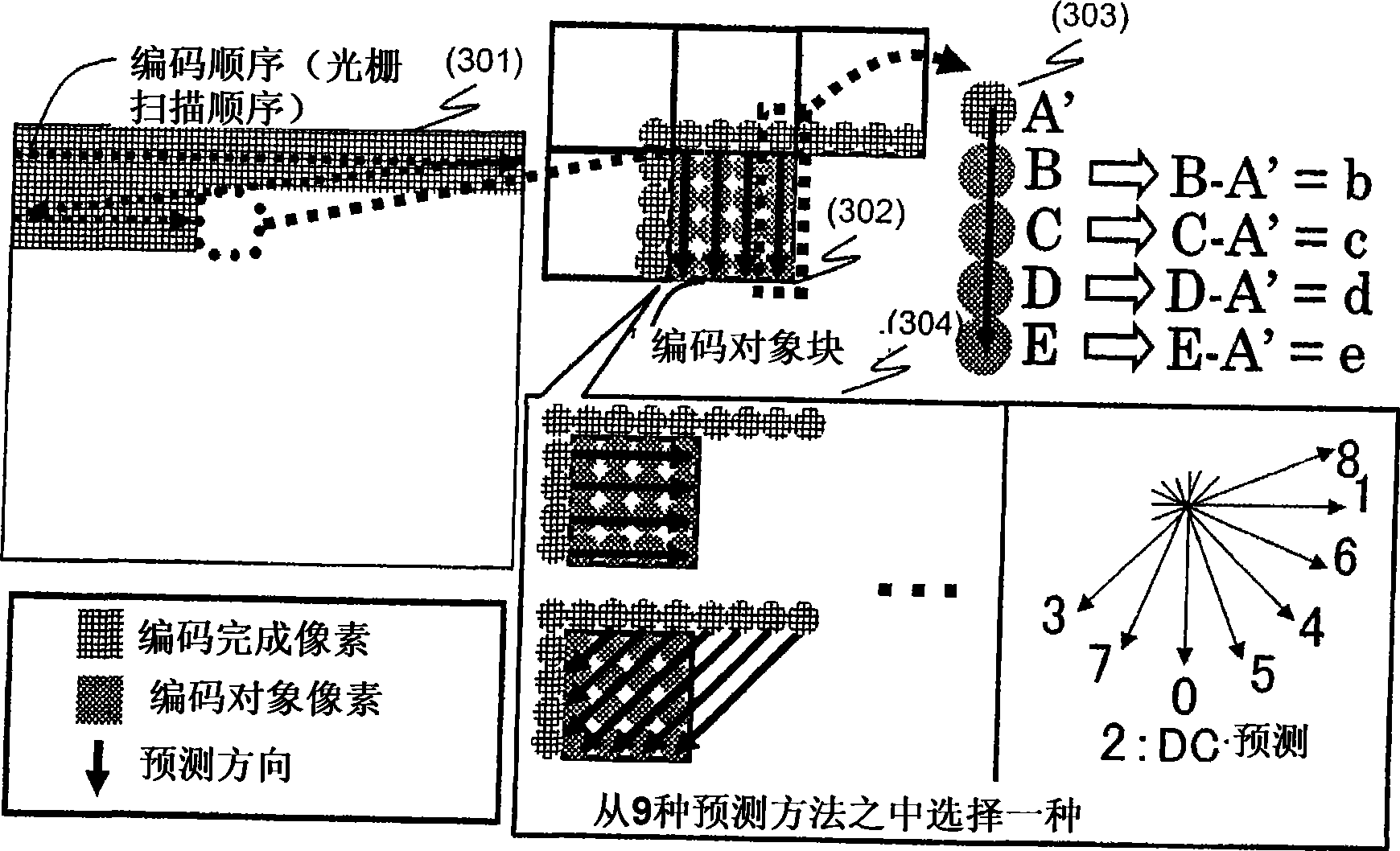

Image encoding device and encoding method, and image decoding device and decoding method

InactiveCN101426141AReduce the amount of codingSuppresses increase in code sizePulse modulation television signal transmissionDigital video signal modificationDecoding methodsComputer vision

In an image encoding / decoding device of the present invention, the prediction direction in a target block, i.e., a block which becomes the target of the intra-frame prediction processing, is estimated by taking advantage of pre-encoded blocks which are adjacent to the target block. First, as edge information on decoded images on the adjacent blocks, intensities and angles of the edges are calculated. Next, of the degrees of likelihood calculated with respect to each prediction direction by taking advantage of this edge information and, e.g., a neural network, the prediction direction whose degree of likelihood is the highest is employed as the prediction direction in the target block. Also, a variable-length code table is dynamically created based on the estimated result, which allows a significant reduction in the prediction-direction representing code amount.

Owner:HITACHI LTD

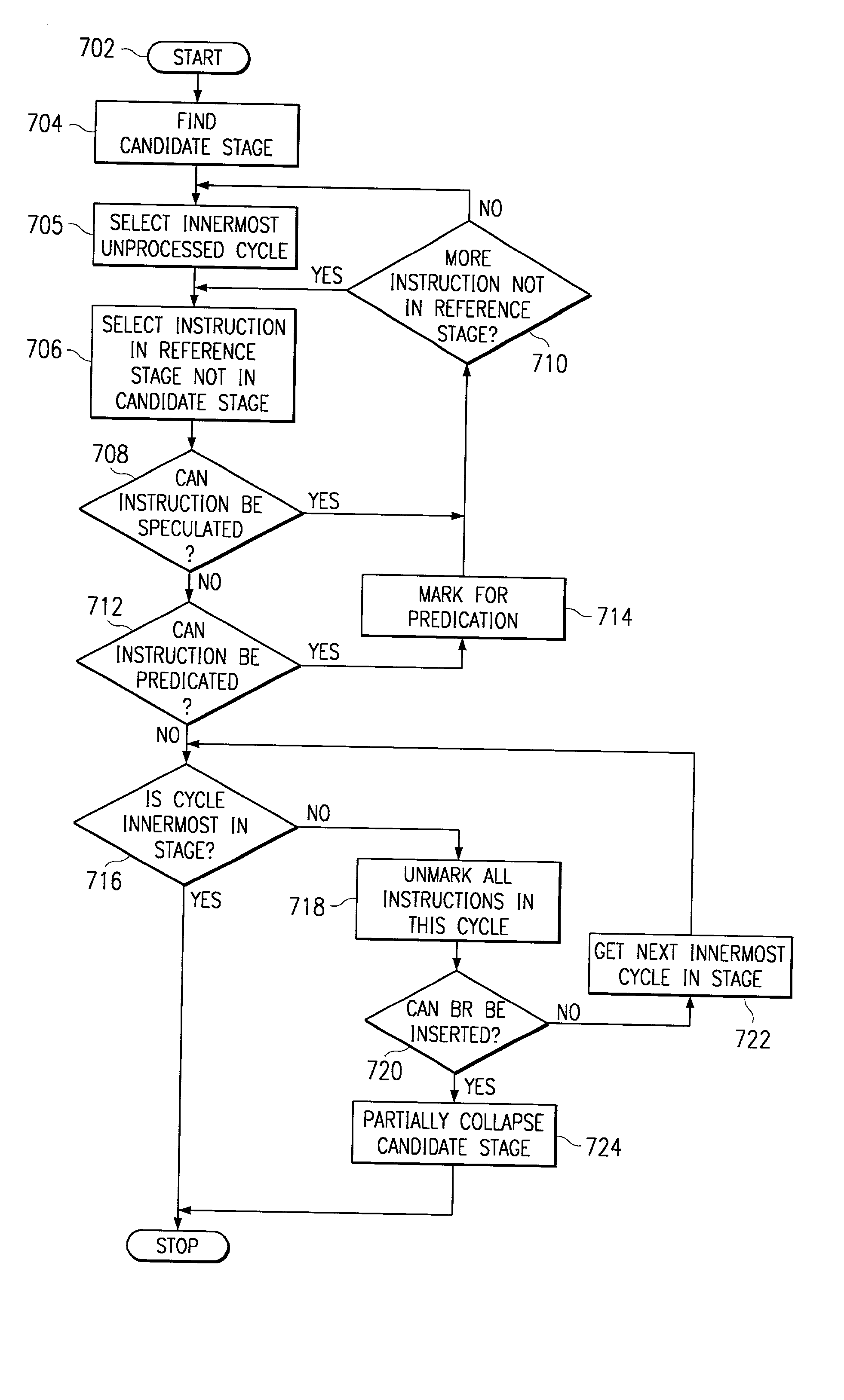

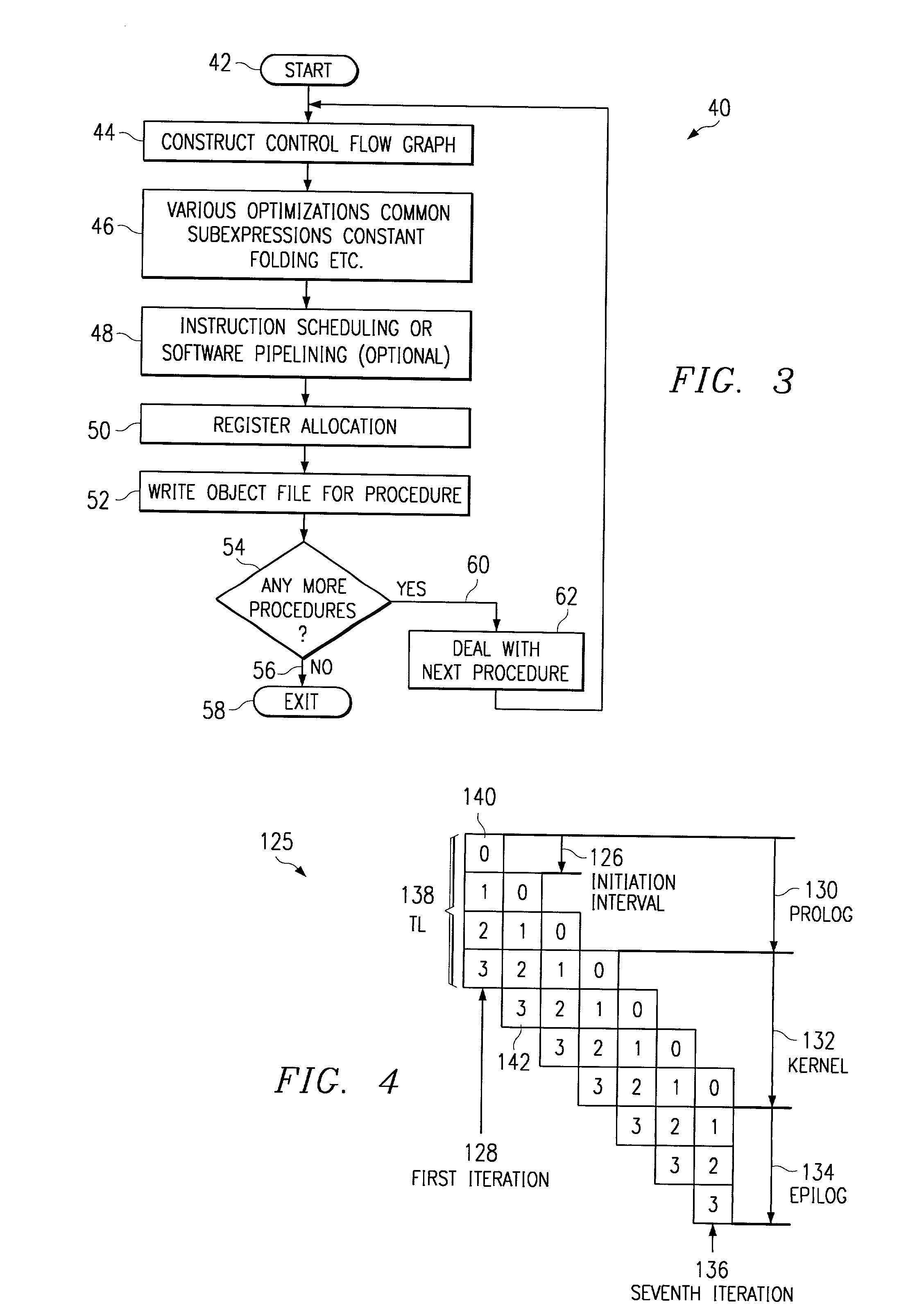

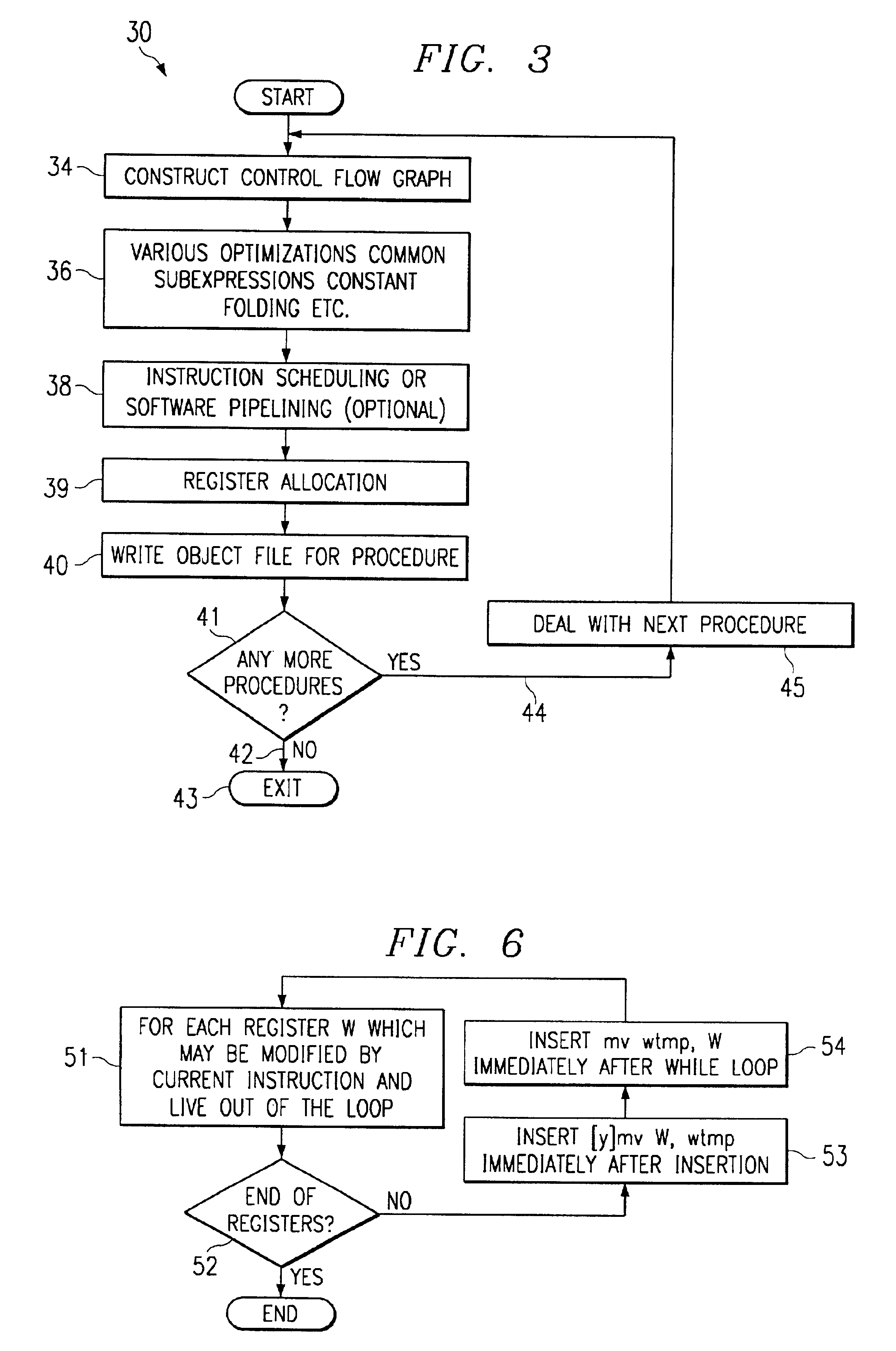

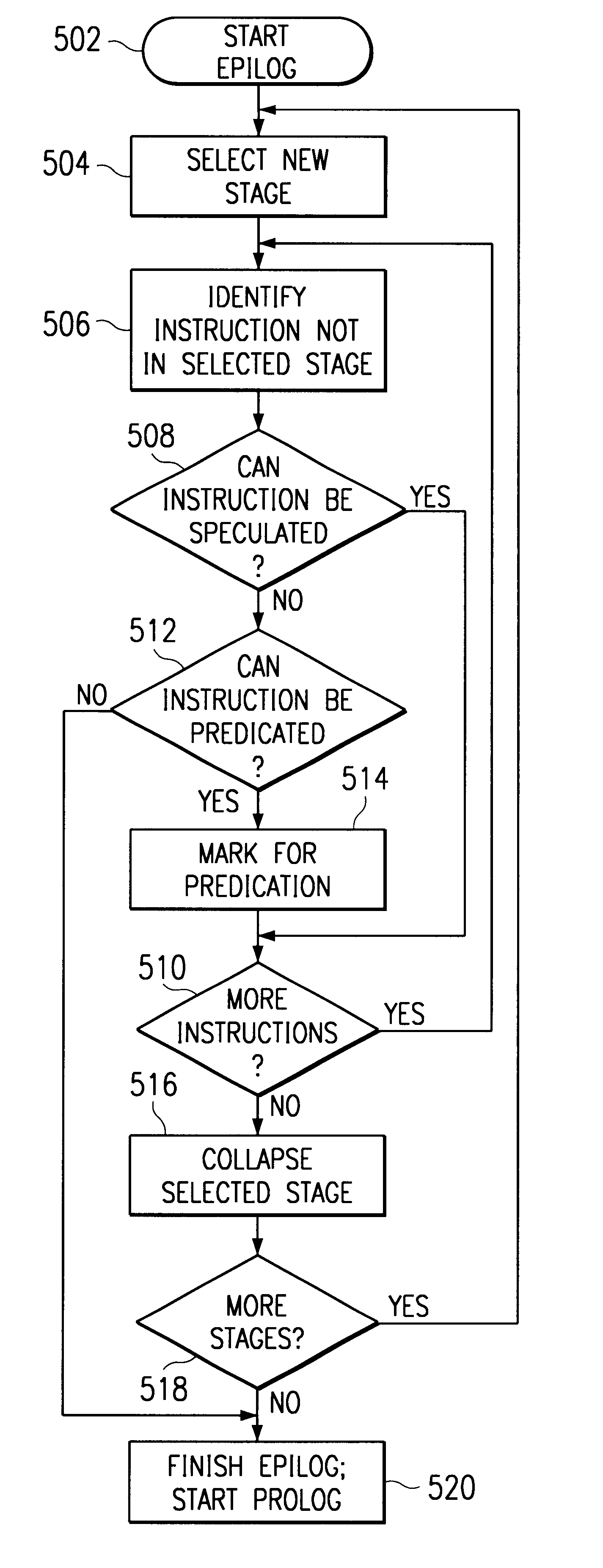

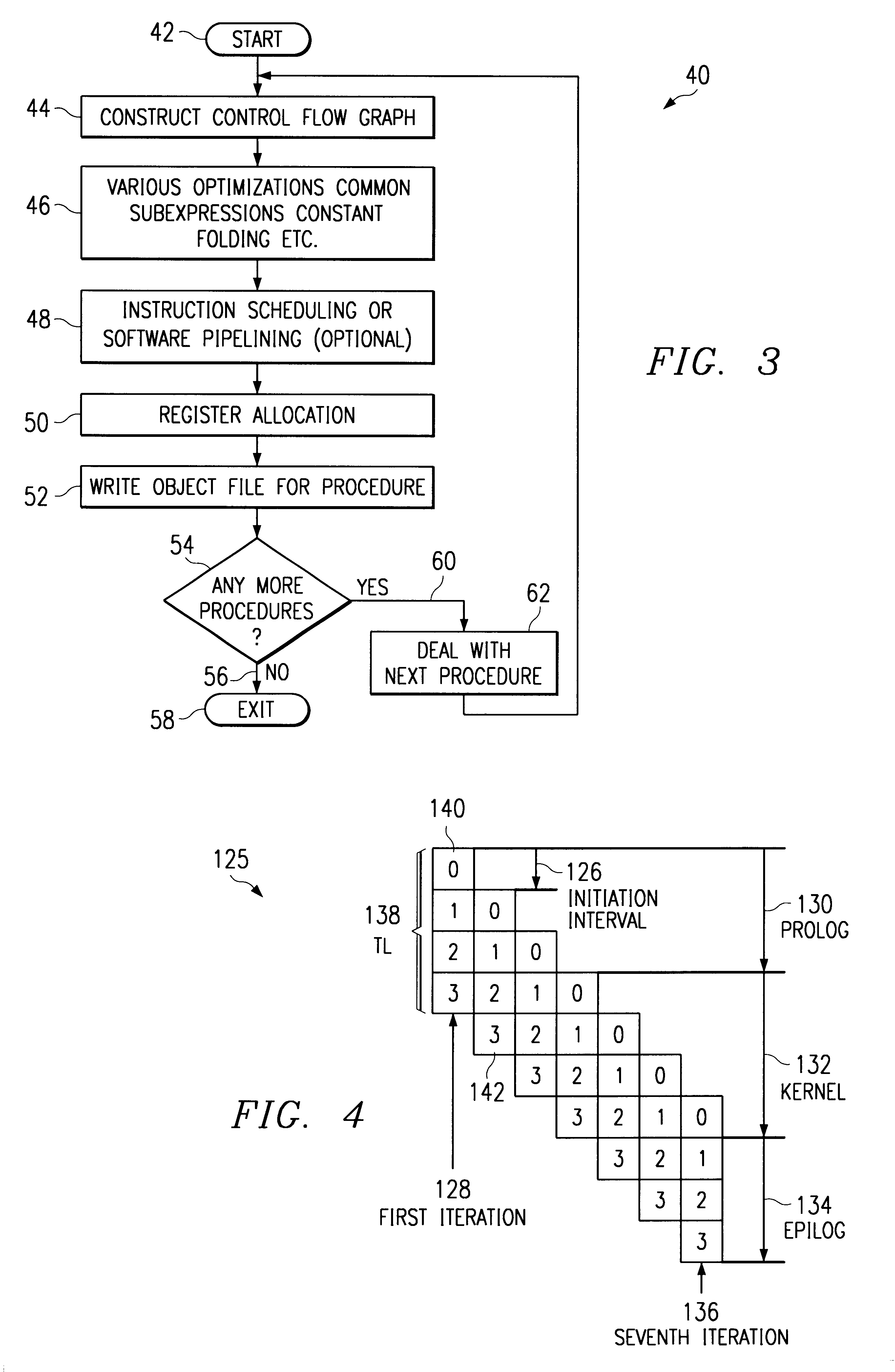

Method for collapsing the prolog and epilog of software pipelined loops

InactiveUS20020112228A1Suppresses increase in code sizeValid encodingSoftware engineeringProgram controlParallel computingSoftware

A method for reducing a code size of a software pipelined loop, the software pipelined loop having a kernel and an epilog. The method includes first evaluating a stage of the epilog. This includes selecting a stage of the epilog to evaluate (504) and evaluating an instruction in a reference stage. This includes identifying an instruction in the reference stage that is not present in the selected stage of the epilog (506) and determining if the identified instruction can be speculated (508). If the identified instruction can be speculated, such is noted. If the instruction cannot be speculated, it is determined whether the identified instruction can be predicated (512). If the instruction can be predicated, it is marked as needing predication (514). Next, it is determined if another instruction in the reference stage is not present in the selected stage of the epilog (510). If there is, the instruction evaluation is repeated. If there is another stage of the epilog to evaluate, the evaluation is repeated (518).

Owner:TEXAS INSTR INC

Data processor

InactiveUS20030061471A1Reduce processReduction of branch penaltyConditional code generationRegister arrangementsParallel computingData processing

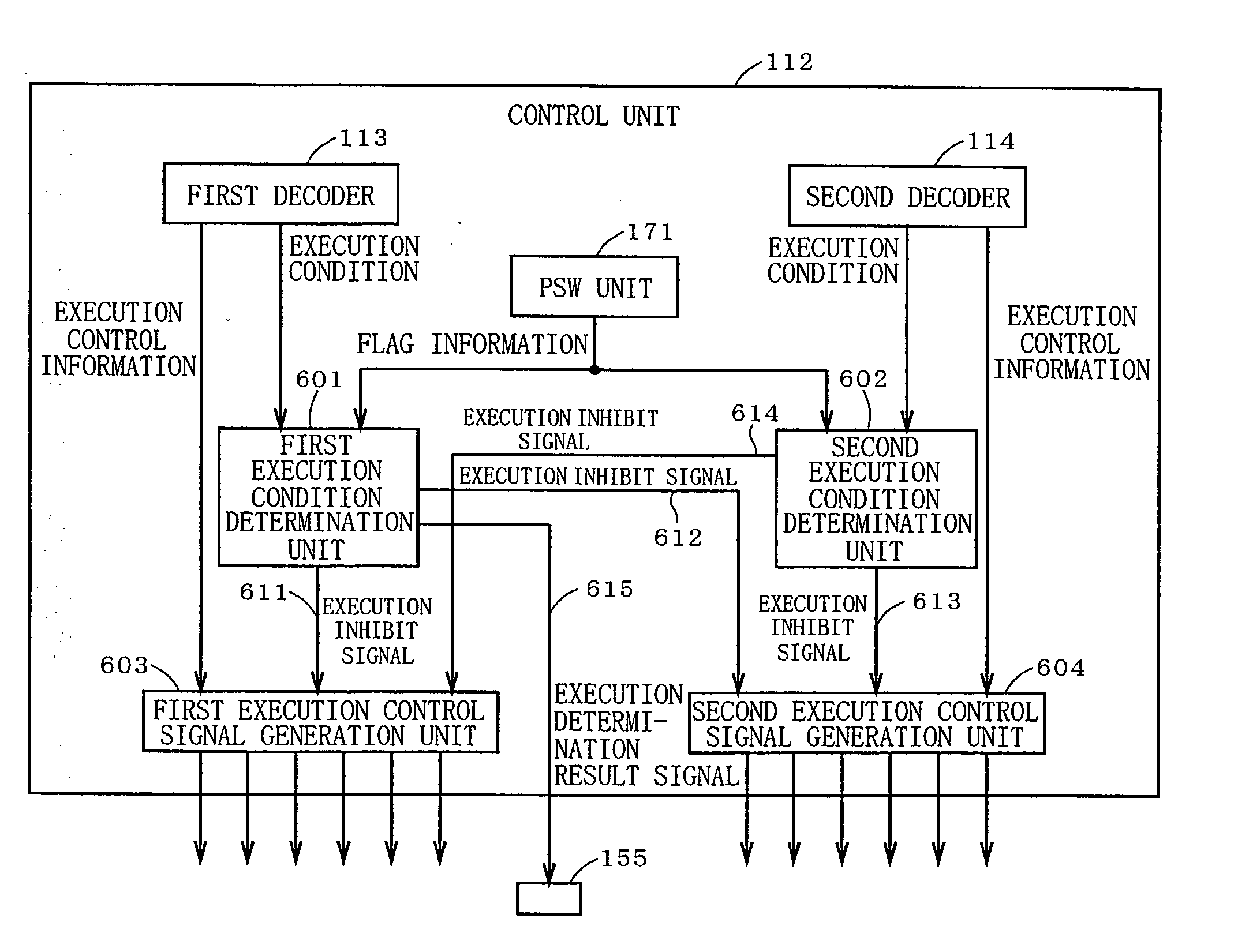

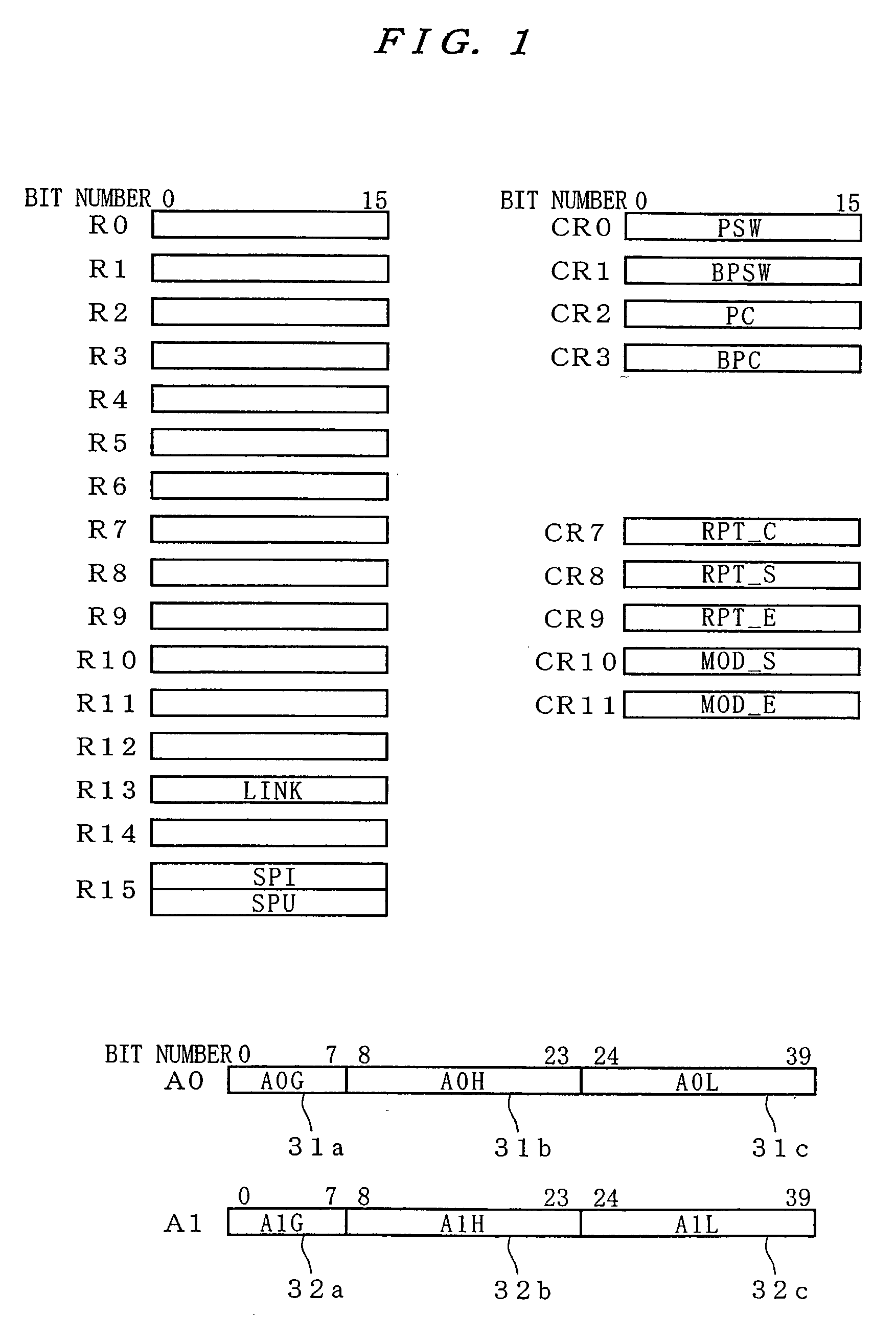

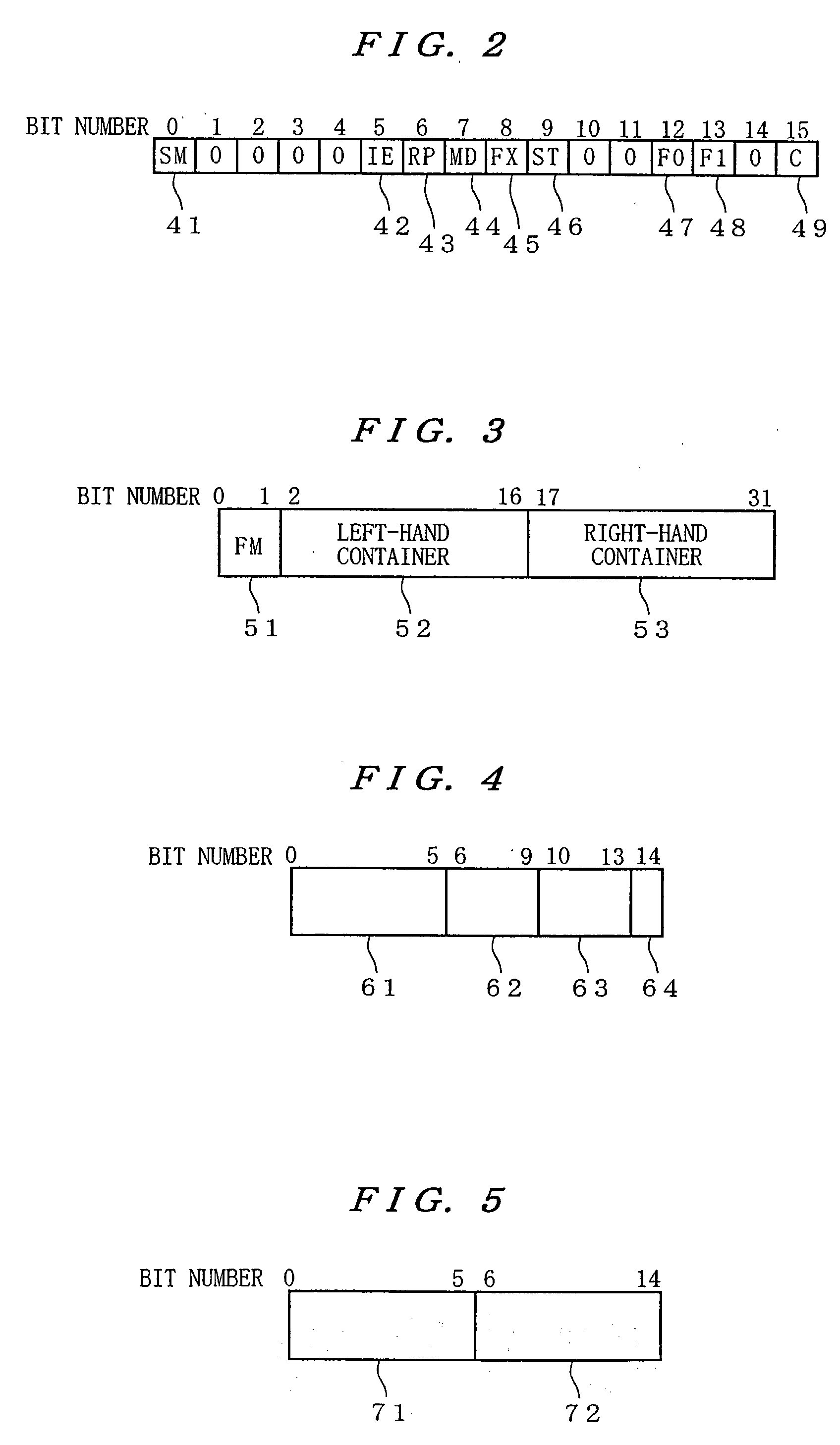

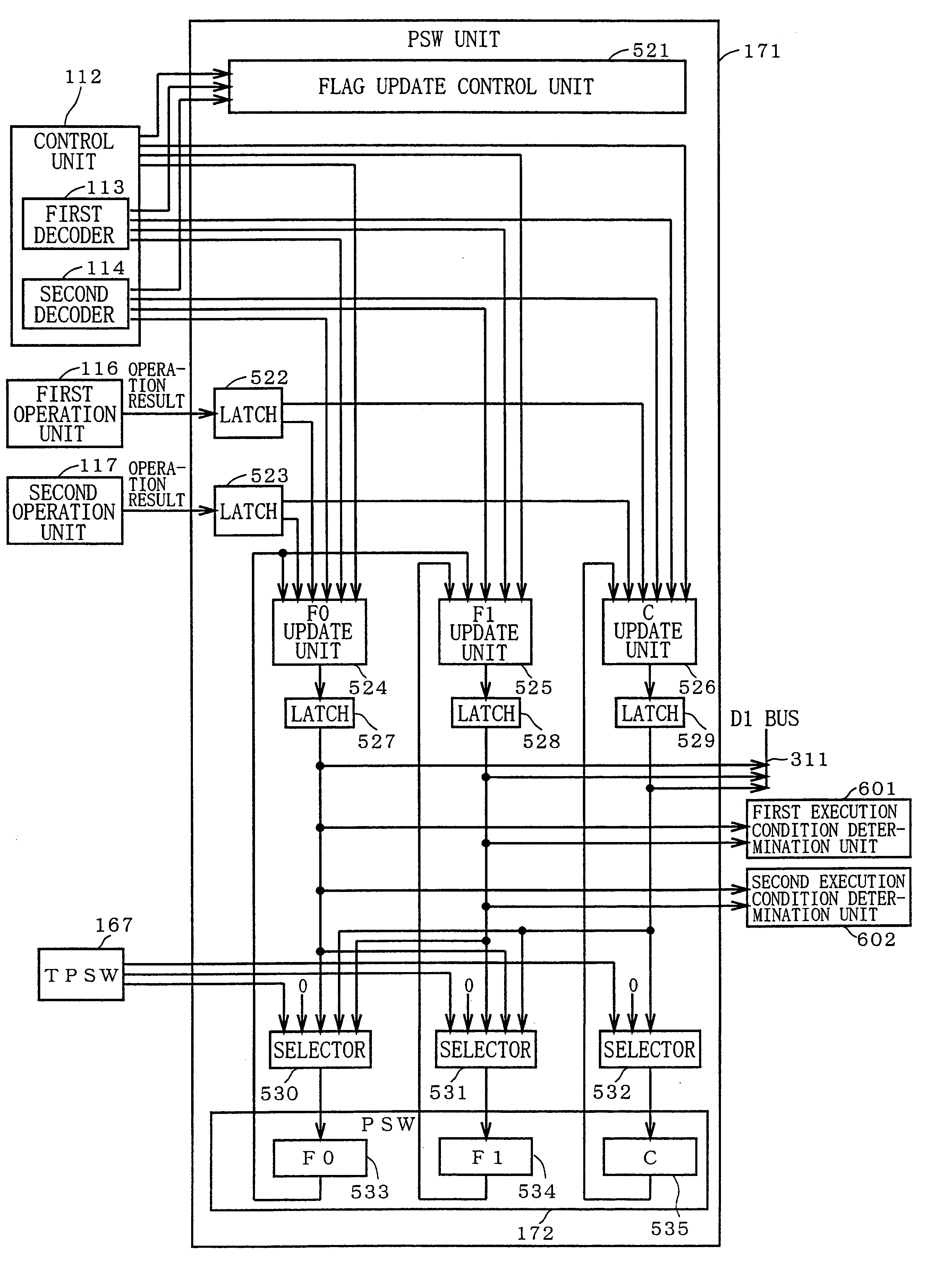

The present invention relates to a data processor, and particularly in a data processor performing condition execution on the basis of flag information, aims at obtaining a data processor having excellent code efficiency, which can reduce branch penalty. In order to attain the aforementioned object, it is so structured that, when a first instruction decoded in a first decoder (113) is an execution condition specifying instruction specifying the execution condition for a pair of second instructions executed in parallel, a first execution condition determination unit (601) performs determination of the execution condition for the second instructions defined by the execution condition specifying instruction on the basis of the flag information and controls assertion / non-assertion of an execution inhibit signal (612) on the basis of whether the execution condition defined by the execution condition specifying instruction is satisfied or not.

Owner:RENESAS TECH CORP

Data processor

InactiveUS6484253B1Reduce processReduction of branch penaltyConditional code generationDigital computer detailsSignal onParallel computing

The present invention relates to a data processor, and particularly in a data processor performing condition execution on the basis of flag information, aims at obtaining a data processor having excellent code efficiency, which can reduce branch penalty. In order to attain the aforementioned object, it is so structured that, when a first instruction decoded in a first decoder is an execution condition specifying instruction specifying the execution condition for a pair of second instructions executed in parallel, a first execution condition determination unit performs determination of the execution condition for the second instructions defined by the execution condition specifying instruction on the basis of the flag information and controls assertion / non-assertion of an execution inhibit signal on the basis of whether the execution condition defined by the execution condition specifying instruction is satisfied or not.

Owner:RENESAS ELECTRONICS CORP

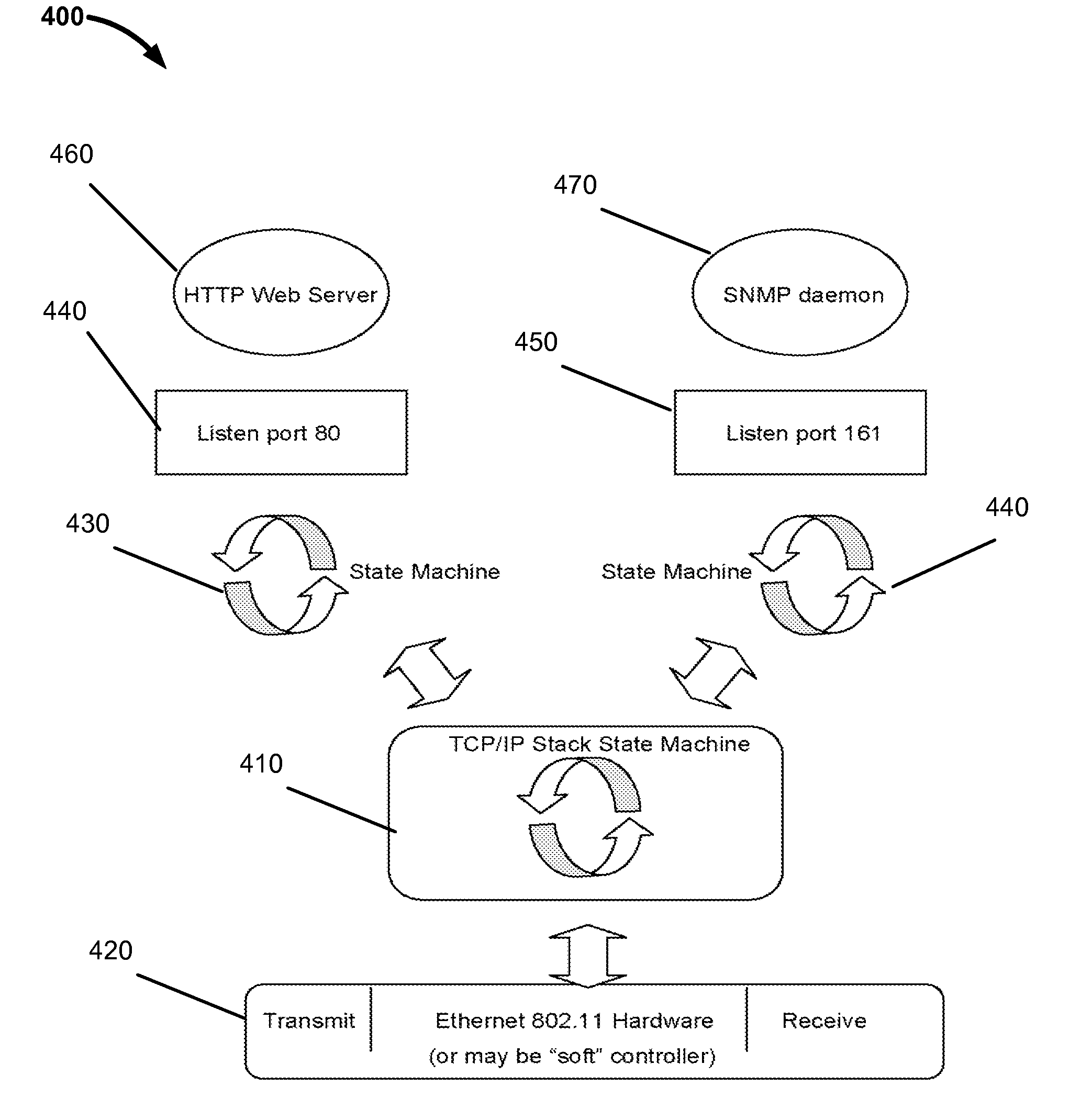

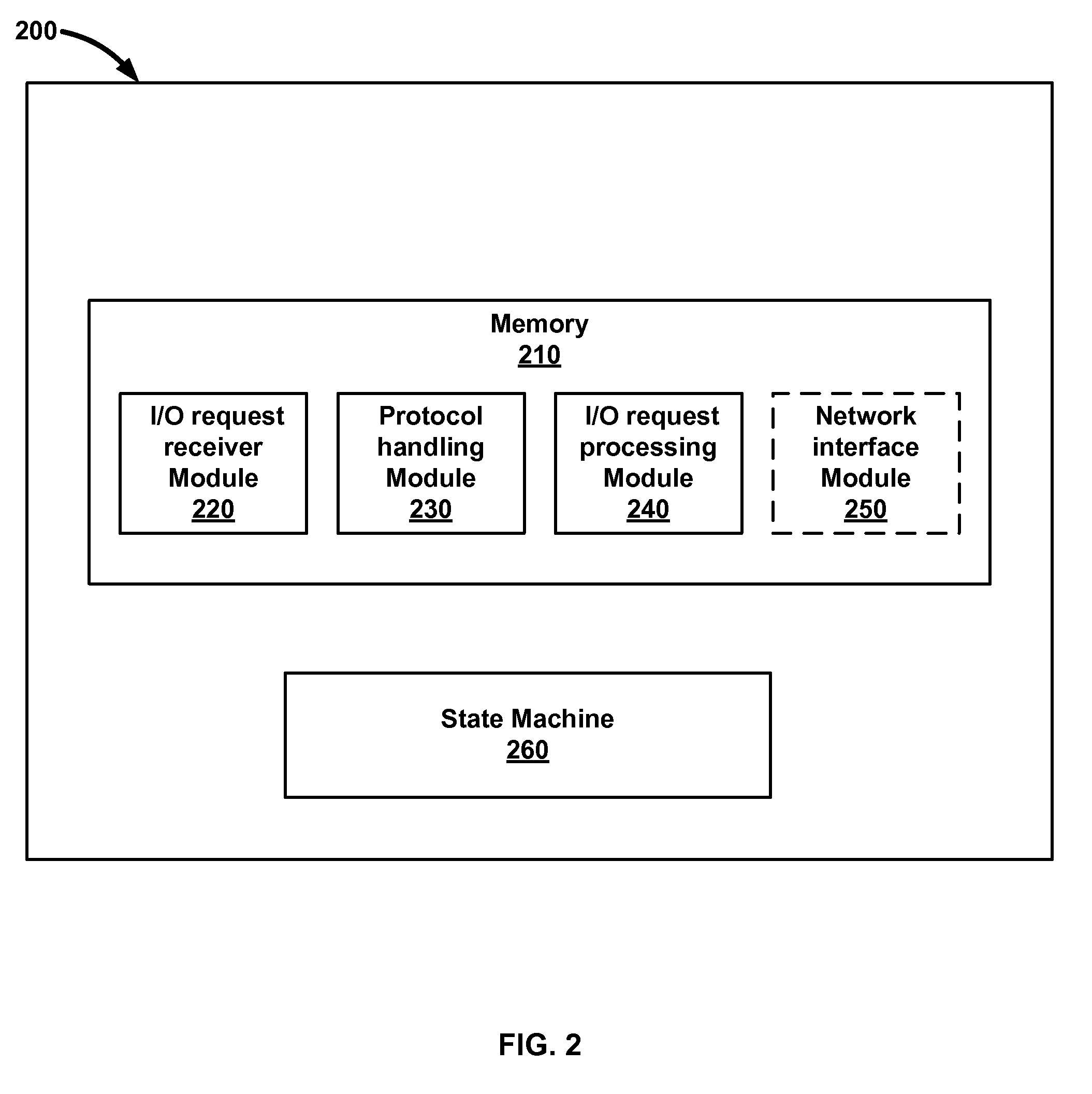

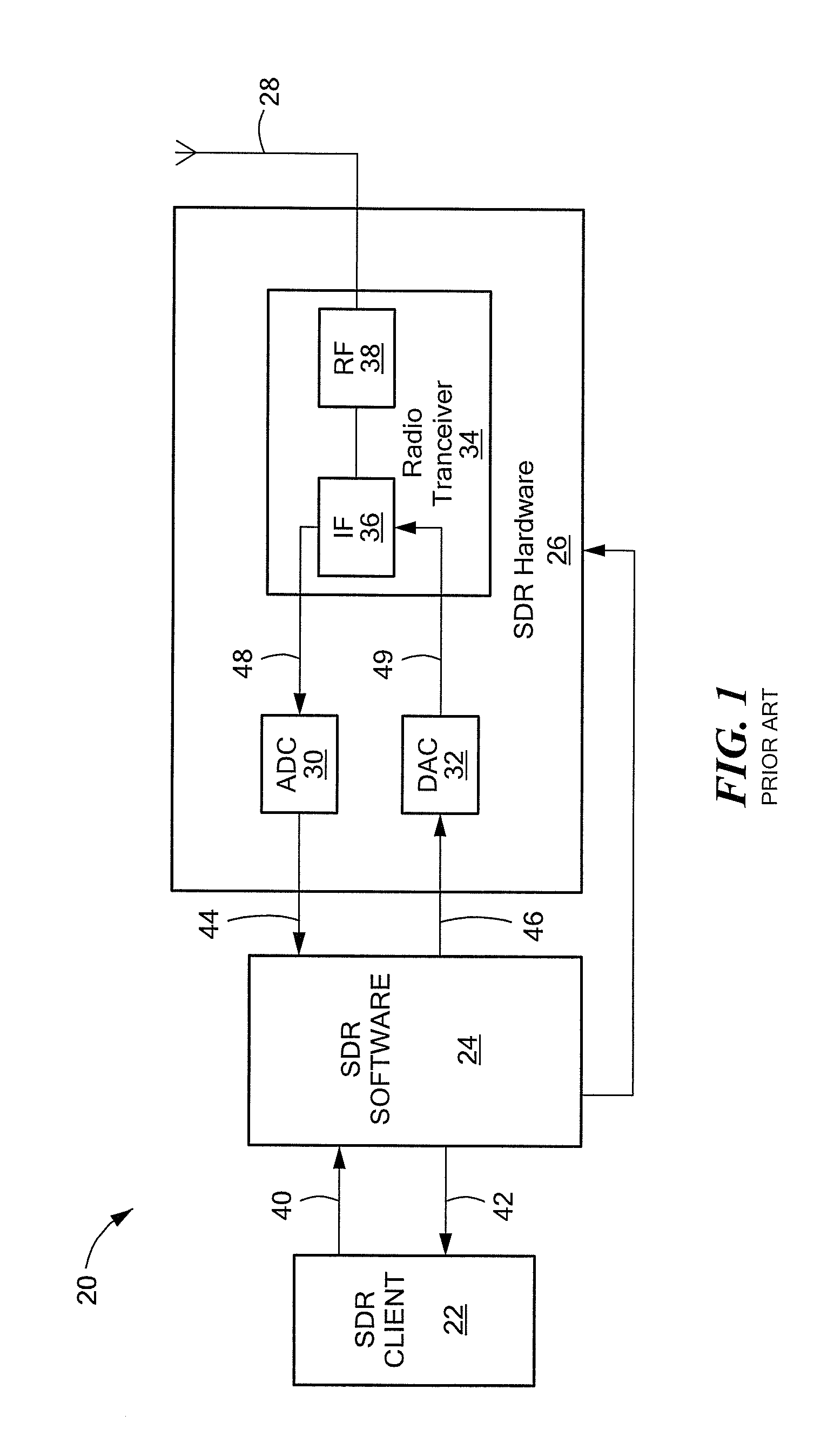

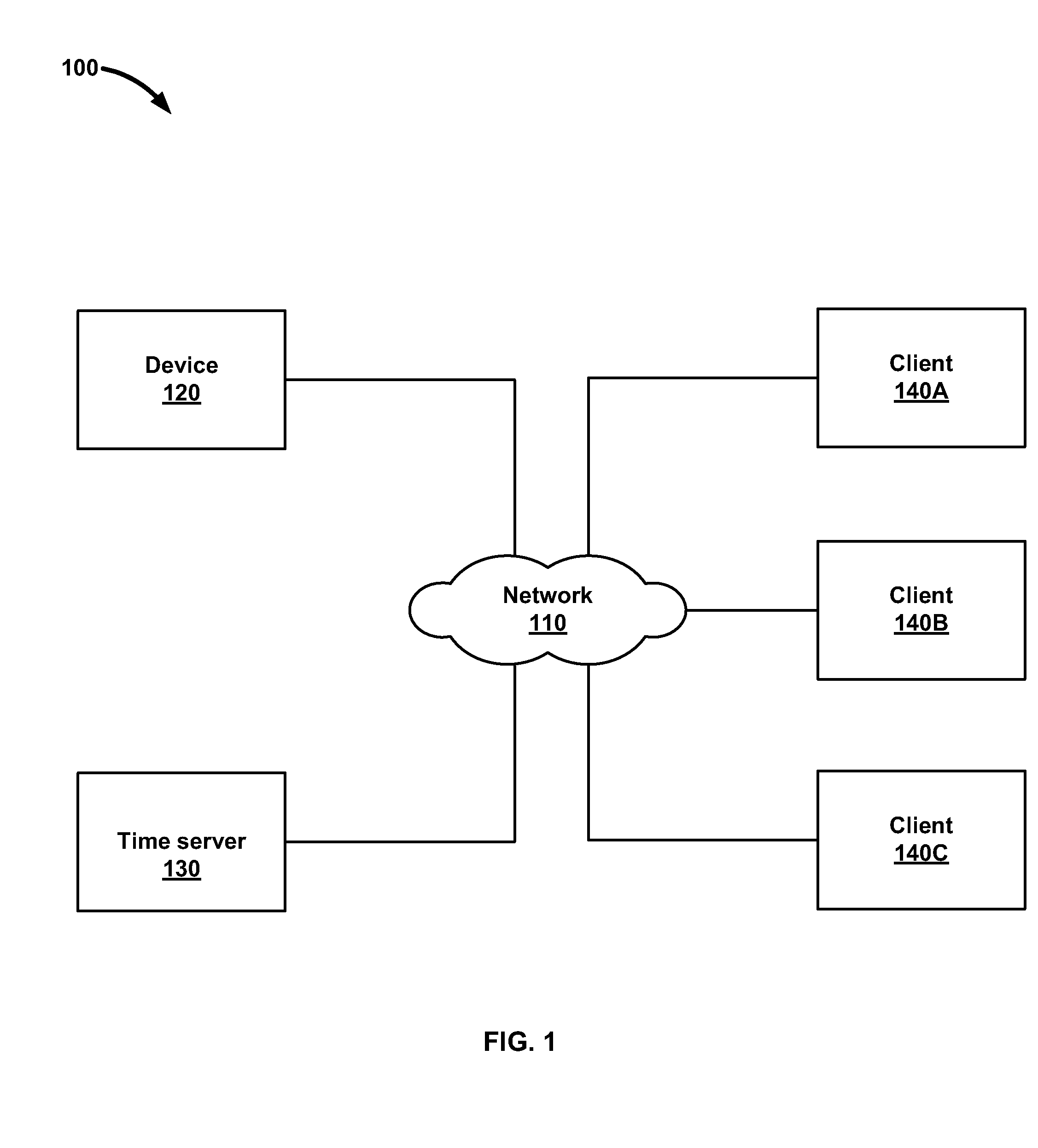

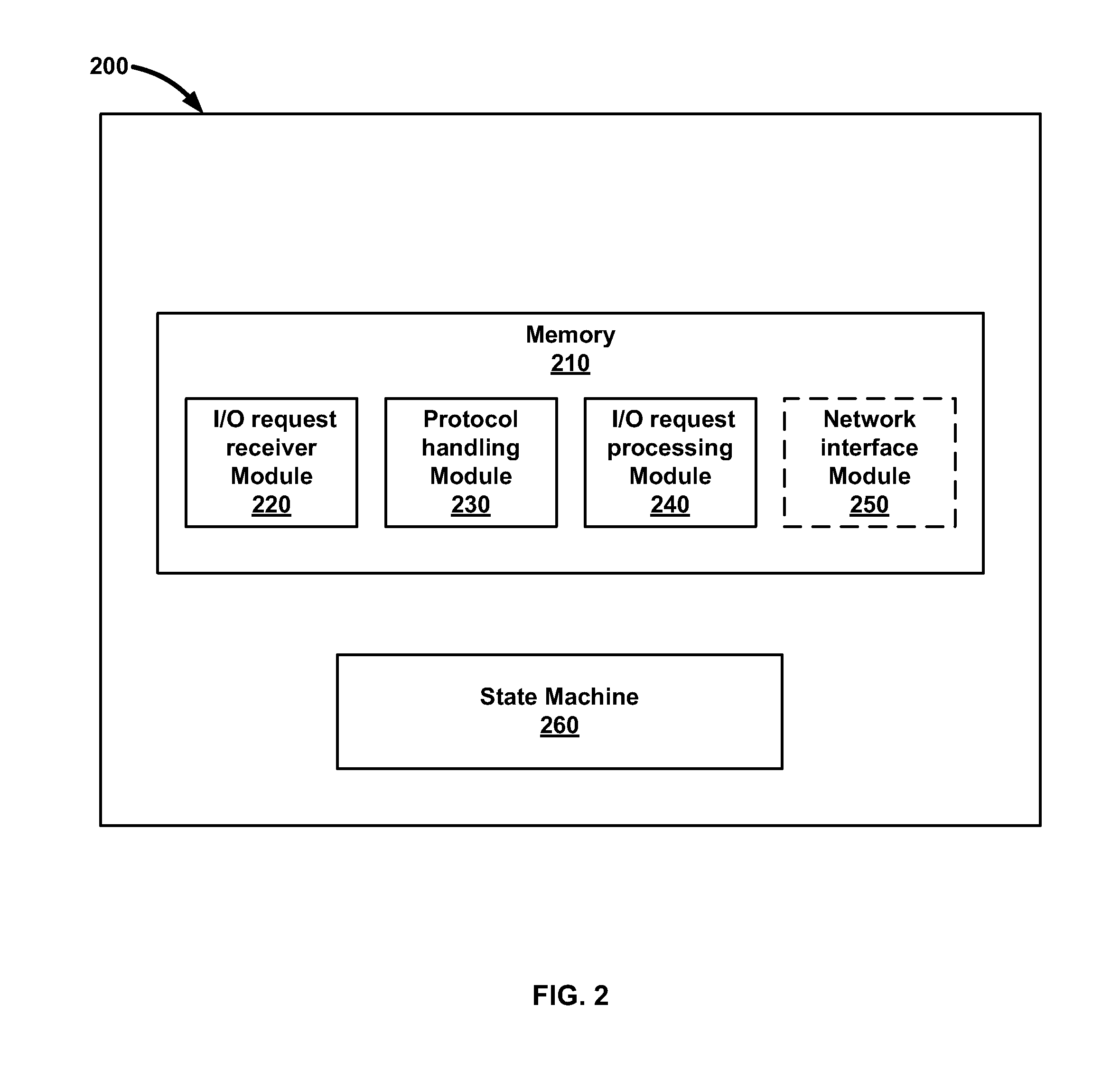

TCP/IP Stack-Based Operating System

InactiveUS20110107357A1Minimize useHighly optimizeInterprogram communicationWireless commuication servicesProtocol for Carrying Authentication for Network AccessUltra low power

Systems and corresponding methods include a system having an operating system based wholly around a protocol stack, such as a Transmission Control Protocol / Internet Protocol (TCP / IP) stack. The system may include a central processing unit (CPU) including the operating system embedded therein, and a network interface coupled with a network and the CPU. The network may be the Internet. The operating system is fundamentally a state machine. The kernel of the operating system is fundamentally just a protocol stack for communicating with one or more devices of the network via the network interface. The protocol stack may be a TCP / IP protocol stack, UDP / IP stack or combinations thereof. A chip may be provided that includes the TCP / IP stack state machine-based operating system embedded in a CPU. The resultant chip may be ultra low power, miniscule in size, and IP-centric.

Owner:IOTA COMPUTING

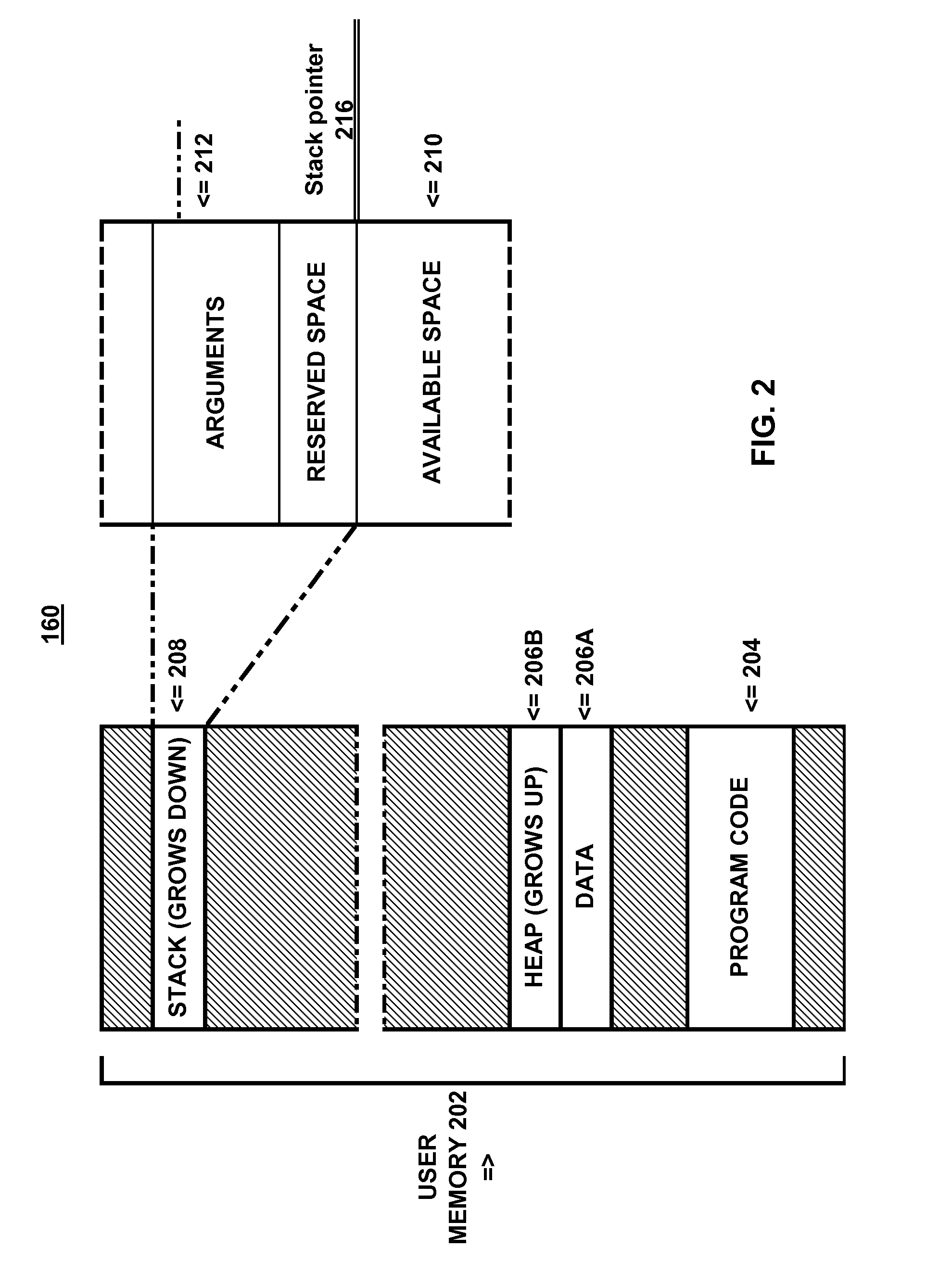

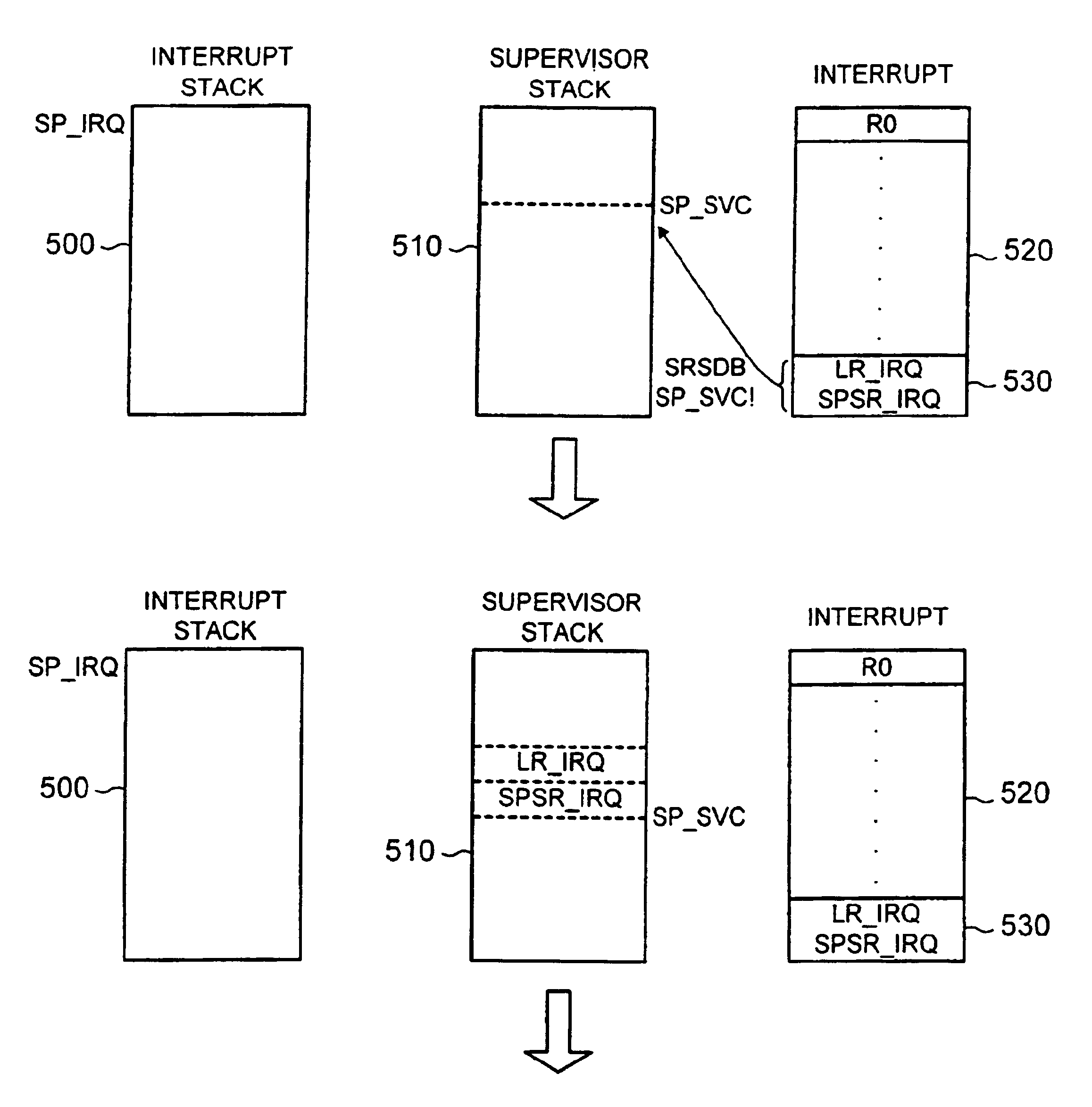

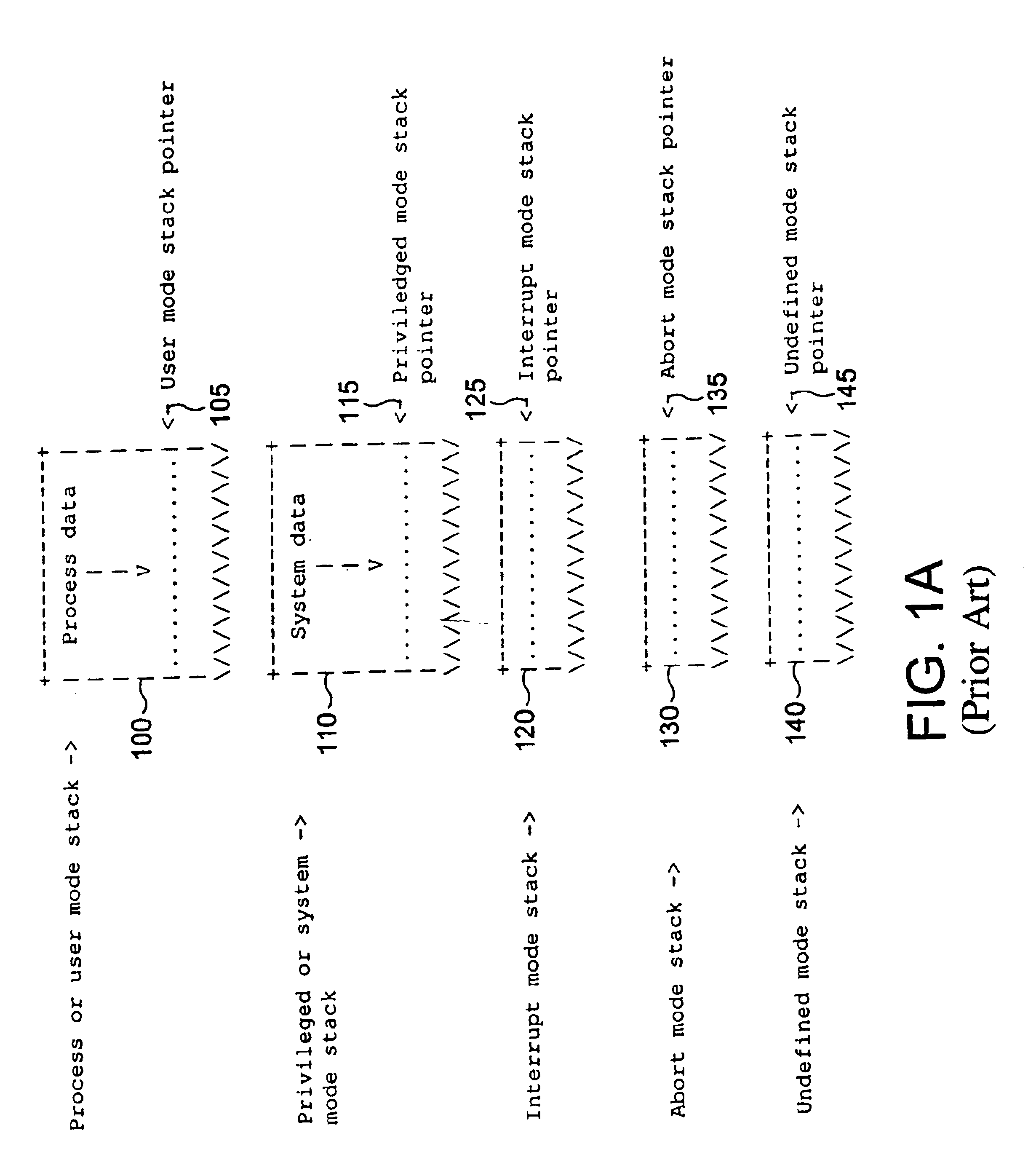

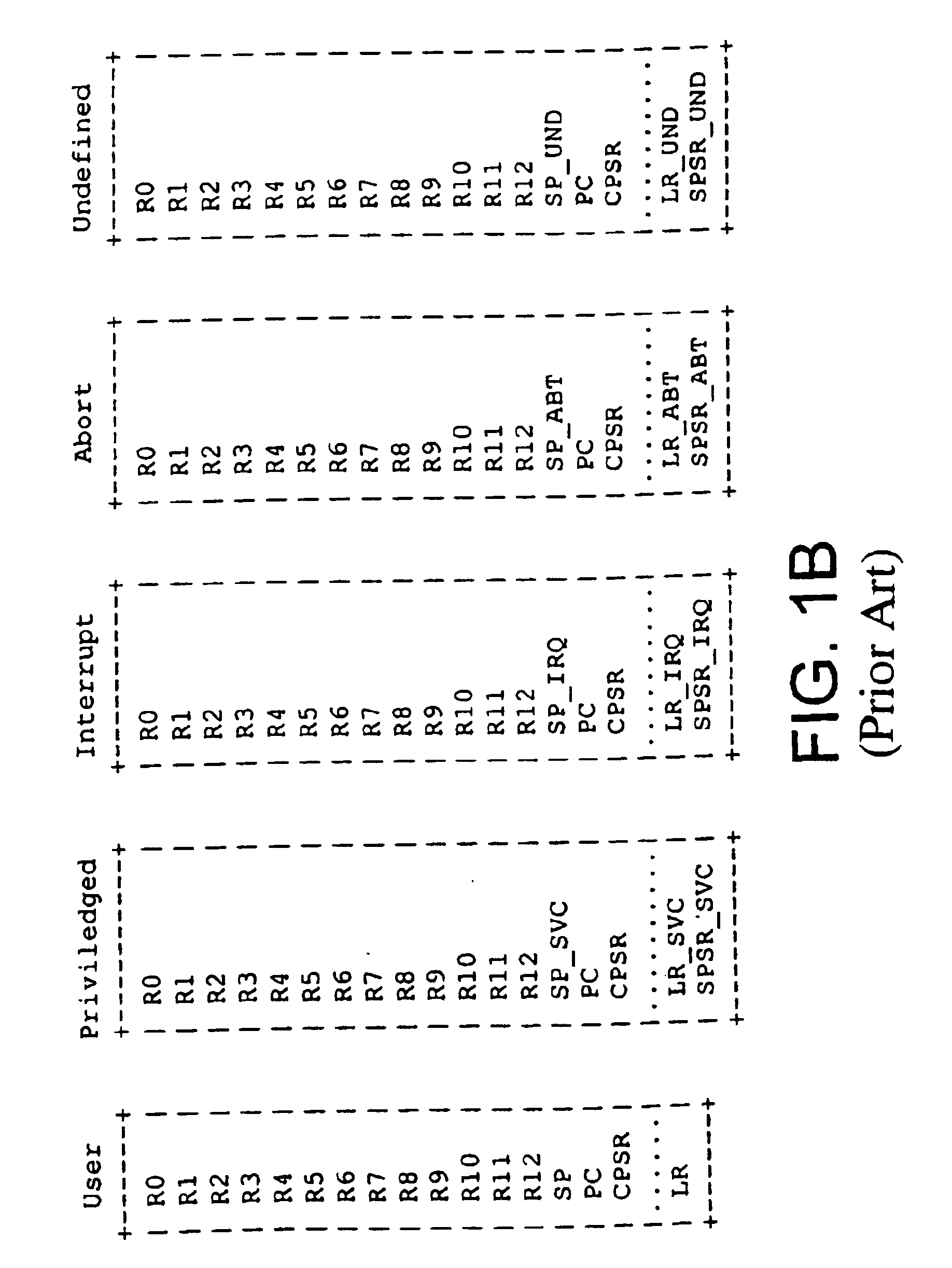

Data processing apparatus and method for saving return state

InactiveUS6904517B2Suppresses increase in code sizeImprove performanceProgram initiation/switchingDigital computer detailsParallel computingOperation mode

The present invention provides a data processing apparatus and method for saving return state. The data processing apparatus comprises a processing unit for executing data processing instructions, the processing unit having a plurality of modes of operation, with each mode of operation having a corresponding stack for storing data associated with that mode. The processing unit is responsive to a return state data processing instruction to write return state data of the processing unit from its current mode of operation to a stack corresponding to a different mode of operation to the current mode of operation. This approach significantly reduces code size and improves interrupt latency over known prior art techniques.

Owner:ARM LTD

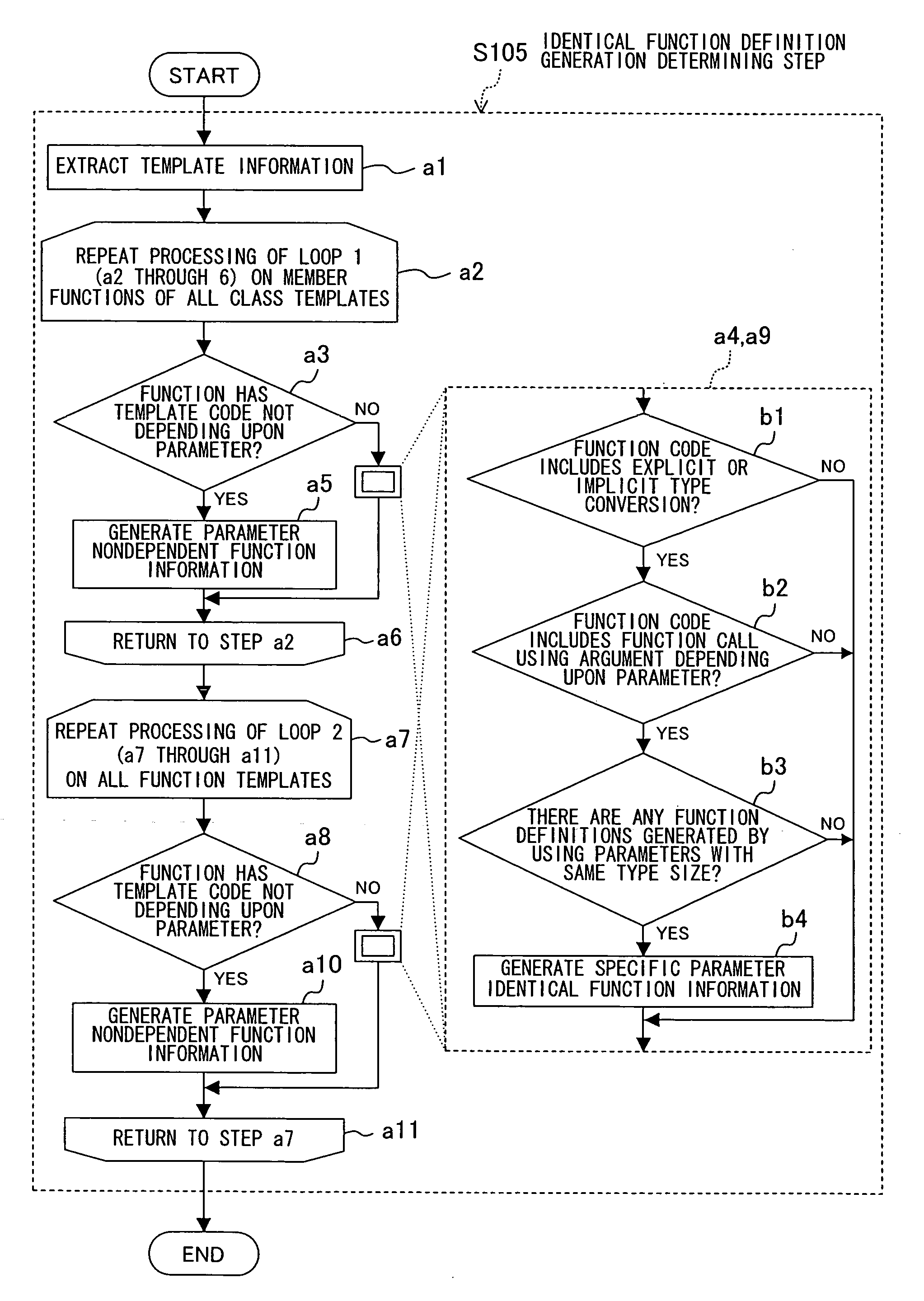

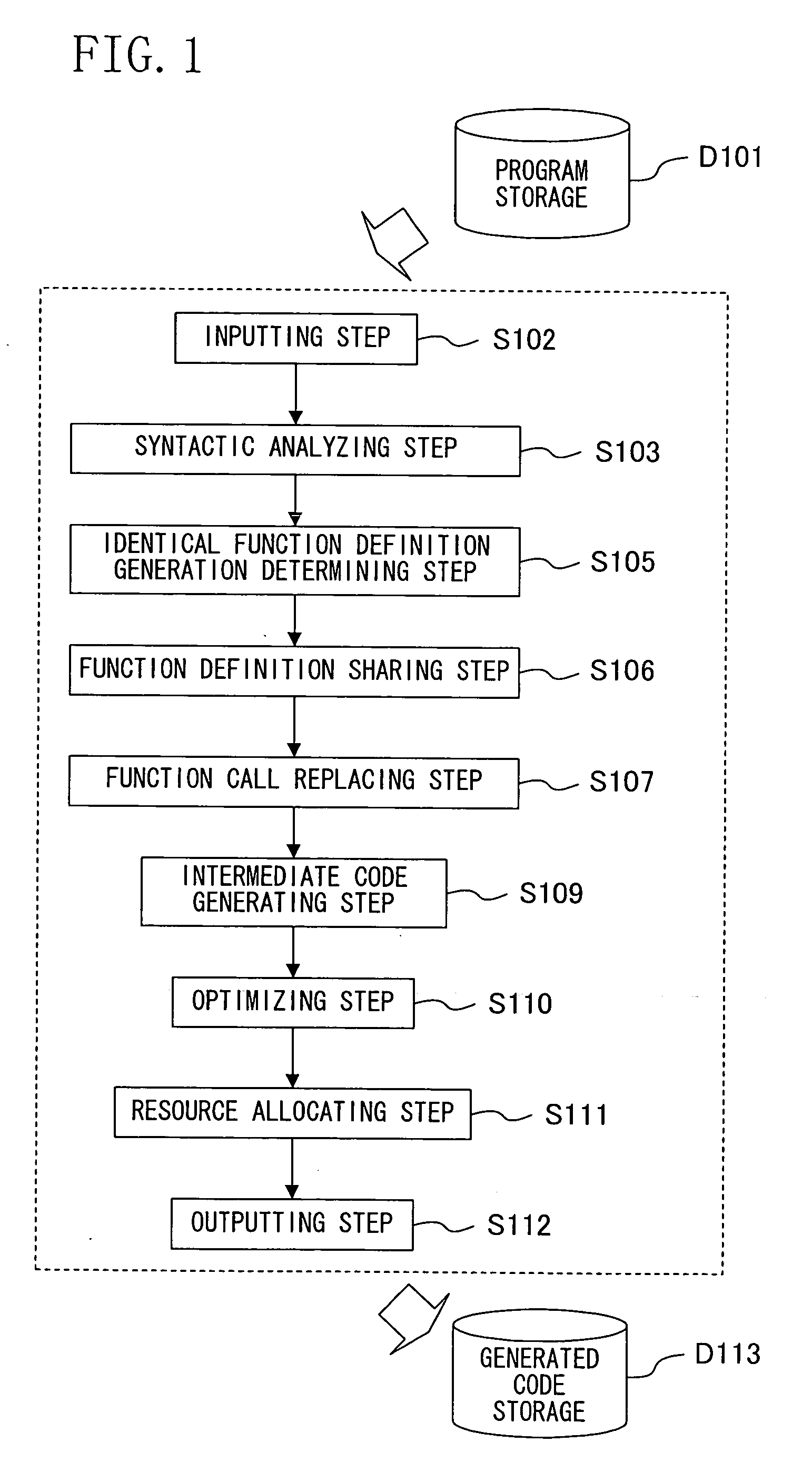

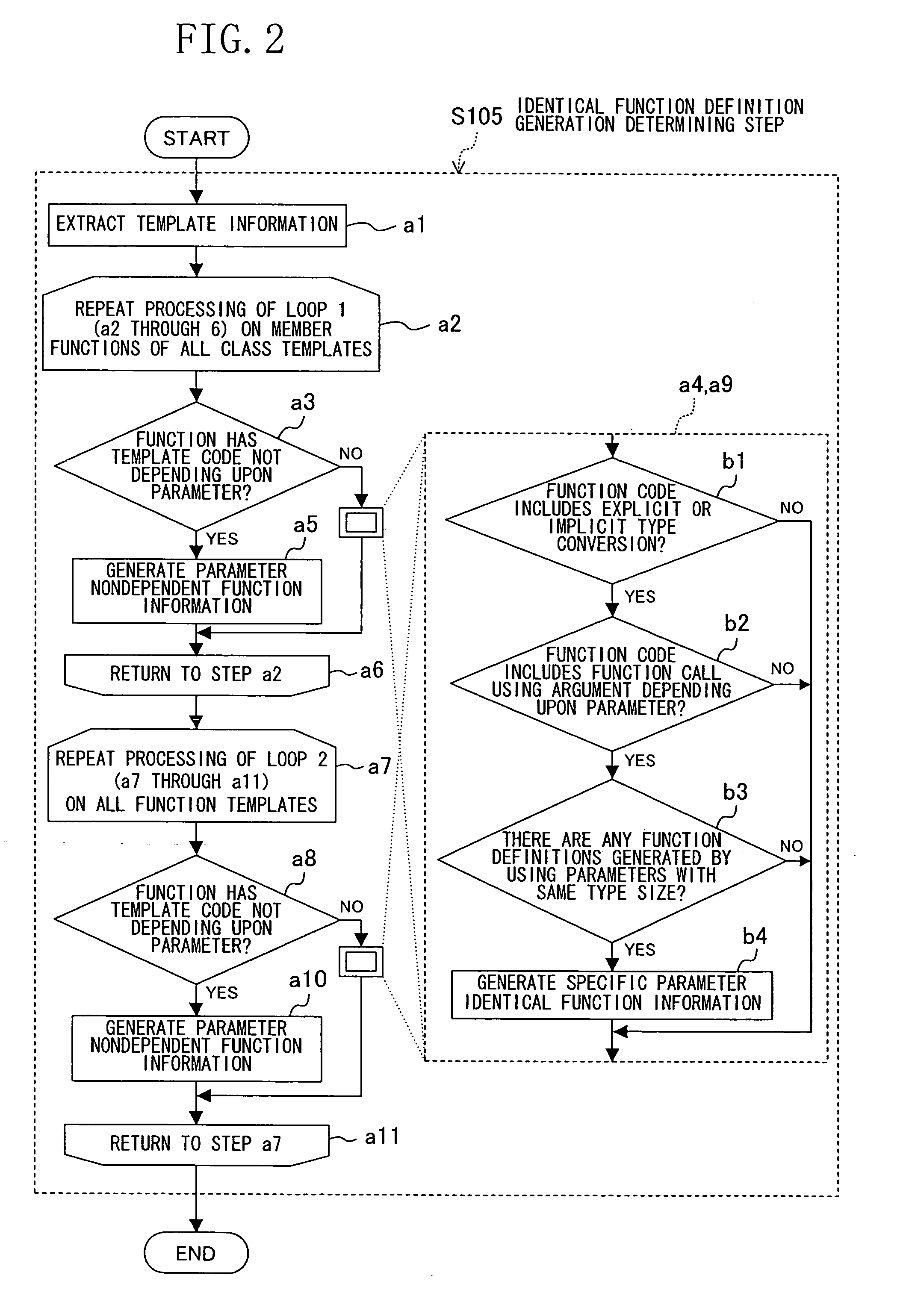

Template compilation method

InactiveUS20050097530A1Generate efficientlySuppresses increase in code sizeProgram controlMemory systemsProgramming languageFunction definition

In an identical function definition generation determining step of a template compilation method, dependency between a function definition code and a template parameter is analyzed, and when there is no dependency, a common function is defined and a plurality of function definitions obtained before defining the common function are deleted in a function definition sharing step. Thereafter, a function call obtained before defining the common function is replaced with a call of the common function in a function call replacing step. Accordingly, among a plurality of function definition codes generated from a template, function definition codes generated as the identical code are shared, so as to reduce the code size that generally increases due to template facilities.

Owner:PANASONIC CORP

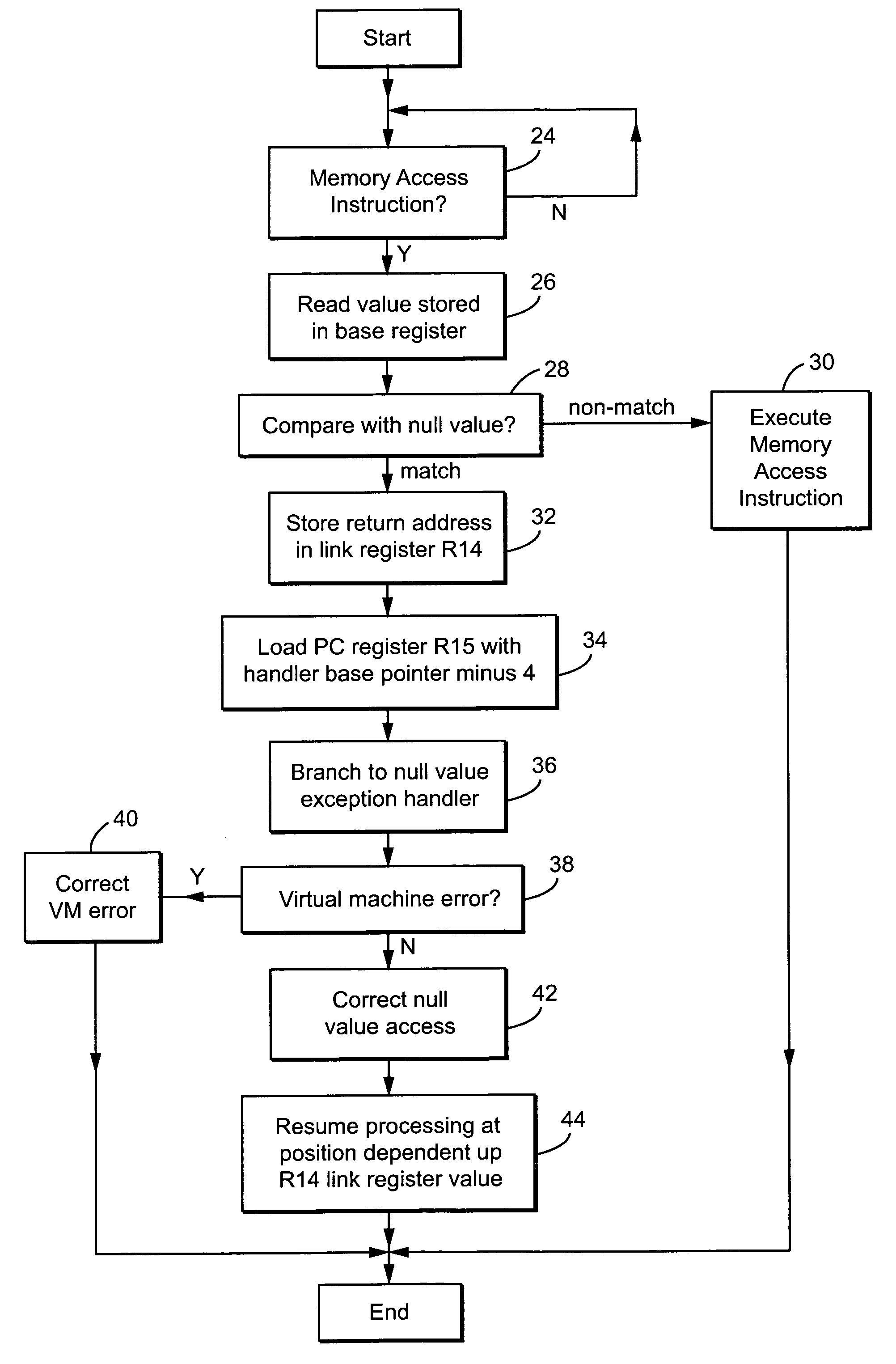

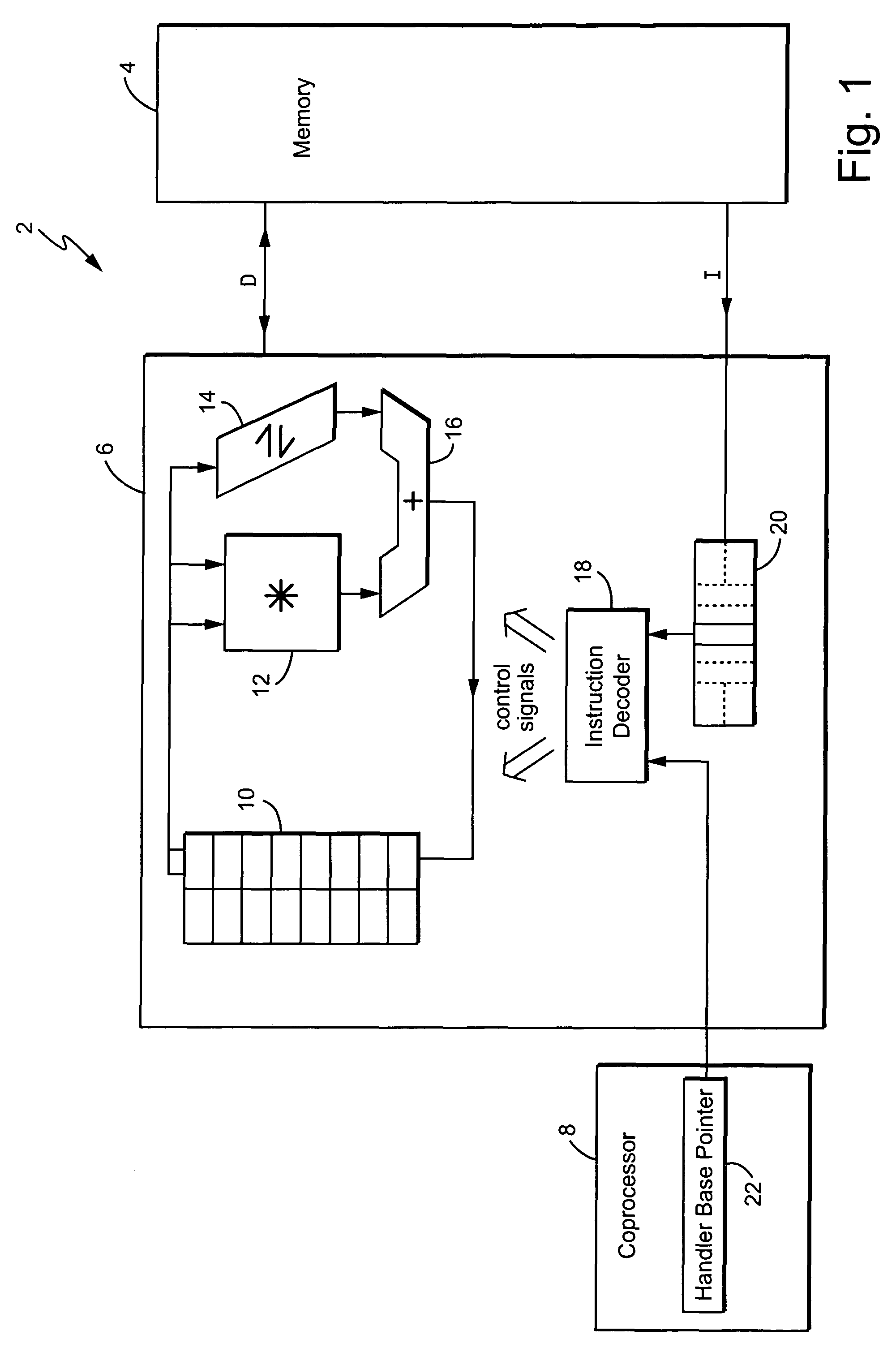

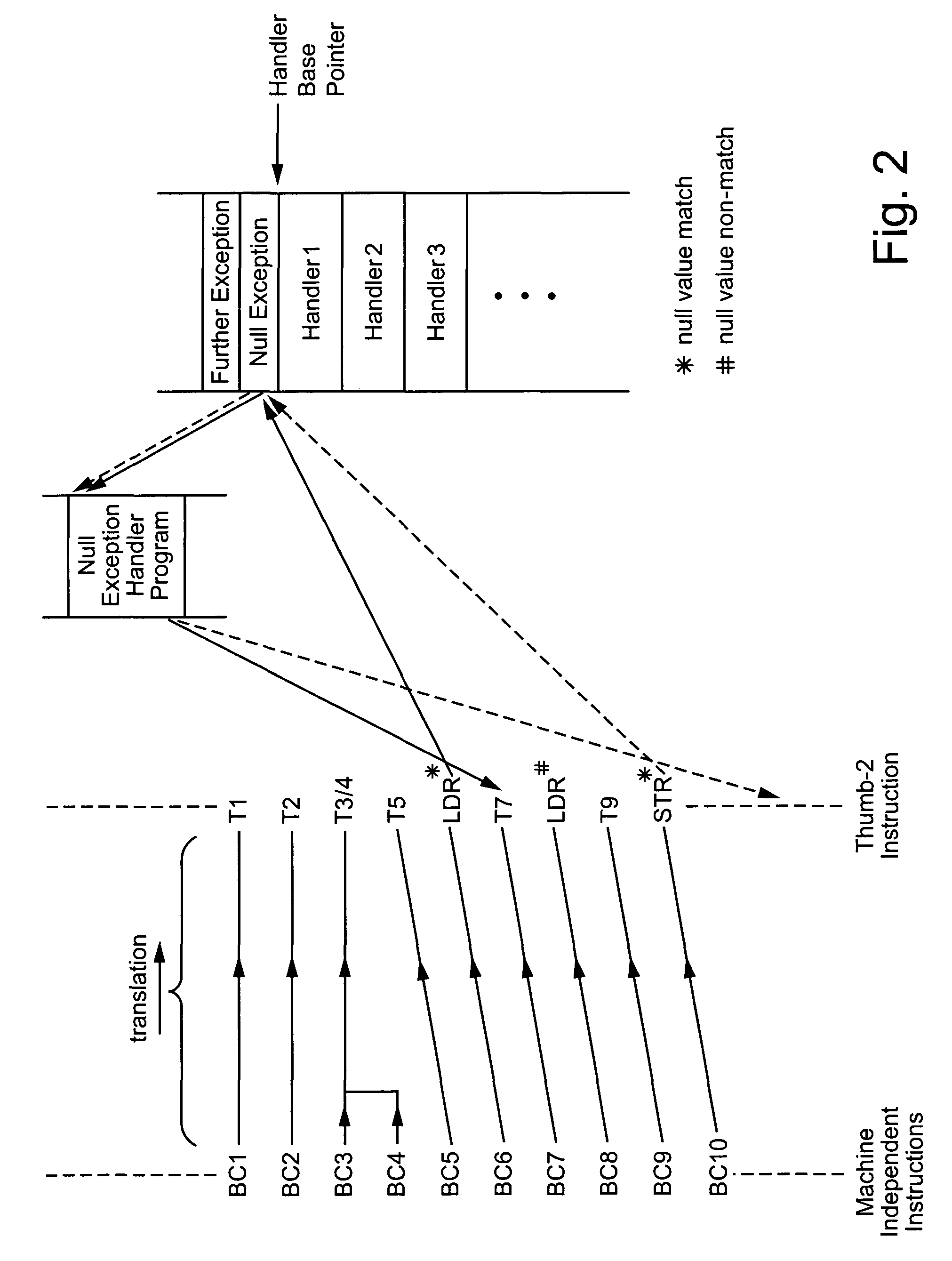

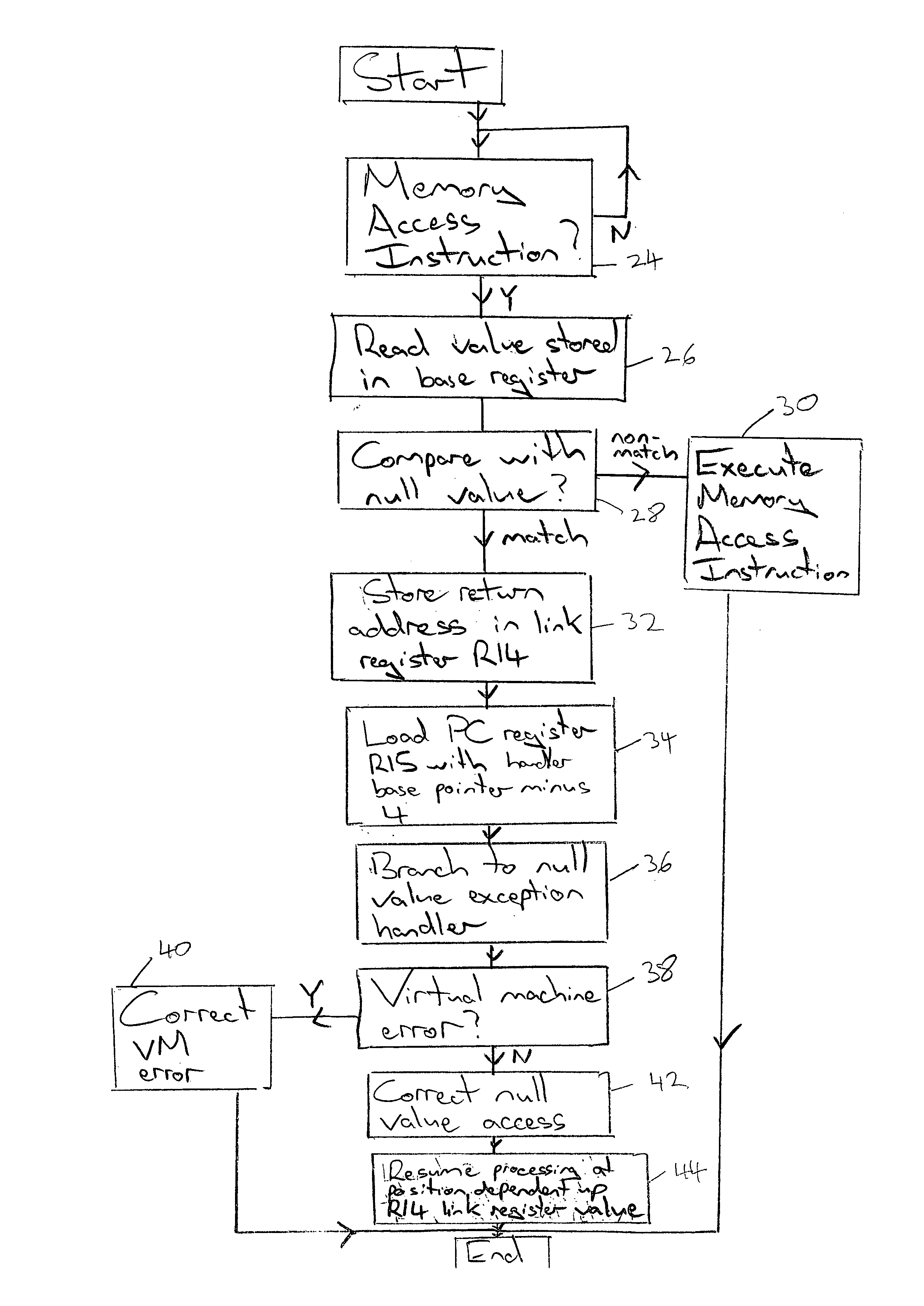

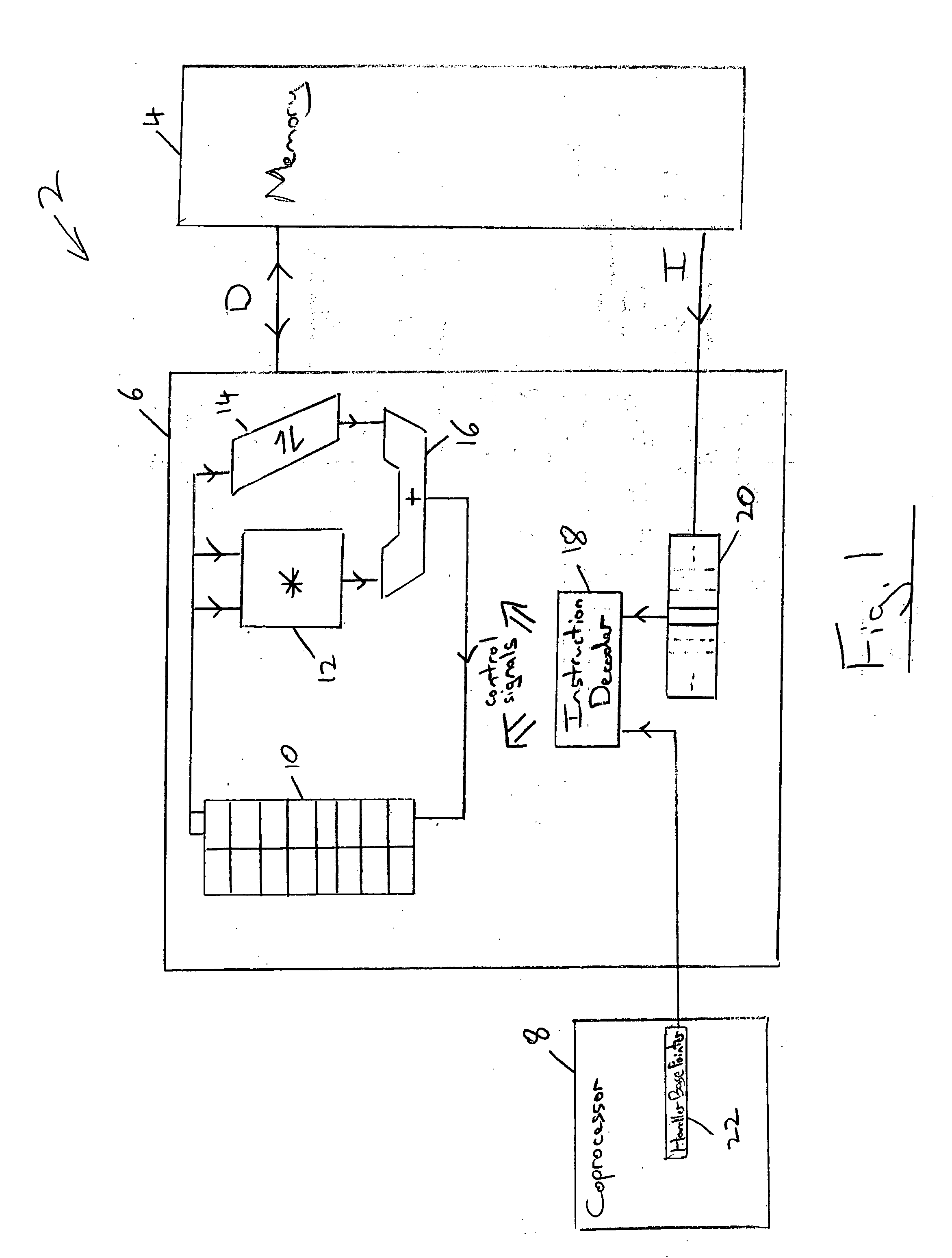

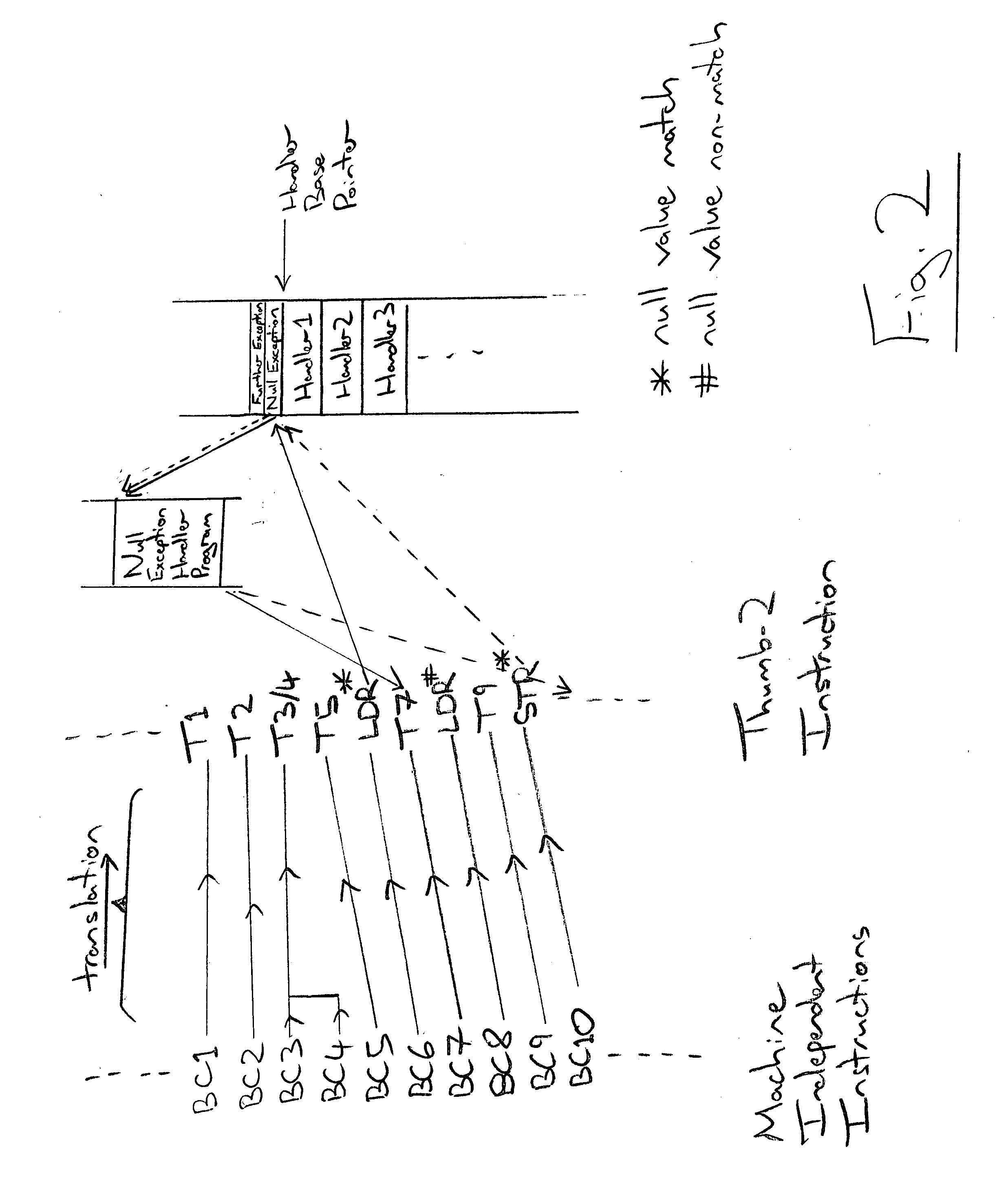

Null exception handling

ActiveUS7802080B2Maximum performanceIncrease in sizeDigital computer detailsConcurrent instruction executionProcessor registerException handling

A processor 6 is provided with an instruction decoder 18 which is responsive to memory access instructions to determine whether the base register value being used matches a null value and if such a match occurs then branches to a null value exception handler.

Owner:ARM LTD

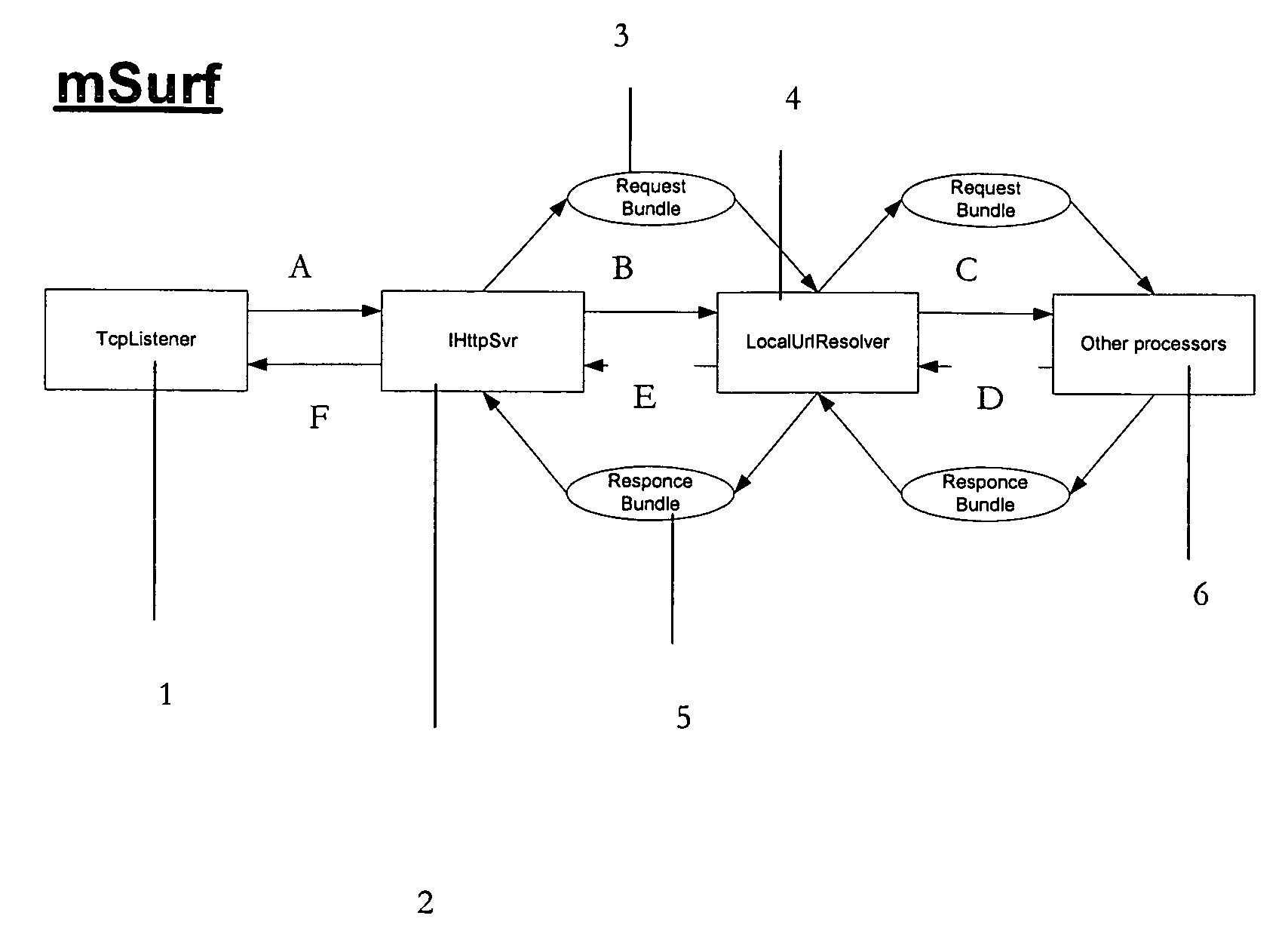

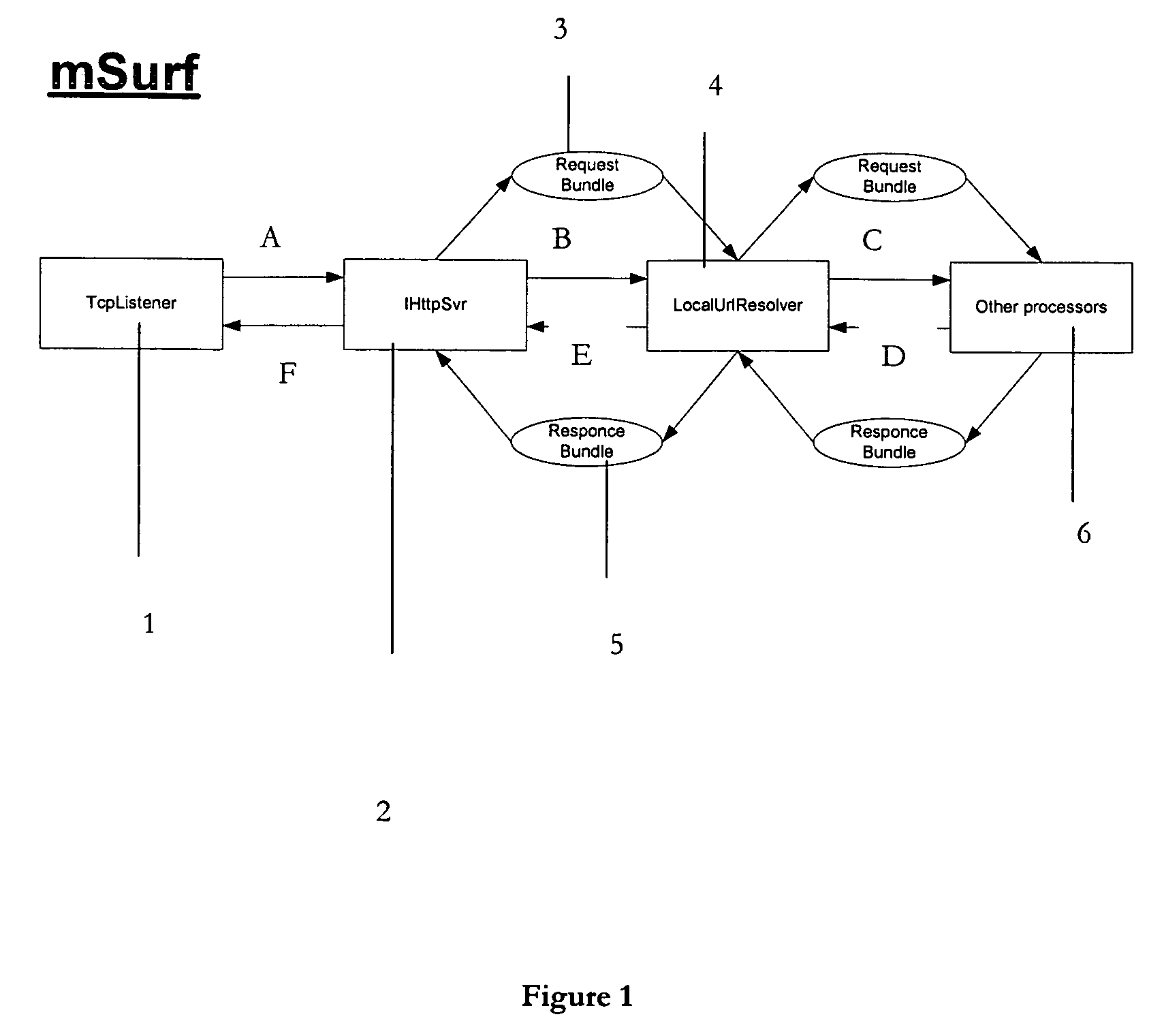

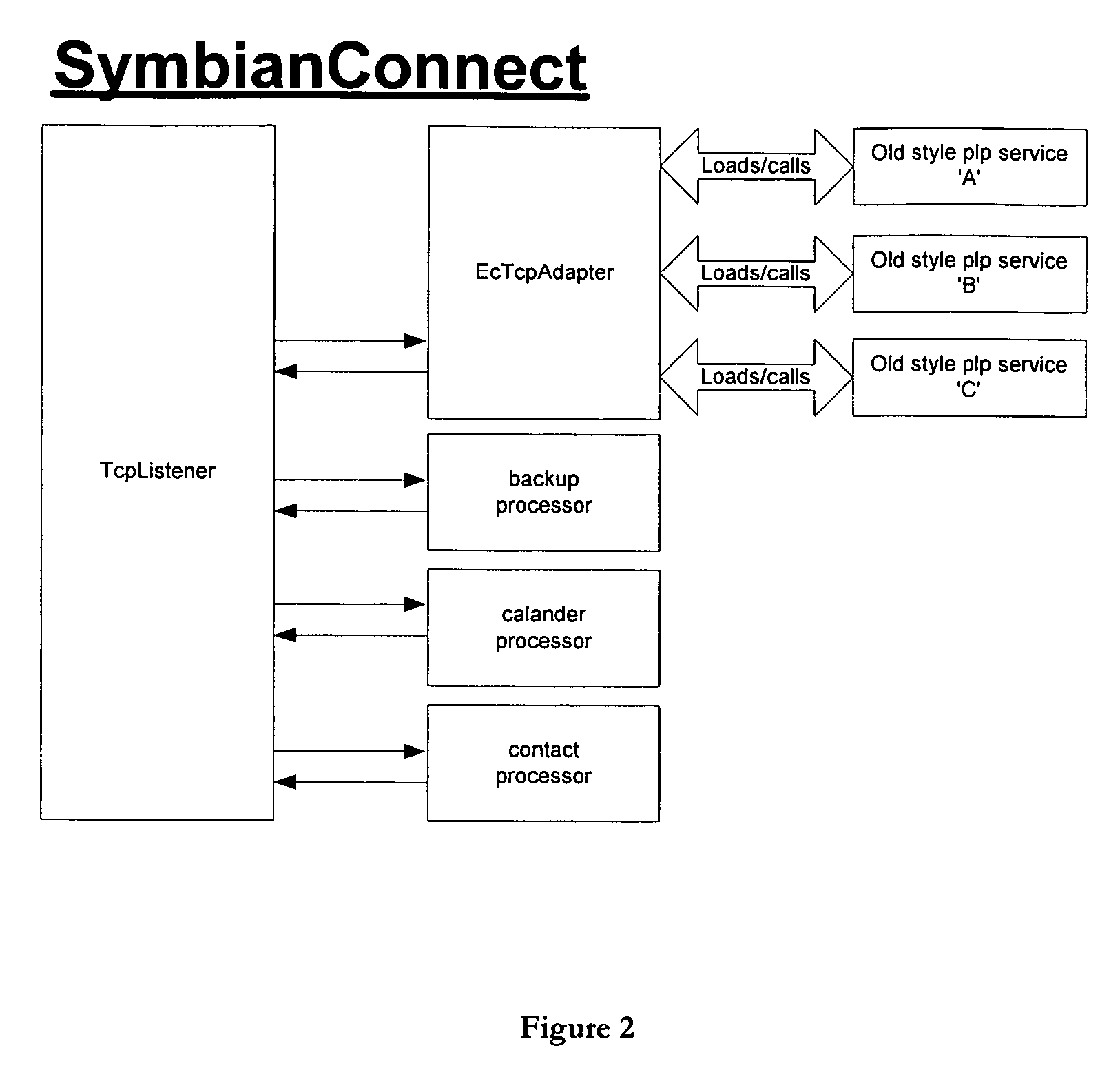

Method of developing software programs for resource constrained mobile computing devices

InactiveUS20050034099A1Readily add new featureFacilitate functioningSoftware reuseSpecific program execution arrangementsVery High LevelSoftware

A method of developing a software program for resource constrained mobile computing devices comprises the step of using a library of three mandatory types of code which enable a system to be modelled, the three types of code being: (a) a first re-useable object which defines the transmission of raw binary data between a writer end and a reader end; (b) a second re-useable object which defines ordered name / value pairs and (c) an abstract API definition that defines how to write, create, call or use a task which handles the first and / or second objects. This very high level abstraction has been found, surprisingly, to apply to virtually all systems which have been analysed by the applicant. Hence, the present invention allows a small (deliberately restricted), core library of “primitives” to be built once and re-used very many times as building blocks by different applications. Re-use of code defining high level abstractions considerably reduces overall code size (a major technical advantage for mobile computing devices) and speeds up developing new programs (major technical advantage in the rapidly moving world of program development for mobile computing devices).

Owner:NOKIA CORP

Instruction packet including multiple instructions having a common destination

ActiveUS20130067205A1Efficient executionFew execution cycleConditional code generationDigital computer detailsComputer hardware

Owner:QUALCOMM INC

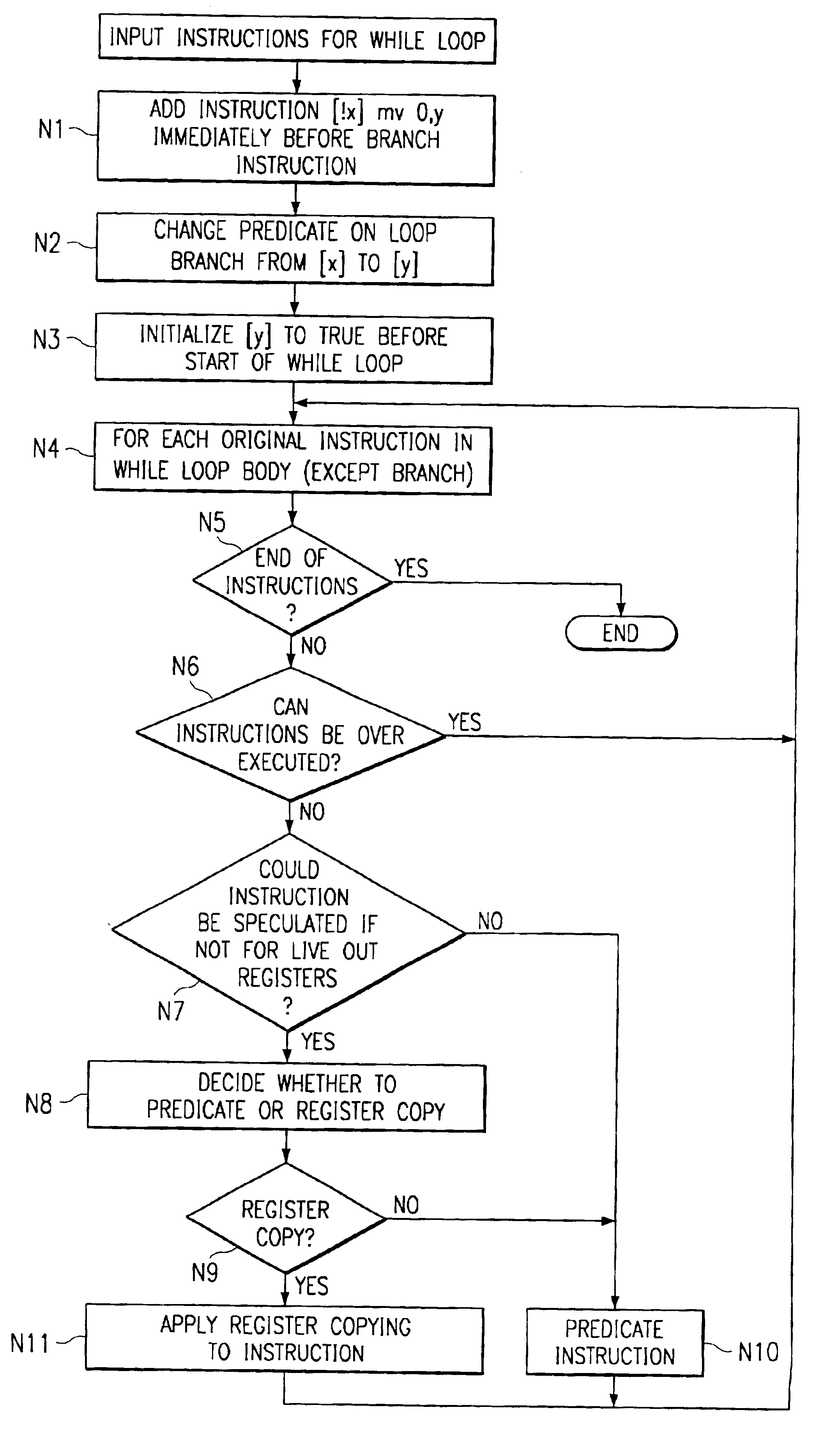

Method for software pipelining of irregular conditional control loops

InactiveUS6892380B2Suppresses increase in code sizeMinimum trip countSoftware engineeringDigital computer detailsProcessor registerParallel computing

A method for software pipelining of irregular conditional control loops including pre-processing the loops so they can be safely software pipelined. The pre-processing step ensures that each original instruction in the loop body can be over-executed as many times as necessary. During the pre-processing stage, each instruction in the loop body is processing in turn (N4). If the instruction can be safely speculatively executed, it is left alone (N6). If it could be safely speculatively executed except that it modifies registers that are live out of the loop, then the instruction can be pre-processed using predication or register copying (N7, N8, N9). Otherwise, predication must be applied (N10). Predication is the process of guarding an instruction. When the guard condition is true, the instruction executes as though it were unguarded. When the guard condition is false, the instruction is nullified.

Owner:TEXAS INSTR INC

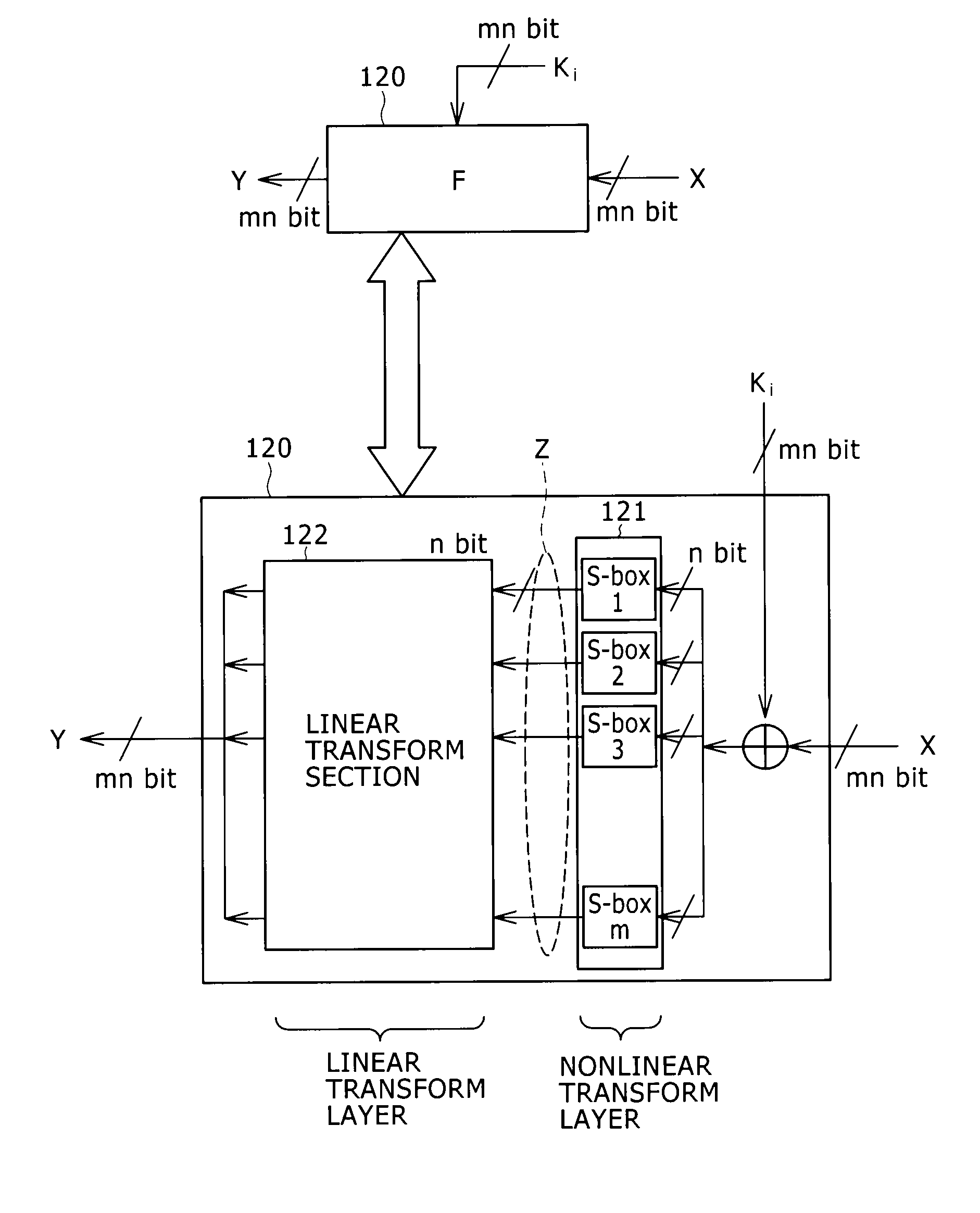

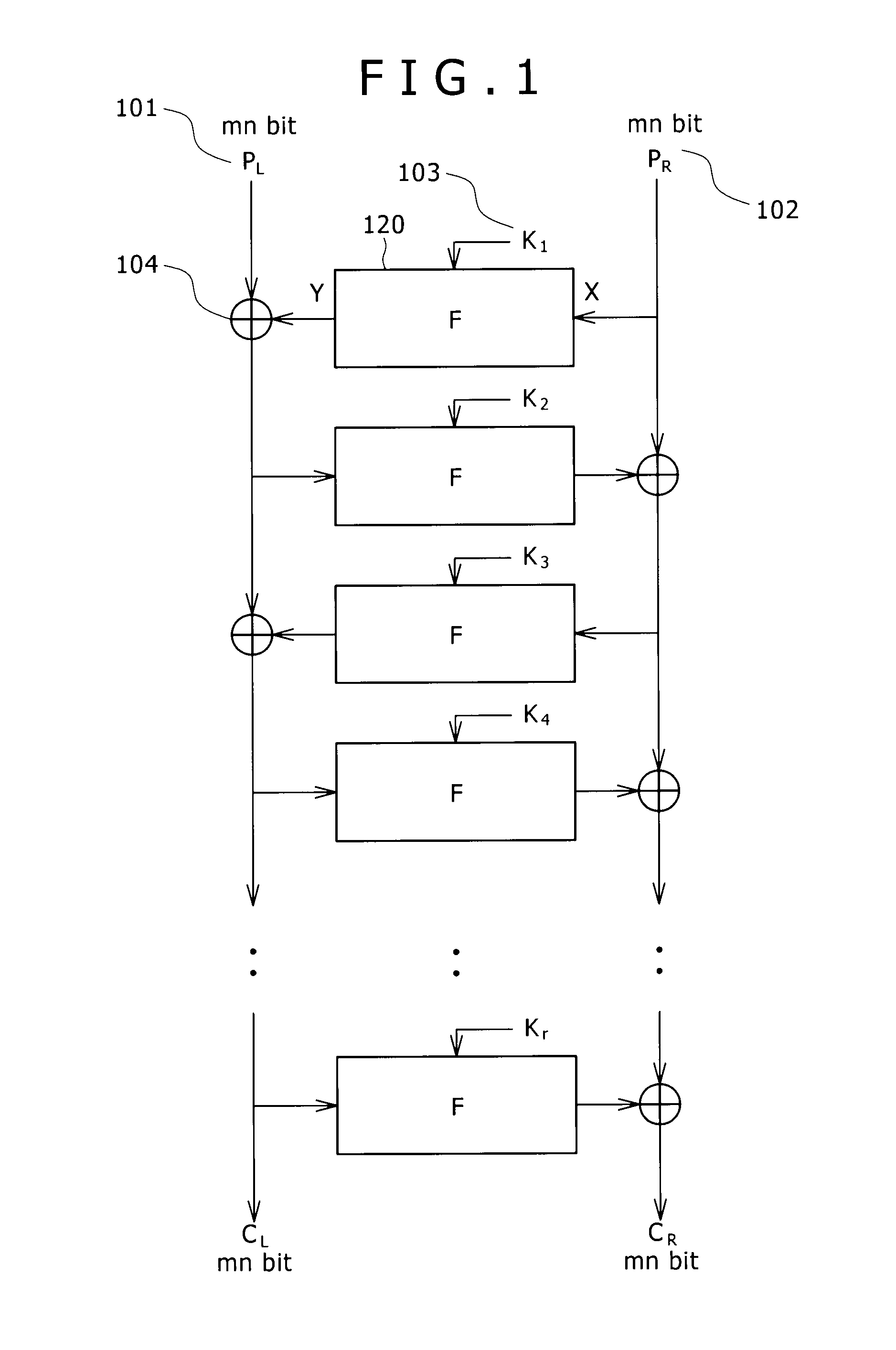

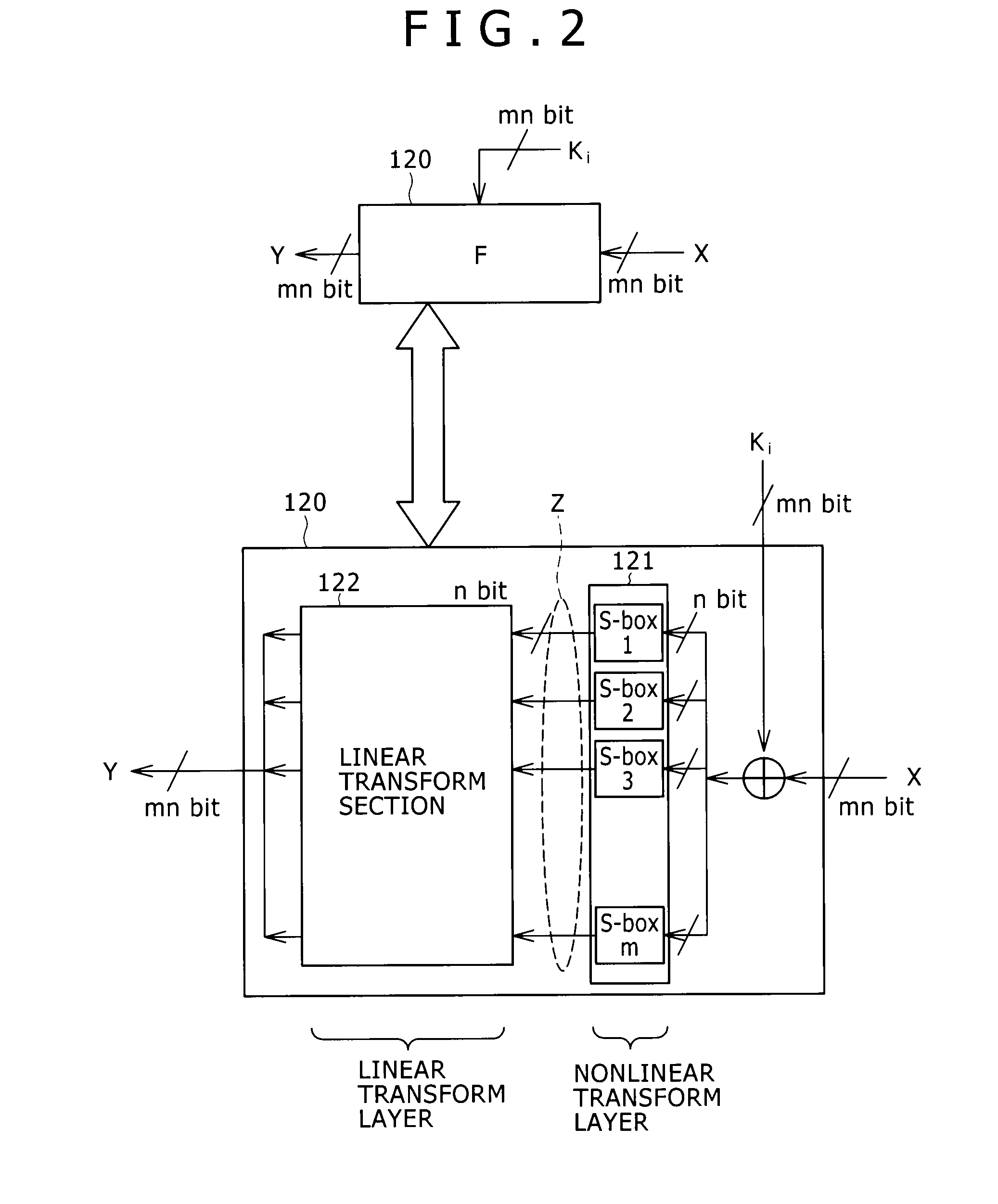

Encryption/decryption device, encryption/decryption method, and computer program

InactiveUS8073140B2Reduce design costReduce data volumeSecret communicationCryptographic attack countermeasuresComputer hardwareHash function

It is possible to realize a Feistel-type common key block encryption / decryption processing configuration capable of reducing data stored in a memory at a low cost. The Feistel-type common key block encryption / decryption processing repeatedly executes an SP-type F function having nonlinear and linear transform sections by several rounds. At least one of the nonlinear and linear transform processes executed in the F function in each round is executed as a transform process identical with a transform process applied to an encryption / decryption algorithm other than a Feistel-type common key block encryption / decryption algorithm and / or another hash function such as AES and Whirlpool. With this configuration, it is possible to reduce the design cost and the amount of data stored in a memory.

Owner:SONY CORP

Method for collapsing the prolog and epilog of software pipelined loops

InactiveUS6754893B2Suppresses increase in code sizeValid encodingSoftware engineeringProgram controlParallel computingSoftware

A method for reducing a code size of a software pipelined loop, the software pipelined loop having a kernel and an epilog. The method includes first evaluating a stage of the epilog. This includes selecting a stage of the epilog to evaluate (504) and evaluating an instruction in a reference stage. This includes identifying an instruction in the reference stage that is not present in the selected stage of the epilog (506) and determining if the identified instruction can be speculated (508). If the identified instruction can be speculated, such is noted. If the instruction cannot be speculated, it is determined whether the identified instruction can be predicated (512). If the instruction can be predicated, it is marked as needing predication (514). Next, it is determined if another instruction in the reference stage is not present in the selected stage of the epilog (510). If there is, the instruction evaluation is repeated. If there is another stage of the epilog to evaluate, the evaluation is repeated (518).

Owner:TEXAS INSTR INC

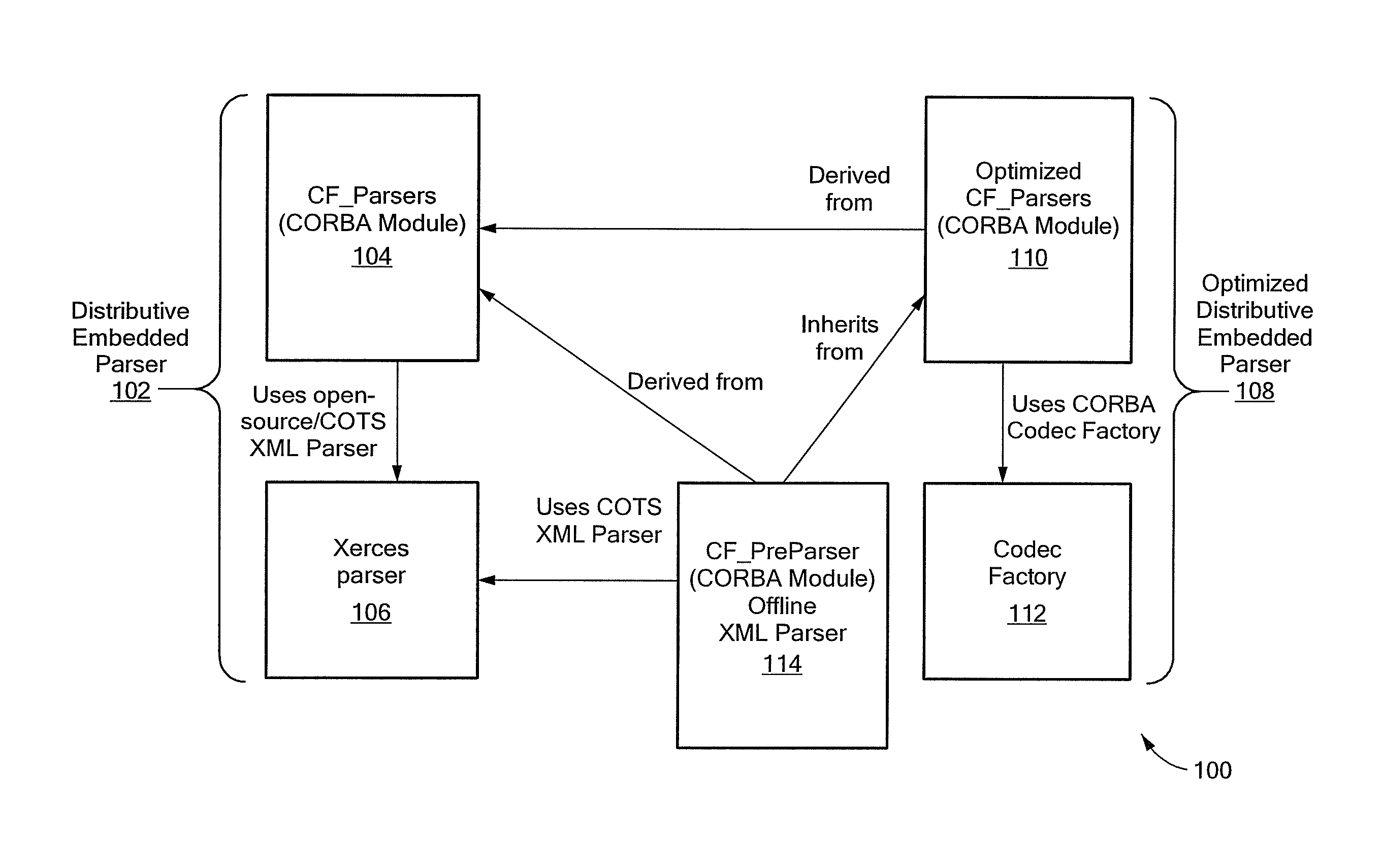

Systems, methods, and language for SCA CORBA descriptor files

ActiveUS20120284288A1Reduce code size and processing timeReduce code sizeDigital data processing detailsSoftware reuseCommon Data RepresentationSoftware Communications Architecture

The invention provides a preparsers tool for converting SCA XML files into CORBA structures usable by a Software Communication Architecture (SCA) Core Framework (CF) and comprises a core framework (CF)_PreParsers interface definition language (IDL) and a first preparser. The CF_IDL is configured to be in operable communication with an XML parser and with at least a first type of preparser. The first type of preparser is in operable communication with the CF_PreParsers IDL, is associated with a first type of descriptor for the CF, and is configured to call the XML parser to request parsing of a first set of first XML files, convert the first parsed set of first XML files into a first CORBA structure type, encode the first CORBA structure type into a first CORBA Common Data Representation (CDR) file; and write the first CORBA CDR to file as a first octet sequence.

Owner:BAE SYST INFORMATION & ELECTRONICS SYST INTERGRATION INC

Variable address length compiler and processor improved in address management

InactiveUS20080320454A1NotSuppresses increase in code sizeBinary to binaryRegister arrangementsParallel computingHuman language

The present invention discloses a program converting unit for generating a machine language instruction from a source program for a processor that manages an N-bit address while processing M-bit data, N being greater than M, and such a processor that runs the converted program. The program converting unit comprising: a parameter holding unit for holding a data width and a pointer width designated by a user; the data width representing the number of bits of data used in the source program while the pointer width representing the number of bits of an address; and a generating unit for generating an instruction to manage the data width when a variable operated by the instruction represents the data, and for generating an instruction to manage the pointer width when a variable operated by the instruction represents the address.

Owner:PANASONIC CORP

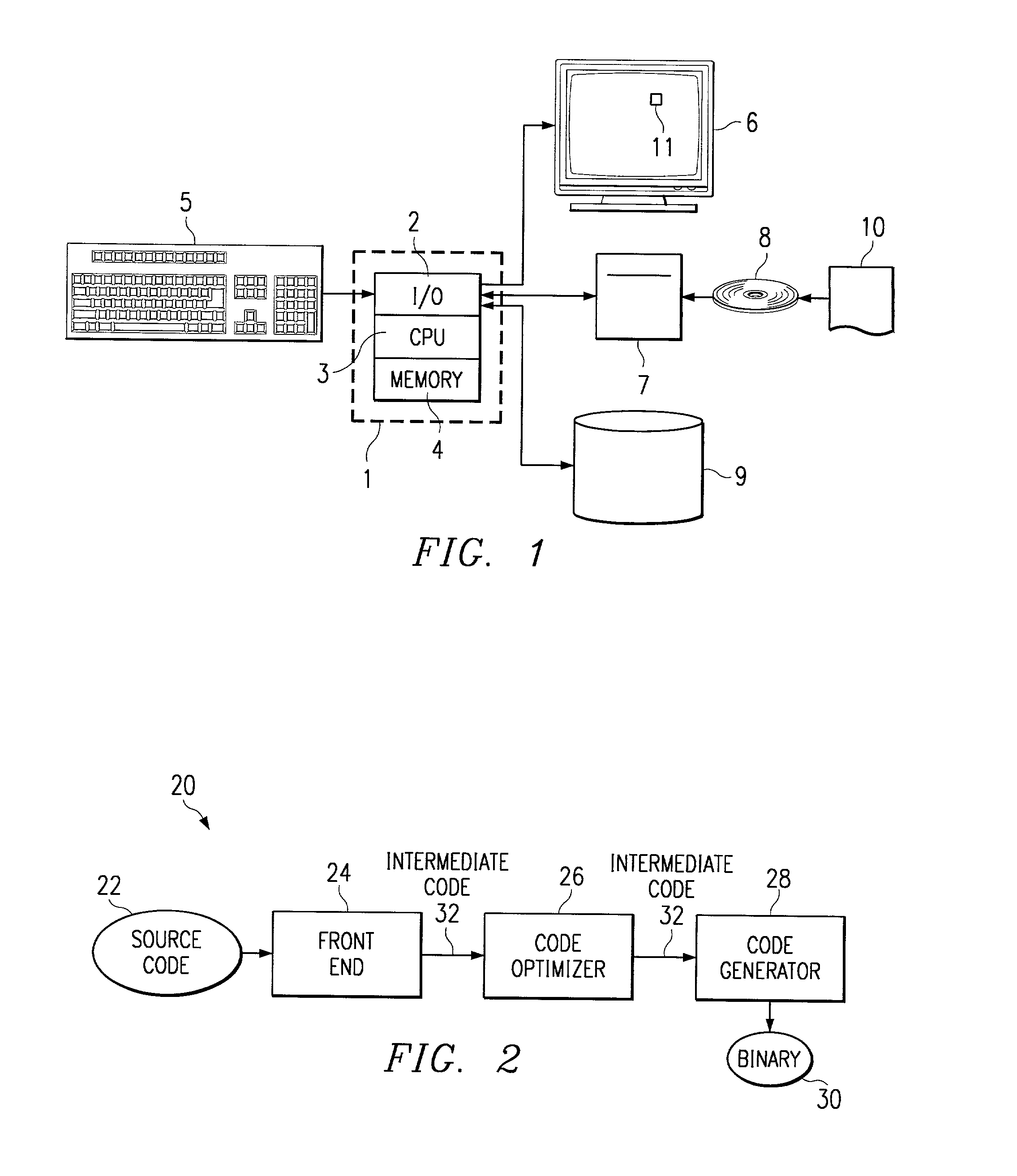

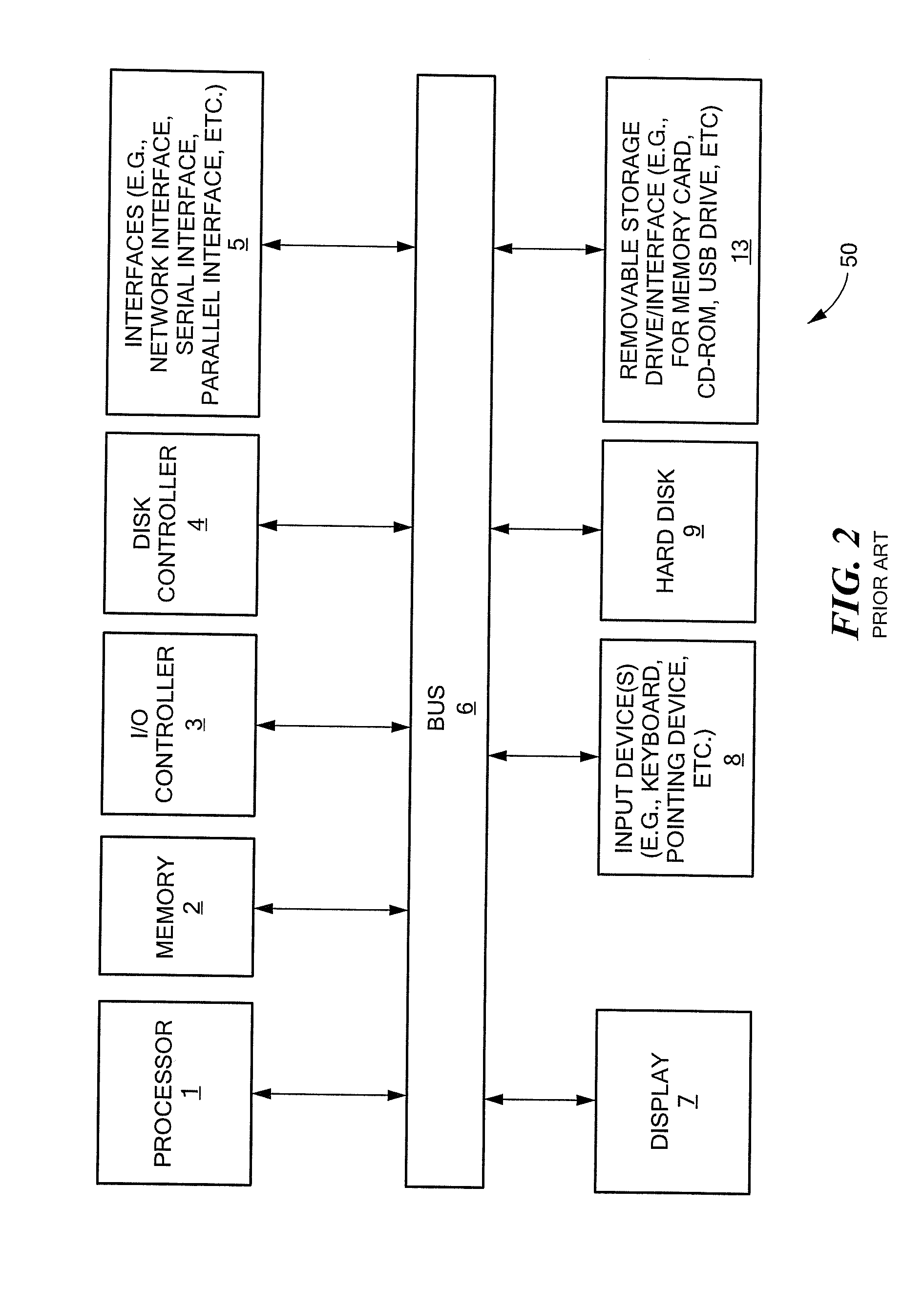

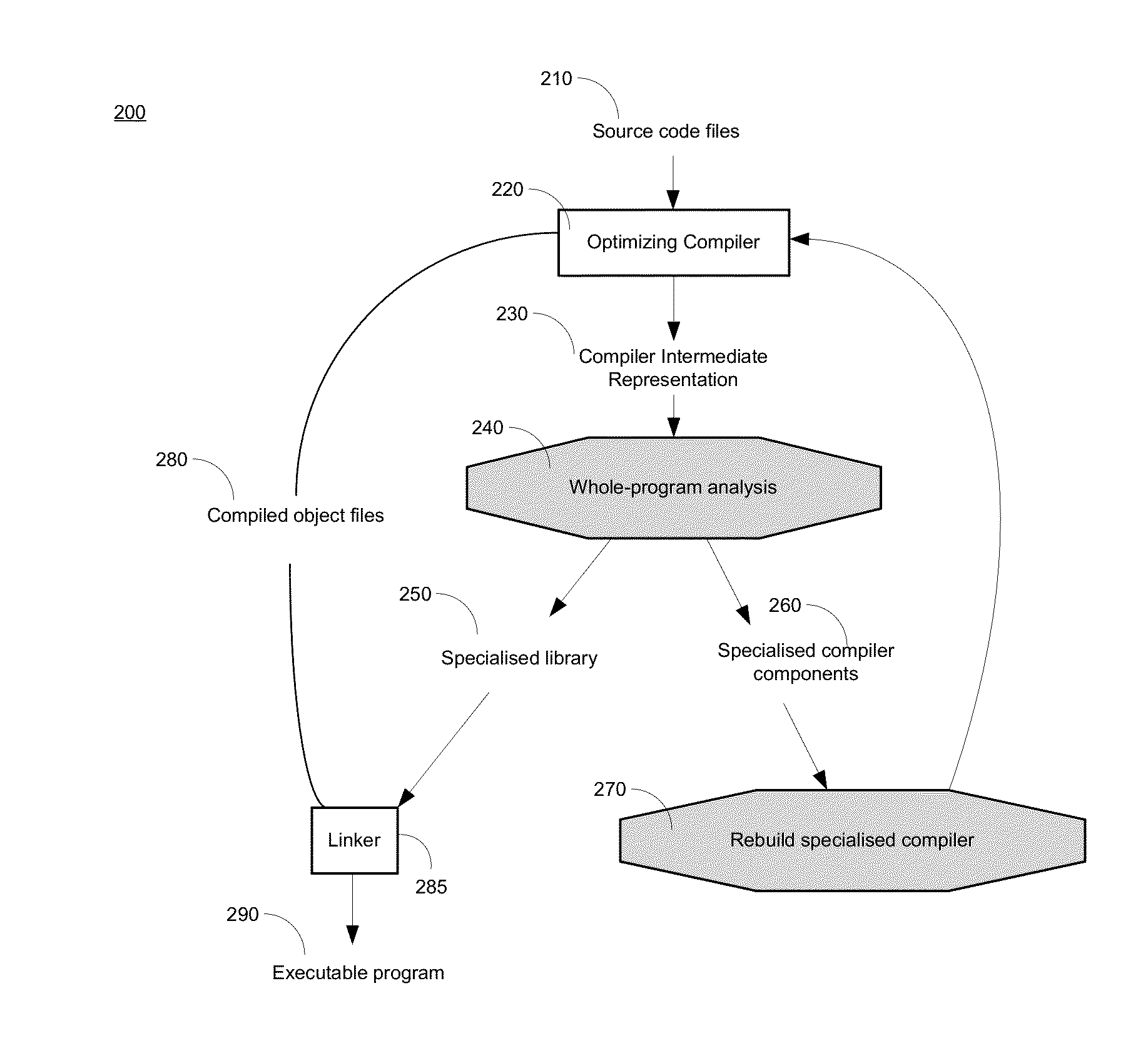

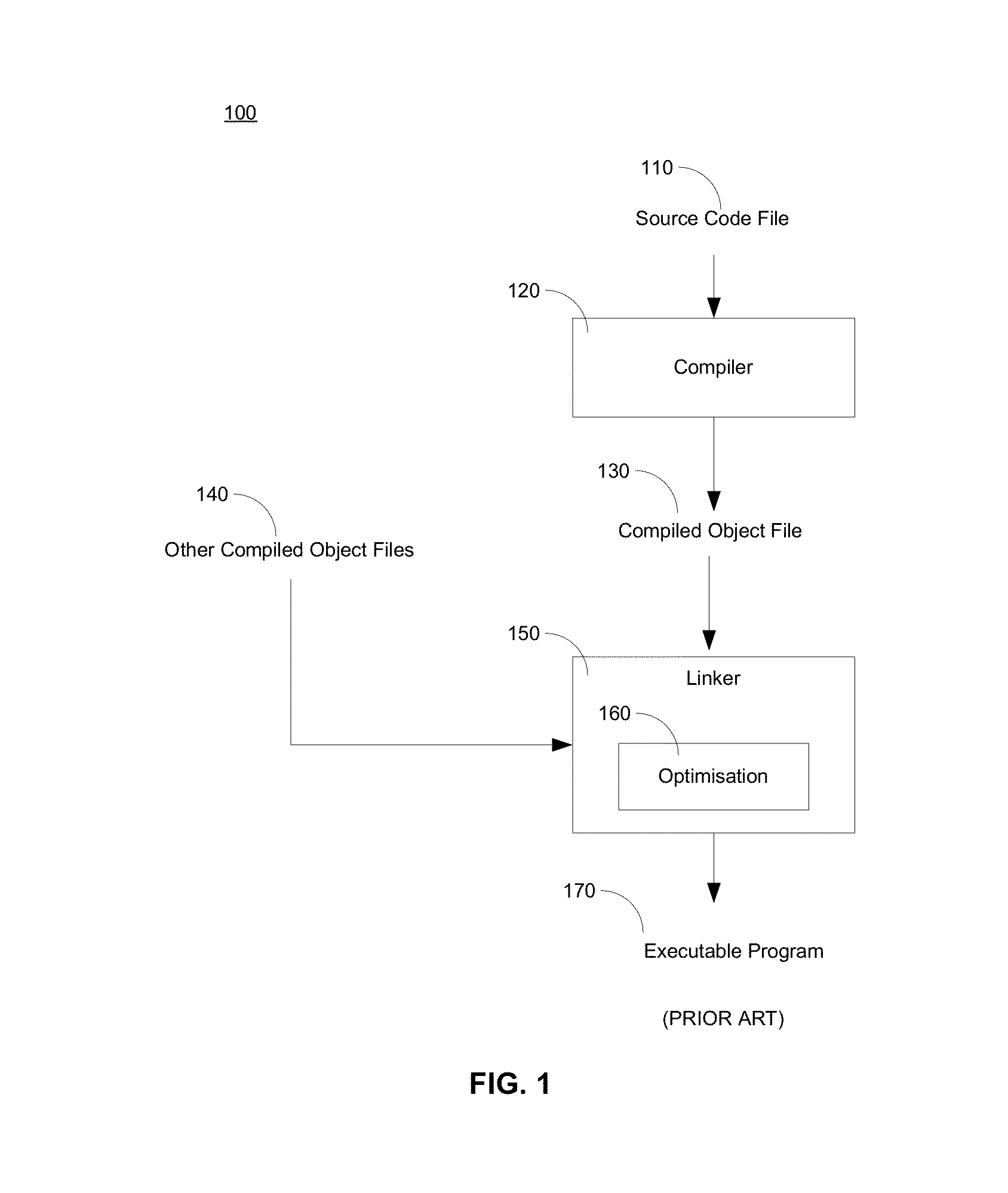

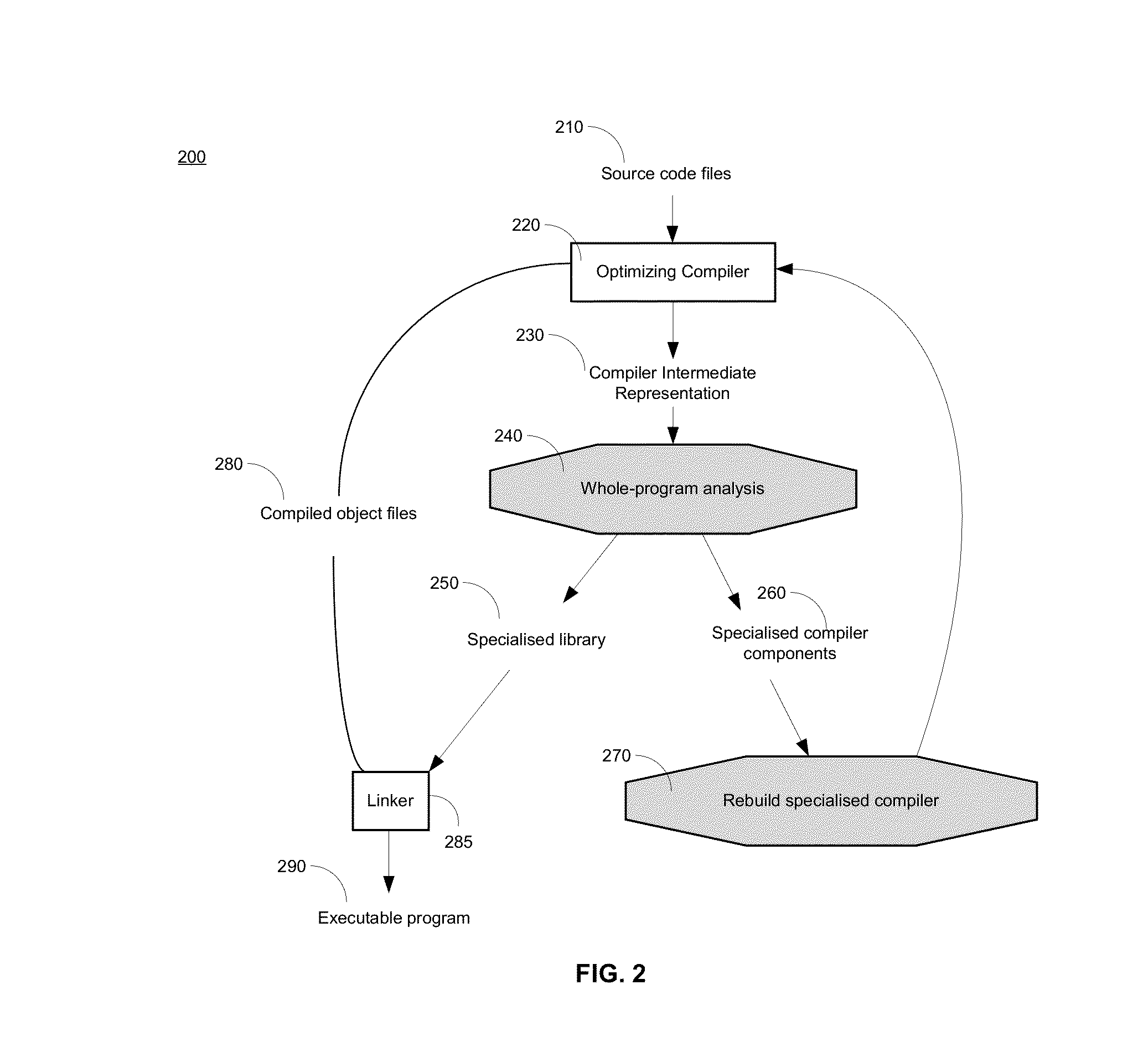

Automated Compiler Specialization for Global Optimization

InactiveUS20140026127A1Little compilerLittle link-time overheadProgram controlCompiler constructionGlobal optimizationStatic analysis

Techniques are provided herein for the offline static analysis of a stable code base in order to build a compiler and tools specialised to that code base. This allows global code base knowledge to be applied earlier in the compilation process giving better opportunities for optimisation. The offline static analysis produces specialized compiler components that are then used to rebuild the compiler. This results, over time, in a compiler specialized to the code base with improved optimization after every compiler release cycle.

Owner:MSTAR SEMICON INC +1

Null exception handling

ActiveUS20050216711A1Increase flexibilityMaximum performanceDigital computer detailsConcurrent instruction executionException handlingInstruction decoder

A processor 6 is provided with an instruction decoder 18 which is responsive to memory access instructions to determine whether the base register value being used matches a null value and if such a match occurs then branches to a null value exception handler.

Owner:ARM LTD

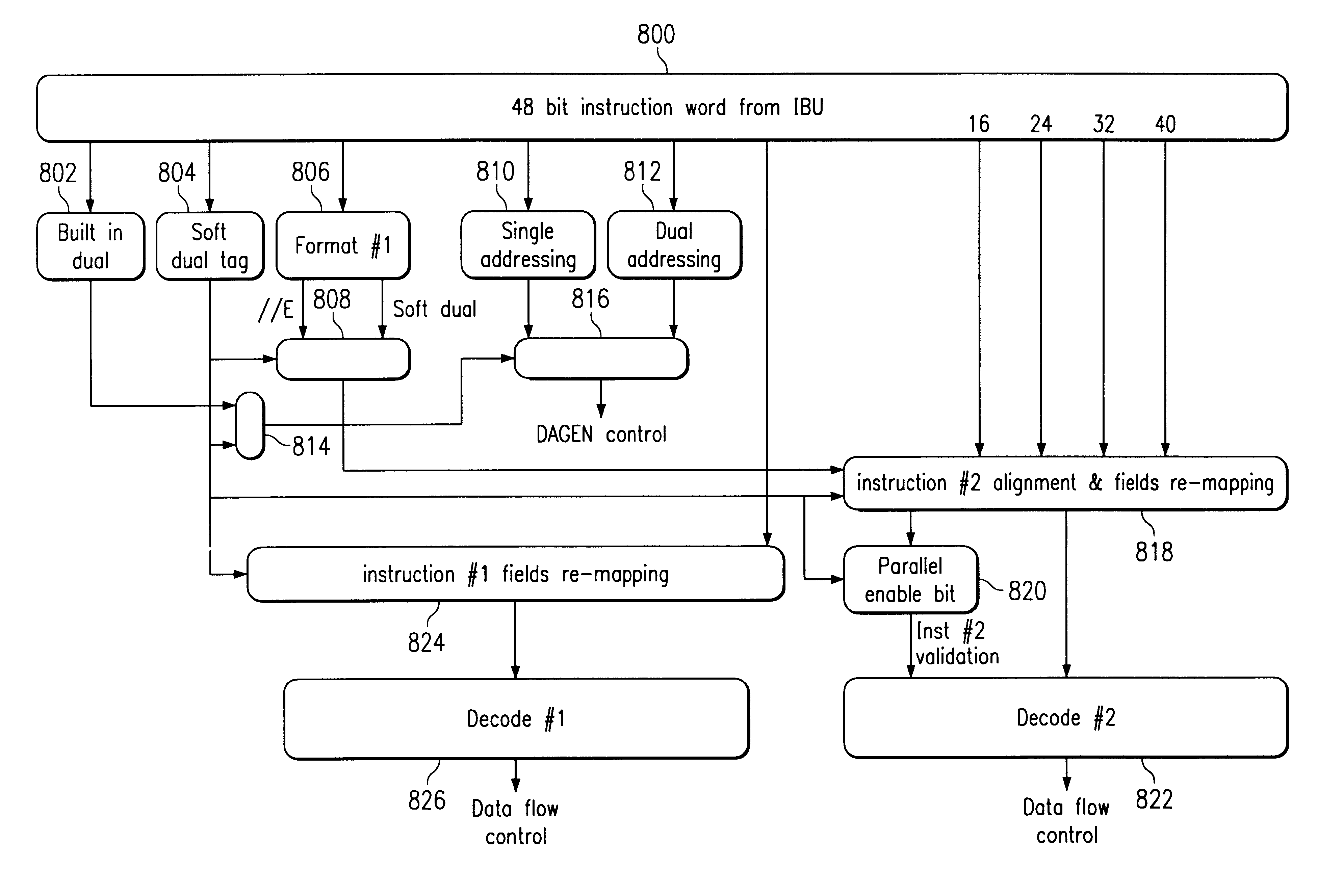

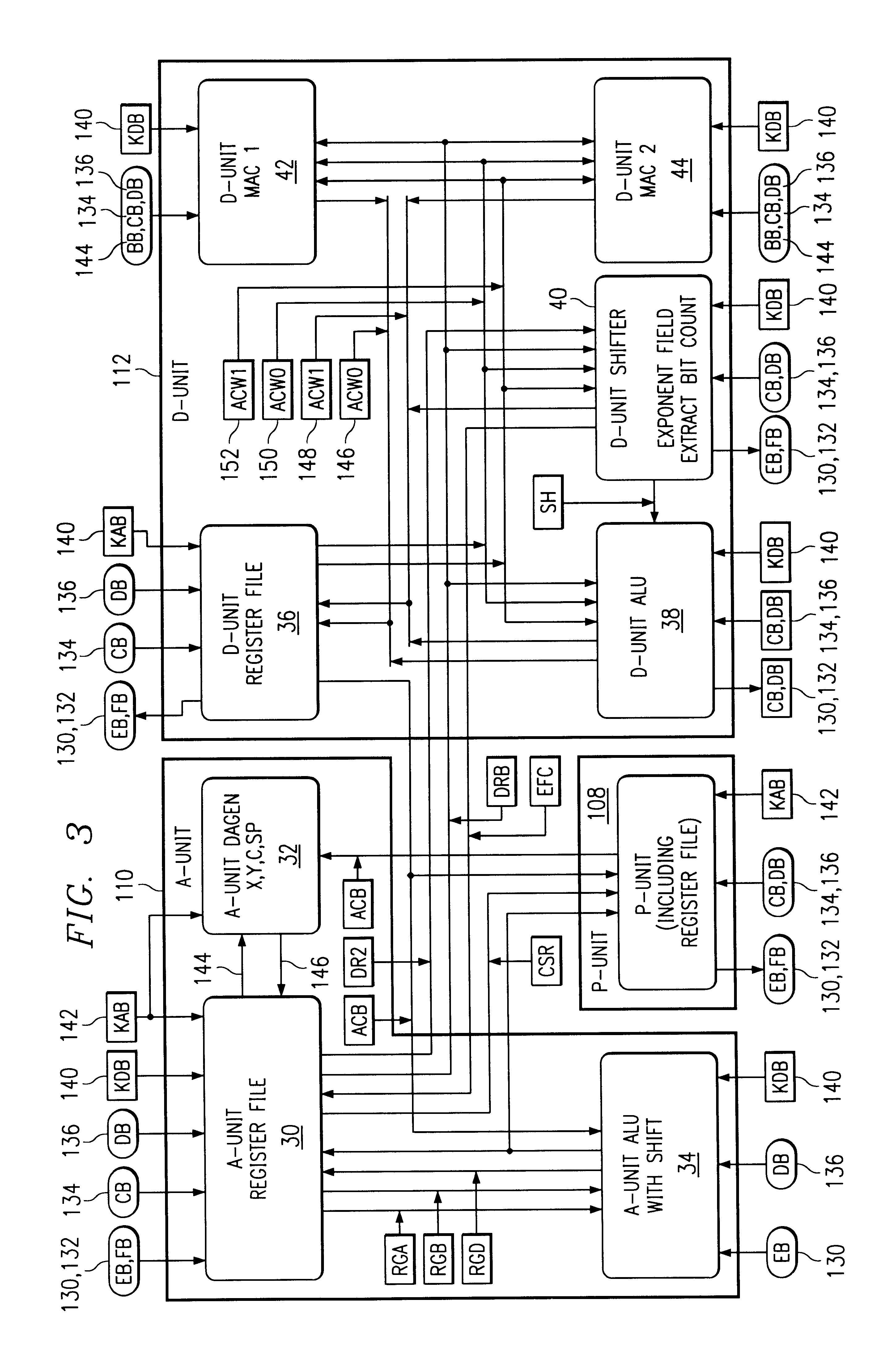

Dual access instruction and compound memory access instruction with compatible address fields

InactiveUS6681319B1Effect instruction throughputReduce in quantityCordless telephonesRegister arrangementsProgram instructionParallel computing

A processing engine 10 includes an instruction buffer 502 operable to buffer single and compound instructions pending execution. A decode mechanism is configured to decode instructions from the instruction buffer. The decode mechanism is arranged to respond to a predetermined tag in a tag field of an instruction, which predetermined tag is representative of the instruction being a compound instruction formed from separate programmed memory instructions. The decode mechanism is operable in response to the predetermined tag to decode at least first data flow control for a first programmed instruction and second data flow control for a second programmed instruction. The use of compound instructions enables effective use of the bandwidth available within the processing engine. A soft dual memory instruction can be compiled from separate first and second programmed memory instructions. A compound address field of the predetermined compound instruction can be arranged at the same bit positions as the address field for a hard compound memory instruction, that is a compound instruction which is programmed. In this case the decoding of the addresses can be started before the operation code of the instructions have been decoded. To reduce the number of bits in the compound instruction, addressing can be restricted to indirect addressing and the operation codes for at least the first instruction can be reduced in size. In this way, the compound instruction can be arranged to have the same number of bits in total as the sum of the bits of the separate programmed instructions.

Owner:TEXAS INSTR INC

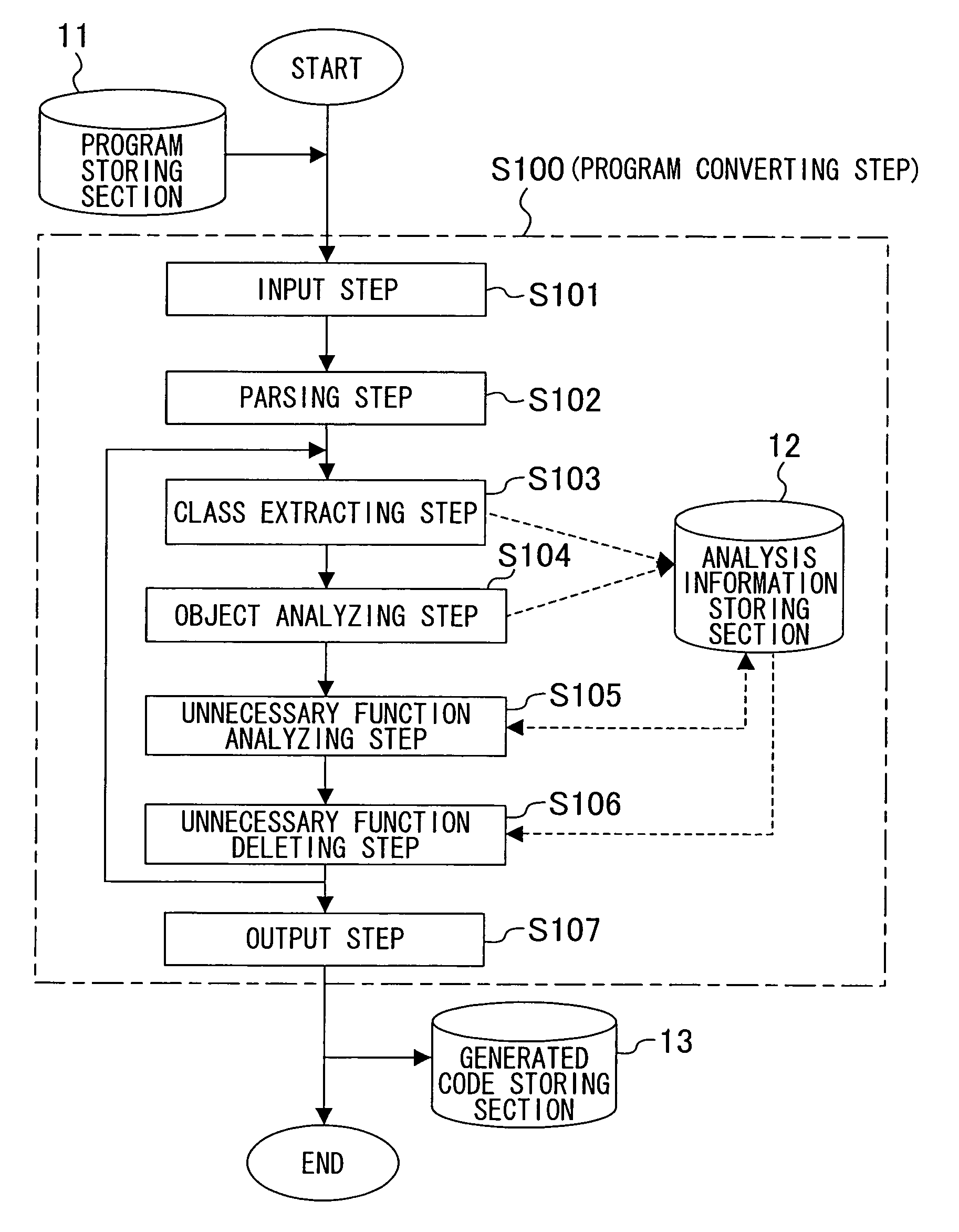

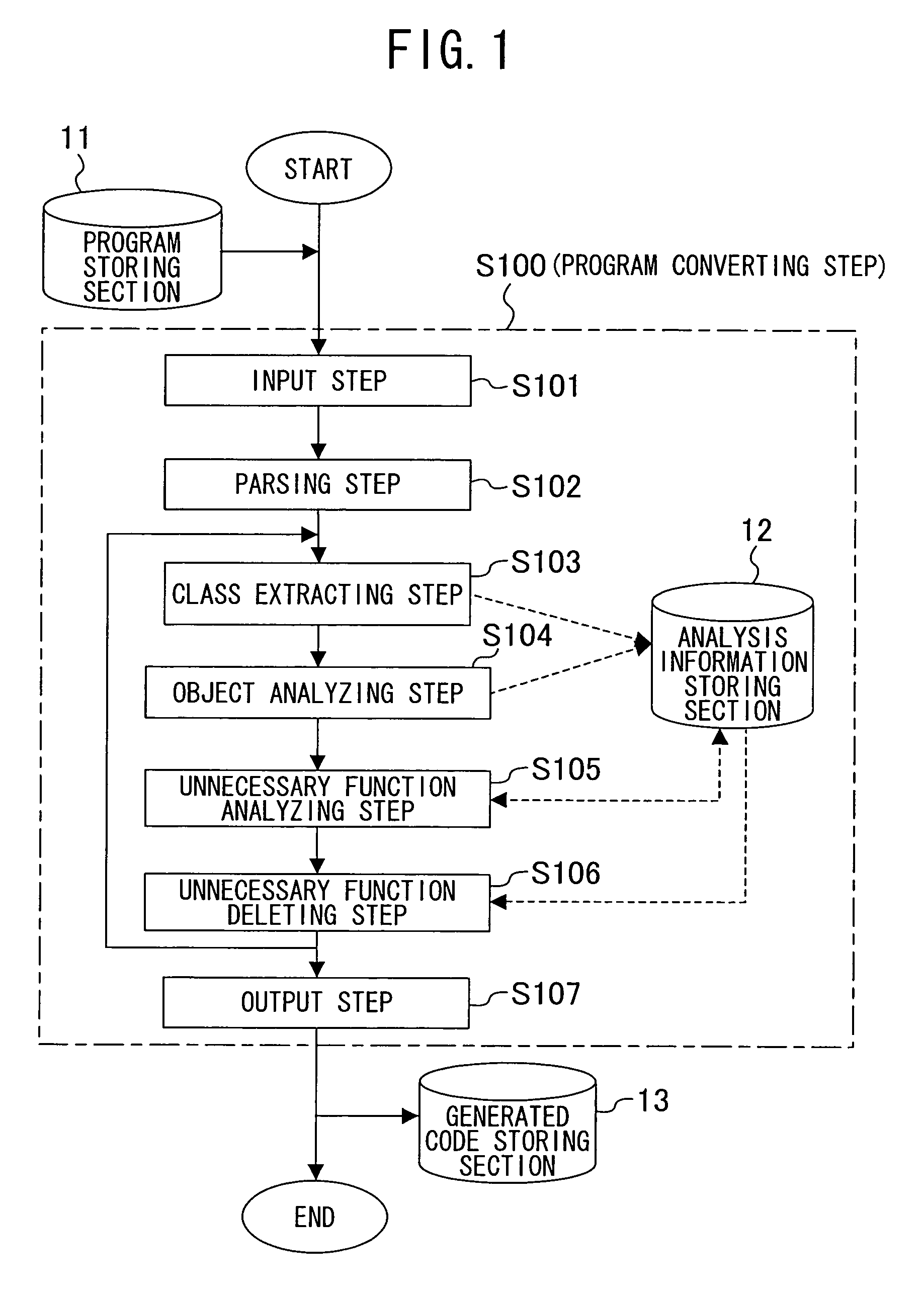

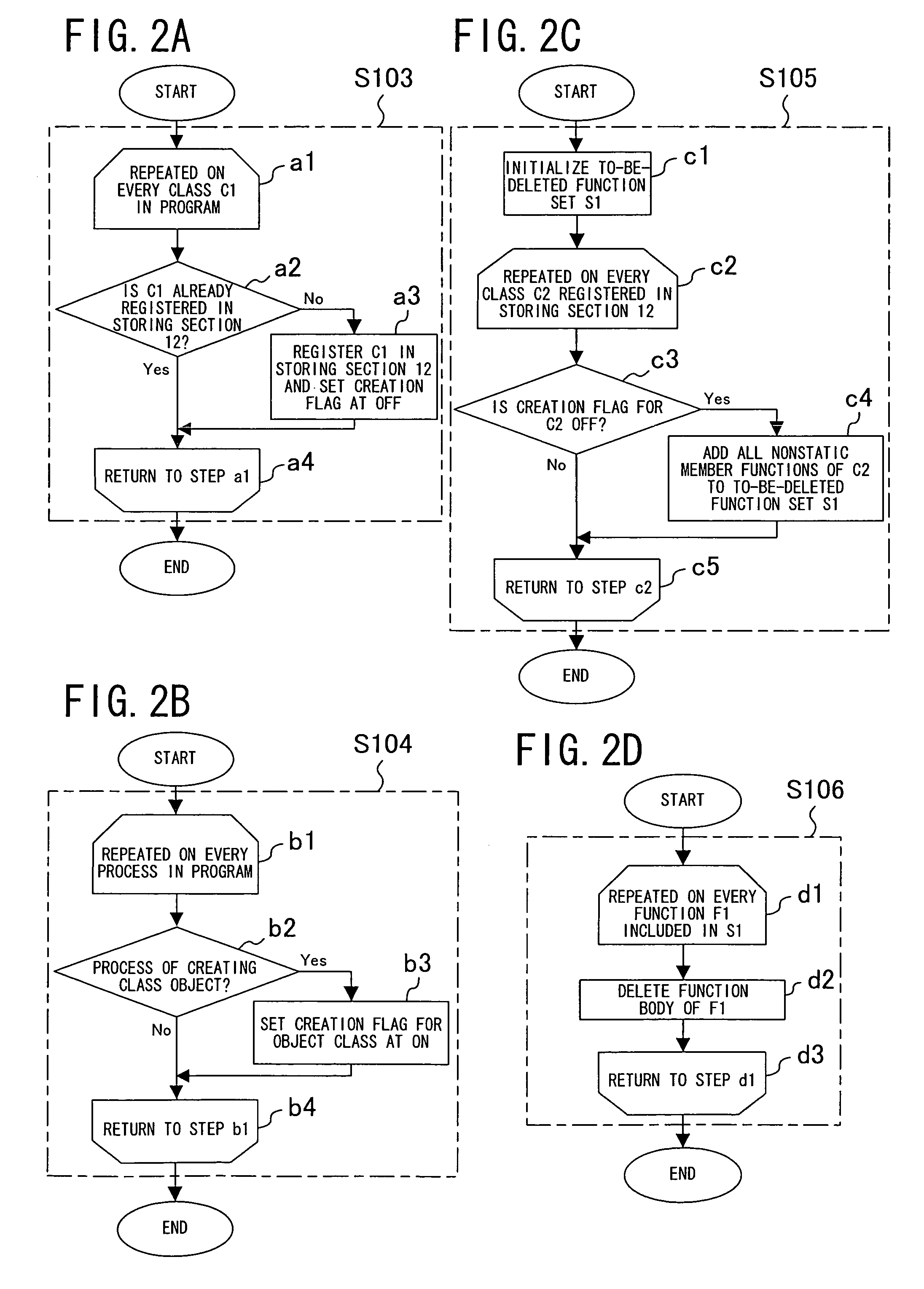

Program converting method and storage medium

InactiveUS7500229B2Efficient methodEnsuring deletionSoftware engineeringSpecific program execution arrangementsFunction analysisProgram transformation

Owner:SOCIONEXT INC

TCP/IP Stack-Based Operating System

InactiveUS20120042088A1Less microprocessor clock cyclesReduce power consumptionInterprogram communicationMultiple digital computer combinationsOperational systemUltra low power

Owner:IOTA COMPUTING

Moving picture coding apparatus, moving picture coding method, and moving picture coding program, and moving picture decoding apparatus, moving picture decoding method, and moving picture decoding program

ActiveUS8976867B2Suppresses increase in code sizeImprove coding efficiencyColor television with pulse code modulationColor television with bandwidth reductionDecoding methodsMotion vector

A motion vector predictor candidate generation unit derives a plurality of motion vector predictor candidates by prediction from first coded prediction blocks neighboring a prediction block subject to coding within the same picture as the prediction block subject to coding, or from a second coded prediction block located at the same position as or in the neighborhood of the prediction block subject to coding in a picture different from that of the prediction block subject to coding, and adds the derived motion vector predictor candidates in a motion vector predictor candidate. The motion vector predictor candidate generation unit determines, for the purpose of obtaining a predetermined number of motion vector predictor candidates, which of first coded prediction blocks provides the motion vector from which to derive the motion vector predictor candidate, organizing the blocks in the order of priority.

Owner:JVC KENWOOD CORP

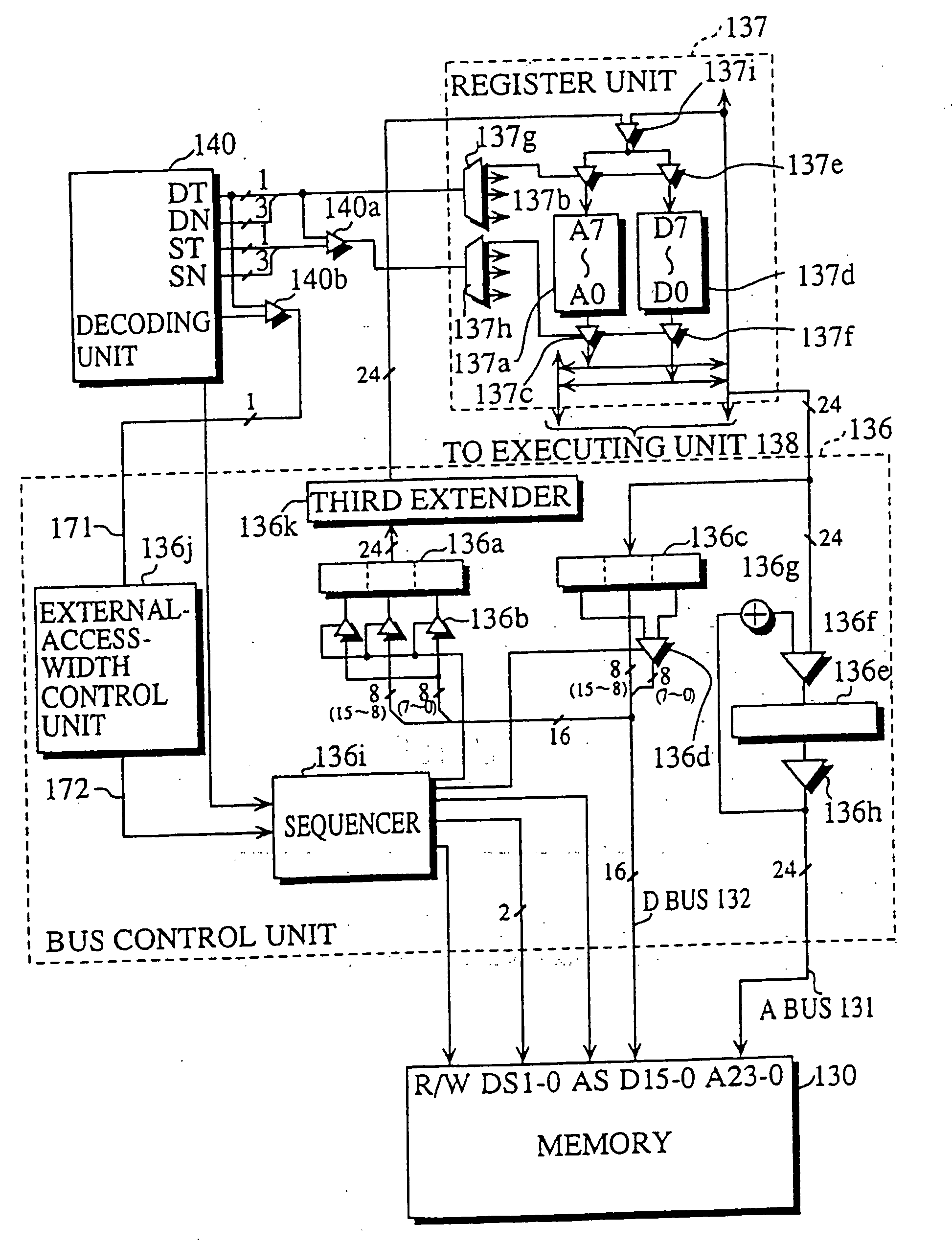

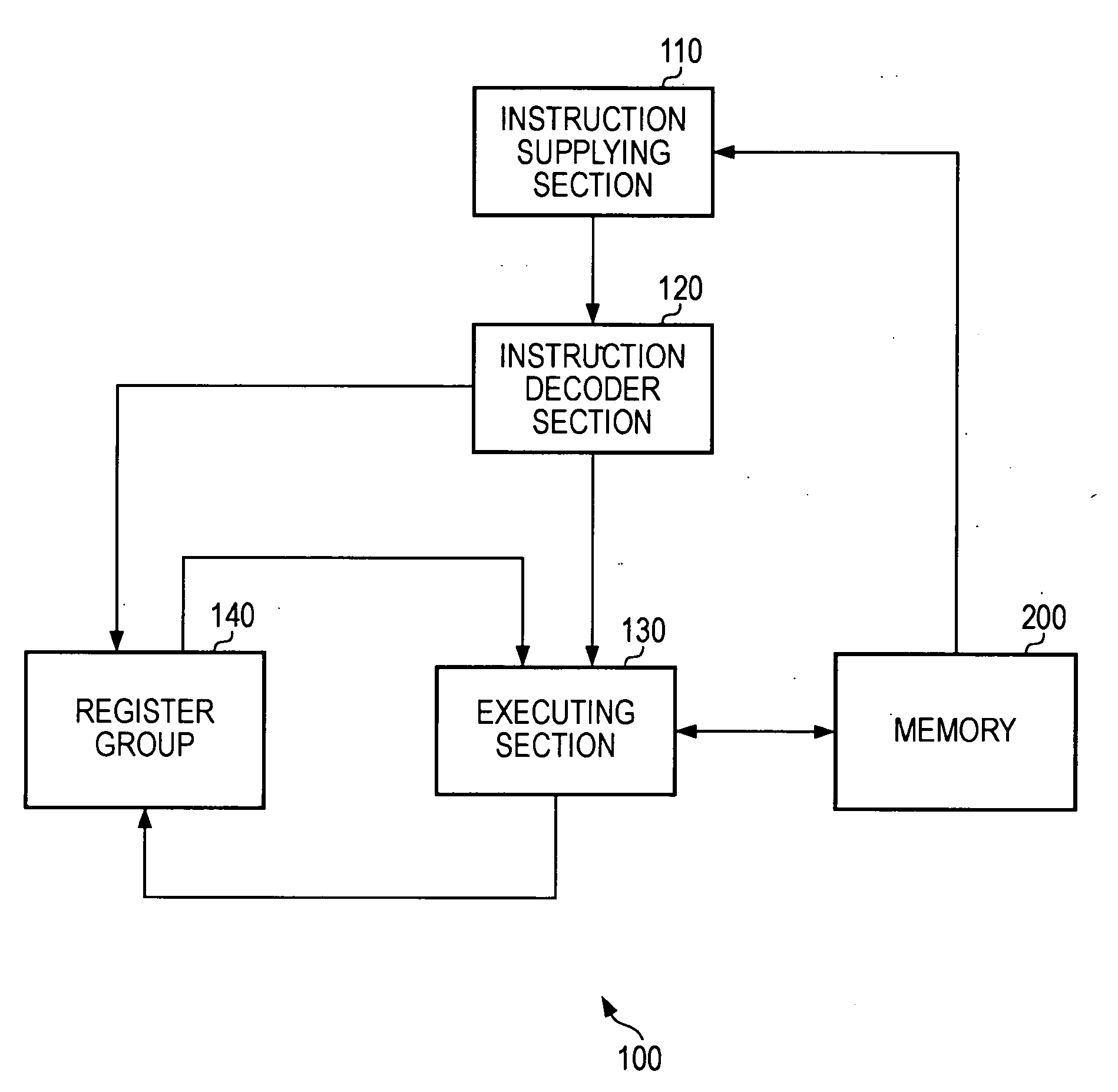

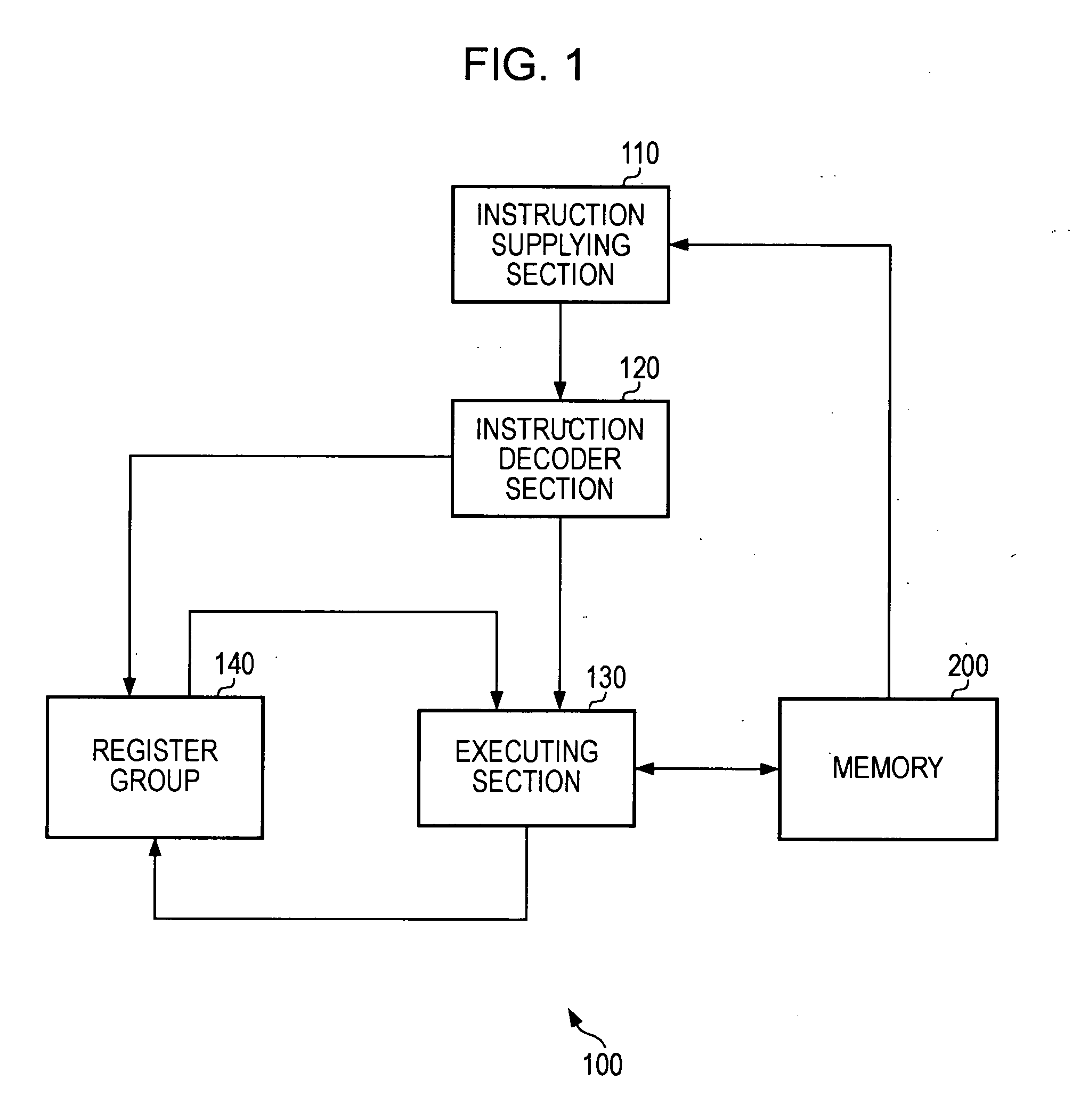

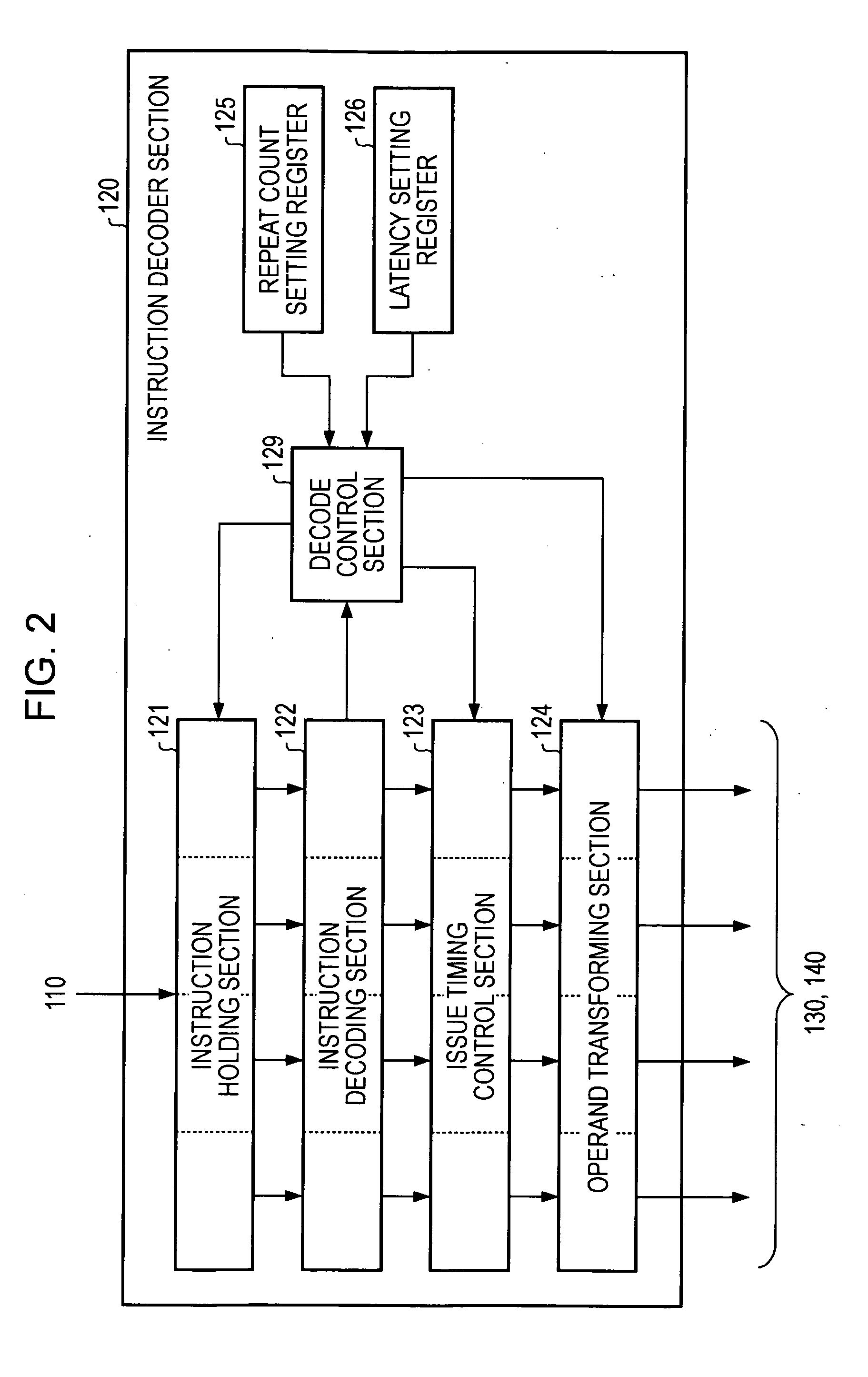

Information processing apparatus and instruction decoder for the information processing apparatus

ActiveUS20110099354A1Suppresses increase in code sizeDigital computer detailsMemory systemsInformation processingOperand

An information processing apparatus includes an instruction supplying section that supplies a plurality of instructions as a single instruction group, an executing section that repetitively executes a plurality of execution processes corresponding to the plurality of instructions in parallel, an issue timing control section that controls an issue timing of each of the instructions to the executing section so that the plurality of execution processes are executed with a timing delayed in accordance with a predetermined latency, and an operand transforming section that transforms an operand register address of each of the instructions in accordance with a predetermined increment value upon every repetition of execution in the executing section.

Owner:SONY CORP

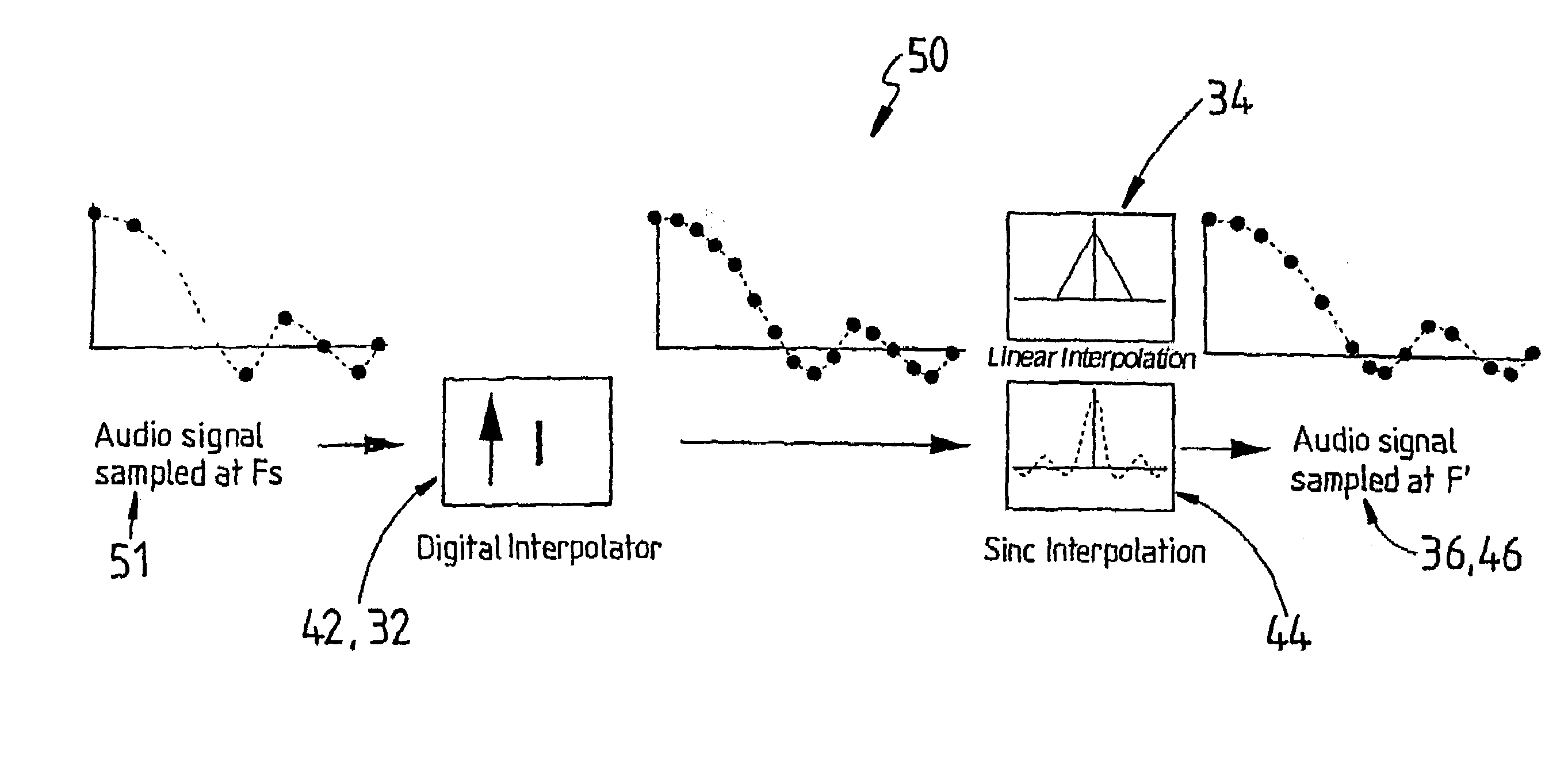

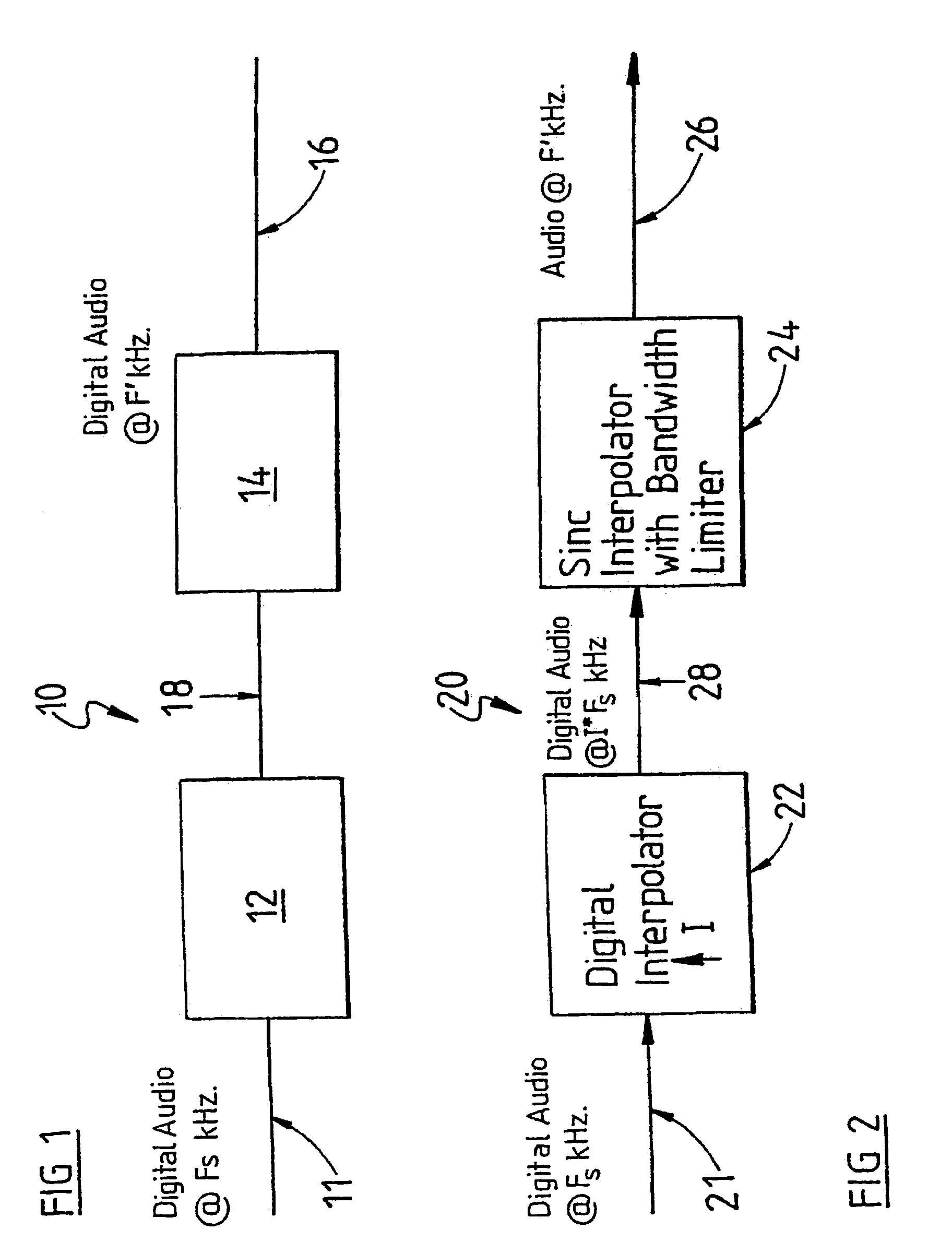

Universal sampling rate converter for digital audio frequencies

InactiveUS7177812B1Reduces program code sizeSimple structureDigital technique networkSpeech synthesisAudio frequencyComputer science

A method for conversion of input audio frequency data, at an input sample frequency, to output audio frequency data, at an output sample frequency. The input data is subjected to expansion to produce expanded data at an output sample frequency. The expanded data is interpolated to produce output data. In one embodiment of the invention the interpolation is effected by a process that also filters the output data. In another embodiment, the input data is sampled by an integer factor to produce expanded data, the expanded data is then interpolated to produce the output data. Also disclosed is a method of transition of a signal output, at one frequency, to a signal output at another frequency. The signal output at said one frequency is faded out over a period, and the signal output at said other frequency is faded in over that period. Both signal outputs are combined to produce the signal output over said period. Apparatus for effecting the methods is also disclosed.

Owner:STMICROELECTRONICS ASIA PACIFIC PTE

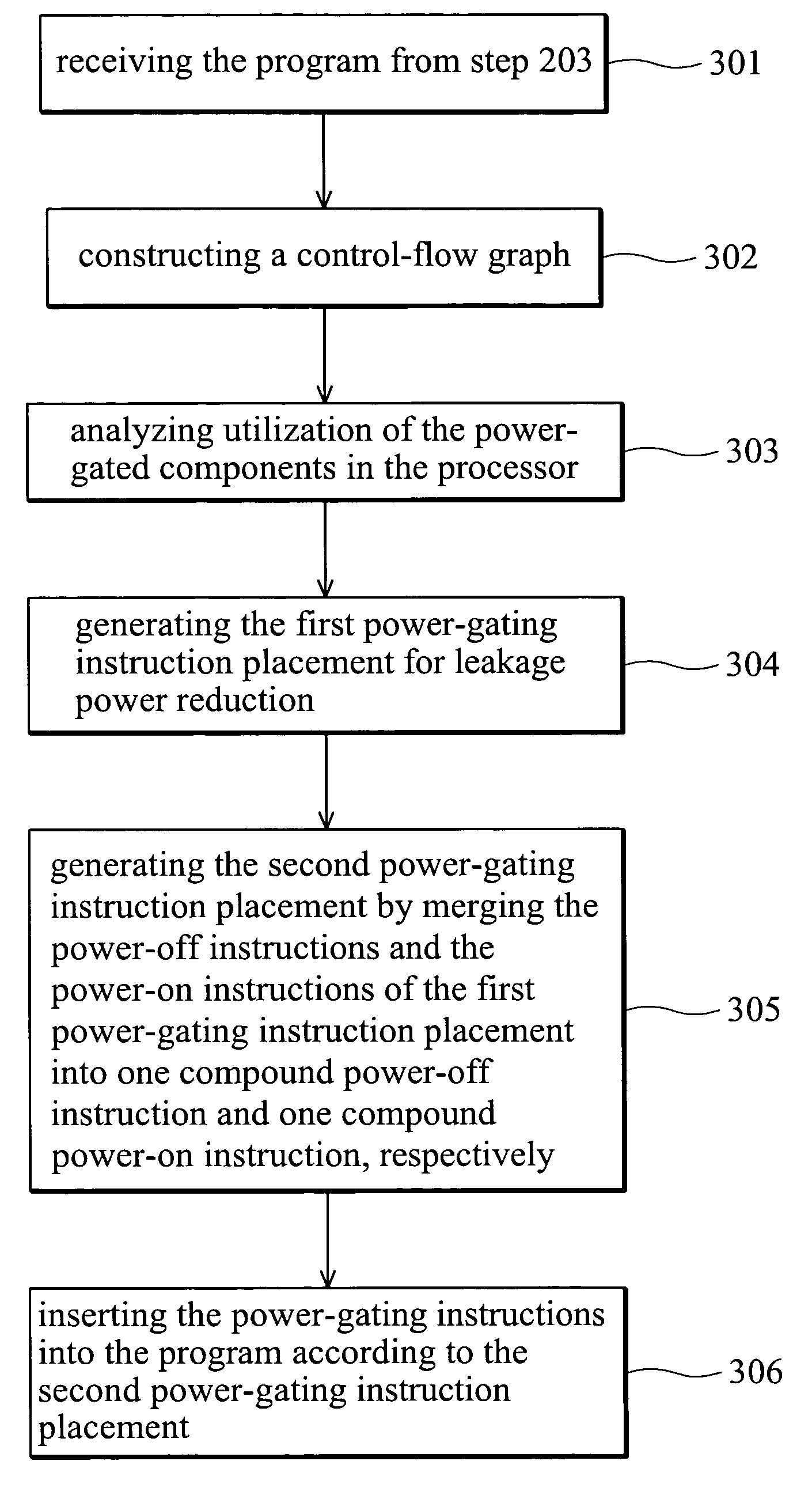

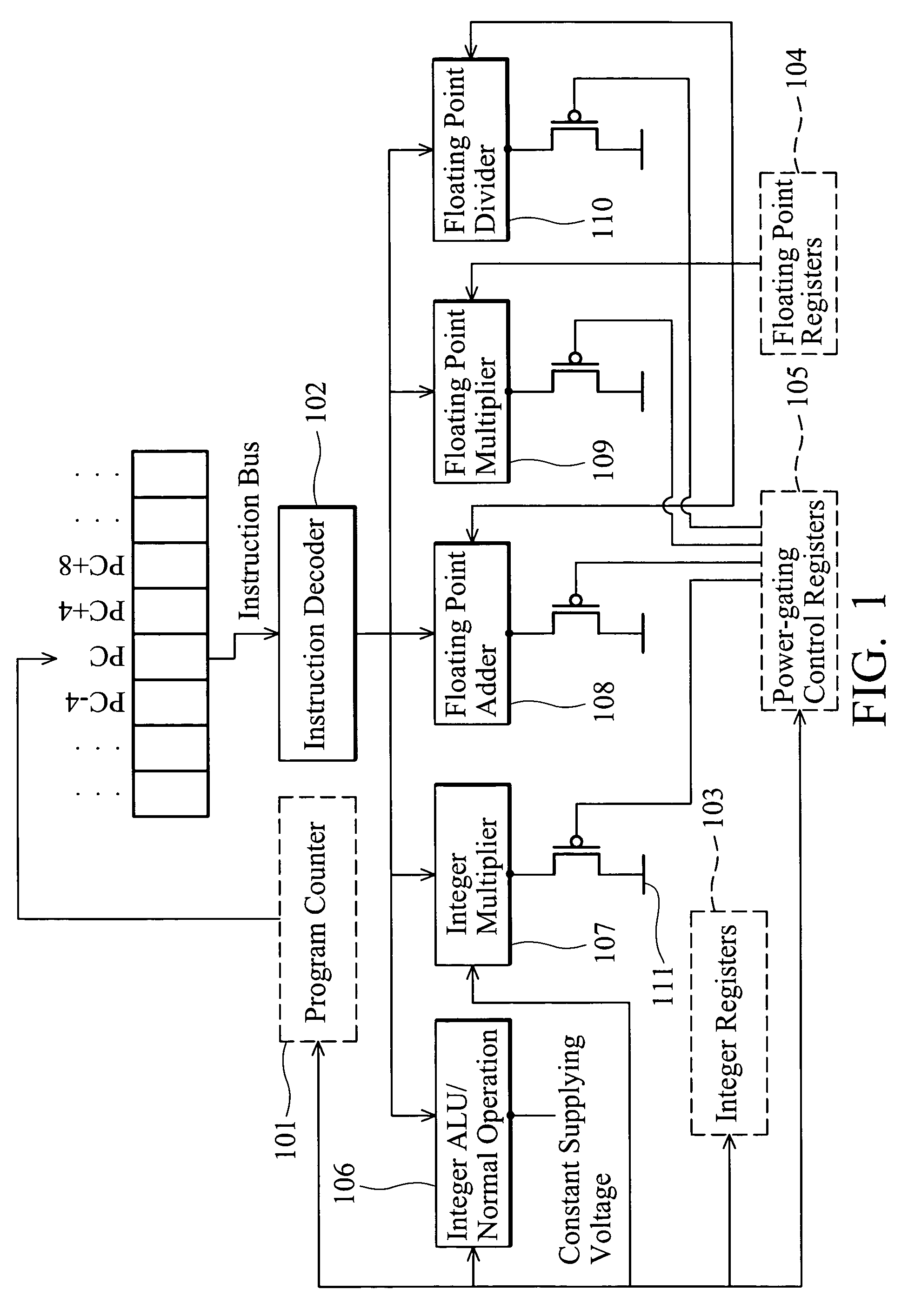

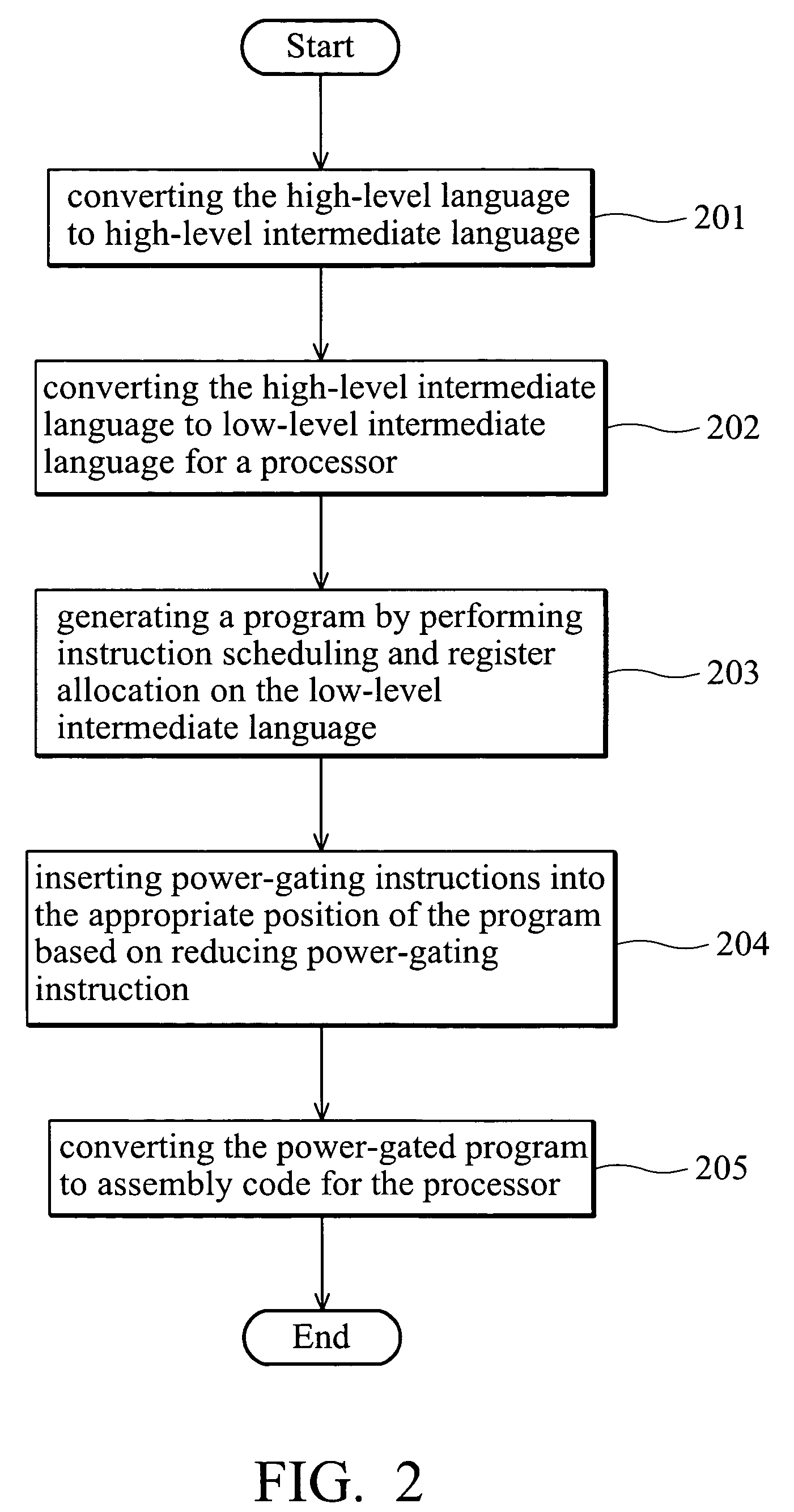

Power-gating instruction scheduling for power leakage reduction

InactiveUS7539884B2Increase powerReducing power-gating instructionsVolume/mass flow measurementPower supply for data processingElectricityScheduling instructions

A method of power-gating instruction scheduling for leakage power reduction comprises receiving a program, generating a control-flow graph dividing the program into a plurality of blocks, analyzing utilization of power-gated components of a processor executing the program, generating the first power-gating instruction placement comprising power-off instructions and power-on instructions to shut down the inactive power-gated components, generating the second power-gating instruction placement by merging the power-off instructions as one compound power-off instruction and merging the power-on instructions as one compound power-on instruction, and inserting power-gating instructions into the program in accordance with the second power-gating instruction placement.

Owner:IND TECH RES INST