Variable address length compiler and processor improved in address management

a compiler and address technology, applied in the field of program conversion, can solve the problems of hardware not fully utilized, performance efficiency significantly degraded, programming efficiency degraded, etc., and achieve the effect of reducing the number of instructions and reducing the overhead at the conditional branch

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

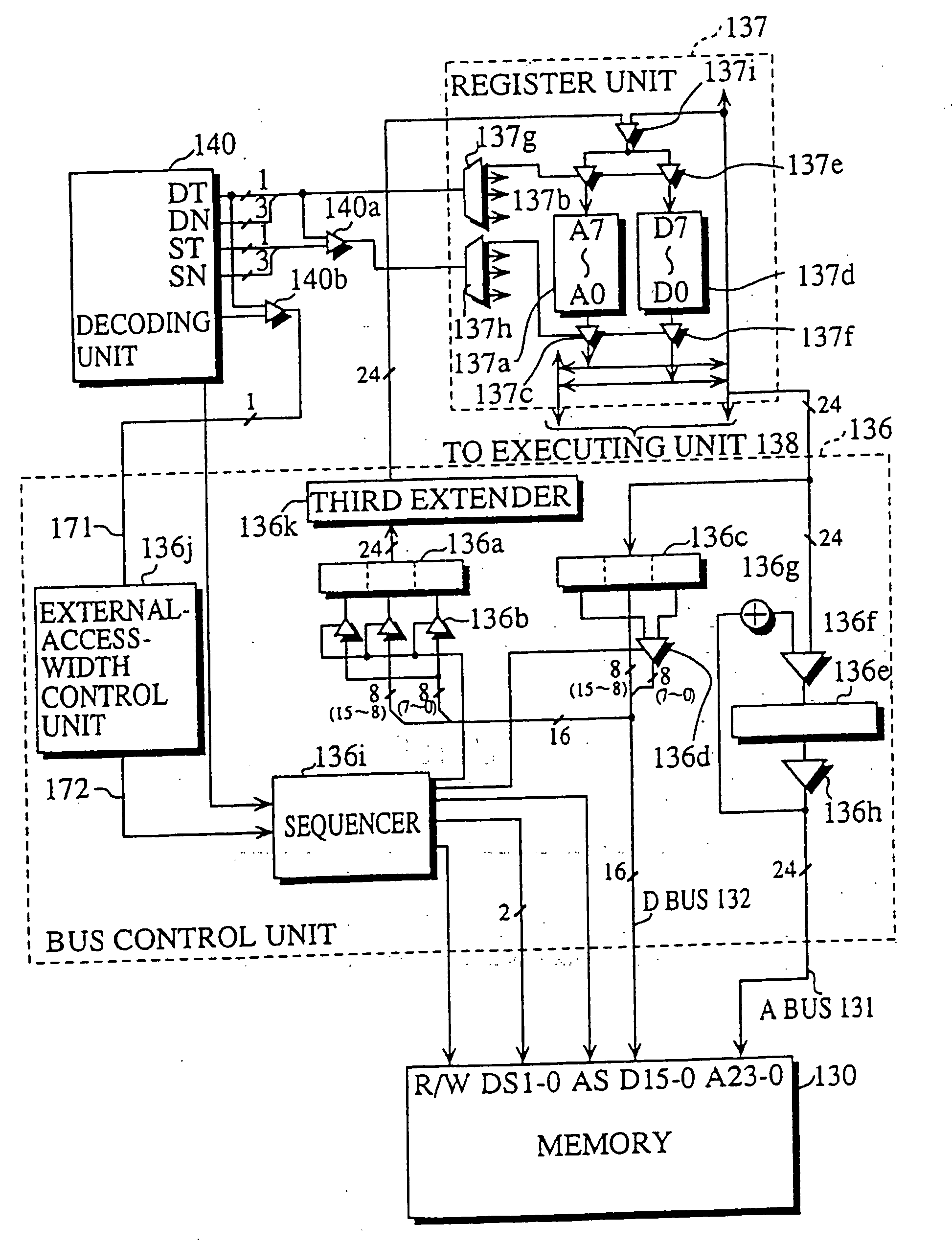

[0144]A hardware structure of a data processing system including a computer and a program converting unit (compiler) is depicted in FIG. 13. The data processing system comprises a storage unit 1 for storing a C language program, a compiler 2 for translating the C language program into a machine language program, and a computer 3 for running an object code; the computer 3 includes a processor and a memory.

[0145]More precisely, the computer 3 includes a memory 130, an address bus 131, a data bus 132, an instruction control unit 134, an operation executing unit 135, and a bus control unit 136.

[0146]The memory 130 stores an object code and data used in a program.

[0147]The address bus 131 is of 24-bit wide and sends an address to the memory 130.

[0148]The data bus 132 is of 16-bit wide and transfers data to each component within the computer 3.

[0149]The instruction control unit 134 includes a fetching unit 139 and a decoding unit 140 to fetch an instruction via the bus control unit 136 an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More