Patents

Literature

917 results about "Machine code" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Machine code is a computer program written in machine language instructions that can be executed directly by a computer's central processing unit (CPU). Each instruction causes the CPU to perform a very specific task, such as a load, a store, a jump, or an ALU operation on one or more units of data in CPU registers or memory.

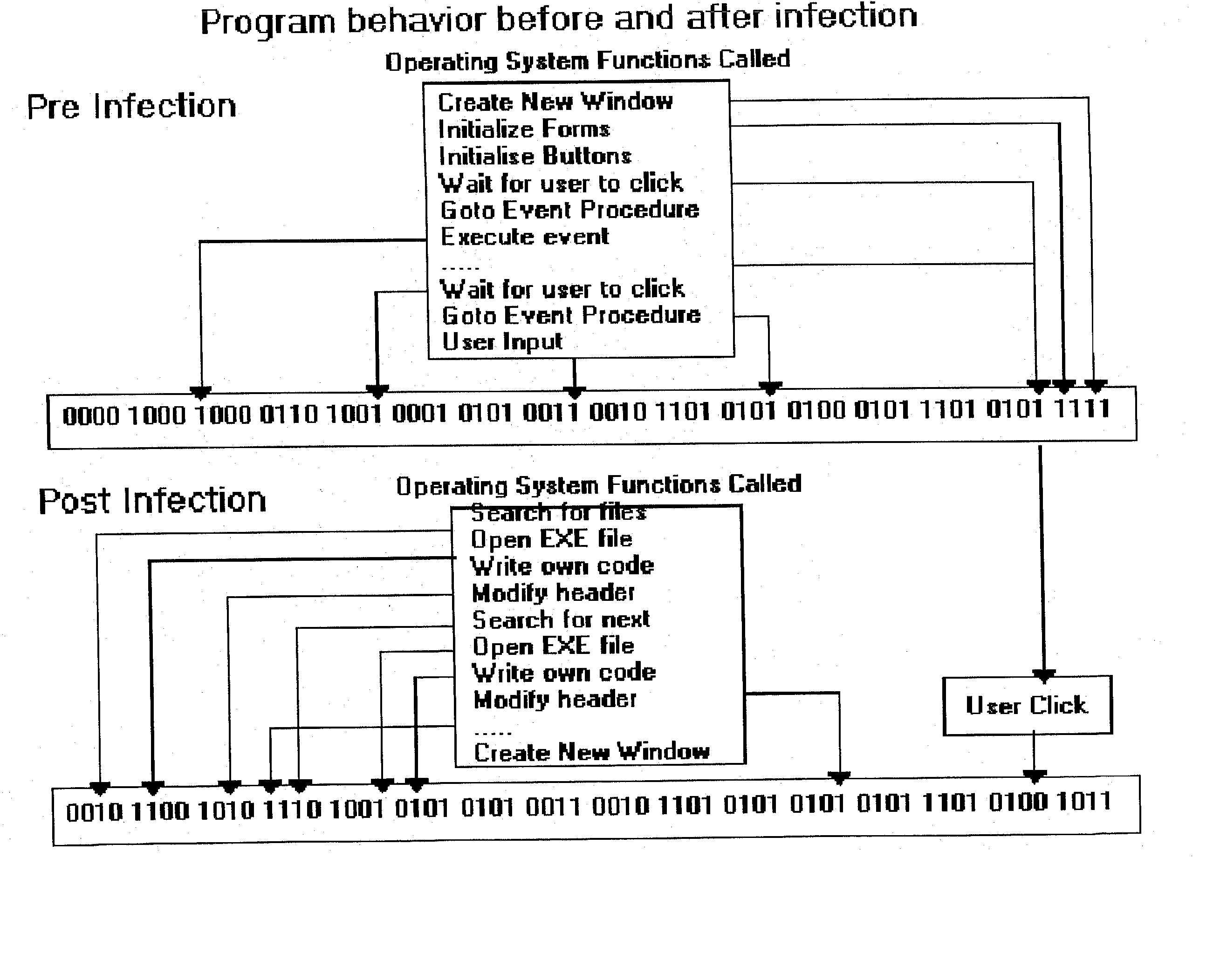

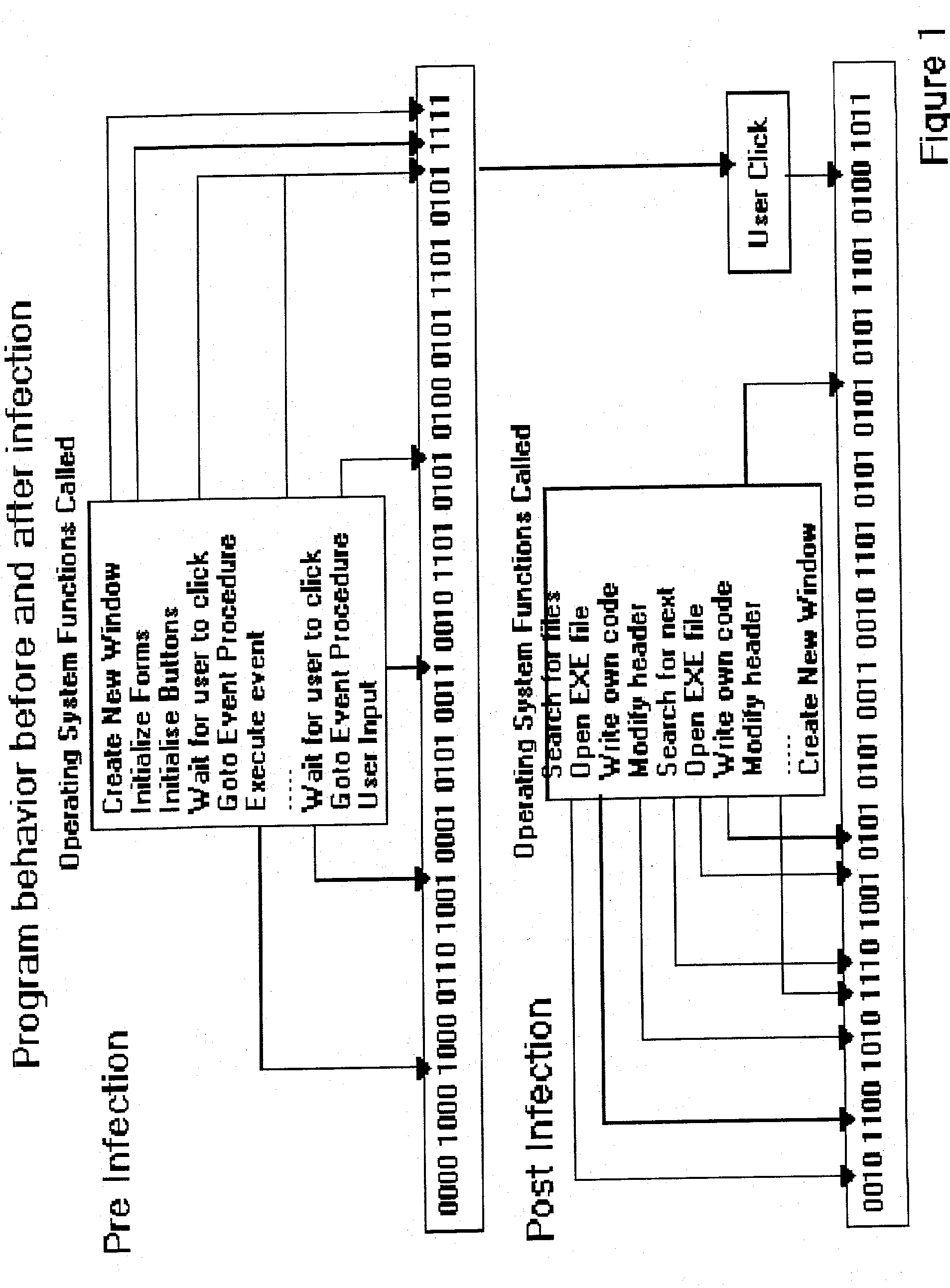

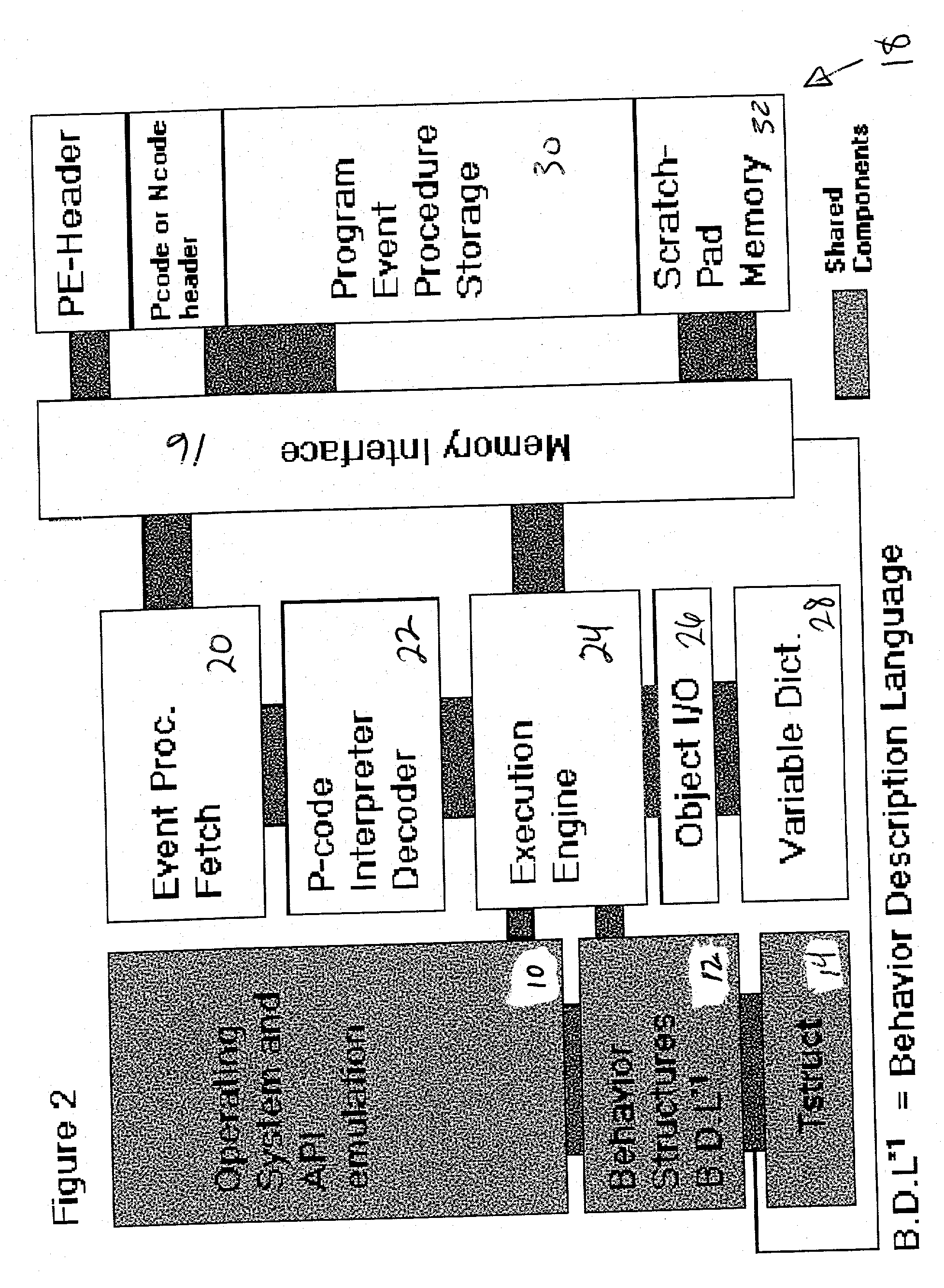

Computer immune system and method for detecting unwanted code in a P-code or partially compiled native-code program executing within a virtual machine

InactiveUS20030212902A1Memory loss protectionDigital data processing detailsComputerized systemBehaviour pattern

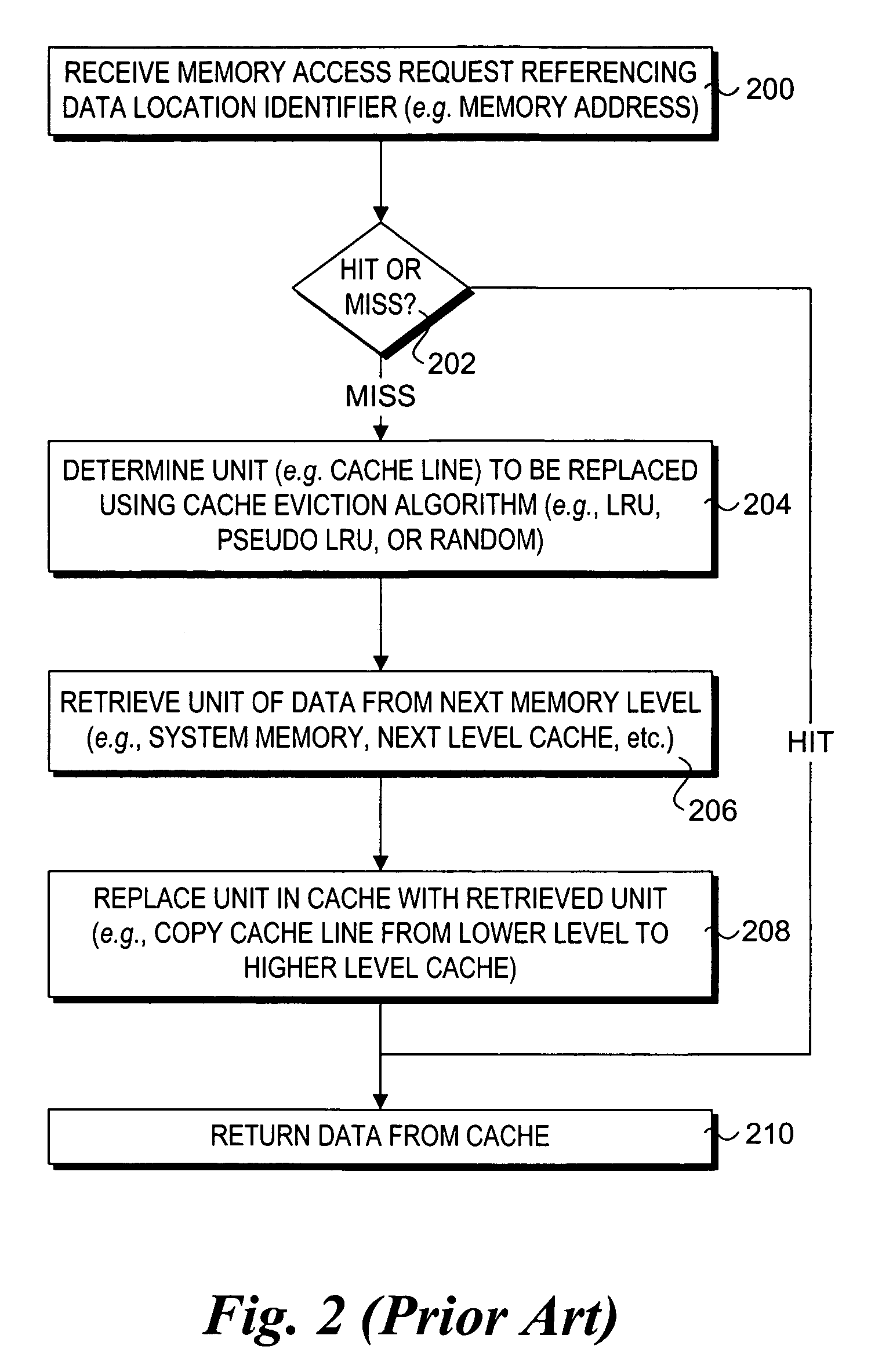

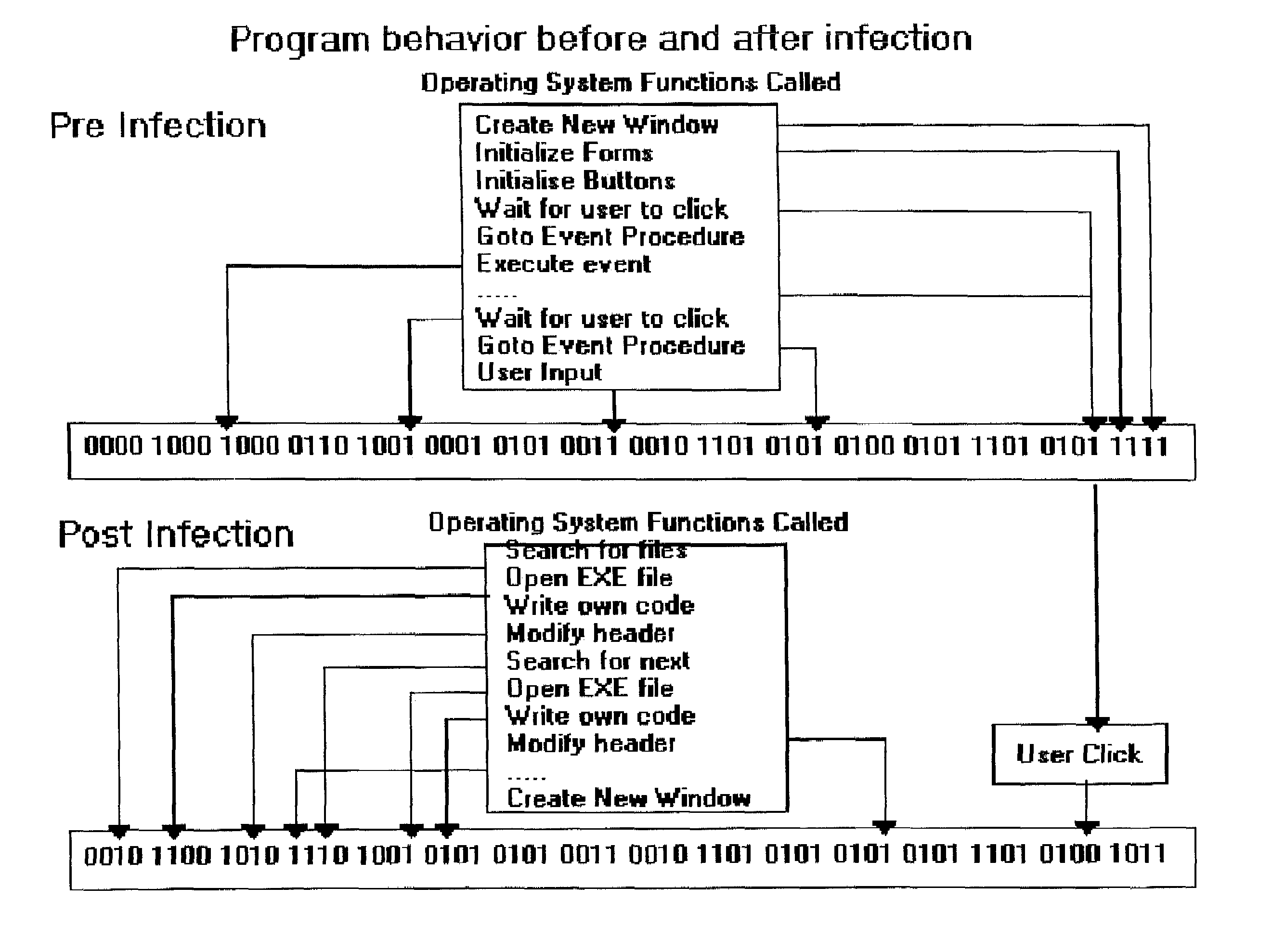

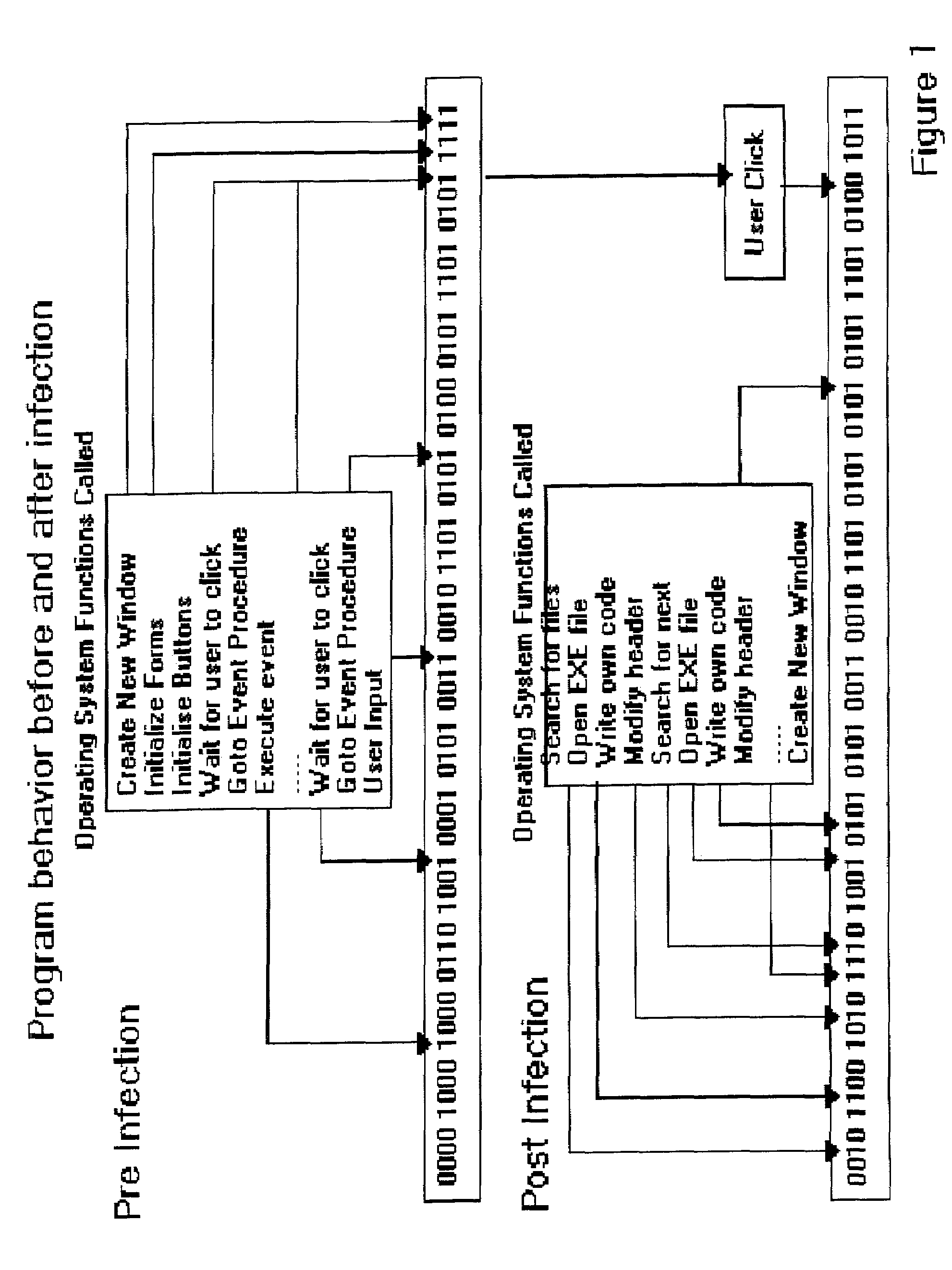

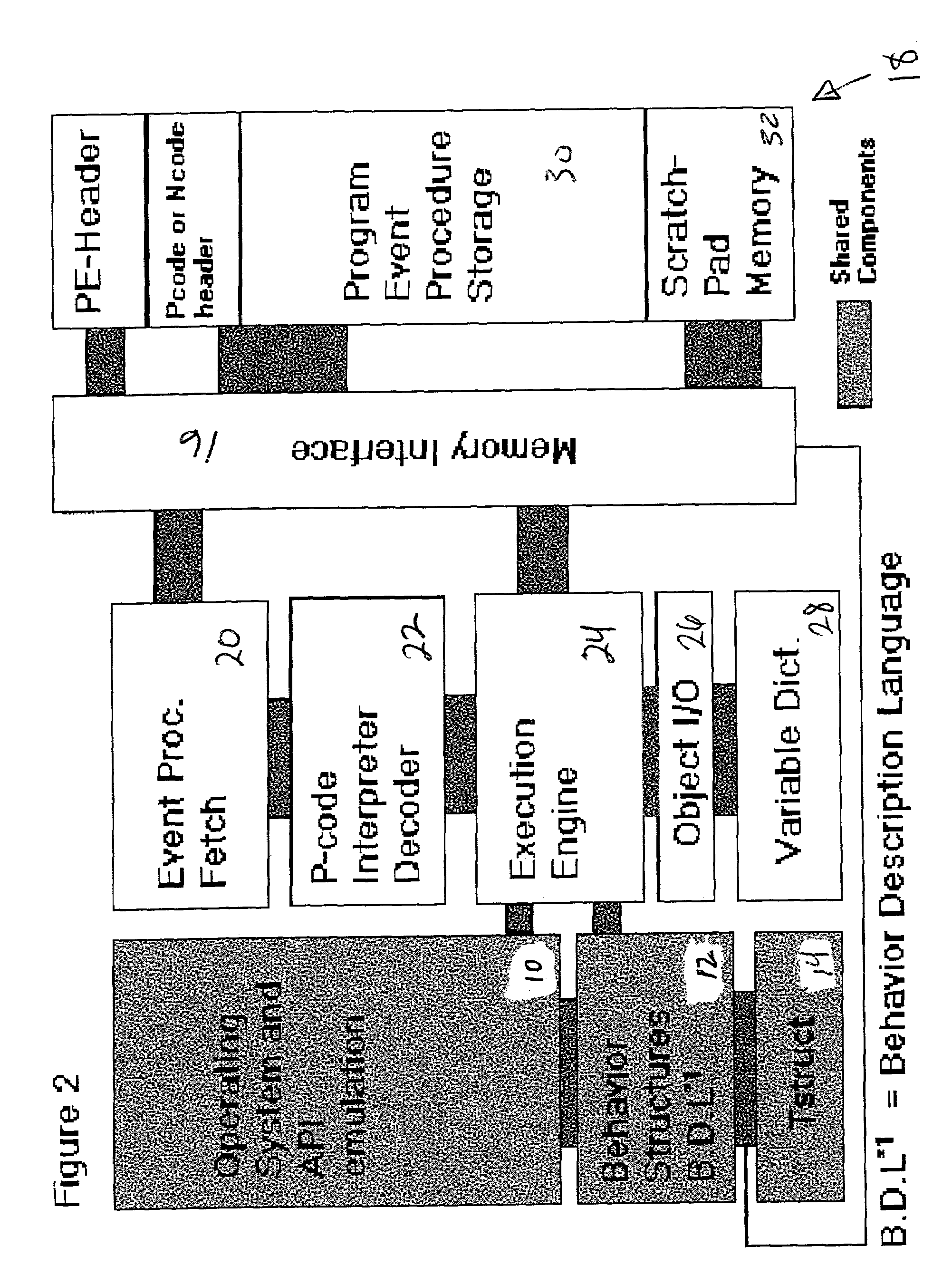

An automated analysis system identifies the presence of malicious P-code or N-code programs in a manner that limits the possibility of the malicious code infecting a target computer. The target computer system initializes an analytical virtual P-code engine (AVPE). As initialized, the AVPE comprises software simulating the functionality of a P-code or intermediate language engine as well as machine language facilities simulating the P-code library routines that allow the execution of N-code programs. The AVPE executes a target program so that the target program does not interact with the target computer. The AVPE analyzes the behavior of the target program to identify occurrence of malicious code behavior and to indicate in a behavior pattern the occurrence of malicious code behavior. The AVPE is terminated at the end of the analysis process, thereby removing from the computer system the copy of the target program that was contained within the AVPE.

Owner:PALO ALTO NETWORKS INC

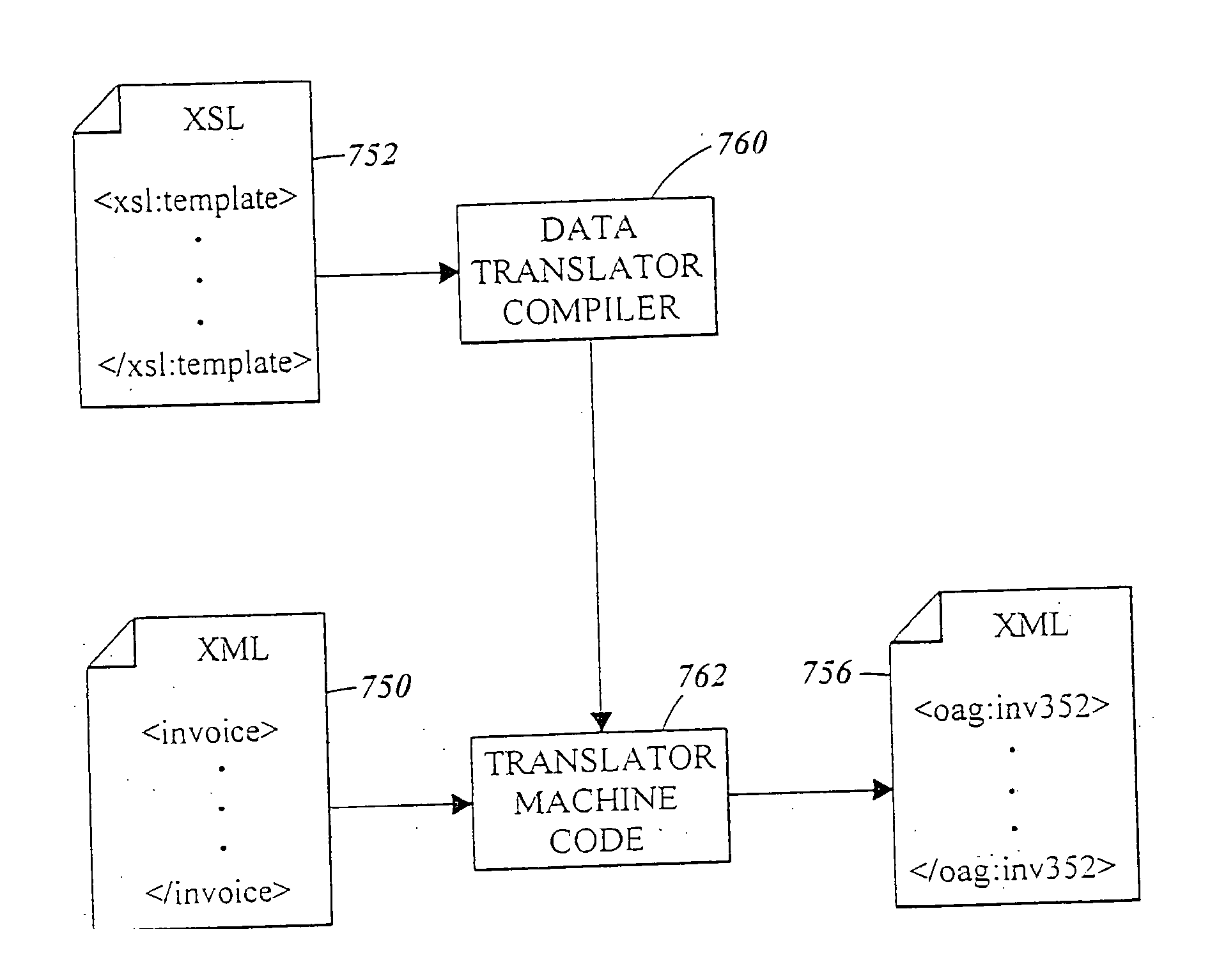

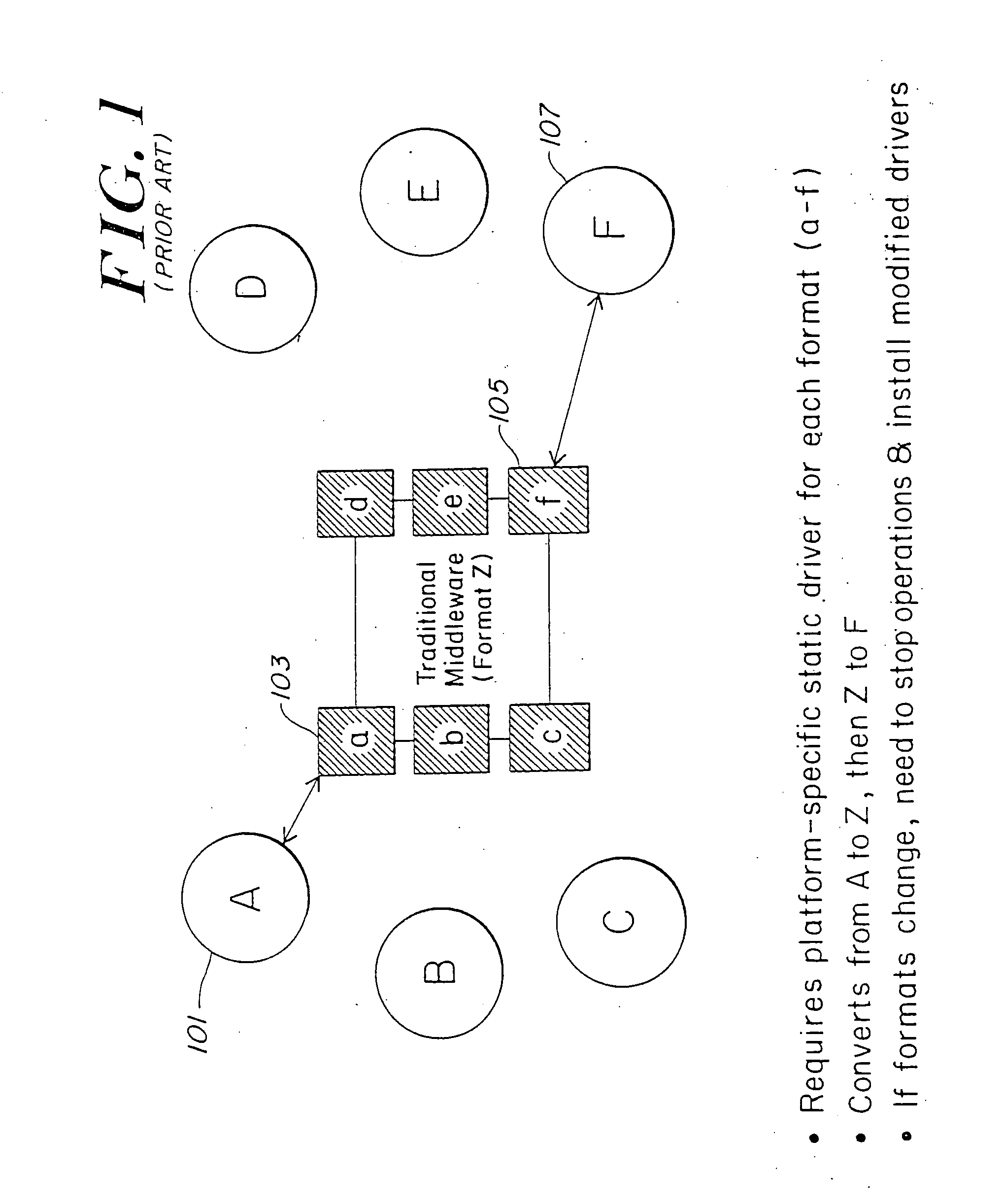

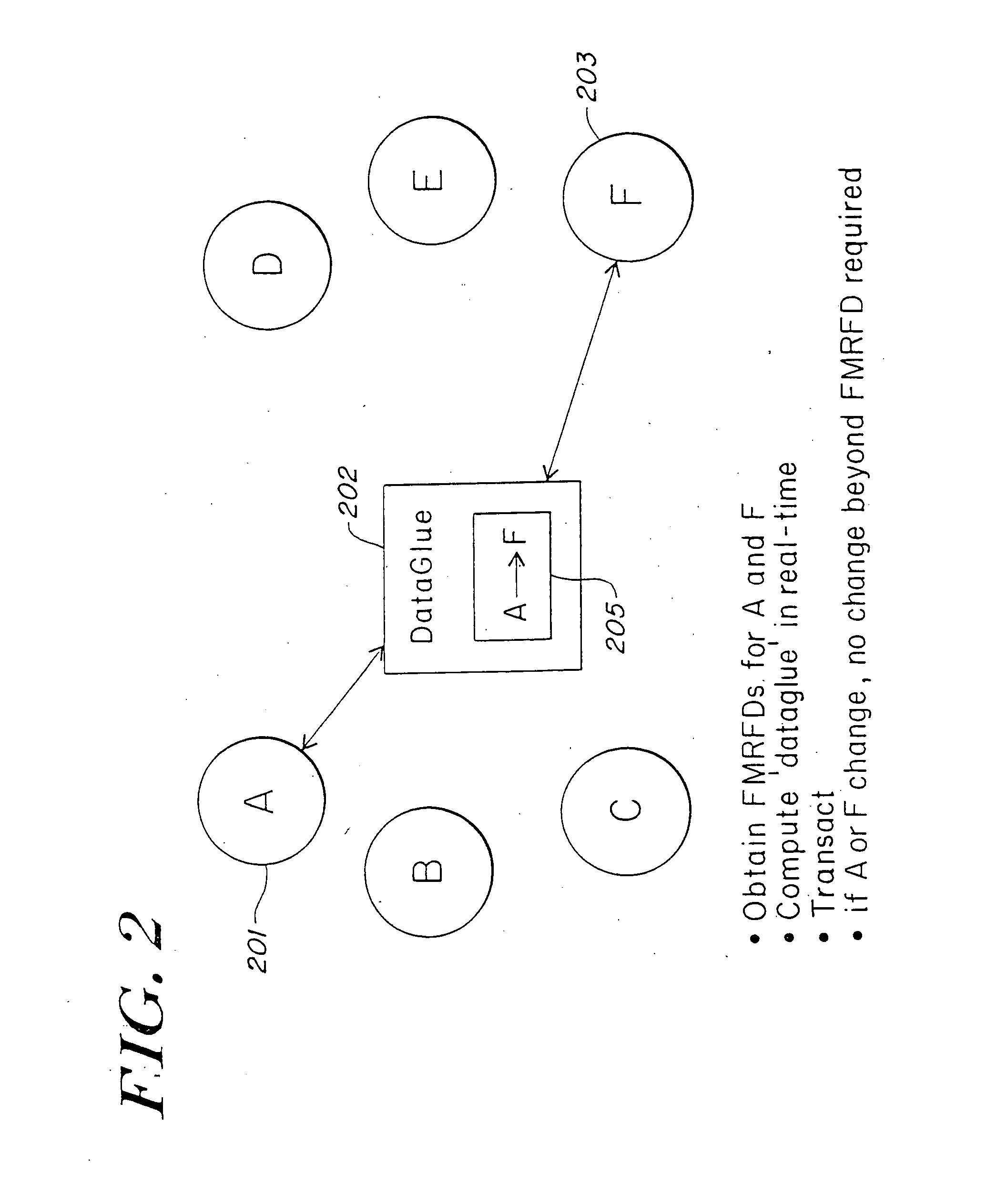

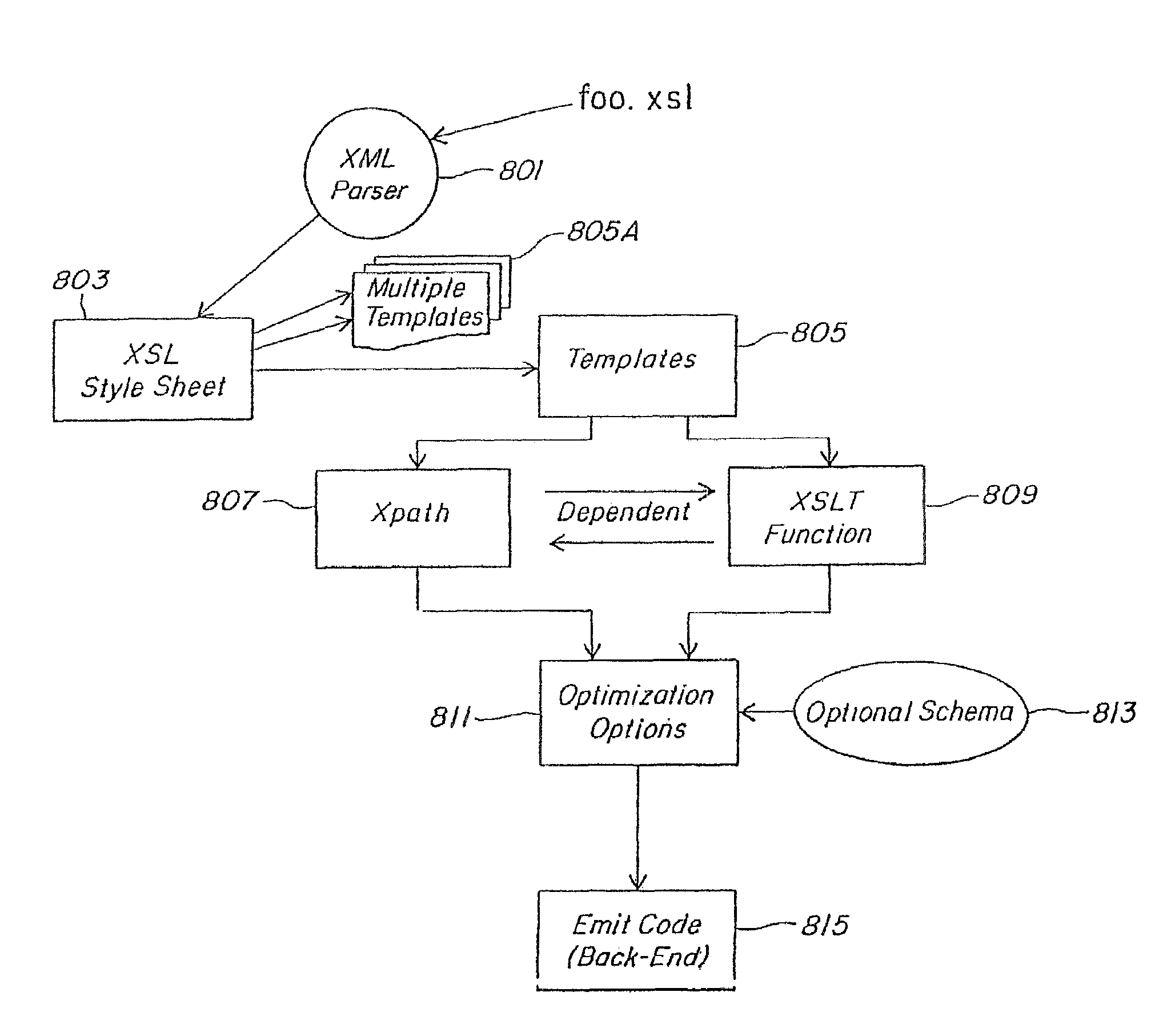

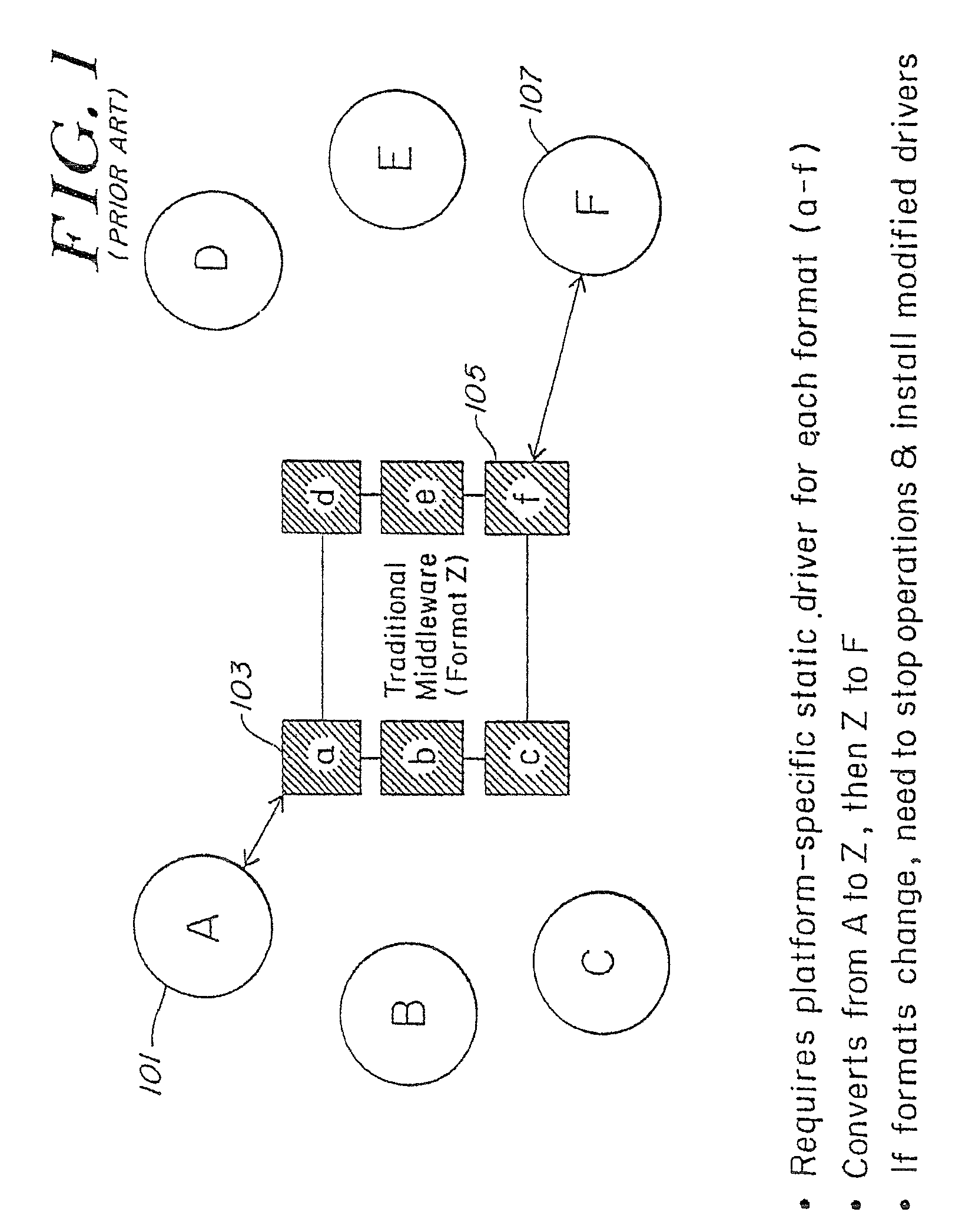

Method and apparatus of streaming data transformation using code generator and translator

InactiveUS20050273772A1Promote generationStay flexibleNatural language data processingMultiple digital computer combinationsStreaming dataObject code

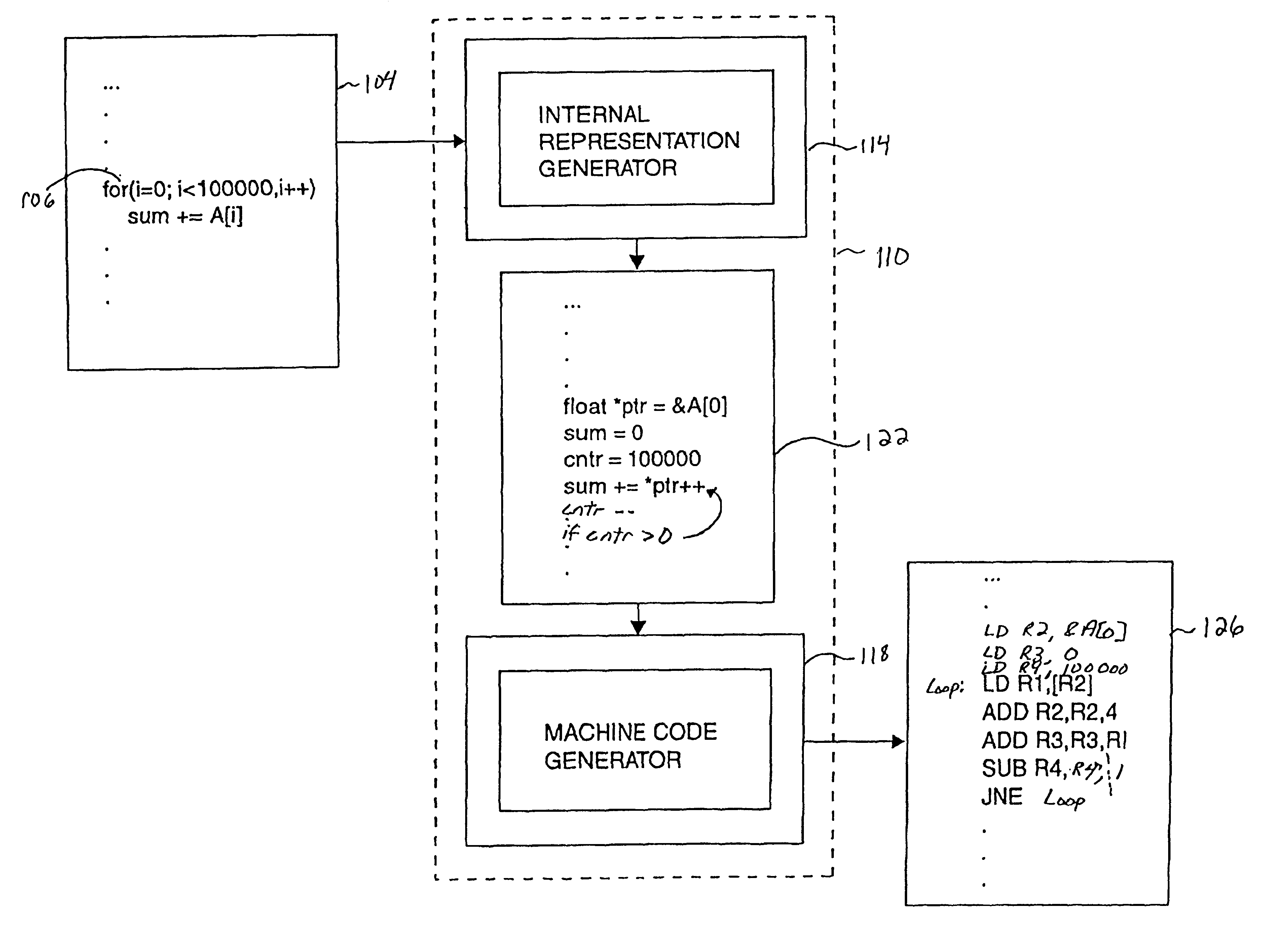

A high level transformation method and apparatus for converting data formats in the context of network applications, among other places. A flexible transformation mechanism is provided that facilitates generation of translation machine code. A translator is dynamically generated by a translator compiler engine. When fed an input stream, the translator generates an output stream by executing the native object code generated on the fly by the translator compiler engine. In addition, the translator may be configured to perform a bi-directional translation between the two streams as well as translation between two distinct protocol sequences. Further a translator may working in streaming mode, to facilitate streaming processing of documents.

Owner:IBM CORP

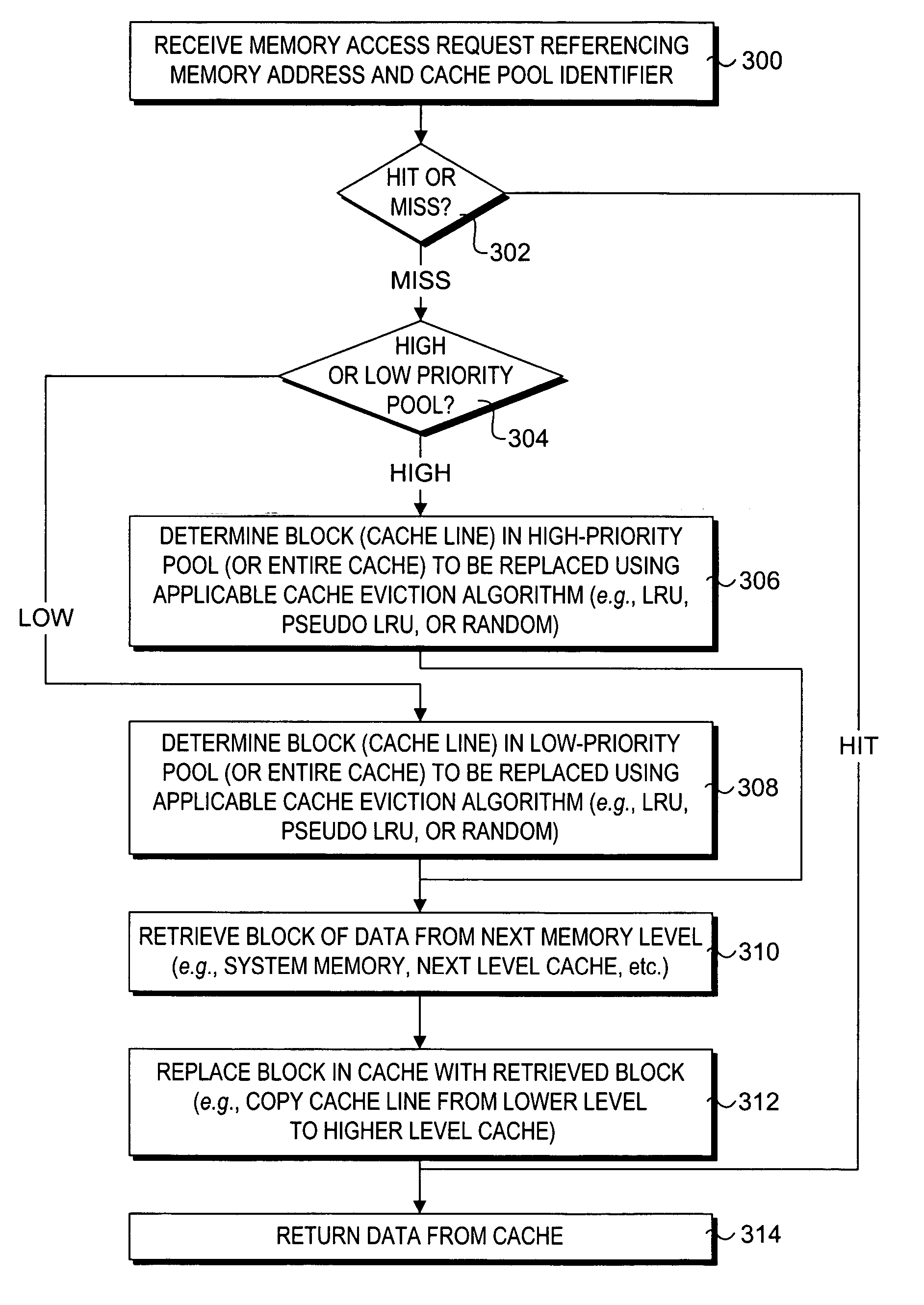

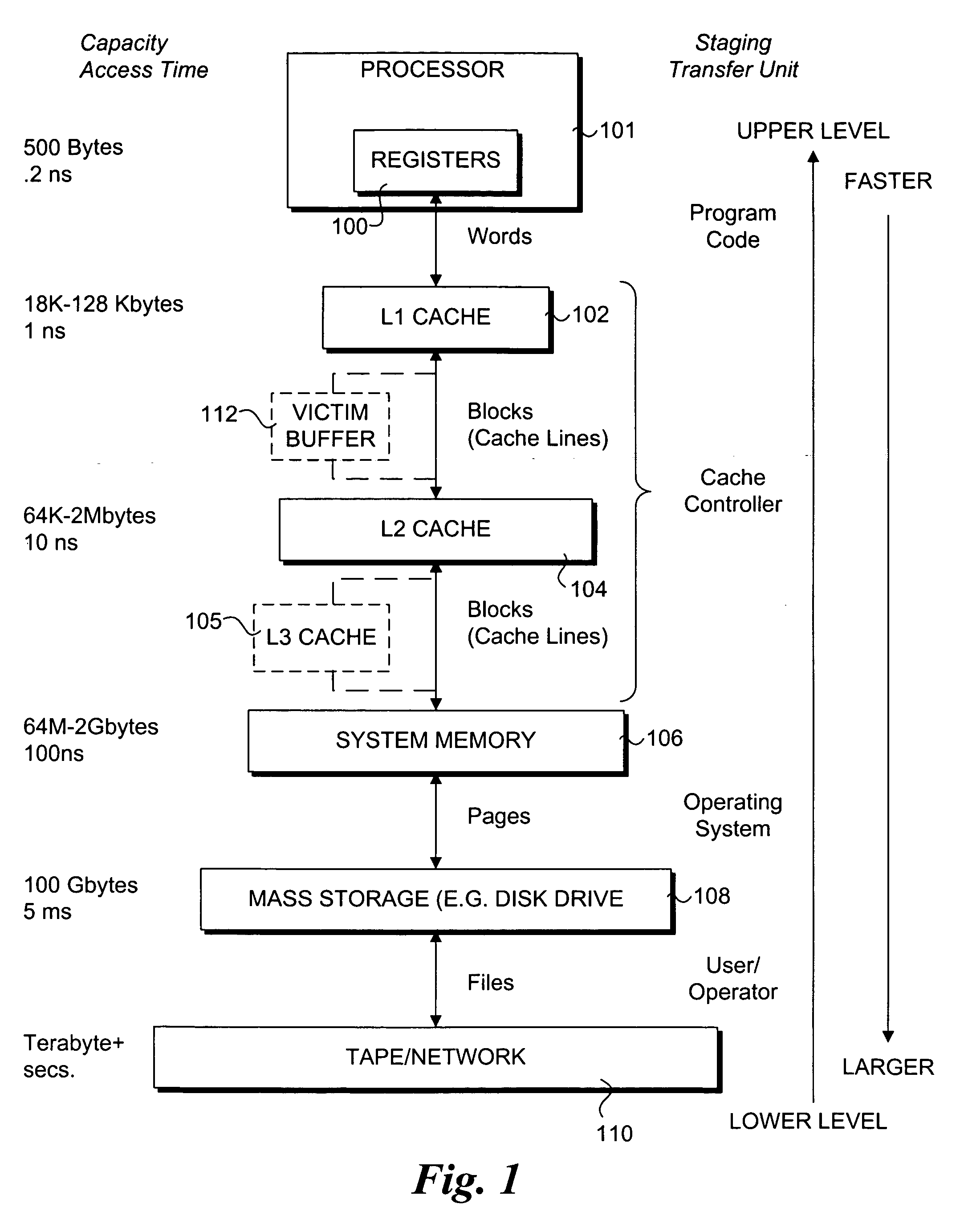

Method for programmer-controlled cache line eviction policy

A method and apparatus to enable programmatic control of cache line eviction policies. A mechanism is provided that enables programmers to mark portions of code with different cache priority levels based on anticipated or measured access patterns for those code portions. Corresponding cues to assist in effecting the cache eviction policies associated with given priority levels are embedded in machine code generated from source- and / or assembly-level code. Cache architectures are provided that partition cache space into multiple pools, each pool being assigned a different priority. In response to execution of a memory access instruction, an appropriate cache pool is selected and searched based on information contained in the instruction's cue. On a cache miss, a cache line is selected from that pool to be evicted using a cache eviction policy associated with the pool. Implementations of the mechanism or described for both n-way set associative caches and fully-associative caches.

Owner:INTEL CORP

Computer immune system and method for detecting unwanted code in a P-code or partially compiled native-code program executing within a virtual machine

InactiveUS7370360B2Memory loss protectionDigital data processing detailsComputerized systemBehaviour pattern

An automated analysis system identifies the presence of malicious P-code or N-code programs in a manner that limits the possibility of the malicious code infecting a target computer. The target computer system initializes an analytical virtual P-code engine (AVPE). As initialized, the AVPE comprises software simulating the functionality of a P-code or intermediate language engine as well as machine language facilities simulating the P-code library routines that allow the execution of N-code programs. The AVPE executes a target program so that the target program does not interact with the target computer. The AVPE analyzes the behavior of the target program to identify occurrence of malicious code behavior and to indicate in a behavior pattern the occurrence of malicious code behavior. The AVPE is terminated at the end of the analysis process, thereby removing from the computer system the copy of the target program that was contained within the AVPE.

Owner:PALO ALTO NETWORKS INC

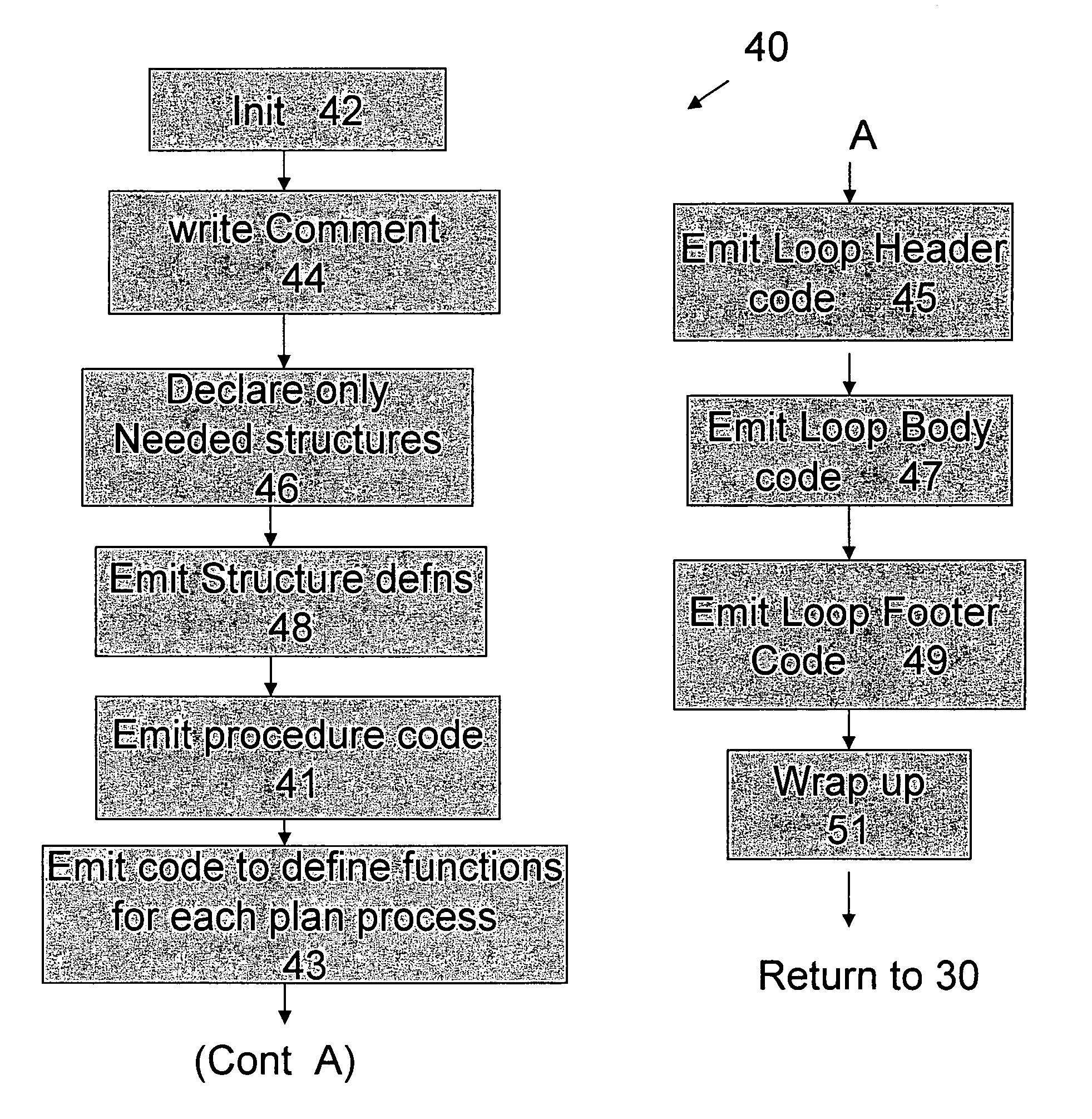

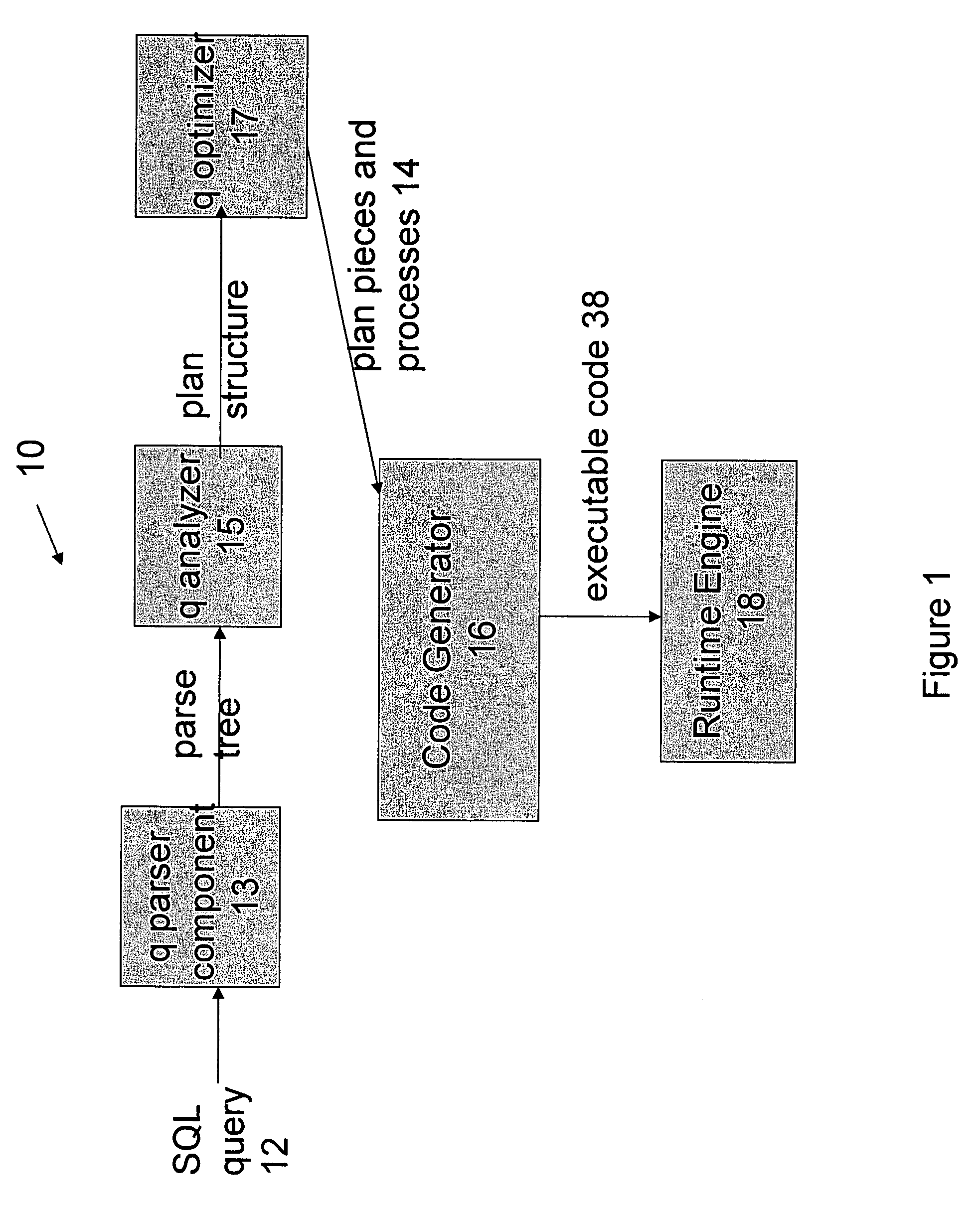

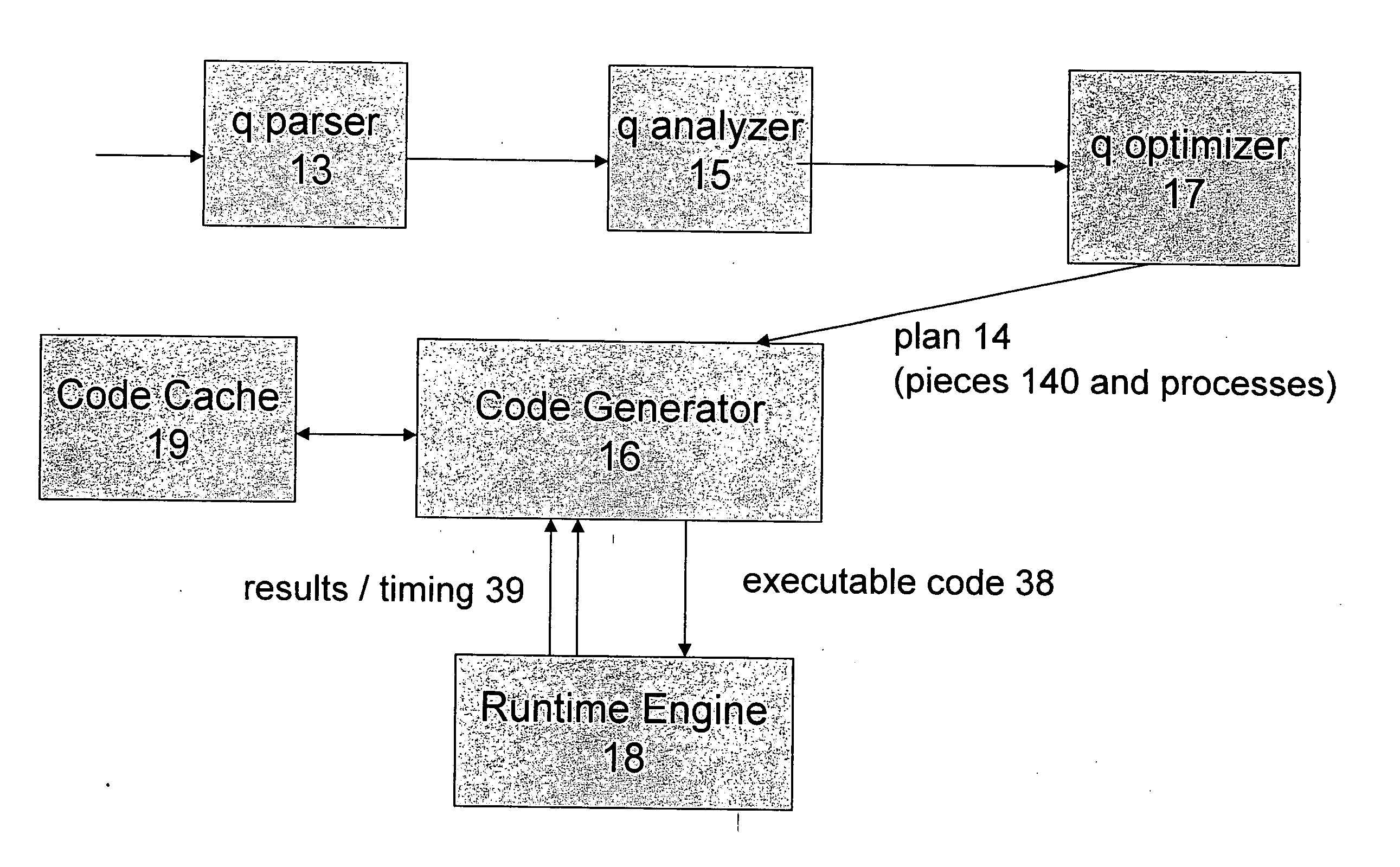

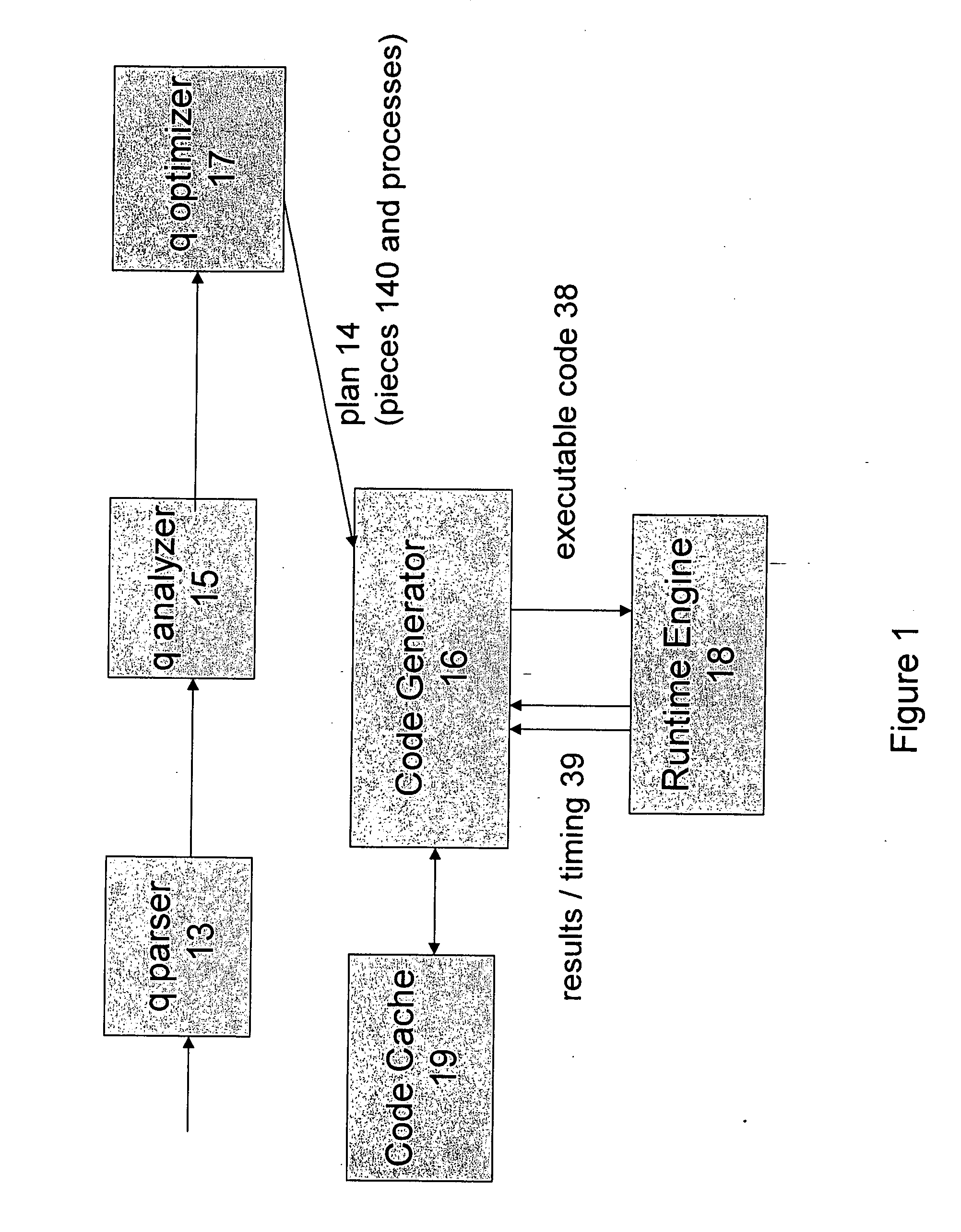

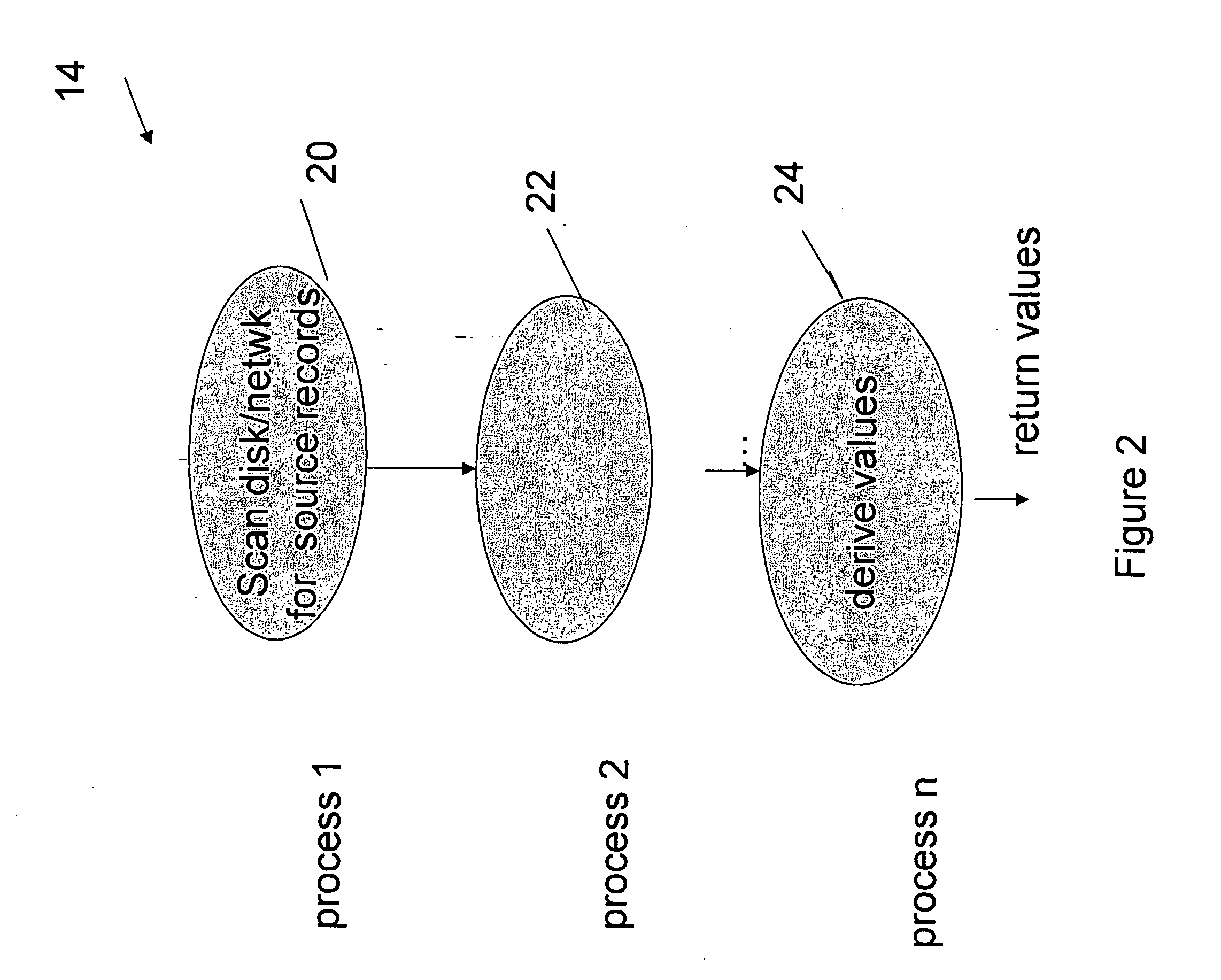

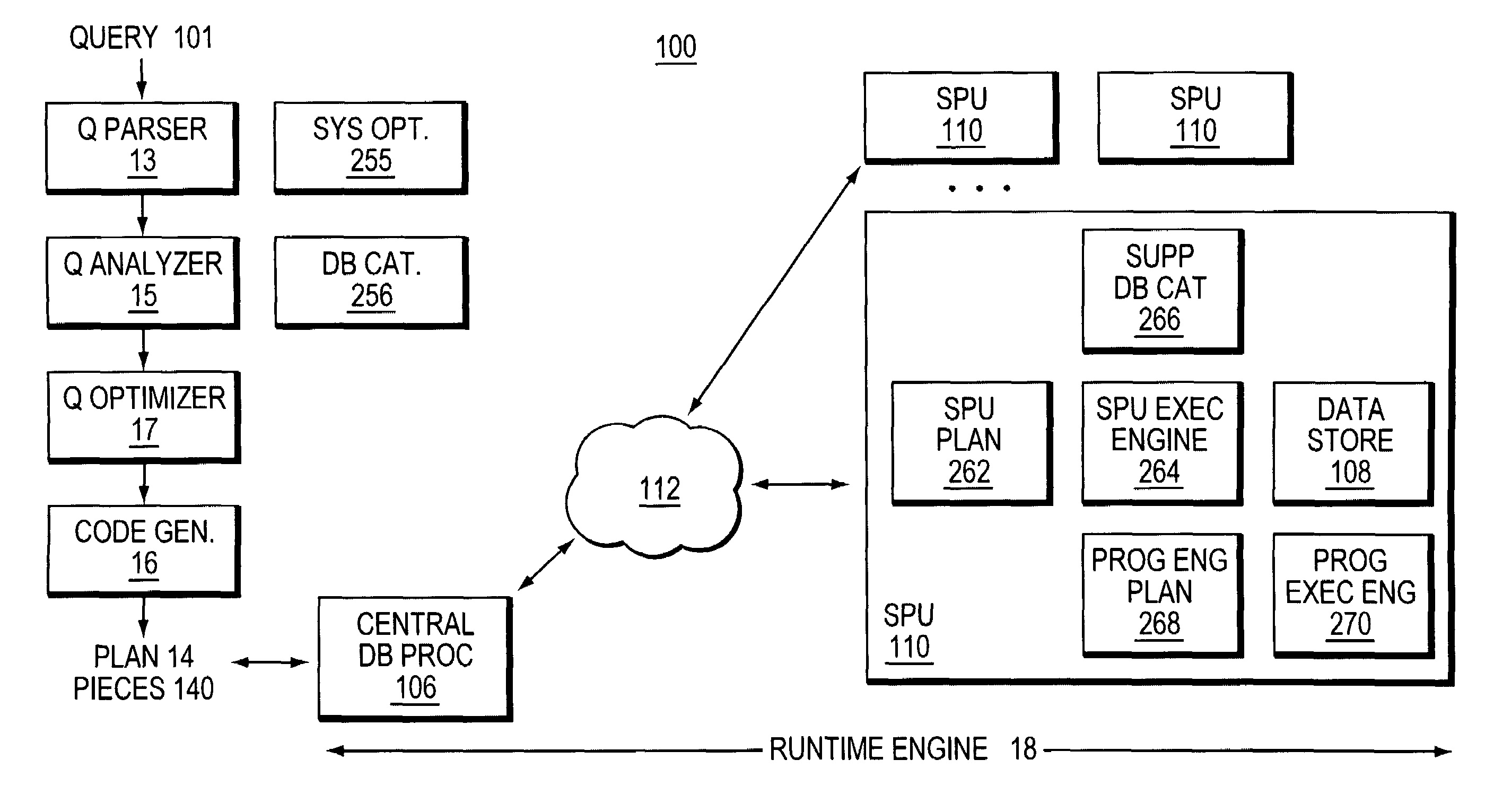

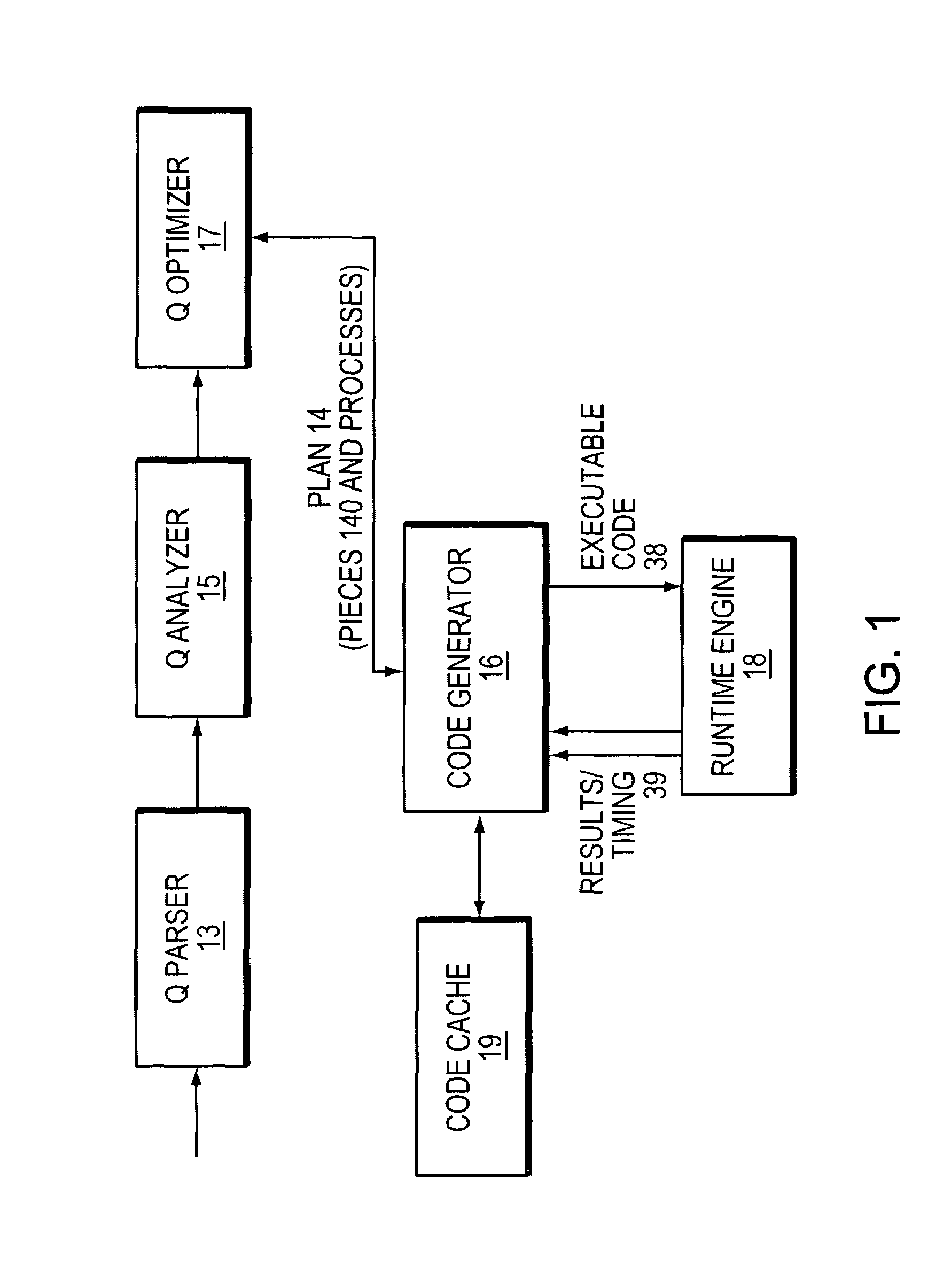

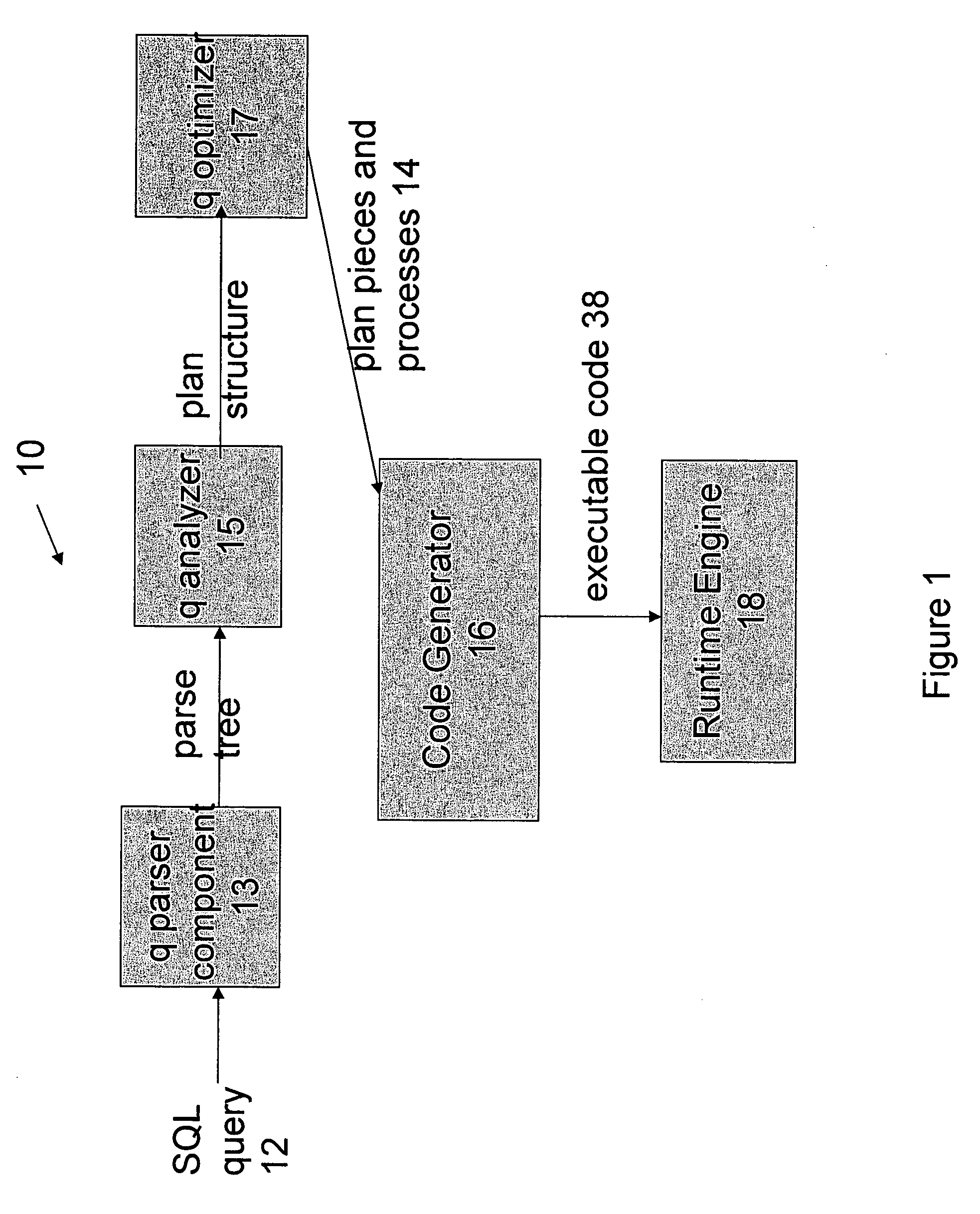

Optimized SQL code generation

ActiveUS7430549B2Reduce and minimize compilation timeReduce and minimize execution timeDigital data information retrievalData processing applicationsExecution planCode generation

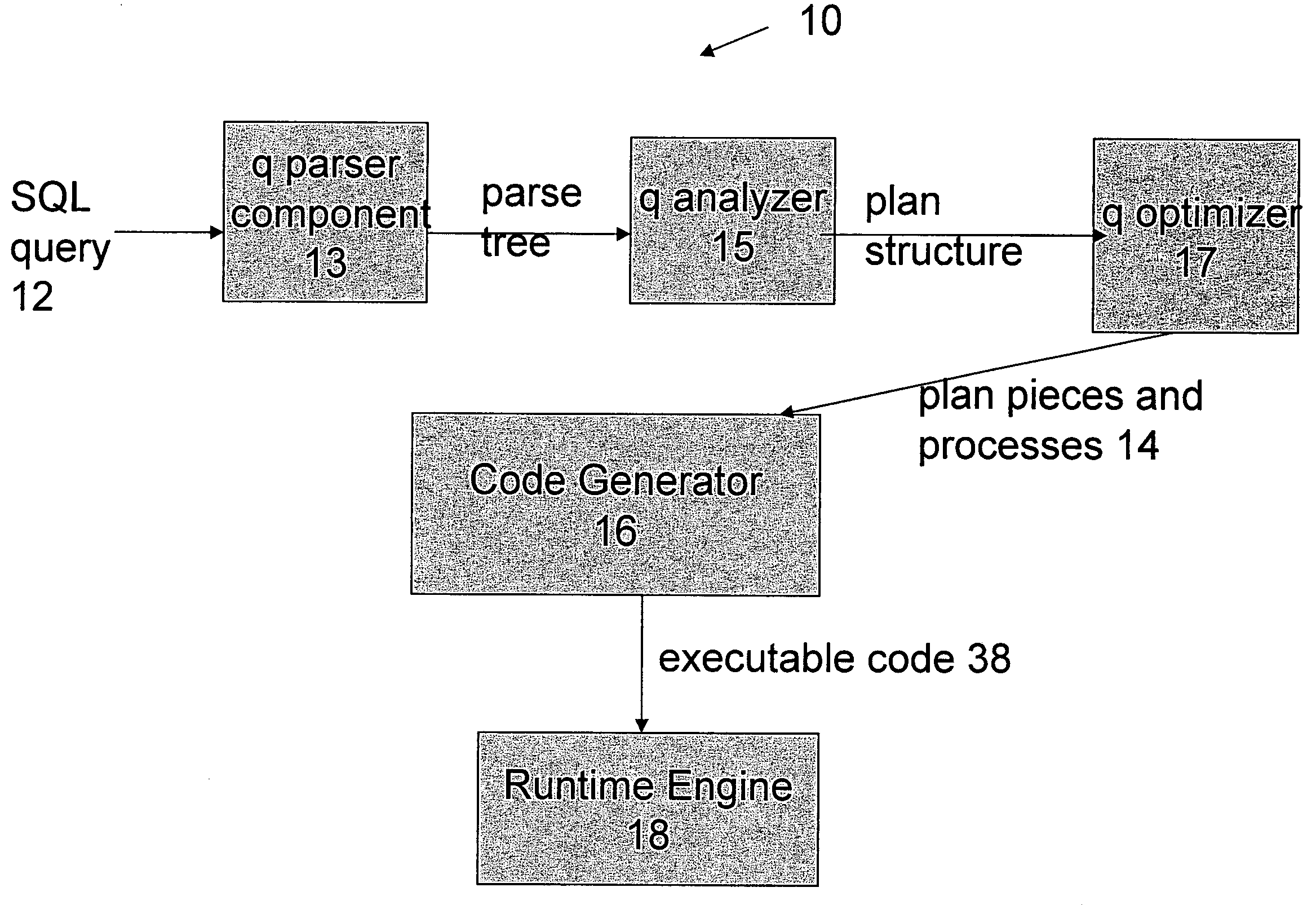

This invention relates generally to a system for processing database queries, and more particularly to a method for generating high level language or machine code to implement query execution plans. The present invention provides a method for generating executable machine code for query execution plans, that is adaptive to dynamic runtime conditions, that is compiled just in time for execution and most importantly, that avoids the bounds checking, pointer indirection, materialization and other similar kinds of overhead that are typical in interpretive runtime execution engines.

Owner:INT BUSINESS MASCH CORP

Method and apparatus of streaming data transformation using code generator and translator

InactiveUS7590644B2Promote generationStay flexibleDigital data processing detailsNatural language data processingStreaming dataObject code

A high level transformation method and apparatus for converting data formats in the context of network applications, among other places. A flexible transformation mechanism is provided that facilitates generation of translation machine code. A translator is dynamically generated by a translator compiler engine. When fed an input stream, the translator generates an output stream by executing the native object code generated on the fly by the translator compiler engine. In addition, the translator may be configured to perform a bi-directional translation between the two streams as well as translation between two distinct protocol sequences. Further a translator may working in streaming mode, to facilitate streaming processing of documents.

Owner:INT BUSINESS MASCH CORP

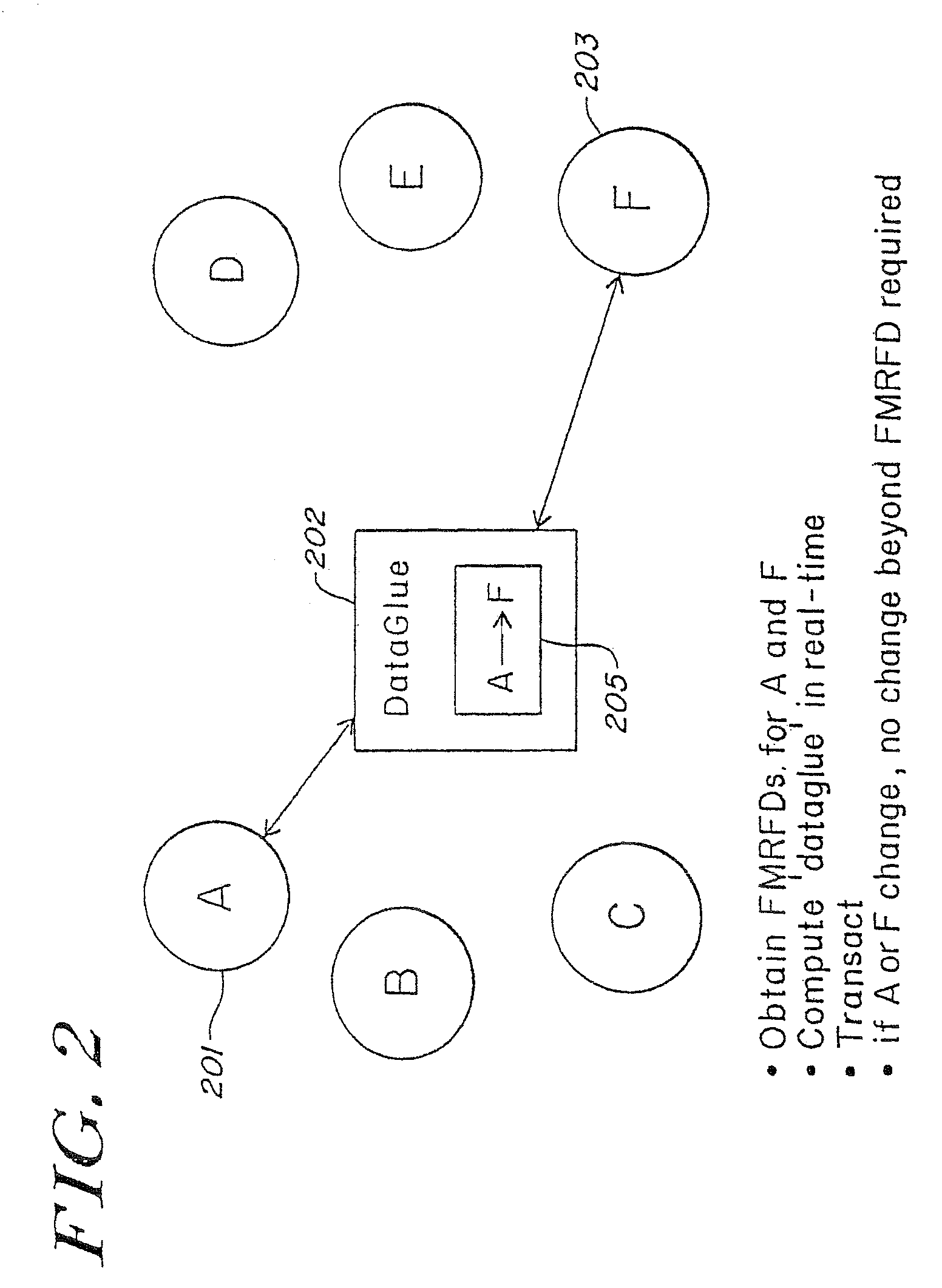

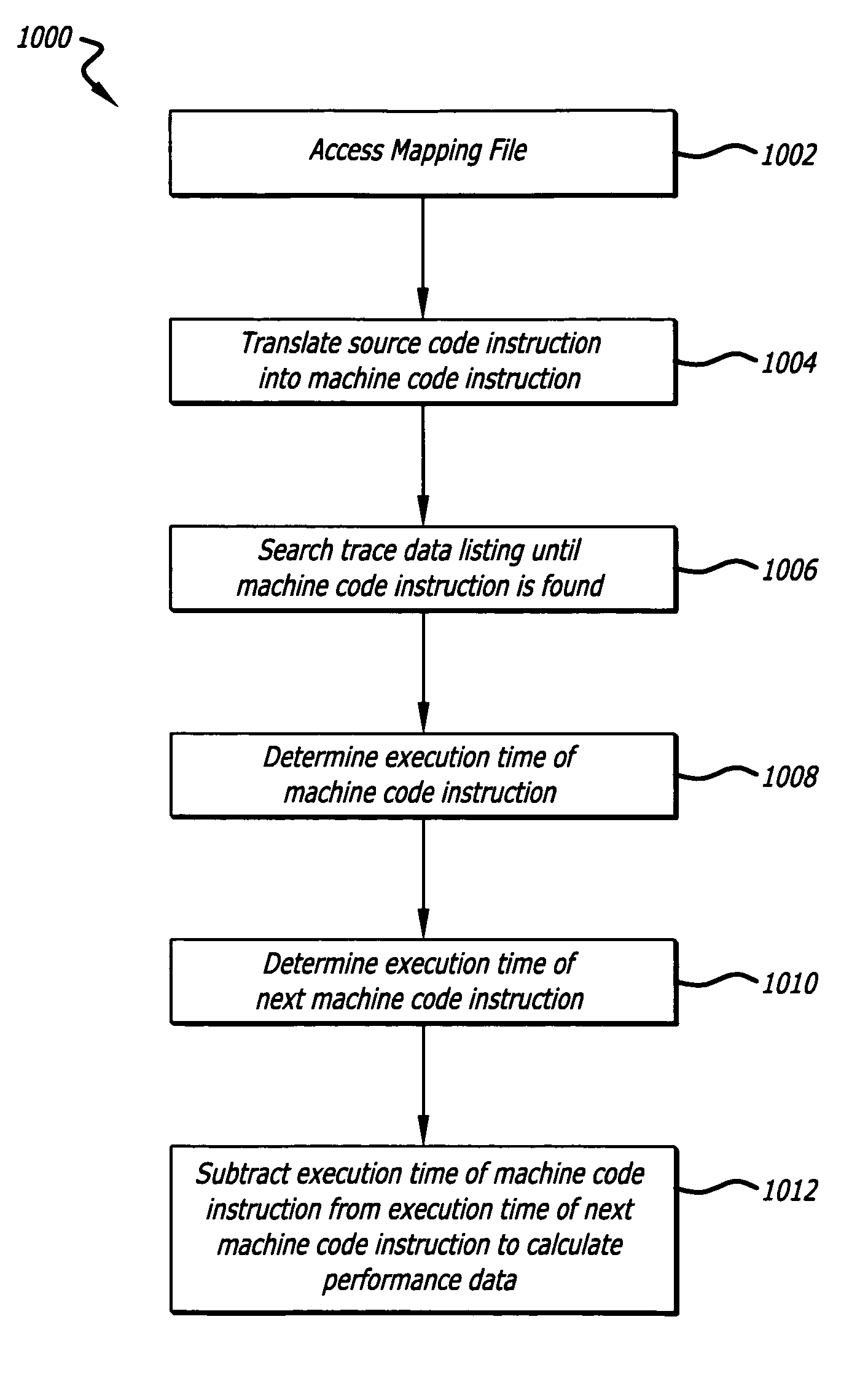

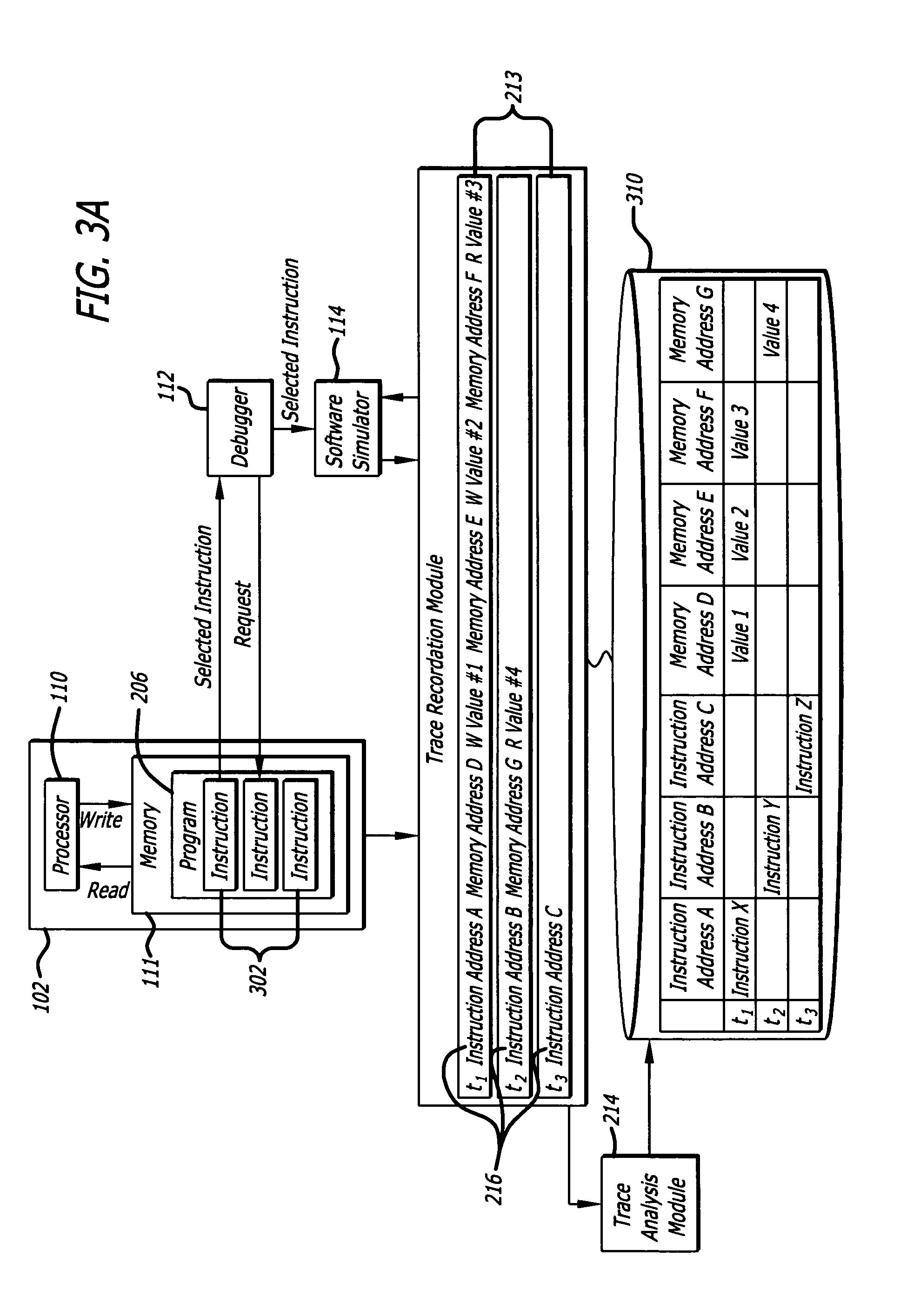

Post-execution software debugger with performance display

ActiveUS7653899B1Error detection/correctionSpecific program execution arrangementsParallel computingMachine instruction

A method for finding an error in a computer program is disclosed. A sequence of machine instructions performed by a processor is recorded as trace data. A mapping file is accessed. A source code instruction is translated into a machine code instruction according to a mapping found in the mapping file. Further, at least a portion of the trace data is searched through until the machine code instruction is found. In addition, a first execution time of the machine code instruction is determined by reviewing the trace data in a first vicinity that an address of the machine code instruction is located. Further, a second execution time of the next machine code instruction is determined by reviewing the trace data in a second vicinity that an address of the next machine code instruction is located. Accordingly, performance data is calculated by subtracting the first execution time from the second execution time. The performance data is displayed.

Owner:GREEN HILLS SOFTWARE

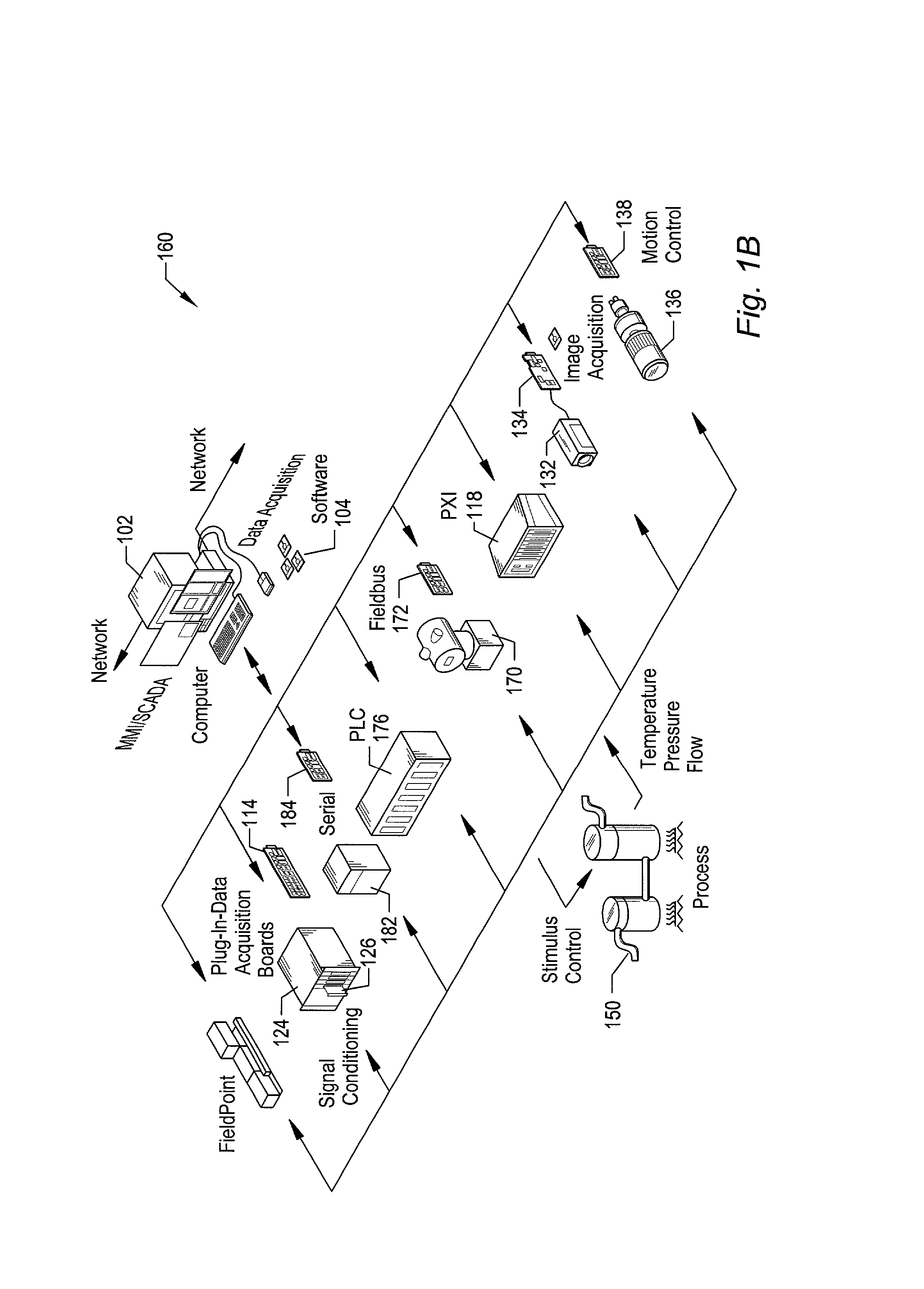

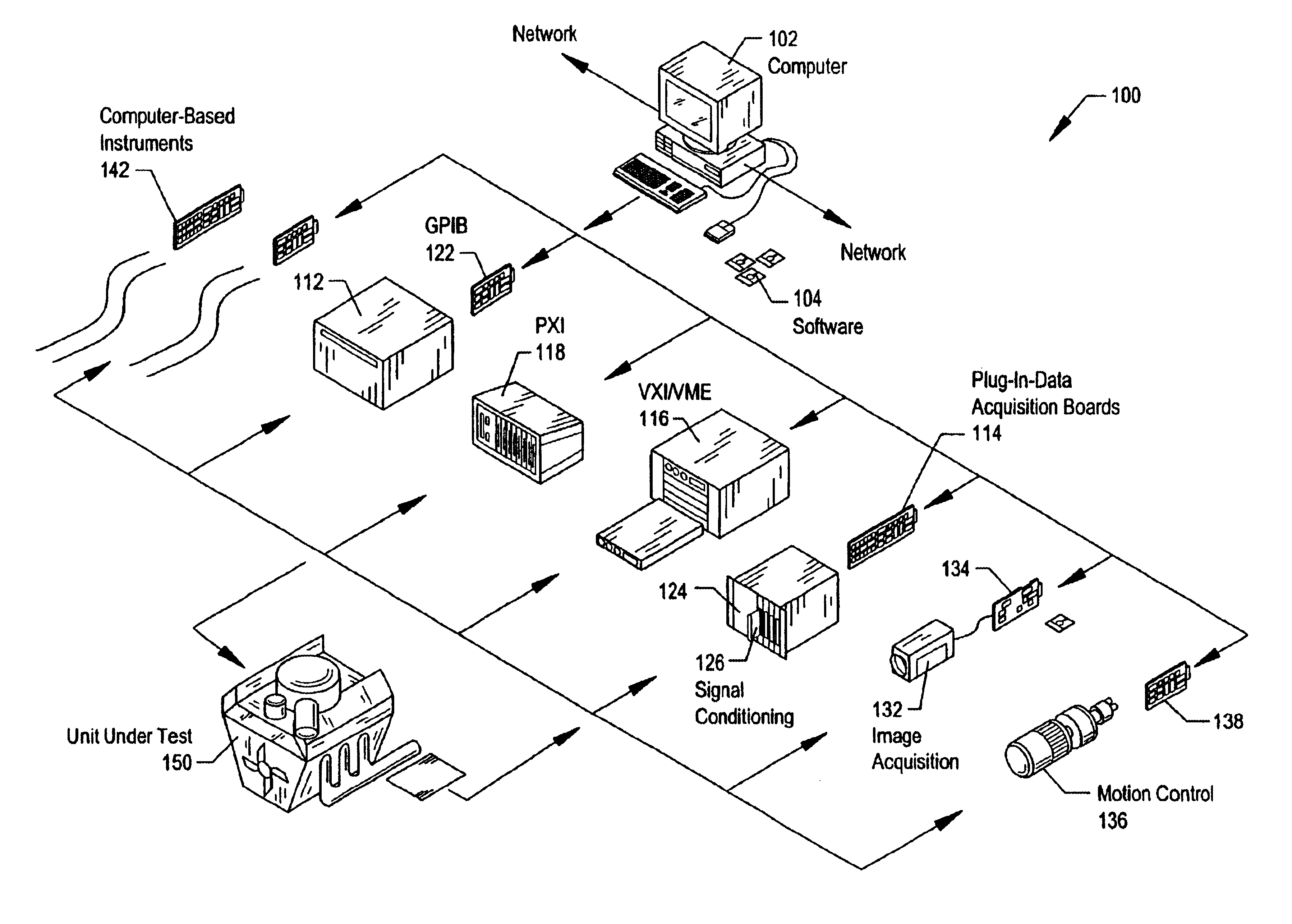

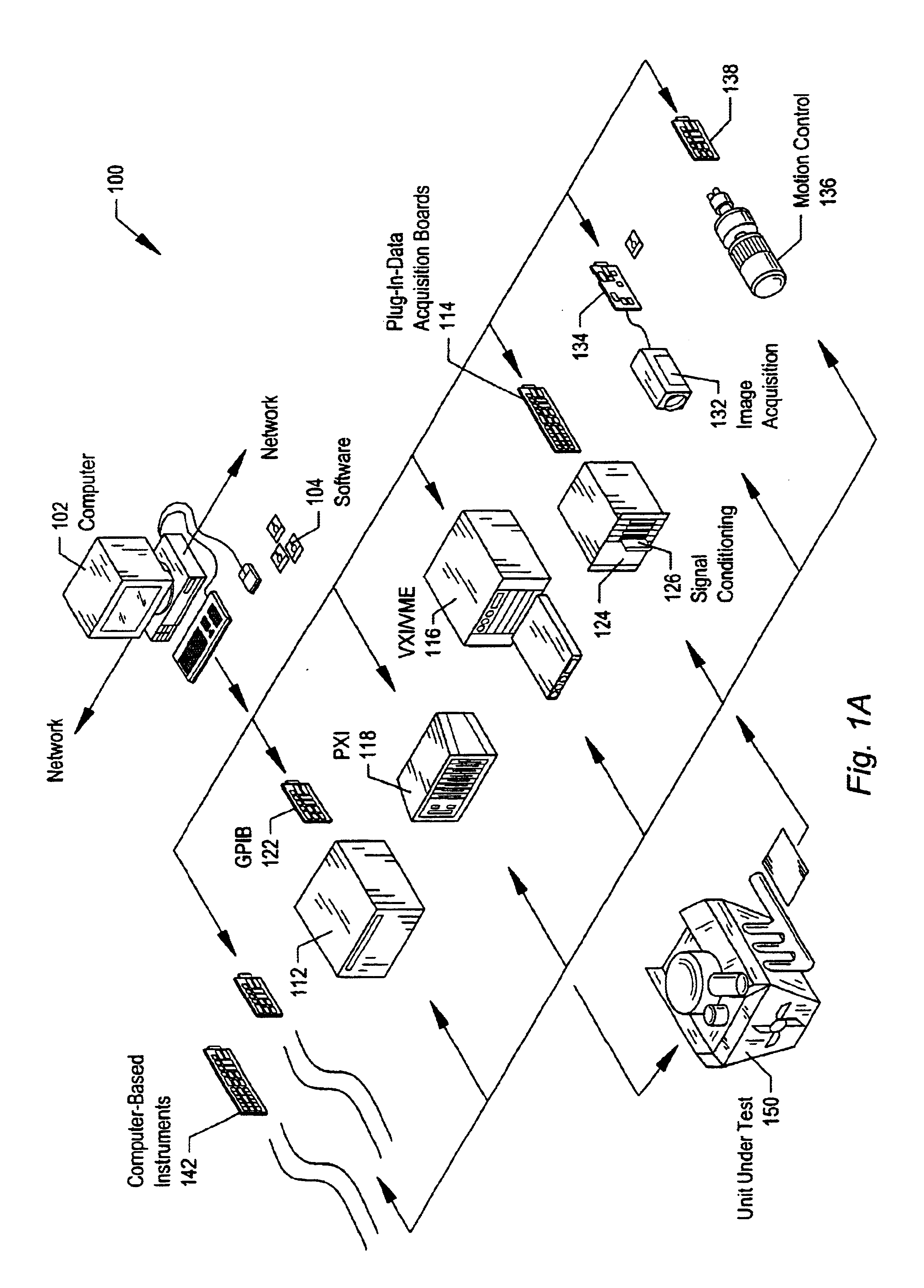

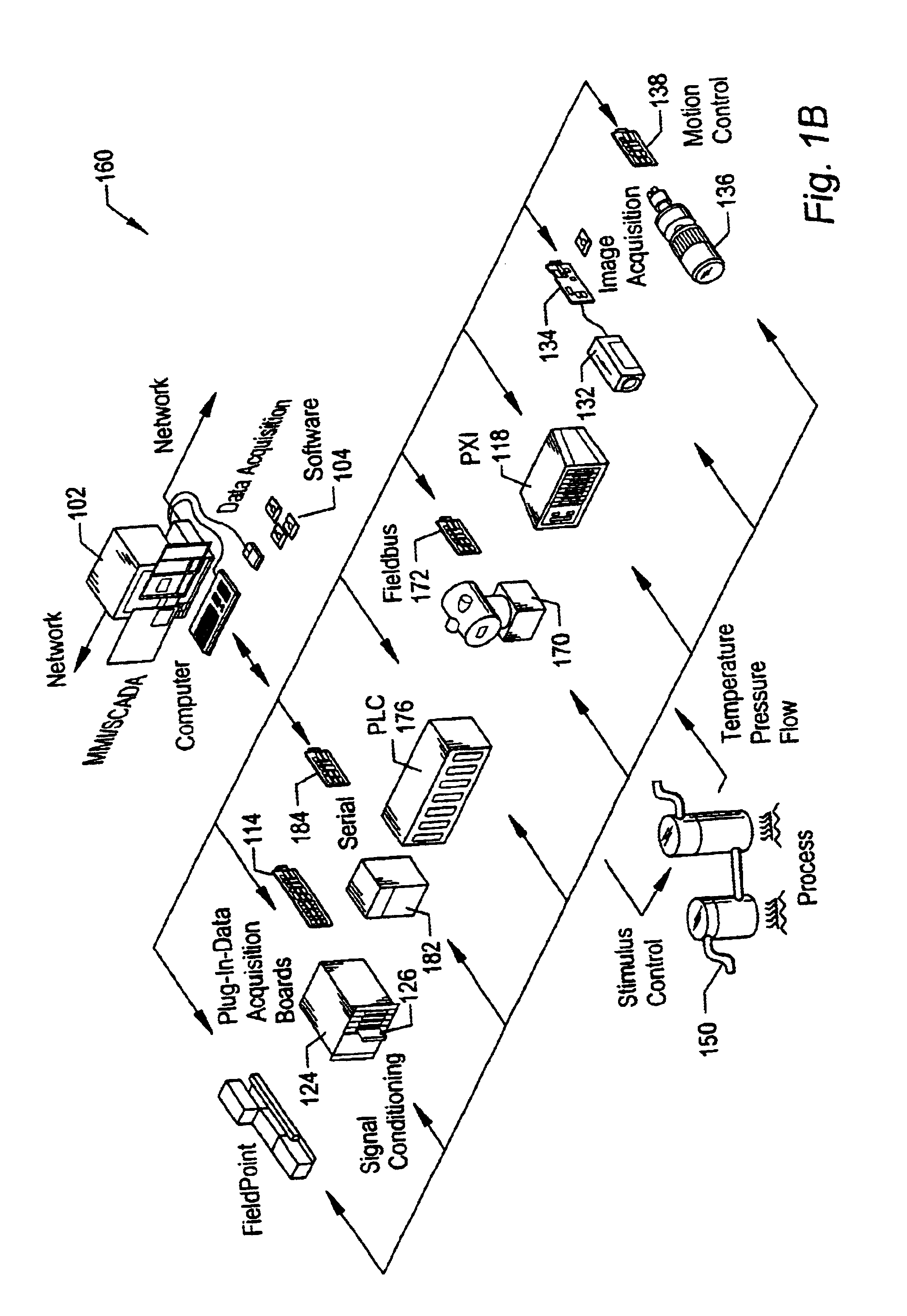

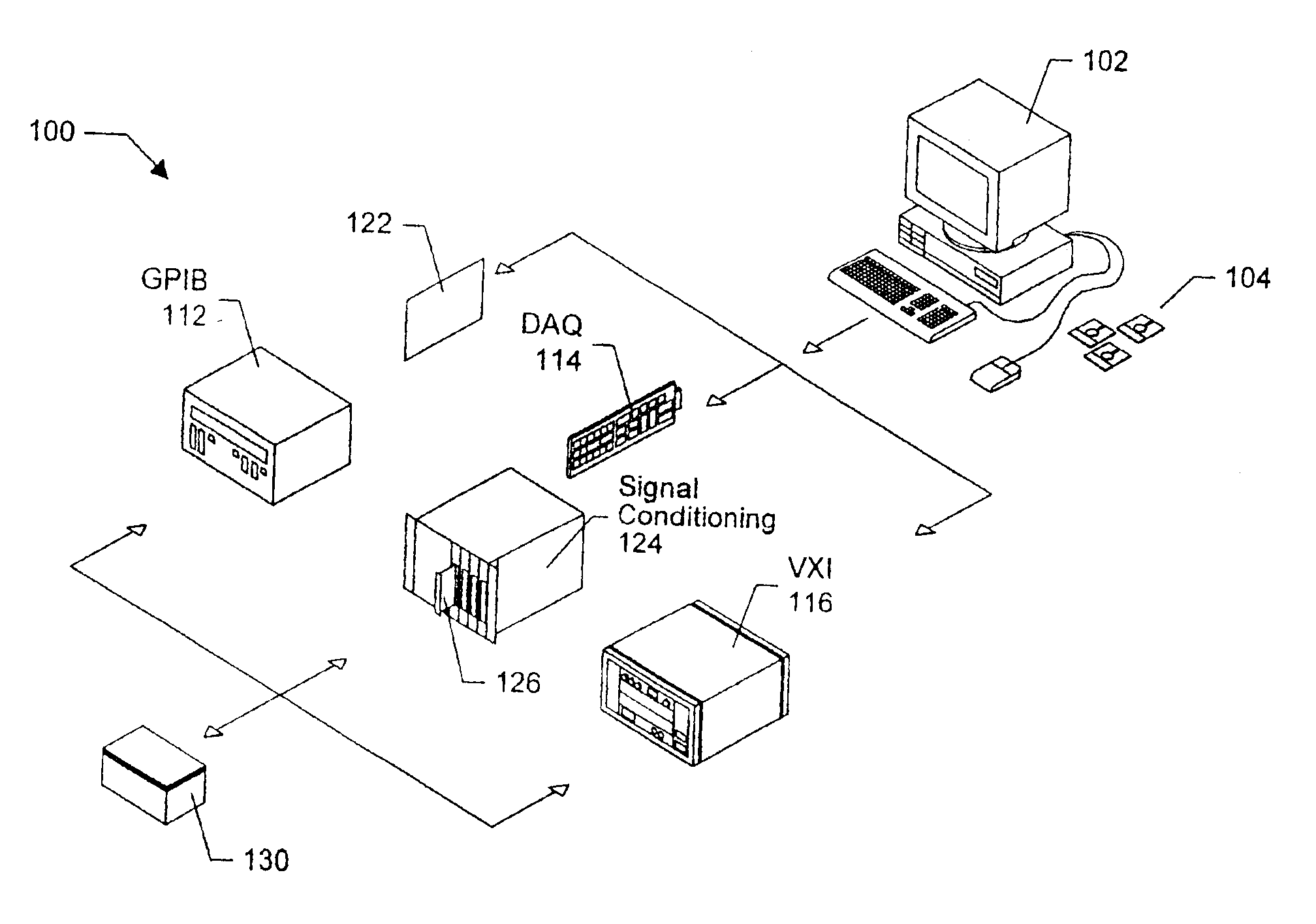

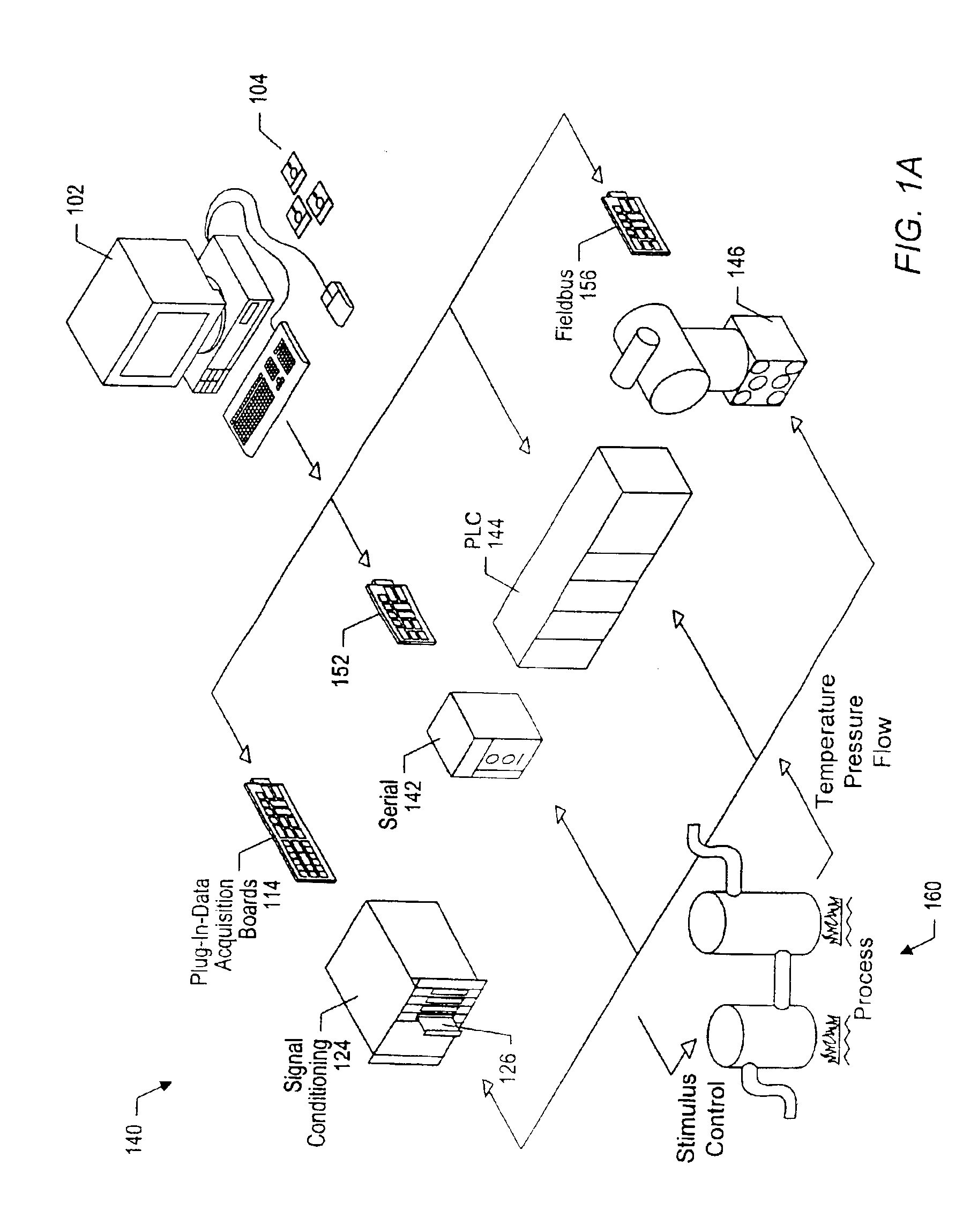

System and method for configuring an instrument to perform measurement functions utilizing conversion of graphical programs into hardware implementations

InactiveUS20020080174A1Detecting faulty hardware by remote testCathode-ray tube indicatorsGraphicsComputer hardware

A computer-implemented system and method for generating a hardware implementation of graphical code. The method may operate to configure an instrument to perform measurement functions, wherein the instrument includes a programmable hardware element. The method comprises first creating a graphical program, wherein the graphical program may implement a measurement function. A portion of the graphical program may be converted into a hardware implementation on a programmable hardware element, and a portion may optionally be compiled into machine code for execution by a CPU. The programmable hardware element is thus configured utilizing a hardware description and implements a hardware implementation of at least a portion of the graphical program.

Owner:NATIONAL INSTRUMENTS

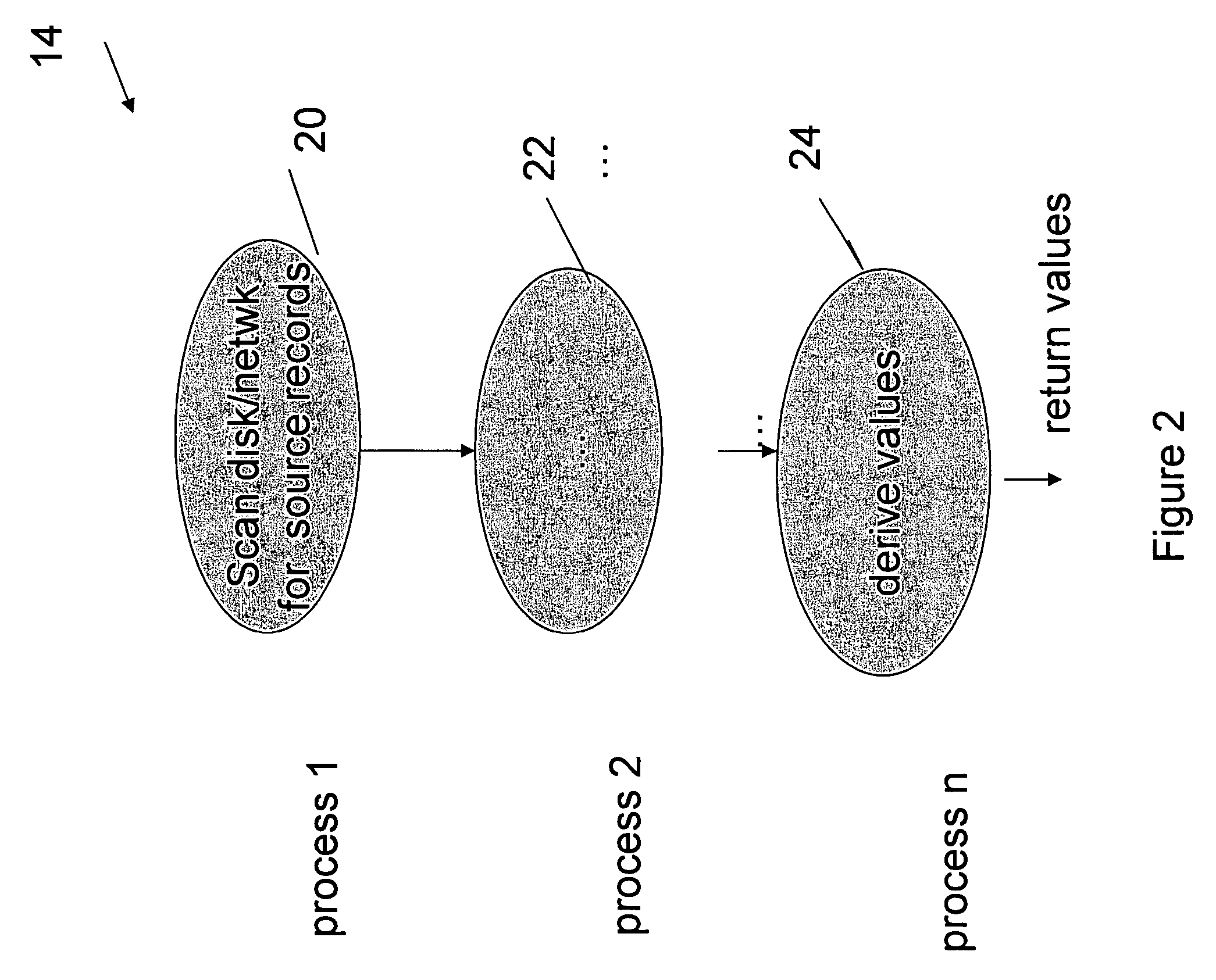

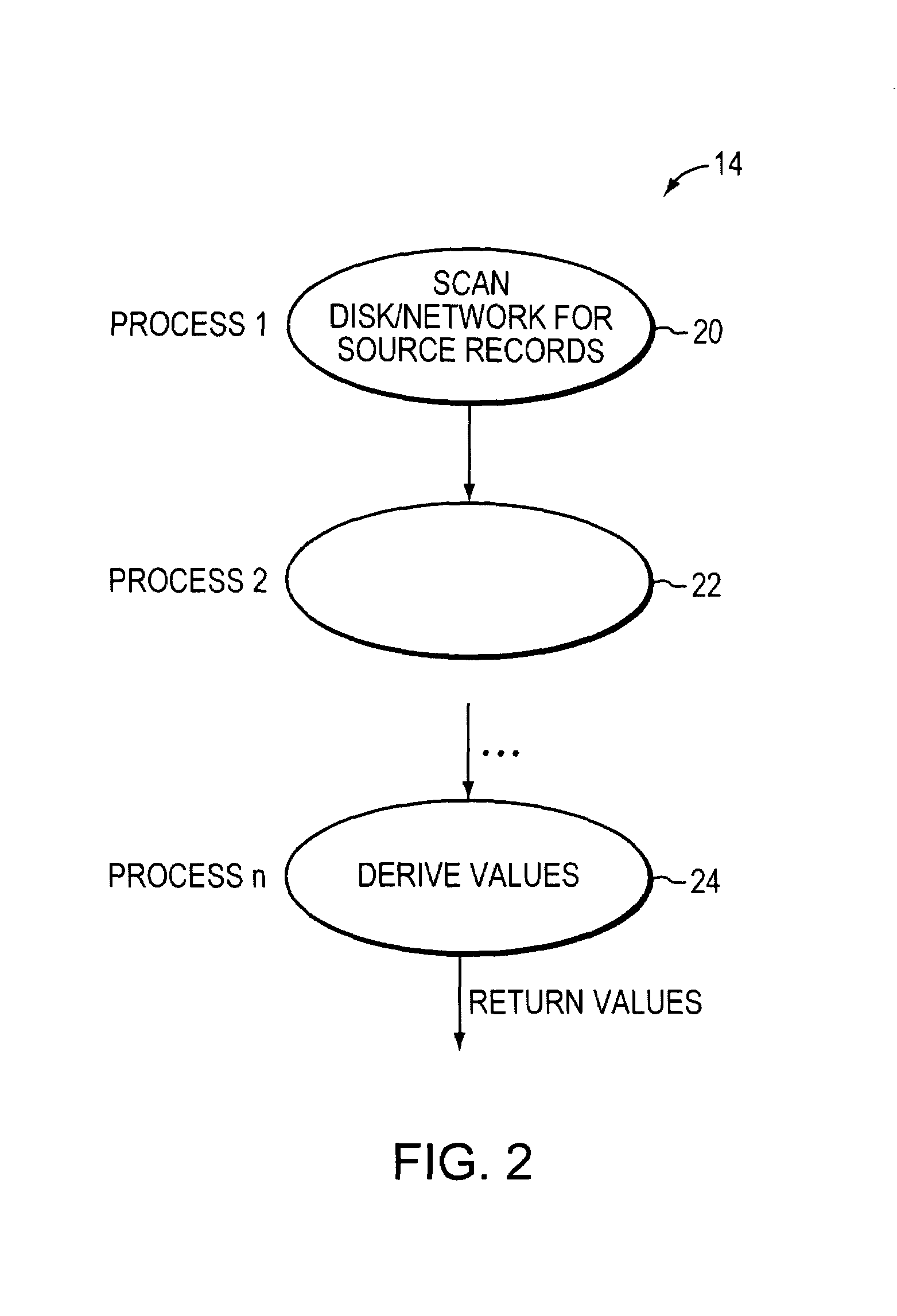

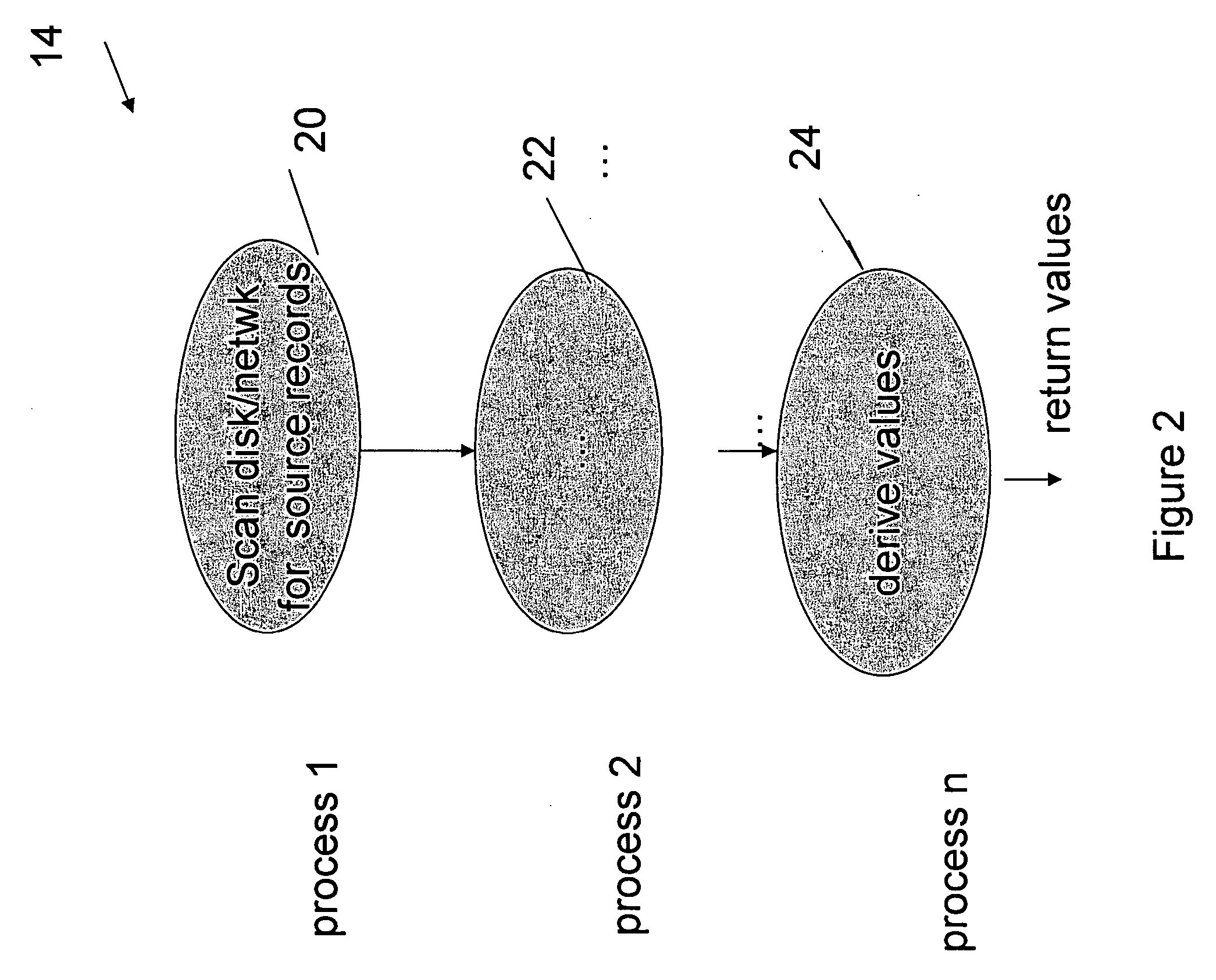

SQL code generation for heterogeneous environment

ActiveUS20050028134A1Avoiding runtime interpretationAnalysis latencyData processing applicationsDigital data information retrievalDatabase queryExecution plan

This invention relates generally to a system for processing database queries, and more particularly to a method for generating high level language or machine code to implement query execution plans. In one preferred embodiment, the method begins by receiving a subject query, and then forming an execution plan corresponding to the subject query. The execution plan will typically have a sequence of component snippets or pieces and corresponding processes for implementing the pieces. For at least one piece in the plan, the process then (a) generates source code using different code generation techniques as a function of expected runtime processing machine types; and then (b) compiles the generated source code to form machine executable code for implementing the subject query. As a result, the query executed directly as machine executable code thereby avoiding runtime interpretation of the pieces in the execution plan.

Owner:IBM CORP

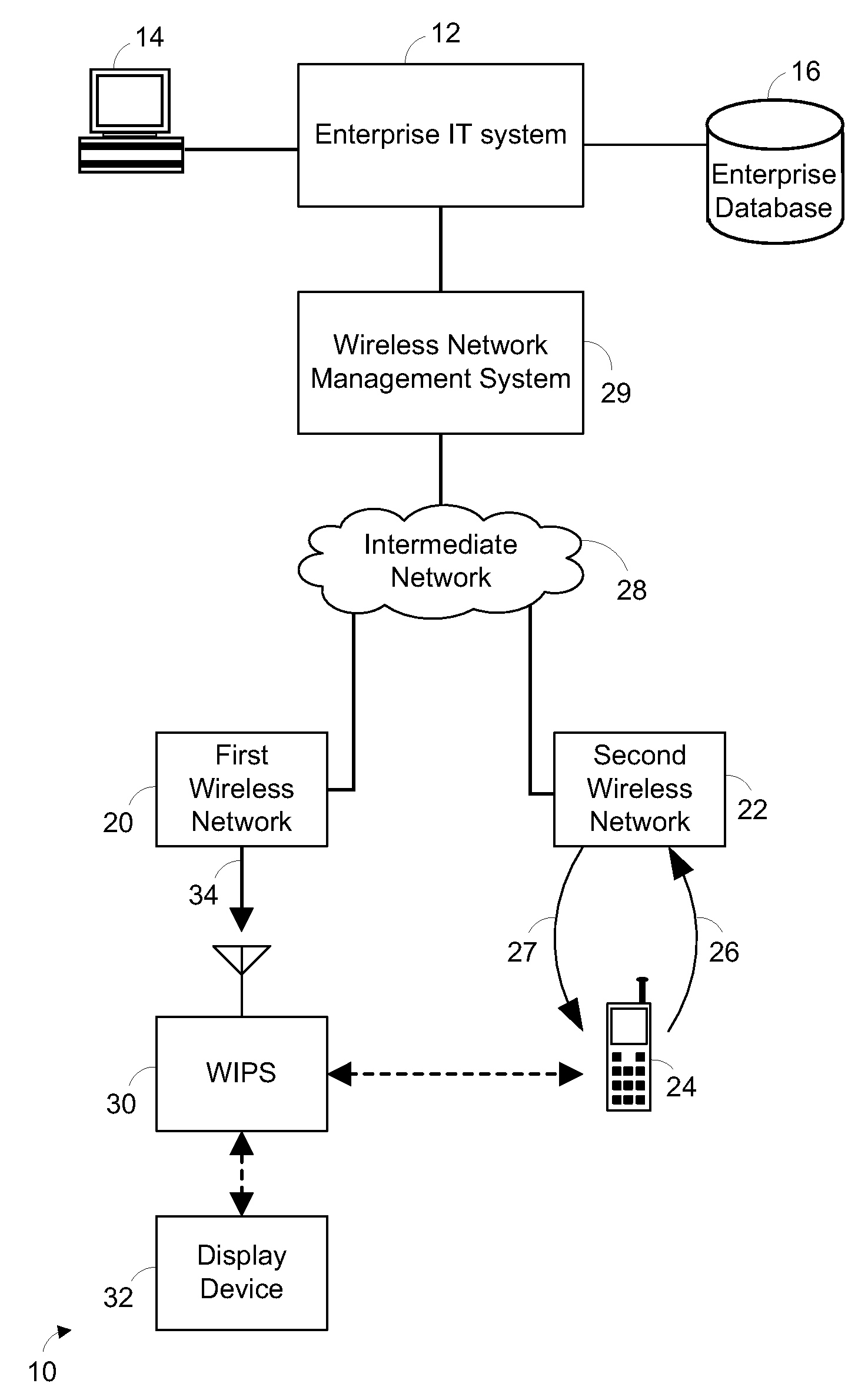

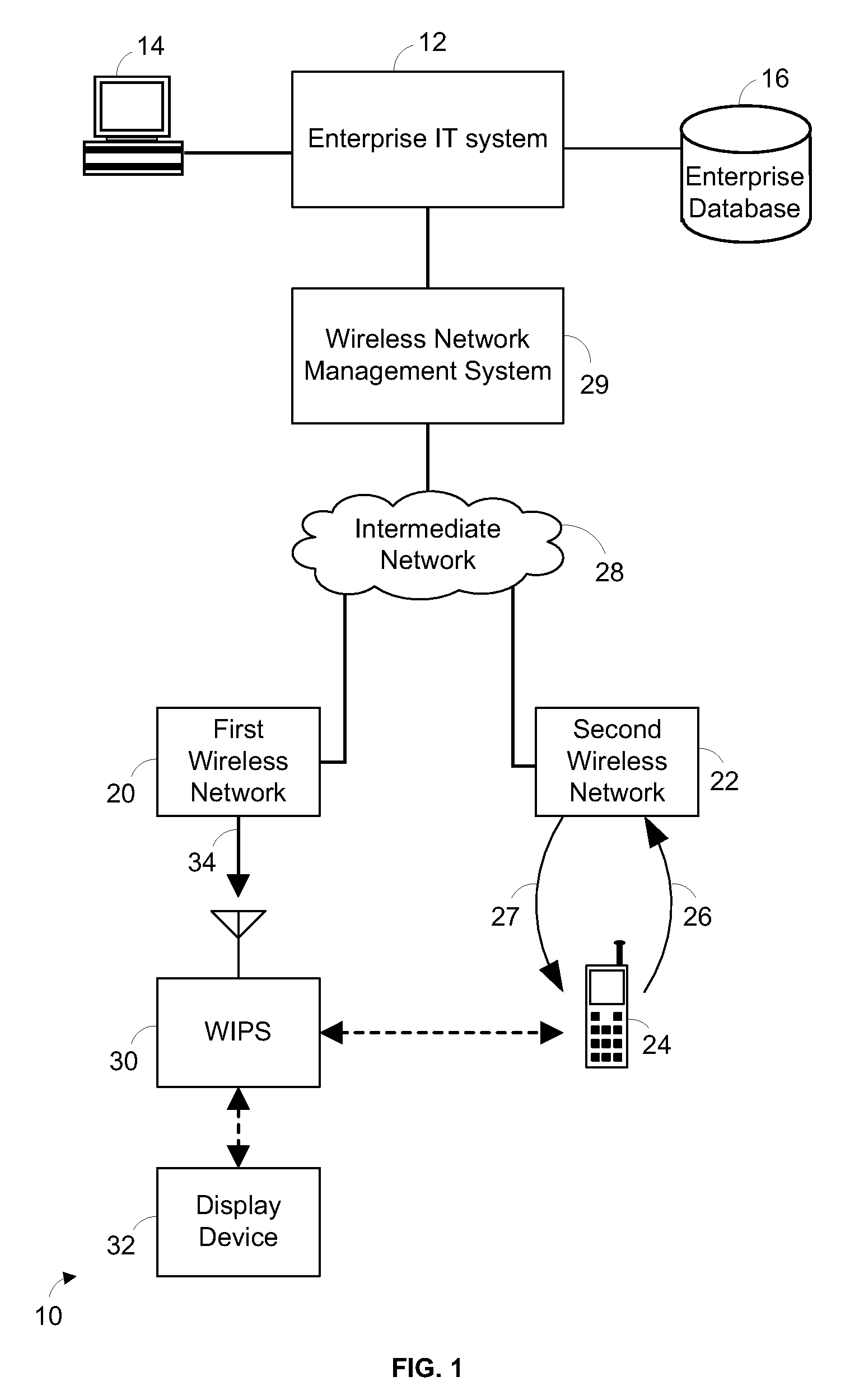

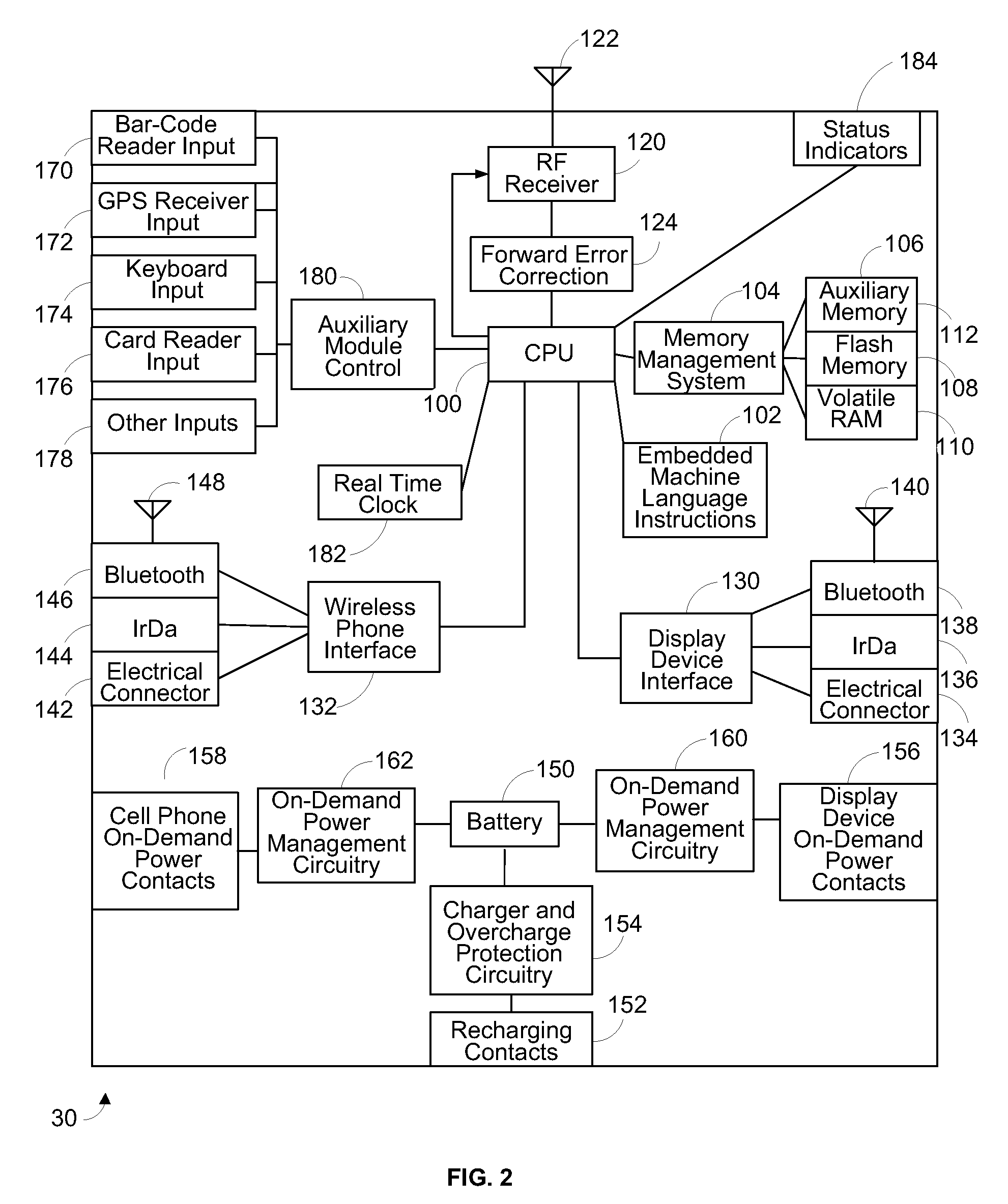

Wireless intelligent personal server

InactiveUS7149511B1Multiple digital computer combinationsRadio/inductive link selection arrangementsDisplay deviceRadio frequency

A wireless intelligent personal server includes a radio frequency (RF) receiver, a memory for storing electronic files, a set of embedded machine language instructions, a central processing unit (CPU), a first interface for a display device, such as a personal digital assistant (PDA), and a second interface for a wireless telephone. The RF receiver receives downstream data transmitted over a downstream wireless communications channel. The CPU executes the machine language instructions to process the downstream data and, thereby, either update an existing target electronic file stored in the memory, so that the target electronic file reflects changes made to a source electronic file, or create a new electronic file in the memory. A display device may be brought into communication with the wireless intelligent personal server, via the first interface, to access the electronic files stored in the memory. The wireless intelligent personal server may also transmit an upstream signal over an upstream wireless communication channel, such as by using a wireless telephone, in communication via the second interface. The upstream signal may acknowledge receipt of the downstream data, or it may include upstream data reflecting changes to the electronic files stored in the memory made by the display device.

Owner:DOUBLE TIME CORP +1

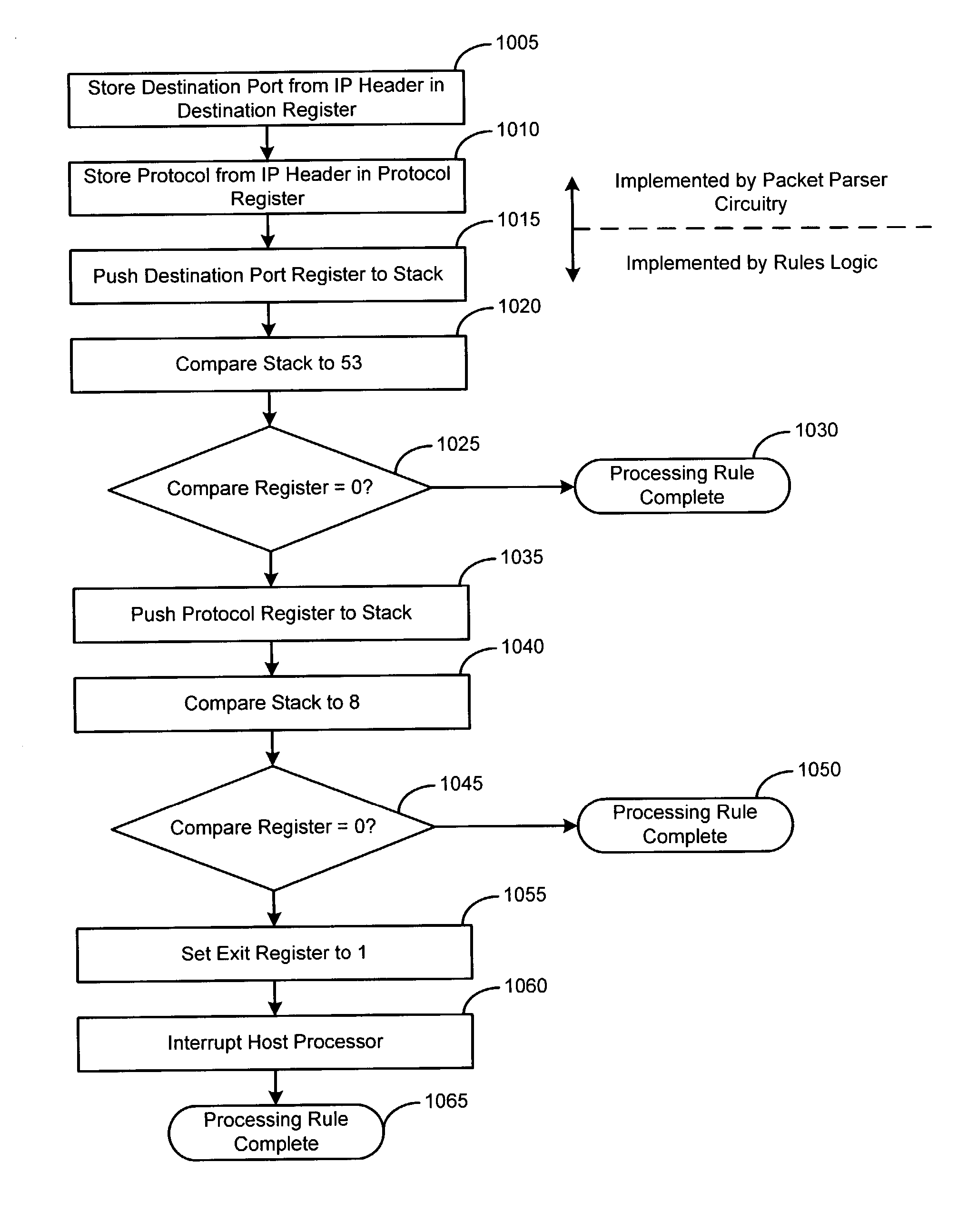

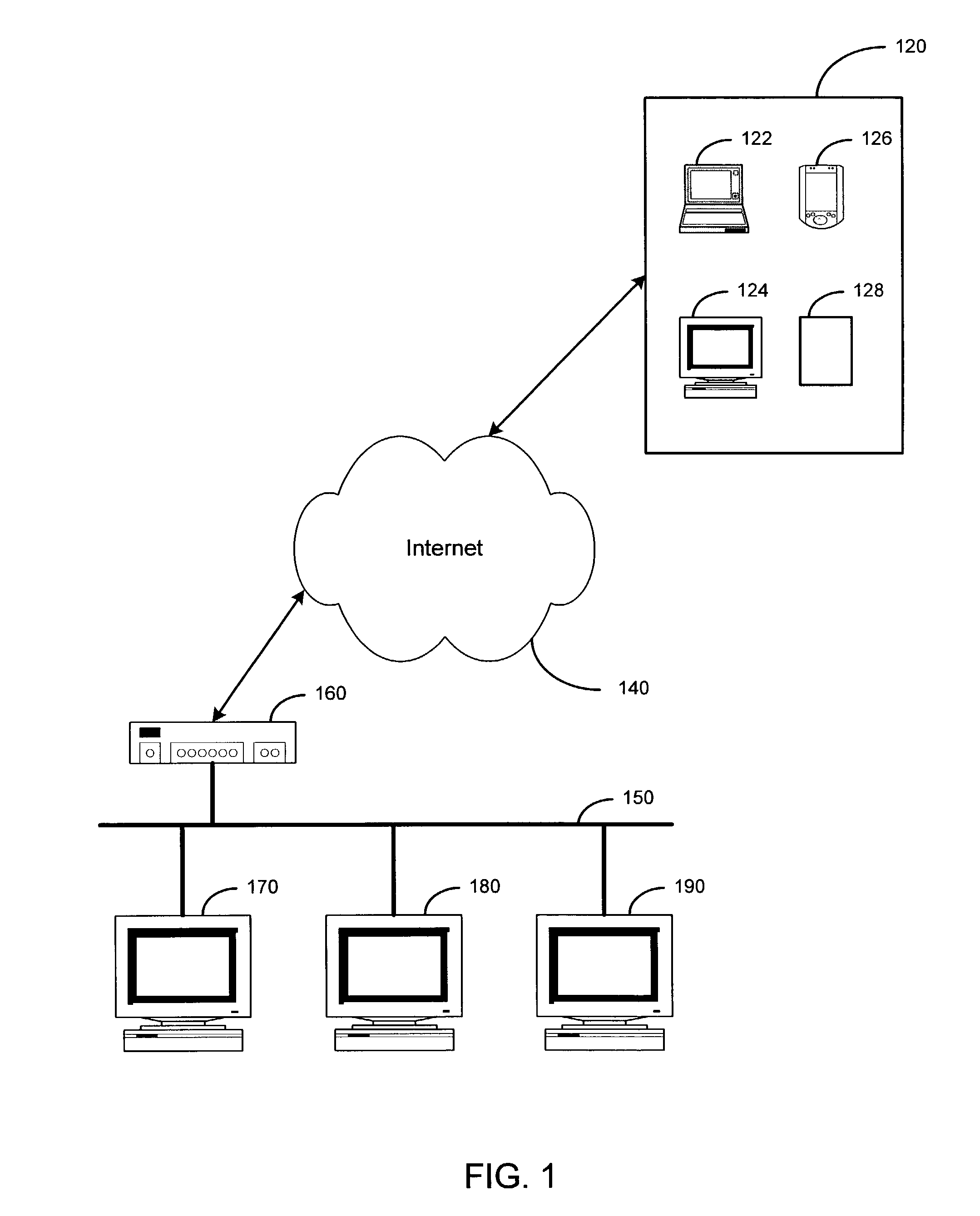

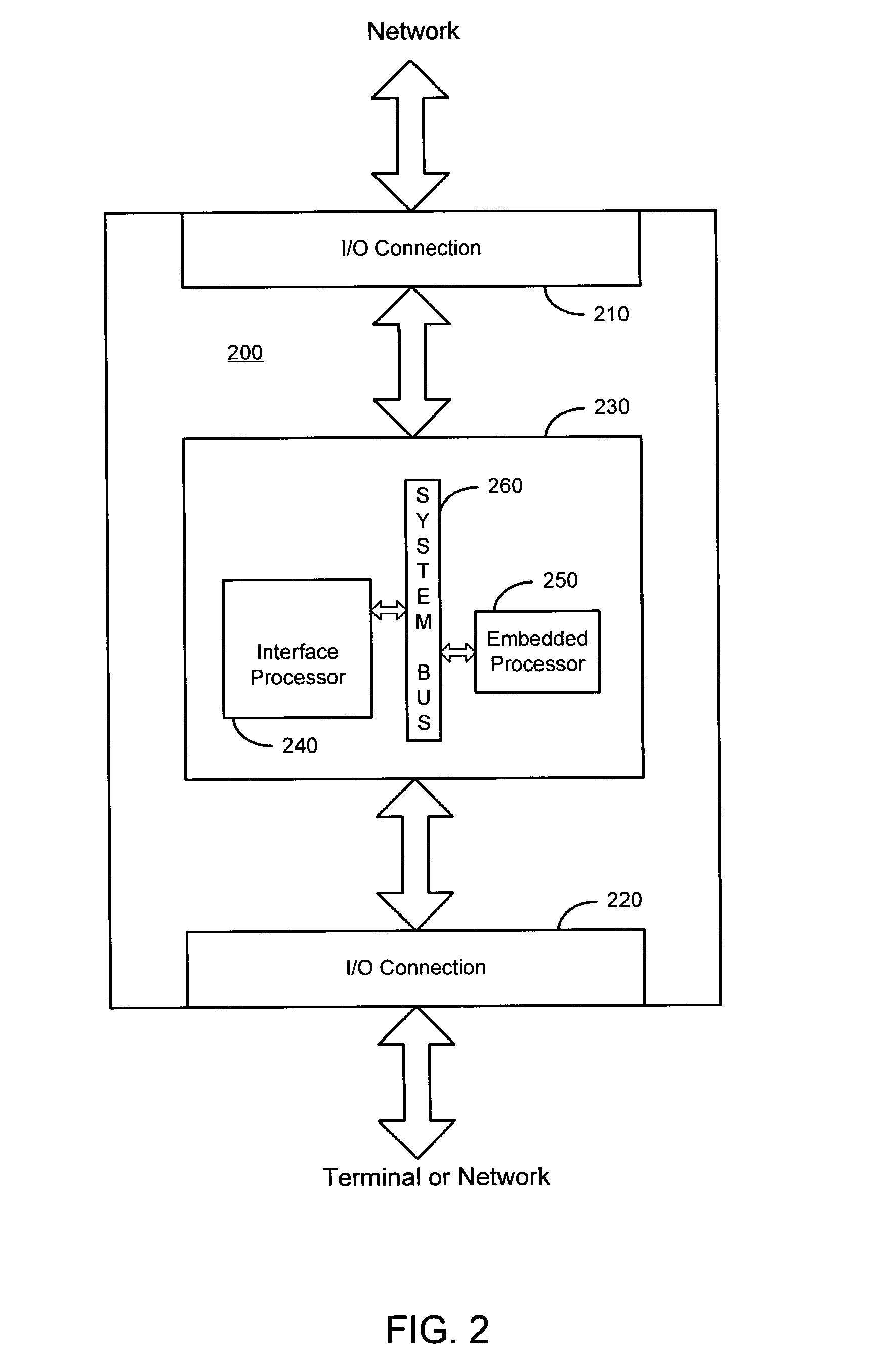

Hardware-based packet filtering accelerator

InactiveUS20040039940A1Digital computer detailsConcurrent instruction executionProcessor registerParallel computing

A data packet filtering accelerator processor operates in parallel with a host processor and is arranged on an integrated circuit with the host processor. The accelerator processor classifies data packets by executing a sequence machine code instructions converted directly from a set of rules. Portions of data packets are passed to the accelerator processor from the host processor. The accelerator processor includes packet parser circuit for parsing the data packets into relevant data units and storing the relevant data units in memory. A packet analysis circuit executes the sequence of machine code instructions converted directly from the set of rules. The machine code instruction sequence operates on the relevant data units to classify the data packet. The packet analysis circuit returns the results of the classification to the host processor by storing the classification results in a register accessible by the host processor.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

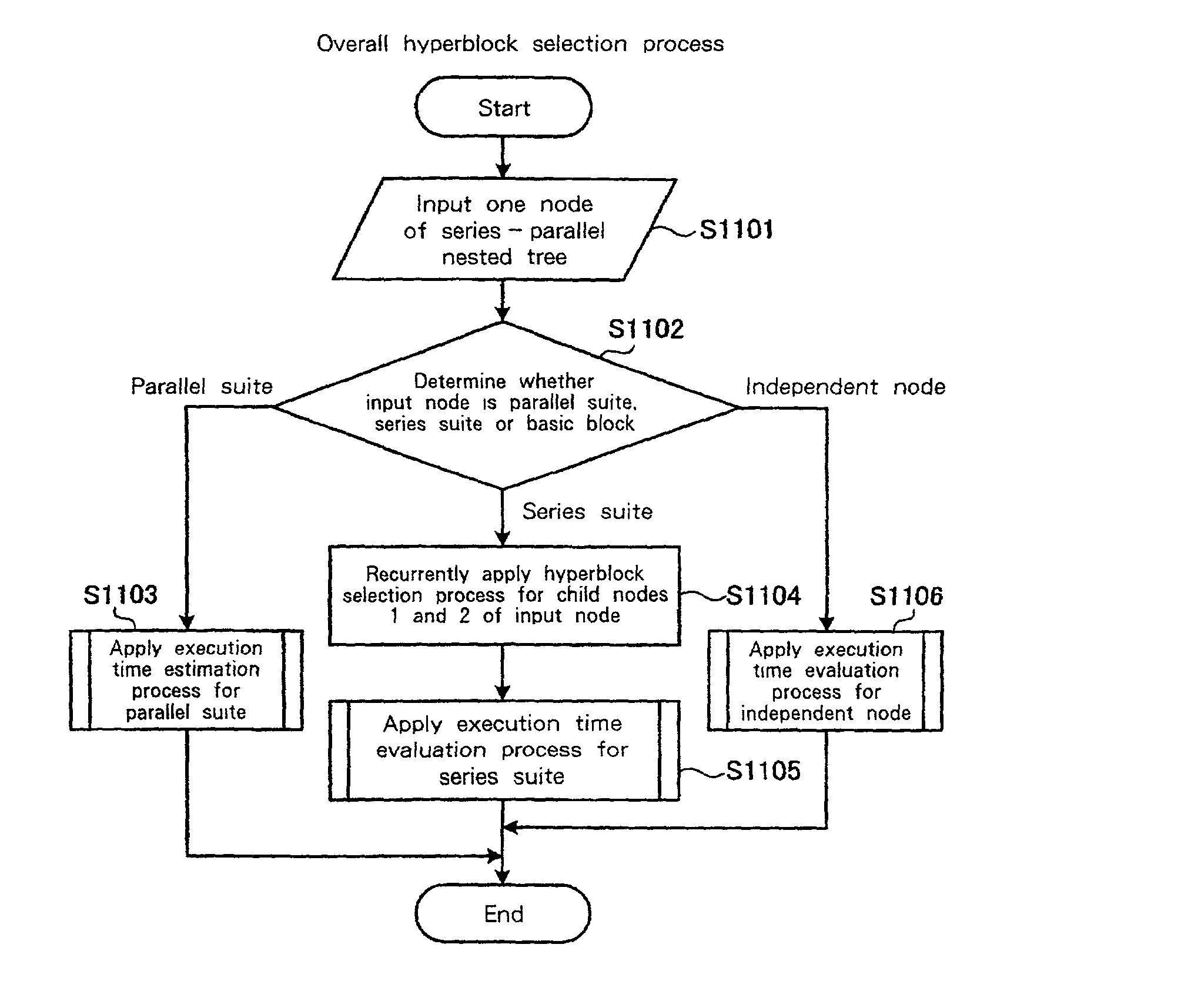

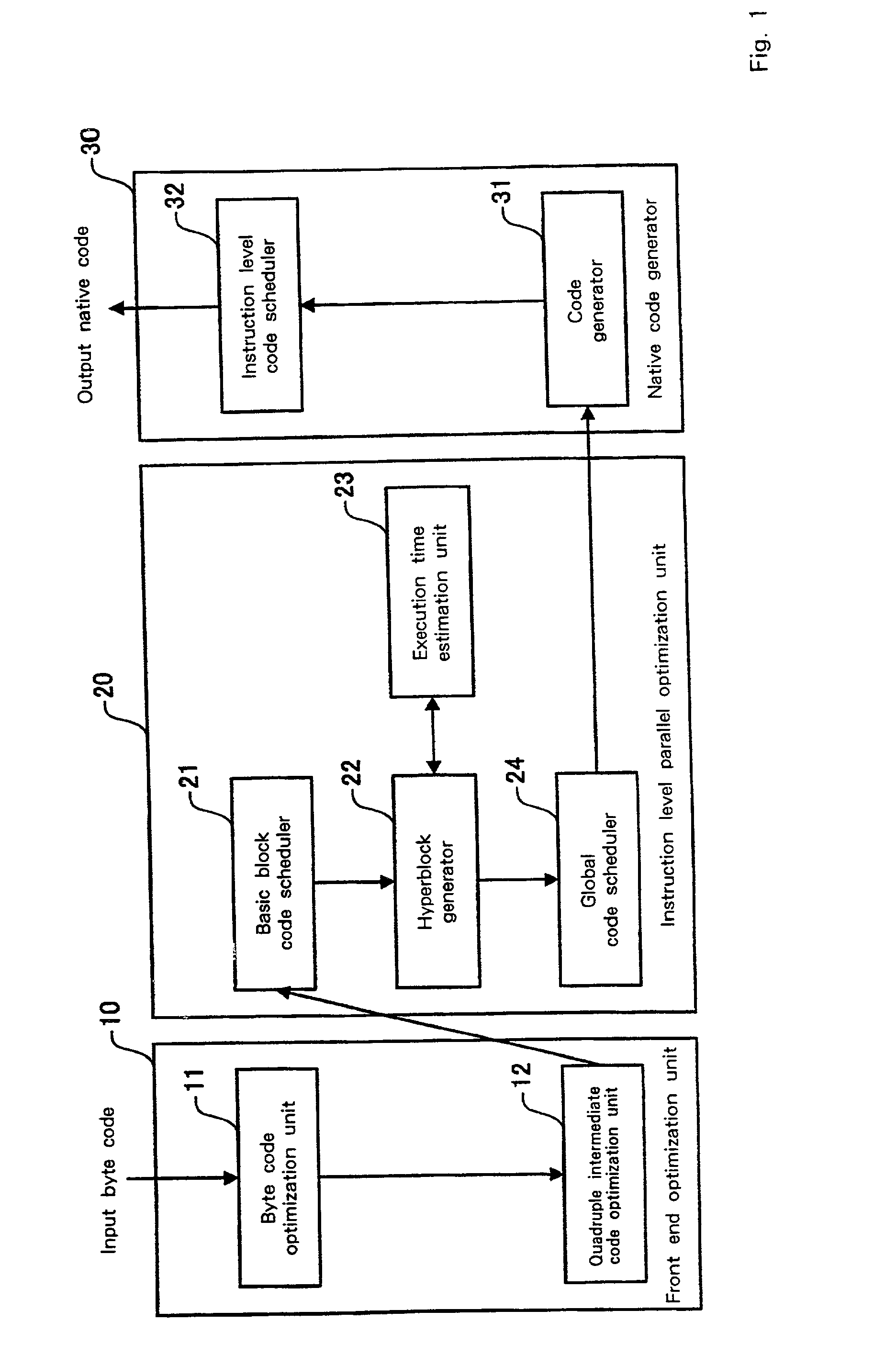

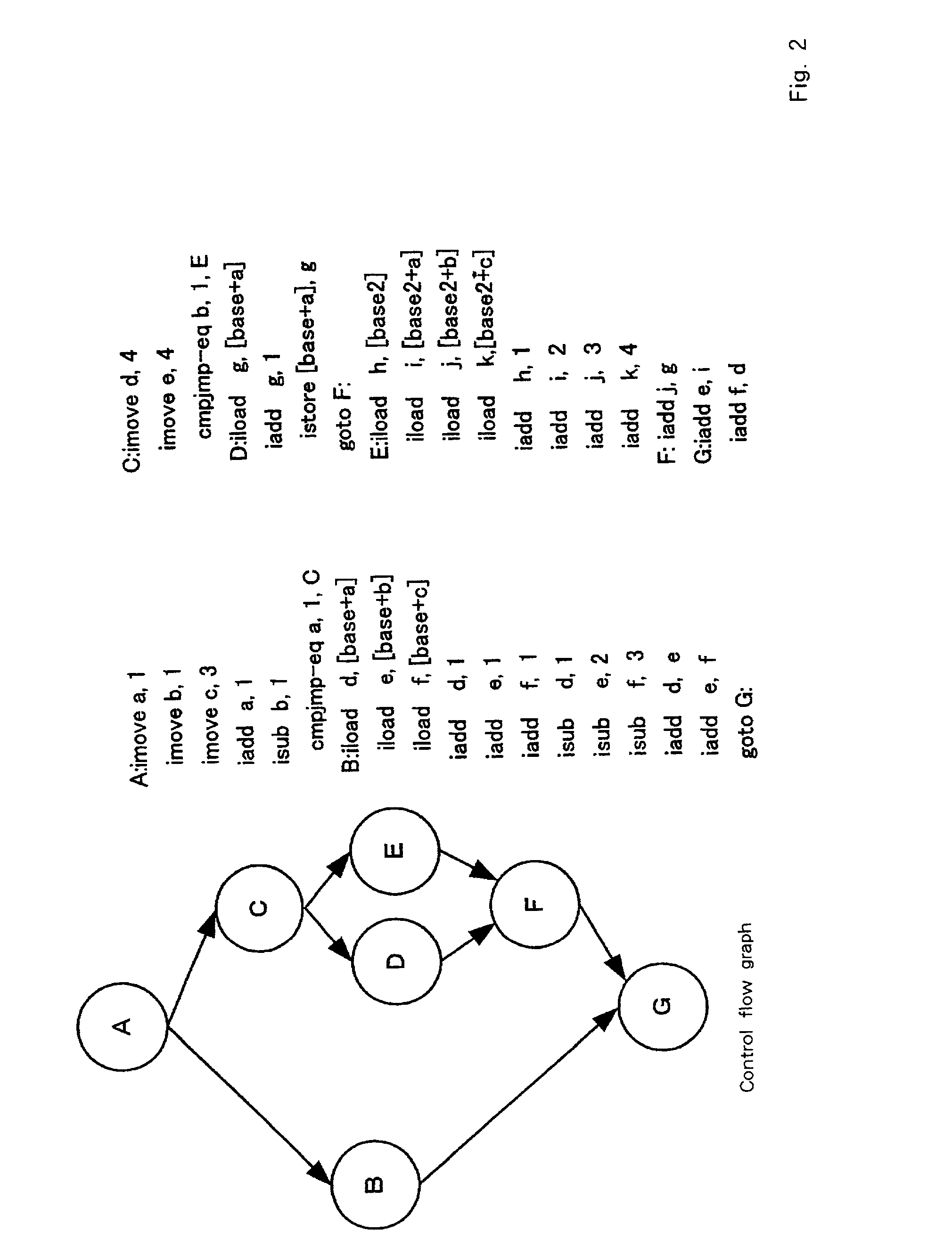

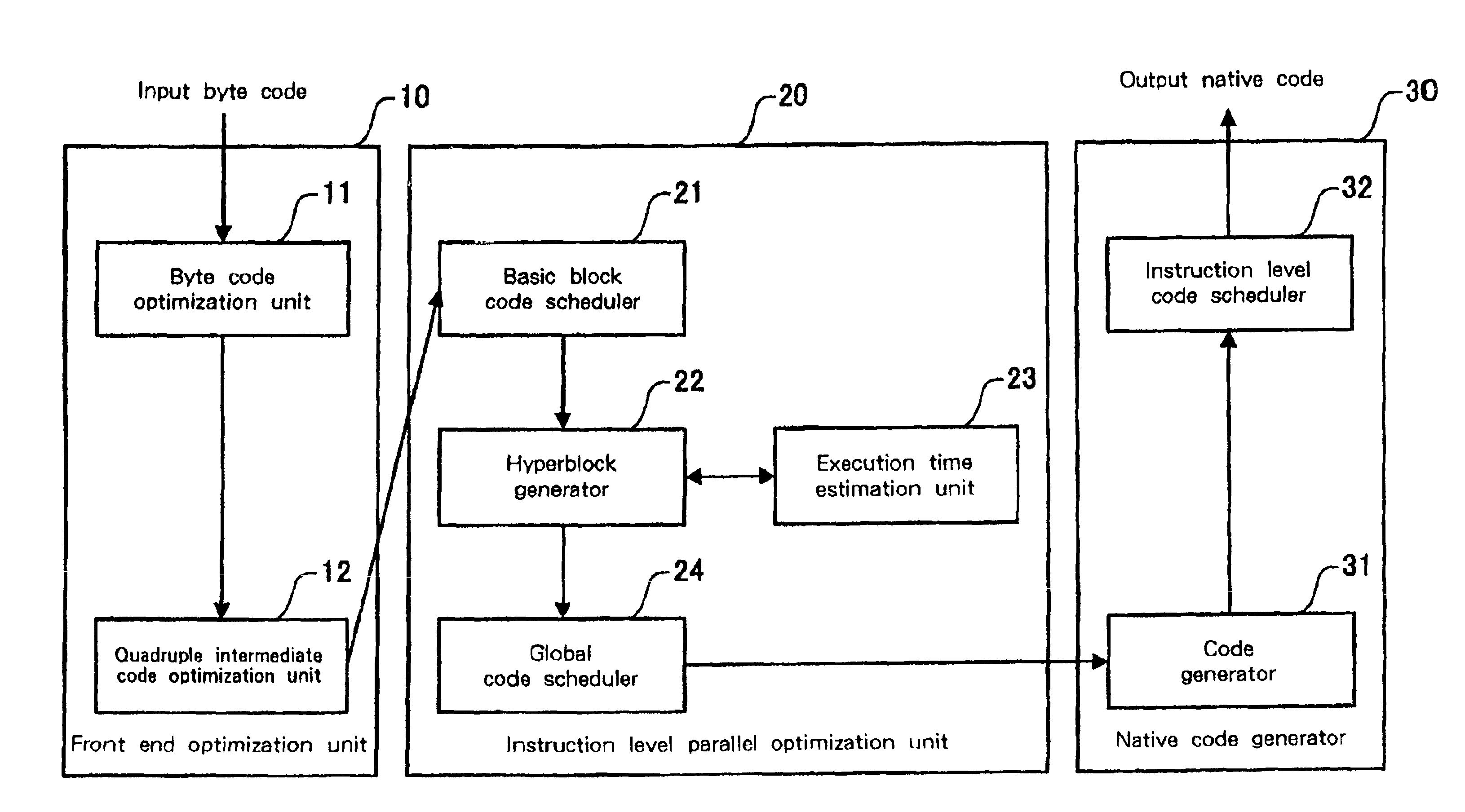

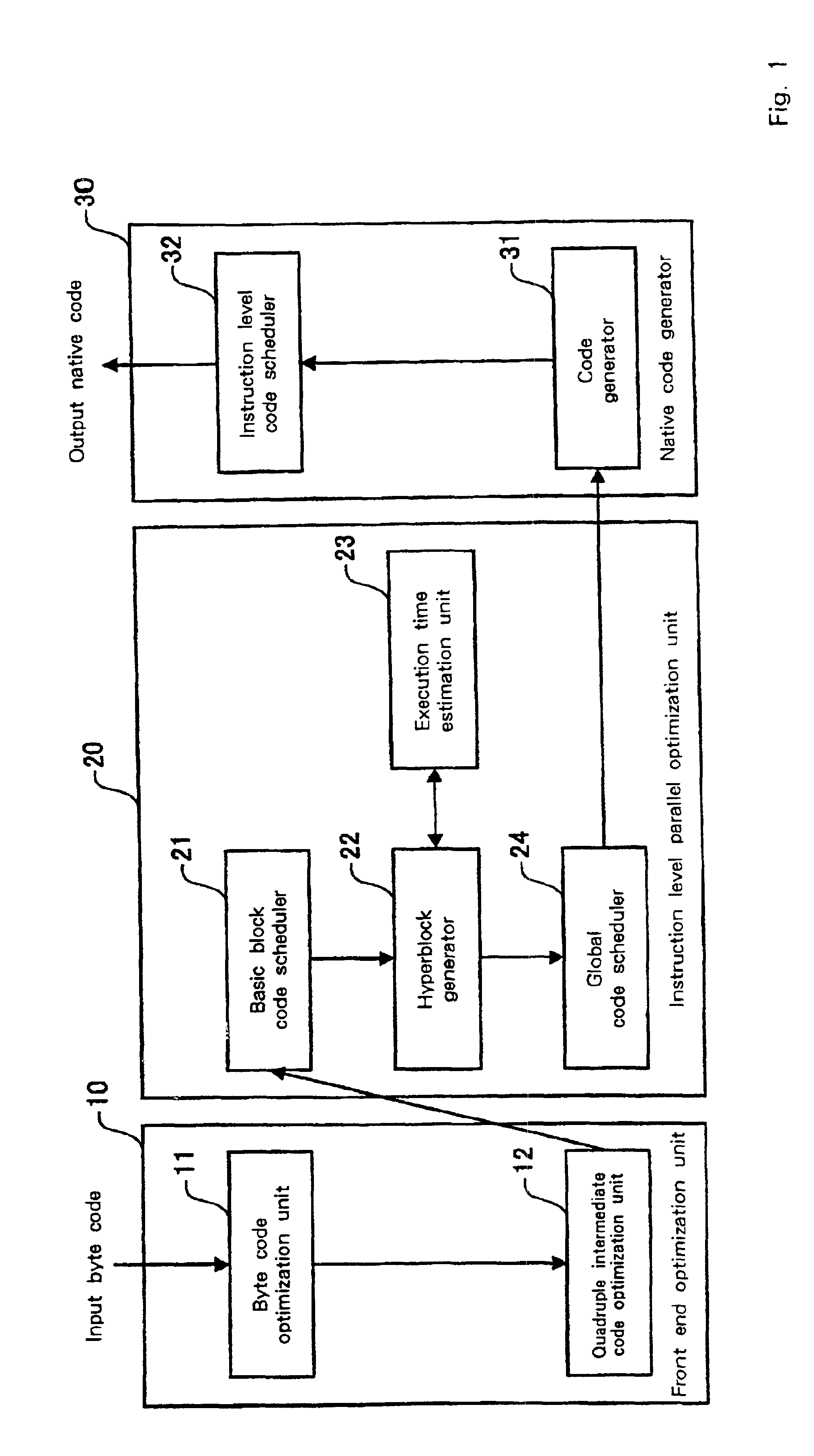

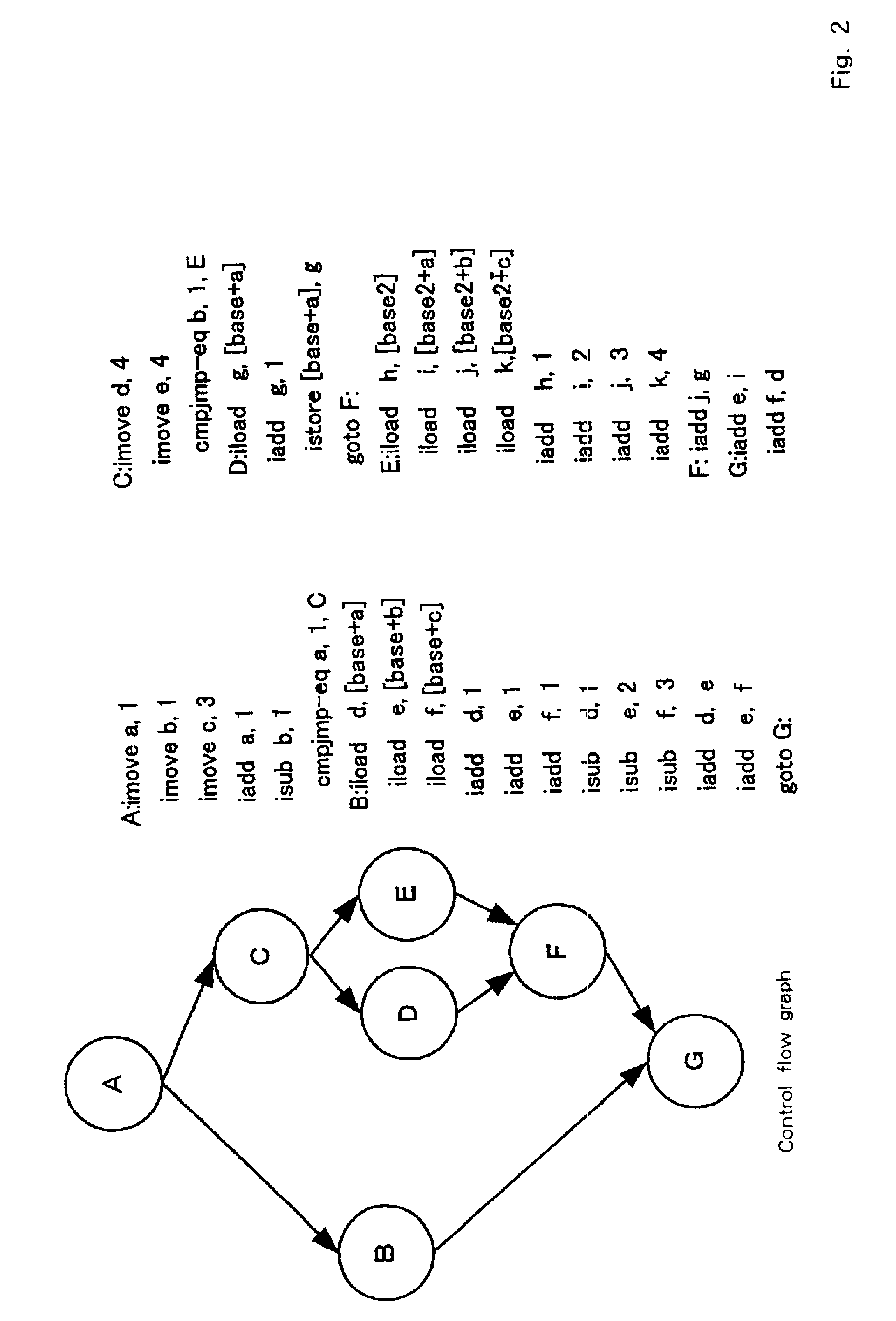

Program optimization method, and compiler using the same

InactiveUS20020095666A1Short processing timeEfficient executionSoftware engineeringDigital computer detailsSource codeBasic block

An optimization method and apparatus for converting source code for a program written in a programming language into machine language and for optimizing the program includes employing a basic block as a unit to estimate an execution time for the program to be processed, generating a nested tree that represents the connections of the basic blocks using a nesting structure, when a conditional branch is accompanied by a node in the nested tree, employing the execution time estimated by using the basic blocks as units to obtain an execution time at the node of the program when a conditional branching portion of a program is directly executed and when the conditional branching portion is executed in parallel, and defining the node as a parallel execution area group when the execution time required for the parallel execution is shorter or dividing multiple child nodes of the nodes into multiple parallel execution areas when the execution time for the conditional branching portion is shorter.

Owner:IBM CORP

SQL code generation for heterogeneous environment

ActiveUS7433863B2Avoid generatingDigital data information retrievalData processing applicationsDatabase queryExecution plan

This invention relates generally to a system for processing database queries, and more particularly to a method for generating high level language or machine code to implement query execution plans. in one preferred embodiment, the method begins by receiving a subject query, and then forming an execution plan corresponding to the subject query. The execution plan will typically have a sequence of component snippets or pieces and corresponding processes for implementing the pieces. For at least one piece in the plan, the process then (a) generates source code using different code generation techniques as a function of expected runtime processing machine types; and then (b) compiles the generated source code to form machine executable code for implementing the subject query. As a result, the query executed directly as machine executable code thereby avoiding runtime interpretation of the pieces in the execution plan.

Owner:INT BUSINESS MASCH CORP

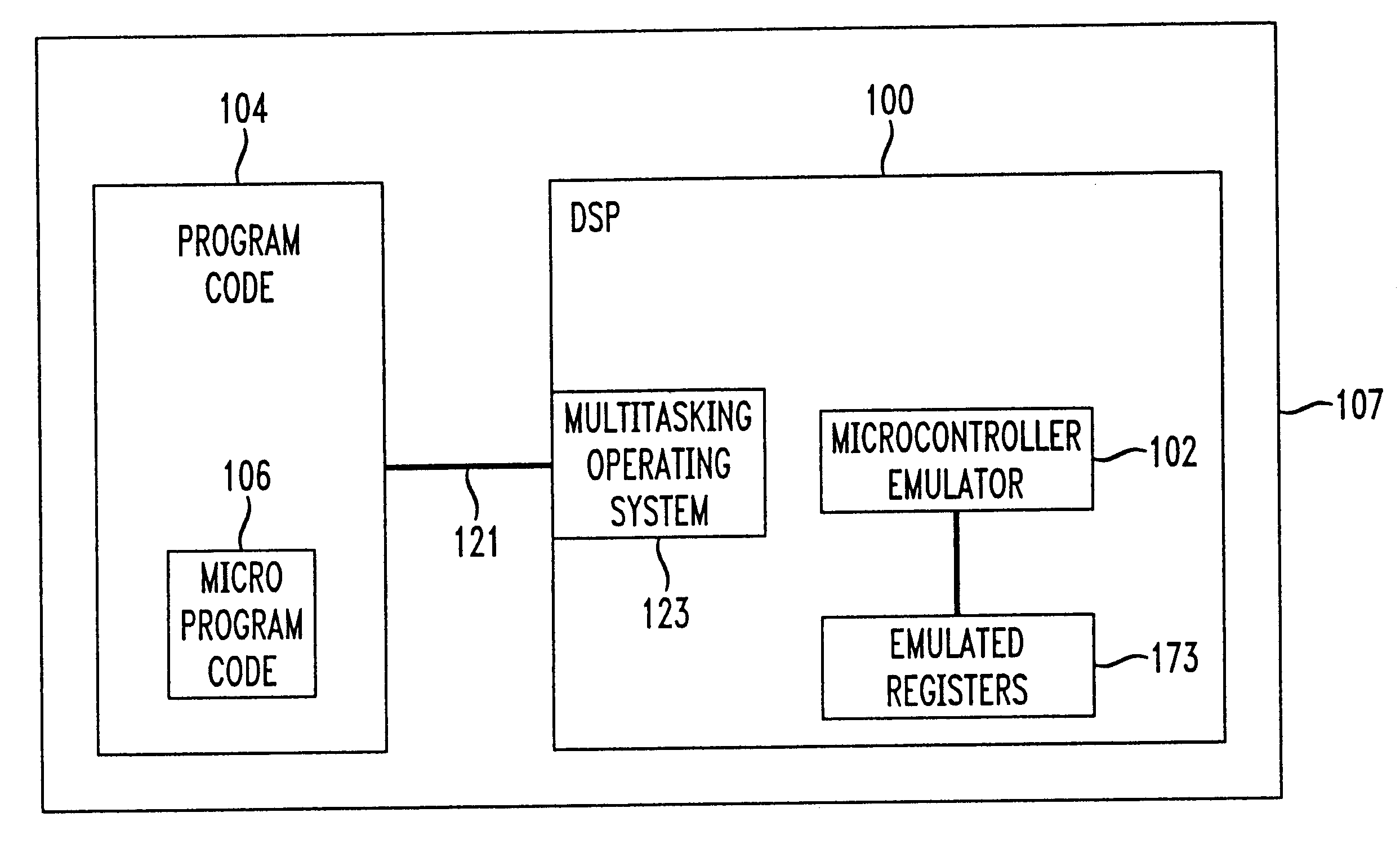

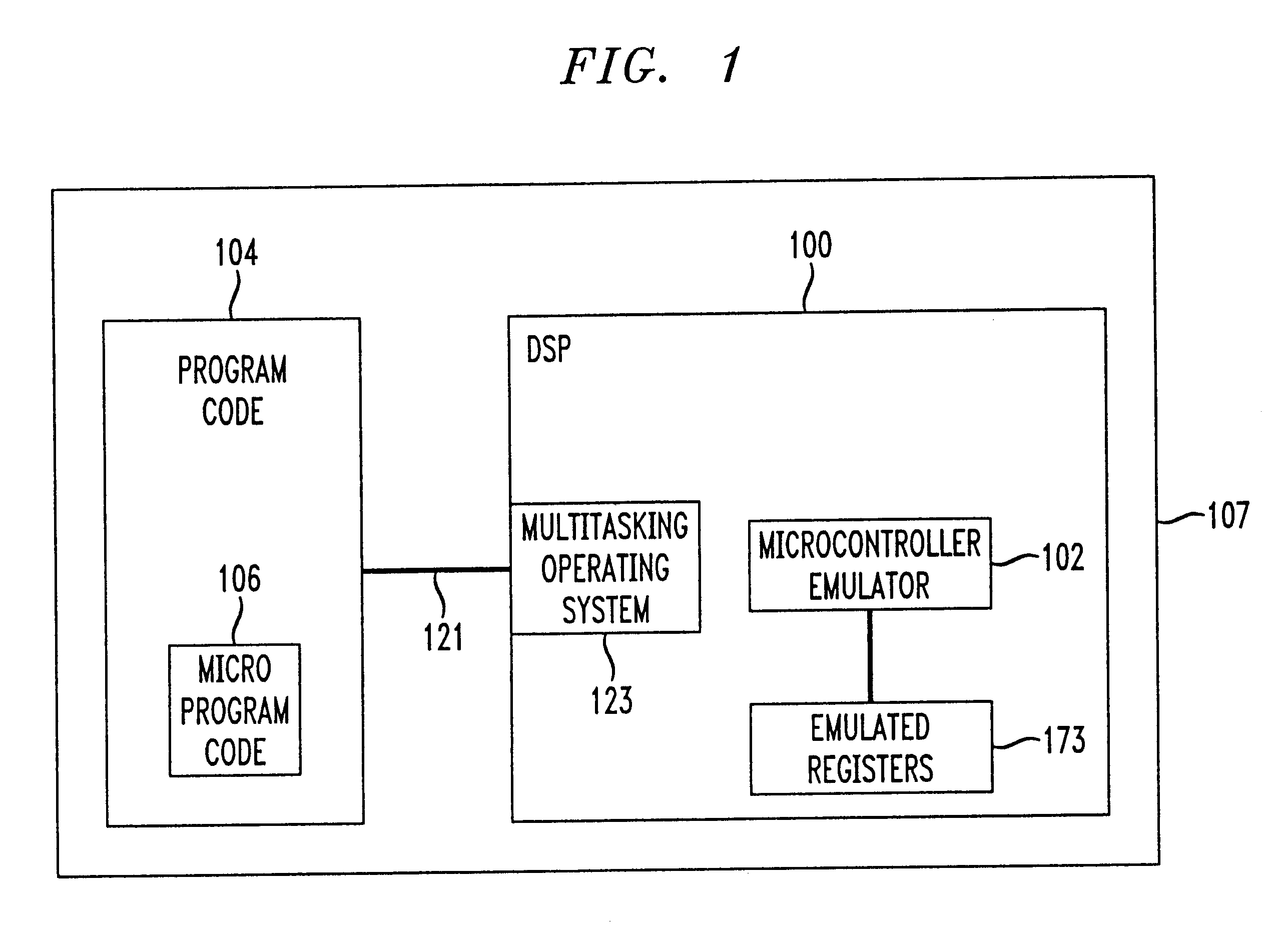

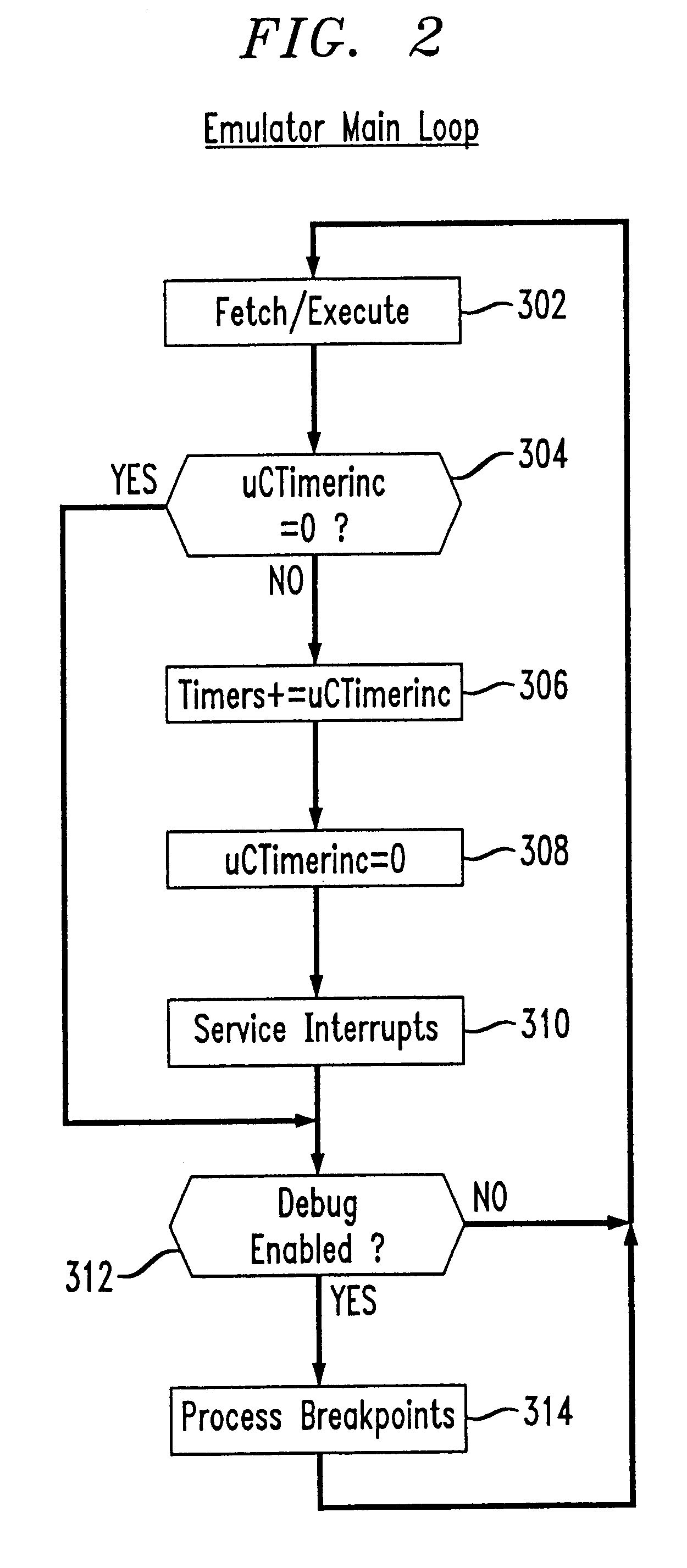

DSP emulating a microcontroller

InactiveUS6564179B1General purpose stored program computerSoftware simulation/interpretation/emulationMicrocontrollerOperational system

The present invention provides a processor device and technique having the capability of providing a two-processor solution with only one processor. In accordance with the principles of the present invention, a host processor is programmed in its native source and machine code language, and an emulated second processor is programmed in a different native source or machine code language particular to that emulated processor, to allow programming specialists in the different processors to develop common code for use on the same host processor. A multitasking operating system is included to allow time sharing operation between instructions from program code relating to the host processor (e.g., a DSP in the disclosed embodiment), and different program code relating to the emulated processor. The program code relating to the host processor (e.g., DSP) is written in program code which is native to the DSP, while the program code relating to the emulated processor (e.g., microcontroller) is written in program code which is native to the microcontroller. The SoftCore emulation module allows both DSP code and control code written for a microcontroller to execute independently on the same processor by multi-tasking resources in the faster, host processor (e.g., in the DSP), giving equal time slots of processor time to each processor (real and emulated).

Owner:LUCENT TECH INC +1

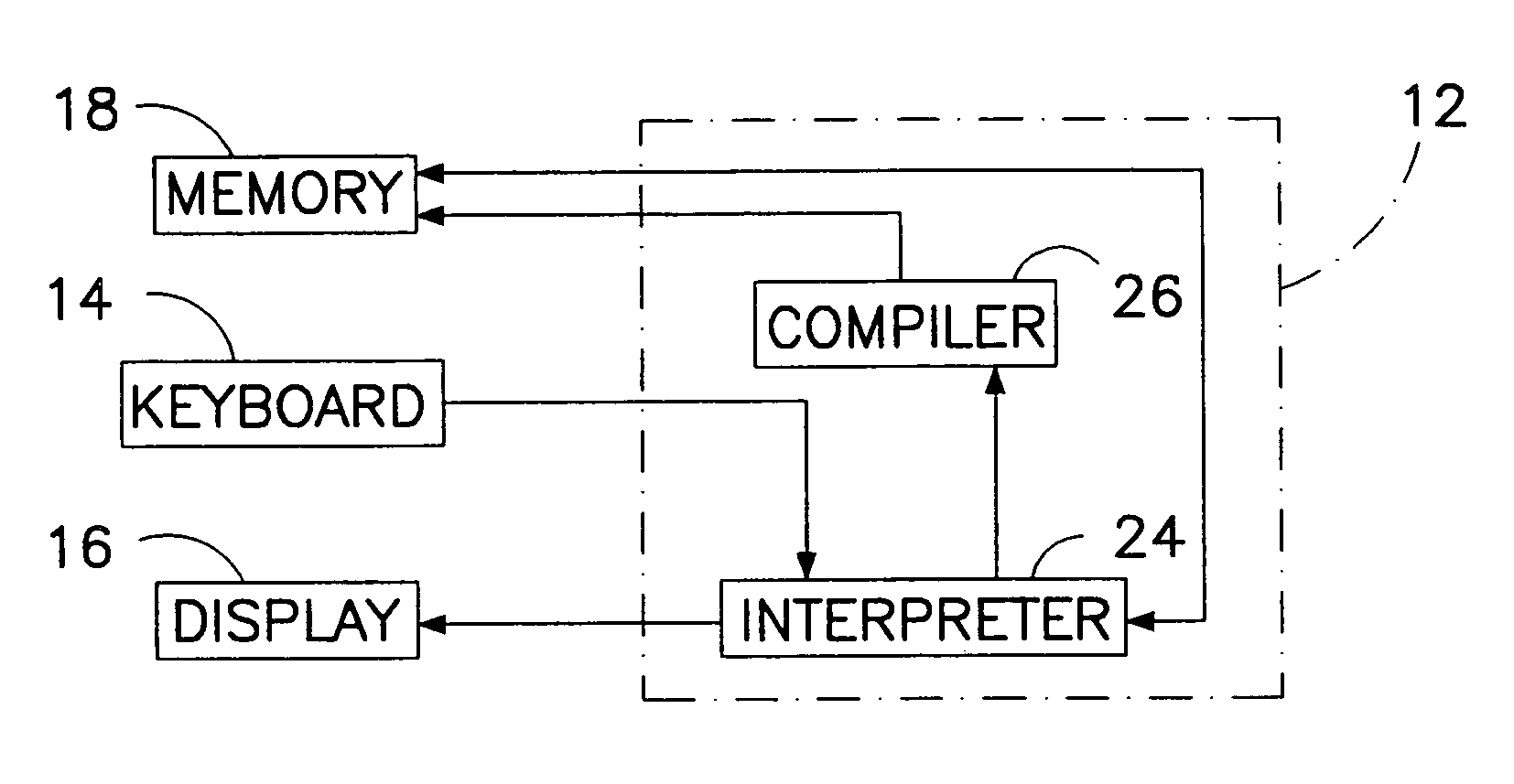

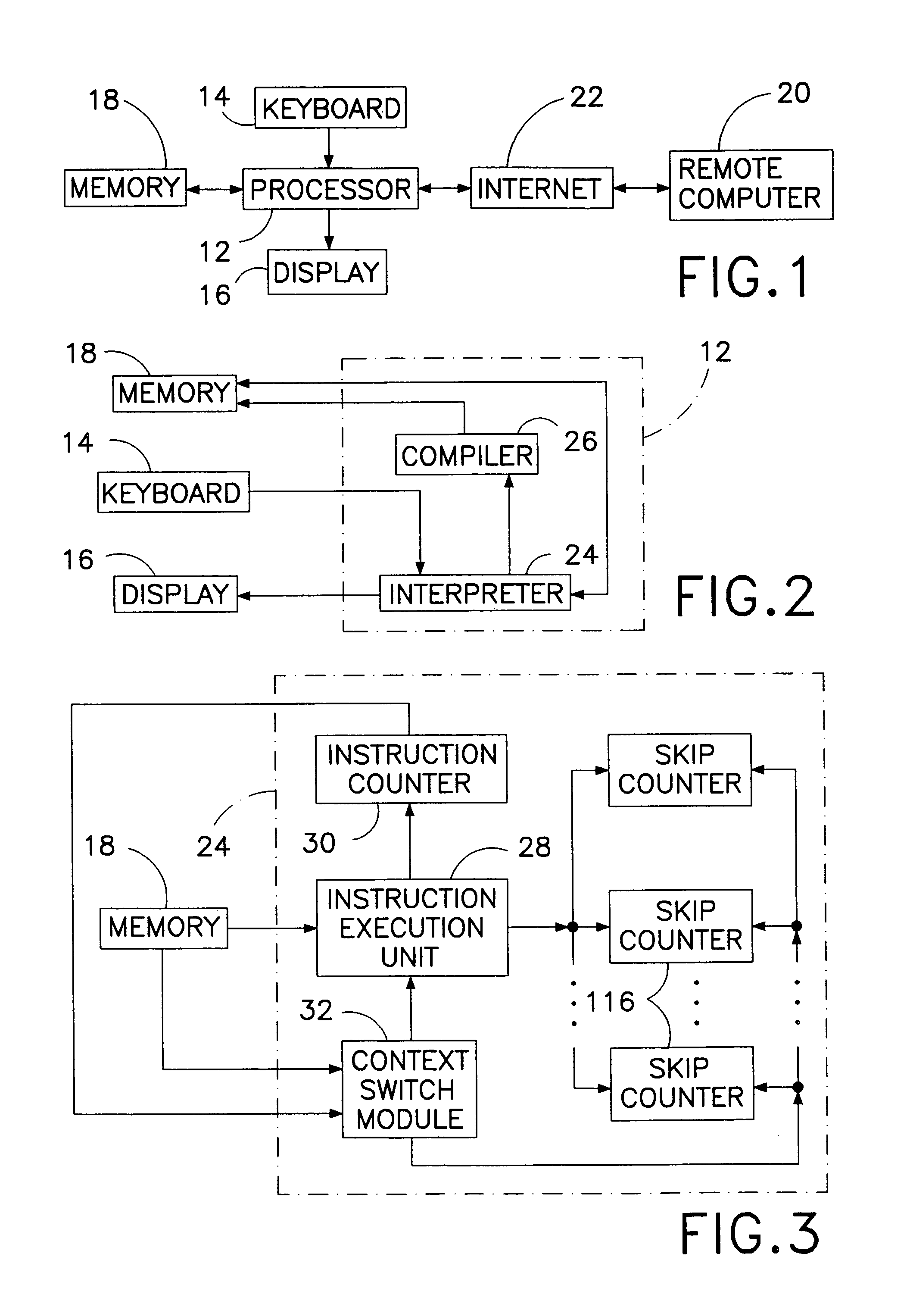

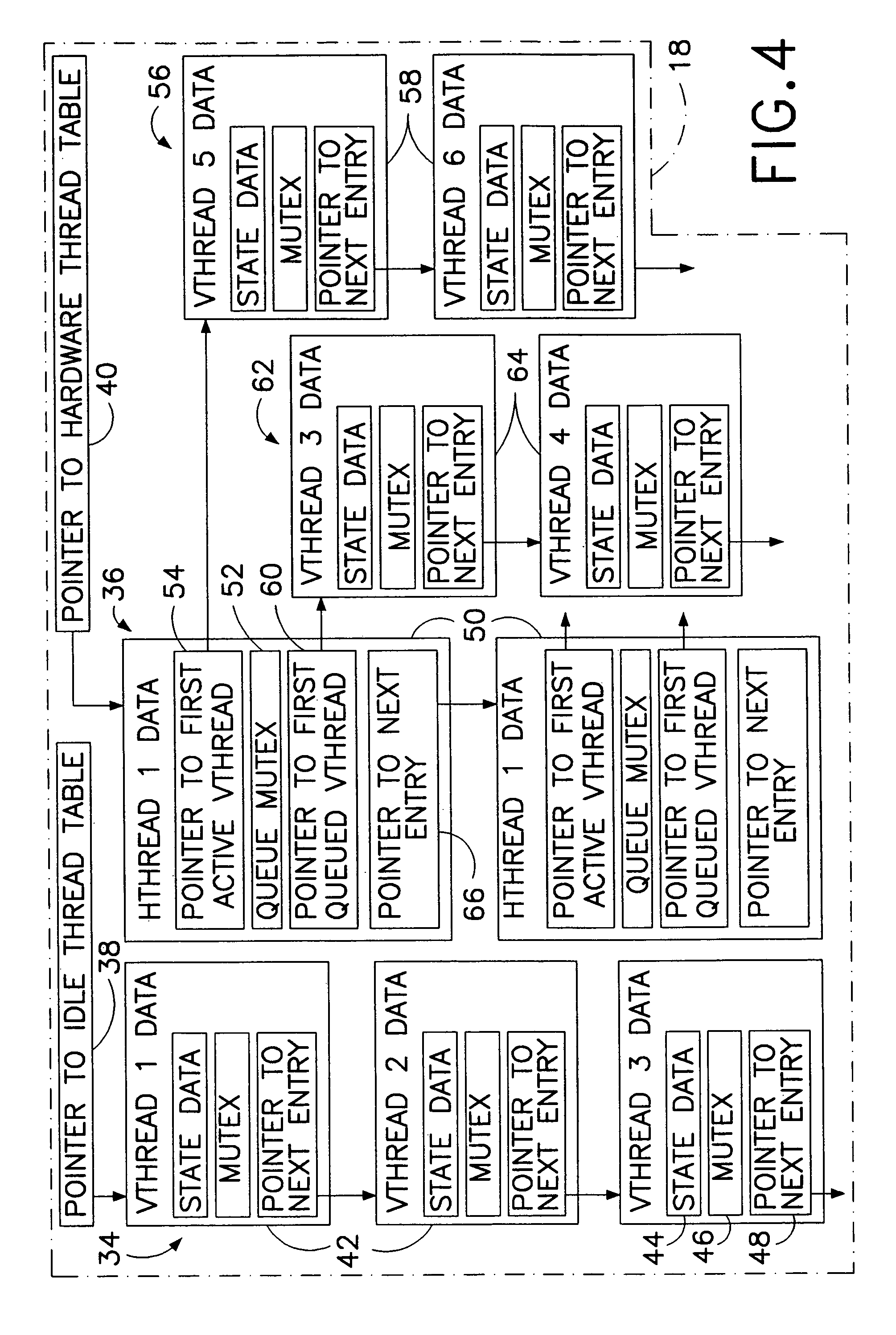

Computer multi-tasking via virtual threading using an interpreter

InactiveUS7234139B1Eliminate dependenciesDifferent operationalProgram initiation/switchingInterprogram communicationLocal variablePseudocode

In the operation of a computer, a plurality of bytecode or pseudocode instructions, at least some of the pseudocode instructions comprising a plurality of machine code instructions, are stored in a computer memory. For each of a plurality of tasks or jobs to be performed by the computer, a respective virtual thread of execution context data is automatically created. The virtual threads each include (a) a memory location of a next one of the pseudocode instructions to be executed in carrying out the respective task or job and (b) the values of any local variables required for carrying out the respective task or job. At least some of the tasks or jobs each entails execution of a respective one of the pseudocode instructions comprising a plurality of machine language instructions. Each of the tasks or jobs are processed in a respective series of time slices or processing slots under the control of the respective virtual thread, and, in every context switch between different virtual threads, such context switch is undertaken only after completed execution of a currently executing one of the pseudocode instructions.

Owner:CERINET USA

System and method for configuring an instrument to perform measurement functions utilizing conversion of graphical programs into hardware implementations

InactiveUS6784903B2Detecting faulty hardware by remote testCathode-ray tube indicatorsGraphicsComputer hardware

A computer-implemented system and method for generating a hardware implementation of graphical code. The method may operate to configure an instrument to perform measurement functions, wherein the instrument includes a programmable hardware element. The method comprises first creating a graphical program, wherein the graphical program may implement a measurement function. A portion of the graphical program may be converted into a hardware implementation on a programmable hardware element, and a portion may optionally be compiled into machine code for execution by a CPU. The programmable hardware element is thus configured utilizing a hardware description and implements a hardware implementation of at least a portion of the graphical program.

Owner:NATIONAL INSTRUMENTS

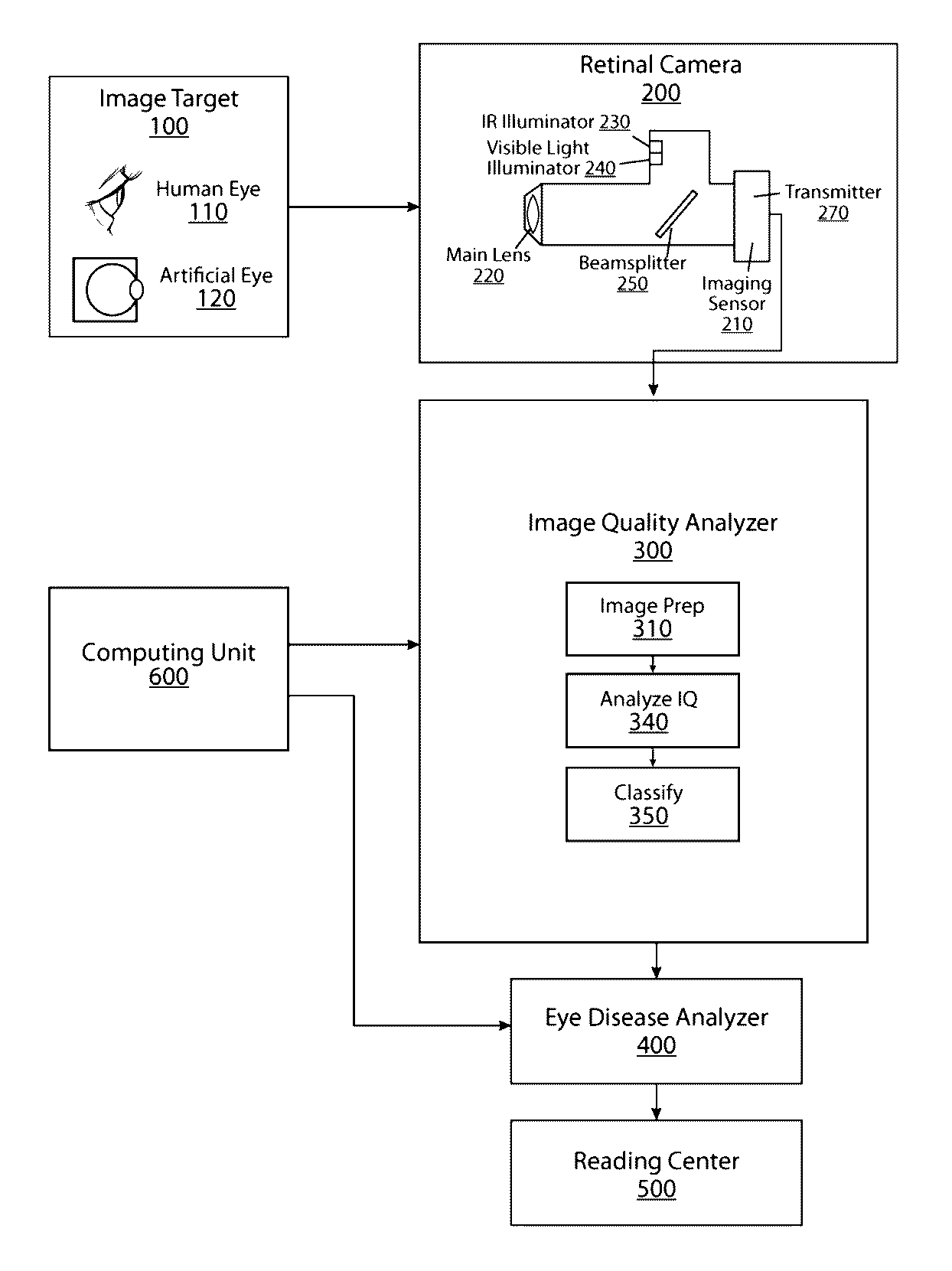

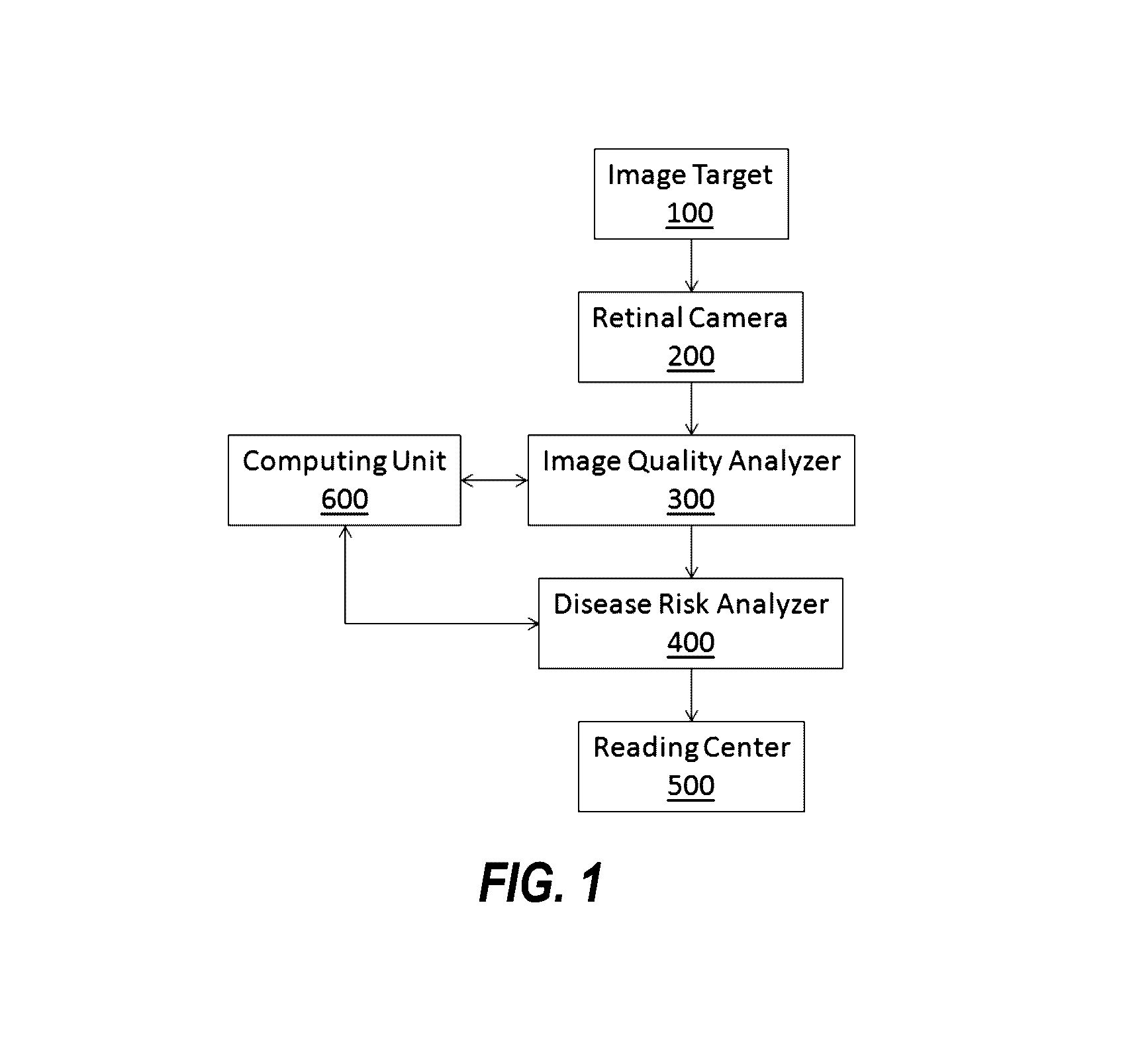

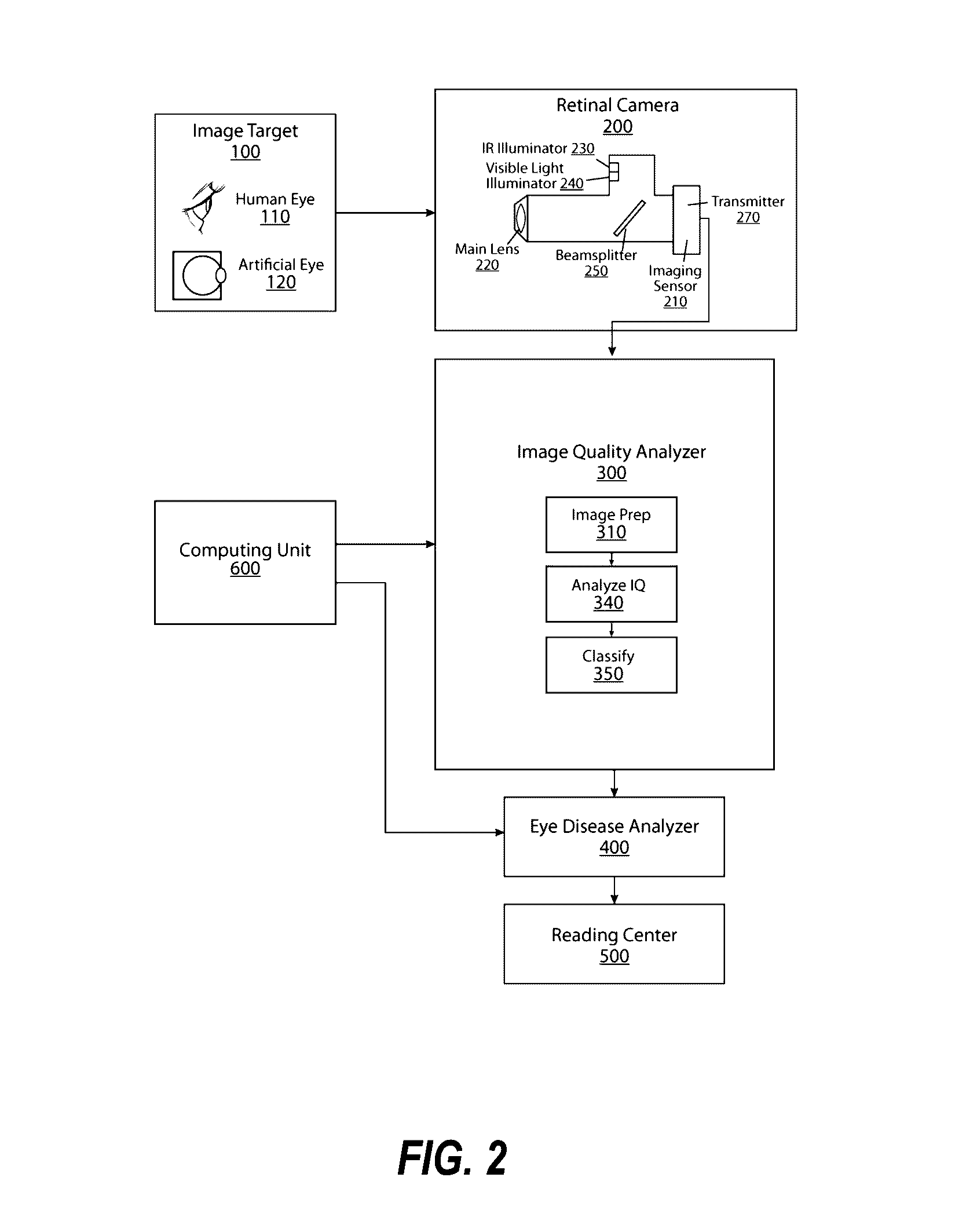

System and methods for automatic processing of digital retinal images in conjunction with an imaging device

Systems and methods of obtaining and recording fundus images by minimally trained persons, which includes a camera for obtaining images of a fundus of a subject's eye, in combination with mathematical methods to assign real time image quality classification to the images obtained based upon a set of criteria. The classified images will be further processed if the classified images are of sufficient image quality for clinical interpretation by machine-coded and / or human-based methods. Such systems and methods can thus automatically determine whether the quality of a retinal image is sufficient for computer-based eye disease screening. The system integrates global histogram features, textural features, and vessel density, as well as a local non-reference perceptual sharpness metric. A partial least square (PLS) classifier is trained to distinguish low quality images from normal quality images.

Owner:VISIONQUEST BIOMEDICAL

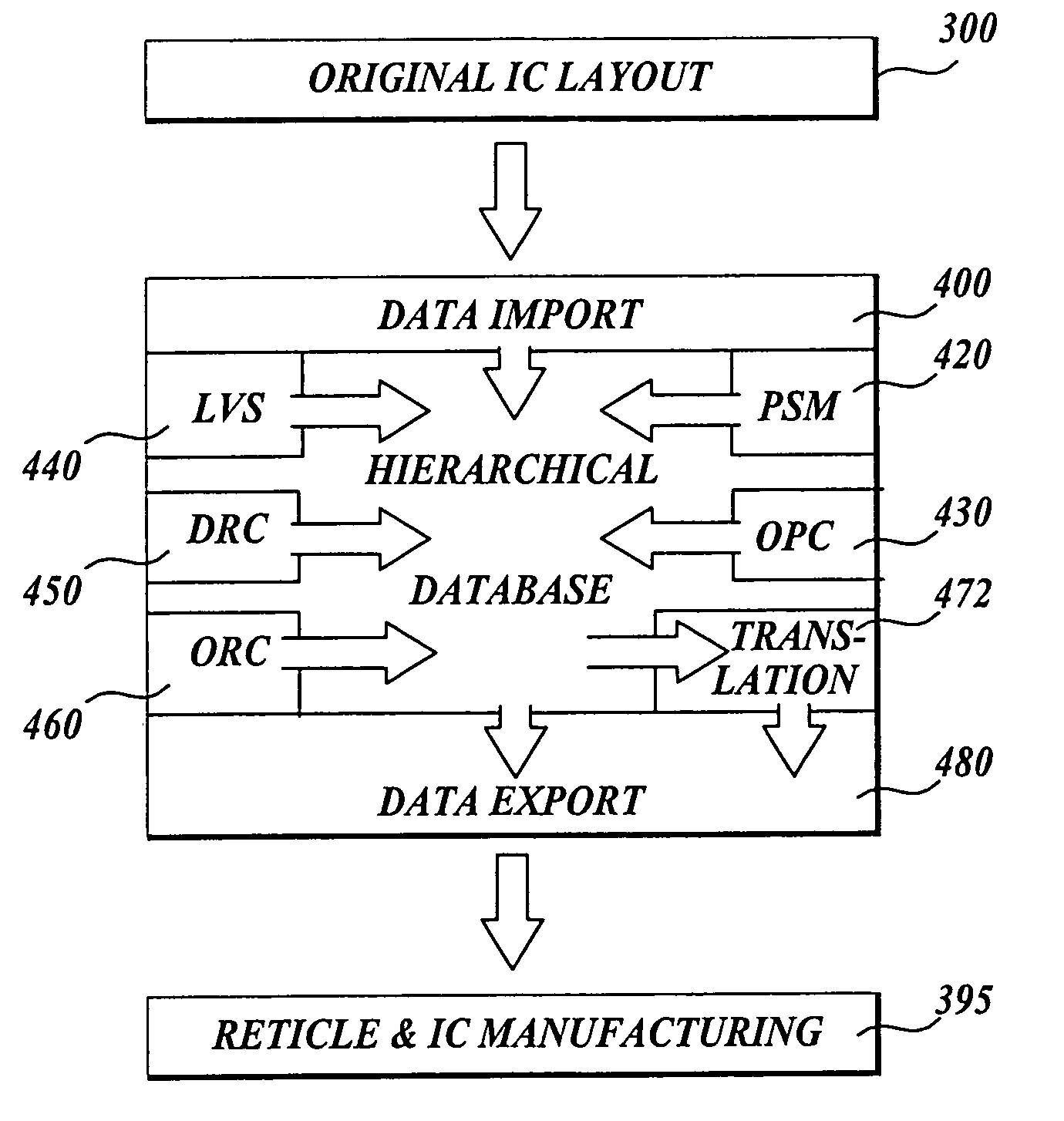

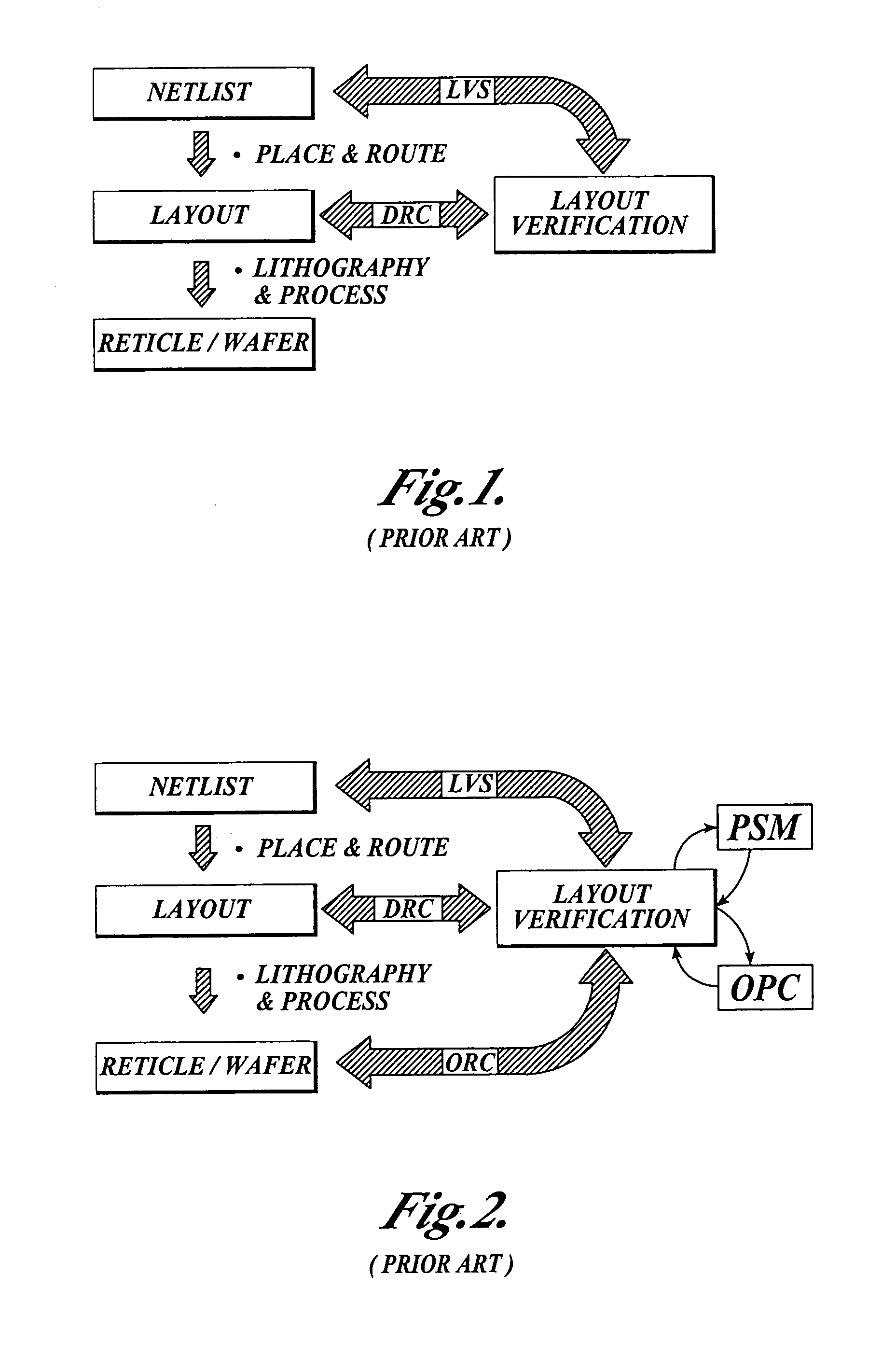

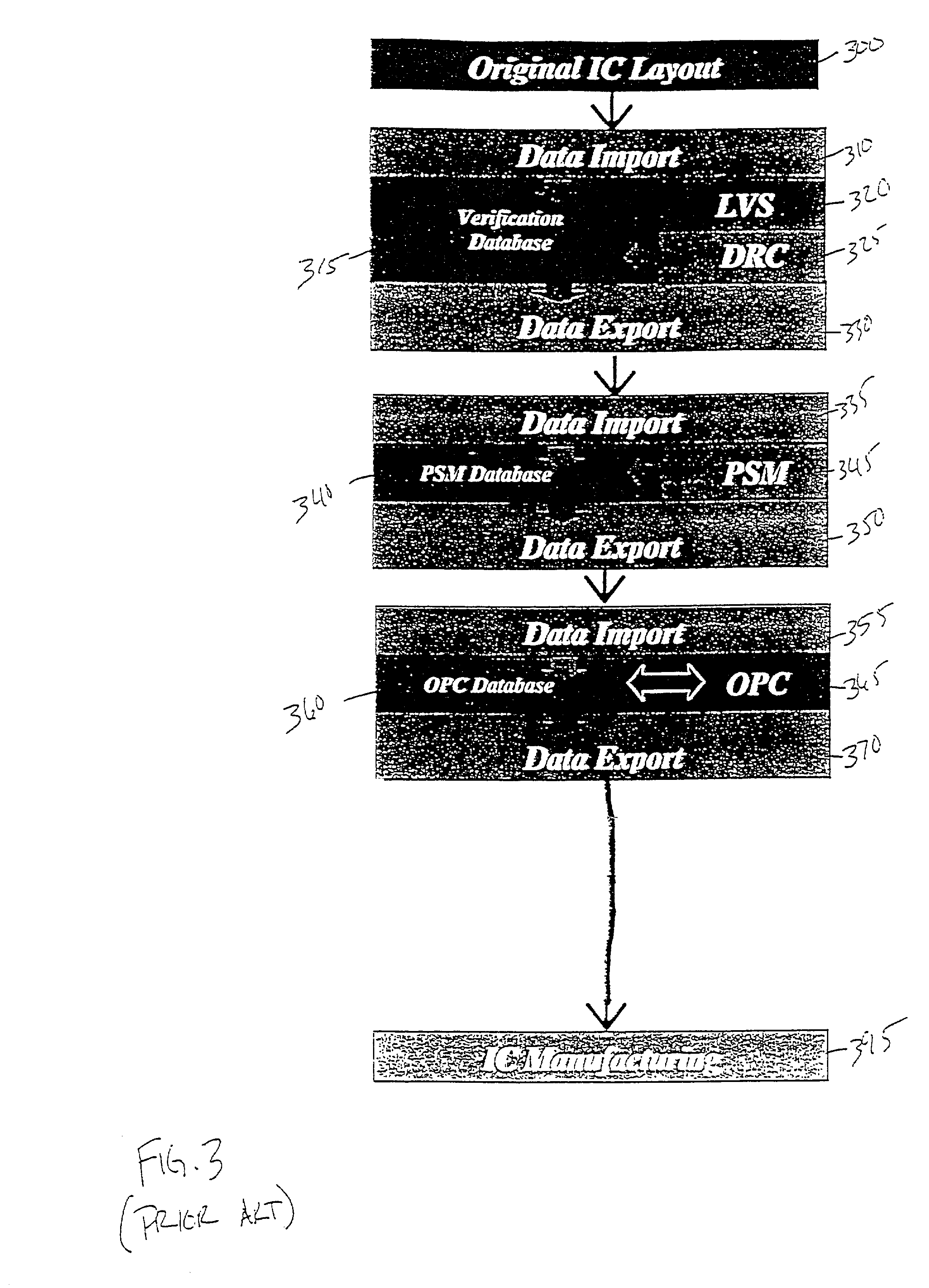

Integrated verification and manufacturability tool

InactiveUS7017141B2Originals for photomechanical treatmentComputer aided designComputer architectureInter layer

An integrated verification and manufacturability tool provides more efficient verification of integrated device designs than verification using several different verification tools. The integrated verification and manufacturability includes a hierarchical database to store shared design data accessed by multiple verification tool components (e.g., layout versus schematic, design rule check, optical process correction, phase shift mask assignment and machine language conversion). The hierarchical database includes representations of one or more additional, or intermediate layer structures that are created and used by the verification tool components for operations performed on the design being verified. Use of a single hierarchical database having shared data for access and use by multiple verification components streamlines the verification process, which provides an improved verification tool.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

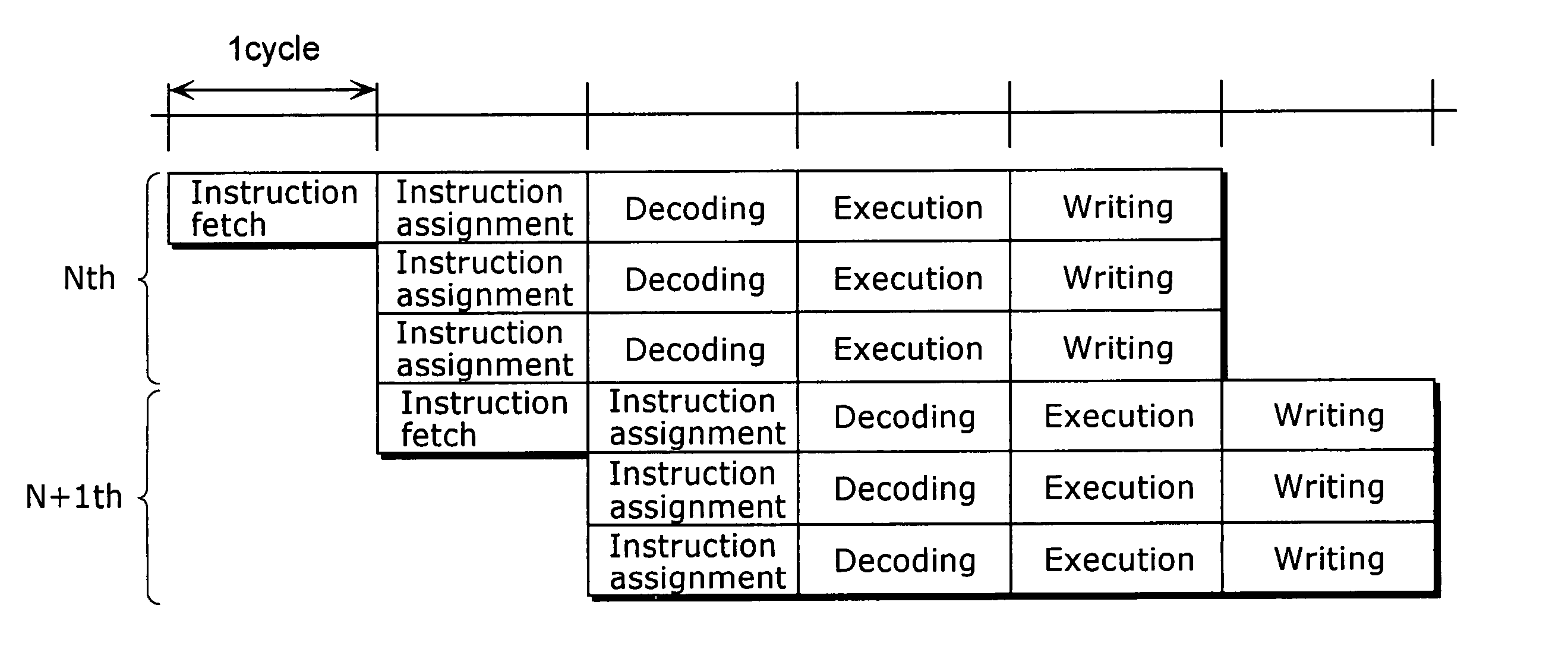

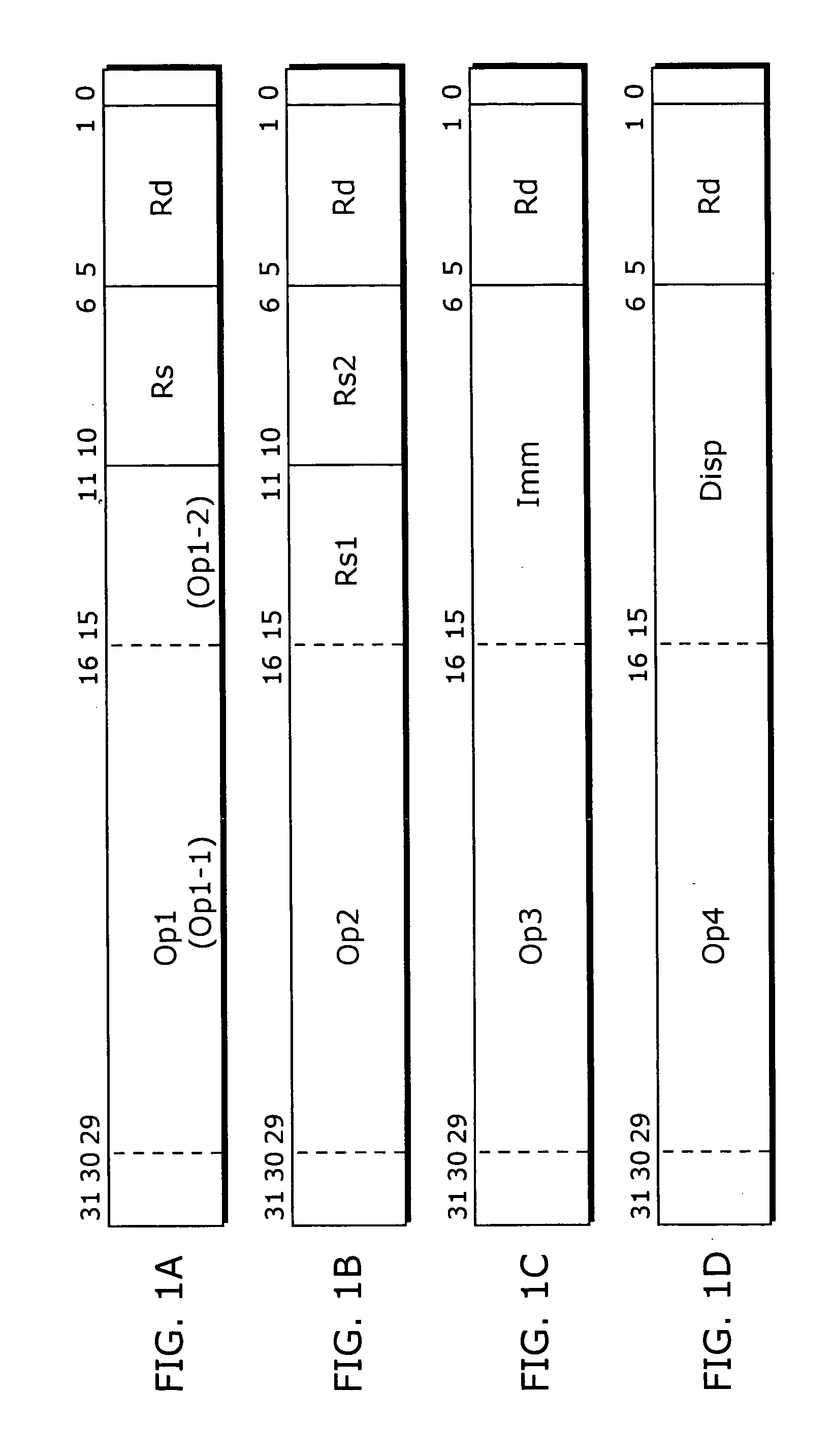

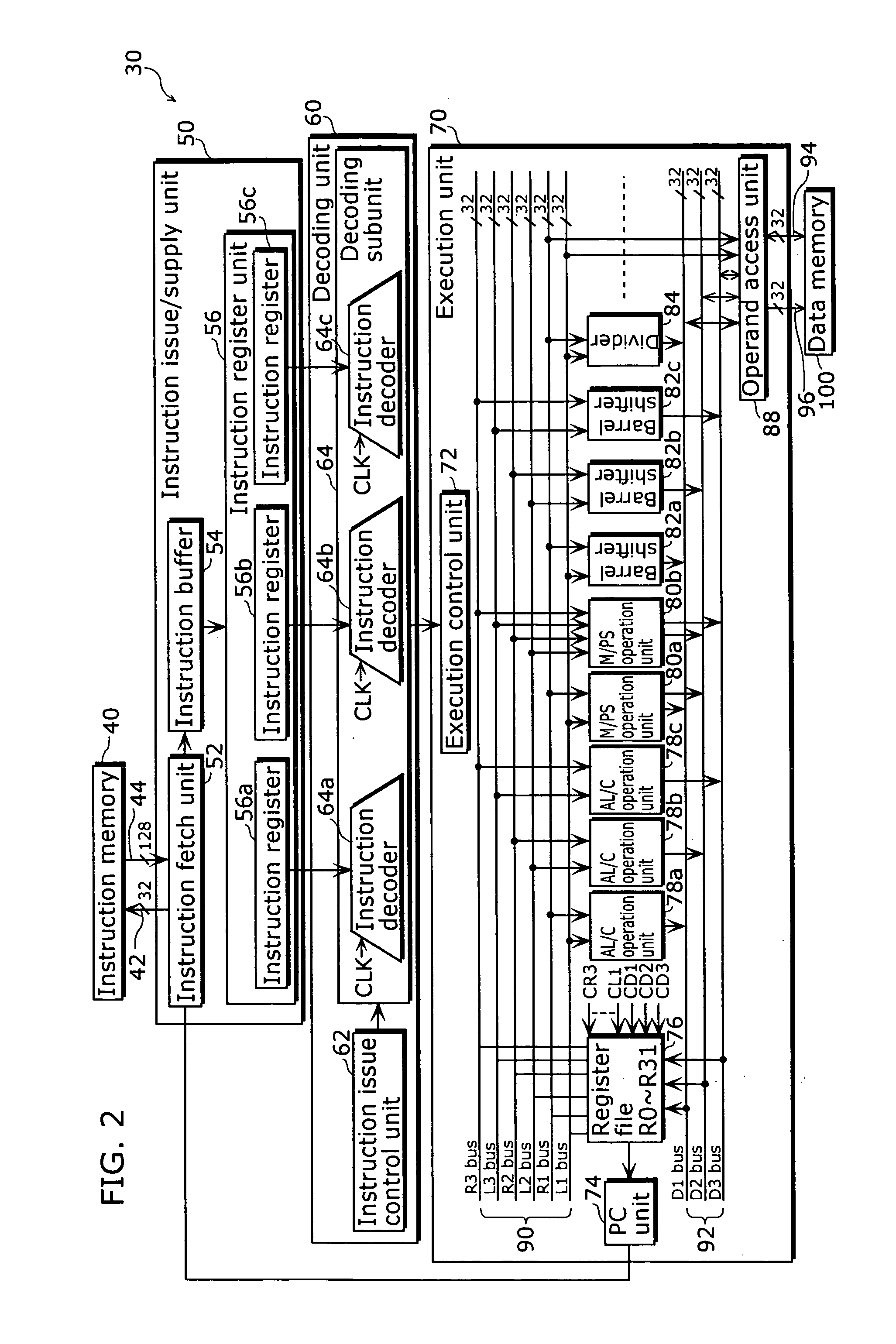

Compiler apparatus and compilation method

InactiveUS20040154006A1Avoid changeReduce power consumptionEnergy efficient ICTSoftware engineeringMachine instructionInstruction cycle

A compiler apparatus that is capable of generating instruction sequences for causing a processor with parallel processing capability to operate with lower power consumption is a compiler apparatus that translates a source program into a machine language program for the processor including a plurality of execution units which can execute instructions in parallel and a plurality of instruction issue units which issue the instructions executed respectively by the plurality of execution units, and includes: a parser unit operable to parse the source program; an intermediate code conversion unit operable to convert the parsed source program into intermediate codes; an optimization unit operable to optimize the intermediate codes so as to reduce a hamming distance between instructions placed in positions corresponding to the same instruction issue unit in consecutive instruction cycles, without changing dependency between the instructions corresponding to the intermediate codes; and a code generation unit operable to convert the optimized intermediate codes into machine language instructions.

Owner:SOCIONEXT INC

Computer implemented machine learning method and system including specifically defined introns

InactiveUS6493686B1Loss in flexibilityImprove efficiencyProgramme-controlled manipulatorDigital computer detailsArray data structureAlgorithm

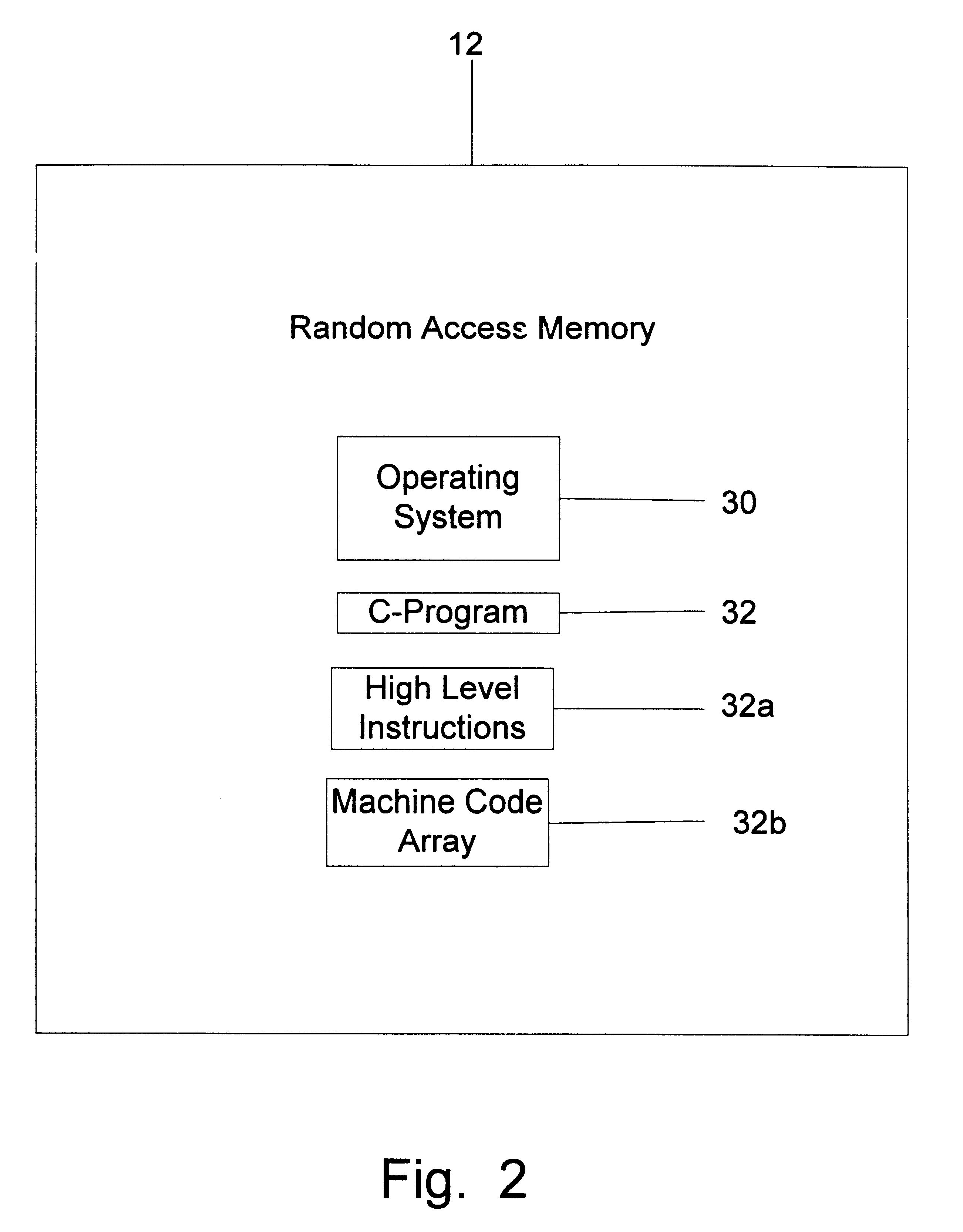

In a computer implemented learning and / or process control system, a computer model is constituted by the most currently fit entity in a population of computer program entities. The computer model defines fitness as a function of inputs and outputs. A computing unit accesses the model with a set of inputs, and determines a set of outputs for which the fitness is highest. This associates a sensory-motor (input-output) state with a fitness in a manner that might be termed "feeling".The learning and / or control system preferably utilizes a Compiling Genetic Programming System (CGPS) in which one or more machine code entities such as functions are created which represent solutions to a problem and are directly executable by a computer. The programs are created and altered by a program in a higher level language such as "C" which is not directly executable, but requires translation into executable machine code through compilation, interpretation, translation, etc. The entities are initially created as an integer array that can be altered by the program as data, and are executed by the program by recasting a pointer to the array as a function type. The entities are evaluated by executing them with training data as inputs, and calculating fitnesses based on a predetermined criterion. The entities are then altered based on their fitnesses using a genetic machine learning algorithm by recasting the pointer to the array as a data (e.g. integer) type. This process is iteratively repeated until an end criterion is reached.

Owner:FRANCONE FR D +2

Optimized SQL code generation

ActiveUS20050027701A1Reduce and minimize compilation timeReduce and minimize execution timeDigital data information retrievalData processing applicationsExecution planSQL

This invention relates generally to a system for processing database queries, and more particularly to a method for generating high level language or machine code to implement query execution plans. The present invention provides a method for generating executable machine code for query execution plans, that is adaptive to dynamic runtime conditions, that is compiled just in time for execution and most importantly, that avoids the bounds checking, pointer indirection, materialization and other similar kinds of overhead that are typical in interpretive runtime execution engines.

Owner:IBM CORP

Program optimization method, and compiler using the same

InactiveUS6817013B2Short processing timeEfficient executionSoftware engineeringDigital computer detailsBasic blockSource code

An optimization method and apparatus for converting source code for a program written in a programming language into machine language. The program includes a basic block as a unit to estimate an execution time for the program to be processed, generating a nested tree that represents the connections of the basic blocks using a nesting structure, when a conditional branch is accompanied by a node in the nested tree, employing the execution time estimated by using the basic blocks as units to obtain an execution time at the node of the program when a conditional branching portion of a program is directly executed and when the conditional branching portion is executed in parallel, and defining the node as a parallel execution area group when the execution time required for the parallel execution is shorter or dividing multiple child nodes of the nodes into multiple parallel execution areas.

Owner:INT BUSINESS MASCH CORP

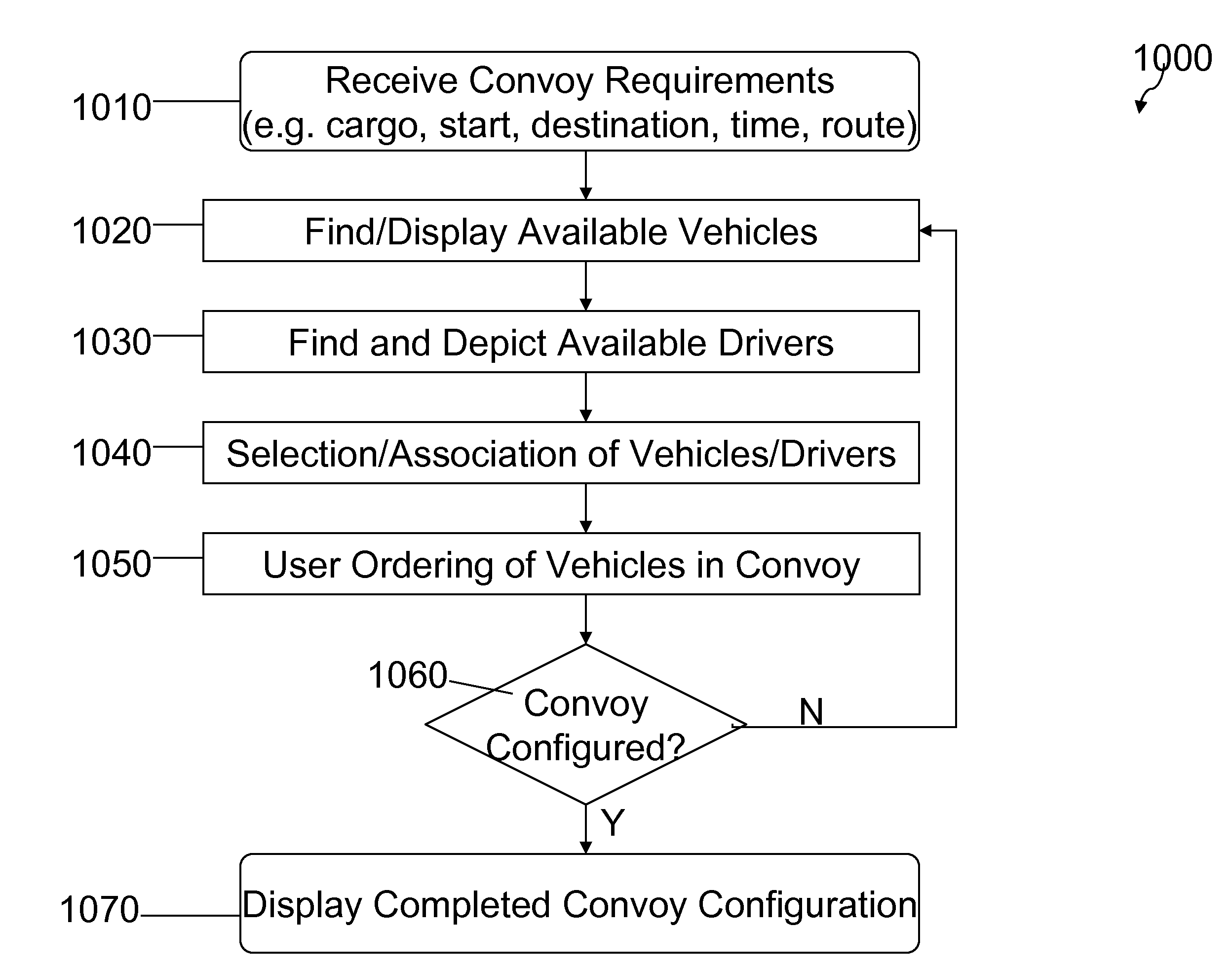

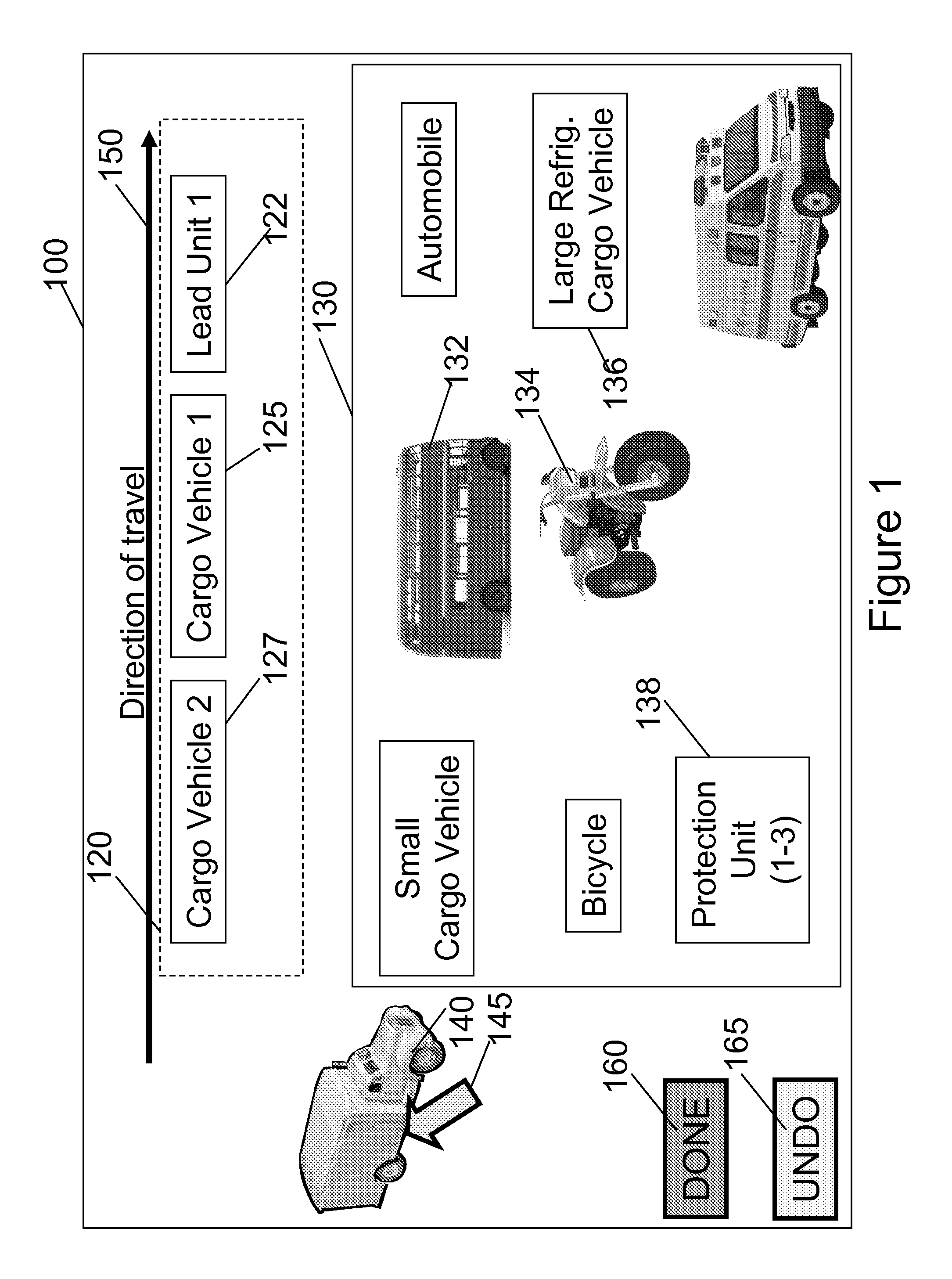

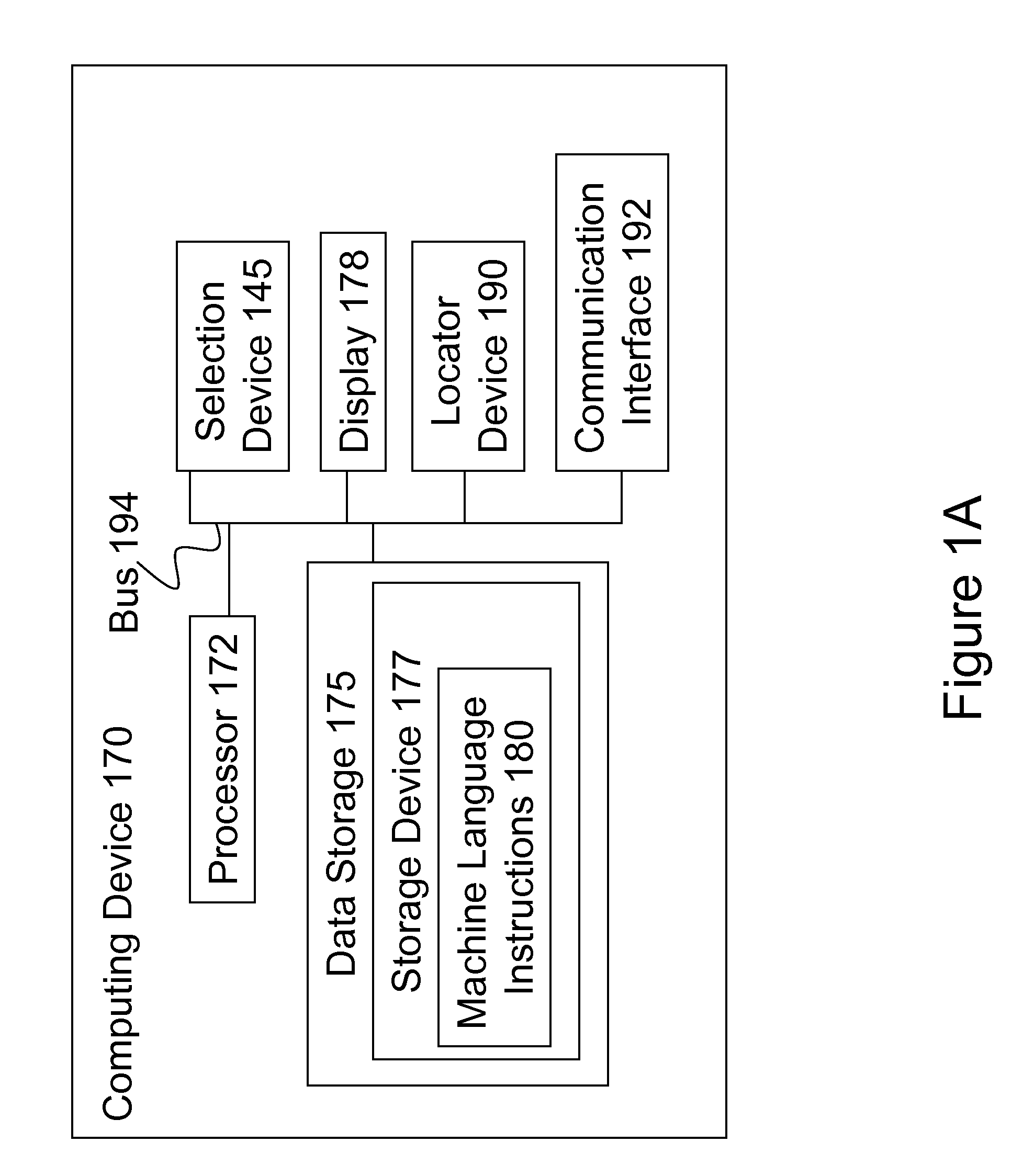

Vehicle deployment planning system

InactiveUS20090157461A1Road vehicles traffic controlNavigation instrumentsPlanning methodMachine code

A vehicle deployment planning method and system are provided for planning a convoy that travels on at least one roadway using a convoy planning tool. The tool includes a computer processor, data storage, and machine language instructions that enable the tool to perform the following tasks. The tool finds one or more available vehicles for the convoy. The tool displays the one or more available vehicles in a vehicle corral. The user of the tool selects one or more vehicles from the vehicle corral. The user places the selected one or more vehicles in a position in the convoy. The tool displays the placed one or more vehicles in the convoy. The tool determines a convoy configuration is complete and then displays the complete convoy configuration.

Owner:HONEYWELL INT INC

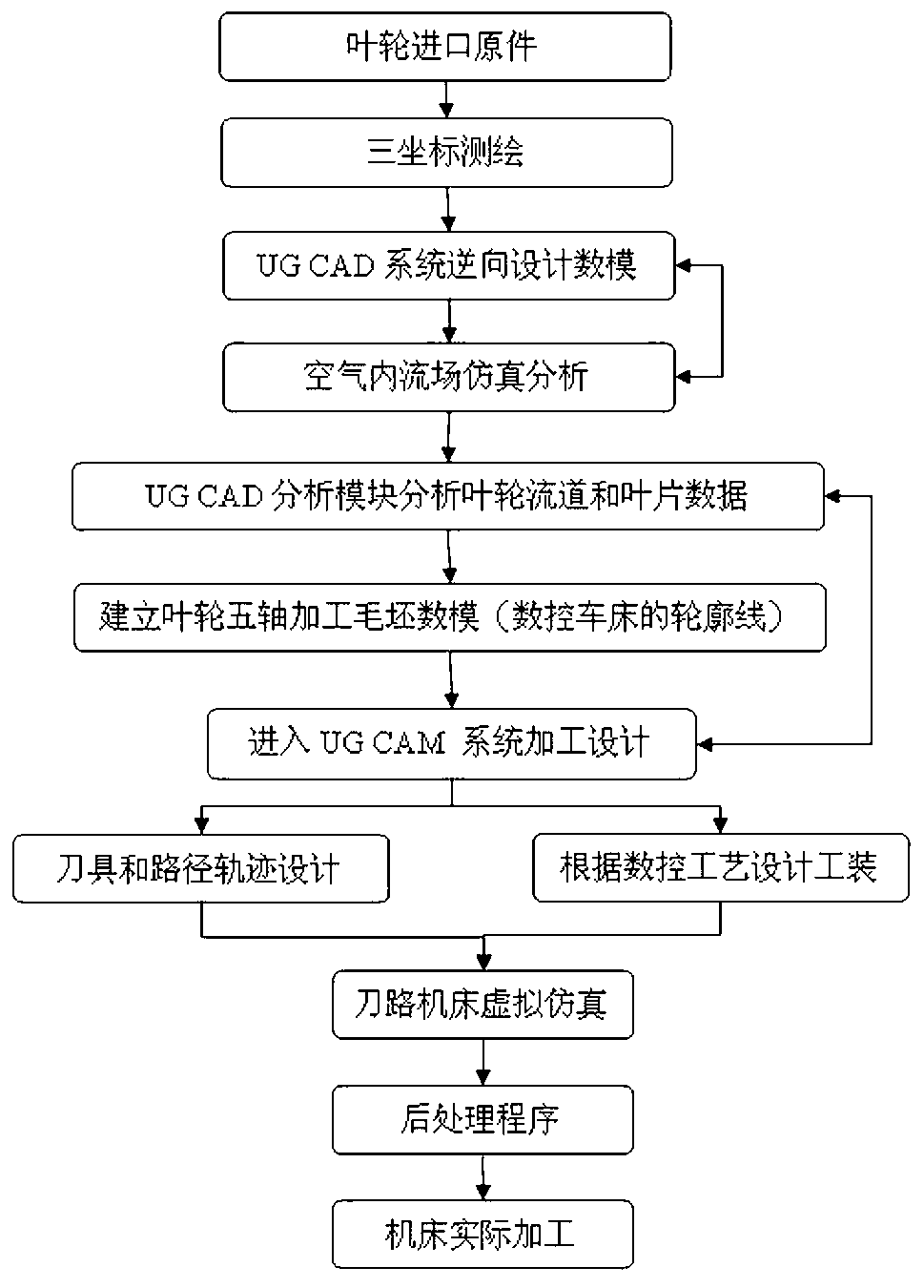

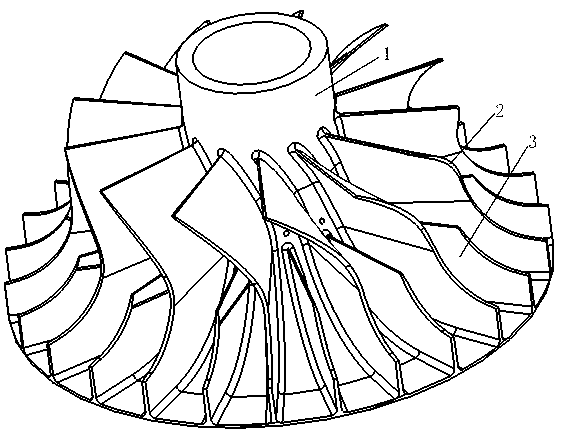

Integral impeller 5-axis machining method based on UG NX system platform

The invention discloses an integral impeller 5-axis machining method based on a UG NX system platform and relates to a technical scheme of a 5-axis numerical control processing technology for an integral impeller researched and developed under a UGNX 7.5 computer-aided design (CAD) system platform. The method comprises using a reversal design technique under the UGNX 7.5 CAD system platform to obtain compressor wheel digifax; acquiring corresponding data from the digifax to establish blank digifax on the digifax according to numerical control technology requirements; selecting a machine tool: using a 5-axis linkage machining center; selecting a cutter according to the geometrical shape and machining materials of an impeller and selecting the cutter with a diameter as large as possible as long as the passage dimension allows; and setting the impeller machining track: UGNX, selecting an appropriate machining method and selecting allowances for rough and finish machining, outputting 5-axis machining center machine tool machining codes for being called by the 5-axis linkage machining center.

Owner:NO 60 RES INST OF GENERAL STAFF DEPT PLA

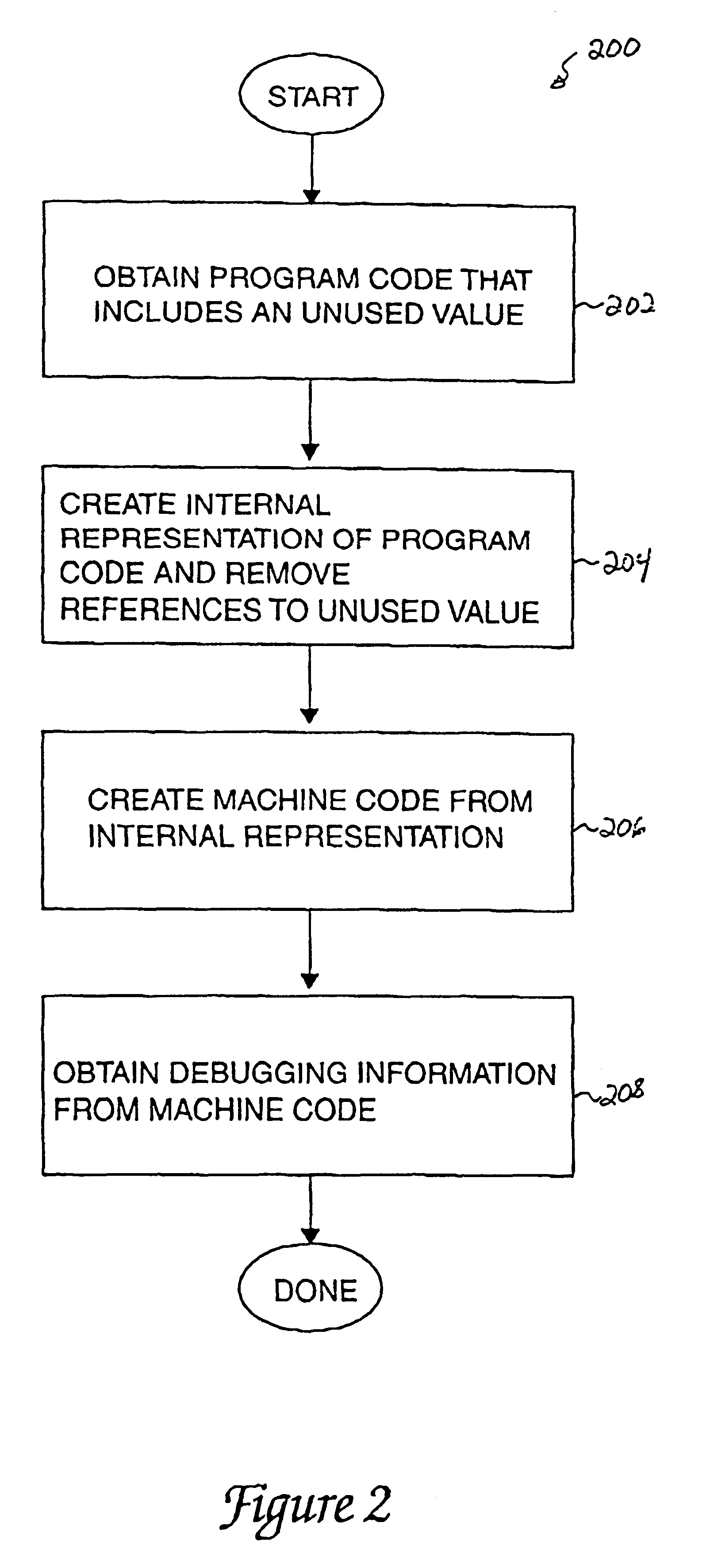

Method and apparatus for debugging optimized code

InactiveUS6553565B2Software testing/debuggingSpecific program execution arrangementsCode segmentBreak point

Methods and apparatus for providing a substantially full set of state information to a debugger, without significantly compromising system performance, in order to debug optimized computer program code are disclosed. According to one aspect of the present invention, a method for obtaining information associated with program code includes adding a segment of code, which includes a representation that is effectively not used after it is computed, to the program code. Debugging code is added in proximity to the segment of code, and machine code is generated from the program code. The machine code includes a break point that is associated with the debugging code, and includes an instruction at the breakpoint. Finally, the method includes replacing the instruction at the break point with a branch instruction that is arranged to cause the debugging code to execute.

Owner:ORACLE INT CORP

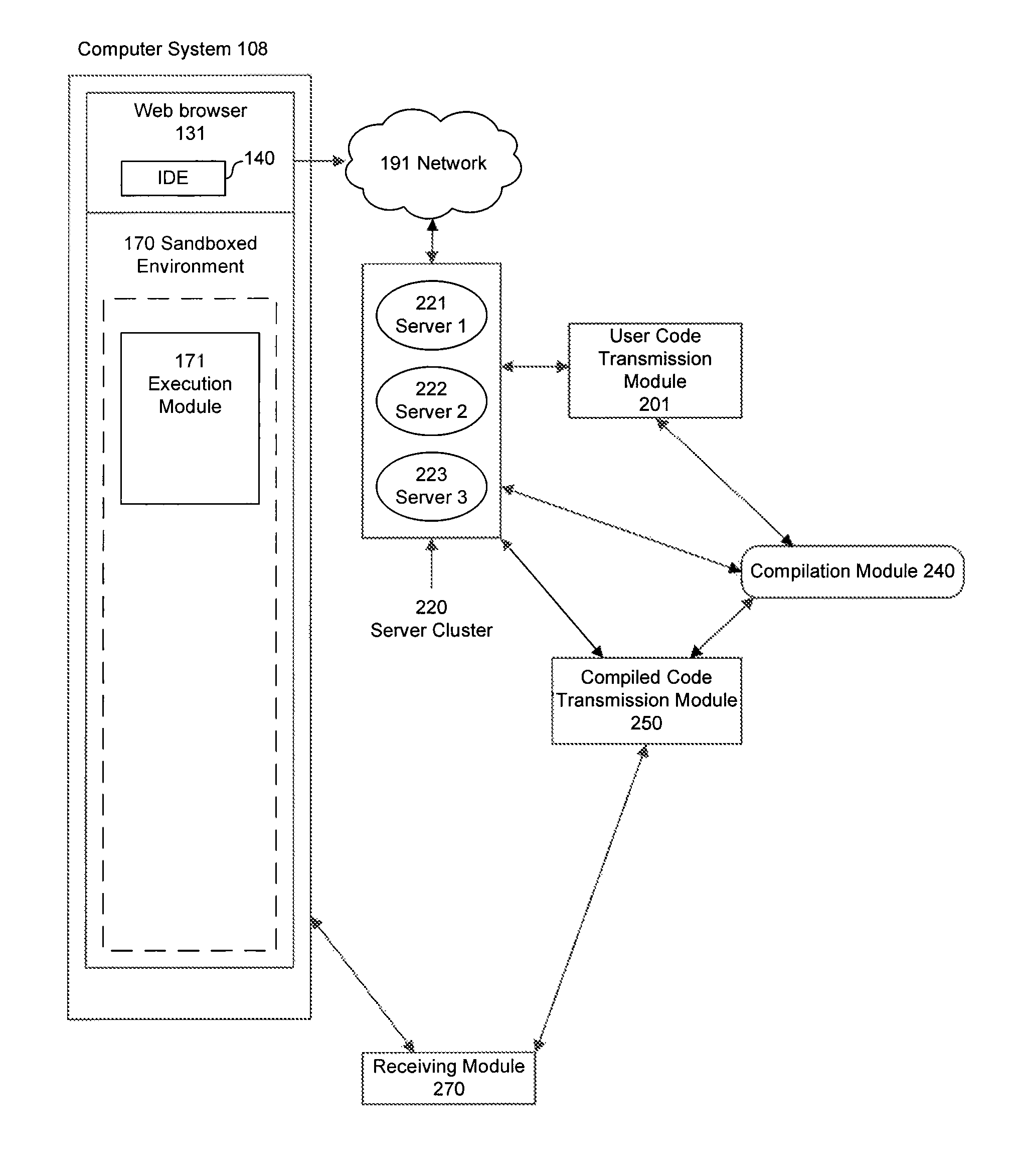

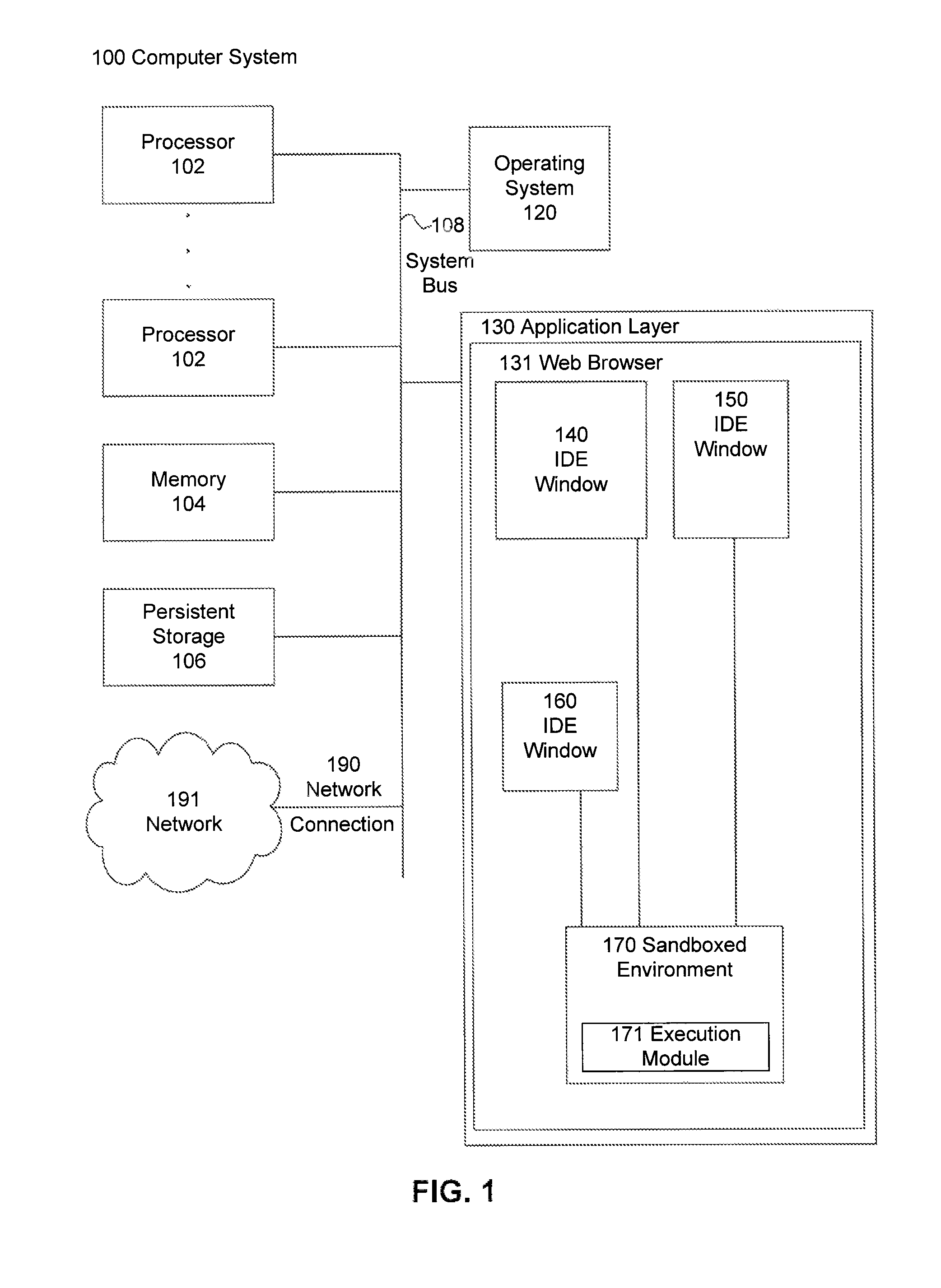

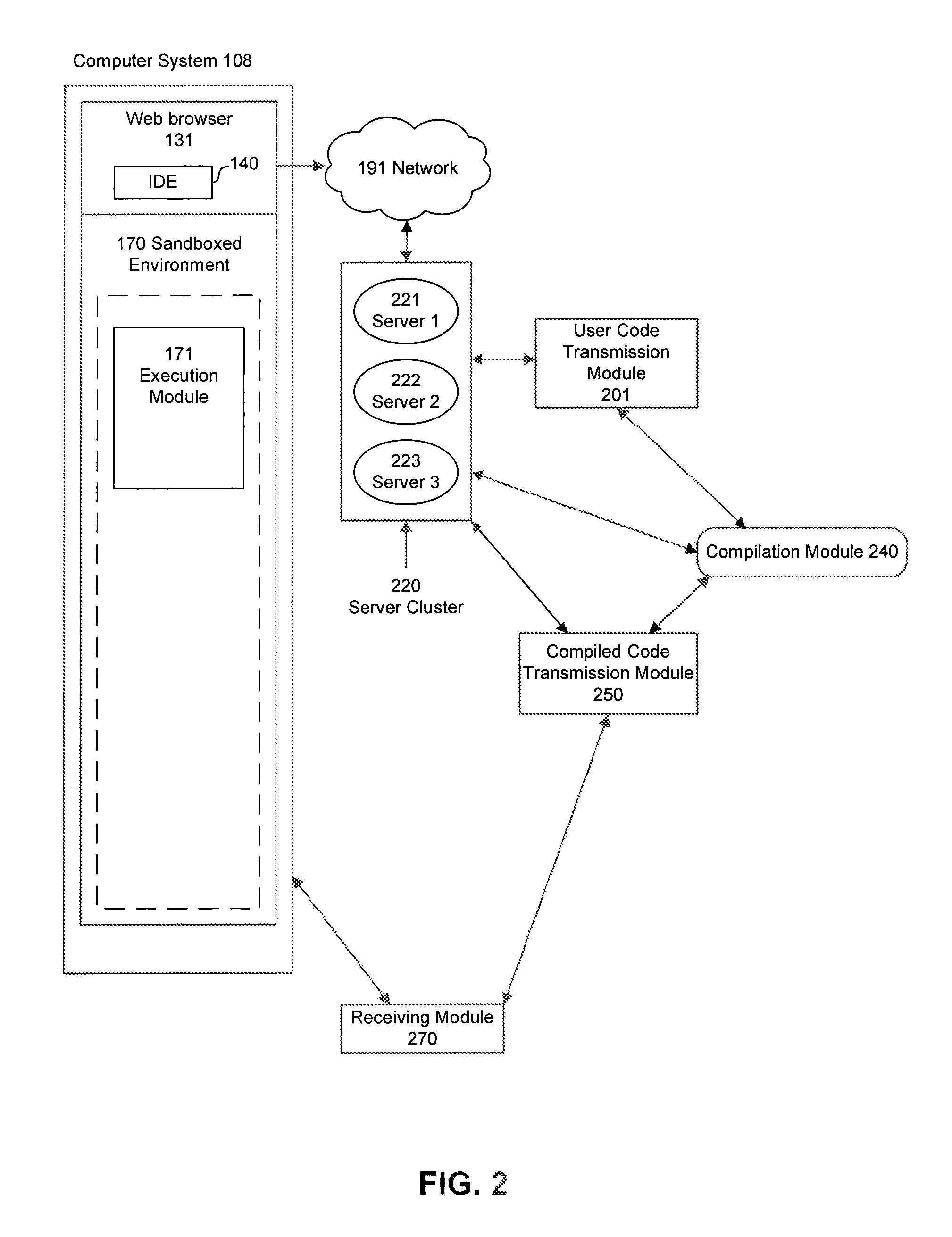

Integrated development environment with network-based compilation and sandboxed native machine-language capabilities

InactiveUS8281288B1Improve performanceEasy to compileMultiple digital computer combinationsSoftware designWeb browserNetwork connection

An IDE is provided by a web browser on a client machine, the IDE having a document editor that allows a user to generate source code. The source code is transmitted from the client machine to one or more servers via a network connection to be compiled into compiled native machine instructions. The compiled native machine instructions are received from the one or more servers by the client machine. The compiled native machine instructions are executed in a sandboxed environment on the client machine, such that system calls originating from the compiled native machine instructions that present a security risk are blocked using the sandboxed environment and system calls originating from the compiled native machine instructions that do not present a security risk are allowed in the sandboxed environment.

Owner:GOOGLE LLC

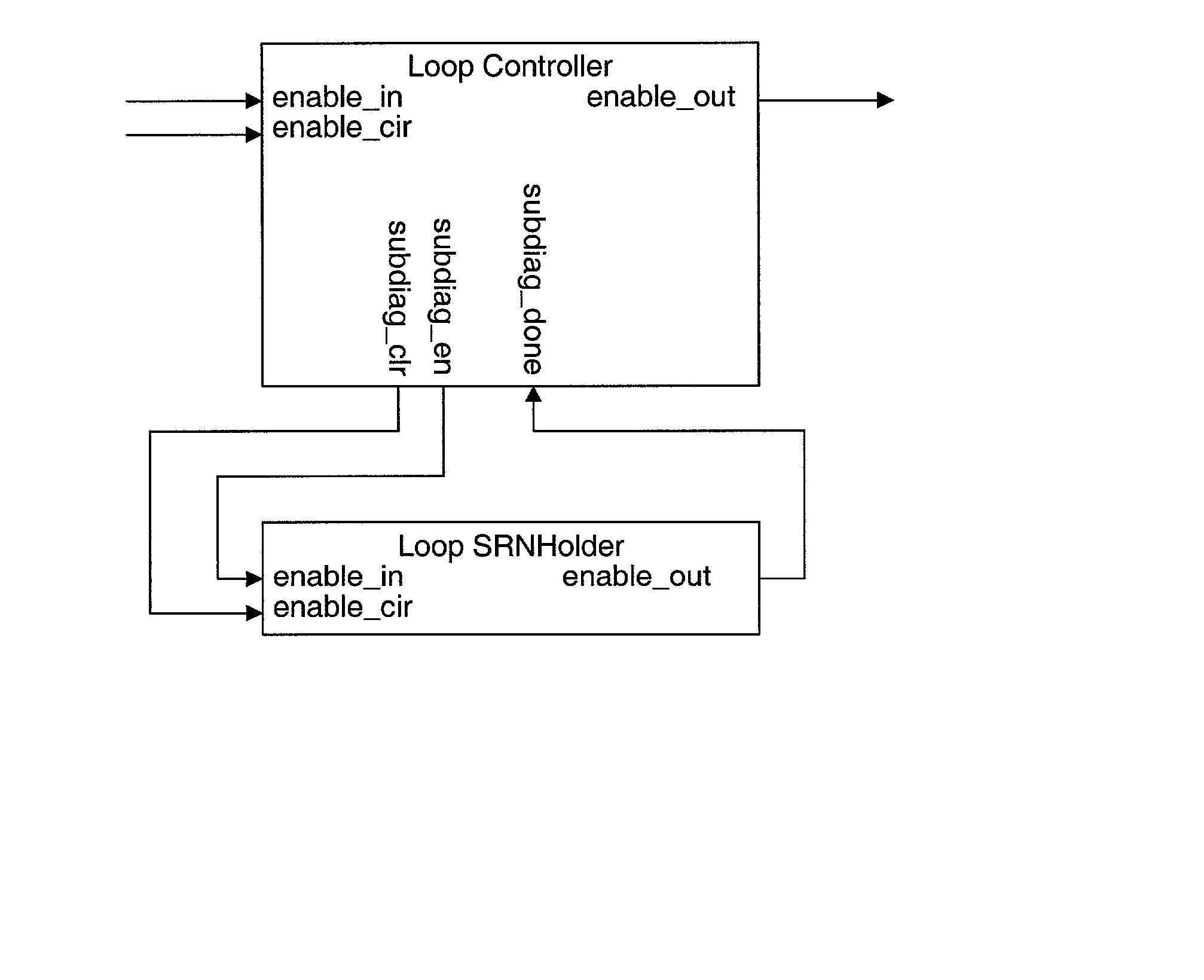

Specifying and targeting portions of a graphical program for execution by multiple targets

InactiveUS6934668B2Detecting faulty hardware by remote testComputation using non-denominational number representationGraphicsComputer architecture

A computer-implemented system and method for generating a hardware implementation of graphical code. The method comprises first creating a graphical program. A first portion of the graphical program may optionally be compiled into machine code for execution by a CPU. A second portion of the graphical program is converted into a hardware implementation according to the present invention. The operation of converting the graphical program into a hardware implementation comprises exporting the second portion of the graphical program into a hardware description, wherein the hardware description describes a hardware implementation of the second portion of the graphical program, and then configuring a programmable hardware element utilizing the hardware description to produce a configured hardware element. The configured hardware element thus implements a hardware implementation of the second portion of the graphical program.

Owner:NATIONAL INSTRUMENTS

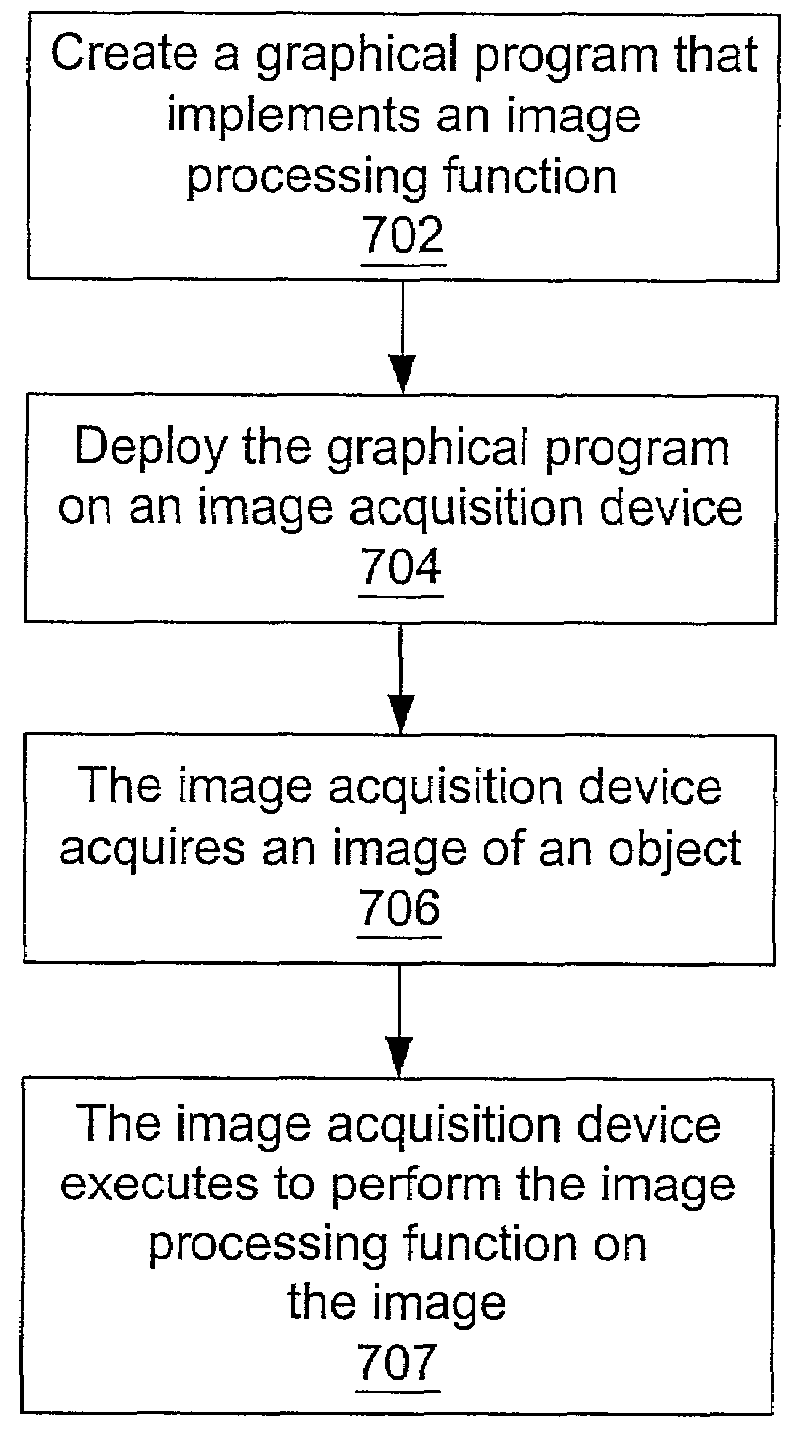

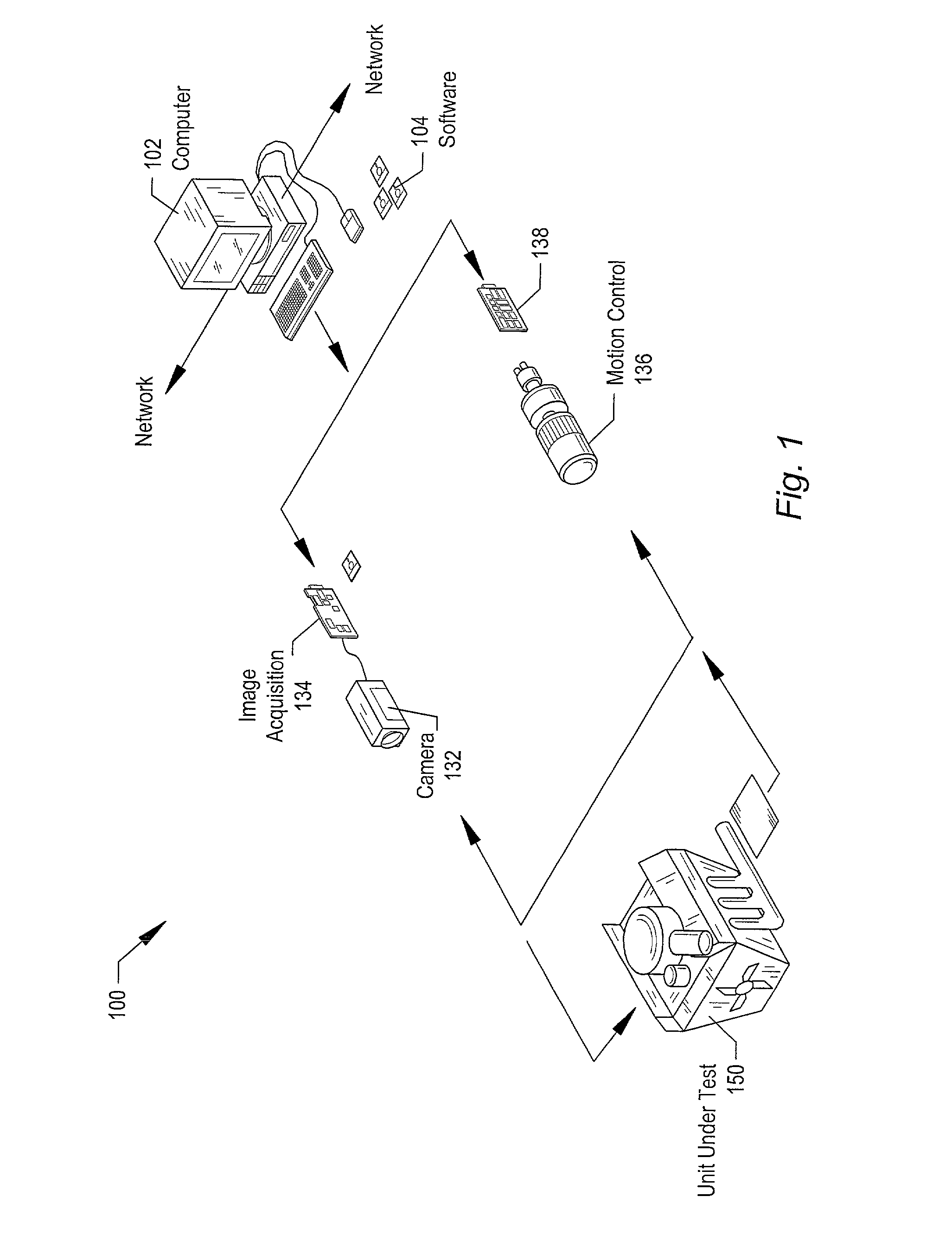

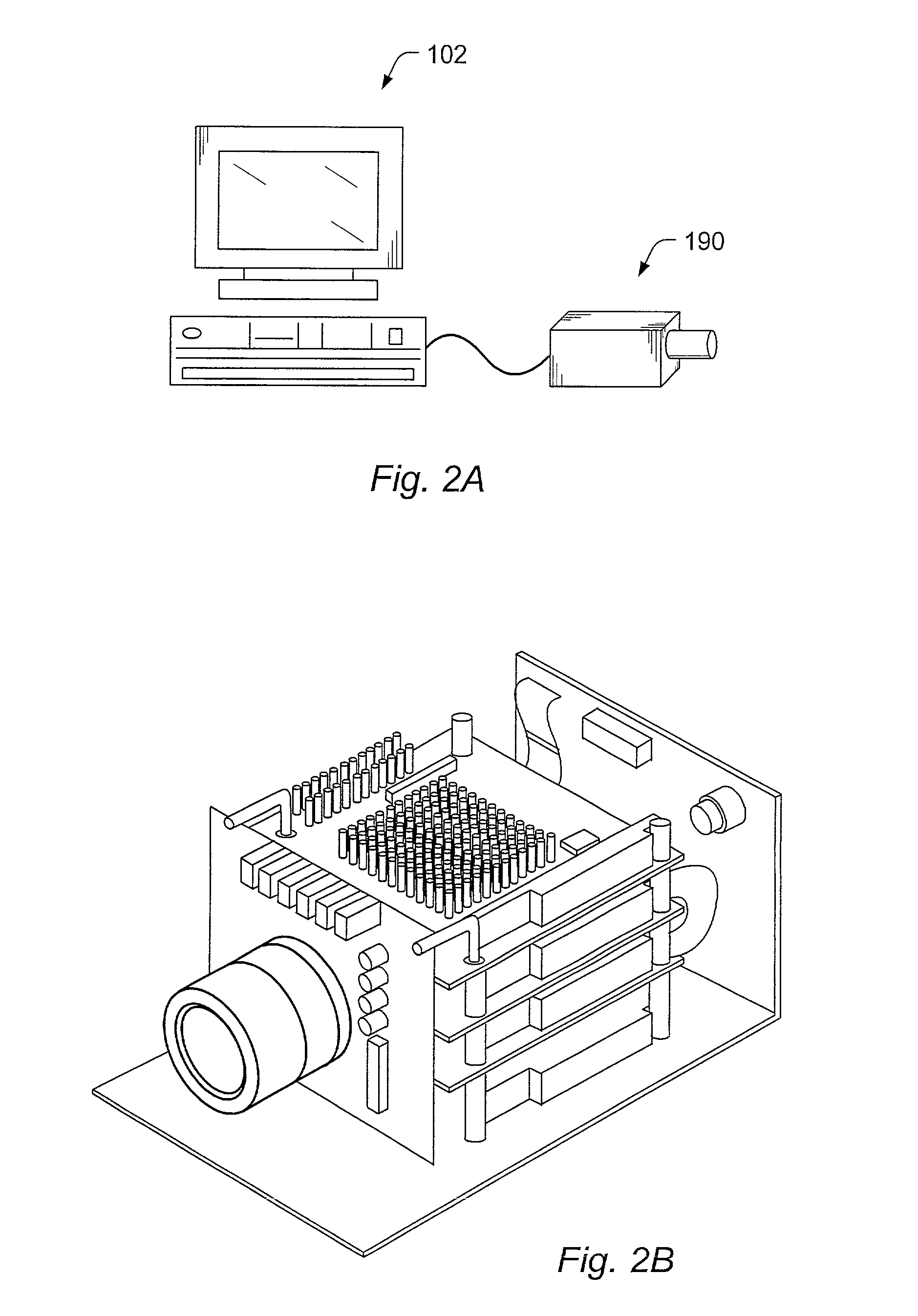

System and method for deploying a graphical program on an image acquisition device

InactiveUS6971066B2Television system detailsDetecting faulty hardware by remote testComputer hardwareComputer architecture

A computer-implemented system and method for deploying a graphical program onto an image acquisition (IMAQ) device. The method may operate to configure an image acquisition (IMAQ) device to perform image processing or machine vision functions, wherein the device includes a programmable hardware element and / or a processor and memory. The method comprises first creating a graphical program which implements the image processing or machine vision function. A portion of the graphical program may be converted into a hardware implementation on a programmable hardware element, and a portion may optionally be compiled into machine code for execution by a CPU. The programmable hardware element is thus configured utilizing a hardware description and implements a hardware implementation of at least a portion of the graphical program. The CPU-executable code may be executed by a computer coupled to the IMAQ device, or by a processor / memory on the IMAQ device.

Owner:NATIONAL INSTRUMENTS

Secure method and system for creating a plug and play network

ActiveUS20060168647A1Improve securityReduce inconvenienceDigital data processing detailsUser identity/authority verificationAuthorizationData library

A first device is automatically authorized to participate in a secure network by associating the first device with network access information in a machine-accessible format that can serve as a basis for the authorization. The network access information may be presented to a machine code reader in communication with a second device participating in the secure network. Upon the network access information being presented to the reader, the second device authorizes the first device associated with the identifier to participate in the secure network. Alternatively, the network access information may be registered with an authorization database in which the network access information is associated with a network identifier or an identifier representing a user associated with the secure network. The second device is signaled, by means of a signal button or comparable act, to access the authorization database to verify the first device is authorized to participate in the network.

Owner:MICROSOFT TECH LICENSING LLC

Same code base in irrigation control devices and related methods

Various embodiments are described in which different irrigation controllers in an irrigation control system have machine code having a same code base. In one implementation, a first irrigation control unit comprises a processor and a medium storing a first set of machine code to be executed by the processor. The first set is based on a portion of source code on which a second set of machine code stored in a second irrigation control unit is based, and the first and second sets not identical to each other. The first and second irrigation control units are in a predefined hierarchical control relationship. In one variation, the first and second control units have at least related operating systems. In another variation, a central controller includes machine code developed from at least a portion of the same source code as machine code in a remote controller for simulation or execution purposes.

Owner:RAIN BIRD CORP