Patents

Literature

2787 results about "Compiler" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

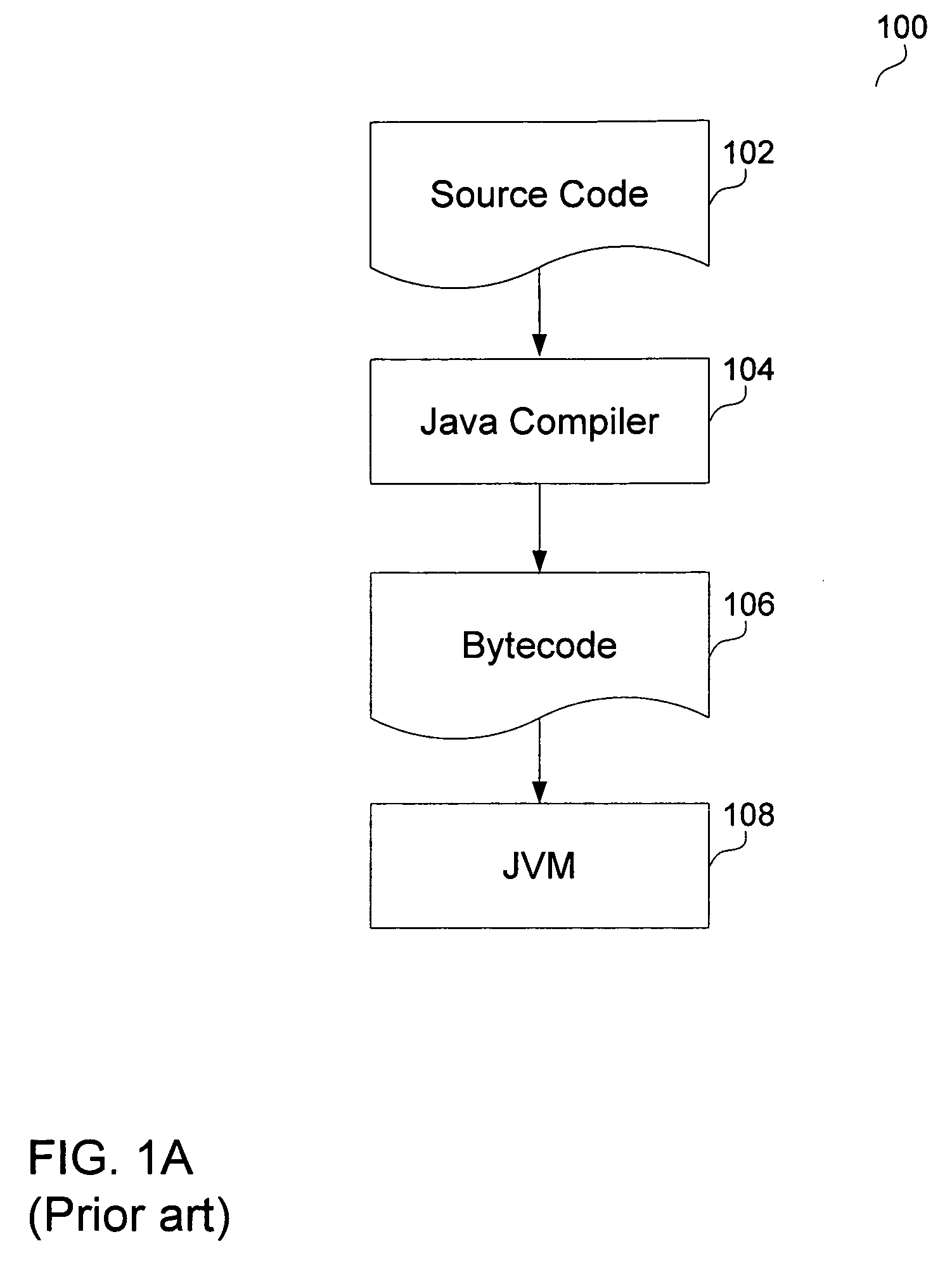

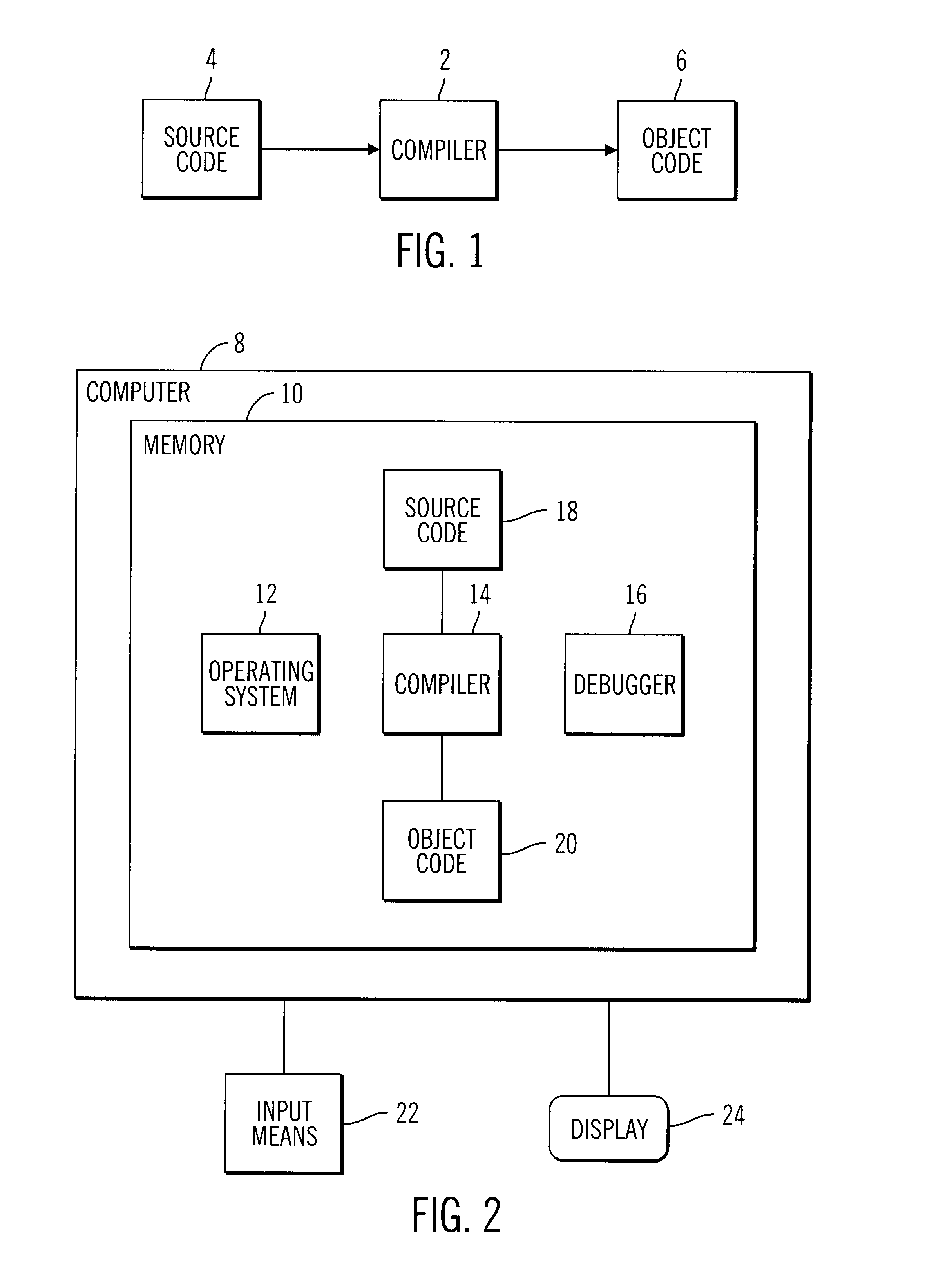

A compiler is a computer program that translates computer code written in one programming language (the source language) into another language (the target language). The name compiler is primarily used for programs that translate source code from a high-level programming language to a lower level language (e.g., assembly language, object code, or machine code) to create an executable program.

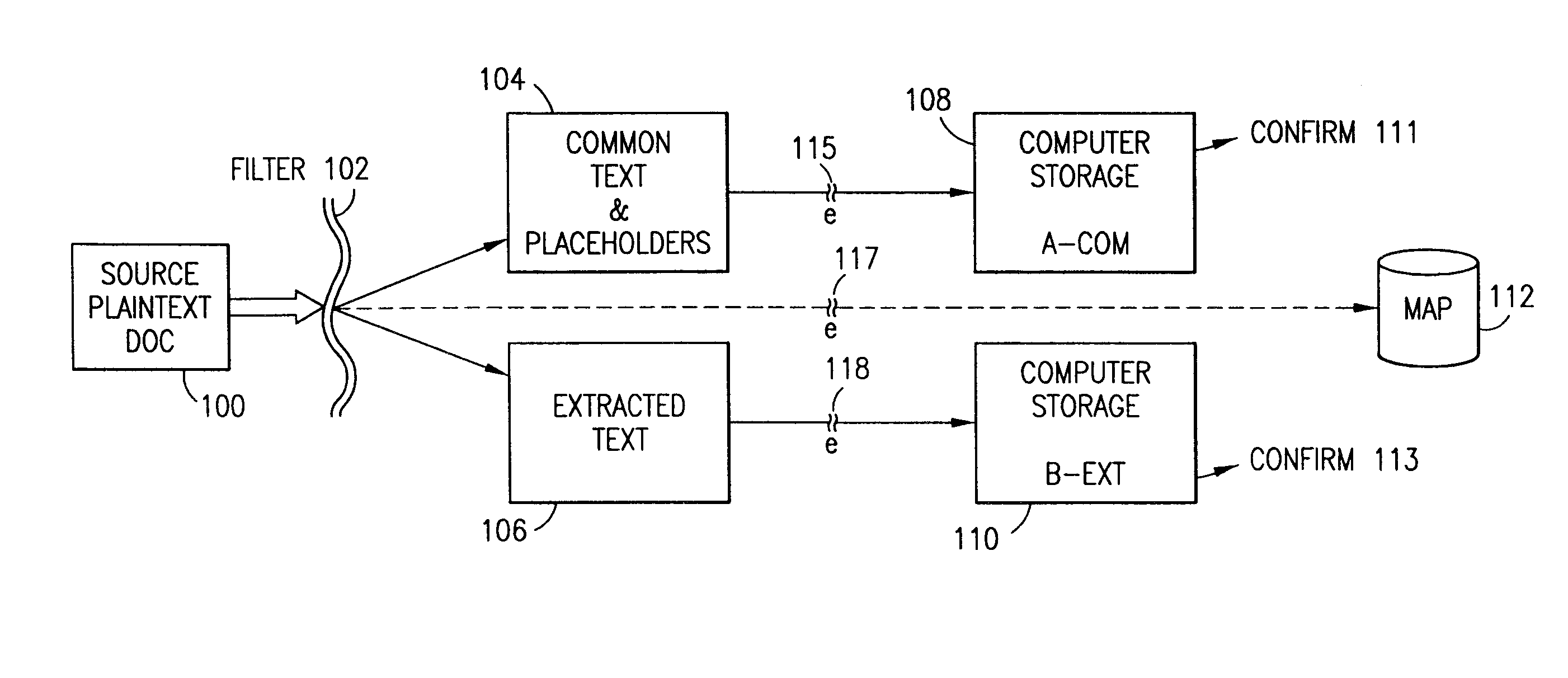

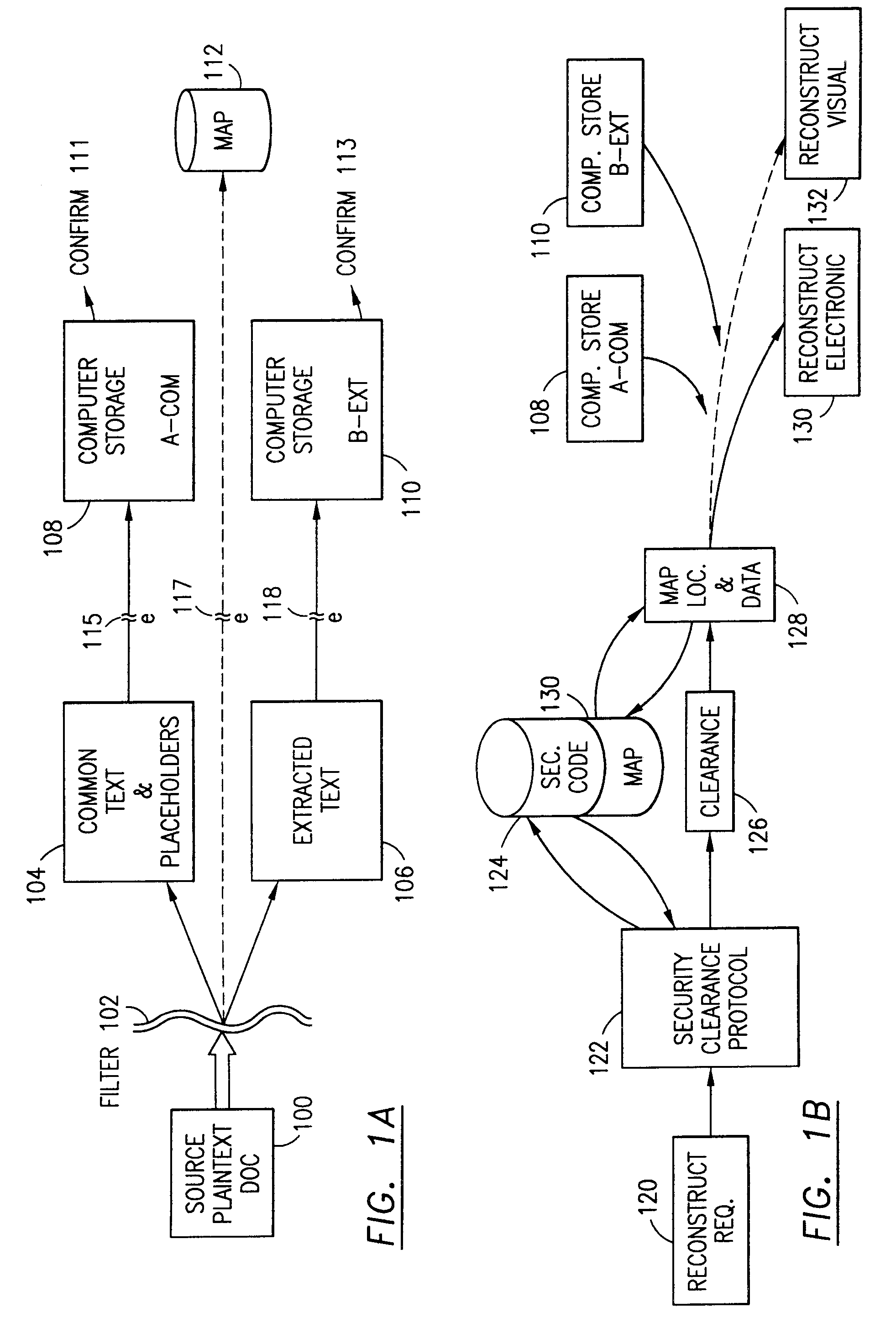

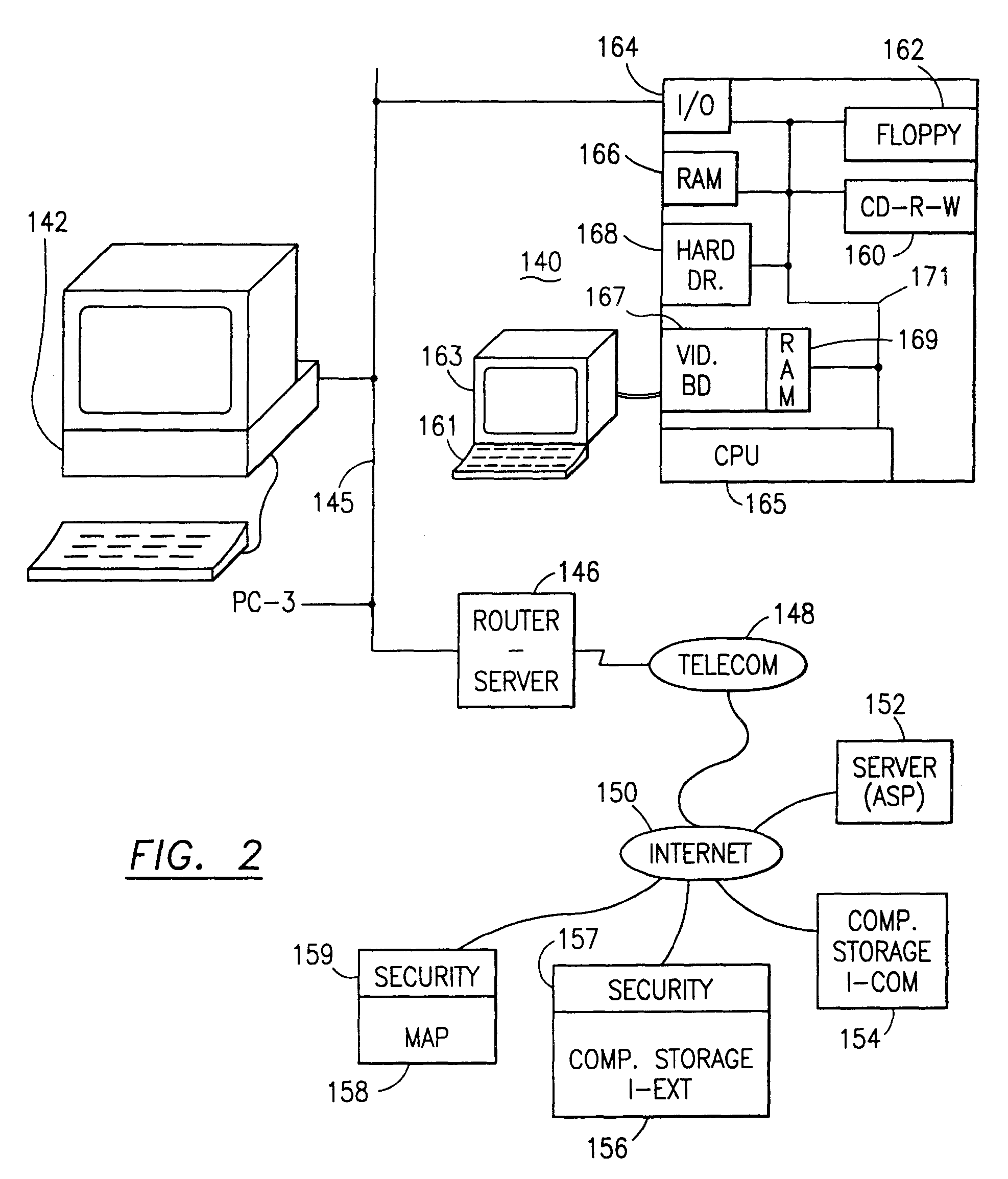

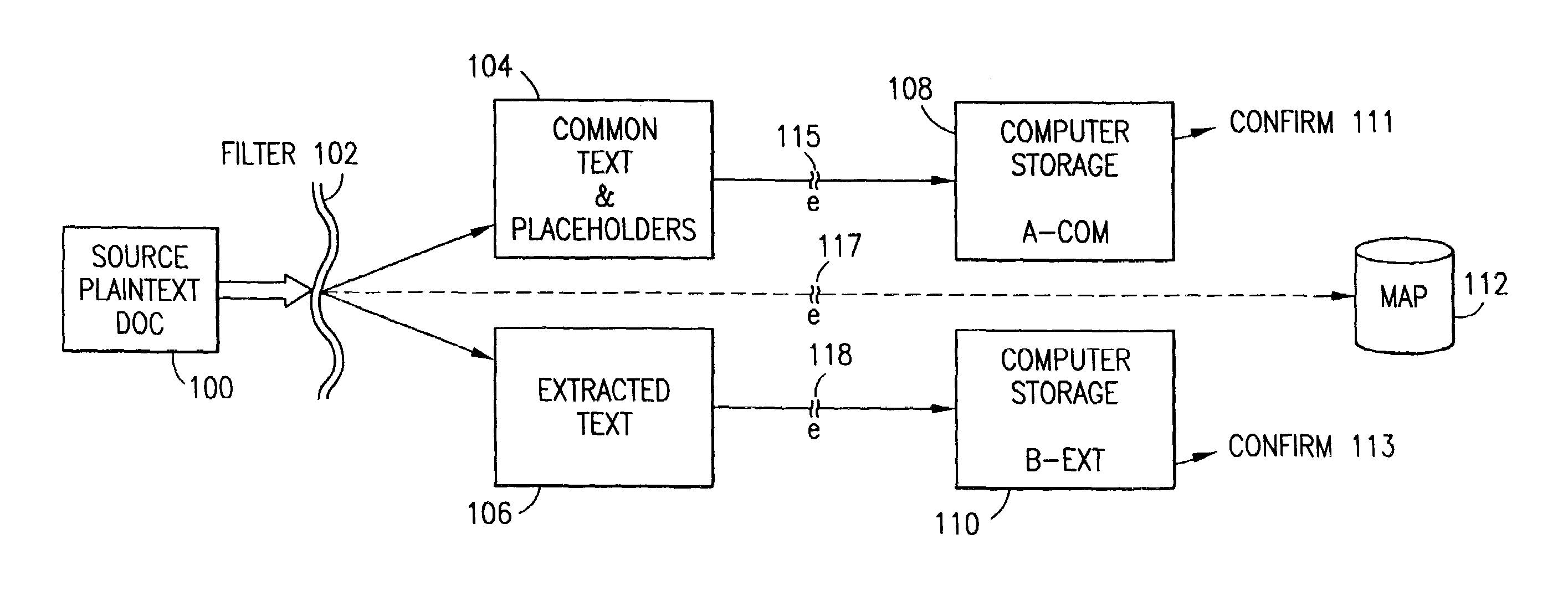

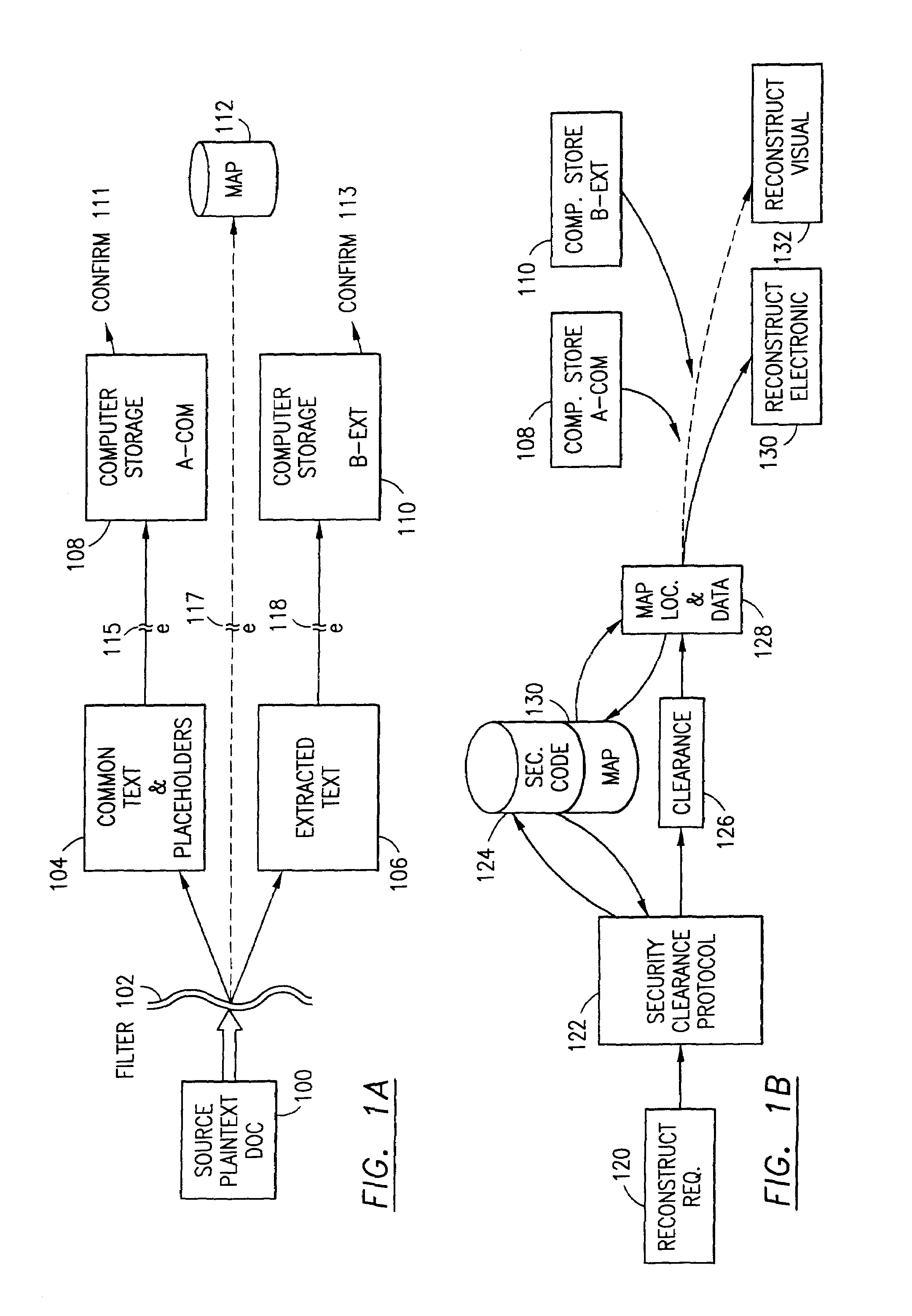

Data security system and method for separation of user communities

InactiveUS7140044B2Multiple keys/algorithms usageDigital data processing detailsInformation processingPlaintext

Data is secured in a computer network to transparently establish and manage a separation of user-based communities of interest based upon crypto-graphically separated, need to know, security levels. Data from a source document, data object or data stream is filtered to form subsets of extracted data and remainder data based upon security levels for the communities. Extracts are stored in assigned memories. Full or partial plaintext reconstruction is permitted only in the presence of assigned security clearance for the community of the inquiring party. Encryption, corresponding to security levels, establishes separation of secured data. The information processing system uses a data filter to extract security sensitive words, data objects, etc., a distributed storage system and a compiler is used to reconstruct plaintext based on security clearance. Multiple level encryption in one document is also available.

Owner:DIGITAL DOORS

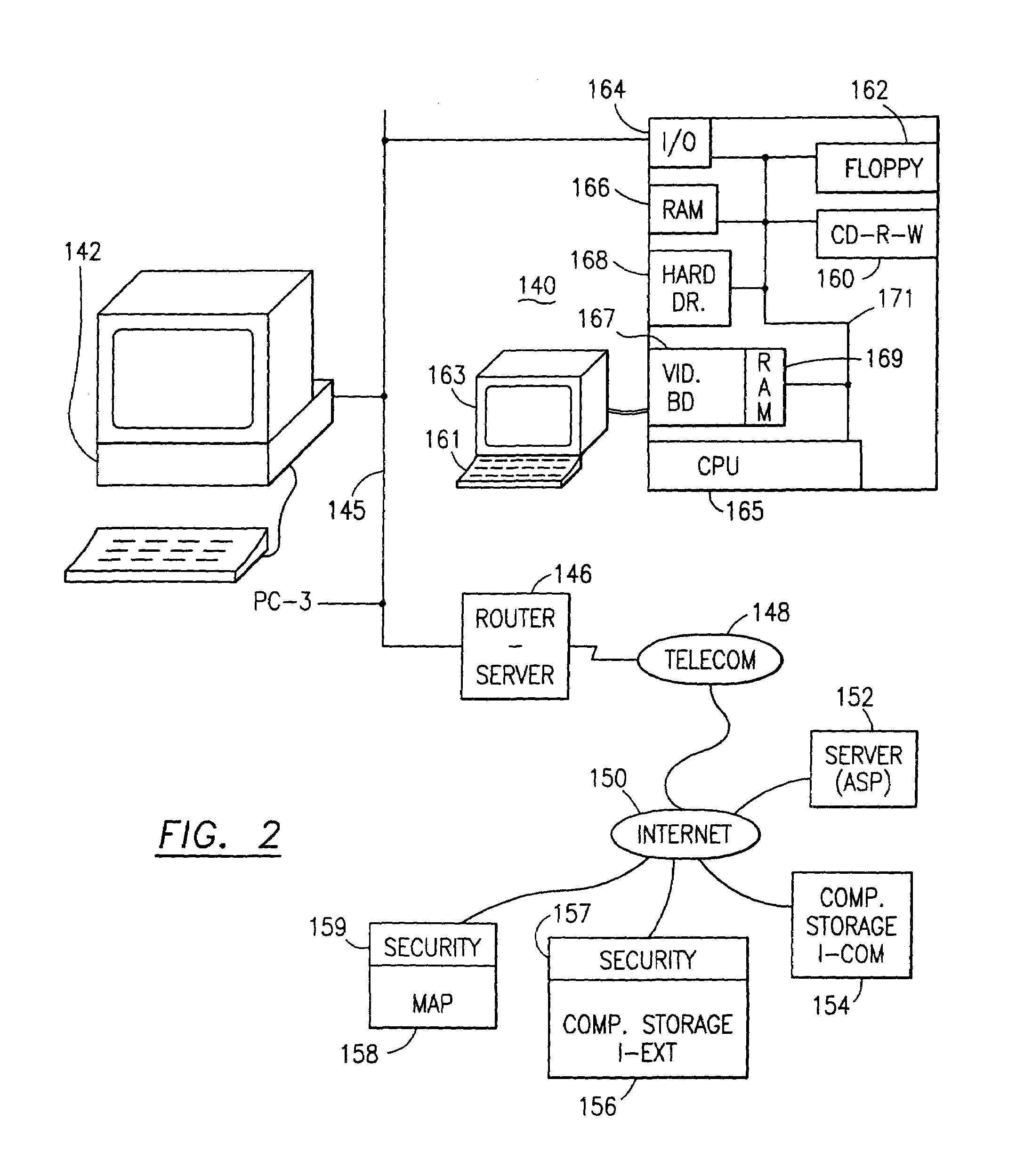

Data security system and method responsive to electronic attacks

ActiveUS7146644B2Ease overhead performanceHigh overhead performanceMemory loss protectionMultiple keys/algorithms usageInformation processingSelf adaptive

An adaptive method, system and program for securing data against a plurality of electronic and environmental events directed at computers utilizes a hacking monitor which generates attack warnings (such as a hacking warning) dependent upon the severity of the attack. Based upon these warnings, data is filtered to extract security sensitive words etc. and the extract and remainder data (if necessary) is stored in assigned memory. Full or partial reconstruction is permitted, manually or automatically, with a security clearance. Encryption is typically used dependent upon the warning. The information processing system includes a filter which is adjusted based upon the degree of attack warning to extract security sensitive words. A storage system stores extracted data and remainder data (if necessary) based upon the level of the warning and a compiler is used to reconstruct the data in the presence of the appropriate security clearance level.

Owner:DIGITAL DOORS

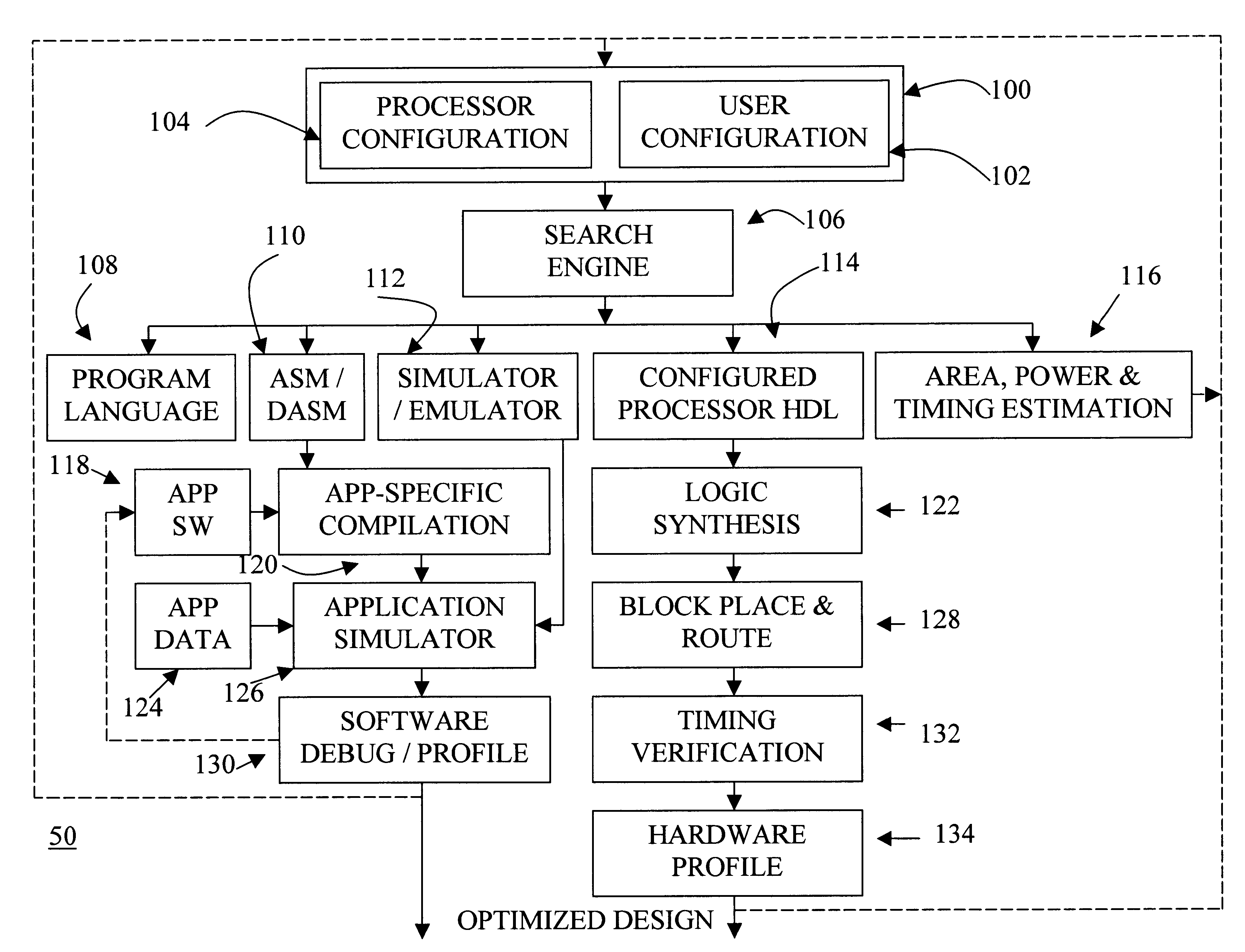

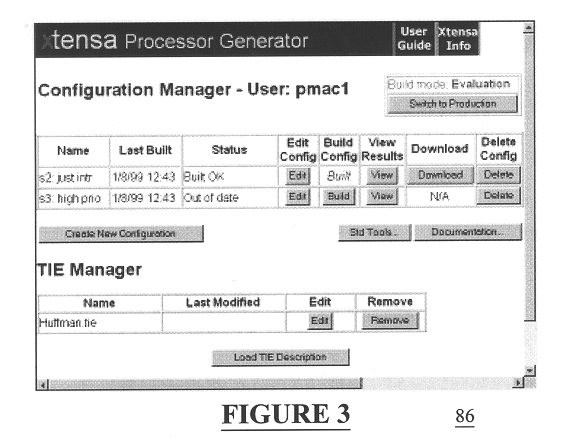

Automated processor generation system for designing a configurable processor and method for the same

InactiveUS6477683B1Decompilation/disassemblyCAD network environmentApplication softwareProcessor design

An automated processor design tool uses a description of customized processor instruction set extensions in a standardized language to develop a configurable definition of a target instruction set, a Hardware Description Language description of circuitry necessary to implement the instruction set, and development tools such as a compiler, assembler, debugger and simulator which can be used to develop applications for the processor and to verify it. Implementation of the processor circuitry can be optimized for various criteria such as area, power consumption, speed and the like. Once a processor configuration is developed, it can be tested and inputs to the system modified to iteratively optimize the processor implementation. By providing a constrained domain of extensions and optimizations, the process can be automated to a high degree, thereby facilitating fast and reliable development.

Owner:TENSILICA

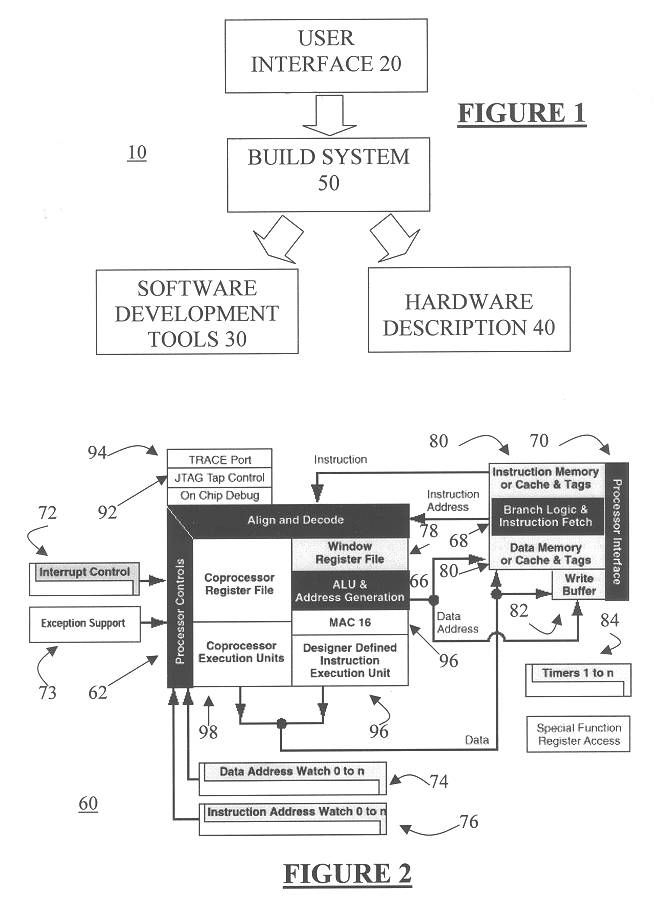

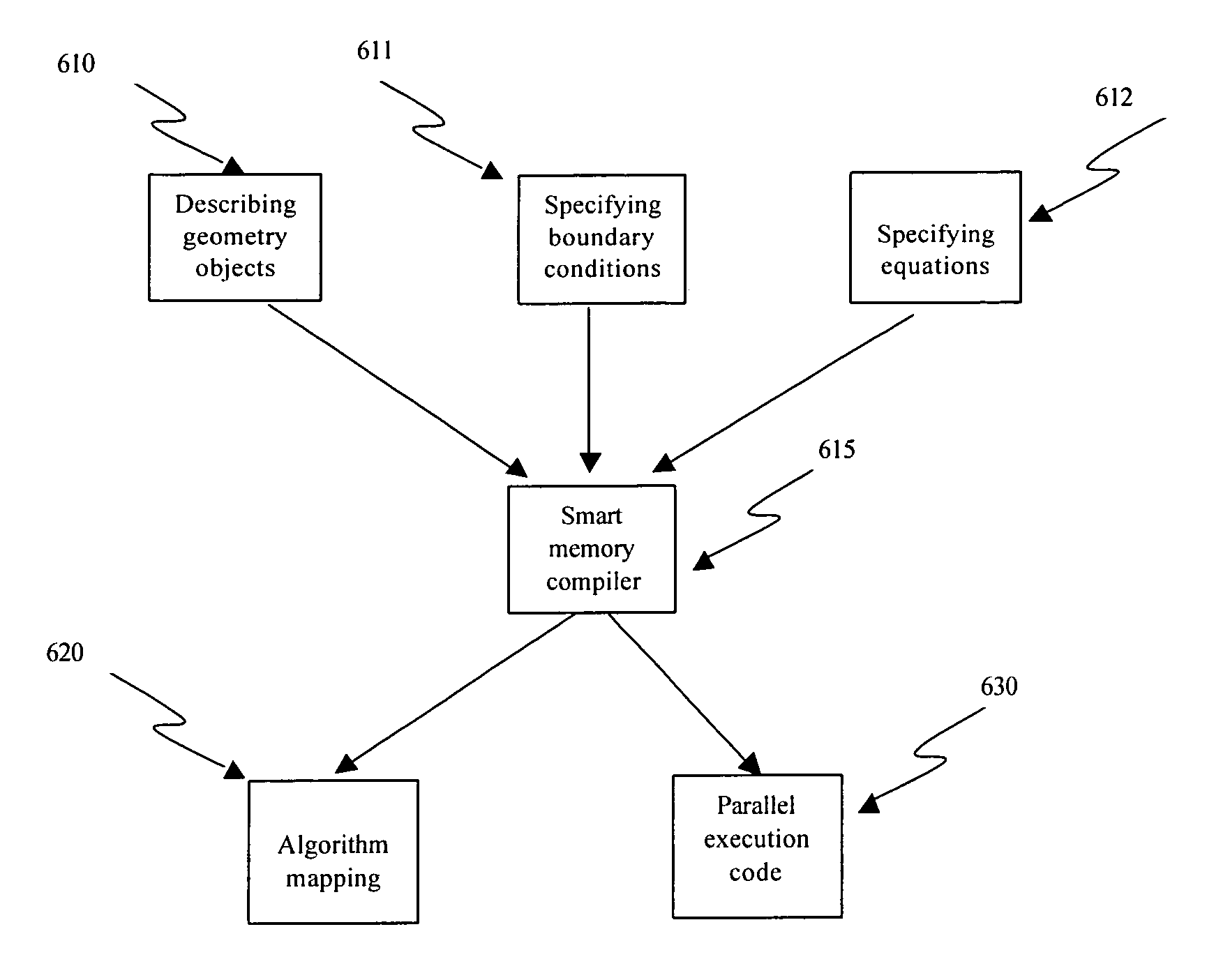

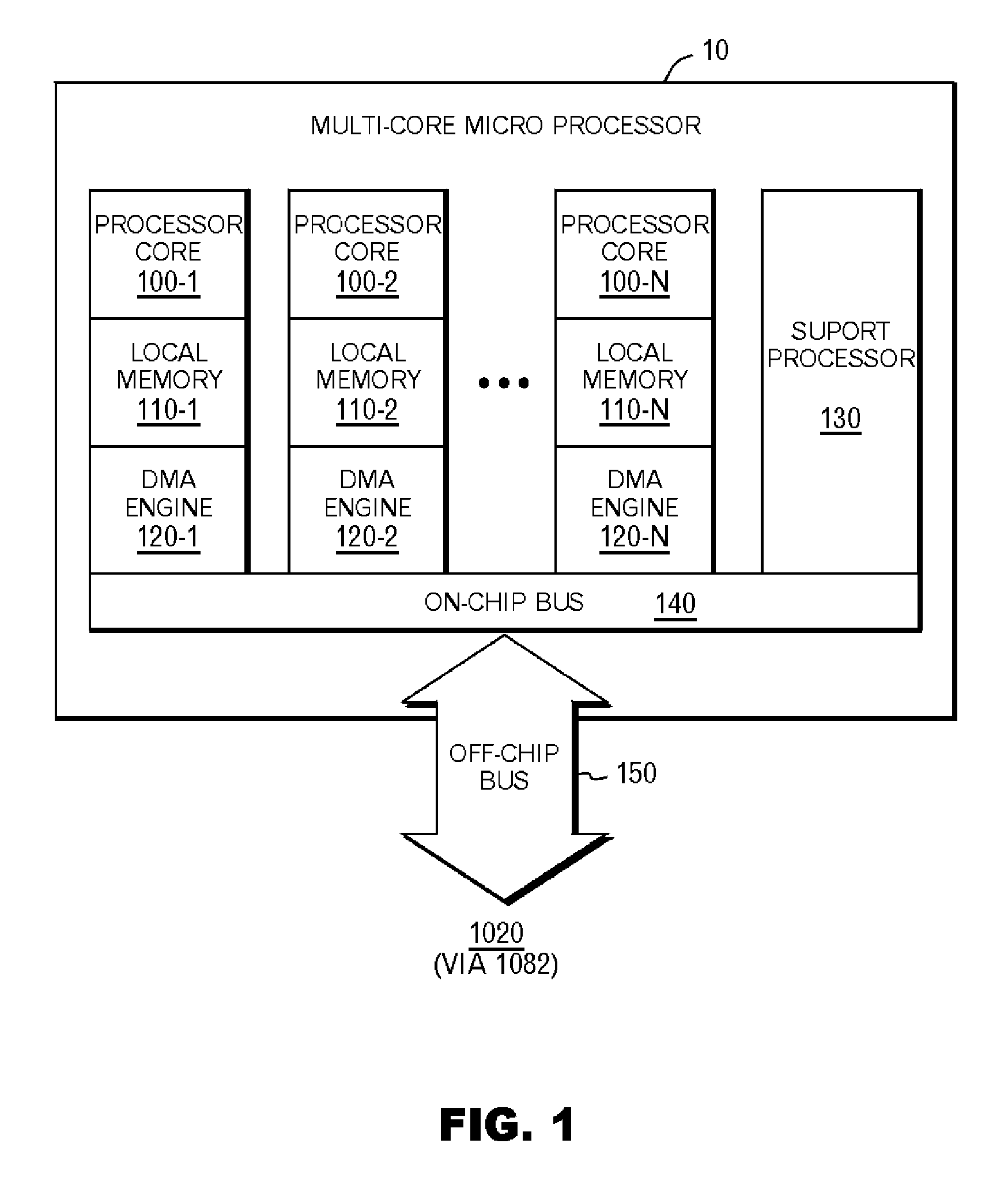

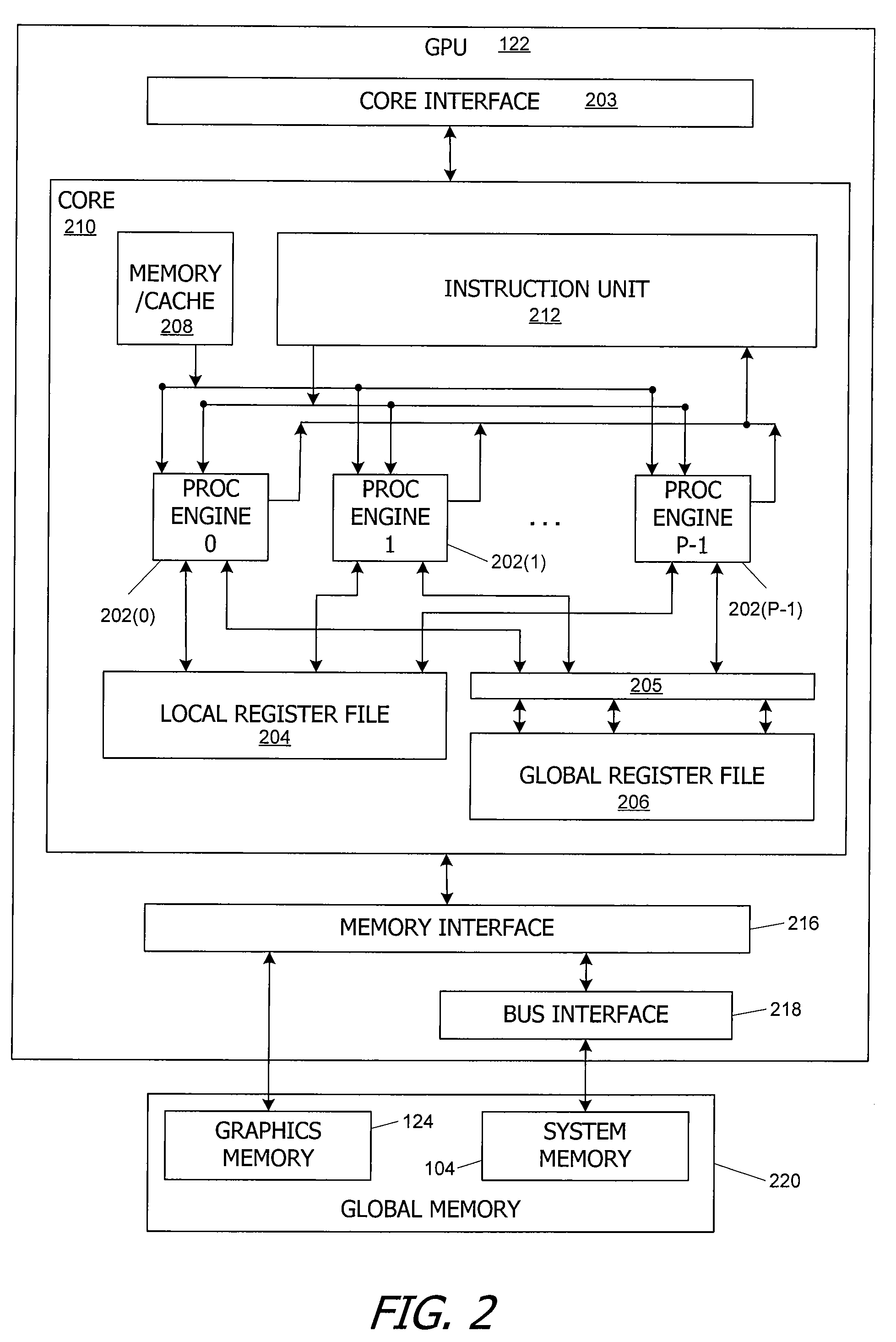

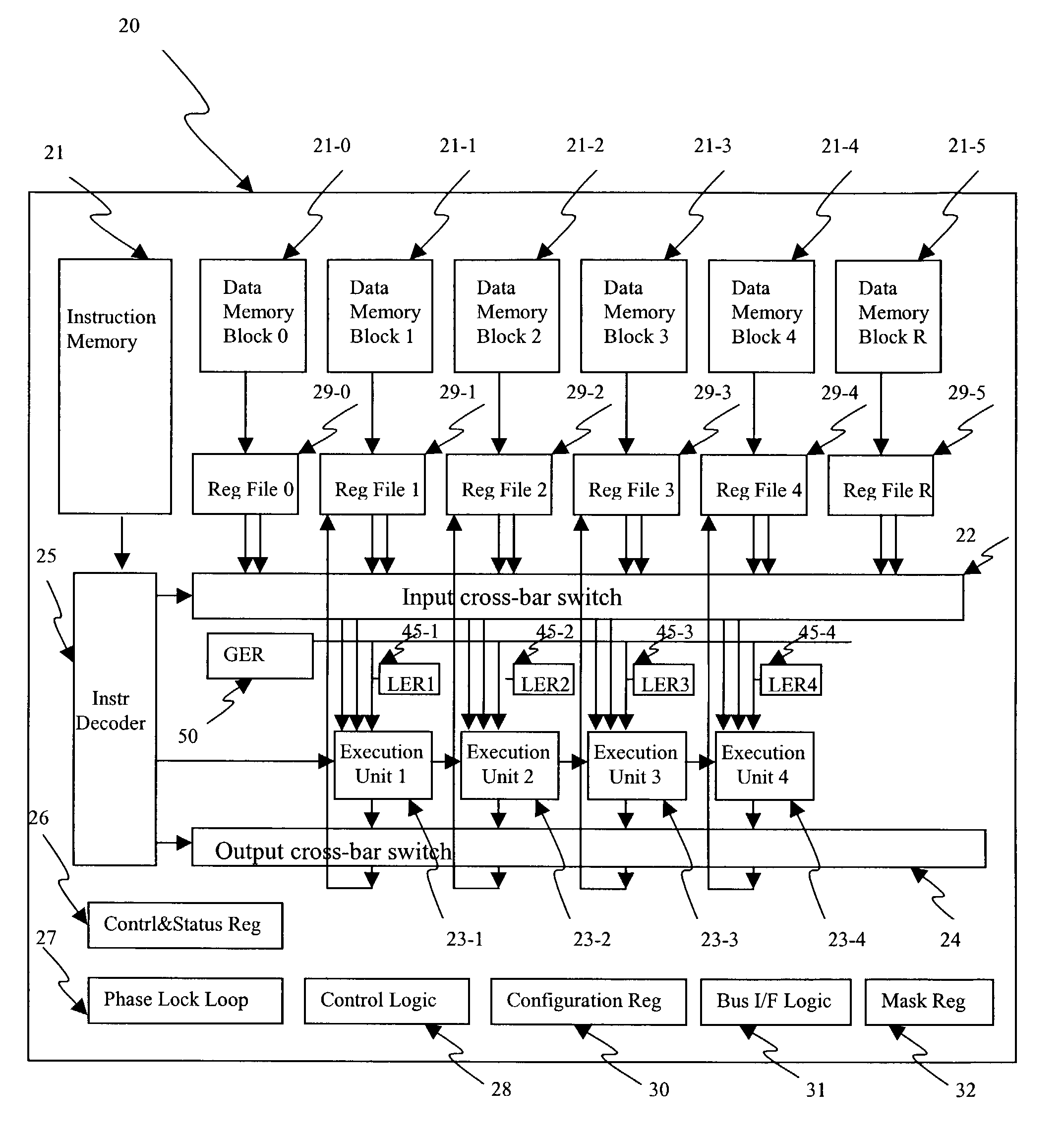

Algorithm mapping, specialized instructions and architecture features for smart memory computing

InactiveUS7546438B2Improve performanceLow costMultiplex system selection arrangementsDigital computer detailsSmart memoryExecution unit

A smart memory computing system that uses smart memory for massive data storage as well as for massive parallel execution is disclosed. The data stored in the smart memory can be accessed just like the conventional main memory, but the smart memory also has many execution units to process data in situ. The smart memory computing system offers improved performance and reduced costs for those programs having massive data-level parallelism. This smart memory computing system is able to take advantage of data-level parallelism to improve execution speed by, for example, use of inventive aspects such as algorithm mapping, compiler techniques, architecture features, and specialized instruction sets.

Owner:STRIPE INC

Specializing write-barriers for objects in a garbage collected heap

ActiveUS7089272B1Reduce in quantityWithout compromising garbage collector performanceData processing applicationsSpecial data processing applicationsParallel computingWaste collection

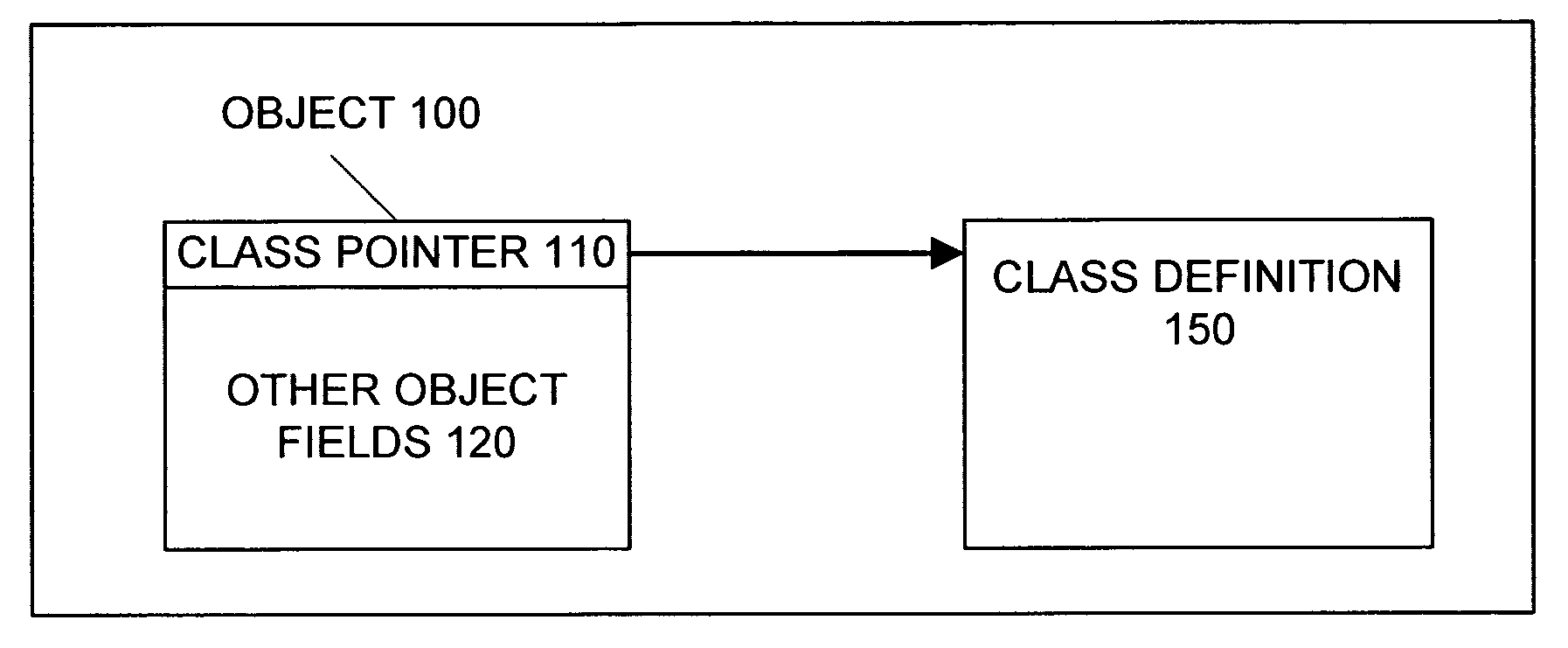

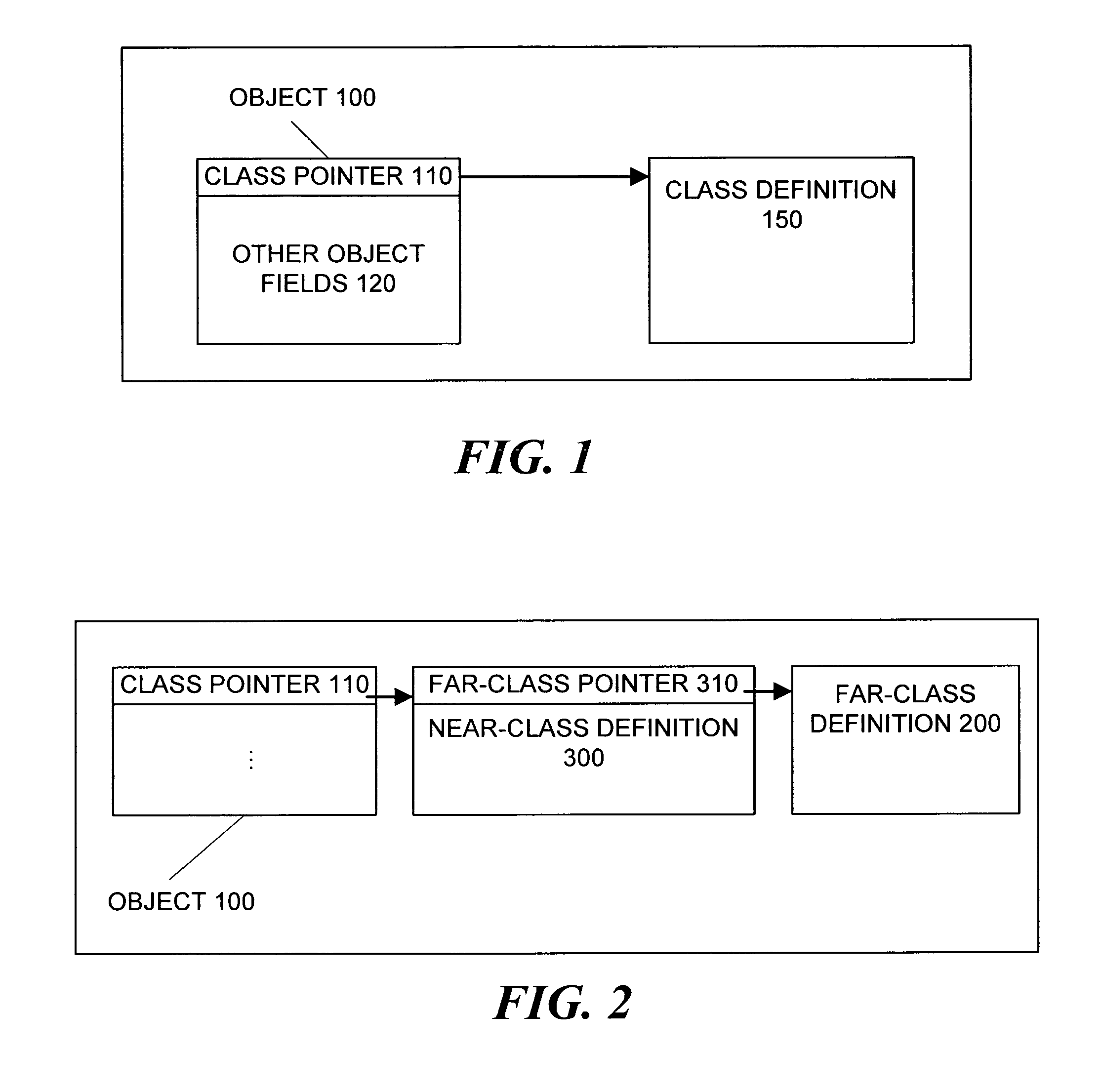

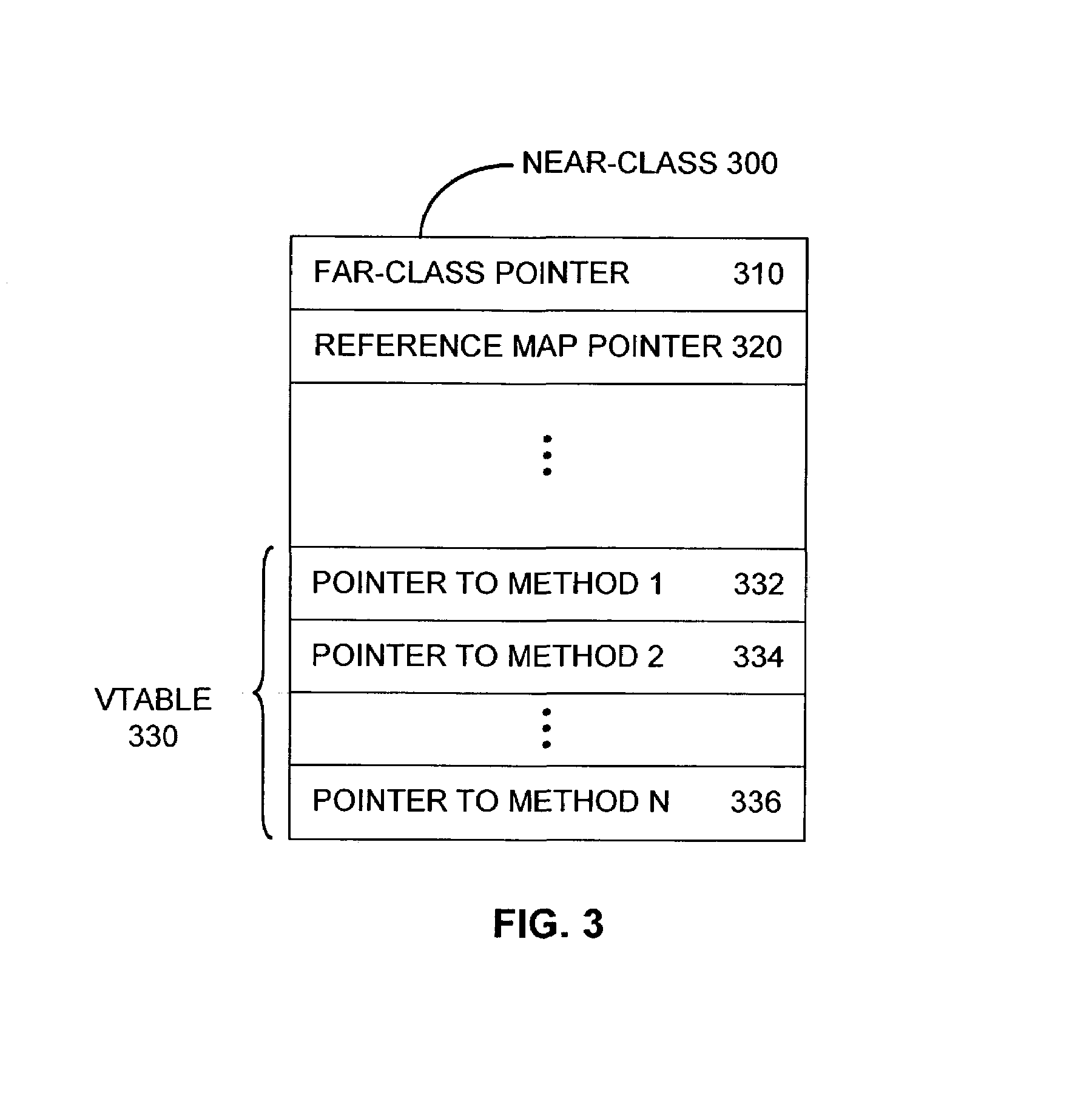

A technique is provided for reducing the number of write barriers executed in mutator code without compromising garbage collector performance. Advantageously, a compiler generates two forms of a mutator code—a first version with write barriers and a second version substantially without write barriers. In operation, the first version of the code may be accessed by a vtable in a “mature” near-class and the second version may be accessed by a vtable in a “nascent” near-class. According to the invention, mapping of functionally equivalent points in the first and second versions of the mutator code may be facilitated by an associated pcmap. Further, each of the first and second versions may also be associated with a respective nr_map that facilitates mapping functionally equivalent points within different branches of guard code sequences corresponding to reference-writes to non-receiver objects.

Owner:ORACLE INT CORP

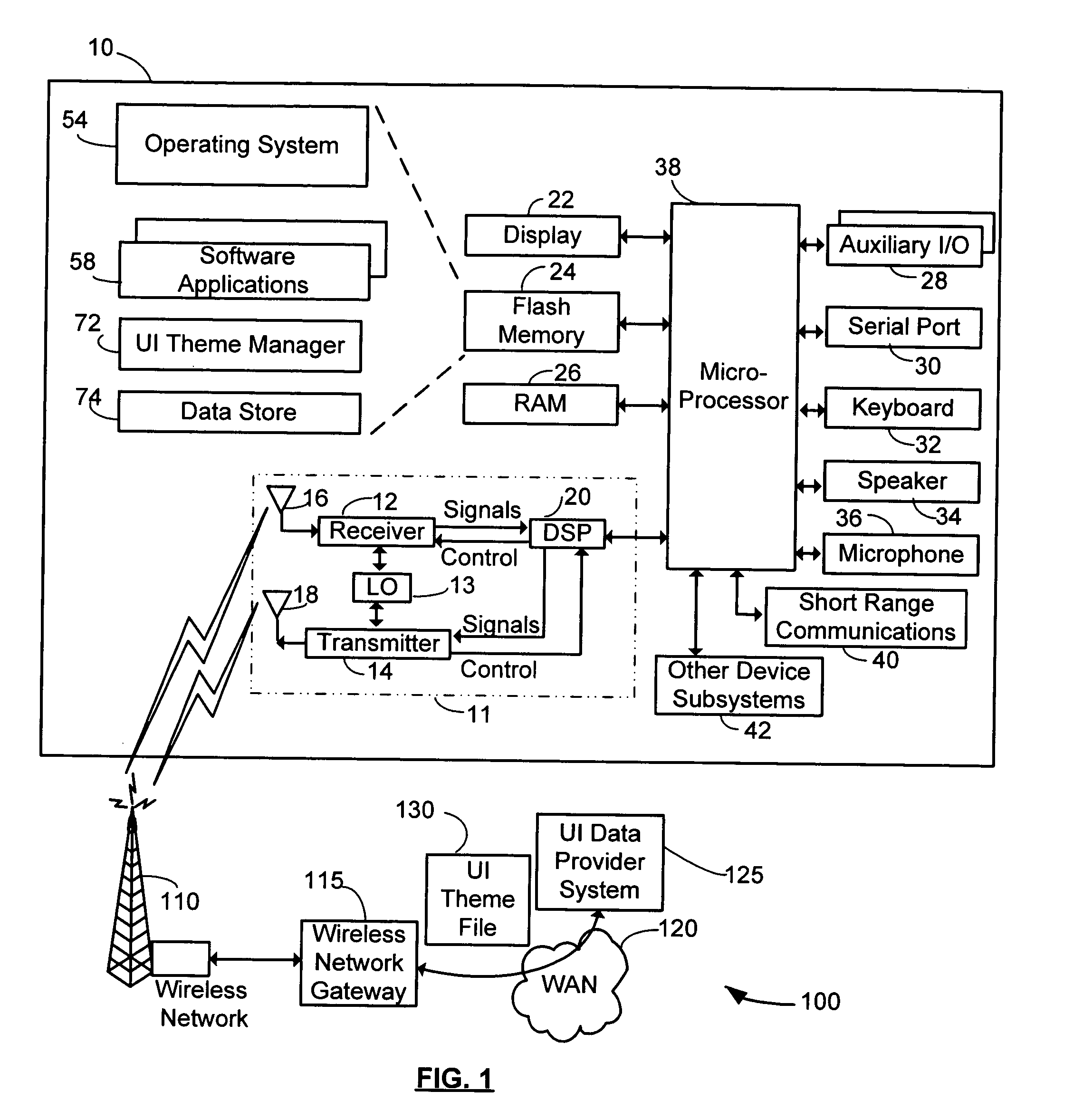

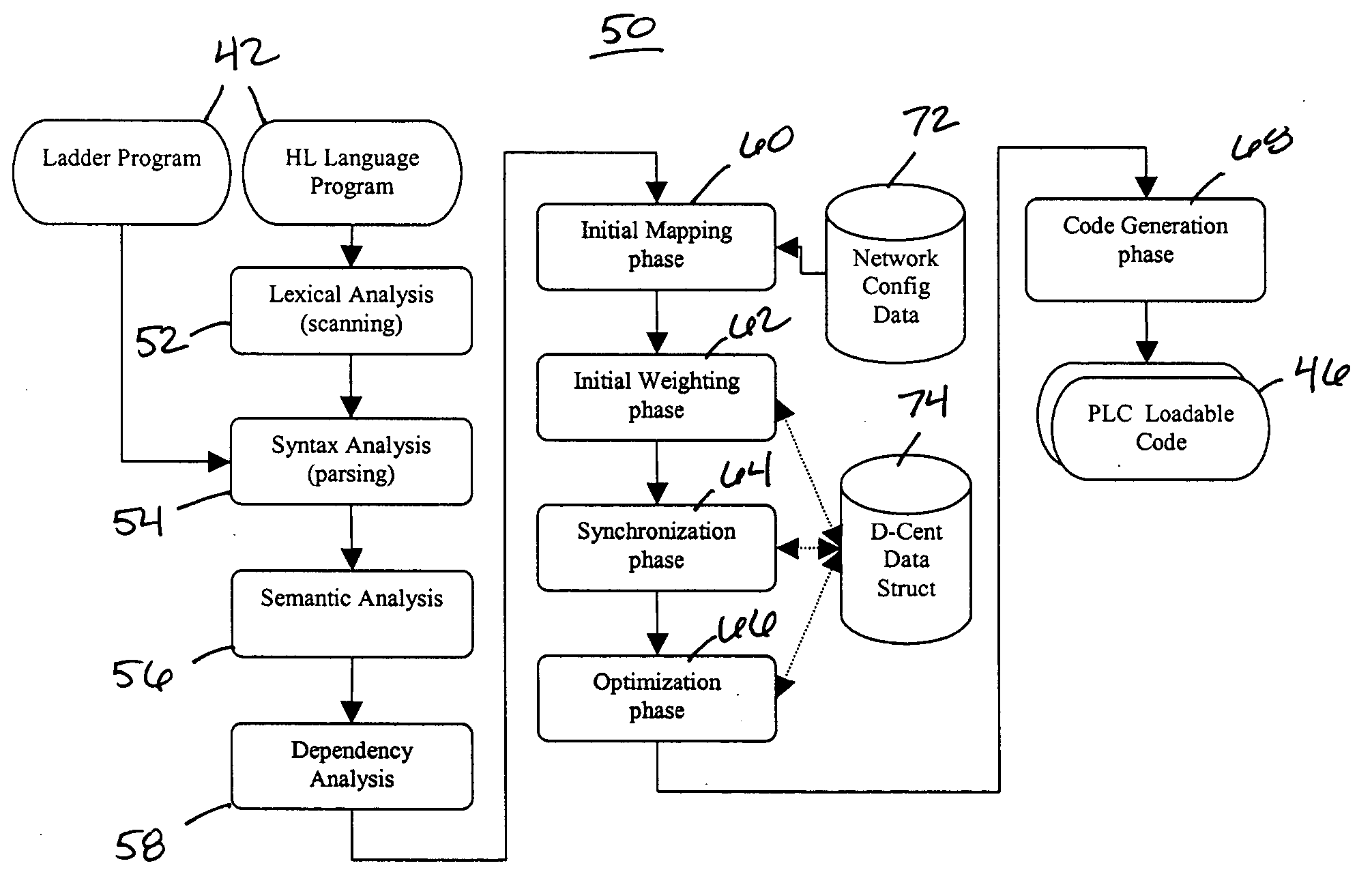

System and method for implementing logic control in programmable controllers in distributed control systems

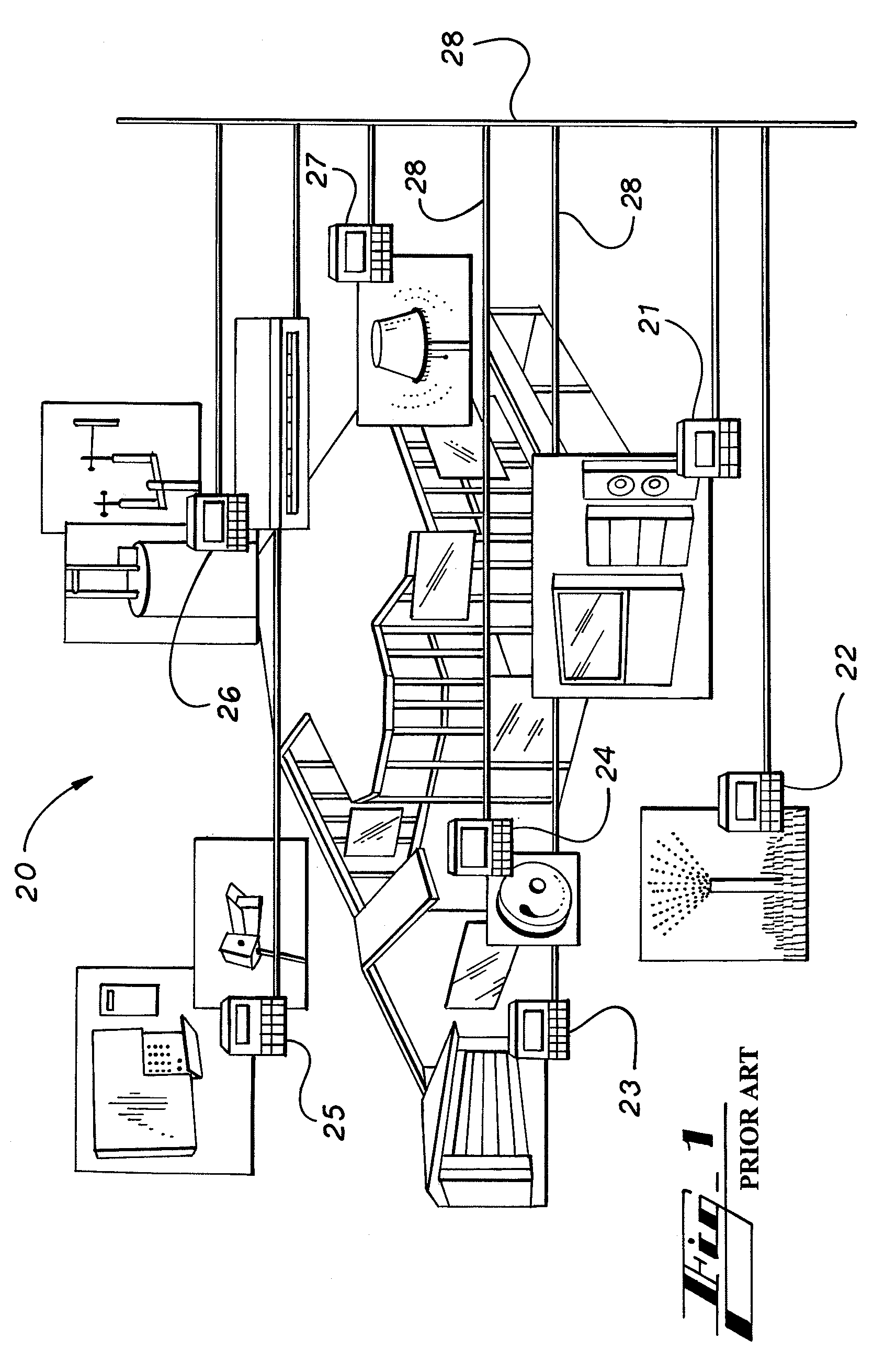

ActiveUS7225037B2Easy to installEasy to modifyTemperatue controlStatic/dynamic balance measurementProgrammable logic controllerDistributed control system

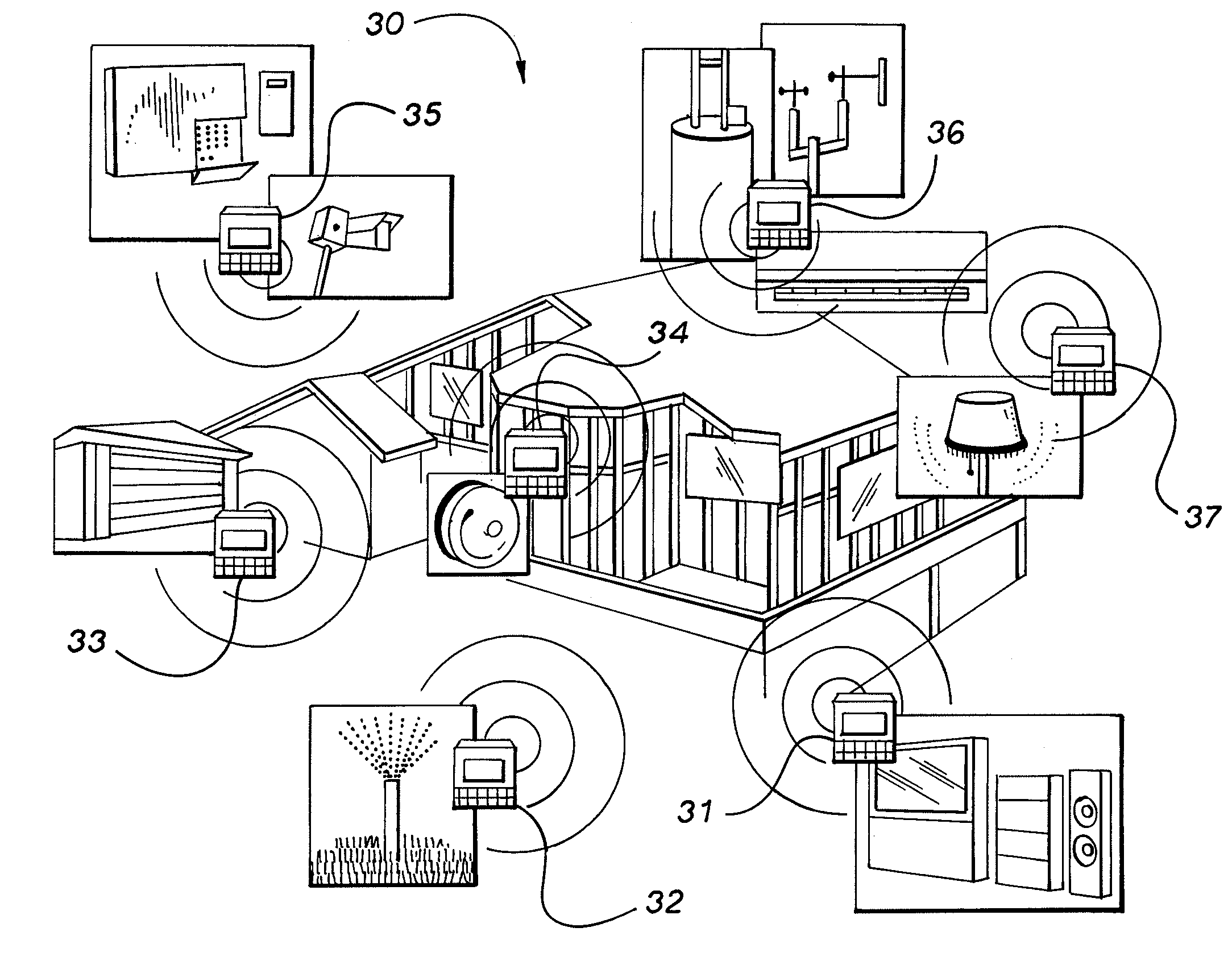

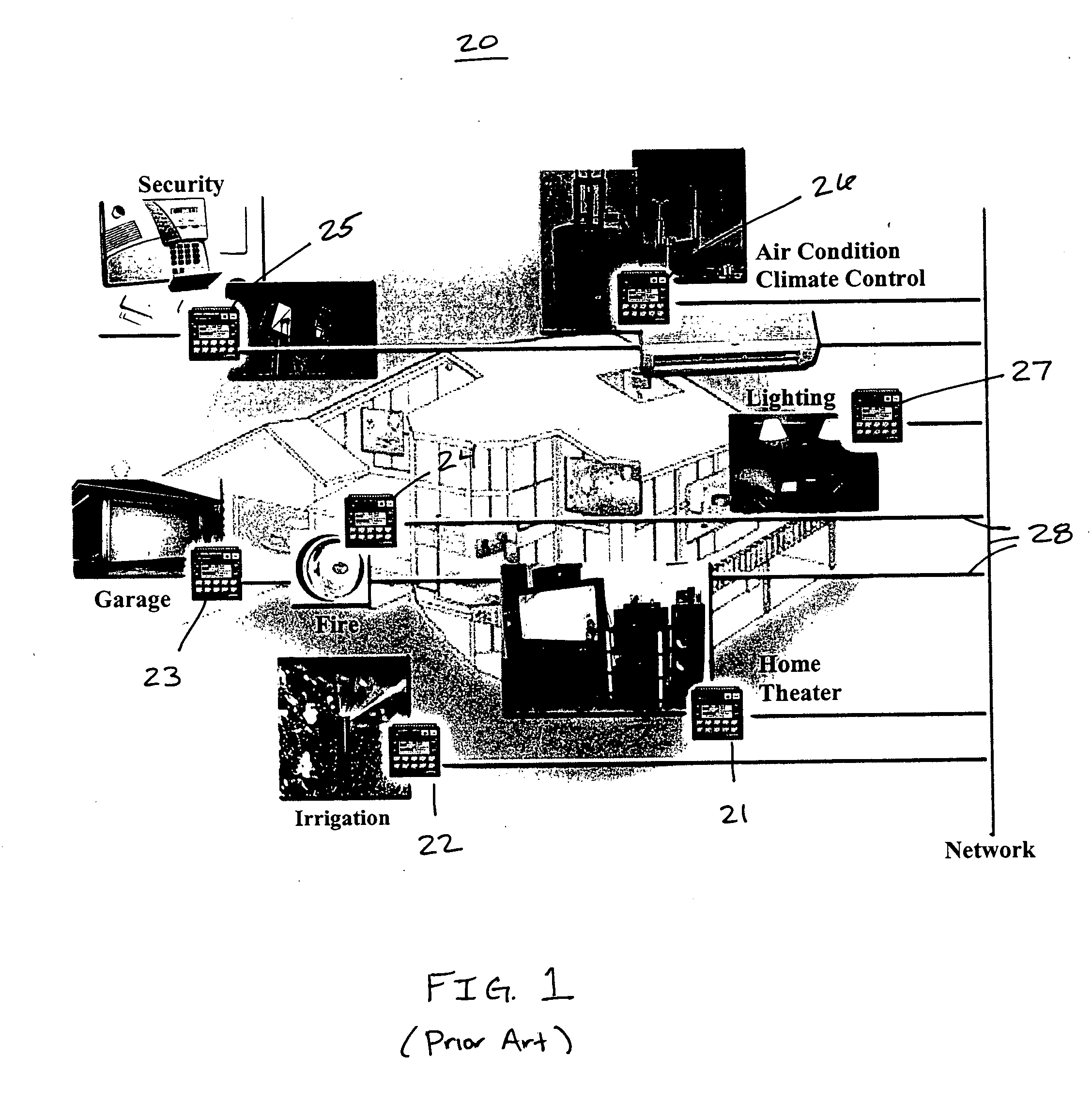

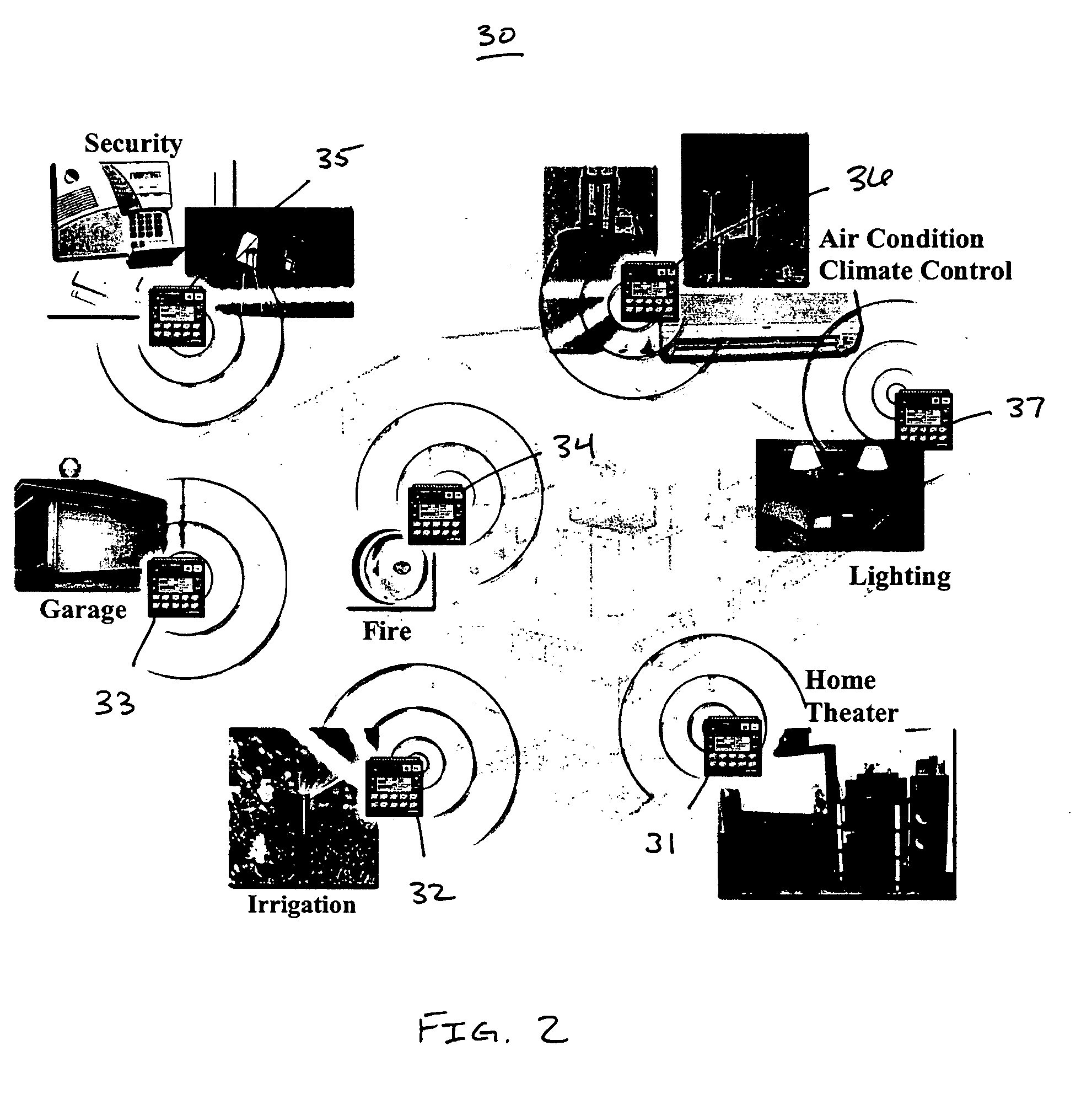

The present invention provides a system and method for implementing logic control in programmable controllers in distributed control systems using a wired or wireless network. A software application is used to define the configuration of the network. Based on the network configuration, a compiler engine automatically assigns each statement of the control program to at least one programmable logic controller in the network. Each statement is then transmitted over a data transmission medium to the programmable logic controller assigned to the statement.

Owner:UNITRONICS 1989 RG

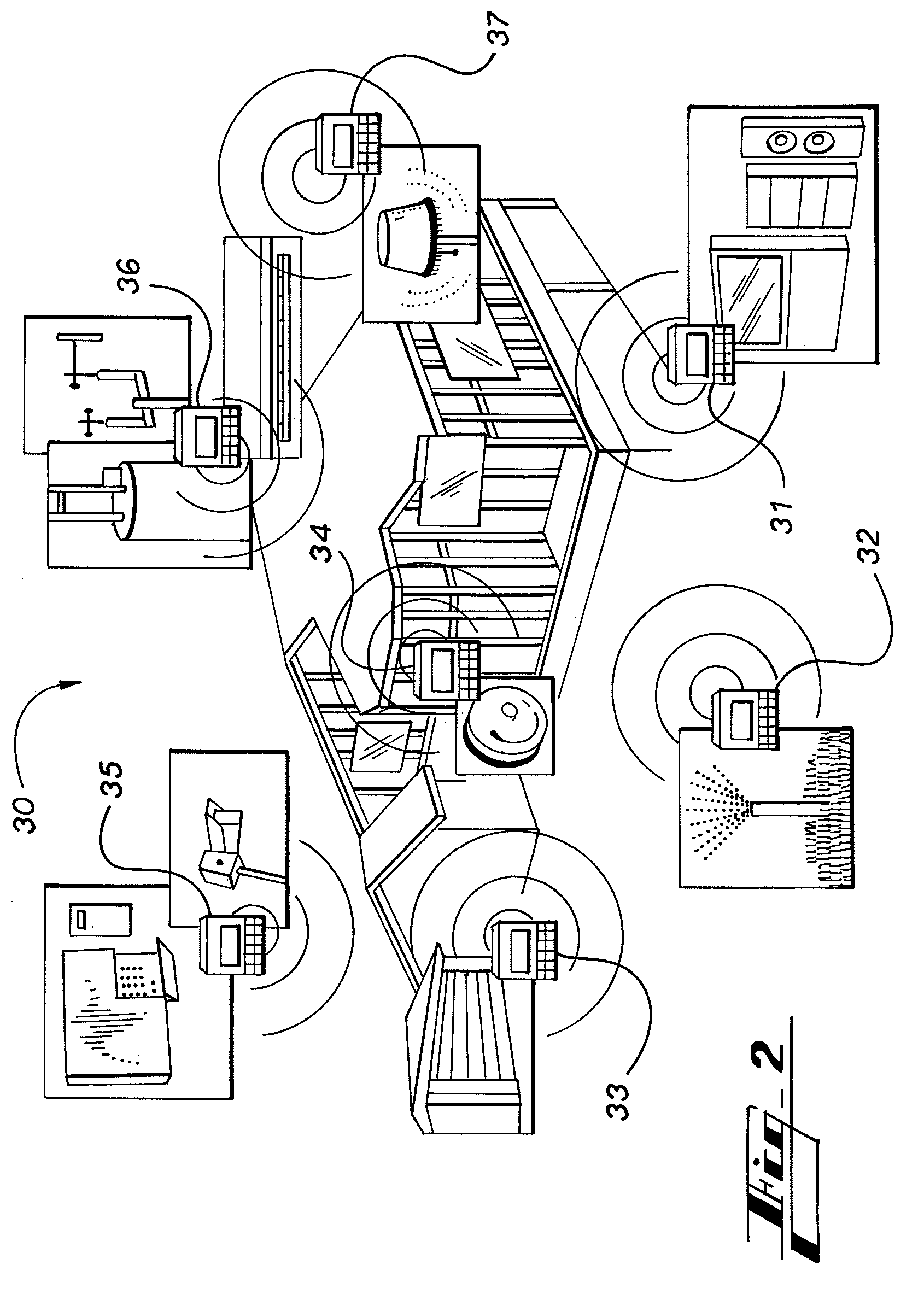

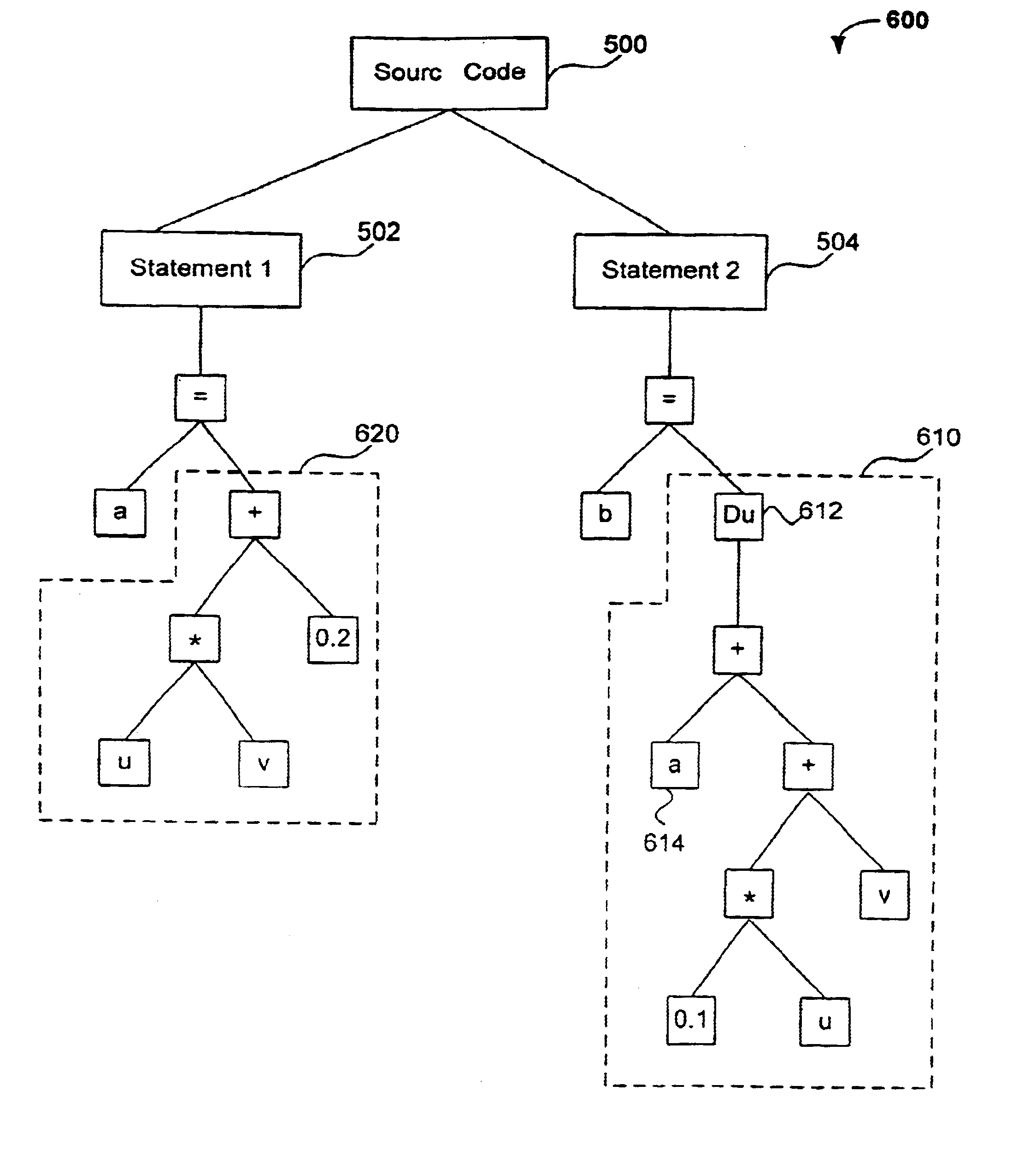

Method, system, and computer program product for implementing derivative operators with graphics hardware

InactiveUS6717599B1Cathode-ray tube indicatorsImage generationApplication programming interfaceTheoretical computer science

Method, system, and computer program product for implementing derivative operators at an interactive rate in computer graphics systems. In an embodiment, a data structure representing the operation of one or more computer program statements is received by a compiler and transformed into a tree data structure. Nodes of the tree data structure that determine derivative information are marked, and a transform rule is applied to the marked nodes to transform the tree data structure into a data structure that can be implemented with graphics hardware interface program statements. In one embodiment of the invention, the compiler transforms shading language statements into graphics application programming interface statements that can be implemented with multiple passes through a graphics pipeline. It is a feature of the present invention that it can be implemented on a wide range of computer graphics systems.

Owner:MICROSOFT TECH LICENSING LLC

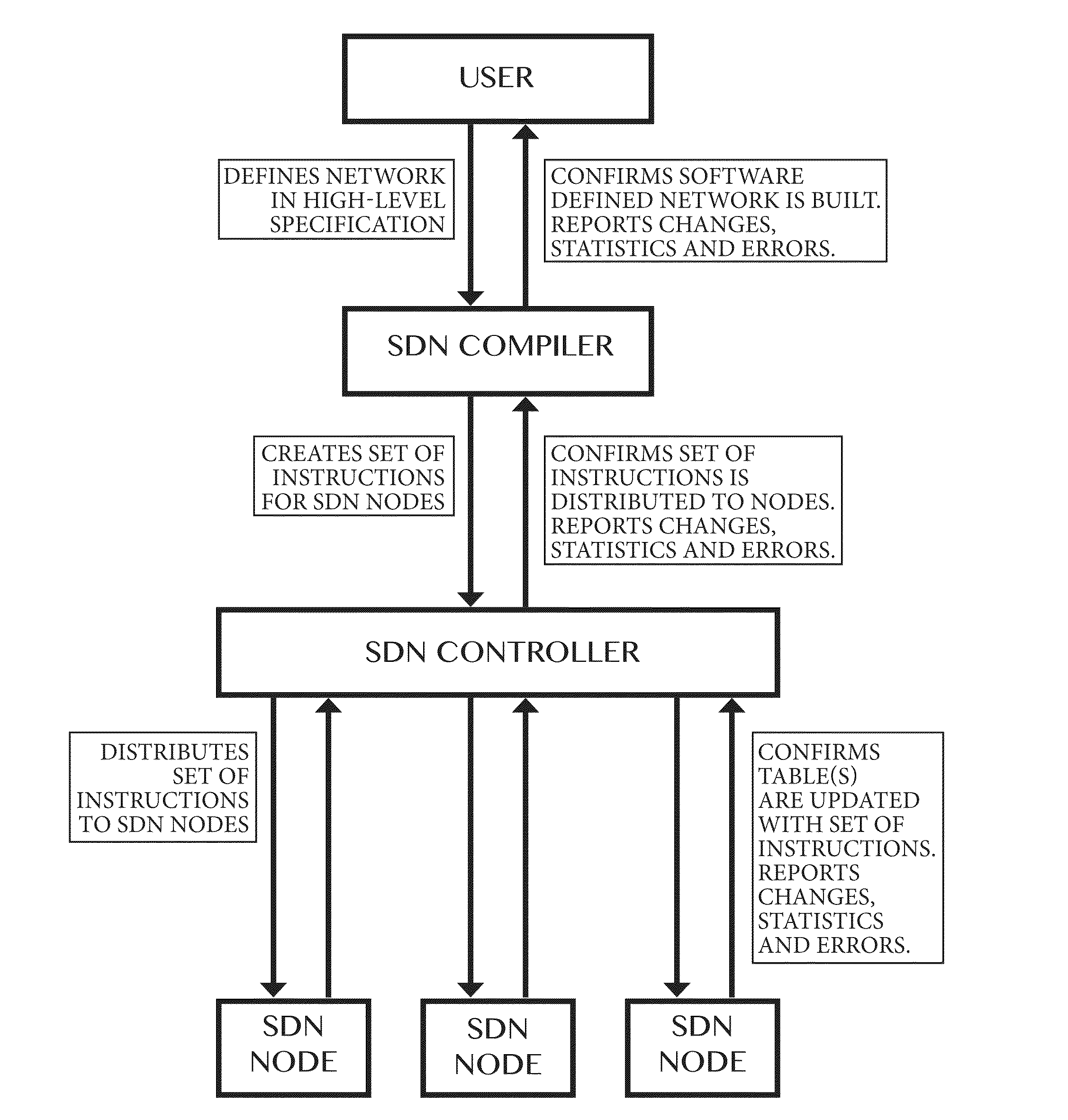

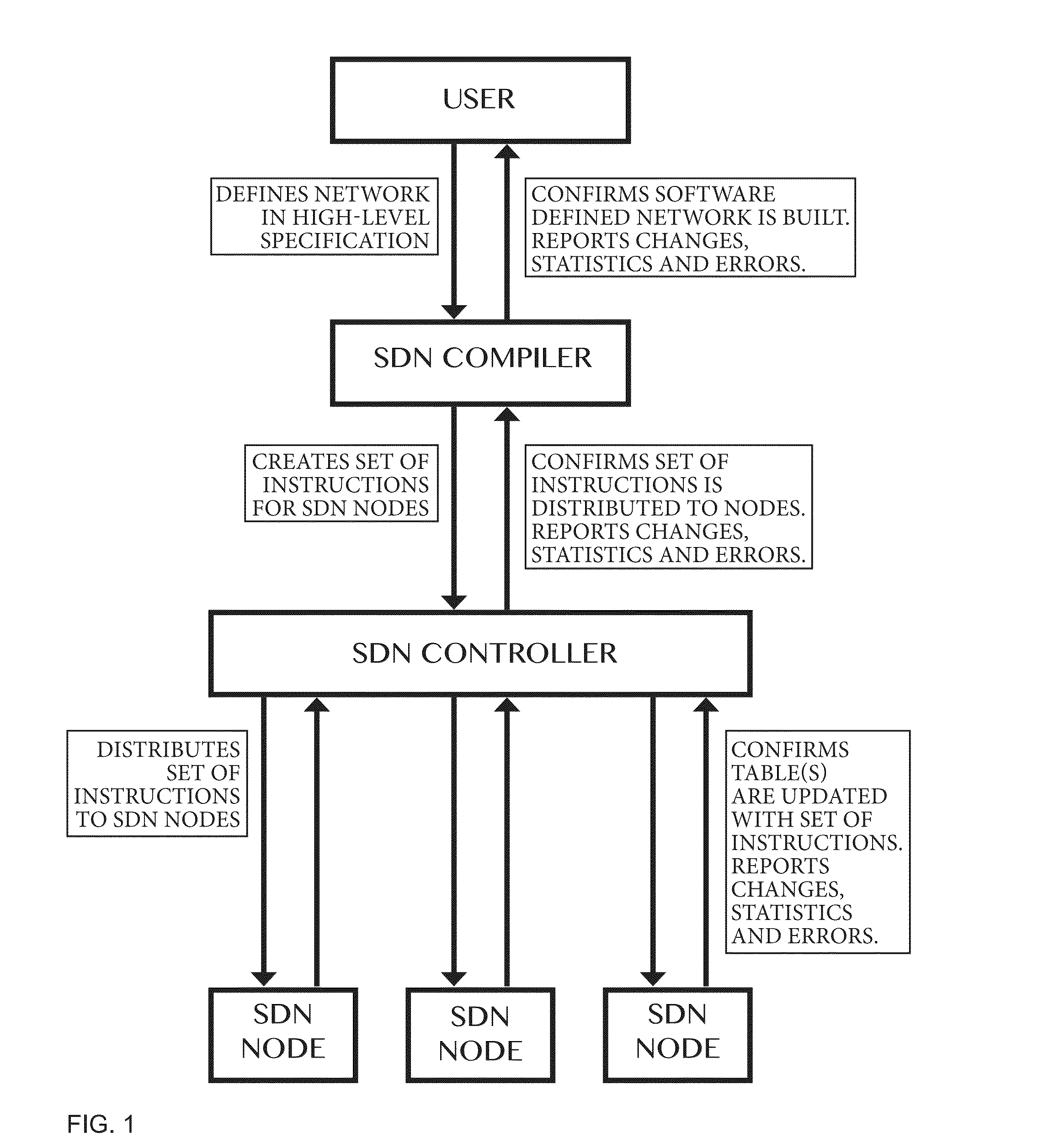

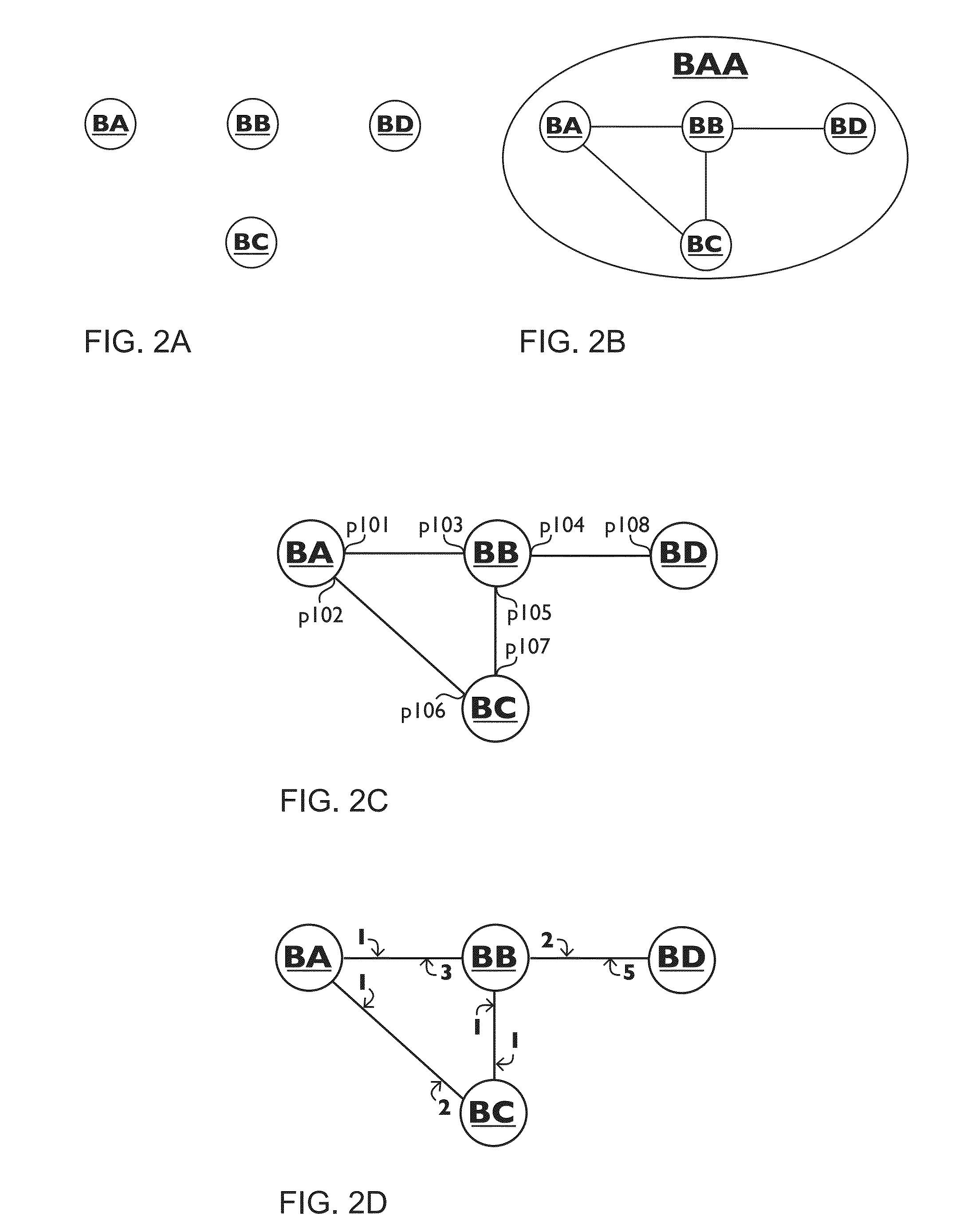

Compiler for and method for software defined networks

ActiveUS20160173338A1Small sizeSpeed up the calculation processDigital computer detailsData switching networksLogical networkSoftware define network

Method of and a compiler for controlling a network based on a logical network model. The network has physical nodes and virtual nodes. The physical nodes are interconnected by physical links in accordance with a physical network layout. The logical network model has logical nodes indicated with a logical node name which refers to at least one physical or at least one virtual node in the network. The method uses a physical forwarding point-of-attachment relation defining physical paths of the physical network in dependence on a physical forwarding policy, a first mapping relation defining how the virtual nodes and the physical nodes are mapped to one another, and a second mapping relation defining how the logical nodes are mapped to the physical nodes and the virtual nodes. The method also includes transforming paths in the physical network to paths between the physical nodes and the virtual nodes.

Owner:WOLTING HLDG

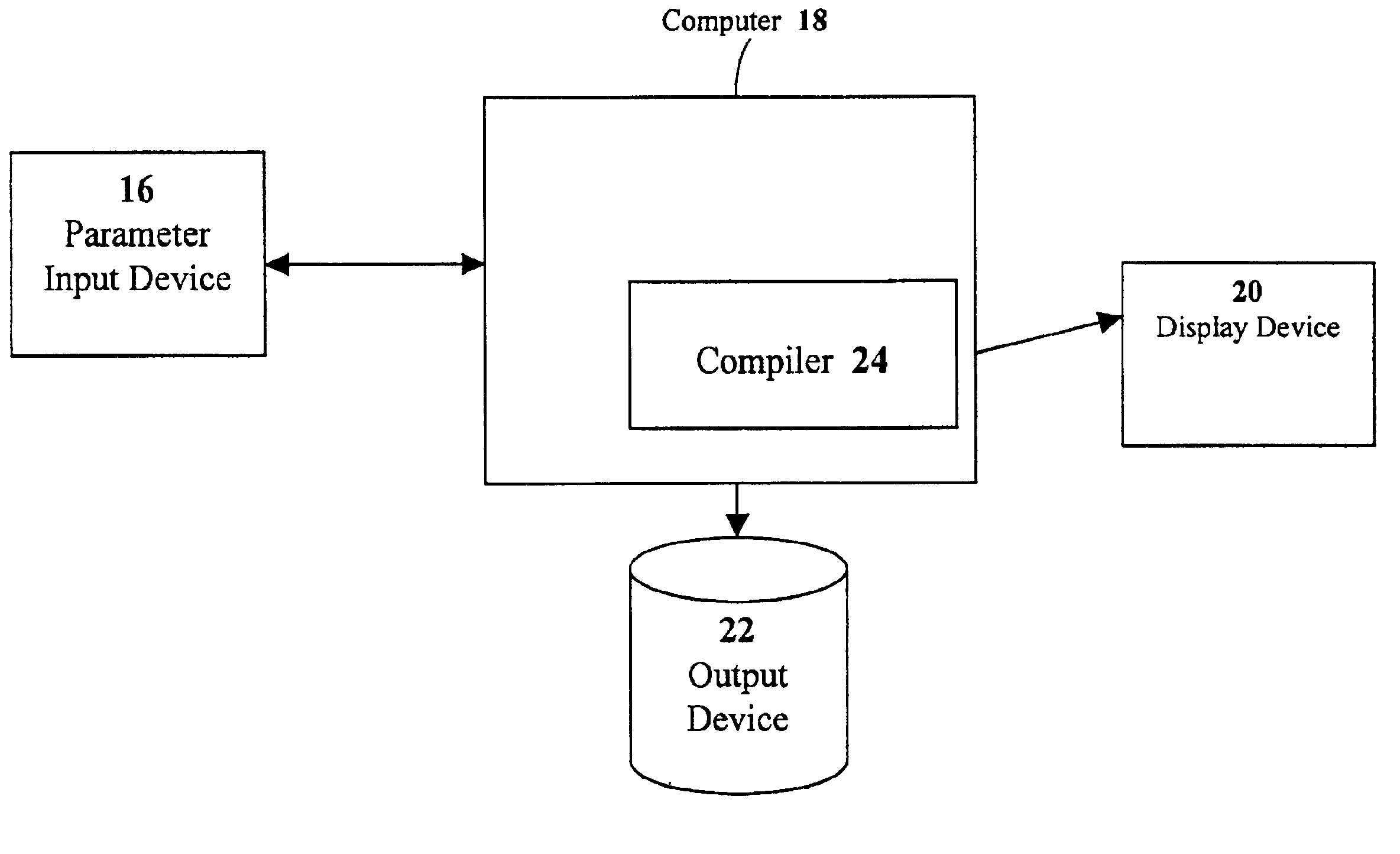

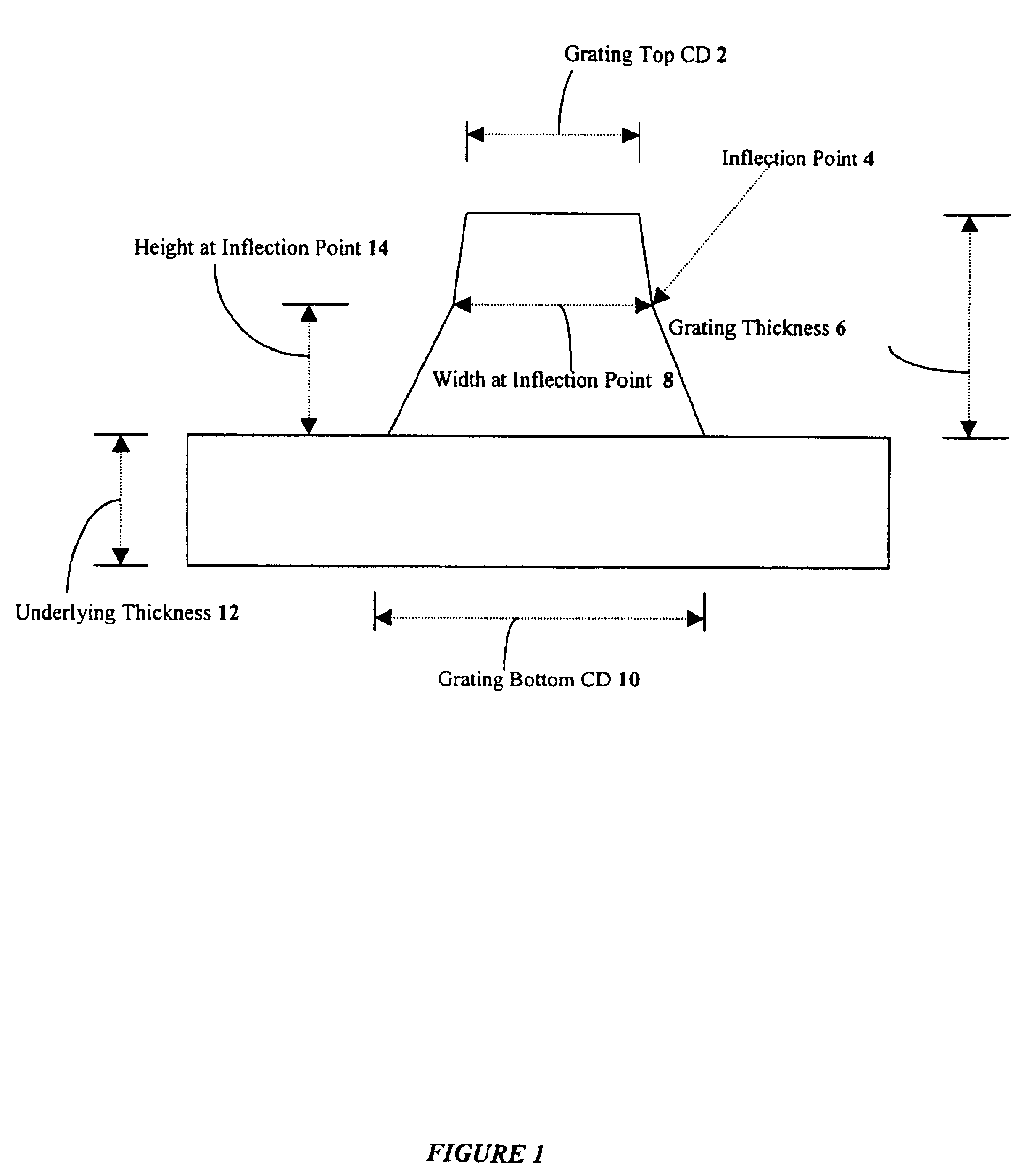

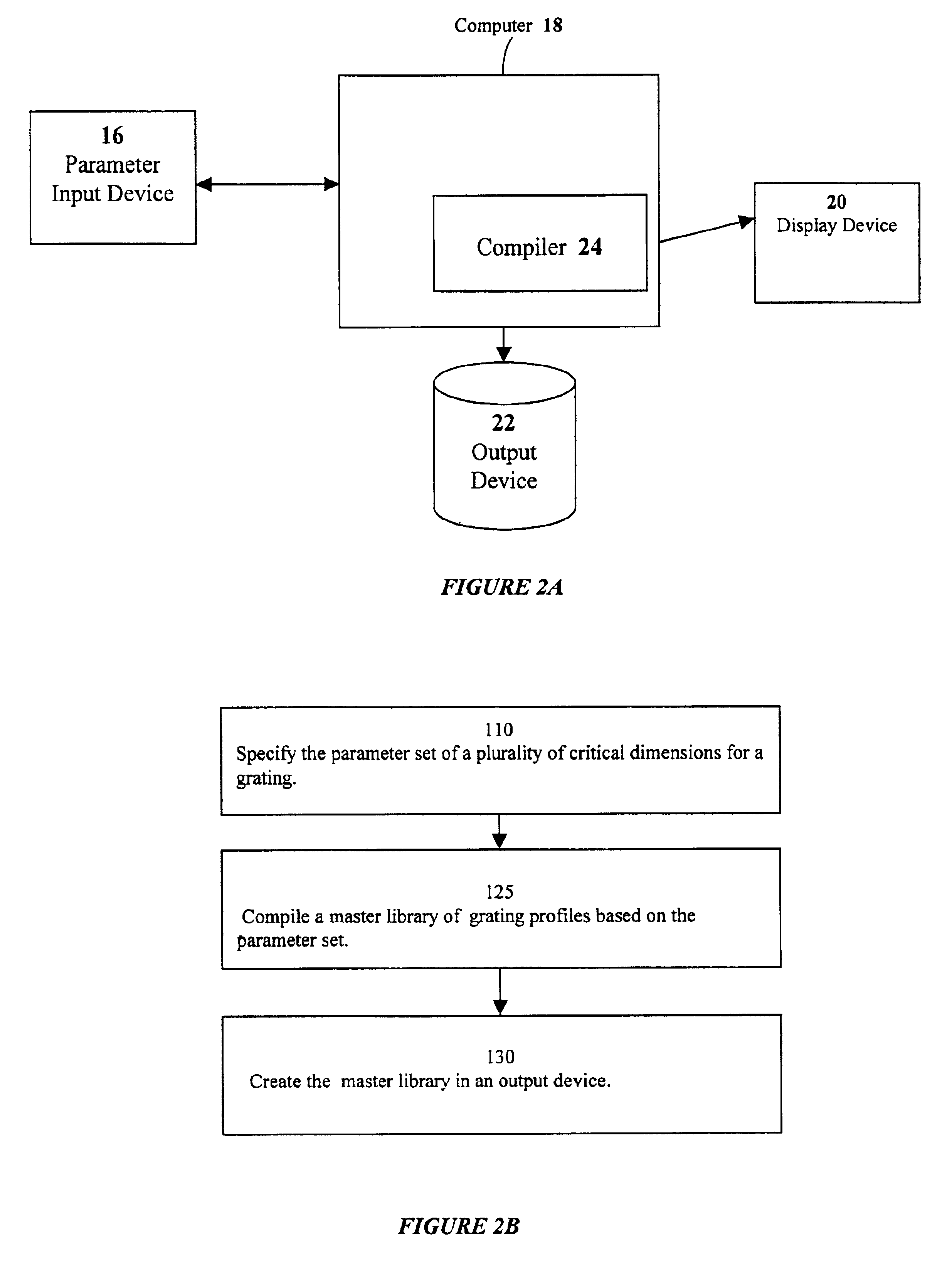

System and method for real-time library generation of grating profiles

The present invention provides a method and a system for a real-time configurable definition and generation of grating profile libraries. A parameter set is used to specify the ranges of grating dimensions and resolutions of the profile library to be generated. In one embodiment, a compiler creates subsets of a large profile library, the subset designed to enable rapid search and validation of real-time data. In another embodiment, an automatic process generates a new parameter set and a new subset of the library when trigger conditions are met. Subsets of the profile library may be used to check if grating spectrum data are within the ranges established for an application and if the dimensions are within the process averages established for a manufacturing run. The system for generation of grating profile libraries is scalable, operable in a distributed environment, and includes application specific items that can be selected or determined by the client.

Owner:TOKYO ELECTRON US HOLDINGS INC

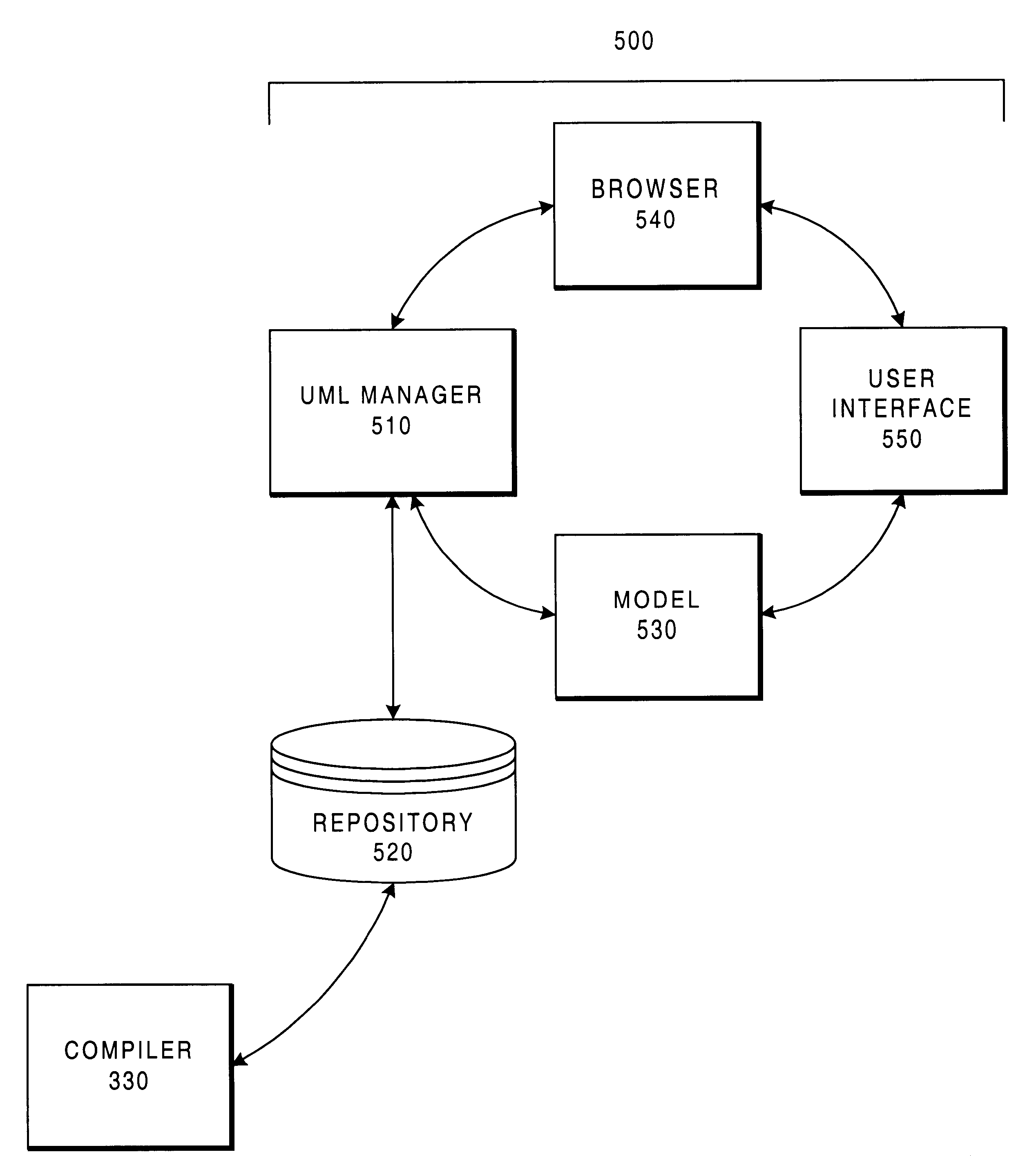

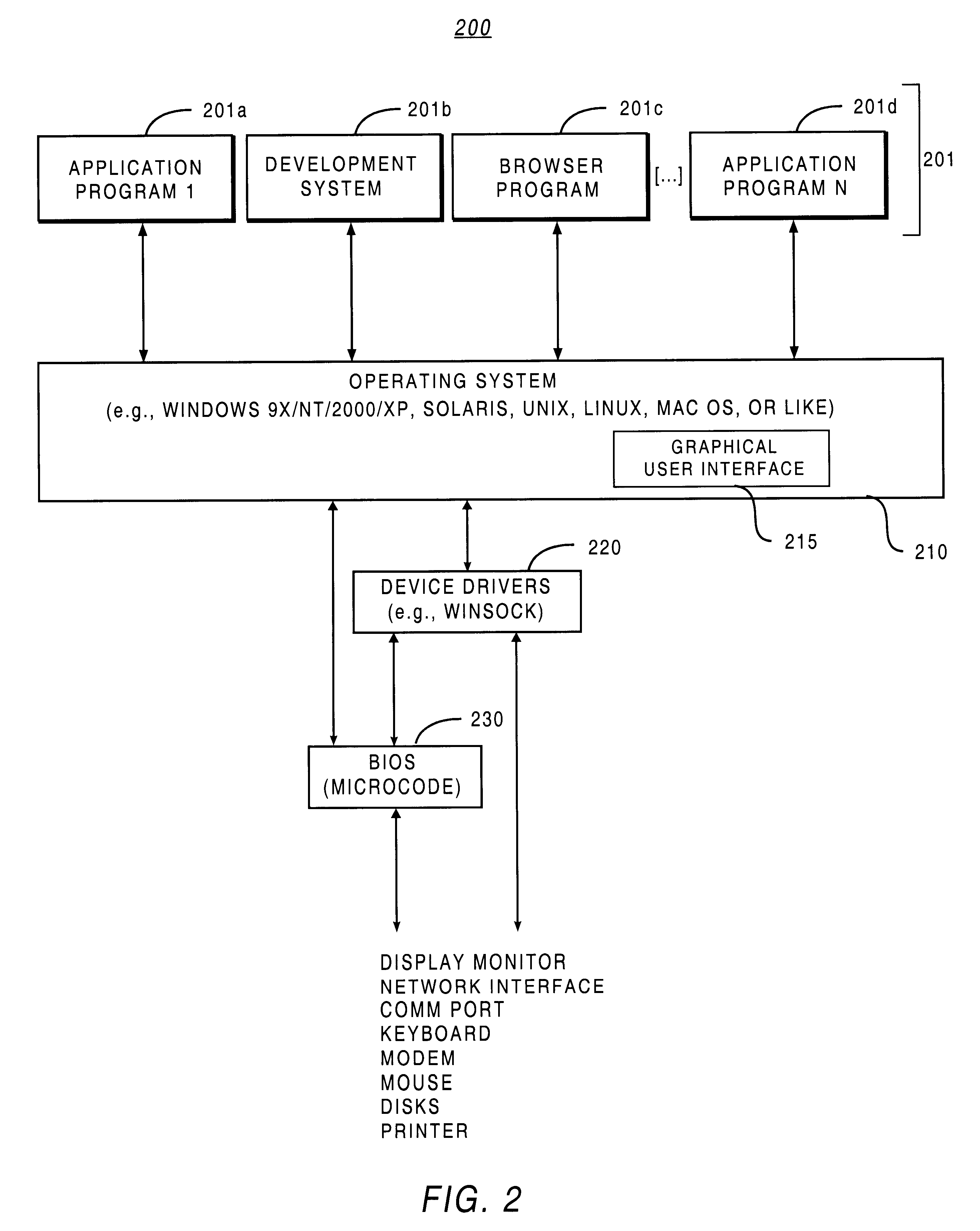

System and methodology for providing fixed UML layout for an object oriented class browser

A system and methodology for providing a Unified Modeling Language (UML) diagram of a program for display in a graphical user interface of a development system is described. Relationships between a plurality of files of a program are determined using a compiler. When a request for display of a UML diagram is received, a UML diagram of the currently selected file is generated based upon the determined relationships between the currently selected file and other files of the program. The UML diagram displayed in the graphical user interface enables a user to navigate to a particular file of the program by selecting one of the nodes of the UML diagram. The system enables a user to view source code or a UML diagram of a particular component displayed in the UML diagram.

Owner:BORLAND

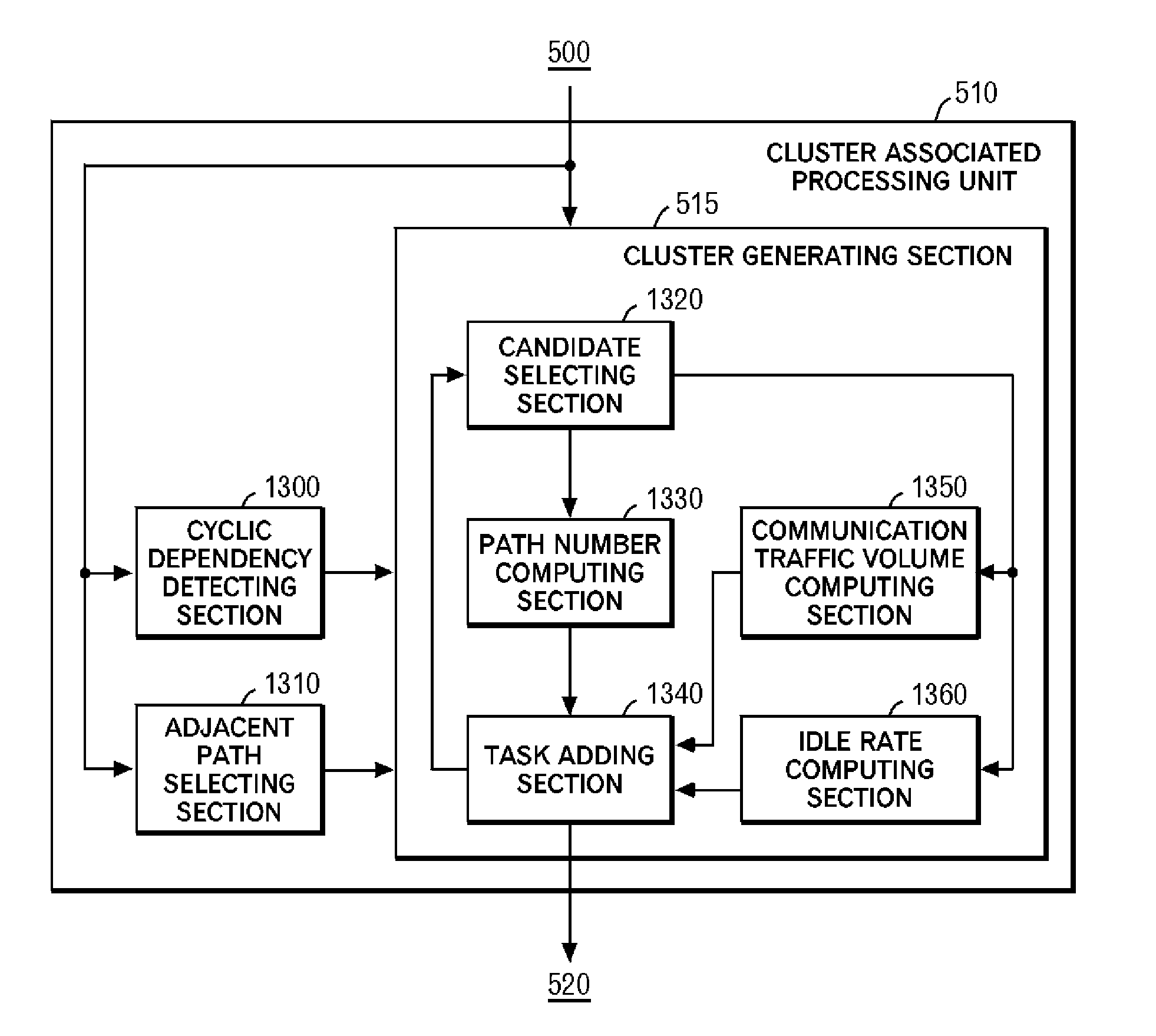

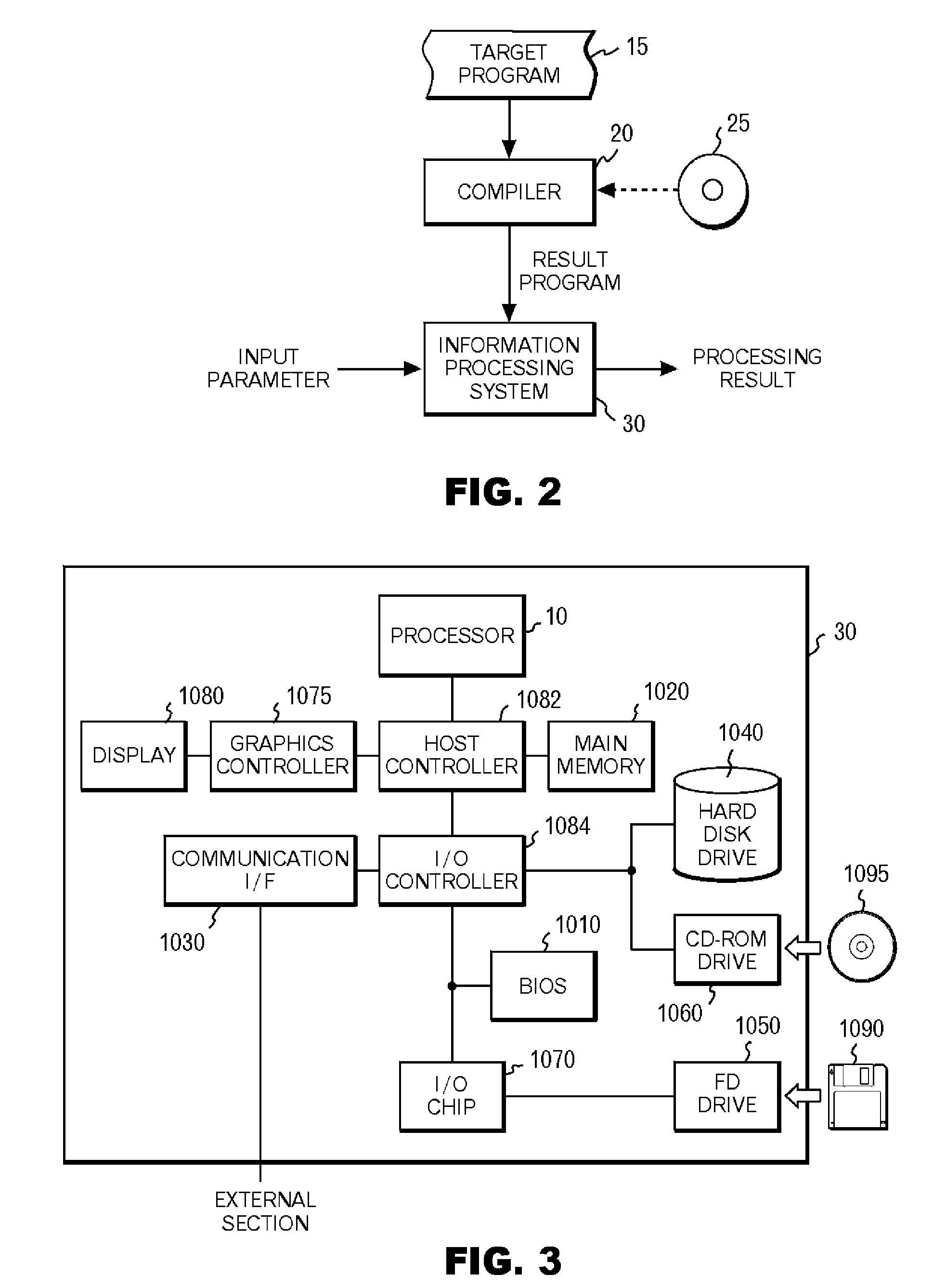

Preprocessor to improve the performance of message-passing-based parallel programs on virtualized multi-core processors

InactiveUS20070038987A1Reduced execution timeEasy to implementMultiprogramming arrangementsMemory systemsCluster basedParallel processing

Provided is a complier which optimizes parallel processing. The complier records the number of execution cores, which is the number of processor cores that execute a target program. First, the compiler detects a dominant path, which is a candidate of an execution path to be consecutively executed by a single processor core, from a target program. Subsequently, the compiler selects dominant paths with the number not larger than the number of execution cores, and generates clusters of tasks to be executed by a multi-core processor in parallel or consecutively. After that, the compiler computes an execution time for which each of the generated clusters is executed by the processor cores with the number equal to one or each of a plurality natural numbers selected from the natural numbers not larger than the number of execution cores. Then, the compiler selects the number of processor cores to be assigned for execution of each of the clusters based on the computed execution time.

Owner:IBM CORP

System and method for mining data

InactiveUS20060235811A1Data processing applicationsConveying record carriersBatch processingBatch extraction

A system and method for extracting data, hereinafter referred to as MitoMine, that produces a strongly-typed ontology defined collection referencing (and cross referencing) all extracted records. The input to the mining process can be any data source, such as a text file delimited into a set of possibly dissimilar records. MitoMine contains parser routines and post processing functions, known as ‘munchers’. The parser routines can be accessed either via a batch mining process or as part of a running server process connected to a live source. Munchers can be registered on a per data-source basis in order to process the records produced, possibly writing them to an external database and / or a set of servers. The present invention also embeds an interpreted ontology based language within a compiler / interpreter (for the source format) such that the statements of the embedded language are executed as a result of the source compiler ‘recognizing’ a given construct within the source and extracting the corresponding source content. In this way, the execution of the statements in the embedded program will occur in a sequence that is dictated wholly by the source content. This system and method therefore make it possible to bulk extract free-form data from such sources as CD-ROMs, the web etc. and have the resultant structured data loaded into an ontology based system.

Owner:FAIRWEATHER JOHN

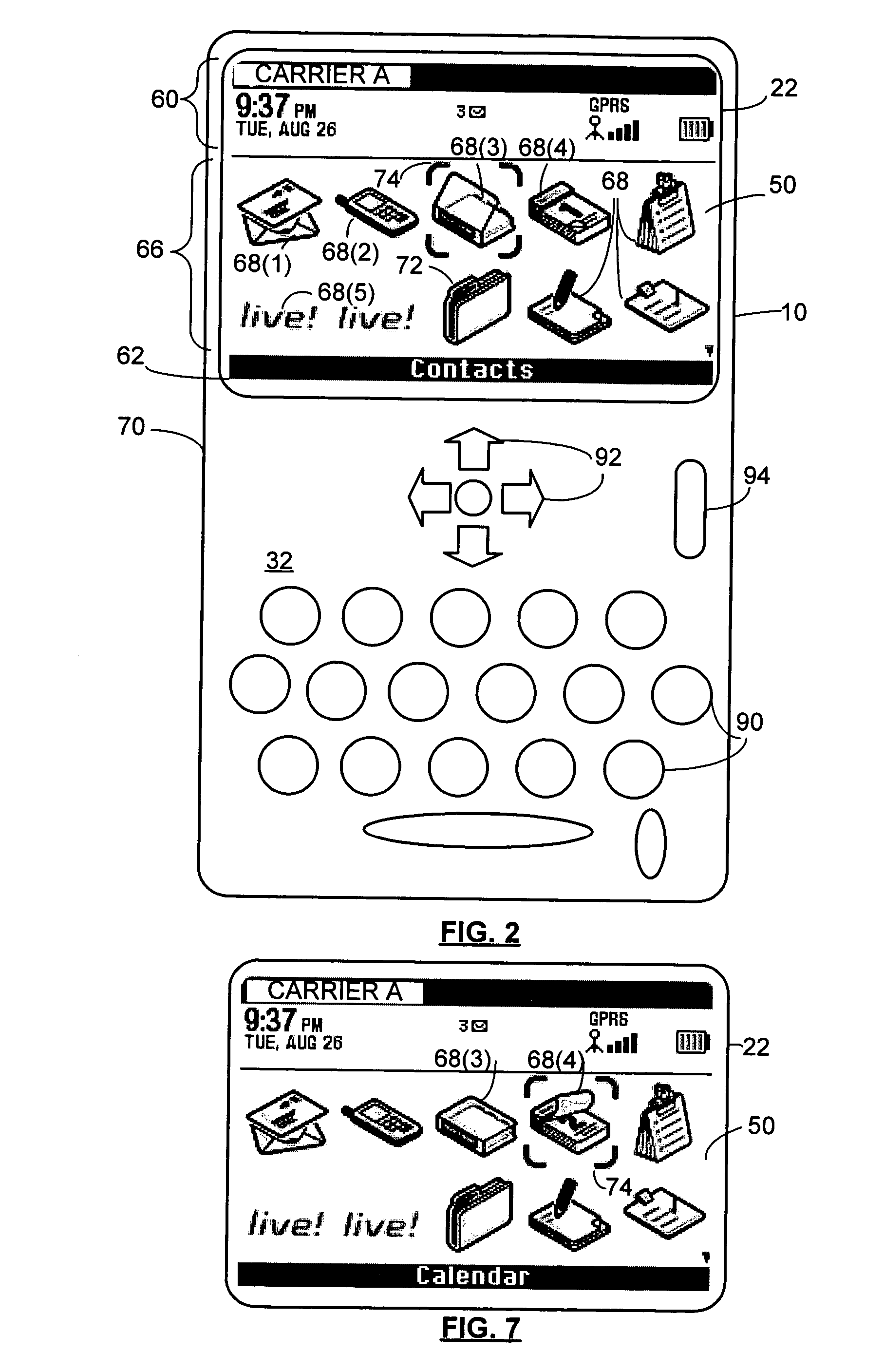

Method and data structure for user interface customization

InactiveUS20050050474A1Software engineeringCathode-ray tube indicatorsGraphicsGraphical user interface

A method for changing visual attributes presented by a graphical user interface of a device such as a mobile electronic device by loading onto the device a file containing information for changing selected visual attributes of the interface. A method or compiler for generating or compiling a file that contains information used by a device to change the user interface presented by the device.

Owner:BLACKBERRY LTD

System and method for implementing logic control in programmable controllers in distributed control systems

ActiveUS20050085928A1EliminateAchieve modularityTemperatue controlStatic/dynamic balance measurementProgrammable logic controllerDistributed control system

Owner:UNITRONICS 1989 RG

Reconfigurable processing

ActiveUS20070198971A1Reduce signal delayReduce areaEnergy efficient ICTSoftware engineeringPathPingComputer architecture

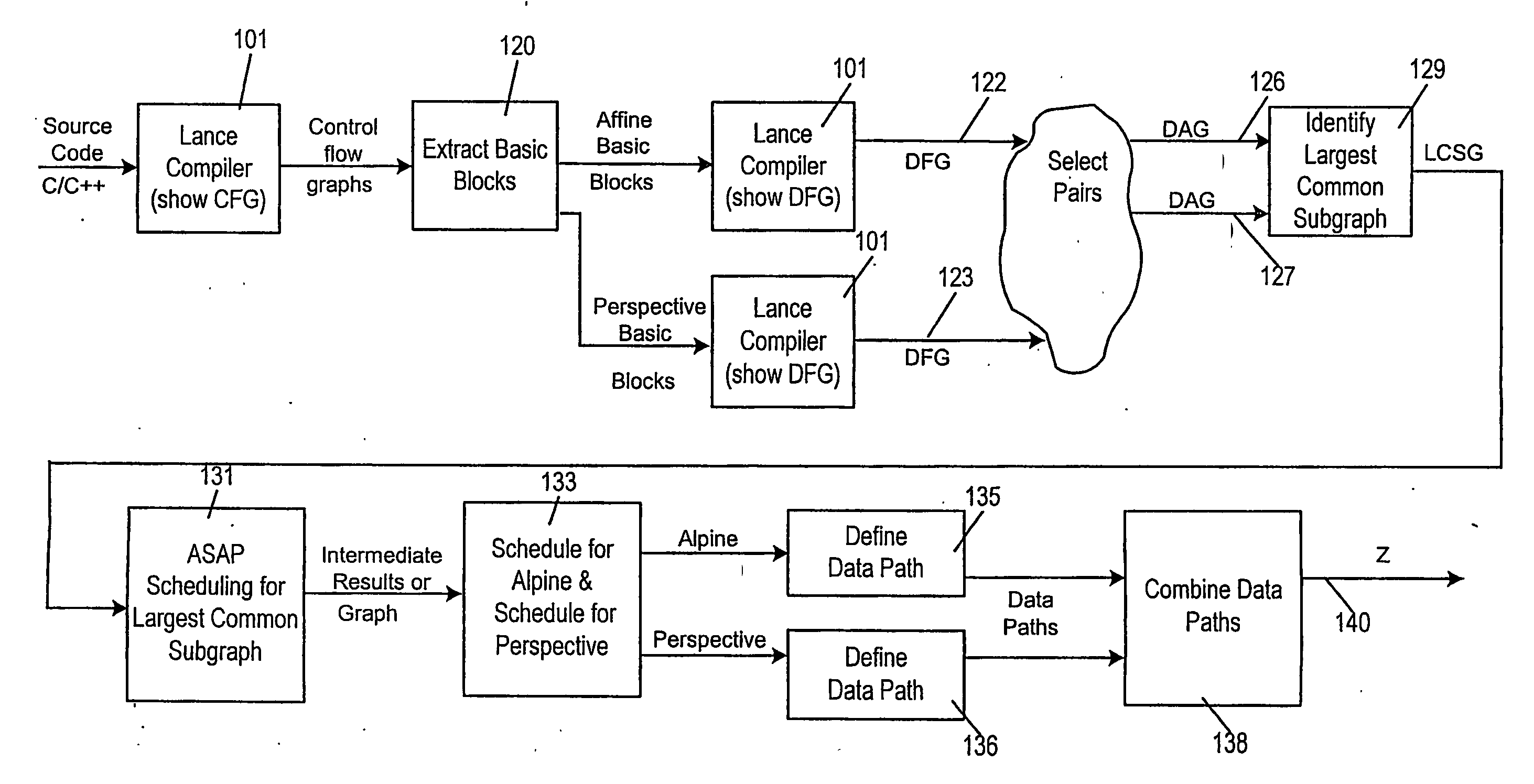

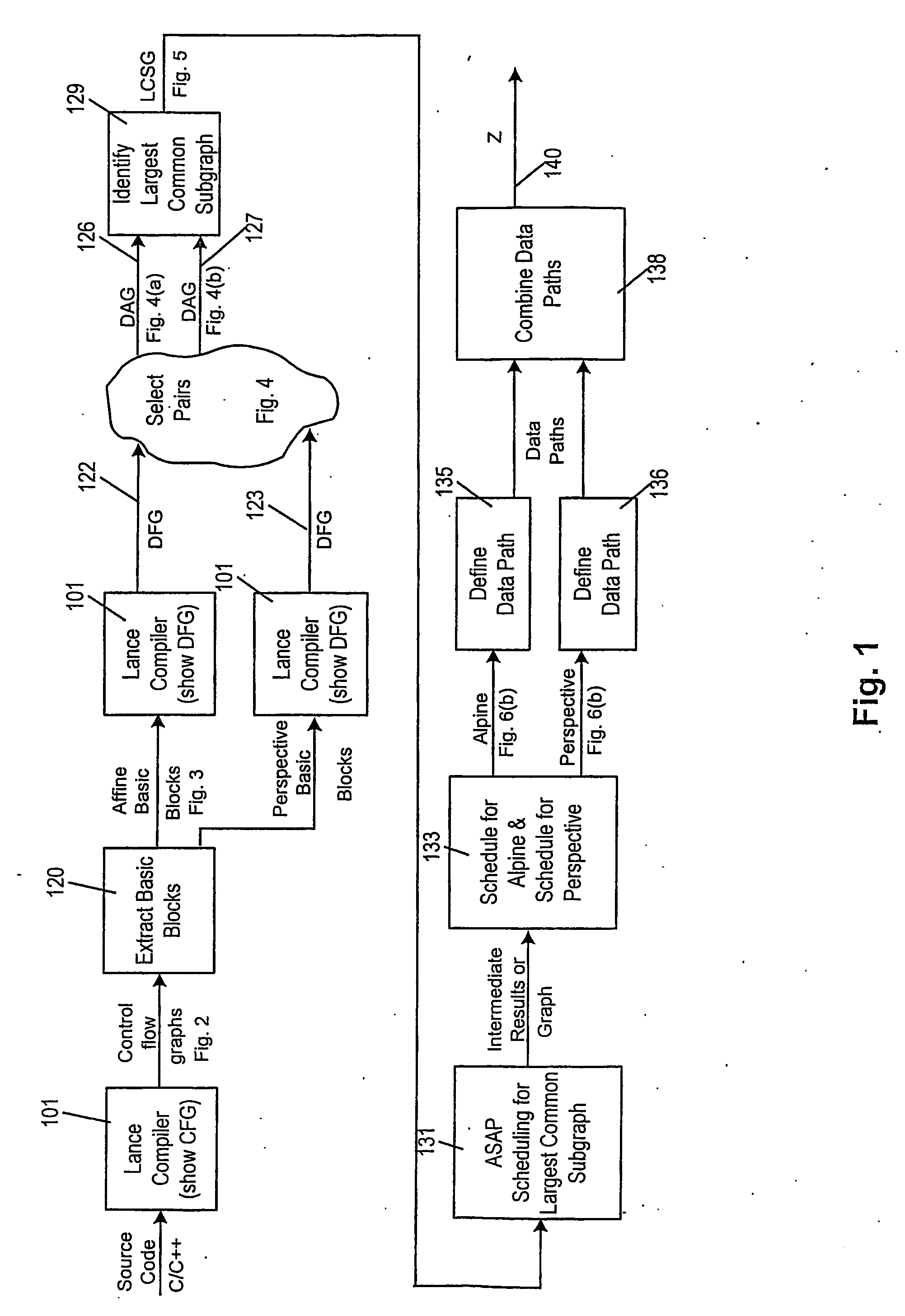

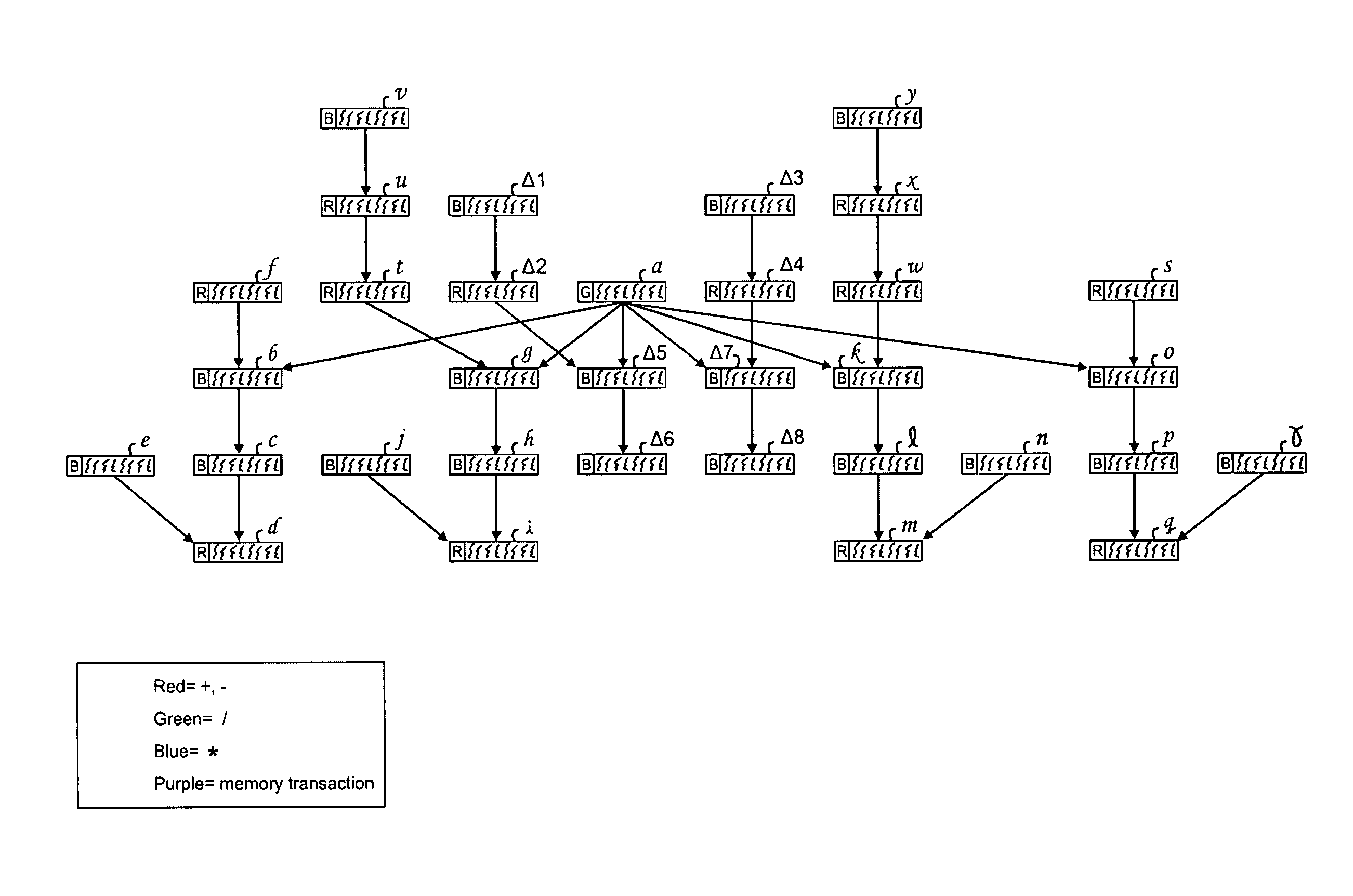

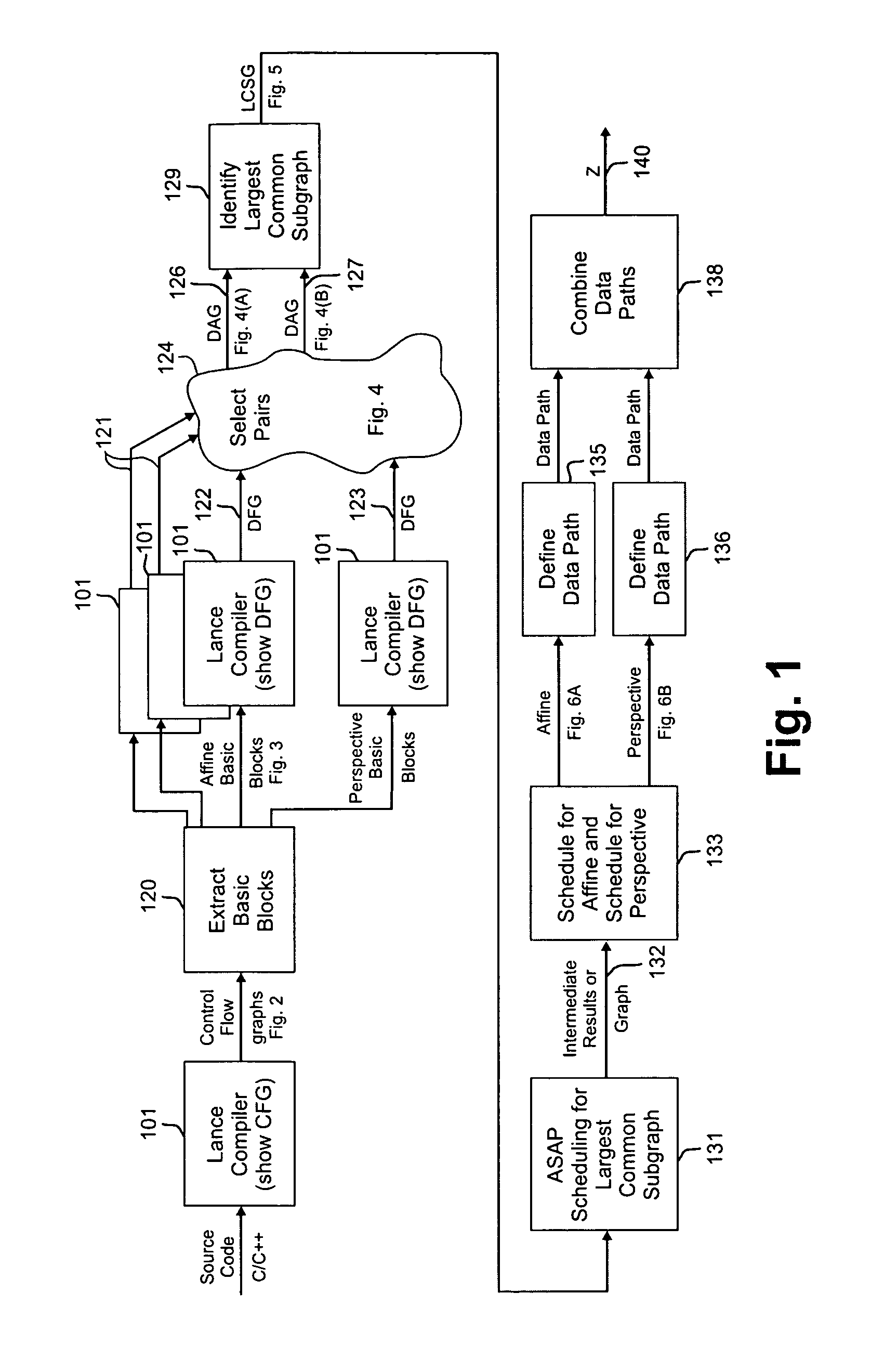

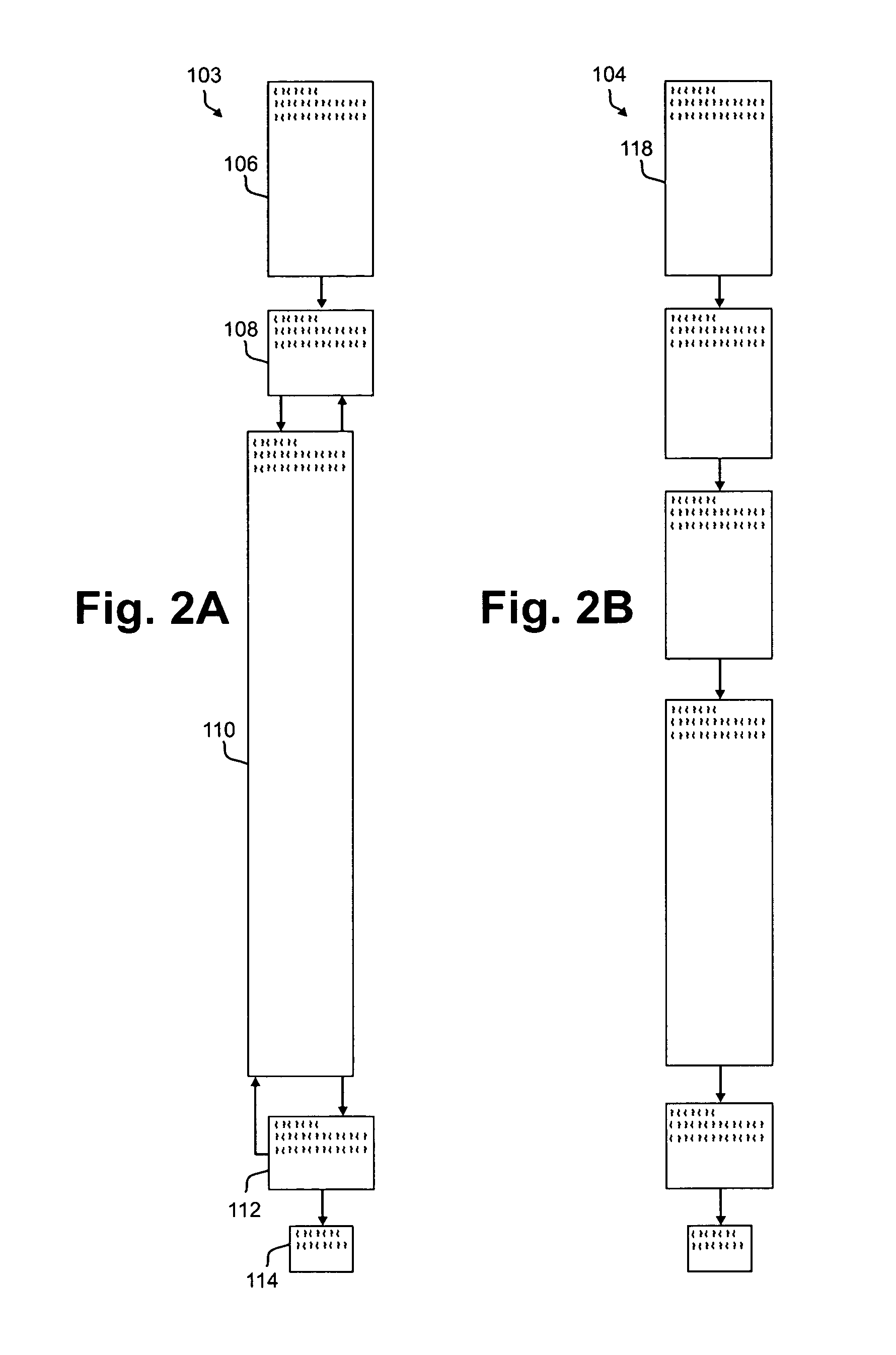

A method of producing a reconfigurable circuit device for running a computer program of moderate complexity such as multimedia processing. Code for the application is compiled into Control Flow Graphs representing distinct parts of the application to be run. From those Control Flow Graphs are extracted basic blocks. The basic blocks are converted to Data Flow Graphs by a compiler utility. From two or more Data Flow Graphs, a largest common subgraph is determined. The largest common subgraph is ASAP scheduled and substituted back into the Data Flow Graphs which also have been scheduled. The separate Data Flow Graphs containing the scheduled largest common subgraph are converted to data paths that are then combined to form code for operating the application. The largest common subgraph is effected in hardware that is shared among the parts of the application from which the Data Flow Graphs were developed. Scheduling of the overall code is effected for sequencing, providing fastest run times and the code is implemented in hardware by partitioning and placement of processing elements on a chip and design of the connective fabric for the design elements.

Owner:ARIZONA STATE UNIVERSITY

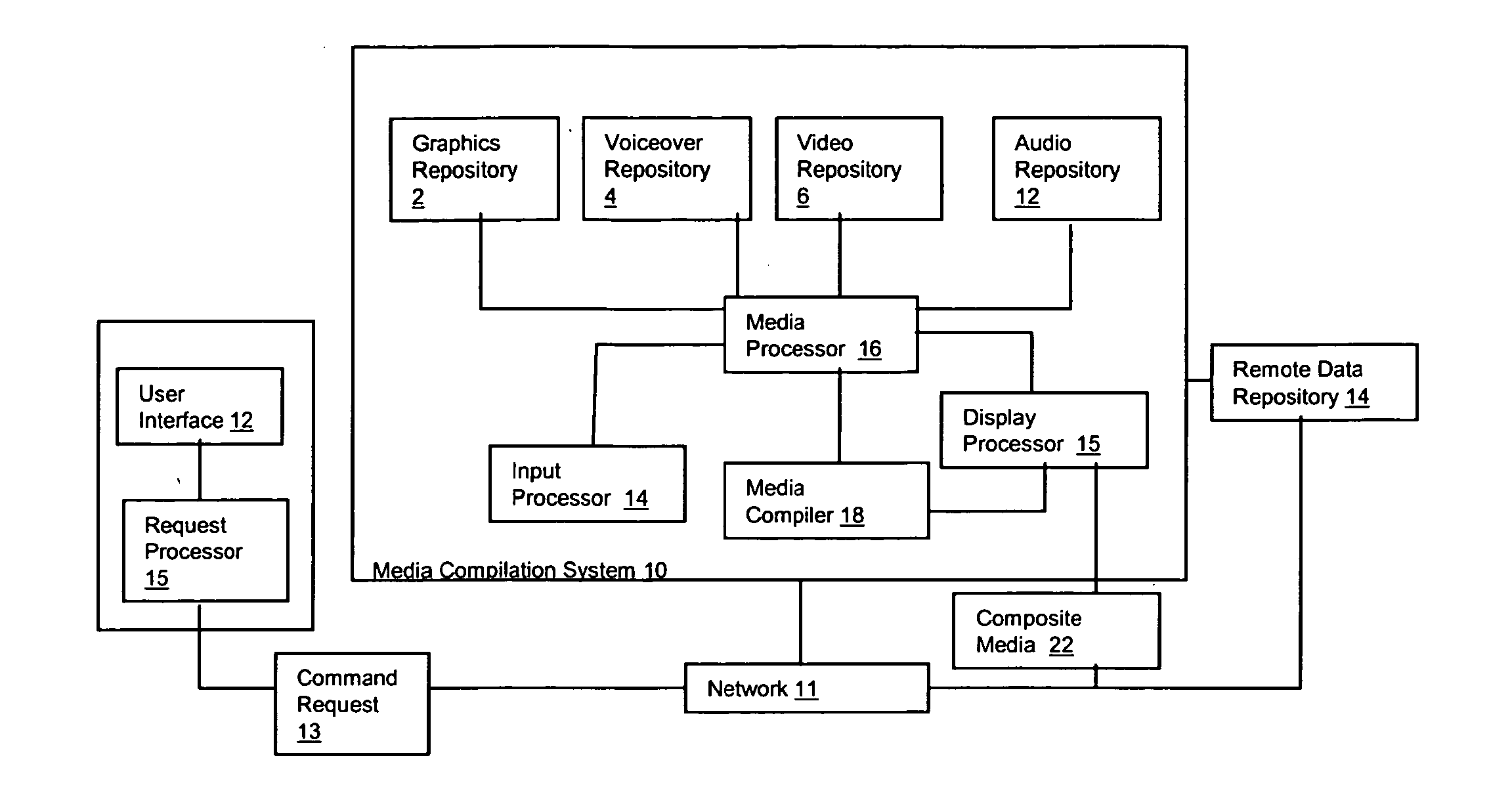

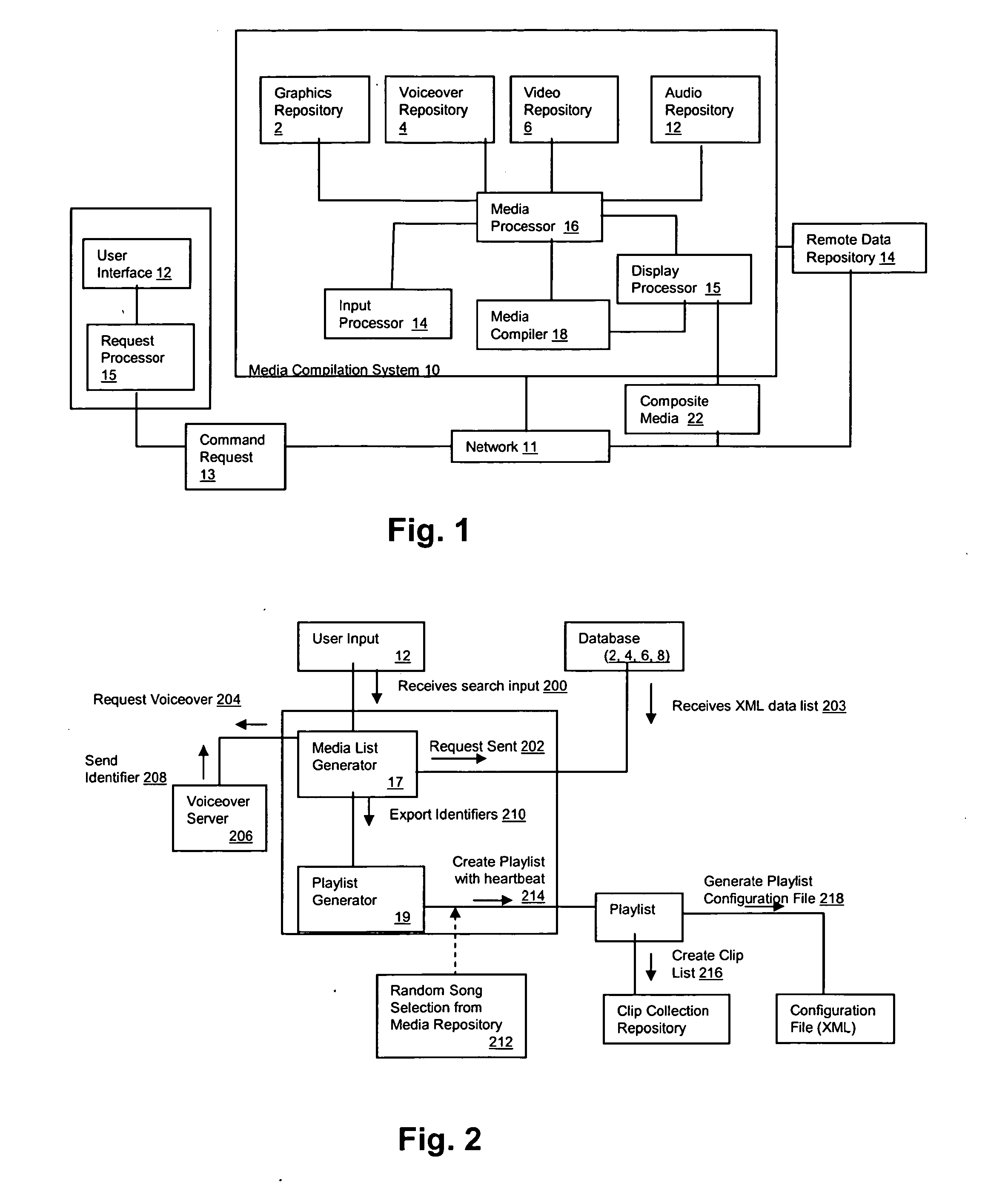

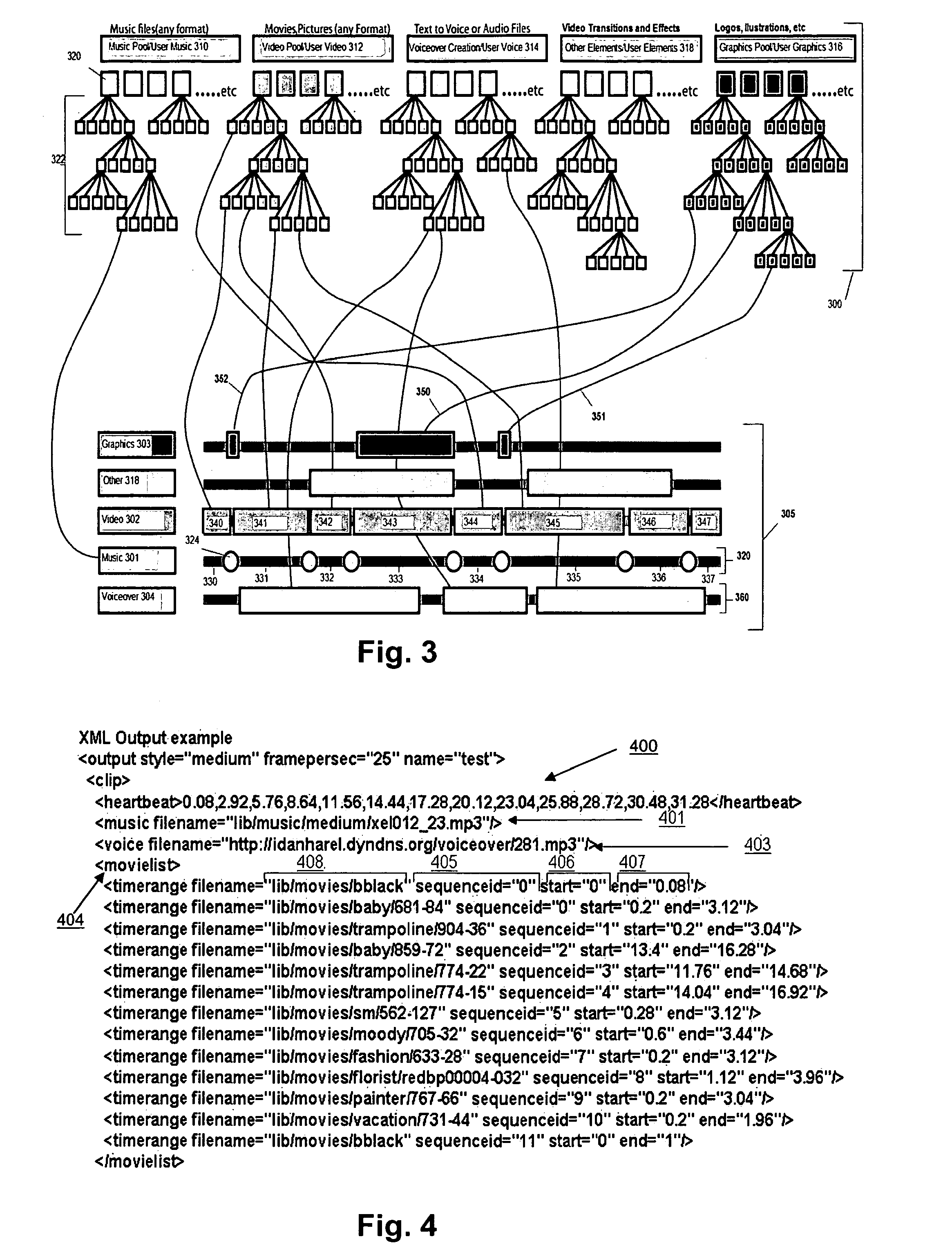

System and Method for Automatically Creating a Media Compilation

InactiveUS20110161348A1Digital data processing detailsElectronic editing digitised analogue information signalsData formatMetadata

A media creation system enabling the automatic compilation file by combining a plurality of different media source files. A media processor automatically initiates a search of media files stored in the repository based on the received criteria data and the metadata associated with the file to produce a list of a plurality of different types of media files wherein each respective media files satisfies the criteria. Media processor automatically and randomly selects a first media file in a first data format from the list and at least one other media file in a second data format. A compiler produces a media compilation file for display including the first and the at least one second media file, the at least one second media file being displayed concurrently with the first media file.

Owner:ORON AVI

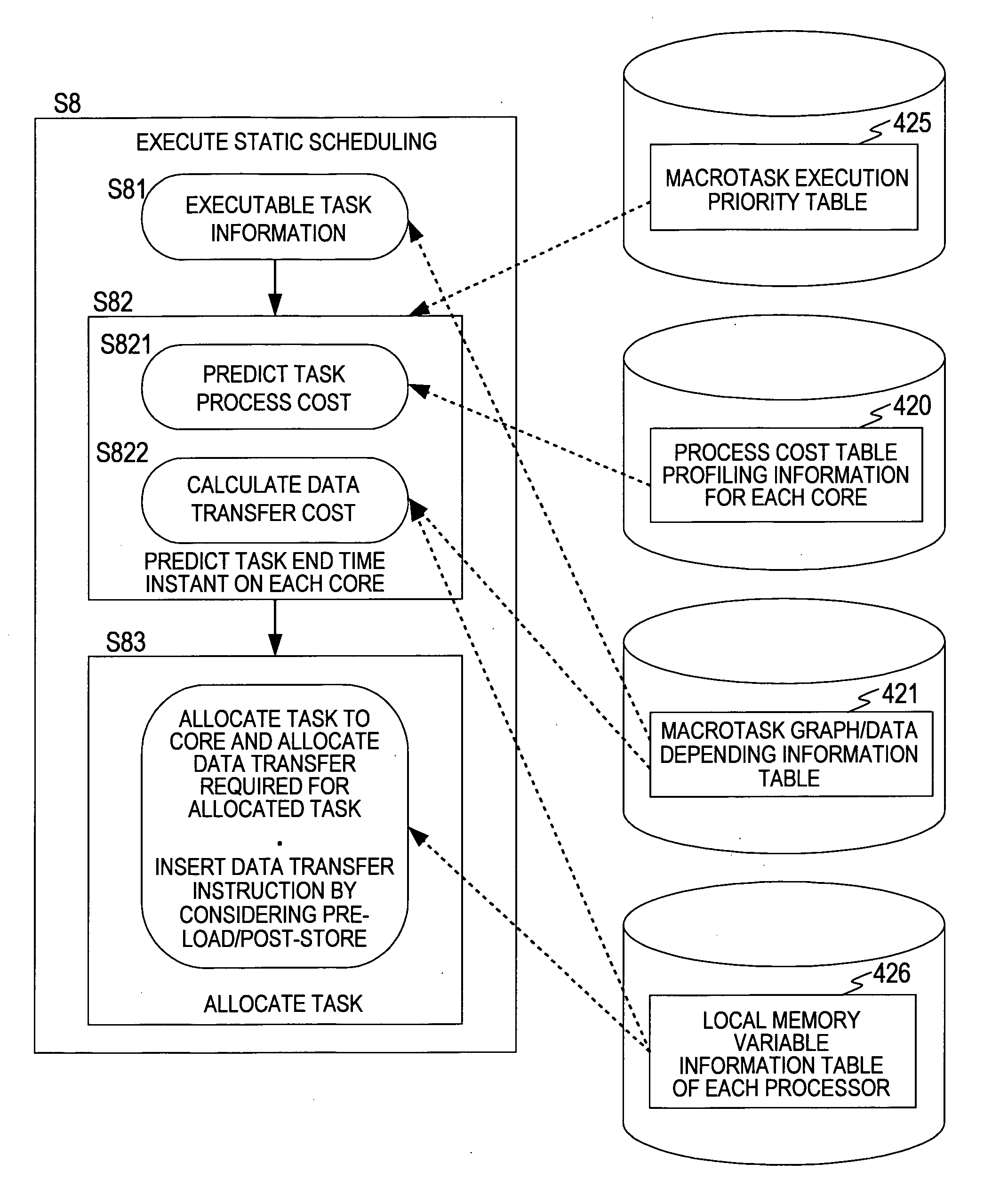

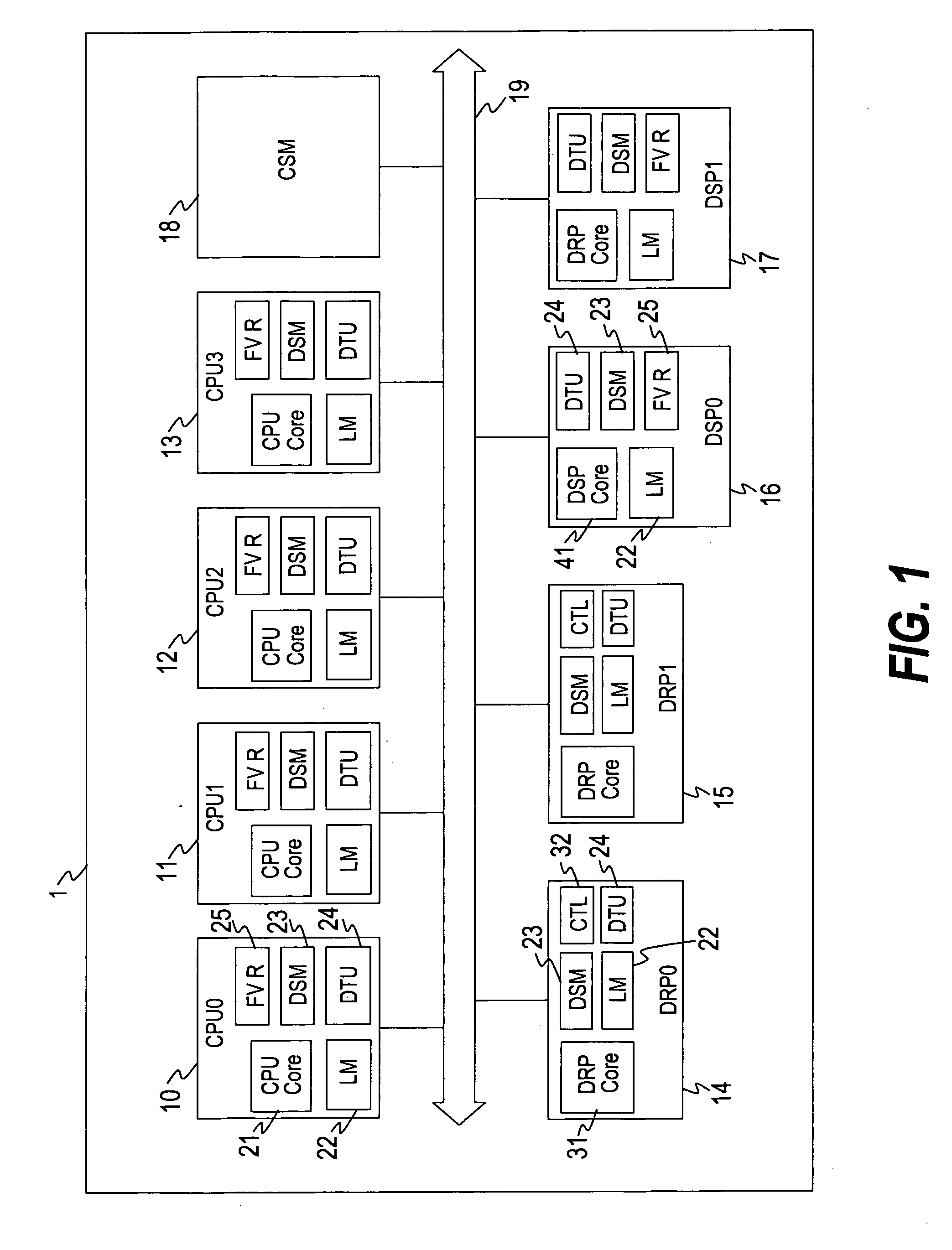

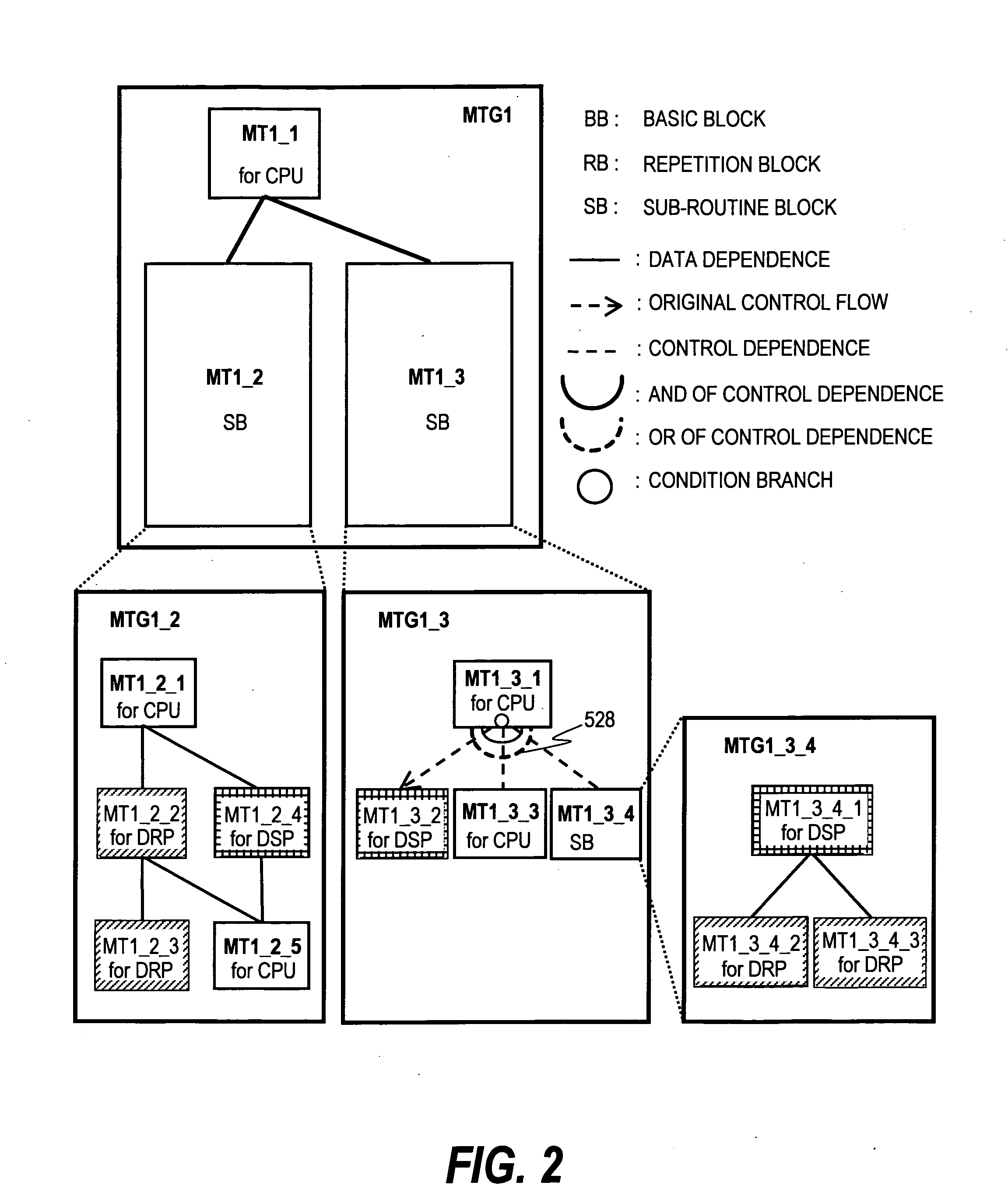

Method for controlling heterogeneous multiprocessor and multigrain parallelizing compiler

ActiveUS20070283358A1Improve efficiencyOverhead required can be suppressedEnergy efficient ICTResource allocationGeneral purposeCost comparison

A heterogeneous multiprocessor system including a plurality of processor elements having mutually different instruction sets and structures avoids a specific processor element from being short of resources to improve throughput. An executable task is extracted based on a preset depending relationship between a plurality of tasks, and the plurality of first processors are allocated to a general-purpose processor group based on a depending relationship among the extracted tasks. A second processor is allocated to an accelerator group, a task to be allocated is determined from the extracted tasks based on a priority value for each of tasks, and an execution cost of executing the determined task by the first processor is compared with an execution cost of executing the task by the second processor. The task is allocated to one of the general-purpose processor group and the accelerator group that is judged to be lower as a result of the cost comparison.

Owner:WASEDA UNIV

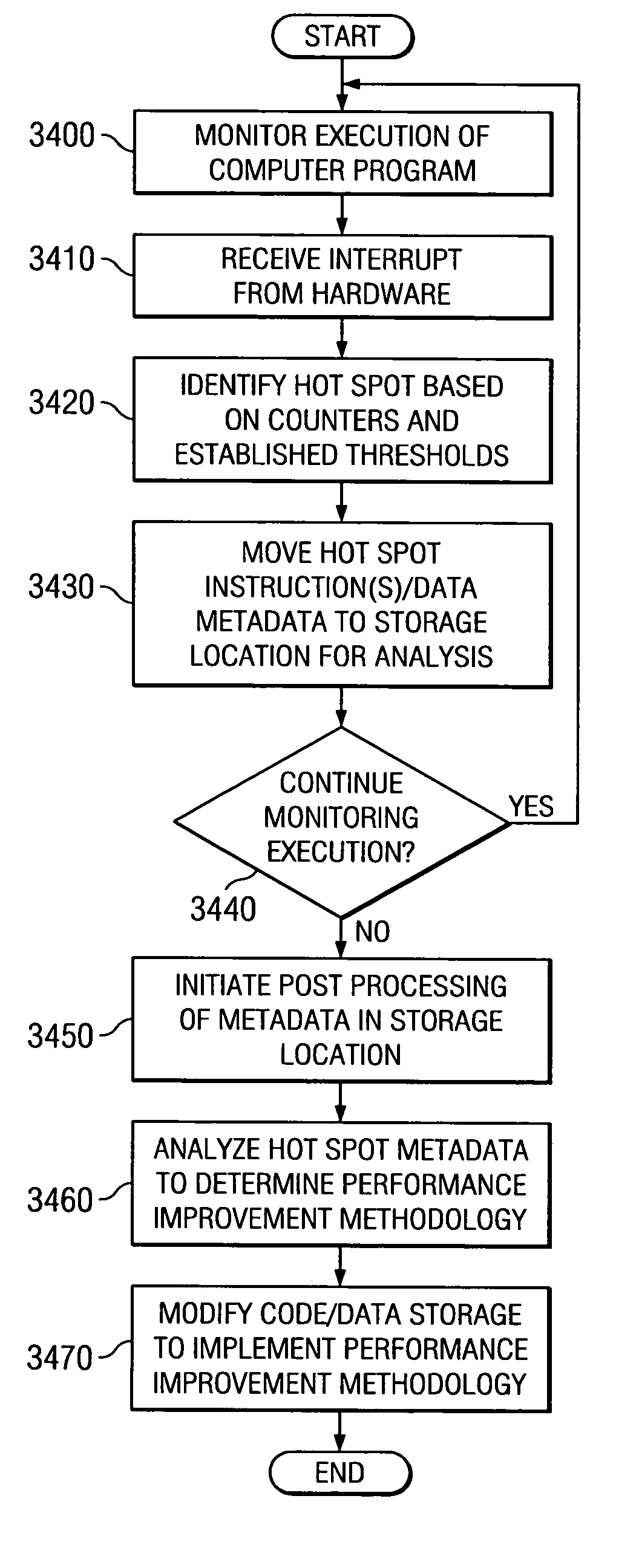

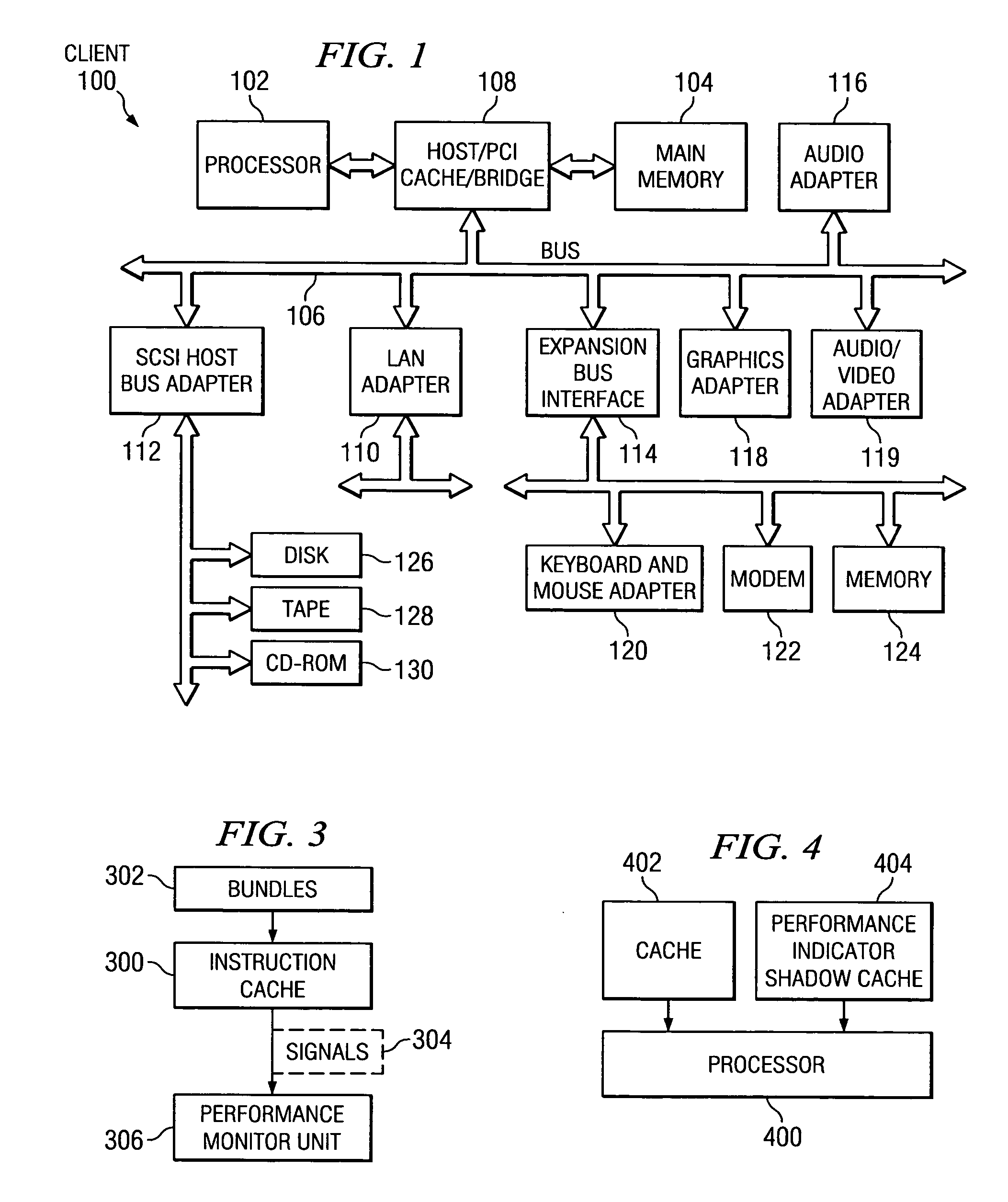

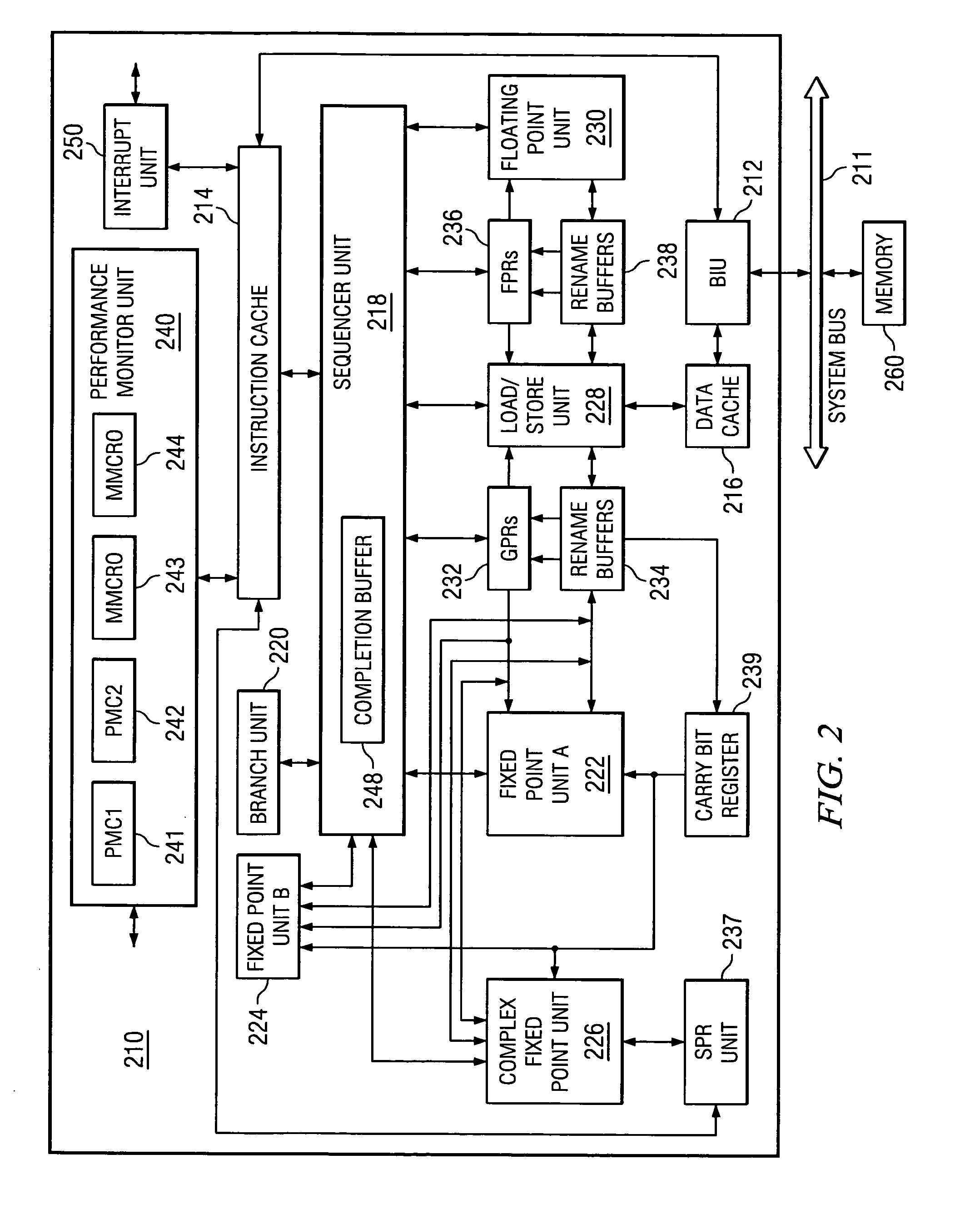

Method and apparatus for optimizing code execution using annotated trace information having performance indicator and counter information

InactiveUS20050155026A1Improve performanceError detection/correctionSoftware engineeringData processing systemProcessing Instruction

A method, apparatus, and computer instructions in a data processing system for processing instructions are provided. Instructions are received at a processor in the data processing system. If a selected indicator is associated with the instruction, counting of each event associated with the execution of the instruction is enabled. In some embodiments, a compiler may obtain performance profile data, annotated by output obtained from the use of the performance indicators and counters, along with the instructions / data of the computer program and use this information to optimize the manner by which the computer program is executed, instructions / data are stored, and the like. The optimizations may be to optimize the instruction paths, optimize the time spent in initial application load, the manner by which the cache and memory is utilized, and the like.

Owner:IBM CORP

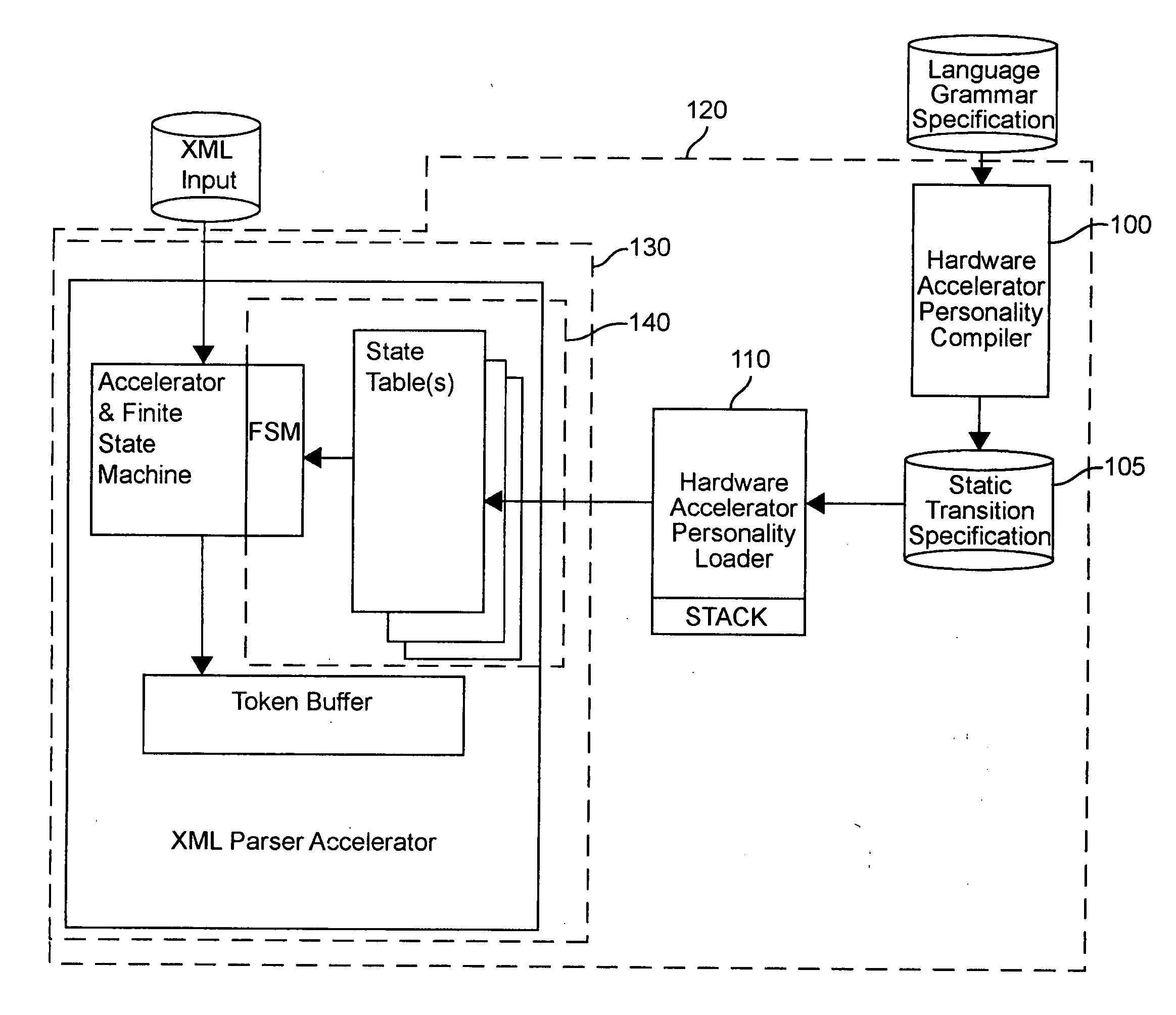

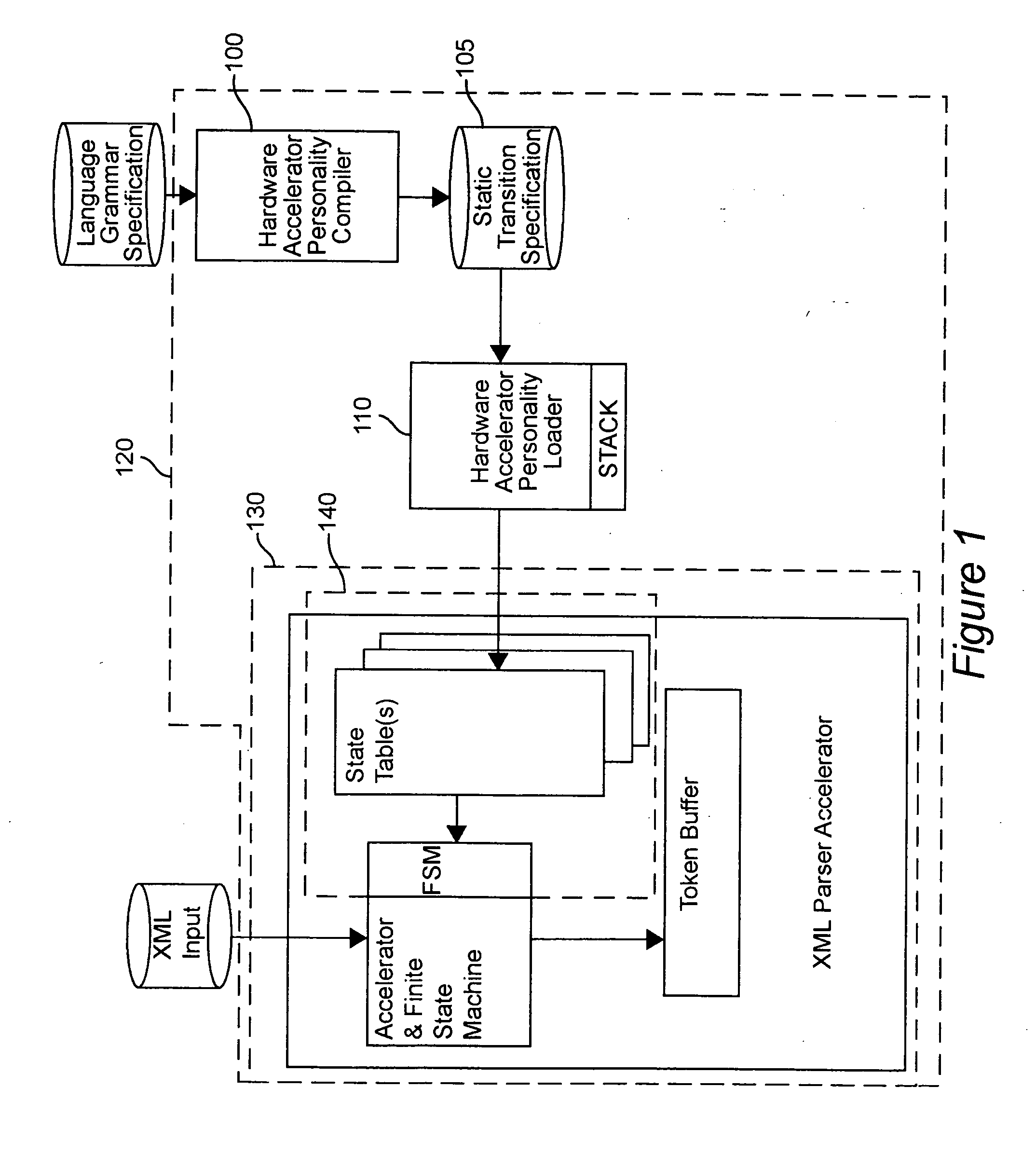

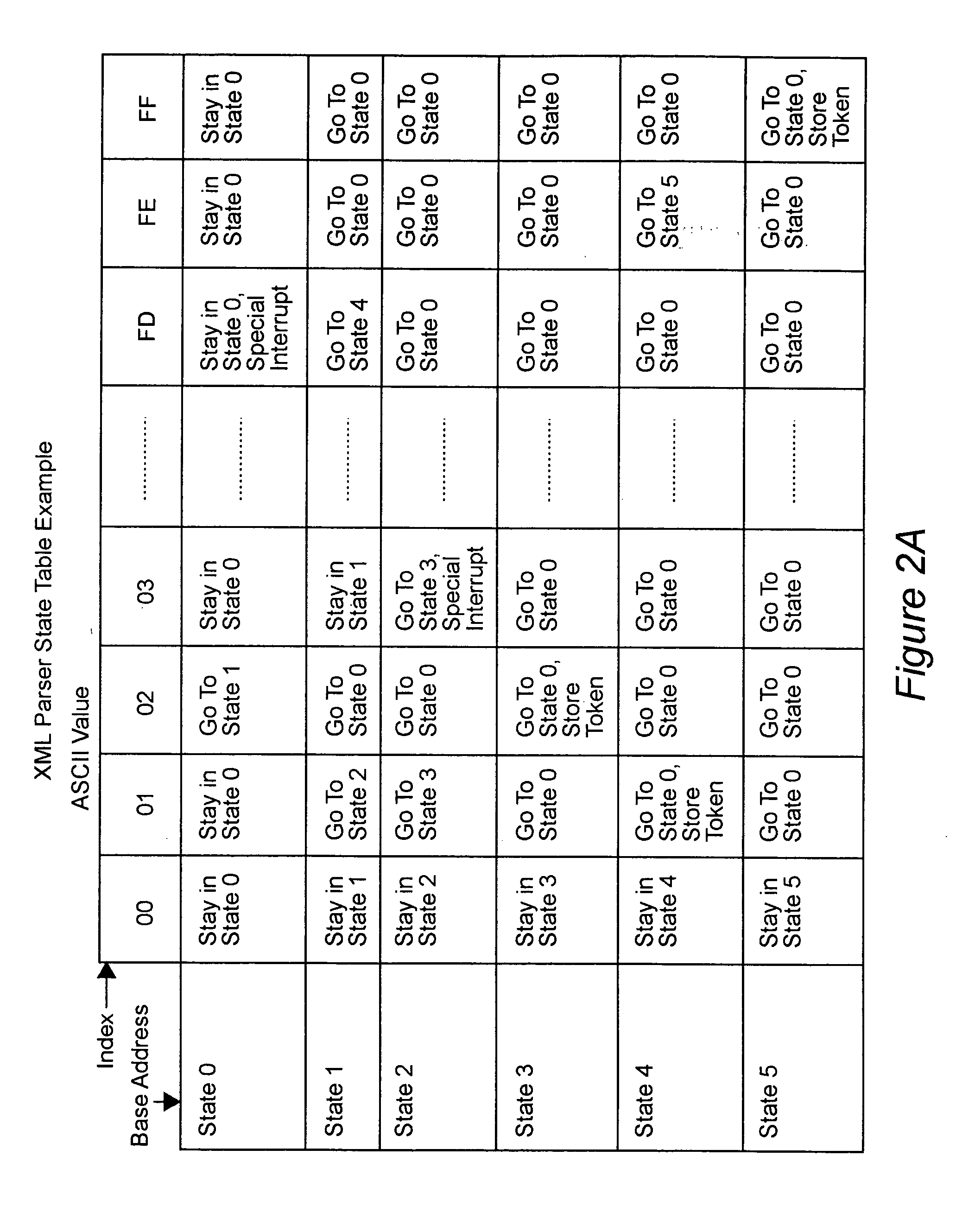

Hardware accelerator personality compiler

InactiveUS20040172234A1Software engineeringSpecial data processing applicationsState switchingAutomaton

Error-free state tables are automatically generated from a specification of a group of desired performable functions, such as are provided in a programming language in a formal notation such as Backus-Naur form or a derivative thereof by discriminating tokens corresponding to respective performable functions, identifications, arguments, syntax, grammar rules, special symbols and the like. The tokens may be recursive (e.g. infinite), in which case they are transformed into a finite automata which may be deterministic or non-deterministic. Non-deterministic finite automata are transformed into deterministic finite automata and then into state transitions which are used to build a state table which can then be stored or, preferably, loaded into a finite state machine of a hardware parser accelerator to define its personality.

Owner:LOCKHEED MARTIN CORP

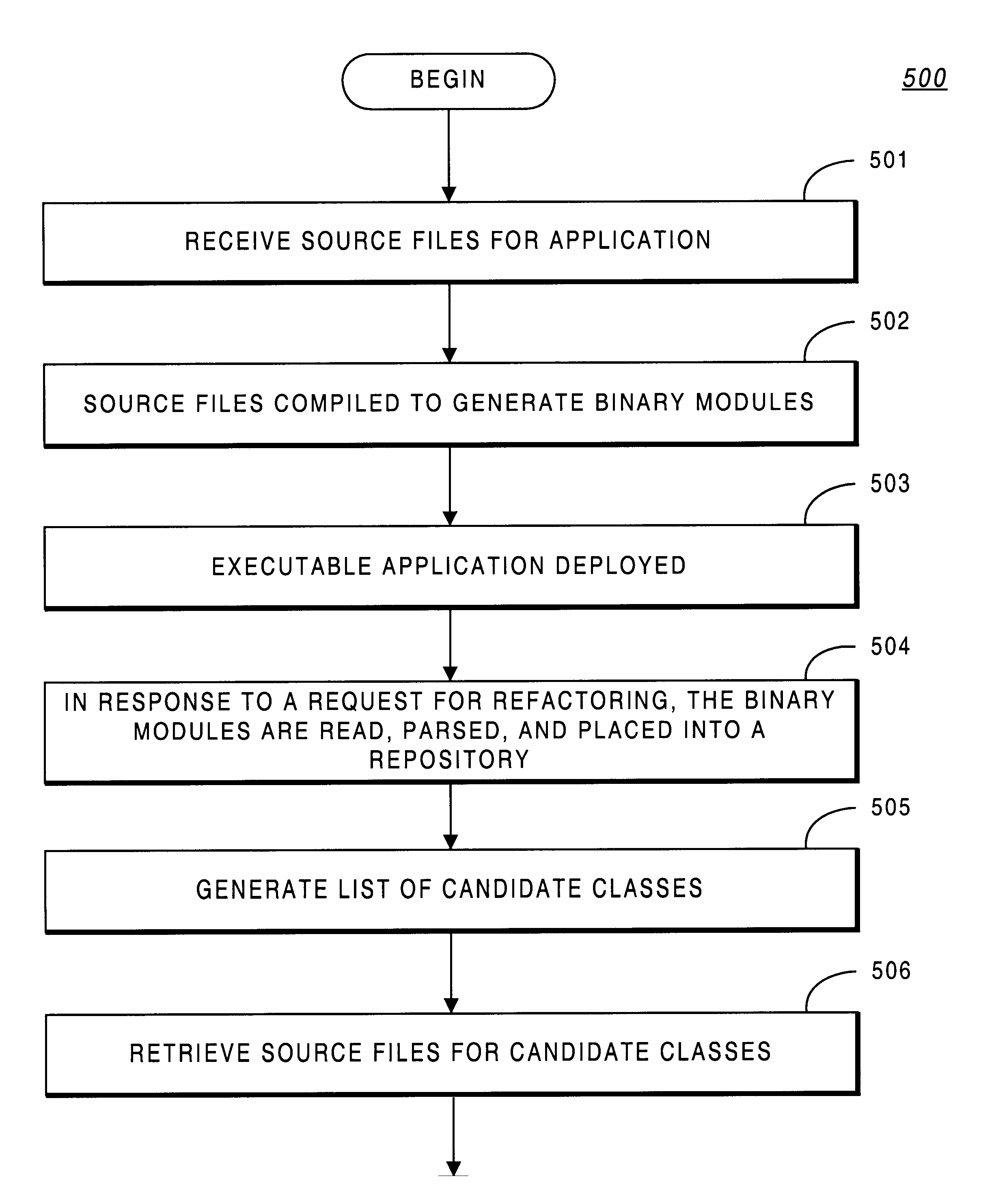

System and methodology providing compiler-assisted refactoring

A system providing an improved method for compiler-assisted refactoring of a software application is described. Upon receiving a request for refactoring of a software application (e.g., changing a given symbol of the application), the binary files of the application are parsed to identify those binary files containing references to the given symbol. The source files of the identified binary files are then retrieved and fed into a compiler. The compiler is used to generate a list of all uses of the given symbol in the software application. This list includes not only the text name of the symbol, but also type information and position information regarding its location(s) in the source file. Based upon the list, changes are applied to the software application.

Owner:CODEGEAR

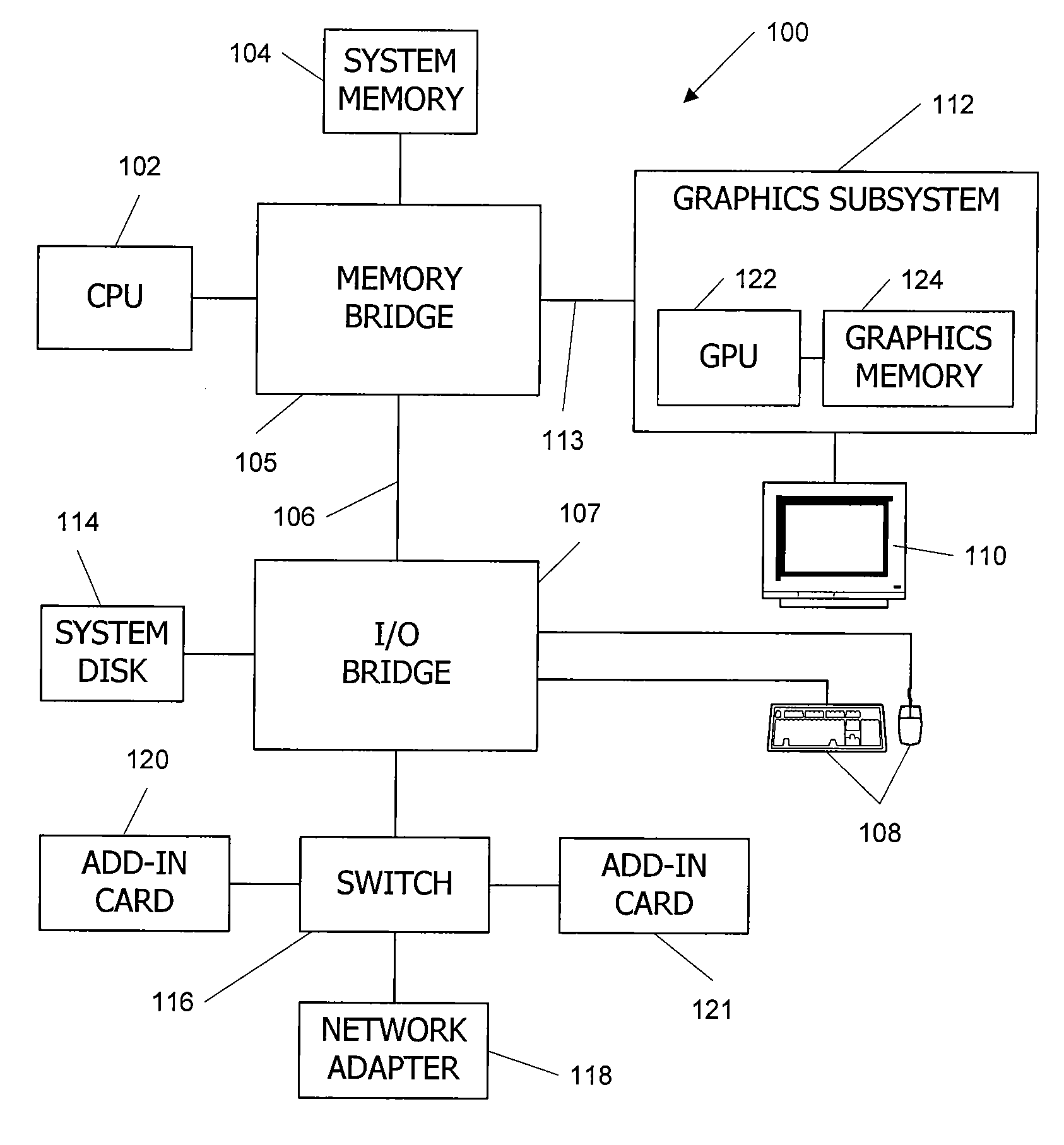

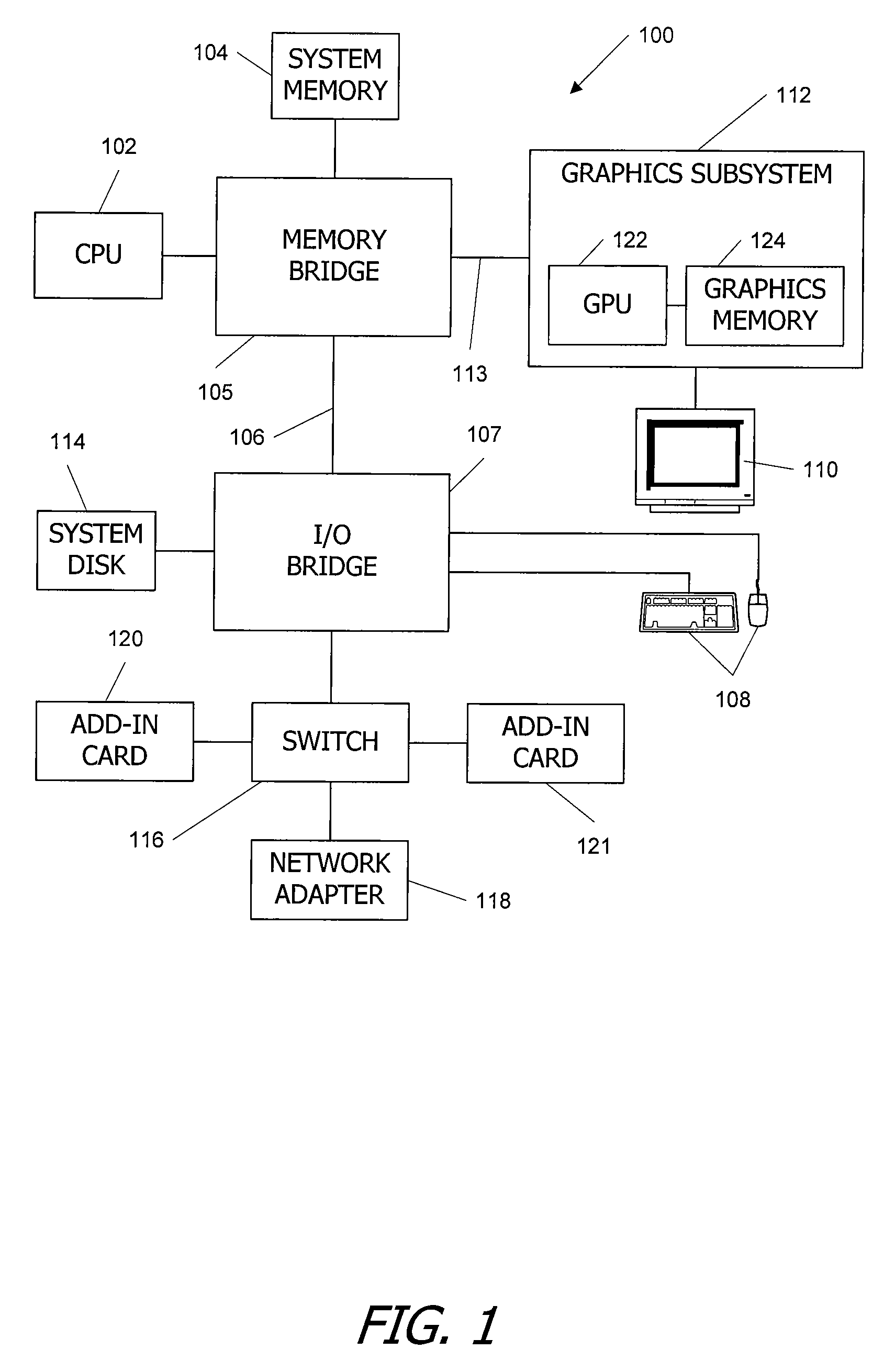

C/c++ language extensions for general-purpose graphics processing unit

A general-purpose programming environment allows users to program a GPU as a general-purpose computation engine using familiar C / C++ programming constructs. Users may use declaration specifiers to identify which portions of a program are to be compiled for a CPU or a GPU. Specifically, functions, objects and variables may be specified for GPU binary compilation using declaration specifiers. A compiler separates the GPU binary code and the CPU binary code in a source file using the declaration specifiers. The location of objects and variables in different memory locations in the system may be identified using the declaration specifiers. CTA threading information is also provided for the GPU to support parallel processing.

Owner:NVIDIA CORP

Algorithm mapping, specialized instructions and architecture features for smart memory computing

InactiveUS6970988B1Improve performanceLow costMultiplex system selection arrangementsProgram controlSmart memoryExecution unit

A smart memory computing system that uses smart memory for massive data storage as well as for massive parallel execution is disclosed. The data stored in the smart memory can be accessed just like the conventional main memory, but the smart memory also has many execution units to process data in situ. The smart memory computing system offers improved performance and reduced costs for those programs having massive data-level parallelism. This smart memory computing system is able to take advantage of data-level parallelism to improve execution speed by, for example, use of inventive aspects such as algorithm mapping, compiler techniques, architecture features, and specialized instruction sets.

Owner:STRIPE INC

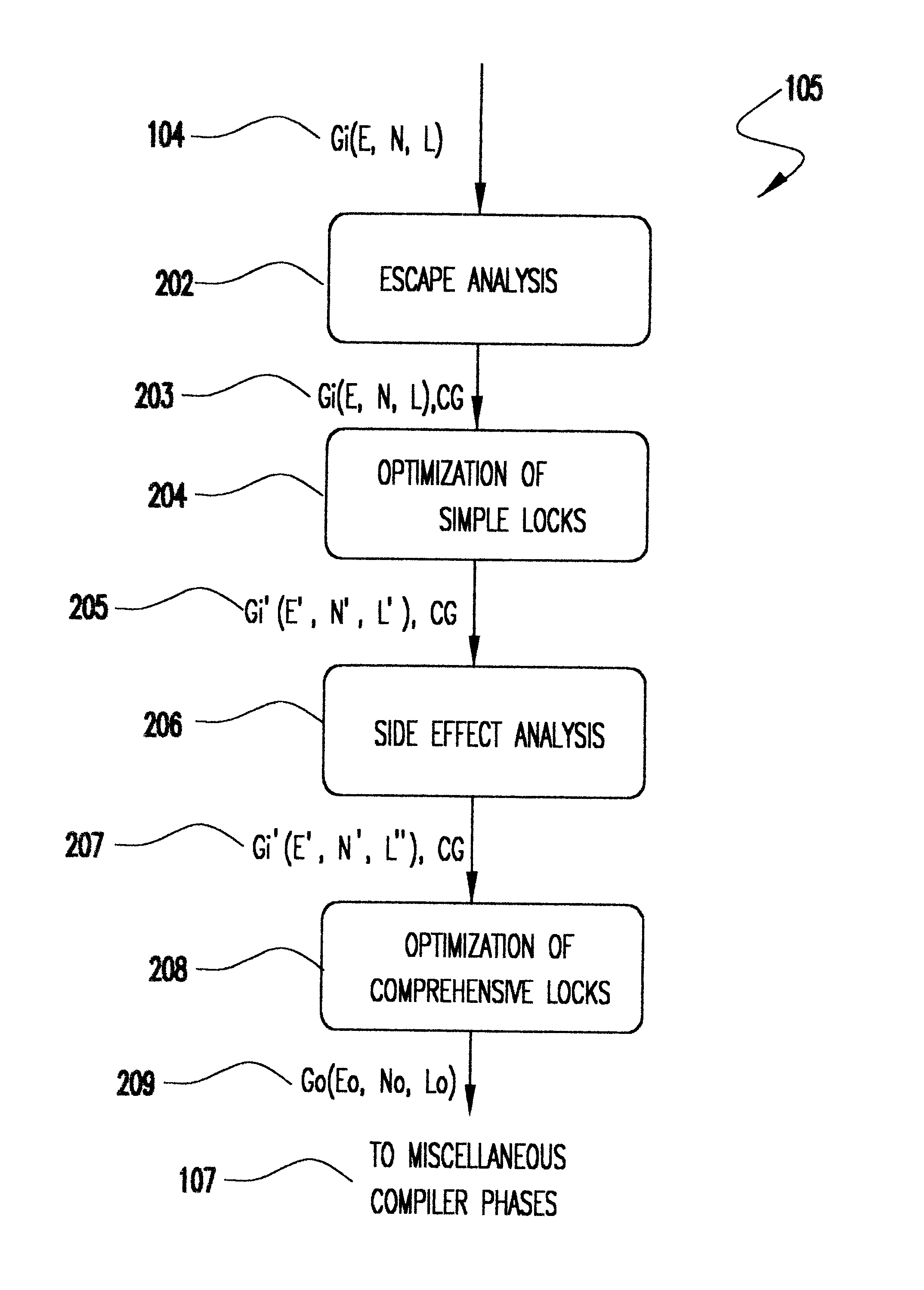

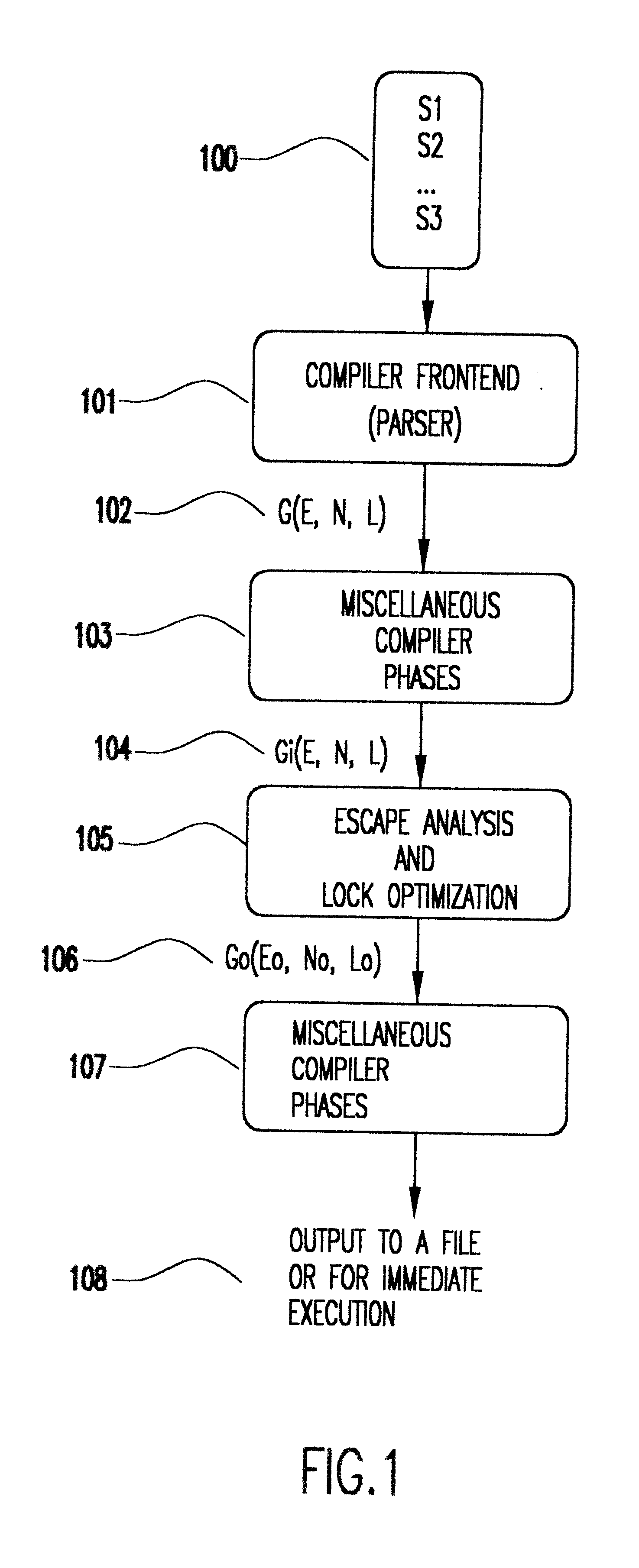

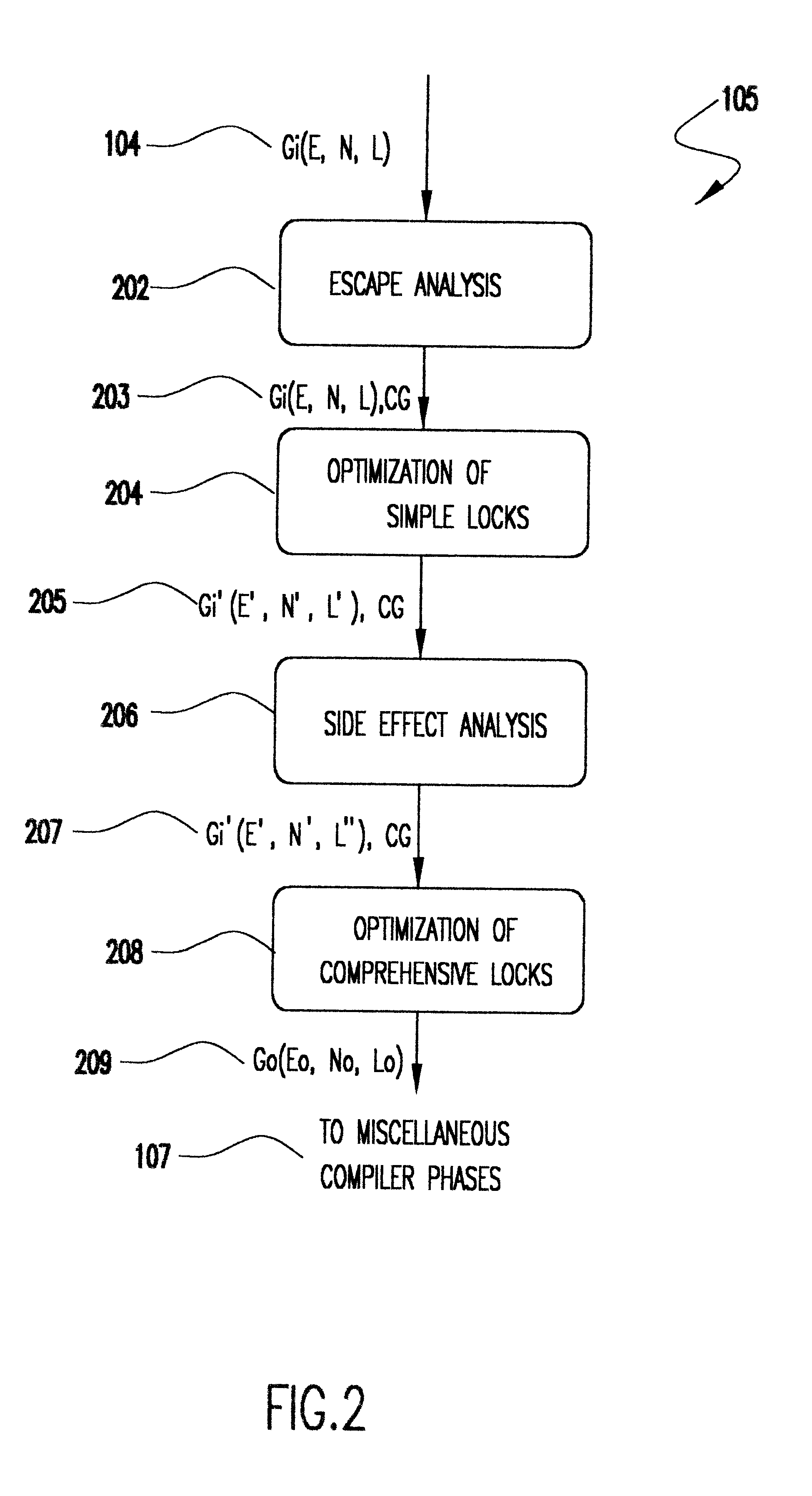

Method for optimizing locks in computer programs

InactiveUS6530079B1Easy to operateProgram synchronisationSoftware engineeringProgram planningSemantics

A method and several variants for using information about the scope of access of objects acted upon by mutual exclusion, or mutex, locks to transform a computer program by eliminating locking operations from the program or simplifying the locking operations, while strictly performing the semantics of the original program. In particular, if it can be determined by a compiler that the object locked can only be accessed by a single thread it is not necessary to perform the "acquire" or "release" part of the locking operation, and only its side effects must be performed. Likewise, if it can be determined that the side effects of a locking operation acting on a variable which is locked in multiple threads are not needed, then only the locking operation, and not the side effects, needs to be performed. This simplifies the locking operation, and leads to faster programs which use fewer computer processor resources to execute; and programs which perform fewer shared memory accesses, which in turn not only causes the optimized program, but also other programs executing on the same computing machine to execute faster. The method also describes how information about the semantics of the locking operation side effects and the information about the scope of access can also be used to eliminate performing the side effect parts of the locking operation, thereby completely eliminating the locking operation. The method also describes how to analyze the program to compute the necessary information about the scope of access. Variants of the method show how one or several of the features of the method may be performed.

Owner:IBM CORP

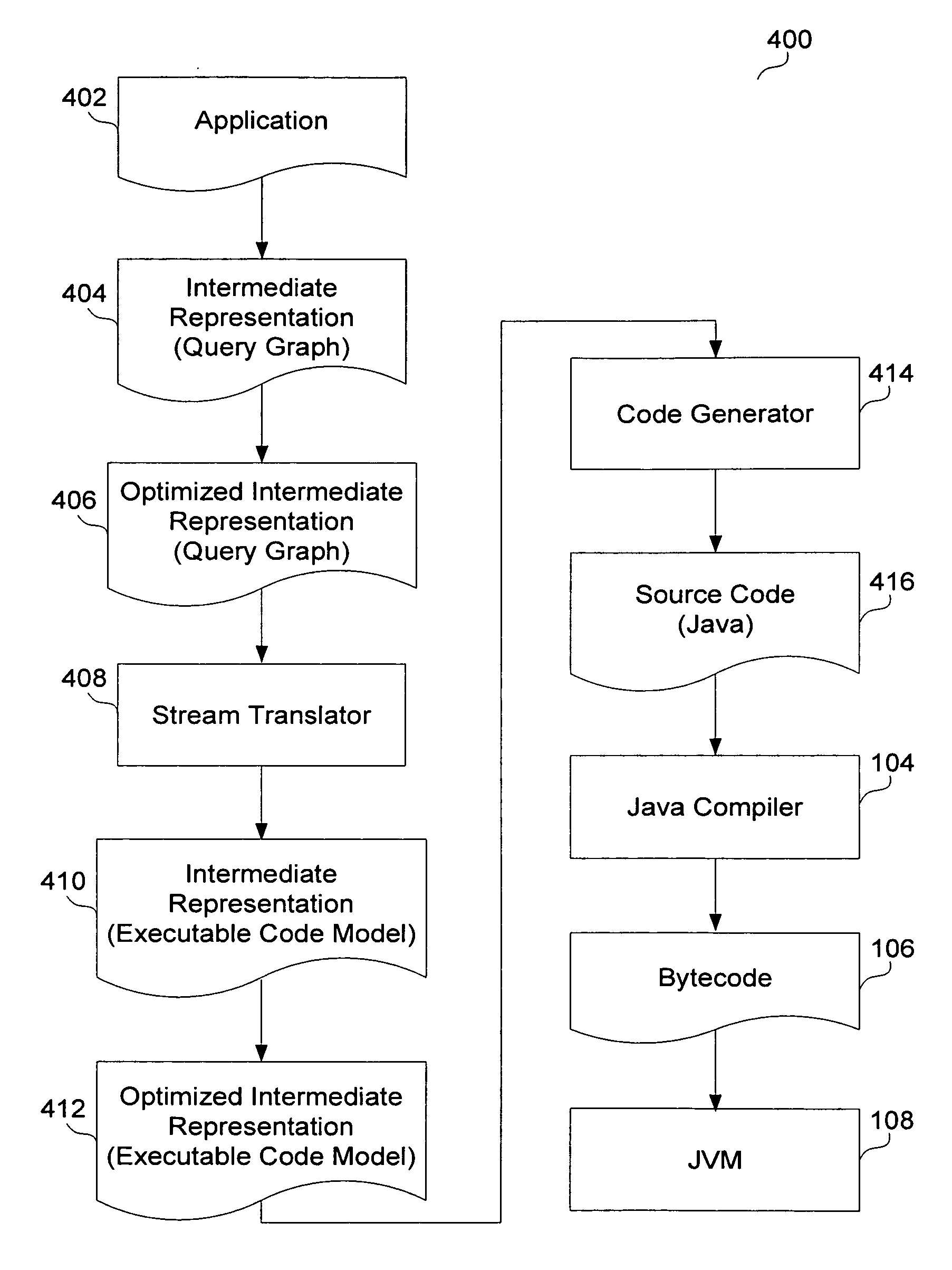

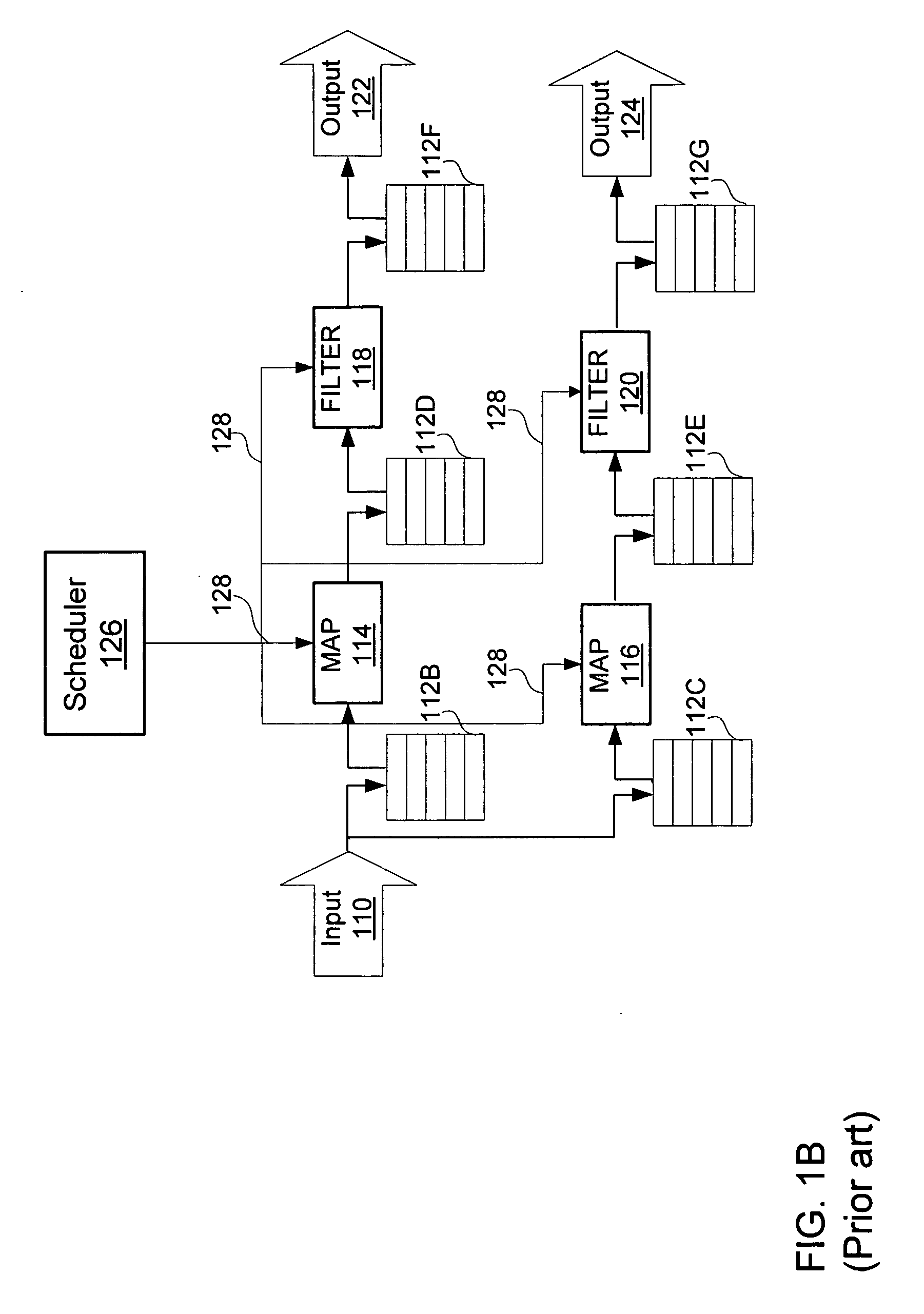

Stream processor with compiled programs

ActiveUS20080134158A1Visual/graphical programmingProgram controlApplication softwareStream processing

A stream processing platform that provides fast execution of stream processing applications within a safe runtime environment. The platform includes a stream compiler that converts a representation of a stream processing application into executable program modules for a safe environment. The platform allows users to specify aspects of the program that contribute to generation of modules that execute as intended. A user may specify aspects to control a type of implementation for loops, order of execution for parallel paths, whether multiple instances of an operation can be performed in parallel or whether certain operations should be executed in separate threads. In addition, the stream compiler may generate executable modules in a way that cause a safe runtime environment to allocate memory or otherwise operate efficiently.

Owner:AUTOLIV DEV AB +1

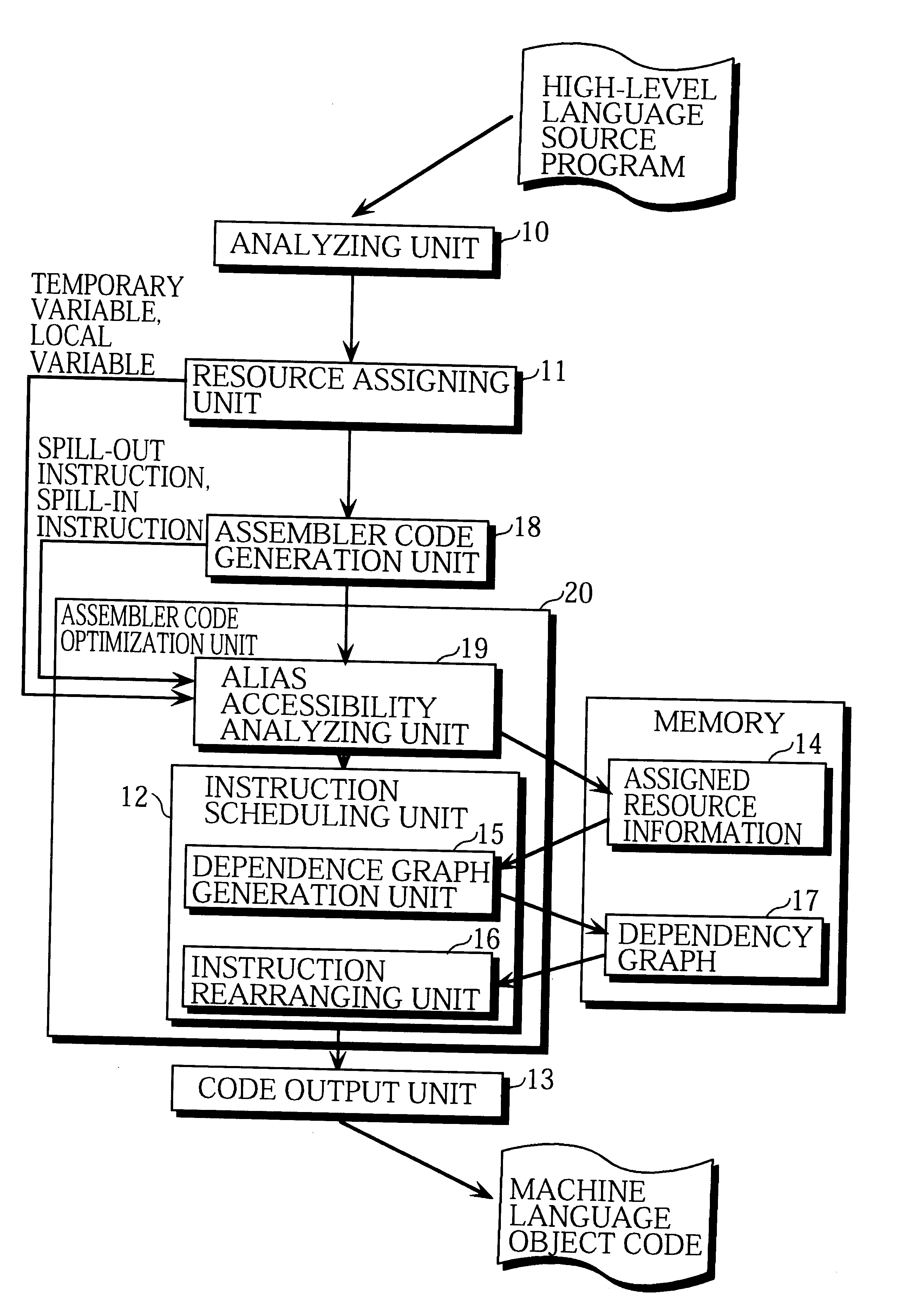

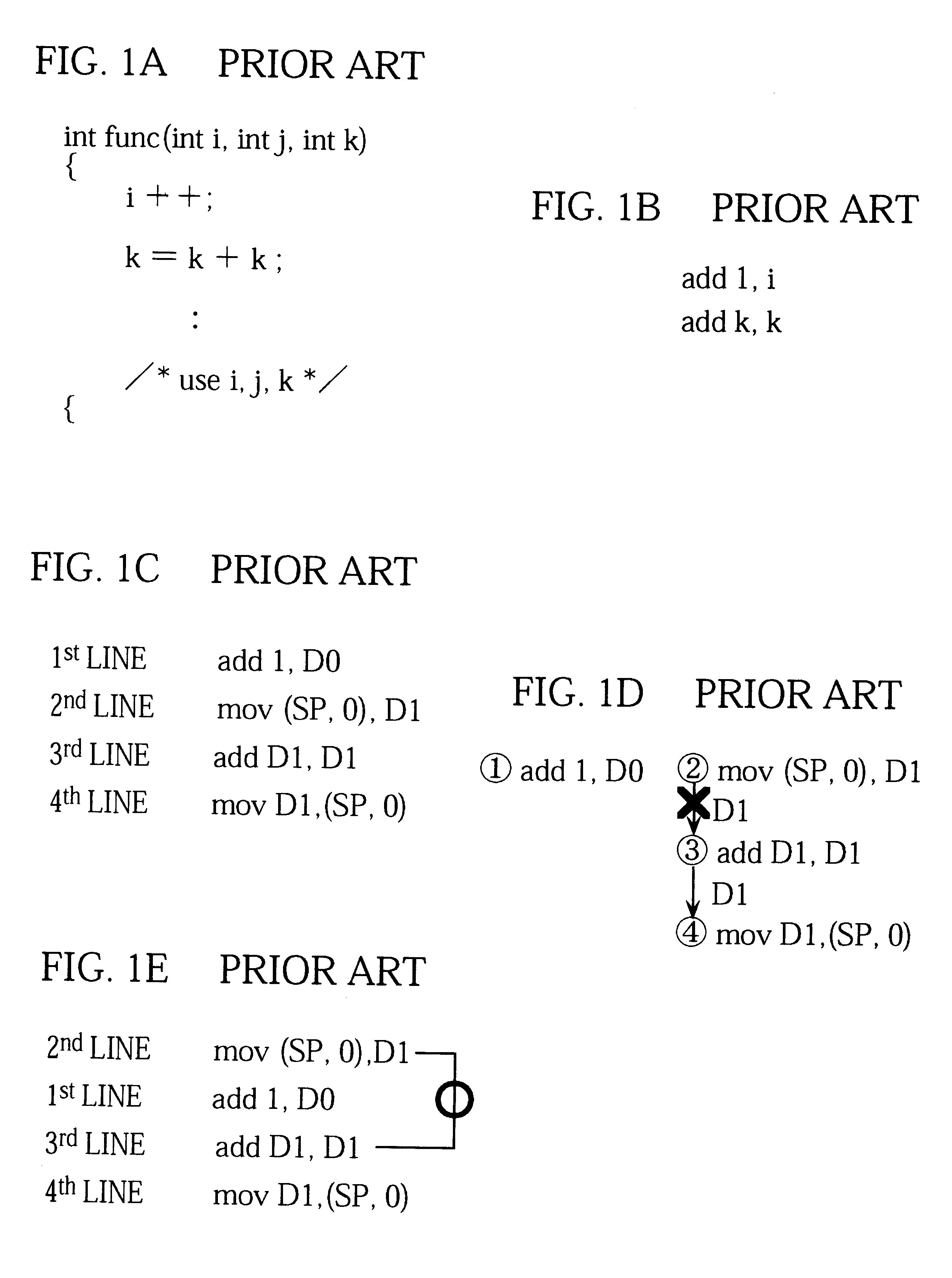

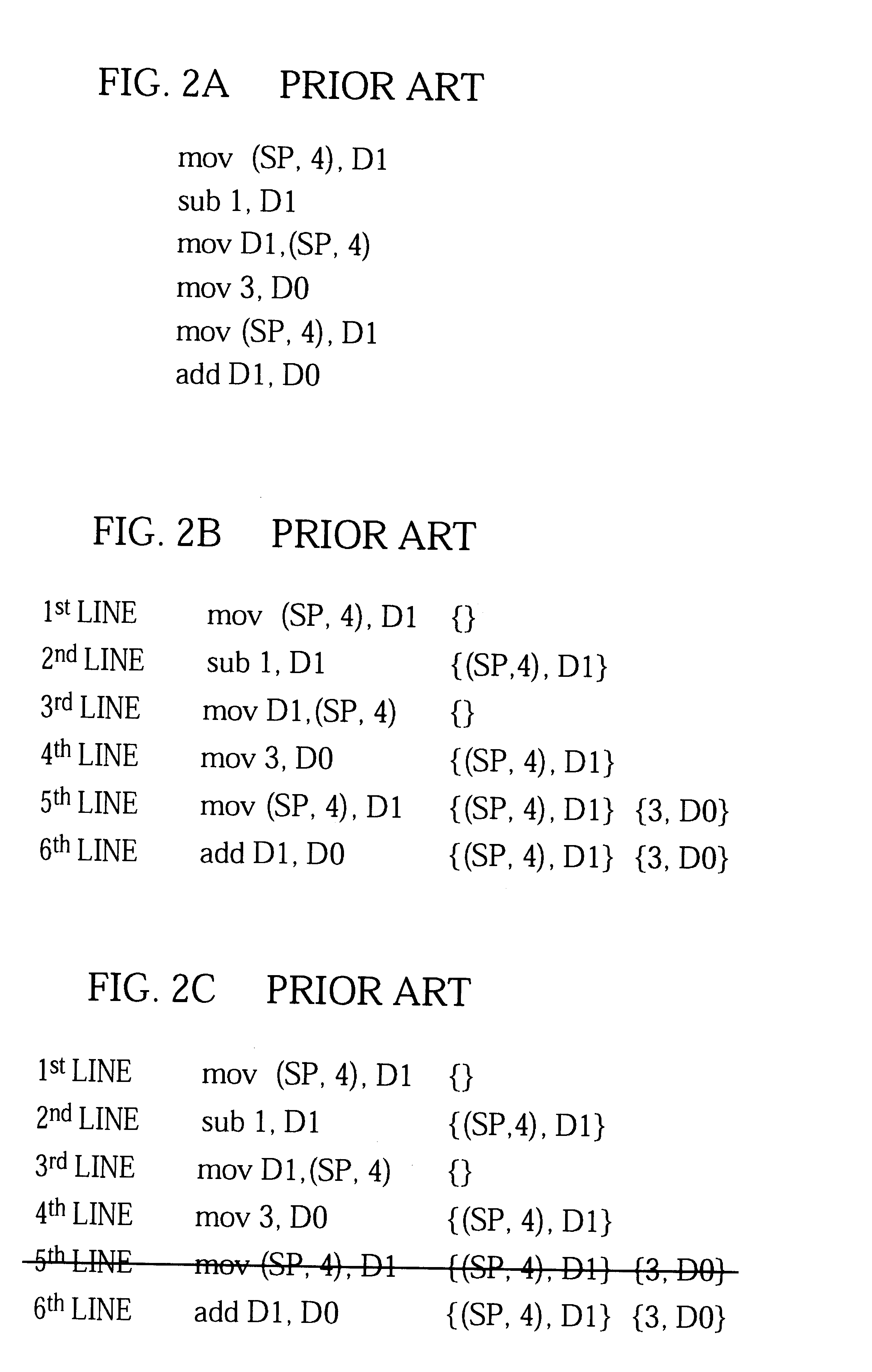

Compiler for optimizing memory instruction sequences by marking instructions not having multiple memory address paths

Internal variables generated by a compiler are assigned to machine resources such as registers and memory by the resource assigning unit 11, and when the assembler code generation unit 18 has outputted an instruction sequence, the alias accessibility analyzing unit 19 registers memory access instructions in the instruction sequence in the assigned resource information 14 according to whether the instructions have a possibility of access by alias. The assembler code optimization unit 20 refers to the assigned resource information 14 and performs optimization at assembler level, thereby reducing the program size and execution time of the instruction sequence.

Owner:SOCIONEXT INC

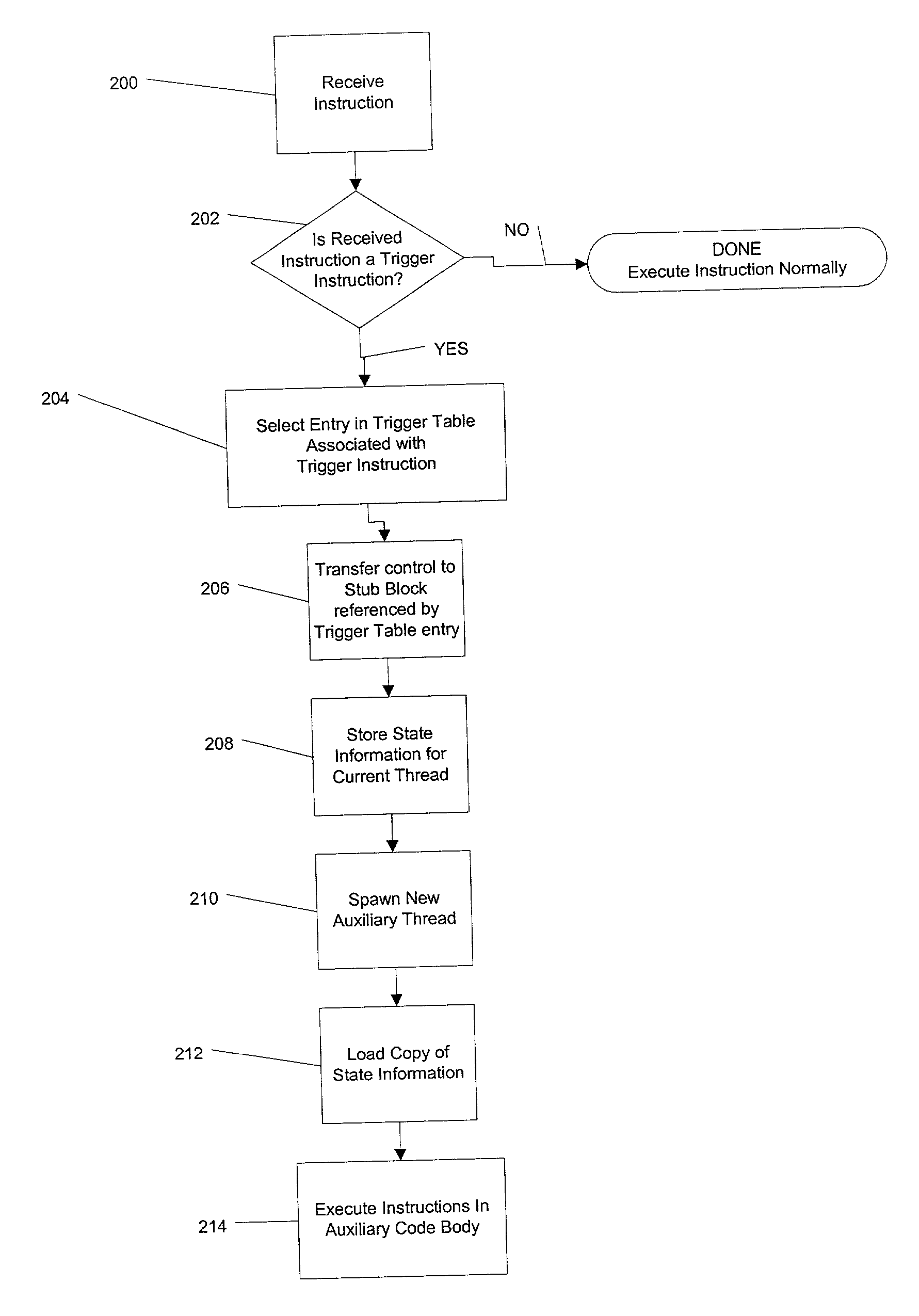

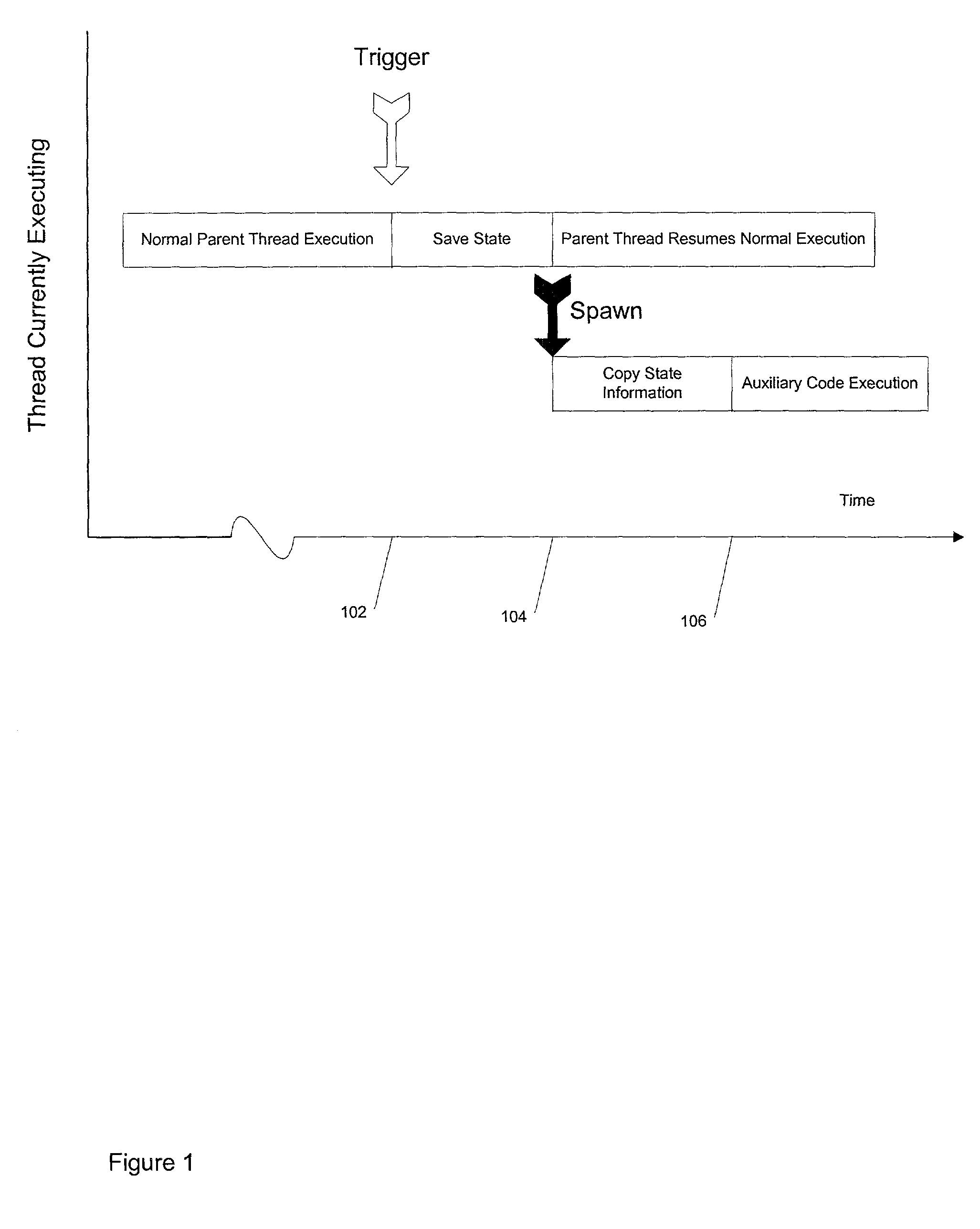

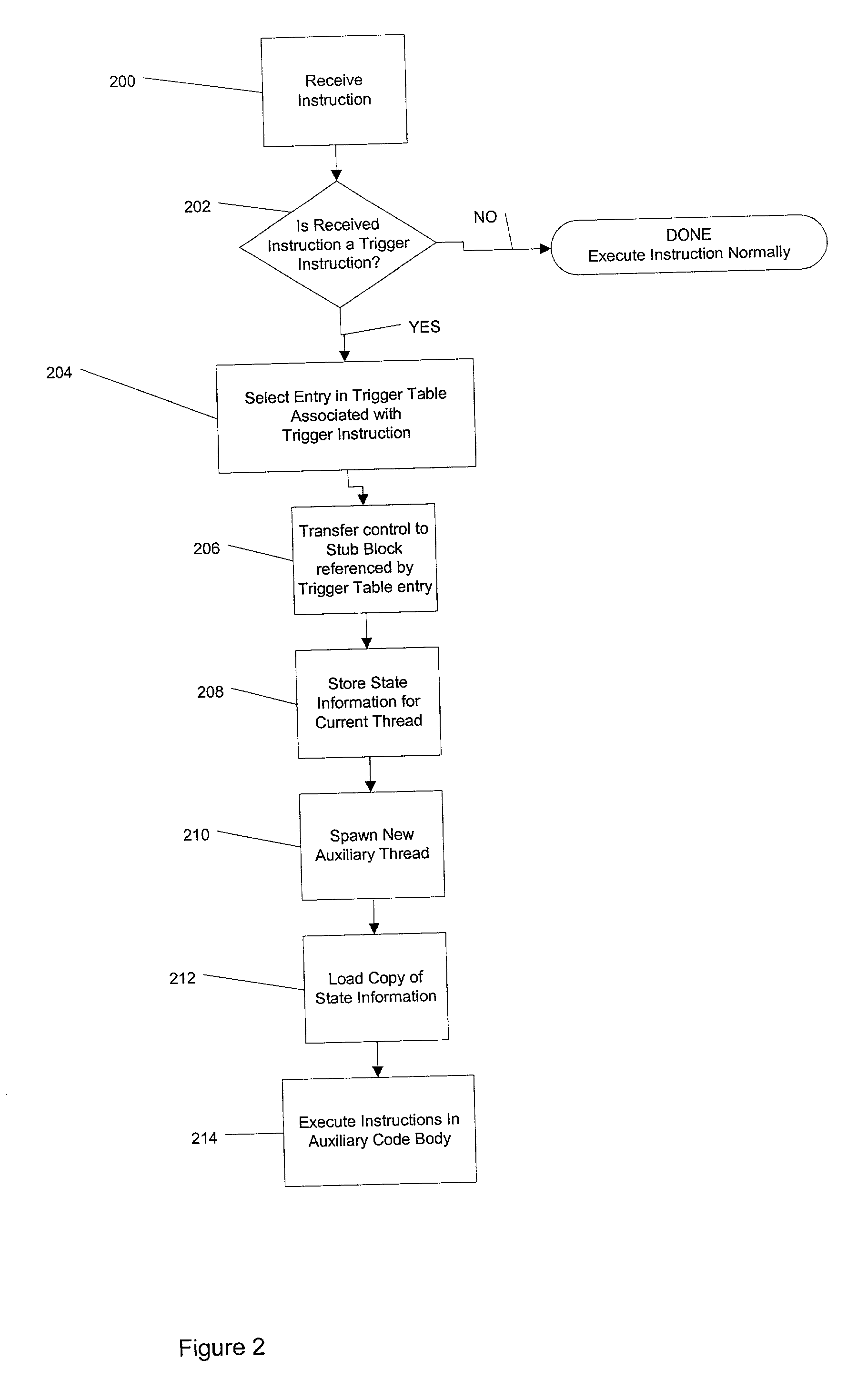

Method and apparatus for compiler-generated triggering of auxiliary codes

InactiveUS20020199179A1Eliminating cache missProgram initiation/switchingSoftware engineeringComputer scienceCompiler

Owner:INTEL CORP

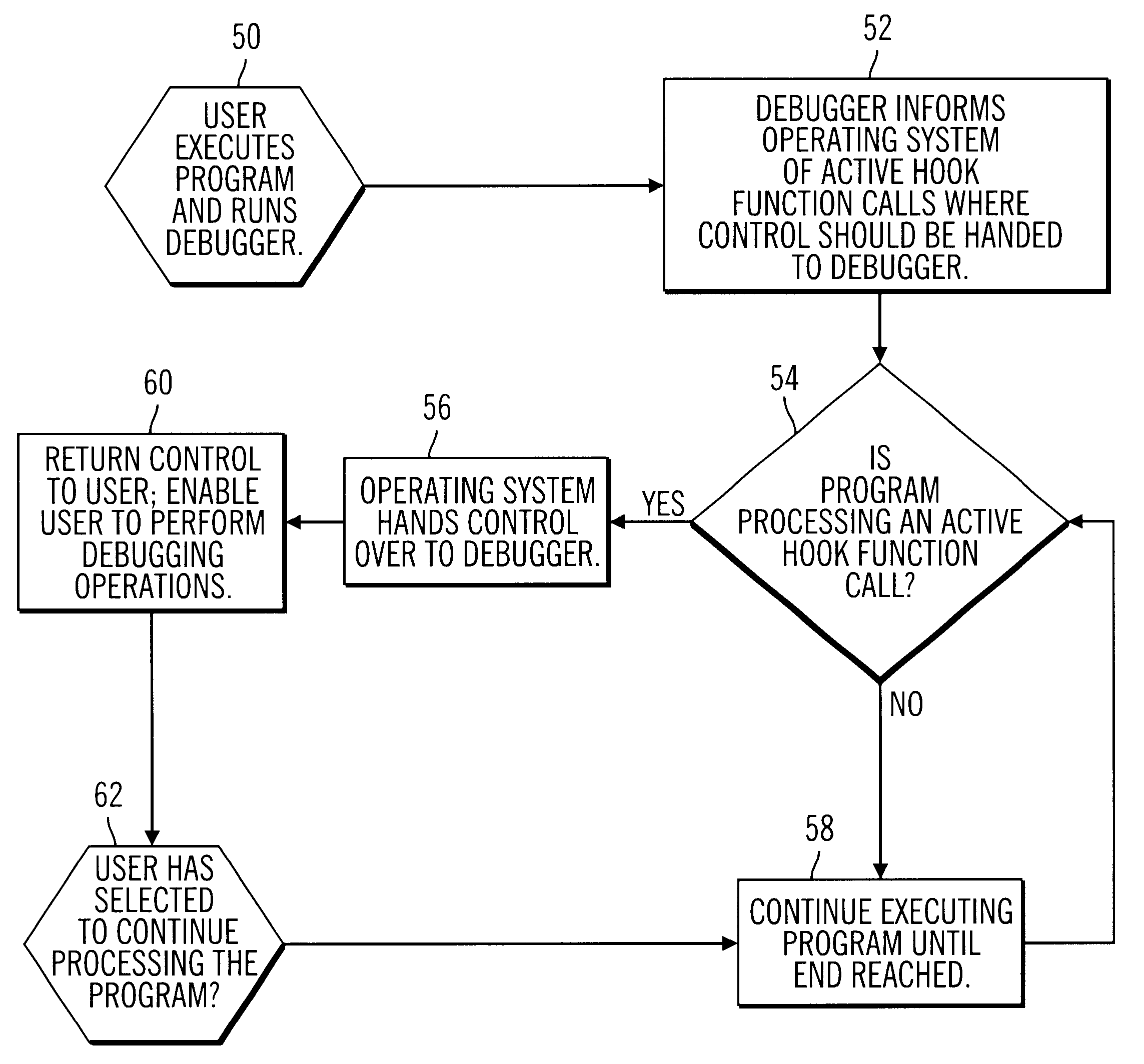

Method system and article of manufacture for debugging a computer program by encoding user specified breakpoint types at multiple locations in the computer program

InactiveUS6249907B1Efficient insertionSoftware testing/debuggingSpecific program execution arrangementsDebuggerComputer program

Disclosed is a system for debugging a computer program. A user indicates a specified breakpoint type, such as a program statement, variable reference, command, etc. The program, including program statements, is then compiled. During compilation, the compiler locates statements in the program corresponding to the breakpoint types and generates a function call into the program at instances in the program of statements corresponding to the user specified breakpoint types. During a debugging phase, a debugger may execute an executable version of the program, including the function calls. Upon processing the function calls, the debugger may stop execution of the program and pass control to the user to perform debugging operations.

Owner:IBM CORP

Reconfigurable processing

ActiveUS8281297B2Reduce the amount requiredQuick switchEnergy efficient ICTSoftware engineeringControl flowProcessing element

A method of producing a reconfigurable circuit device for running a computer program of moderate complexity such as multimedia processing. Code for the application is compiled into Control Flow Graphs representing distinct parts of the application to be run. From those Control Flow Graphs are extracted basic blocks. The basic blocks are converted to Data Flow Graphs by a compiler utility. From two or more Data Flow Graphs, a largest common subgraph is determined. The largest common subgraph is ASAP scheduled and substituted back into the Data Flow Graphs which also have been scheduled. The separate Data Flow Graphs containing the scheduled largest common subgraph are converted to data paths that are then combined to form code for operating the application. The largest common subgraph is effected in hardware that is shared among the parts of the application from which the Data Flow Graphs were developed. Scheduling of the overall code is effected for sequencing, providing fastest run times and the code is implemented in hardware by partitioning and placement of processing elements on a chip and design of the connective fabric for the design elements.

Owner:ARIZONA STATE UNIVERSITY

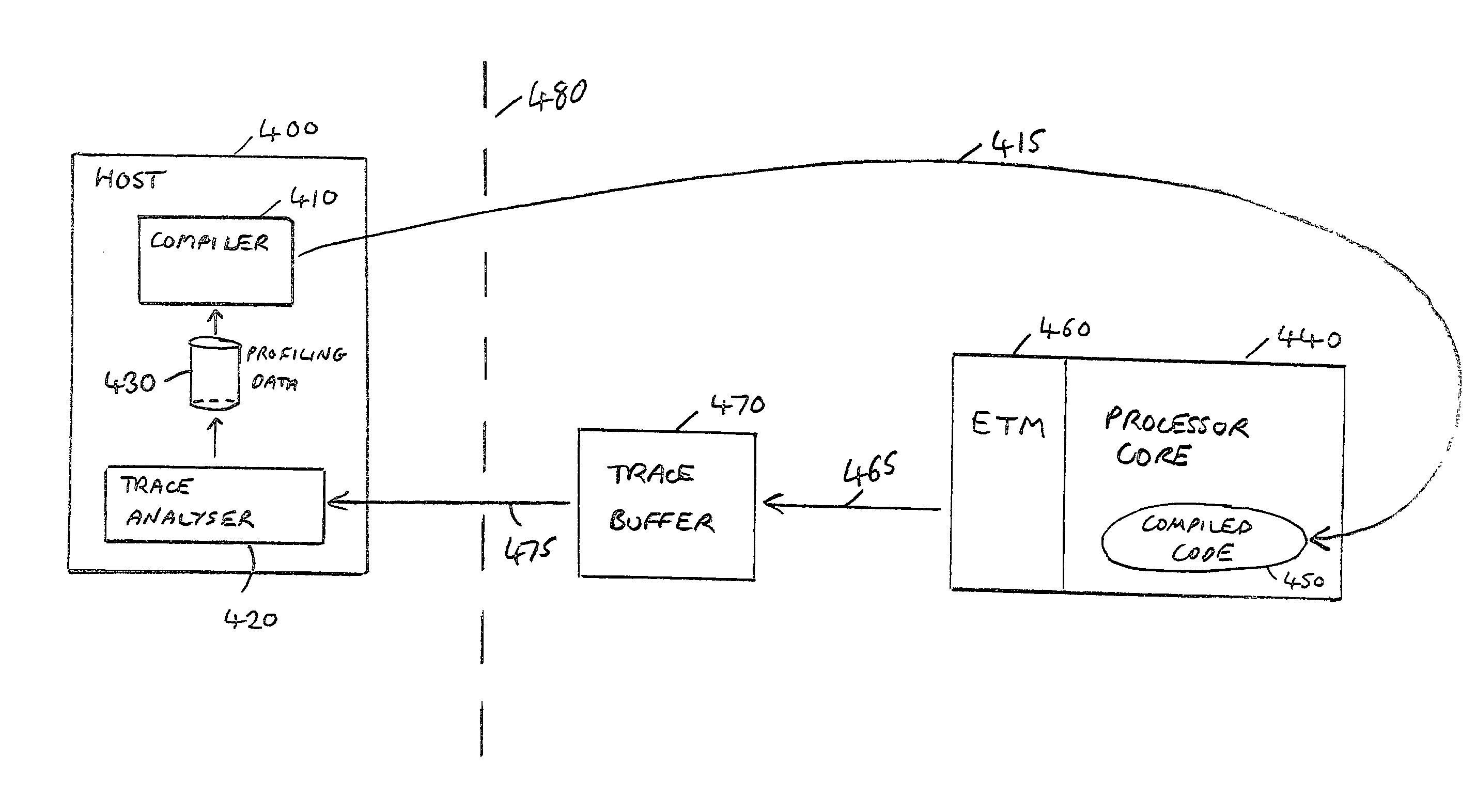

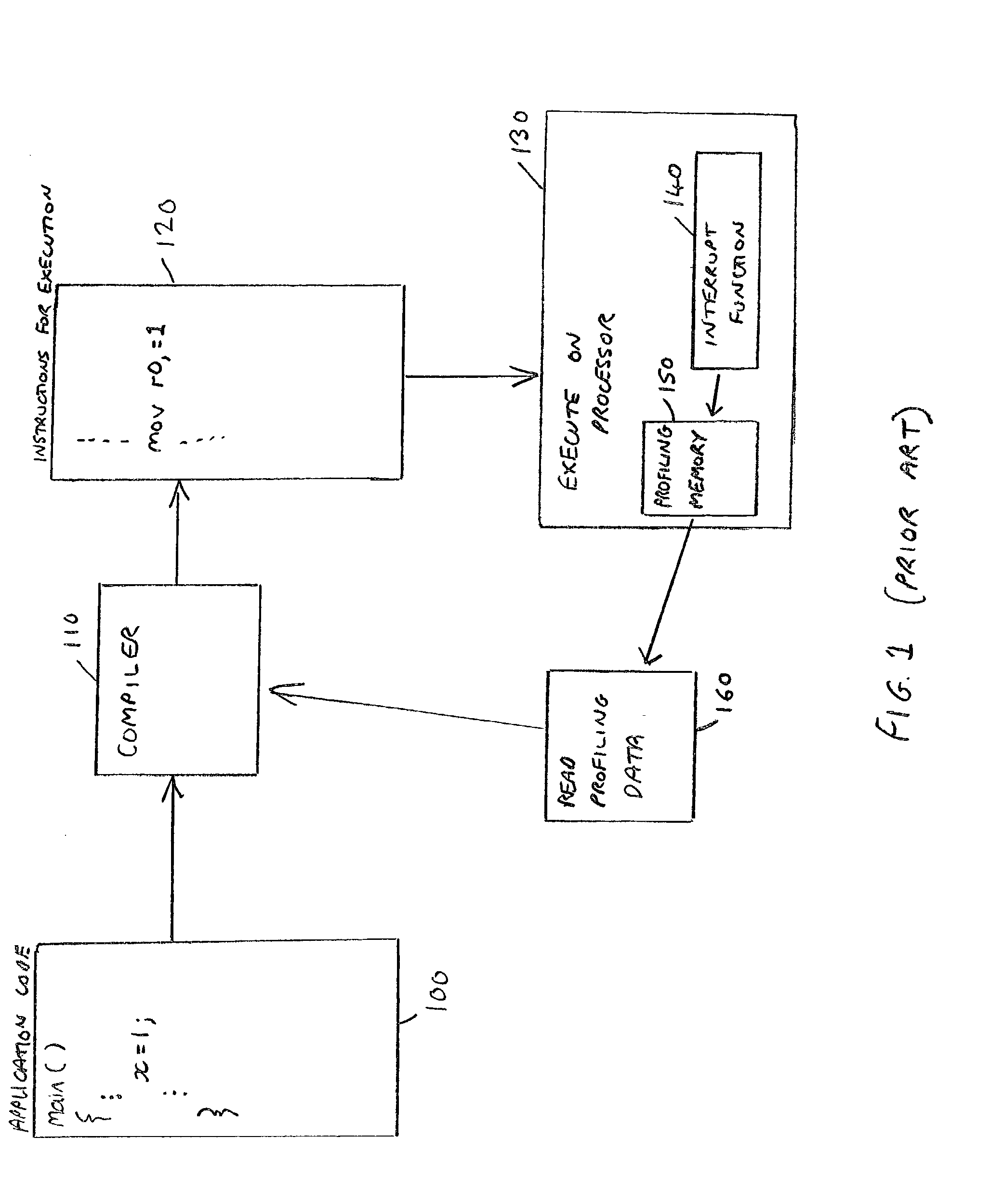

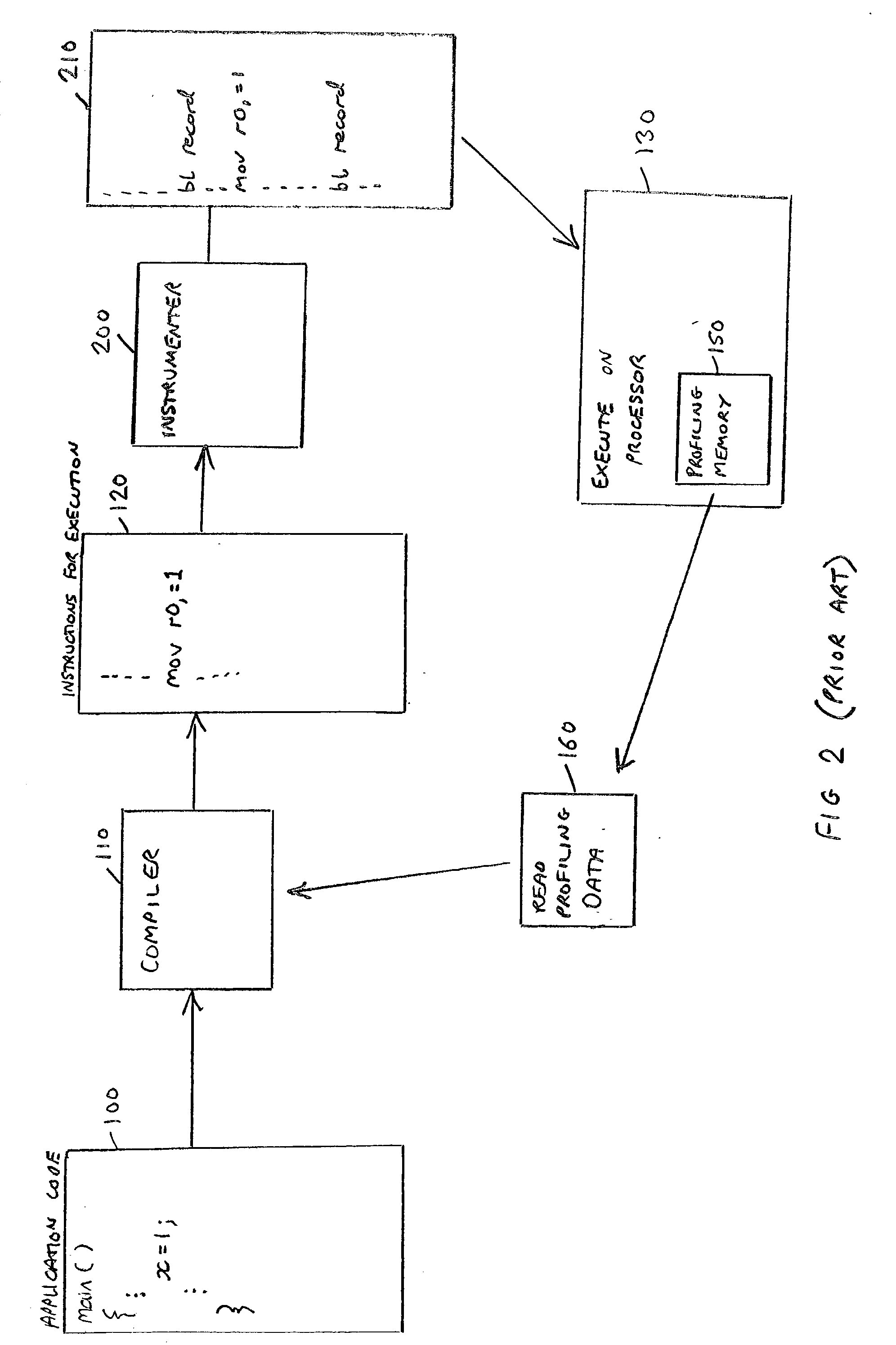

Compilation of application code in a data processing apparatus

ActiveUS20040019886A1Reduce decreaseImprove performanceSoftware engineeringHardware monitoringProgram codeComputer engineering

The present invention relates to a data processing apparatus and method for compiling application code. The data processing apparatus comprises a processor, and a compiler for compiling application code to generate instructions for execution by the processor. Furthermore, a non-invasive trace unit is coupled to the processor for generating, from input signals received from the processor, trace signals indicative of the instructions being executed by the processor. The compiler is then arranged to control the compilation of the application code dependent on the trace signals. The non-invasive nature of the trace unit enables it to generate trace signals that can be used to produce profiling information for use by the compiler without altering the behaviour of the code being executed by the processor, and accordingly provides a significantly improved technique for obtaining profiling information for use in feedback driven optimisation compilation techniques.

Owner:ARM LTD

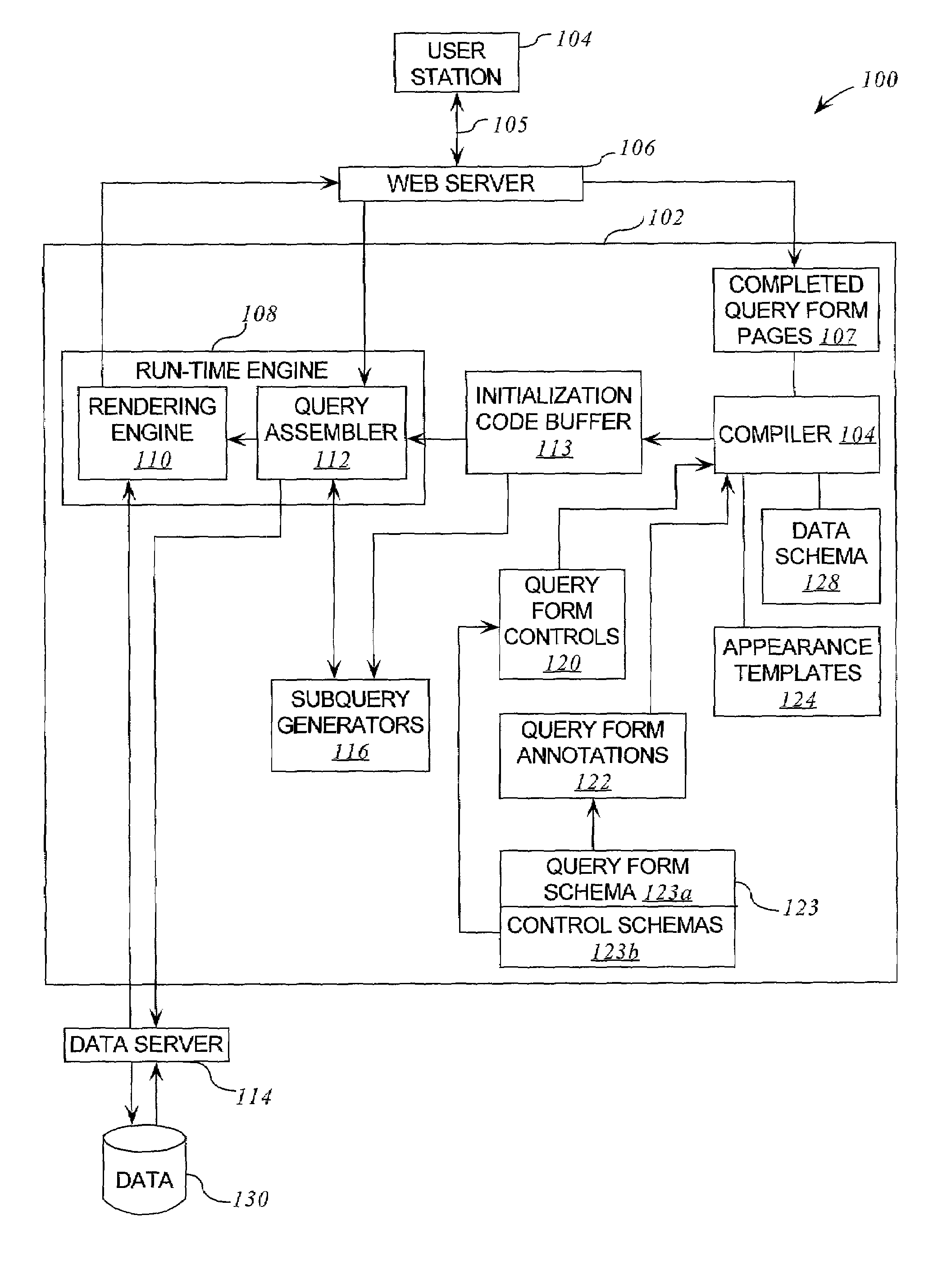

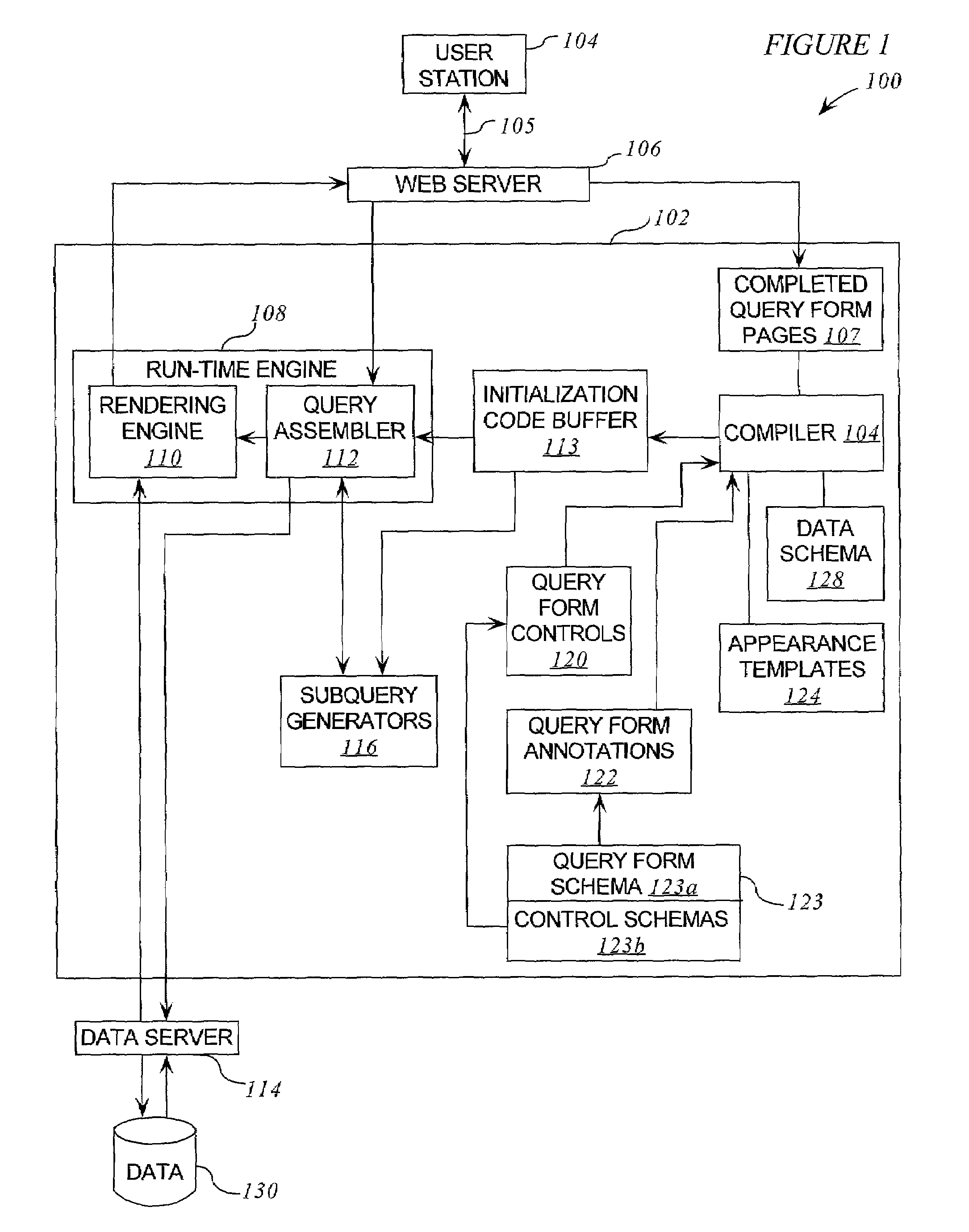

Reconfigurable query generation system for web browsers

ActiveUS7203678B1Simple procedureAvoid time-consuming reprogrammingData processing applicationsWeb data indexingWeb browserData query

A reconfigurable web-browser compatible data query system. The invention provides an XML platform enabling web-based forms that query data modeled by data schemas. This platform comprises a collection of query form controls, an annotation scheme for attaching these controls to the data schema, a compiler for creating a web-browser-compatible representation of the query form, and a run-time engine for constructing queries against the data and rendering query results.

Owner:ORACLE INT CORP