Patents

Literature

92 results about "Smart memory" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

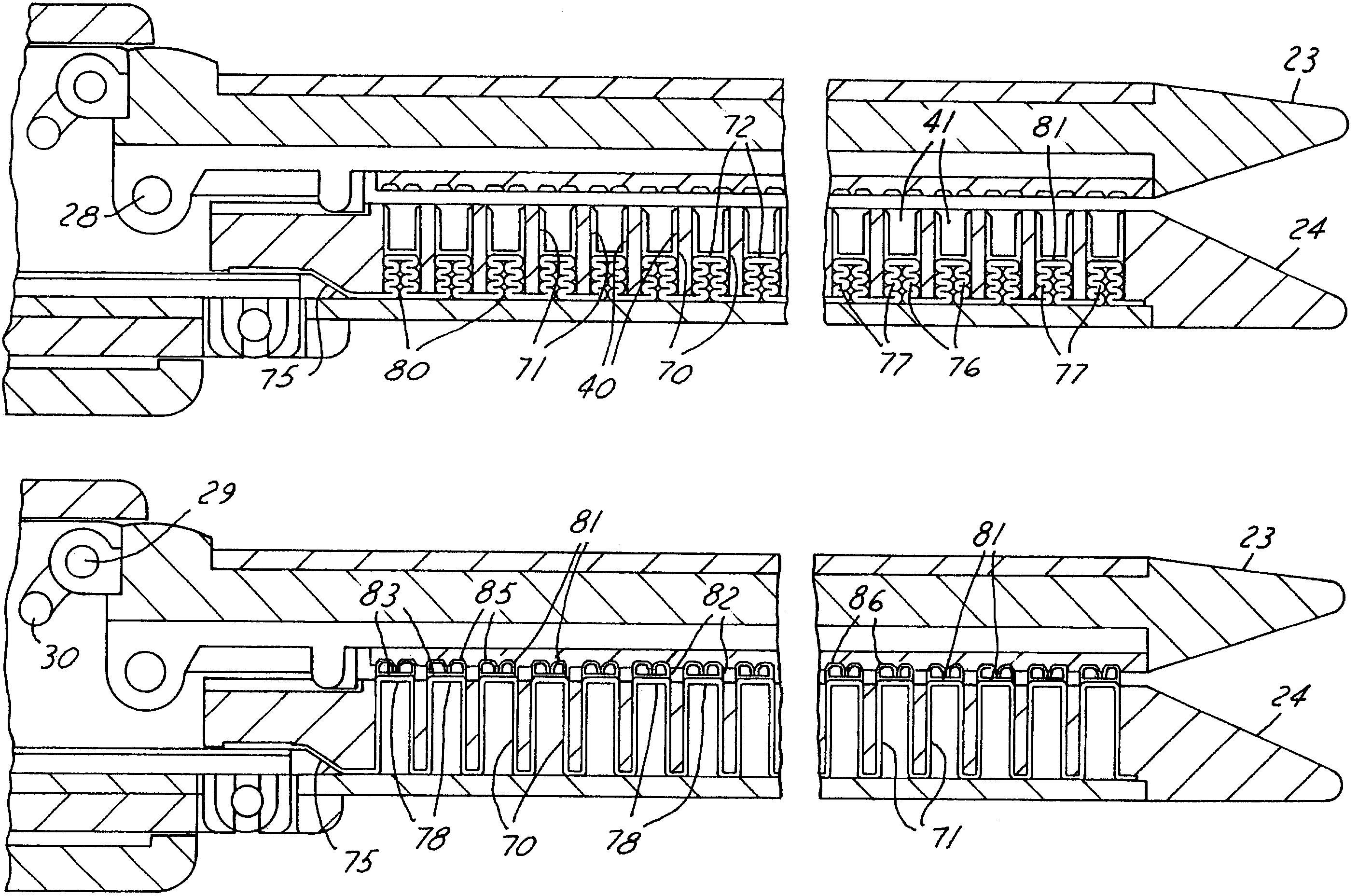

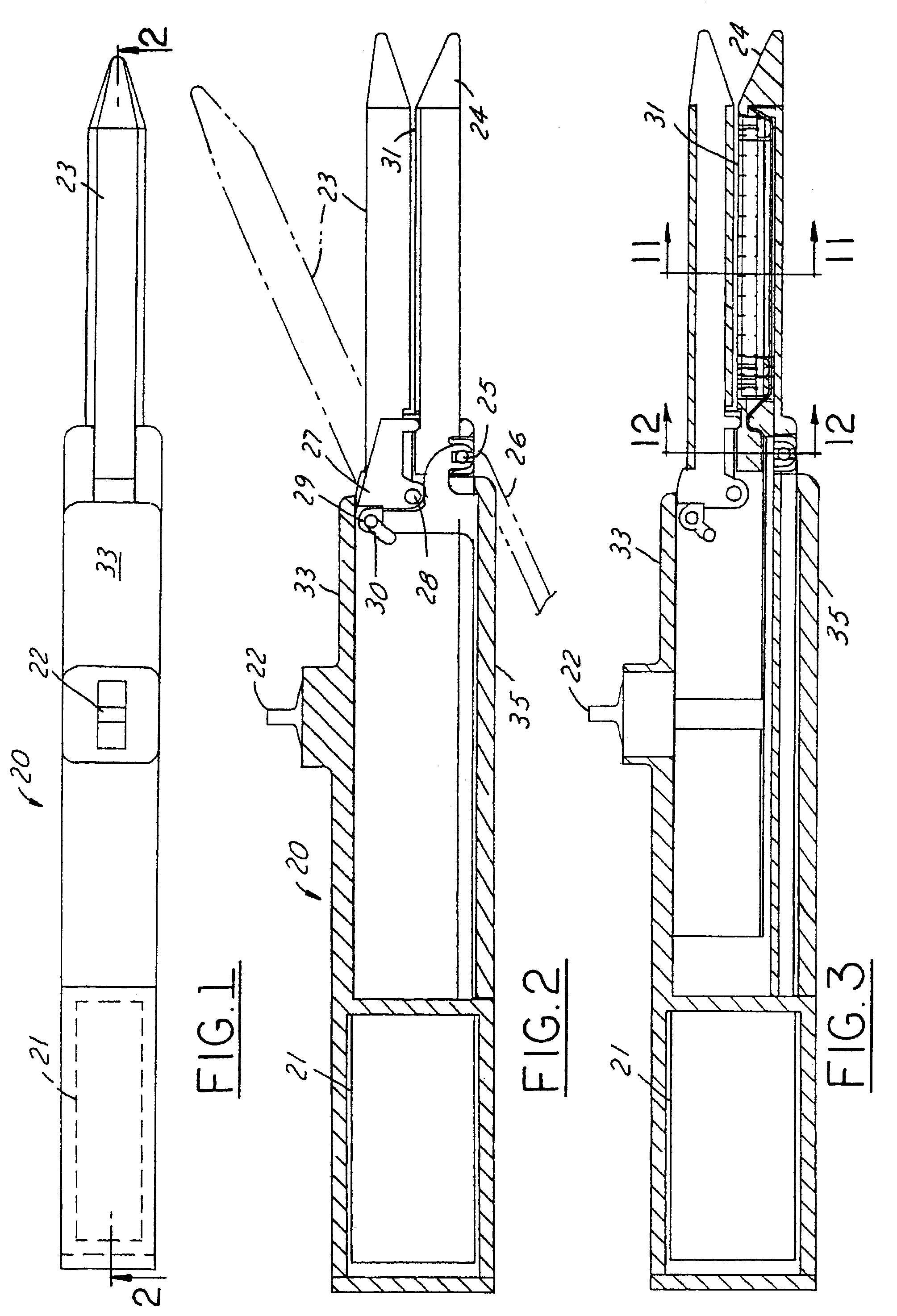

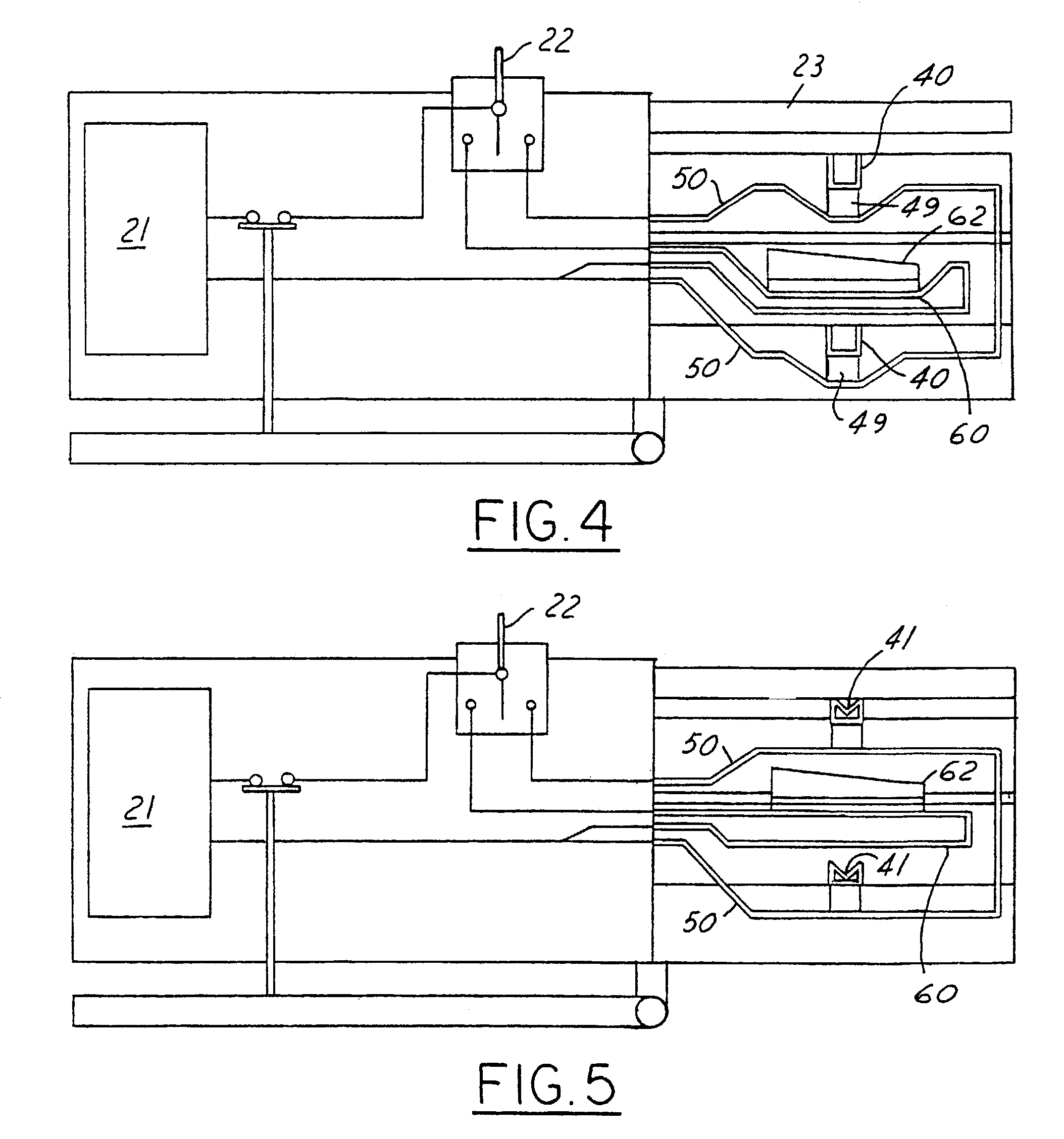

Surgical device and method

Owner:EZZAT HAZEM +2

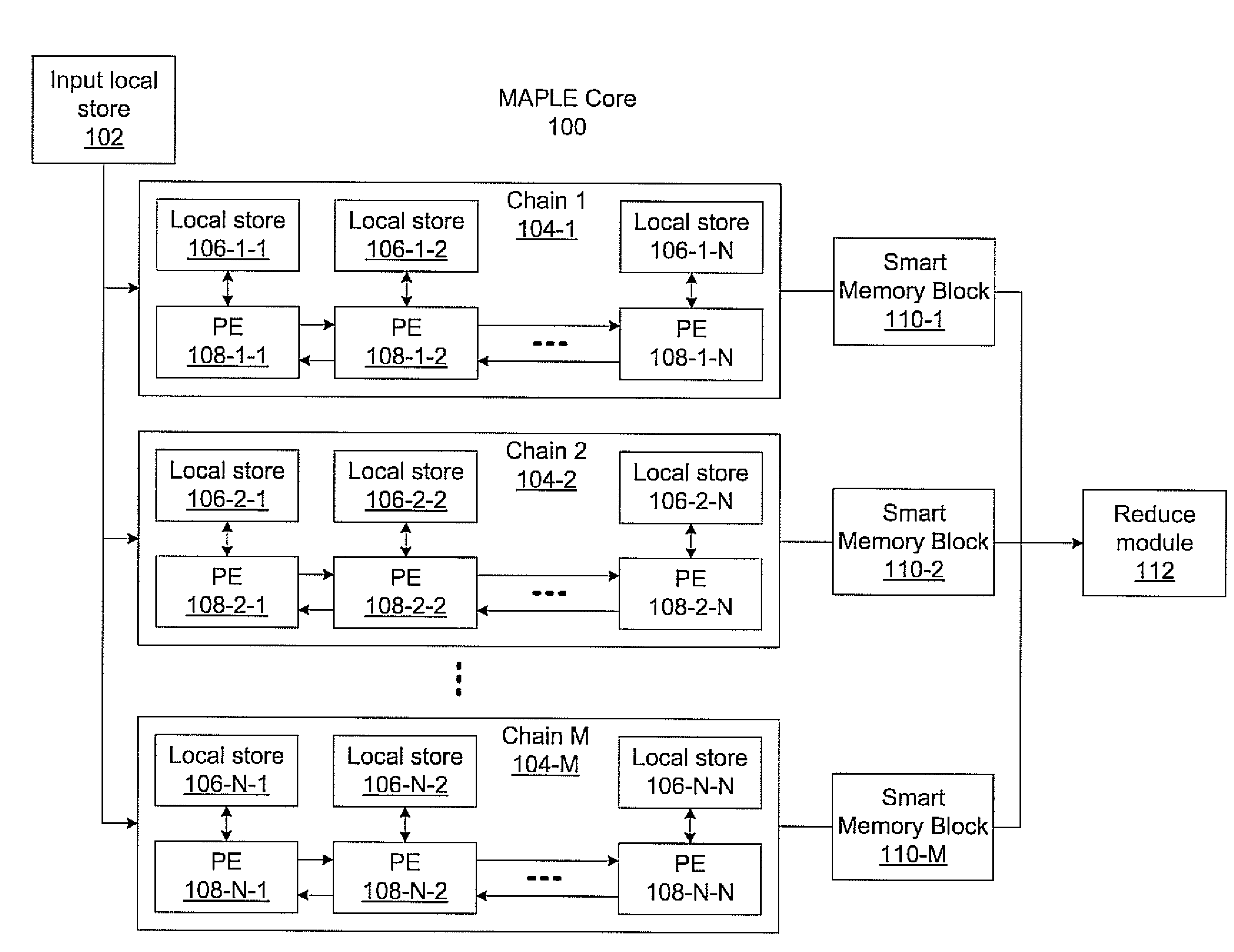

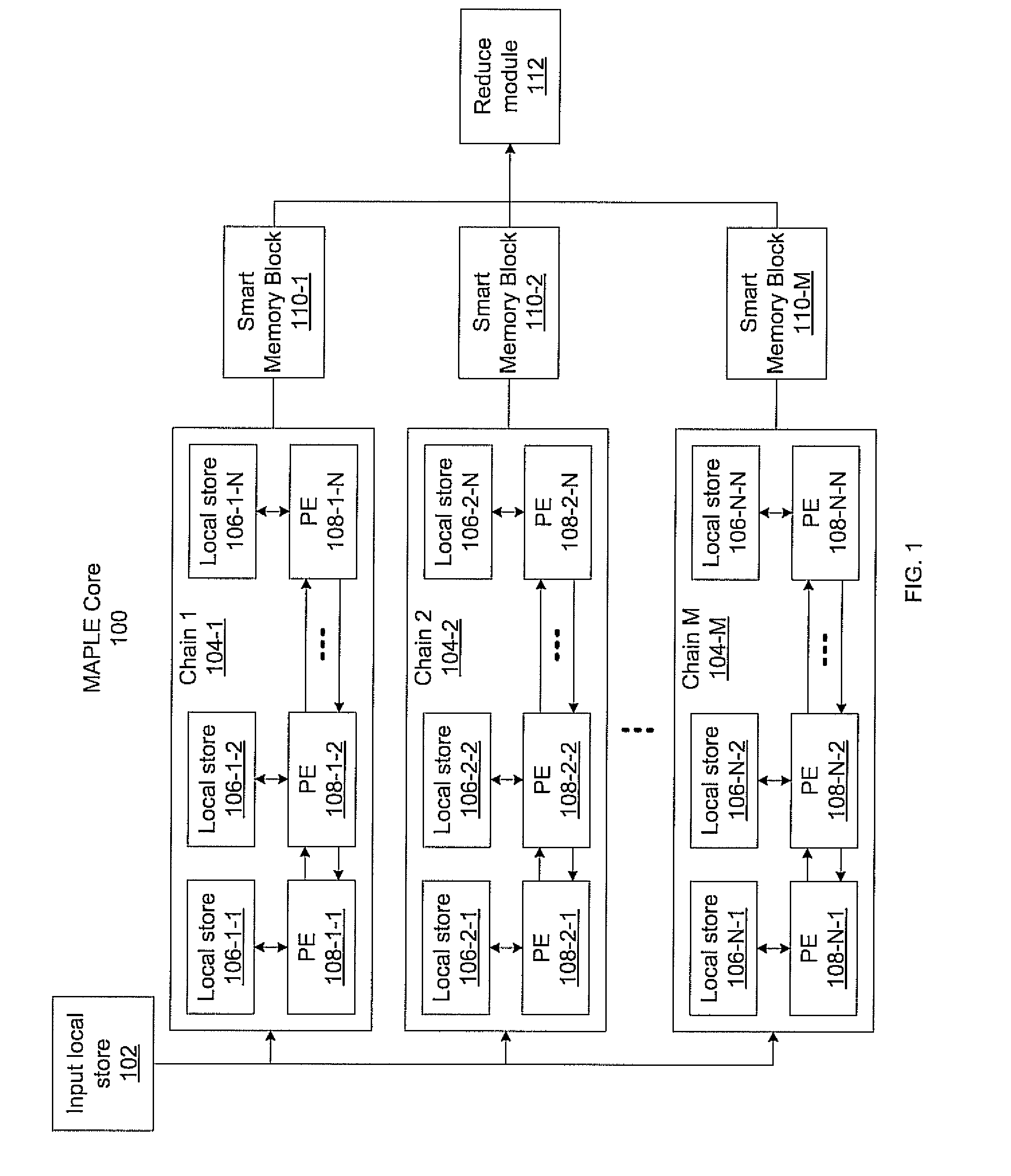

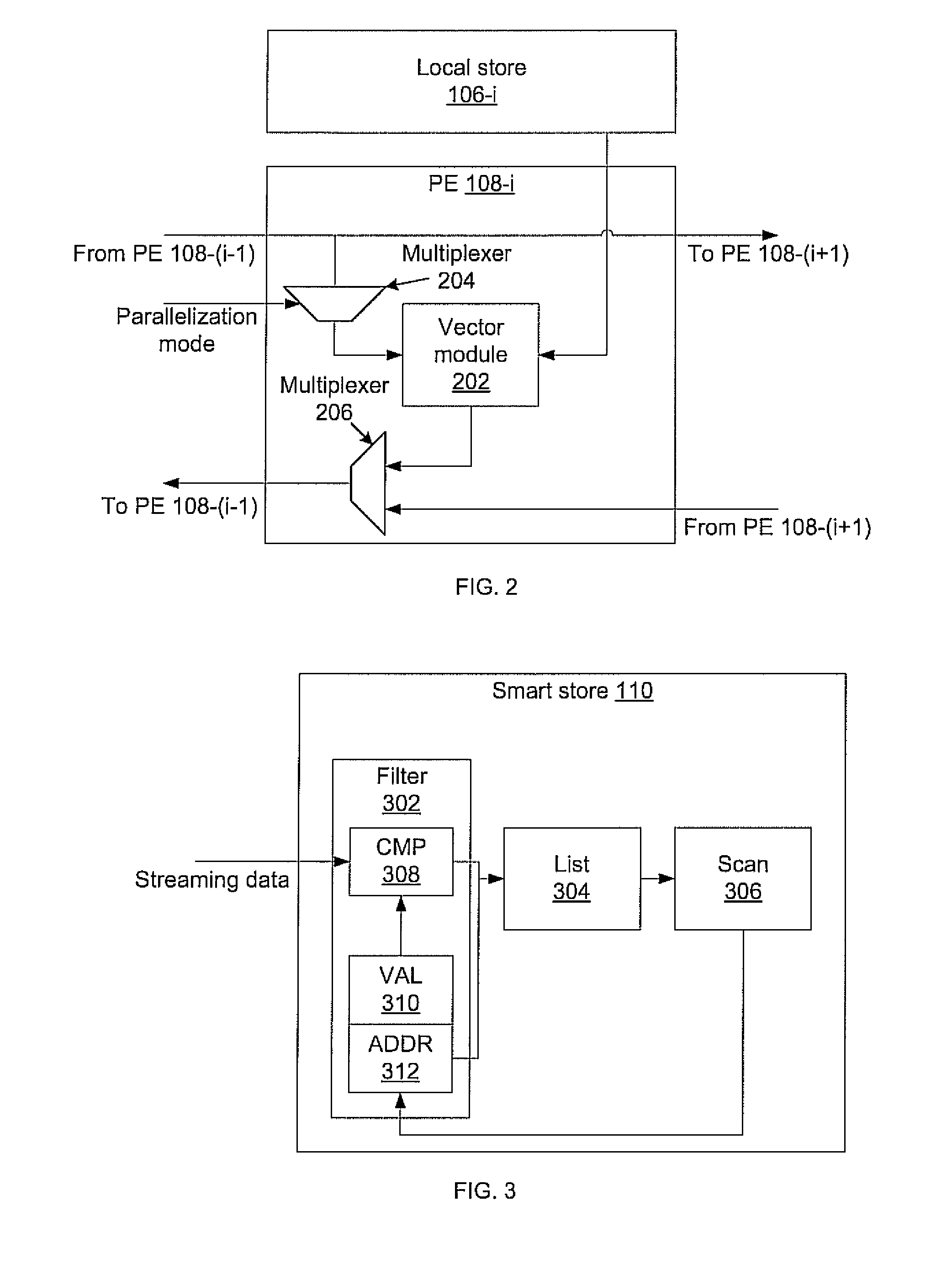

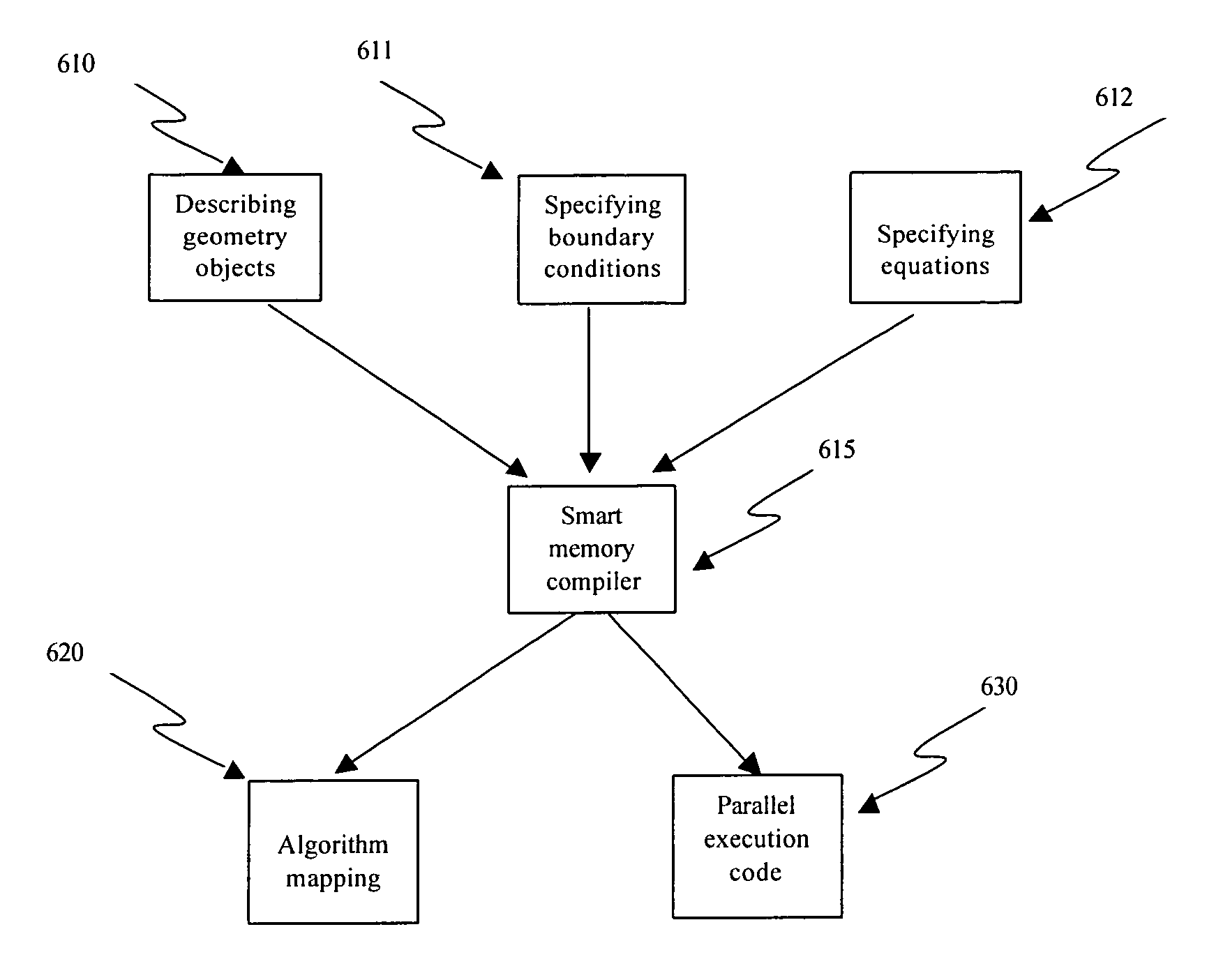

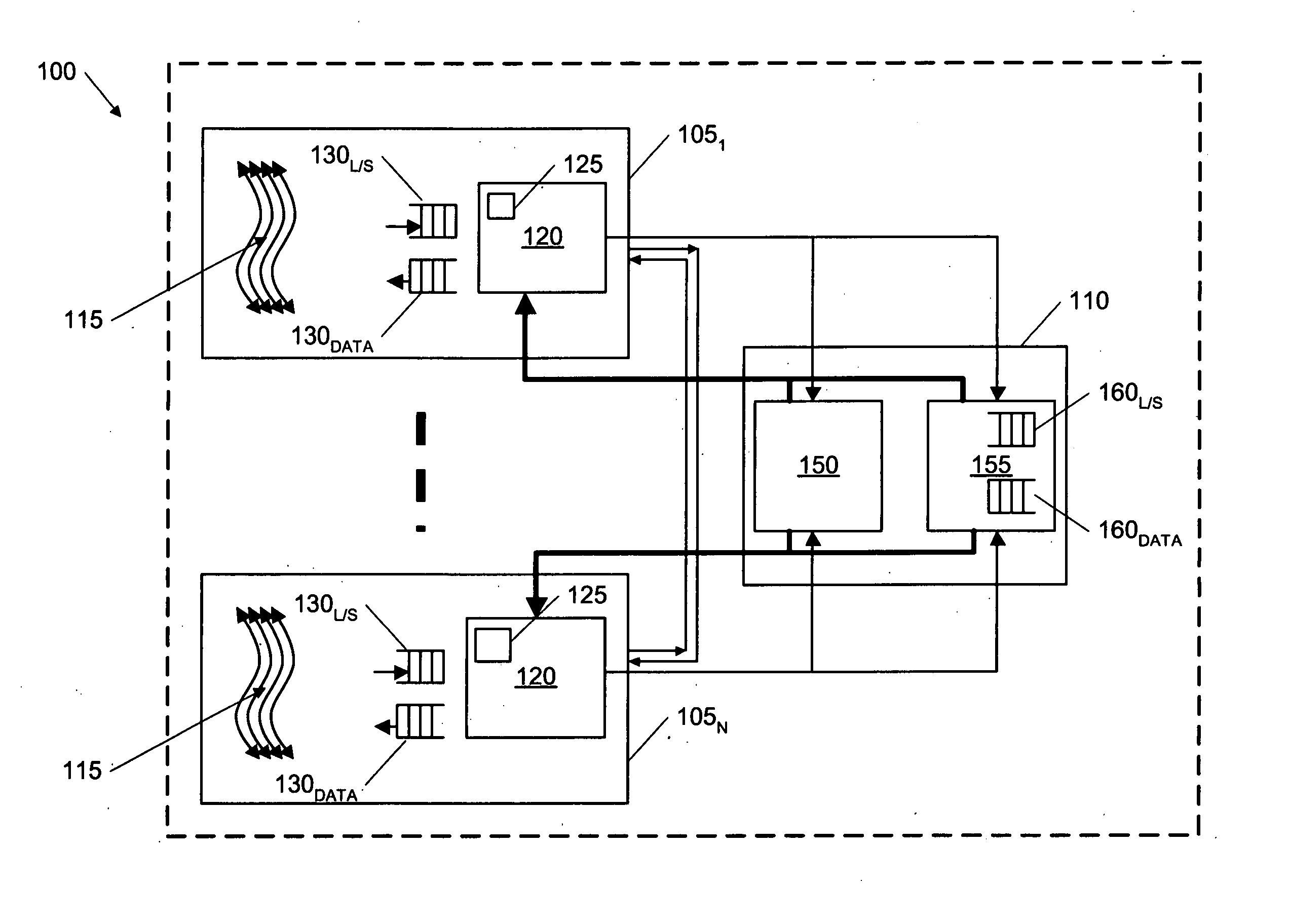

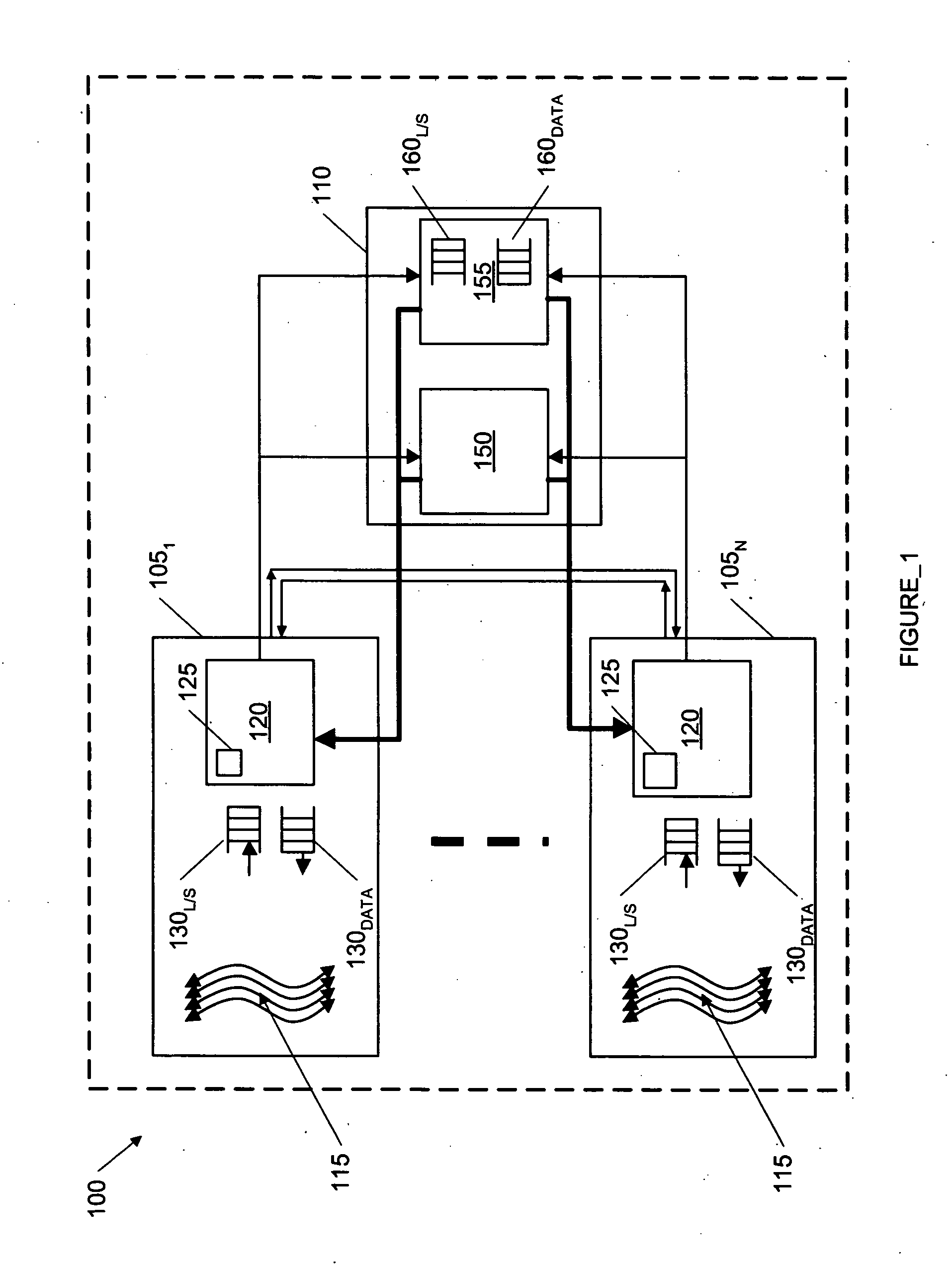

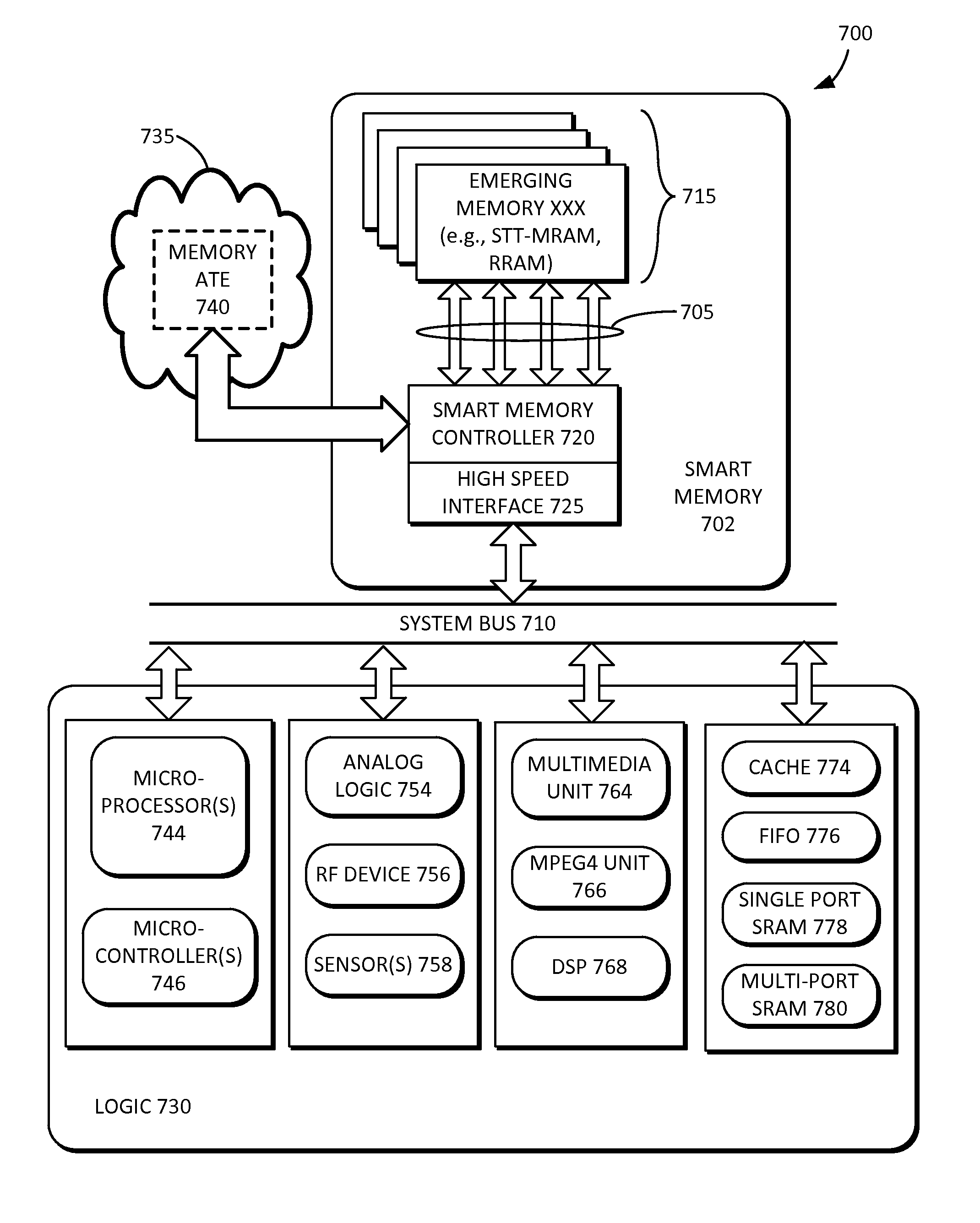

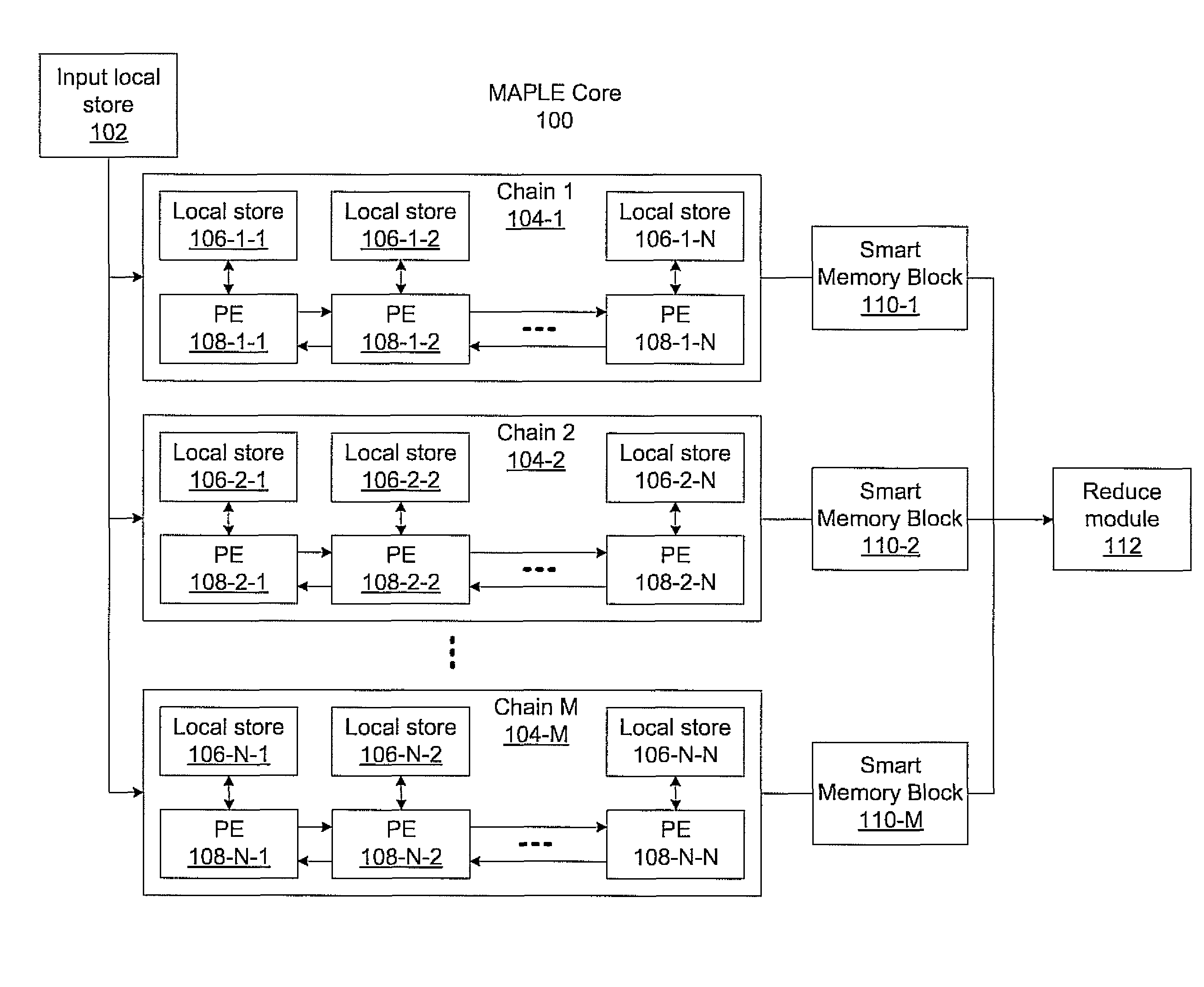

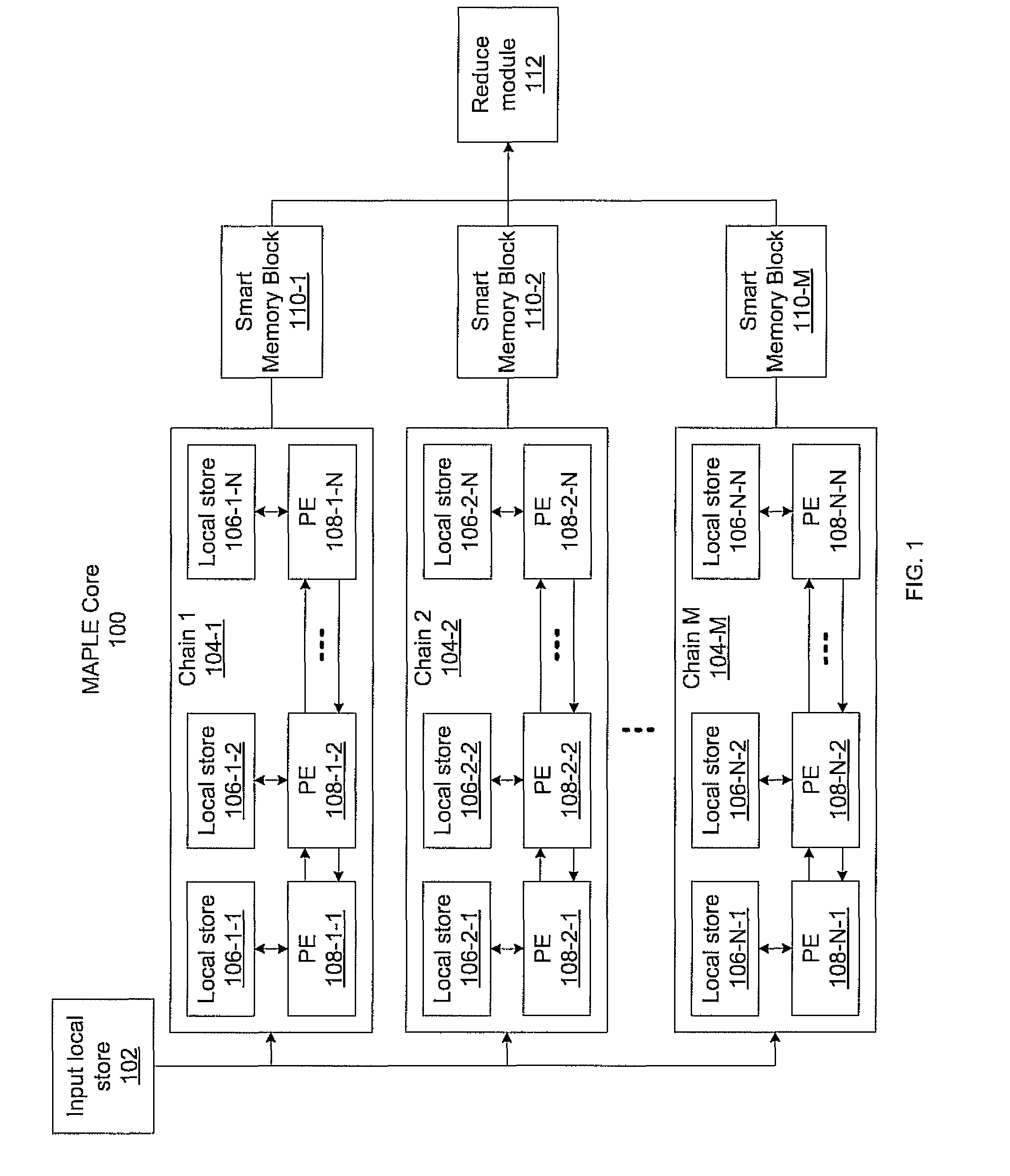

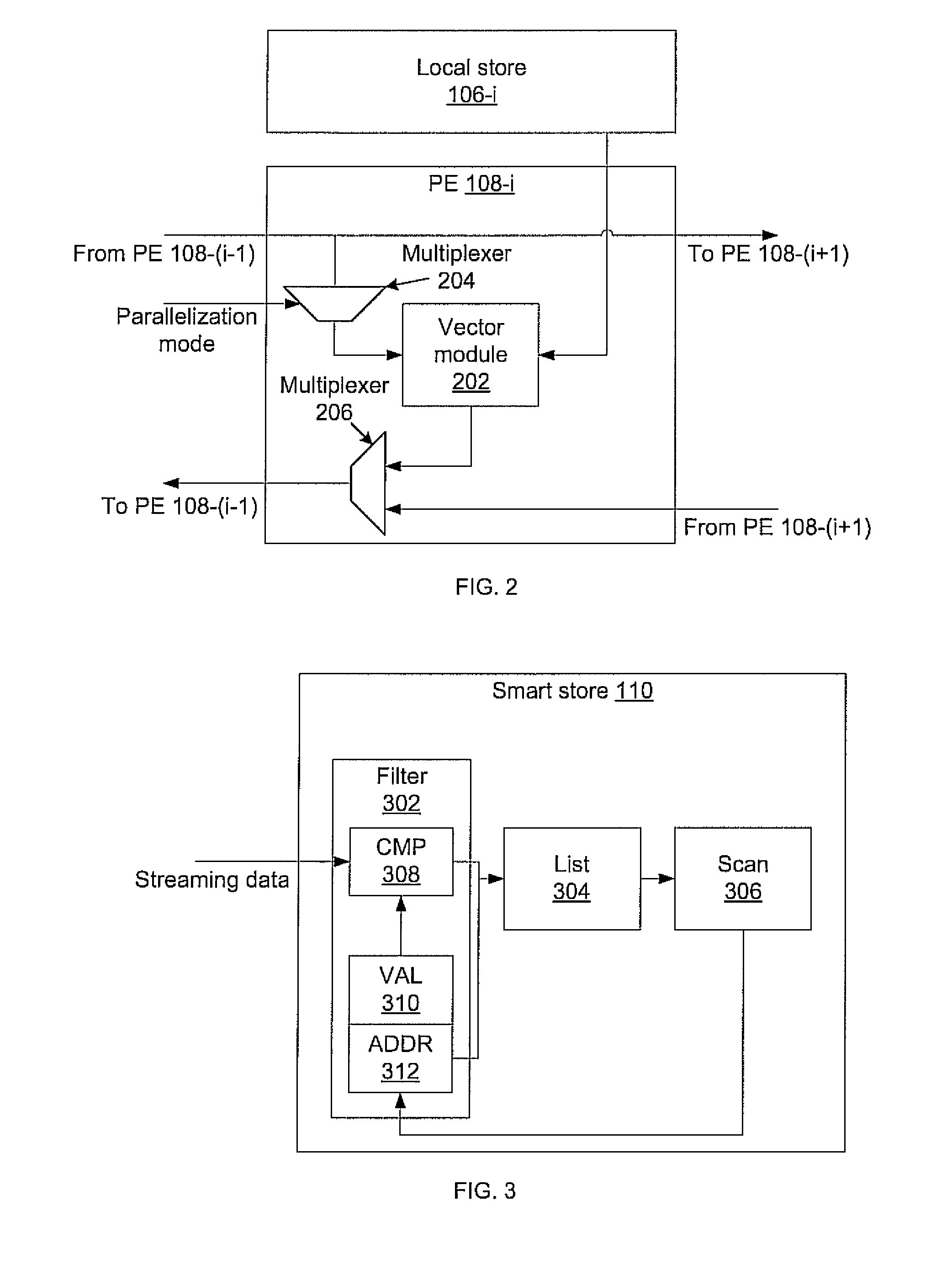

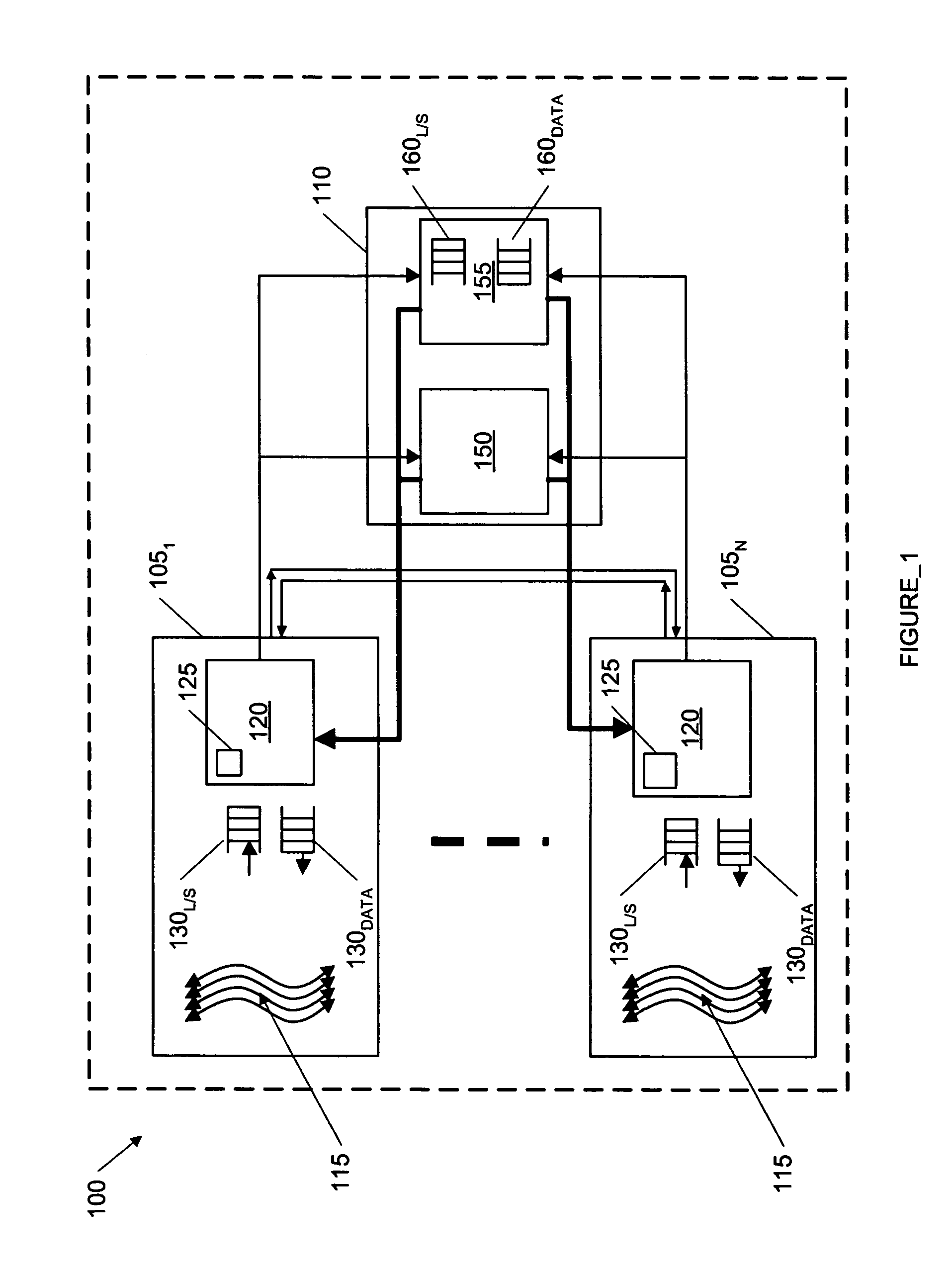

Massively parallel, smart memory based accelerator

Systems and methods for massively parallel processing on an accelerator that includes a plurality of processing cores. Each processing core includes multiple processing chains configured to perform parallel computations, each of which includes a plurality of interconnected processing elements. The cores further include multiple of smart memory blocks configured to store and process data, each memory block accepting the output of one of the plurality of processing chains. The cores communicate with at least one off-chip memory bank.

Owner:NEC CORP

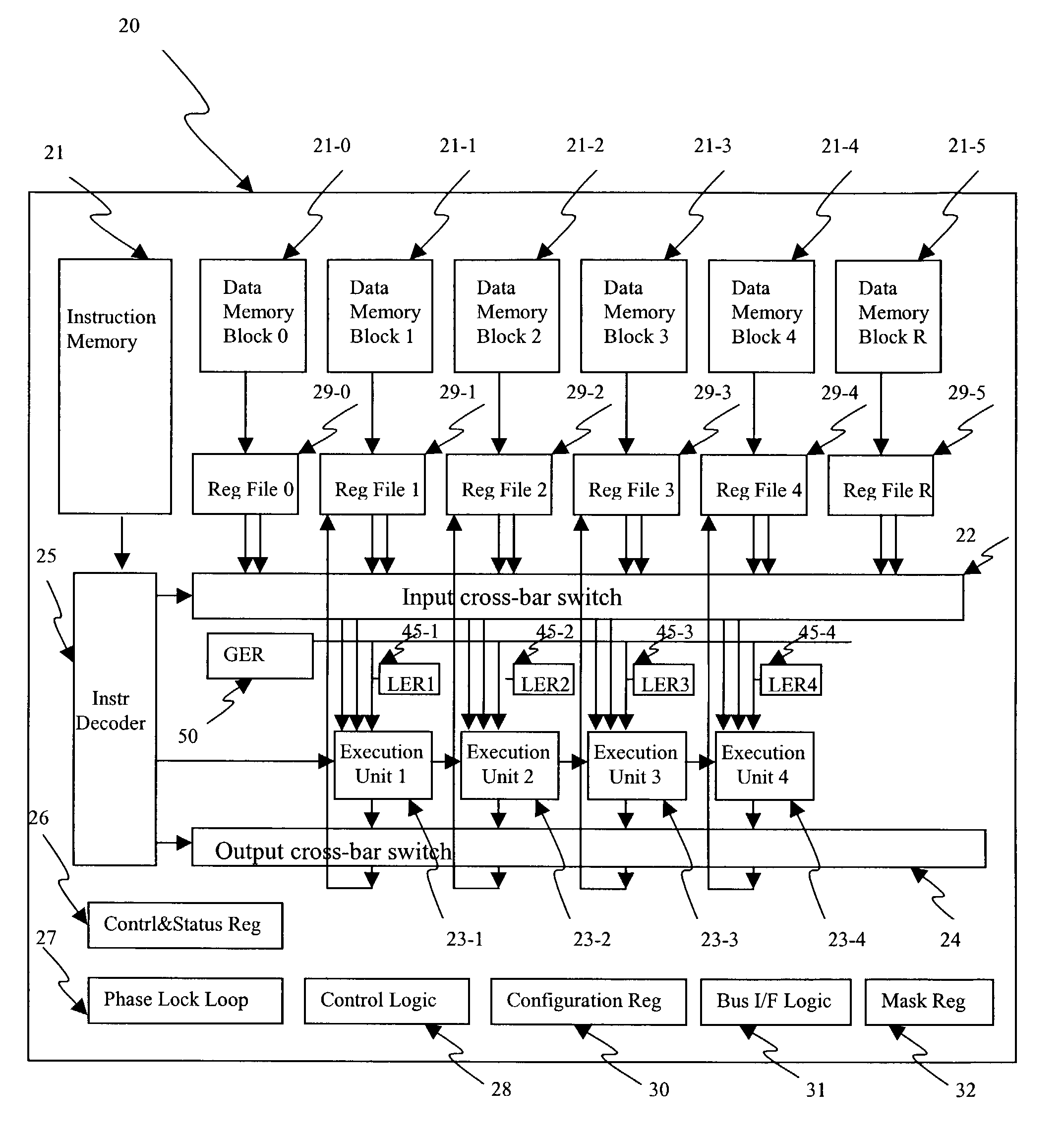

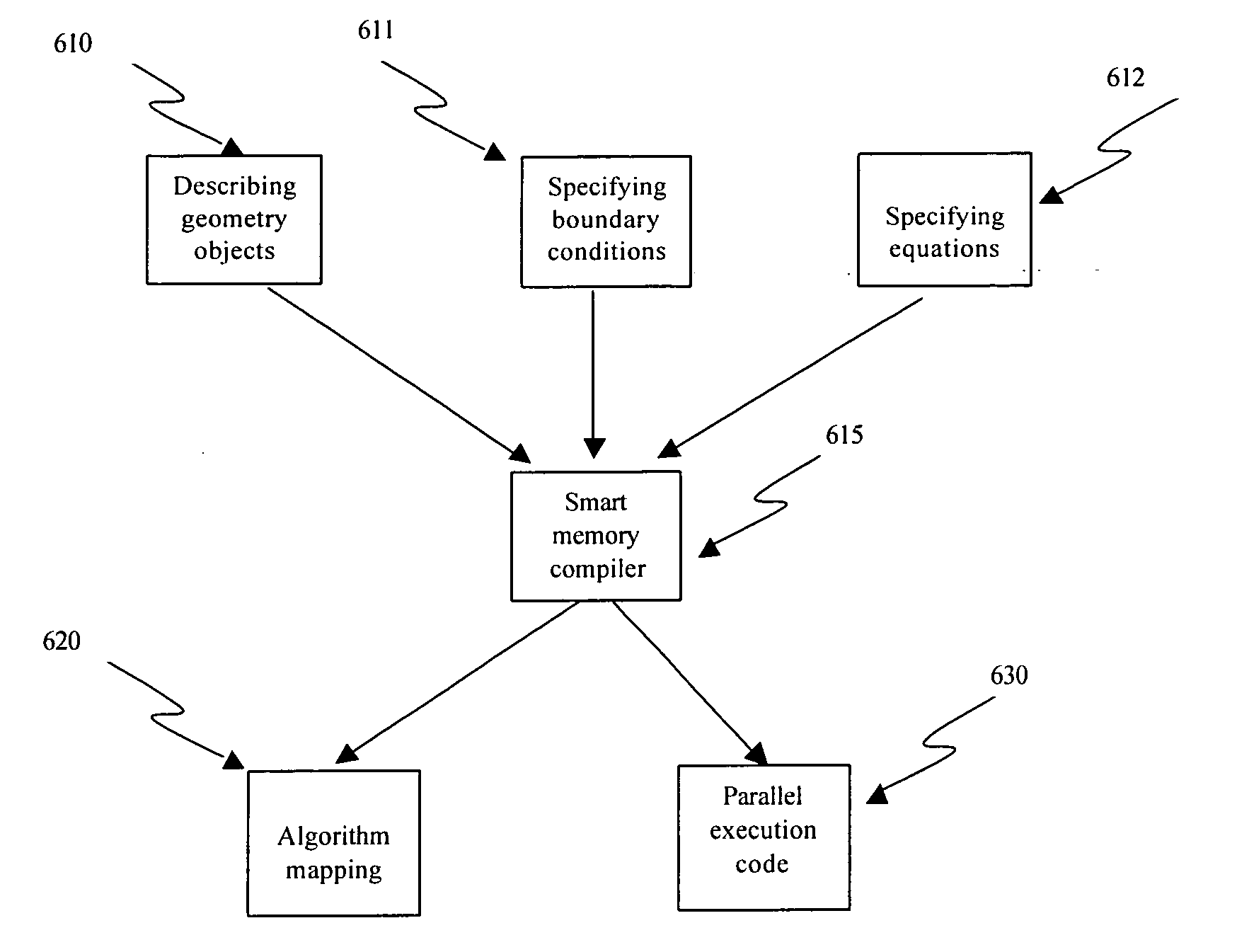

Algorithm mapping, specialized instructions and architecture features for smart memory computing

InactiveUS7546438B2Improve performanceLow costMultiplex system selection arrangementsDigital computer detailsSmart memoryExecution unit

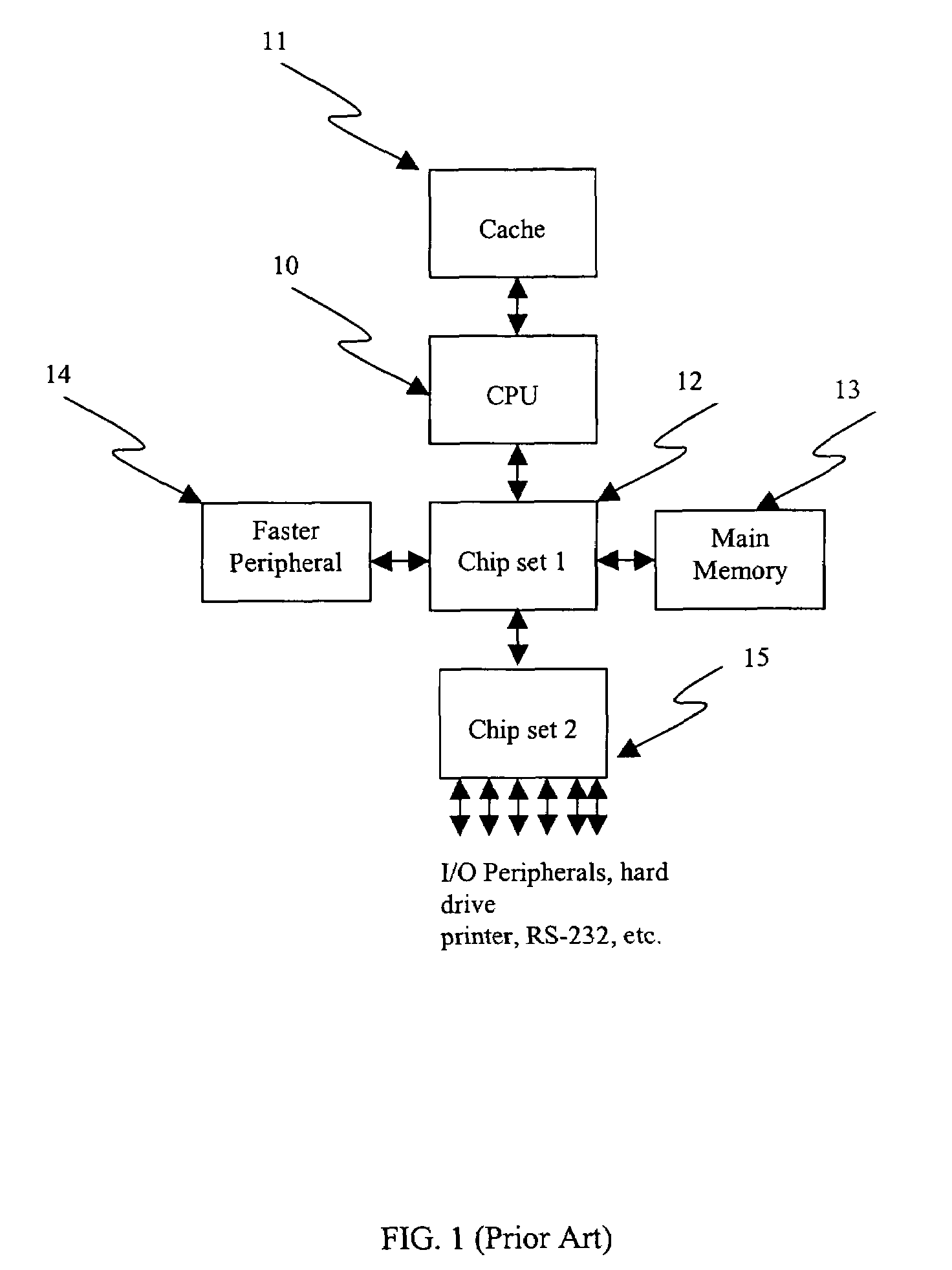

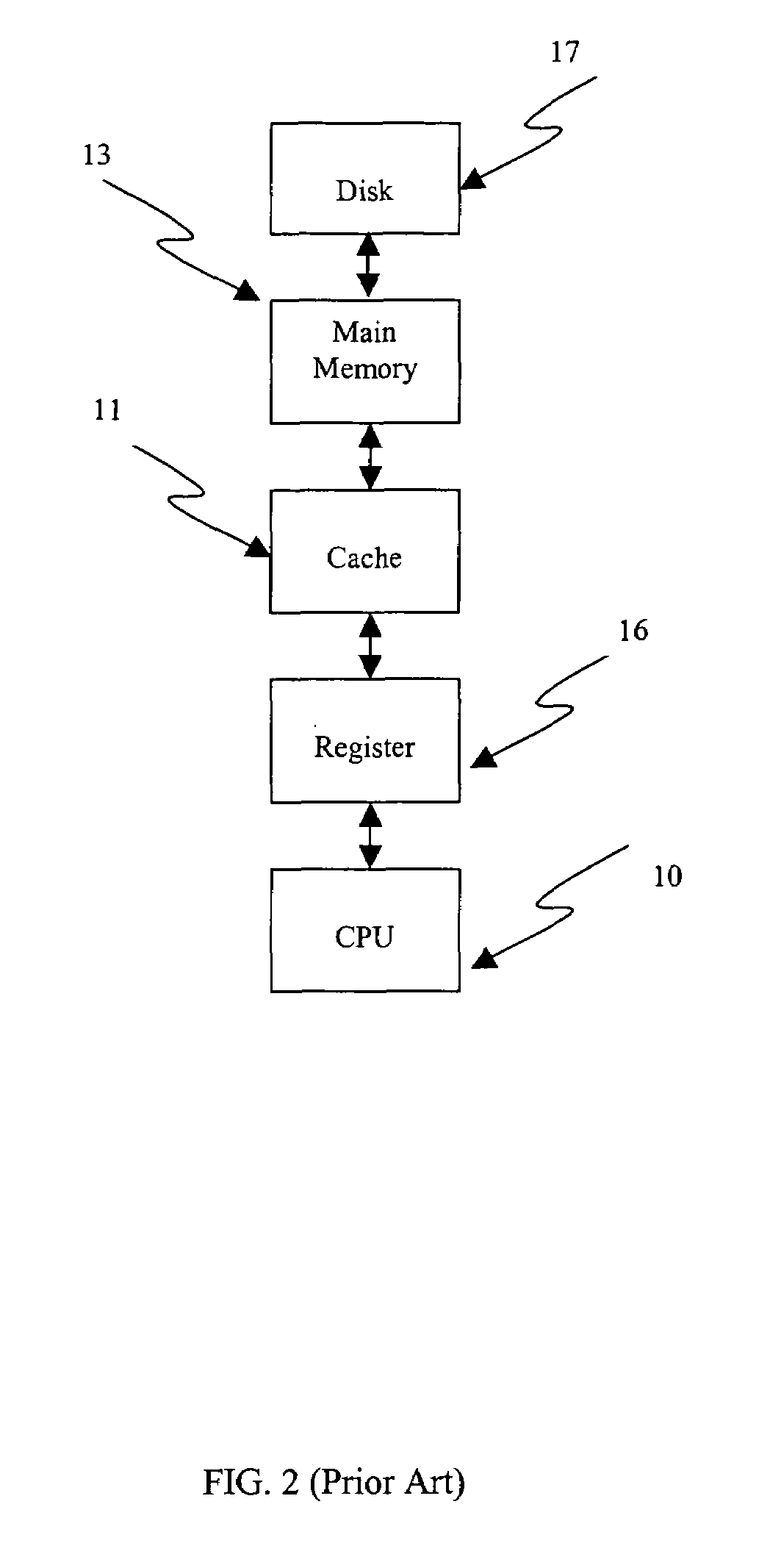

A smart memory computing system that uses smart memory for massive data storage as well as for massive parallel execution is disclosed. The data stored in the smart memory can be accessed just like the conventional main memory, but the smart memory also has many execution units to process data in situ. The smart memory computing system offers improved performance and reduced costs for those programs having massive data-level parallelism. This smart memory computing system is able to take advantage of data-level parallelism to improve execution speed by, for example, use of inventive aspects such as algorithm mapping, compiler techniques, architecture features, and specialized instruction sets.

Owner:STRIPE INC

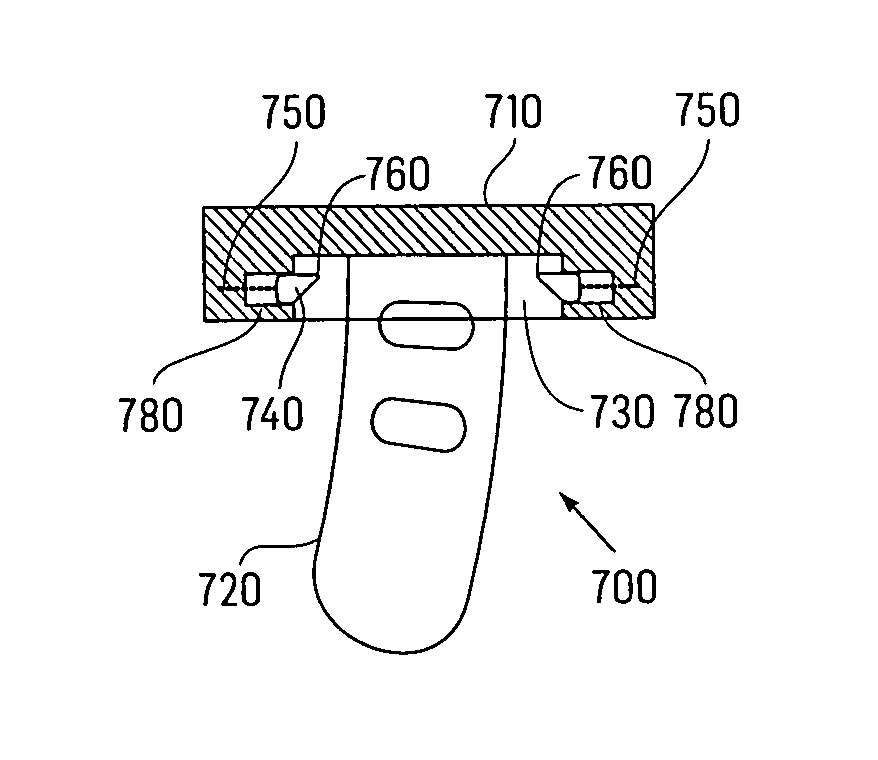

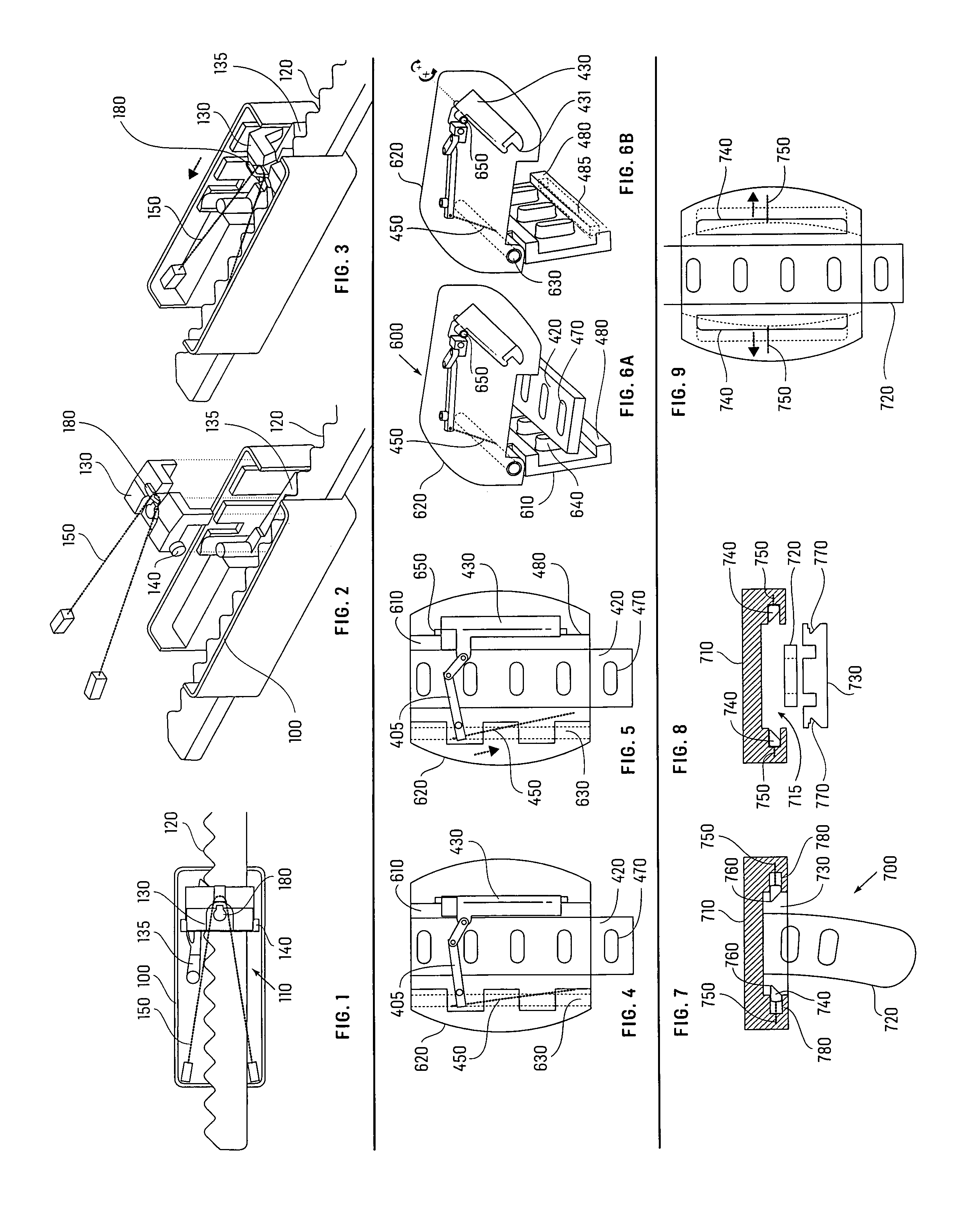

Surgical device and method

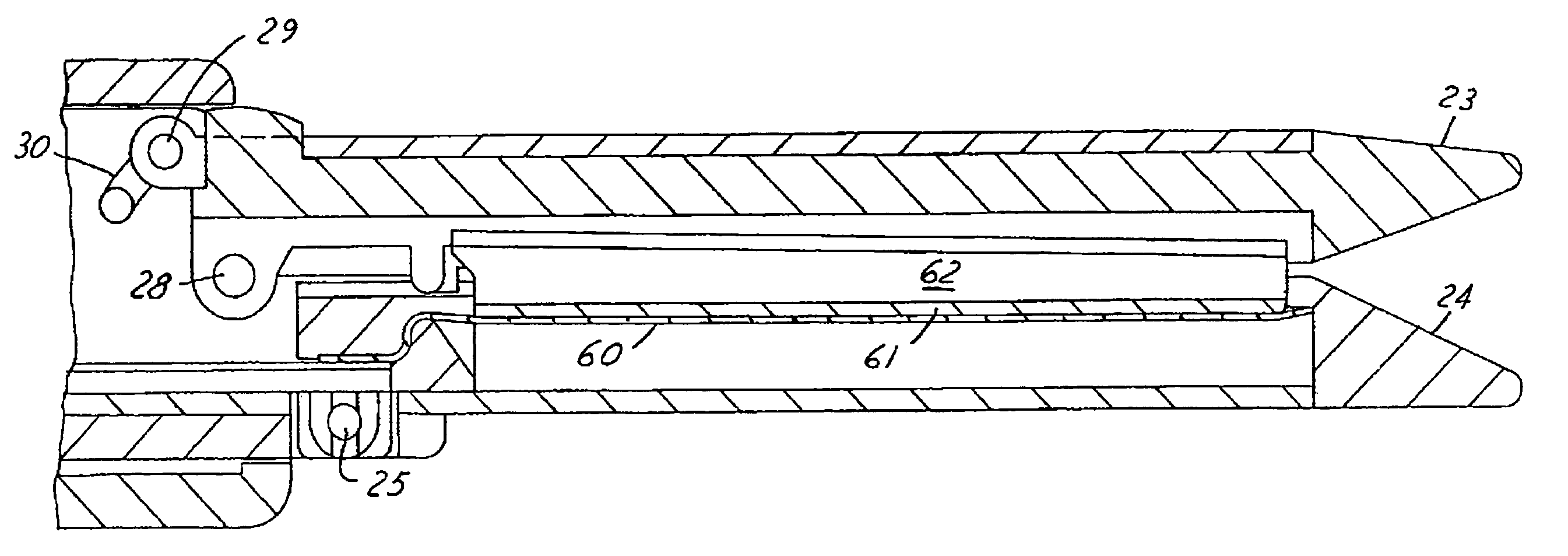

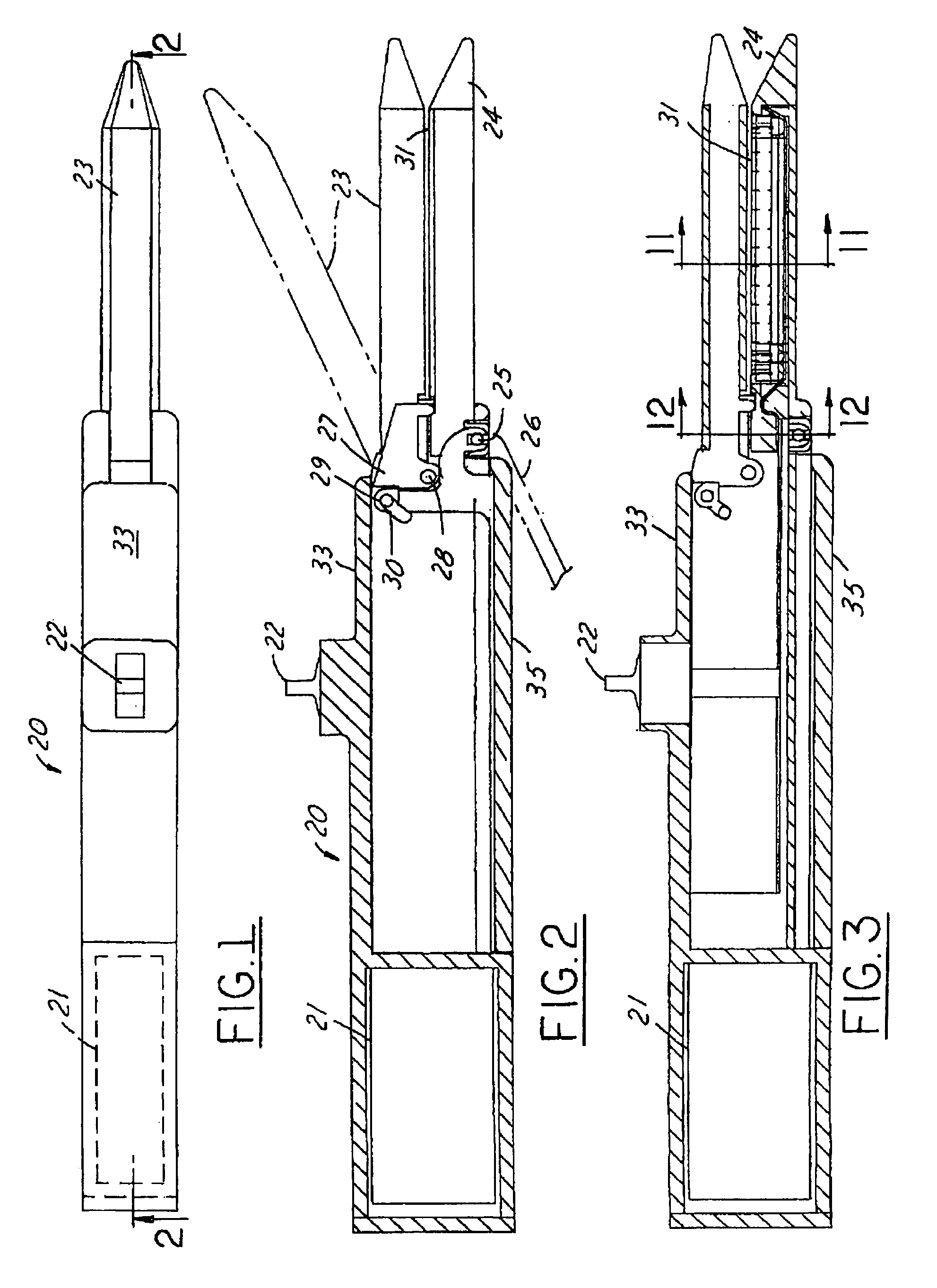

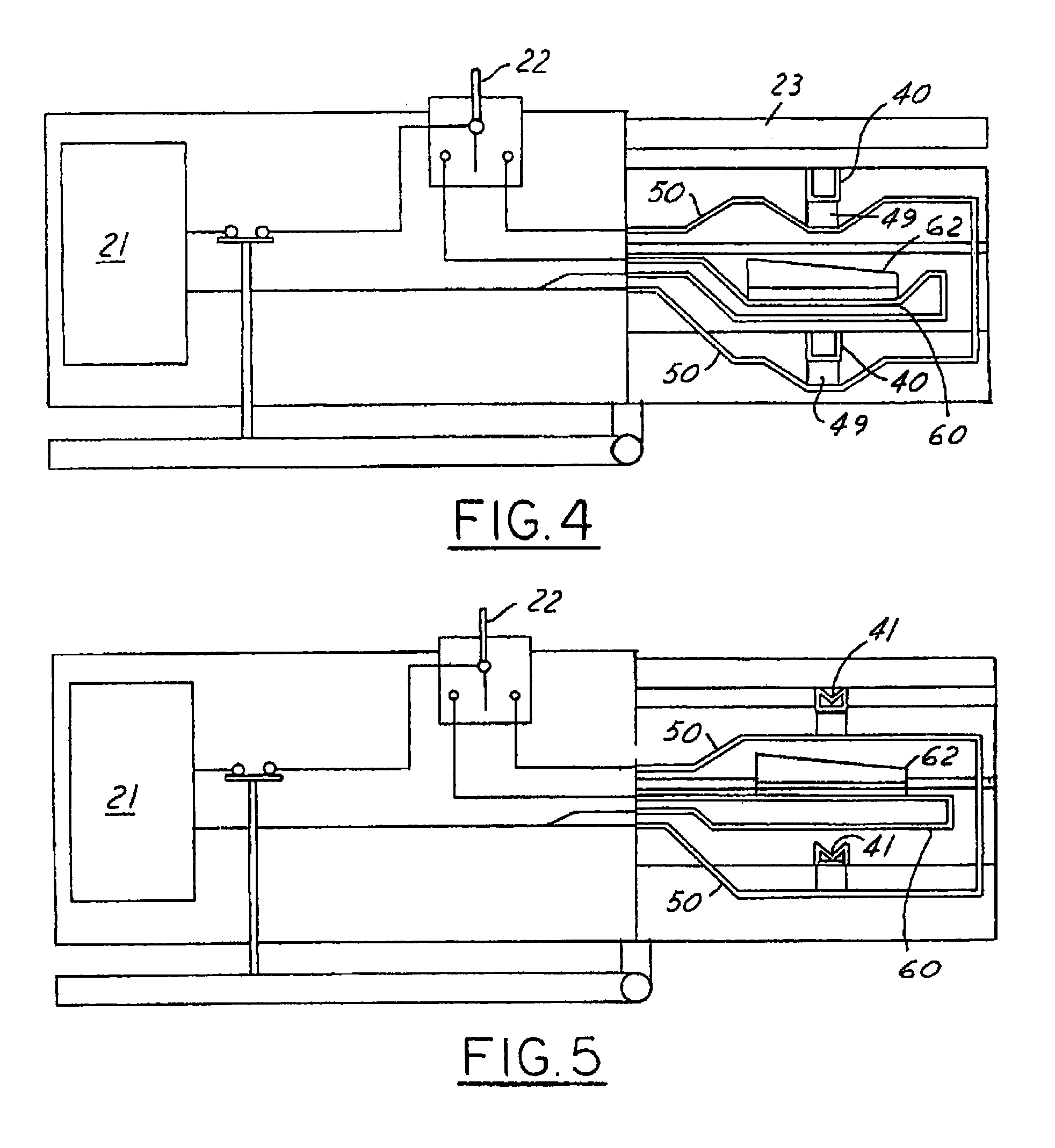

A surgical device 20 for attaching staples 40 to a portion of a body comprising an anvil 23; a smart memory material (SMM) 50, 75 capable of going from one physical state to another physical state; a supply of staples in communication with the smart memory material and placed near the anvil; and an activating apparatus 21 which is in communication with the smart memory material and which can cause the change in the physical state of the smart memory material, which change in state causes the movement of the staples against the anvil thereby securing the staples 40 to the desired body portion. The device utilizes a source of electricity which when activated causes the SMM to expand in volume thereby moving an individual staple from the supply of staples. The device may also contain a surgical knife 62 to cut a body portion wherein a SMM is in communication with the knife whereby when the SMM expands it engages the knife causing the knife to cut the desired body portion.

Owner:EZZAT HAZEM +2

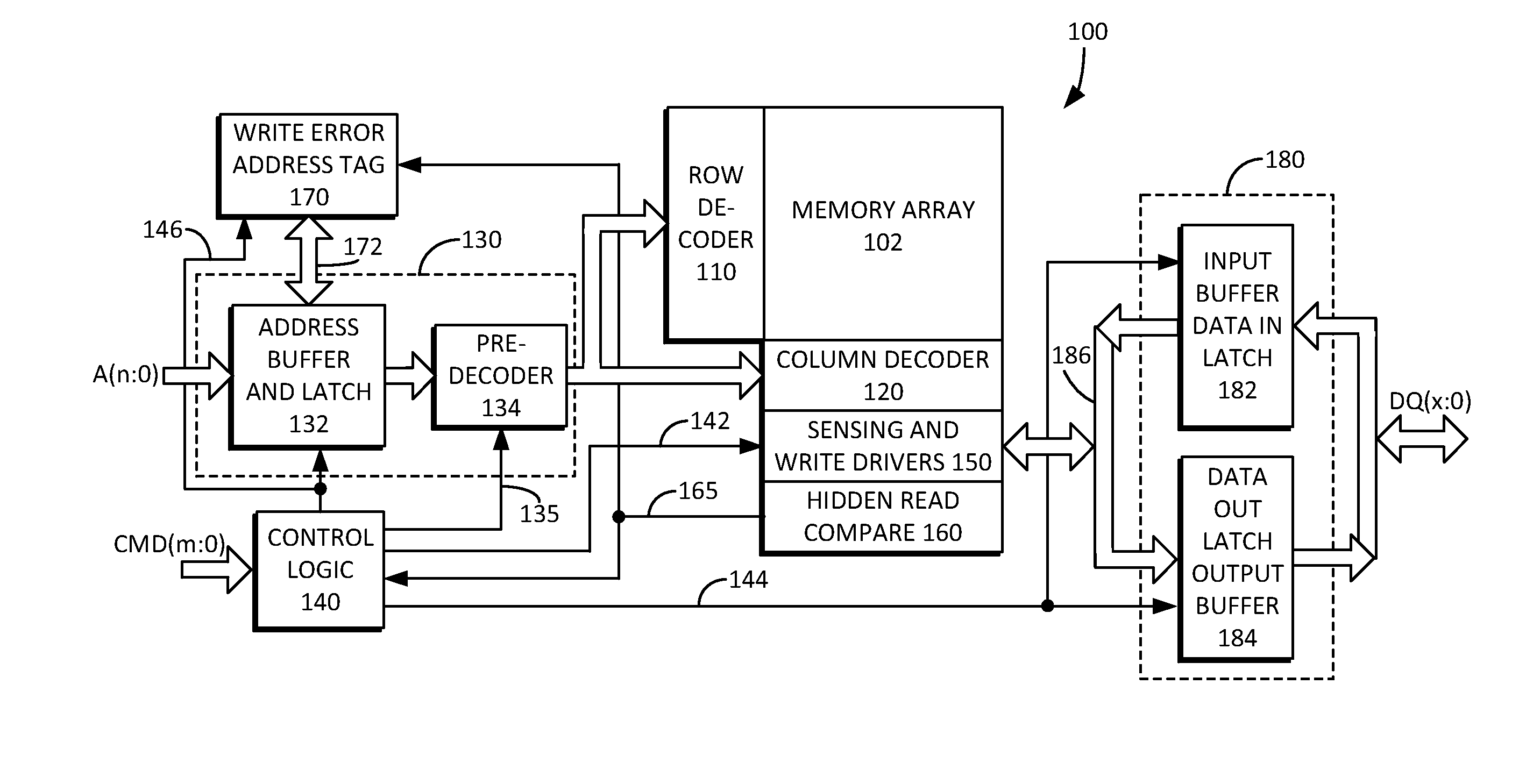

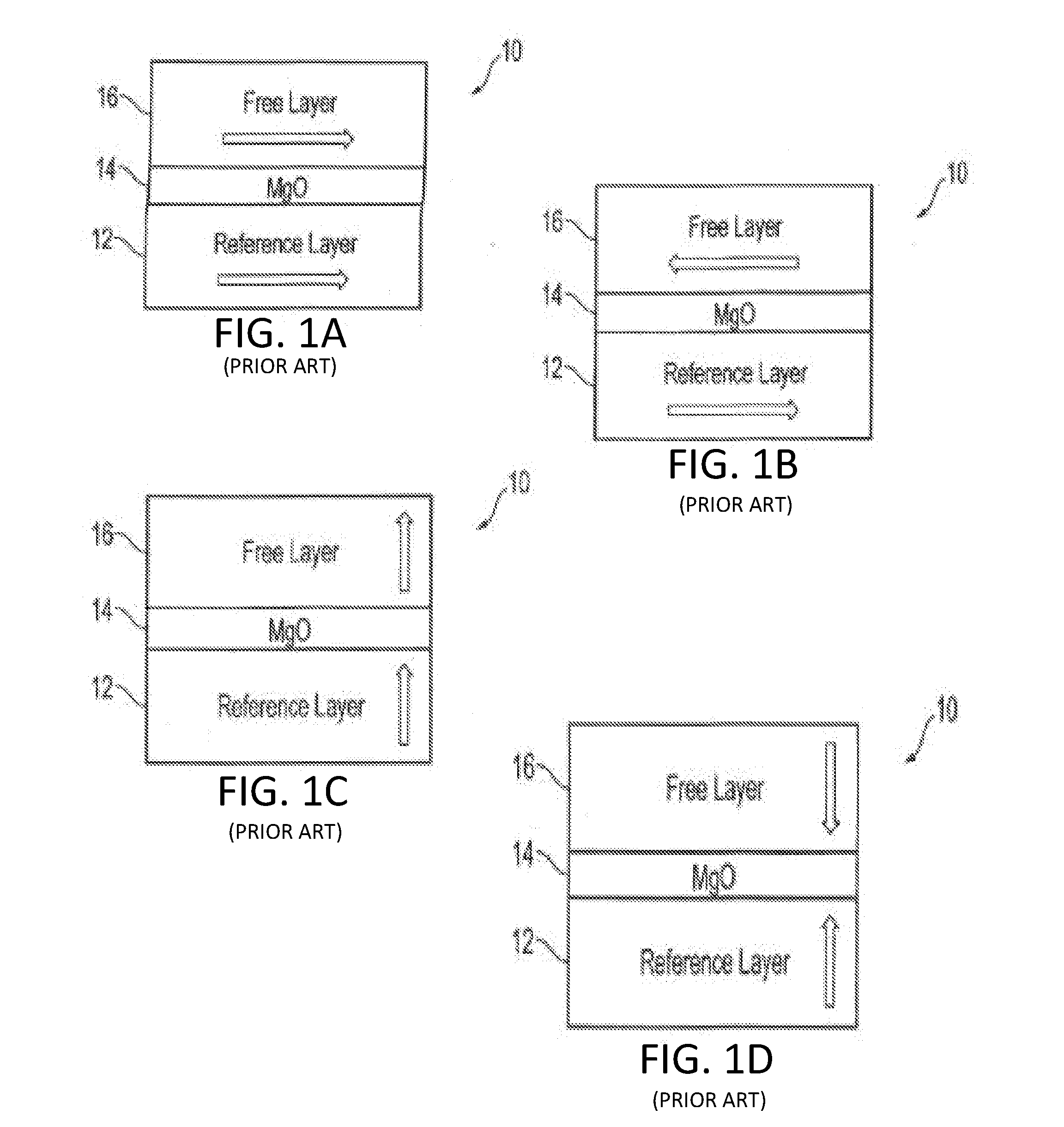

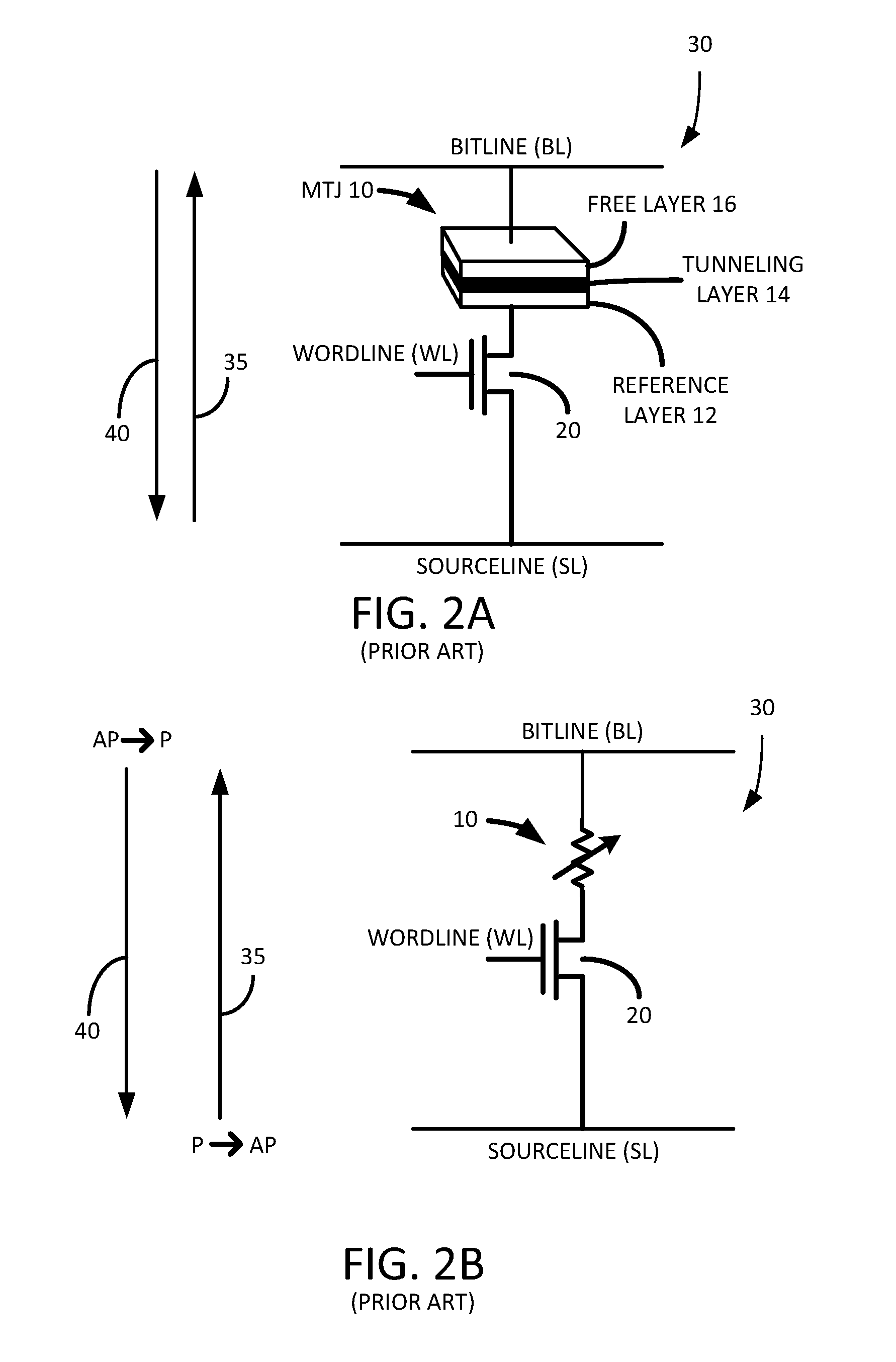

Method and system for providing a smart memory architecture

ActiveUS20140157065A1High rateHigh error rateError detection/correctionDigital computer detailsMemory chipSmart memory

A smart memory system preferably includes a memory including one or more memory chips, and a processor including one or more memory processor chips. The system may include a smart memory controller capable of performing a bit error rate built-in self test. The smart memory control may include bit error rate controller logic configured to control the bit error rate built-in self test. A write error rate test pattern generator may generate a write error test pattern for the bit error rate built-in self test. A read error rate test pattern generator may generate a read error test pattern for the built-in self test. The smart memory controller may internally generate an error rate timing pattern, perform built-in self test, measure the resulting error rate, automatically adjust one or more test parameters based on the measured error rate, and repeat the built-in self test using the adjusted parameters.

Owner:SAMSUNG ELECTRONICS CO LTD

Algorithm mapping, specialized instructions and architecture features for smart memory computing

InactiveUS6970988B1Improve performanceLow costMultiplex system selection arrangementsProgram controlSmart memoryExecution unit

A smart memory computing system that uses smart memory for massive data storage as well as for massive parallel execution is disclosed. The data stored in the smart memory can be accessed just like the conventional main memory, but the smart memory also has many execution units to process data in situ. The smart memory computing system offers improved performance and reduced costs for those programs having massive data-level parallelism. This smart memory computing system is able to take advantage of data-level parallelism to improve execution speed by, for example, use of inventive aspects such as algorithm mapping, compiler techniques, architecture features, and specialized instruction sets.

Owner:STRIPE INC

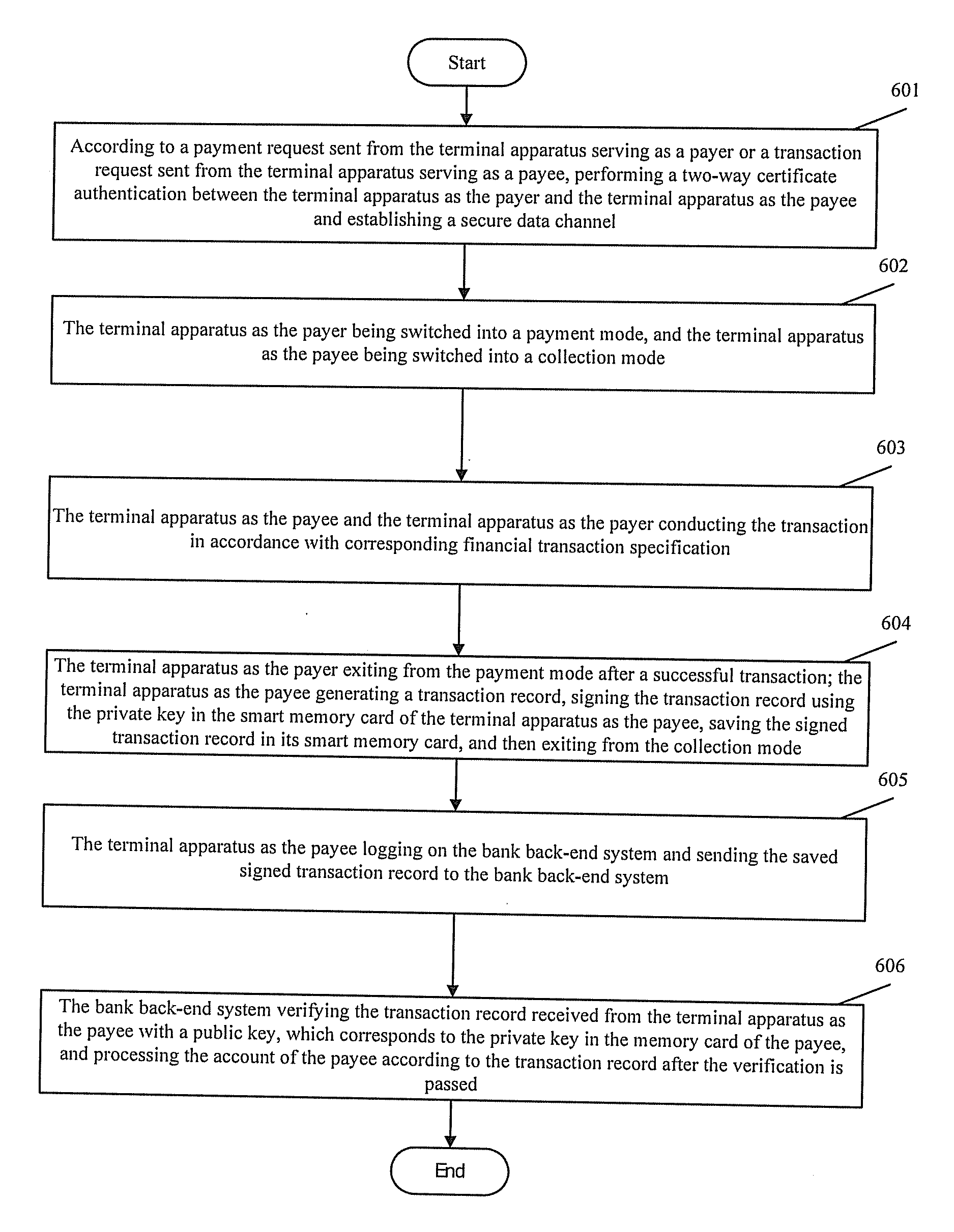

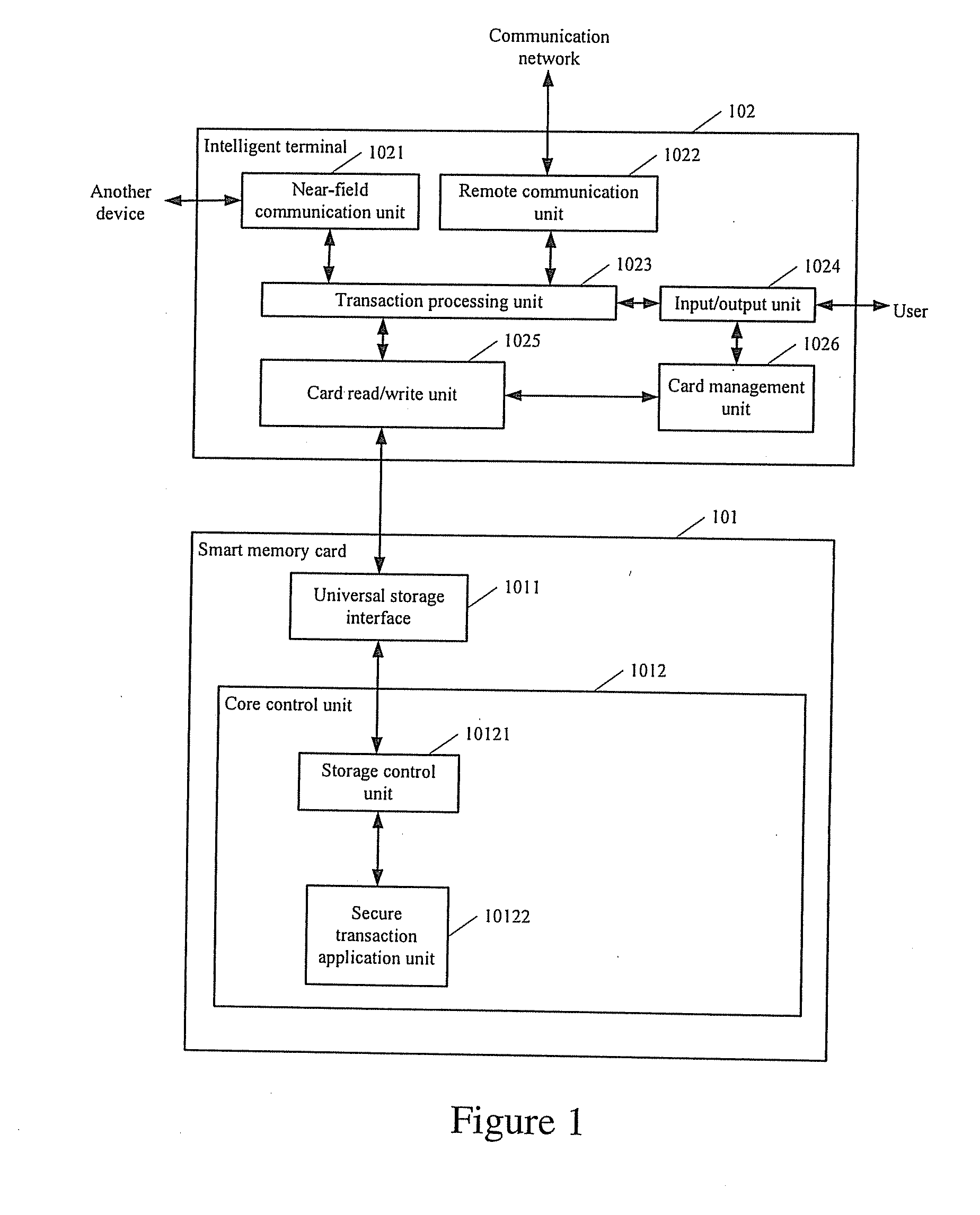

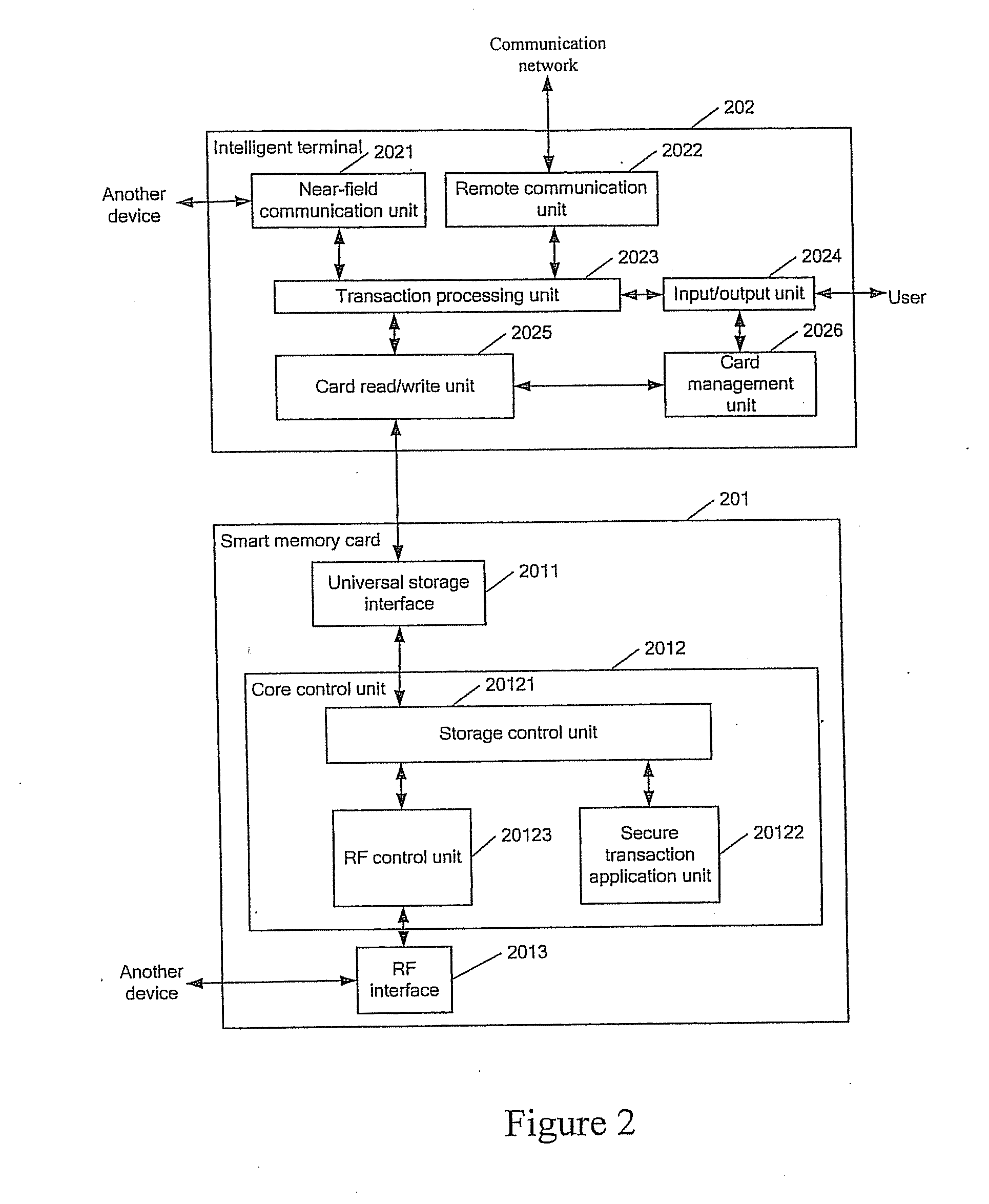

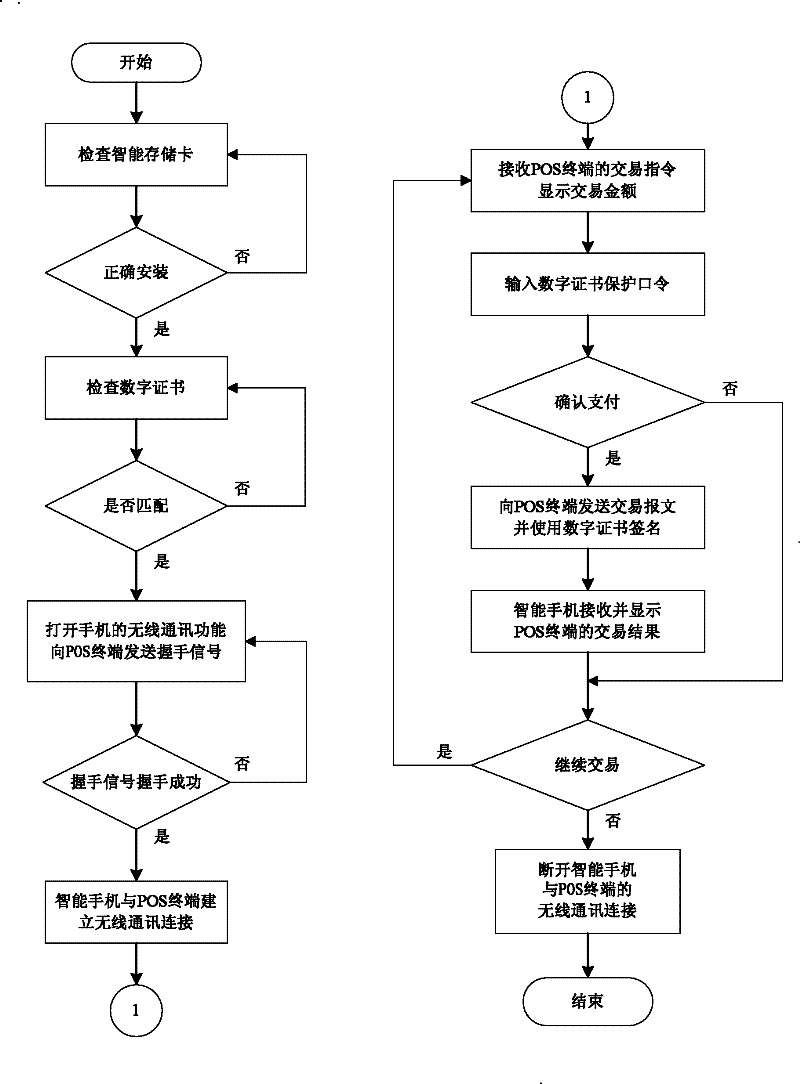

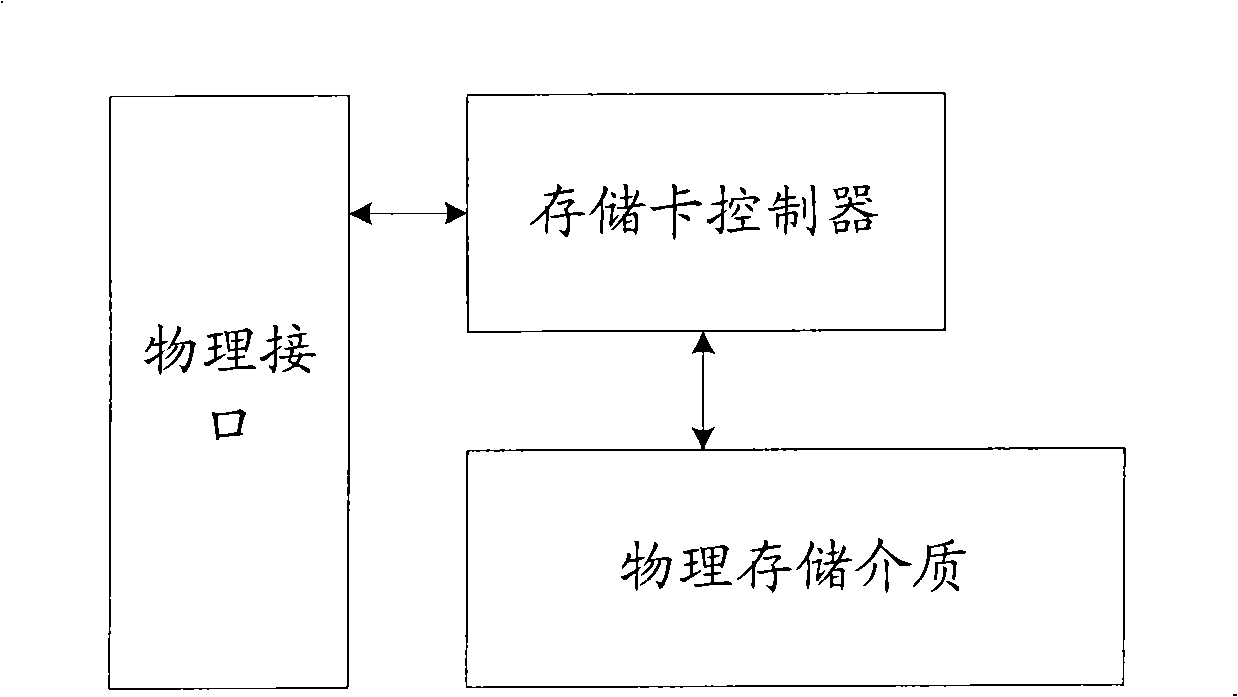

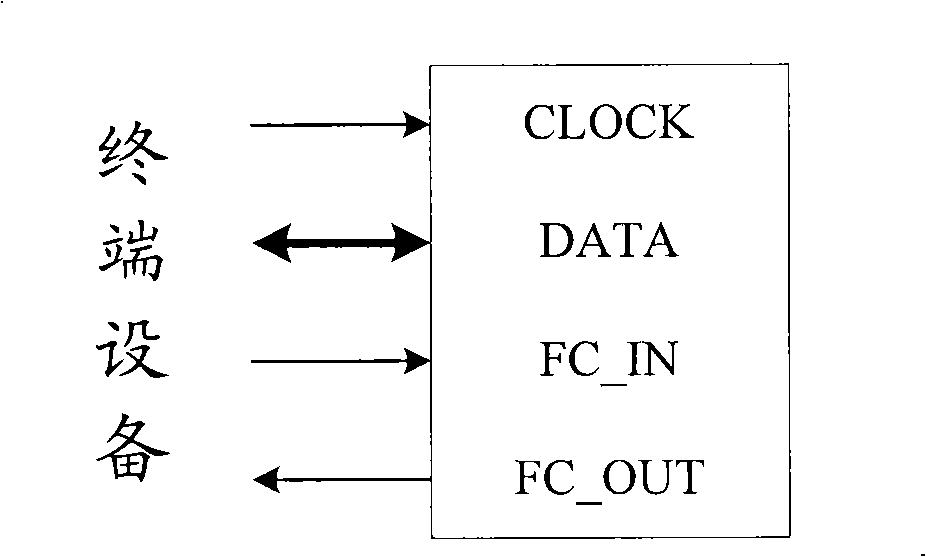

Device, system and transaction method for integrating payment function and receipt function

InactiveUS20120089507A1Easy to popularizeBroaden applicationFinancePayment architecturePaymentTransaction management

A device integrated with payment function and collection function, includes a smart memory card and an intelligent terminal. The intelligent terminal is adapted to generate a secure transaction management instruction, send the secure transaction management instruction to the smart memory card and notify an execution result of the secure transaction management instruction; to interact with a bank side system via a remote communication network; to interact with user via a user interface; to interact with another device in near field communication mode; to process transaction instruction, generate a secure transaction application instruction and send the secure transaction application instruction to the smart memory card; and to notify an execution result of the secure transaction application instruction. The smart memory card is adapted to execute the safe transaction management instruction and the safe transaction application instruction.

Owner:POTEVIO INST OT TECH

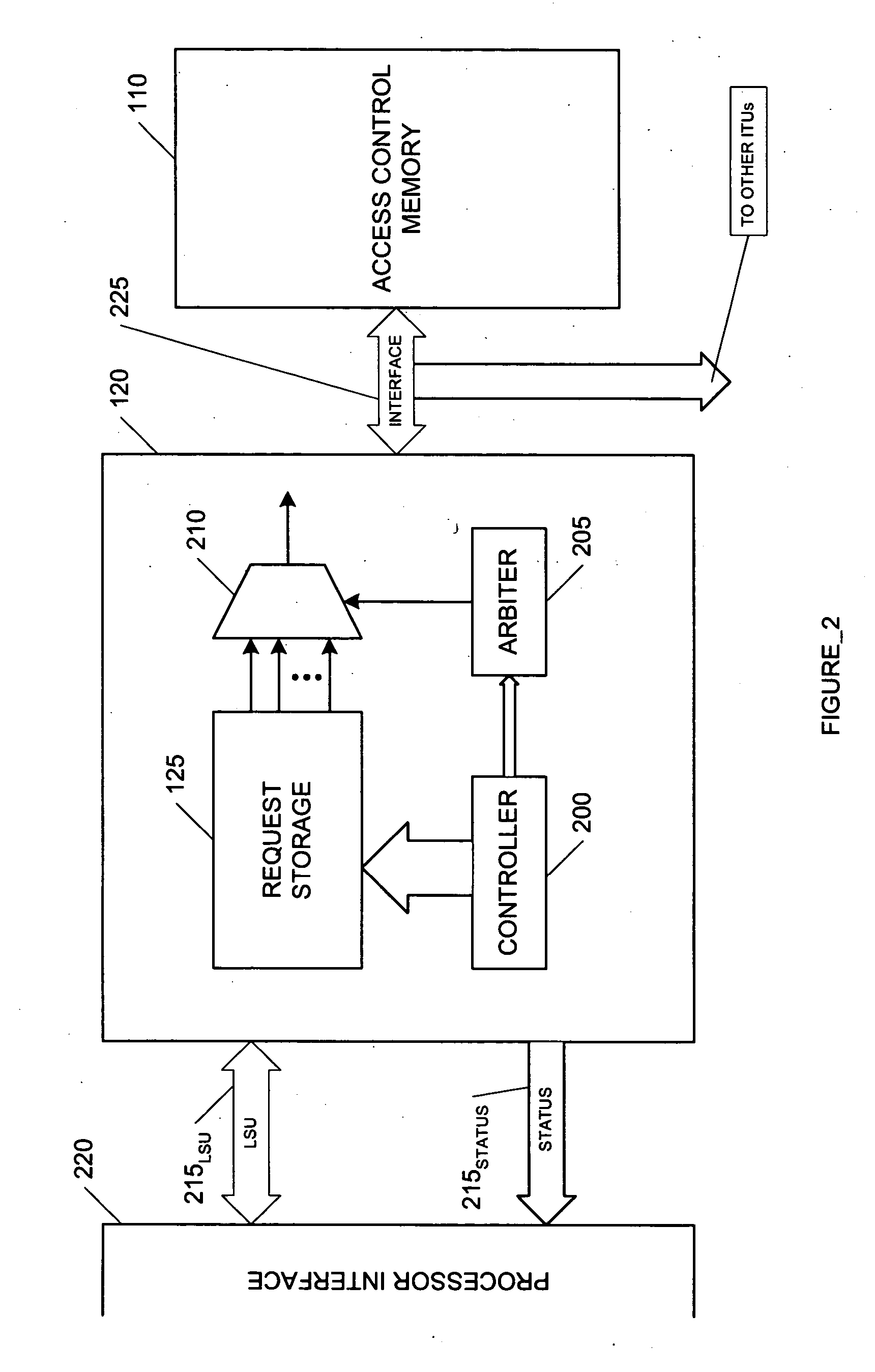

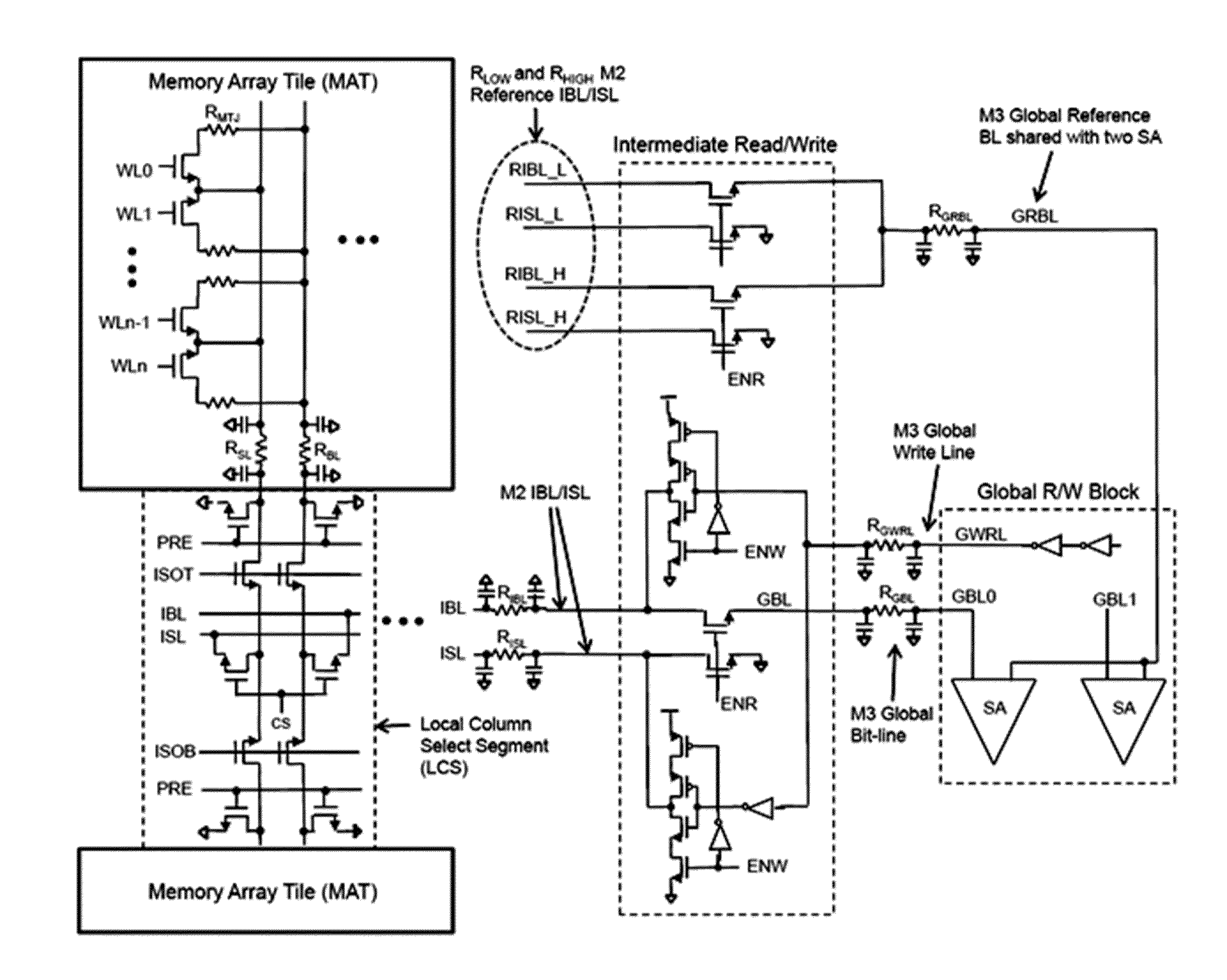

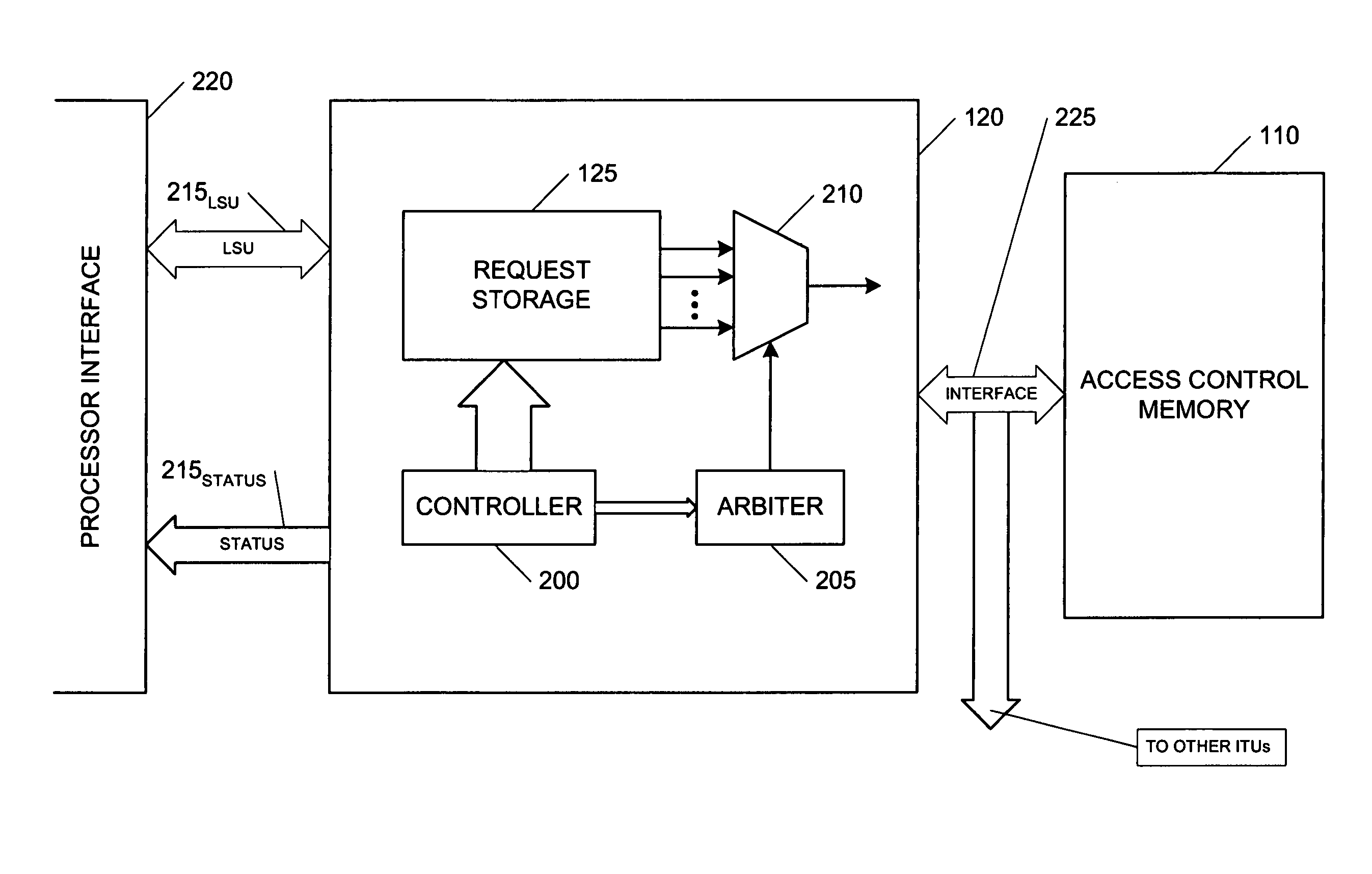

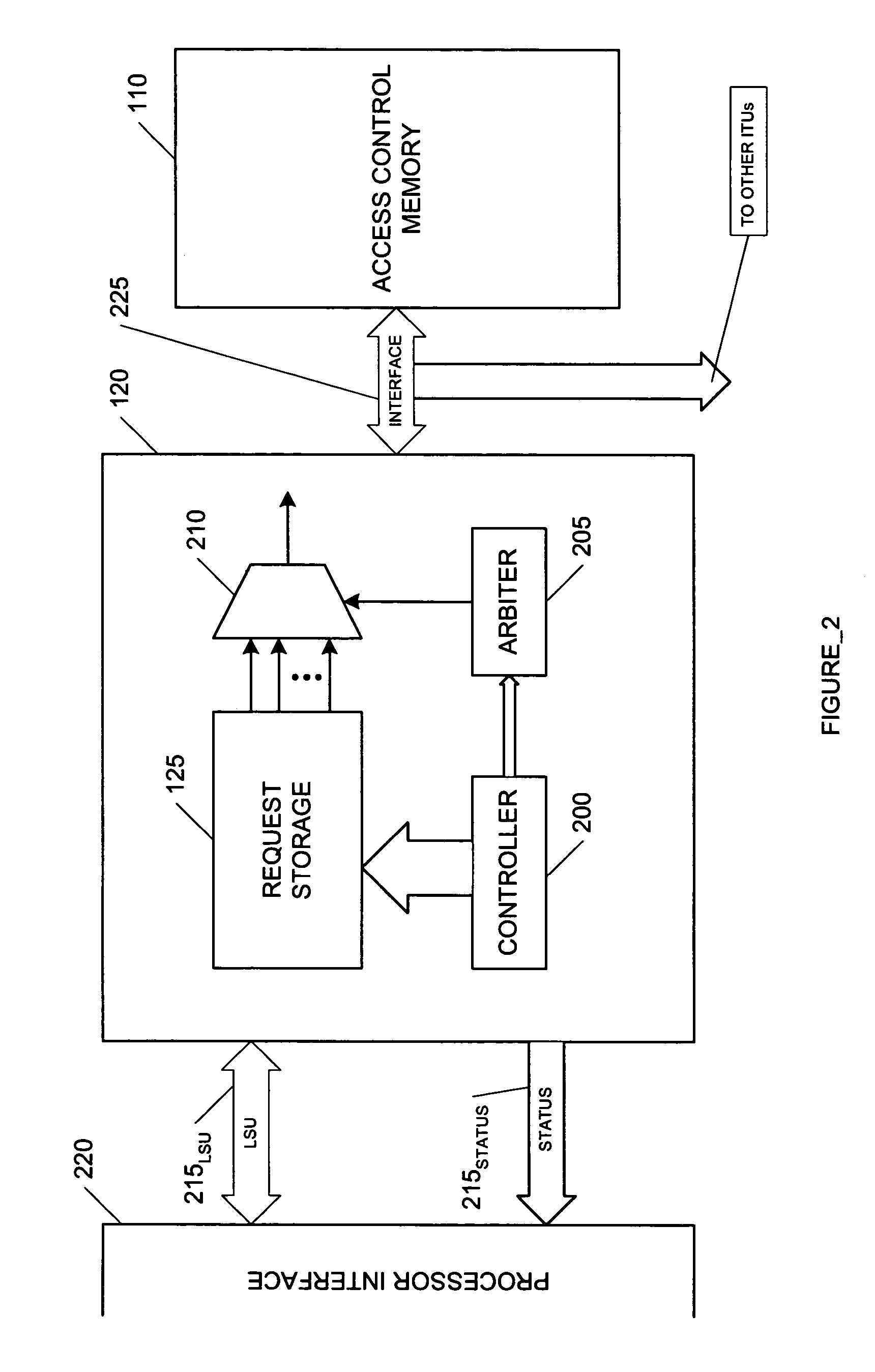

Smart memory based synchronization controller for a multi-threaded multiprocessor SoC

A memory interface for use with a multiprocess memory system having a gating memory, the gating memory associating one or more memory access methods with each of a plurality of memory locations of the memory system wherein the gating memory returns a particular one access method for a particular one memory location responsive to a memory access instruction relating to the particular one memory location, the interface including: a request storage for storing a plurality of concurrent memory access instructions for one or more of the particular memory locations, each the memory access instruction issued from an associated independent thread context; an arbiter, coupled to the request storage, for selecting a particular one of the memory access instructions to apply to the gating memory; and a controller, coupled to the request storage and to the arbiter, for: storing the plurality of memory access instructions in the request storage; initiating application of the particular one memory access instruction selected by the arbiter to the gating memory; receiving the particular one access method associated with the particular one memory access method from the gating memory; and initiating a communication of the particular access method to the thread context associated with the particular one access instruction.

Owner:MIPS TECH INC

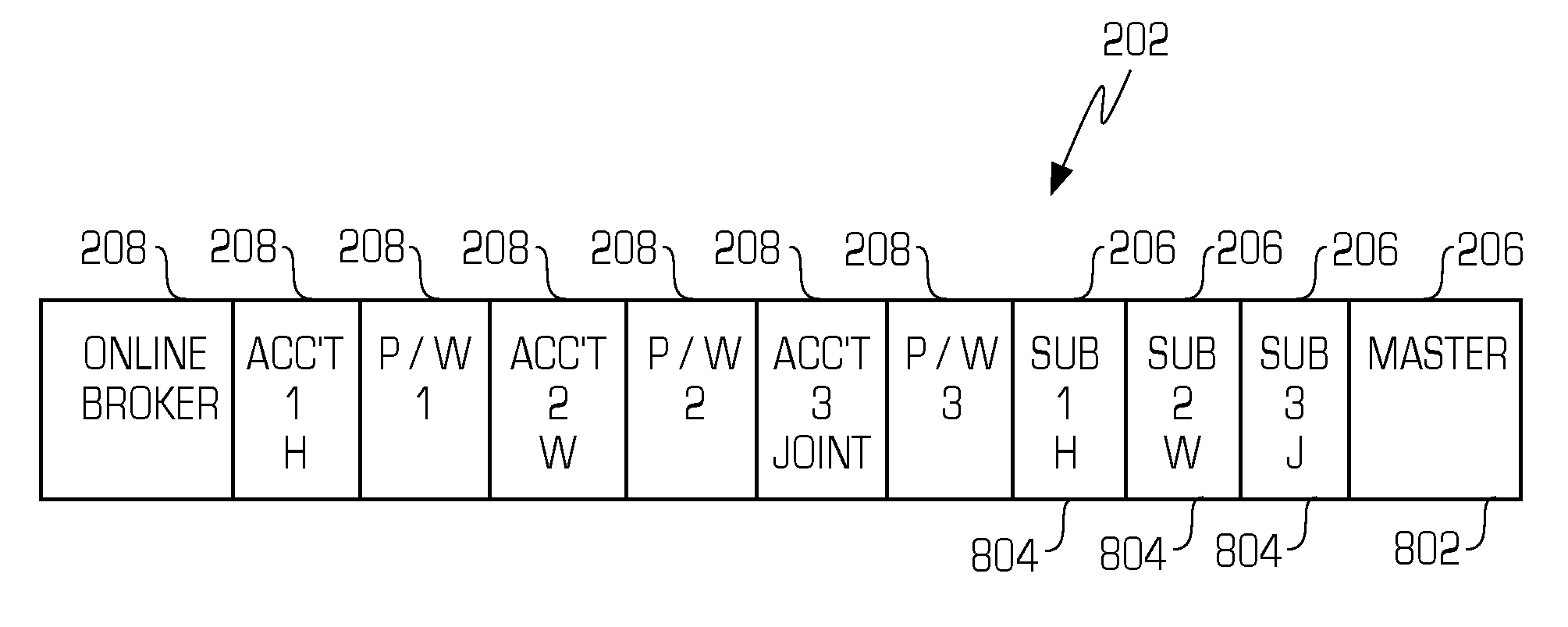

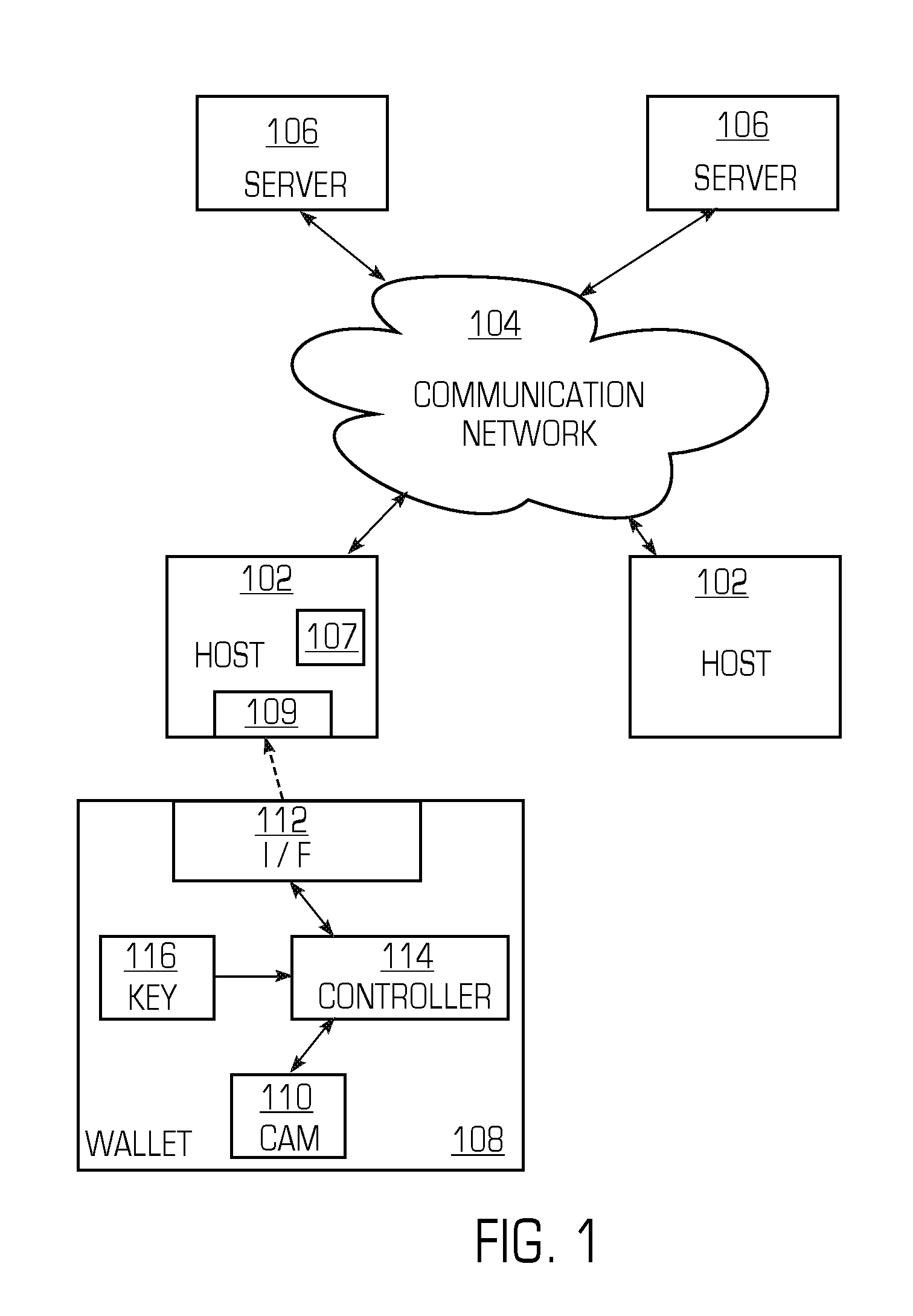

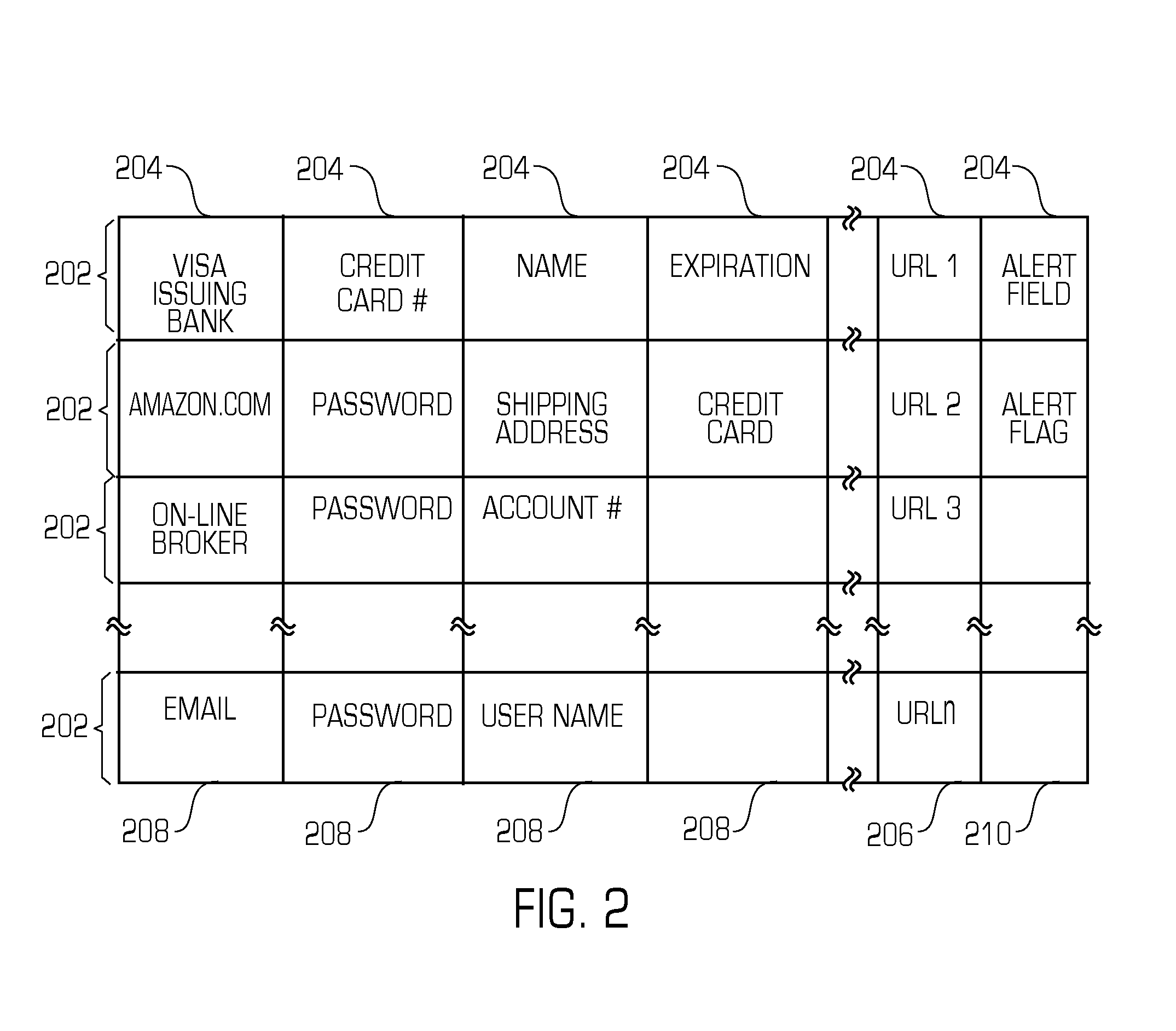

Smart memory card wallet

InactiveUS7533063B2Coded identity card or credit card actuationProtocol authorisationUser inputPassword

A system includes at least one server and at least one host computer coupled to a communication network. A memory card wallet includes a content addressable memory that stores server identifiers, such as URLs, and user information associated with the resource provider, such as user identification numbers and passwords. The user inserts the memory card wallet into the host computer, and instead of entering user identifiers and passwords, the memory card wallet can provide such information to the server. When the user enters a server identifier that matches a server identifier stored in the content addressable memory, the memory card wallet provides the user information associated with the matched sever identifier.

Owner:SILICON STORAGE TECHNOLOGY

Word memory intelligent learning method and system thereof

InactiveCN103413478AShorten the timeSave energyEnergy efficient computingSpecial data processing applicationsLTM - Long-term memoryShort-term memory

The invention belongs to the technical field of an intelligent memory method, and particularly relates to a word memory intelligent learning method and a system thereof. According to the memory ability of different learners, times spent on the memory of words in each day and the degree of difficulty of memorizing different words, the forgetting models of each word in different periods (transient memory, short-term memory and long-term memory) are calculated, then according to a forgetting critical point, the optimal review time of each word is accurately calculated, thus new word amount of each memory and old word amount of review are planned, and the overall learning progress can be predicated. The learning system established according to the above method is accurate and rapid, a lot of times and energy are saved for the learner, thus the efficiency of word memory is raised, and the system is especially suitable for memorizing a large amount of words. This system is applied to a computer or various smart mobile devices.

Owner:FUDAN UNIV

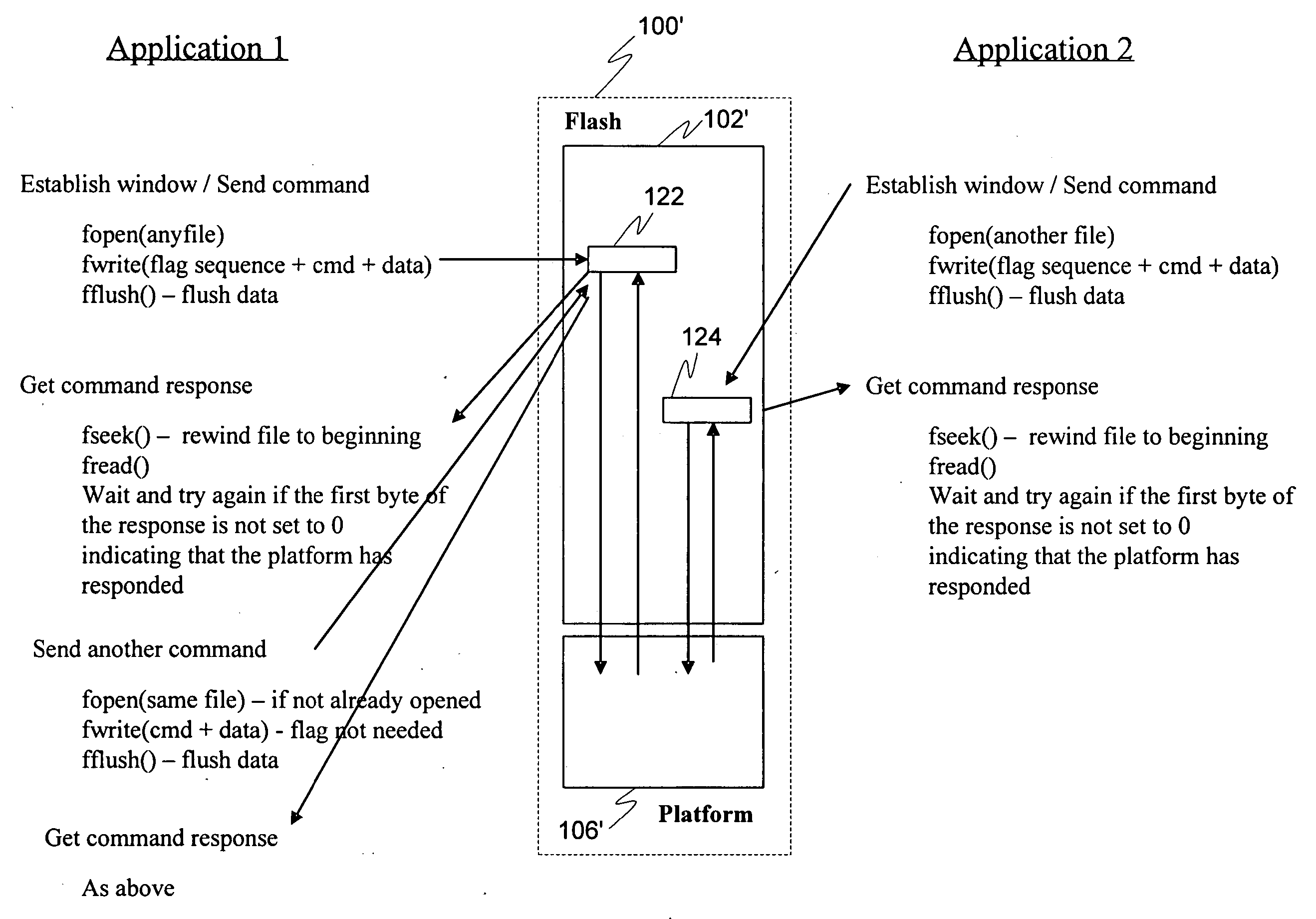

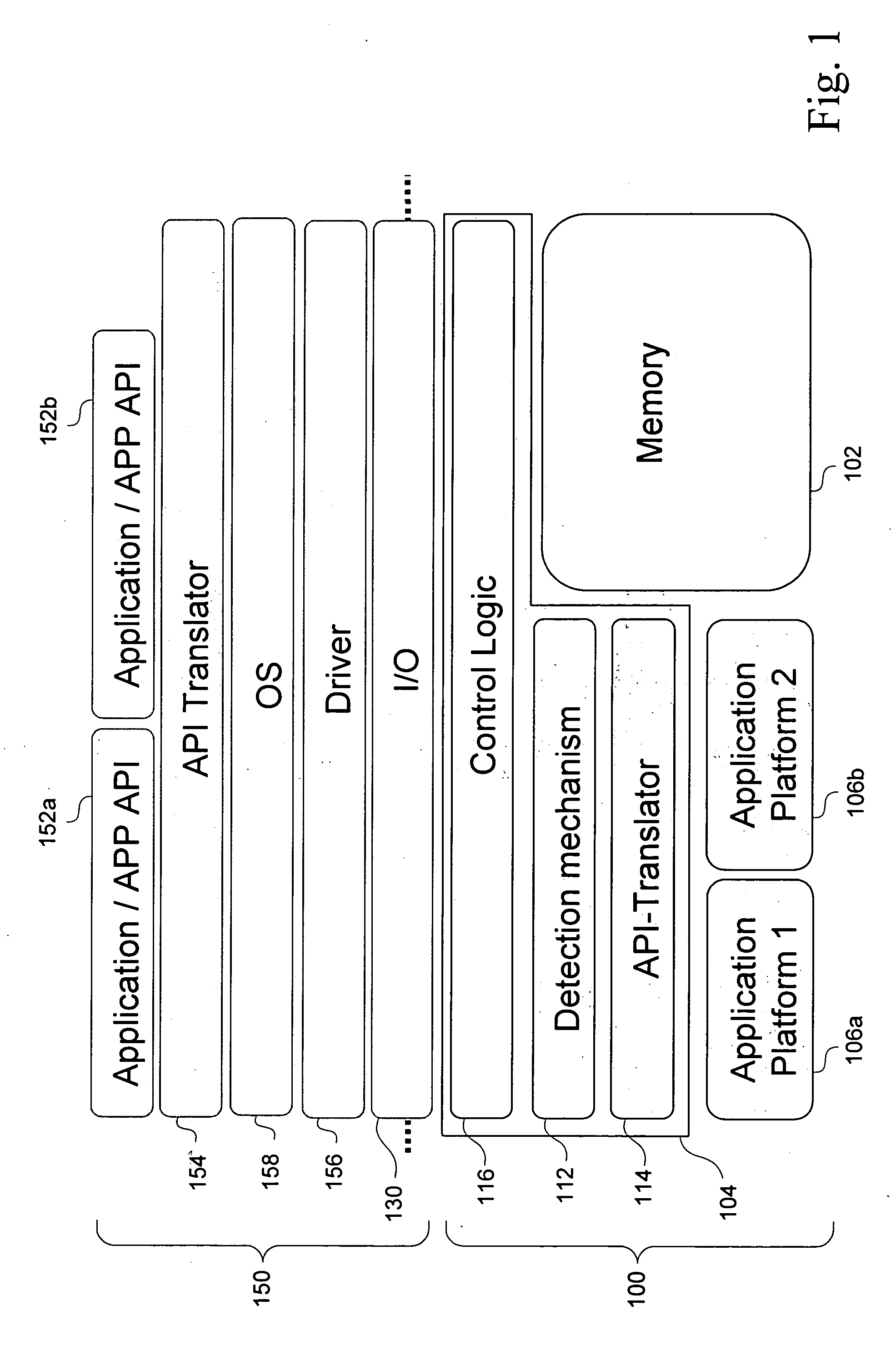

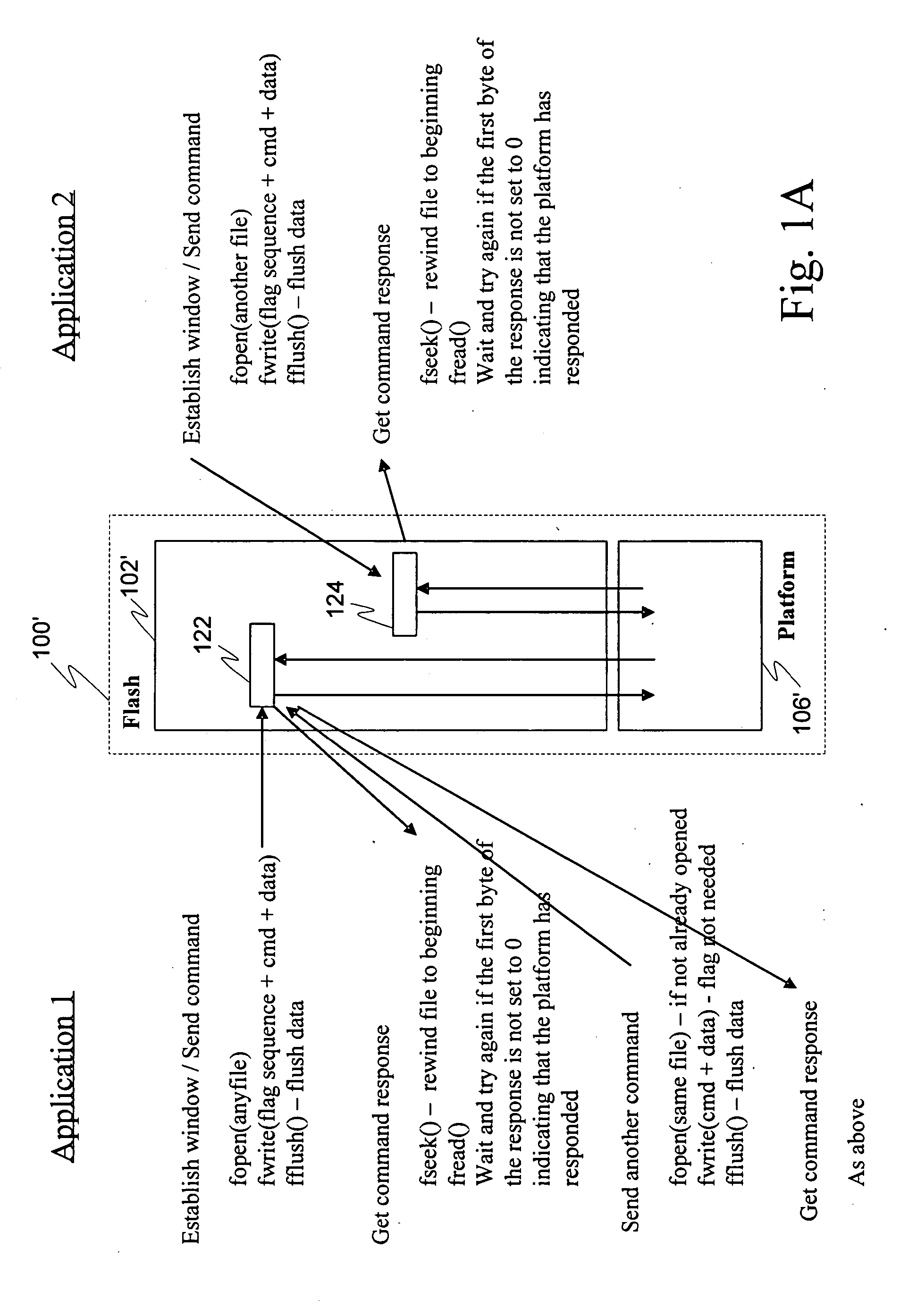

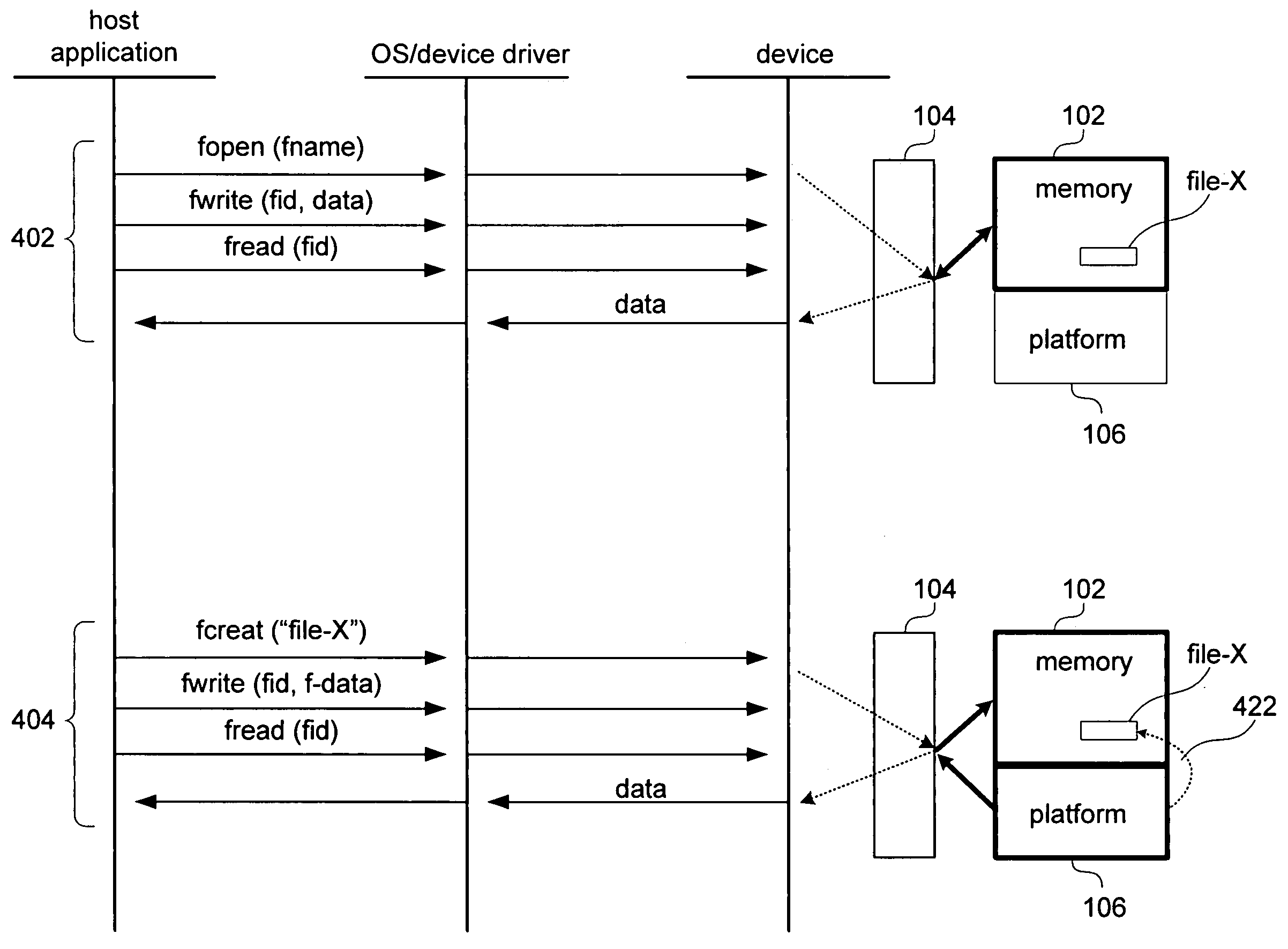

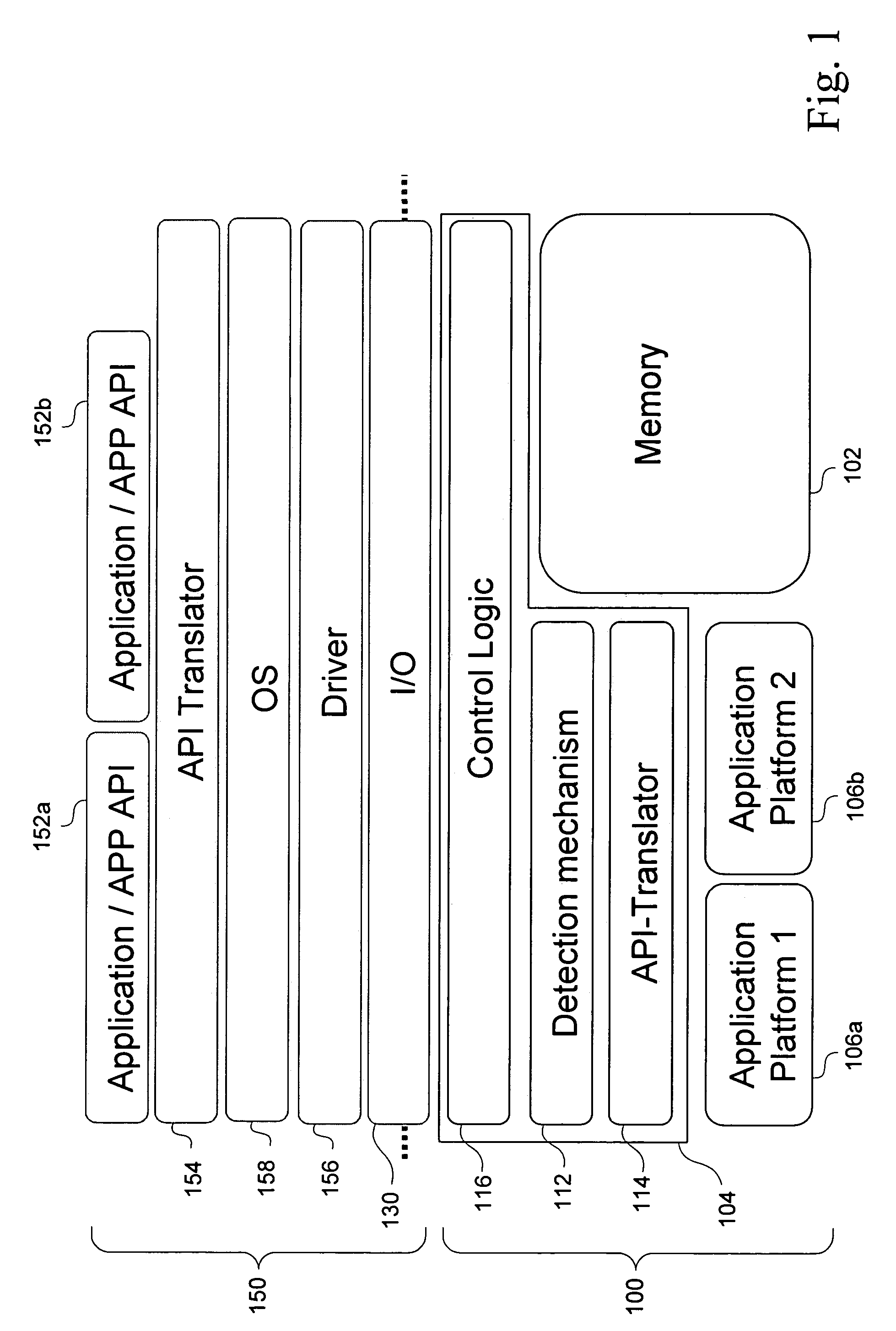

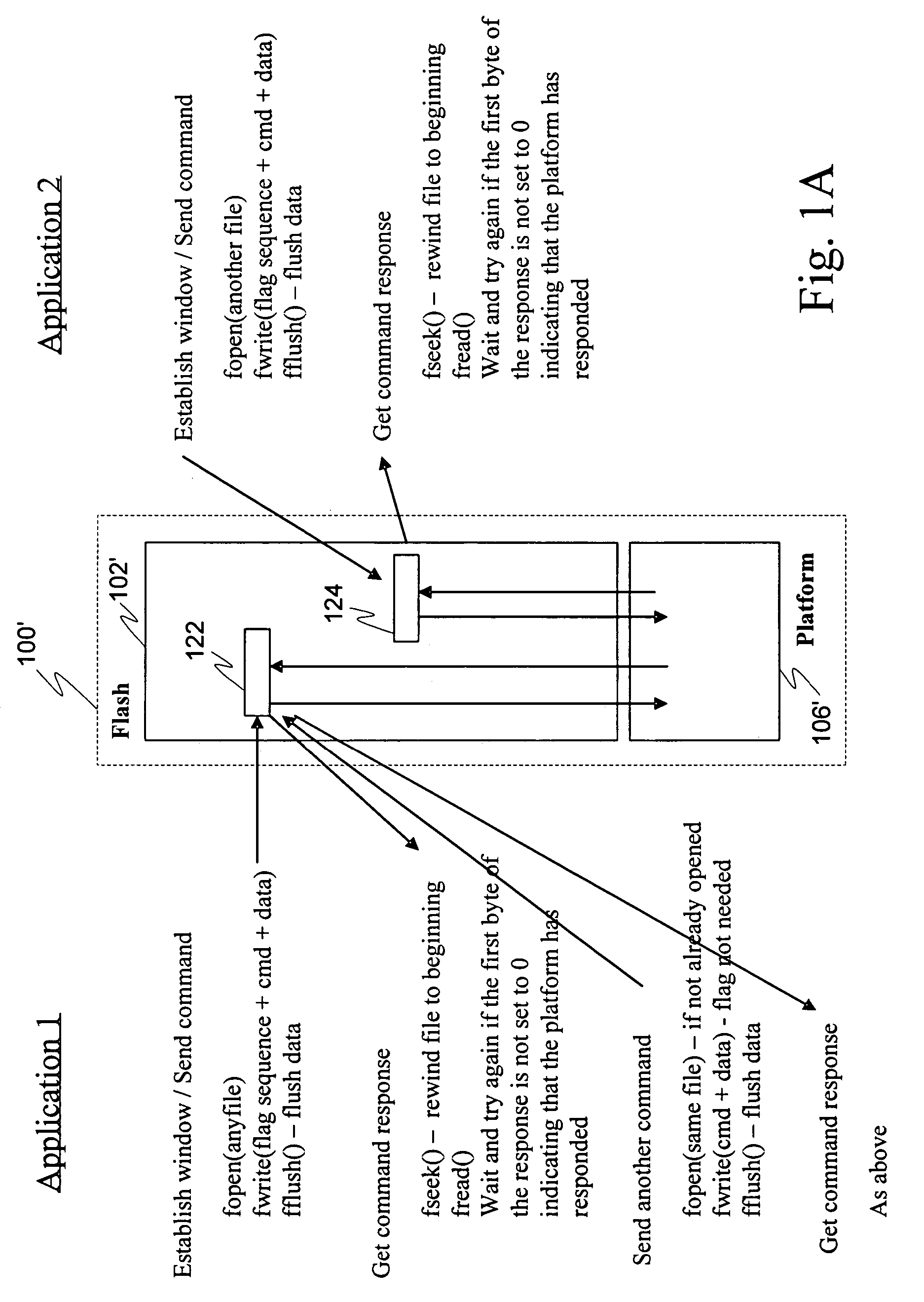

Method and apparatus for smart memory pass-through communication

ActiveUS20050086421A1Add featureInput/output to record carriersData processing applicationsSmart memoryData sequences

Enhanced functionality is provided in memory devices by enhancing the control logic to recognize predetermined data sequences. Standard (legacy) device operations are used to communicate the predetermined data sequences, thereby allowing existing device drivers to be used with the enhanced devices.

Owner:RENESAS ELECTRONICS AMERICA

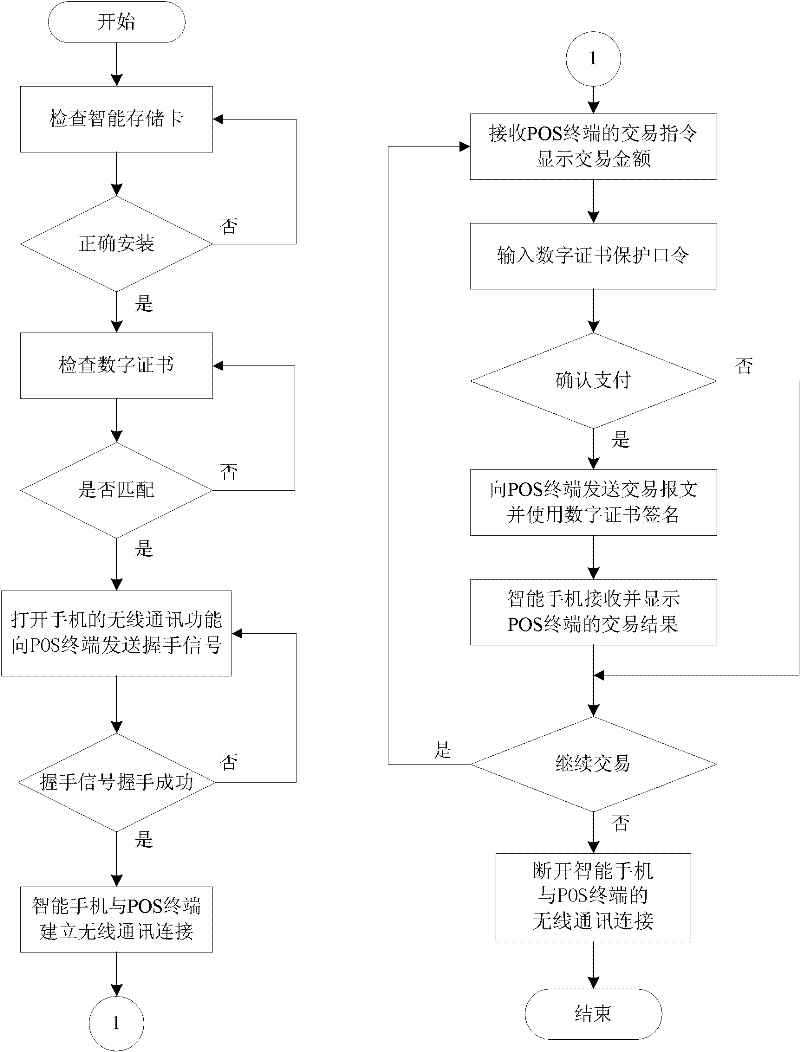

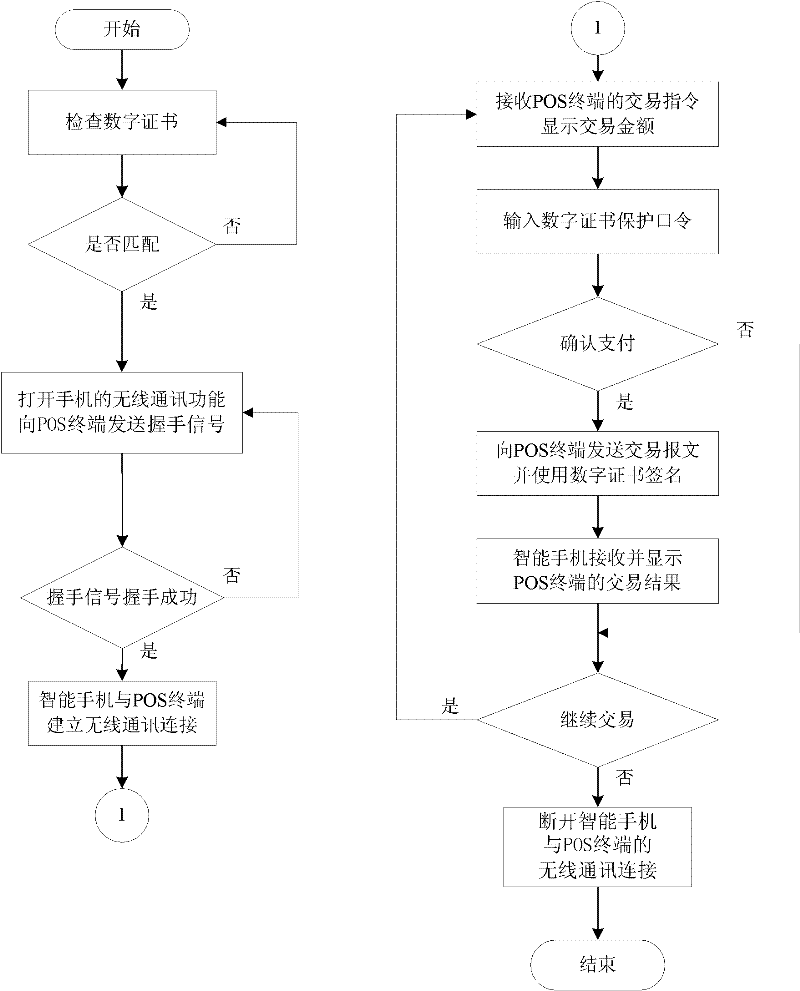

Near field payment method for smart phone

The invention discloses a near field payment method for a smart phone. The scheme is that: the phone without a near field communication (NFC) chip and a smart memory card with an encryption algorithm are adopted, a digital certificate of a bank card is downloaded into the smart memory card matched with the digital certificate as a payment voucher, the smart memory card is inserted into the smart phone, and near field communication trading software is installed in a memory of a body of the smart phone or in the smart memory card. The smart phone is held close to a point of sale (POS) terminal,performs near field communication with the POS terminal by utilizing own wireless communication technology of the phone and obtains bank card operation authority by authenticating the digital certificate, and a trading amount is displayed on the POS terminal and the phone. The near field communication trading software in the smart phone realizes mobile payment. In the method, the use of the NFC chip is avoided and an NFC antenna is not required to be arranged or modified in the smart phone. When NFC mobile phones are not popularized in China, the method can be used as a transitional scheme for the near field payment of the phone.

Owner:SHANGHAI HUASHEN INTELLIGENT IC CARD APPL SYST

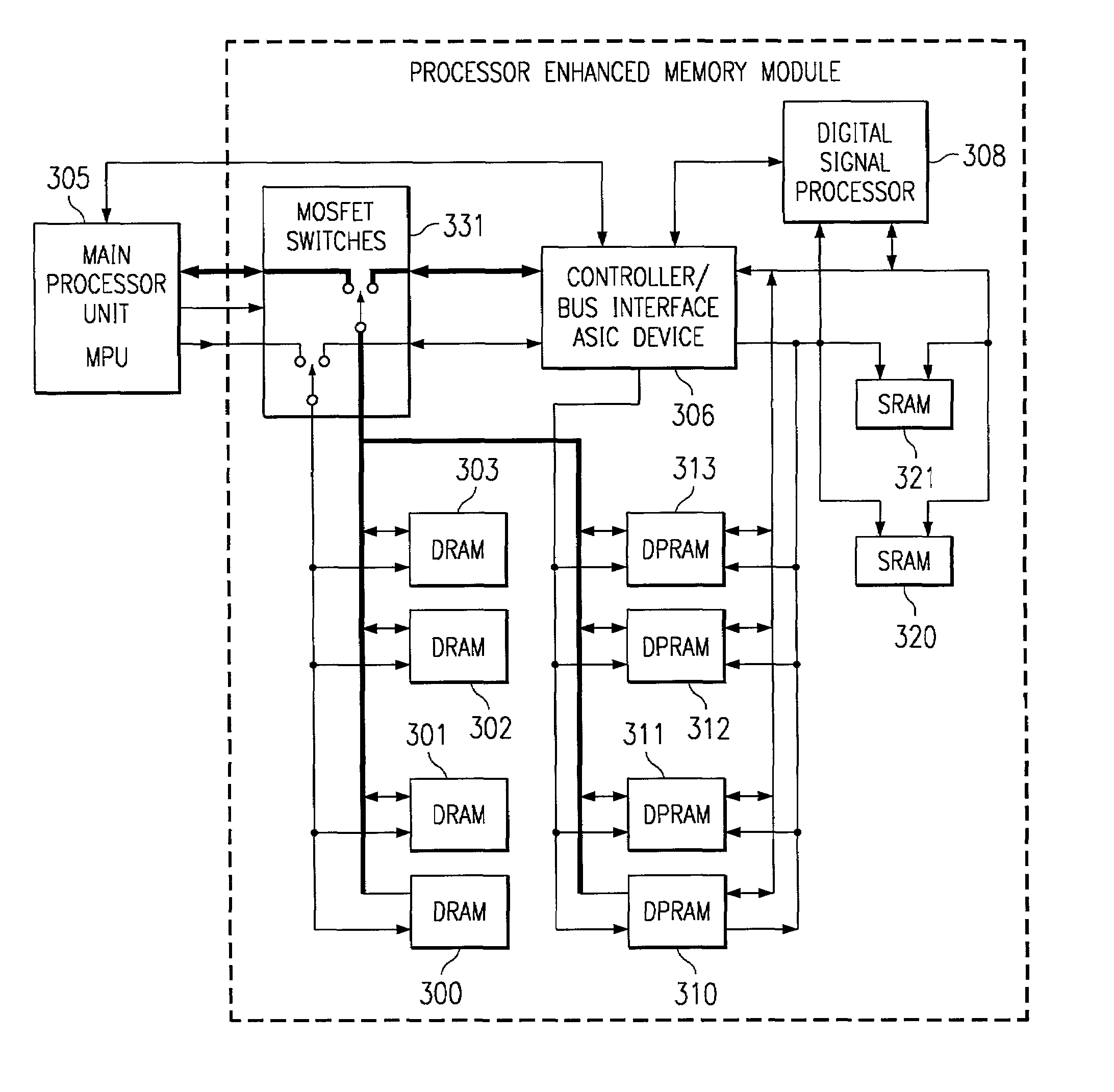

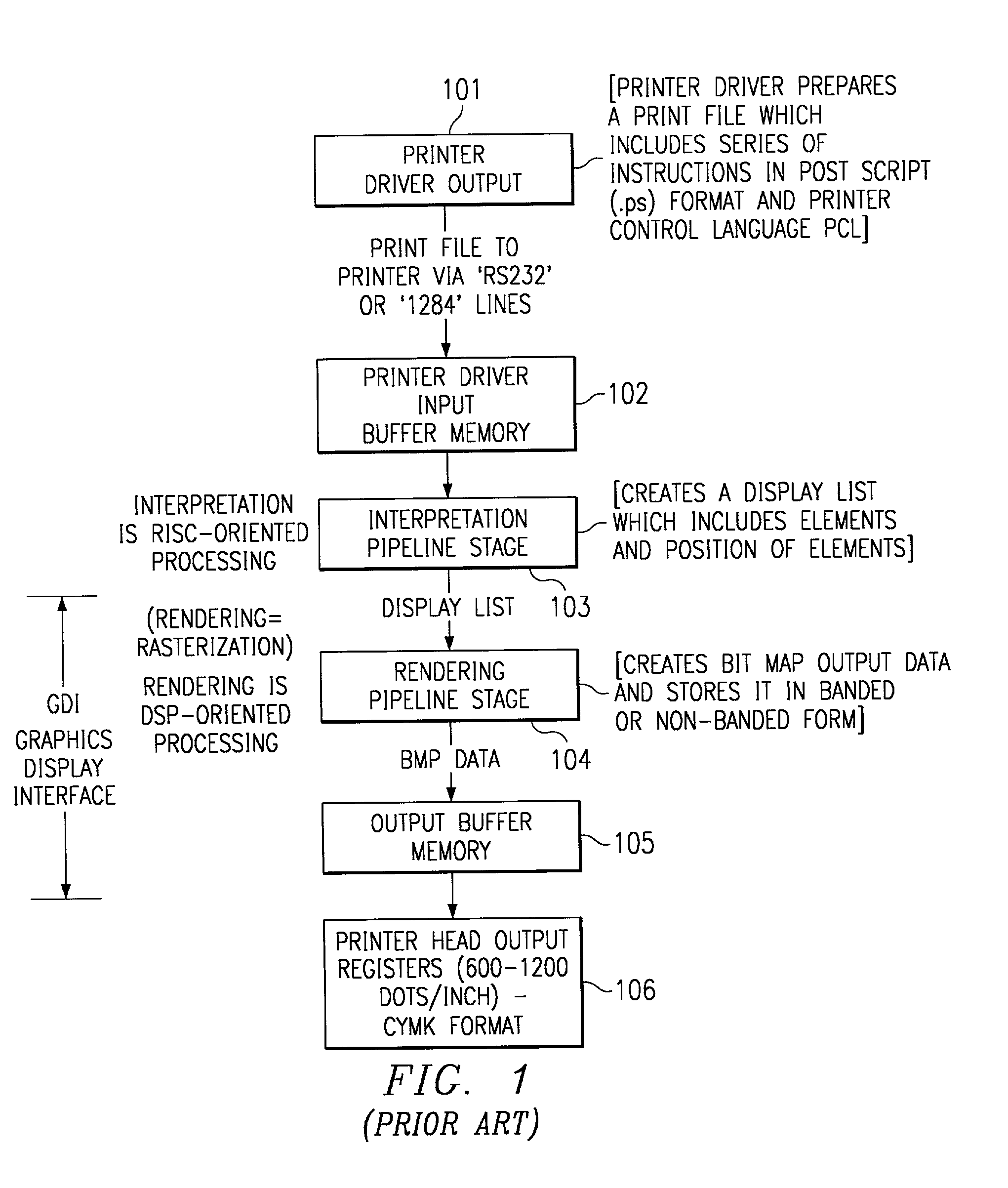

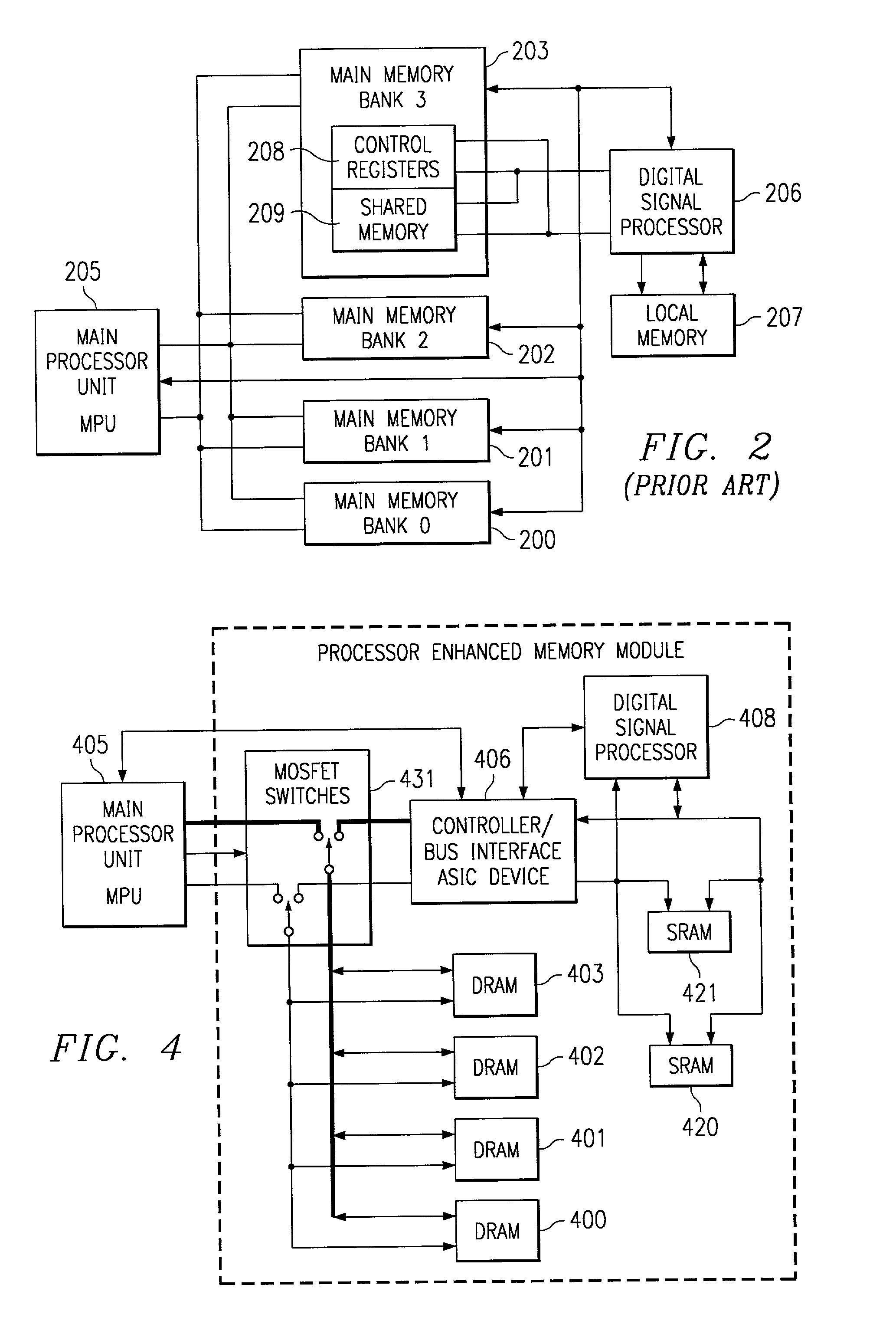

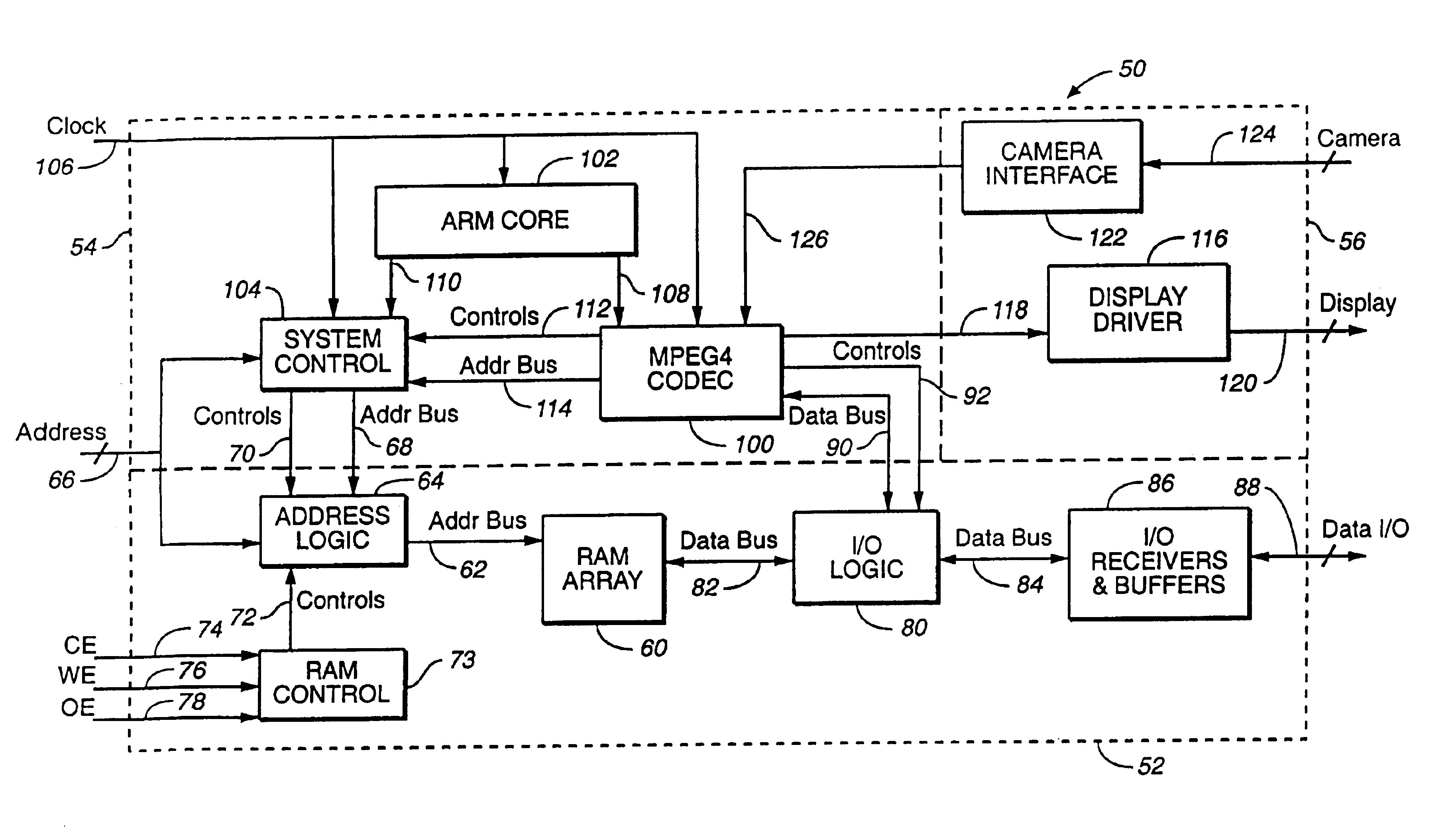

Using a processor enhanced memory module to accelerate hardcopy image processing within existing printer controller

ActiveUS7034955B2Increase system bandwidthDigital computer detailsHandling output dataImaging processingSmart memory

The processor enhanced memory module PEMM can be incorporated into the hardcopy image processing pipeline of existing printer controllers by using the smart memory model. Here the data generated from RISC based PDL interpretation or pre-rasterized data can be processed in an accelerated fashion into page bit maps, color space converted, and compressed by the PEMM. Since the DSP on the PEMM is programmable, the resolution, color space, and type of compression along with other printer specific processing can have formats other than those determined by the fixed functionality of the ASIC devices present in the pipeline.

Owner:TEXAS INSTR INC

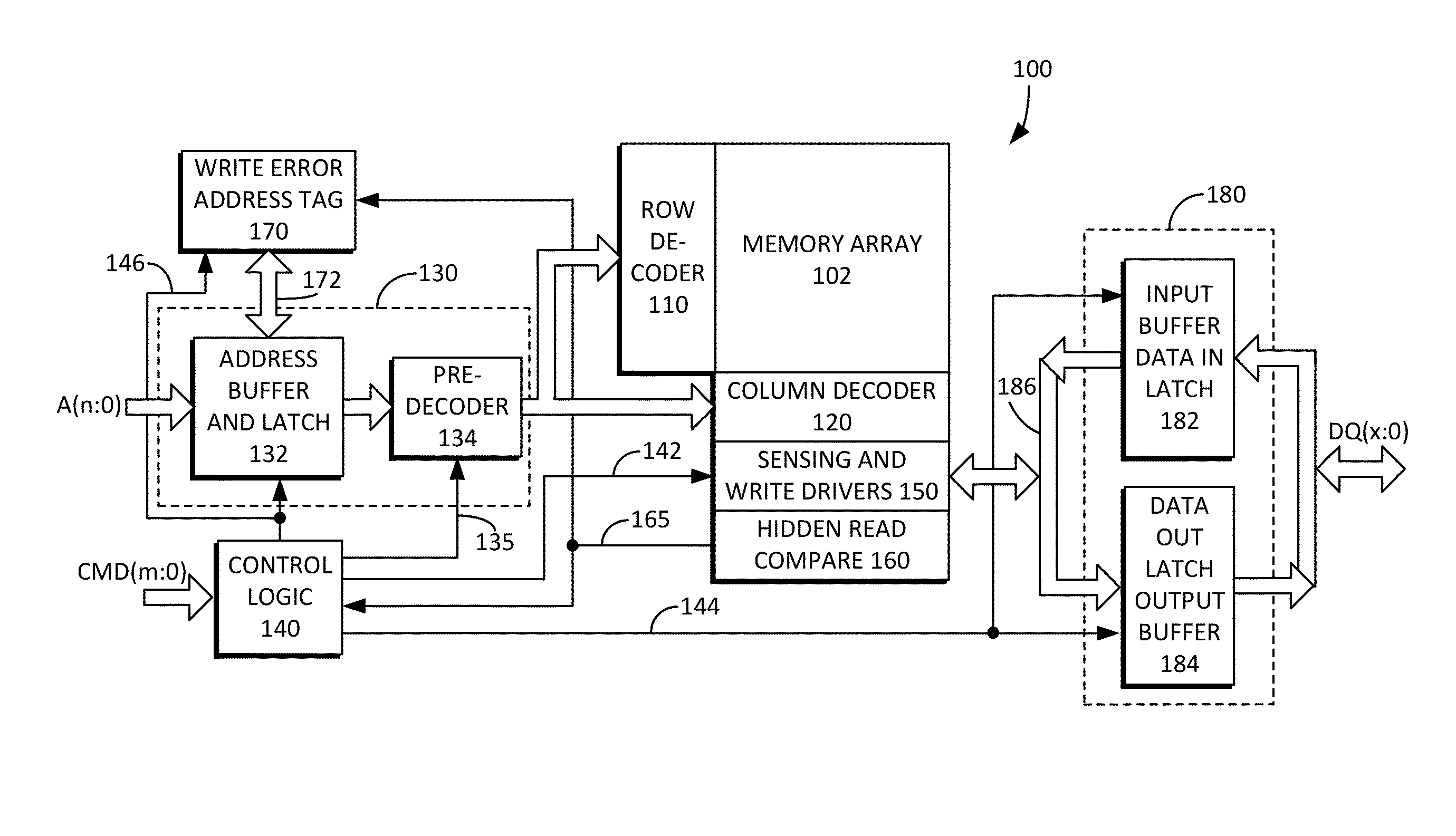

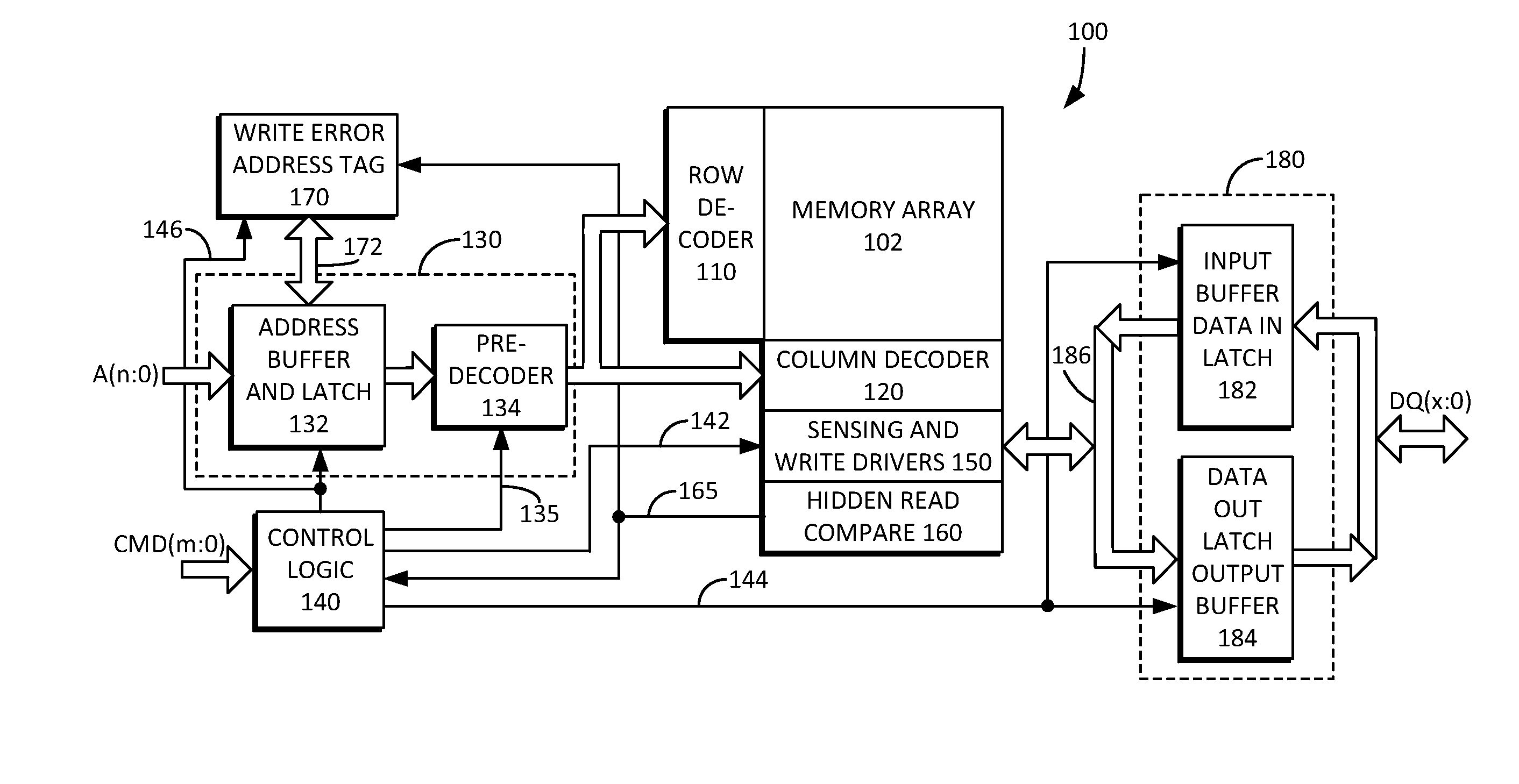

Method and system for providing a smart memory architecture

ActiveUS20130212431A1High rateHigh error rateDigital computer detailsComputer security arrangementsMemory addressSmart memory

A smart memory system preferably includes a memory including one or more memory chips, and a processor including one or more memory processor chips. The processor may include a common address / data / control memory bus that is configured to provide an asynchronous handshaking interface between the memory array and the memory processor. The processor can offload error data from the memory chip for analysis, and can store poor retention bit address information for memory refreshing in a non-volatile error retention memory. Program logic can also be included for memory address re-configuration. Power management logic can also be included, which may have a process-voltage-temperature compensation voltage generator for providing stable and constant read currents. An asynchronous handshaking interface is provided between the memory array and the memory processor. Write error tagging and write verification circuits can also be included.

Owner:SAMSUNG ELECTRONICS CO LTD

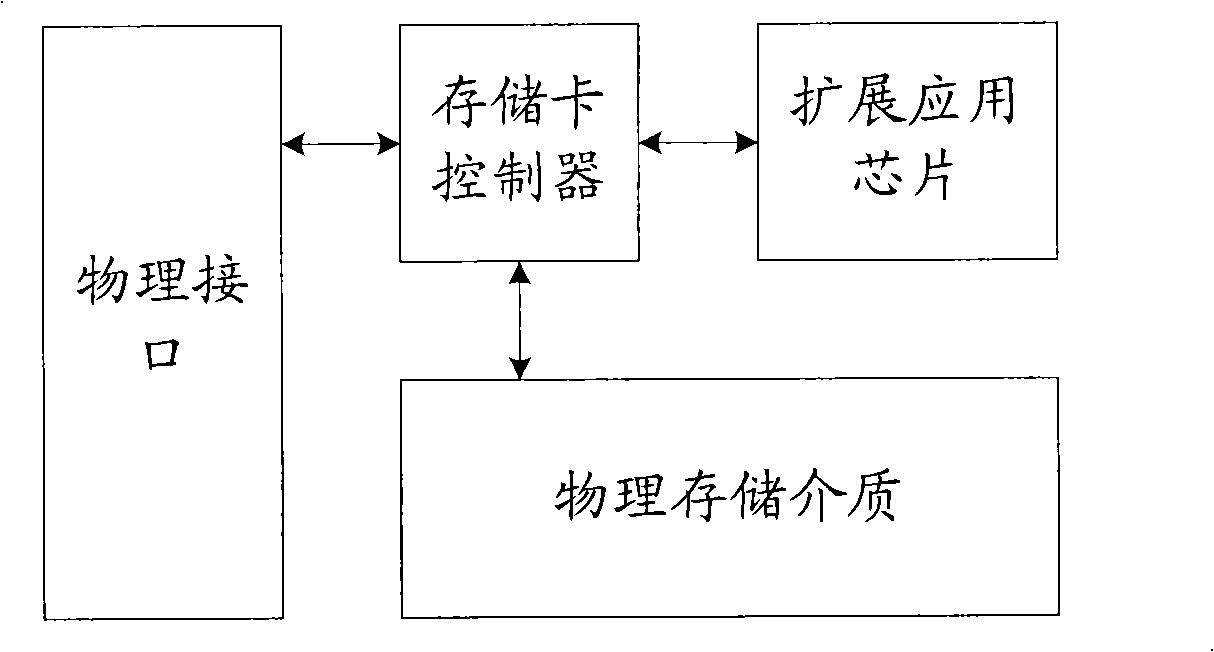

Smart memory card system and method for implementing interaction by the system

InactiveCN101340663ARealize managementRadio/inductive link selection arrangementsProgram loading/initiatingApplication serverSmart memory

Owner:POTEVIO INFORMATION TECH

Architecture and method for remote memory system diagnostic and optimization

InactiveUS20130212207A1Easy diagnosisPromote repairDigital computer detailsComputer security arrangementsSpecific testSmart memory

A smart memory system preferably includes a memory including one or more memory chips and a smart memory controller. The smart memory controller includes a transmitter communicatively coupled to the cloud. The transmitter securely transmits a product identification (ID) associated with the memory to the cloud. A cloud-based data center receives and stores the product ID and related information associated with the memory. A smart memory tester receives a product specific test program from the cloud-based data center. The smart memory tester may remotely test the memory via the cloud in accordance with the product specific test program. The information stored in the cloud-based data center can be accessed anywhere in the world by authorized personnel. Repair solutions can be remotely determined based on the test results and the diagnostic information. The repair solutions are transmitted to the smart memory controller, which repairs the memory.

Owner:SAMSUNG ELECTRONICS CO LTD

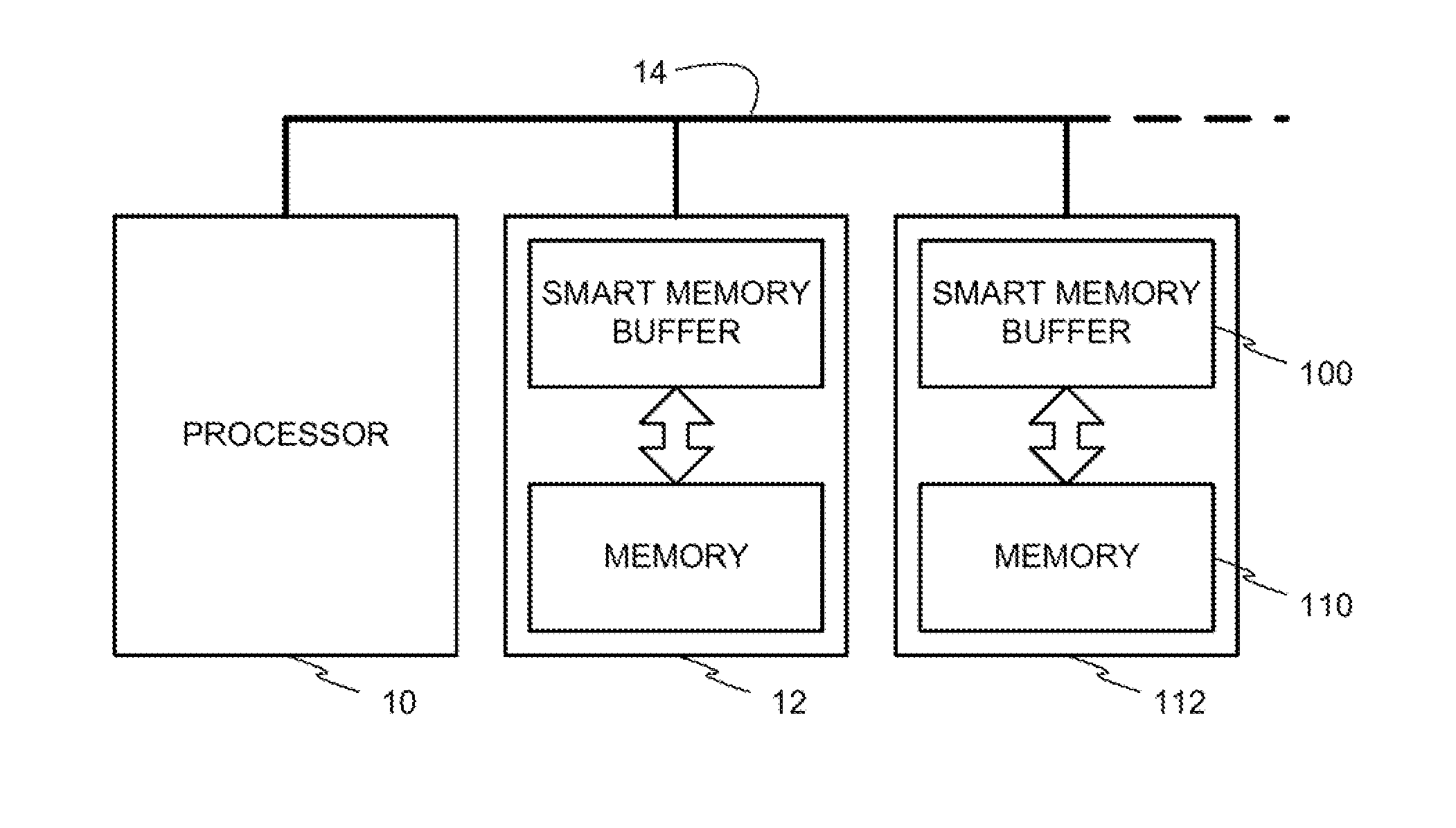

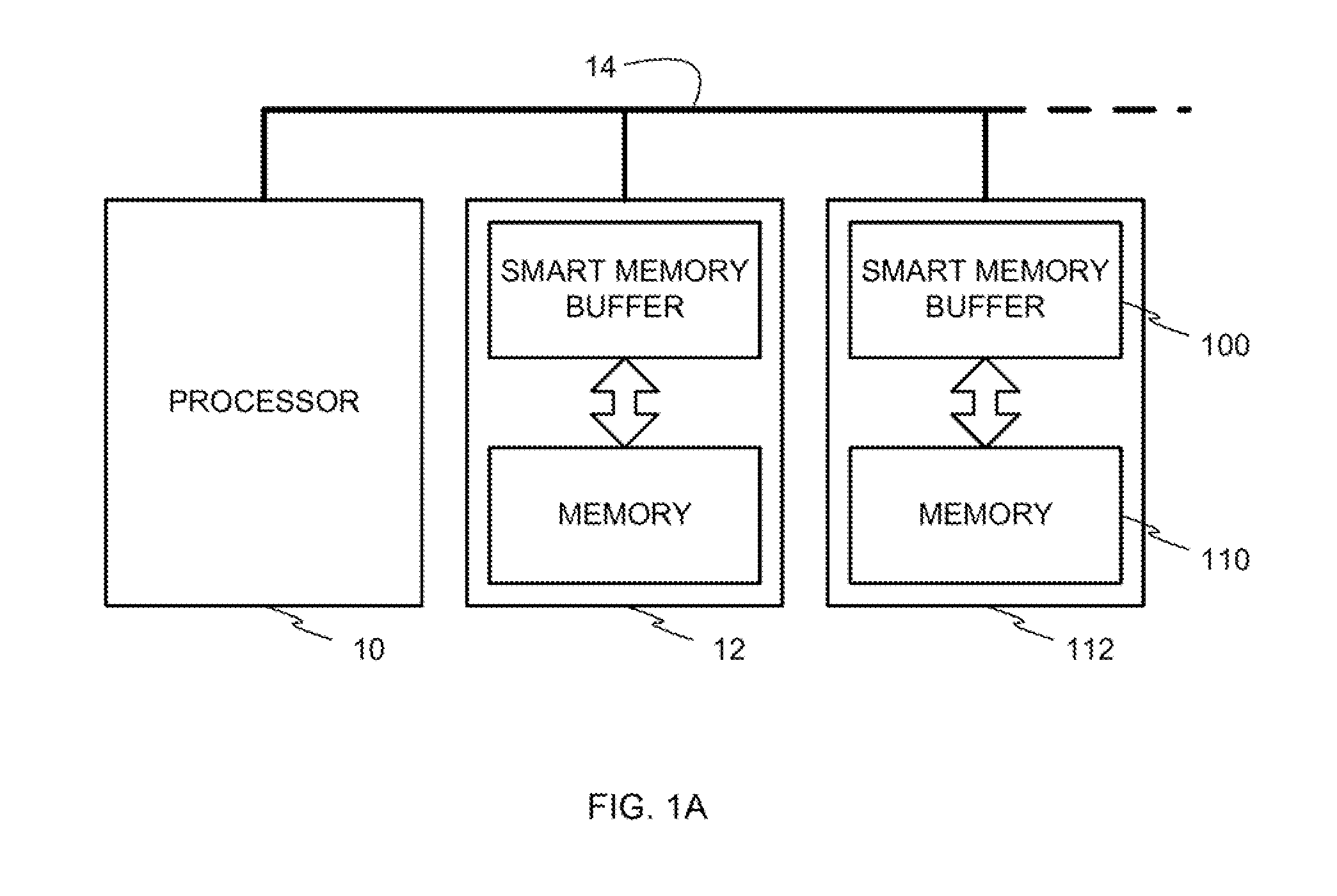

Massively parallel processing core with plural chains of processing elements and respective smart memory storing select data received from each chain

Systems and methods for massively parallel processing on an accelerator that includes a plurality of processing cores. Each processing core includes multiple processing chains configured to perform parallel computations, each of which includes a plurality of interconnected processing elements. The cores further include multiple of smart memory blocks configured to store and process data, each memory block accepting the output of one of the plurality of processing chains. The cores communicate with at least one off-chip memory bank.

Owner:NEC CORP

Intelligent maze robot

InactiveCN1888995AReduce in quantityReduce misusePosition/course control in two dimensionsElectric machineSmart memory

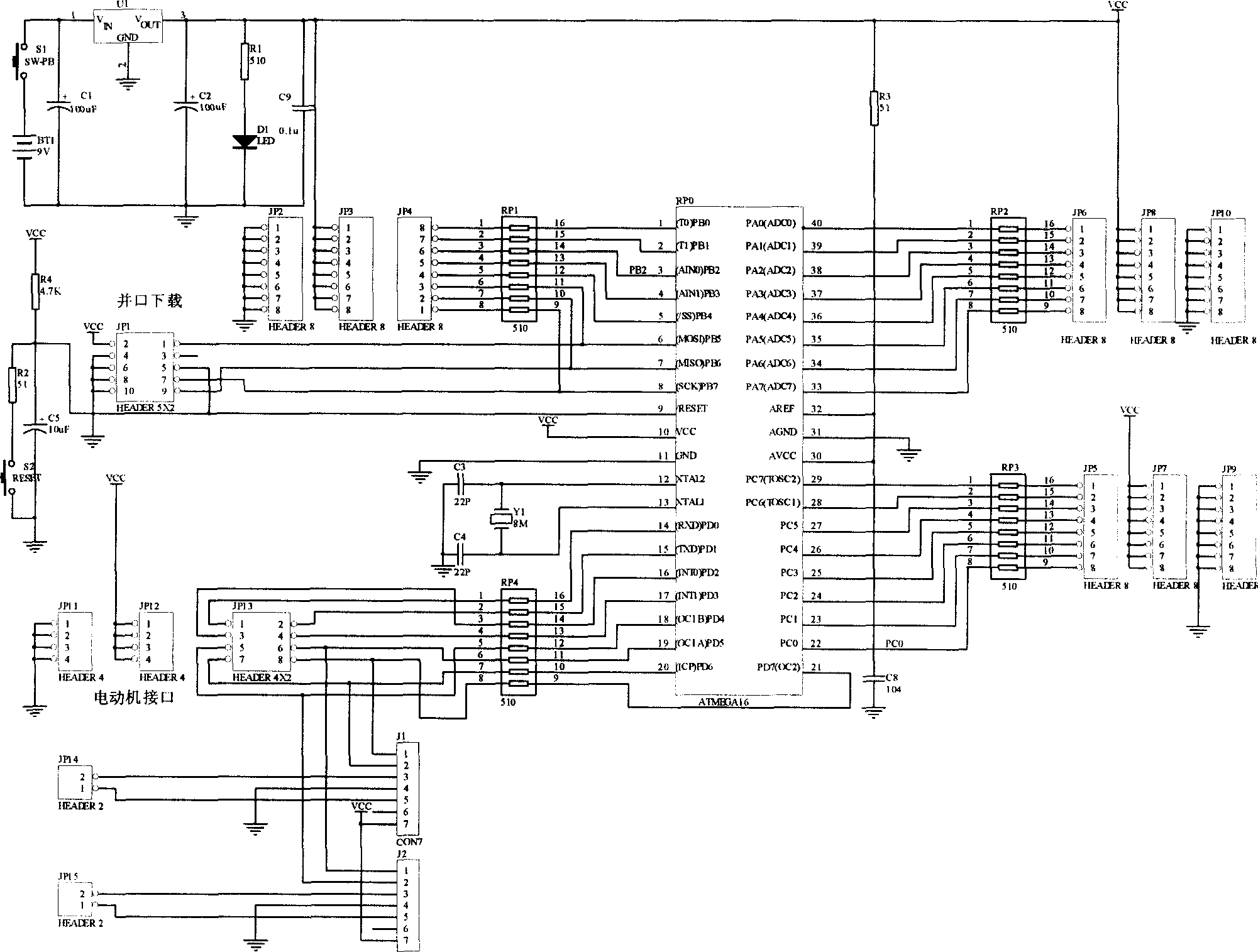

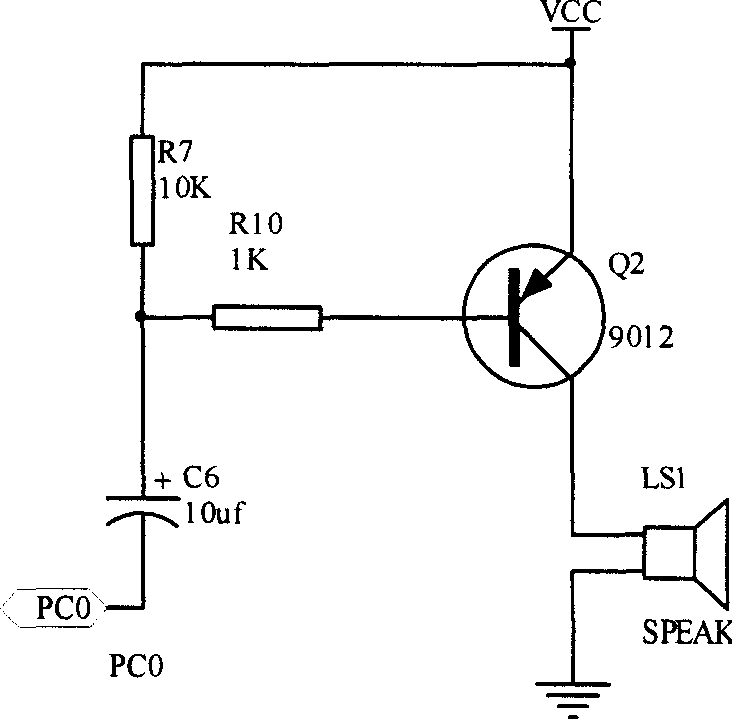

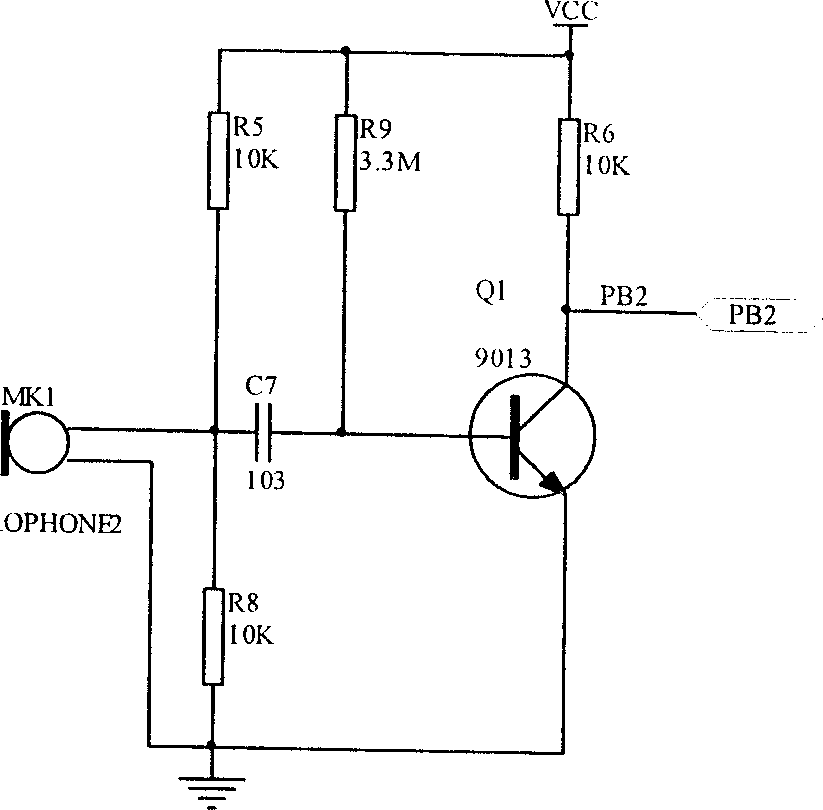

The invention relates to an intelligent maze robot which includes two independent controlling action wheels, the universal wheel in the front middle, the carriage, the microprocessor and the sensing system which includes the three infrared emission receiving sensor, the first photoelectric sensorand the second photoelectric sensor. The two action wheels are connected to the universal wheel by the carriage and all sensors are connected to the microprocessors. The microprocessor controls the motion of the electric machine according to the inputting signal to control the moving and the direction of the robot. The invention can reach the function of the auto searching maze and detecting the best way in the support of the software, also it can decrease the probability of the mishandling and improve the system stability because of using less sensors.

Owner:BEIJING UNIV OF TECH

Method for Increasing the Fluid Productivity of a Hydraulically Fractured Well

InactiveUS20090205826A1Increasing fluid productivity of wellReduce productionFluid removalDrilling compositionParticulatesProduction rate

A method for increasing the fluid productivity of a hydraulically fractured well and reducing the production of particulate proppant plugging during production of fluids from a hydraulic fracture in a subterranean formation penetrated from an earth surface by a well by the use of smart memory particles and dissolvable proppant particles in the fracturing fluid.

Owner:BP CORP NORTH AMERICA INC

Method and apparatus for smart memory pass-through communication

ActiveUS7334077B2Add featureData processing applicationsInput/output to record carriersSmart memoryData sequences

Enhanced functionality is provided in memory devices by enhancing the control logic to recognize predetermined data sequences. Standard (legacy) device operations are used to communicate the predetermined data sequences, thereby allowing existing device drivers to be used with the enhanced devices.

Owner:RENESAS ELECTRONICS AMERICA

Smart memory based synchronization controller for a multi-threaded multiprocessor SoC

A memory interface for use with a multiprocess memory system having a gating memory, the gating memory associating one or more memory access methods with each of a plurality of memory locations of the memory system wherein the gating memory returns a particular one access method for a particular one memory location responsive to a memory access instruction relating to the particular one memory location, the interface including: a request storage for storing a plurality of concurrent memory access instructions for one or more of the particular memory locations, each the memory access instruction issued from an associated independent thread context; an arbiter, coupled to the request storage, for selecting a particular one of the memory access instructions to apply to the gating memory; and a controller, coupled to the request storage and to the arbiter, for: storing the plurality of memory access instructions in the request storage; initiating application of the particular one memory access instruction selected by the arbiter to the gating memory; receiving the particular one access method associated with the particular one memory access method from the gating memory; and initiating a communication of the particular access method to the thread context associated with the particular one access instruction.

Owner:MIPS TECH INC

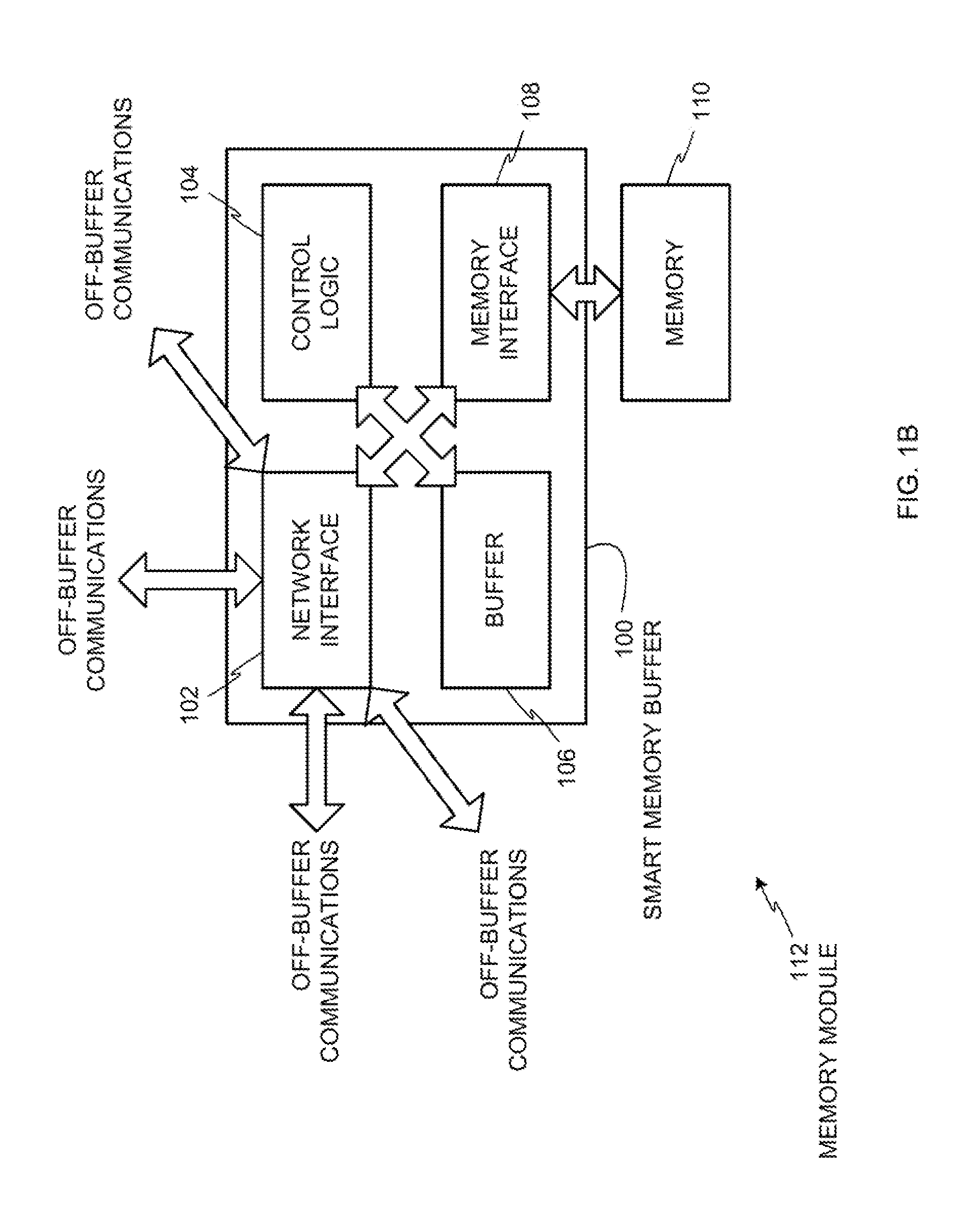

Smart memory buffers

ActiveUS20150193158A1Input/output to record carriersError detection/correctionSmart memoryData storing

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

Algorithm mapping, specialized instructions and architecture features for smart memory computing

InactiveUS20050246698A1Improve performanceLow costMultiplex system selection arrangementsDigital computer detailsMassively parallelSmart memory

A smart memory computing system that uses smart memory for massive data storage as well as for massive parallel execution is disclosed. The data stored in the smart memory can be accessed just like the conventional main memory, but the smart memory also has many execution units to process data in situ. The smart memory computing system offers improved performance and reduced costs for those programs having massive data-level parallelism. This smart memory computing system is able to take advantage of data-level parallelism to improve execution speed by, for example, use of inventive aspects such as algorithm mapping, compiler techniques, architecture features, and specialized instruction sets.

Owner:STRIPE INC

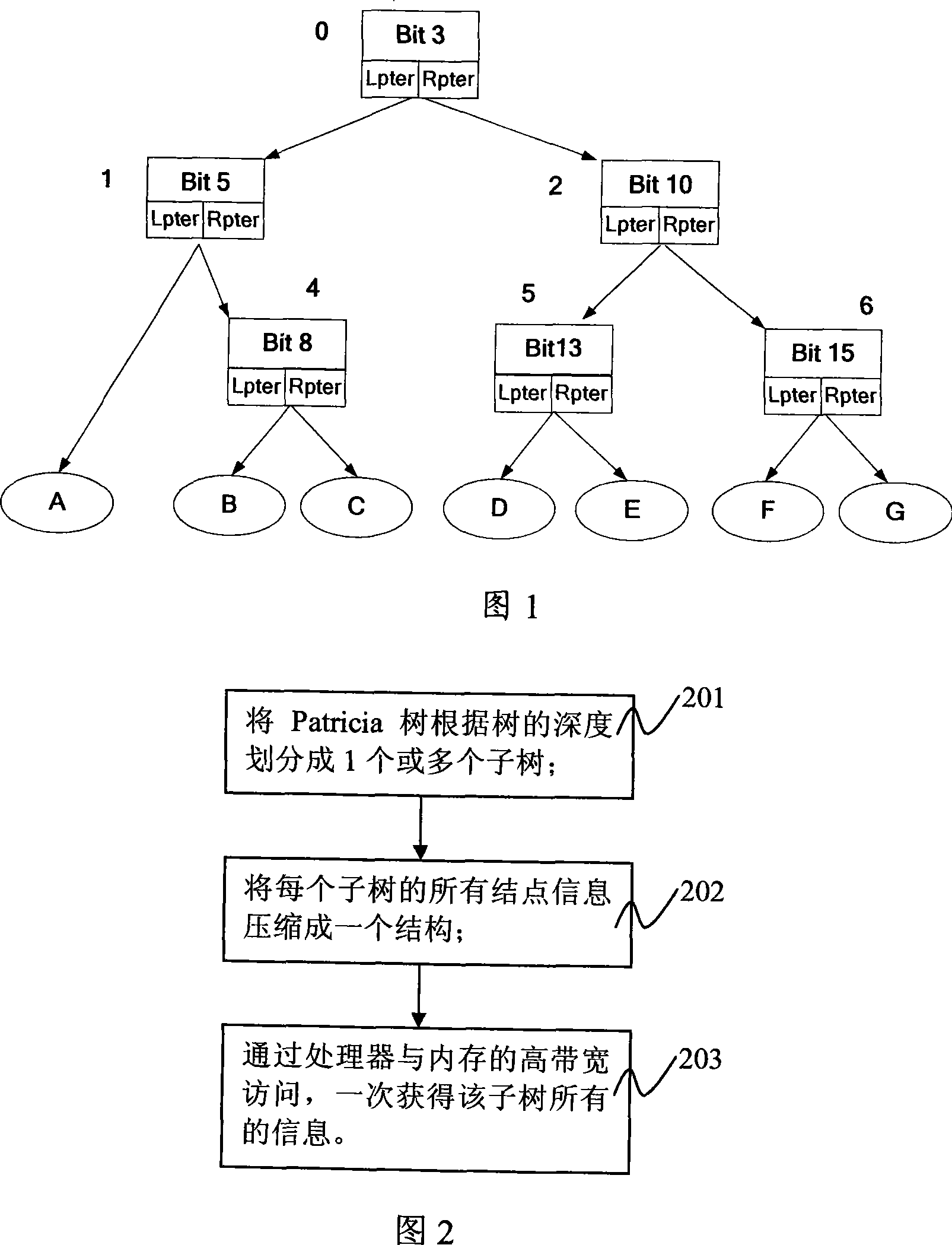

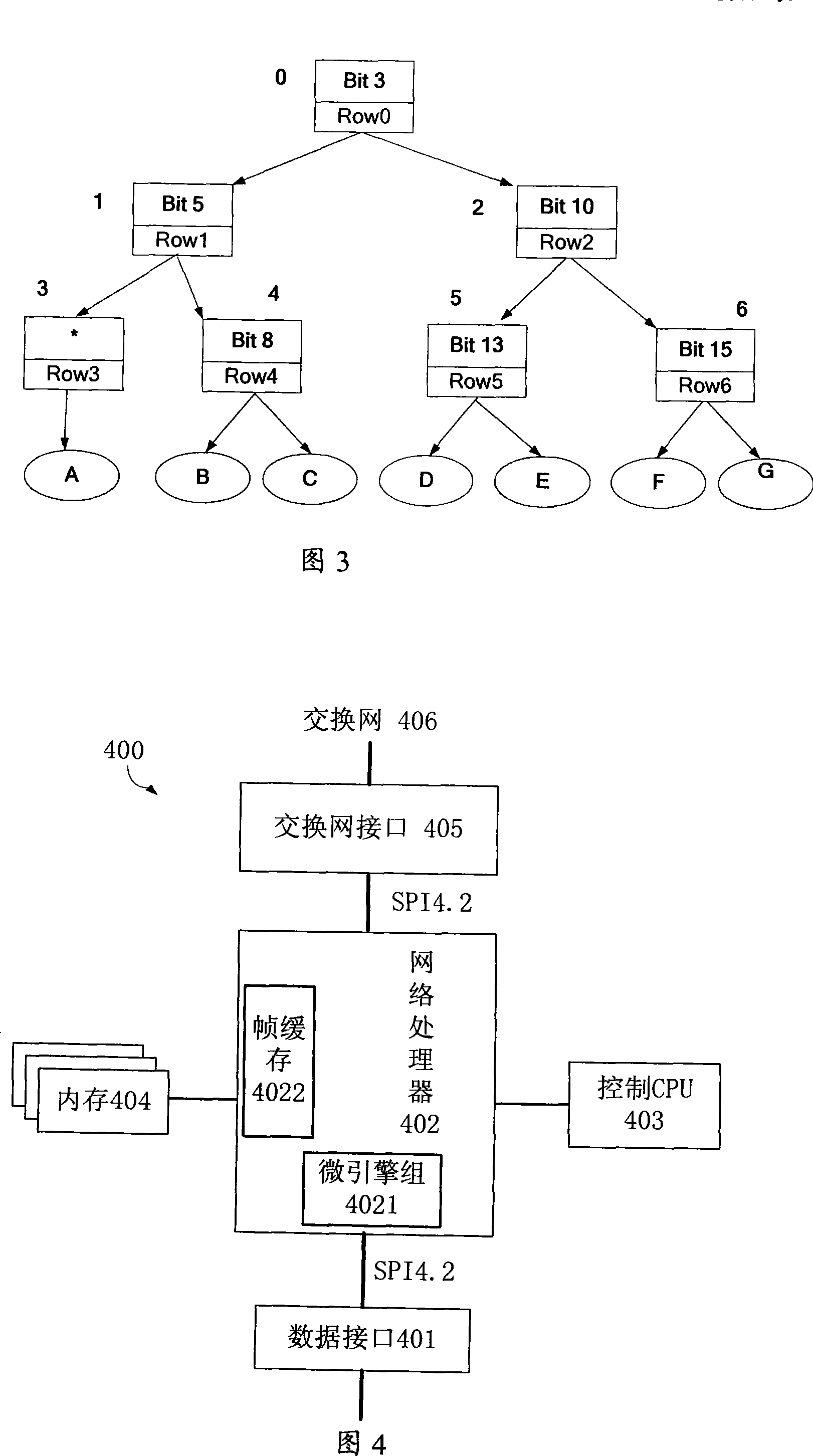

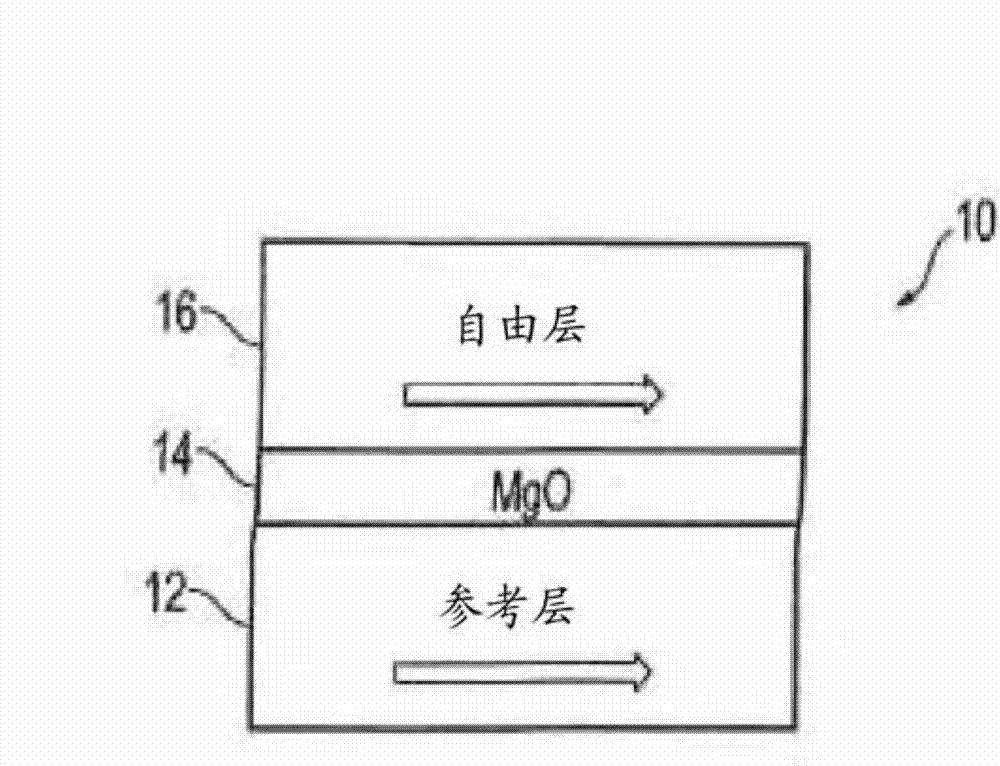

Patricia tree rapid lookup method

ActiveCN101241499AImprove effective useImprove search efficiencySpecial data processing applicationsHigh bandwidthDirect memory access

The present invention provides a method of Patricia tree rapid inquiry, including following steps: (a) dividing Patricia tree into one or more subtrees according to depth of tree; (b) compressing all node information of each subtree to a compressing tree structure; (c) accessing high bandwidth of the EMS memory via the processor, acquiring all information of a subtree by reading once memory, the method of Patricia tree rapid inquiry can reduce times of smart memory access of Patricia inquiry tree computing and improve finding efficiency.

Owner:ZTE CORP

Method and system for providing smart memory architecture

A smart memory system preferably includes a memory including one or more memory chips, and a processor including one or more memory processor chips. The processor includes a common address / data / control memory bus that is configured to provide an asynchronous handshaking interface between the memory array and the memory processor. The processor can offload error data from the memory chip for analysis, and can store poor retention bit address information for memory refreshing in a non-bolatile error retention memory. Porgram logic can also be included for memory address re-configuration. Power management logic can also be included, which can have a process-voltage-temperature compensation voltage generator for providing stable and constant read currents. An asynchronous handshaking interface is provided between the memory array and the memory processor. Write error tagging and write verification circuits can also be included.

Owner:SAMSUNG ELECTRONICS CO LTD

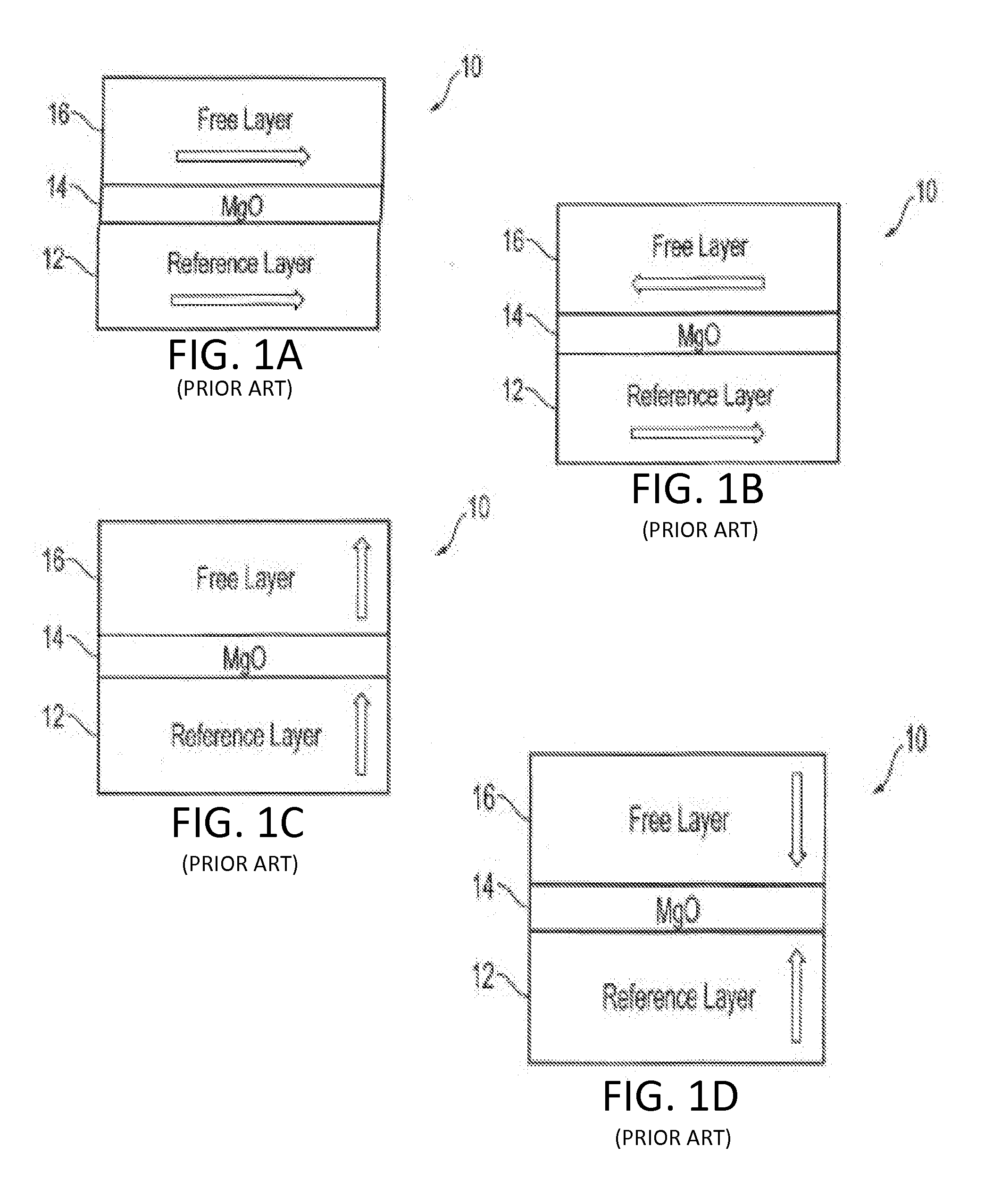

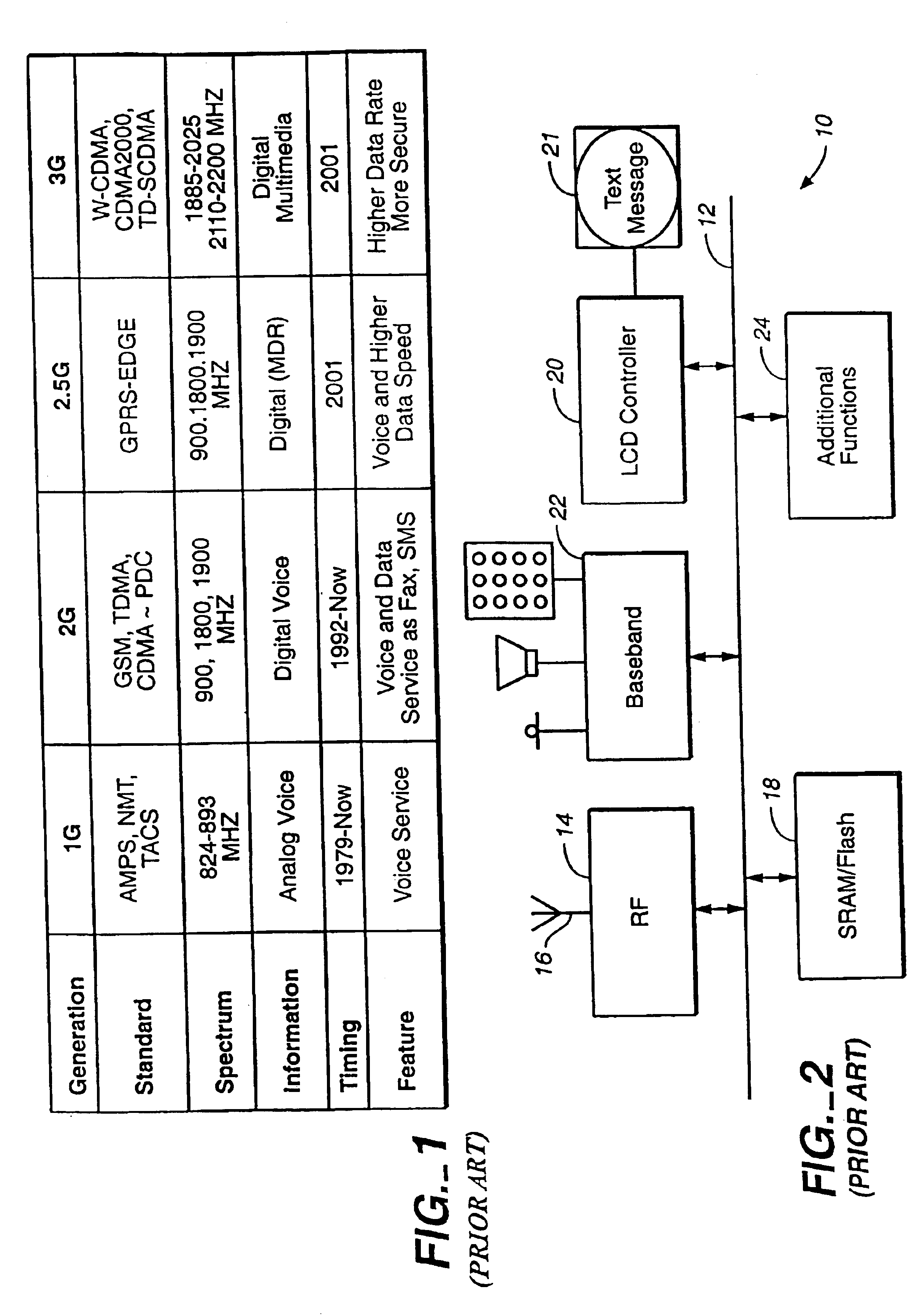

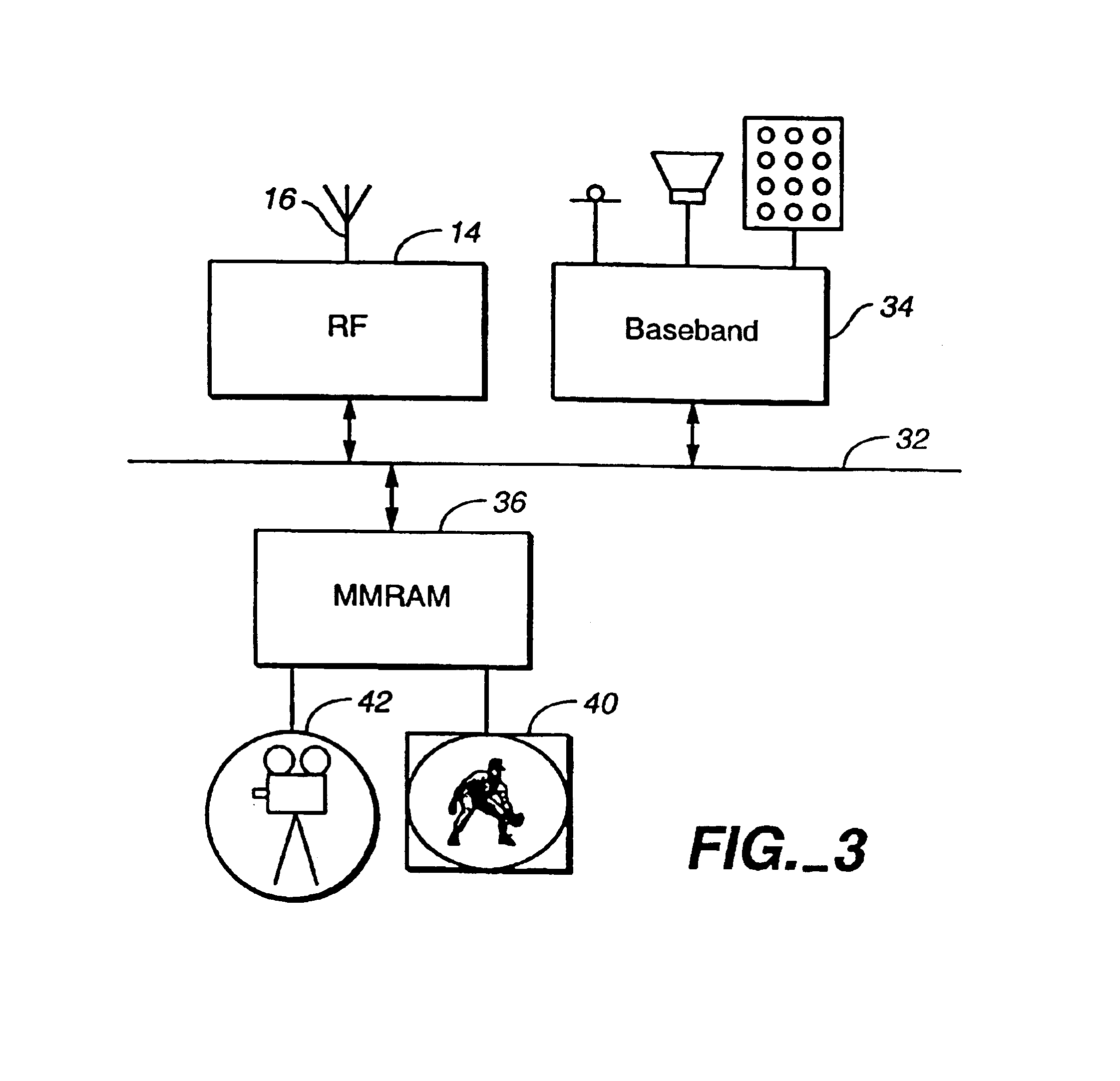

Smart memory

InactiveUS6920528B1Increase power consumptionFunction increaseDigital storageRecord carriers used with machinesClock rateSmart memory

A smart memory includes a memory array and one or more memory-intensive additional functions, all packaged in a standard memory package that has substantially the same fit and form as a standard integrated-circuit memory. One type of smart memory chip is a multi-media RAM (MMRAM) chip that provides on a single integrated-circuit chip a memory array and a compressor / decompressor (CODEC) section where connections between the memory array section and the CODEC section are on the single integrated-circuit die. The smart memory eliminates the need for additional special function integrated-circuit packages and significantly reduces the clock rate and the power consumption of a baseband chip in a personal communication device.

Owner:NANOAMP SOLUTIONS

Method and system for providing a smart memory architecture

ActiveUS9069719B2High rateHigh error rateInput/output to record carriersDigital computer detailsMemory addressSmart memory

A smart memory system preferably includes a memory including one or more memory chips, and a processor including one or more memory processor chips. The processor may include a common address / data / control memory bus that is configured to provide an asynchronous handshaking interface between the memory array and the memory processor. The processor can offload error data from the memory chip for analysis, and can store poor retention bit address information for memory refreshing in a non-volatile error retention memory. Program logic can also be included for memory address re-configuration. Power management logic can also be included, which may have a process-voltage-temperature compensation voltage generator for providing stable and constant read currents. An asynchronous handshaking interface is provided between the memory array and the memory processor. Write error tagging and write verification circuits can also be included.

Owner:SAMSUNG ELECTRONICS CO LTD

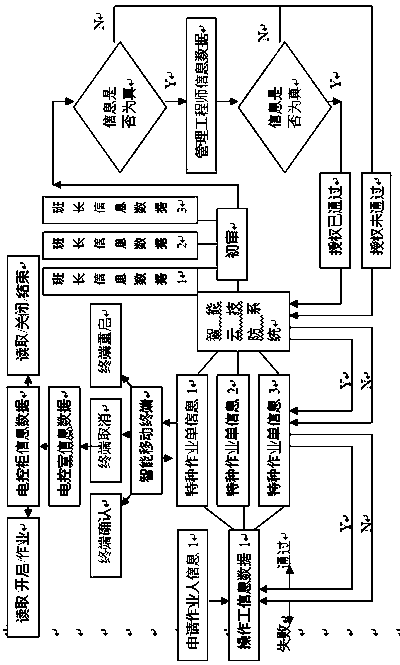

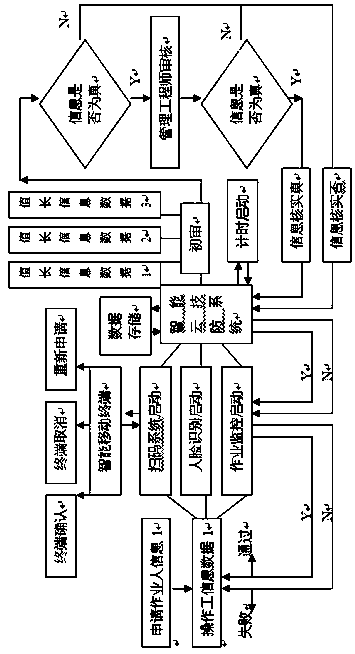

Two-dimensional code identity recognition based intelligent technical protection and control method for electric control room

InactiveCN107622546AEnsure safetyGuaranteed operational safetyIndividual entry/exit registersResourcesCloud systemsIdentity recognition

The invention discloses a two-dimensional code identity recognition based intelligent technical protection and control method for an electric control room. Identity information is pre-acquired throughan intelligent technical protection cloud system, identity information and human face information of personnel possibly accessing to the electric control room, information of the electric control room and information of electric control cabinets are pre-acquired, electric control special operation sheet applying, examining, checking and operation authorizing are preset, identity recognition and operation authorization are performed on personnel accessing to the electric control room through two-dimensional code scanning to confirm electric control room accessing operation purposes, to-be-operated electric control cabinets, routing inspection, troubleshooting and control selection are assigned, access time of operating personnel and operating records are intelligently memorized and remotely transmitted to the intelligent technical protection cloud system in case of transmission and query, an electric control room management system can be perfected, control is facilitated, and safety and stability are remarkably improved. The method can be widely applied to two-dimensional code identity recognition based intelligent technical protection and control of electric control rooms in significant electric control facilities at different industrial, agricultural and office places.

Owner:石河子天域新实化工有限公司 +1

Method and system for providing a smart memory architecture

ActiveUS20160284422A9High rateHigh error rateError detection/correctionDigital computer detailsMemory chipTest error rate

A smart memory system preferably includes a memory including one or more memory chips, and a processor including one or more memory processor chips. The system may include a smart memory controller capable of performing a bit error rate built-in self test. The smart memory control may include bit error rate controller logic configured to control the bit error rate built-in self test. A write error rate test pattern generator may generate a write error test pattern for the bit error rate built-in self test. A read error rate test pattern generator may generate a read error test pattern for the built-in self test. The smart memory controller may internally generate an error rate timing pattern, perform built-in self test, measure the resulting error rate, automatically adjust one or more test parameters based on the measured error rate, and repeat the built-in self test using the adjusted parameters.

Owner:SAMSUNG ELECTRONICS CO LTD

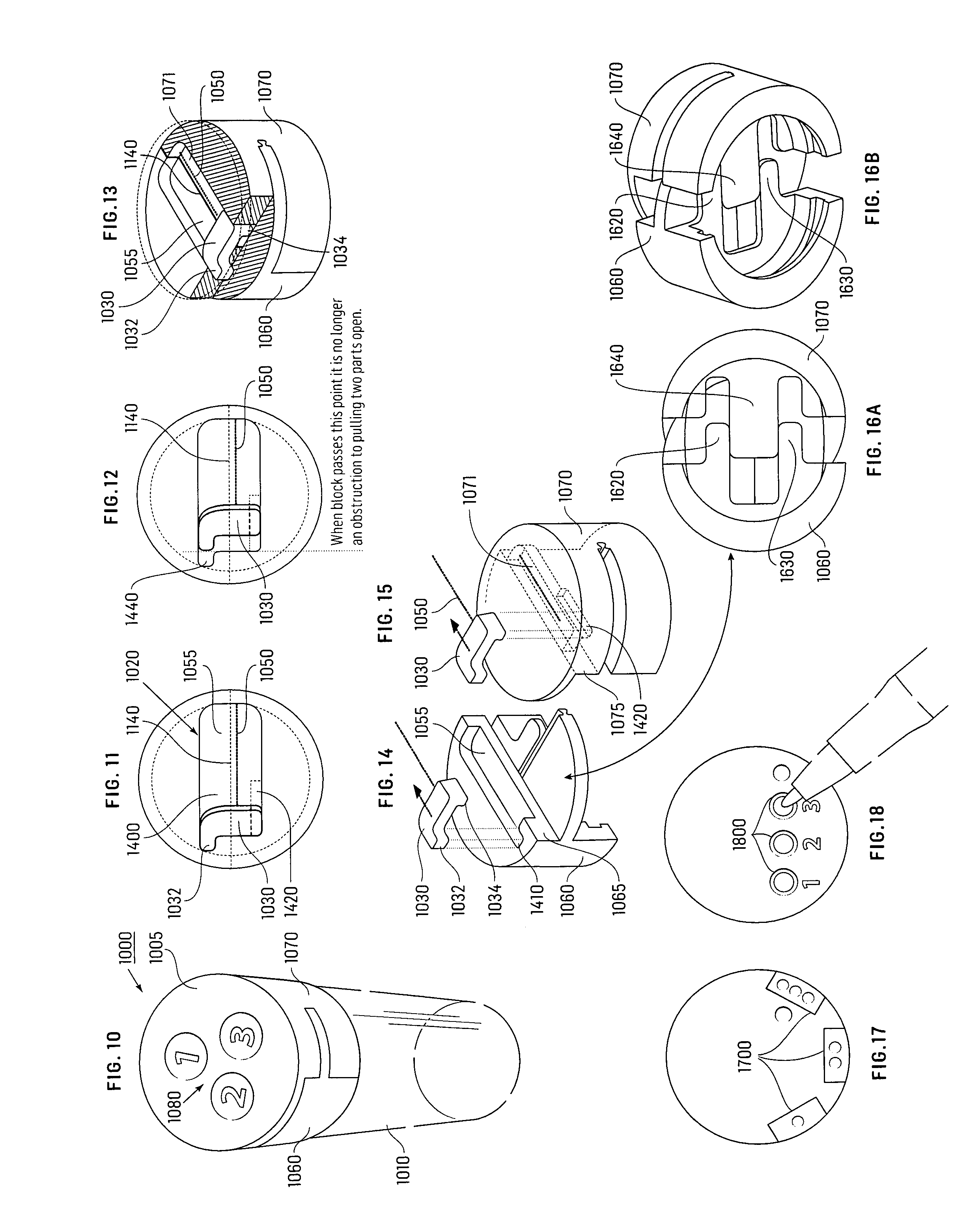

Smart memory material lock devices

ActiveUS9424722B2Avoid separationBurglar alarm by openingNon-mechanical controlsSmart memoryLocking mechanism

Owner:UNLIMITED LIABILITY