Patents

Literature

256 results about "Processor design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Processor design is the design engineering task of creating a processor, a key component of computer hardware. It is a subfield of computer engineering (design, development and implementation) and electronics engineering (fabrication). The design process involves choosing an instruction set and a certain execution paradigm (e.g. VLIW or RISC) and results in a microarchitecture, which might be described in e.g. VHDL or Verilog. For microprocessor design, this description is then manufactured employing some of the various semiconductor device fabrication processes, resulting in a die which is bonded onto a chip carrier. This chip carrier is then soldered onto, or inserted into a socket on, a printed circuit board (PCB).

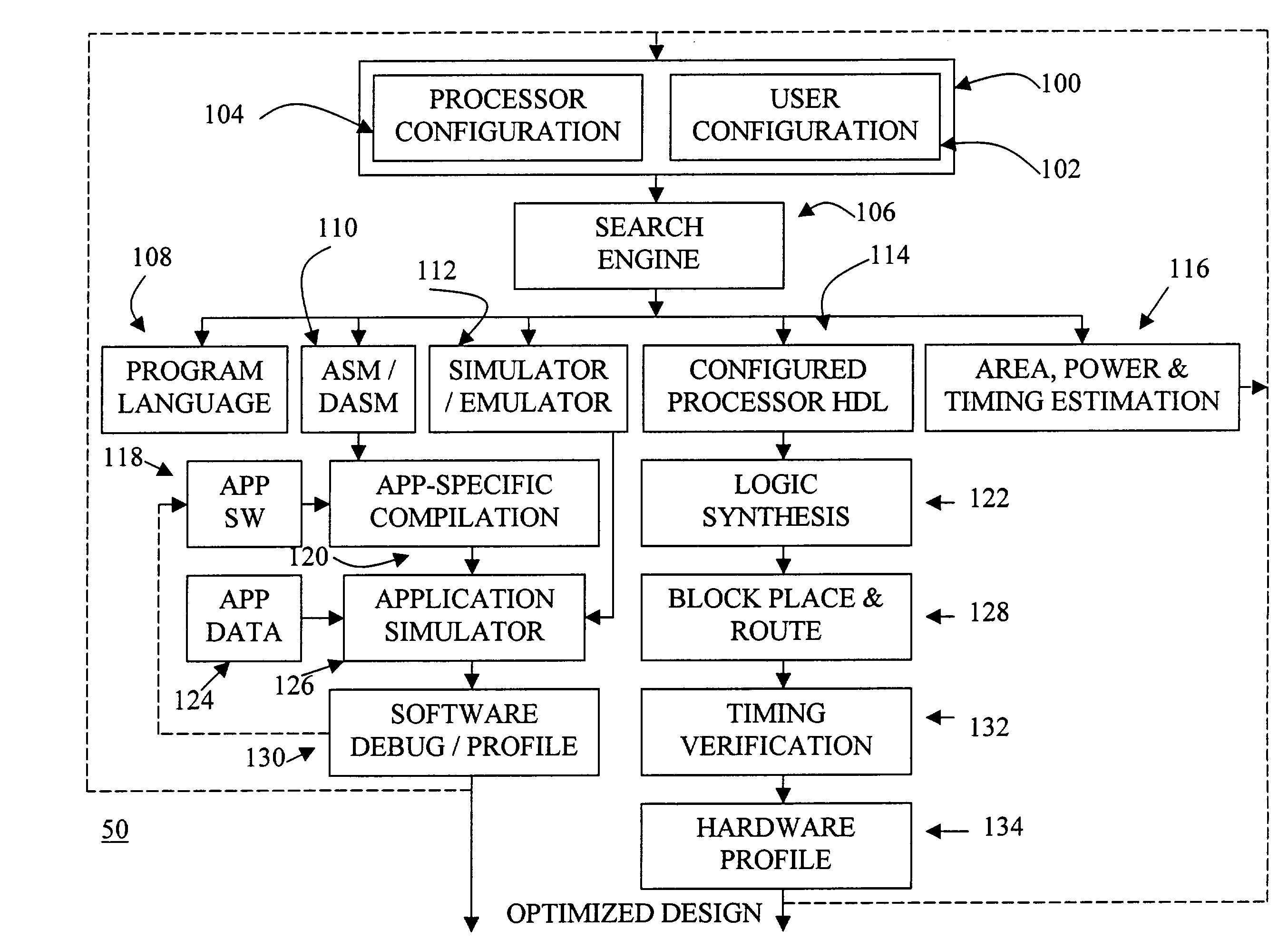

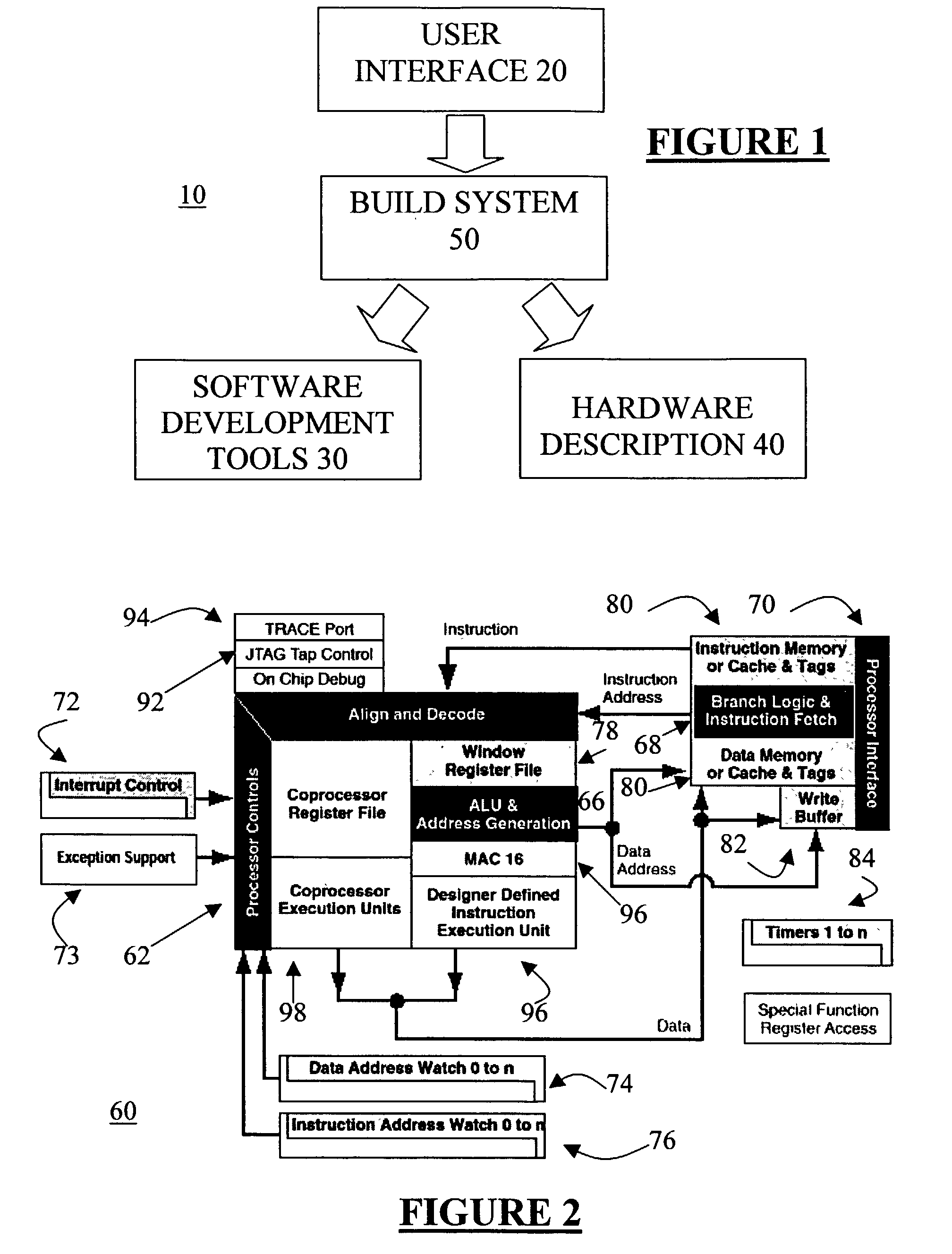

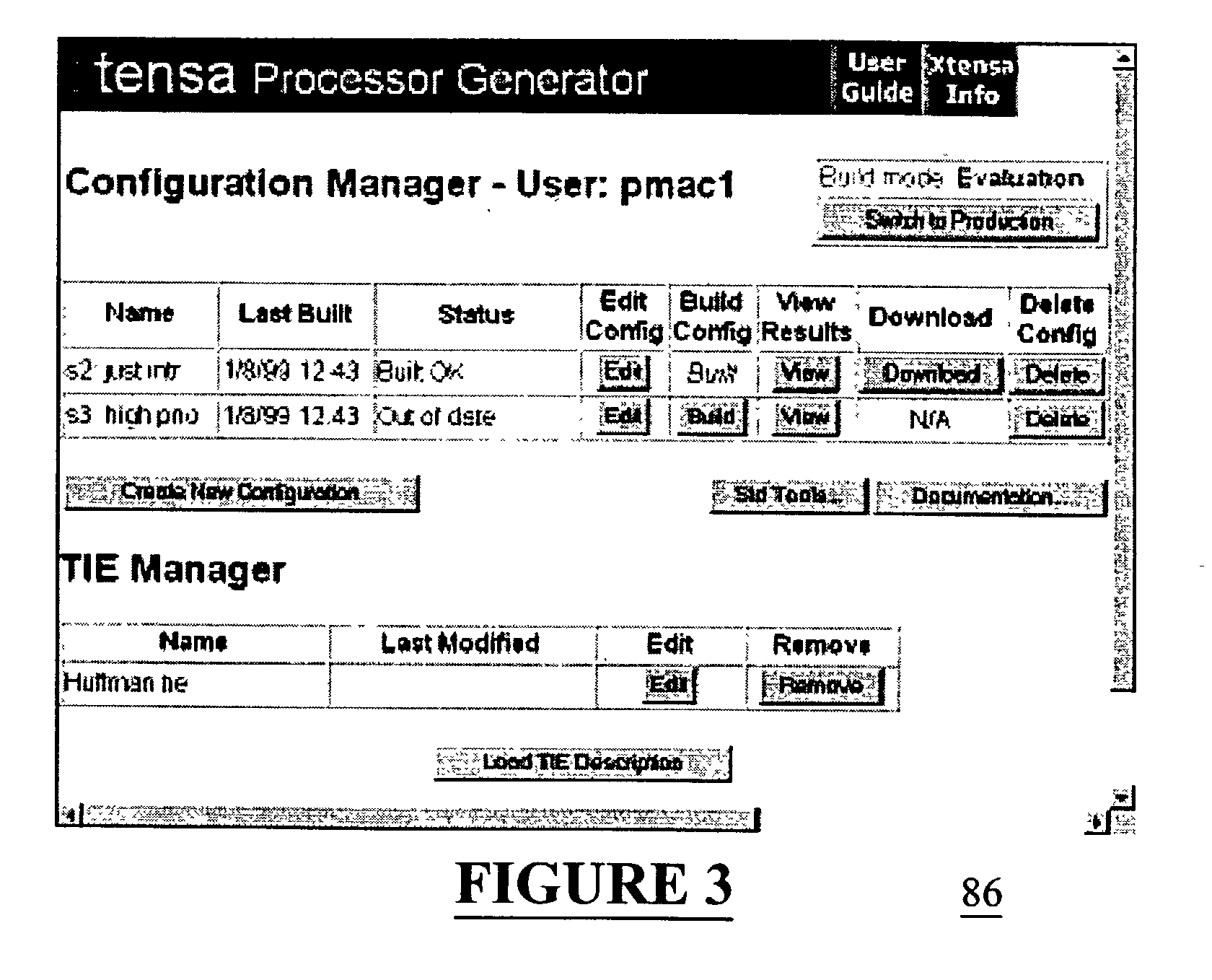

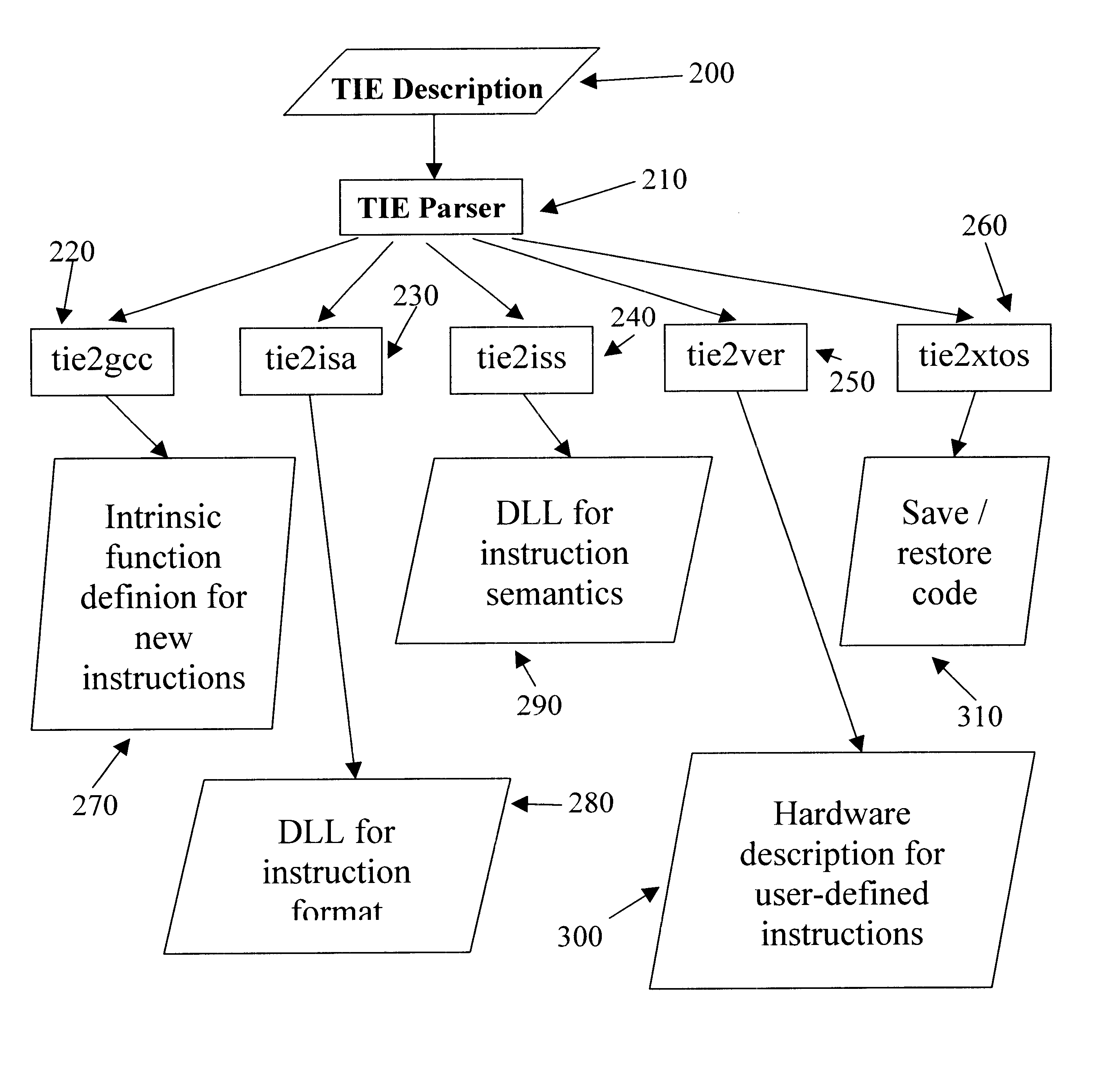

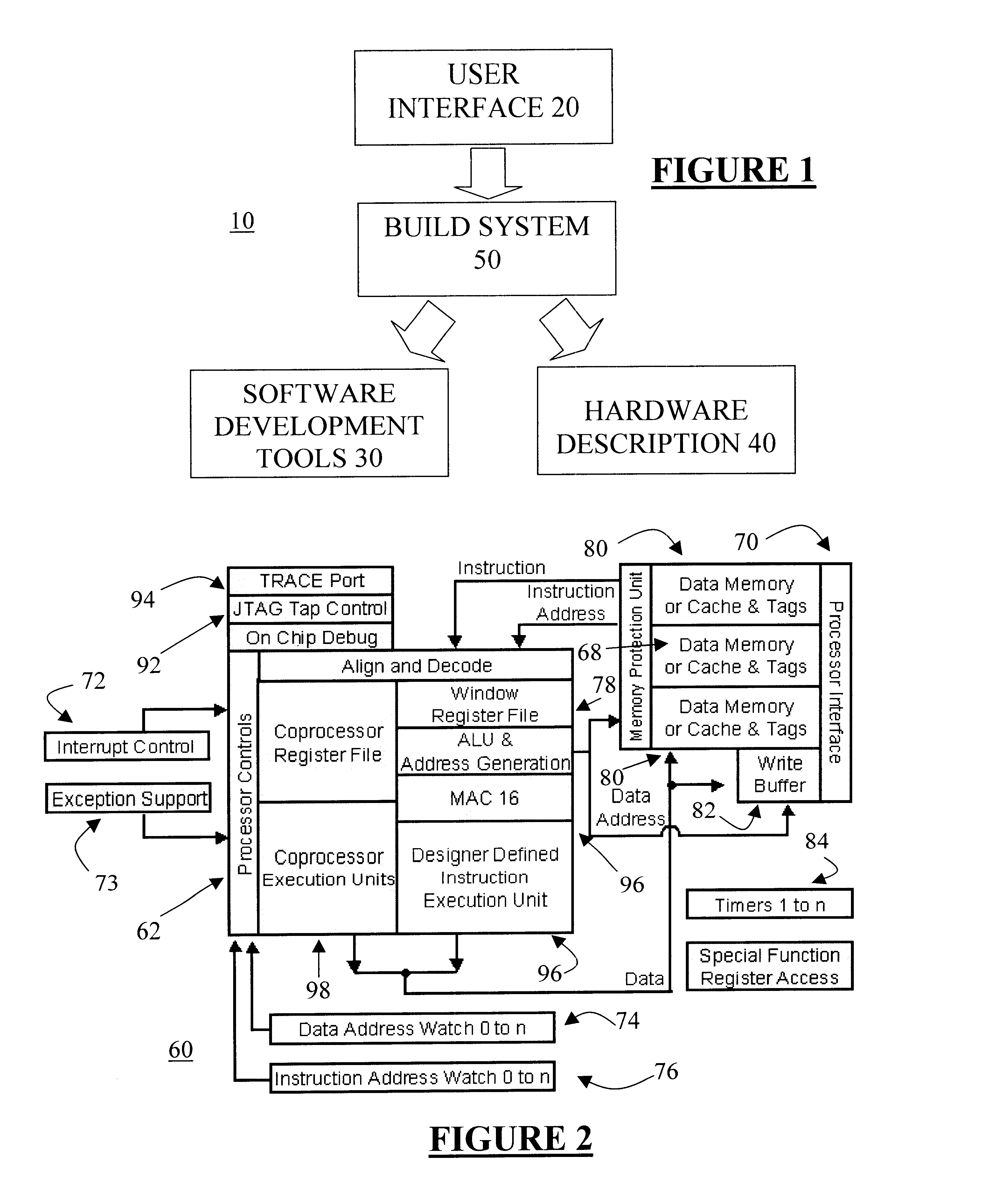

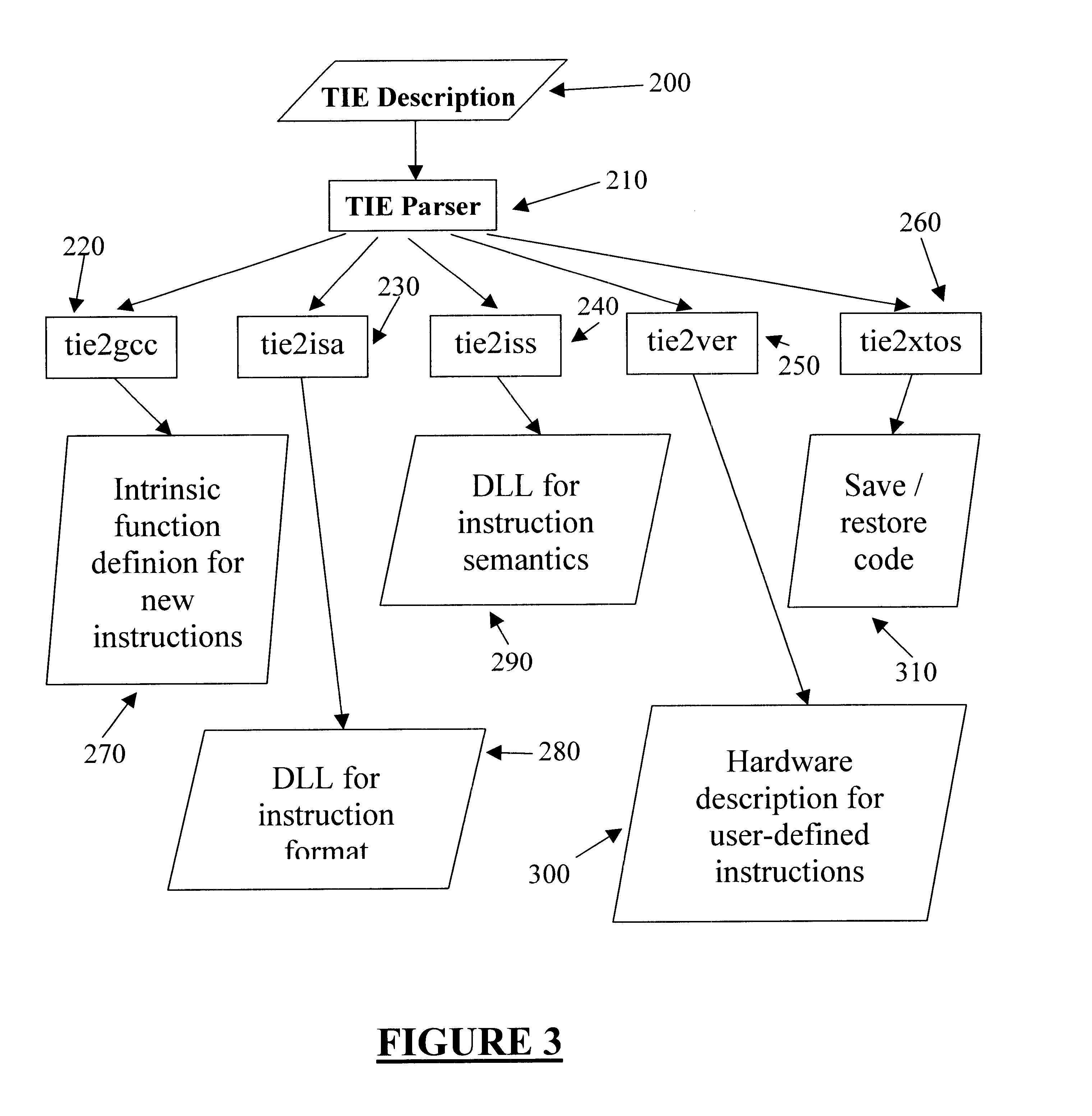

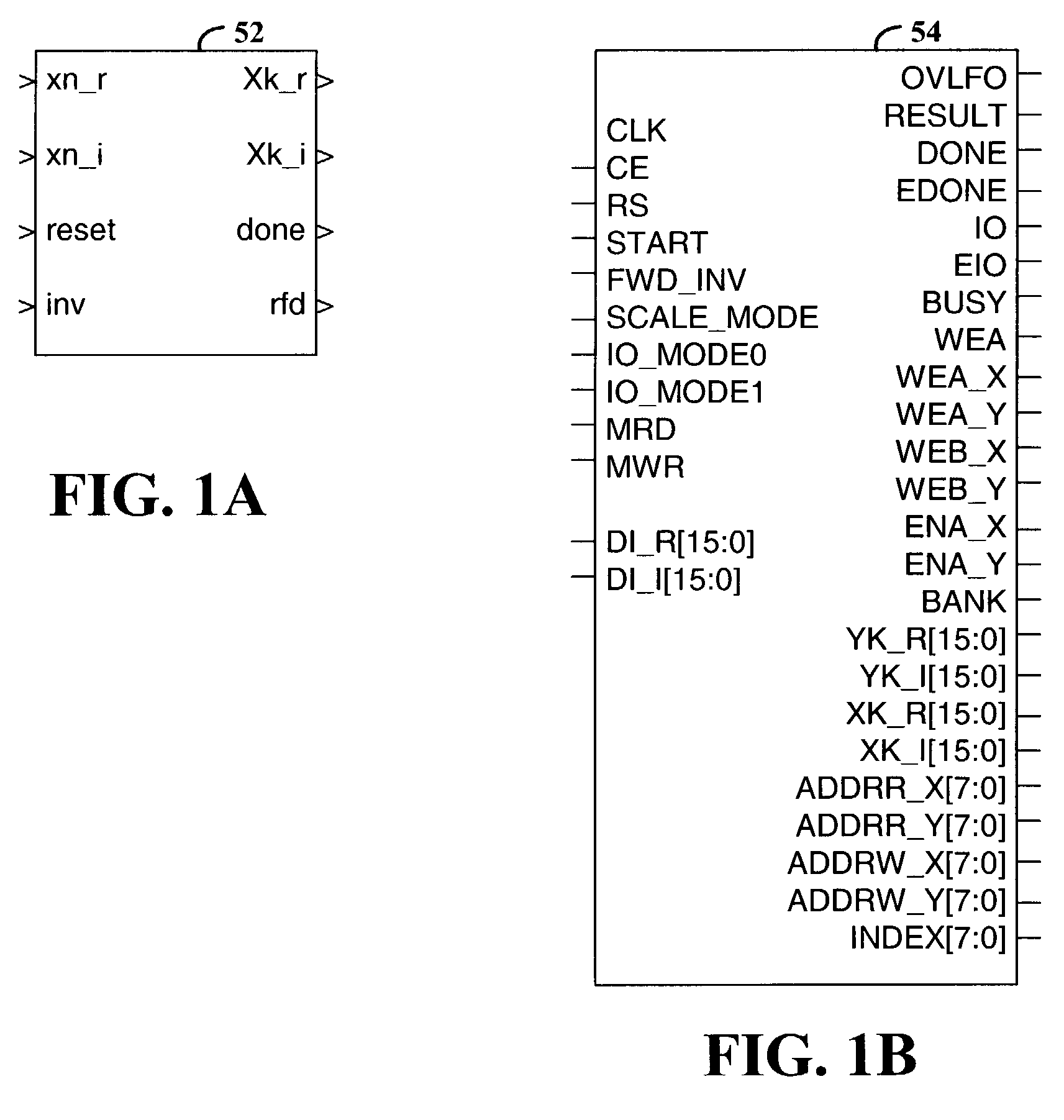

Automated processor generation system for designing a configurable processor and method for the same

InactiveUS6477683B1Decompilation/disassemblyCAD network environmentApplication softwareProcessor design

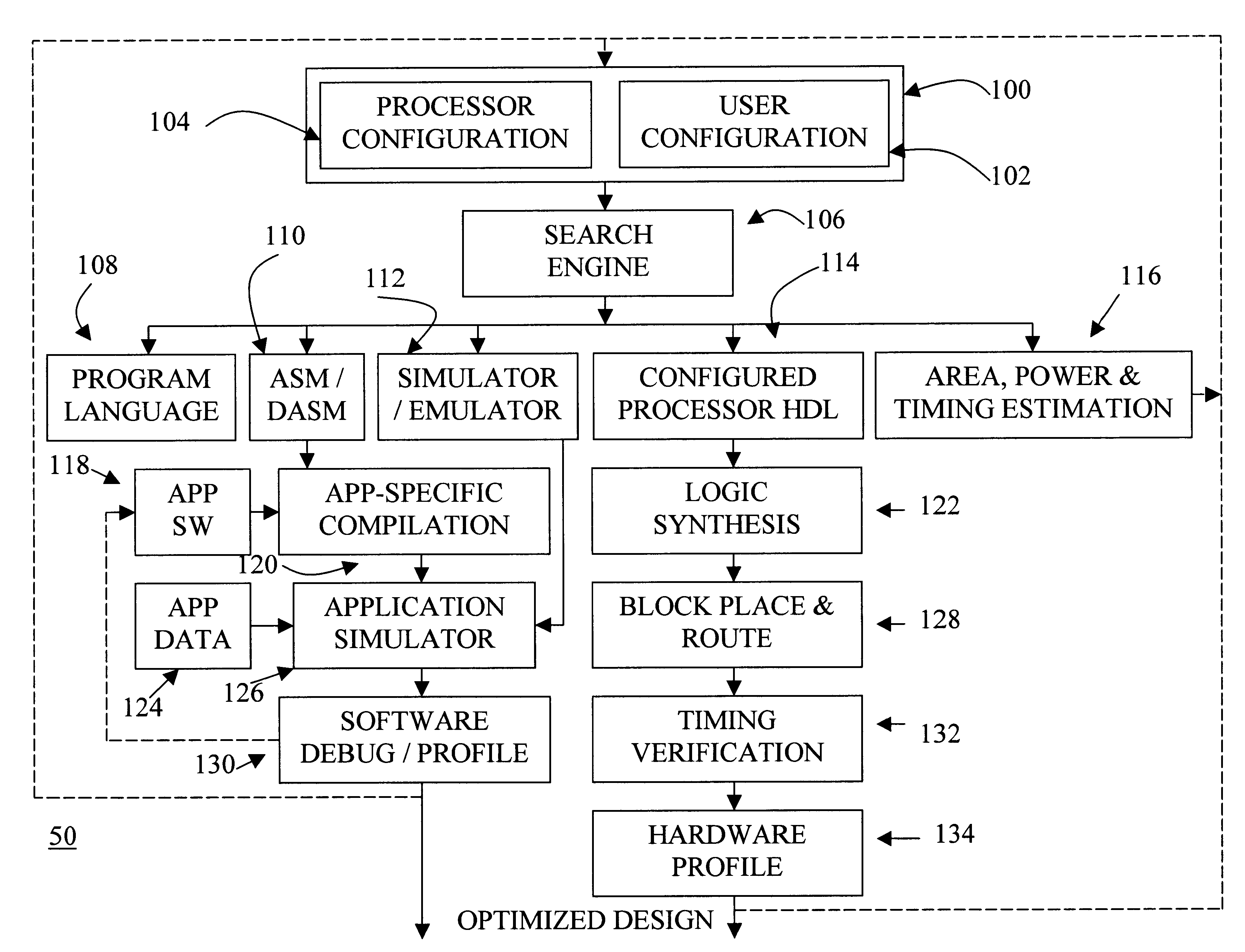

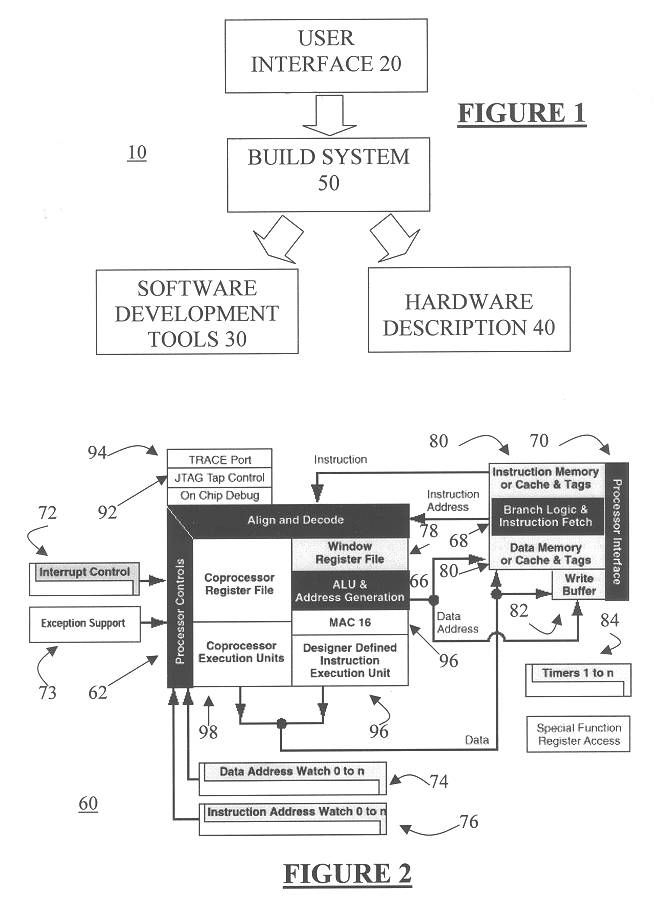

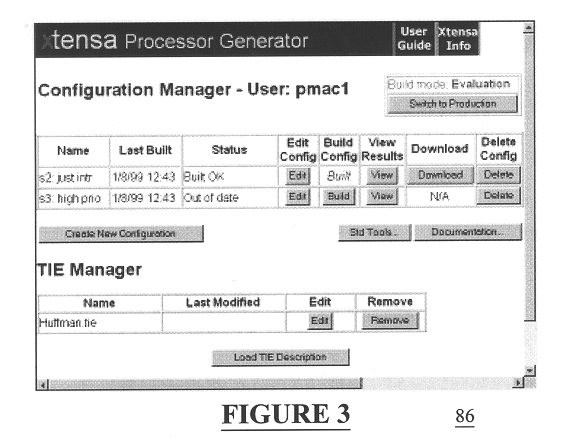

An automated processor design tool uses a description of customized processor instruction set extensions in a standardized language to develop a configurable definition of a target instruction set, a Hardware Description Language description of circuitry necessary to implement the instruction set, and development tools such as a compiler, assembler, debugger and simulator which can be used to develop applications for the processor and to verify it. Implementation of the processor circuitry can be optimized for various criteria such as area, power consumption, speed and the like. Once a processor configuration is developed, it can be tested and inputs to the system modified to iteratively optimize the processor implementation. By providing a constrained domain of extensions and optimizations, the process can be automated to a high degree, thereby facilitating fast and reliable development.

Owner:TENSILICA

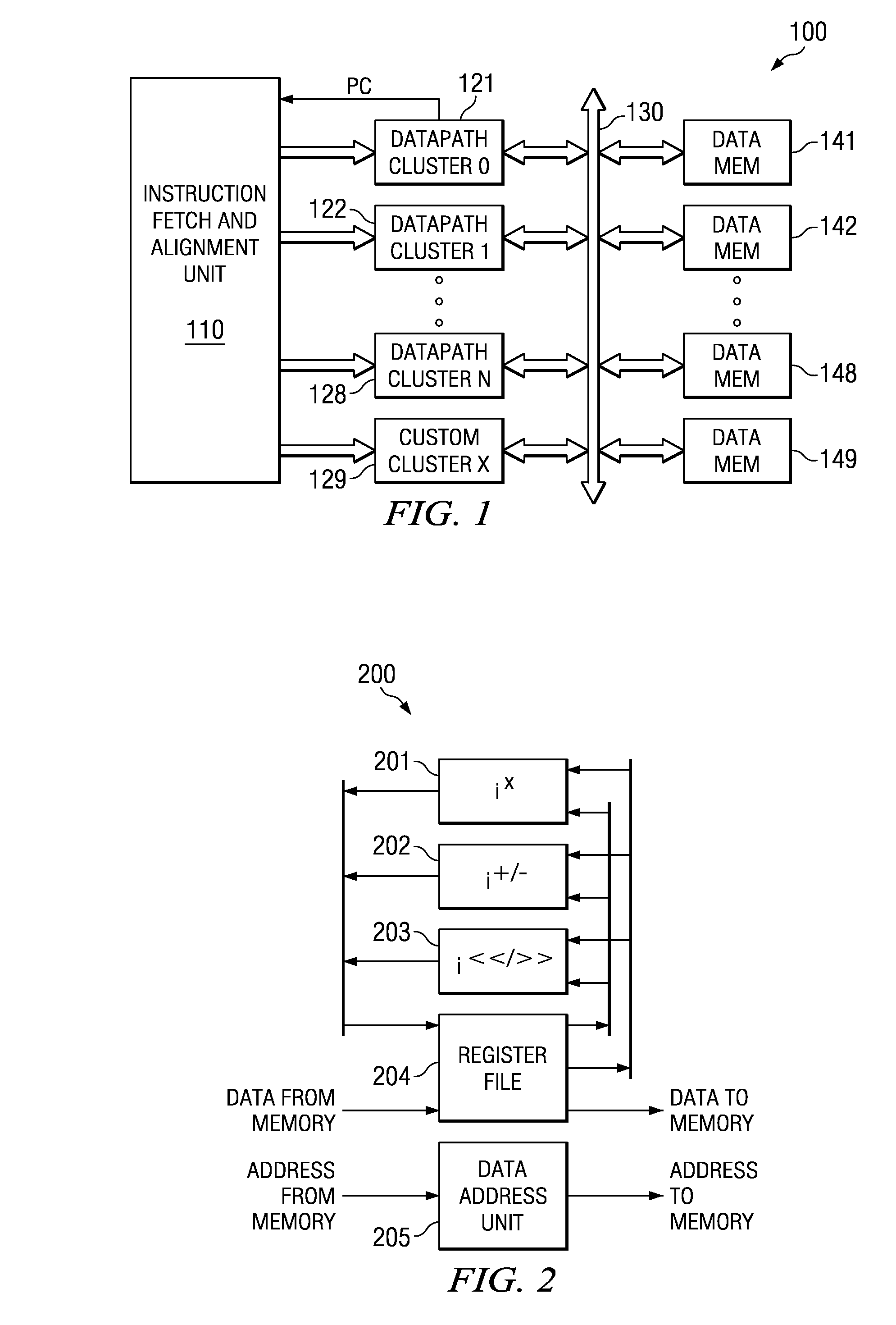

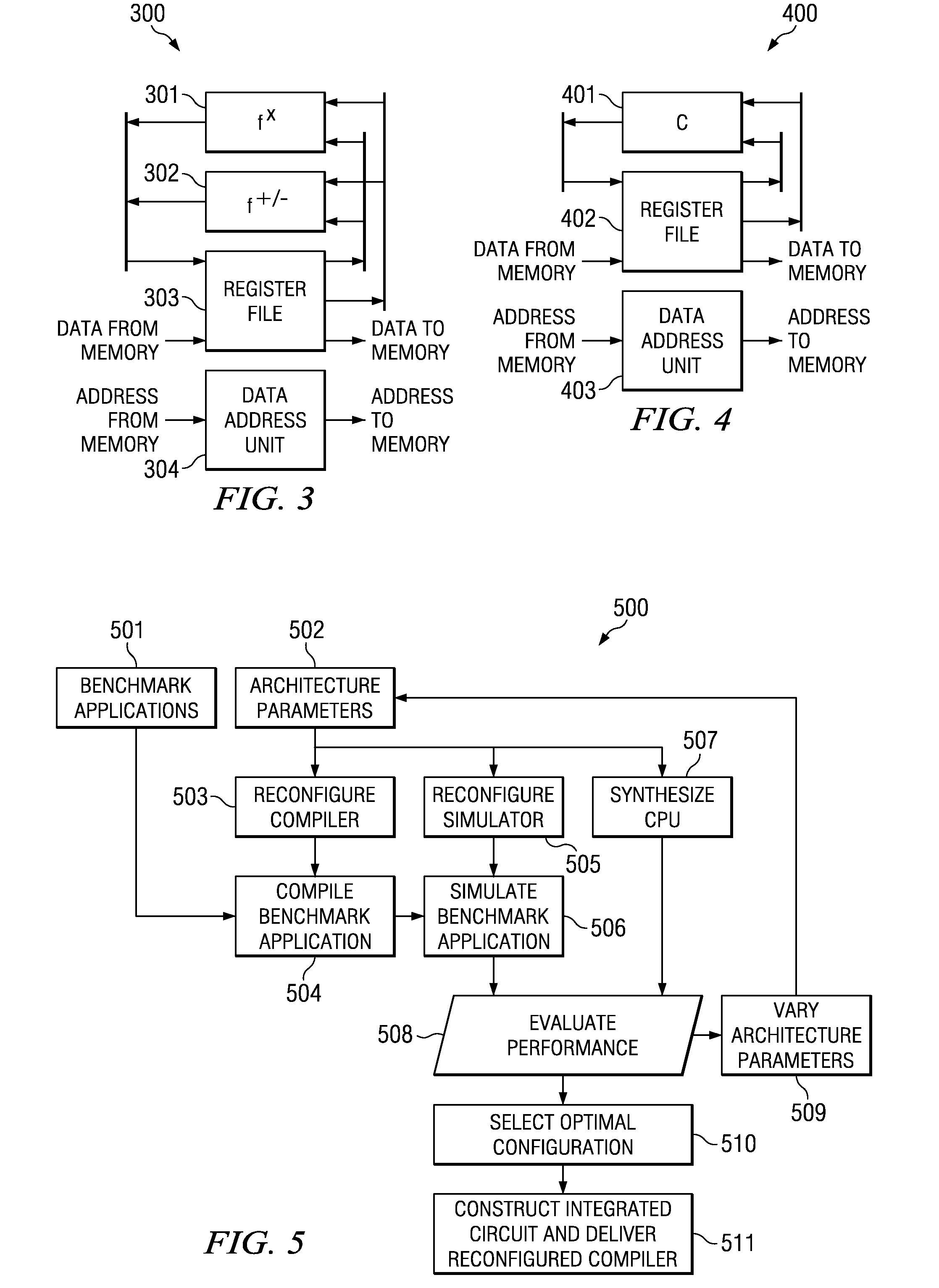

SIMD datapath coupled to scalar/vector/address/conditional data register file with selective subpath scalar processing mode

InactiveUS6839828B2Not compromise SIMD data processing performanceReduce consumptionRegister arrangementsDigital data processing detailsProcessor registerOperation mode

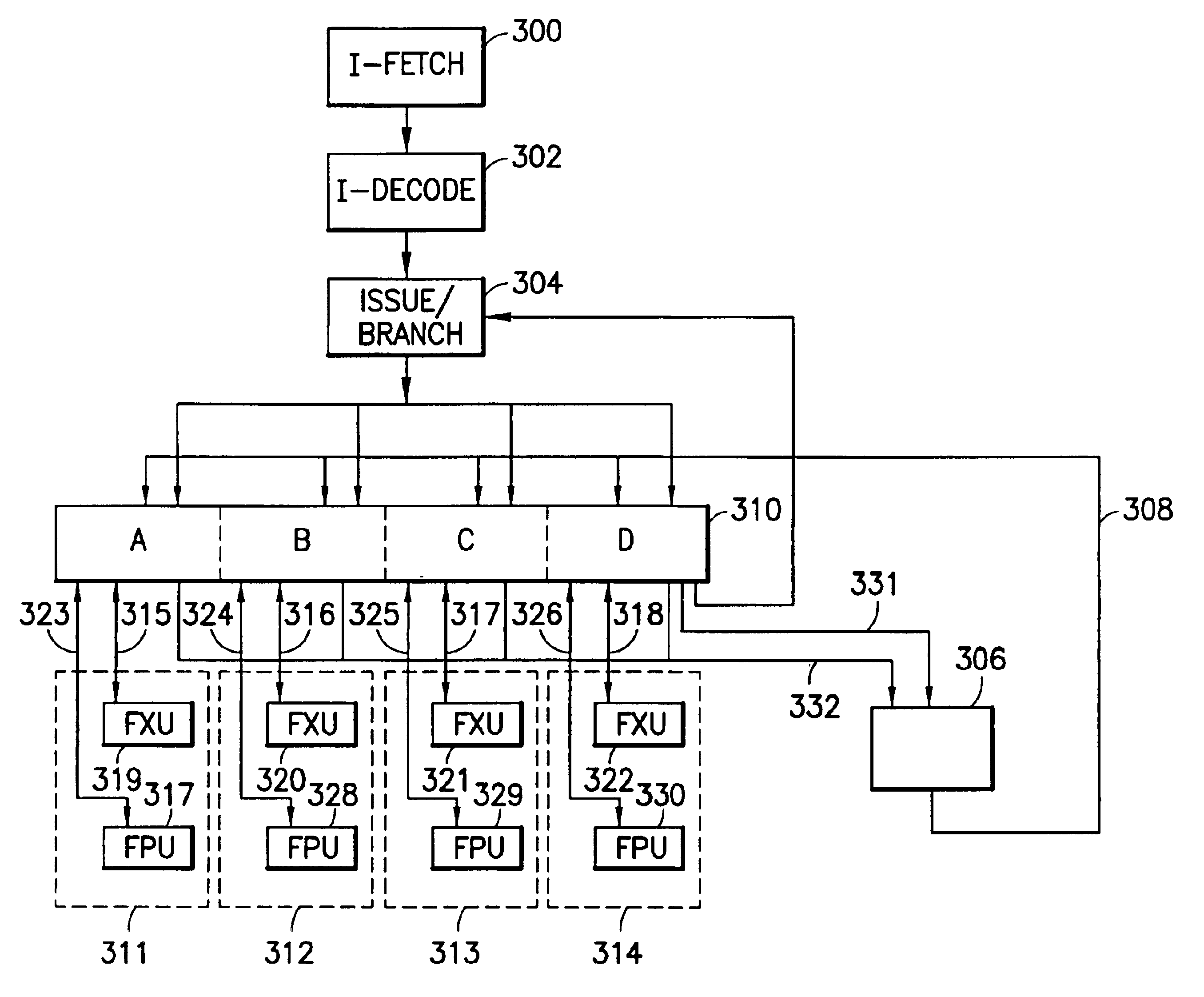

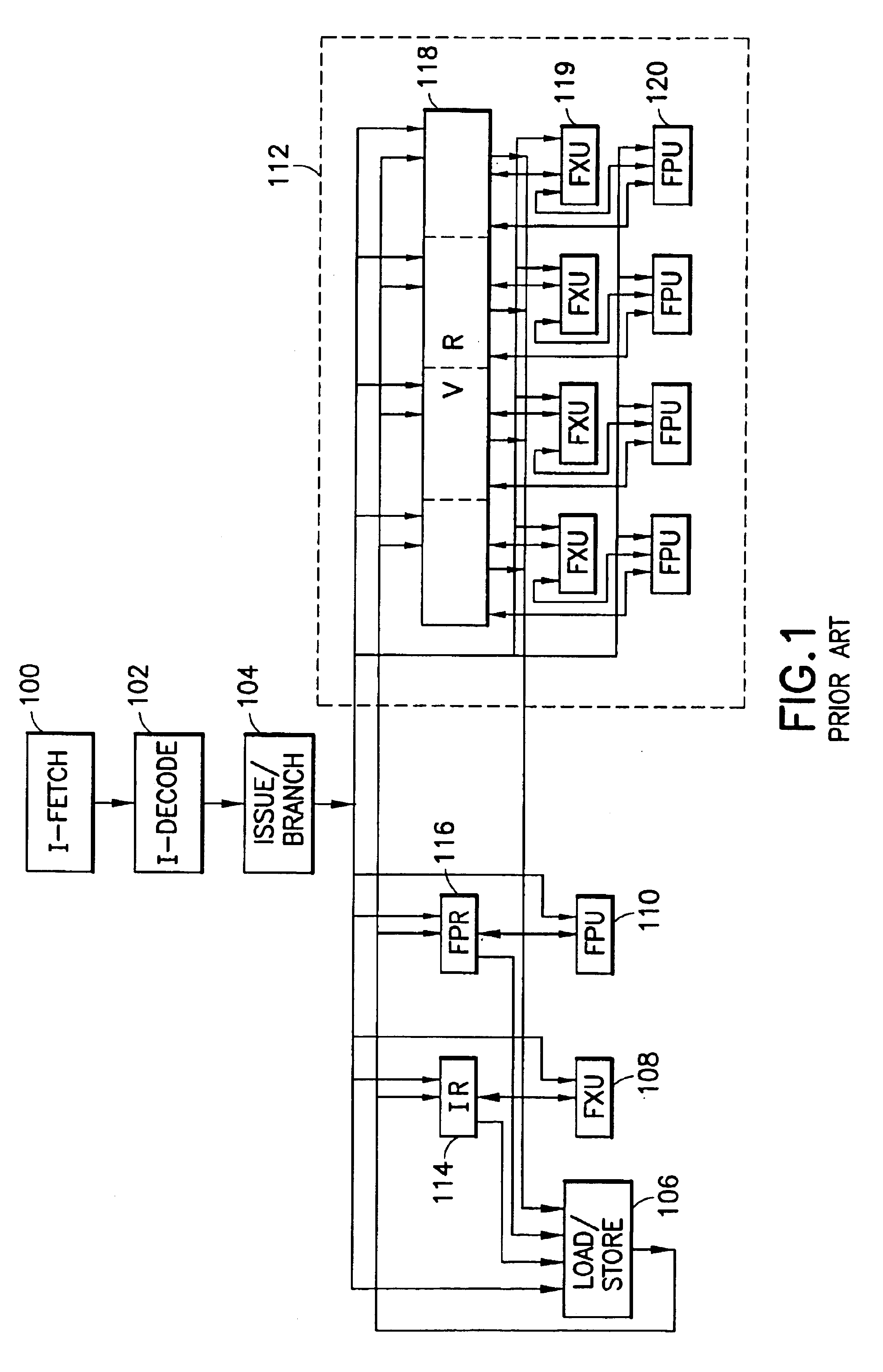

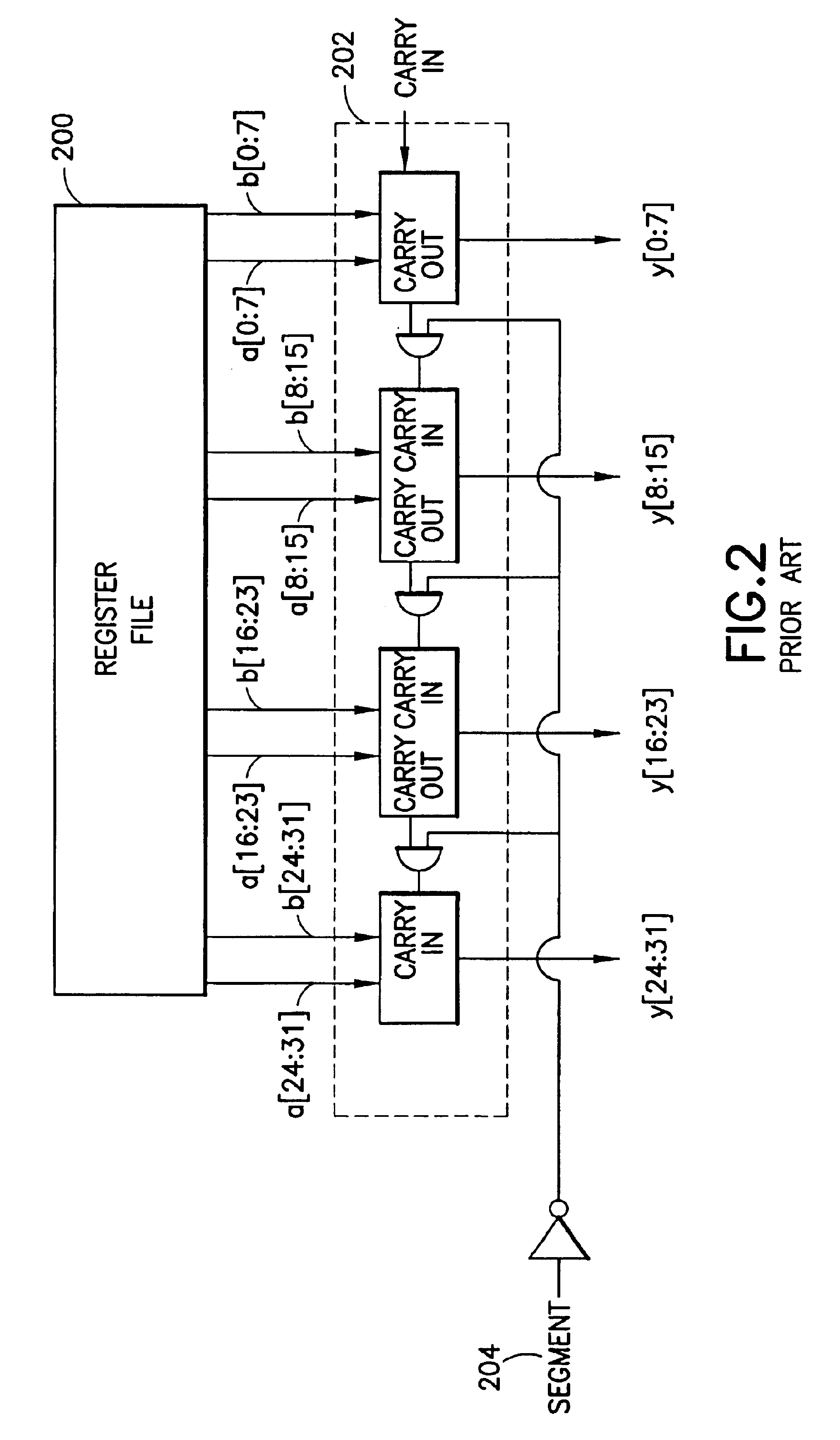

There is provided a processor designed to operate in a plurality of modes for processing vector and scalar instructions. Register files are each for storing scalar and vector data and address information. A parallel vector unit, coupled to the register files, includes functional units configurable to operate in a vector operation mode and a scalar operation mode. The vector unit includes an apparatus for tightly coupling the functional units to perform an operation specified by a current instruction. Under a vector operation mode, the vector unit performs, in parallel, a single vector operation on a plurality of data elements. The operations performed on the plurality of data elements are each performed by a different functional unit of the vector unit. Under a scalar operation mode, the vector unit performs a scalar operation on a data element received from the register files in a functional unit within the vector unit.

Owner:INTEL CORP

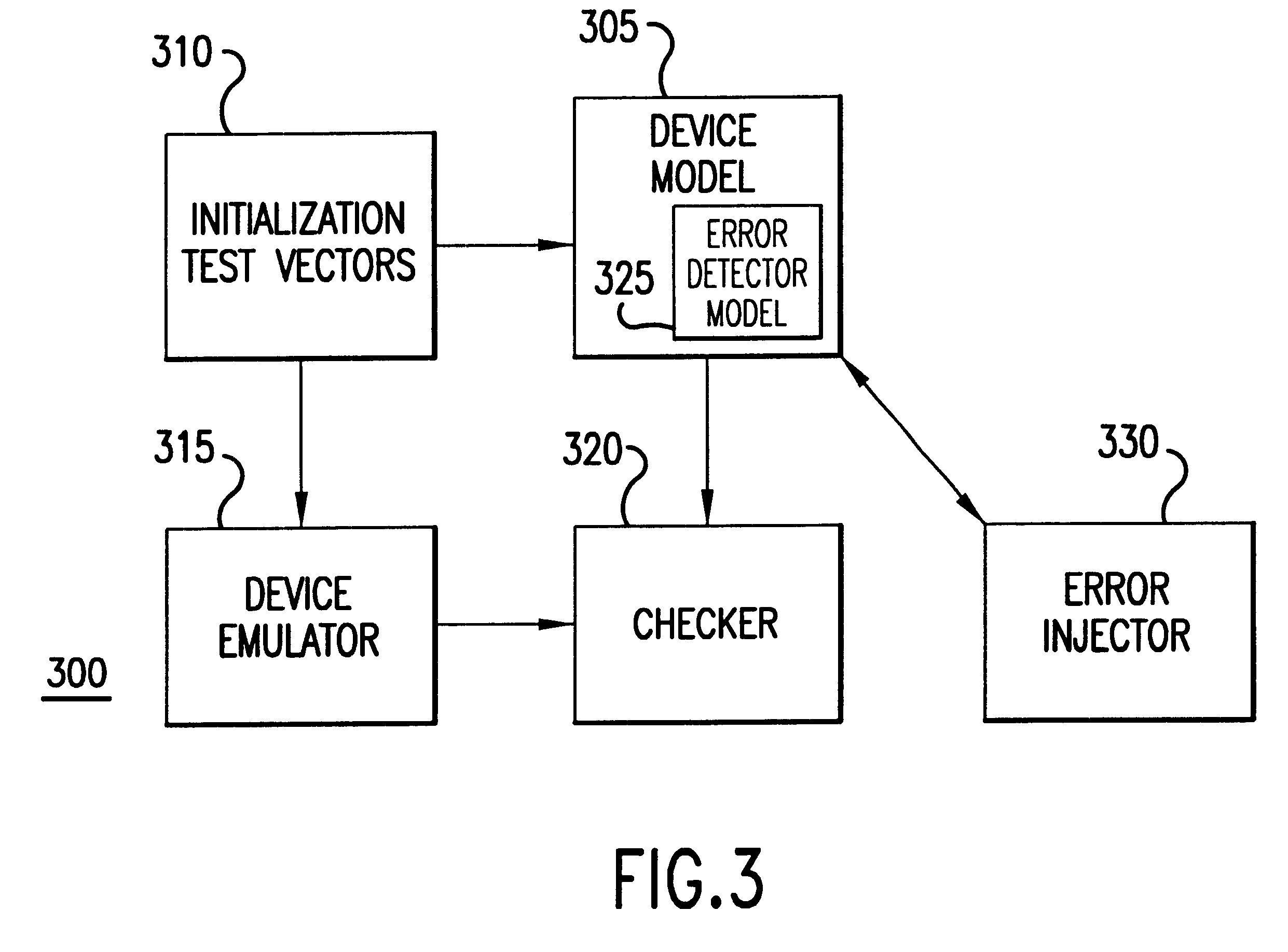

Method and apparatus for testing error detection

InactiveUS6539503B1Easy to testFocusElectronic circuit testingError detection/correctionComputer softwareProcessor design

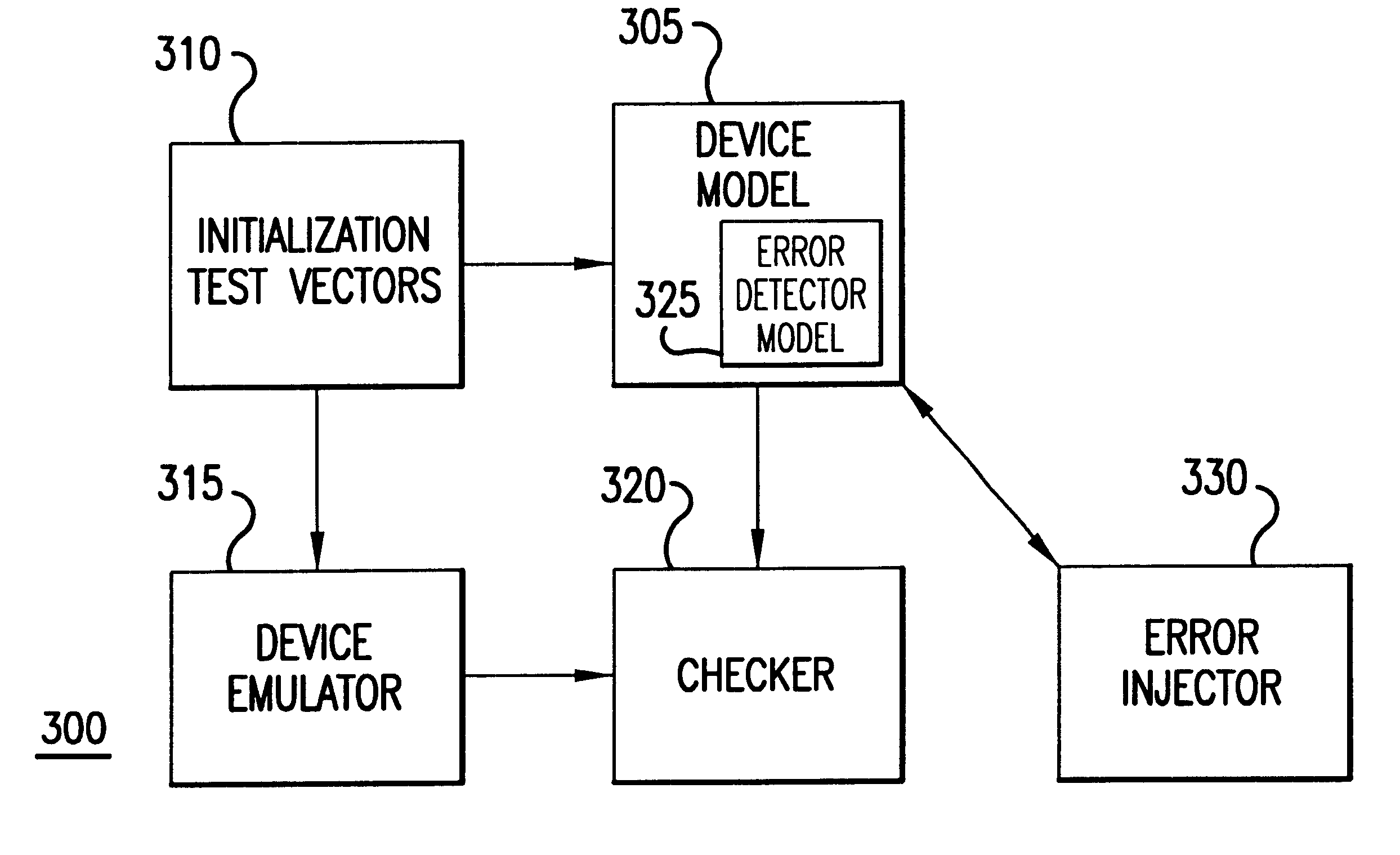

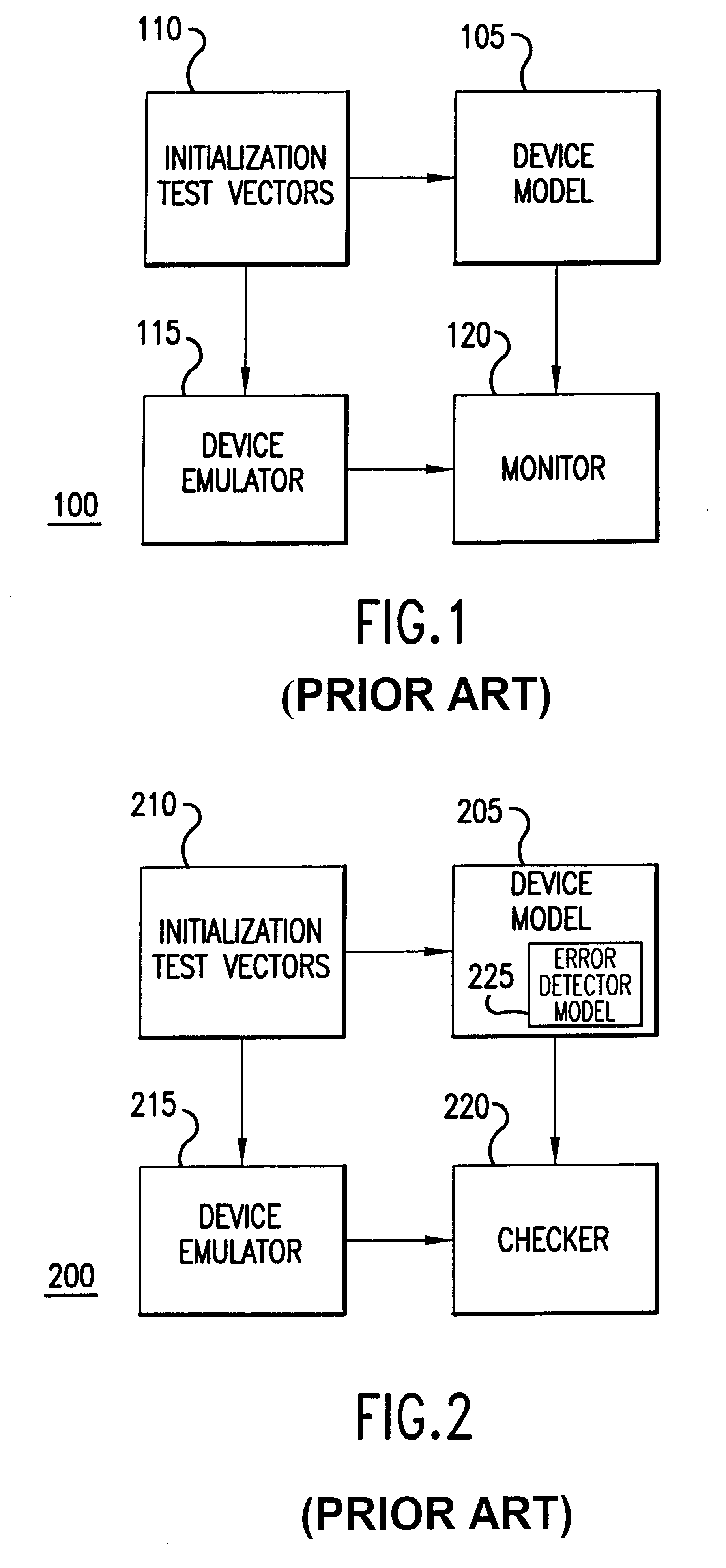

Disclosed is a device and method for testing of a program or a design of an electronic device comprising digital logic circuitry. The method comprises testing the design of software or an electronic device and injecting, after initiation of the testing step, a predetermined error pattern into a value operated upon by the design of the digital logic circuitry. In a preferred embodiment, the software is a simulation of the design of a processor having a cache with error detection and / or correction circuitry. A triggering condition is preferably a cache hit, in response to which a detectable error is injected into the cache. The simulated operations of the model are observed to determine whether the injected error is detected, as should happen if the processor's error detection circuitry has been designed properly. In another respect, the invention is an apparatus, or computer software embedded on a computer readable medium, for testing a program comprising an error detector. The apparatus or software comprises the program, an error injector module connected to the program; and a checker module connected to the program. The checker module is capable of determining whether the program responds appropriately to an error dynamically produced by the error injector module during execution of the program. By injecting errors dynamically the invention easily facilitates precisely focused testing at any time during simulated operation regardless of initialization conditions.

Owner:SAMSUNG ELECTRONICS CO LTD

Automated processor generation system for designing a configurable processor and method for the same

InactiveUS20030208723A1Decompilation/disassemblyGeneral purpose stored program computerApplication softwareProcessor design

An automated processor design tool uses a description of customized processor instruction set extensions in a standardized language to develop a configurable definition of a target instruction set, a Hardware Description Language description of circuitry necessary to implement the instruction set, and development tools such as a compiler, assembler, debugger and simulator which can be used to develop applications for the processor and to verify it. Implementation of the processor circuitry can be optimized for various criteria such as area, power consumption, speed and the like. Once a processor configuration is developed, it can be tested and inputs to the system modified to iteratively optimize the processor implementation. By providing a constrained domain of extensions and optimizations, the process can be automated to a high degree, thereby facilitating fast and reliable development.

Owner:TENSILICA

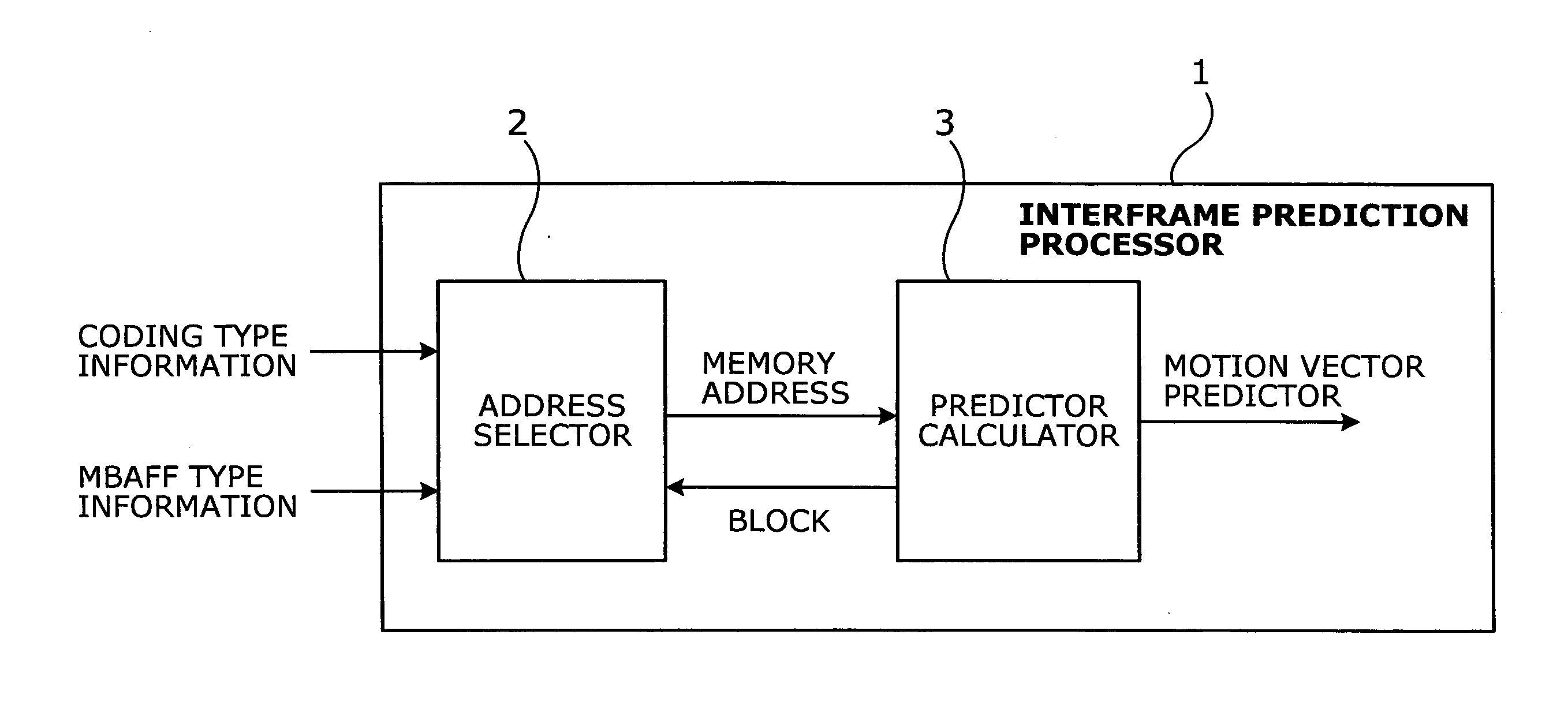

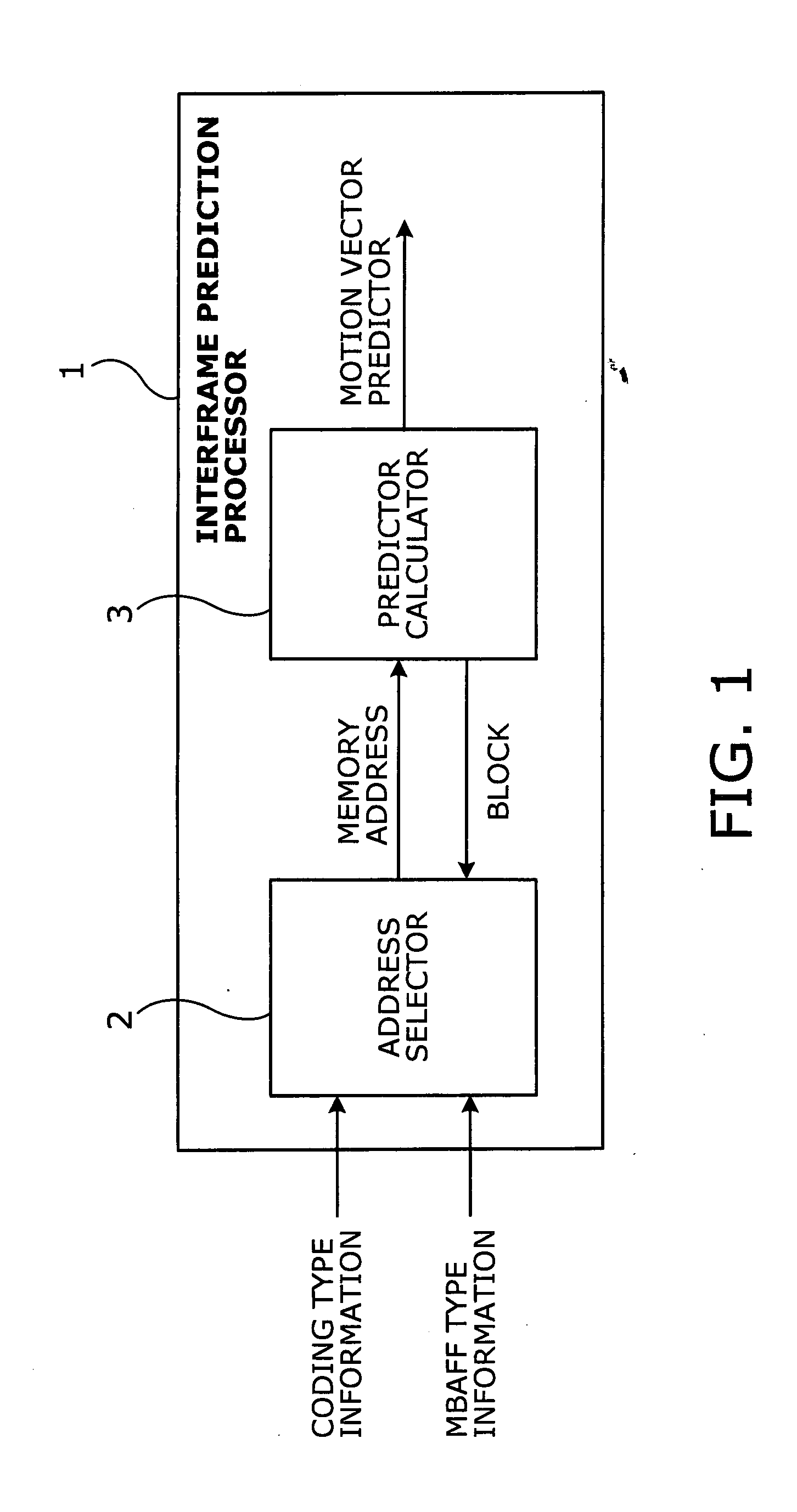

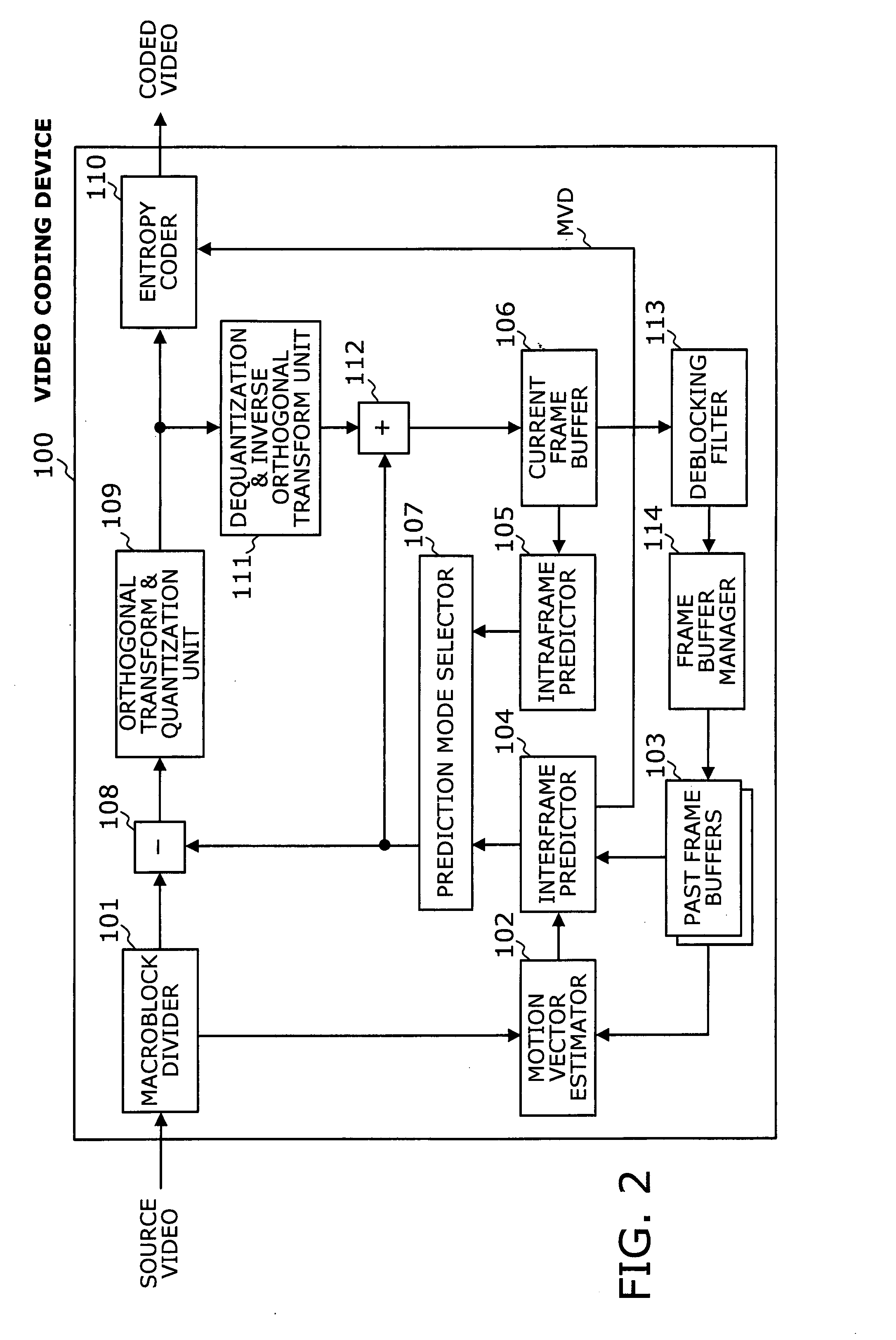

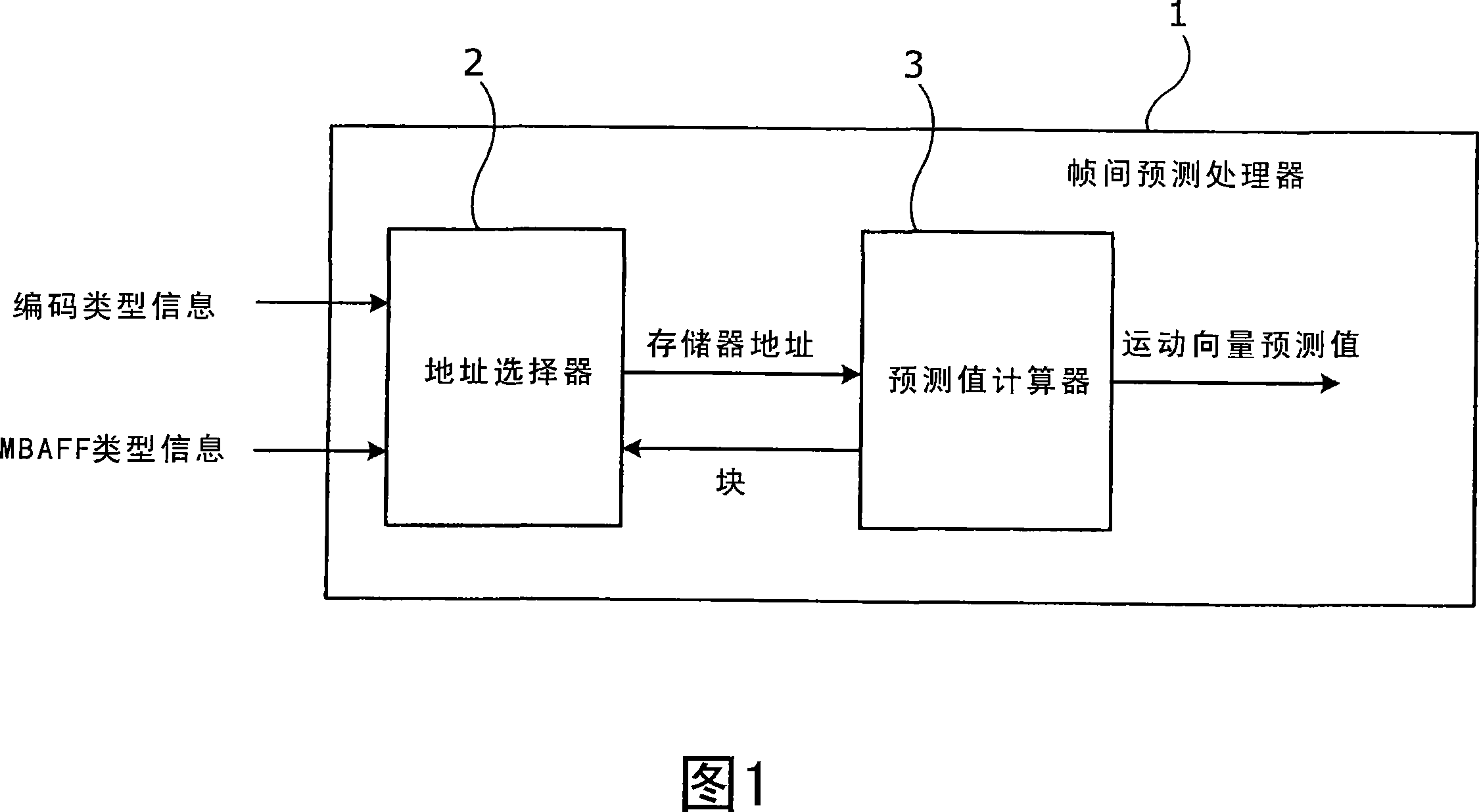

Interframe prediction processor with mechanism for providing locations of reference motion vectors used in macroblock adaptive field/frame mode

InactiveUS20080043843A1Increase speedColor television with pulse code modulationColor television with bandwidth reductionMemory addressMotion vector

An interframe prediction processor designed for high-speed video coding and decoding. The interframe prediction processor has an address selector and a predictor calculator. The address selector receives information about MBAFF type and coding type. When performing motion compensation for a given MBAFF picture with reference to blocks surrounding a current block, the address selector provides memory addresses of reference motion vectors according to the coding type of the current block pair, as well as to the coding type of the reference blocks. The predictor calculator that determines a motion vector predictor for each constituent block of the current block pair based on reference motion vectors read out of the provided memory addresses.

Owner:SOCIONEXT INC

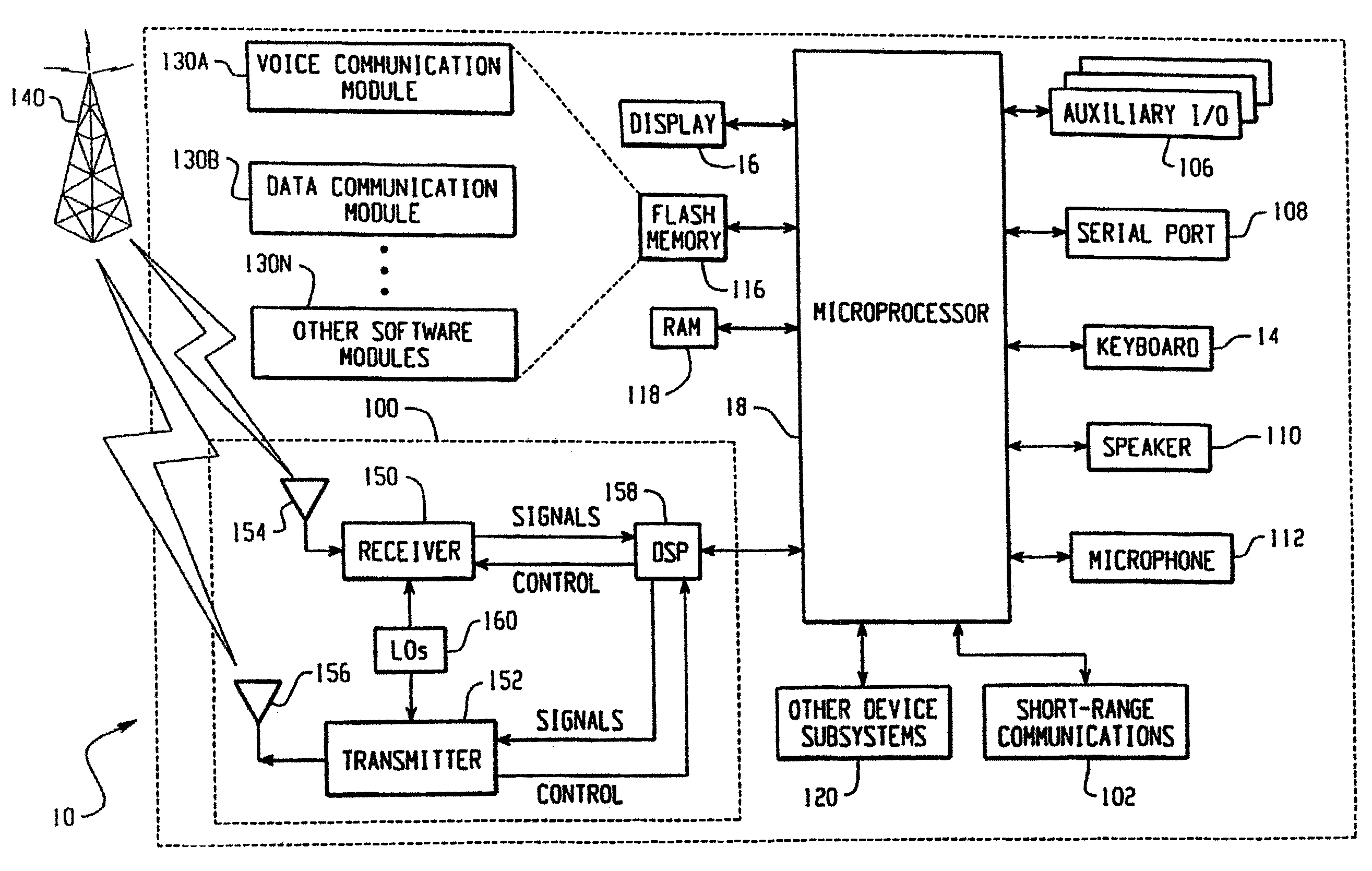

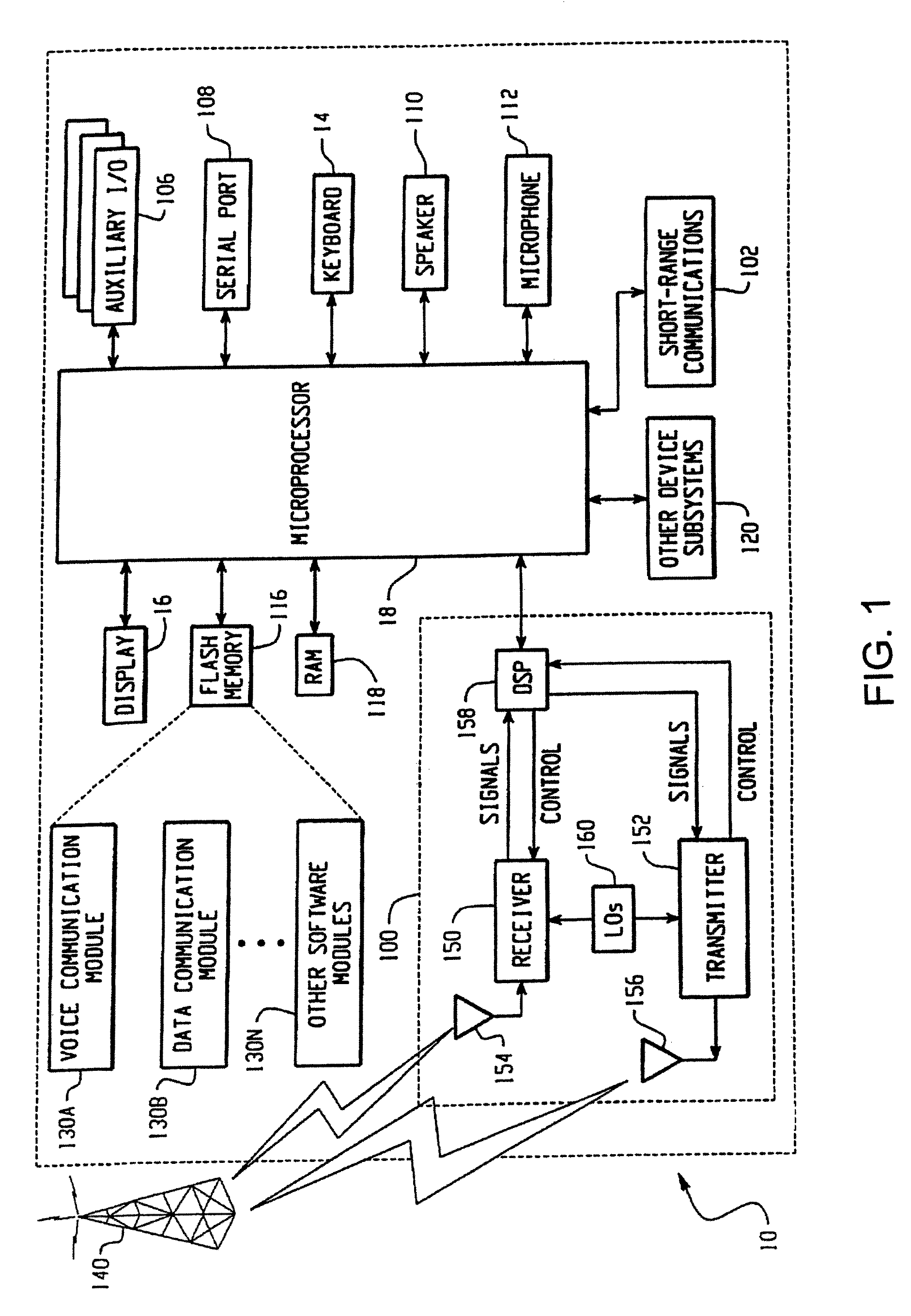

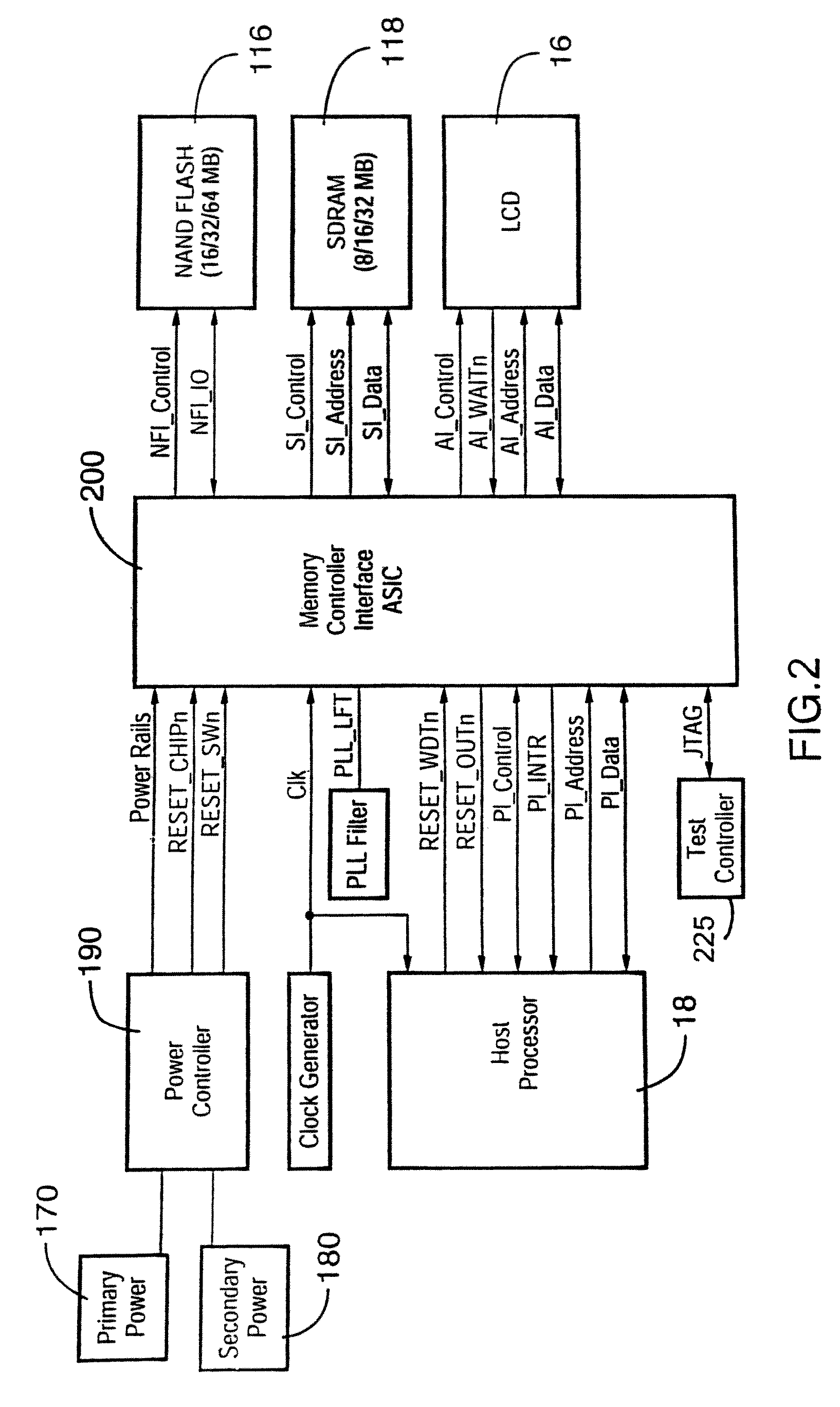

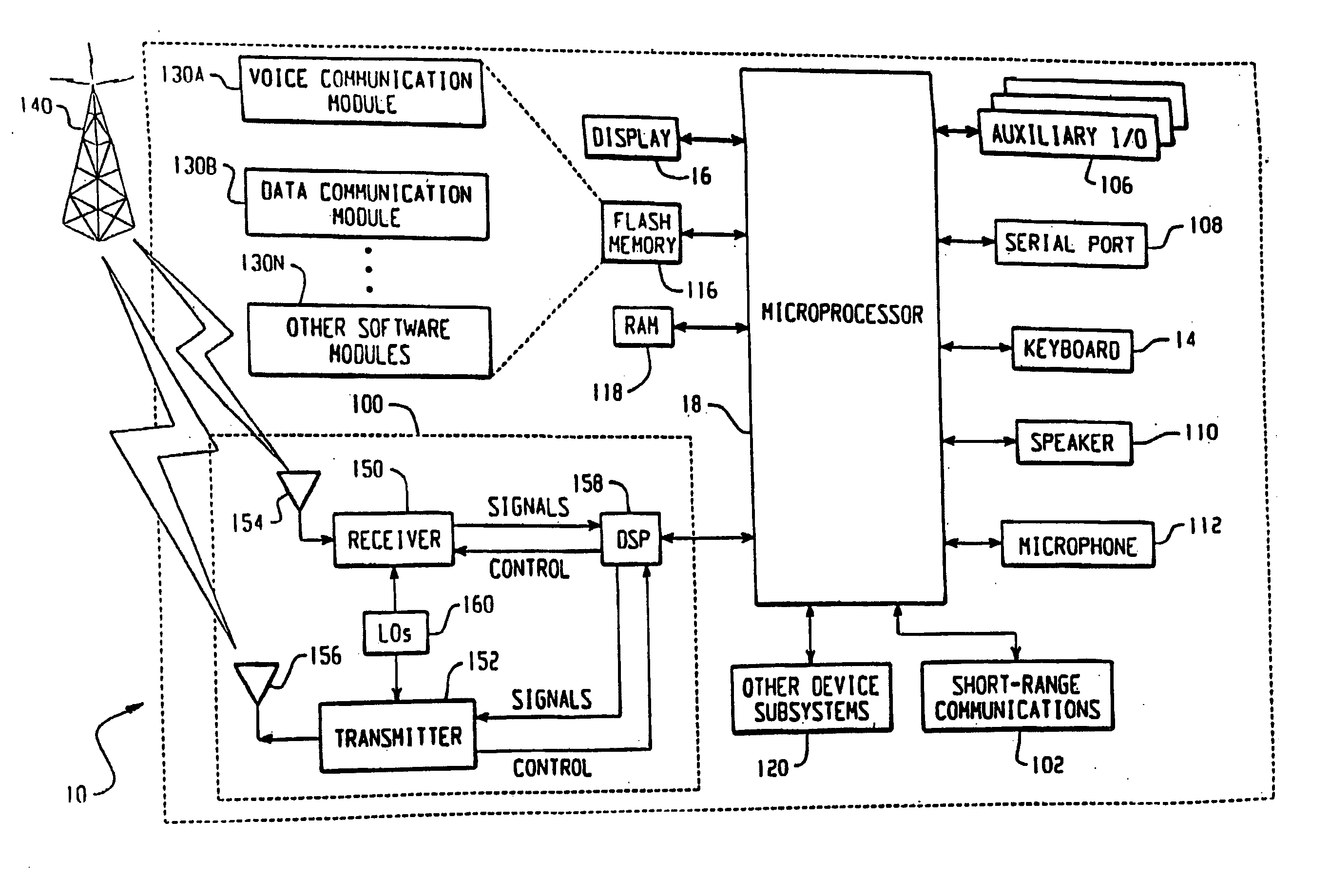

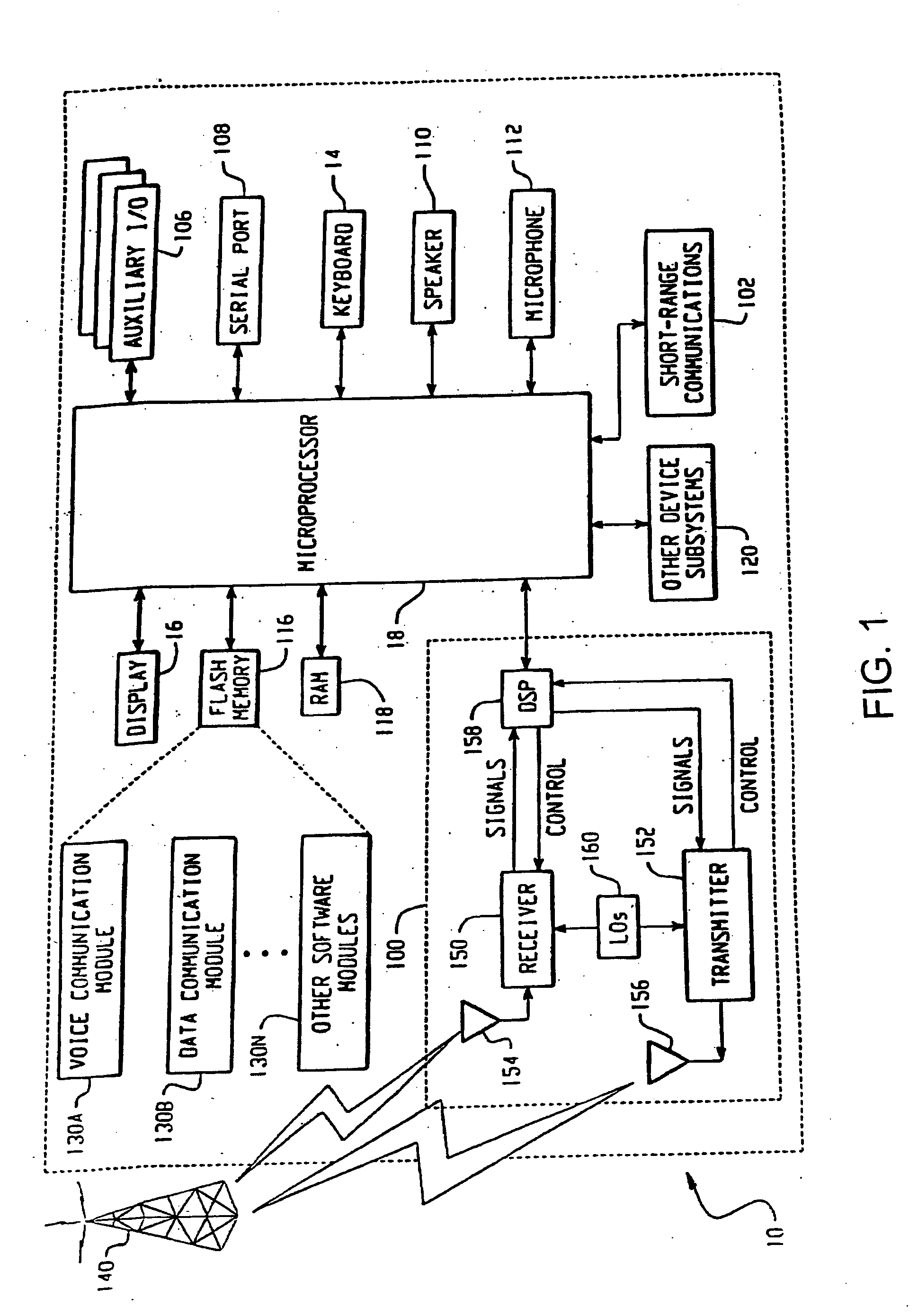

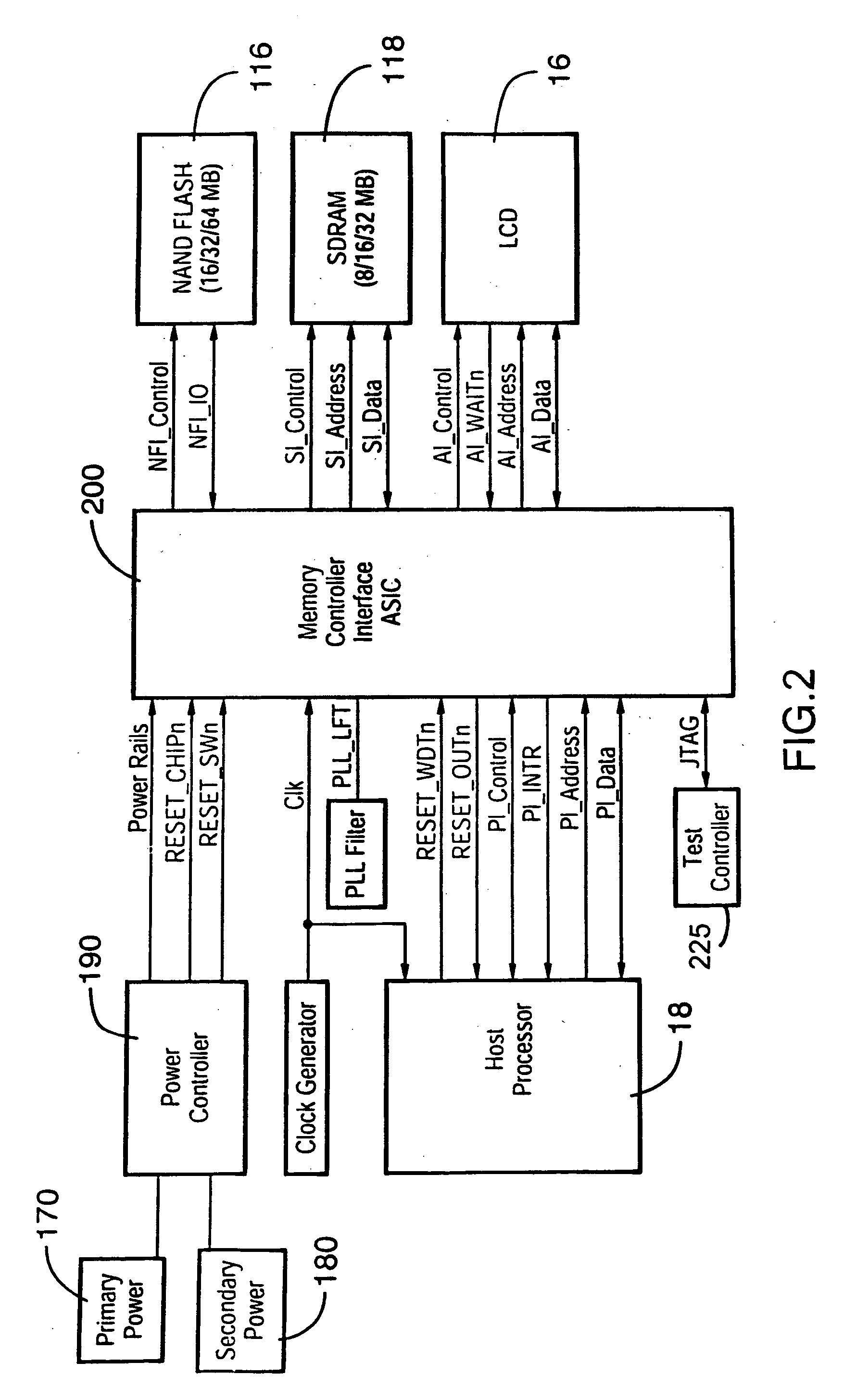

Memory controller interface

ActiveUS7610433B2Memory architecture accessing/allocationMemory loss protectionStatic random-access memoryMemory interface

A memory interface controller and method to allow a processor designed and configured to operate with NOR flash and static random access memory (SRAM) memory devices to instead operate using NAND flash and synchronous dynamic random access memory (SDRAM). The system accomplishes this by caching sectors out of NAND flash into SDRAM, where the data can be randomly accessed by the processor as though it were accessing data from NOR flash / SRAM. Sectors containing data required by the processor are read out of NAND flash and written into SDRAM, where the data can be randomly accessed by the processor.

Owner:MALIKIE INNOVATIONS LTD

Adding complex instruction extensions defined in a standardized language to a microprocessor design to produce a configurable definition of a target instruction set, and hdl description of circuitry necessary to implement the instruction set, and development and verification tools for the instruction set

InactiveUS6477697B1Fast and reliable developmentGeneral purpose stored program computerCAD network environmentApplication softwareProcessor design

An automated processor design tool uses a description of customized processor instruction set extensions in a standardized language to develop a configurable definition of a target instruction set, a Hardware Description Language description of circuitry necessary to implement the instruction set, and development tools such as a compiler, assembler, debugger and simulator which can be used to develop applications for the processor and to verify it. The standardized language is capable of handling instruction set extensions which modify processor state or use configurable processors. By providing a constrained domain of extensions and optimizations, the process can be automated to a high degree, thereby facilitating fast and reliable development.

Owner:TENSILICA

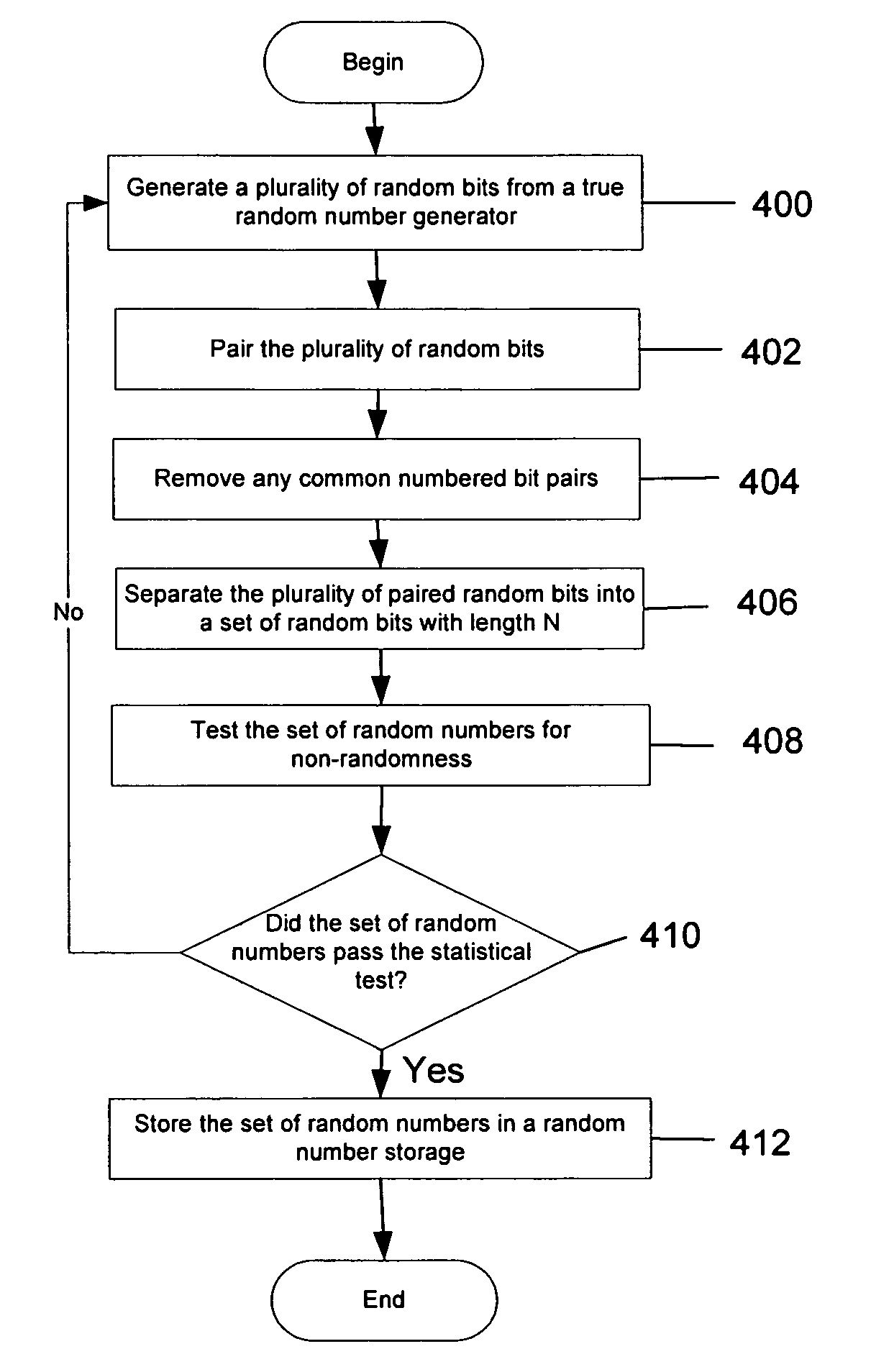

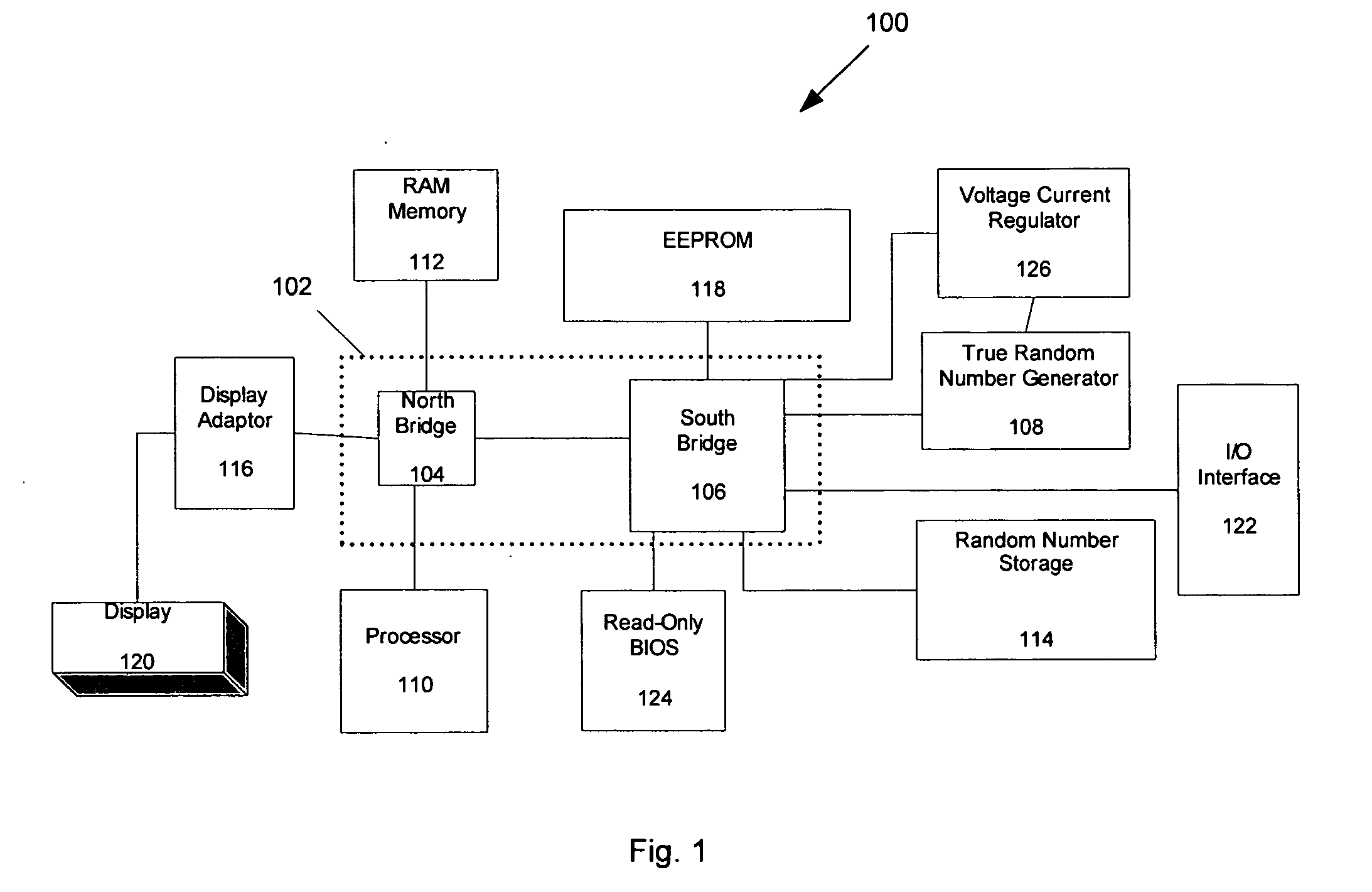

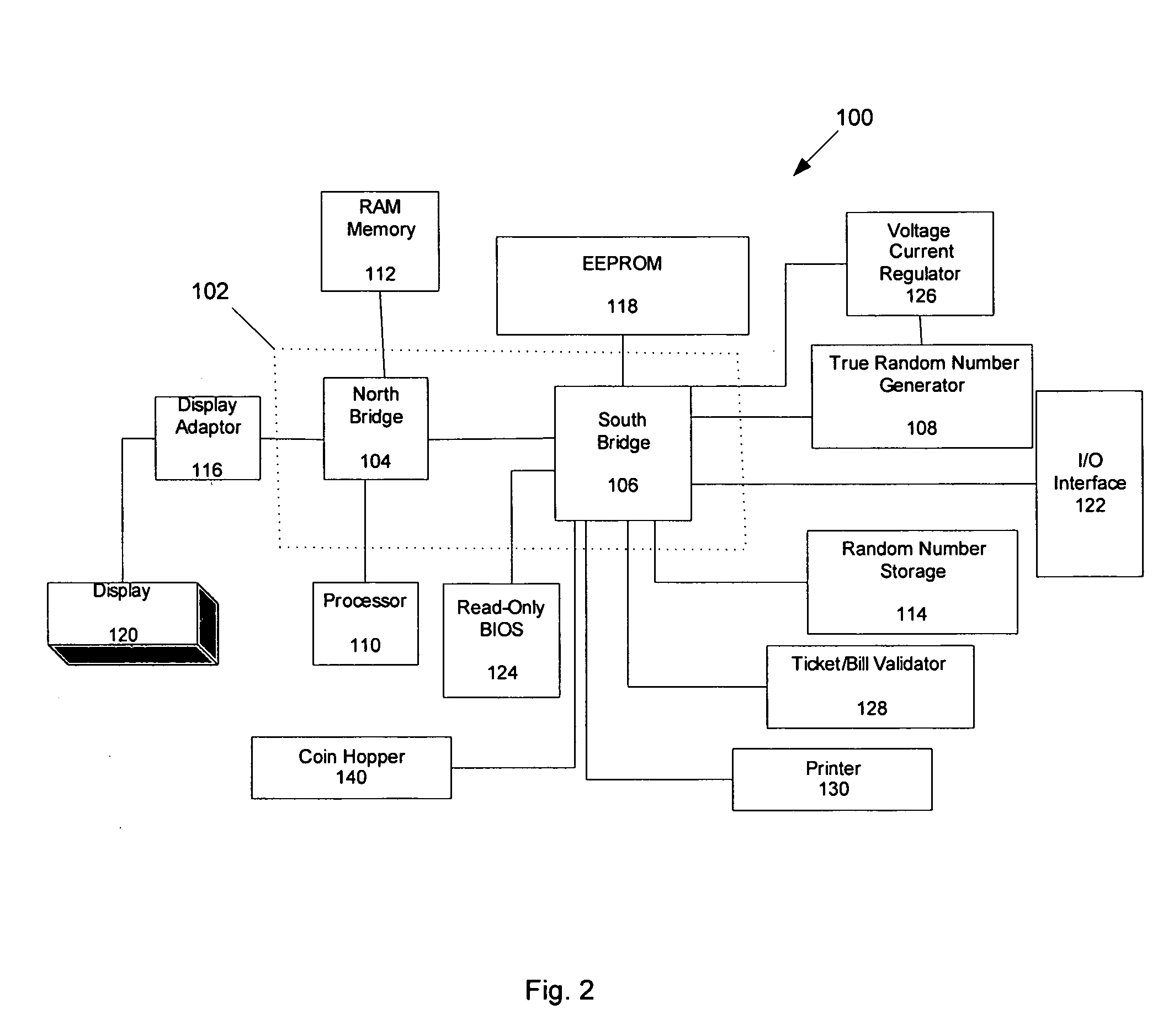

Quantum gaming system

Owner:IGT

Heterogeneous multiprocessor design for power-efficient and area-efficient computing

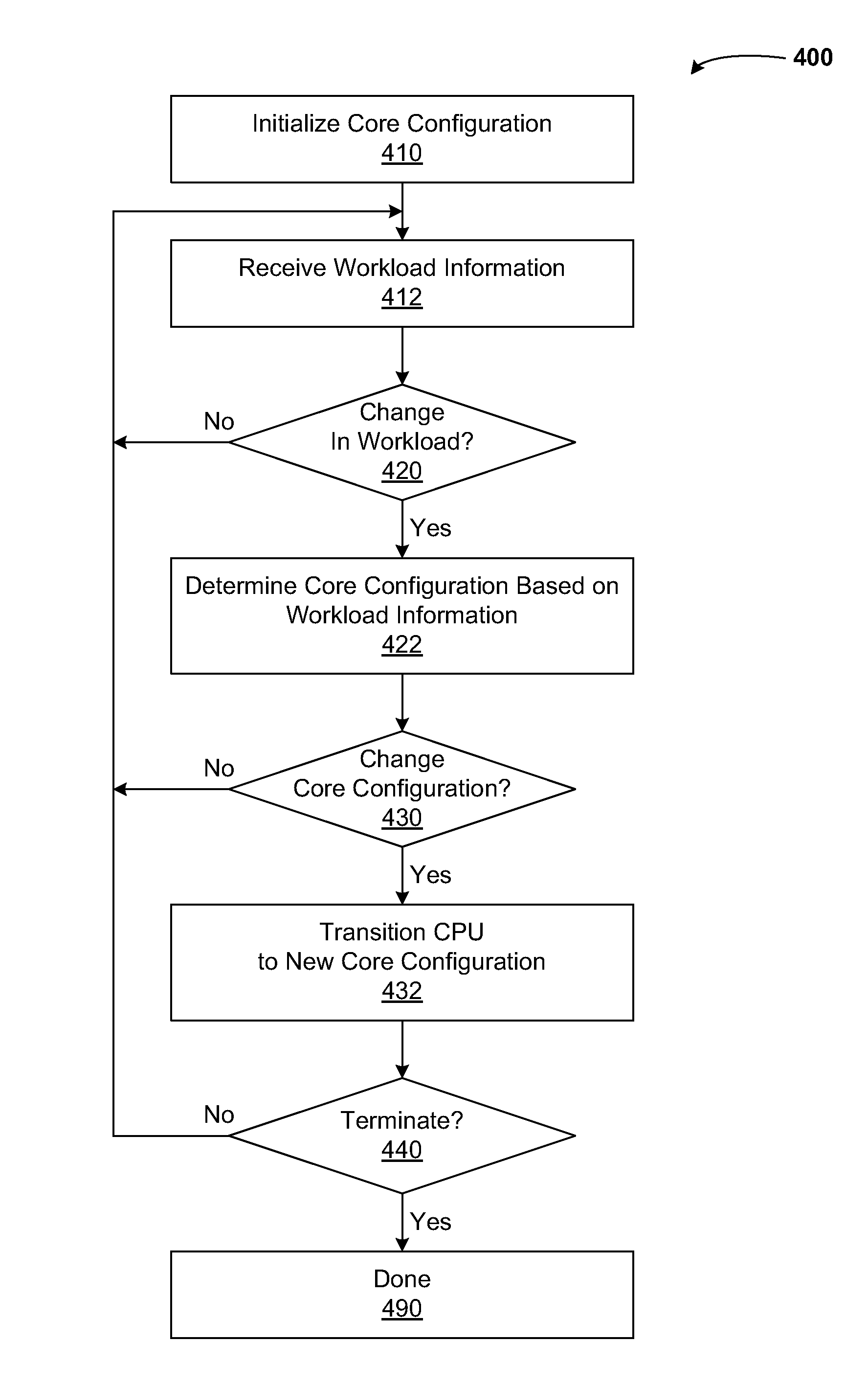

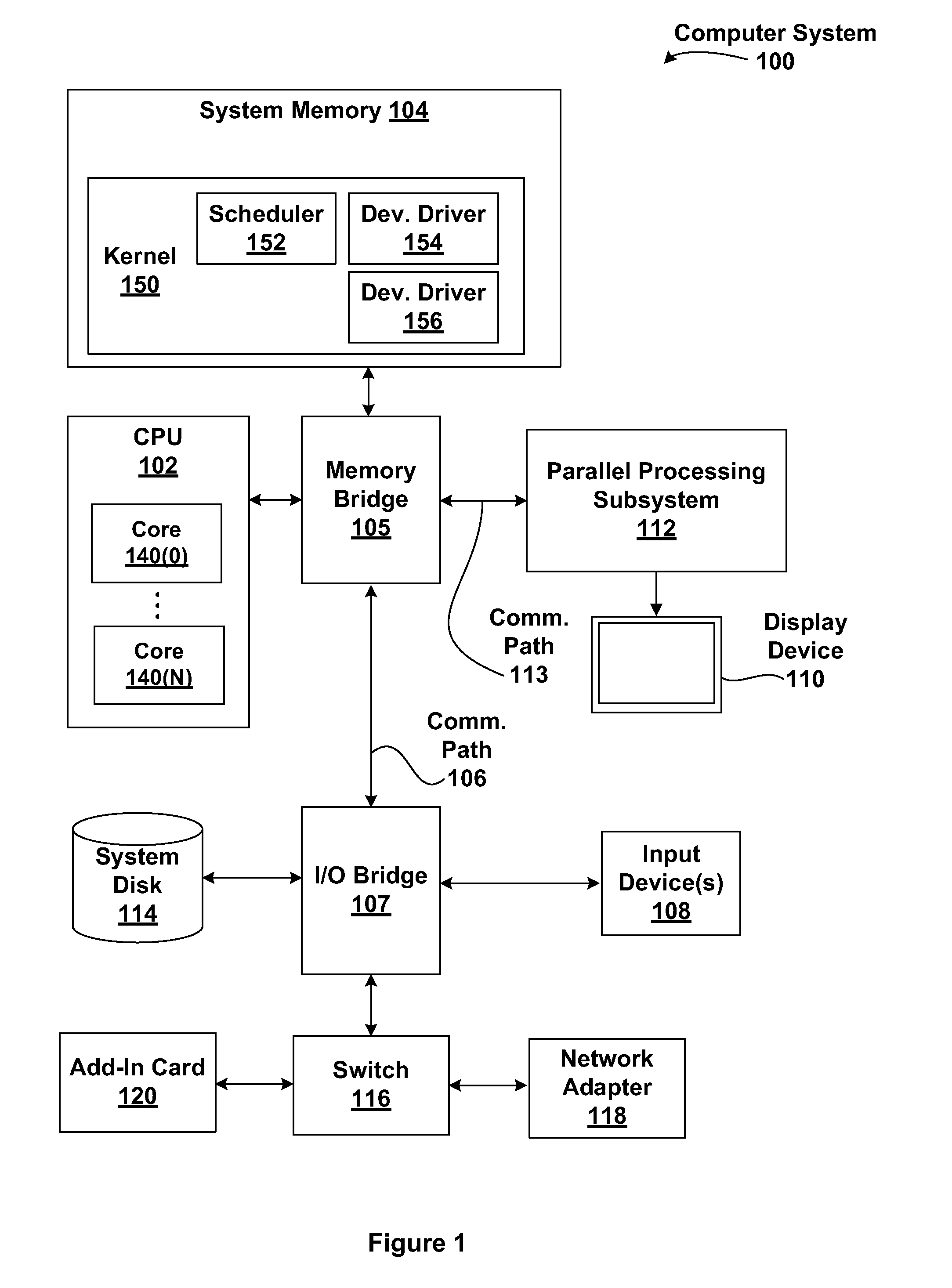

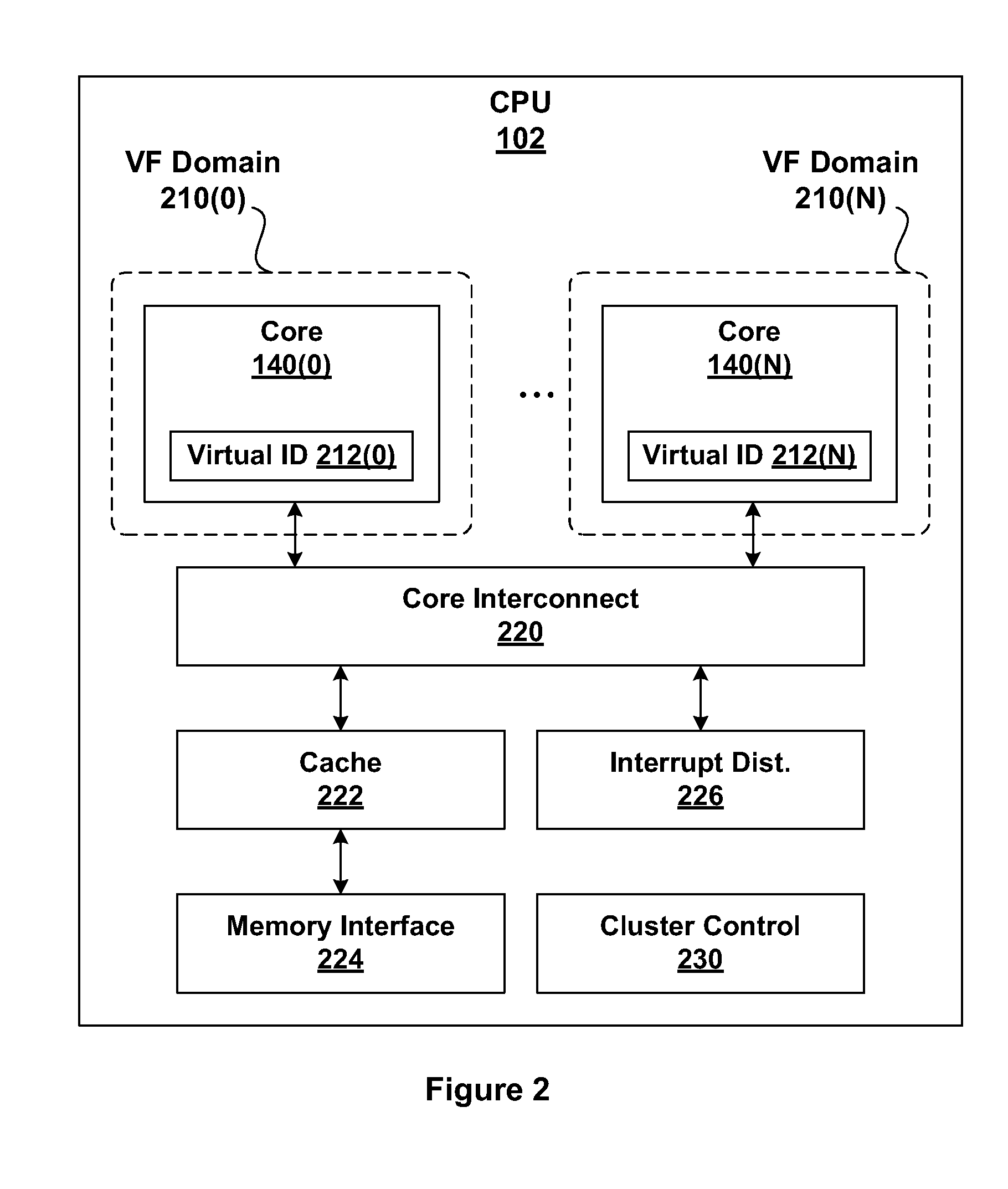

ActiveUS20140181501A1Improve power efficiencyEfficient use ofData resettingProgram loading/initiatingPower efficientResource utilization

A technique for managing processor cores within a multi-core central processing unit (CPU) provides efficient power and resource utilization over a wide workload range. The CPU comprises at least one core designed for low power operation and at least one core designed for high performance operation. For low workloads, the low power core executes the workload. For certain higher workloads, the high performance core executes the workload. For certain other workloads, the low power core and the high performance core both share execution of the workload. This technique advantageously enables efficient processing over a wider range of workloads than conventional systems.

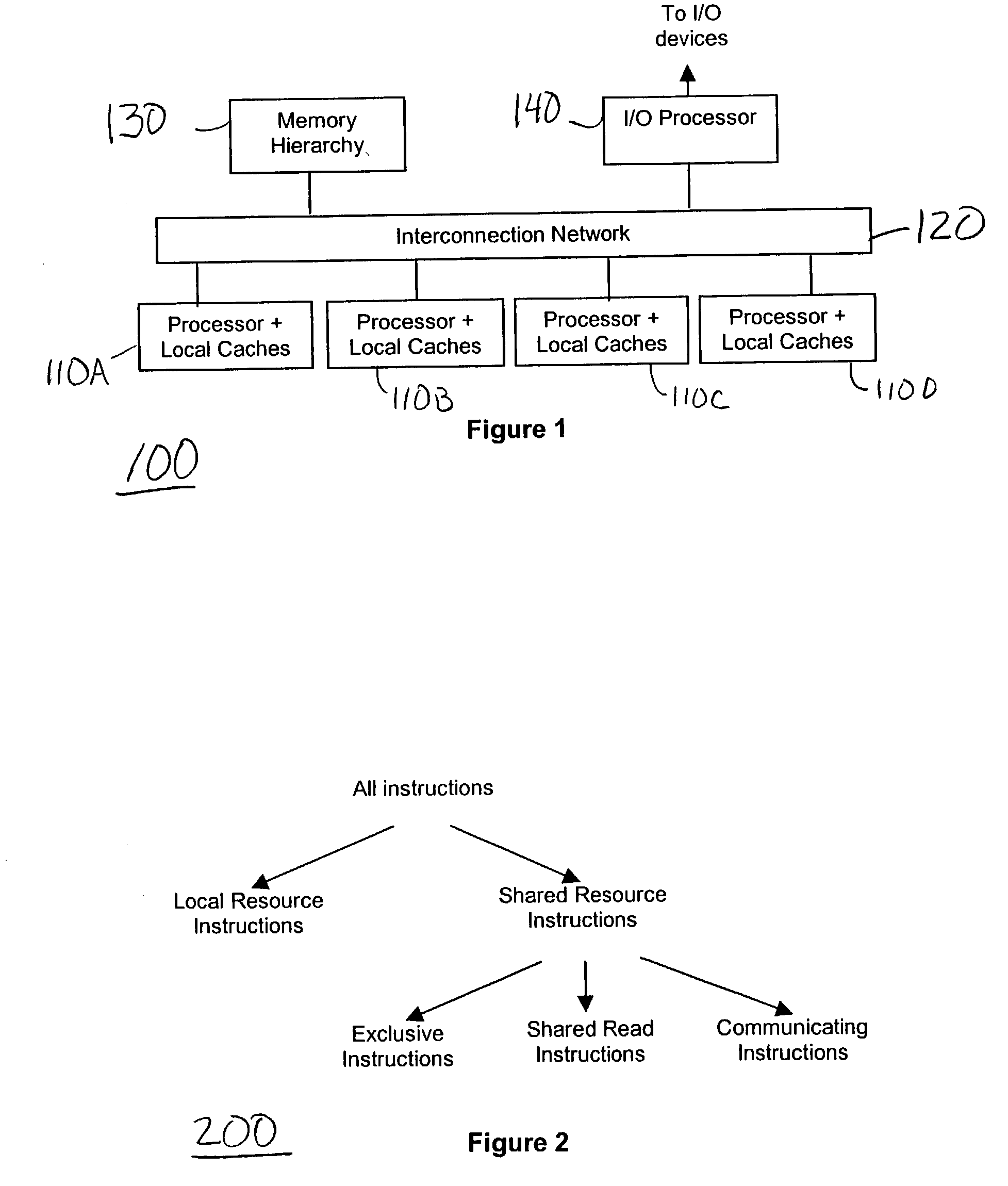

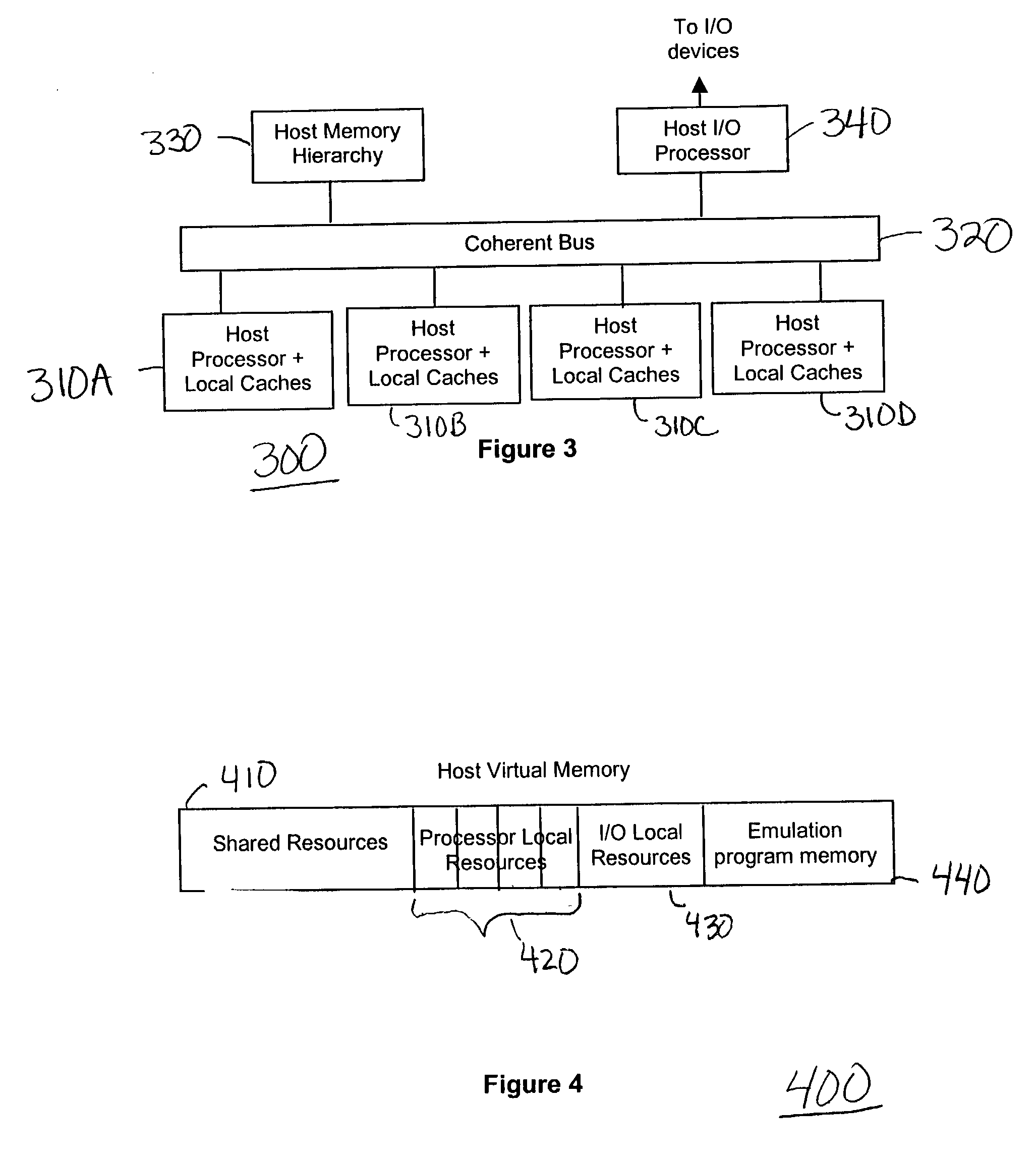

Method and system for multiprocessor emulation on a multiprocessor host system

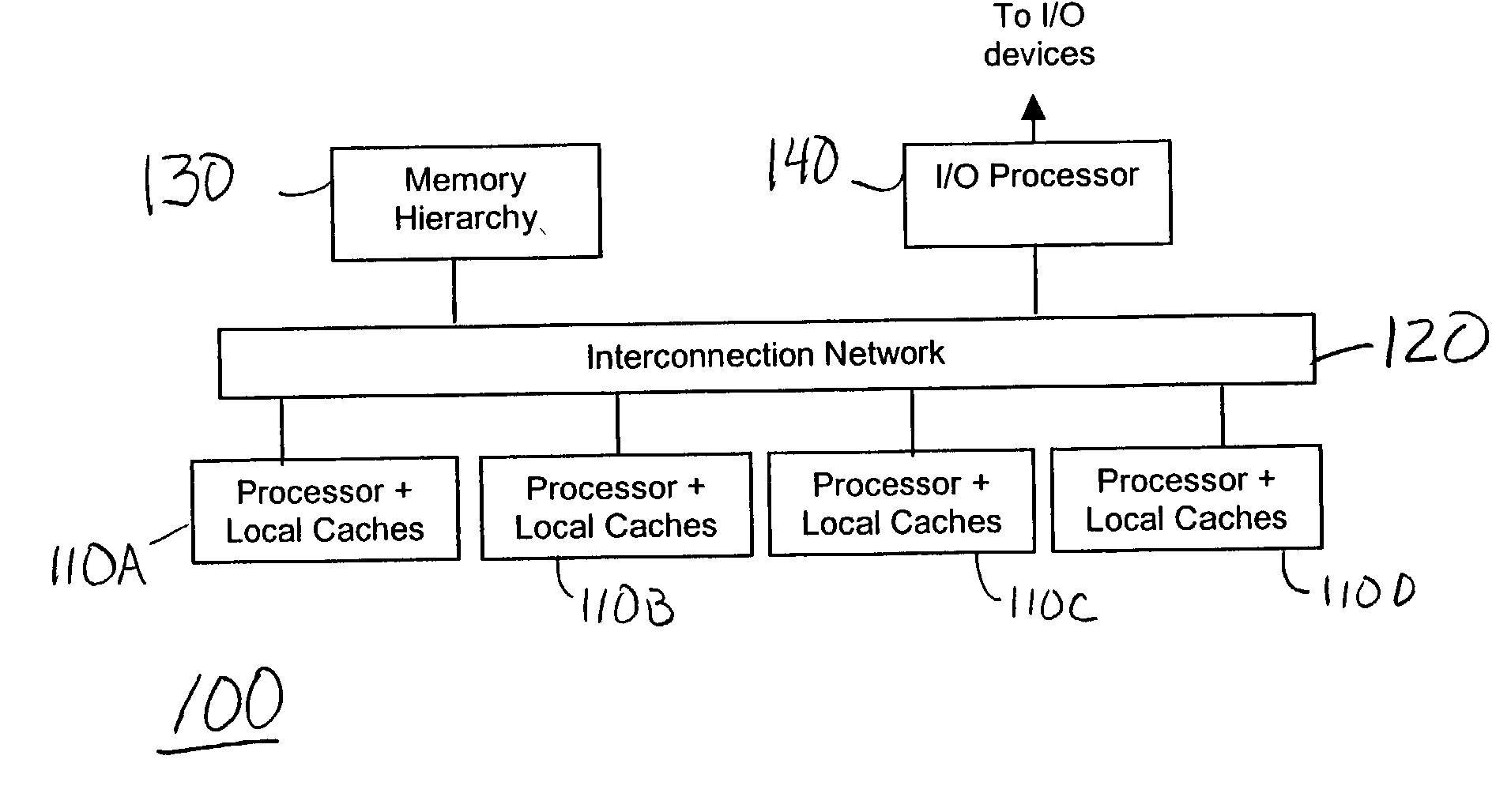

InactiveUS20040054517A1Improve performanceEfficient executionResource allocationConcurrent instruction executionMulti processorProgram Thread

A method (and system) for executing a multiprocessor program written for a target instruction set architecture on a host computing system having a plurality of processors designed to process instructions of a second instruction set architecture, includes representing each portion of the program designed to run on a processor of the target computing system as one or more program threads to be executed on the host computing system.

Owner:IBM CORP

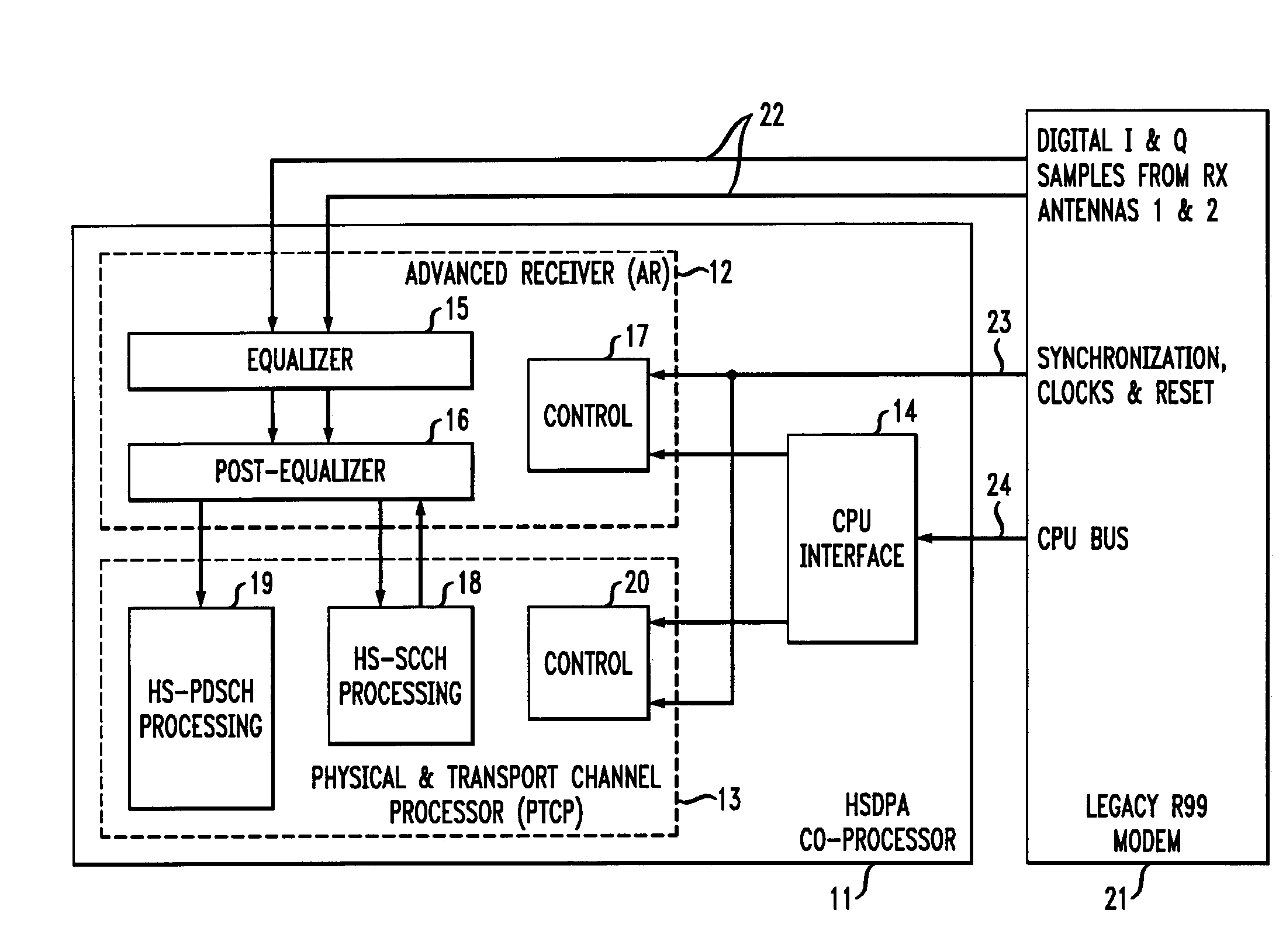

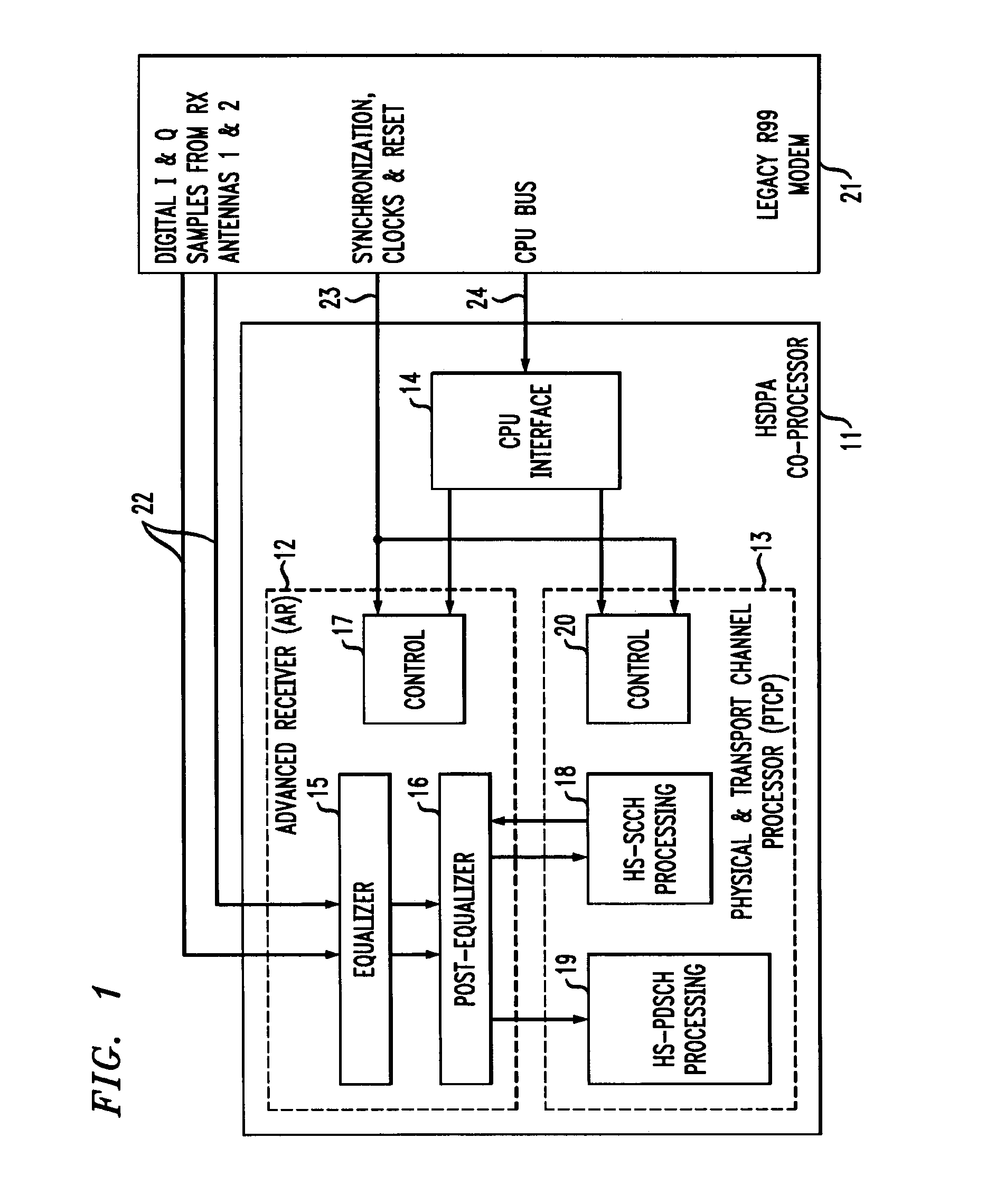

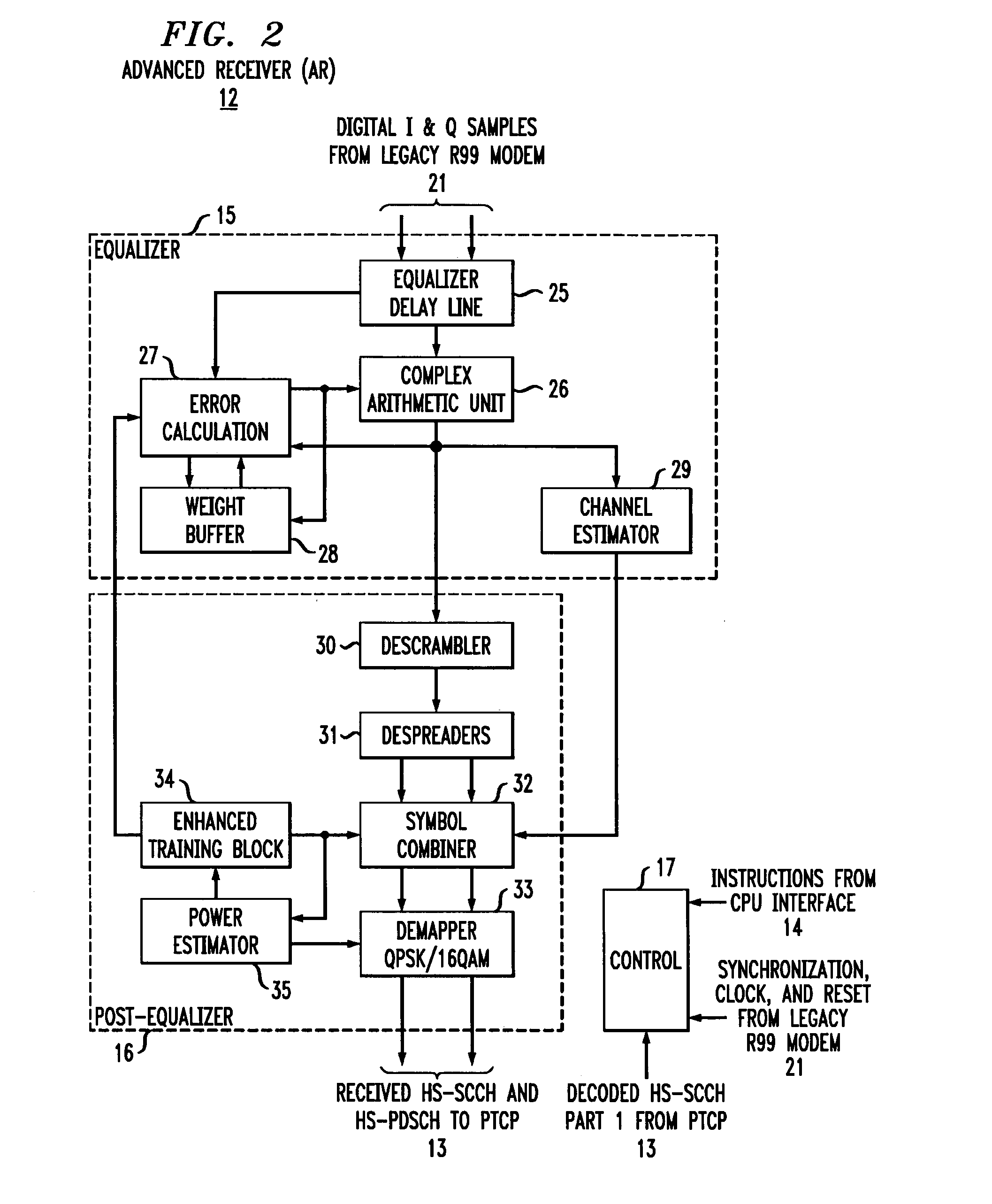

Hsdpa co-processor for mobile terminals

InactiveUS20090296798A1Improve reception performanceMultiple-port networksDelay line applicationsCMOSCoprocessor

In one embodiment, an HSDPA co-processor for 3GPP Release 6 Category 8 (7.2 Mb / s) HSDPA that provides all chip-rate, symbol-rate, physical-channel, and transport-channel processing for HSDPA in 90 nm CMOS. The co-processor design is scalable to all HSDPA data rates up to 14 Mb / s. The coprocessor implements an Advanced Receiver based on an NLMS equalizer, supports RX diversity and TX diversity, and provides up to 6.4 dB better performance than a typical single-antenna rake receiver. Thus, 3GPP R6 HSDPA functionality can be added to a legacy R99 modem using an HSDPA co-processor consistent with embodiments of the present invention, at a reasonable incremental cost and power.

Owner:AGERE SYST INC

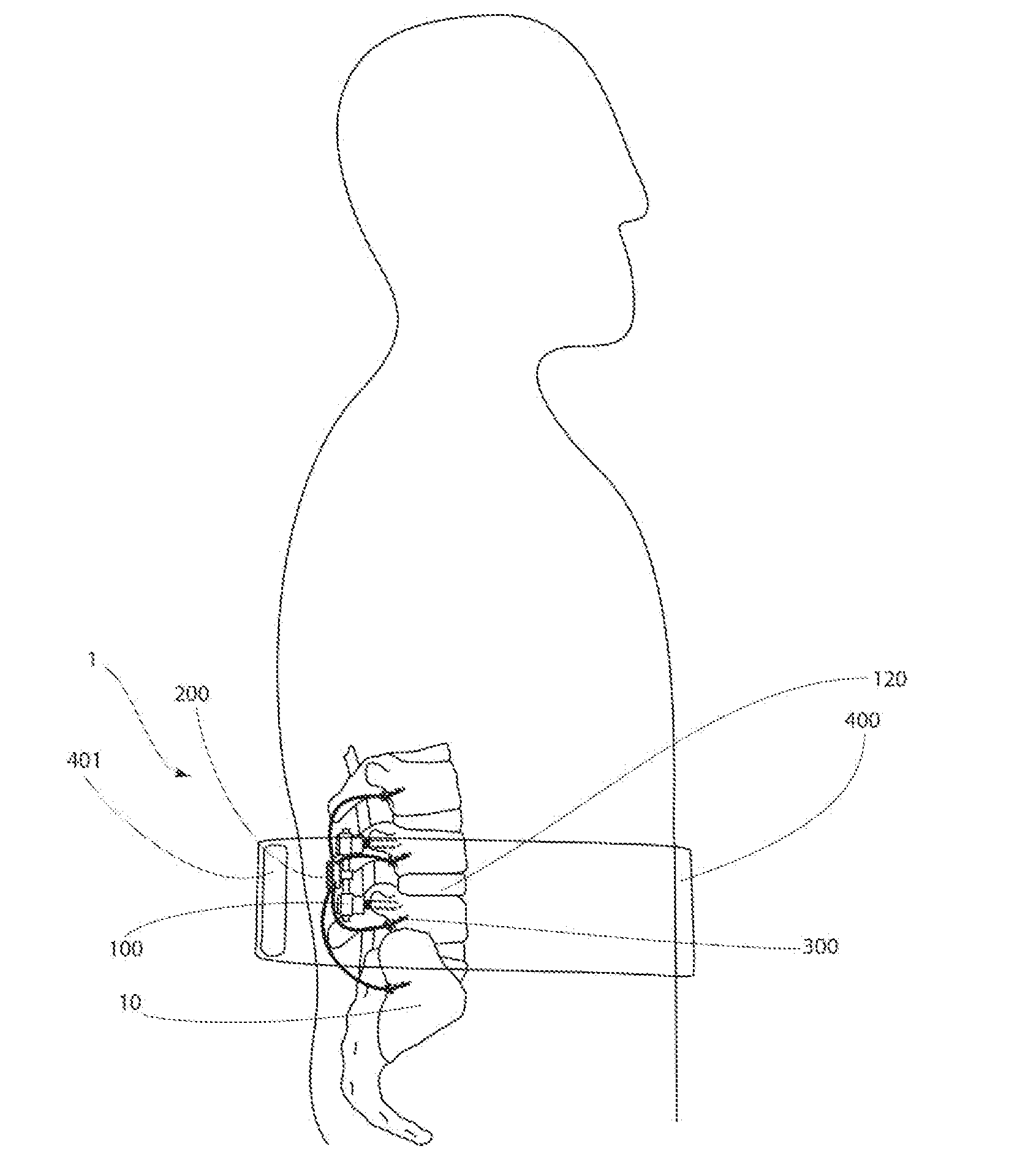

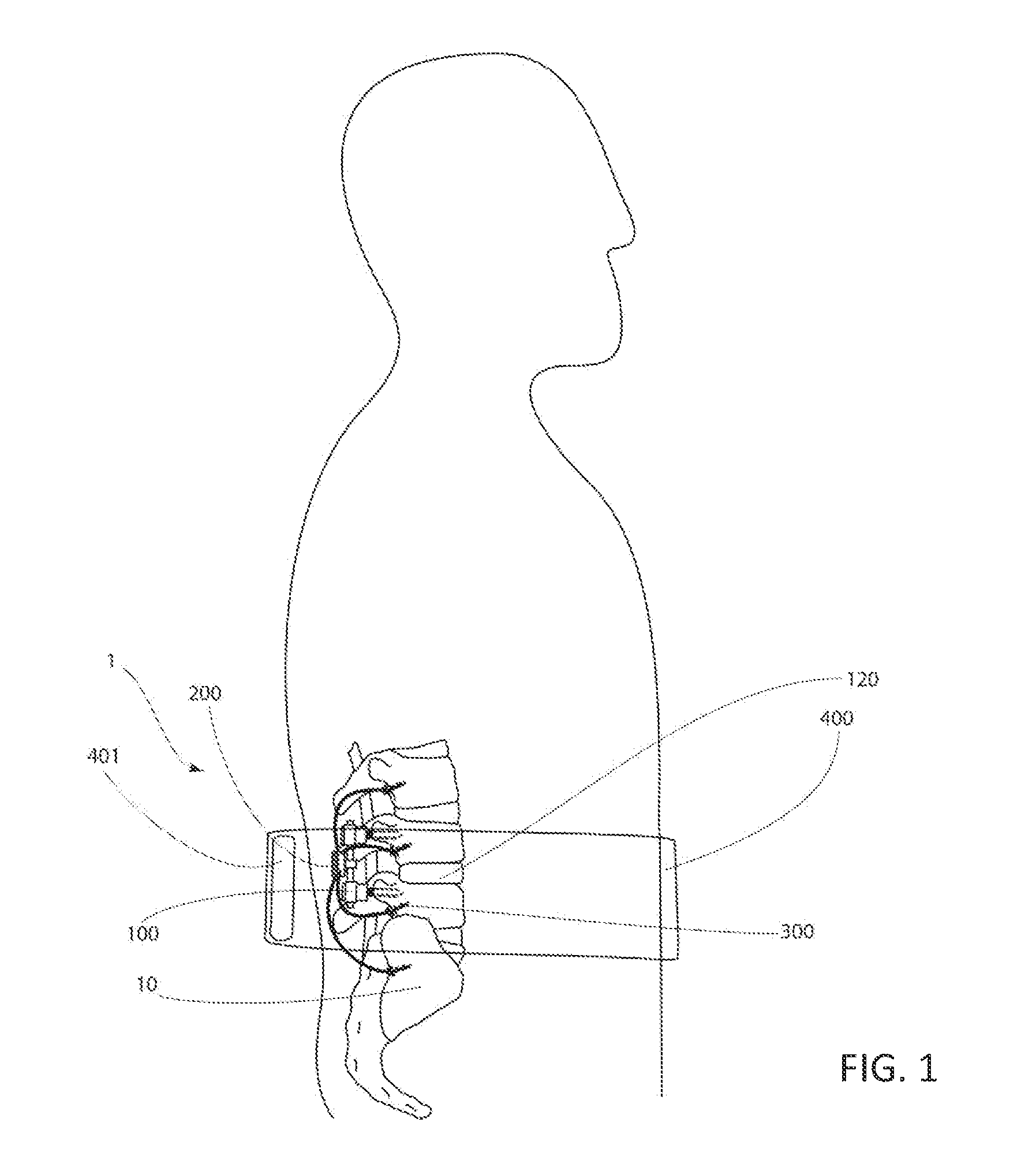

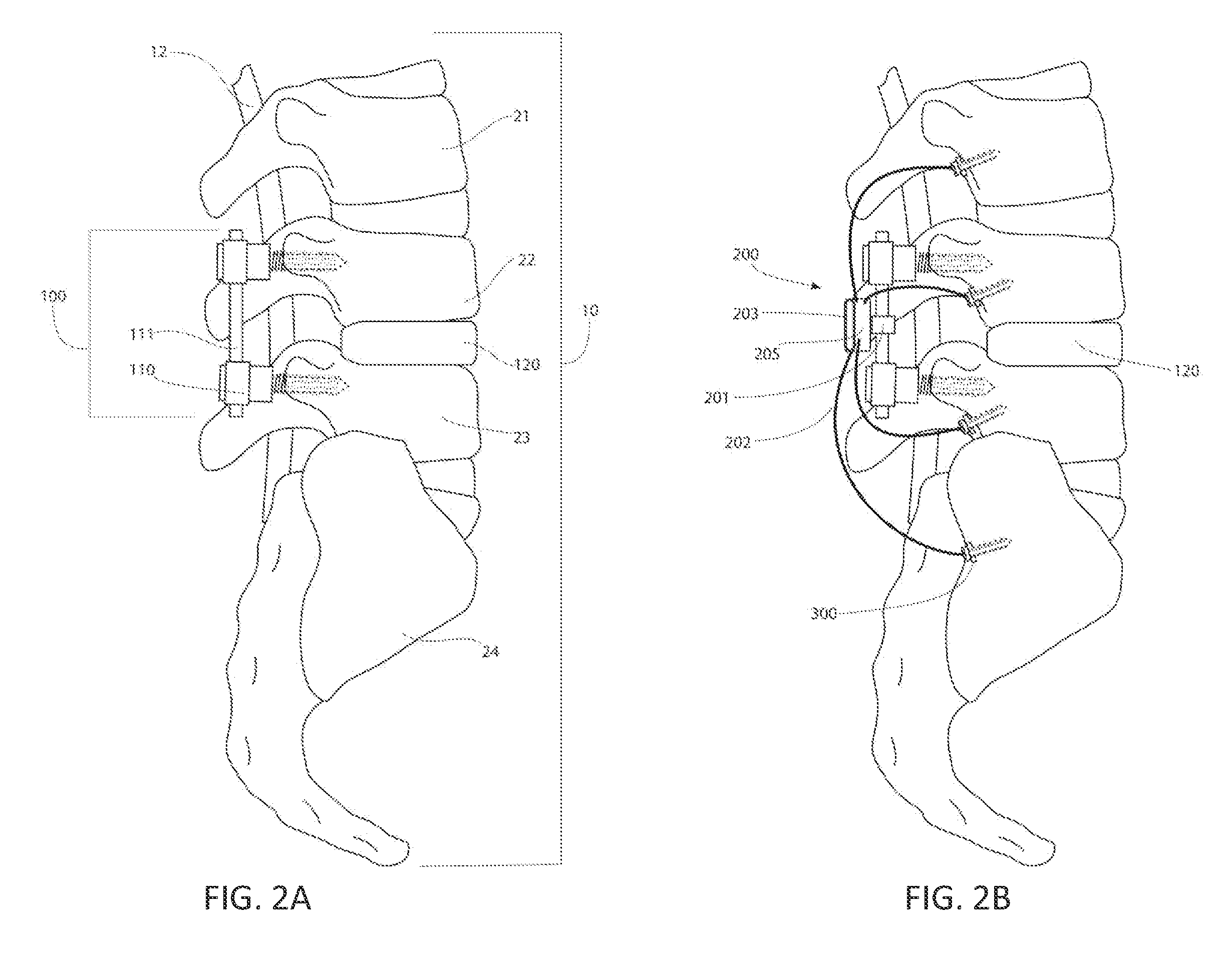

Method and Apparatus for an Implantable Inertial-Based Sensing System for Real-Time, In Vivo Detection of Spinal Pseudarthrosis and Adjacent Segment Motion

InactiveUS20110295159A1Extended range of motionRange of motionMusculoskeletal system evaluationInternal osteosythesisAccelerometerIn vivo

A vertebral processor designed to collect and interpret data from multiple surgically implanted accelerometers. Each accelerometer is surgically implanted into a vertebra of a patient utilizing a bone screw. Additional accelerometers are implanted in adjacent vertebrae. The data from the accelerometers is compared by an algorithm to determine the relative movement of the accelerometers implanted in adjacent vertebrae. Data is generated via the algorithm and compared against the expected behavior of the surgically implanted accelerometers as if they were connected to a rigid body, thus determining the level of success of a spinal fusion procedure for those adjacent segments. The apparatus may be utilized with or without spinal stabilization hardware, and with or without fusion cages or artificial discs. The vertebral processor is supplemented by an external system worn by the patient, which provides for an inductive charging power source and for data transfer.

Owner:PHARMACO KINESIS

Memory controller interface

ActiveUS20050185472A1Memory architecture accessing/allocationMemory loss protectionMemory interfaceMemory controller

A memory interface controller and method to allow a processor designed and configured to operate with NOR flash and SRAM memory devices to instead operate using NAND flash and SDRAM. The system accomplishes this by caching sectors out of NAND flash into SDRAM, where the data can be randomly accessed by the processor as though it were accessing data from NOR flash / SRAM. Sectors containing data required by the processor are read out of NAND flash and written into SDRAM, where the data can be randomly accessed by the processor.

Owner:MALIKIE INNOVATIONS LTD

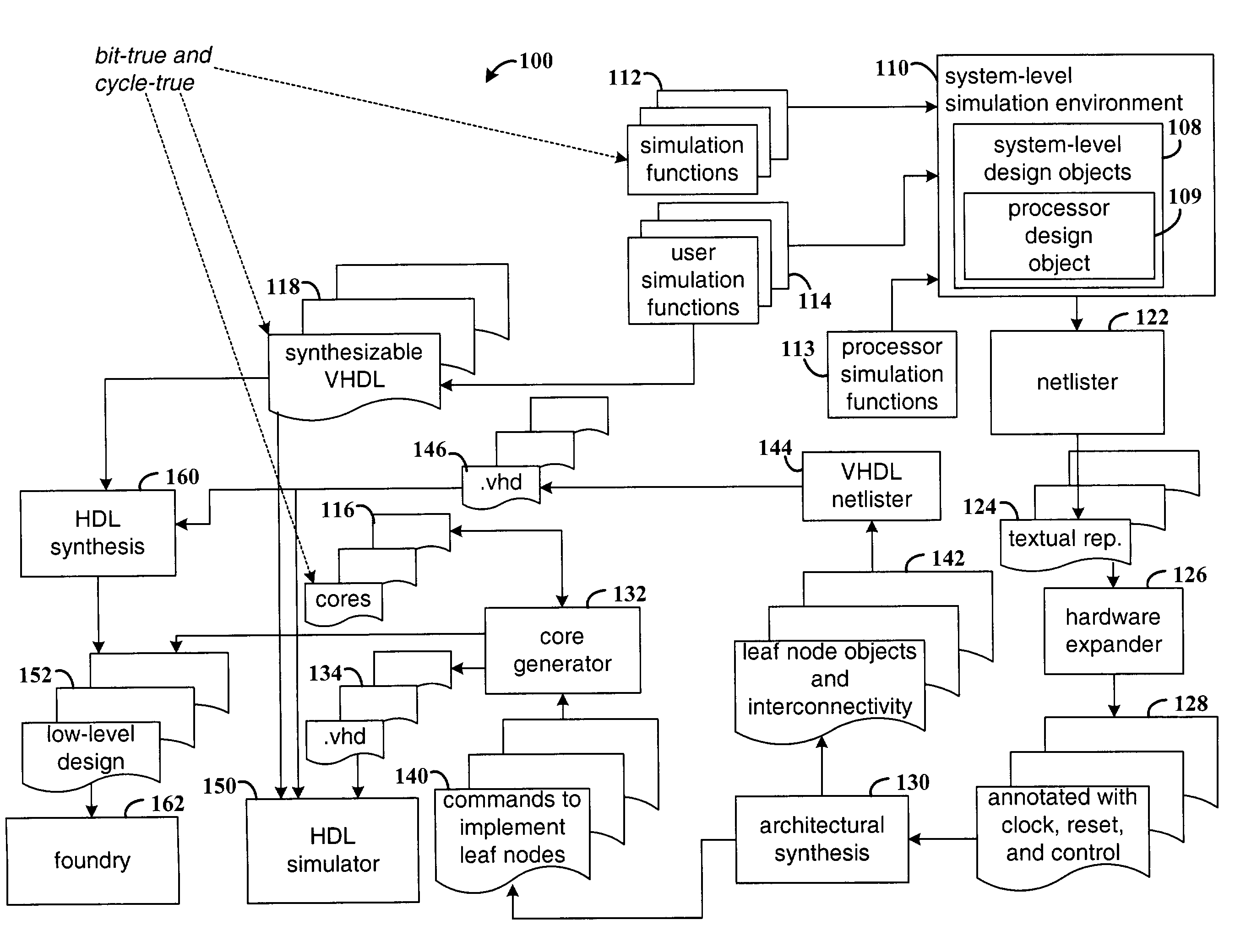

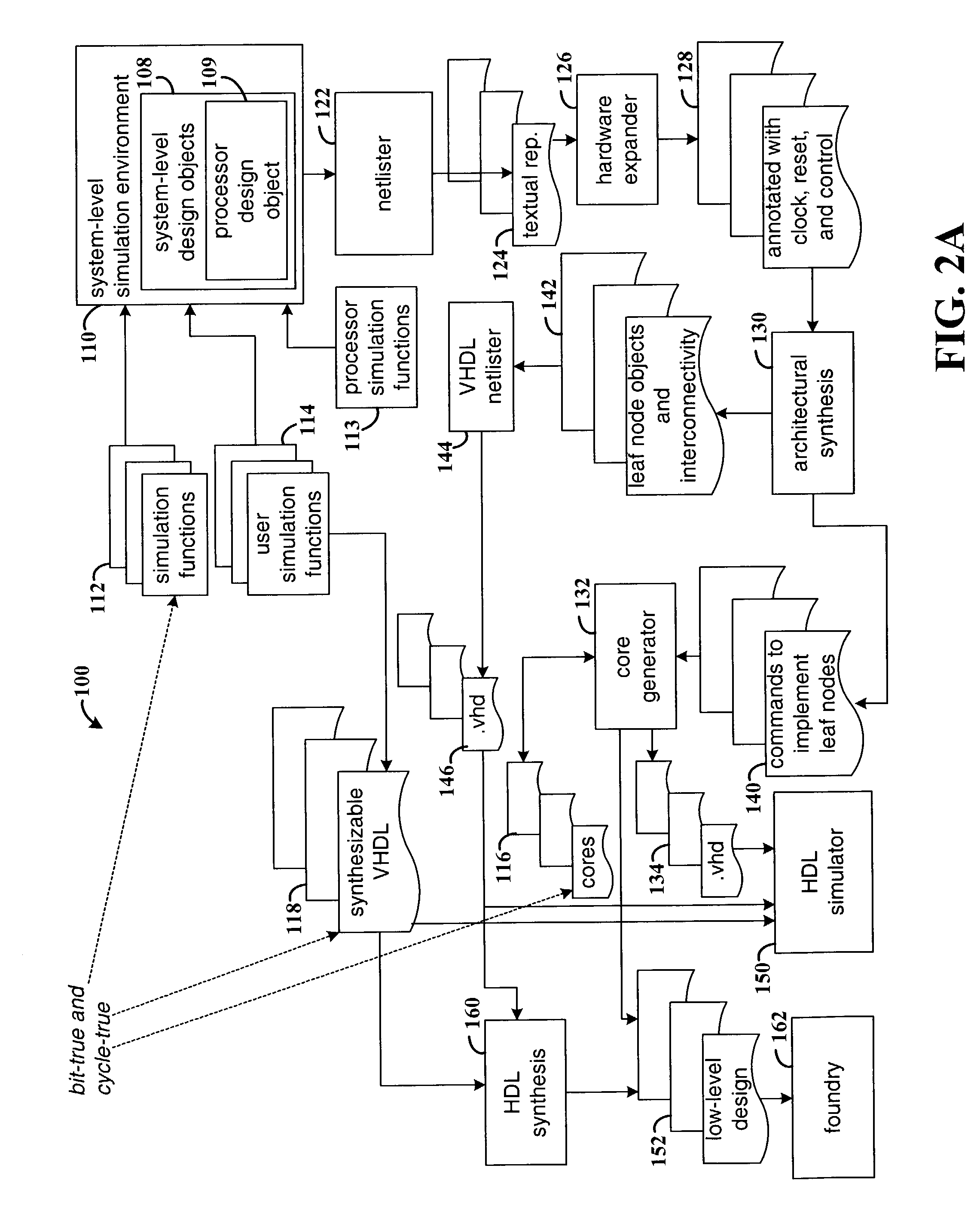

Method and system for modeling and automatically generating an embedded system from a system-level environment

InactiveUS7085702B1Electric pulse generatorAnalogue computers for nuclear physicsLevel designProcessor design

Method and system for modeling and automatically generating an embedded system from a system-level environment. A plurality of user-selectable system-level design objects are provided in the system-level environment. Each system-level design object is defined by a system-level function and is selectable by a system-level designer. A plurality of hardware-level design objects are also provided. Each hardware-level design object is configured to generate a hardware definition of a hardware-level function. Each system-level design object maps to one or more hardware-level design objects. A processor design object is provided which defines a processor. In response to selections made by the designer, a system-level design is instantiated in a system-level design file. The system-level design includes user-selected ones of the system-level and processor design objects. The system simulates behavior of the system-level design consistent with the processor, system-level functions, and behavior of a hardware definition from the hardware-level design objects that implement the user-selected ones of the system-level design objects.

Owner:XILINX INC

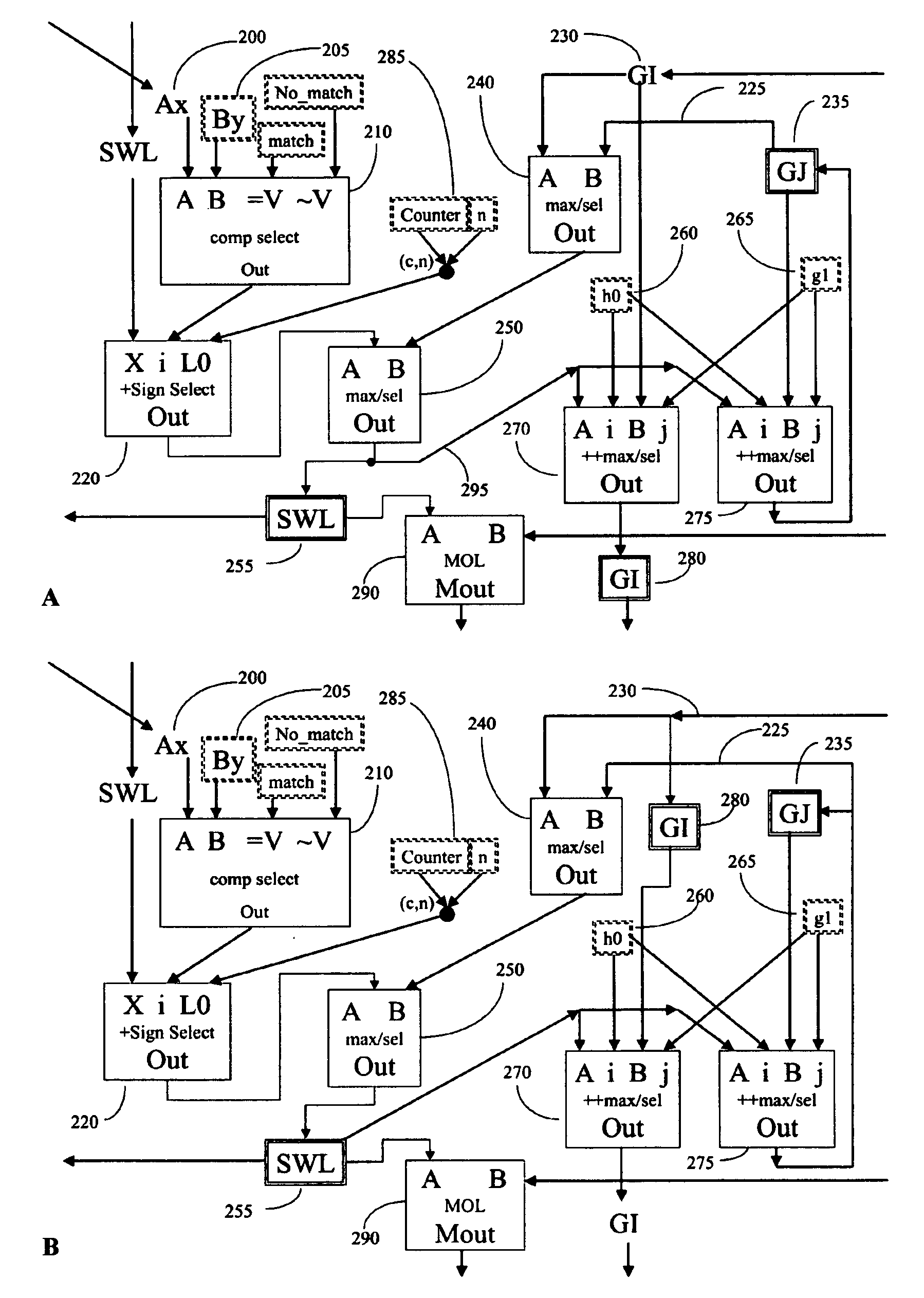

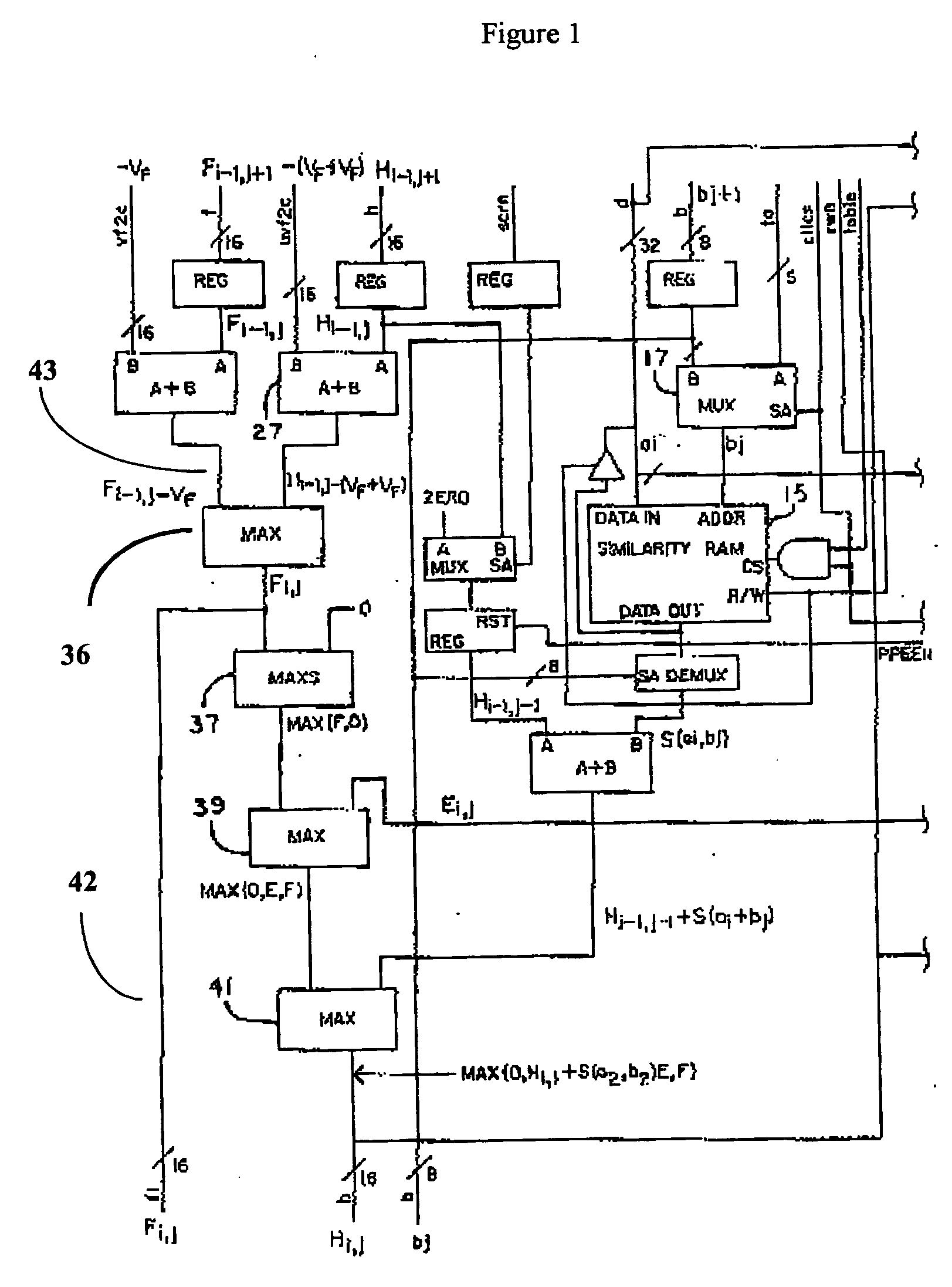

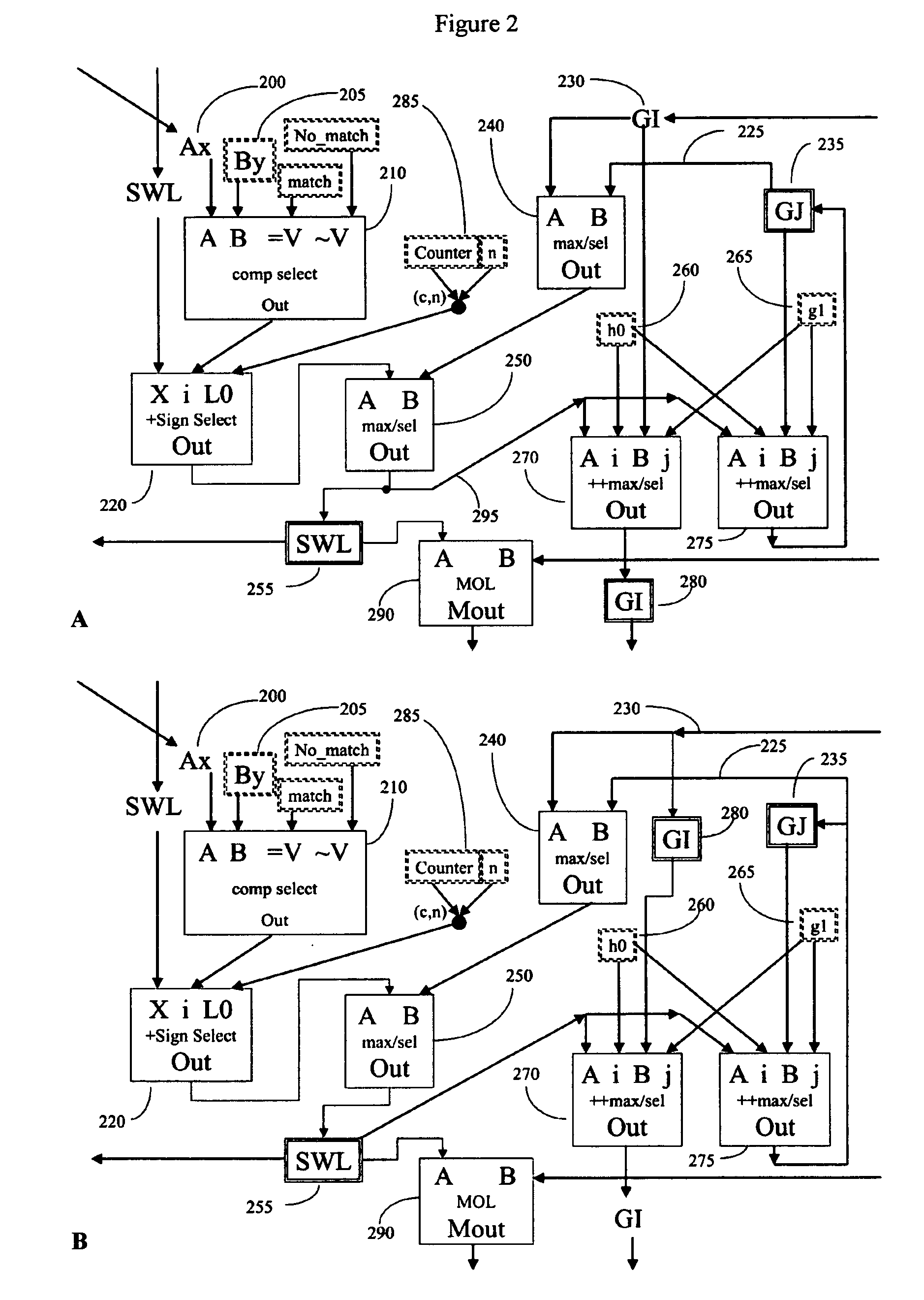

Processors for multi-dimensional sequence comparisons

InactiveUS20050228595A1Requirement to reduce computing speedEffect on its overall performanceDigital computer detailsBiological testingRecursive analysisHigh dimensional

Improved processors and processing methods are disclosed for high-speed computerized comparison analysis of multiple linear symbol or character sequences, such as biological nucleic acid sequences, protein sequences, or other long linear arrays of characters. These improved processors and processing methods, which are suitable for use with recursive analytical techniques such as the Smith-Waterman algorithm, and the like, are optimized for minimum gate count and maximum clock cycle computing efficiency. This is done by interleaving multiple linear sequence comparison operations per processor, which optimizes use of the processor's resources. In use, a plurality of such processors are embedded in high-density integrated circuit chips, and run synchronously to efficiently analyze long sequences. Such processor designs and methods exceed the performance of currently available designs, and facilitate lossless higher dimensional sequence comparison analysis between three or more linear sequences.

Owner:COOKE LAURENCE H +1

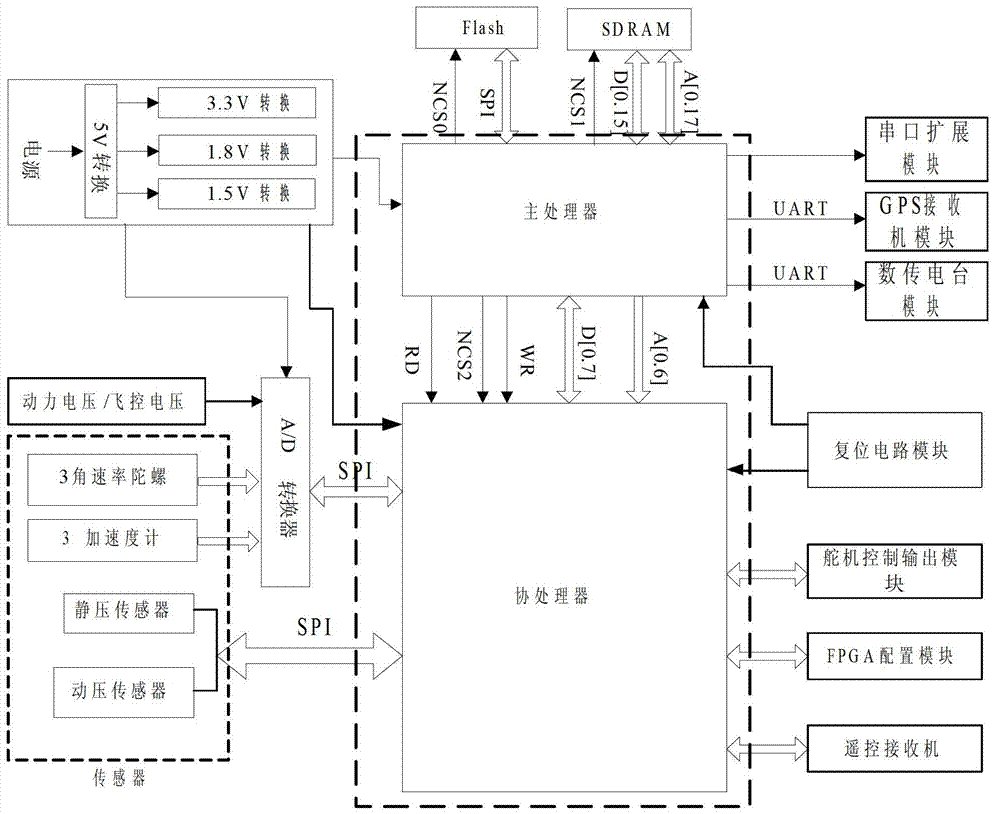

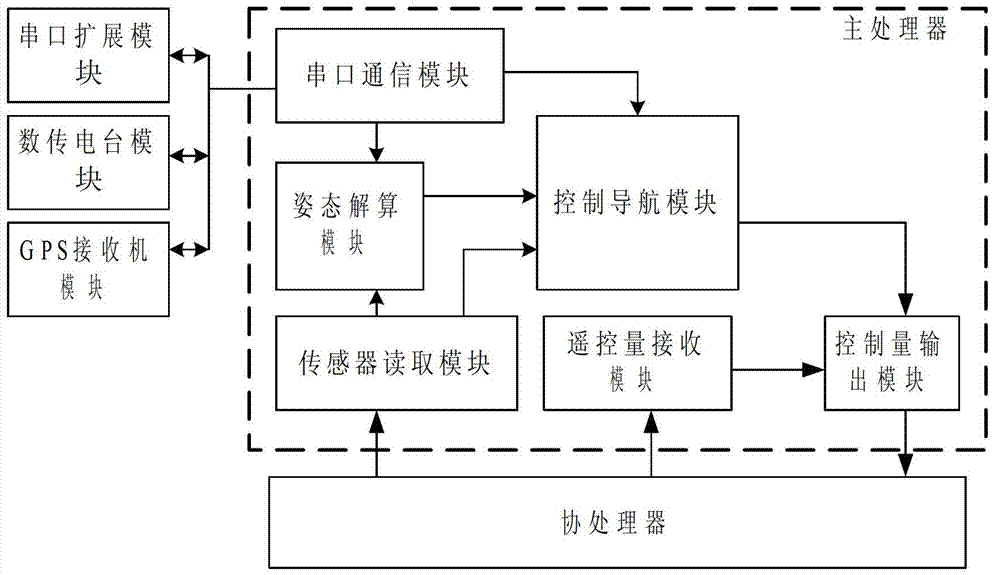

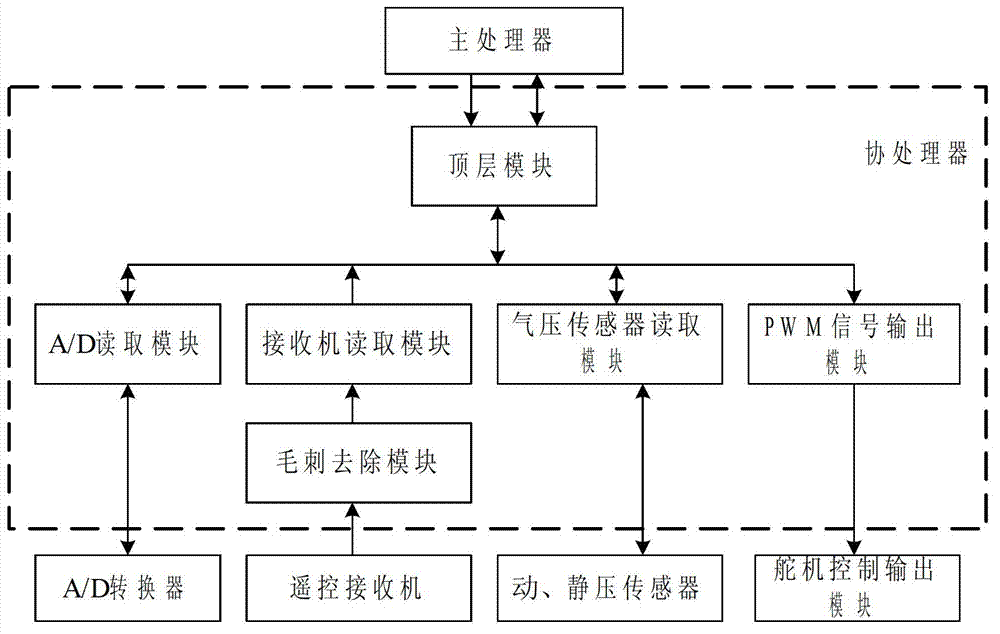

ARM and FPGA (Field Programmable Gate Array) architecture based autopilot of fixed wing unmanned aerial vehicle

InactiveCN102830708AClear division of laborImprove efficiencyPosition/course control in three dimensionsComputer moduleWorkload

The invention relates to an ARM and FPGA (Field Programmable Gate Array) architecture based autopilot of a fixed wing unmanned aerial vehicle, which belongs to the technical field of an embedded-control unmanned aerial vehicle. The autopilot uses two processors. The main processor is responsible for controlling calculation while the slave processor is responsible for collecting and outputting signals. The slave processor is designed as a peripheral device of the main processor. The main processor can operate the slave processor by way of operating the self storage space, so that extra workload due to data exchange between two processors is reduced, work is divided clearly, and the system response speed is fast. A design ideal of a top layer module with multiple bottom layers is adopted with distinct gradations, and operation is carried out by using a state machine in reading of an A / D (Analog / Digital) module, so that the work efficiency is higher.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

Interframe prediction processor with mechanism for providing locations of reference motion vectors

InactiveCN101127913APulse modulation television signal transmissionDigital video signal modificationMemory addressMotion vector

An interframe prediction processor designed for high-speed video coding and decoding. The interframe prediction processor has an address selector and a predictor calculator. The address selector receives information about MBAFF type and coding type. When performing motion compensation for a given MBAFF picture with reference to blocks surrounding a current block, the address selector provides memory addresses of reference motion vectors according to the coding type of the current block pair, as well as to the coding type of the reference blocks. The predictor calculator that determines a motion vector predictor for each constituent block of the current block pair based on reference motion vectors read out of the provided memory addresses.

Owner:SOCIONEXT INC

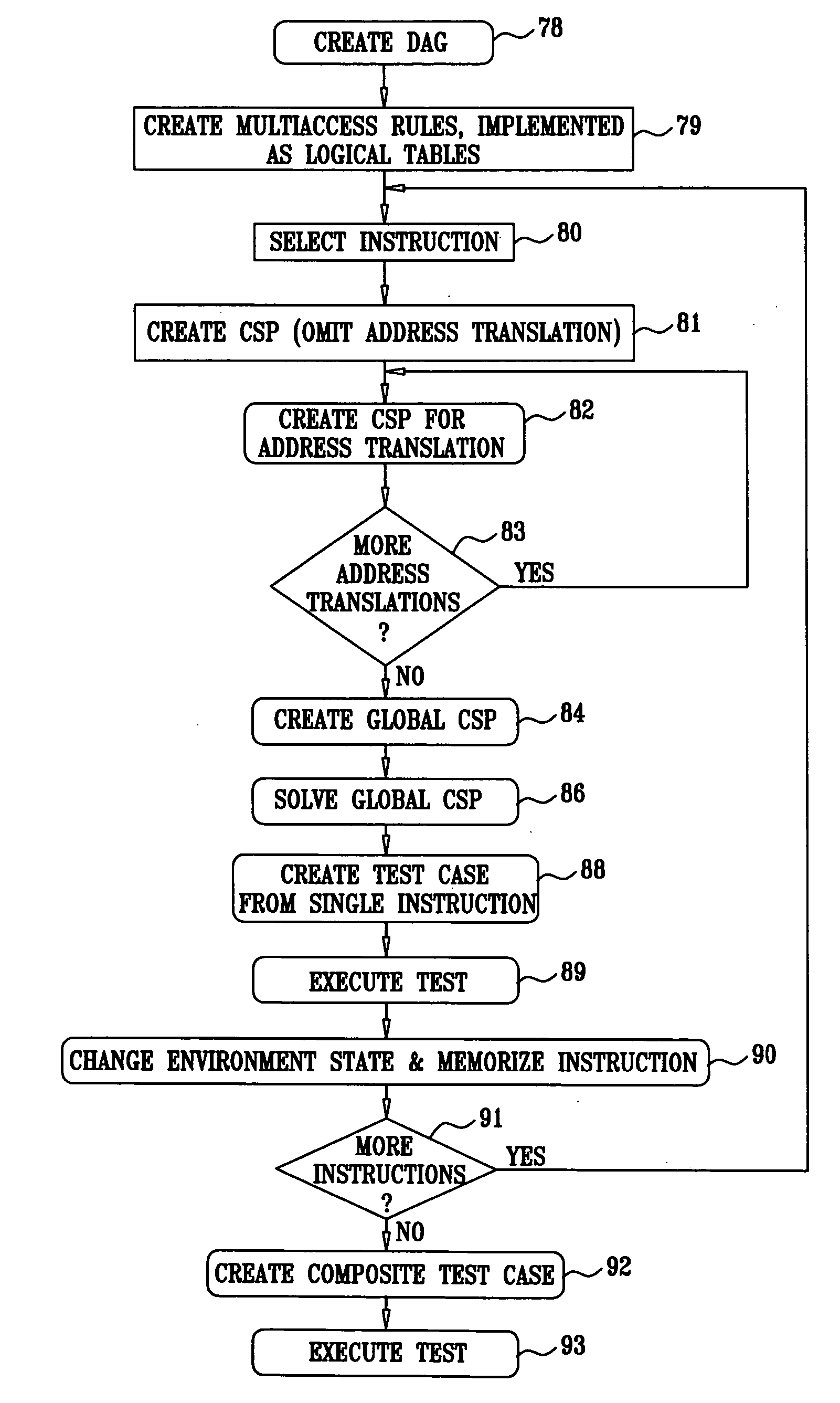

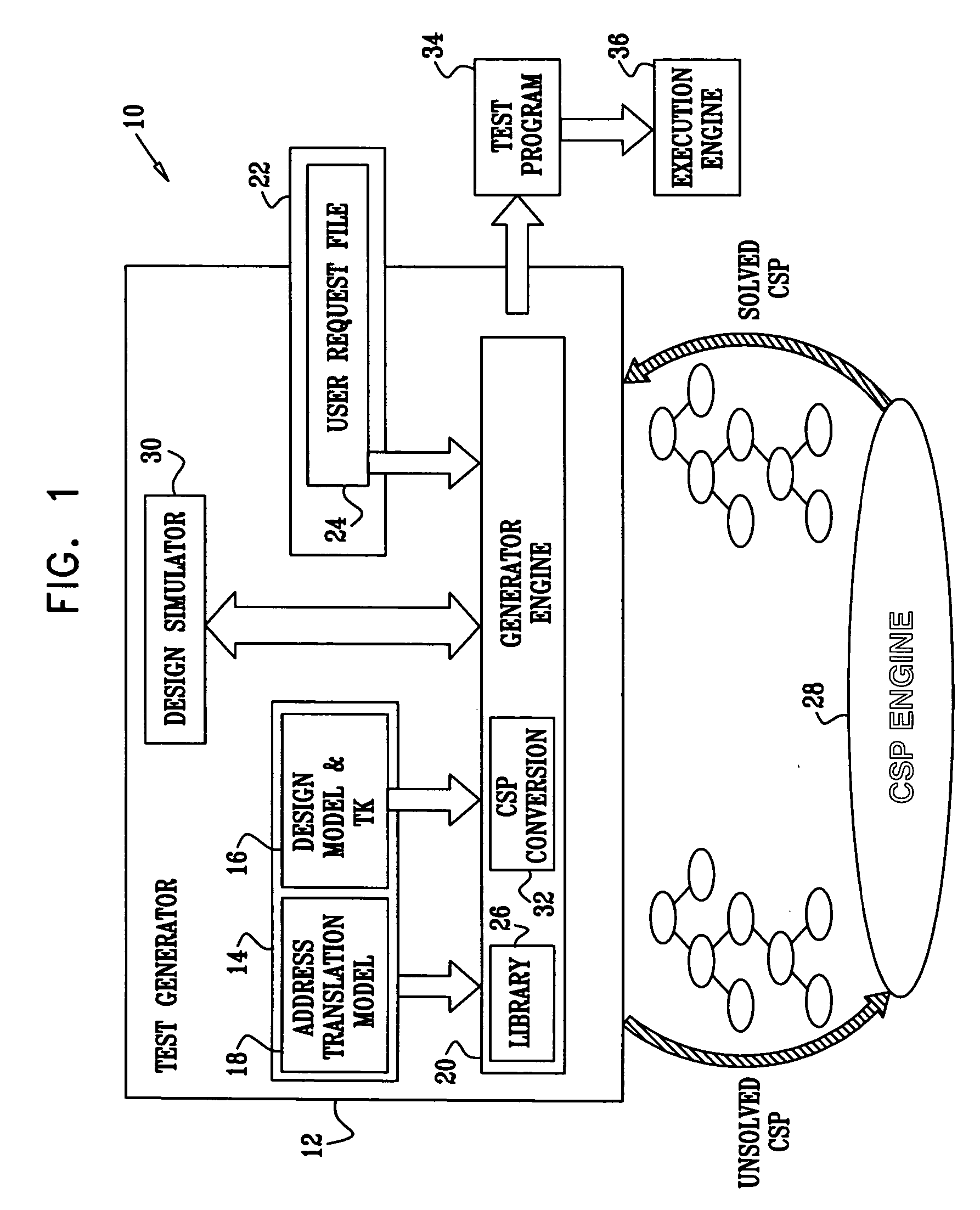

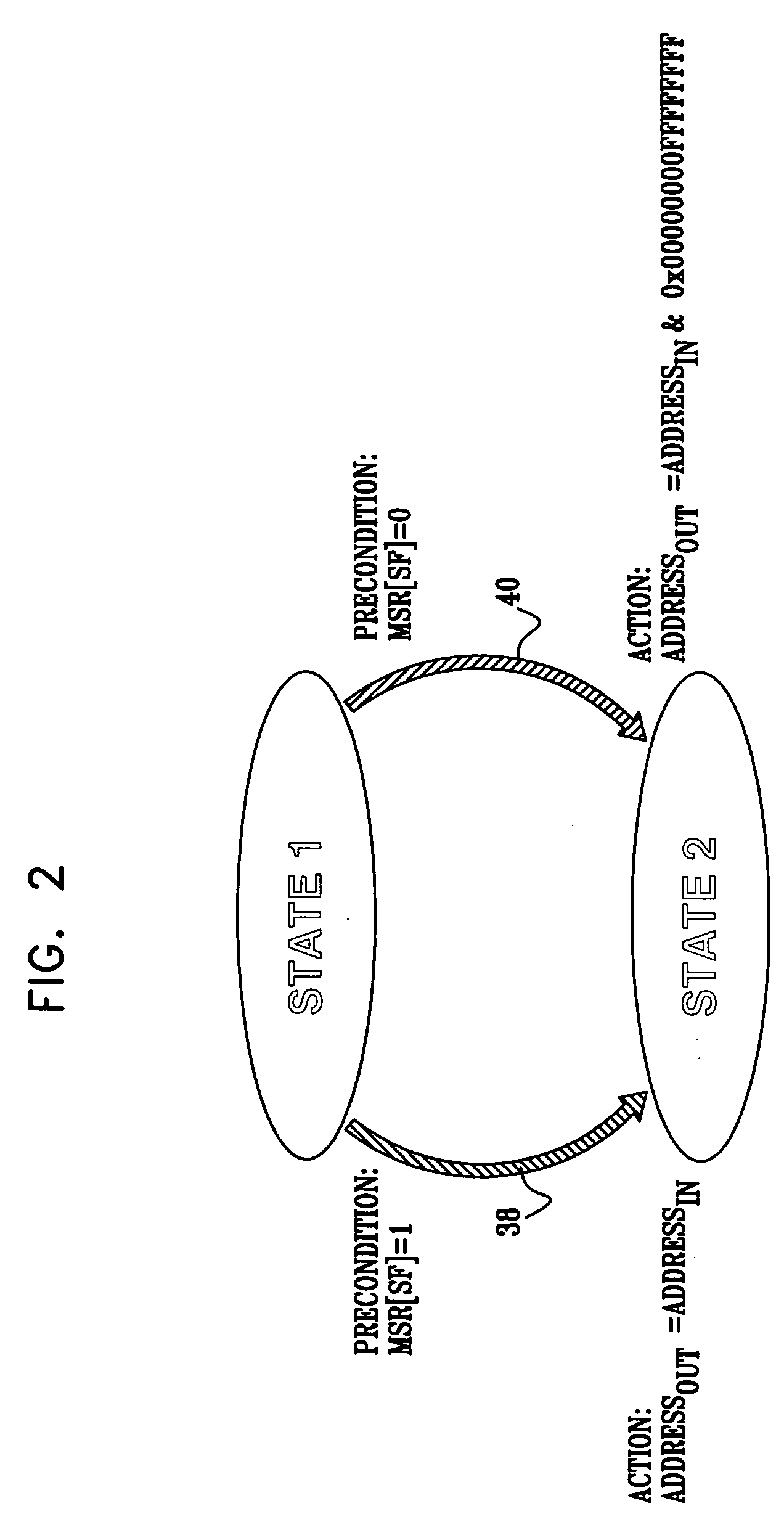

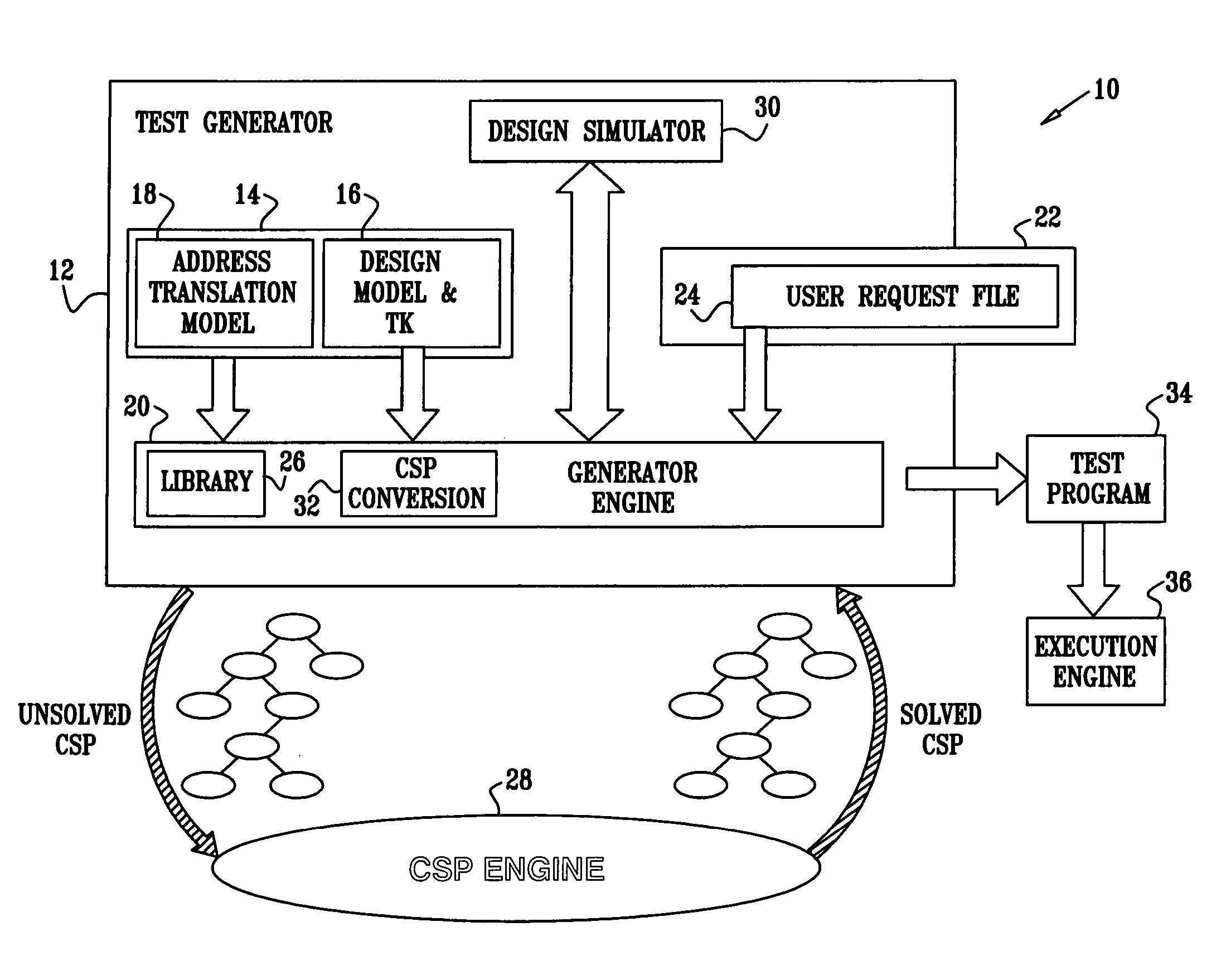

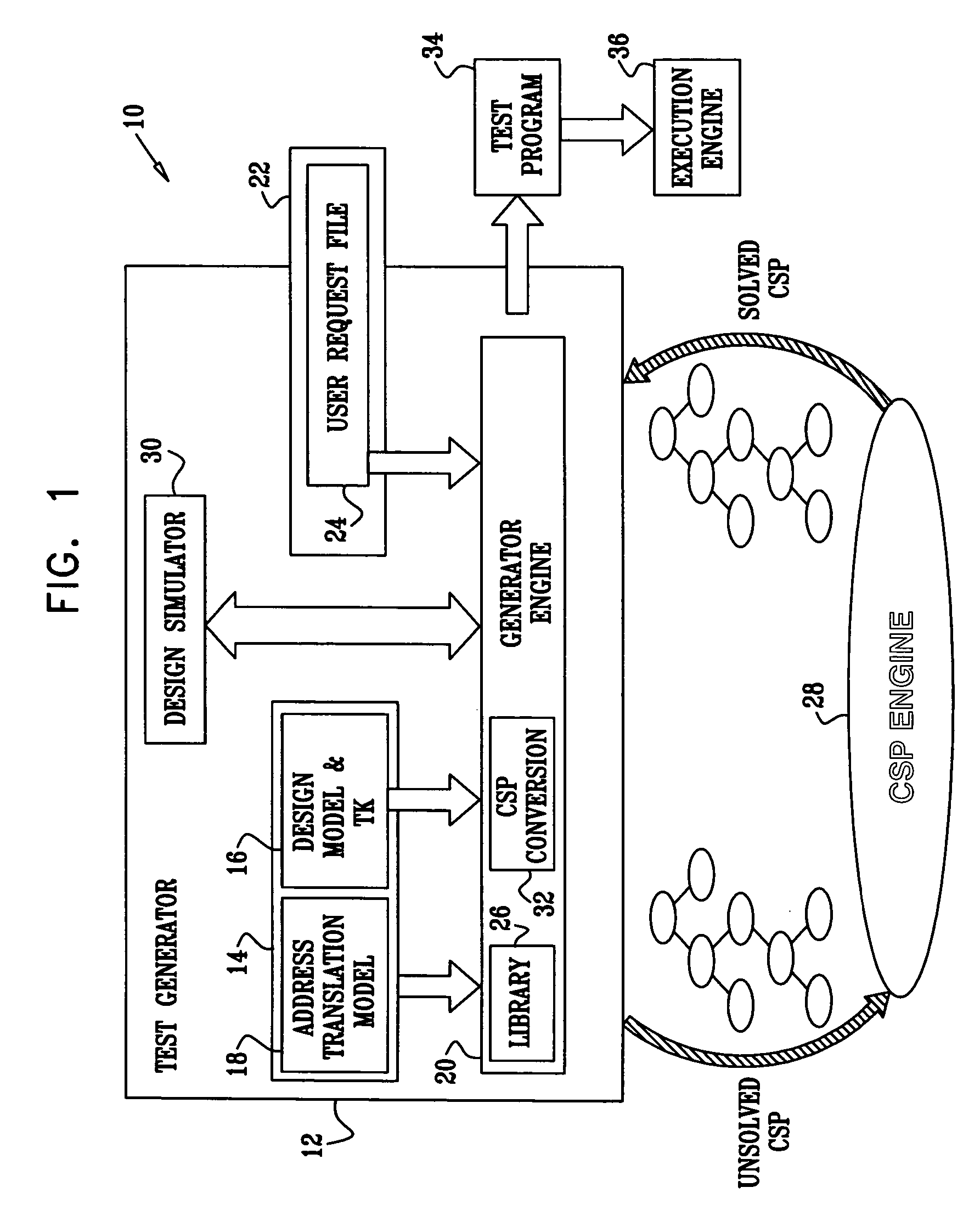

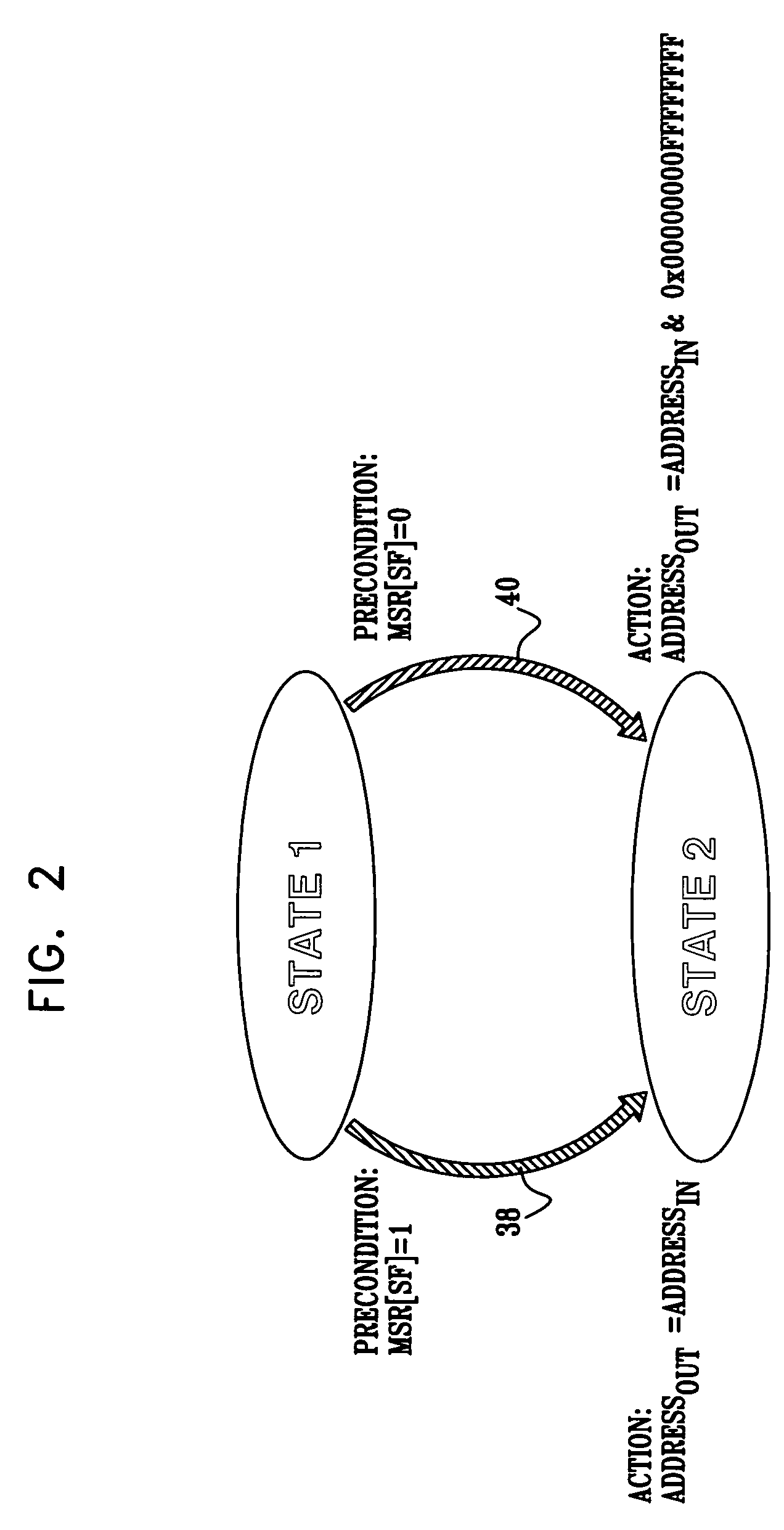

Modeling language and method for address translation design mechanisms in test generation

InactiveUS20050278702A1Large coverageLogical operation testingSoftware simulation/interpretation/emulationConstraint satisfaction problemModeling language

Methods and systems are disclosed that enhance the ability of a test generator to automatically deal with address translation in a processor design, and without need for creating specific code. A model of the address translation mechanism of a design-under-test is represented as a directed acyclic graph and then converted into a constraint satisfaction problem. The problem is solved by a CSP engine, and the solution used to generate test cases for execution. Using the model, testing knowledge can be propagated to models applicable to many different designs to produce extensive coverage of address translation mechanisms.

Owner:GLOBALFOUNDRIES INC

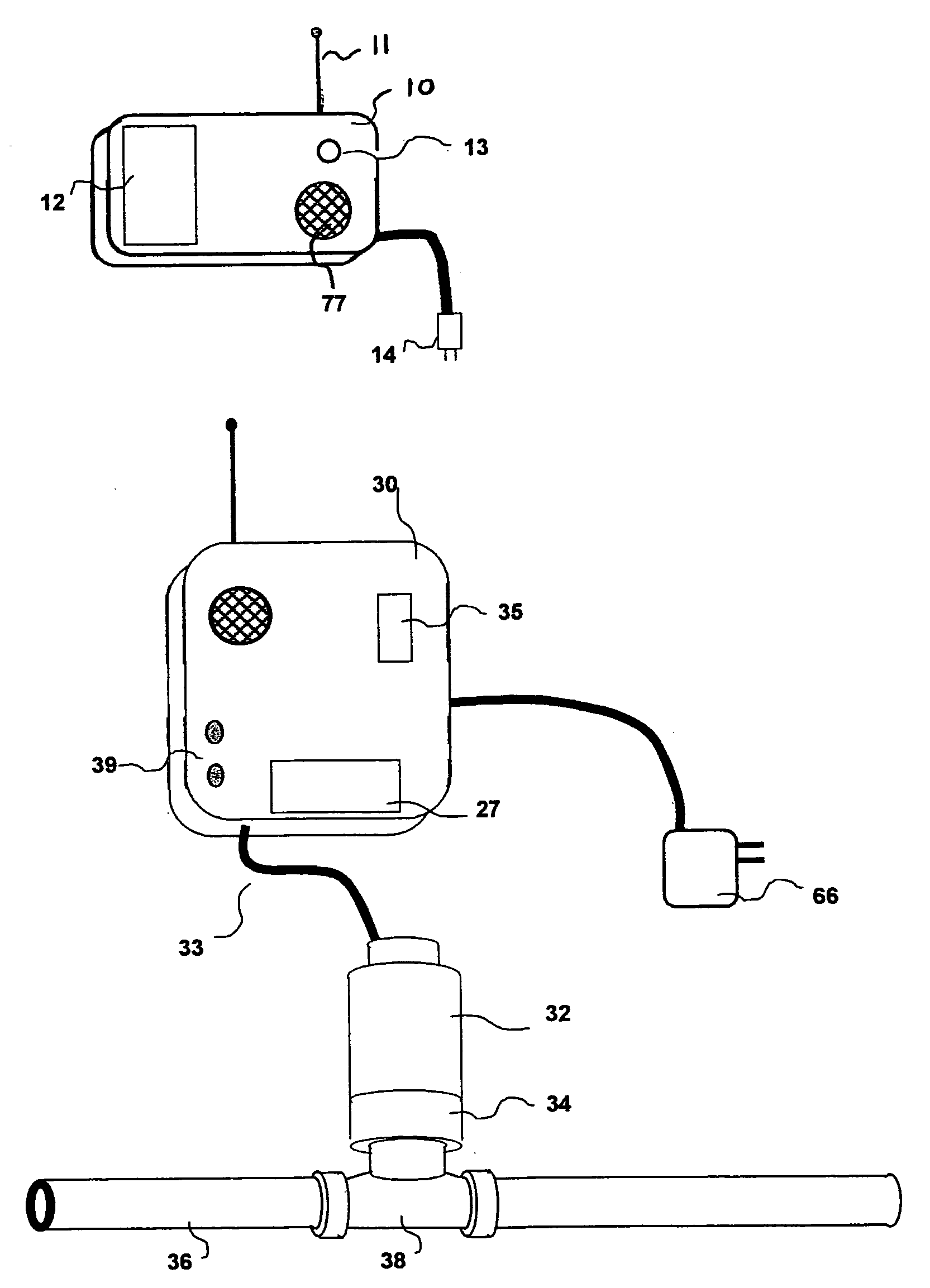

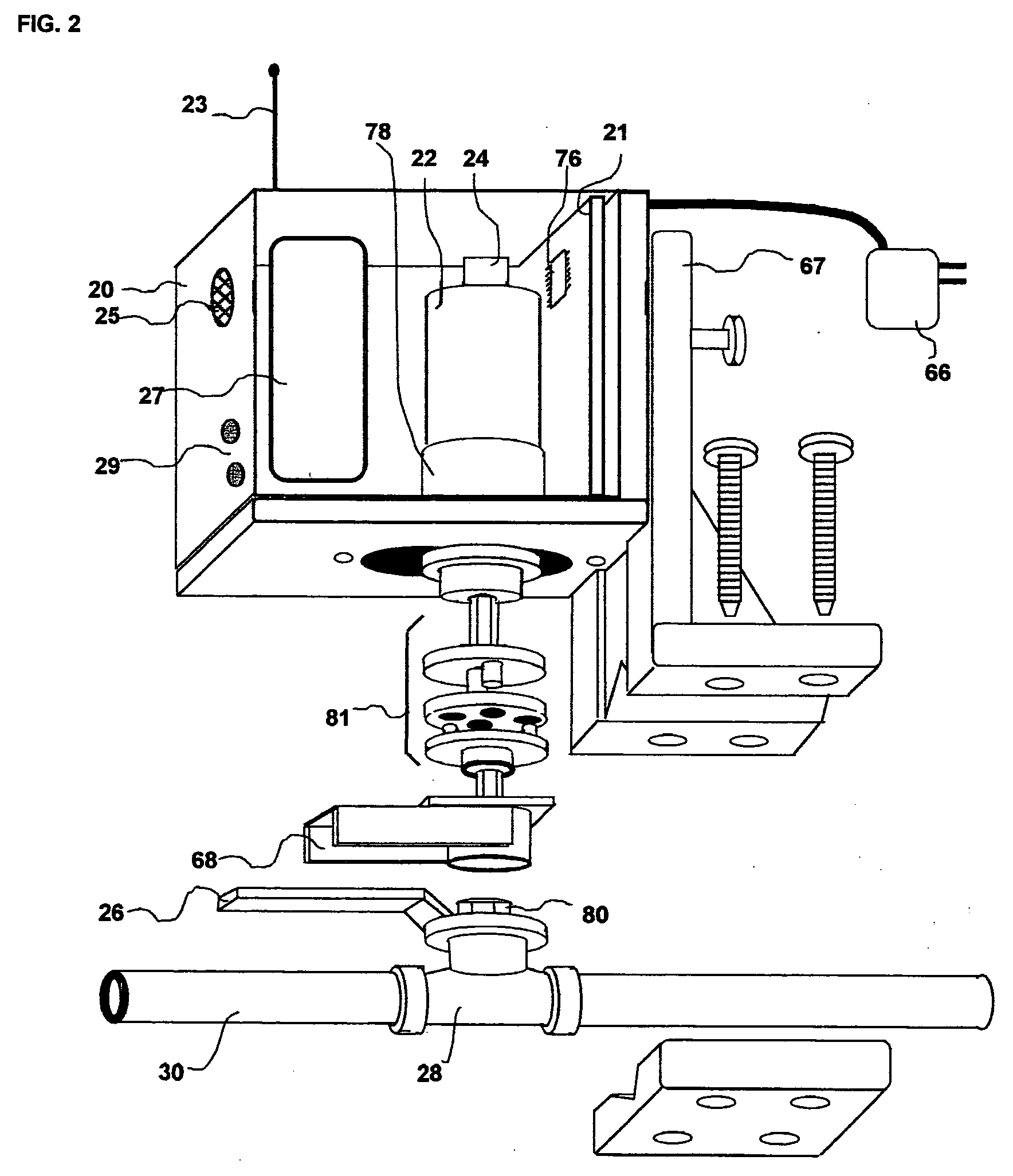

Secure wireless leak detection system

InactiveUS20060124171A1Easy to installReduce power consumptionDetection of fluid at leakage pointOther washing machinesTransceiverMagnetic valve

A method utilizing a wireless leak detection and prevention system, used for preventing property damage and personal injury caused by liquid or gas leak. The system comprised of a wireless, battery operated apparatus having sensor(s) incorporated with an RF transmitter, used for detecting liquid or gas leaks, and transmits signal(s) to a wireless valve shutoff control unit. The valve shutoff control unit containing an RF transceiver and a processor designed to receive the detected signals and activate a supervised solenoid or motorized valve shut-off mechanism to stop the detected leak. In a preferred embodiment of the invention, the wireless valve control unit is connected to a motor, which is mounted on manual shutoff valve. Wherein the valve control unit activates the motor to produce torque to turn the valve towards a close position in response to a received detected leak signal from a sensor. An electronic or electromechanical circuitry is provided, to detect motor or gear turn cycles. The motor rotation is being controlled by the valve control unit processor, which stops motor rotation in response to a detected preset number of motor turn cycles. A digital, voice, SMS text message phone dialer is add to dispatch the detected leak signals, and notify monitoring personnel of the supervised system operation status. And provide user access to turn on or off a valve(s) from a remote location.

Owner:RUGGIERI MONICA L +1

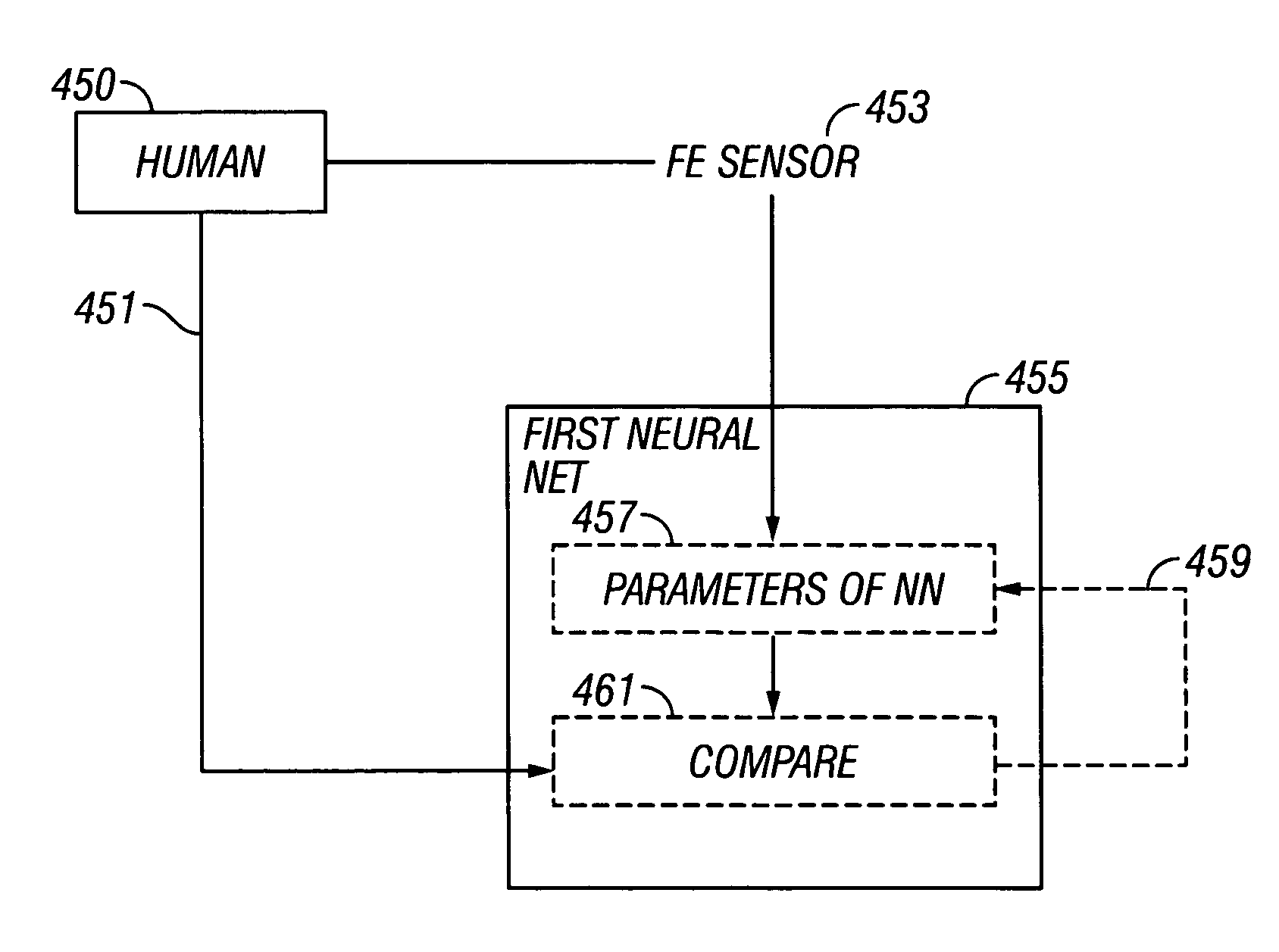

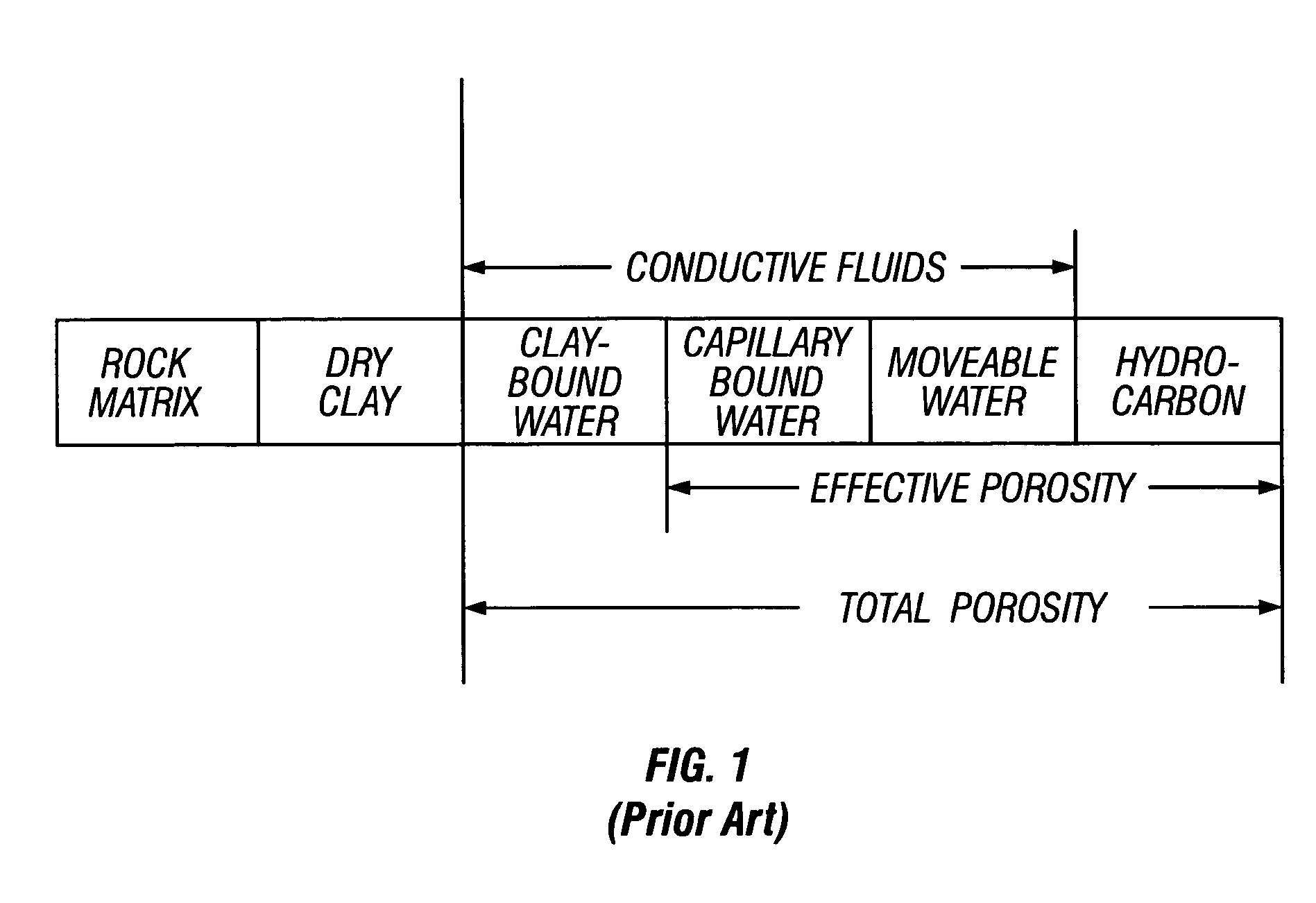

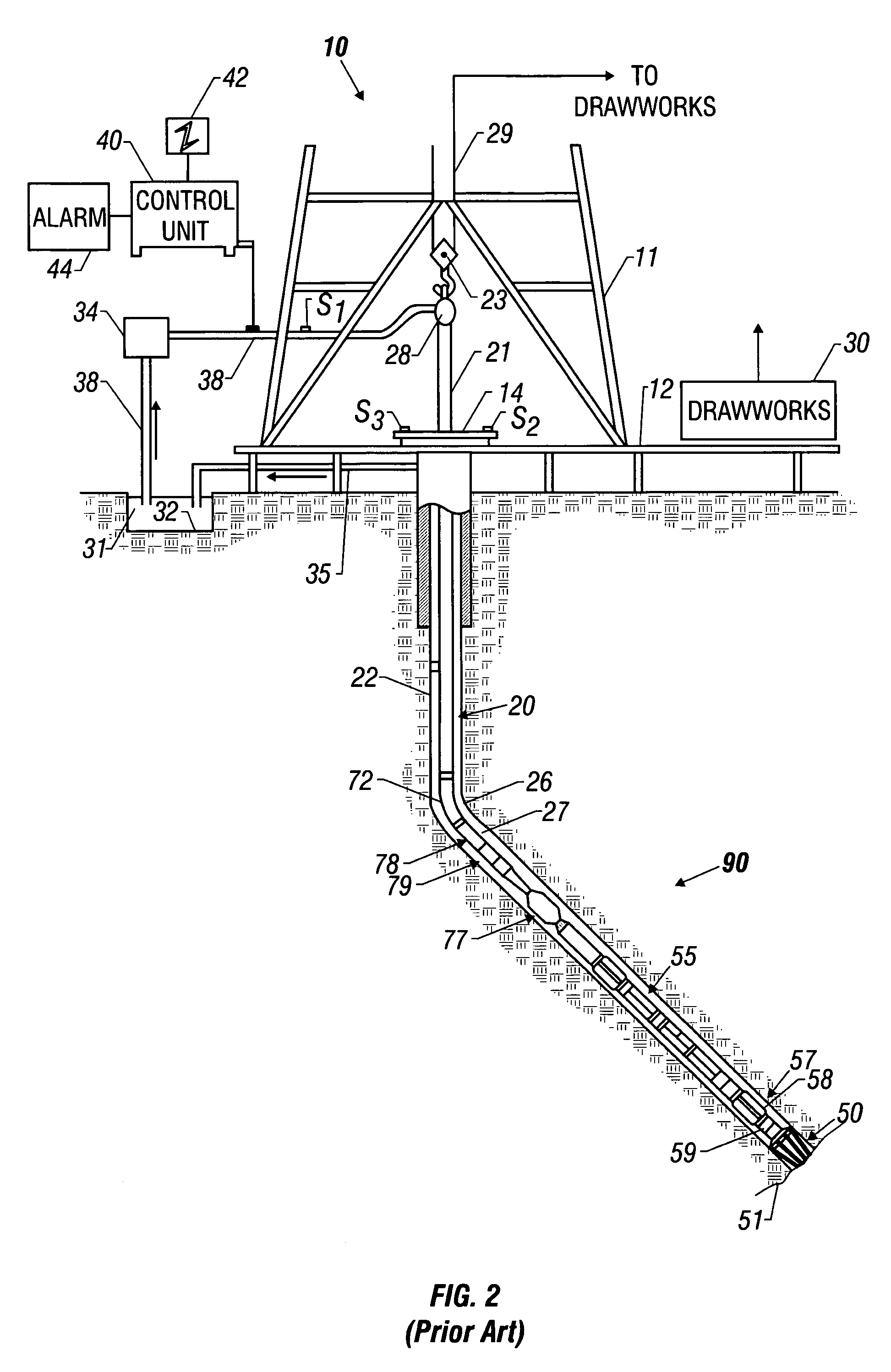

Downhole NMR processing

InactiveUS7193414B2Reduce power consumptionElectric/magnetic detection for well-loggingConstructionsLithologyPulse sequence

An expert system is included in a downhole processor designed to acquire and process NMR data downhole in real time. The downhole processor controls the acquisition of the NMR data based at least in part on instructions transmitted downhole from a surface location and at least in part on evaluation of downhole conditions by the expert system. The downhole conditions include drilling operation conditions (including motion sensors) as well as lithology and fluid content of the formation obtained from other MWD data. The wait time, number of echos, number of repetitions of an echo sequence, interecho time, bandwidth and shape of the tipping and refocusing pulses may be dynamically changed. Data processing is a combination of standard evaluation techniques. Selected data and diagnostics are transmitted uphole. The expert system may be implemented as a two stage neural net. The first stage does the formation evaluation and the second stage controls the NMR pulse sequence.

Owner:BAKER HUGHES INC

Processing core with programmable microcode unit

A method and circuit arrangement utilize a programmable microcode unit that is capable of being programmed via software to modify the instruction sequences output by the microcode unit in response to microcode instructions issued to the microcode unit. Among other benefits, a programmable microcode unit consistent with the invention enables customization of a processor design to handle specific applications or tasks, as well as to support specific hardware configurations such as specific execution units. In addition, a programmable microcode unit may be updatable, e.g., to correct bugs or faults found in previous instruction sequences supported by the unit.

Owner:IBM CORP

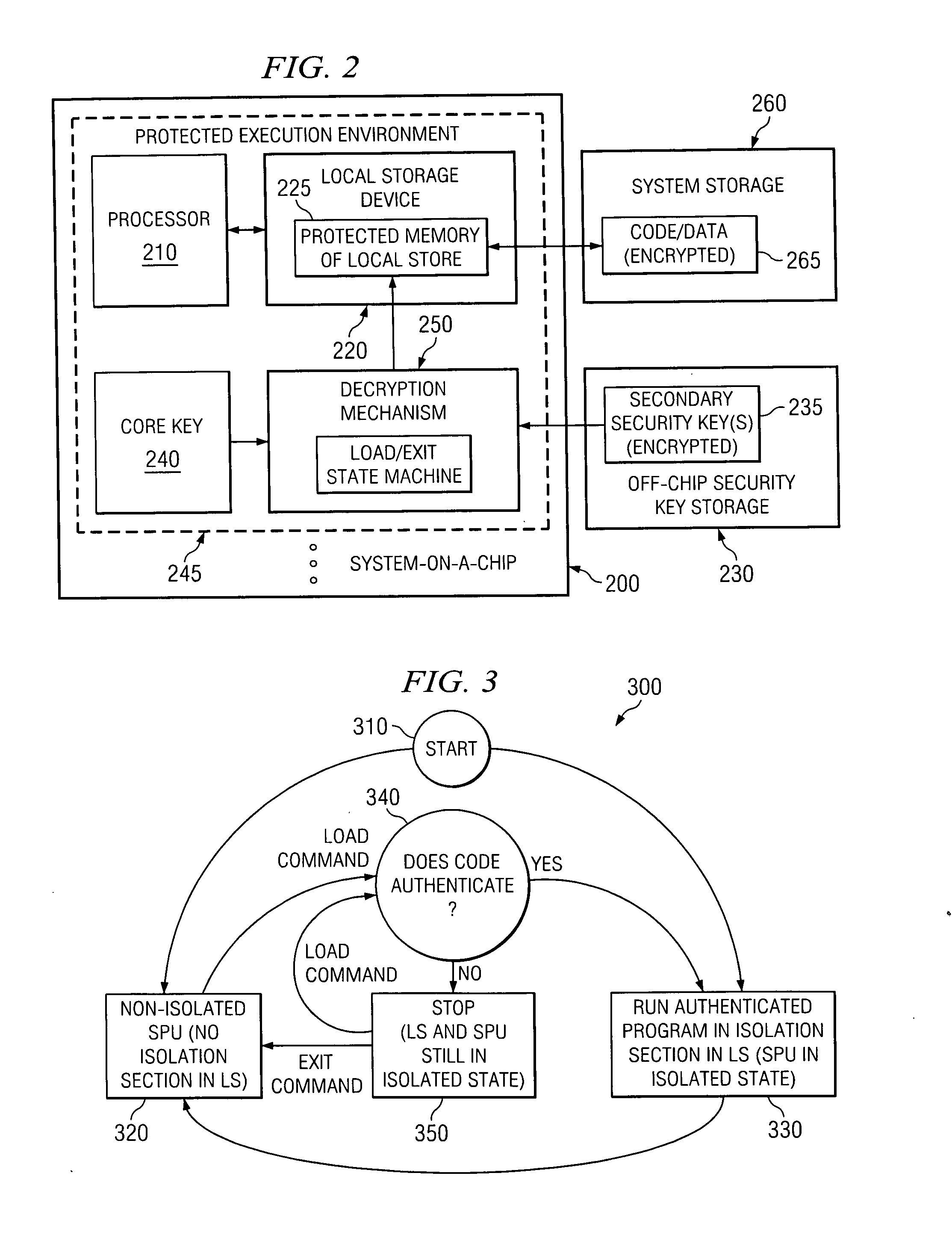

Apparatus and method for providing key security in a secure processor

InactiveUS20070180271A1Volume/mass flow measurementUser identity/authority verificationKey storageProcessor design

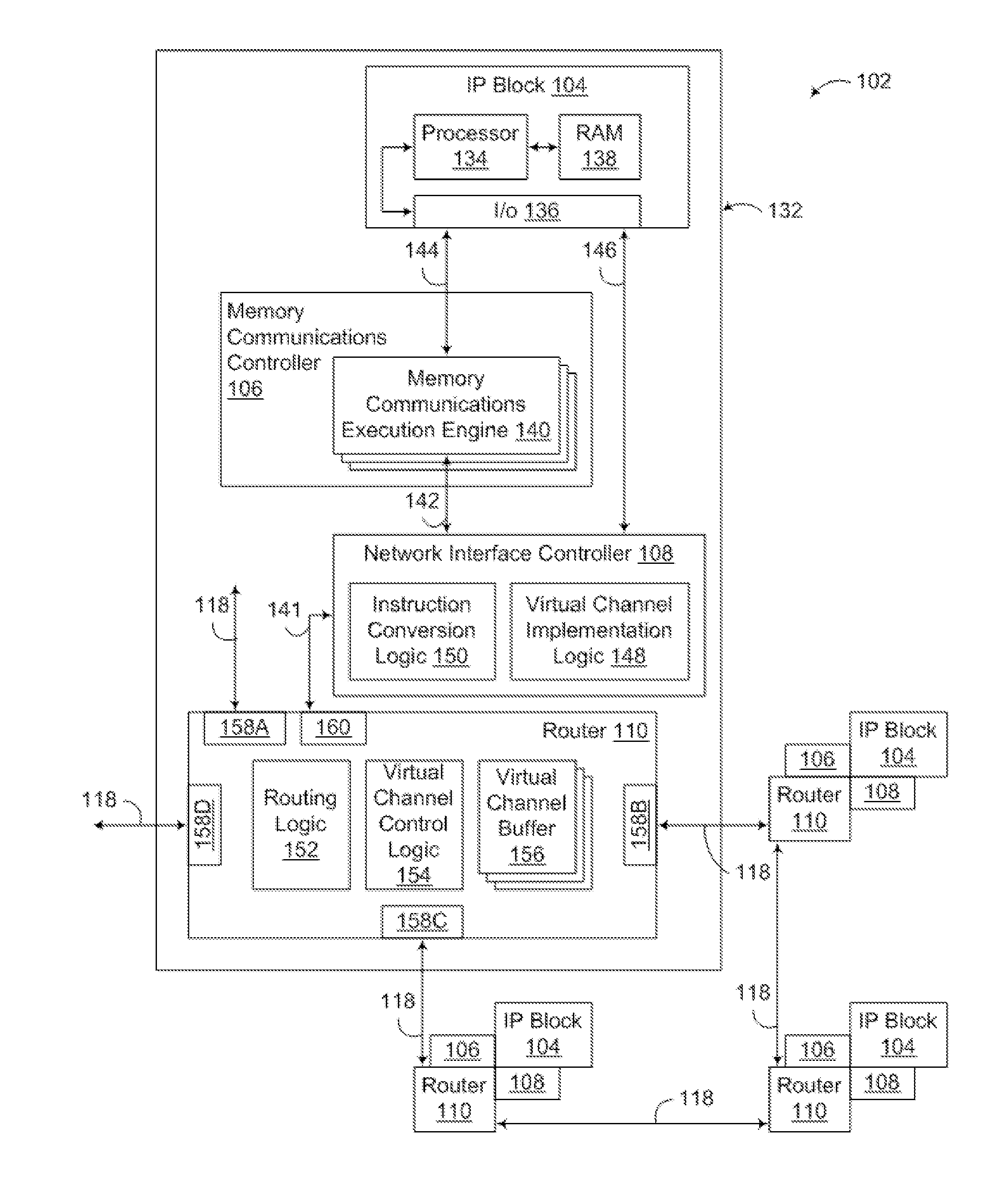

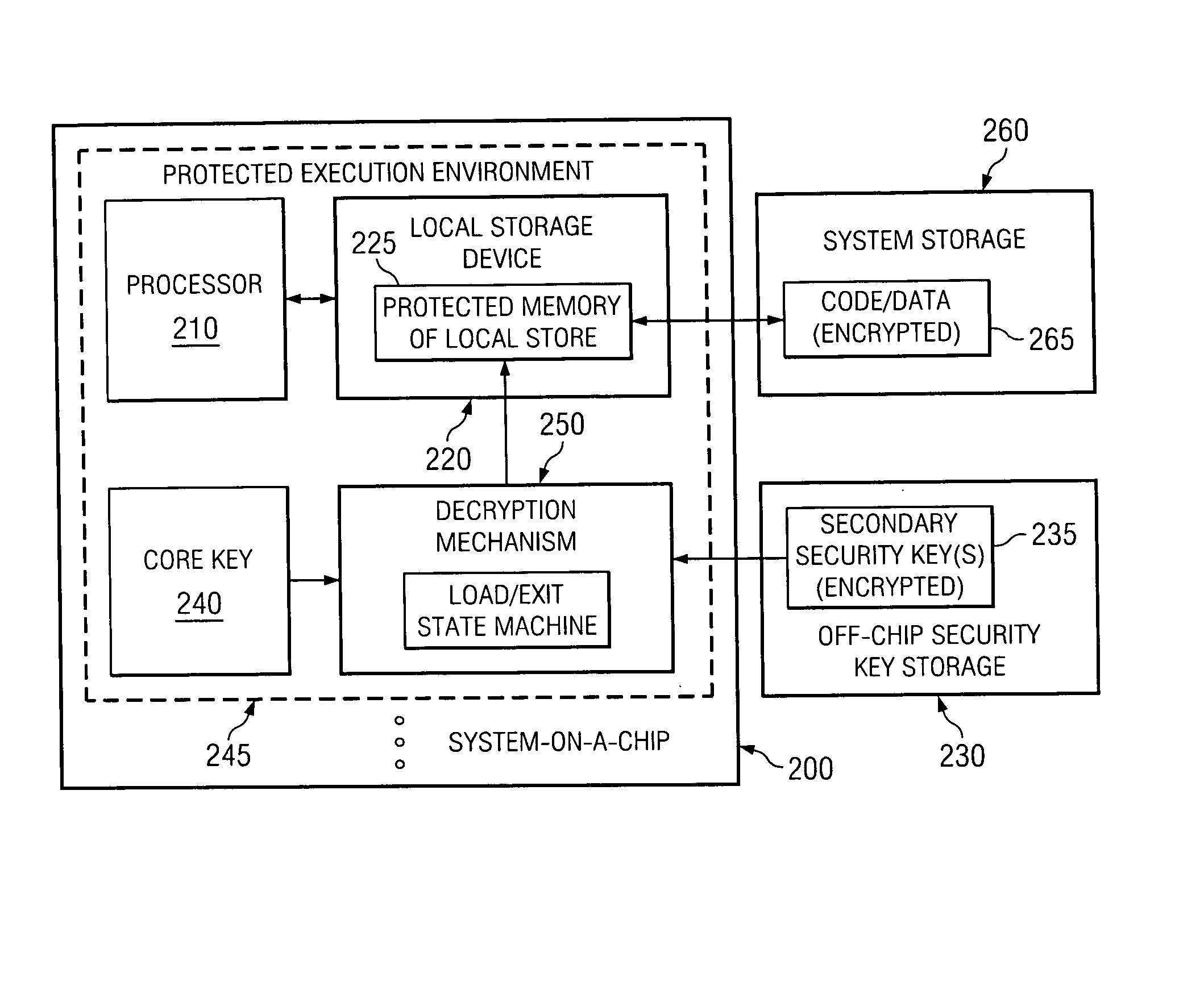

An apparatus and method for providing key security in a secure processor are provided. With the apparatus and method, a two-tiered key security mechanism is provided. On a first tier, a decryption mechanism and a fixed size storage area for a core key are hard-wired into the chip design. It is this first tier that is common to all systems and customers utilizing the processor design. On a second tier, off-chip but within the system is a secondary security key storage device that stores all the keys that are required by the particular system architecture. The off-chip storage device is programmed with the necessary keys before the system is shipped to the customer and thus, provides the needed flexibility. For protection, the keys are stored as an encrypted image using the core key stored on-chip.

Owner:IBM CORP +1

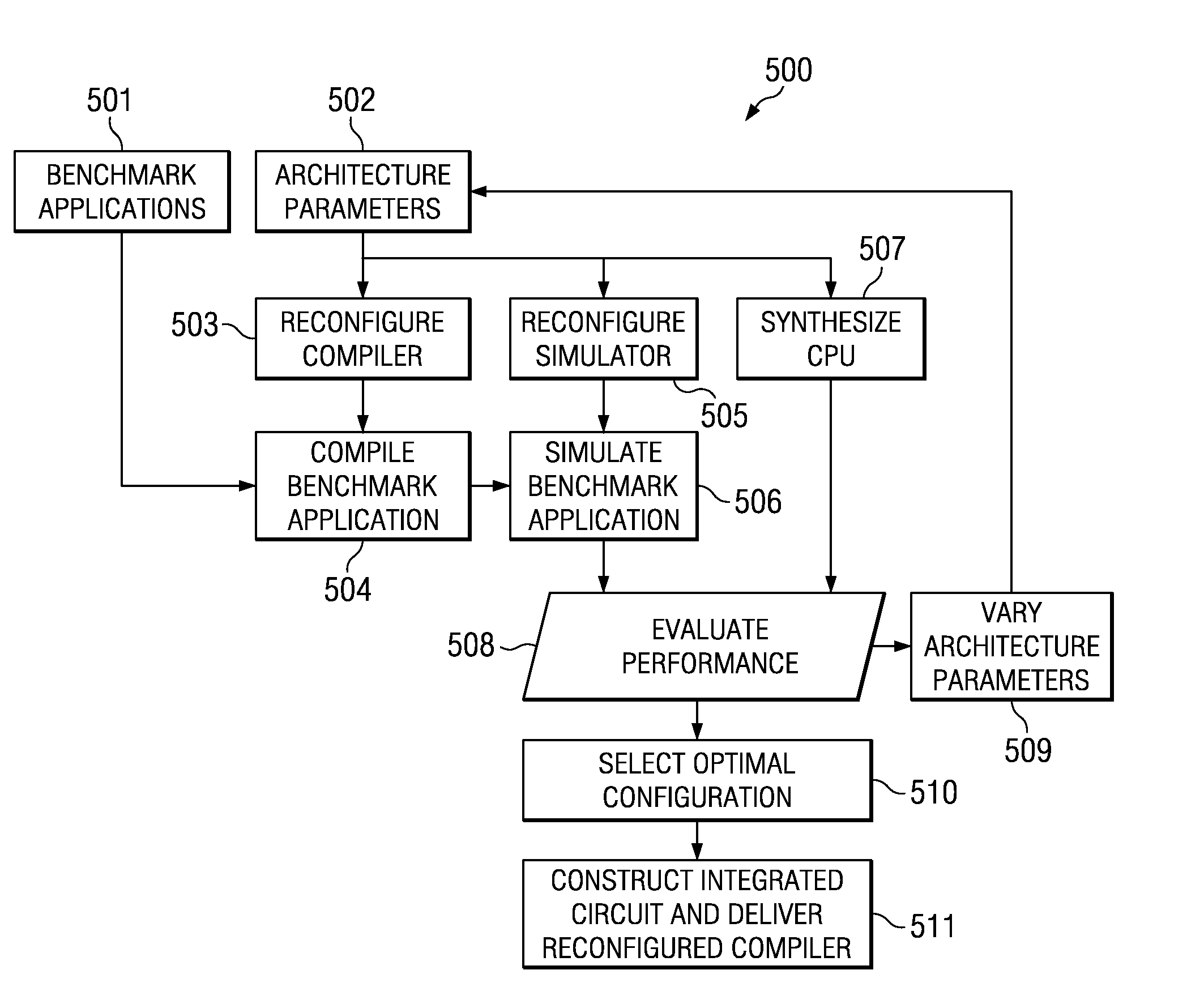

Method for Design of Programmable Data Processors

ActiveUS20080177996A1Short timeRapidly evaluate architecture alternativeDigital computer detailsData resettingIC programmingProcessor design

A method of integrated circuit programmed data processor design includes selecting a benchmark application, selecting an initial set of architecture parameters, reconfiguring a compiler for the selected architecture parameters, compiling the benchmark, reconfiguring a data processor simulator to the selected architecture parameters, running the complied benchmark on the reconfigured simulator, automatically synthesizing an integrated circuit physical layout and evaluating performance of the selected architecture parameters against predetermined criteria. The method varies the selected architecture parameters upon failure to meet criteria until evaluation of the selected architecture parameters meets the criteria.

Owner:TEXAS INSTR INC

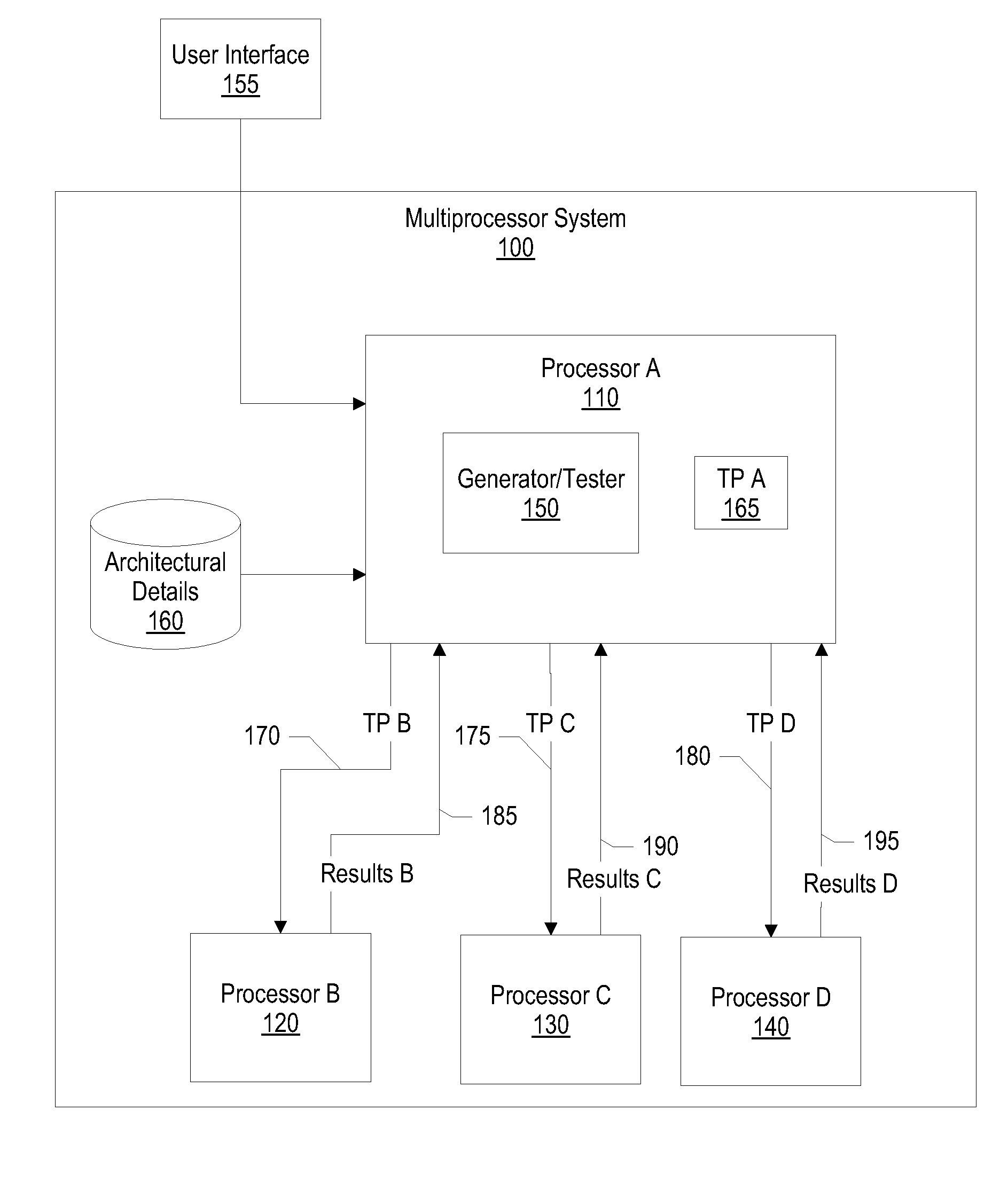

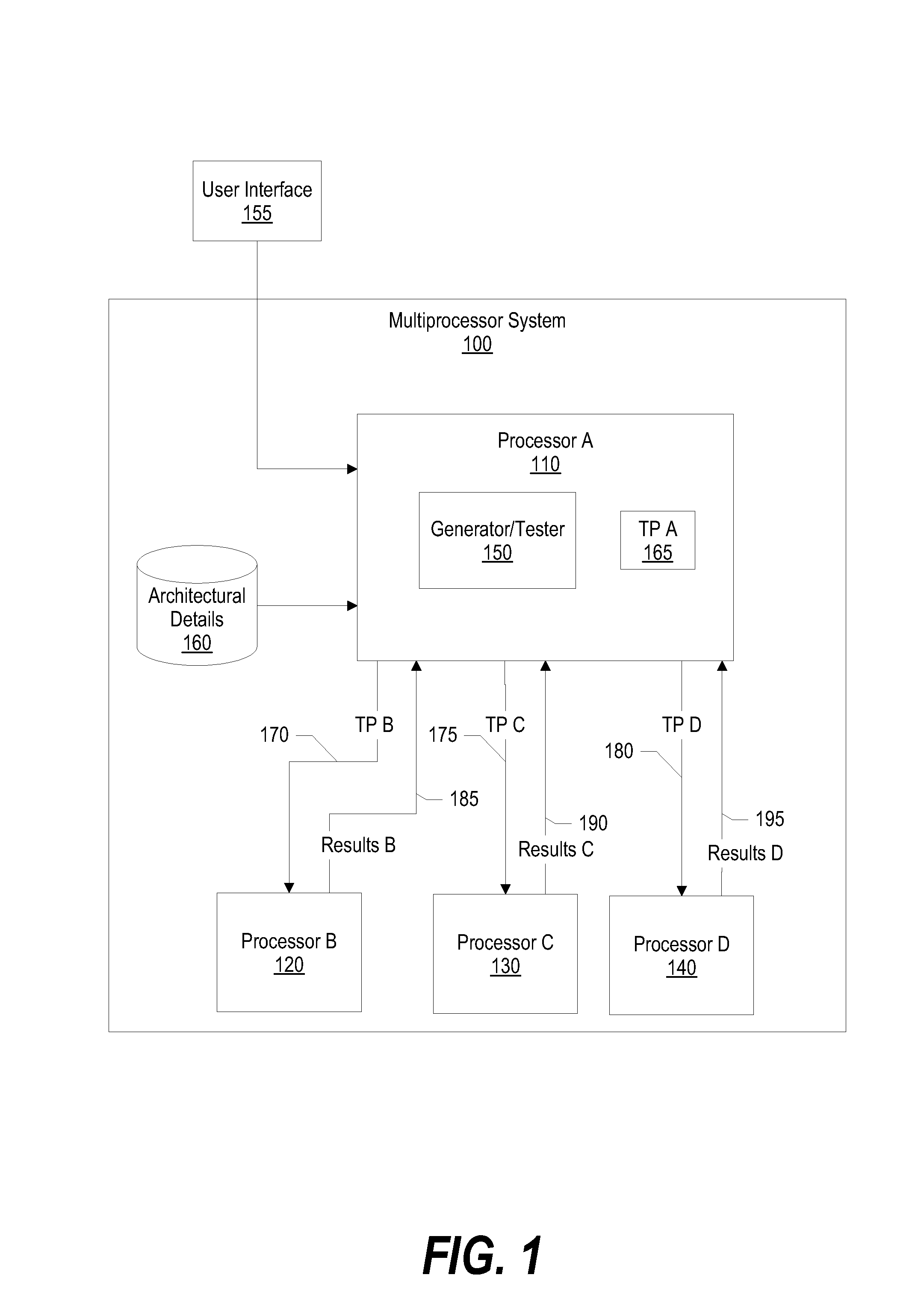

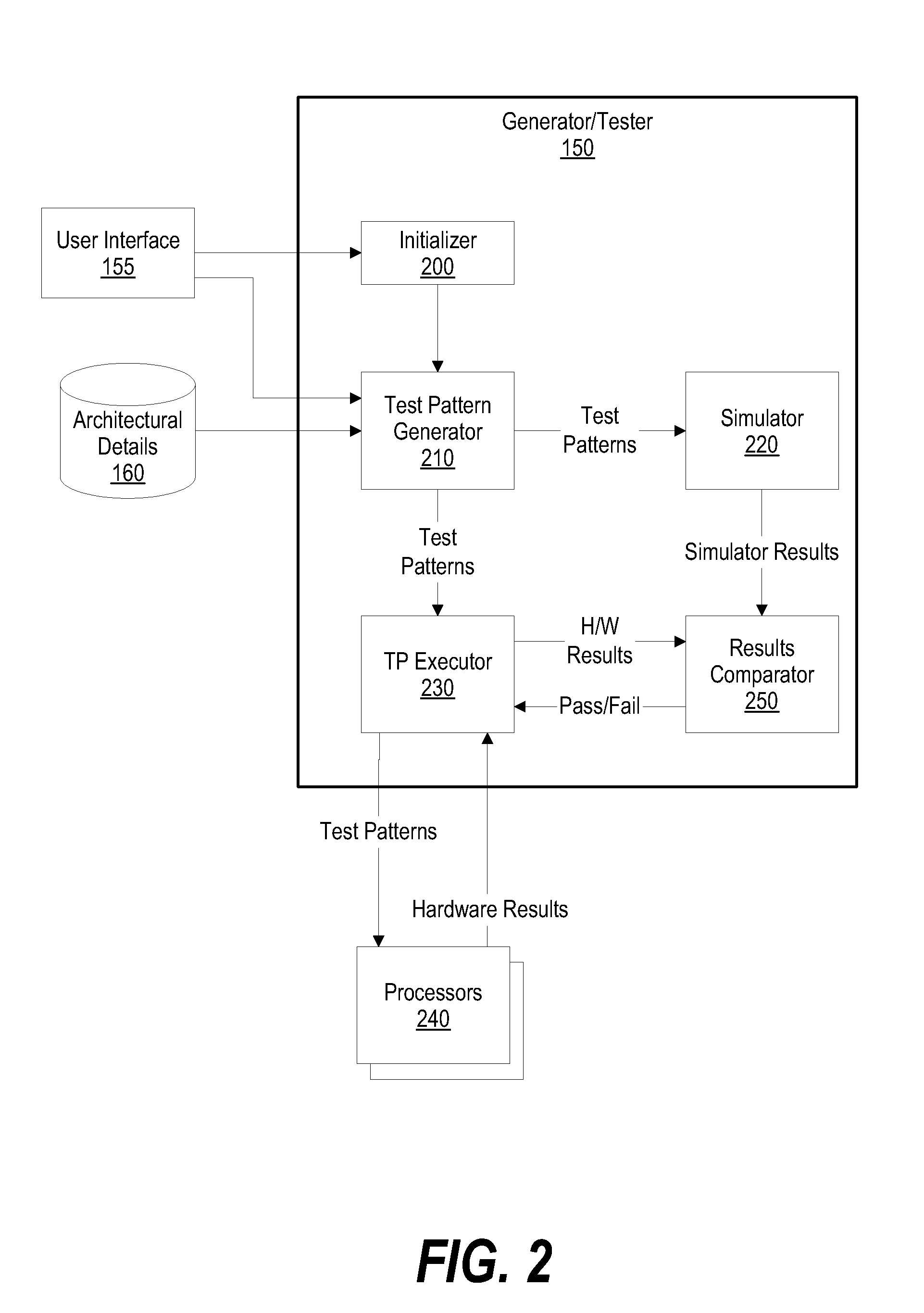

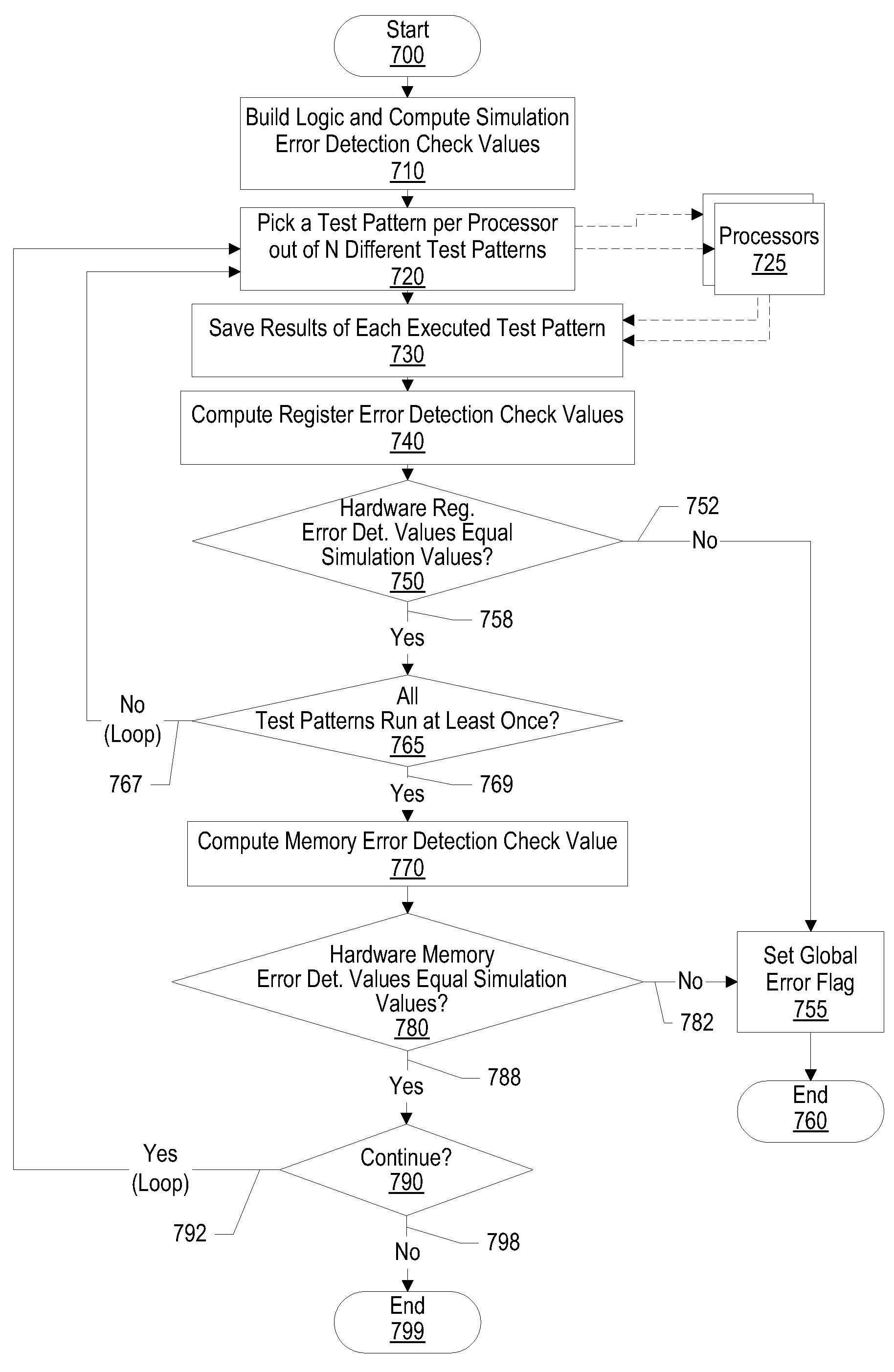

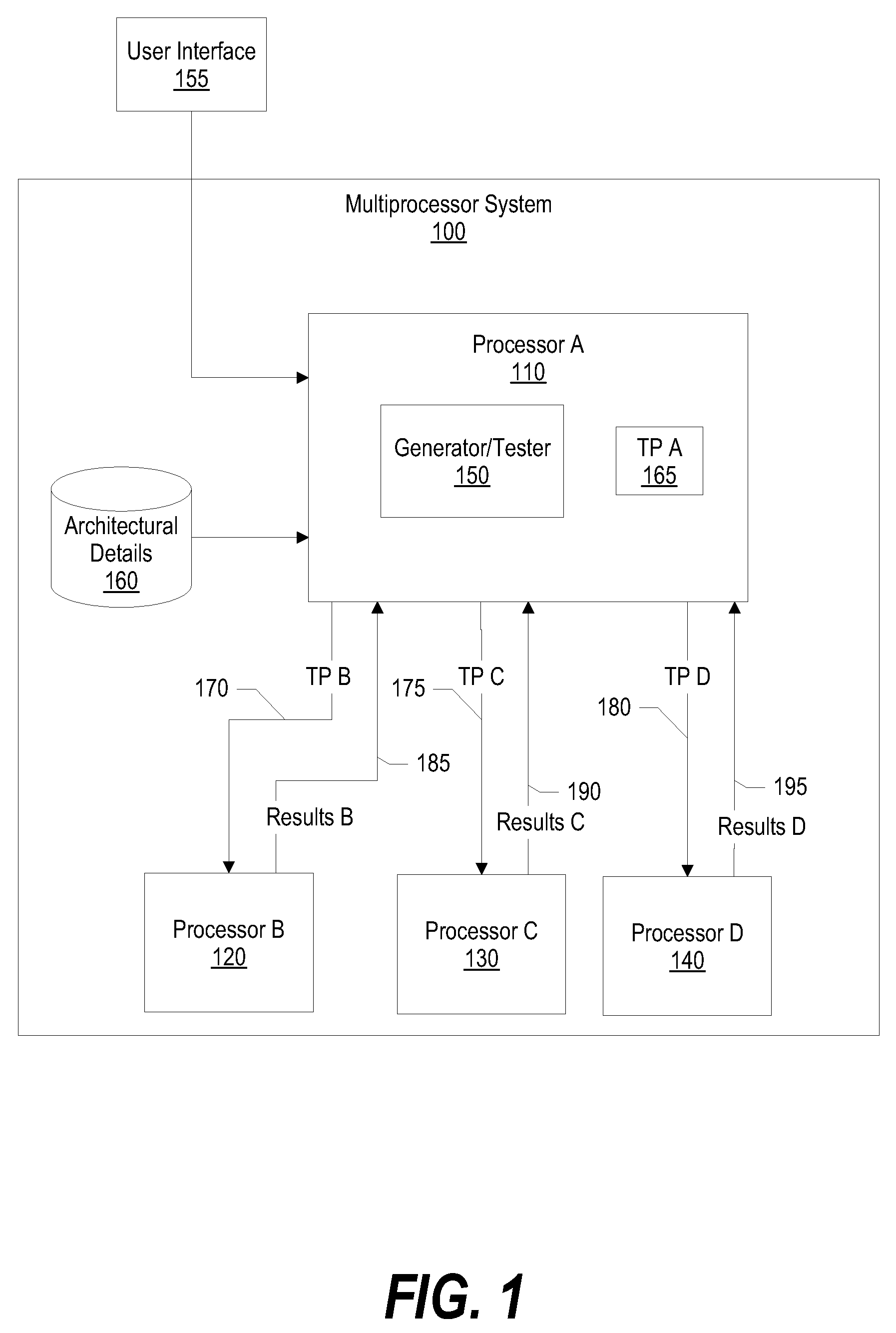

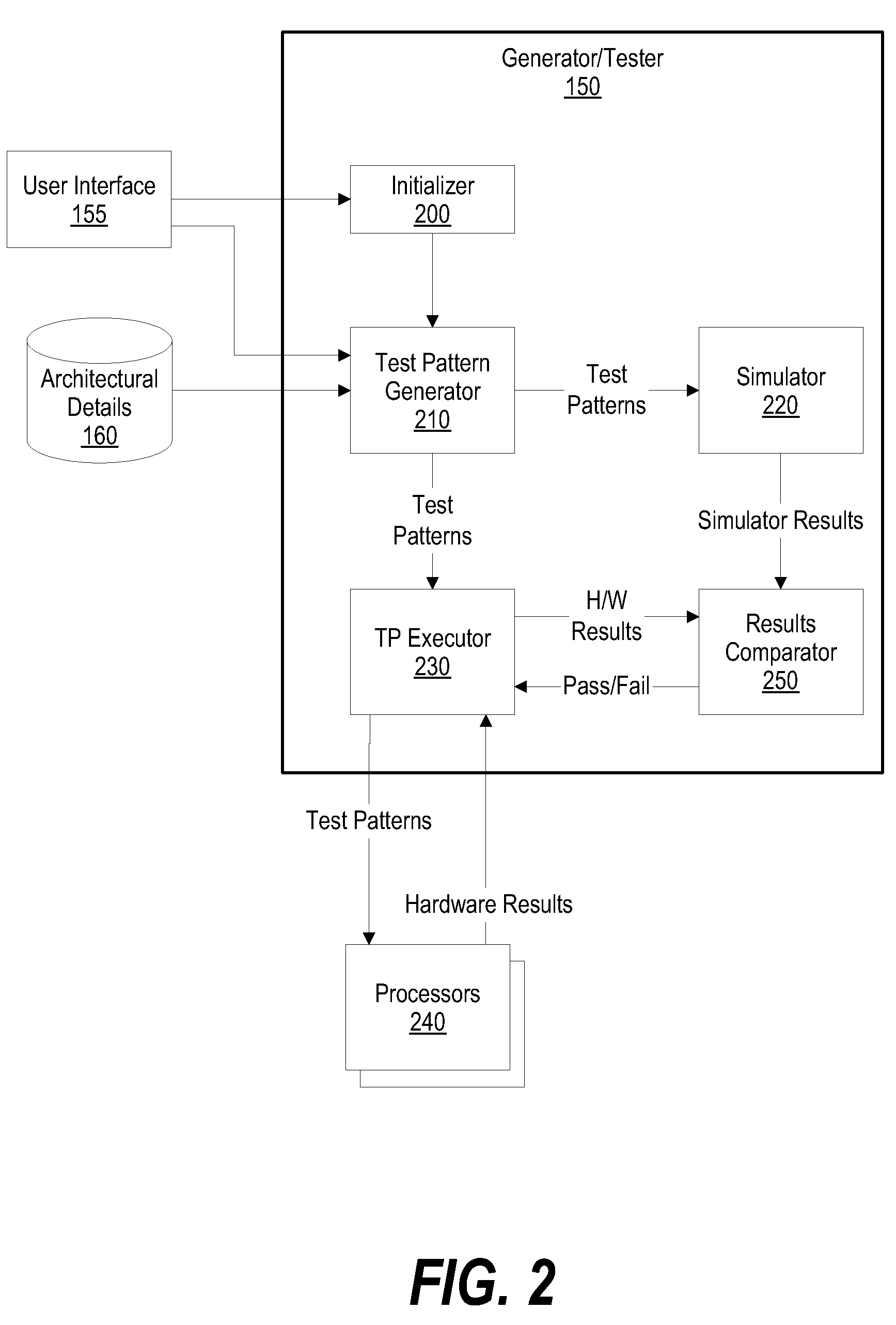

System and Method of Testing using Test Pattern Re-Execution in Varying Timing Scenarios for Processor Design Verification and Validation

ActiveUS20090024892A1Reduce test pattern build timeIncrease system test coverageElectronic circuit testingError detection/correctionError checkingProcessor design

A system and method processor testing using test pattern re-execution is presented. A processor re-executes test patterns using different timing scenarios in order to reduce test pattern build time and increase system test coverage. The invention described herein varies initial states of a processor's memory (cache, TLB, SLB, etc.) that, in turn, varies the timing scenarios when re-executing test patterns. By re-executing the test patterns instead of rebuilding new test patterns, verification quality is improved since more time is available for execution, verification and validation. In addition, since the test patterns result in the same final state, the invention described herein also simplifies error checking.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

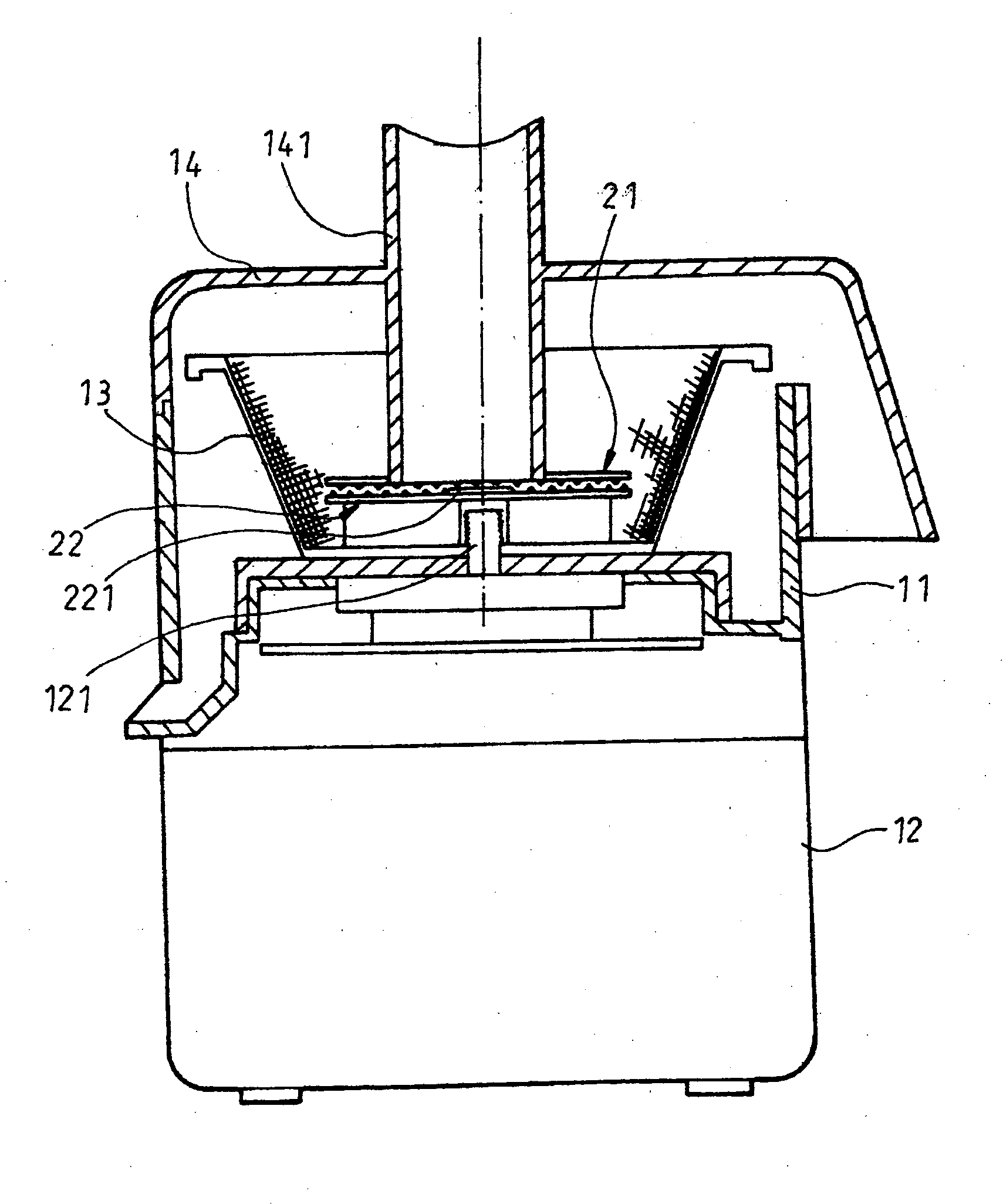

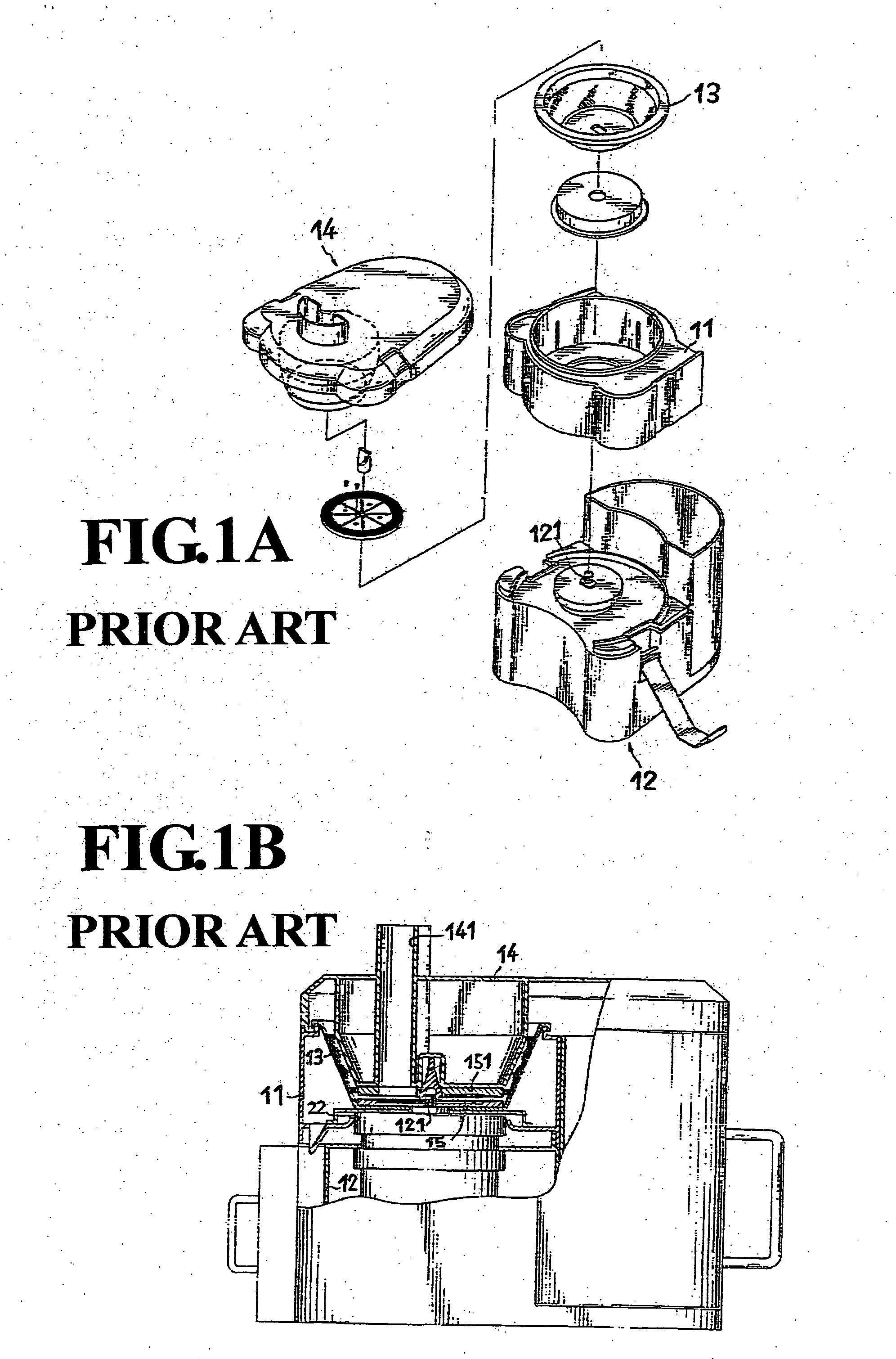

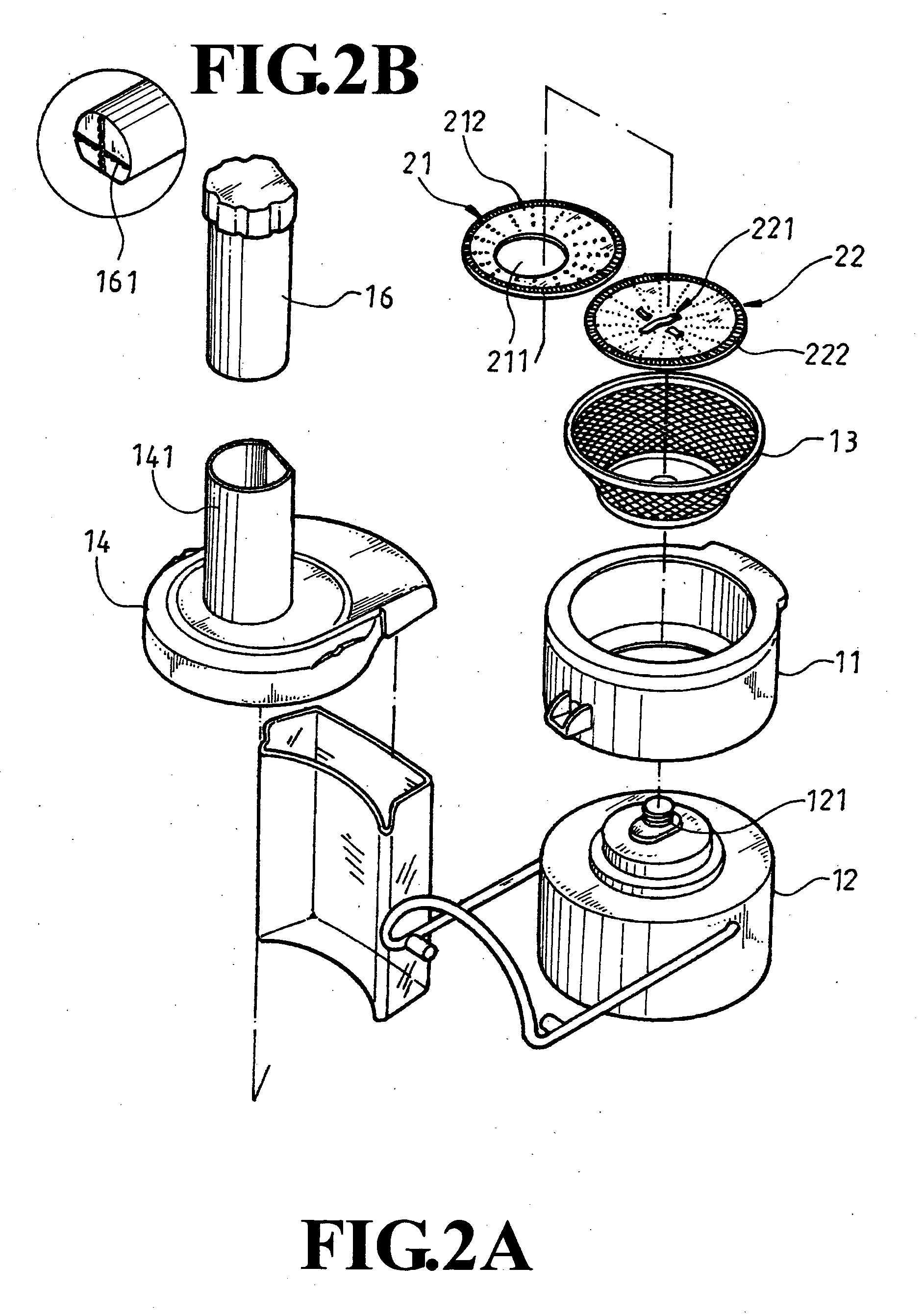

Food processor with combined grinding and juice extracting functions

InactiveUS20080115677A1Increase the areaEliminate dead areasJuice extractionGrain treatmentsEngineeringProcessor design

A food processor designed for grinding beans and cereals as well as extracting juice from fruits and vegetables includes a bowl, a base, a strainer basket, a cover, an upper grinding disc fixedly mounted around a bottom of a feed tube formed on the cover, and a lower grinding disc firmly connected to and driven by a driving mechanism on the base to rotate at high speed. Since the lower grinding disc is provided at a central area with differently shaped central blades and along a circumferential edge with multiple grinding teeth, the feed tube is offset from but overlaps a center of the lower grinding disc, and the upper grinding disc is provided with grinding teeth corresponding to the lower grinding disc, an expanded grinding area is available on and between the two grinding discs, and any dead area of grinding may be eliminated.

Owner:GREAT YEN ELECTRIC FOOD GRINDER

Modeling language and method for address translation design mechanisms in test generation

InactiveUS7370296B2Large coverageLogical operation testingSoftware simulation/interpretation/emulationConstraint satisfaction problemTheoretical computer science

Methods and systems are disclosed that enhance the ability of a test generator to automatically deal with address translation in a processor design, and without need for creating specific code. A model of the address translation mechanism of a design-under-test is represented as a directed acyclic graph and then converted into a constraint satisfaction problem. The problem is solved by a CSP engine, and the solution used to generate test cases for execution. Using the model, testing knowledge can be propagated to models applicable to many different designs to produce extensive coverage of address translation mechanisms.

Owner:GLOBALFOUNDRIES INC

System and method of testing using test pattern re-execution in varying timing scenarios for processor design verification and validation

ActiveUS7647539B2Reduce build timeImprove test coverageElectronic circuit testingError detection/correctionError checkingSystem testing

A system and method processor testing using test pattern re-execution is presented. A processor re-executes test patterns using different timing scenarios in order to reduce test pattern build time and increase system test coverage. The invention described herein varies initial states of a processor's memory (cache, TLB, SLB, etc.) that, in turn, varies the timing scenarios when re-executing test patterns. By re-executing the test patterns instead of rebuilding new test patterns, verification quality is improved since more time is available for execution, verification and validation. In addition, since the test patterns result in the same final state, the invention described herein also simplifies error checking.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

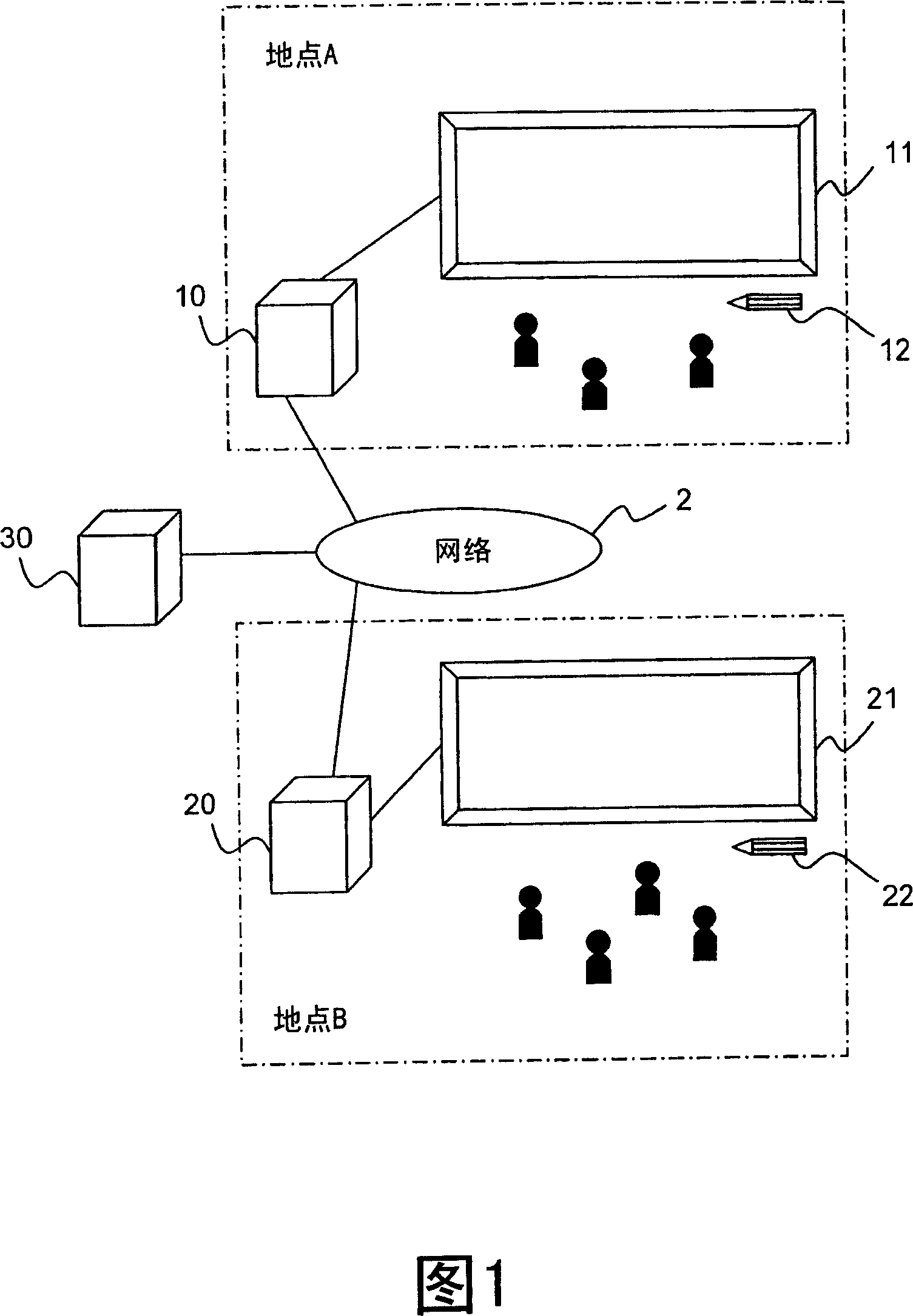

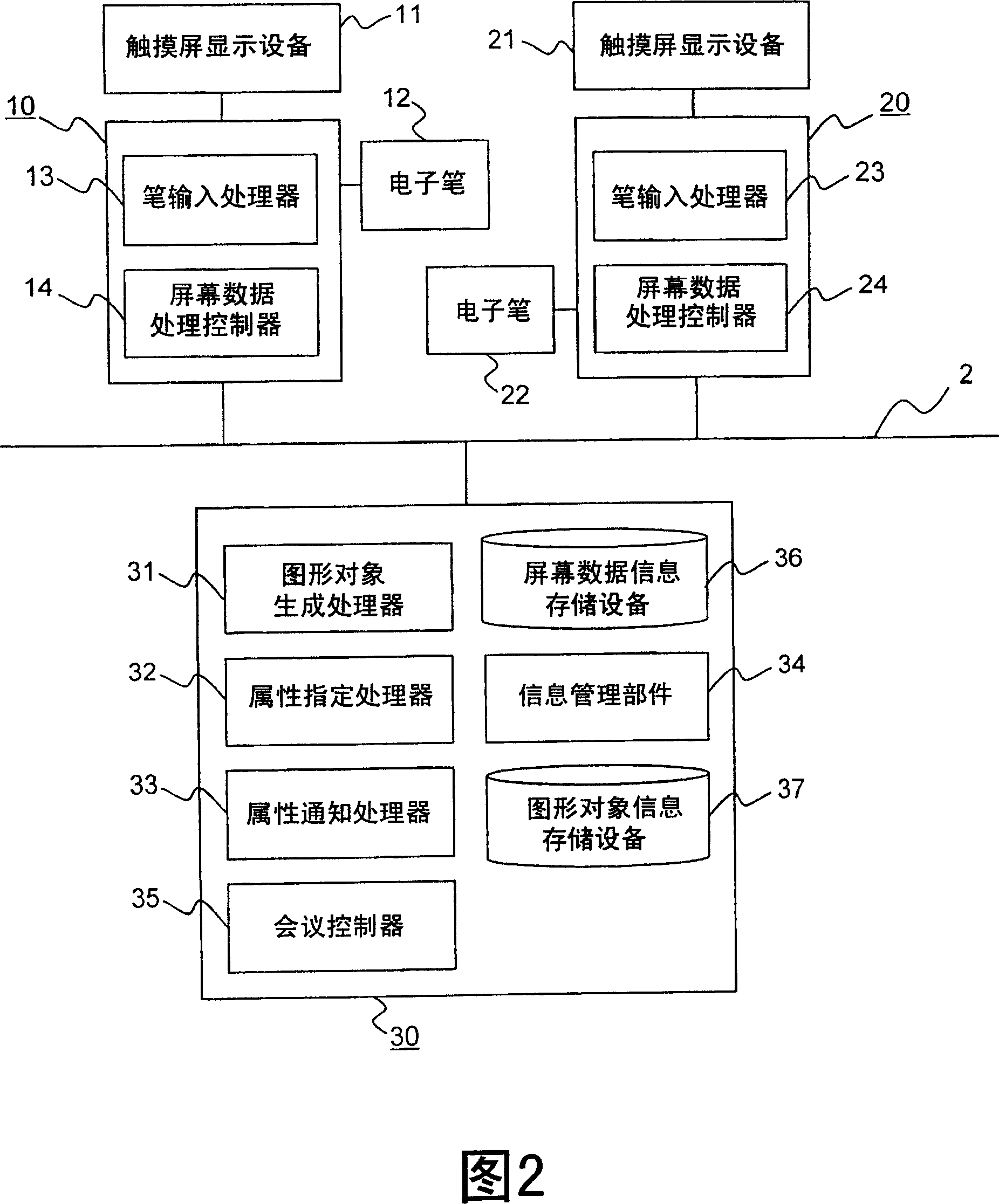

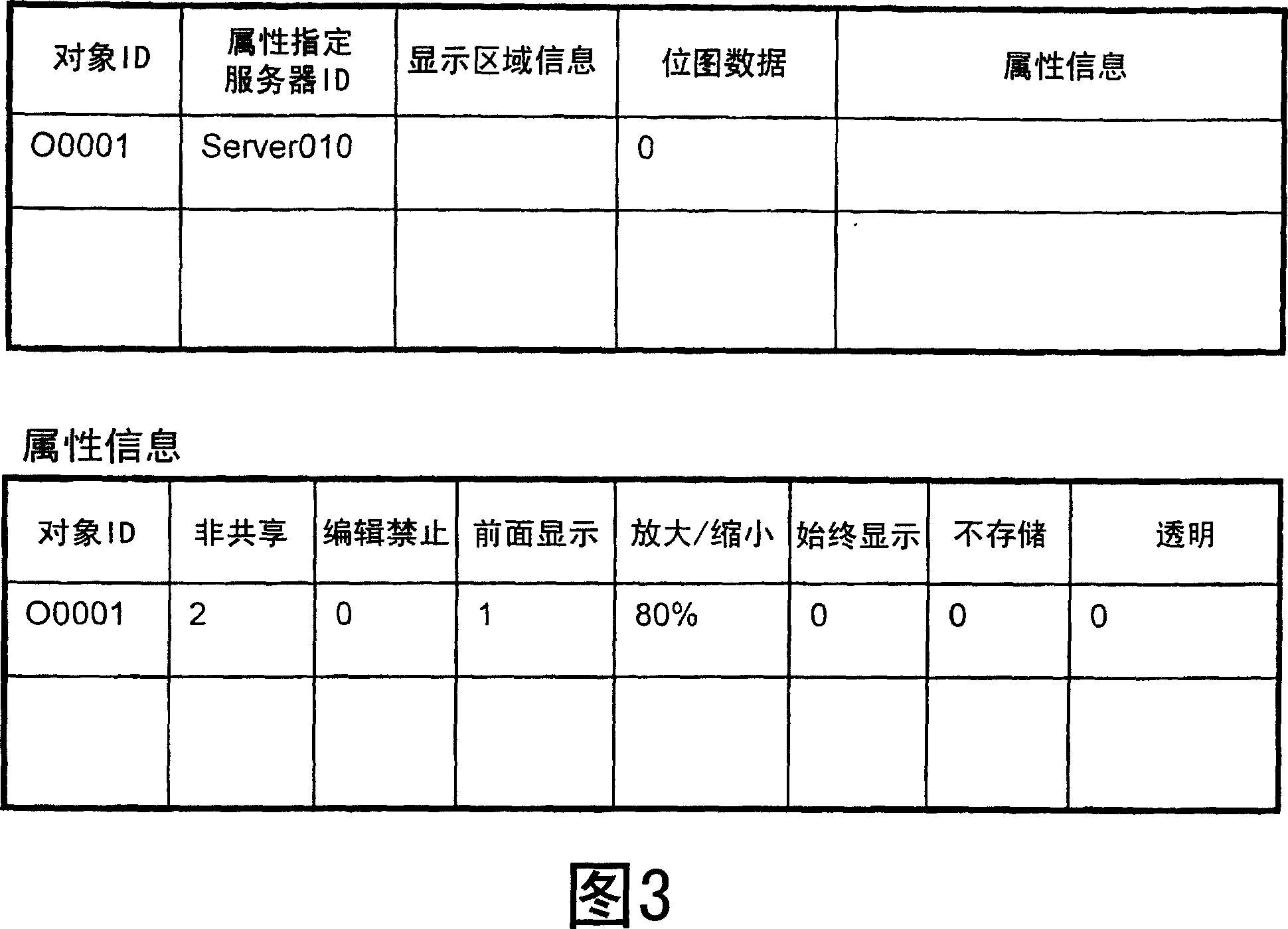

Electronic conference system, electronic conference support method, electronic conference support device, and conference server

InactiveCN101031063ATelevision conference systemsSpecial service for subscribersGraphicsDisplay device

A conference server computer connected with a display device is provided, which comprises: a unit designed to obtain input and assign attribute information to the graphic objects contained in screen images displayed on the display device; a controller, designed to process the graphic objects according to the attribute information; and, a unit designed to transmit the obtained attribute information to an electronic conference control device. The electronic conference control device comprises: a unit designed to manage some images in the screen images formed when the screen data is displayed as graphic objects; a processor designed to receive attribute information transmitted from a conference server computer; and, a processor designed to notify other conference server computers (except for the conference server computer for which the attribute information is inputted and specified) of the attribute information on the graphic objects.

Owner:FUJIFILM BUSINESS INNOVATION CORP

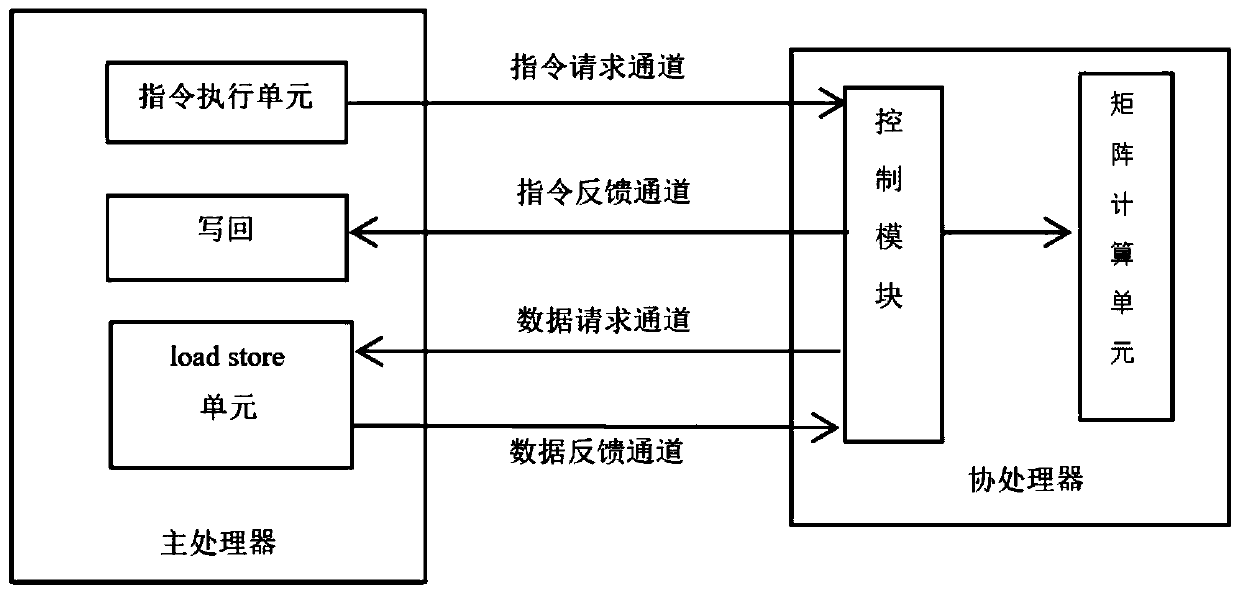

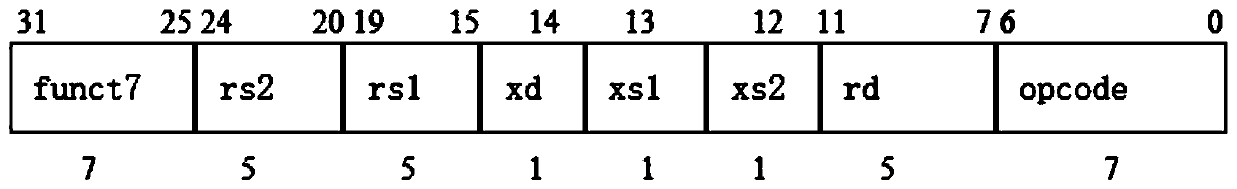

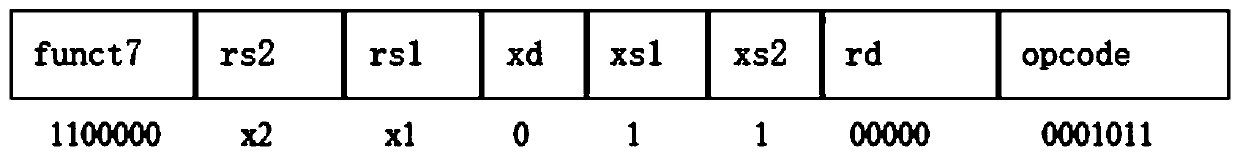

Matrix convolution calculation method, interface, coprocessor and system based on RISC-V architecture

ActiveCN109857460ACalculation speedReduce the number of memory accessesConcurrent instruction executionNeural architecturesExtensibilityProcessor design

The invention discloses a set based on RISC-. According to the method and system complete mechanism of the instruction, the interface and the coprocessor for matrix convolution calculation of the V instruction set architecture, traditional matrix convolution calculation is efficiently achieved in a software and hardware combined mode, and RISC-is utilized. Extensibility of V instruction sets, a small number of instructions and a special convolution calculation unit (namely a coprocessor) are designed; the memory access times and the execution period of a matrix convolution calculation instruction are reduced, the complexity of application layer software calculation is reduced, the efficiency of large matrix convolution calculation is improved, the calculation speed of matrix convolution isincreased, flexible calling of upper-layer developers is facilitated, and the coding design is simplified. Meanwhile, RISC-is utilized. The processor designed by the V instruction set also has greatadvantages in power consumption, size and flexibility compared with ARM, X86 and other architectures, can adapt to different application scenes, and has a wide prospect in the field of artificial intelligence.

Owner:NANJING HUAJIE IMI TECH CO LTD

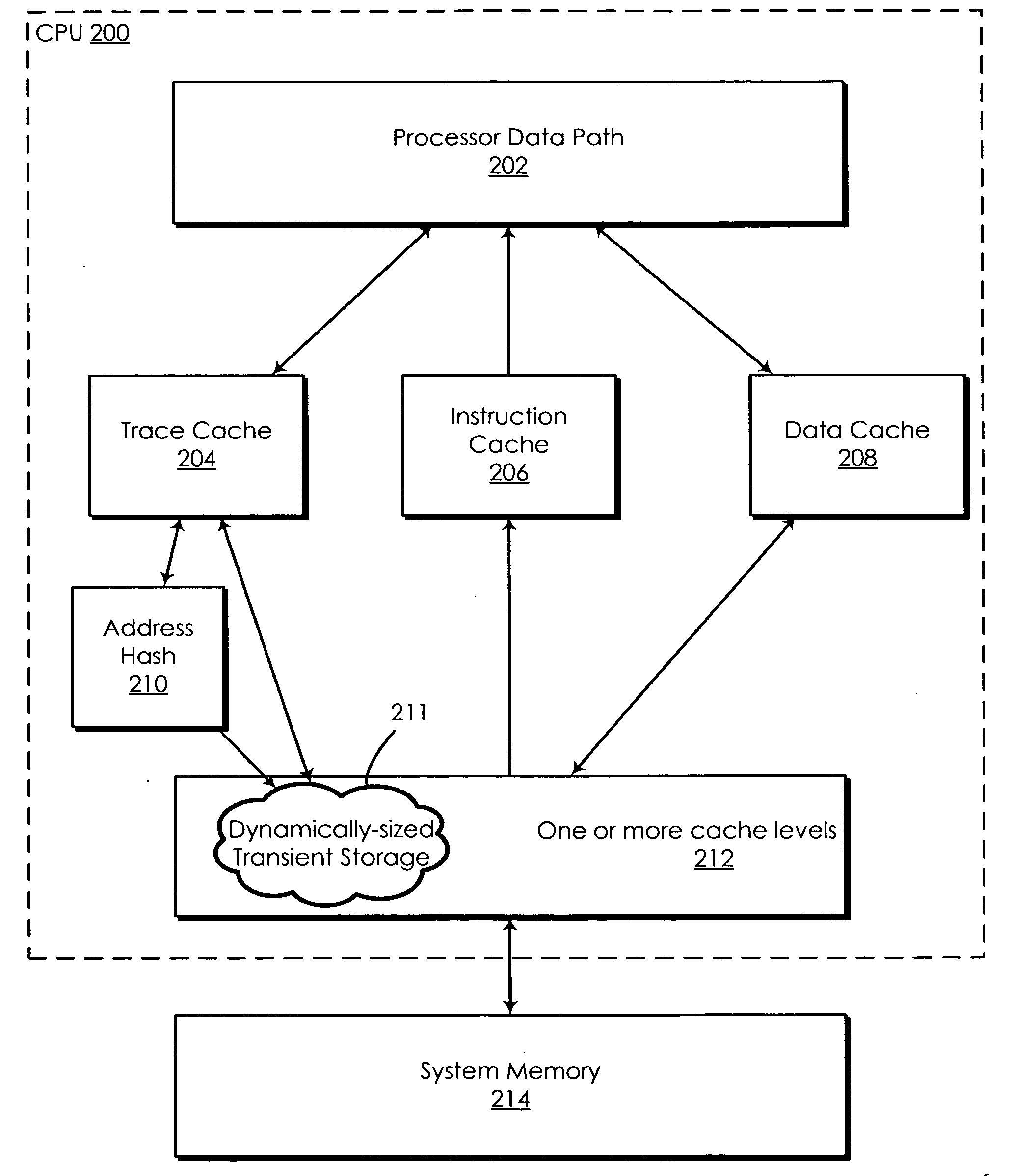

Transient cache storage

ActiveUS20070130237A1Low costMemory adressing/allocation/relocationProgram controlCache hierarchyExternal storage

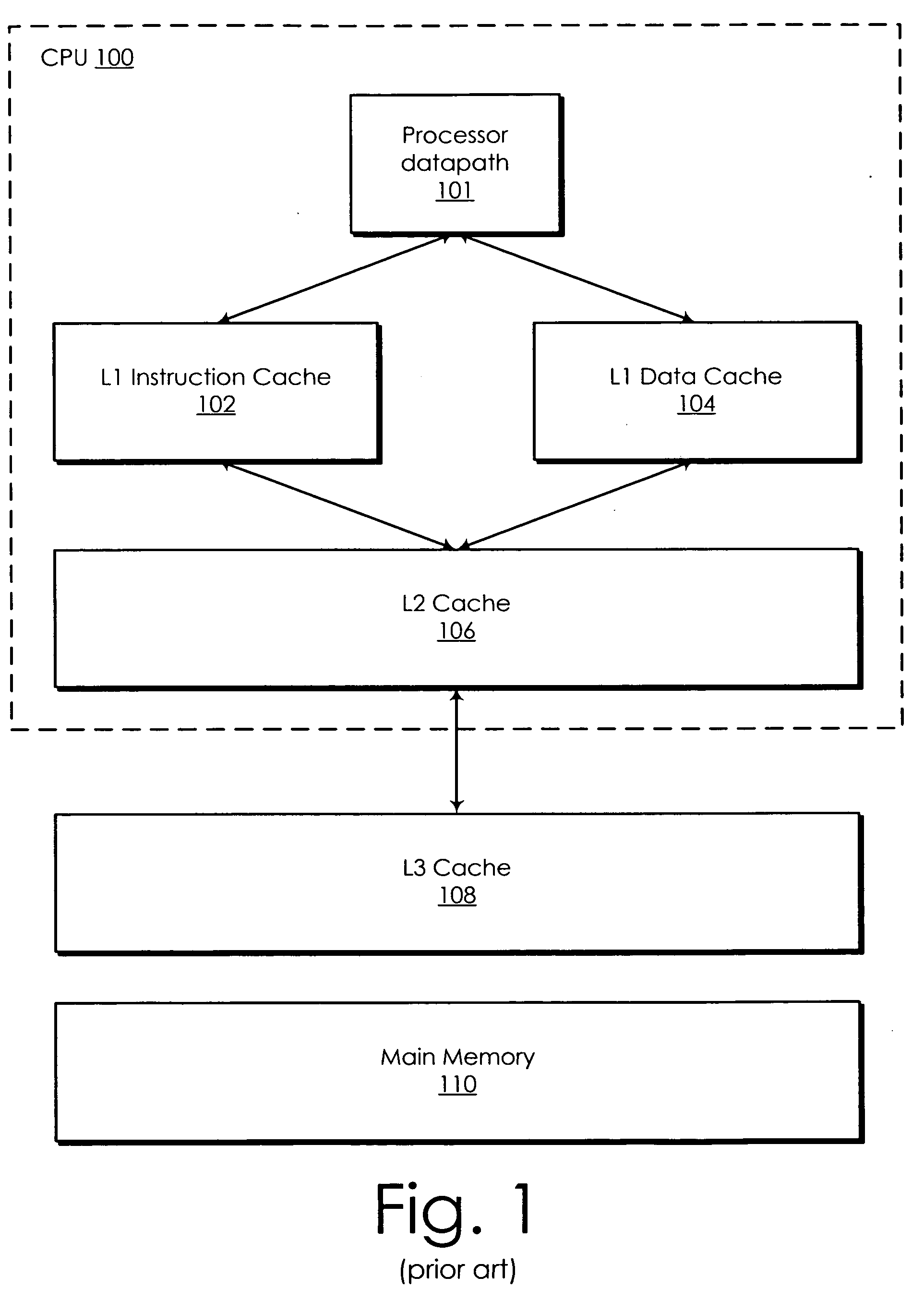

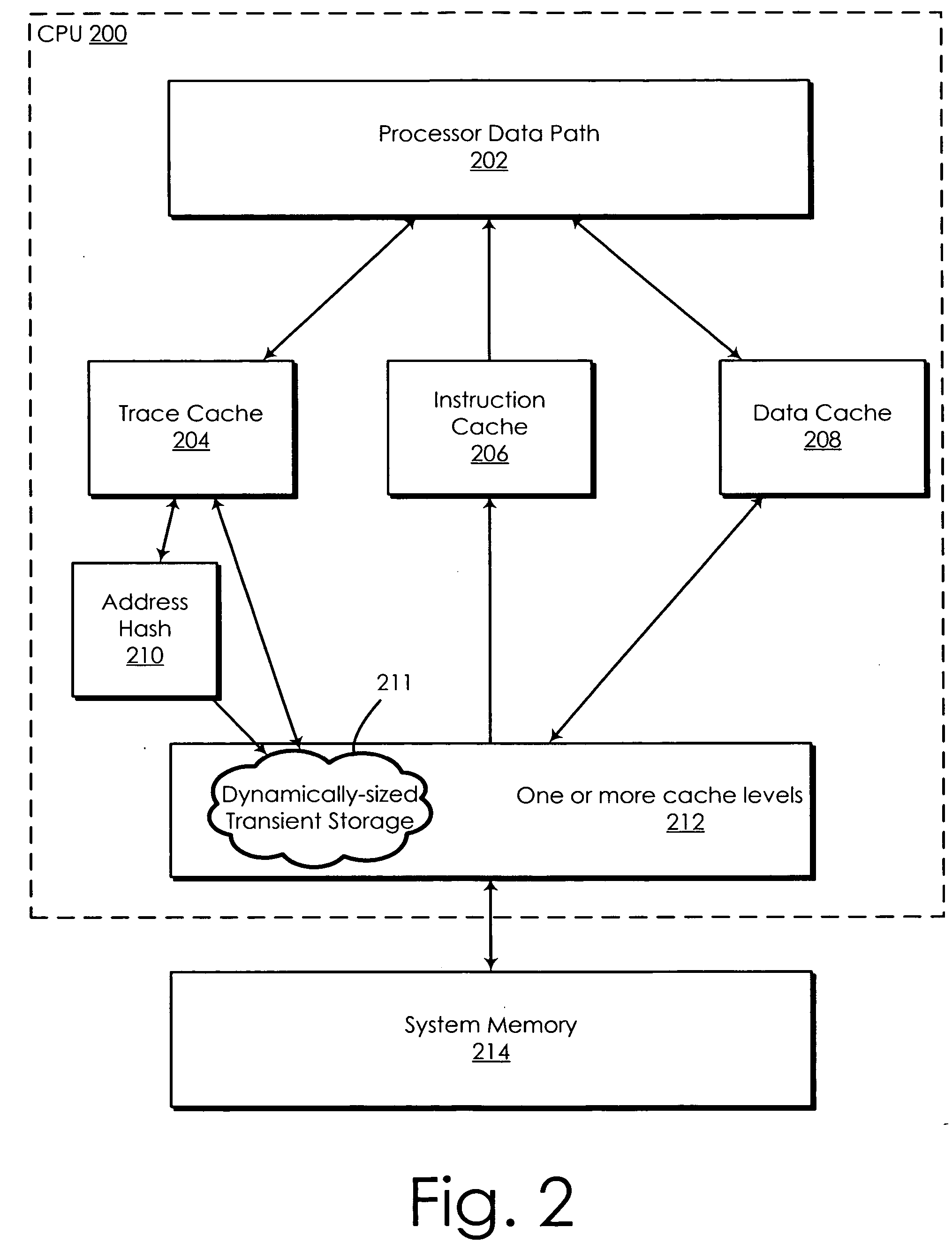

A method and apparatus for storing non-critical processor information without imposing significant costs on a processor design is disclosed. Transient data are stored in the processor-local cache hierarchy. An additional control bit forms part of cache addresses, where addresses having the control bit set are designated as “transient storage addresses.” Transient storage addresses are not written back to external main memory and, when evicted from the last level of cache, are discarded. Preferably, transient storage addresses are “privileged” in that they are either not accessible to software or only accessible to supervisory or administrator-level software having appropriate permissions. A number of management functions / instructions are provided to allow administrator / supervisor software to manage and / or modify the behavior of transient cache storage. This transient storage scheme allows the cache hierarchy to store data items that may be used by the processor core but that may be too expensive to allocate to external memory.

Owner:MACHINES INT BUSINESS