Patents

Literature

70results about How to "Effect on its overall performance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

TCP/IP offload network interface device

InactiveUS20020156927A1Negligibly effectMove quicklyMultiple digital computer combinationsNetwork connectionsFast pathGeneral purpose

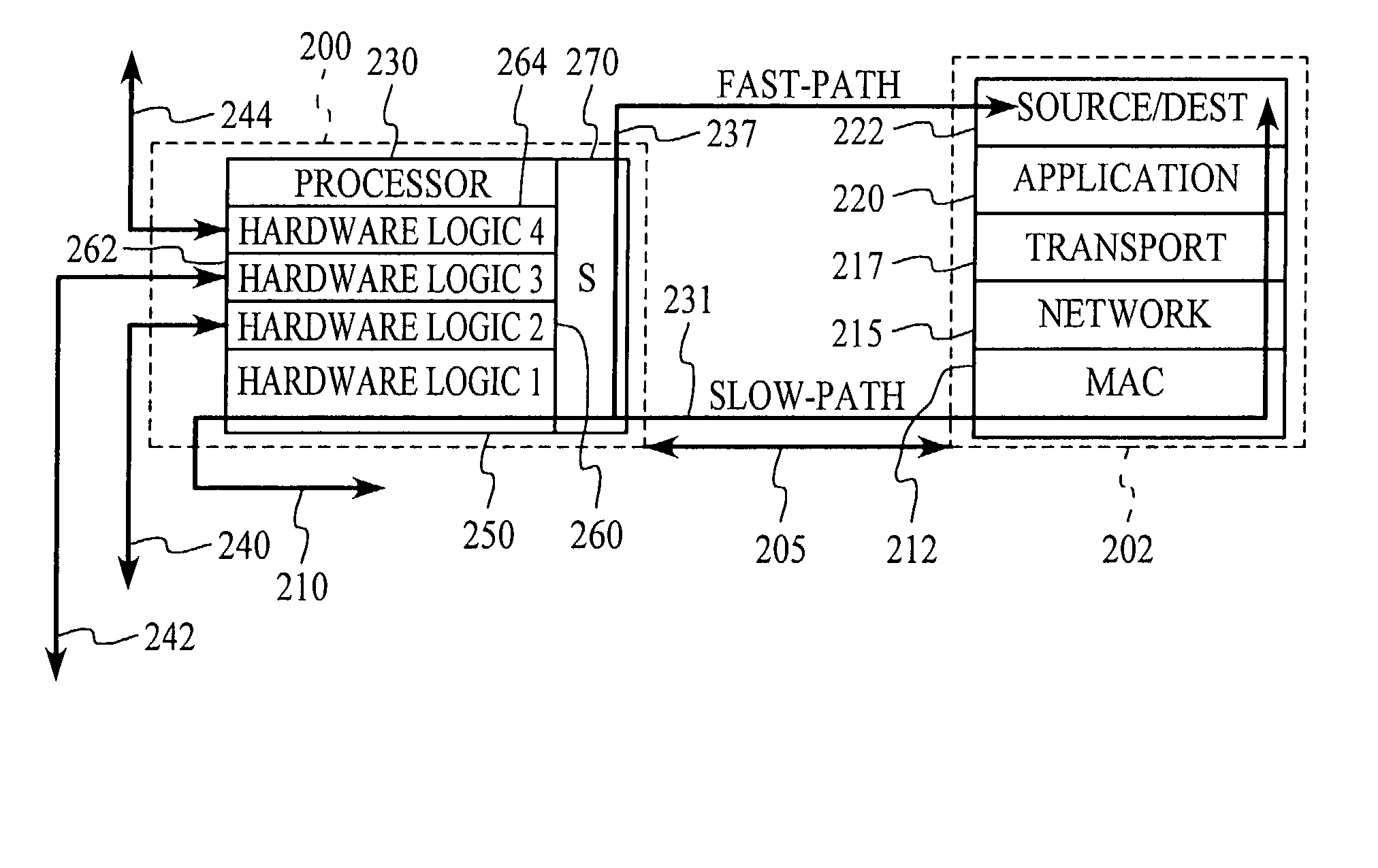

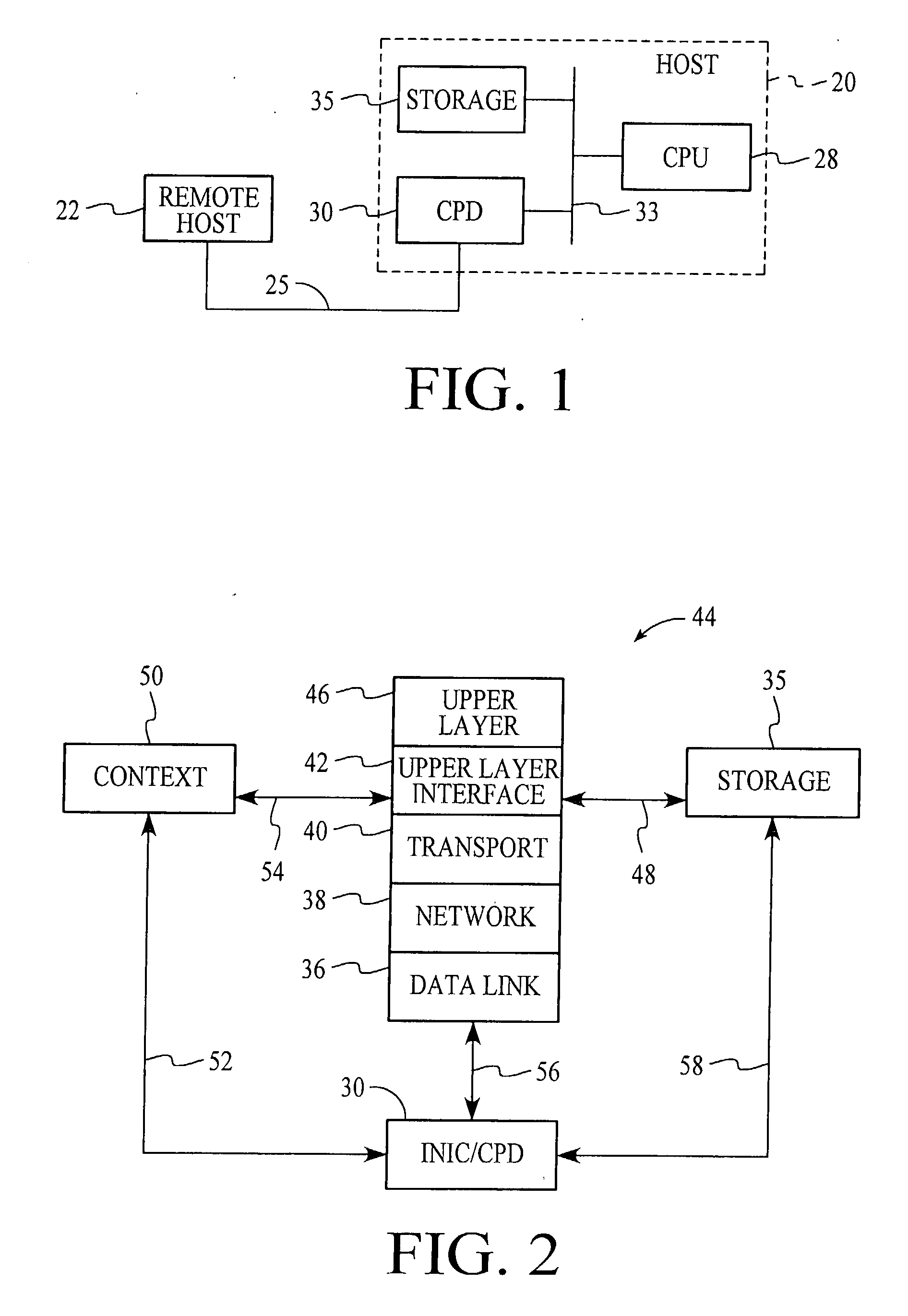

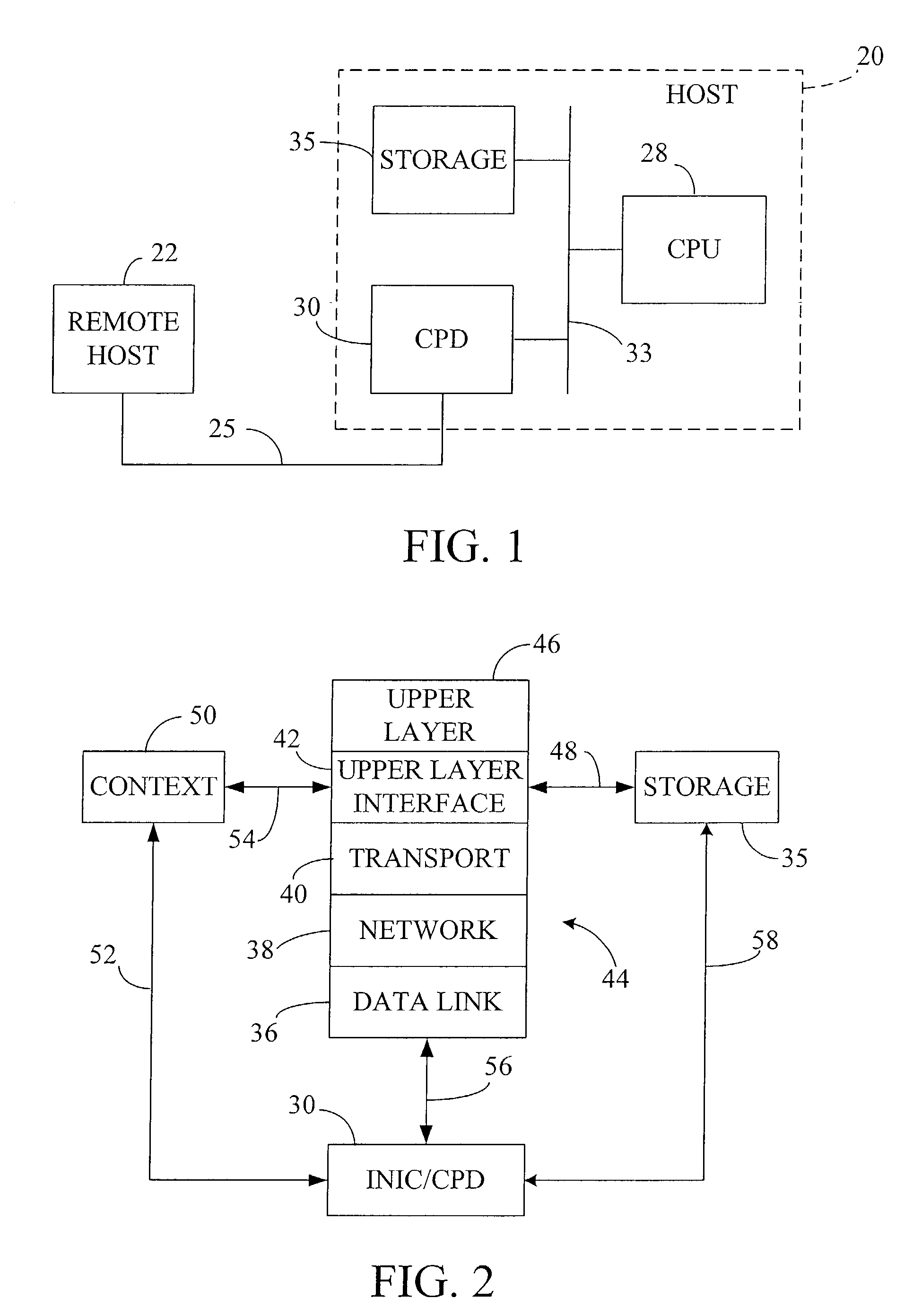

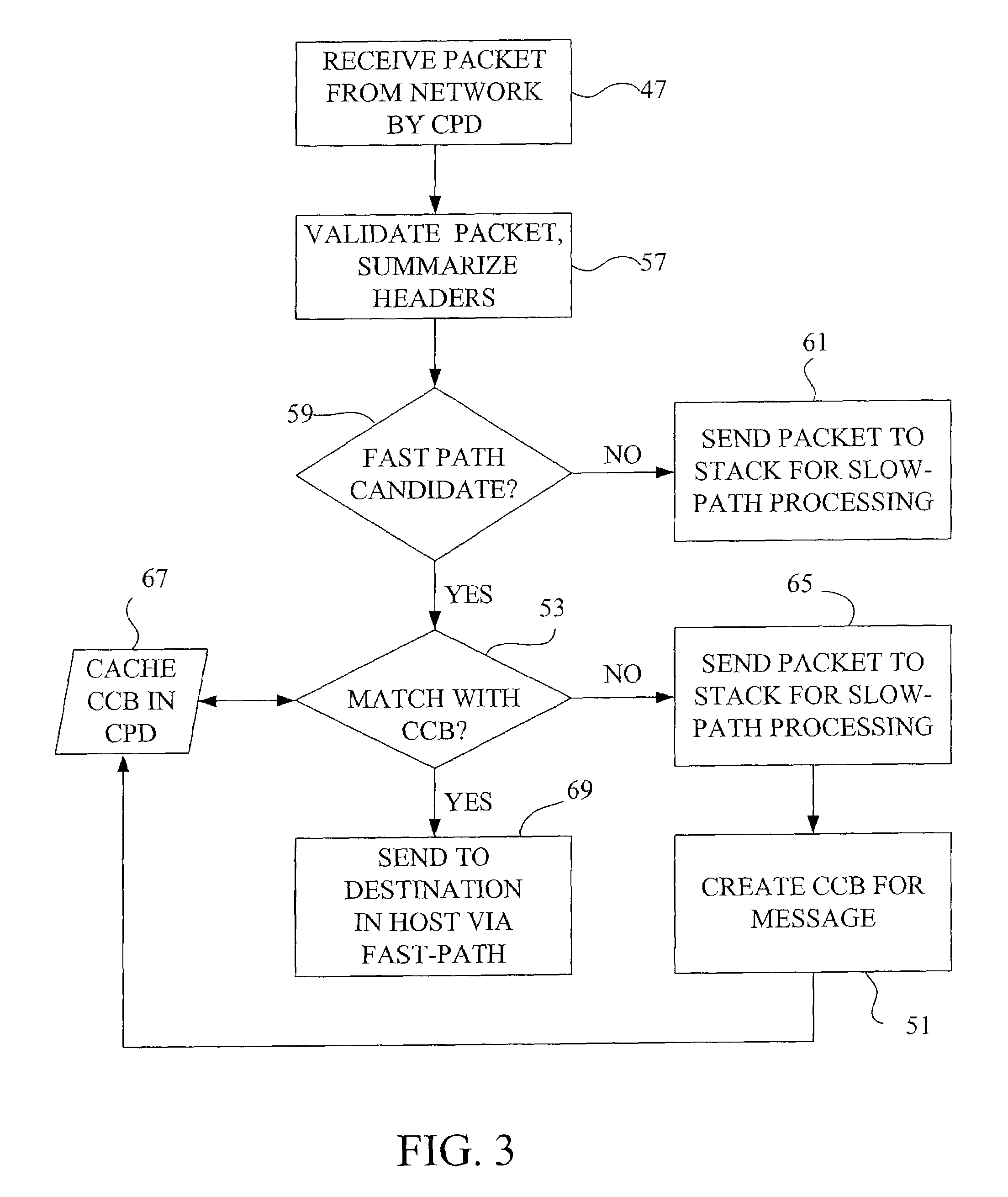

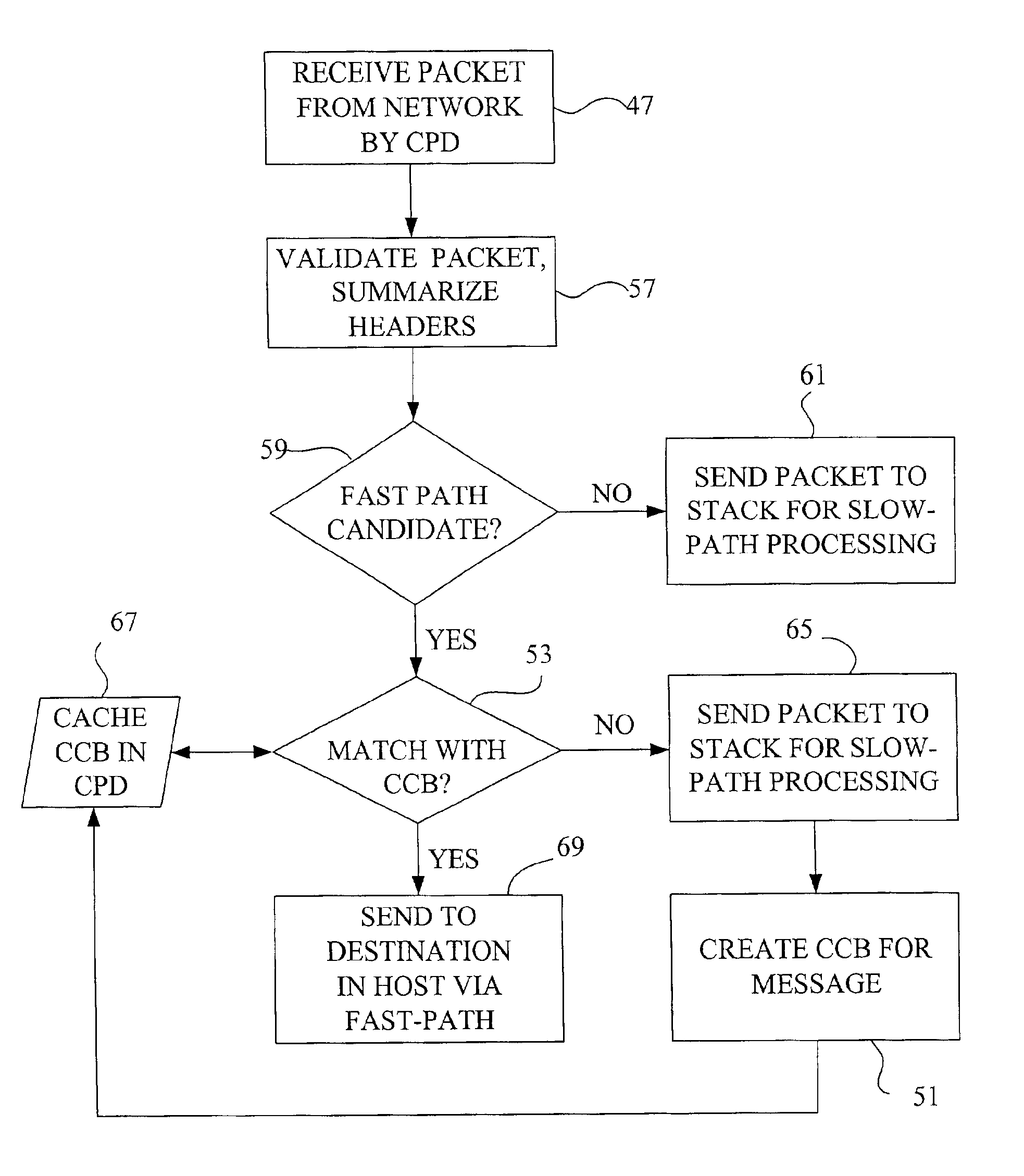

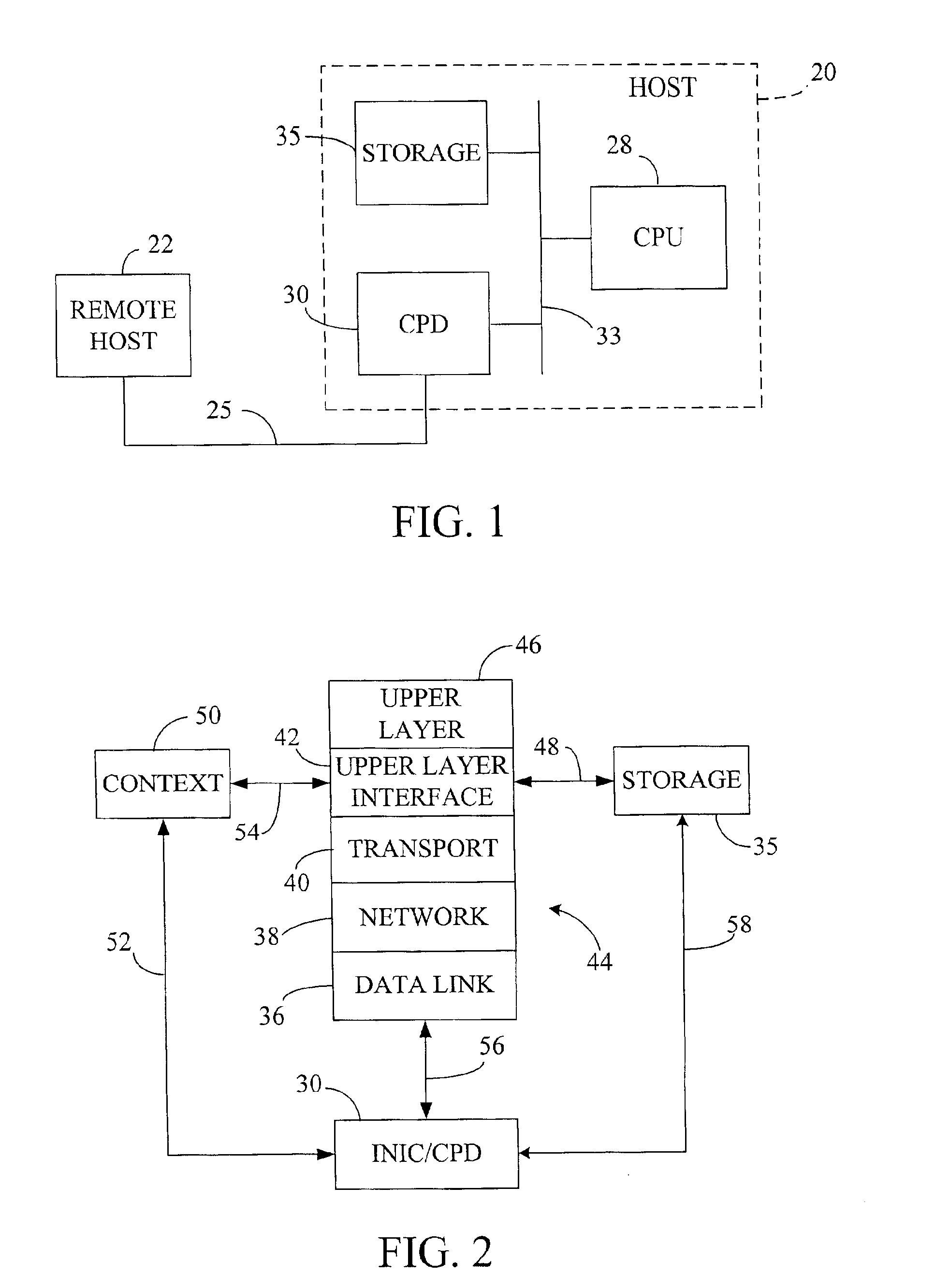

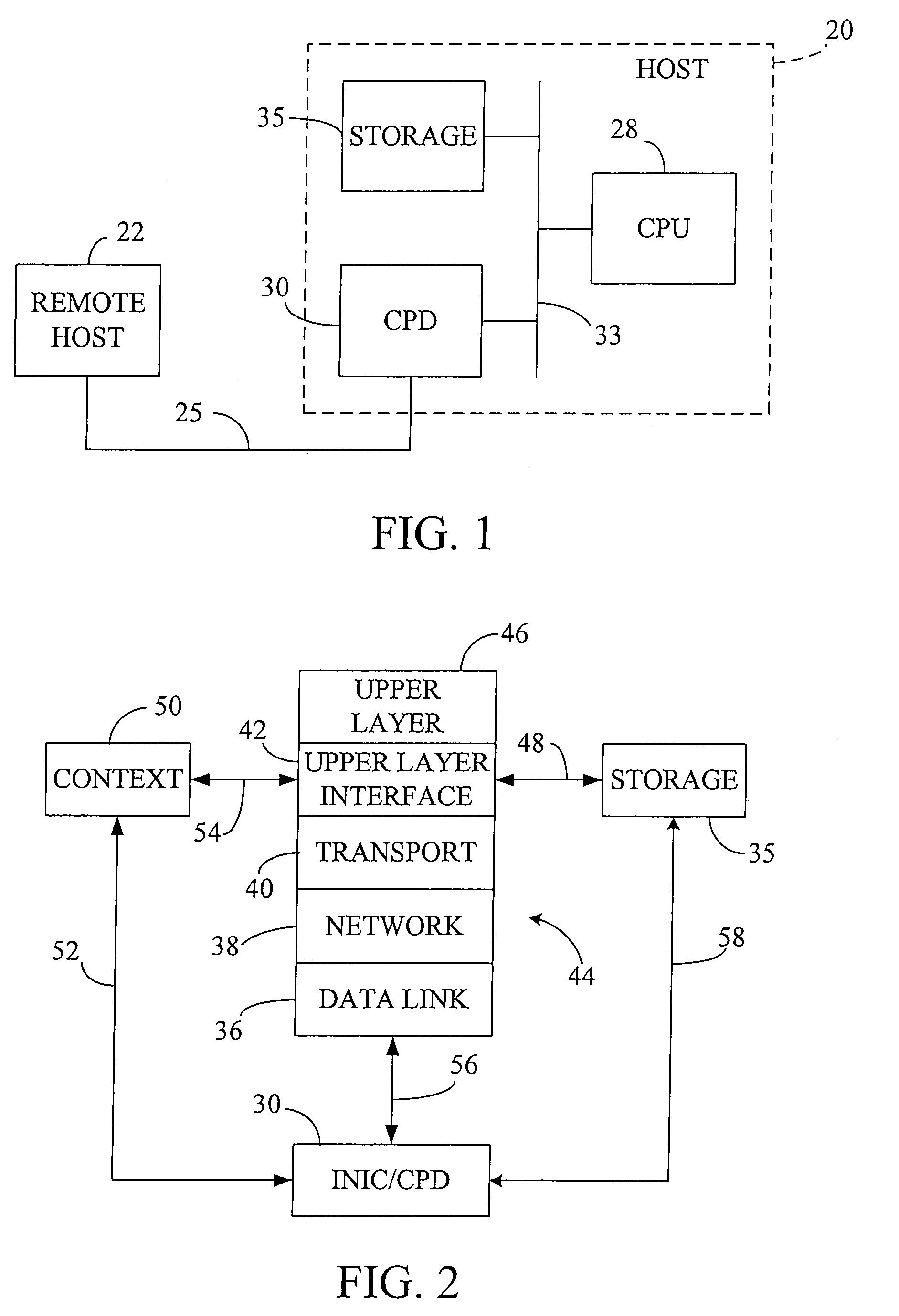

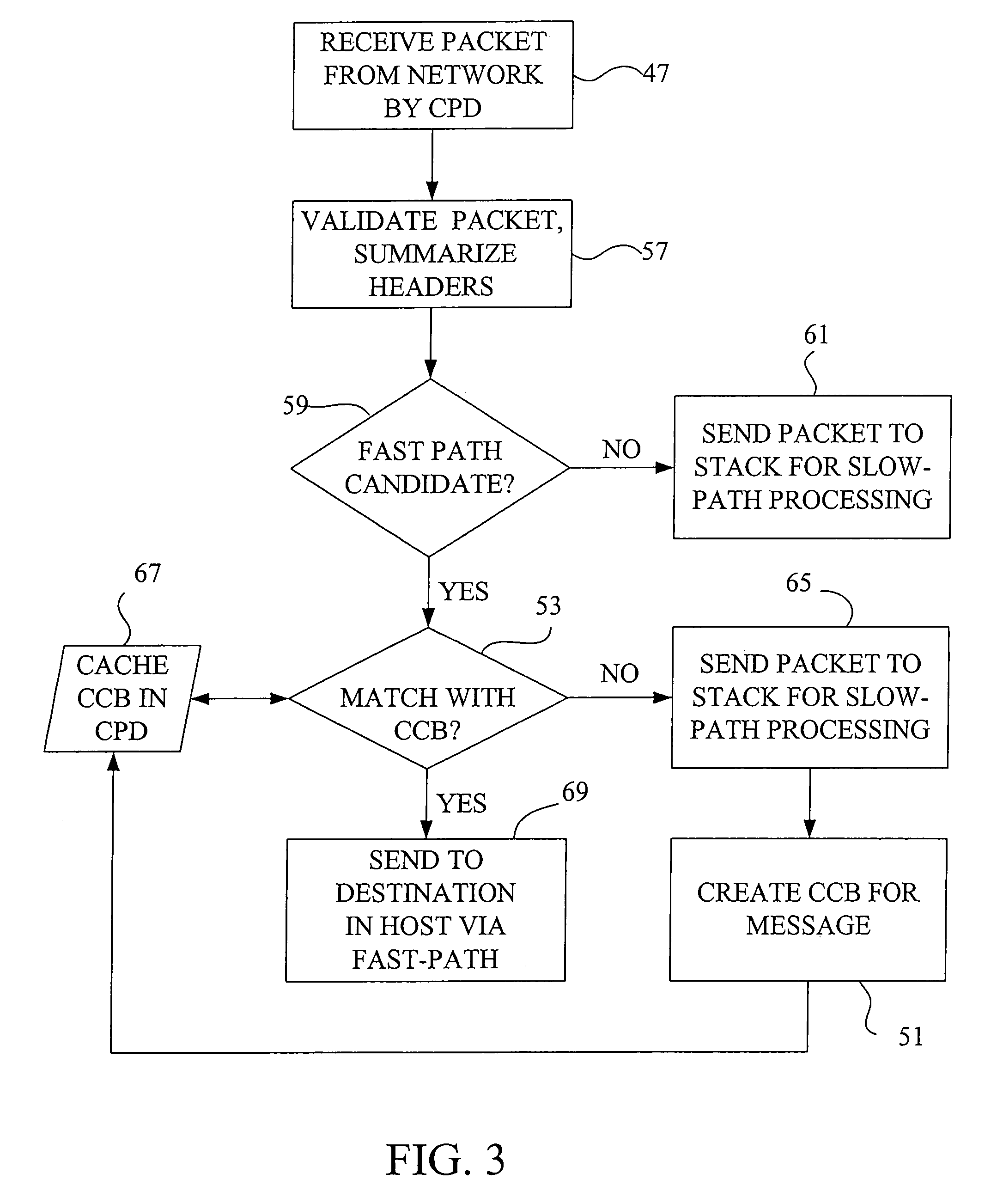

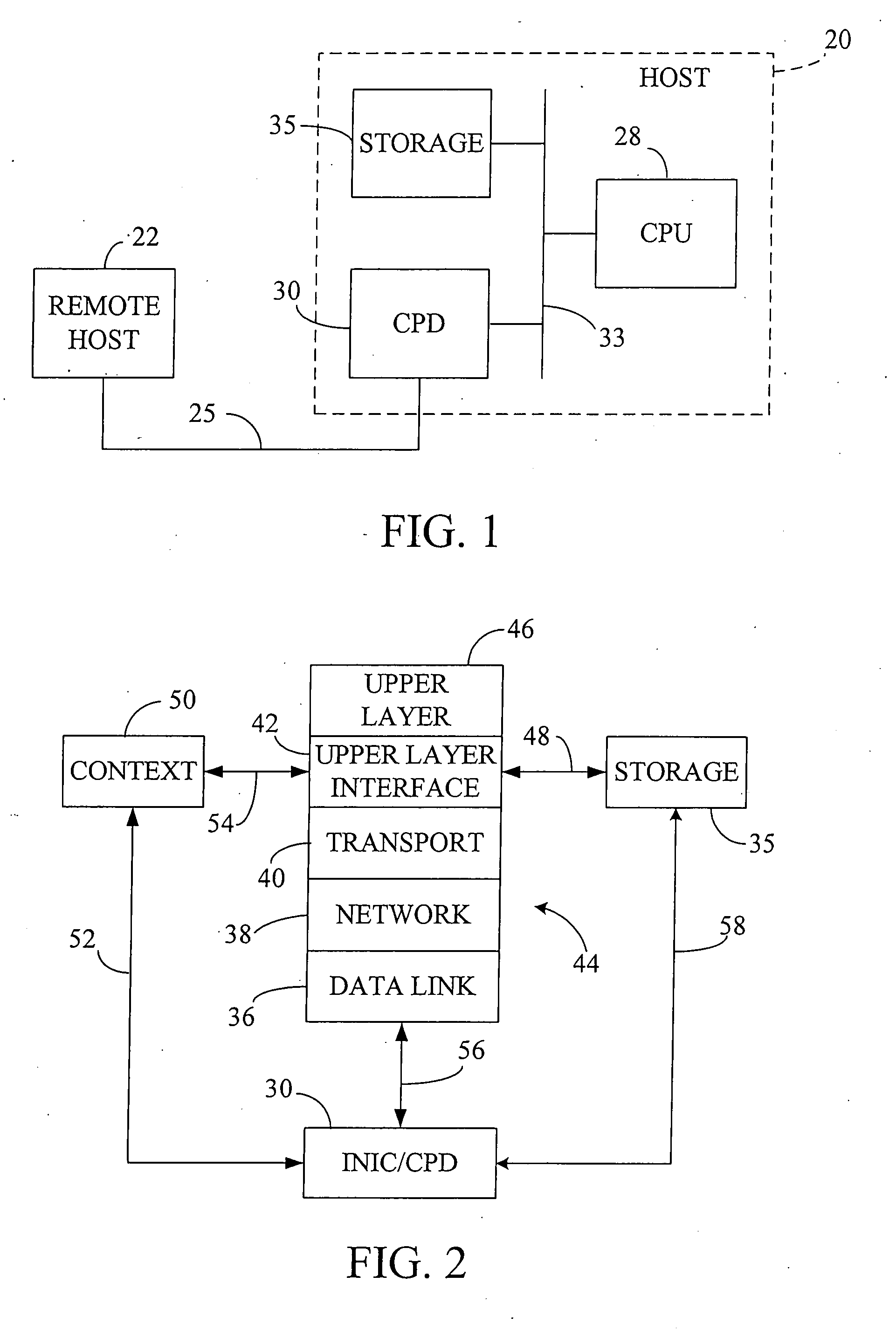

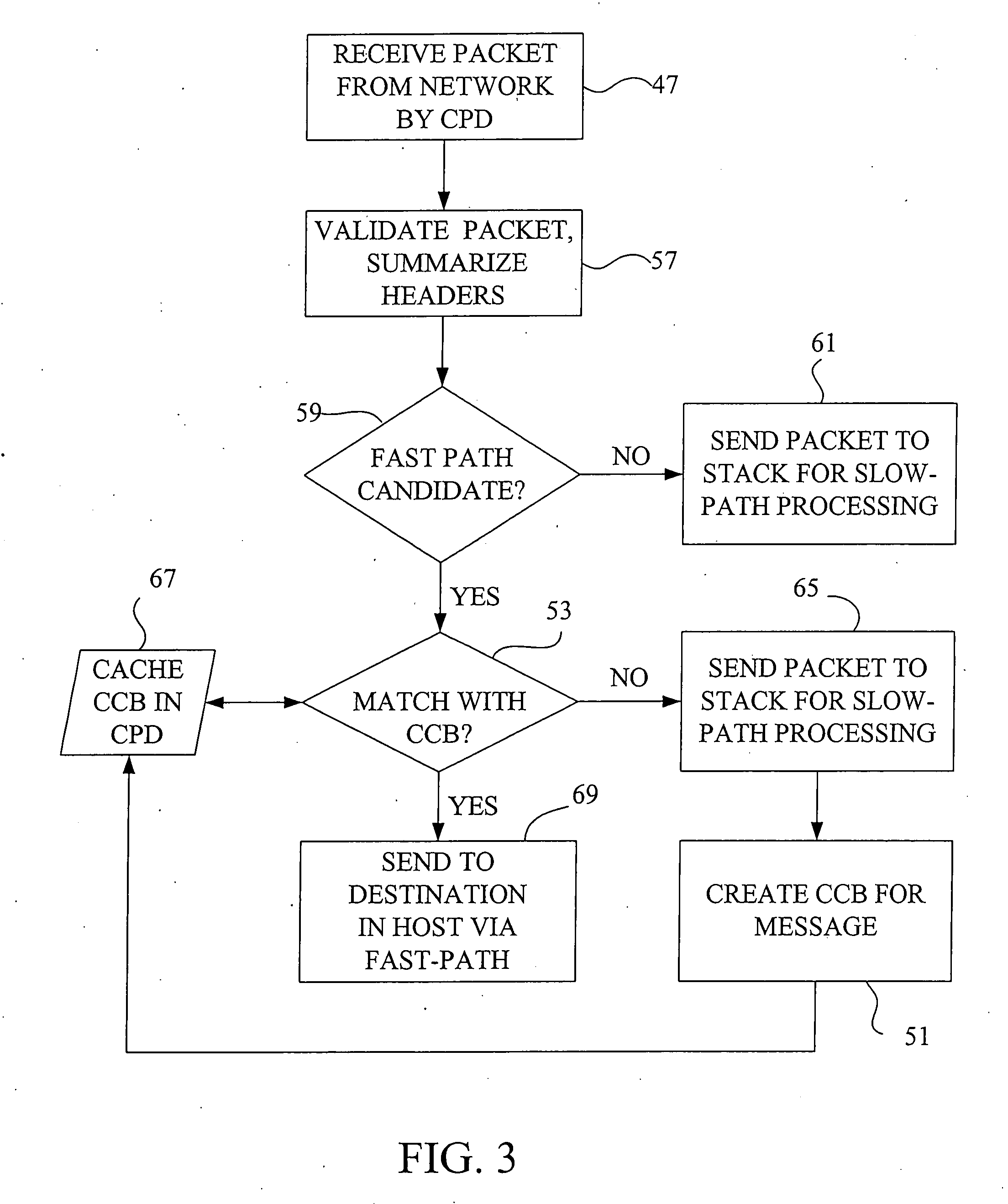

A system for protocol processing in a computer network has a TCP / IP Offload Network Interface Device (TONID) associated with a host computer. The TONID provides a fast-path that avoids protocol processing for most large multi-packet messages, greatly accelerating data communication. The TONID also assists the host for those message packets that are chosen for processing by host software layers. A communication control block for a message is defined that allows DMA controllers of the TONID to move data, free of headers, directly to or from a destination or source in the host. The context is stored in the TONID as a communication control block (CCB) that can be passed back to the host for message processing by the host. The TONID contains specialized hardware circuits that are much faster at their specific tasks than a general purpose CPU. A preferred embodiment includes a trio of pipelined processors with separate processors devoted to transmit, receive and management processing, with full duplex communication for four fast Ethernet nodes.

Owner:ALACRITECH

Fast-path apparatus for receiving data corresponding a TCP connection

InactiveUS7237036B2Negligibly effectMove fastTime-division multiplexData switching by path configurationMessage passingProtocol processing

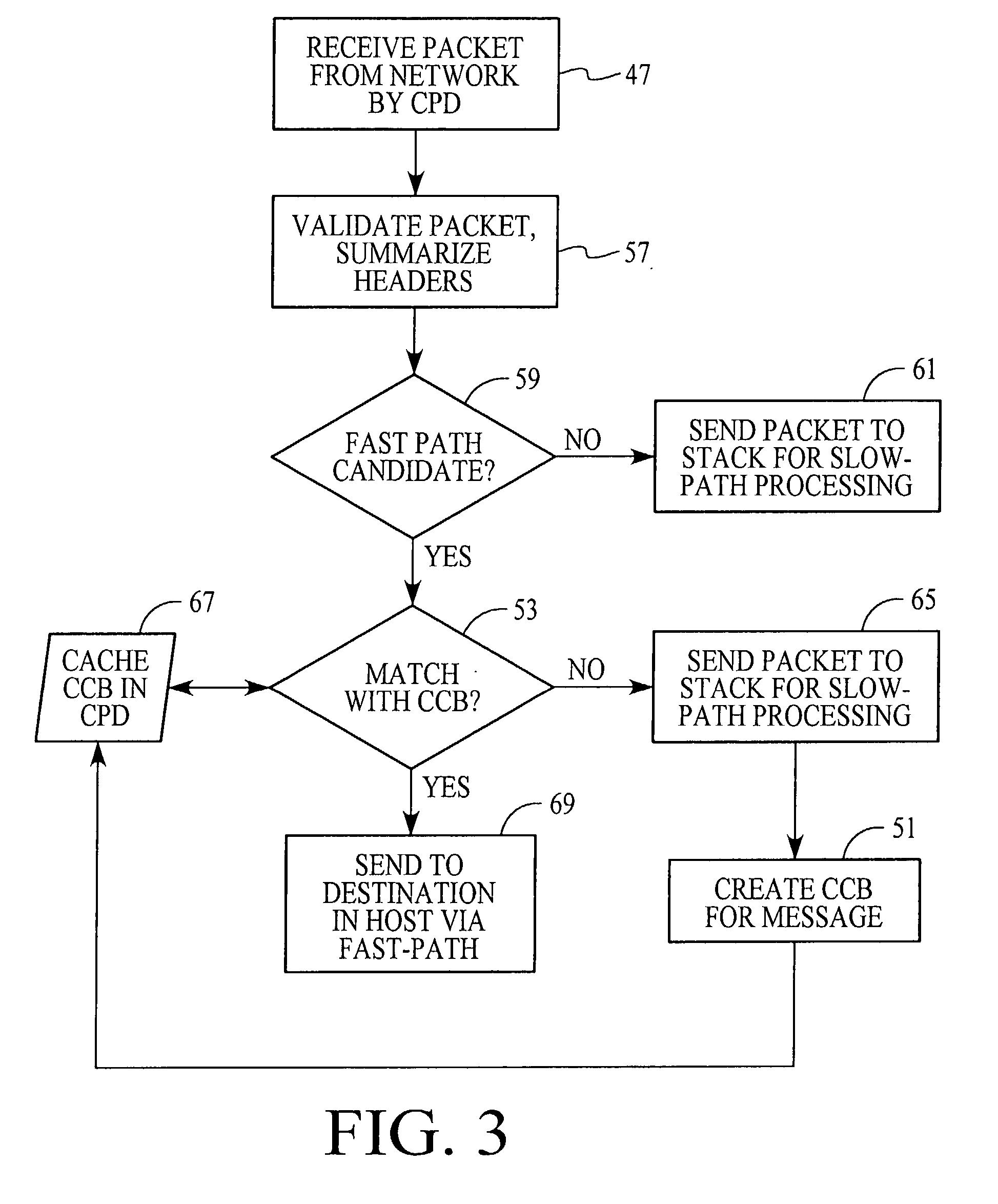

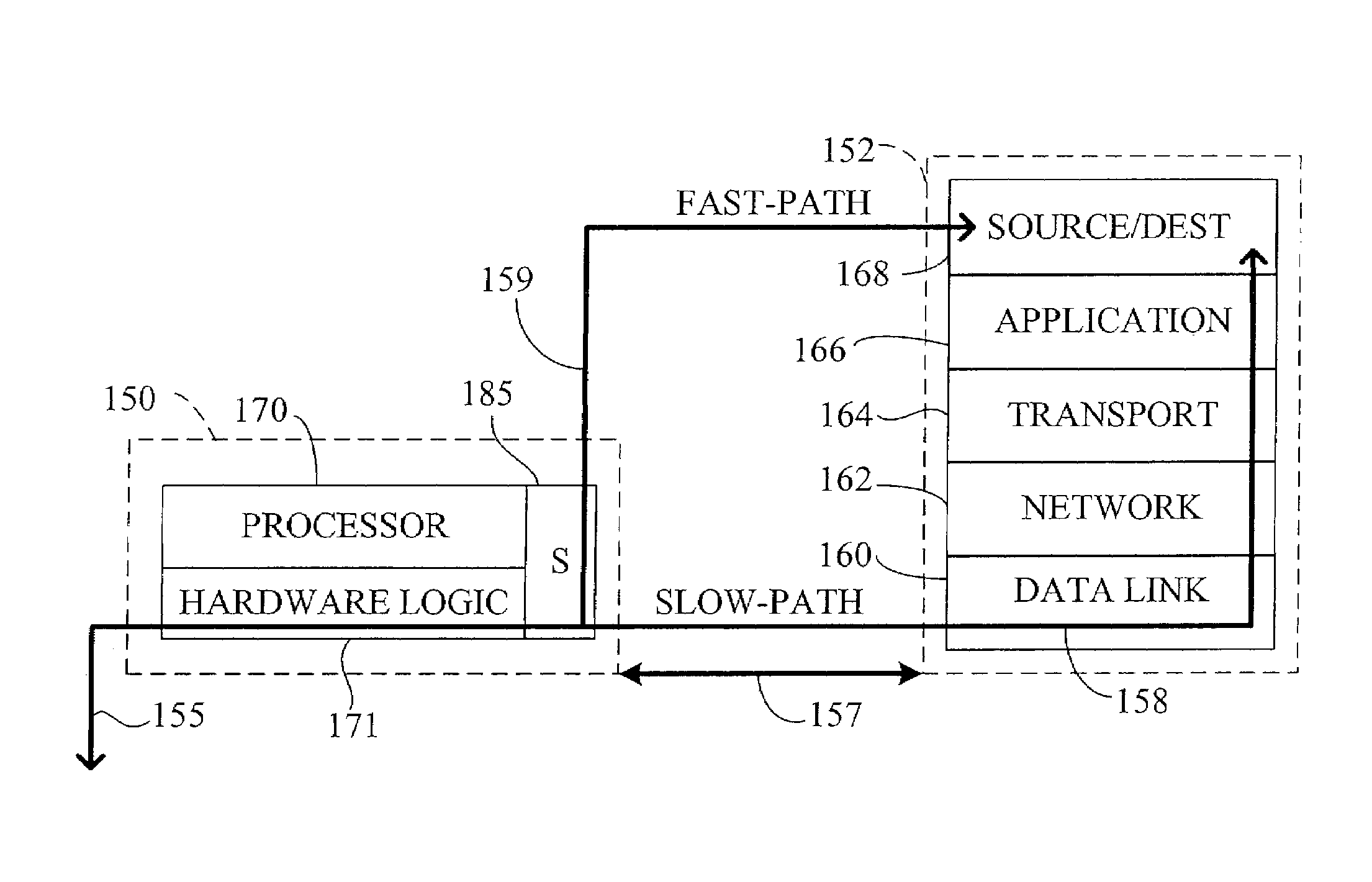

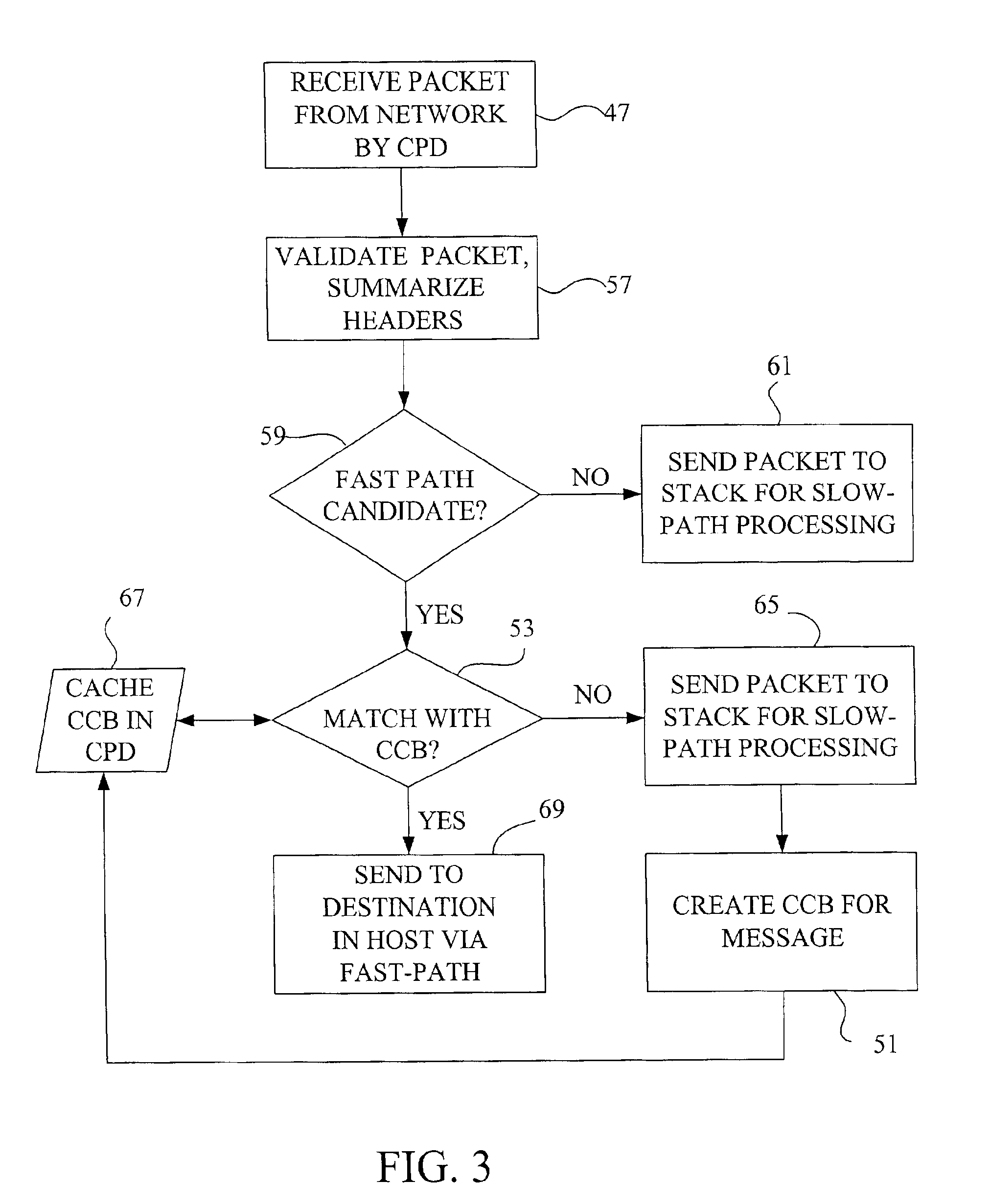

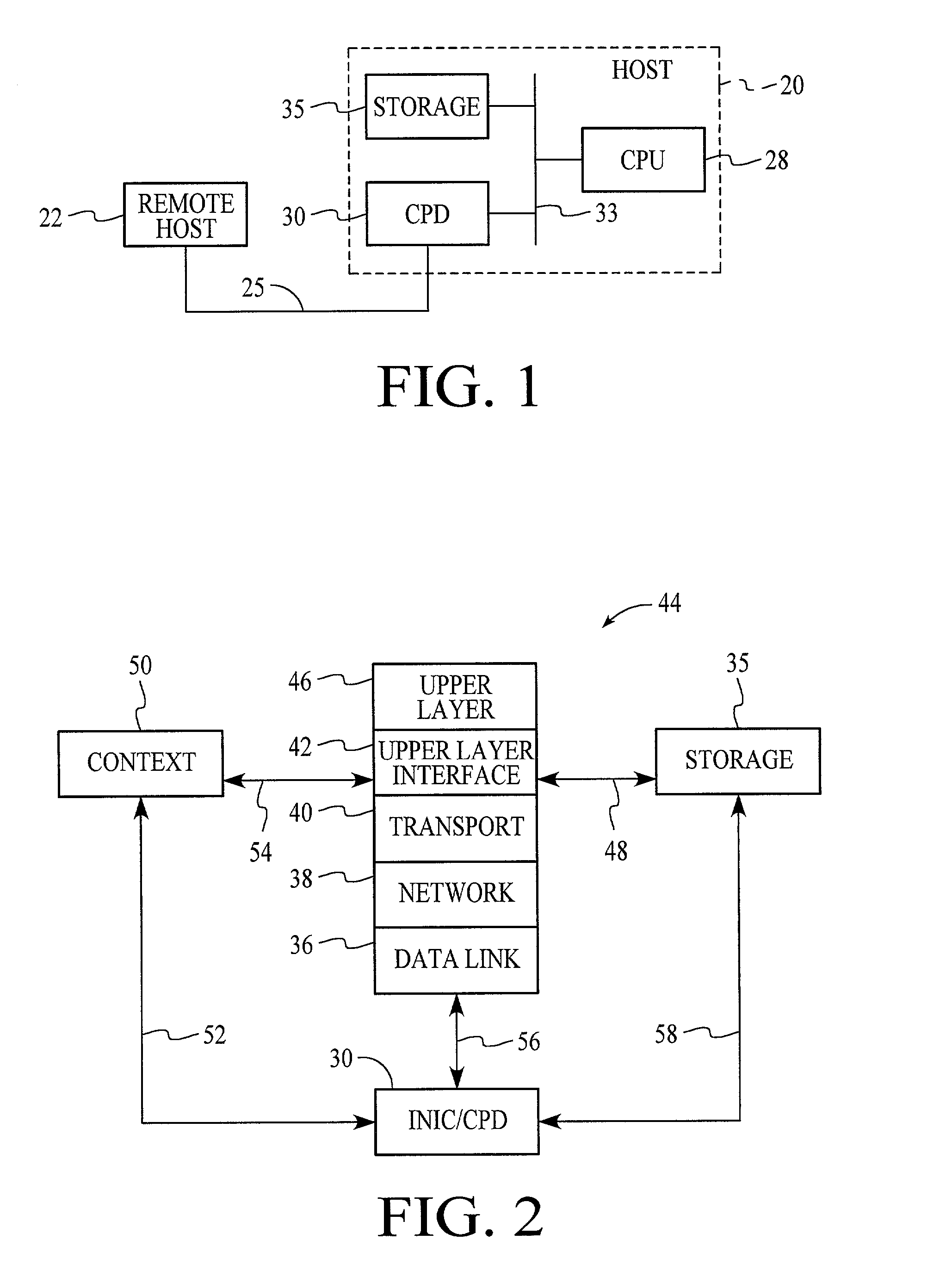

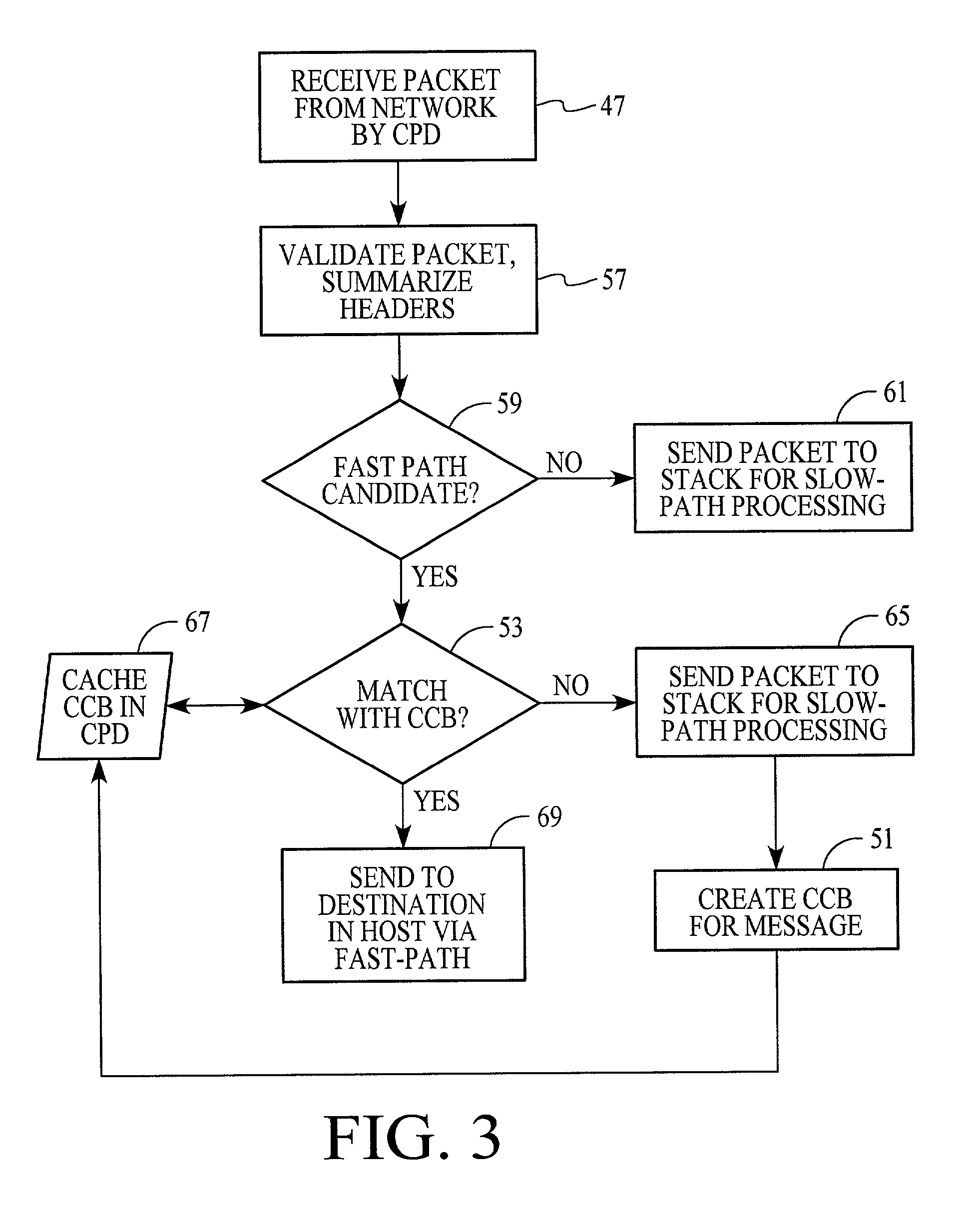

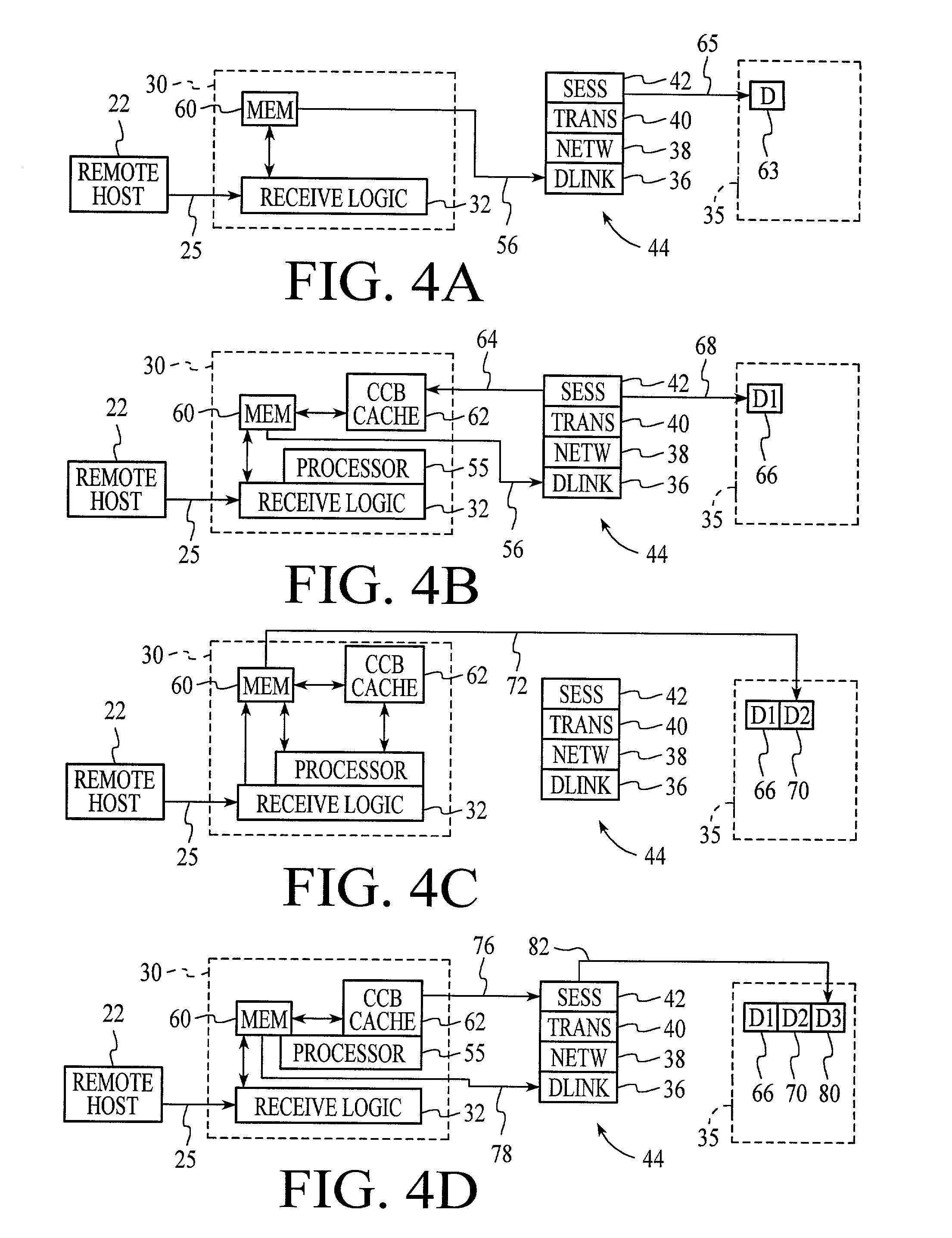

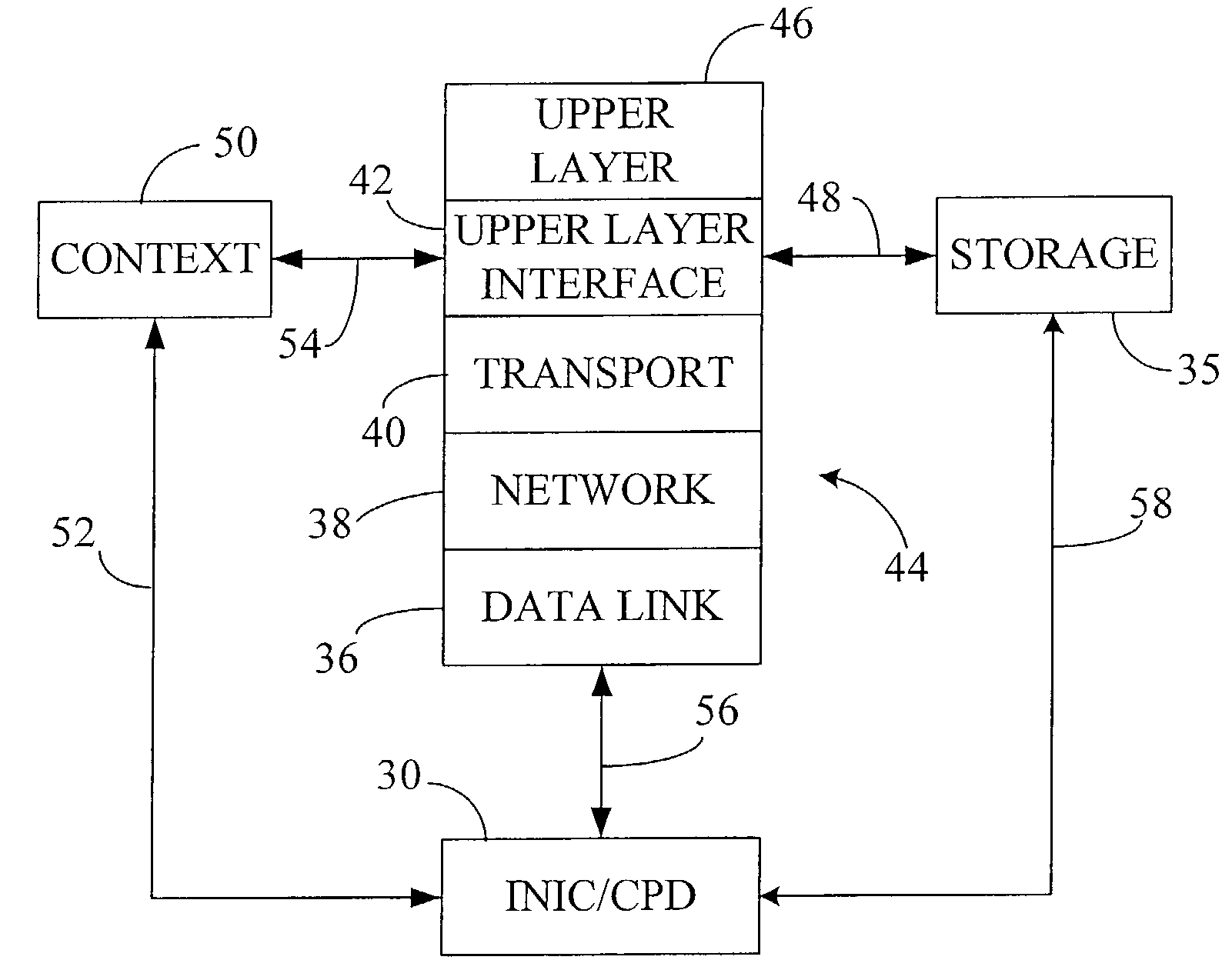

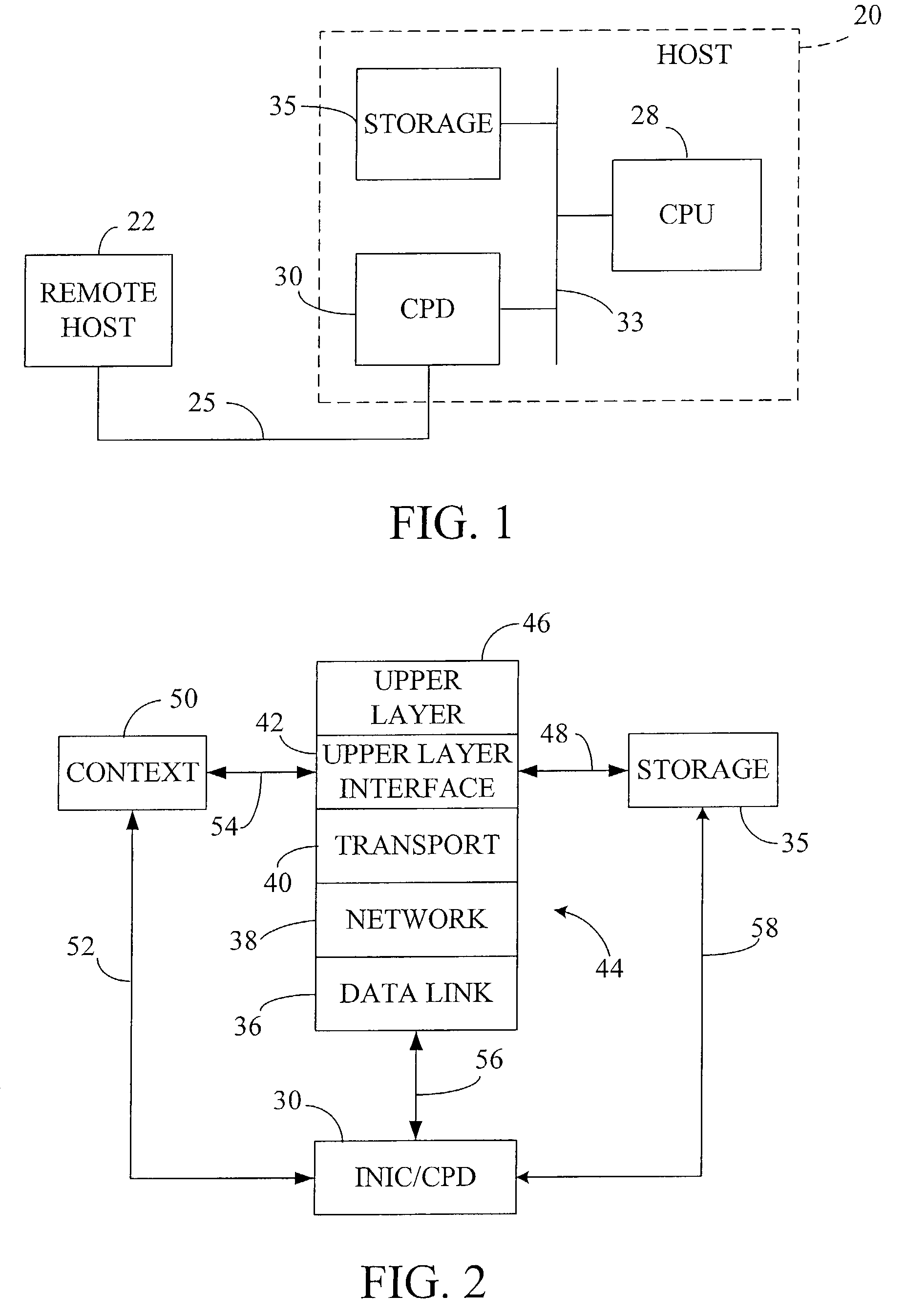

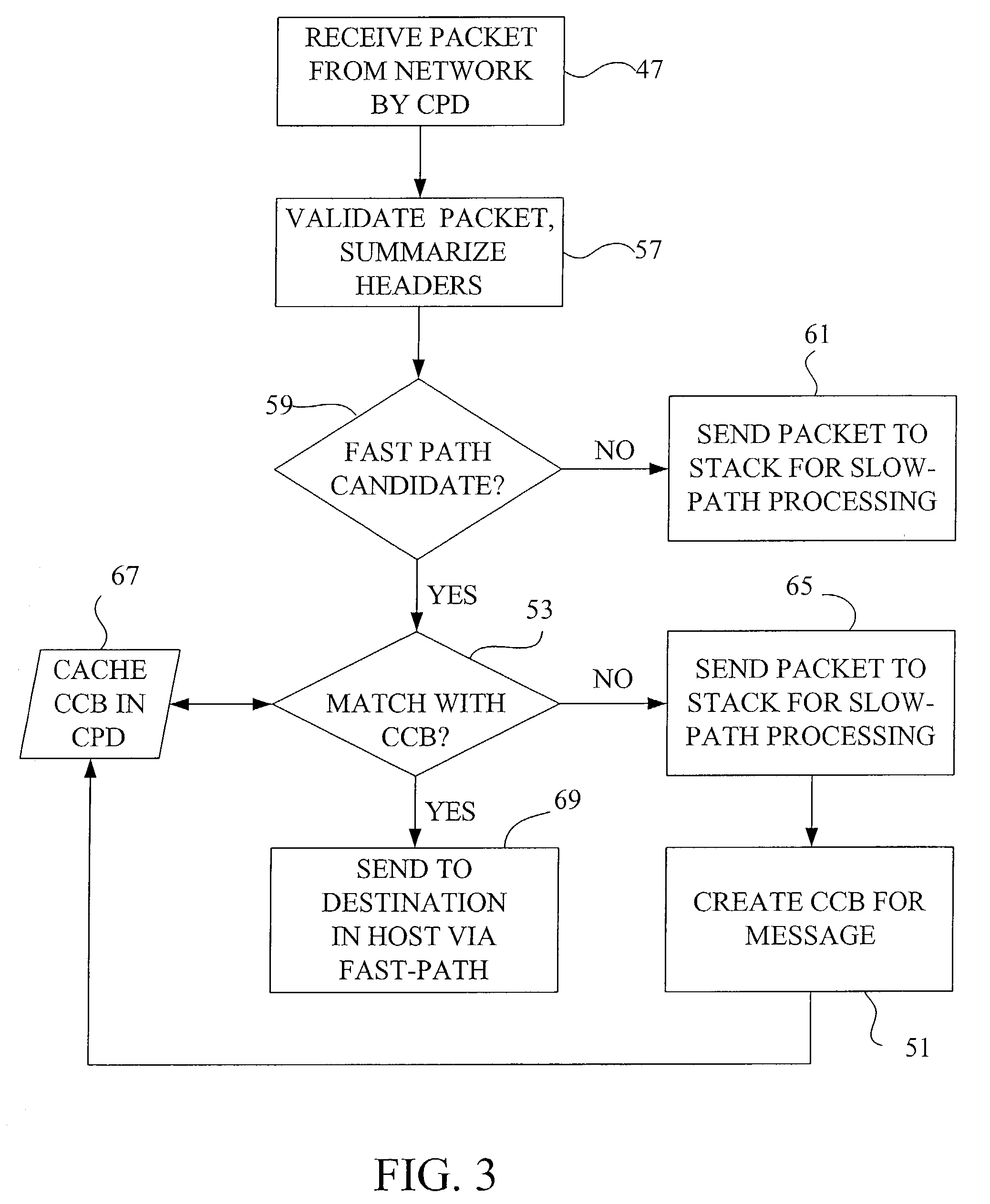

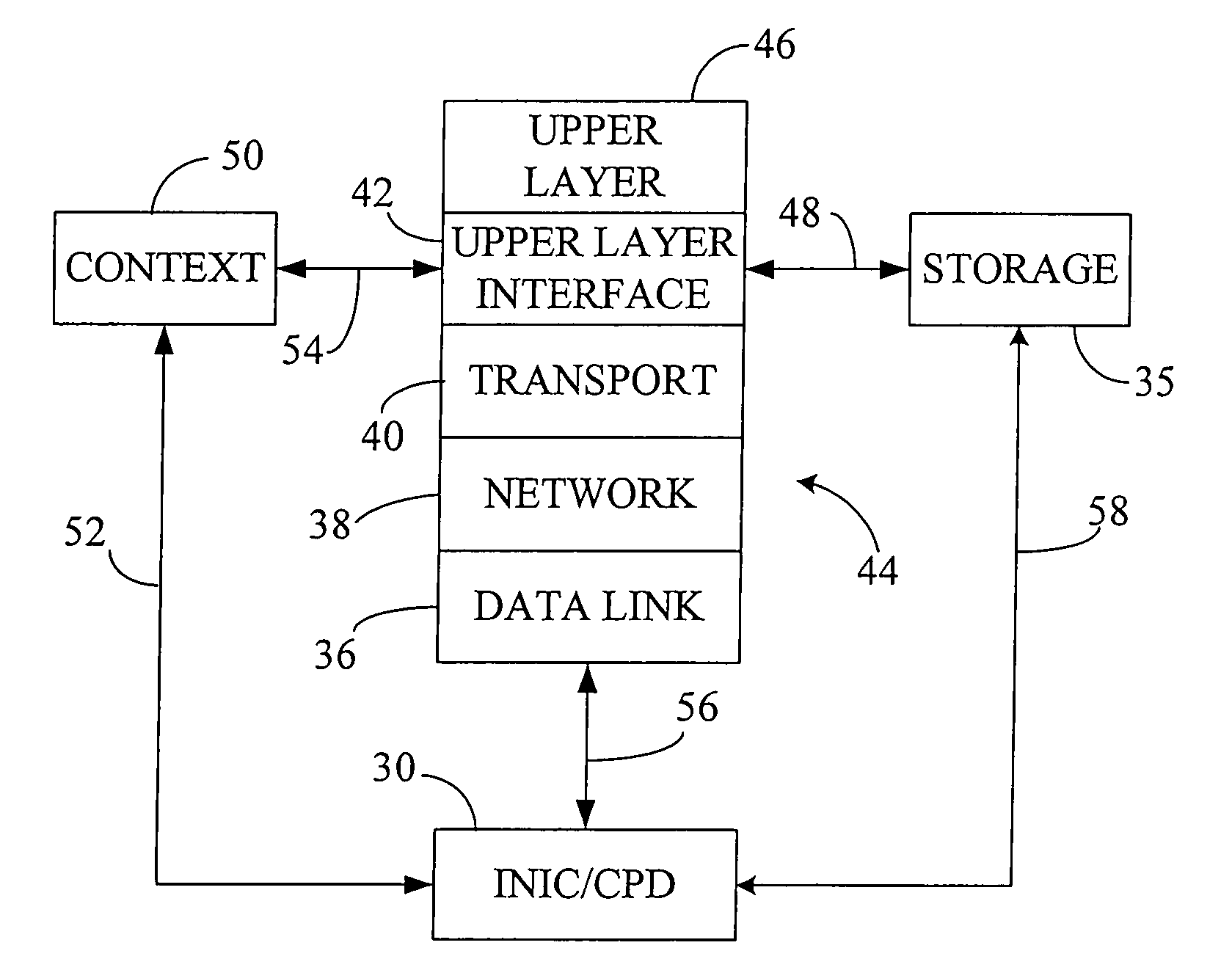

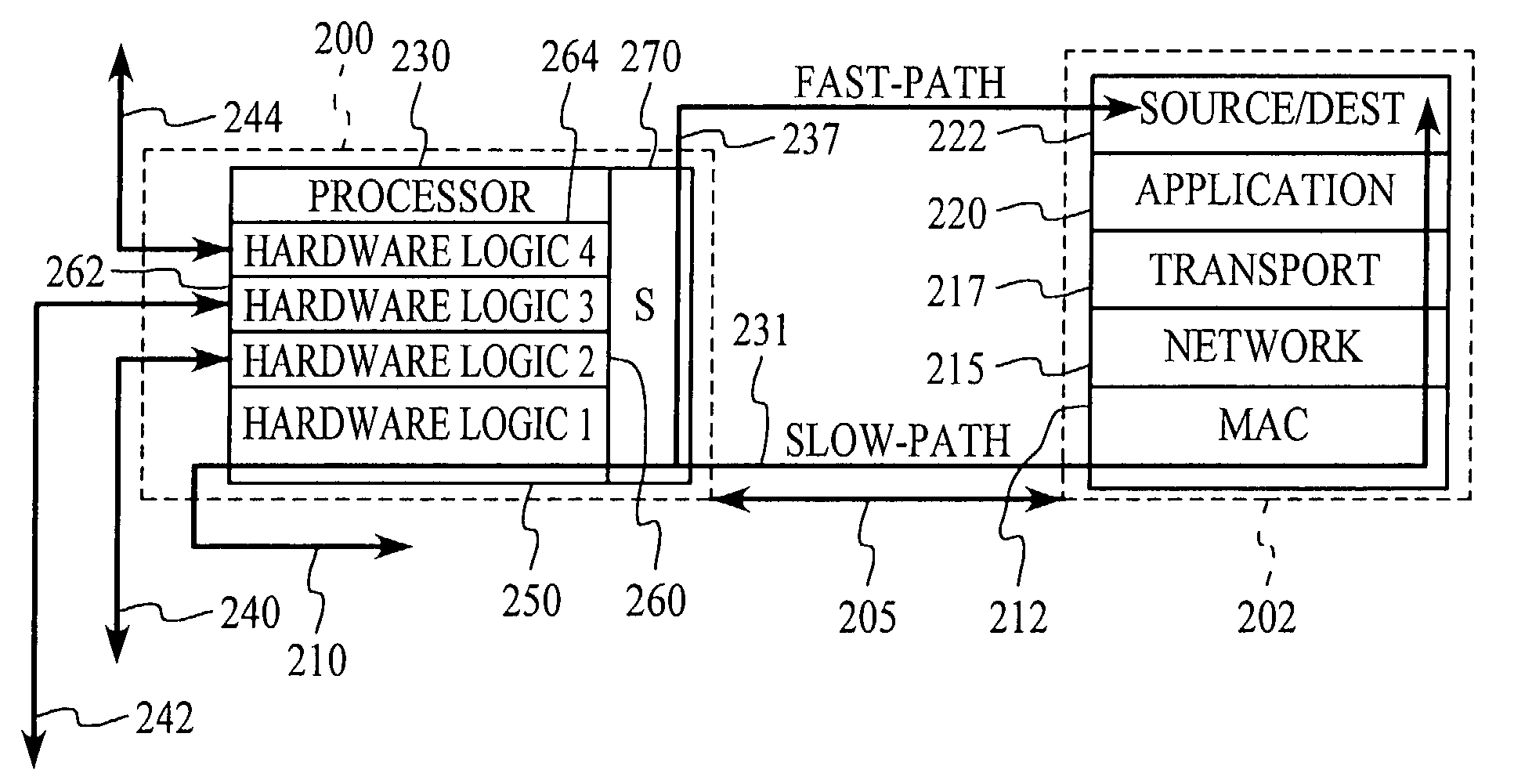

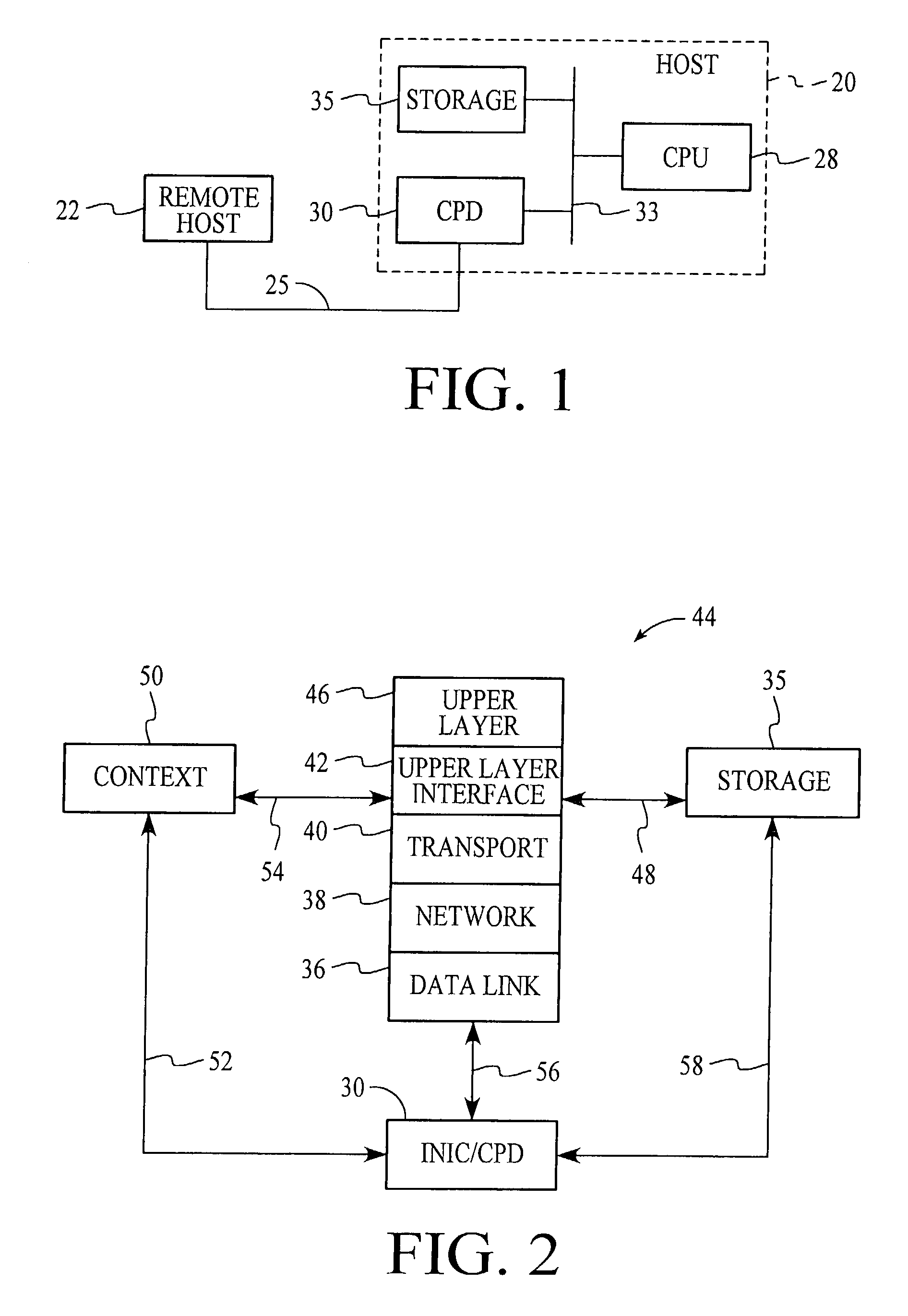

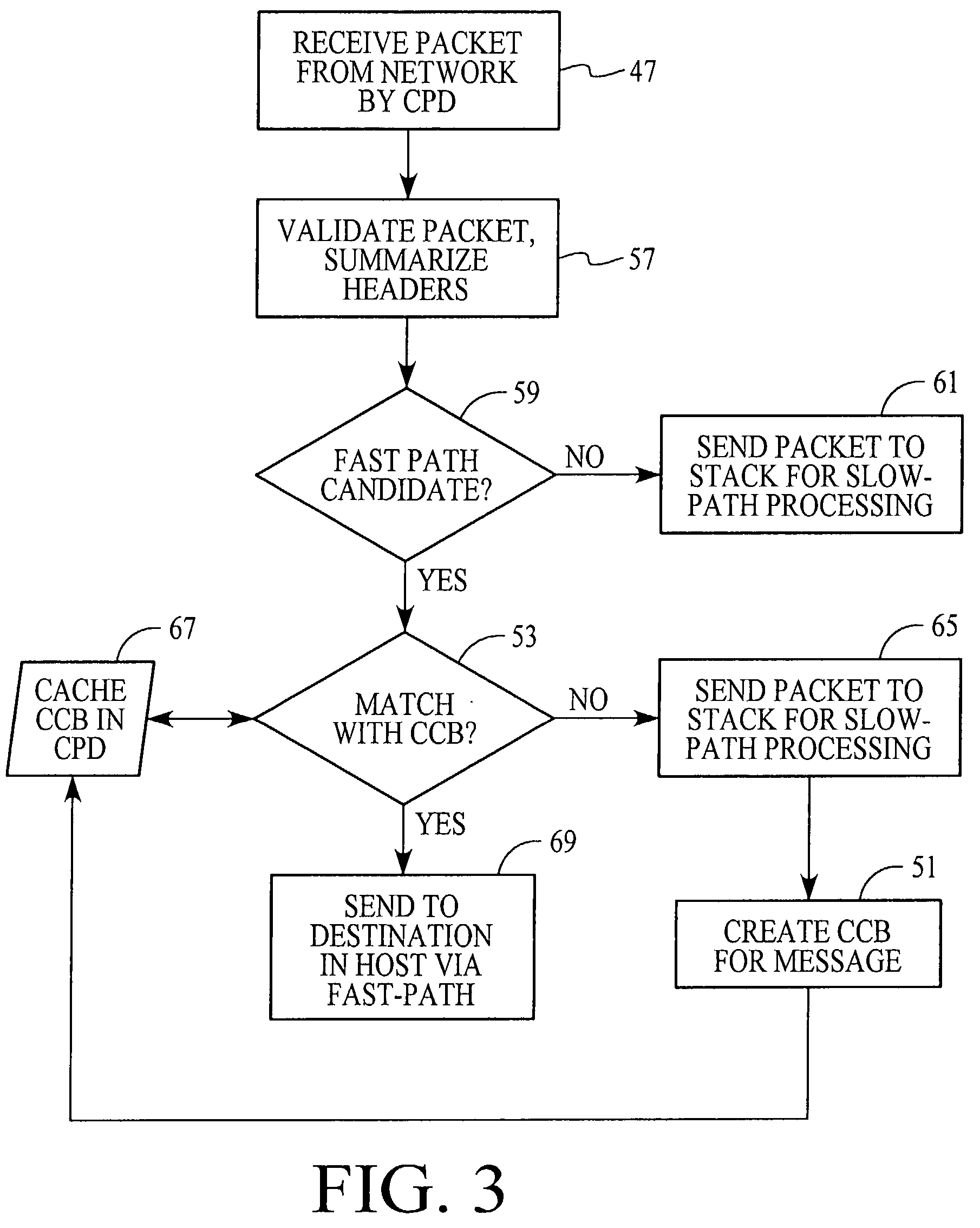

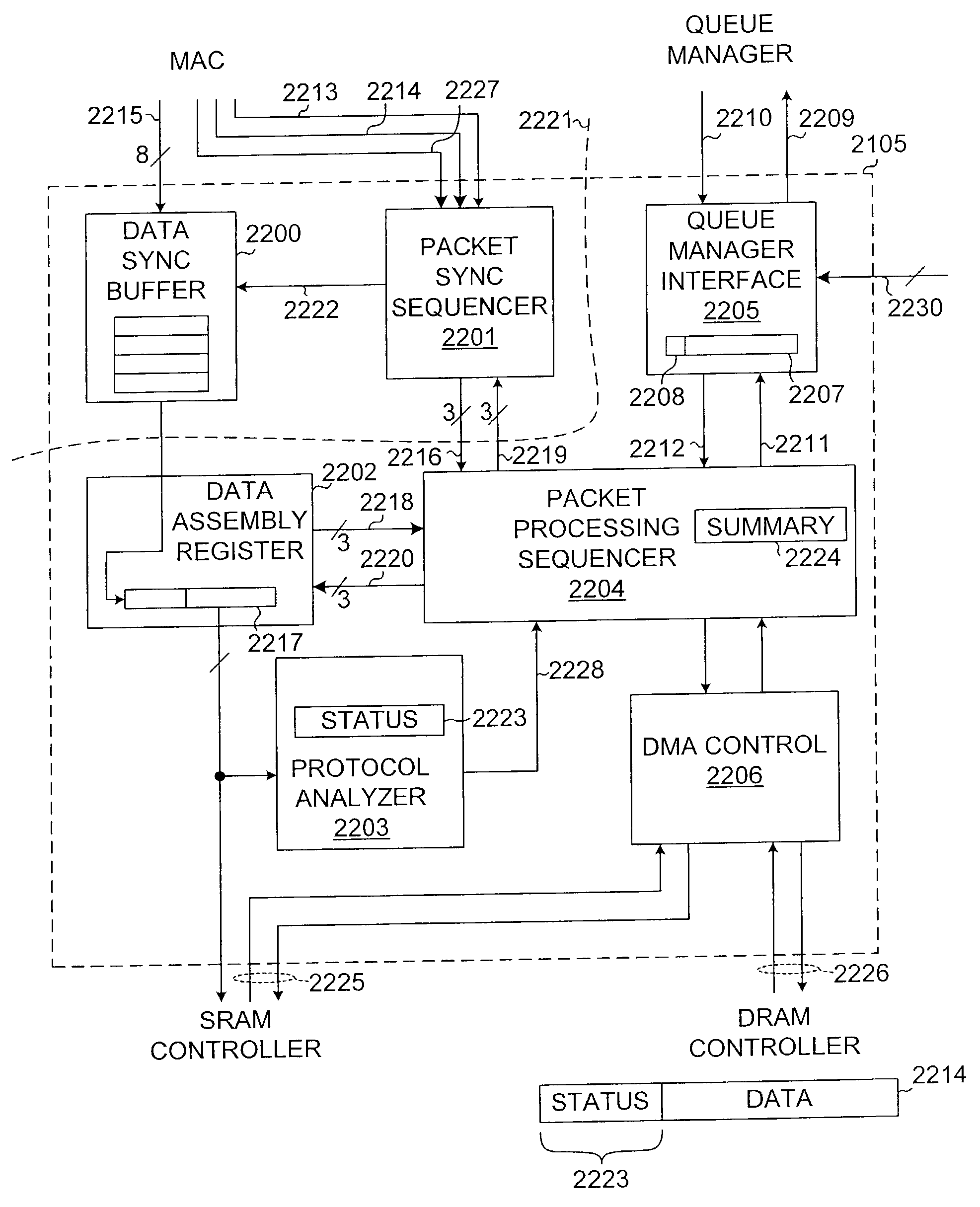

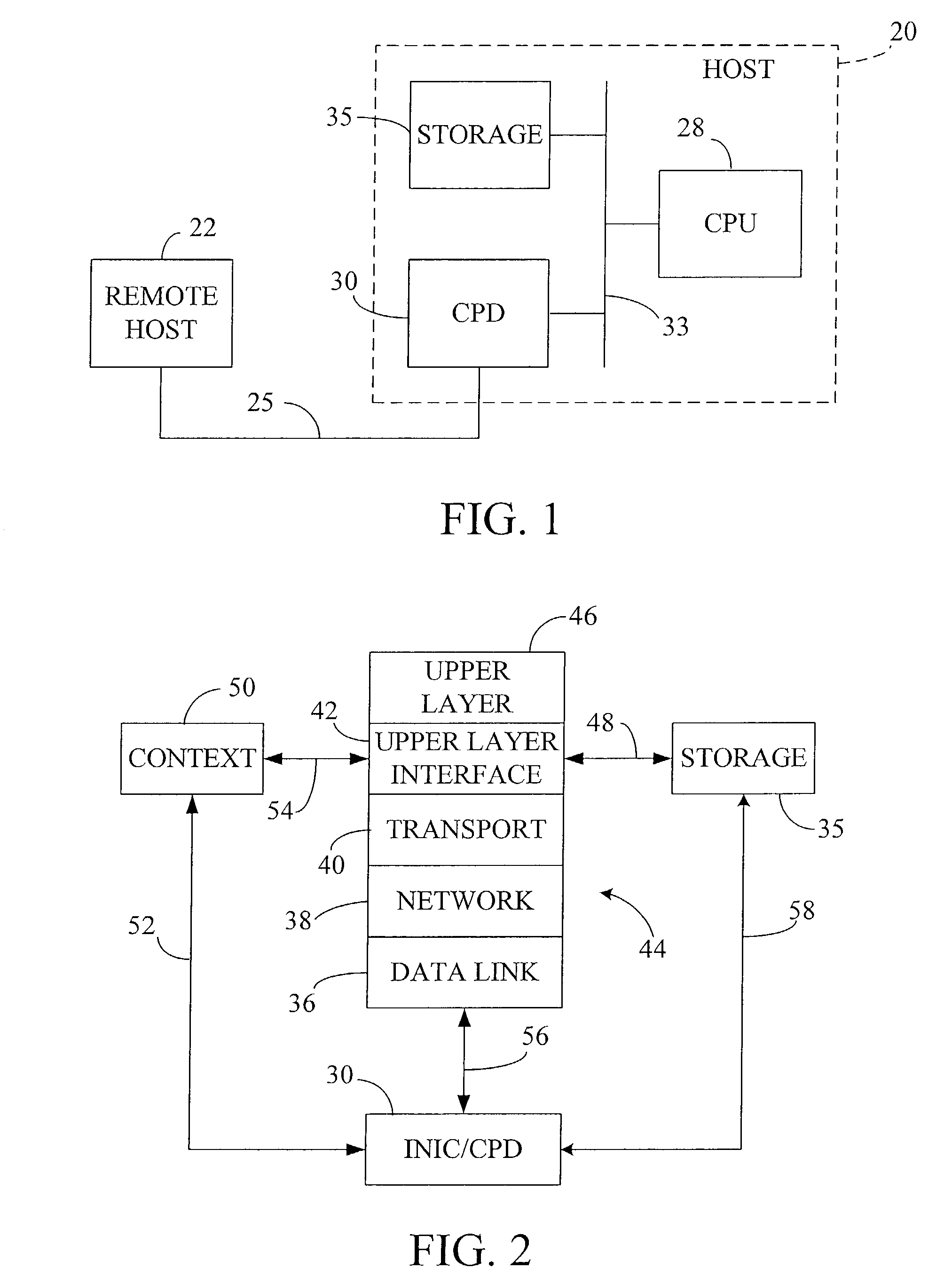

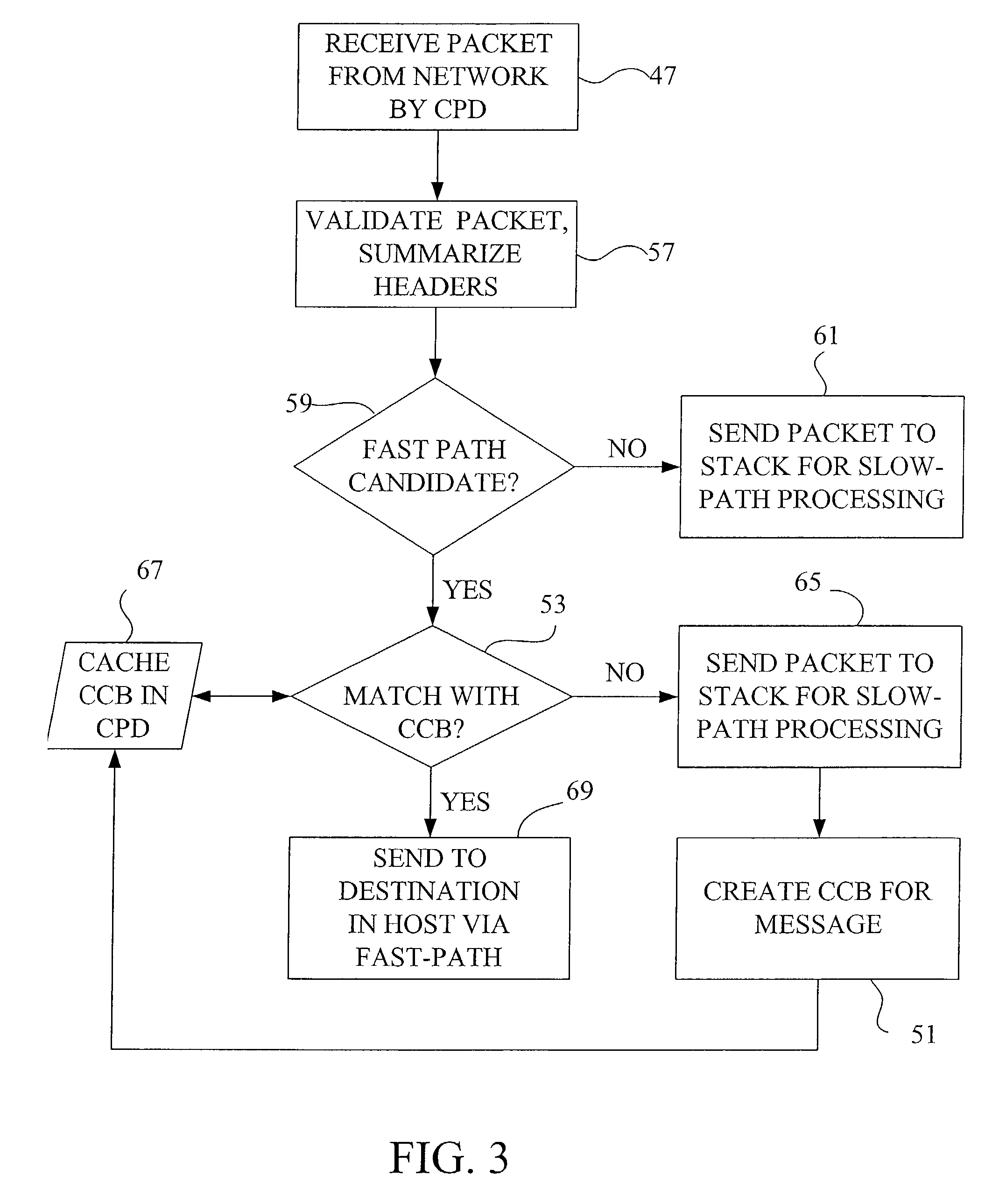

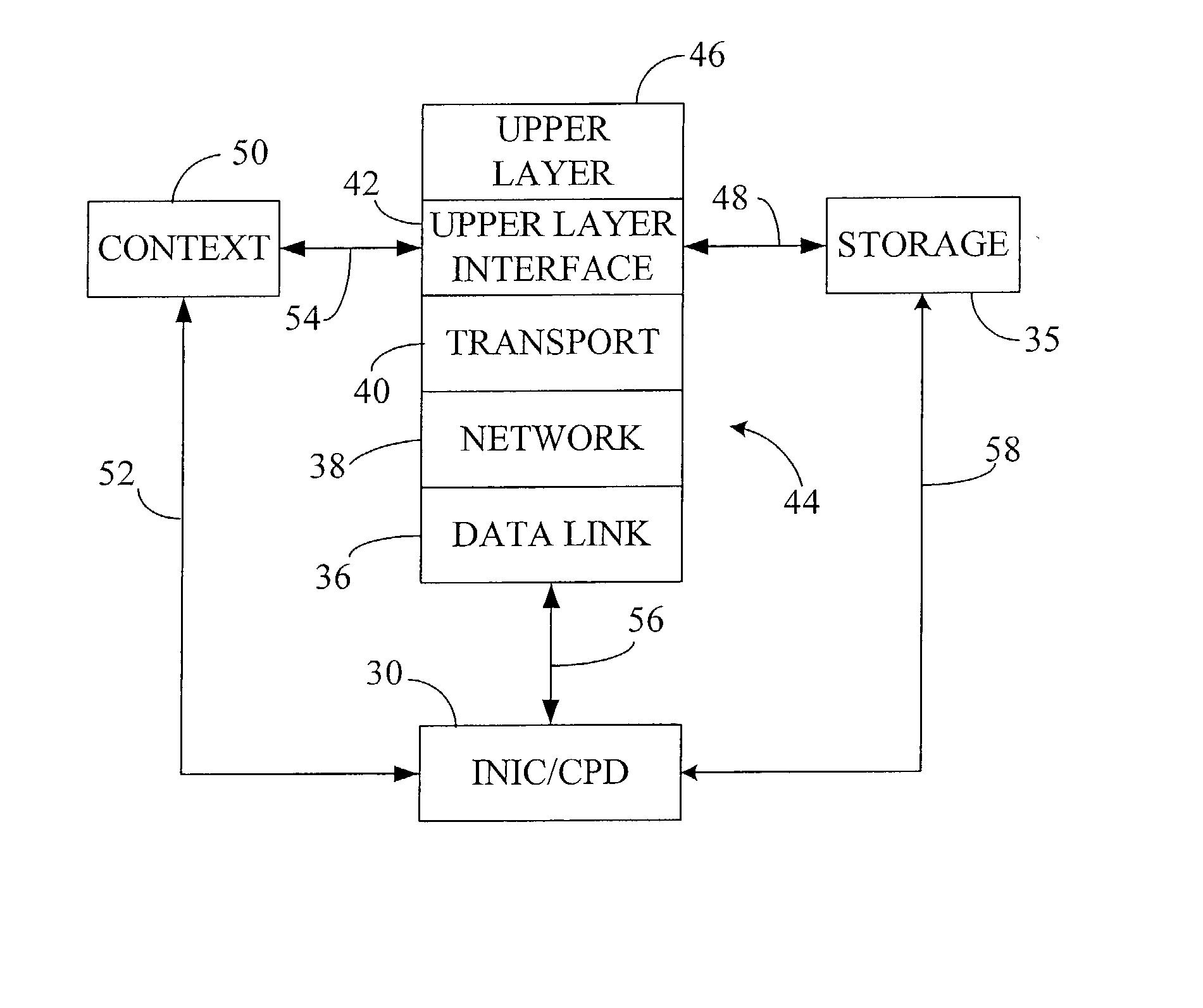

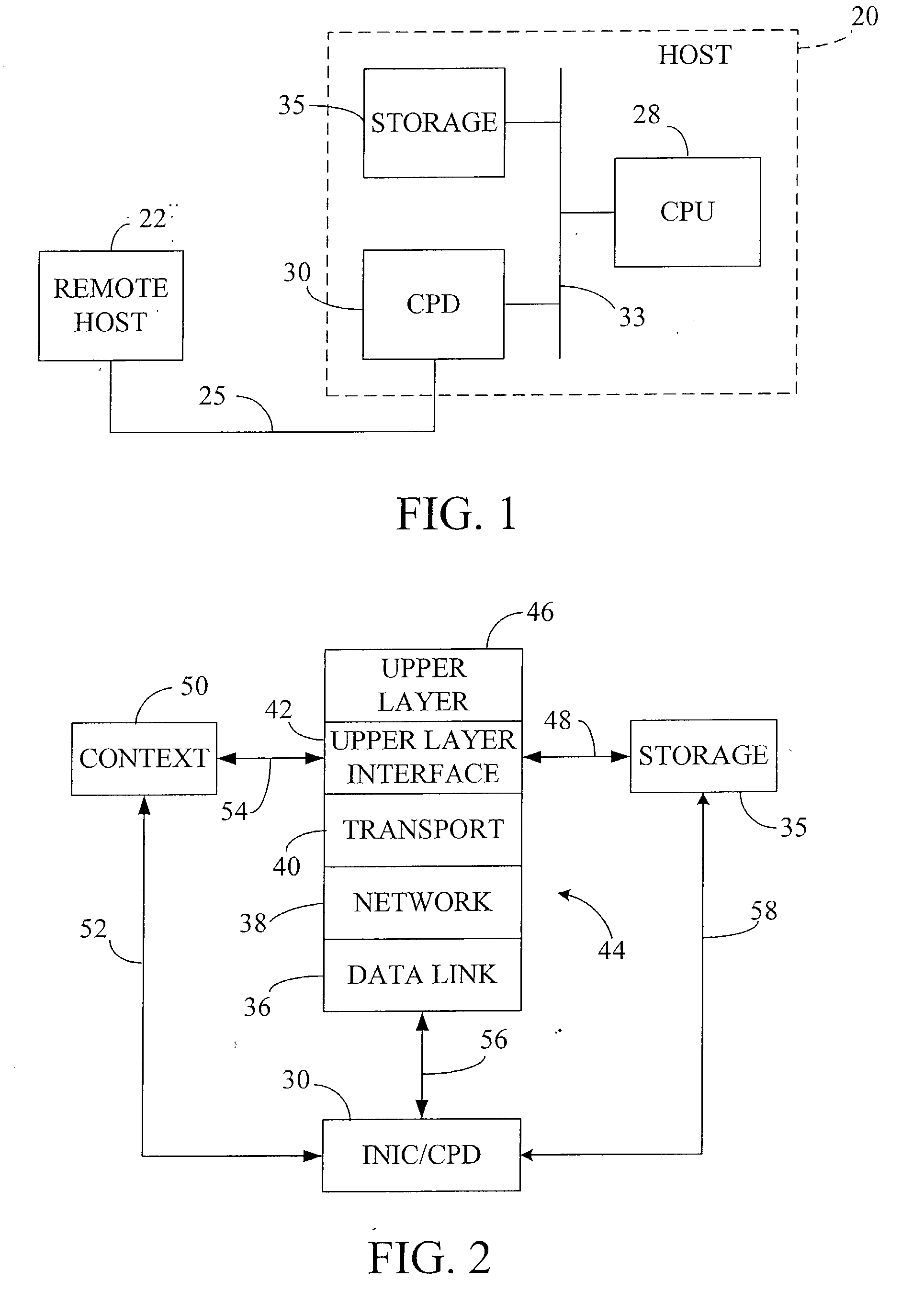

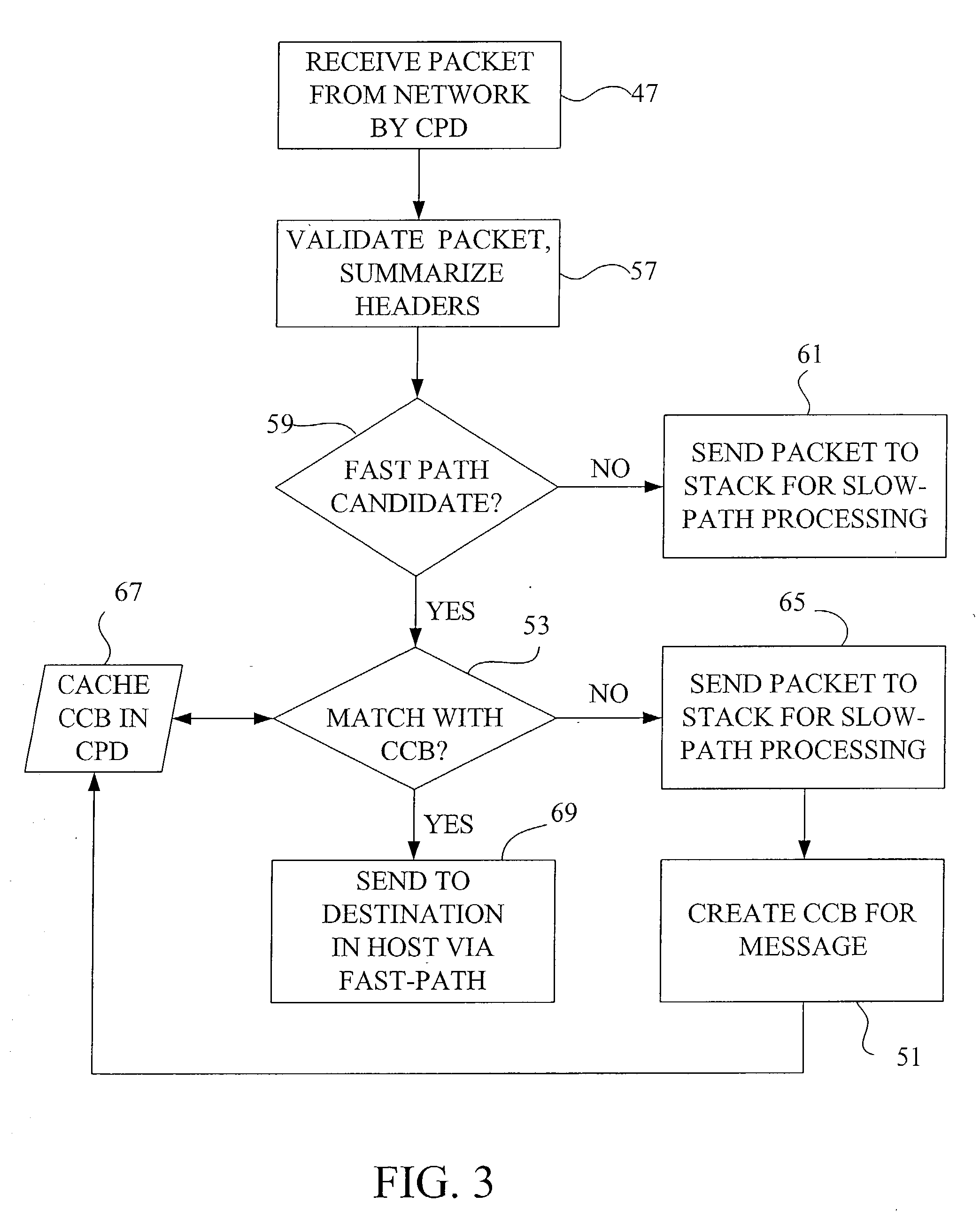

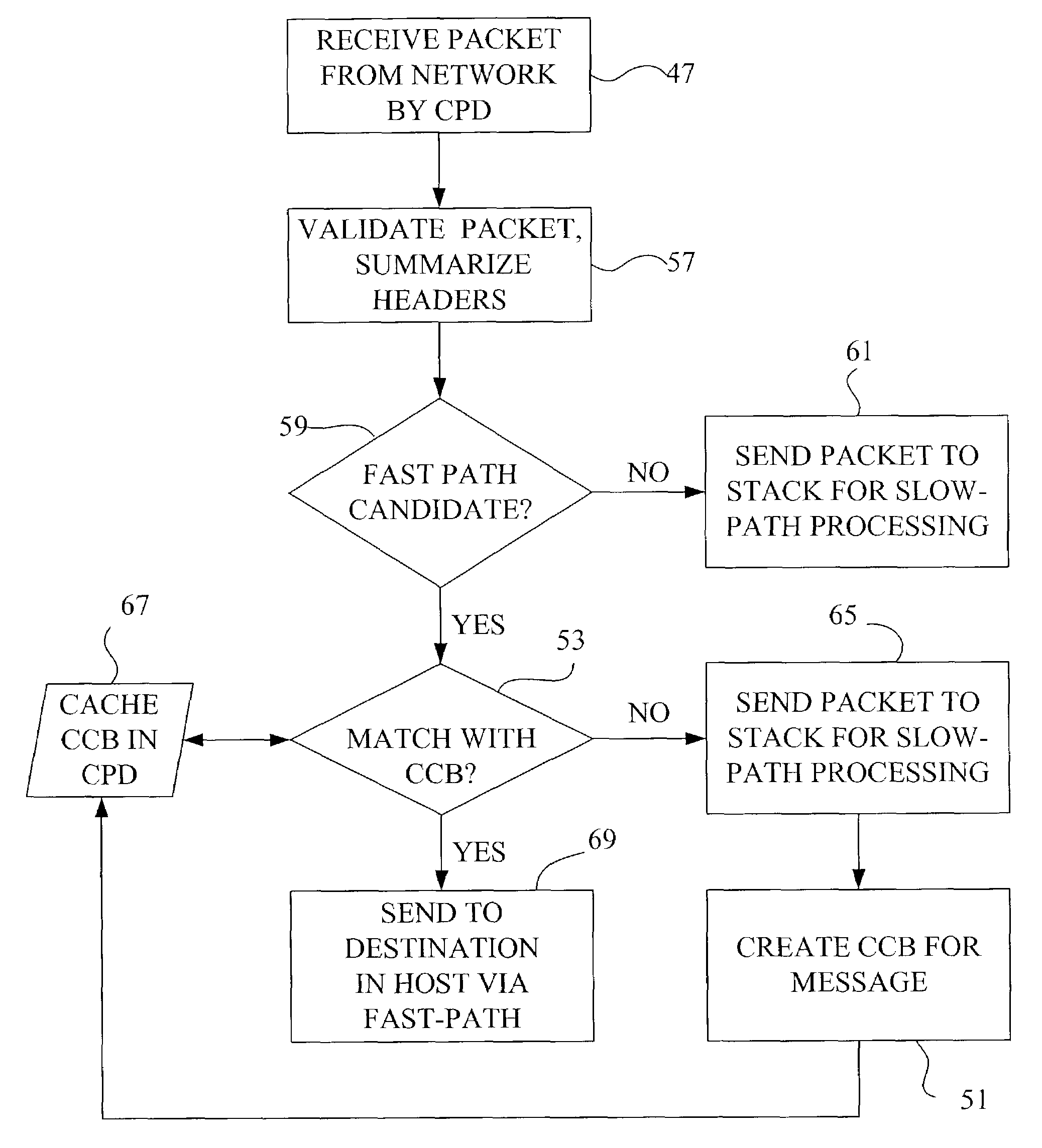

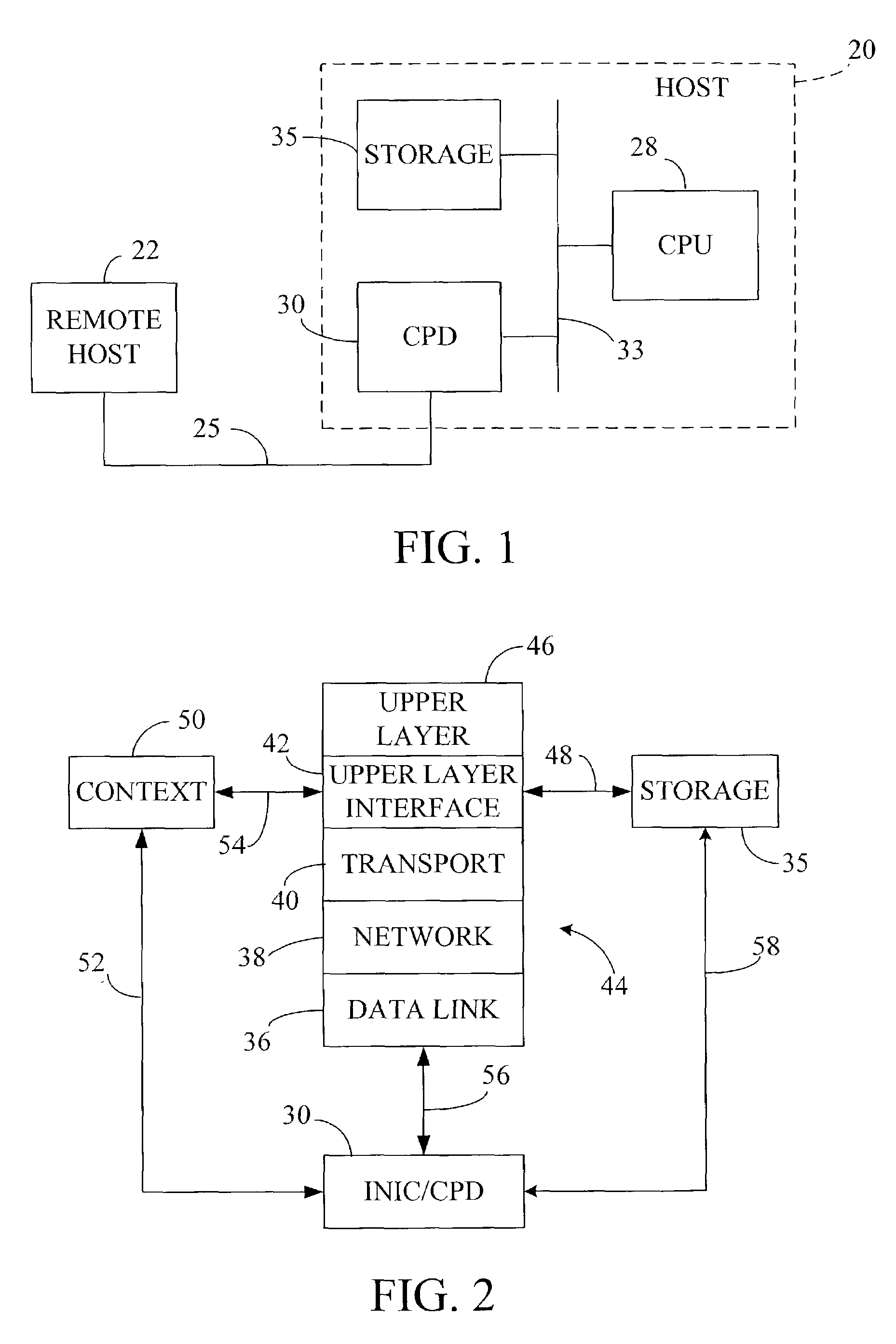

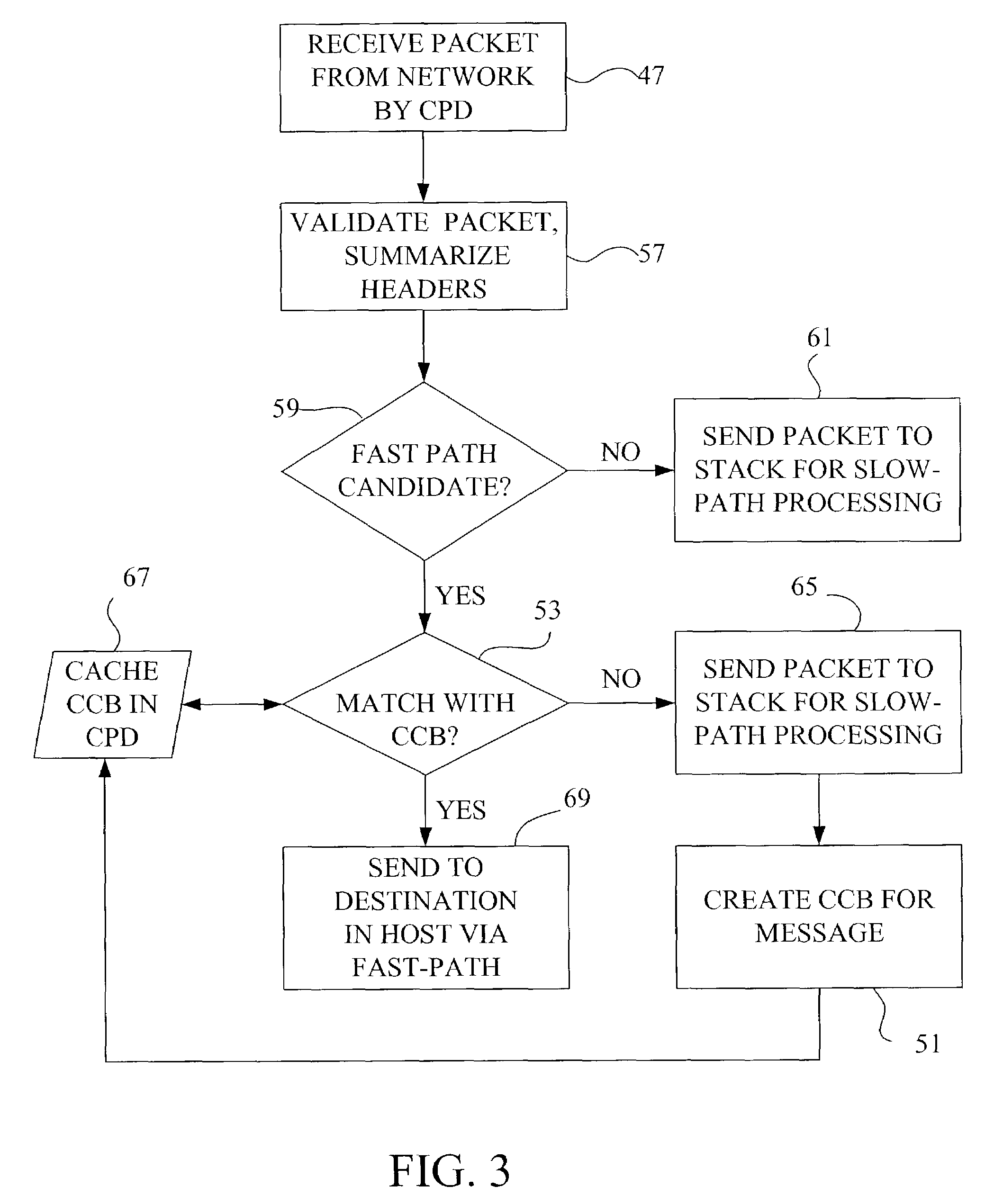

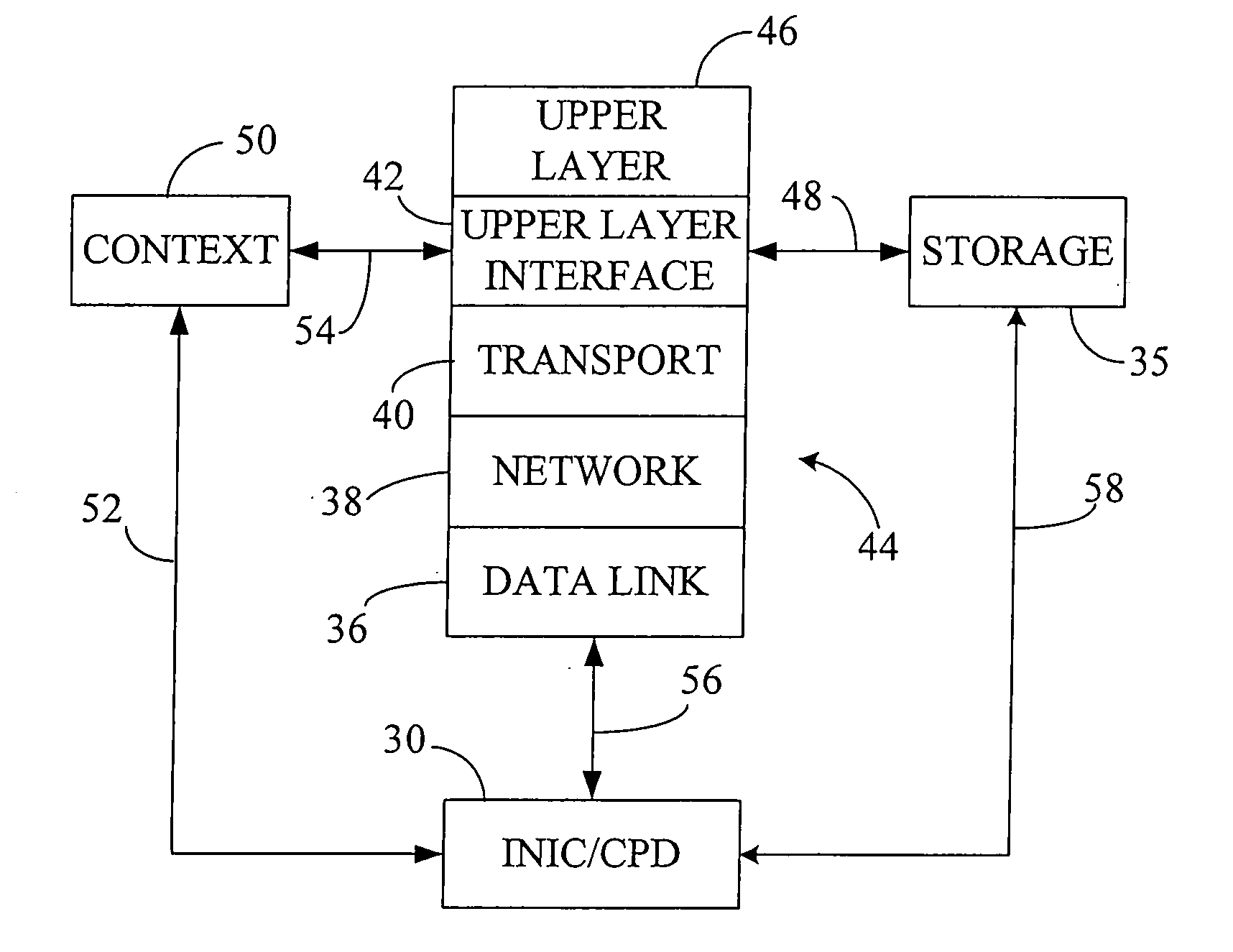

A system for protocol processing in a computer network has an intelligent network interface card (INIC) or communication processing device (CPD) associated with a host computer. The INIC provides a fast-path that avoids protocol processing for most large multi-packet messages, greatly accelerating data communication. The INIC also assists the host for those message packets that are chosen for processing by host software layers. A communication control block for a message is defined that allows DMA controllers of the INIC to move data, free of headers, directly to or from a destination or source in the host. The context is stored in the INIC as a communication control block (CCB) that can be passed back to the host for message processing by the host. The INIC contains specialized hardware circuits that are much faster at their specific tasks than a general purpose CPU. A preferred embodiment includes a trio of pipelined processors with separate processors devoted to transmit, receive and management processing, with full duplex communication for four fast Ethernet nodes.

Owner:ALACRITECH

Transmit fast-path processing on TCP/IP offload network interface device

InactiveUS6965941B2Little and no performance benefitMove quicklyMultiplex system selection arrangementsMultiple digital computer combinationsFast pathProtocol processing

Owner:ALACRITECH

Passing a communication control block from host to a local device such that a message is processed on the device

InactiveUS20010023460A1Unnecessary load on be avoidEffect on it overall performanceMultiplex system selection arrangementsMultiple digital computer combinationsProtocol processingIntelligent network interface card

A system for protocol processing in a computer network has an intelligent network interface card (INIC) or communication processing device (CPD) associated with a host computer. The INIC provides a fast-path that avoids protocol processing for most large multi-packet messages, greatly accelerating data communication. The INIC also assists the host for those message packets that are chosen for processing by host software layers. A communication control block for a message is defined that allows DMA controllers of the INIC to move data, free of headers, directly to or from a destination or source in the host. The context is stored in the INIC as a communication control block (CCB) that can be passed back to the host for message processing by the host. The INIC contains specialized hardware circuits that are much faster at their specific tasks than a general purpose CPU. A preferred embodiment includes a trio of pipelined processors with separate processors devoted to transmit, receive and management processing, with full duplex communication for four fast Ethernet nodes.

Owner:ALACRITECH

Fast-path apparatus for receiving data corresponding to a TCP connection

ActiveUS7337241B2Little and no performance benefitMove quicklyMultiple digital computer combinationsSecuring communicationFast pathGeneral purpose

A system for protocol processing in a computer network has an intelligent network interface card (INIC) or communication processing device (CPD) associated with a host computer. The INIC provides a fast-path that avoids protocol processing for most large multi-packet messages, greatly accelerating data communication. The INIC also assists the host for those message packets that are chosen for processing by host software layers. A communication control block for a message is defined that allows DMA controllers of the INIC to move data, free of headers, directly to or from a destination or source in the host. The context is stored in the INIC as a communication control block (CCB) that can be passed back to the host for message processing by the host. The INIC contains specialized hardware circuits that are much faster at their specific tasks than a general purpose CPU. A preferred embodiment includes a trio of pipelined processors with separate processors devoted to transmit, receive and management processing, with full duplex communication for four fast Ethernet nodes.

Owner:ALACRITECH

Fast-path apparatus for transmitting data corresponding to a TCP connection

InactiveUS7673072B2Little and no performance benefitMove quicklyError preventionFrequency-division multiplex detailsGeneral purposeFast path

A system for protocol processing in a computer network has an intelligent network interface card (INIC) or communication processing device (CPD) associated with a host computer. The INIC provides a fast-path that avoids protocol processing for most large multi-packet messages, greatly accelerating data communication. The INIC also assists the host for those message packets that are chosen for processing by host software layers. A communication control block for a message is defined that allows DMA controllers of the INIC to move data, free of headers, directly to or from a destination or source in the host. The context is stored in the INIC as a communication control block (CCB) that can be passed back to the host for message processing by the host. The INIC contains specialized hardware circuits that are much faster at their specific tasks than a general purpose CPU. A preferred embodiment includes a trio of pipelined processors with separate processors devoted to transmit, receive and management processing, with full duplex communication for four fast Ethernet nodes.

Owner:ALACRITECH

TCP/IP offload network interface device

InactiveUS7174393B2Little and no performance benefitMove quicklyMultiple digital computer combinationsData switching networksGeneral purposeFast path

A system for protocol processing in a computer network has a TCP / IP Offload Network Interface Device (TONID) associated with a host computer. The TONID provides a fast-path that avoids protocol processing for most large multi-packet messages, greatly accelerating data communication. The TONID also assists the host for those message packets that are chosen for processing by host software layers. A communication control block for a message is defined that allows DMA controllers of the TONID to move data, free of headers, directly to or from a destination or source in the host. The context is stored in the TONID as a communication control block (CCB) that can be passed back to the host for message processing by the host. The TONID contains specialized hardware circuits that are much faster at their specific tasks than a general purpose CPU. A preferred embodiment includes a trio of pipelined processors with separate processors devoted to transmit, receive and management processing, with full duplex communication for four fast Ethernet nodes.

Owner:ALACRITECH

Fast-path apparatus for receiving data corresponding to a TCP connection

InactiveUS7191241B2Little and no performance benefitMove quicklyMultiple digital computer combinationsTransmissionFast pathGeneral purpose

A system for protocol processing in a computer network has an intelligent network interface card (INIC) or communication processing device (CPD) associated with a host computer. The INIC provides a fast-path that avoids protocol processing for most large multi-packet messages, greatly accelerating data communication. The INIC also assists the host for those message packets that are chosen for processing by host software layers. A communication control block for a message is defined that allows DMA controllers of the INIC to move data, free of headers, directly to or from a destination or source in the host. The context is stored in the INIC as a communication control block (CCB) that can be passed back to the host for message processing by the host. The INIC contains specialized hardware circuits that are much faster at their specific tasks than a general purpose CPU. A preferred embodiment includes a trio of pipelined processors with separate processors devoted to transmit, receive and management processing, with full duplex communication for four fast Ethernet nodes.

Owner:ALACRITECH

Fast-path apparatus for receiving data corresponding to a TCP connection

ActiveUS20040064578A1Negligibly effectMove quicklyMultiple digital computer combinationsSecuring communicationGeneral purposeFast path

A system for protocol processing in a computer network has an intelligent network interface card (INIC) or communication processing device (CPD) associated with a host computer. The INIC provides a fast-path that avoids protocol processing for most large multi-packet messages, greatly accelerating data communication. The INIC also assists the host for those message packets that are chosen for processing by host software layers. A communication control block for a message is defined that allows DMA controllers of the INIC to move data, free of headers, directly to or from a destination or source in the host. The context is stored in the INIC as a communication control block (CCB) that can be passed back to the host for message processing by the host. The INIC contains specialized hardware circuits that are much faster at their specific tasks than a general purpose CPU. A preferred embodiment includes a trio of pipelined processors with separate processors devoted to transmit, receive and management processing, with full duplex communication for four fast Ethernet nodes.

Owner:ALACRITECH

System for and method of golf performance recordation and analysis

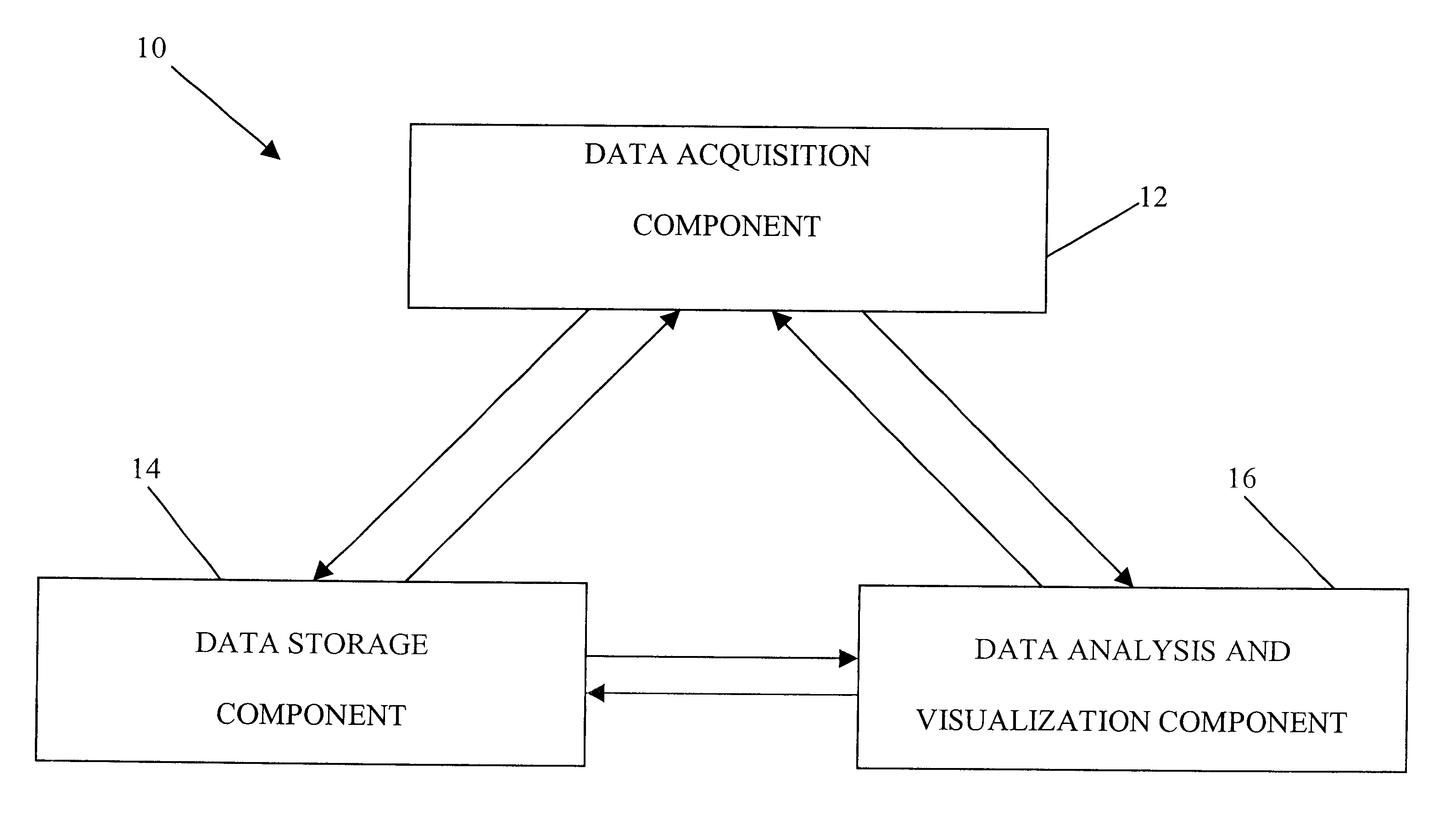

InactiveUS6697820B1Improve performanceEffect on its overall performanceBall sportsSpecial data processing applicationsData acquisitionCentralized database

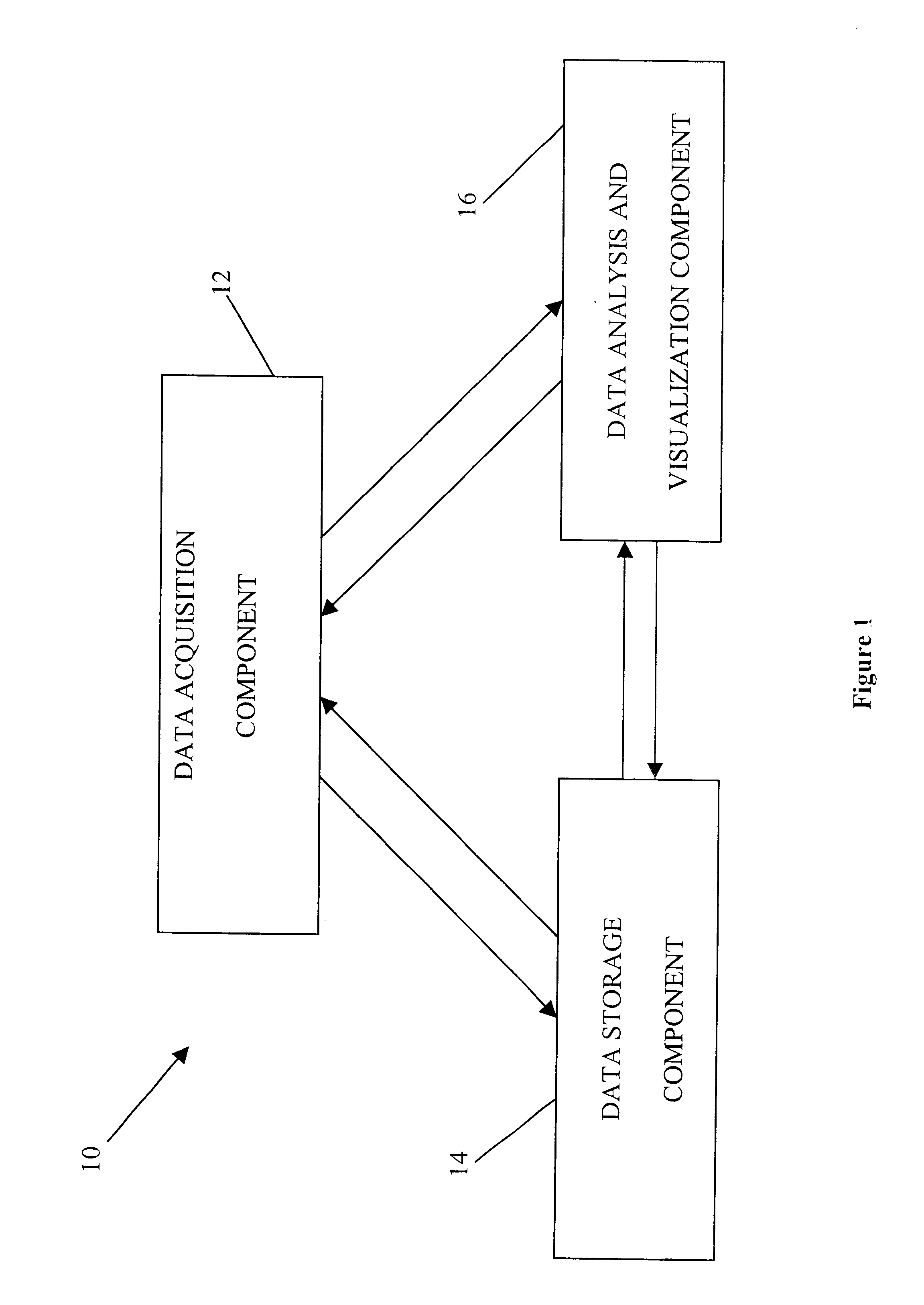

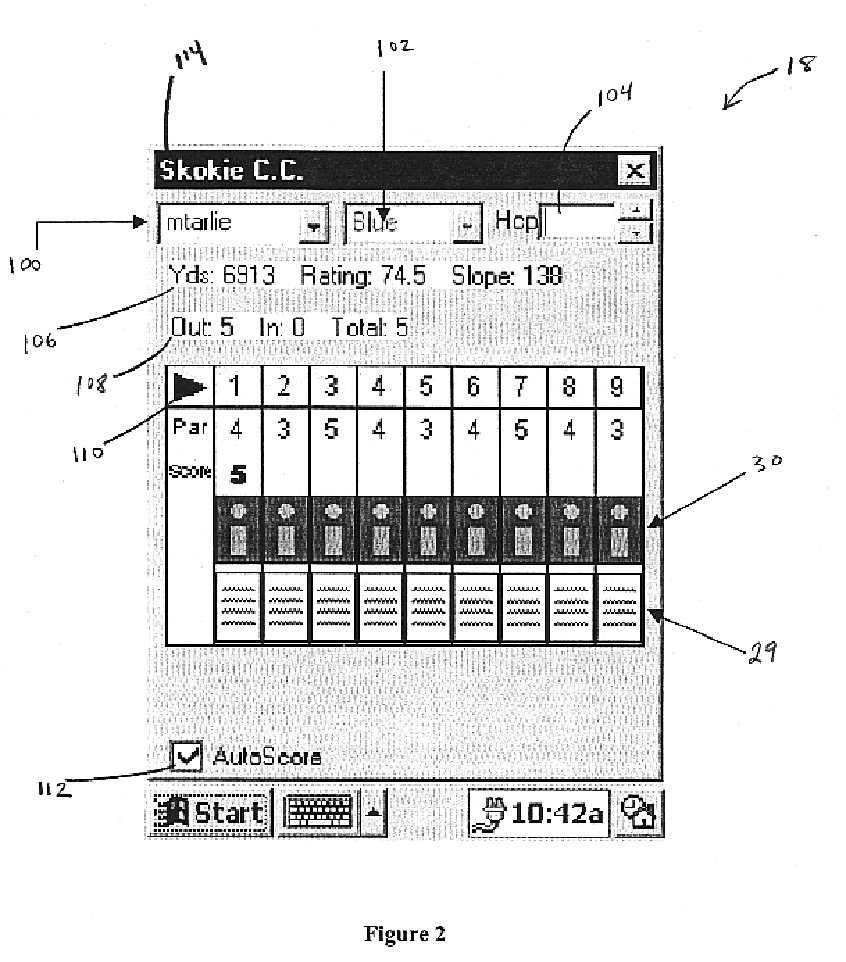

A system for and method of golf performance recordation and analysis are provided. In accordance with the present invention, a user records hole-level and shot-level performance data for rounds of golf played by one or more players in a data acquisition component and uploads the performance data to a centralized database. The stored information can later be retrieved from the database by the user for visualization and analysis.

Owner:TARLIE MARTIN B

TCP offload network interface device

InactiveUS7284070B2Negligibly effectMove quicklyMultiple digital computer combinationsTransmissionFast pathGeneral purpose

A system for protocol processing in a computer network has an intelligent network interface card (INIC) or communication processing device (CPD) associated with a host computer. The INIC provides a fast-path that avoids protocol processing for most large multi-packet messages, greatly accelerating data communication. The INIC also assists the host for those message packets that are chosen for processing by host software layers. A communication control block for a message is defined that allows DMA controllers of the INIC to move data, free of headers, directly to or from a destination or source in the host. The context is stored in the INIC as a communication control block (CCB) that can be passed back to the host for message processing by the host. The INIC contains specialized hardware circuits that are much faster at their specific tasks than a general purpose CPU. A preferred embodiment includes a trio of pipelined processors with separate processors devoted to transmit, receive and management processing, with full duplex communication for four fast Ethernet nodes.

Owner:ALACRITECH

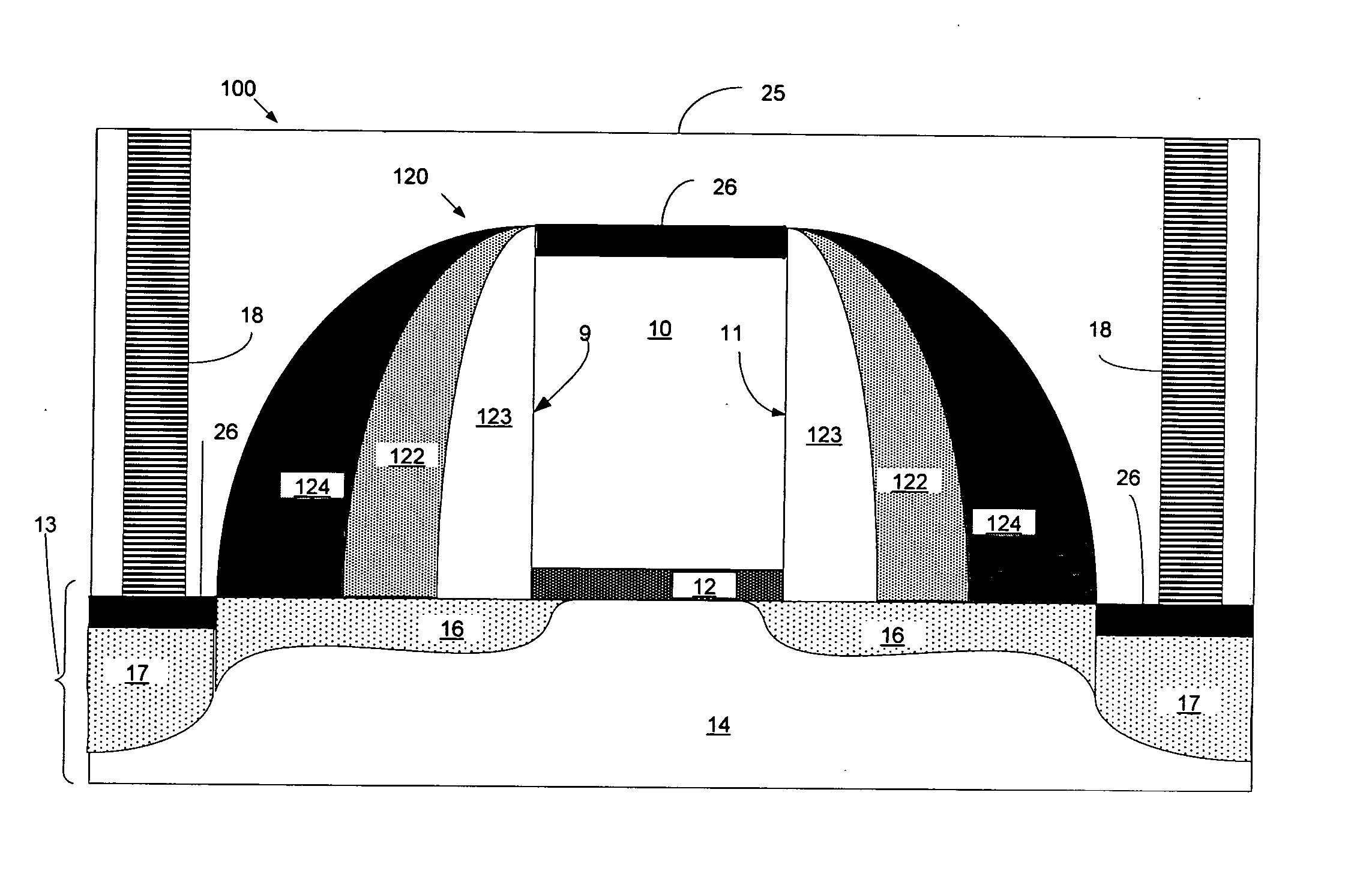

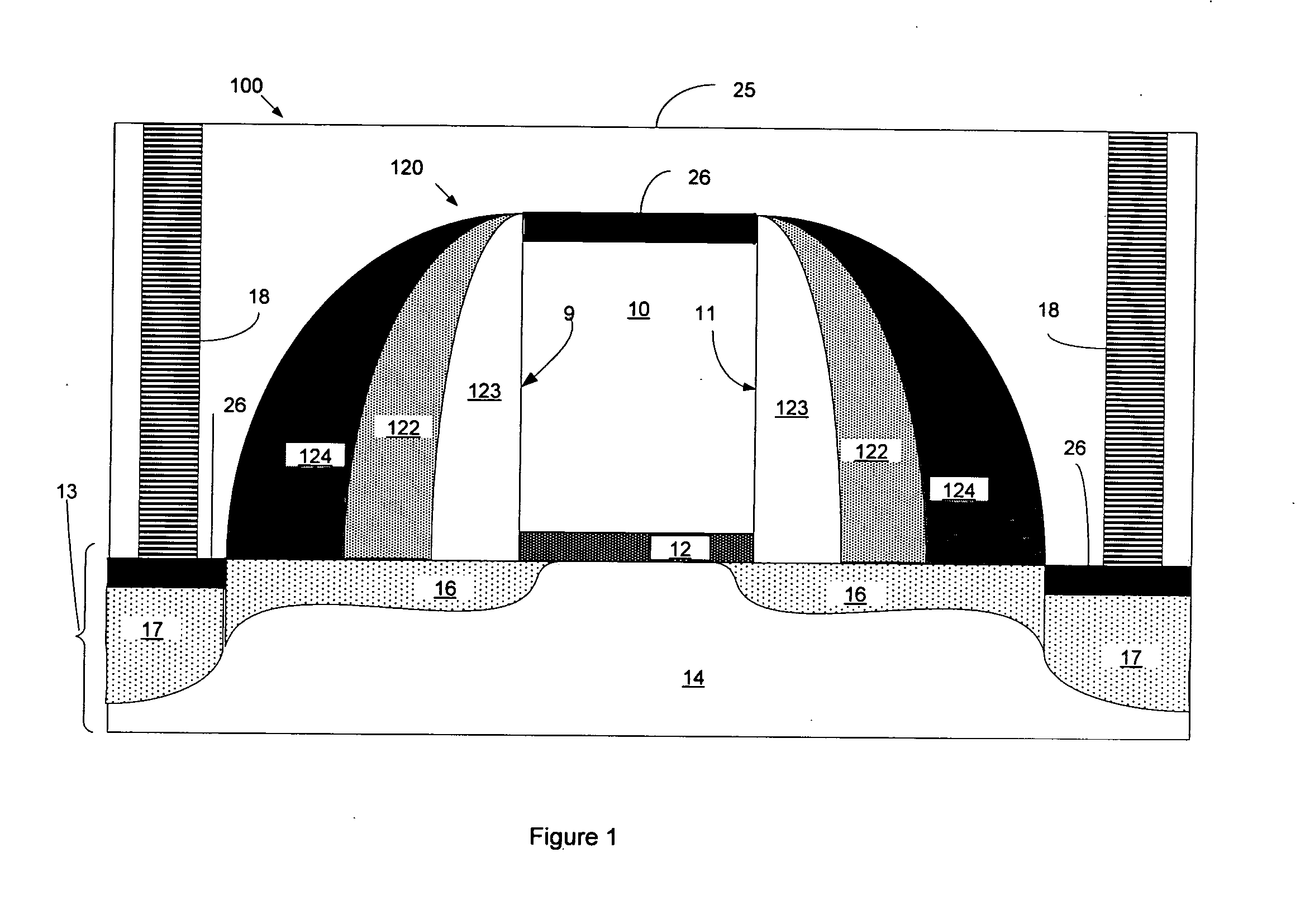

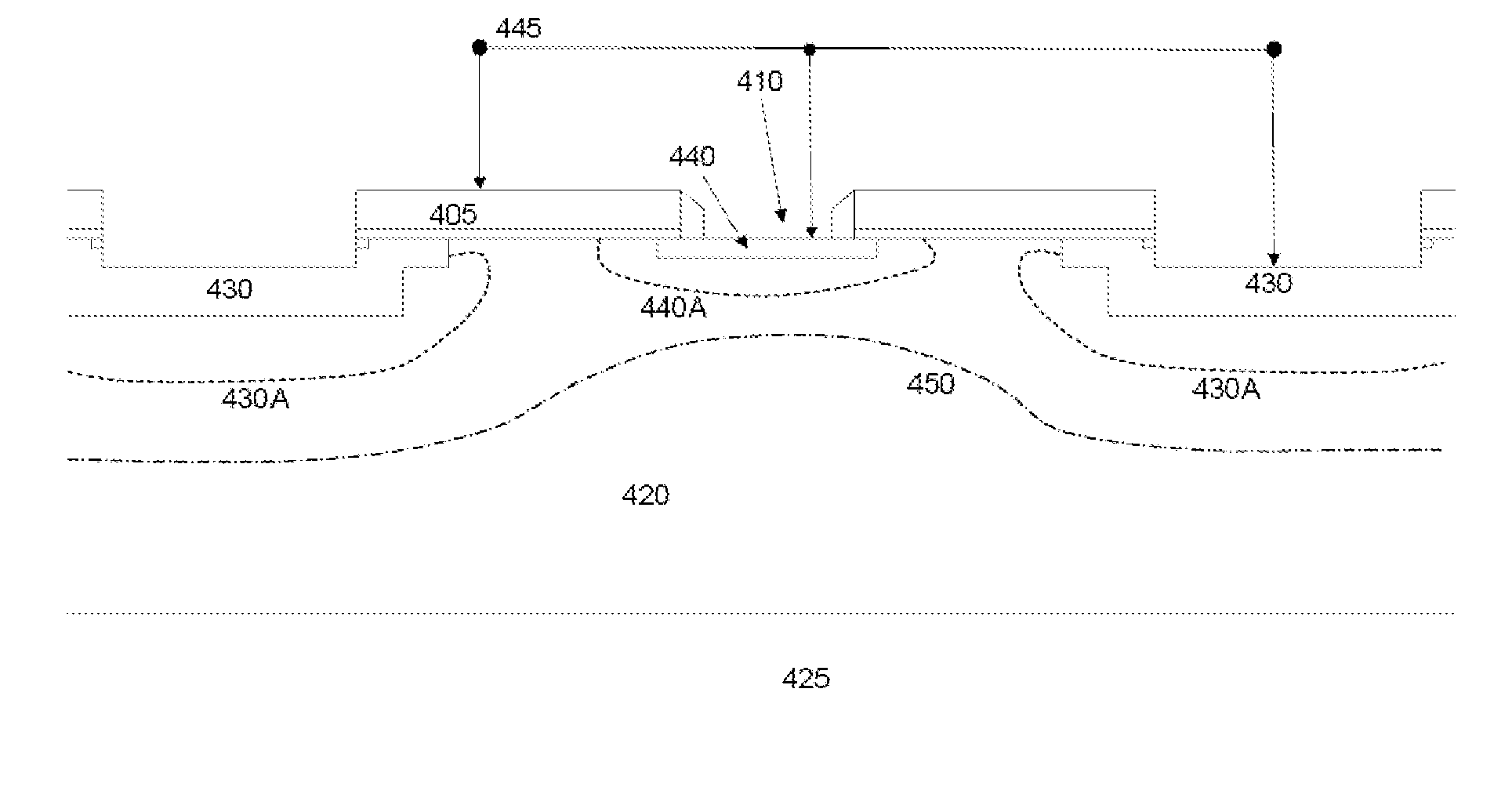

High performance FET with elevated source/drain region

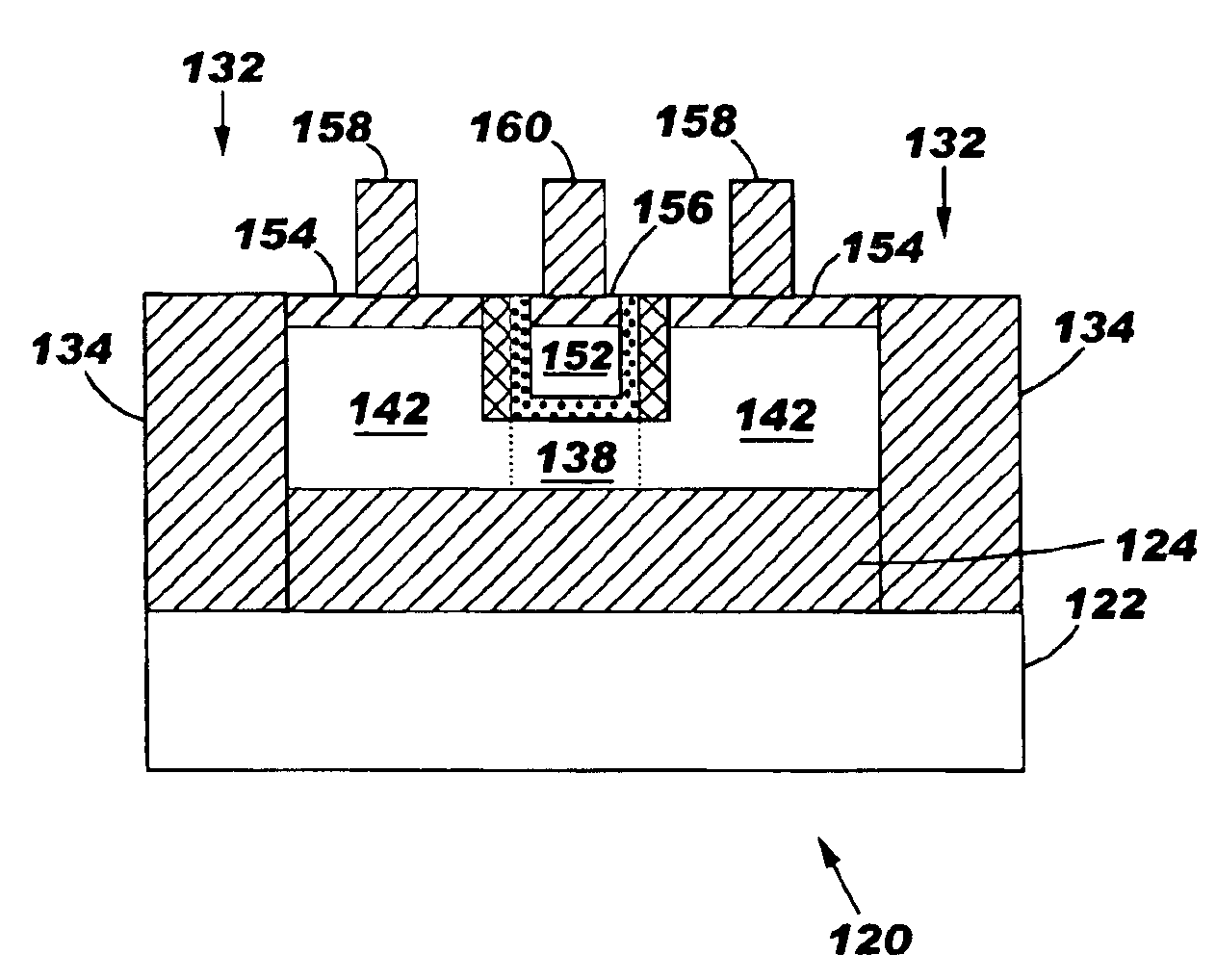

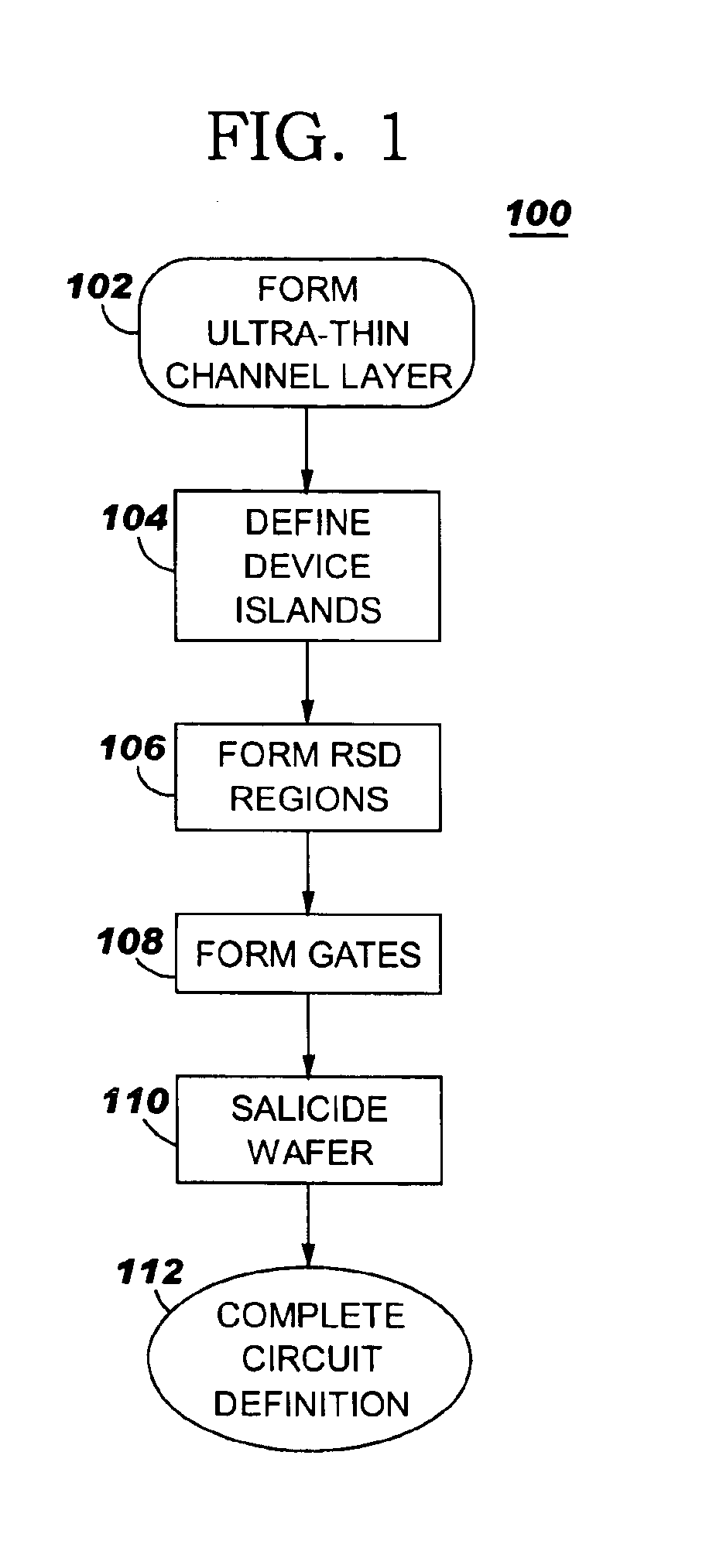

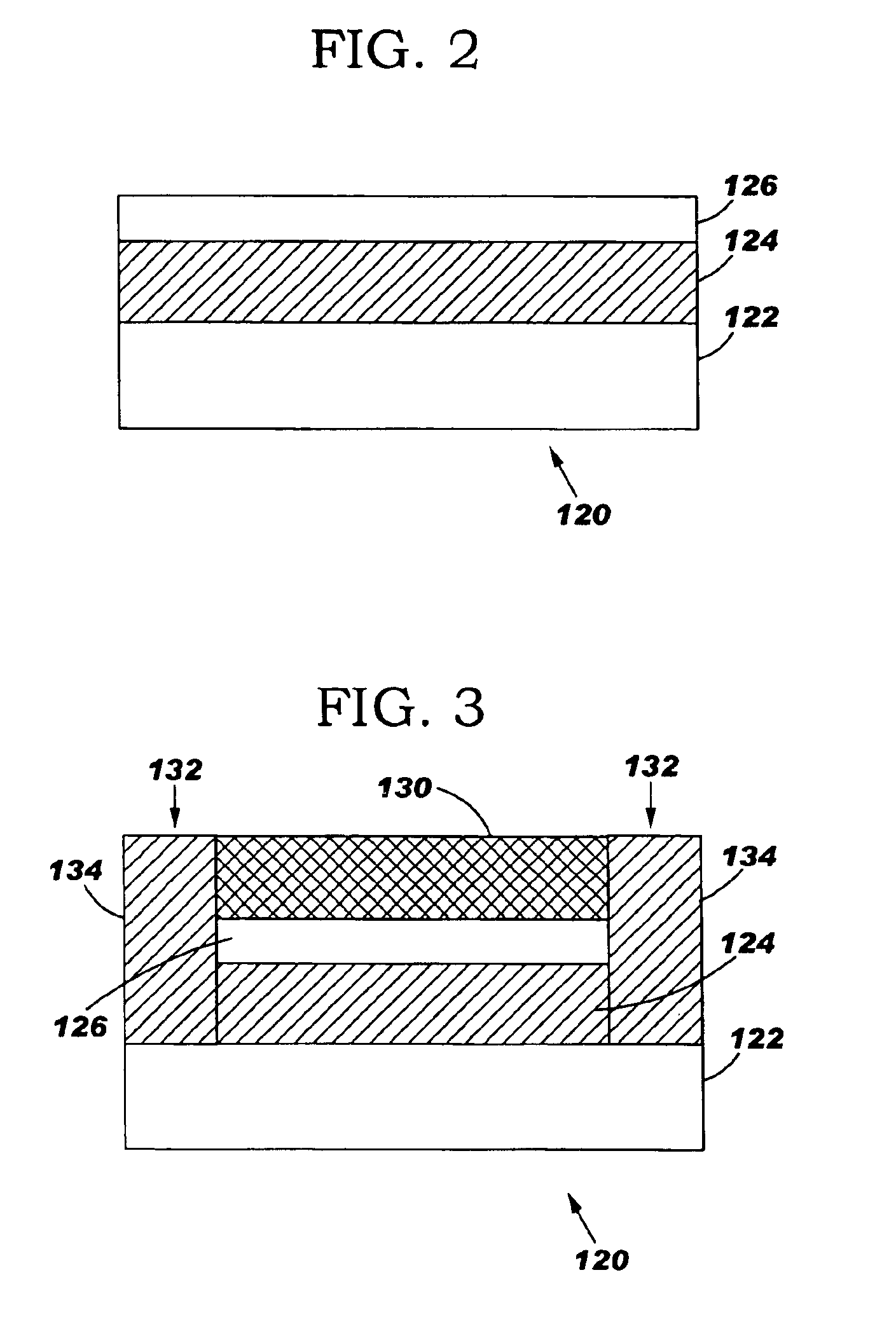

InactiveUS6864540B1Improve field effect transistor (FET) performanceReduce ultra-thin channel FET series resistanceTransistorSolid-state devicesDielectricSalicide

The invention includes a field effect transistor (FET) on an insulator layer, and integrated circuit (IC) on SOI chip including the FETs and a method of forming the IC. The FETs include a thin channel with raised source / drain (RSD) regions at each end on an insulator layer, e.g., on an ultra-thin silicon on insulator (SOI) chip. Isolation trenches at each end of the FETs, i.e., at the end of the RSD regions, isolate and define FET islands. Insulating sidewalls at each RSD region sandwich the FET gate between the RSD regions. The gate dielectric may be a high K dielectric. Salicide on the RSD regions and, optionally, on the gates reduce device resistances.

Owner:IBM CORP

Fast-path apparatus for transmitting data corresponding to a TCP connection

InactiveUS20080126553A1Little and no performance benefitMove quicklyError preventionTransmission systemsGeneral purposeFast path

Owner:ALACRITECH

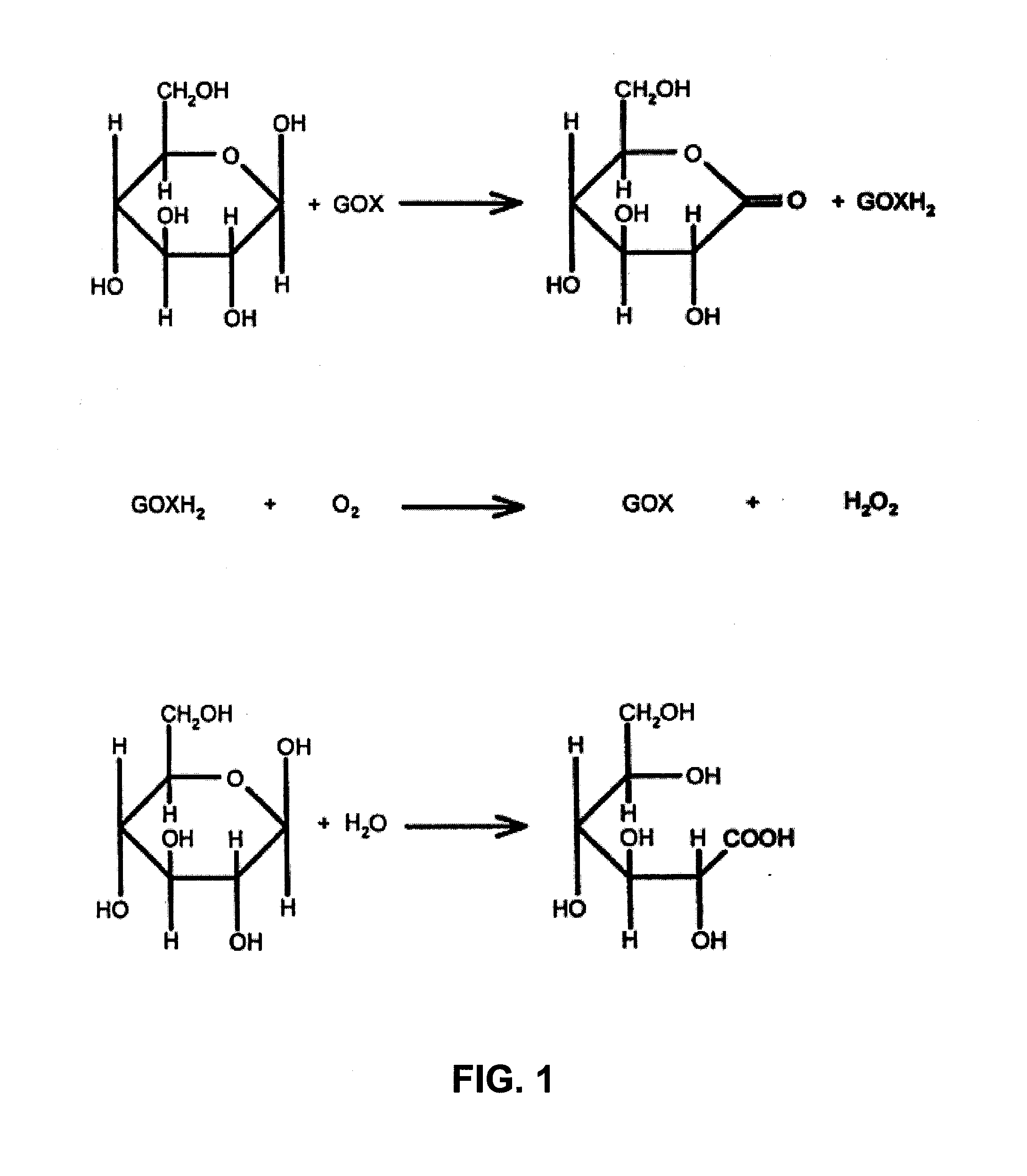

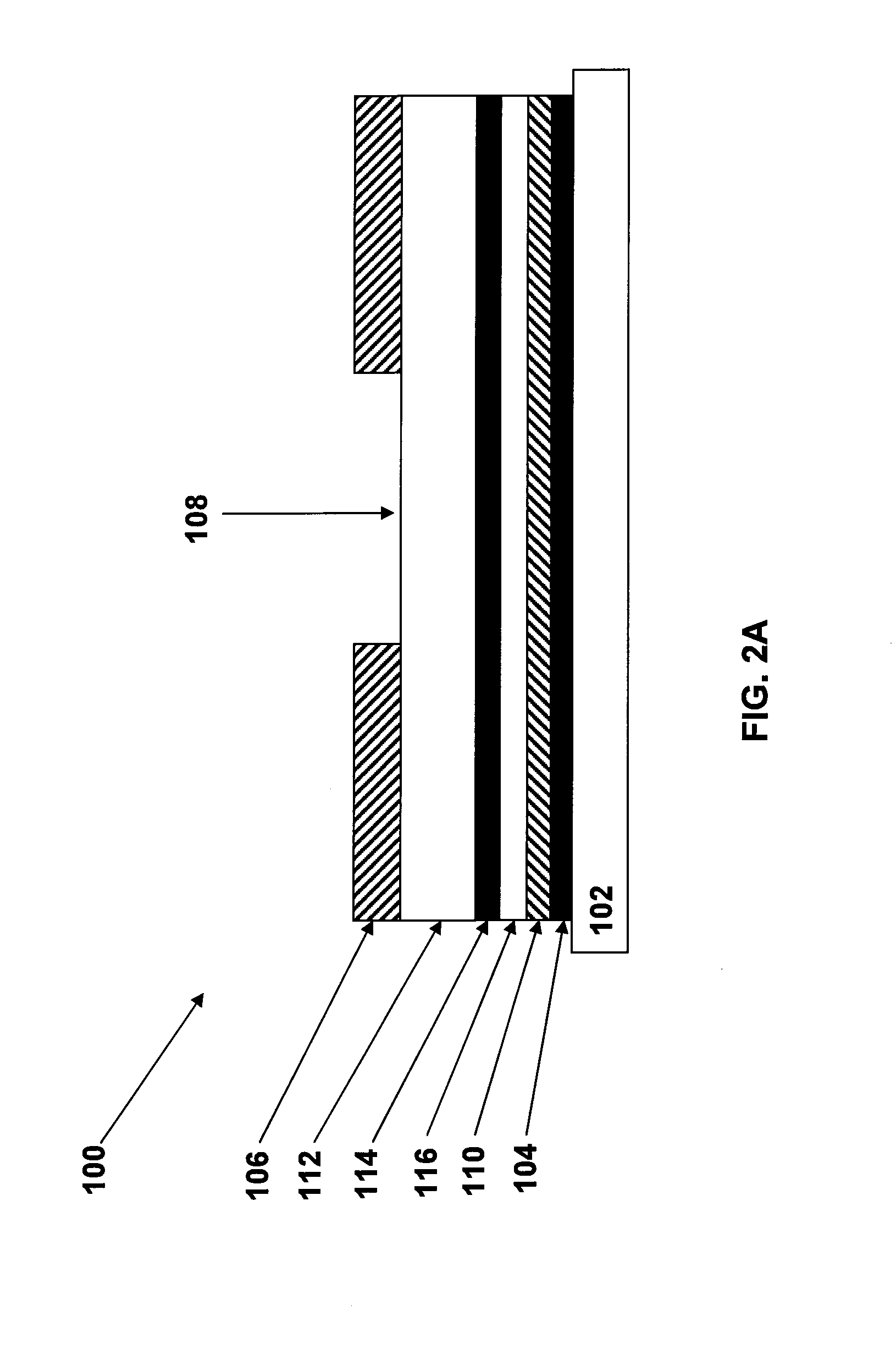

Layered enzyme compositions for use with analyte sensors

ActiveUS20120186997A1Effect on its overall performanceImmobilised enzymesBioreactor/fermenter combinationsPlatinumGlucose sensors

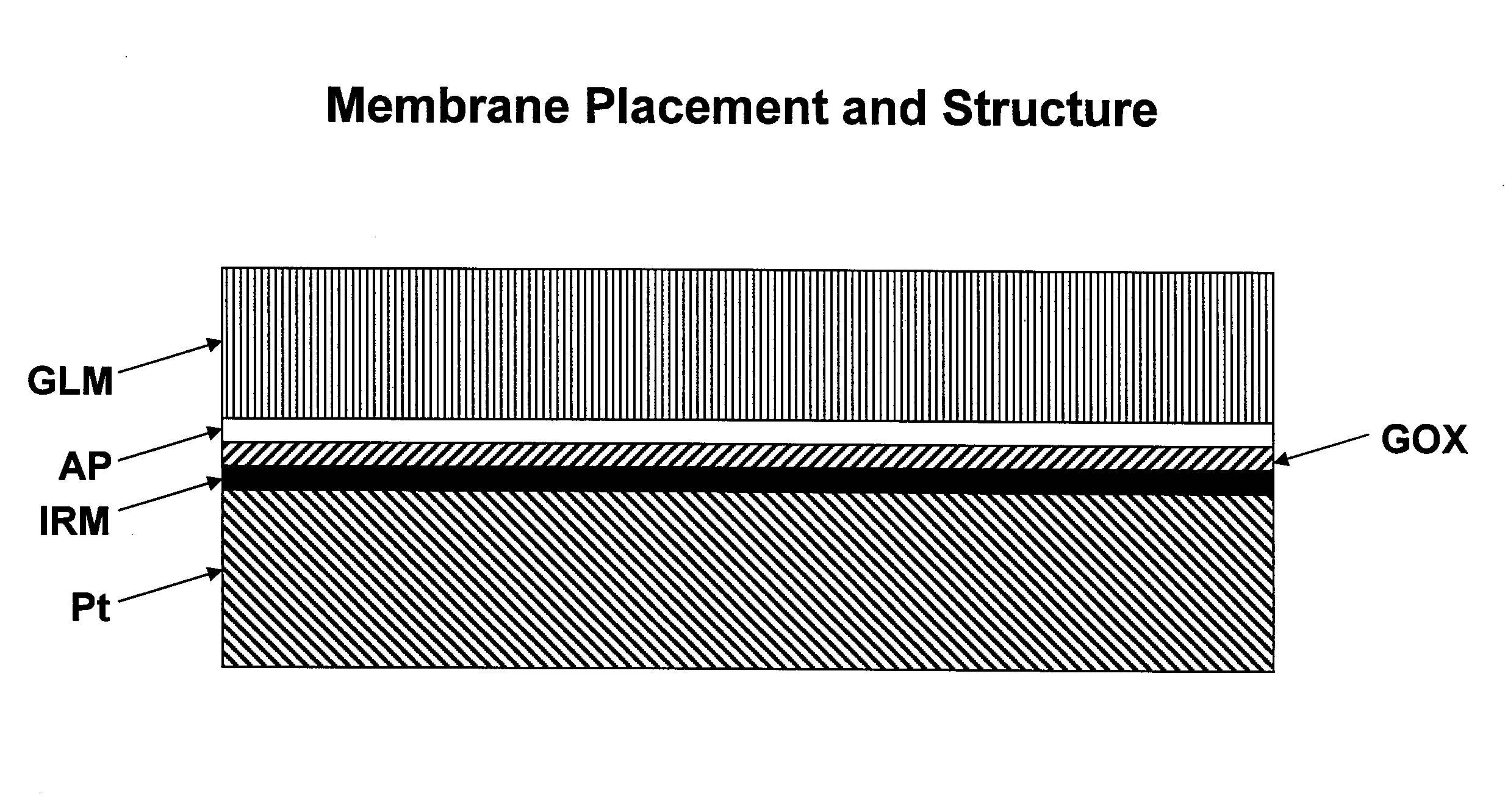

Embodiments of the invention provide amperometric analyte sensors having optimized elements such as electrodes formed from sputtered platinum compositions as well as layers of material selected to optimize the characteristics of a wide variety of sensor elements and sensors. While embodiments of the innovation can be used in a variety of contexts, typical embodiments of the invention include glucose sensors used in the management of diabetes.

Owner:MEDTRONIC MIMIMED INC

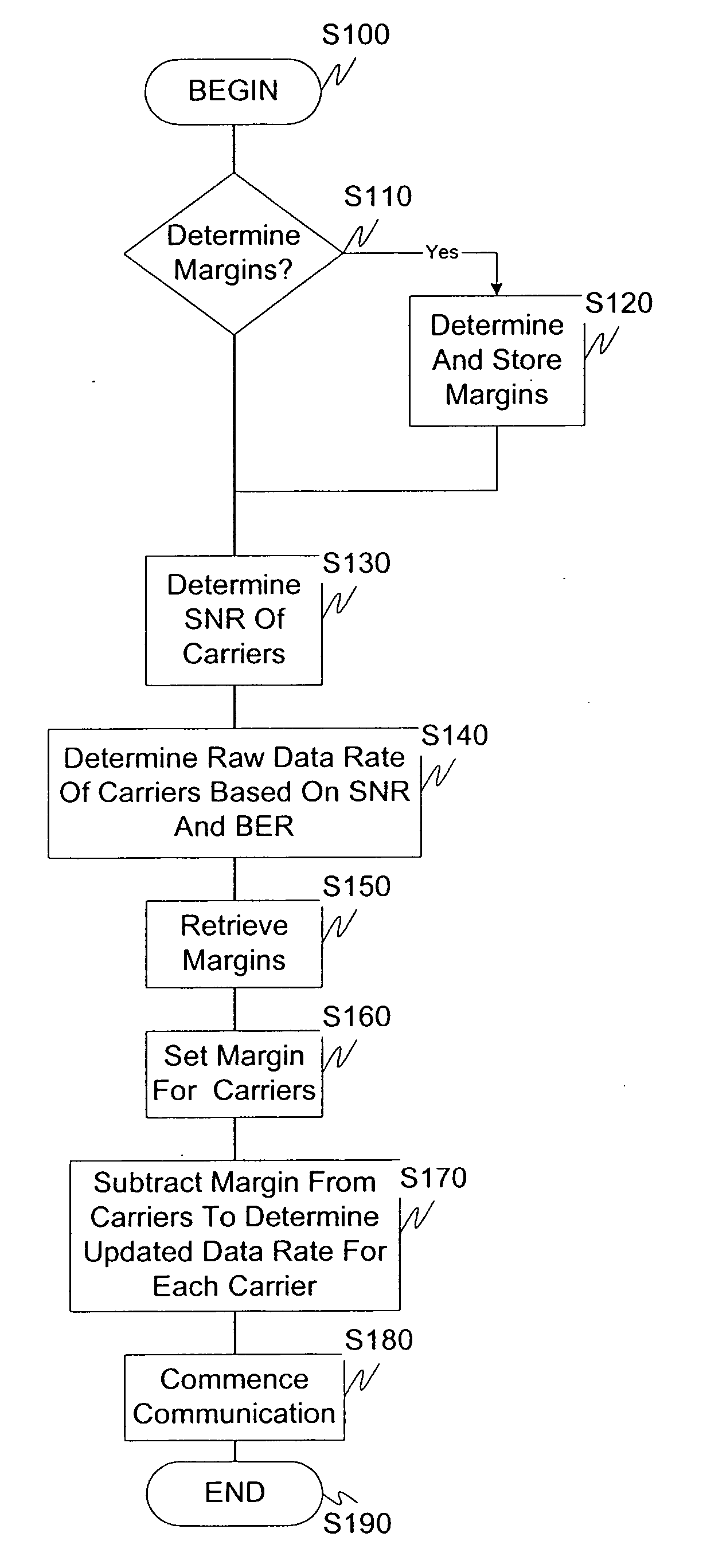

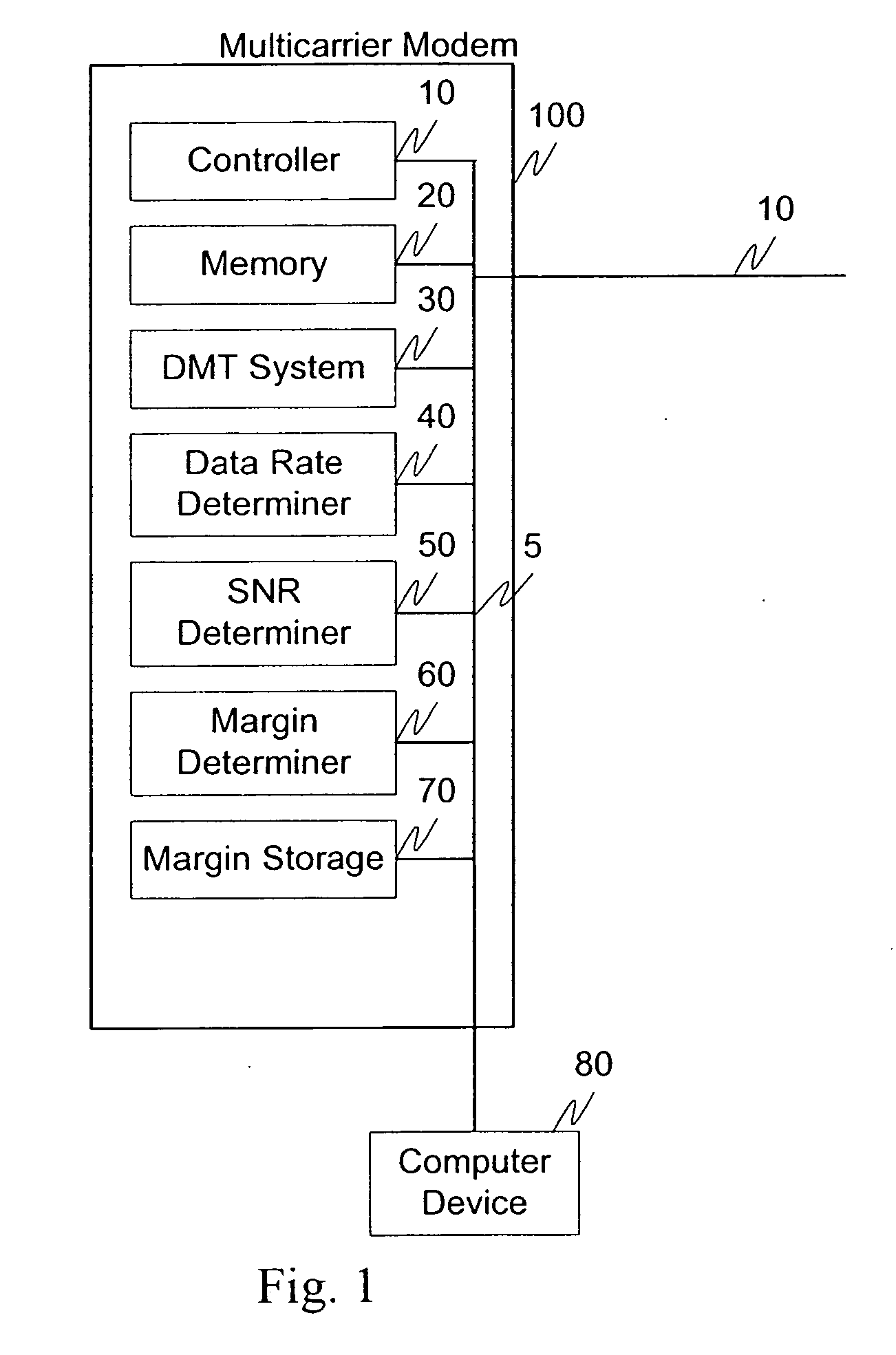

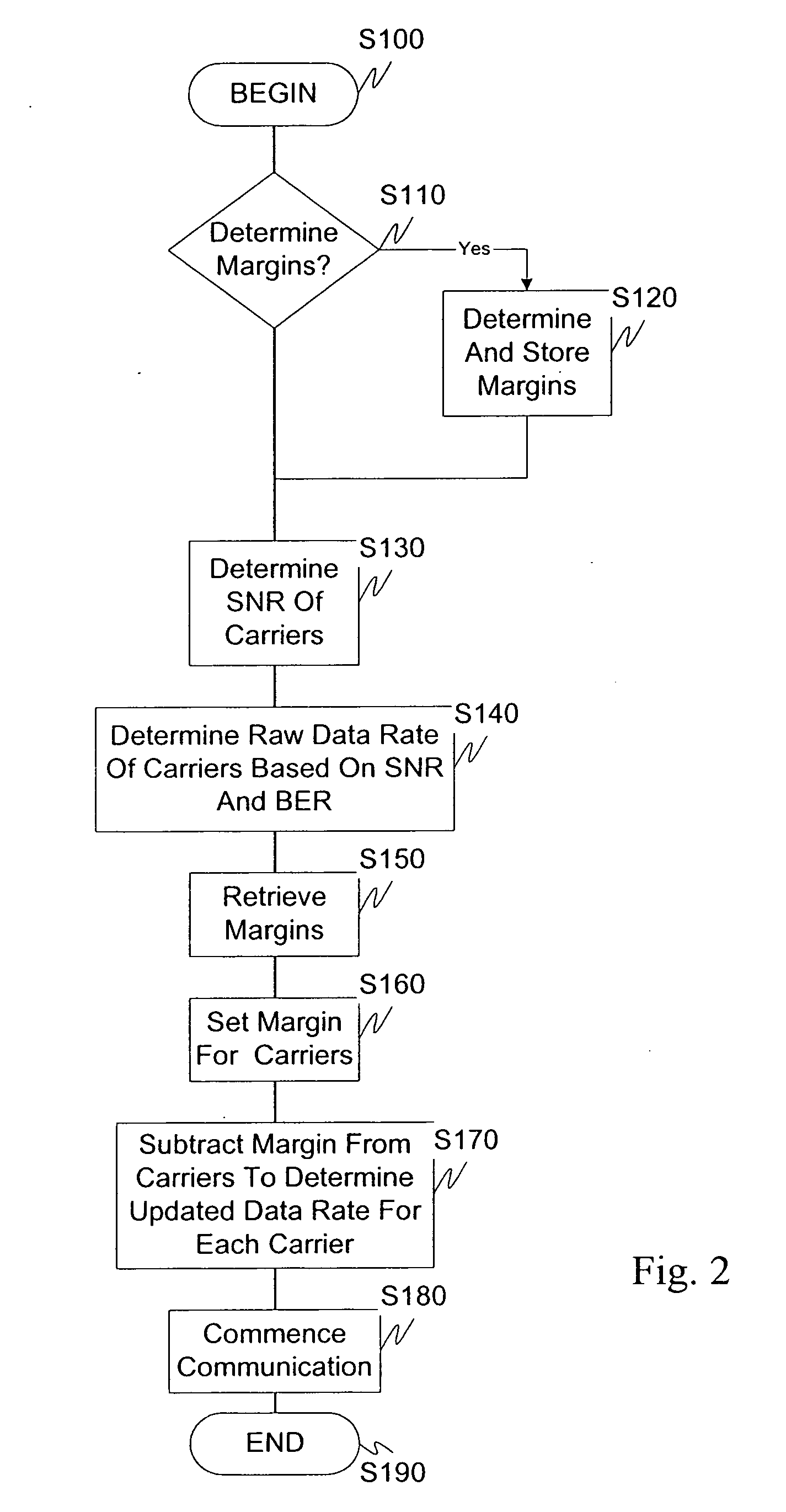

Systems and methods for a multicarrier modulation system with a variable margin

InactiveUS20060018395A1Effect on its overall performanceHigh levelError preventionFrequency-division multiplex detailsModem deviceData rate

Owner:AWARE INC

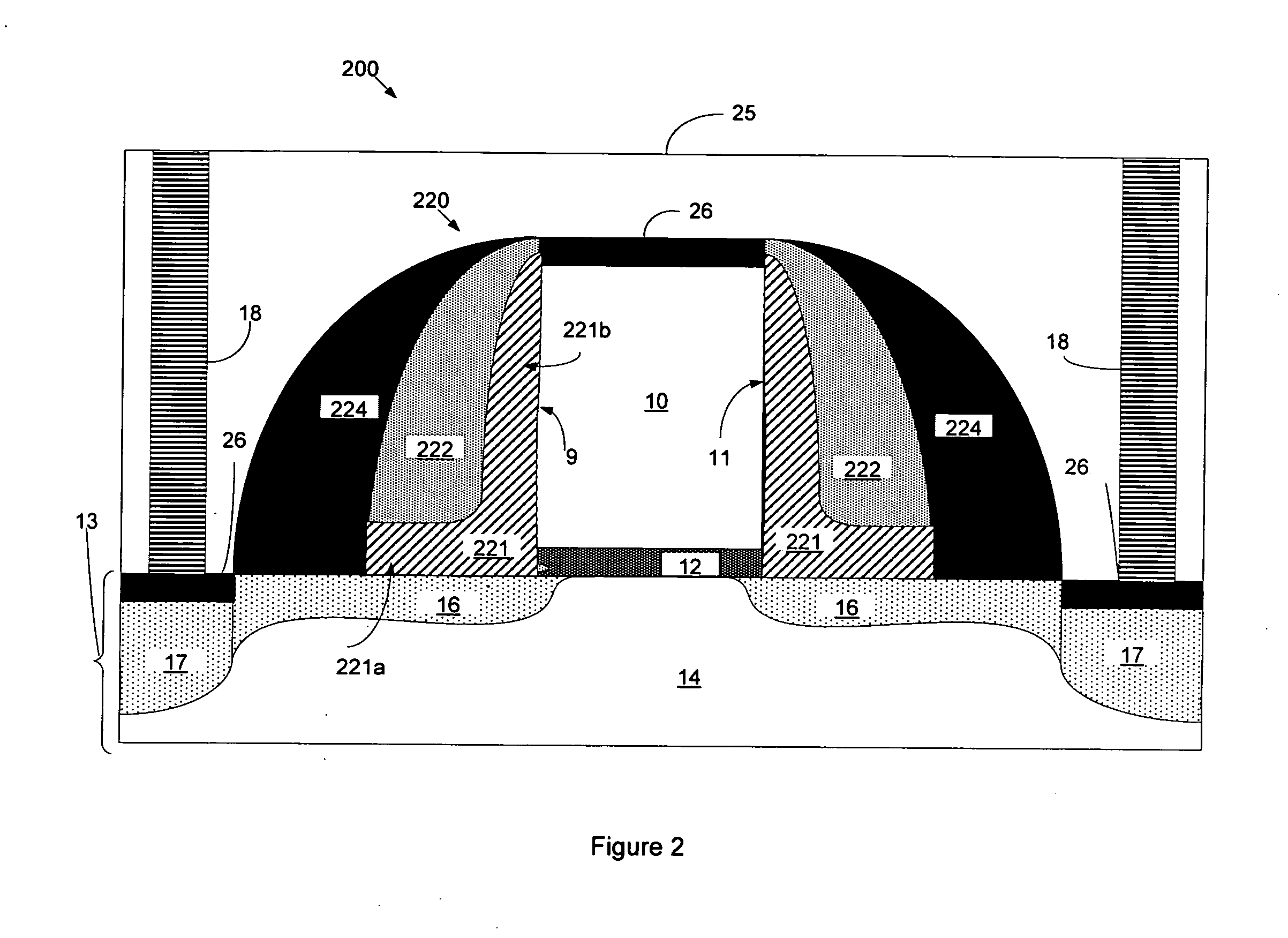

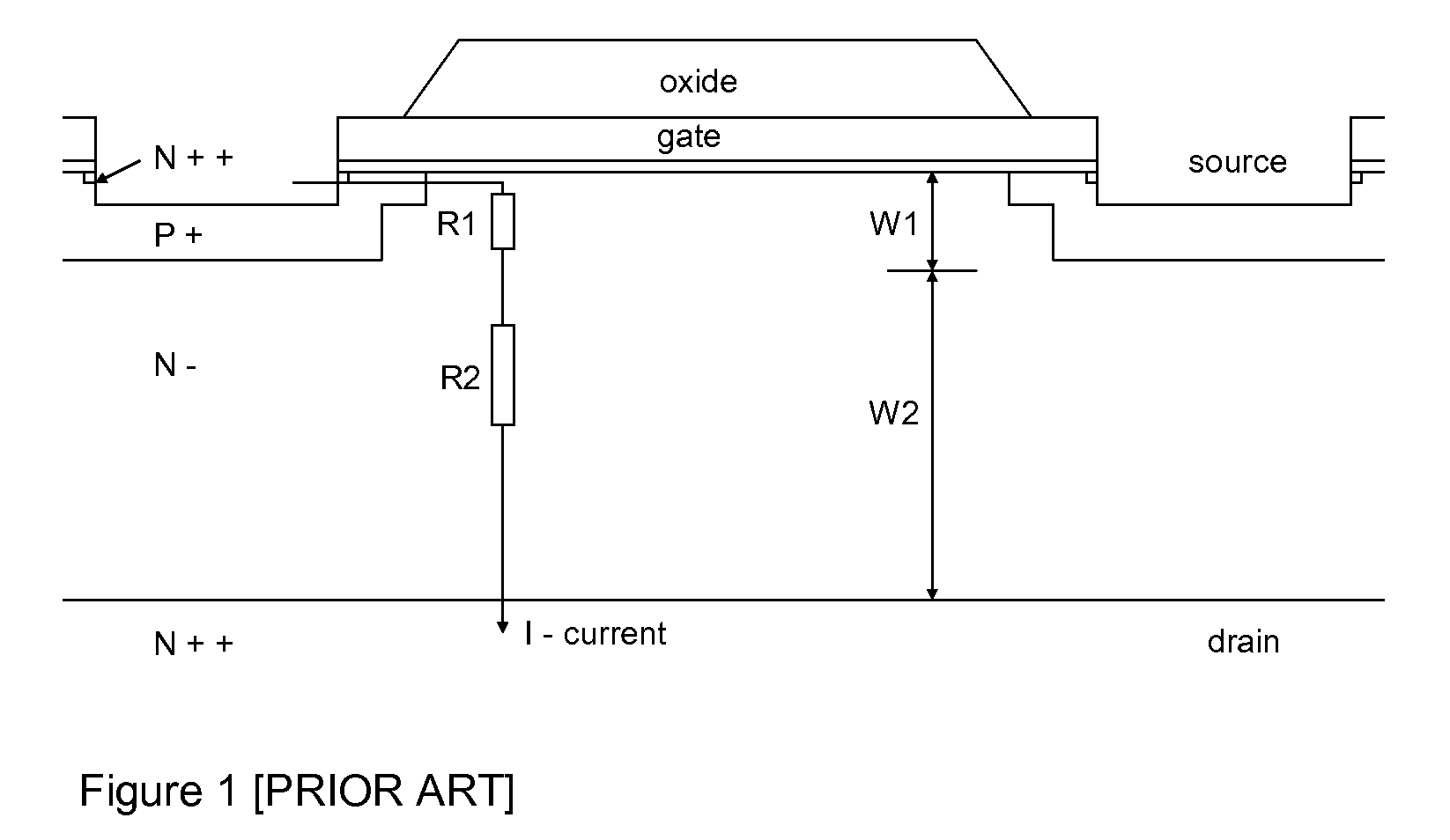

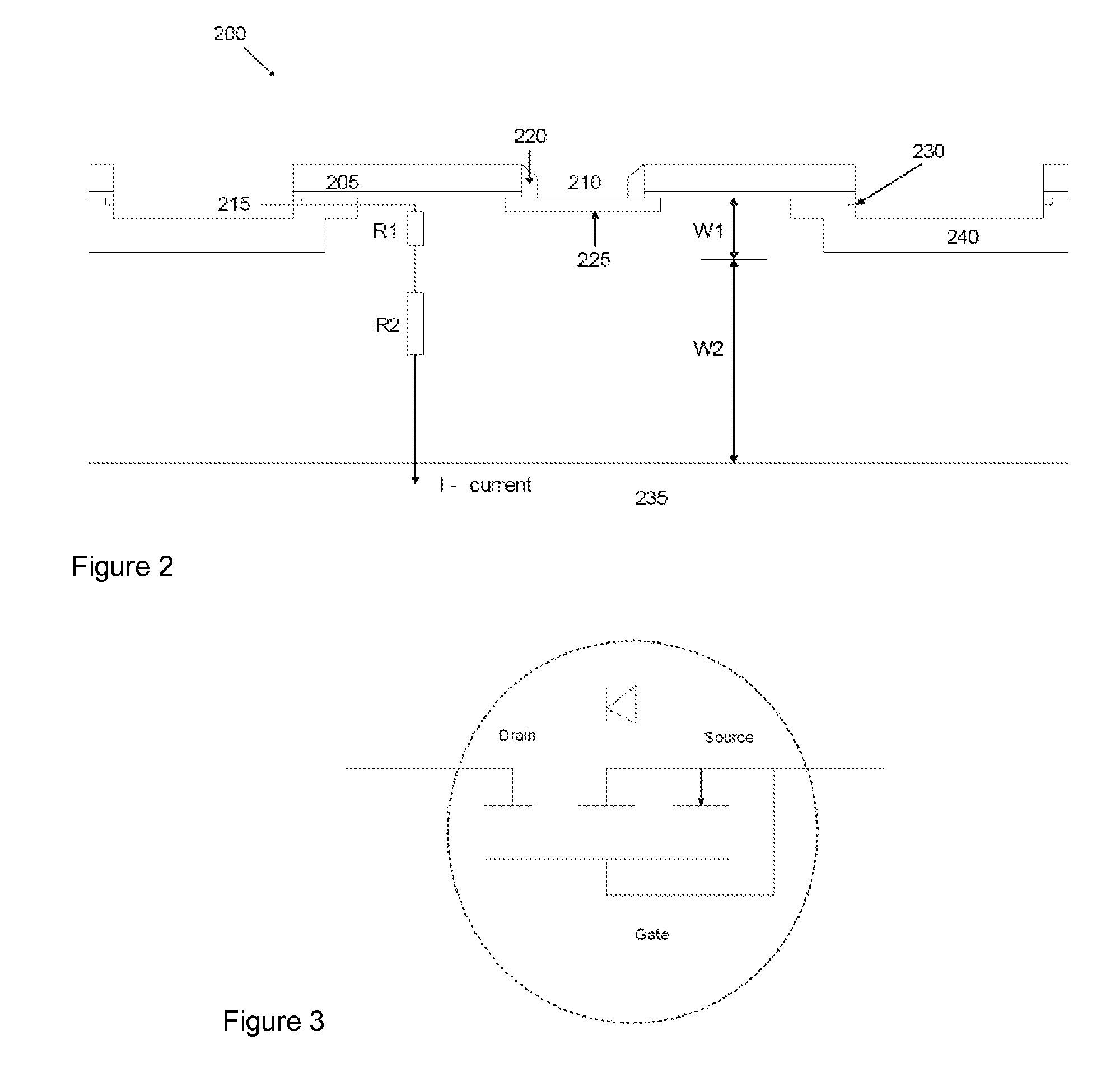

MOSFET structure with ultra-low K spacer

InactiveUS20060220152A1Suppress parasitic overlap capacitanceEffect on its overall performanceTransistorSemiconductor/solid-state device detailsMOSFETCapacitance

Disclosed is a MOSFET structure and method of fabricating the structure that incorporates a multi-layer sidewall spacer to suppress parasitic overlap capacitance between the gate conductor and the source / drain extensions without degrading drive current and, thereby, effecting overall MOSFET performance. In one embodiment, the multi-layer sidewall spacer is formed with a gap layer having a dielectric constant equal to one and a permeable low-K (e.g., less than 3.5) dielectric layer. In another embodiment, the multi-layer sidewall spacer is formed with a first L-shaped dielectric layer having a permittivity value of less than approximately three and a second dielectric layer. Either embodiment may also have a third nitride or oxide spacer layer. This third spacer layer provides increased structural integrity.

Owner:GOOGLE LLC

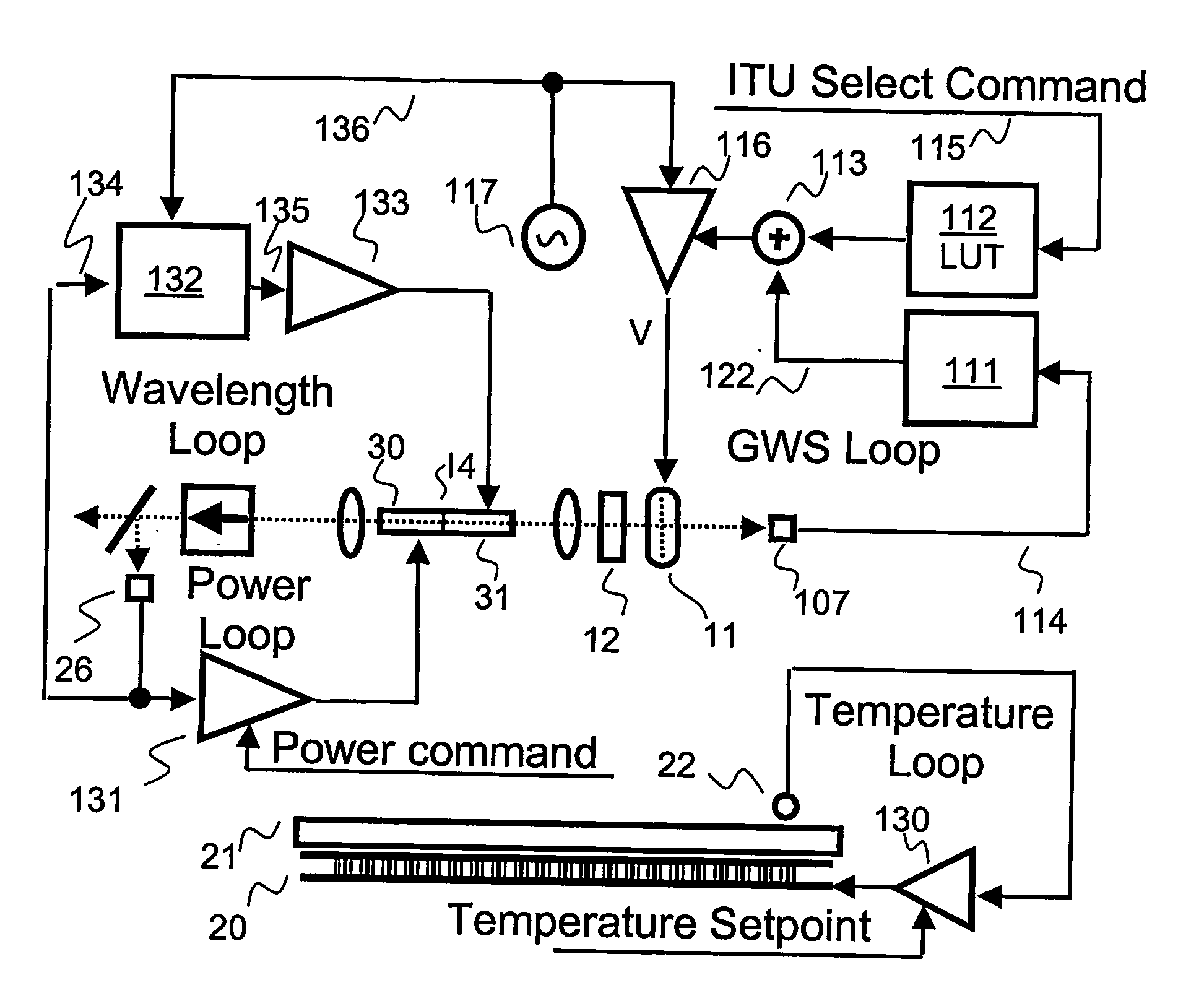

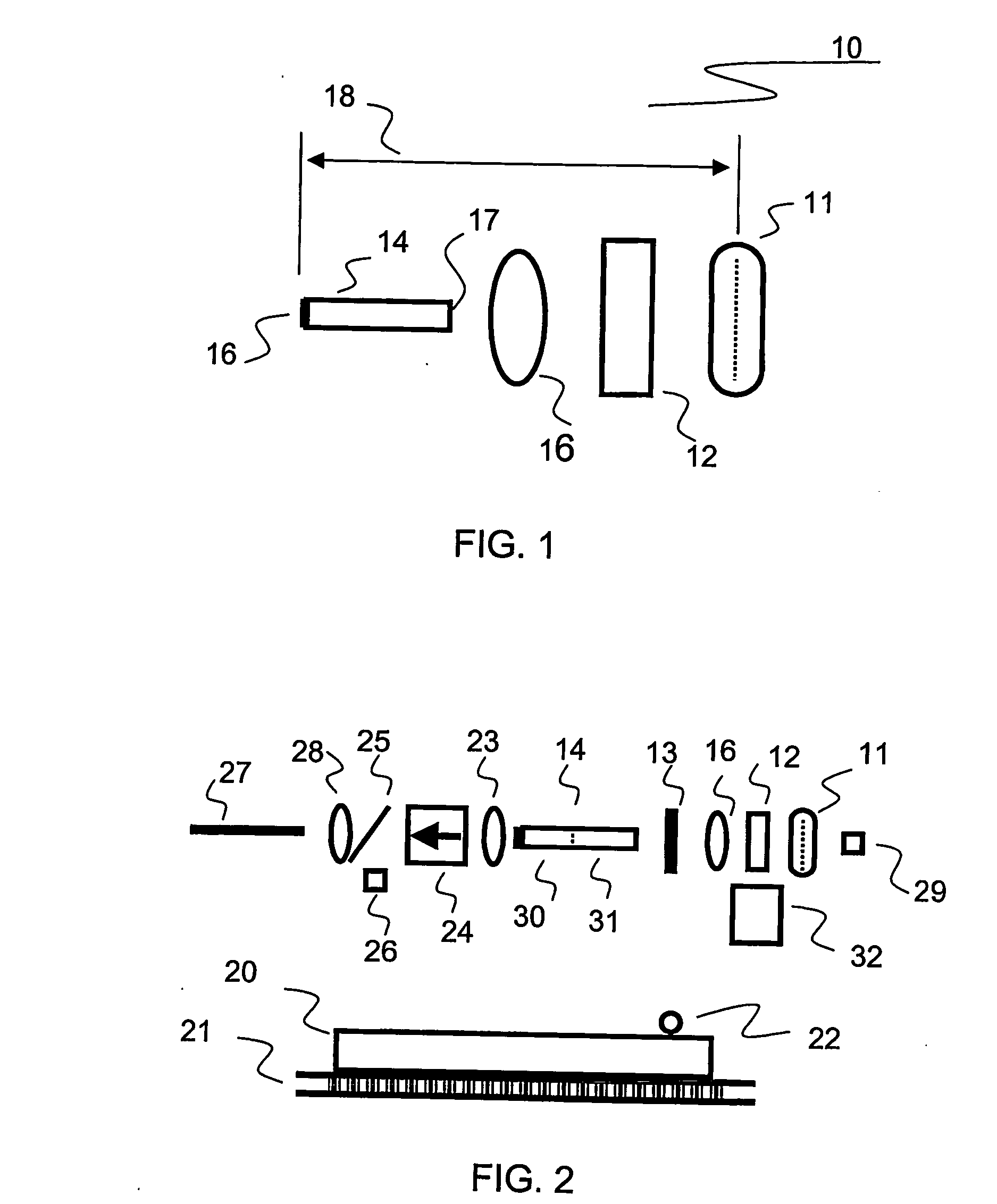

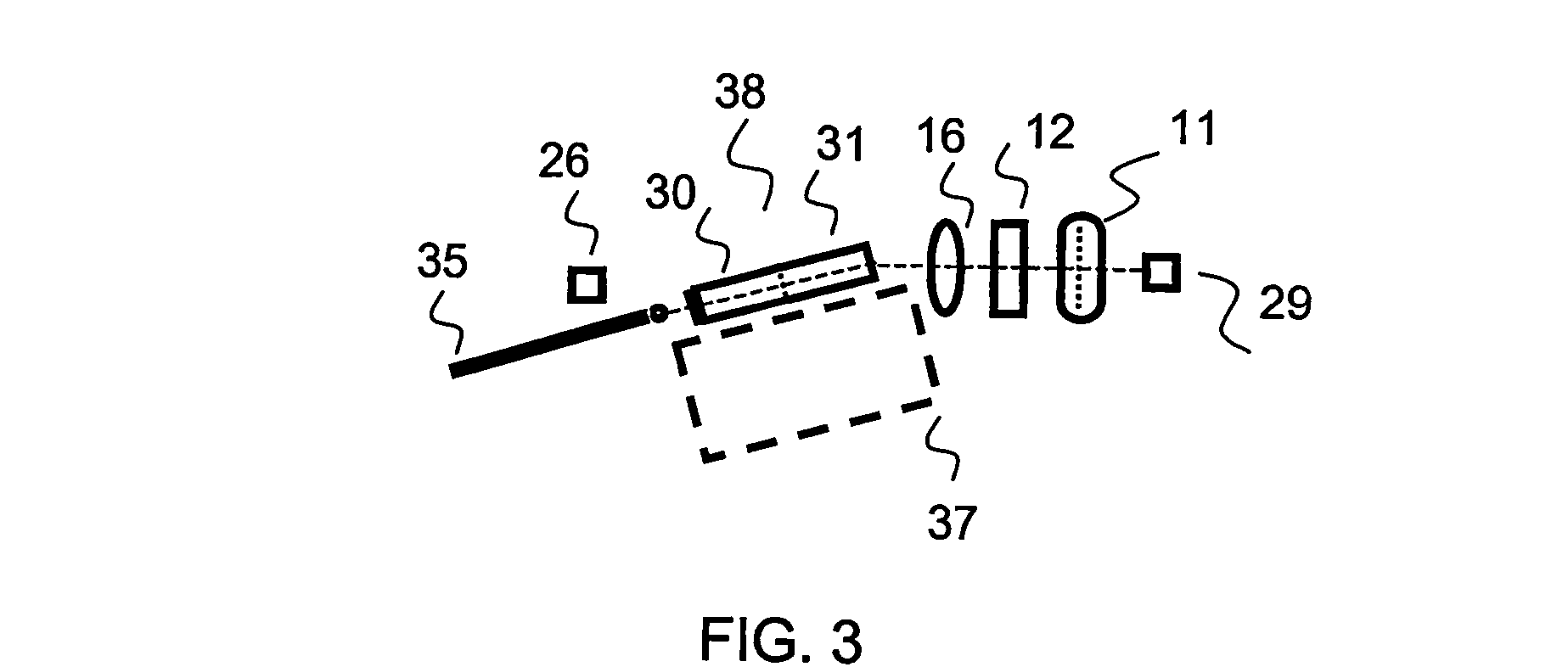

External Cavity Tunable Laser and Control

InactiveUS20060193354A1Avoid lasing instabilityEffect on its overall performanceLaser optical resonator constructionOptical resonator shape and constructionGratingPhase shifted

An optical lasing device, comprising (i) a lasing medium disposed in a lasing cavity, (ii) an etalon disposed within the lasing cavity, and (iii) an electrically tuned filter device, such as a grating waveguide structure device. The lasing device also comprises a detector for determining the lasing power of the lasing device, and a controllable phase shift capability, and the device is preferably locked to a maximum of the lasing power by adjusting the phase, thereby achieving locking to a wavelength predetermined by the etalon, aligned to an ITU grid wavelength. Adjusting the phase shift to achieve the maximum of the lasing power is preferably performed using a closed loop system. Furthermore, adjusting of the phase shift to achieve a maximum of the lasing power is preferably also operative to wave lock the lasing device to a peak wavelength of the etalon.

Owner:ROSENBLATT YEHUDA

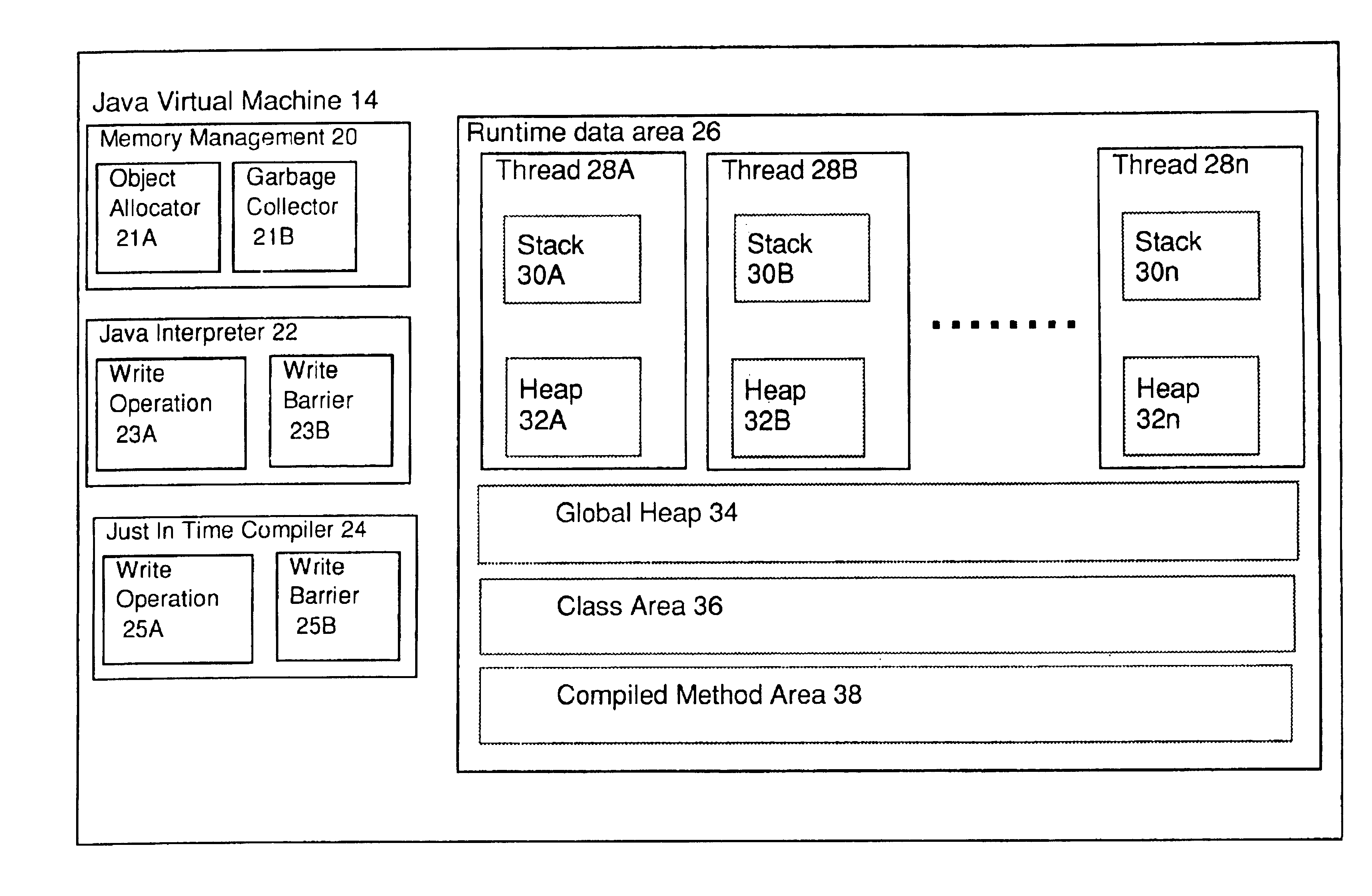

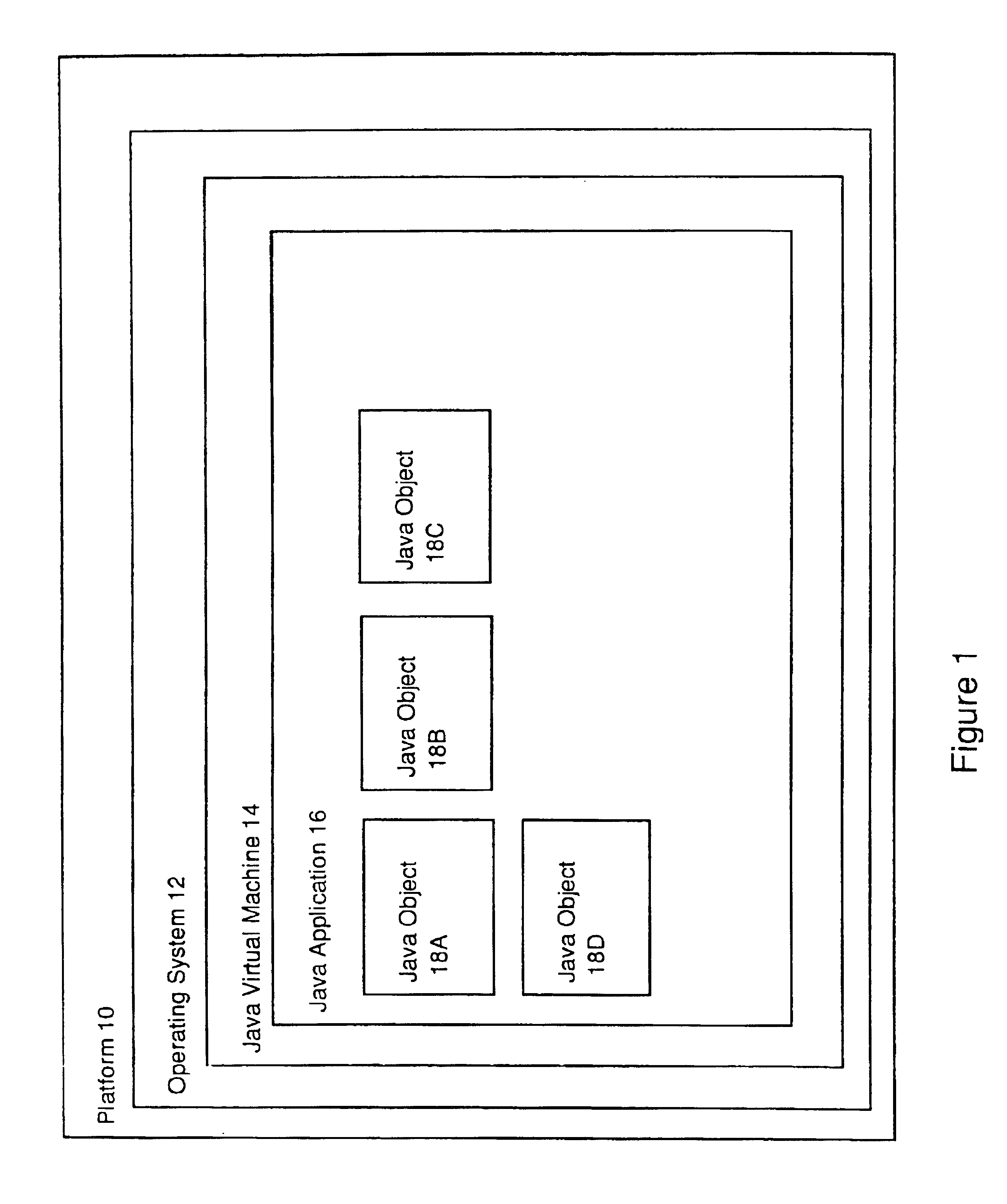

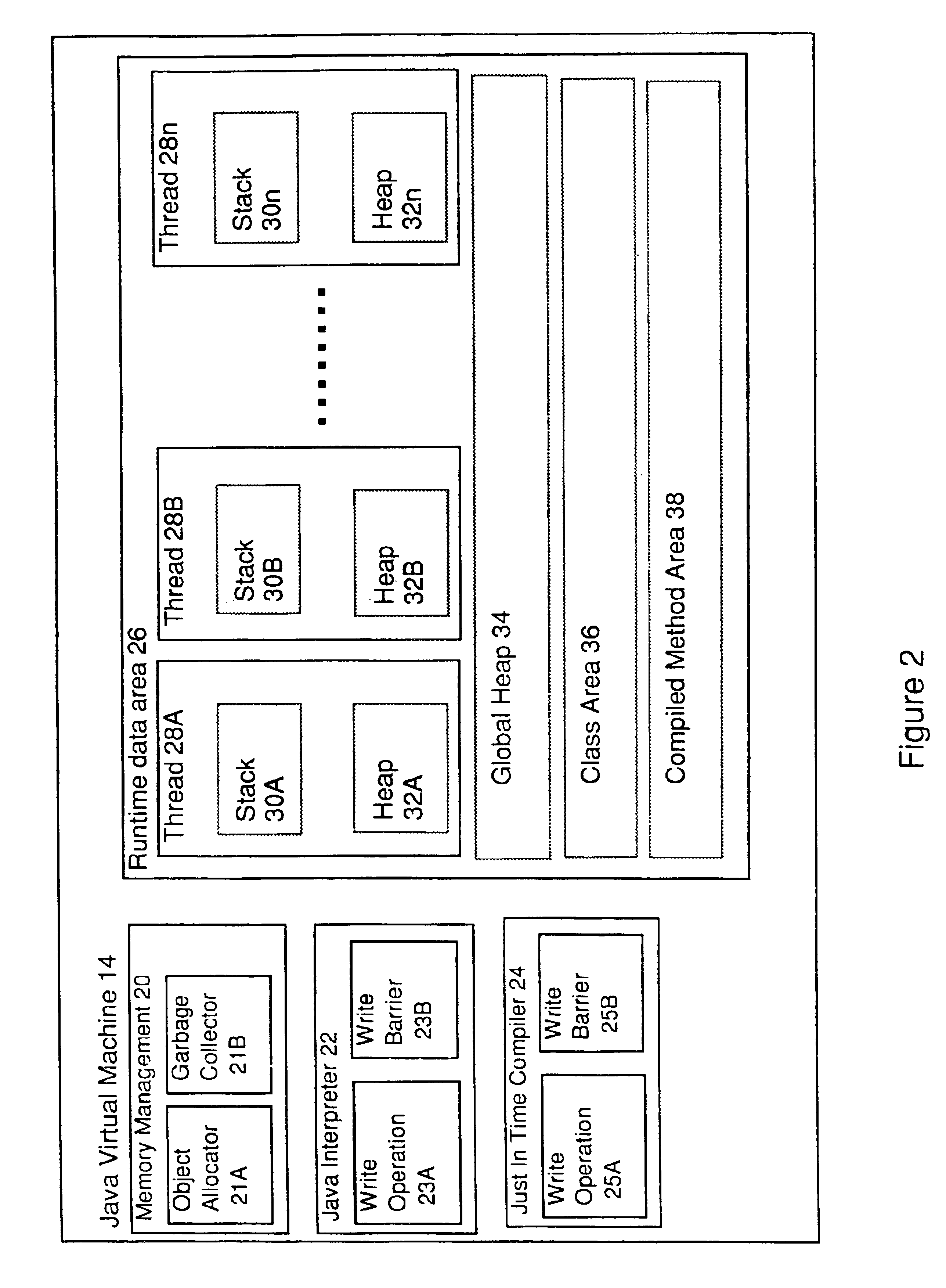

Virtual machine memory management

InactiveUS6912553B1Little effectEffect on its overall performanceData processing applicationsMemory adressing/allocation/relocationOperational systemWaste collection

This invention relates to memory management in a virtual machine or operating system and in particular to object creation and garbage collection. There is described a method and system of managing memory in a multi-threaded processing environment such as a java virtual machine comprising: creating an object in a thread heap; associating a status with the object and setting the status as local; using write barriers to change the status to global if the object is assigned to a static variable or if the object is assigned to a field in a global object; changing the status of all objects referenced by that object to global; and performing garbage collection by deleting from the thread heap, when memory space in the thread heap is required, one or more local objects which can not be traced to the thread stack.

Owner:IBM CORP

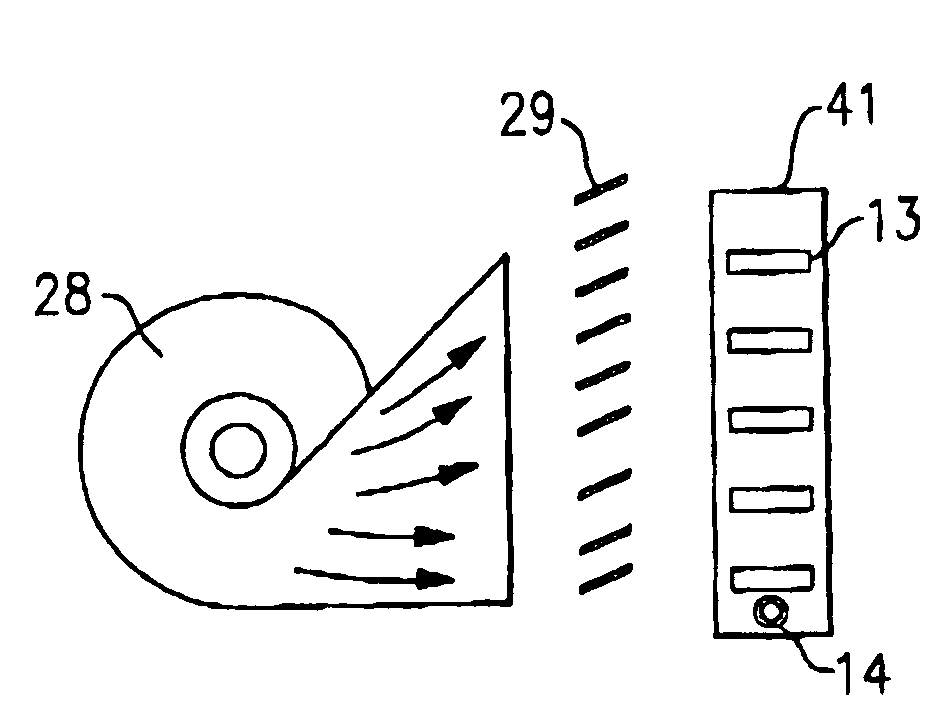

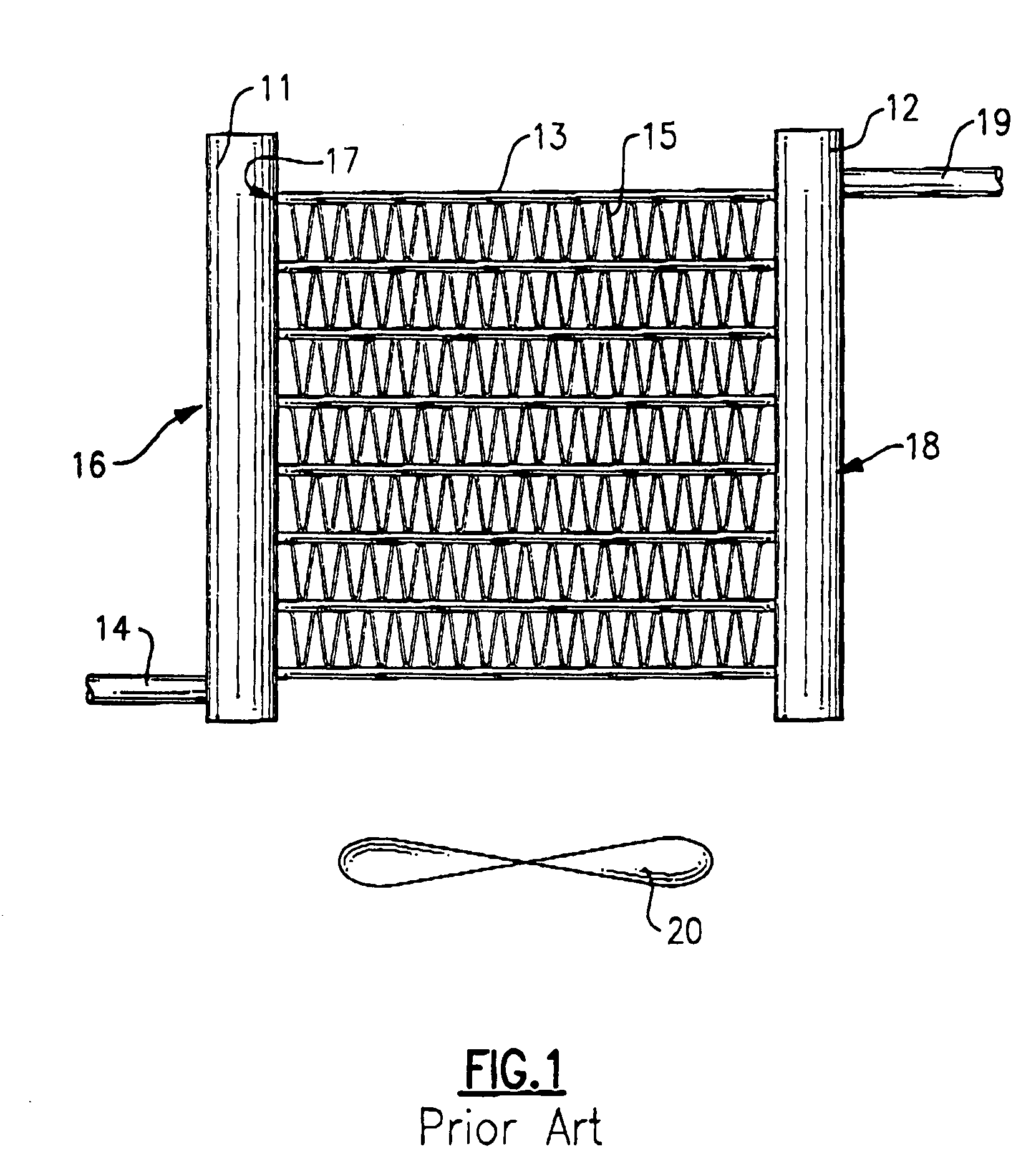

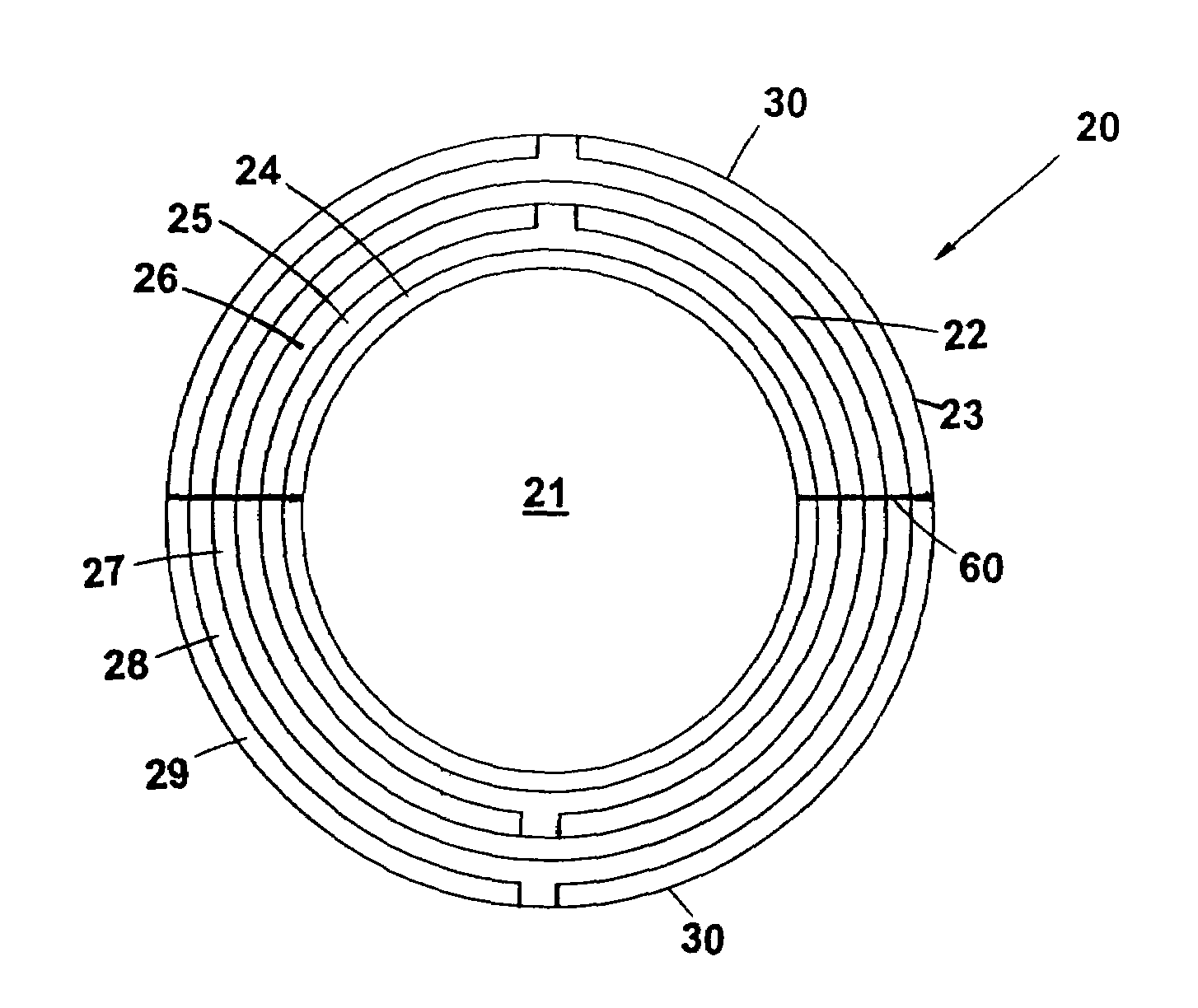

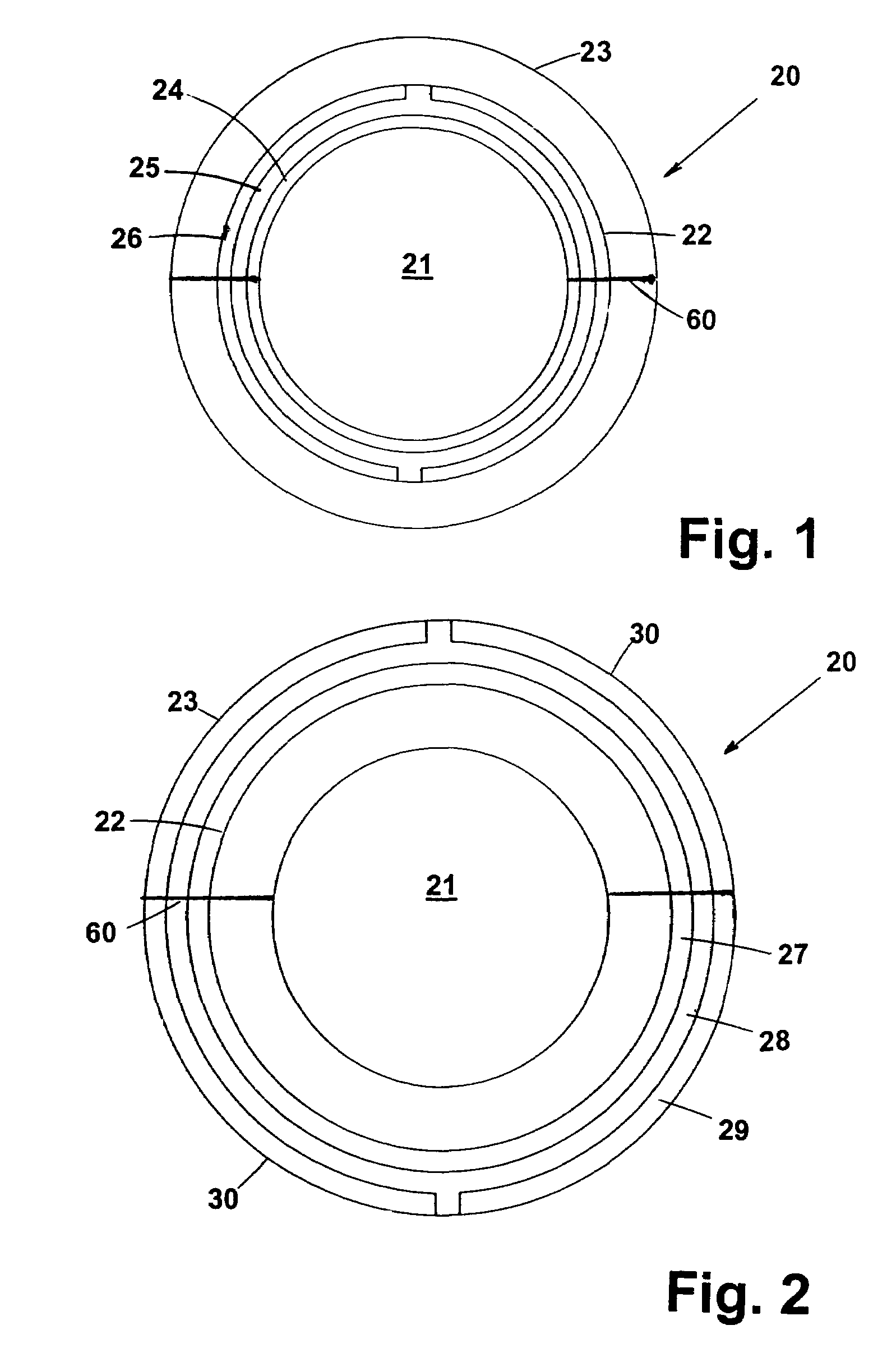

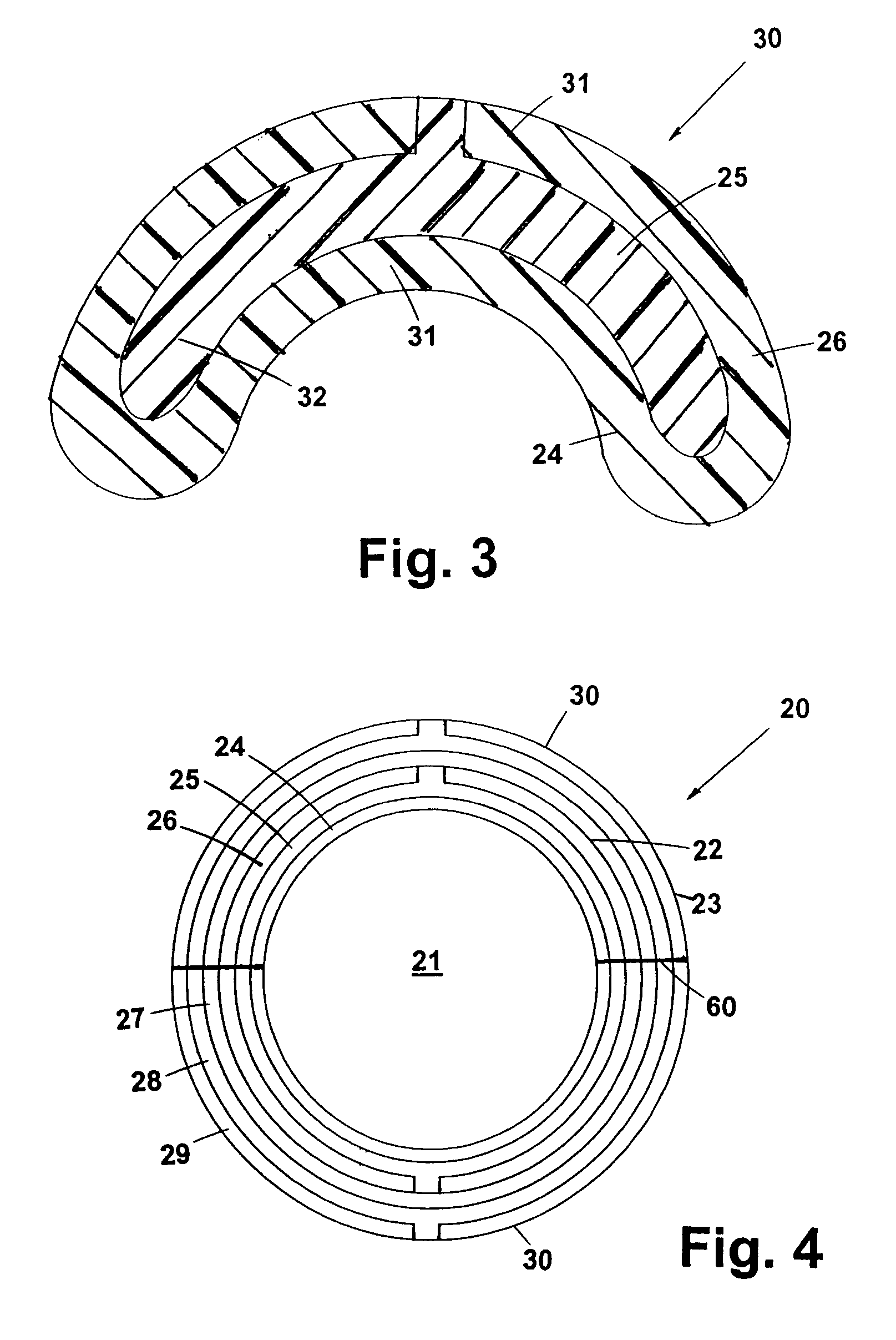

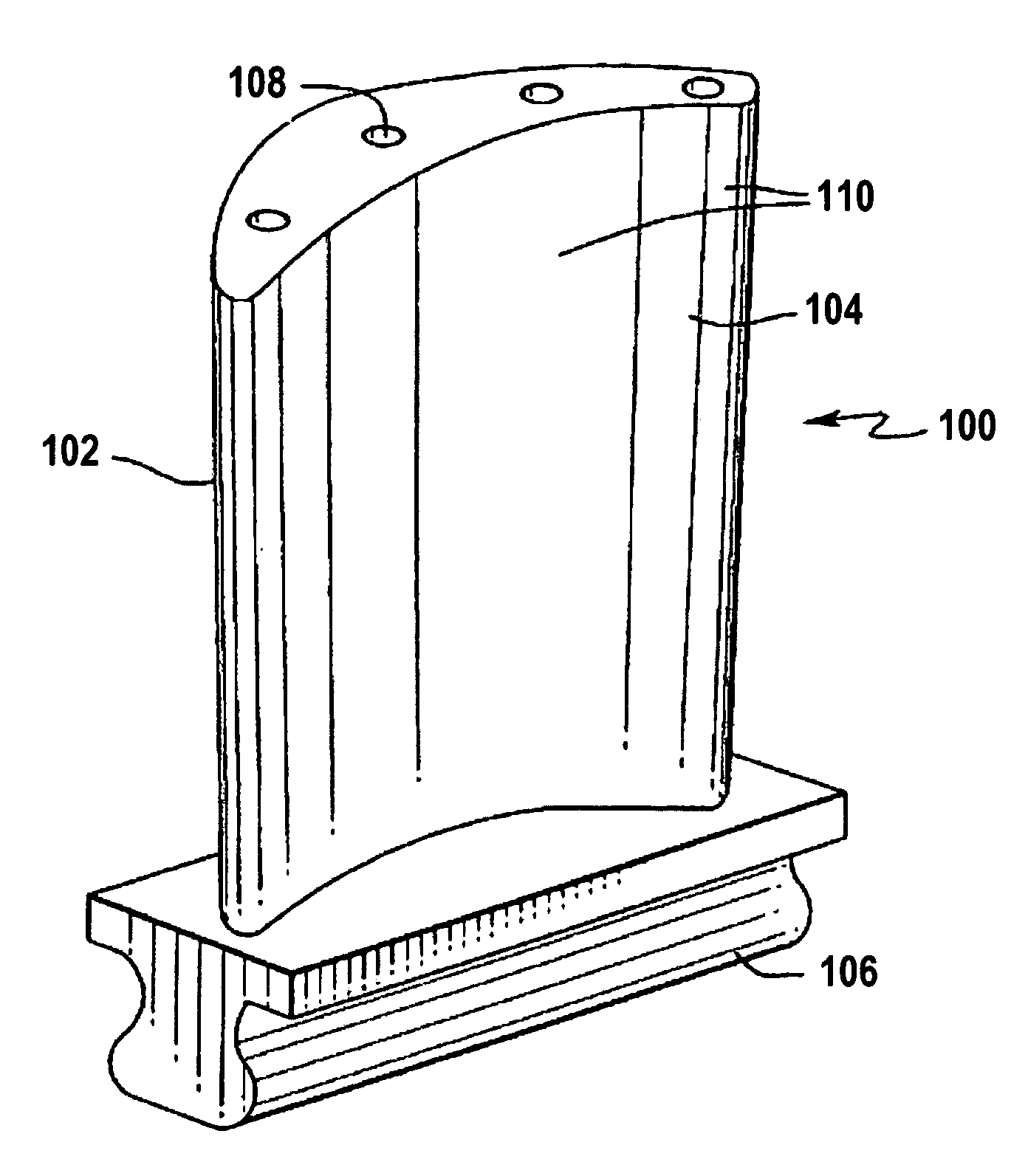

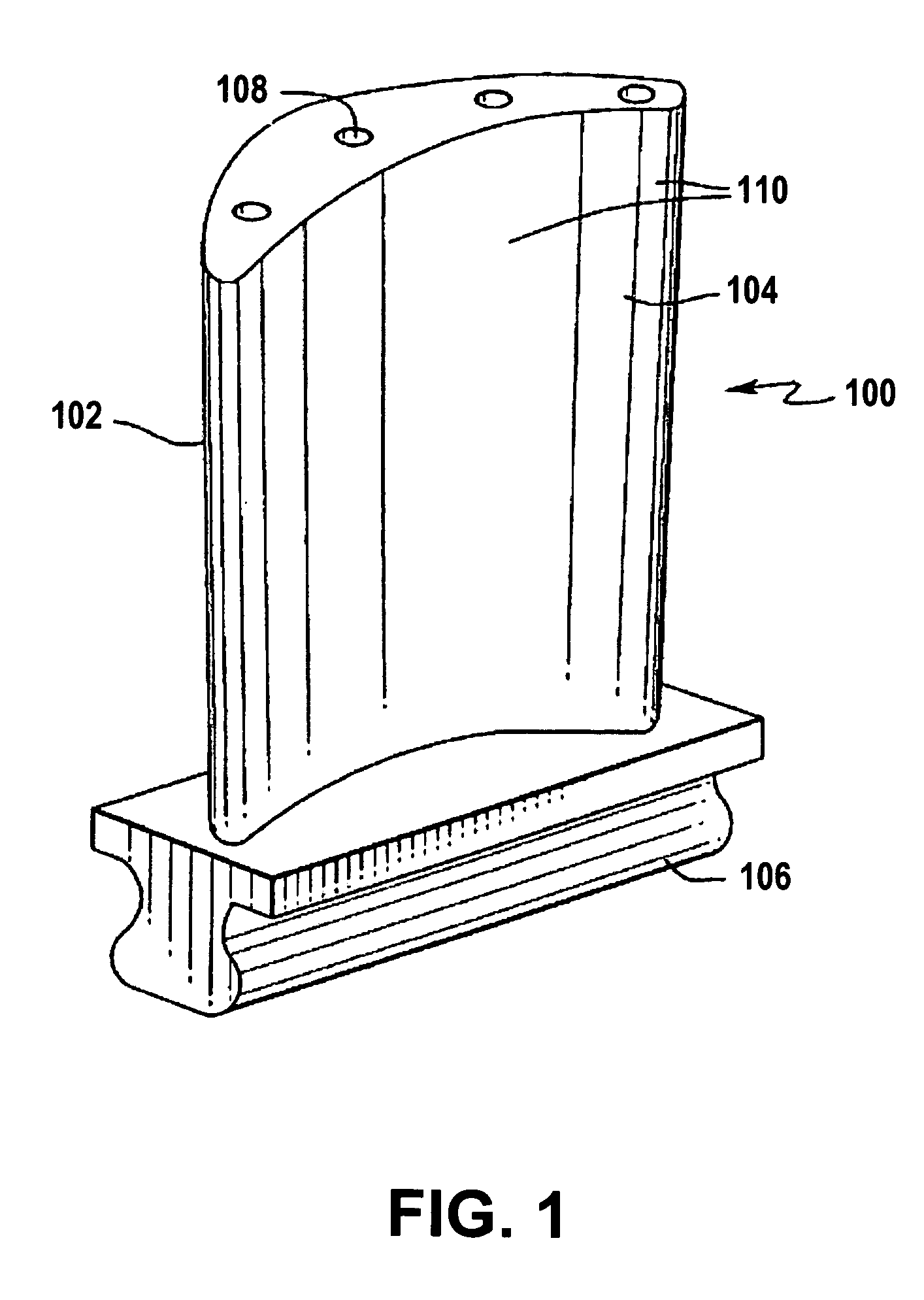

Parallel flow evaporator with non-uniform characteristics

InactiveUS7163052B2Effect on its overall performanceEliminate the effects ofEvaporators/condensersStationary conduit assembliesVariable CharacteristicEngineering

In a parallel flow heat exchanger, which is susceptible to having a non-uniform distribution of a two-phase refrigerant flow to the individual channels, the resultant differences in the refrigerant flow therethrough are compensated and counter-balanced by a corresponding difference in the external heat transfer rate for the respective channels. In one embodiment, these differences are accomplished by variable characteristics of extended heat transfer surface elements such as fin type, fin density, fin geometry and difference in construction materials, and in another embodiment, by varying the airflow distribution over the cross-section area of the heat exchanger.

Owner:CARRIER CORP

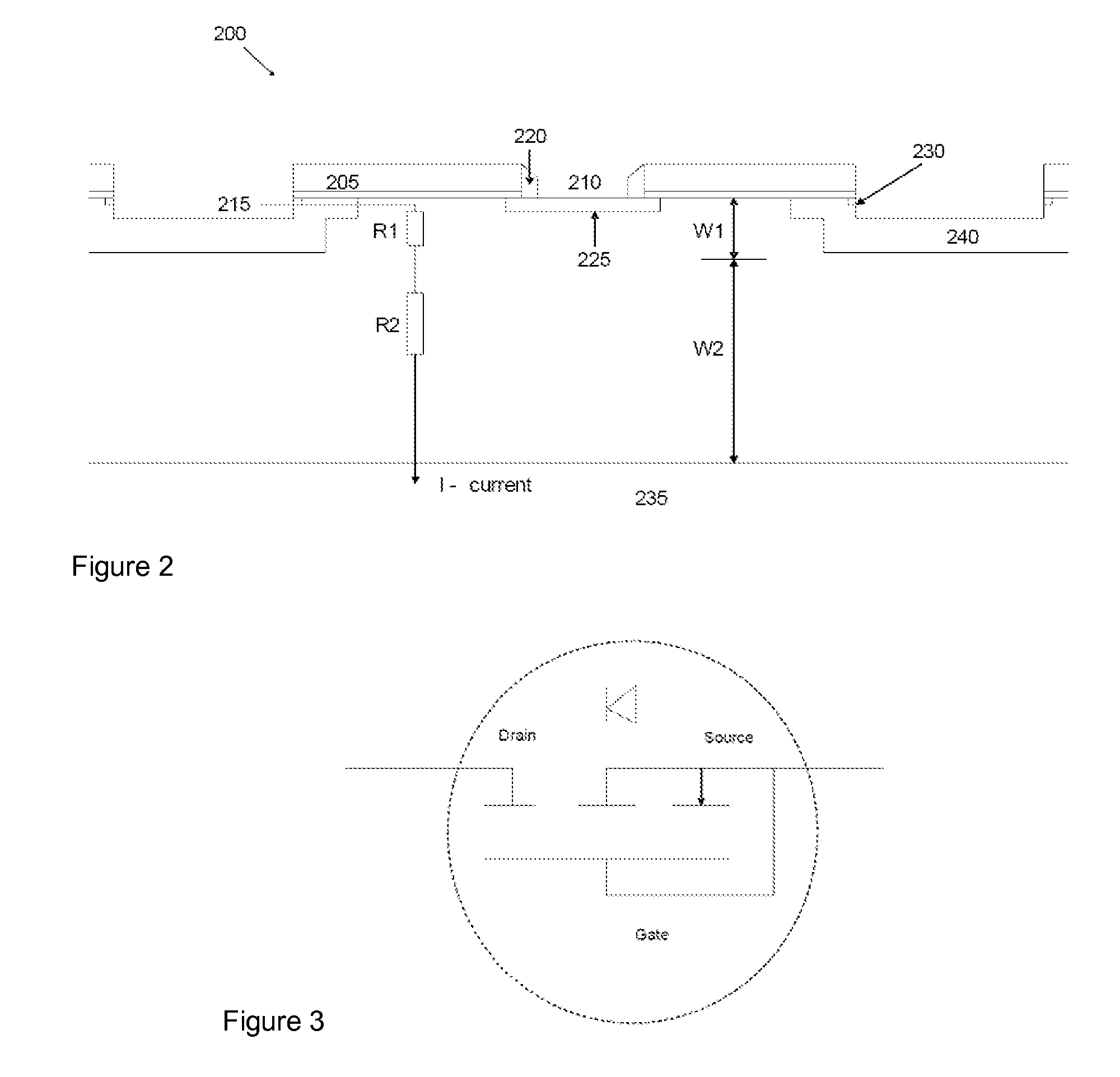

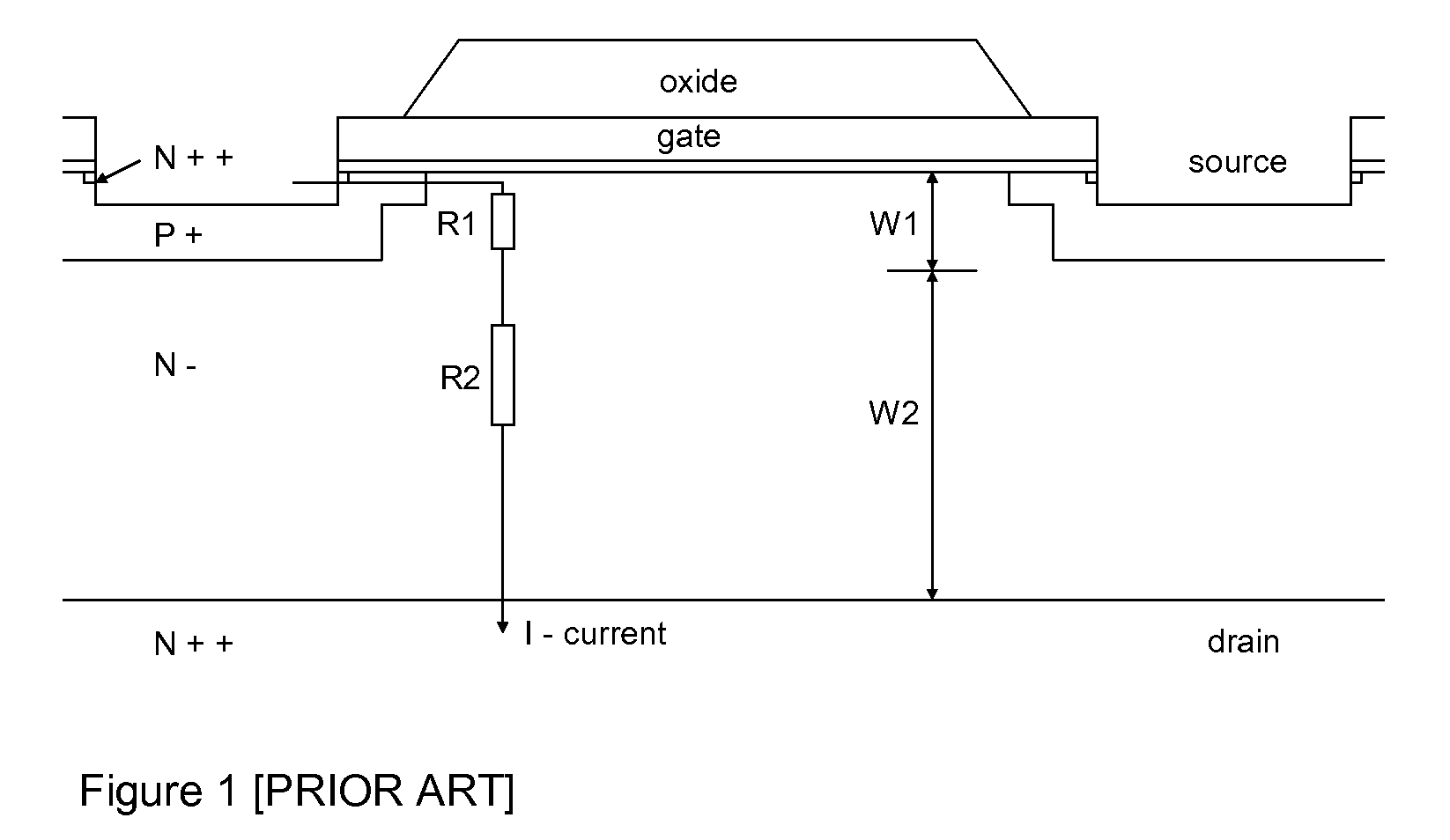

Adjustable Field Effect Rectifier

ActiveUS20090078962A1Function reliably and efficientlyFast recoveryThyristorMOSFETElectromagnetic interference

An Adjustable Field Effect Rectifier uses aspects of MOSFET structure together with an adjustment pocket or region to result in a device that functions reliably and efficiently at high voltages without significant negative resistance, while also permitting fast recovery and operation at high frequency without large electromagnetic interference.

Owner:STMICROELECTRONICS INT NV

Method for making golf ball with co-injected inner cover

The present invention is directed towards a method of manufacturing a multi-layered golf ball, with at least an inner cover having multiple layers formed by a sandwich injection molding process. The multi-layered inner cover comprises an inner layer and an outer layer of a first material and an intermediate layer therebetween of a second material. The materials having different properties.

Owner:ACUSHNET CO

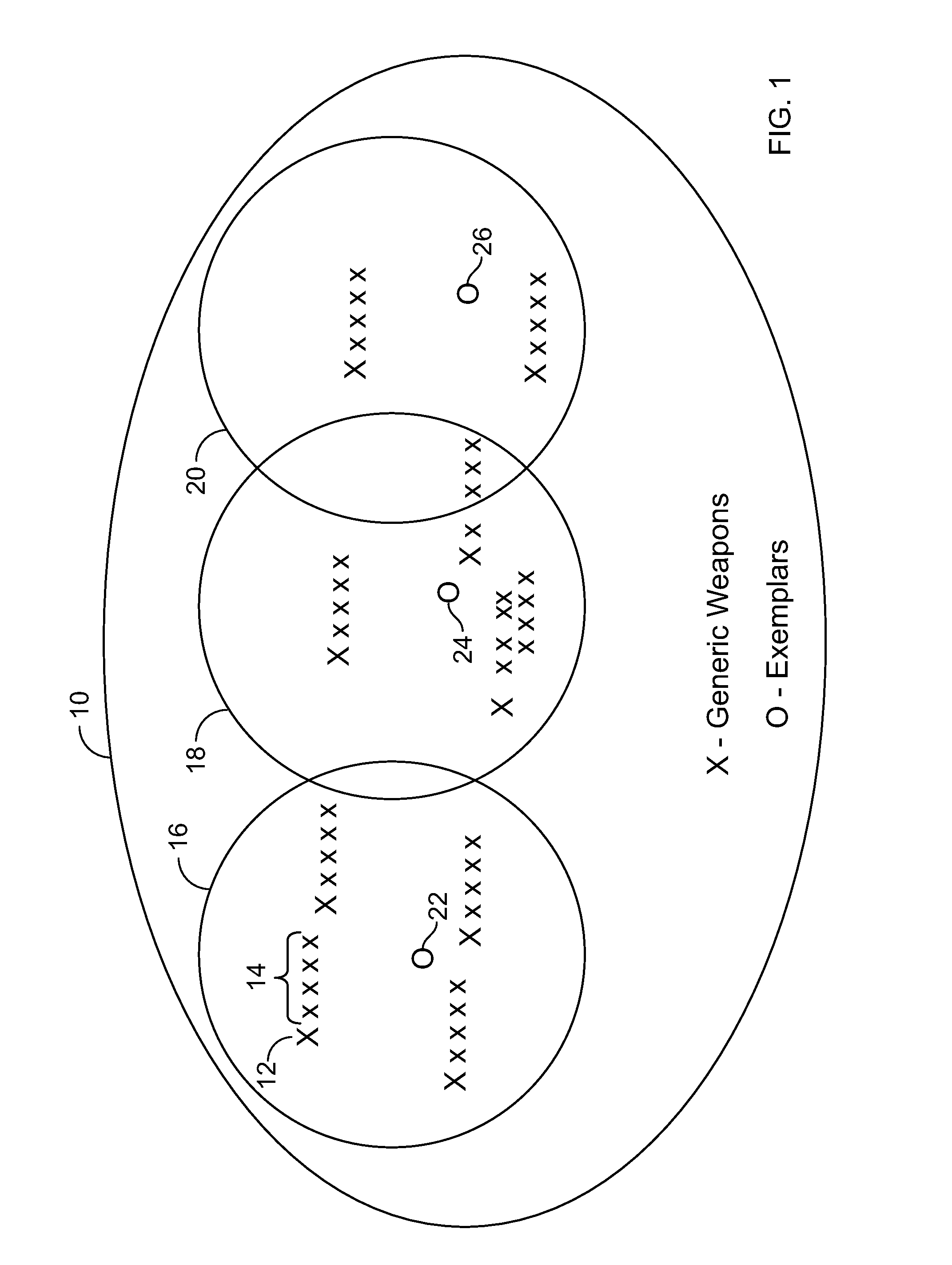

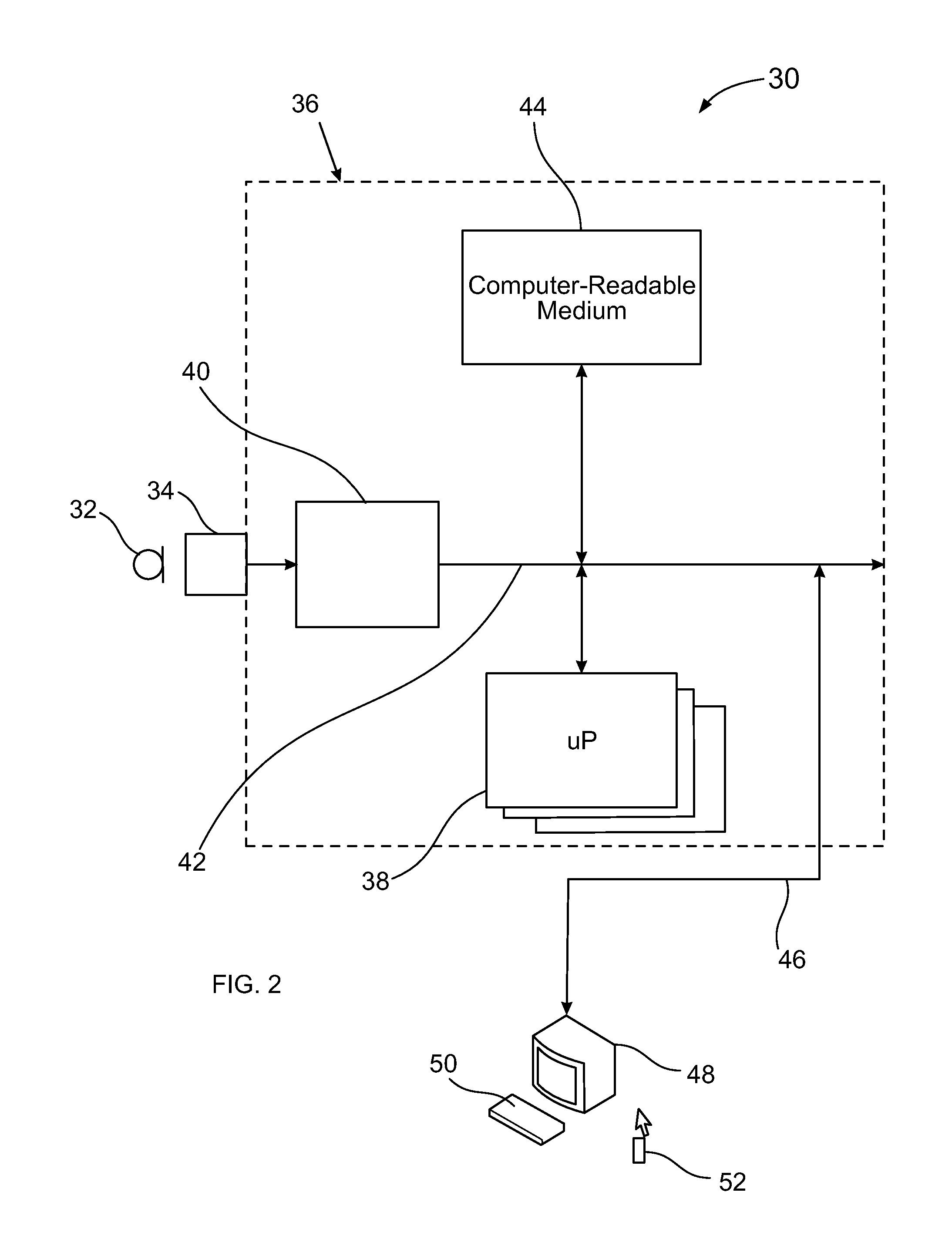

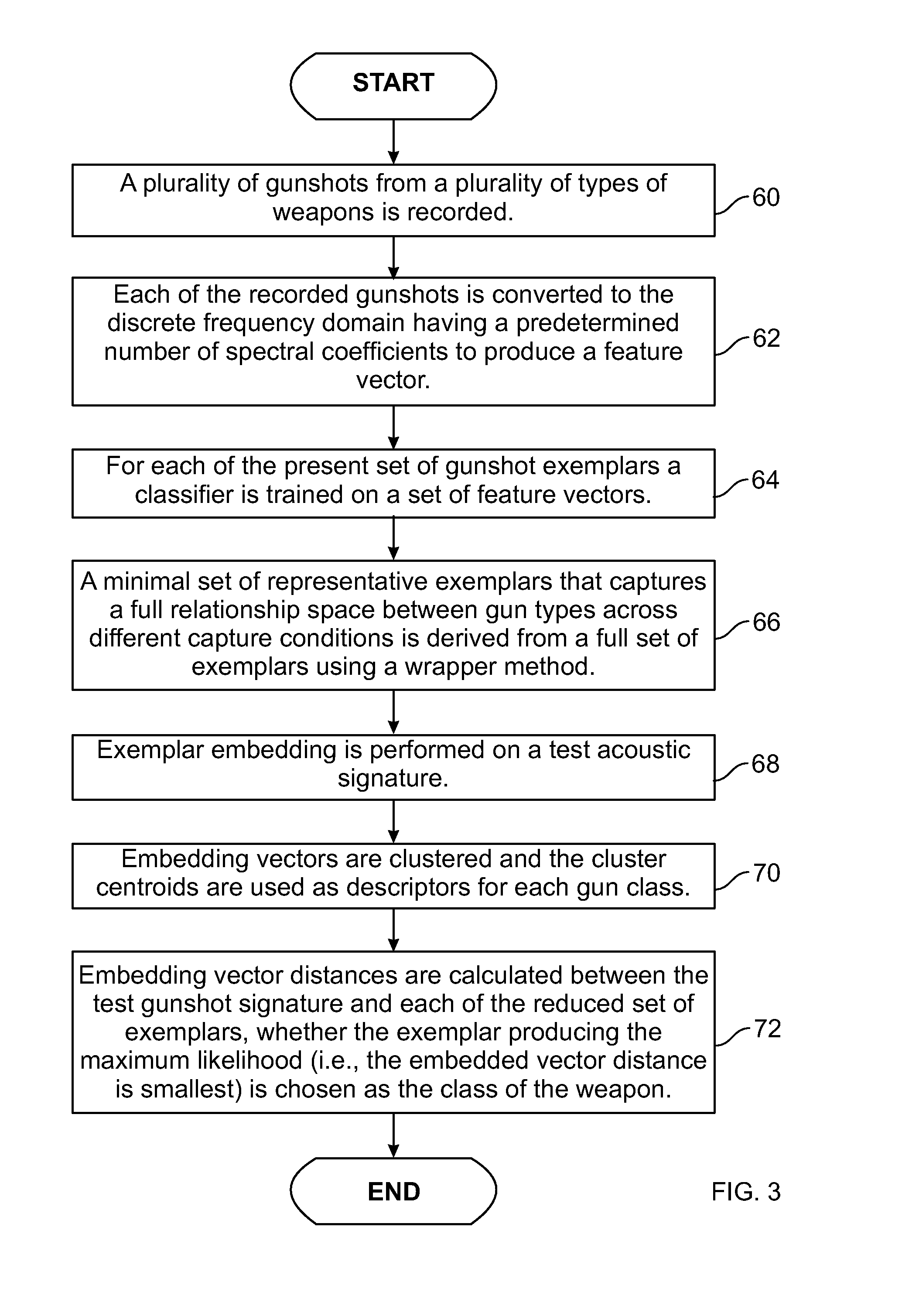

Weapon identification using acoustic signatures across varying capture conditions

ActiveUS20100271905A1Effect on its overall performanceLow errorDirection finders using ultrasonic/sonic/infrasonic wavesSpeech analysisSpeech soundAcoustic signature

A computer implemented method for automatically detecting and classifying acoustic signatures across a set of recording conditions is disclosed. A first acoustic signature is received. The first acoustic signature is projected into a space of a minimal set of exemplars of acoustic signature types derived from a larger set of exemplars using a wrapper method. At least one vector distance is calculated between the projected acoustic signature and each exemplar of the minimal set of exemplars. An exemplar is selected from the minimal set of exemplars having the smallest vector distance to the projected acoustic signature as a class corresponding to and classifying the first acoustic signature. The first acoustic signature and the plurality of acoustic signatures may correspond to one of gunshots, musical instruments, songs, and speech. The minimal set of exemplars may correspond to a hierarchy of acoustic signature types.

Owner:SRI INTERNATIONAL

Adjustable field effect rectifier

ActiveUS8148748B2Improve performanceImproving reverse recovery characteristicThyristorMOSFETHigh voltage igbt

An Adjustable Field Effect Rectifier uses aspects of MOSFET structure together with an adjustment pocket or region to result in a device that functions reliably and efficiently at high voltages without significant negative resistance, while also permitting fast recovery and operation at high frequency without large electromagnetic interference.

Owner:STMICROELECTRONICS INT NV

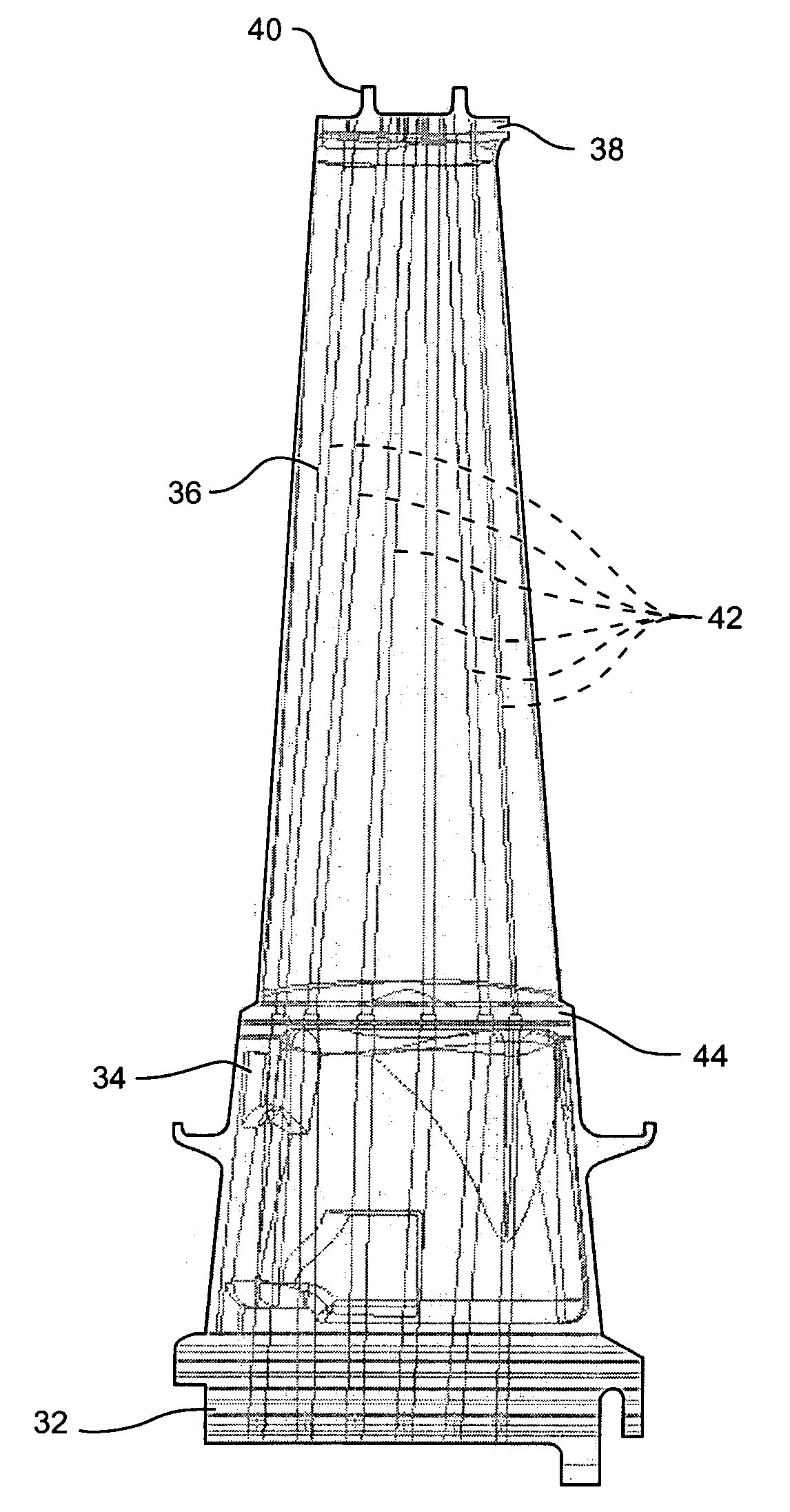

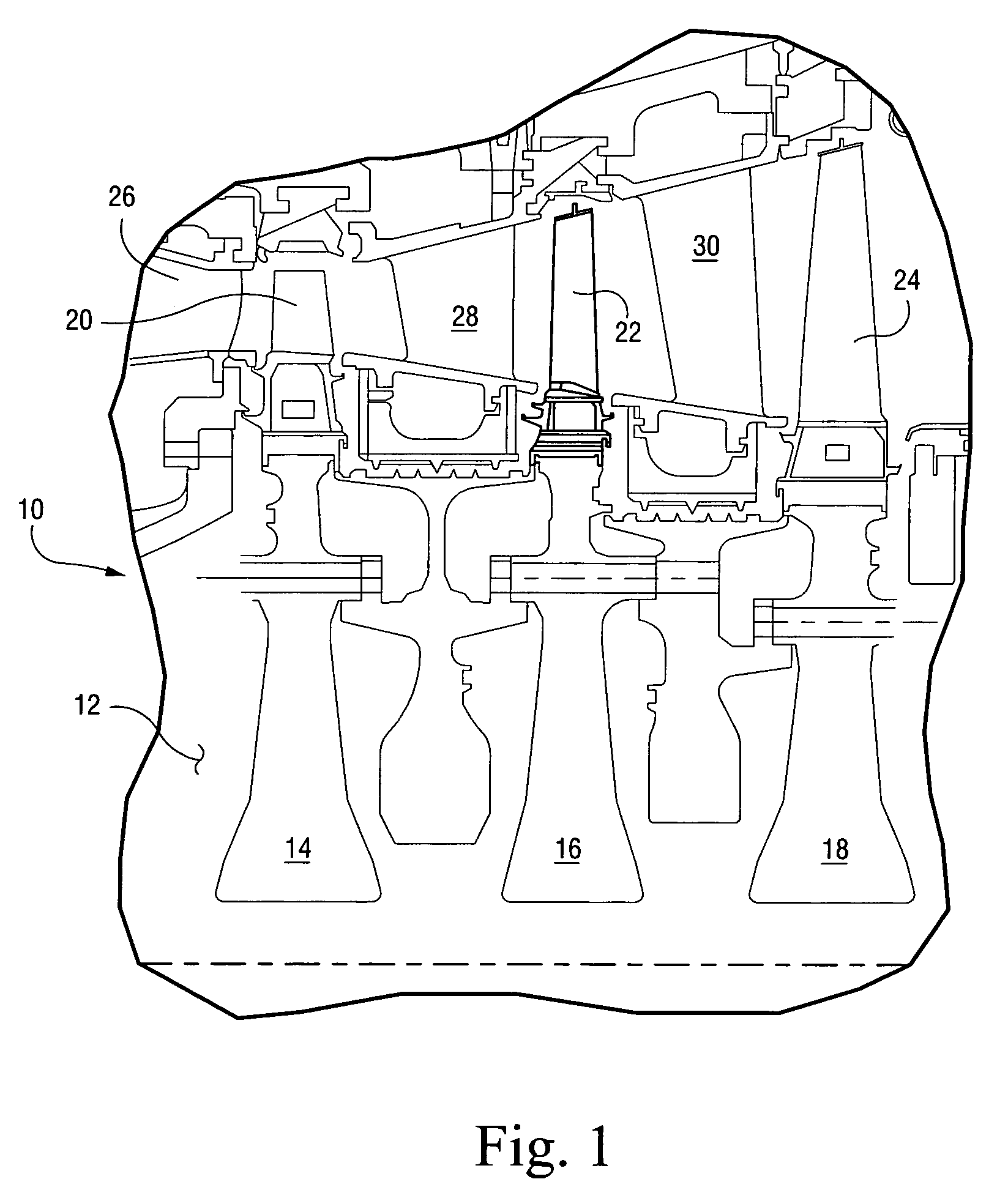

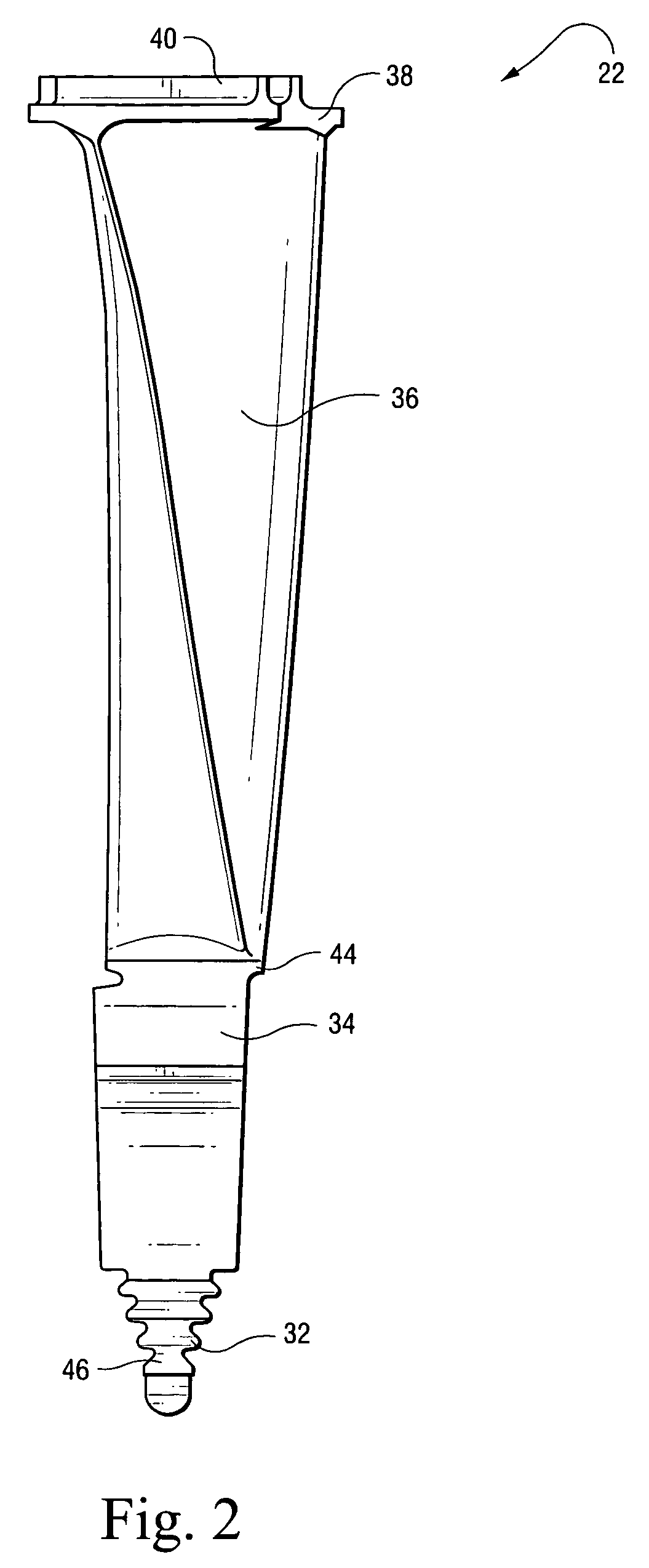

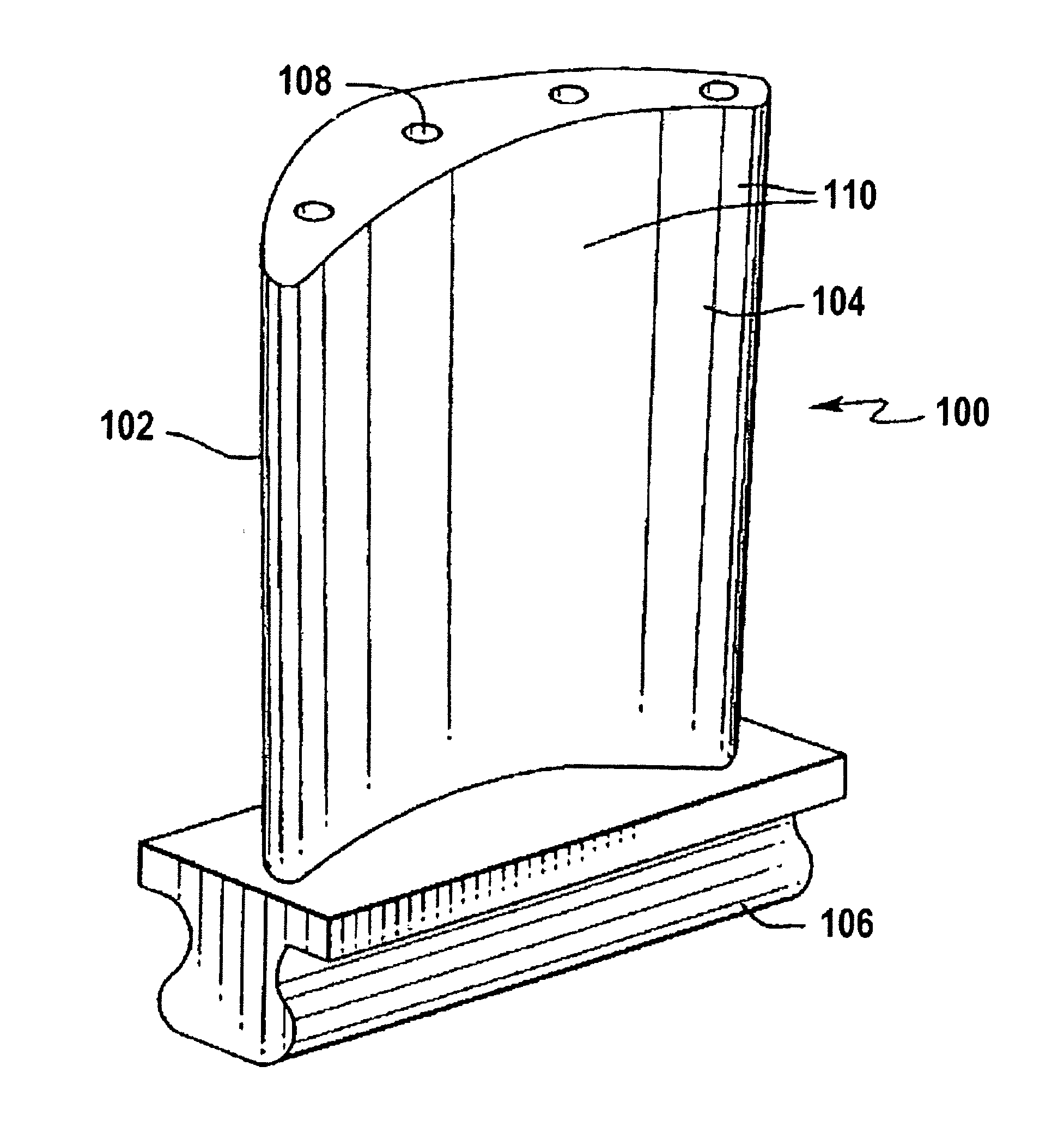

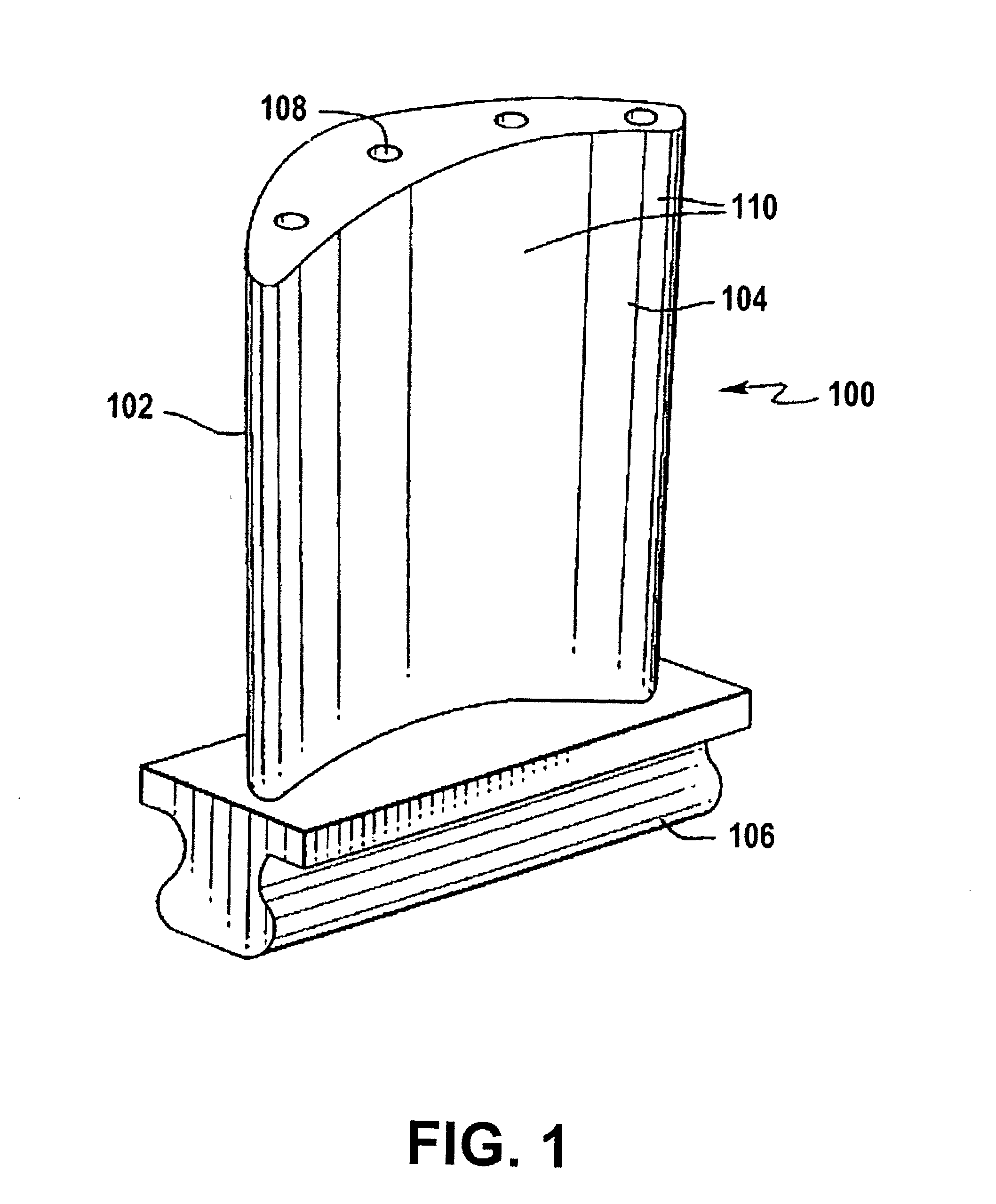

Turbine bucket with optimized cooling circuit

ActiveUS7207775B2Improve cooling effectMaximize useful life at base load operationEngine fuctionsBlade accessoriesTrailing edgeTurbine

A turbine bucket includes a cooling circuit through a dovetail section, a shank section and an airfoil section. The cooling circuit is configured to maximize cooling ability and maximize a useful life at base load operation at firing temperatures of up to 2084° F. while minimizing negative effects on performance. The cooling circuit includes a plurality of cooling holes having predetermined positions and sizes, resulting in increased cooling flow near a trailing edge of the airfoil section and effecting turbulation in the airfoil section to increase bulk and local creep margins throughout the airfoil section.

Owner:GENERAL ELECTRIC CO

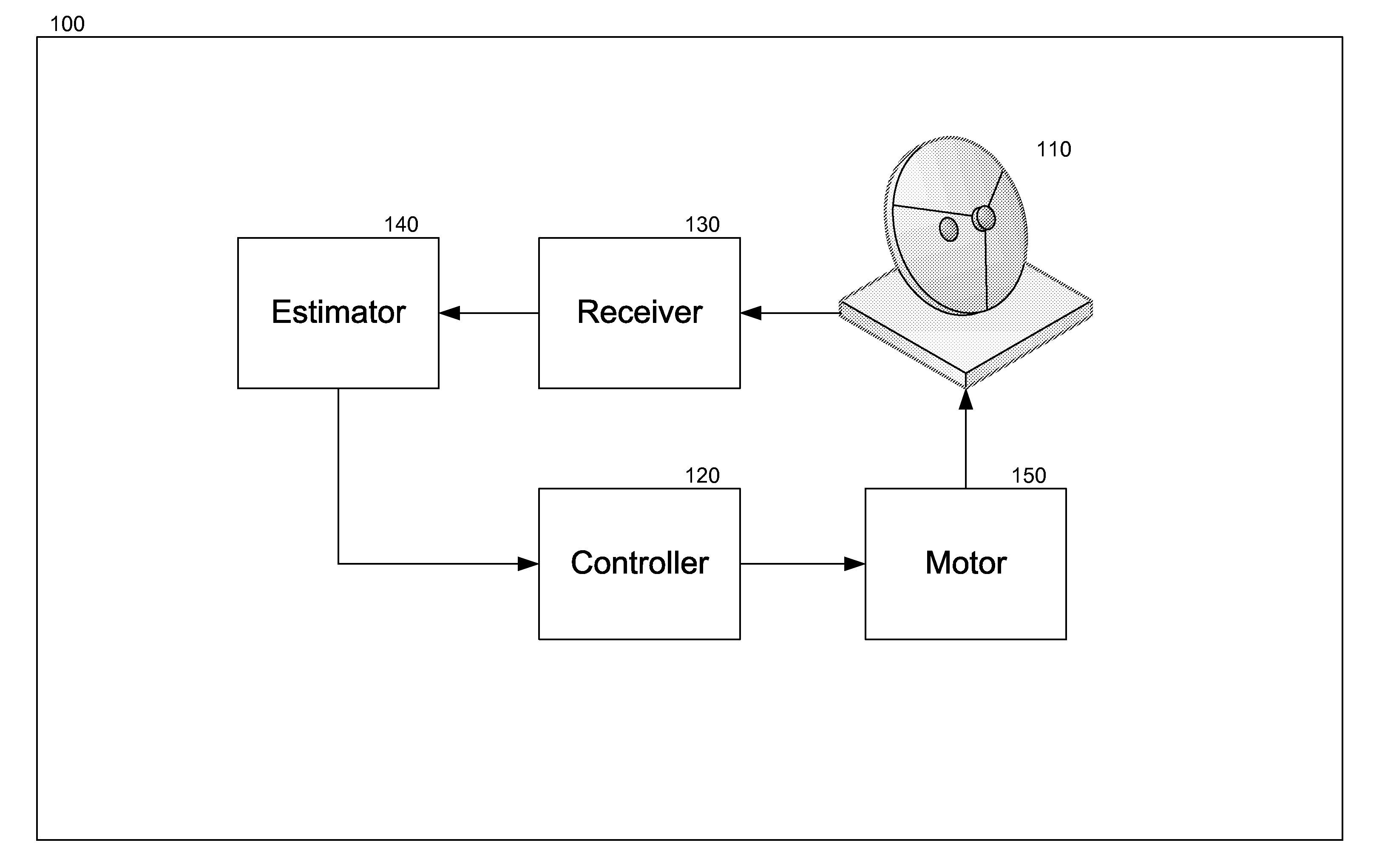

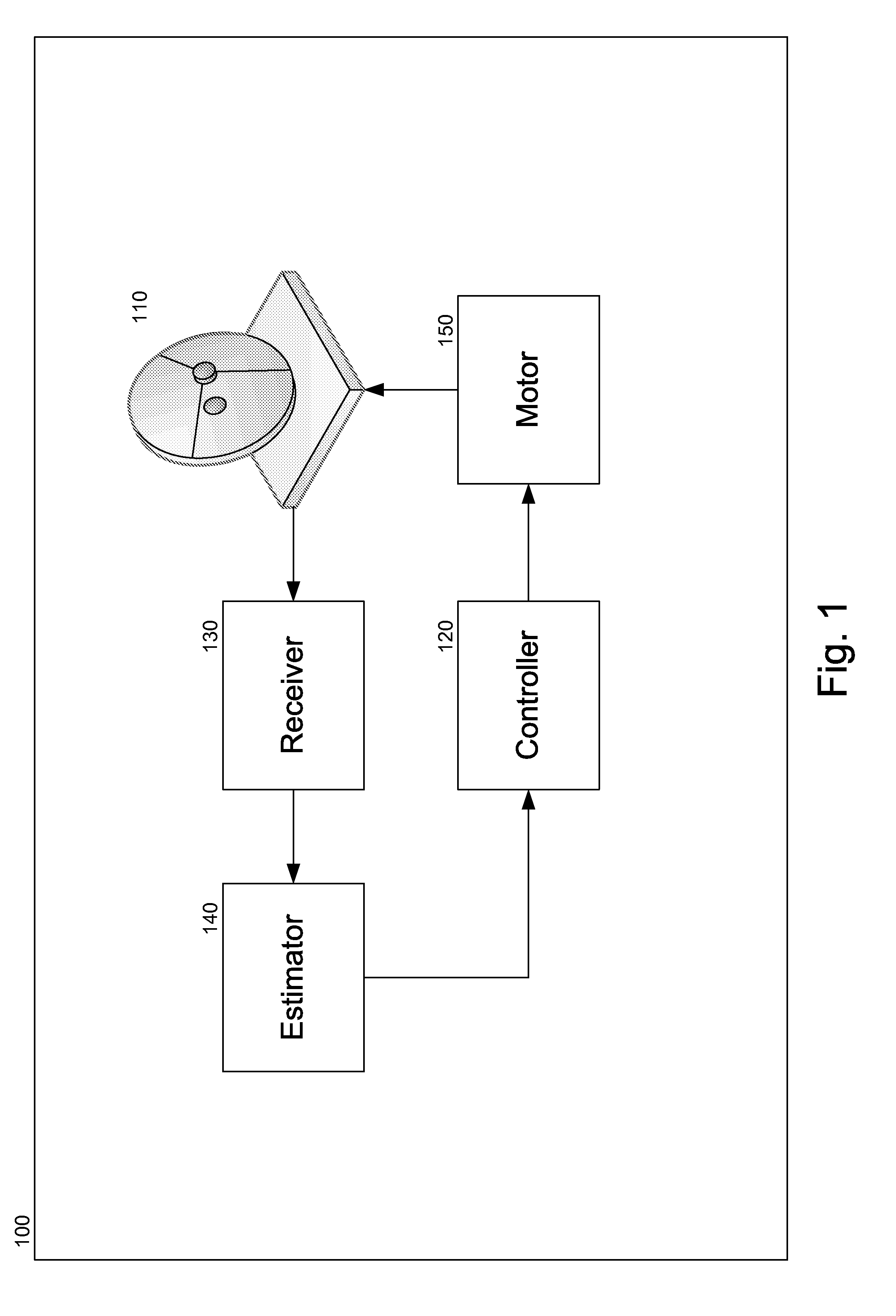

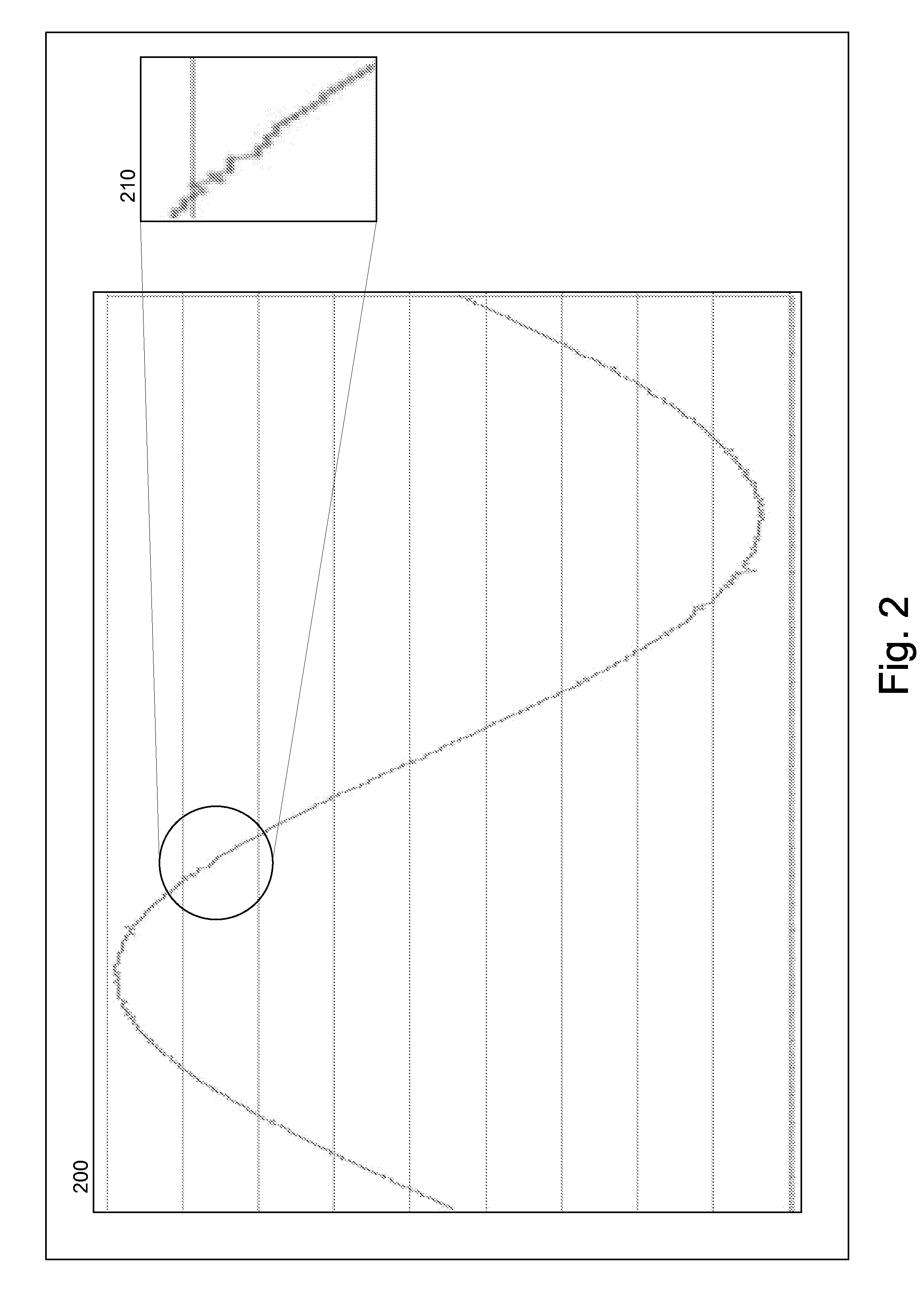

Satellite Tracking Method and Apparatus Thereof

InactiveUS20120013506A1Reduce alignment errorsReduce signalingCosmonautic vehicle trackingAntenna detailsSatellite trackingInclined orbit

A satellite communication ground station configured for communicating over an inclined orbit geostationary satellite may include a tracking antenna having three fixed axis and one moving axis, a motor for swinging the antenna along the moving axis, a controller for controlling the motor, a receiver configured to receive a signal arriving from the satellite via the tracking antenna and an estimator configured to estimate reception quality of a signal received by the receiver. The invention described herein presents a method for tracking an inclined orbit geostationary satellite, the method comprising a learning step and a tracking step, wherein the learning step includes use of a filter for reducing alignment errors and reducing the amount of peaking required for aligning the antenna with the satellite and tracking its movement.

Owner:GILAT SATELLITE NETWORKS

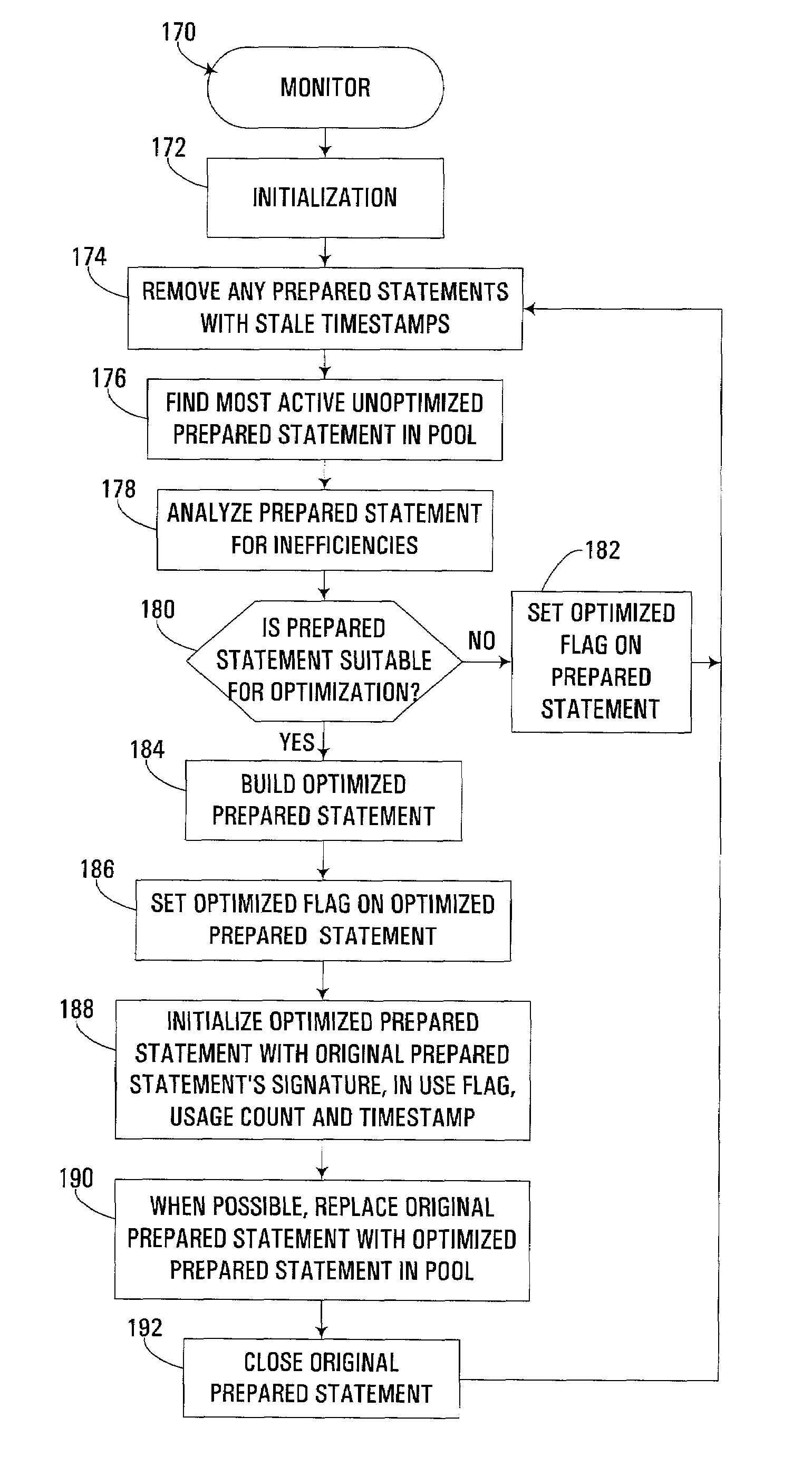

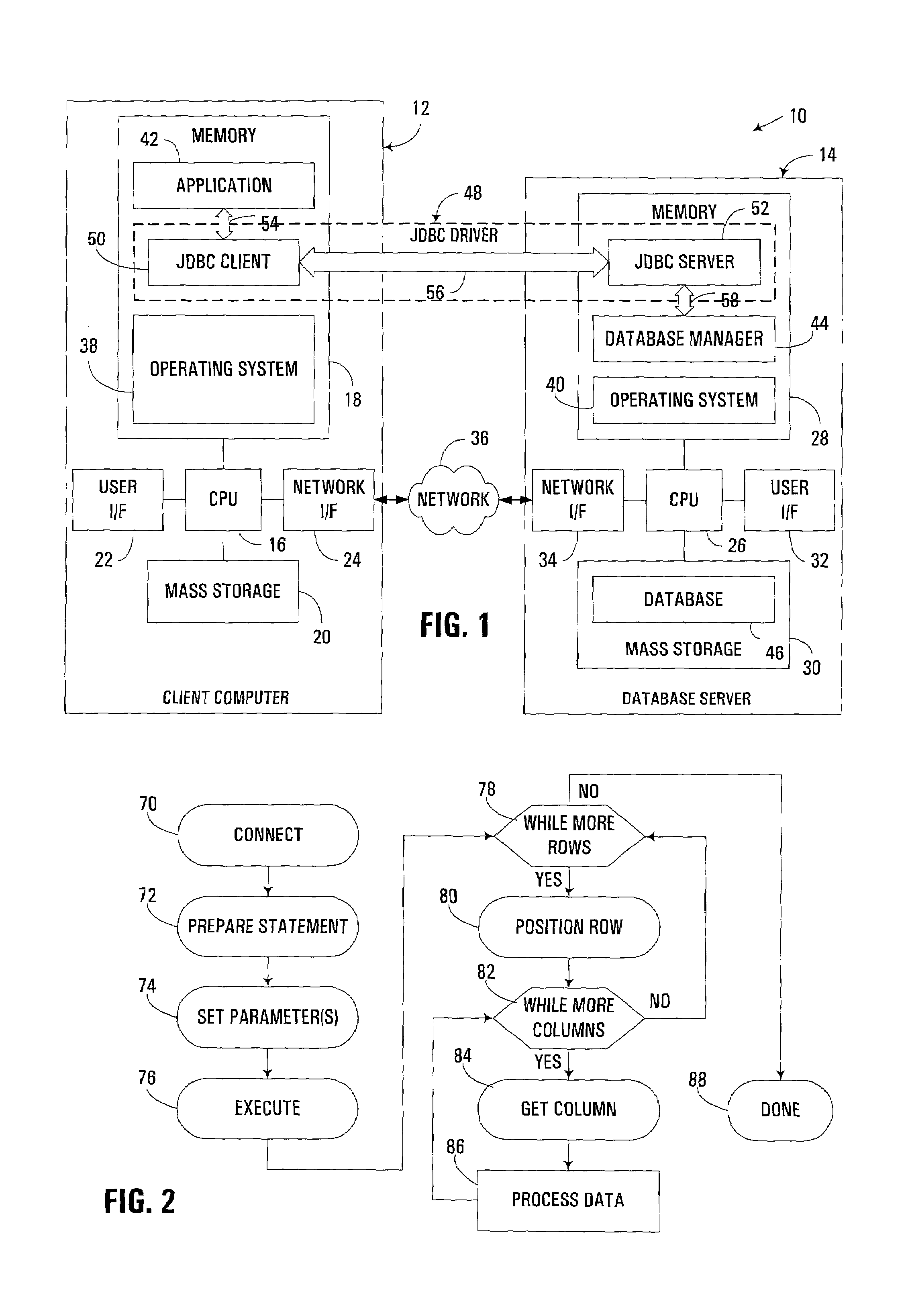

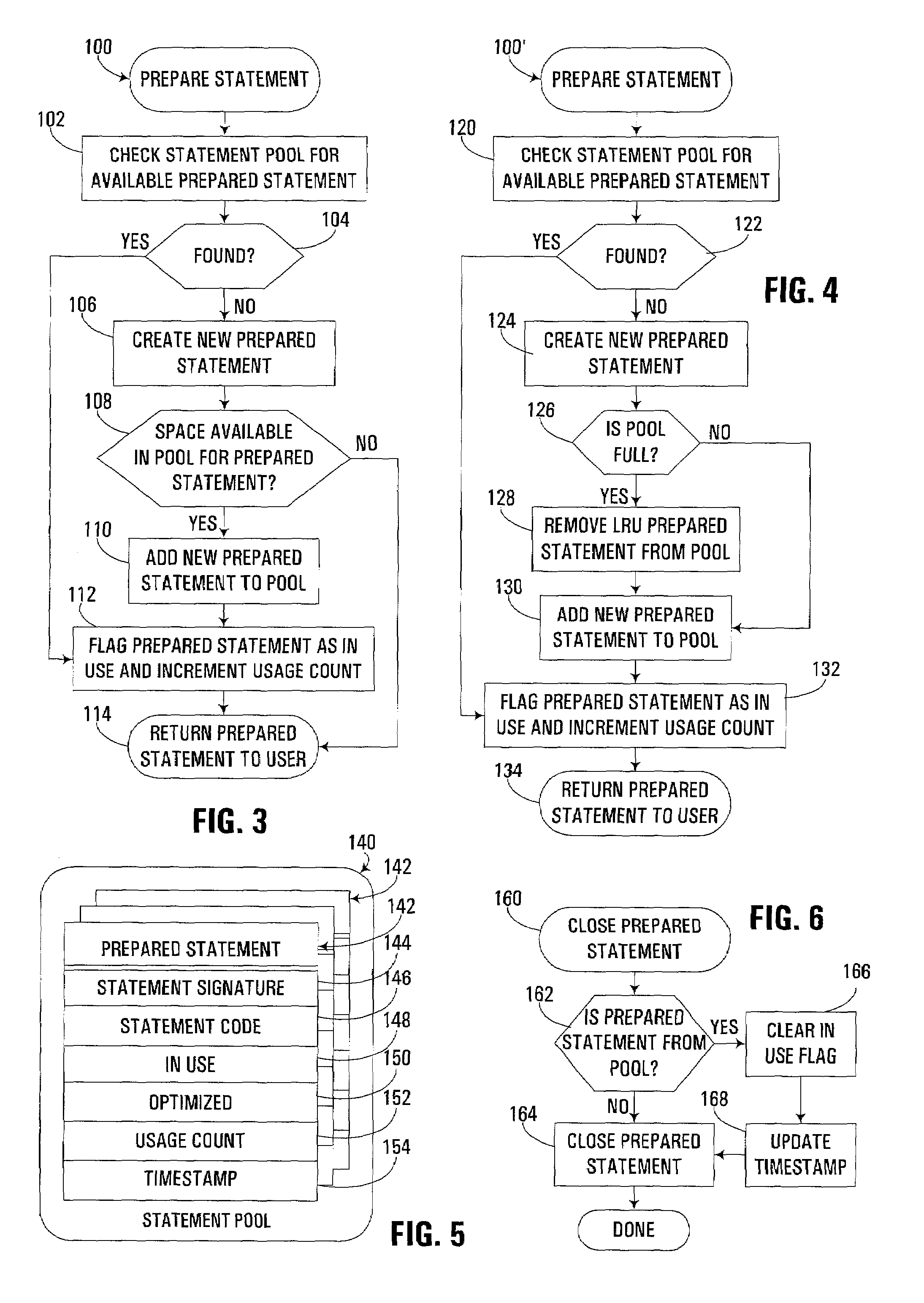

Dynamic optimization of prepared statements in a statement pool

ActiveUS7356523B2Improve performanceAffect applicationData processing applicationsDigital data information retrievalDynamical optimizationPrepared statement

An apparatus, program product and method dynamically optimize prepared statements resident in a statement pool to permit subsequent reuses of such statements to utilize the optimized representations of such statements. The optimization of pooled statements may be performed responsive to the tracked usage of the statements in a statement pool, to direct the overhead associated with such optimization to those statements that are more likely to be utilized in the future. Among a multitude of possible optimizations, a pooled statement that requests data in a format other than that utilized by the database being accessed may be modified to request the data in the format used by the database, thereby decreasing the overhead in the database associated with format conversions.

Owner:META PLATFORMS INC

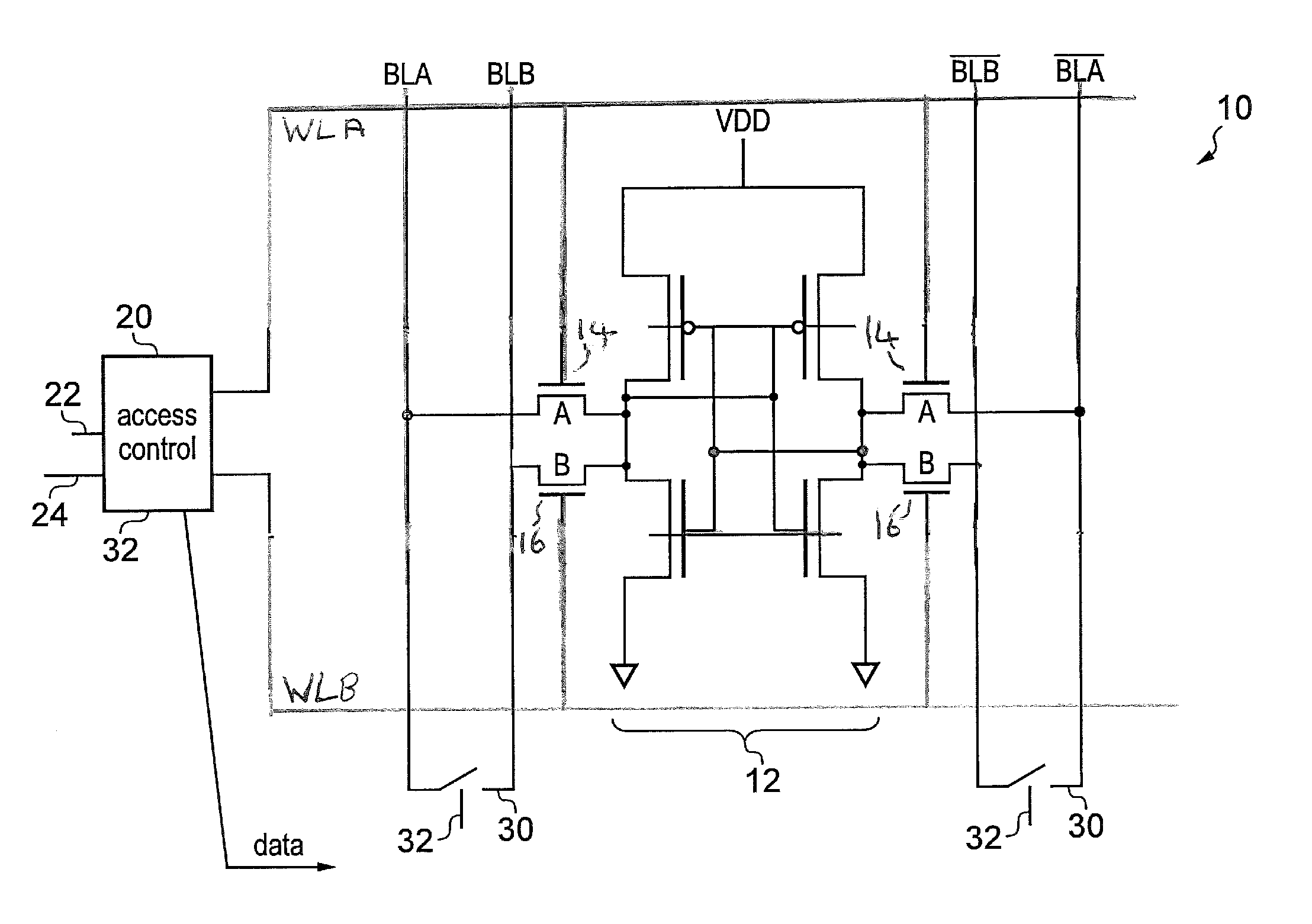

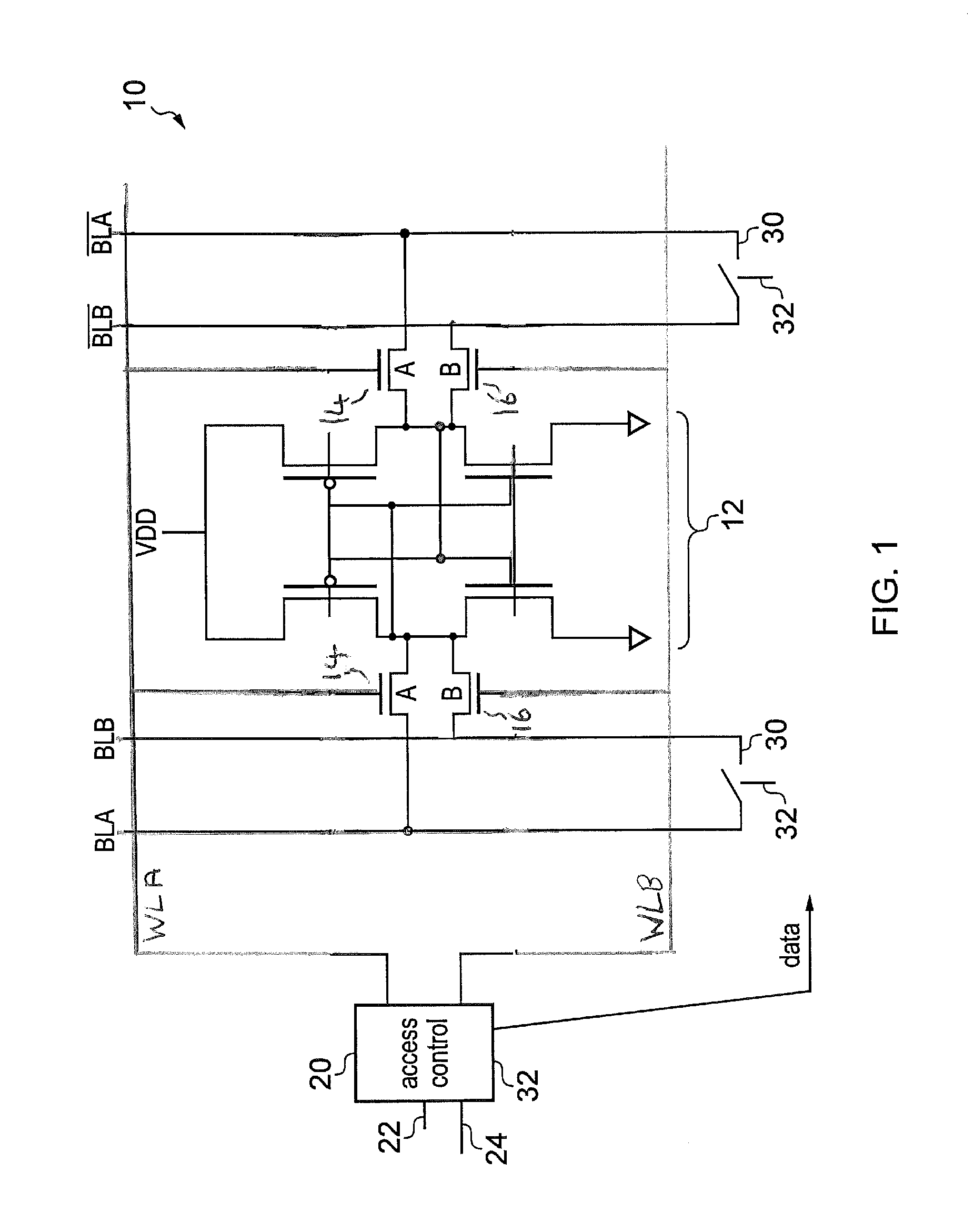

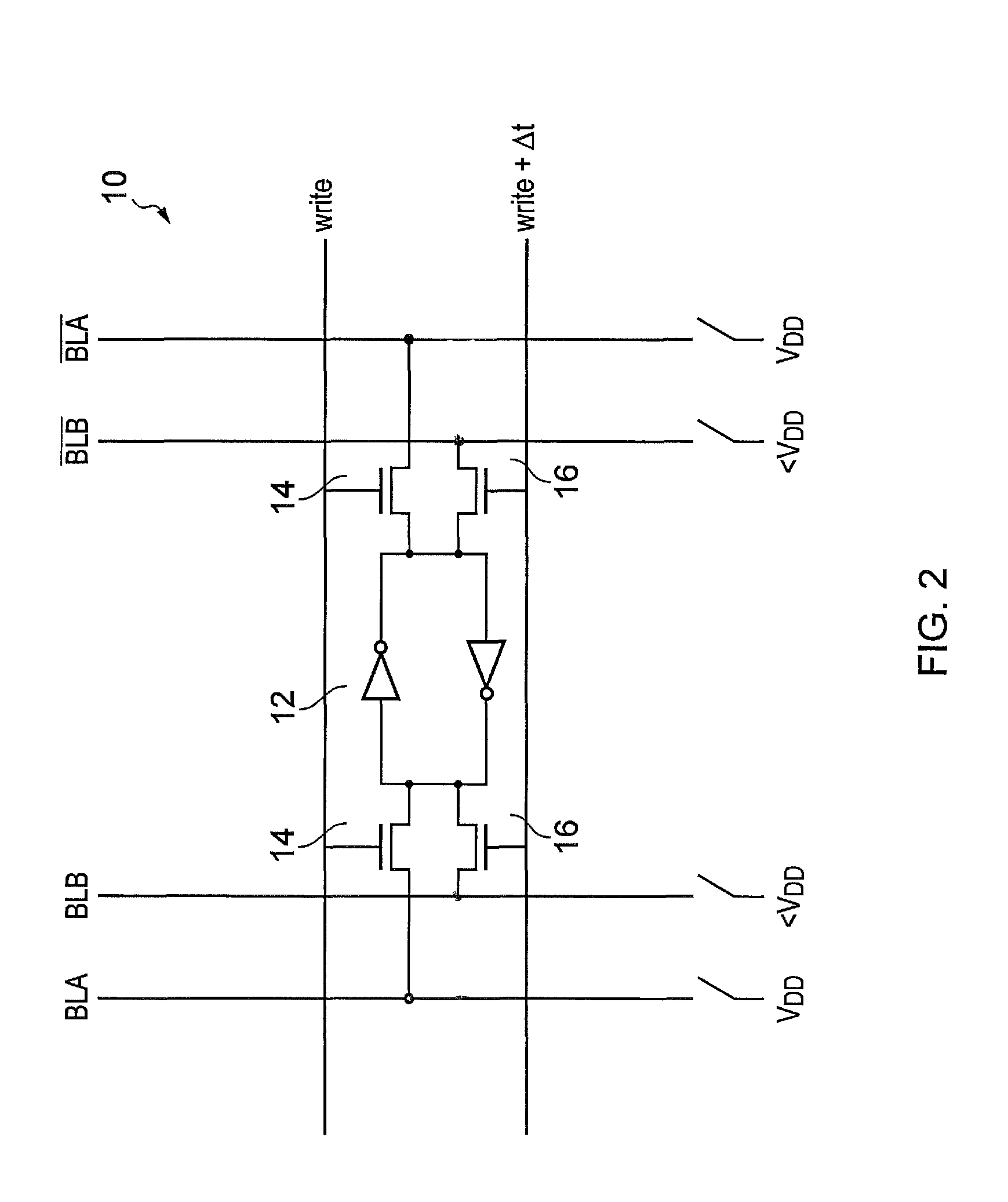

Write assist in a dual write line semiconductor memory

A semiconductor memory storage device with a plurality of storage cells, each cell includes two access control devices, each providing the cell with access to or isolation from a respective one of two data lines in response to an access control signal provided by access control circuitry. The control devices are controlled to provide the storage cell with access to or isolation from either of the first and second of the two data lines. The access control circuitry is responsive to a data access request, the data access request being a write request, to apply a data value to be written to both of the first and second data lines and to apply the access control signal to both of the first and second access control lines.

Owner:ARM LTD

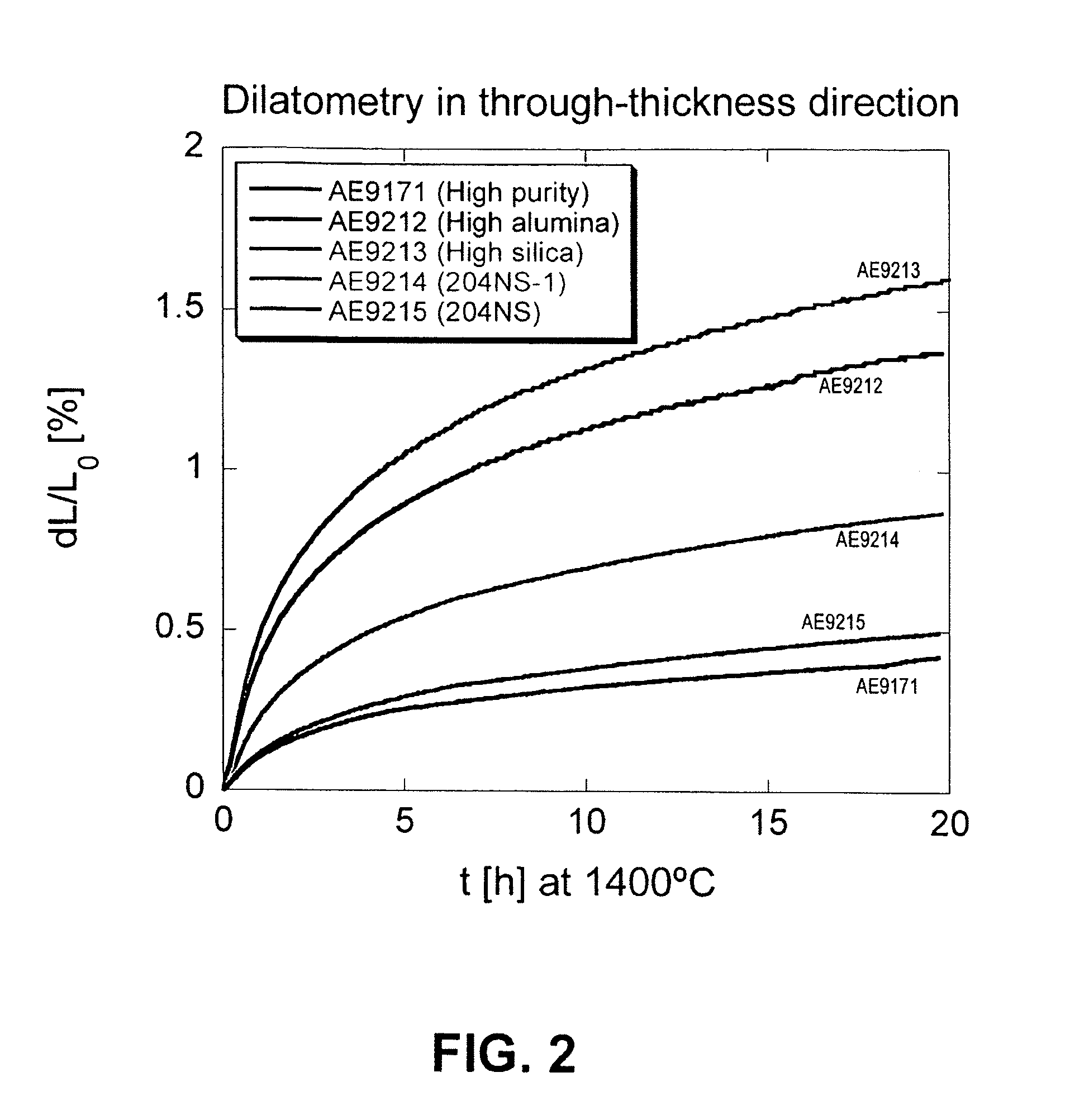

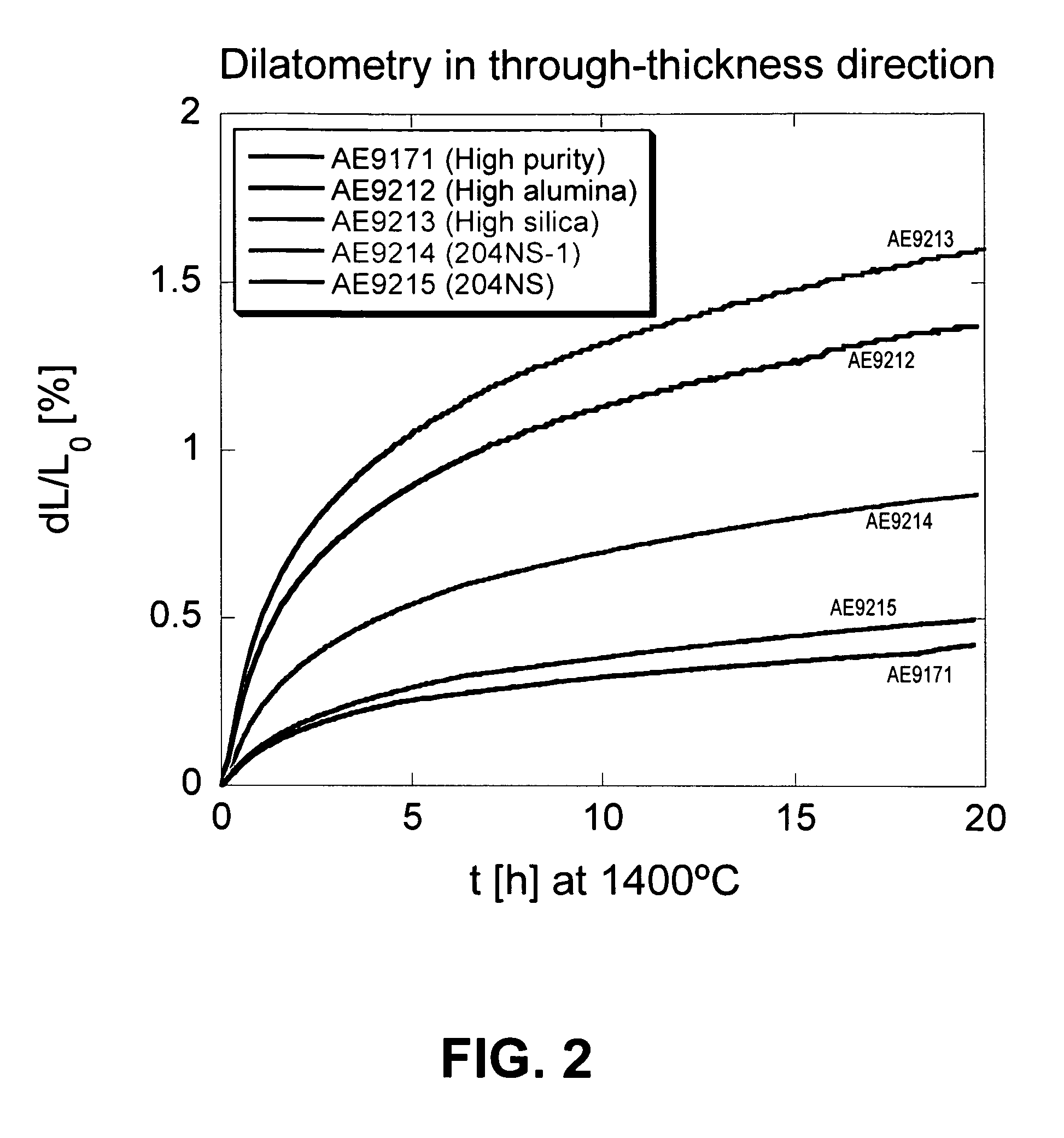

Ceramic material for high temperature service

ActiveUS20130295326A1Improve stabilizerEffect on its overall performanceMolten spray coatingLayered productsCoated surfaceMetallurgy

Owner:SULZER METCO (US) INC

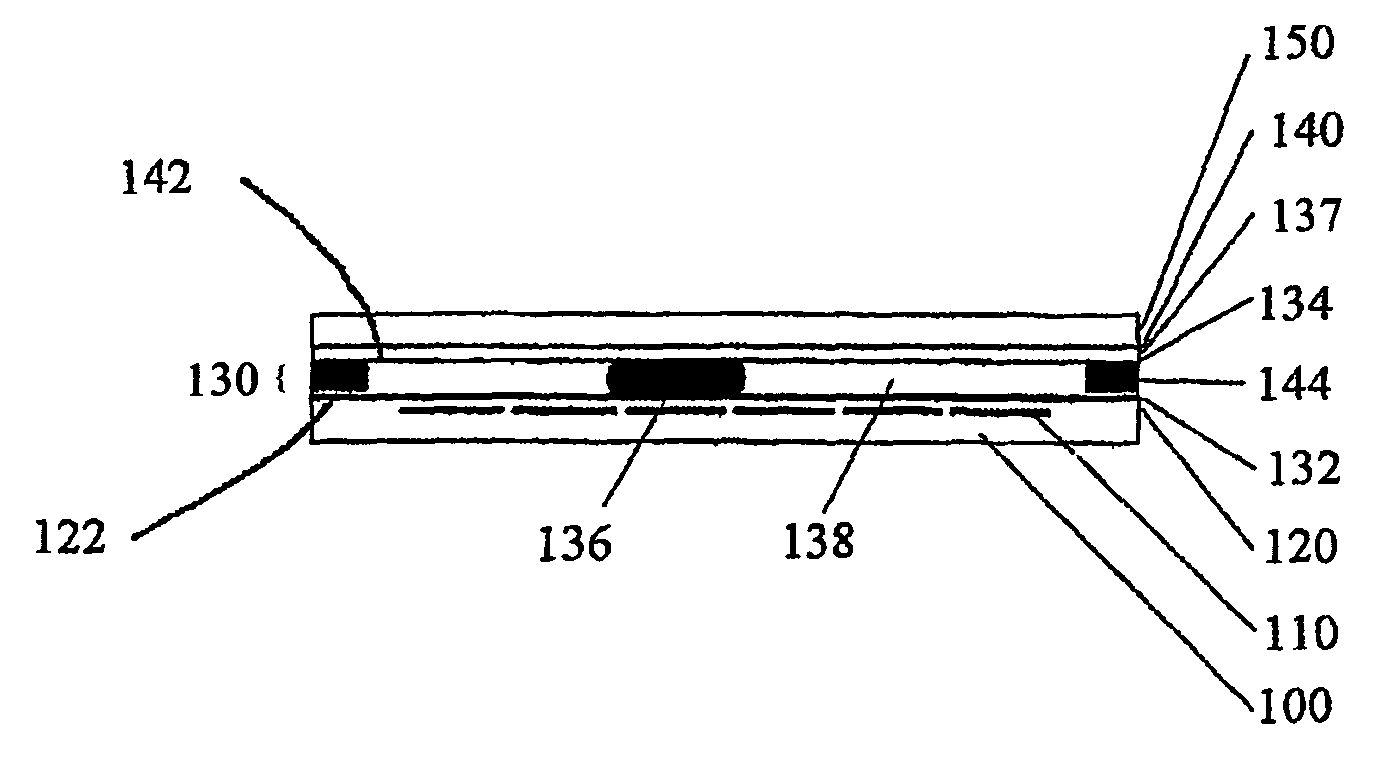

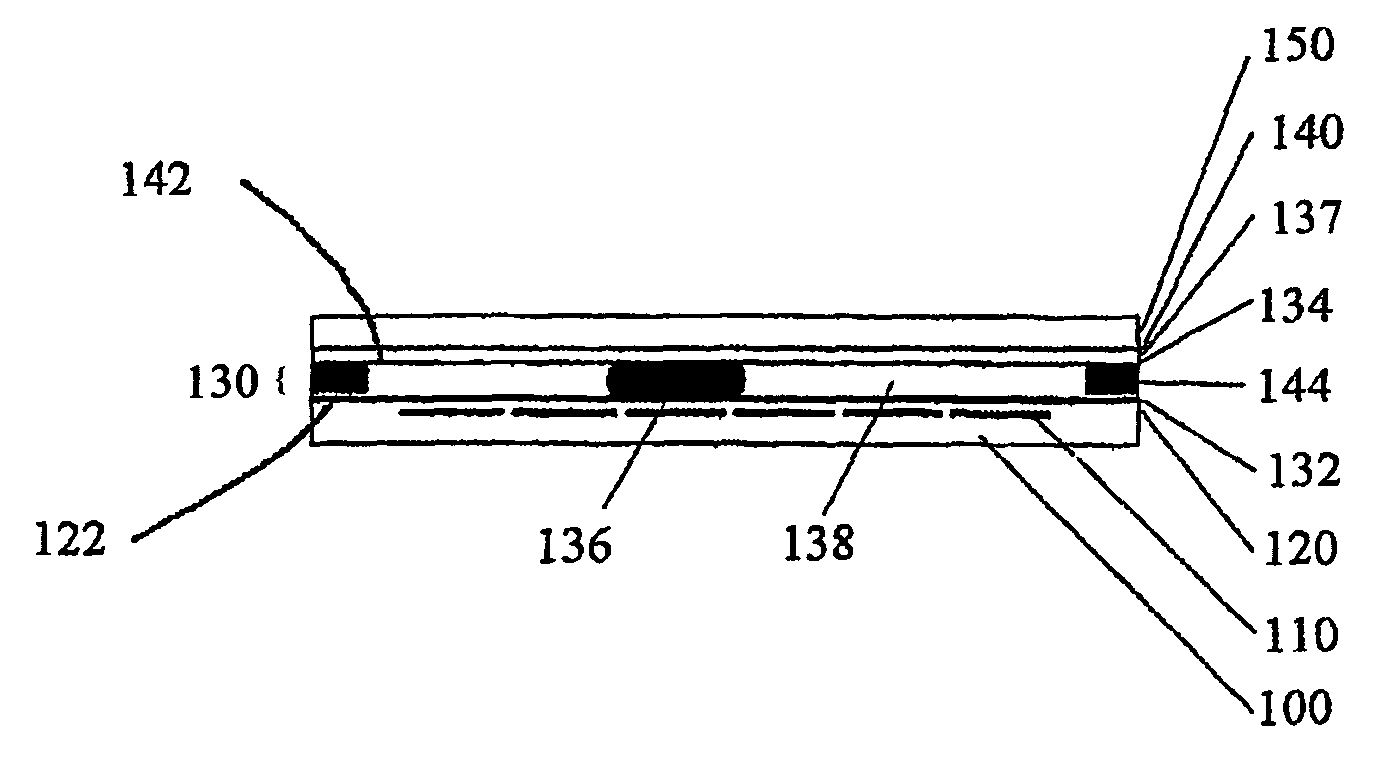

Layer composition of an electrowetting system

InactiveUS7909974B2High dielectric constantIncrease valueElectrostatic separatorsSludge treatmentFluid layerPermittivity

A layer composition of an electrowetting system with a first electrode layer, an insulator layer on the first electrode layer, and a fluid layer over the insulator layer, wherein the fluid layer comprises at least two immiscible fluids which, under the influence of an applied voltage, reversibly change their wetting behavior of a surface allocated to the insulator layer, wherein the insulator layer being at least in part built of a material with a permittivity of ∈r≧20. The fluid layer is adjacent to at least one layer being repellent for the at least one of the fluids. On the surface of the repellent layer pointing away from the fluid layer is provided an adhesion enhancing layer before the subsequent layer.

Owner:ADVANCED DISPLAY TECH

Ceramic material for high temperature service

ActiveUS20100075147A1Improve stabilizerEffect on its overall performanceMolten spray coatingVacuum evaporation coatingAlloyProviding material

Owner:SULZER METCO (US) INC