Patents

Literature

504 results about "Intermediate code" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

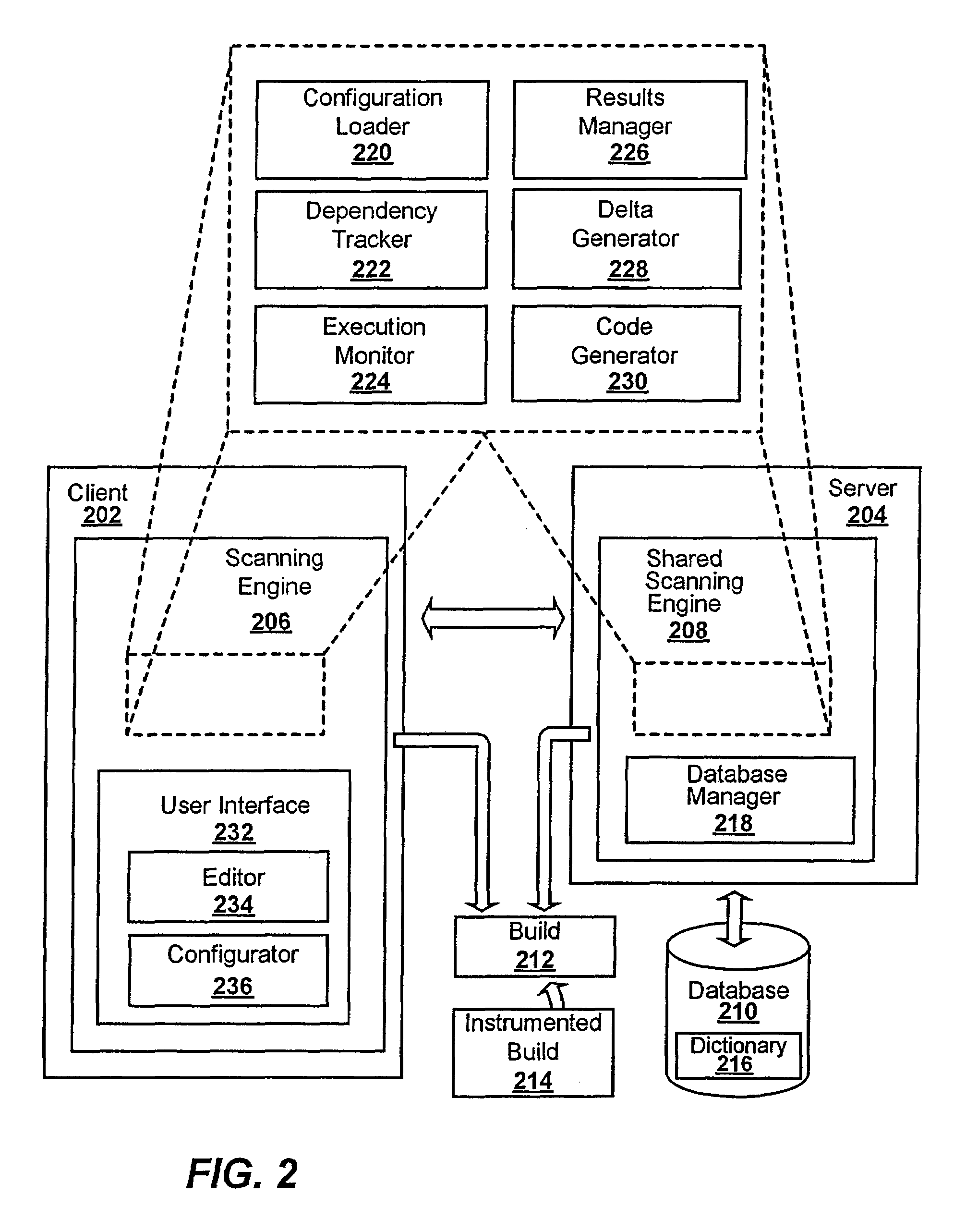

Method and system for automatically testing a software build

InactiveUS20050071818A1Error detection/correctionSpecific program execution arrangementsSoftware buildIntermediate code

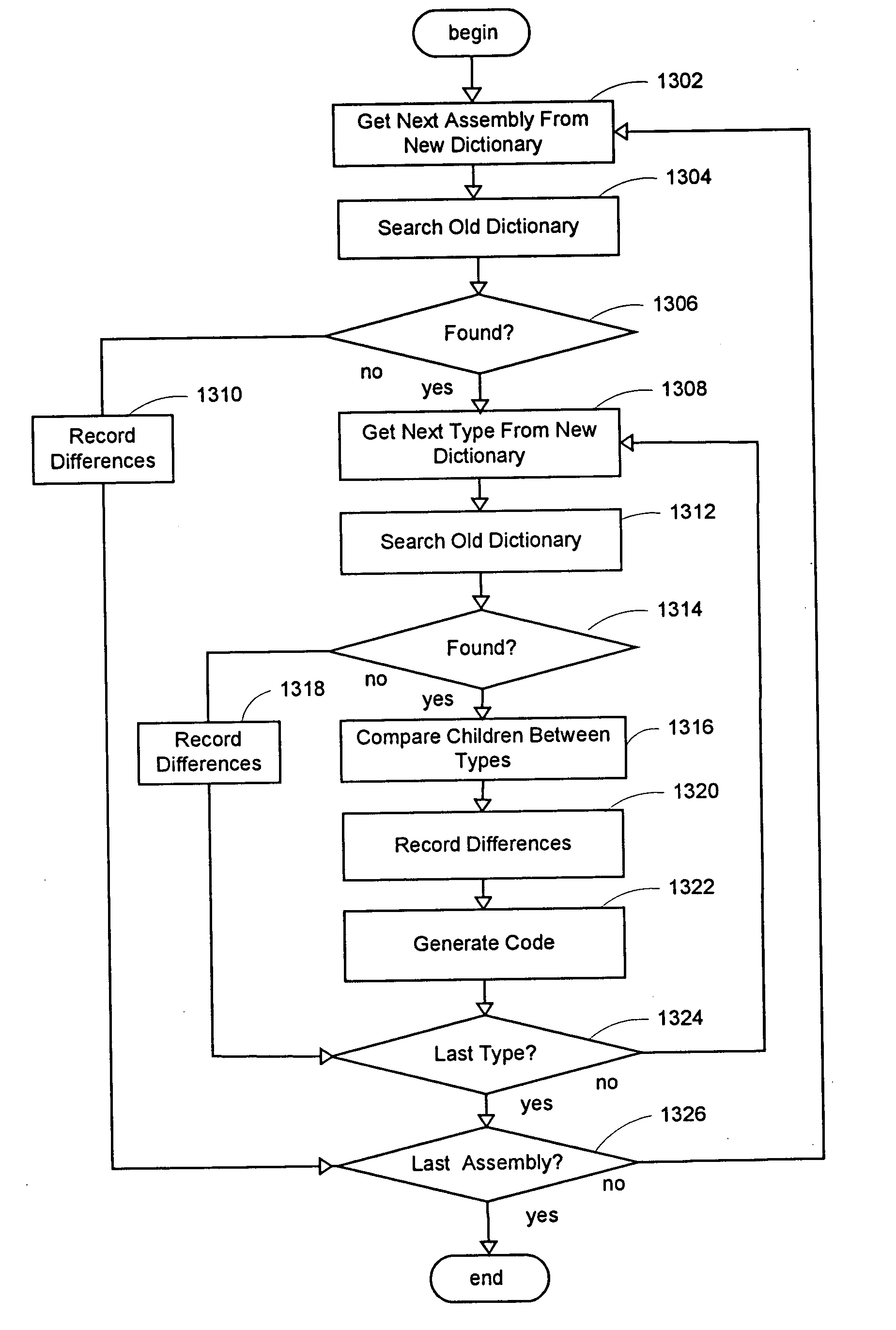

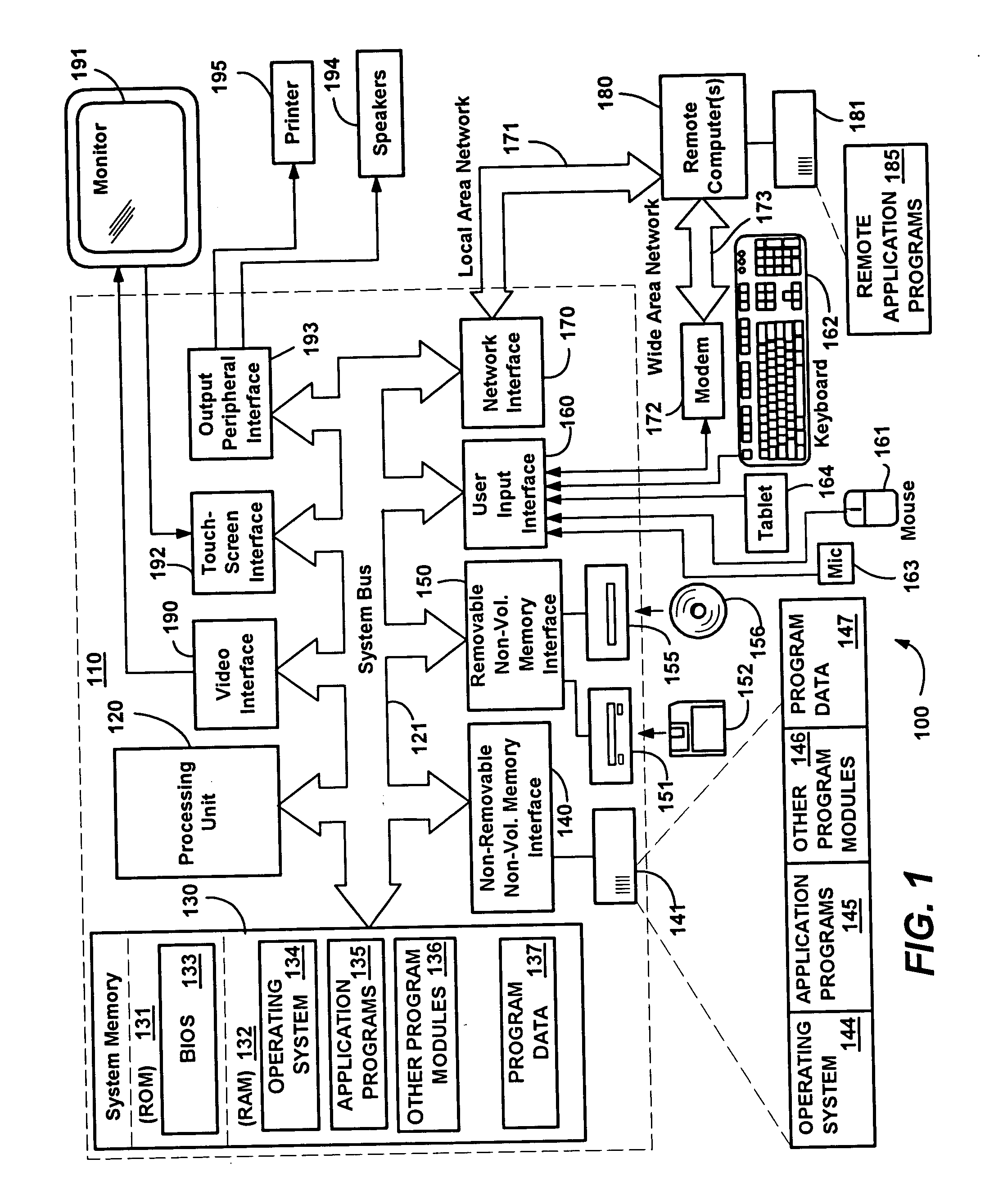

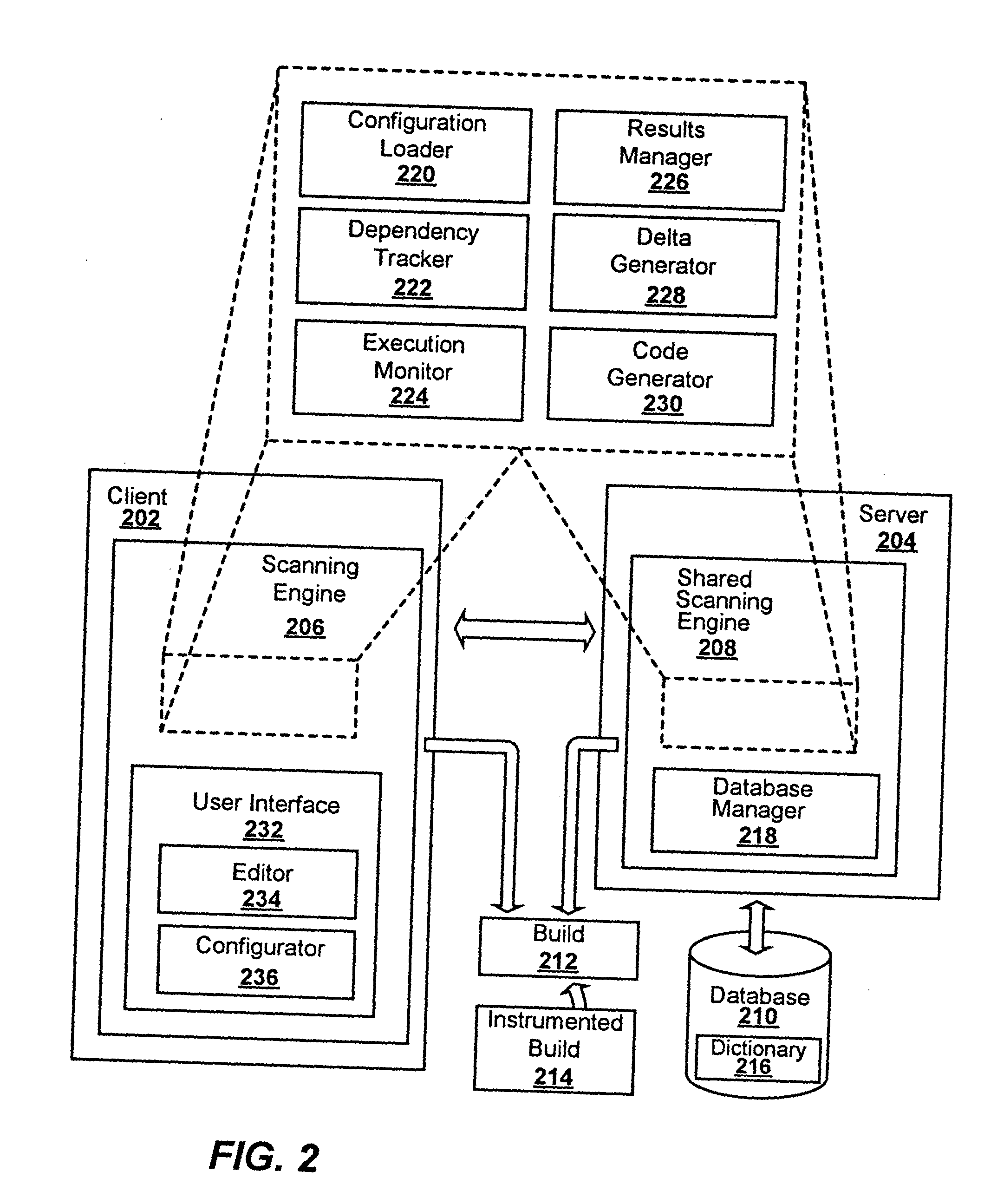

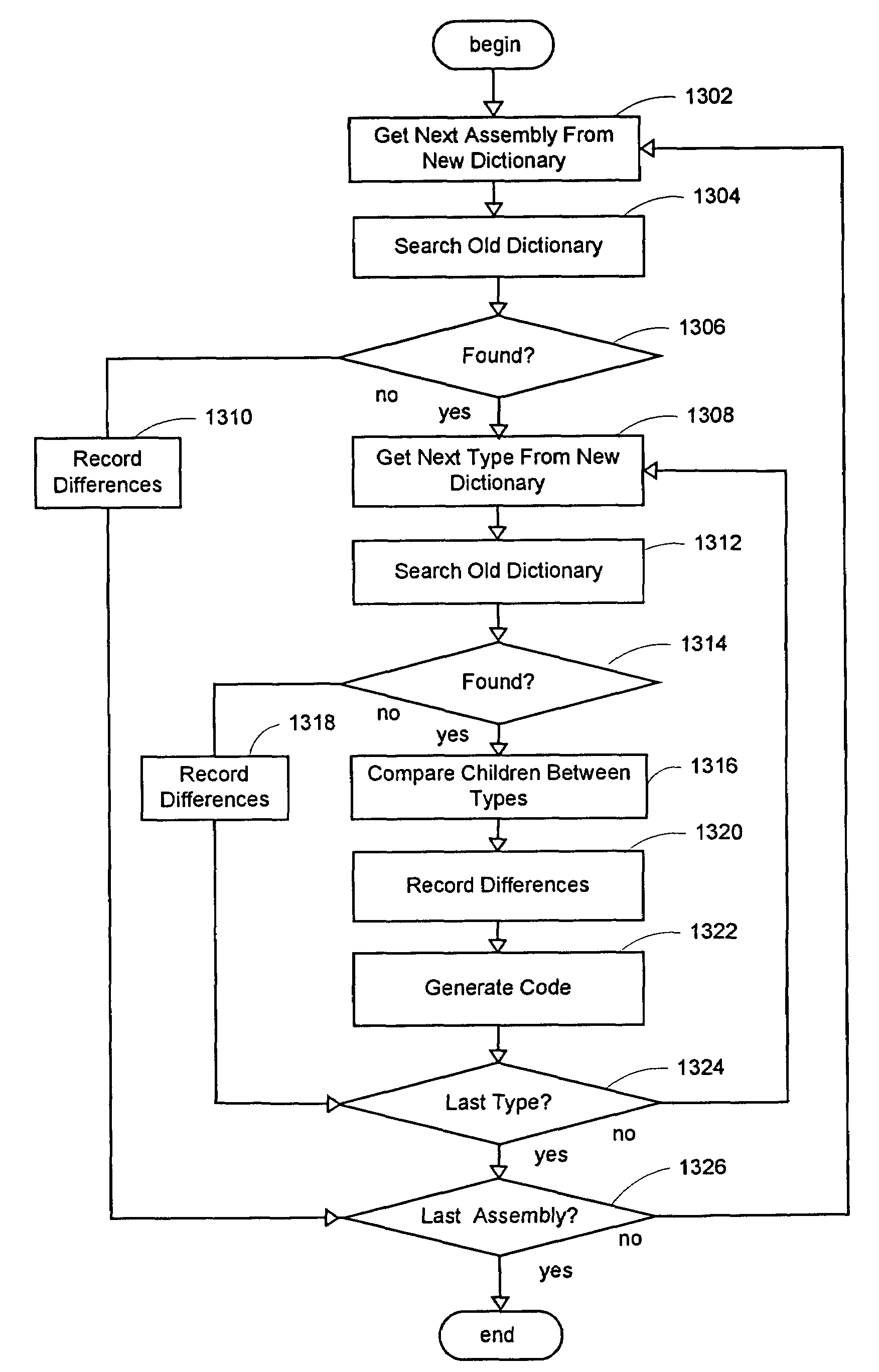

A system and method for improved testing of a software build is provided. The system and method automatically track differences between software builds by scanning the binaries of a software product to automatically discover its classes. The system and method then build a detailed dictionary that captures static and dynamic information of that build, including class dependencies. A comparison may be made with another build, so that the present invention may automatically execute selective tests on any types, and their dependencies, that have had a structural or behavioral modification since the last build. Testers may load a set of constructors for any specific types to further increase coverage of types (or classes) tested. The present invention may also provide detailed reports that may be used to drive future testing work and target specific areas of the code for additional testing. The system and method may further provide code generation from intermediate code to specified targets to aid in reproducing and fixing bugs.

Owner:MICROSOFT TECH LICENSING LLC

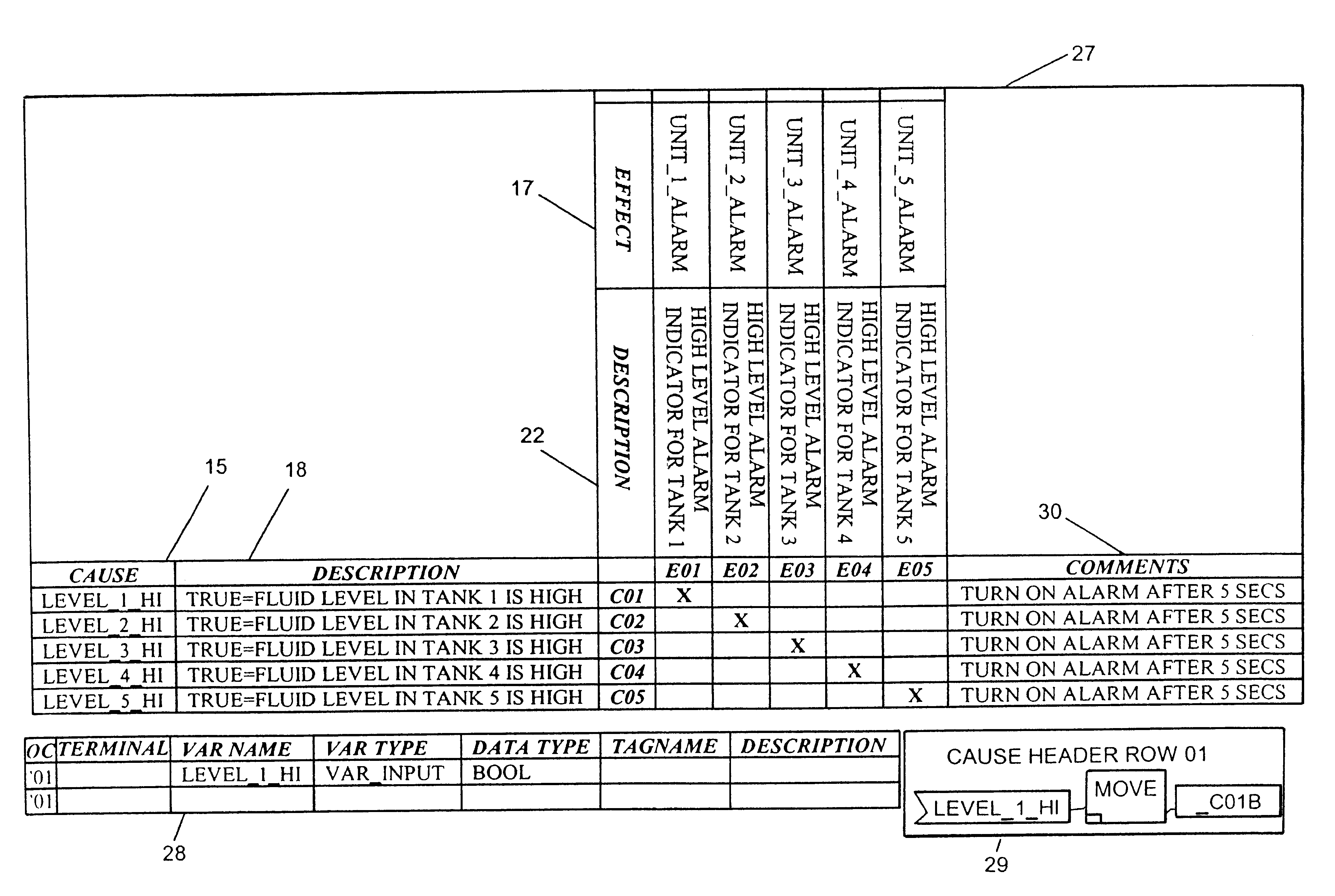

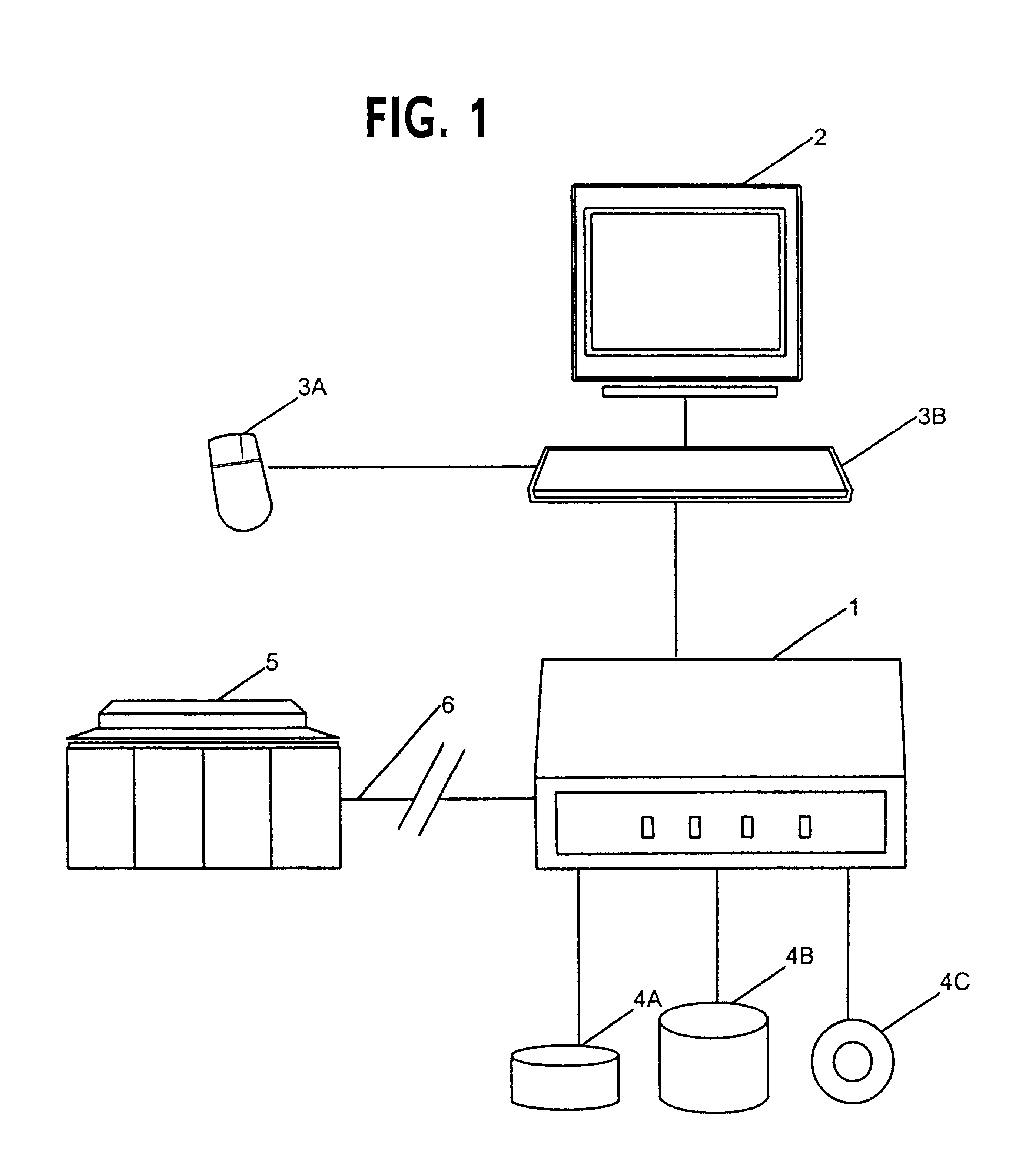

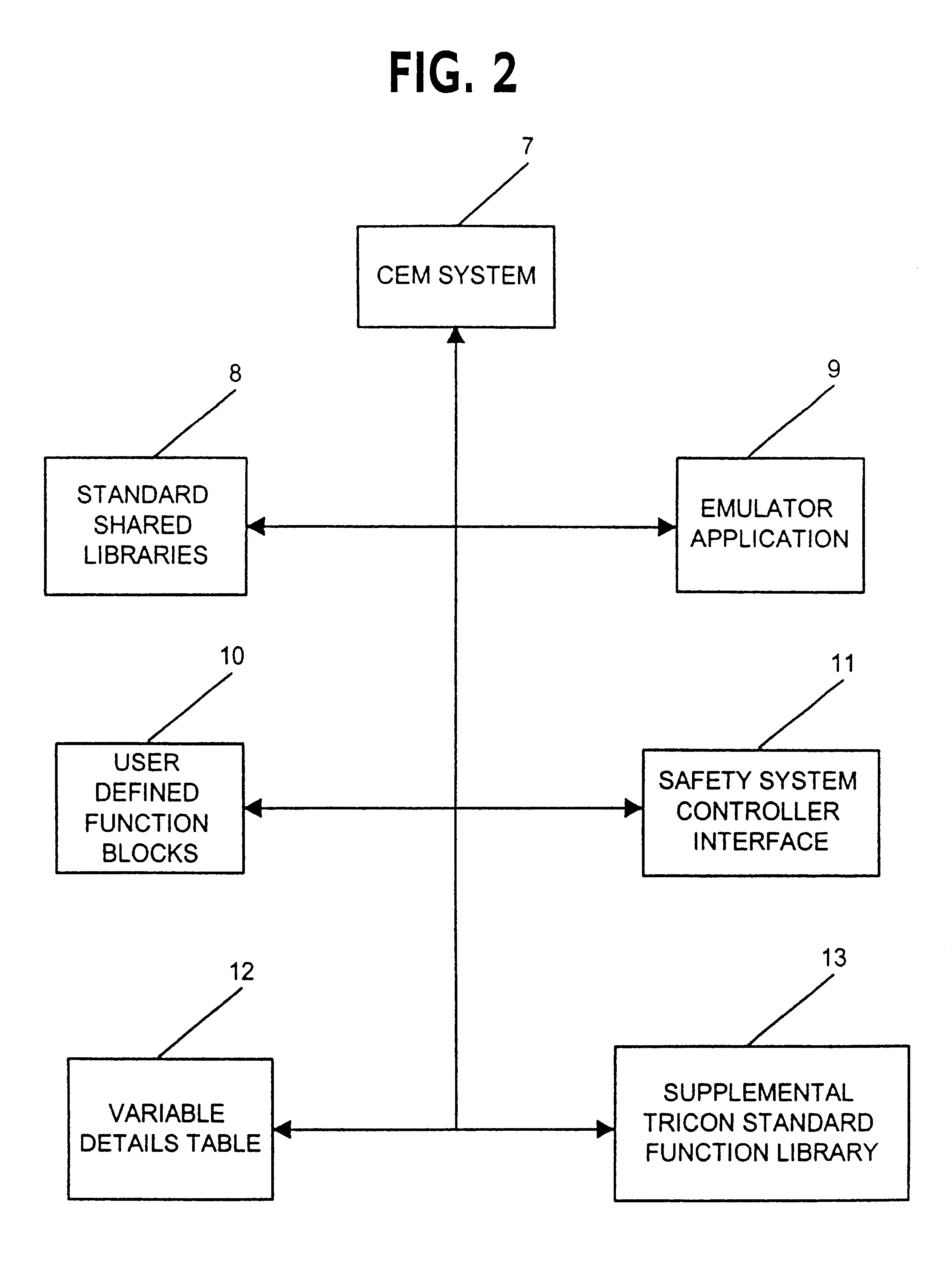

Cause effect diagram program

A computer system for generating a cause effect matrix as a user interface to develop a control program based on the cause effect matrix and to compile and download the resulting program into a programmable controller. A cause effect matrix diagram is used to develop a function block diagram program which is a standard IEC 1131-3 language. The function block diagram is translated into structured text which is compiled into intermediate code. The intermediate code is translated into the native code for the micro-processor of the target control system, including but not necessarily limited to the Motorola processor MPC-860. The automation of a cause effect matrix diagram to generate a function block diagram permits additional capability by allowing functions for causes, intersections, and effects. Because special functions may be included, the results of a cause generate timing functions or other computations before initiating the effect.

Owner:SCHNEIDER ELECTRIC SYST USA INC

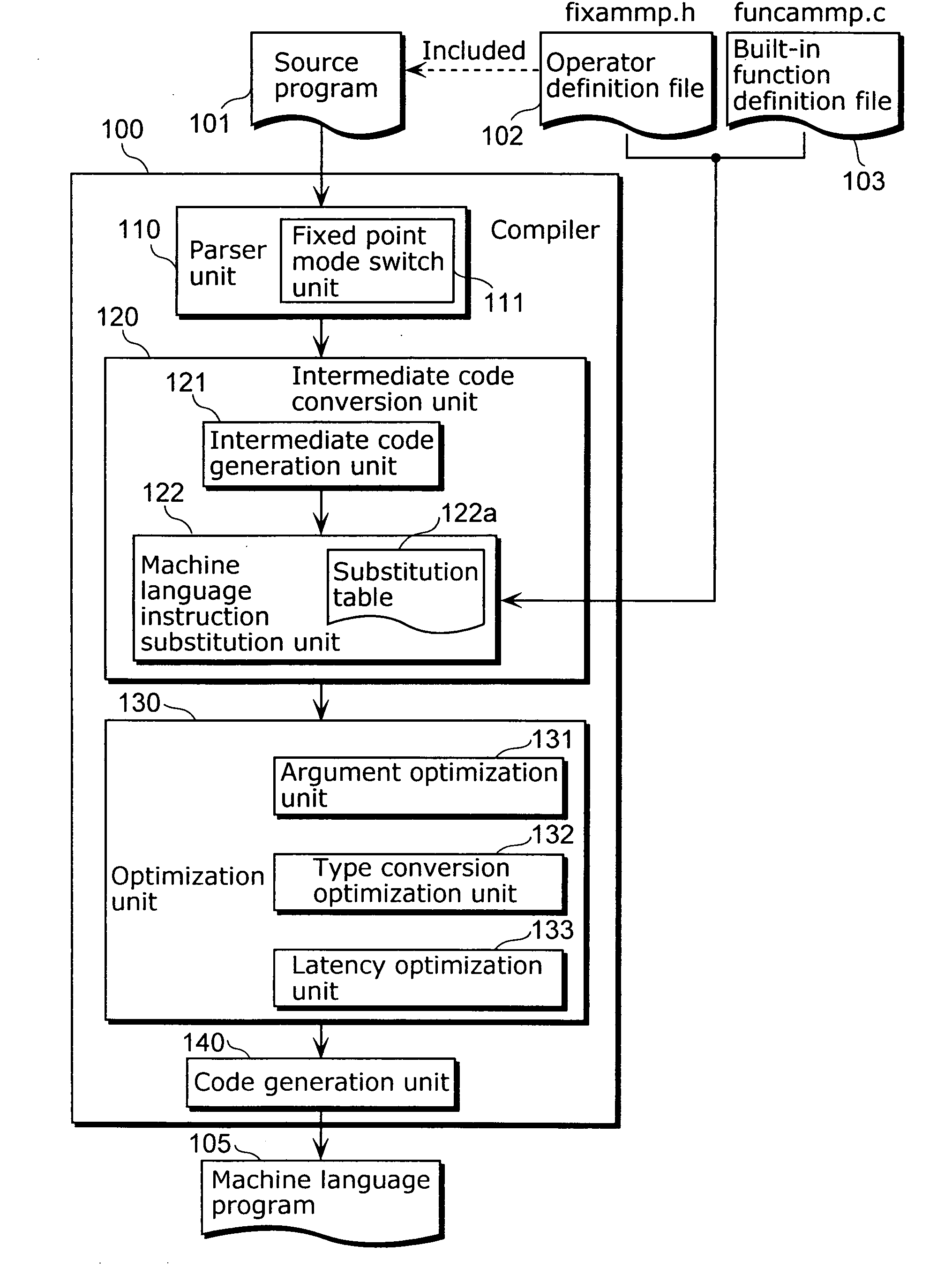

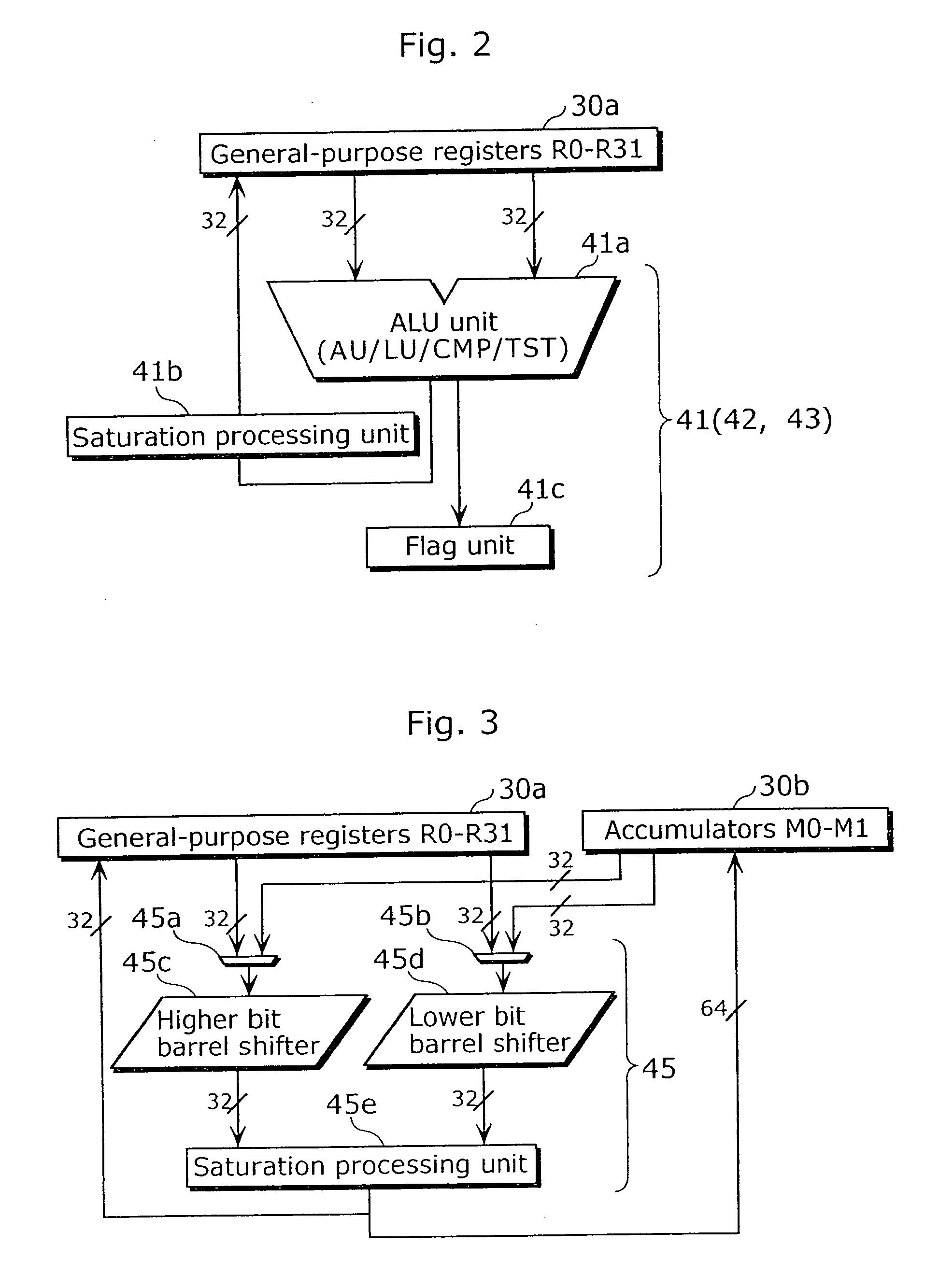

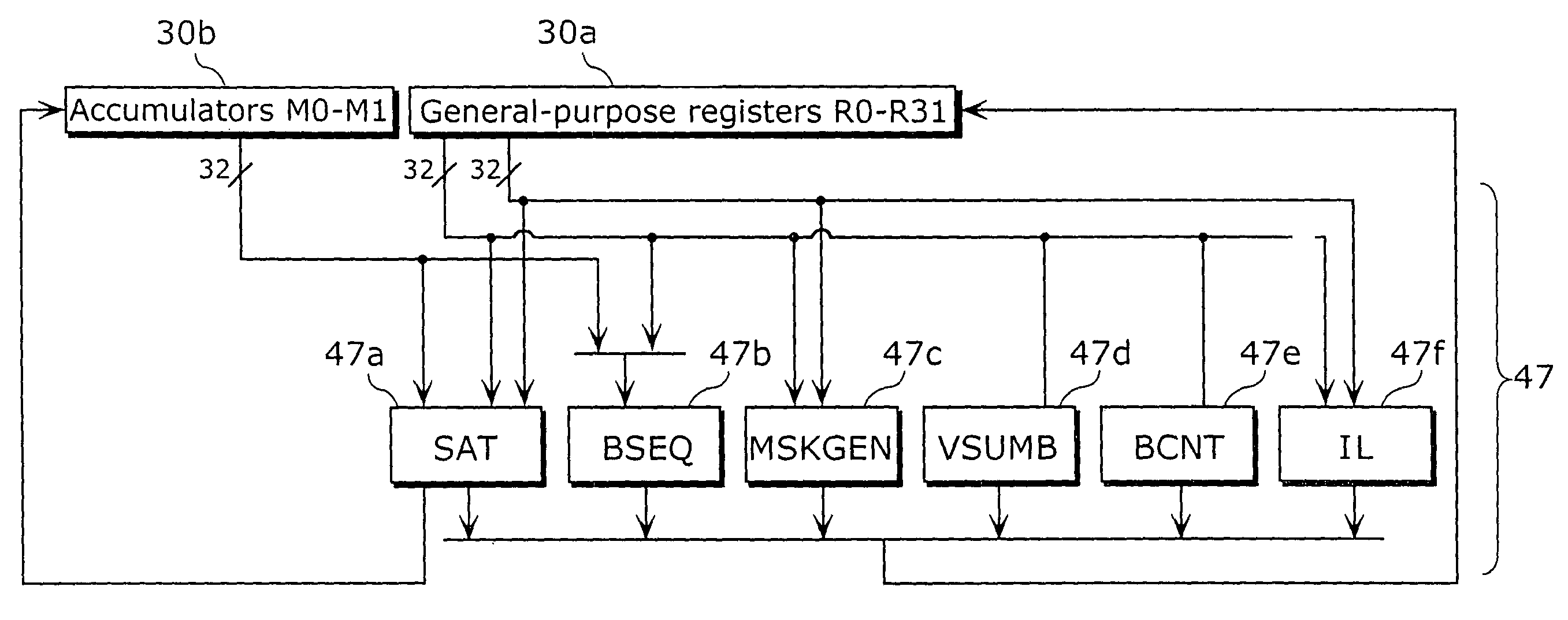

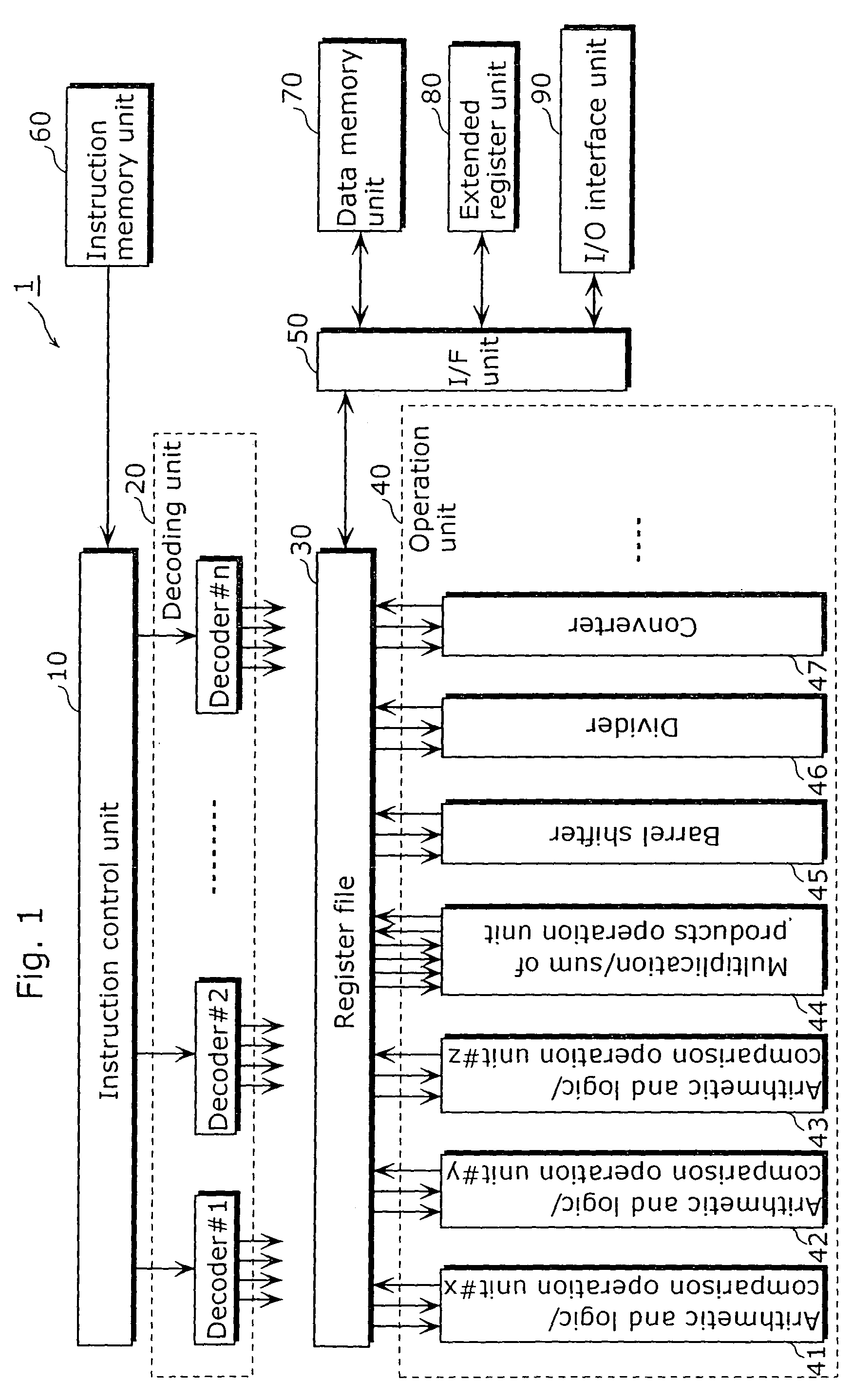

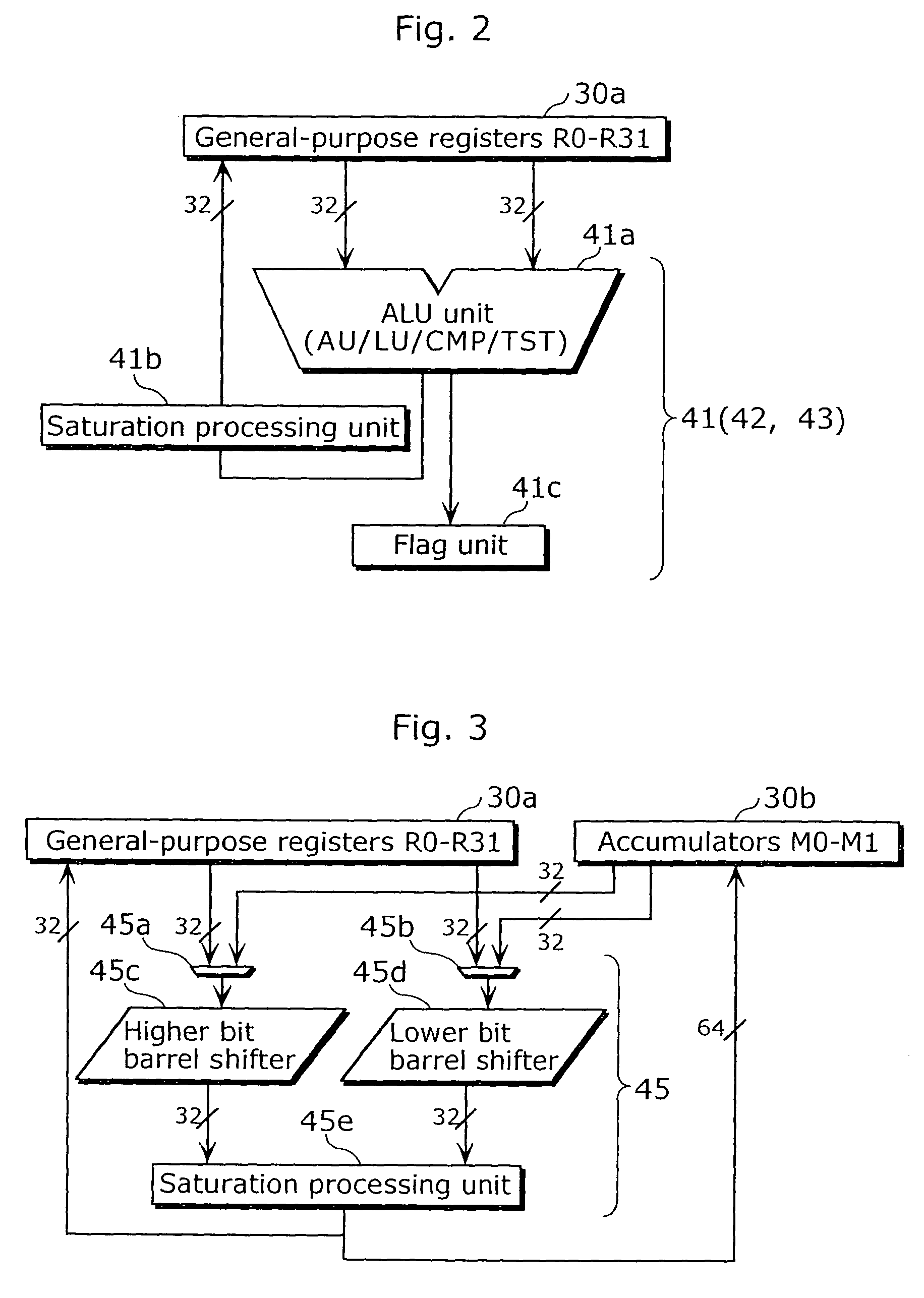

Compiler, compiler apparatus and compilation method

ActiveUS20070256065A1Generate efficientlyImprove the level ofSoftware engineeringProgram controlIntermediate codeHuman language

An operator definition file 102 and the like included in a source program 101 and a compiler 100 that translates the source program 101 into a machine language program 105 are provided. The operator definition file 102 includes definitions of various fixed point type operators by class definitions. The compiler 100 can generate effectively advanced and specific instructions that a processor executes and make improvements through expanding functions and the like without repeating frequently upgrading of the version of the compiler itself. The compiler 100 is made up of an intermediate code generation unit 121 that generates intermediate codes, a machine language instruction substitution unit 122 that substitutes the intermediate codes referring to classes defined by the operator definition file 102 with machine language instructions and an optimization unit 130 that performs optimization targeting the intermediate codes including the substituted machine language instructions.

Owner:SOCIONEXT INC

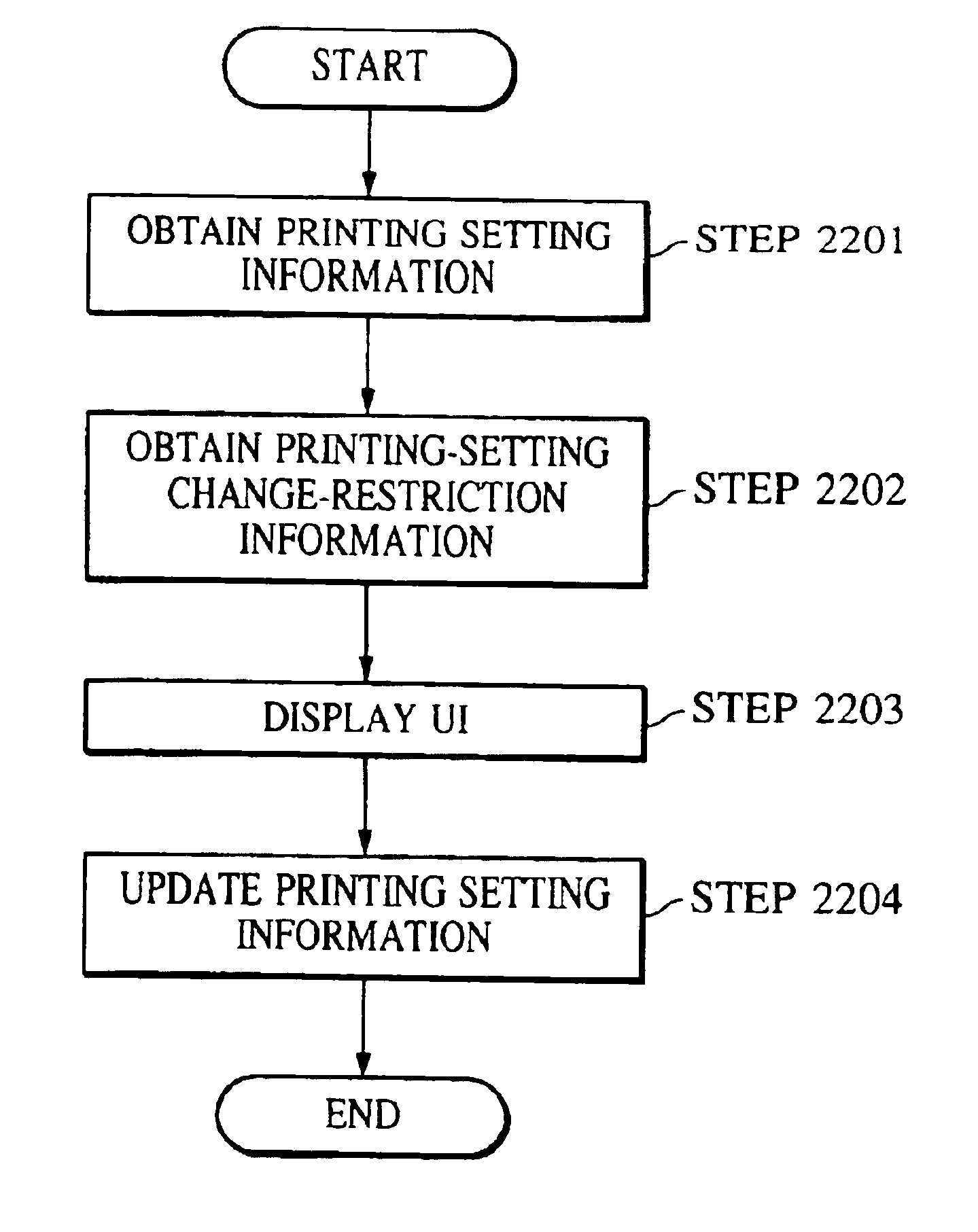

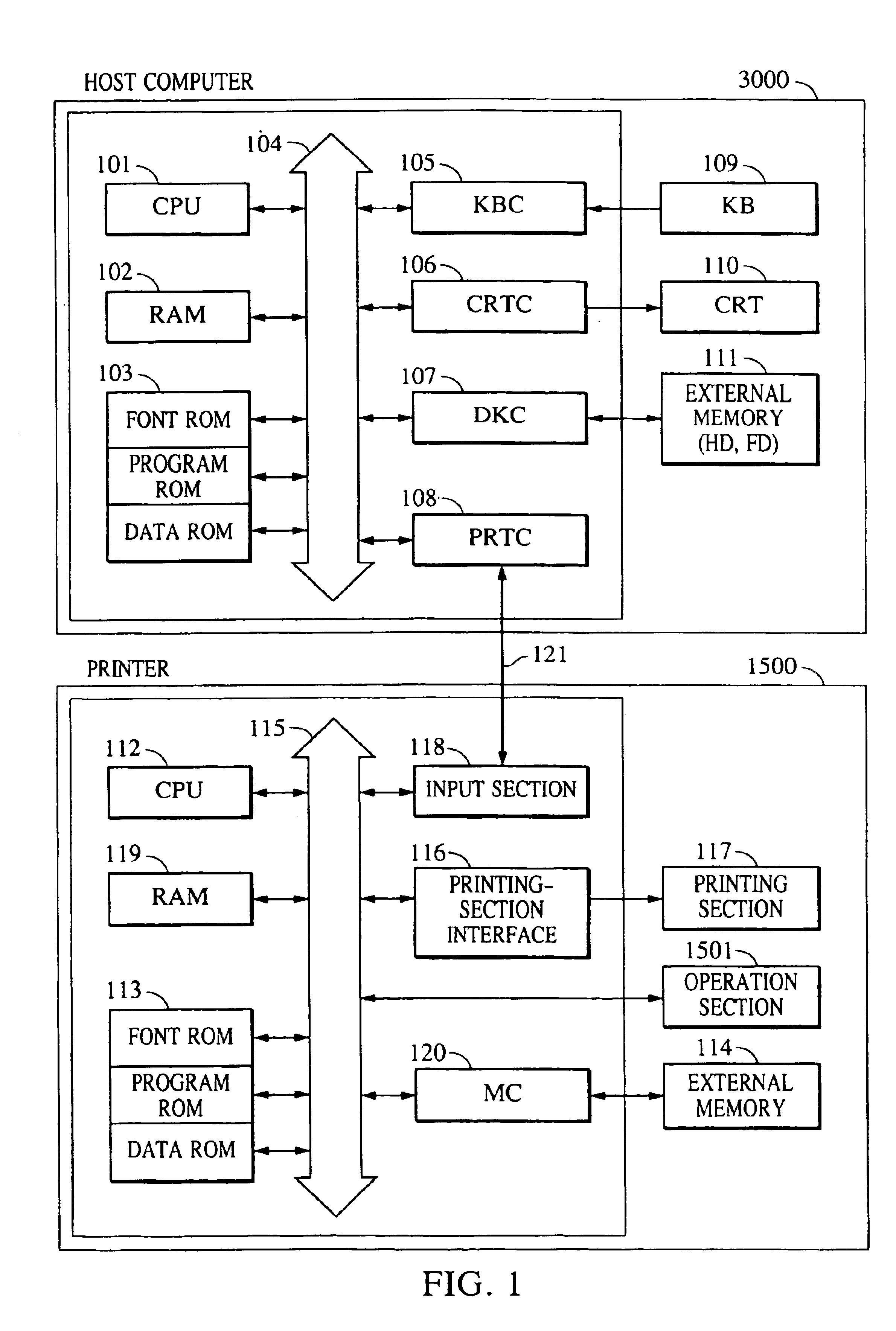

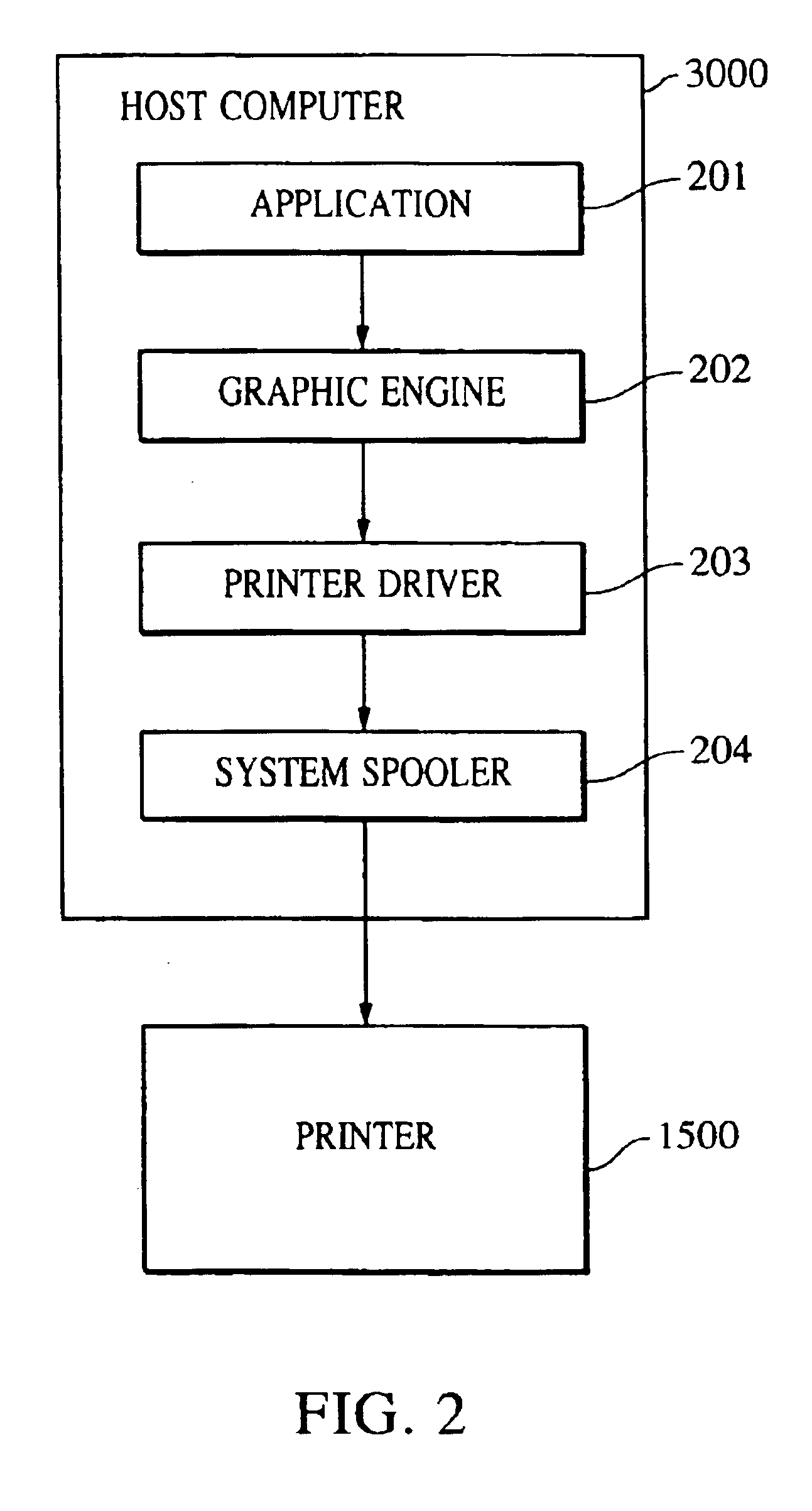

Information processing apparatus, information processing method, and storage medium storing computer-readable program

InactiveUS6924826B1Control changesDigital computer detailsCathode-ray tube indicatorsInformation processingUser interface

Editing a printing job of printing data temporarily stored in an intermediate-code format is restricted such that an error does not occur in the result of printing. A user interface for editing the printing-setting information of the data temporarily stored in the intermediate-code format is controlled such that a change of printing settings which can be edited is restricted and the printing settings are displayed.

Owner:CANON KK

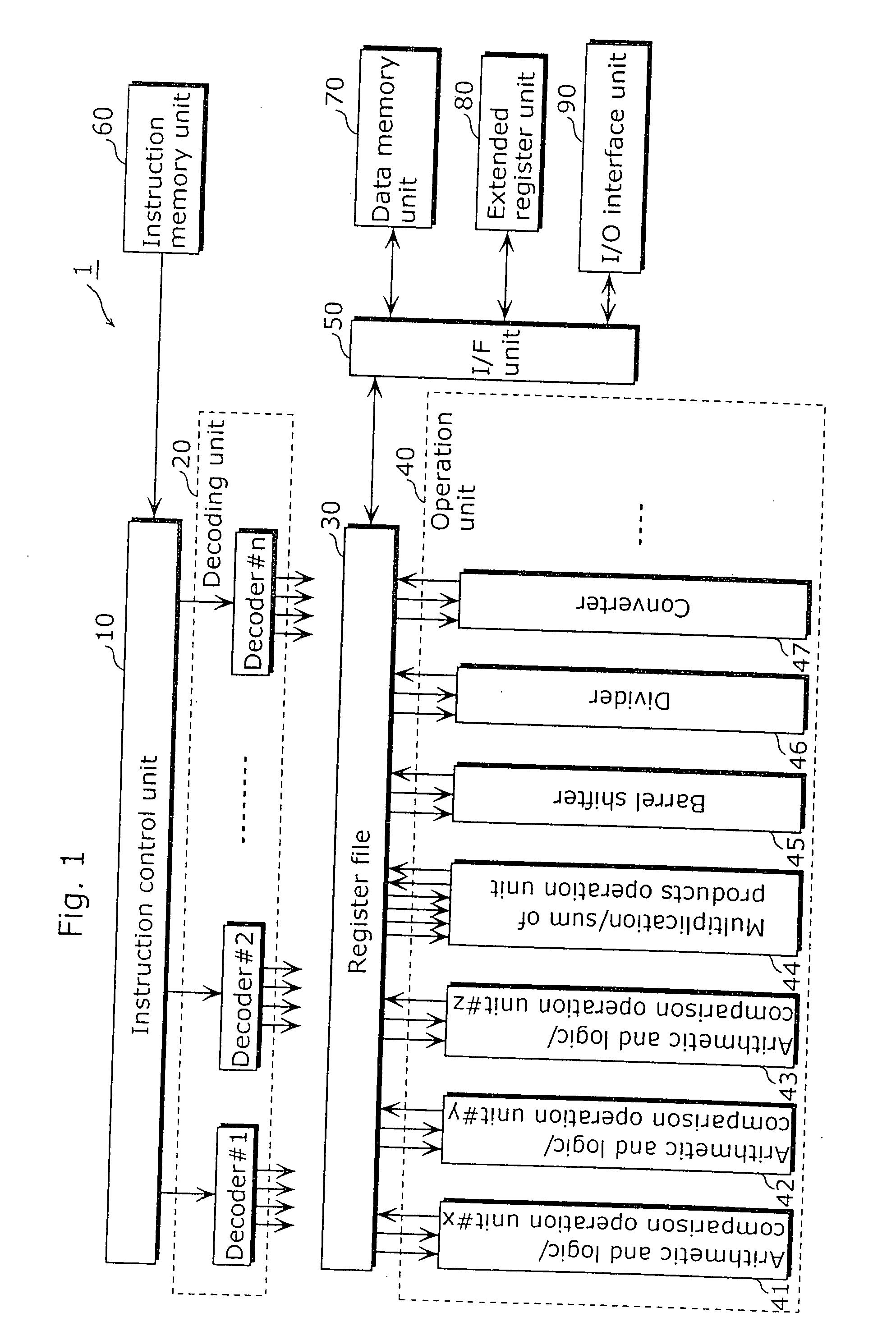

Compiler apparatus and compilation method

InactiveUS20040154006A1Avoid changeReduce power consumptionEnergy efficient ICTSoftware engineeringMachine instructionInstruction cycle

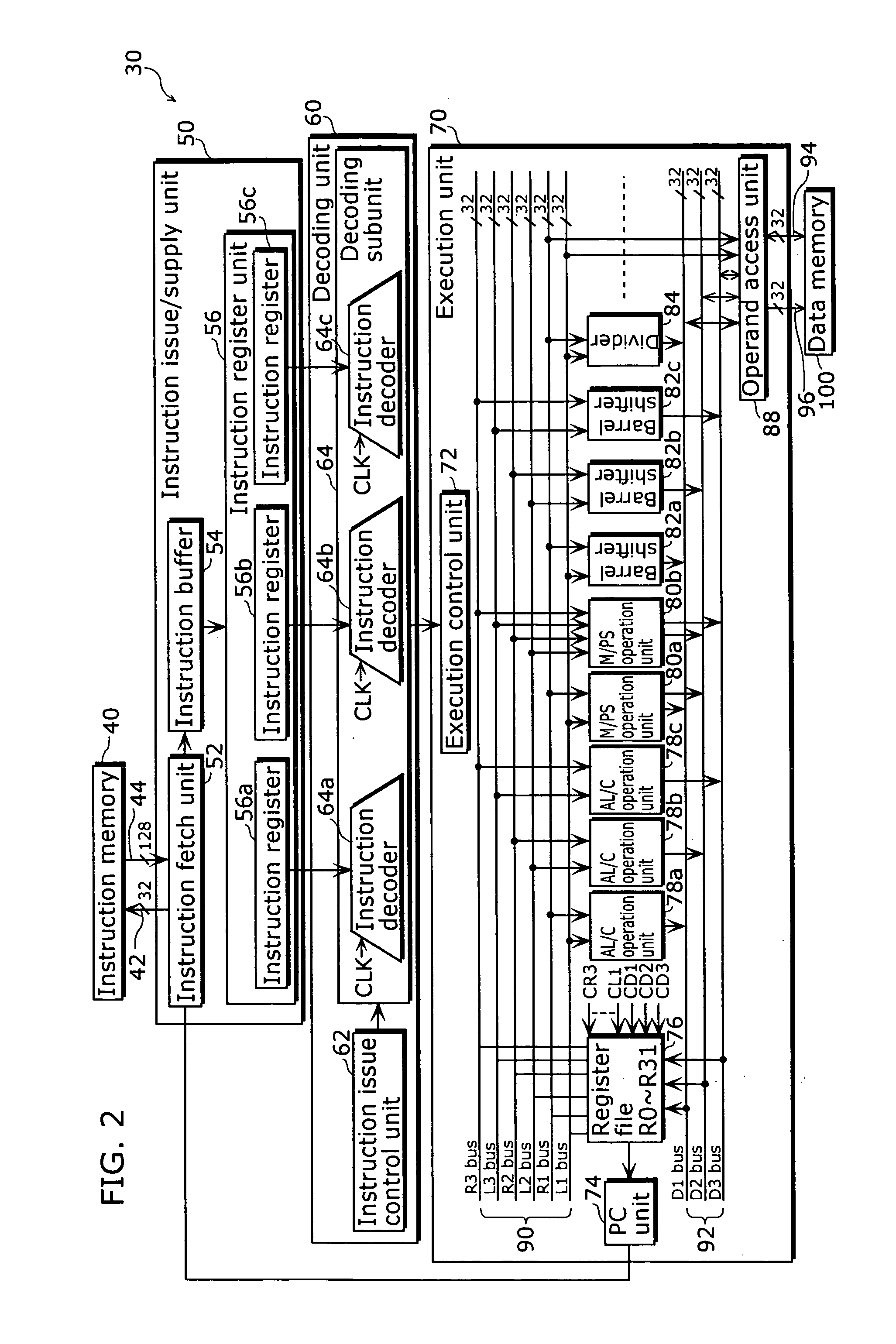

A compiler apparatus that is capable of generating instruction sequences for causing a processor with parallel processing capability to operate with lower power consumption is a compiler apparatus that translates a source program into a machine language program for the processor including a plurality of execution units which can execute instructions in parallel and a plurality of instruction issue units which issue the instructions executed respectively by the plurality of execution units, and includes: a parser unit operable to parse the source program; an intermediate code conversion unit operable to convert the parsed source program into intermediate codes; an optimization unit operable to optimize the intermediate codes so as to reduce a hamming distance between instructions placed in positions corresponding to the same instruction issue unit in consecutive instruction cycles, without changing dependency between the instructions corresponding to the intermediate codes; and a code generation unit operable to convert the optimized intermediate codes into machine language instructions.

Owner:SOCIONEXT INC

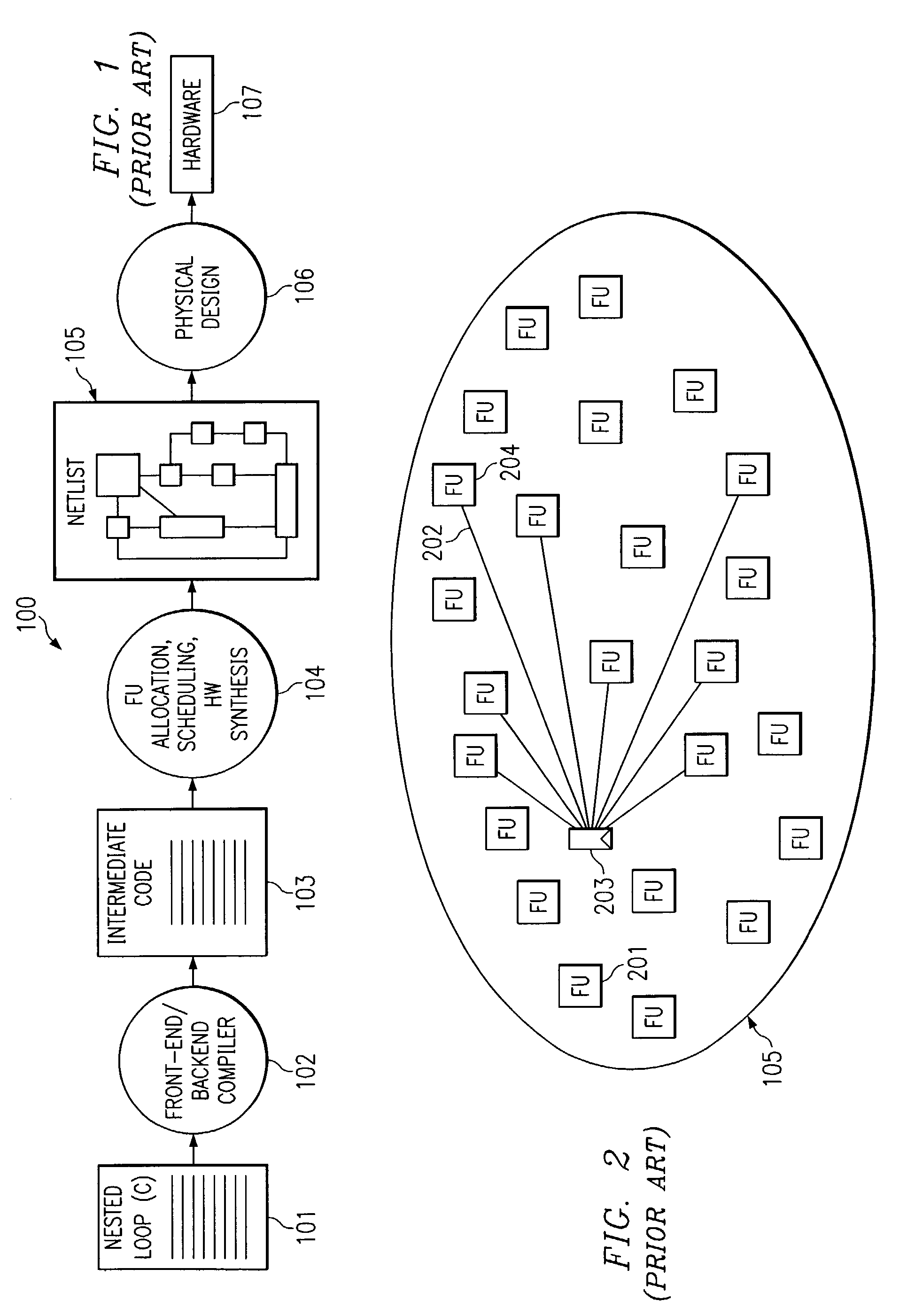

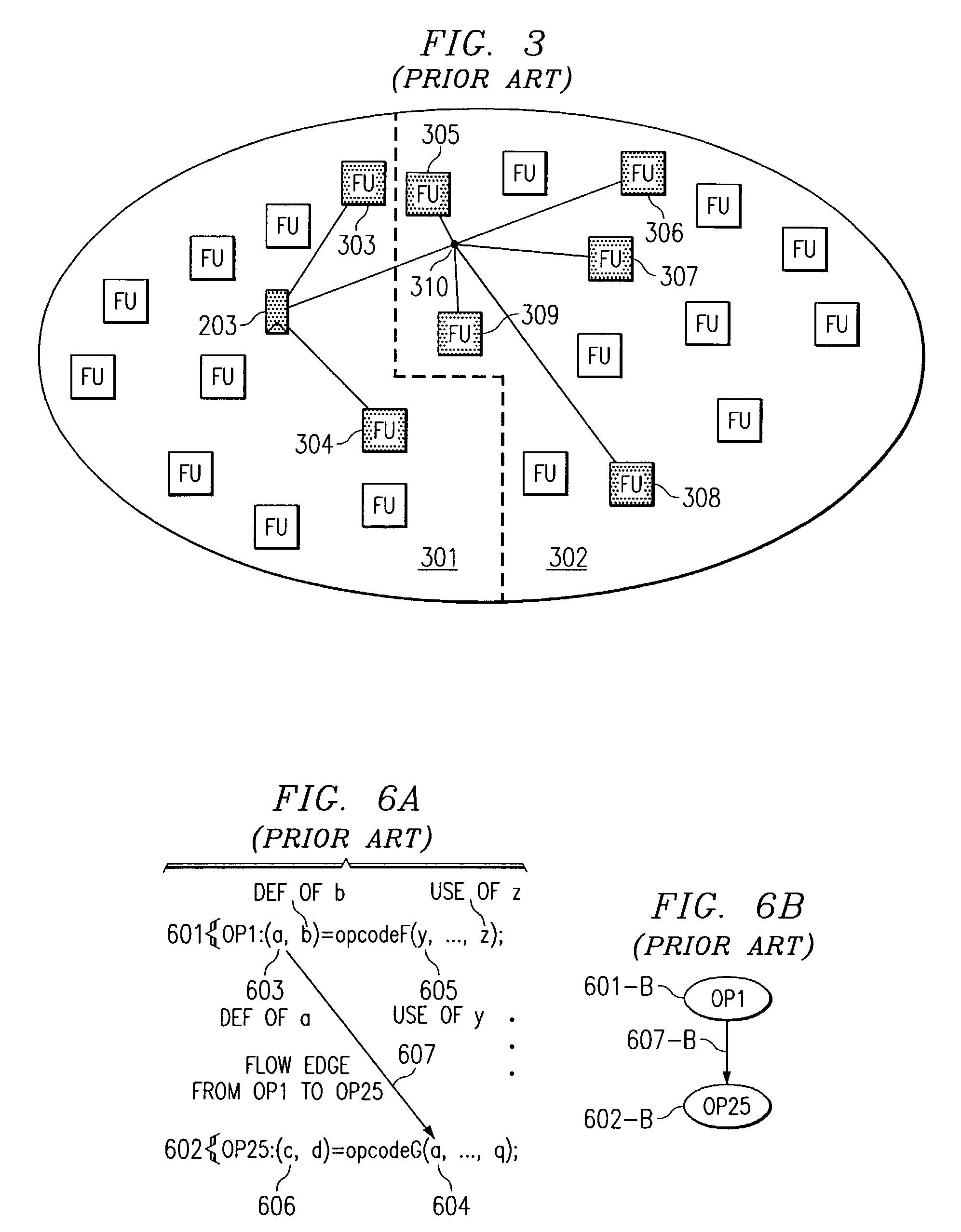

System and method for reducing wire delay or congestion during synthesis of hardware solvers

ActiveUS7107568B2CAD circuit designSoftware simulation/interpretation/emulationTheoretical computer scienceIntermediate code

One embodiment of the invention is a method for producing a hardware solver for intermediate code comprising analyzing intermediate code for at least one instantiation that may cause at least one of wire delay and congestion in the solver, forming compensation for the at least one instantiation, and forming the solver in accordance with the compensation.

Owner:SAMSUNG ELECTRONICS CO LTD

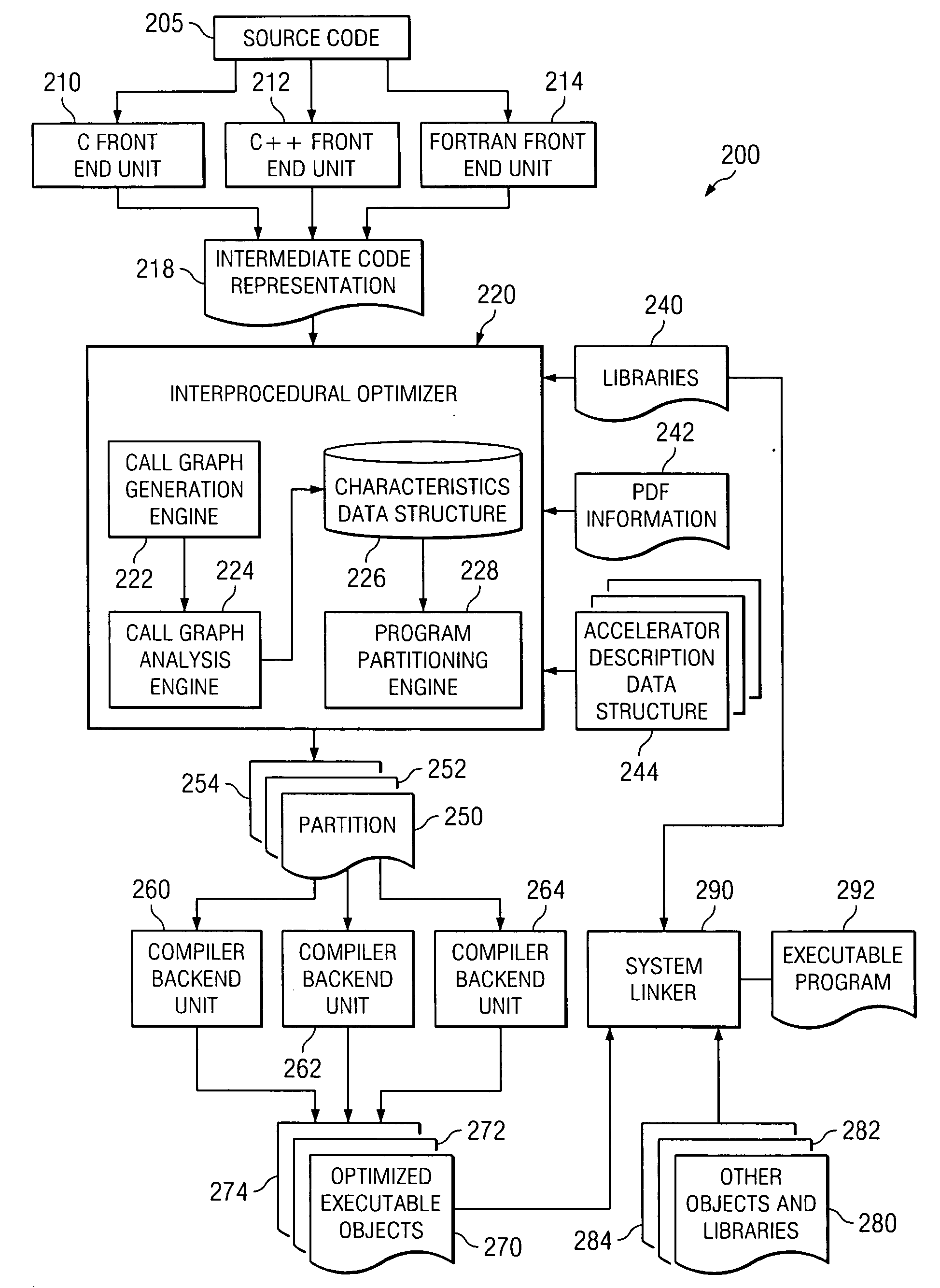

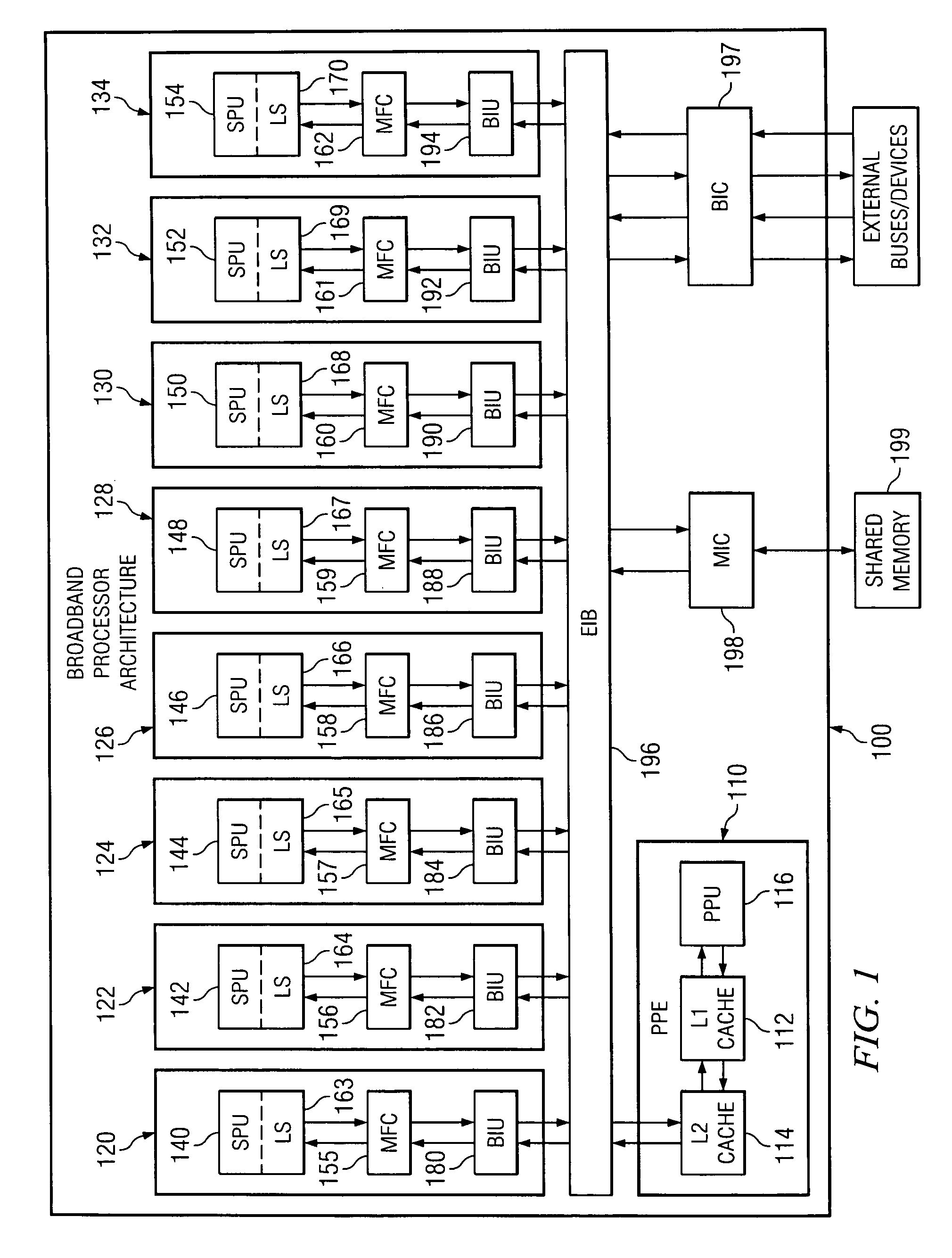

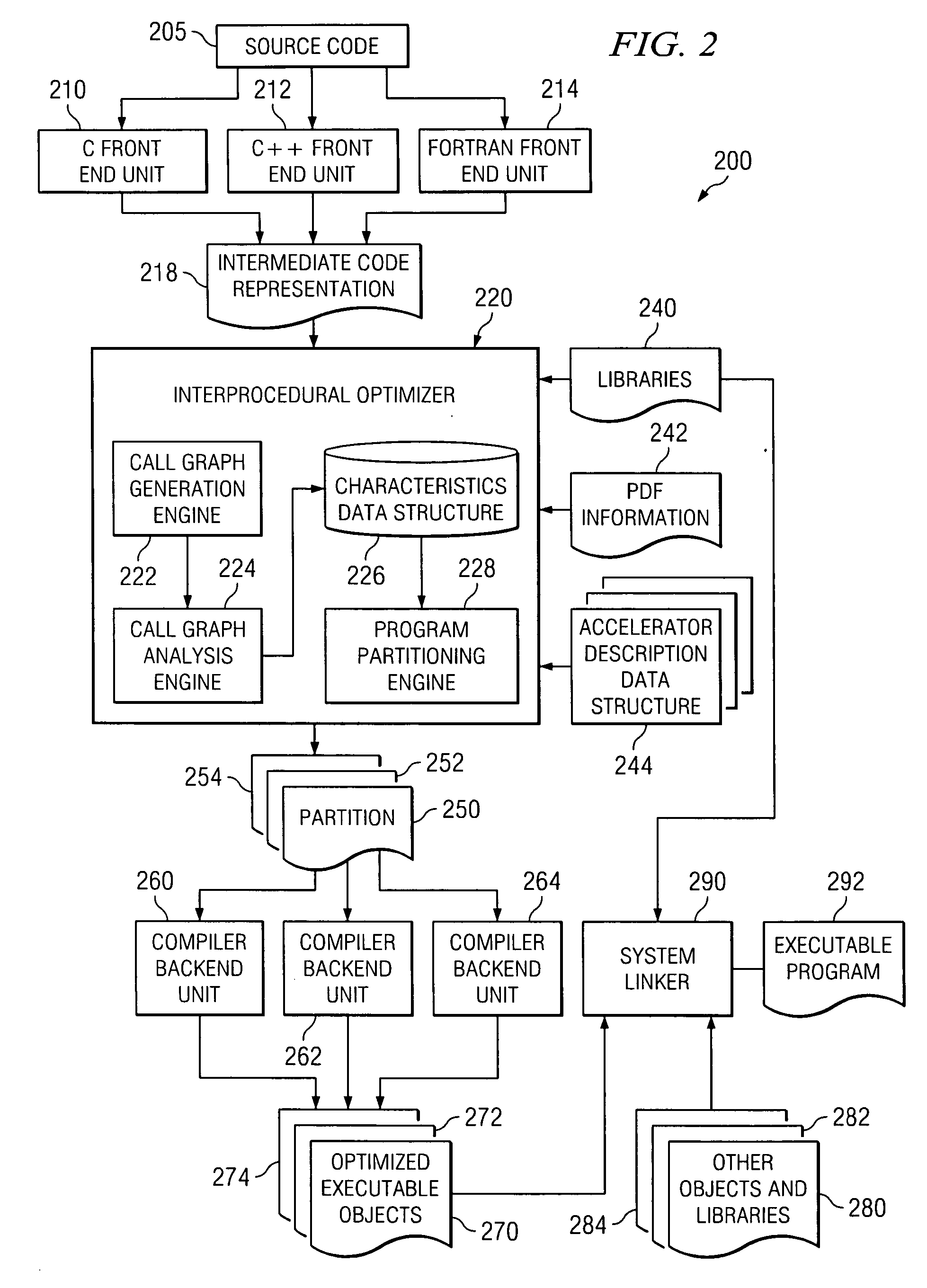

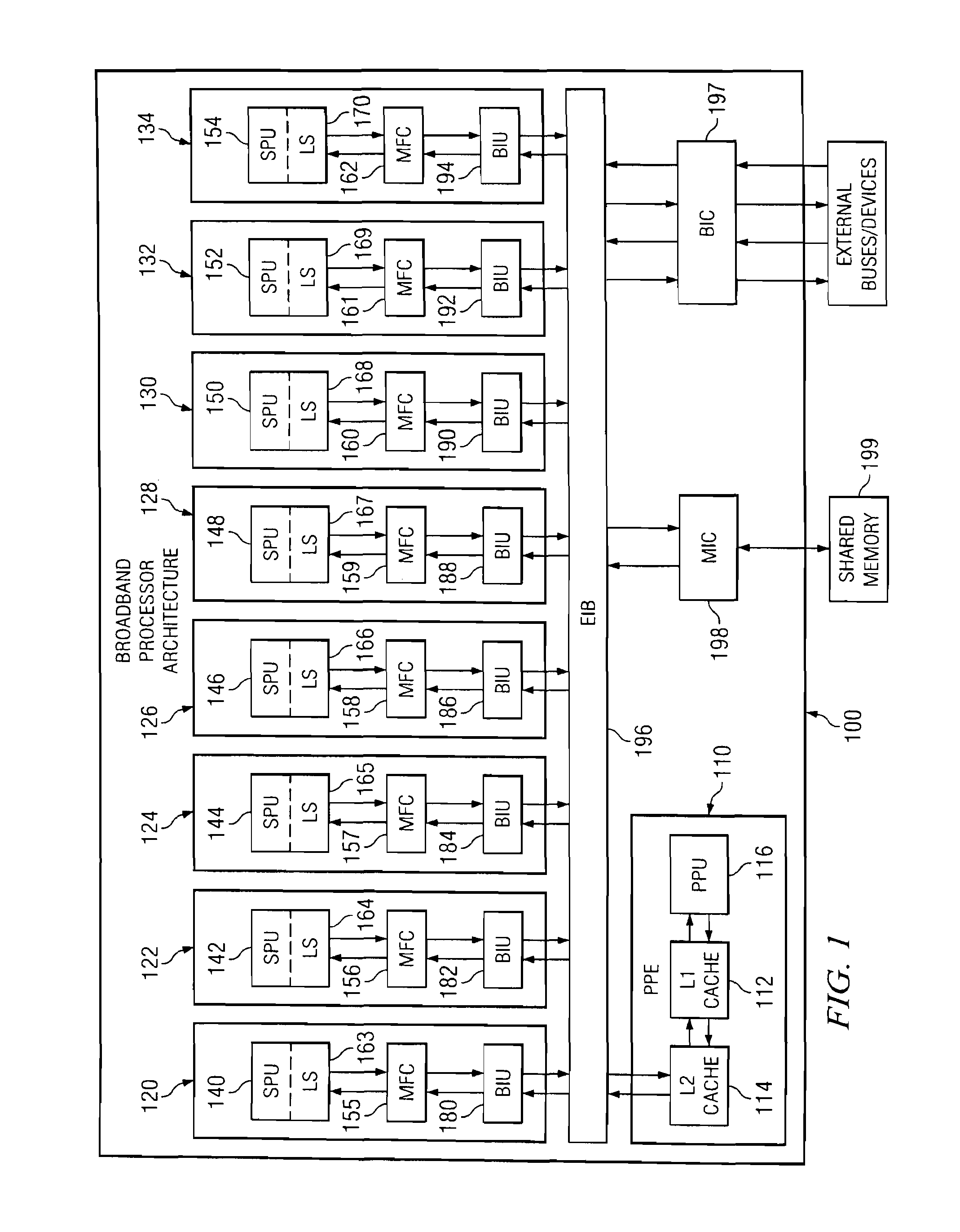

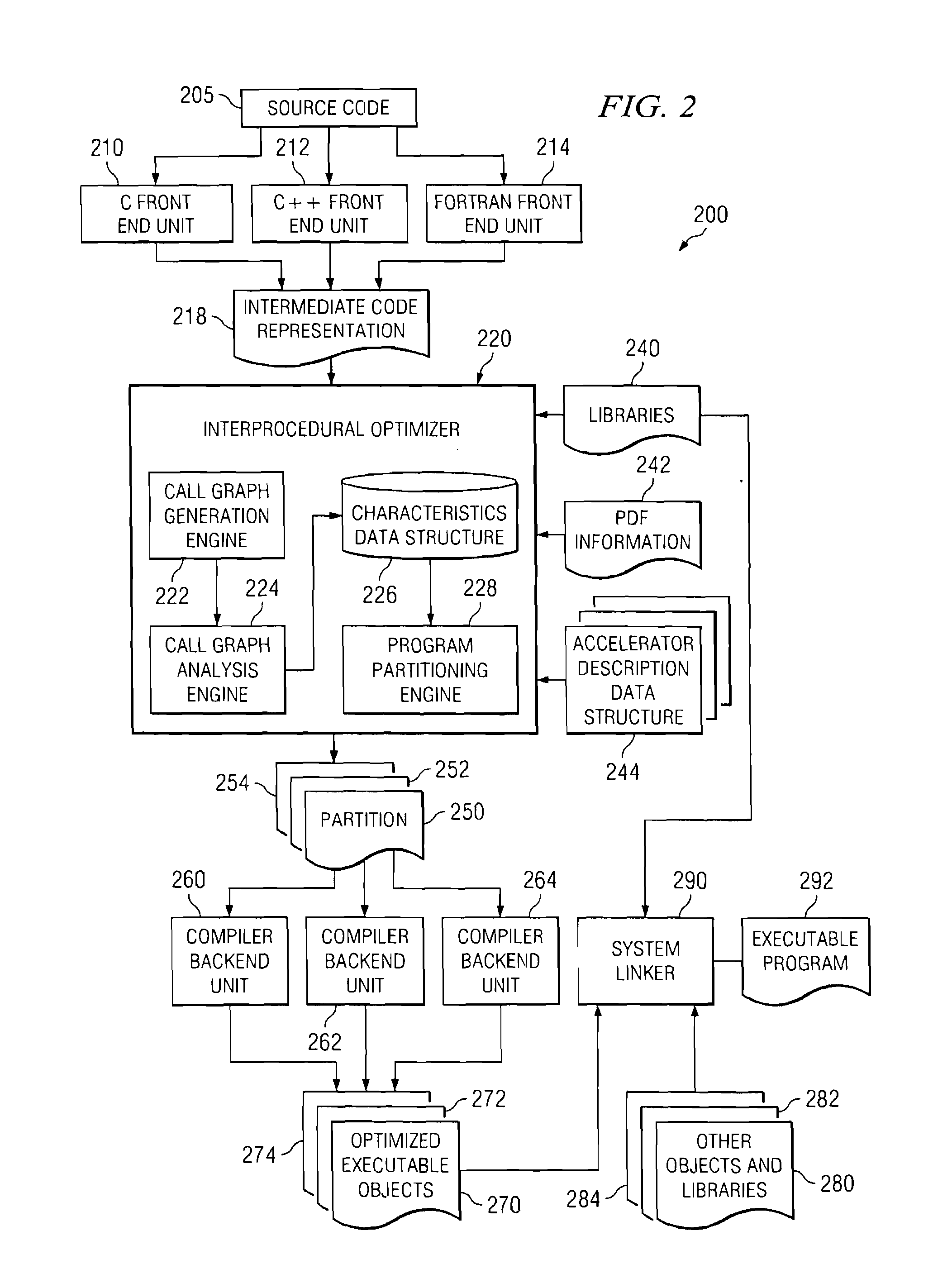

Apparatus and method for partitioning programs between a general purpose core and one or more accelerators

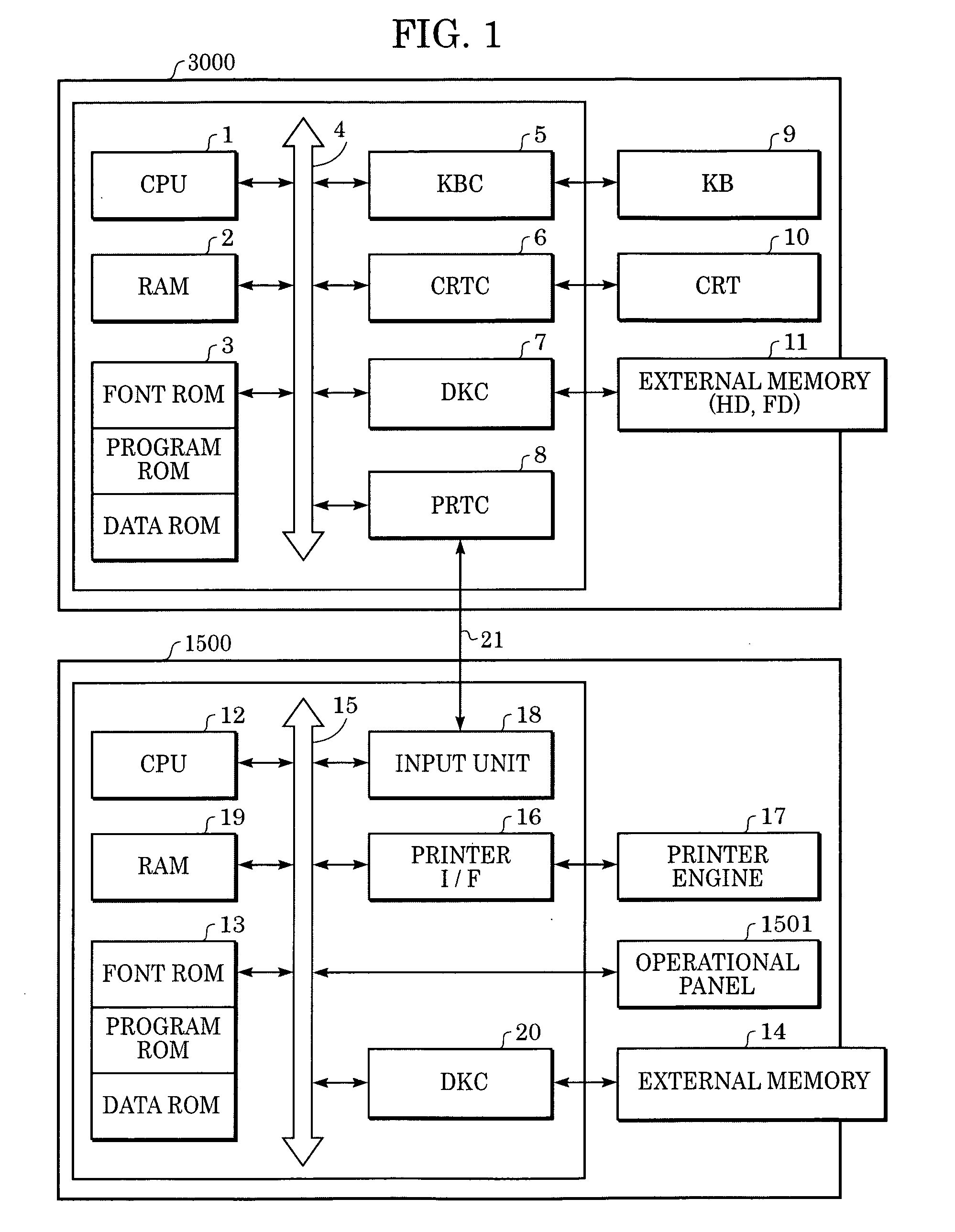

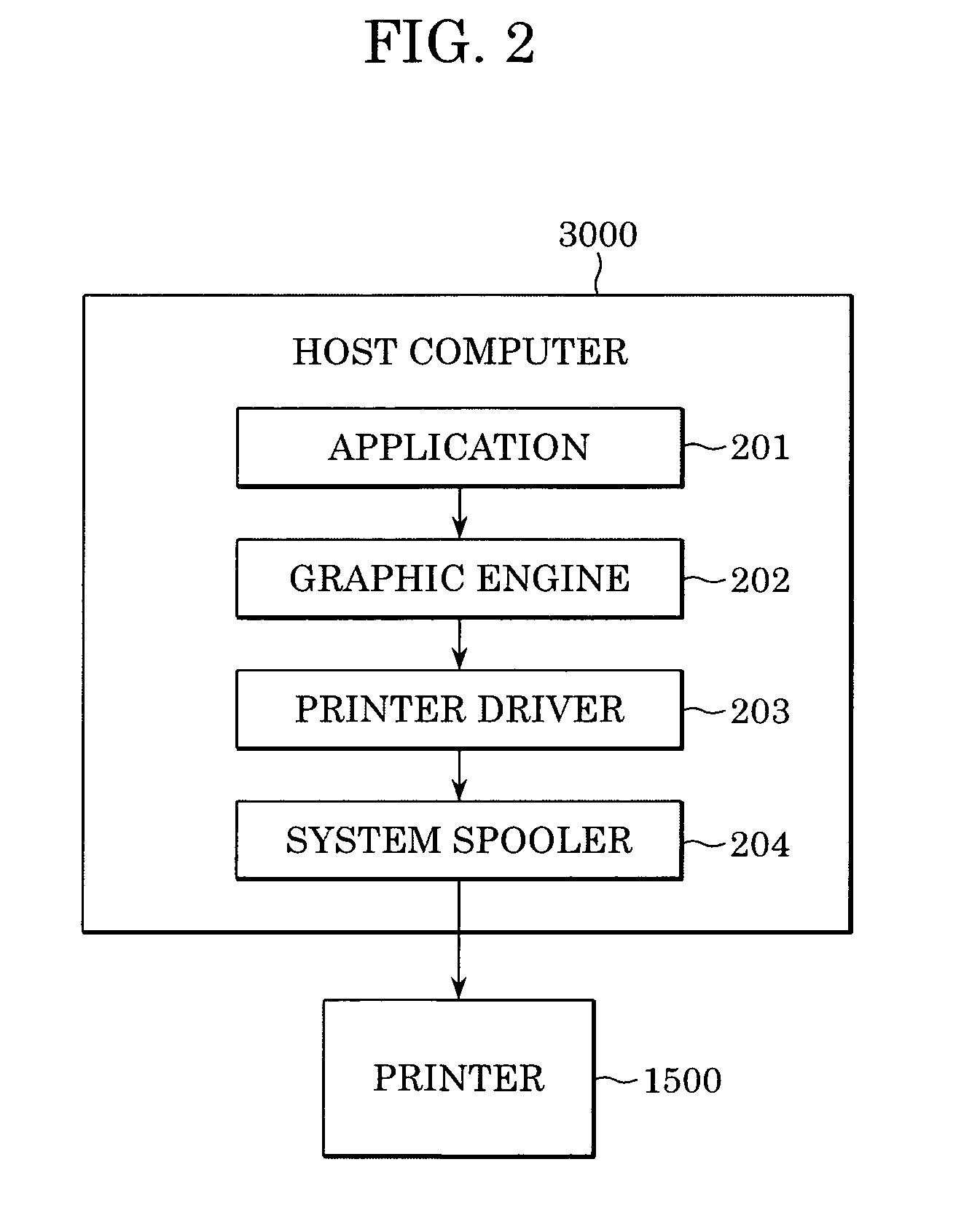

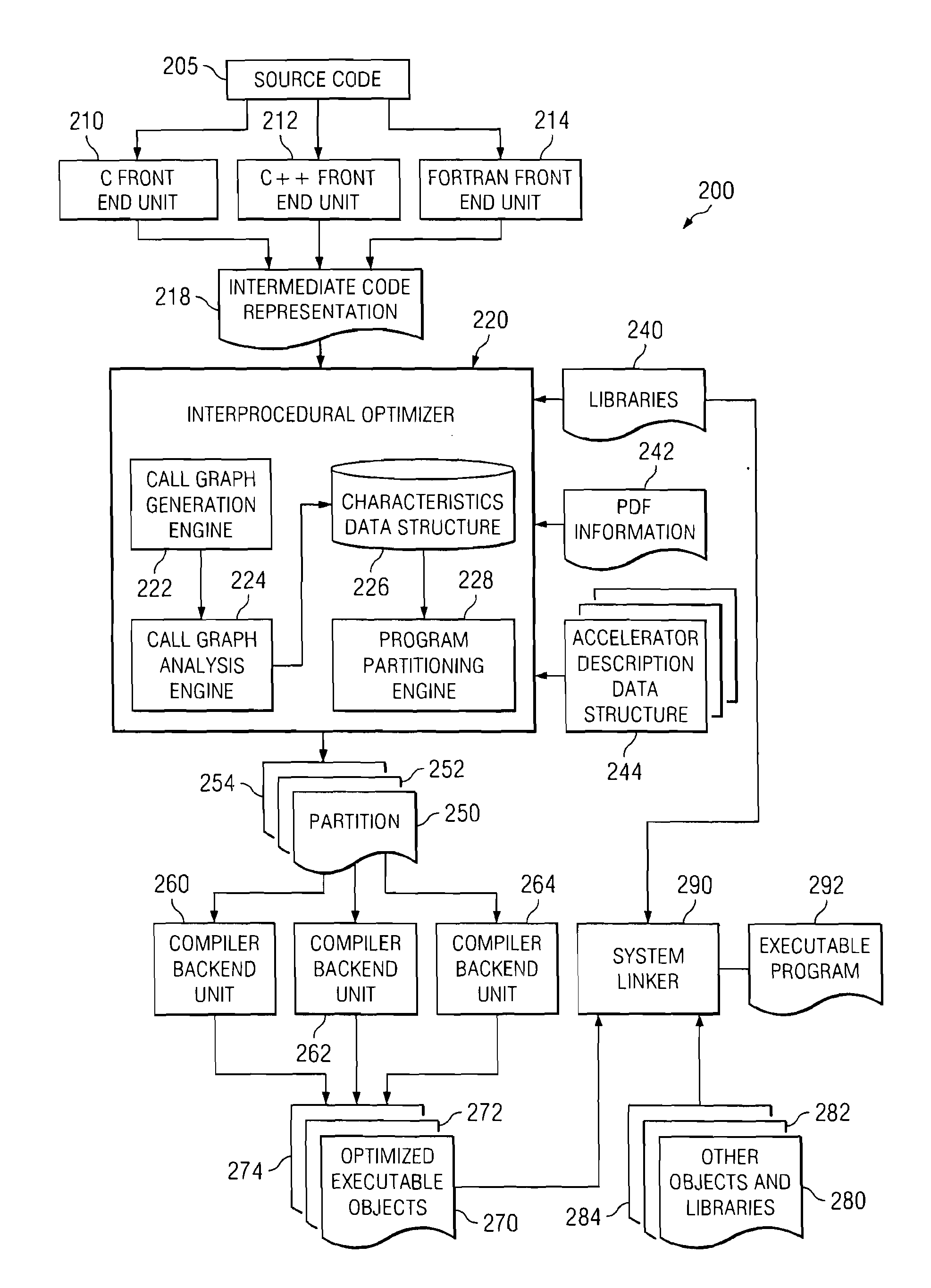

An apparatus and method for partitioning programs between a general purpose core and one or more accelerators are provided. With the apparatus and method, a compiler front end is provided for converting a program source code in a corresponding high level programming language into an intermediate code representation. This intermediate code representation is provided to an interprocedural optimizer which determines which core processor or accelerator each portion of the program should execute on and partitions the program into sub-programs based on this set of decisions. The interprocedural optimizer may further add instructions to the partitions to coordinate and synchronize the sub-programs as required. Each sub-program is compiled on an appropriate compiler backend for the instruction set architecture of the particular core processor or accelerator selected to execute the sub-program. The compiled sub-programs and then linked to thereby generate an executable program.

Owner:MACHINES CORP INT BUSINESS +1

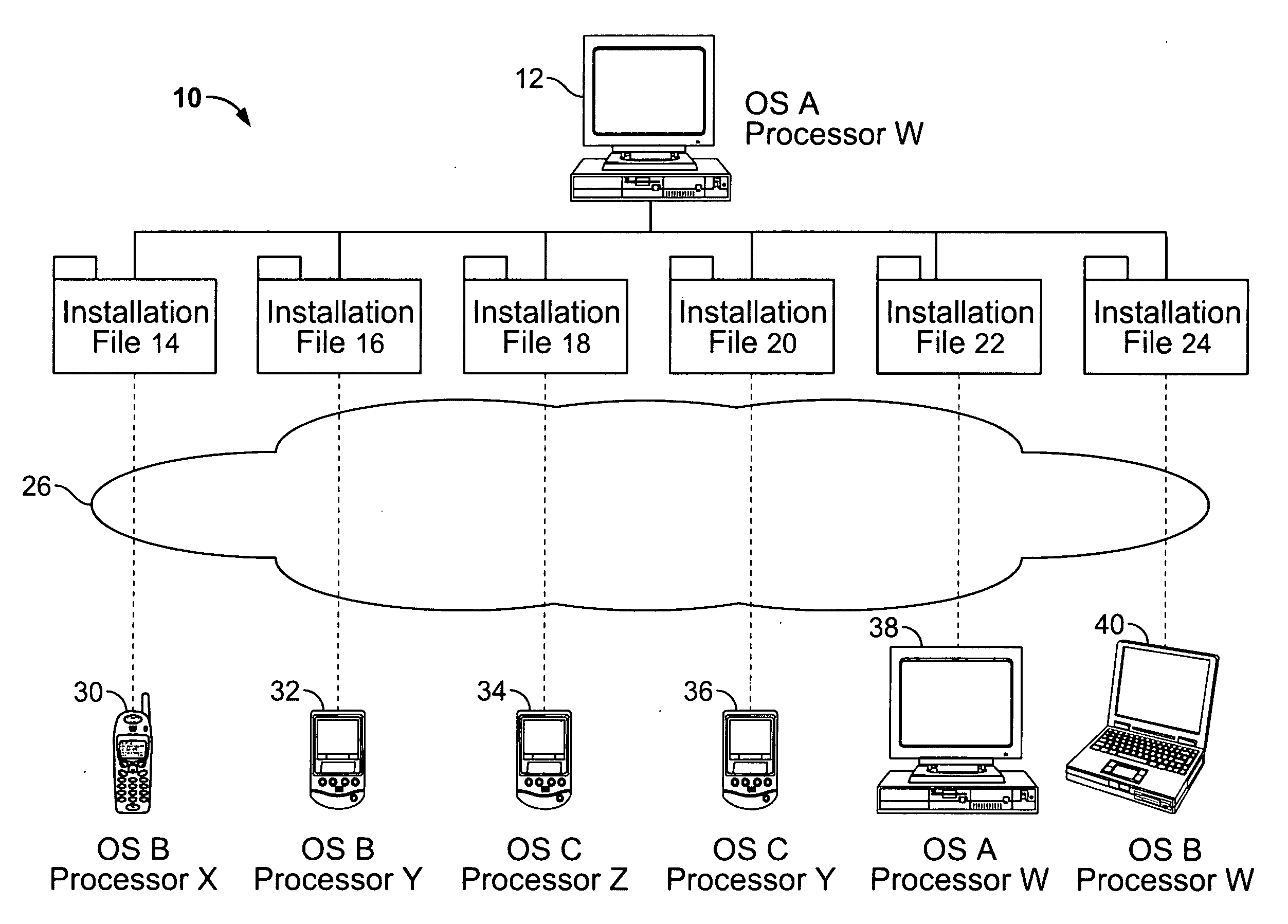

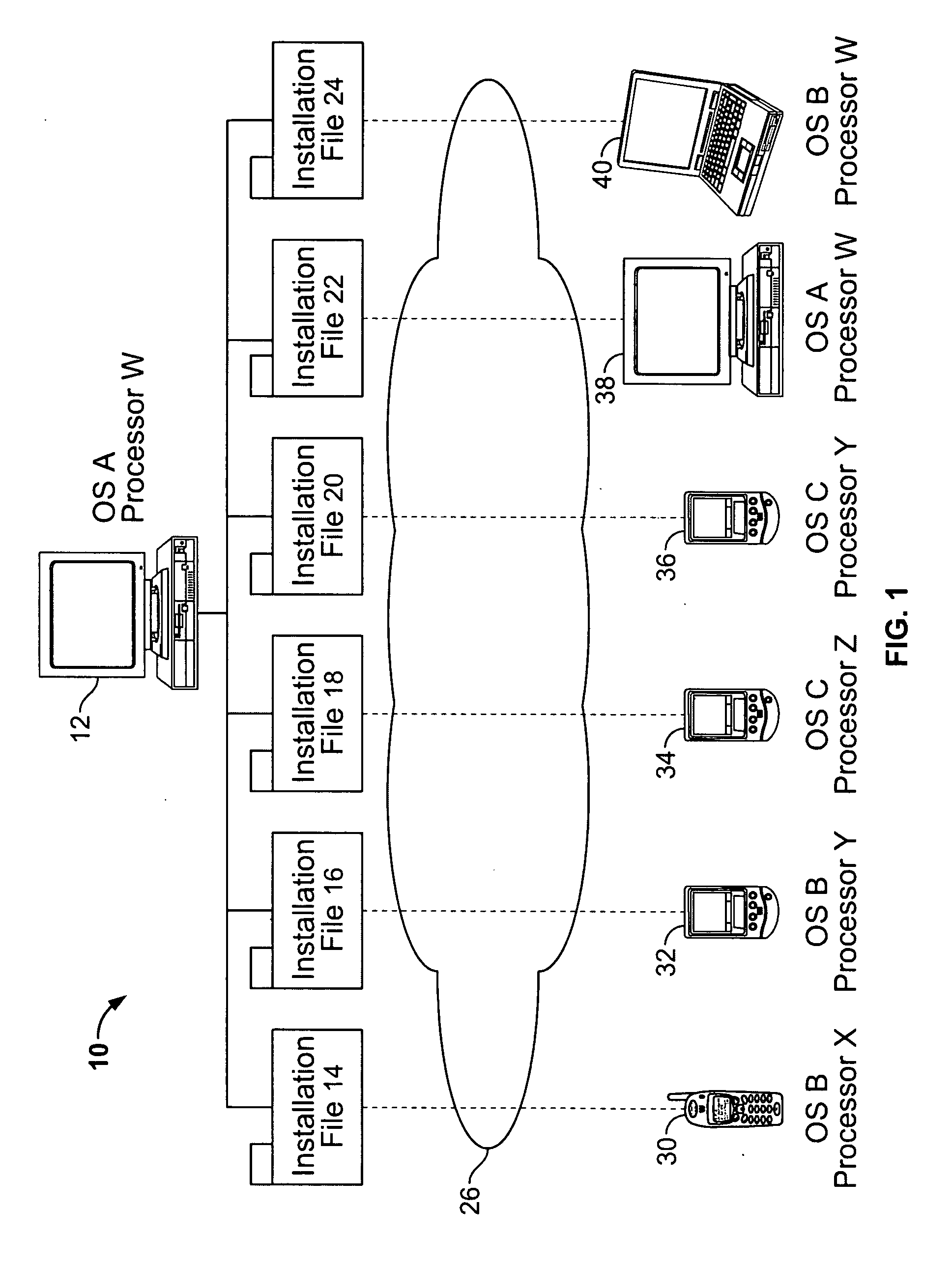

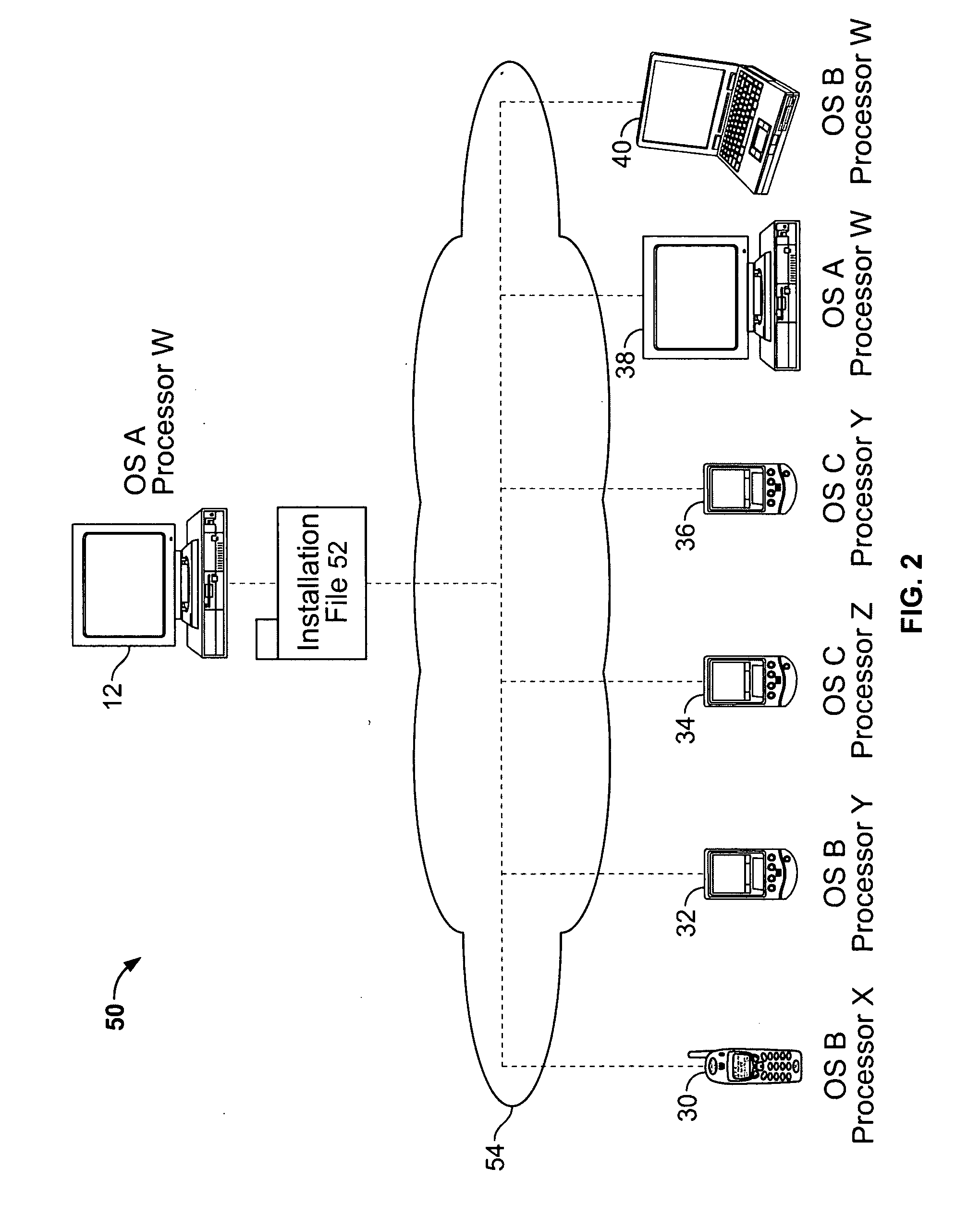

System and method for common file installation

ActiveUS20060248524A1Program loading/initiatingMemory systemsProgramming languageJust-in-time compilation

The invention provides a method and system for creating a single, common installation file for multiple target device types. In one approach, the method comprises providing a base engine, compiling the engine into an intermediate language code, and just-in-time compiling the intermediate code into executable code. The latter code is executed to gather the appropriate data sets and concatenate the data sets with the engine to form the installation file. The present invention also provides a method and system for utilizing the installation file to retrieve the appropriate data set(s) for the identified target device type, and to install the retrieved data set(s) onto the target device.

Owner:INTERMEC IP

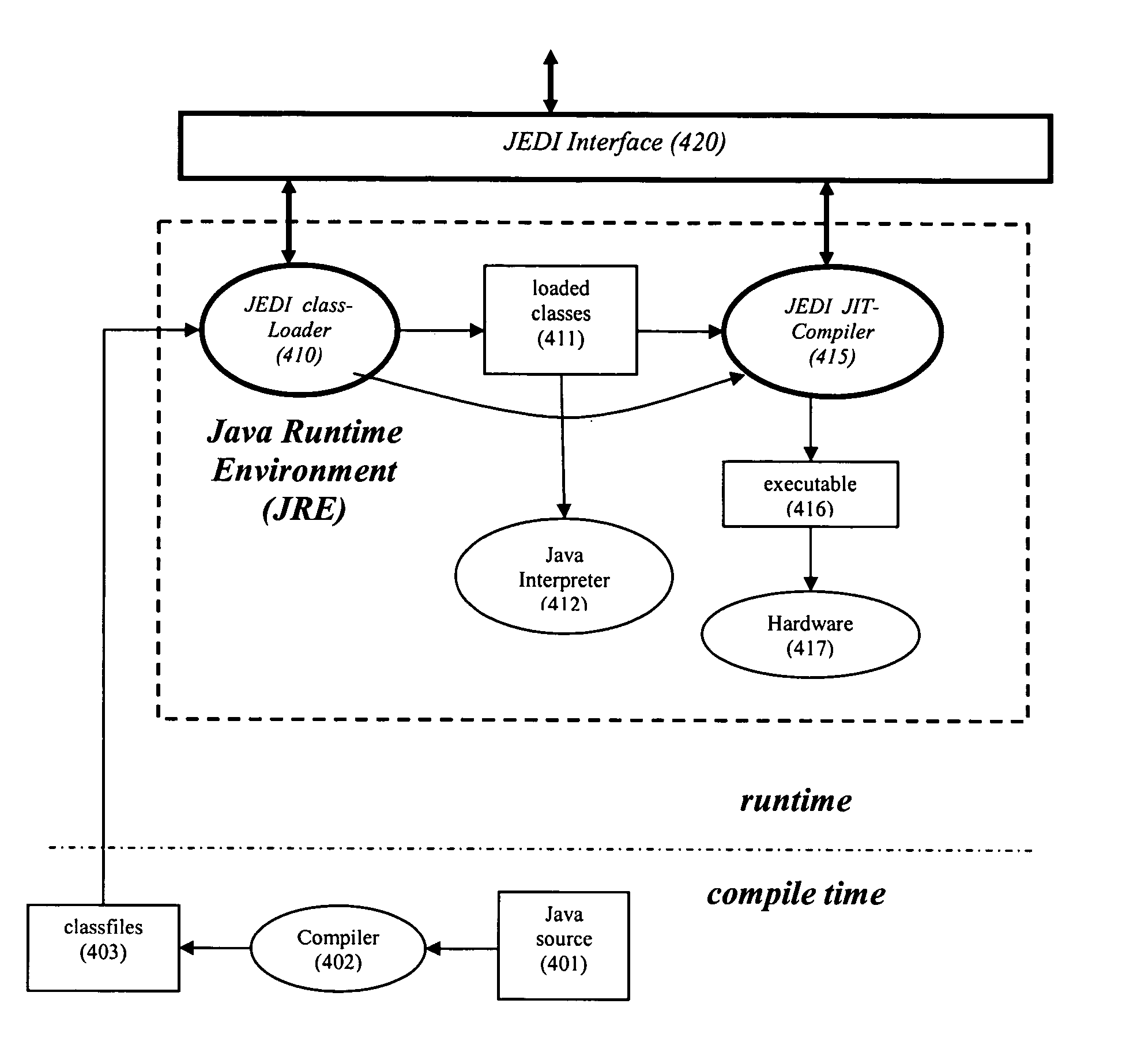

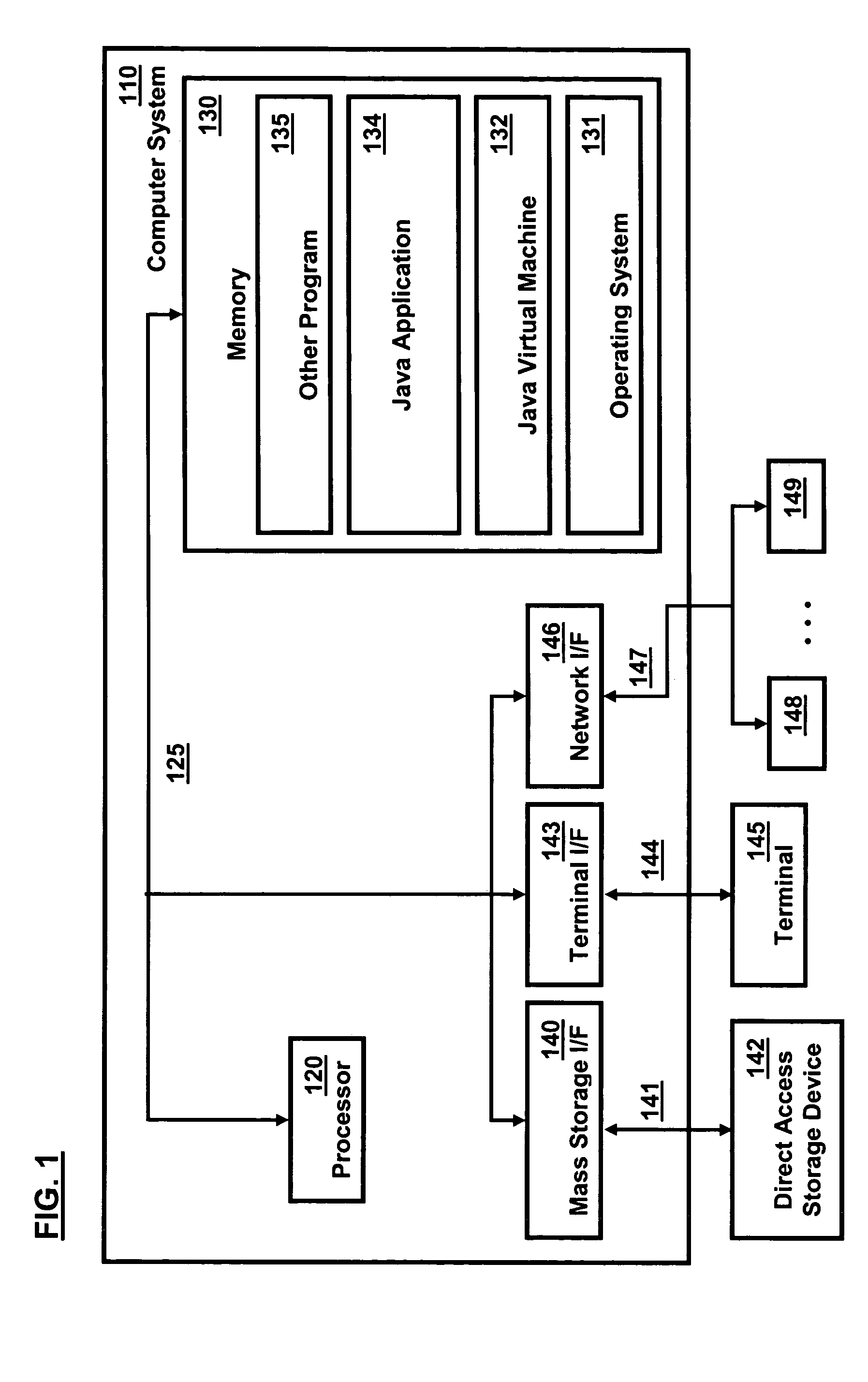

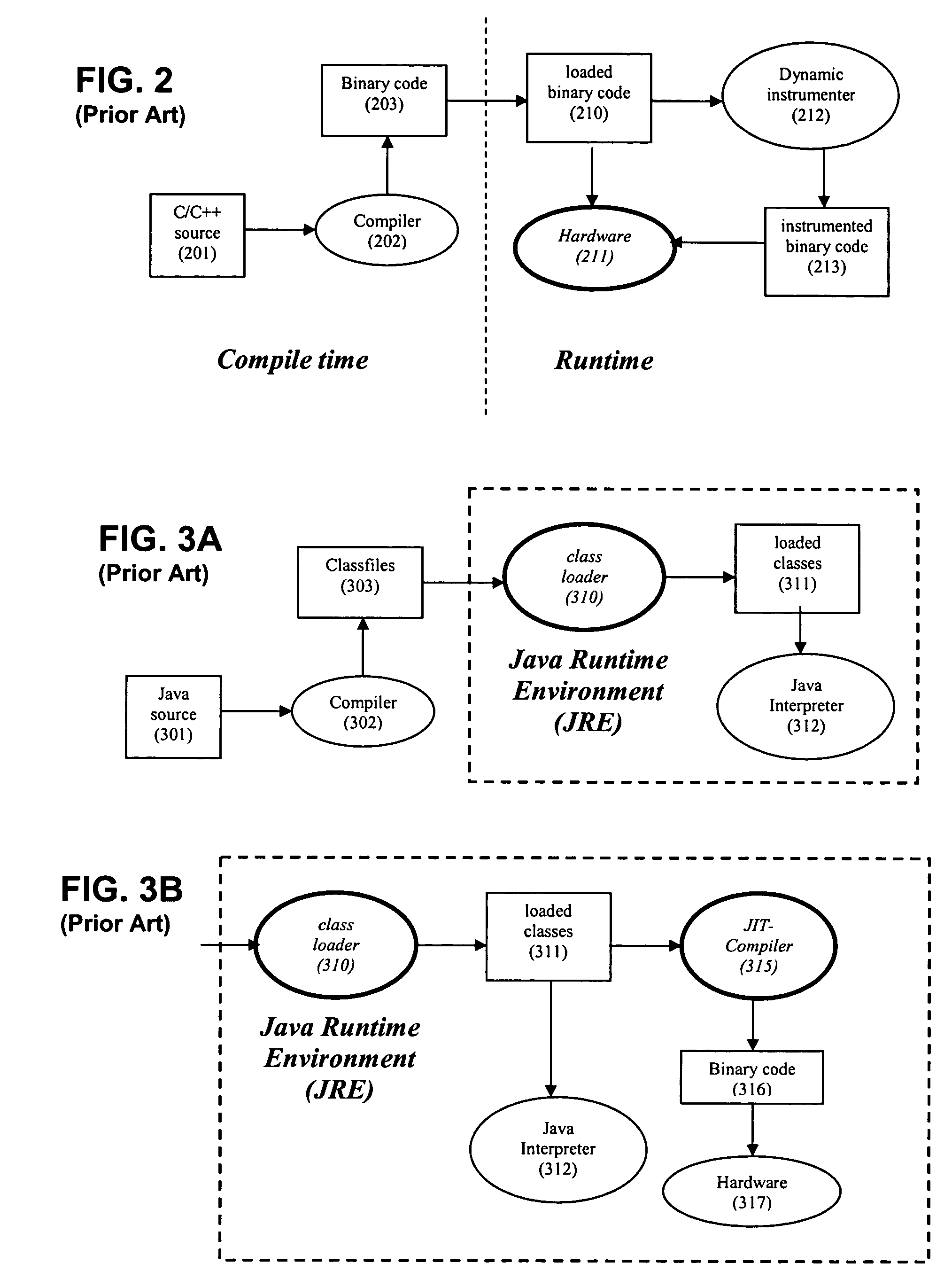

Dynamic instrumentation for a mixed mode virtual machine

Owner:GOOGLE LLC

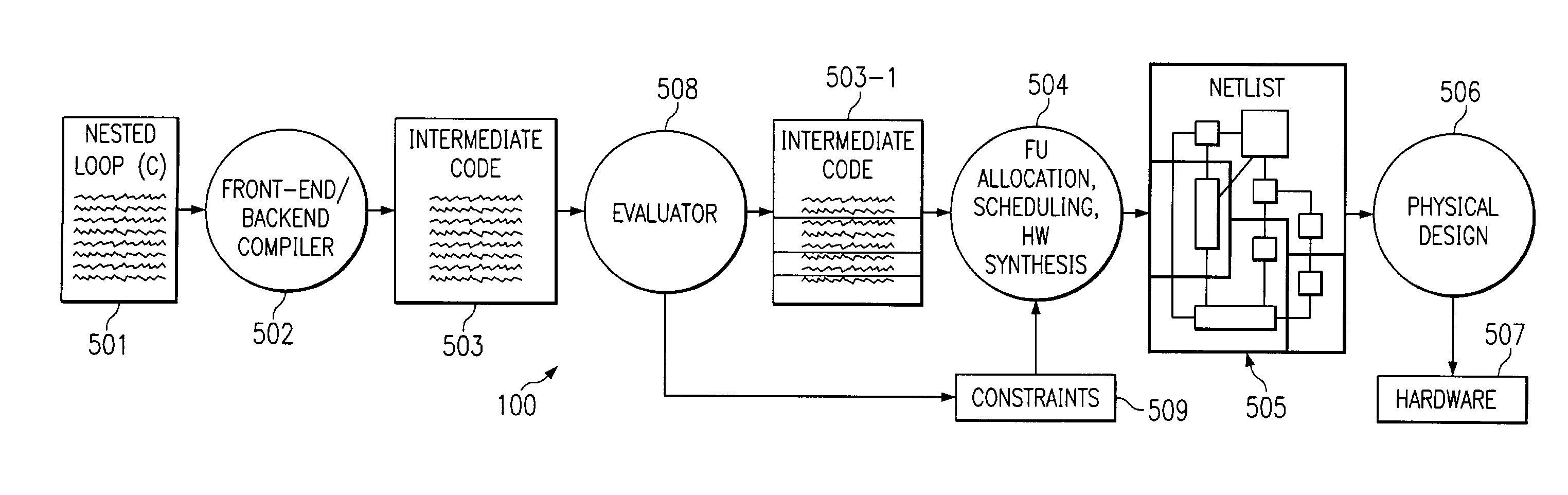

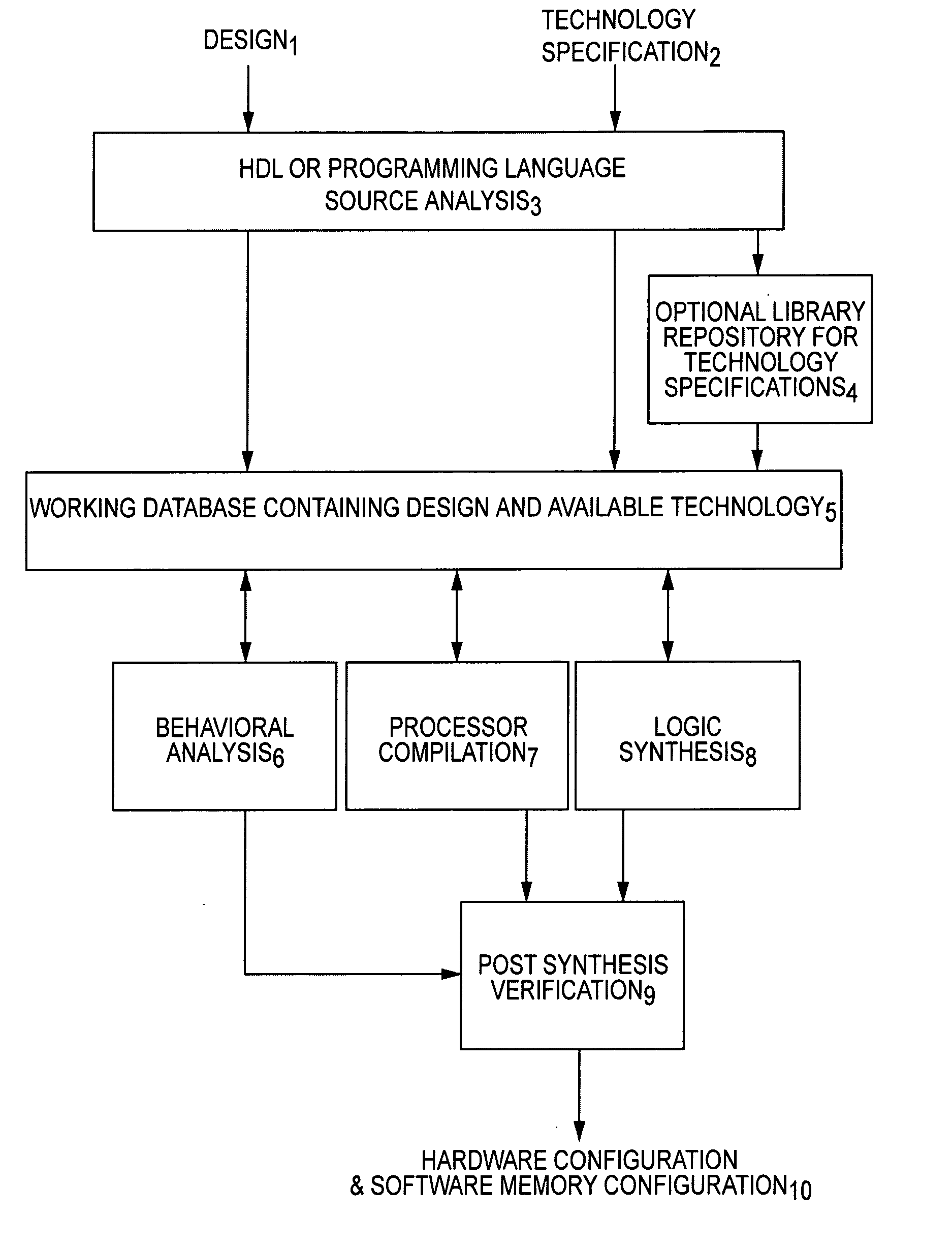

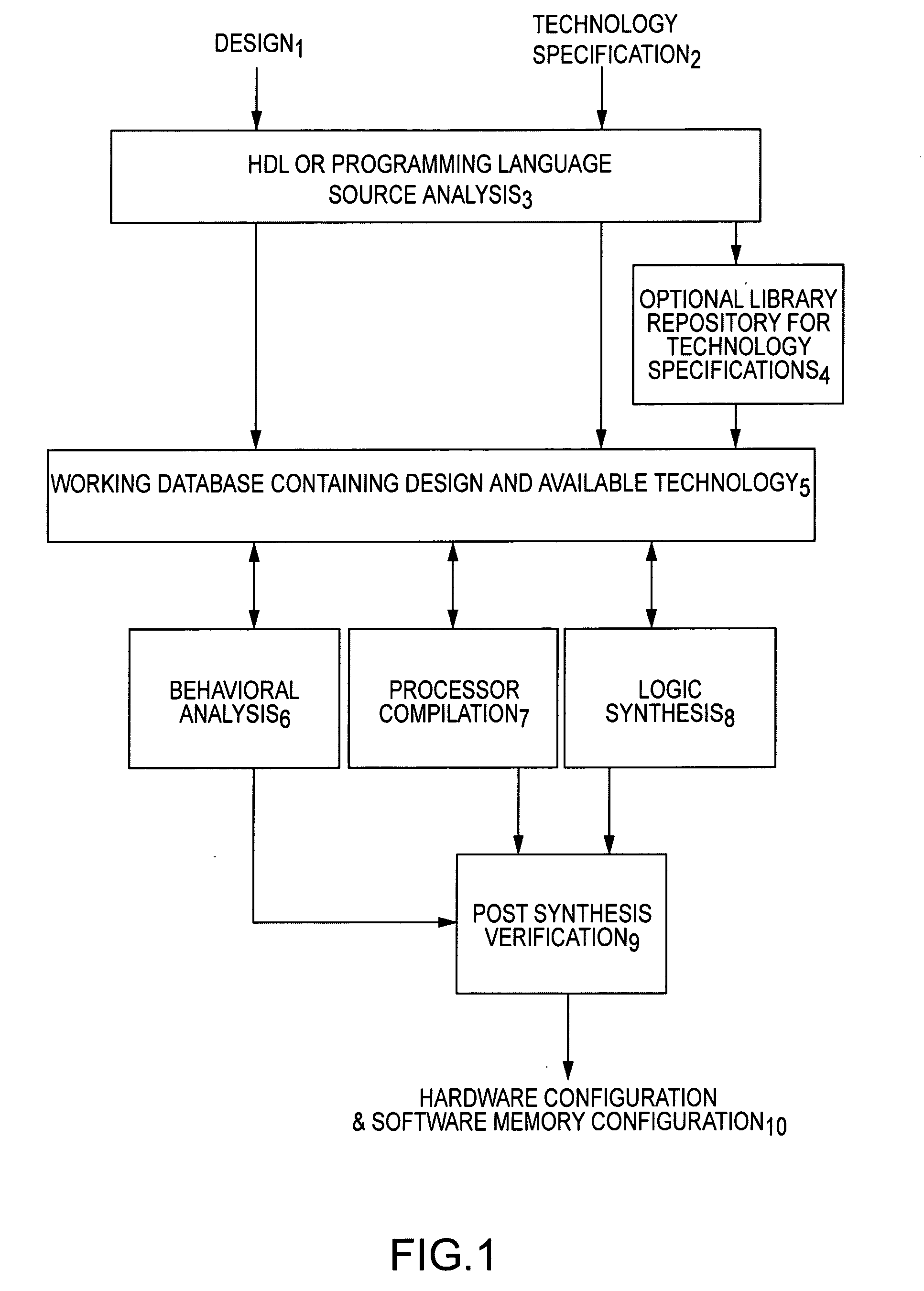

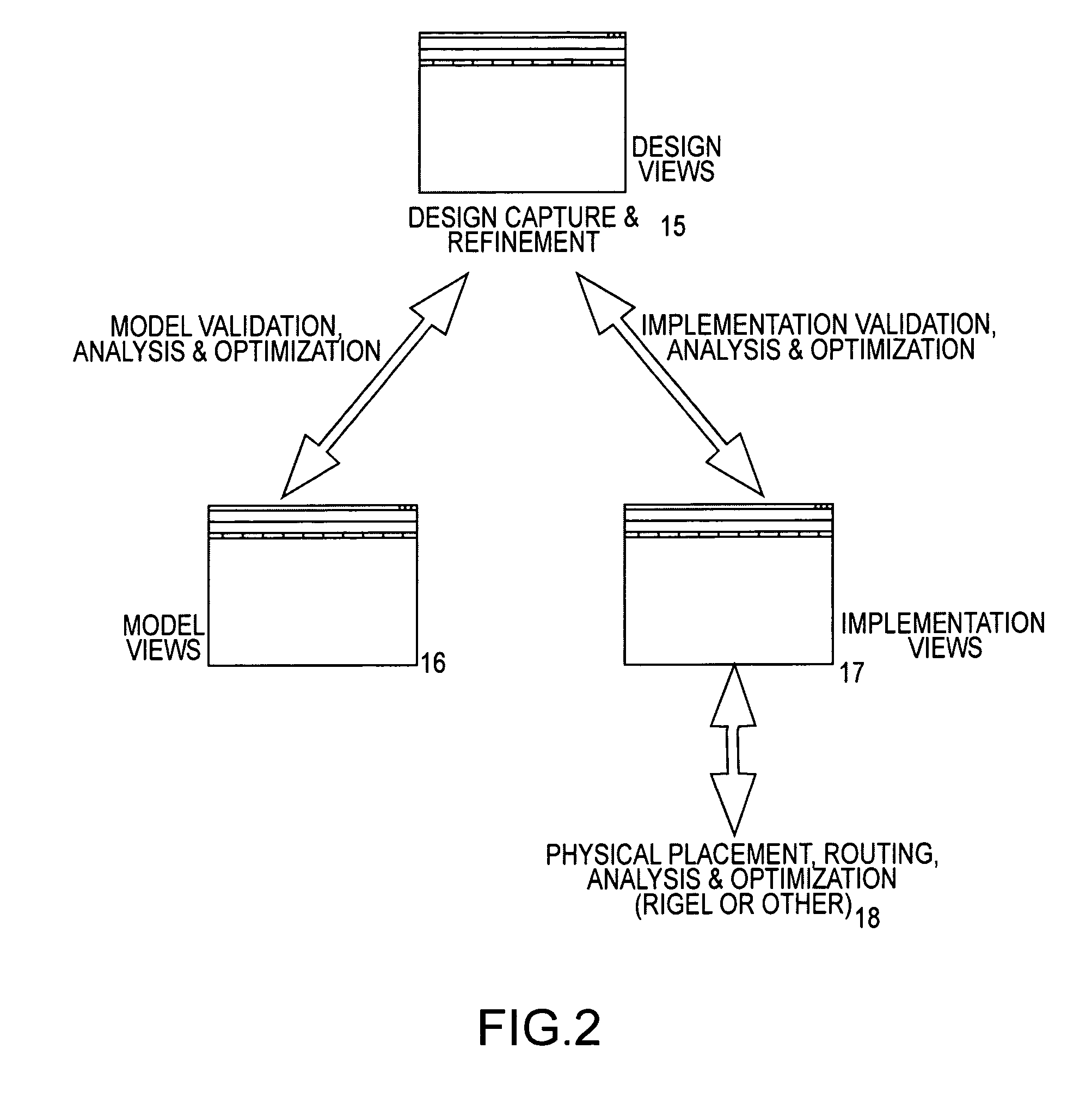

Hardware/software design tool and language specification mechanism enabling efficient technology retargeting and optimization

InactiveUS20050289485A1More compactEfficient designElectrical testingDigital computer detailsComputer architectureSoftware system

An innovative hardware / software design tool provides four modes of operation for converting an electronic design specification and zero or more technology specifications into realization of the electronic design in computer hardware, software and firmware. The first mode of operation compiles design and logic technology specifications into a model which can be utilized for behavioral analysis (such as simulation or formal verification) of logical characteristics (the model). The second mode of operation translates (compiles) partitions of the design and one or more logic technologies into one or more processor intermediates or binaries (embedded binary) suitable for execution on multi-purpose processing units (embedded or general purpose processors). The third mode of operation translates (synthesizes) partitions of the design and logic technology into a collection of cells and interconnects (net-list implementation) suitable for input to physical design processes such as is required to target a field-programmable logic array (FPGA), application specific integrated circuit (ASIC), system-on-a-chip (SOC) or custom logic). The fourth mode of operation analyzes (verifies) behavior of the embedded binaries running on processing units and implementations augmented by additional physical technology and parameters, yielding a more detailed (accurate) prediction of the resulting hardware / software system behavior when realized through manufacturing. Critically, the design specification, logic specifications, physical specifications and definition of each multi-purpose processing unit may be defined external to the hardware / software design tool using an innovative augmentation of standard hardware description or programming languages taught in this patent application. In the prior art, specification of the logic technology, physical technology and embedded or general purpose processor architecture are either incorporated directly into the design tool by the tool developer or are maintained entirely external to the design tool (such as an encapsulated component model or intermediate code interpreter). The present invention is an innovative and valuable improvement over prior art in that design specifications are combined by the tool from distinct specification(s) of generalized logic, physical and processor technology, leading to more efficient behavioral design, opportunities for third parties to add functionality by incorporating generalized logic and physical technology modules into the analysis and synthesis process and opportunities for semi-automatic, goal-directed optimization through application of various logic, physical and processor technologies by the design tool.

Owner:FTL SYST

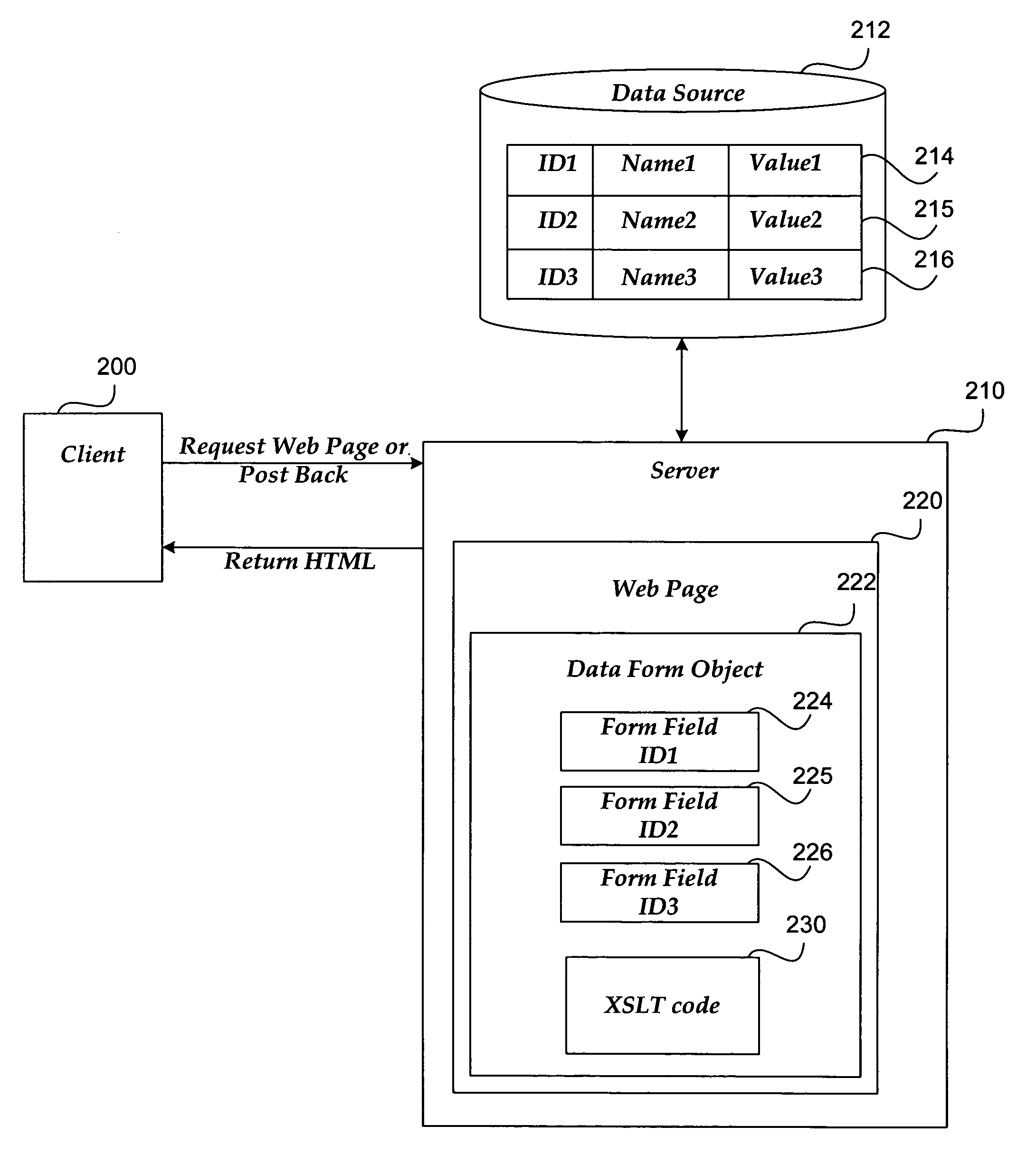

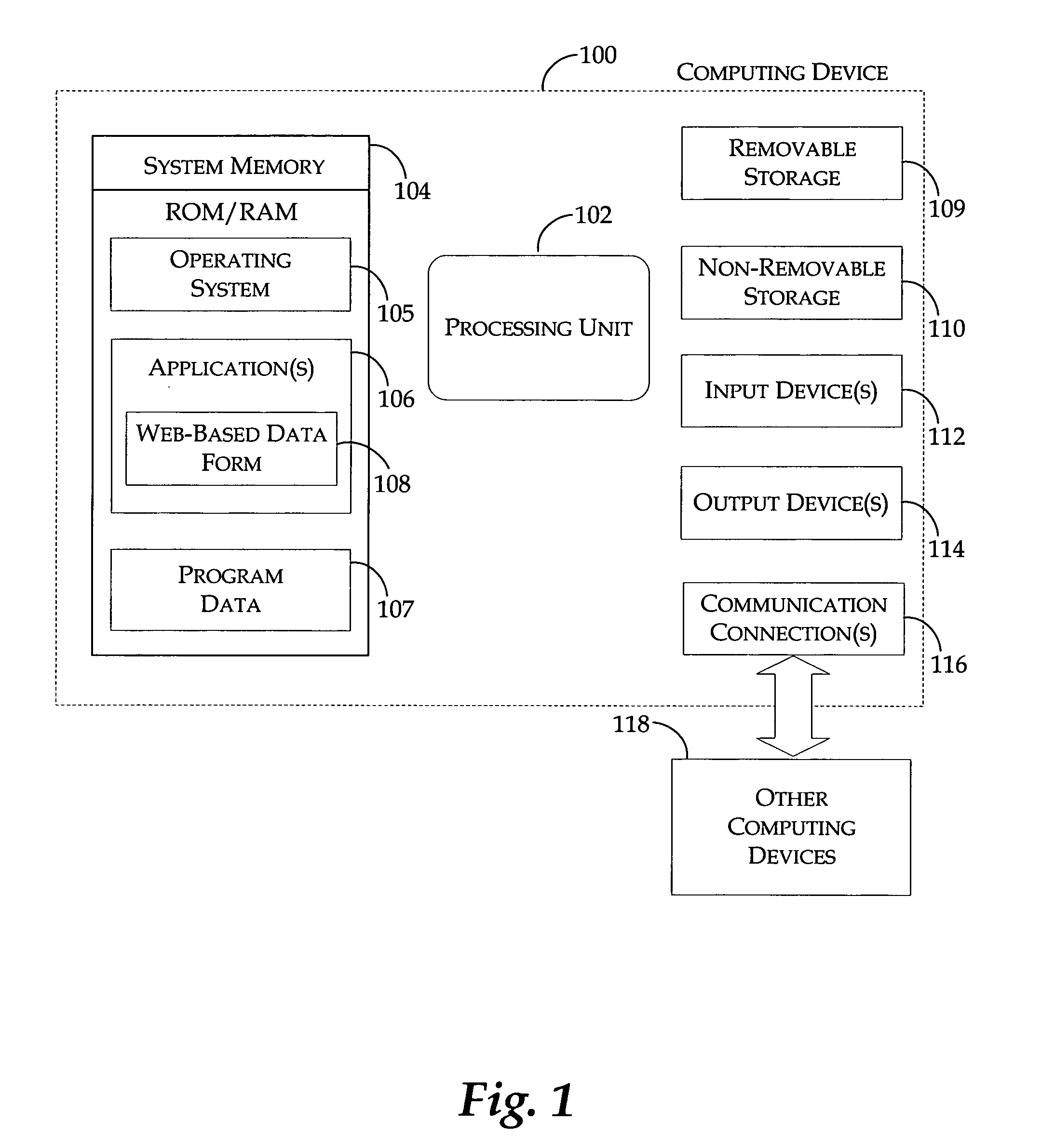

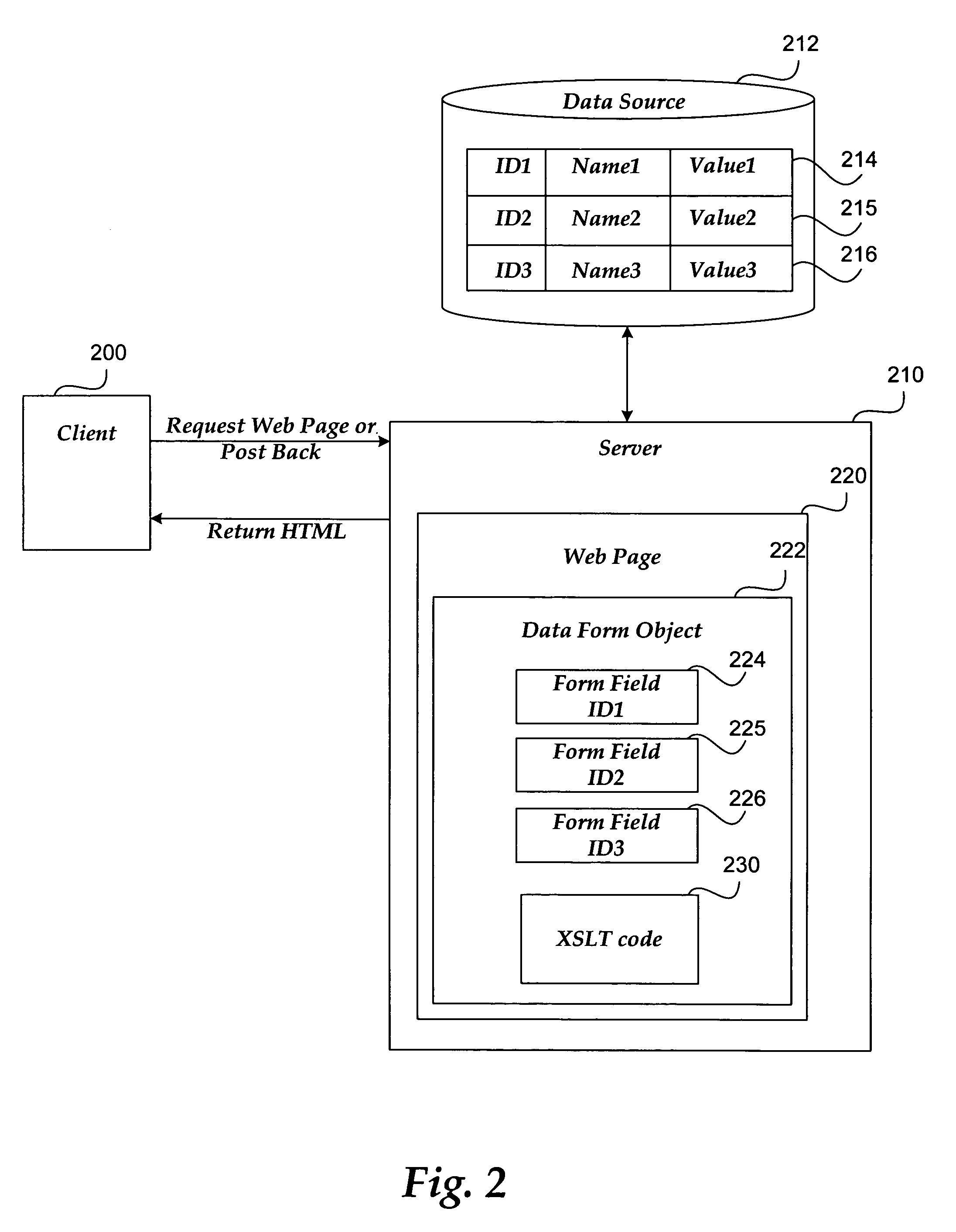

Web-based data form

InactiveUS20060074981A1Natural language data processingSpecial data processing applicationsXSLTData source

A web-based data form enables modifications made to values in the data form to be dynamically implemented in a data source. Form fields of the data form are associated with items in the data source using data binding information. Data from the data source is transformed into intermediate code using Extensible Stylesheet Language Transformation (XSLT) code. Form controls of the data form are instantiated using the intermediate code. Hypertext Markup Language (HTML) is generated from the intermediate code including the form controls.

Owner:MICROSOFT TECH LICENSING LLC

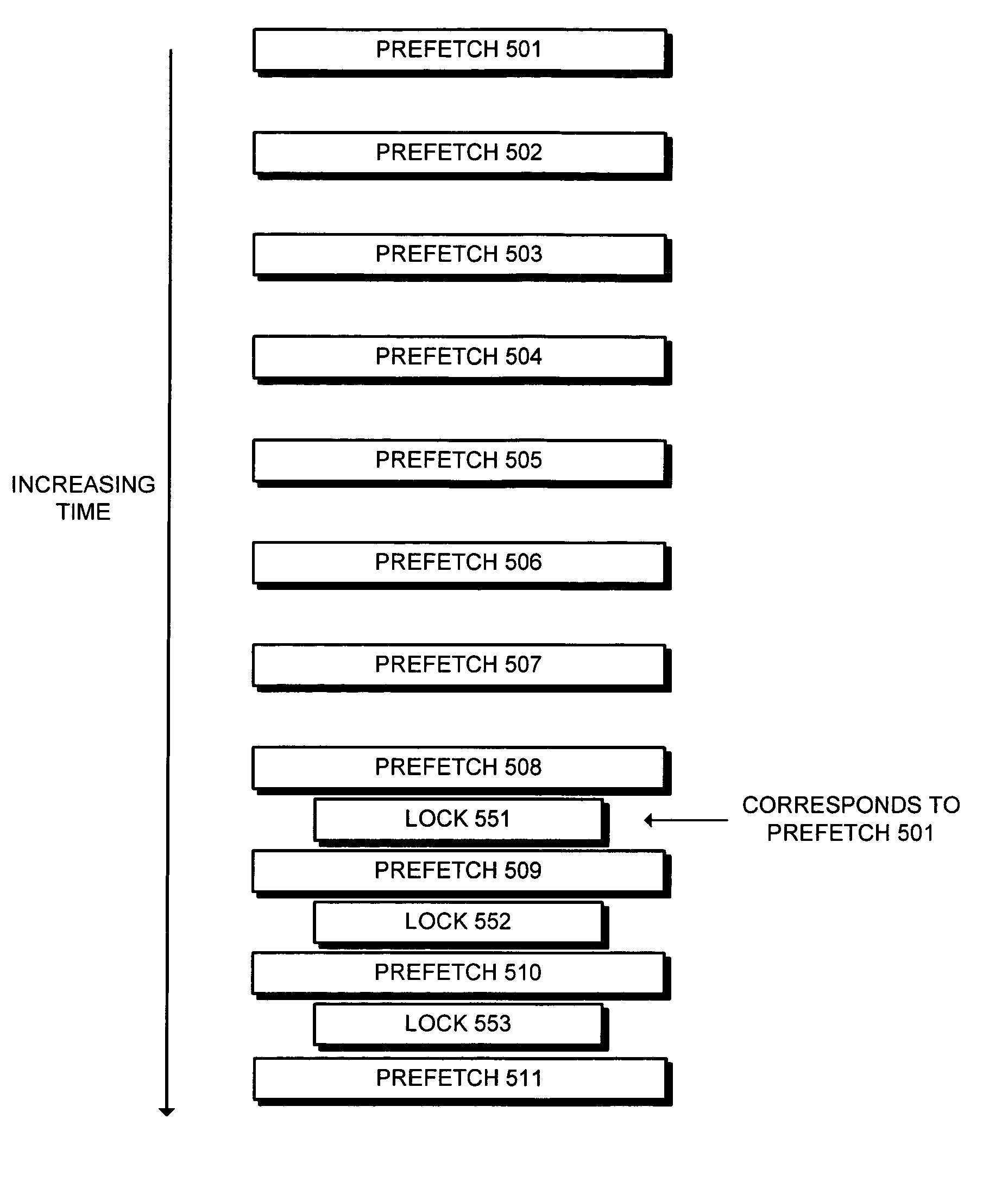

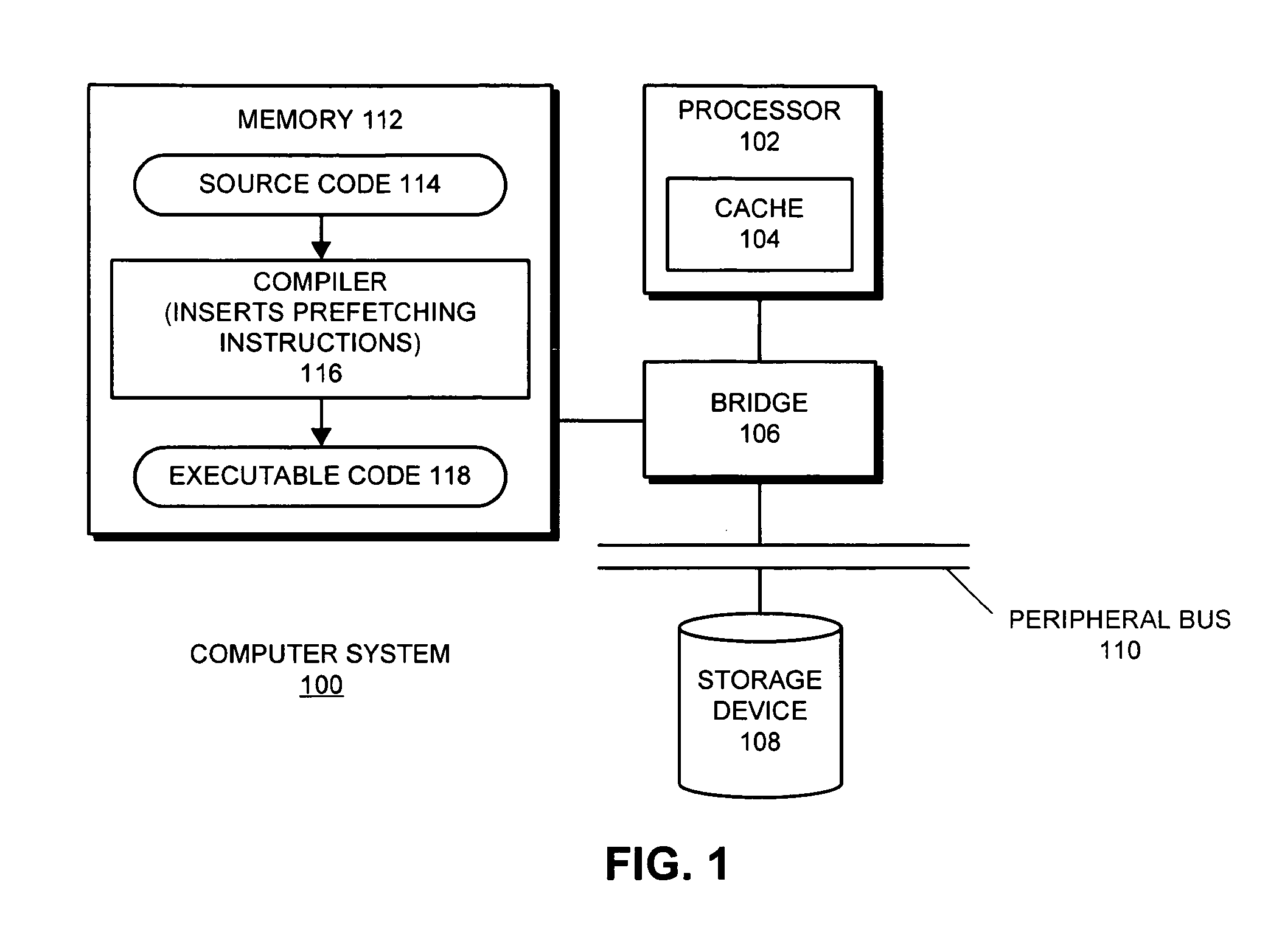

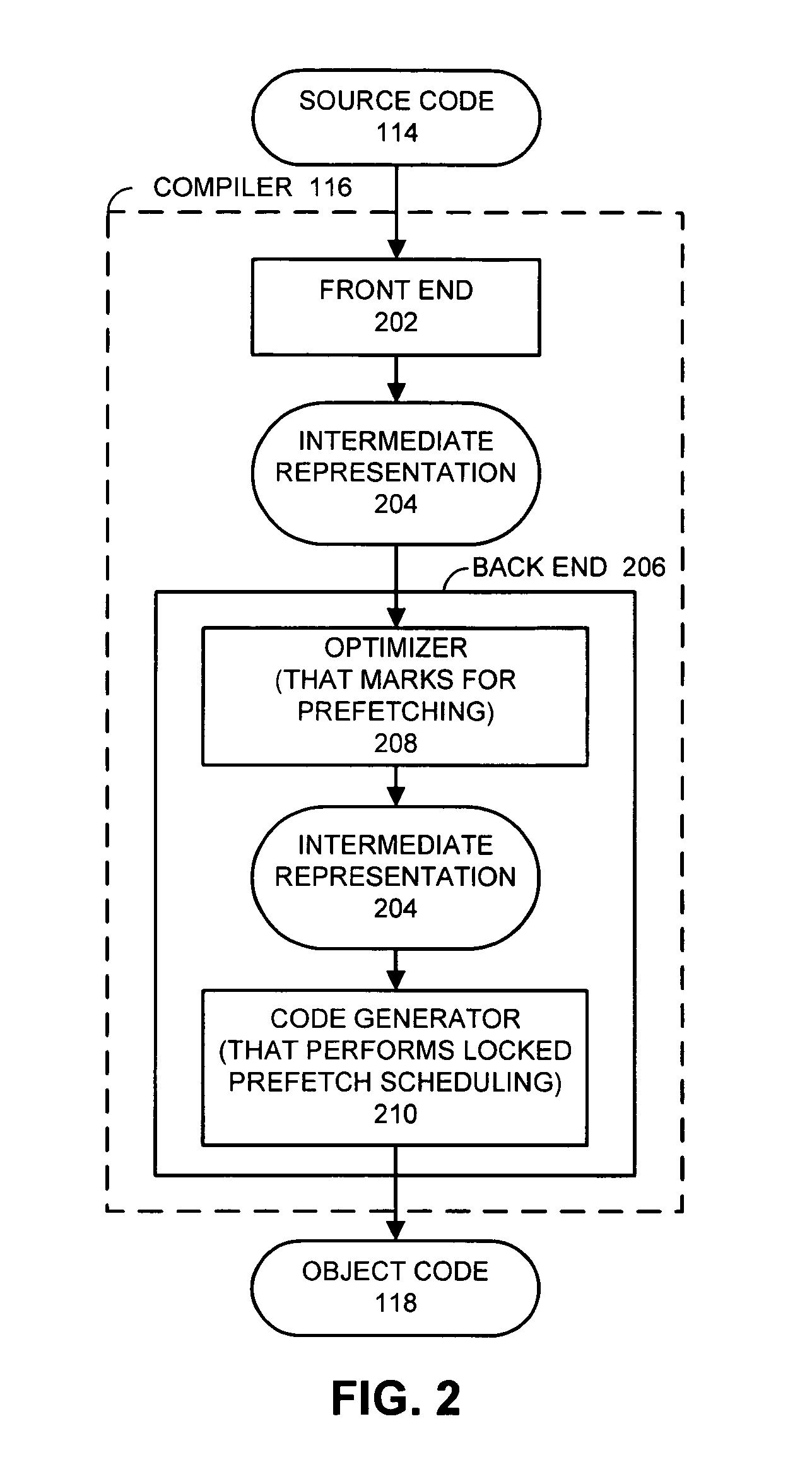

Locked prefetch scheduling in general cyclic regions

ActiveUS7681188B1Facilitates locked prefetch schedulingSoftware engineeringDigital computer detailsParallel computingSource code

One embodiment of the present invention provides a system that facilitates locked prefetch scheduling in general cyclic regions of a computer program. The system operates by first receiving a source code for the computer program and compiling the source code into intermediate code. The system then performs a trace detection on the intermediate code. Next, the system inserts prefetch instructions and corresponding locks into the intermediate code. Finally, the system generates executable code from the intermediate code, wherein a lock for a given prefetch instruction prevents subsequent prefetches from being issued until the data value returns for the given prefetch instruction.

Owner:ORACLE INT CORP

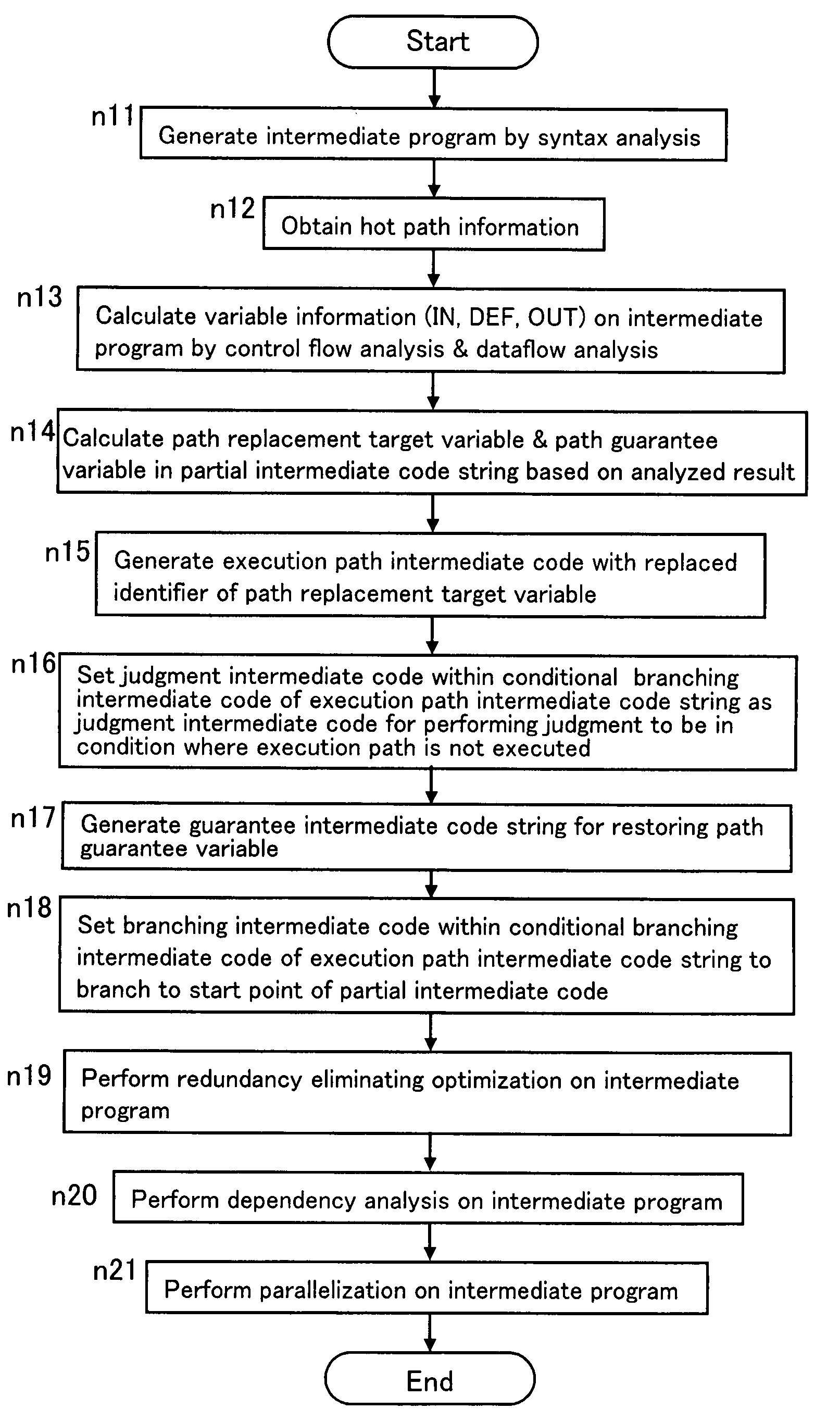

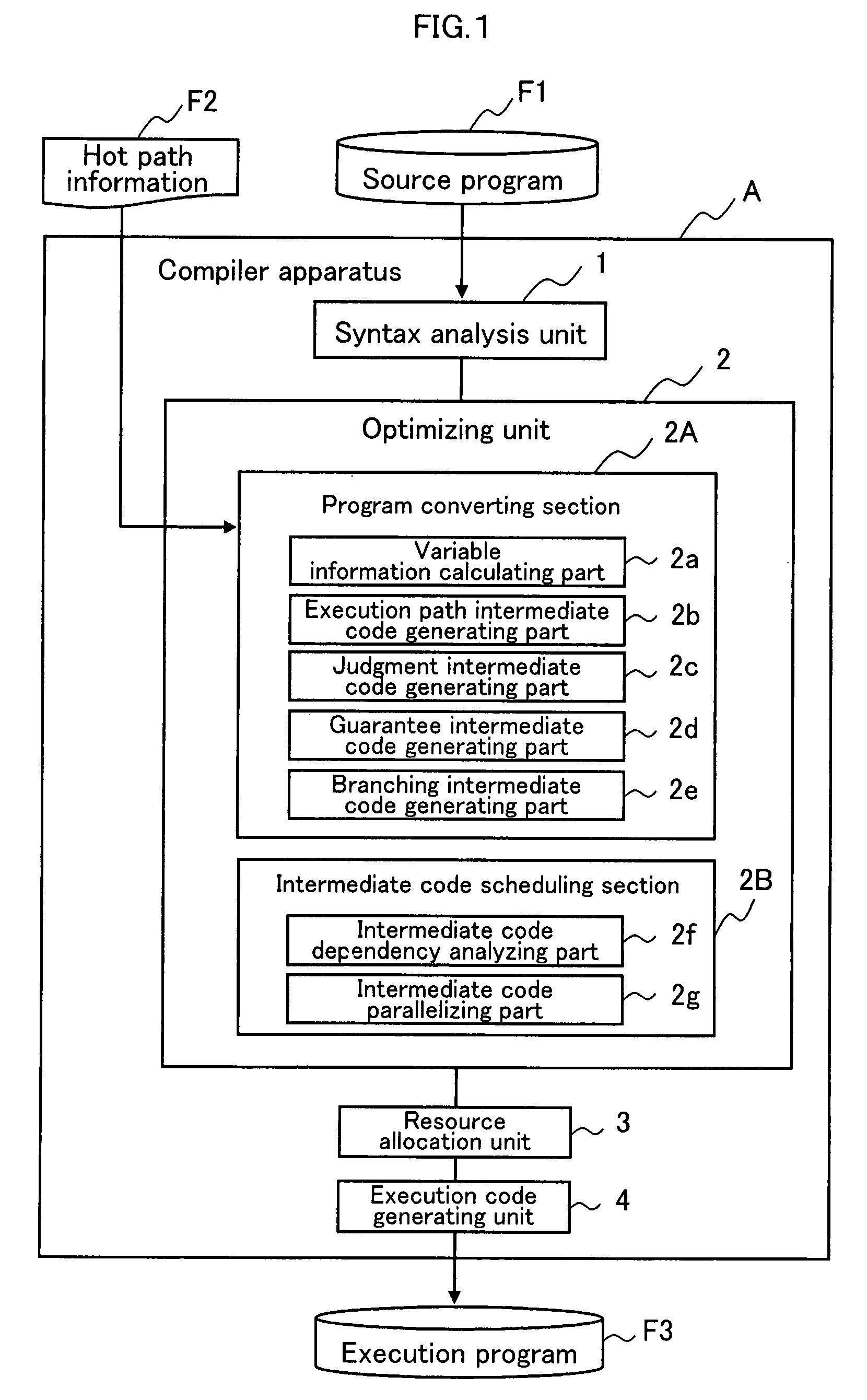

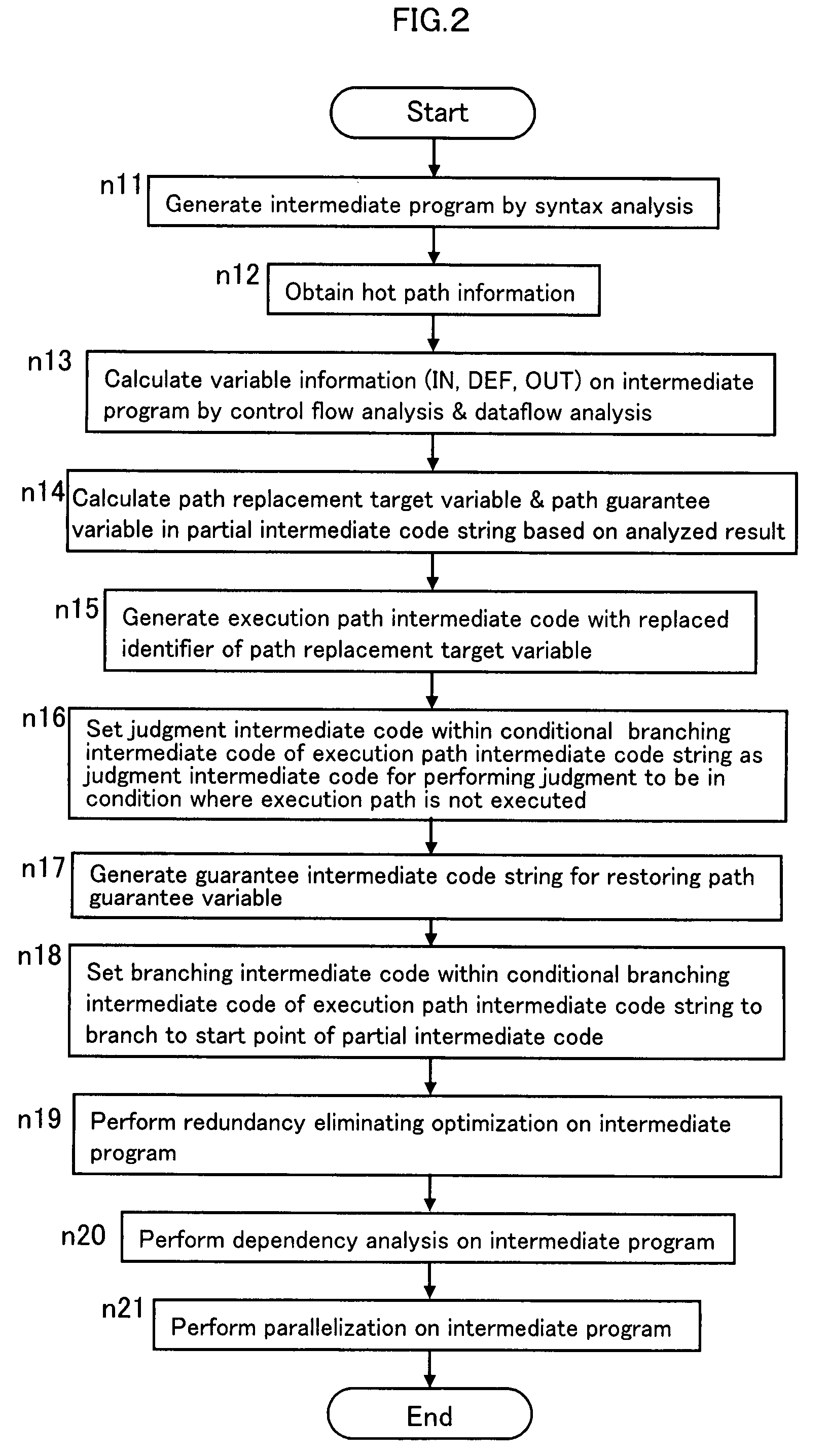

Compiler apparatus, compiler method, and compiler program

InactiveUS20070277162A1Maintain consistencySoftware engineeringProgram controlBasic blockIntermediate code

A high-sped block is formed by generating and connecting a new basic block (contains an intermediate code obtained by performing variable replacing processing to a path replacement target variable of the intermediate code on a hot path of an original partial program and contains a branching intermediate code where a branching instruction on the hot path is converted so as to execute the hot path), and a basic block with an intermediate code for restoring value of path guarantee variable among the path replacement target variables to a value of an original variable. When an execution result of a conditional branching intermediate code is true, the speeding up of the original program is achieved through executing the basic block, and performing dependency analysis and dependency generation between the intermediate codes in the high-speed block and scheduling of the instructions.

Owner:PANASONIC CORP

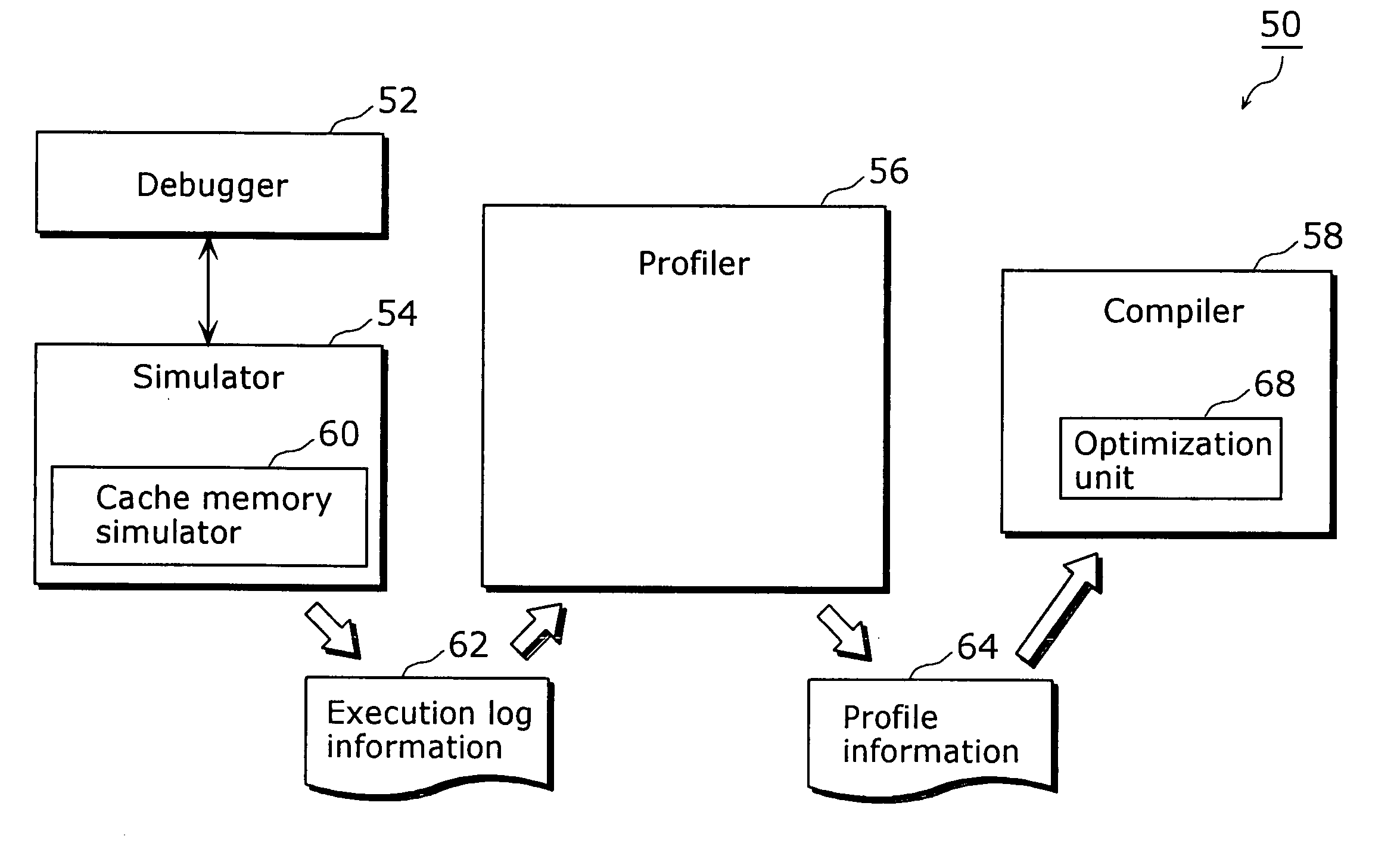

Compiler apparatus

A compiler 58, which is a compiler that realizes program development in a fewer man hours, translates a source program 72 written in a high-level language into a machine language program. This compiler 58 is comprised of: a directive obtainment unit that obtains a directive that a machine language program to be generated should be optimized; a parser unit 76 that parses the source program 72; an intermediate code conversion unit 78 that converts the source program 72 into intermediate codes based on a result of the parsing performed by the parser unit 76; an optimization unit 68 that optimizes the intermediate codes according to the directive; and a code generation unit 90 that converts the intermediate codes into the machine language program. The above directive is a directive to optimize the machine language program targeted at a processor that uses a cache memory.

Owner:SOCIONEXT INC

Method and system for automatically testing a software build

InactiveUS7519953B2Error detection/correctionDigital data processing detailsSoftware buildIntermediate code

Testing of a software build. Differences between software builds are tracked by scanning the binaries of a software product to automatically discover its classes. A detailed dictionary is built that captures static and dynamic information of that build, including class dependencies. A comparison may be made with another build, so that selective tests may be automatically executed on any types, and their dependencies, that have had a structural or behavioral modification since the last build. Testers may load a set of constructors for any specific types to further increase coverage of types (or classes) tested. Detailed reports may also be provided that may be used to drive future testing work and target specific areas of the code for additional testing. Code generation from intermediate code to specified targets may also be performed to aid in reproducing and fixing bugs.

Owner:MICROSOFT TECH LICENSING LLC

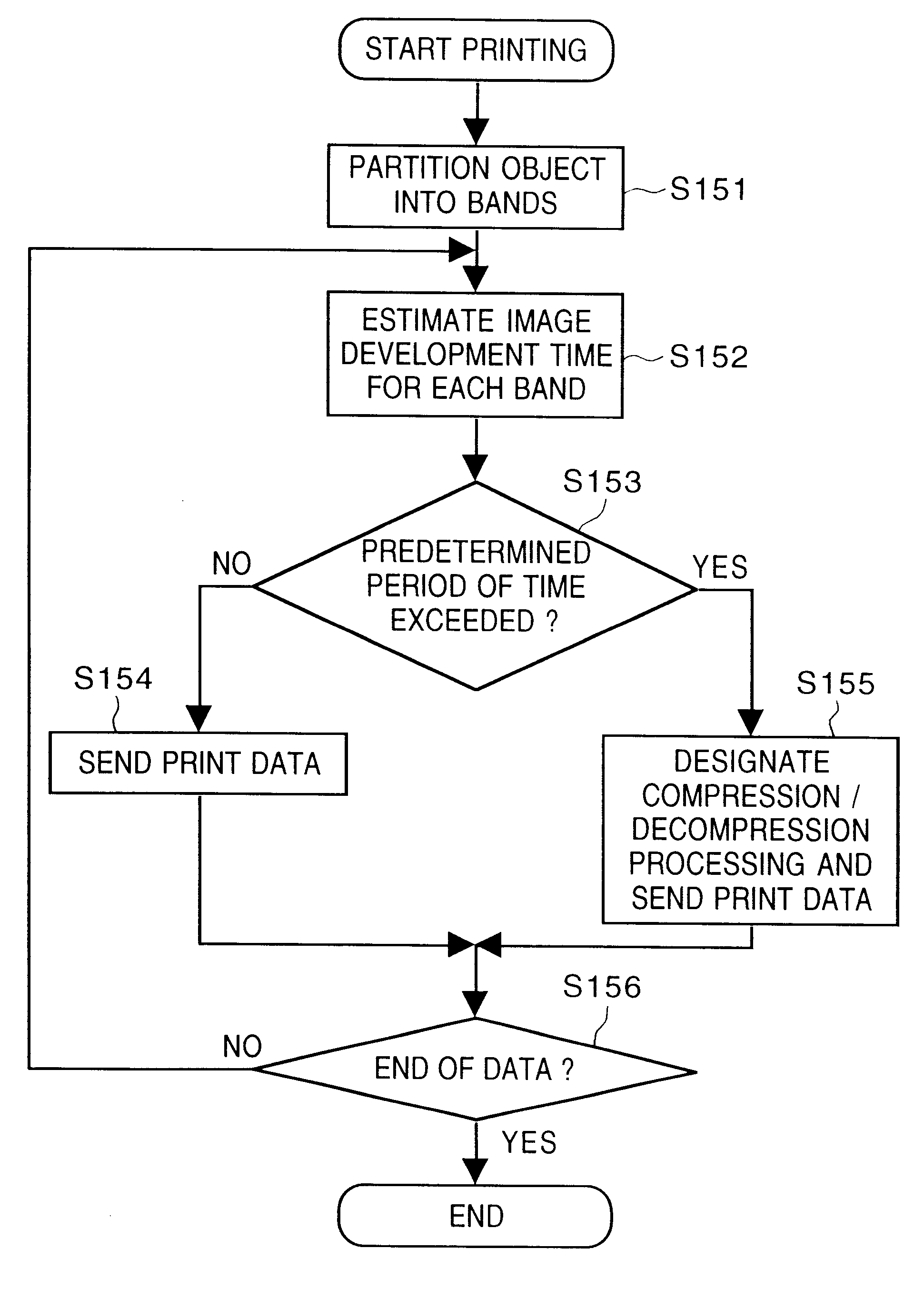

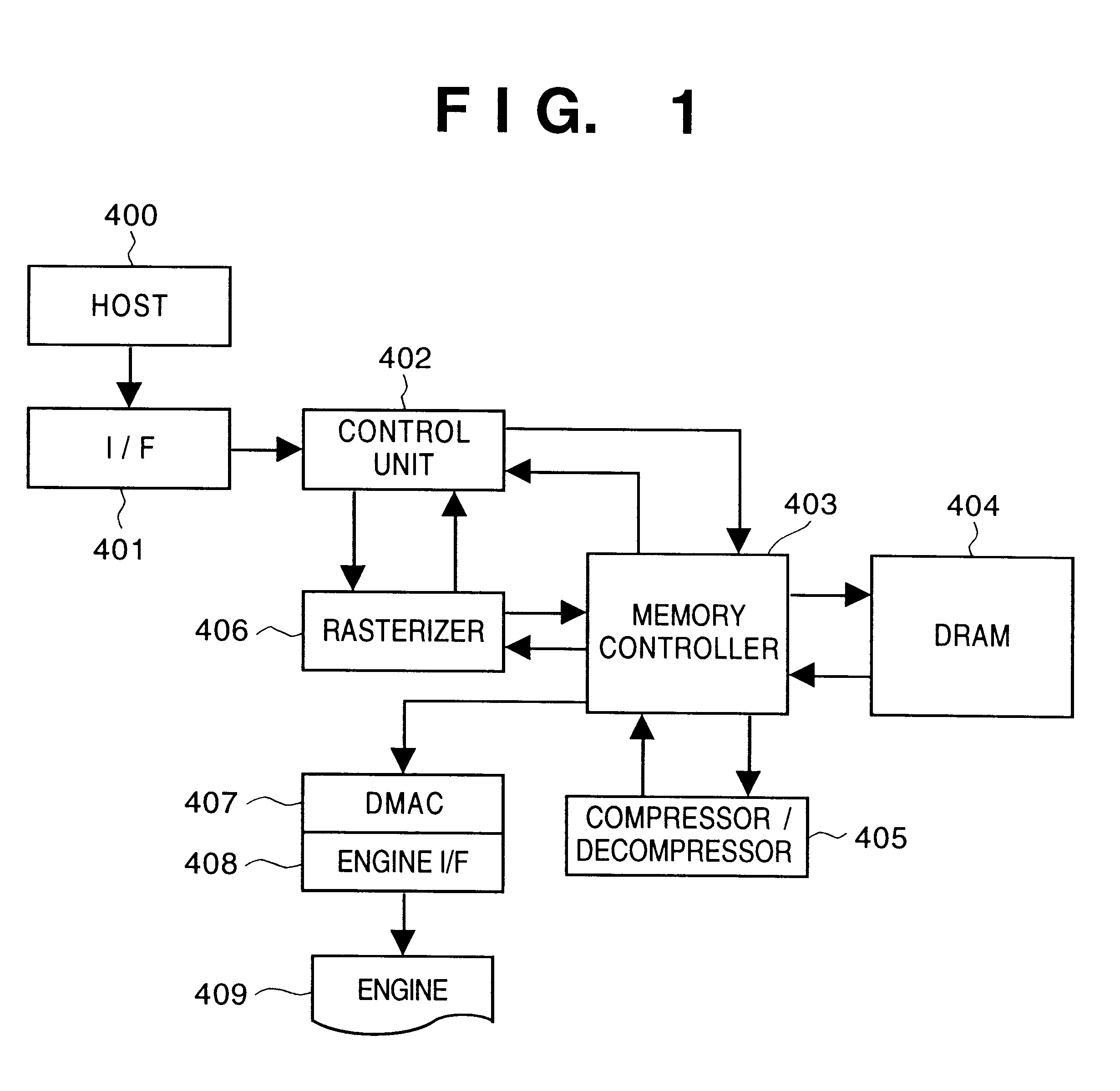

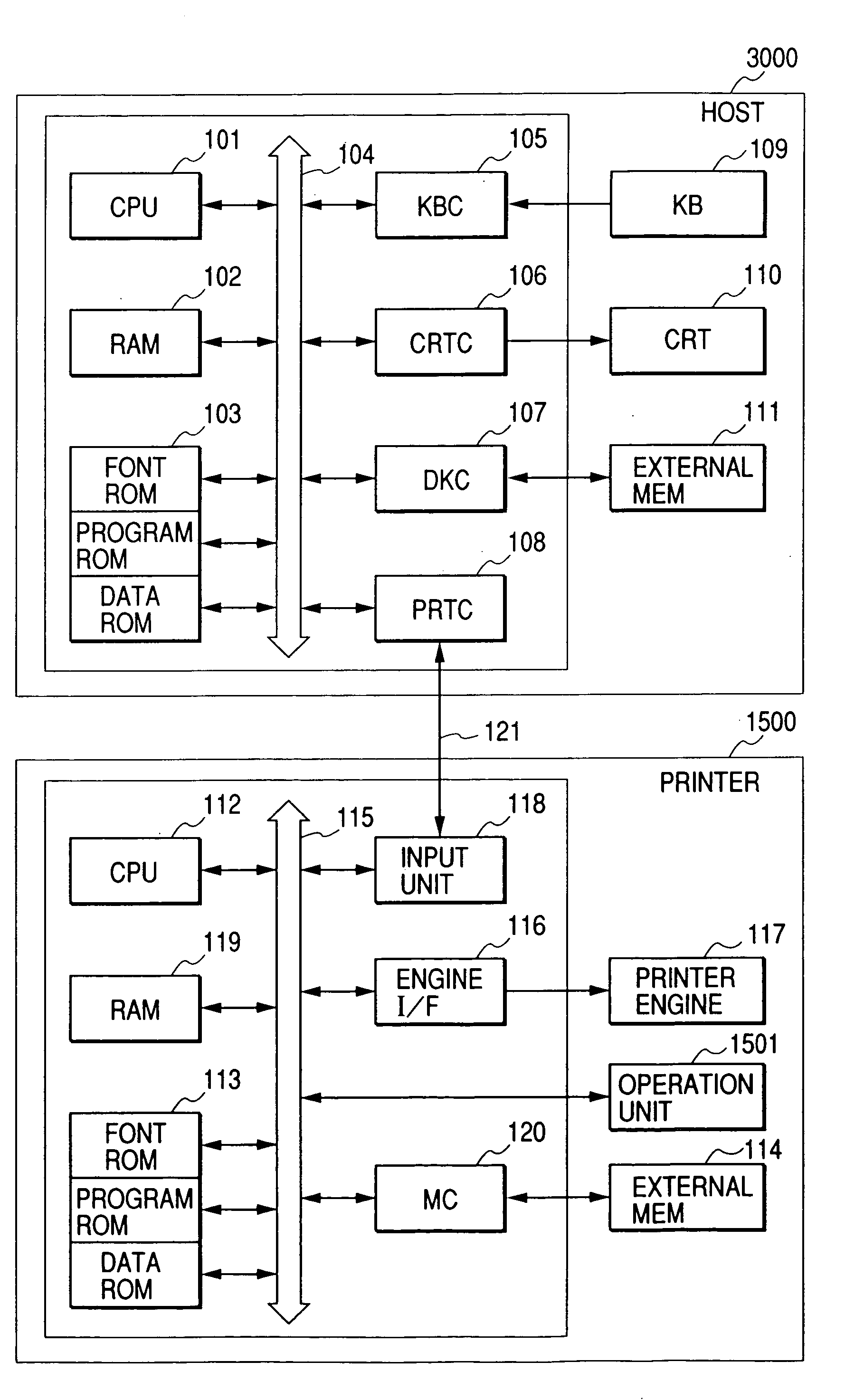

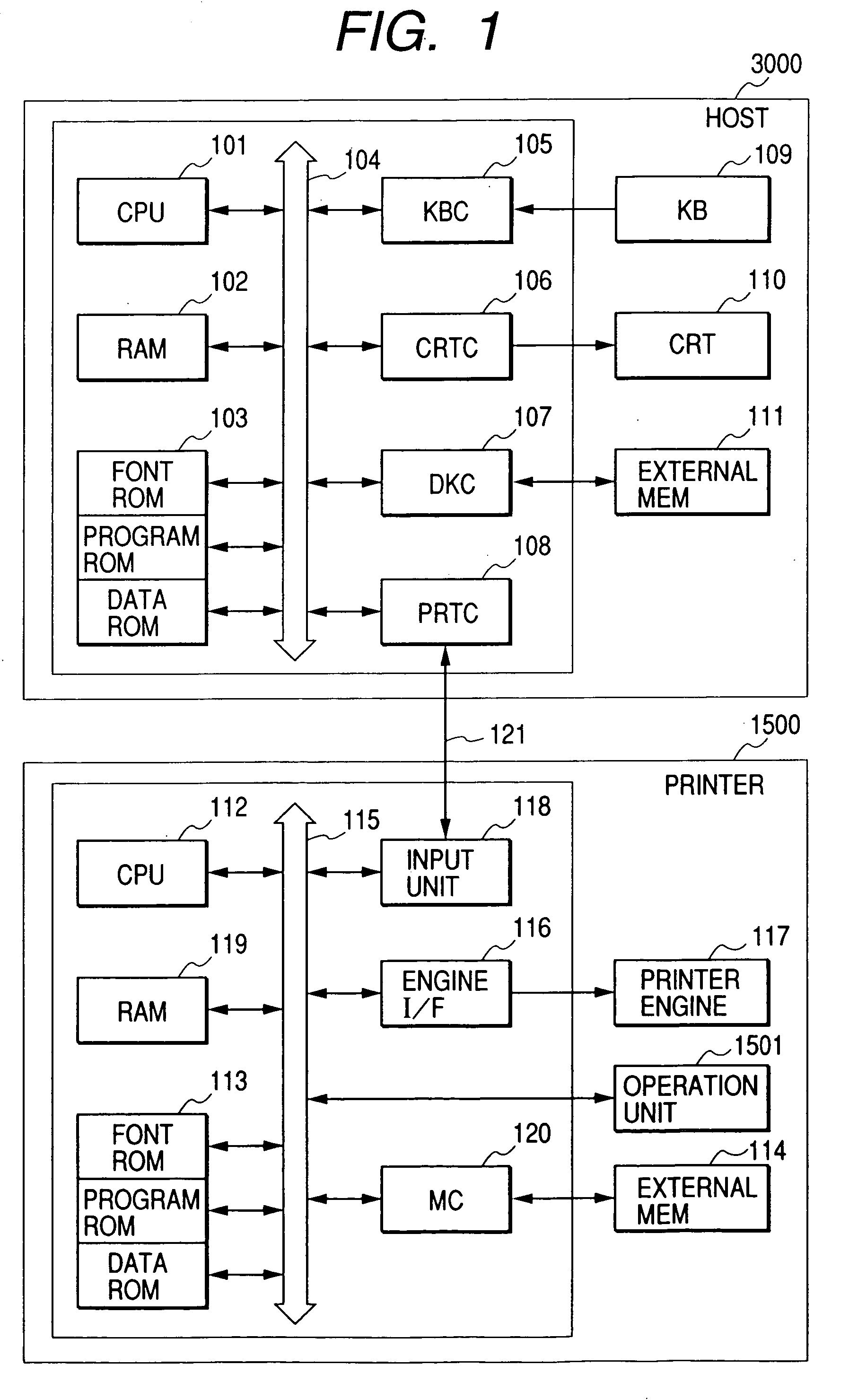

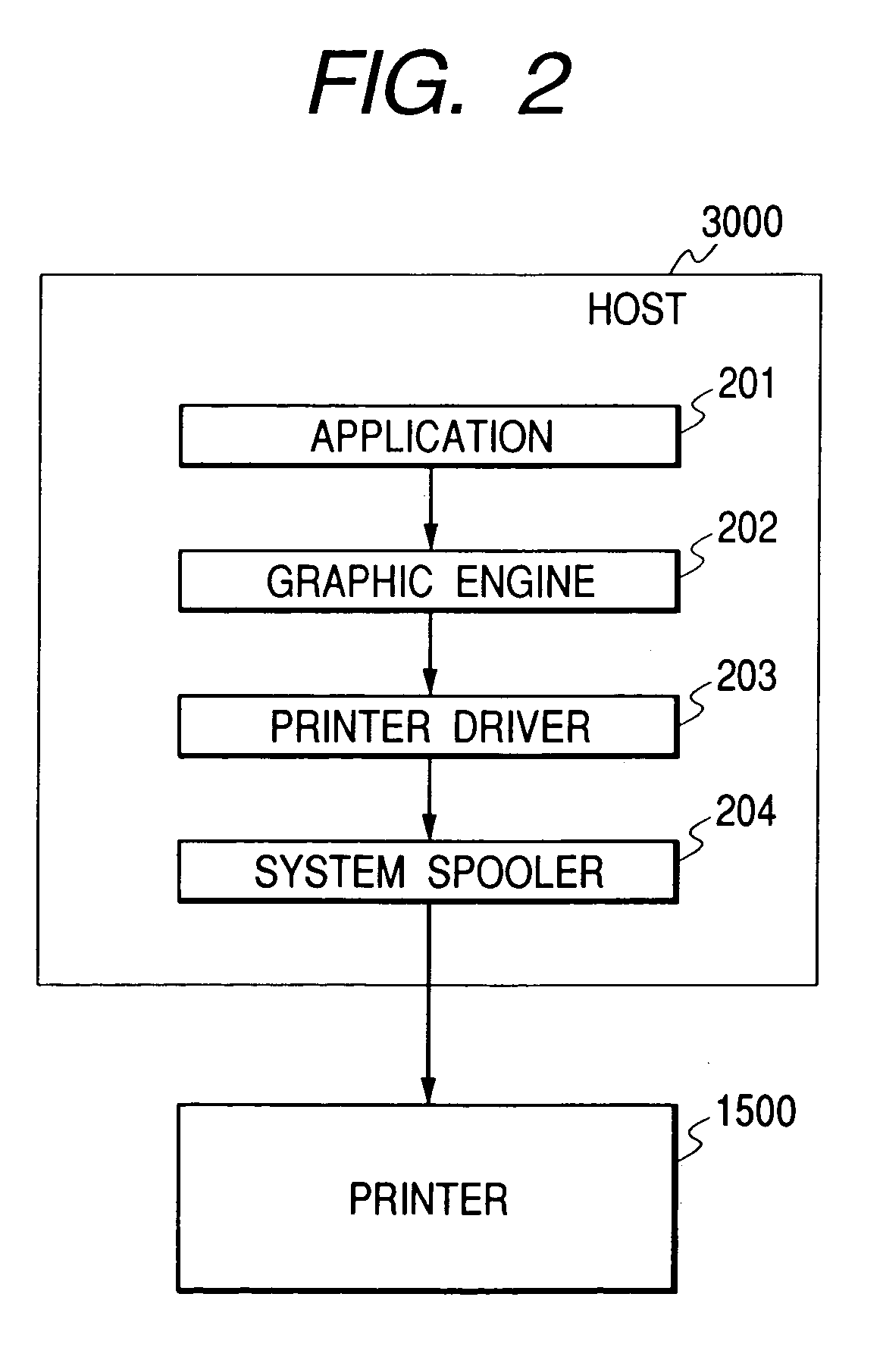

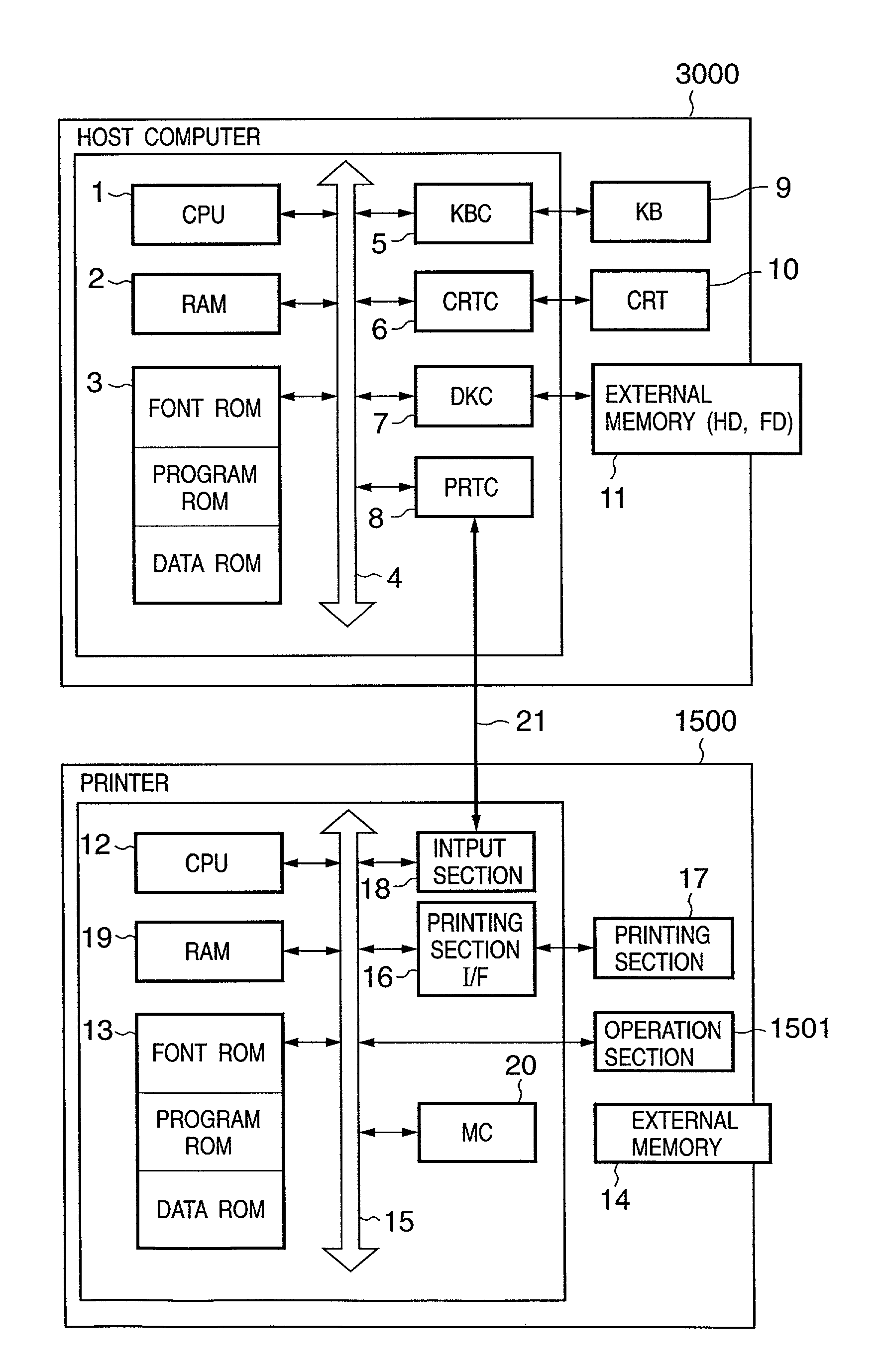

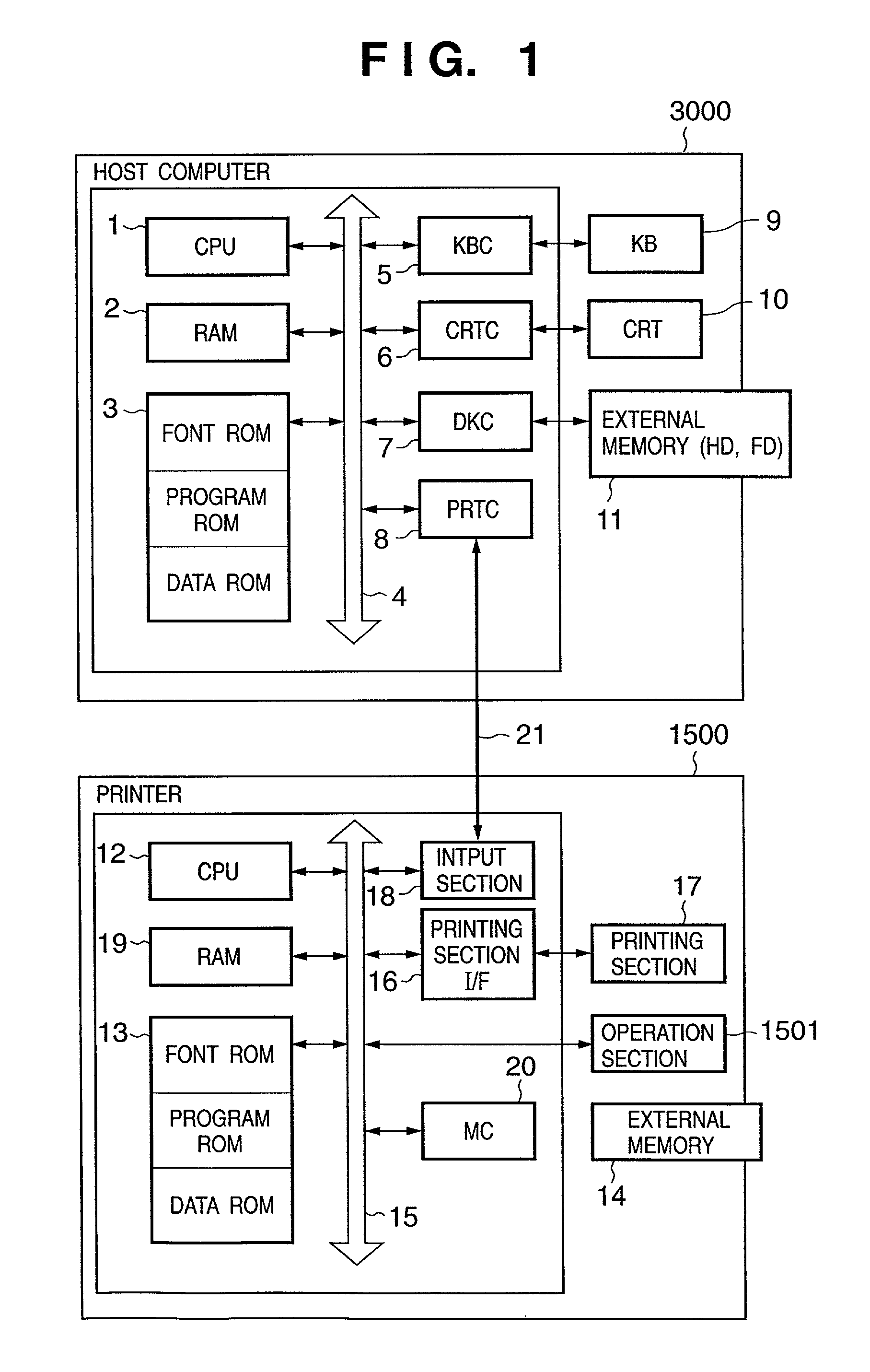

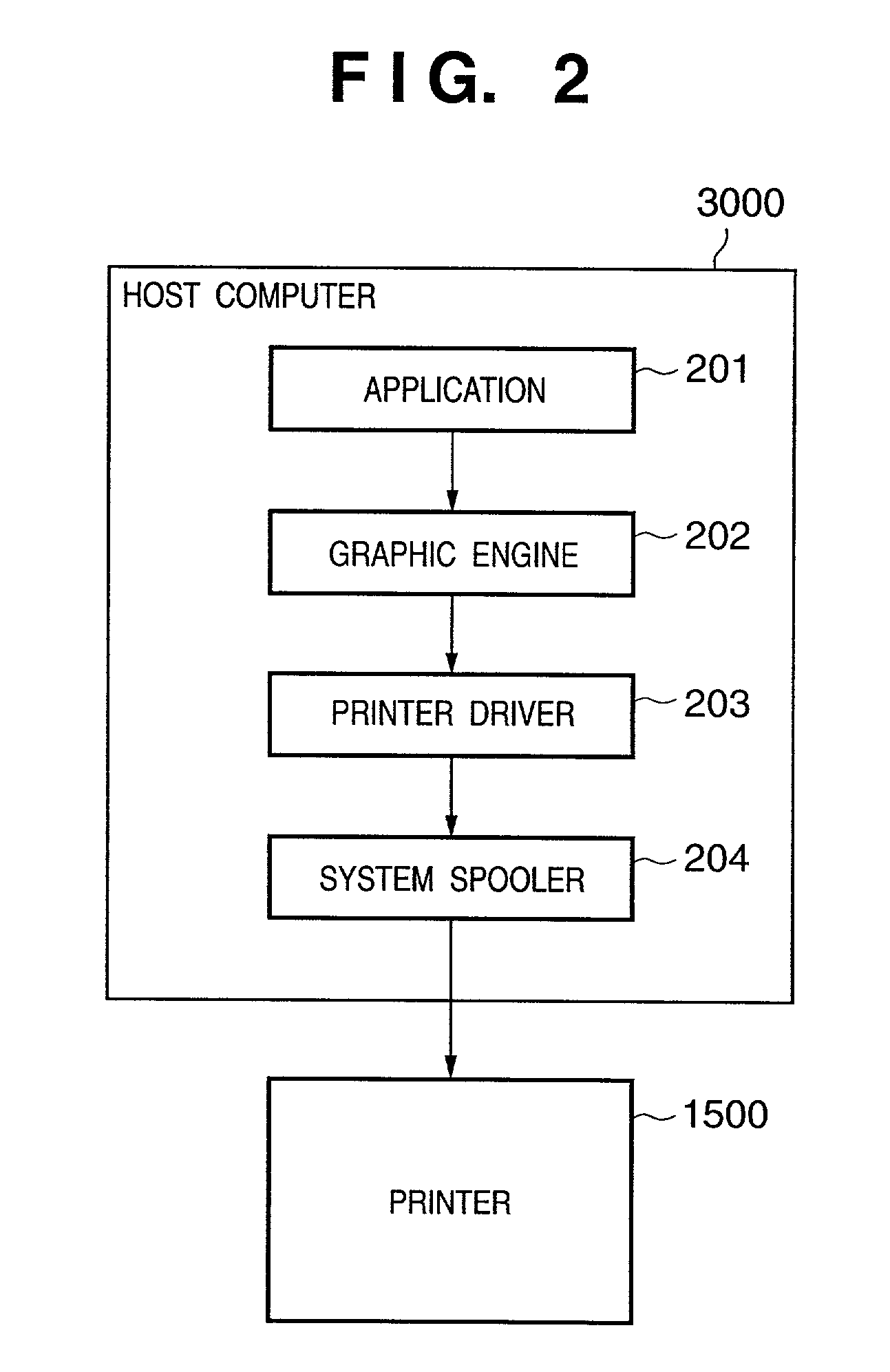

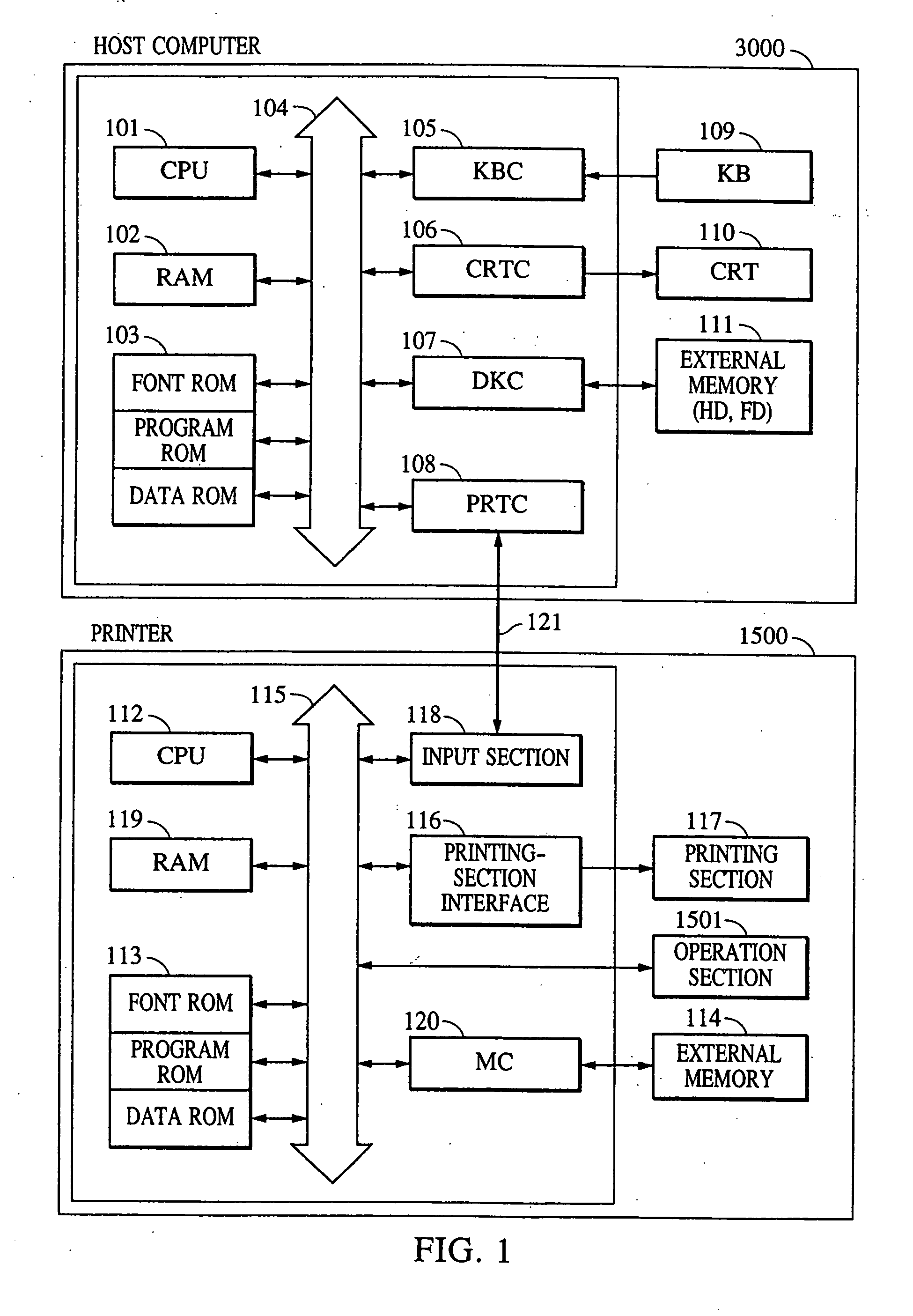

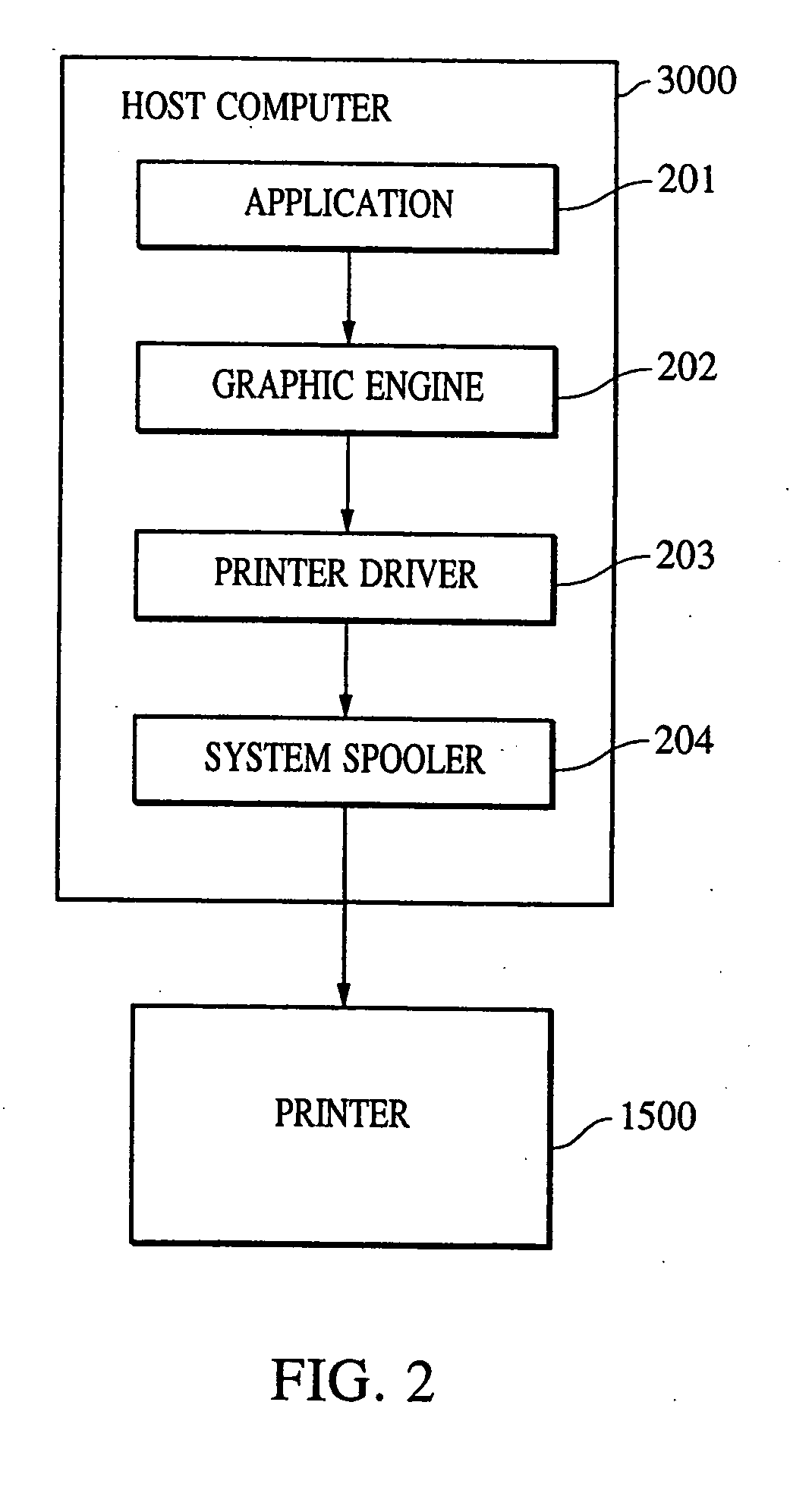

Printing with designation of processing

InactiveUS6348969B1Visual representatino by photographic printingOther printing apparatusComputer scienceImaging data

When a host computer transmits print data to a printer, the computer investigates the possibility of overrun per each band of band obtained by partitioning a page into bands. The host computer designates pre-rendering processing in regard to bands in which overrun is judged to be possible. Upon receiving the print data, the printer generates and compresses image data beforehand in regard to a band for which pre-rendering has been designated and stores the compressed image data. In case of a band for which pre-rendering has not been designated, the printer generates an intermediate code at a stage prior to the generation of image data from the print data. At the time of printing, image data is generated in one of two band buffers and image data is output from one band buffer. At this time the compressed image data is decompressed in case of a band for which pre-rendering has been designated, and image data is generated from an intermediate code in case of a band for which an intermediate code has been generated.

Owner:CANON KK

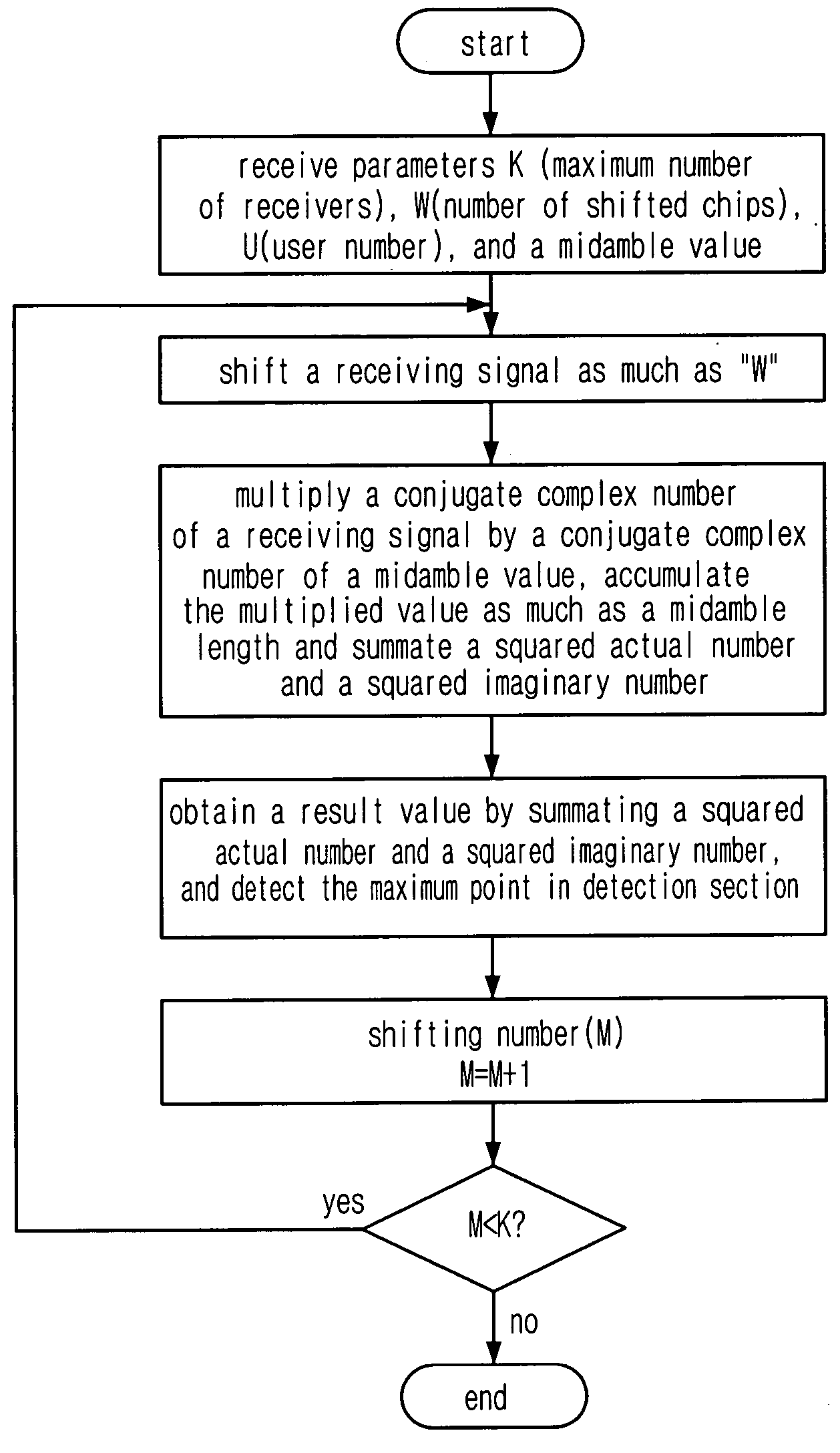

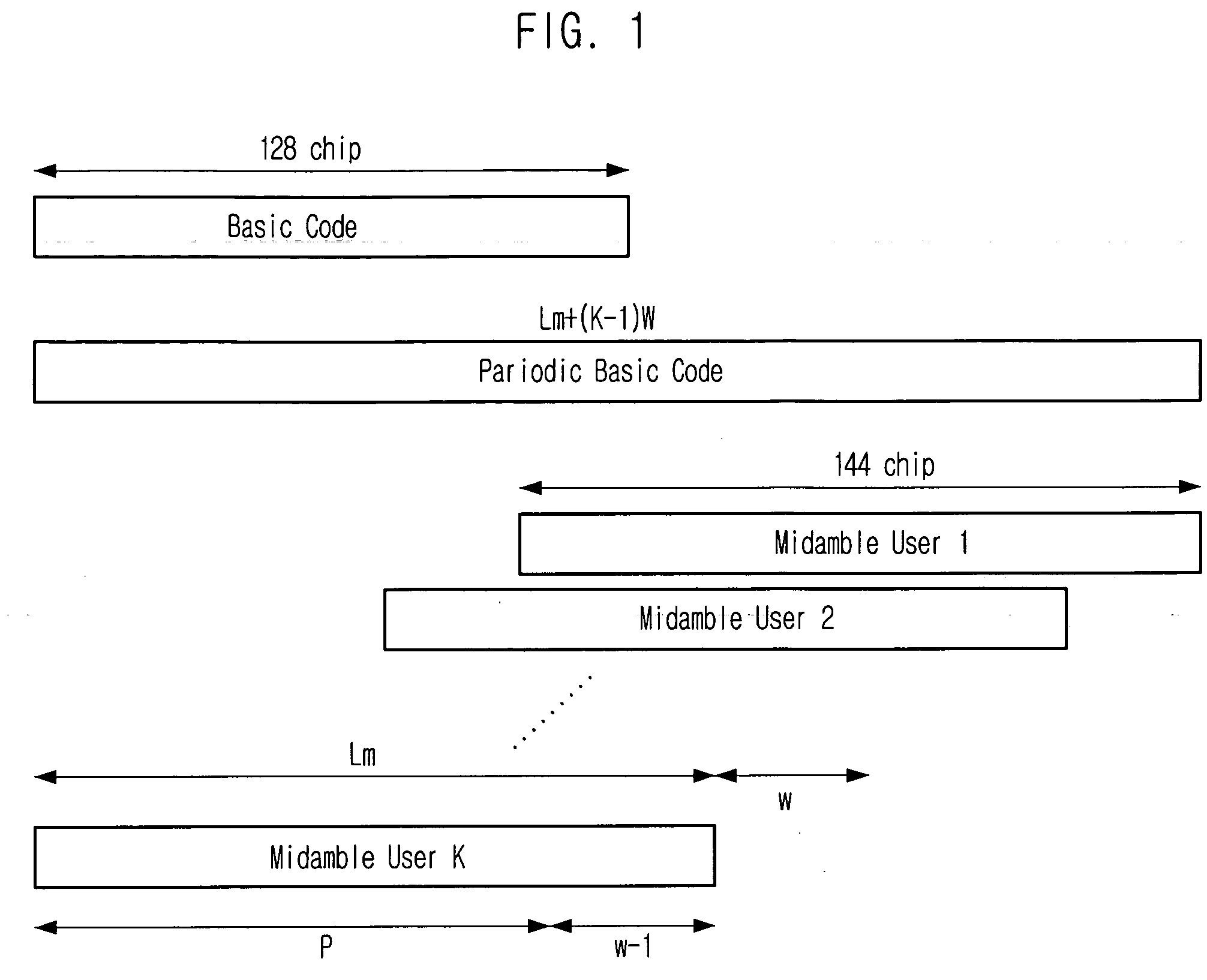

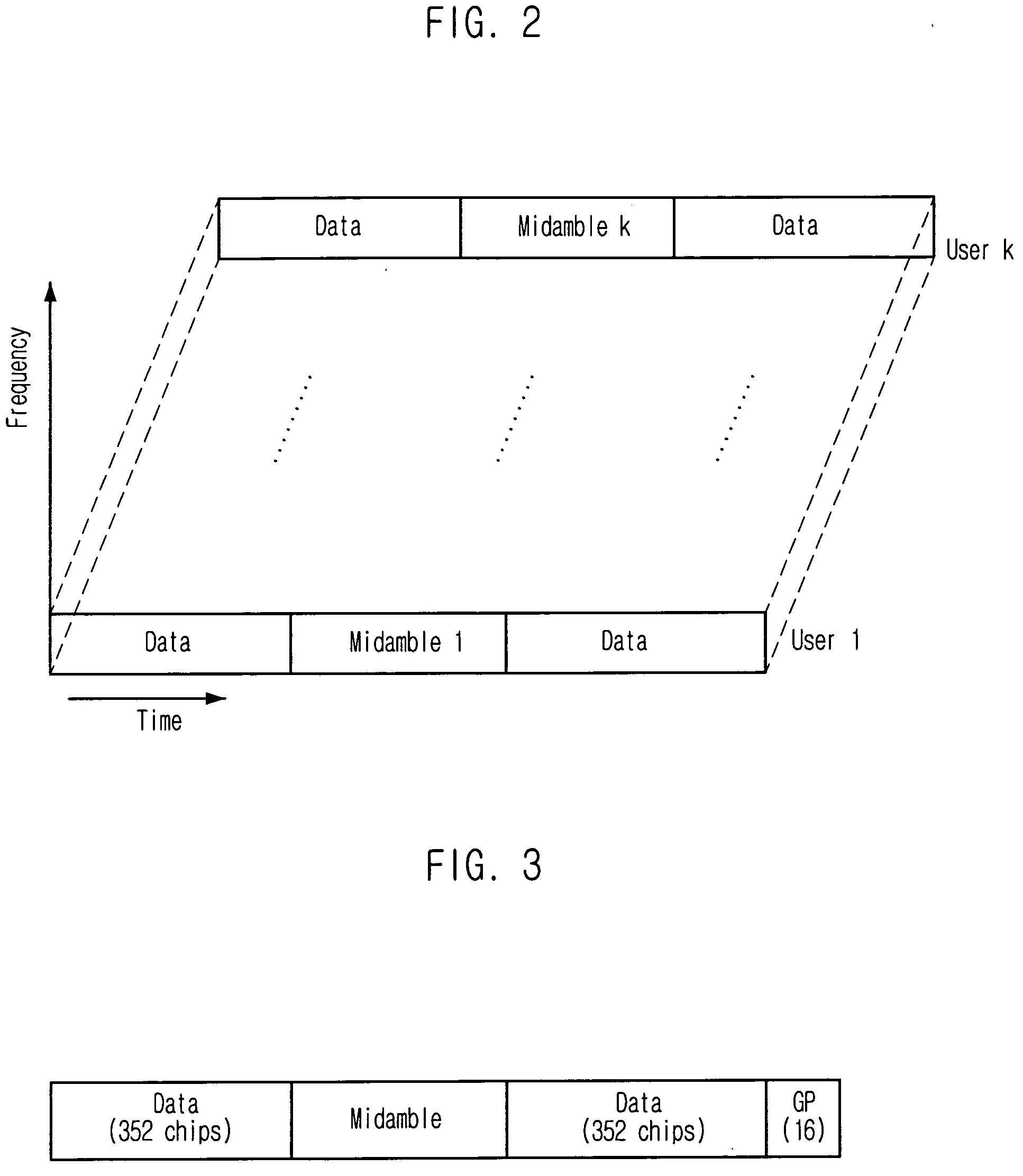

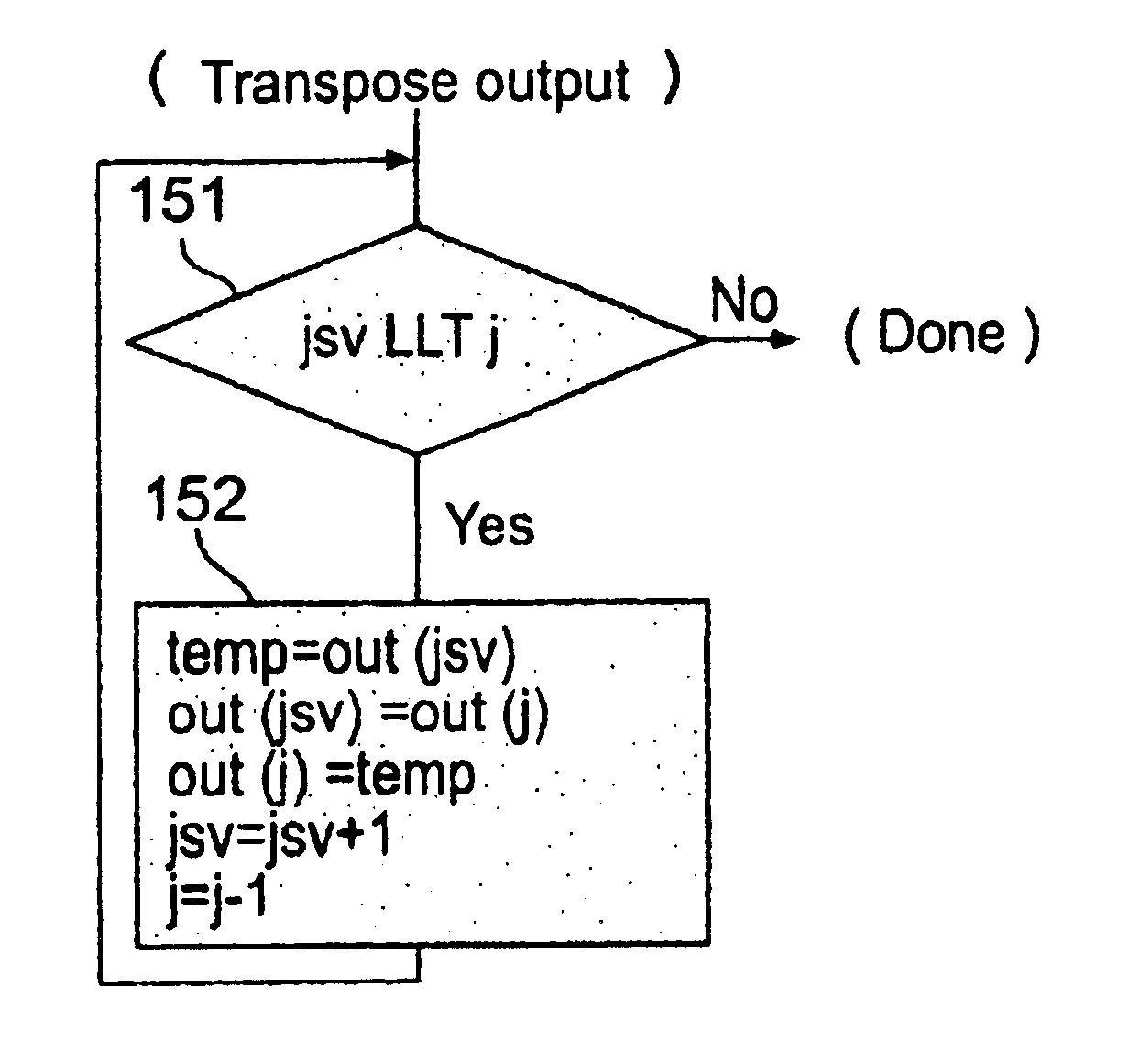

Apparatus and method for detecting timing error based on cyclic correlation

InactiveUS20060126765A1Reduce complexityReduce processing timeTime-division multiplexAmplitude-modulated carrier systemsShift registerTiming error detector

Provided is an apparatus and method for detecting timing errors based on characteristics of cyclic correlation. The apparatus and method can detect the timing errors of many users by using the cyclic characteristics of a midamble code at a time and detects the timing errors based on the characteristics of cyclic correlation to reduce the time required for detecting the users and lower the complexity in terms of Hardware. The apparatus includes a detection section controller, a register, a midamble generator, a midamble shifter, an accumulator, an adder, a shift register and a timing error detector.

Owner:ELECTRONICS & TELECOMM RES INST

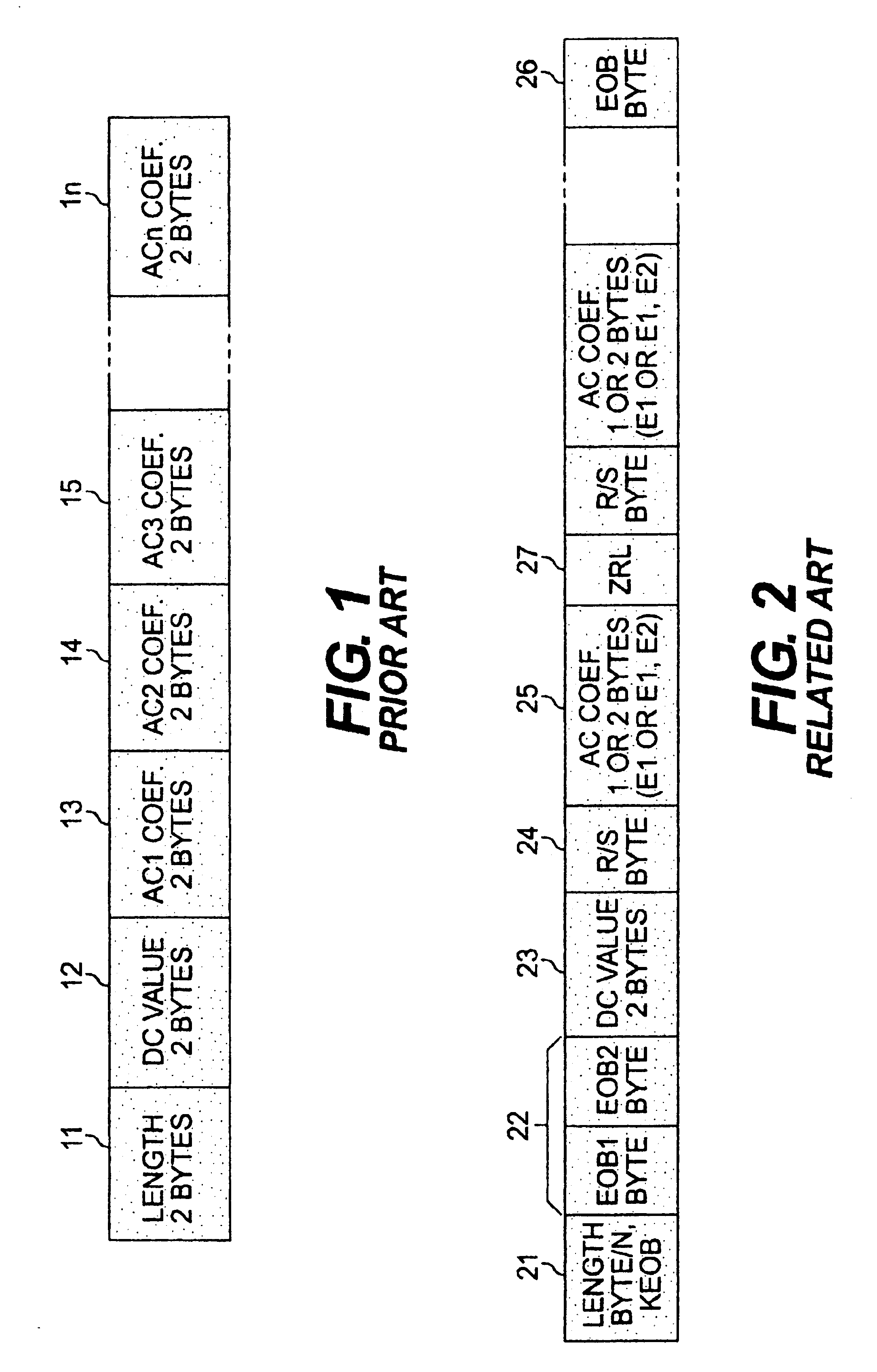

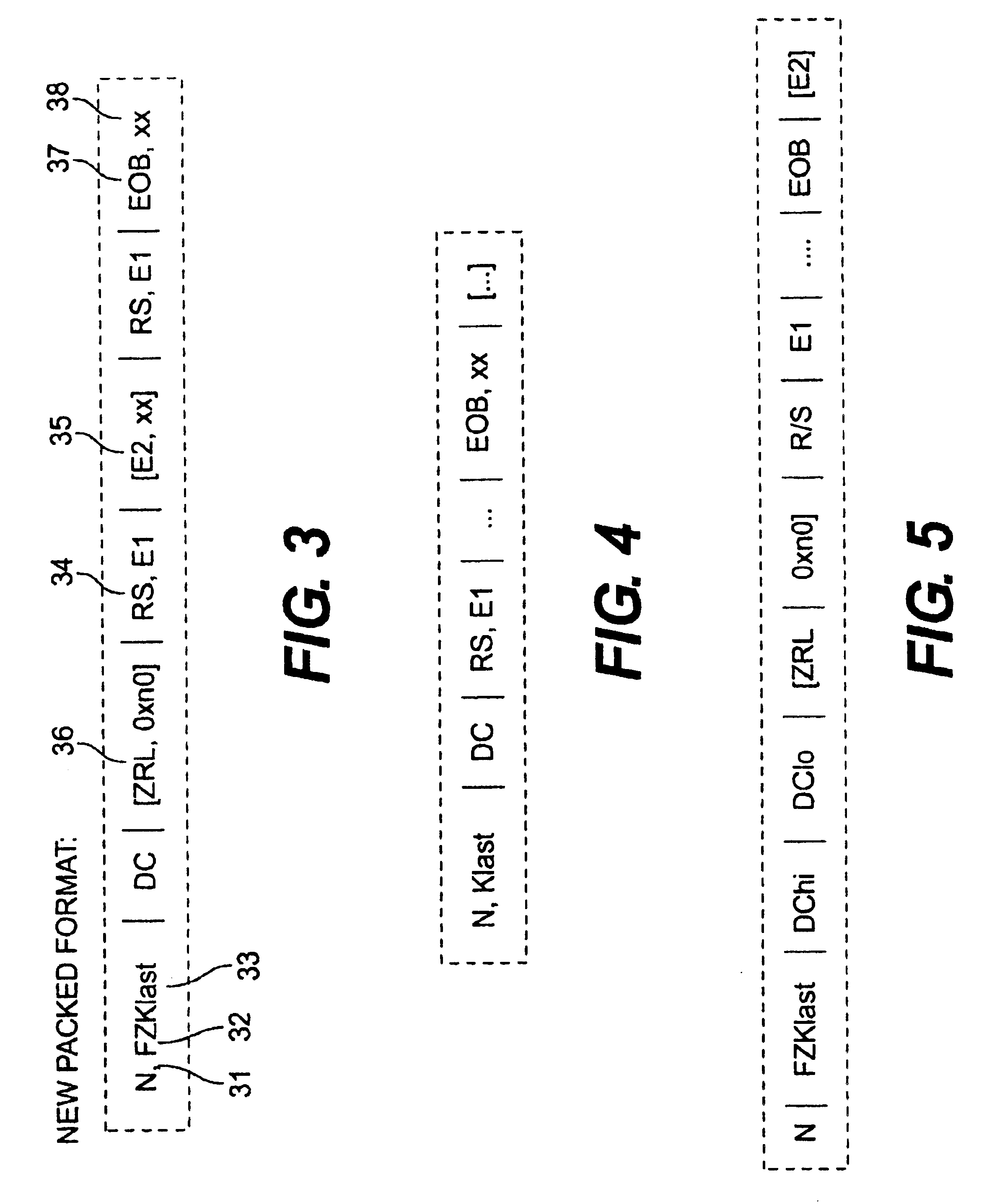

Faster lossless rotation of JPEG images

InactiveUS6819803B2Easy to implementReduce processing timeGeometric image transformationCharacter and pattern recognitionJPEGGlyph

Image rotations of 90°, 180° and 270° and horizontal and vertical mirroring image transformations are performed losslessly and with greatly enhanced speed by processing orthogonal transform coefficients in a zig-zag order with direct storage of S (size) values, reassociated R (run of zero valued coefficients) from an adjacent coded orthogonal transform value and a non-zero valued transformation coefficient in reverse zig-zag order. Cache misses are avoided by processing values which are not widely separated in the coded data and other features of the technique and memory accesses are reduced to accelerate processing while extremely little computation is required. These effects are substantially augmented when intermediate codes having certain attributes including coding of zero valued coefficients and flagging certain code features are employed.

Owner:PENDRAGON NETWORKS

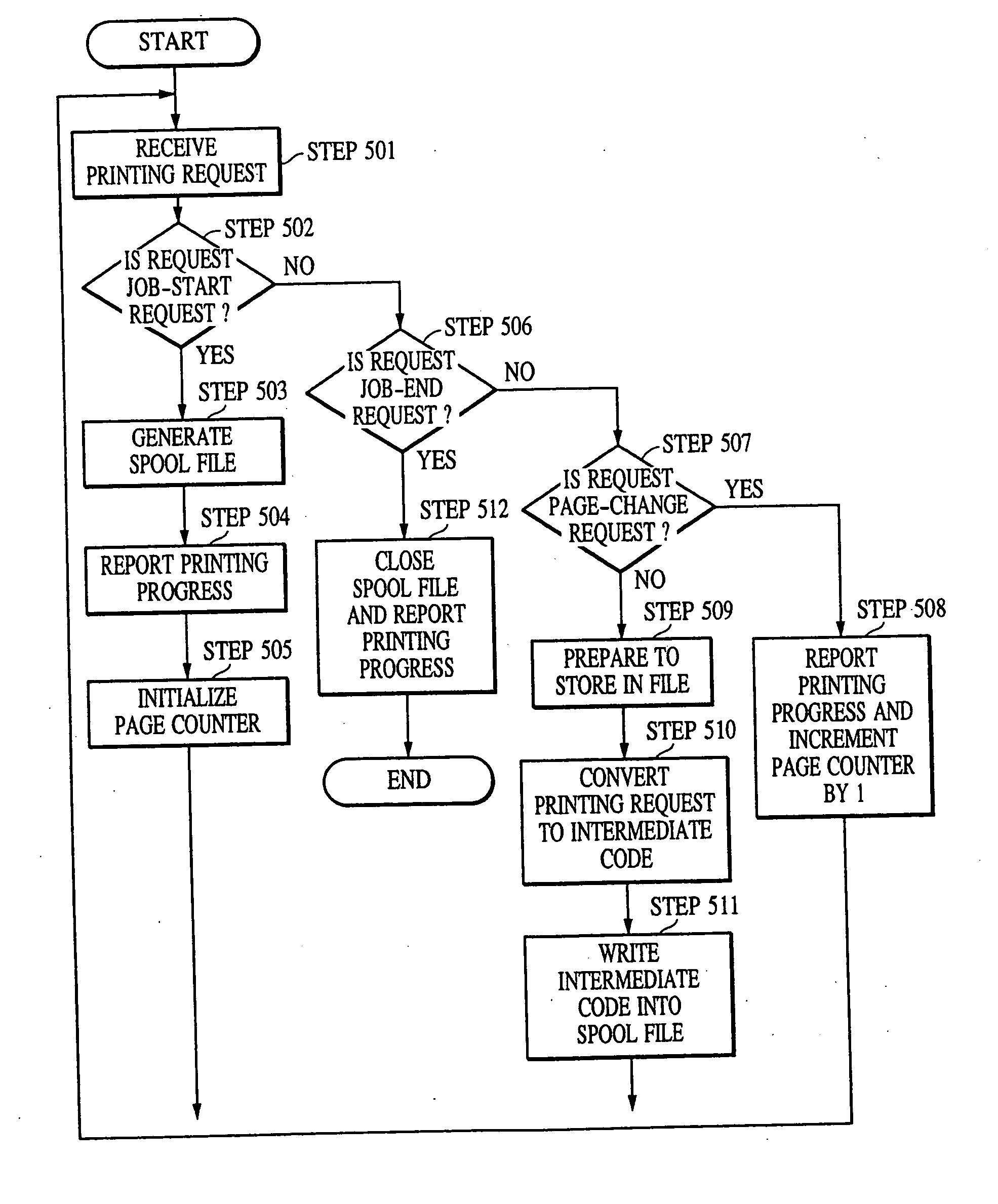

Information processing apparatus, information processing method, and storage medium storing computer-readable program therein

InactiveUS7301656B1Digital computer detailsNatural language data processingInformation processingData transformation

When a preview of a composed job is performed by composing data outputted from an application for printing, in order to provide a method for enabling the preview to be performed in consideration of a layout of each print job, one composed job is formed by composing the print jobs obtained by converting the data to be printed into the data in an intermediate code format and this method is realized by controlling so as to display the preview of the composed job on the basis of layout information of each print job in the composed job.

Owner:CANON KK

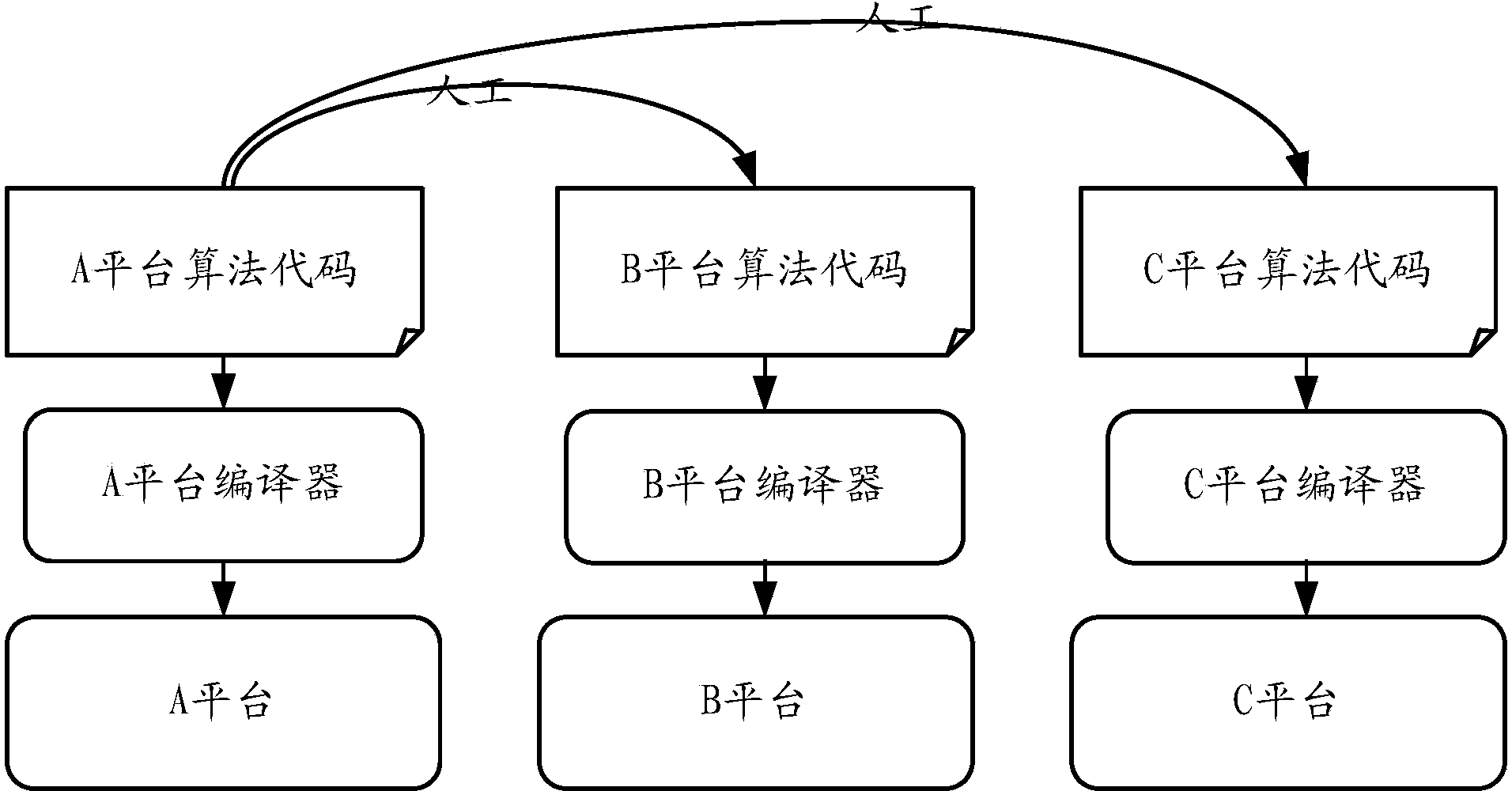

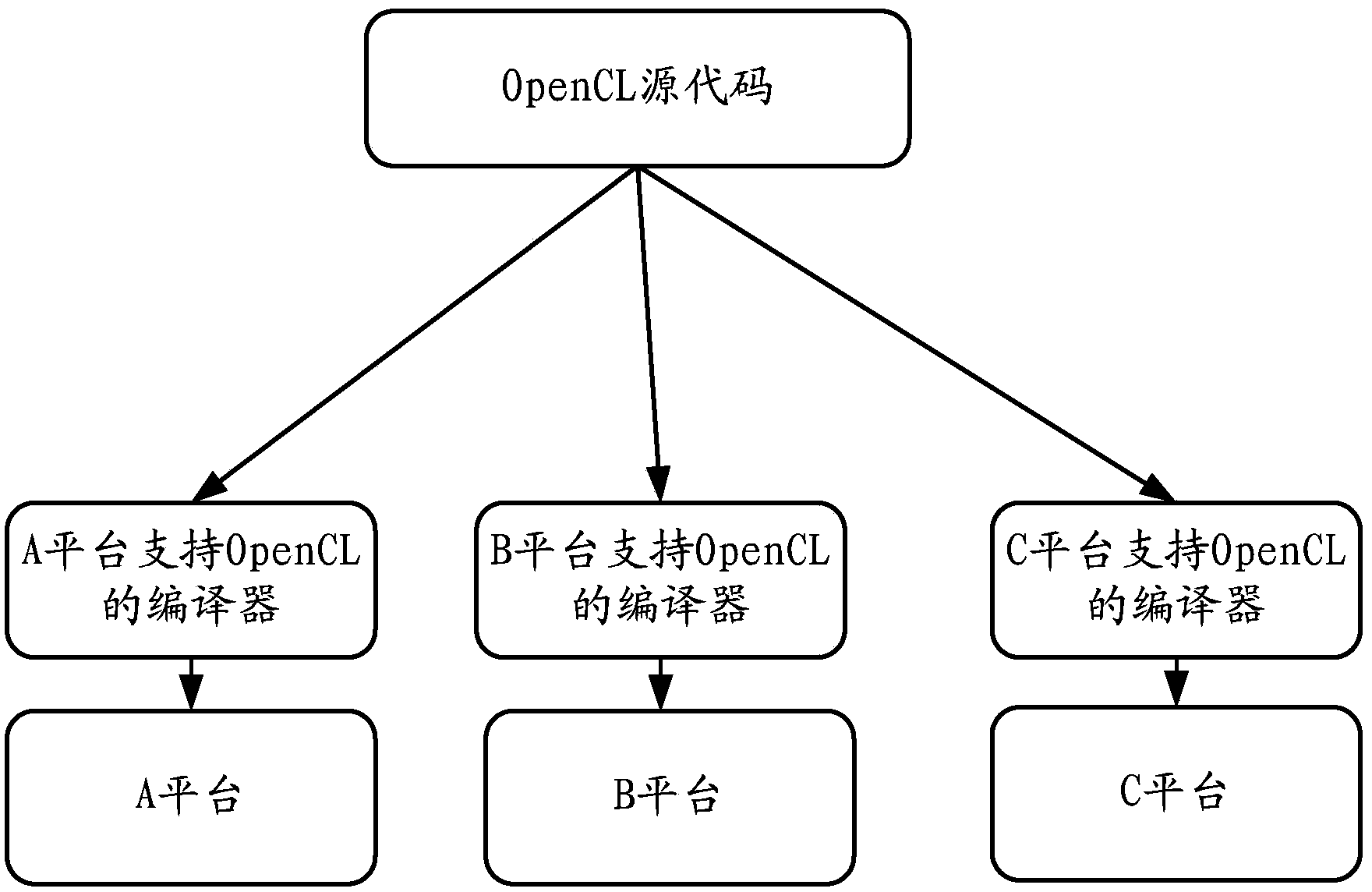

Transplantation method and source to source compiler

InactiveCN103631632AAchieve portingSolve the problem that cross-platform source-to-source conversion cannot be achievedSpecific program execution arrangementsMemory systemsTheoretical computer scienceSource code

The embodiment of the invention discloses a transplantation method and a source to source compiler, and aims to solve the problem in the prior art that the application program can not carry out cross-platform transplantation. The method comprises the following steps of receiving a common platform algorithm source code which is irrelevant with a platform chip framework, is compiled by aiming at an application program and adopts a common operator and a common data type; converting the common operator and the common data type in the common platform algorithm source code to obtain a target platform algorithm source code which conforms to the target platform requirement; and sending the target platform algorithm source code to a target platform complier. In the embodiment, the common platform algorithm source code is used as an intermediate code, the common operator and the common data type of the common platform algorithm source code are converted to obtain the target platform algorithm source code which conforms to the target platform requirement; the conversion of the common operator and the common data type is the conversion to the basic operation; therefore, cross-platform source to source conversion can be realized; and the problem in the prior art that cross-platform source to source conversion can not be realized is solved.

Owner:HUAWEI TECH CO LTD

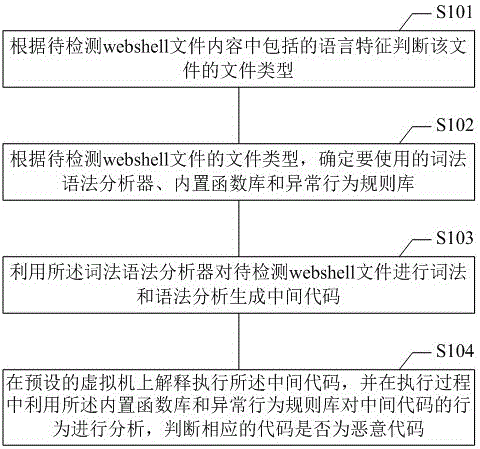

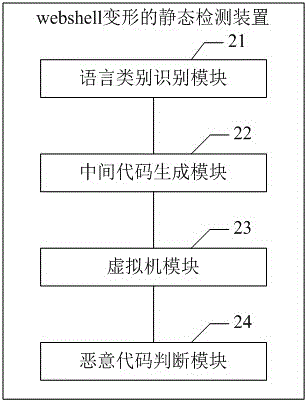

Static detection method and apparatus for webshell deformation

The application provides a static detection method and apparatus for webshell deformation. The method comprises: according to voice features contained in the content of a to-be-detected webshell file, judging the type of the file; according to the type of the file, determining a lexical and syntax analyzer, a built-in function library and an abnormal behavior rule library which are to be used; performing lexical and syntax analysis on the to-be-detected webshell file by utilizing the lexical and syntax analyzer to generate an intermediate code; and interpretively executing the intermediate code in a preset virtual machine, analyzing a behavior of the intermediate code by utilizing the built-in function library and the abnormal behavior rule library in the execution process, and judging whether a corresponding code is a malicious code. According to the scheme of the application, the problem that an existing hook mode possibly influences normal business can be avoided while the deformed webshell code is effectively identified.

Owner:XIAMEN MEIYA PICO INFORMATION

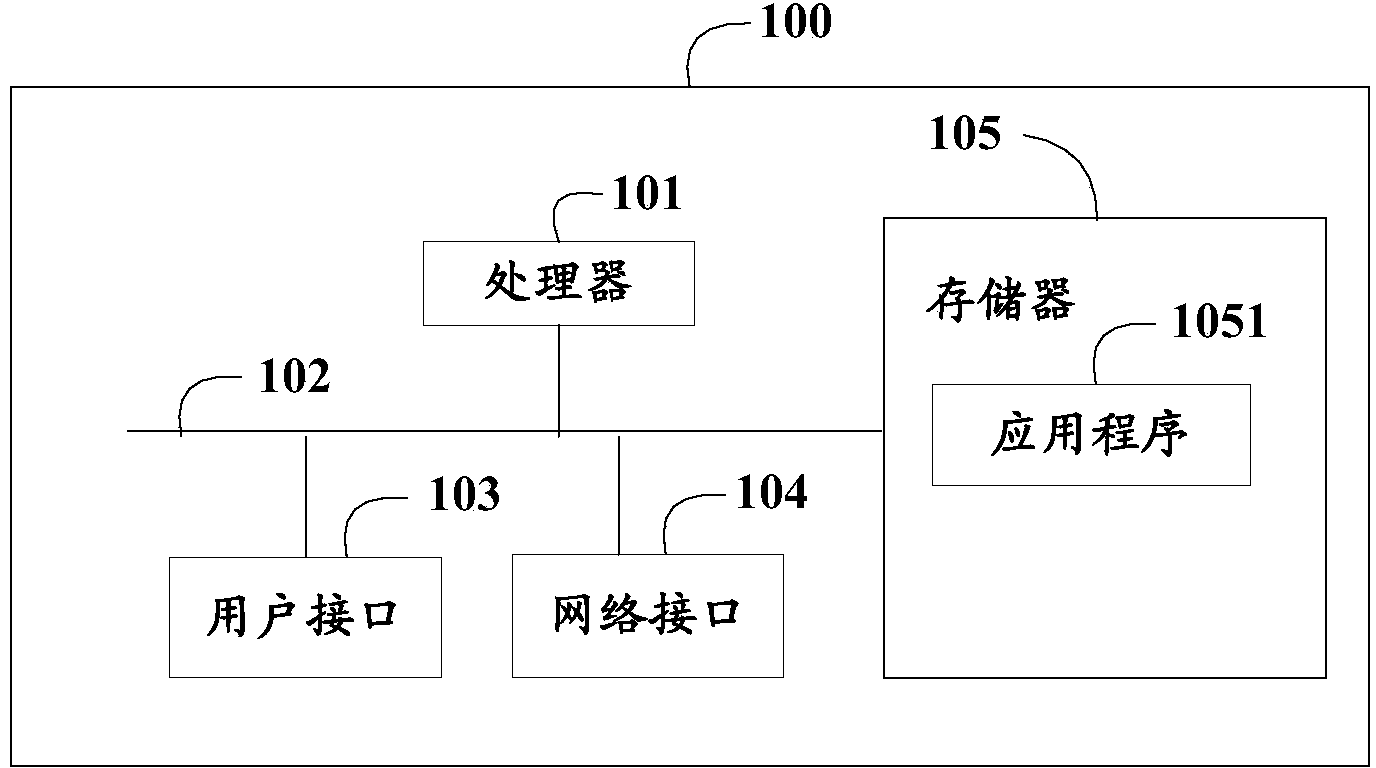

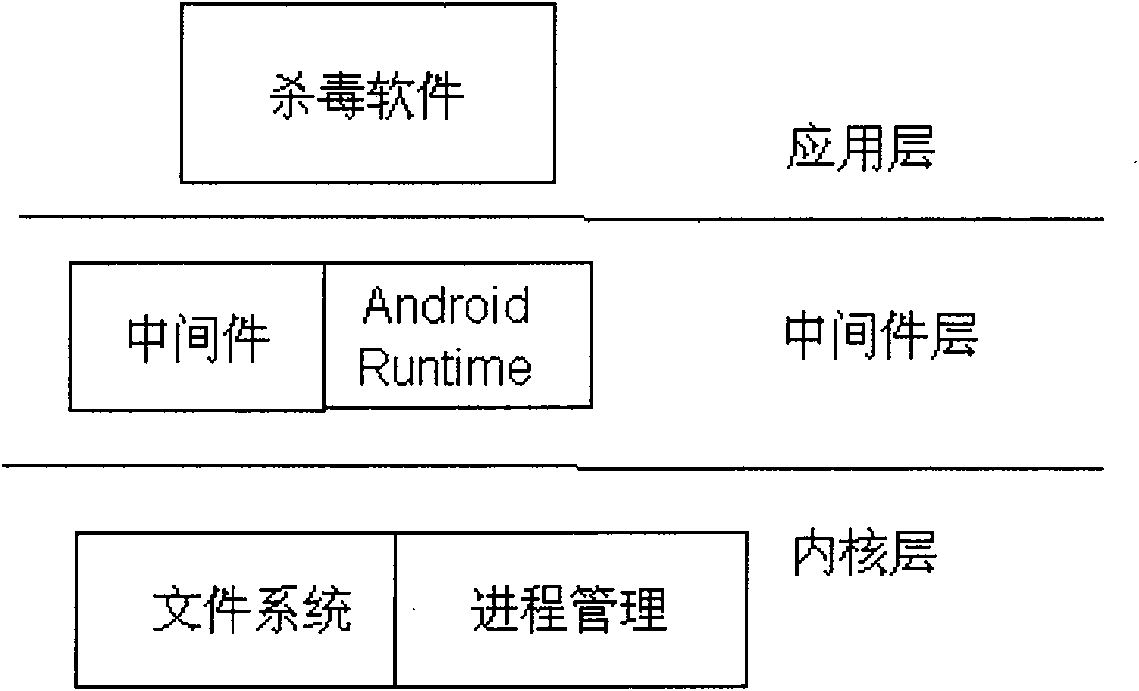

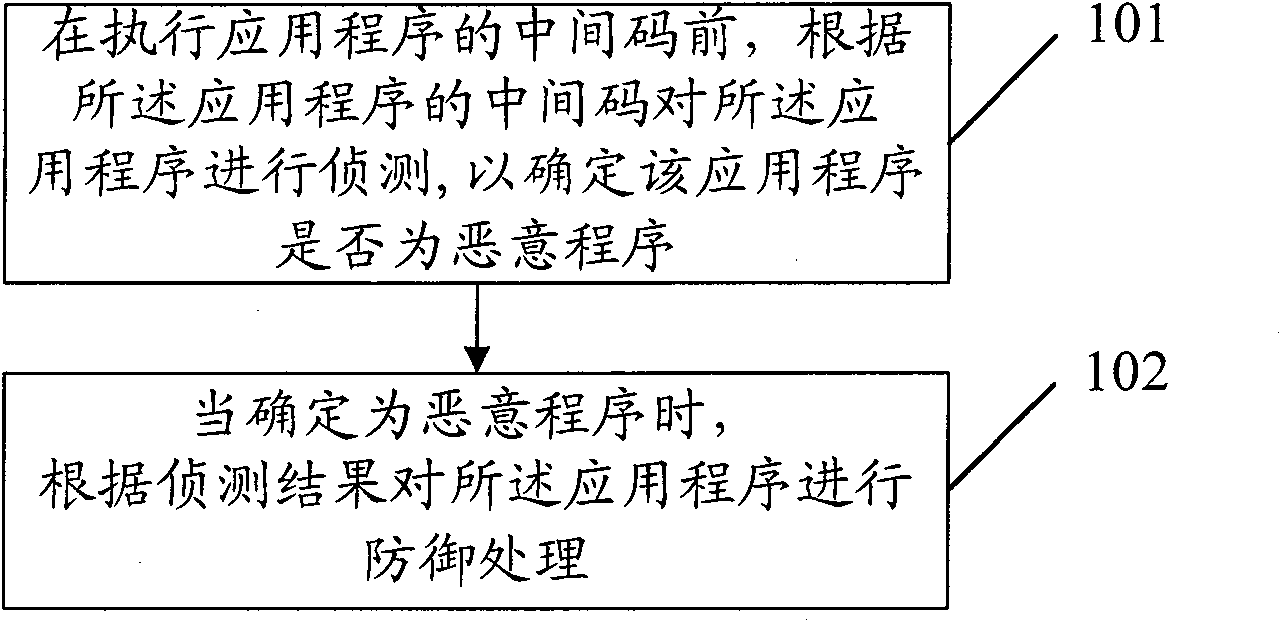

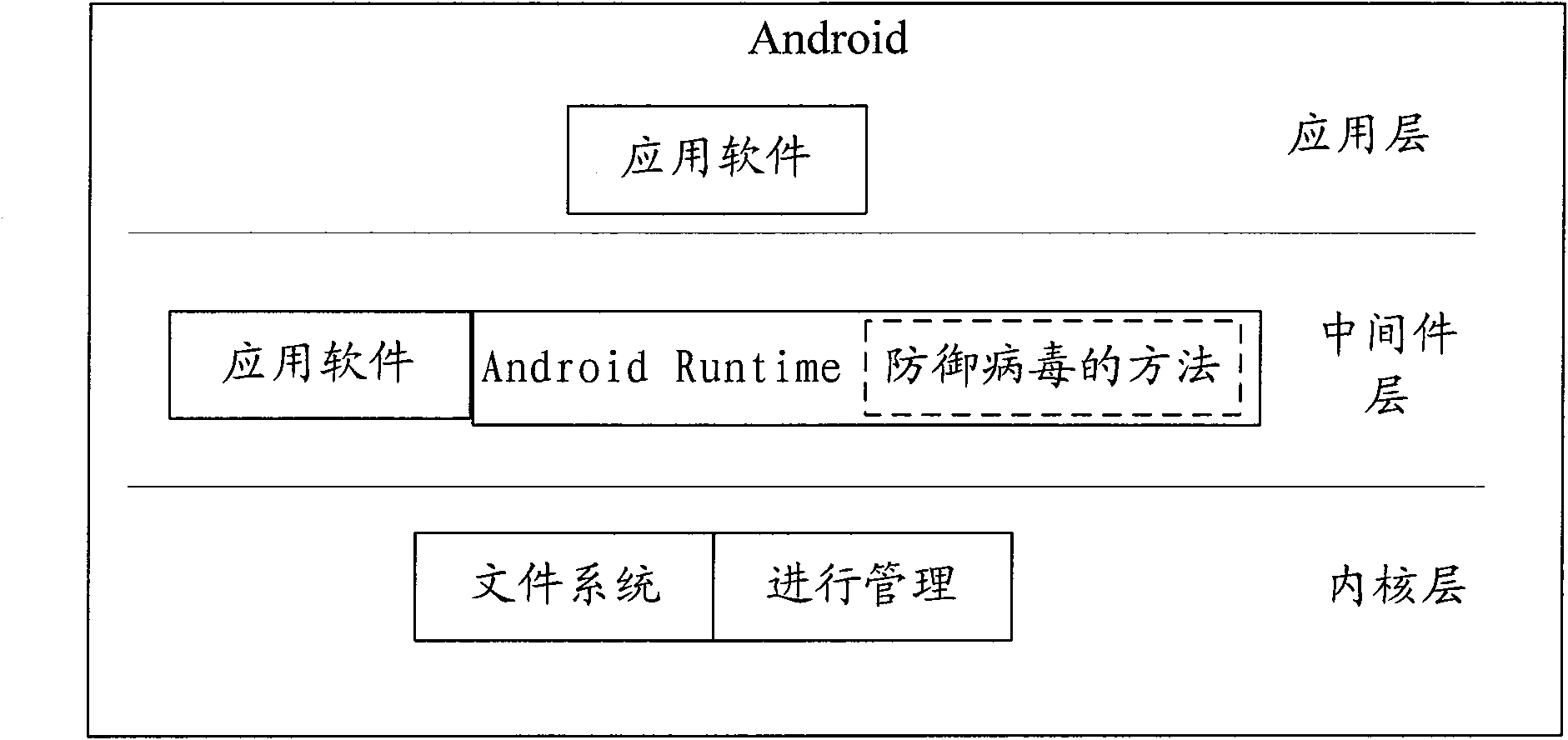

Method, device and system for defending malicious program for terminal

InactiveCN101901321AAvoid harmImprove protection against malicious programsPlatform integrity maintainanceApplication softwareInformation security

The embodiment of the invention discloses a method, a device and a system for defending a malicious program for a terminal, relates to the technical field of information security and communication and solves the technical problem of poor security of an antivirus scheme used in terminals such as a mobile phone and the like in the prior art. The method in the embodiment of the invention mainly comprises the following steps of: before executing an intermediate code of an application program, detecting the application program according to the intermediate code of the application program to determine whether the application program is a malicious program or not; and performing defense treatment on the application program if the application program is a malicious program. The method, the device and the system in the embodiment of the invention are mainly used for improving the information security.

Owner:HUAWEI DEVICE CO LTD

Information processing apparatus and method for creating print data and storage medium

InactiveUS7161711B2Digitally marking record carriersDigital computer detailsInformation processingApplication software

When a preview of a job that combines data to be printed output from an application is presented, an information processing apparatus includes, for the purpose of presenting a preview considering the setting of each print job, an intermediate data conversion unit that converts print data created by the application to an intermediate code format and stores the converted intermediate code format data and processing conditions of the print data, an editing unit that edits the data converted to an intermediate code format or processing conditions of the print data, a data creation unit that creates print data and processing conditions that implement print processing different from the print data created by the application based on the edited data and a preview display control unit for displaying the print processing result in advance based on the created print data and processing conditions.

Owner:CANON KK

Compiler, compiler apparatus and compilation method

ActiveUS7284241B2Convenient teachingImprove the level ofSoftware engineeringGeneral purpose stored program computerCode generationIntermediate code

An operator definition file 102 and the like included in a source program 101 and a compiler 100 that translates the source program 101 into a machine language program 105 are provided. The operator definition file 102 includes definitions of various fixed point type operators by class definitions. The compiler 100 can generate effectively advanced and specific instructions that a processor executes and make improvements through expanding functions and the like without repeating frequently upgrading of the version of the compiler itself. The compiler 100 is made up of an intermediate code generation unit 121 that generates intermediate codes, a machine language instruction substitution unit 122 that substitutes the intermediate codes referring to classes defined by the operator definition file 102 with machine language instructions and an optimization unit 130 that performs optimization targeting the intermediate codes including the substituted machine language instructions.

Owner:SOCIONEXT INC

Information processing apparatus, information processing method, and storage medium storing computer-readable program

InactiveUS20050200879A1Control changesDigital computer detailsCathode-ray tube indicatorsInformation processingUser interface

Owner:CANON KK

Programming language compiling method of PLC (Programmable Logic Controller)

InactiveCN104239115AIncrease profitClear logical relationshipProgram controlMemory systemsObject codeSystem hardware

The invention relates to the field of industrial control and particularly relates to a programming language compiling method of a PLC (Programmable Logic Controller). The programming language compiling method comprises the following steps: converting an instruction list, analyzing an instruction, generating an intermediate code and generating an object code. According to the method, a trapezoid language program is converted into an instruction list source program by utilizing an instruction list language as a medium according to the one-to-one correspondence relation between the trapezoid language and the instruction list language, and then an instruction list is further processed, compiled and translated into the object code, so that the language logic relation is clear, the writing format is simple, the code utilization rate is high and the compiling effect is good. The programming language compiling method is conductive to providing a soft PLC control scheme applicable to multiple hardware platforms and developing a development system applicable to multiple operating system hardware platforms. When using hardware platforms of different manufacturers as soft PLC operating systems, a user can use the development tool without relearning programming of a new hardware platform, so that a lot of time spent in relearning programming is omitted, and the method has great practical significance in PLC development.

Owner:SHANTOU UNIV +1

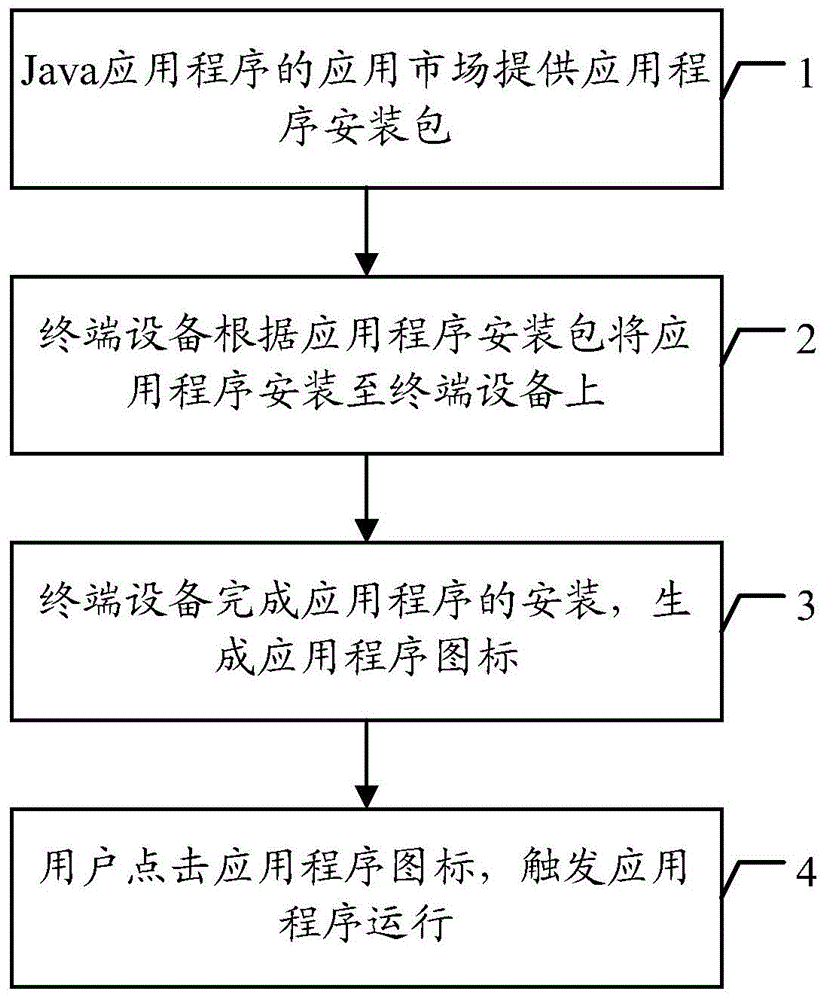

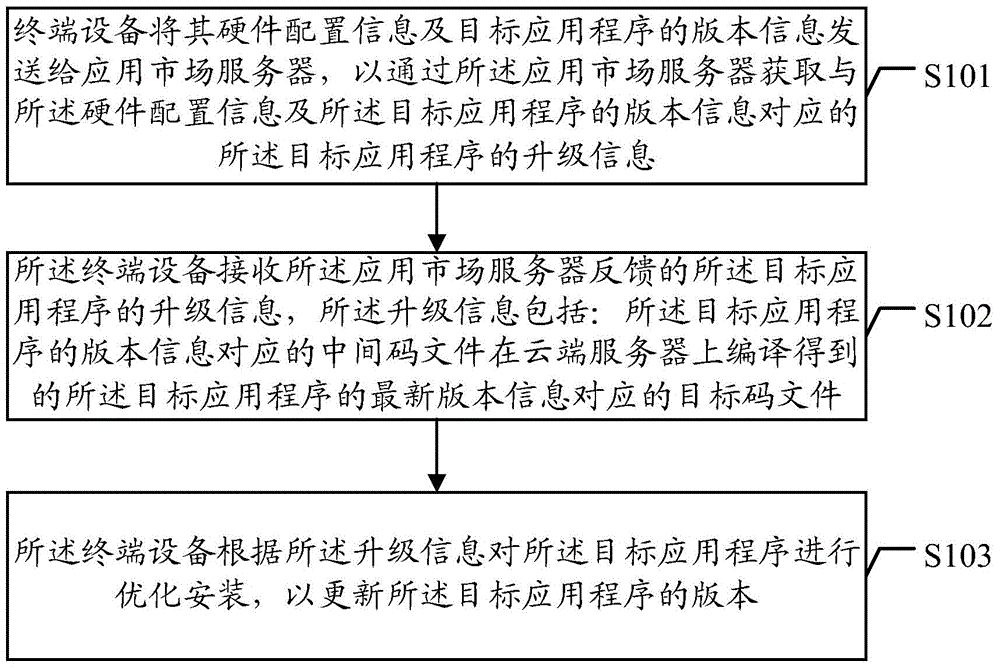

Method, device and system for realizing Java application installation via cloud compilation

ActiveCN105100191AReduce memory spaceReduce storage spaceTransmissionSoftware deploymentTerminal equipmentApplication software

The embodiment of the invention discloses a method for realizing Java application installation via cloud compilation. The method comprises the following steps that: terminal equipment transmits the hardware configuration information of the terminal equipment and the version information of a target application to an application market server in order to obtain the upgrade information of the target application corresponding to the hardware configuration information and the version information of the target application through the application market server; the terminal equipment receives the upgrade information of the target application fed back by the application market server, wherein the upgrade information includes a target code file corresponding to newest version information obtained by compilation of an intermediate code file corresponding to the version information of the target application on a cloud server; and the terminal equipment performs optimal installation of the target application according to the upgrade information in order to update the version of the target application. Through adoption of the embodiment of the invention, the method has the advantages that the equipment memory occupied by the optimal installation of the application can be reduced specifically; the efficiency of optimal installation of the application is increased; and the user experience of application installation is enhanced.

Owner:HUAWEI TECH CO LTD

Data processor, data processing method, storage medium for storing computer-readable program, and program

InactiveUS20050168764A1Visual presentation using printersOther printing apparatusComputer printingPaper document

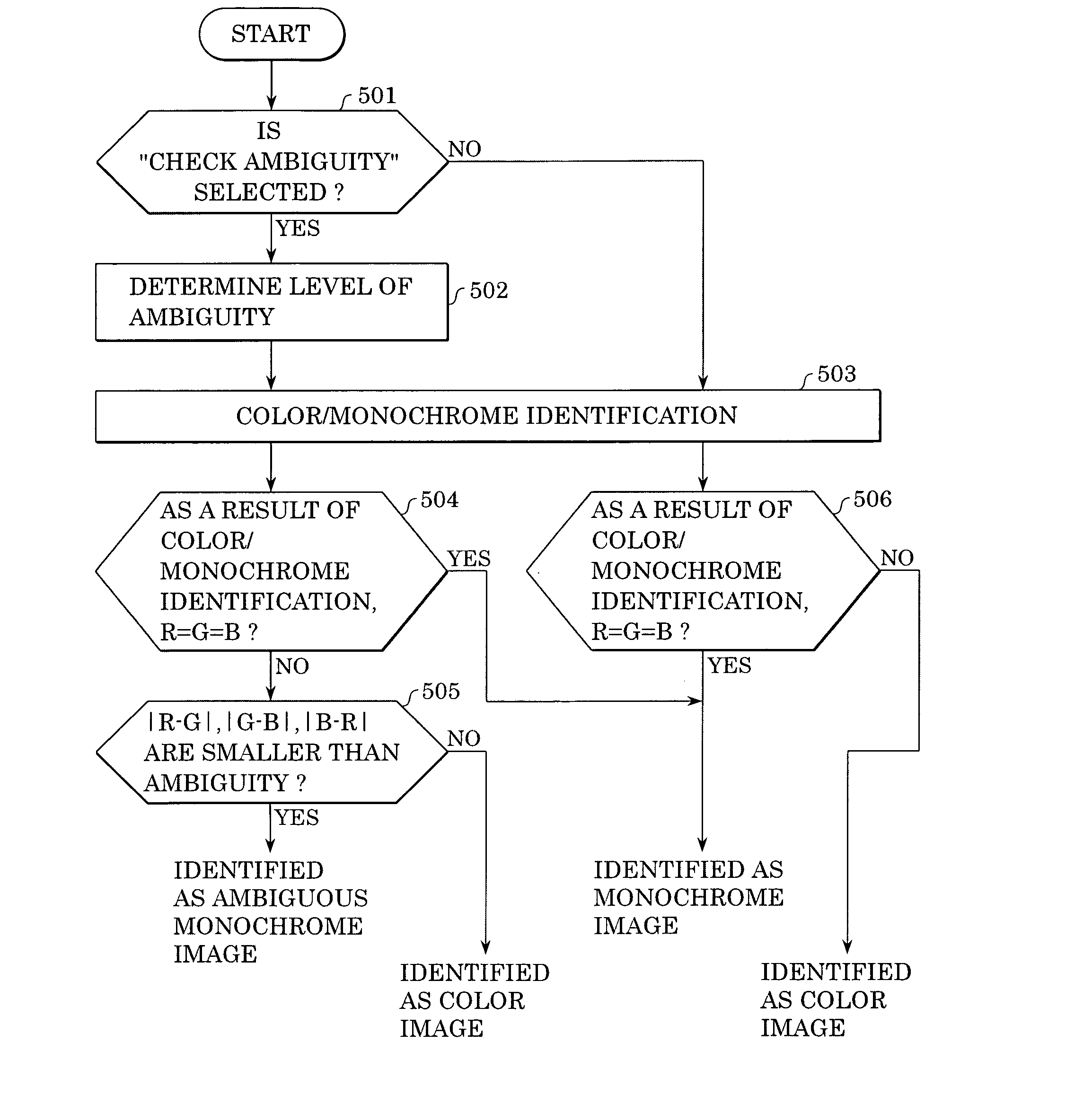

The printing mode for each page of a document can be efficiently selected at a preferable timing. A printer driver identifies a spooled intermediate code as color data or monochrome data, based on selected criteria. Based on the identification results, a page that has been identified as being ambiguous is displayed on a screen. The printing mode of the ambiguous page can be changed. Then, the change of the printing mode is confirmed. After the change is confirmed, the intermediate code is printed in accordance with the confirmed printing mode.

Owner:CANON KK

Apparatus and Method for Partitioning Programs Between a General Purpose Core and One or More Accelerators

InactiveUS20080256521A1Multiprogramming arrangementsSpecific program execution arrangementsGeneral purposeHigh-level programming language

An apparatus and method for partitioning programs between a general purpose core and one or more accelerators are provided. With the apparatus and method, a compiler front end is provided for converting a program source code in a corresponding high level programming language into an intermediate code representation. This intermediate code representation is provided to an interprocedural optimizer which determines which core processor or accelerator each portion of the program should execute on and partitions the program into sub-programs based on this set of decisions. The interprocedural optimizer may further add instructions to the partitions to coordinate and synchronize the sub-programs as required. Each sub-program is compiled on an appropriate compiler backend for the instruction set architecture of the particular core processor or accelerator selected to execute the sub-program. The compiled sub-programs and then linked to thereby generate an executable program.

Owner:INT BUSINESS MASCH CORP

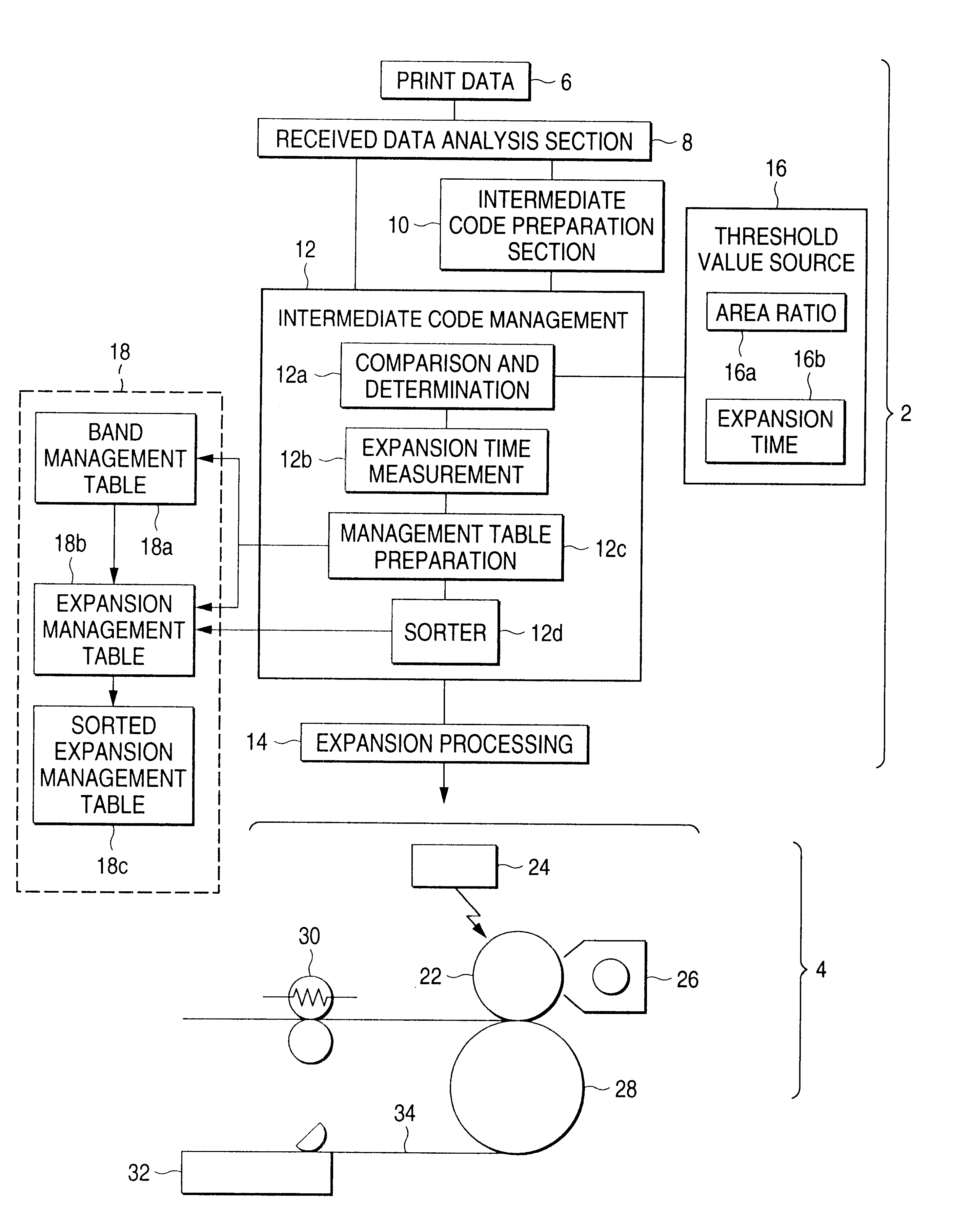

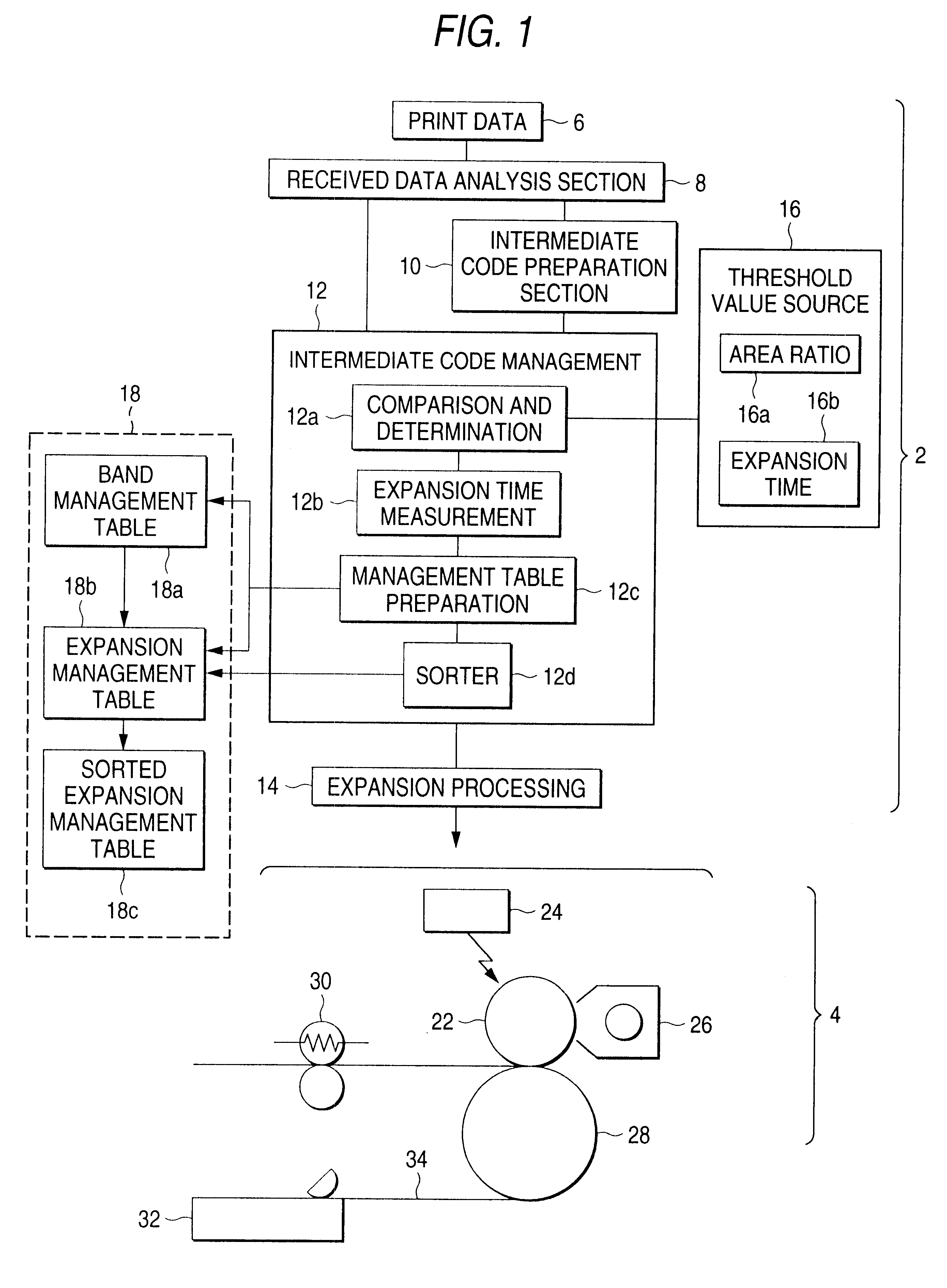

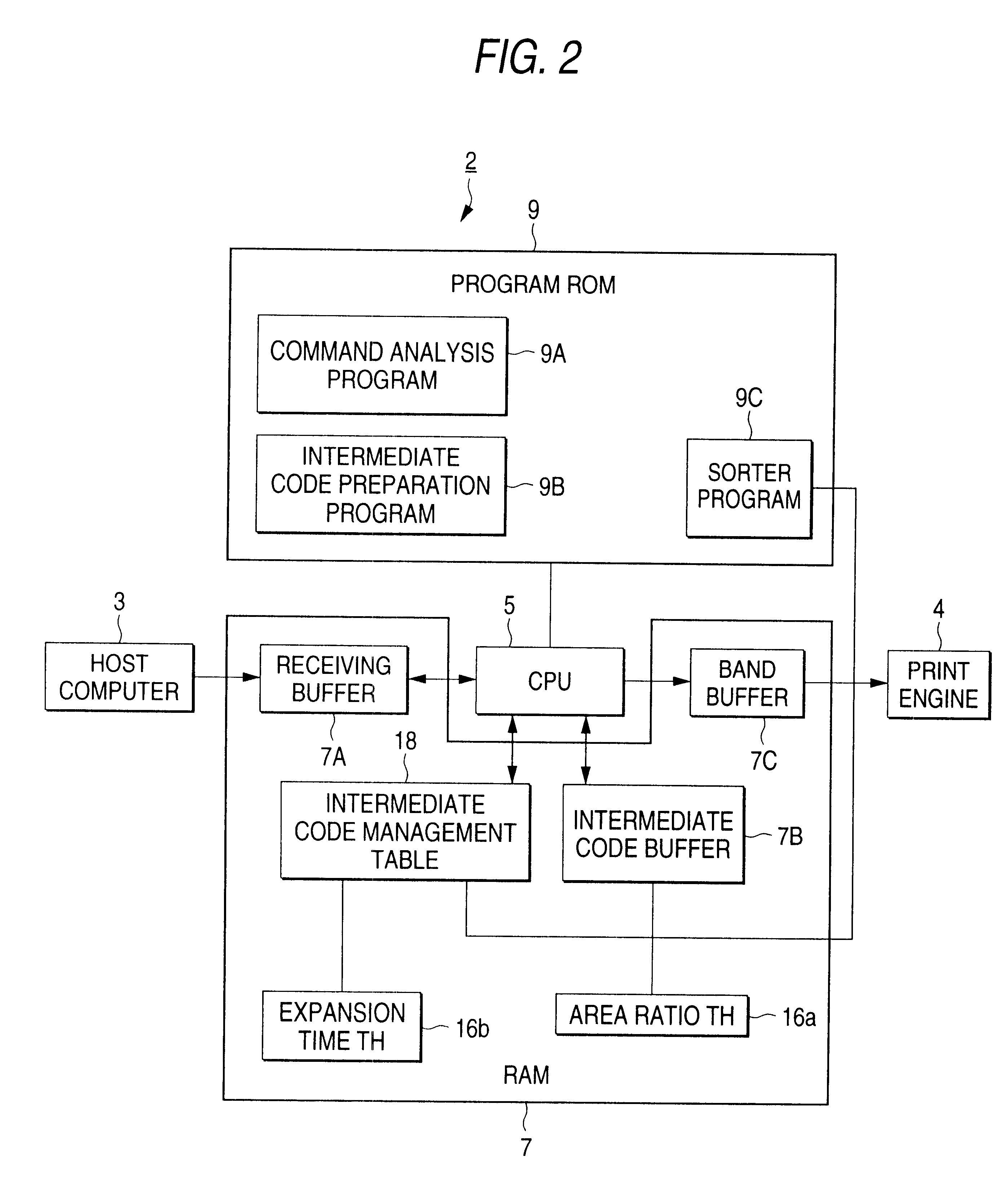

Printer, printer controller, and image input/output apparatus and method of printing

InactiveUS6574003B1Visual presentation using printersOther printing apparatusComputer architectureComputer printing

A printer includes an intermediate code preparation section that converts print data into intermediate codes for each band, and the thus-converted intermediate code is stored in memory. The intermediate code is expanded to bit-map data, and the bit-map data are transferred to a print engine. An expansion time measurement section measures the time required for expanding the intermediate code for each band. A comparison-and-determination section determines, for each band, whether or not the time required for expanding the intermediate code into the bit-map data exceeds a threshold value, thereby preparing a band management table. With regard to only the bands which exceed a threshold value, an expansion management table is prepared by copying the band management table. The expansion management table is converted into a sorted expansion management table in which bands are sorted in descending order of expansion time. Intermediate codes for the bands are expanded beforehand into bit-map data in descending order from a higher band to a lower order band in the sorted expansion management table, so long as memory for expansion is reserved.

Owner:SEIKO EPSON CORP