Patents

Literature

666 results about "Design specification" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A Product design specification is a detailed document providing information about a designed product or process. For example, the design specification must include all necessary drawings, dimensions, environmental factors, ergonomic factors, aesthetic factors, maintenance that will be needed, etc. It may also give specific examples of how the design should be executed, helping others work properly (a guideline for what the person should do).

Systems And Methods For Wireless Power System With Improved Performance and/or Ease of Use

ActiveUS20140142876A1Easy to deployFacilitate communicationNear-field transmissionTransformersElectric power systemPower grid

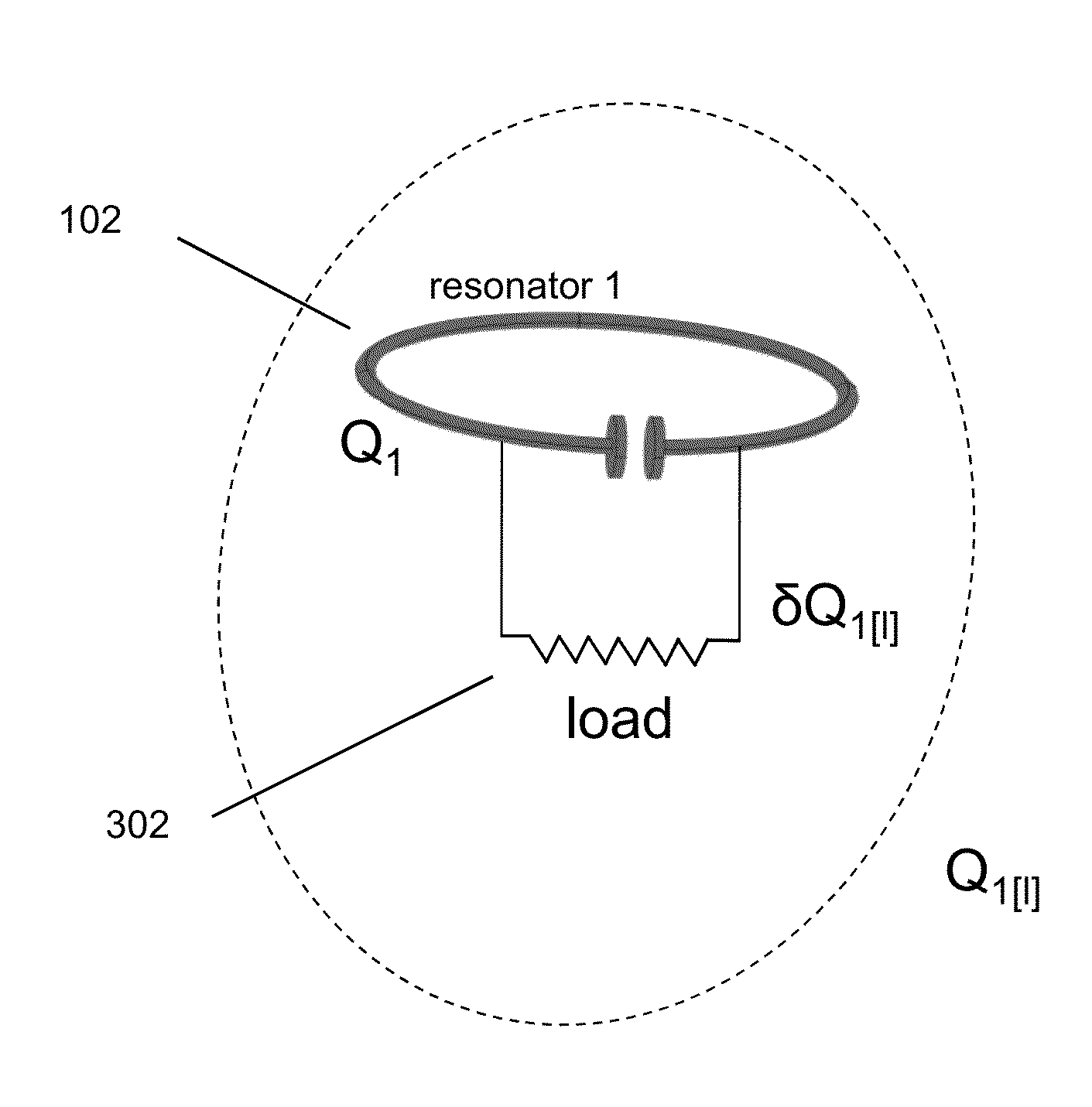

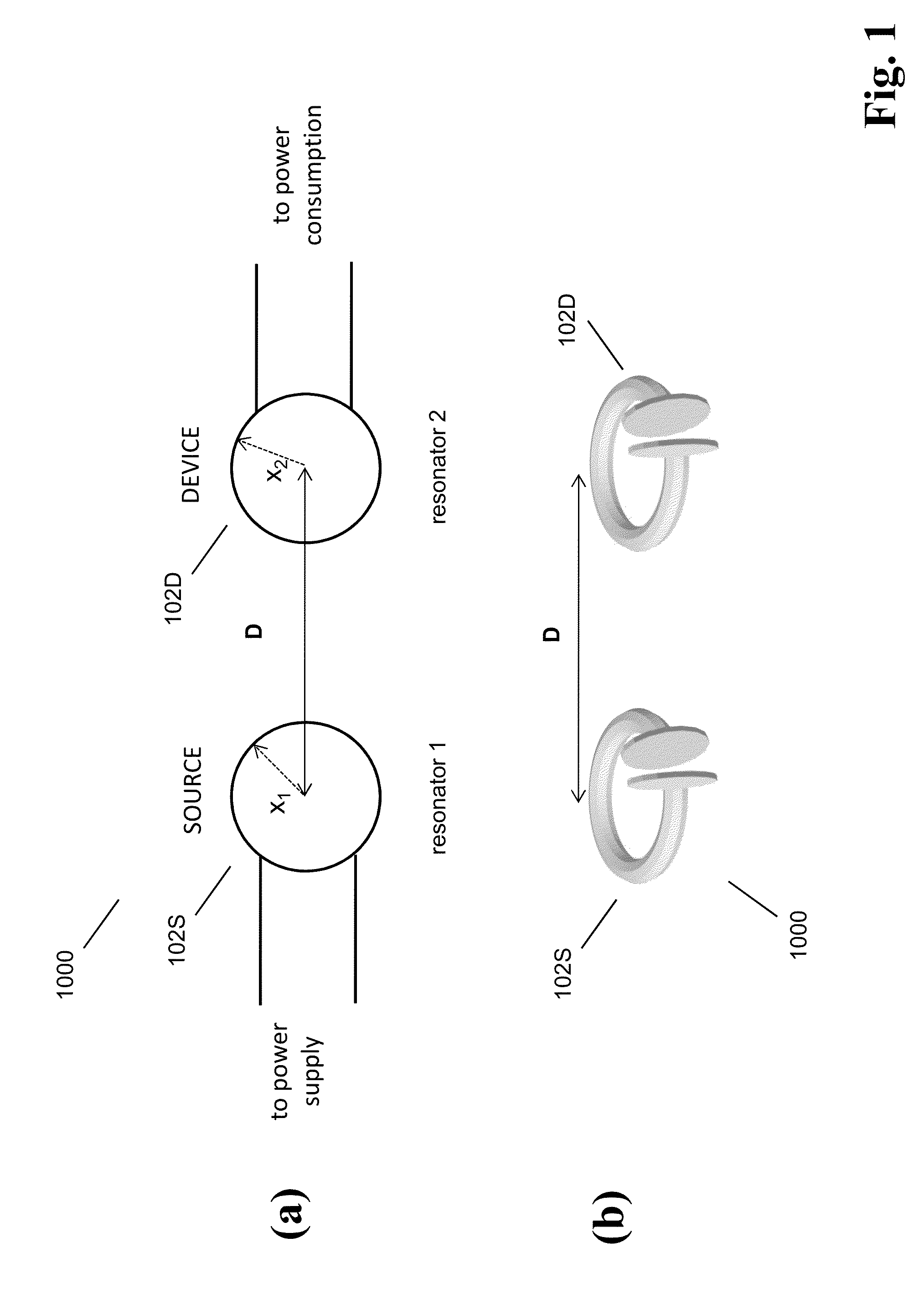

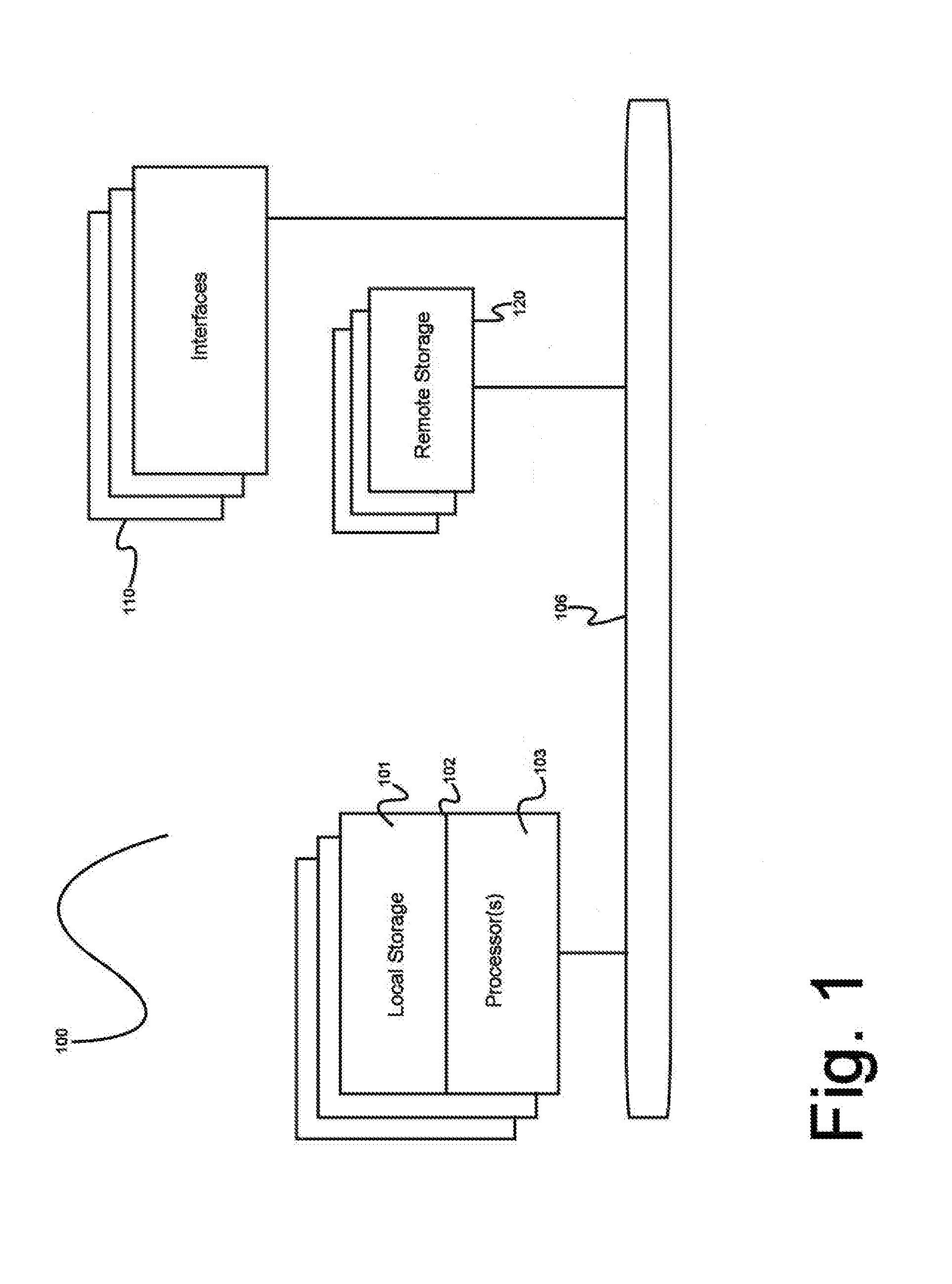

A device for testing a wireless power network is disclosed. The network includes at least one power source, at least one load, and multiple resonators configured to couple wireless power from the at least one power source to the at least one load. The device includes: a user interface for receiving input from a user and providing information to the user; a measurement module for measuring, whether directly or indirectly, at least one operational characteristic of the wireless power network and information about the geometric arrangement of the multiple resonators in the wireless power network; a memory for storing design specifications about the wireless power network; and an electronic processor configured to calculate information about a performance of the wireless power network based on the measured operational characteristic, the information about the geometric arrangement of the multiple resonators, and the stored design specifications, and further configured to provide the performance information to the user through the user interface.

Owner:WITRICITY CORP

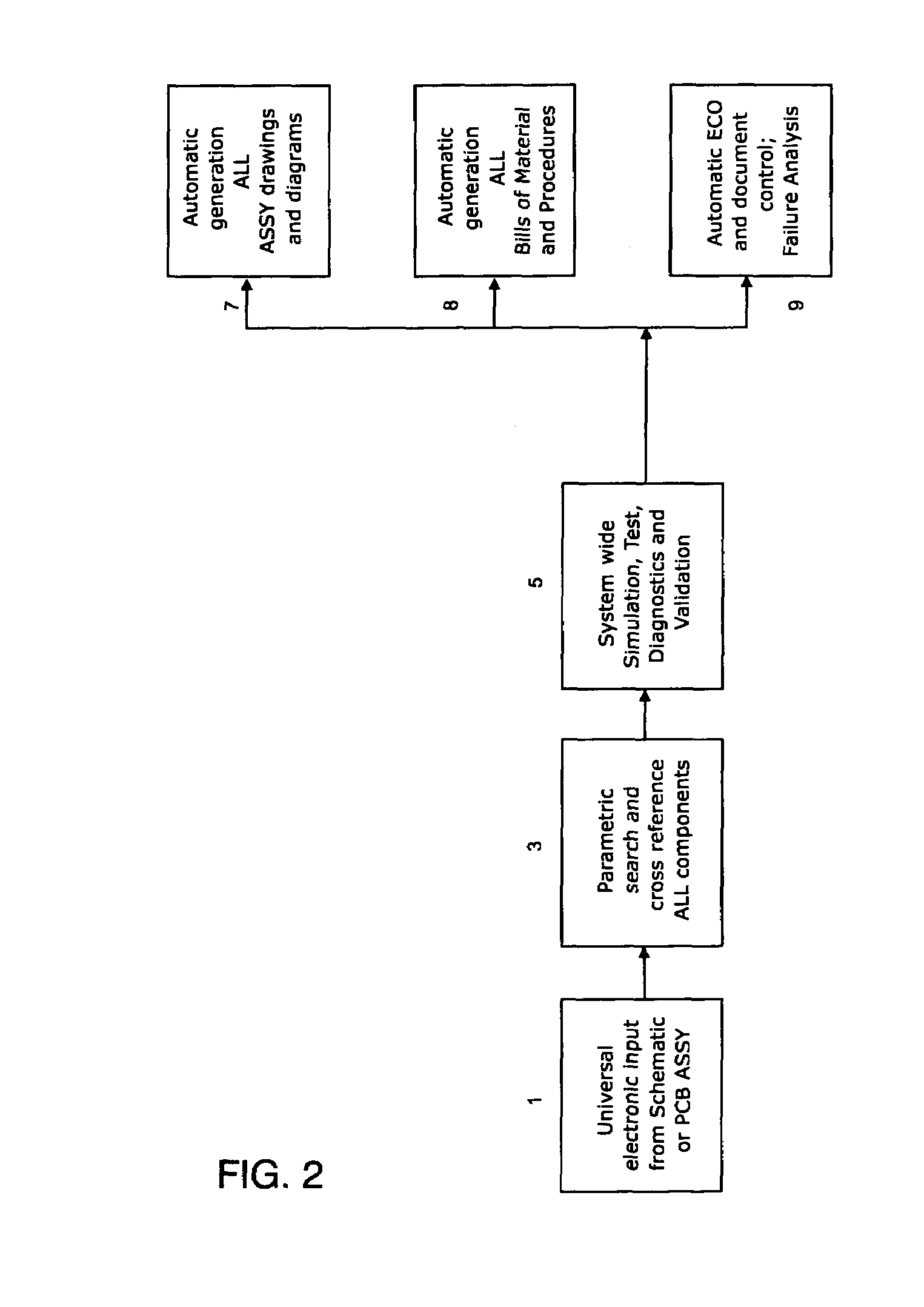

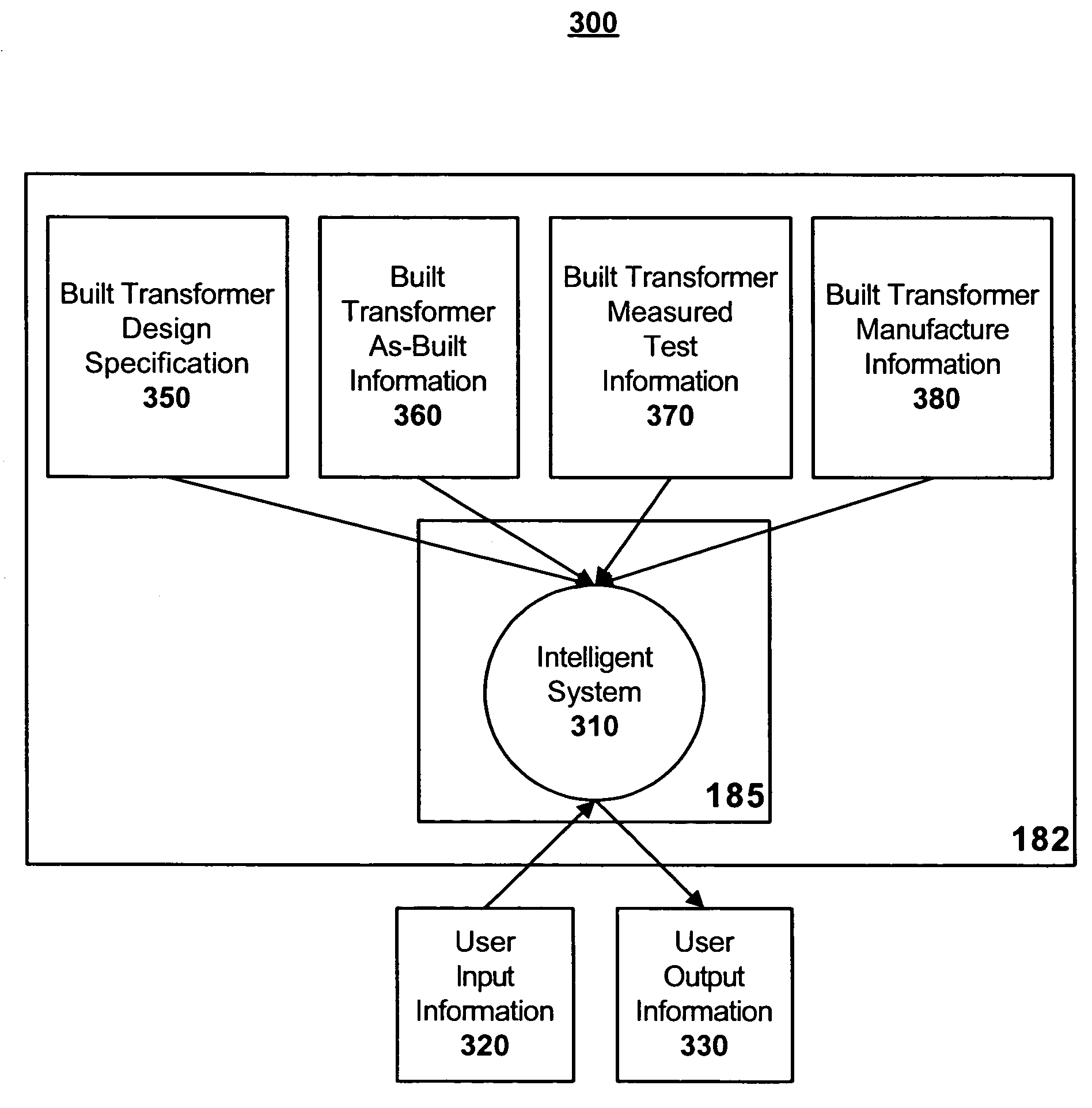

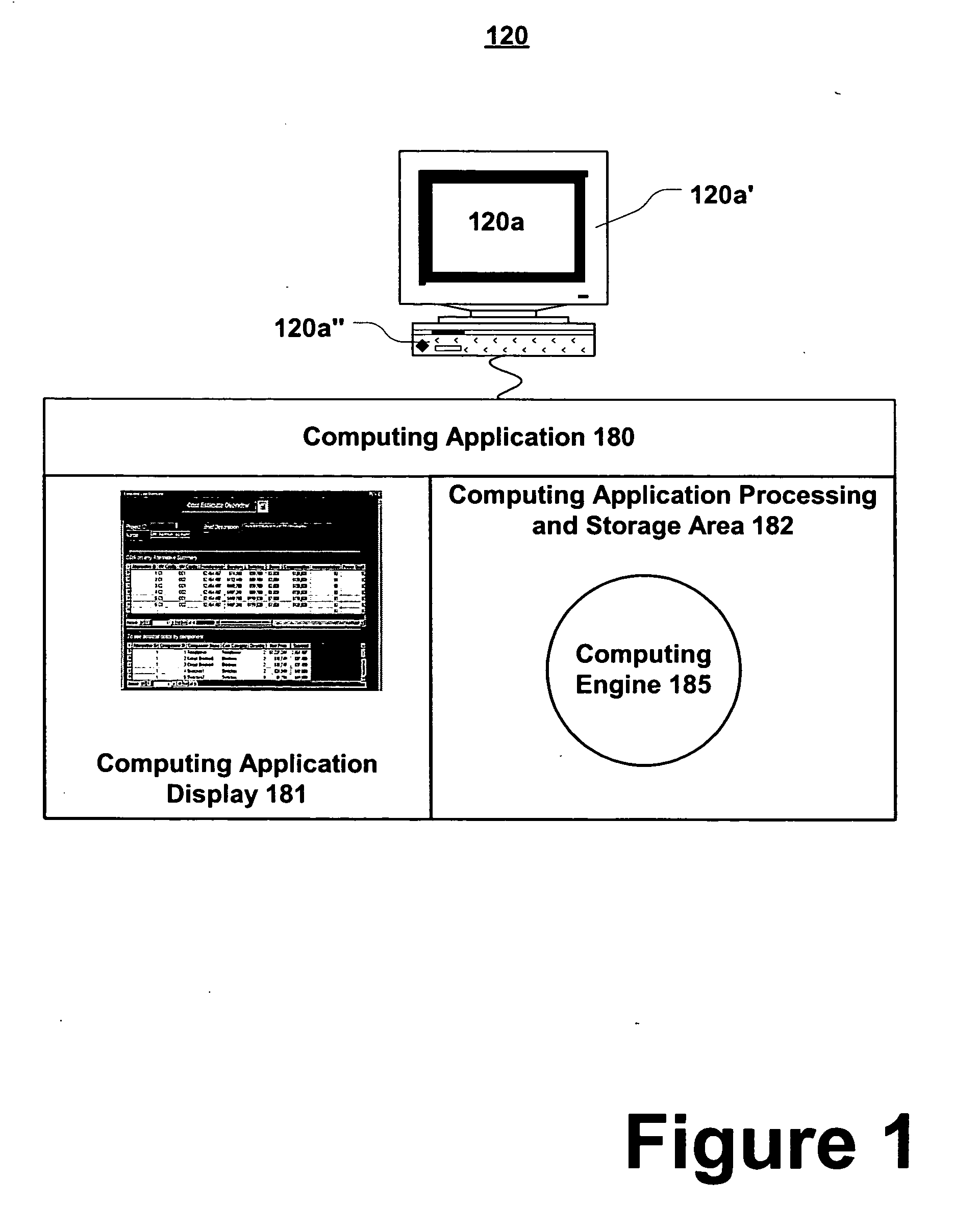

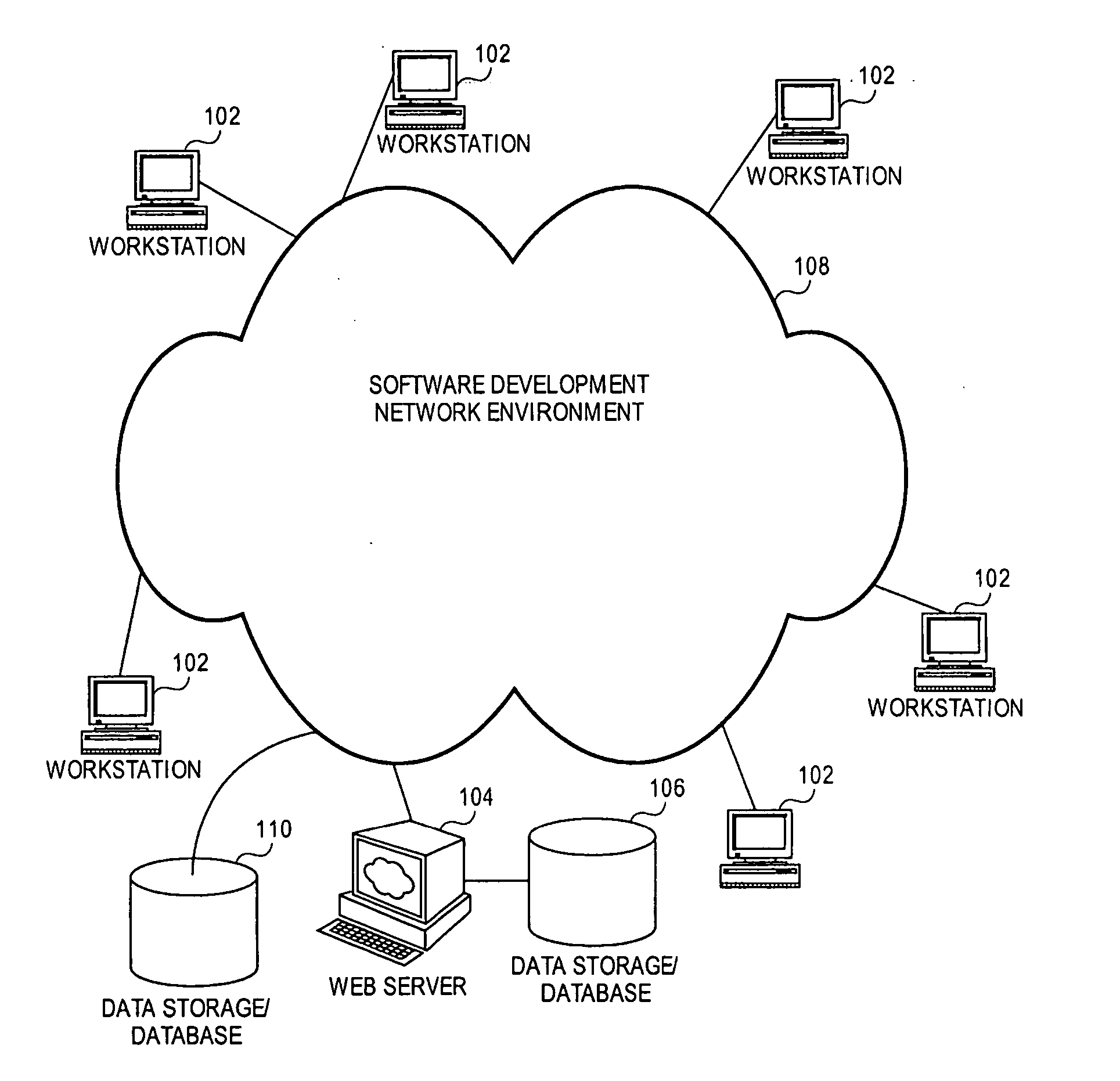

PLM-supportive CAD-CAM tool for interoperative electrical & mechanical design for hardware electrical systems

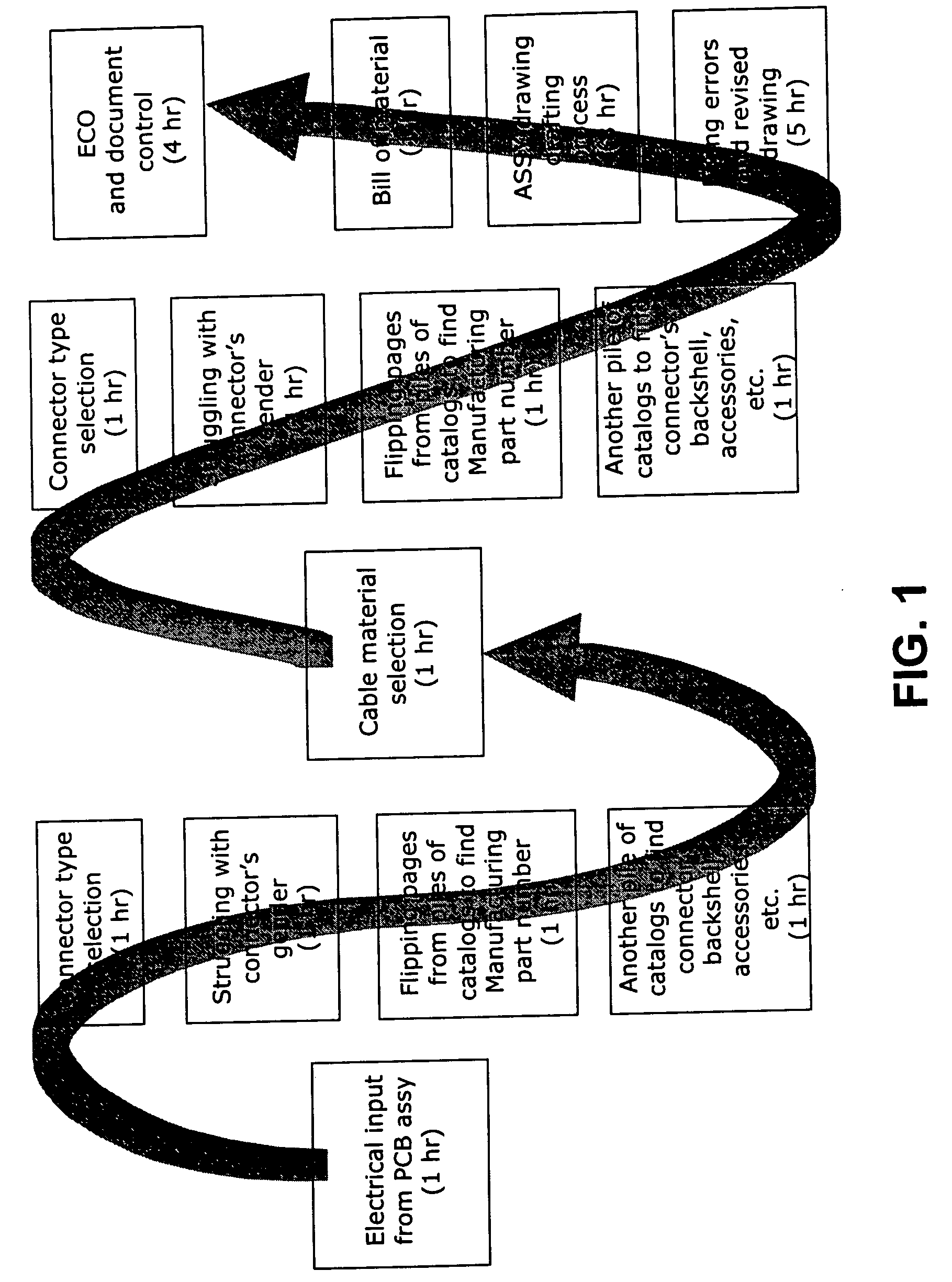

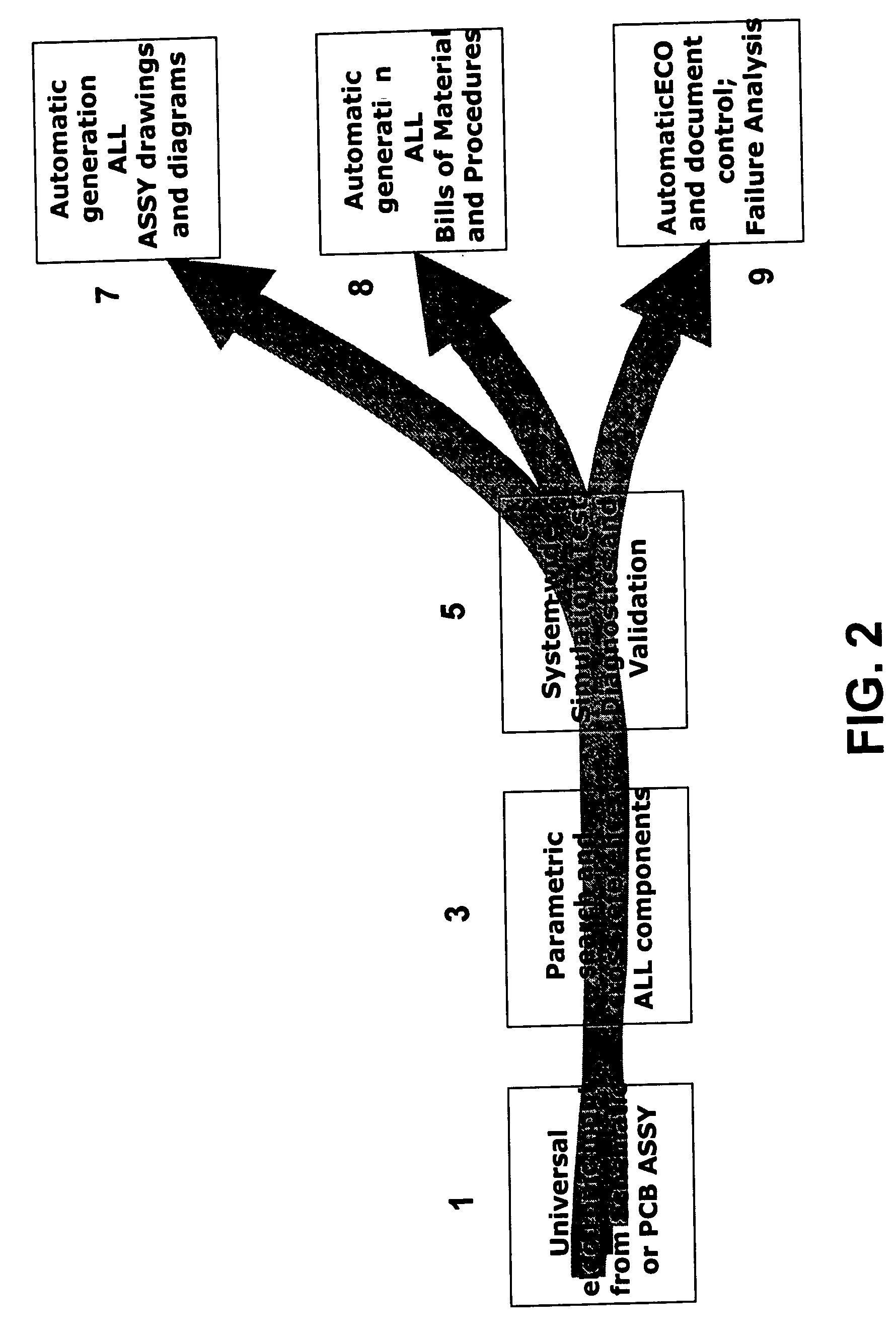

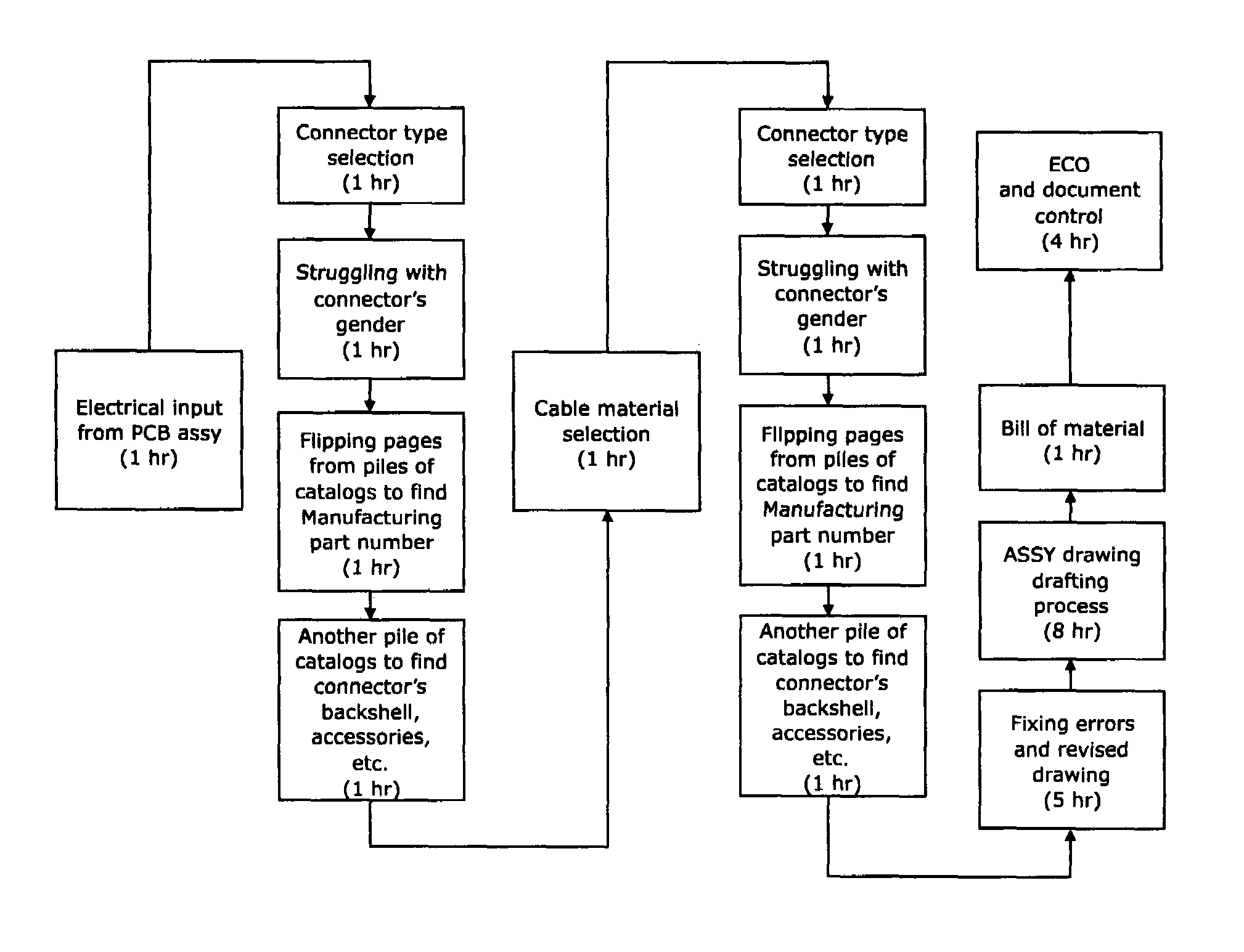

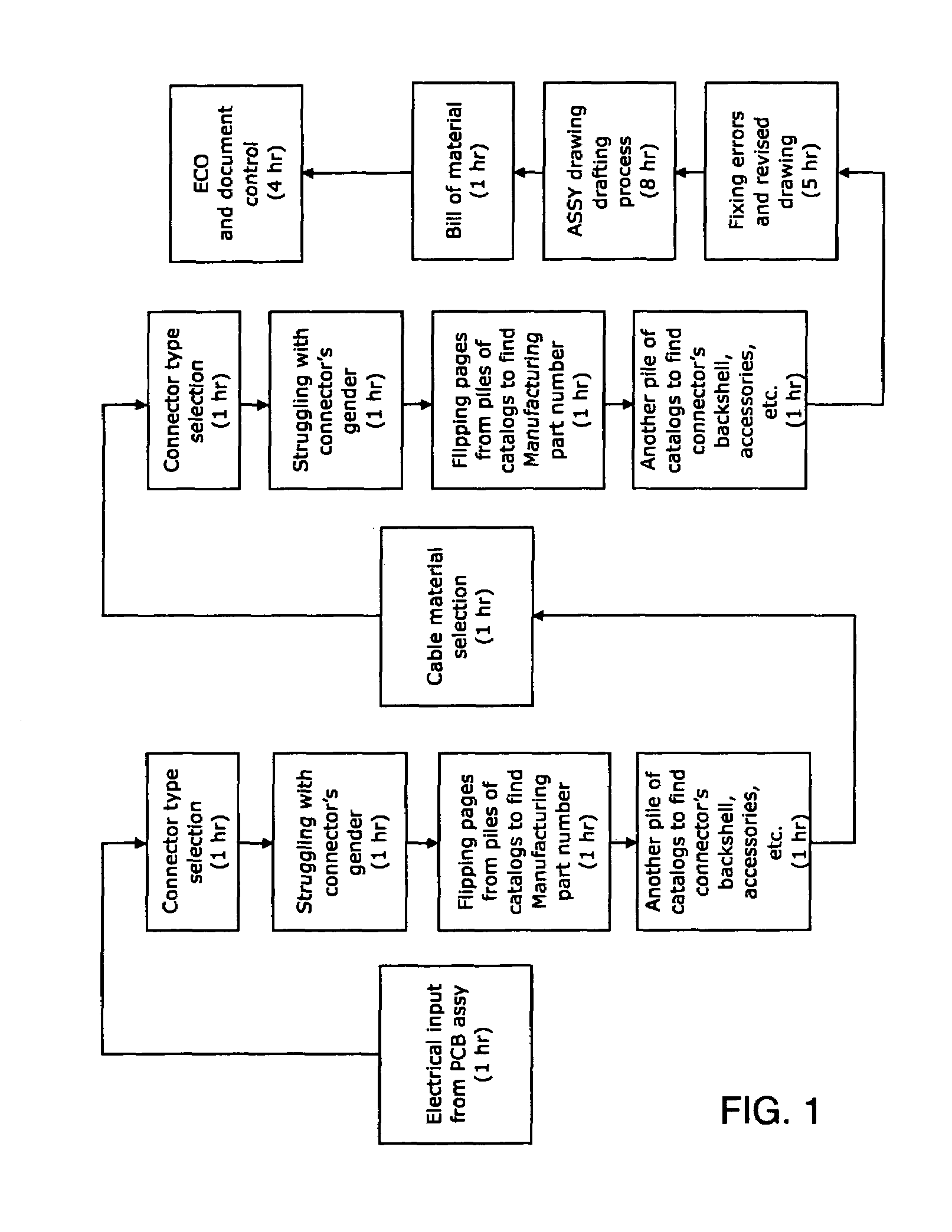

InactiveUS20050080502A1Reduce frictionCAD network environmentComputer programmed simultaneously with data introductionTask completionBill of materials

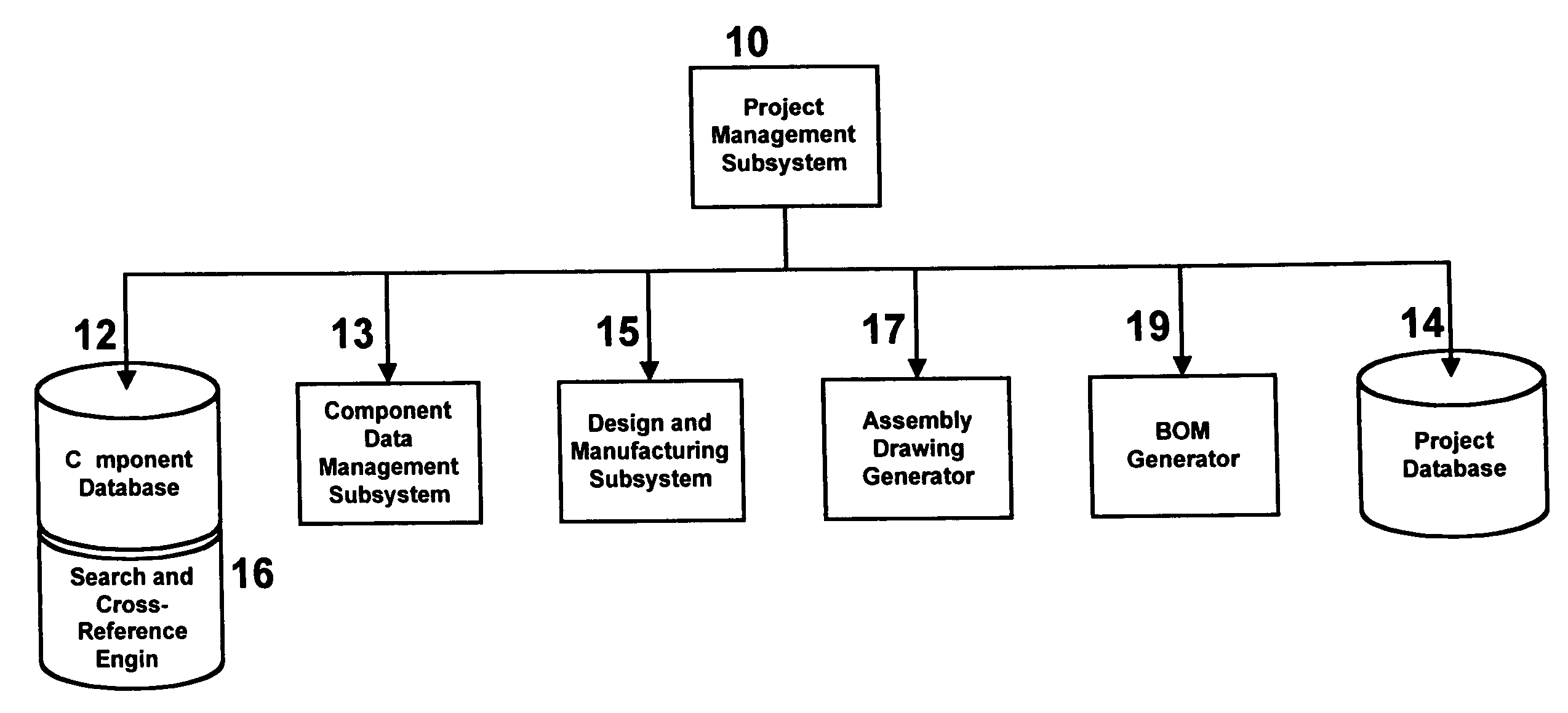

This invention is a tool for computer-aided design, computer-aided manufacturing forming a Project Management System, comprising: (1) a Component Database; (2) a Component Data Management System; (3) a Design and Manufacturing System; (4) an Assembly Drawing Generator; (5) a Bill of Materials Generator; and, (7) a Project Database. The Project Manager tracks the process and actions, recording and supervising version and change order compliance and task completion, from the start through verification of a production-ready finished version. Each project uses a master workbench. On it design specifications are entered for each subassembly element and connector. Then the user consults the Component Database using a Search and Cross Reference engine for components meeting those design specifications, until a constraint-satisfying design is completed. The tool generates a Bill of Materials, Assembly Drawings, and process records for the project in process.

Owner:CHERNYAK ALEX H +3

PLM-supportive CAD-CAM tool for interoperative electrical and mechanical design for hardware electrical systems

InactiveUS7103434B2Reduce frictionCAD network environmentComputer programmed simultaneously with data introductionTask completionBill of materials

Owner:CHERNYAK ALEX H +3

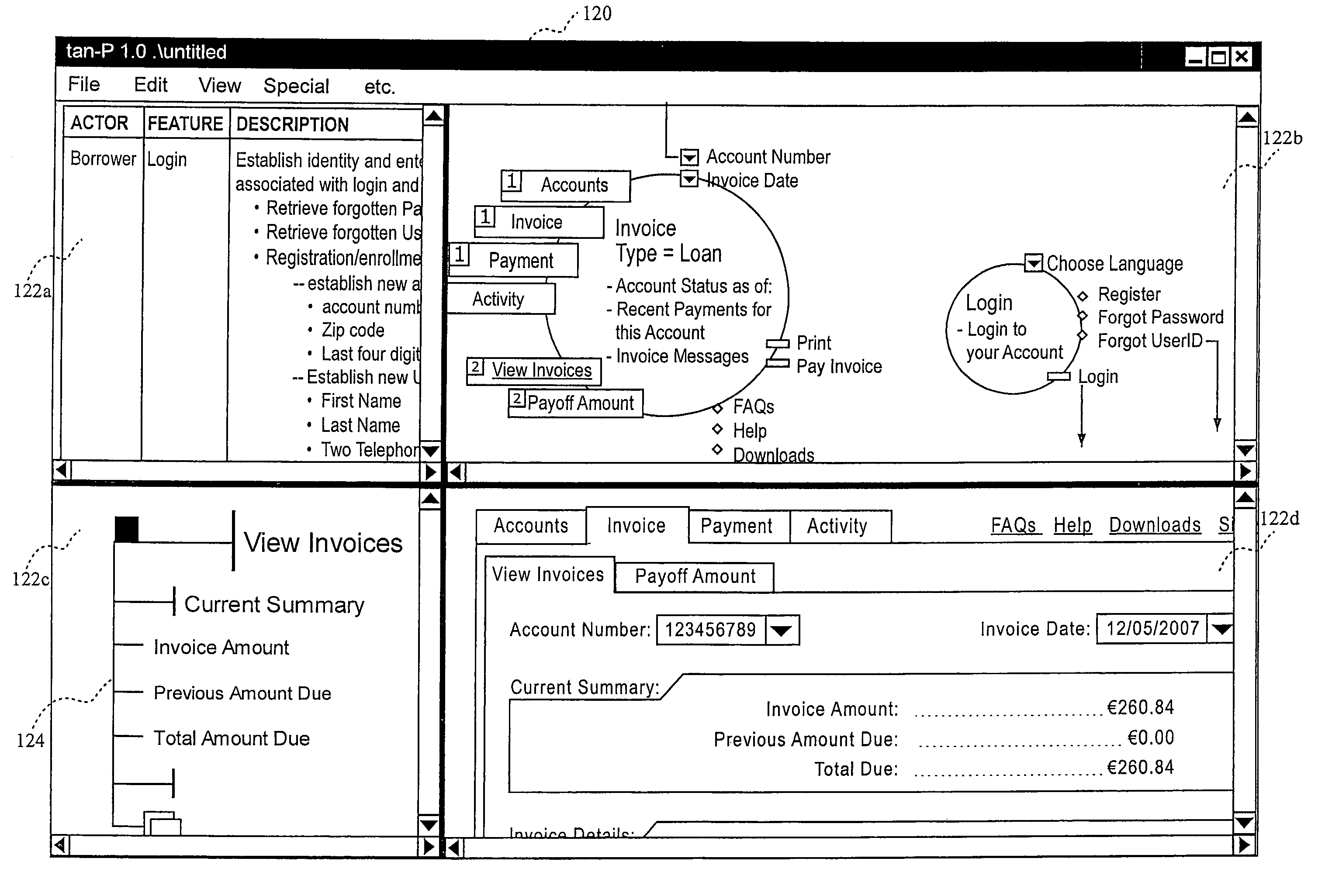

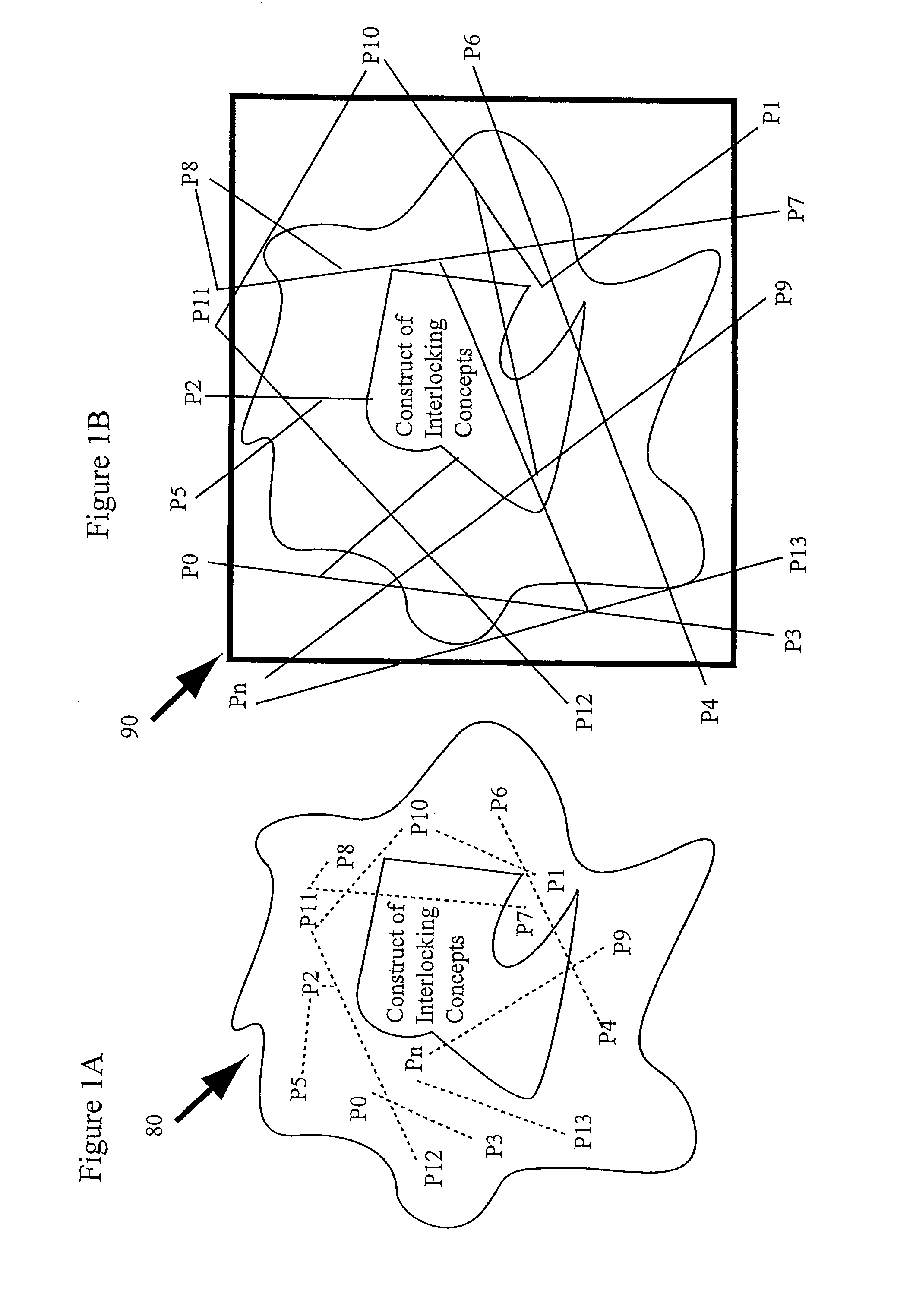

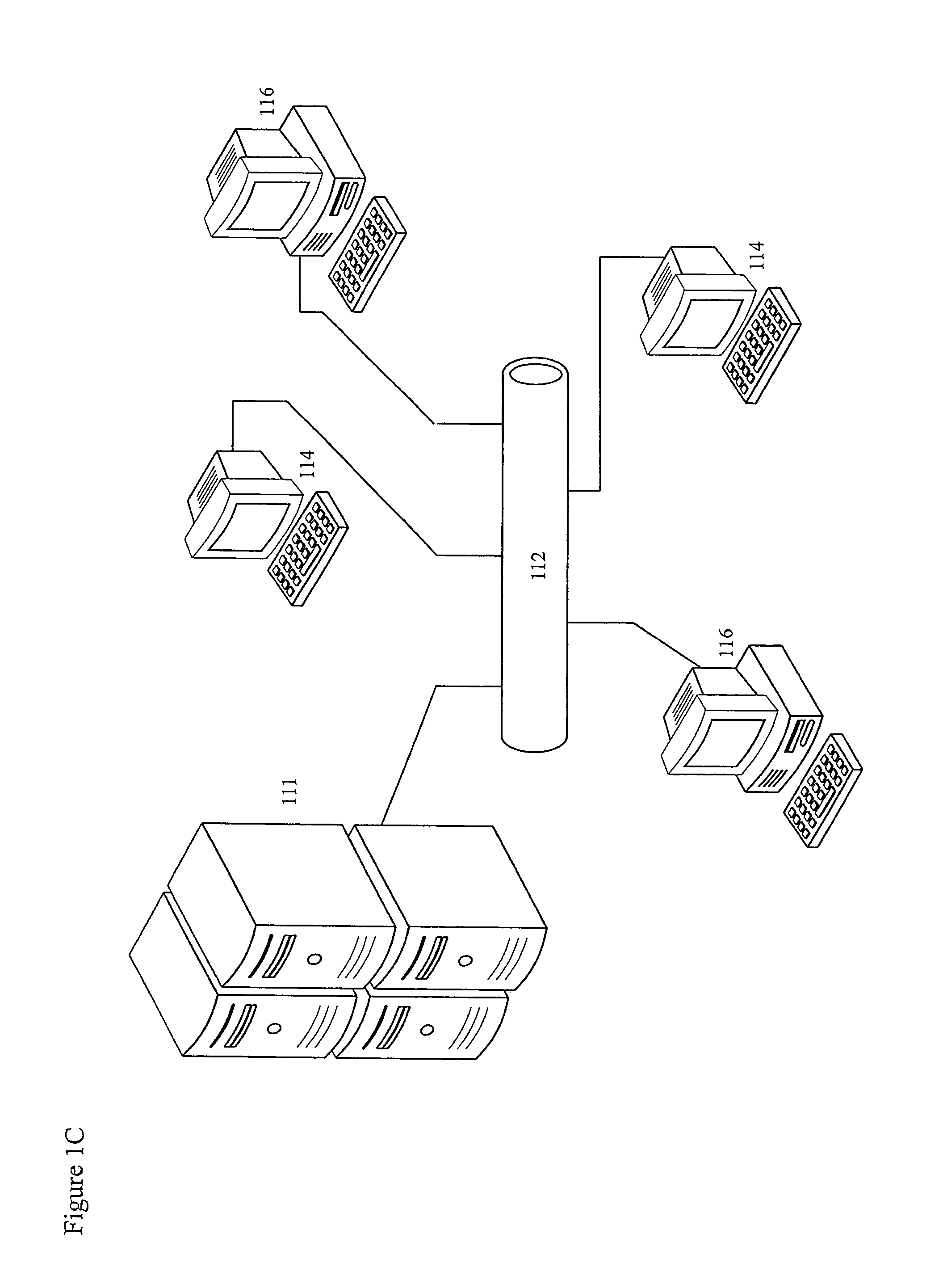

Design tool and methodology for enterprise software applications

ActiveUS7644390B2Easy to createEfficient communicationProgram documentationDesign optimisation/simulationProject managementApplication software

A system for creating and viewing simulation models that are used for managing requirements and design specifications for complex systems. Users simultaneously collaborate on the description of a complex system such as an enterprise software project throughout its life cycle. User interfaces, designed to assist in the visualization of a particular form of knowledge, allow users to describe the complex system with simple interactive elements. Information in all perspectives is presented so that it is legible and discernable to a non-technical audience. Multi-dimensional data structures record all the resulting information, creating a simulation model of the complex system, and the tasks required for construction and maintenance. Tasks are driven from the specifications not as a separate activity, but as part of the same activity to facilitate project management by allowing decisions to be tracked virtually throughout the simulation model.

Owner:KHODABANDEHLOO PAYMAN +1

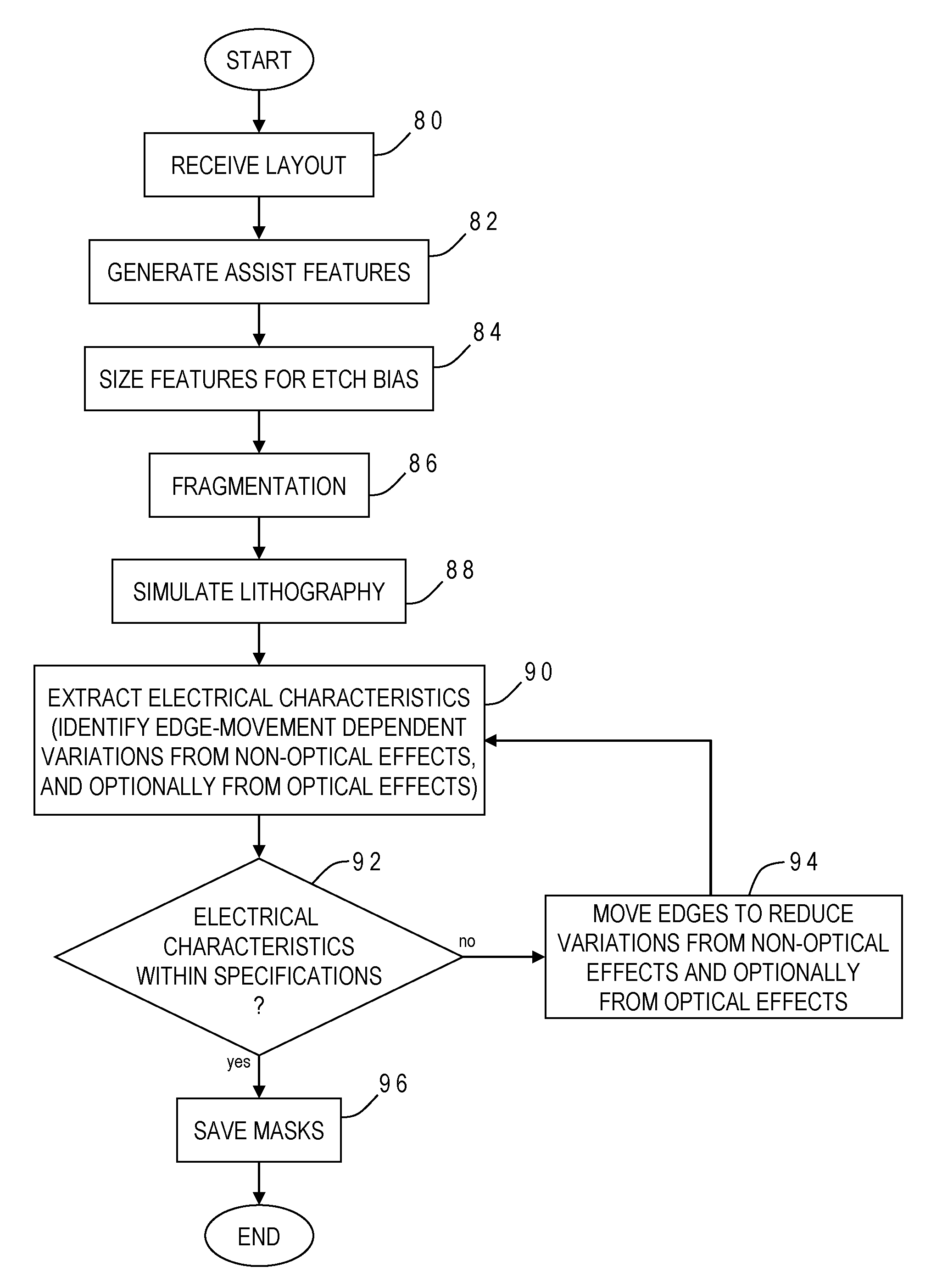

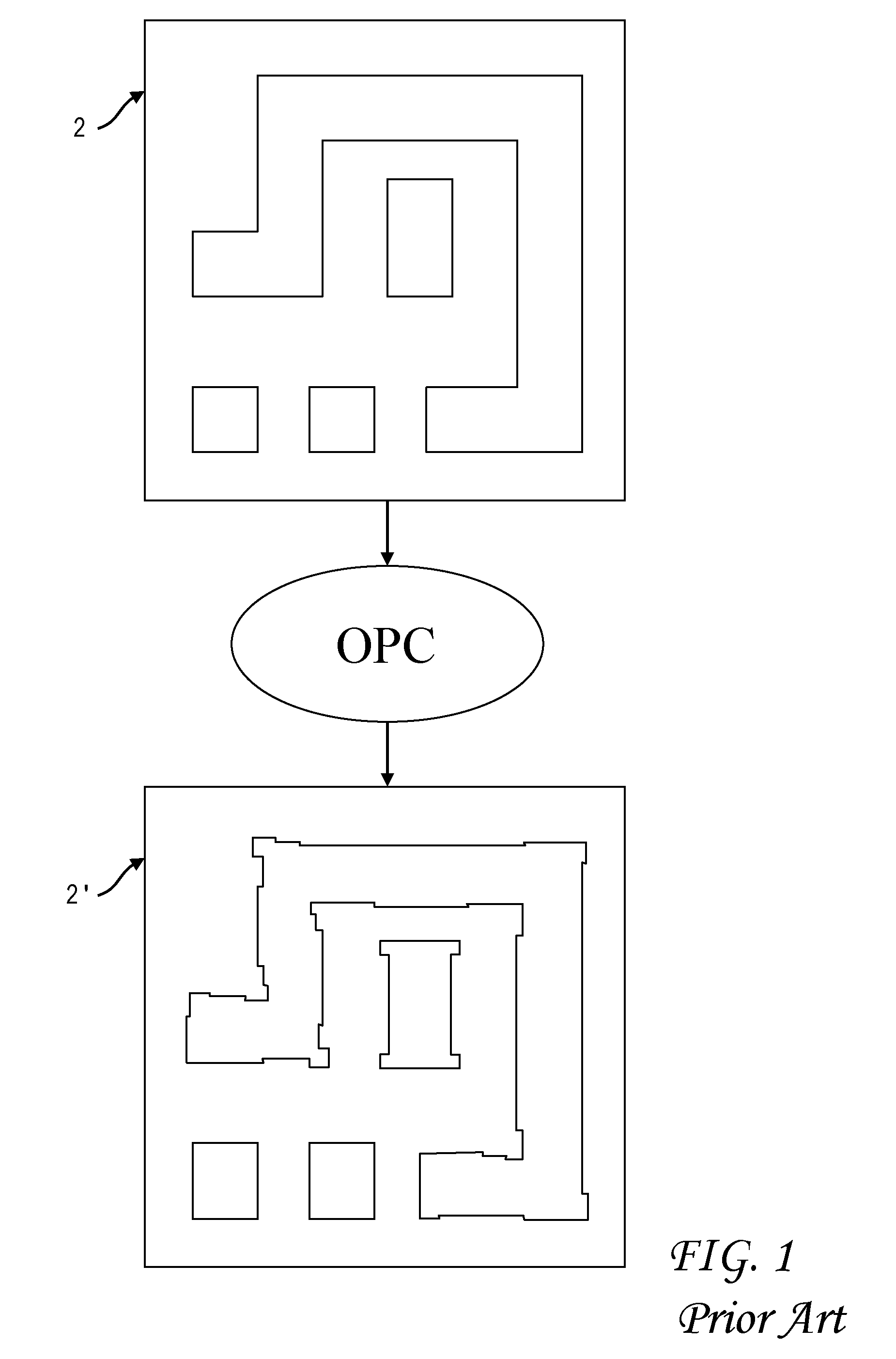

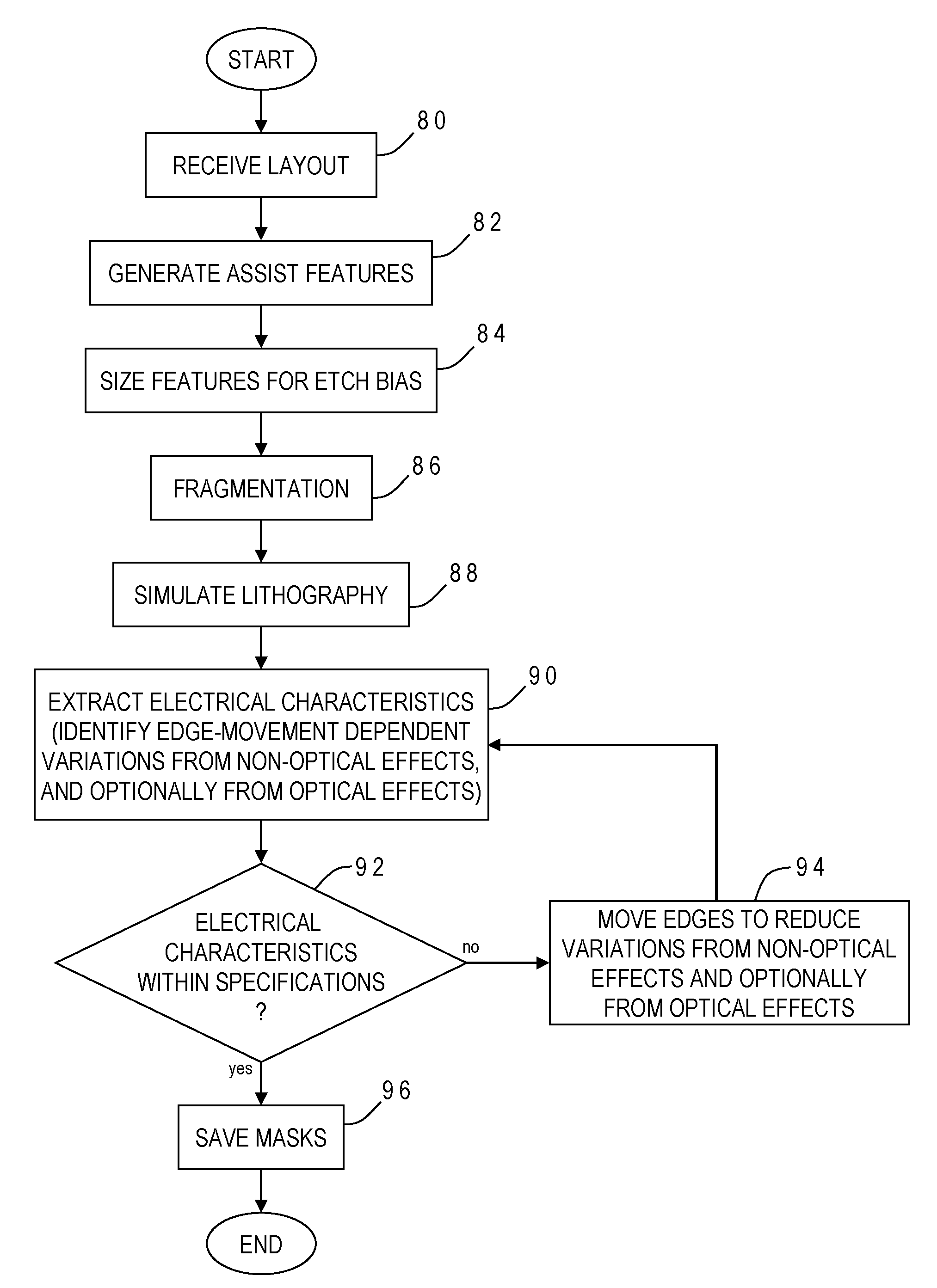

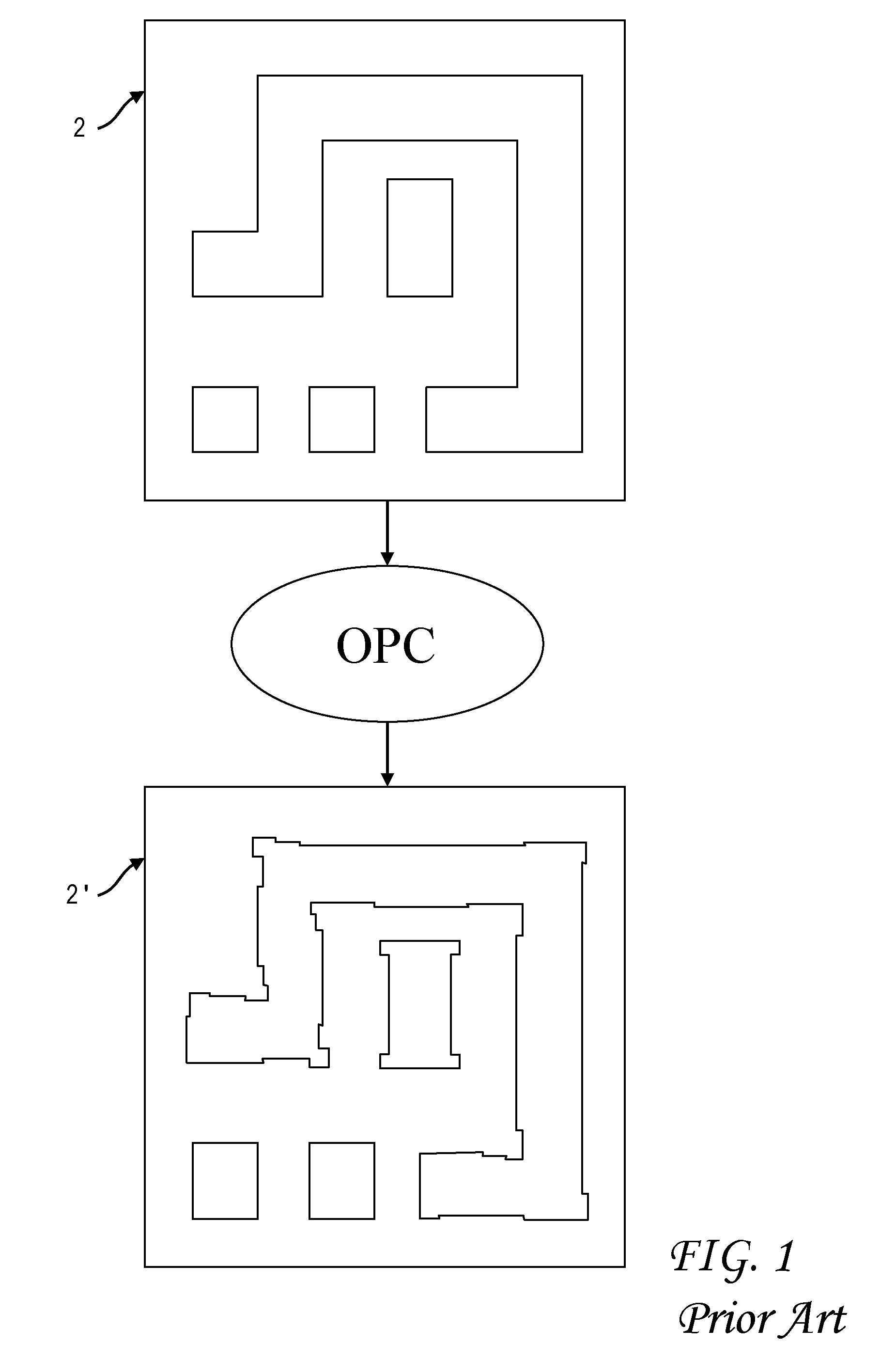

Electrically-driven optical proximity correction to compensate for non-optical effects

ActiveUS8103983B2Improve performancePhotomechanical apparatusOriginals for photomechanical treatmentCapacitanceEngineering

A contour of a mask design for an integrated circuit is modified to compensate for systematic variations arising from non-optical effects such as stress, well proximity, rapid thermal anneal, or spacer thickness. Electrical characteristics of a simulated integrated circuit chip fabricated using the mask design are extracted and compared to design specifications, and one or more edges of the contour are adjusted to reduce the systematic variation until the electrical characteristic is within specification. The particular electrical characteristic preferably depends on which layer is to be fabricated from the mask: on-current for a polysilicon; resistance for contact; resistance and capacitance for metal; current for active; and resistance for vias. For systematic threshold voltage variation, the contour is adjusted to match a gate length which corresponds to an on-current value according to pre-calculated curves for contour current and gate length at a nominal threshold voltage of the chip.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

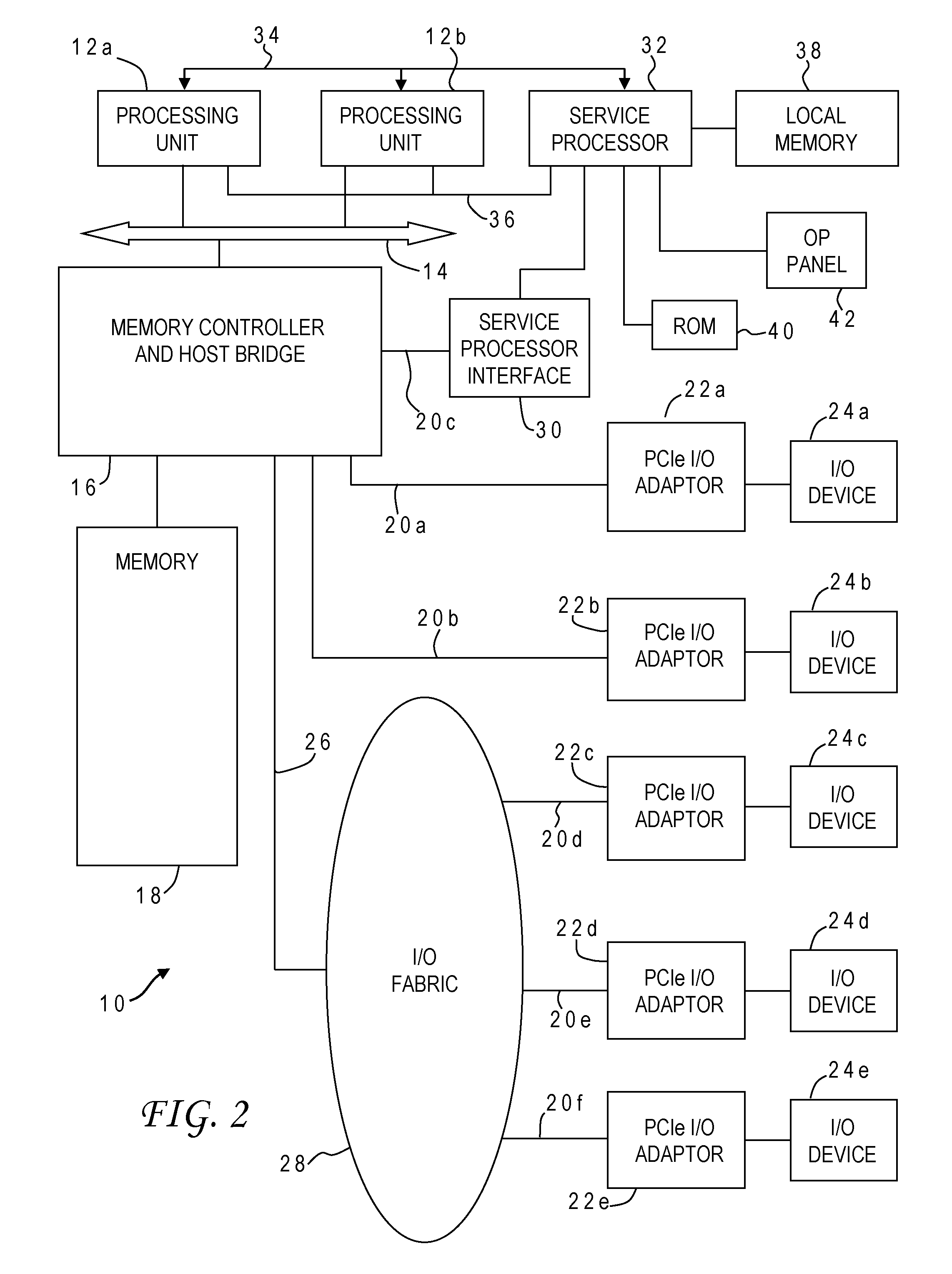

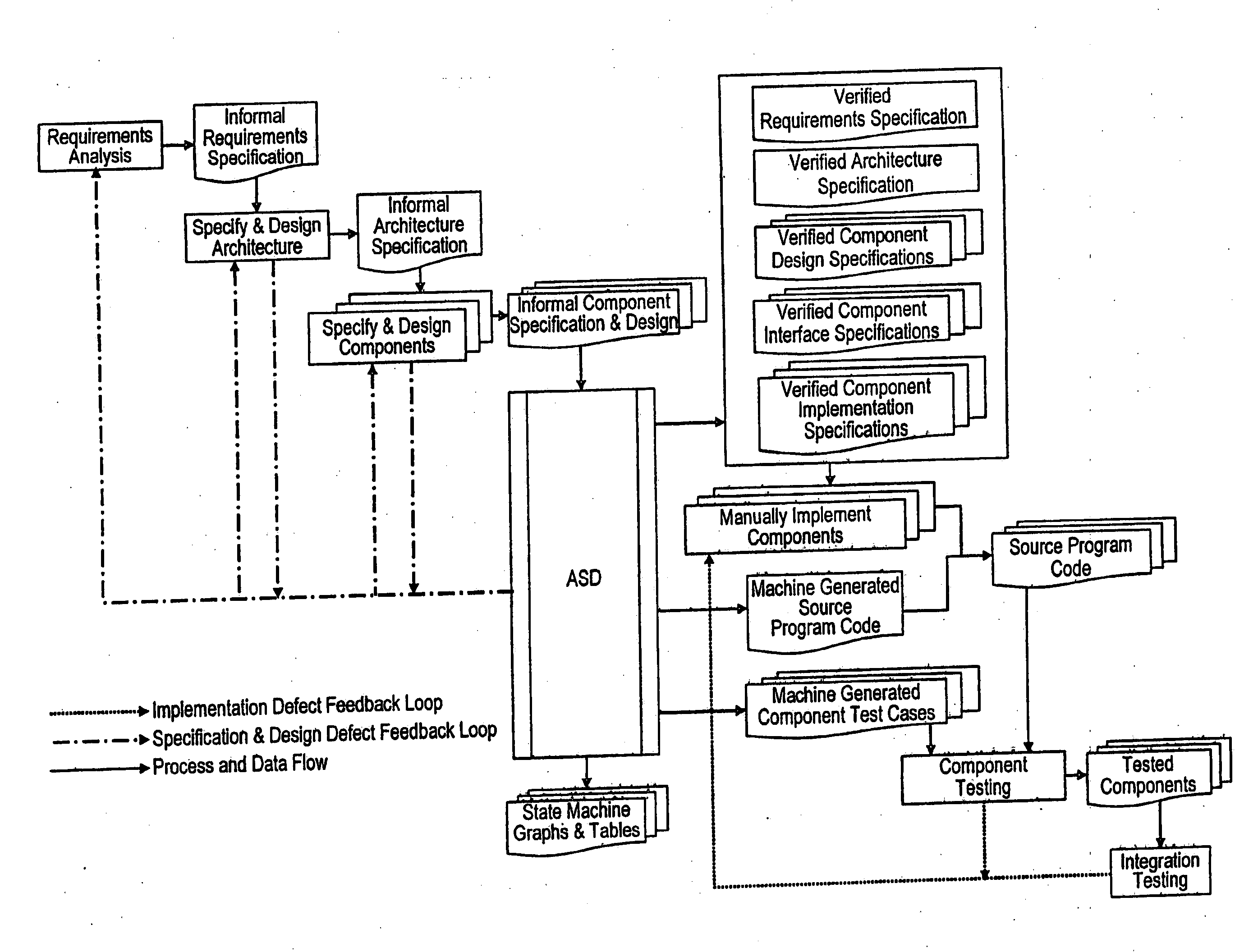

Analytical Software Design System

ActiveUS20080263506A1Improve effectivenessExpand coverageSoftware designRequirement analysisSystems designMathematical model

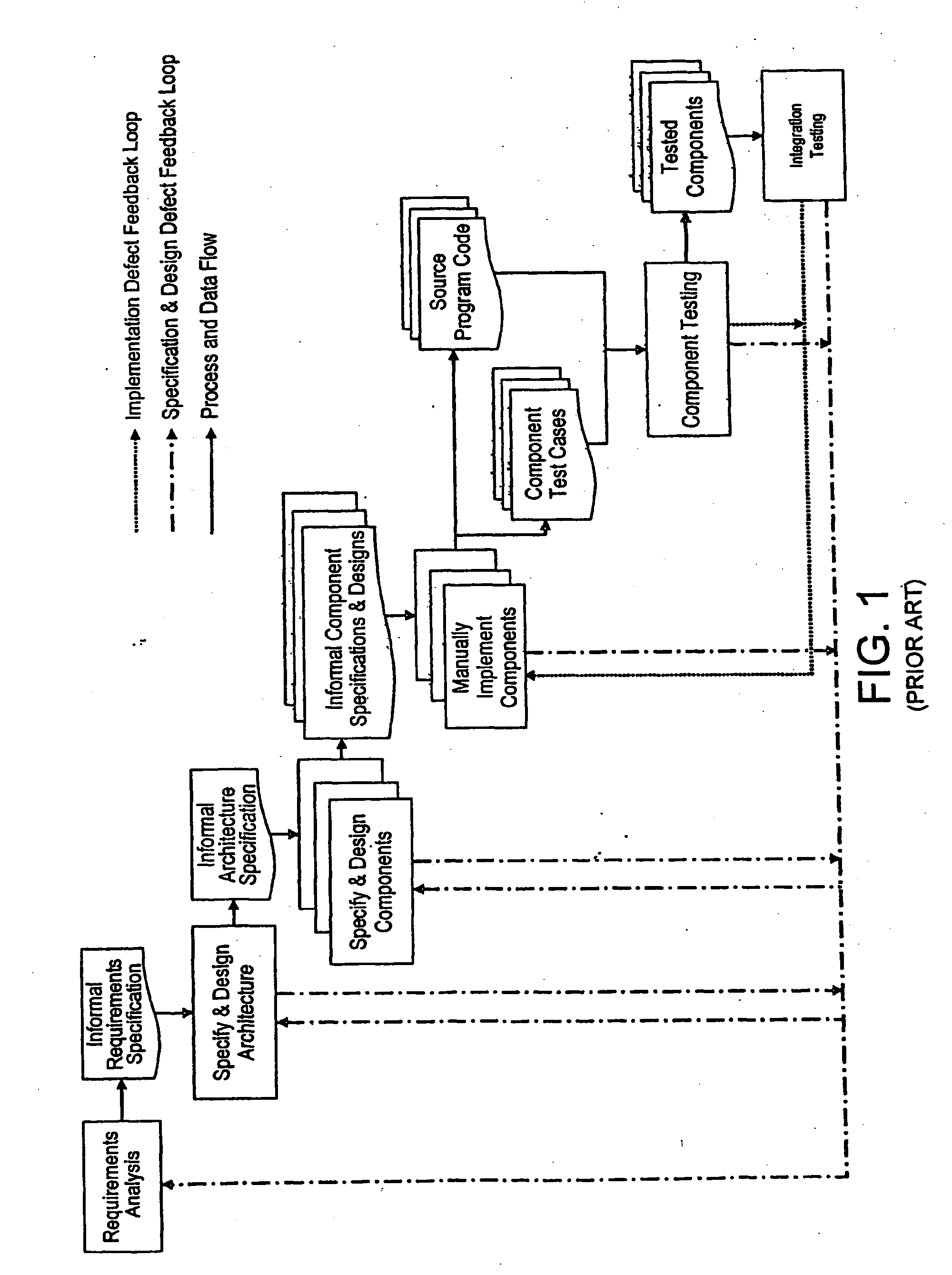

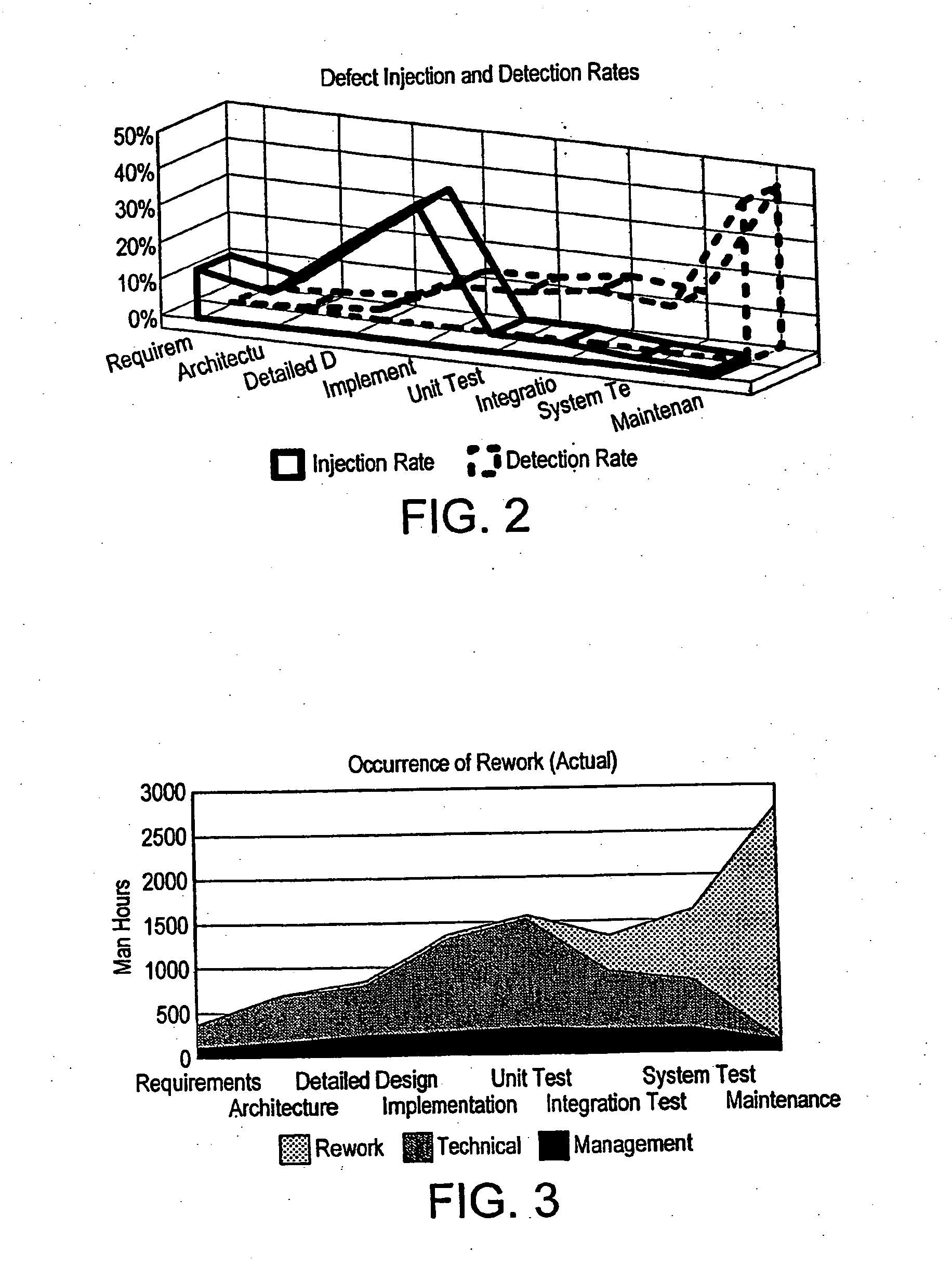

An analytical software design system arranged to receive informal system design specifications and to convert them into verified design specifications for use in creating source code and carrying out implementation testing of the source code is described. The system comprises a verified black box specification generator arranged to process the received informal system design specifications to create formal specifications; to generate from the formal specifications mathematical models representing the system behaviour; to analyse the mathematical models to determine if they have the required behaviour; to adjust the formal specifications until the required behaviour is achieved; and to derive the required verified design specifications from the mathematical models.

Owner:COCOTEC LTD

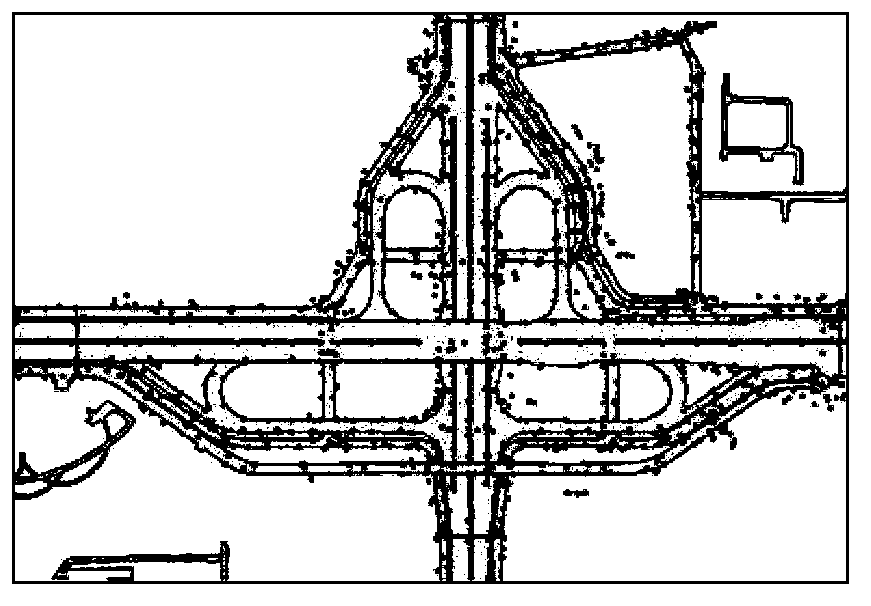

Method of constructing fine discrete road grid in urban drainage simulation system

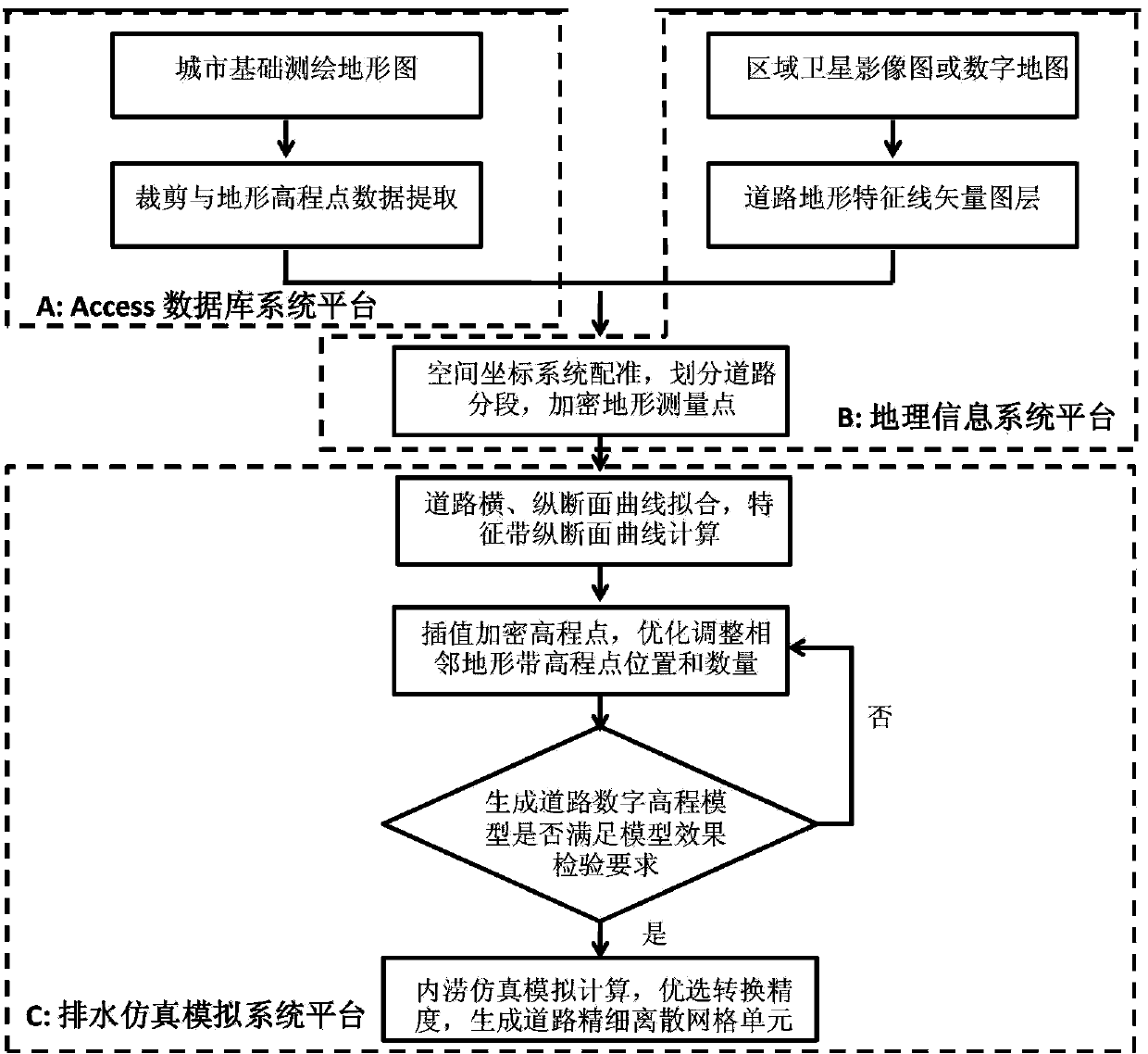

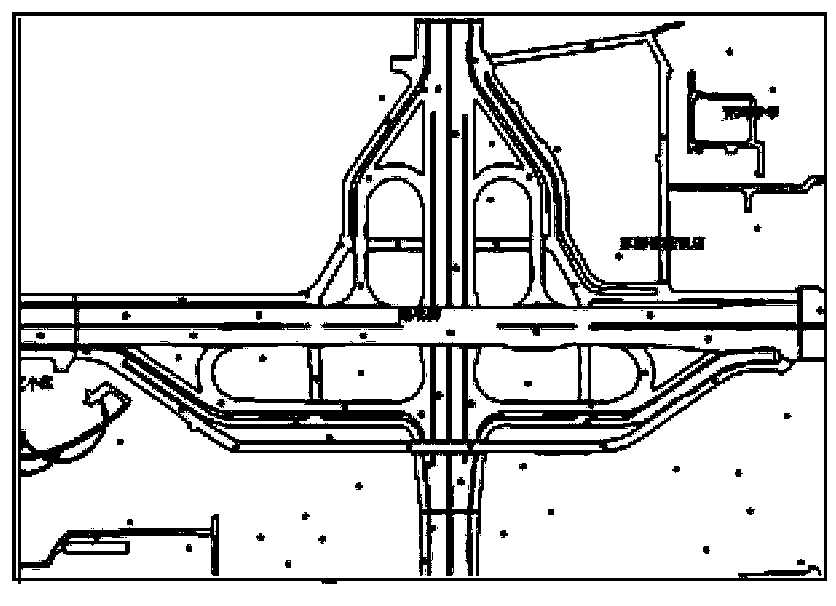

InactiveCN103399990ARealize the expression of micro-topographic featuresBuild accuratelySpecial data processing applicationsTerrainMathematical model

The invention relates to a method of constructing a fine discrete road grid in an urban drainage simulation system and belongs to the cross field of municipal engineering information technology, database technology and geologic information system technology. From the demand on construction of a waterlogging simulation model, under the restraint conditions in road design specifications and on the basis of conventional map measured elevation points, the number and positions of interpolation points are optimized under the drainage simulation system platform by the fitting method of local elevation change curves of cross-longitudinal road section and by road characteristic terrain vector layers according to mathematical model interpolation encryption plane and elevation information of physical road tomography; accordingly, a fine discrete road elevation grid unit is constructed, true tomographic road features are expressed quickly and economically, the demand on precise simulation of waterlogging models is met, especially the dredging and resisting actions of road micro-tomographic features upon waterflow can be correctly expressed, and the method is significant to promotion and application of the drainage simulation technology.

Owner:BEIJING UNIV OF TECH

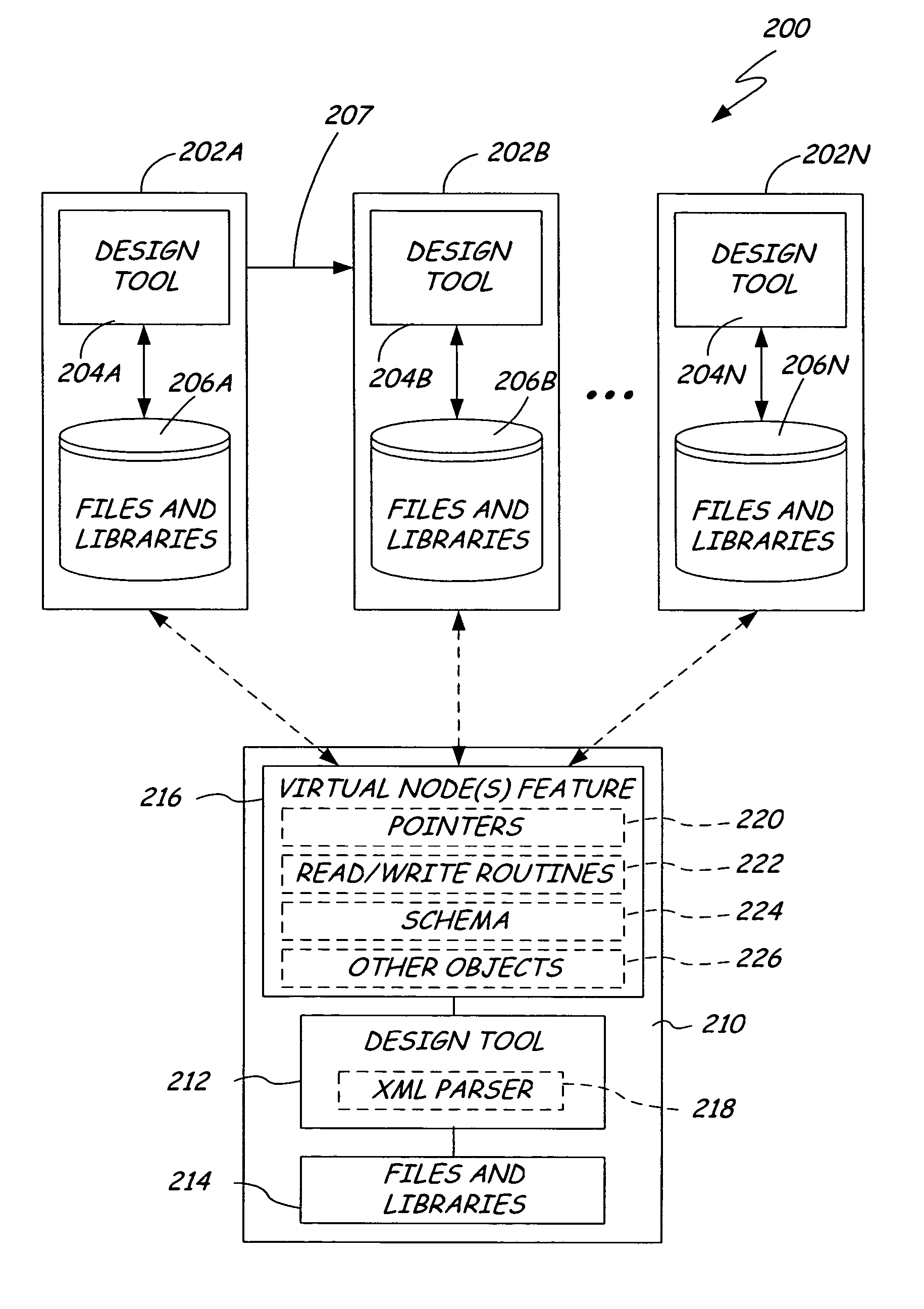

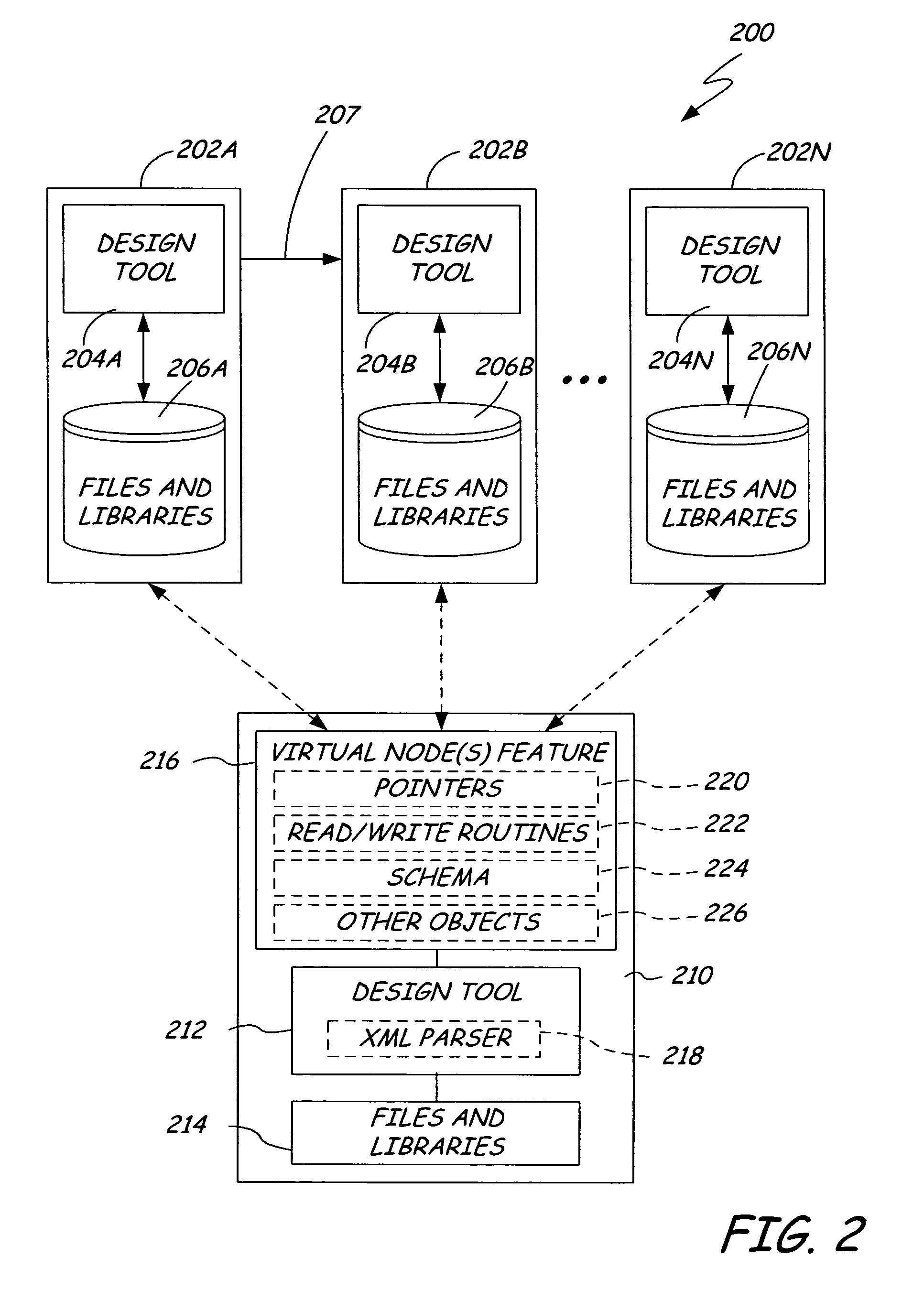

Virtual data representation through selective bidirectional translation

InactiveUS20060112376A1Software designProgram controlComputer architectureComputer aided circuit design

A computer-aided circuit design application has a virtual node feature and a design tool. The virtual node feature is adapted to access design specification information in a first data format and to represent the accessed design specification information as a virtual data node object within a list of node objects in a second data format. The design tool is operable on the list of node objects and the virtual data node object.

Owner:BELL SEMICON LLC

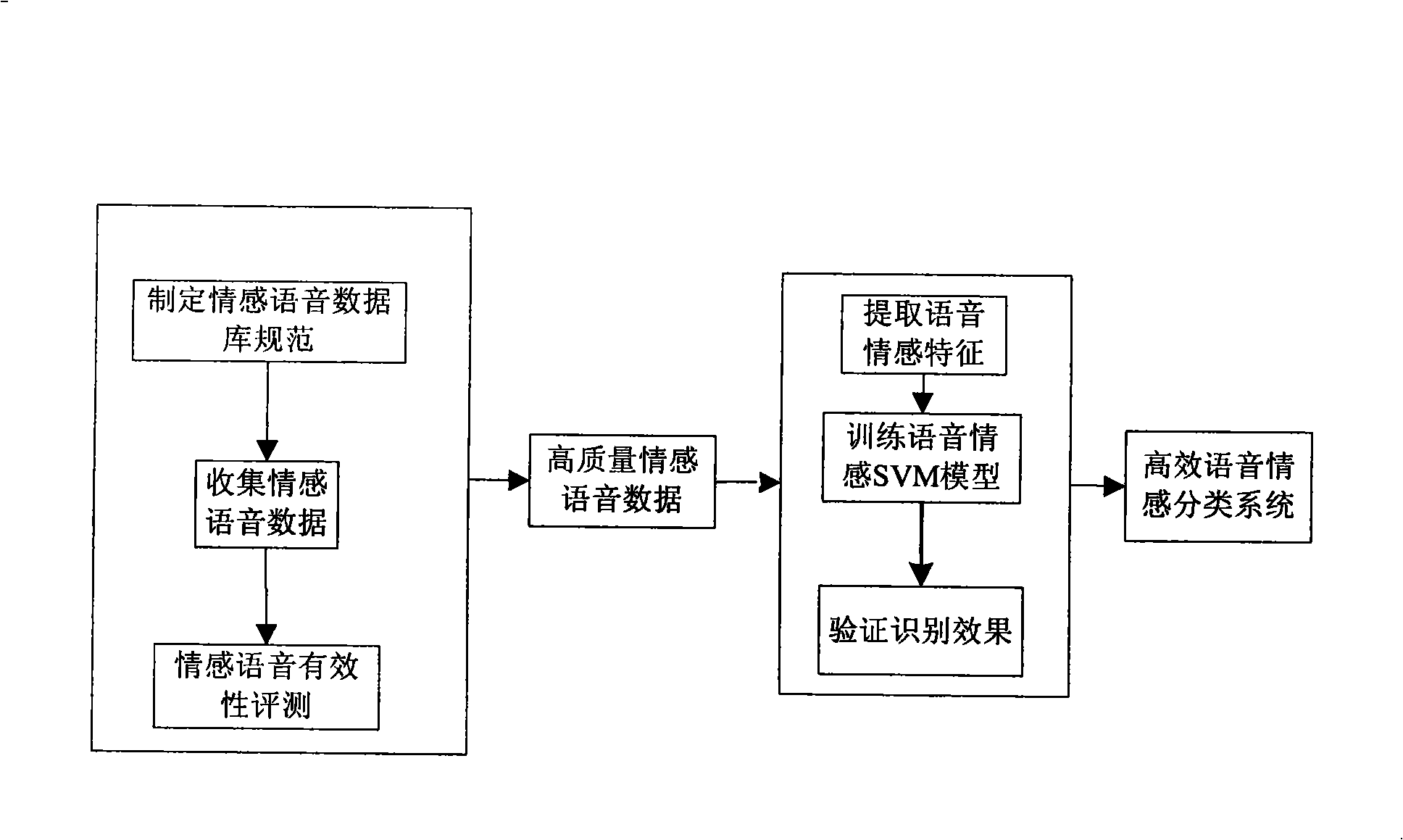

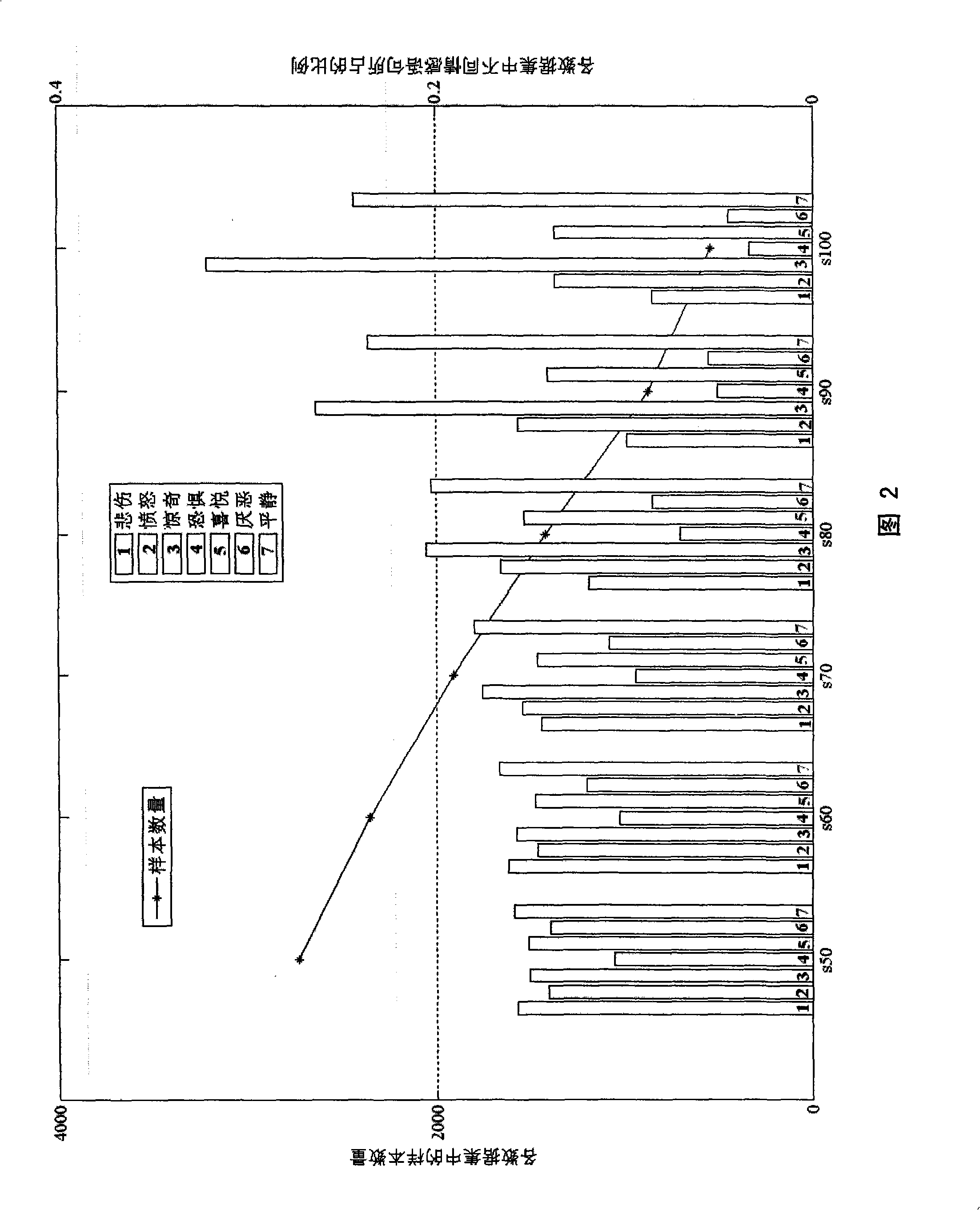

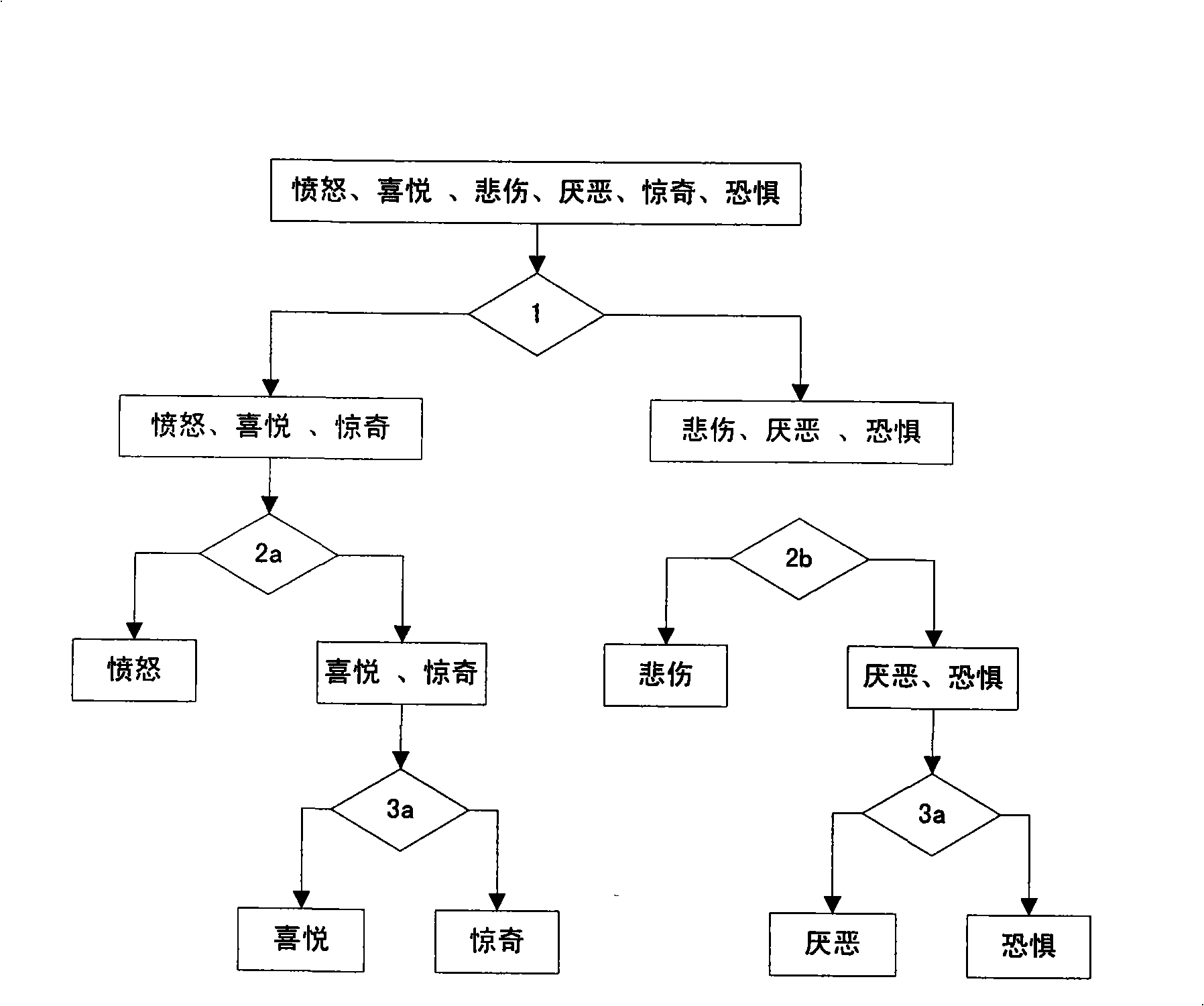

Extraction and modeling method for Chinese speech sensibility information

InactiveCN101261832AAvoid missingSolve quality problemsSpeech recognitionEmotion identificationDatabase Specification

The invention provides a method for extracting and modeling the emotional information of a Chinese sound; the extracting method for the emotional information of the Chinese sound is that: formulate the specification of a emotional speech database, which includes the pronouncer specification, the recording play book design specification and the naming specification of audio files and so on; collect the emotional speech data; evaluate the validity of the emotional speech, namely, at least ten evaluators apart from a speaker carry out a subjective listen evaluation experiment on the emotional speech data. The modeling method of the emotional information of the Chinese sound is that: extract the emotional characteristics of the sound, define and distinguish the characteristic combination of each emotion type; adopt different characteristic combinations to train the SVM model of a multilevel sound emotion recognition system; verify the identification effect of the classifying models, namely, verify the classification effect of the multilevel classification models of sound emotion in a situation unrelated to the speaker by adopting a cross leave-one-out method. The method solves the problems that the domestic emotional speech databases are less in emotion type and the number of the domestic emotional speech database is very limited; at the same time, the method realizes an efficient speech emotion identification system.

Owner:BEIHANG UNIV

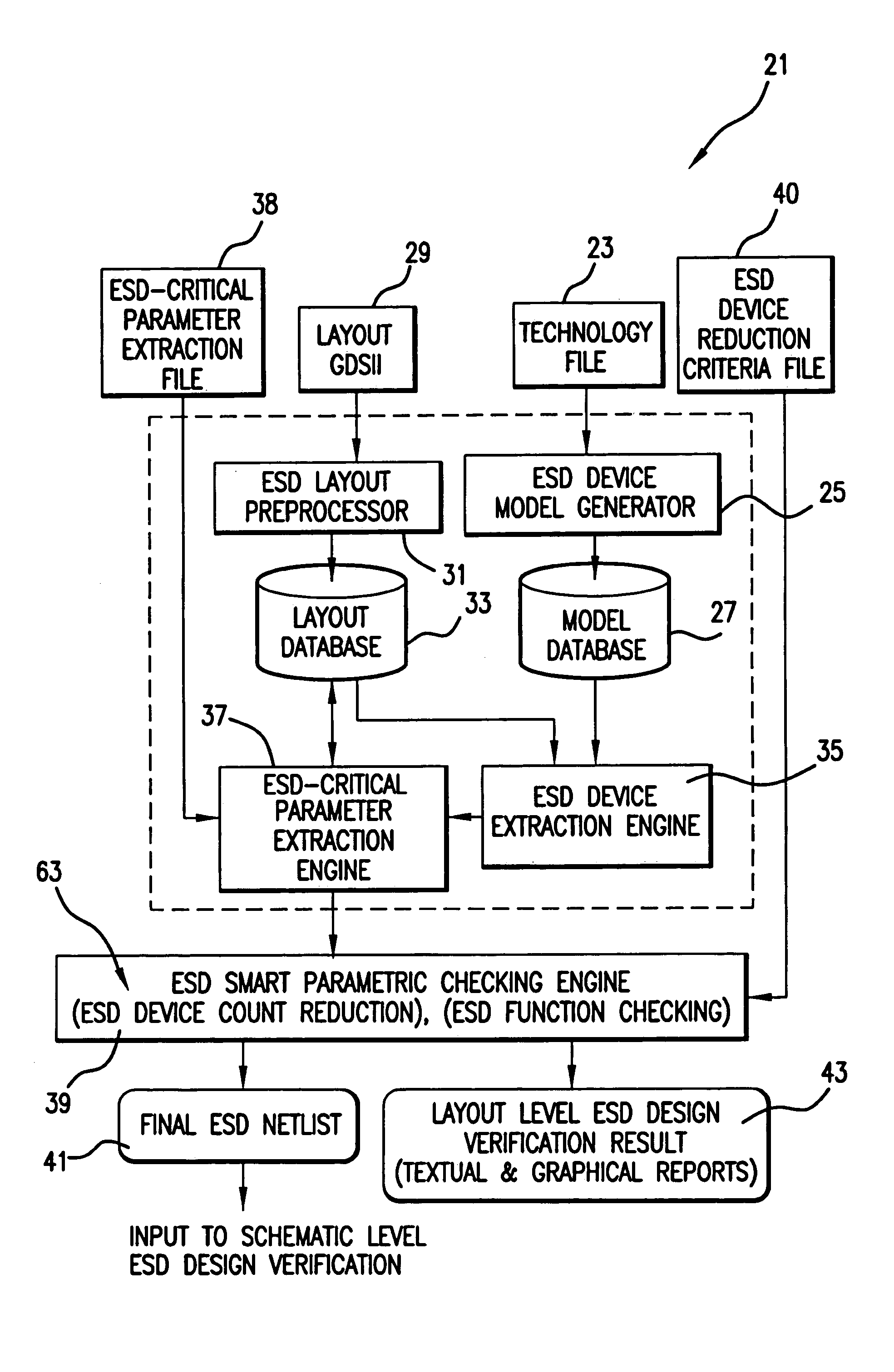

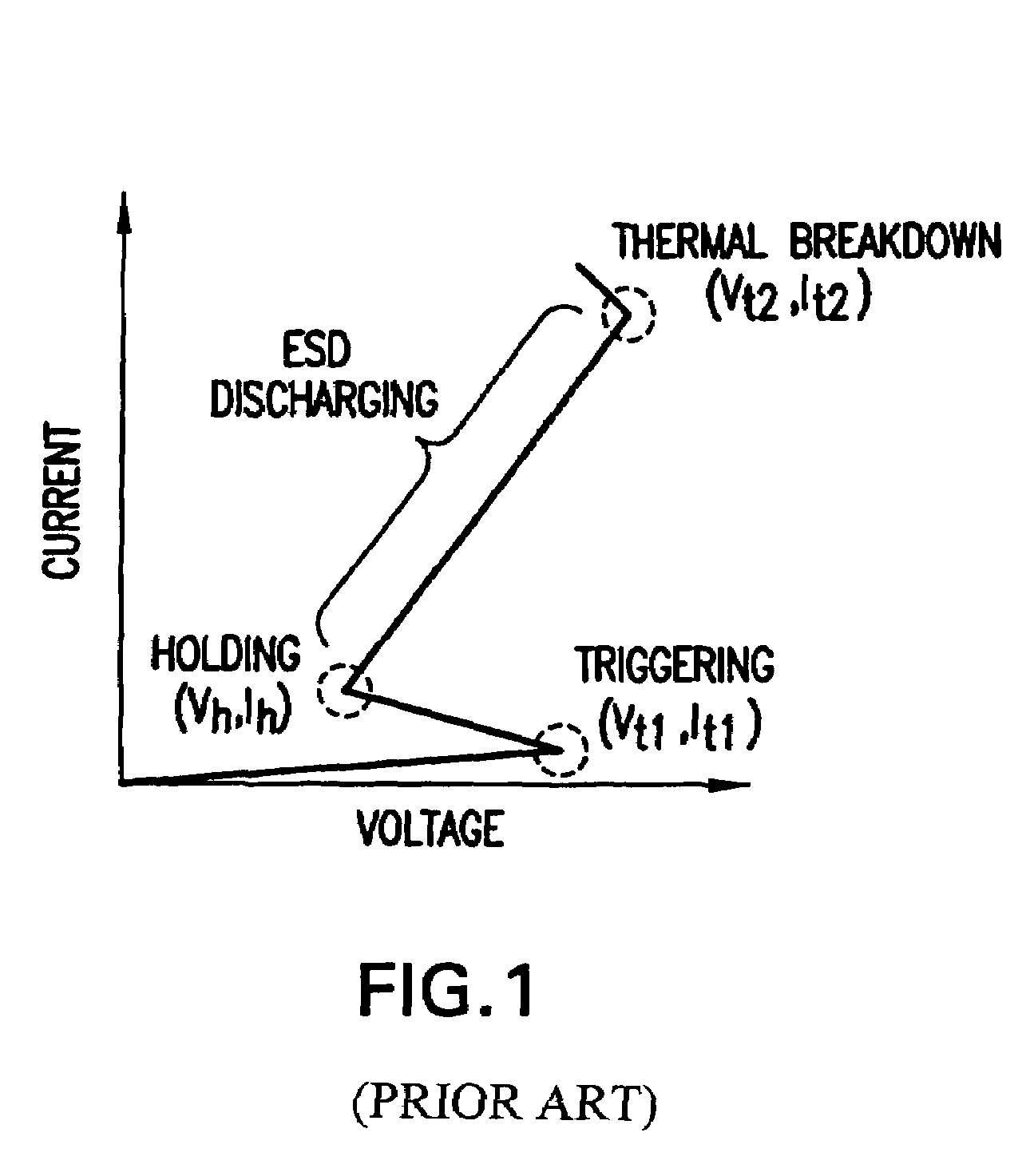

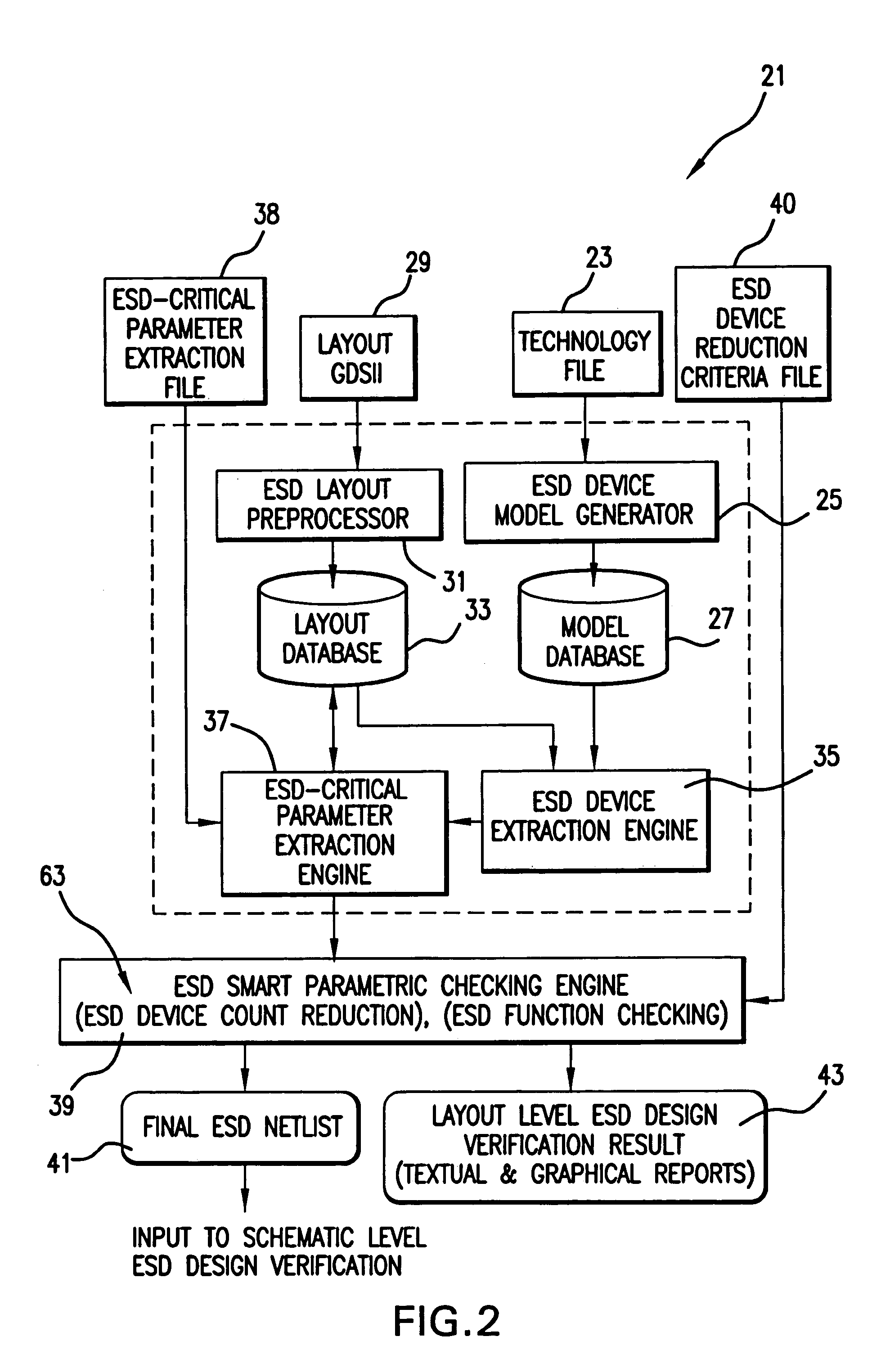

Parameter checking method for on-chip ESD protection circuit physical design layout verification

ActiveUS7243317B2Precise designEasy to disassembleComputer aided designSoftware simulation/interpretation/emulationEngineeringNetlist

A checking mechanism for complete full-chip ESD protection circuit design and layout verification at layout level identifies all of both intentional and parasitic ESD devices contained in the design layout file and compiles a netlist. The checking mechanism then determines the critical operating parameters of the identified ESD devices and determines if the parasitic devices will negatively effect ESD protection performance. The checking mechanism then determines if the intentional devices meet design specifications; eliminates parasitic devices which will not negatively effect ESD protection from the netlist, and retains those parasitic devices which may lead to ESD protection malfunction. Design layout verification and faults are then reported.

Owner:TRUSTCHIP TECH

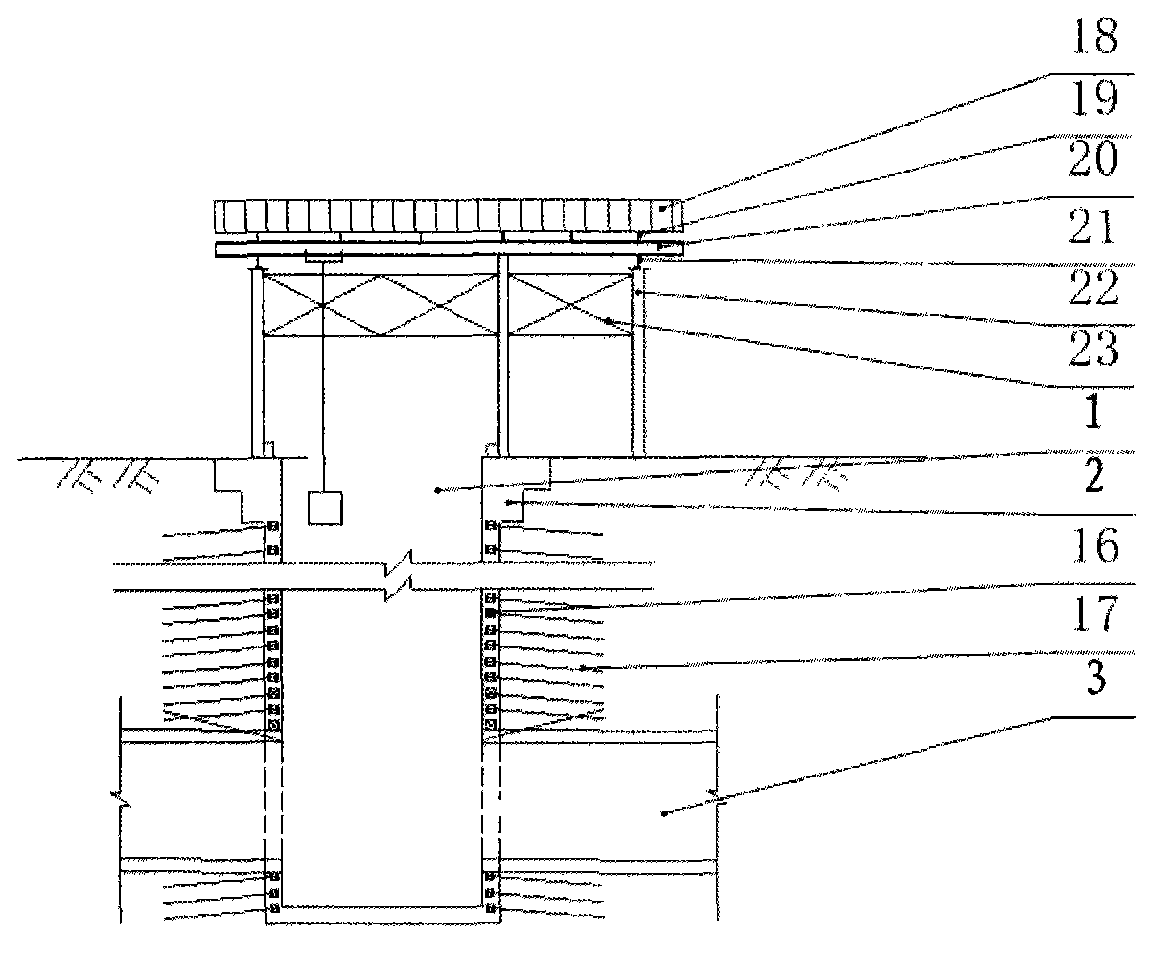

Bidirectional punching method for underground excavation of subway station

InactiveCN102953739AShorten the construction periodReduce interactionUnderground chambersSocial benefitsPunching

The invention provides a bidirectional punching method for underground excavation of a subway station. A light-section five-layer channel is arranged at the middle part of the station and runs through the station horizontally; the excavation is carried out from the middle part to the two sides of the station; and with adopting of a layering excavation mode and a crossed and segmented excavation mode as well as necessary preliminary bracing construction measures, the variation, caused by large-area multi-direction excavation, of surrounding rock stress around pilot tunnels can be distributed reasonably, the influences of surrounding soil bodies on the excavation among the different pilot tunnels are alleviated, a multi-cavity effect is prevented, and the top arch settling and lateral convergence and deformation in preliminary bracing of the pilot tunnels are alleviated so as to ensure that the preliminary bracing deformation of the pilot tunnels can meet design specification requirements; and meanwhile, the pilot tunnels can be excavated in advance at the middle part of the station, and can be excavated synchronously with the symmetrical excavation of air ducts toward the station direction, so that the integral preliminary bracing construction period of the station can be shortened by half, and comprehensive economic and social benefits are obvious.

Owner:中铁城建集团第三工程有限公司 +1

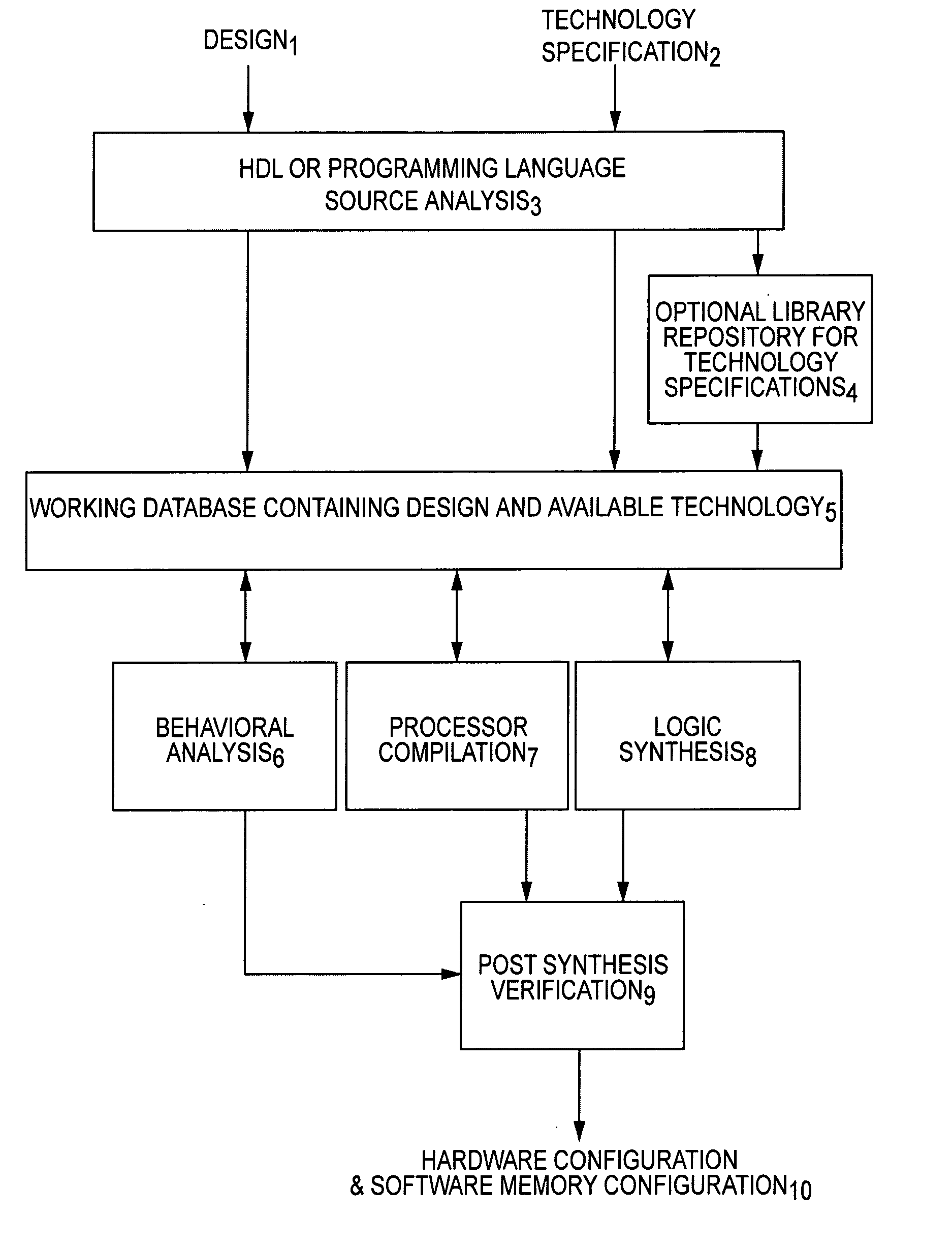

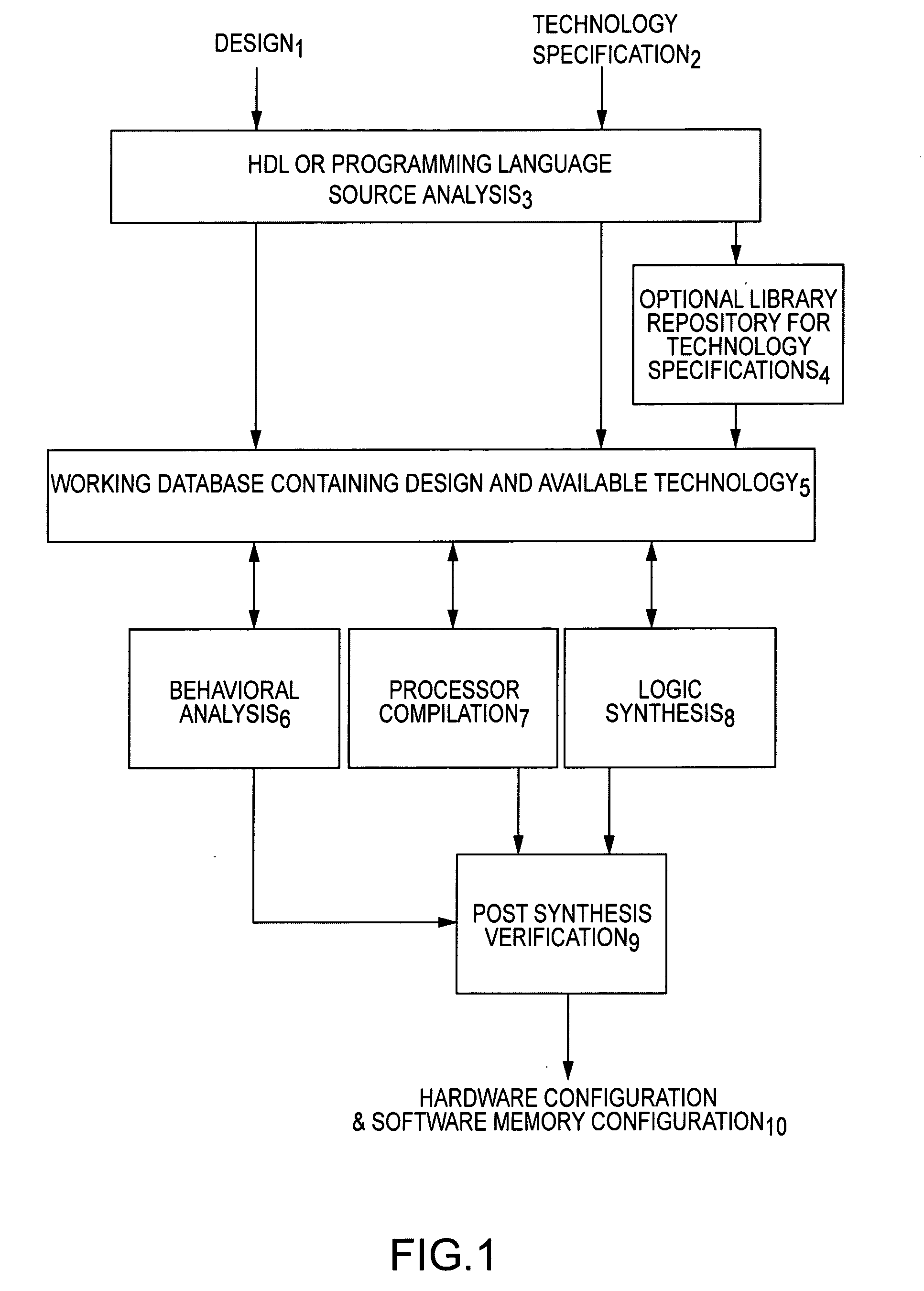

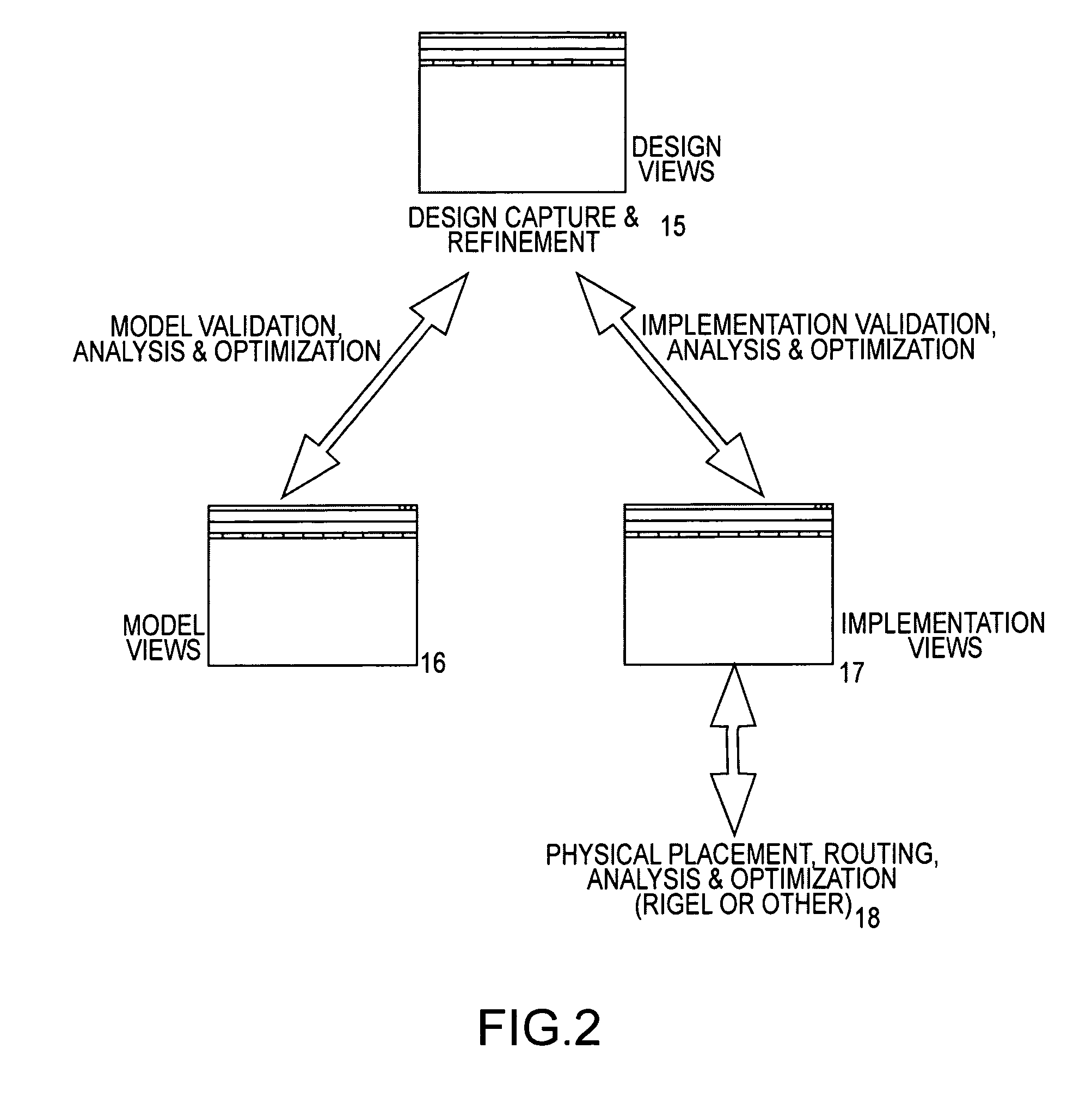

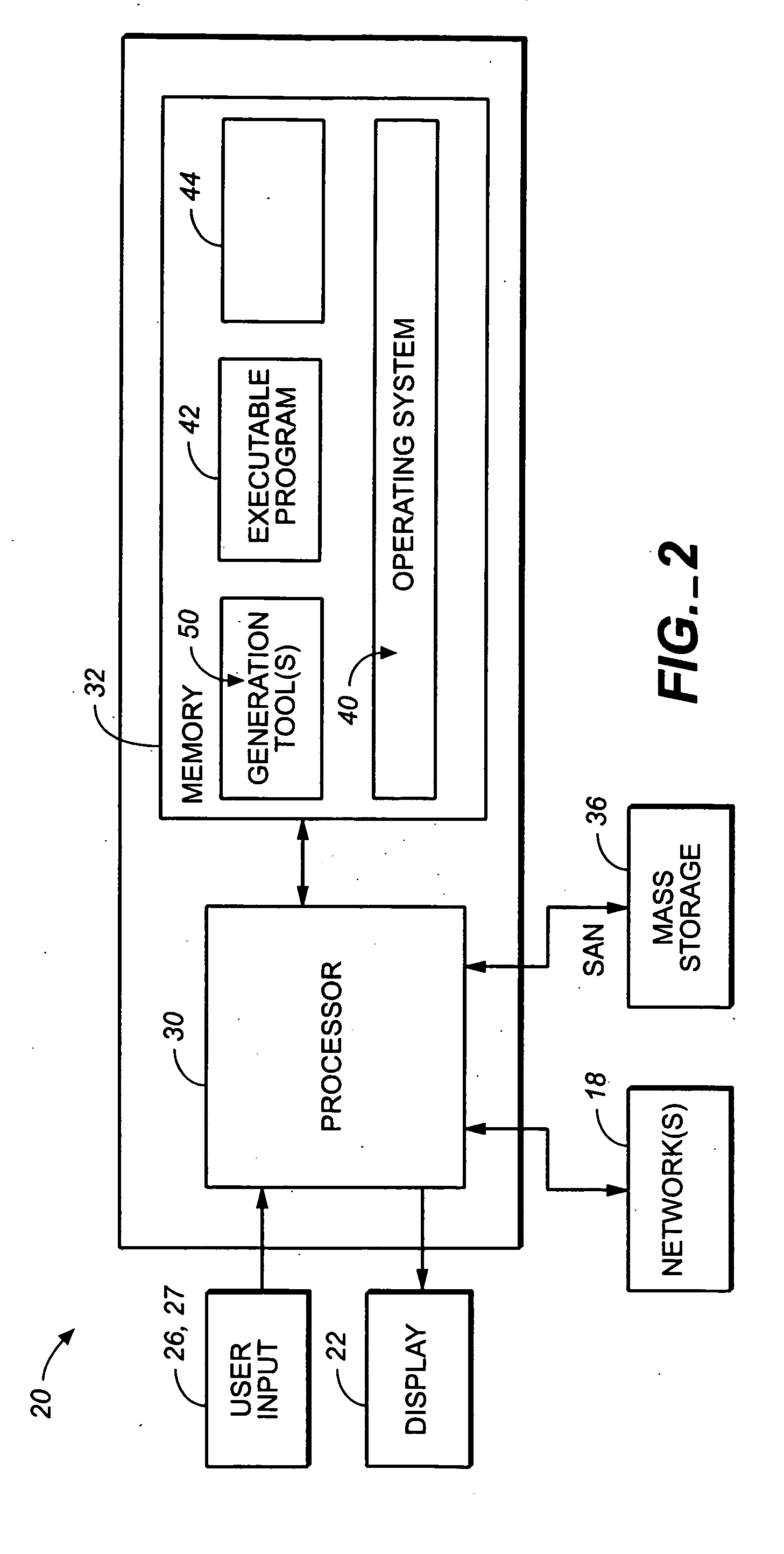

Hardware/software design tool and language specification mechanism enabling efficient technology retargeting and optimization

InactiveUS20050289485A1More compactEfficient designElectrical testingDigital computer detailsComputer architectureSoftware system

An innovative hardware / software design tool provides four modes of operation for converting an electronic design specification and zero or more technology specifications into realization of the electronic design in computer hardware, software and firmware. The first mode of operation compiles design and logic technology specifications into a model which can be utilized for behavioral analysis (such as simulation or formal verification) of logical characteristics (the model). The second mode of operation translates (compiles) partitions of the design and one or more logic technologies into one or more processor intermediates or binaries (embedded binary) suitable for execution on multi-purpose processing units (embedded or general purpose processors). The third mode of operation translates (synthesizes) partitions of the design and logic technology into a collection of cells and interconnects (net-list implementation) suitable for input to physical design processes such as is required to target a field-programmable logic array (FPGA), application specific integrated circuit (ASIC), system-on-a-chip (SOC) or custom logic). The fourth mode of operation analyzes (verifies) behavior of the embedded binaries running on processing units and implementations augmented by additional physical technology and parameters, yielding a more detailed (accurate) prediction of the resulting hardware / software system behavior when realized through manufacturing. Critically, the design specification, logic specifications, physical specifications and definition of each multi-purpose processing unit may be defined external to the hardware / software design tool using an innovative augmentation of standard hardware description or programming languages taught in this patent application. In the prior art, specification of the logic technology, physical technology and embedded or general purpose processor architecture are either incorporated directly into the design tool by the tool developer or are maintained entirely external to the design tool (such as an encapsulated component model or intermediate code interpreter). The present invention is an innovative and valuable improvement over prior art in that design specifications are combined by the tool from distinct specification(s) of generalized logic, physical and processor technology, leading to more efficient behavioral design, opportunities for third parties to add functionality by incorporating generalized logic and physical technology modules into the analysis and synthesis process and opportunities for semi-automatic, goal-directed optimization through application of various logic, physical and processor technologies by the design tool.

Owner:FTL SYST

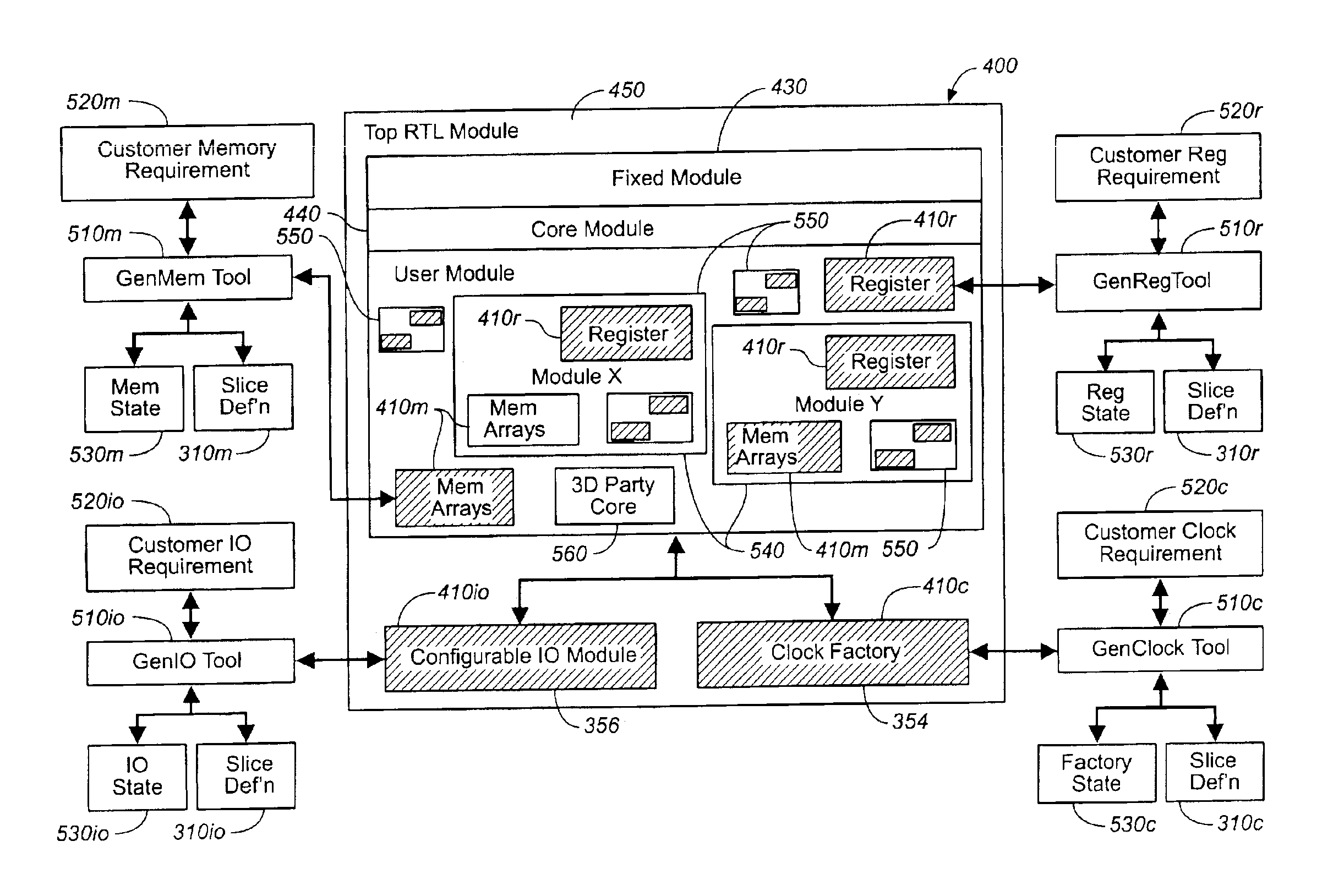

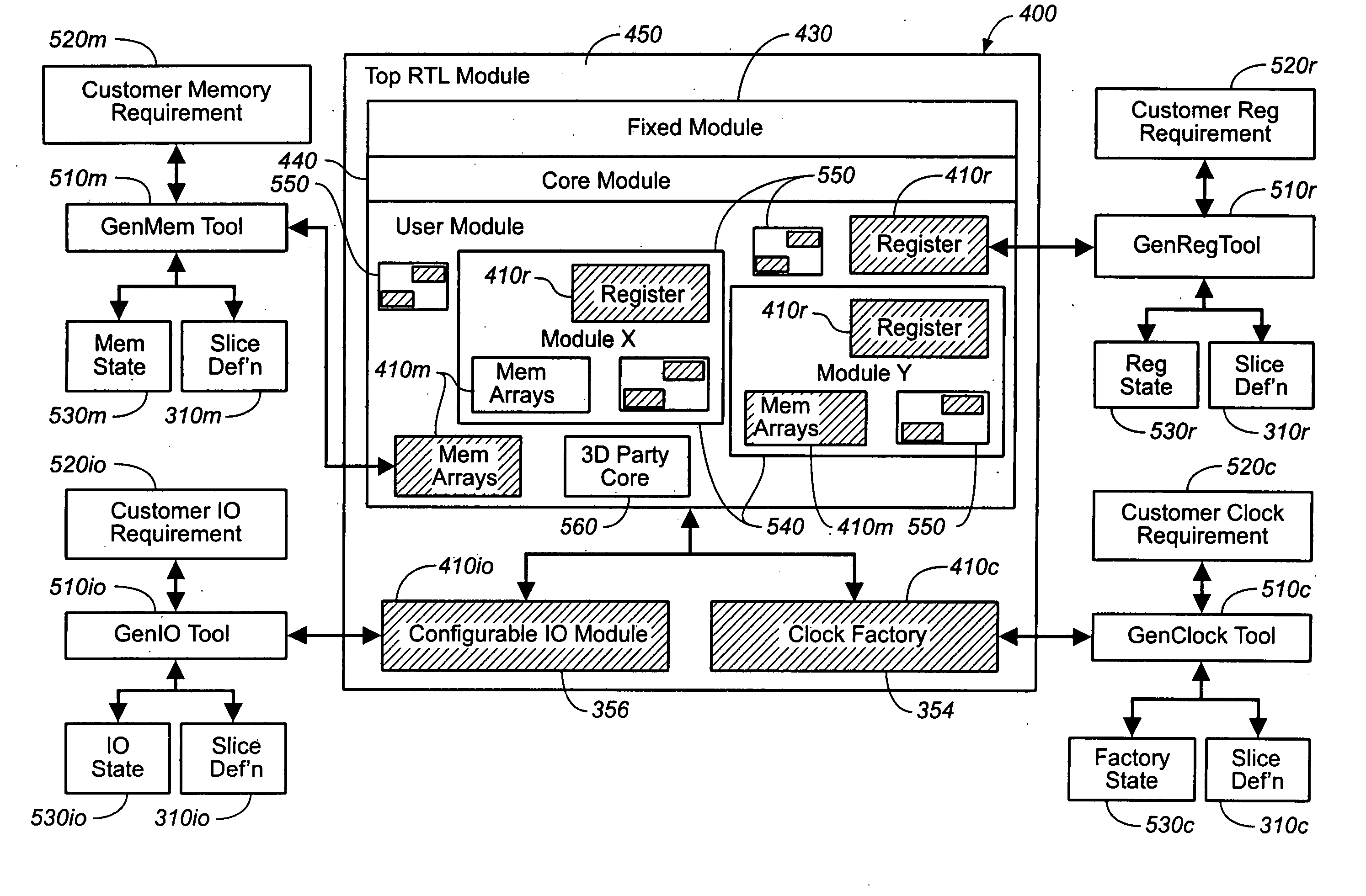

Simplified process to design integrated circuits

ActiveUS7055113B2Computer aided designSoftware simulation/interpretation/emulationCustomer requirementsFoundry

A set of tools is provided herein that produces useful, proven, and correct integrated semiconductor chips. Having as input either a customer's requirements for a chip, or a design specification for a partially manufactured semiconductor chip, the tools generate the RTL for control plane interconnect; memory composition, test, and manufacture; embedded logic analysis, trace interconnection, and utilization of spare resources on the chip; I / O qualification, JTAG, boundary scan, and SSO analysis; testable clock generation, control, and distribution; interconnection of all of the shared logic in a testable manner from a transistor fabric and / or configurable blocks in the slice. The input customer requirements are first conditioned by RTL analysis tools to quickly implement its logic. The slice definition and the RTL shell provides the correct logic for a set of logic interfaces for the design specification to connect. The tools share a common database so that logical interactions do not require multiple entries. The designs are qualified, tested, and verified by other tools. The tools further optimize the placement and timing of the blocks on the chip with respect to each other and with respect to placement on a board. The suite may be run as batch processes or can be driven interactively through a common graphical user interface. The tools also have an iterative mode and a global mode. In the iterative mode, one or more of the selected tools can generate the blocks or modify a design incrementally and then look at the consequences of the addition, or change. In the global mode, the semiconductor product is designed all at once in a batch process as above and then optimized altogether. This suite of generation tools generates design views including a qualified netlist for a foundry to manufacture.

Owner:BELL SEMICON LLC

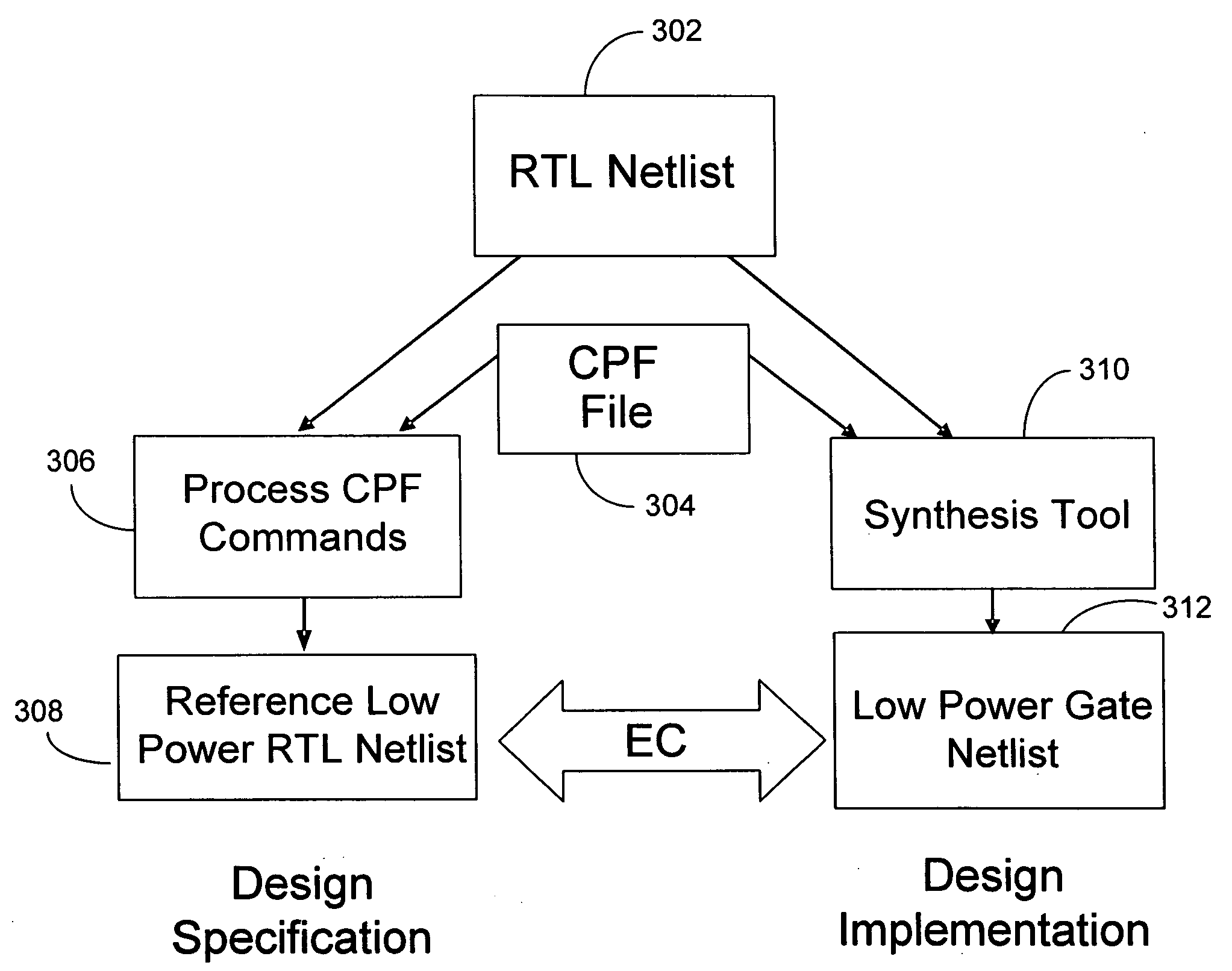

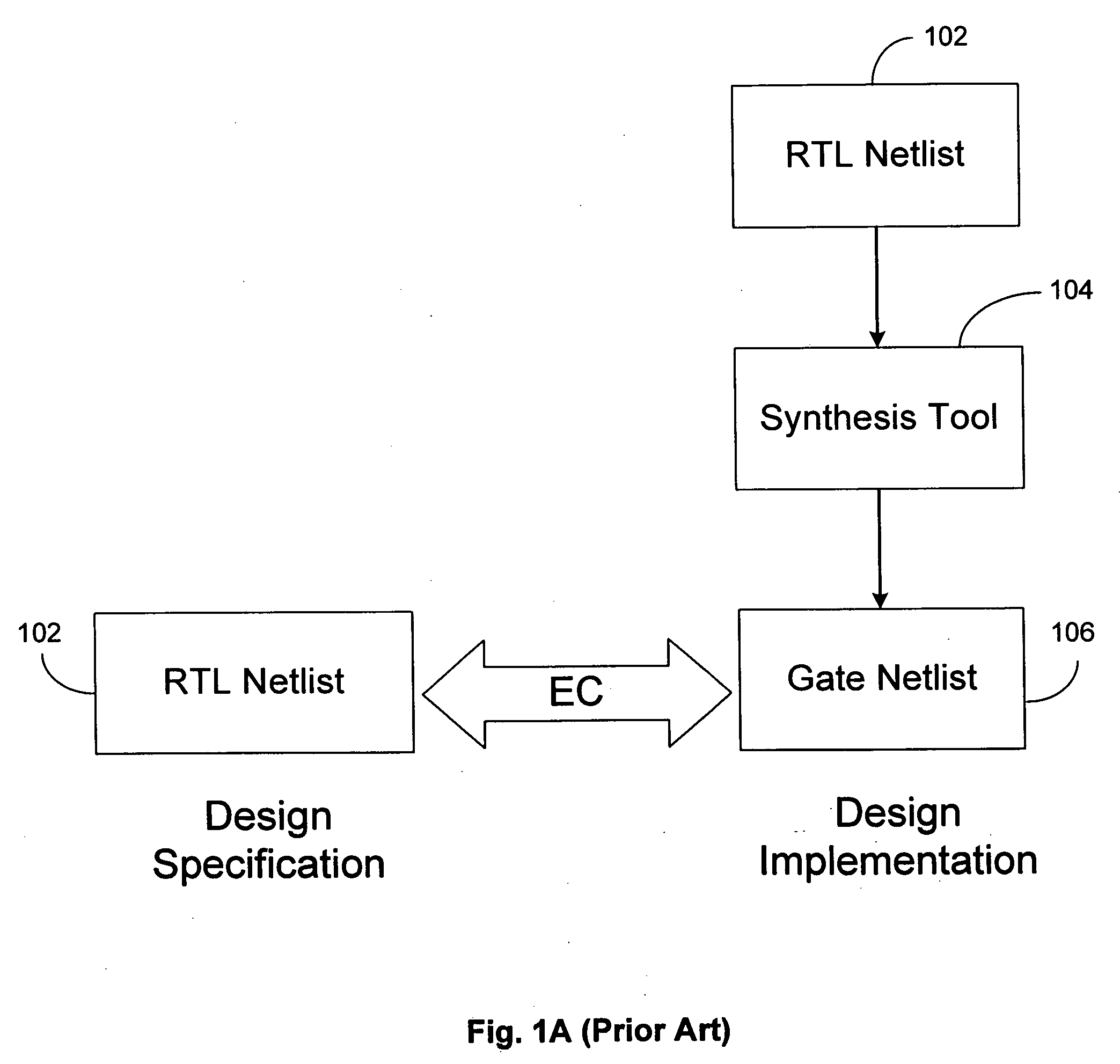

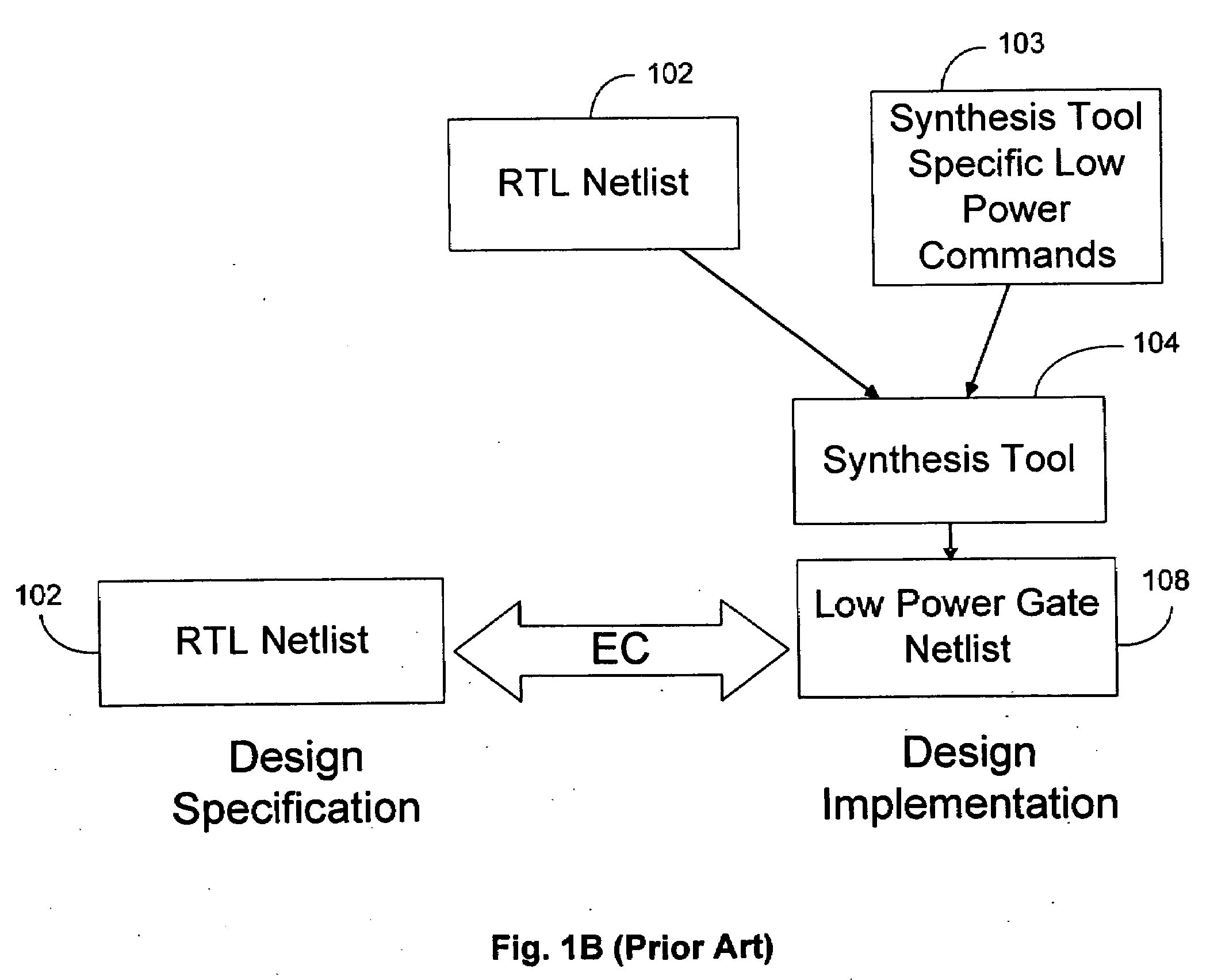

Method and system for equivalence checking of a low power design

ActiveUS20080127014A1CAD circuit designSoftware simulation/interpretation/emulationProcessor registerEngineering

Method and system for equivalence checking of a low power design are disclosed. The method includes receiving a register-transfer level (RTL) netlist representation of a circuit, receiving a power specification file for describing power requirements of the circuit, creating a low power gate netlist for representing a design implementation of the circuit using the RTL netlist and the power specification file, creating a reference low power RTL netlist for representing a design specification of the circuit using the RTL netlist and the power specification file, and performing equivalence checking between the low power gate netlist and the reference low power RTL netlist. The method further includes annotating low power information described in the power specification file into the reference low power RTL netlist, and creating low power logic in the reference low power RTL netlist.

Owner:CADENCE DESIGN SYST INC

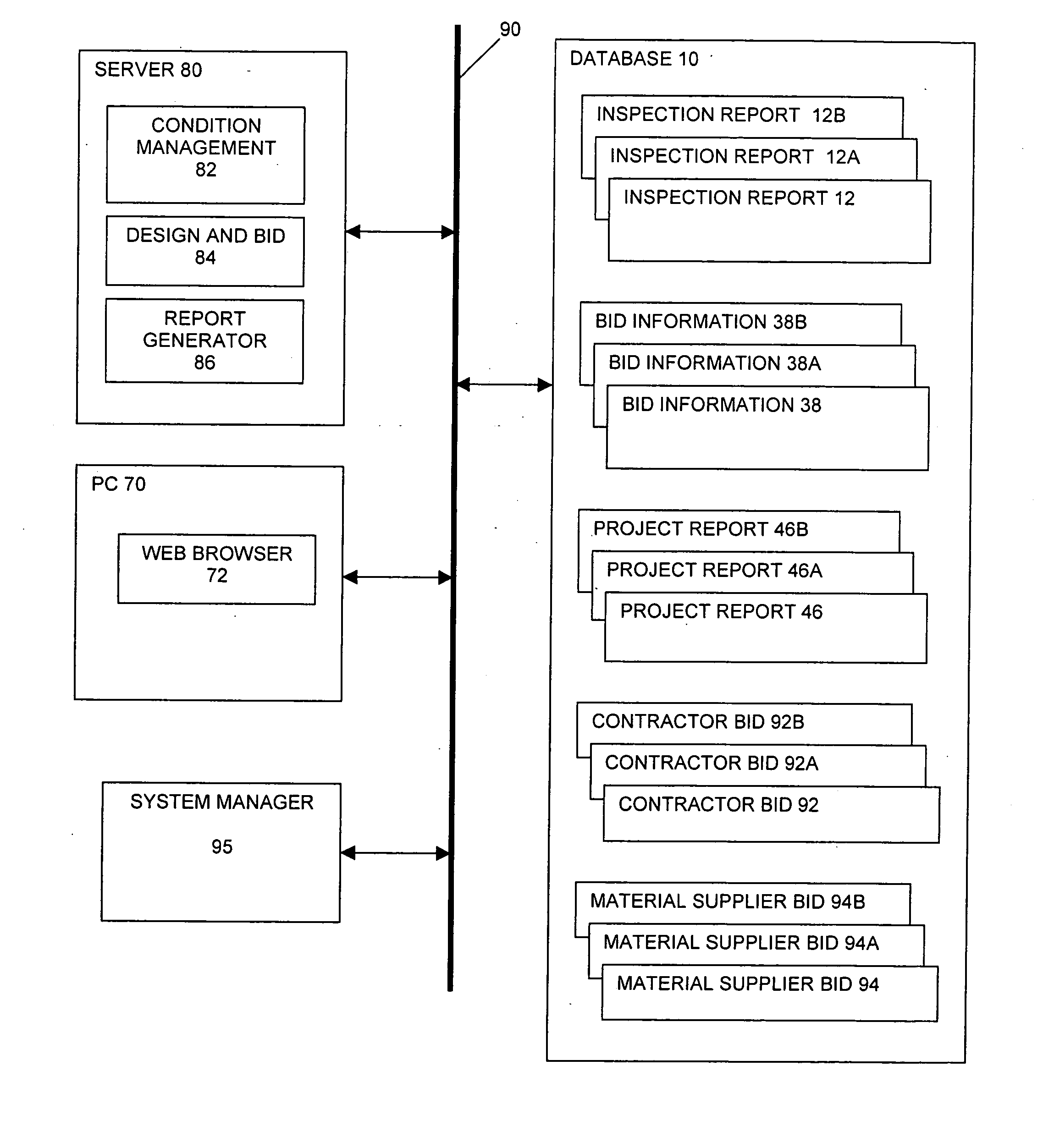

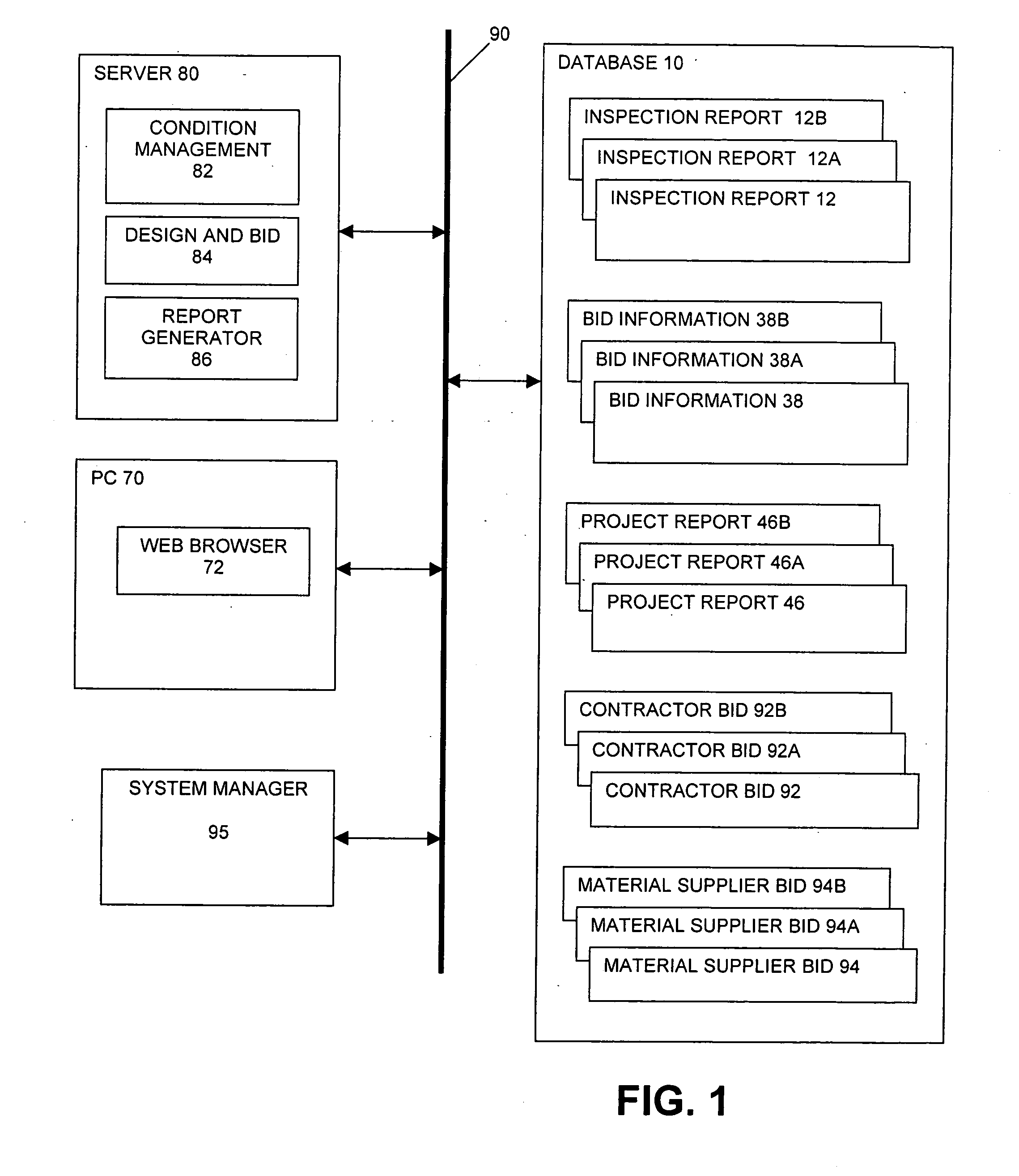

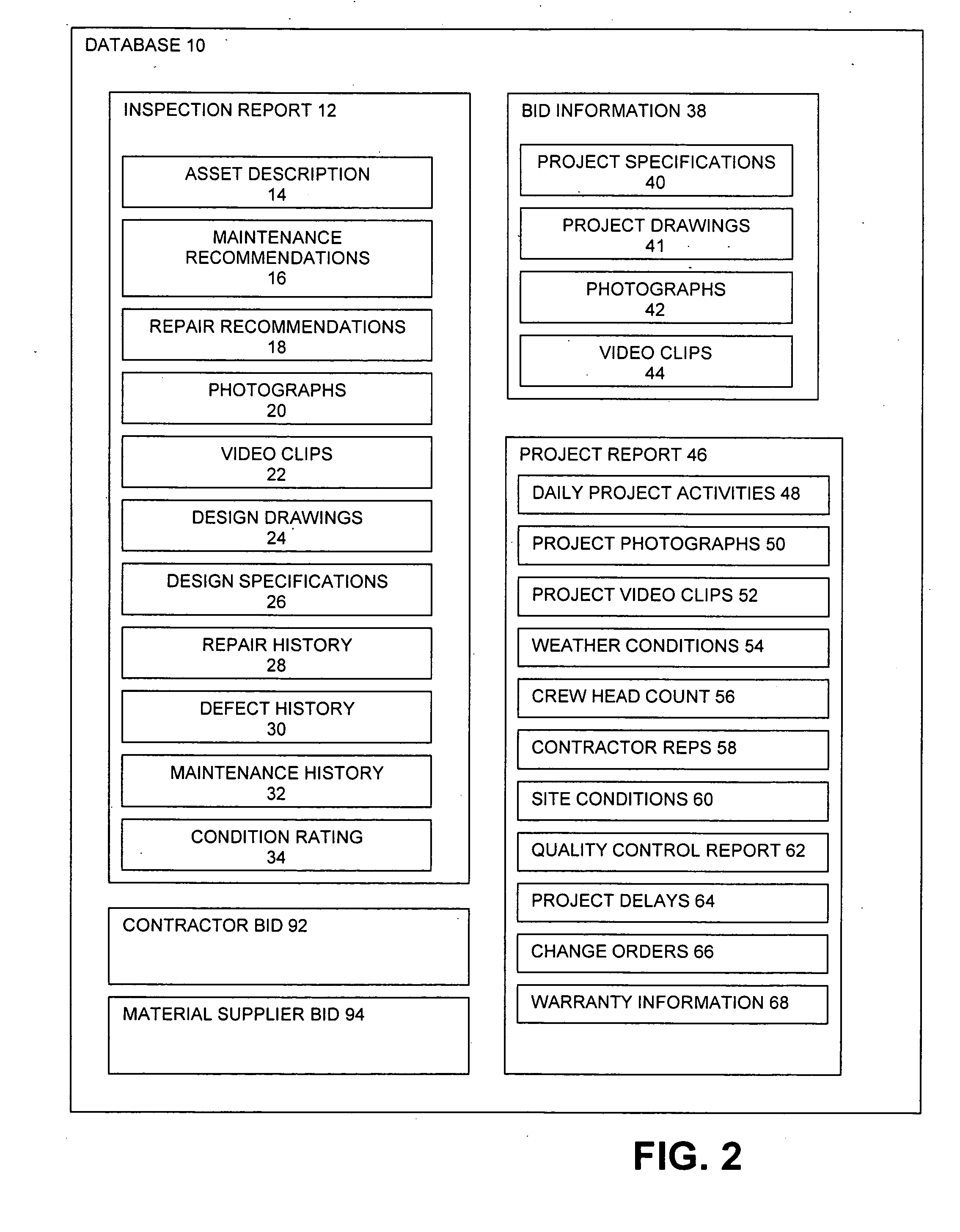

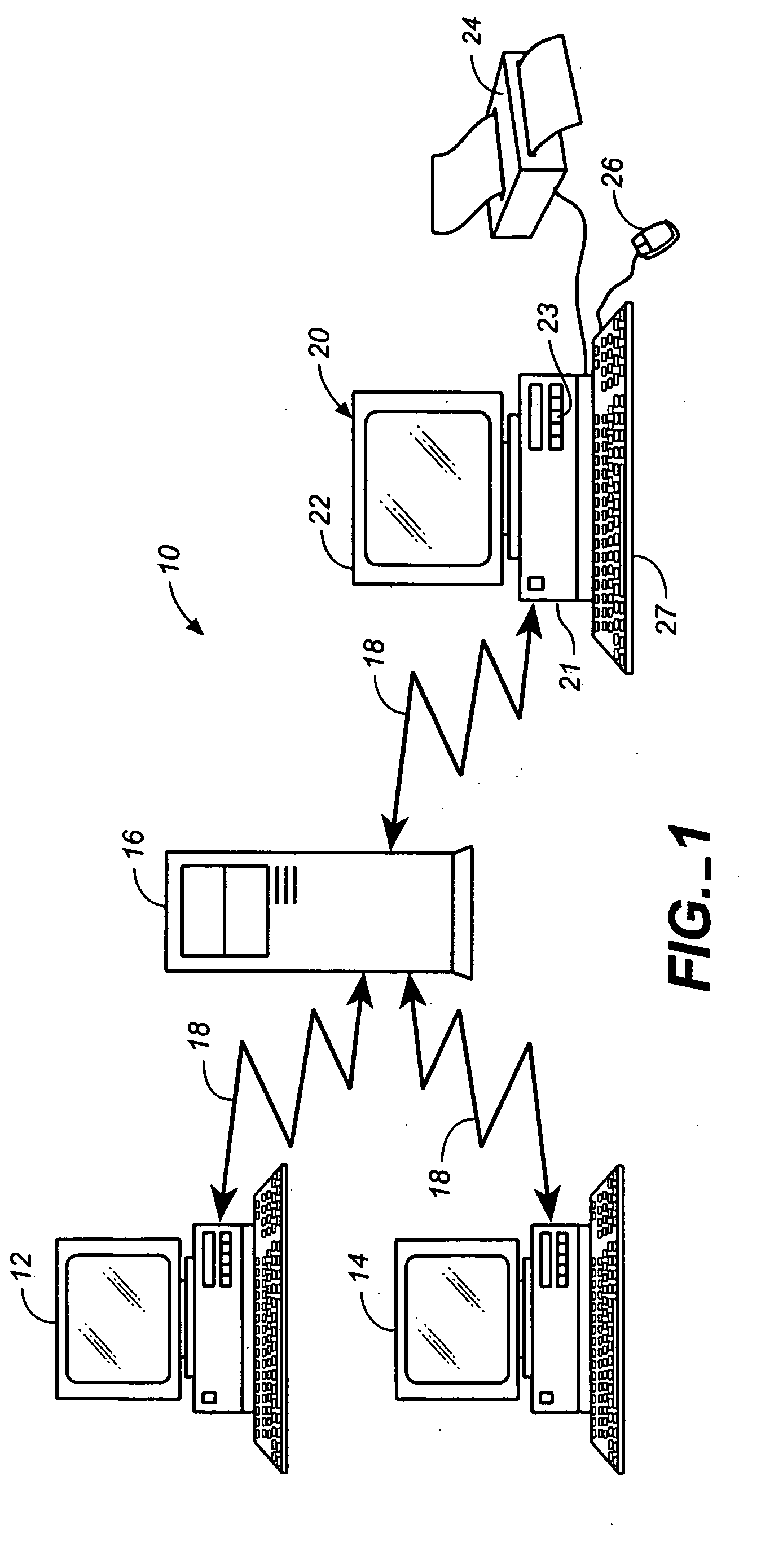

Methods and systems for online management of construction assets

The present invention provides methods and systems for online management of construction assets. An online inspection report relating to a current condition of a construction asset is provided. The inspection report is archived (e.g., uploaded to a database accessible via a server). An asset owner is then provided with online access to the archived inspection report. The inspection report may include a description of the construction asset, recommendations regarding maintenance of the construction asset, recommendations regarding current repairs to the construction asset, photographs of the construction asset, video clips of the construction asset, design drawings of the construction asset, design specifications of the construction asset, repair history, defect history, maintenance history, and the like. A plurality of inspection reports corresponding to a plurality of construction assets of the asset owner may be archived. Computerized reports may be generated relating to one or more of the plurality of construction assets.

Owner:SWEENEY THOMAS

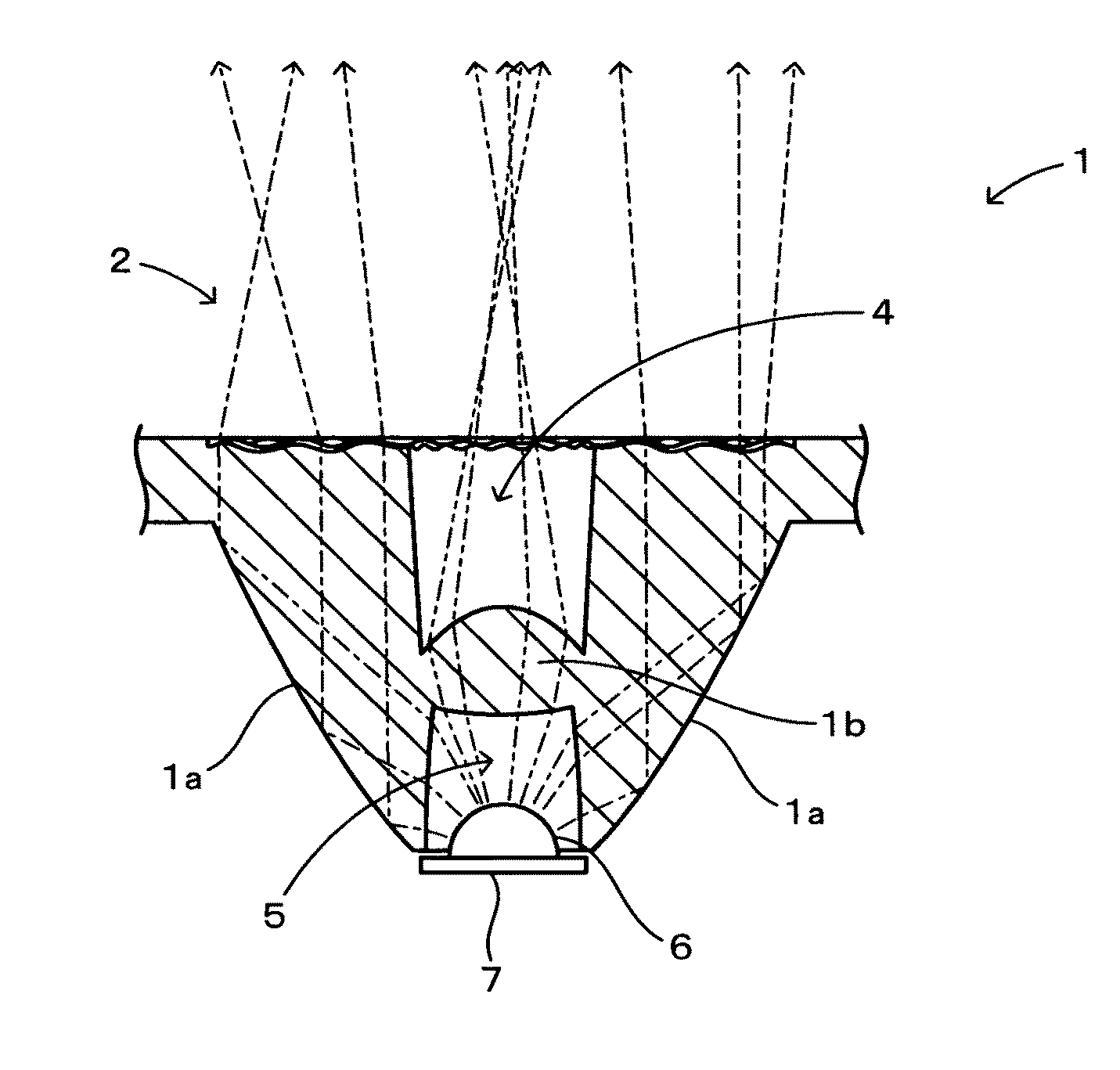

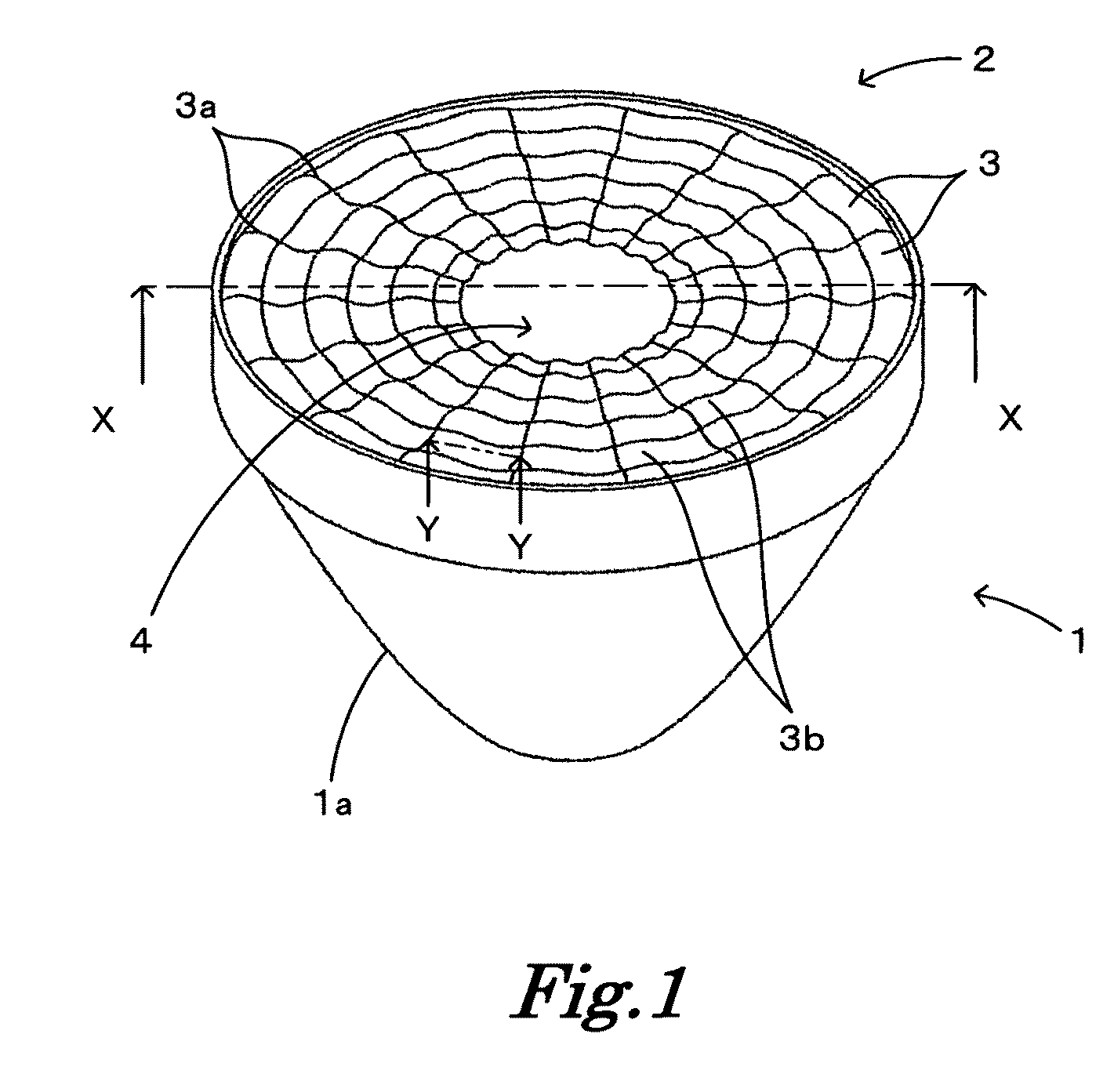

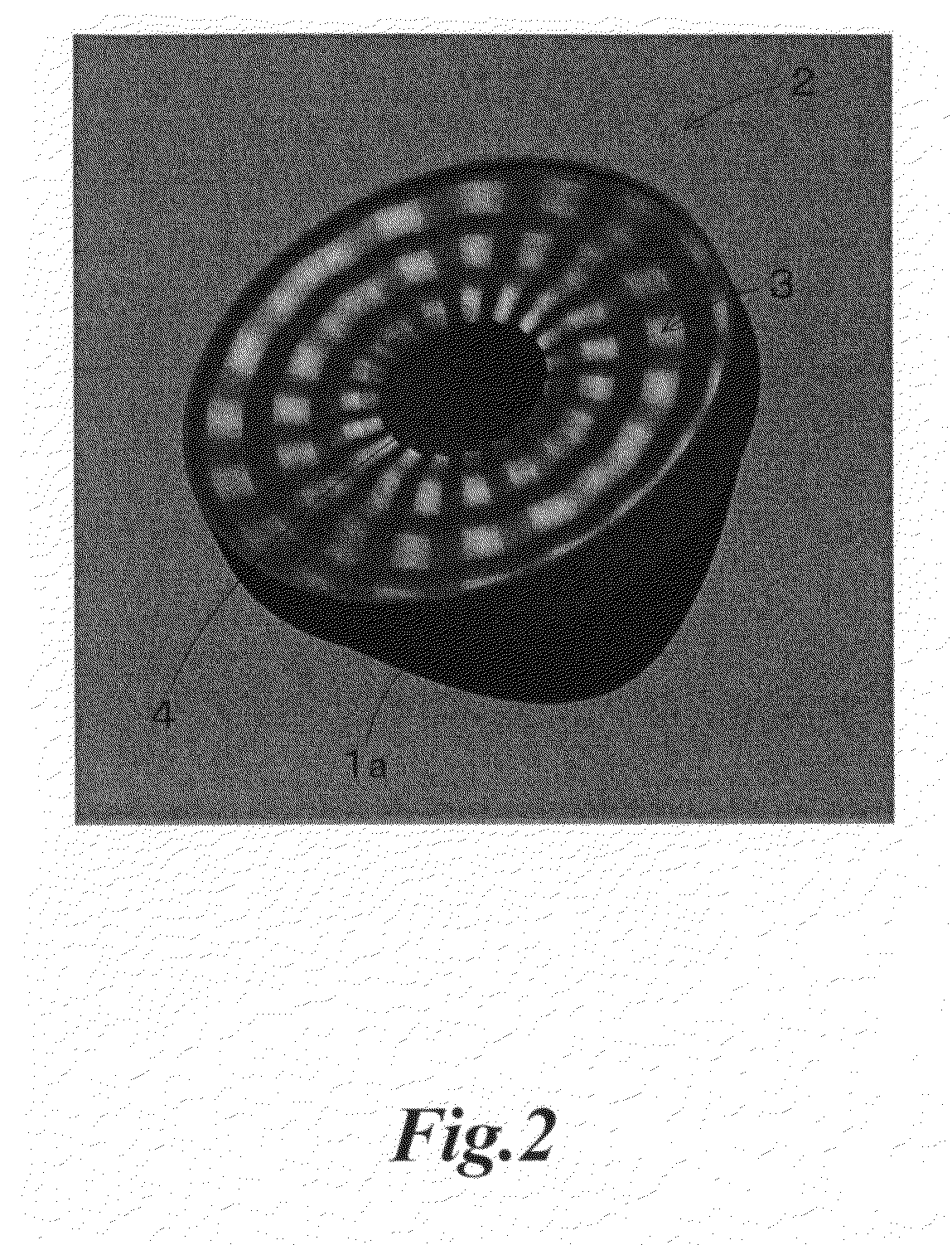

LED light distribution lens, LED lighting module having LED light distribustion lens and lighting equipment having LED lighting module

InactiveUS20110096553A1Low production costLight extraction efficiencyPoint-like light sourceLighting support devicesLight equipmentComputer module

LED light distribution lens having a light emitting surface whose shape is circular in its plan view, which emits forward light from LED disposed in its center.The LED light distribution lens is characterized by the construction of the emitting surface which is low at production cost and so designed as not to cause the diffuse reflection and unintended diffusion. Such emitting surface has a plural convex surfaces formed both in its radial and its circumferential directions in a manner that the convex surfaces surround the circumference of the LED and has continuous surfaces formed such that the boundary portions of the convex surfaces constitute the concave surfaces, thereby realizing expected light distribution based on design specification.

Owner:ENDO LIGHTING CORP

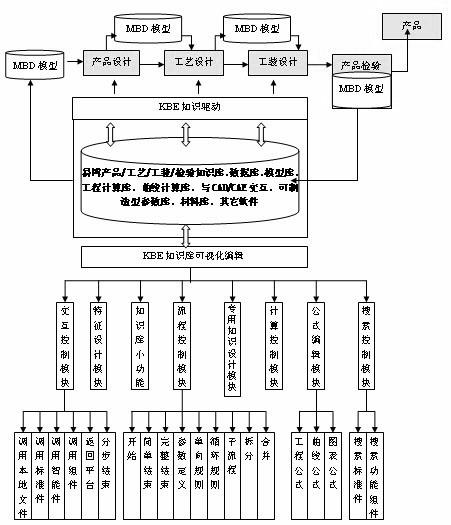

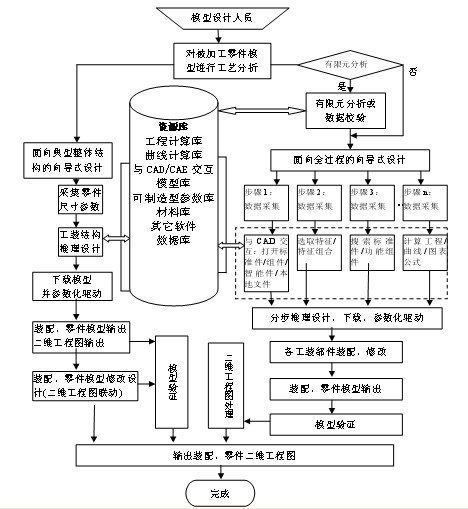

Full three-dimensional digital knowledge base system and application method of knowledge base

ActiveCN102324072AImprove general performanceDo not disclose design experienceData processing applicationsSpecial data processing applicationsData acquisitionDigitization

The invention discloses a full three-dimensional digital knowledge base system and an application method of a knowledge base. The knowledge base system comprises a flow control module, a specific knowledge design module, an interaction control module, an equation editing module, a search control module, a computing control module and a knowledge base small functional module and is an independent knowledge driving system capable of being hung on different CAD (Computer-Aided Design). The application method of the knowledge base can be applied to various fields such as products, processes, tool design, product inspection and the like in the mechanism manufacture industry. A designer expresses knowledge such as purposes, industry design specifications, standard manuals, design experience, computational formulas and the like through an open programming-free visual knowledge editing function and stores the knowledge into the knowledge base, a database and a model base for reusing; and wizard design is realized through parameter passing, data acquisition and interaction and platform interaction. The system has the advantages of strong generality, convenience and rapidness, no leakage of enterprise core technology experience knowledge and the like and provides means for technical innovation and knowledge and experience accumulation.

Owner:西安易博软件有限责任公司

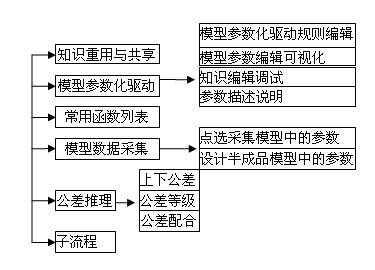

Transformer performance prediction

A method for predicting transformer performance includes receiving information representative of a plurality of built transformers, the information comprising a design specification for each built transformer, and measured test information for each built transformer, receiving a second transformer design specification, and determining, via an intelligent system, a predicted test result for the second transformer design specification based on the second transformer design specification and the information representative of the plurality of built transformers.

Owner:ABB RES LTD

Suite of tools to design integrated circuits

InactiveUS20050240892A1Accelerate Design CycleI/O can be optimizedDetecting faulty computer hardwareComputer programmed simultaneously with data introductionFoundryCustomer requirements

A set of tools is provided herein that produces useful, proven, and correct integrated semiconductor chips. Having as input either a customer's requirements for a chip, or a design specification for a partially manufactured semiconductor chip, the tools generate the RTL for control plane interconnect; memory composition, test, and manufacture; embedded logic analysis, trace interconnection, and utilization of spare resources on the chip; I / O qualification, JTAG, boundary scan, and SSO analysis; testable clock generation, control, and distribution; interconnection of all of the shared logic in a testable manner from a transistor fabric and / or configurable blocks in the slice. The input customer requirements are first conditioned by RTL analysis tools to quickly implement its logic. The slice definition and the RTL shell provides the correct logic for a set of logic interfaces for the design specification to connect. The tools share a common database so that logical interactions do not require multiple entries. The designs are qualified, tested, and verified by other tools. The tools further optimize the placement and timing of the blocks on the chip with respect to each other and with respect to placement on a board. The suite may be run as batch processes or can be driven interactively through a common graphical user interface. The tools also have an iterative mode and a global mode. In the iterative mode, one or more of the selected tools can generate the blocks or modify a design incrementally and then look at the consequences of the addition, or change. In the global mode, the semiconductor product is designed all at once in a batch process as above and then optimized altogether. This suite of generation tools generates design views including a qualified netlist for a foundry to manufacture.

Owner:BELL SEMICON LLC

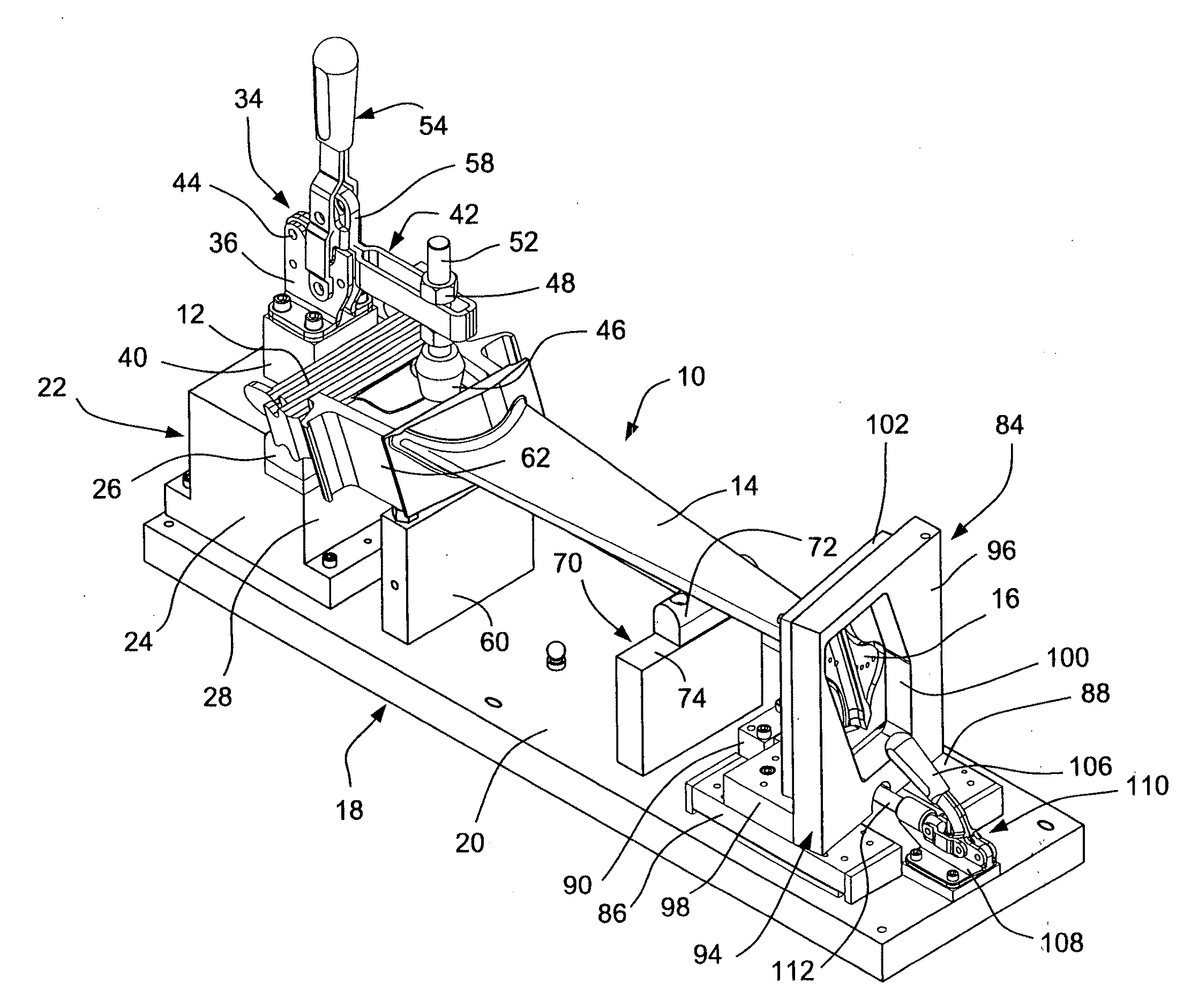

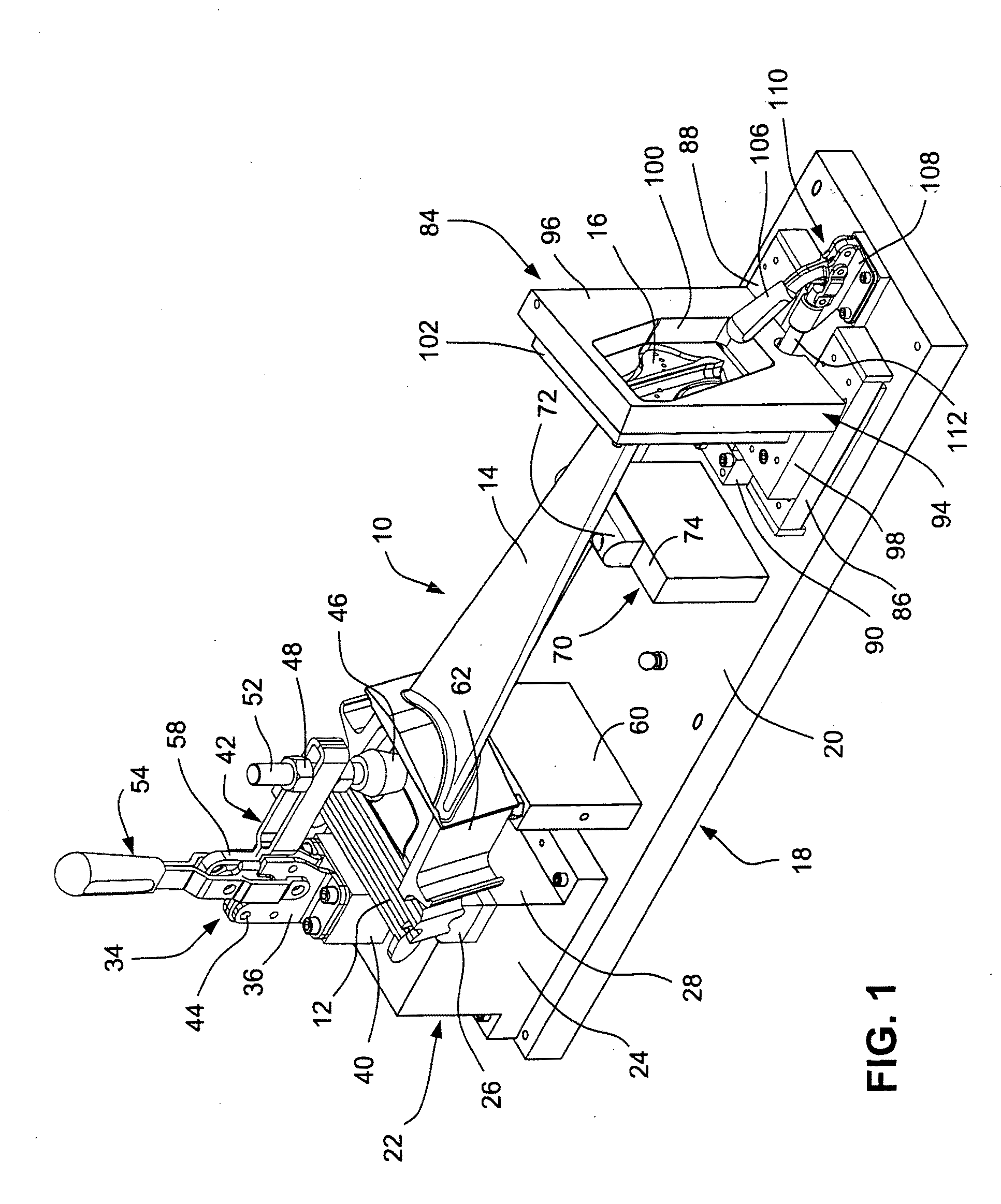

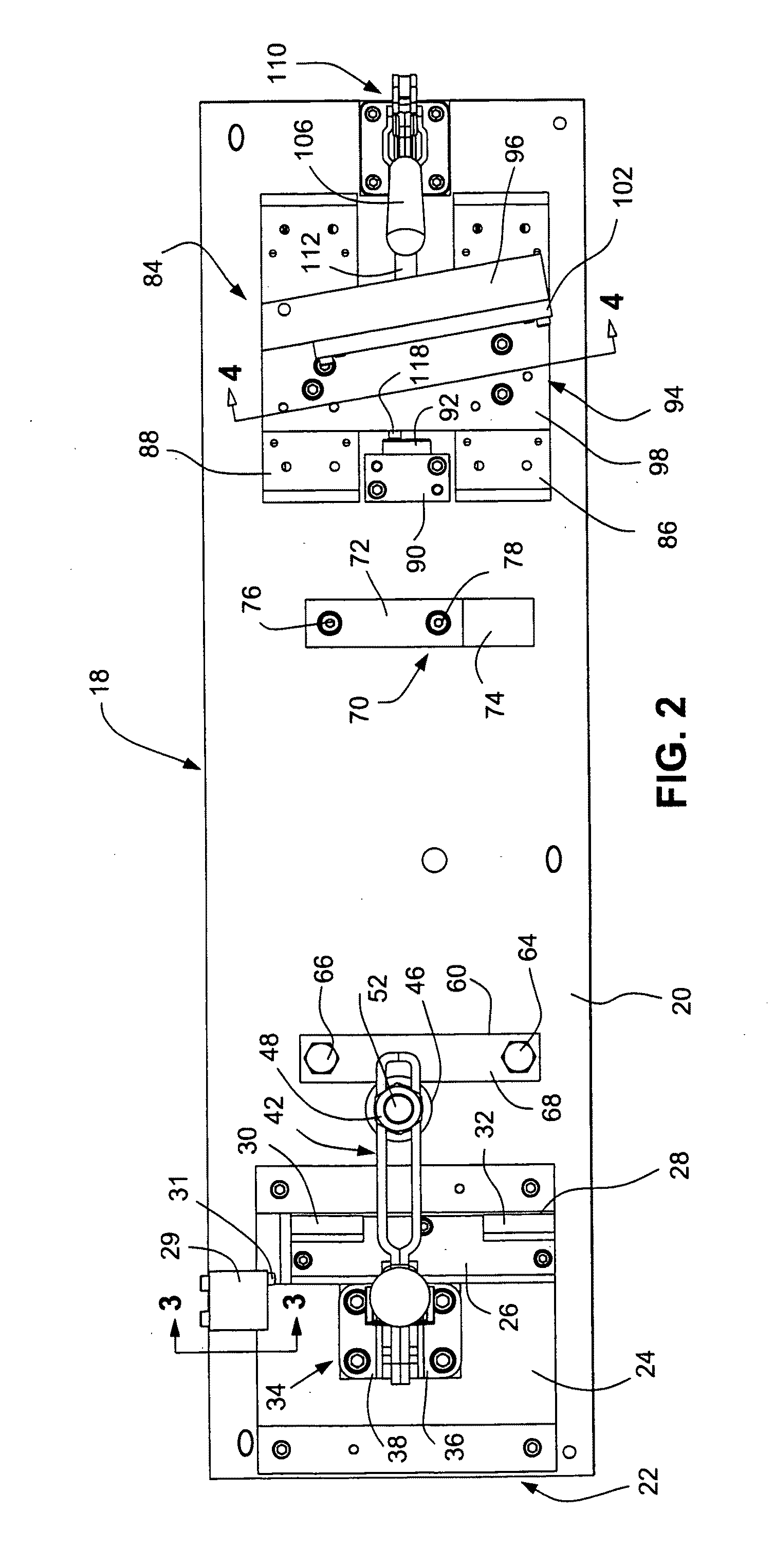

Inspection tool for measuring bucket Z notch position

An inspection tool for a turbine bucket shroud includes: a clamp device for clamping a dovetail portion of a turbine bucket; a template plate provided with an aperture defined by a edge shaped to conform to a specified shape of the turbine bucket shroud, wherein the template is moveable to a location over the turbine bucket shroud in a direction toward the clamp device, and wherein, at the location, the aperture represents a design specification location for the turbine bucket shroud relative to the dovetail portion of the bucket. A measurement gauge is provided for measuring gaps between edges of the shroud and edges of the template aperture.

Owner:GENERAL ELECTRIC CO

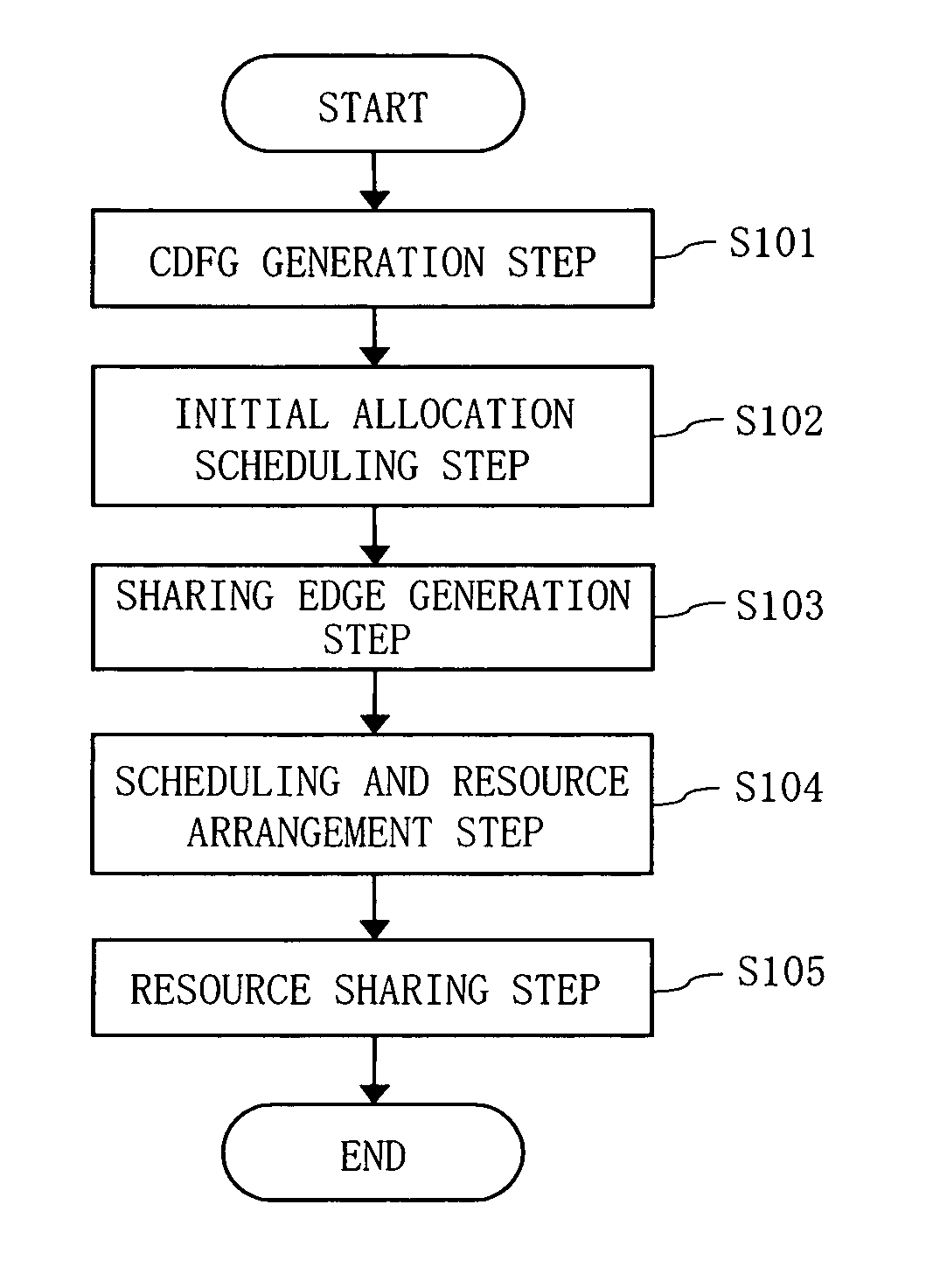

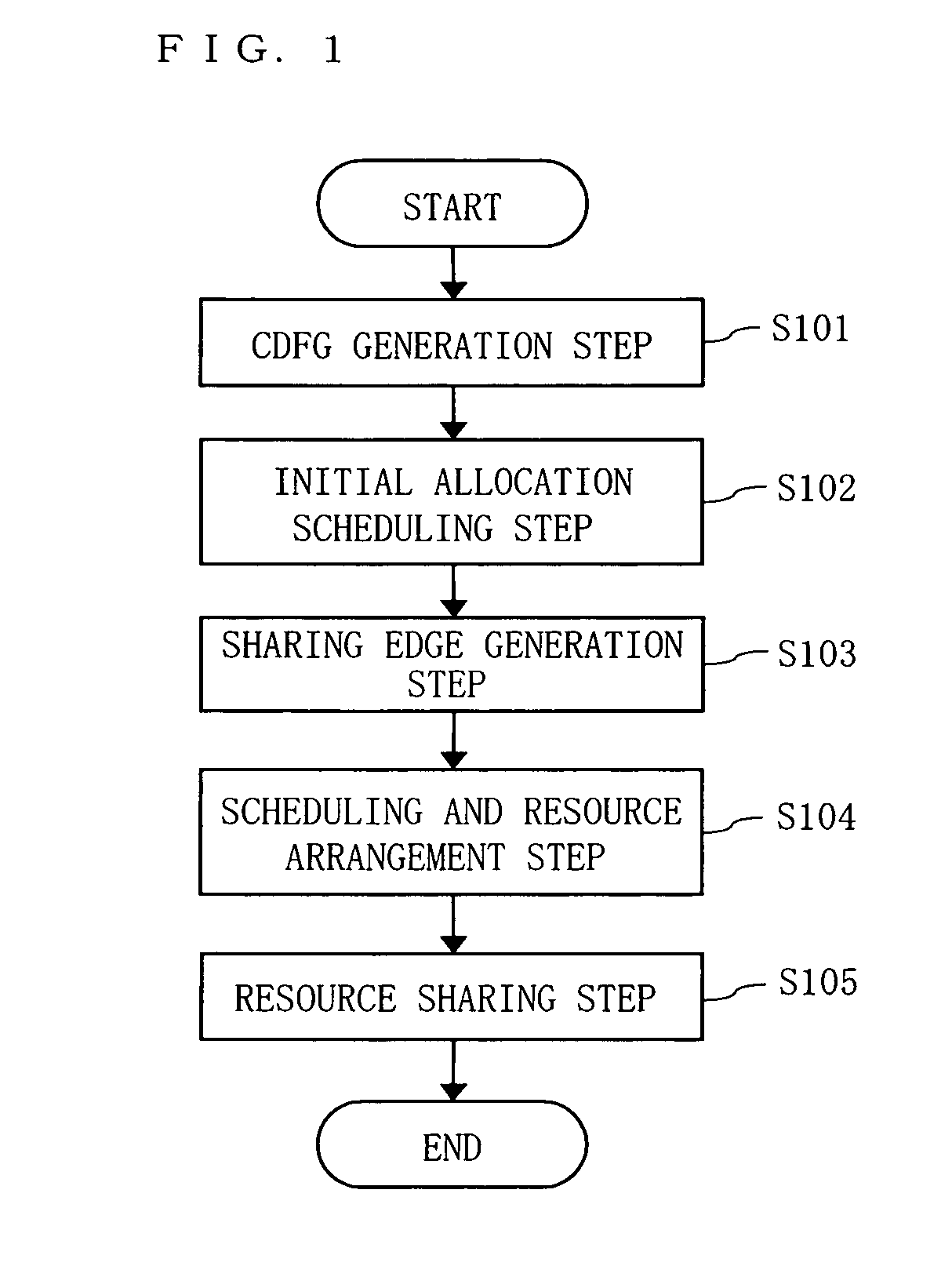

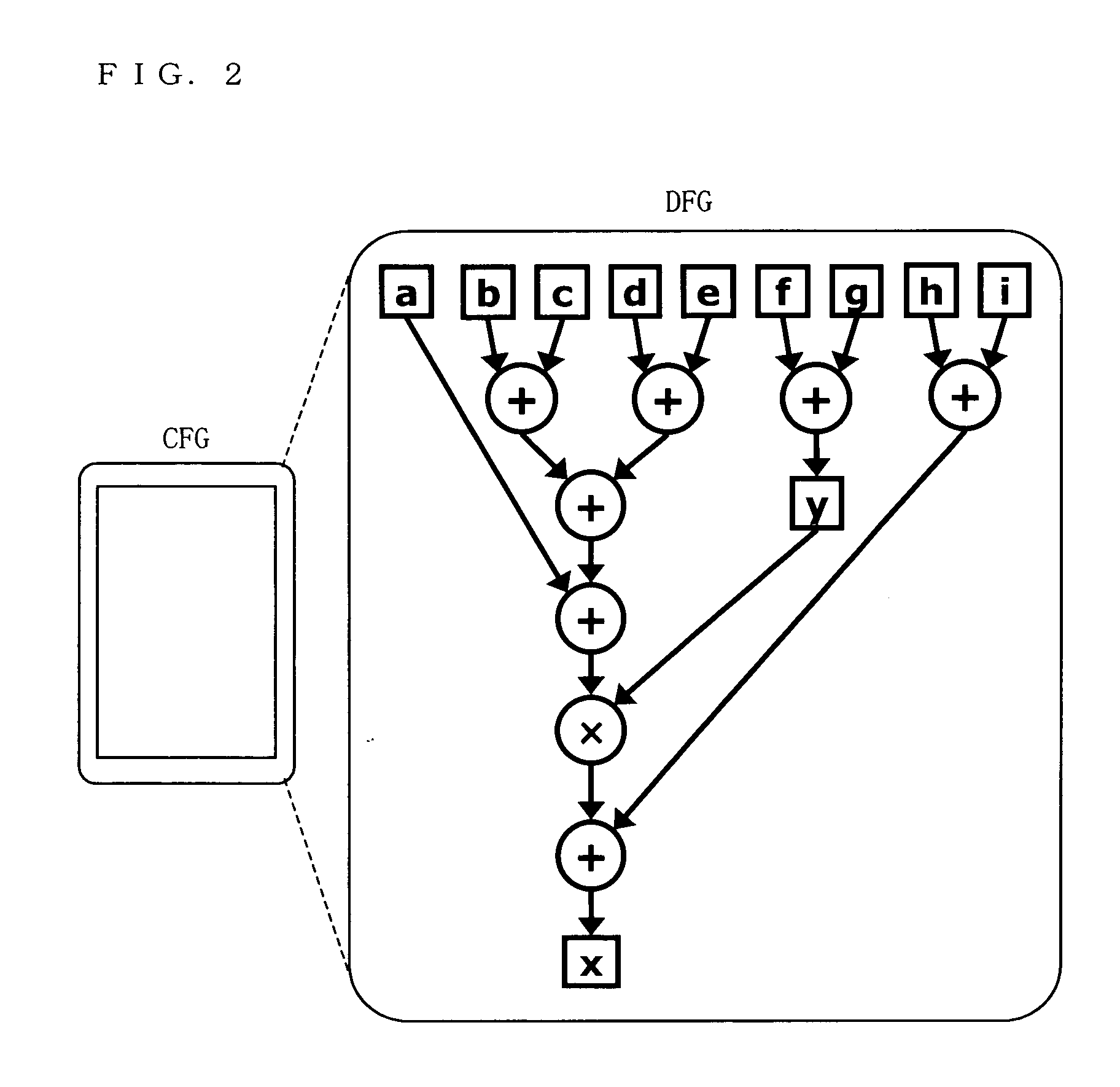

High level synthesis method for semiconductor integrated circuit

InactiveUS20050289499A1Efficient sharingLess attractiveCAD circuit designSoftware simulation/interpretation/emulationGraphicsData stream

A CDFG which is a graph representing calculations and a data flow included in the design specifications of a circuit is generated S101, a clock cycle required for the processing is obtained and thus an allocated resource connection graph is generated S102. When the allocated resource connection graph includes nodes to which hardware resources having the same function are allocated, a sharing edge for controlling sharing of the nodes is added between the nodes S103. A provisional layout of the allocated resource connection graph having the sharing edge added thereto is provided S104, and the nodes of the allocated resource connection graph are shared based on the layout result S105. The sharing edge is provided with attribute or weight such as attraction or repulsion. Thus, the distance between the nodes in the layout result is controlled and the degree at which the resources are shared is controlled.

Owner:SOCIONEXT INC

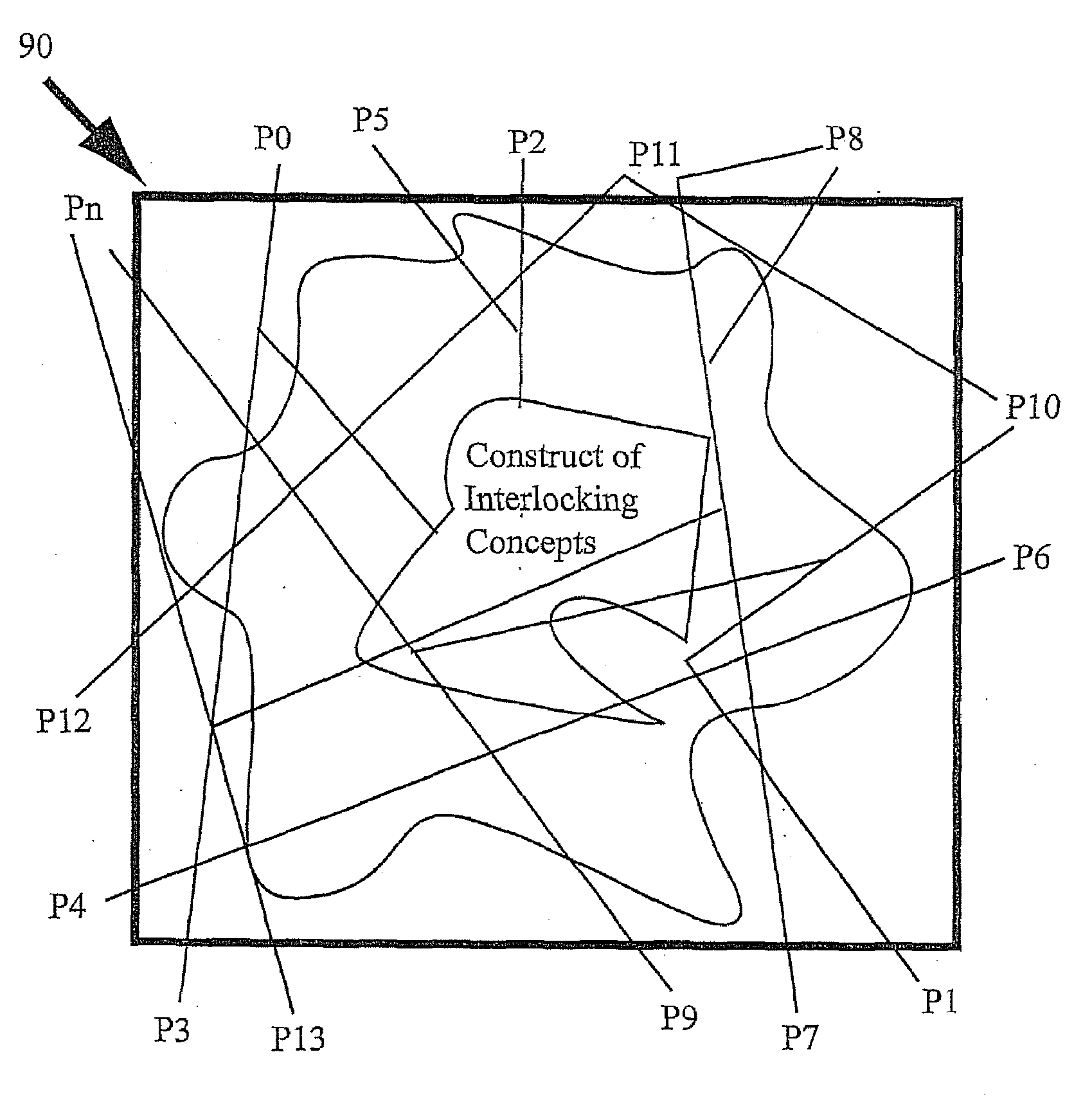

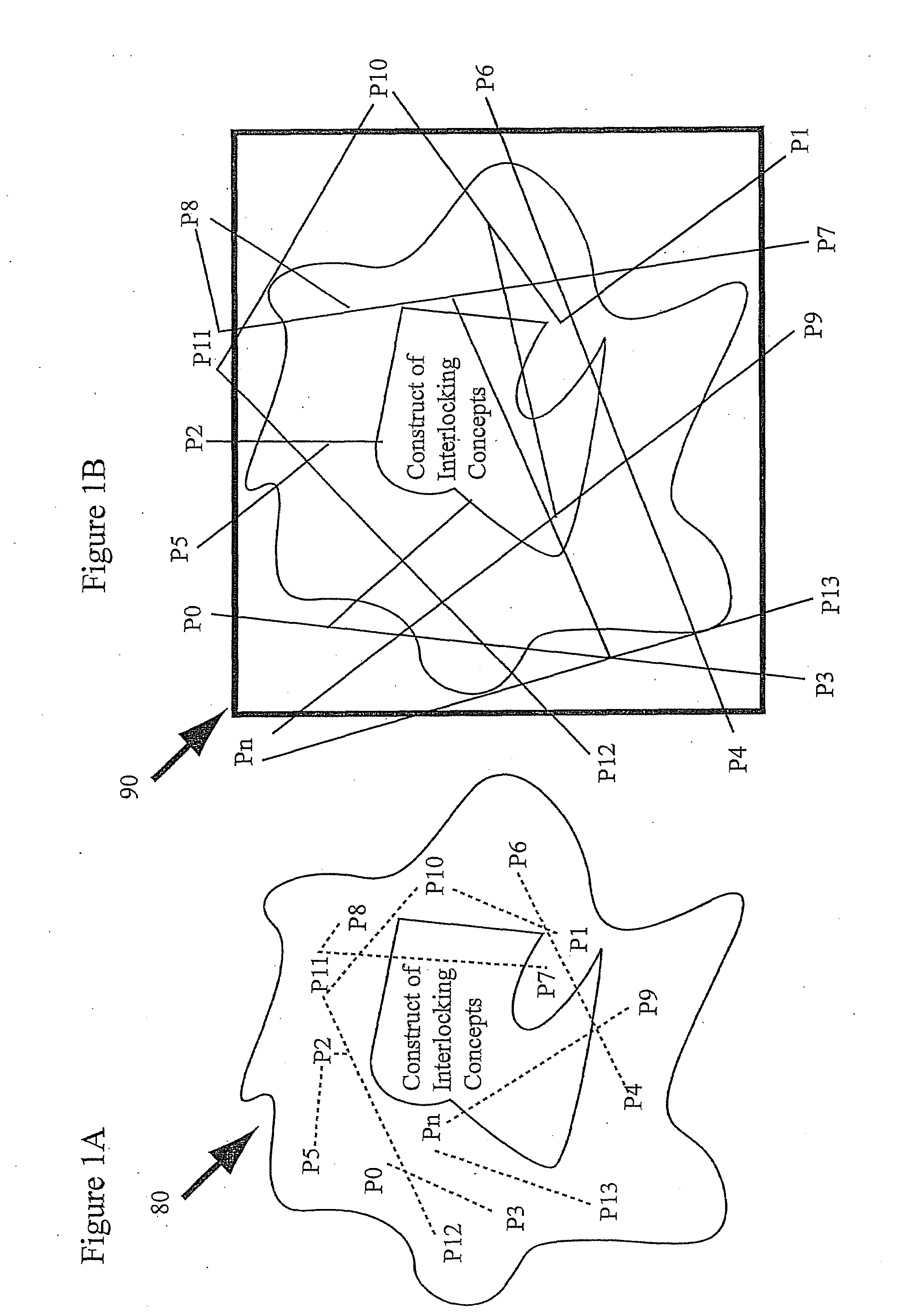

Design tool and methodology for enterprise software applications

ActiveUS20100088664A1Easy to createEfficient communicationSoftware designSpecific program execution arrangementsProject managementApplication software

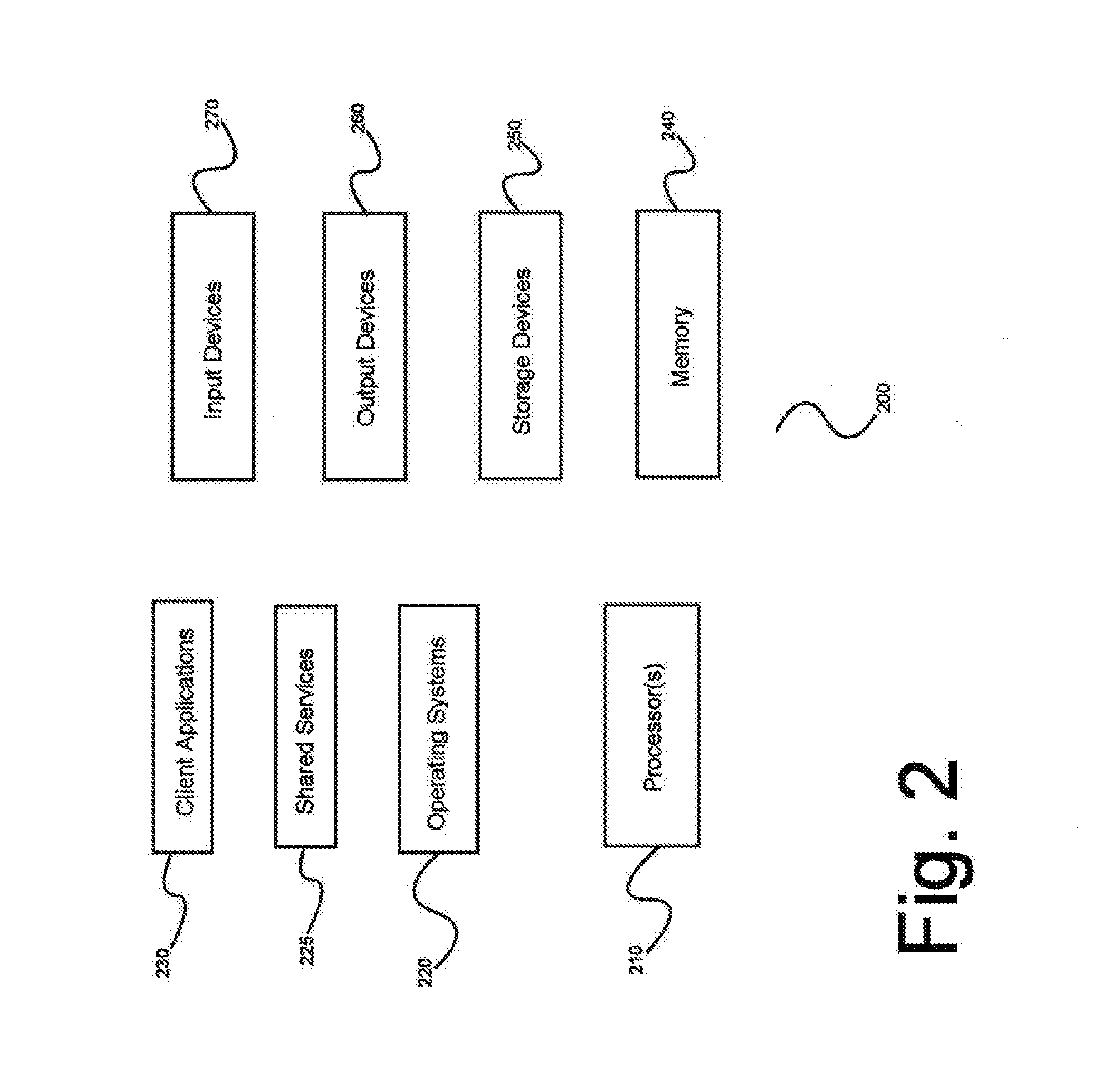

A system for creating and viewing simulation models that are used for managing requirements and design specifications for complex systems. Users simultaneously collaborate on the description of a complex system such as an enterprise software project throughout its life cycle. User interfaces, designed to assist in the visualization of a particular form of knowledge, allow users to describe the complex system with simple interactive elements. Information in all perspectives is presented so that it is legible and discernable to a non-technical audience. Multi-dimensional data structures record all the resulting information, creating a simulation model of the complex system, and the tasks required for construction and maintenance. Tasks are driven from the specifications not as a separate activity, but as part of the same activity to facilitate project management by allowing decisions to be tracked virtually throughout the simulation model.

Owner:KHODABANDEHLOO PAYMAN +1

Electrically-driven optical proximity correction to compensate for non-optical effects

ActiveUS20100122231A1Simple methodImprove performancePhotomechanical apparatusOriginals for photomechanical treatmentCapacitanceEngineering

A contour of a mask design for an integrated circuit is modified to compensate for systematic variations arising from non-optical effects such as stress, well proximity, rapid thermal anneal, or spacer thickness. Electrical characteristics of a simulated integrated circuit chip fabricated using the mask design are extracted and compared to design specifications, and one or more edges of the contour are adjusted to reduce the systematic variation until the electrical characteristic is within specification. The particular electrical characteristic preferably depends on which layer is to be fabricated from the mask: on-current for a polysilicon; resistance for contact; resistance and capacitance for metal; current for active; and resistance for vias. For systematic threshold voltage variation, the contour is adjusted to match a gate length which corresponds to an on-current value according to pre-calculated curves for contour current and gate length at a nominal threshold voltage of the chip.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

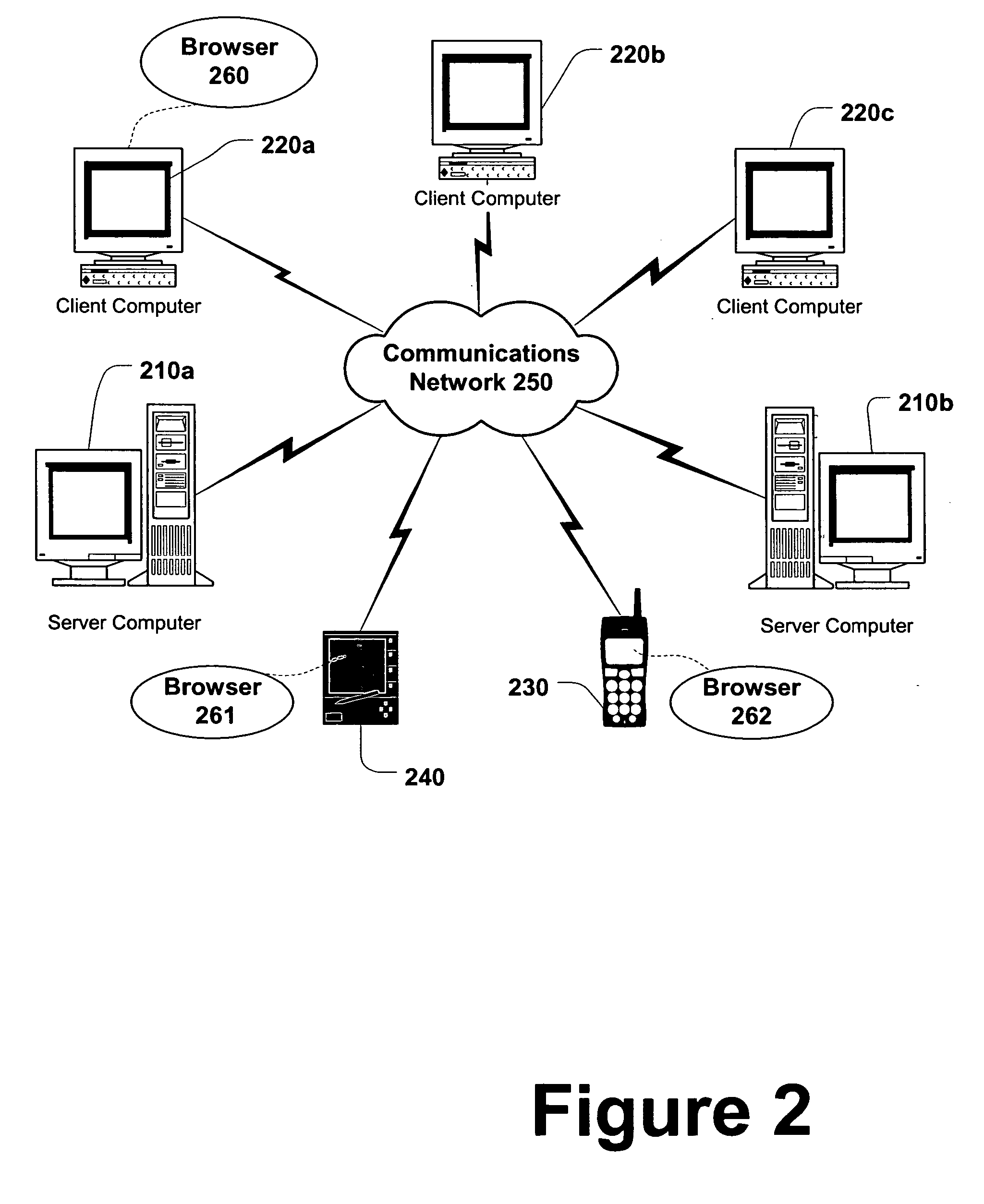

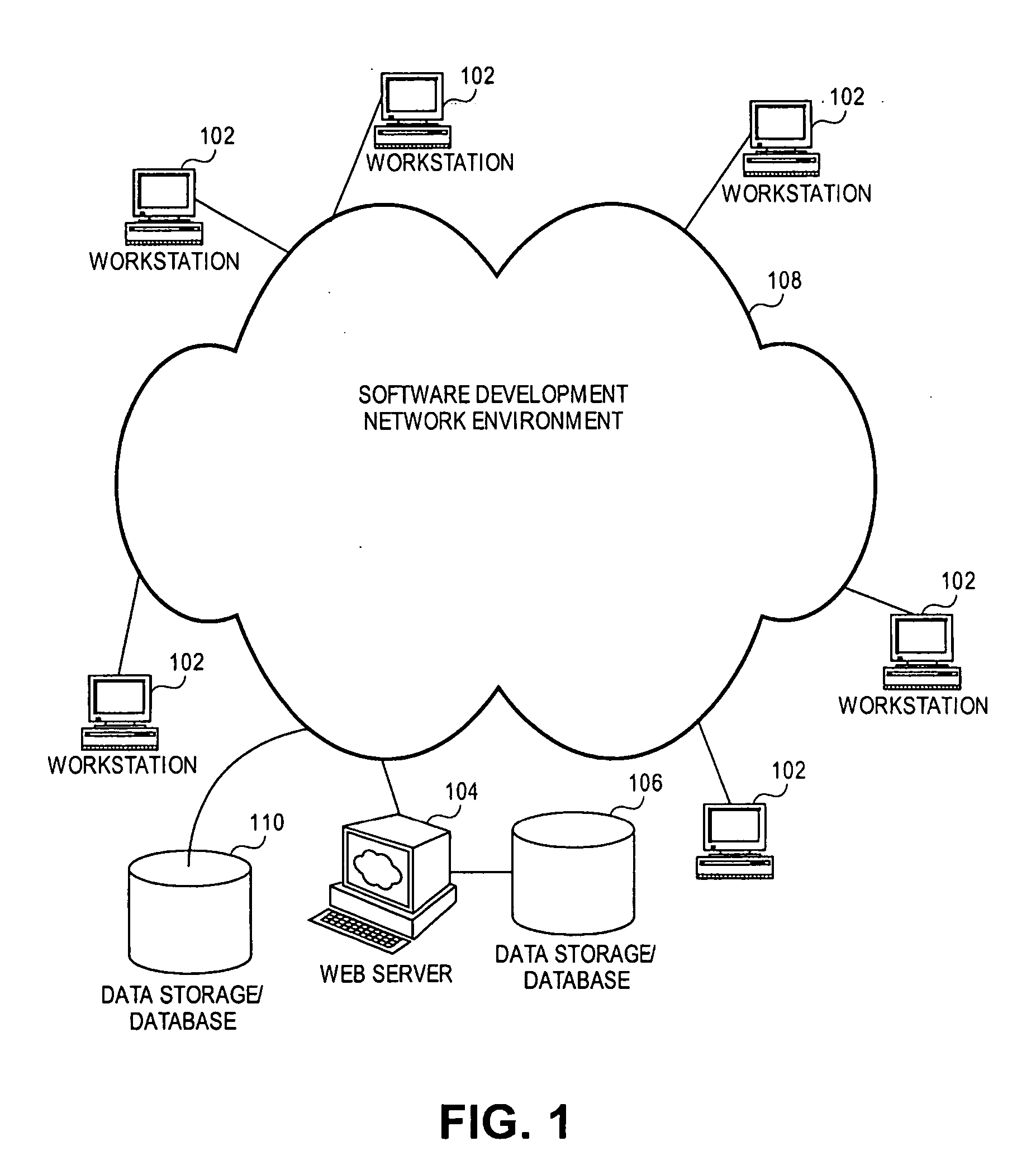

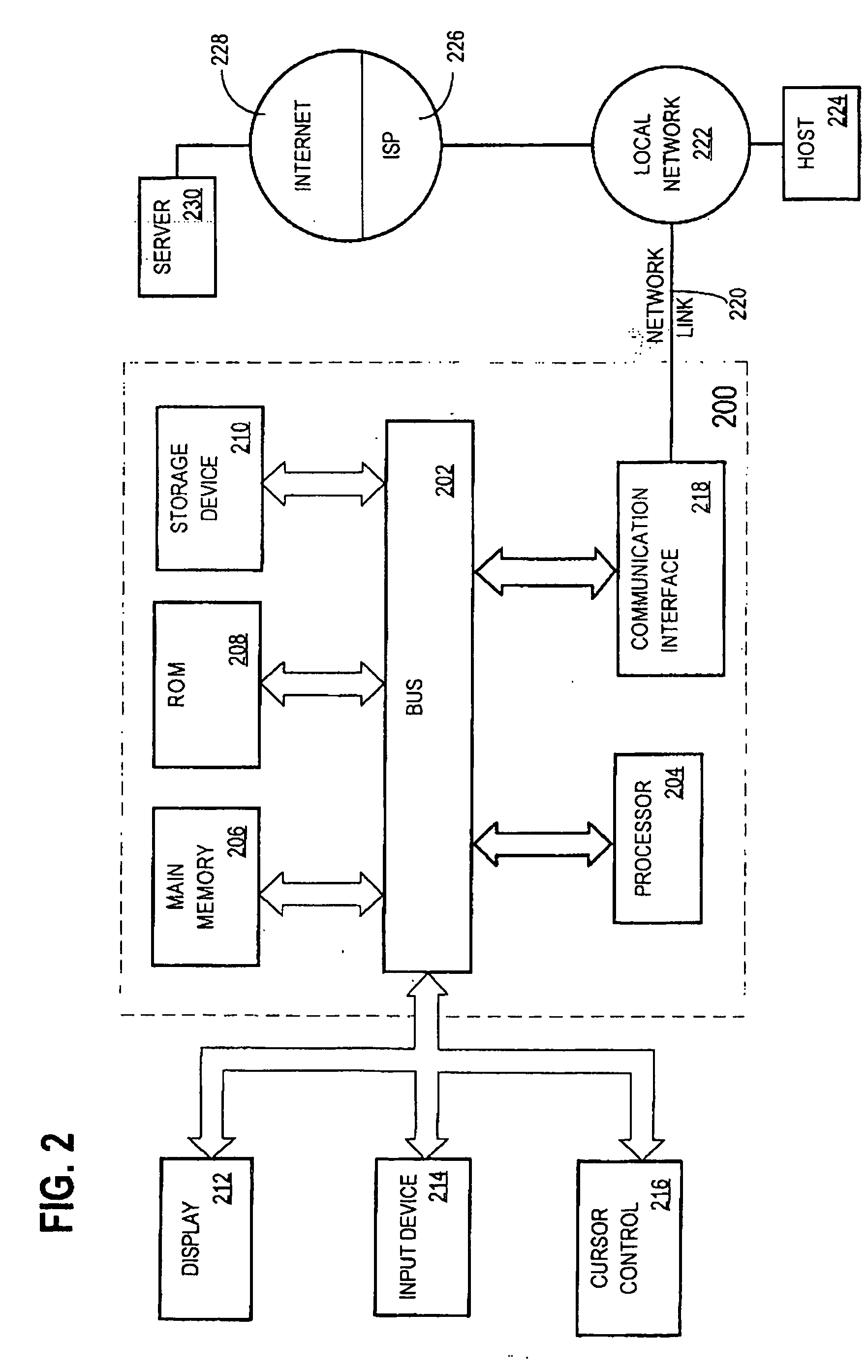

Software development environment with design specification validation tool

InactiveUS20060265690A1Errors can be reduced and avoidedSoftware testing/debuggingRequirement analysisFunction definitionLocal variable

An automated software class specification validation tool automatically determines, for functions defined in a function definition section of a class specification, whether the function is properly declared throughout one or more other sections of the same class specification. Further, it can be determined whether variables, i.e., attributes, parameters, and local variables, associated with respective functions in the function definition section are properly specified throughout one or more other sections of the same class specification. The functions and variables that are validated include attributes and functions that are specified for structures and nested classes defined in a defined type section of the class specification. The validation tool is accessible over a network via a web page, and results of the validation process are also displayed on a web page.

Owner:RICOH KK

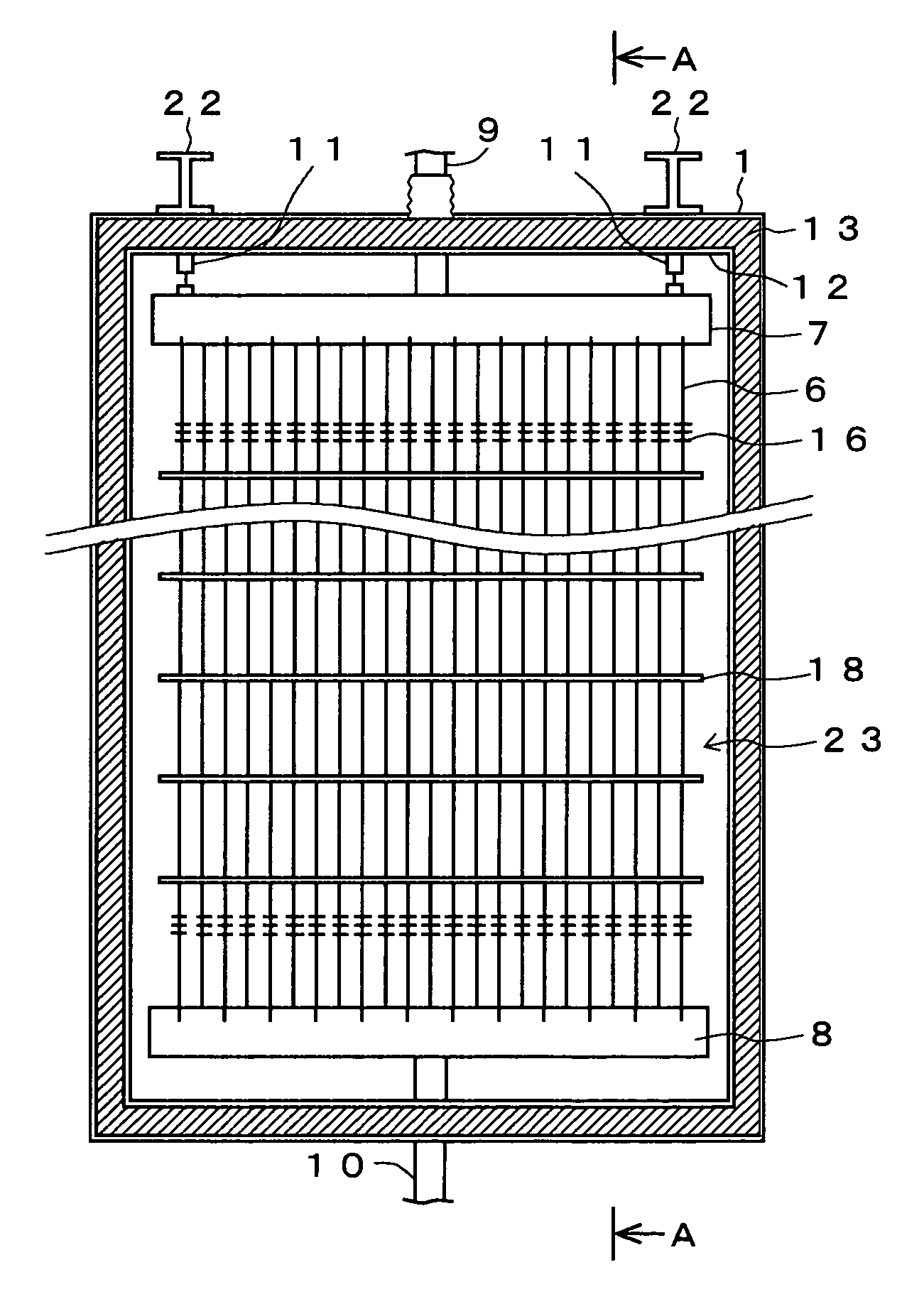

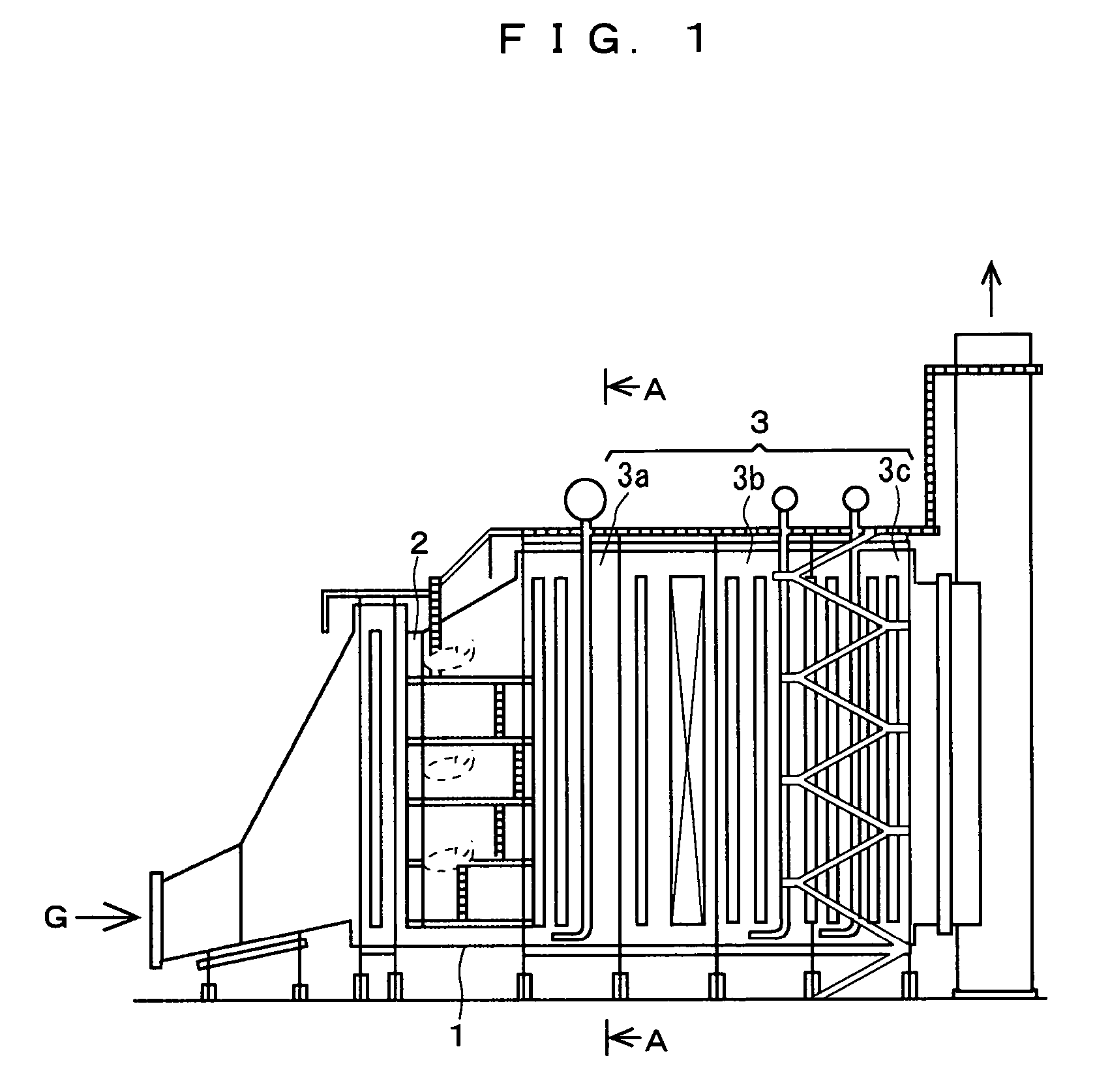

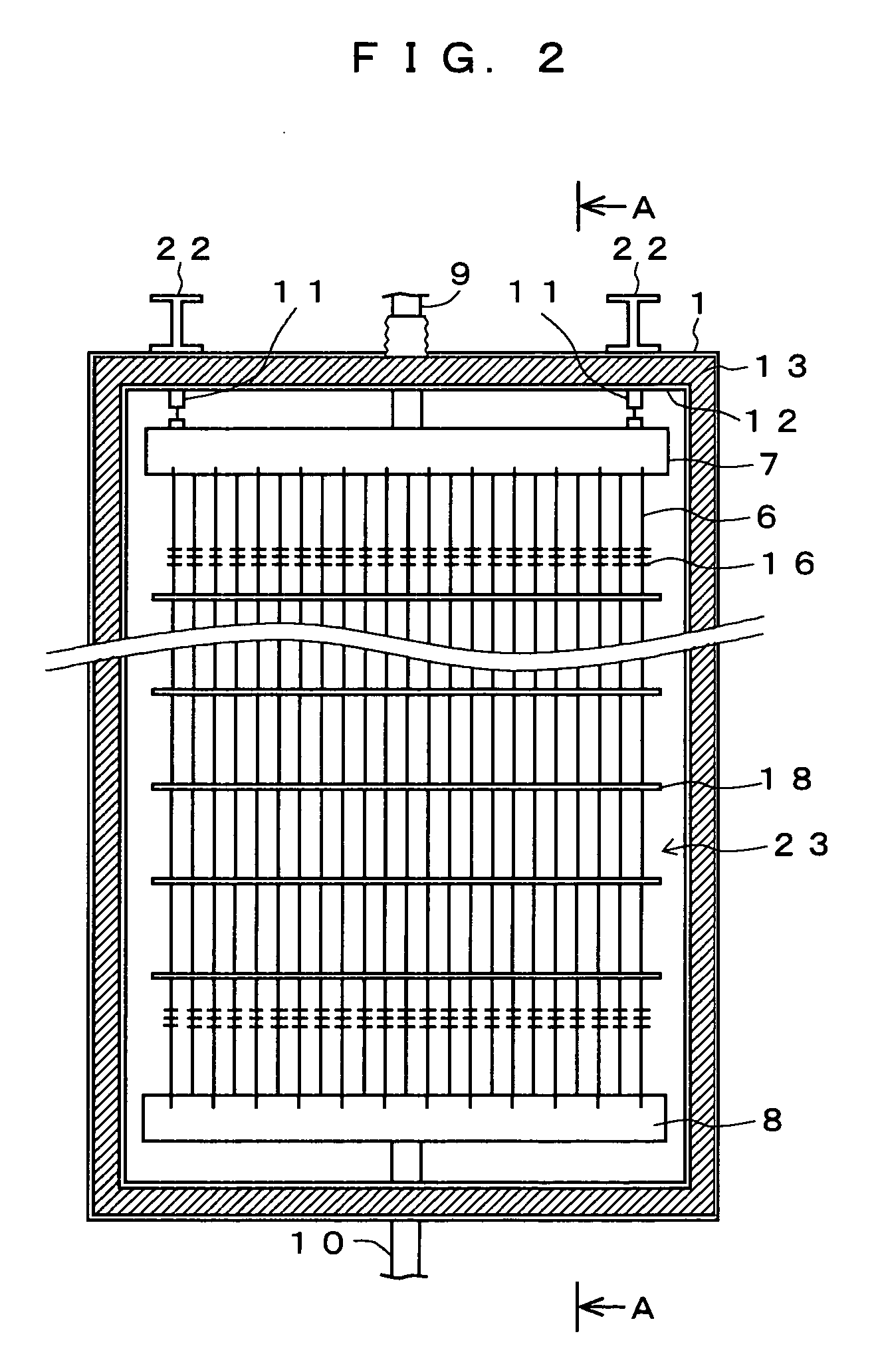

Heat exchanger tube panel module, and method of constructing exhaust heat recovery boiler using the same

InactiveUS20070119388A1Easy to installShort timeBoiler supporting/setting arrangementsBoiler flue tubes/fire tubesEngineeringRecovery boiler

A necessary size and number of modules each obtained by housing a member including heat exchanger tube panels each comprising a heat exchanger tube bundle and headers for the heat exchanger tube bundle, an upper casing of an exhaust heat recovery boiler (HRSG), provided above the heat exchanger tube panels, heat insulators, and heat exchanger tube panel support beams provided on the upper surface of the upper casing into a transportation frame, are prepared according to design specifications of the HRSG, and side casings and a bottom casing except for the ceiling part casing are constructed in advance at a construction site of the HRSG, and the modules are suspended from above between adjacent support beams of the ceiling part to dispose the heat exchanger tube panel support beams of the modules at the set heights of the ceiling part support beams, and the support beams and the ceiling part support beams are connected and fixed via connecting steel plates, whereby the respective modules are transported to the HRSG construction site and can be easily constructed.

Owner:MITSUBISHI HITACHIPOWER SYST LTD

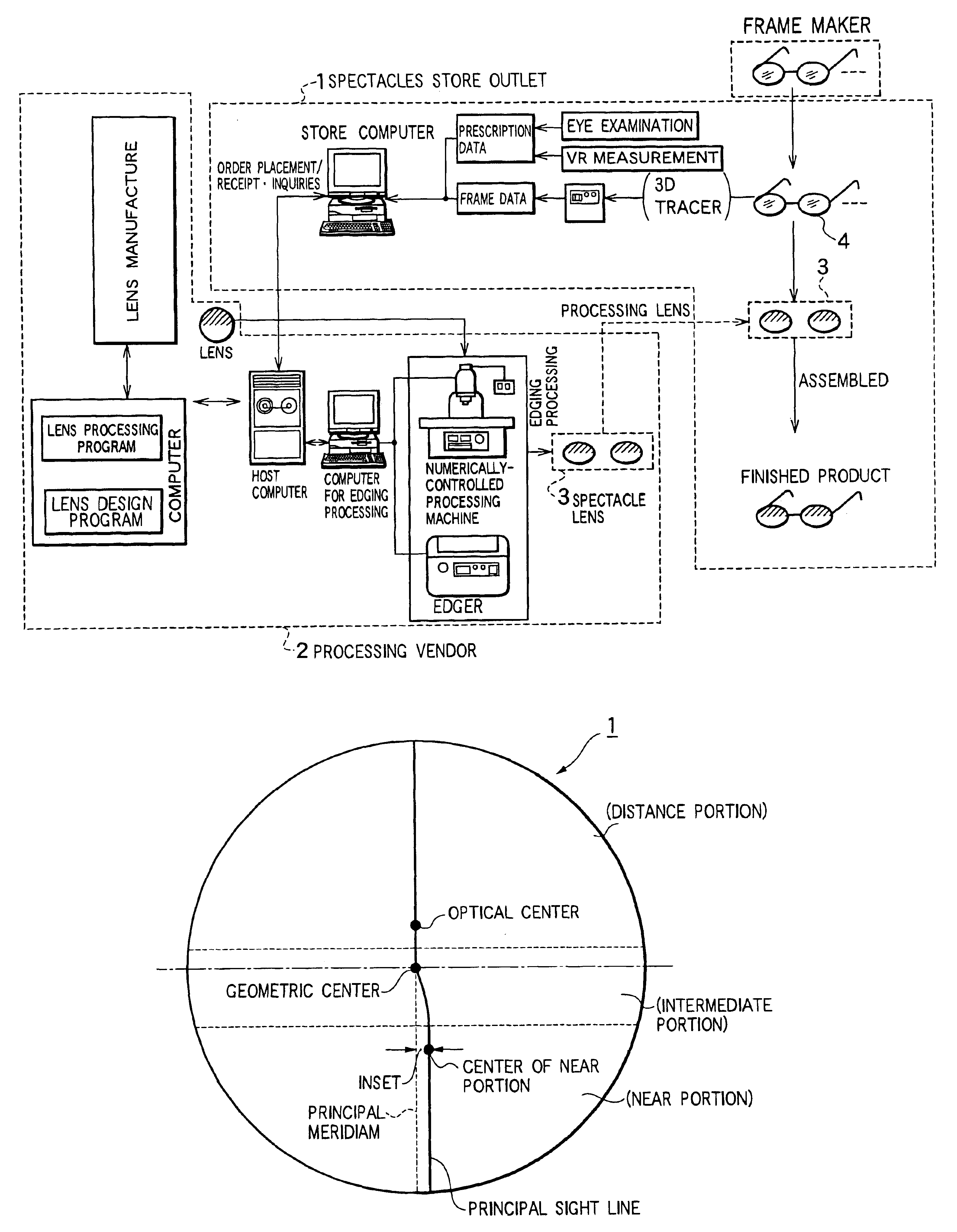

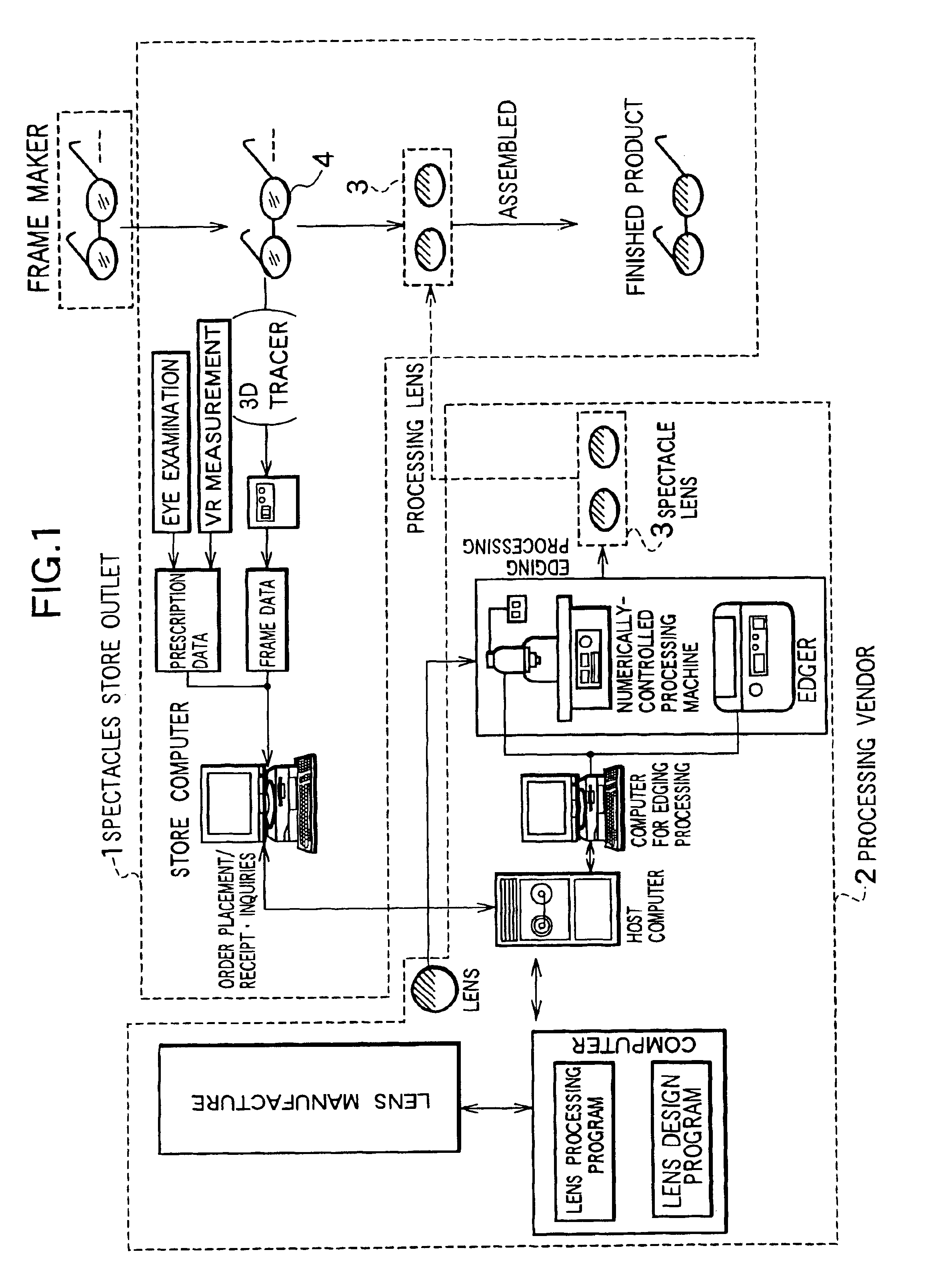

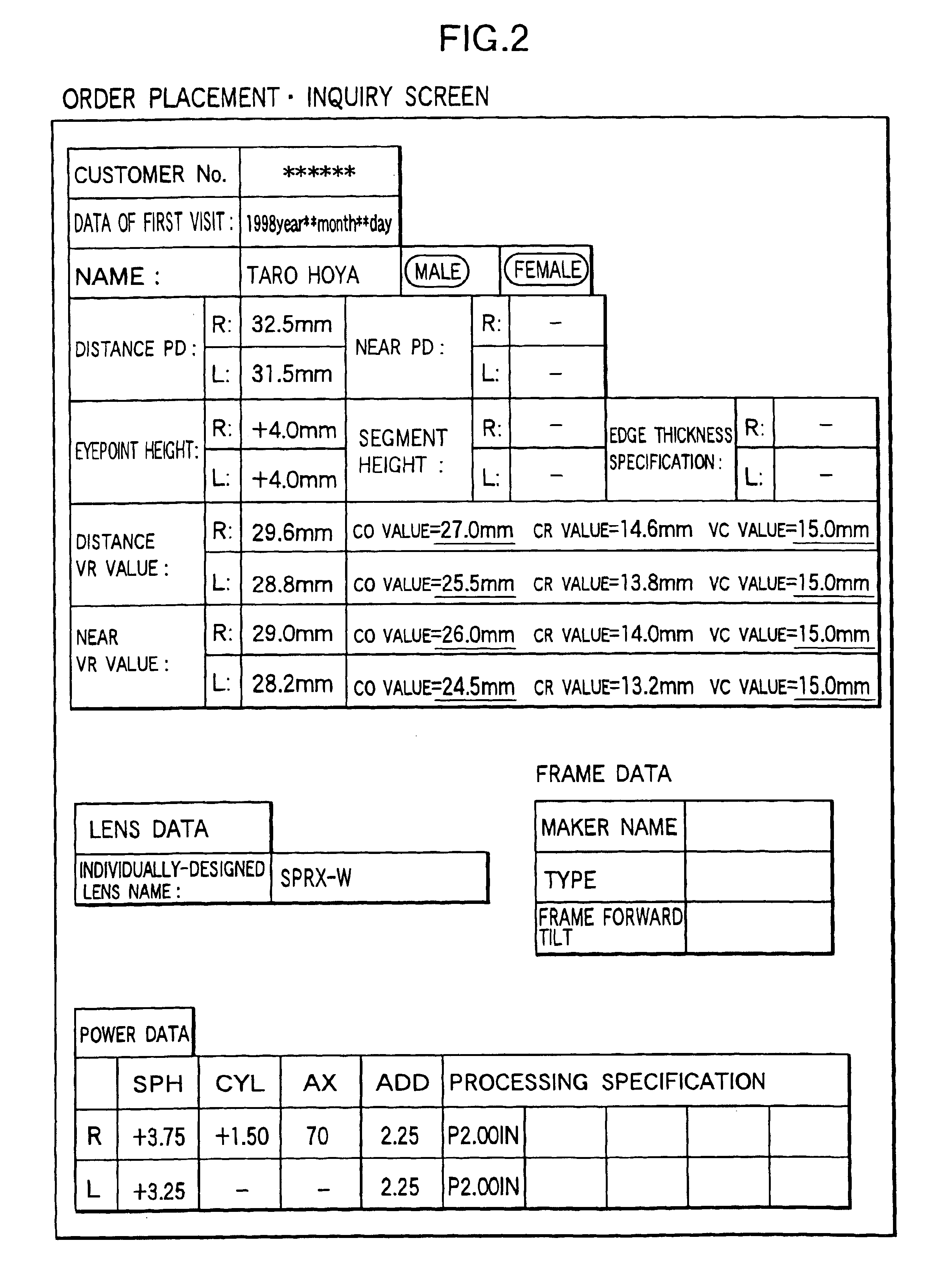

Spectacle lens and manufacturing method therefor

InactiveUS6871955B2Improve performanceSpectales/gogglesProgramme controlUses eyeglassesCentre of rotation

A spectacle lens is designed by using a value determined by either measuring or specifying for an individual spectacles wearer the value of the distance VR from a reference point on the back surface of a spectacle lens to the center of rotation of the eye, which adds together the value of the distance VC from a reference point of the back surface of a spectacle lens to the vertex of the cornea of the eye of the spectacles wearer at spectacle lenses wearing time, which is one of the required data in spectacle lens design, and the distance CR from the above-mentioned vertex of the cornea to the center of rotation of the eye, and manufacturing a spectacle lens based on this design specification.

Owner:HOYA CORP

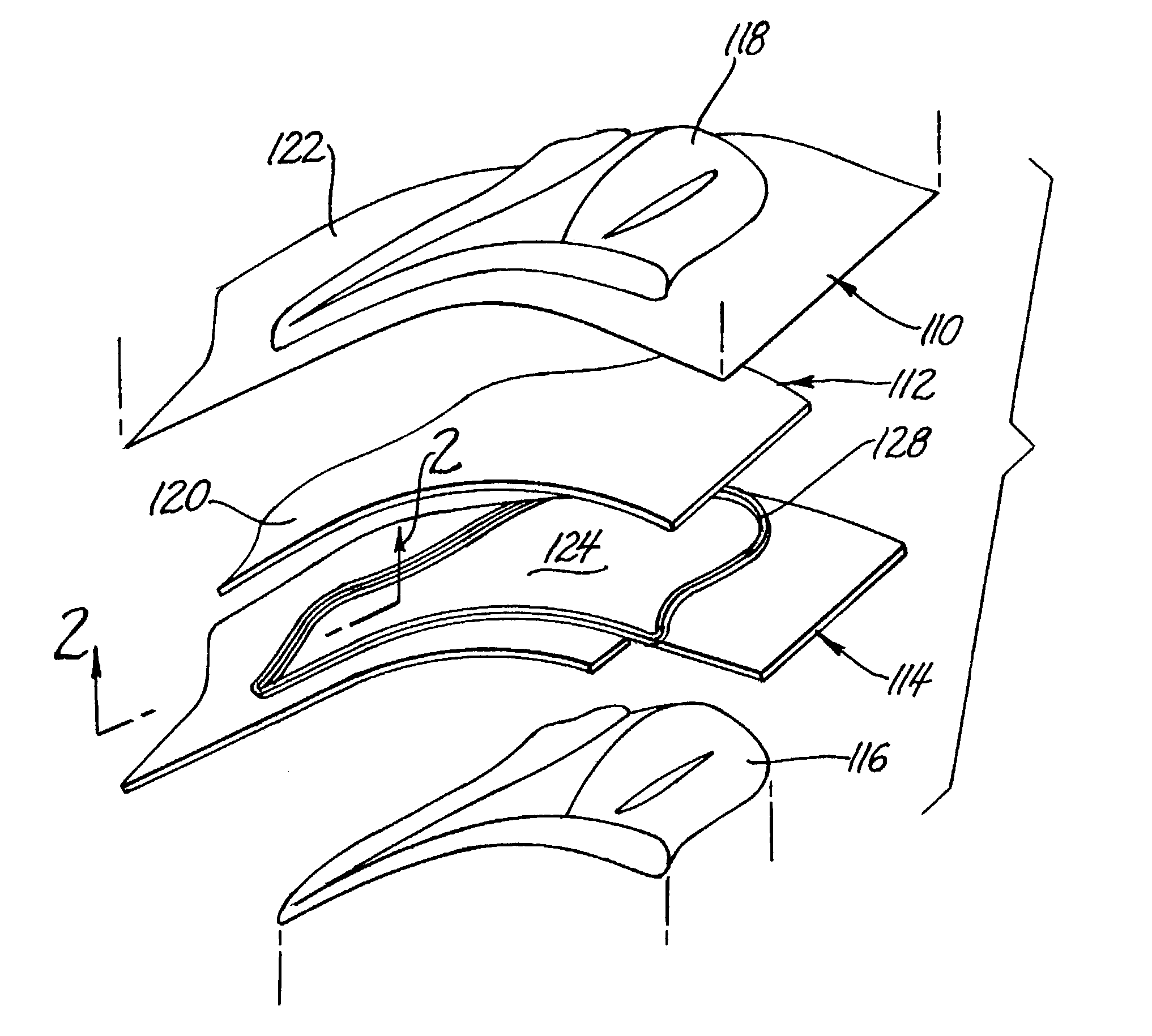

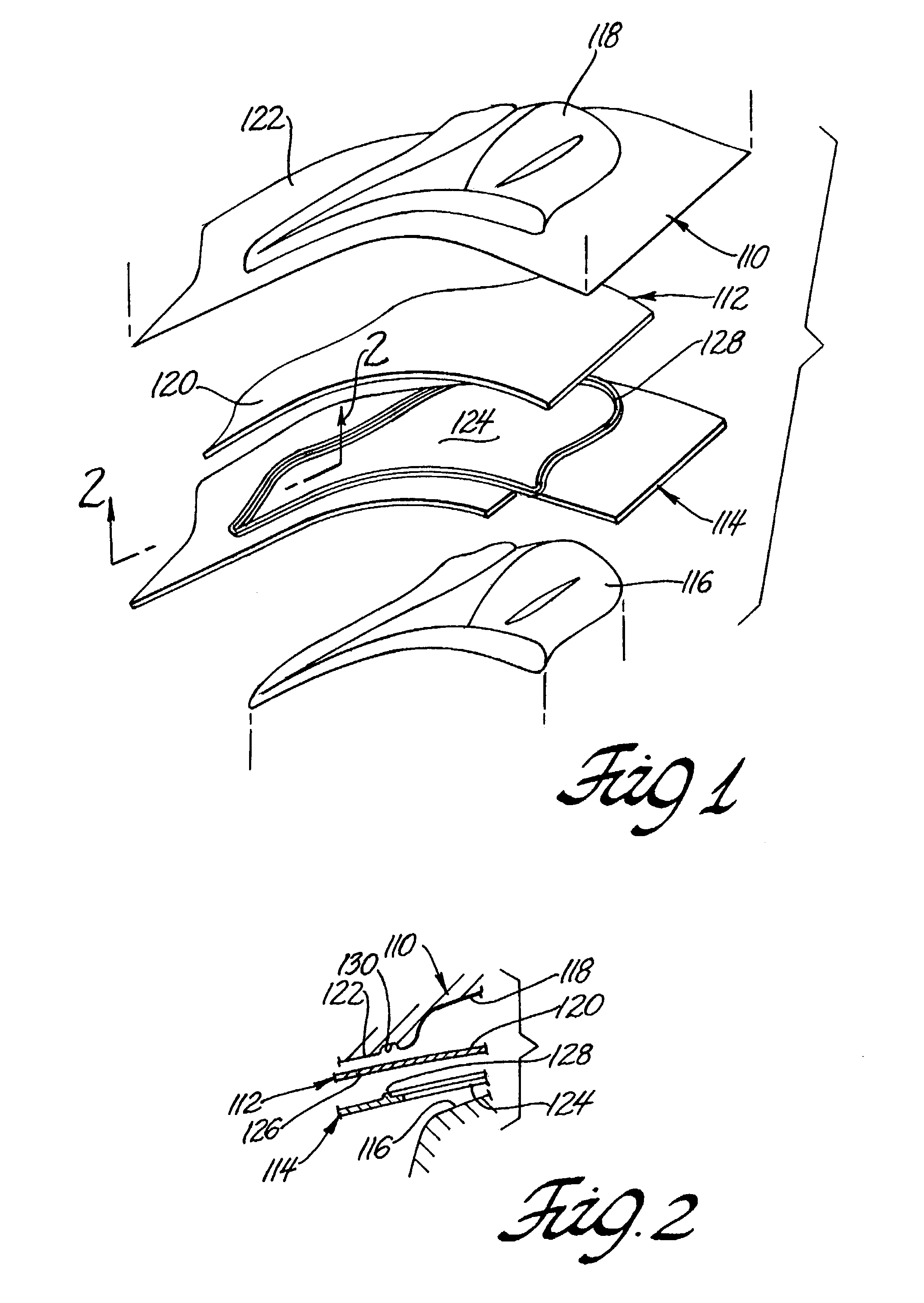

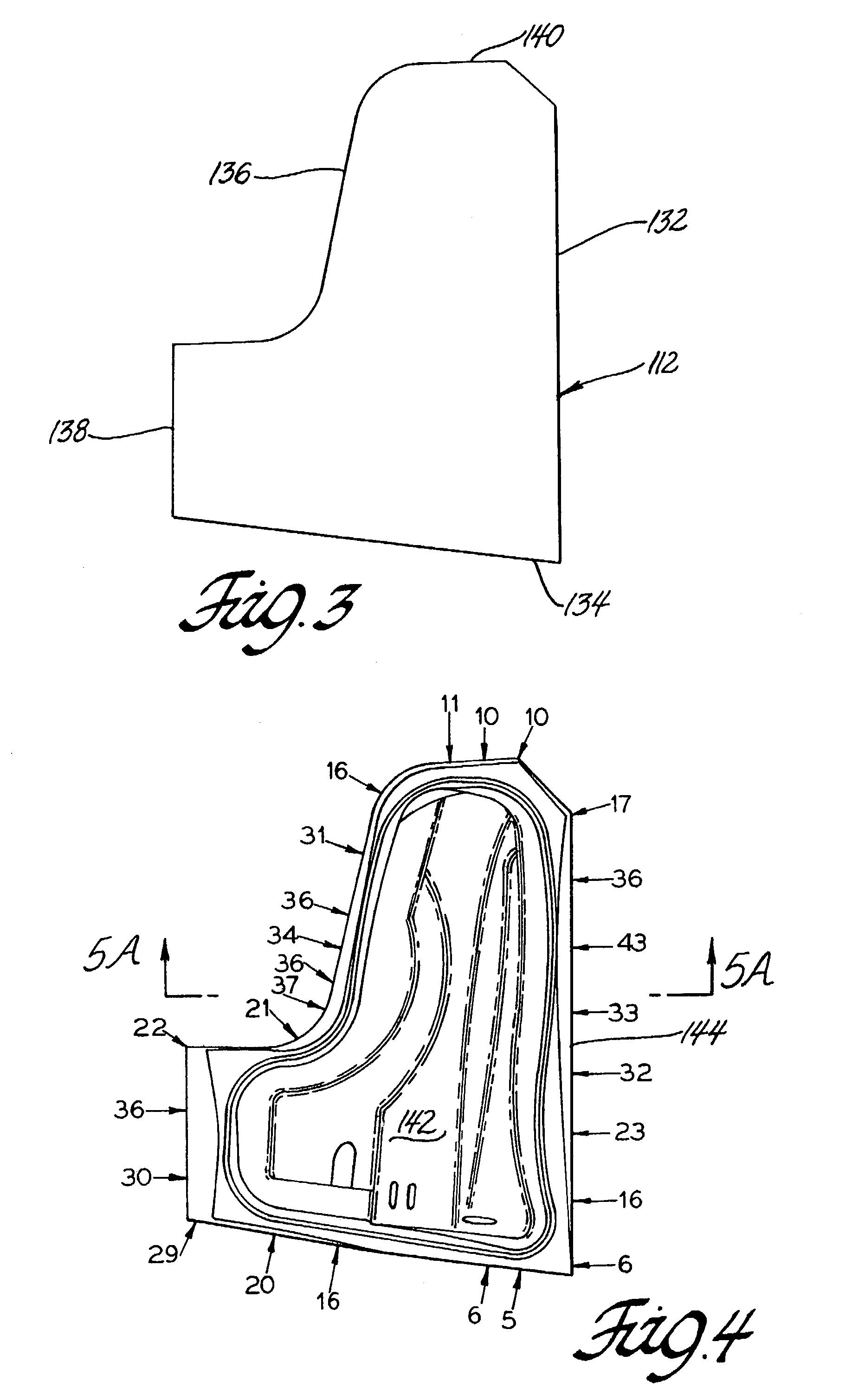

Draw-in map for stamping die tryout

ActiveUS7130708B2Rapid productionMinimum effortShaping toolsSpecial data processing applicationsMetal formingSize determination

Sheet metal forming is a manufacturing process in which flat sheet metal is drawn into a die cavity to form a product shape. Draw-in amount is the single most important stamping index that controls all forming characteristics (strains and stresses), formability failures (splits, wrinkles) and surface quality (distortions) on a panel. Adaptation of a new die set for repetitively stamping sheet metal parts to a part design specification is simplified by using a math-based simulation of the stamping operation under specified engineering stamping conditions for the specified part. The stamping simulations are used to create an engineered draw-in map comparing selected locations on the peripheral edge of the stamped part with corresponding locations on the peripheral edge of its original sheet metal blank. The resulting map of sheet metal draw-in dimensions reflect suitable displacements of the metal sheet between the binder ring and binder surface of the female die member at all such locations as the punch member of the die set executes its stamping operation. The engineered draw-in dimensions for a simulated part identify specific locations for adjustment of the binder ring / binder surface system in adapting the die set for production of parts.

Owner:GM GLOBAL TECH OPERATIONS LLC

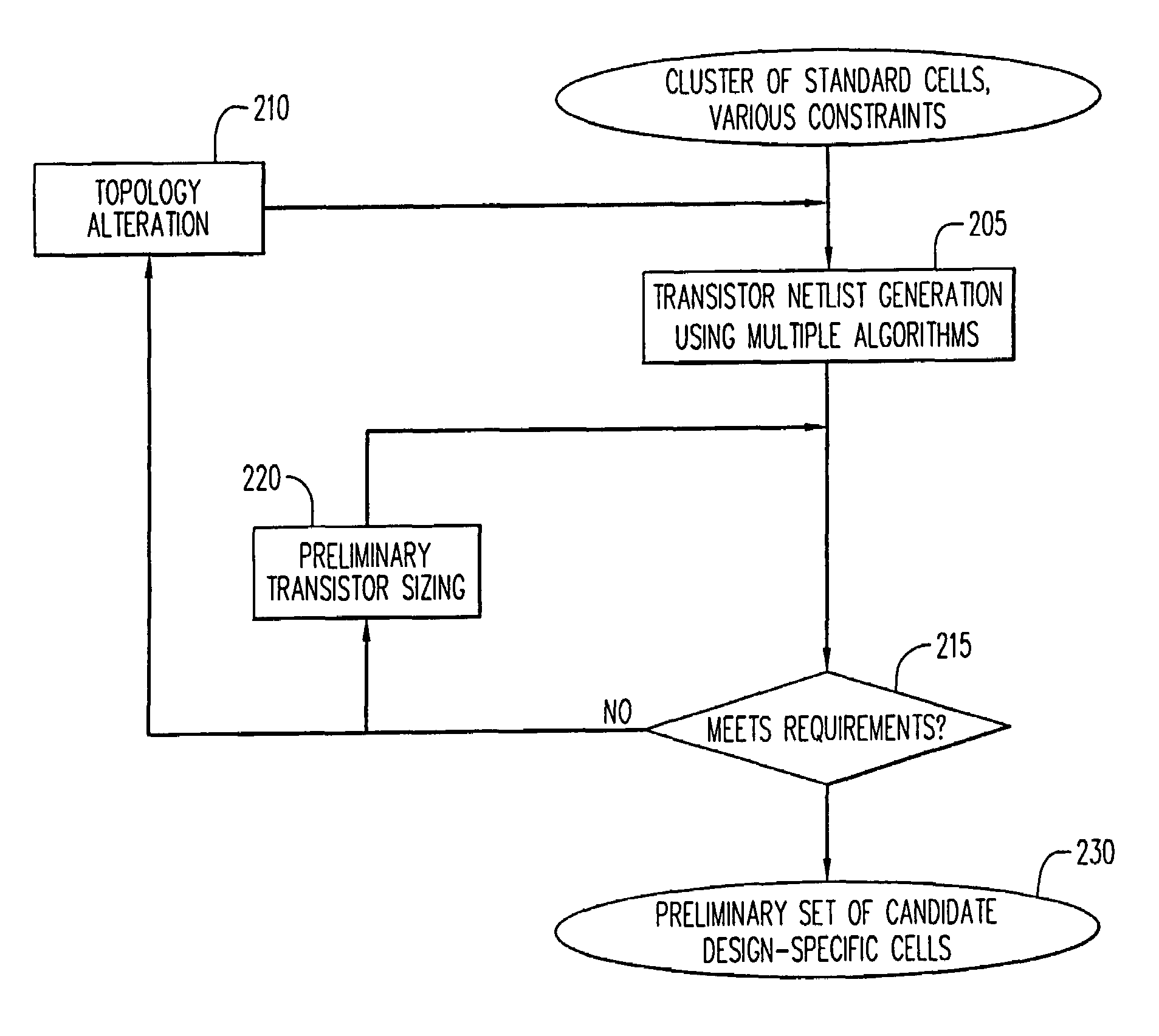

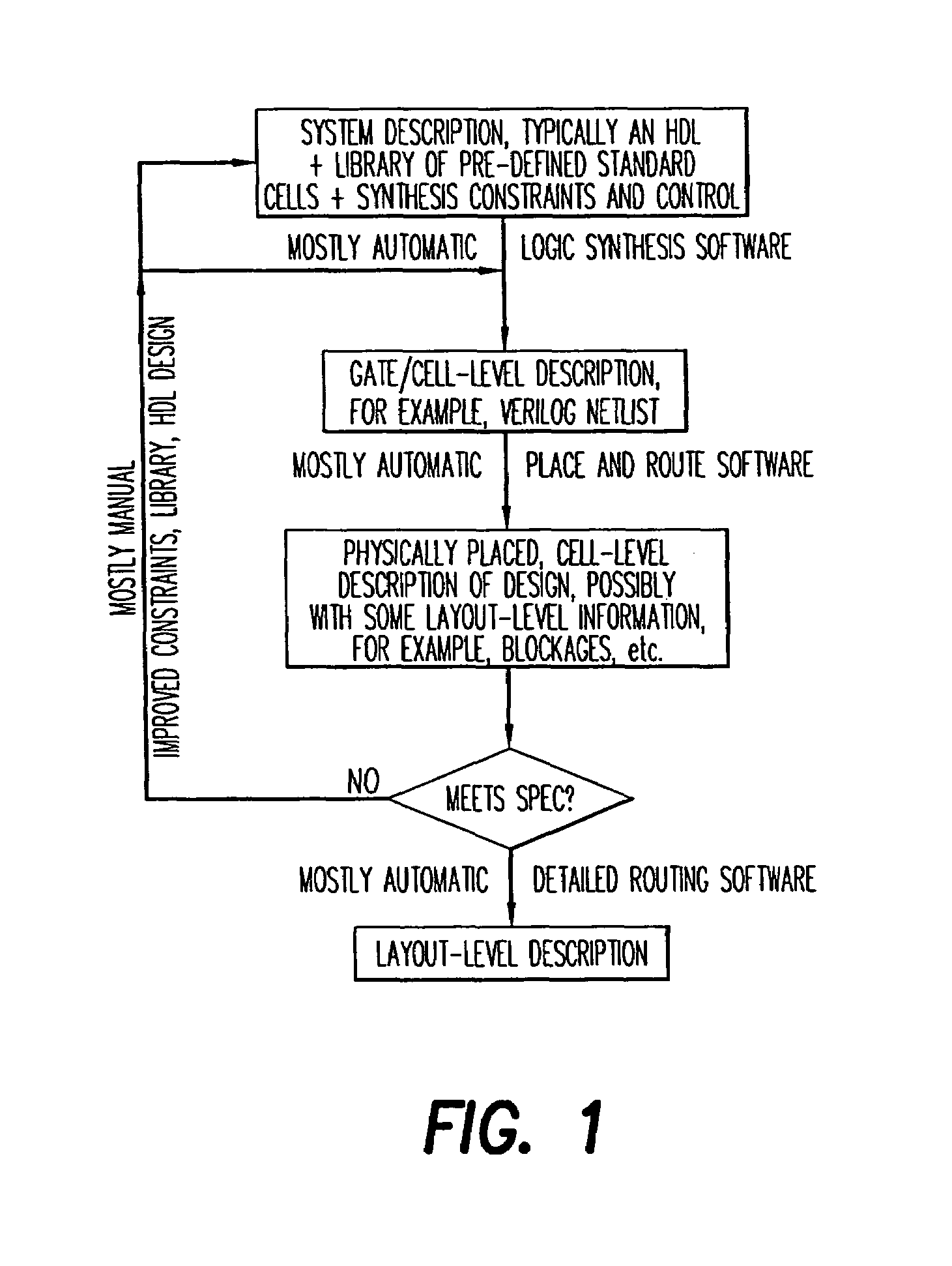

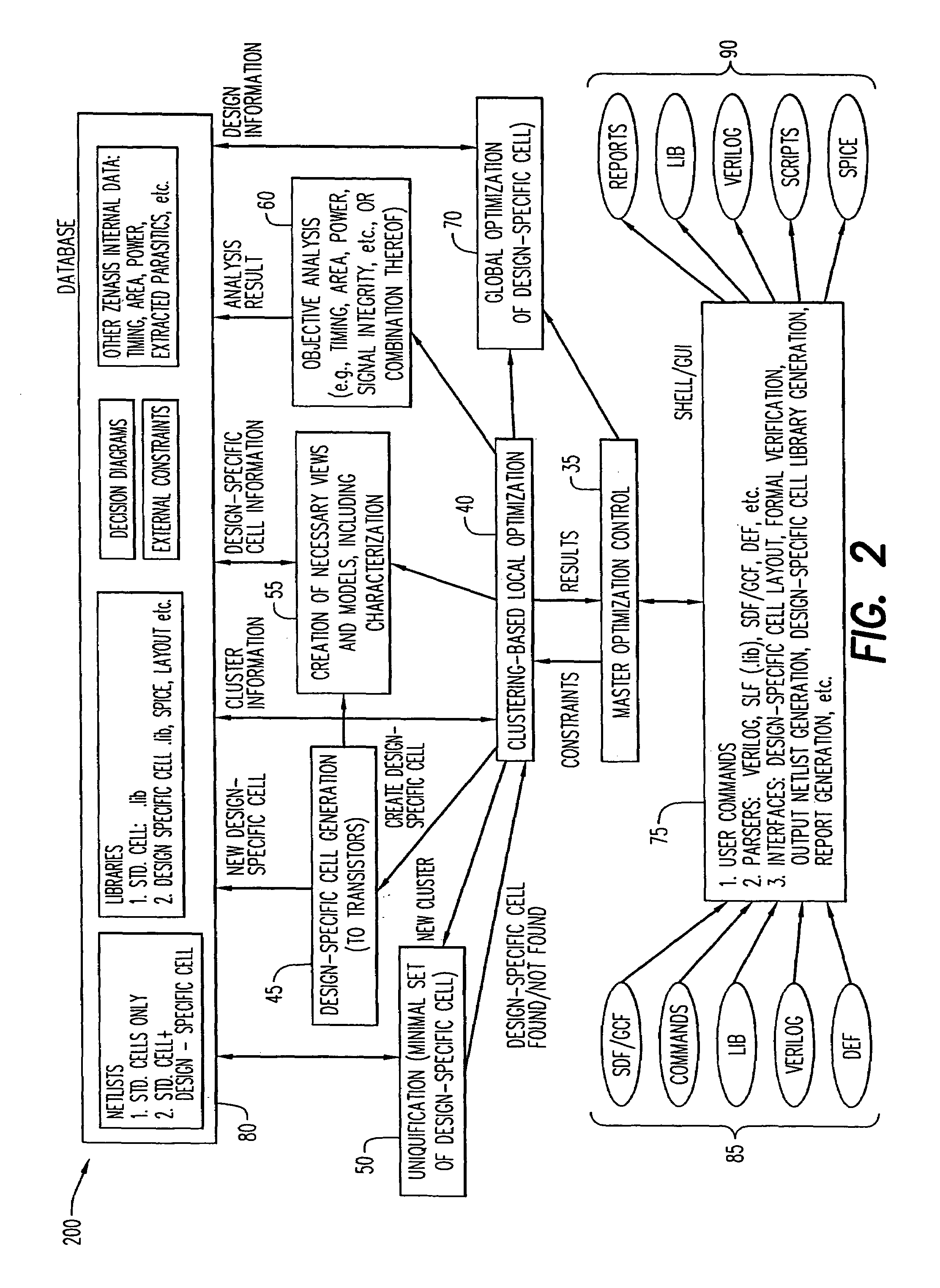

Process for automated generation of design-specific complex functional blocks to improve quality of synthesized digital integrated circuits in CMOS using altering process

InactiveUS7003738B2Small sizeCAD circuit designSoftware simulation/interpretation/emulationCMOSGenerative Design

The present invention pertains to an automated method for designing a integrated circuit (IC) design-specific cell, the method includes the steps of receiving a design specification for the design-specific cell, mapping a transistor-level representation of the design-specific cell, wherein the mapping is based on at least one, but perhaps plural design specifications, and evaluating the transistor-level representation of the design-specific cell for satisfaction of the design specification.

Owner:OPEN-SILICON

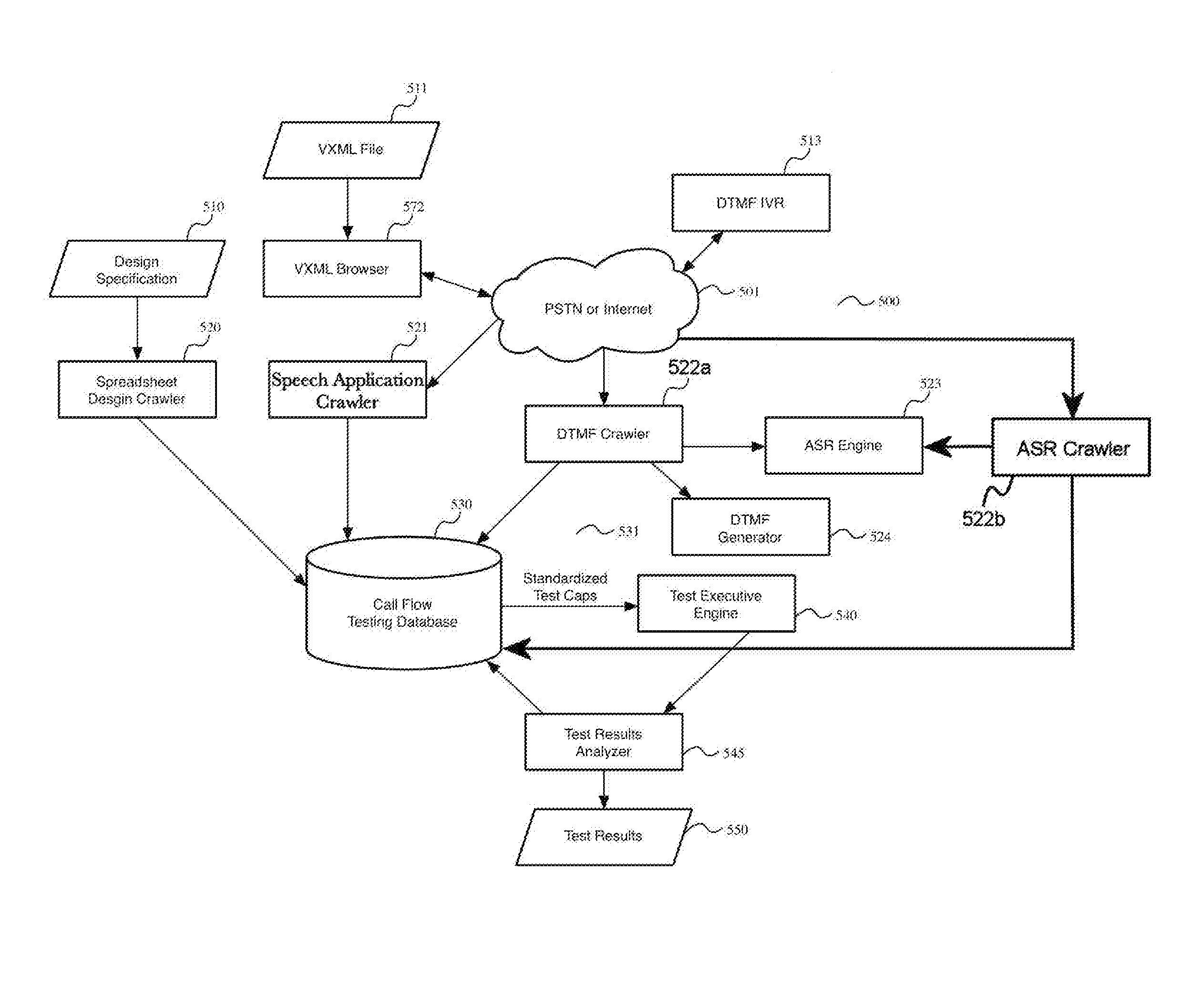

Interactive voice response system crawler

ActiveUS20160227034A1Interconnection arrangementsSupervisory/monitoring/testing arrangementsComputer networkInteractive voice response system

A system for interactive voice response system crawling, comprising an IVR crawler that may be VXML, design specification, DTMF or ASR / NLSR speech-based in nature and traverses an IVR menu to discover possible interaction paths and produces test cases based on those paths, and a database that stores test cases produced by the IVR crawler during operation, and a method for using an IVR crawler to perform a system migration.

Owner:CYARA SOLUTIONS

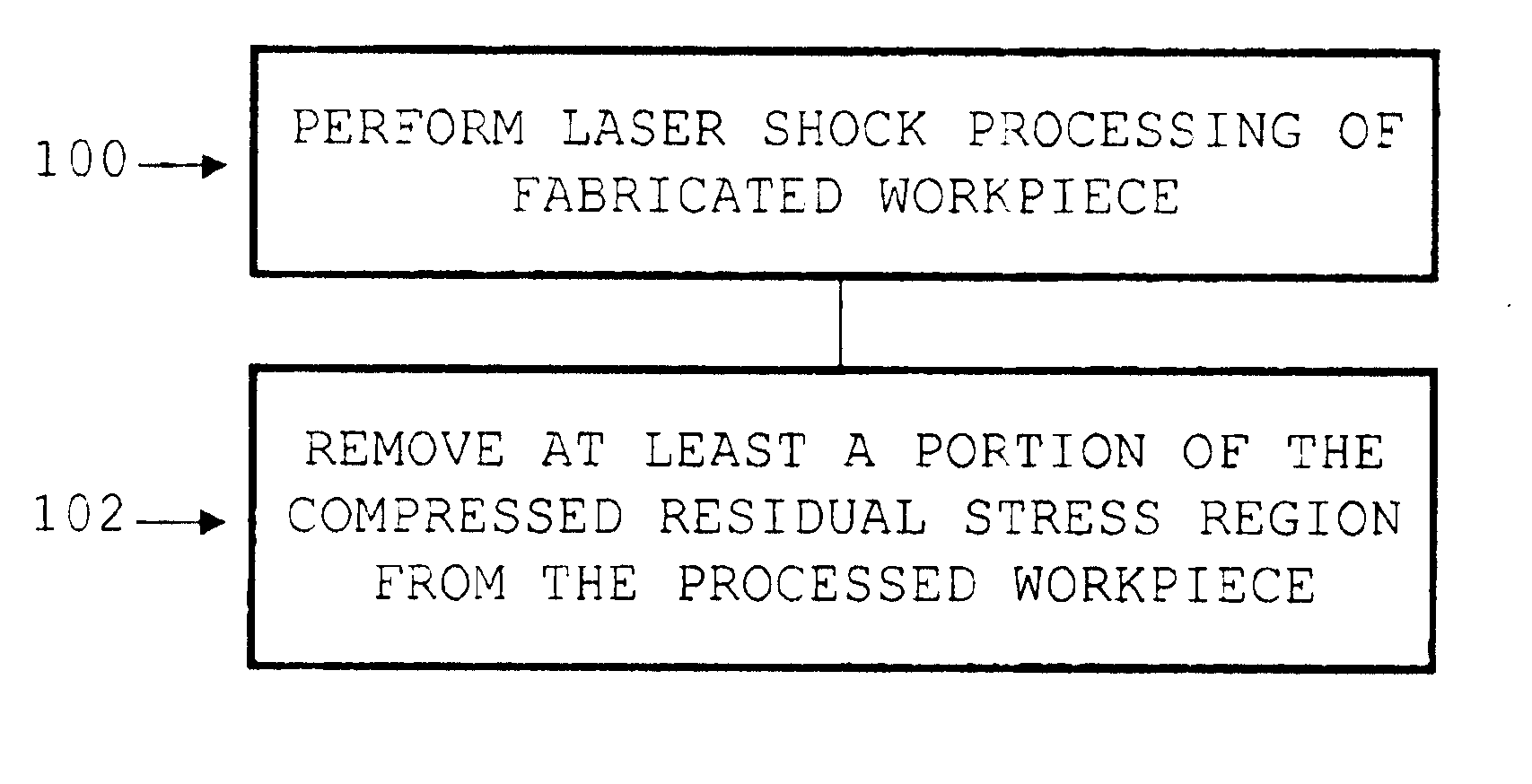

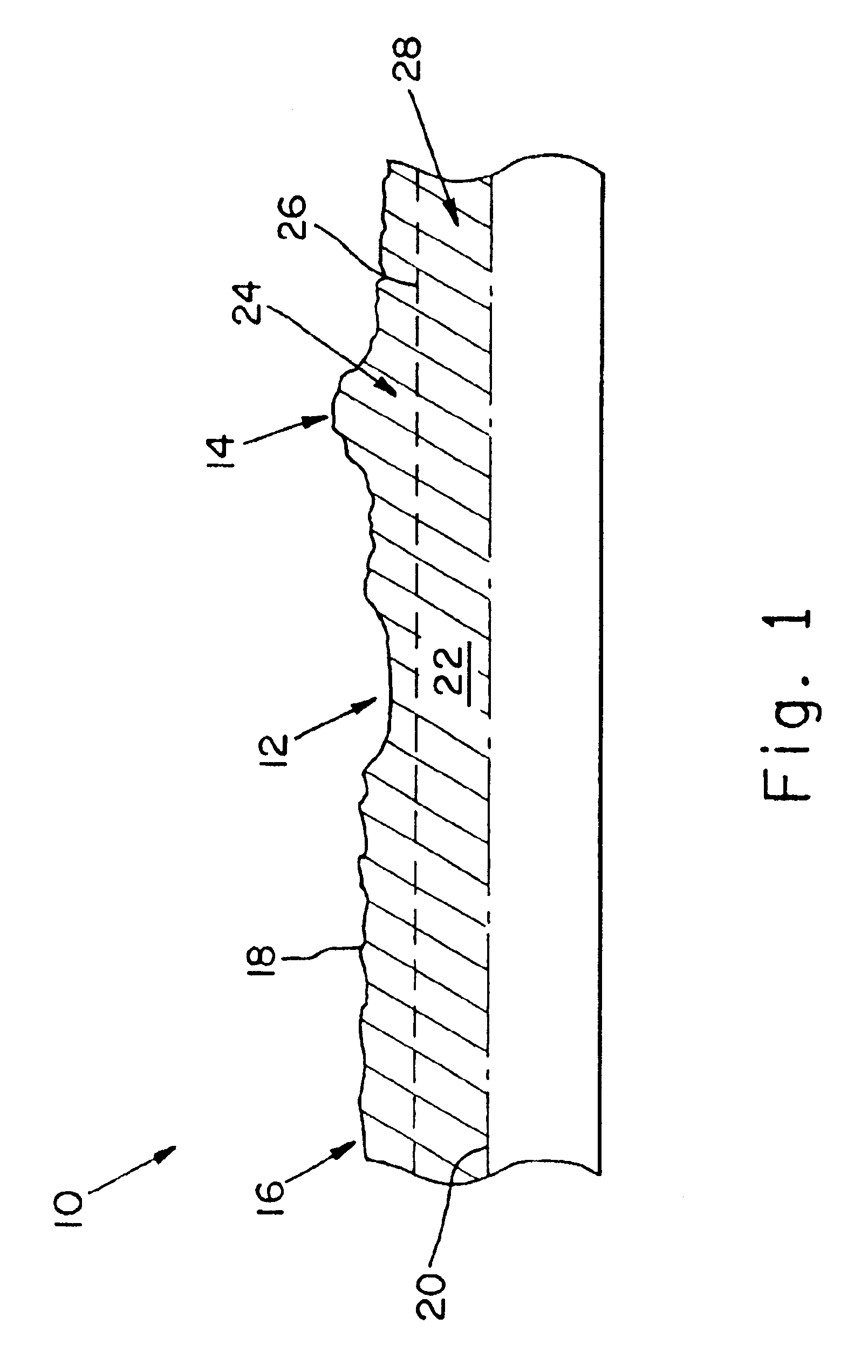

Method of modifying a workpiece following laser shock processing

InactiveUS6852179B1Improve fatigue performanceThin material handlingLaser beam welding apparatusMaterial removalHigh intensity

A method of manufacturing a workpiece involves performing any one of various post-processing part modification steps on a workpiece that has been previously subjected to laser shock processing. In one step, material is removed from the compressive residual stress region of the processed workpiece. Alternately, the workpiece may be provided with oversized dimensions such that the removal process removes an amount of material sufficient to generate a processed workpiece having dimensions substantially conforming to design specifications. Alternately, the material removal process is adapted to establish a penetration depth for material removal that coincides with the depth at which the workpiece exhibits maximum compressive residual stress. Alternately, a first high-intensity laser shock processing treatment is performed on the workpiece, followed by the removal of material from the compressive residual stress region, and then a second low-intensity laser shock processing treatment is performed on the workpiece. Material may be removed from the compressive residual stress region through a workpiece surface different from the laser shock processed surface. Material may also be deposited onto the laser shock processed surface.

Owner:LSP TECH INC