Patents

Literature

466 results about "Electronic design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Supplant design rules in electronic designs

ActiveUS20080163141A1Interaction be complexComputer aided designSoftware simulation/interpretation/emulationFoundryComputer architecture

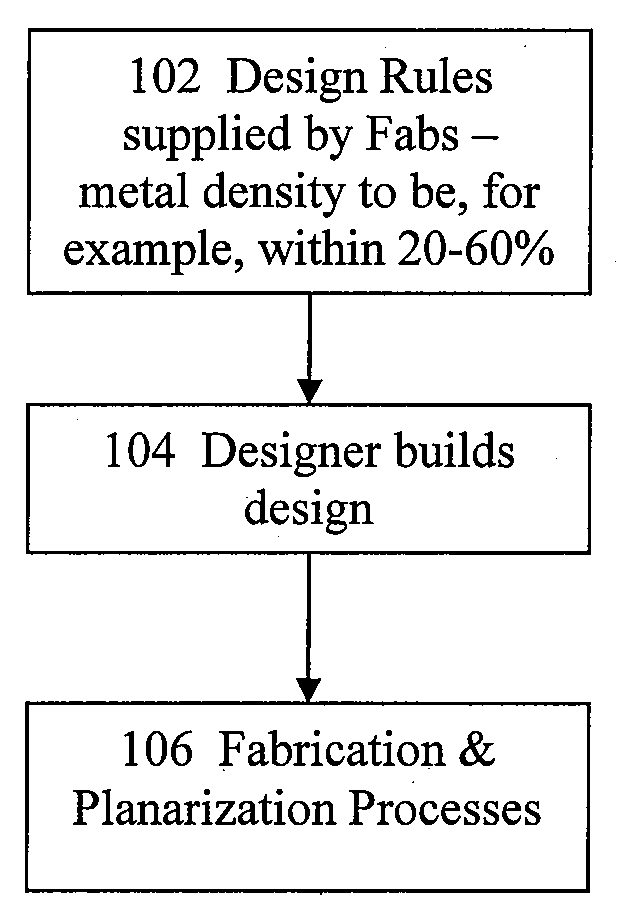

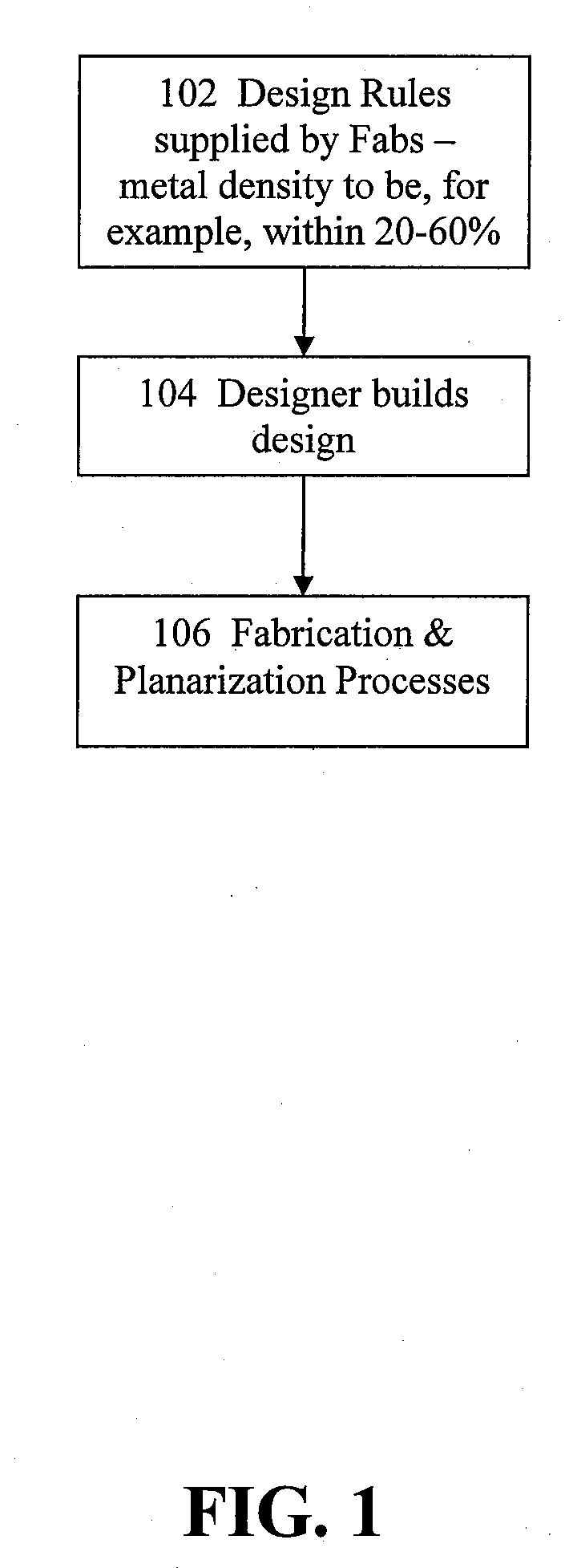

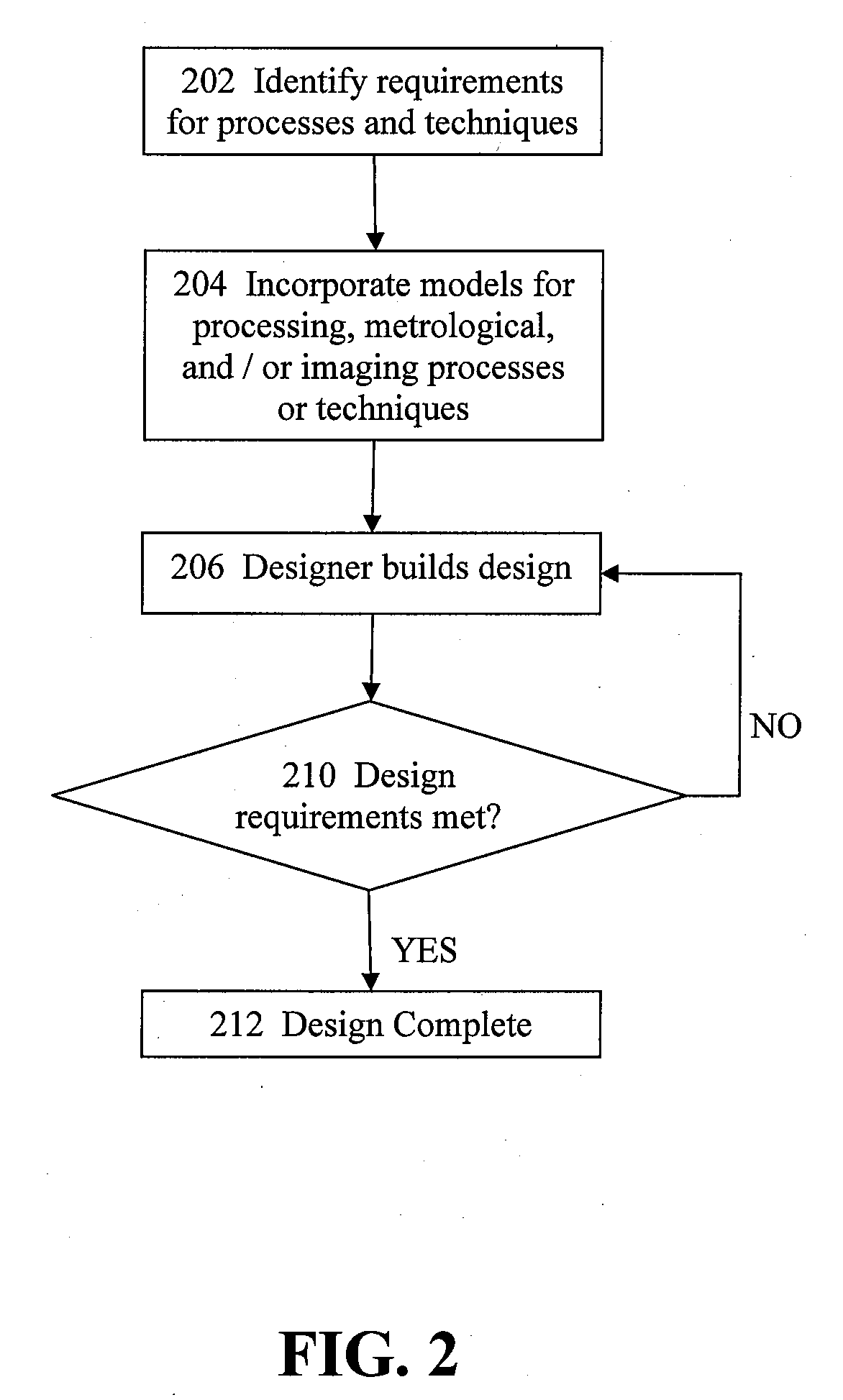

Disclosed is an improved method, system, and computer program product for electronic designs with supplant design rules. According to some embodiments of the invention, the foundry-imposed design rules are replaced by one or more supplant design requirements which define absolute or relative threshold(s) for a design feature characteristic. Some other embodiments of the invention, the foundry-imposed design rules are replaced by one or more supplant design requirements which define one or more ranges of absolute or relative values for a design feature characteristic. Some other embodiments of the invention further provide an EDA tool which takes into account a model for the electronic design, the processing, metrological, lithographic, or imaging processing processes or techniques, and the supplant design requirements to determine whether the features of an electronic design meet the design requirements.

Owner:CADENCE DESIGN SYST INC

Electronic design automation system and methods utilizing groups of multiple cells having loop-back connections for modeling port electrical characteristics

InactiveUS6539536B1CAD circuit designSoftware simulation/interpretation/emulationLoopbackElectricity

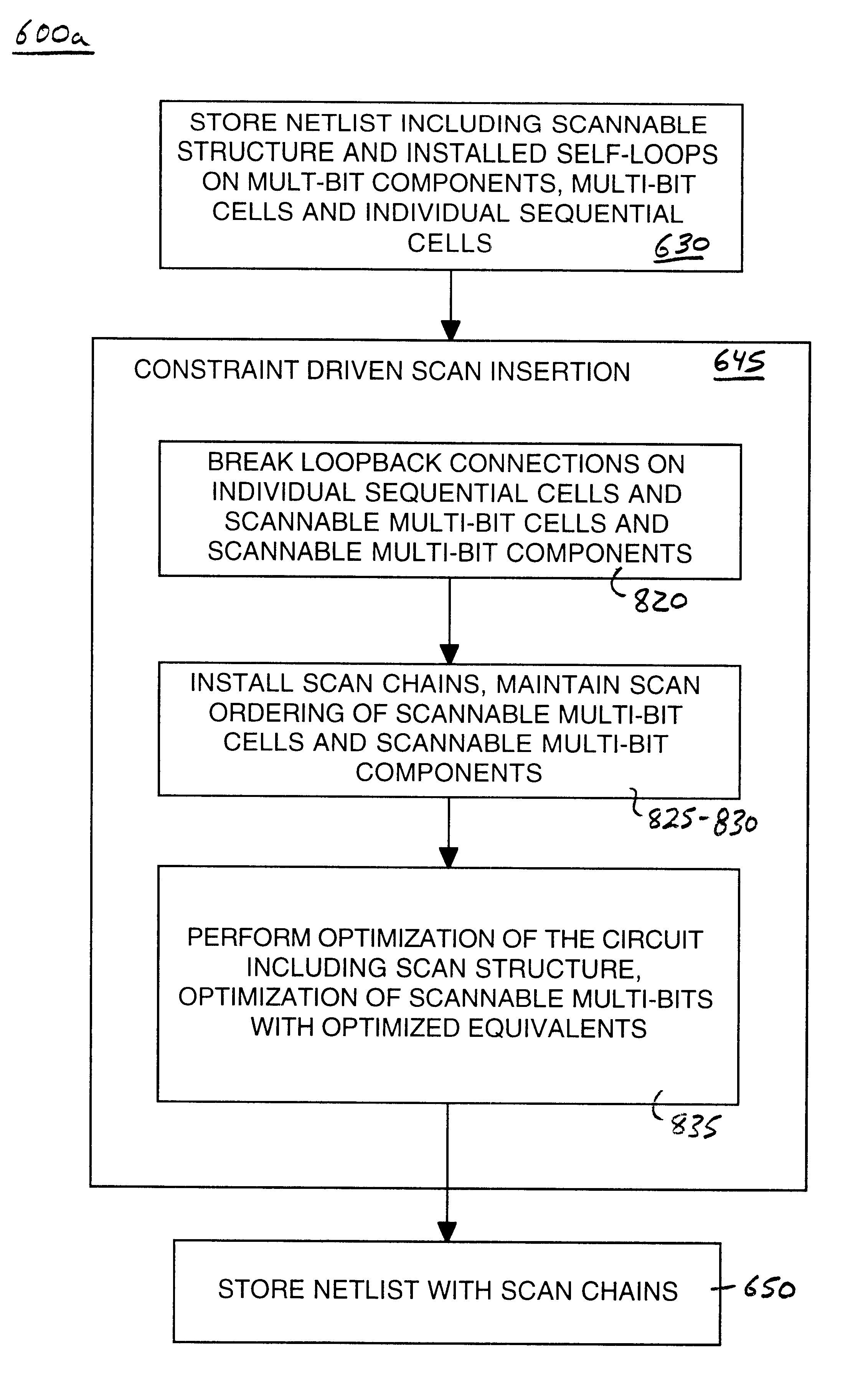

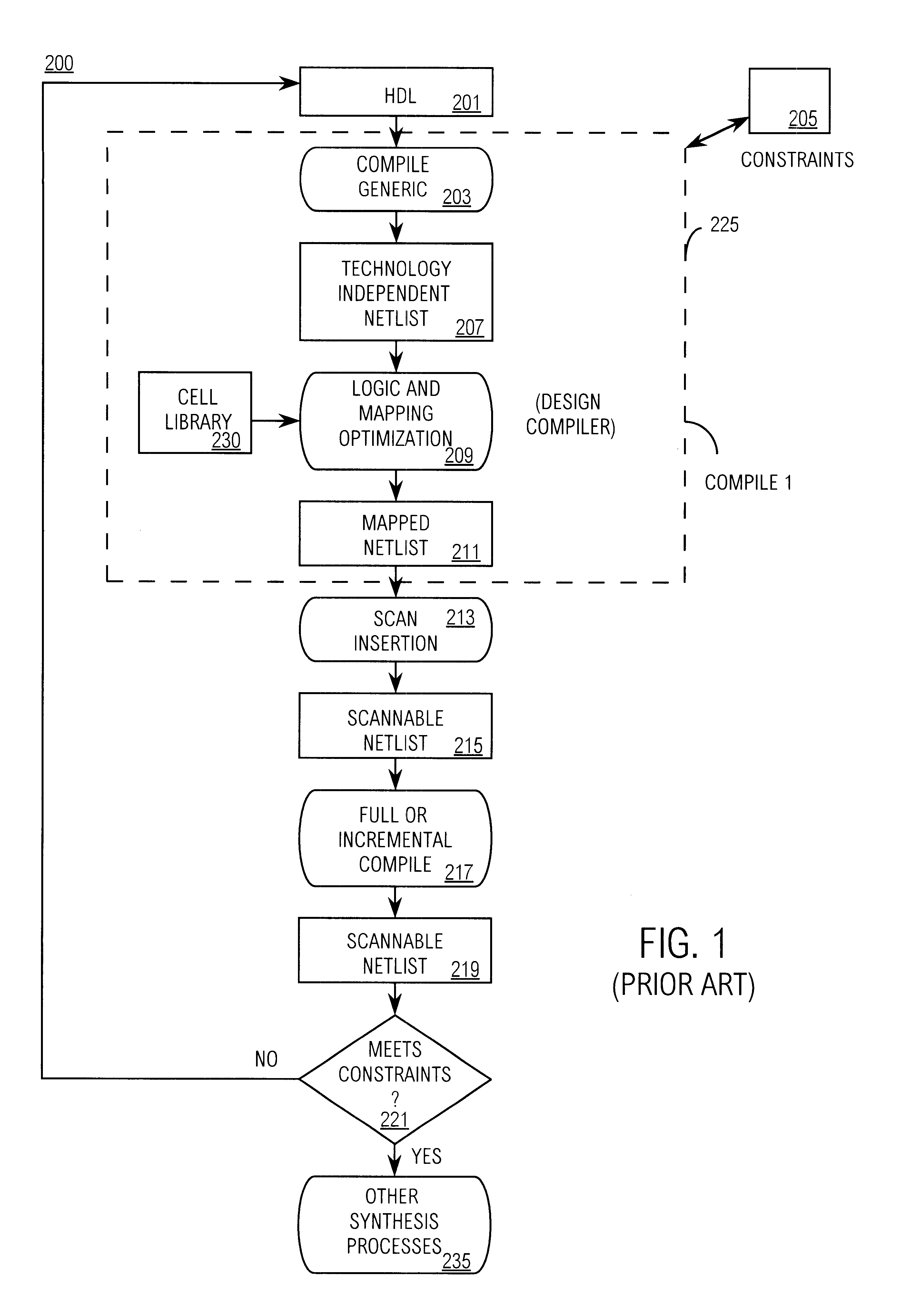

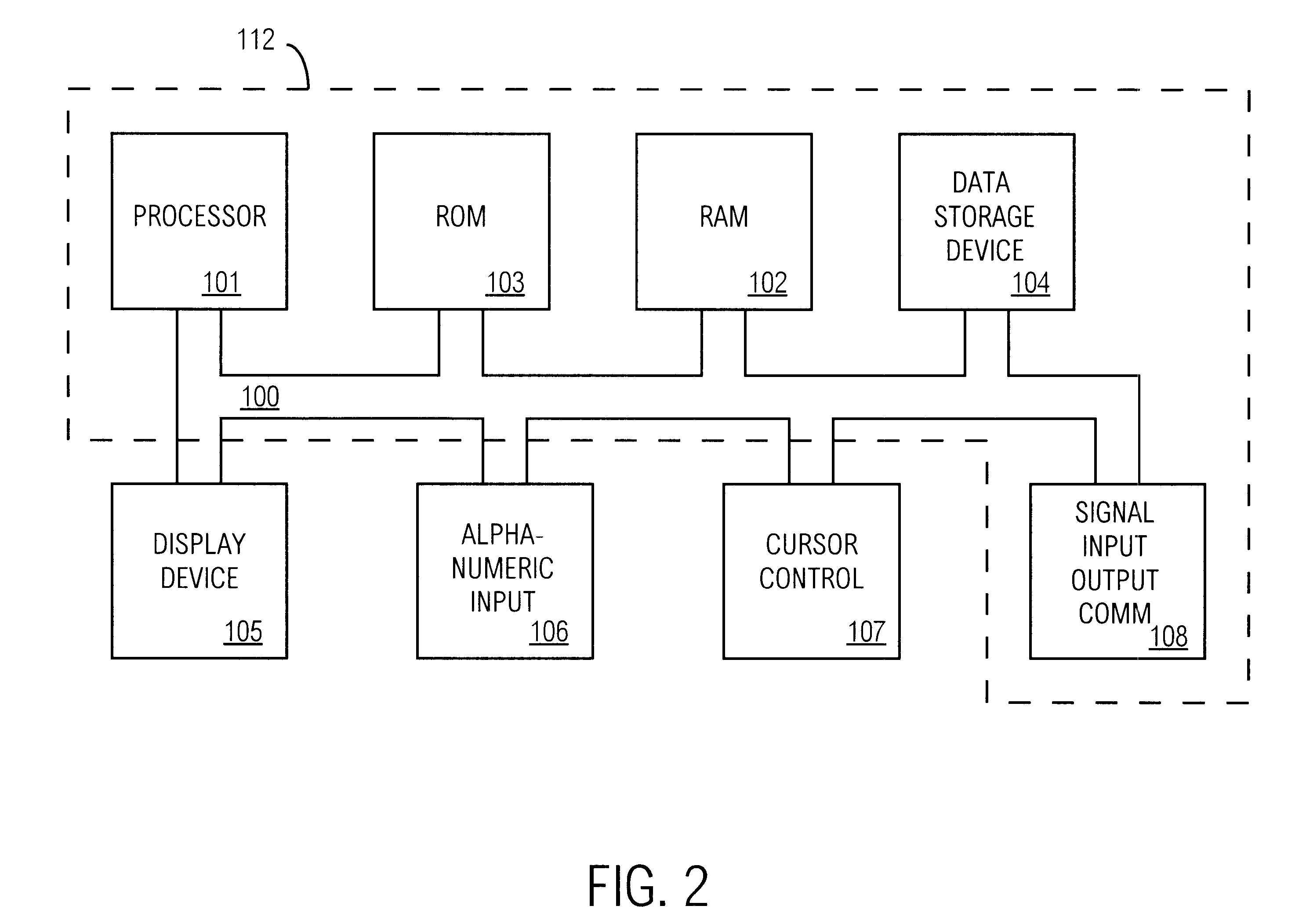

A computer implemented process and system for electronic design automation (EDA) using groups of multiple cells having loop-back connections for modeling port electrical characteristics. Multi-bit cells have multiple gates of the same function implemented within a same cell. Multi-bit components have multiple multi-bit cells implemented within a same component. Scannable multi-bit cells and components are similar to multi-bit cells and components but contain scannable sequential elements with scan chains installed. Multi-bit cells may or may not have each sequential cells' input and each sequential cells' output available externally. The scannable sequential elements of a multi-bit component are ordered into a predefined scan chain which is defined by the library containing the multi-bit component or multi-bit cell. During scan replacement processes of the EDA compile process, multi-bit cells and components of the netlist are replaced with scannable multi-bit cells and components. Also, during optimization, multi-bit cells and components undergo equivalence replacement to meet specified constraints (e.g., area, performance, etc.). To model the electrical characteristics of the port during certain optimizations, loopback connections are applied to the multi-bit components from the scan out port to the scan in port of the multi-bit cell or component, therefore, one loopback connection spans multiple sequential cells within the multi-bit cell or component. During certain optimizations, loopback connections are applied to multiple sequential cells that are coupled together but do not necessarily reside in a multi-bit cell or component. By spanning multiple sequential cells, circuit degeneration is reduced thereby providing better circuit optimizations for netlists having scan circuitry.

Owner:SYNOPSYS INC

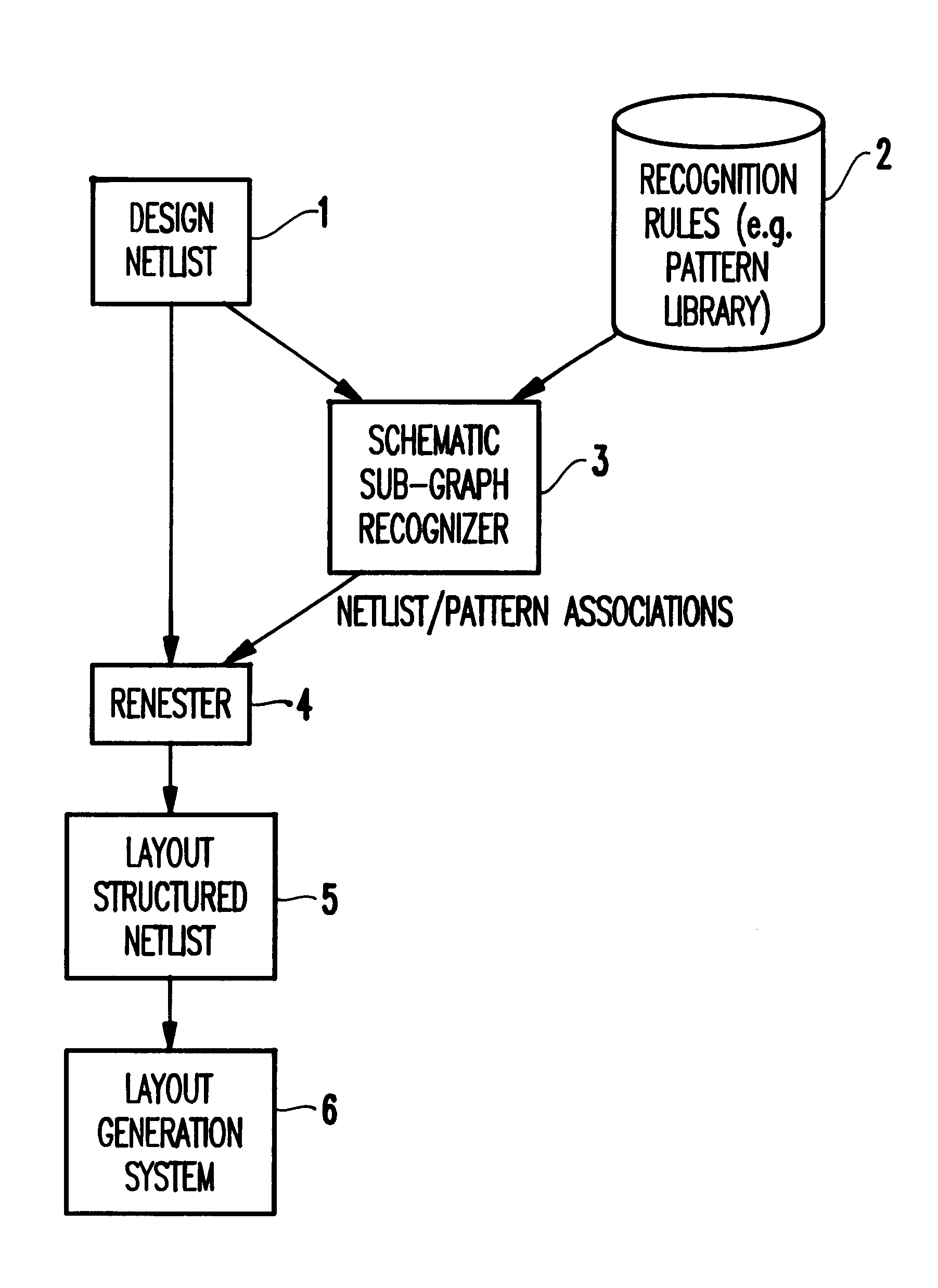

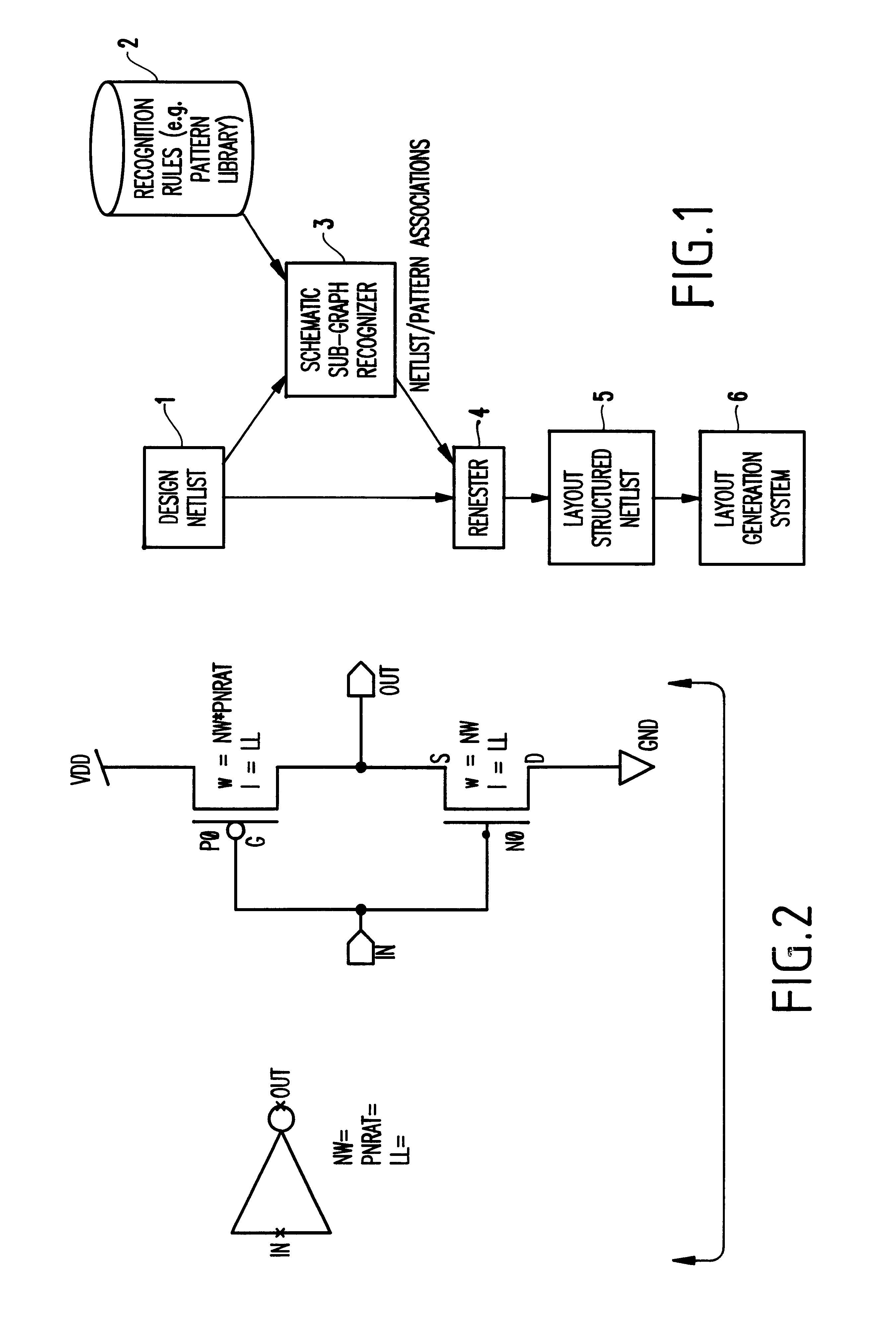

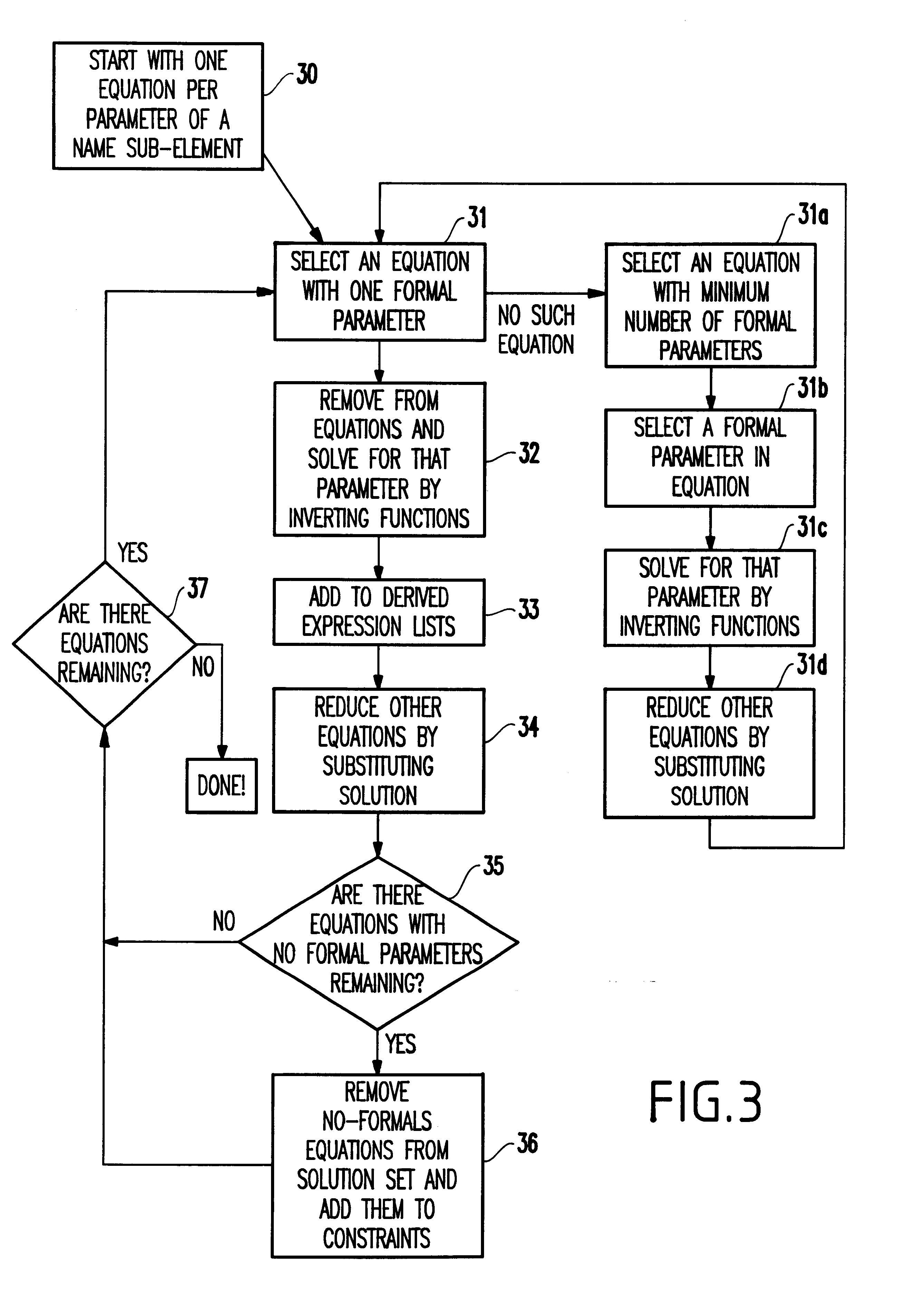

Hierarchical layout method for integrated circuits

InactiveUS20020194575A1Easy to modifyIncrease production capacityCAD circuit designProgram controlComputer architectureGenerative Design

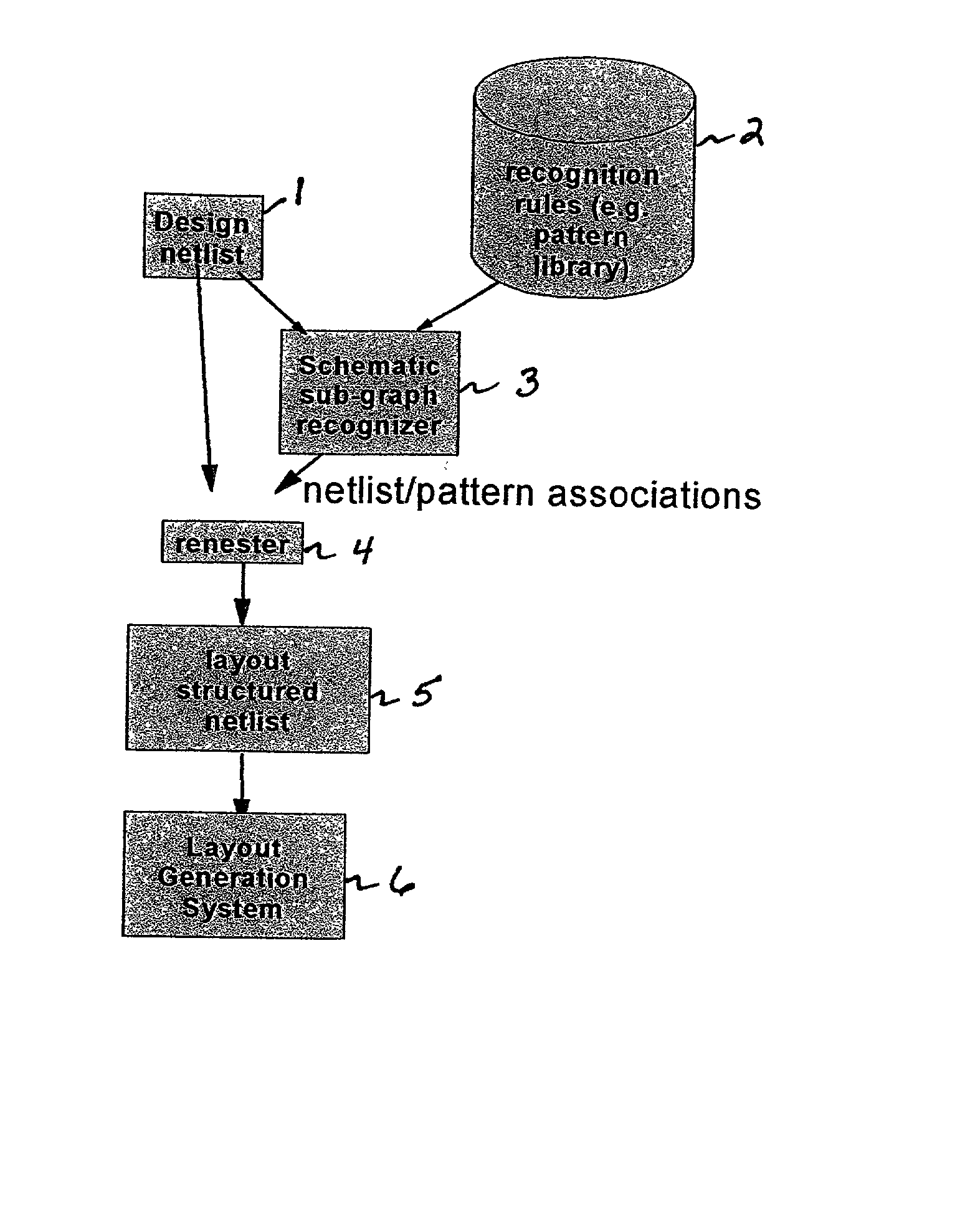

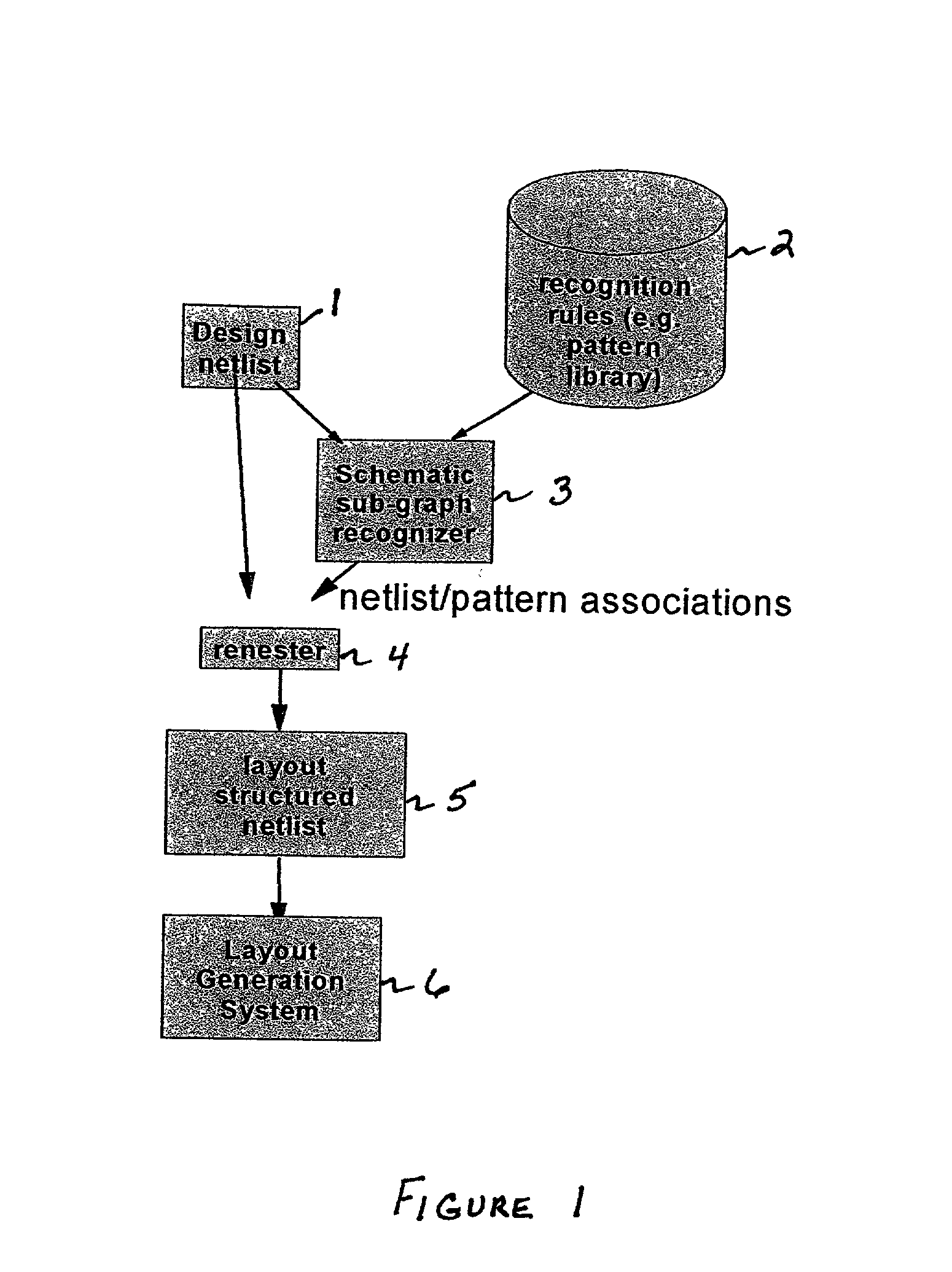

A method for hierarchical layout of an electronic design using an electronic computer aided design system, wherein the method includes generating a parameterized pattern library and using an existing netlist and analyze in a pattern recognizer, from which a list of associations between the pattern library and the netlist is created. Renesting then occurs wherein the netlist using the list of associations is used for generating a hierarchical layout of the electronic components in the design.

Owner:IBM CORP

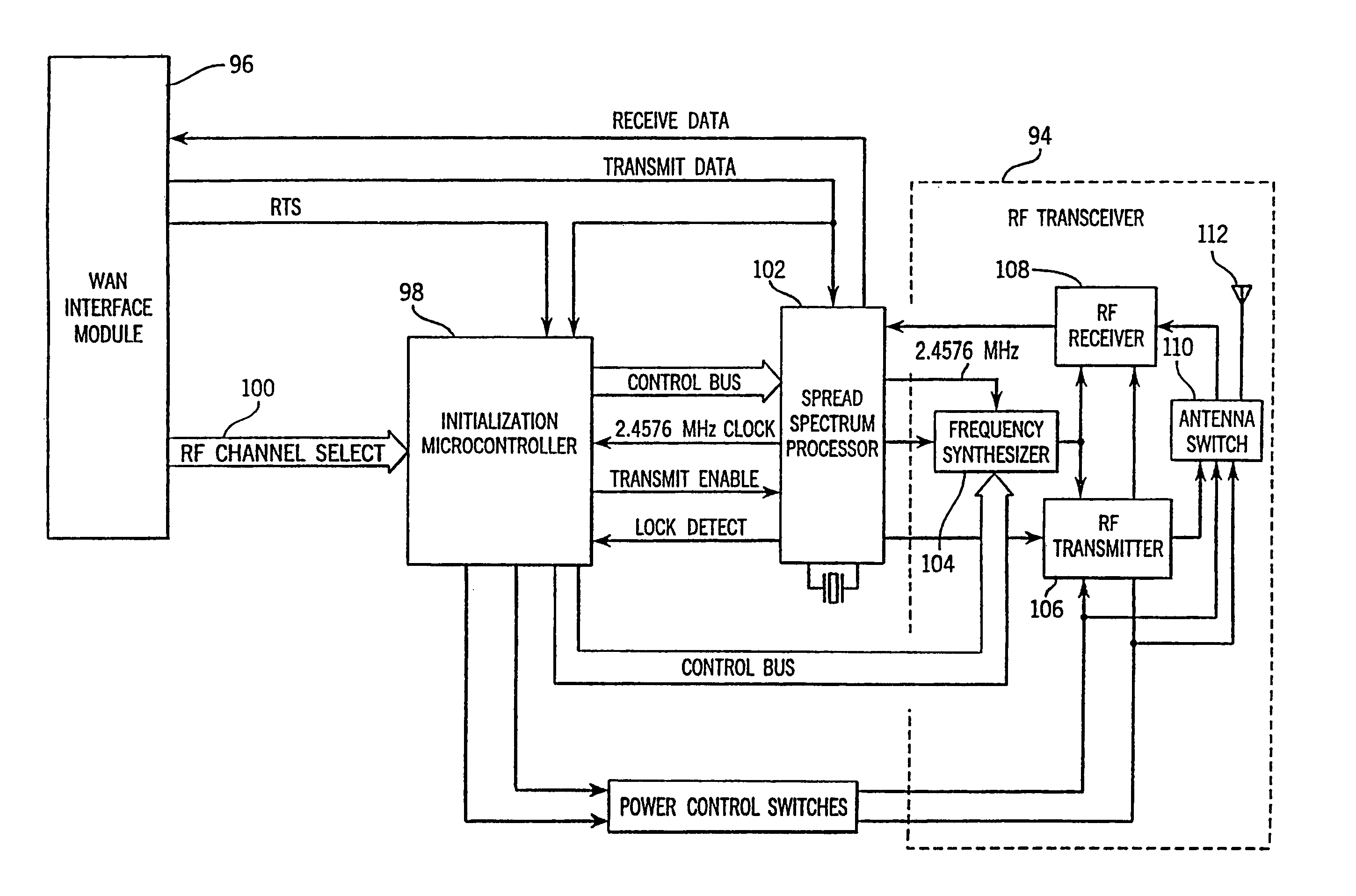

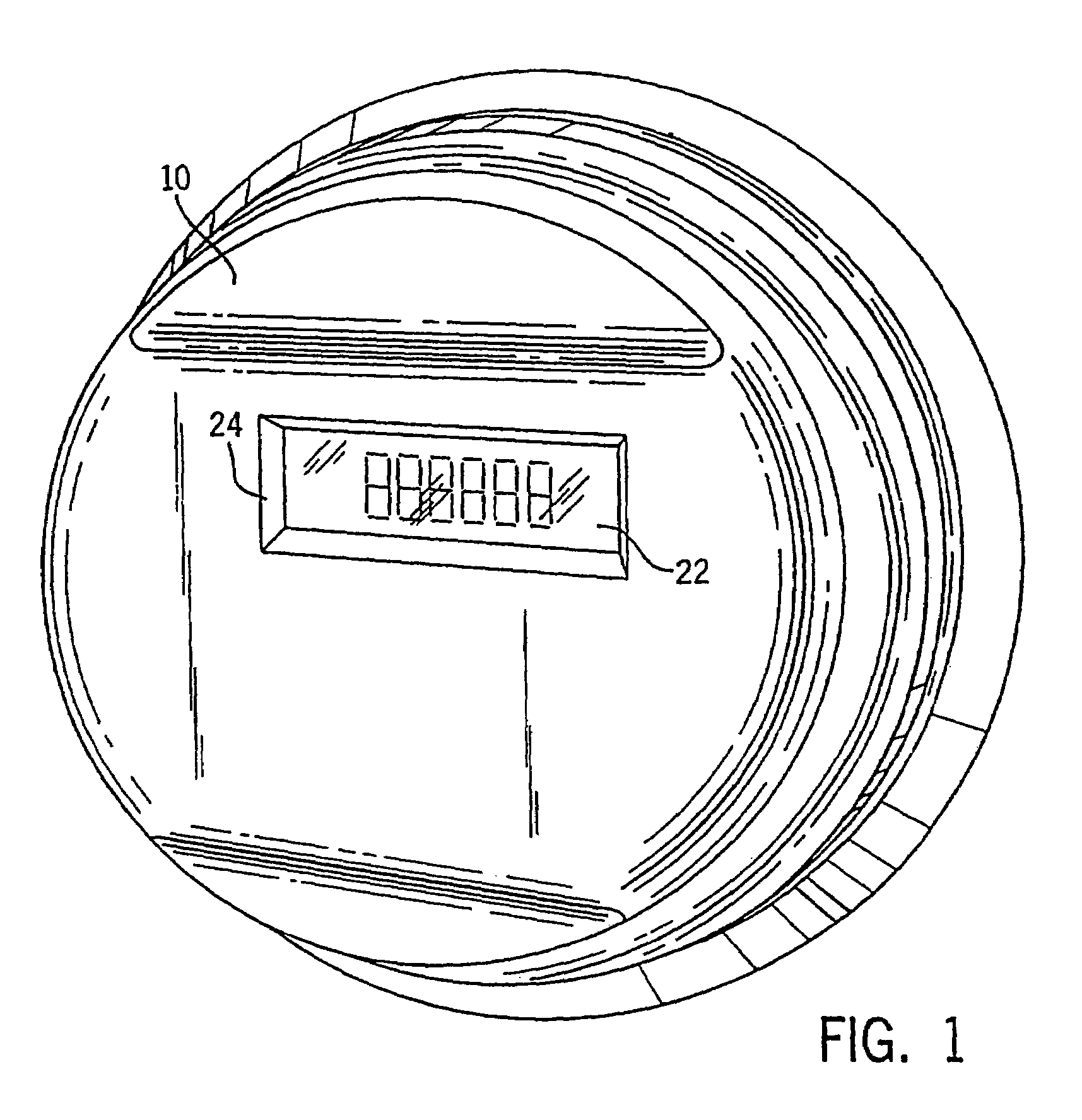

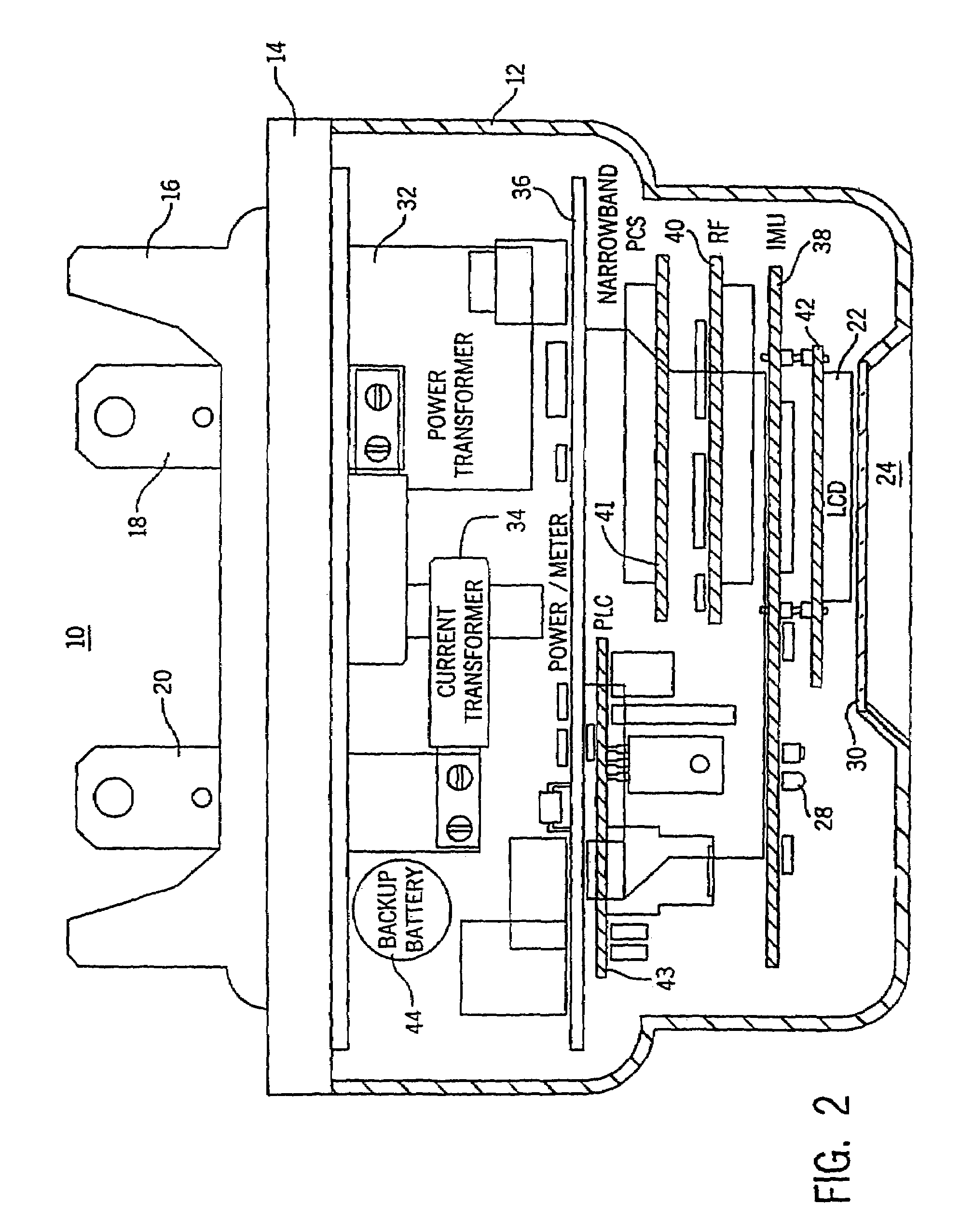

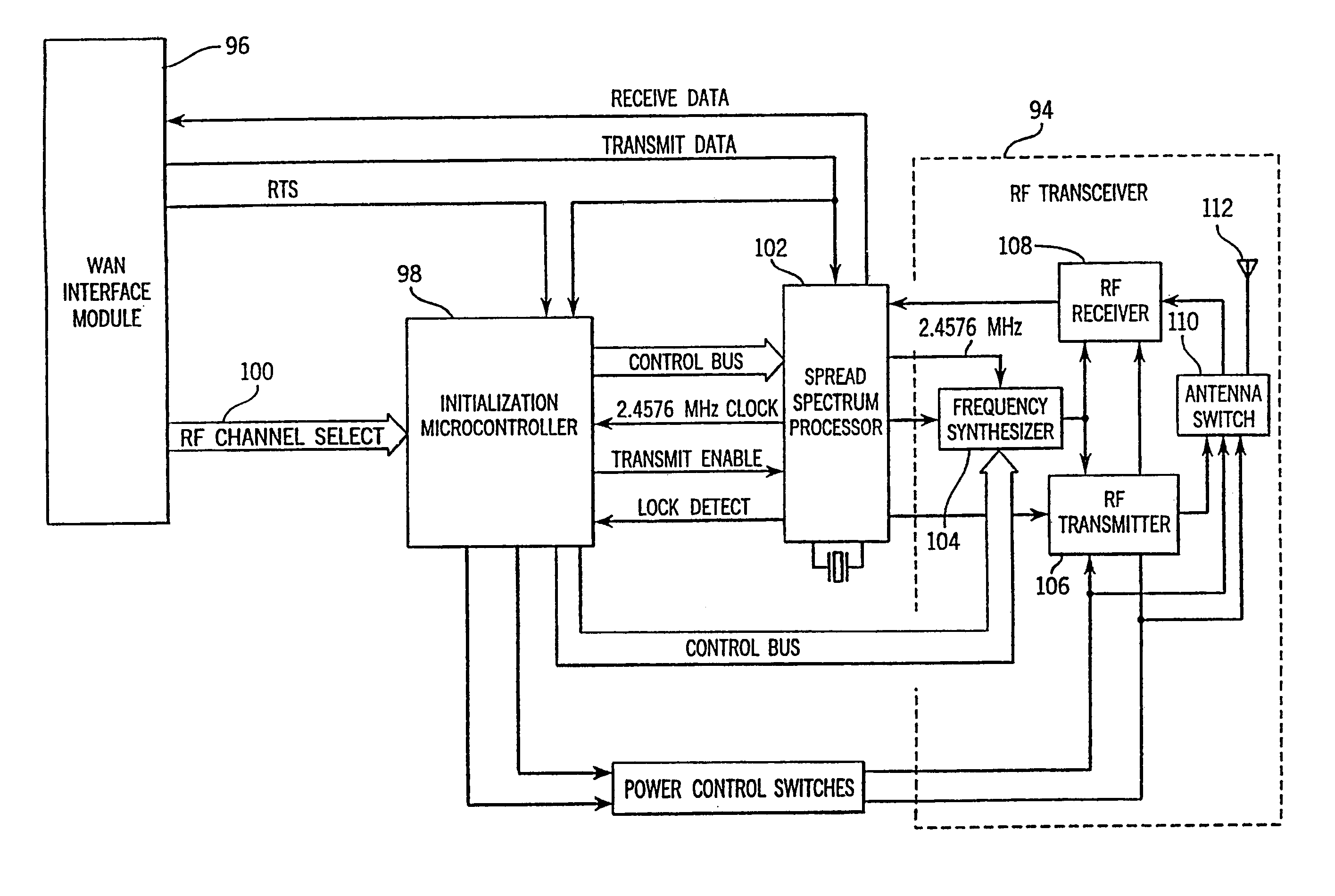

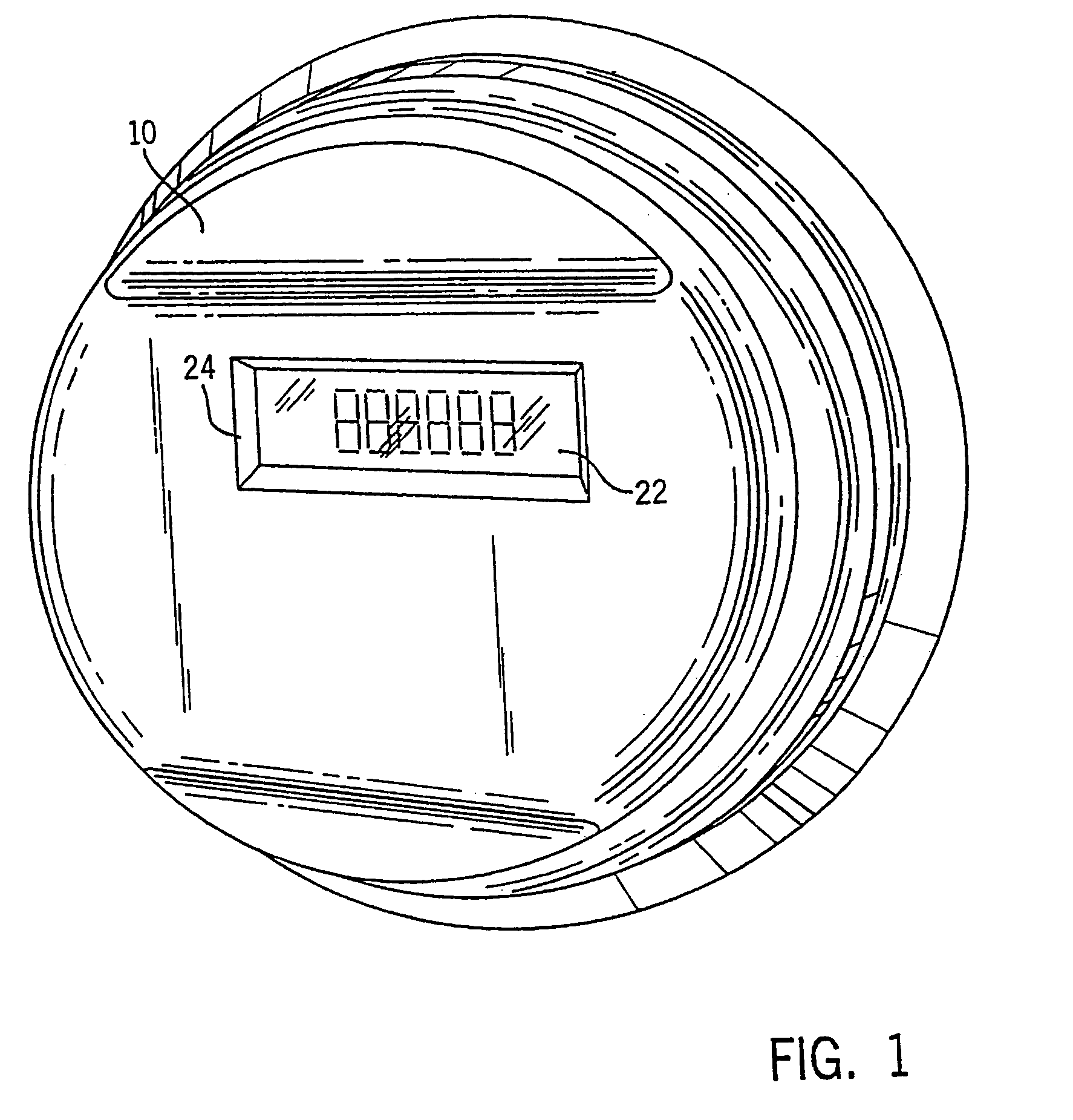

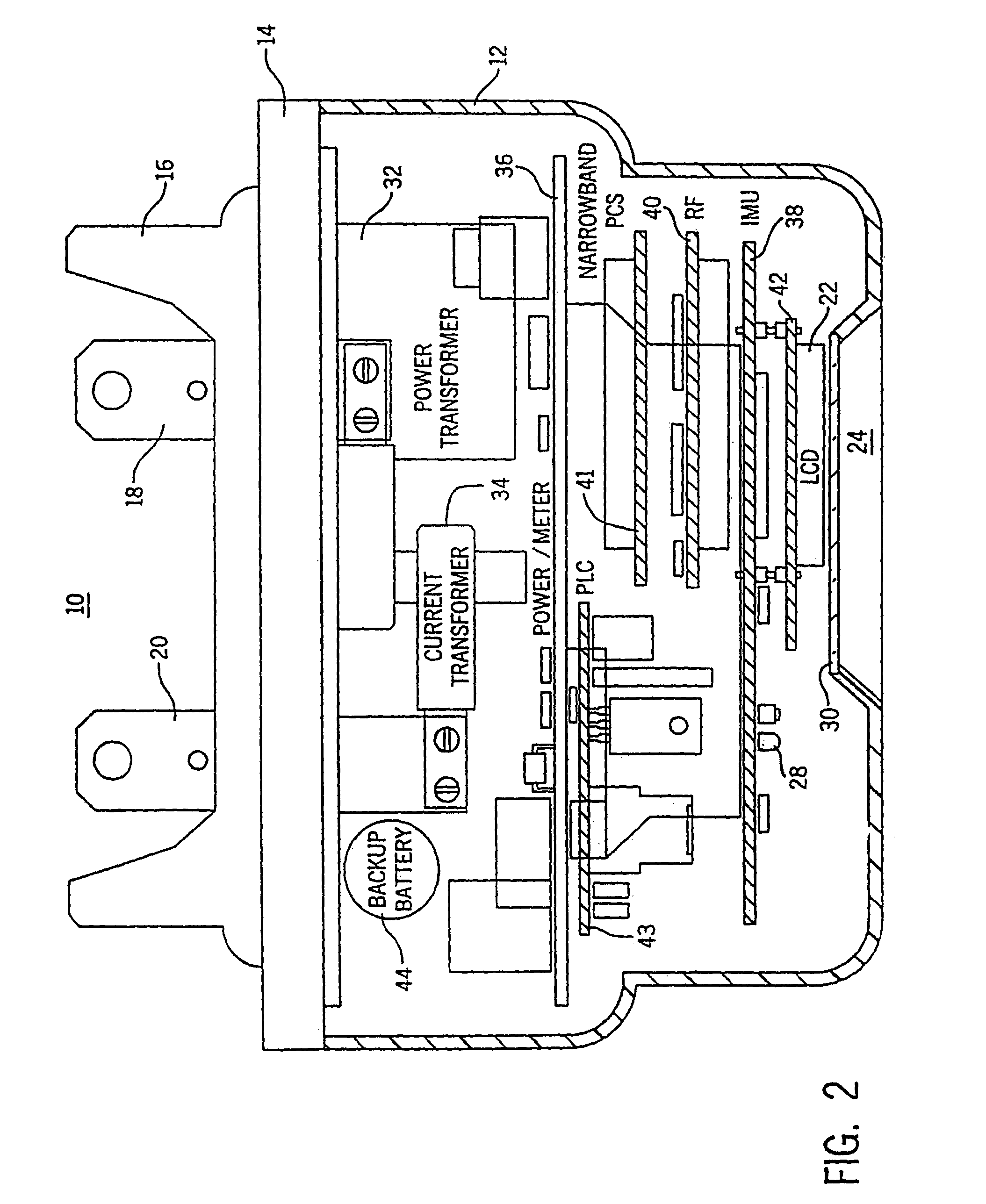

Electronic electric meter for networked meter reading

InactiveUS7064679B2Easy to changeElectric signal transmission systemsTariff metering apparatusMicrocontrollerCommunication link

An electronic electric meter for use in a networked automatic meter reading environment. The electric meter retrofits into existing meter sockets and is available for new meter installations for both single phase and three phase electric power connections. The meter utilizes an all electronic design including a meter microcontroller, a measurement microcontroller, a communication microcontroller and spread spectrum processor, and a plurality of other communication interface modules for communicating commodity utilization and power quality data to a utility. The electric meter utilizes a modular design which allows the interface modules to be changed depending upon the desired communication network interface. The meter measures electricity usage and monitors power quality parameters for transmission to the utility over a two-way 900 MHz spread spectrum local area network (LAN) to a remotely located gateway node. The gateway node transmits this data to the utility over a commercially available fixed wide area network (WAN). The meter also provides direct communication to the utility over a commercially available network interface that plugs into the meter's backplane or bus system bypassing the local area network communication link and gateway node.

Owner:SILVER SPRING NETWORKS

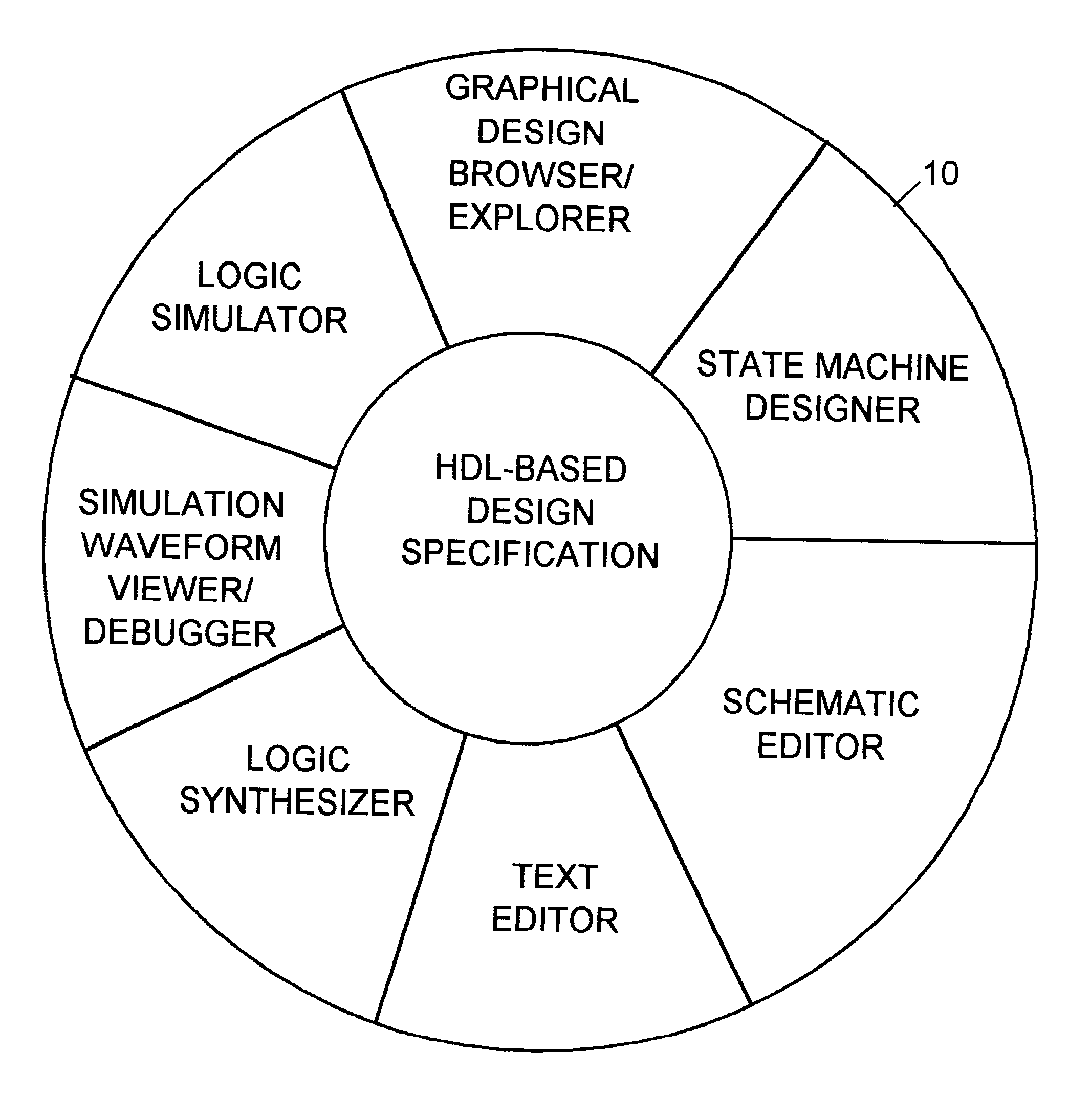

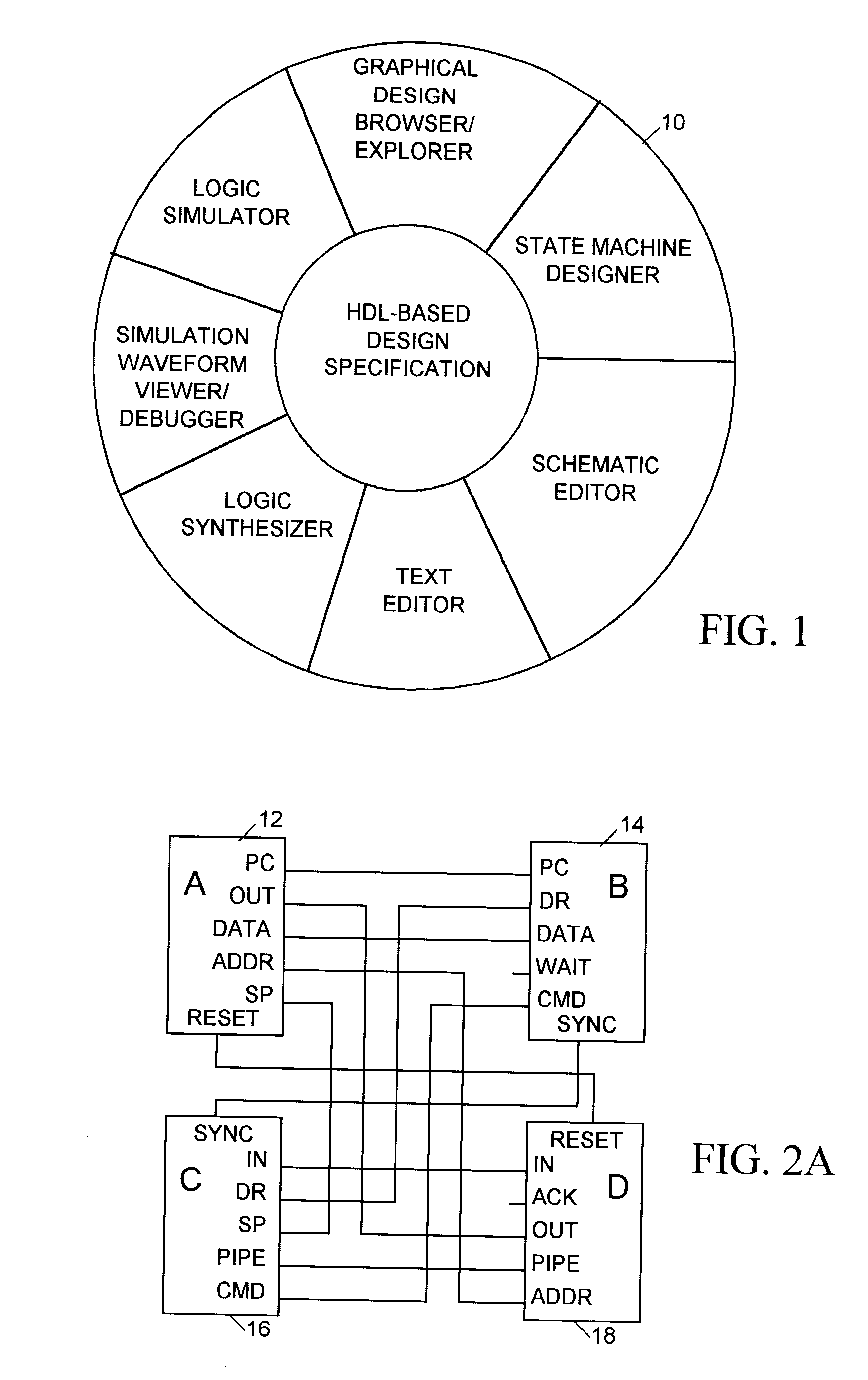

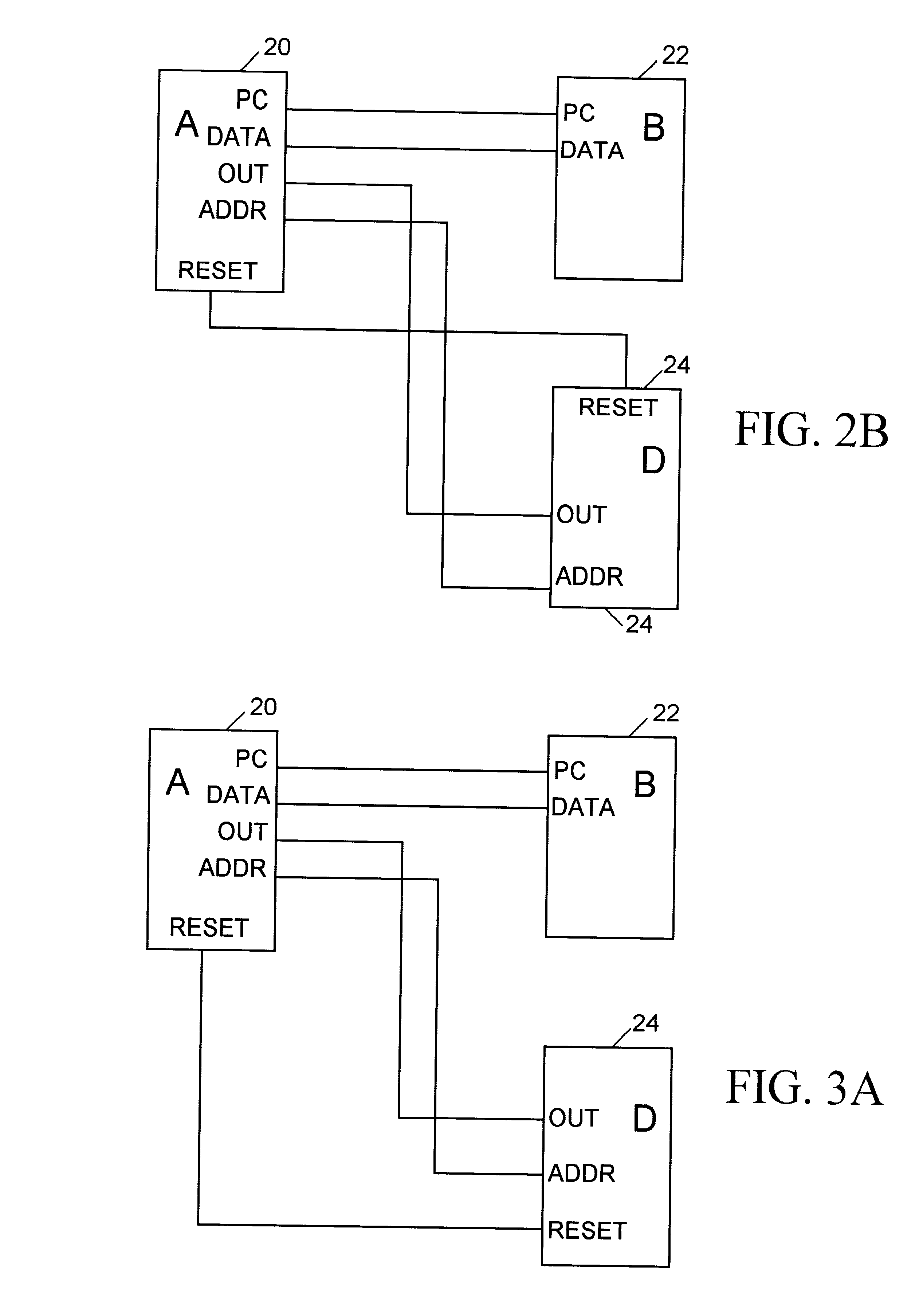

System and method for browsing graphically an electronic design based on a hardware description language specification

InactiveUS6366874B1CAD circuit designSoftware simulation/interpretation/emulationGraphicsProgramming language

Hardware description language (HDL)-centered design system and methodology uses HDL specification effectively as master depository for design intent or knowledge. Through network browser, designers conveniently navigate or explore design graphically. Designers selectively review or save design in entirety or portions. Design capture, analysis, and manipulation are based on HDL specification, either directly through text file editing, or indirectly through use of graphical tools.

Owner:SYNOPSYS INC

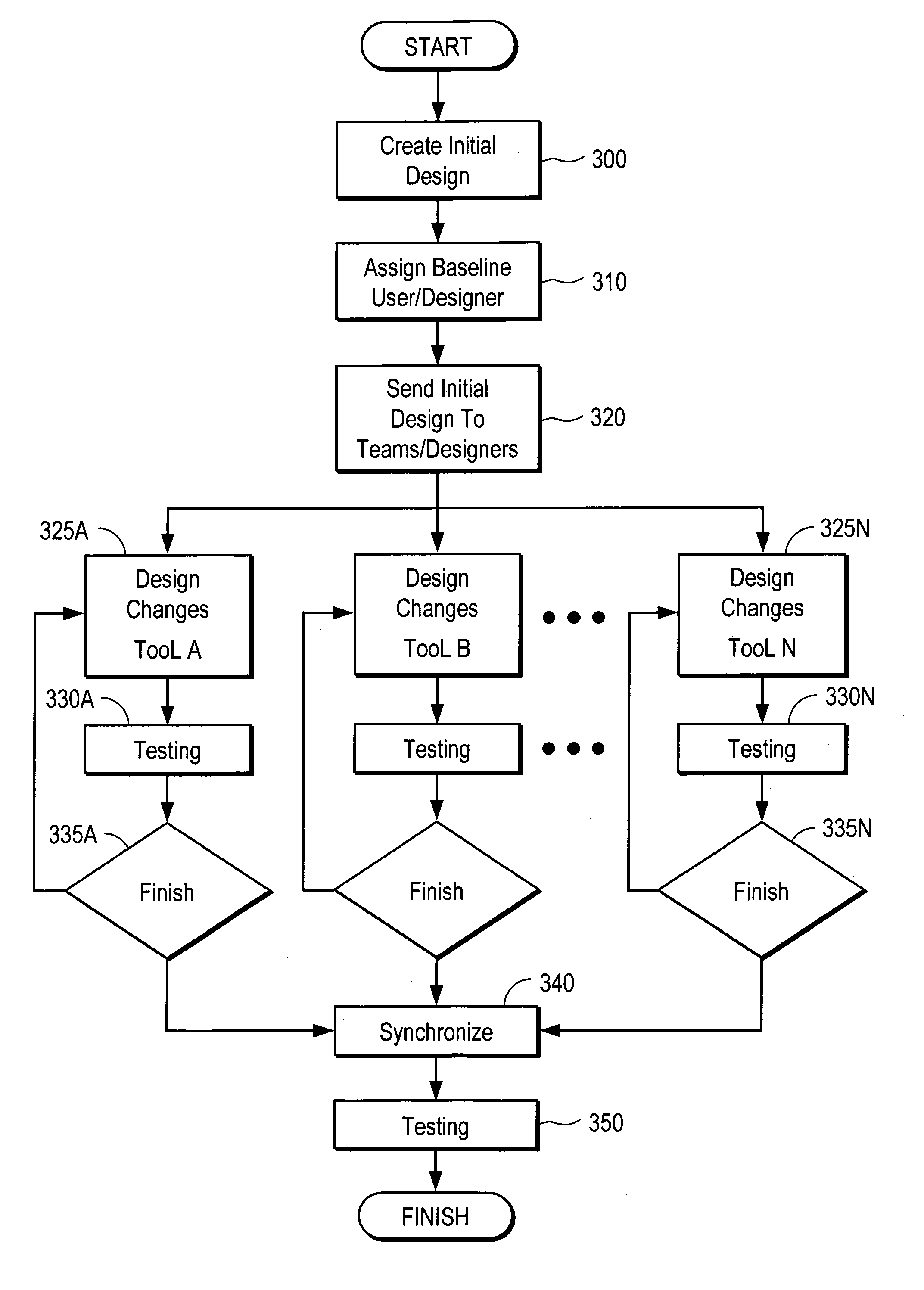

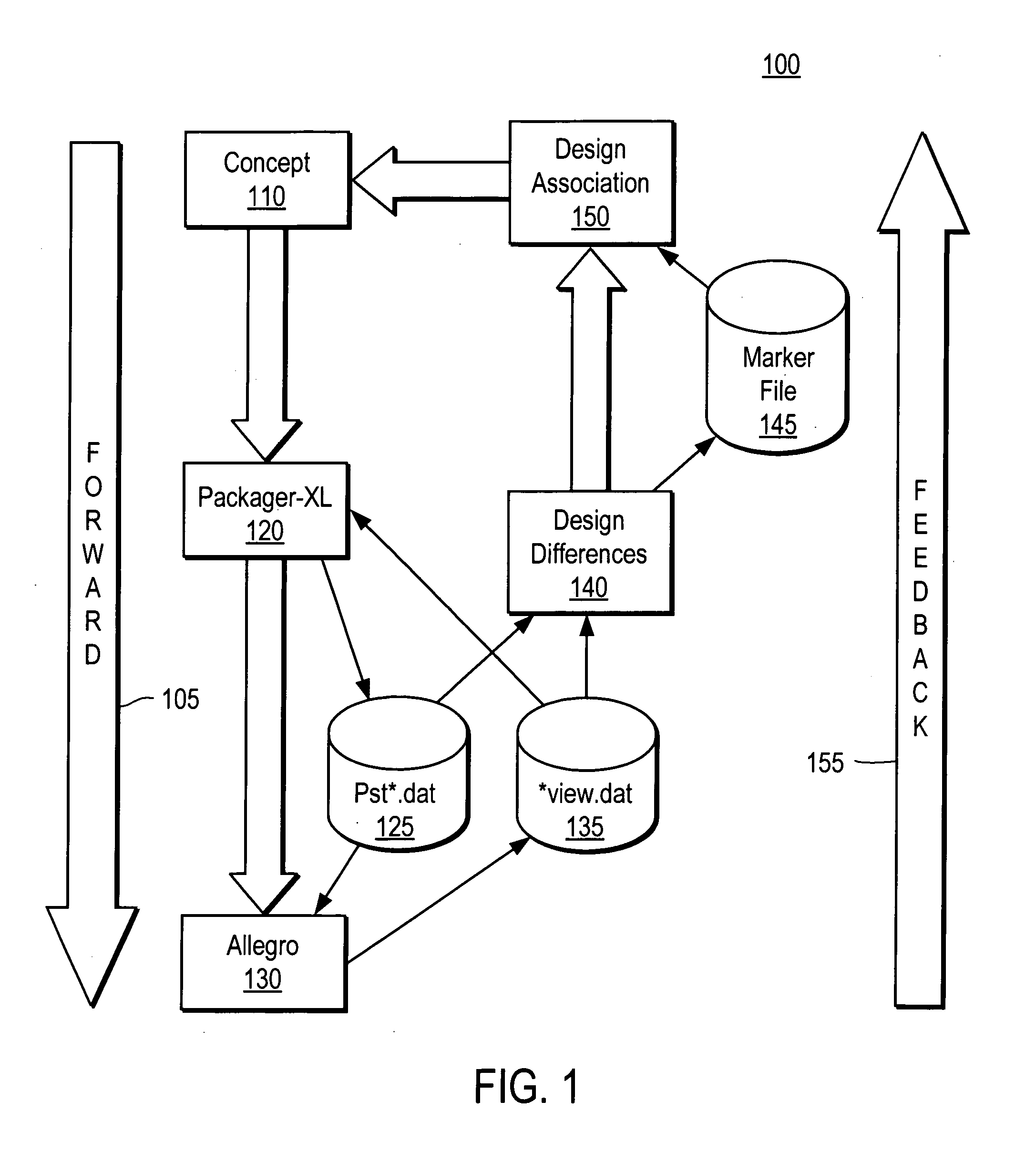

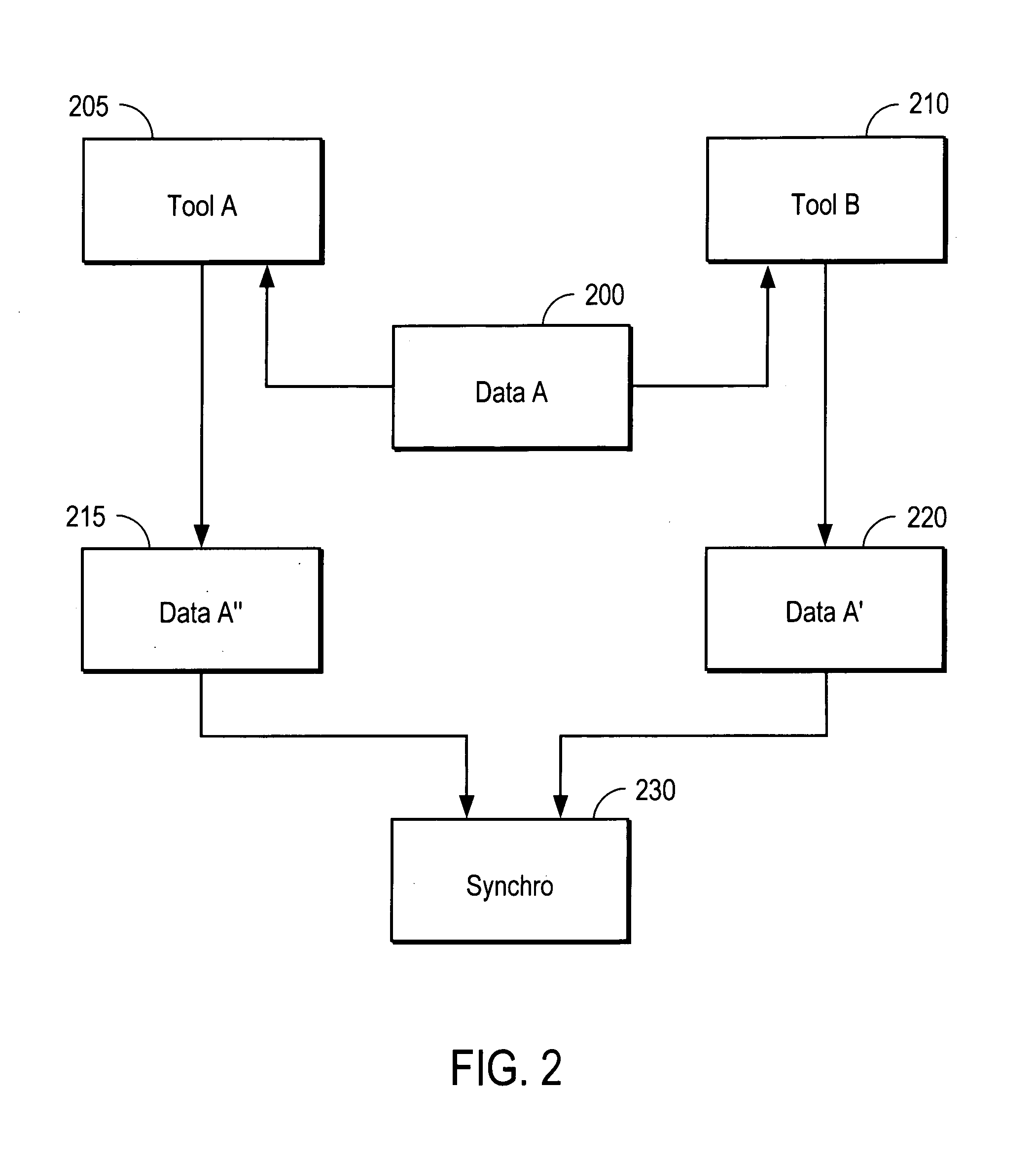

Method and apparatus for concurrent engineering and design synchronization of multiple tools

ActiveUS7143341B1Easy to controlGood synchronizationDigital computer detailsComputer aided designData synchronizationConcurrent engineering

Concurrent engineering among multiple design groups is facilitated by maintaining design changes in a data model of a design being developed. Design changes for each group are made from a baseline design. Changes are tracked by maintaining change information from all but an owner of the original baseline design. Changes are synchronized by identifying owner and non-owner changes and merging the changes to produce a final design. Since non-owner changes are tracked, the baseline design is not needed in synchronization. Preferably the invention is applied to electronic designs made by multiple design groups at geographically diverse locations. The invention may also be applied to any system where configuration management of developed software, parts, or any design is needed.

Owner:CADENCE DESIGN SYST INC

Electronic electric meter for networked meter reading

InactiveUS7277027B2Easy to changeElectric signal transmission systemsTariff metering apparatusMicrocontrollerCommunication link

Owner:ITRON NETWORKED SOLUTIONS INC

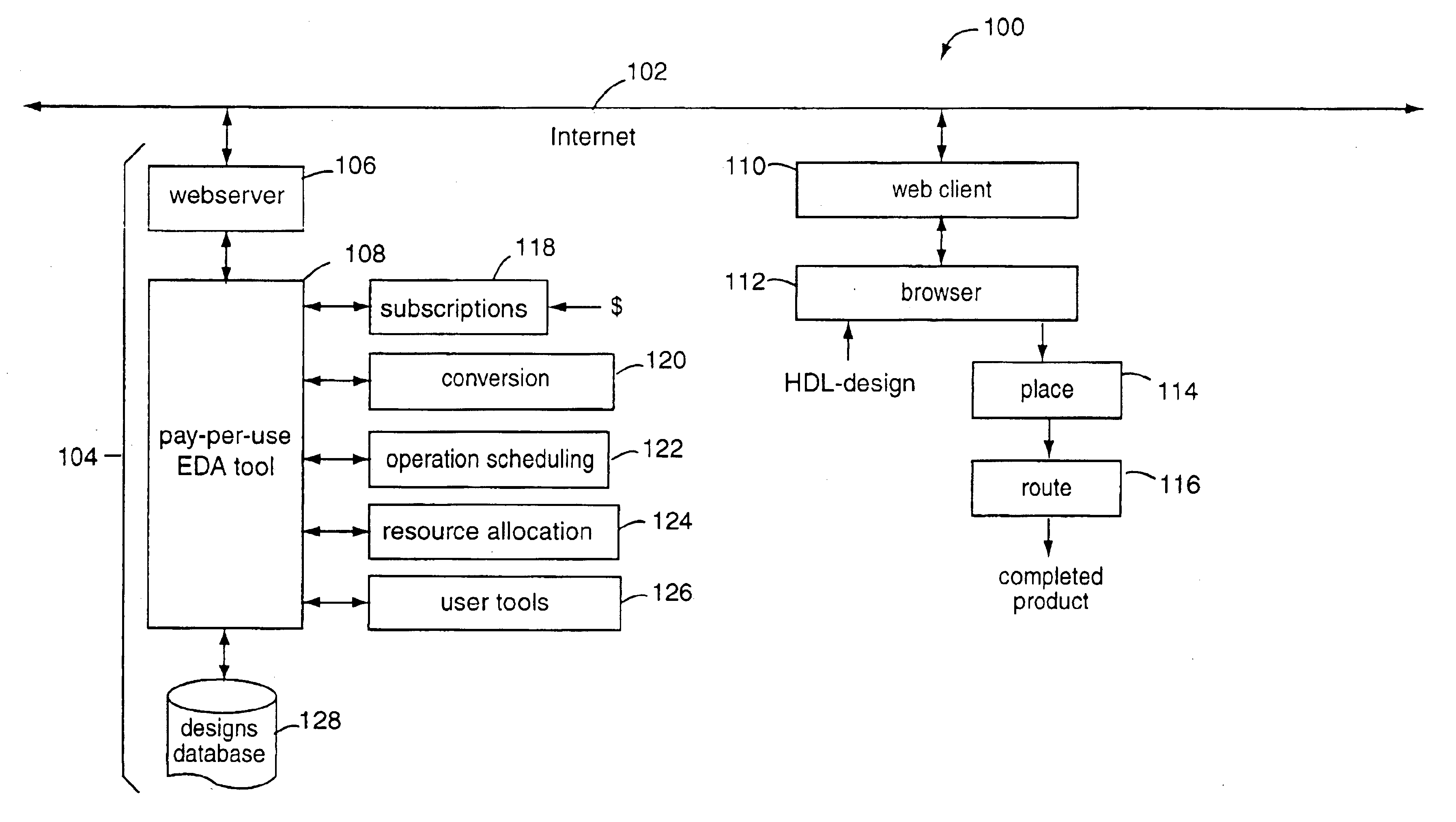

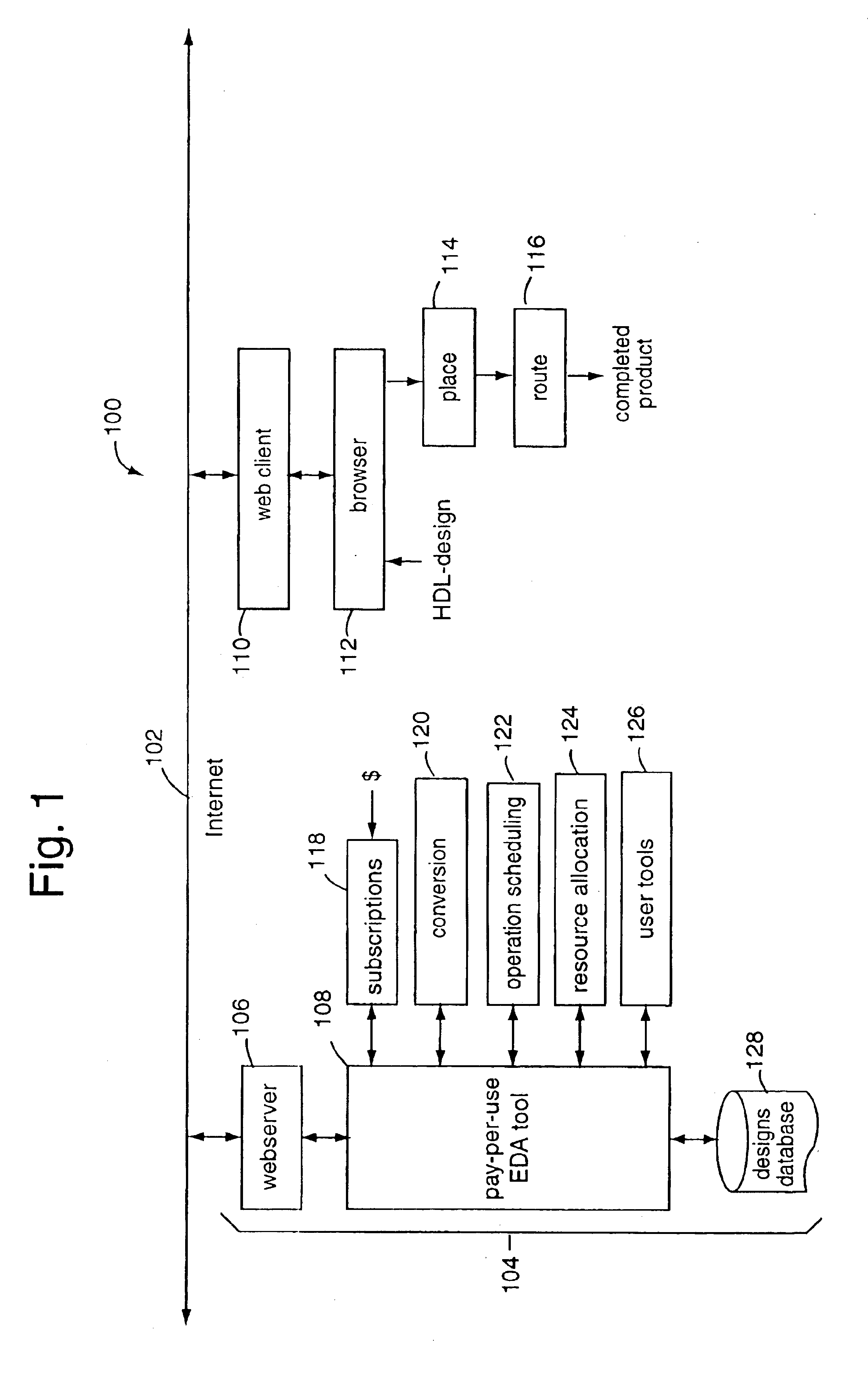

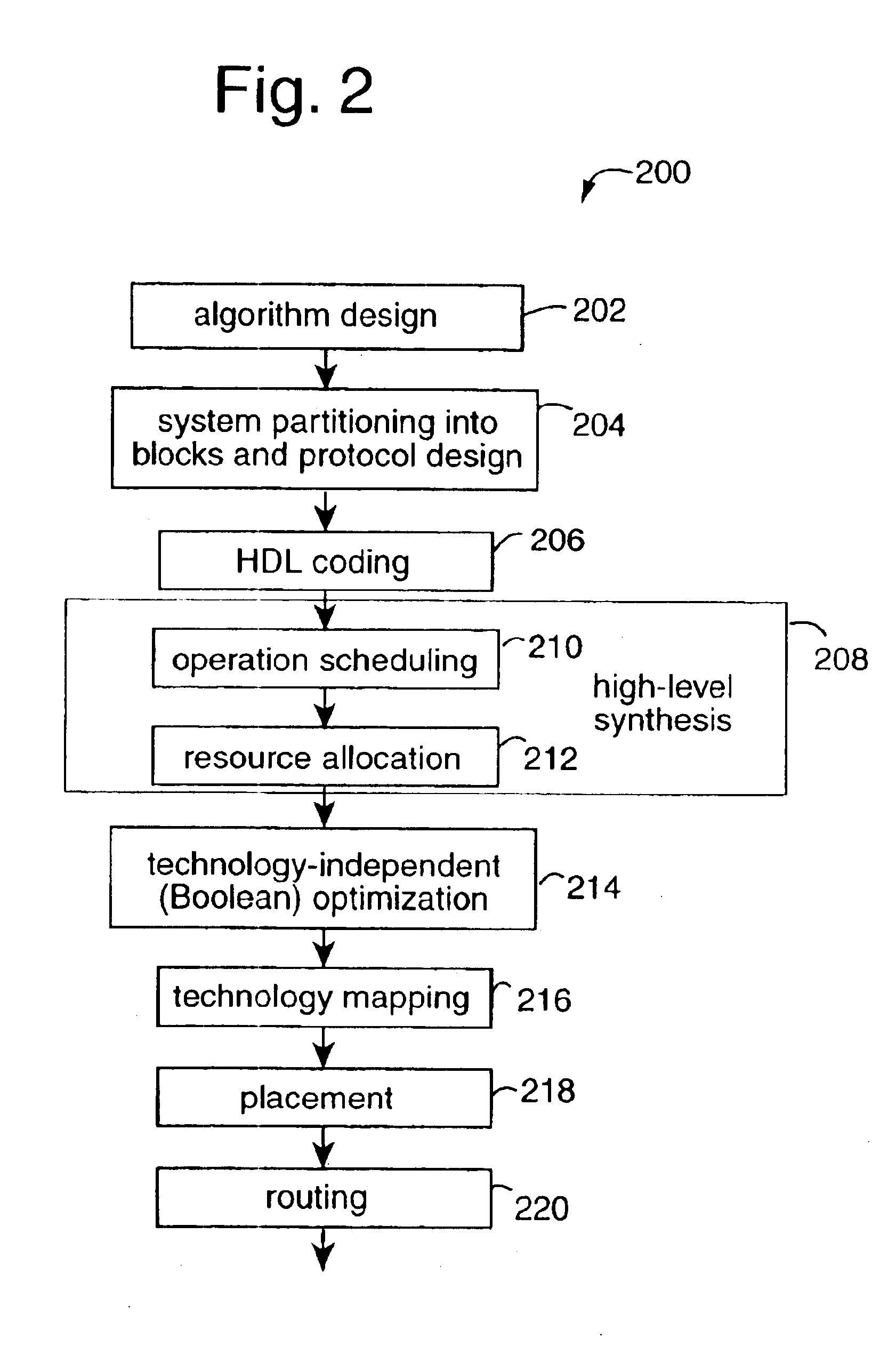

Behavioral-synthesis electronic design automation tool business-to-business application service provider

InactiveUS6782511B1Distributed efficiently and easilyCAD circuit designSoftware simulation/interpretation/emulationWeb serviceIntellectual property

A business-to-business application service provider includes an Internet website and webserver with EDA-on-demand solutions for system-on-a-chip designers. Such website allows electronic designs in hardware description language to be uploaded into a front-end EDA design environment. A behavioral model simulation tool hosted privately on the webserver tests and validates the design. Such tool executes only in the secure environment of the business-to-business application service provider. The validated solution is then downloaded back over the Internet for a pay-per-use fee to the customer, and in a form ready to be placed and routed by a back-end EDA tool. Such validated design solutions are also downloadable to others in exchange for other designs, or available in technology libraries. The intellectual property created can be re-used, sold, shared, exchanged, and otherwise distributed efficiently and easily from a central for-profit clearinghouse.

Owner:CADENCE DESIGN SYST INC

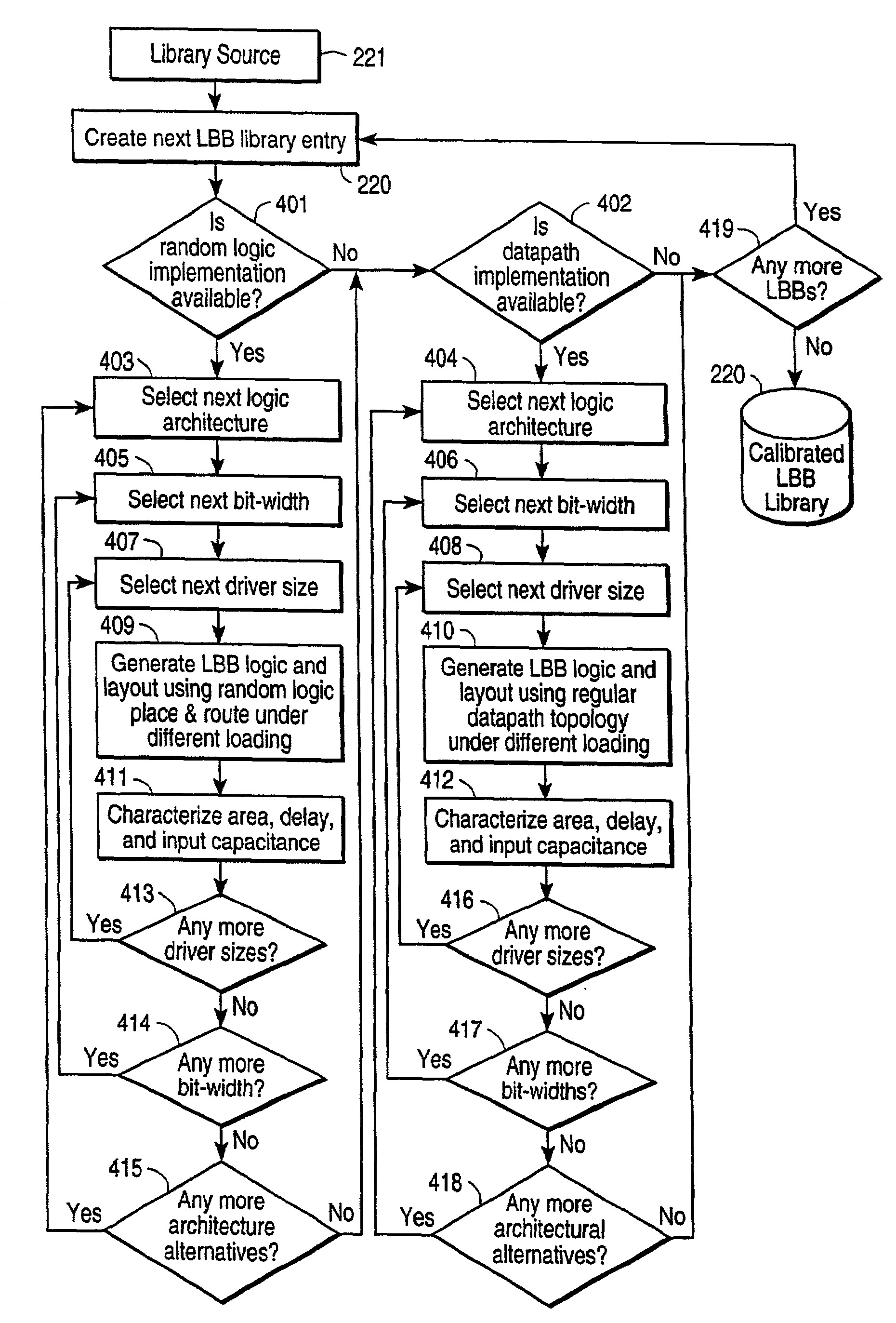

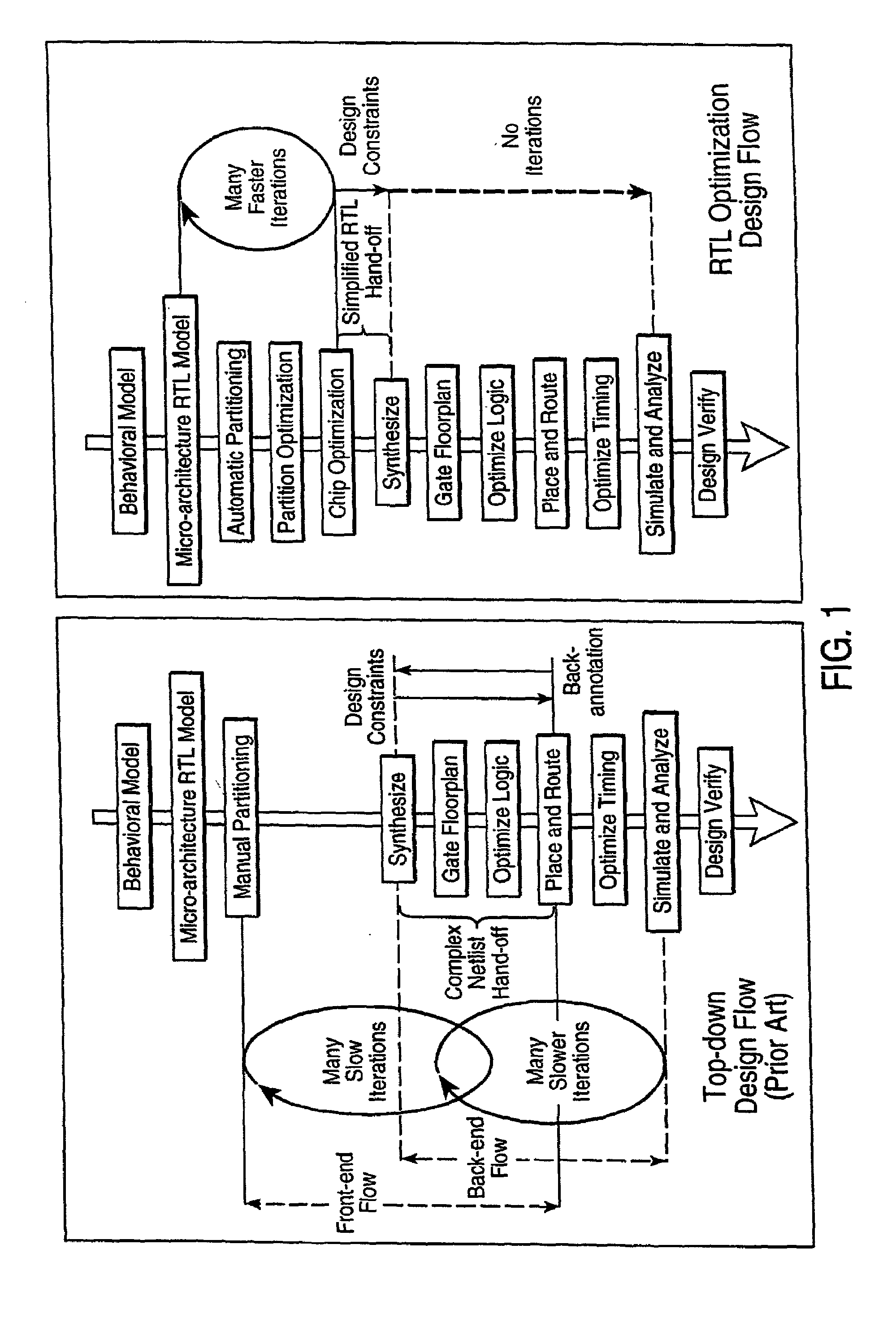

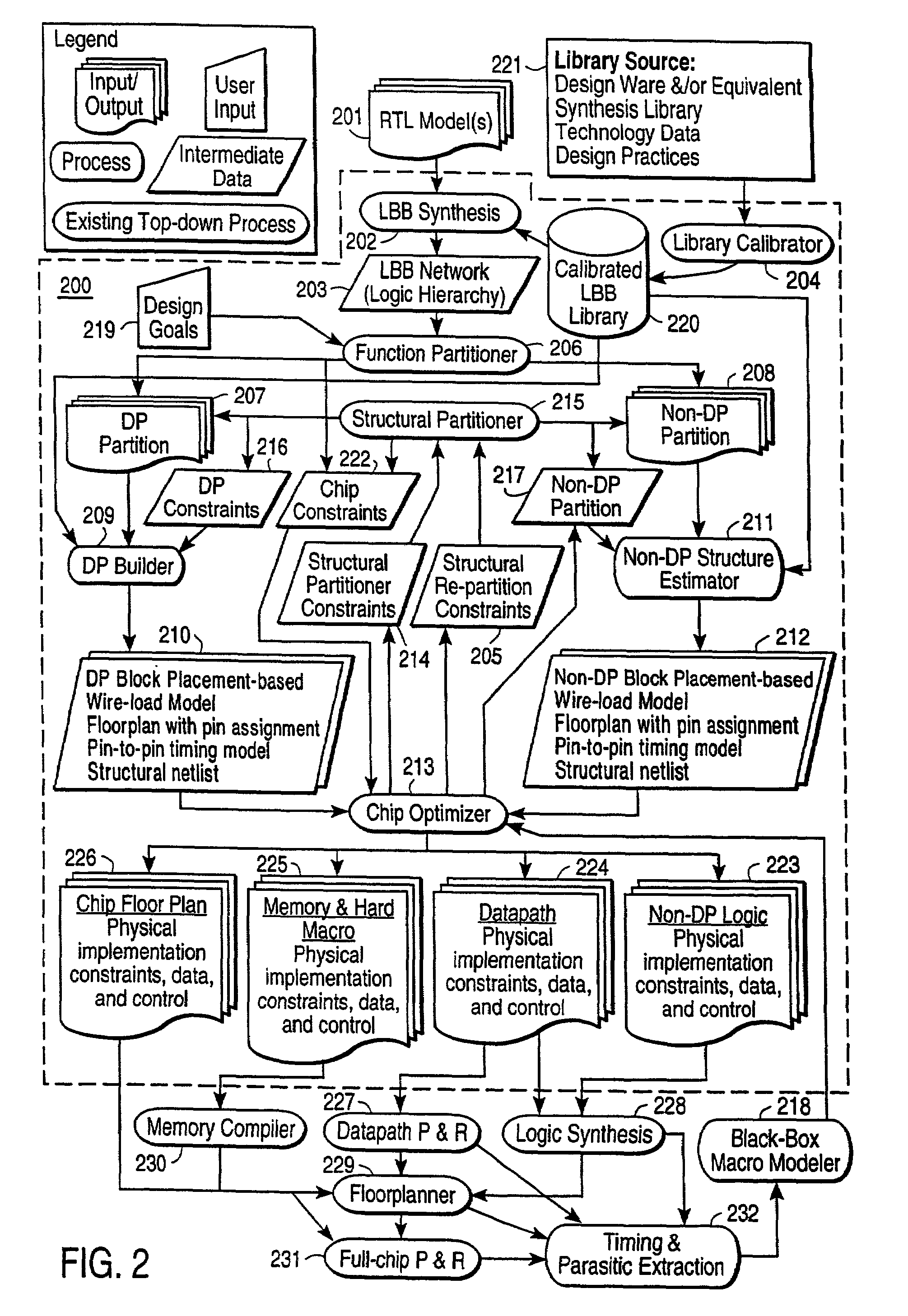

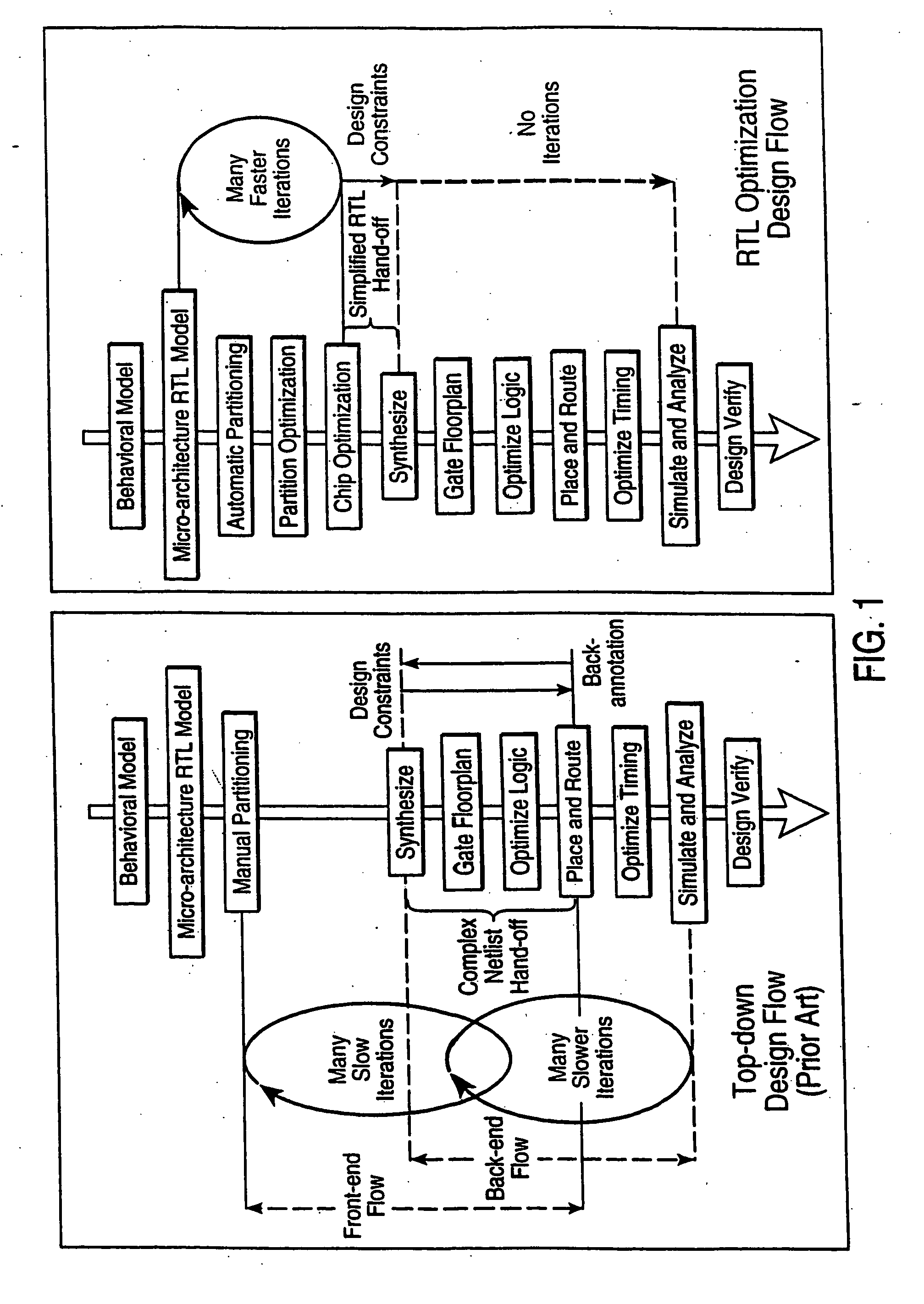

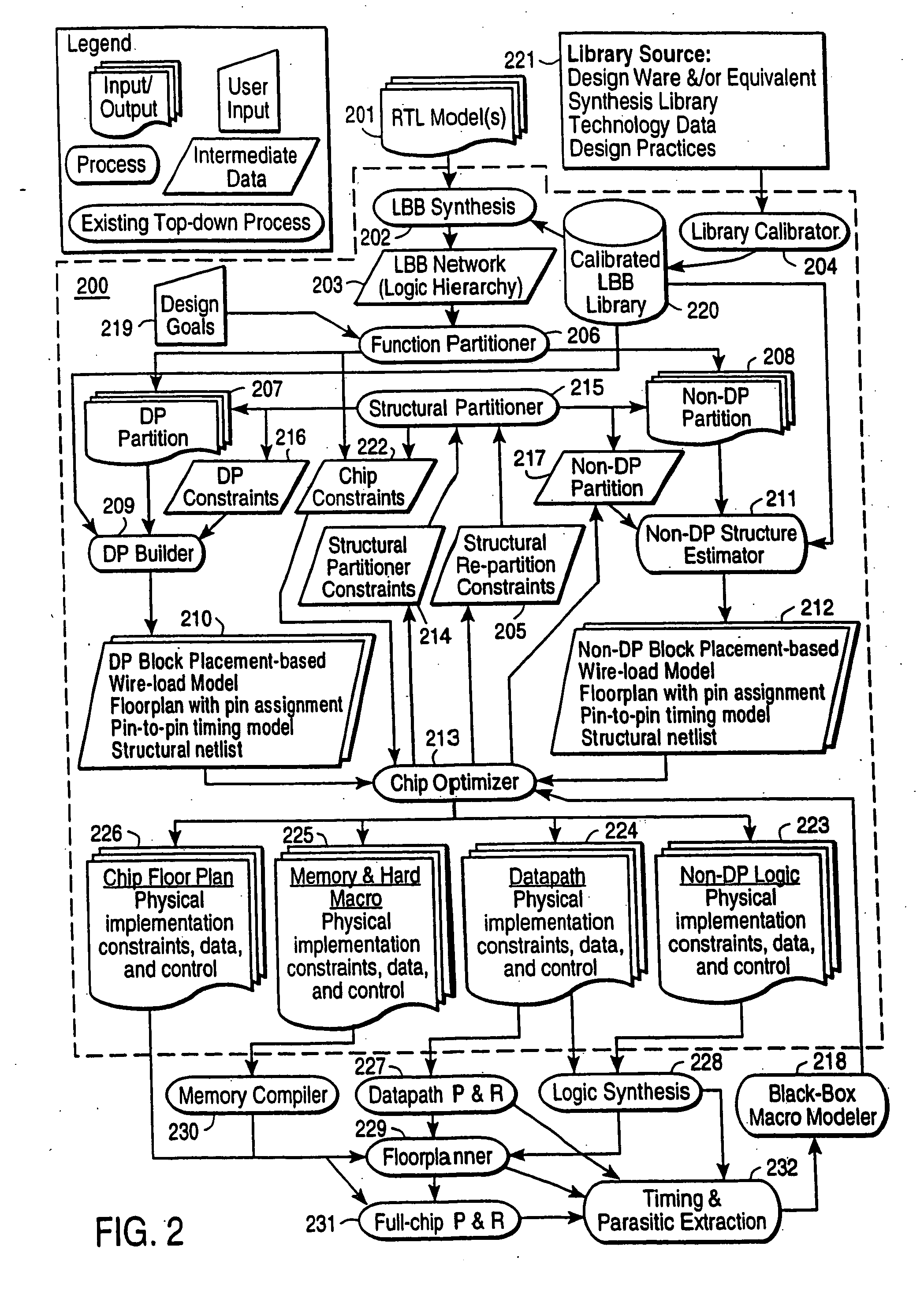

Creating optimized physical implementations from high-level descriptions of electronic design using placement-based information

InactiveUS7143367B2Enhances existing top-down EDA systemsHigh densityDetecting faulty computer hardwareCAD circuit designComputer architectureLoad model

Owner:SYNOPSYS INC

Hierarchical layout method for integrated circuits

InactiveUS6574779B2Easy to modifyIncrease production capacityCAD circuit designProgram controlComputer architectureGenerative Design

Owner:INT BUSINESS MASCH CORP

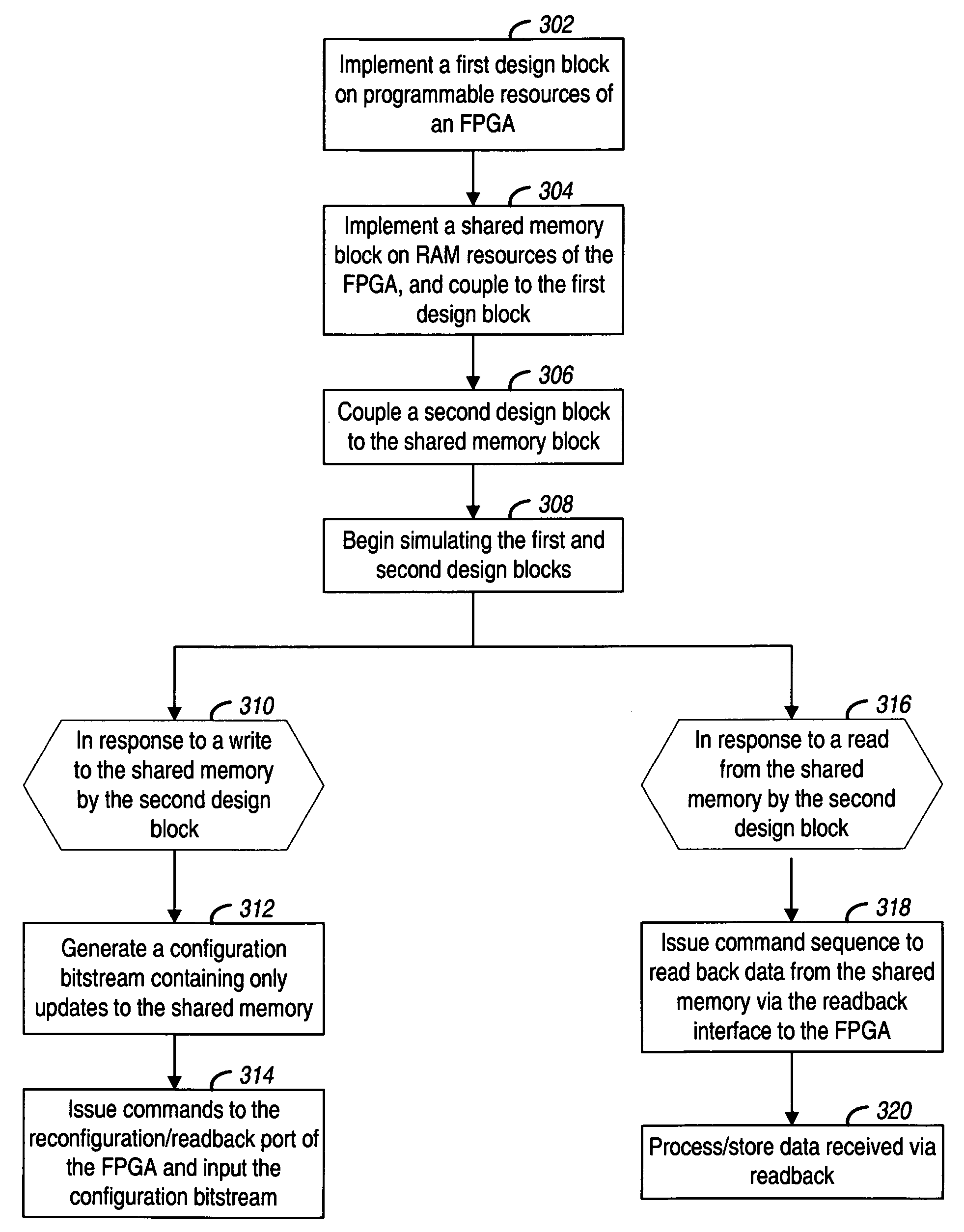

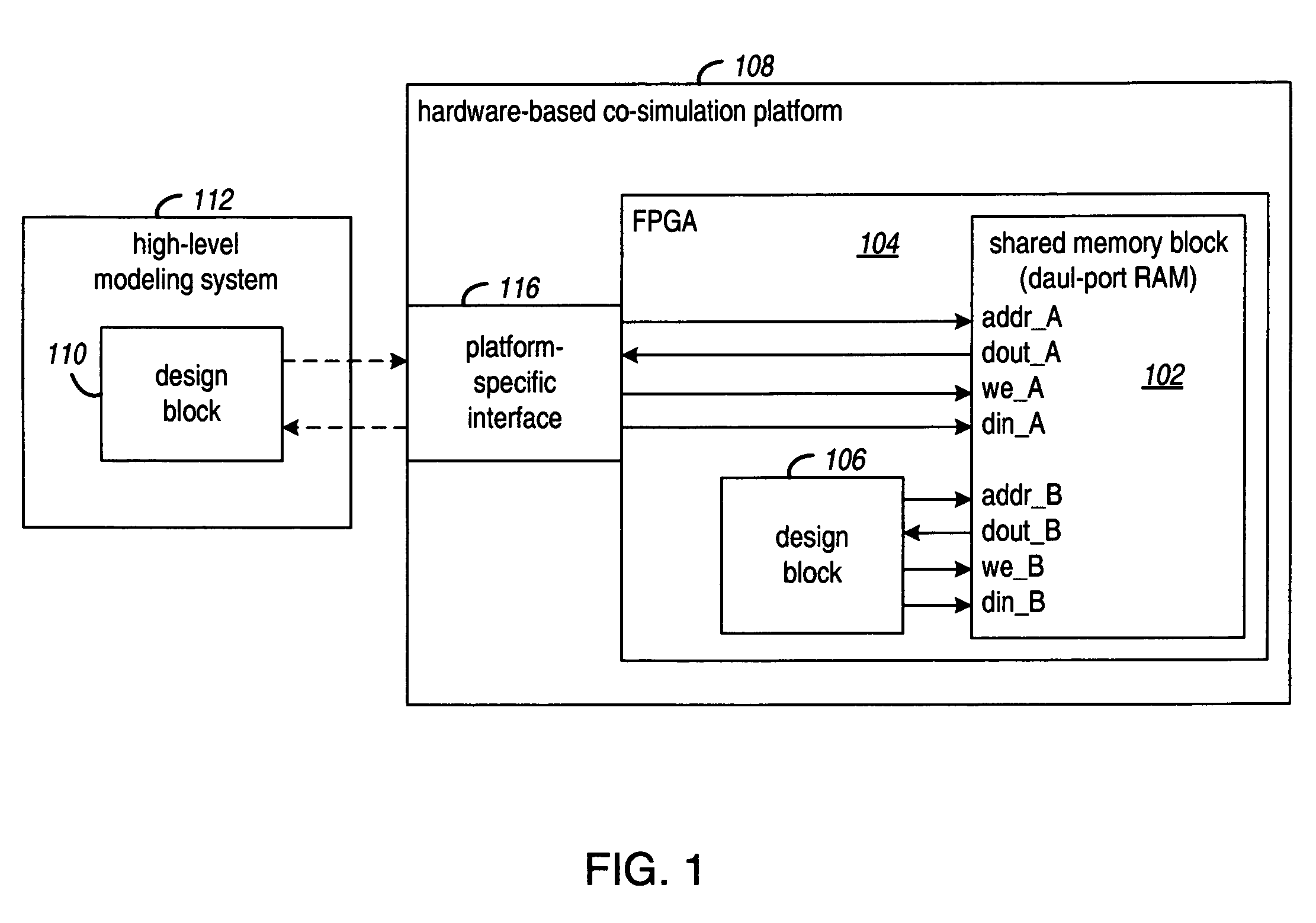

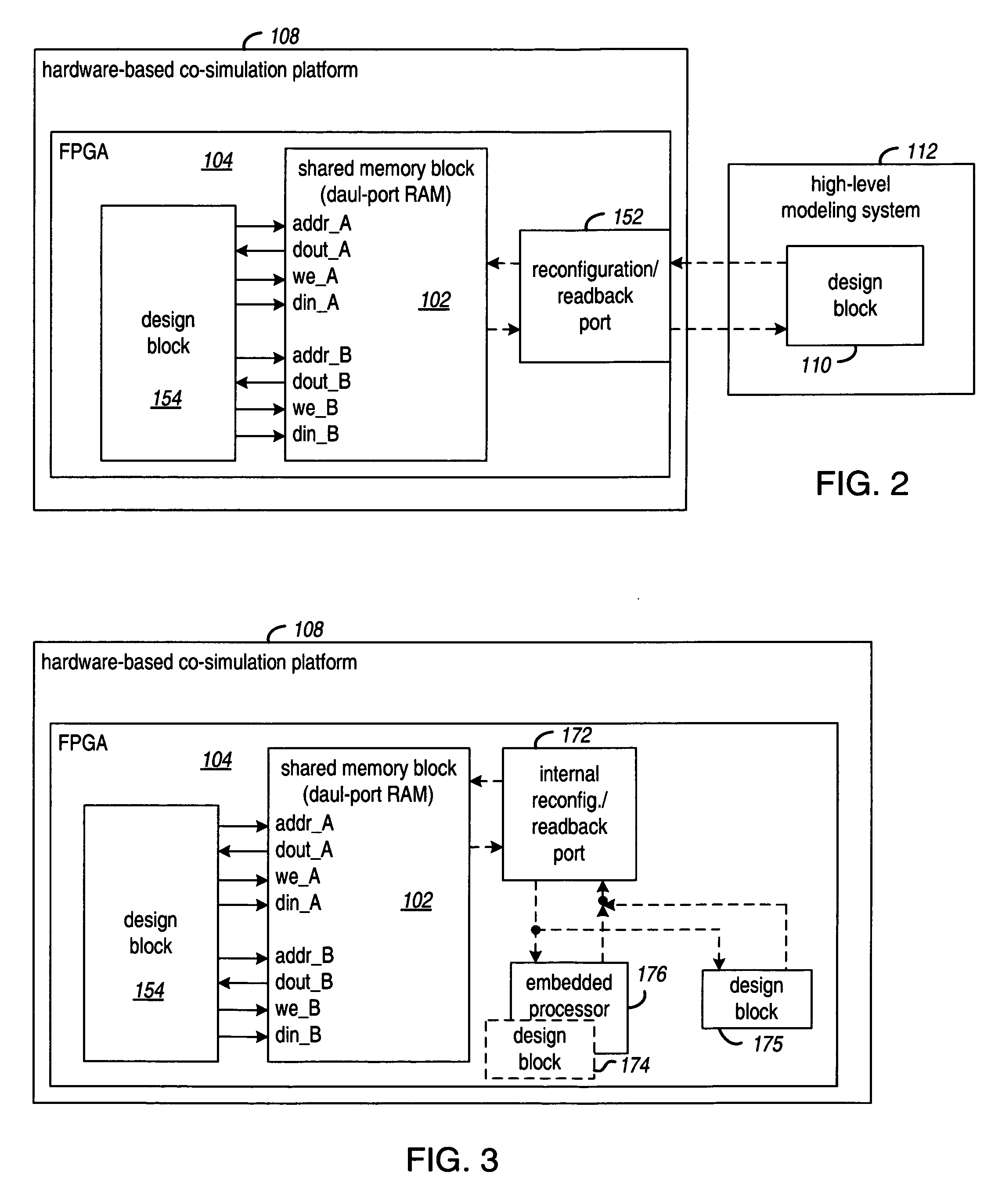

Shared memory interface in a programmable logic device using partial reconfiguration

ActiveUS7546572B1Electronic switchingSpecial data processing applicationsMemory addressMemory interface

Partial reconfiguration of a programmable logic device is used in combination with a shared memory block for communicating between two blocks of an electronic circuit design. In one embodiment, a shared memory is implemented on RAM resources of a field programmable gate array (FPGA), and a first design block implemented in resources of the FPGA is coupled to the shared memory. A second design block is also coupled to the shared memory. In response to a write request by the second design block, a process determines the RAM resources of the FPGA that correspond to the shared memory address in the write request. A configuration bitstream is generated to include configuration data for partial reconfiguration of the FPGA with the data from the write request at the appropriate RAM resources. The FPGA is partially reconfigured with the configuration bitstream via a configuration port of the FPGA.

Owner:XILINX INC

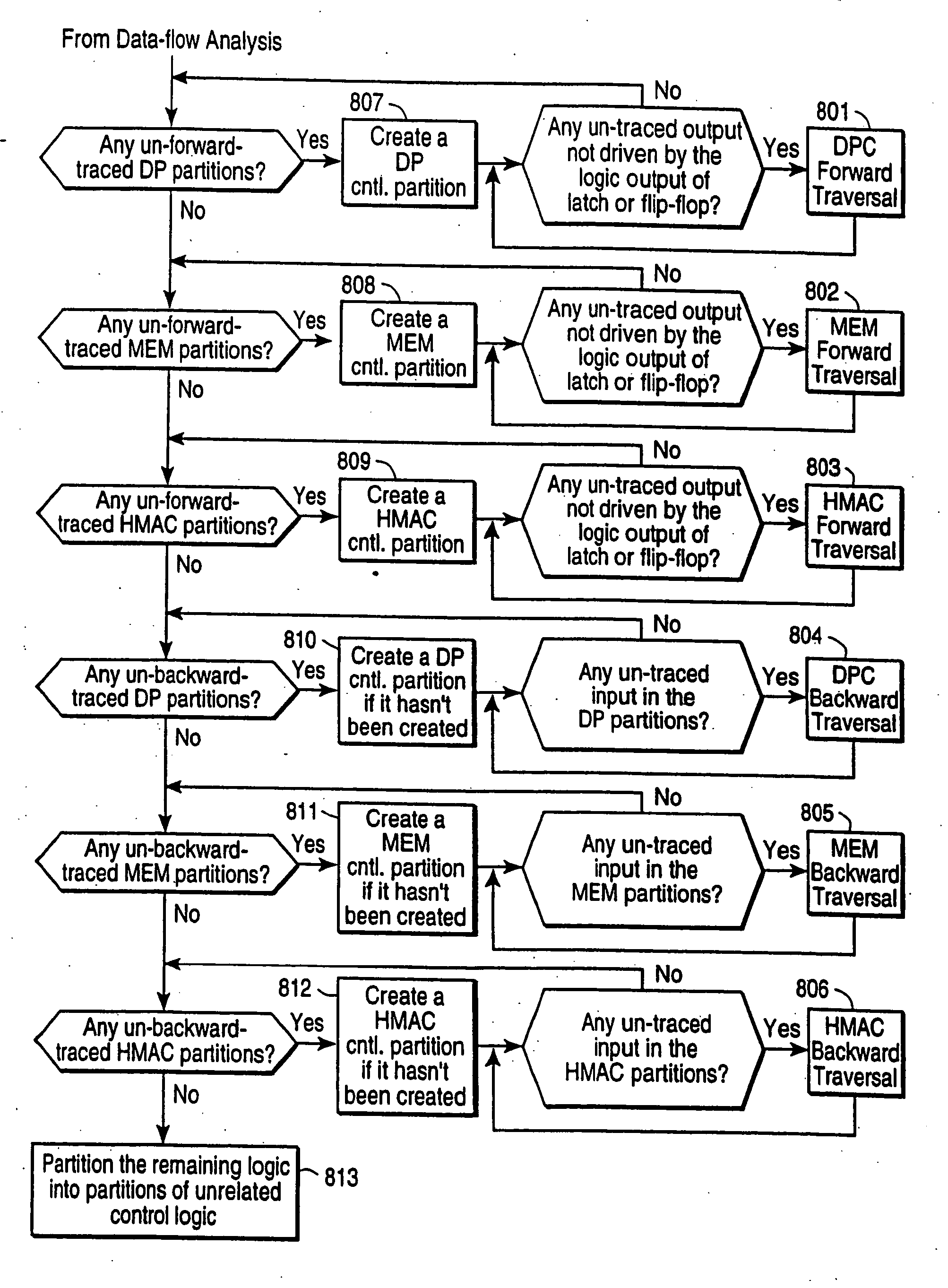

Creating optimized physical implementations from high-level descriptions of electronic design using placement-based information

InactiveUS20060053396A1Improve performanceHigh densityCAD circuit designSoftware simulation/interpretation/emulationComputer architectureData file

An electronic design automation system provides optimization of RTL models of electronic designs, to produce detailed constraints and data precisely defining the requirements for the back-end flows leading to design fabrication. The system takes a RTL model of an electronic design and maps it into an efficient, high level hierarchical representation of the hardware implementation of the design. Automatic partitioning partitions the hardware representation into functional partitions, and creates a fully characterized performance envelope for a range of feasible implementations for each of the partitions, using accurate placement based wire load models. Chip-level optimization selects and refines physical implementations of the partitions to produce compacted, globally routed floorplans. Chip-level optimization iteratively invokes re-partitioning passes to refine the partitions and to recompute the feasible implementations. In this fashion, a multiple-pass process converges on an optimal selection of physical implementations for all partitions for the entire chip that meet minimum timing requirements and other design goals. The system outputs specific control and data files which thoroughly define the implementation details of the design through the entire back-end flow process, thereby guaranteeing that the fabricated design meets all design goals without costly and time consuming design iterations.

Owner:MAGMA DESIGN AUTOMATION

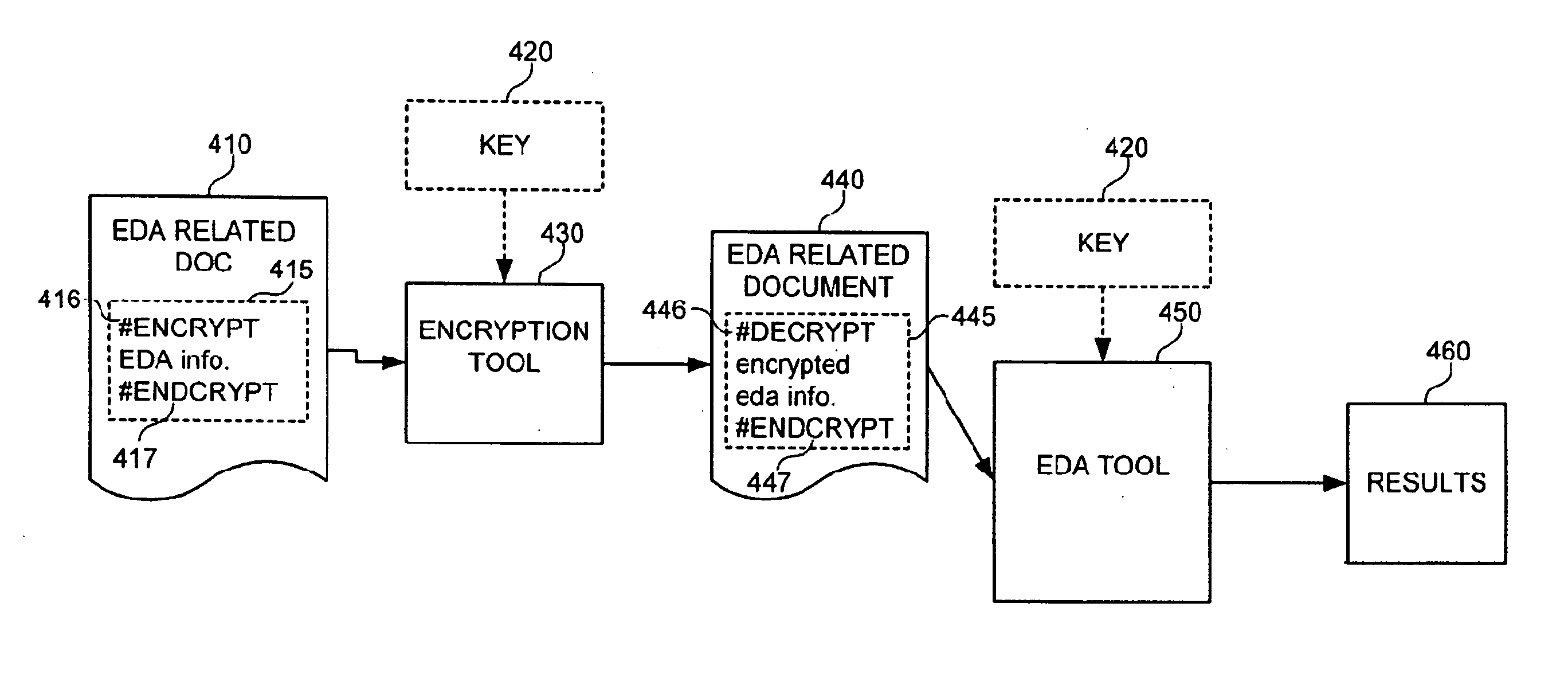

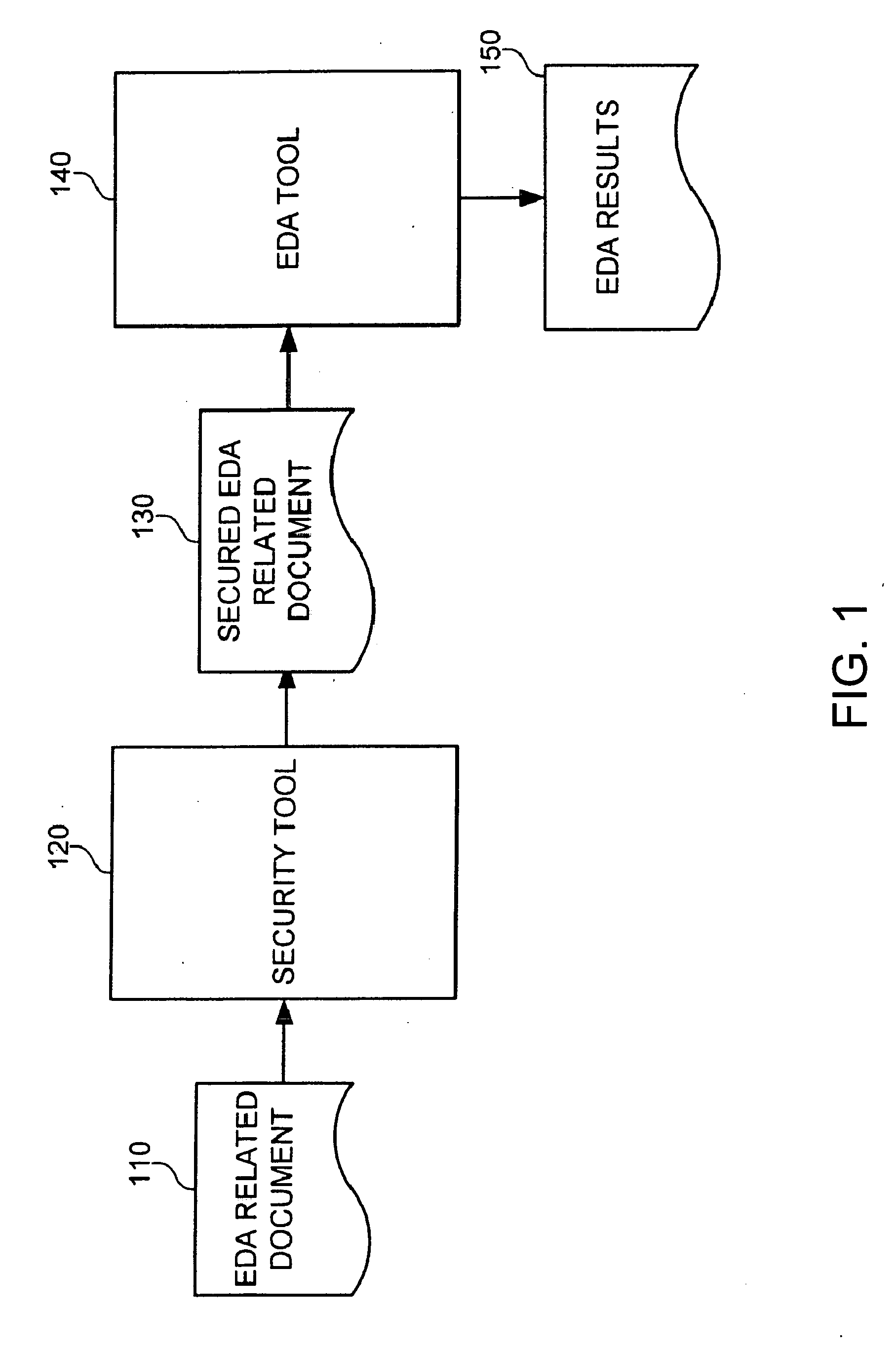

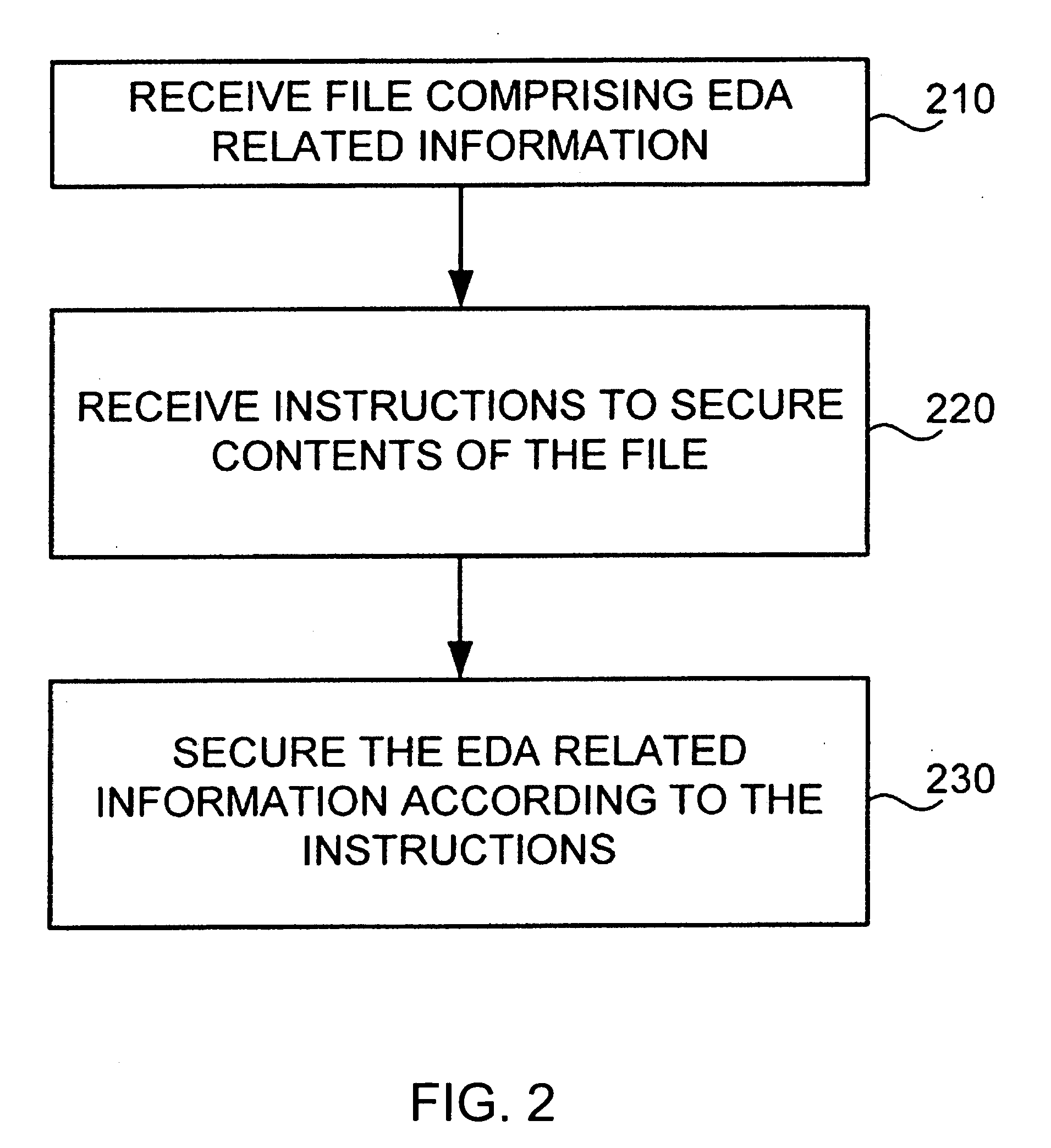

Concealment of information in electronic design automation

InactiveUS20070055892A1Digital data processing detailsUser identity/authority verificationEngineeringInformation hiding

An electronic design automation tool may receive information related to electronic design automation that contains secured information, such as physically secured information, and annotations to indicate the secured portions of the information. Upon receiving such information, the electronic design automation tool may identify those portions of the information comprising secured information related to electronic design automation, and unlock the secured information for processing. The electronic design automation tool may process at least some of the secured electronic design automation information without revealing that secured information to unauthorized persons, tools, systems, or otherwise compromising the protection of that secured information. That is, the design automation tool may process the secured electronic design automation information so that the secured information is concealed both while it is being processed and by the output information generated from processing the secured information.

Owner:MENTOR GRAPHICS CORP

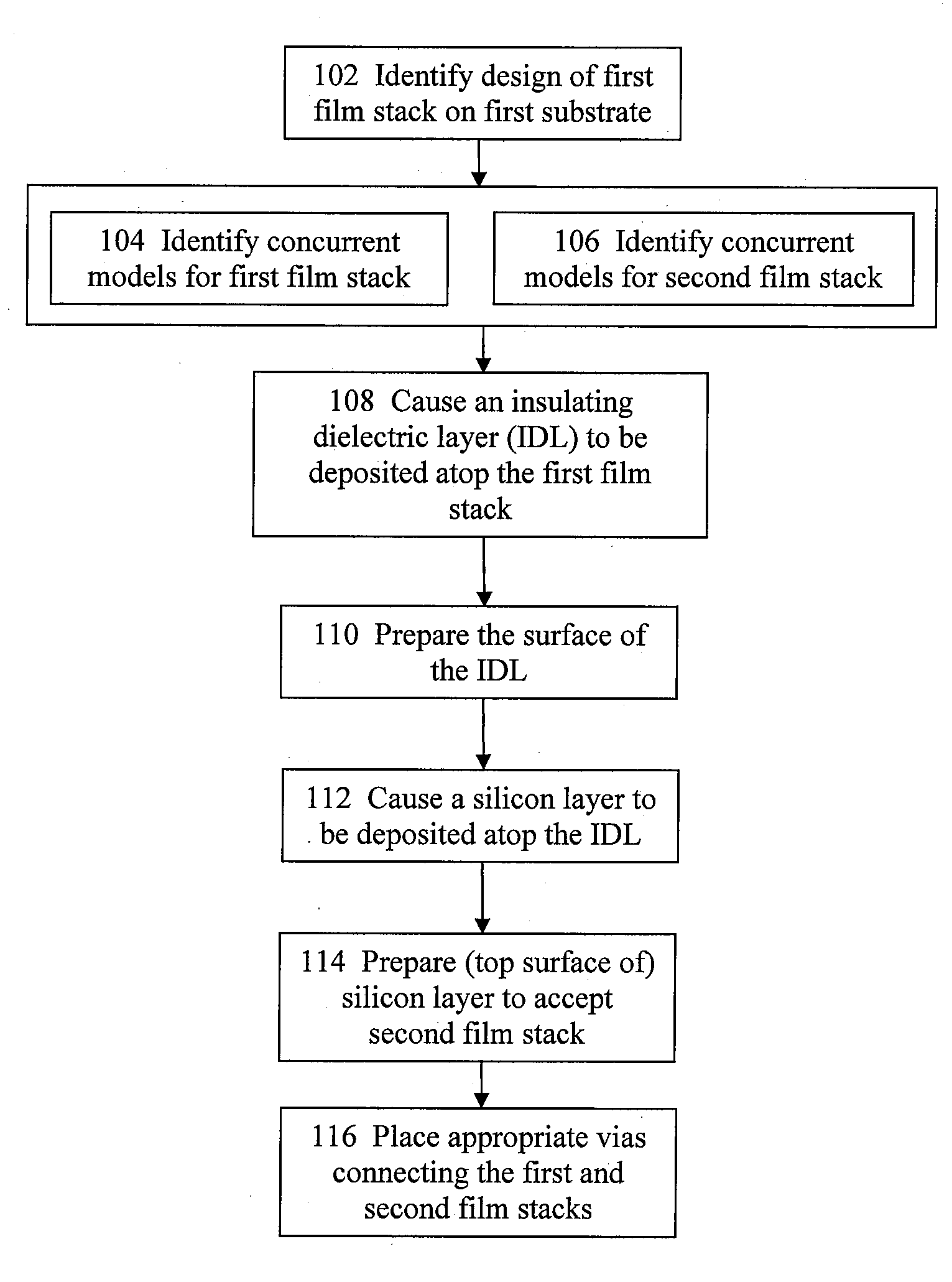

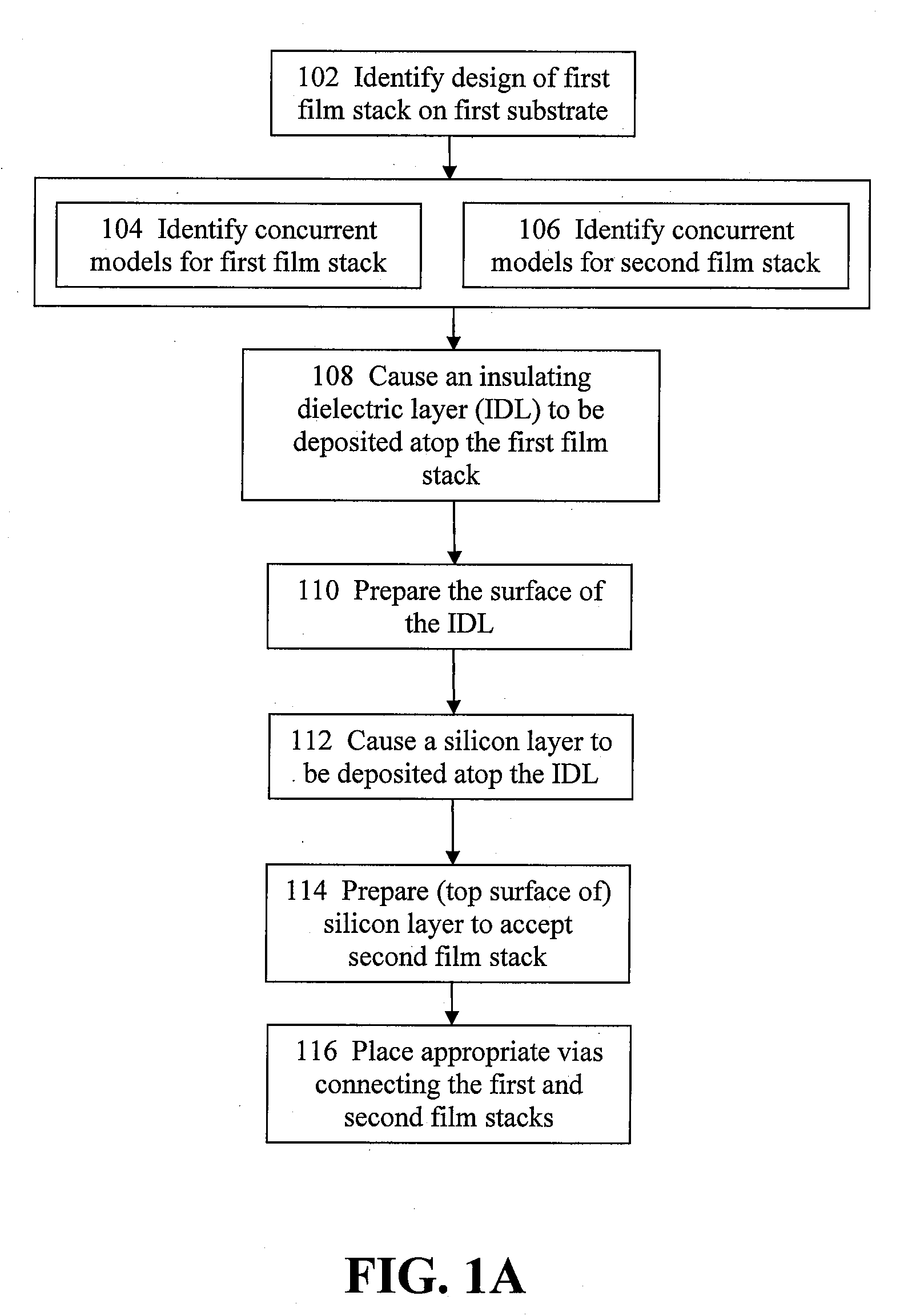

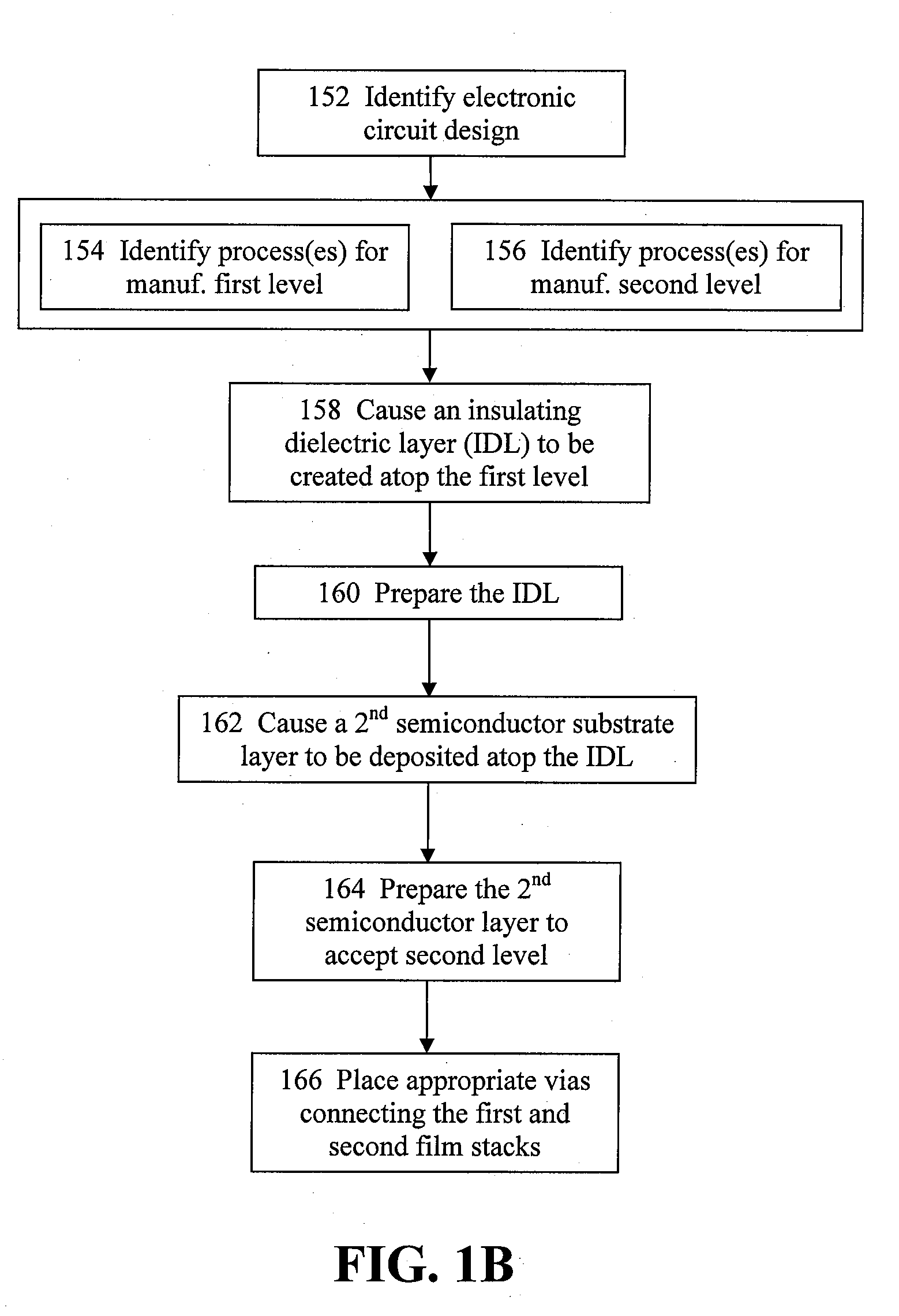

Method, system, and computer program product for preparing multiple layers of semiconductor substrates for electronic designs

ActiveUS20080163139A1Simple methodSemiconductor/solid-state device testing/measurementDetecting faulty computer hardwareEngineeringElectronic design

Disclosed is an improved method, system, and computer program product for preparing multiple levels of semiconductor substrates for three-dimensional IC integration. Some embodiments utilize the process and design models to check and fabricate the insulating dielectric layer (IDL) separating the first and the second film stacks on separate substrates and then prepare the surface of the IDL to receive an additional layer of semiconductor substrate for further fabrication of the chips. Yet some other embodiments further employ the design and process models to ensure the IDL and the semiconductor substrate are sufficiently flat, or are otherwise satisfactory, so the three-dimensional integrated circuits meet the reliability, manufacturability, yield, or performance requirements. Yet some other embodiments further employ design and process models to place the vias connecting the multiple film stacks.

Owner:CADENCE DESIGN SYST INC

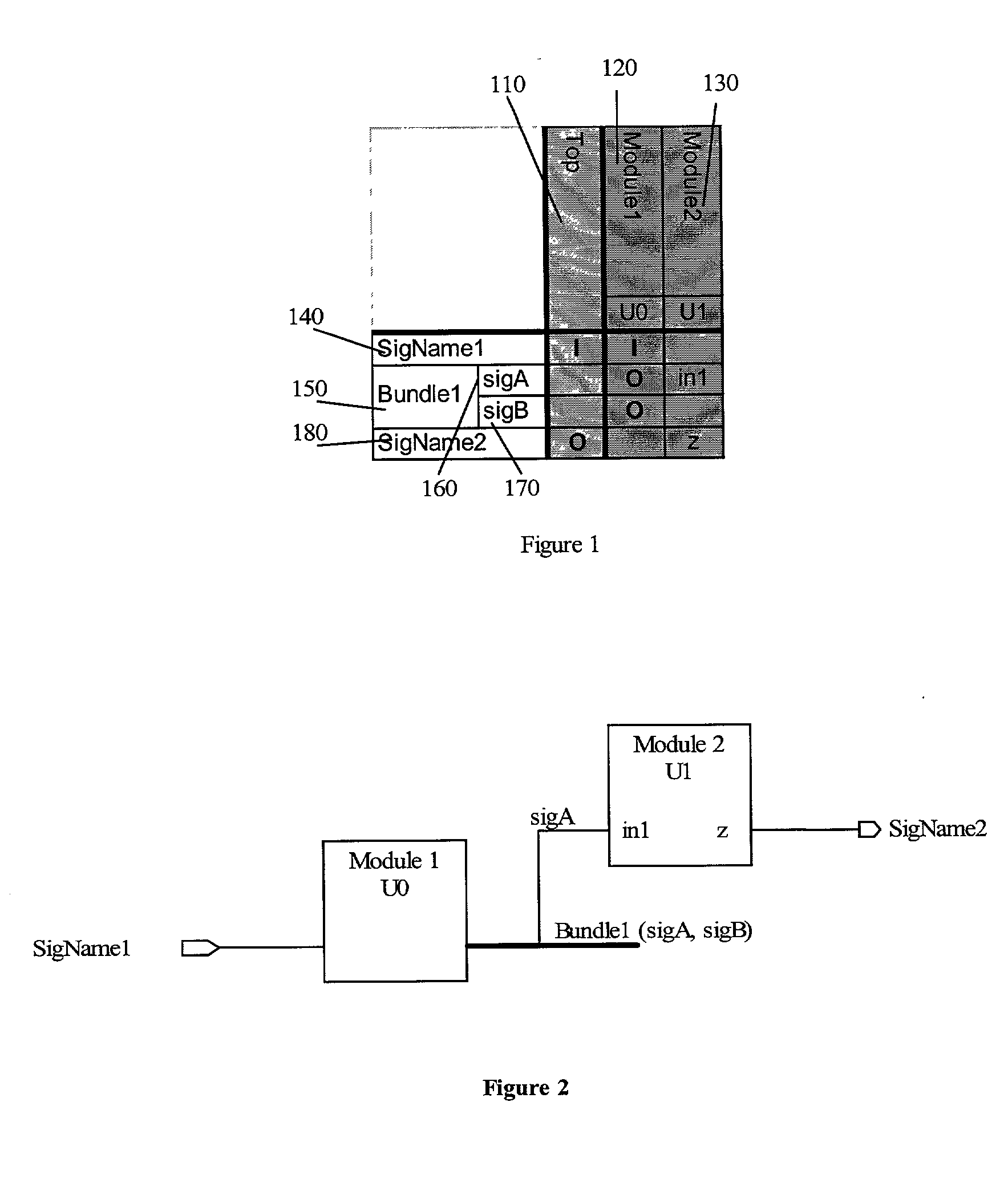

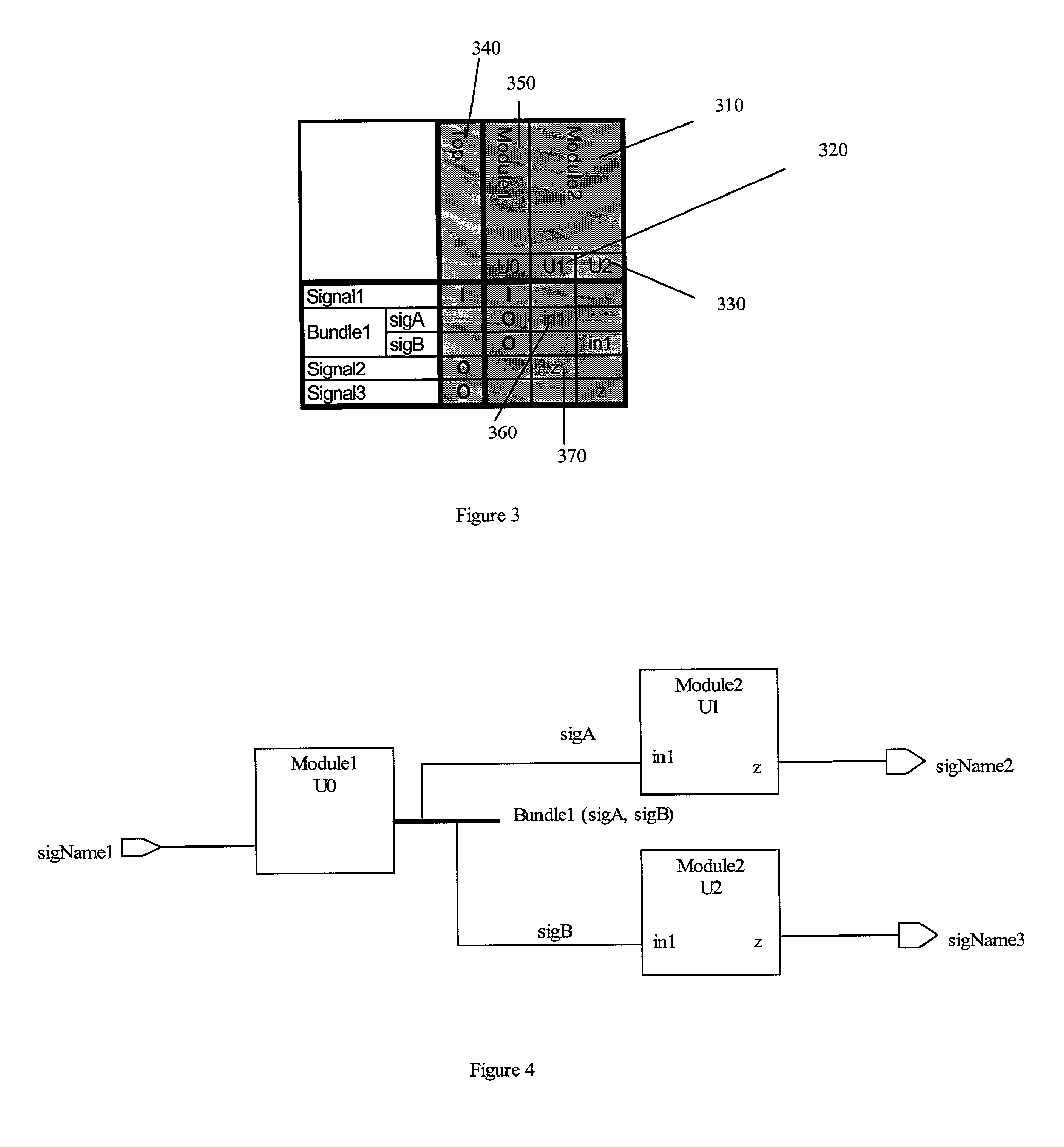

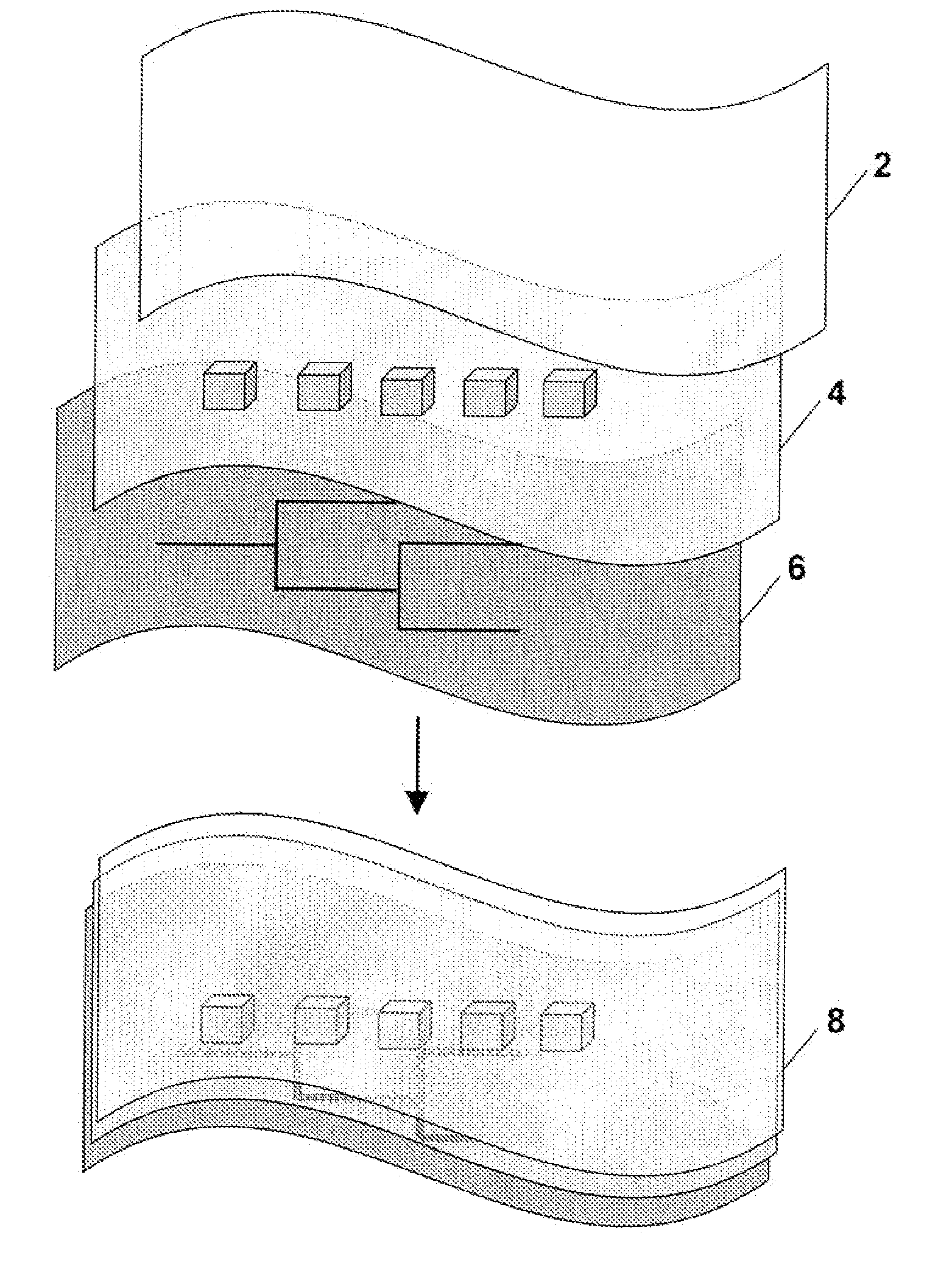

Interface based design using a tabular paradigm

InactiveUS20020129334A1Semiconductor/solid-state device manufacturingCAD circuit designComputer architectureElectronic design

A method of creating an interfaced based representation of an electronic design is provided. Rows and columns are added to tables. These rows and columns represent signals and instances in the electronic design being represented by the description. The cells created by the table that results from the rows and column provide interconnect information.

Owner:MENTOR GRAPHICS CORP

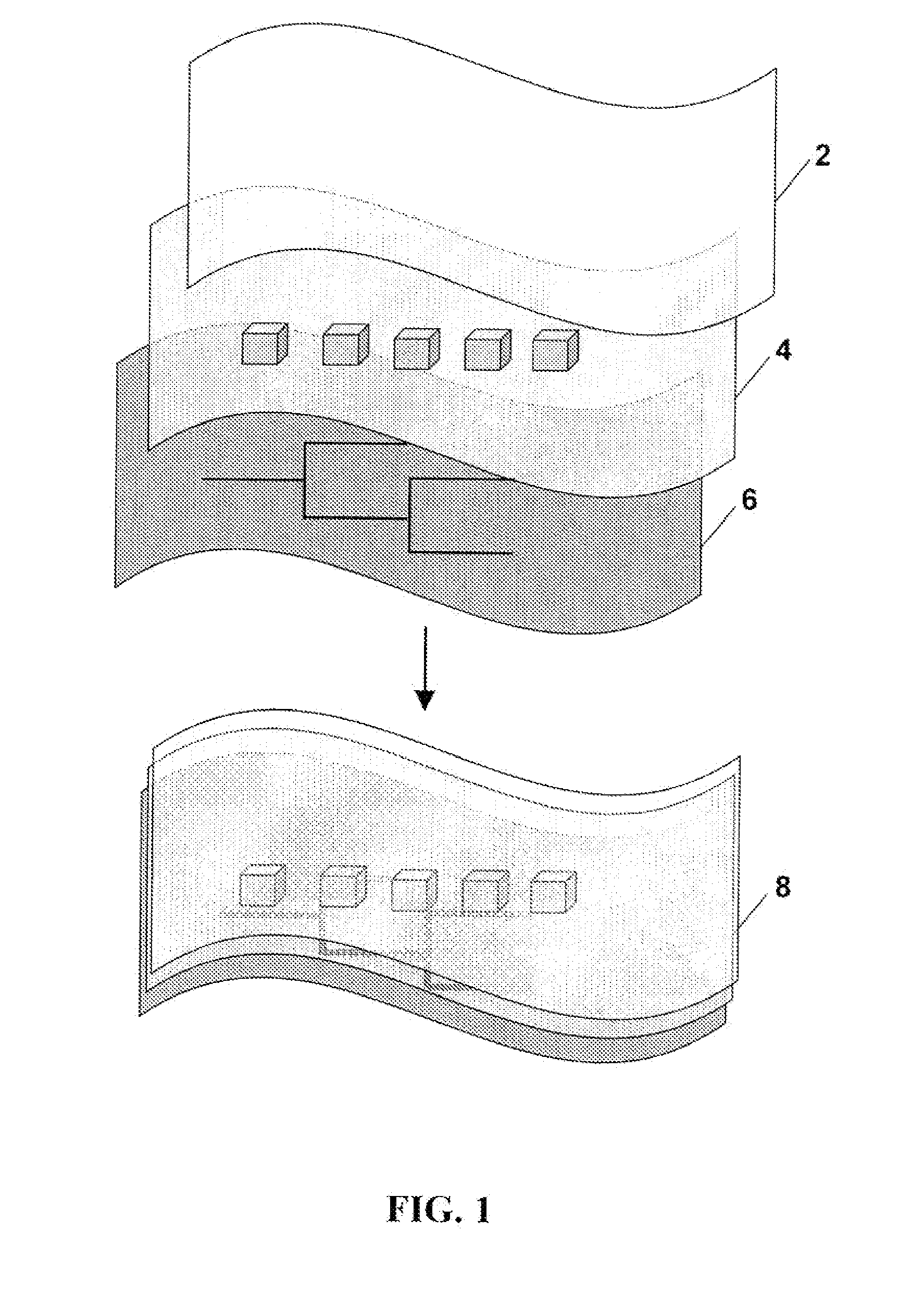

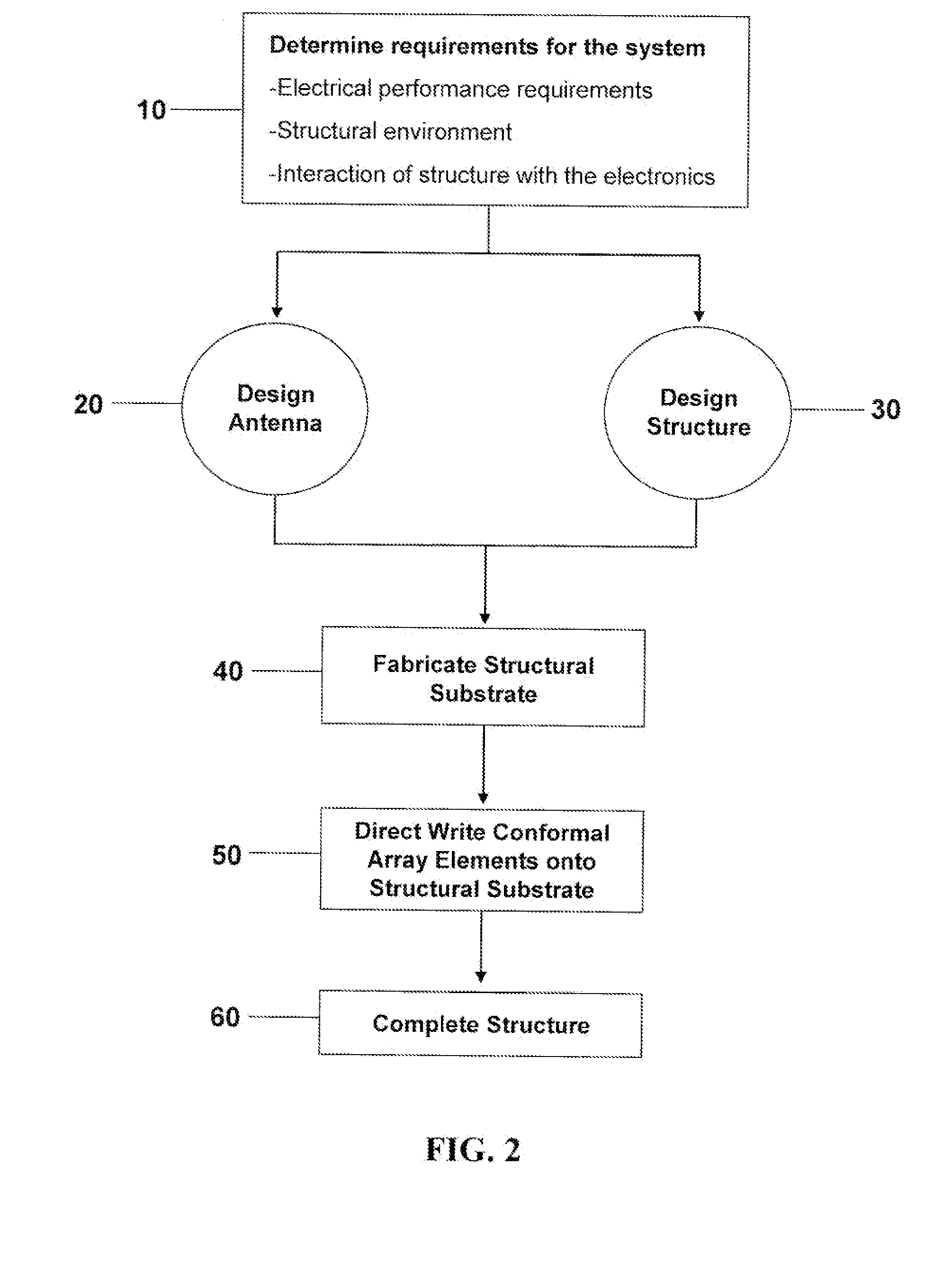

Arbitrarily-shaped multifunctional structures and method of making

ActiveUS20080218416A1Improve performanceImprove functionalityAntenna arraysSimultaneous aerial operationsManufacturing technologyEngineering

Multifunctional structures and methods of manufacturing multifunctional structures which function as both electronic devices and load-bearing elements are disclosed. The load-bearing elements are designed to have electronic functionality using electronics designed to be load-bearing. The method of manufacturing the multifunctional structure comprises forming an electronic element directly on at least one ply of arbitrarily shaped load-bearing material using conventional lithographic techniques and / or direct write fabrication techniques, and assembling at least two plies of arbitrarily shaped load-bearing material into a multifunctional structure. The multifunctional structure may be part of an aerospace structure, part of a land vehicle, pan of a watercraft or part of a spacecraft.

Owner:SI2 TECH

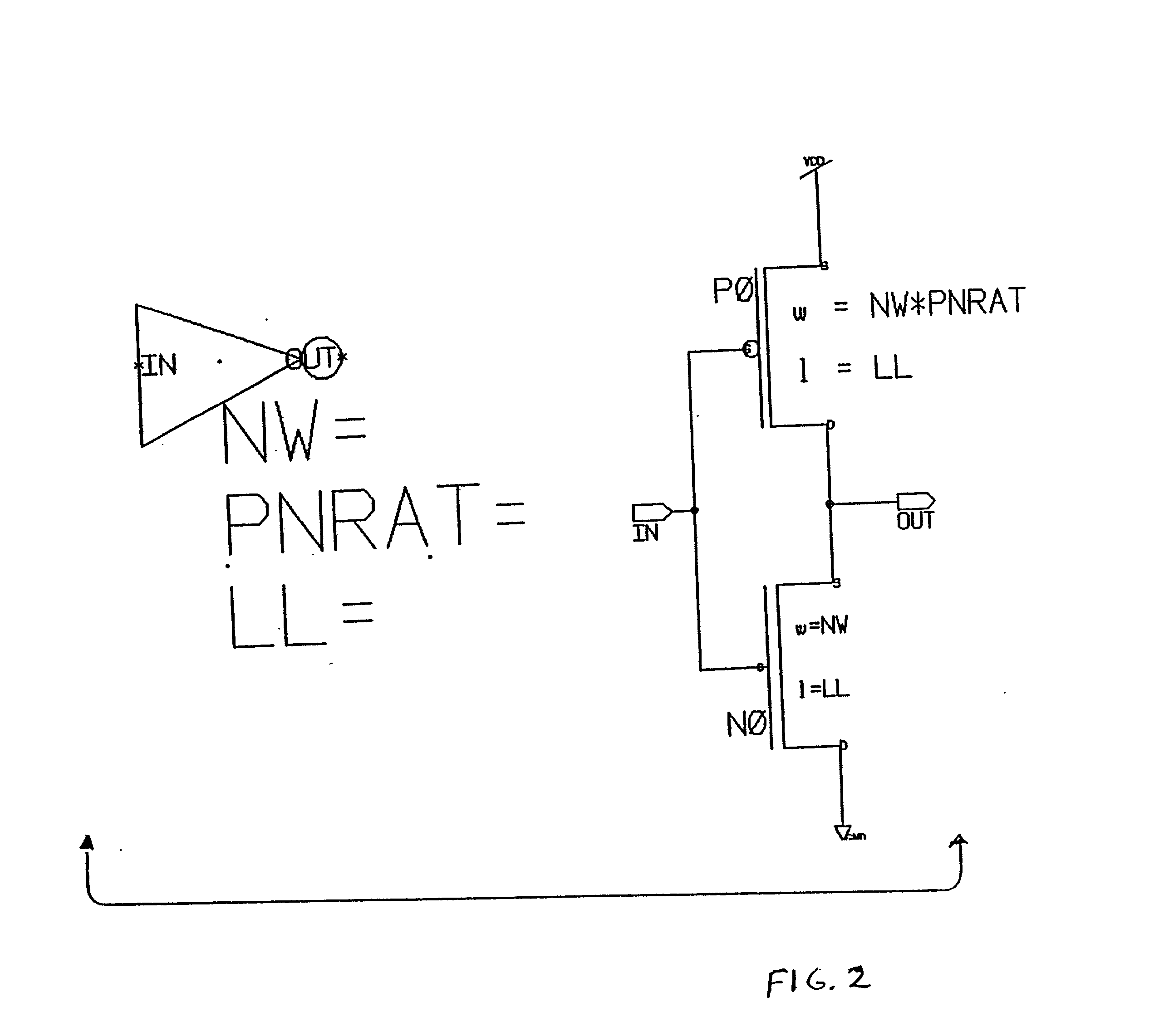

Electronic design protection circuit

InactiveUS7107567B1Accurate operationCAD circuit designSoftware simulation/interpretation/emulationElectronic designEmbedded system

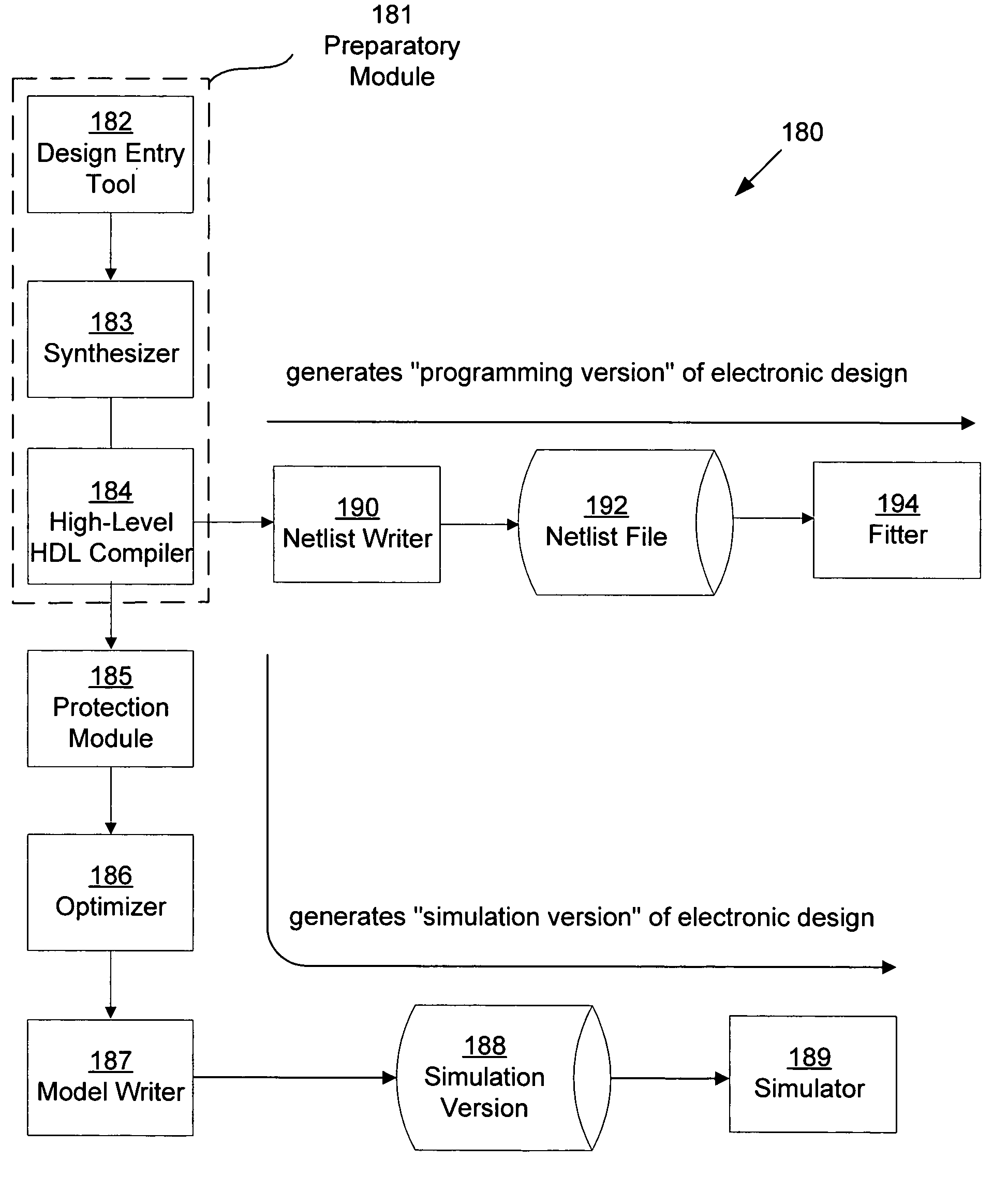

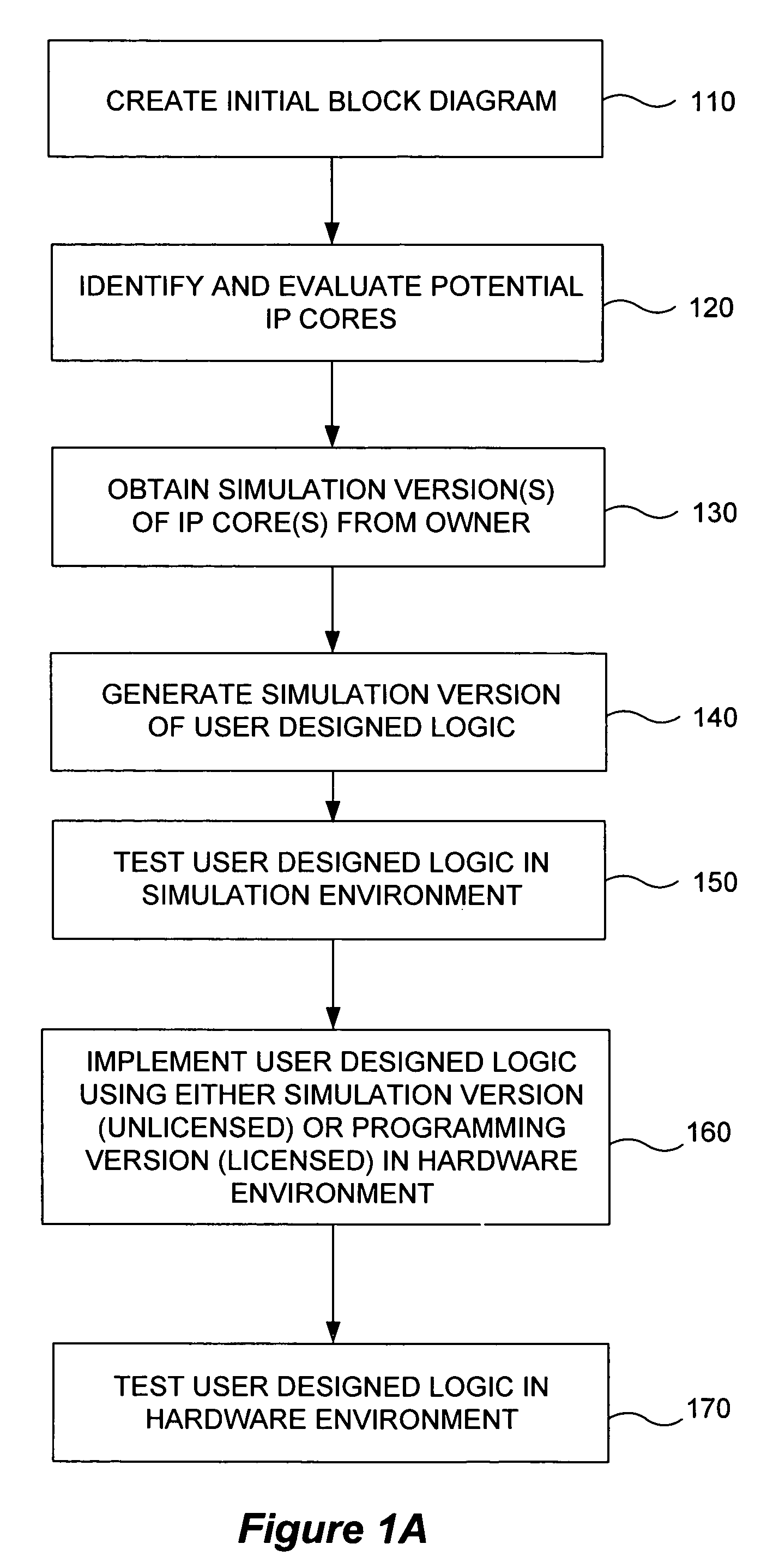

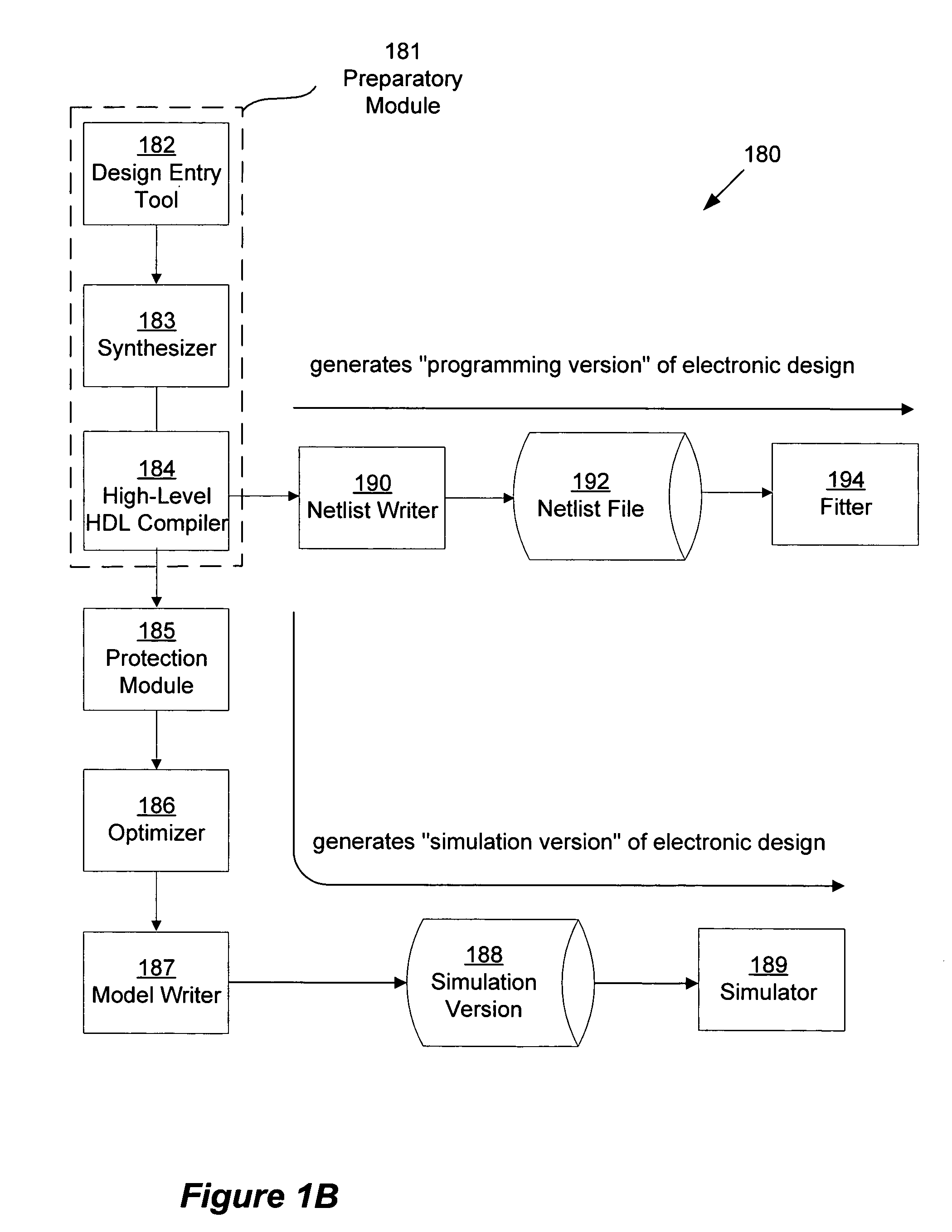

Protected electronic designs permit appropriate simulation and testing of the electronic design in a simulation environment, while preventing a correctly operating unauthorized implementation of the electronic design in a hardware environment such as a programmable device. An unprotected version of the simulation version of an electronic design is augmented by adding protection circuitry to the unprotected version to create a protected version of the electronic design, which operates correctly in a simulation environment but which fails to operate correctly in a hardware environment. In some embodiments of the present invention, a separate programming version which does not incorporate the protection circuitry of the simulation version may also be provided for licensed / authorized users of the electronic design, which may be an IP core or other design.

Owner:ALTERA CORP

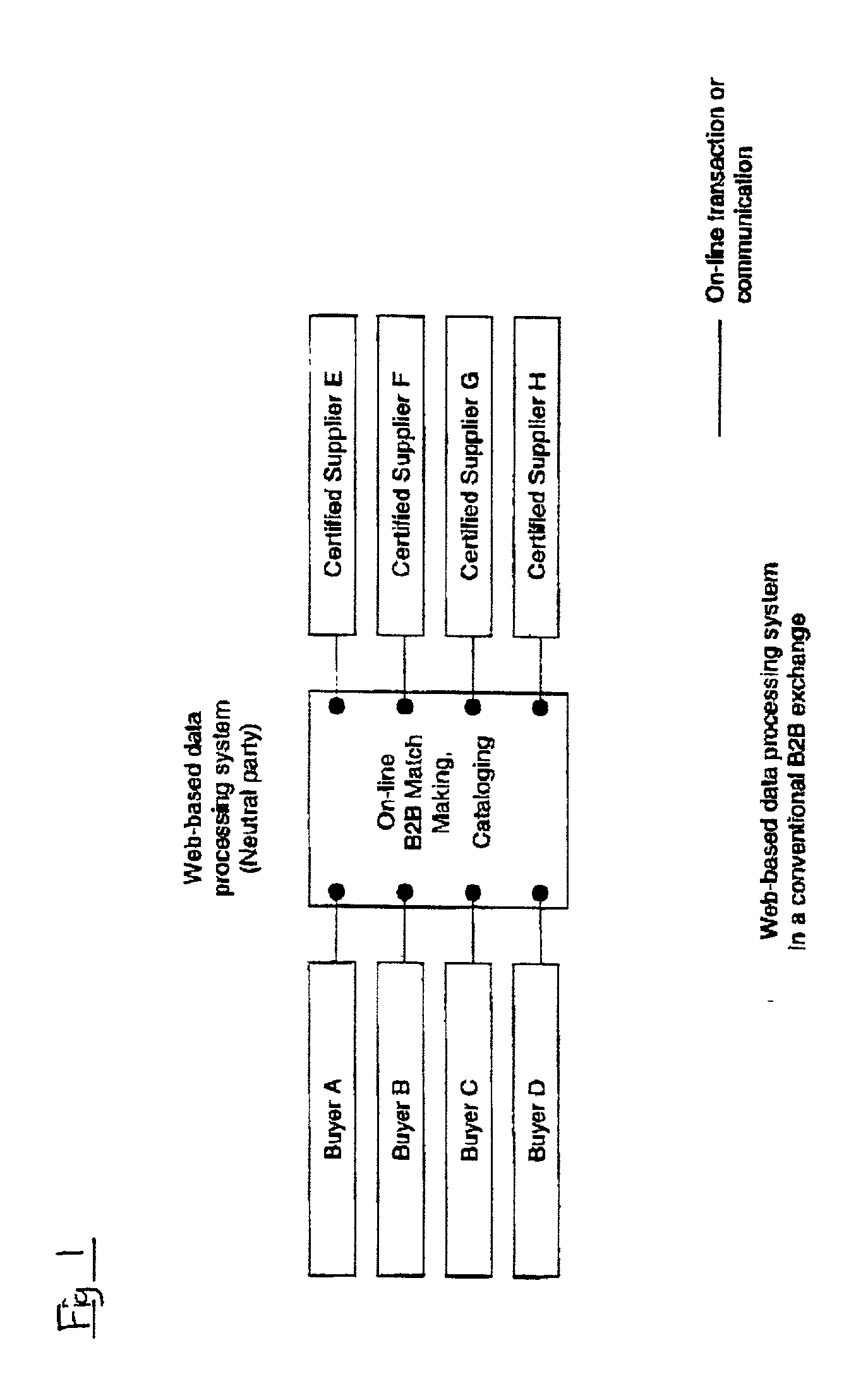

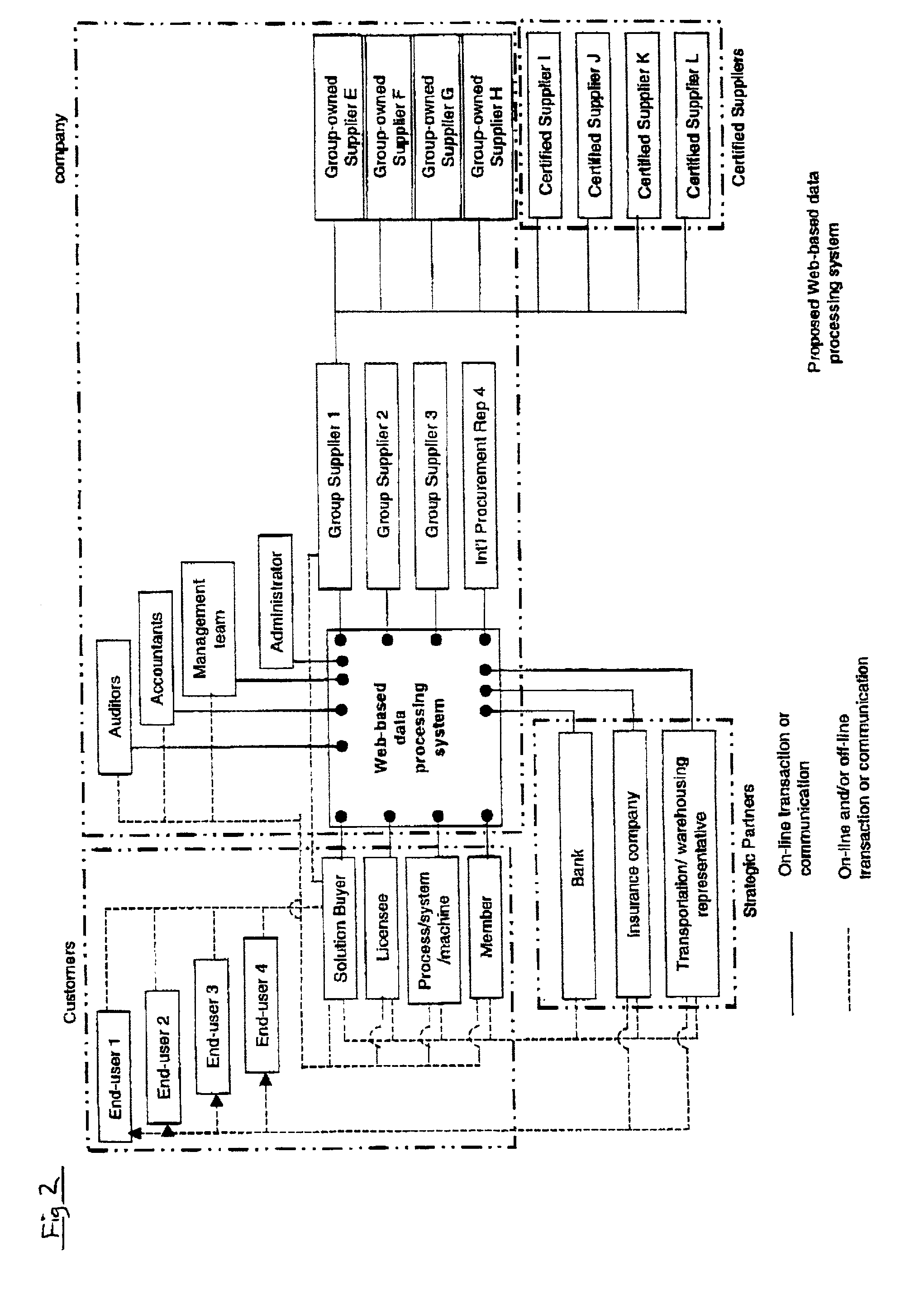

Data processing system for implementing an exchange

InactiveUS20020138166A1ResourcesSpecial data processing applicationsBusiness-to-businessEnterprise resource planning

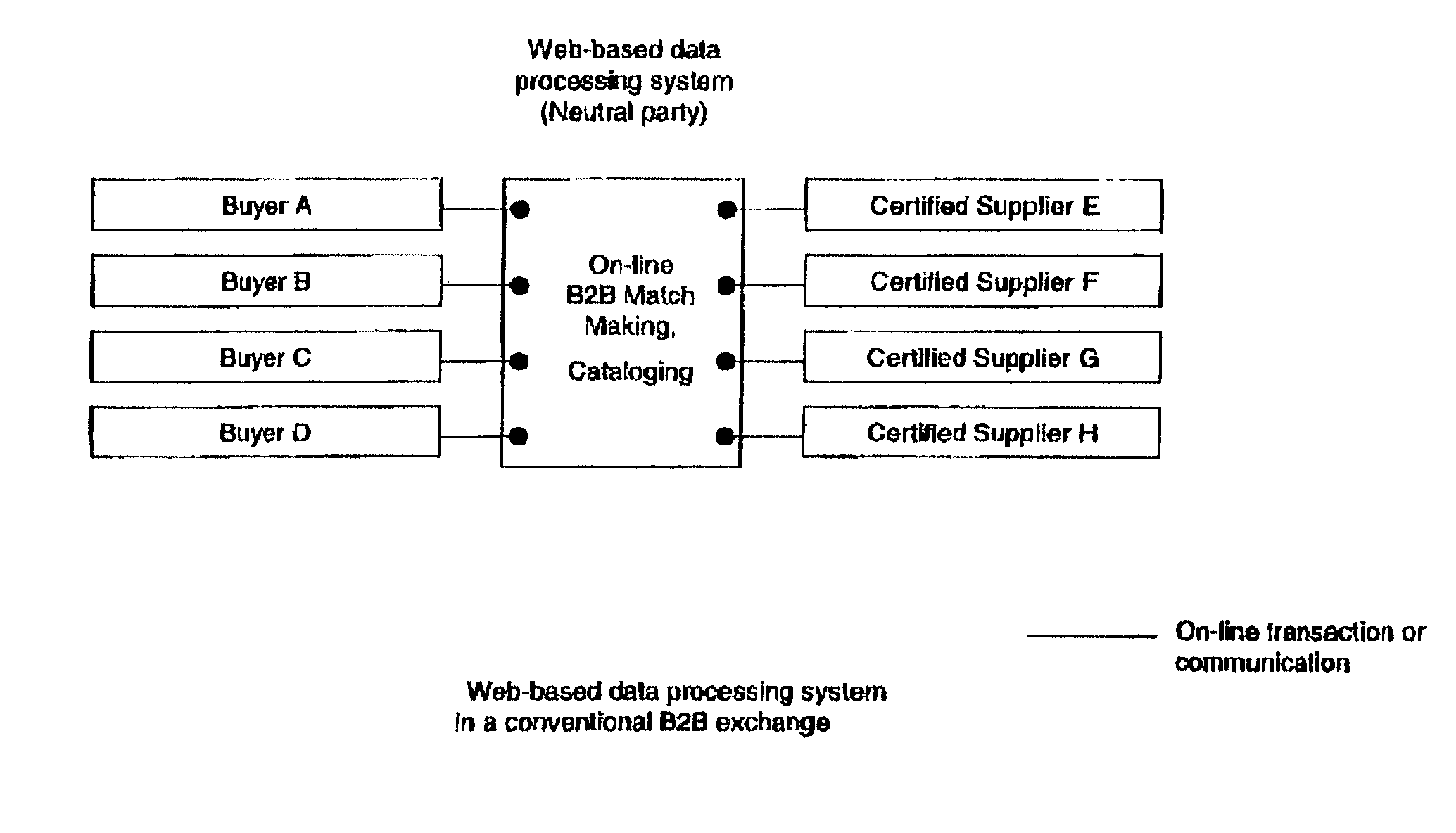

A web-based data processing system is used in a Business-to-Business (B2B) exchange for providing one-stop manufacturing solutions. In a B2B exchange, this system provides a moderator desktop for project planning, quoting, coordination and supervisory of all web-based business transactions from mechanical / electronic design and production of first article, tooling, production, financing, insurance, warehousing to end-product delivery. Also, this system provides a machine web communication desktop for web-based maintenance and support to members, process lines, systems and machines, and web-based resource sharing to "pay as you go" members and "flat fee" members. Likewise, this system provides dedicated desktops for other participants in the B2B exchange for direct and critical communication, collaboration and commerce transaction with moderator and machine web communication center. Said participants include Customers, Process lines / systems / machines, Strategic Partners, Suppliers and Management team / account / audit / administrator. This system also distributes and manages Request for Quotations (RFQs) for said B2B exchange in NAFTA, Asia Pacific and Europe data servers. Besides, the web-based data processing system provides a direct communication with a collaborative platform. Said collaborative platform may be integrated with existing web-based Enterprise Resource Planning (ERP) and Supply Chain Management (SCM).

Owner:MILLING SYST & CONCEPTS PTE

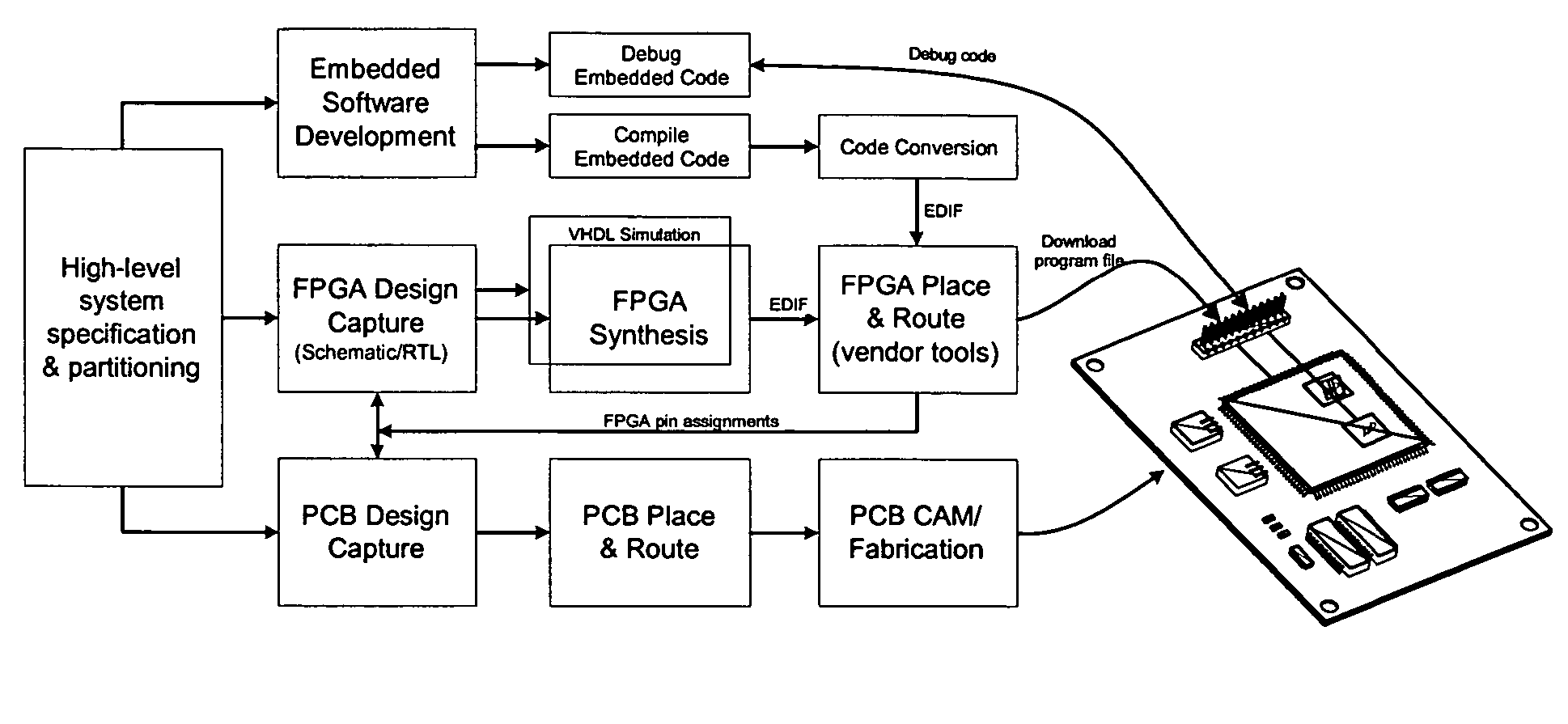

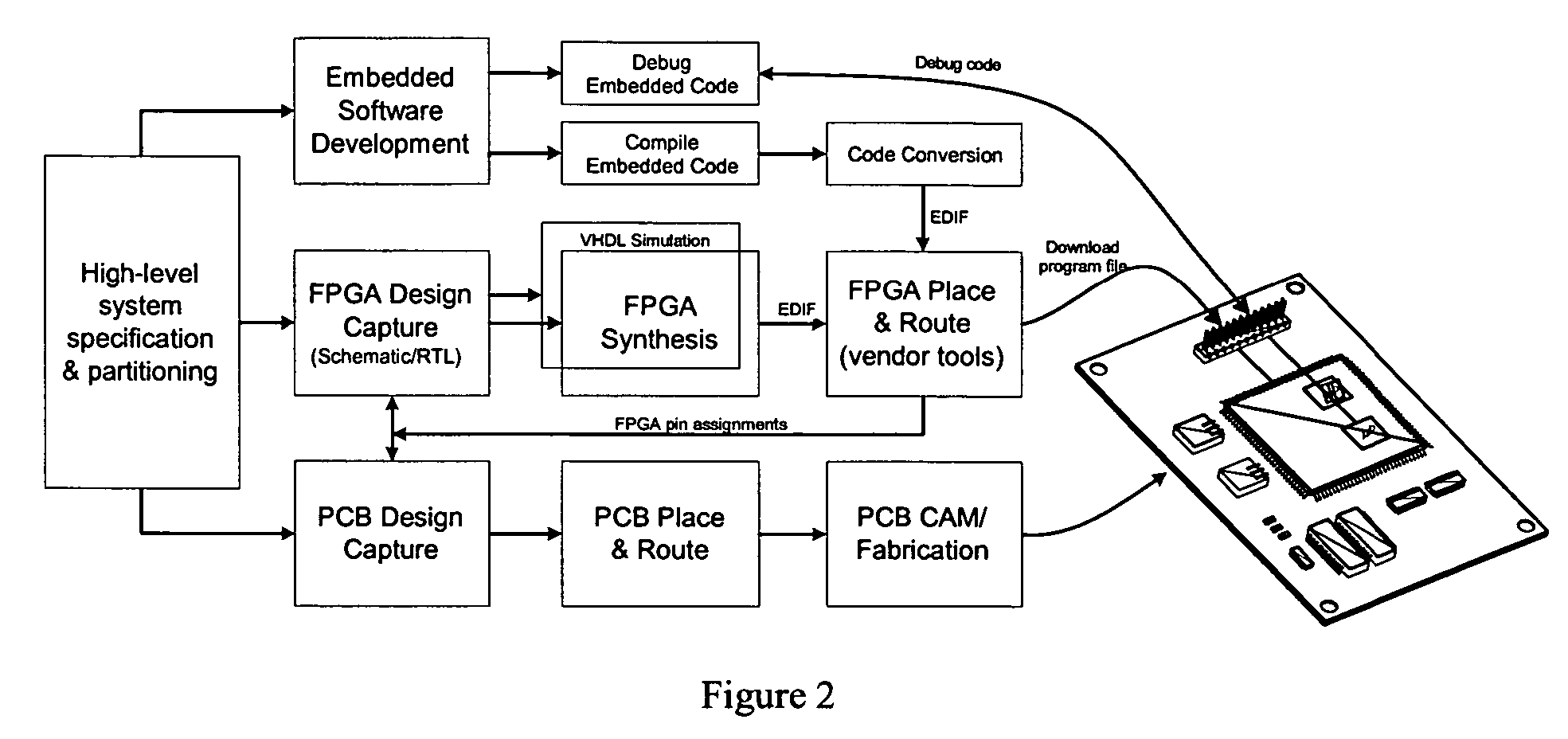

System for designing re-programmable digital hardware platforms

InactiveUS7340693B2Assembly is complexEasy to moveCAD circuit designSpecial data processing applicationsComputer hardwareComputer architecture

A digital design system and method are provided for re-programmable hardware platforms, such as field programmable gate arrays (FPGAs) and other re-programmable system designs. The design system and method bridge the gap between what has previously been a development and prototyping platform used during the design phase of an electronic design system (EDS) project, and commercially viable re-programmable product platforms to replace non-programmable platforms, such as discrete processors and ASICs.

Owner:MITSUBISHI CABLE IND LTD

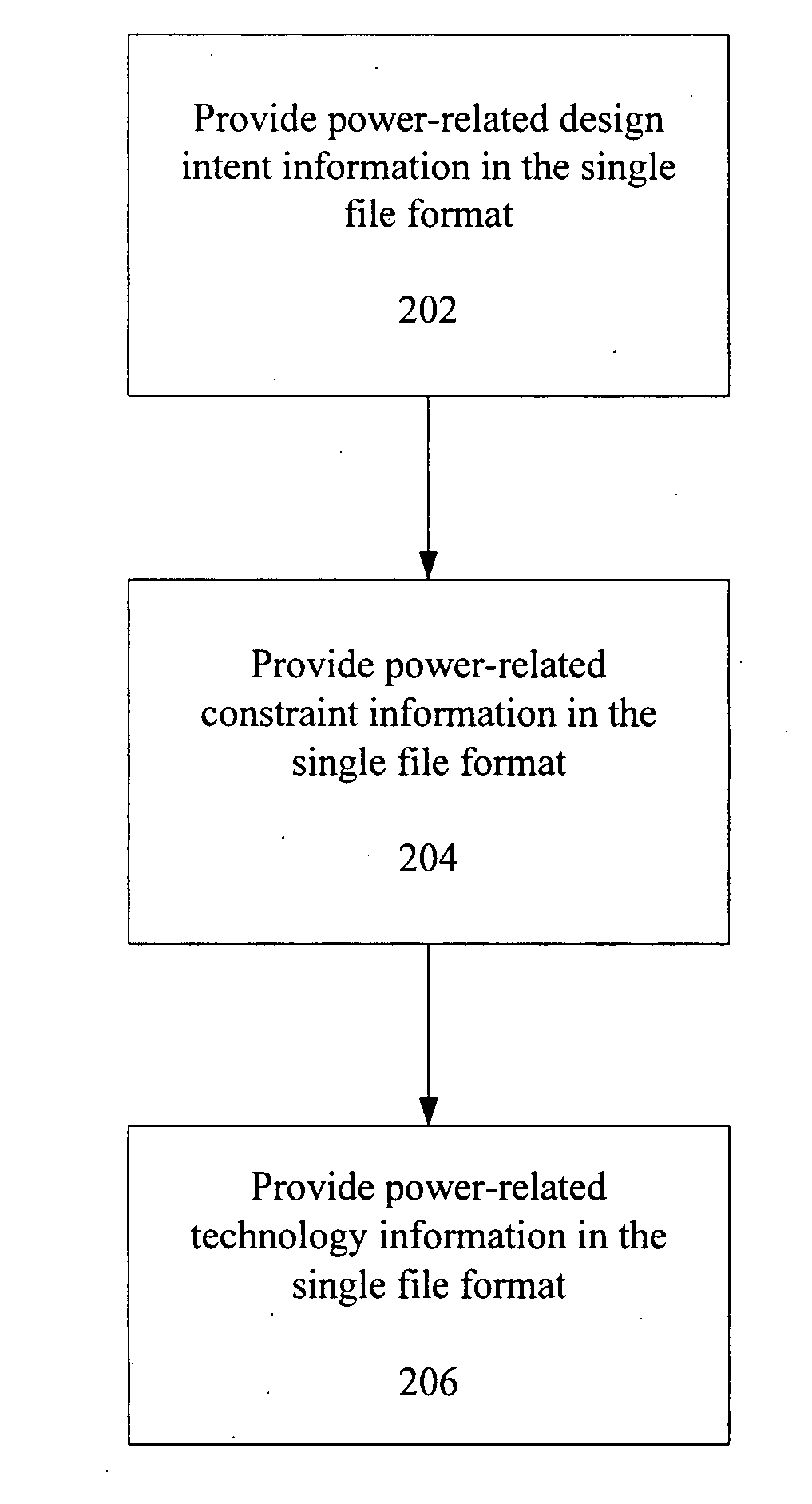

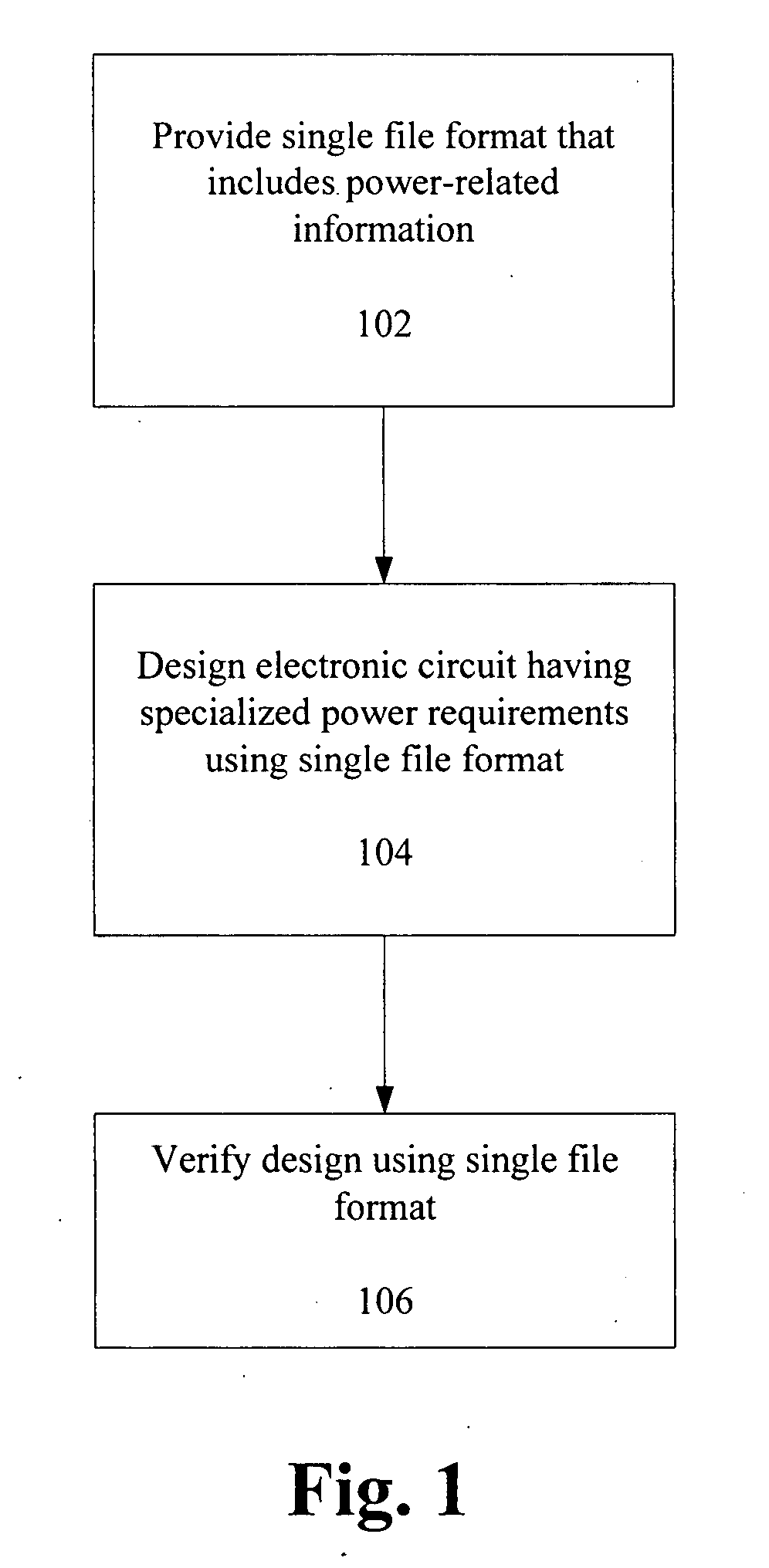

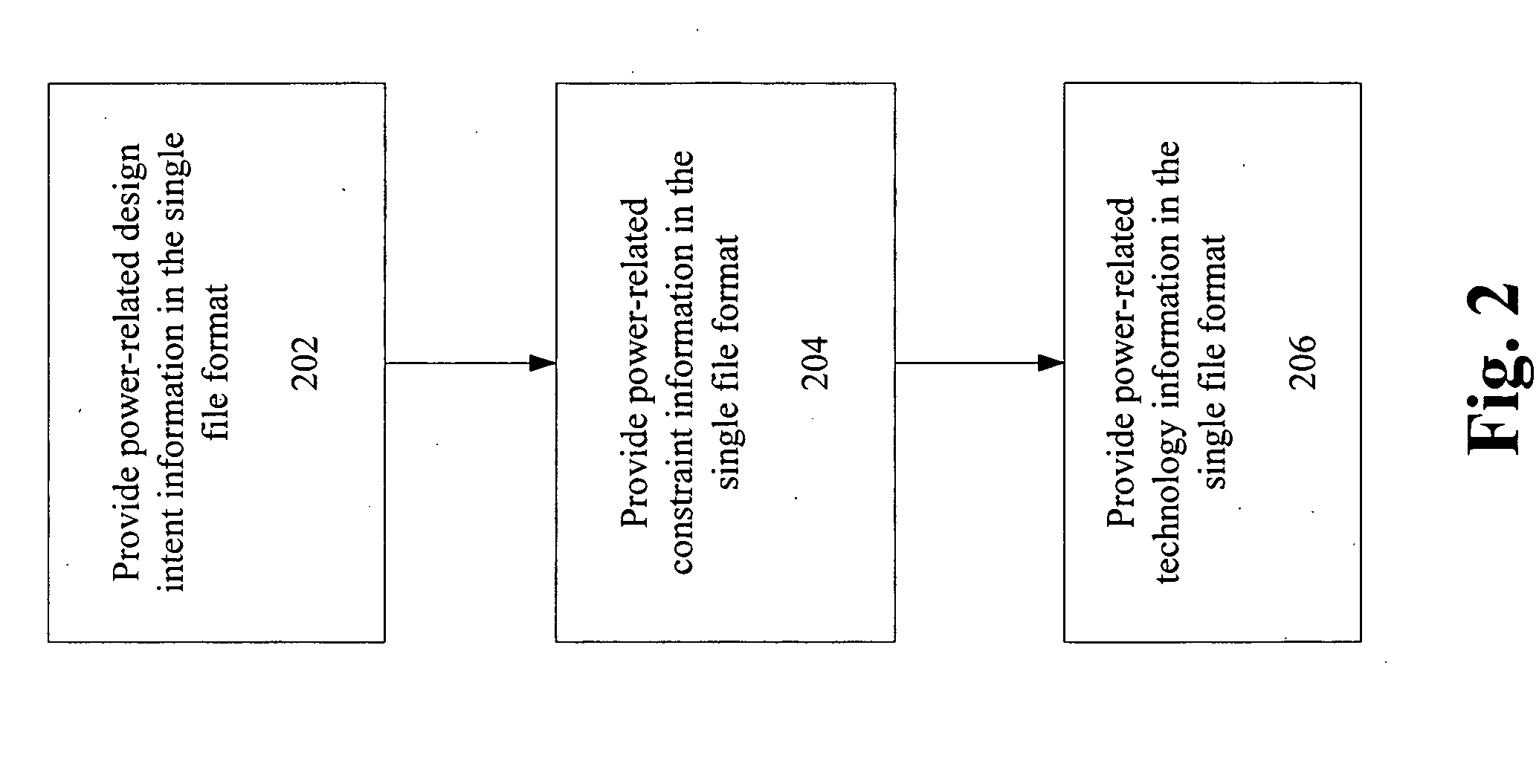

Method and mechanism for implementing electronic designs having power information specifications background

ActiveUS20070245285A1Low power designCAD circuit designSoftware simulation/interpretation/emulationPower modeElectronic design

A method of adding power control circuitry to a circuit design at each of an RTL and a netlist level comprising: demarcating multiple power domains within the circuit design; specifying multiple power modes each power mode corresponding to a different combination of on / off states of the multiple demarcated power domains; and defining isolation behavior relative to respective power domains.

Owner:CADENCE DESIGN SYST INC

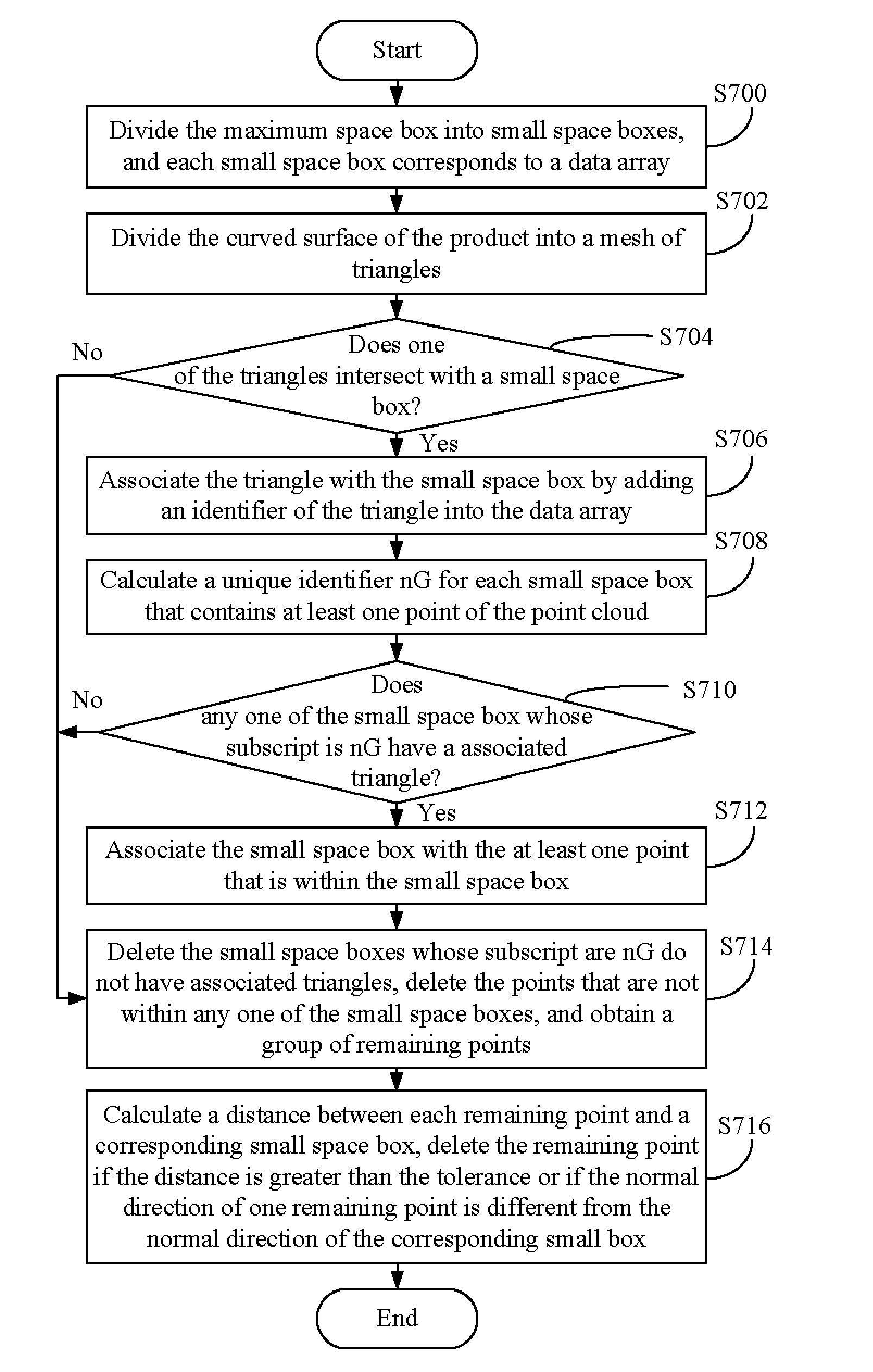

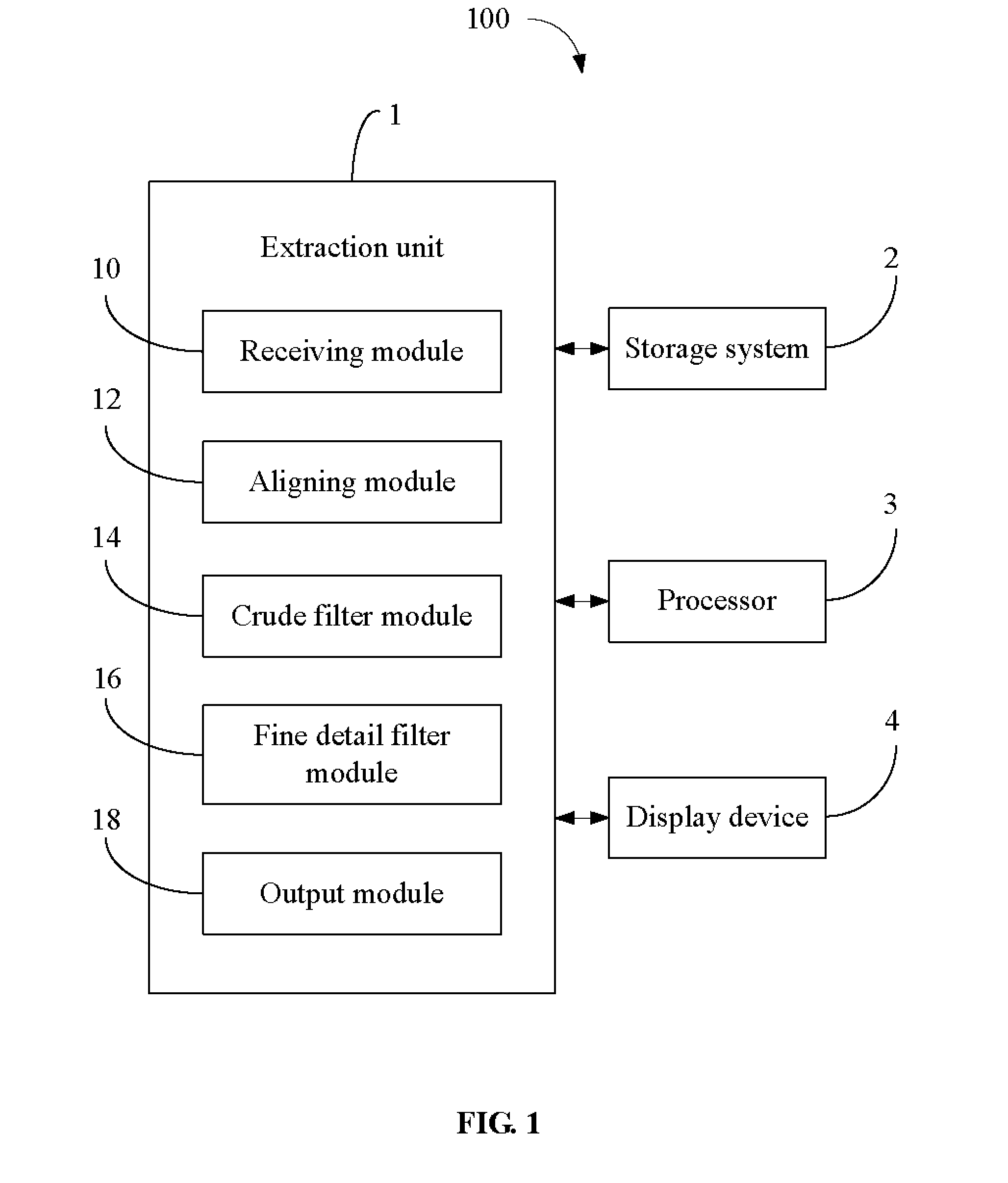

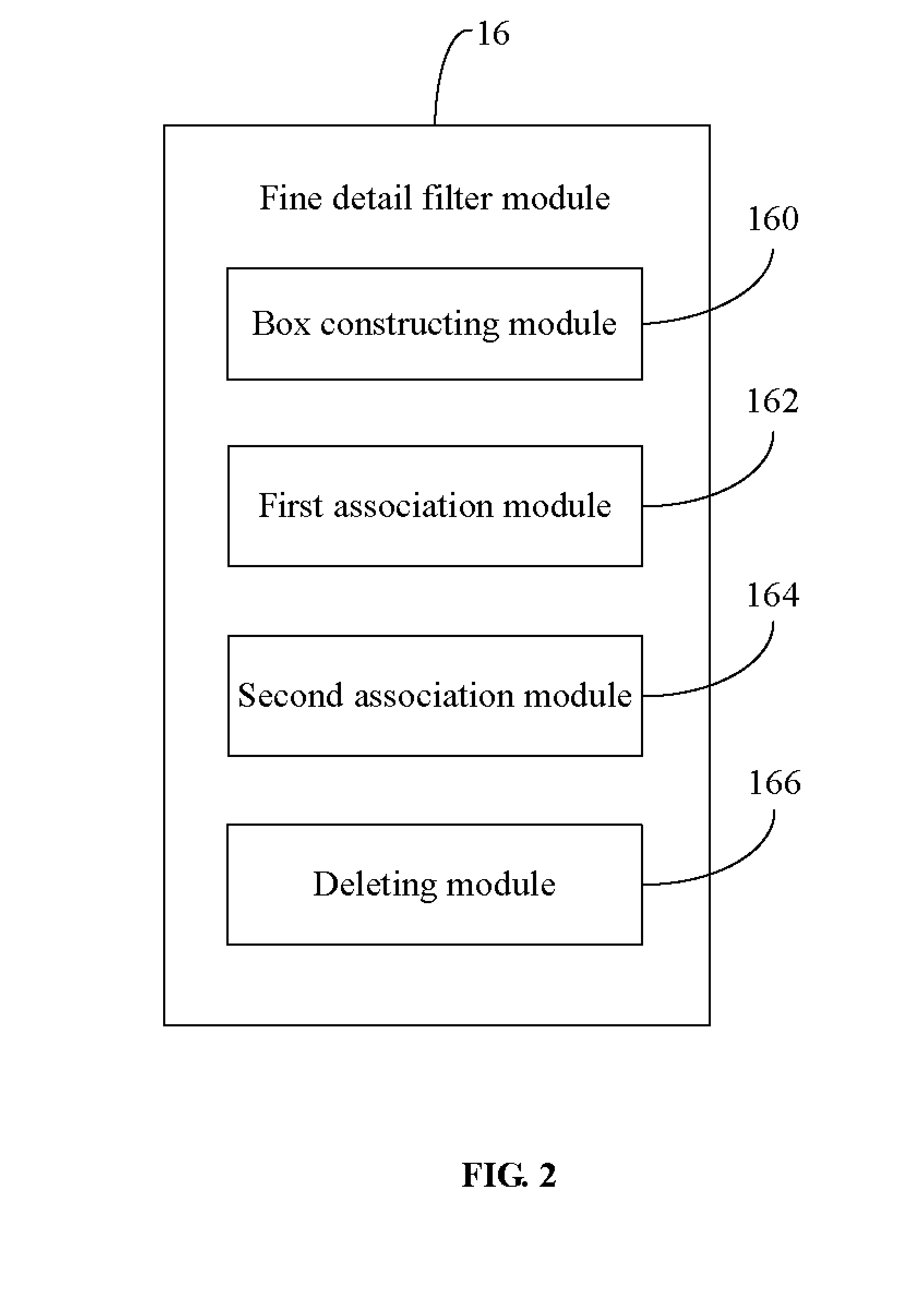

Computing device and method for extracting data of product for use in construction of point cloud

InactiveUS20130156292A1Pointing accuratelyImage enhancementImage analysisPoint cloudElectronic design

In a method for extracting data of a product, an electronic design document related to the product and point cloud created using actual measurements of the product are received. The point cloud includes points of the product. The method aligns the curved surface of the product with the corresponding portion of the point cloud using a best-fit method, creates a maximum space box for a feature element of the product, and deletes points that are not within the maximum space box. According to an average distance between two neighboring points of the point cloud, the maximum space box can be divided into many small space boxes. Using the small space boxes, the points are filtered to form a feature element.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

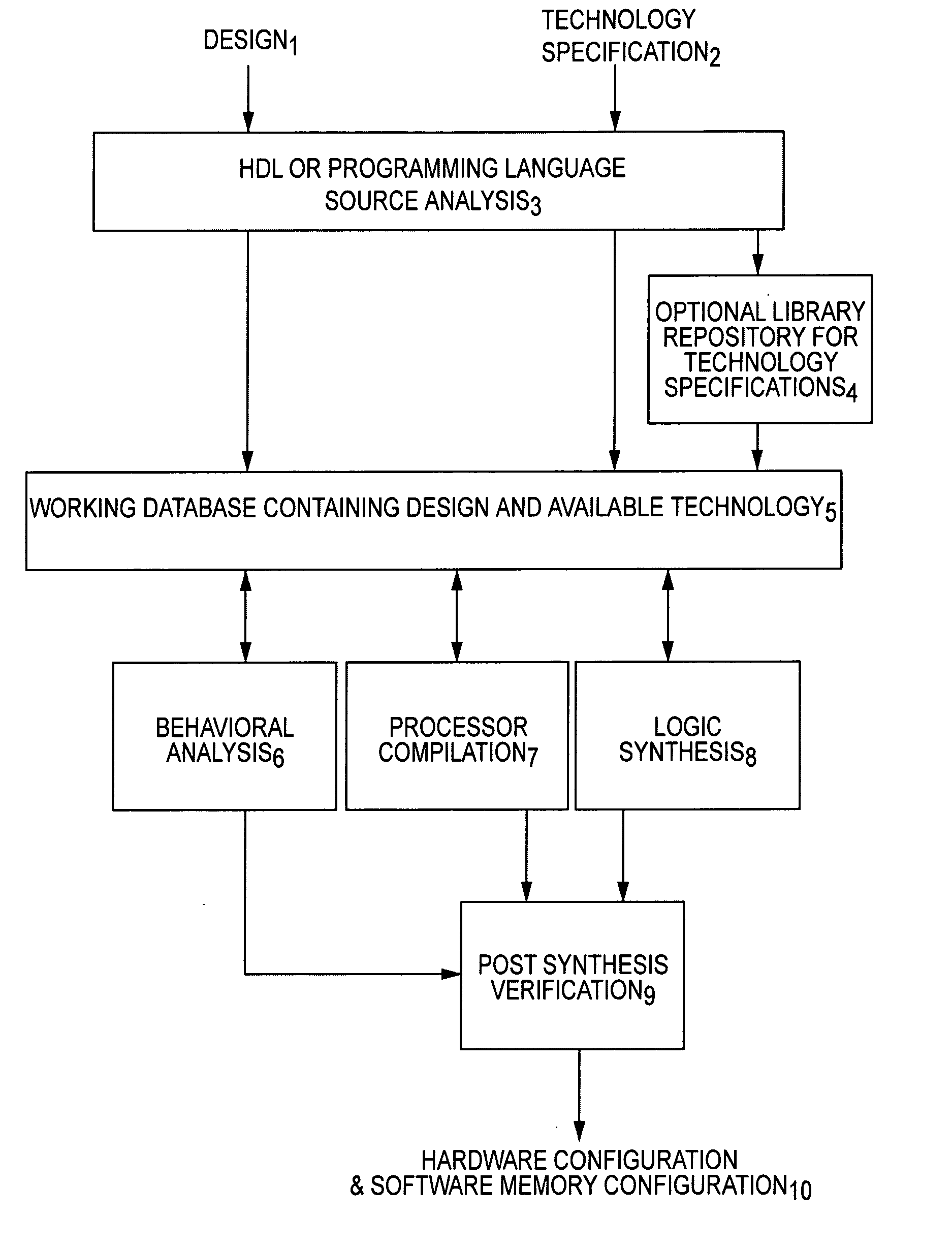

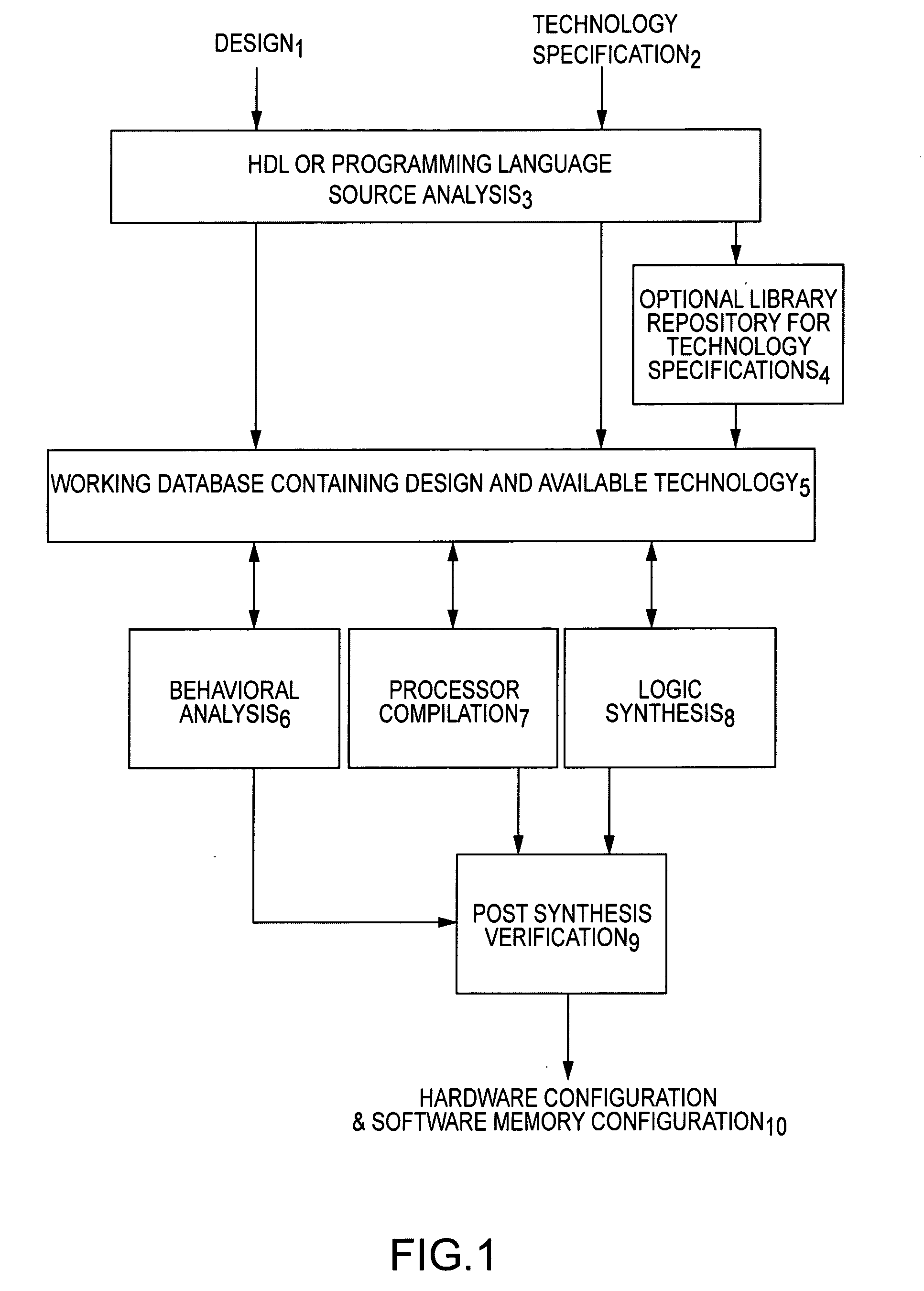

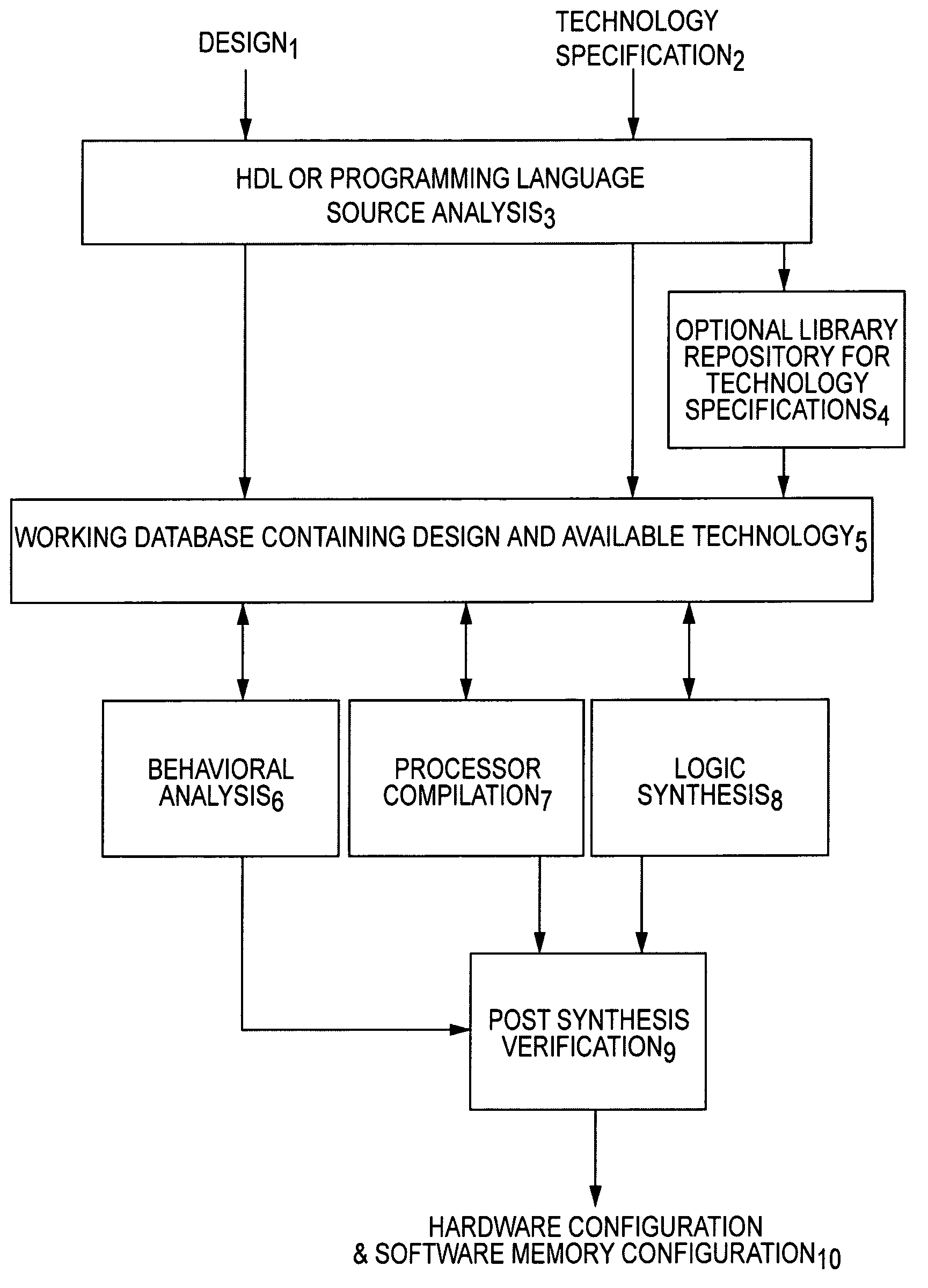

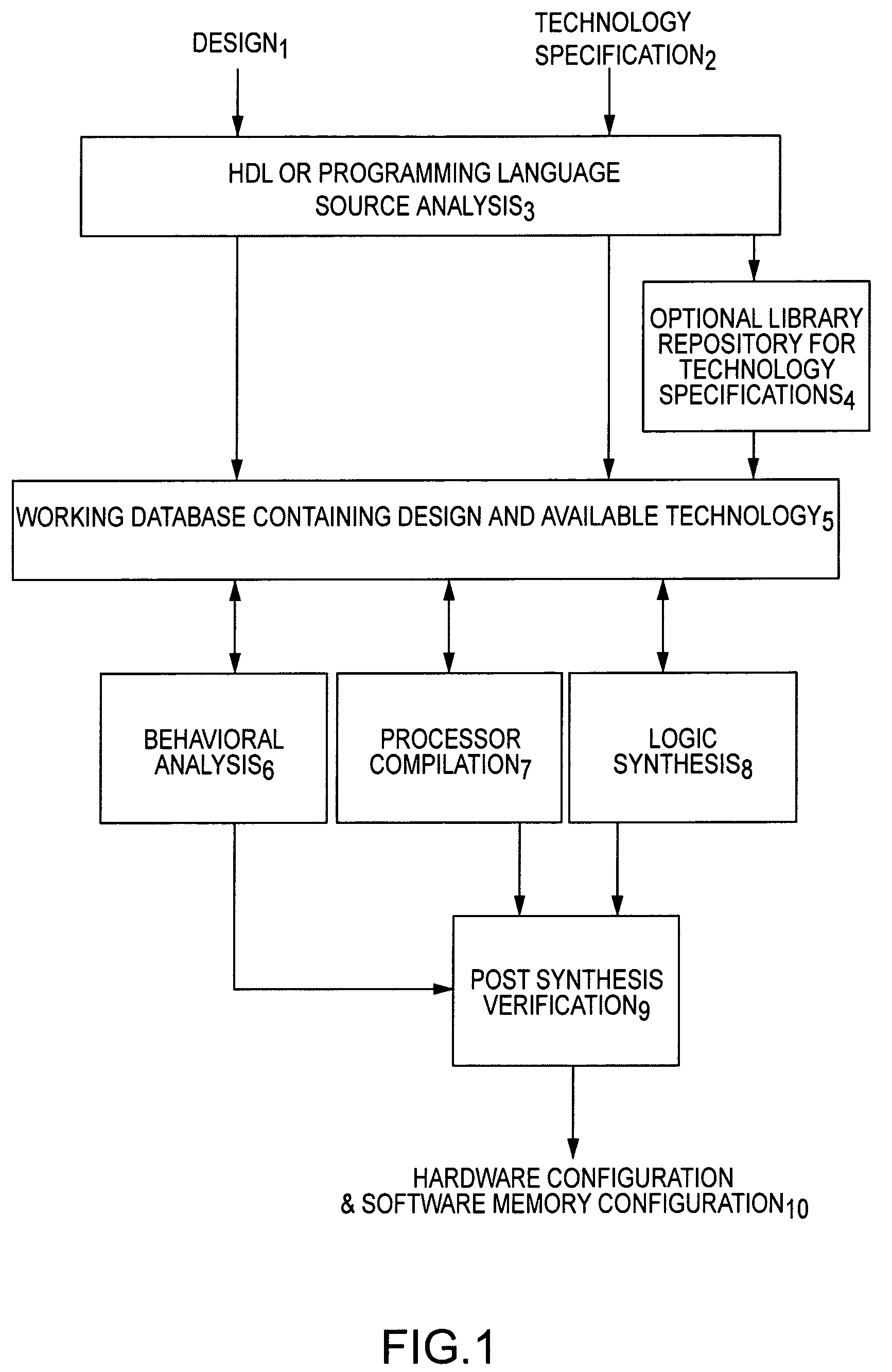

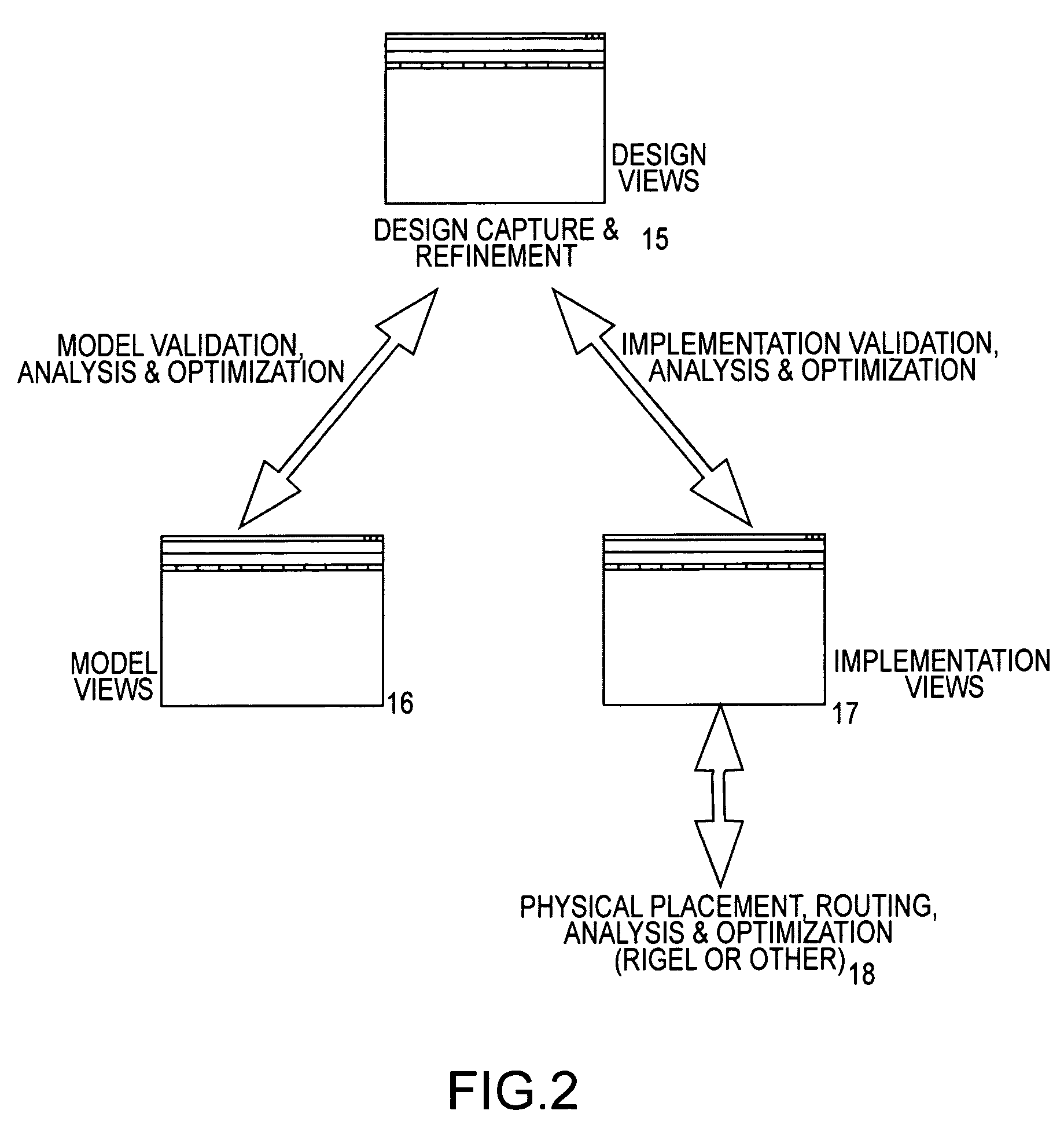

Hardware/software design tool and language specification mechanism enabling efficient technology retargeting and optimization

InactiveUS20050289485A1More compactEfficient designElectrical testingDigital computer detailsComputer architectureSoftware system

An innovative hardware / software design tool provides four modes of operation for converting an electronic design specification and zero or more technology specifications into realization of the electronic design in computer hardware, software and firmware. The first mode of operation compiles design and logic technology specifications into a model which can be utilized for behavioral analysis (such as simulation or formal verification) of logical characteristics (the model). The second mode of operation translates (compiles) partitions of the design and one or more logic technologies into one or more processor intermediates or binaries (embedded binary) suitable for execution on multi-purpose processing units (embedded or general purpose processors). The third mode of operation translates (synthesizes) partitions of the design and logic technology into a collection of cells and interconnects (net-list implementation) suitable for input to physical design processes such as is required to target a field-programmable logic array (FPGA), application specific integrated circuit (ASIC), system-on-a-chip (SOC) or custom logic). The fourth mode of operation analyzes (verifies) behavior of the embedded binaries running on processing units and implementations augmented by additional physical technology and parameters, yielding a more detailed (accurate) prediction of the resulting hardware / software system behavior when realized through manufacturing. Critically, the design specification, logic specifications, physical specifications and definition of each multi-purpose processing unit may be defined external to the hardware / software design tool using an innovative augmentation of standard hardware description or programming languages taught in this patent application. In the prior art, specification of the logic technology, physical technology and embedded or general purpose processor architecture are either incorporated directly into the design tool by the tool developer or are maintained entirely external to the design tool (such as an encapsulated component model or intermediate code interpreter). The present invention is an innovative and valuable improvement over prior art in that design specifications are combined by the tool from distinct specification(s) of generalized logic, physical and processor technology, leading to more efficient behavioral design, opportunities for third parties to add functionality by incorporating generalized logic and physical technology modules into the analysis and synthesis process and opportunities for semi-automatic, goal-directed optimization through application of various logic, physical and processor technologies by the design tool.

Owner:FTL SYST

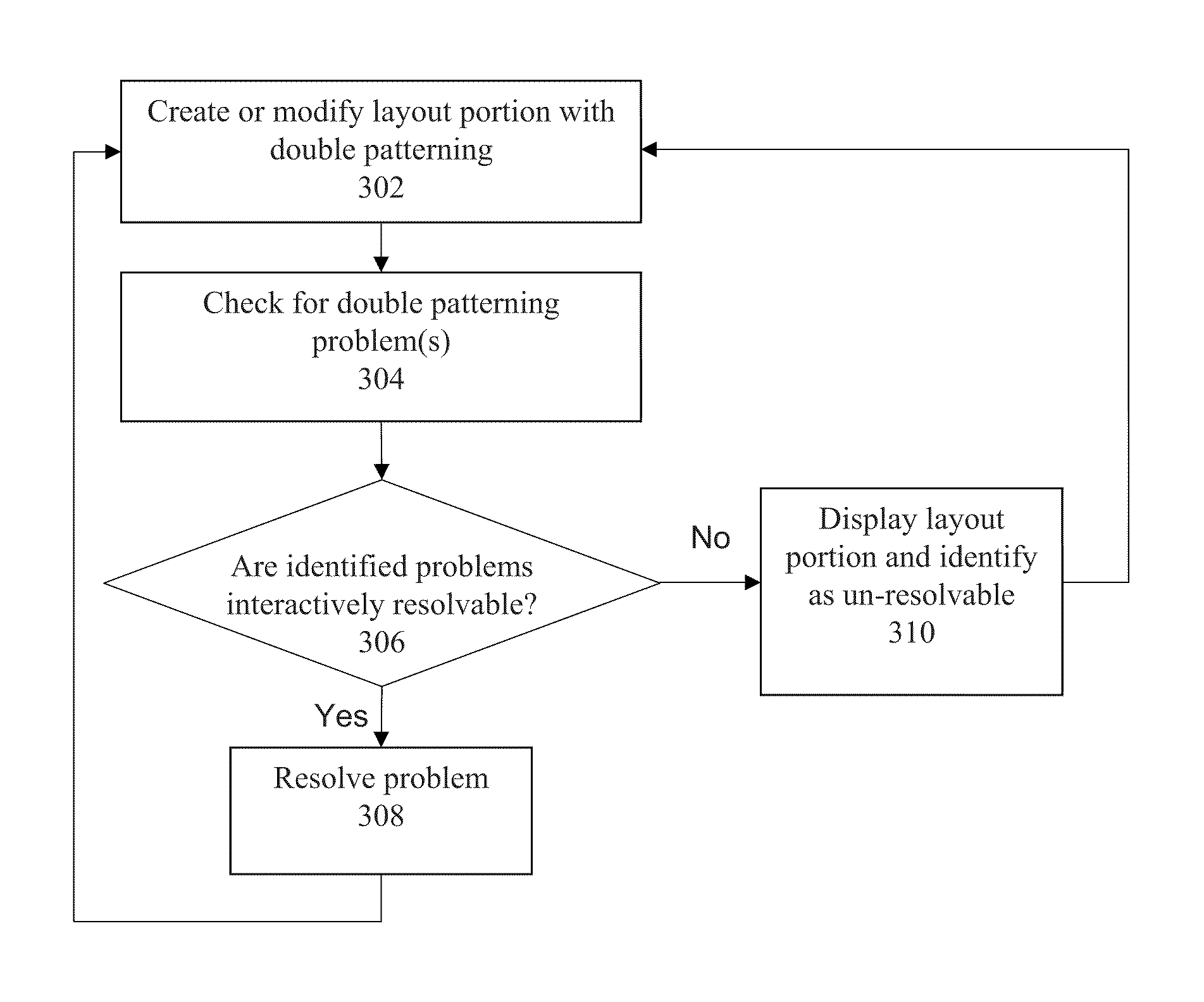

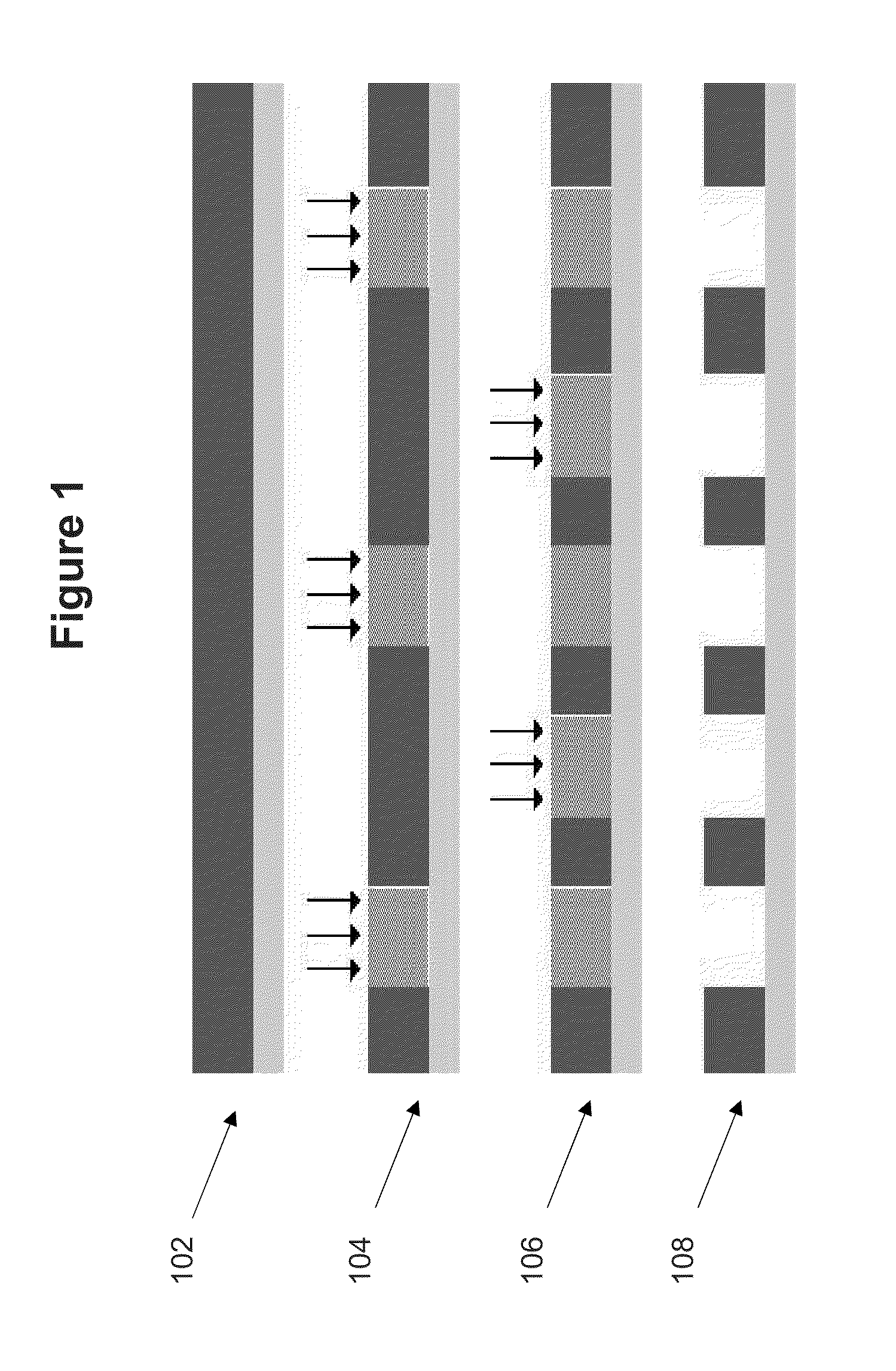

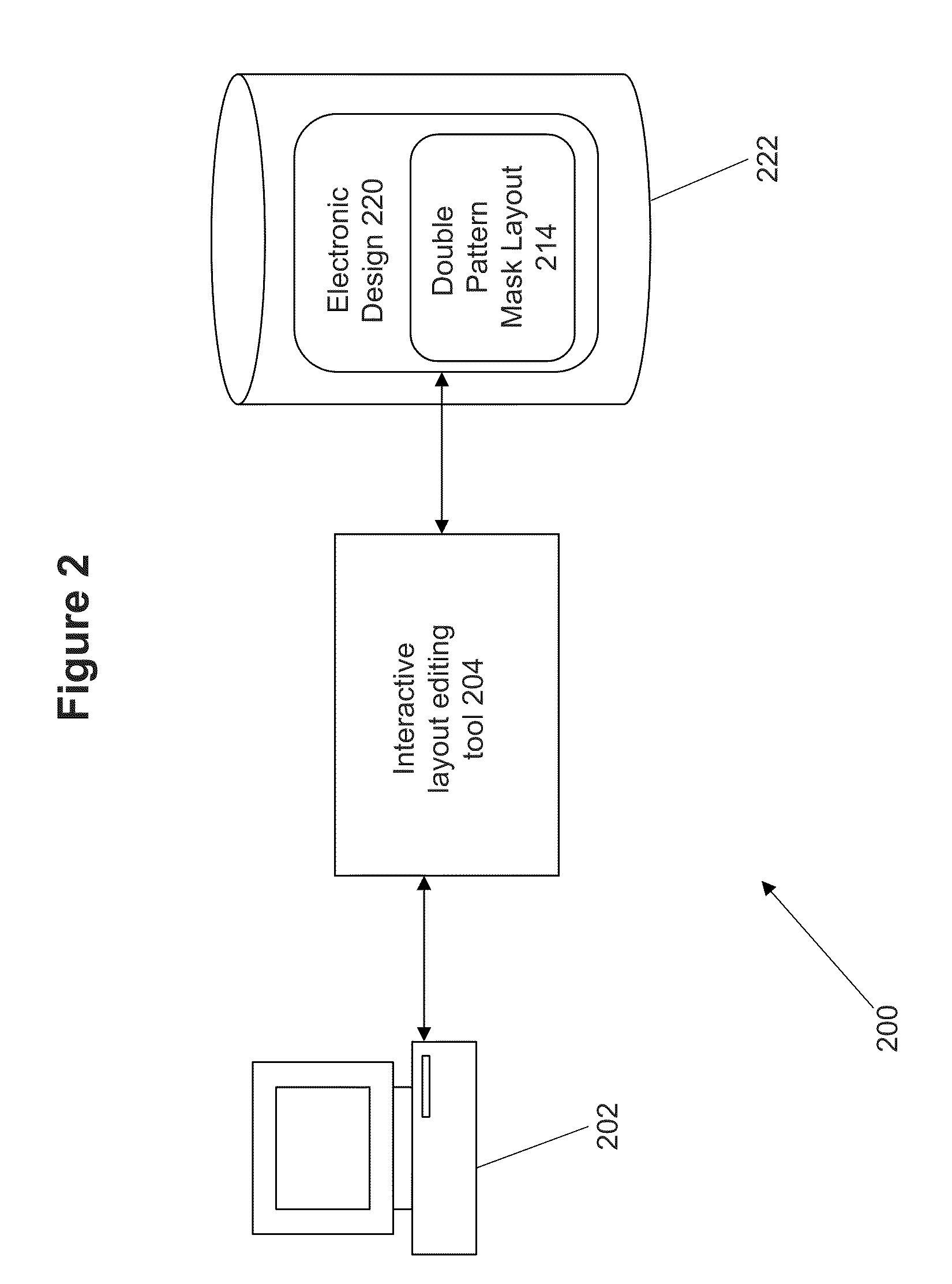

Method, system, and program product for interactive checking for double pattern lithography violations

ActiveUS20110219341A1CAD circuit designOriginals for photomechanical treatmentLithographic artistElectronic design

Disclosed are a method, apparatus, and computer program product for performing interactive layout editing to address double patterning approaches to implement lithography of electronic designs. A spatial query is performed around the shape(s) being created during editing with the distance of allowed spacing in a single mask. If a design error is encountered, corrective editing may occur to correct the error. Checking may occur to make sure that the error detection and corrective actions can be performed interactively.

Owner:CADENCE DESIGN SYST INC

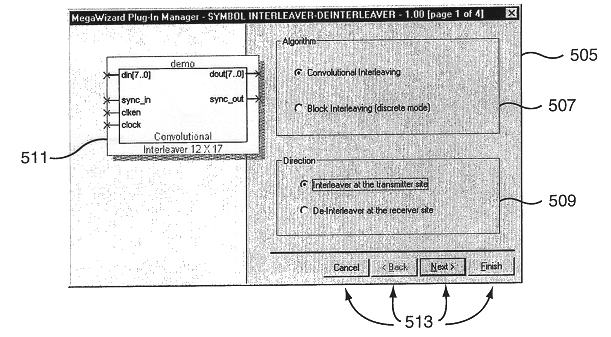

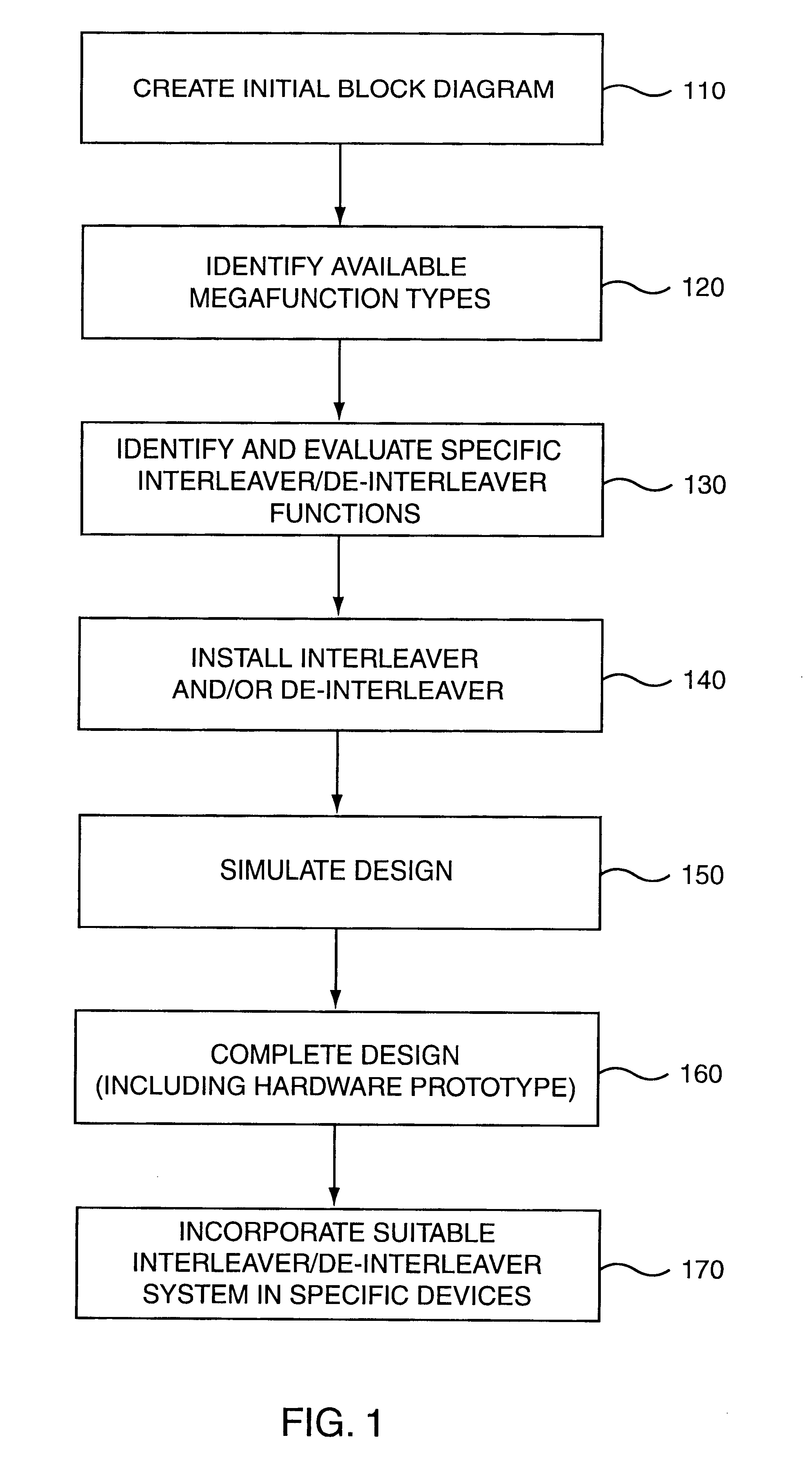

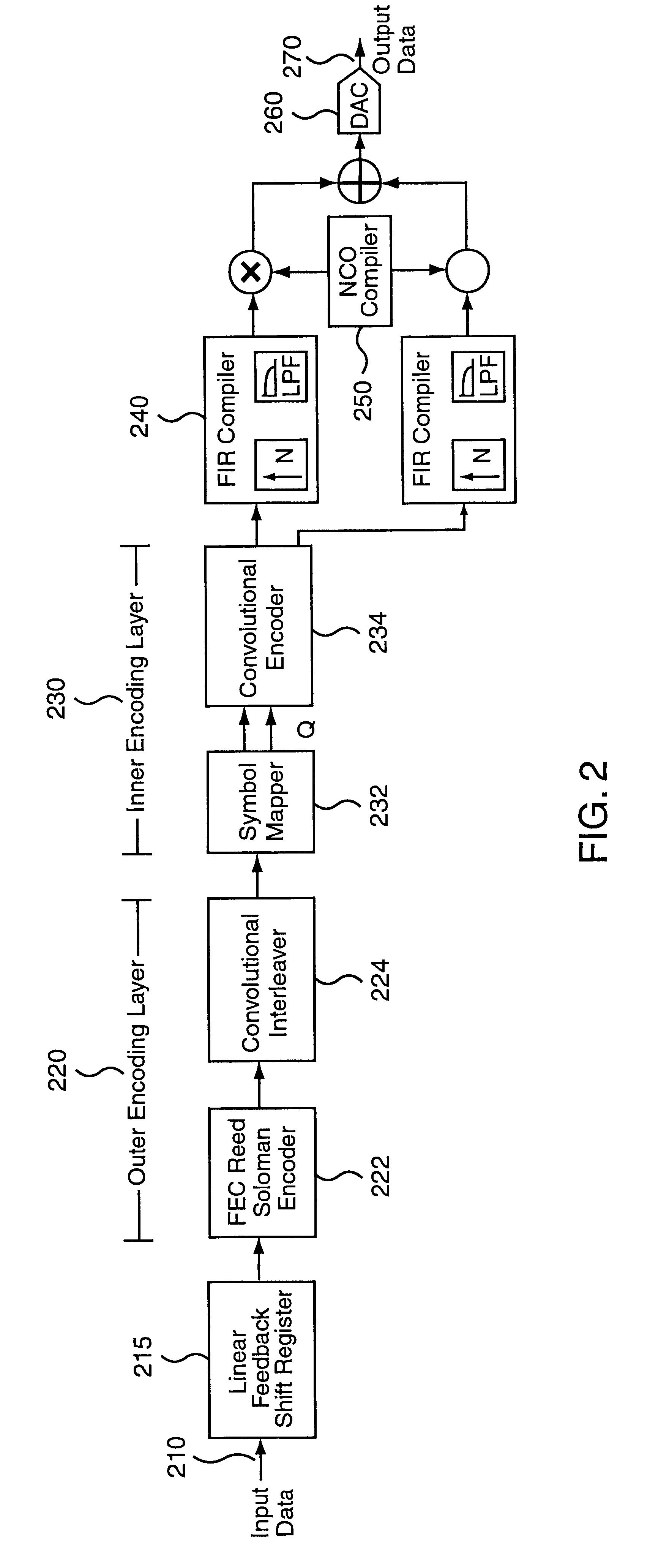

Interleaver-deinterleaver megacore

Methods and apparatuses are disclosed for creating a parameterized interleaver / de-interleaver megafunction for use in an electronic design, where the interleaver / de-interleaver megafunction requires specific setting of at least one variable parameter value. The method includes presenting a user with the opportunity to specify an adjustable parameter value for at least one interleaver / de-interleaver parameter. The specified parameter value then is received and a suitable interleaver and / or de-interleaver system is generated.< / PTEXT>

Owner:ALTERA CORP

Hardware/software design tool and language specification mechanism enabling efficient technology retargeting and optimization

InactiveUS7278122B2More compactEfficient designElectrical testingDigital computer detailsComputer architectureBehavioral analytics

A hardware / software design tool converts an electronic design specification and zero or more technology specifications into realization of the electronic design in computer hardware, software and firmware. It compiles design and logic technology specifications into a model which can be utilized for behavioral analysis of logical characteristics. It translates partitions of the design and one or more logic technologies into one or more processor intermediates or binaries suitable for execution on multi-purpose processing units. It translates partitions of the design and logic technology into a collection of cells and interconnects suitable for input to physical design processes such as is required to target, a FPGA, system-on-a-chip or custom logic. It analyzes behavior of the embedded binaries running on processing units and implementations augmented by additional physical technology and parameters, yielding a more detailed prediction of the resulting hardware / software system behavior when realized through manufacturing.

Owner:FTL SYST

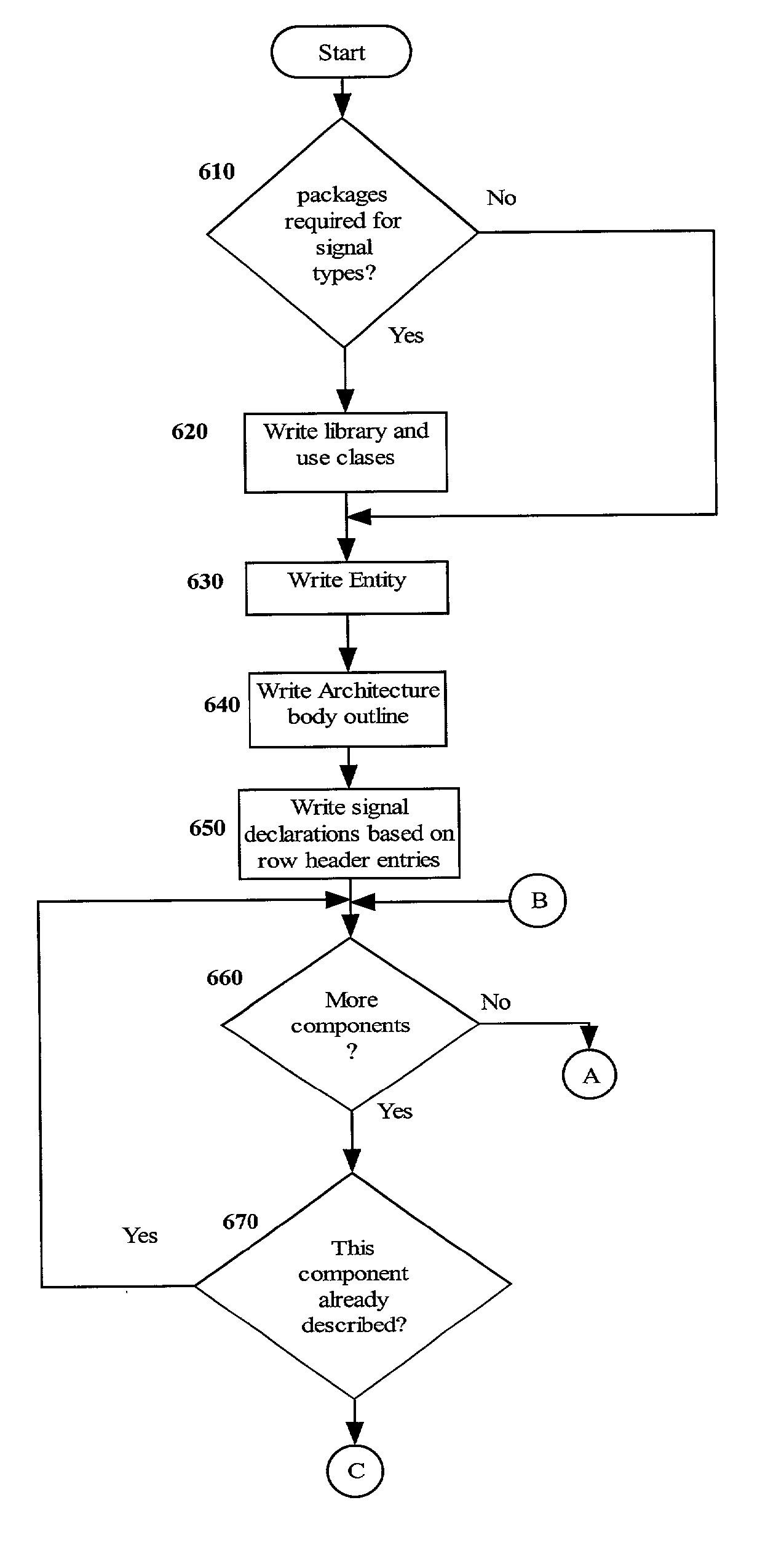

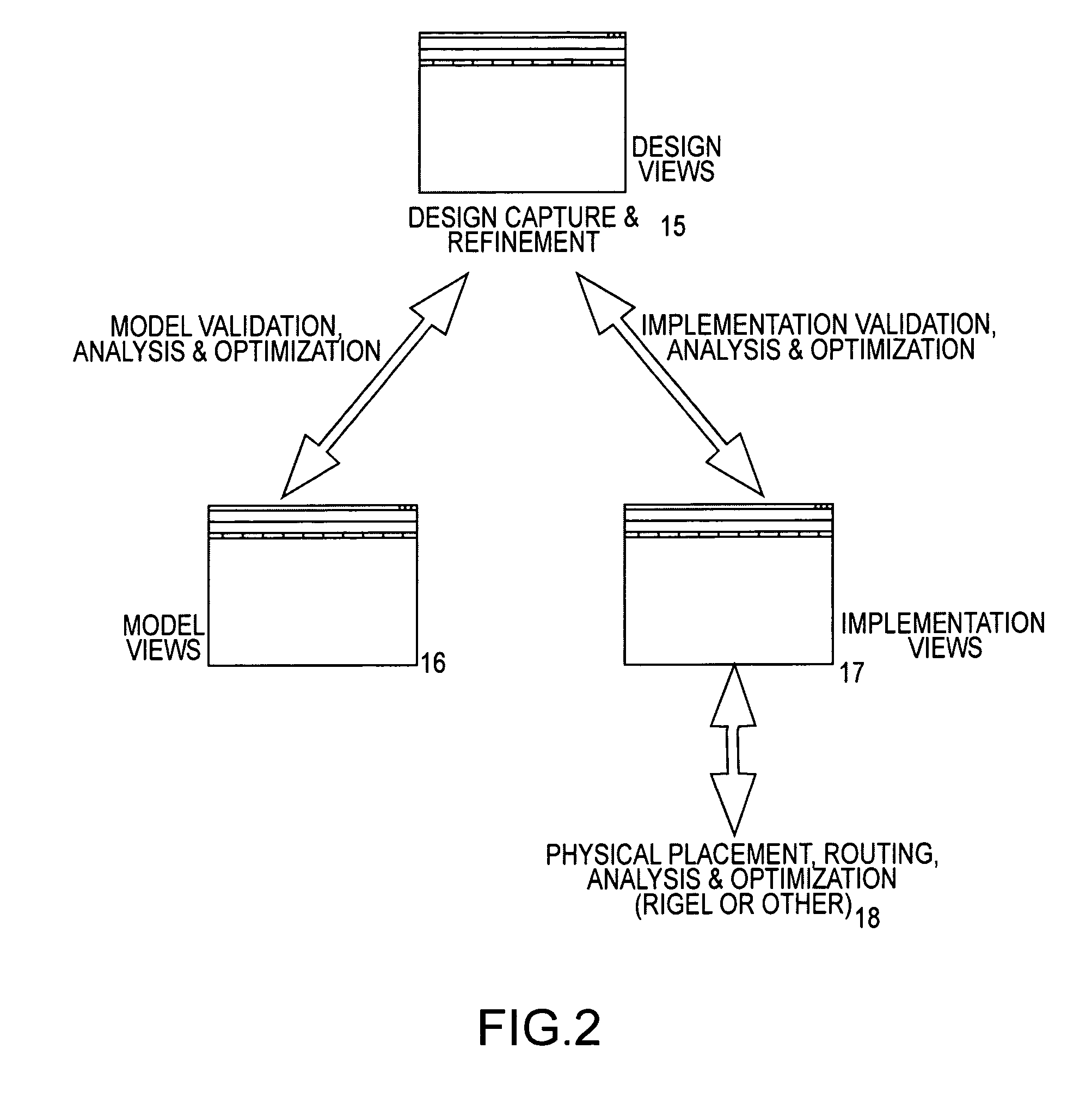

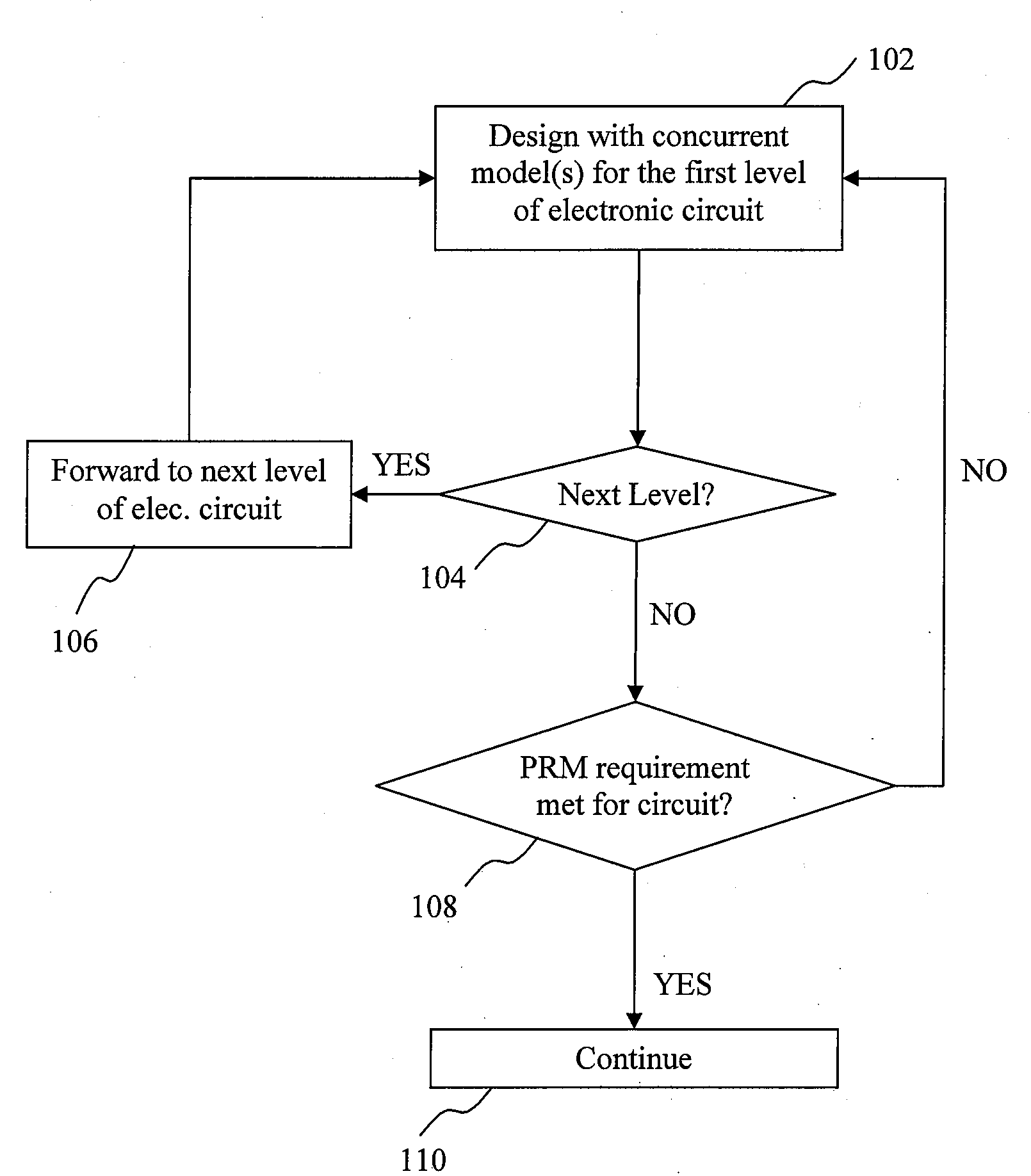

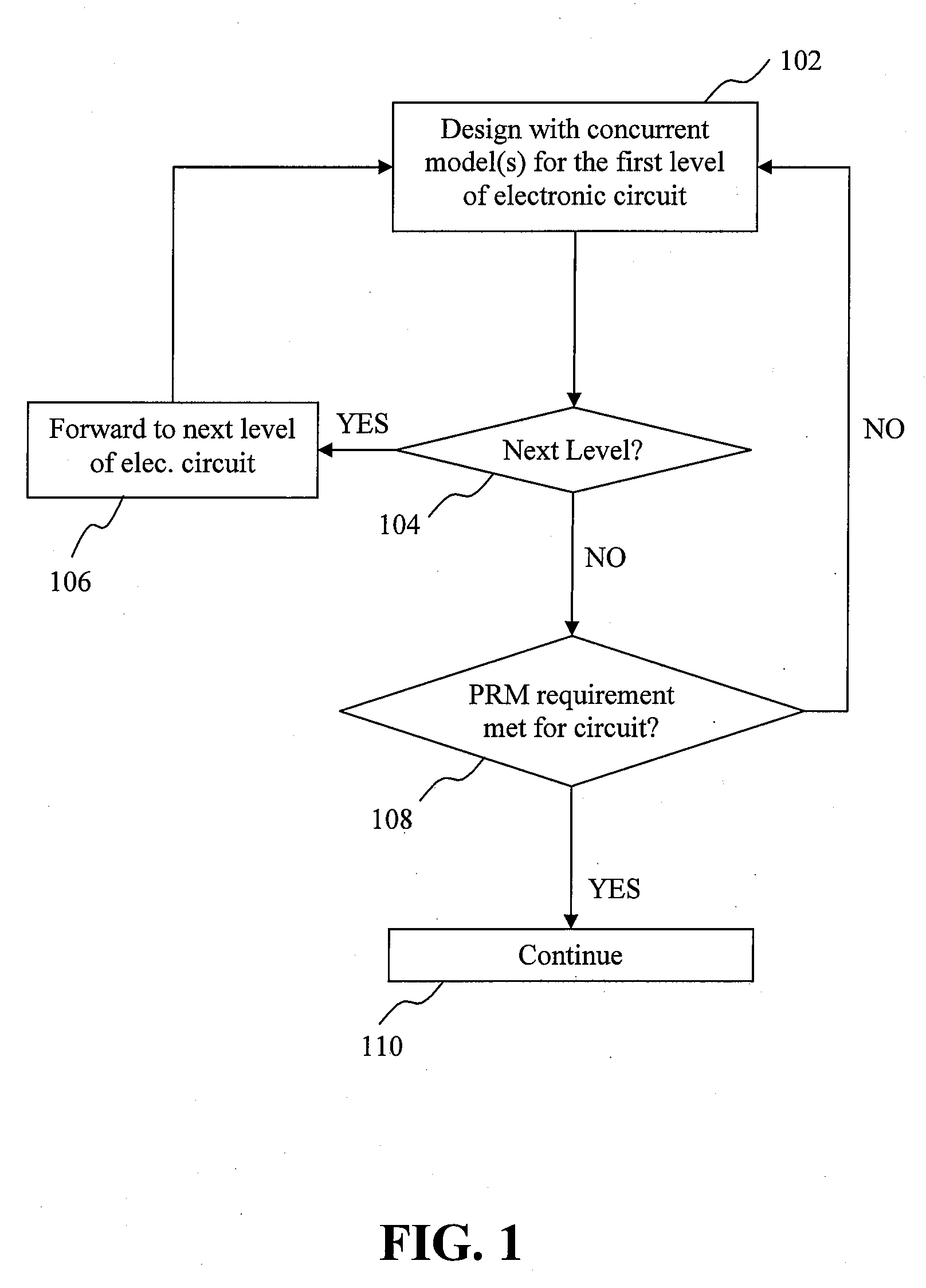

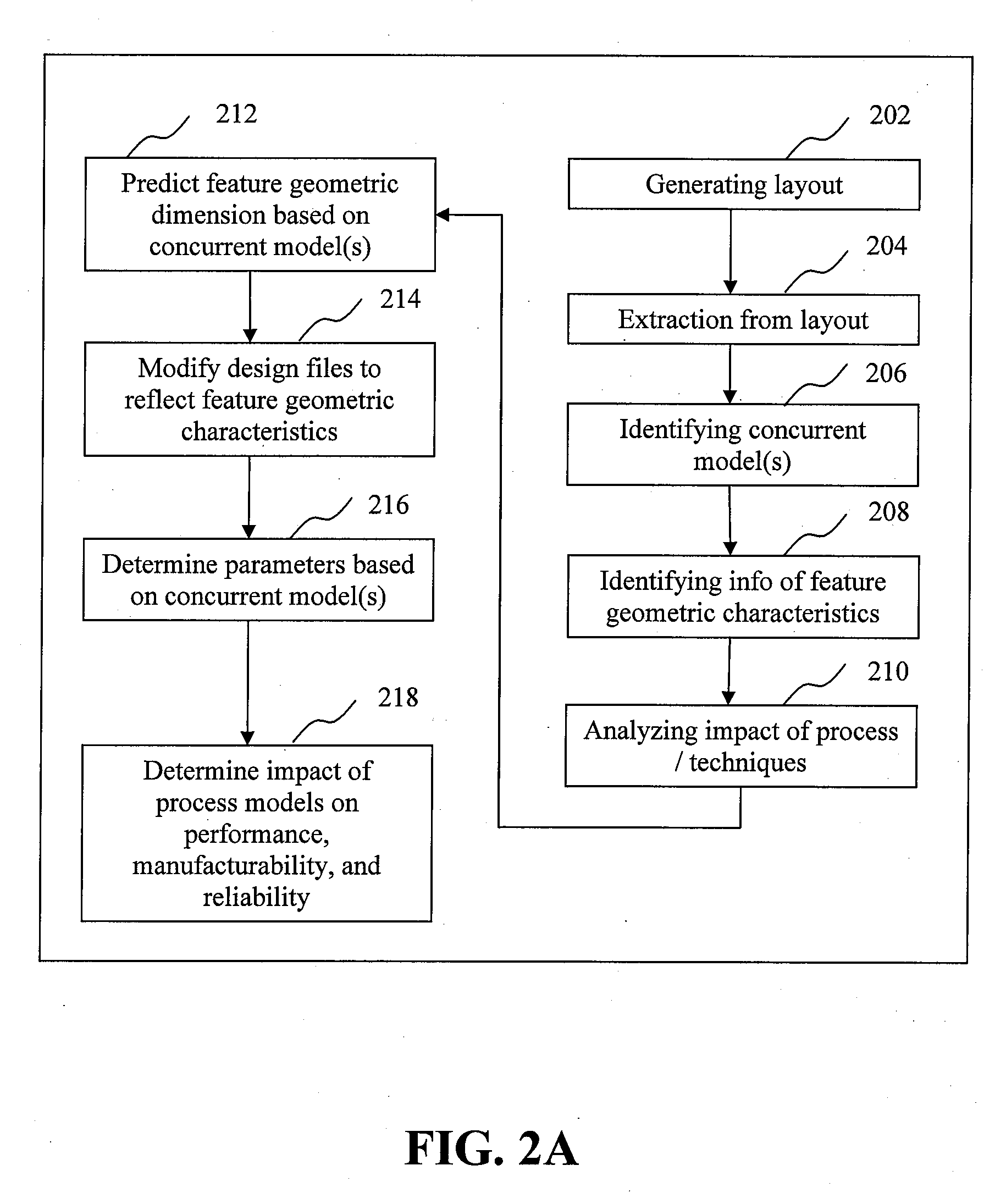

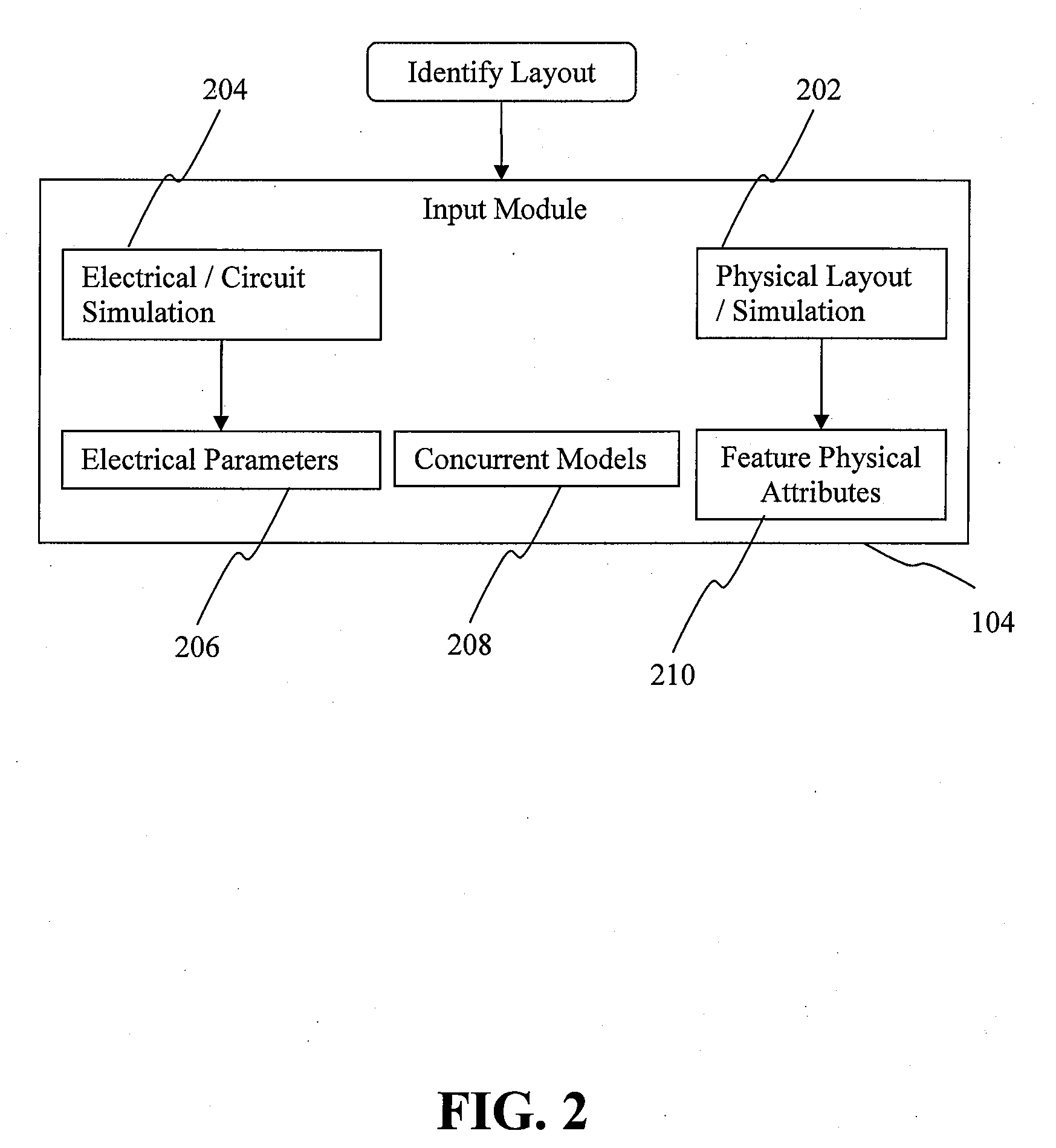

Method, system, and computer program product for concurrent model aided electronic design automation

InactiveUS20080162103A1Effective and accurate methodologyAccurate predictionAnalogue computers for electric apparatusPhotomechanical apparatusComputer architectureGenerative Design

Disclosed are improved methods, systems, and computer program products for predicting performance, manufacturability, and reliability (PMR) using concurrent model analyses for electronic designs. Various embodiments of the present invention disclose a method for predicting PMR with concurrent process model analysis in which a method with concurrent model(s) generate a design for the one or more layers in the electronic circuit. The method then analyzes the impact of the processes or techniques for feature geometric characteristic predictions or PMR evaluations, based upon the concurrent models. Results may be reported to the users, or the method may modify the designs to accommodate the variations and determines one or more parameters based upon the concurrent models. One embodiment determines the impact of concurrent model on one or more of performance, manufacturability, and reliability criteria.

Owner:CADENCE DESIGN SYST INC

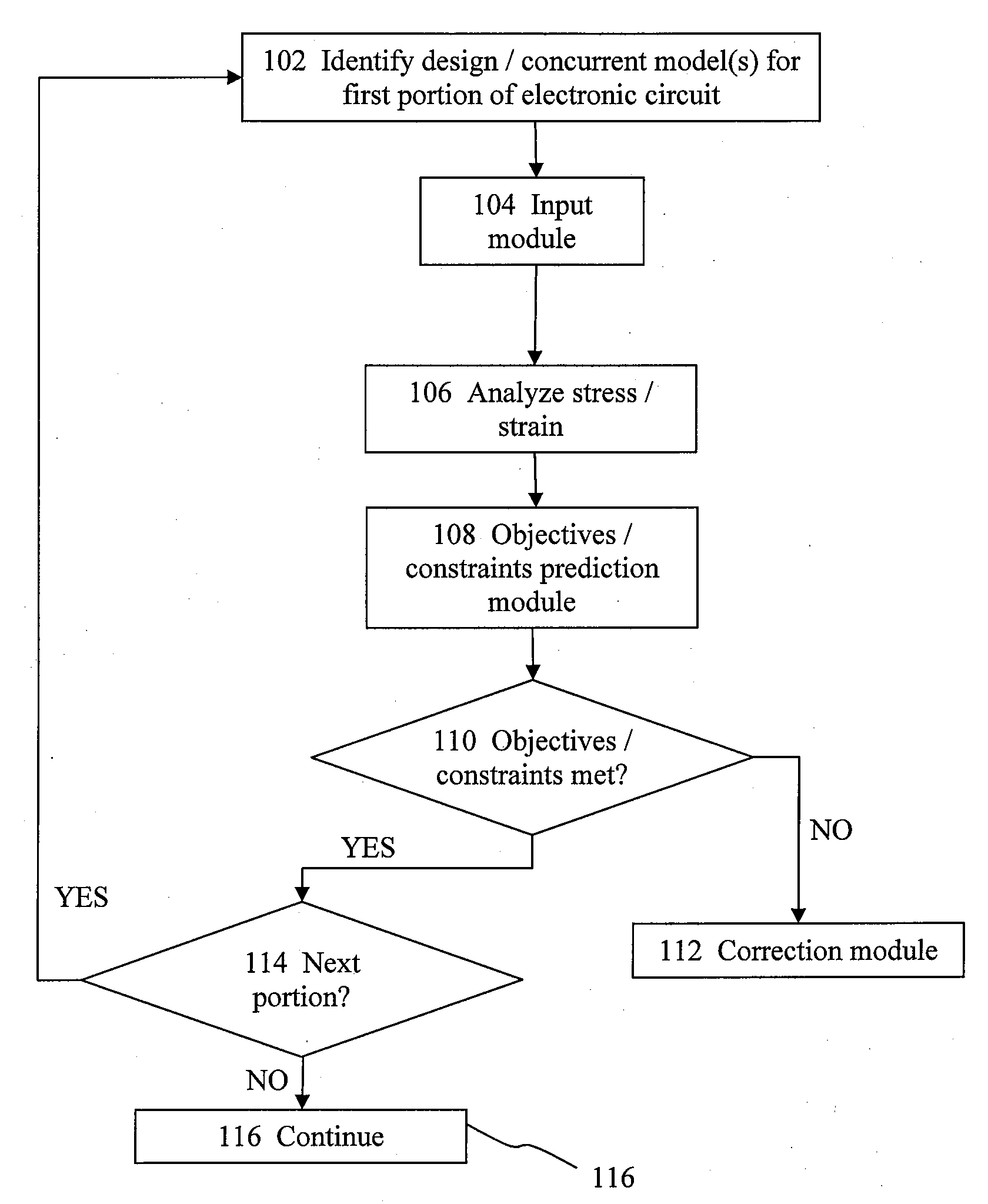

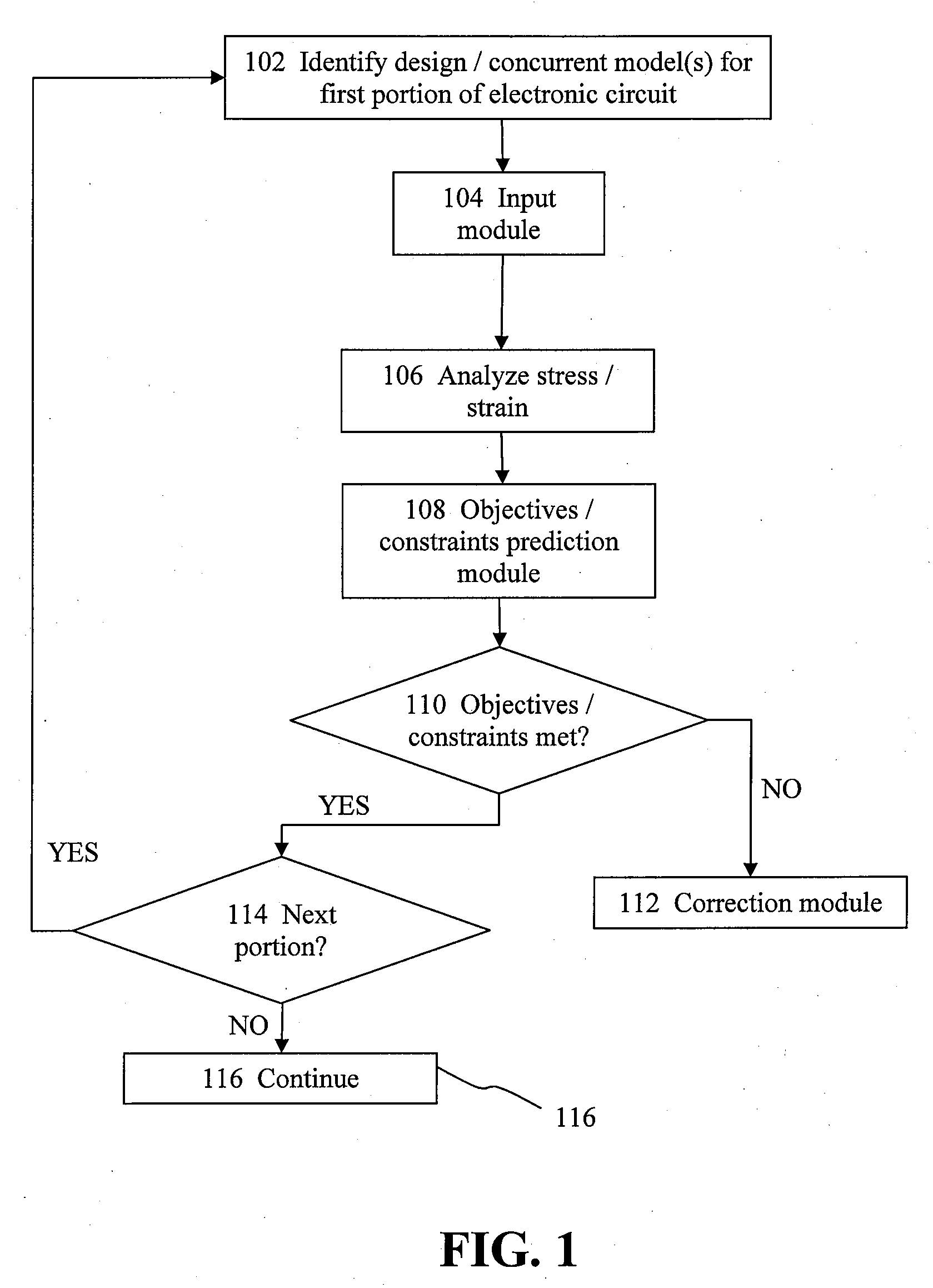

Method, system, and computer program product for predicting thin film integrity, manufacturability, reliability, and performance in electronic designs

ActiveUS20080160646A1Semiconductor/solid-state device testing/measurementResistance/reactance/impedenceImproved methodElectronic design

Disclosed is an improved method, system, and computer program product for predicting and improving the integrity, manufacturability, reliability, and performance of an electronic circuit feature based on the stresses or strains of design features of electronic designs. Some embodiments identify the design, the concurrent model(s), design feature physical or electrical parameters or attributes, analyzes the stresses or strains to predict the integrity of the design and determines whether the design meets the design objectives or constraints. Some other embodiments make corrections to the designs or the processes based upon the determination of whether the design meets the design objectives or constraints. Some other embodiments compute the variations of the design features as a result of the stresses or strains and determine their impact on the subsequent processes.

Owner:CADENCE DESIGN SYST INC

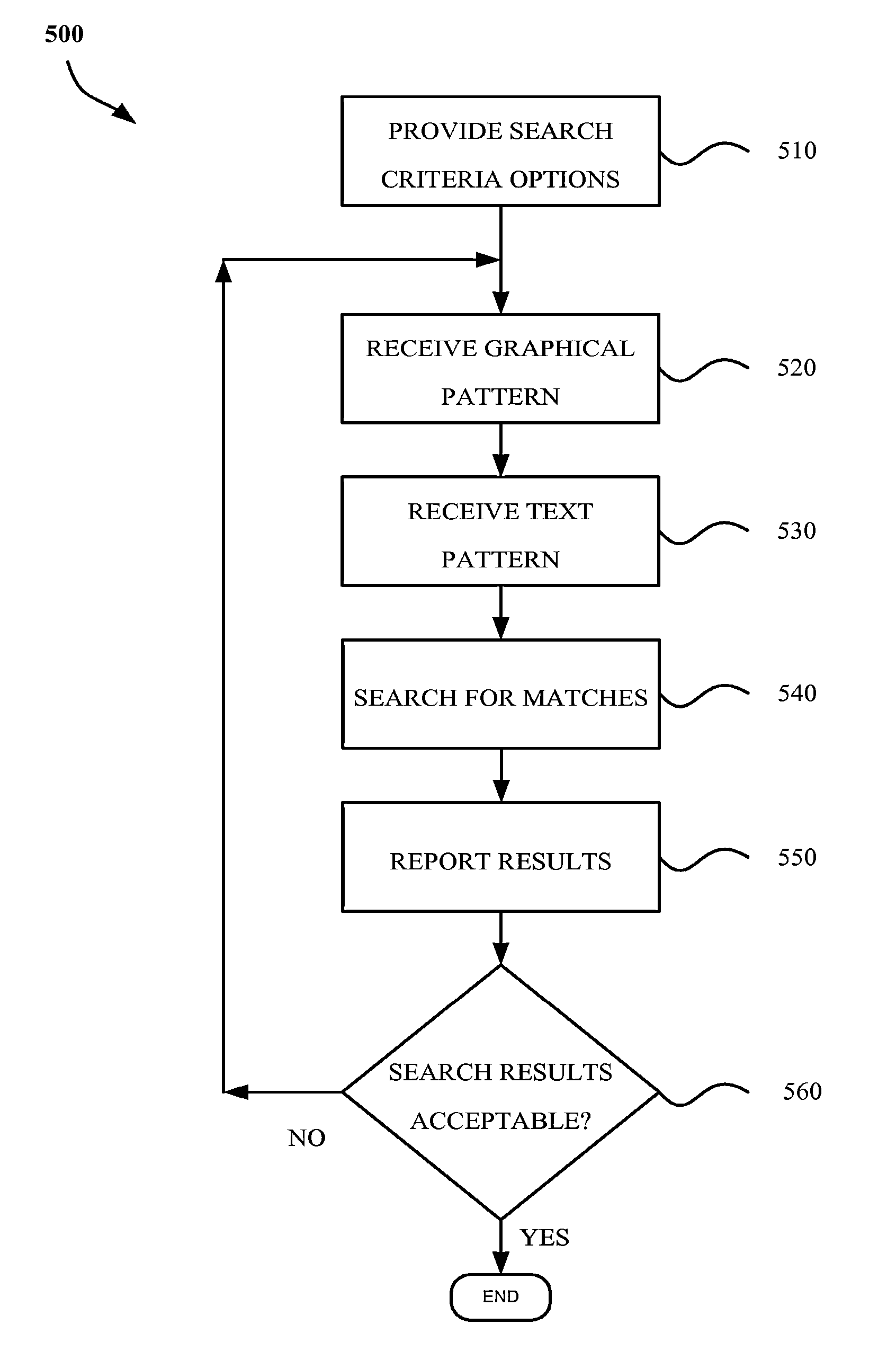

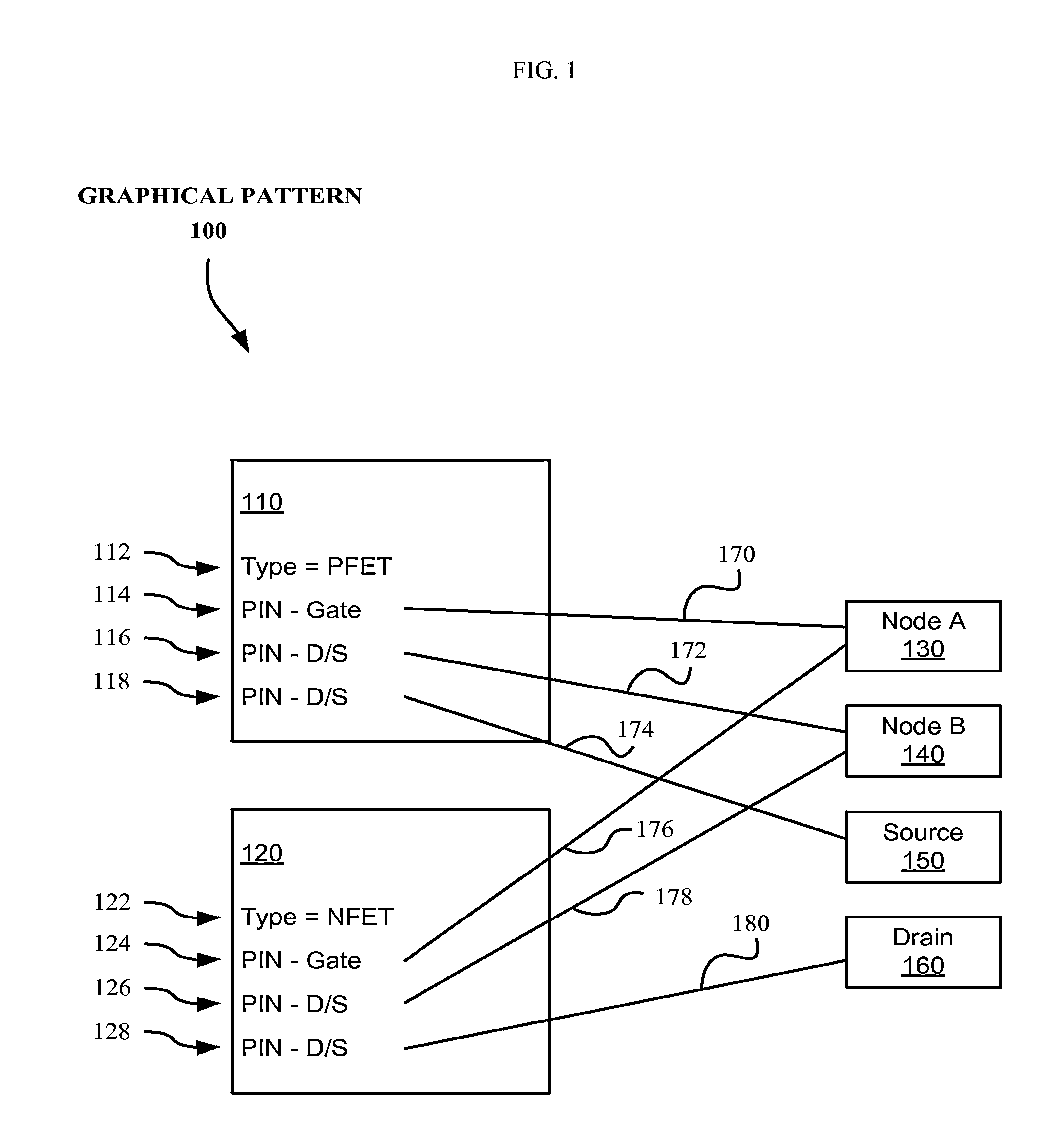

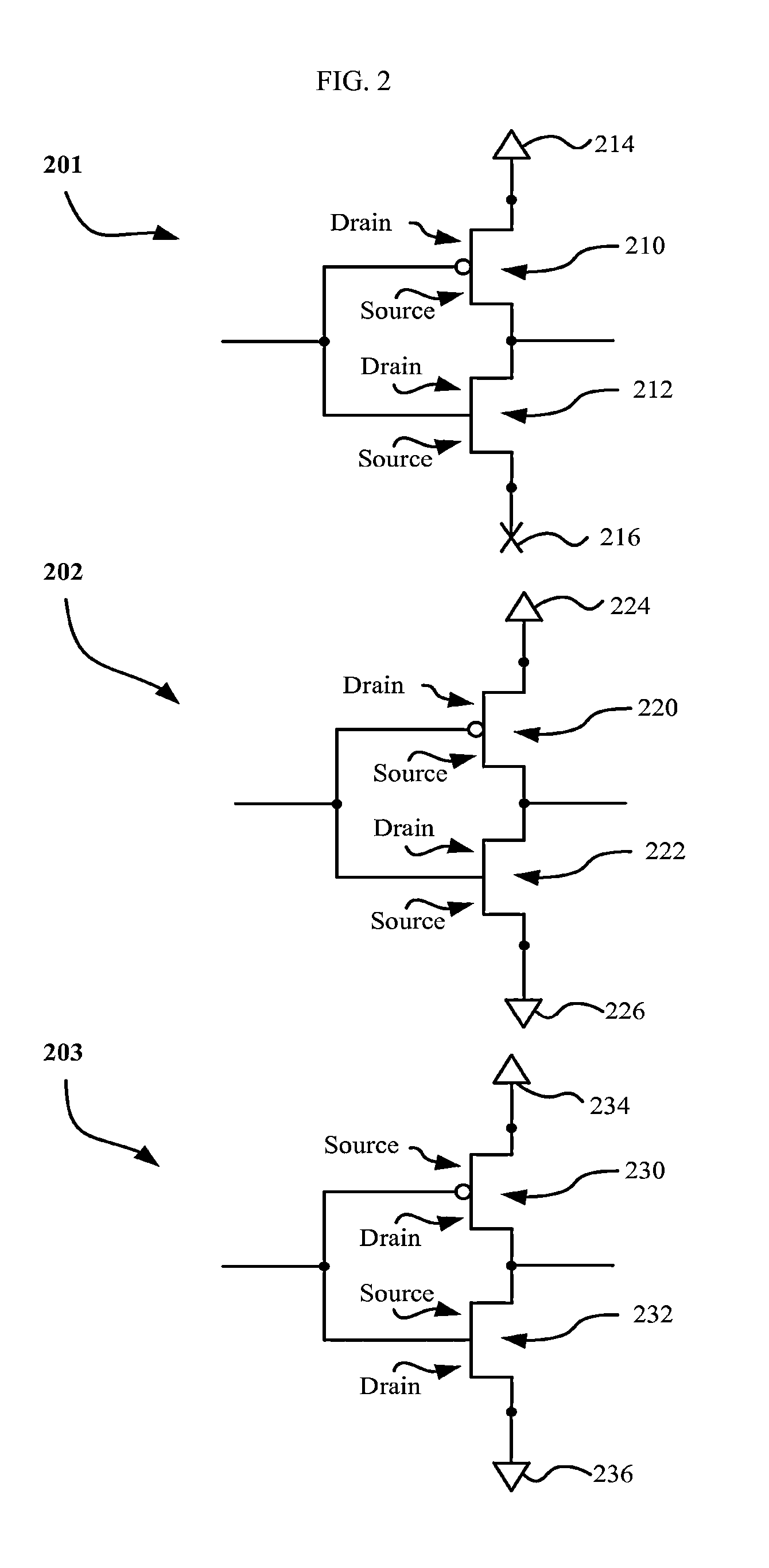

System and method of detecting design rule noncompliant subgraphs in circuit netlists

ActiveUS20130125072A1Increase flexibilityEasy to useCAD circuit designSoftware simulation/interpretation/emulationGraphicsTheoretical computer science

An automated system and method of performing electronic design rule checking on the netlist of an integrated circuit composed of a plurality of subgraphs. The electronic design rule is embodied as a two part template with a target subgraph specification and a design rule compliance check specification. The target subgraph specification often is at least partially defined by an interactive visual programming section that allows the user to construct a graphic specification of the target netlist. The method first searches the netlist for target subgraphs that match the target subgraph specification, and the user can verify proper target selection. The method then performs rule checks on these search targets, and non compliant subnets identified. Flexibility is enhanced by use of search wildcards, attribute ranges, and various short user scripts which may contain various Boolean logical operations.

Owner:INSIGHT EDA

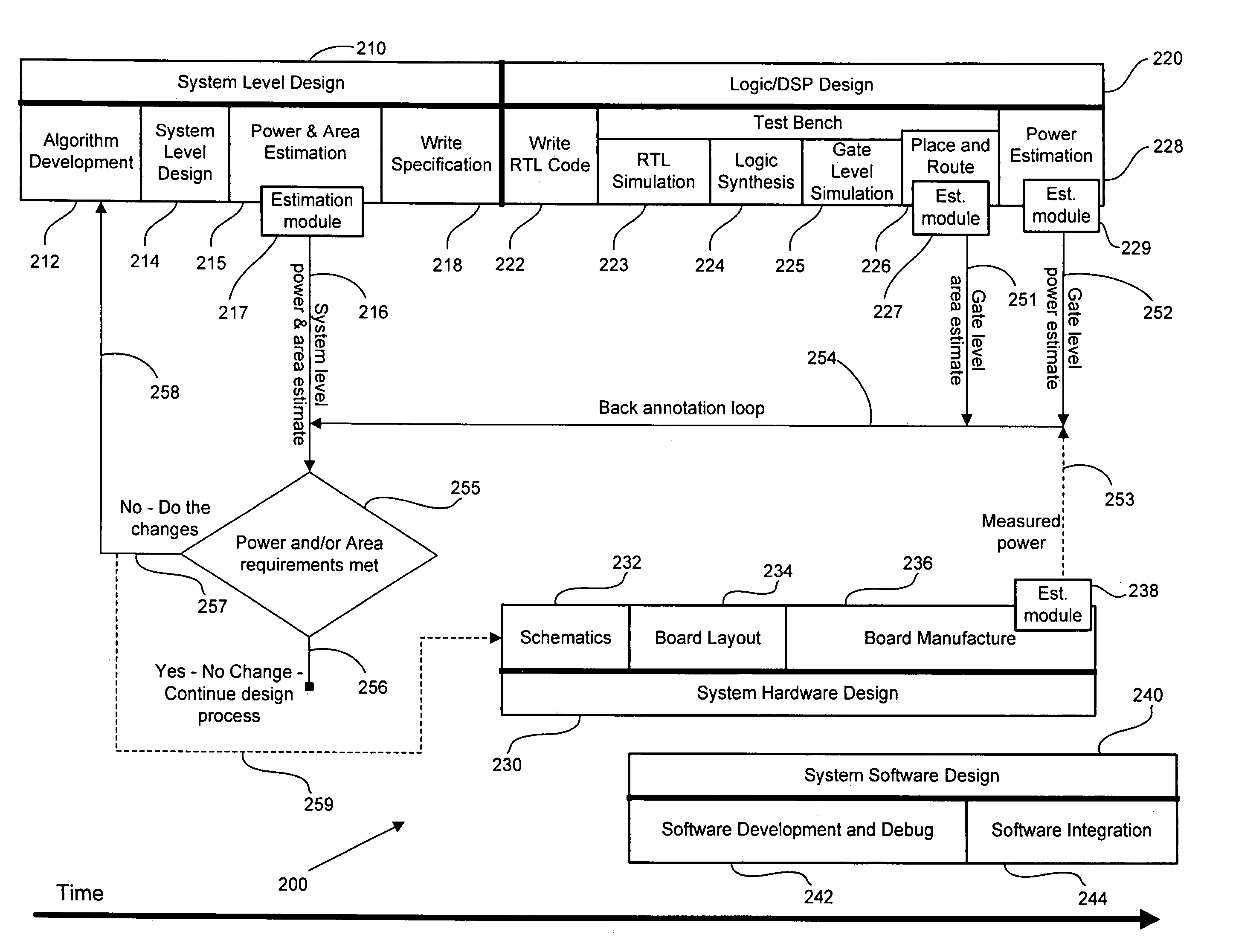

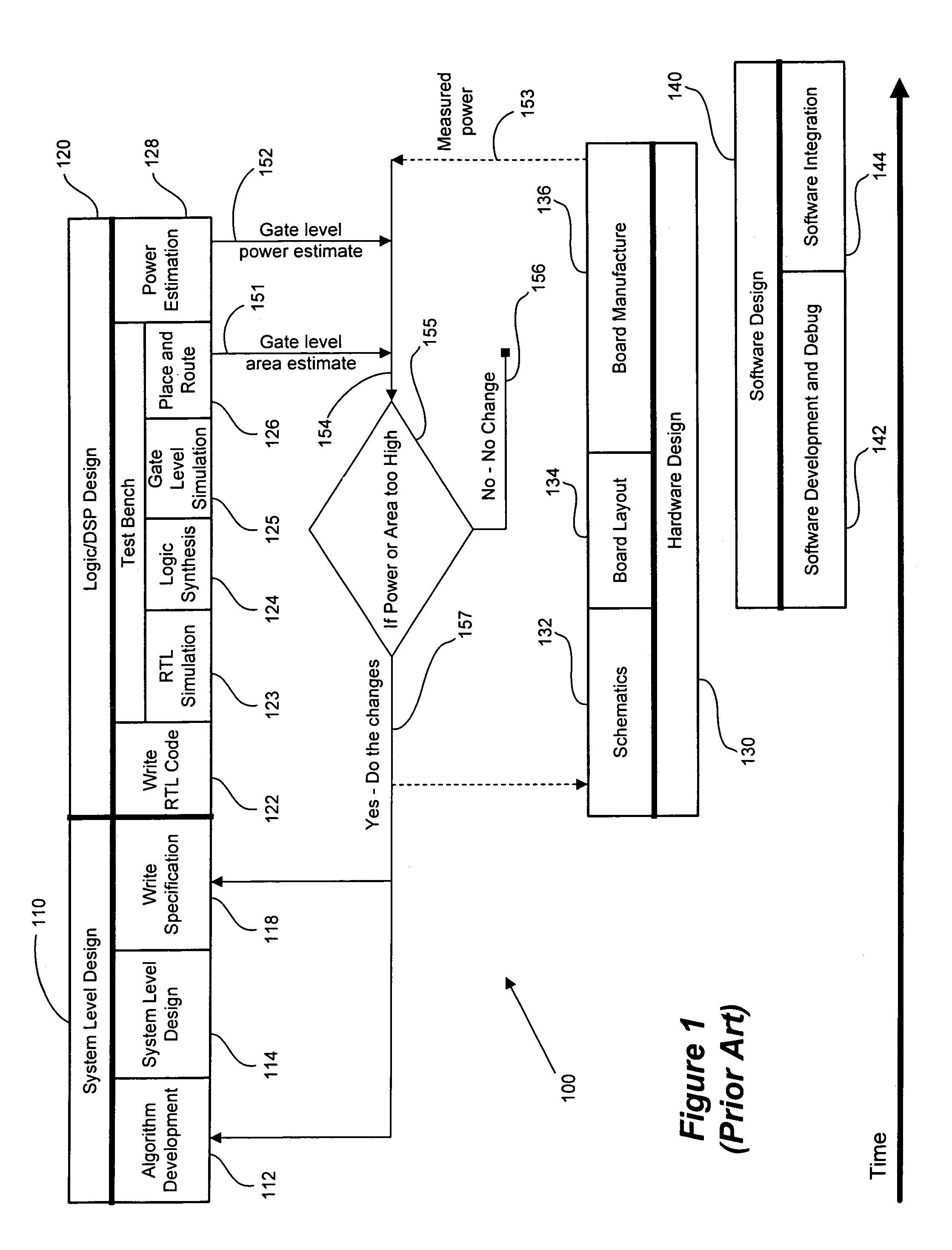

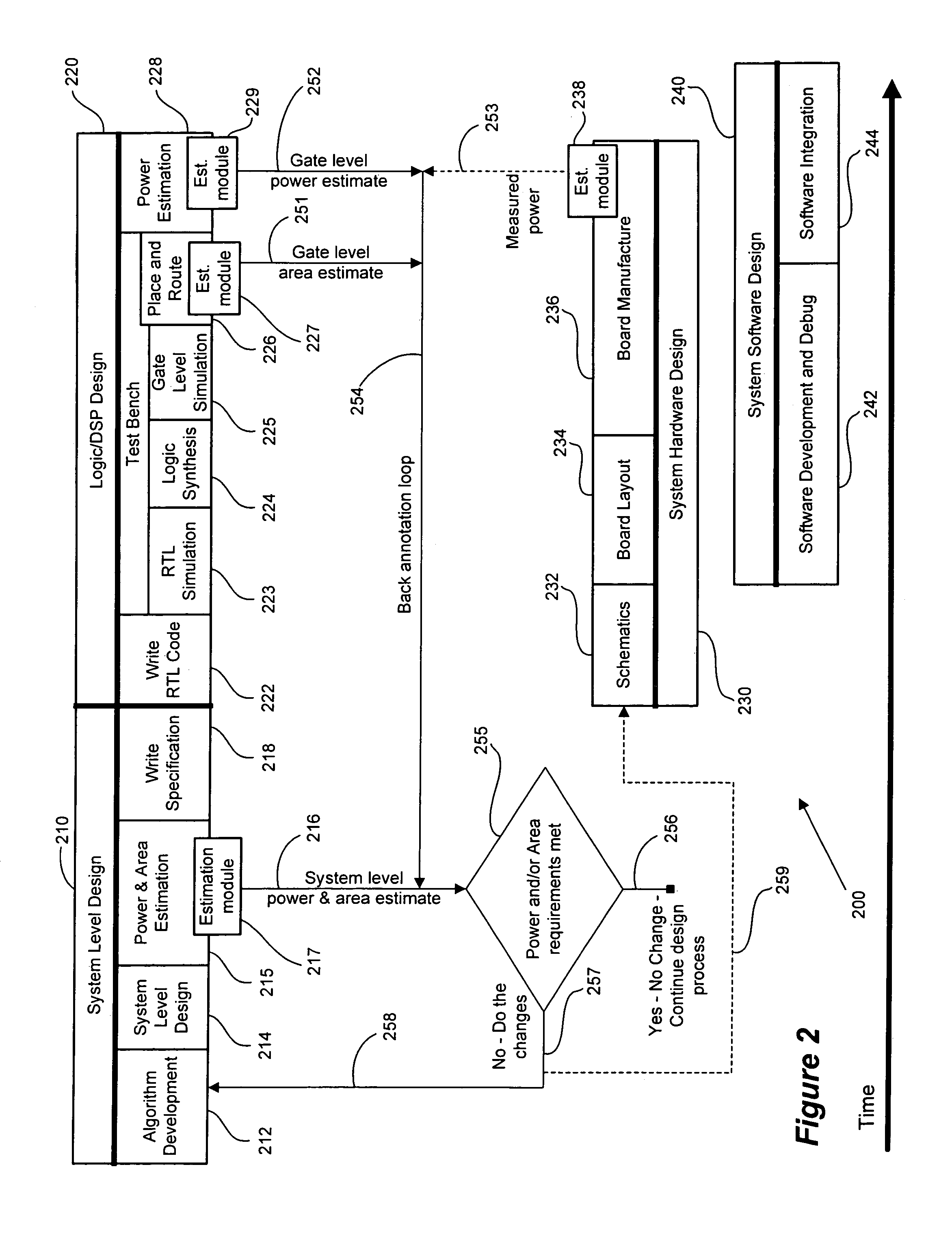

DSP design system level power estimation

ActiveUS7143368B1Save resourcesCAD circuit designSoftware simulation/interpretation/emulationEngineeringElectronic design

Power consumption estimation is performed at the system level in a design process, thus allowing early evaluation of feasibility and other considerations relating to logic / DSP design and hardware implementation of a proposed electronic design. Evaluation of the system level power consumption estimate(s) permits adjustment of a system level representation of the proposed electronic design, prior to investment of substantial resources in the electronic design. Other estimates, including other power consumption estimates, may be performed to adjust the proposed electronic design as well. Such estimates may be made in response to gate level power consumption estimates and / or hardware level power consumption estimates.

Owner:ALTERA CORP

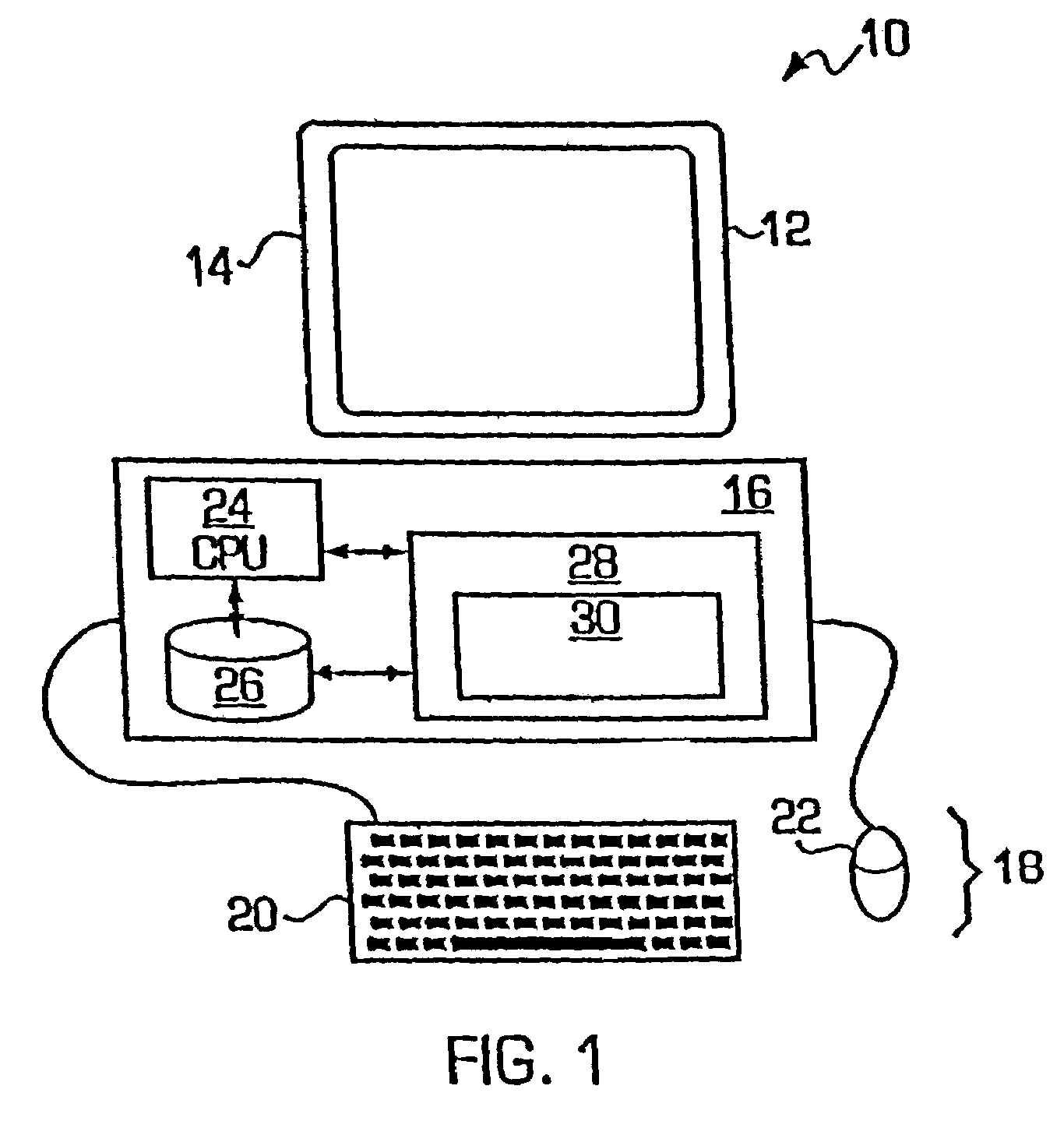

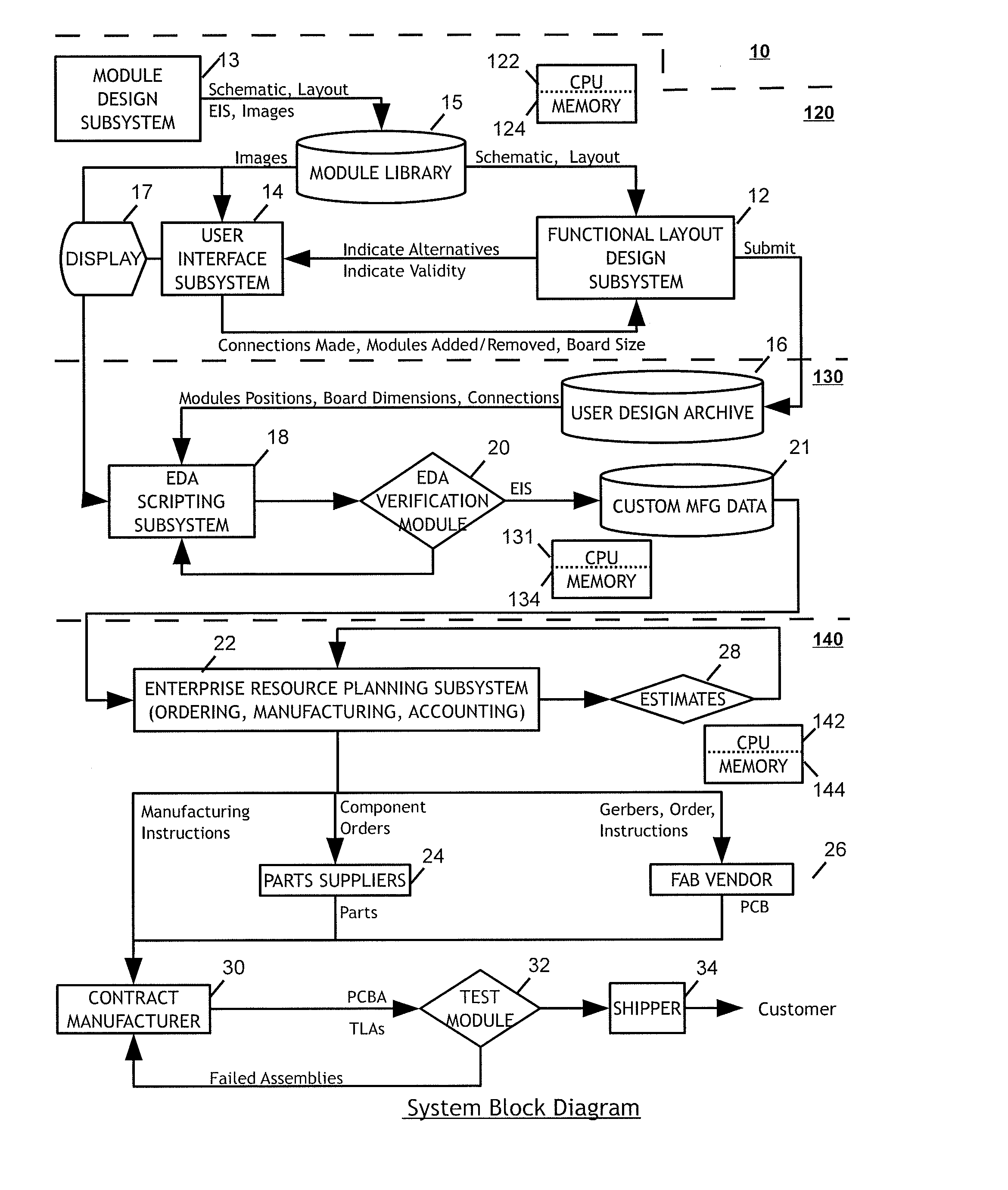

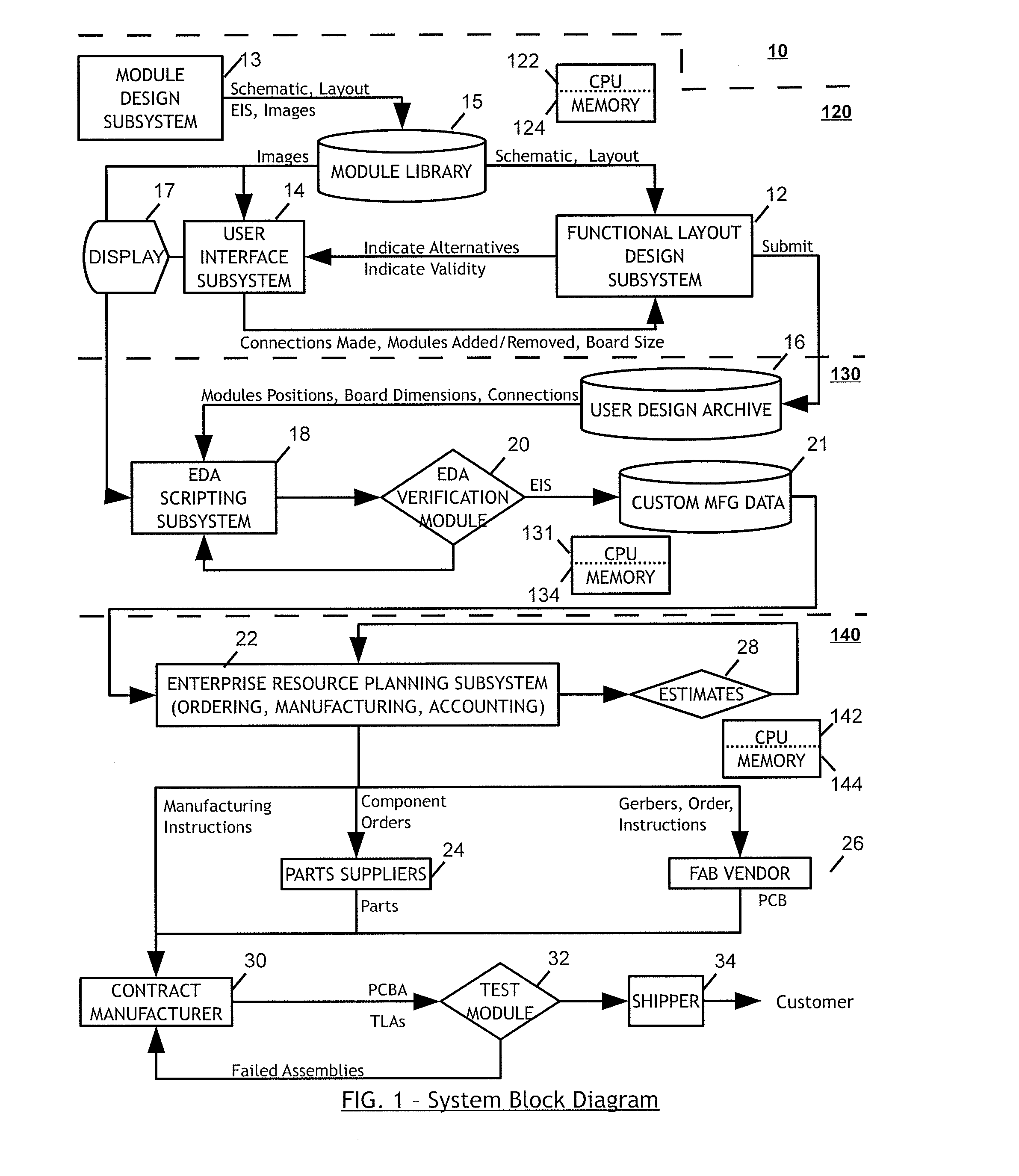

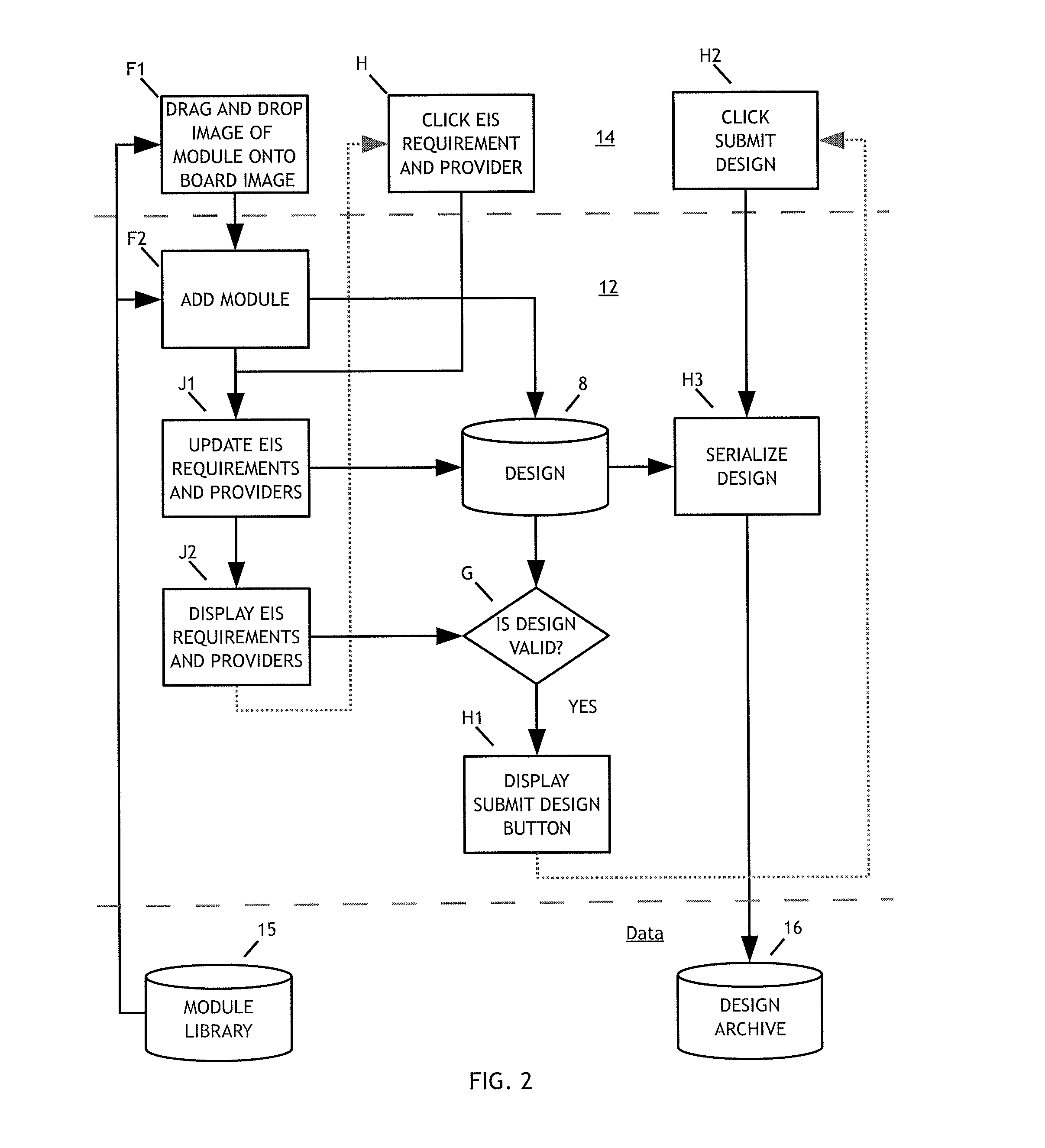

Integrated electronic design automation system

ActiveUS20130326457A1Minimal human interventionEliminate needConfiguration CADTotal factory controlManufacturing execution systemElectronic design automation

An electronic design automation system combines features of discrete EDA / CAD systems and manufacturing systems into a monolithic system to enable a layperson to efficiently design, construct and have manufactured a specific class of custom electronic device, namely a computer processing unit with embedded software. A Graphical User Interface (GUI) is provided as the front-end to a Computer Aided Design (CAD) server that generates sophisticated control and manufacturing instructions that are delivered to a fabrication supply chain, which produces a specified device that is then transported via managed logistics into inventory and ordering systems at vendors for delivery to a designated customer.

Owner:ALTIUM LLC