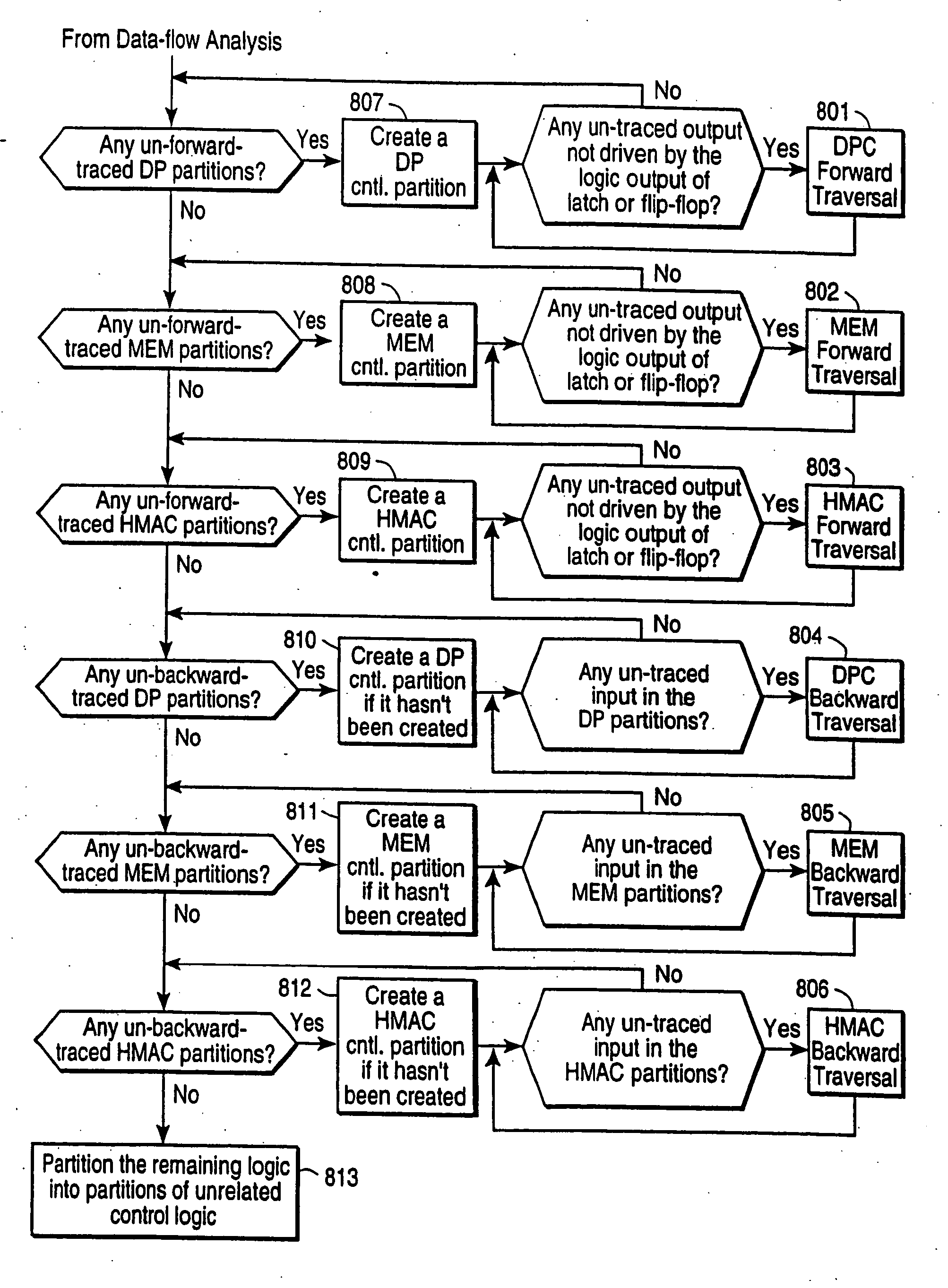

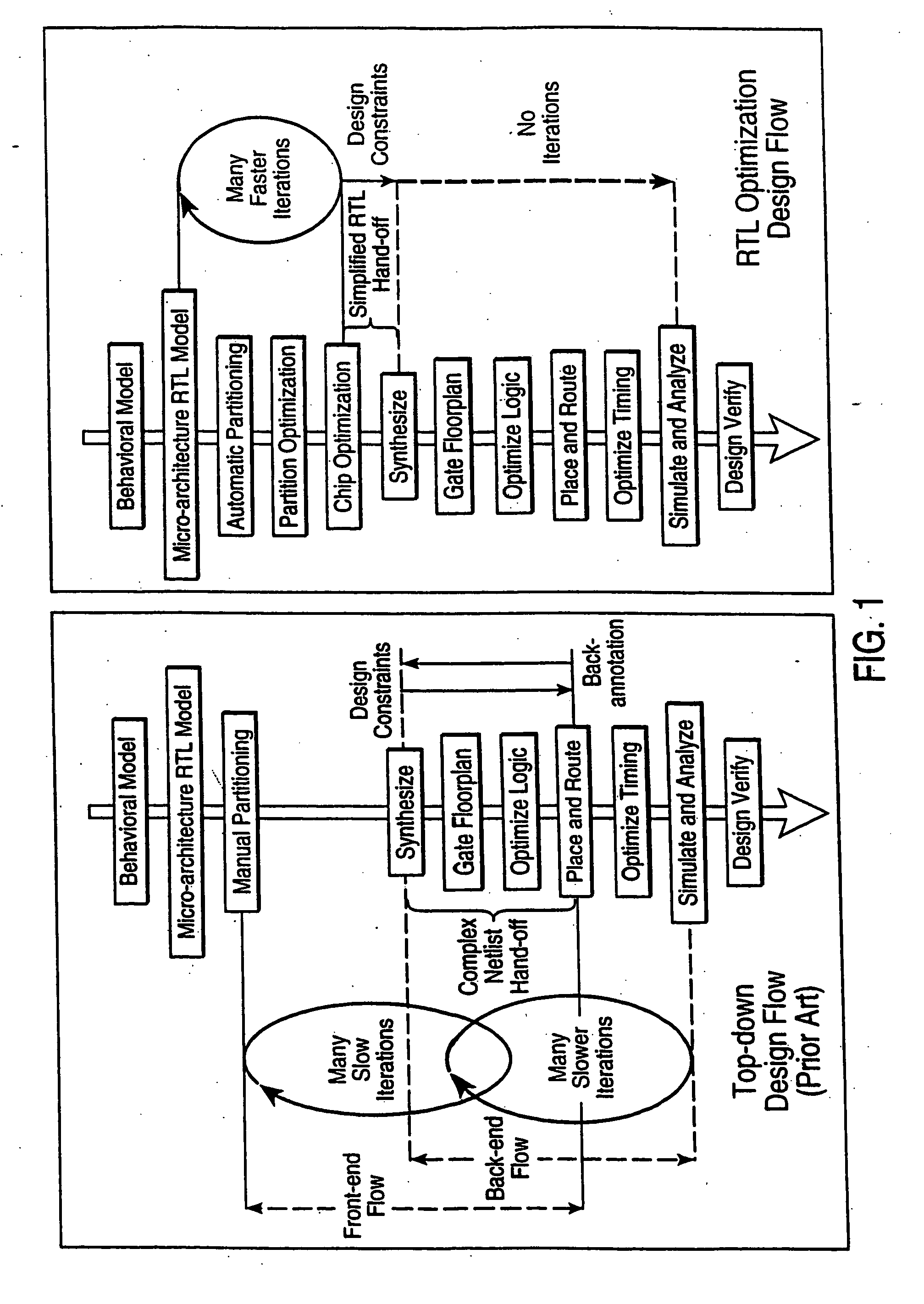

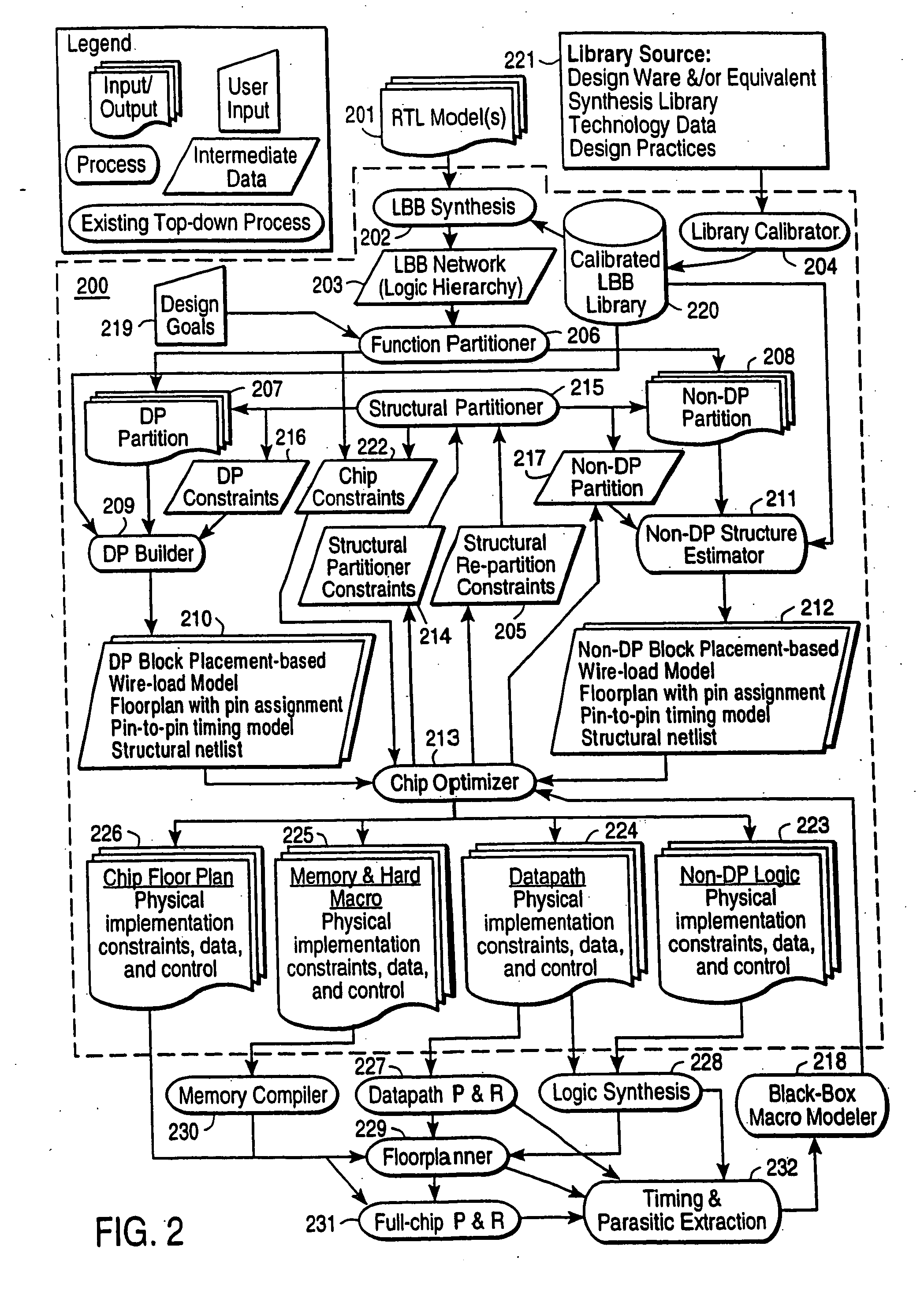

Each of these flows involve multiple

time consuming iterations, and the exchange of very complex information.

While the synthesis and place-and-

route automation represent a significant productivity improvement over an otherwise tedious and error-prone manual

design process, the top-down design methodology has failed to produce efficient physical implementations of many circuit designs that take full

advantage of the capability of advanced

IC manufacturing processes.

In contrast, designers using conventional top-down EDA tools struggle with the creation, analysis, and

verification of integrated circuits having 0.5-1 million gates, running at 150 MHz.

The primary inefficiency of the top-down methodology arises from its reliance on statistical wire-load models proved to be inadequate in wire-

delay dominated deep sub-micron digital systems.

These tools use inaccurate, statistical wire-load estimates to model wiring parasitics at early stages in the

design cycle, and the effects of these inaccuracies are propagated throughout the rest of the design methodology.

The large discrepancy between statistical wire-

load model and actual wire-load means that circuit designers must wait until gate-level floorplanning and

place and route tasks are complete to begin

chip-level optimization.

Place-and-

route execution times for these circuits can also consume many hours.

During manual partitioning, however, the designer has little or no accurate information on the back-end physical effect of the partitioning, and in particular, on the effect of such partitions on timing, area, and

power consumption.

The failure to predict accurate back-end physical effect at or above the RTL

design stage results in local optimization and a sub-optimal

functional description of the design.

Design efficiency suffers due to design over-constraint (timing non-convergence) or under-constraint (loss of performance and density), or some combination of both for various different partitions of the

integrated circuit.

Sub-optimal RTL descriptions and partitioning serve as a poor starting point for logic synthesis, which propagates and amplifies the design deficiencies, eventually leading to

silicon inefficiency (e.g., excessive area or

power consumption, slower

operating frequency), even after long iteration and manual intervention.

Further inefficiency in the top-down design methodology is introduced because logic synthesis tools treat all logic as

random logic.

Consequently, logic synthesis typically fails to recognize and take

advantage of more efficient

silicon structures such as datapaths, which are commonly used and expressed in the high level description of the design.

This is equivalent to writing a gate-level

netlist, an onerous, low-productivity, and error-prone task.

Another deficiency of the top-down methodology is that it requires a cumbersome

netlist hand-off between front-end and back-end design cycles.

The diverse design expertise required to effectively manage the top-down

design process is rare and not commonly available to a typical

design team.

Design inefficiency causes the costly under-utilization of advanced

IC manufacturing processes.

The iterative nature of the top-down design methodology requires long design time and large design teams, often not available or even feasible in a competitive design environment characterized by short product life-cycles and short time-to-market requirements.

Thus, achieving rapid timing convergence while satisfying density, power, and productivity constraints for high performance complex systems is a daunting challenge facing the

electronic design industry today.

Login to View More

Login to View More  Login to View More

Login to View More