Patents

Literature

391 results about "Ic manufacturing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

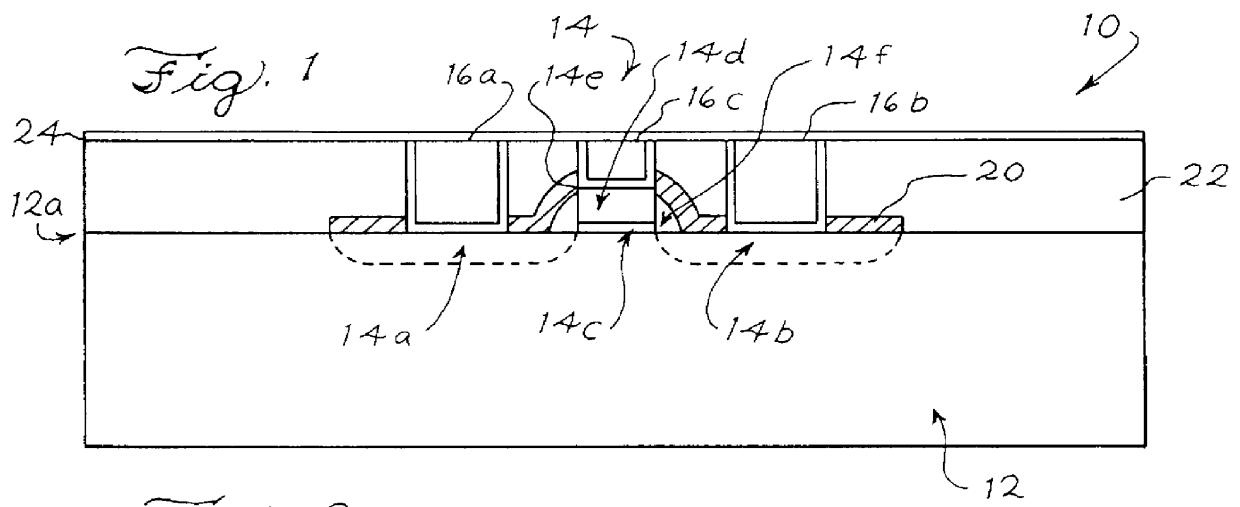

Apparatus of antenna with heat slug and its fabricating process

ActiveUS20060071308A1Simple structureEasy to makeAntenna supports/mountingsSemiconductor/solid-state device detailsEngineeringDual band antenna

An apparatus of antenna with heat slug and its fabricating process are provided, in which the antenna with heat slug can be realized with a single sheet or double sheets of metal. A dual-band antenna module with a mask cover is taken as an example to realize the apparatus. Each single sheet of metal can be achieved by simply cutting and bending a metal plate. Thereby, it is a simple and low-cost fabricating process. In the known fabricating process of integrated circuit, the heat slug and the antenna can be combined in a module at the same step. Therefore, integrating the antenna with heat slug in a fabricating process needs not to develop a new process.

Owner:IND TECH RES INST

Process for reducing copper oxide during integrated circuit fabrication

InactiveUS6033584ADecorative surface effectsSemiconductor/solid-state device manufacturingCopper interconnectCopper oxide

A method of integrated circuit fabrication creating copper interconnect structures wherein the formation of copper oxide is reduced or eliminated by etching away the copper oxide performing an H2 plasma treatment in a plasma enhanced chemical vapor deposition chamber.

Owner:ADVANCED MICRO DEVICES INC

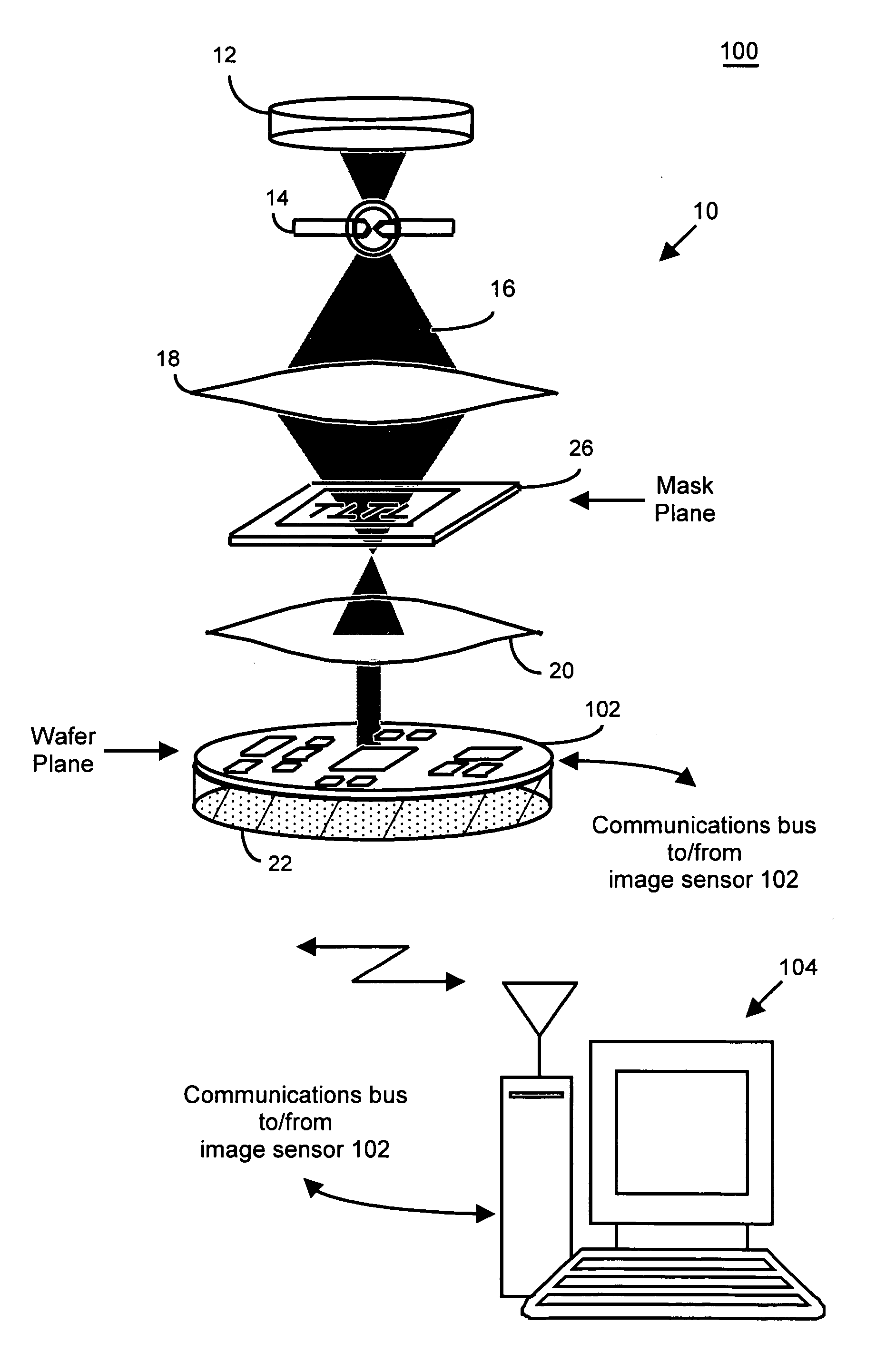

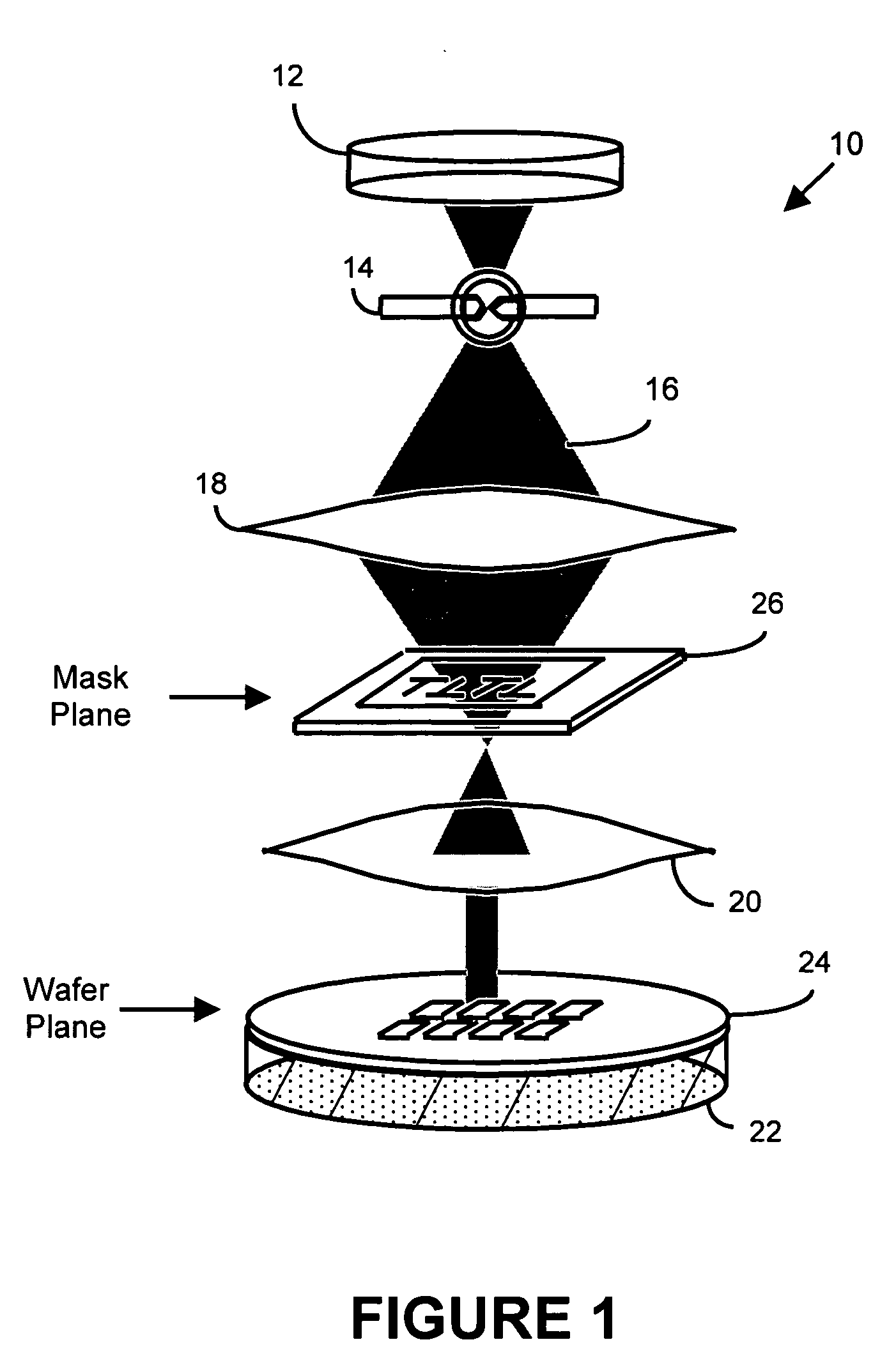

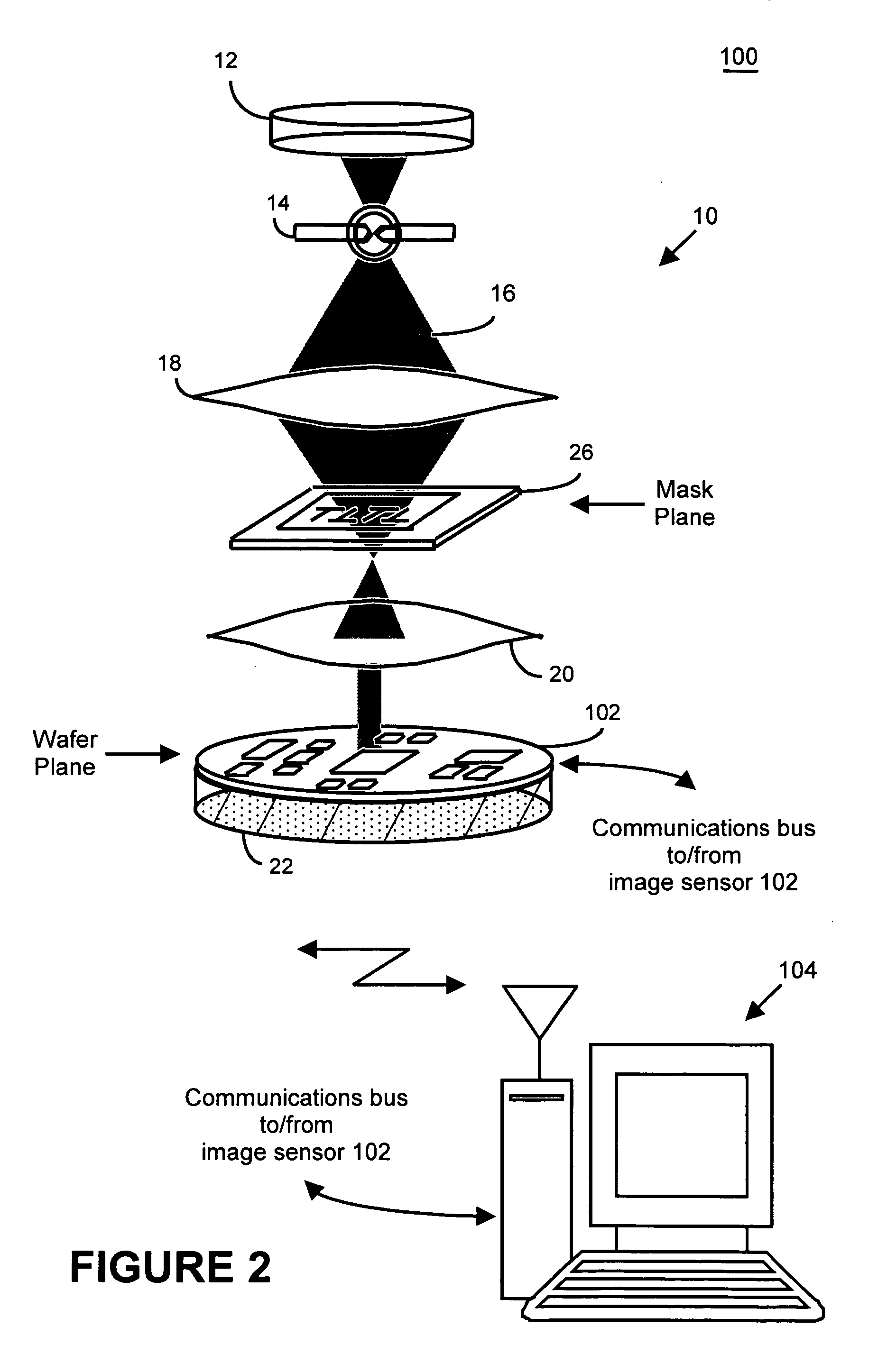

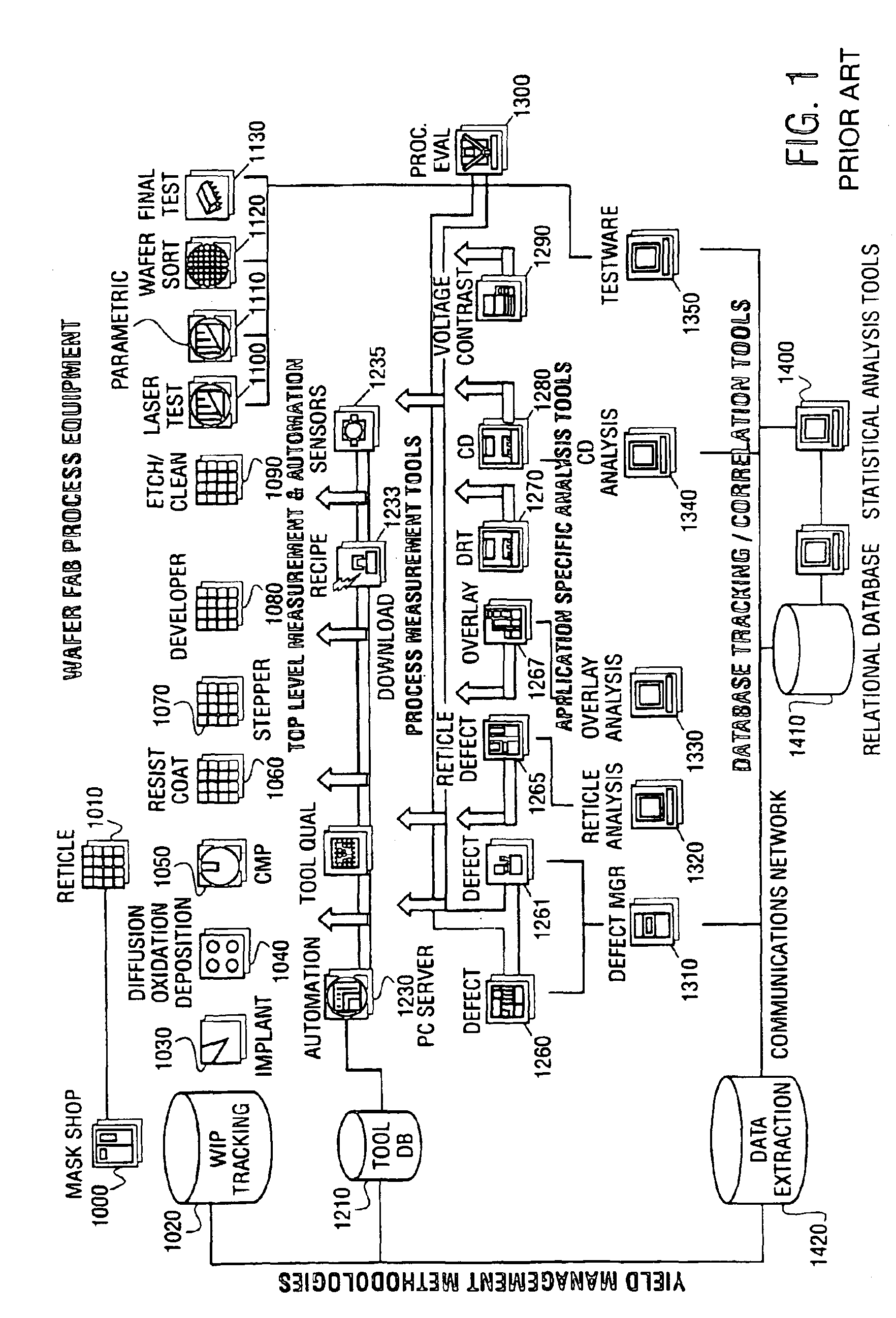

System and method for lithography process monitoring and control

InactiveUS20060000964A1Highly precise moveable platformSolid-state devicesPhotomechanical apparatusIntegrated circuit manufacturingLithography process

In one aspect, the present invention is a technique of, and a system and sensor for measuring, inspecting, characterizing and / or evaluating optical lithographic equipment, methods, and / or materials used therewith, for example, photomasks. In one embodiment, the system, sensor and technique measures, collects and / or detects an aerial image produced or generated by the interaction between the photomask and lithographic equipment. An image sensor unit may measure, collect, sense and / or detect the aerial image in situ—that is, the aerial image at the wafer plane produced, in part, by a product-type photomask (i.e., a wafer having integrated circuits formed during the integrated circuit fabrication process) and / or by associated lithographic equipment used, or to be used, to manufacture of integrated circuits. In this way, the aerial image used, generated or produced to measure, inspect, characterize and / or evaluate the photomask is the same aerial image used, generated or produced during wafer exposure in integrated circuit manufacturing. In another embodiment, the system, sensor and technique characterizes and / or evaluates the performance of the optical lithographic equipment, for example, the optical sub-system of such equipment. In this regard, in one embodiment, an image sensor unit measures, collects, senses and / or detects the aerial image produced or generated by the interaction between lithographic equipment and a photomask having a known, predetermined or fixed pattern (i.e., test mask). In this way, the system, sensor and technique collects, senses and / or detects the aerial image produced or generated by the test mask—lithographic equipment in order to inspect, evaluate and / or characterize the performance of the lithographic equipment.

Owner:ASML NETHERLANDS BV

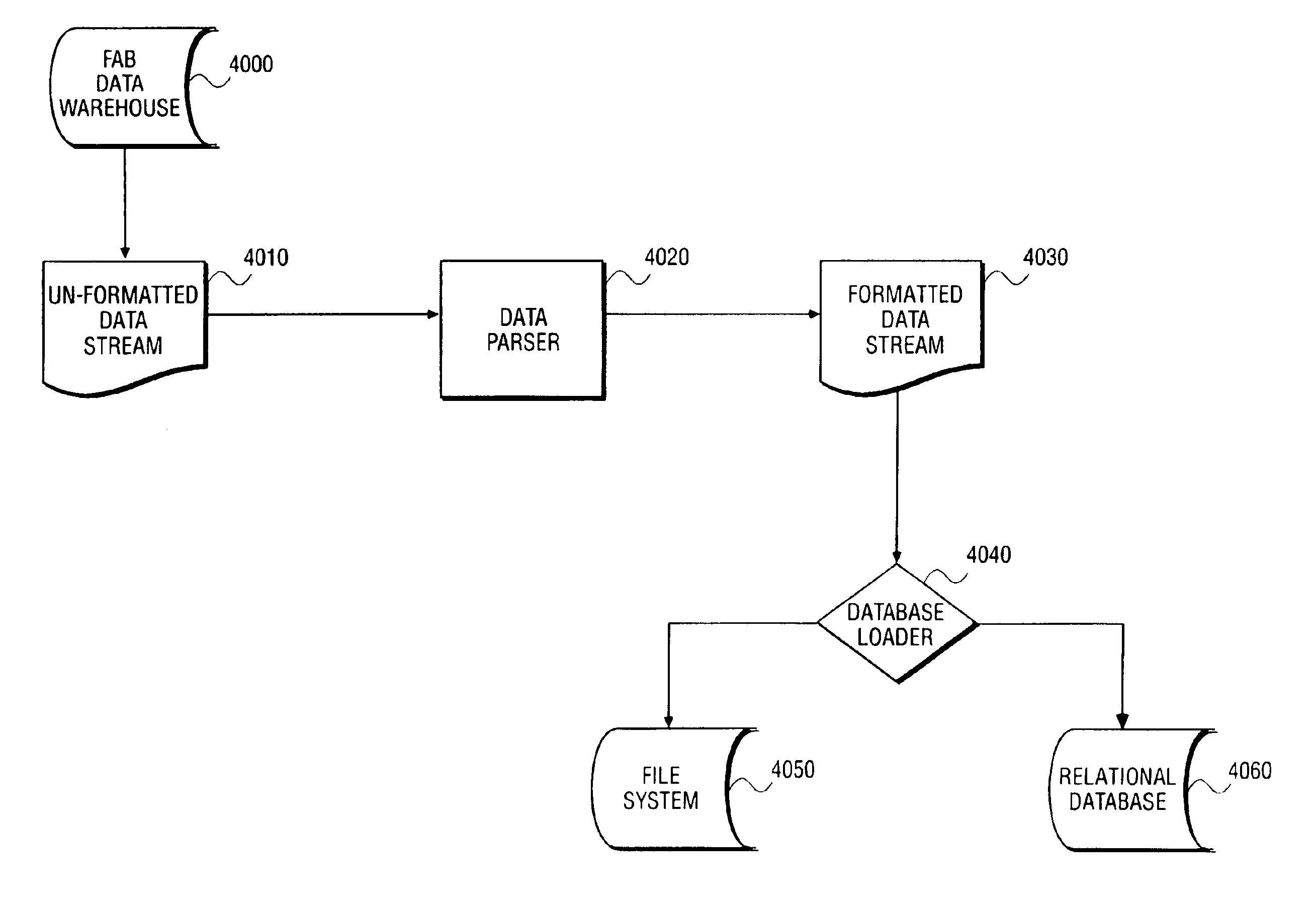

Method and apparatus for analyzing manufacturing data

A method for data mining information obtained in an integrated circuit fabrication factory (“fab”) that includes steps of: (a) gathering data from the fab from one or more of systems, tools, and databases that produce data in the fab or collect data from the fab; (b) formatting the data and storing the formatted data in a source database; (c) extracting portions of the data for use in data mining in accordance with a user specified configuration file; (d) data mining the extracted portions of data in response to a user specified analysis configuration file; (e) storing results of data mining in a results database; and (f) providing access to the results.

Owner:APPLIED MATERIALS INC

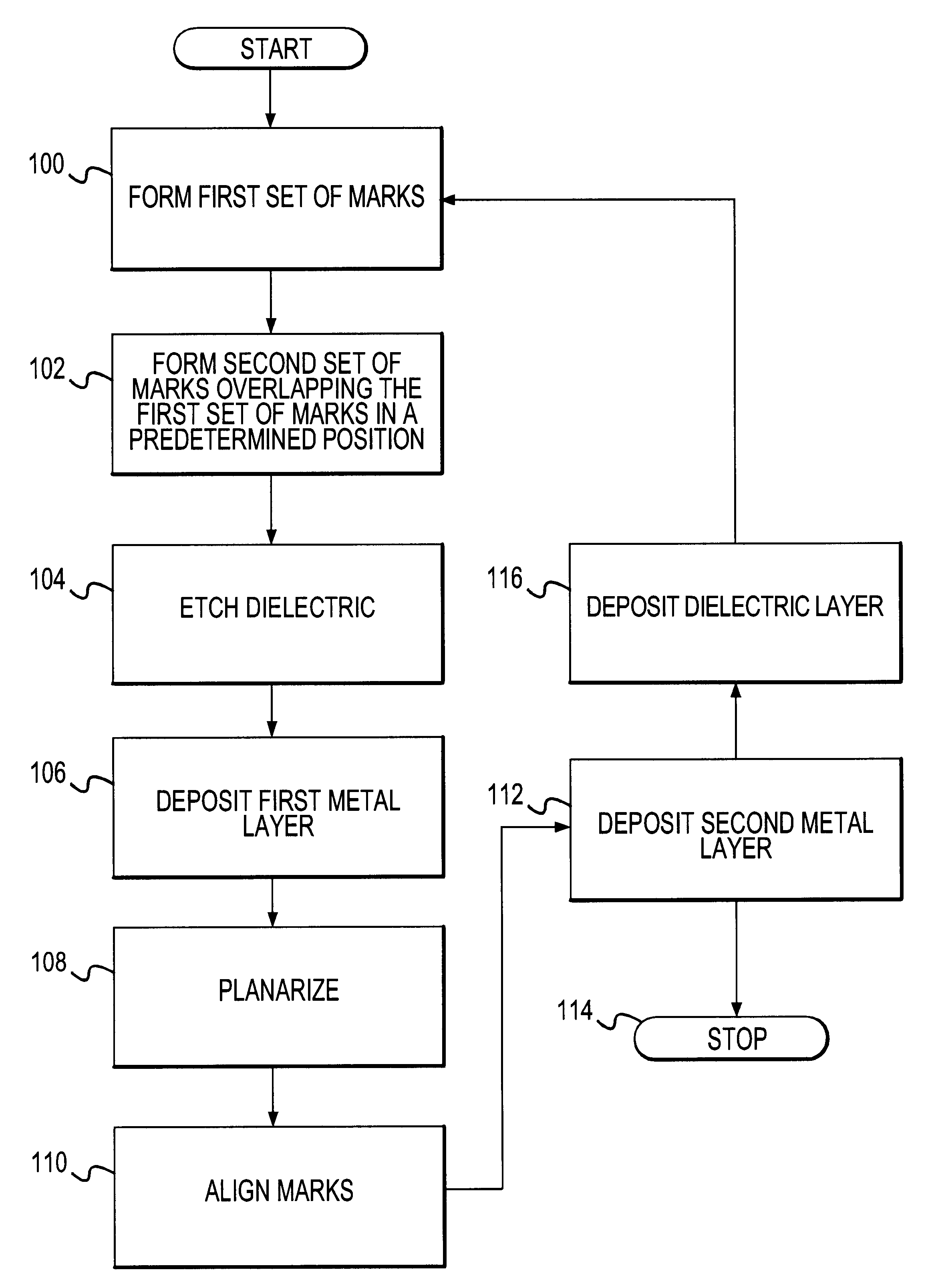

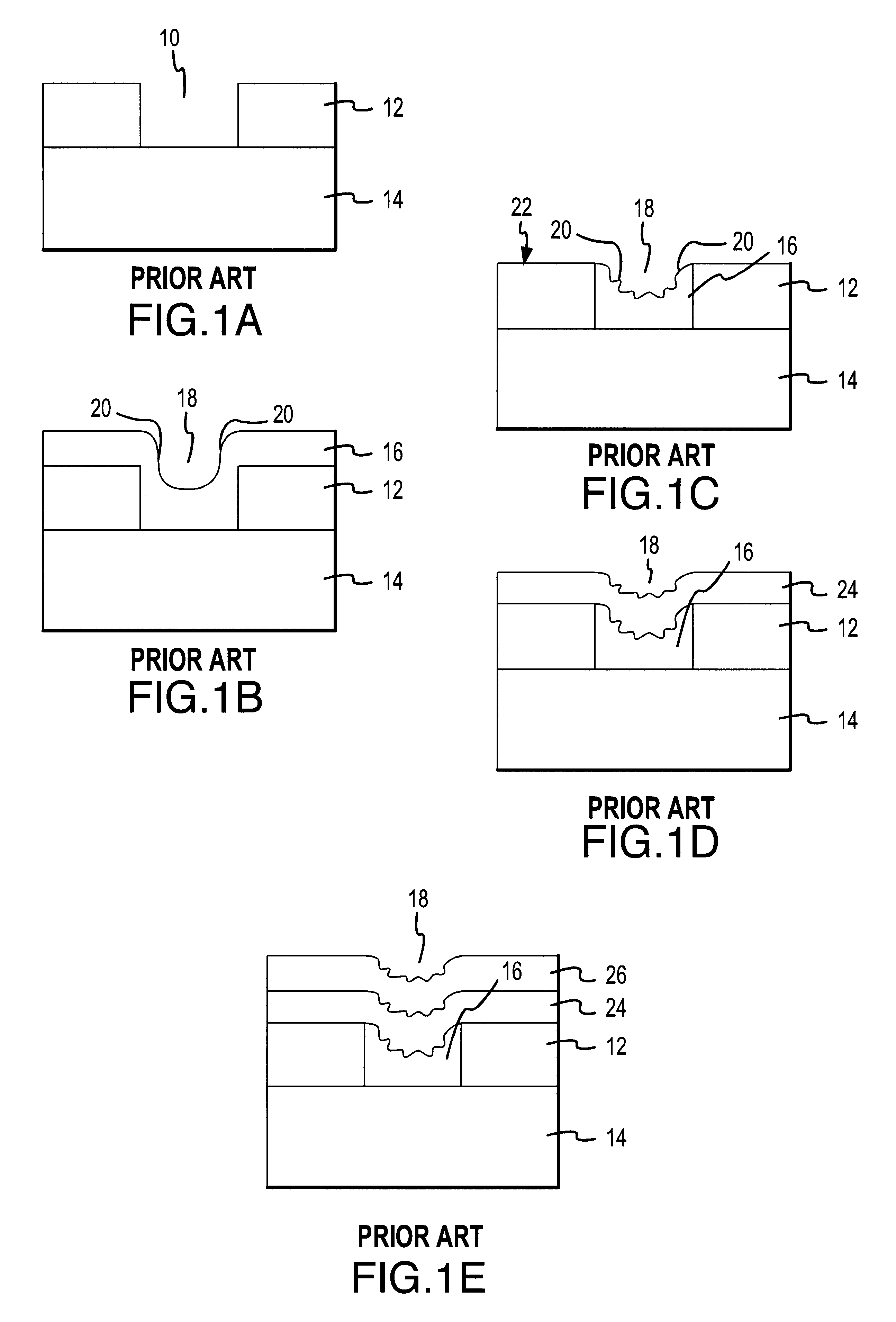

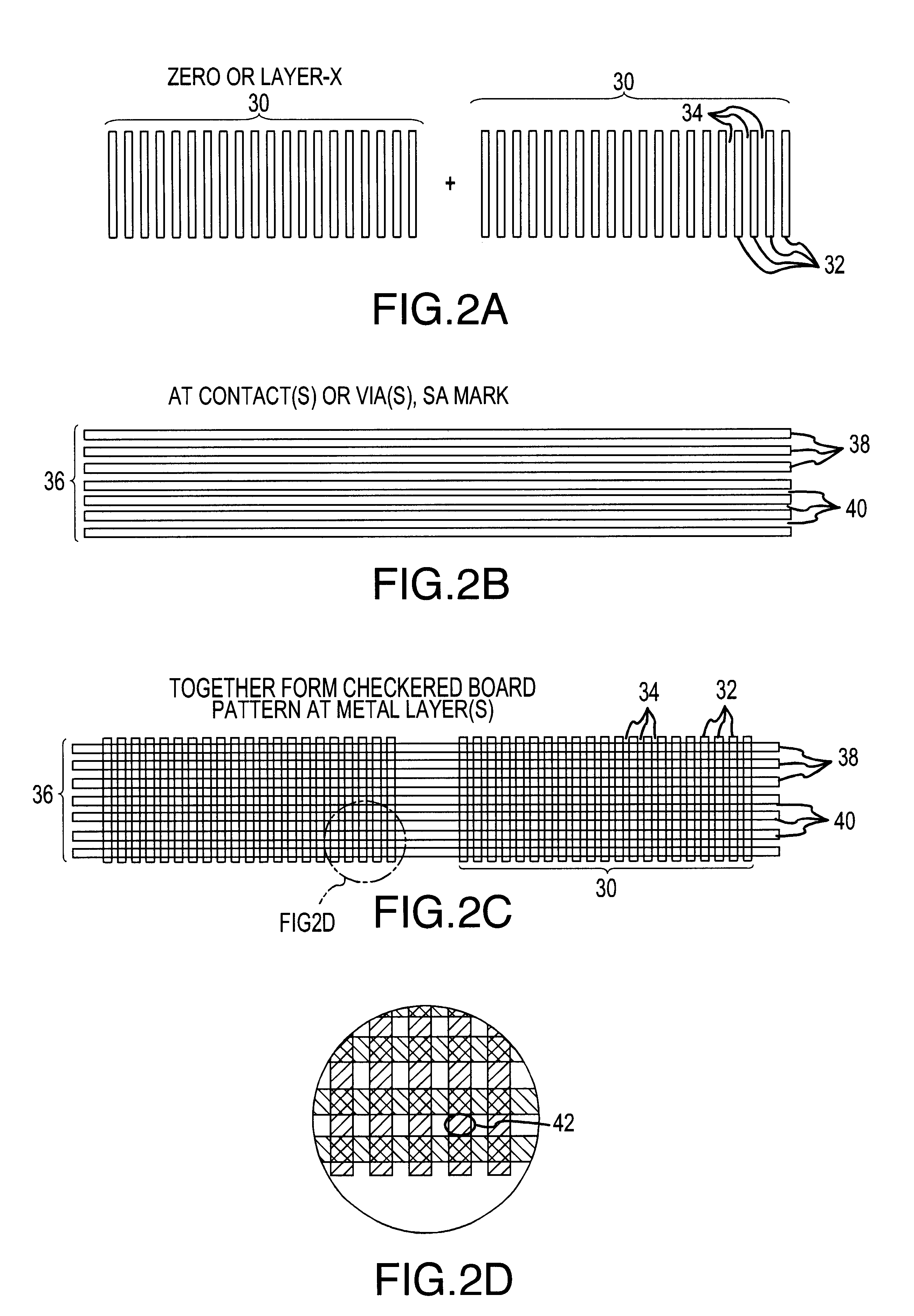

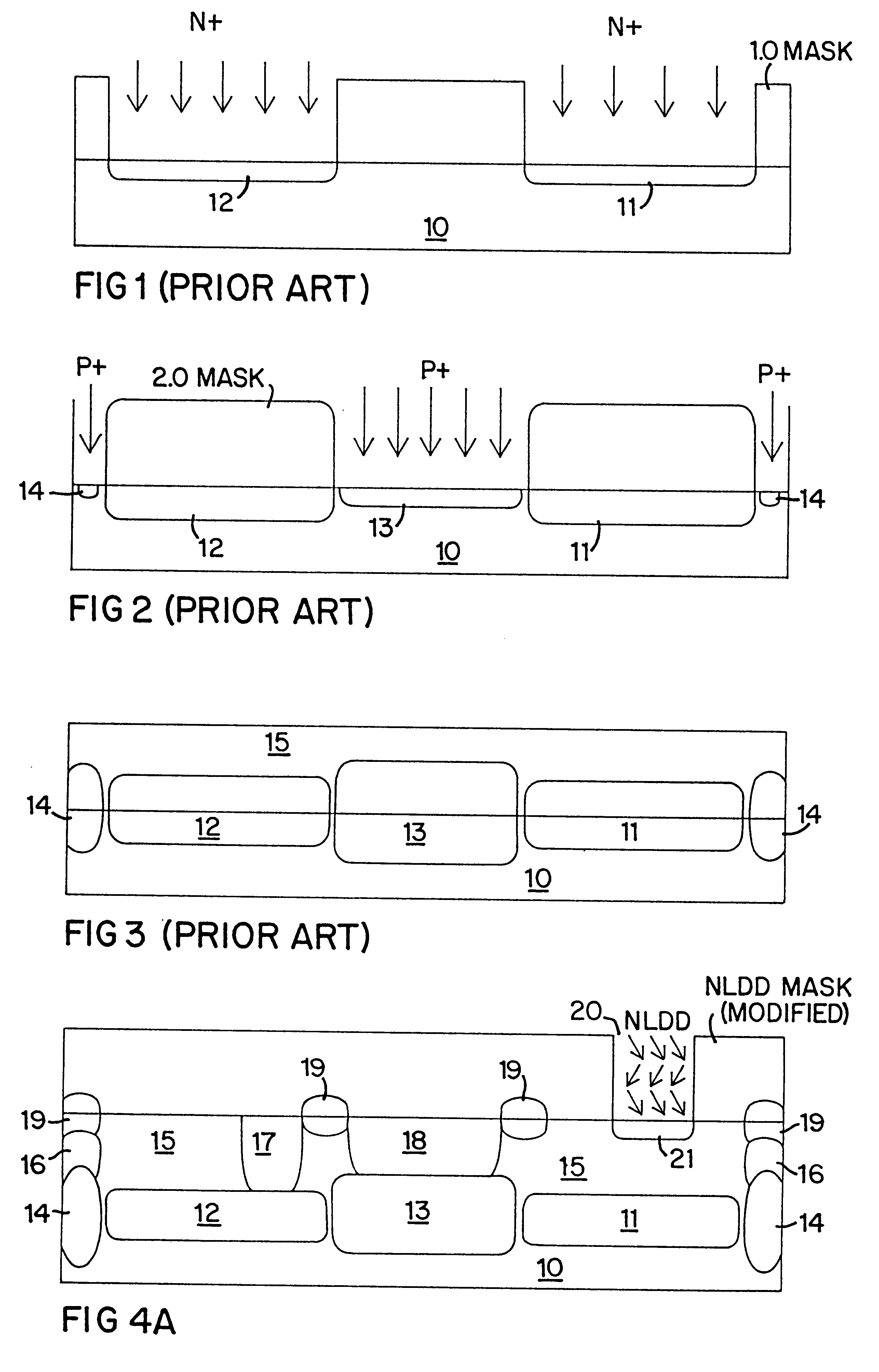

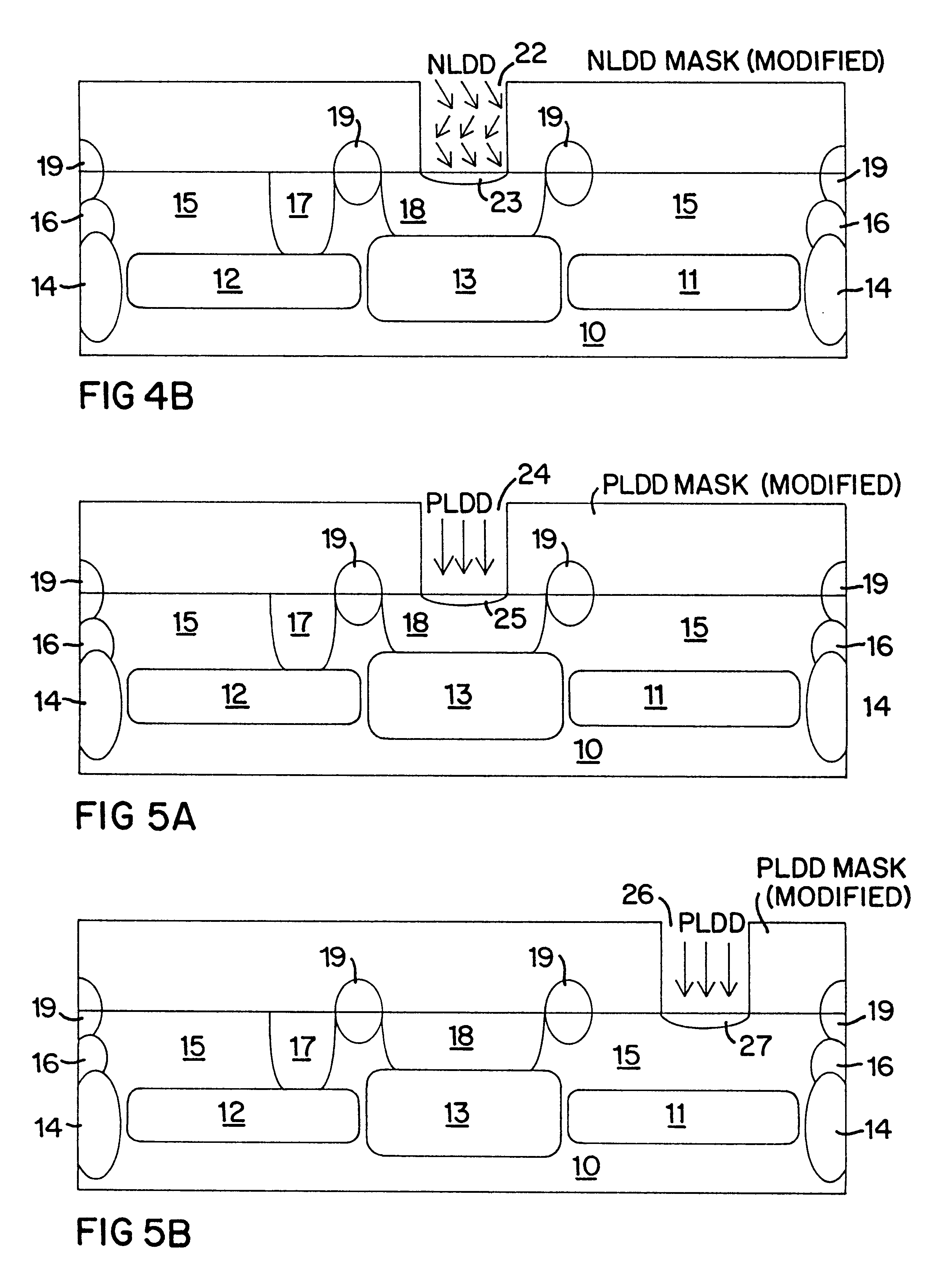

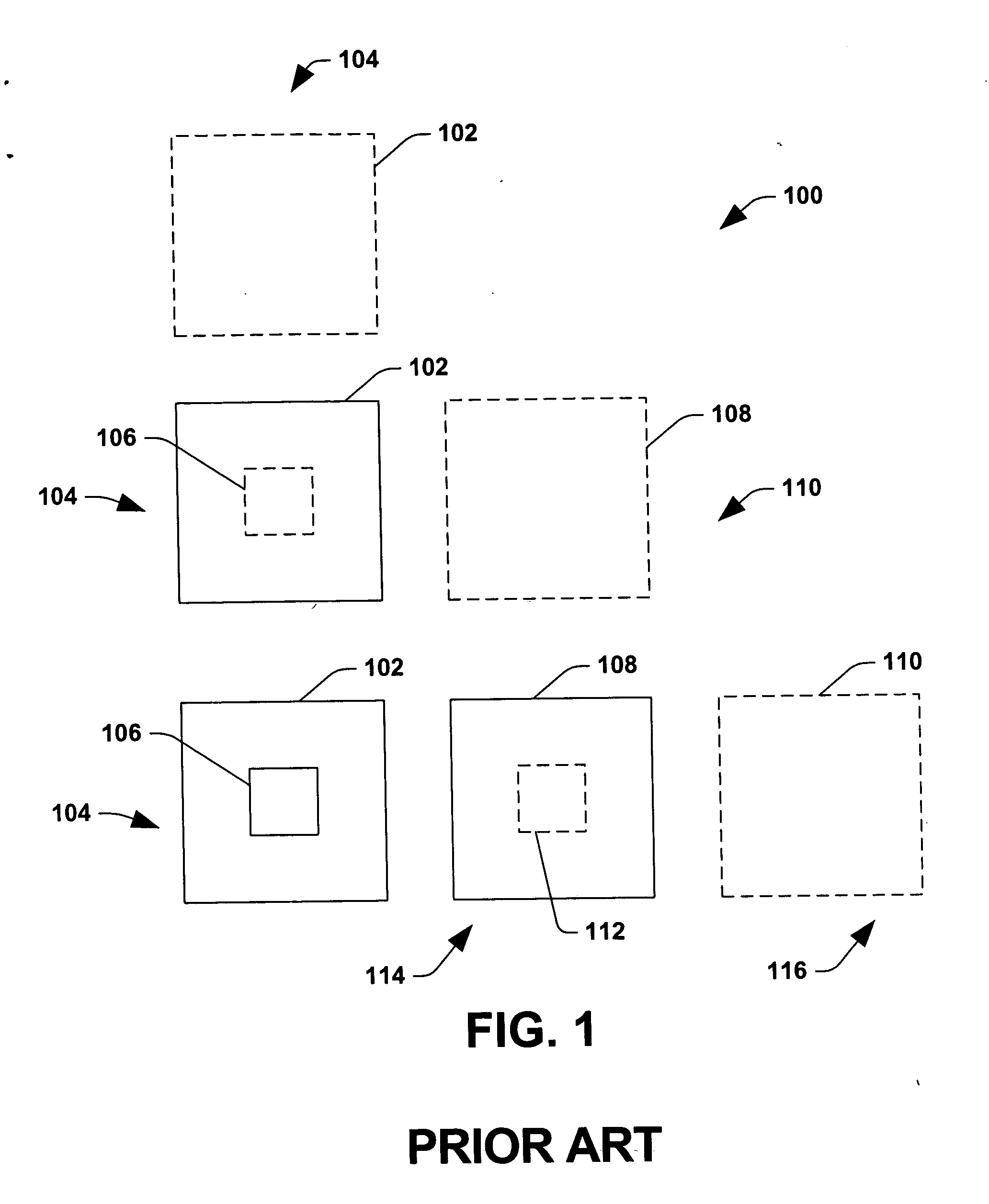

Method for creating and preserving alignment marks for aligning mask layers in integrated circuit manufacture

InactiveUS6261918B1Semiconductor/solid-state device detailsSolid-state devicesEngineeringIntegrated circuit

A method for creating and preserving alignment marks used for aligning mask layers in integrated circuit formation including the steps of creating a first set of marks within a reference layer to form a basic alignment mark, creating a second set of marks overlapping the first set of marks and positioned perpendicular to the first set of marks in the same reference layer to form a preservation pattern, and etching the reference layer to form a substantially checkerboard-type pattern where portions of the first set of marks are recessed within a thickness of the reference layer. After creating the checkerboard-type pattern formed from the first and second marks, a first metal a layer may be deposited to fill in any recesses contained within the pattern. CMP follows without damaging the segmented portions of the first set of marks which lie recessed within a thickness of the reference layer. Finally, the preserved portions of the first set of marks are aligned with pattern marks for a second metal layer.

Owner:NEWPORT FAB

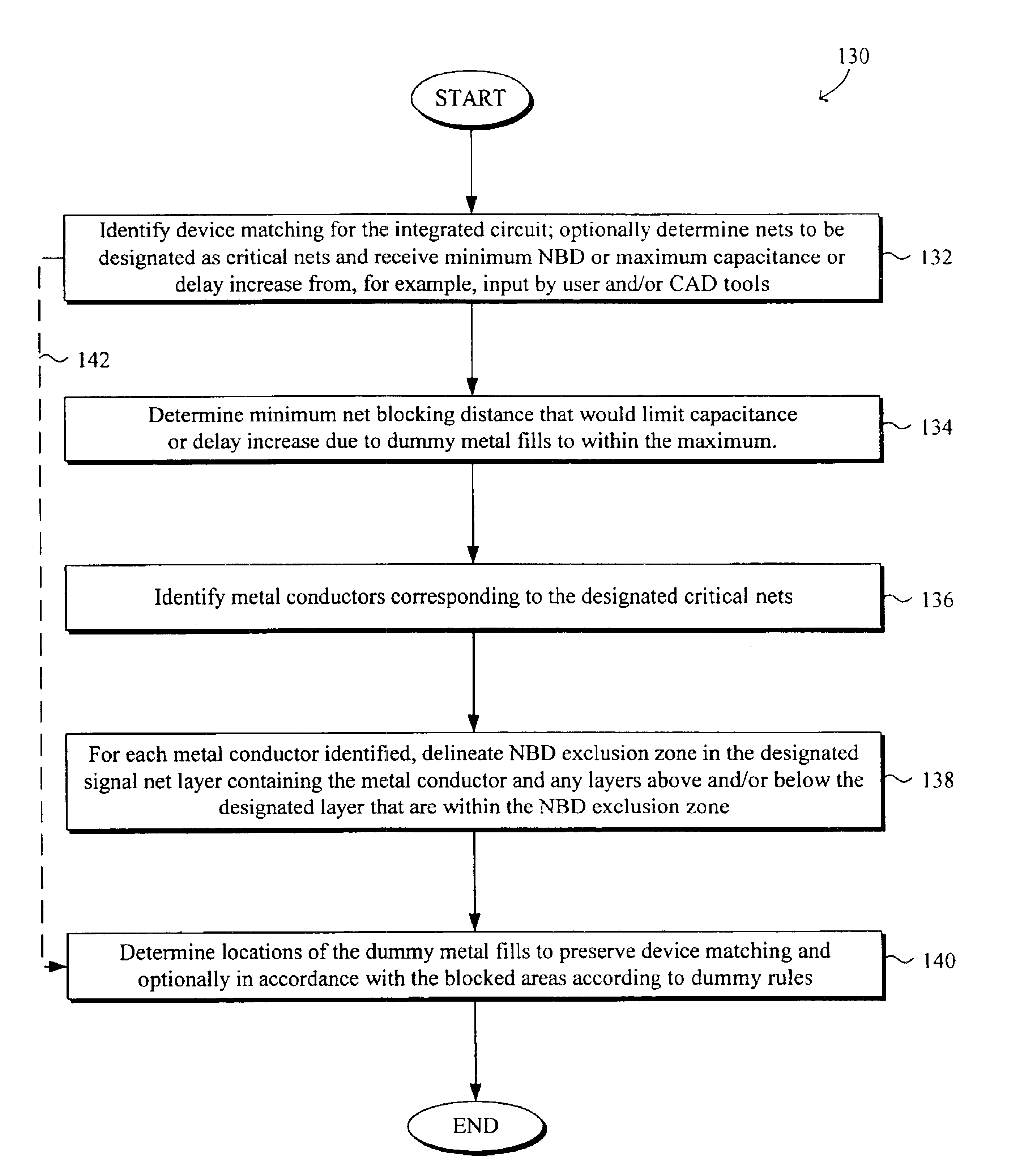

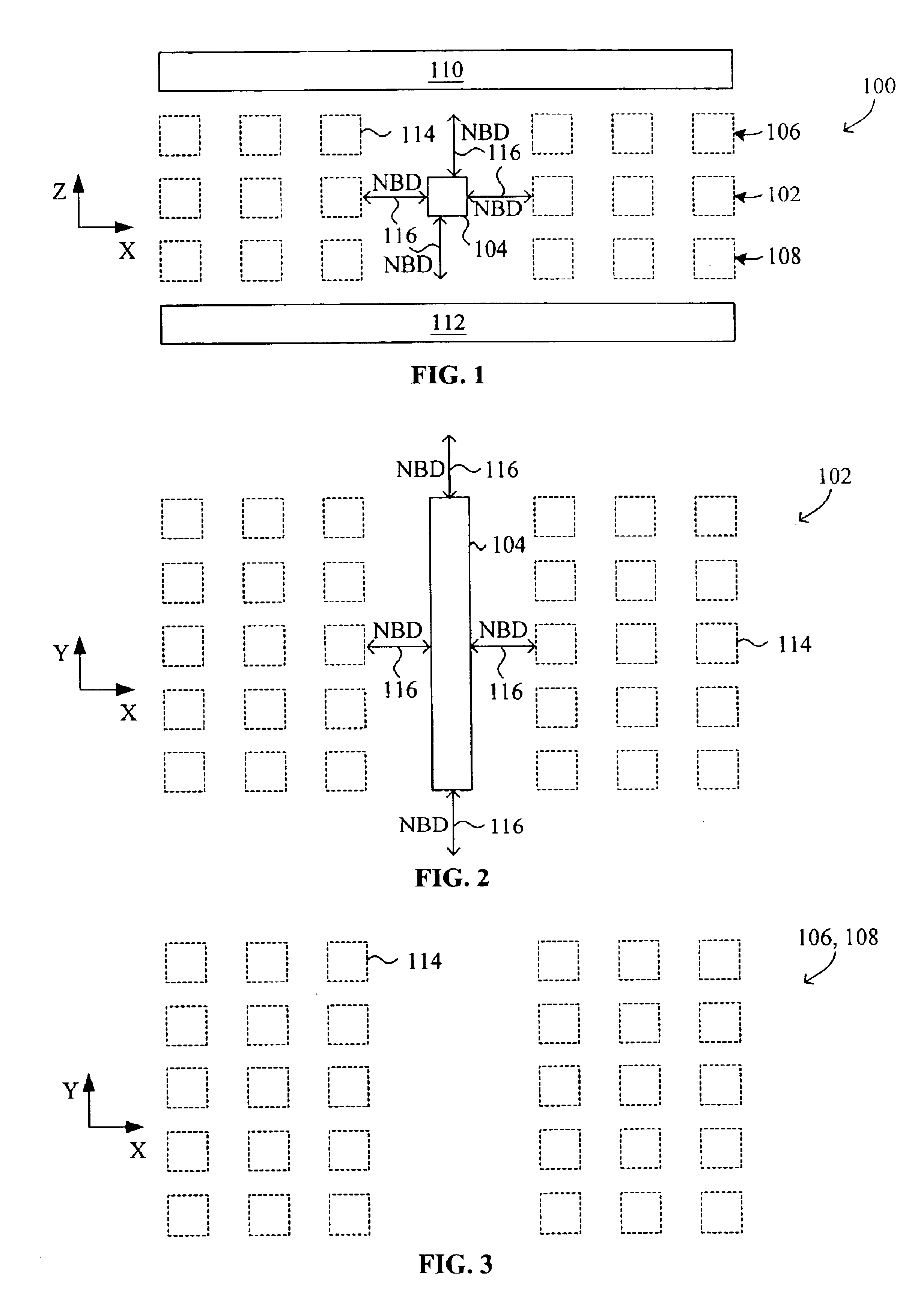

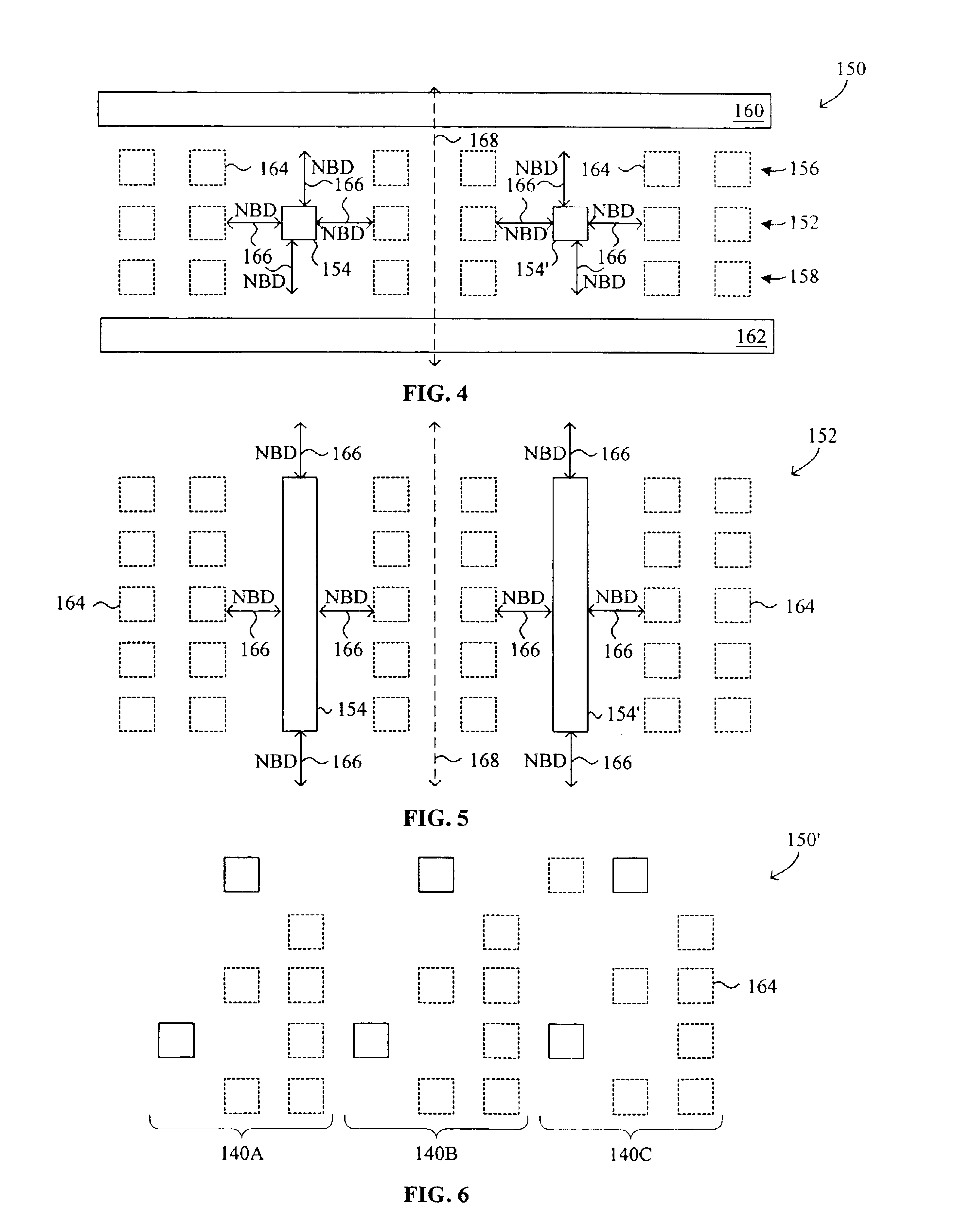

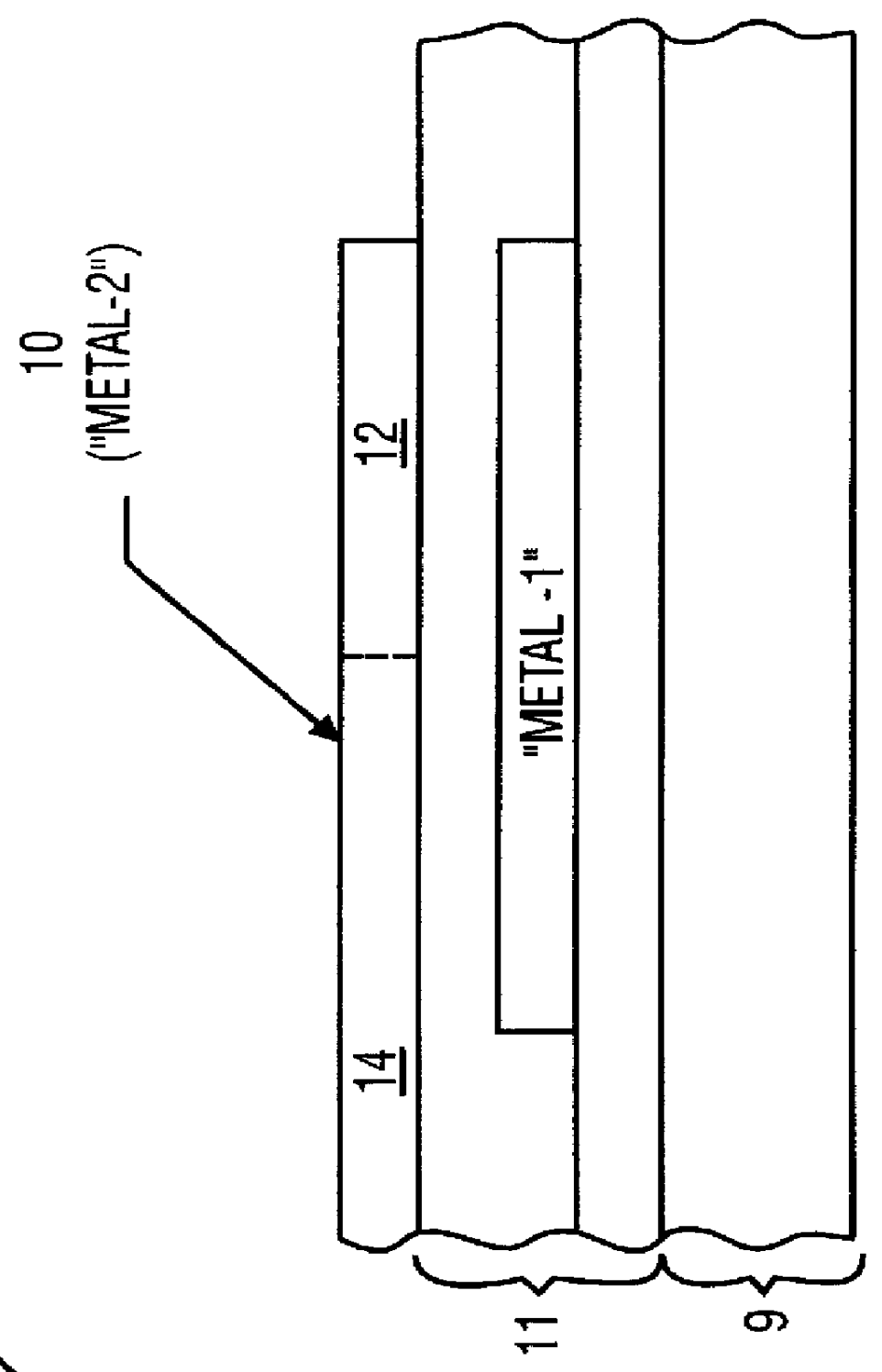

System and method for placement of dummy metal fills while preserving device matching and/or limiting capacitance increase

InactiveUS6904581B1CAD circuit designSoftware simulation/interpretation/emulationCapacitanceElectrical conductor

Systems and methods for placement of dummy metal fills while preventing disturbance of device matching and optionally limiting capacitance increase are disclosed. A computer-automated method for locating dummy fills in an integrated circuit fabrication process generally comprises receiving an input layout of the integrated circuit and specification of device matching for the integrated circuit and locating the dummy fills in the integrated circuit according to dummy rules while preserving device matching. Locating the dummy fills may include locating the dummy fills along the at least one axis of symmetry where device matching is along an axis of symmetry and locating the dummy fills so as to preserve matching of the repeated elements where device matching is repeated matched elements. The method may also include designating at least one net of the integrated circuit as a critical net, the critical nets being only a subset of all nets of the integrated circuit, identifying metal conductors corresponding to each designated critical net from the layout file, and delineating a net blocking exclusion zone extending a distance of a minimum net blocking distance (NBD) from the metal conductor for each metal conductor identified, wherein the step of locating locates the dummy fills outside of the net blocking exclusion zone.

Owner:MAGMA DESIGN AUTOMATION

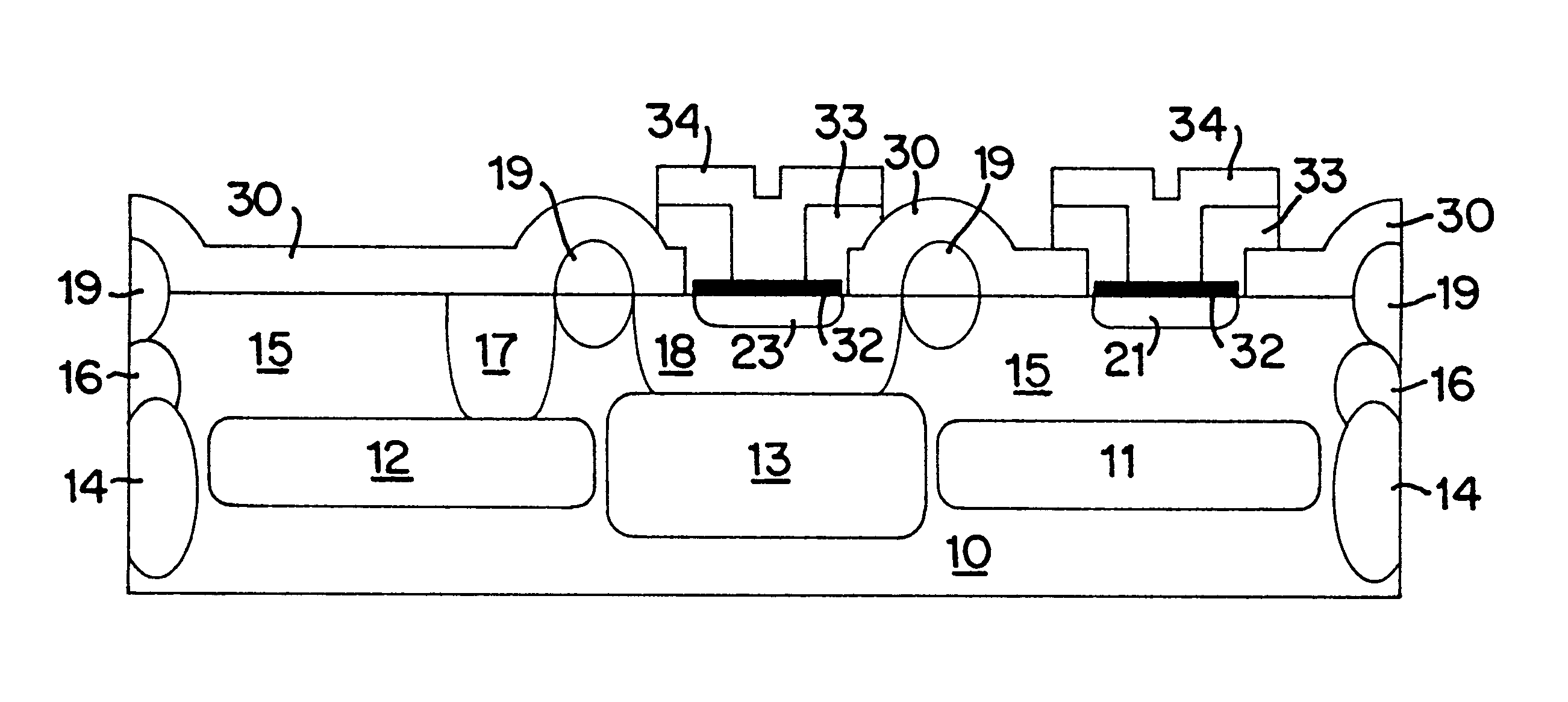

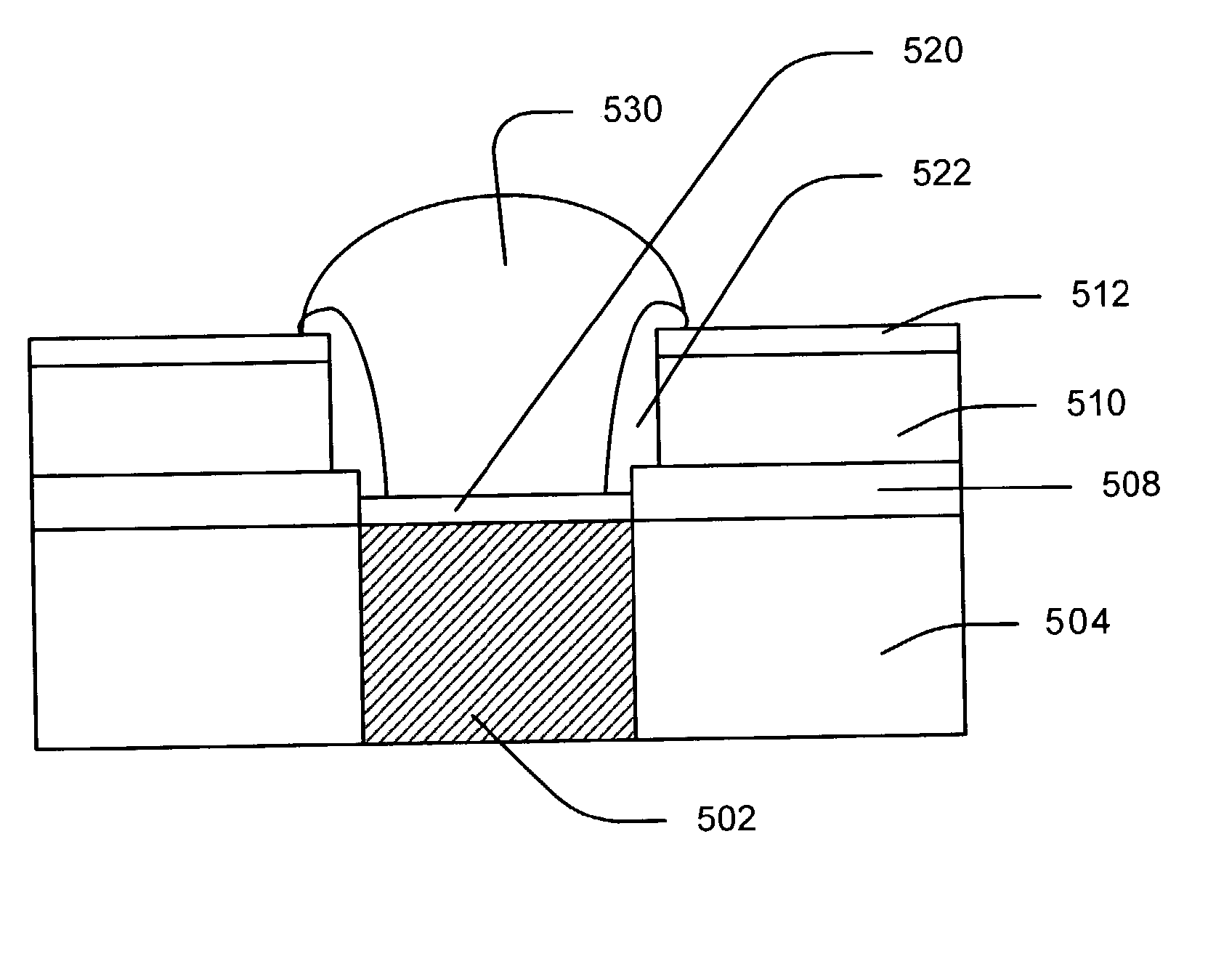

Method of fabricating Schottky diode and related structure

InactiveUS6261932B1Easy to optimizeReduce parasitic capacitanceTransistorSolid-state devicesDopantMetal silicide

A method of forming an improved Schottky diode structure as part of an integrated circuit fabrication process that includes the introduction of a selectable concentration of dopant into the surface of an epitaxial layer so as to form a barrier-modifying surface dopant layer. The epitaxial layer forms the cathode of the Schottky diode and a metal-silicide layer on the surface of the epitaxial layer forms the diode junction. The surface dopant layer positioned between the cathode and the diode junction is designed to raise or lower the barrier height between those two regions either to reduce the threshold turn-on potential of the diode, or to reduce the reverse leakage current of the transistor. The particular dopant conductivity used to form the surface dopant layer is dependent upon the conductivity of the epitaxial layer and the type of metal used to form the metal-silicide junction.

Owner:SEMICON COMPONENTS IND LLC

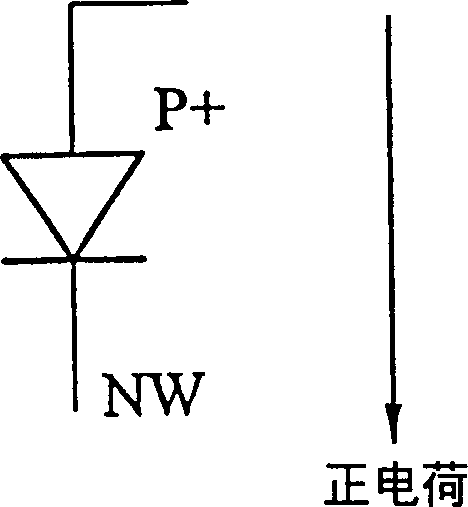

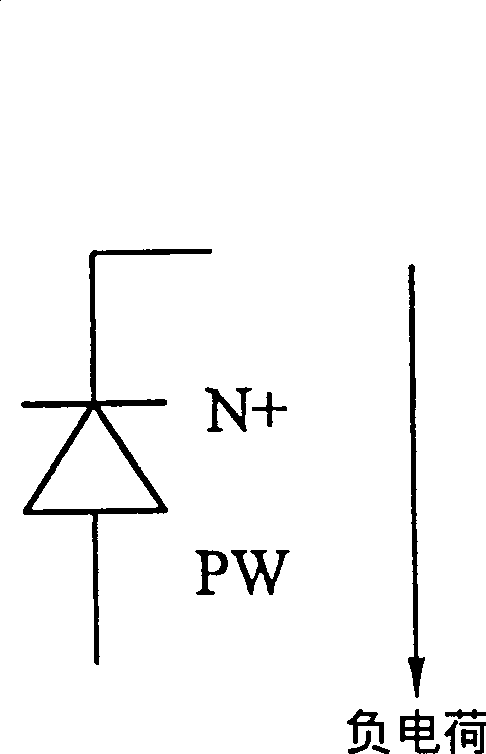

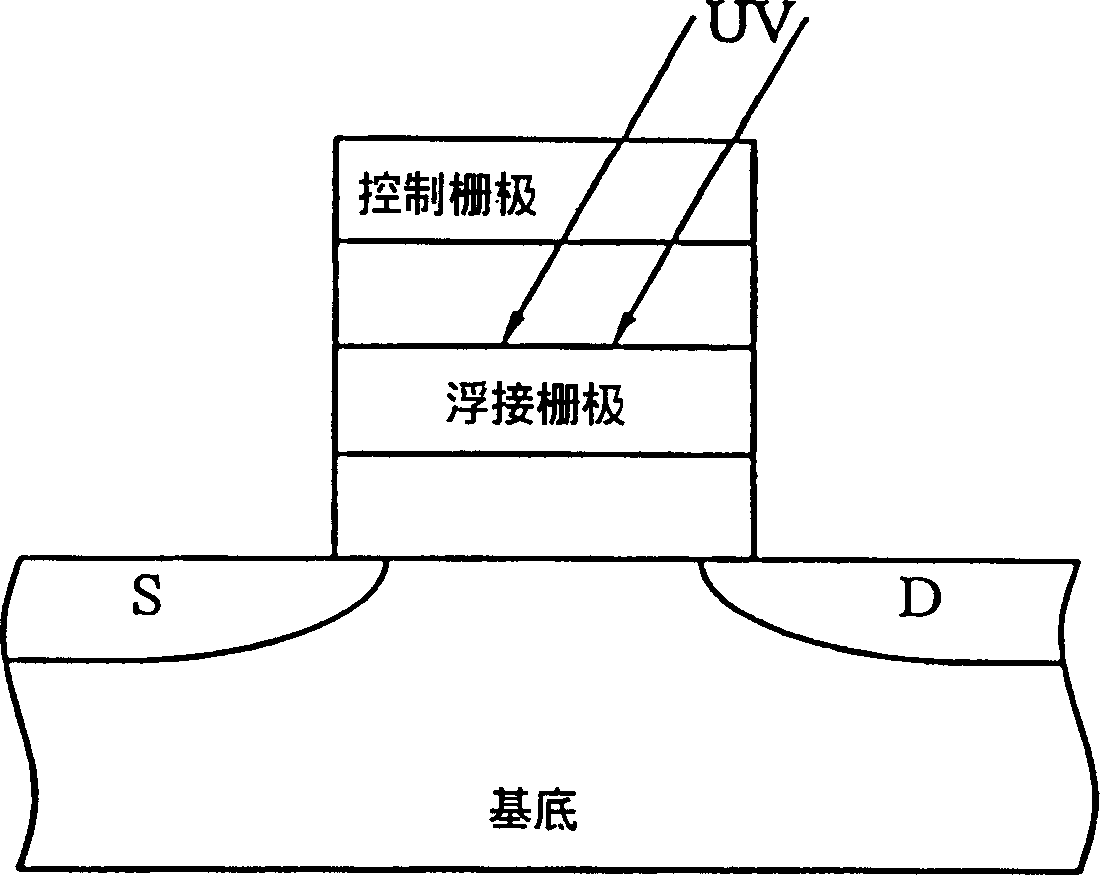

IC device and its manufacture

InactiveCN1469473AAvoid damageProtection from positive chargesTransistorSemiconductor/solid-state device detailsIc devicesSemiconductor

The present invention relates to one kind of protection device and IC manufacturing process. The protection device includes one NMOS / PMOS pair with a dynamic initial voltage, and the NMOS and the PMOS have separate grids coupled to the semiconductor in the channel area. Cooperating with proper metal connection, the said structure can protect IC in manufacture from plasma and charge damage and protect IC in operation from abnormal voltage.

Owner:MACRONIX INT CO LTD

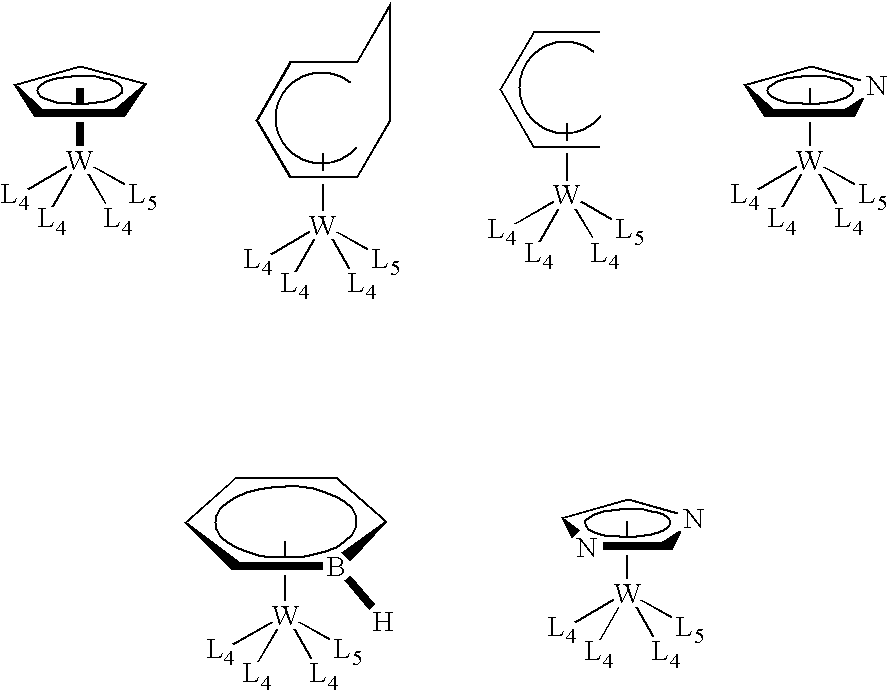

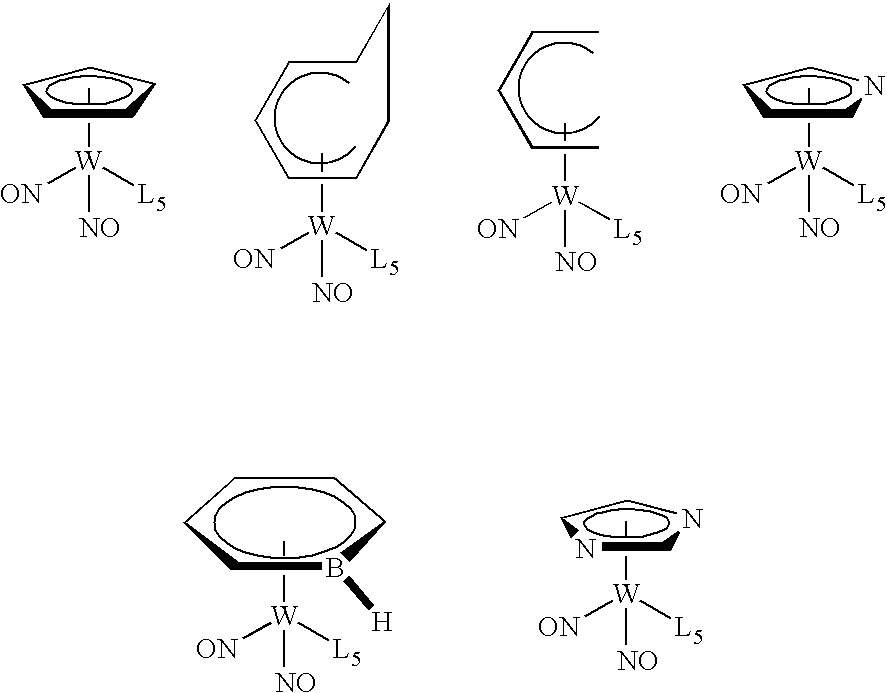

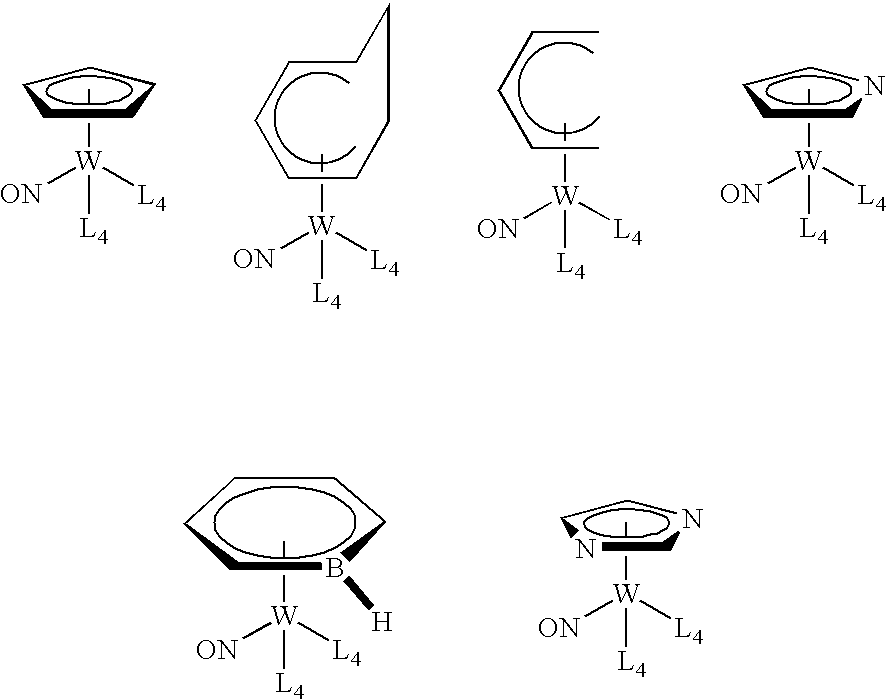

Organometallic compounds, processes for the preparation thereof and methods of use thereof

ActiveUS20080081127A1Improve responseReduce usageGroup 5/15 element organic compoundsSolid-state devicesIntegrated circuit manufacturingElectron donor

This invention relates to organometallic compounds represented by the formula (L1)yM(L2)z-y wherein M is a Group 5 metal or a Group 6 metal, L1 is a substituted or unsubstituted anionic 6 electron donor ligand, L2 is the same or different and is (i) a substituted or unsubstituted anionic 2 electron donor ligand, (ii) a substituted or unsubstituted cationic 2 electron donor ligand, or (iii) a substituted or unsubstituted neutral 2 electron donor ligand; y is an integer of 1, and z is the valence of M; and wherein the sum of the oxidation number of M and the electric charges of L1 and L2 is equal to 0.; a process for producing the organometallic compounds; and a method for depositing a metal and / or metal carbide / nitride layer, e.g., a tungsten, tungsten nitride, tungsten carbide, or tungsten carbonitride layer, on a substrate by the thermal or plasma enhanced dissociation of the organometallic precursor compounds, e.g., by CVD or ALD techniques. The metal and / or metal carbide layer is useful as a liner or barrier layer for conducting metals and high dielectric constant materials in integrated circuit manufacturing.

Owner:PRAXAIR TECH INC

Composition and process for ashless removal of post-etch photoresist and/or bottom anti-reflective material on a substrate

InactiveUS20060063687A1Non-surface-active detergent compositionsDetergent mixture composition preparationDielectricIntegrated circuit manufacturing

An aqueous-based composition and process for removing photoresist and / or bottom anti-reflective coating (BARC) material from a substrate having such material(s) thereon. The aqueous-based composition includes a quaternary ammonium base, at least one co-solvent, and optionally a chelator. The composition achieves high-efficiency removal of photoresist and / or BARC material in the manufacture of integrated circuitry without adverse effect on metal species on the substrate, such as copper, and without damage to SiOC-based dielectric materials employed in the semiconductor architecture.

Owner:ADVANCED TECH MATERIALS INC

Hardmask materials

ActiveUS20110135557A1Poor pattern alignmentReduce stressLiquid surface applicatorsElectric discharge tubesMaterials sciencePost treatment

Hardmask films having high hardness and low stress are provided. In some embodiments a film has a stress of between about −600 MPa and 600 MPa and hardness of at least about 12 GPa. In some embodiments, a hardmask film is prepared by depositing multiple sub-layers of doped or undoped silicon carbide using multiple densifying plasma post-treatments in a PECVD process chamber. In some embodiments, a hardmask film includes a high-hardness boron-containing film selected from the group consisting of SixByCz, SixByNz, SixByCzNw, BxCy, and BxNy. In some embodiments, a hardmask film includes a germanium-rich GeNx material comprising at least about 60 atomic % of germanium. These hardmasks can be used in a number of back-end and front-end processing schemes in integrated circuit fabrication.

Owner:NOVELLUS SYSTEMS

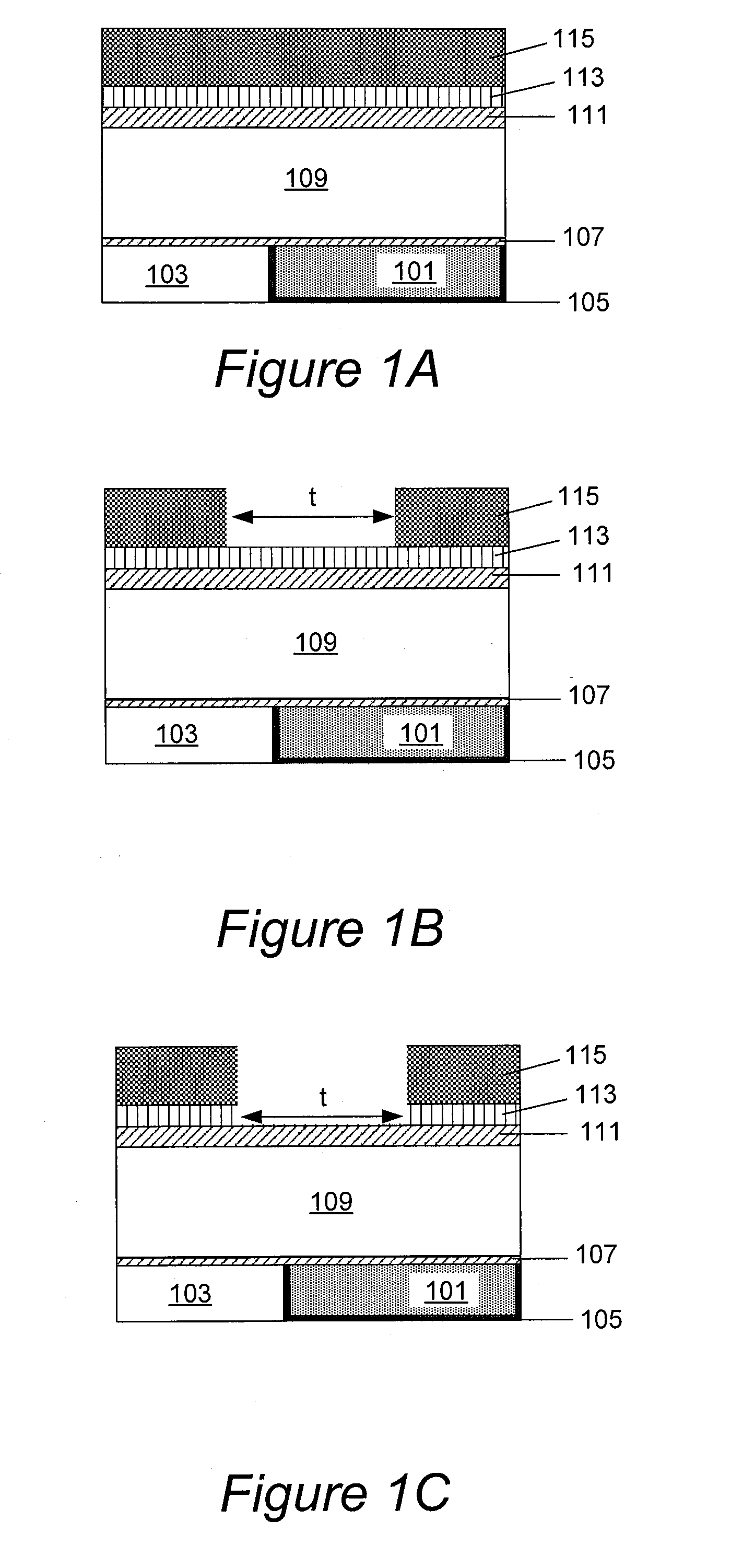

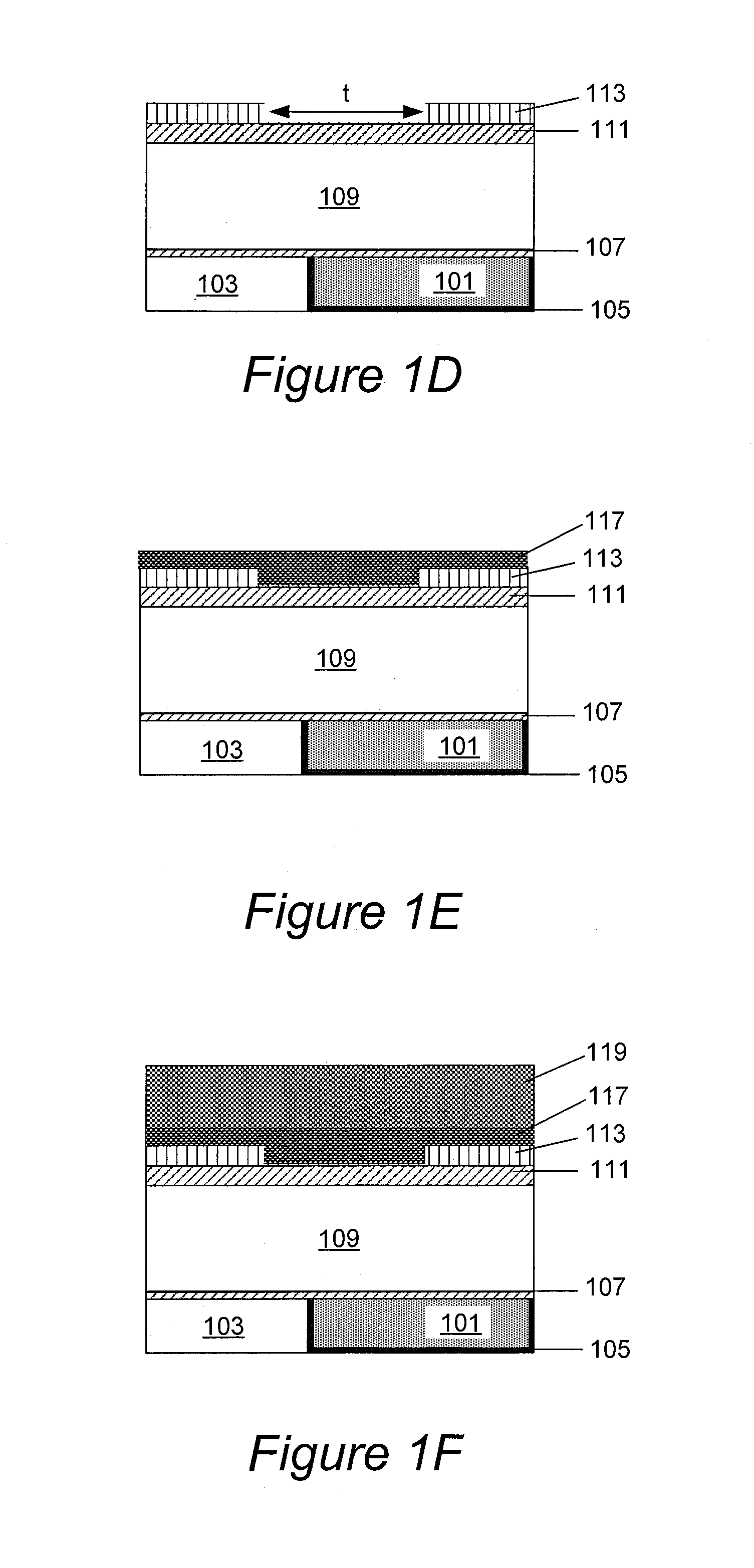

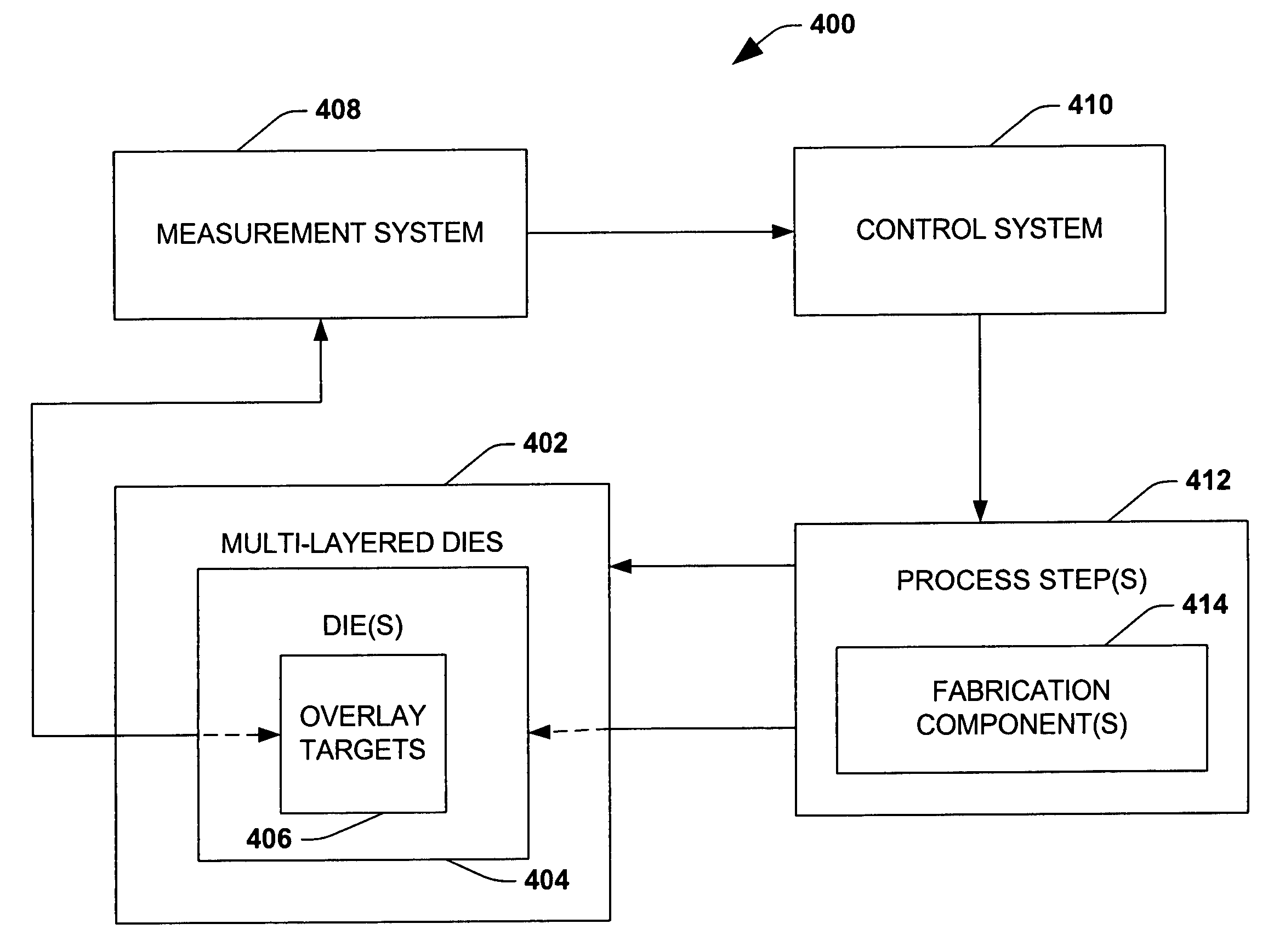

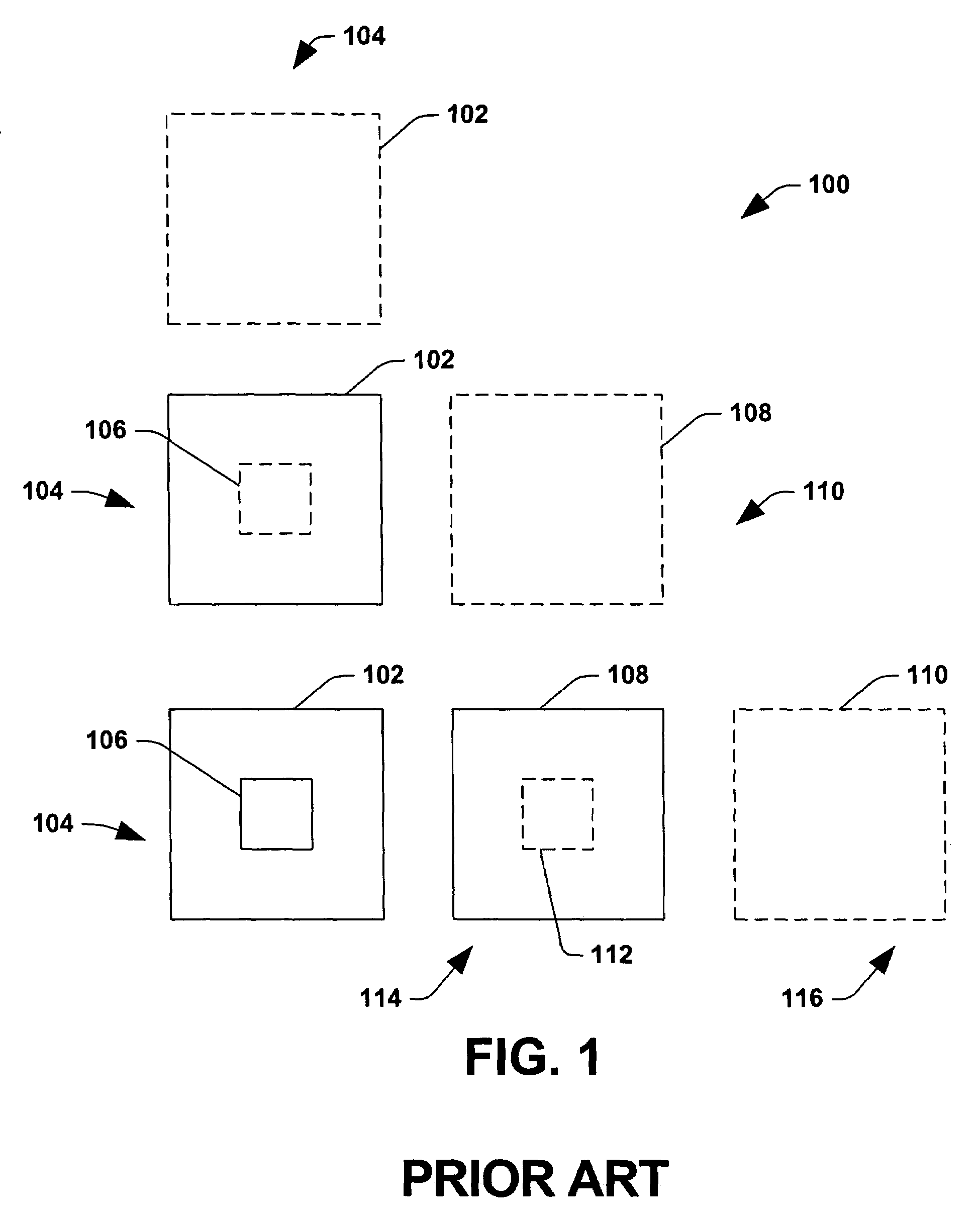

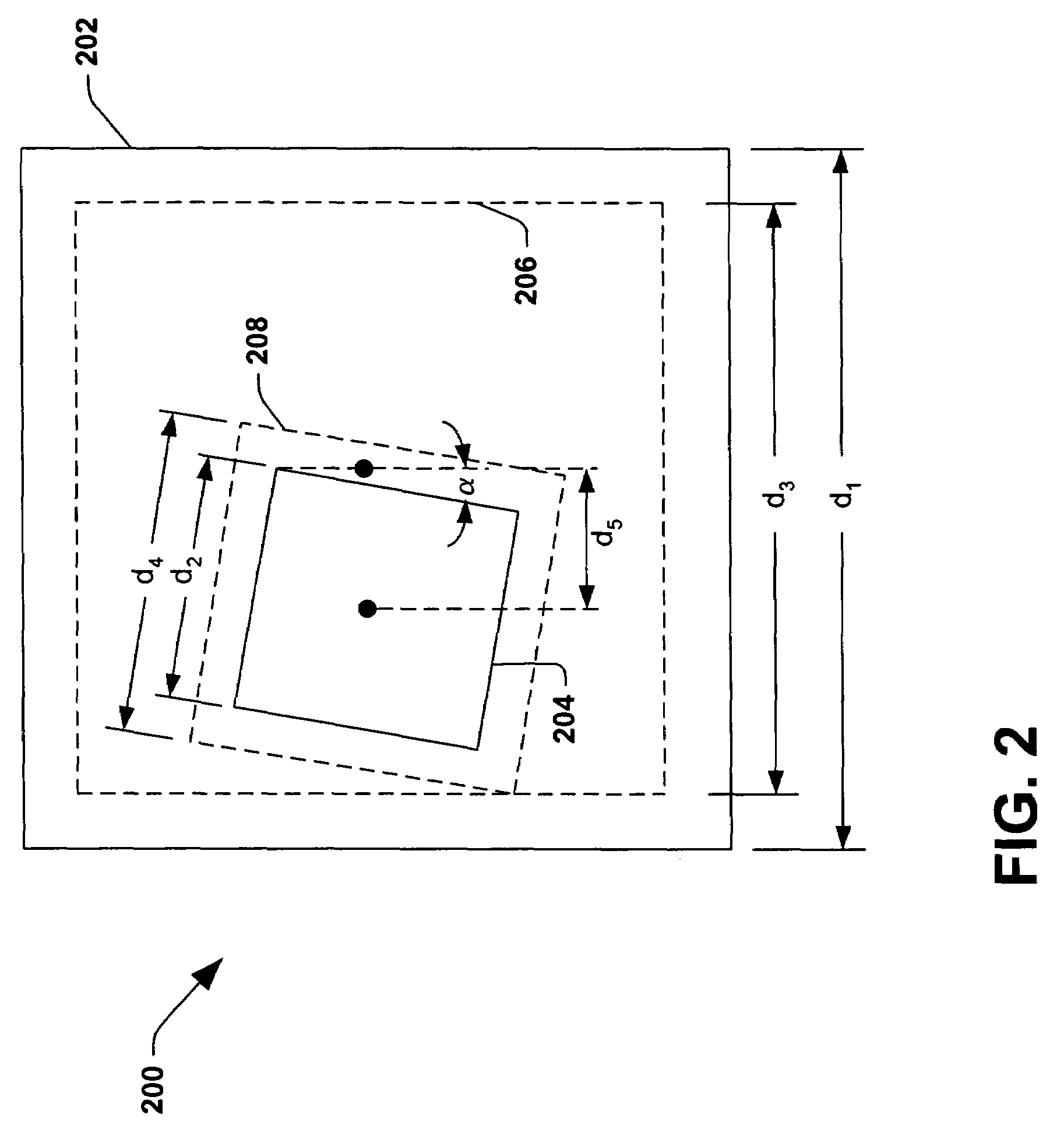

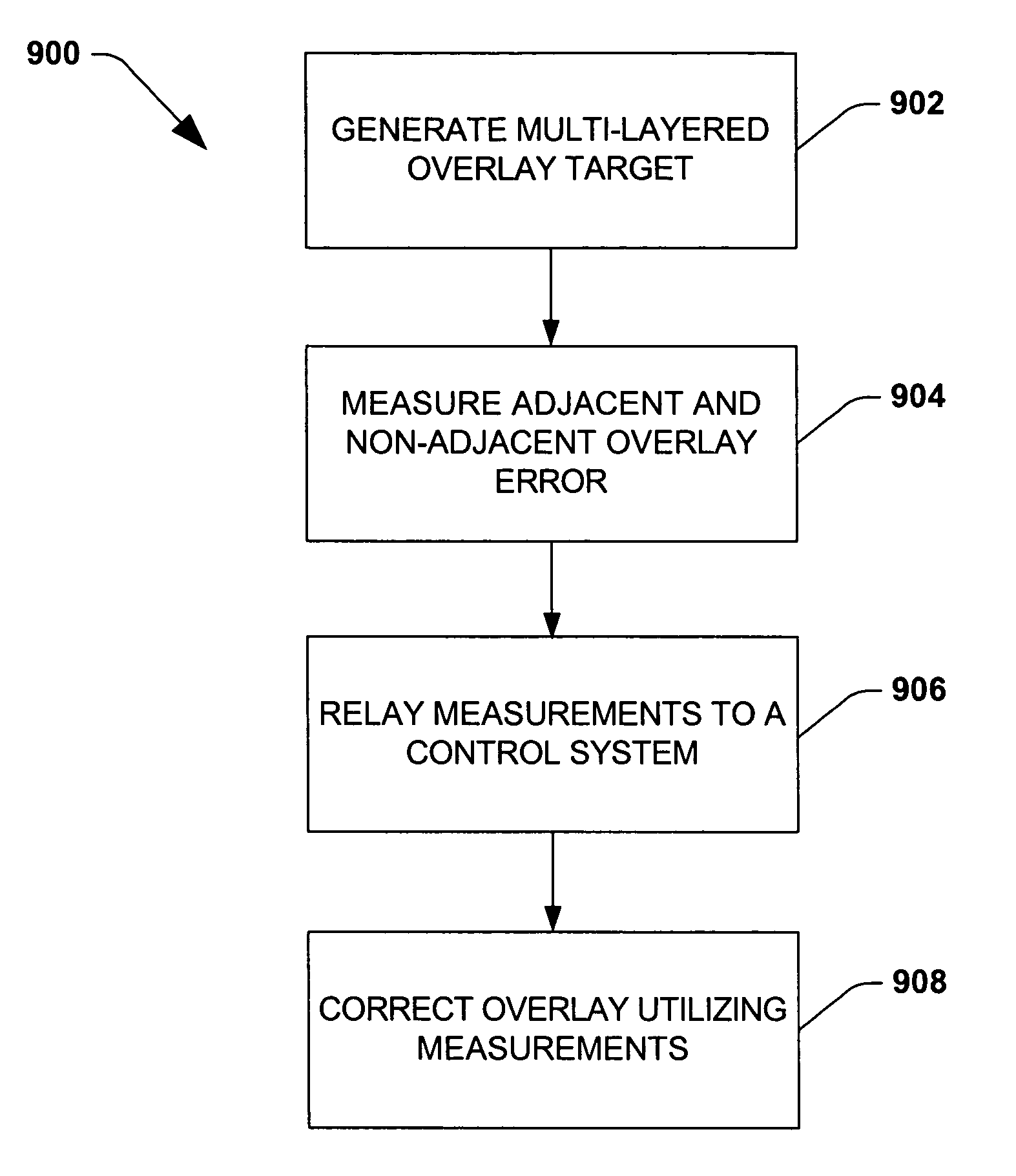

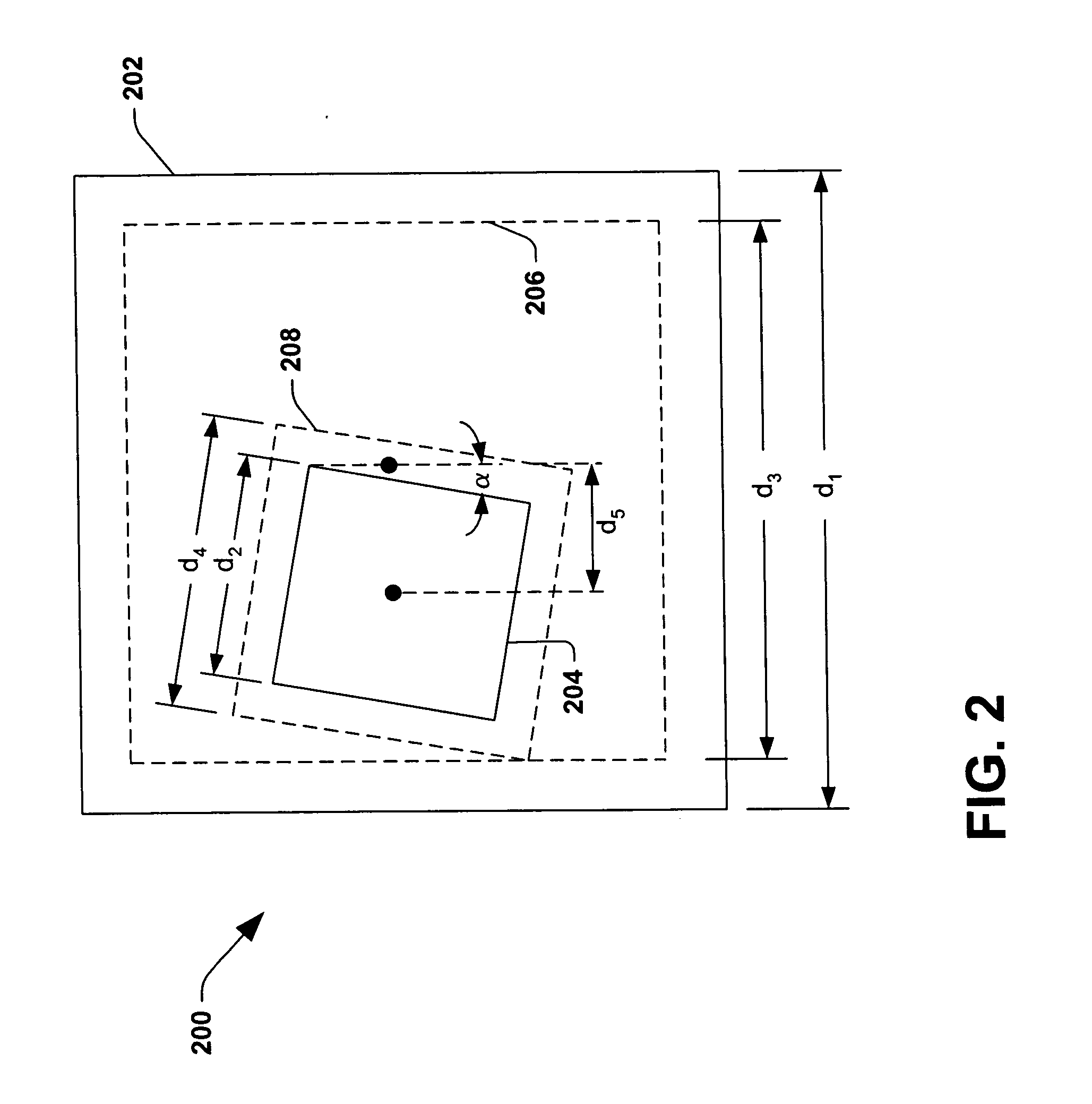

Multi-layer overlay measurement and correction technique for IC manufacturing

InactiveUS7065737B2Reduce recurrenceCorrection errorSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsCorrection techniqueComputer science

A system facilitating measurement and correction of overlay between multiple layers of a wafer is disclosed. The system comprises an overlay target that represents overlay between three or more layers of a wafer and a measurement component that determines overlay error existent in the overlay target, thereby determining overlay error between the three or more layers of the wafer. A control component can be provided to correct overlay error between adjacent and non-adjacent layers, wherein the correction is based at least in part on measurements obtained by the measurement component.

Owner:GLOBALFOUNDRIES INC

Multi-layer overlay measurement and correction technique for IC manufacturing

InactiveUS20050193362A1Reduce recurrenceCorrection errorSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsCorrection techniqueComputer science

A system facilitating measurement and correction of overlay between multiple layers of a wafer is disclosed. The system comprises an overlay target that represents overlay between three or more layers of a wafer and a measurement component that determines overlay error existent in the overlay target, thereby determining overlay error between the three or more layers of the wafer. A control component can be provided to correct overlay error between adjacent and non-adjacent layers, wherein the correction is based at least in part on measurements obtained by the measurement component.

Owner:GLOBALFOUNDRIES INC

Method to form alpha phase Ta and its application to IC manufacturing

InactiveUS20040131878A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor structurePhysical chemistry

A method of sputtering a Ta layer comprised of alpha phase Ta on a Cu layer. An embodiment includes a Ta sputter deposition on a Cu surface at a substrate temperature less than 200° C. Another embodiment has a pre-cooling step at a temperature less than 100° C. prior to Ta layer sputter deposition. In another non-limiting example embodiment, a pre-clean step comprising an inert gas sputter is performed prior to the tantalum sputter. Another non-limiting example embodiment provides a semiconductor structure comprising: a semiconductor structure; a copper layer over the semiconductor structure; a tantalum layer on the copper layer; the tantalum layer comprised alpha phase Ta; a metal layer on the tantalum layer.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

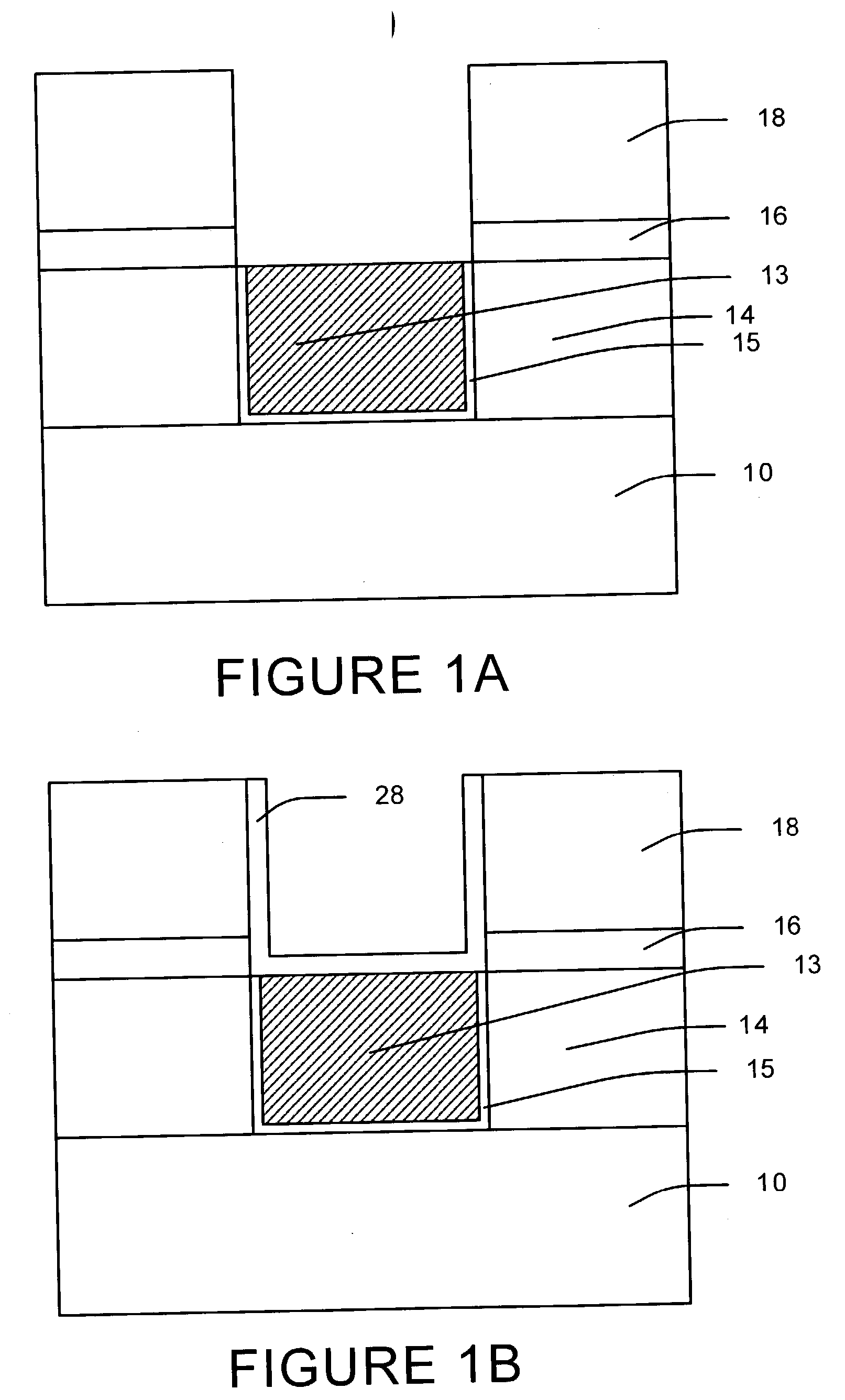

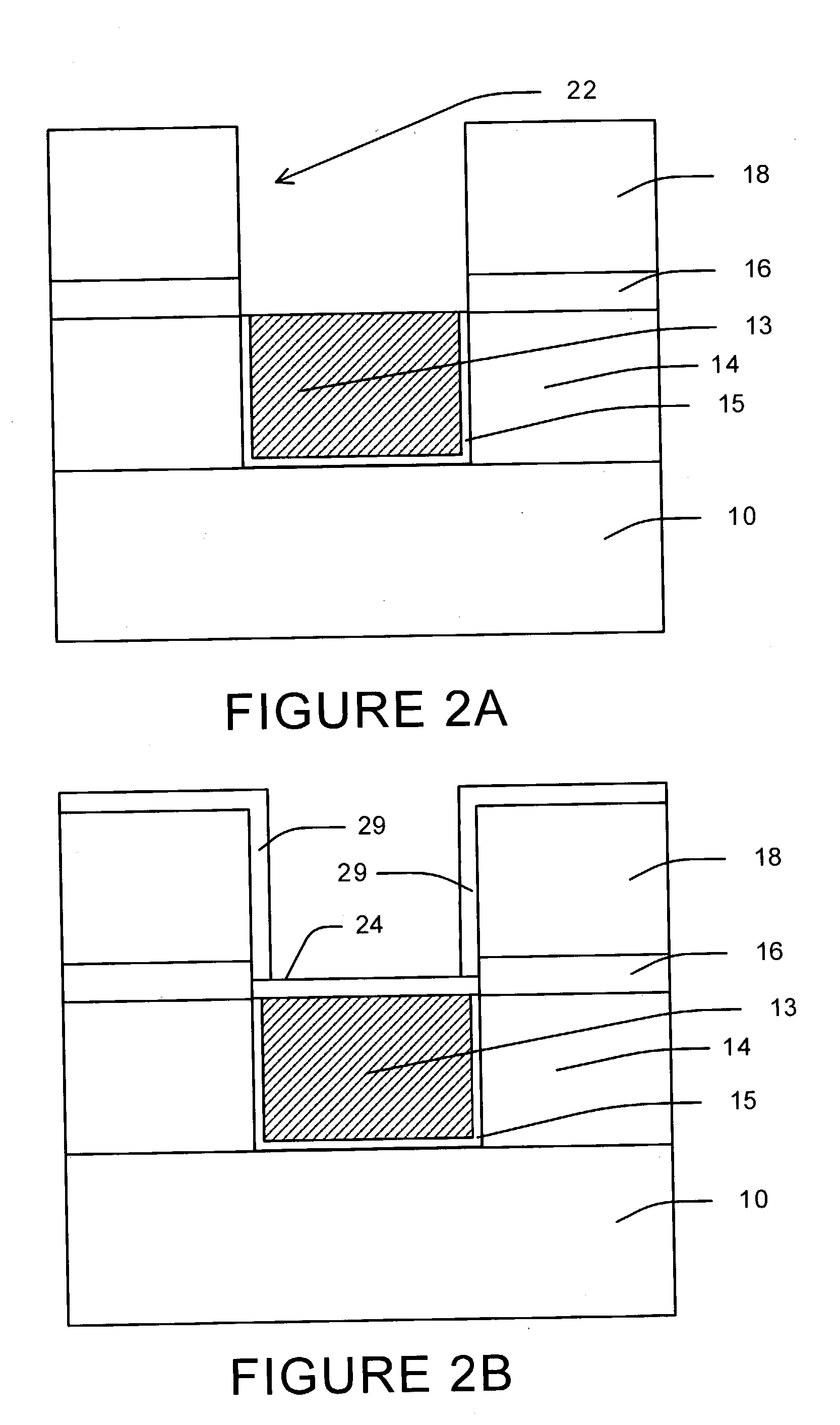

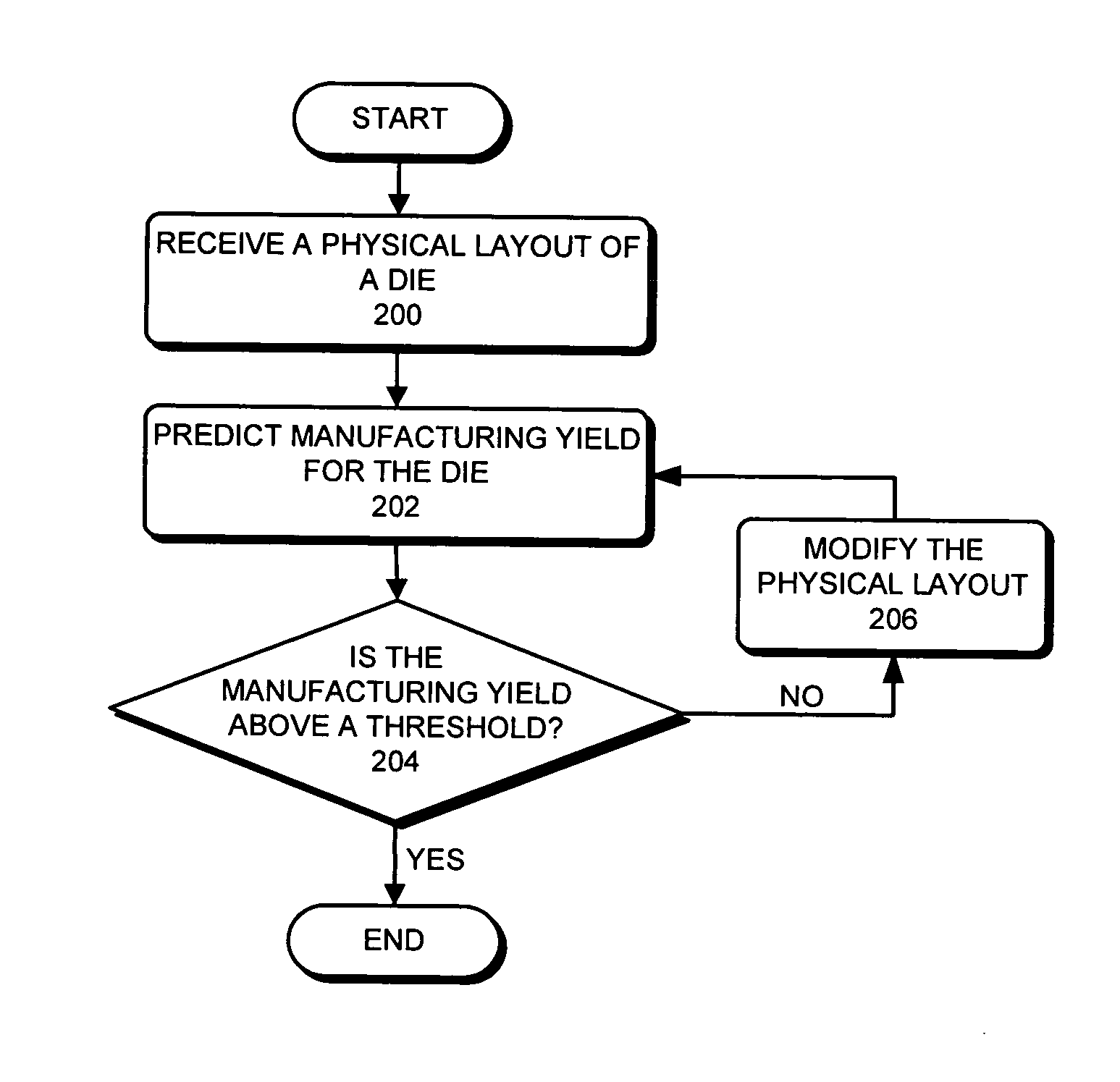

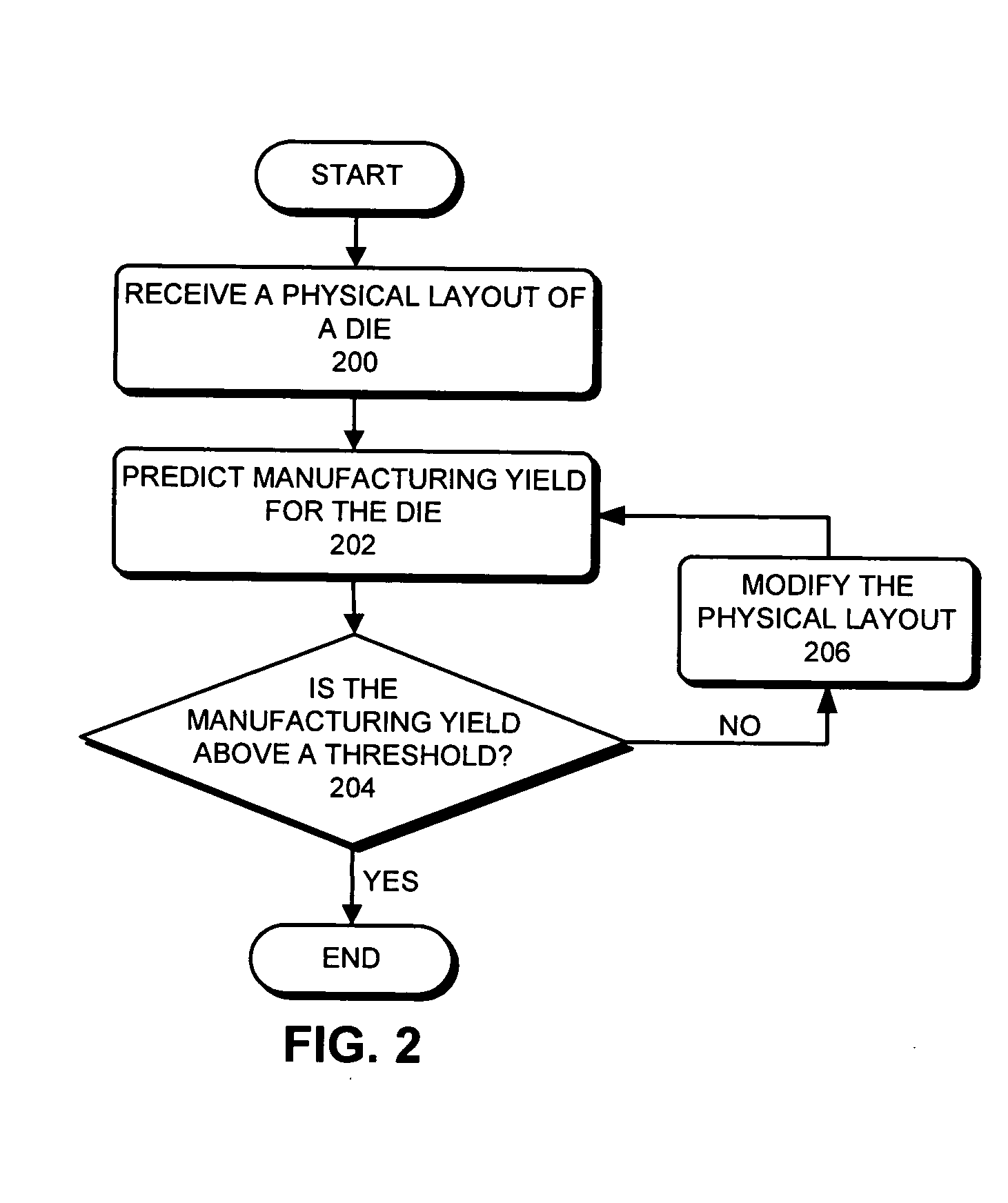

Predicting IC manufacturing yield by considering both systematic and random intra-die process variations

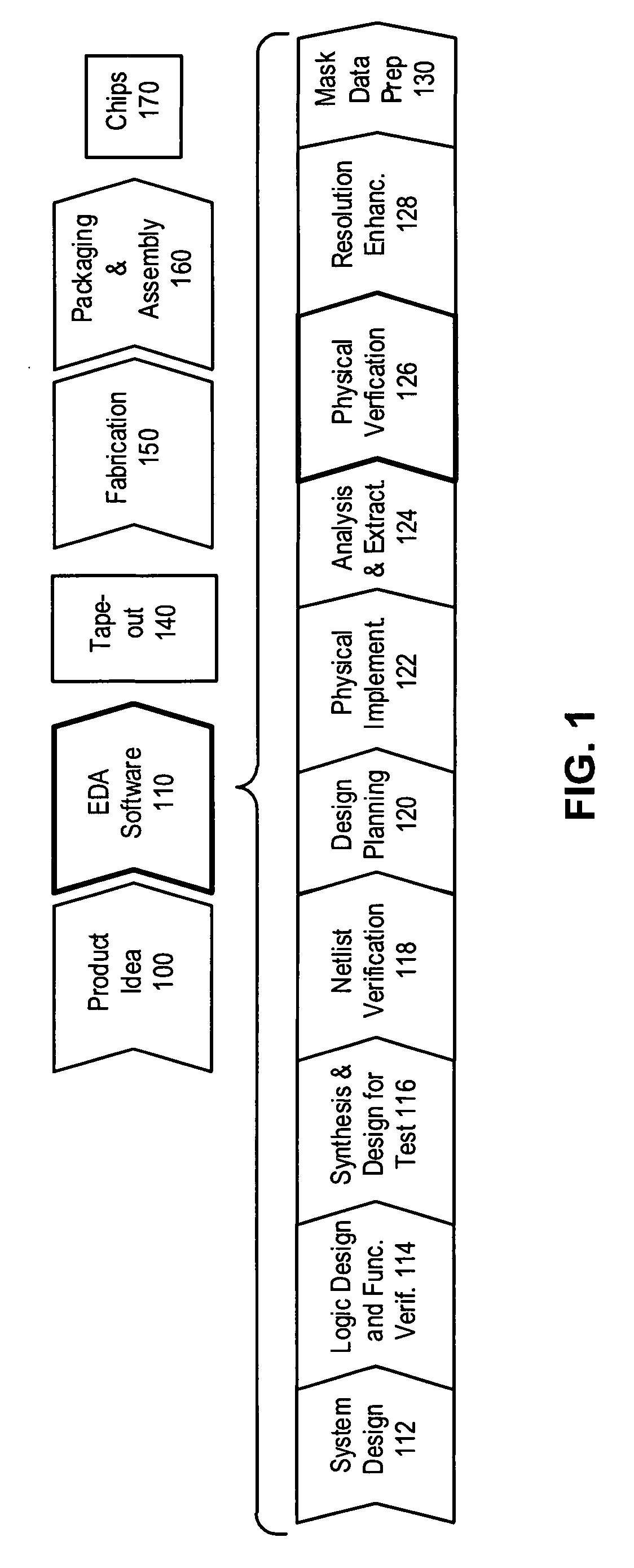

ActiveUS20070174797A1Reduce complexityProgramme controlSemiconductor/solid-state device detailsSystematic variationDying processes

One embodiment of the present invention provides a system that predicts manufacturing yield for a die within a semiconductor wafer. During operation, the system first receives a physical layout of the die. Next, the system partitions the die into an array of tiles. The system then computes systematic variations for a quality indicative value to describe a process parameter across the array of tiles based on the physical layout of the die. Next, the system applies a random variation for the quality indicative parameter to each tile in the array of tiles. Finally, the system obtains the manufacturing yield for the die based on both the systematic variations and the random variations.

Owner:SYNOPSYS INC

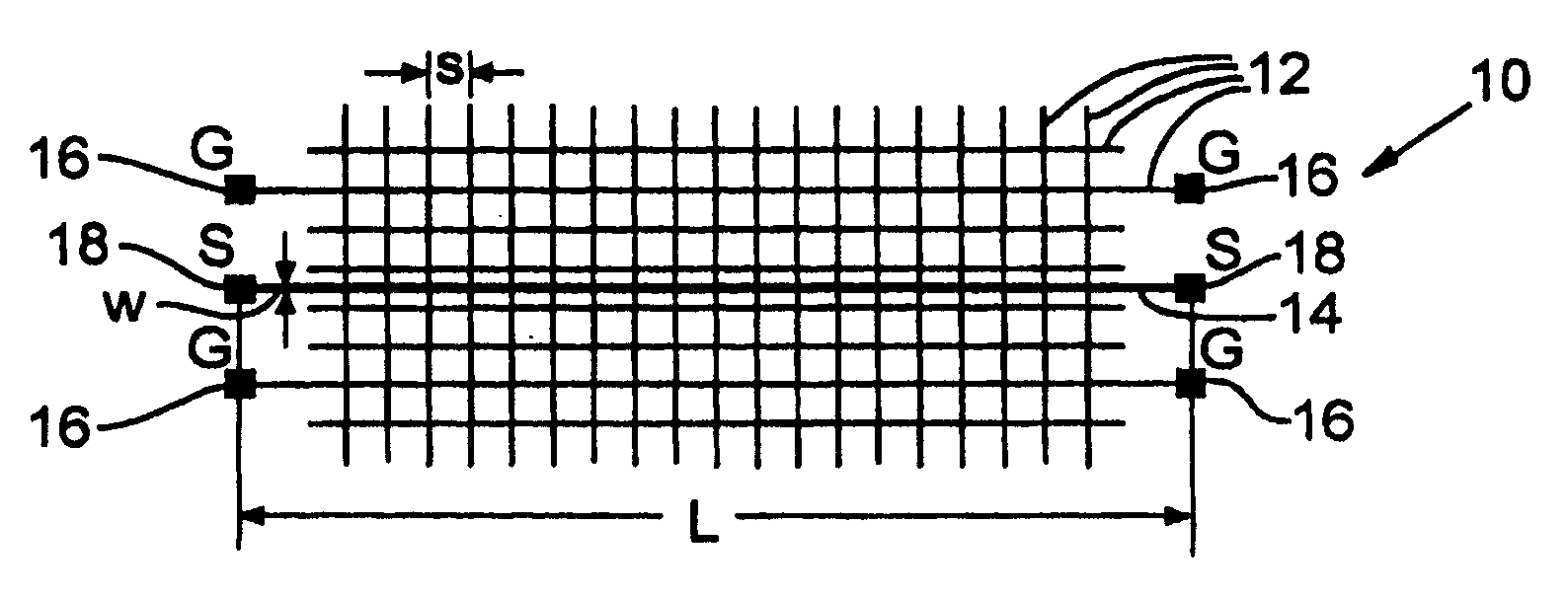

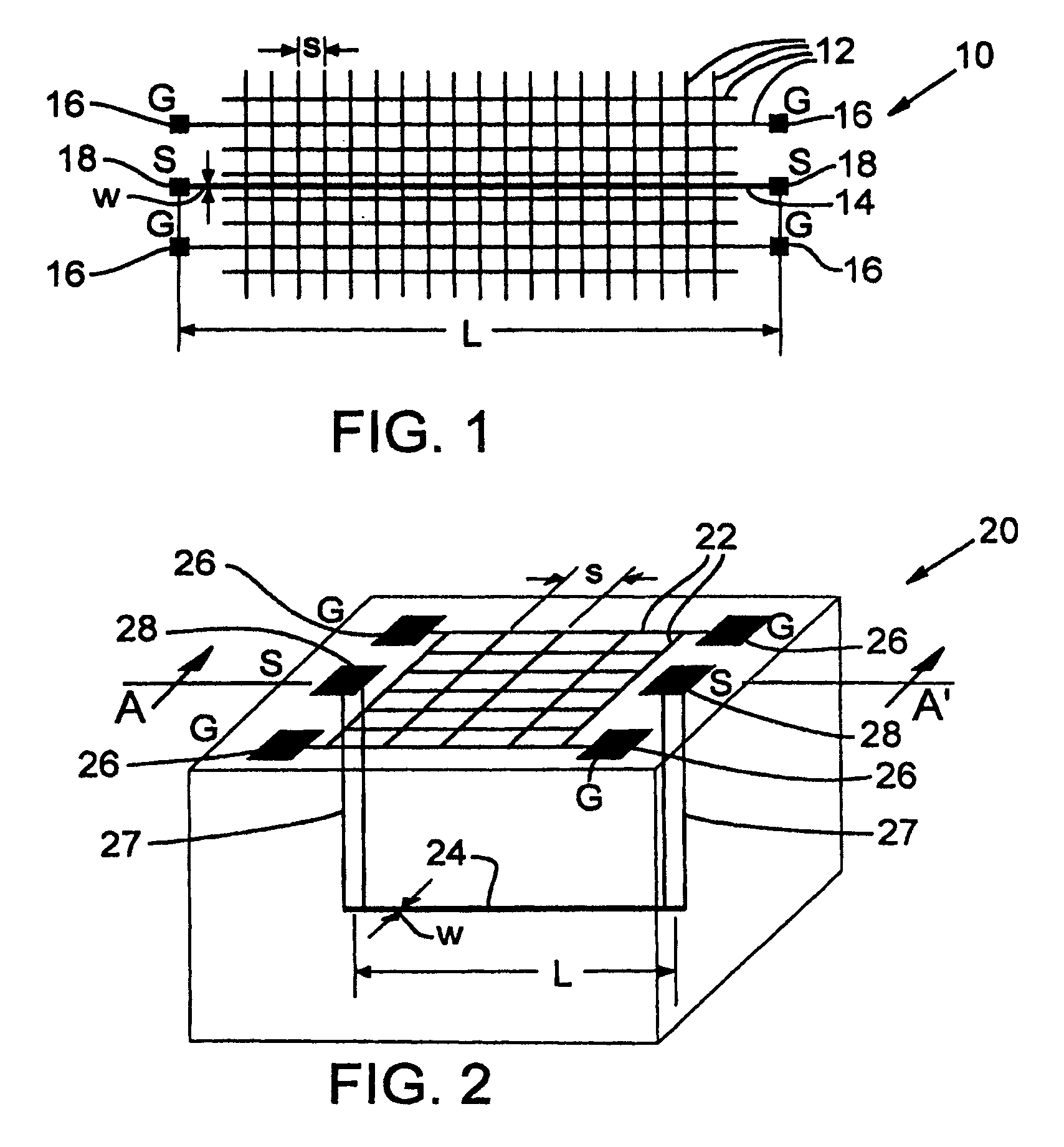

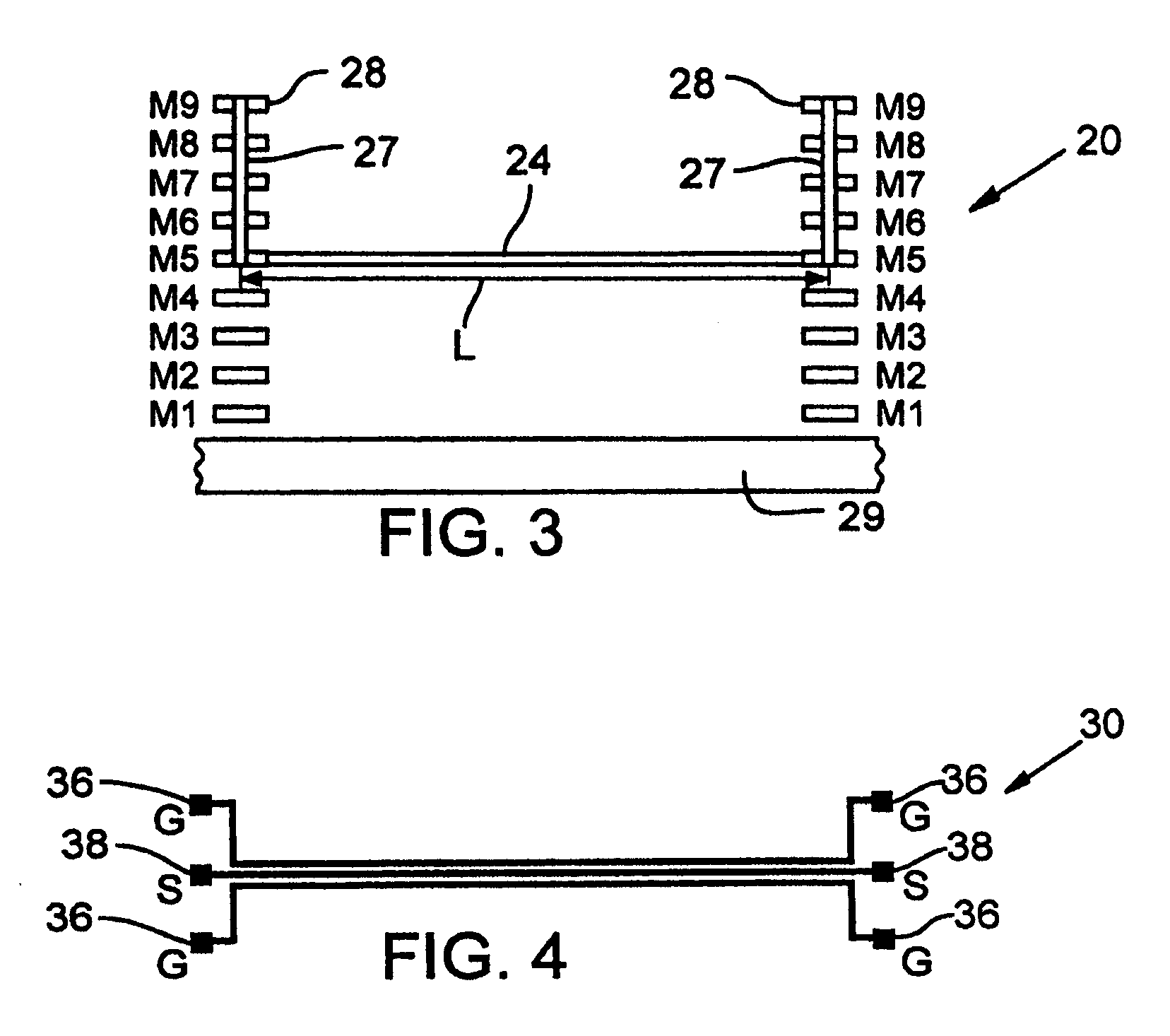

Test structures and method for interconnect impedance property extraction

ActiveUS20060022678A1Easy to understandResistance/reactance/impedenceSemiconductor/solid-state device detailsGrounding gridGrid density

A method and test structures are disclosed for characterizing interconnects of an integrated circuit. The method provides a set of test structures and determines a unit impedance property of each test structure, desirably using S-parameter measurements. A reference impedance data set is then formulated that characterizes the impedance of an integrated circuit manufacturing technology and that can be used to characterize the impedance of interconnects of the chip made by the technology. Each test structure desirably comprises a ground grid and a signal line, and is characterized by values of a set of predetermined attributes such as layer location of the respective ground grid, grid density, layer association, width and length of the respective signal line.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

Process for forming features of 50 nm or less half-pitch with chemically amplified resist imaging

InactiveUS20040265747A1High resolutionElimination of blurSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusIntegrated circuit manufacturingActivation energy

Lithographic imaging of 50 nm (or less) half-pitch features in chemically amplified resists (commonly used in the manufacture of integrated circuits) is enabled by the use of reduced temperature post-exposure processing and low activation energy chemically amplified resists. The post-exposure processing preferably involves ambient to moderately elevated temperature and the presence of a deprotection reaction-dependent co-reactant (e.g., water).

Owner:IBM CORP

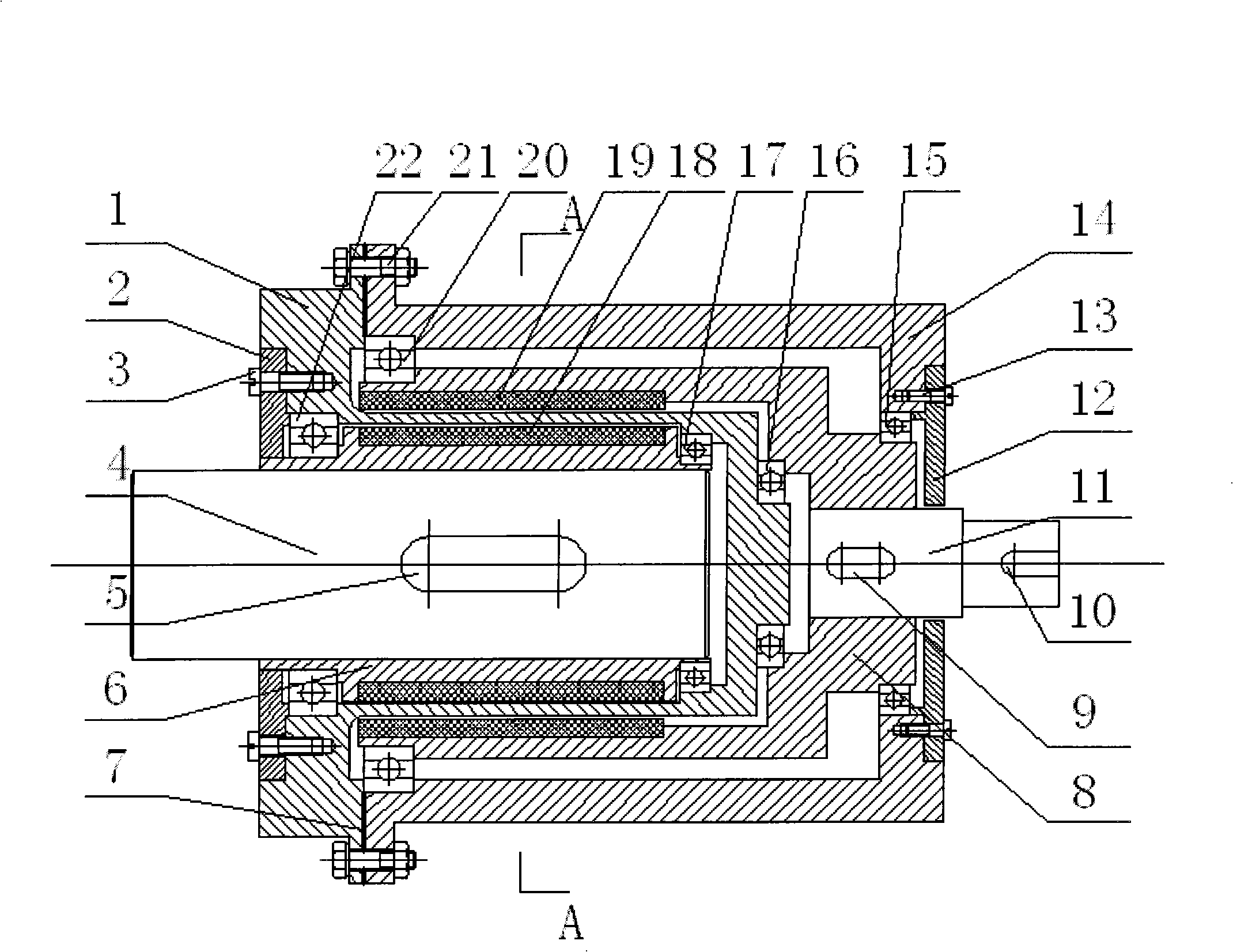

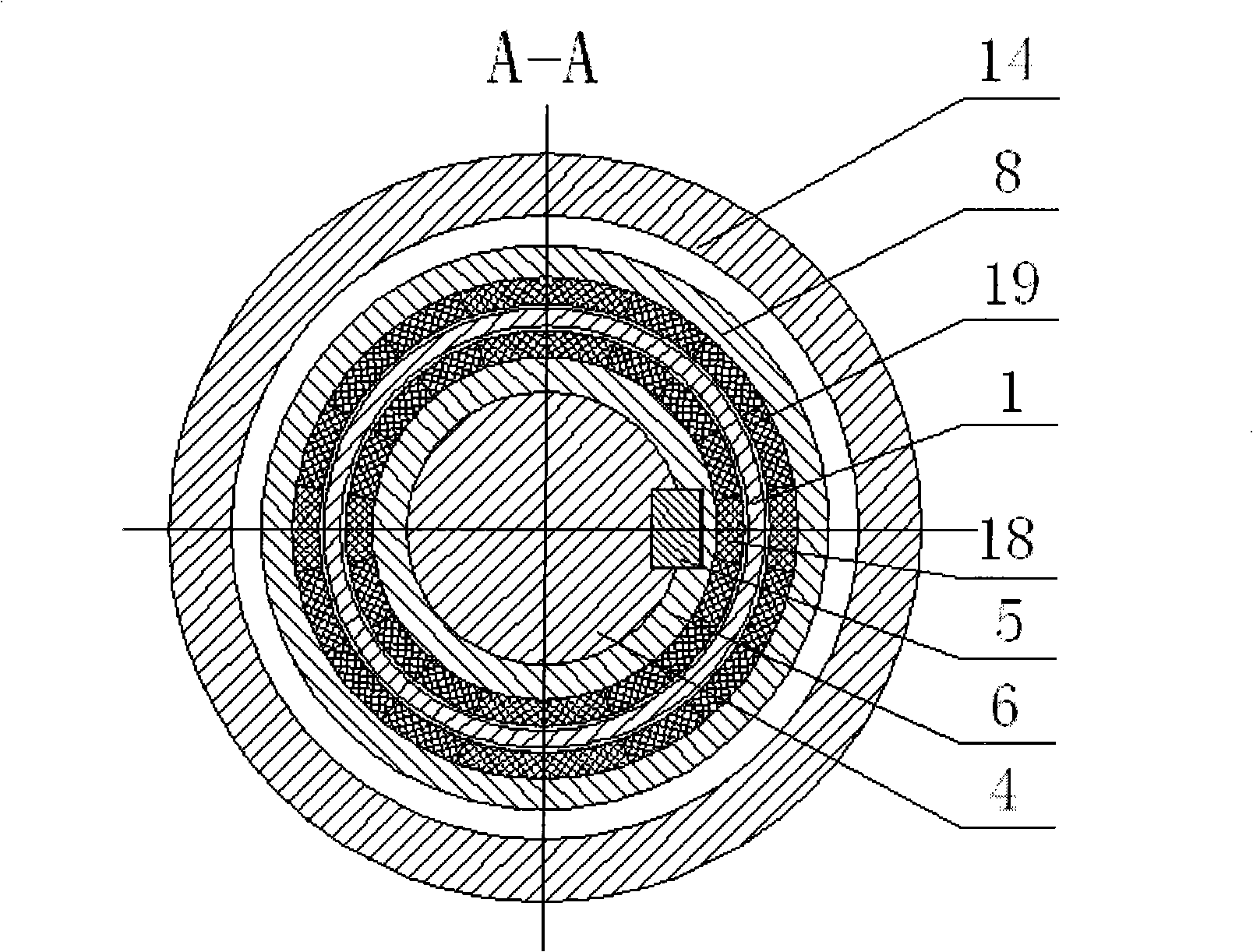

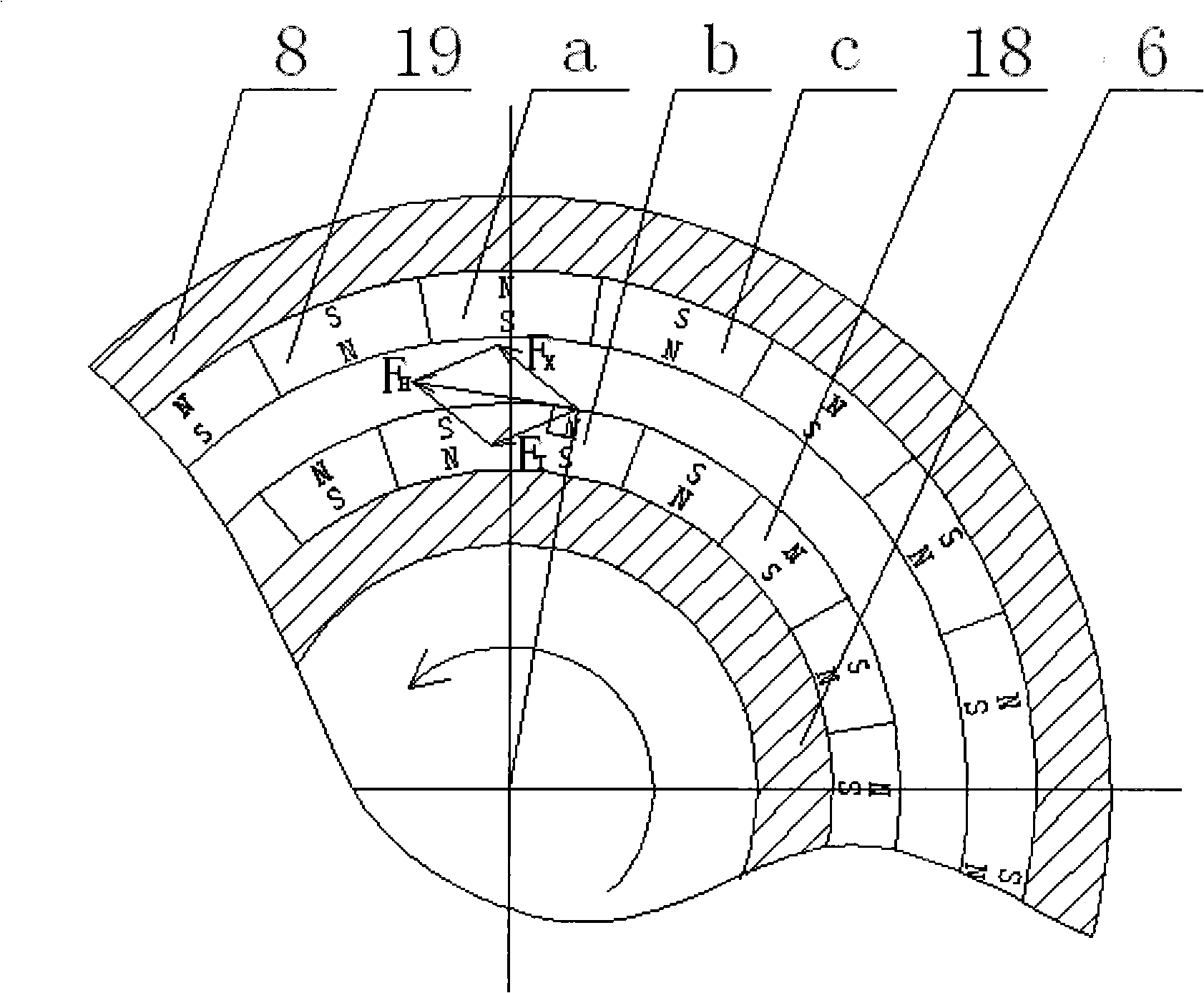

Magnetic force driver

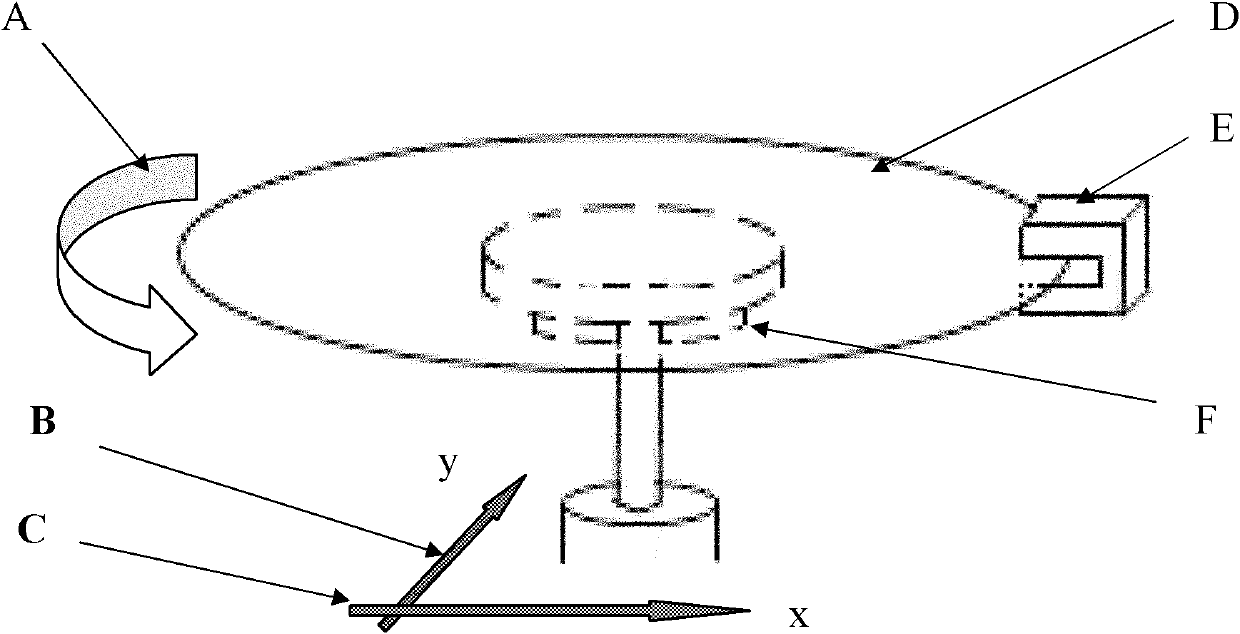

InactiveCN101325360AReduce volumeCompact structureDynamo-electric gearsMagnetic tension forceBall bearing

The invention belongs to the technical field of the industrial robot, particularly to a magnetic driver used in the silicon slice transmission robot playing the silicon slice transmission and positioning action in the vacuum in the IC manufacturing industry. The magnetic driver comprises a drive input part for realizing the torque introduction, a drive output part for realizing the torque output, a case part and a magnetic circuit part; in the drive input part, the drive input part is connected with an input axis through an end bond, and the external rotor is connected with the input axis through the bond, and fixed with the case through a deep groove ball bearing. In the magnetic circuit part, the internal rotor and the internal permanent magnet, the external rotor and the external permanent magnet all adopt the glue joint. The magnetic driver of the invention has compact structure, tight magnet distribution, small volume, large transmission torque, easy control, stable operation, convenient dismounting, small sport inertia, applied in the vacuum robot with higher cleanness.

Owner:DALIAN UNIV OF TECH

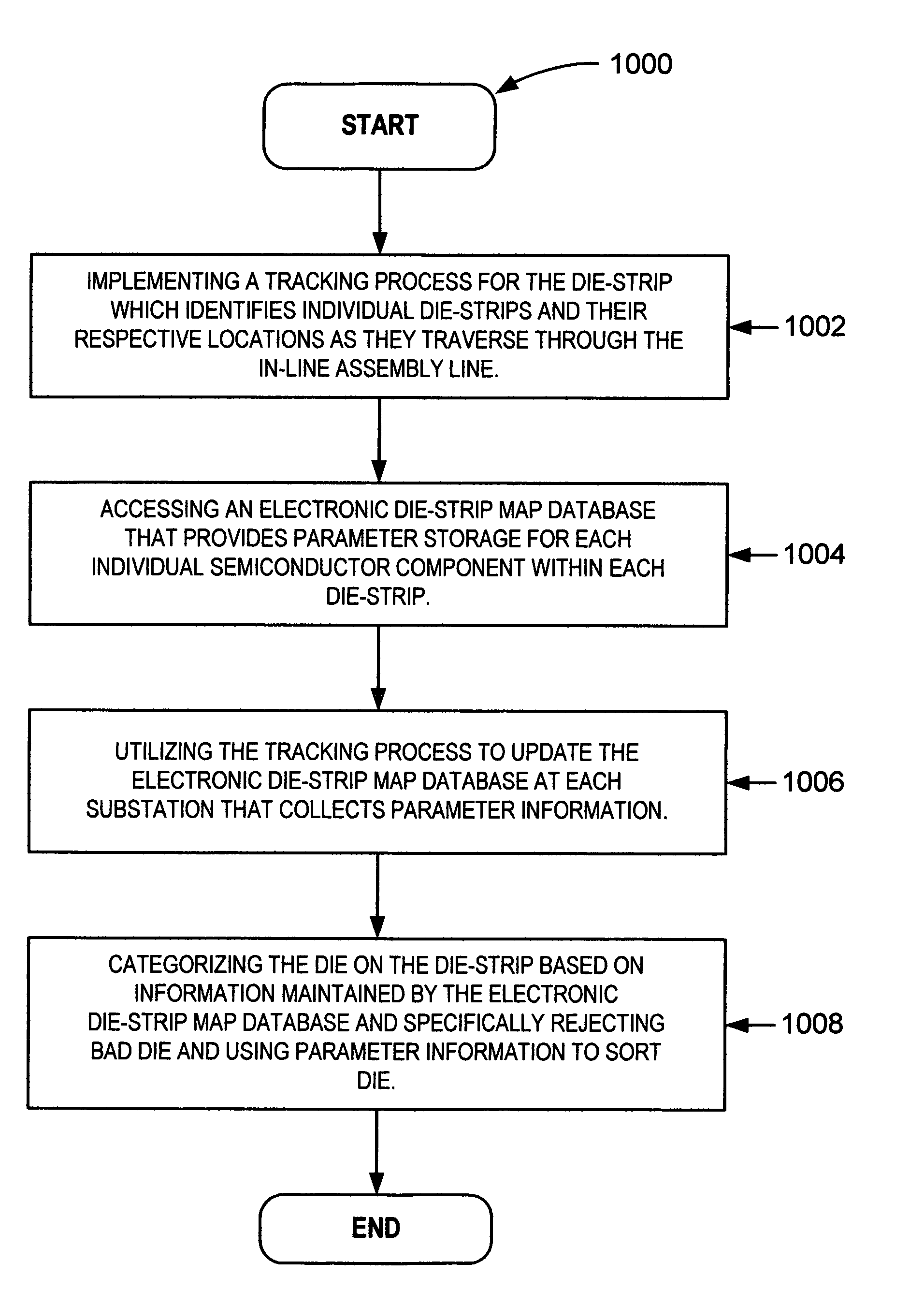

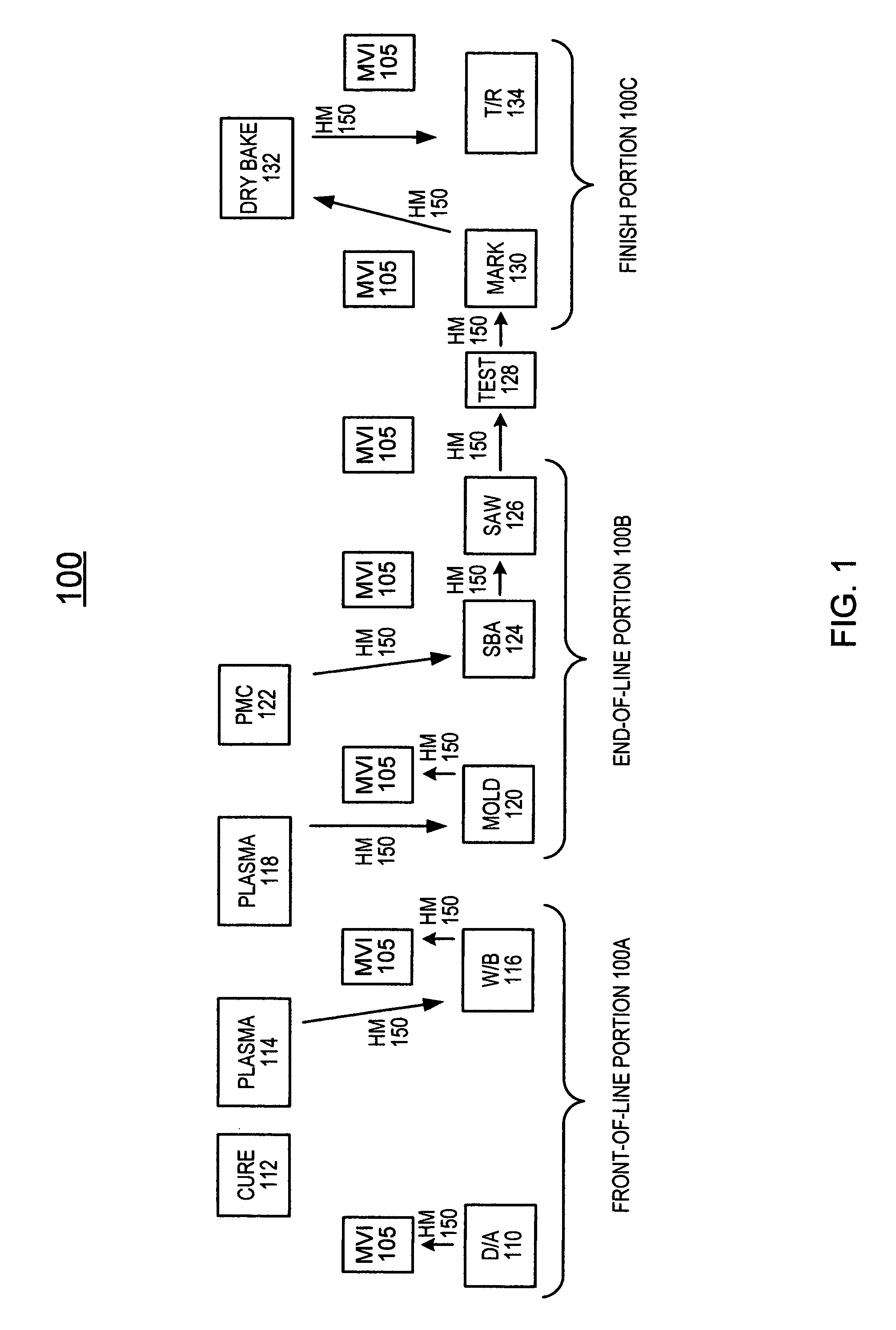

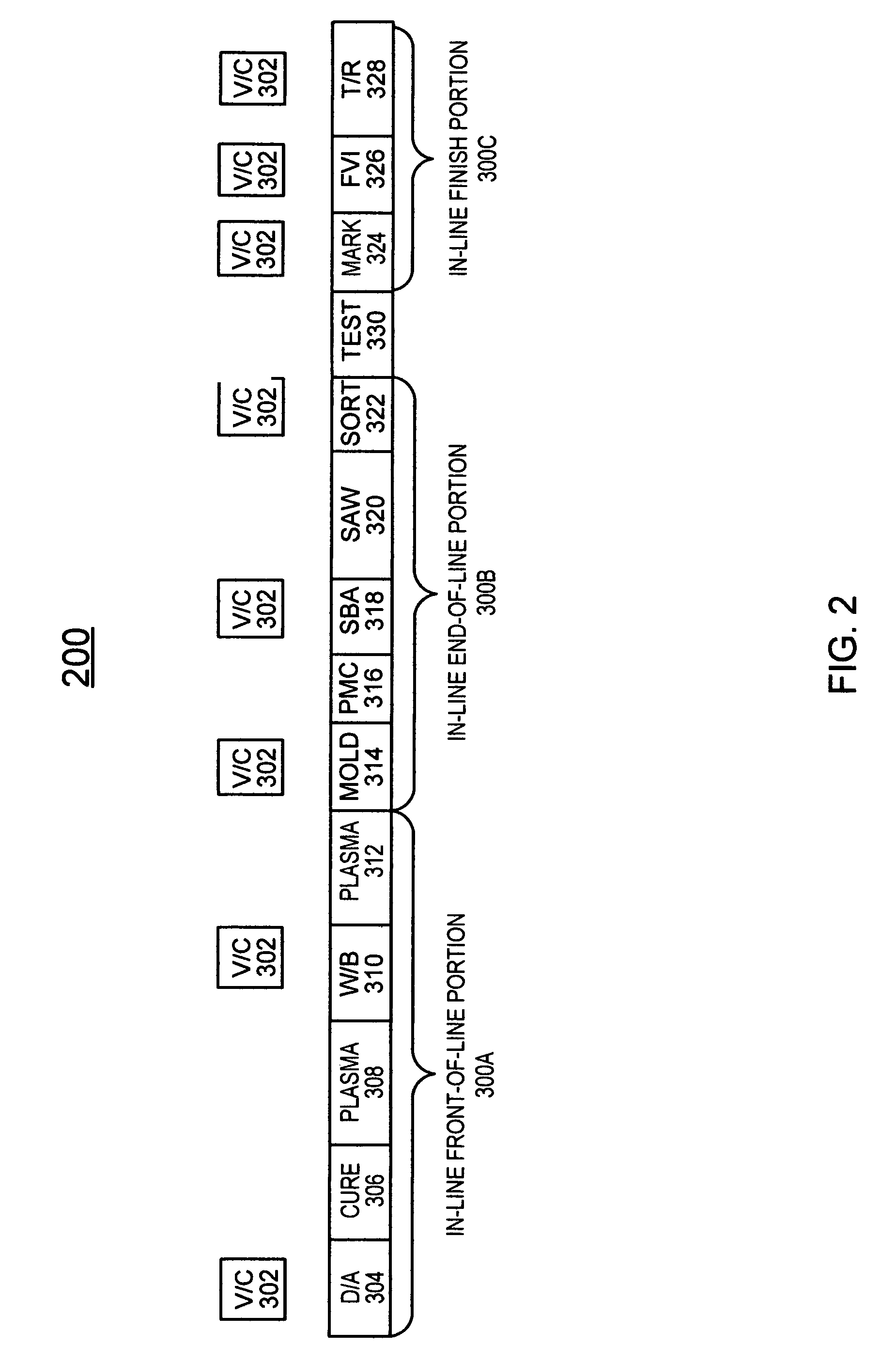

Method and system for a reject management protocol within a back-end integrated circuit manufacturing process

InactiveUS7031791B1Increase throughput timeShorten cycle timeSemiconductor/solid-state device testing/measurementResistance/reactance/impedenceQuality assuranceComputer science

A method and system for a reject management protocol within a back-end IC manufacturing process. In one method embodiment, the present invention implements a tracking process for a die-strip. The present invention also maintains an electronic die-strip map database, and utilizes the tracking process to update the electronic die-strip map database as the die-strip moves in an in-line fashion from one sub-station to another within the manufacturing process. Information used to update the database can originate from one or more automated visual camera systems used for quality assurance. In so doing, the present invention categorizes the die on the die-strip based on information maintained by the electronic die-strip map database. This information can be used for die sorting and for die rejection. In one embodiment, an identifying code is placed on each die strip that can automatically identify the die-strip using the automated camera systems.

Owner:MONTEREY RES LLC

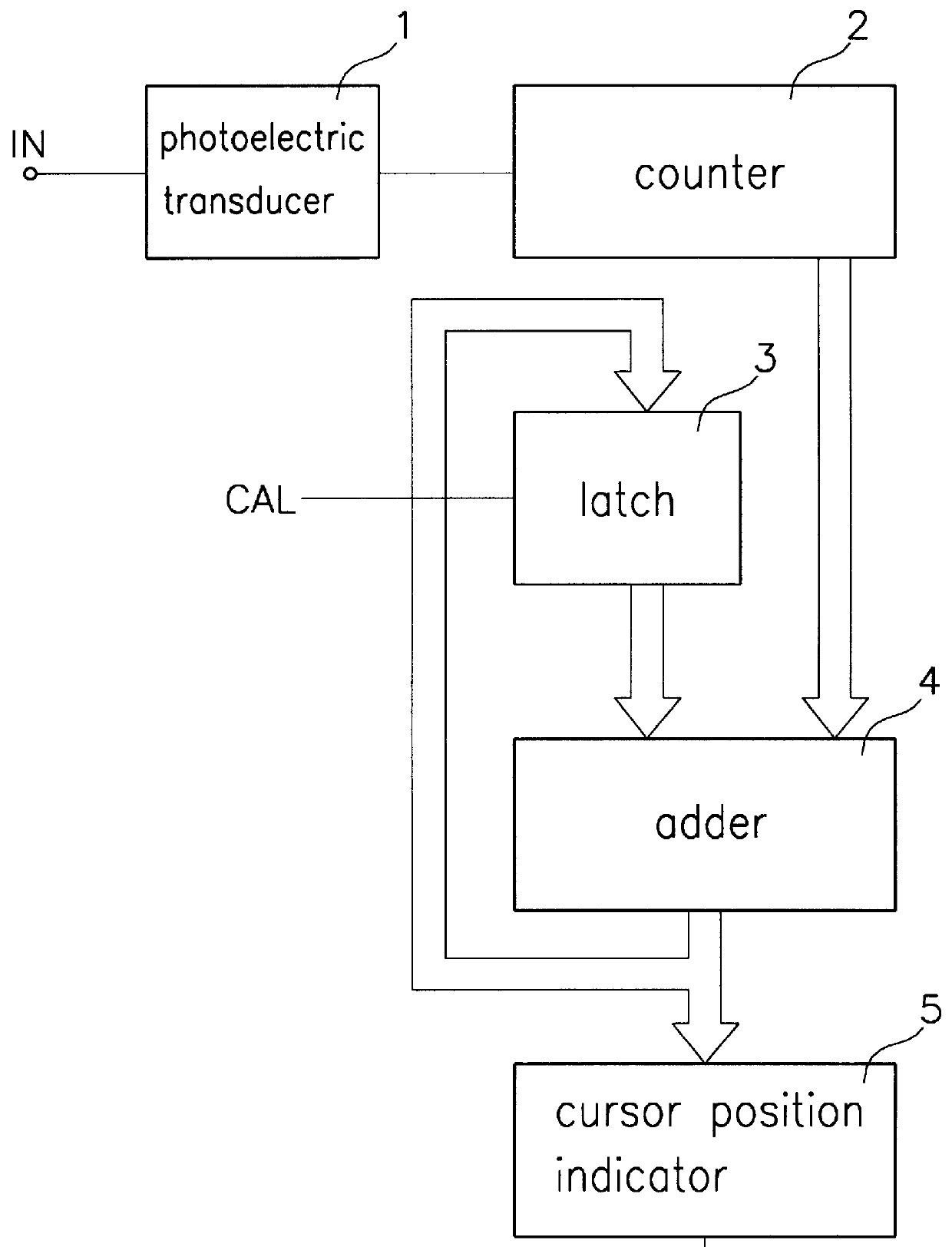

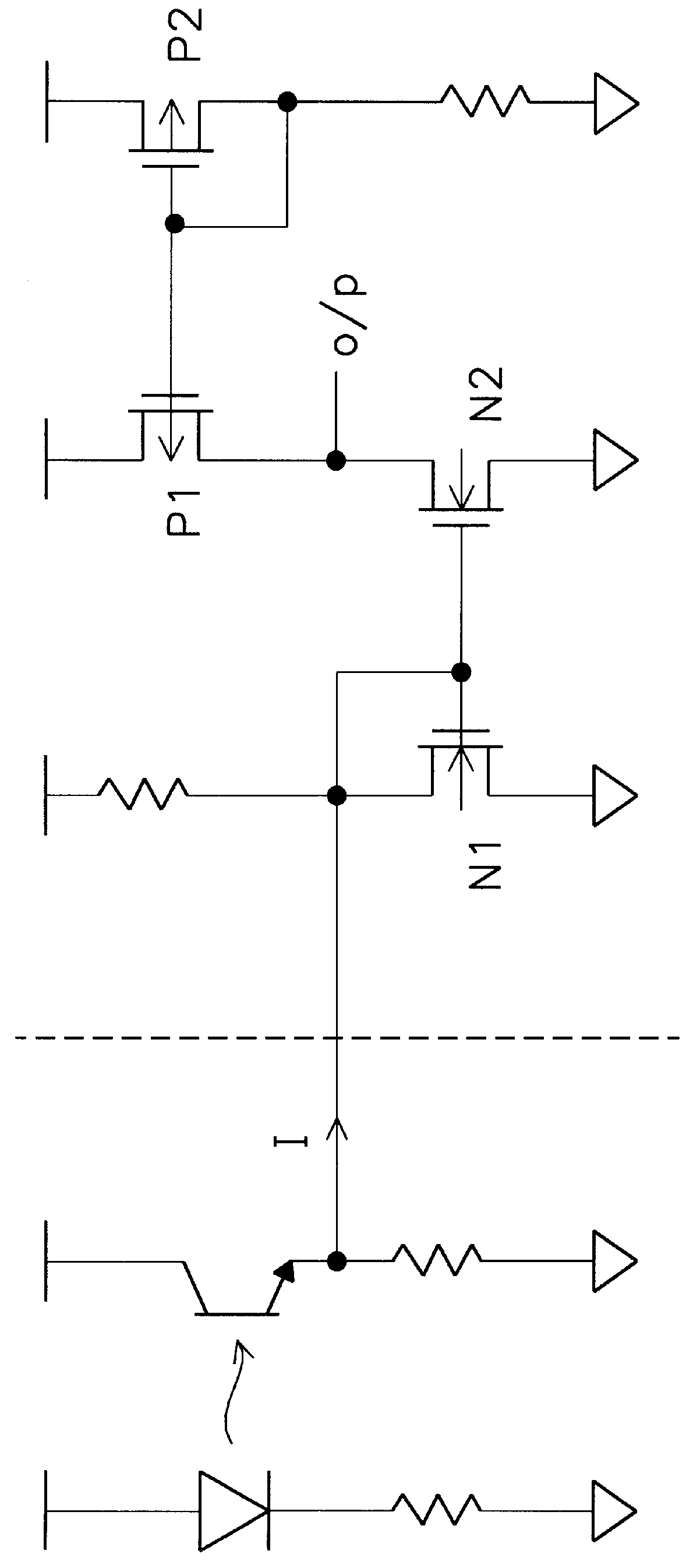

Joystick control device having cursor correcting function

InactiveUS6034669AEliminate bad effectsEasy to correctManual control with multiple controlled membersCathode-ray tube indicatorsJoystickMechanical wear

A joystick control device having cursor correcting function, in which the conventional adjustable resistor is replaced by a photoelectric element for detecting the movement of the joystick, thereby eliminates the ill effects caused by mechanical attrition of resistor. Additionally, the parameter drifts caused by IC manufacturing processes are corrected using shift correction of joystick; therefore, every individual mass-produced IC shows similar good behavior.

Owner:REALTEK SEMICON CORP

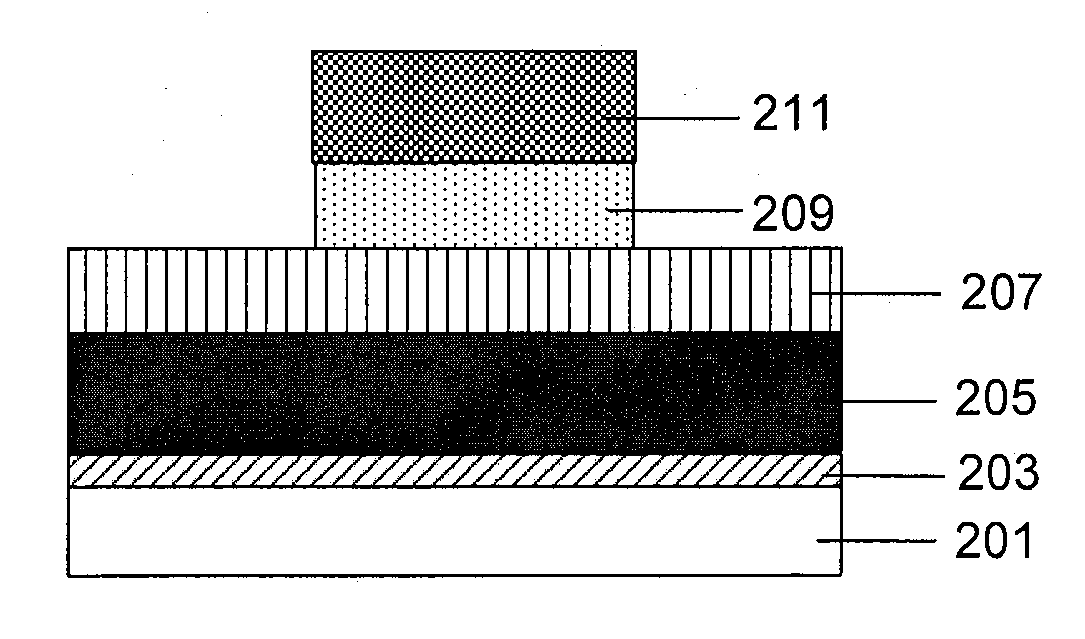

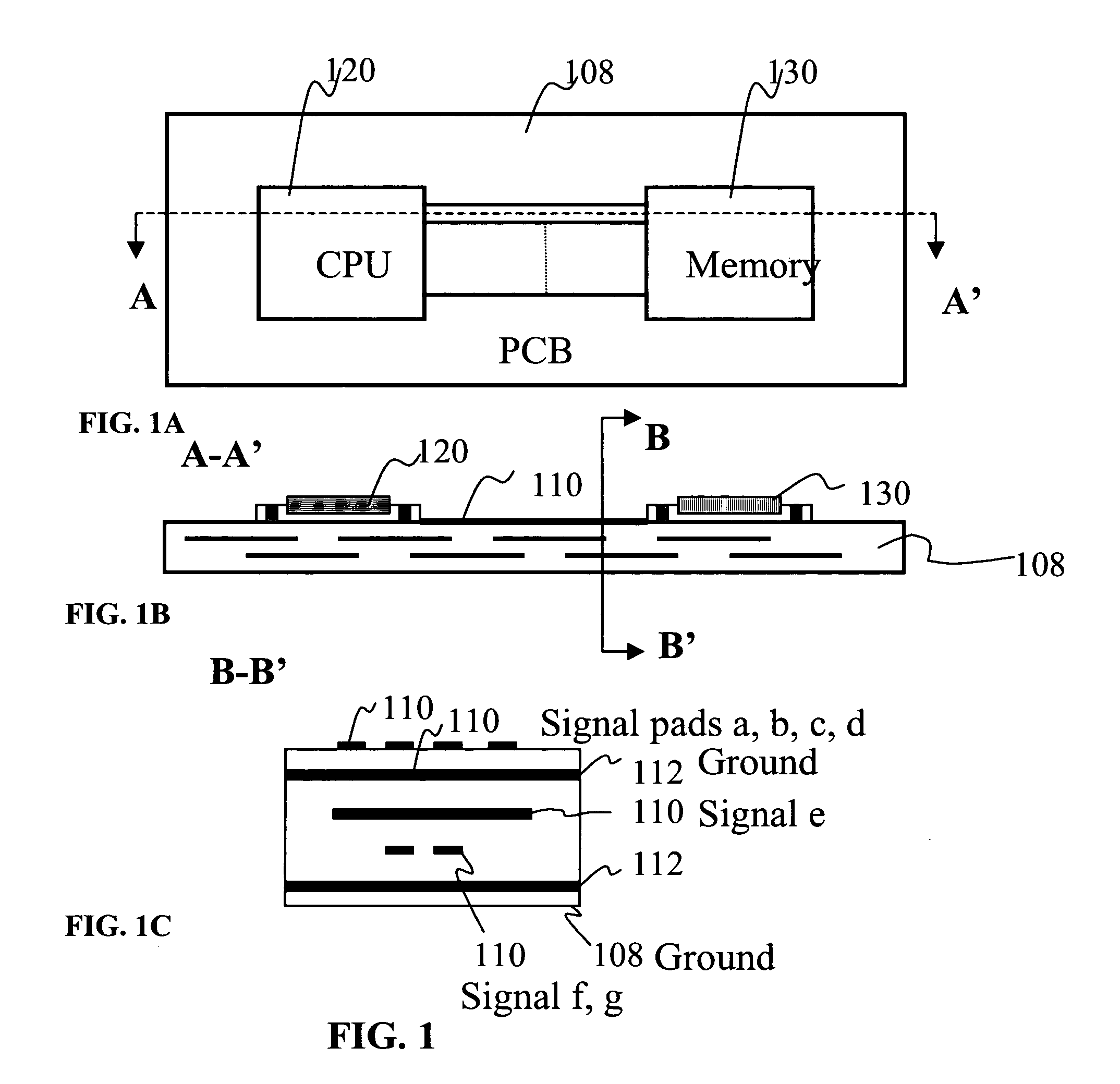

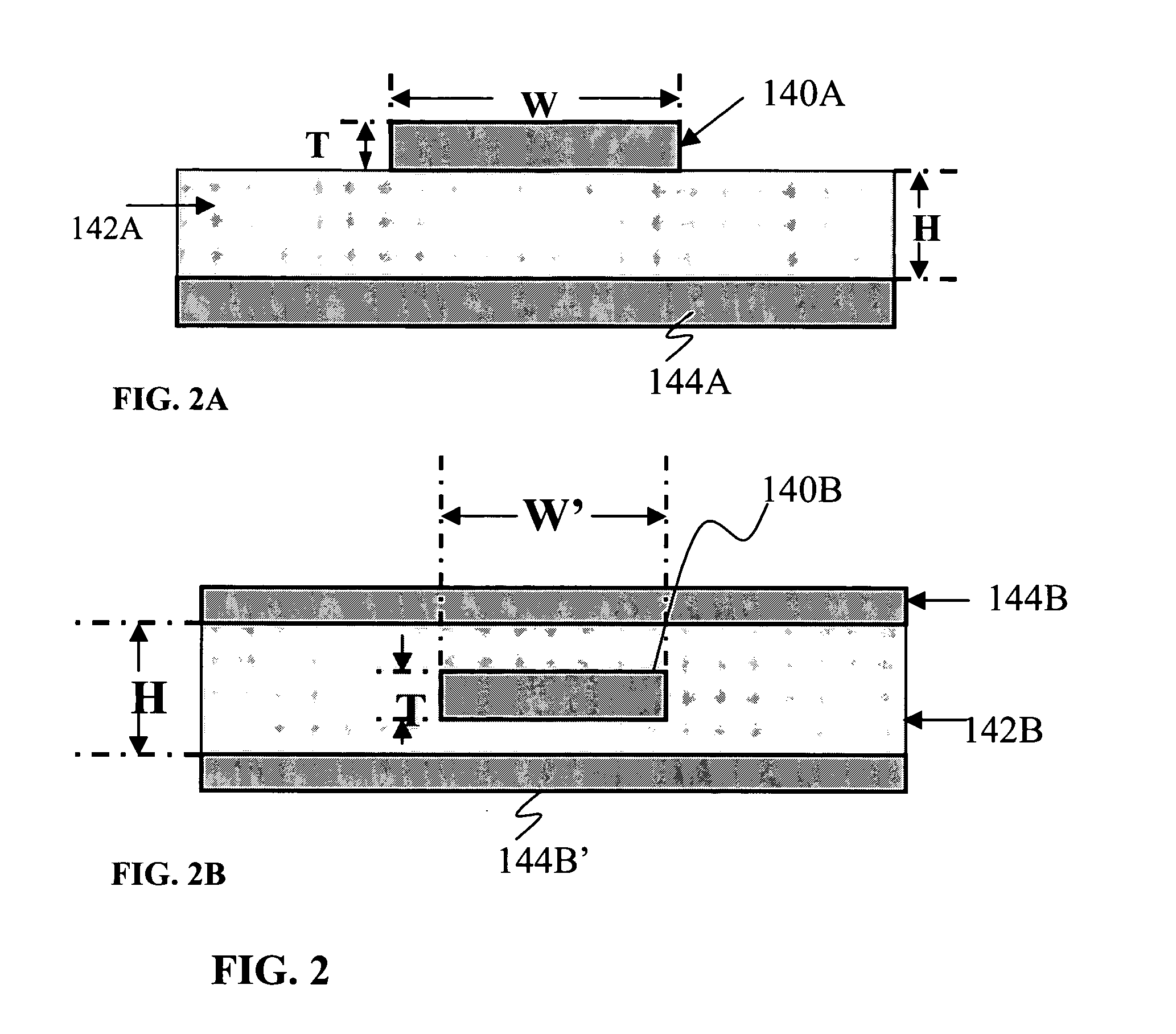

High Speed Electrical On-Chip Interconnects and Method of Manufacturing

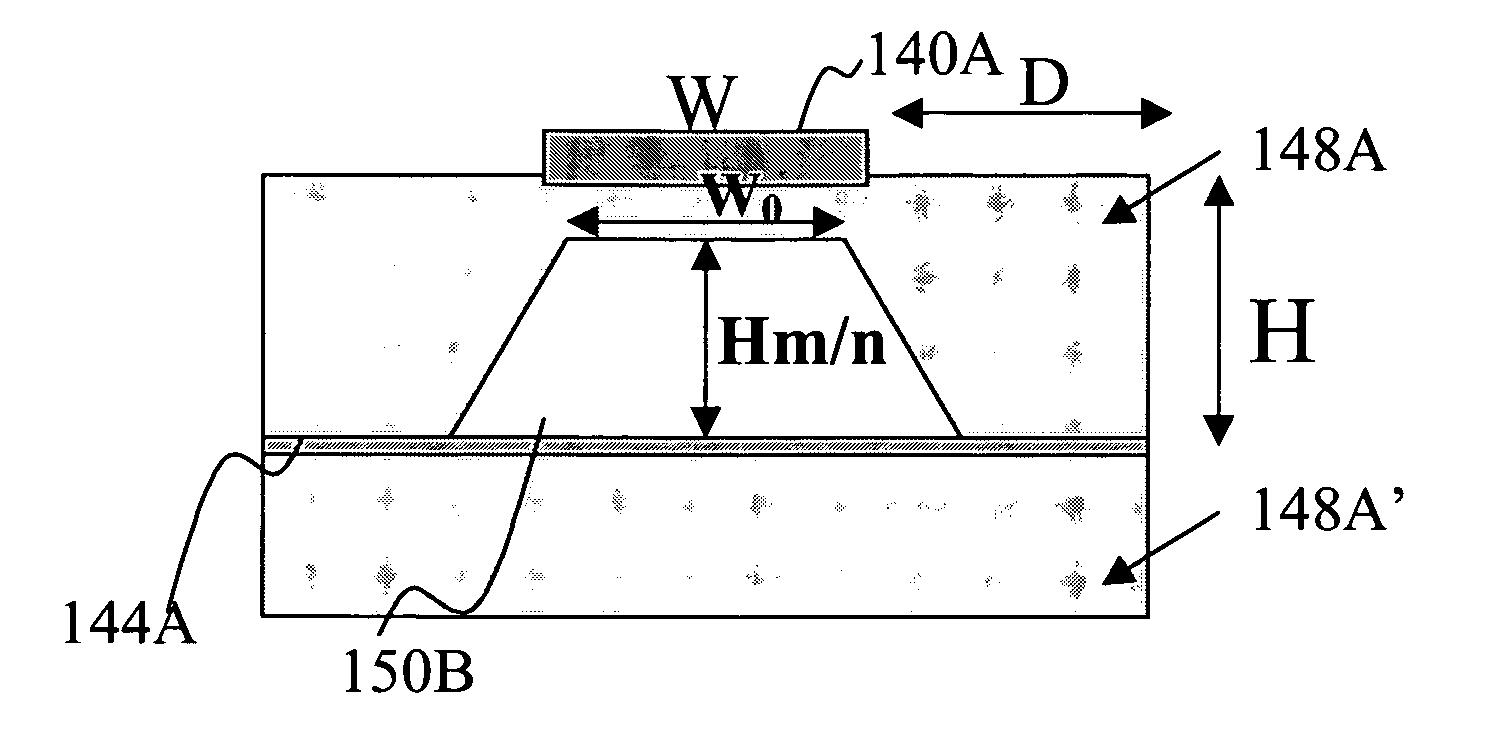

InactiveUS20050110138A1Reduce effective loss-tangentHigh bandwidthSemiconductor/solid-state device detailsSolid-state devicesDielectric substrateIc manufacturing

High-speed interconnect systems for connecting two or more electrical elements are provided for on-chip interconnects. The manufacturing process to fabricate the interconnect structure using standard IC process is also provided. The interconnect systems consists of the electrical signal line, inhomogeneous dielectric systems, and with and without ground line, wherein inhomogeneous dielectric system consisting of the opened-trenches into the dielectric substrate or comb-shaped dielectrics to reduce the microwave loss. The signal lines located below and / or above the opened trenches. The opened trenches helps to reduce the microwave-loss induced due to the dielectric material and increases the on-chip interconnects bandwidth. Alternatively, dielectric system can have the structure based on fully electronic or electromagnetic crystal or quasi crystal with the line defect. The interconnect system, can be made in IC for on-chip interconnects using conventional IC manufacturing technology and yet to increase the interconnects-bandwidth.

Owner:BANPIL PHOTONICS

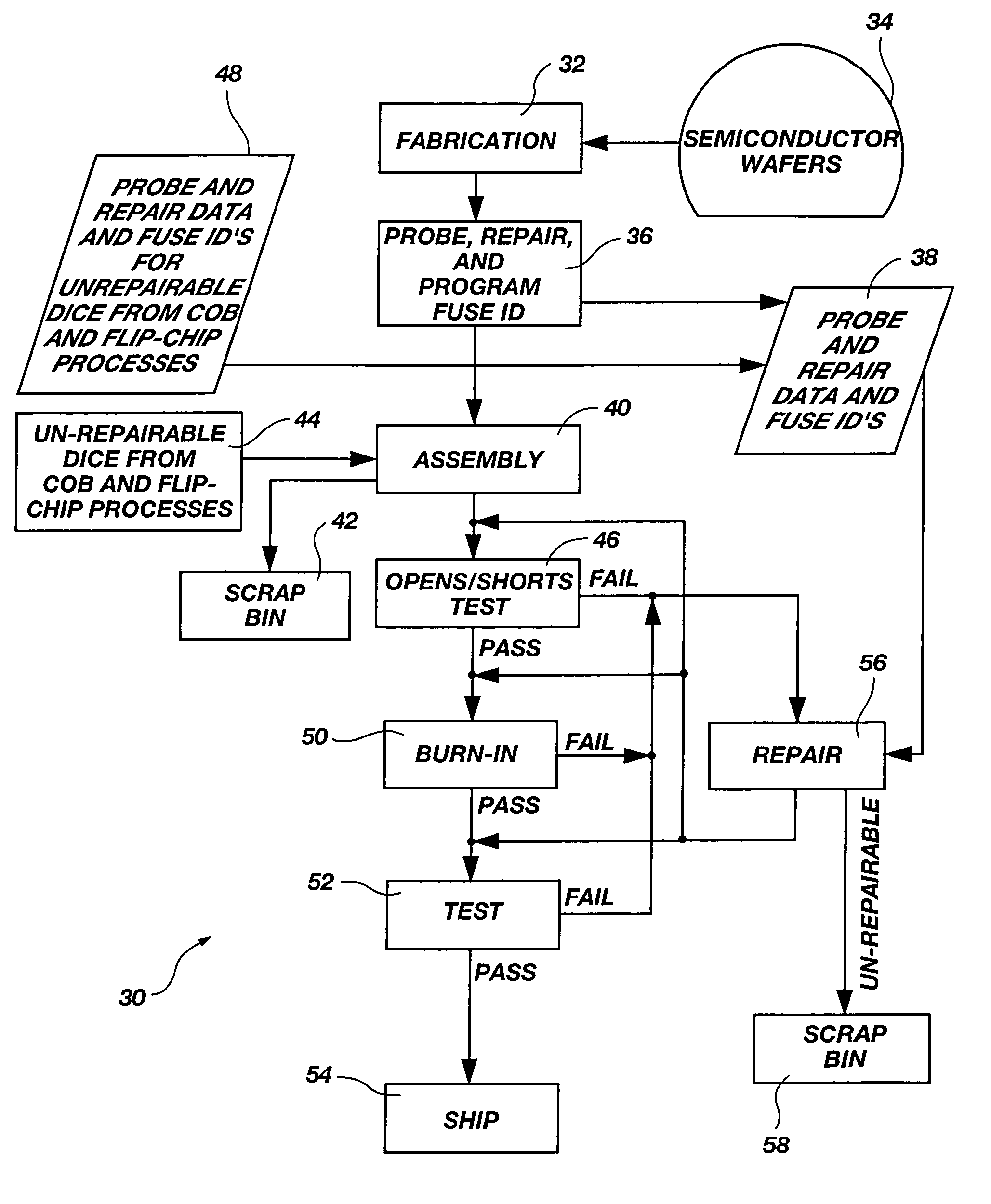

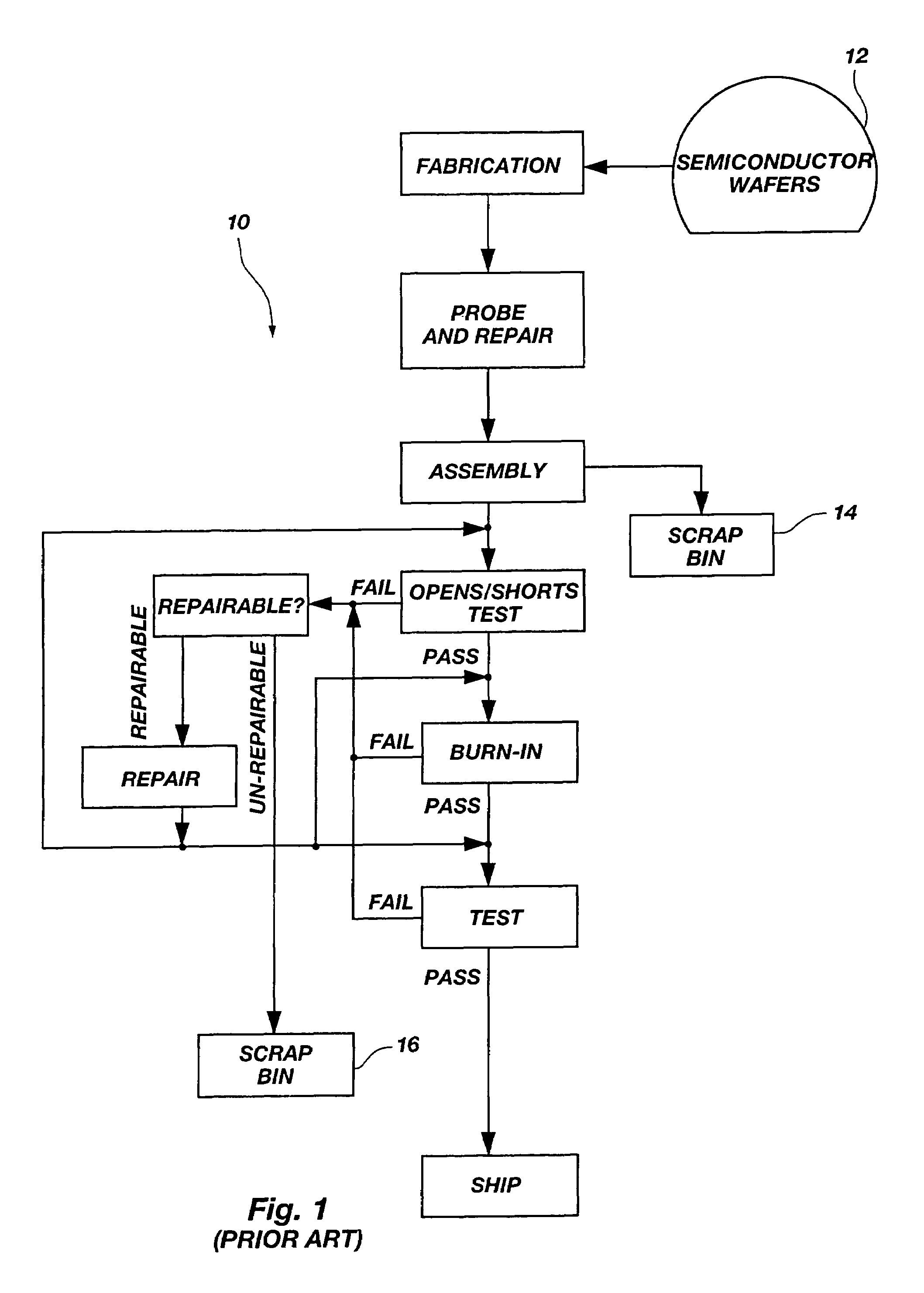

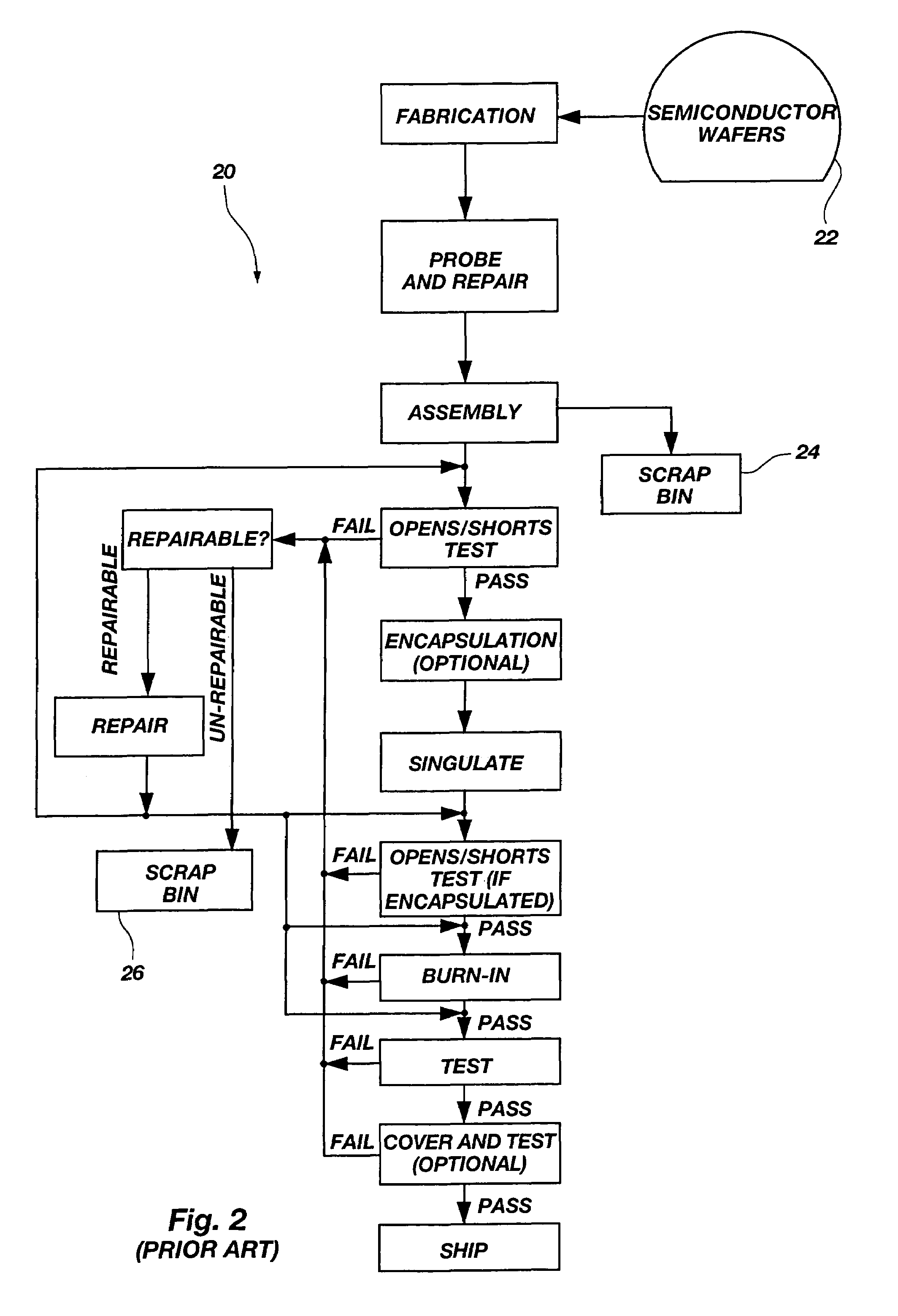

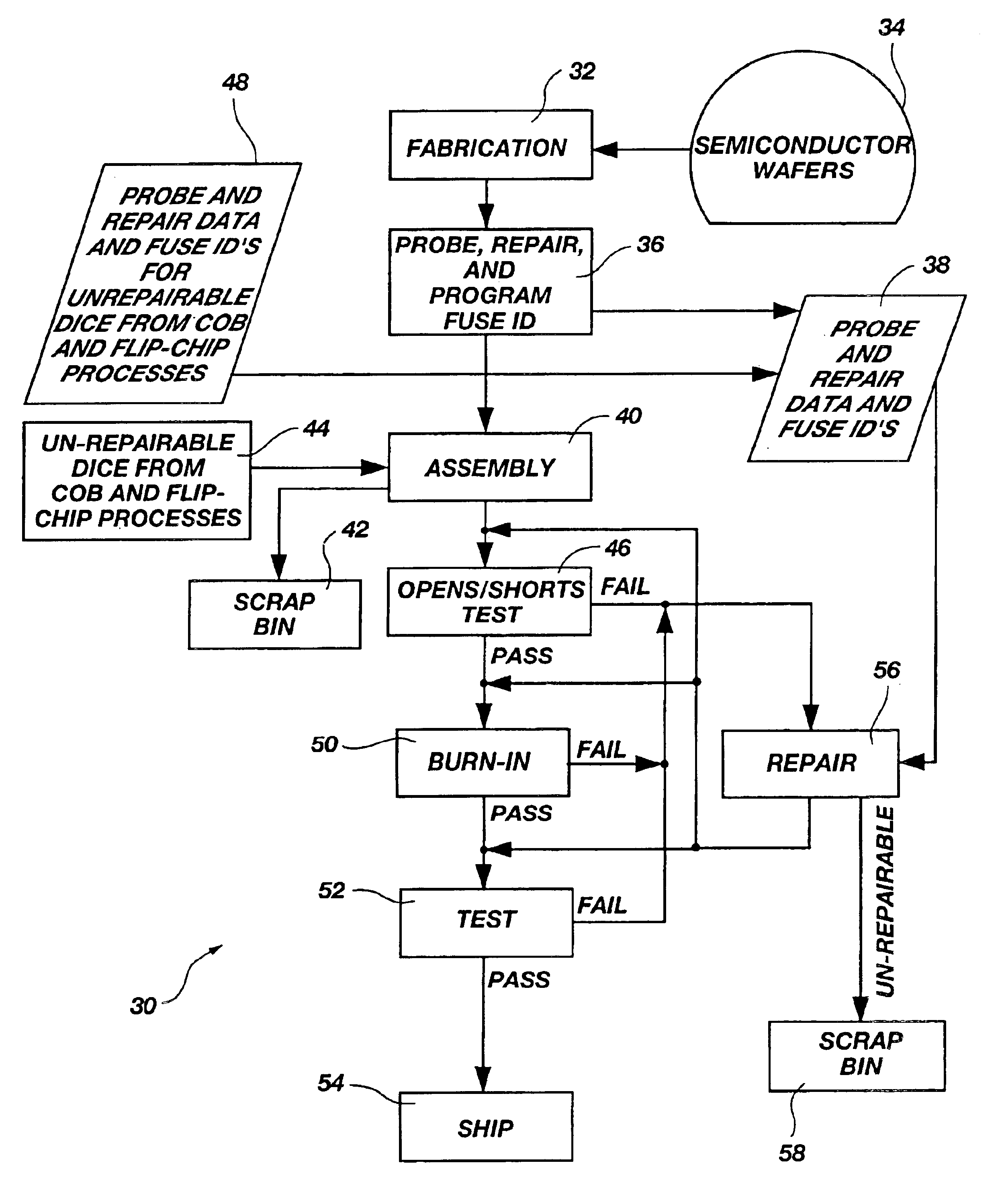

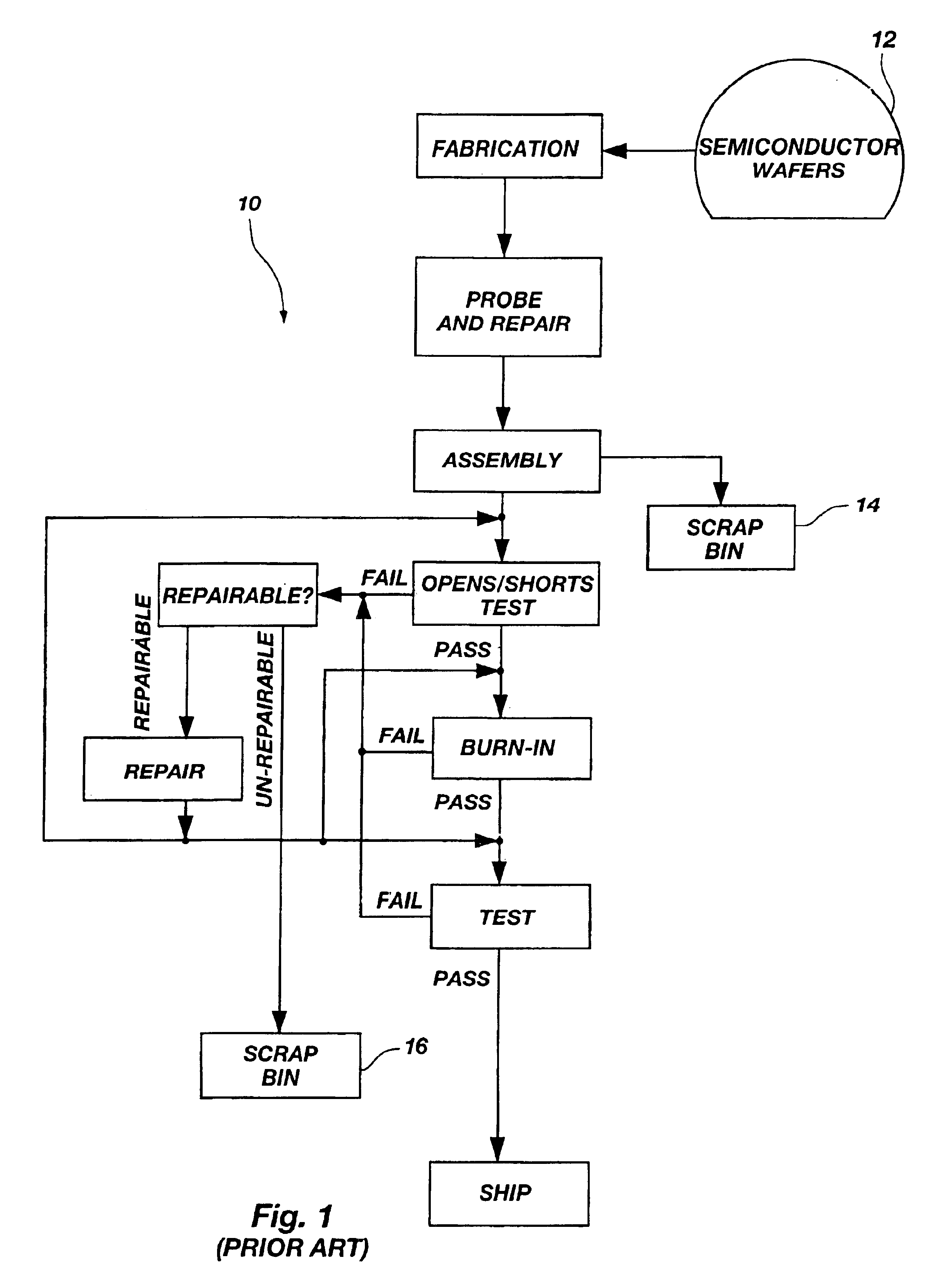

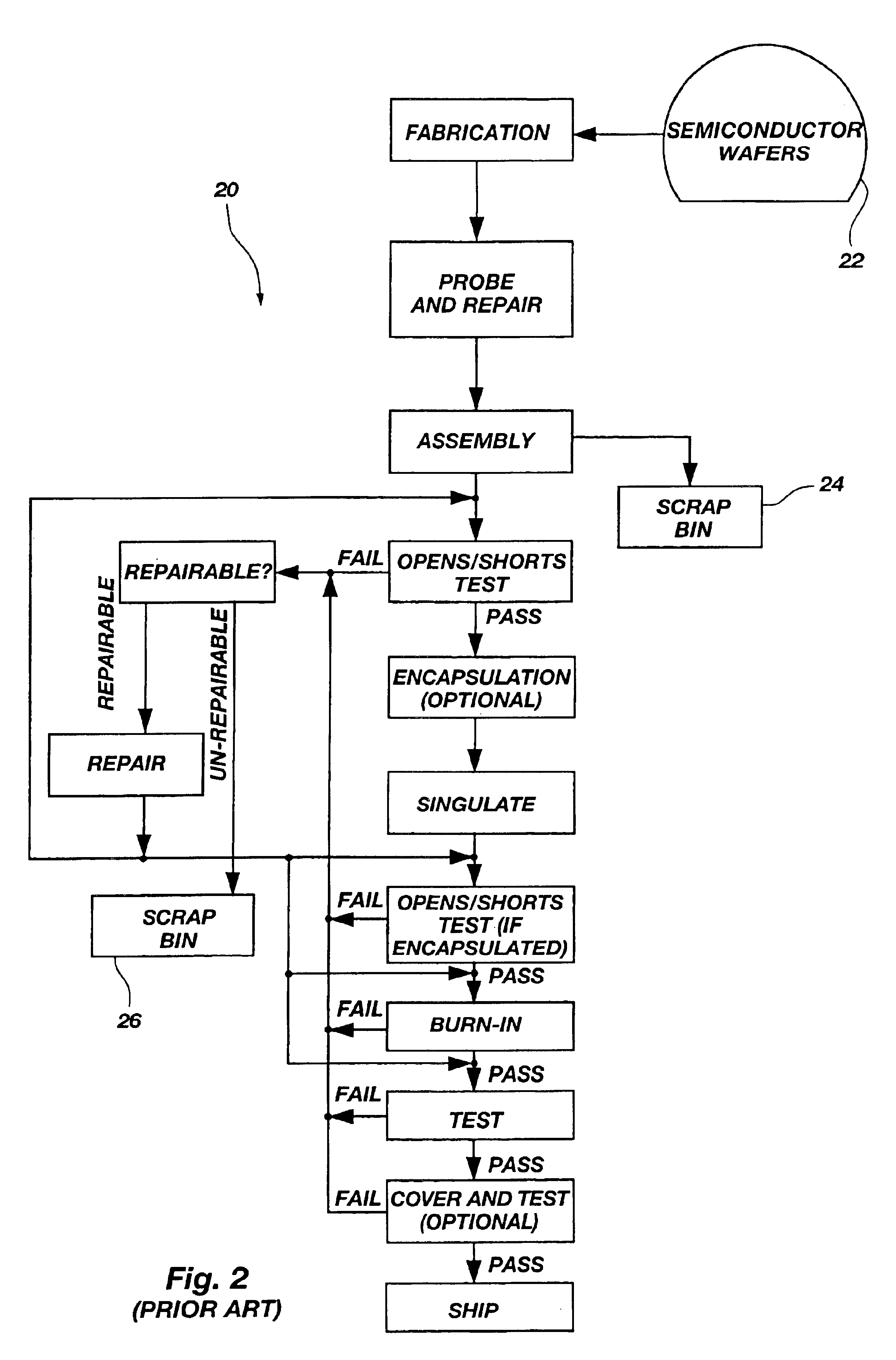

Method for using data regarding manufacturing procedures integrated circuits (ICS) have undergone, such as repairs, to select procedures the ICS will undergo, such as additional repairs

InactiveUS7120513B1Save time wastingResistance/reactance/impedenceSolid-state devicesEngineeringData storing

An inventive method in an integrated circuit (IC) manufacturing process for using data regarding repair procedures conducted on IC's at probe to determine whether any further repairs will be conducted later in the manufacturing process includes storing the data in association with a fuse ID of each of the IC's. The ID codes of the IC's are automatically read, for example, at an opens / shorts test during the manufacturing process. The data stored in association with the ID codes of the IC's is then accessed, and additional repair procedures the IC's may undergo are selected in accordance with the accessed data. Thus, for example, the accessed data may indicate that an IC is unrepairable, so the IC can proceed directly to a scrap bin without having to be queried to determine whether it is repairable, as is necessary in traditional IC manufacturing processes.

Owner:MICRON TECH INC

Method for using data regarding manufacturing procedures integrated circuits (IC's) have undergone, such as repairs, to select procedures the IC's will undergo, such as additional repairs

InactiveUS7155300B2Save time wastingSemiconductor/solid-state device testing/measurementResistance/reactance/impedenceShort-circuit testData storing

An inventive method in an integrated circuit (IC) manufacturing process for using data regarding repair procedures conducted on IC's at probe to determine whether any further repairs will be conducted later in the manufacturing process includes storing the data in association with a fuse ID of each of the IC's. The ID codes of the IC's are automatically read, for example, at an opens / shorts test during the manufacturing process. The data stored in association with the ID codes of the IC's is then accessed, and additional repair procedures the IC's may undergo are selected in accordance with the accessed data. Thus, for example, the accessed data may indicate that an IC is unrepairable, so the IC can proceed directly to a scrap bin without having to be queried to determine whether it is repairable, as is necessary in traditional IC manufacturing processes.

Owner:MICRON TECH INC

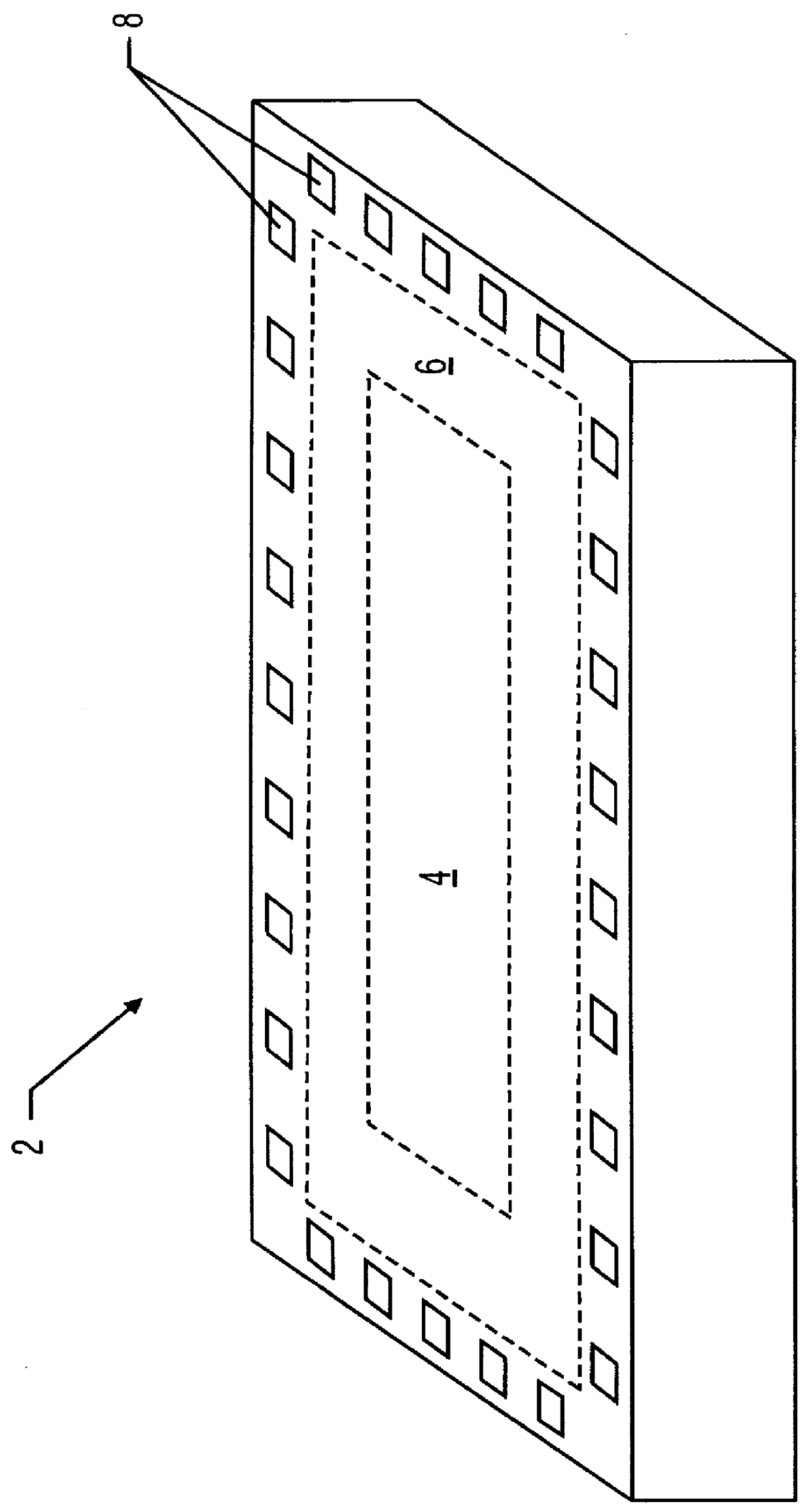

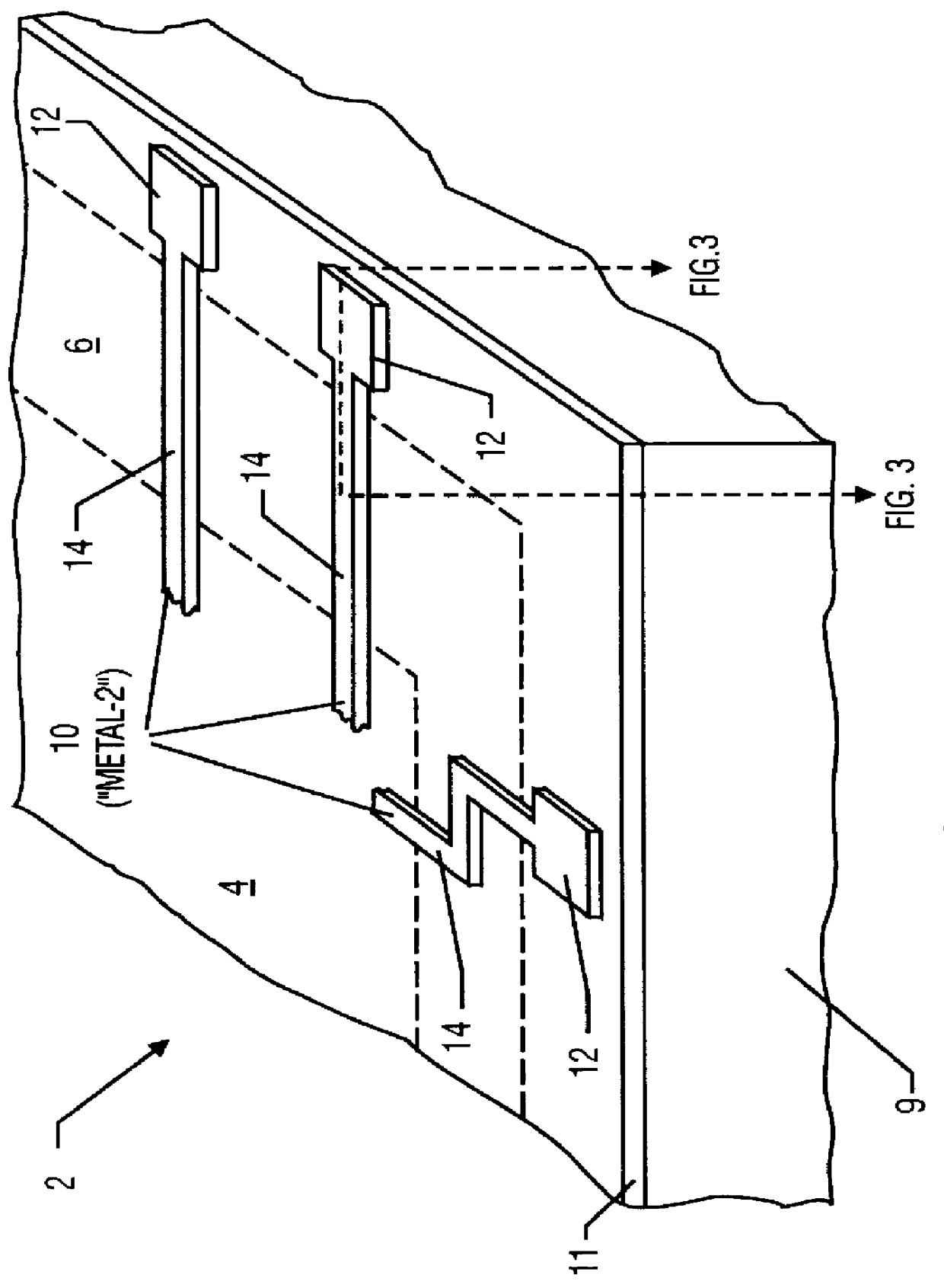

Methods and structures for pad reconfiguration to allow intermediate testing during manufacture of an integrated circuit

InactiveUS6054334ASemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsEmbedded systemIntegrated circuit

Methods and structures for pad reconfiguration to allow intermediate testing during the manufacture of an integrated circuit are disclosed. The methods and structures disclosed are particularly useful in testing an embedded subcircuit, such as a memory array within an embedded chip product. A bond pad reconfiguration etch and other means for reconfiguring a bond pad are also disclosed.

Owner:ROUND ROCK RES LLC

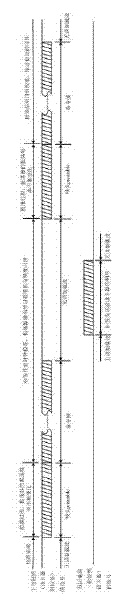

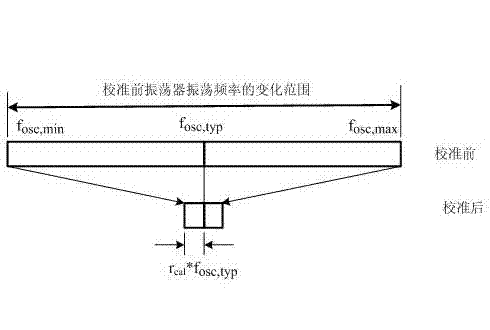

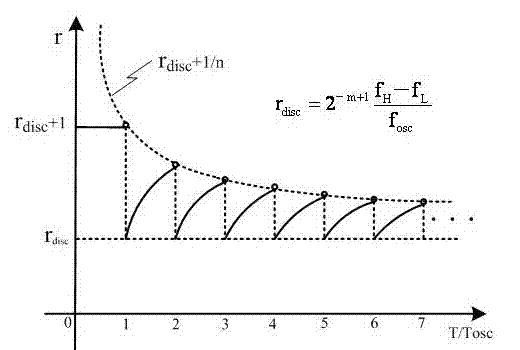

Clock generating circuit for radio frequency identification (RFID) tag and calibrating method of clock generating circuit

ActiveCN102682330ACompensation for discretenessOscillation frequency consistentElectric pulse generator circuitsSensing record carriersComputer hardwarePower-on reset

The invention discloses a clock generating circuit for a radio frequency identification (RFID) tag and the calibrating method of the clock generating circuit and relates to the technical field of RFID. The clock generating circuit provided by the invention comprises a numerical control tuned oscillator, a controller, a counter and a digital baseband processing circuit. A demodulation signal Rx output by tag radio frequency is input to the tag digital baseband processing circuit and the controller, and a power-on reset signal Rst output by a reset signal generating circuit arranged at the front end of the tag radio frequency is input to the controller, the counter and the tag digital baseband processing circuit. A calibration-enable signal Calib_en output by the tag digital baseband processing circuit is connected to the input ends of the controller and the counter. The count output Count of the counter is connected to the input end of the controller, and Rst_cnt output by the controller is connected to the input end of the counter. By using the clock generating circuit and the calibrating method thereof, the influences of an integrated circuit manufacturing process, an application environment and temperature on the bit rate precision, the code, the duty ratio and the like of the chip of the RFID tag can be avoided, the power consumption of the chip of the tag can be reduced, and the finished product rate of the chip can be increased.

Owner:BEIJING TONGFANG MICROELECTRONICS

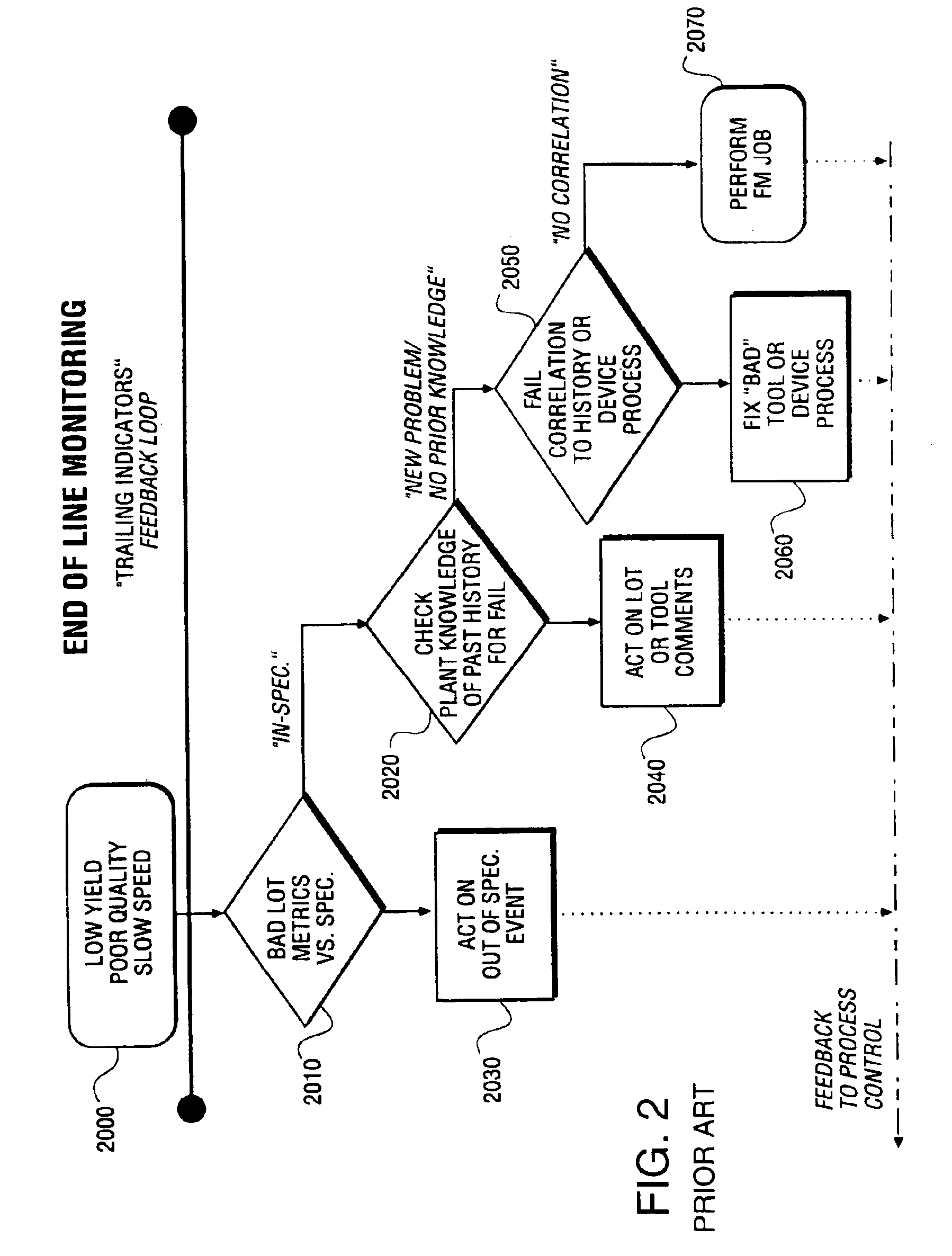

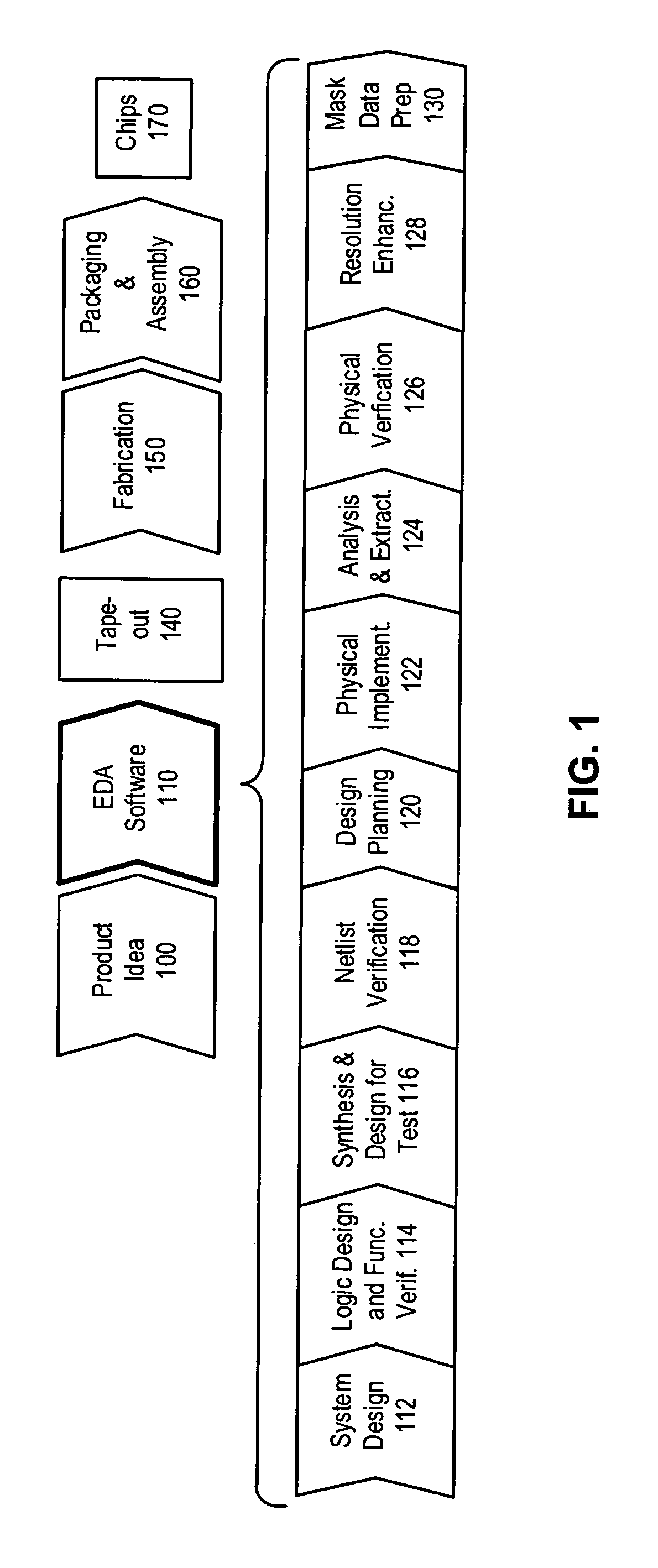

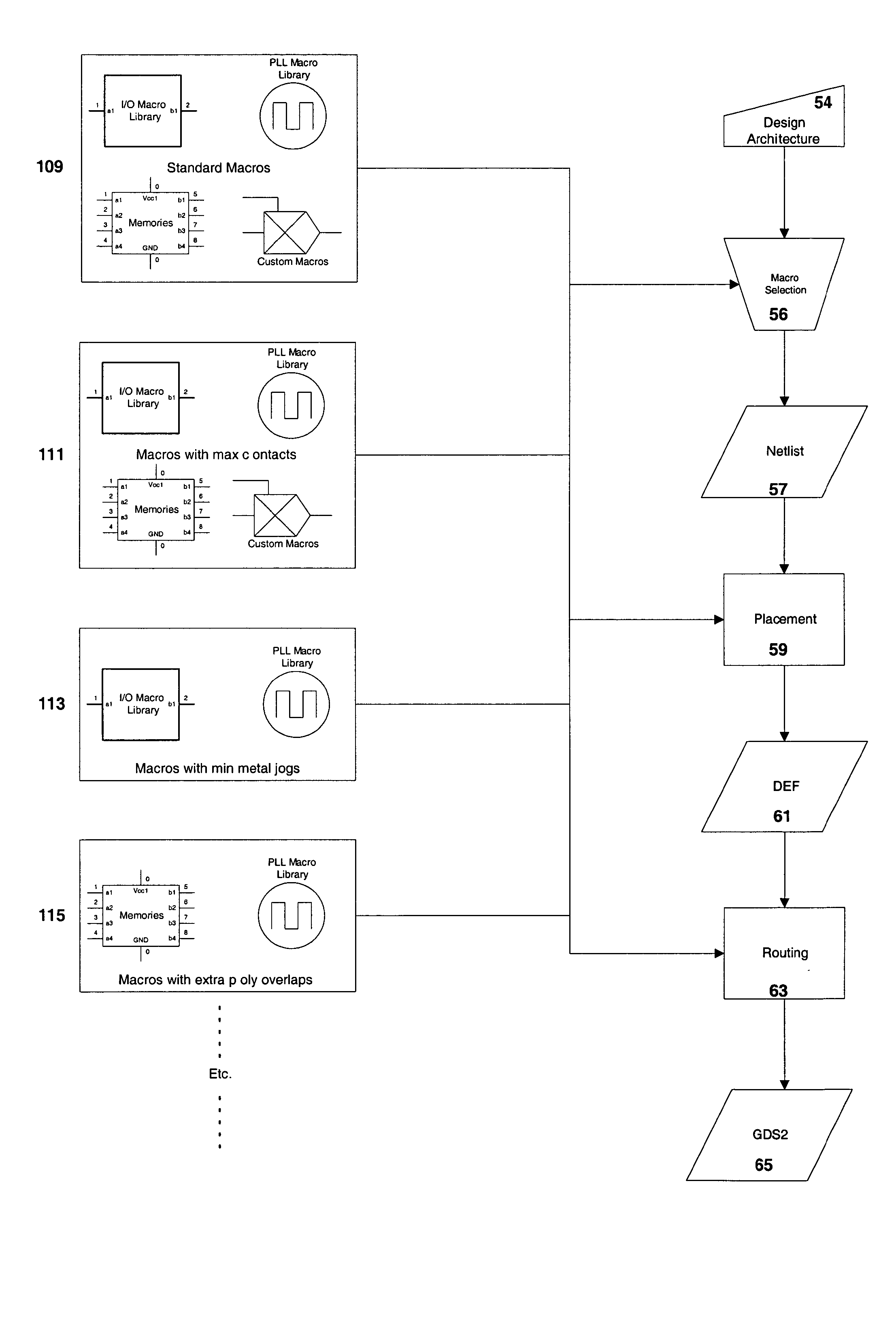

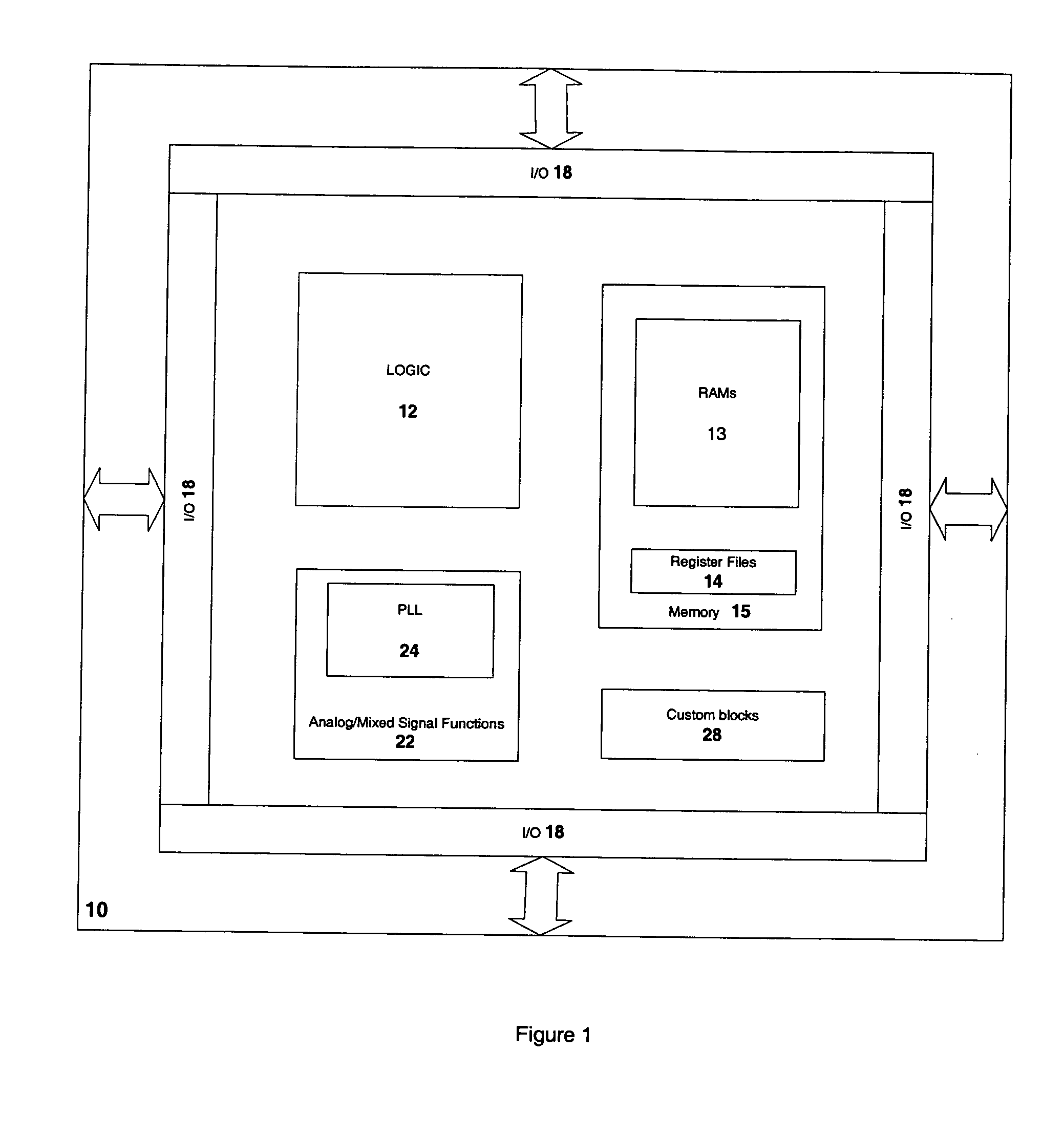

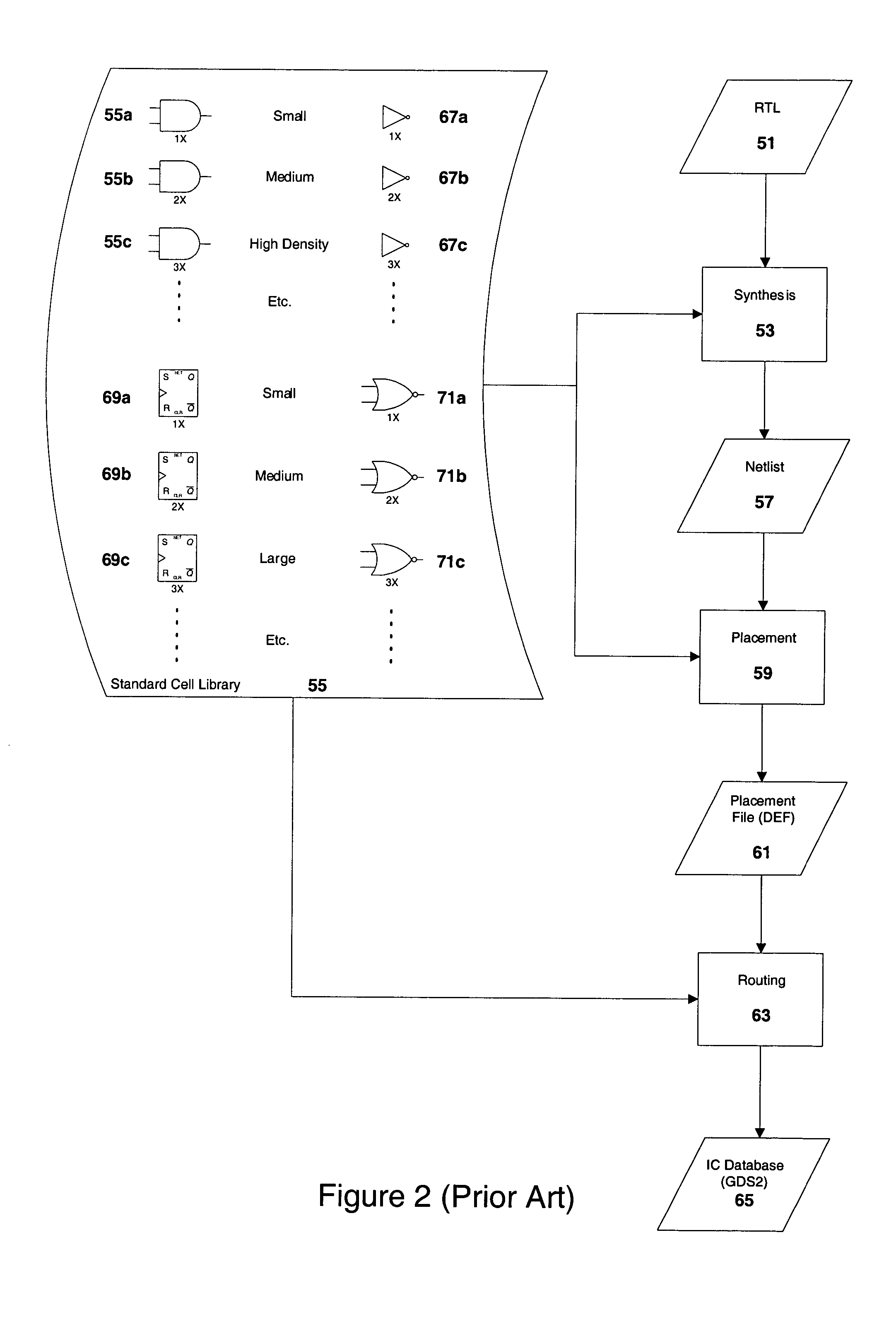

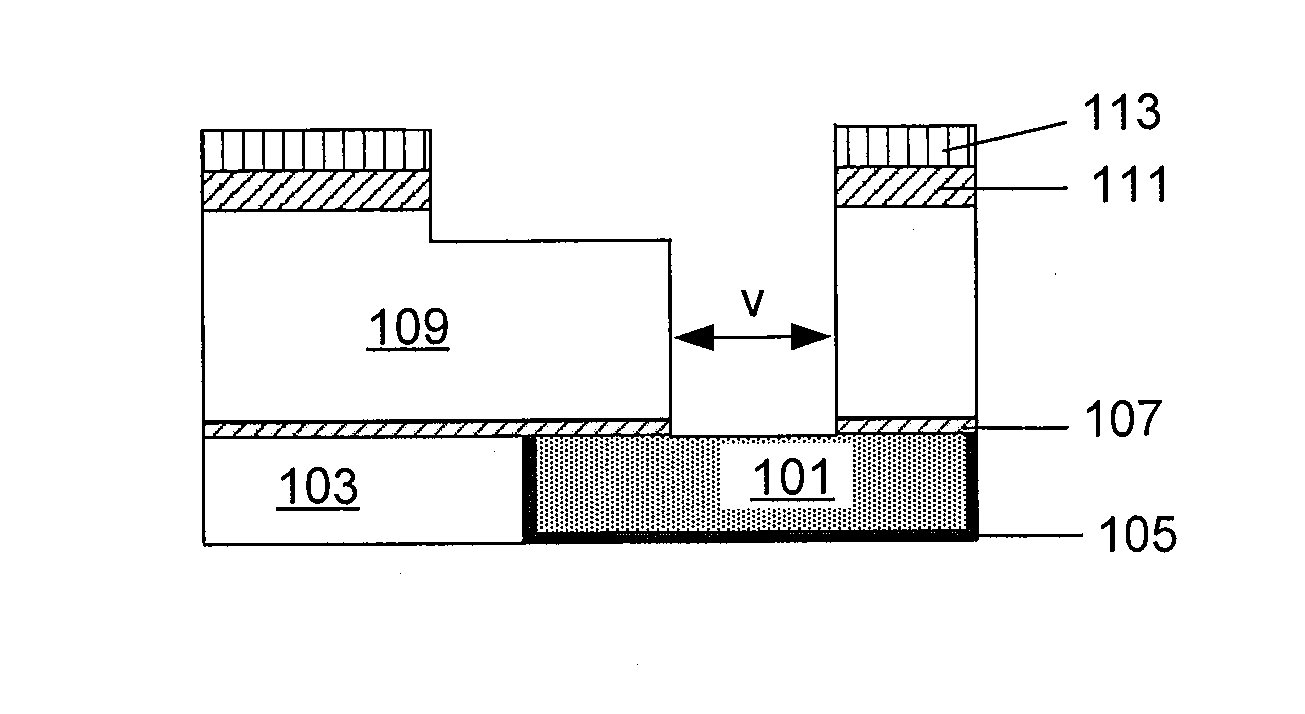

Yield maximization in the manufacture of integrated circuits

ActiveUS20050066294A1Increase productionHigh yieldSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingManufacturing technologyEngineering

A method and apparatus for improving the manufacturability of Integrated Circuits (ICs) formed on semiconductor dies is described. A plurality of different designs for some or all of the standard cells are made available to the circuit designer. Each different design may address a different problem associated with different manufacturing processes or a different design related yield limiter. Each of the design variants is characterized indicating its relative ease of manufacture, or it's yield sensitivity to certain IC design factors. The designer, typically with assistance from computer aided tools, can then select the standard cell variant for each of the cell used in the IC design that best addresses his or her design constraints. In other embodiments, variant versions of I / O cells and memory cells could also be created and made available to the designer in a similar fashion.

Owner:ARM INC

Hardmask materials

ActiveUS20110133313A1Poor pattern alignmentReduce stressLiquid surface applicatorsElectric discharge tubesPost treatmentIntegrated circuit fabrication

Hardmask films having high hardness and low stress are provided. In some embodiments a film has a stress of between about −600 MPa and 600 MPa and hardness of at least about 12 GPa. In some embodiments, a hardmask film is prepared by depositing multiple sub-layers of doped or undoped silicon carbide using multiple densifying plasma post-treatments in a PECVD process chamber. In some embodiments, a hardmask film includes a high-hardness boron-containing film selected from the group consisting of SixByCz, SixByNz, SixByCzNw, BxCy, and BxNy. In some embodiments, a hardmask film includes a germanium-rich GeNx material comprising at least about 60 atomic % of germanium. These hardmasks can be used in a number of back-end and front-end processing schemes in integrated circuit fabrication.

Owner:NOVELLUS SYSTEMS

Method for preventing metals from being damaged by high density plasma chemical vapor deposition

InactiveCN1831190AAvoid damageImprove protectionSemiconductor/solid-state device manufacturingChemical vapor deposition coatingHigh densityGas phase

The invention relates to a method to avoid damage to metal from high density plasma CVD that adopts plasma assistant CVD method to etch surface sediment a SiO2 layer after finishing etching the metal in IC manufacturing process. It induces sediment thin film medium to decrease the damage to metal from high density plasma CVD sediment process. It uses tetraethylorthosilicate as front driving material to form a SiO2 layer to supply good protection for metal.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT +1

Method for doubly setting and accurately positioning centre of silicon slice

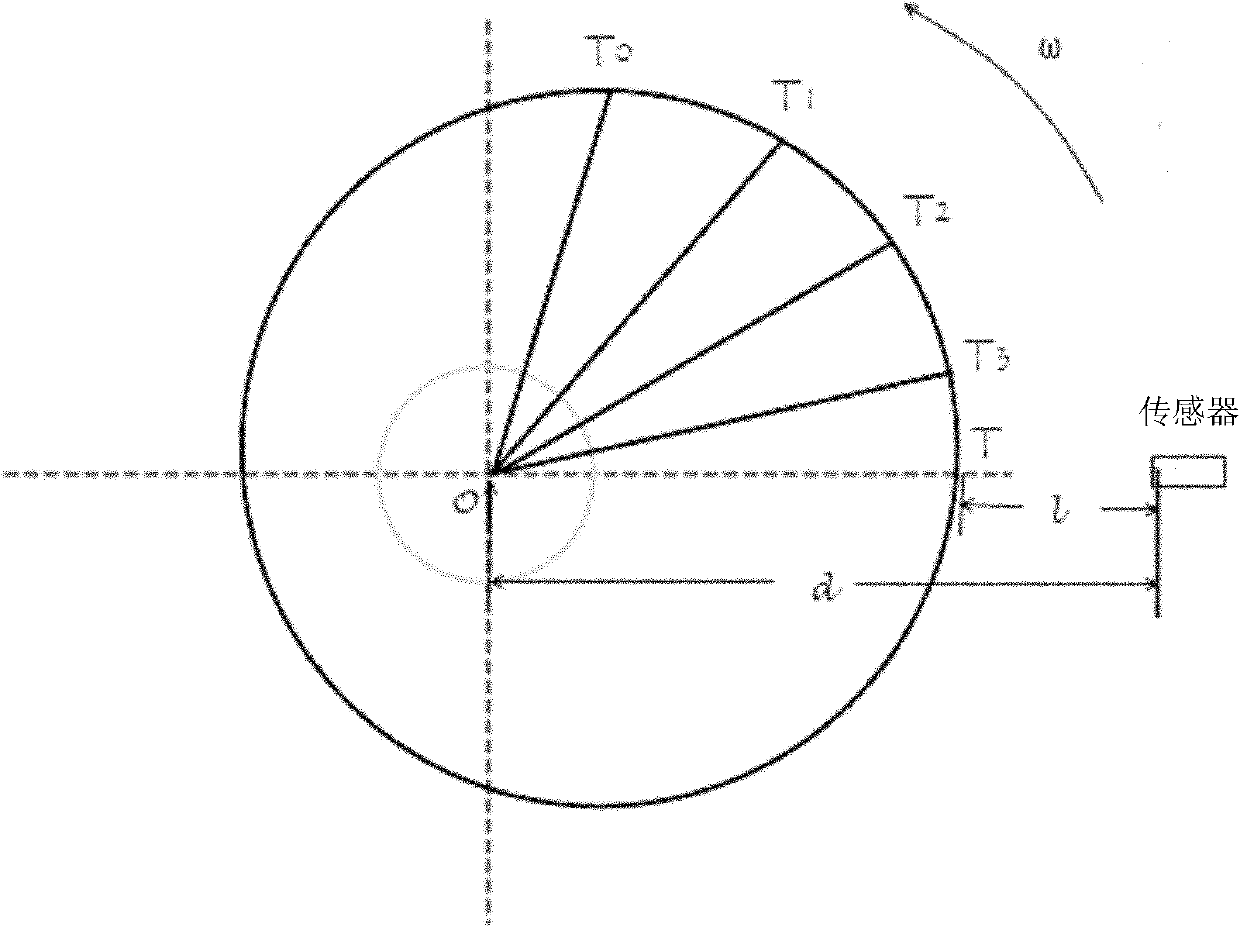

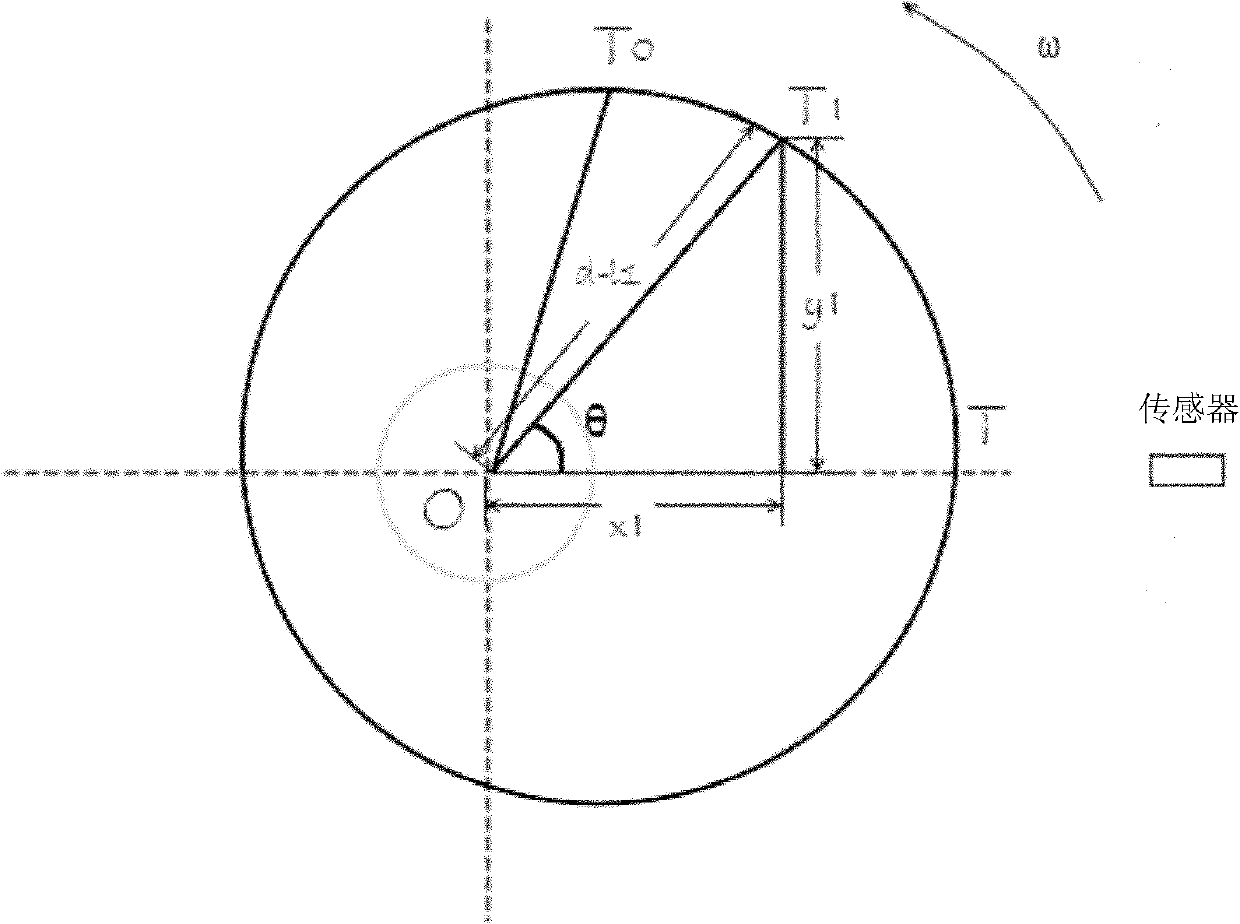

ActiveCN102169822AEliminate errorsAvoid quadratic errorsSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingProcess equipmentSilicon

The invention relates to a processing technology of a silicon slice for manufacturing of an integrated circuit, in particular to a method for doubly setting and accurately positioning the centre of the silicon slice. The method comprises the following steps of: rotating the silicon slice along centre direction; identifying edges of the silicon slice sequentially by linear image identification sensors having different precisions; determining positions of a flat edge or a notch; determining the offset of the centre of the silicon slice; and moving the silicon slice by using a bidirectional movement motor to make the centre of the silicon slice overlapped with a designed position. Therefore, a transmission error of the silicon slice existing in processing equipment in the process of semiconductor industry is avoided, and the precision of the set centre of the silicon slice is equal to 1 mu m by using the double-setting method.

Owner:SHENYANG KINGSEMI CO LTD

Predicting IC manufacturing yield based on hotspots

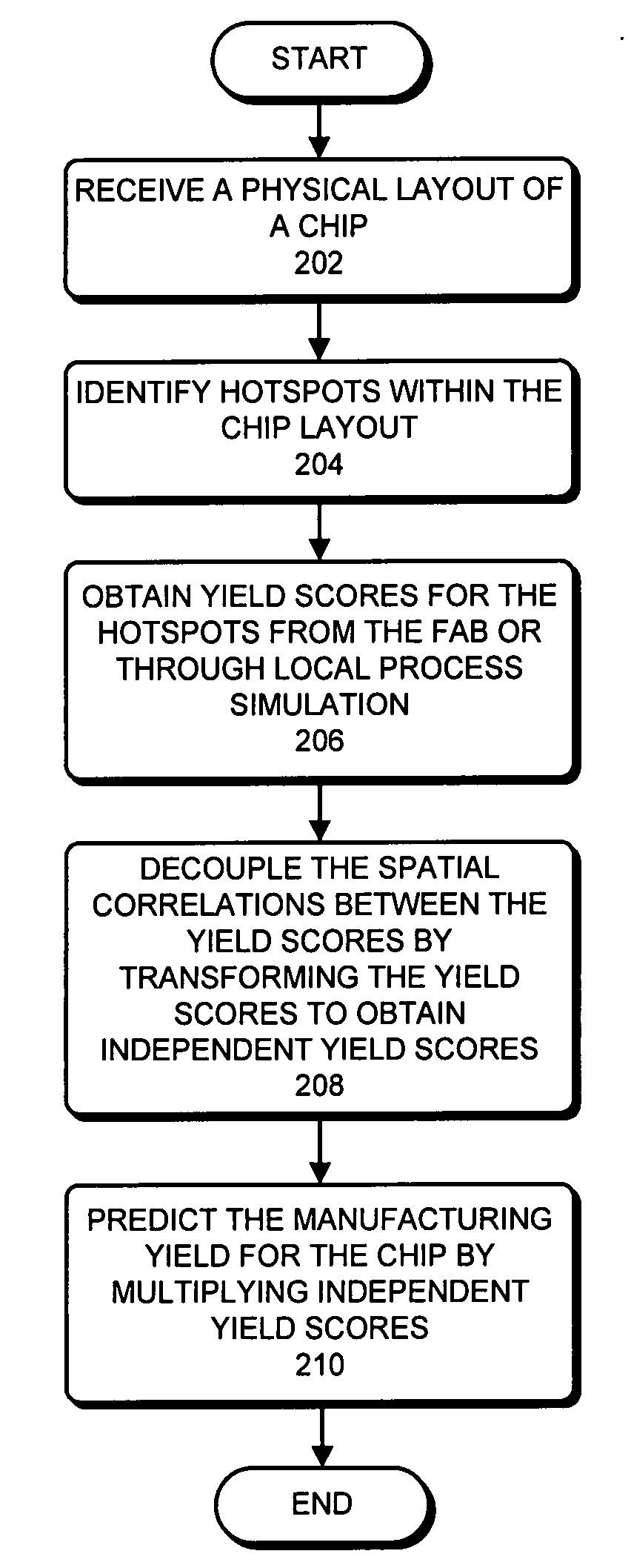

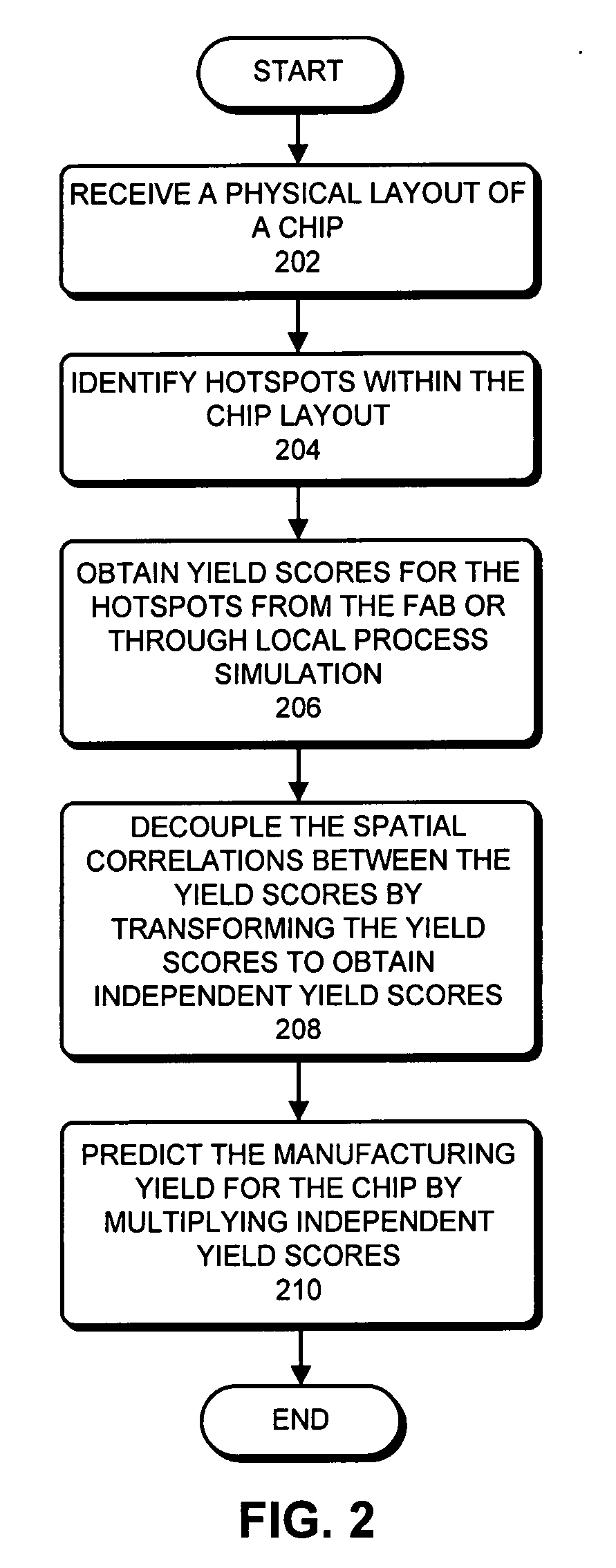

ActiveUS20080295046A1Detecting faulty computer hardwareCAD circuit designEngineeringSystem identification

One embodiment of the present invention provides a system that predicts a manufacturing yield of a chip. During operation, the system first receives a chip layout. Next, the system identifies hotspots within the chip layout, wherein a hotspot is a location within the chip layout wherein a yield-indicative variable value falls in a low manufacturable range. The system then obtains yield scores for the hotspots, wherein a yield score indicates a failure probability for a corresponding hotspot. Next, the system predicts the manufacturing yield for the chip based on the hotspots and the yield scores for the hotspots.

Owner:SYNOPSYS INC