Clock generating circuit for radio frequency identification (RFID) tag and calibrating method of clock generating circuit

A technology for clock generation circuits and radio frequency identification tags, which is applied to electric pulse generator circuits, record carriers used by machines, instruments, etc., can solve the problems of increased power consumption, decreased recognition distance performance indicators of tag chips, and reduced chip yield, etc. question

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

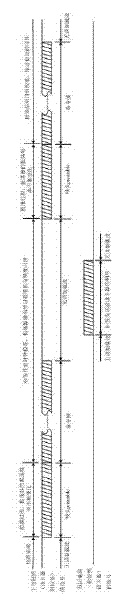

[0089] see Figure 5 , when the oscillator frequency modulation control word Ctrl and the oscillator output frequency f clk When there is a positive correlation, the calibration steps of the self-calibrating clock generation circuit are as follows:

[0090] Passive RF tags enter the RF field of the card reader, the tag power recovery circuit restores the DC power supply voltage on the tag chip, the digitally controlled tuned oscillator starts to oscillate freely, and the reset signal generating circuit generates a power-on reset signal Rst, which is to the The controller and the counter are reset asynchronously, and the frequency modulation control word Ctrl[m-1:0] register of the controller is asynchronously reset to 2 m-1 -1. At this time, the calibration enable signal Calib_en output by the digital baseband processing circuit of the tag is at an invalid level.

[0091] The analog front end of the tag chip demodulates the forward link communication signal from the car...

Embodiment 2

[0101] see Figure 6 , when the oscillator frequency modulation control word Ctrl and the oscillator output frequency f clk When there is a negative correlation, the calibration steps of the self-calibrating clock generating circuit are as follows:

[0102] Passive RF tags enter the RF field of the card reader, the tag power recovery circuit restores the DC power supply voltage on the tag chip, the digitally controlled tuned oscillator starts to oscillate freely, and the reset signal generating circuit generates a power-on reset signal Rst, which is to the The controller and the counter are reset asynchronously, and the frequency modulation control word Ctrl[m-1:0] register of the controller is asynchronously reset to 2 m-1 . At this time, the calibration enable signal Calib_en output by the digital baseband processing circuit of the tag is at an invalid level.

[0103] The analog front end of the tag chip demodulates the forward link communication signal from the card ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More