Patents

Literature

87 results about "Functional description" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A functional specification (or sometimes functional specifications) is a formal document used to describe in detail for software developers a product's intended capabilities, appearance, and interactions with users. The functional specification is a kind of guideline and continuing reference point as the developers write the programming code.

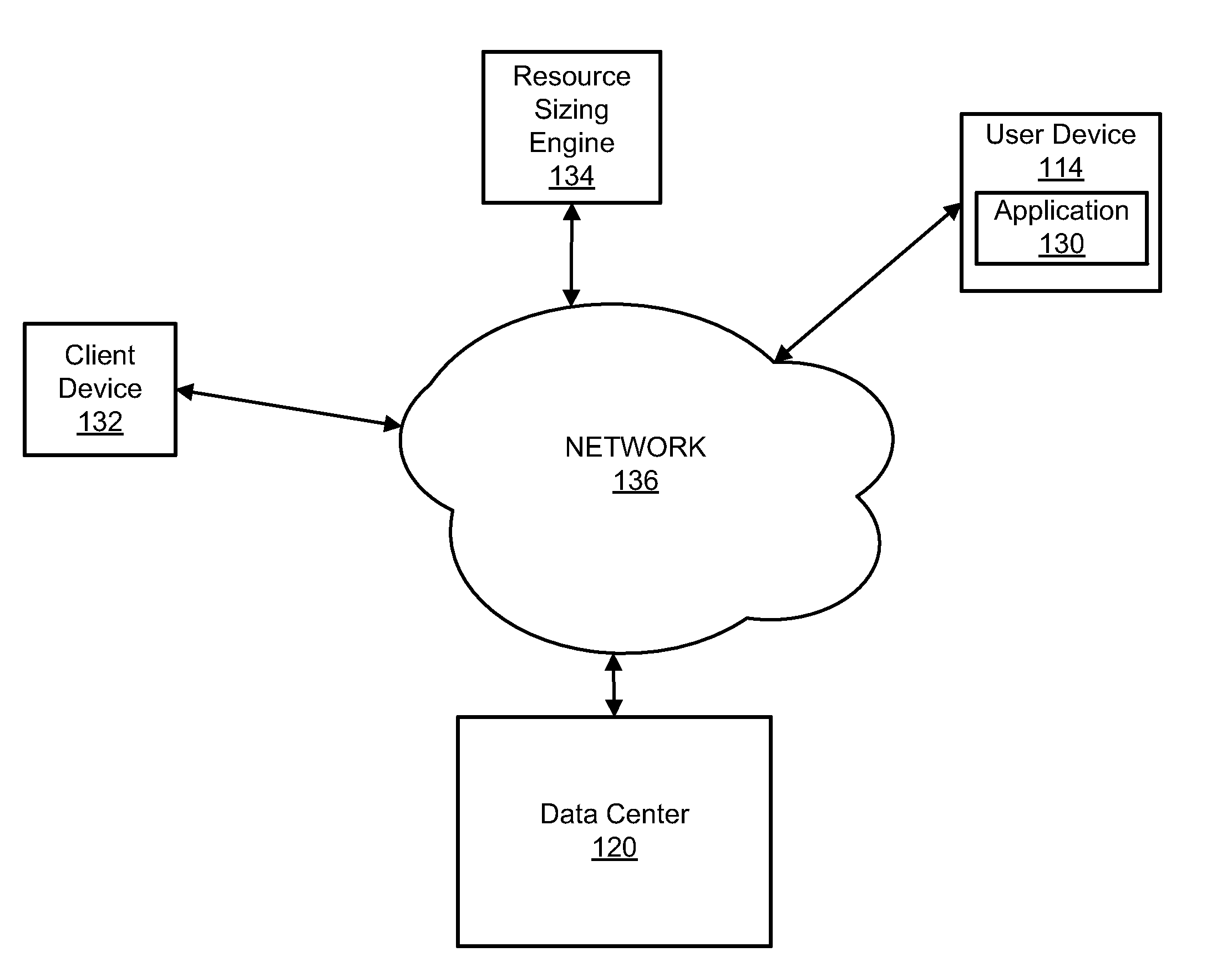

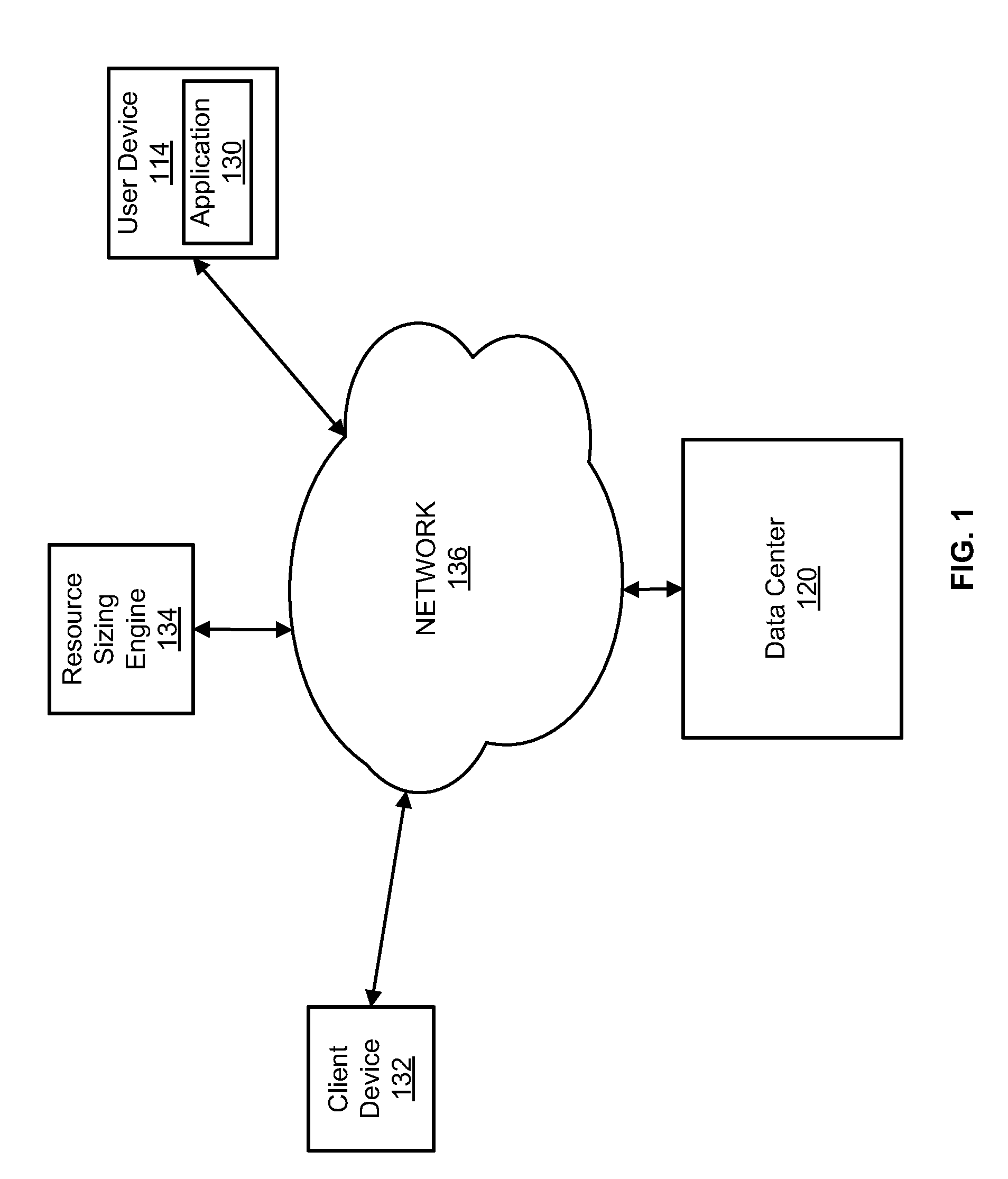

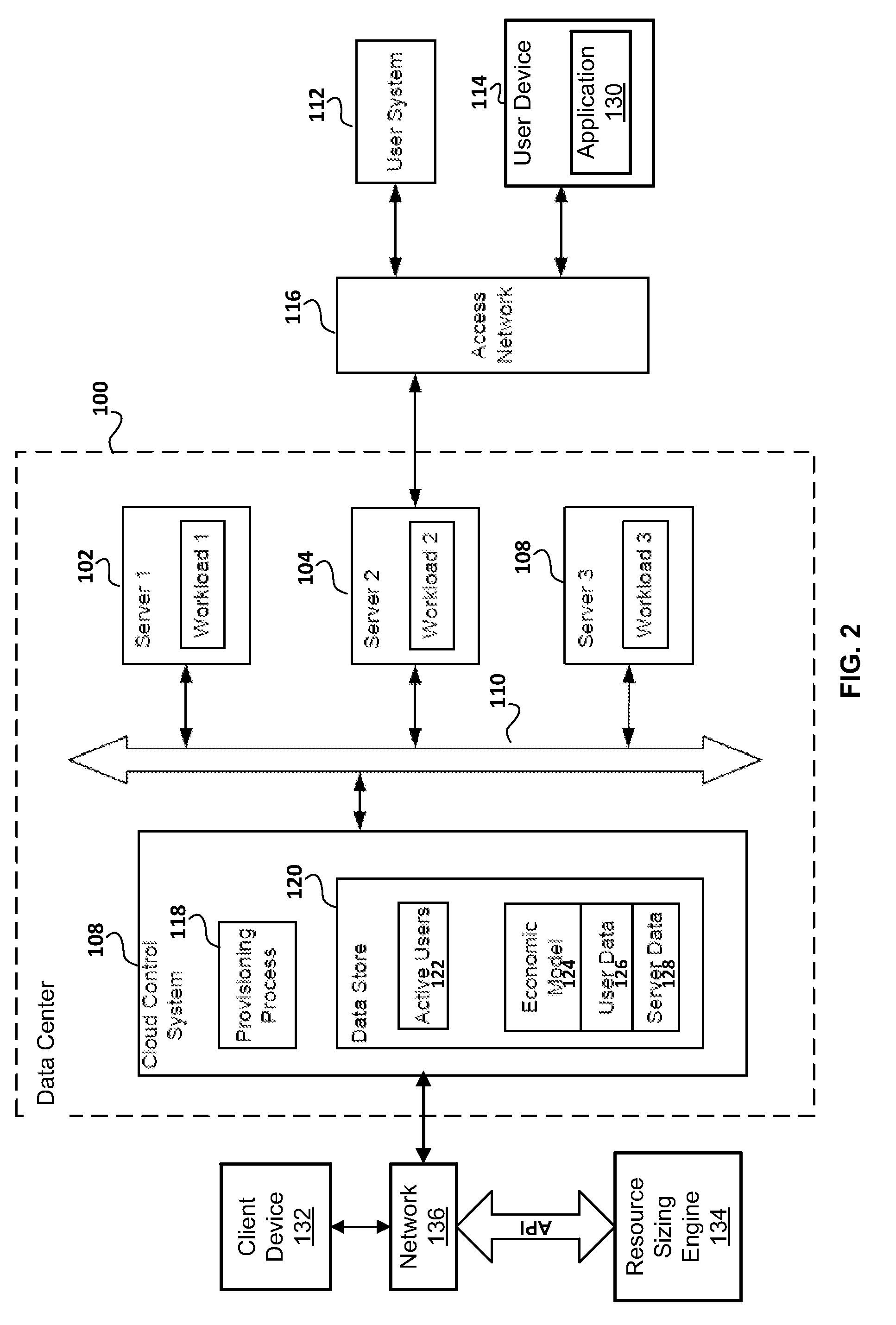

Systems and methods for sizing resources in a cloud-based environment

InactiveUS20120233315A1Well formedDigital computer detailsProgram controlQuality of serviceData center

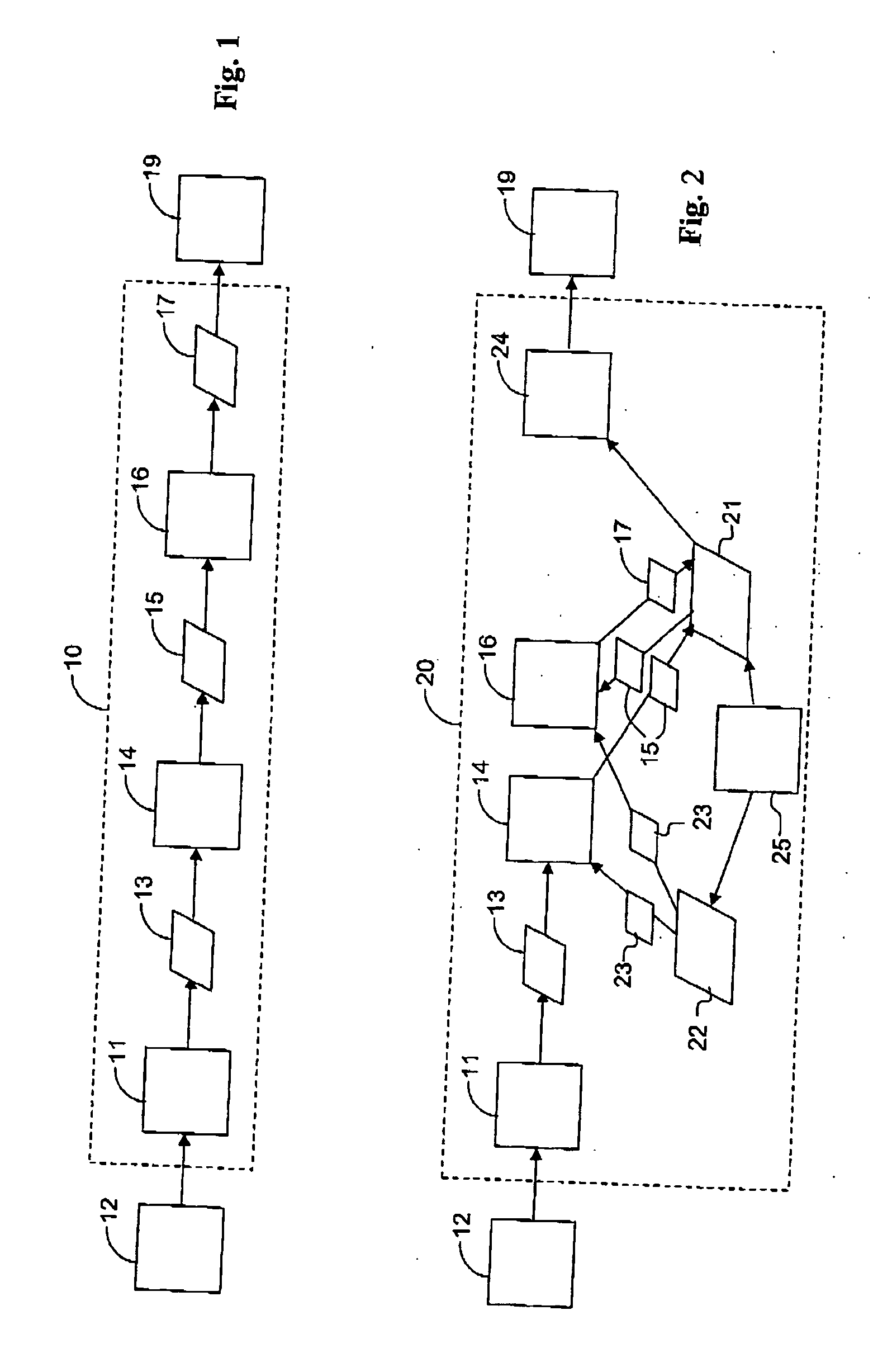

Systems and methods for sizing resources in a cloud-based environment are provided. In an exemplary embodiment, a method includes receiving quality of service requirements and a functional description of a cloud architecture associated with the application, including application resources and relations between the application resources, performing latency analysis of data packets in a compute layer of the cloud architecture, with the latency analysis including comparing size per time metrics of the data packets, determining minimal resources to guarantee the quality of service requirements based on the latency analysis and the quality of service requirements, and providing to the data center the minimal resources.

Owner:JOYENT

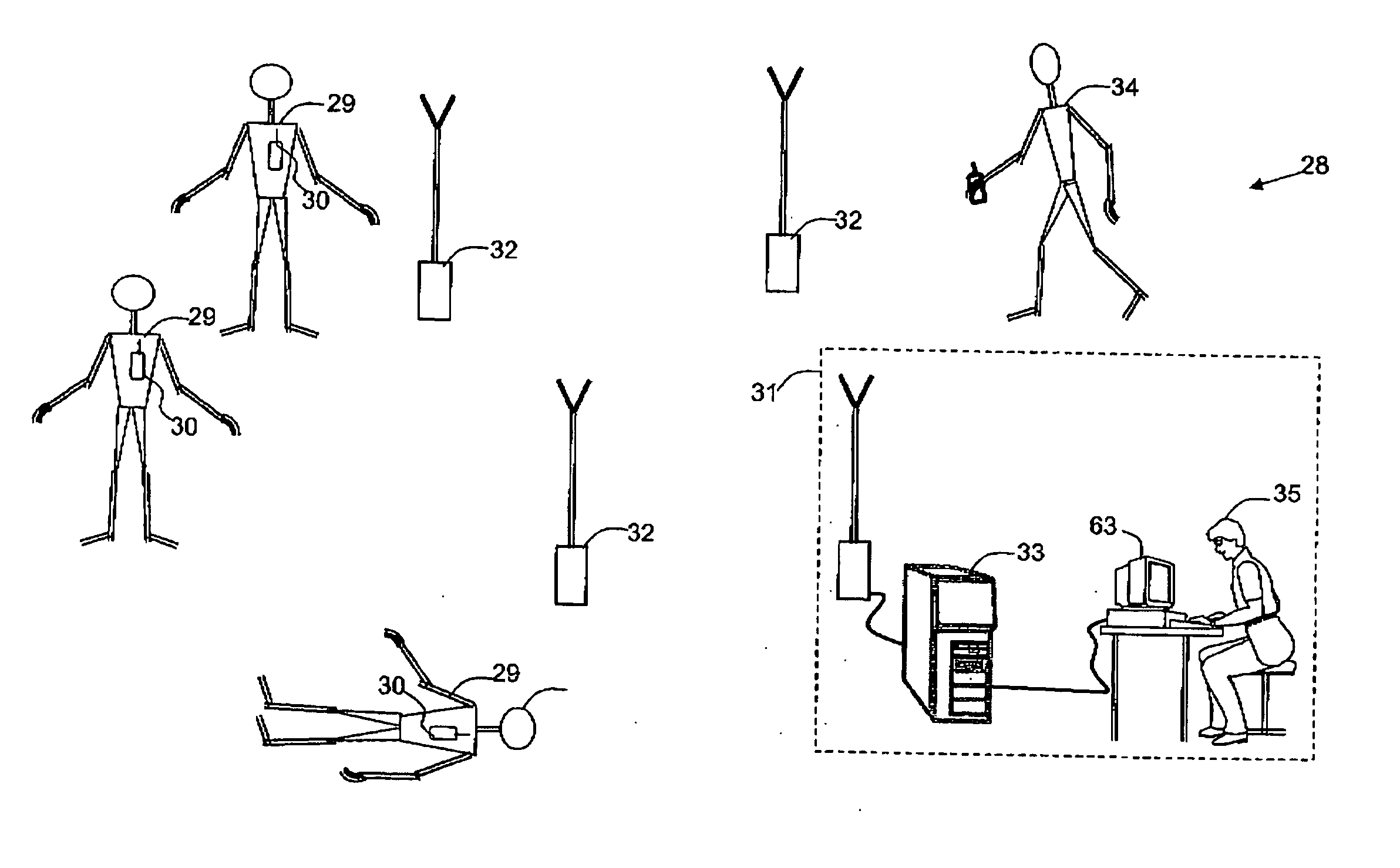

System for automatic structured analysis of body activities

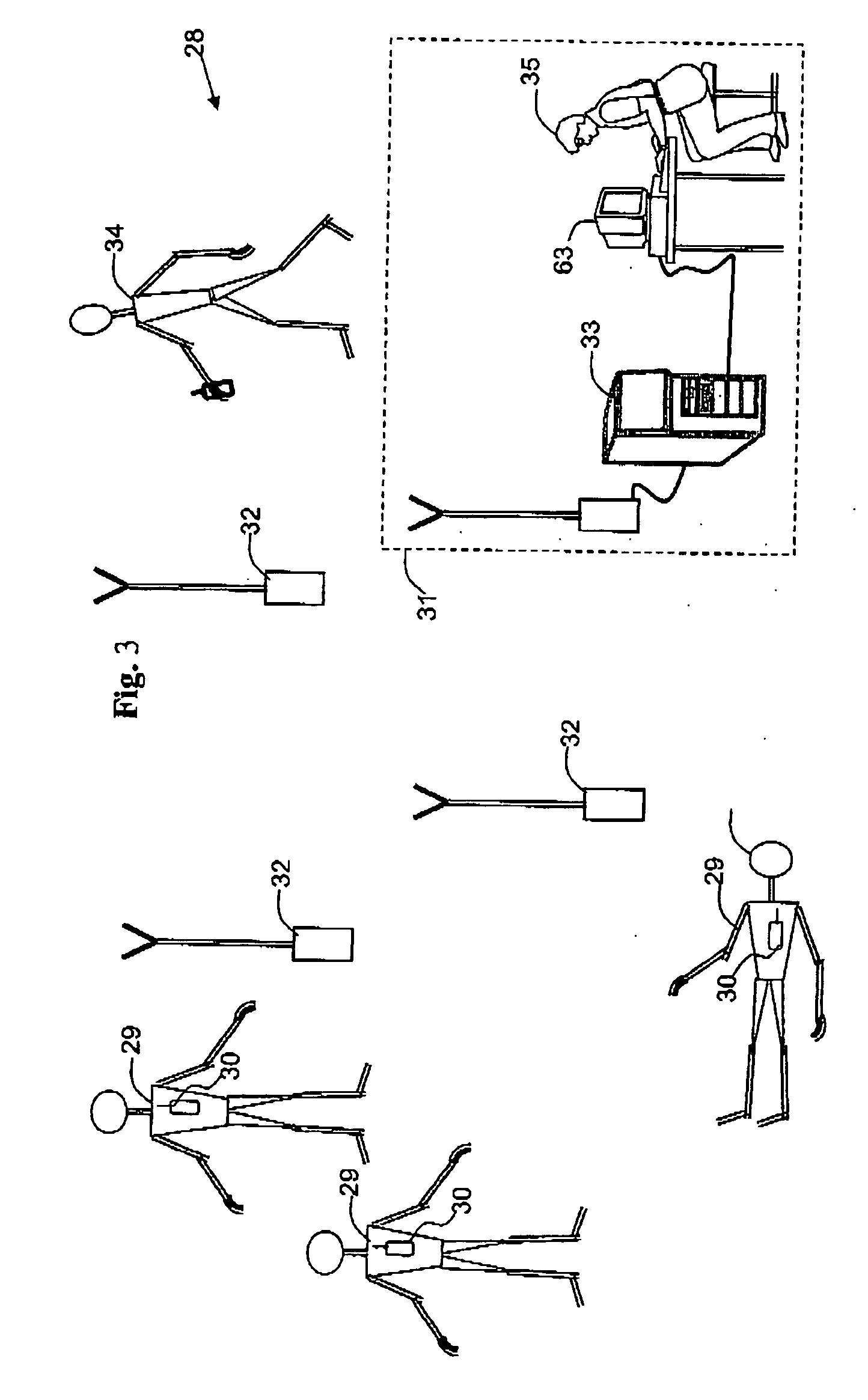

A personal emergency response system employs a structured terminology of body activities. Measurements of primary body activities using accelerometers, heart-bit monitors, etc. are converted to secondary and tertiary level body activities such as walk and fall, further sequenced and combined to determine a personal condition such as walk, stumble and fall, and to identify sequences of such conditions. The structured terminology enables a language supporting a functional description of body activities associated with physical and physiological measurements and enables a machine to understand physical activities.

Owner:COHEN

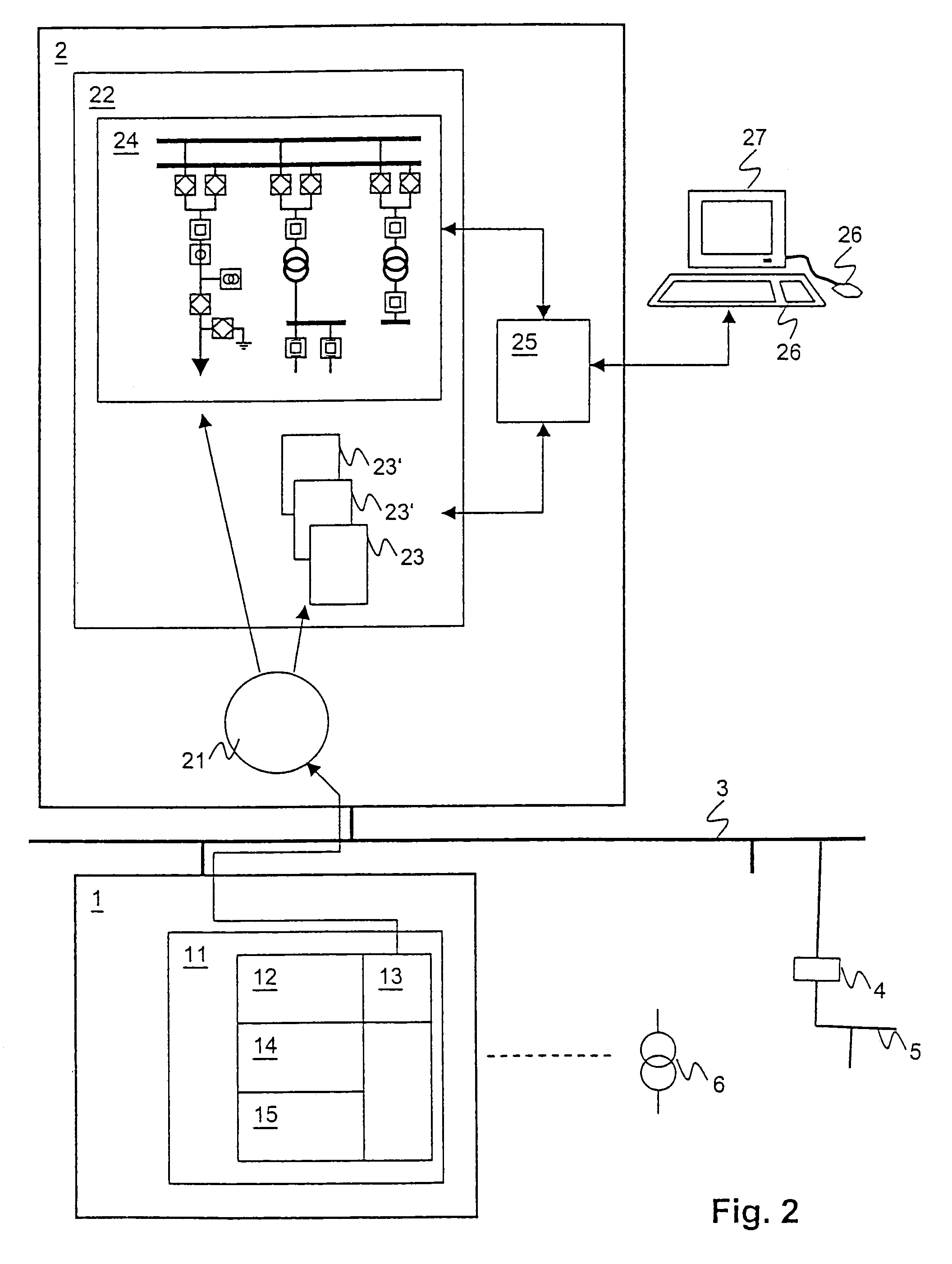

Integration of a field device in an installation control system

InactiveUS6970771B1Save effortReduce effortLevel controlCircuit arrangementsTelecommunications linkControl system

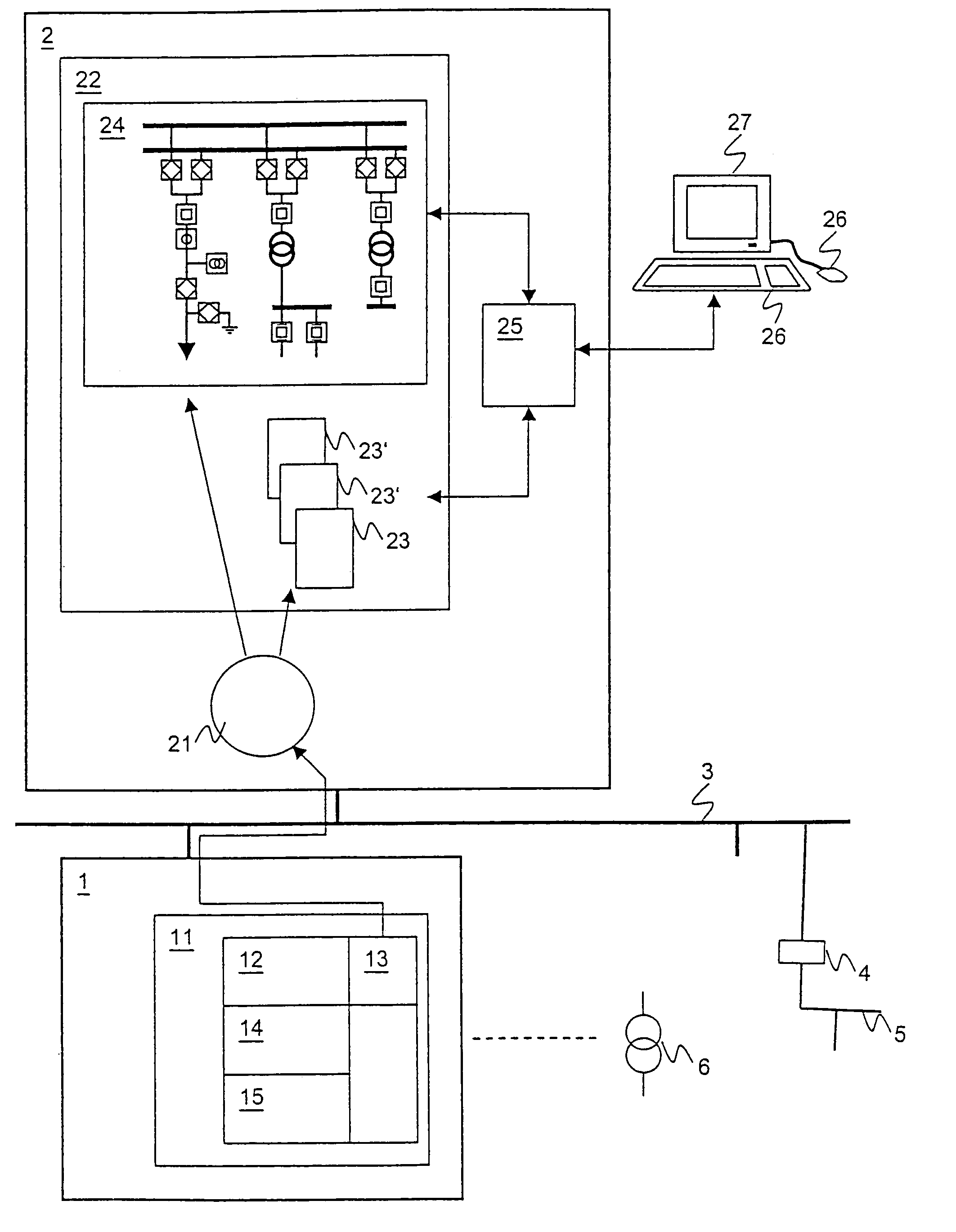

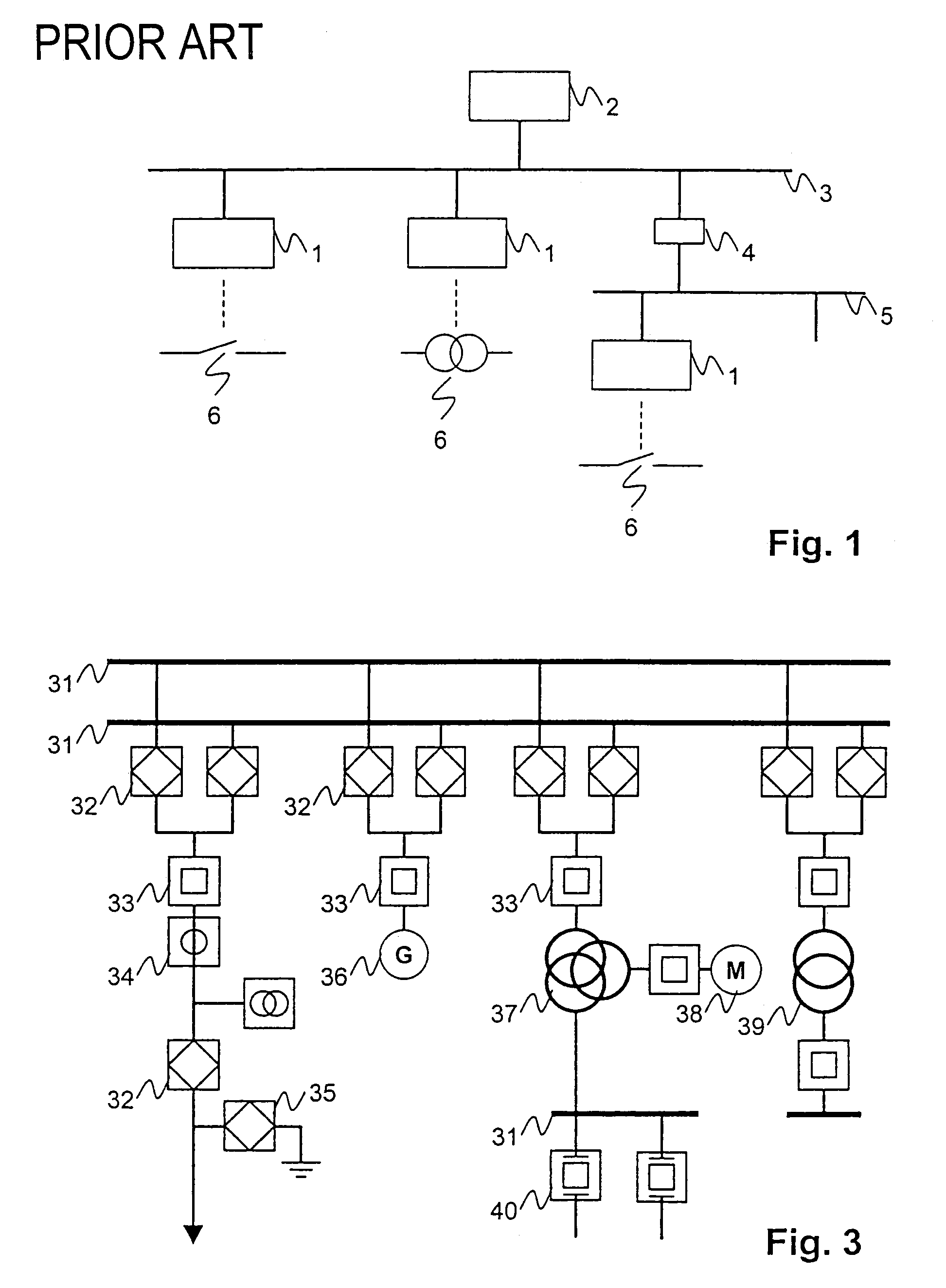

A method and a system for integration of a field device in an installation control system having a communications network and a control station functions in that a field device transmits a functional description of device functions to the control station in a standardized form, whereupon functions associated with the field device are installed on the control station, and communications links are set up between the device functions of the field device and the functions of the control station. In one preferred version of the invention, device functions are automatically or manually combined with an installation structure. The invention is preferably used with high voltage or medium voltage switchgear assemblies and leads to a considerable reduction in the complexity for specification and commissioning of installation internal communications links and to higher quality of a resulting installation control system.

Owner:ABB RES LTD

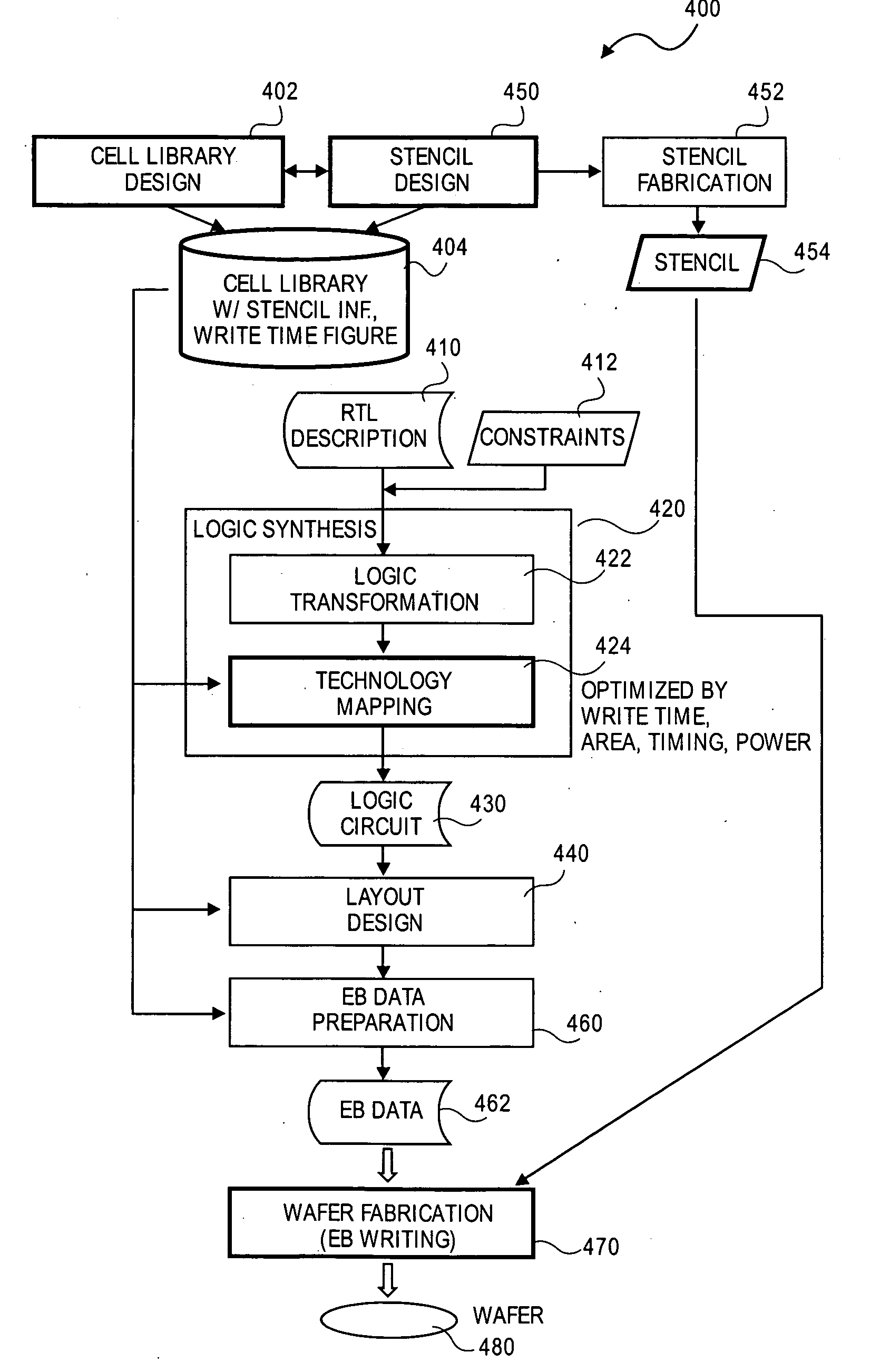

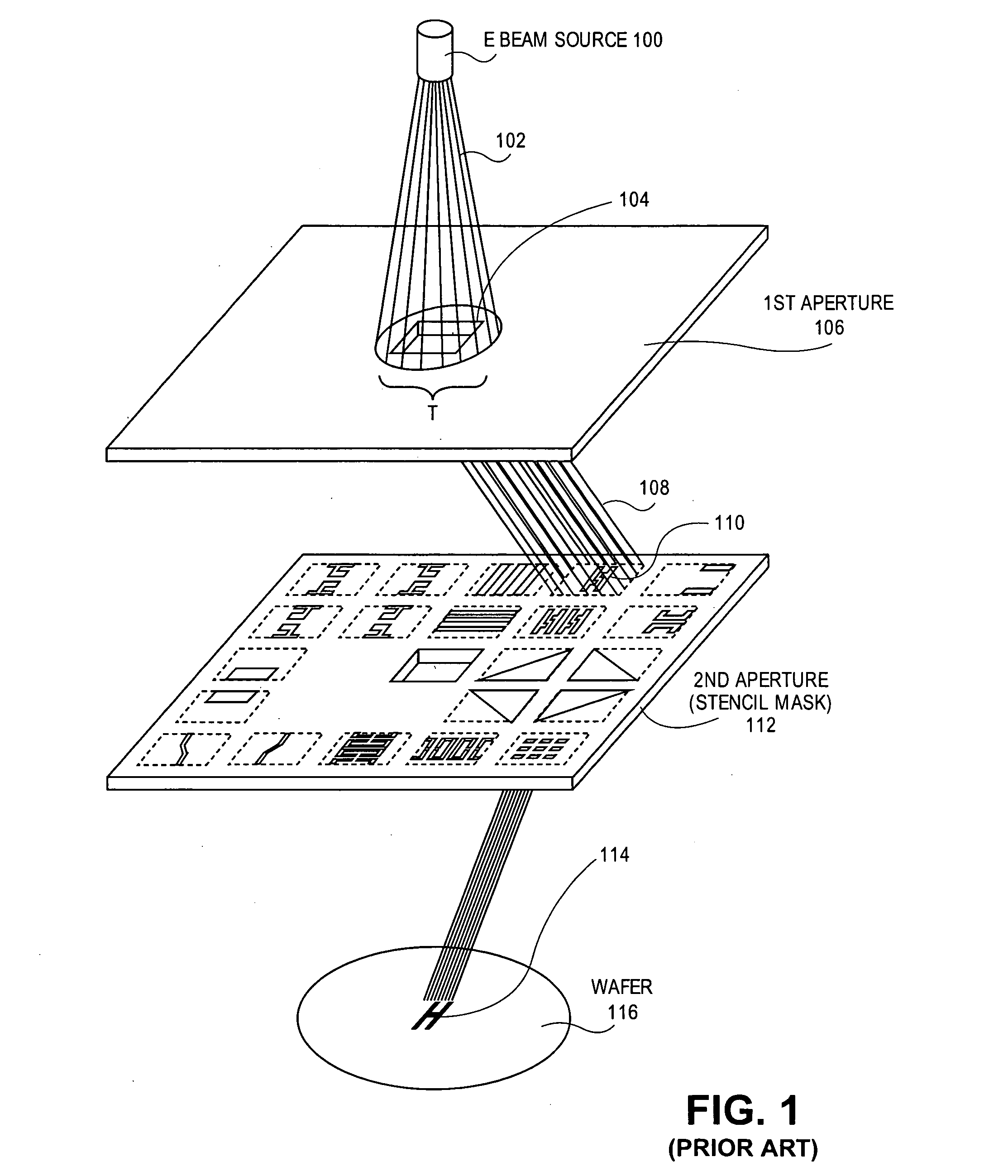

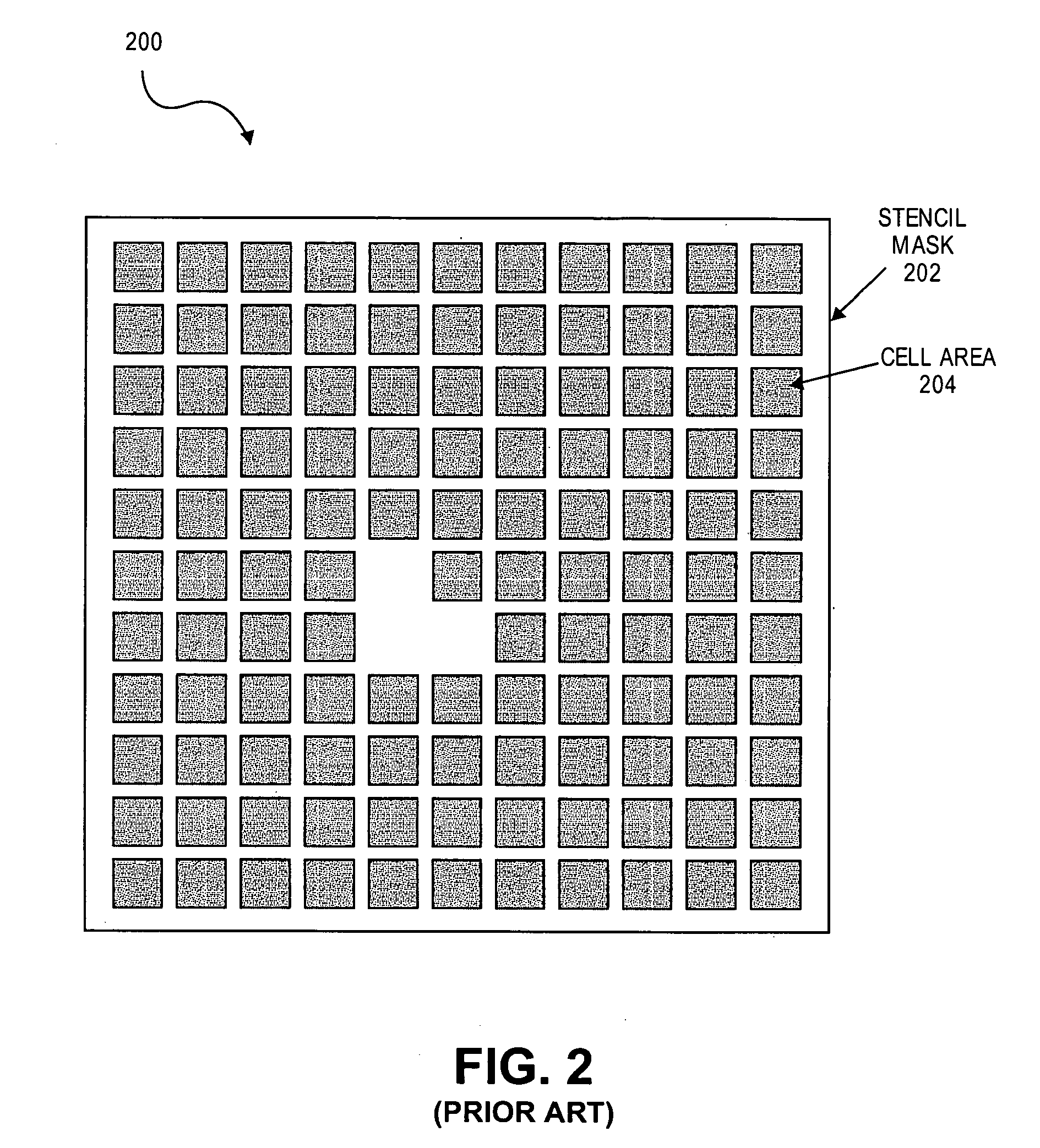

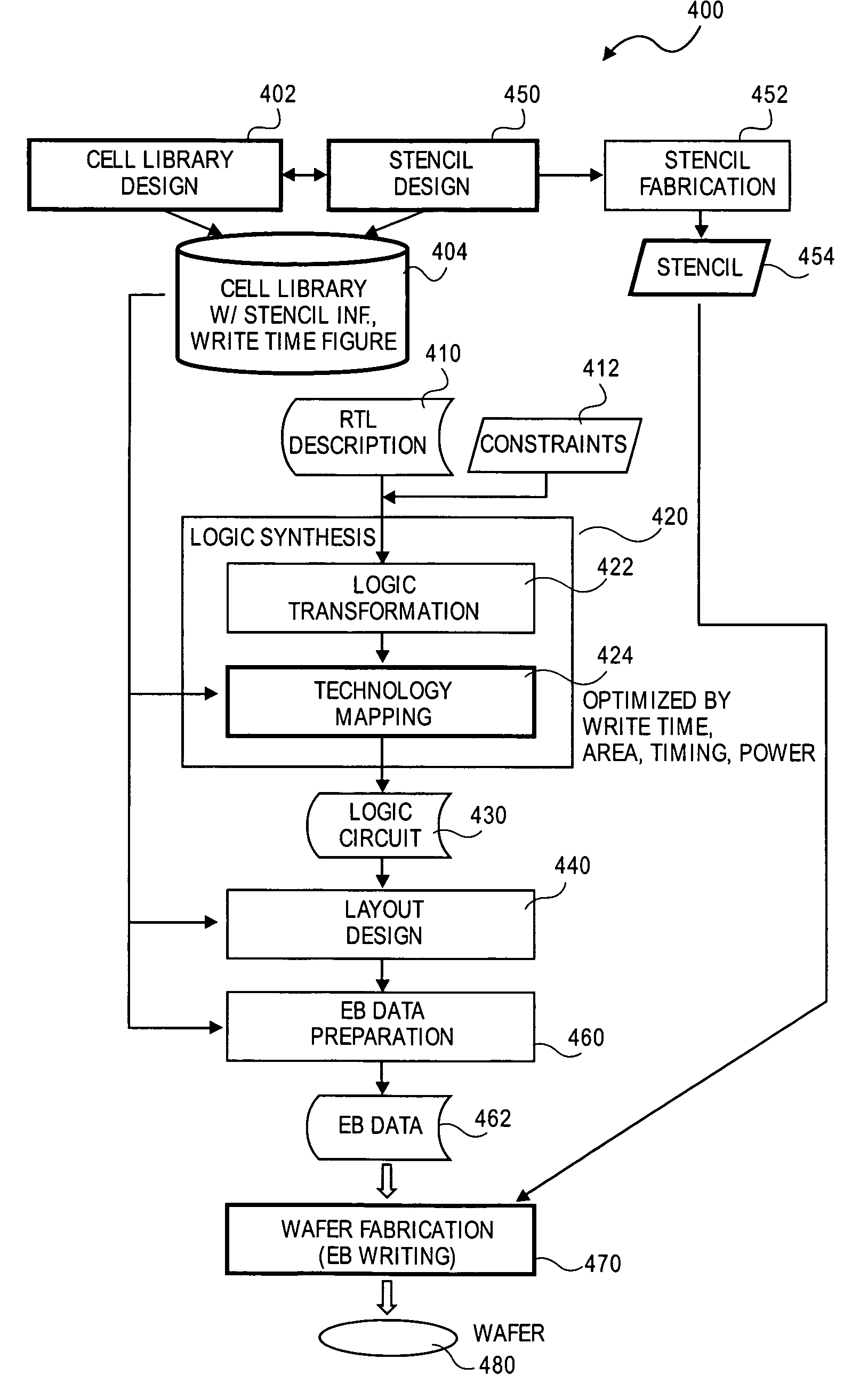

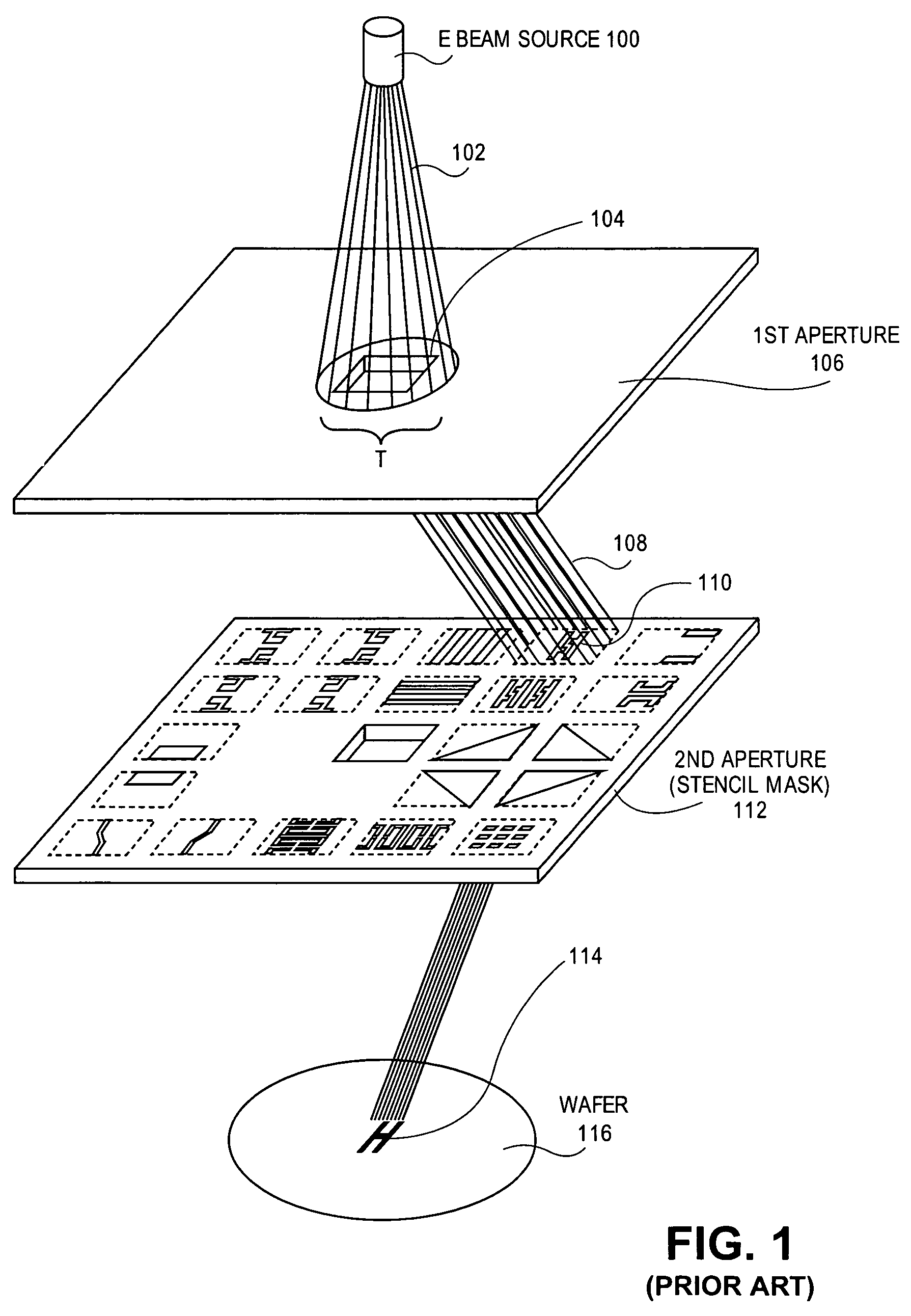

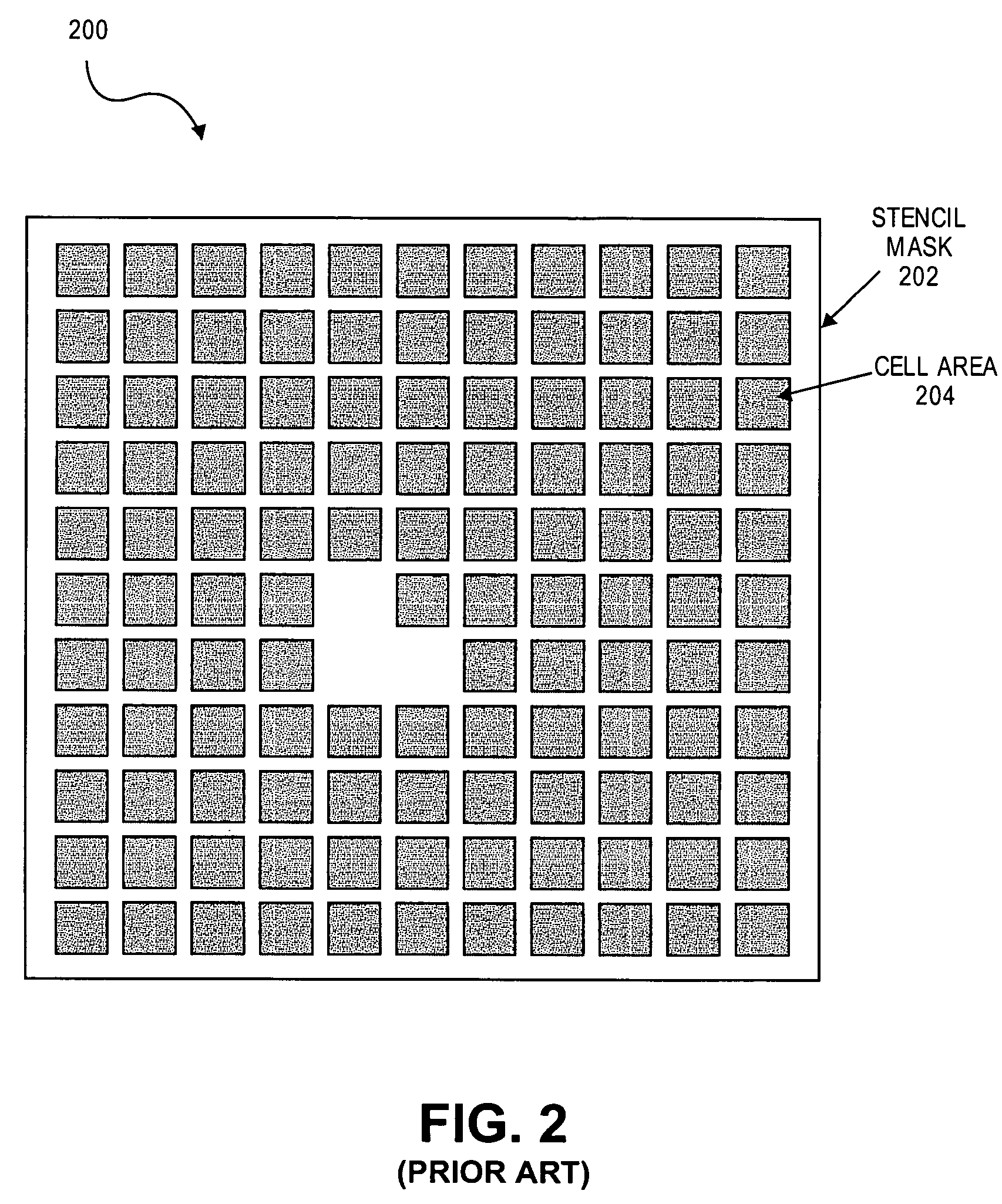

Method and system for logic design for cell projection particle beam lithography

InactiveUS20080128637A1Short EB writing timeShorten write timeElectric discharge tubesNanoinformaticsCell patternLithographic artist

A method for particle beam lithography, such as electron beam (EB) lithography, includes predefining a stencil design having a plurality of cell patterns with information from a cell library, fabricating the stencil design, synthesizing a functional description into a logic circuit design after predefining the stencil design so that one or more characteristics of the stencil design are considered during synthesizing of the functional description into the logic circuit design, optimizing the logic circuit design, generating a layout design from the optimized logic circuit design, and forming the logic circuit on a substrate according to the stencil design and the layout design.

Owner:D2S

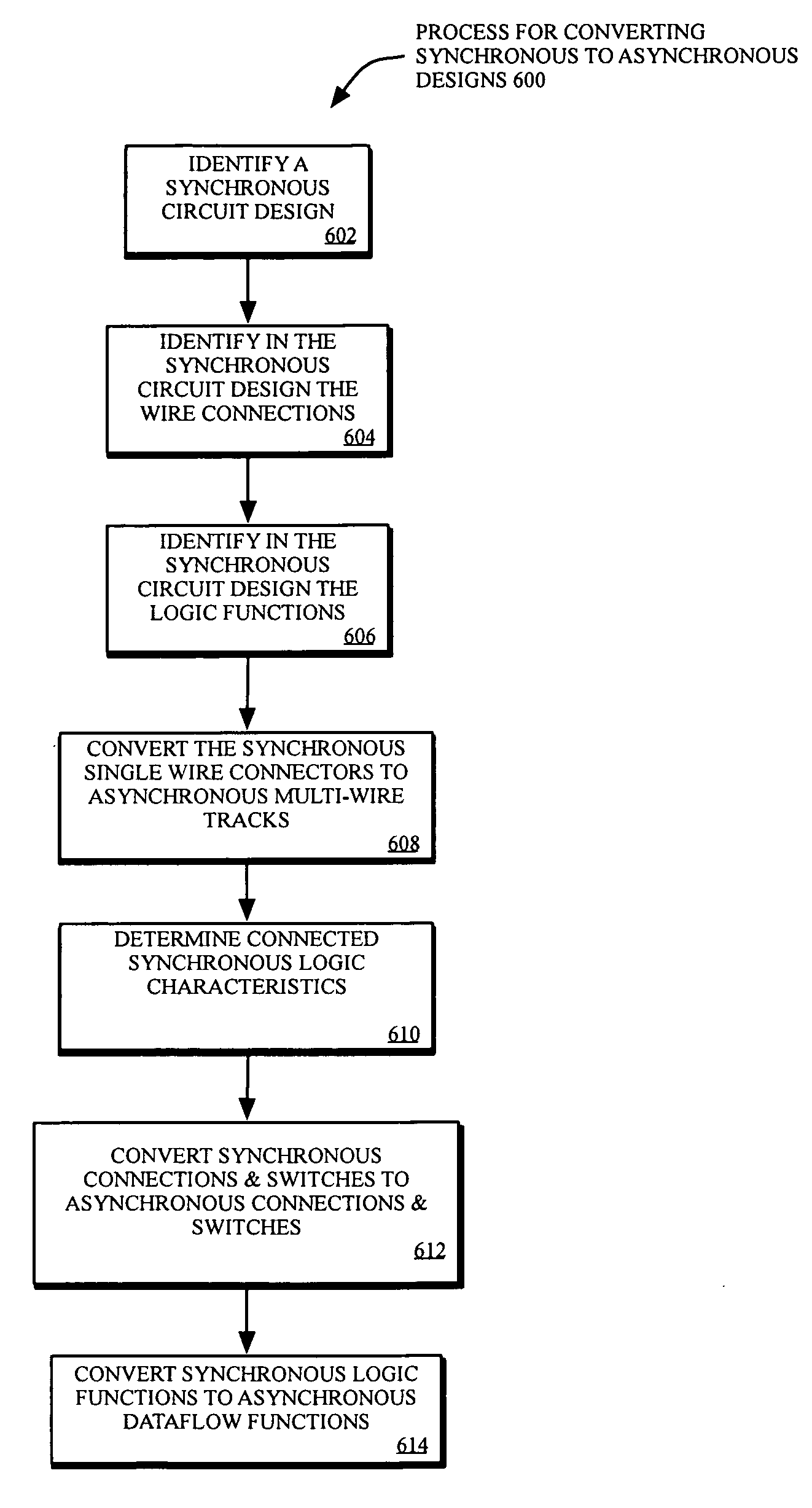

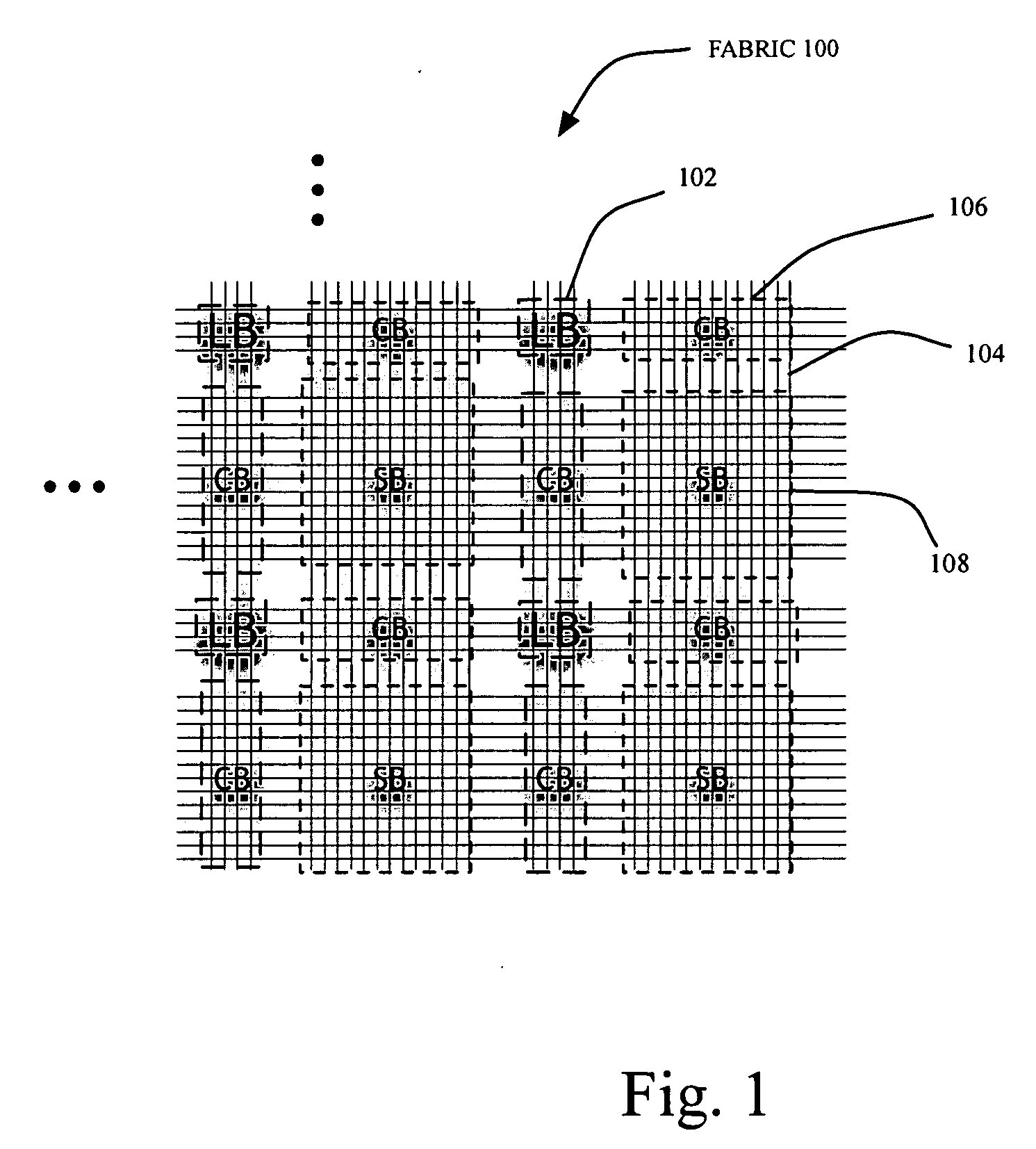

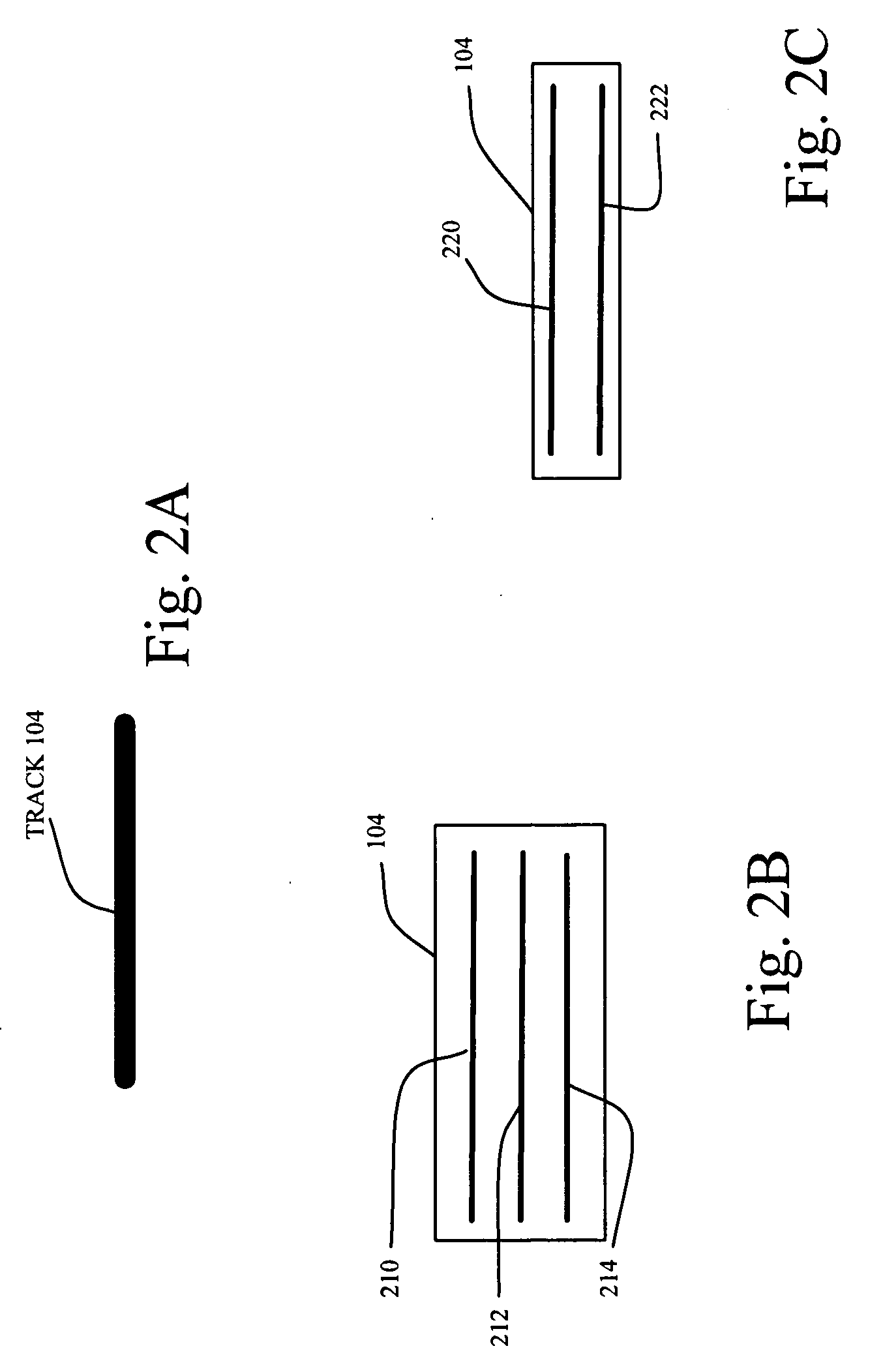

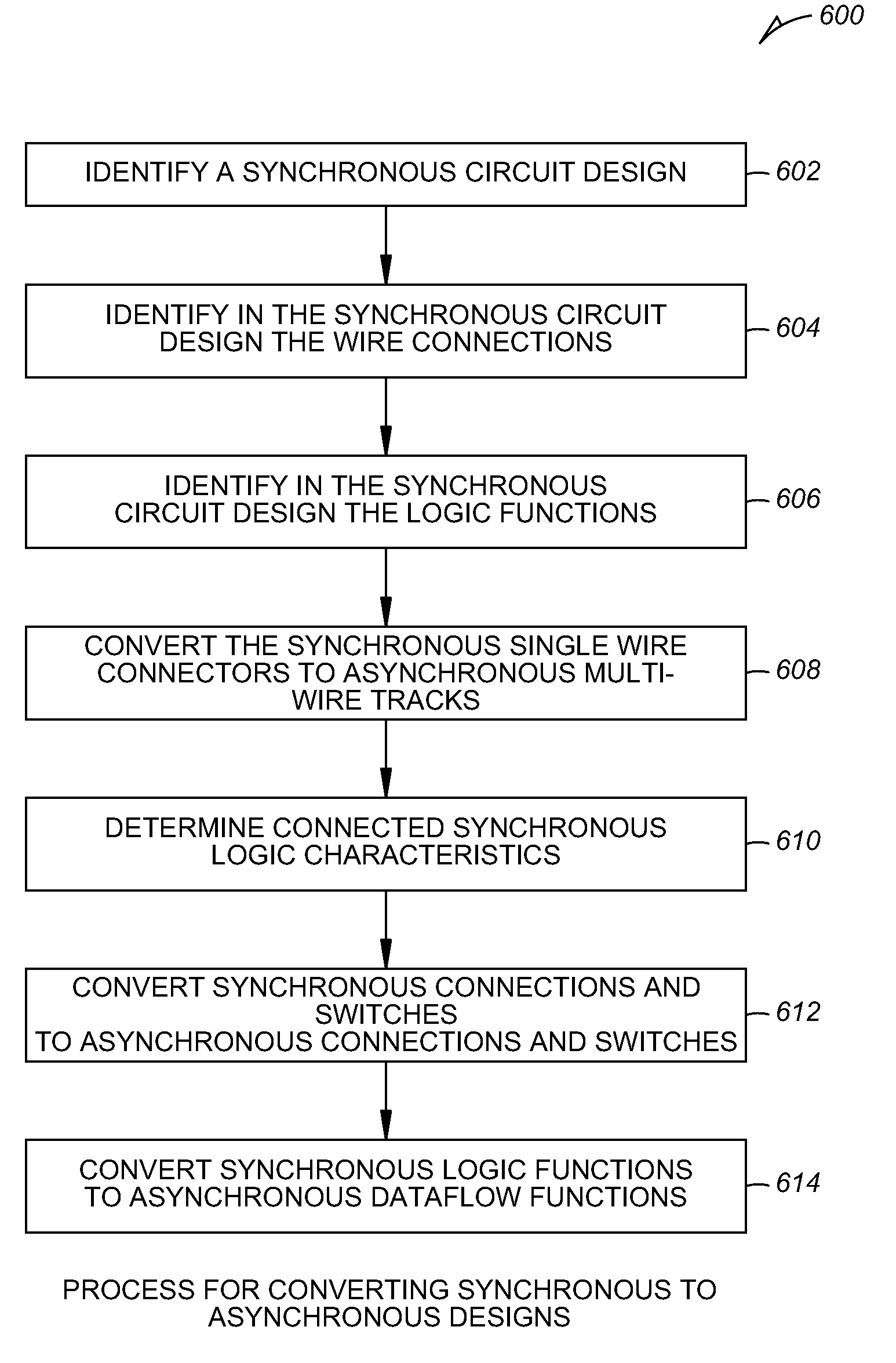

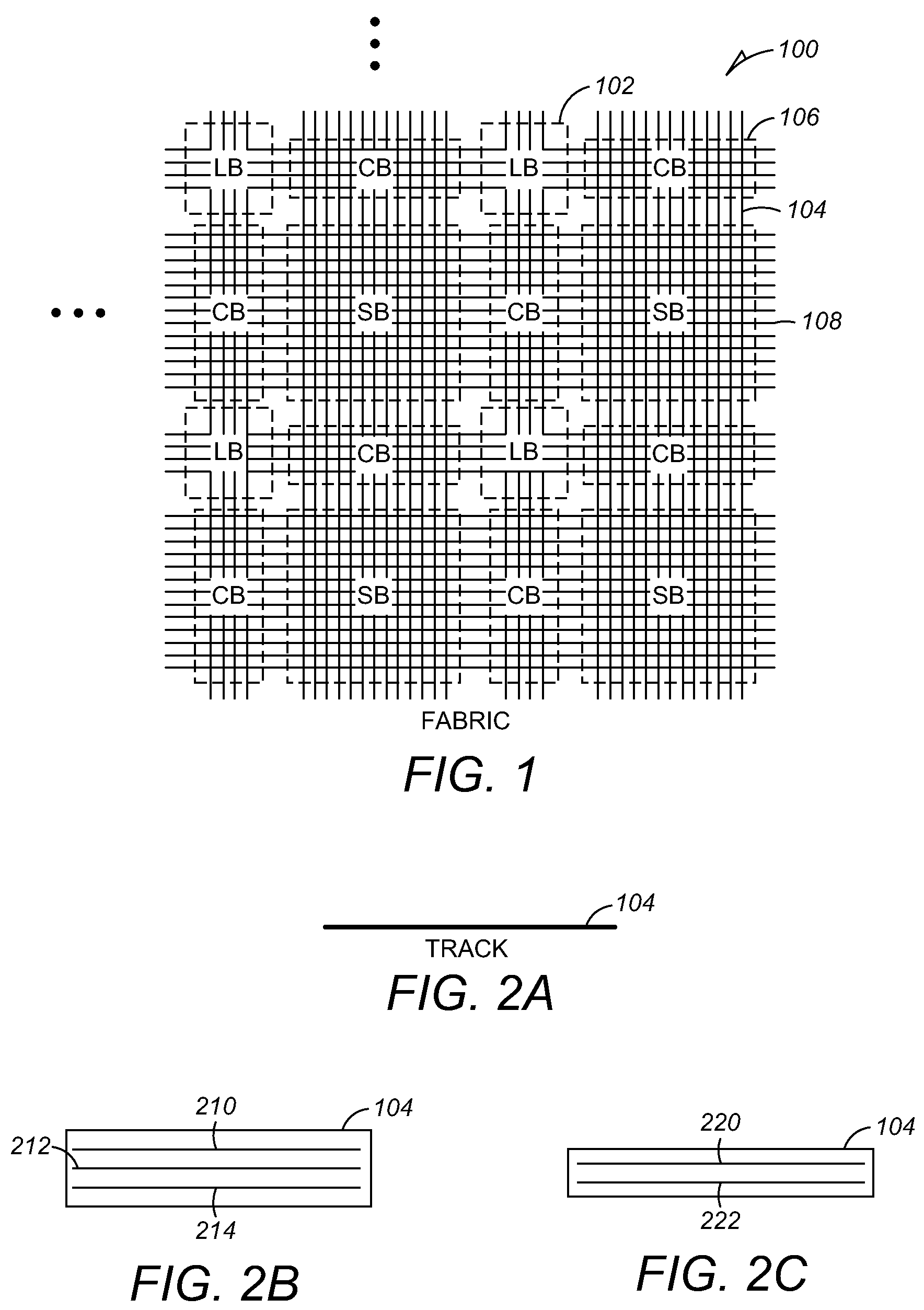

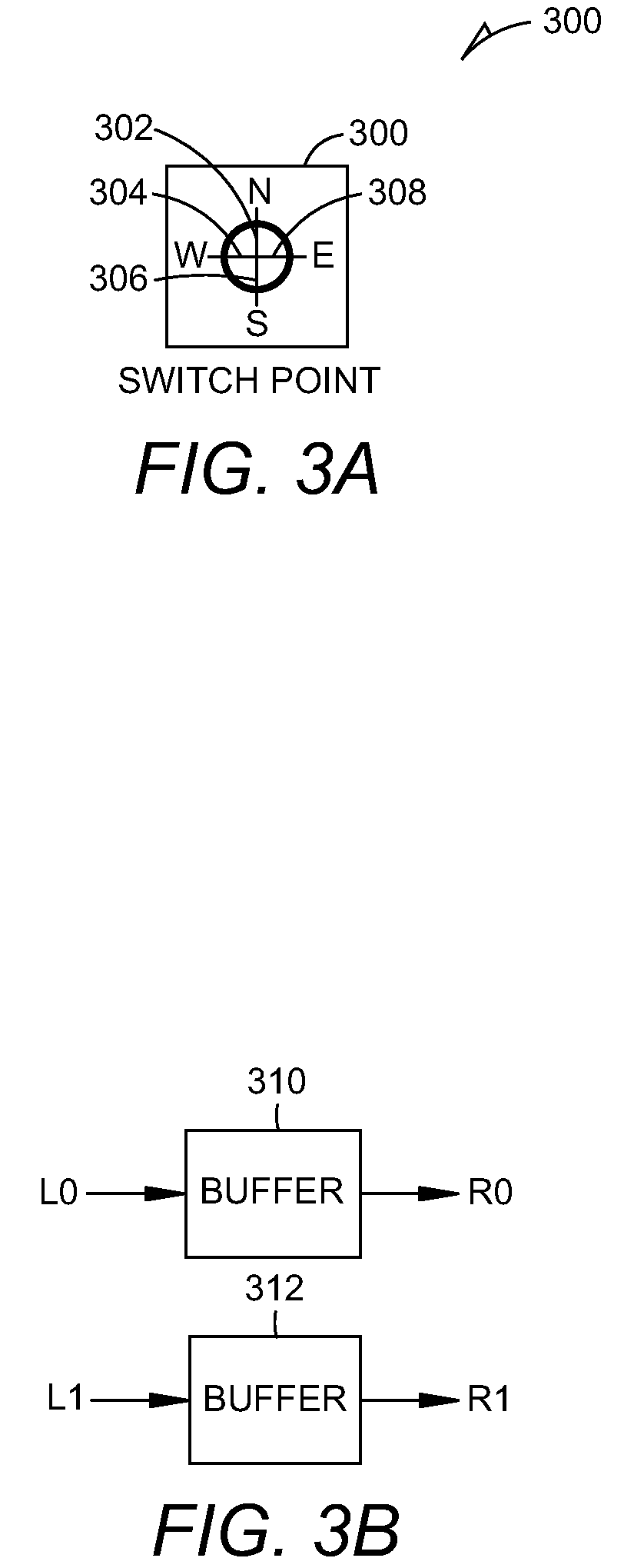

Methods and systems for converting a synchronous circuit fabric into an asynchronous dataflow circuit fabric

Methods and systems for converting synchronous circuit designs to asynchronous circuit designs, and particularly programmable asynchronous circuit designs. Provide is a systematic, workable and repeatable process for evaluating synchronous circuit designs, converting the wires, switches / connections and logic functions to equivalent-function asynchronous circuit designs and hence implementing a functionally equivalent asynchronous circuit with all the benefits thereof. Further provided are a process for systematically doing the conversion and hardware equivalents (in form or functional description) for the asynchronous components. Using the present invention, any synchronous circuit design can be converted to an asynchronous equivalent, typically with no change to the original design implementation.

Owner:ACHRONIX SEMICON CORP

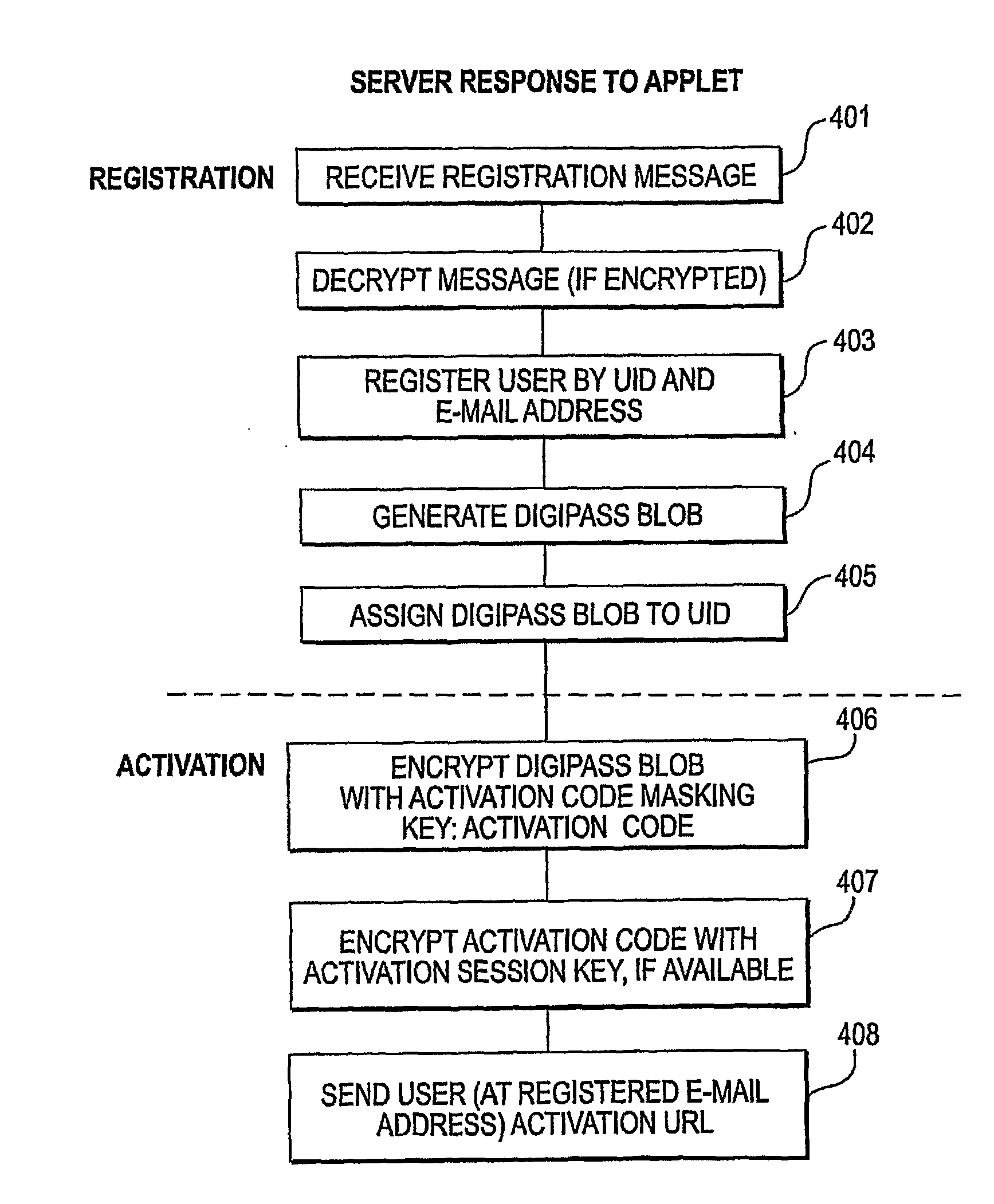

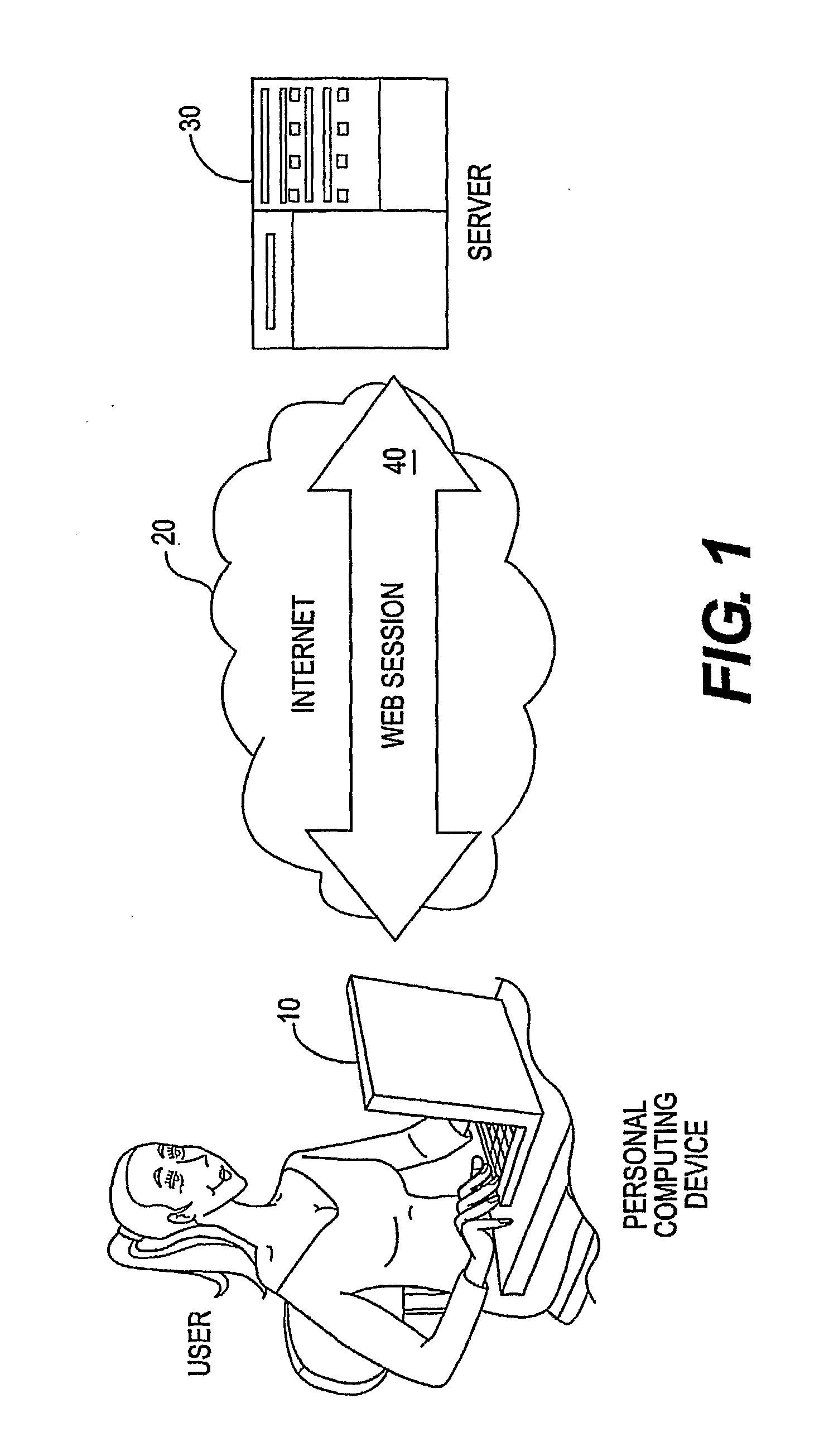

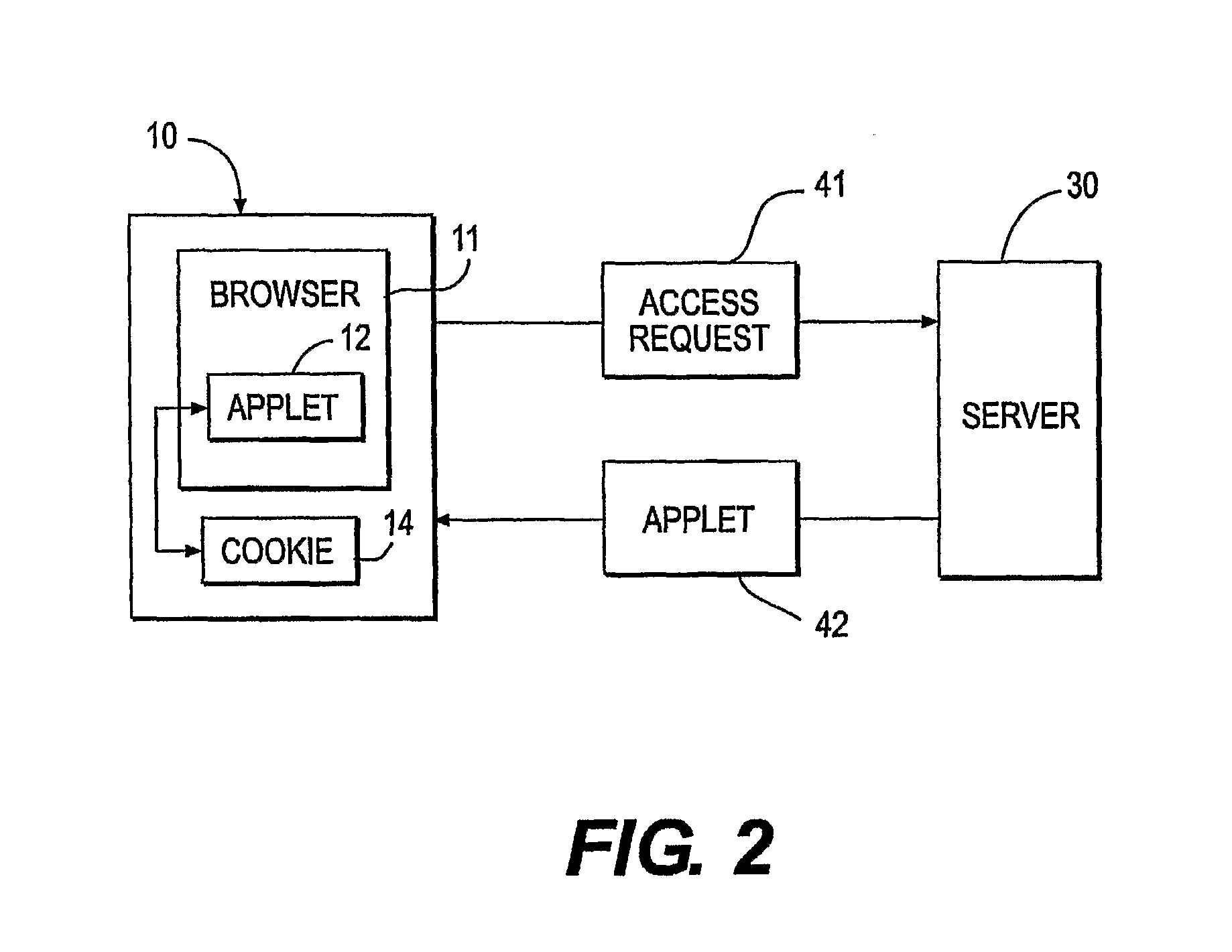

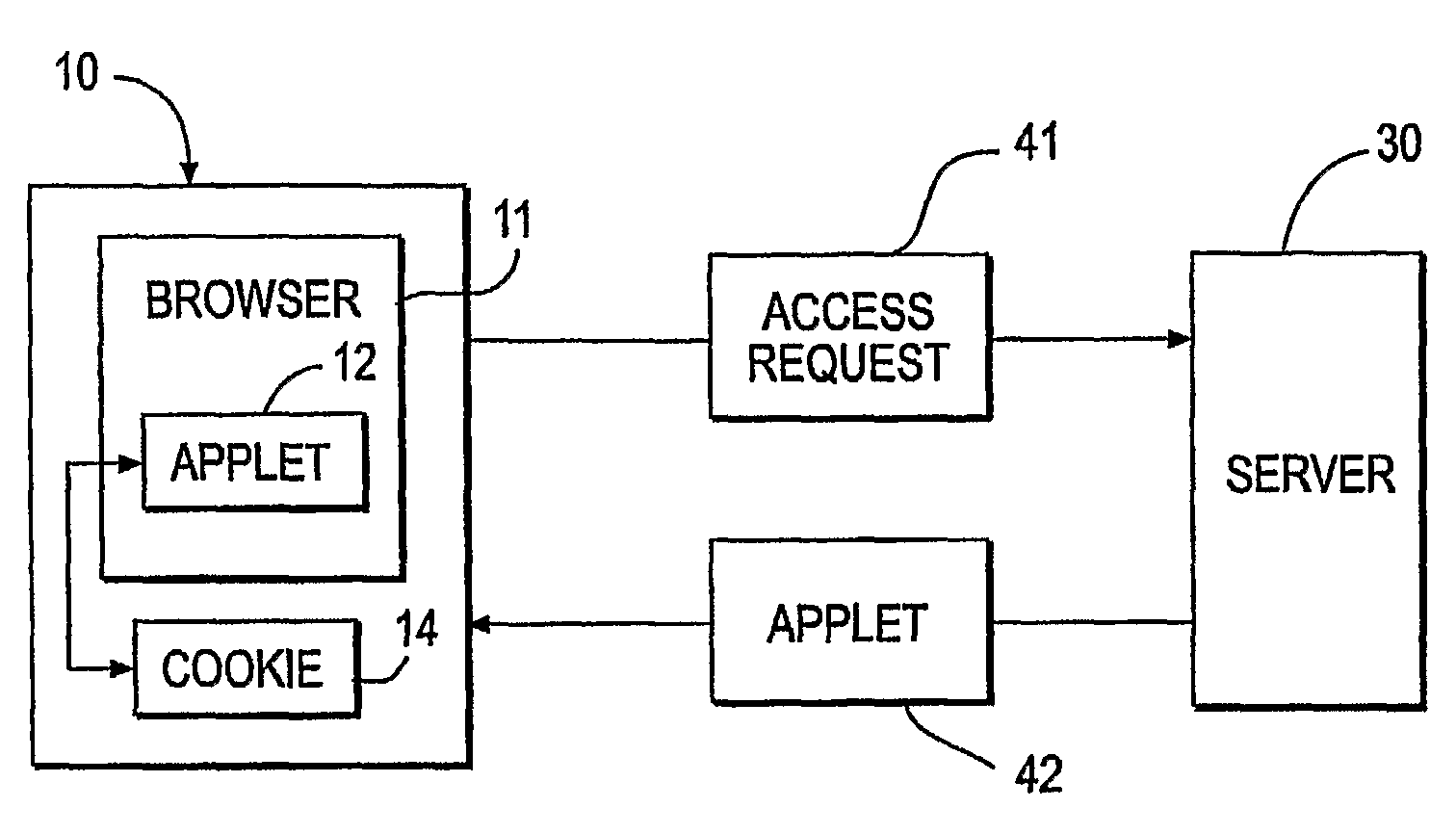

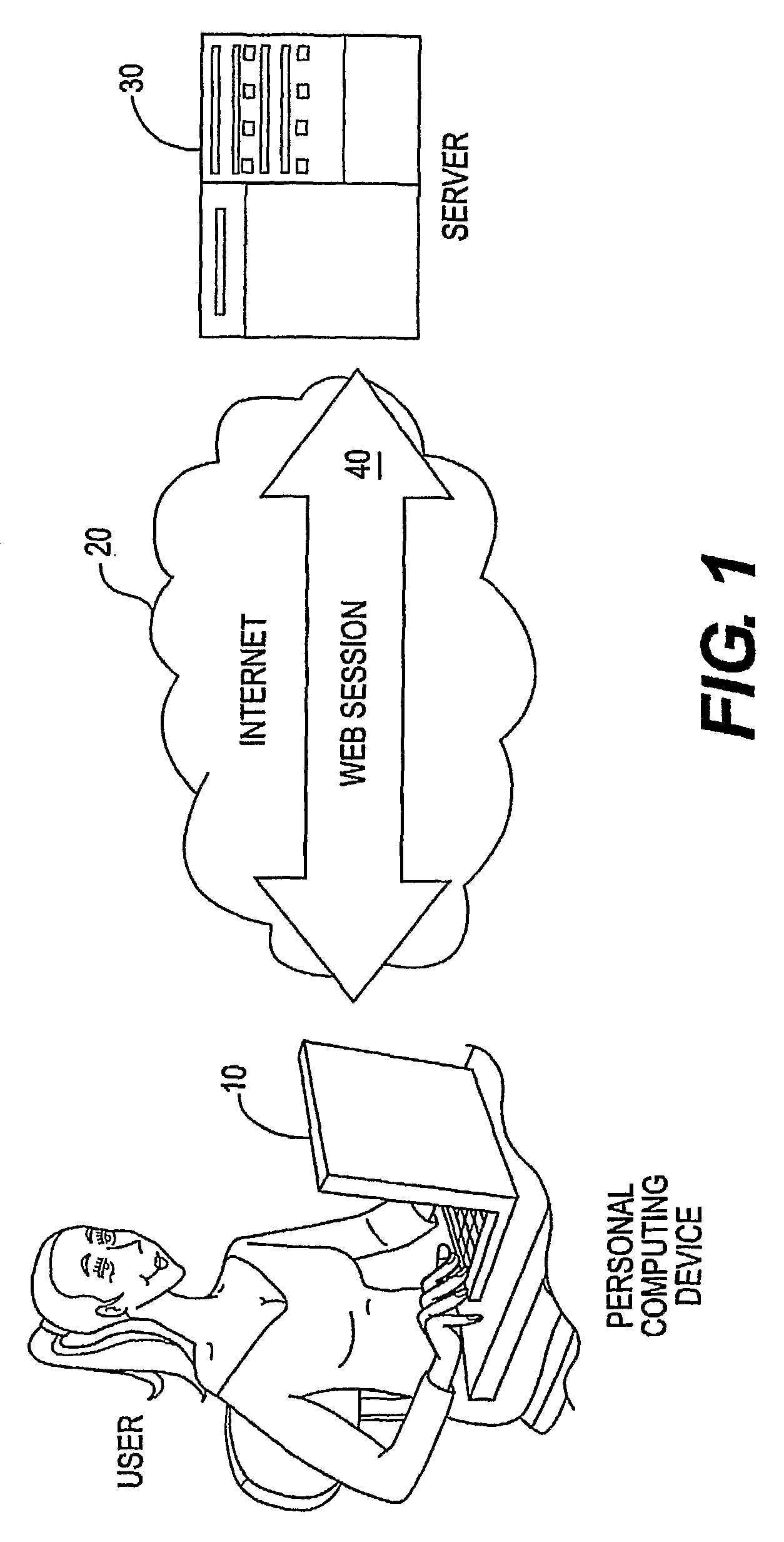

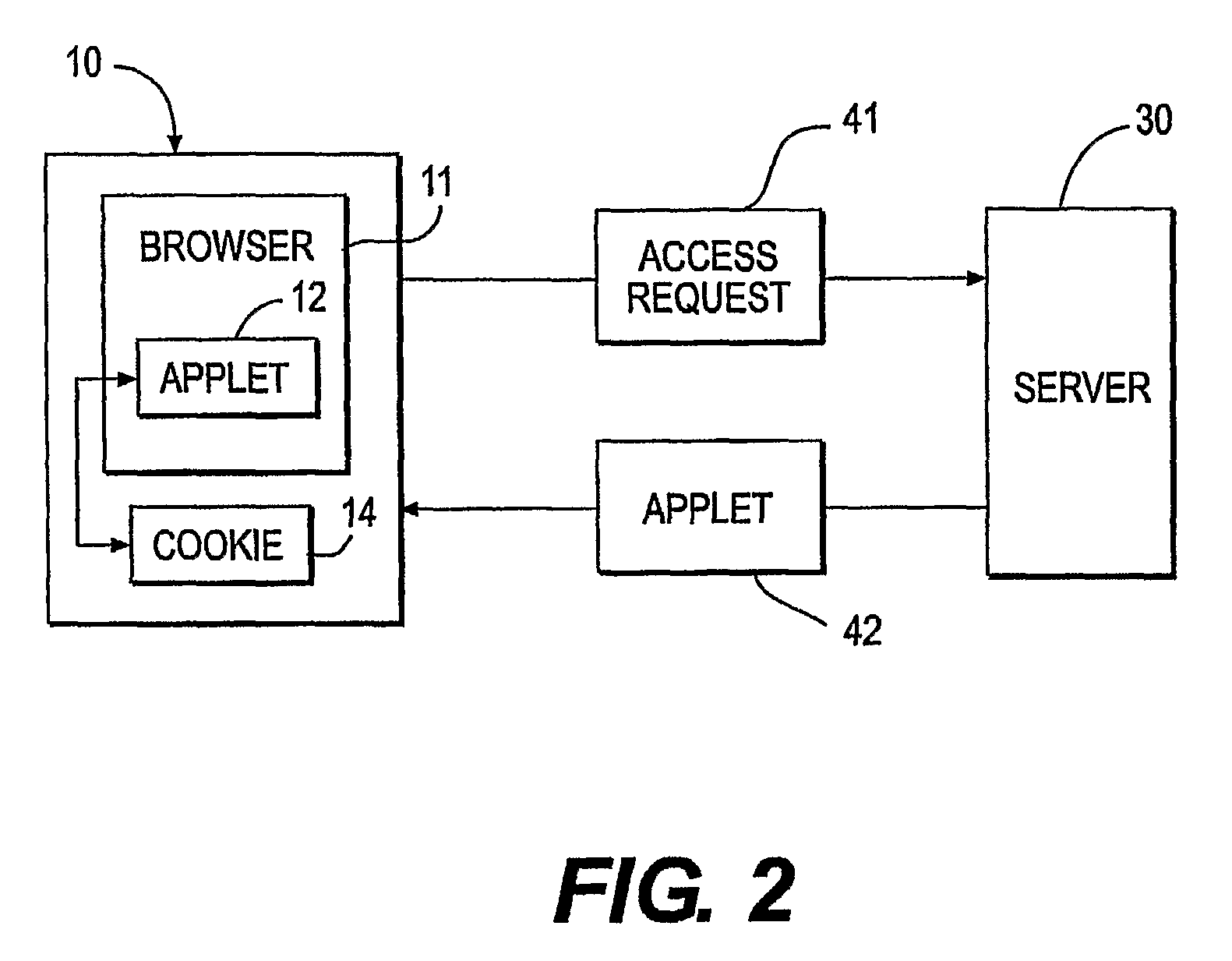

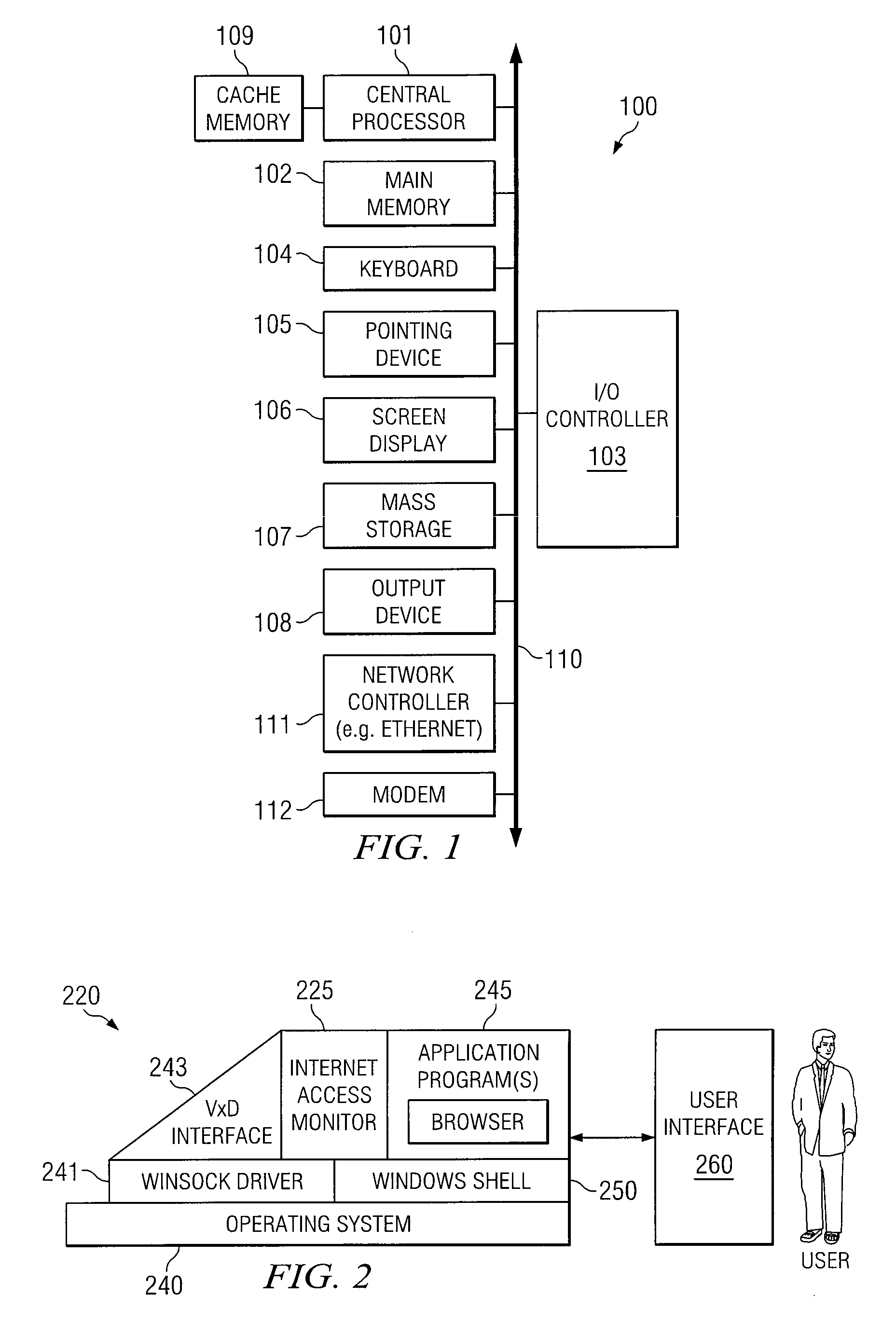

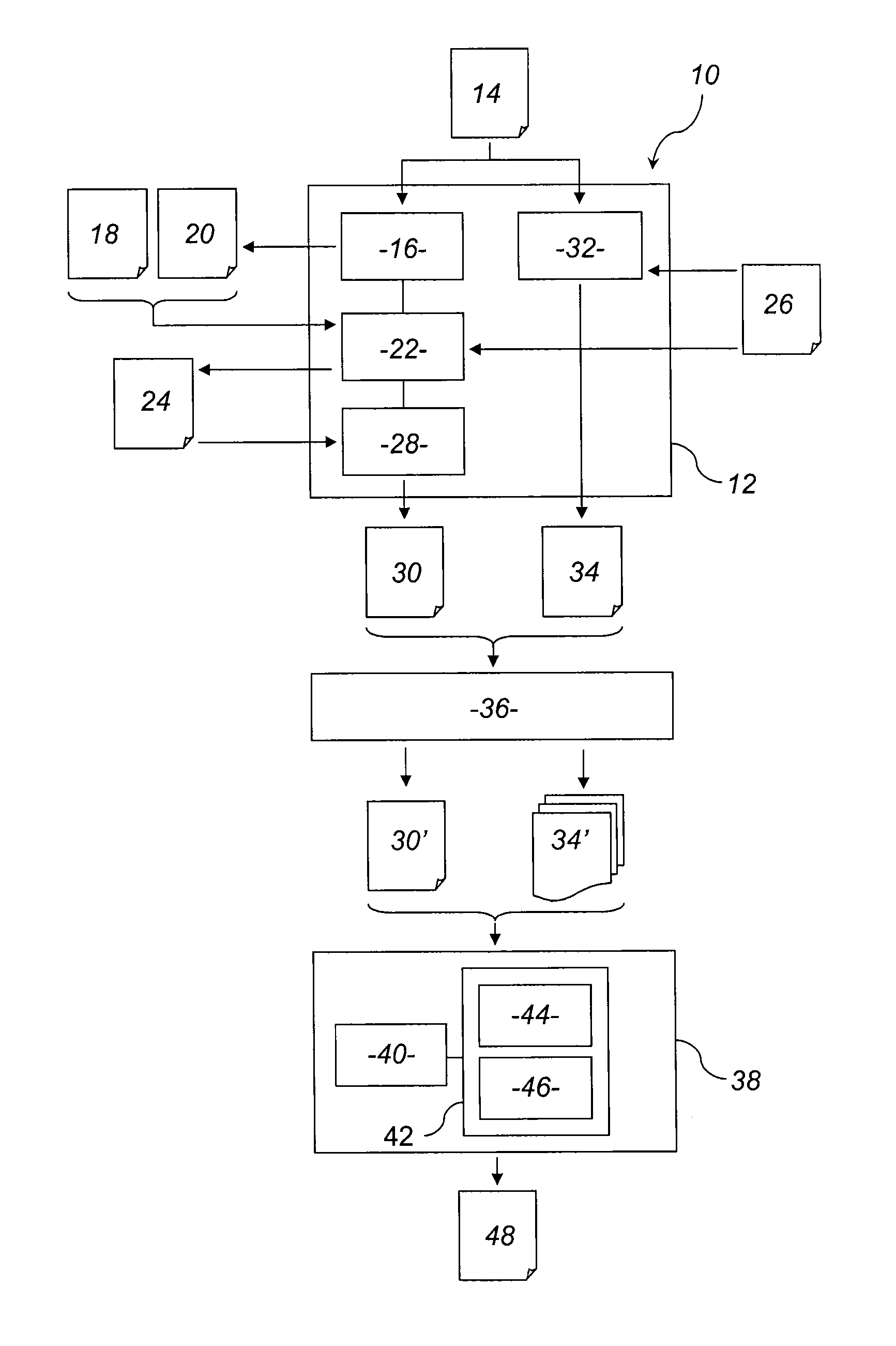

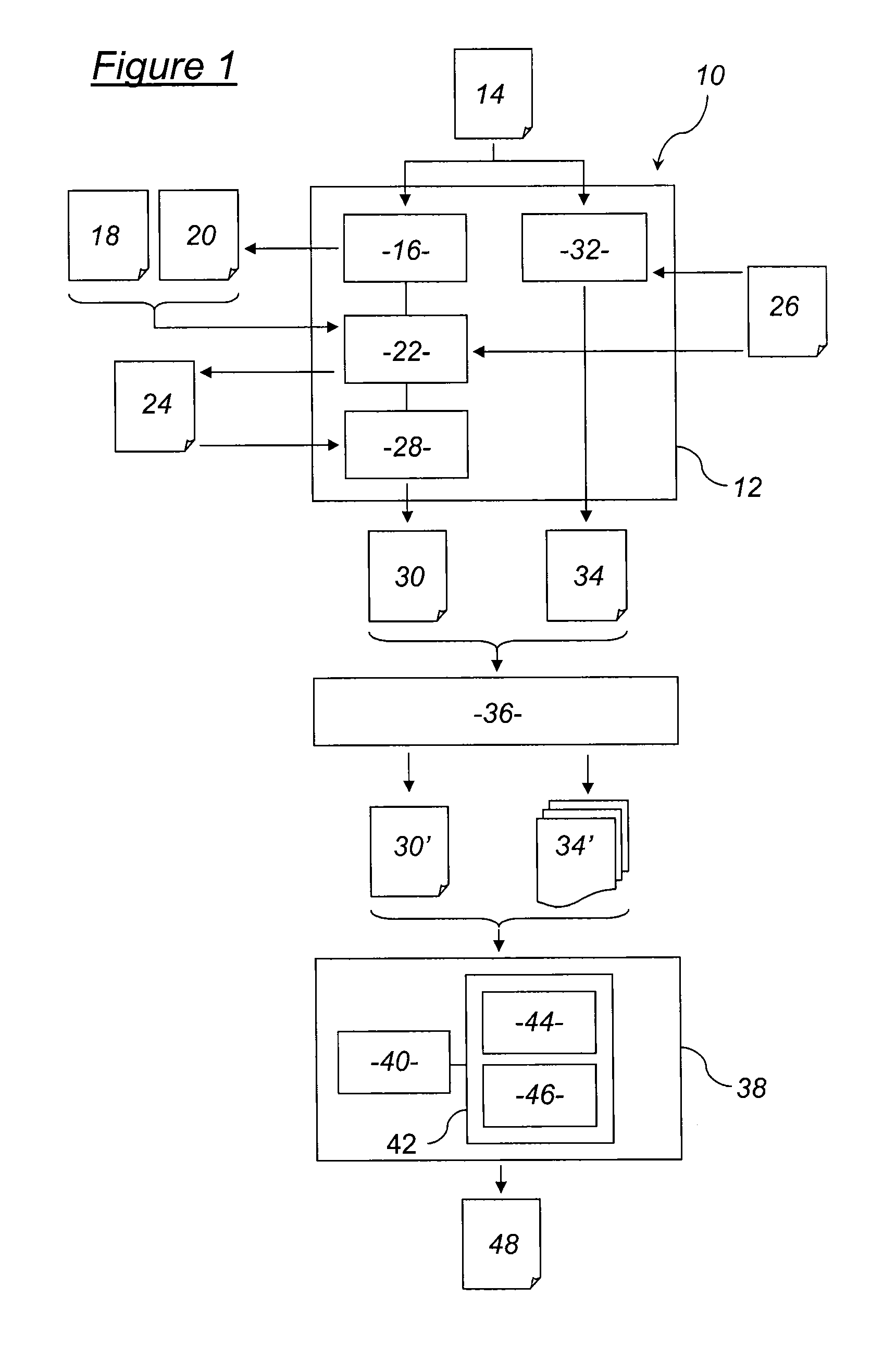

Digipass for web-functional description

ActiveUS20110314290A1Improve securityCost effectiveDigital data processing detailsUser identity/authority verificationUser needsInternet communication

The DigiPass for the Web provides security for internet communication greater than that achieved by the use of a static password without requiring the user to install any software or to possess or use dedicated hardware of any kind. The user merely access an appropriate website which downloads an applet to the user's browser. This is a conventional function which is handled by the browser and does not require any expertise on the part of the user. The browser relies on a password known only to the user for authenticating the user to the browser / applet. The browser / applet interacts with the server to create an authentication key which is then stored on the user's computer. The user can invoke the authentication key dependent on the user's presentation to the browser / applet of the password. Since the password is not used outside the user-browser / applet interaction it is not subject to attacks by hackers. The authentication key is also protected from attacks by encryption although the user need not memorize any information other than the password.

Owner:ONESPAN NORTH AMERICA INC

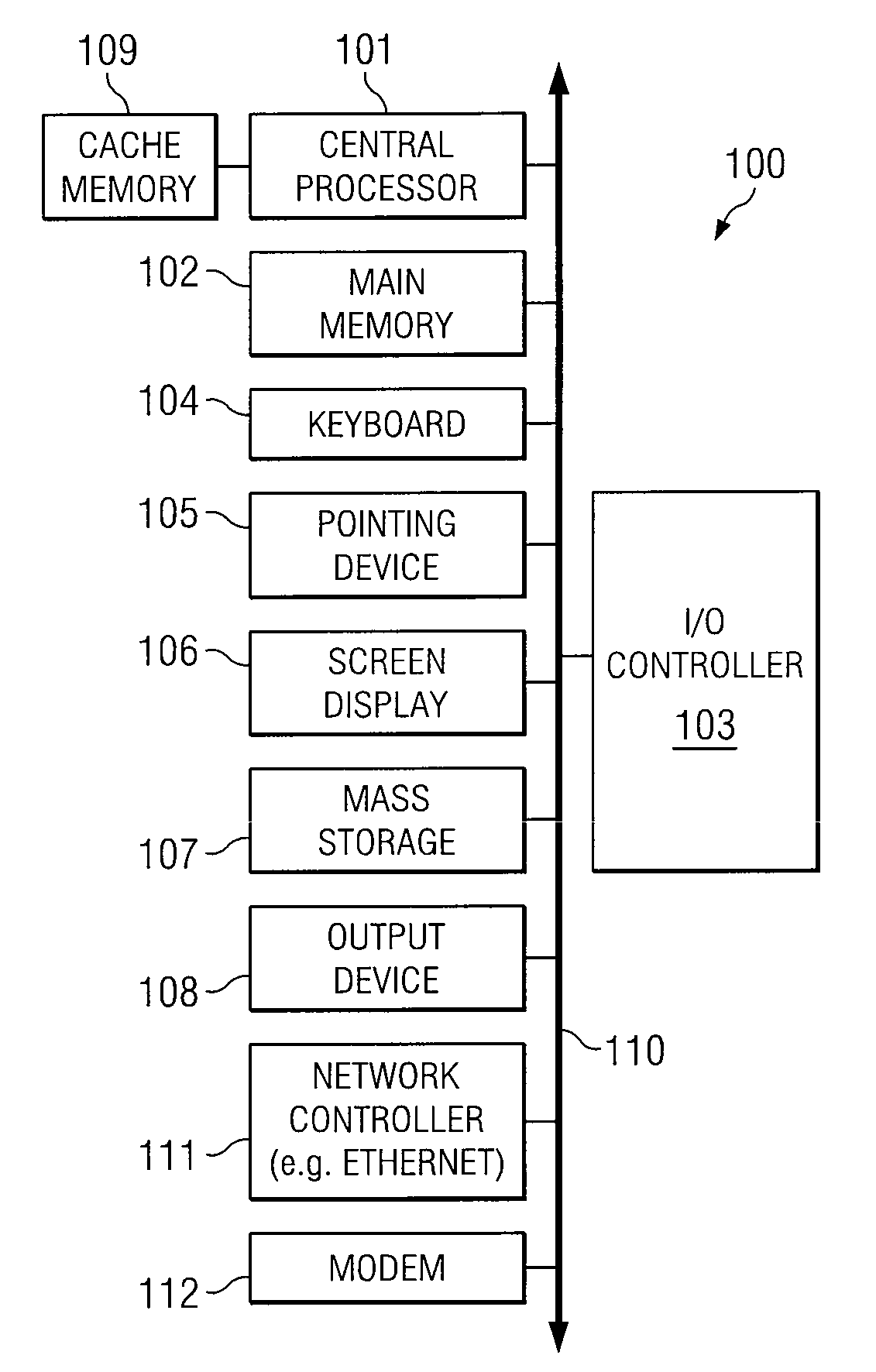

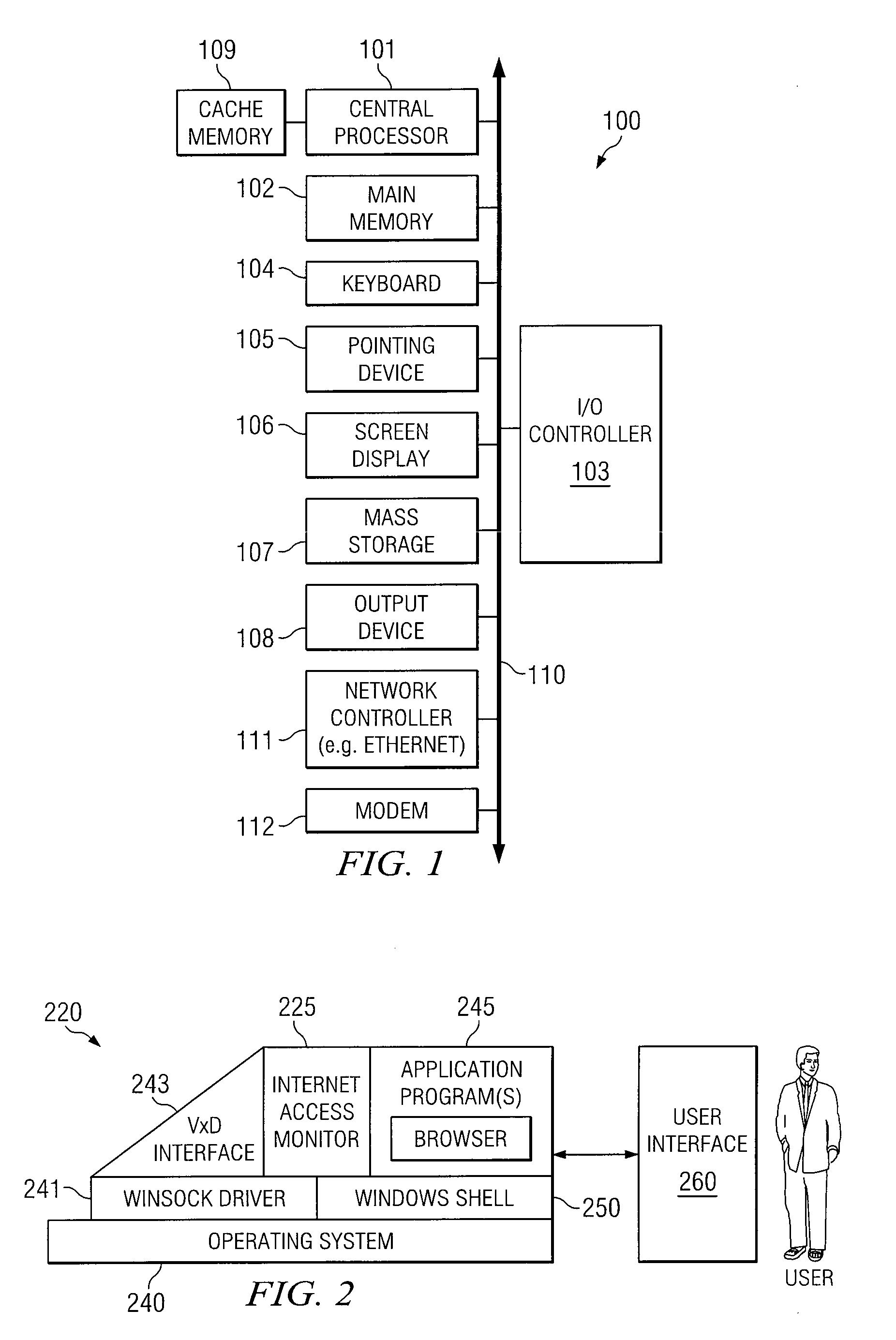

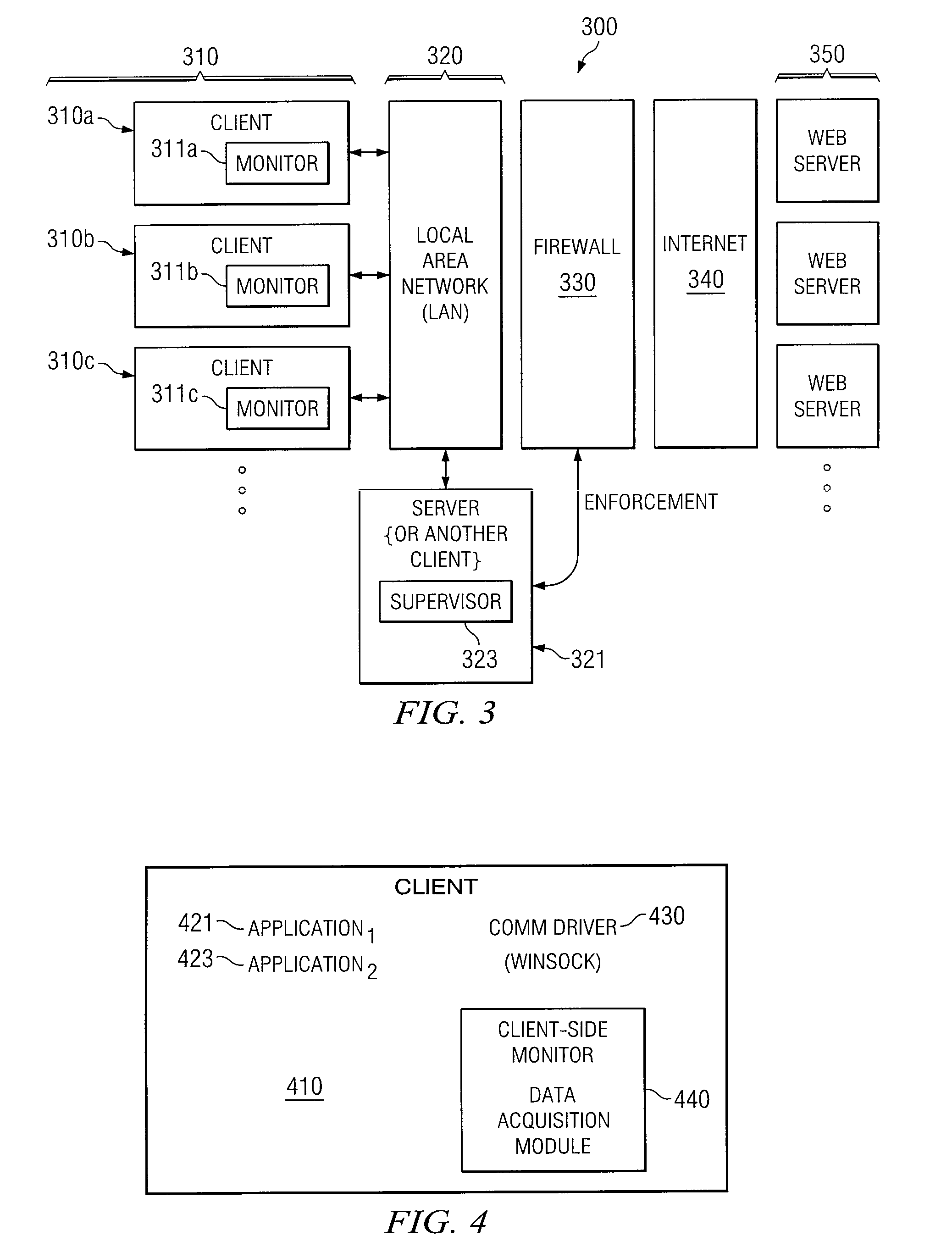

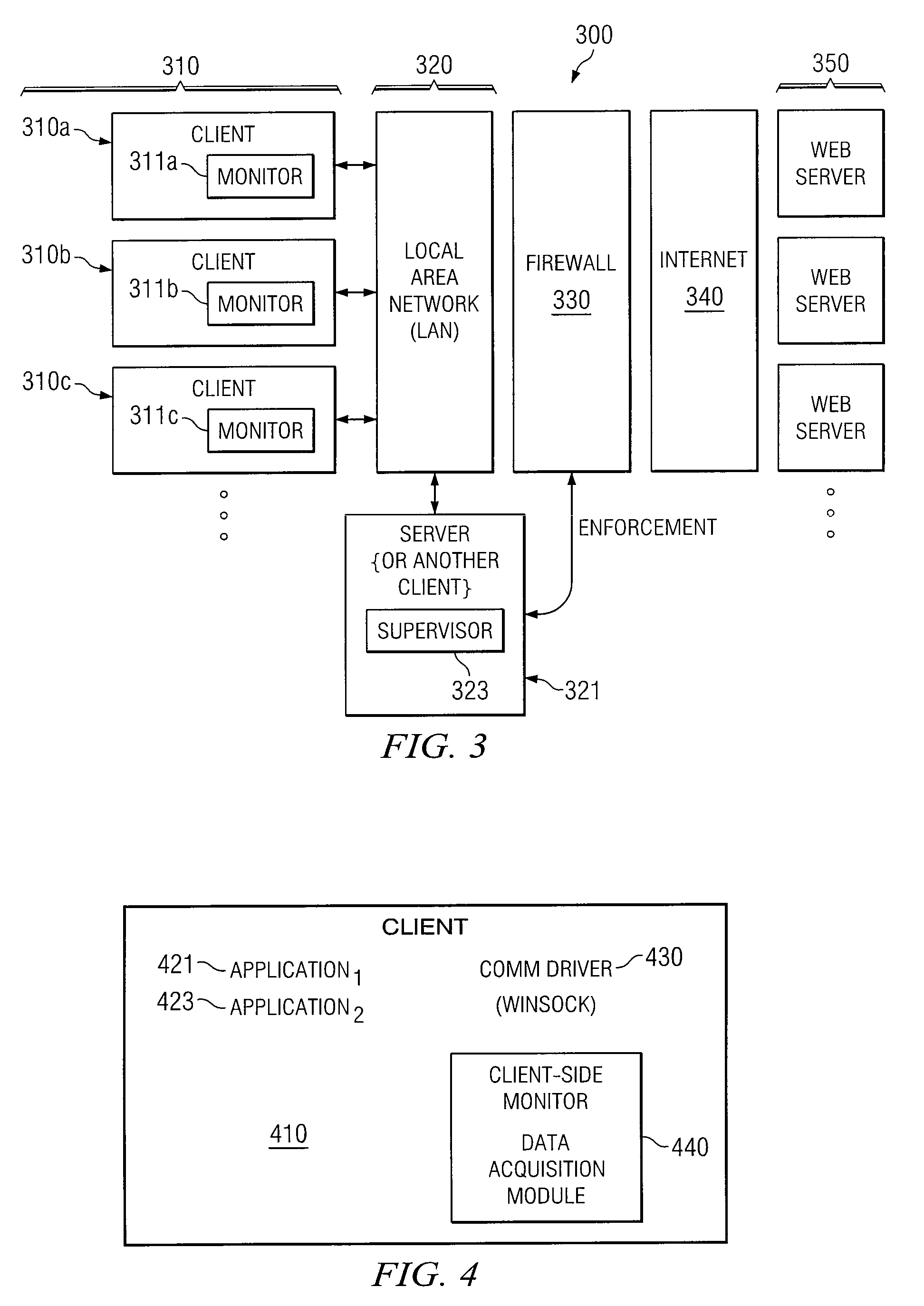

Dynamic threat event management system and method

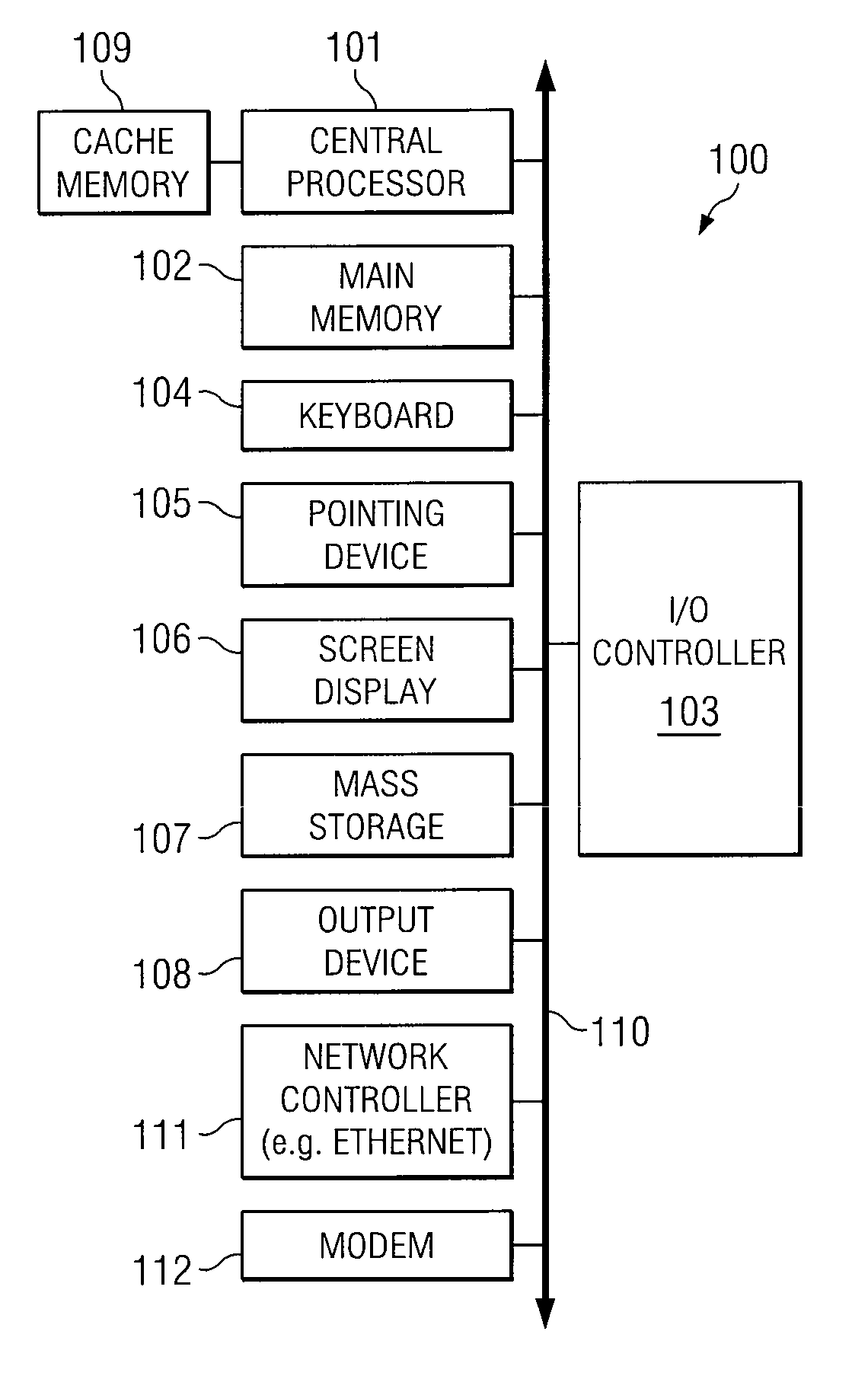

ActiveUS20070192865A1Improve performanceImprove securityMemory loss protectionError detection/correctionInternet privacyPersonal computer

According to various illustrative embodiments of the present invention, a method for a content-driven threat management system includes creating a threat detection primary object with threat mitigation data using at least one researcher of at least one of software and malicious code, encoding the threat detection primary object with threat mitigation data within an object capable of being transmitted to a personal computer system using a transmission vector update function, and transmitting the threat detection primary object with threat mitigation data to a threat agent using the transmission vector update function. The method also includes updating at least one threat function using the threat agent to update at least one threat functional description of the at least one threat function to include the threat detection primary object with threat mitigation data, and using the threat detection primary object with threat mitigation data to be capable of recognizing at least one threat event based upon the threat detection primary object with threat mitigation data.

Owner:CA TECH INC

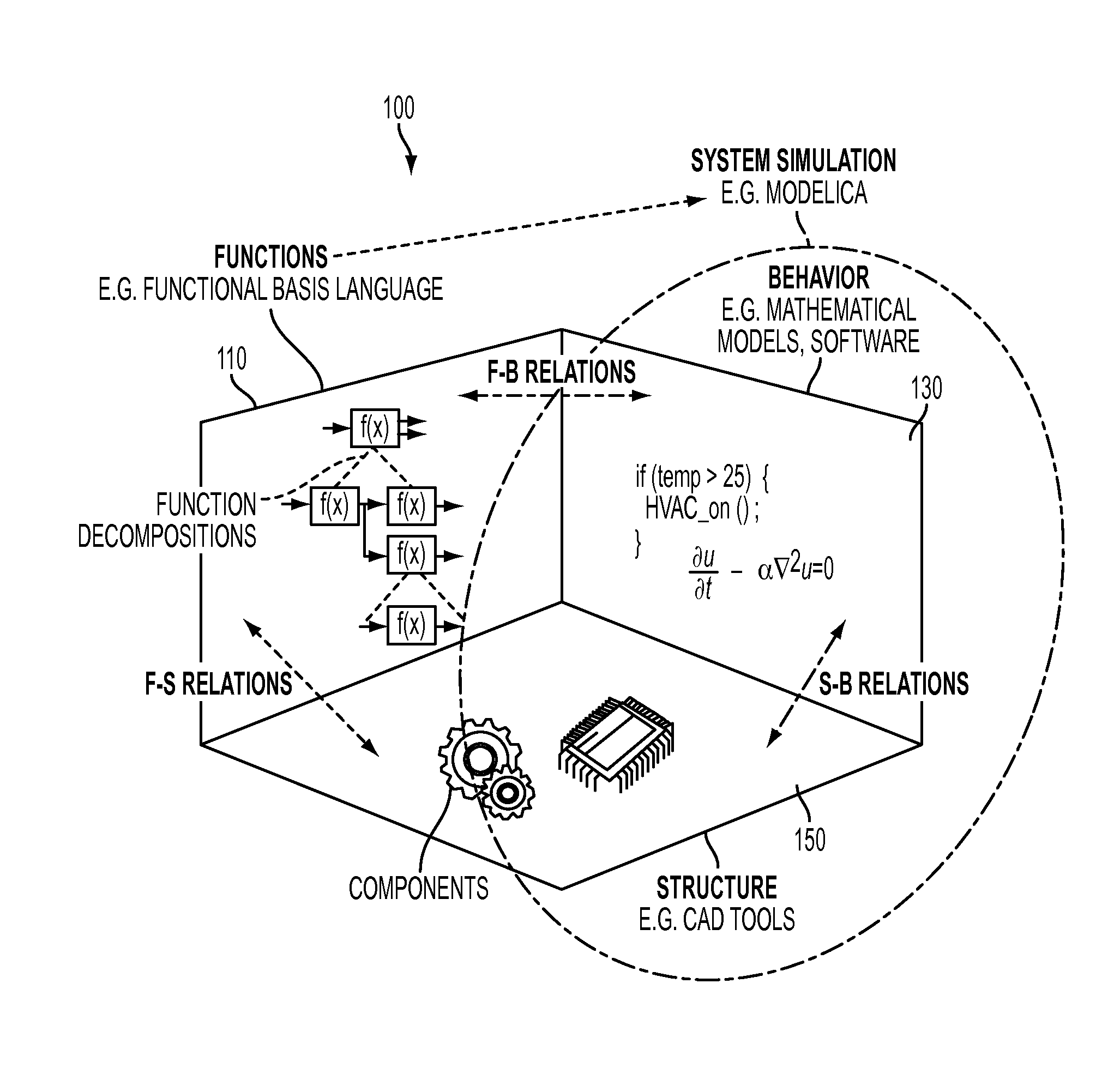

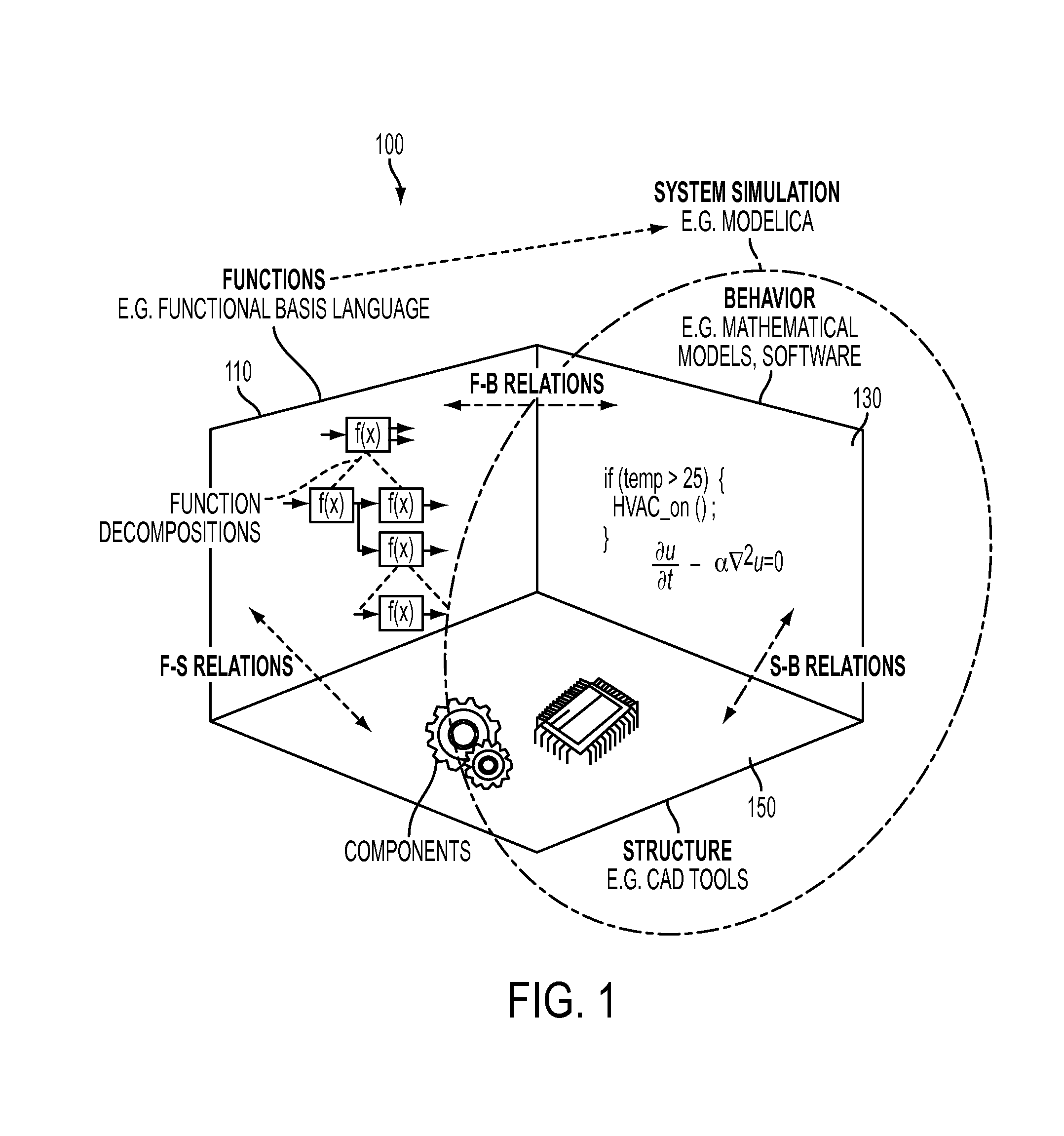

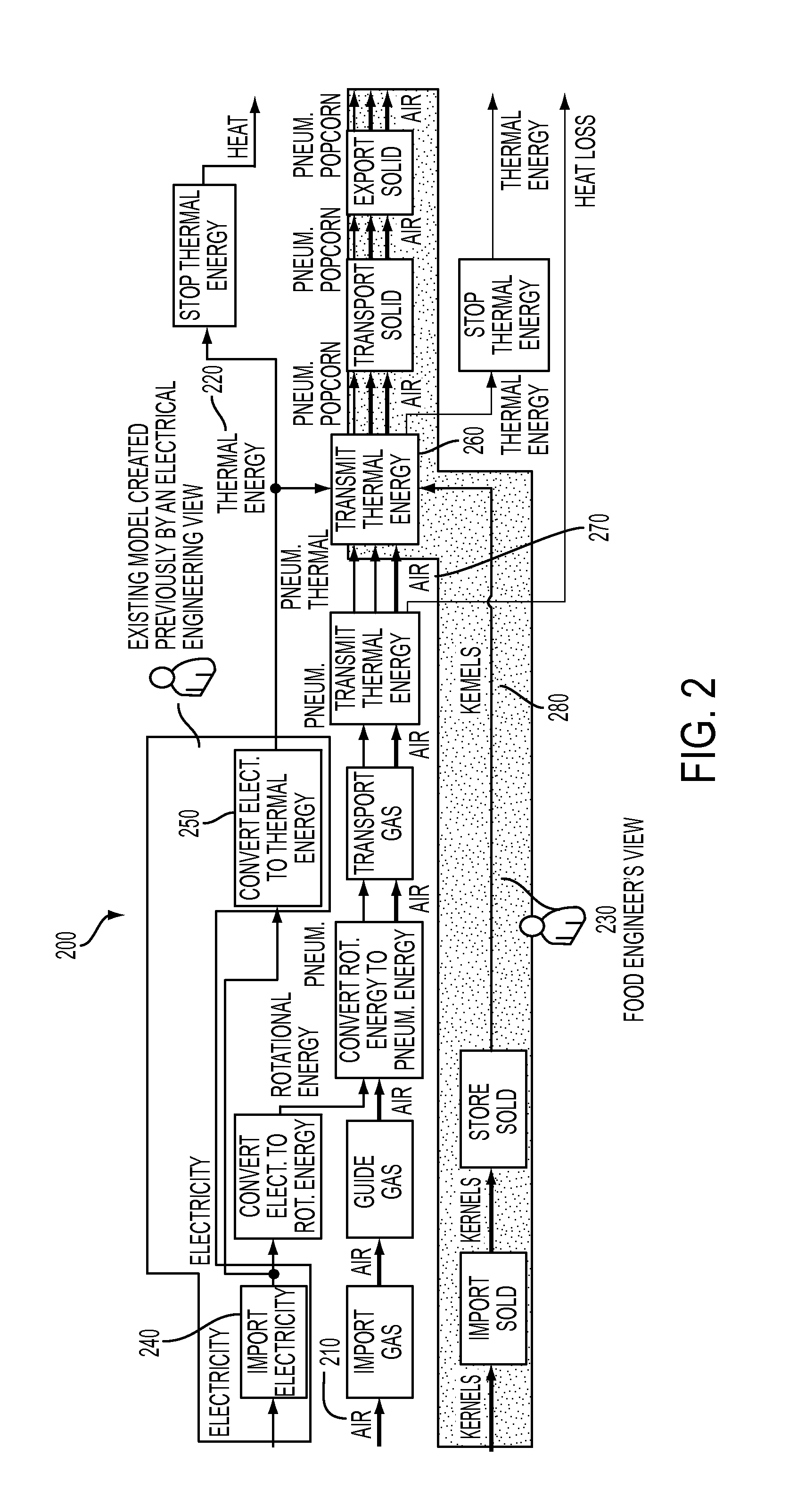

Context-based synthesis of simulation models from functional models of cyber-physical systems

ActiveUS20140019104A1Design optimisation/simulationSpecial data processing applicationsSystems designSimulation

An approach and tool integrate cyber-physical systems design based on the function-behavior-state (FBS) methodology where multi-domain simulation models capturing both the behavioral and structural aspects of a system are automatically generated from its functional description. The approach focuses on simulation-enabled FBS models using automatic and context-sensitive mappings of functional basis elementary functions to simulation components described in physical modeling languages. Potentially beneficial process loops are recognized and inserted in the functional model.

Owner:SIEMENS AG

Method and system for logic design for cell projection particle beam lithography

A method for particle beam lithography, such as electron beam (EB) lithography, includes predefining a stencil design having a plurality of cell patterns with information from a cell library, fabricating the stencil design, synthesizing a functional description into a logic circuit design after predefining the stencil design so that one or more characteristics of the stencil design are considered during synthesizing of the functional description into the logic circuit design, optimizing the logic circuit design, generating a layout design from the optimized logic circuit design, and forming the logic circuit on a substrate according to the stencil design and the layout design.

Owner:D2S

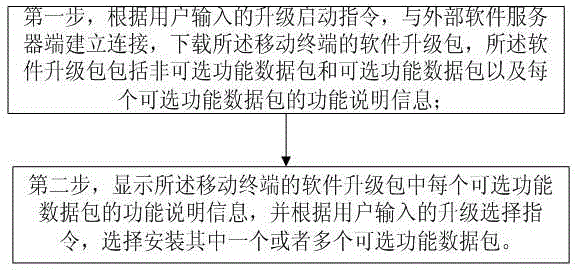

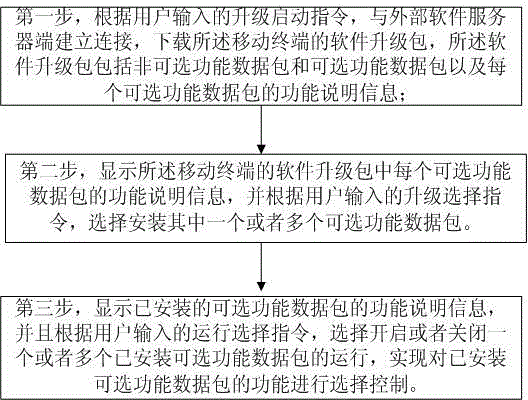

Software upgrading method for mobile terminal

The invention discloses a software upgrading method for a mobile terminal. The software upgrading method comprises the following steps of: 1, establishing connection with an external software server end according to an upgrading starting instruction input by a user, and downloading a software upgrading packet of the mobile terminal, wherein the software upgrading packet comprises a non-optional functional data packet, optional functional data packets and functional description information of each optional functional data packet; and 2, displaying the functional description information of each optional functional data packet in the software upgrading packet of the mobile terminal, and selectively installing one or more optional functional data packets according to an upgrading selection instruction input by the user. According to the software upgrading method for the mobile terminal, a function to be upgraded can be freely selected according to the favor of a user when the mobile terminal such as a mobile phone is subjected to software version upgrading, so that daily control and use of the mobile terminal by the user are facilitated.

Owner:TIANJIN SAMSUNG OPTO ELECTRONICS +1

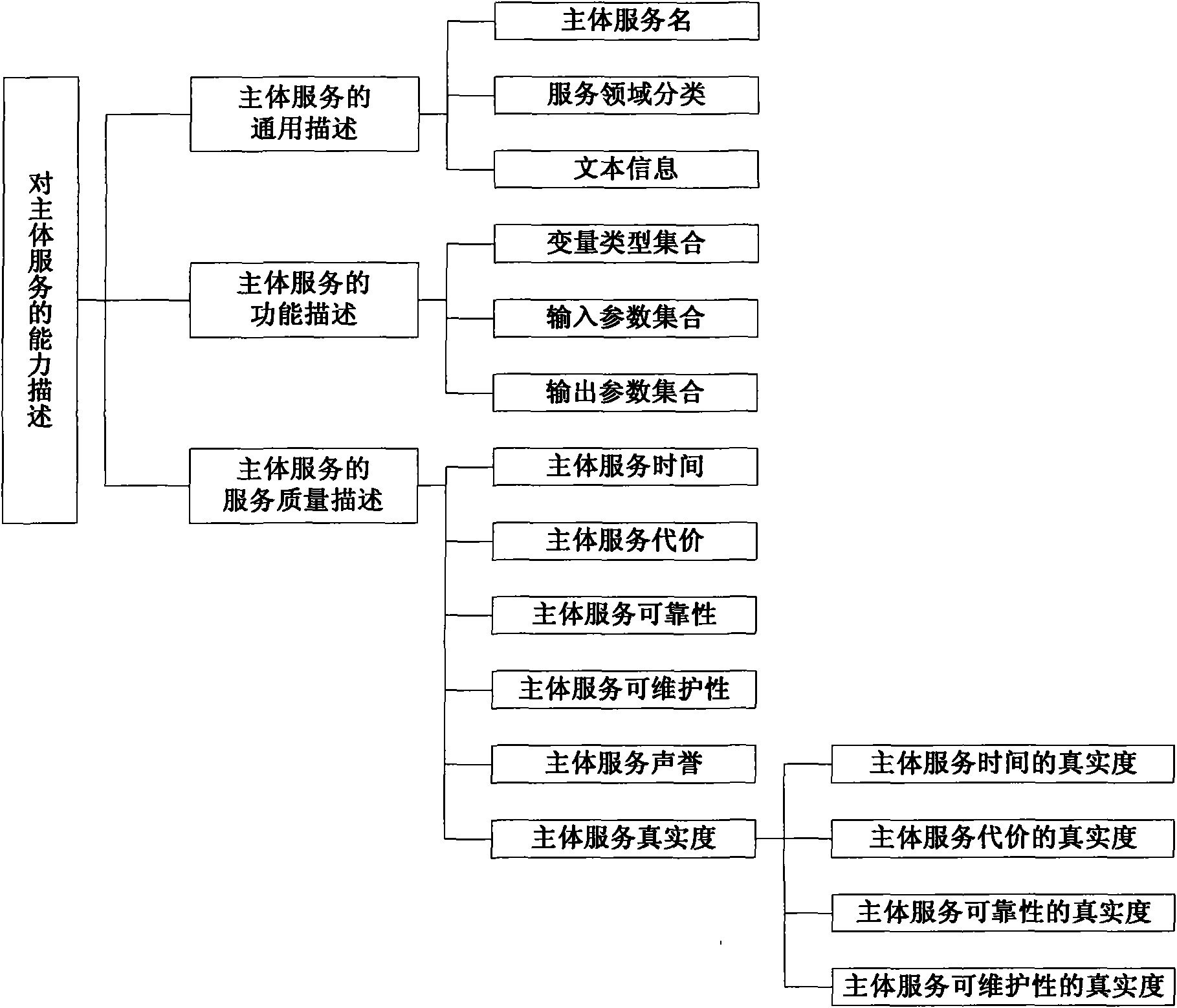

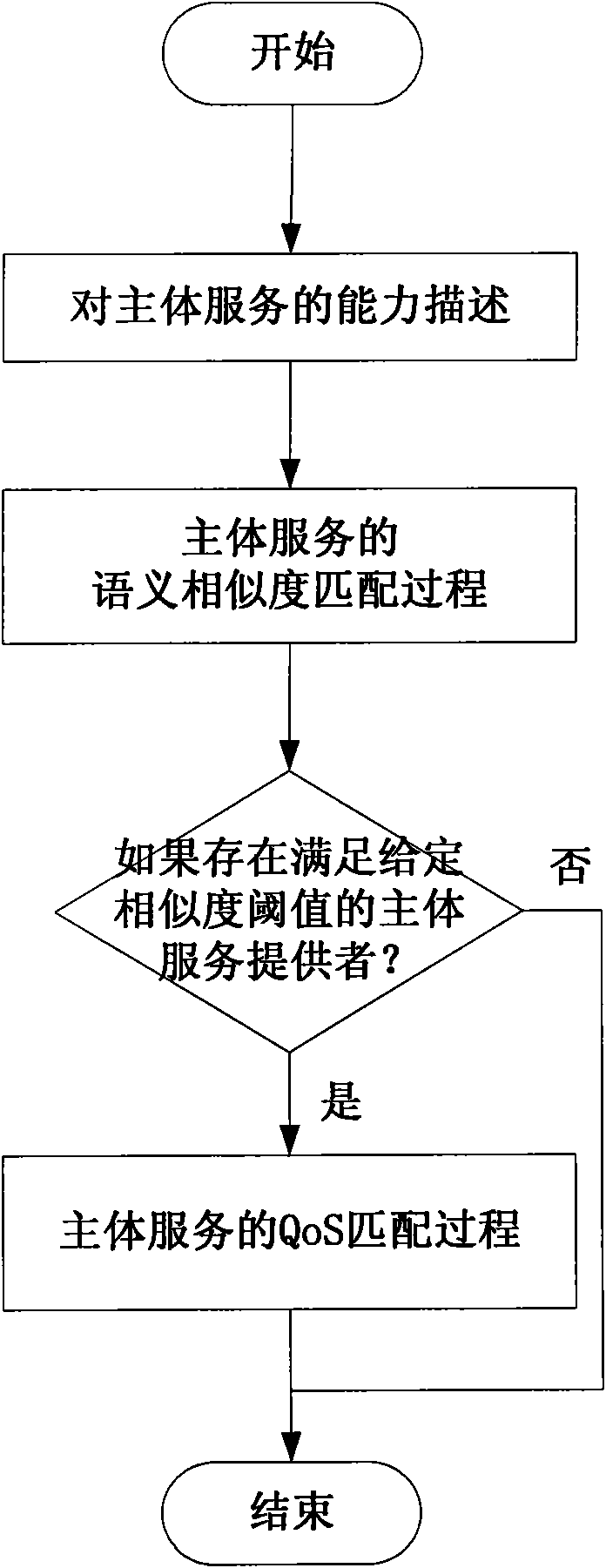

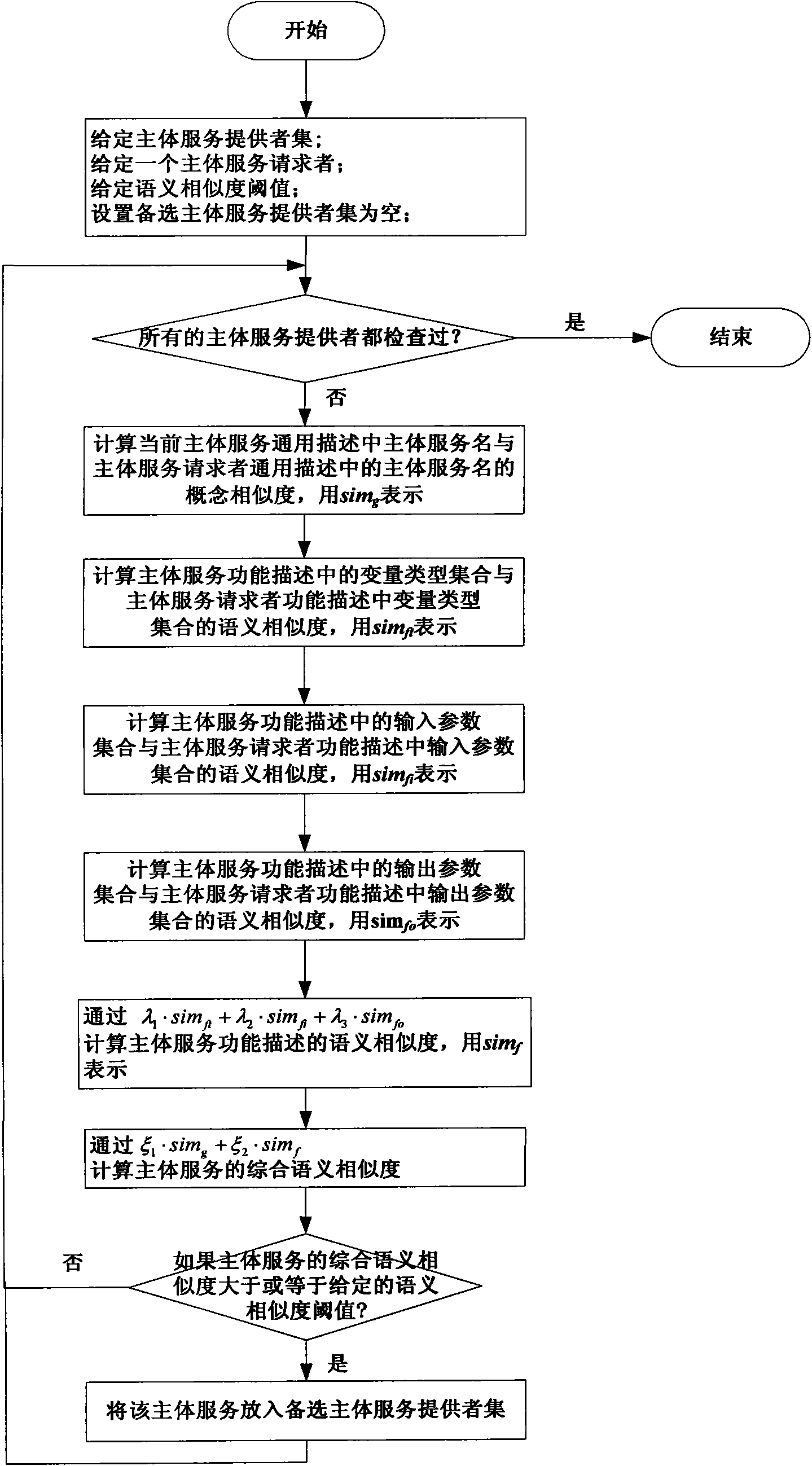

Subject service describing and matching method based on semantic and QoS constraint

ActiveCN101674328AImprove accuracyFully reflect different needsTransmissionCommerceSemanticsWorld Wide Web

The invention discloses a subject service describing and matching method based on semantic and QoS constraint, which comprehensively considers semantic and QoS attributes and describes and matches the subject service. The invention is composed of processes of subject service describing and subject service matching, wherein, the subject service describing process can carry out general description,functional description and service quality attribute description on the subject service, the subject service matching process can intensively find one or a plurality of subject services satisfying semantic similarity threshold value and featuring the optimal QoS in subject service suppliers according to a subject service requester. The invention can perform comprehensive capacity description on the subject service, comprehensively considers semantic and QoS influences on subject service matching, and objectively and impartially selects one or a plurality of subject services satisfying semantic condition and featuring the optimal QoS according to subject service request, thus solving the problems that service quality and semantics are not well combined, matching effect is not accurate, thematching process is subjective and unfair, etc. in the existing methods.

Owner:NANJING UNIV OF SCI & TECH

Automated multiple voltage/power state design process and chip description system

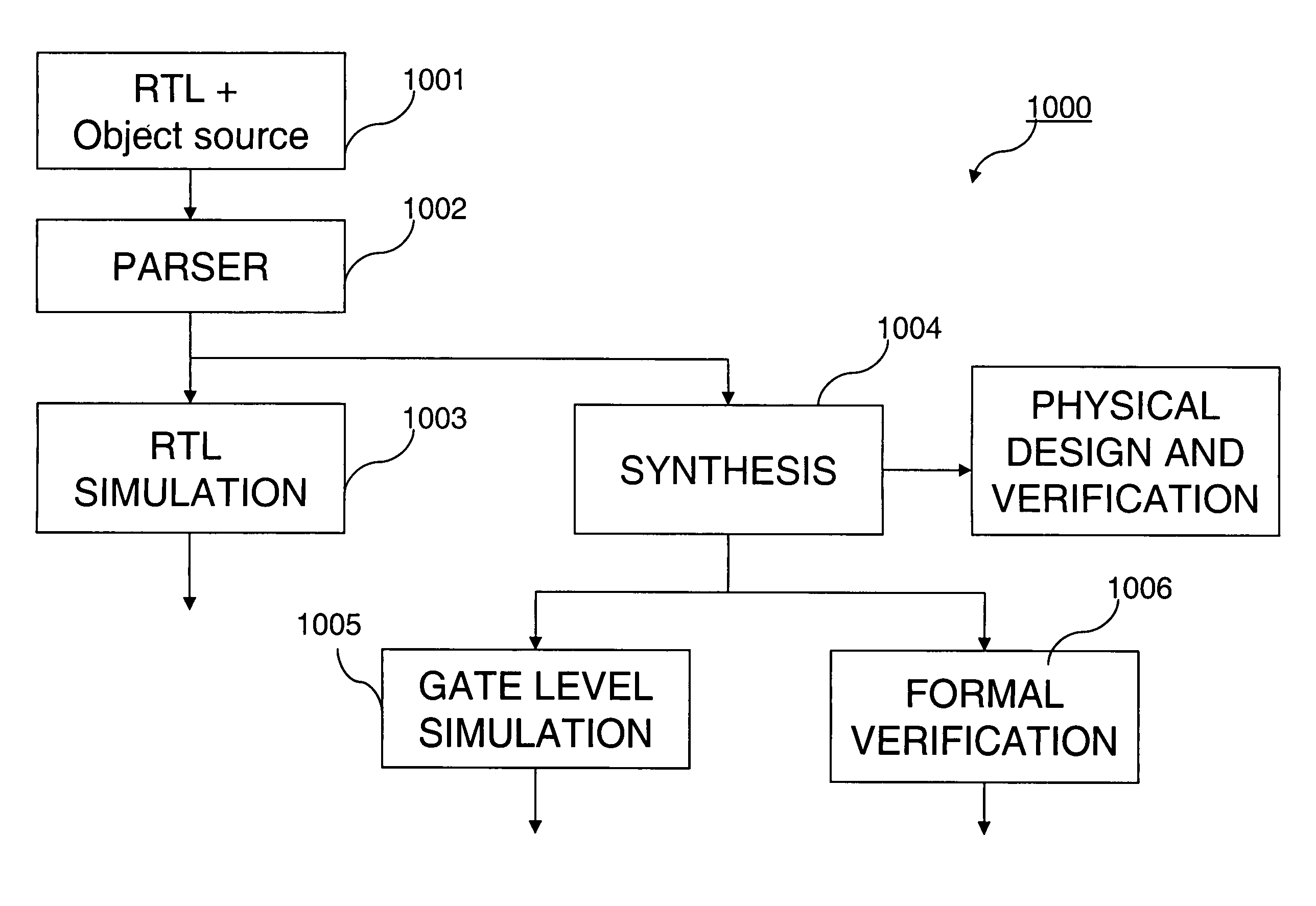

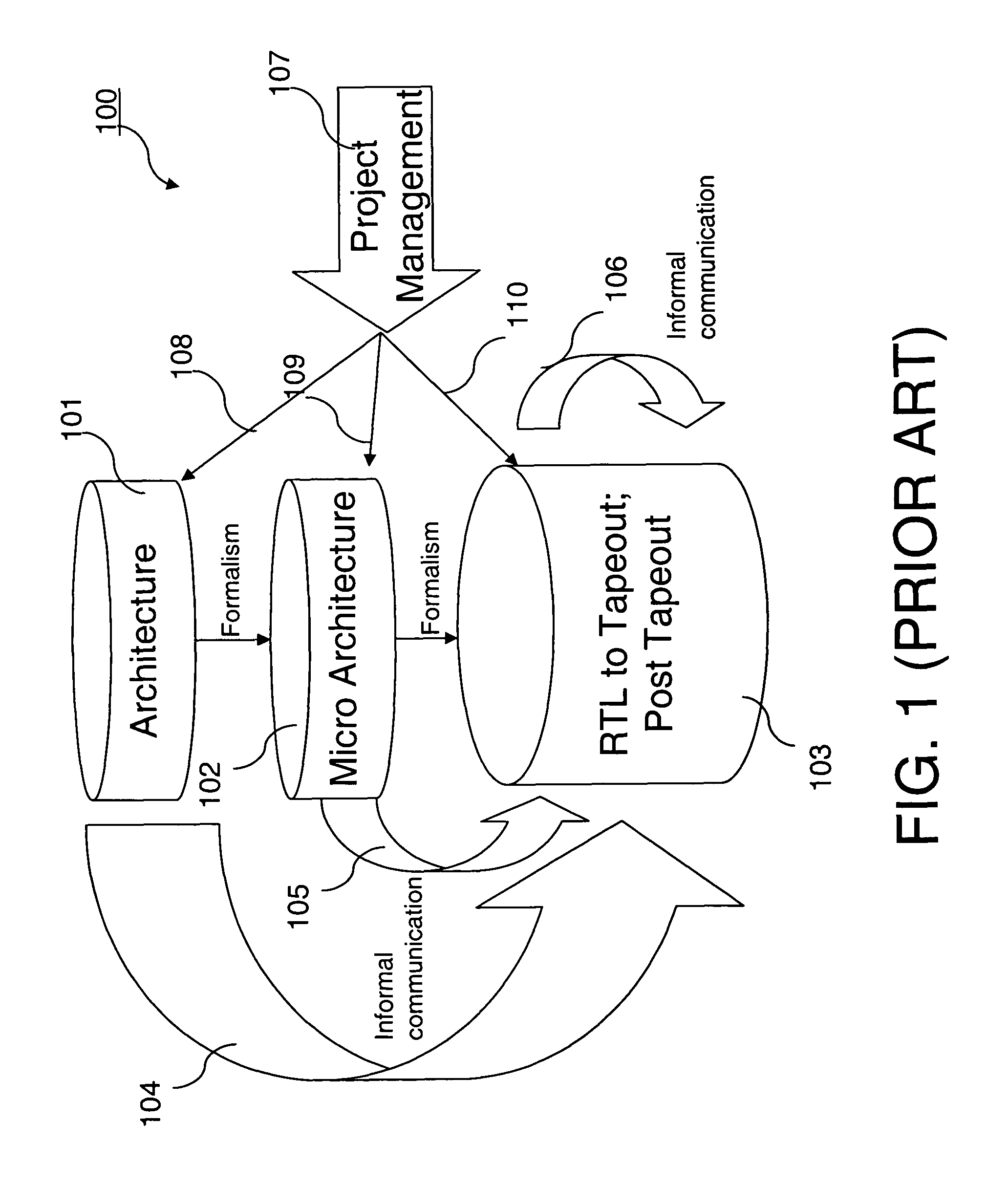

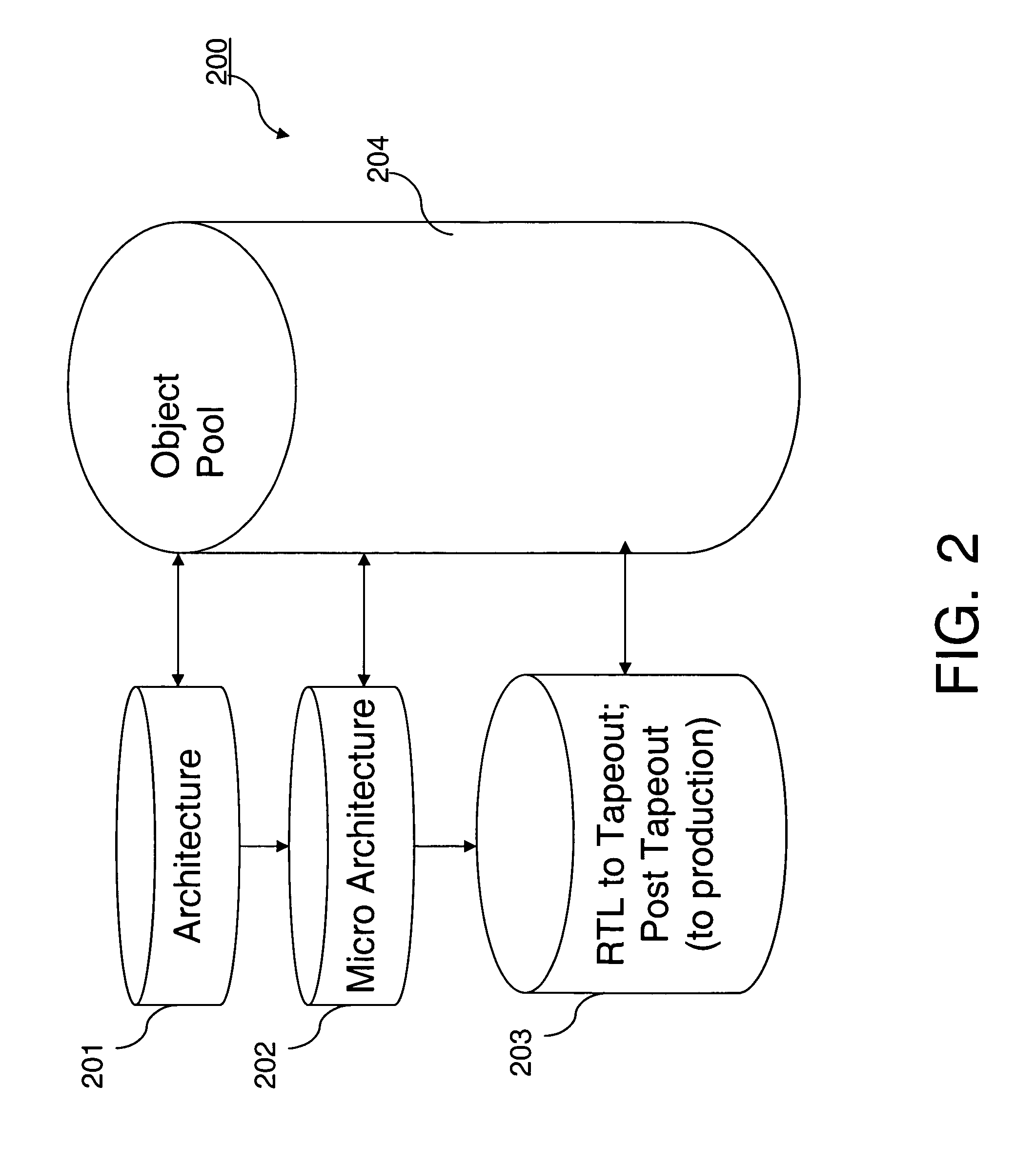

ActiveUS7984398B1Computer aided designSoftware simulation/interpretation/emulationDesign informationEngineering

Systems and methods are disclosed herein which compensate for the loss in design information that occurs when the design is represented in traditional functional descriptions. An automated multiple voltage / power state design process includes creating a plurality of design objects; processing a design definition according to the voltage effects design object; and generating a modified design output such that communication between a plurality of design process steps, wherein the plurality of design process steps include a parsing step, a RTL simulation step, a synthesis step, a gate simulation step, formal verification step, and physical design and verification step in accordance with the voltage effects design object. A system for automating a multiple voltage / power state design process includes a design definition module; a parser module, a RTL simulation module, a synthesis module, a gate simulation module, and a formal verification module wherein the automation of a multiple voltage / power state design process is achieved. The system can include a physical design and verification module coupled to the synthesis module.

Owner:SYNOPSYS INC

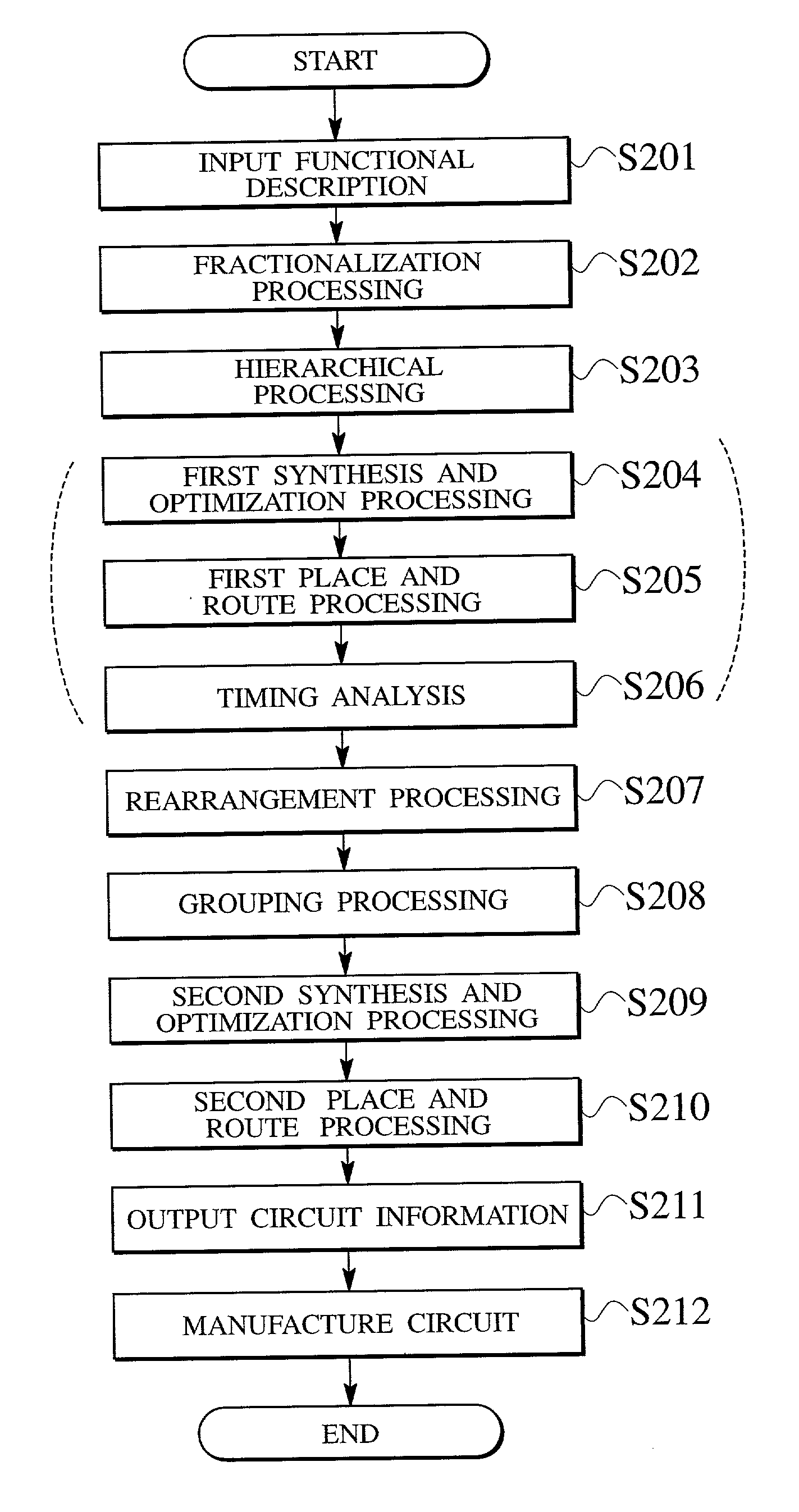

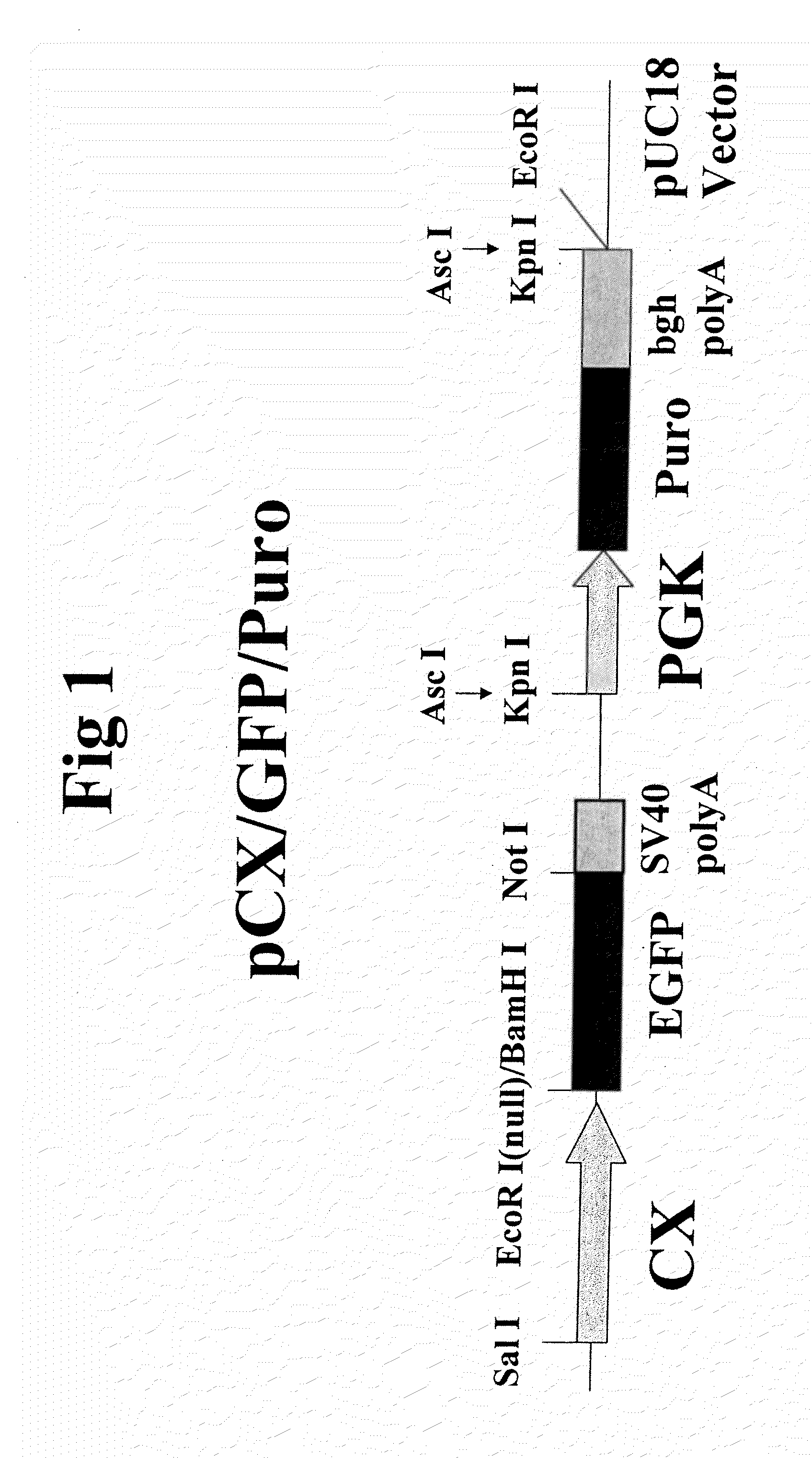

Logical synthesizing apparatus for converting a hardware functional description into gate-level circuit information

InactiveUS20020049958A1CAD circuit designSoftware simulation/interpretation/emulationComputer architectureFeature description

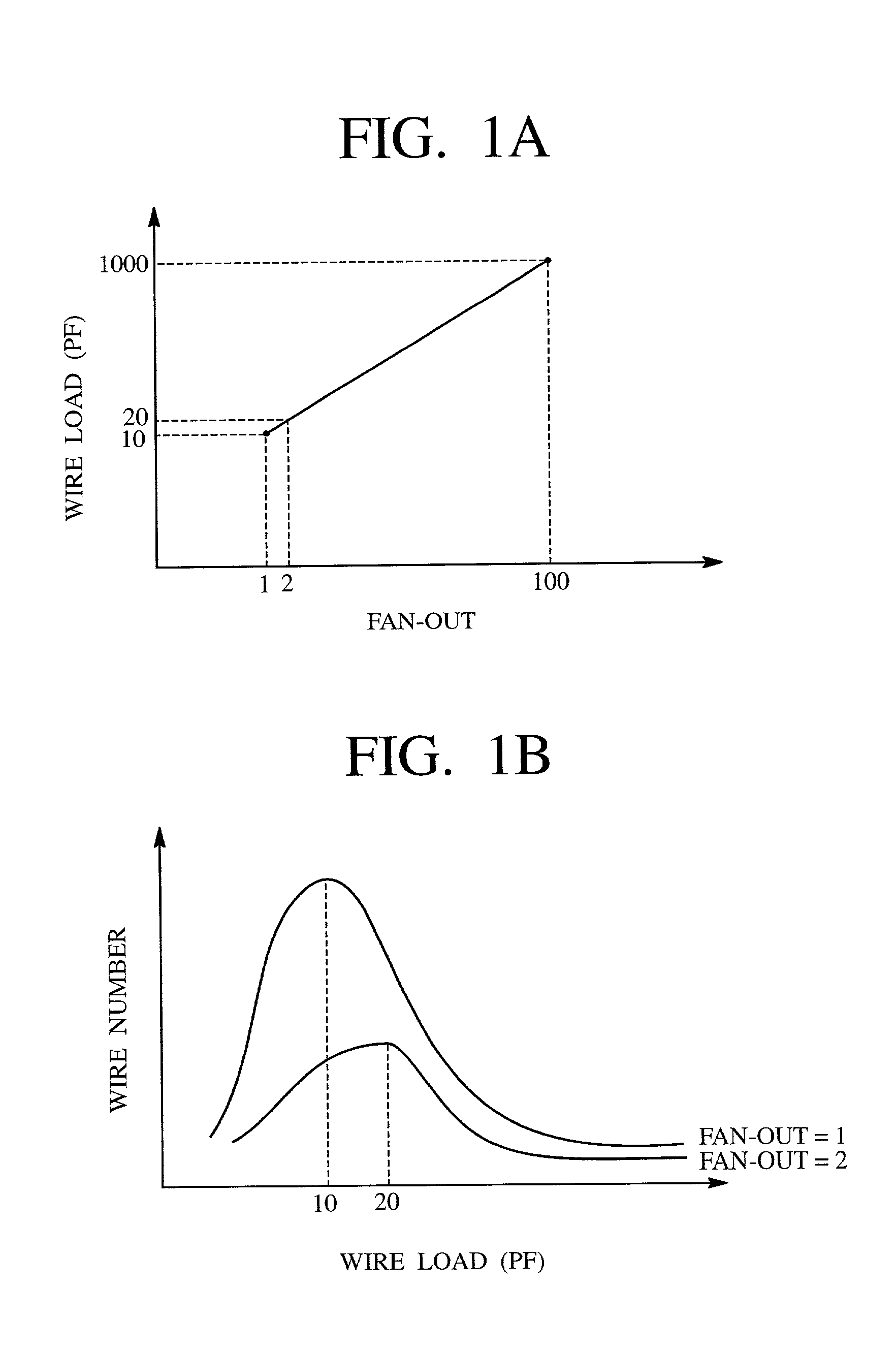

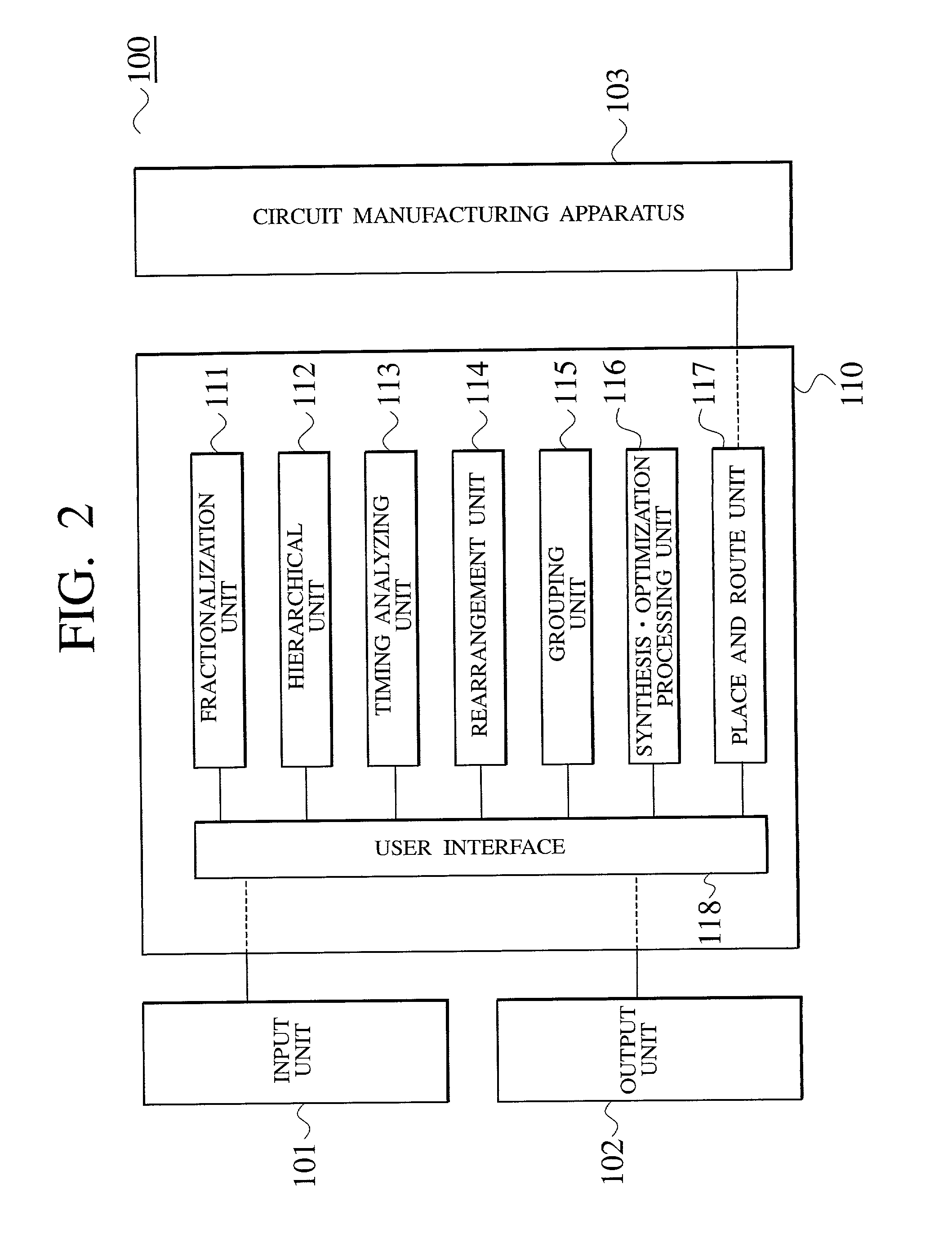

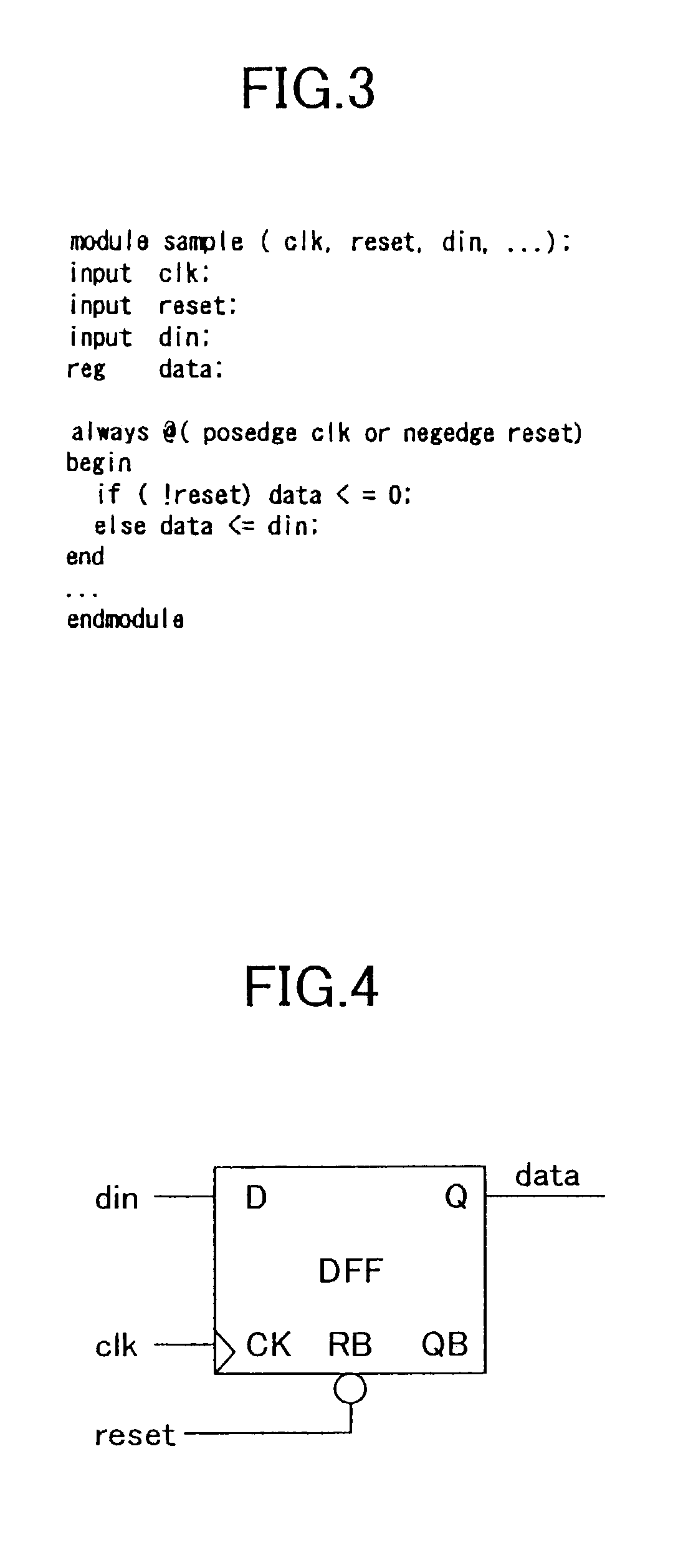

In the disclosed invention, a module in the functional description is fractionalized according to functions, the functional description is converted into two hierarchies and then the fractionalized modules are rearranged so as to decrease a critical path; and the rearranged modules are grouped to generate an intermediate hierarchy and a logical synthesis and optimization processing and a place and route processing are executed using the functional description after the formation of the intermediate hierarchy.

Owner:KK TOSHIBA

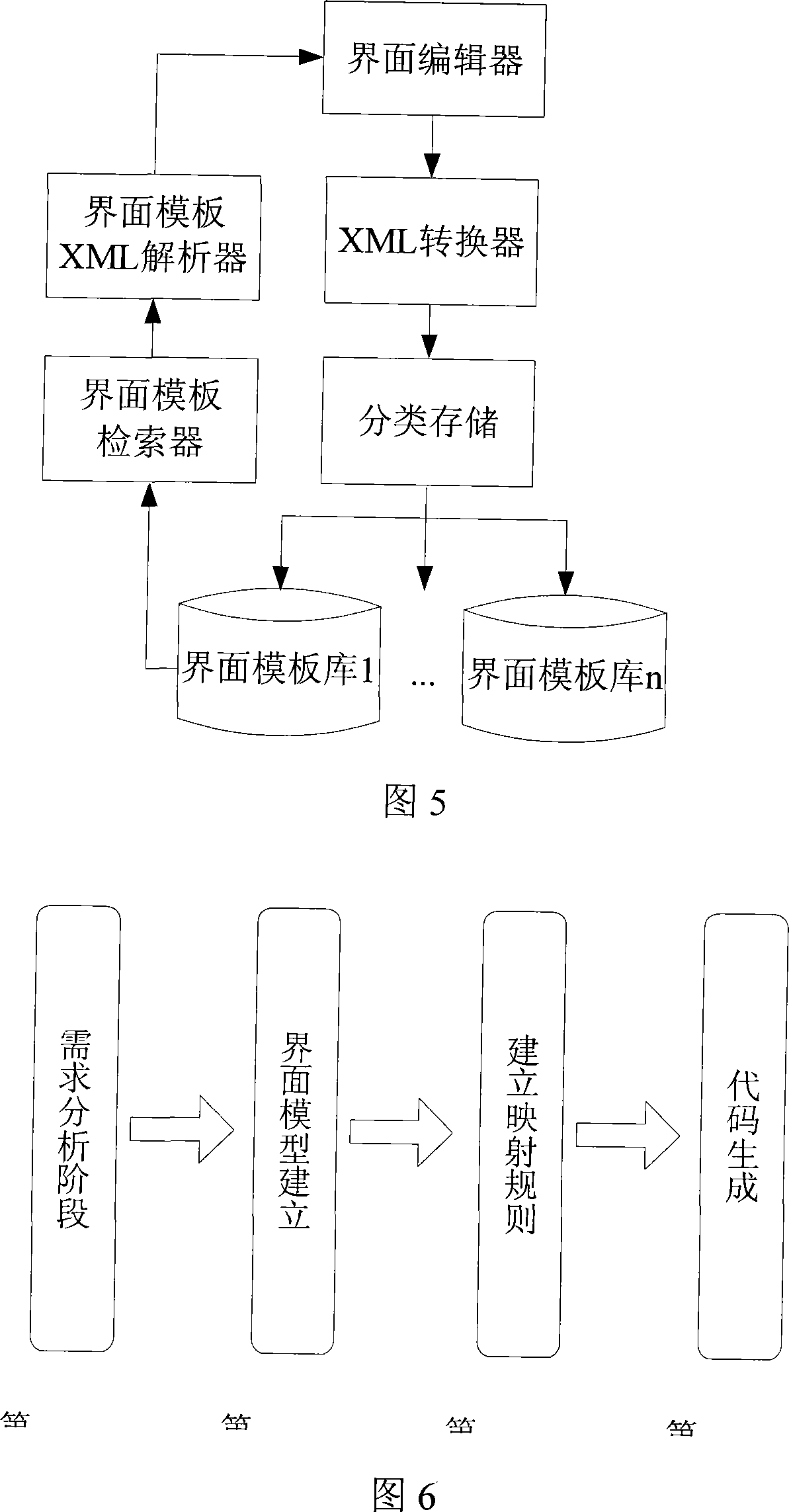

A GUI creation model for mobile terminal

InactiveCN101146281AImprove development efficiencyImprove reusabilityRadio/inductive link selection arrangementsTelephone sets with user guidance/featuresGraphical user interface testingUser interface

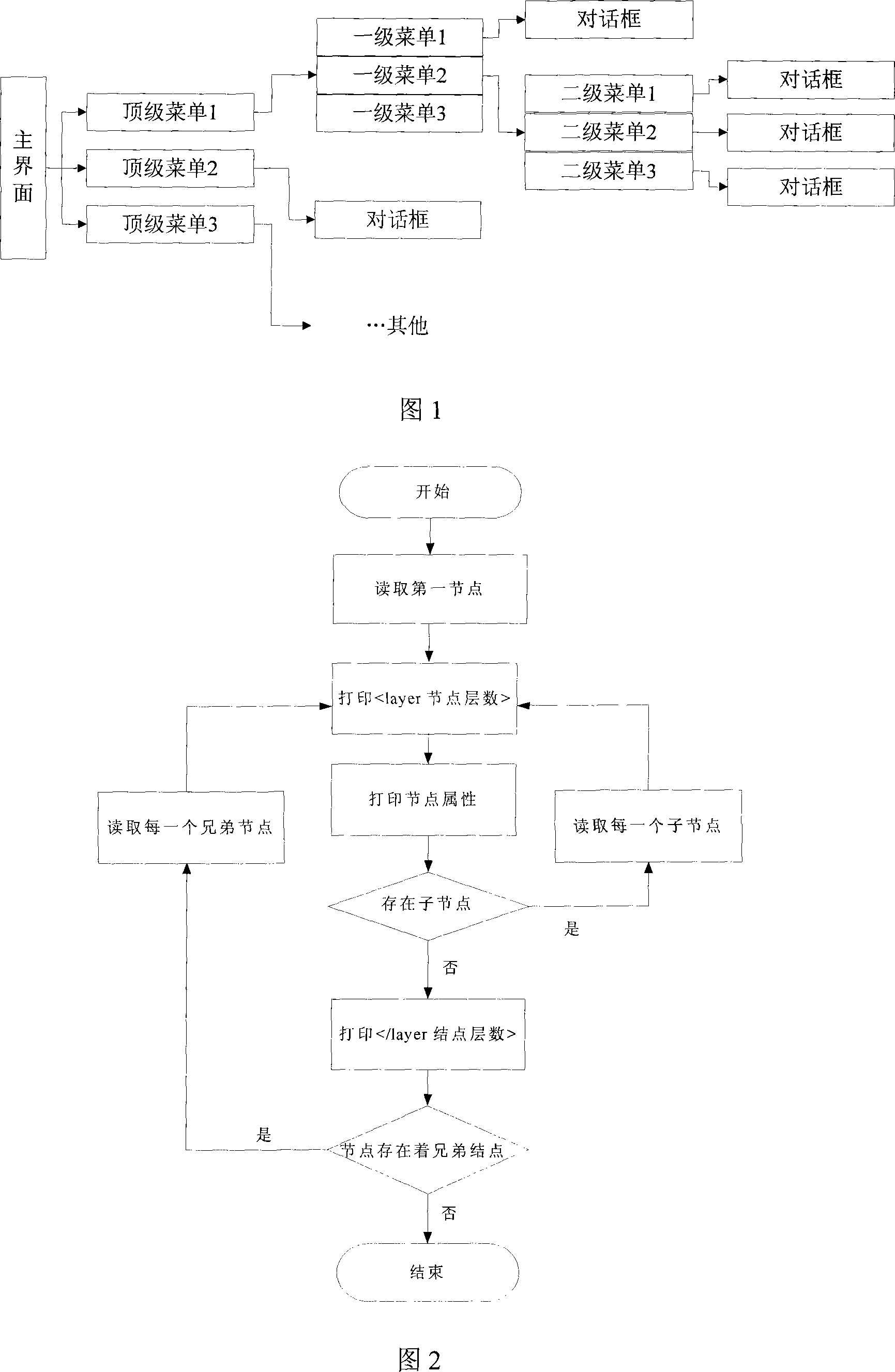

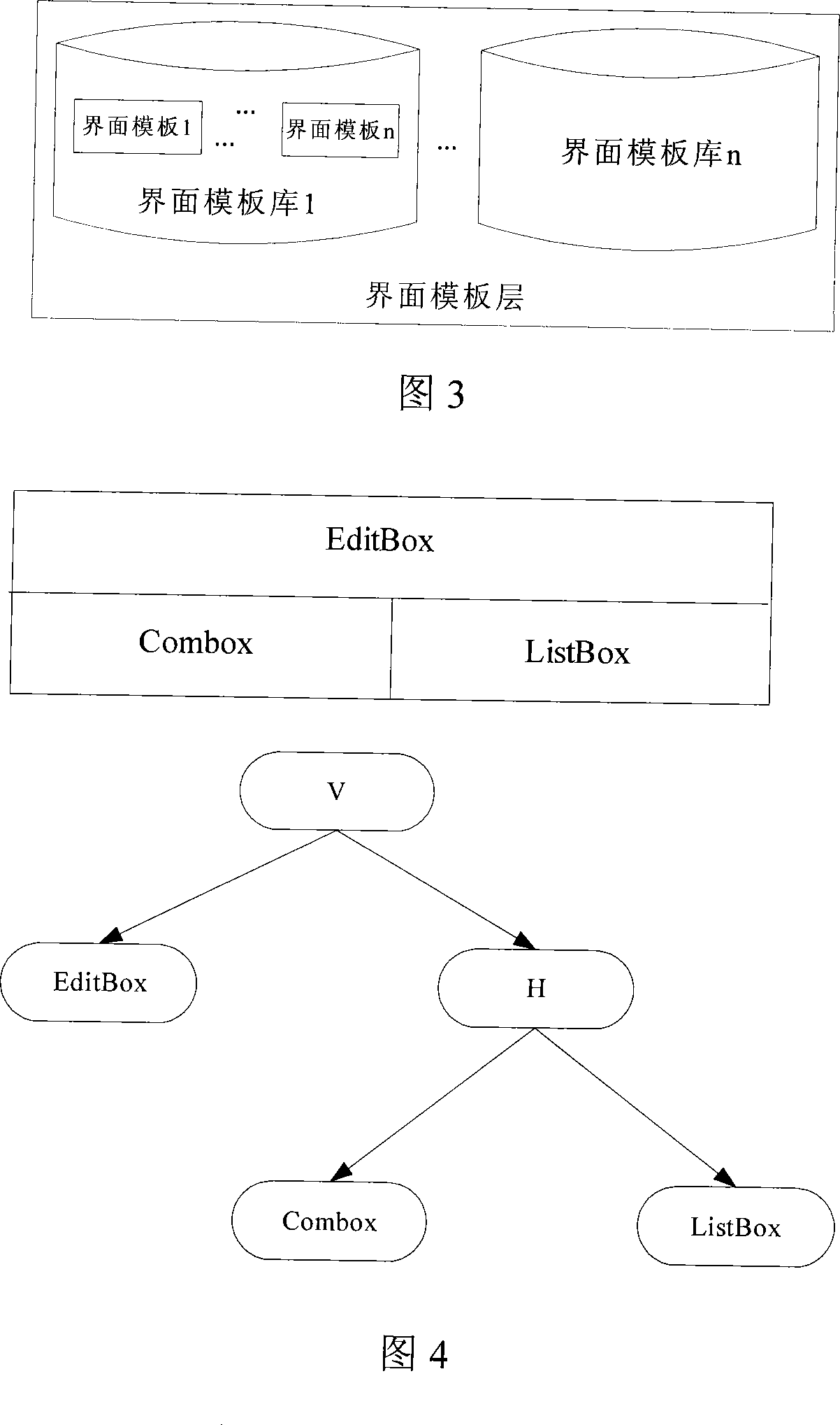

The invention discloses a graphical user interface model set up towards a mobile terminal, which belongs to the field of graphical interface development. The model comprises a functional layer, an objective layer and an interface template layer. The functional layer is the functional description of the whole system and used to produce an interface frame, relationship among the interfaces and requirement of the interface for the objective layer by means of demand analysis. The objective layer, as an intermediate layer in the whole graphical user interface model, exhibits the relationship between the interface and the internal data, and describes the data member characteristics of the object and the basic data type of the object member. The interface template layer is used to set up the corresponding relationship between the internal data and the external display element. The graphical user interface of the mobile terminal has a tree structure as a hierarchical structure. Excepting the root node of the tree structure, the node of the tree structure has two types, one is menu node and the other is dialog box node, wherein each menu node has sub-nodes. The invention can increase the efficiency of interface development for the mobile terminals and improve the reusability of codes.

Owner:SUN YAT SEN UNIV

Methods and systems for converting a synchronous circuit fabric into an asynchronous dataflow circuit fabric

Methods and systems for converting synchronous circuit designs to asynchronous circuit designs, and particularly programmable asynchronous circuit designs. Provide is a systematic, workable and repeatable process for evaluating synchronous circuit designs, converting the wires, switches / connections and logic functions to equivalent-function asynchronous circuit designs and hence implementing a functionally equivalent asynchronous circuit with all the benefits thereof. Further provided are a process for systematically doing the conversion and hardware equivalents (in form or functional description) for the asynchronous components. Using the present invention, any synchronous circuit design can be converted to an asynchronous equivalent, typically with no change to the original design implementation.

Owner:ACHRONIX SEMICON CORP

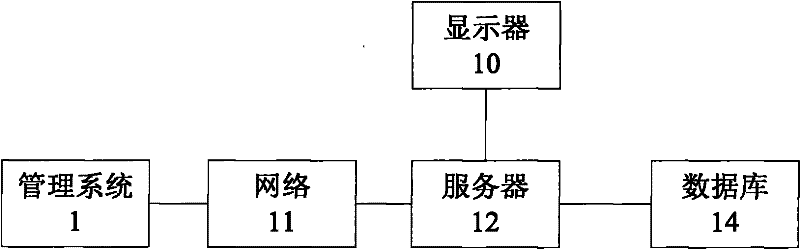

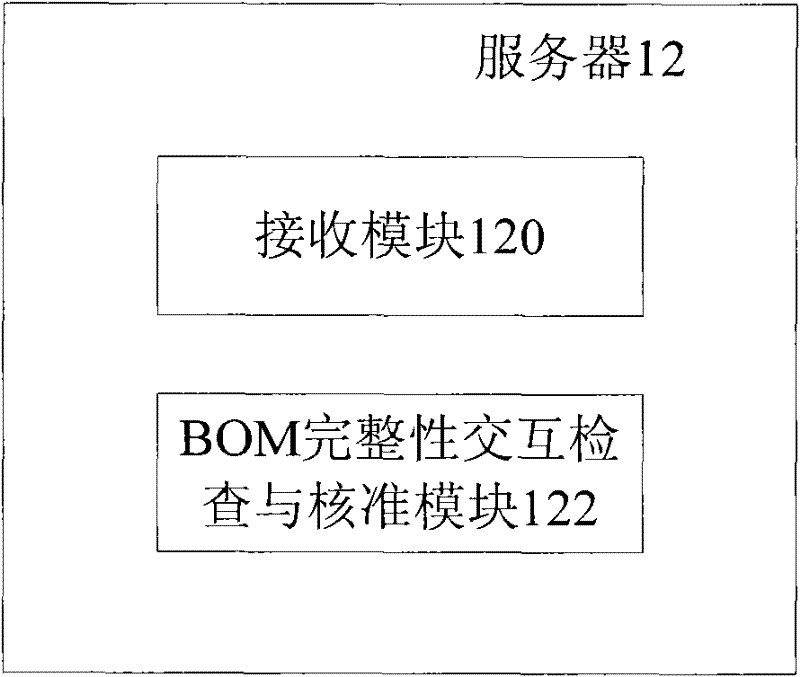

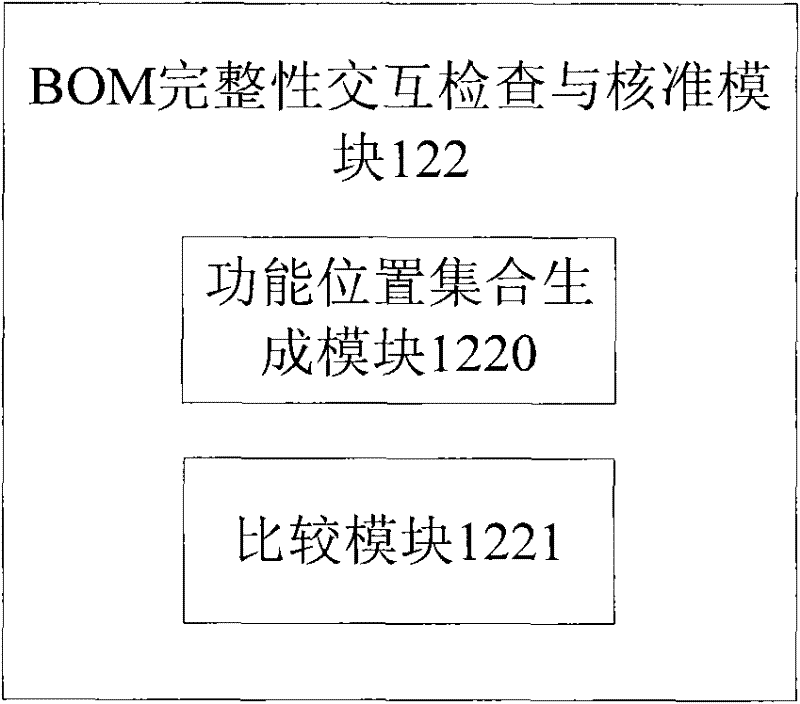

Configurable BOM completeness interactive check and approval system

The invention provides a configurable BOM integrity interactive checking and approval system, the system is connected with at least one management system, the BOM integrity interactive checking and approval system includes a database and a server communicating with the database, the management system includes a full-featured The location description library, the full-configuration feature base library, and the BOM; the server includes a receiving module for receiving the full-function location description library, the full-configuration feature base library, and the BOM from the management system, and a BOM integrity interactive check and approval module, It is used to generate the functional location usage set based on the full-function location description library, full-configuration feature base library and BOM, and to check and approve the integrity of the functional location usage set. Integrity analysis can be performed on the multi-platform, multi-project configurable BOM and the sub-BOM of its sub-projects, which improves the accuracy and efficiency of BOM integrity verification and approval.

Owner:SAIC MOTOR

Digipass for web-functional description

ActiveUS8261087B2Improve securityCost effectiveDigital data processing detailsUser identity/authority verificationInternet communicationUser needs

The DigiPass for the Web provides security for internet communication greater than that achieved by the use of a static password without requiring the user to install any software or to possess or use dedicated hardware of any kind. The user merely access an appropriate website which downloads an applet to the user's browser. This is a conventional function which is handled by the browser and does not require any expertise on the part of the user. The browser relies on a password known only to the user for authenticating the user to the browser / applet. The browser / applet interacts with the server to create an authentication key which is then stored on the user's computer. The user can invoke the authentication key dependent on the user's presentation to the browser / applet of the password. Since the password is not used outside the user-browser / applet interaction it is not subject to attacks by hackers. The authentication key is also protected from attacks by encryption although the user need not memorize any information other than the password.

Owner:ONESPAN NORTH AMERICA INC

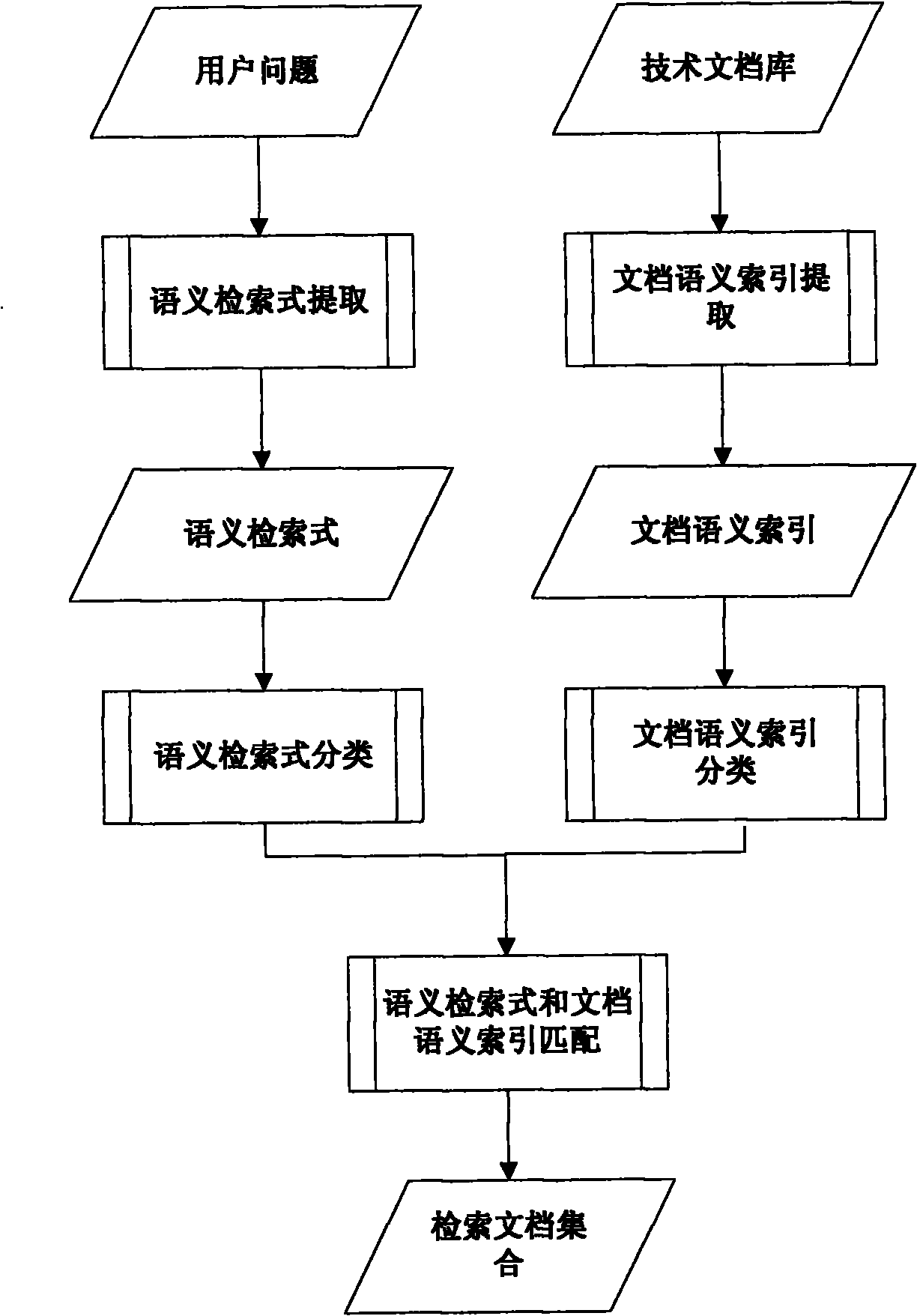

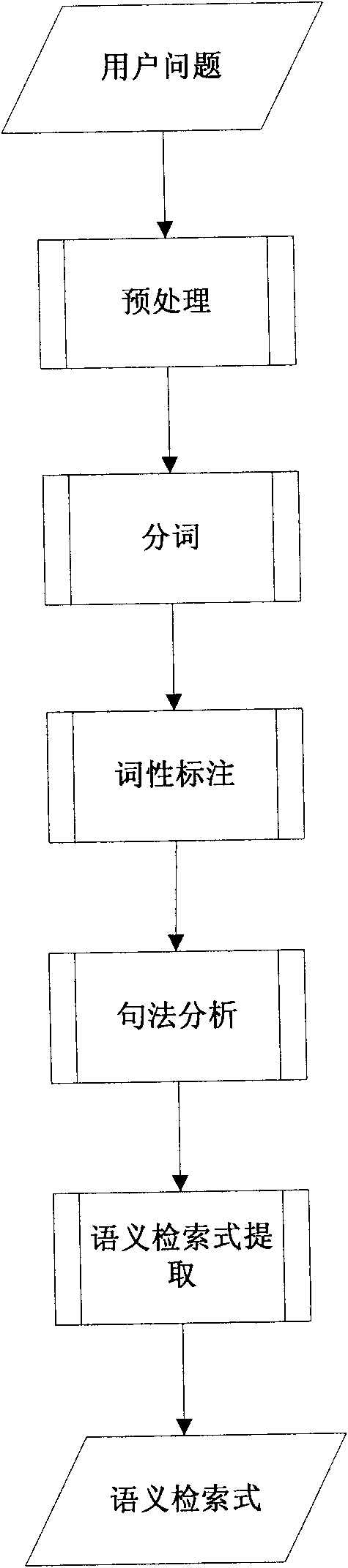

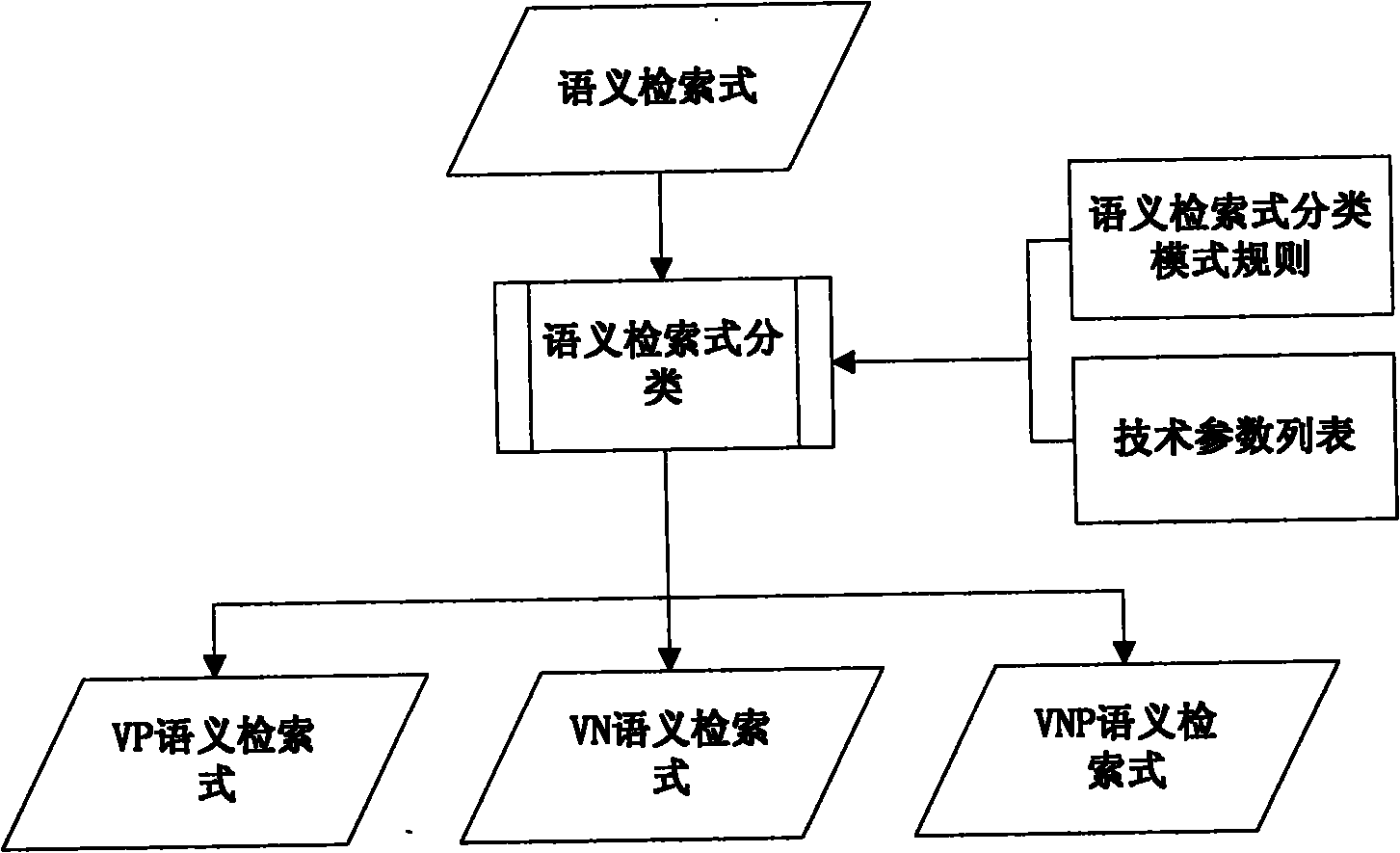

Semantic indexing-based data retrieval method

InactiveCN102117283AImprove effectivenessSpecial data processing applicationsData retrievalAutomatic indexing

The invention provides a semantic indexing-based data retrieval method, which comprises the following steps of: performing semantic analysis on a user question, and extracting the functional description of the user question as a semantic retrieval formula, wherein the functional description is represented by 'action-object'; performing the semantic analysis on a technical document, and extracting the functional description of the technical document as a document semantic index; and matching the semantic retrieval formula with the document semantic index. By the method, the timeliness of technical data and a technical manual in assistance in the maintenance of a technical system is effectively improved, and the document effectively answering the user question can be retrieved with higher quality.

Owner:PERA

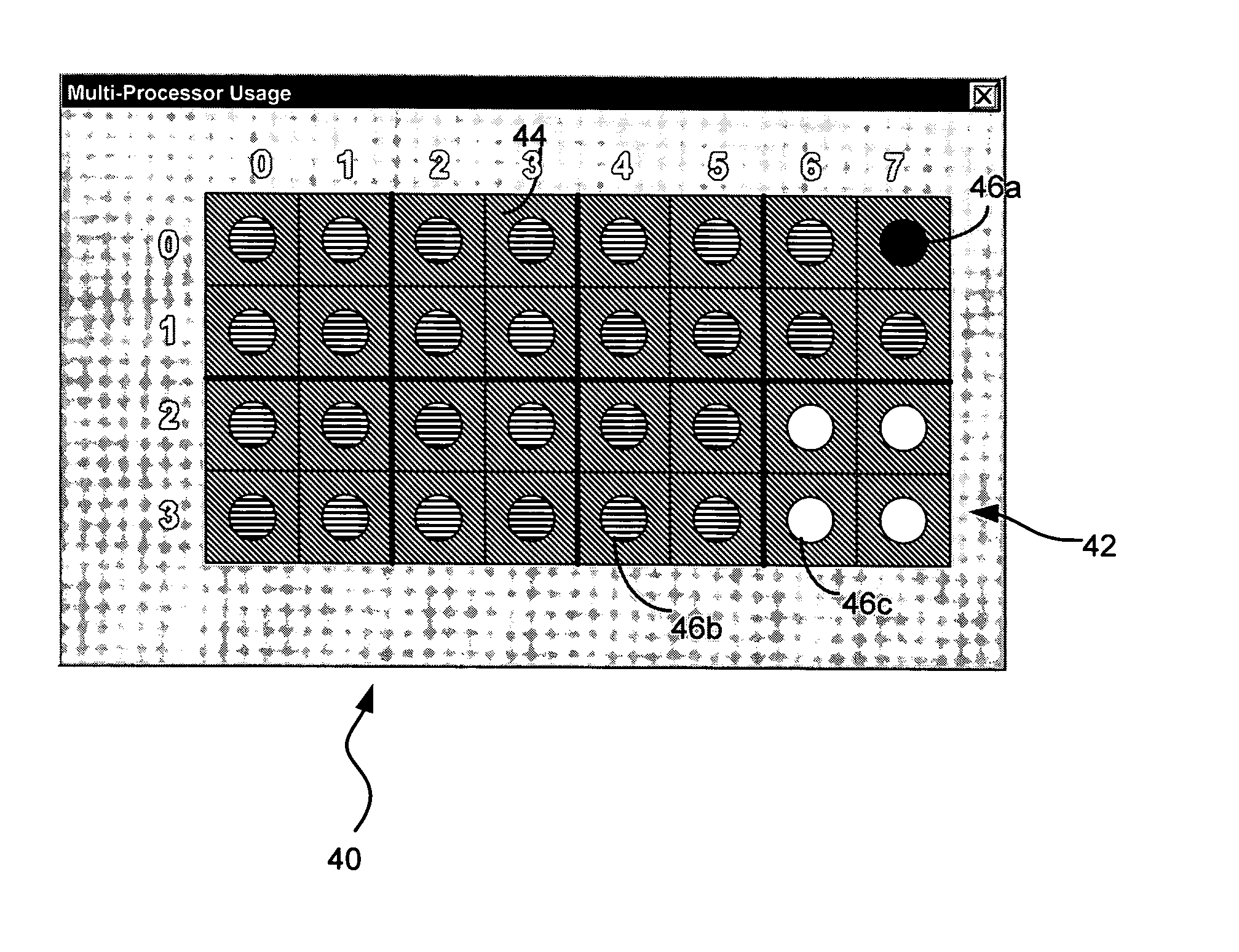

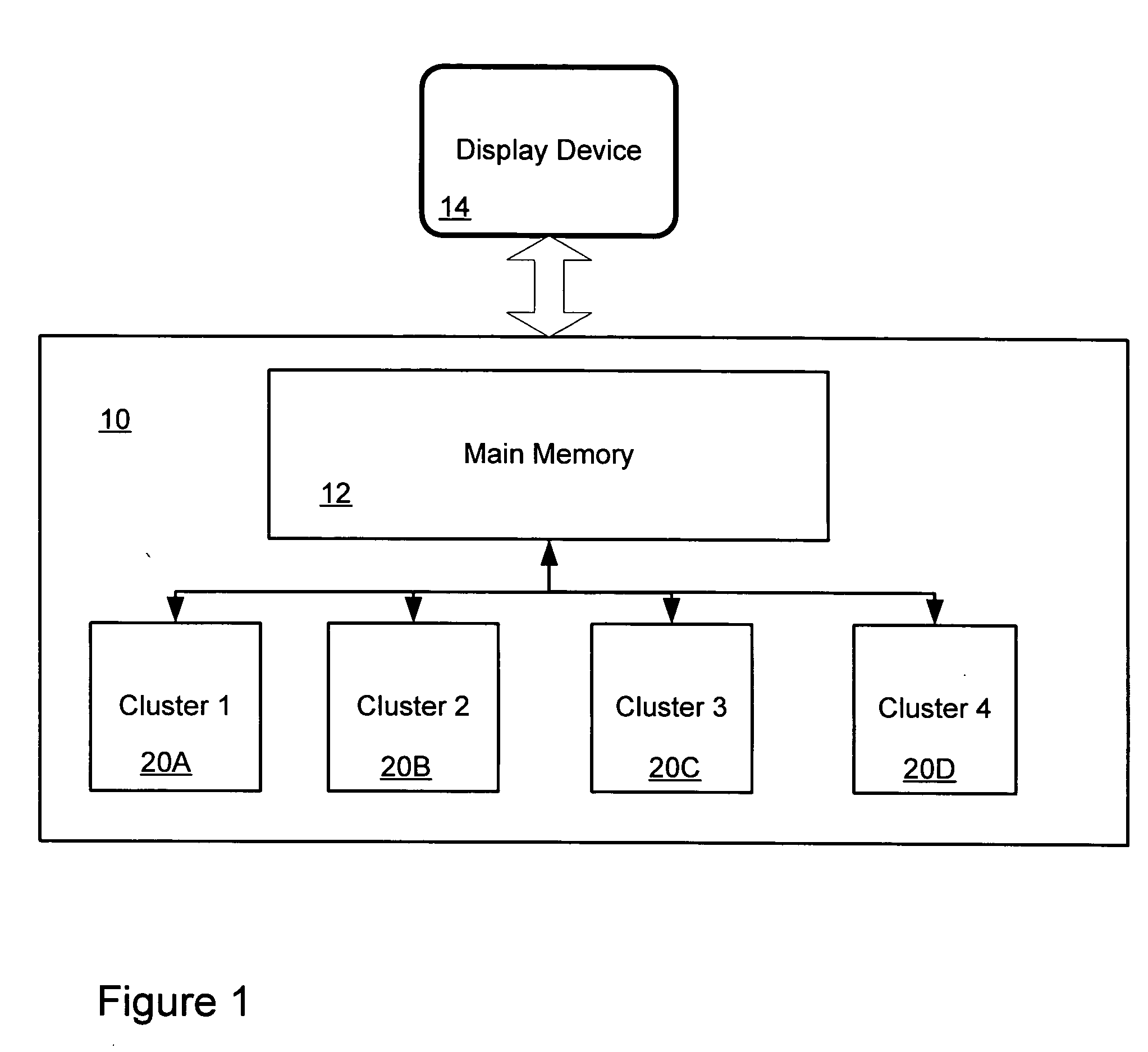

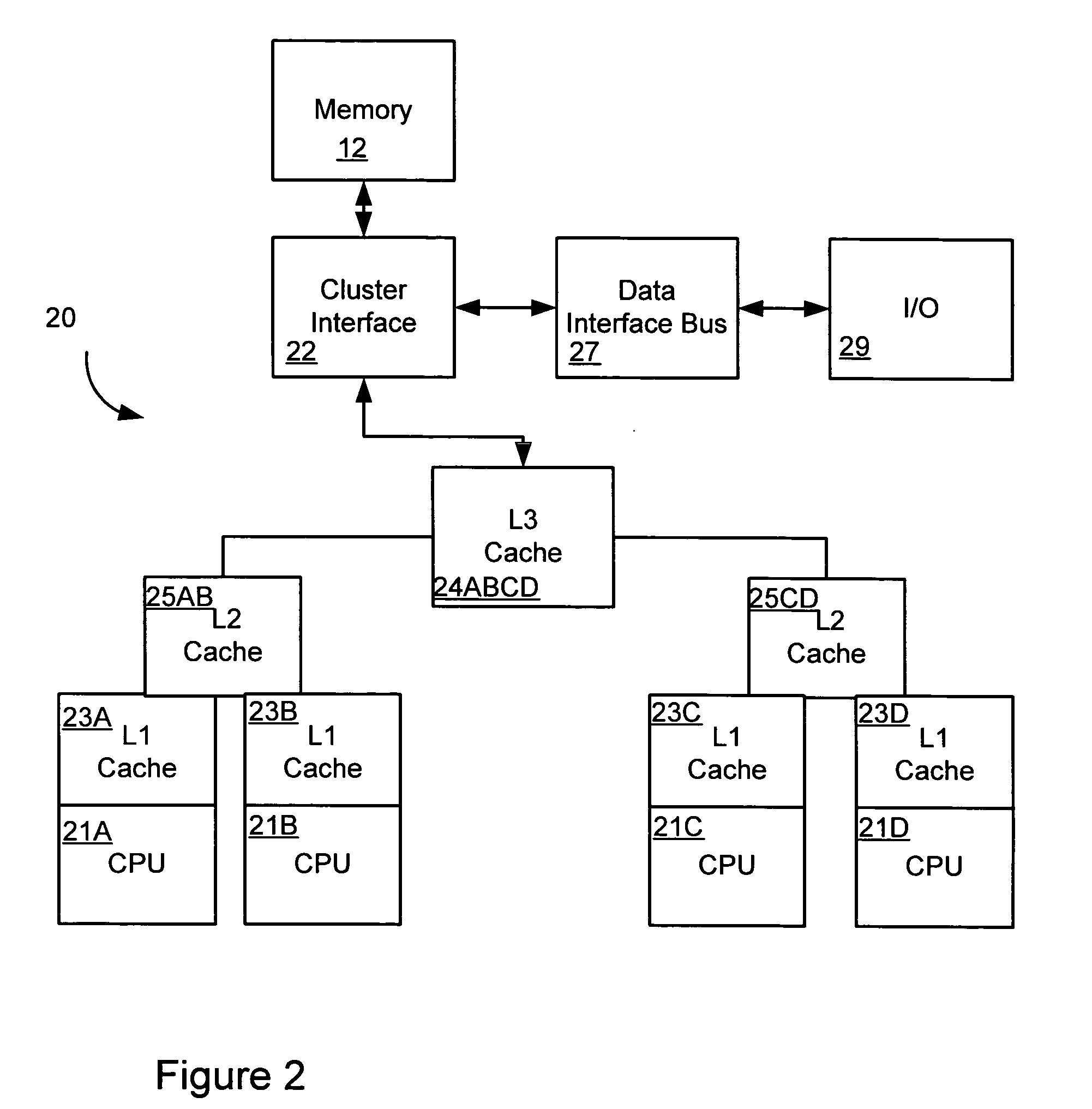

Systems and methods for displaying individual processor usage in a multiprocessor system

A display of CPU utilization in a multiprocessor system is provided. This feature illustrates processor utilization and application group assignments to CPUs and clusters of CPUs. Various graphic indicator are described that can be used to display processor utilization and indicate processors that have no application group assignments. For example, bar graphs as well as gauge displays can be used to visually convey processor utilization. As a result, a user can visually determine the processor utilization and application group assignments across a multiprocessor system. Additionally, various colors and shadings can be used to visually convey application group assignments.

Owner:UNISYS CORP

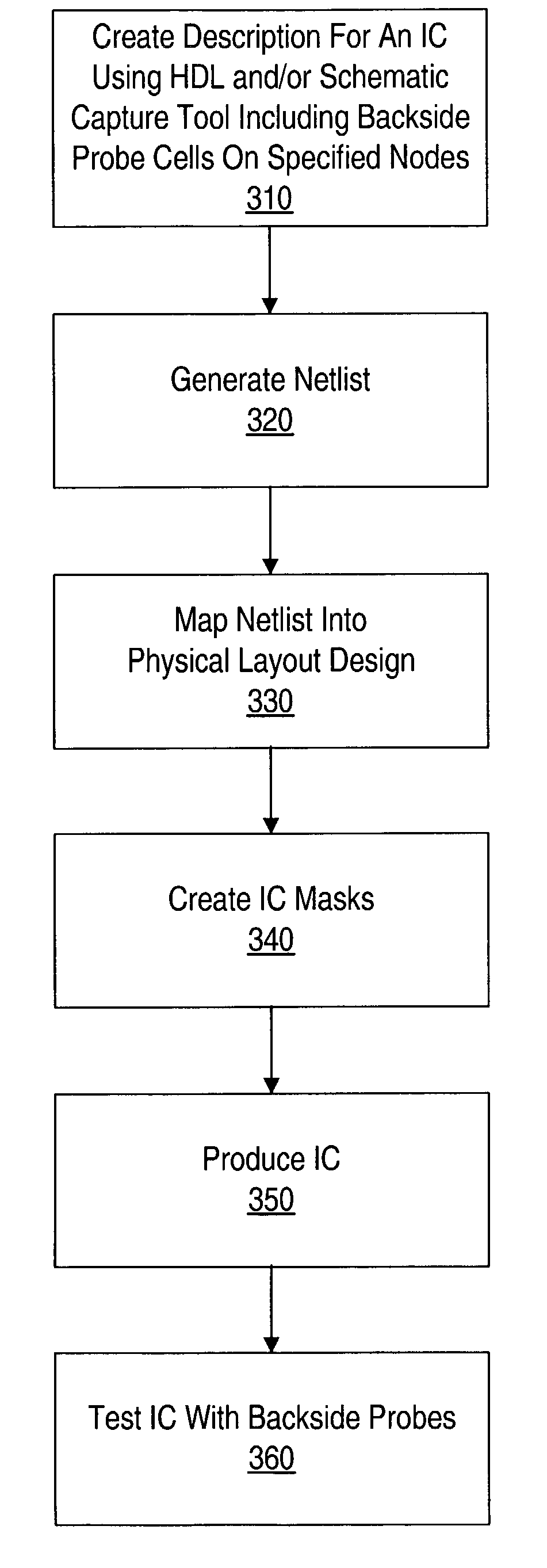

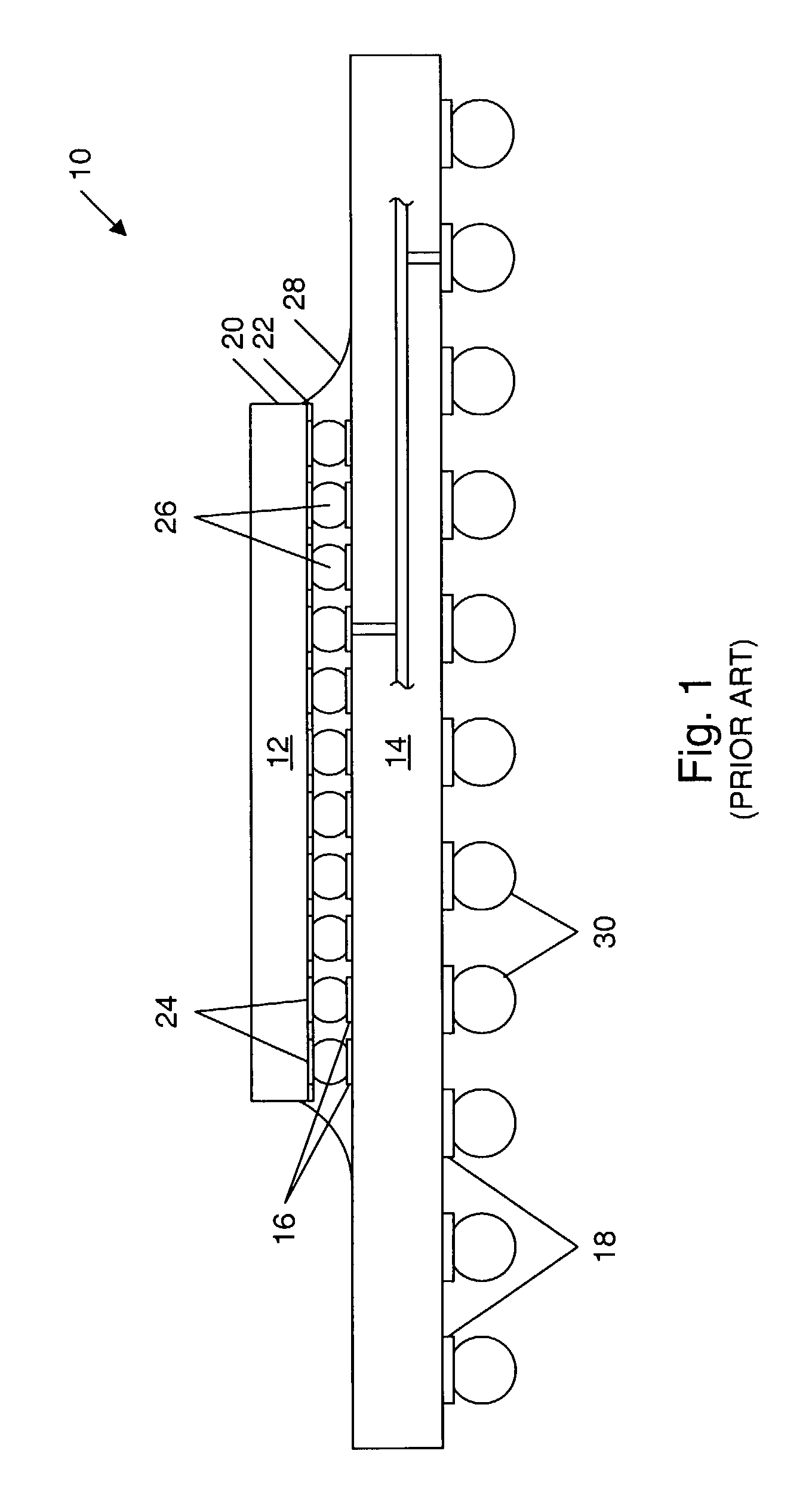

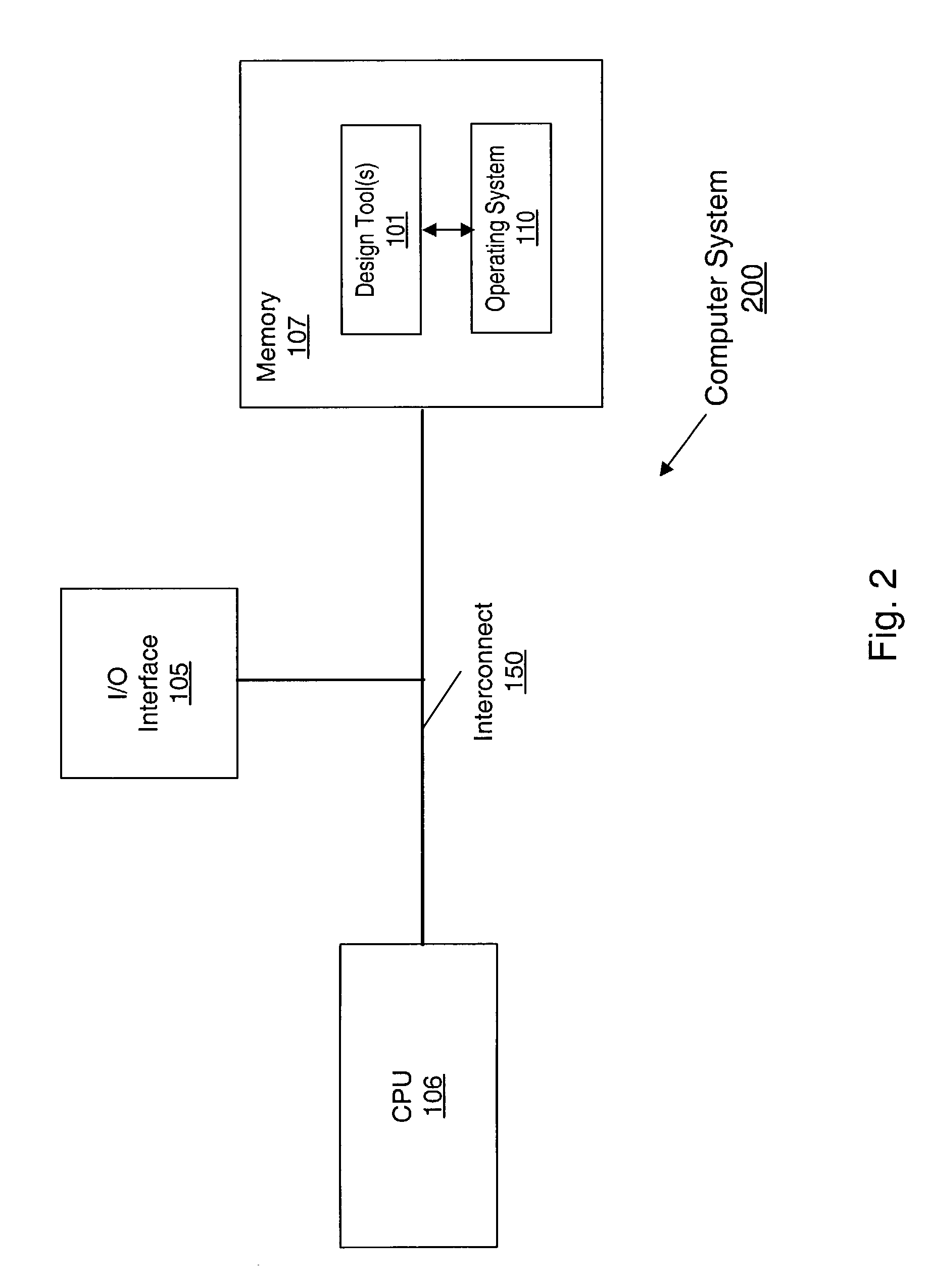

System and method for specifying integrated circuit probe locations

A method for including probe locations in an integrated circuit may include specifying probe cells prior to the place and route stage of the design process. The probe cell locations may be specified in a functional description of the integrated circuit, such as an HDL description from which a netlist may be generated. Alternatively, an existing netlist may be edited to include the probe cells on specified nets. The probe locations are included in the physical layout design along with the rest of the integrated circuit components during place and route. The integrated circuit may be fabricated according to the physical layout design so that the fabricated integrated circuit includes the one or more probe locations.

Owner:GLOBALFOUNDRIES INC

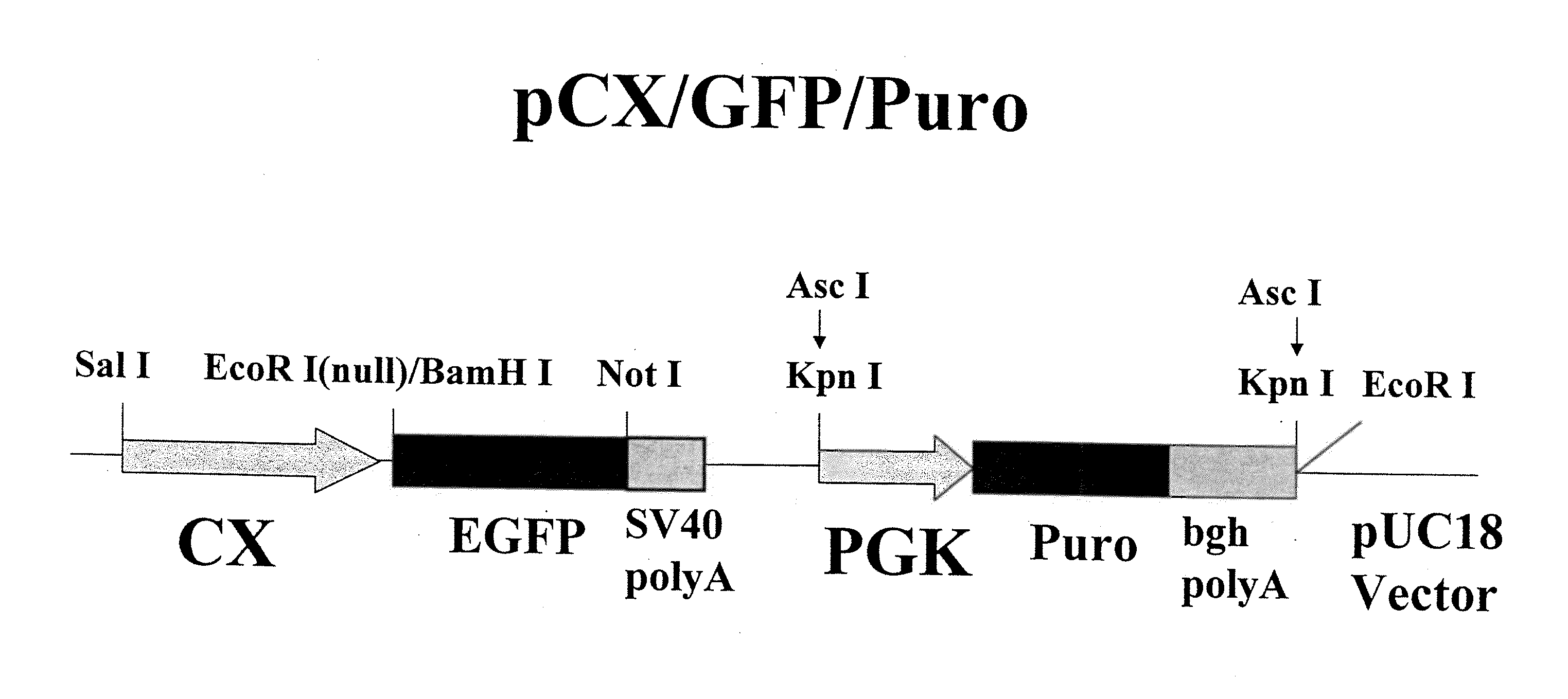

Transgenic Aves Producing Human Polyclonal Antibodies

Owner:SYNAGEVA BIOPHARMA CORP

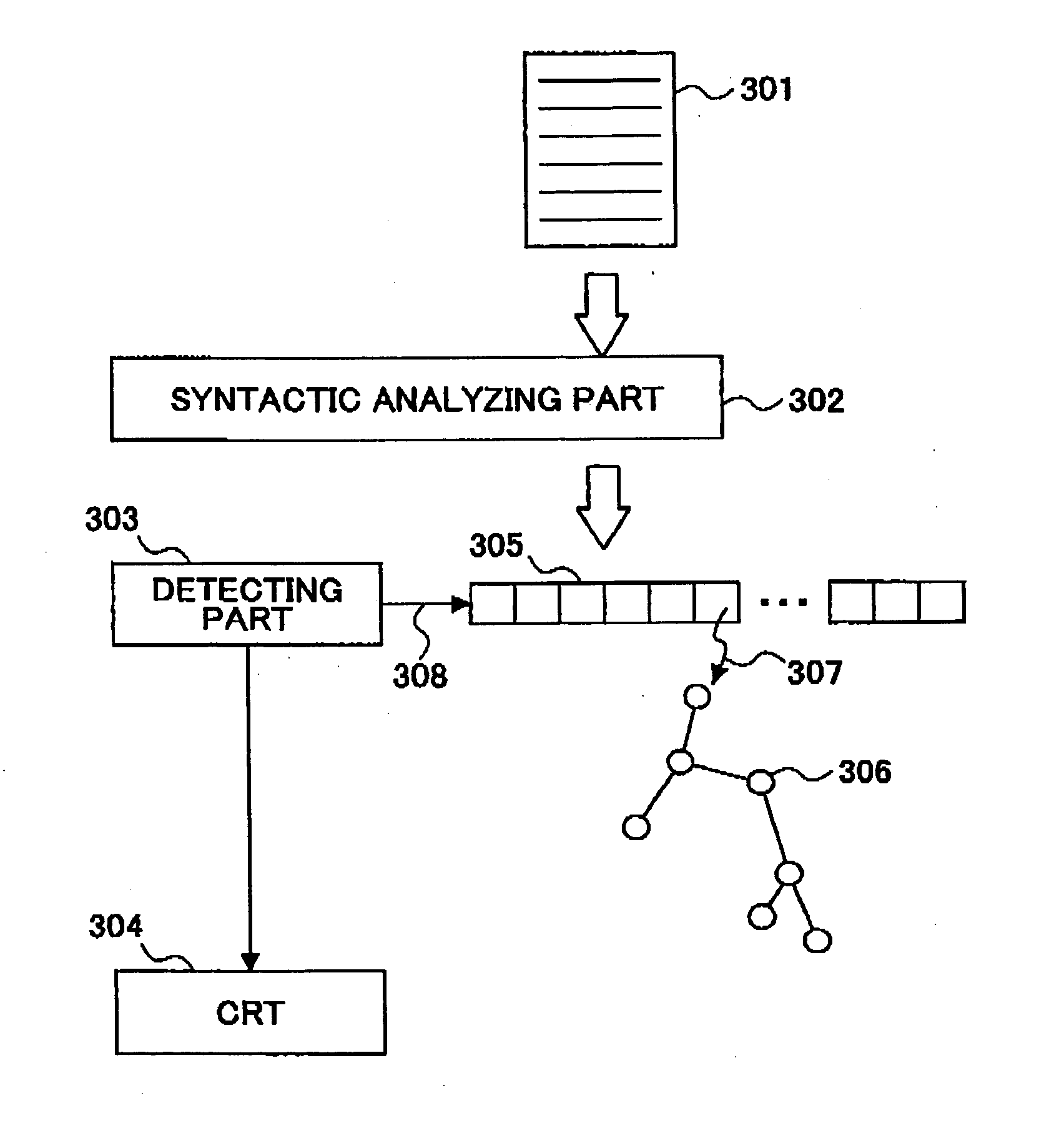

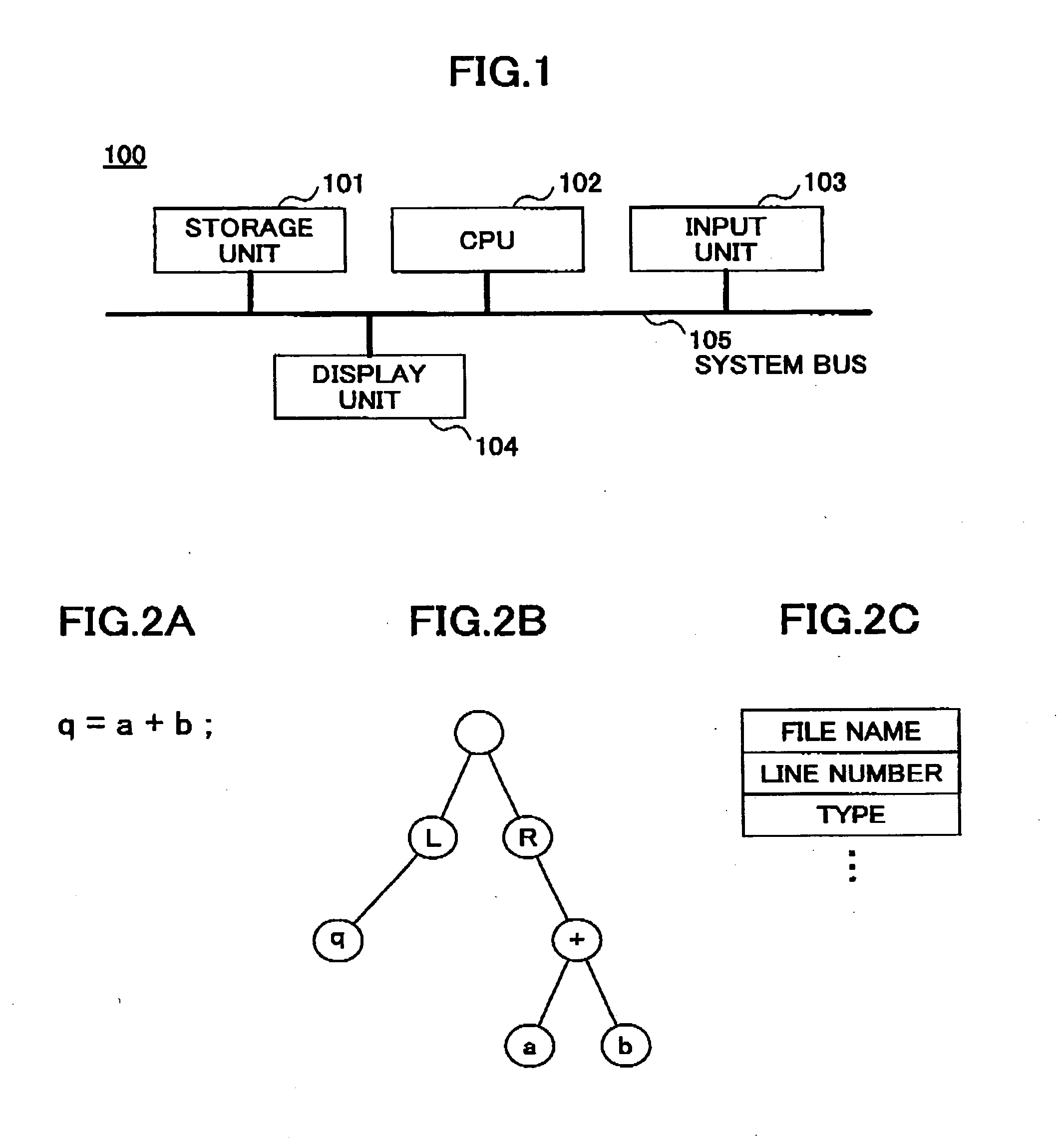

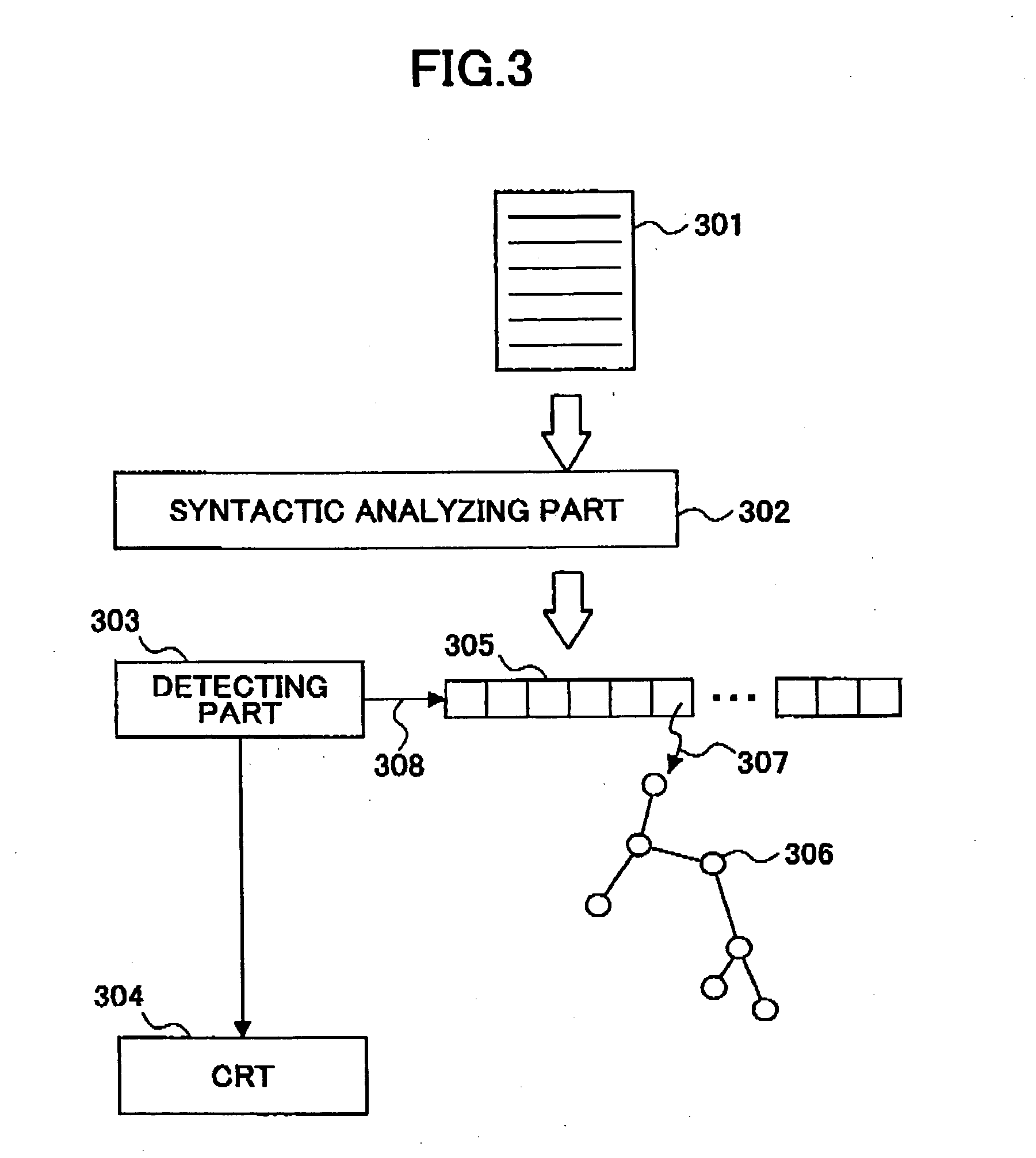

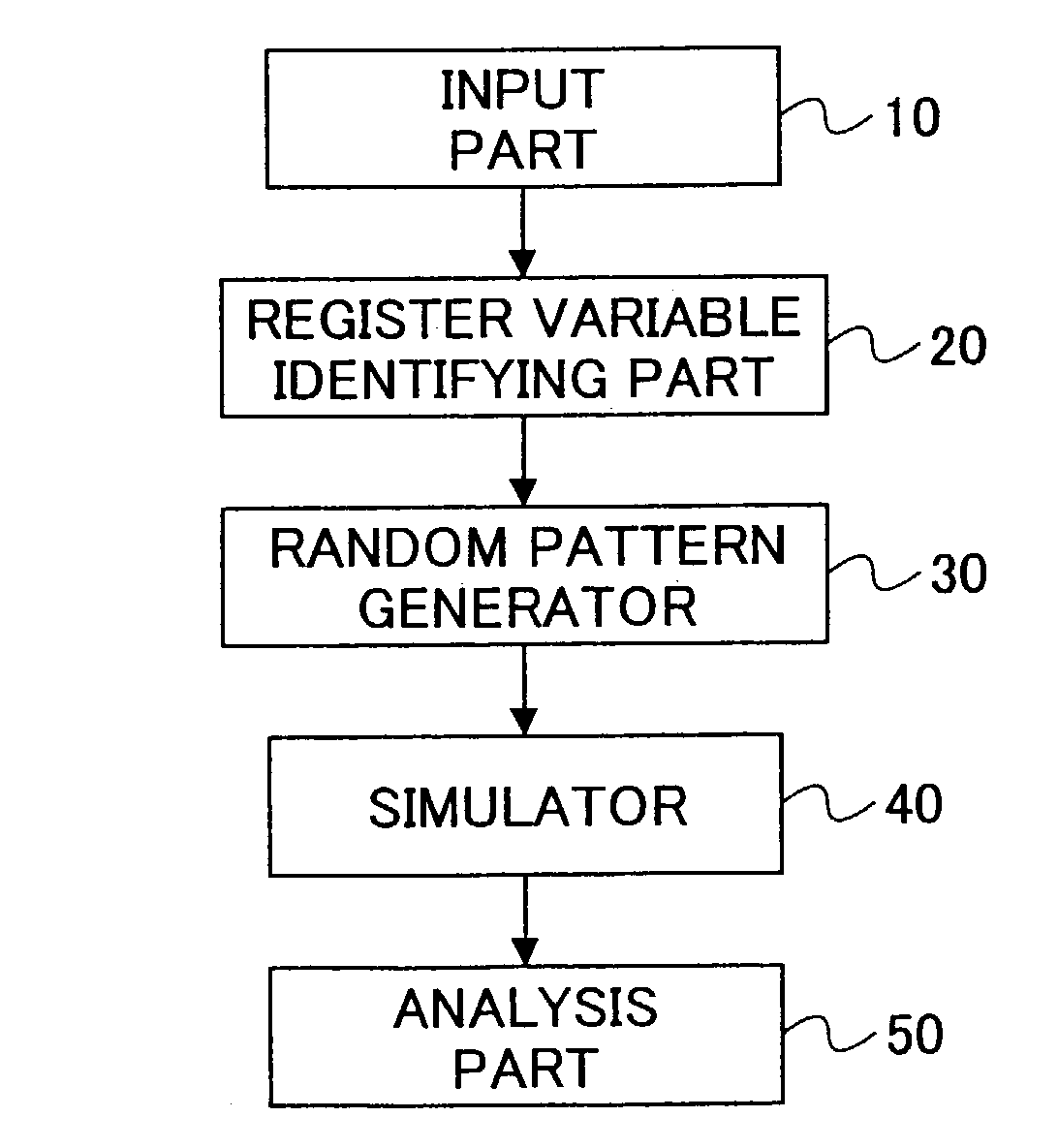

Design supporting apparatus

InactiveUS20050055612A1Improve test qualityEliminate the problemElectronic circuit testingDetecting faulty computer hardwareTheoretical computer scienceLogic built-in self-test

A design supporting apparatus is disclosed, including: an inputting part; a syntactic analyzing part; and a scanning and searching part. The inputting part inputs functional description data of a register transfer level. The syntactic analyzing part conducts a syntactic analysis for the functional description data and develops a parse tree. The scanning and searching part scans and searches for the parse tree being developed by the syntactic analyzing part and searches for a description representing a comparison operator having multiple bits, the comparison operator being difficult to detect a fault by test data formed by pseudo-random numbers, which are applied from a pseudo-random number generator of a logic built-in self-test.

Owner:RICOH KK

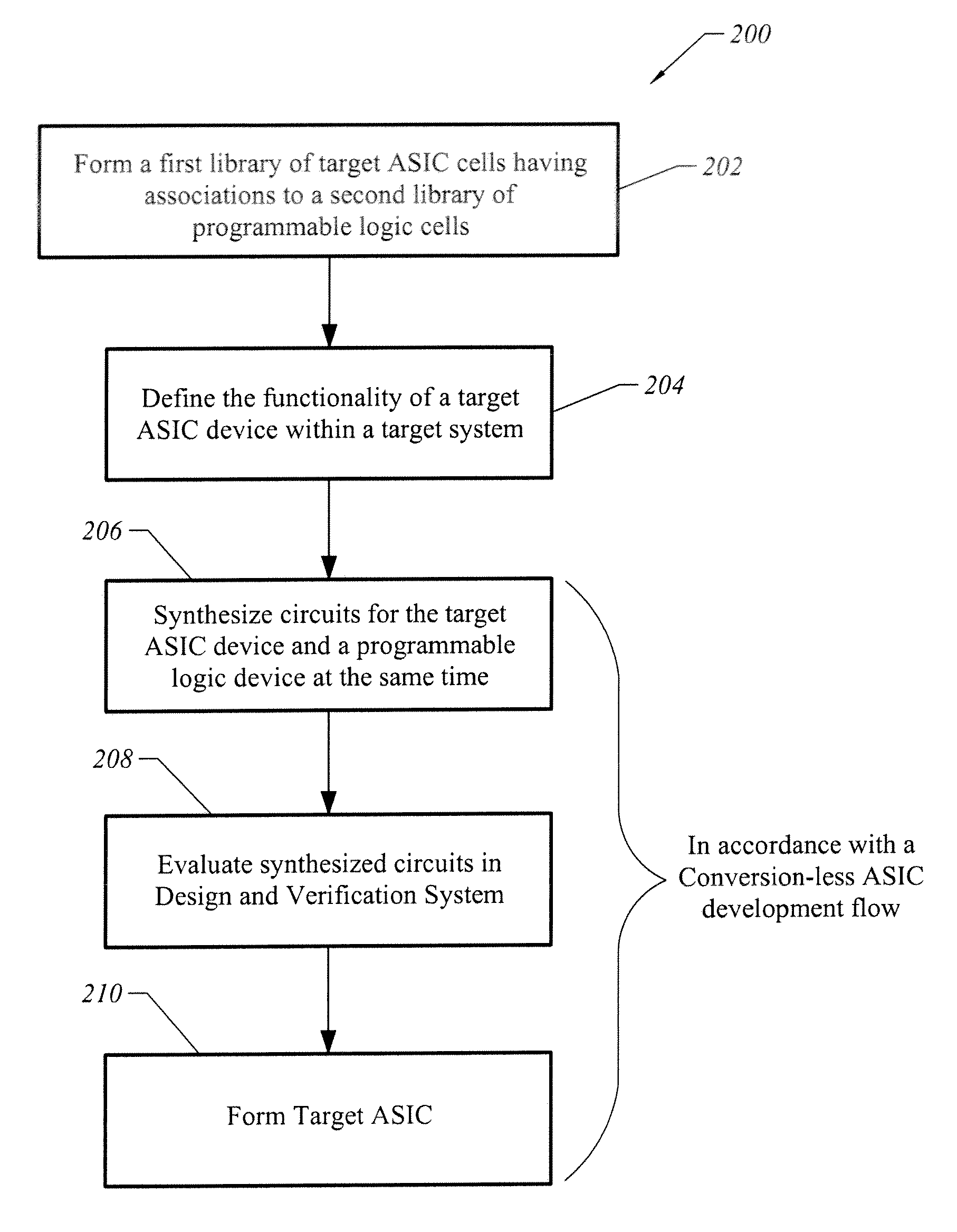

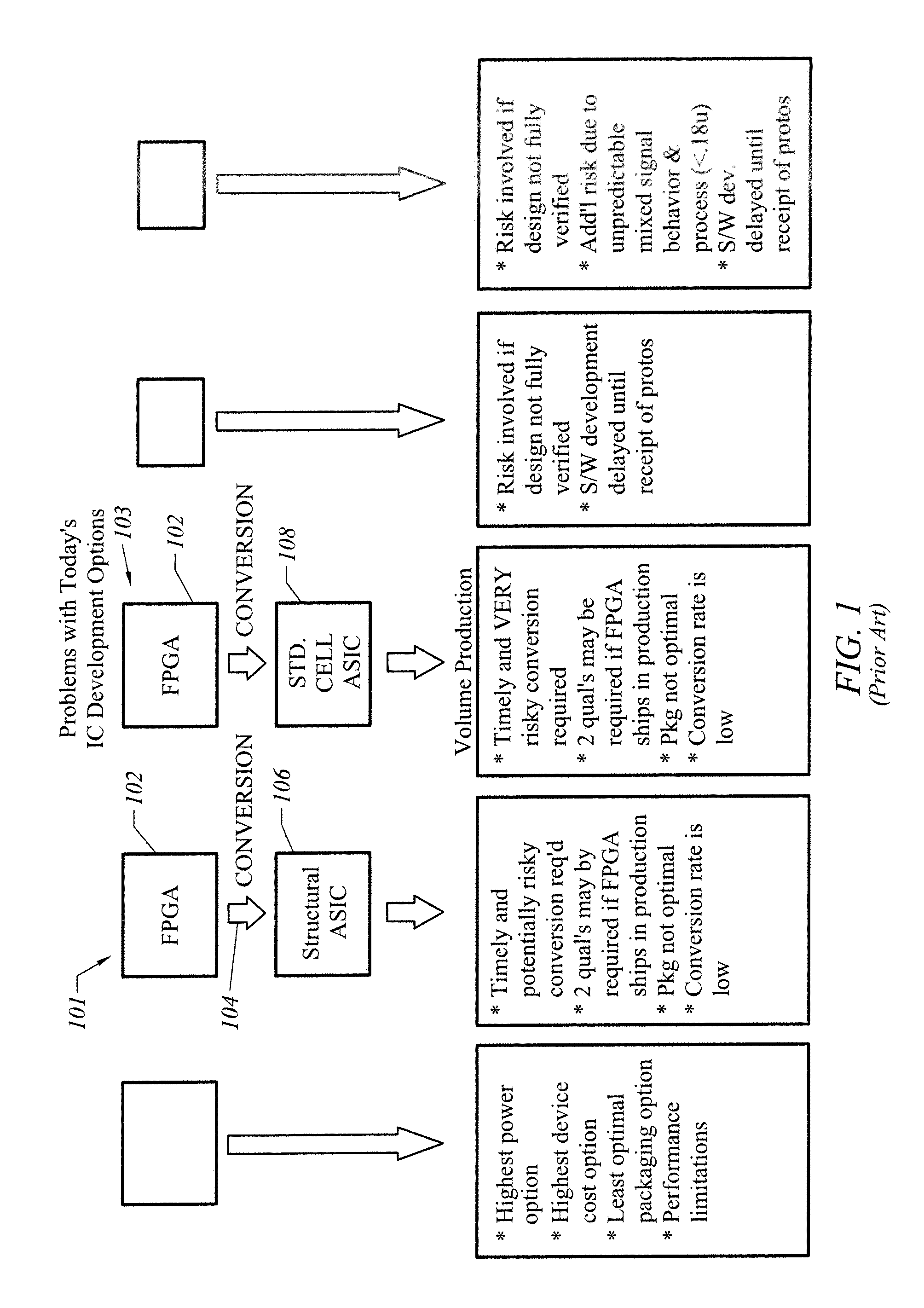

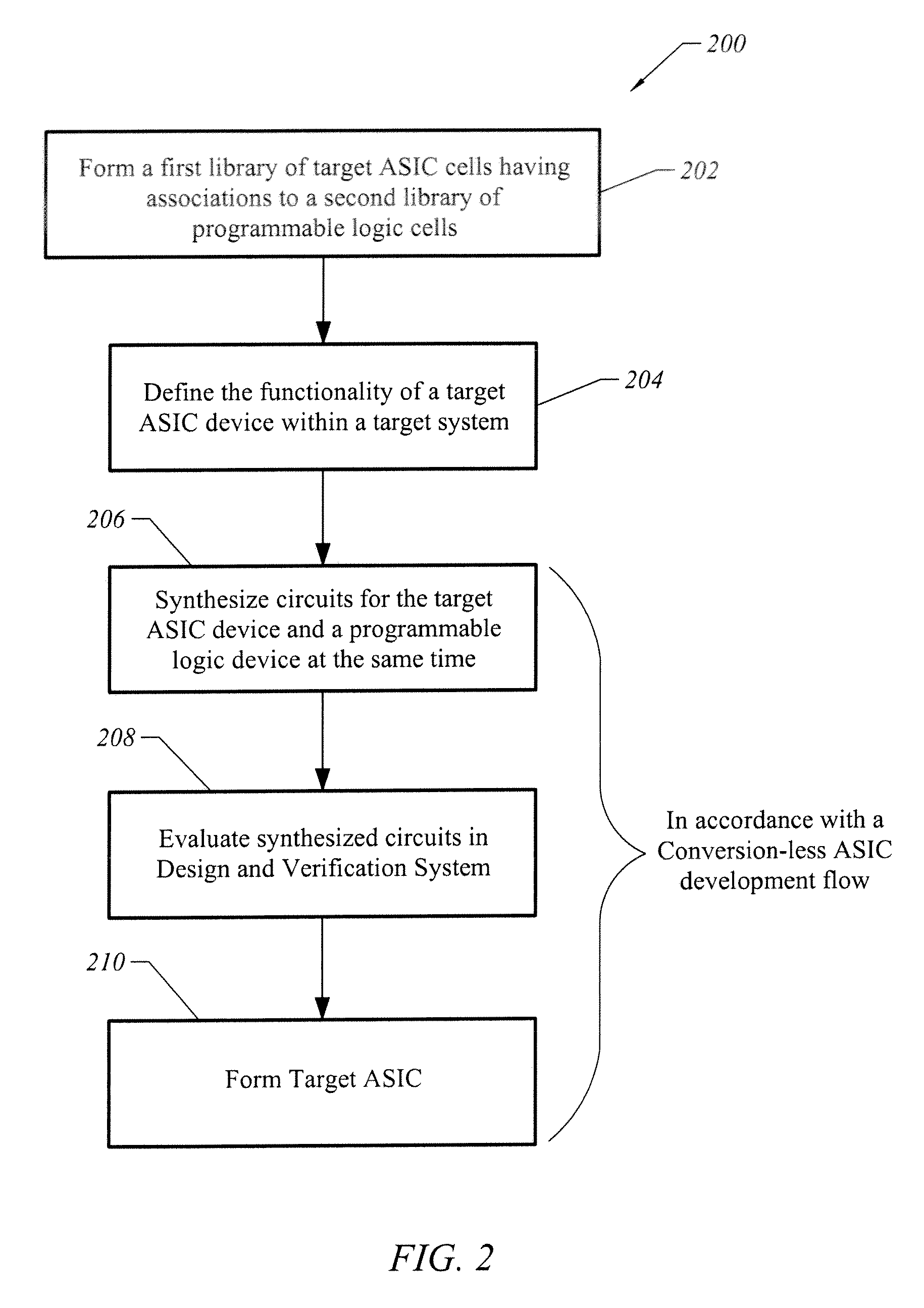

Method of developing application-specific integrated circuit devices

InactiveUS7500215B1Shorten the timeCAD circuit designProgram controlProgrammable logic deviceApplication-specific integrated circuit

A method, computer readable medium apparatus and system for developing an Application-Specific Integrated Circuit (“ASIC”) are disclosed. In one embodiment, a method includes defining the functionality of a target ASIC device within a target system, as well as synthesizing circuits for the target ASIC device and a programmable logic device concurrently or nearly concurrently, thereby providing a conversion-less ASIC development flow using one or more programmable devices. In a specific embodiment, the conversion-less ASIC development flow requires no subsequent step of modifying a functional description for the target ASIC device from a functional description expressed in terms of the programmable logic device, thereby reducing an amount of time required to produce the target ASIC device.

Owner:SILICON VALLEY BANK

Dynamic threat event management system and method

InactiveUS9167000B2Improve performanceImprove securityMemory loss protectionError detection/correctionPersonal computerManagement system

According to various illustrative embodiments of the present invention, a method for a content-driven threat management system includes creating a threat detection primary object with threat mitigation data using at least one researcher of at least one of software and malicious code, encoding the threat detection primary object with threat mitigation data within an object capable of being transmitted to a personal computer system using a transmission vector update function, and transmitting the threat detection primary object with threat mitigation data to a threat agent using the transmission vector update function. The method also includes updating at least one threat function using the threat agent to update at least one threat functional description of the at least one threat function to include the threat detection primary object with threat mitigation data, and using the threat detection primary object with threat mitigation data to be capable of recognizing at least one threat event based upon the threat detection primary object with threat mitigation data.

Owner:CA TECH INC

System and method for improving testability independent of architecture

InactiveUS7103859B2Eliminate the problemImprove testabilityCorrect operation testingElectronic circuit testingFault coverageProcessor register

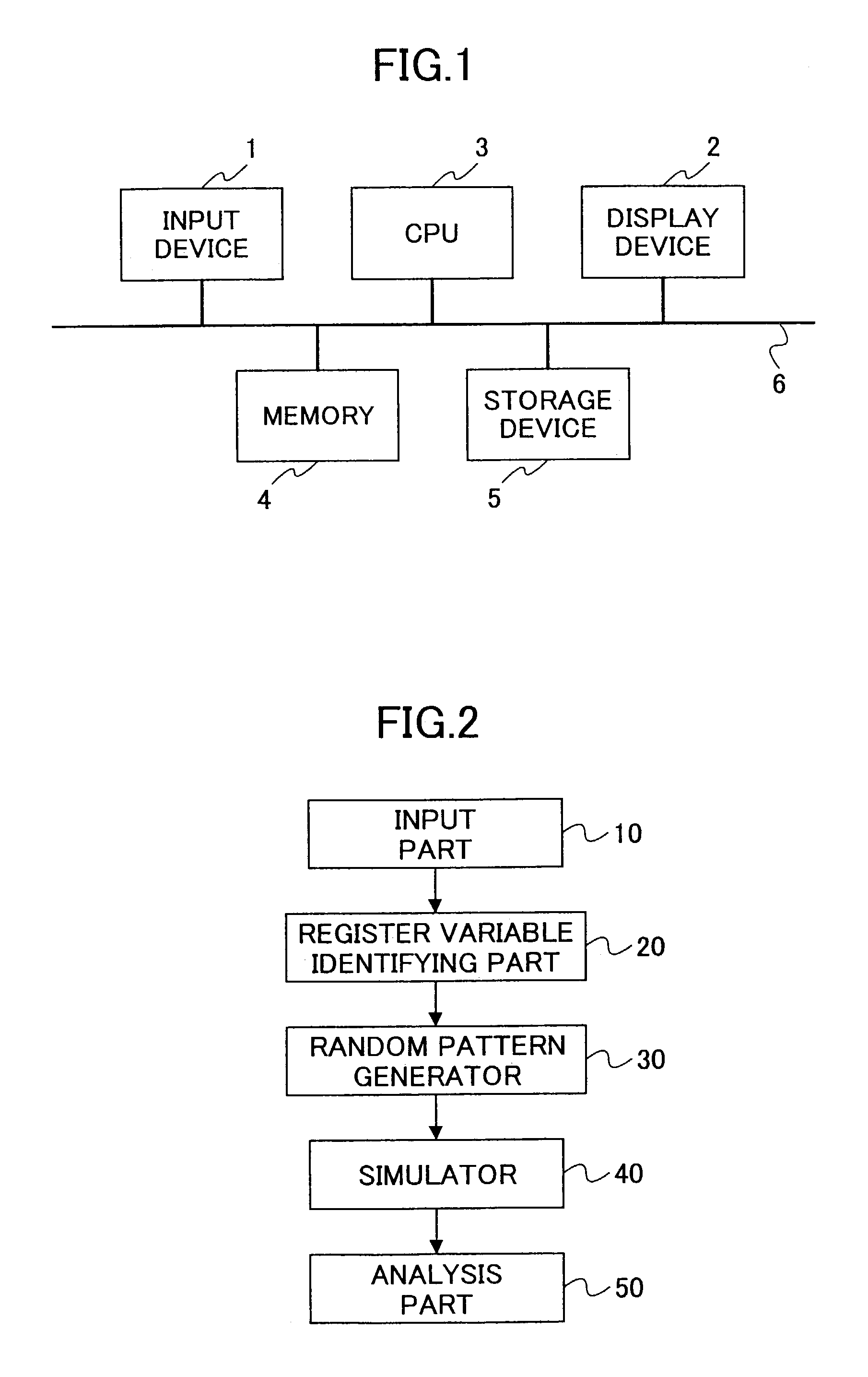

A testability analysis system analyzes testability by evaluating controllability and observability at the level of a hardware functional description independent of architecture. The testability analysis system comprises: an input part inputting functional description data to define a hardware function; a register variable identifying part identifying register variables whereby memory elements such as a flip-flop in said functional description data are inferred; a random pattern generator applying random patterns to the register variable identified by said register variable identifying part; a simulator conducting a simulation on an event caused by applying the random patterns; and an analysis part analyzing a cause of decrease of a fault coverage by LogicBIST, which is mainly caused by the difficulty of detecting faults by the random pattern test that PRPG (Pseudo Random Pattern Generator) of the Scan-Based LogicBIST executes, based upon toggle rates and simulation events of variables (such as net and bus) in said functional description data in accordance with a result of said simulation.

Owner:RICOH KK

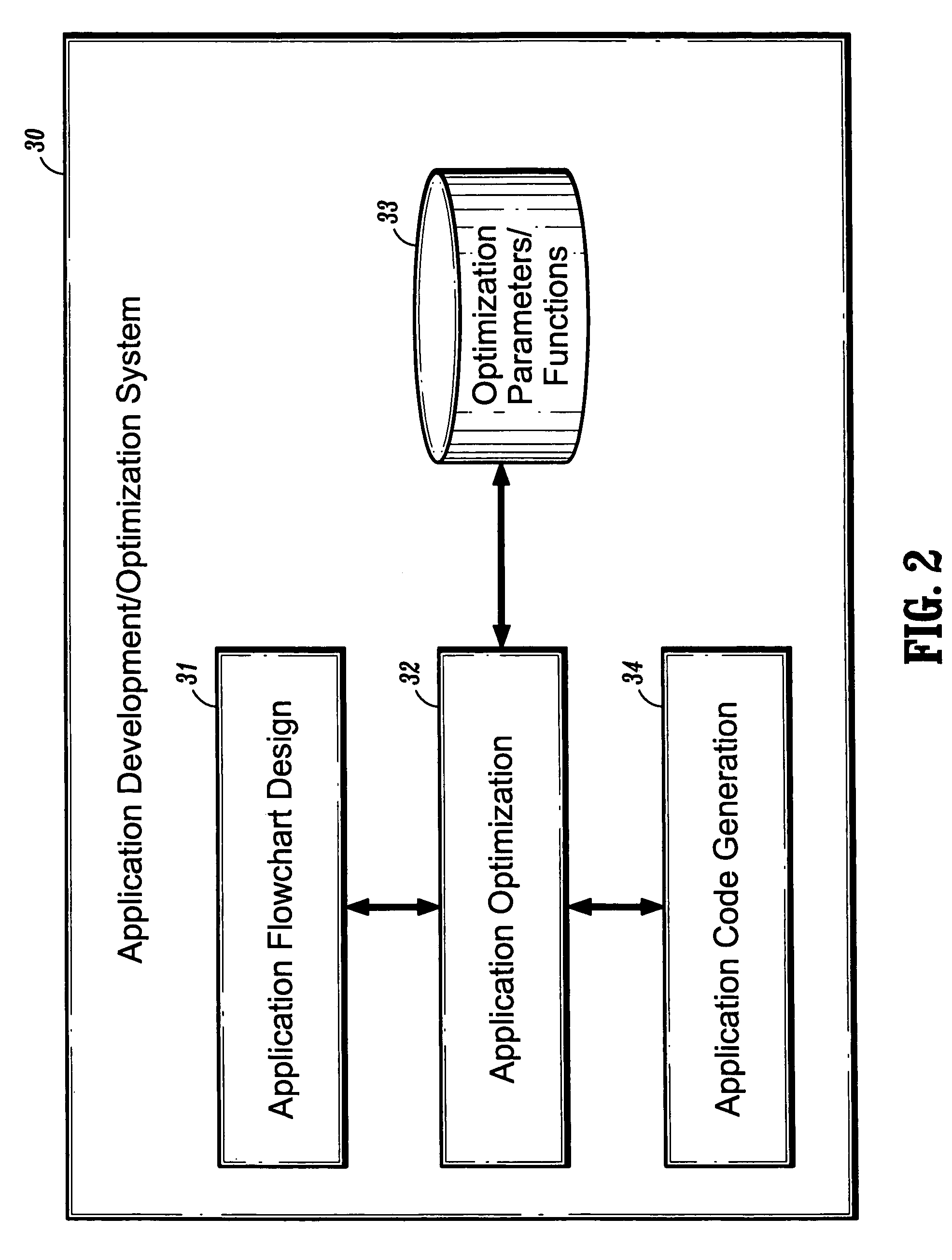

Systems and methods for generating applications that are automatically optimized for network performance

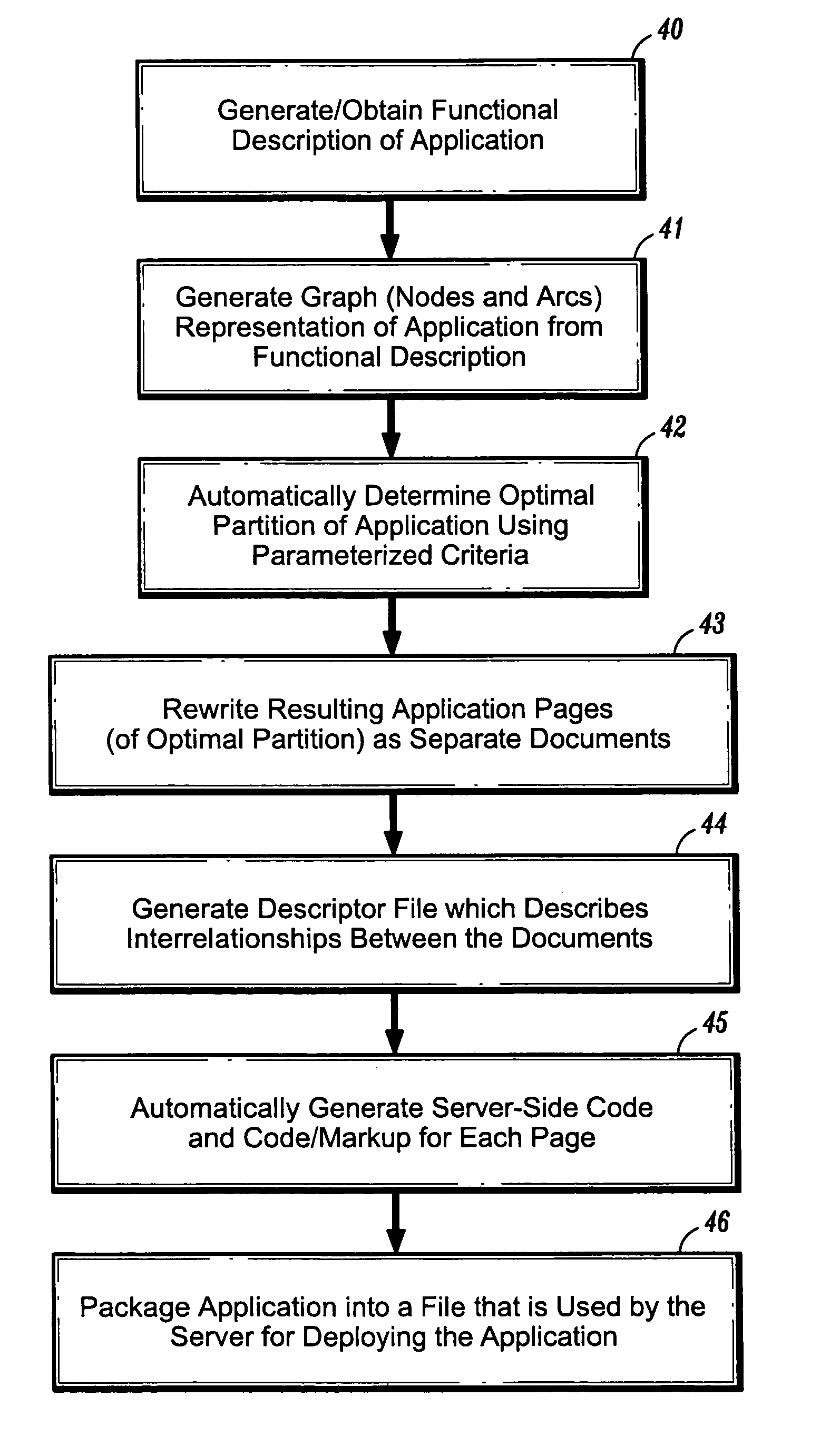

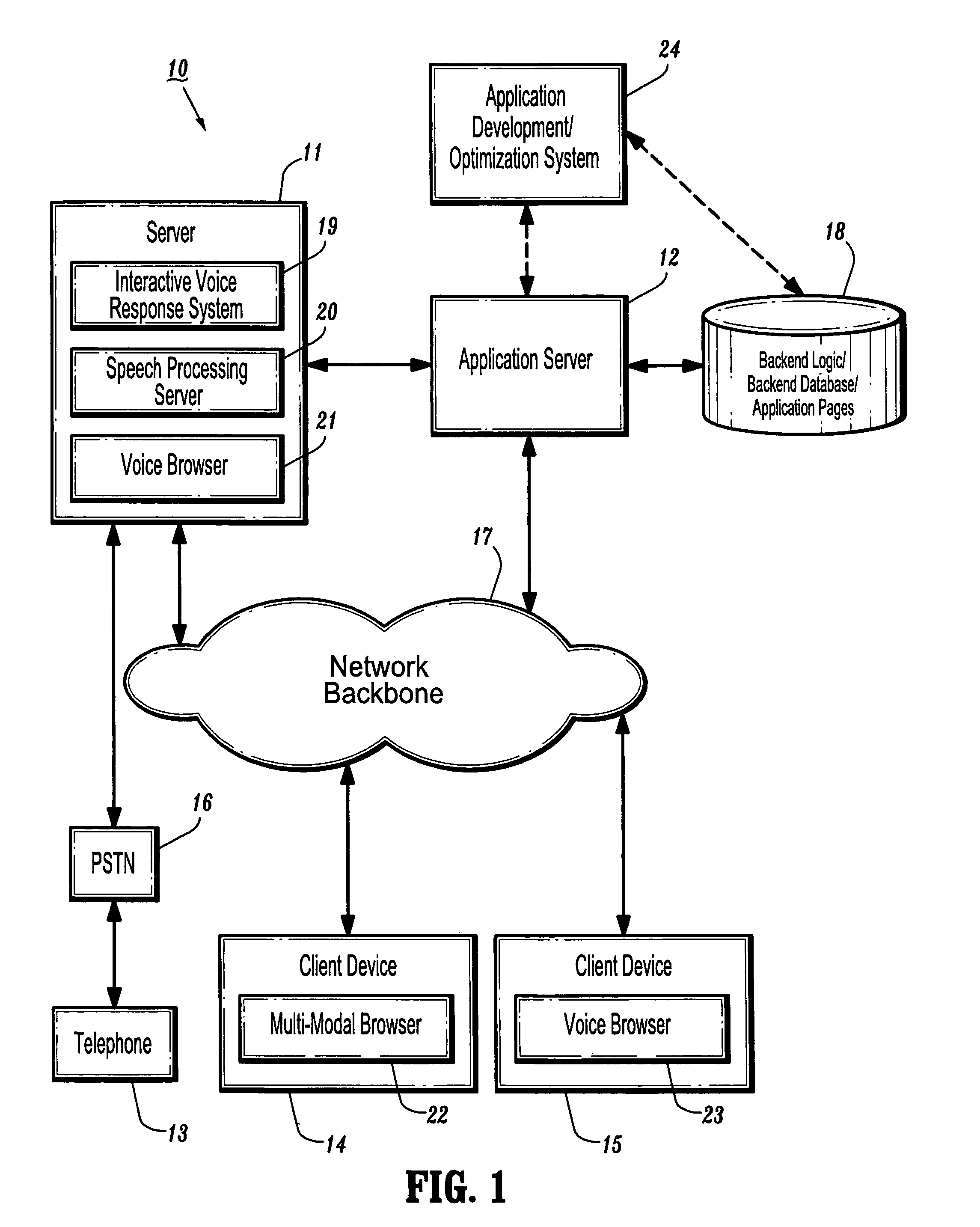

ActiveUS7437707B2Improve performanceDelay minimizationMultiple digital computer combinationsSoftware designApplication softwareApplication module

Owner:GOOGLE LLC

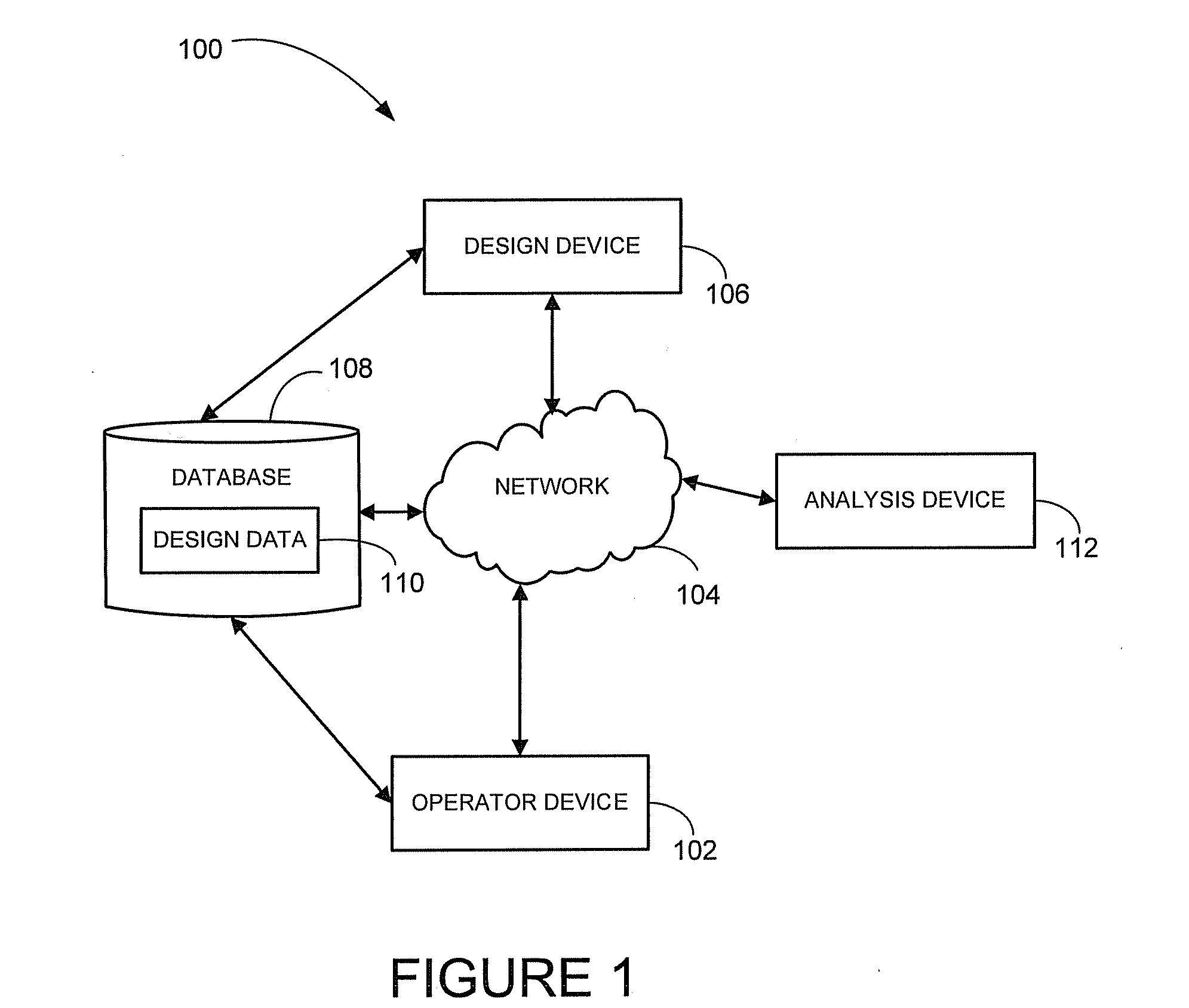

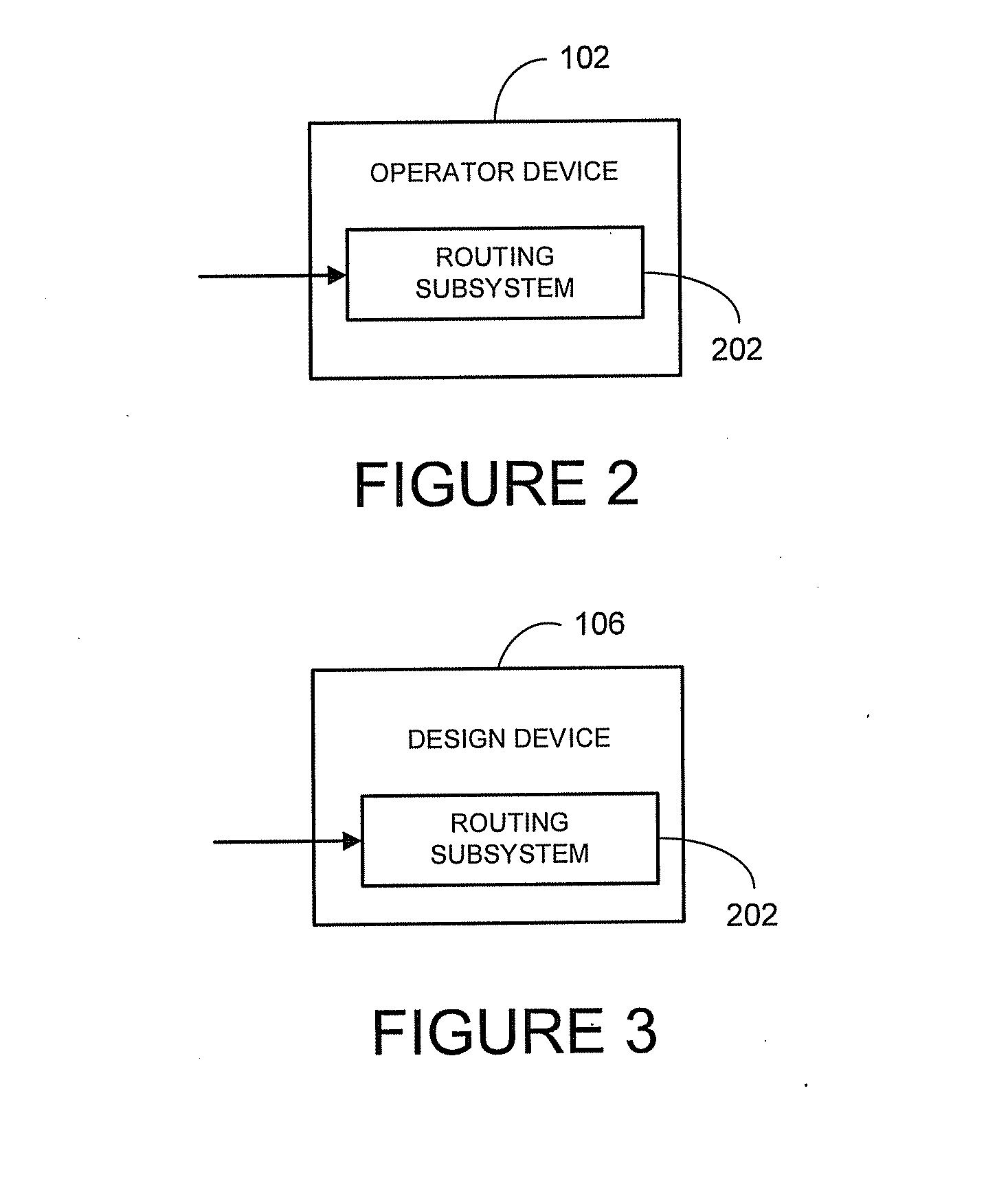

Methods and systems for flexible and repeatable pre-route generation

ActiveUS20120110537A1Computer aided designSpecial data processing applicationsComputer architectureFeature description

Methods and systems for flexible and repeatable pre-route generation are described. In one embodiment, a routing selection is received. The routing selection is for a path between at least a first cell and a second cell. The first and second cell are associated with a functional description of an integrated circuit. A floorplan associated with the functional description is modified to create a modified floorplan. The modified floorplan has a physical design change relative to the floorplan. A pre-route is automatically generated based on receipt of the routing selection and the modified floorplan. The pre-route is added to a physical design of the chip to create a pre-routed physical design. Additional methods and systems are disclosed.

Owner:ORACLE INT CORP

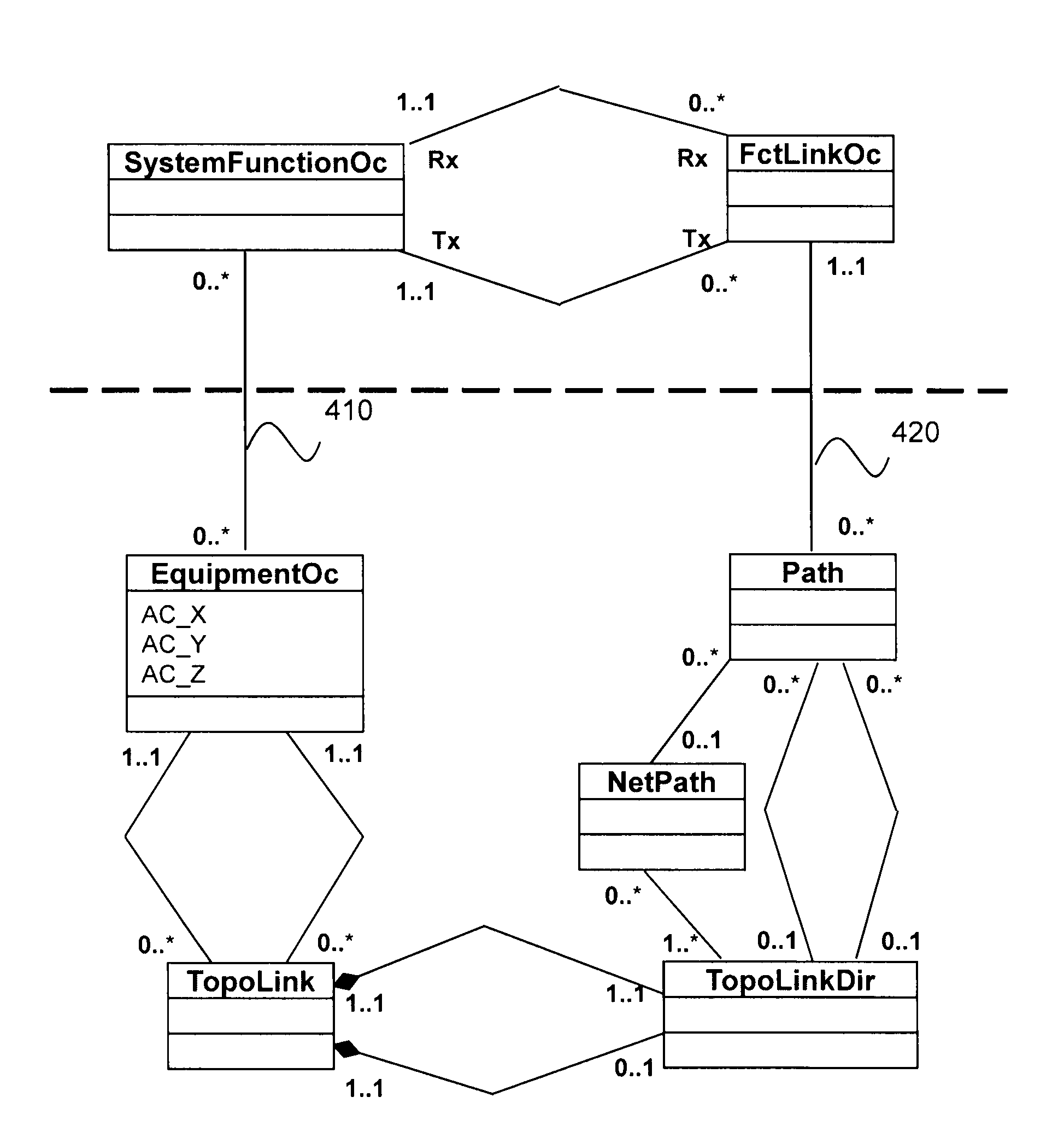

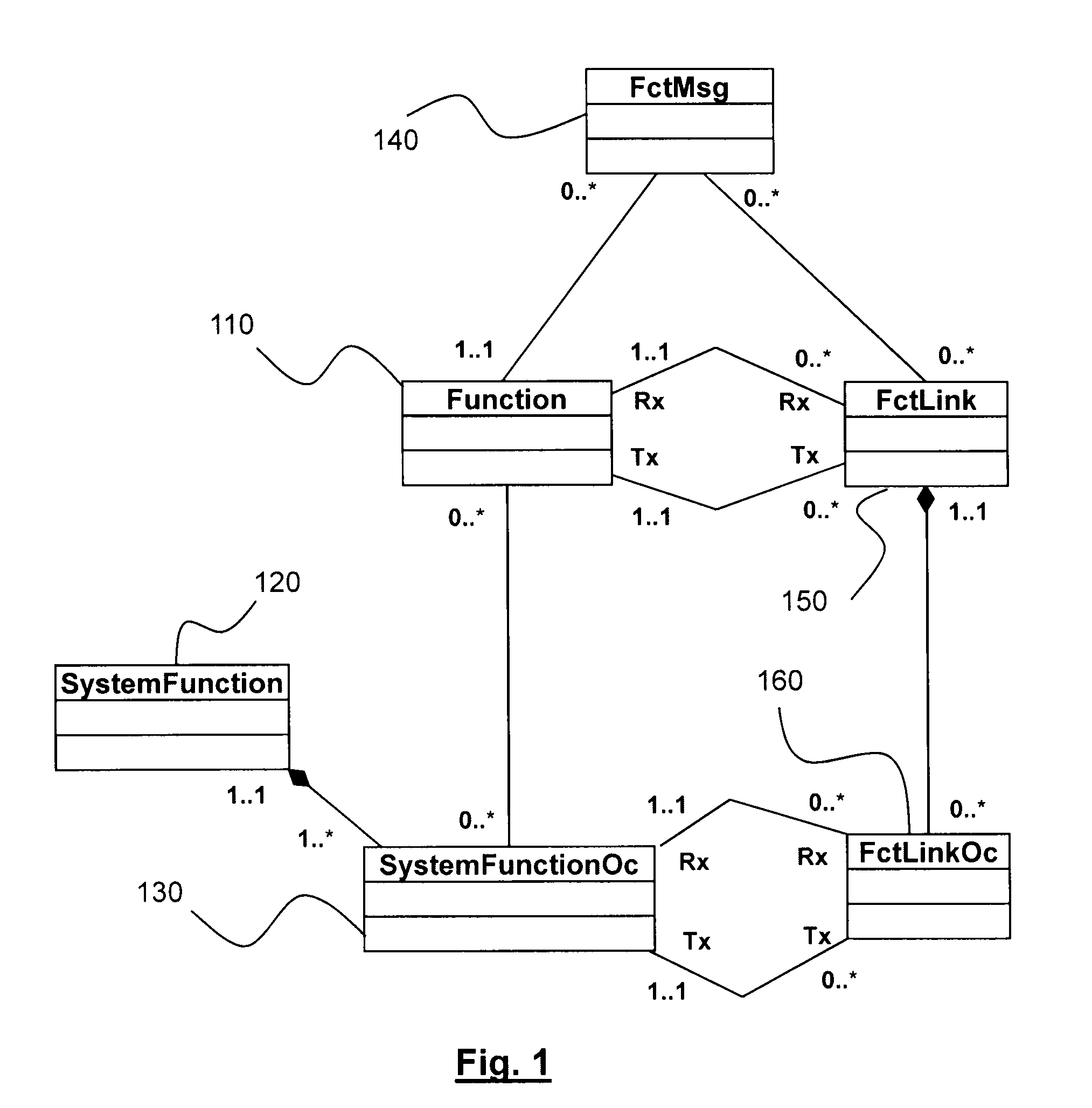

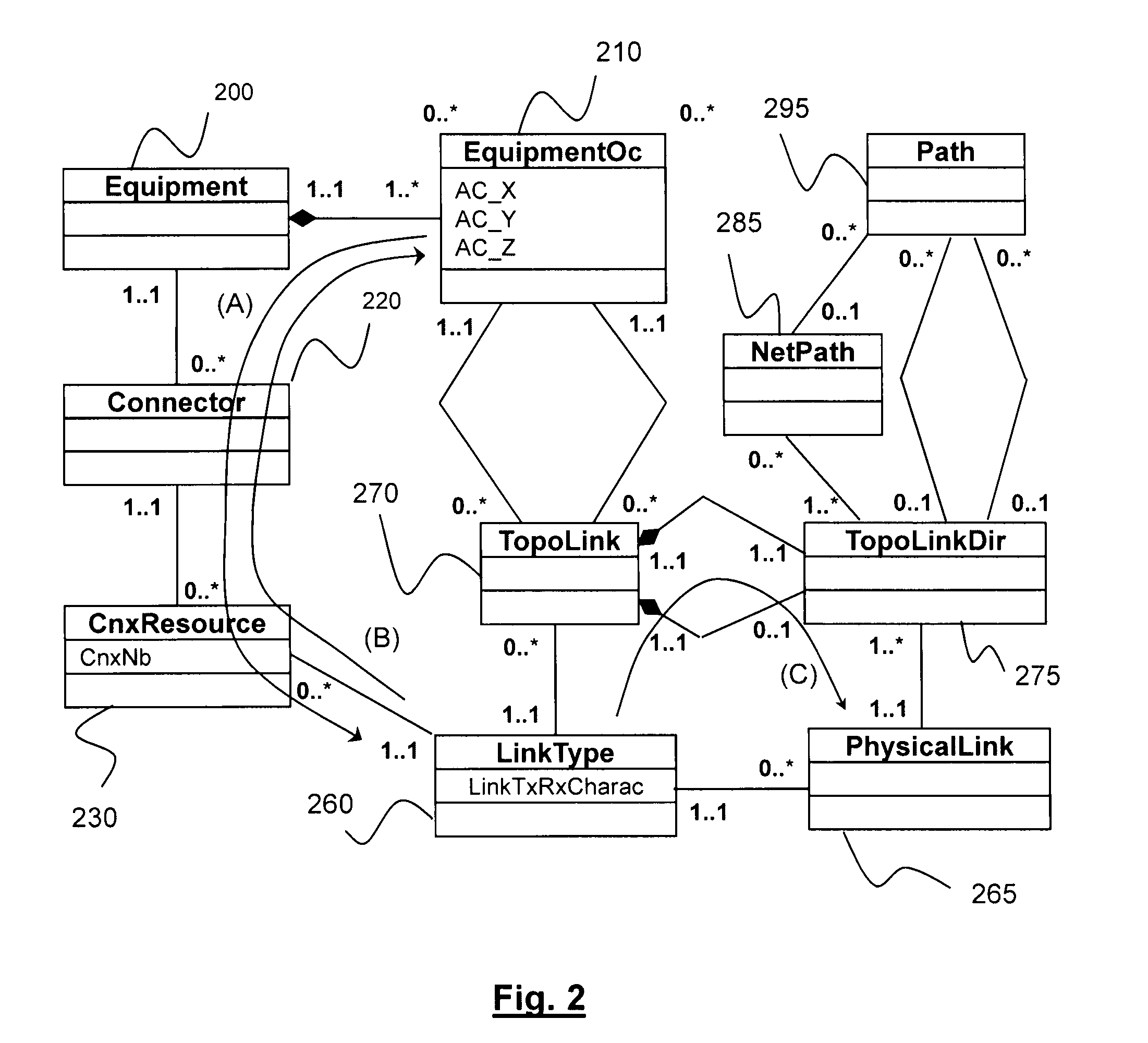

Method for assistance with the construction and validation of an avionics platform

InactiveUS20100292979A1Geometric CADAnalogue computers for electric apparatusAviationMaterial Description

The invention concerns a method for assisting the construction and validation of an avionics platform. It uses, on the one hand, a functional description of the platform using avionics functions, software modules suitable for executing these functions, and functional link occurrences between these modules and, on the other hand, a material description of this platform using calculation or communication items of equipment and physical links between these equipment. The method according to the invention enables to generate paths between the various items of equipment by using direct physical links and / or physical links belonging to one or more network(s), and subsequently to associate at least one such path to be each functional link occurrence. It also enables to associate to each software module an item of equipment adapted to host it.

Owner:AIRBUS OPERATIONS (SAS)

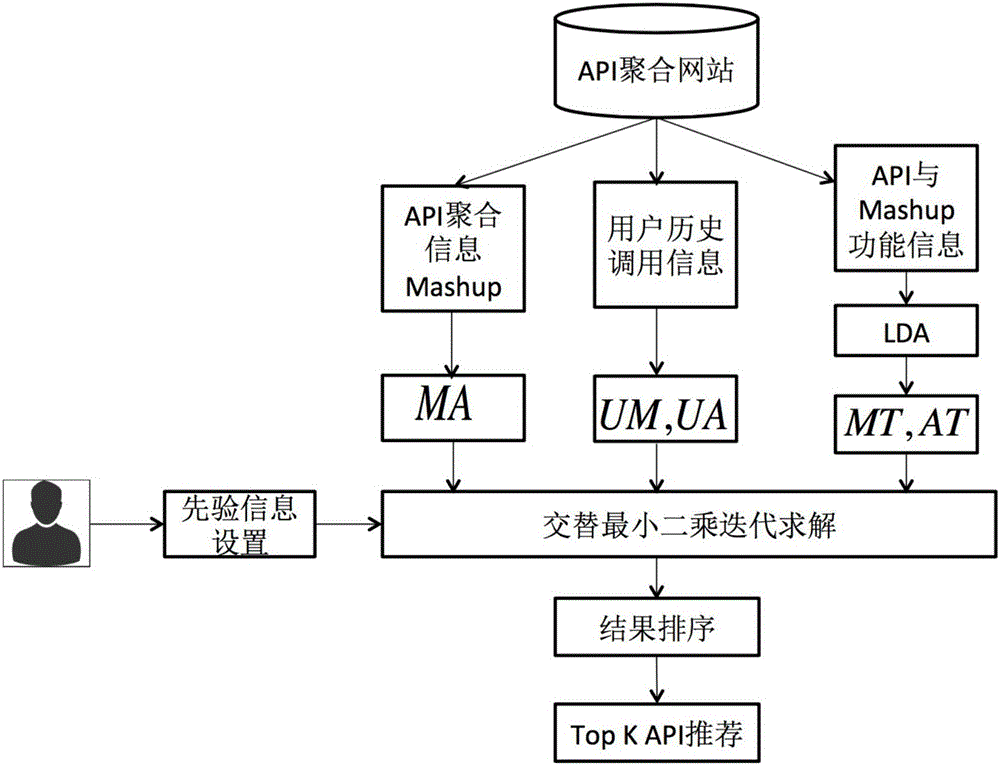

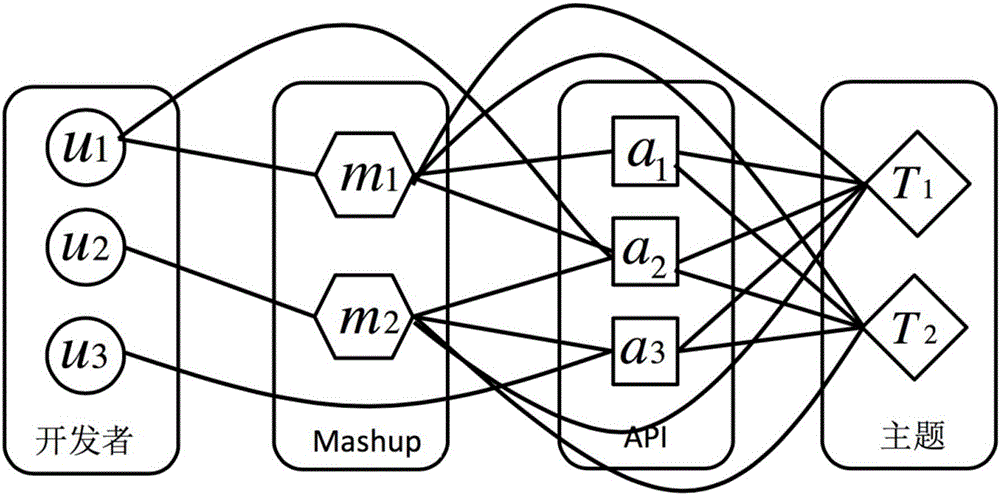

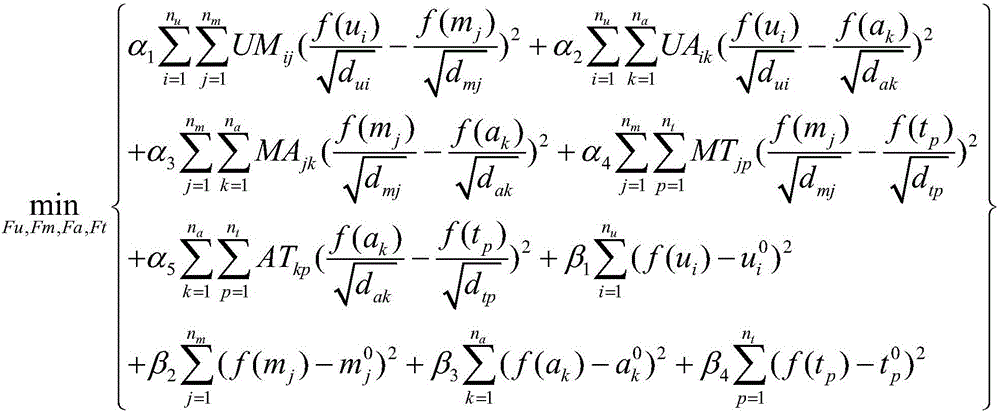

Service aggregation and functional information-based API recommendation method

The invention discloses a service aggregation and functional information-based API (Application Programming Interface) recommendation method. According to the method, an API is recommended to different users by utilizing historical call information of the users, functional description information of the API and aggregation Mashup information of the API. An existing method either only considers the functional information of the API and does not consider the aggregation information of the API, or only utilizes the aggregation information of the API and does not consider the functional information of the API; and the method provided by the invention fuses the functional information and the aggregation information of the API, and performs unified modeling on all the information through a graphic model, so that the effect of API recommendation implemented by the method provided by the invention is remarkably improved in comparison with the effect of API recommendation implemented by the existing method.

Owner:ZHEJIANG UNIV

System and method for designing digital circuitry with an activity sensor

InactiveUS20130125074A1Reduce the valueReduce in quantityCAD circuit designSoftware simulation/interpretation/emulationControl signalComputer science

A system for designing digital circuitry comprising: a digital circuit simulator based on a file containing a functional description of this digital circuit; means for estimating an output variable from the digital circuit when executing a test bench supplied to the simulator; event counters, the events being detected using control signals provided by the simulator when executing the test bench. Said system further comprises means for selecting a portion of the event counters by iteratively optimizing a model for calculating the output variable of the digital circuit using output data from the event counters and means for registering the selected portion of event counters and the optimized calculation model.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES