Patents

Literature

60 results about "Floorplan" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

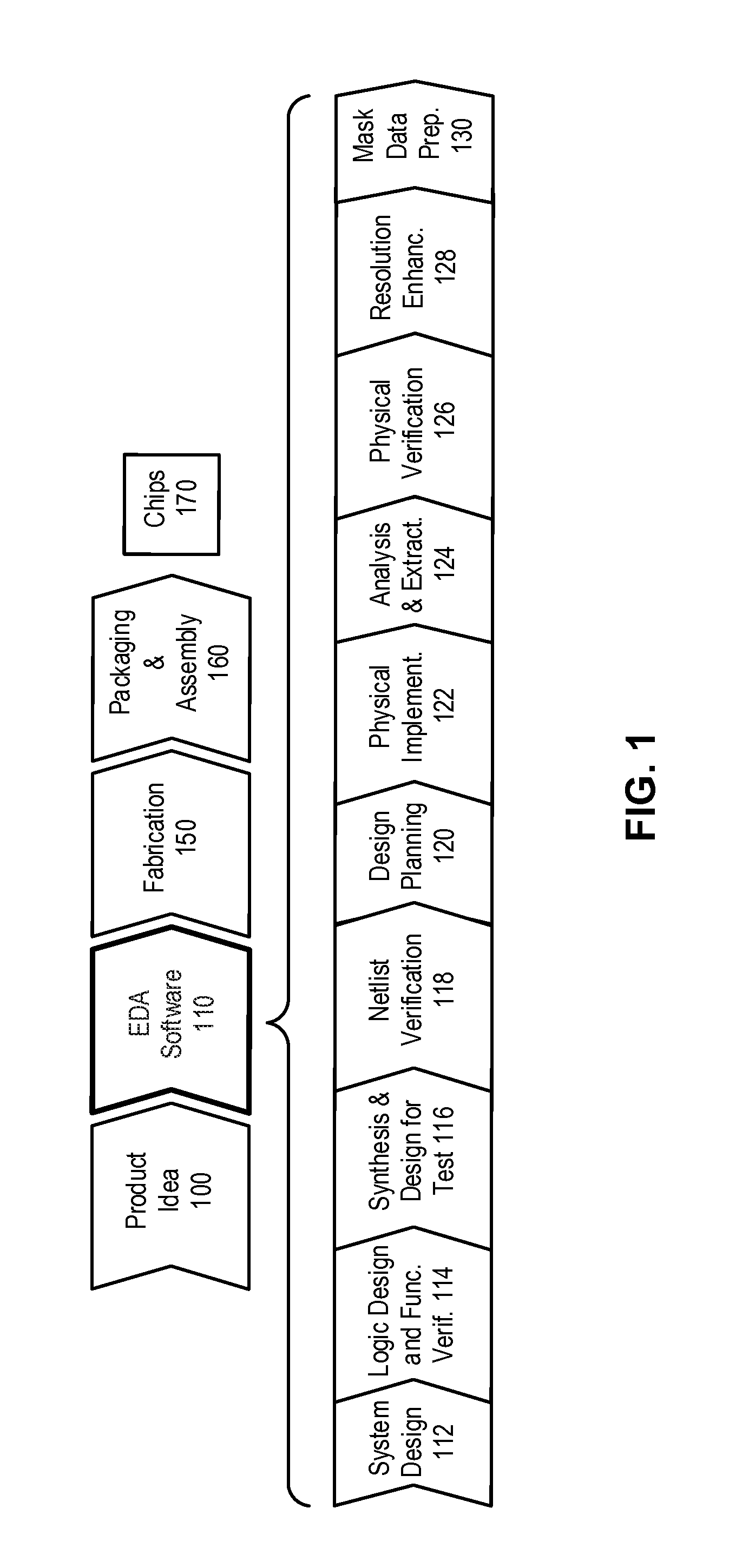

In electronic design automation, a floorplan of an integrated circuit is a schematic representation of tentative placement of its major functional blocks. In modern electronic design process floorplans are created during the floorplanning design stage, an early stage in the hierarchical approach to integrated circuit design.

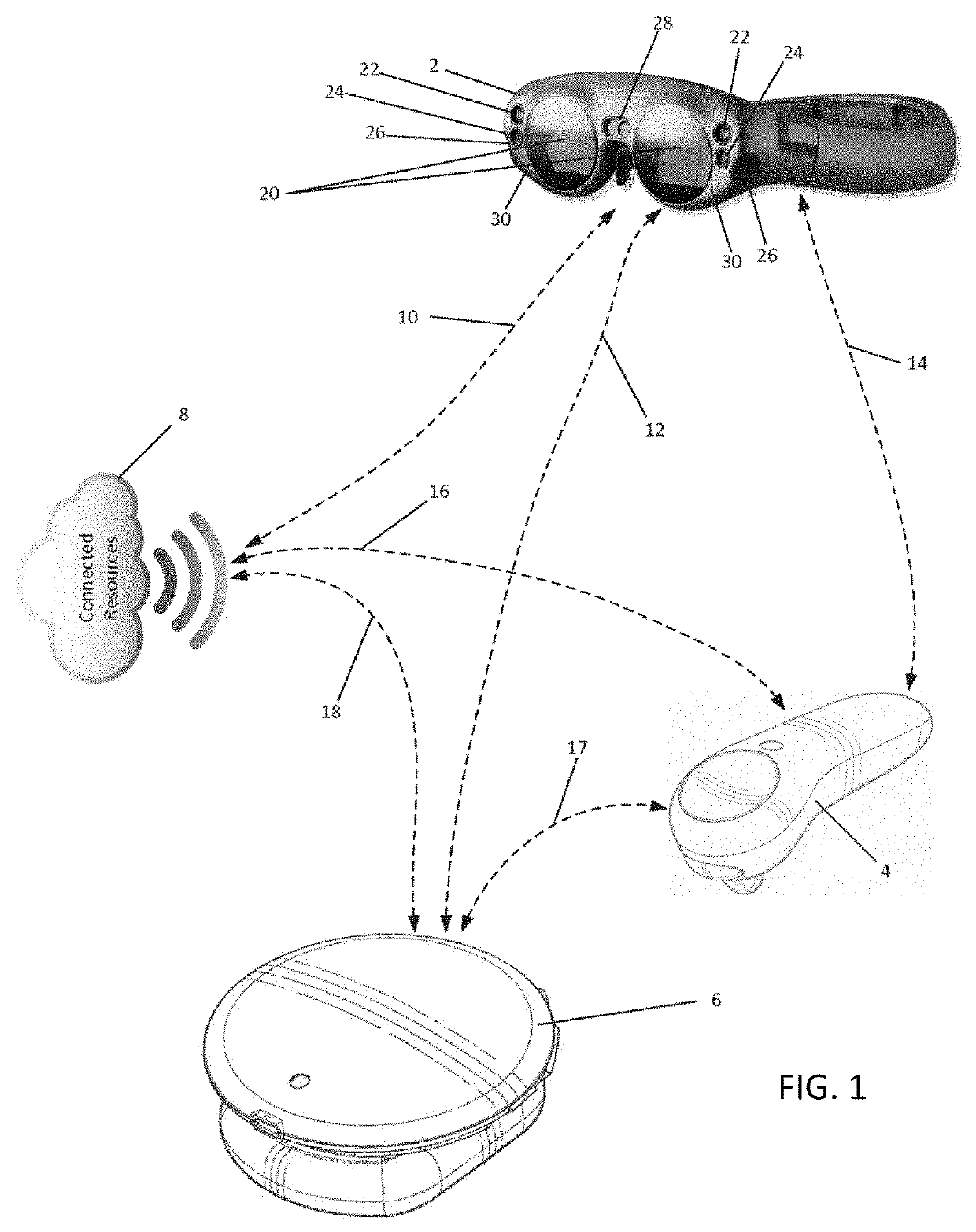

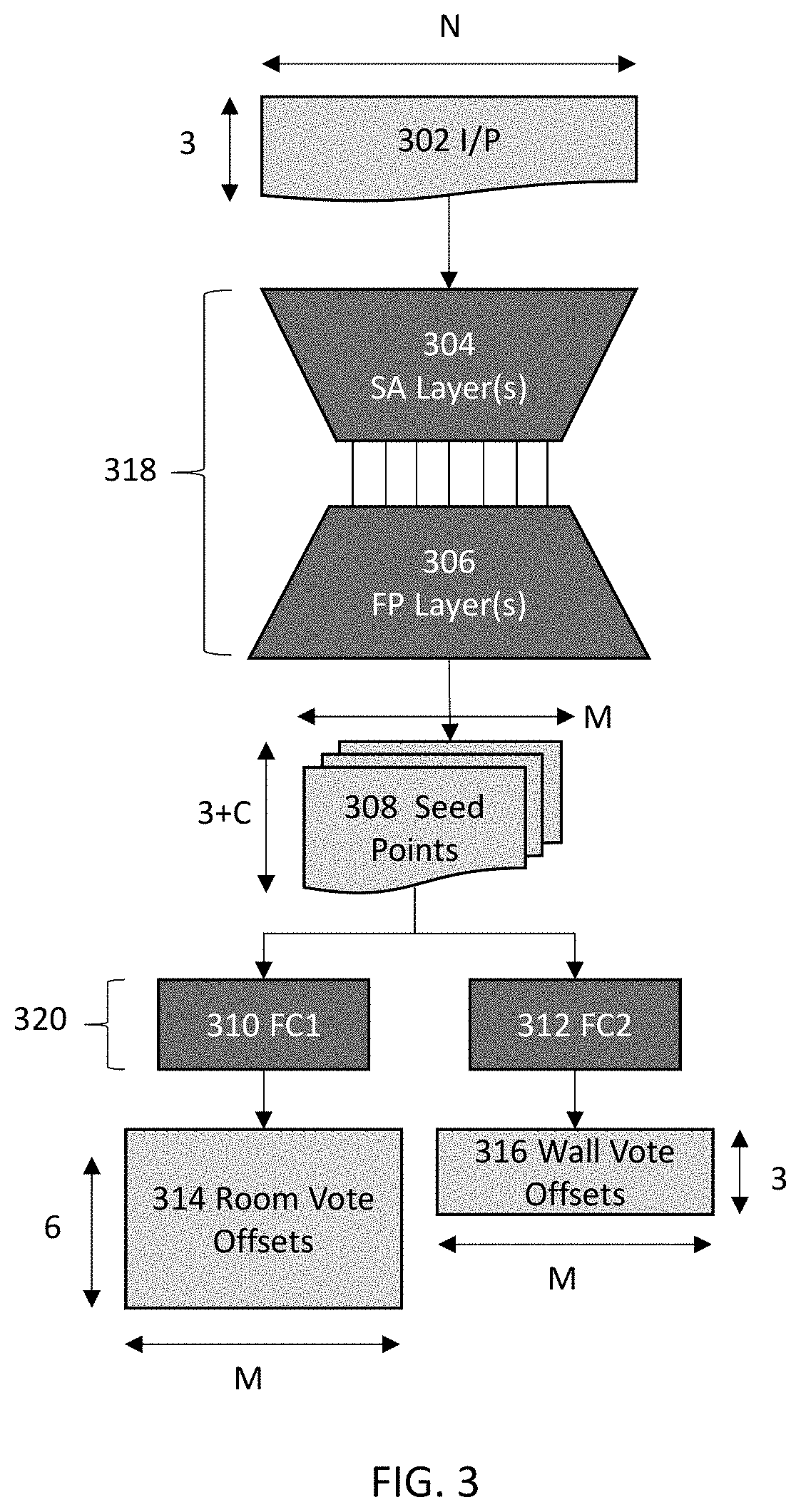

Systems and methods for efficient floorplan generation from 3D scans of indoor scenes

Methods, systems, and wearable extended reality devices for generating a floorplan of an indoor scene are provided. A room classification of a room and a wall classification of a wall for the room may be determined from an input image of the indoor scene. A floorplan may be determined based at least in part upon the room classification and the wall classification without constraining a total number of rooms in the indoor scene or a size of the room.

Owner:MAGIC LEAP

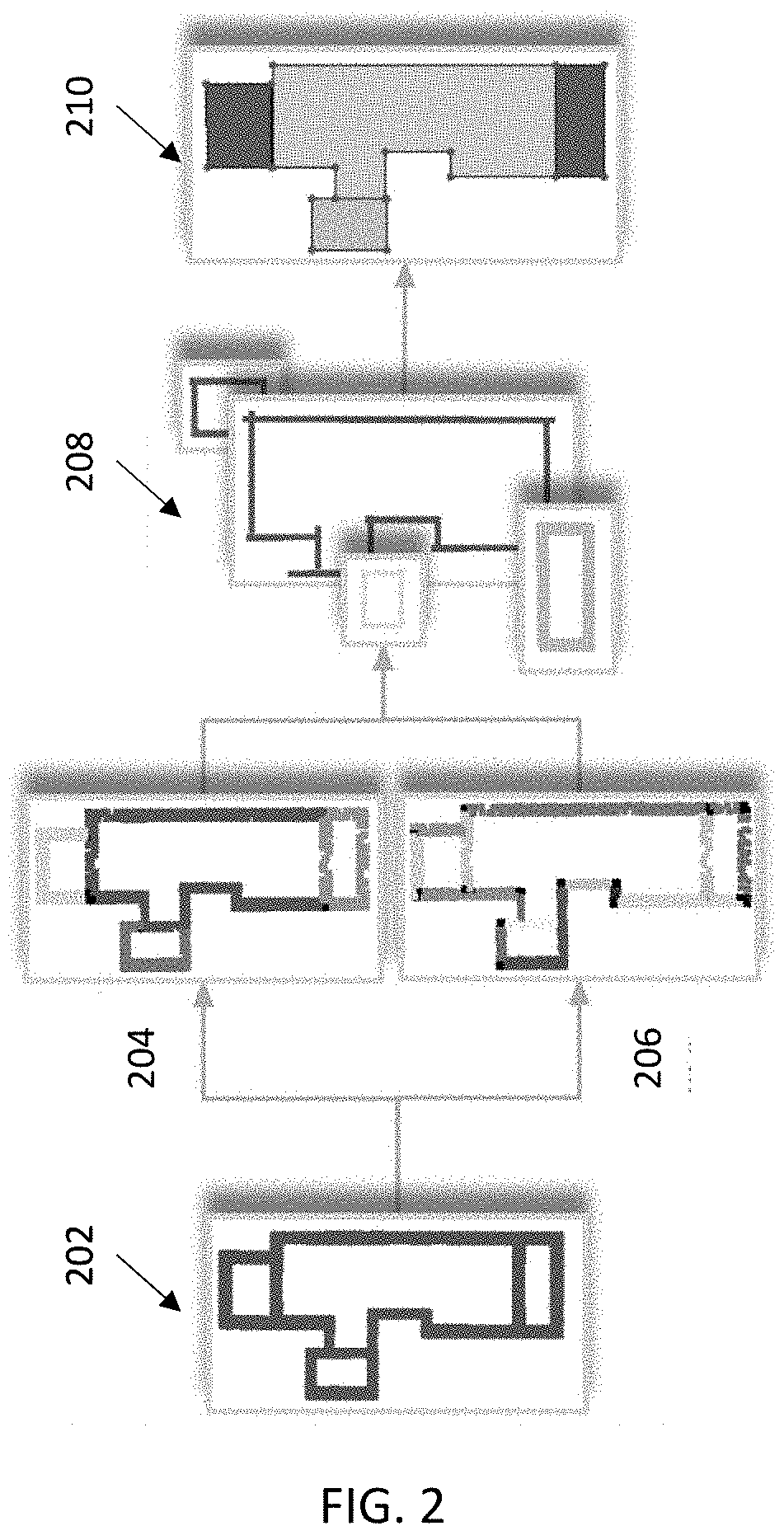

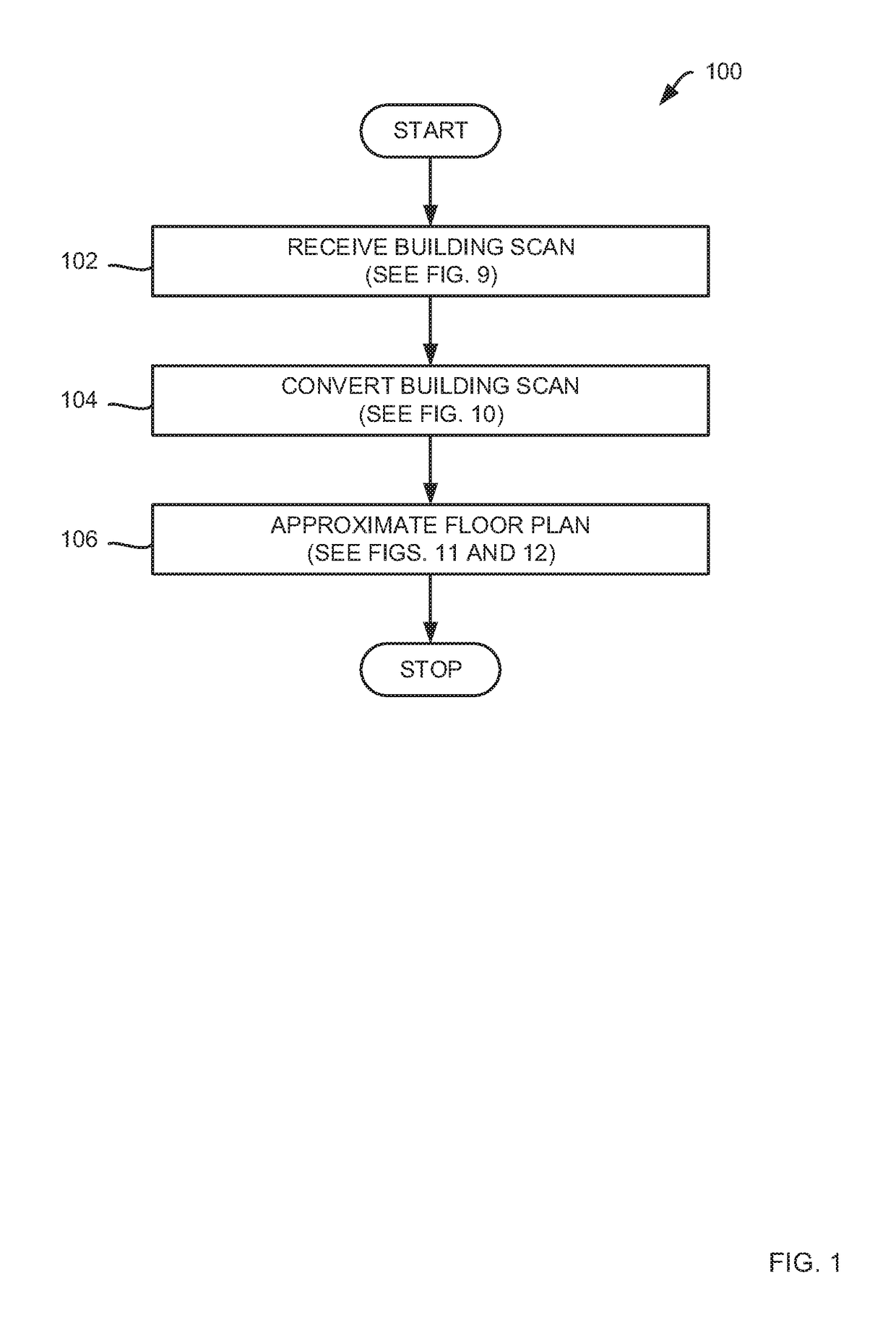

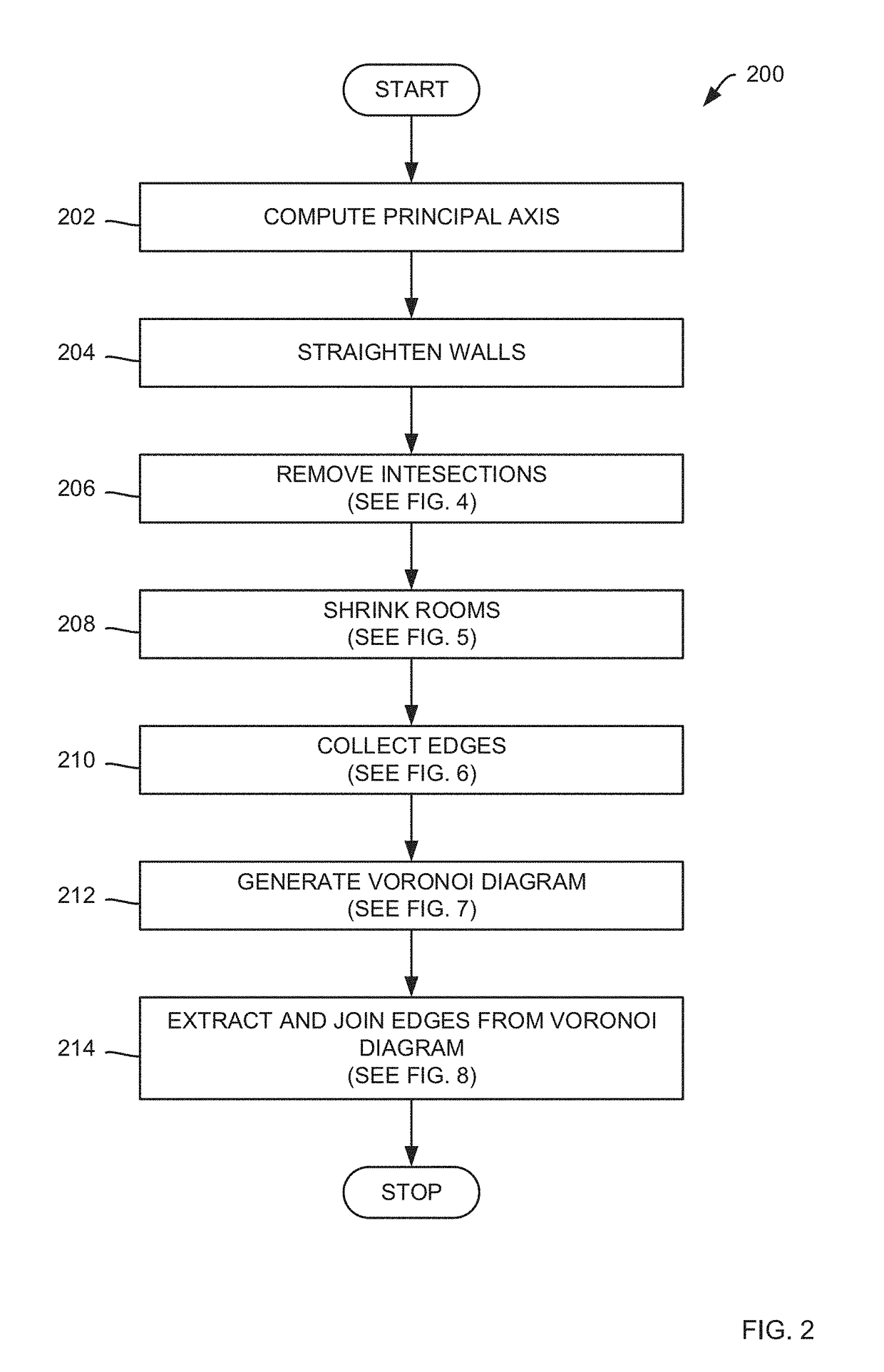

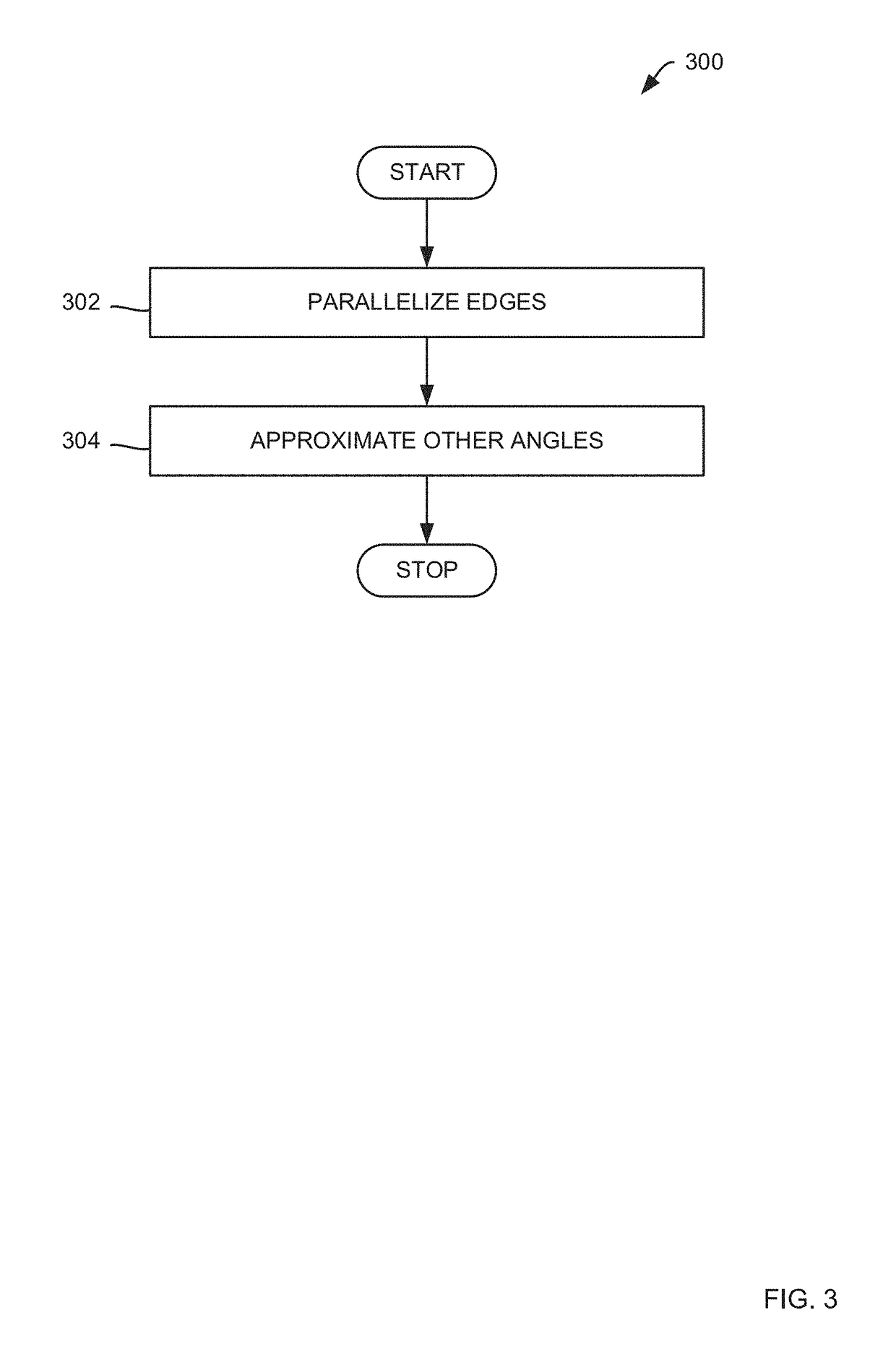

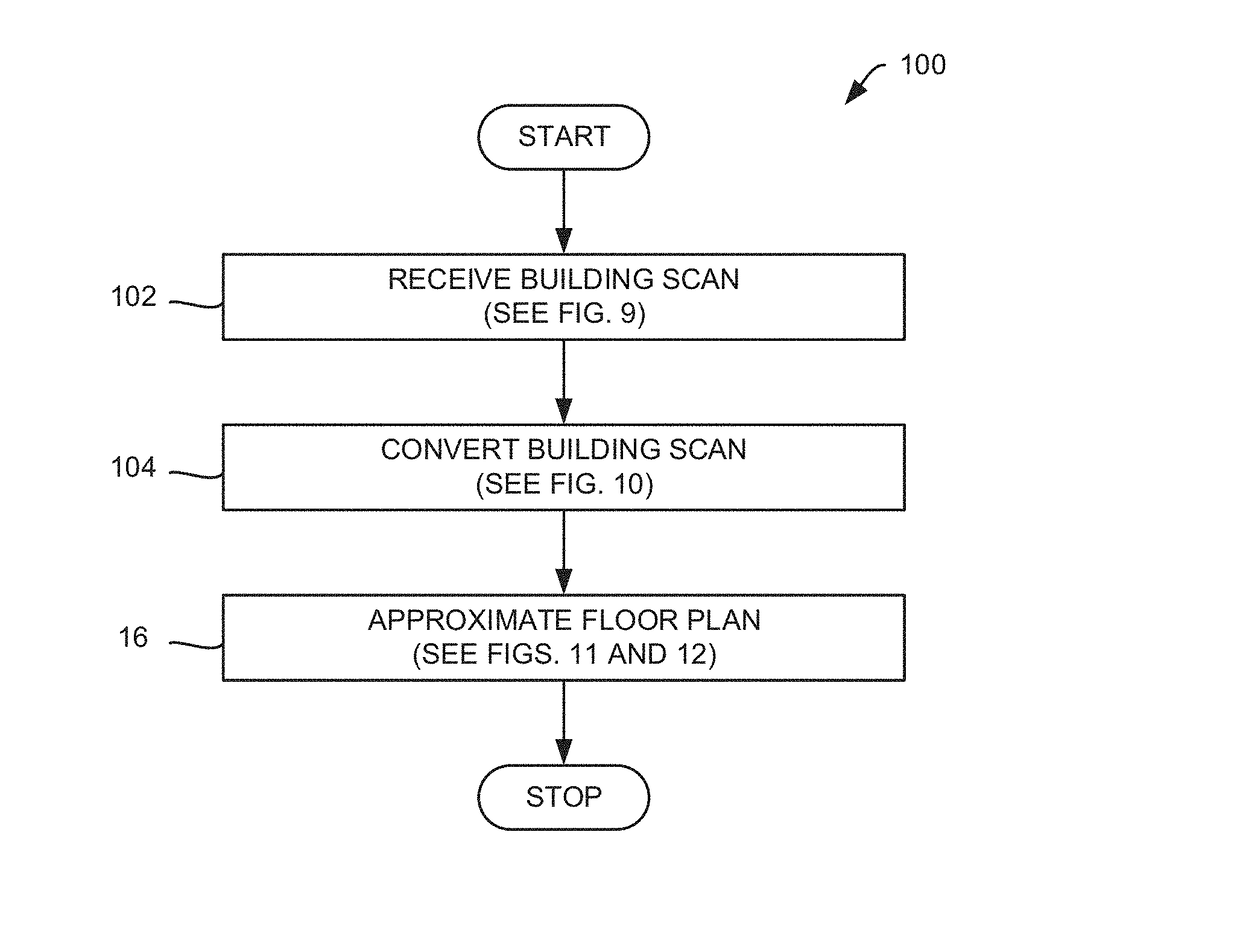

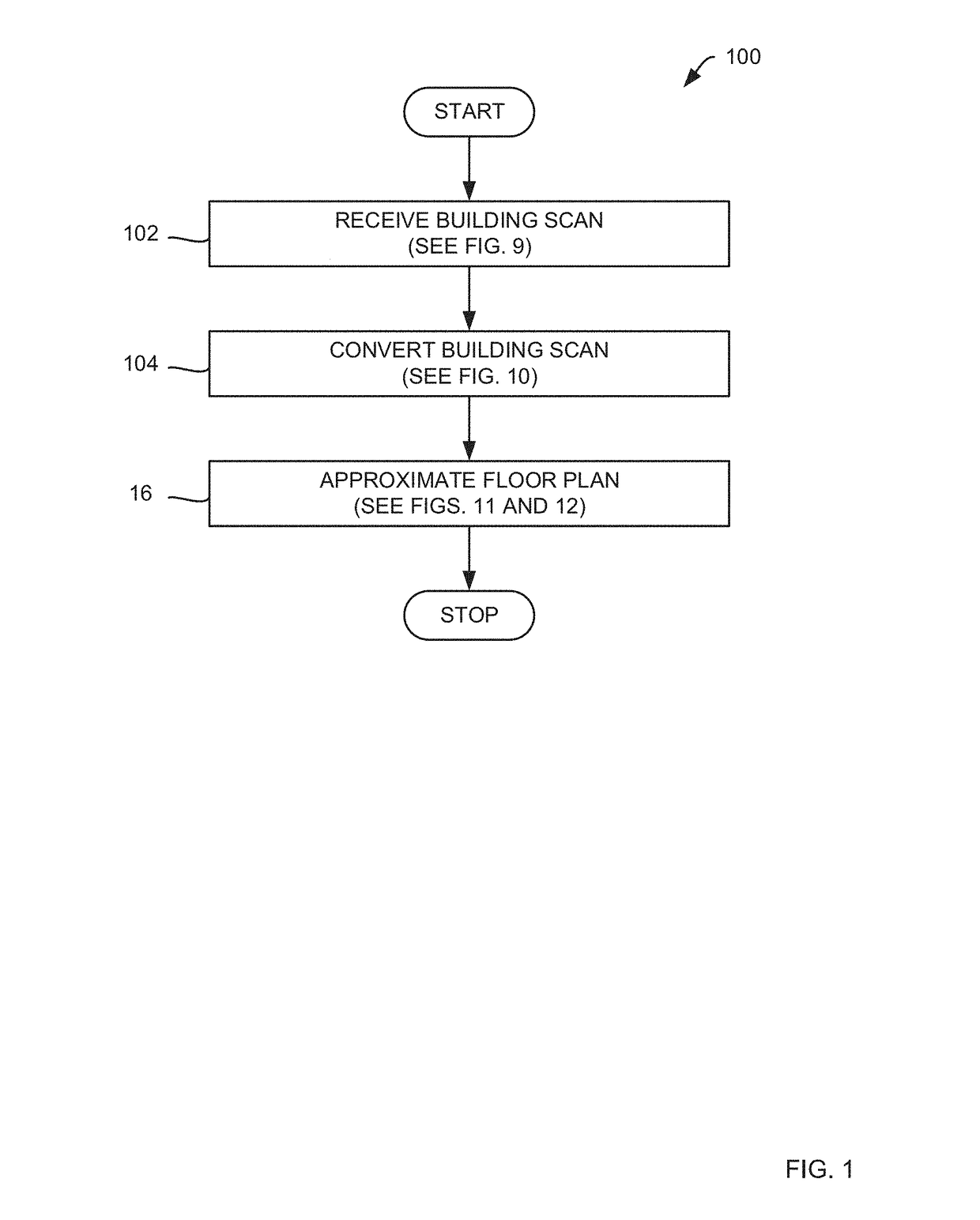

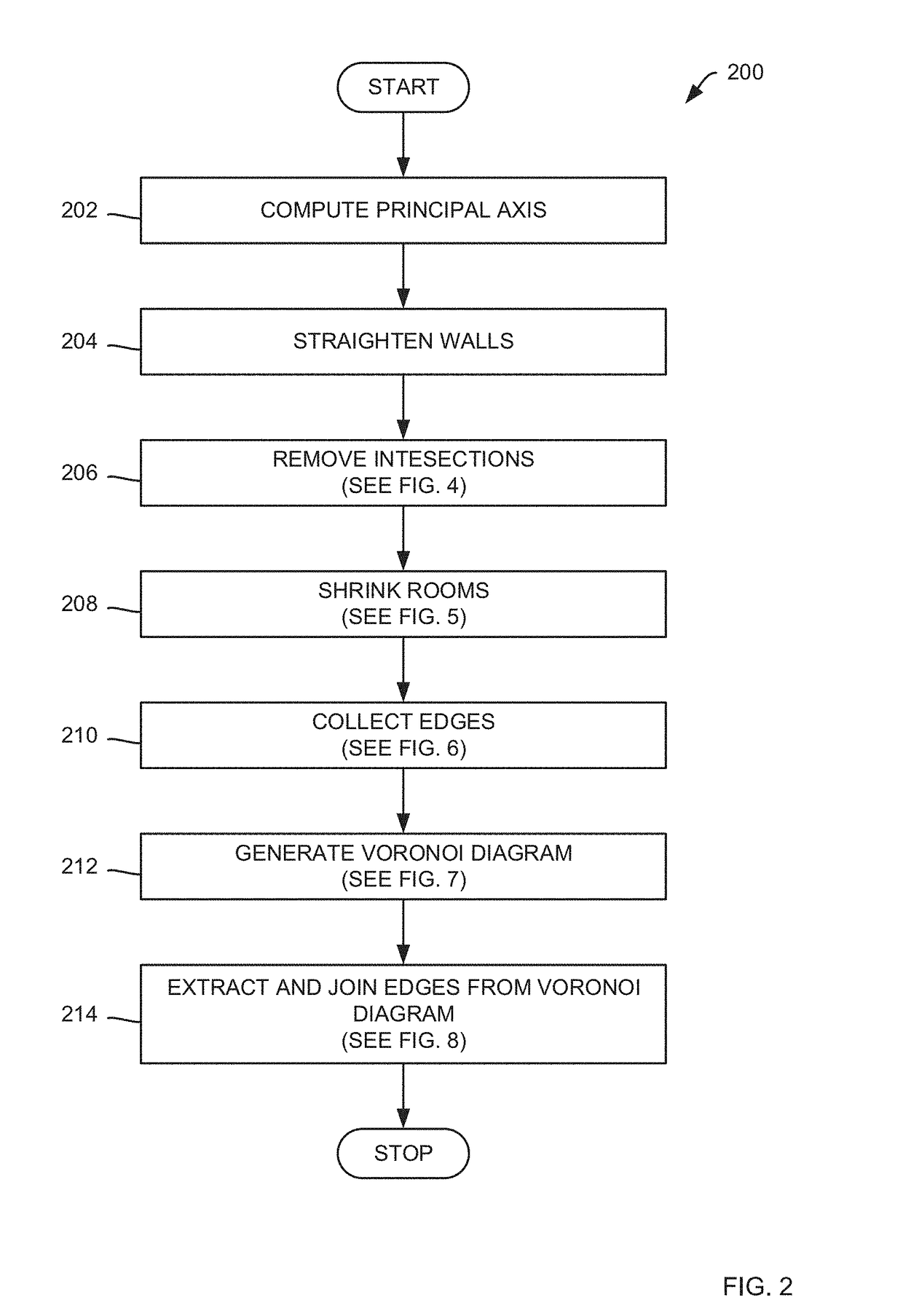

Methods for generating a floor plan from a building scan

Methods for generating a floor plan from a building scan of a building using an electronic computing device are presented, the method including: causing the electronic computing device to receive the building scan; converting the building scan to a floor plan; and refining the floor plan to approximate the building. In some embodiments, the causing the electronic computing device to receive the building scan further includes: extracting information from an input file to obtain a representation of a number of rooms and walls corresponding with the building scan, where the information is selected from the group consisting of: a set of vertices, a set of triangles, and a set of rooms.

Owner:HILTI AG

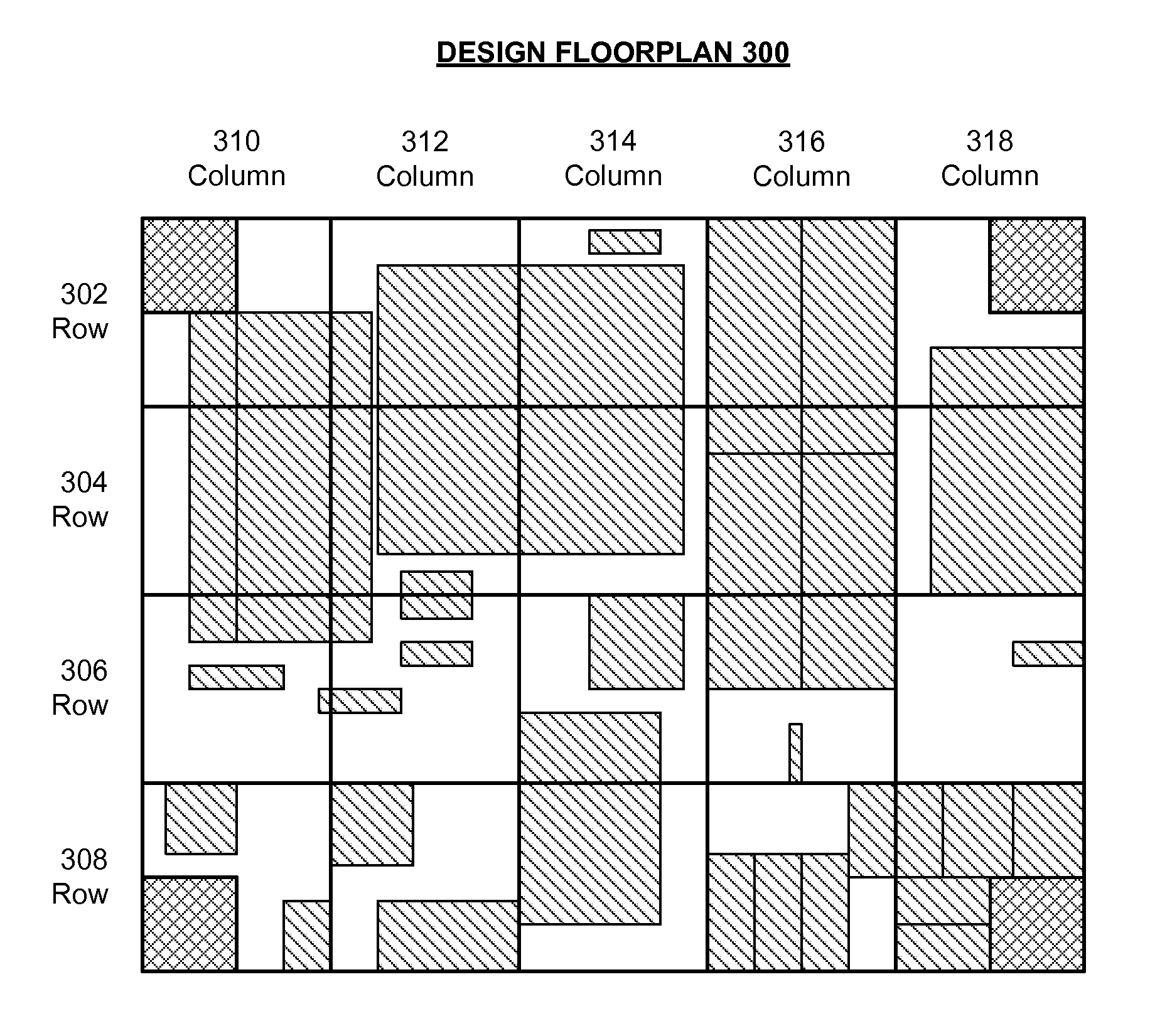

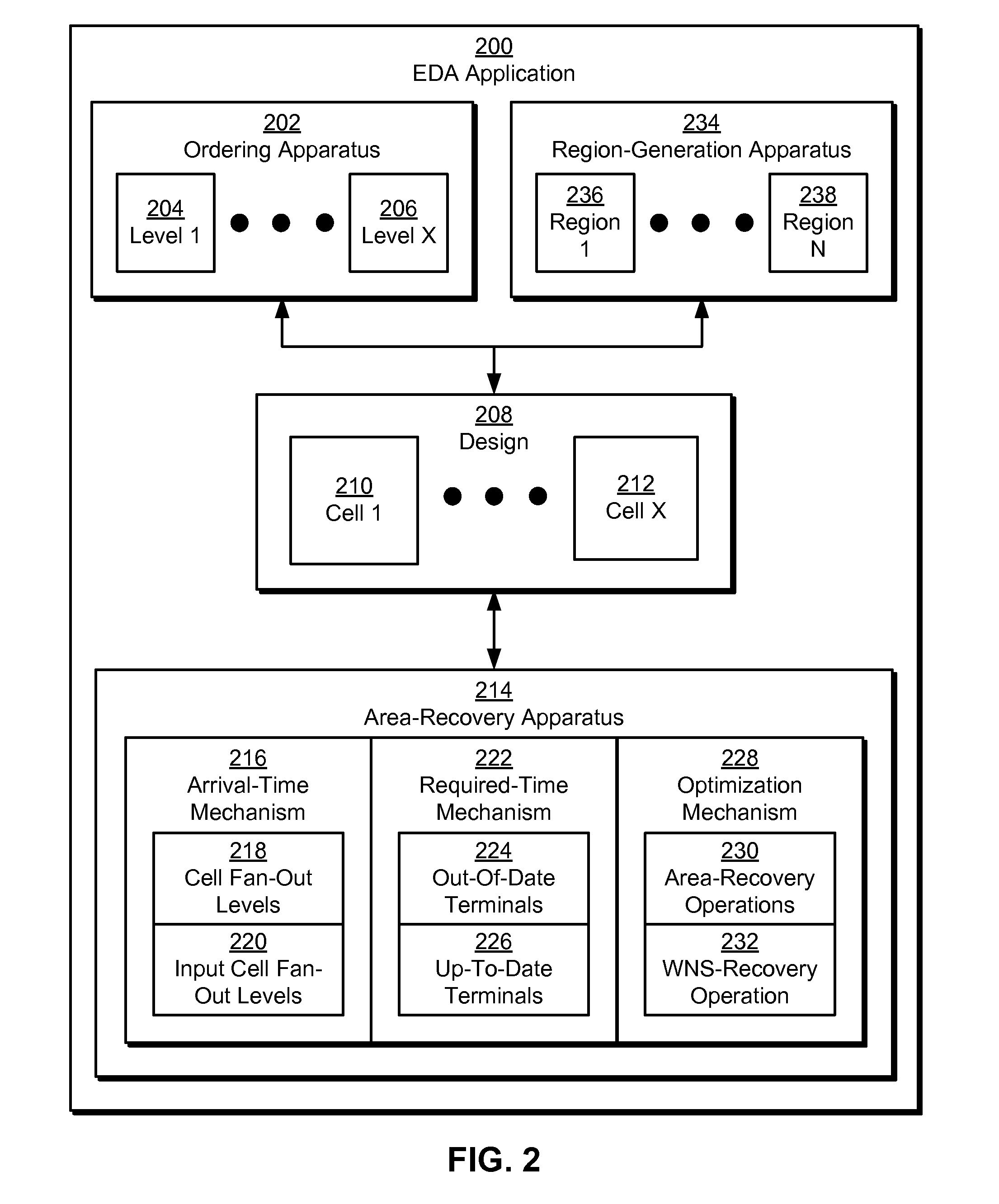

Density-based area recovery in electronic design automation

ActiveUS20110191738A1Improve efficiencyCAD circuit designSpecial data processing applicationsDensity basedEngineering

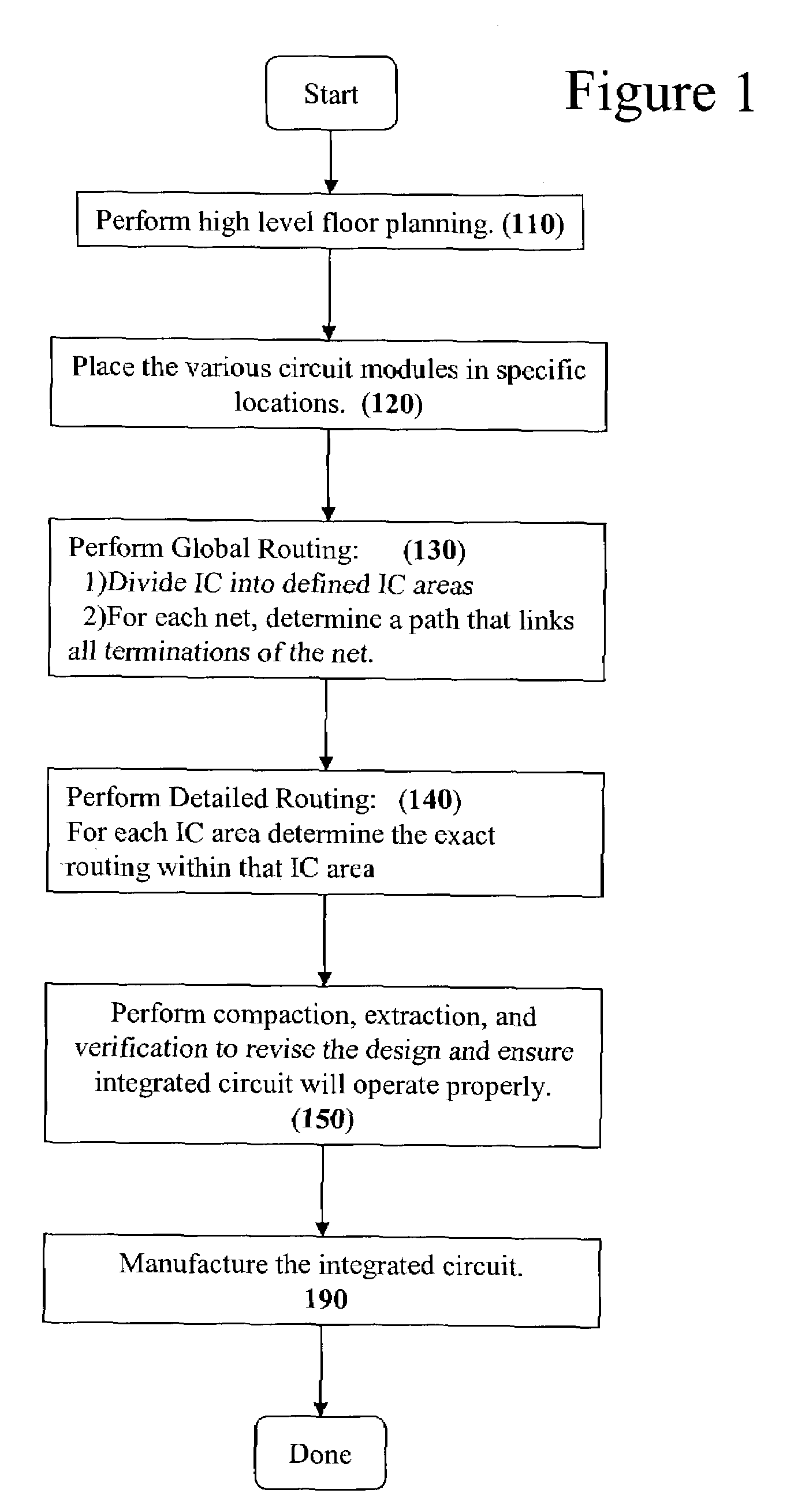

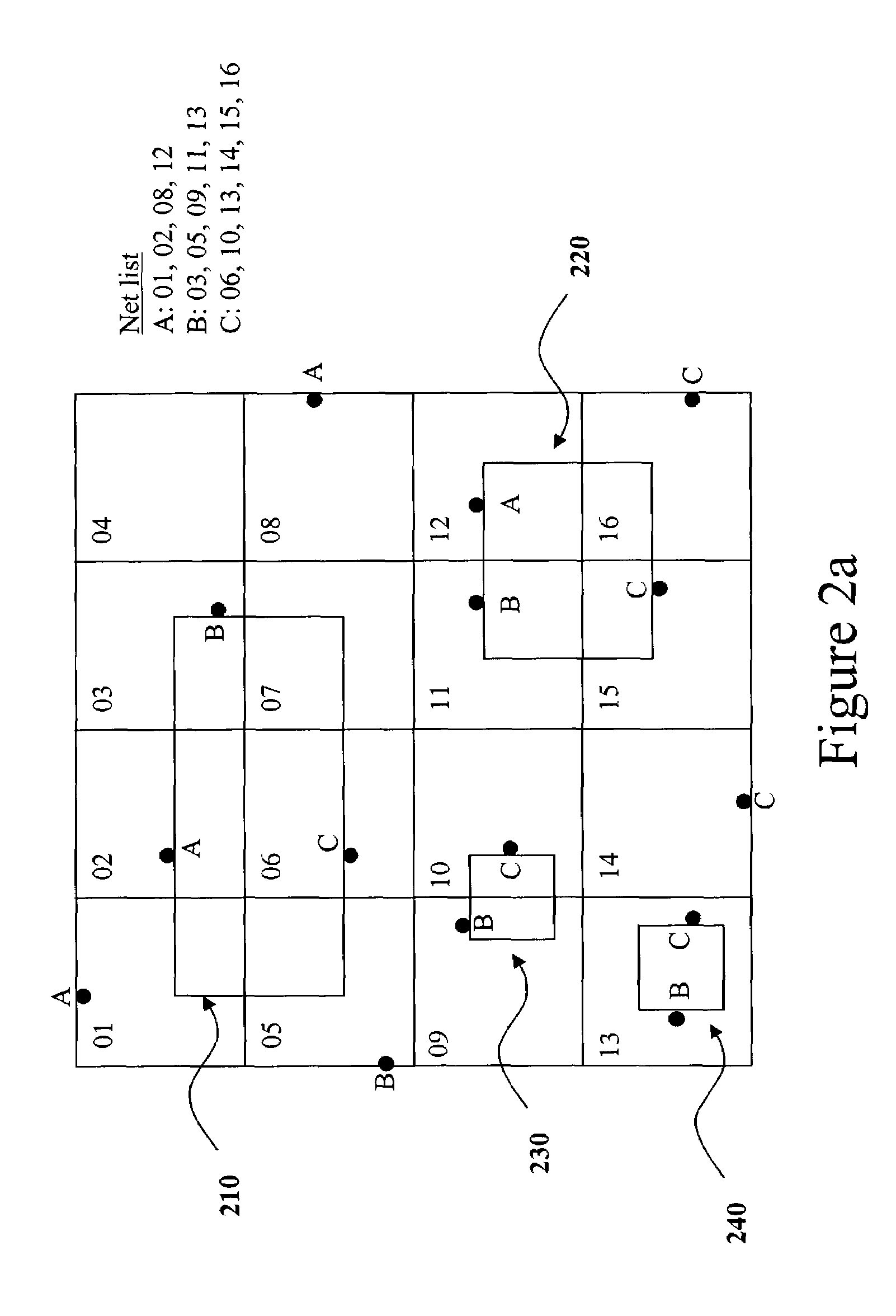

Some embodiments provide techniques and systems for improving the efficiency of area recovery in an electronic design automation (EDA) flow. During operation, the system determines a utilization of a region from a set of regions in a design floorplan. Next, the system performs area recovery (e.g., by using a processor) on the region based at least on the utilization. Specifically, the system can overlay the design floorplan with a grid, wherein the grid comprises a set of grid cells and uses the grid cells as the set of regions. The grid can be associated with a predetermined number of rows and a predetermined number of columns. The system can determine the utilization of the region by calculating the utilization as a cell area of the region divided by a placement area of the region. The utilization can be incrementally calculated during the creation and optimization of the design.

Owner:SYNOPSYS INC

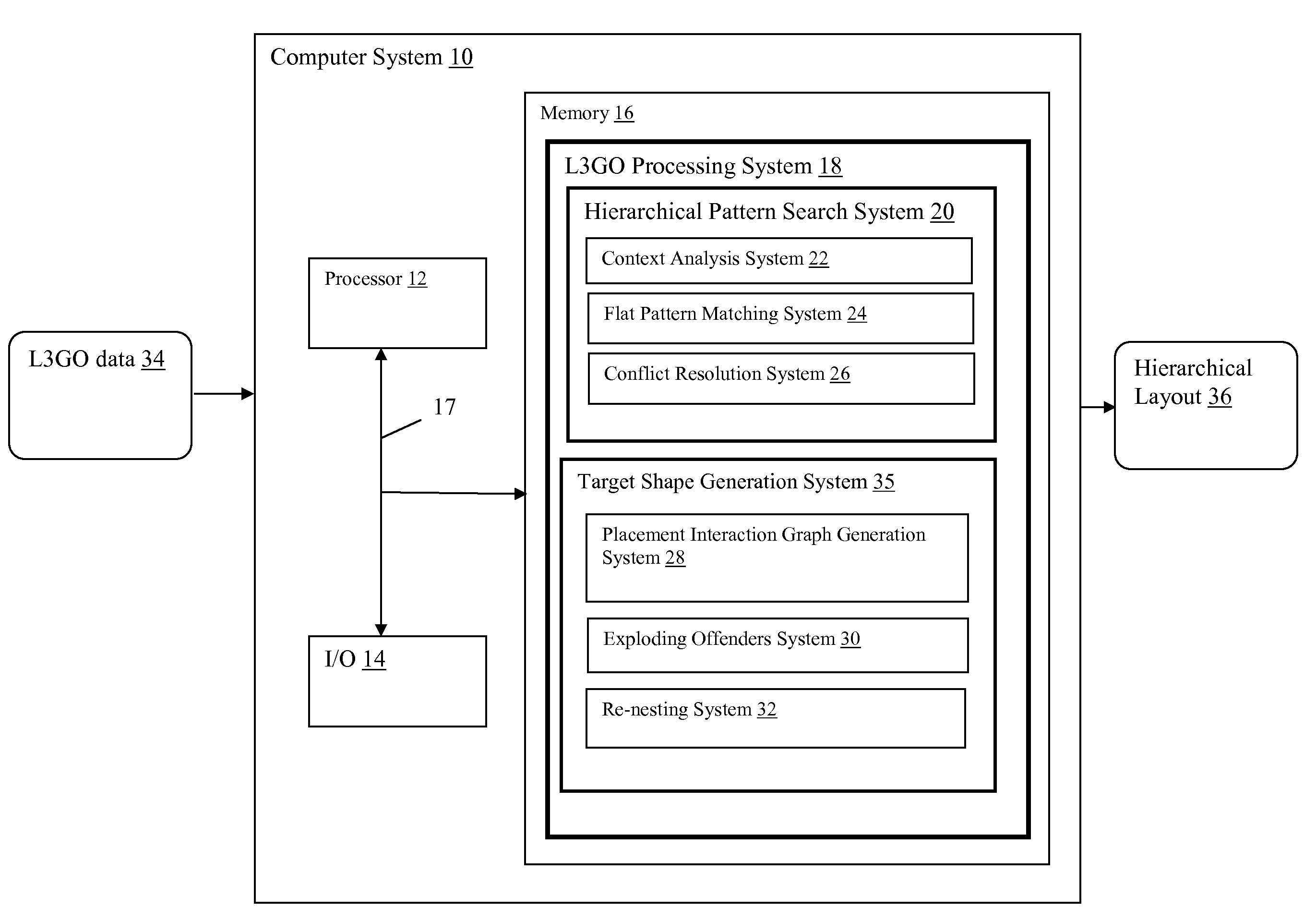

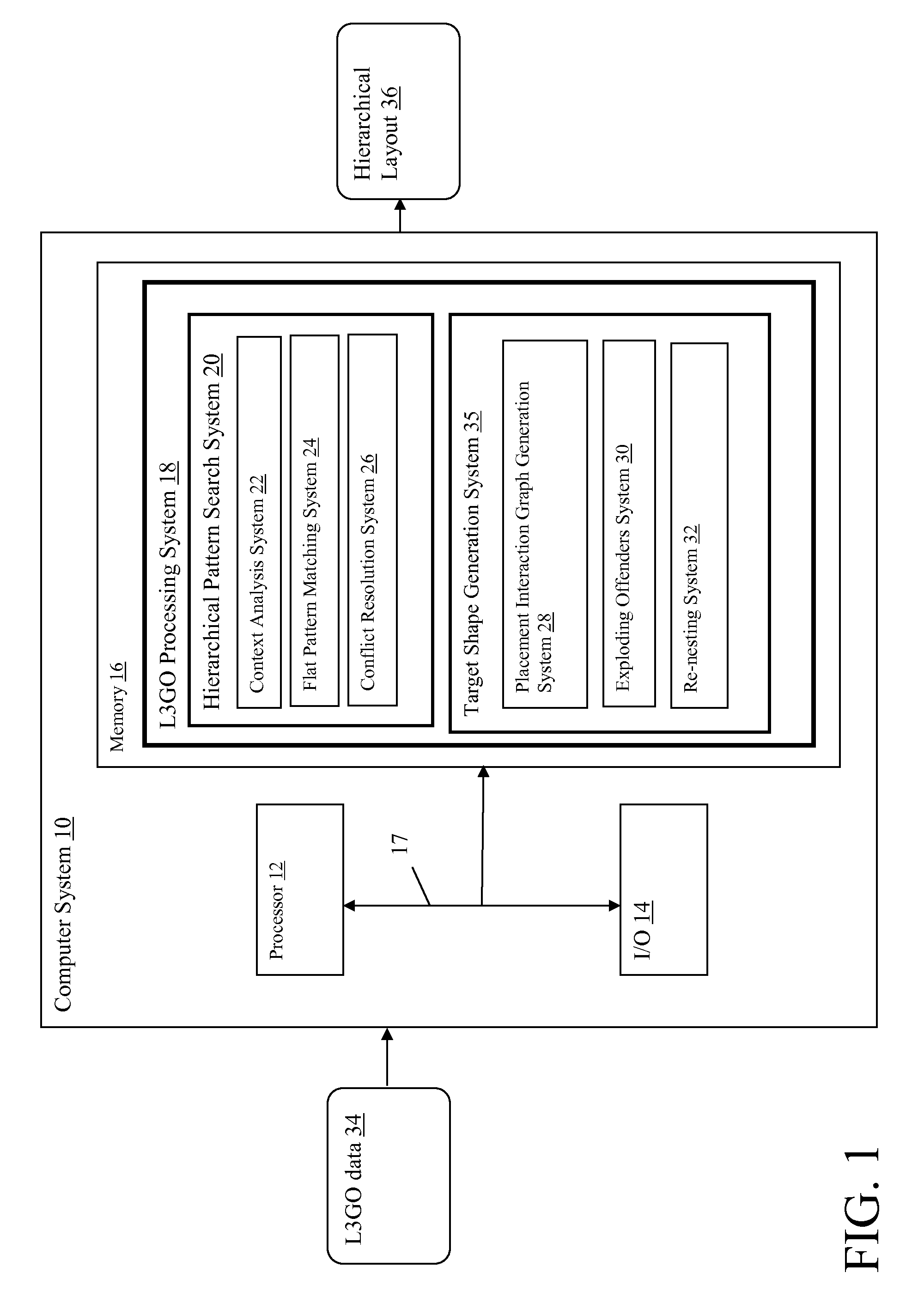

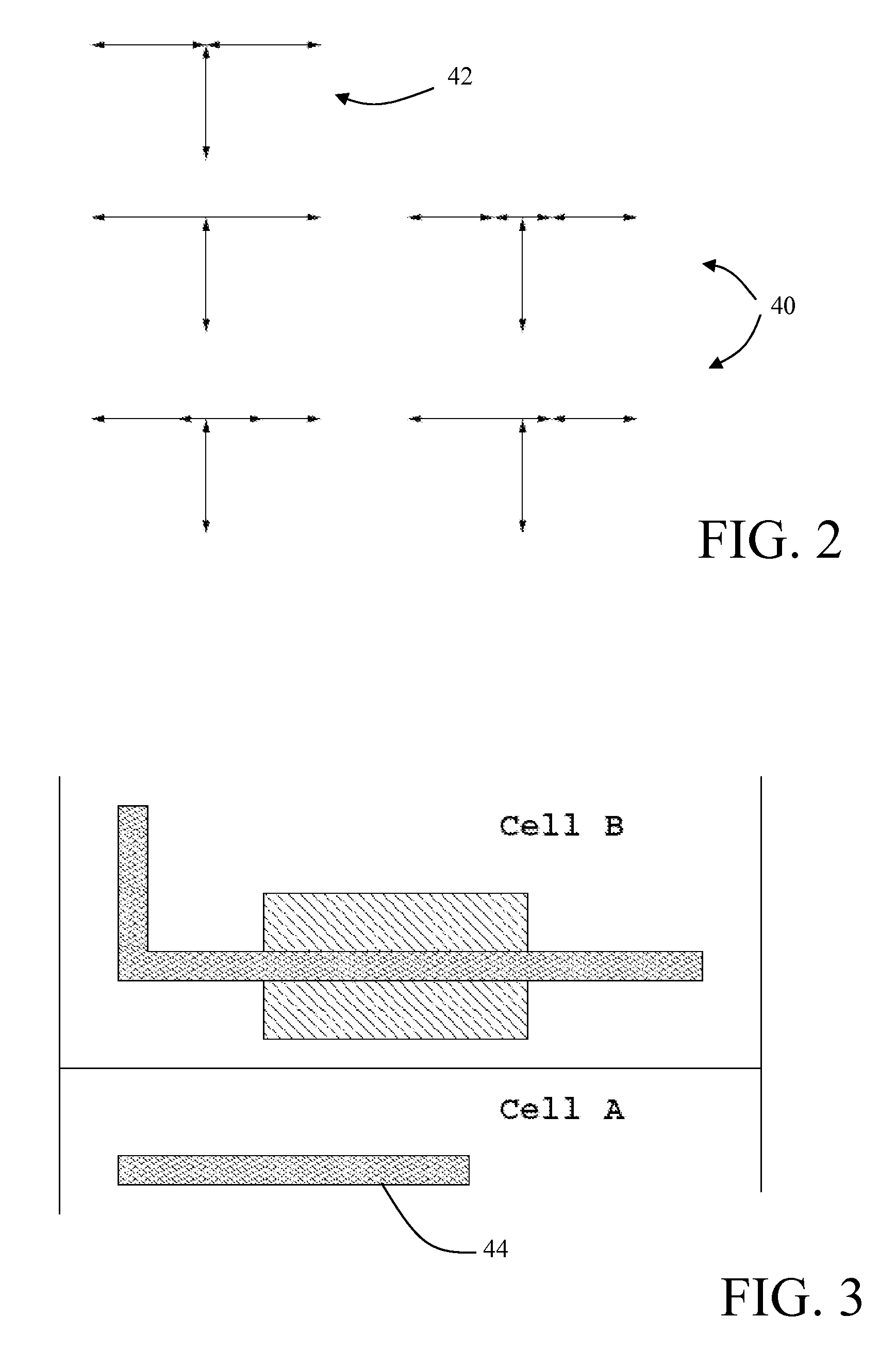

Pattern based elaboration of hierarchical l3go designs

InactiveUS20080244493A1The result is accurateCAD circuit designRecord carriers used with machinesGlyphHierarchical design

A system, method and program product that utilizes flat pattern based L3GO elaboration in a hierarchical environment to create a nested conventional layout. A system is provide for processing a glyph layout to generate shapes for use in a VLSI (very large scale integrated circuit) design process, including: a hierarchical pattern search system that matches patterns from a pattern library to a set of glyph data, wherein the patterns have dependencies that cross hierarchical design boundaries; and a target shape generation system that selects patterns from a set of matching patterns and generates associated shapes.

Owner:IBM CORP

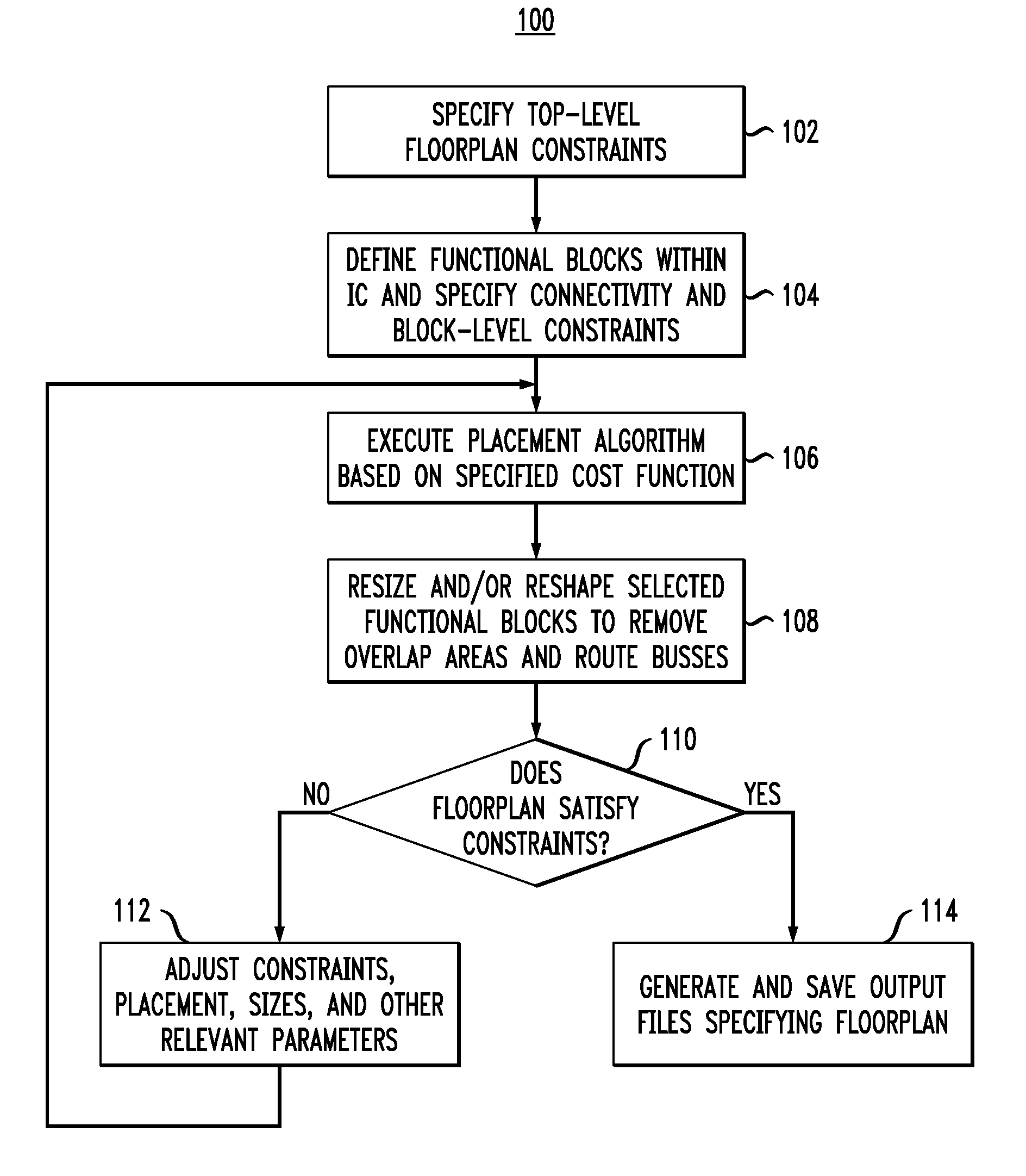

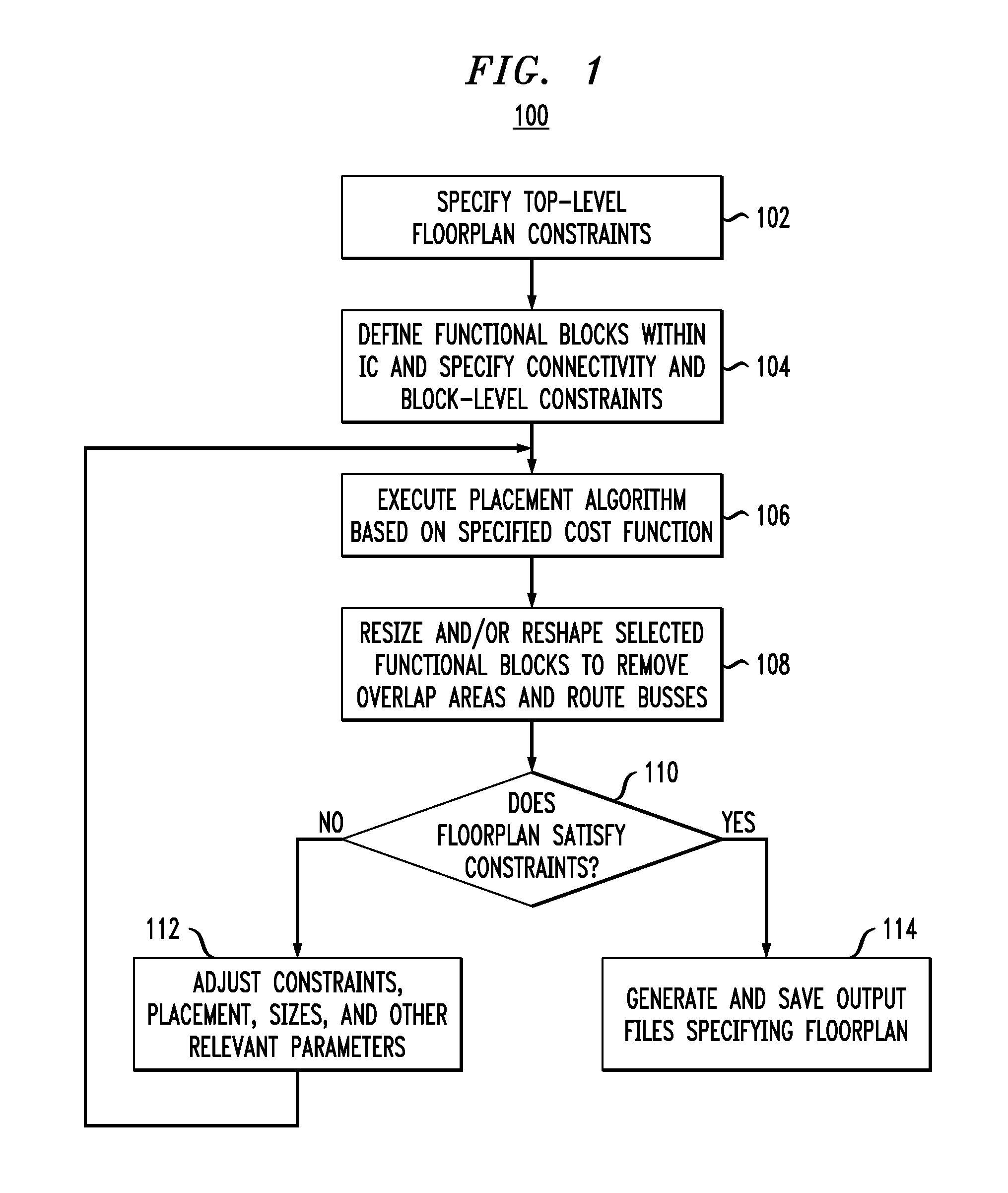

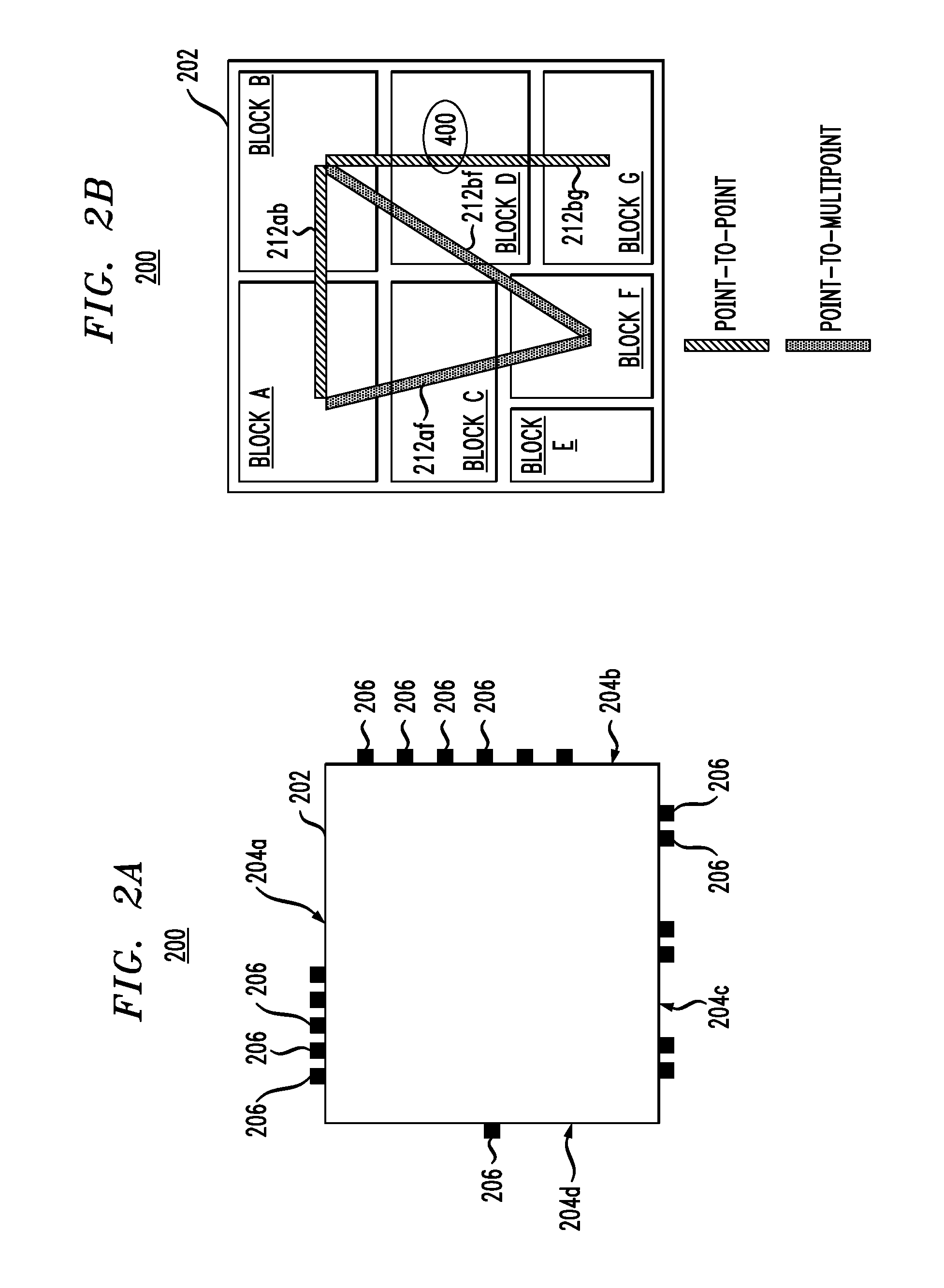

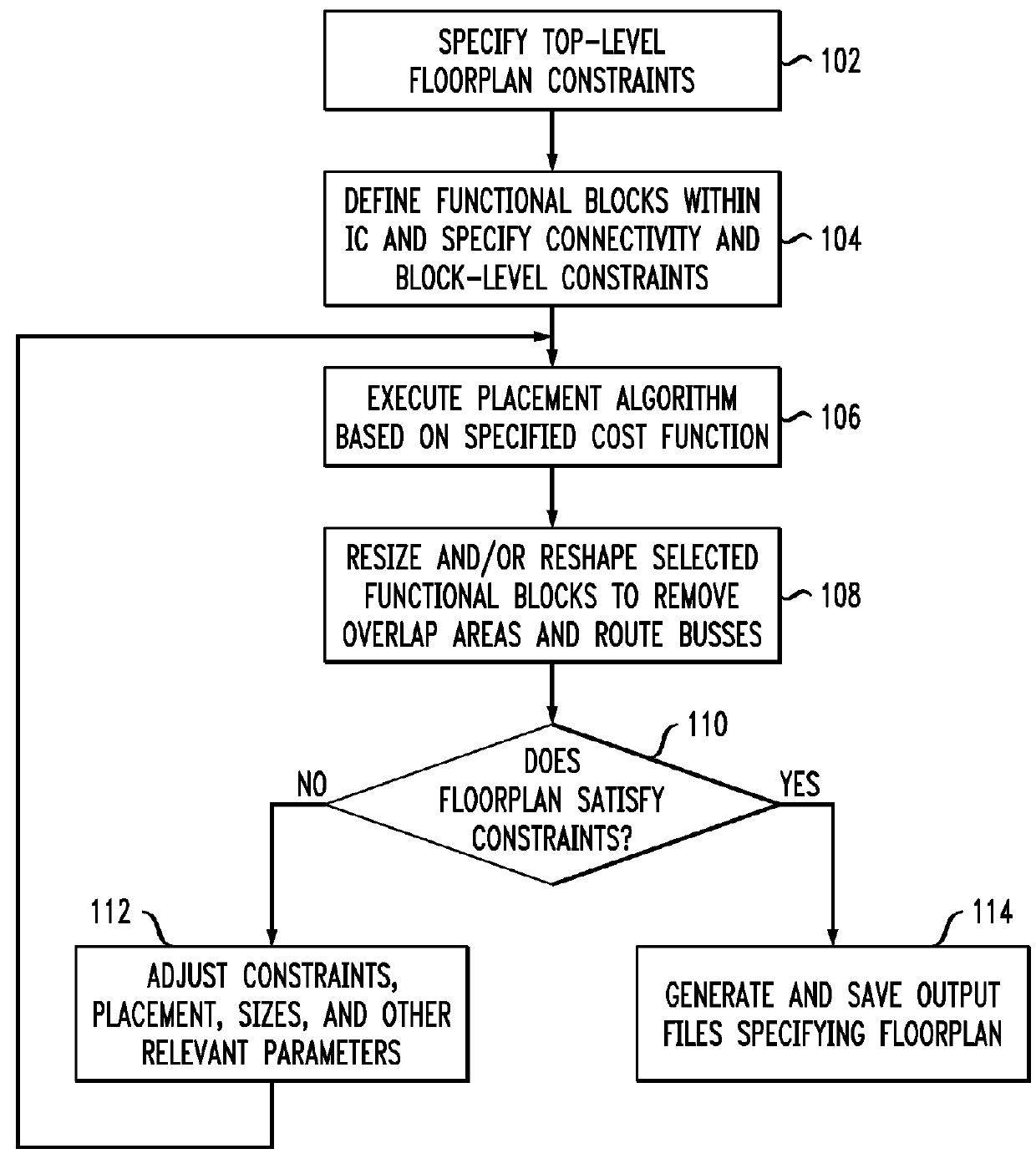

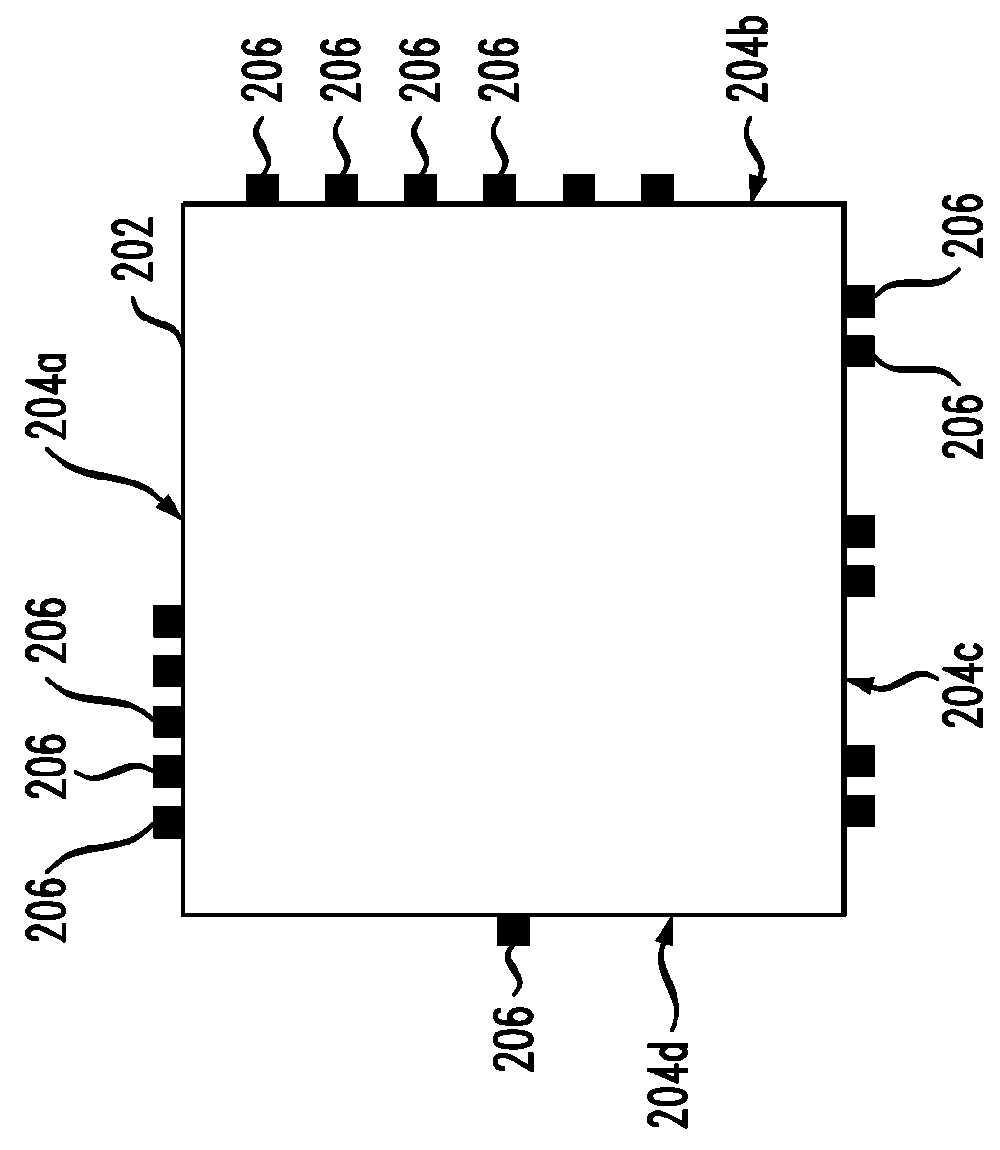

Generating integrated circuit floorplan layouts

InactiveUS20110023000A1Little informationGood informationComputer aided designSpecial data processing applicationsComputer Aided DesignComputer architecture

A method of generating a floorplan layout of an integrated circuit (IC) that is amenable to implementation in a computer-aided design tool. The method is capable of performing placement and routing processing for the IC while requiring very little information about the specific circuitry used in various functional blocks of the IC. For example, at the time of the placement and routing processing, one or more functional blocks of the IC can be specified as empty functional blocks and / or functional blocks that are only partially rendered in gates.

Owner:BELL SEMICON LLC

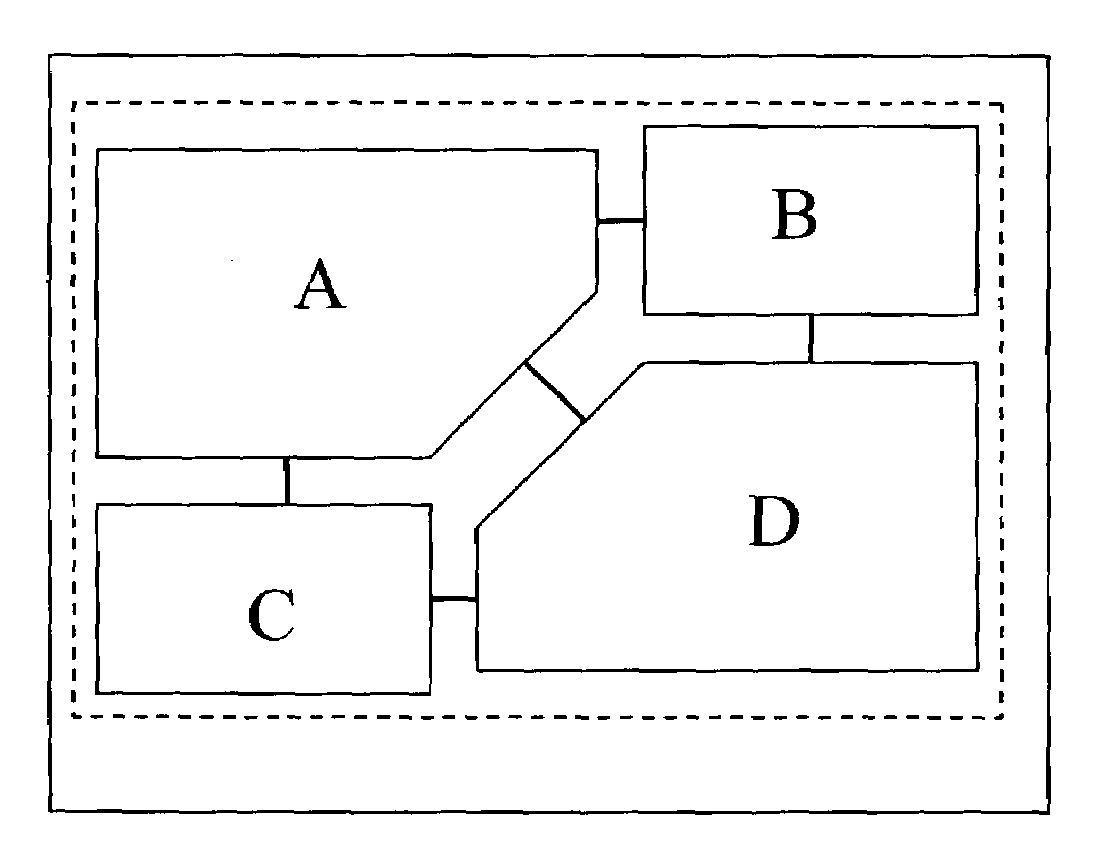

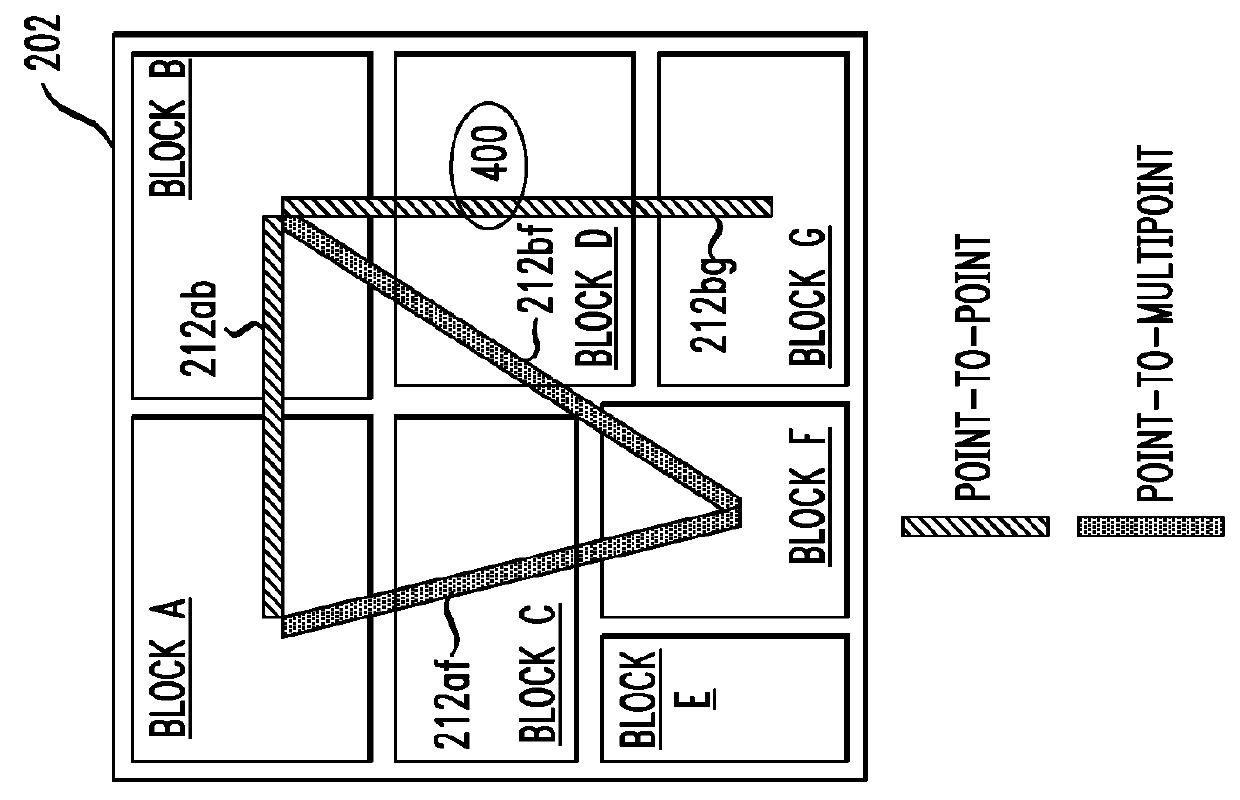

Non manhattan floor plan architecture for integrated circuits

InactiveUS7506295B1Improve routing densityDie sizeComputer aided designSoftware simulation/interpretation/emulationPost processorDiagonal

The present invention introduces methods of creating floor plans and placements for non Manhattan integrated circuits with existing electronic design automation tools. To create a floor plan, an existing Manhattan based floor planning tool is used. The die size for the floor plan is reduced to take into account the improved wiring density of non Manhattan wiring. A non Manhattan global router is then used on the floor plan to create pin placements. The floor plan may create a floor plan having circuit modules with beveled corners to take advantage of diagonal wiring. To create a placement, an existing Manhattan based placer is first used to create an initial placement. The initial placement is then processed by a non Manhattan aware post processor. The post processor performs local optimizations on the initial placement to improve the placement for a non Manhattan routed integrated circuit.

Owner:CADENCE DESIGN SYST INC

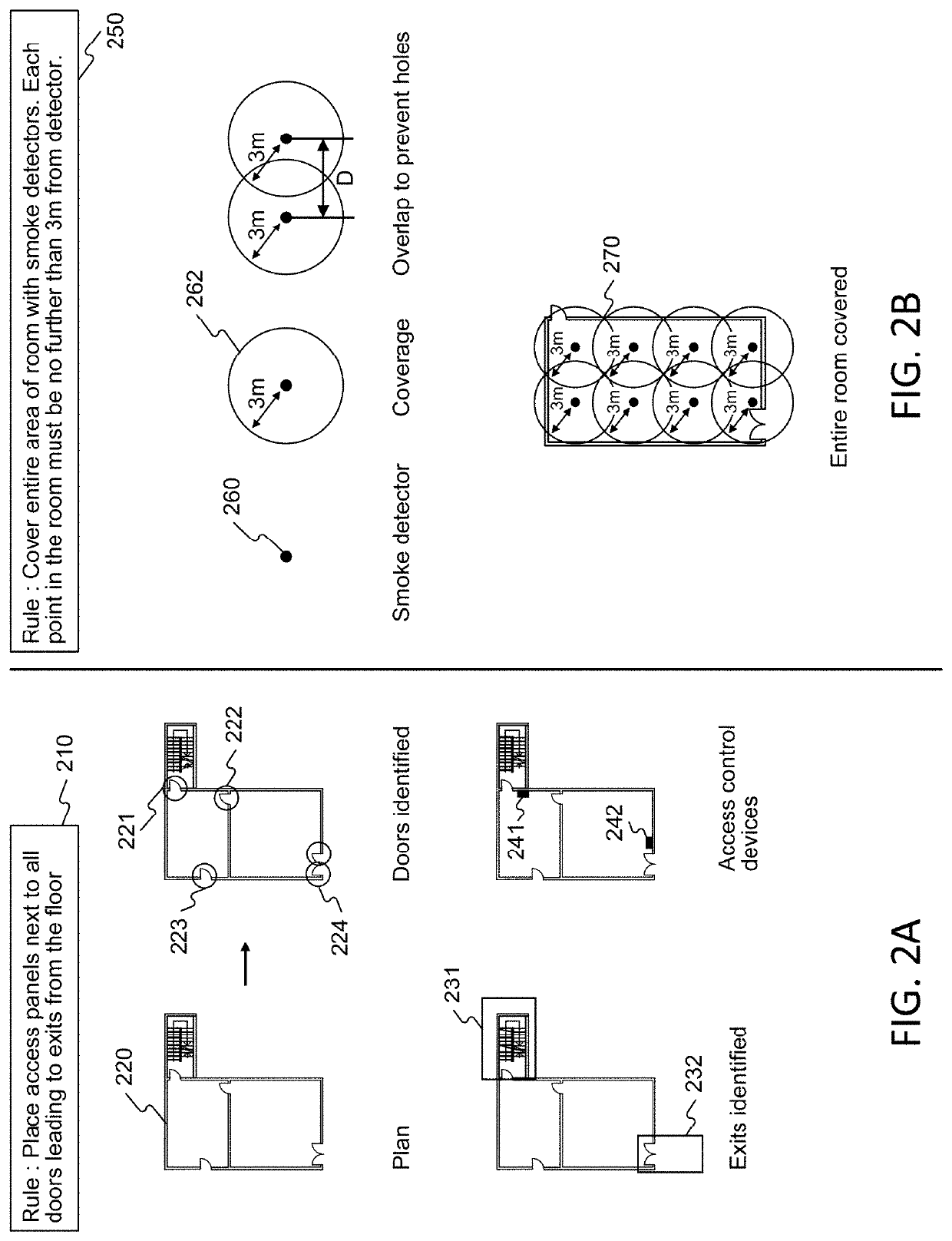

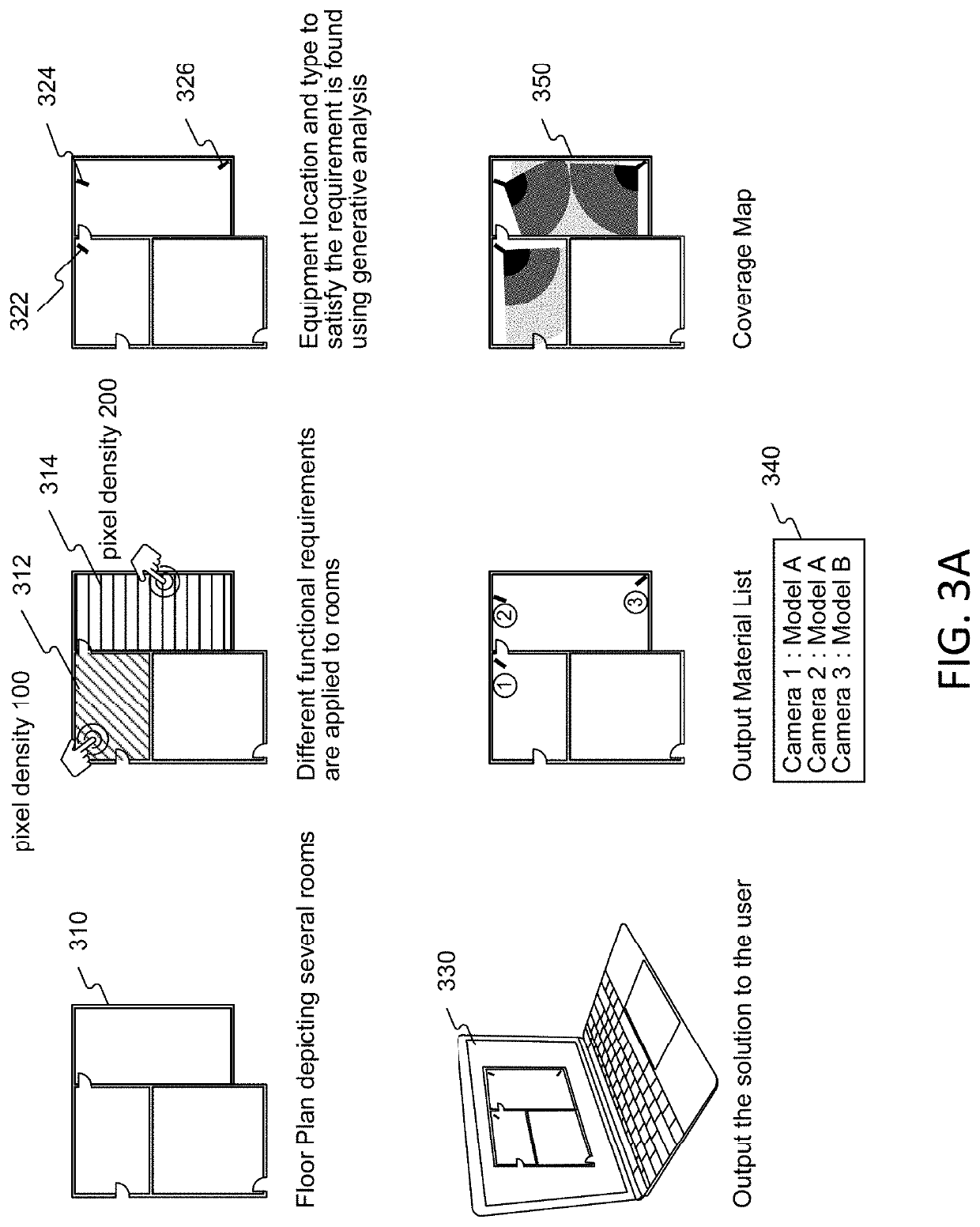

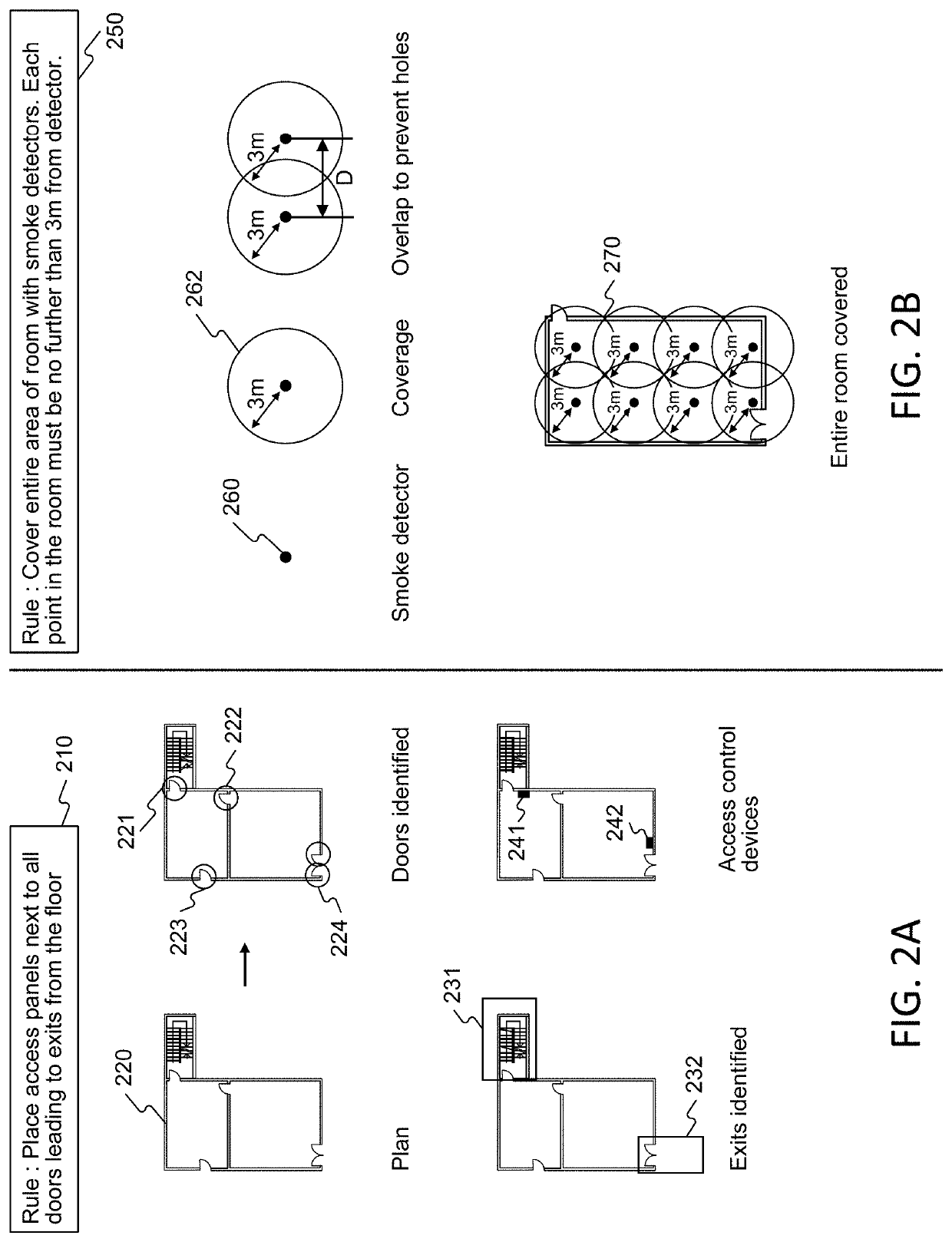

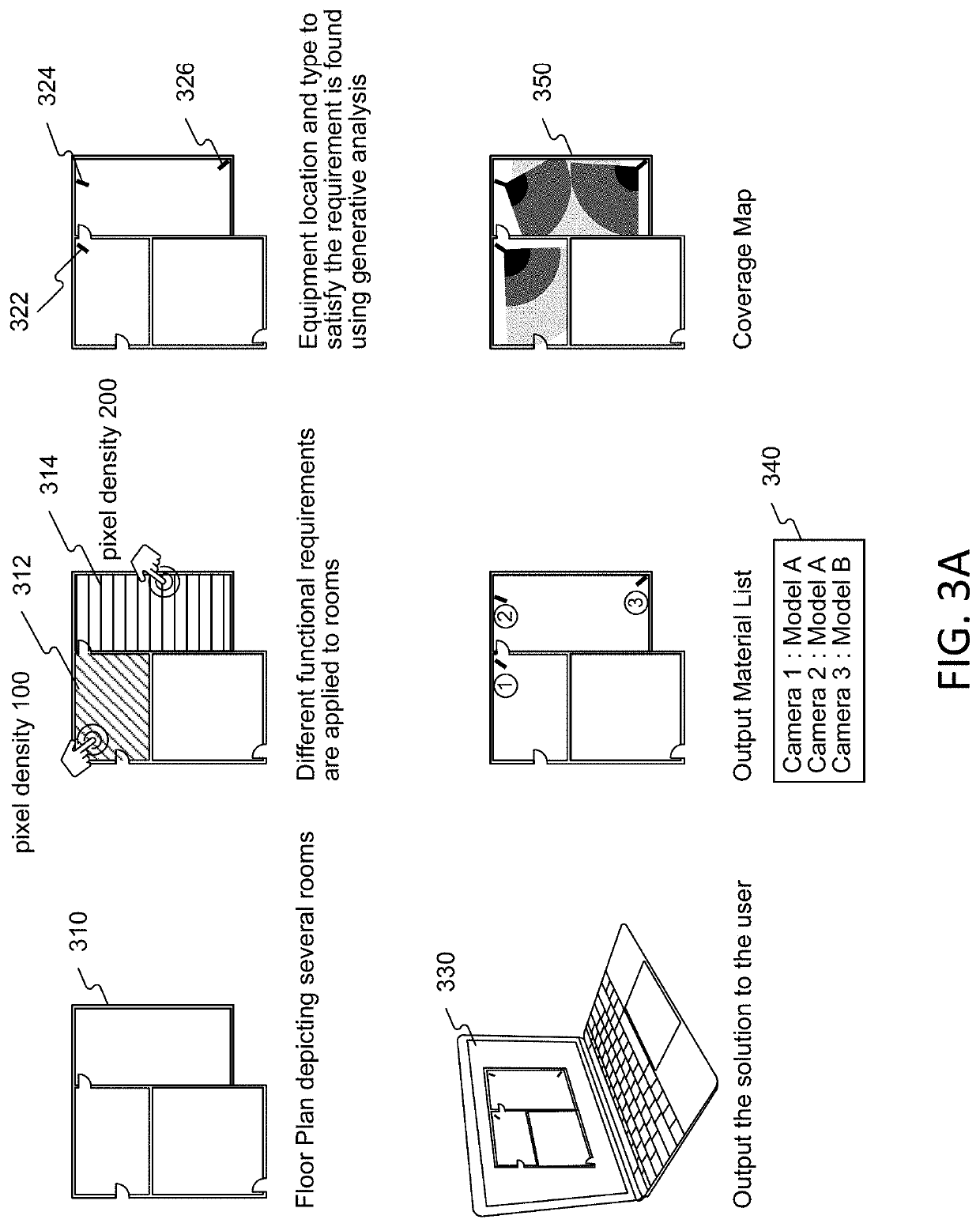

Structural design systems and methods for automatic selection of equipment and generation of wiring diagrams by modeling and simulation

Systems and methods for generating wiring diagrams for equipment are disclosed. The system may include at least one processor configured to perform operations that may include accessing a floor plan defining a plurality of rooms, receiving input associating at least one of a plurality of functional requirements with at least one room of the plurality of rooms, and accessing, in a data structure, technical specifications associated with electrical equipment. Operations may include selecting, from the data structure, a plurality of the technical specifications, generatively analyzing the at least one room in conjunction with the functional requirement and the selected technical specifications in order to select a piece of equipment for the at least one room and select an equipment placement location, accessing structural data associated with the at least one room, and generating a wiring diagram for the at least one room using the selected technical specifications and the structural data.

Owner:BEAMUP LTD

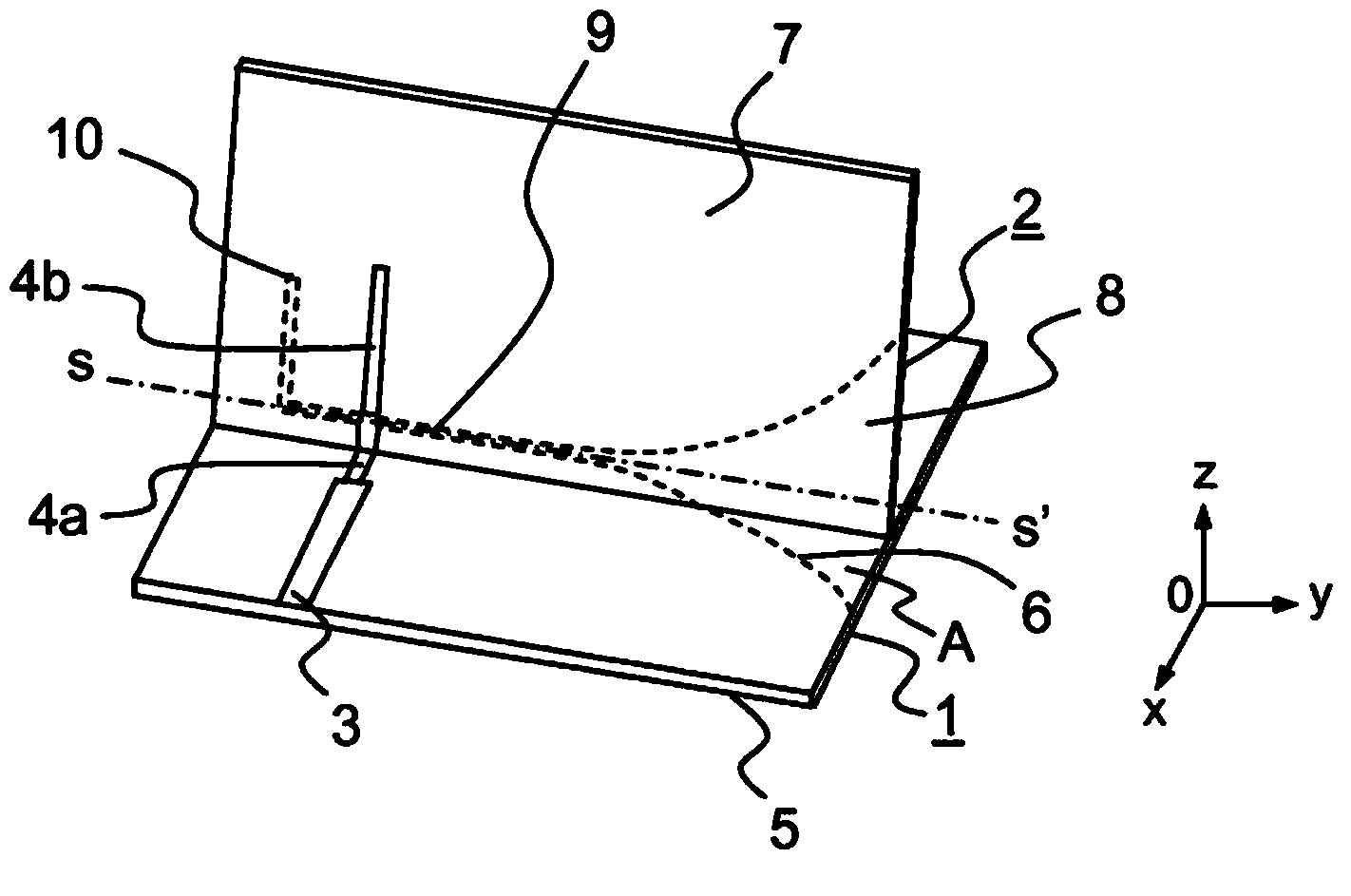

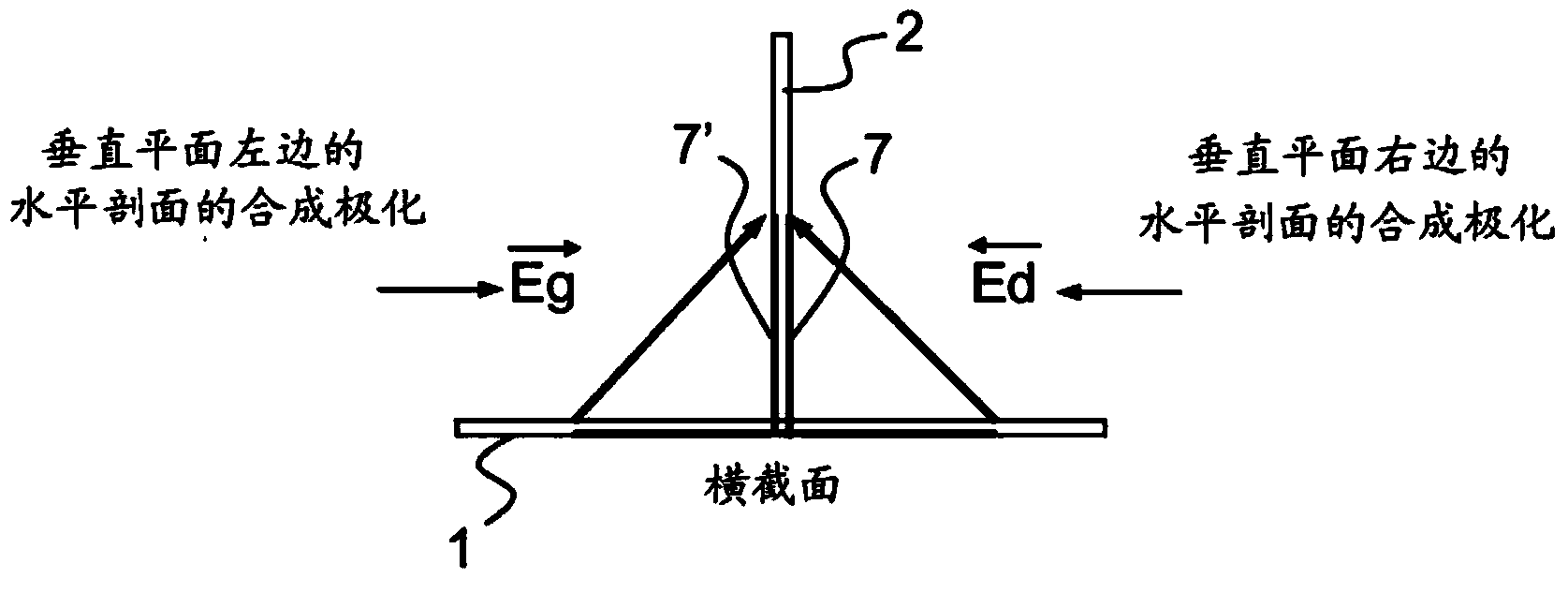

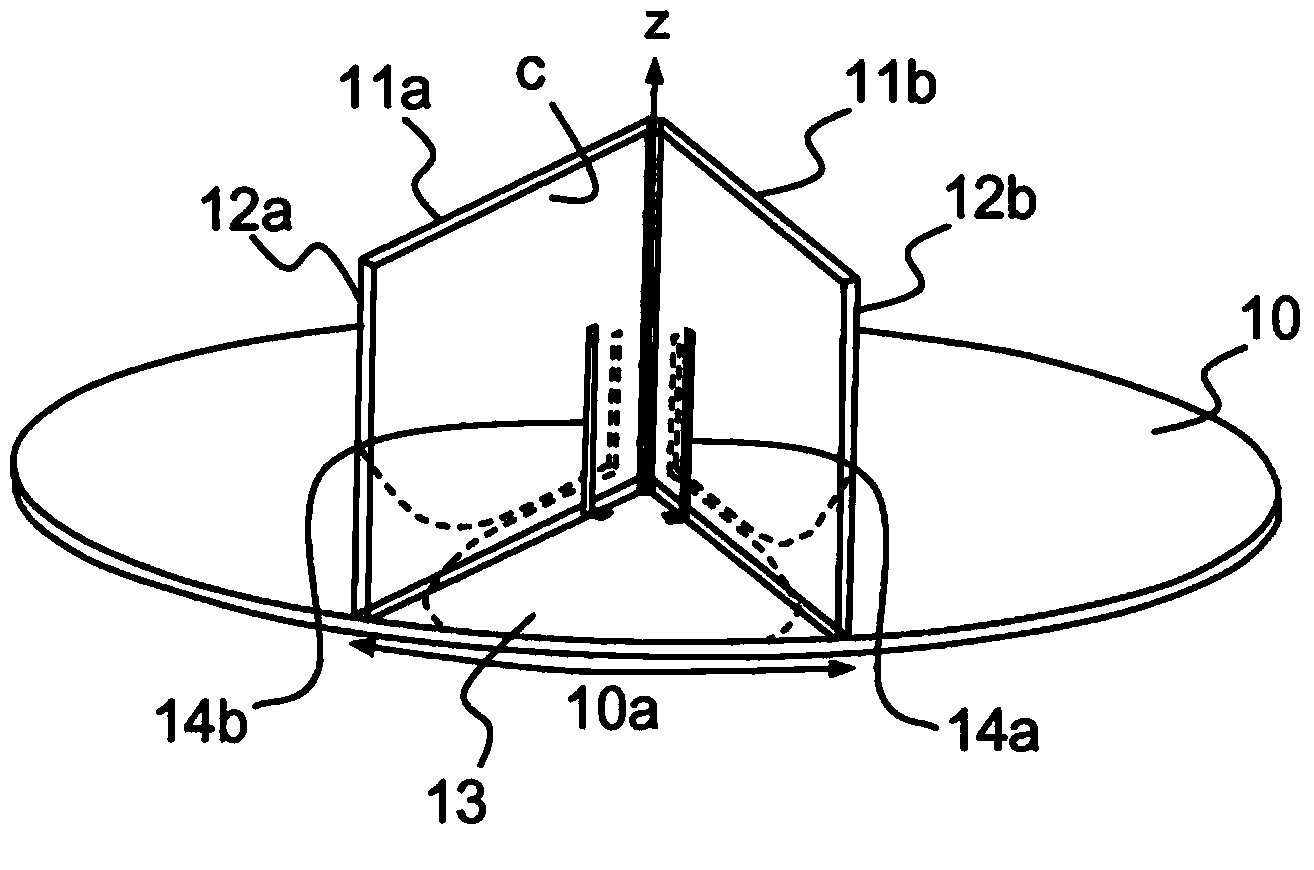

Printed slot-type directional antenna, and system comprising an array of a plurality of printed slot-type directional antennas

InactiveCN103597661AIndividually energised antenna arraysPolarised antenna unit combinationsEngineeringMechanical engineering

The present invention relates to a printed slot-type directional antenna. The invention also relates to antenna systems formed by arranging a plurality of such antennas in an array. The flared printed slot-type directional antenna includes a substrate having a floorplan, in which the slot is etched along a profile having a longitudinal axis, and a line for supplying power to the slot, and is characterized in that the substrate comprises at least one first and one second portion which are folded along an axis that is parallel to said longitudinal axis, and which form an angle A relative to one another.

Owner:THOMSON LICENSING SA

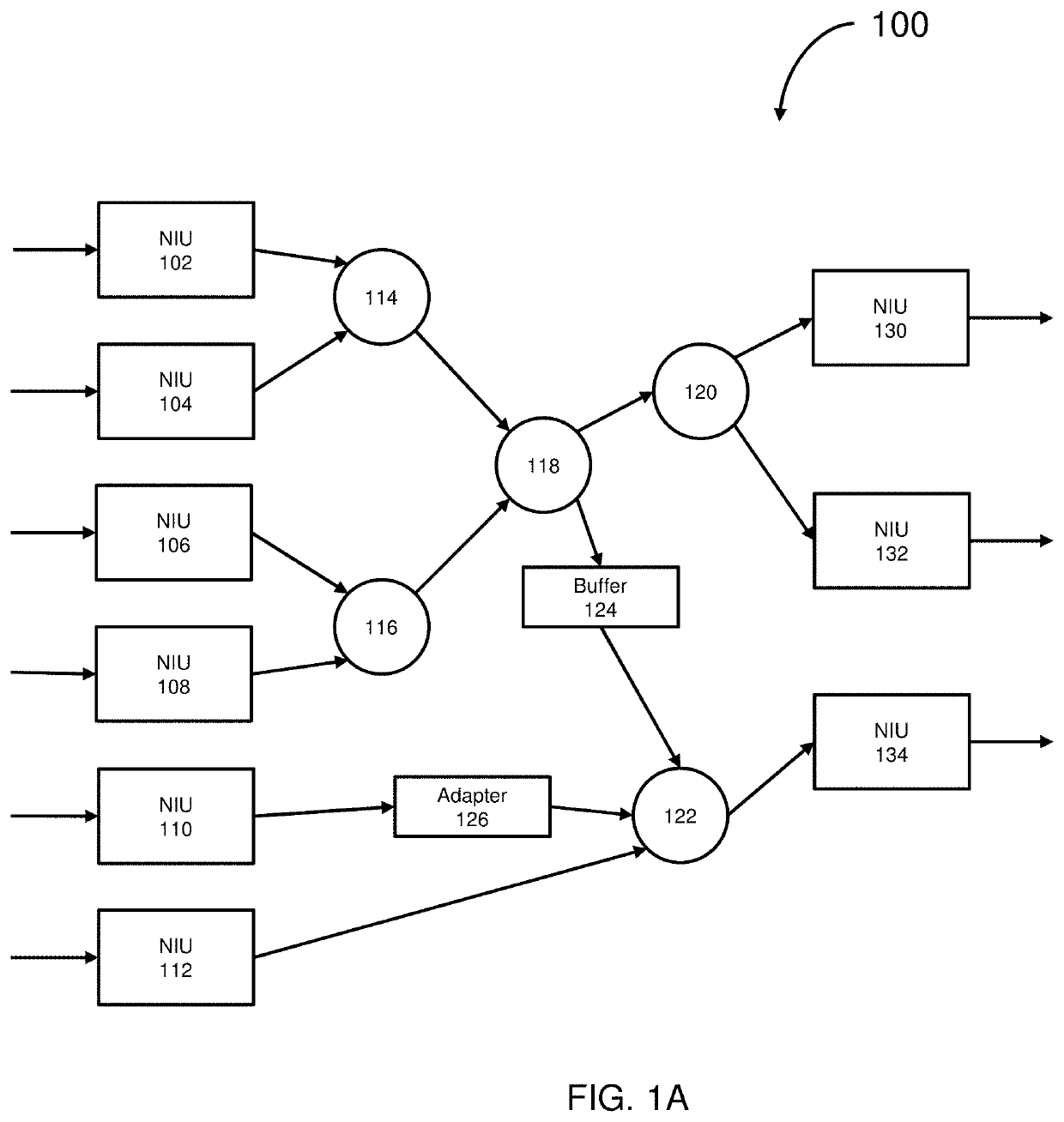

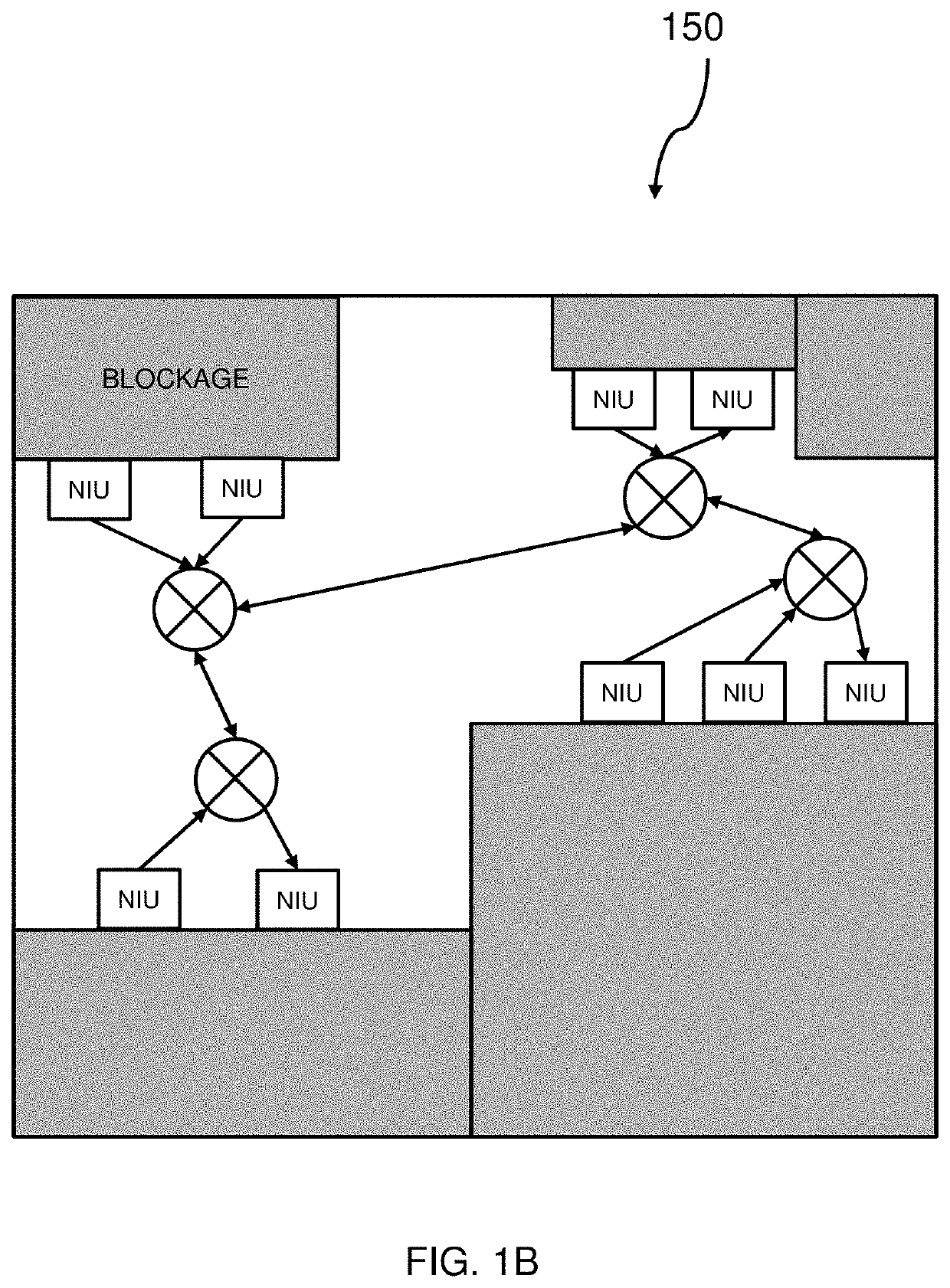

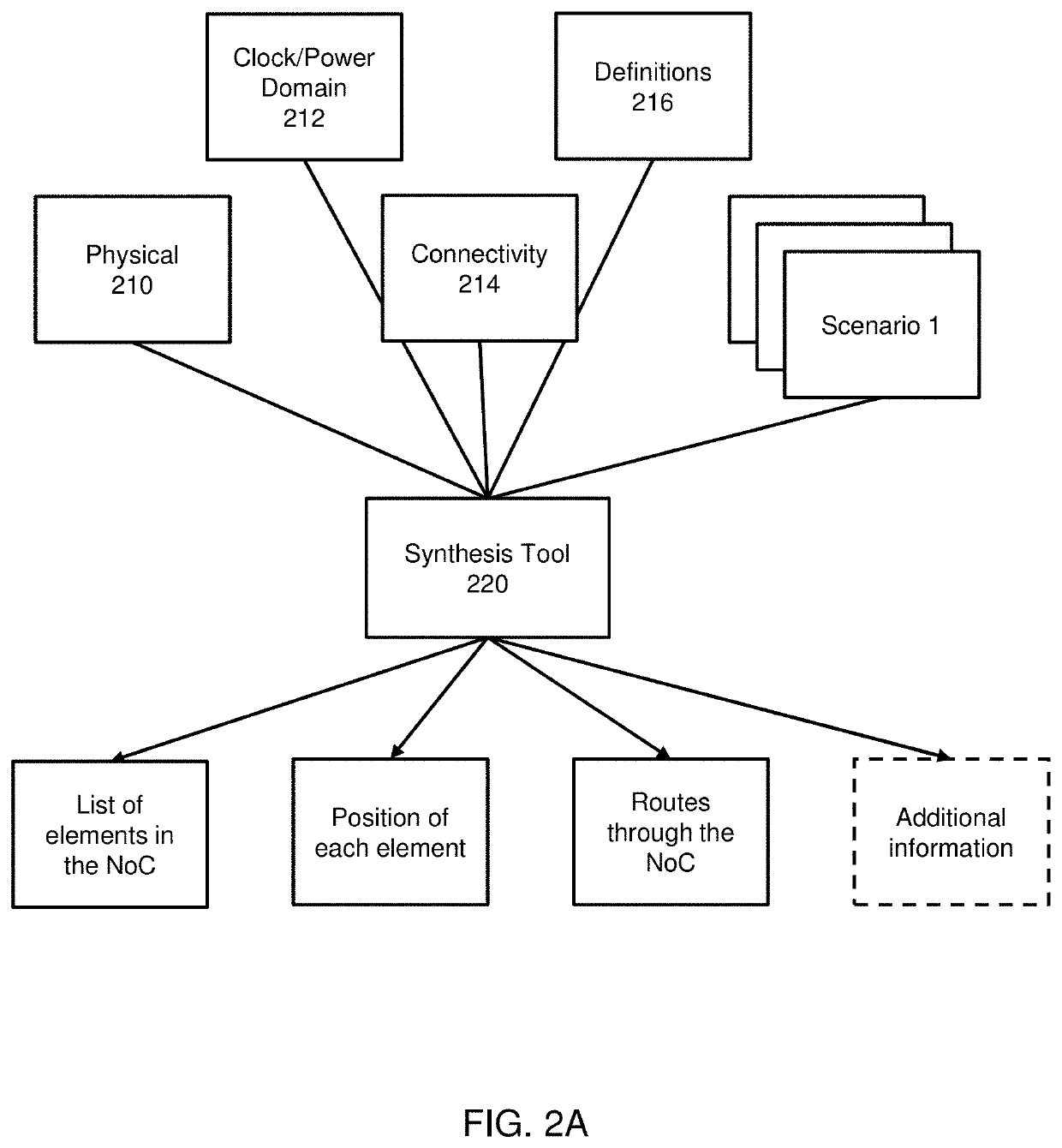

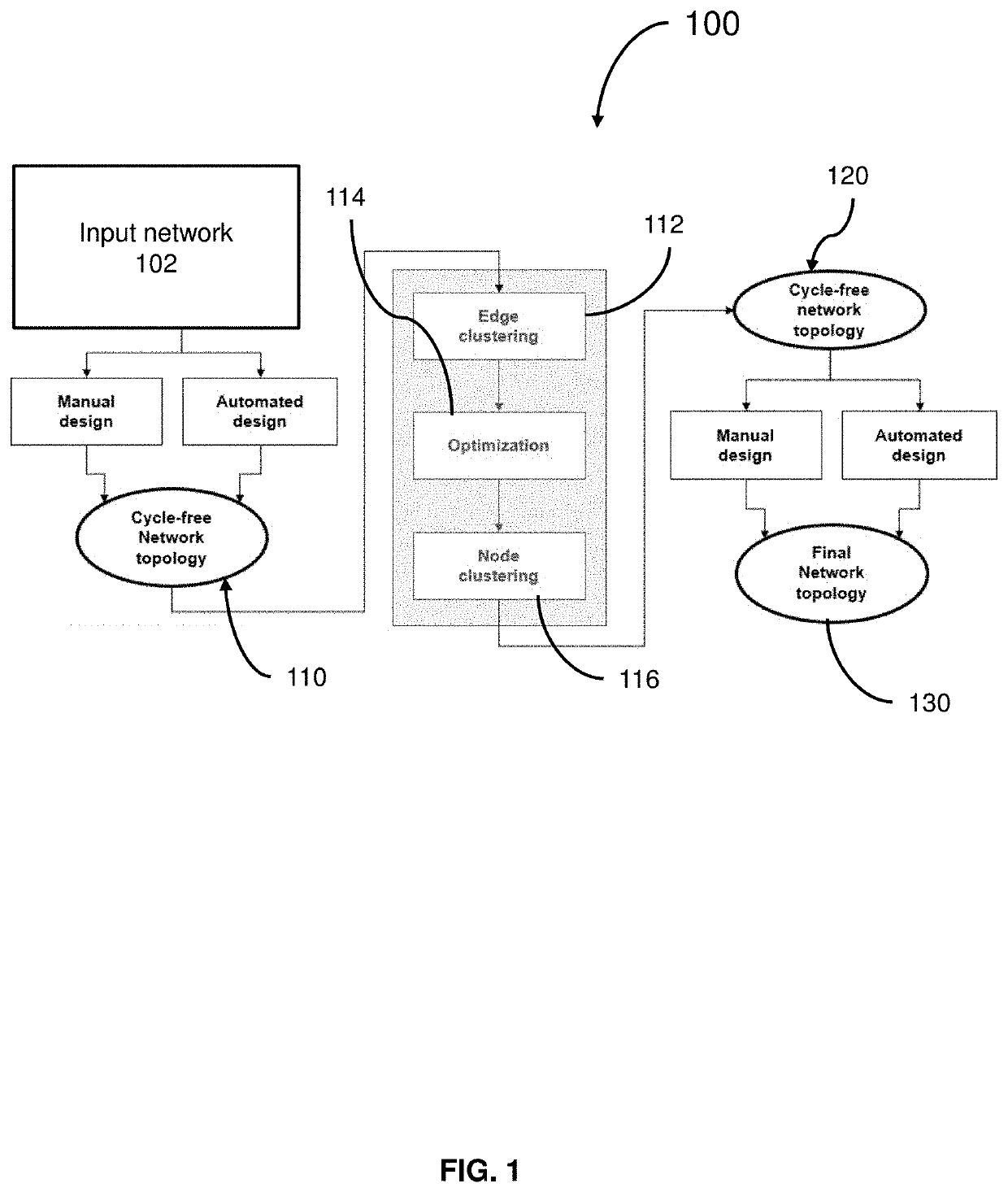

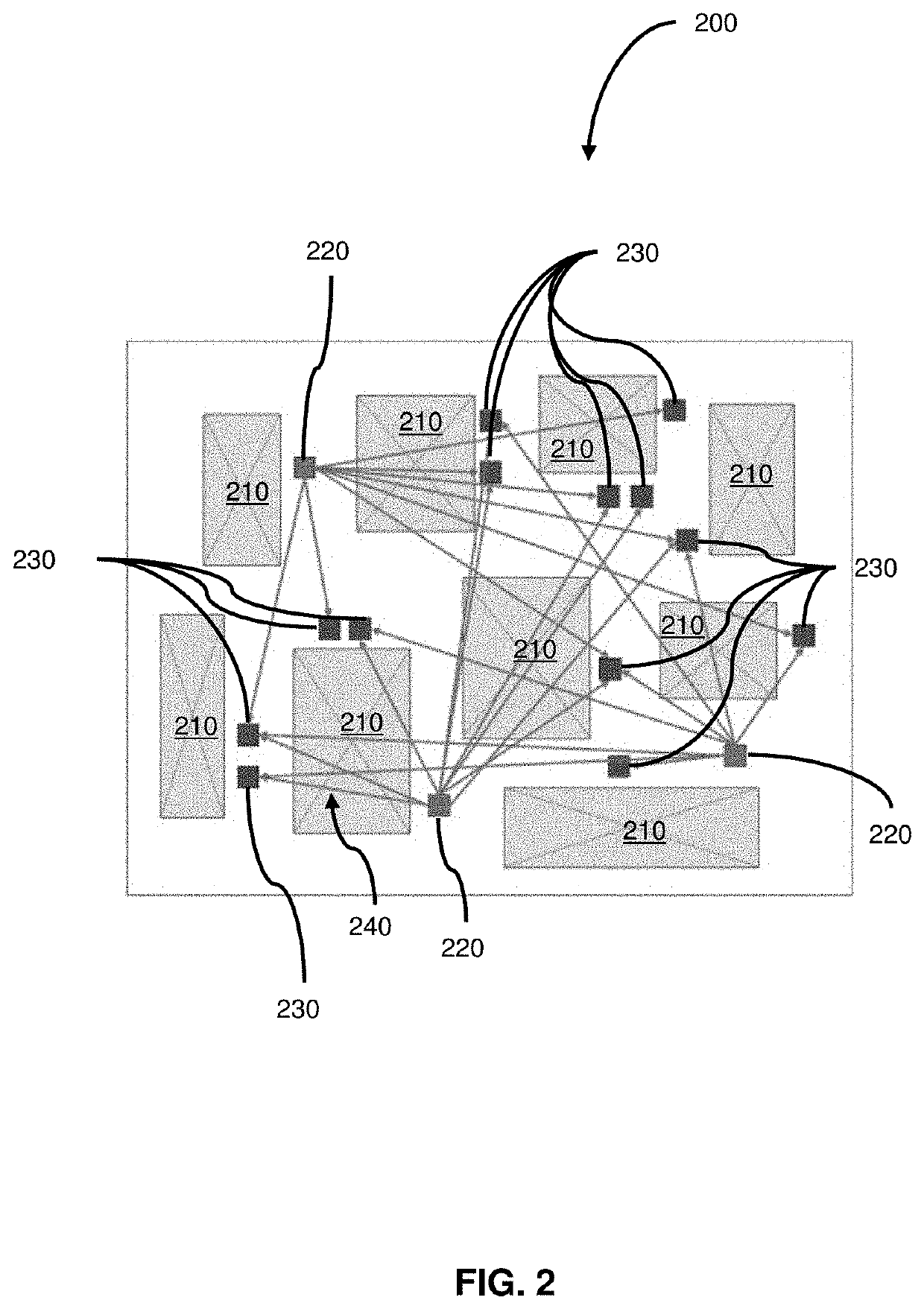

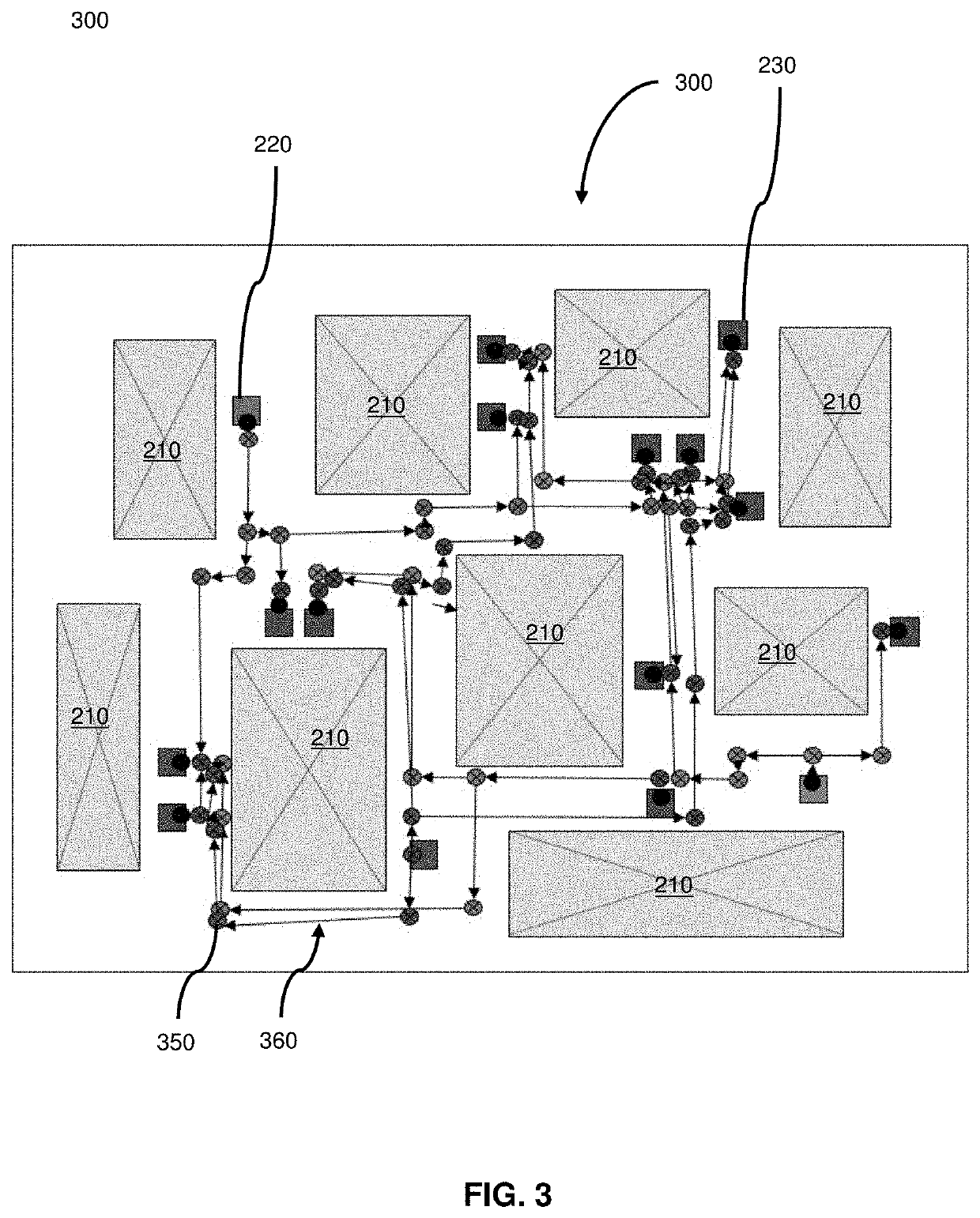

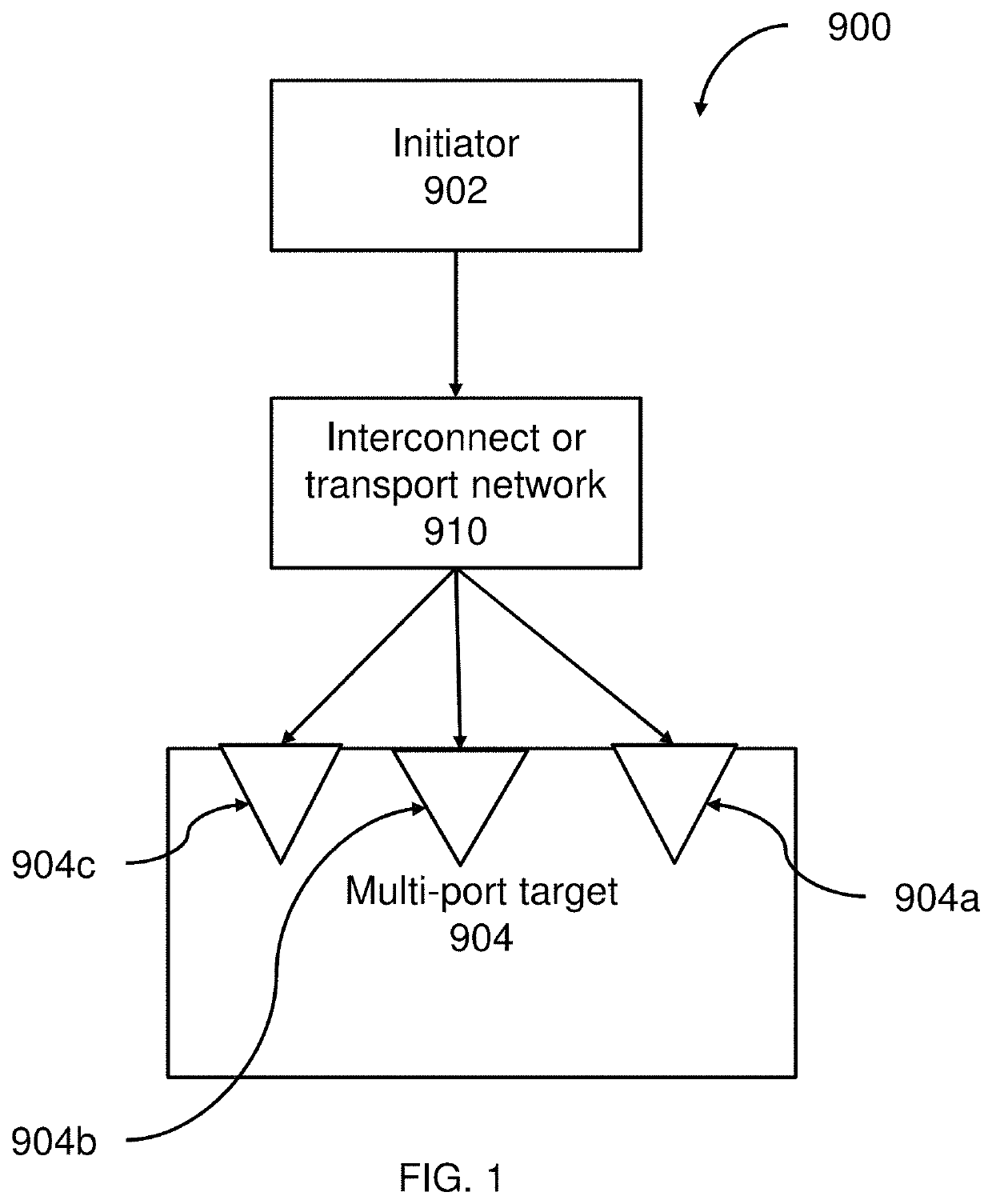

Physically aware topology synthesis of a network

ActiveUS11121933B2Simplify the design processMultiple digital computer combinationsCAD circuit designComputer networkEngineering

System and methods are disclosed for synthesis of network, such as a network-on-chip (NoC), to generate a network description. The system generates a NoC from a set of physical constraints and performance constraints as well as a set of inputs to a sequencer. The system produces the NoC with all its elements. The resulting output includes placement of the elements on a floorplan of a chip that represents the network, such as the NoC.

Owner:ARTERIS

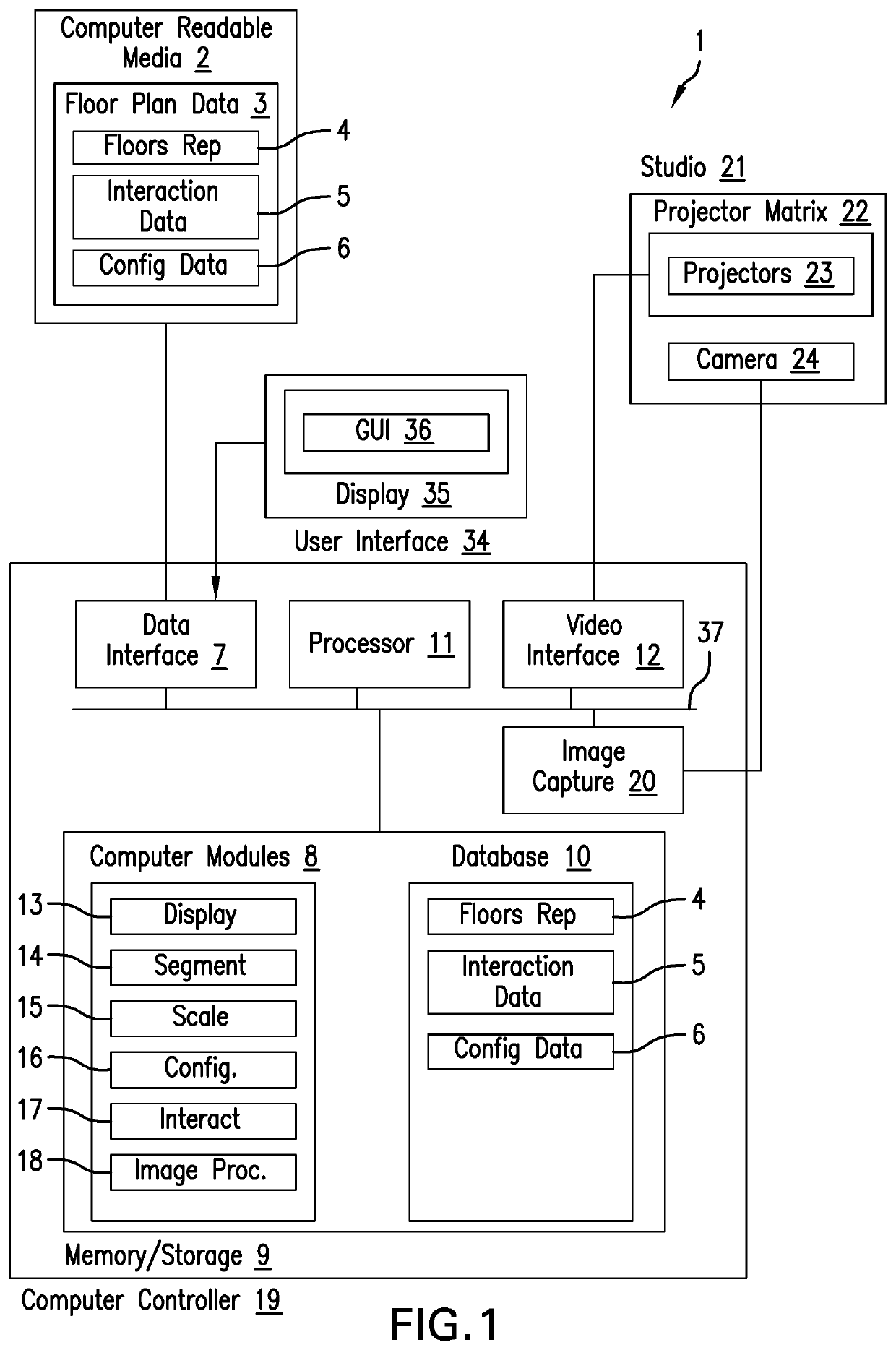

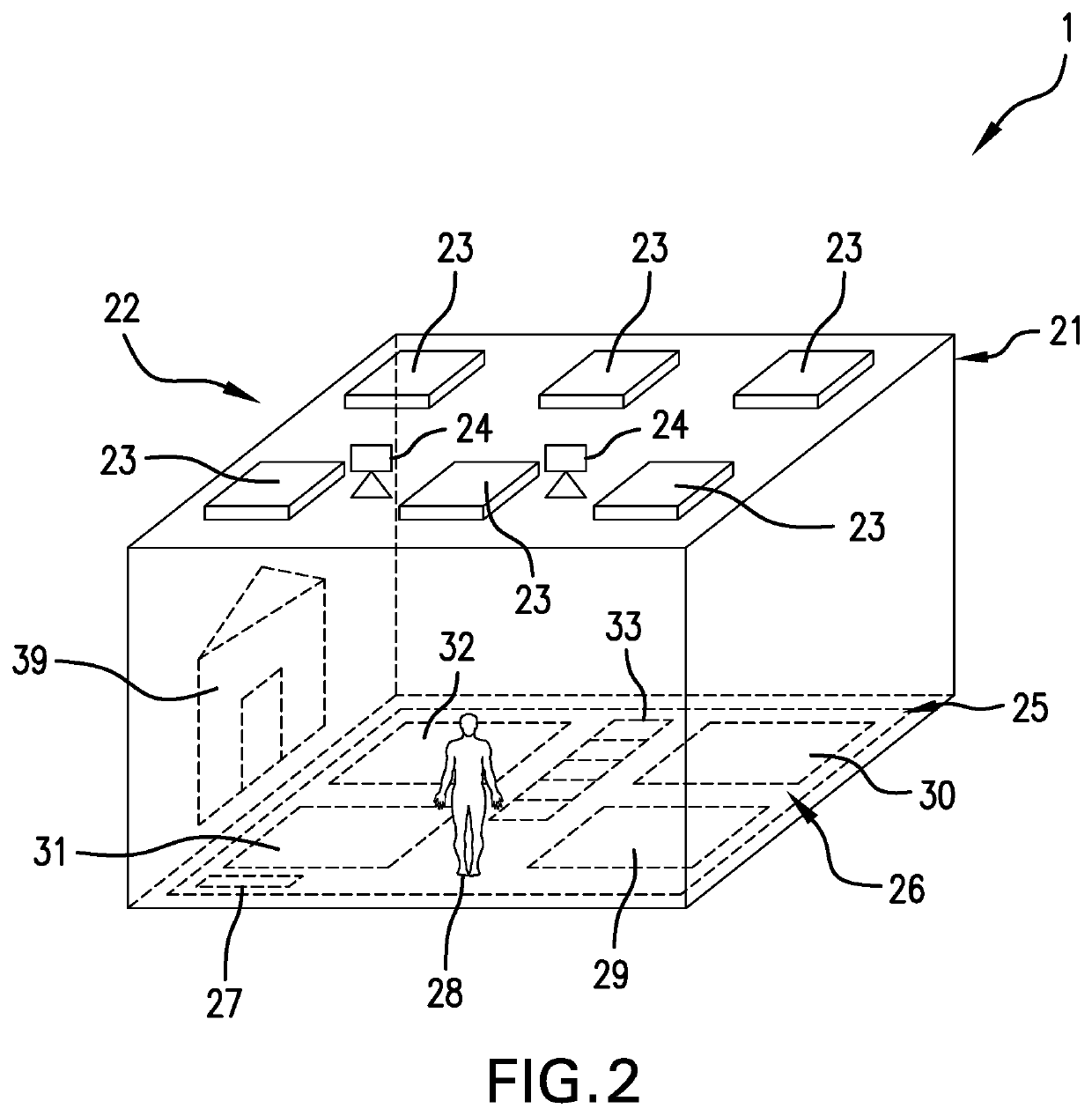

Floorplan visualisation system

ActiveUS10861241B2Accurate measurementGeometric CADInput/output for user-computer interactionComputer graphics (images)Engineering

There is provided a floorplan visualisation system comprising a visualisation studio; a matrix of ceiling mounted edge-blended overlapping projectors projecting onto a floor surface of the visualisation studio; a controller computer comprising: a user interface; and a video output operably coupled to the matrix of projectors for controlling the video projected from such. In use the controller computer is configured for: receiving floor plan representative data; segmenting the floor plan representation data into a plurality of display segments; and outputting the plurality of display segments to respective projectors, and wherein the controller computer is configured to receiving scale adjustment commands via a scale adjustment control of the user interface and adjusting the scale of the segments to display a floor plan representation on the floor surface to a real world scale.

Owner:GHALEB CHRISTOPHER

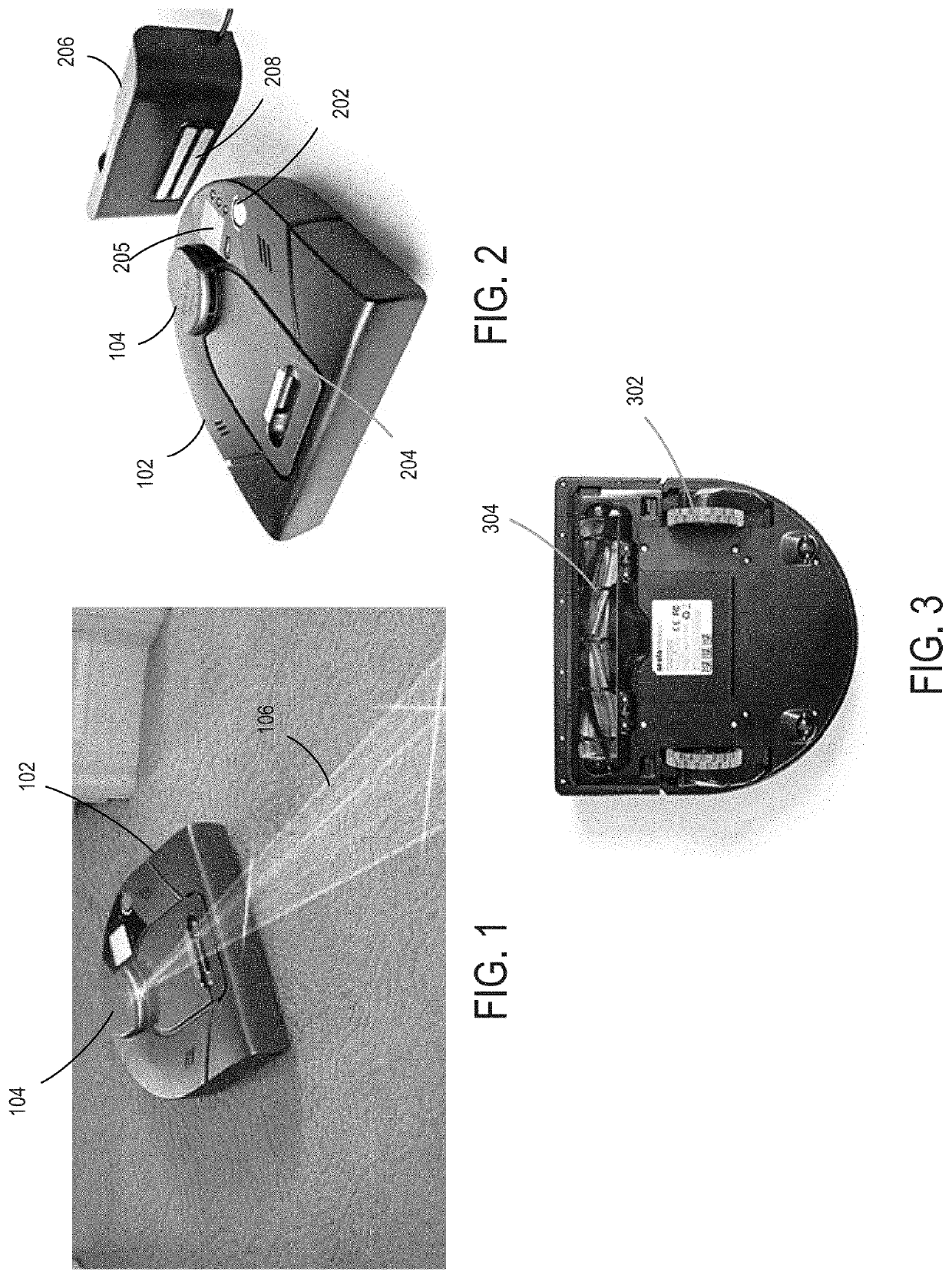

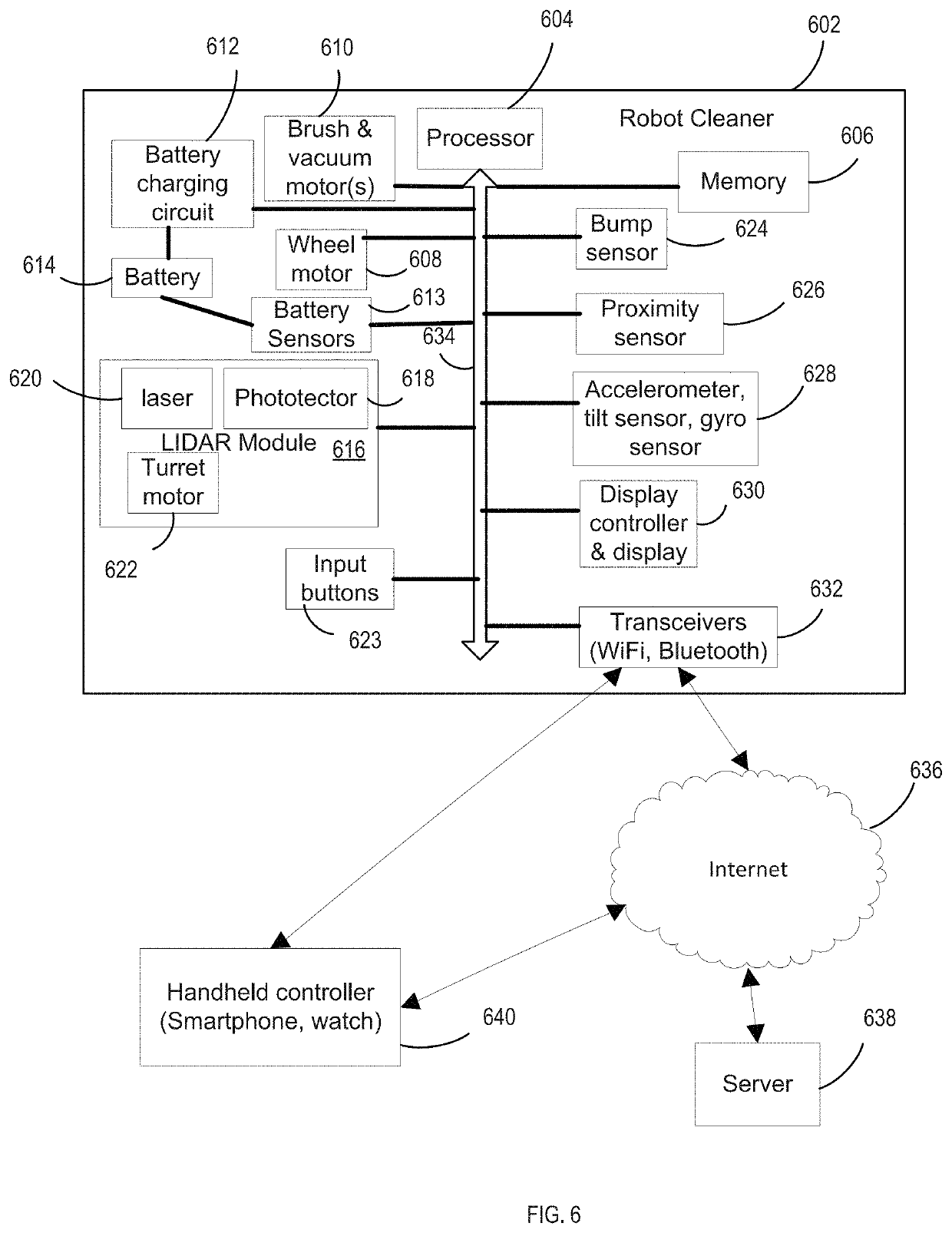

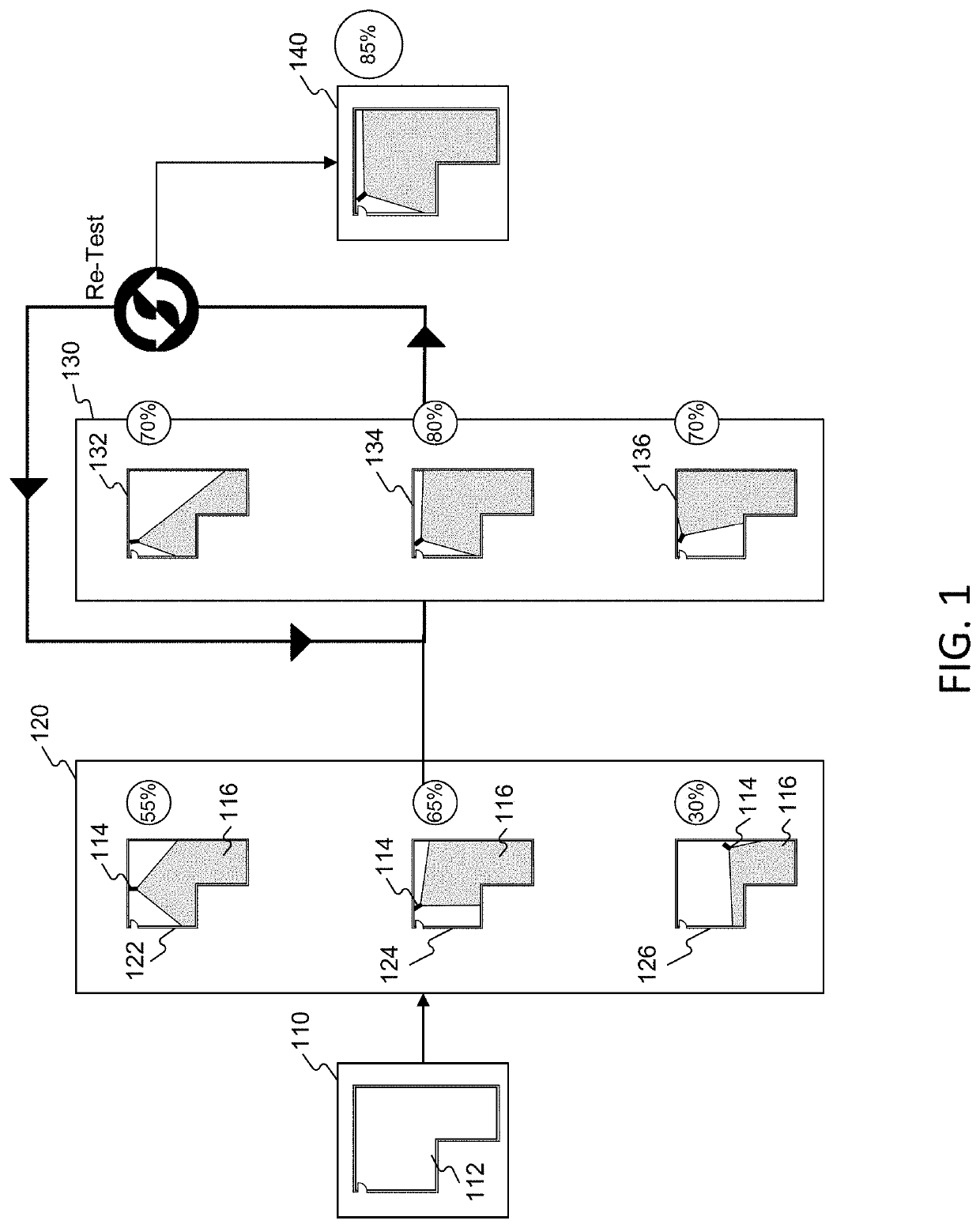

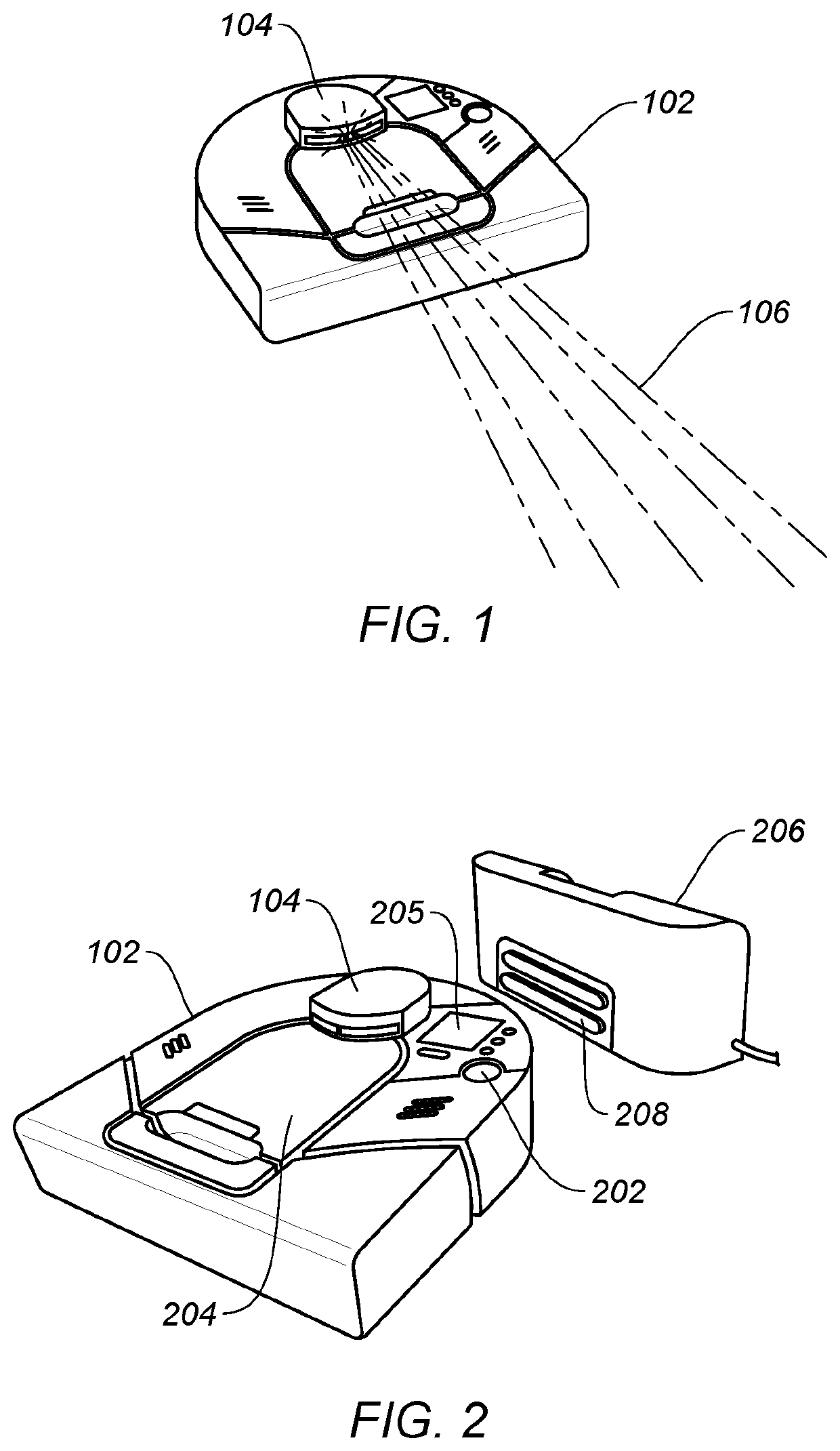

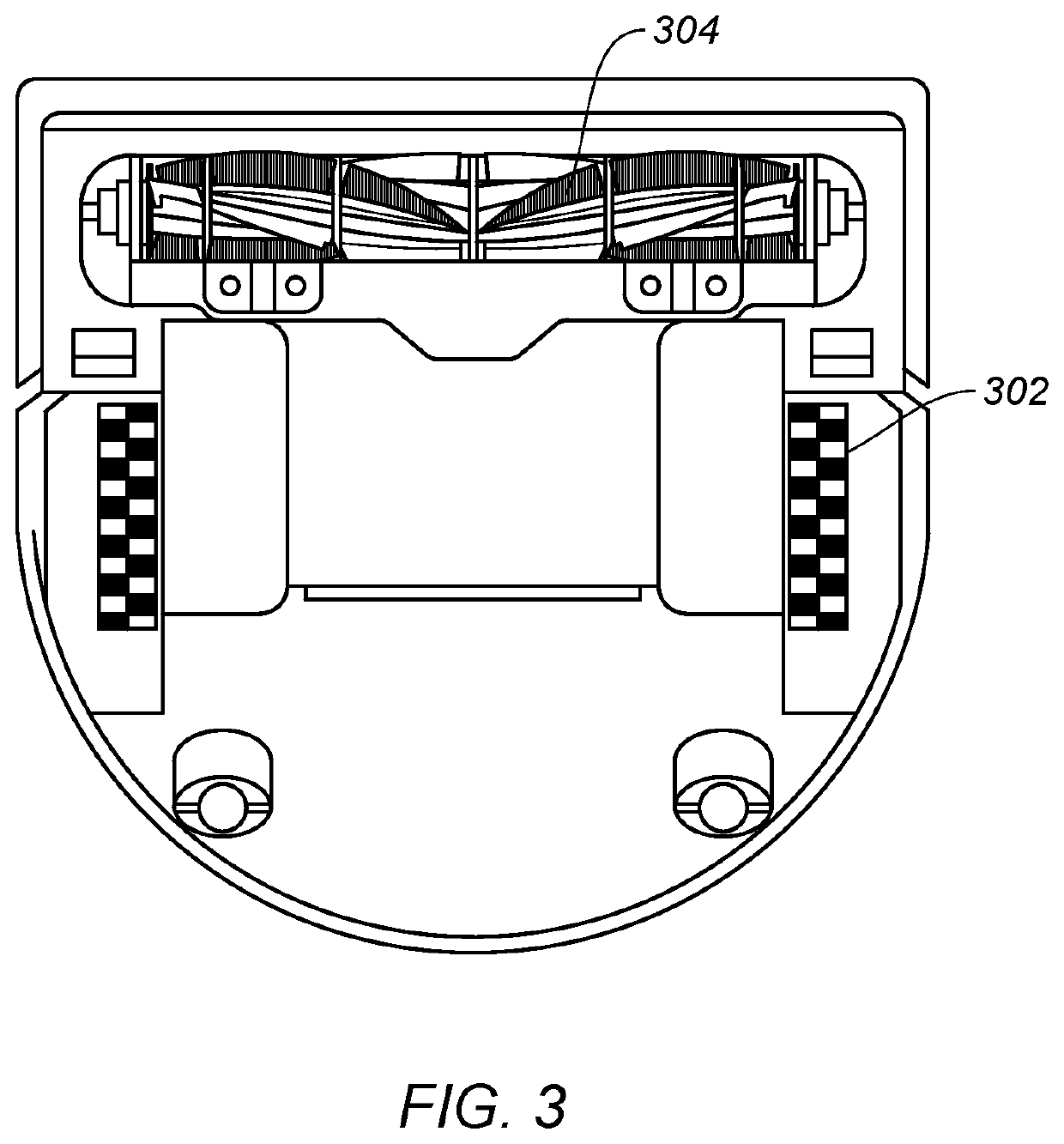

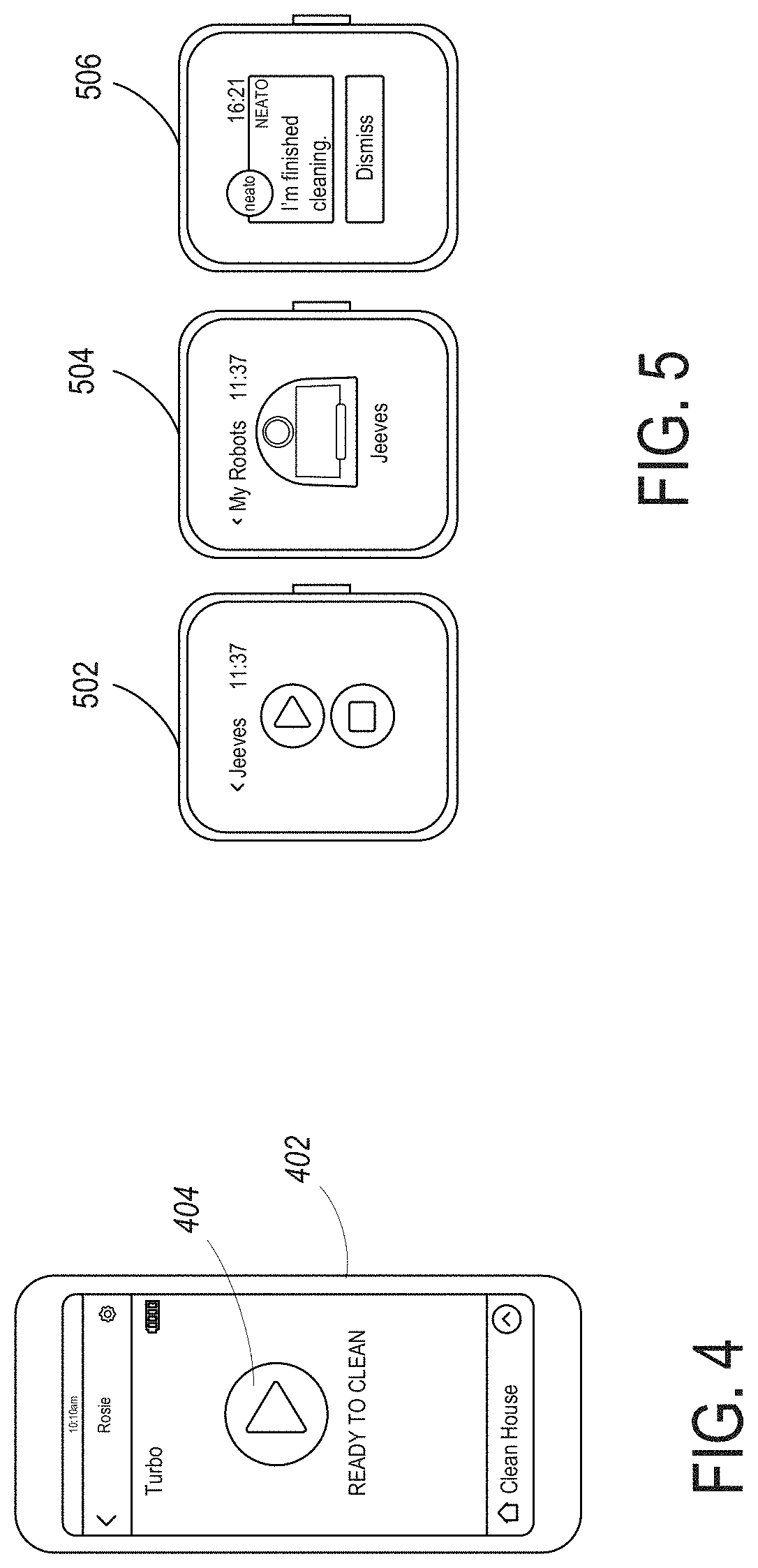

Automatic Recognition of Multiple Floorplans by Cleaning Robot

ActiveUS20200019169A1Automatic obstacle detectionAutonomous decision making processSimulationComputer vision

In one embodiment, a cleaning robot stores multiple floorplans. The robot automatically determines which floorplan it is in by localizing and trying to match its detected environment to the stored map. The best fit is the map for the current floor. If there is no match above a confidence threshold, the robot assumes it is a new floor or the floorplan has changed (e.g., furniture has moved), and the robot initiates a discovery mode to map the floorplan and add it to the robot's memory.

Owner:VORWERK & CO INTERHOLDING GMBH

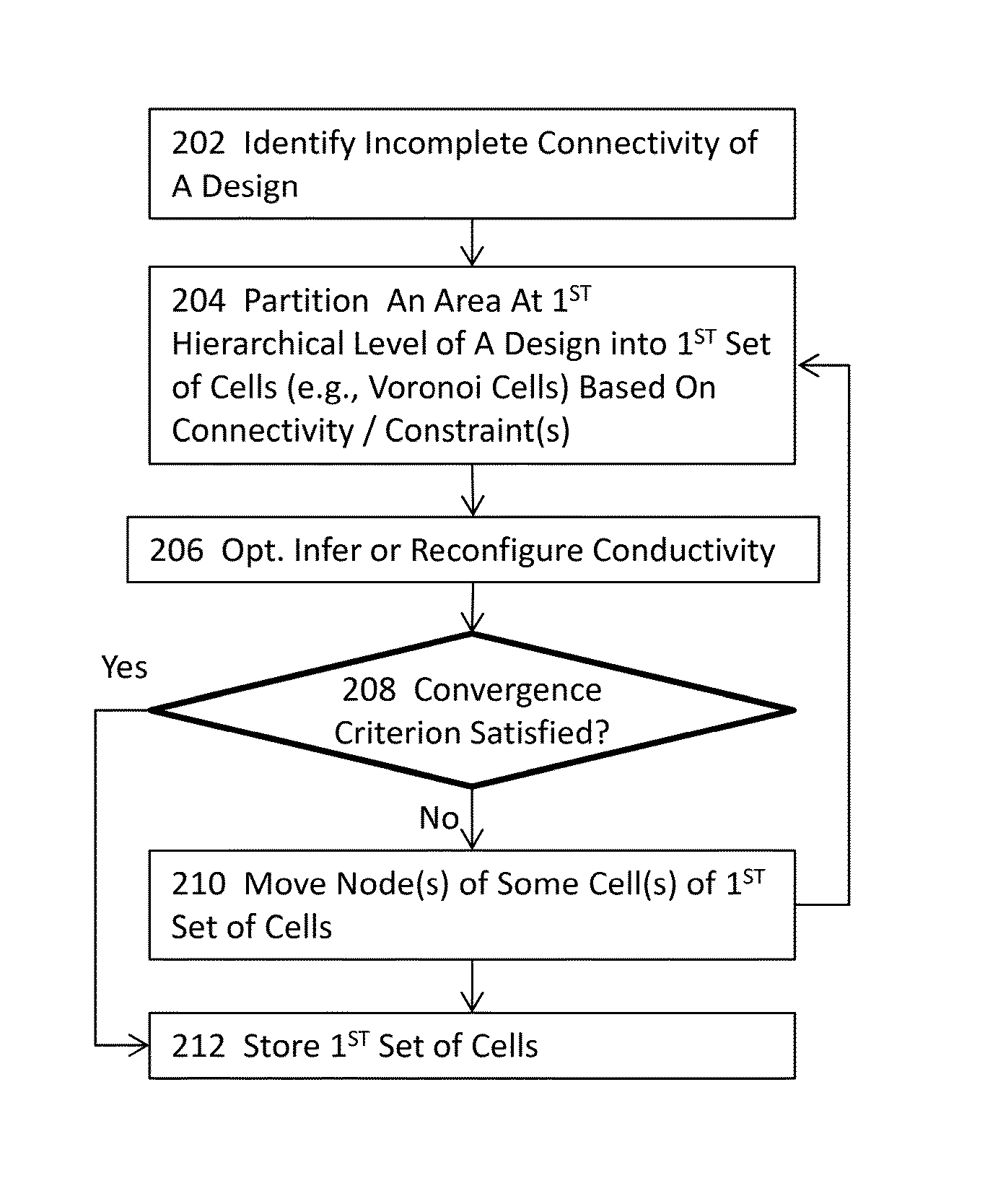

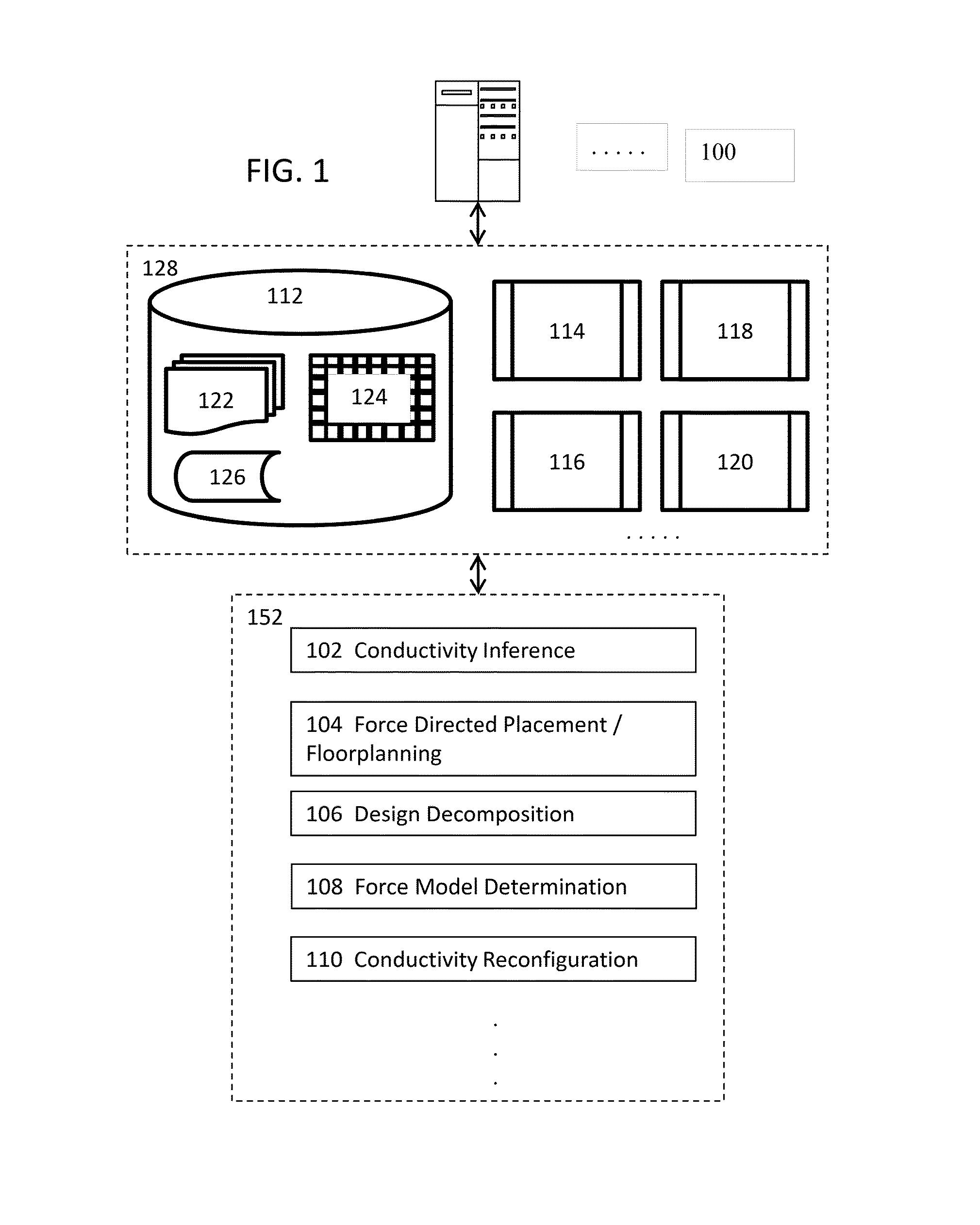

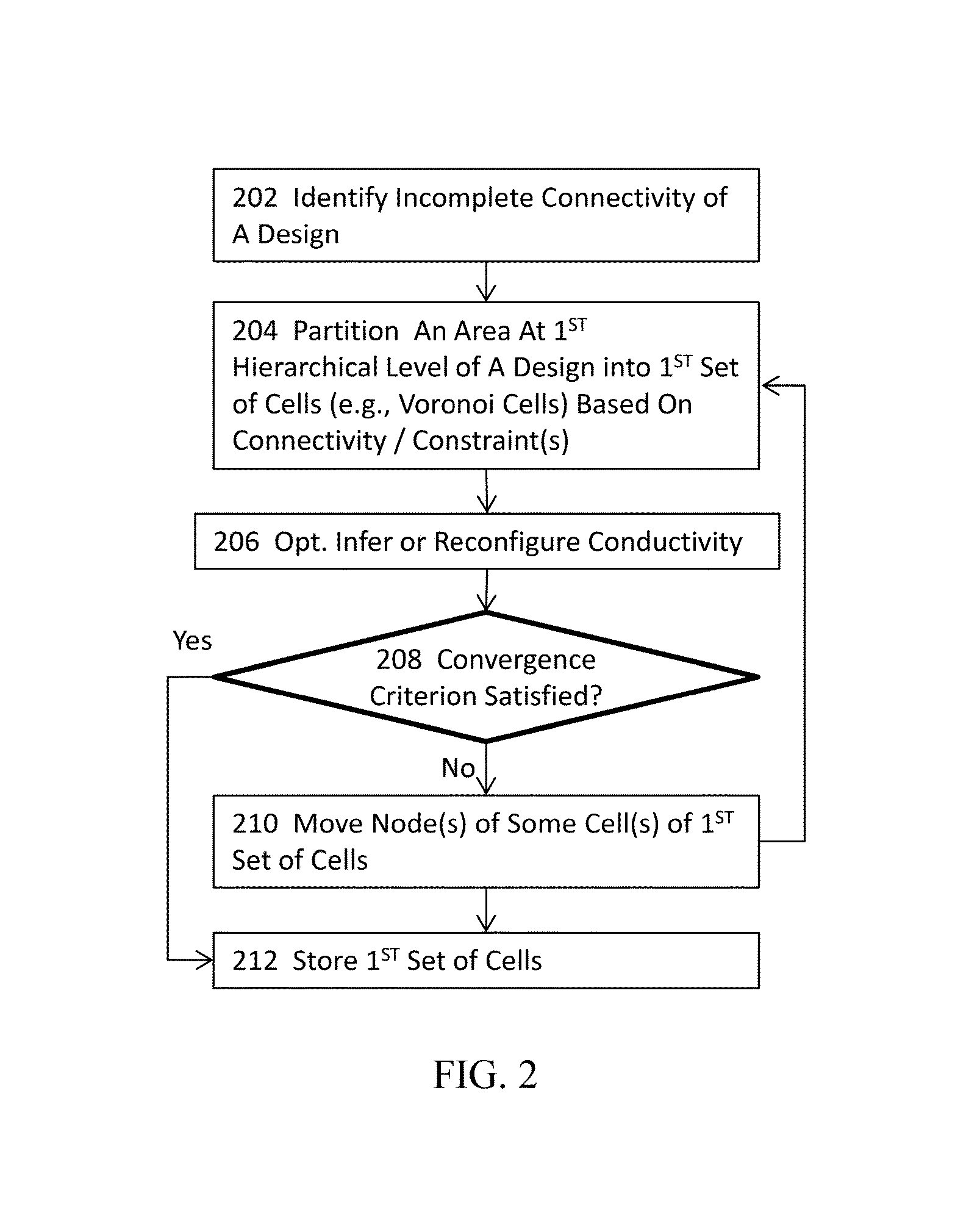

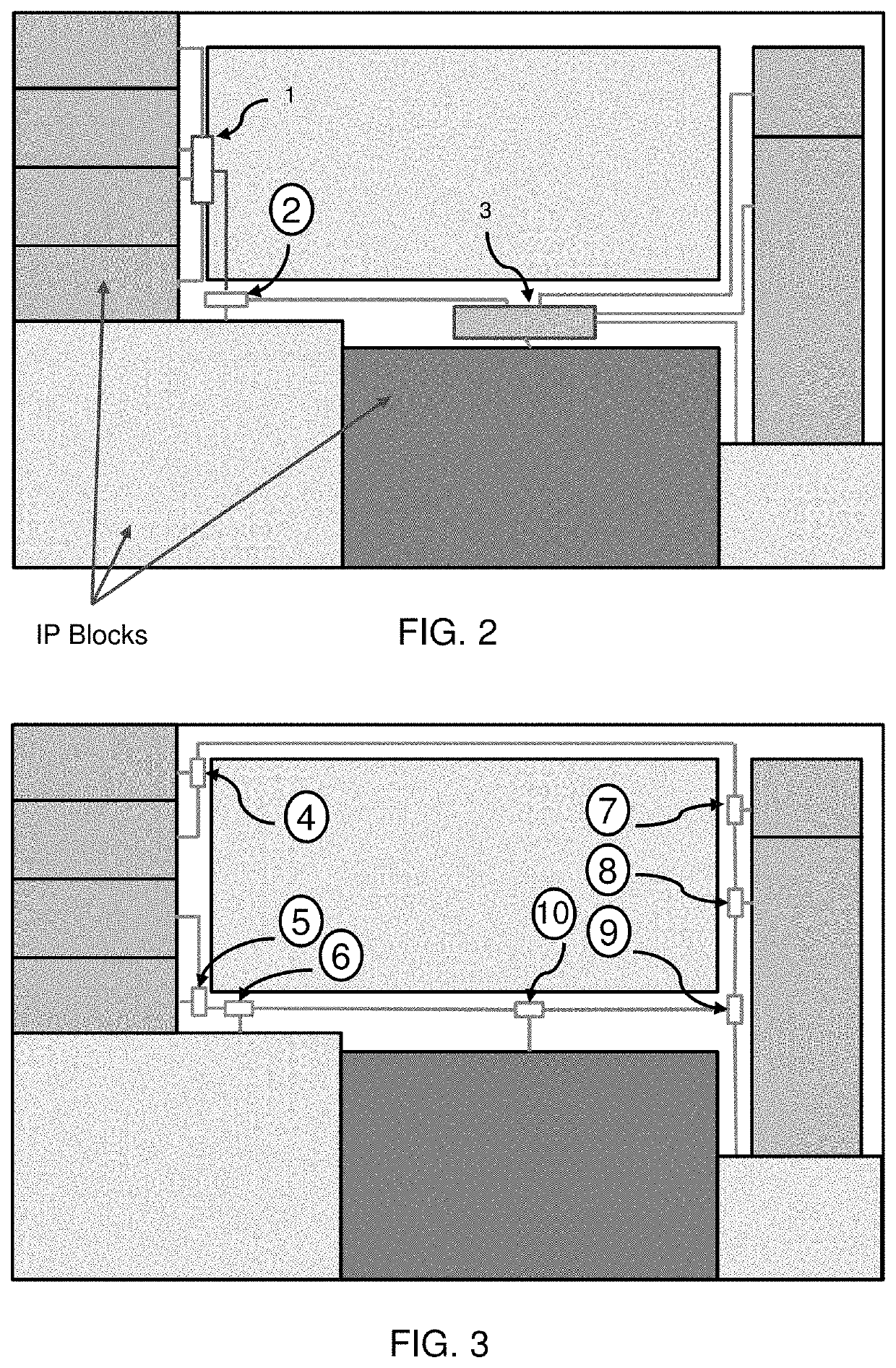

Methods, systems, and articles of manufacture for implementing physical design decomposition with custom connectivity

InactiveUS8918751B1Computer aided designSpecial data processing applicationsNODALComputer architecture

Disclosed are methods, systems, and articles of manufactures for implementing physical design decomposition with custom conductivity by identifying custom, incomplete conductivity for an electronic design, partitioning a physical design space multiple non-overlapping cells, and iteratively moving at least some of the nodes of these multiple cells to generate a floorplan or a placement layout until one or more convergence criteria are satisfied while maintaining the custom, incomplete conductivity. The floorplan or a placement layout generated resembles the final floorplan obtained through a floorplanner or the final placement layout through a placement tool without requiring that complete conductivity information be provided to the floorplanner or placement tool.

Owner:CADENCE DESIGN SYST INC

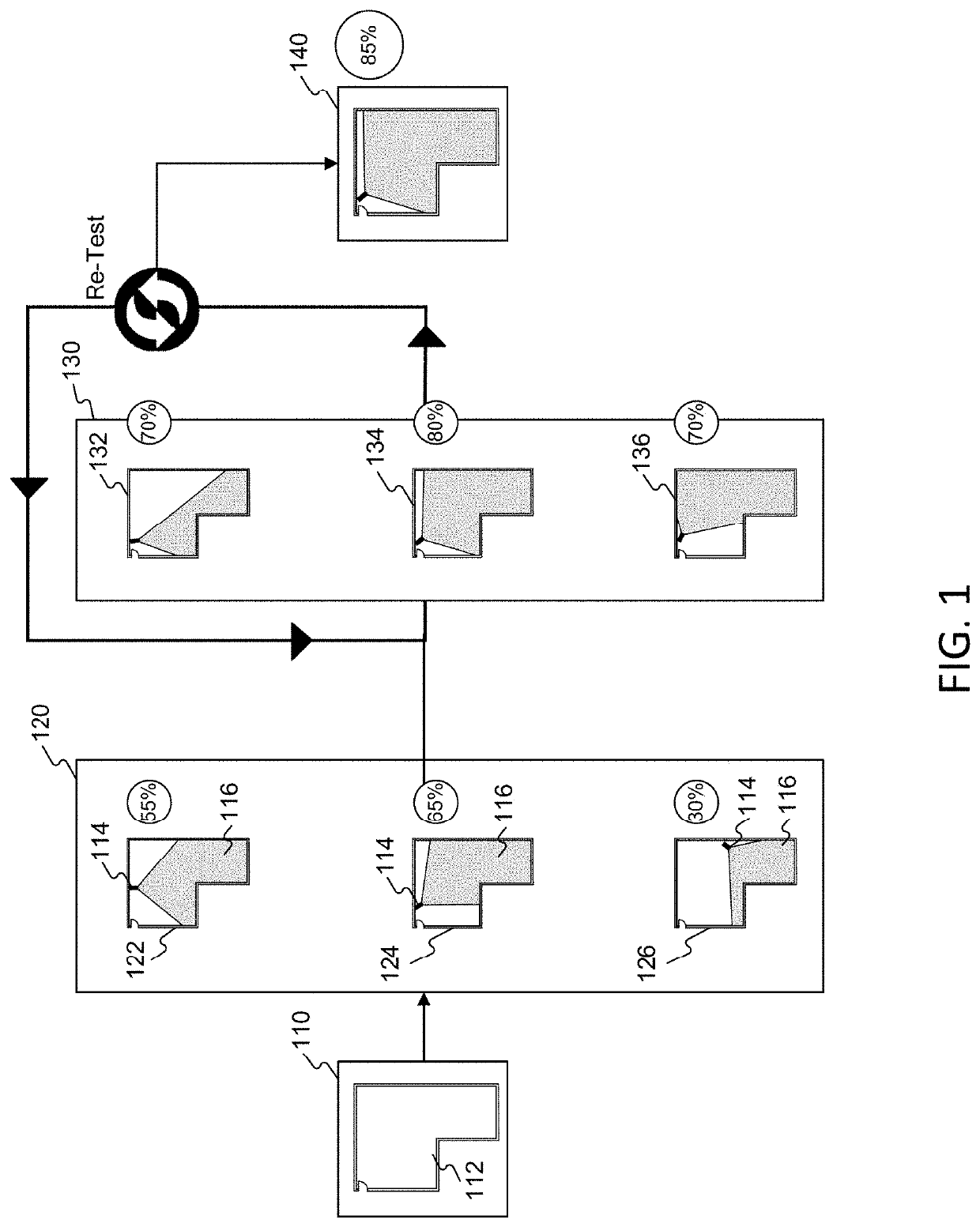

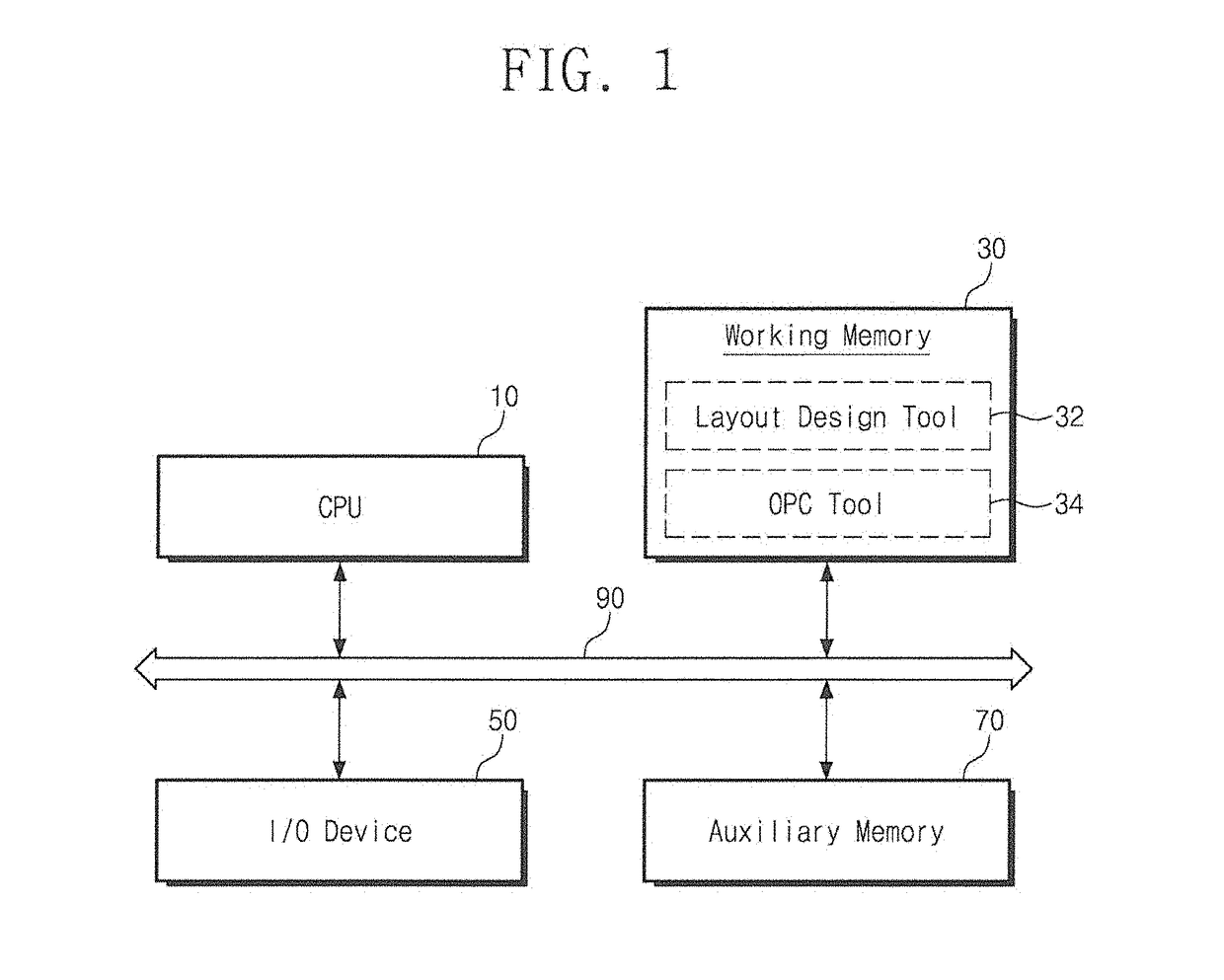

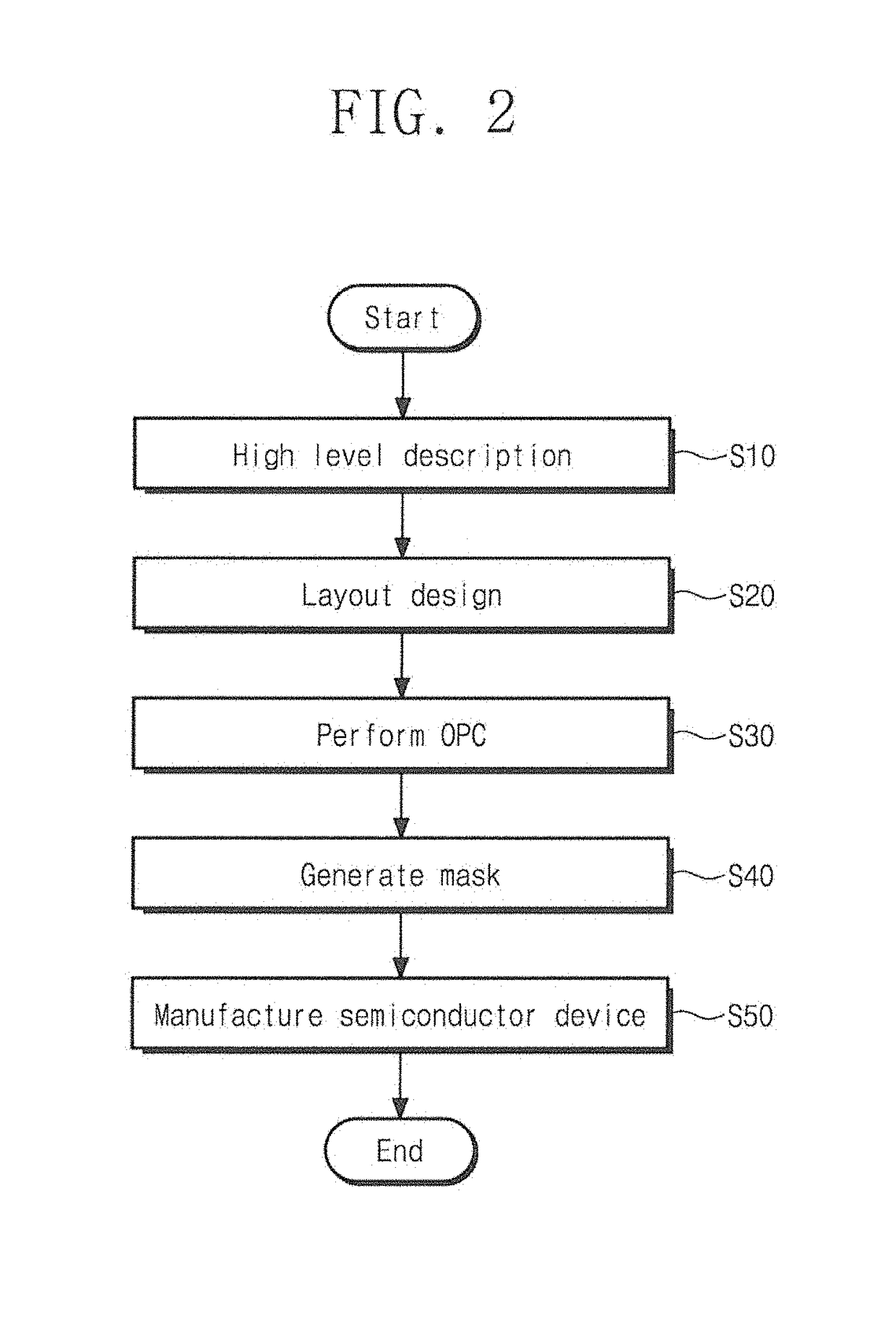

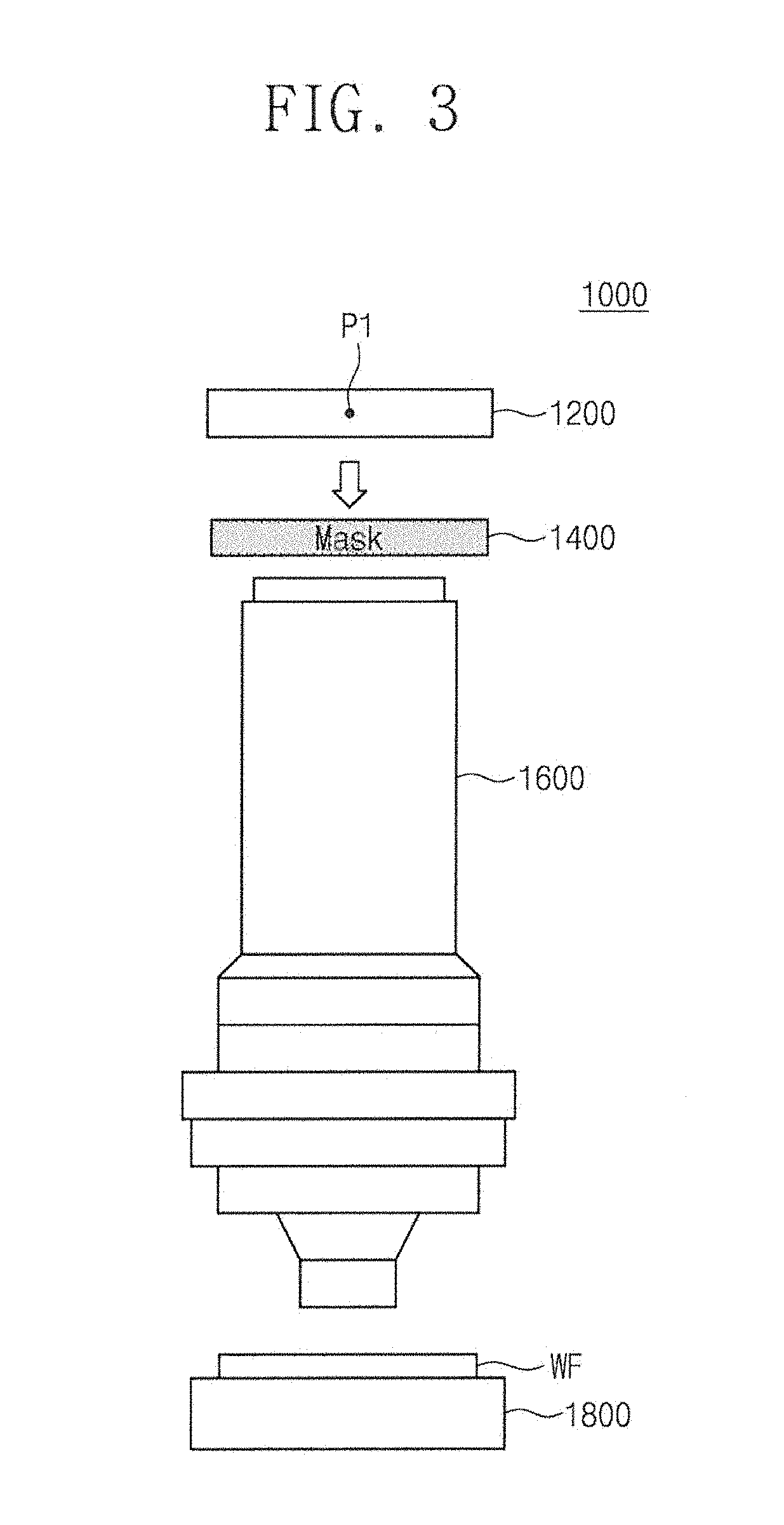

Methods of improving optical proximity correction models and methods of fabricating semiconductor devices using the same

ActiveUS20190004418A1Easy to optimizeImprove reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingDevice materialEngineering

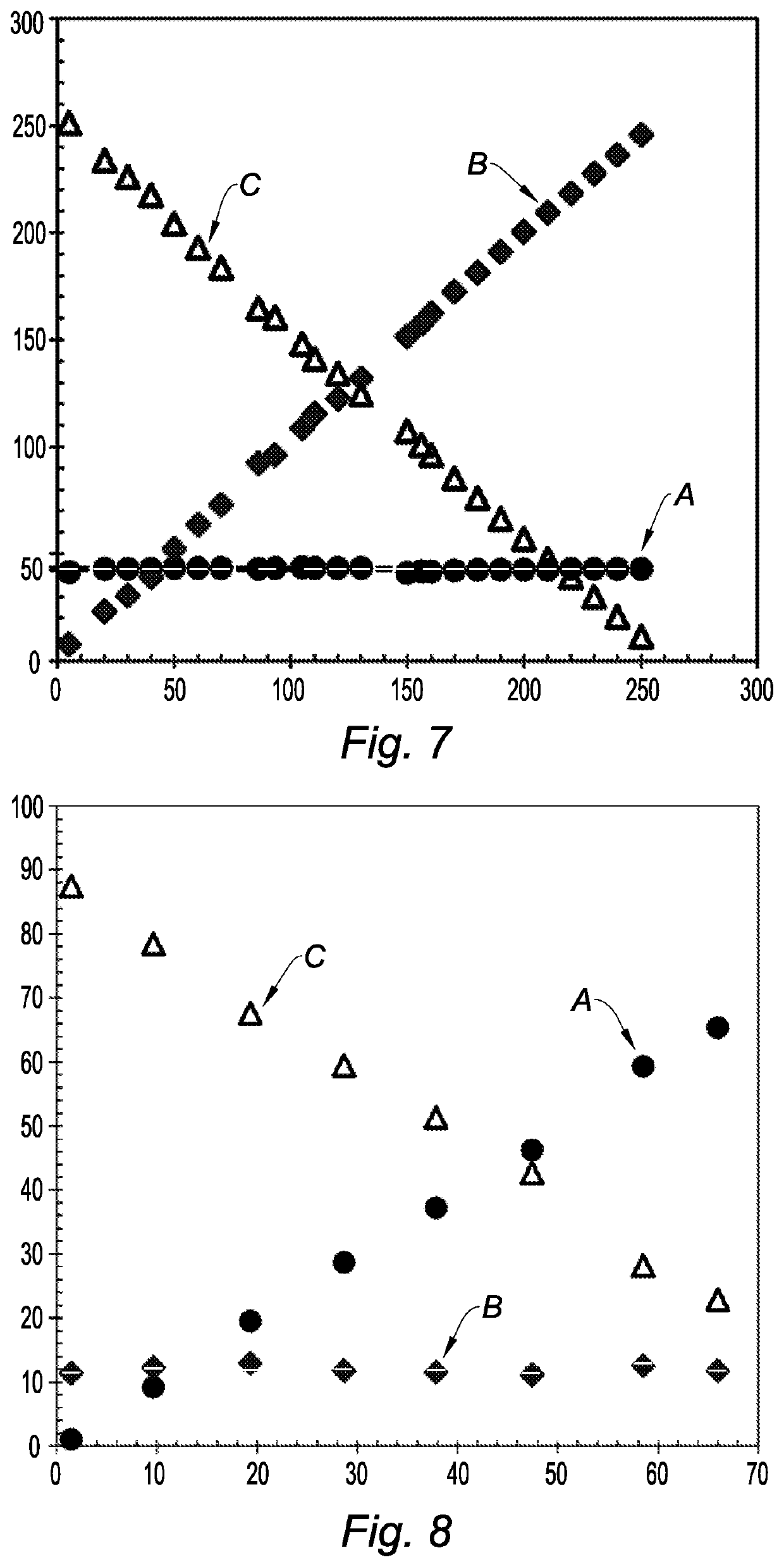

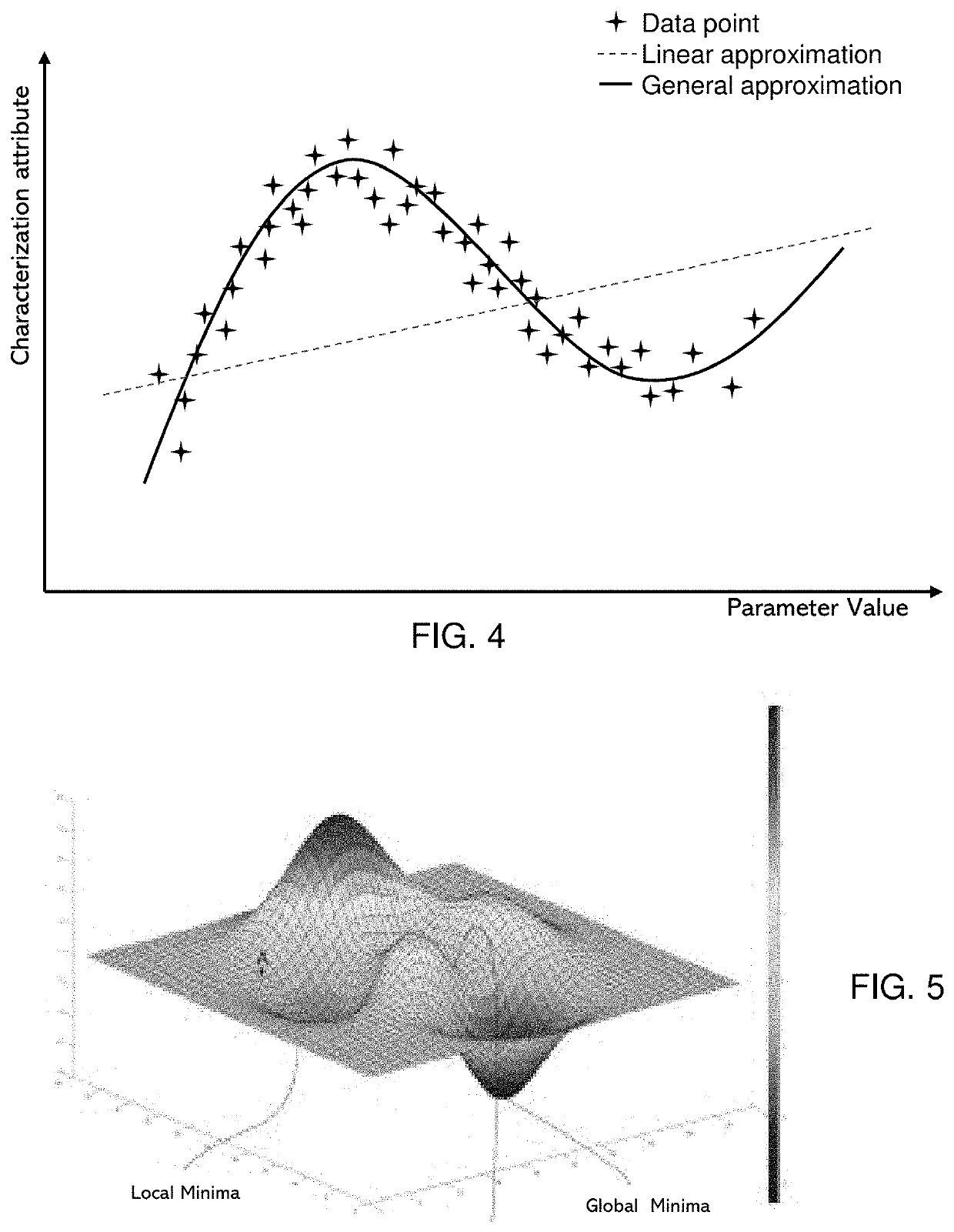

A method of fabricating a semiconductor device includes designing a layout, performing an optical proximity correction (OPC) process to correct the designed layout, fabricating a first photomask using the corrected layout, and forming patterns on a substrate using the first photomask. The OPC process includes generating an OPC model and correcting the designed layout using the generated OPC model. The generation of the OPC model includes rasterizing a planar image of an actual pattern to obtain first label data, rasterizing a simulation image of a simulation pattern to obtain second label data, the simulation pattern being obtained using the OPC model, in which a parameter set including process parameters is set, comparing the first label data with the second label data to obtain comparison data, and correcting the process parameters of the parameter set, based on the comparison data.

Owner:SAMSUNG ELECTRONICS CO LTD

Structural design systems and methods for optimizing equipment selection in floorplans using modeling and simulation

Systems and methods for selecting equipment models and optimizing placement of equipment in floor plans are disclosed. Operations may include access a floor plan demarcating a plurality of rooms, where the floor plan includes a plurality of equipment symbols, enable a user to select an equipment symbol for analysis, access functional requirements for a set of rooms in the plurality of rooms containing the instances of the selected equipment symbols, access equipment technical specifications to identify equipment technical specifications associated with the functional requirements, perform a generative analysis on the identified equipment technical specifications within identified walls of each room in the set of rooms to select an equipment model that at least partially conforms to the functional requirements, update the floor plan by associating the selected equipment model with the instances of the selected equipment symbols, and output a bill of material based on the updated floor plan.

Owner:BEAMUP LTD

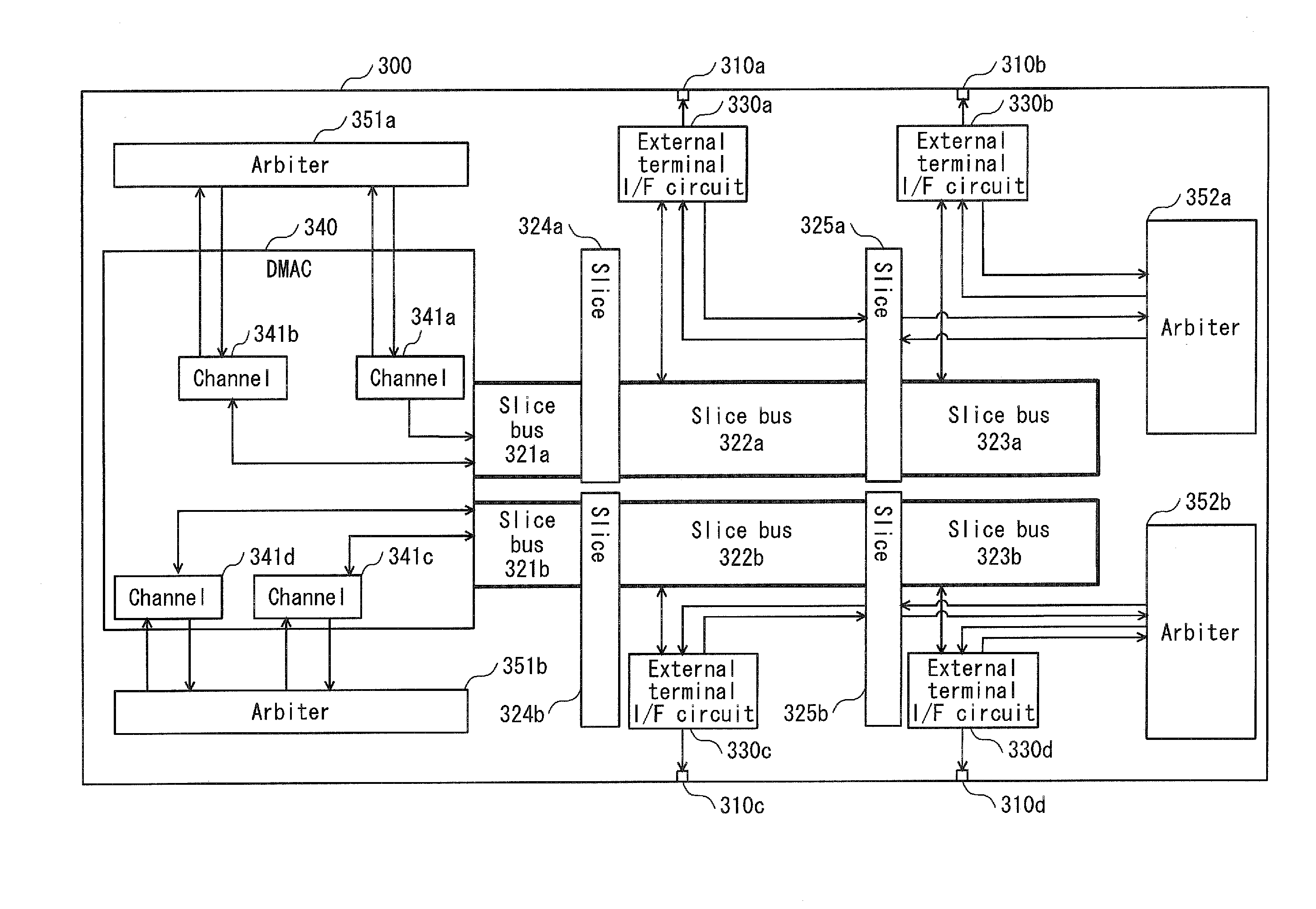

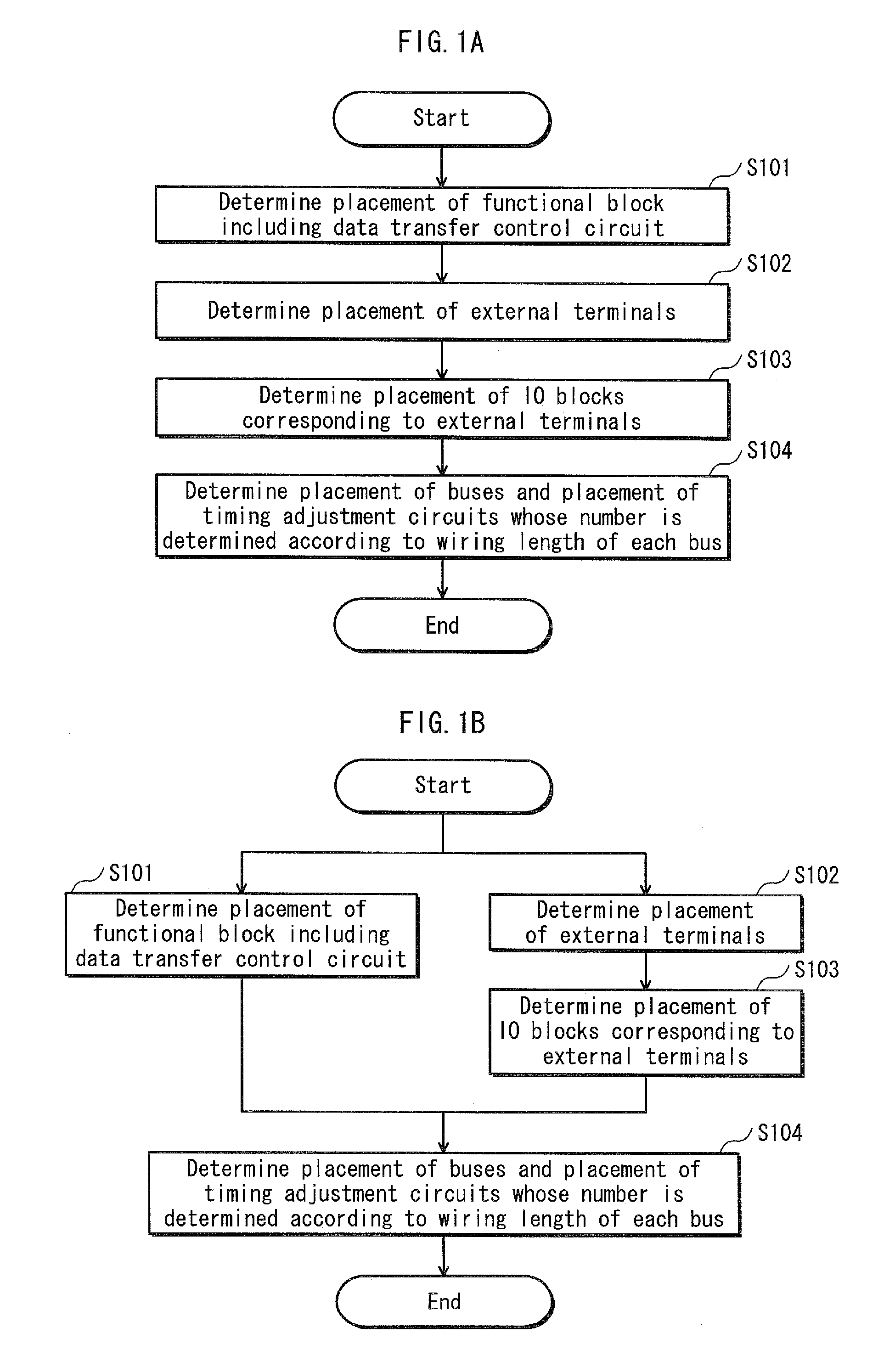

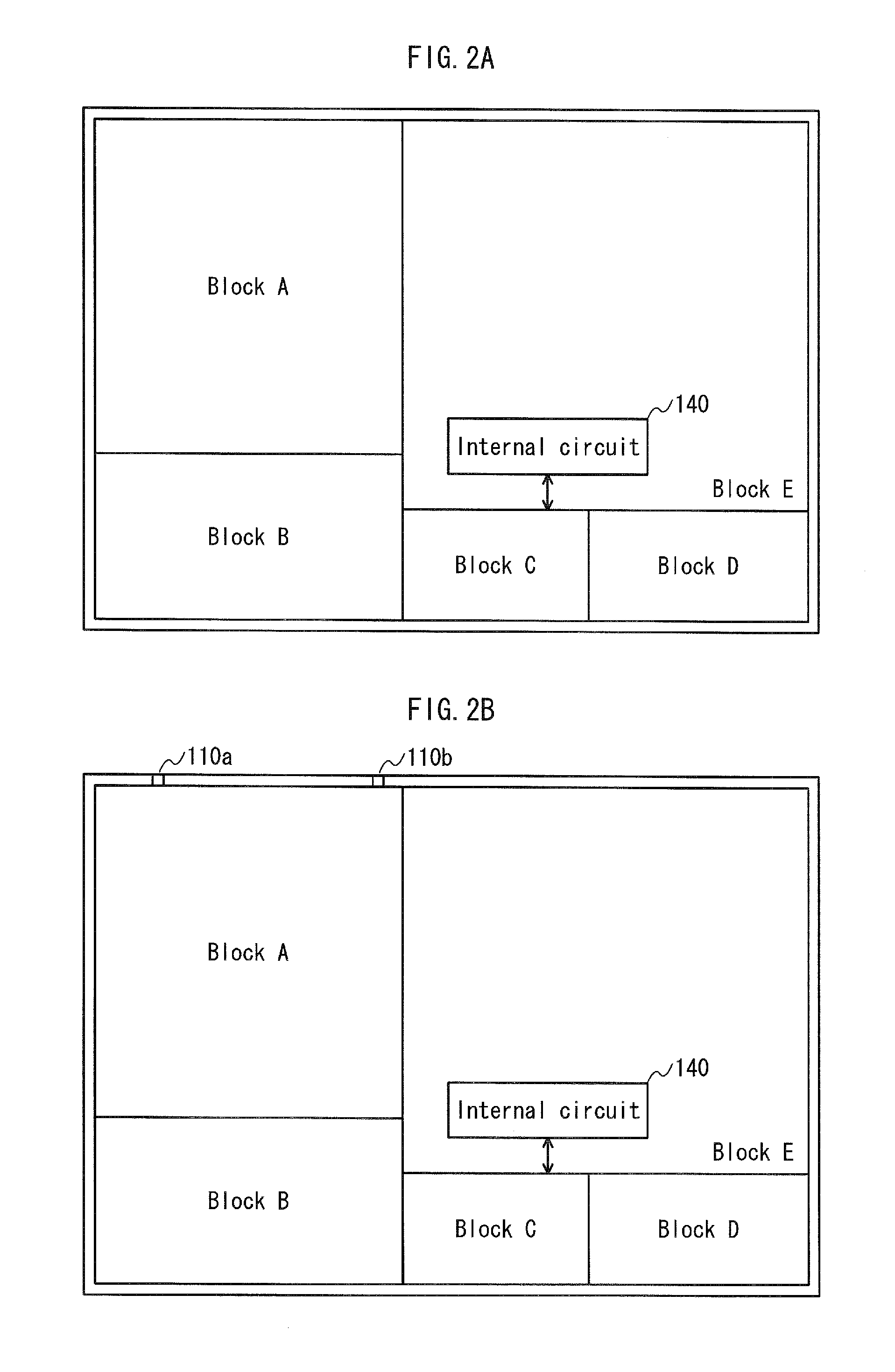

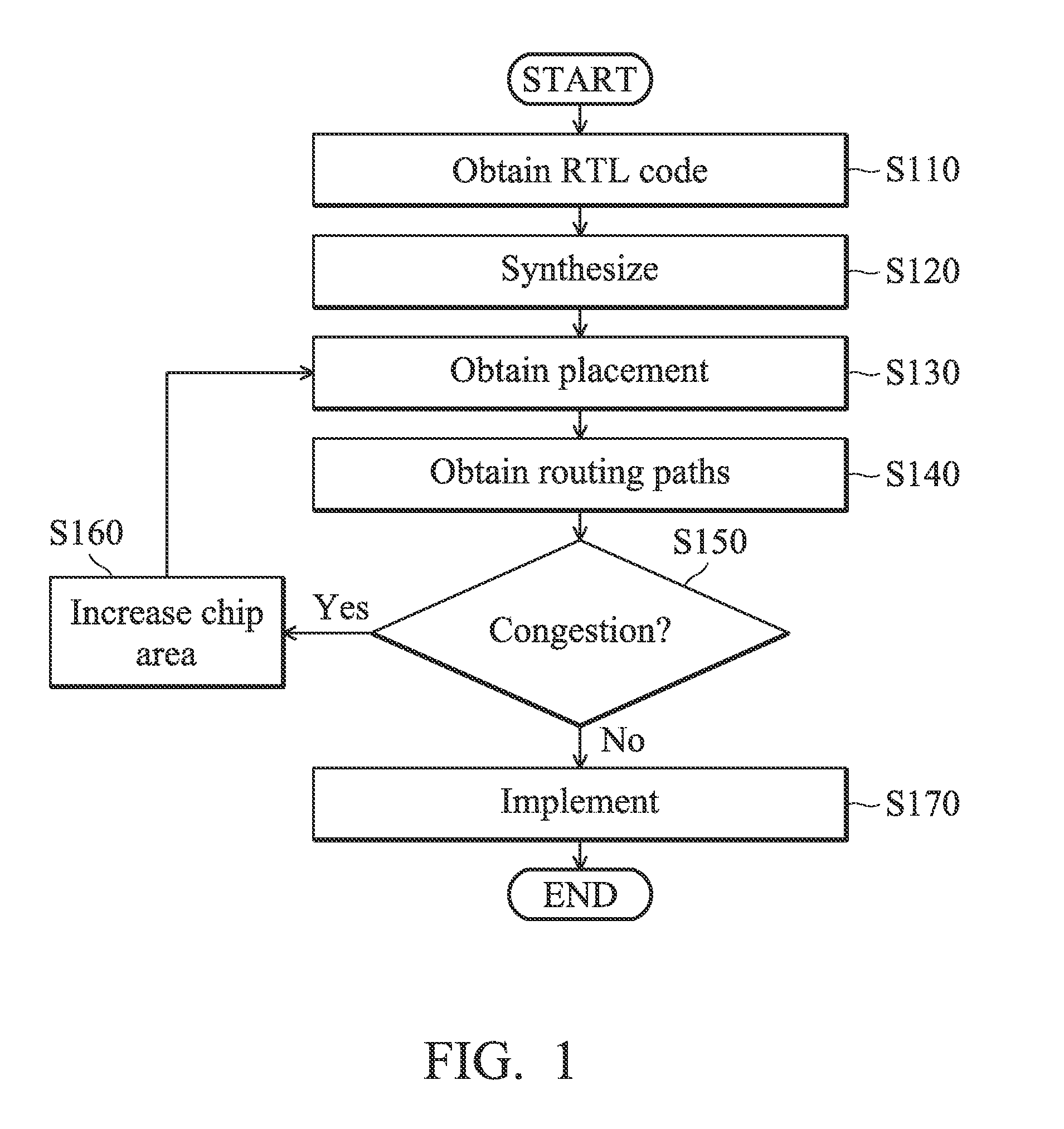

Integrated circuit manufacturing method and semiconductor integrated circuit

InactiveUS20120110535A1Avoid transmission delaysLow costSolid-state devicesSpecial data processing applicationsIntegrated circuit manufacturingSemiconductor

In layout design step of the semiconductor integrated circuit manufacturing method, when it is found that the wiring length between an external terminal and an IO block (external terminal I / F circuit) corresponding to the external terminal increases after a floorplan of a circuit including a functional block and the IO block is determined, placement of the IO block is determined such that the IO block is placed close to the external terminal to alleviate constraints on the wiring between the IO block and the external terminal, and timing adjustment circuits whose number is determined according to the wiring length of a bus (or a shared bus) connecting a data transfer circuit and the IO block is inserted into the bus.

Owner:PANASONIC CORP

Methods for generating a floor plan from a building scan

Methods for generating a floor plan from a building scan of a building using an electronic computing device are presented, the method including: causing the electronic computing device to receive the building scan; converting the building scan to a floor plan; and refining the floor plan to approximate the building. In some embodiments, the causing the electronic computing device to receive the building scan further includes: extracting information from an input file to obtain a representation of a number of rooms and walls corresponding with the building scan, where the information is selected from the group consisting of: a set of vertices, a set of triangles, and a set of rooms.

Owner:HILTI AG

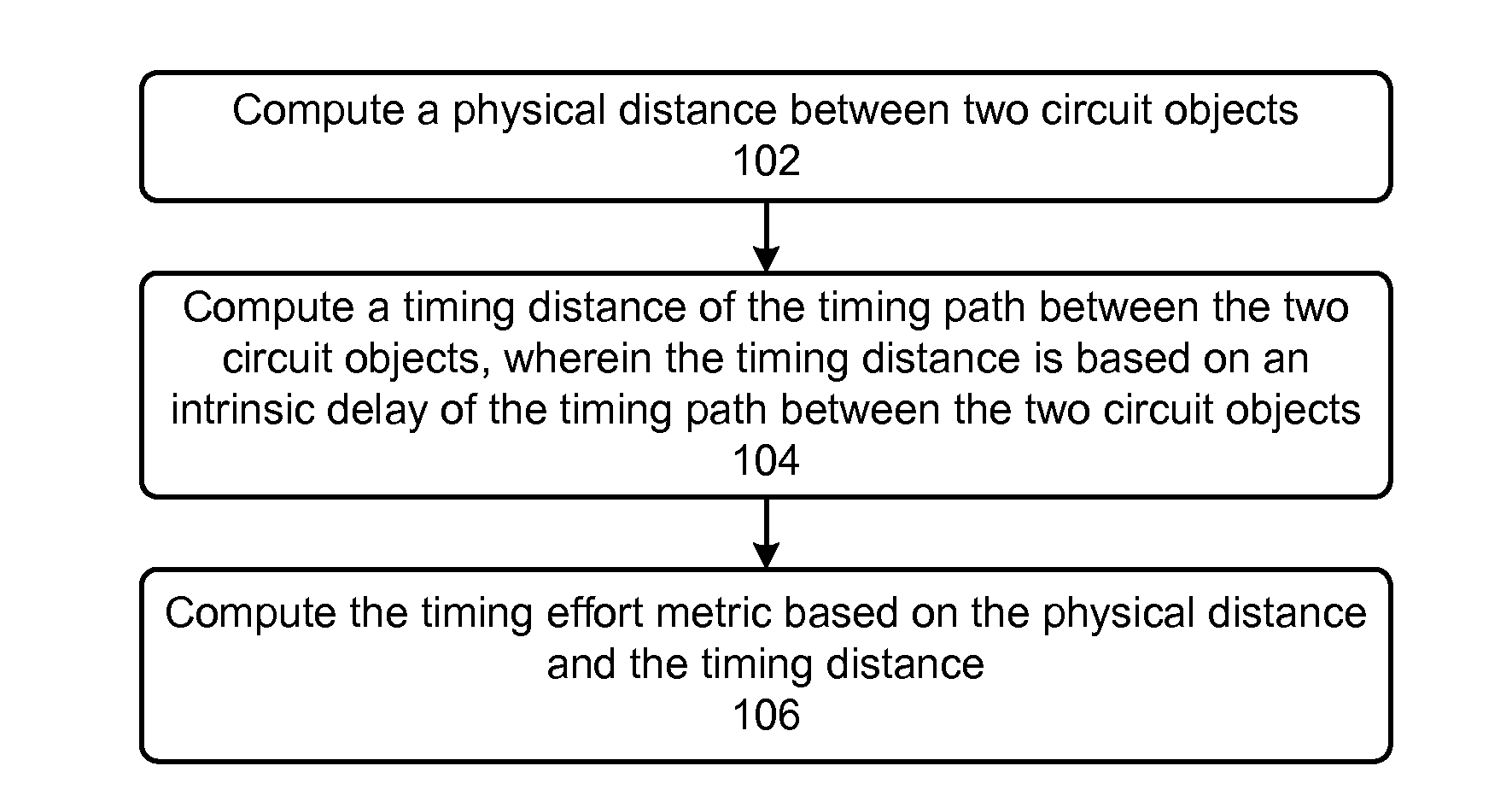

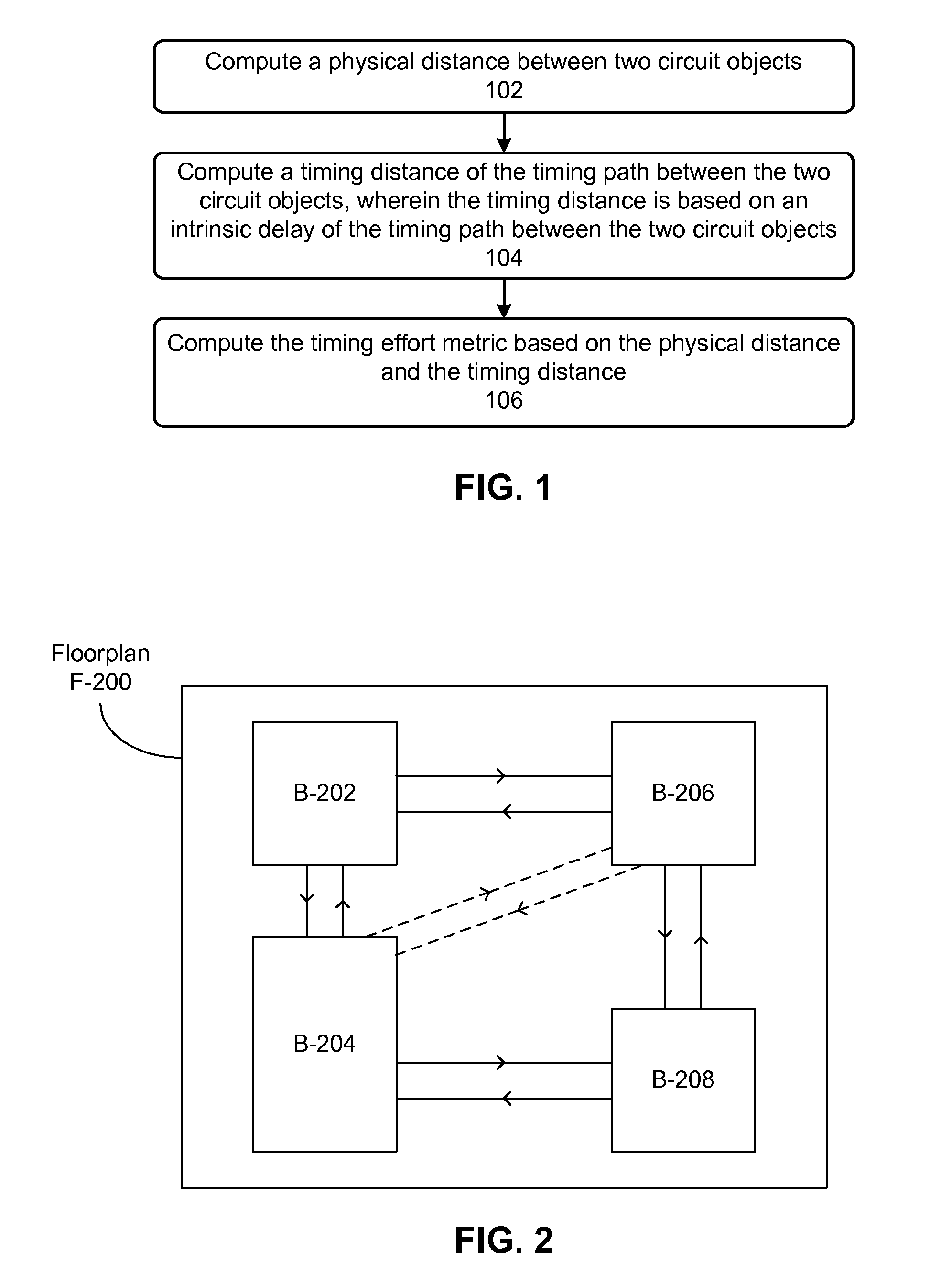

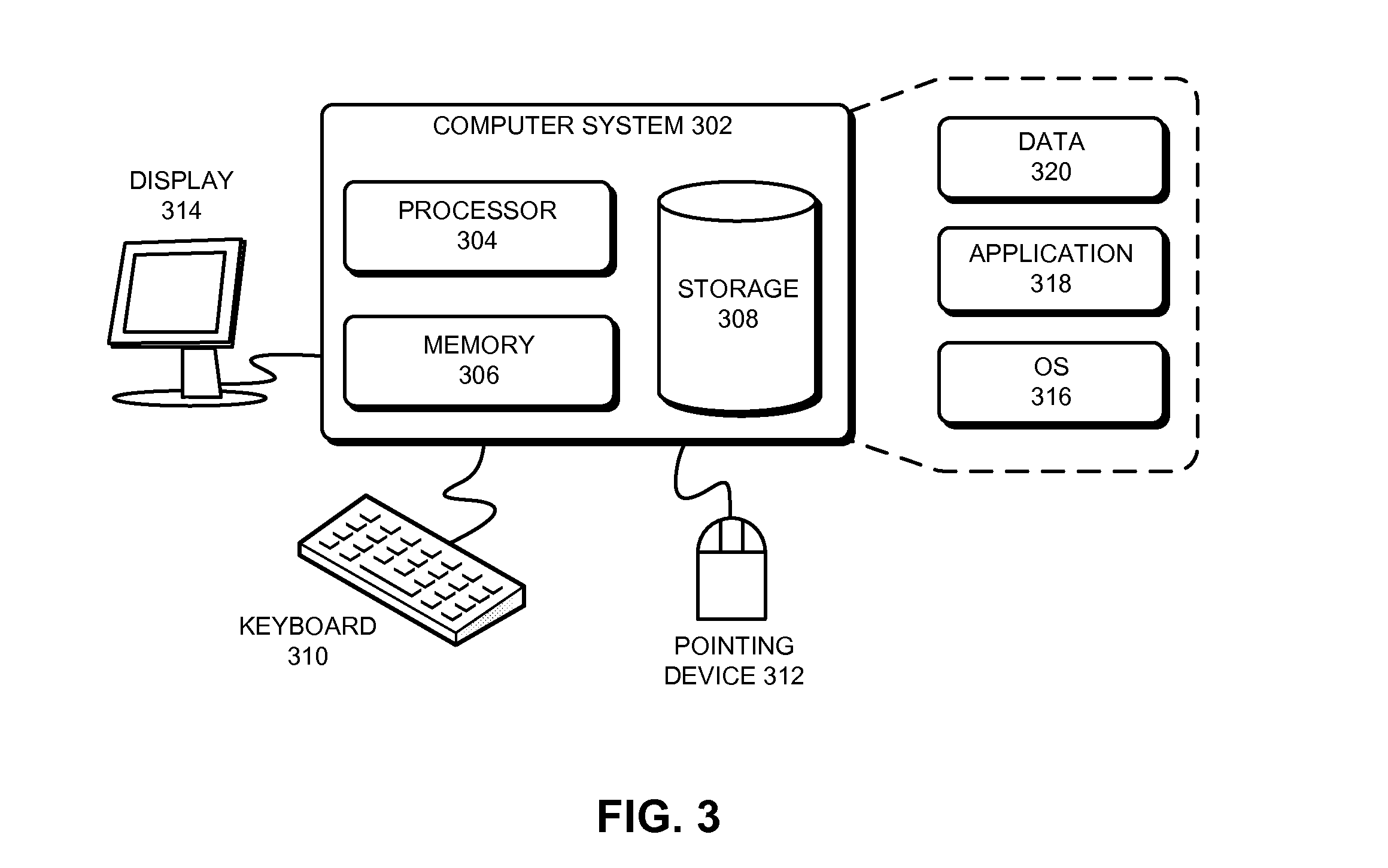

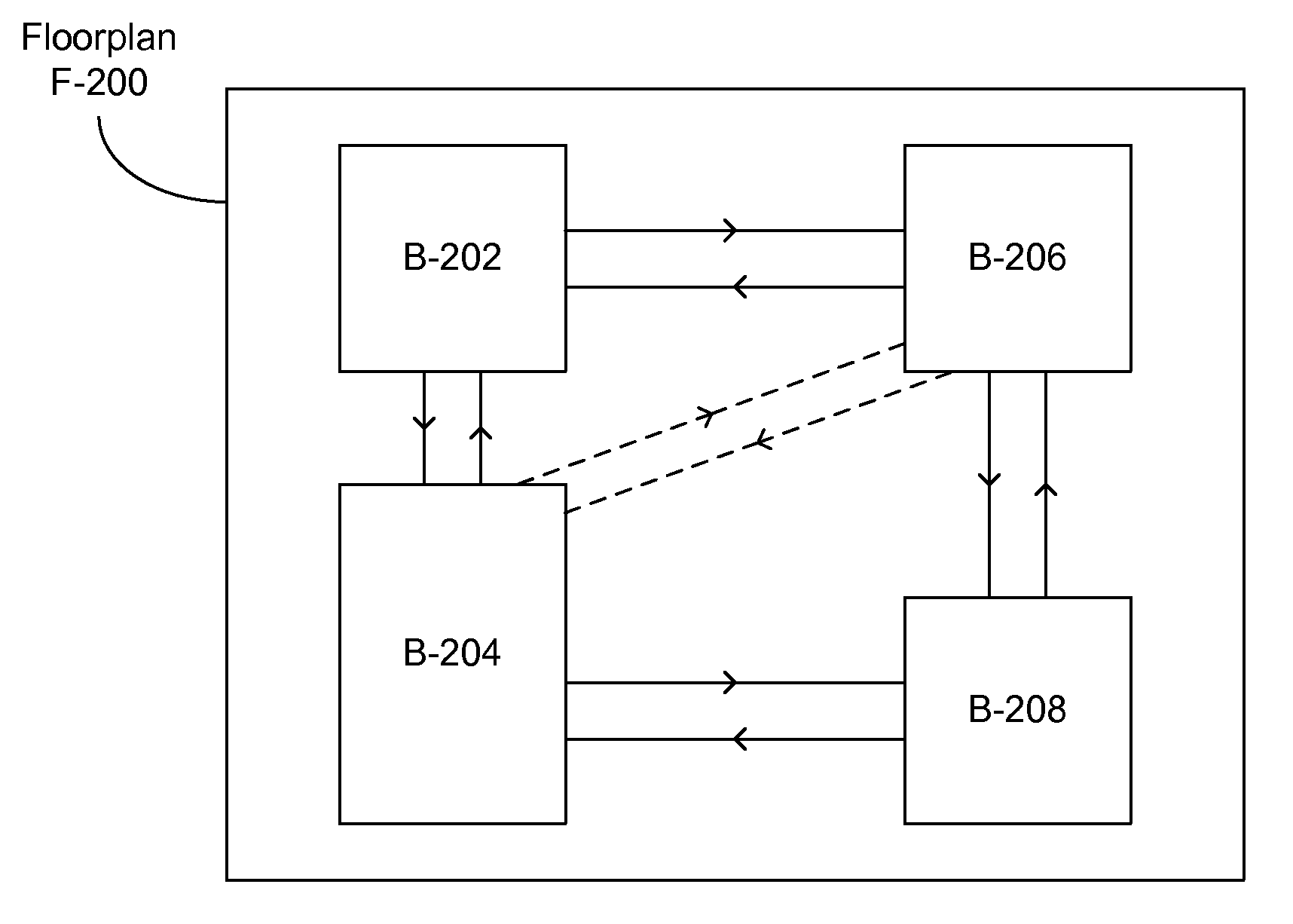

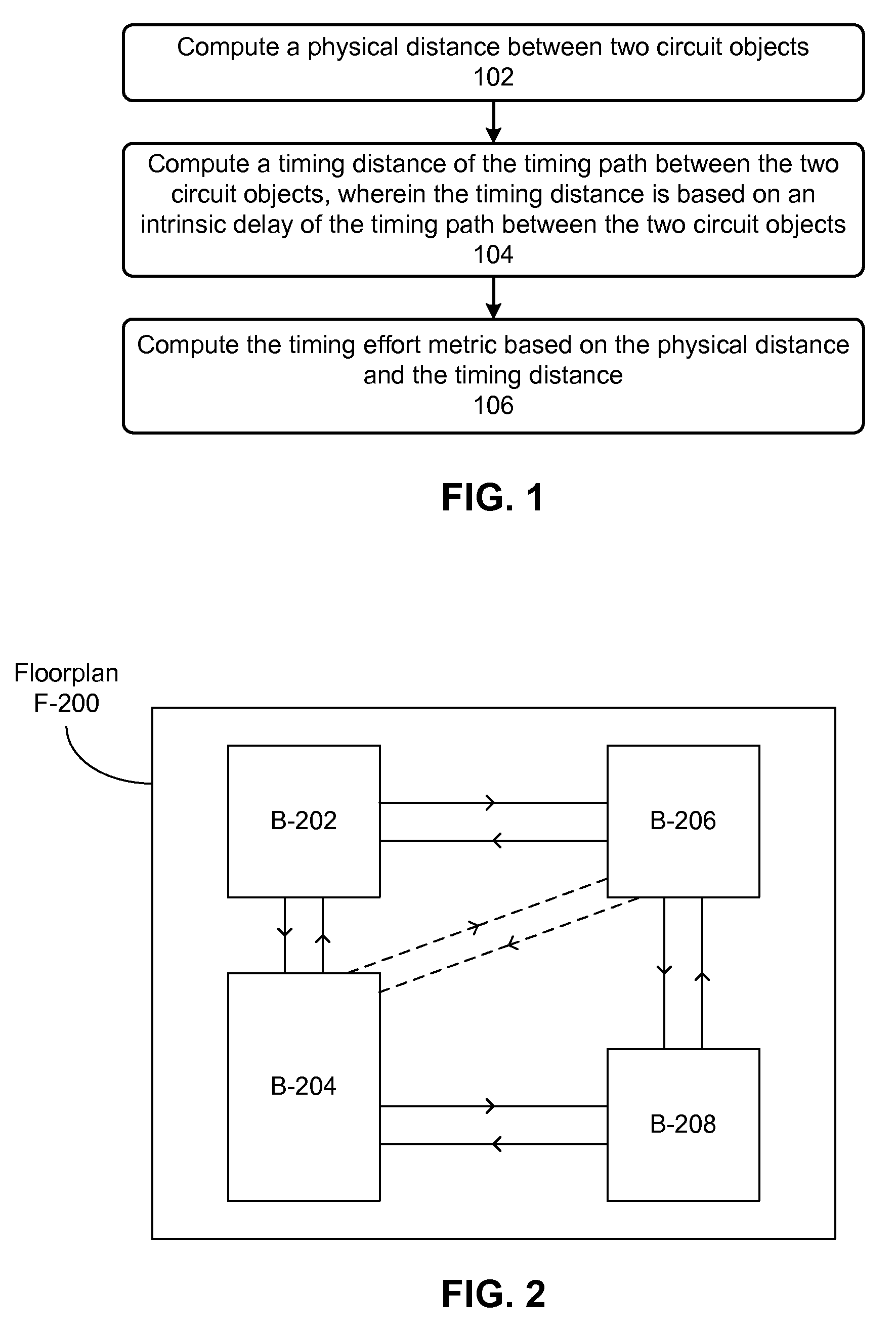

Path-based floorplan analysis

ActiveUS20150121328A1Computer aided designSoftware simulation/interpretation/emulationCircuit designWork Measurement

Systems and techniques for computing a timing effort metric are described. According to one definition, the computed timing effort metric indicates a level of difficulty of fixing a timing violation associated with a timing path between two circuit objects in a circuit design layout.

Owner:SYNOPSYS INC

Path-based floorplan analysis

ActiveUS20160042115A1Detecting faulty computer hardwareComputer aided designPathPingParallel computing

Systems and techniques for computing a timing effort metric are described. According to one definition, the computed timing effort metric indicates a level of difficulty of fixing a timing violation associated with a timing path between two circuit objects in a circuit design layout.

Owner:SYNOPSYS INC

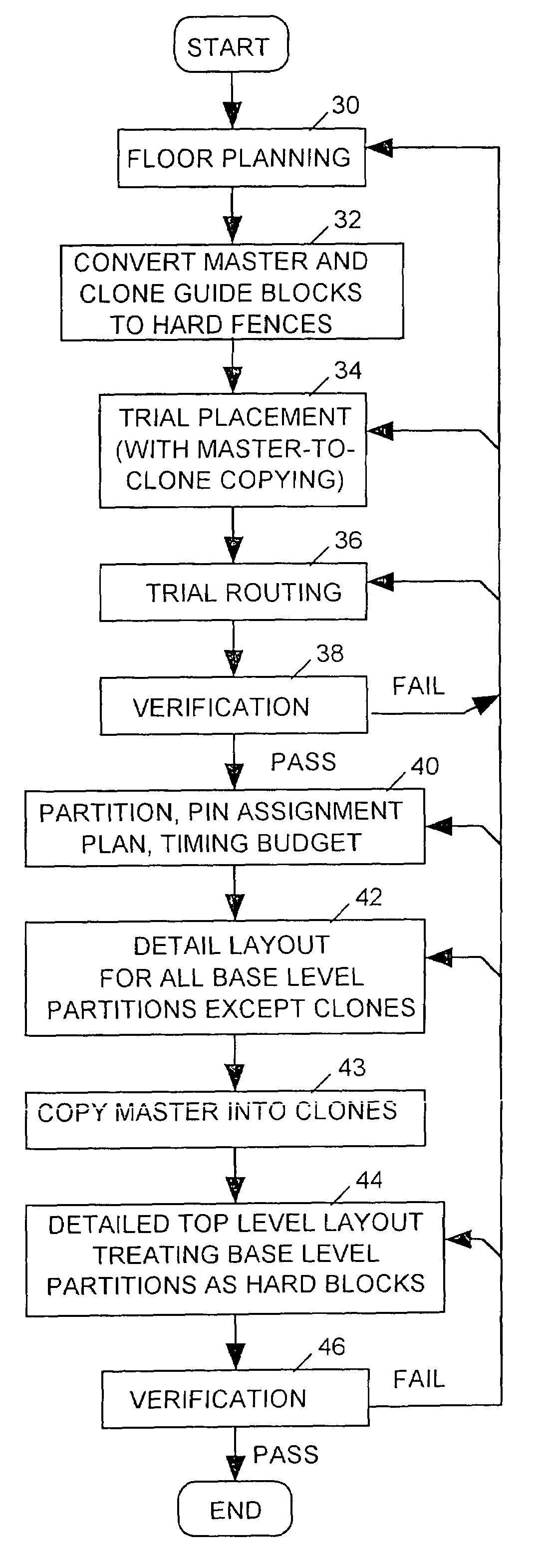

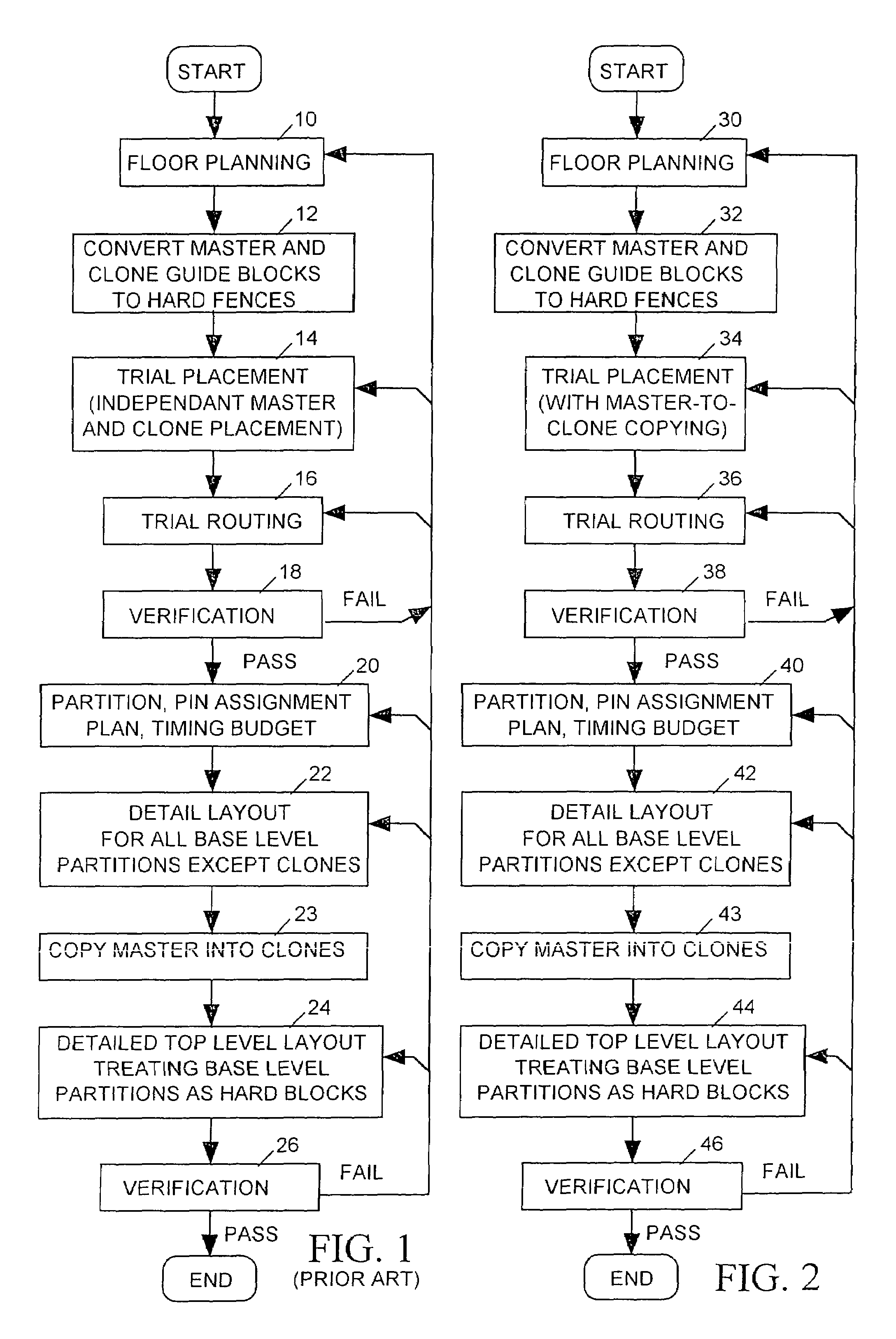

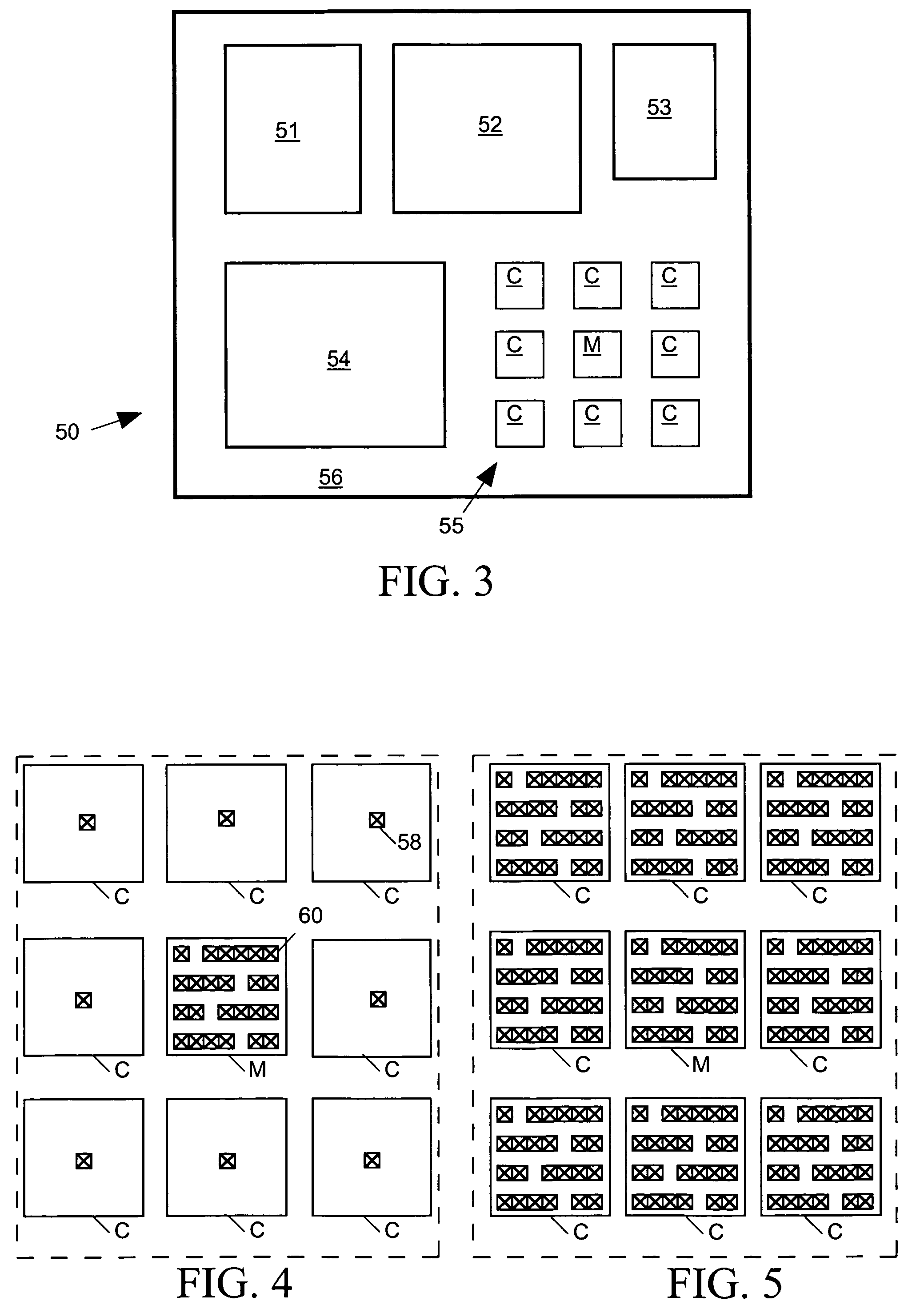

Trial placement system with cloning

InactiveUS7155694B2Computer aided designSoftware simulation/interpretation/emulationSoftware engineeringOperating system

Owner:CADENCE DESIGN SYST INC

Automatic recognition of multiple floorplans by cleaning robot

ActiveUS11157016B2Automatic obstacle detectionAutonomous decision making processComputer graphics (images)Engineering

In one embodiment, a cleaning robot stores multiple floorplans. The robot automatically determines which floorplan it is in by localizing and trying to match its detected environment to the stored map. The best fit is the map for the current floor. If there is no match above a confidence threshold, the robot assumes it is a new floor or the floorplan has changed (e.g., furniture has moved), and the robot initiates a discovery mode to map the floorplan and add it to the robot's memory.

Owner:VORWERK & CO INTERHOLDING GMBH

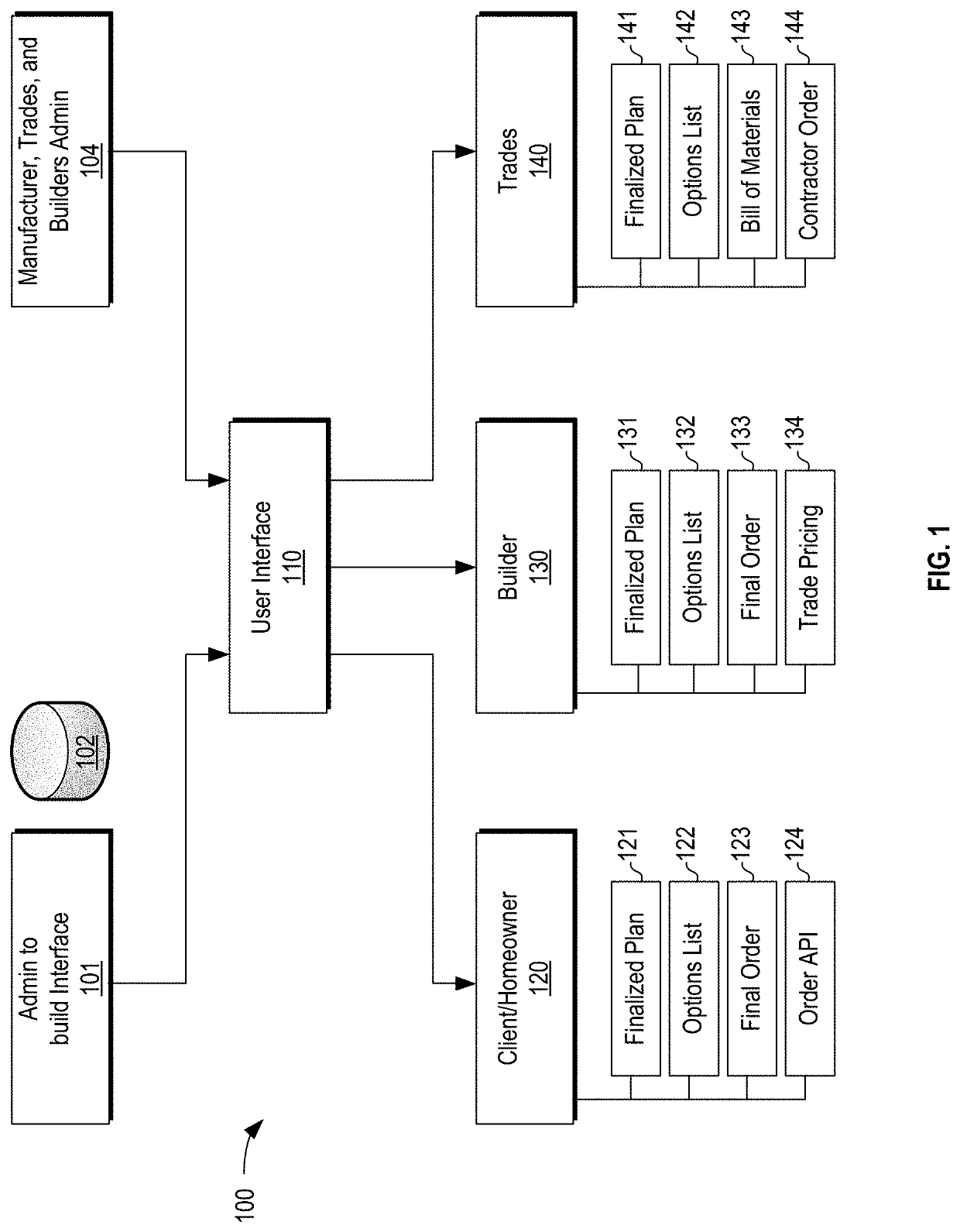

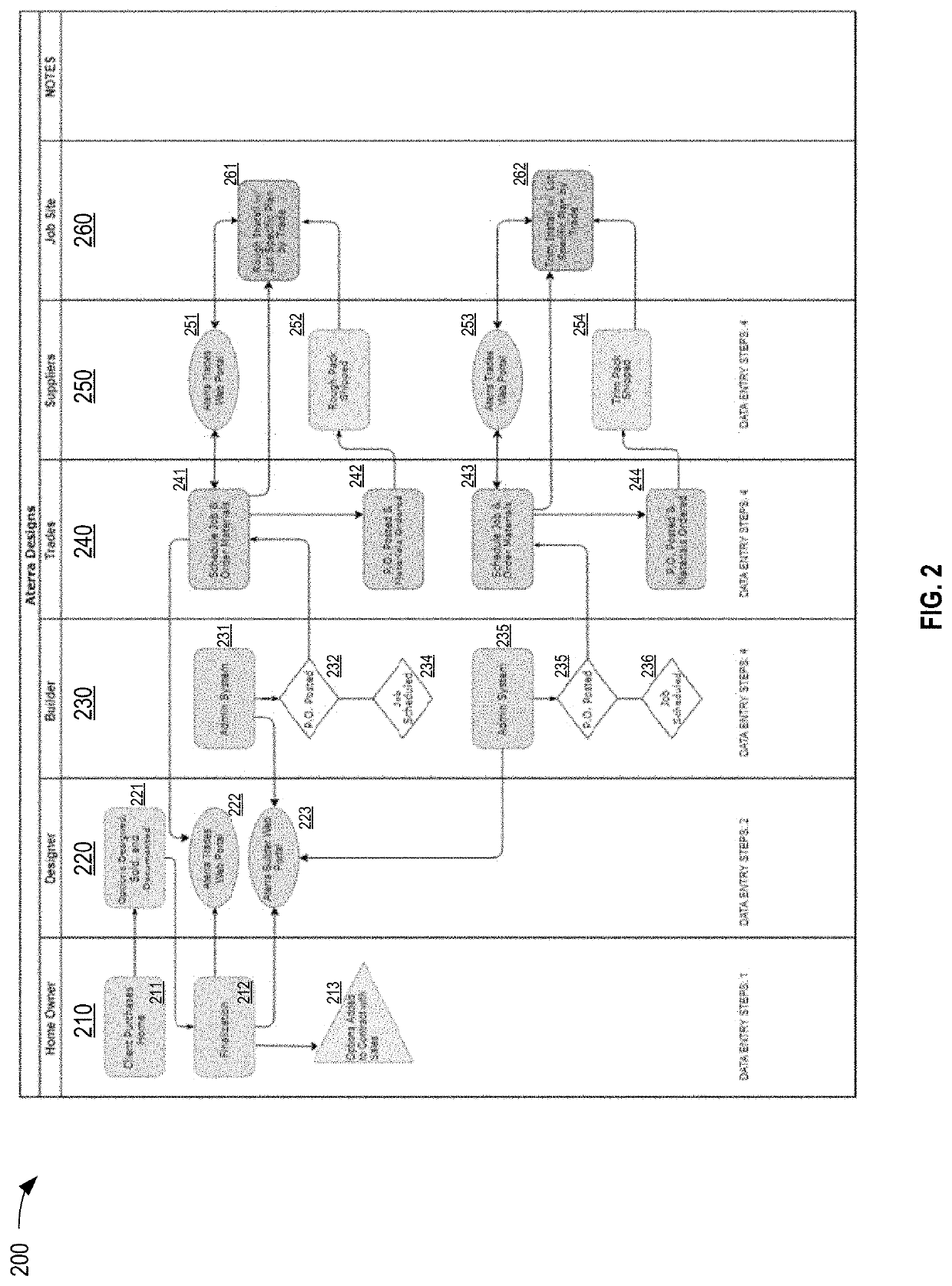

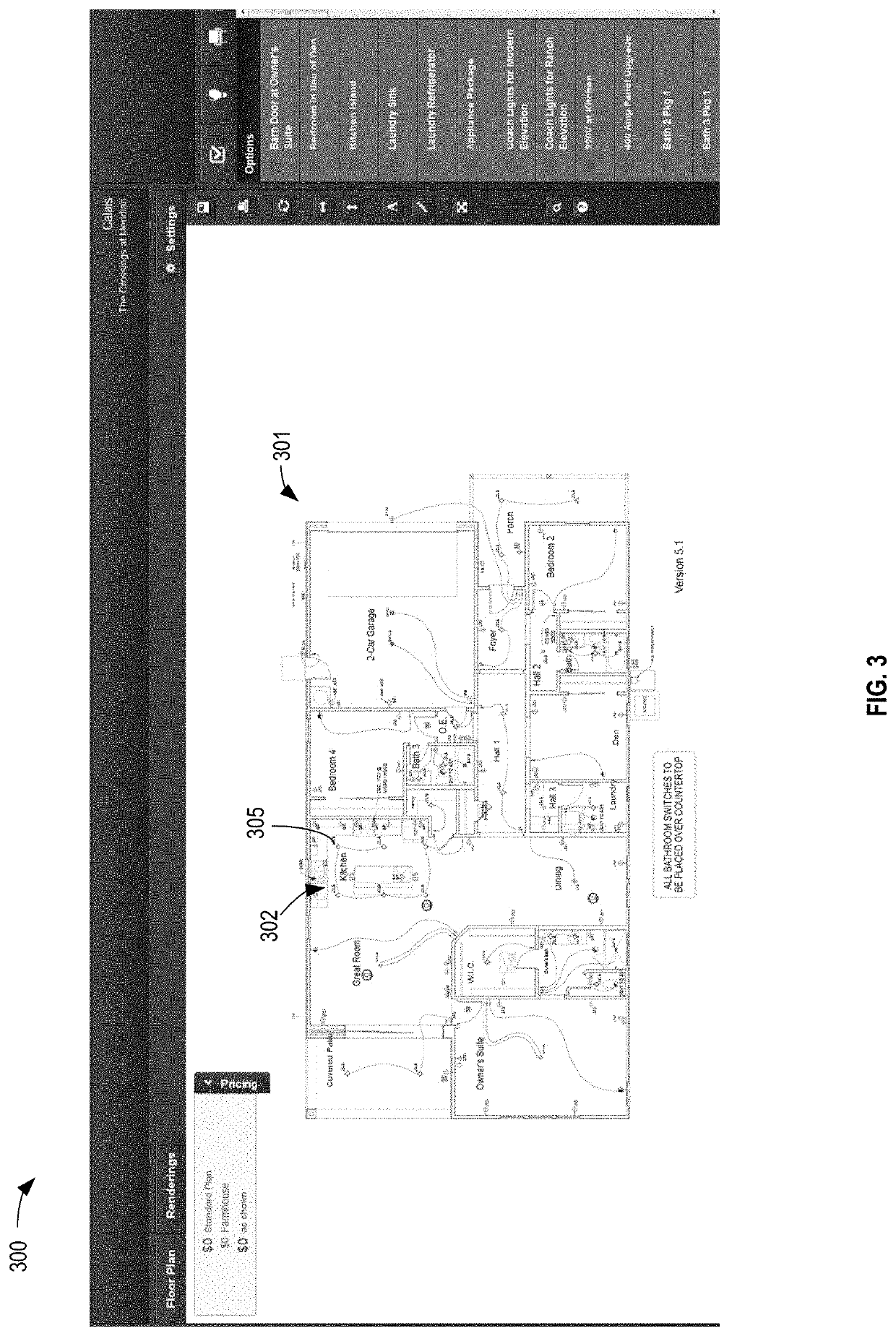

Systems and Methods for Implementing an Interactive Virtual Design Tool

PendingUS20200410576A1Efficiently specifiedReduces construction cycle-timeBuying/selling/leasing transactionsImage generationGraphicsEngineering

A virtual, interactive floorplan system includes a database system configured to store data associated with a plurality of home interior options, and a web-based portal communicatively coupled to the database system, wherein the web-based portal is configured to provide a user interface. The user interface provides: (a) an option-selection mechanism through which a user can select, for a specified home design, one or more options from the plurality of home interior options; (b) a graphical visualization of the specified home design from a 2D plan view and a 3D virtual interactive mode that together display the effect of selecting the home interior options; (c) a report generation mechanism through which the user can generate purchase orders and trade specific installation instructions in the form of at least lot-specific plans, orders, and a bill of materials.

Owner:SALMONSON PAUL R

Generating integrated circuit floorplan layouts

InactiveUS8219959B2Amenable to implementationComputer aided designSoftware simulation/interpretation/emulationComputer hardwareComputer Aided Design

A method of generating a floorplan layout of an integrated circuit (IC) that is amenable to implementation in a computer-aided design tool. The method is capable of performing placement and routing processing for the IC while requiring very little information about the specific circuitry used in various functional blocks of the IC. For example, at the time of the placement and routing processing, one or more functional blocks of the IC can be specified as empty functional blocks and / or functional blocks that are only partially rendered in gates.

Owner:BELL SEMICON LLC

Temperature-sensitive mixed storage framework and data distribution strategy thereof

InactiveCN103176799ARaise priorityReduce the temperatureInput/output to record carriersMemory adressing/allocation/relocationGreedy algorithmParallel computing

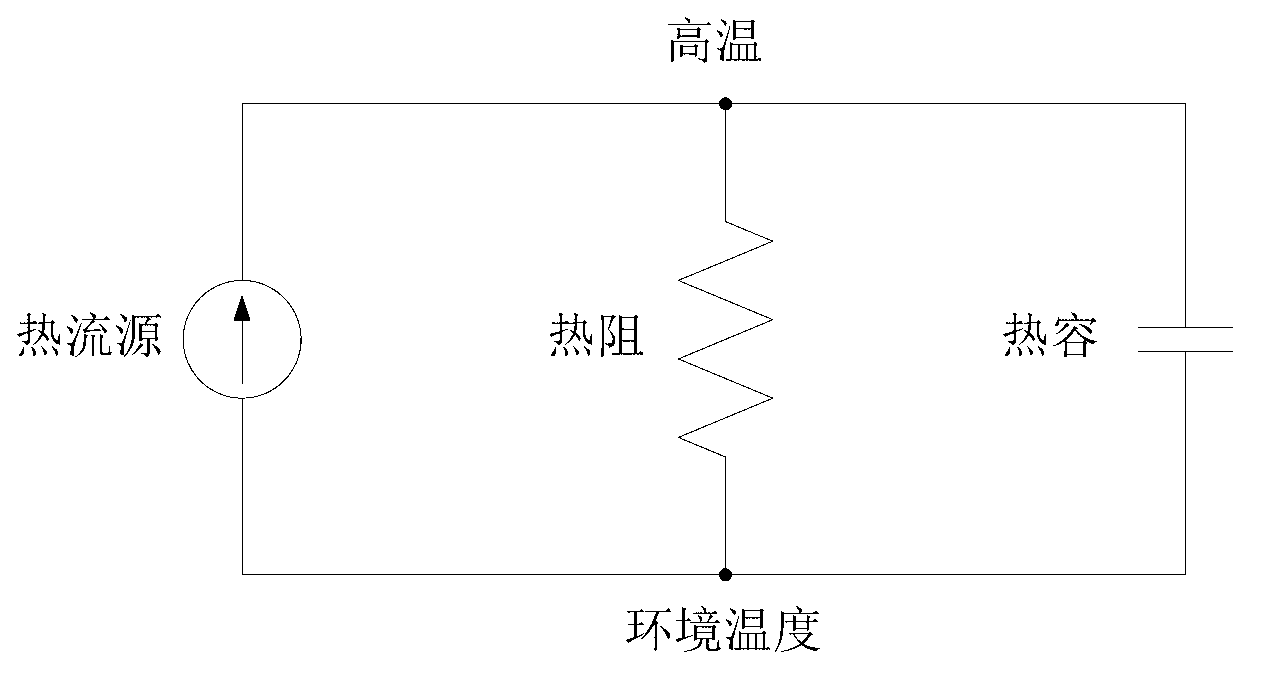

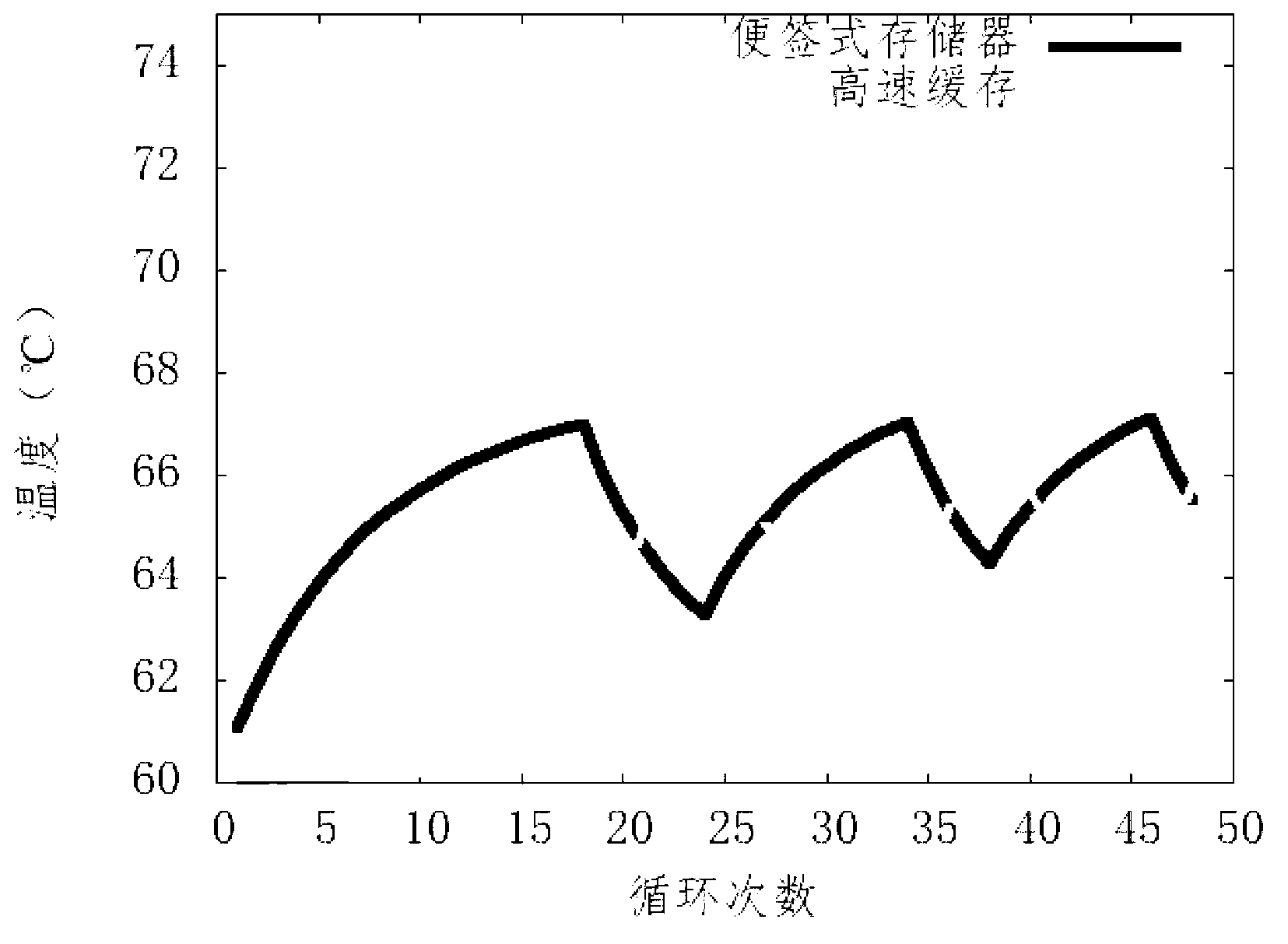

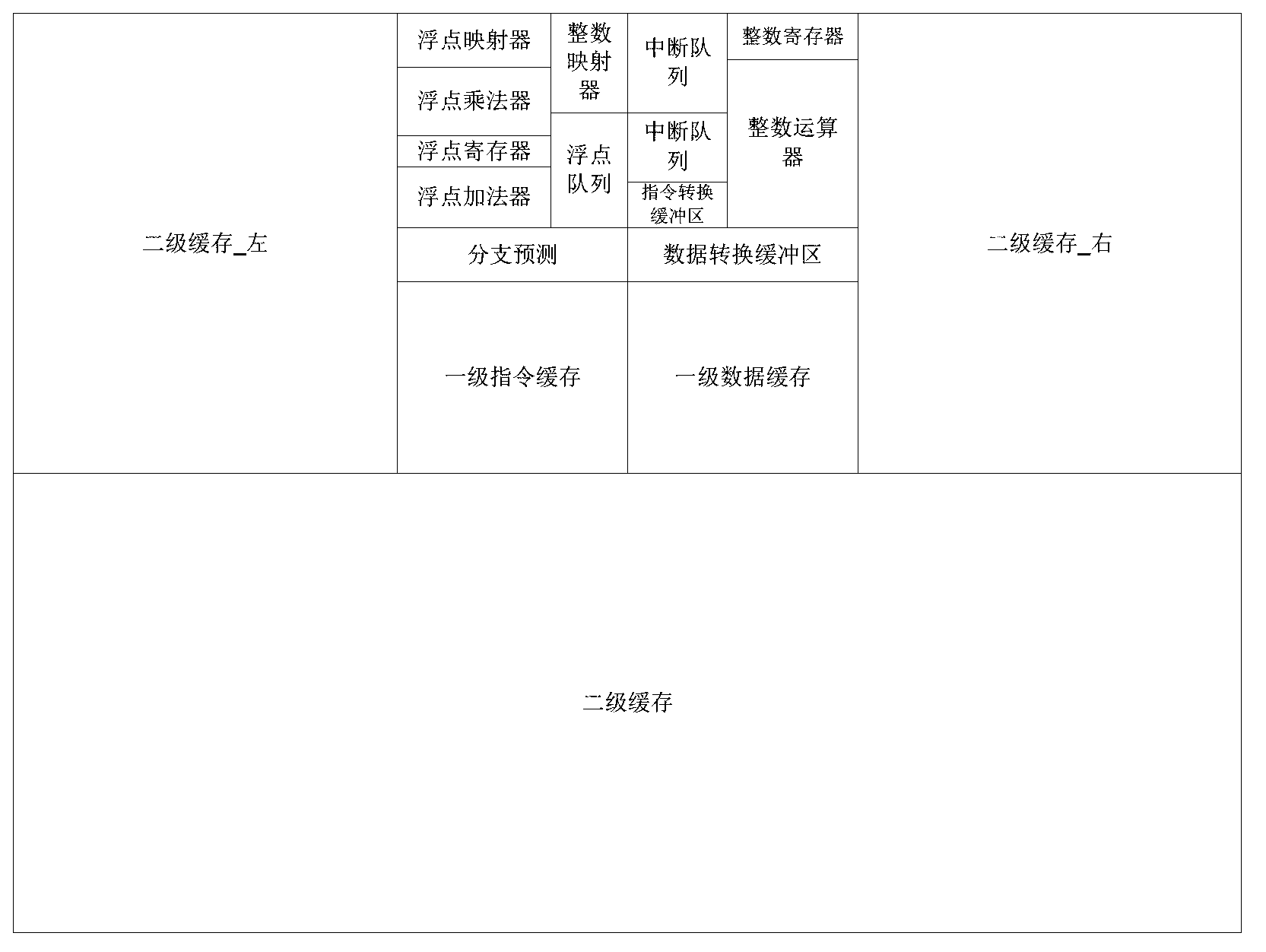

The invention discloses a temperature-sensitive mixed storage framework and a data distribution strategy of the temperature-sensitive mixed storage framework. The method comprises the following steps: (1) according to a storage component cache and an area model of a (scratch pad memory) SPM, designing floorplans with different cache / SPM capacity ratios; (2) according to a temperature model of an embedded processor, working out cache / SPM usage time t1 / t2 ratios in storage system temperature changing periods aiming at different cache / SPM capacity ratios, choosing a floorplan with the maximal t1 / t2 ratio as a designing scheme; (3) according to the designing scheme obtained from the step (2), designing the data distribution strategy; and under the condition of limiting peak temperature, using a greedy algorithm to achieve the data distributed to the cache or the SPM to obtain shortest data access time.

Owner:SHANDONG UNIV

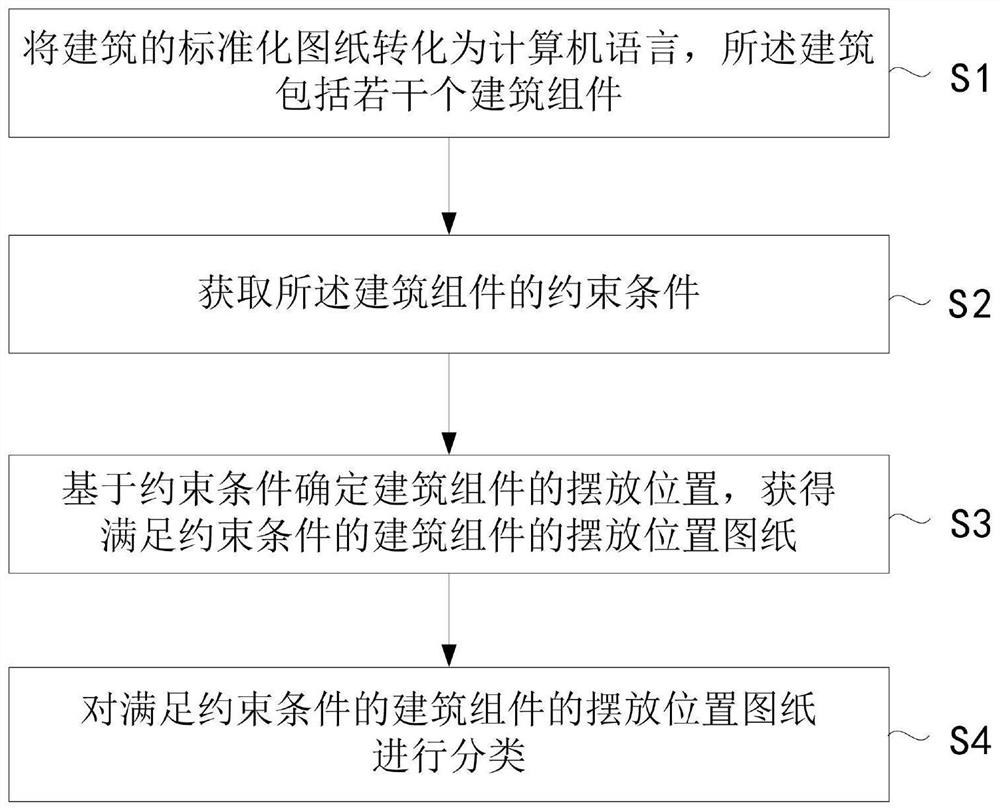

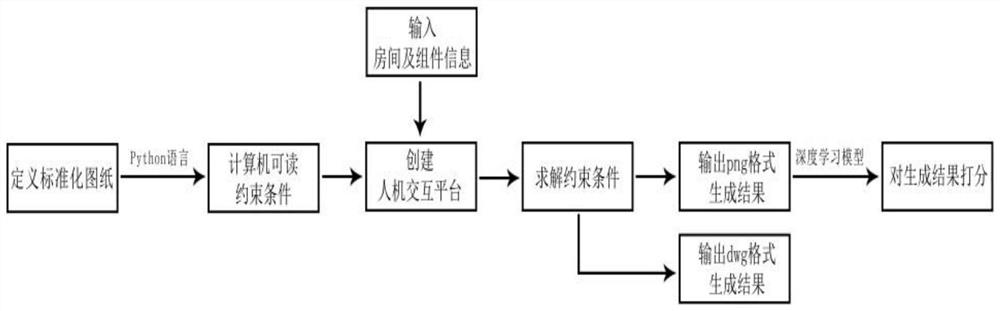

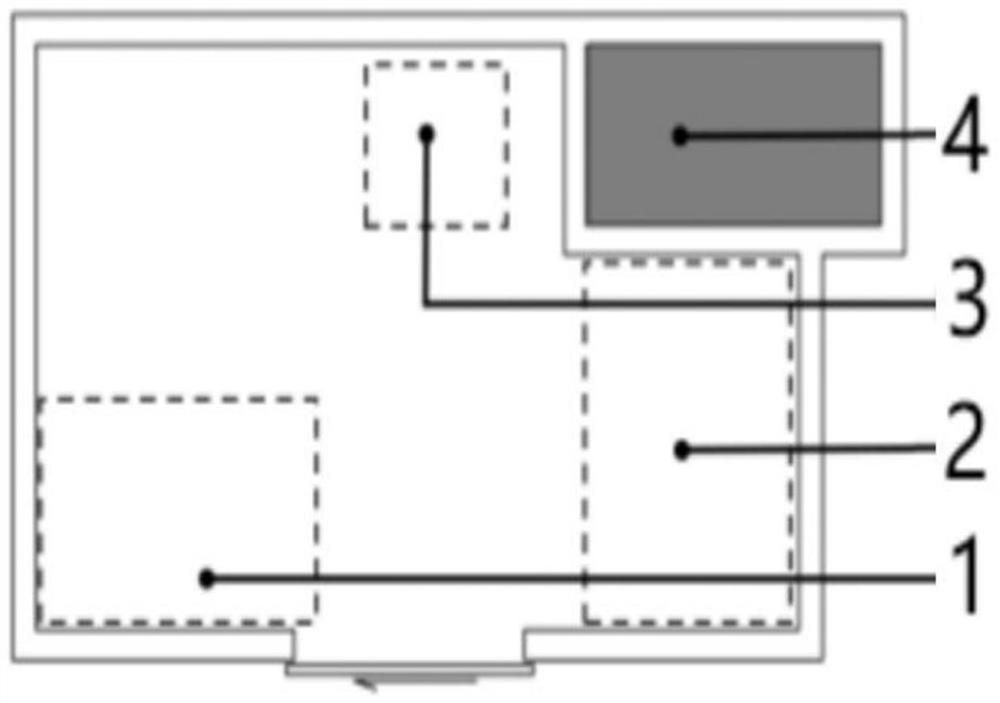

Building plane layout method and device and electronic equipment

PendingCN114169063AImprove work efficiencyGeometric CADCharacter and pattern recognitionSoftware engineeringLayout

The invention provides a building plane layout method and device and electronic equipment, relates to the technical field of building plane layout, and aims to improve the working efficiency of designers and standardize the drawing design by solving constraint conditions, obtaining the placement positions of building components meeting the constraint conditions and automatically generating a building plane drawing. The method comprises the following steps: converting a standardized drawing of a building into a computer language, wherein the building comprises a plurality of building components; obtaining constraint conditions of the building component; determining the placement position of the building component based on the constraint condition, and obtaining the placement position of the building component meeting the constraint condition; and classifying the placement positions of the building components meeting the constraint conditions. The building plane layout device is applied to the building plane layout method. The building plane layout method is applied to the electronic equipment.

Owner:北京奥科博思创新科技有限公司

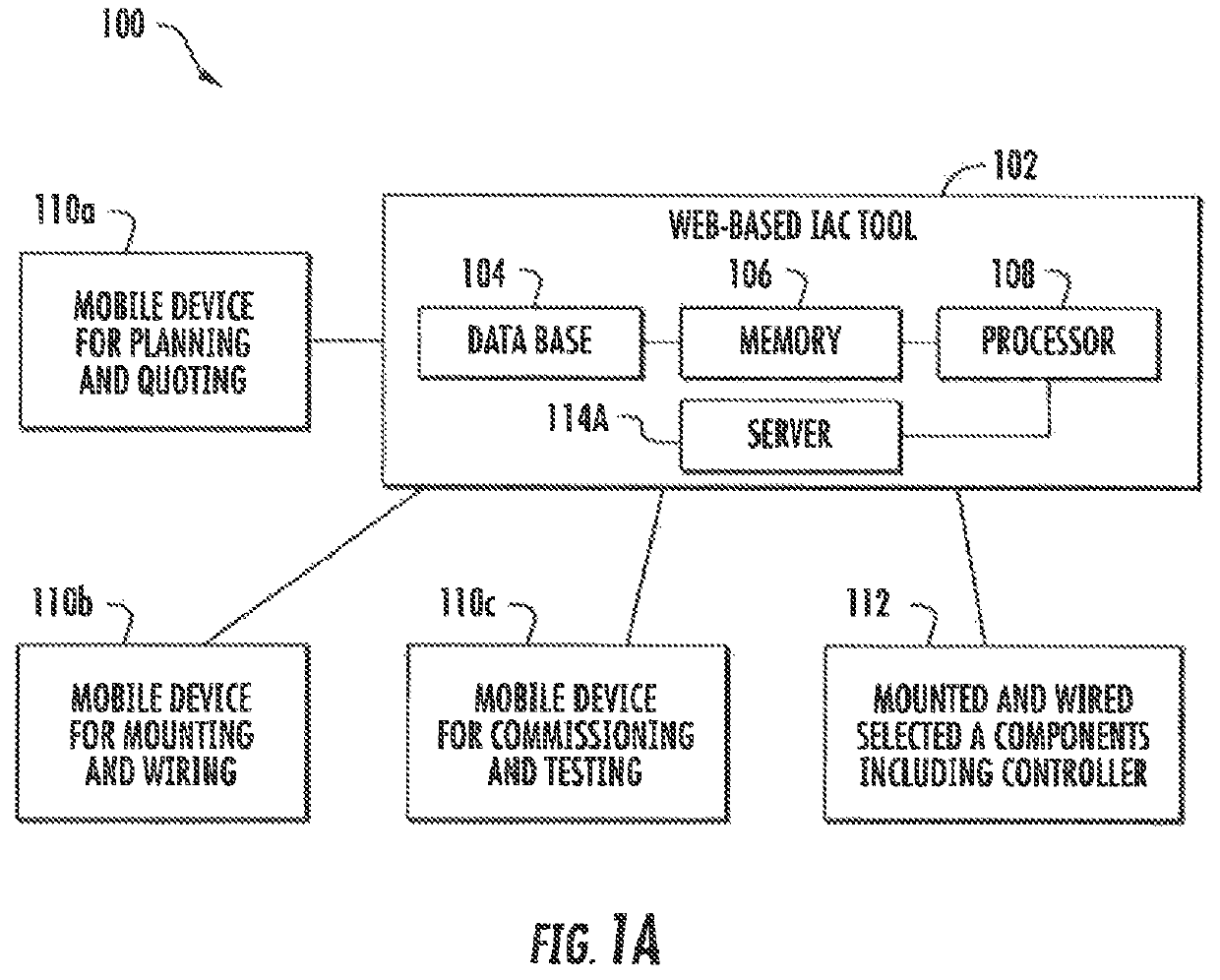

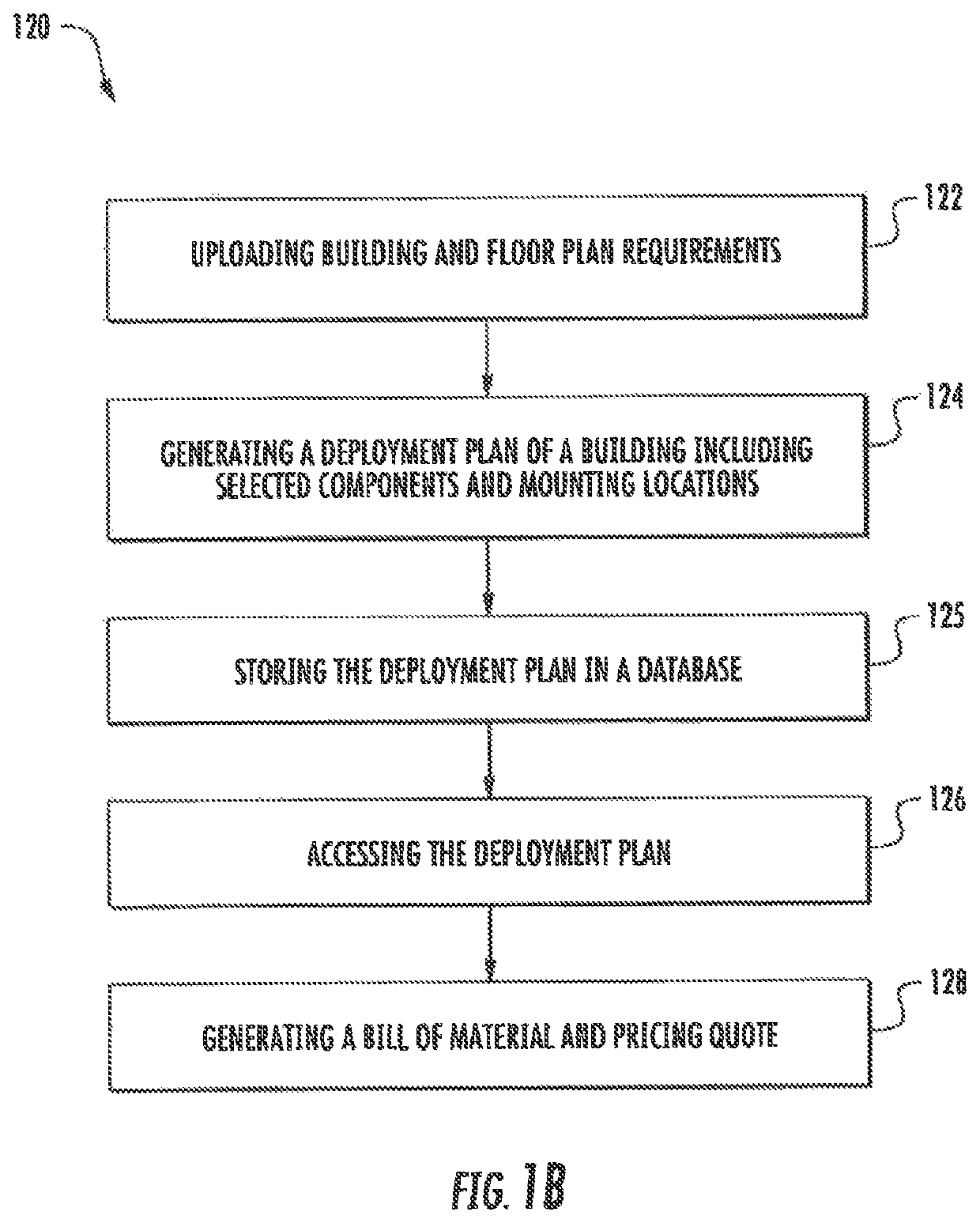

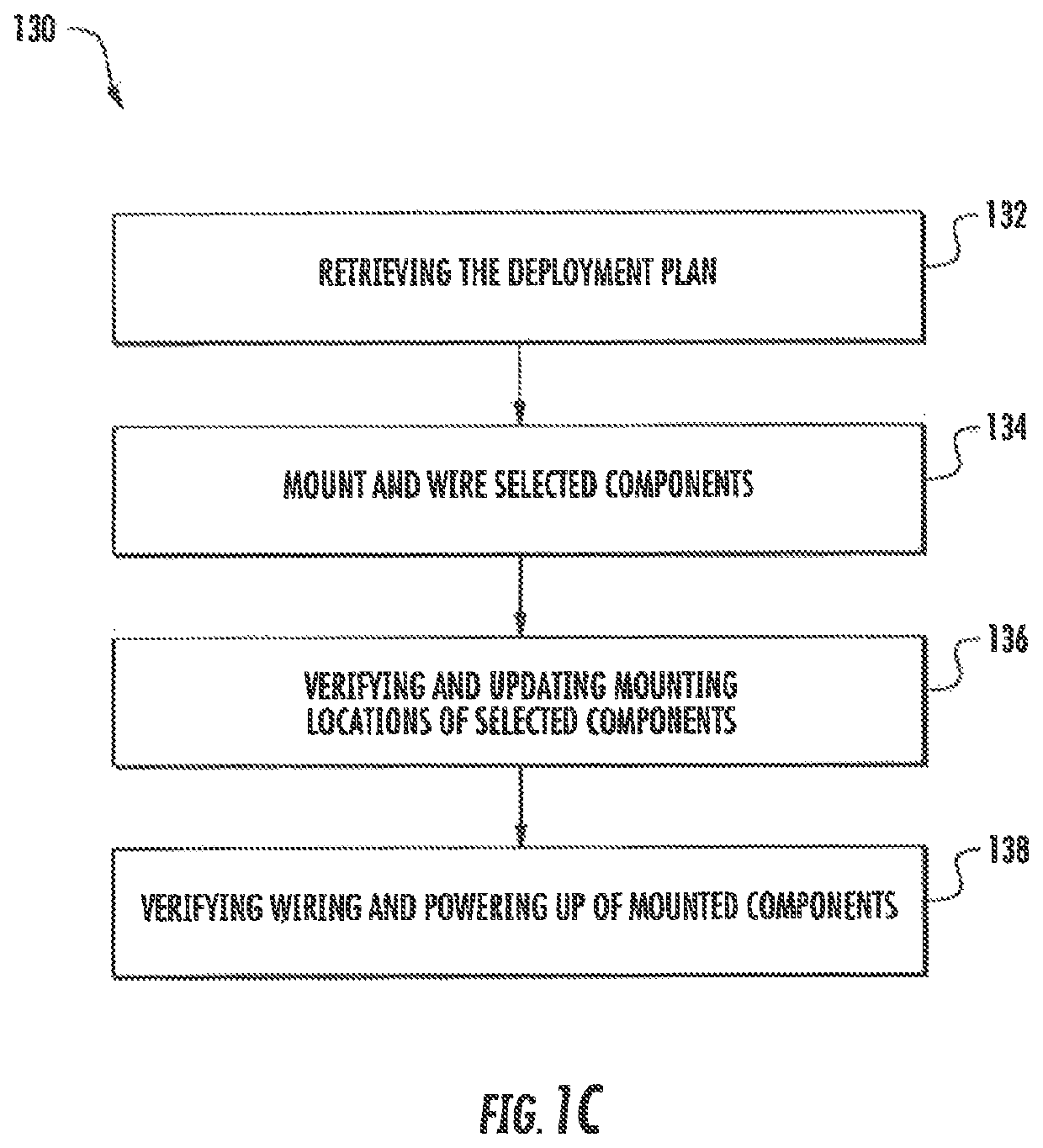

Floor-plan based learning and registration of distributed devices

ActiveUS10944837B2Maximizing global similarityComputer controlPosition fixationSignal qualityMobile device

A method of registering distributed devices includes discovering a plurality of devices at a central panel or server, localizing the devices, and authorizing the devices with a mobile device communicating with the central panel or server. The method also includes registering the devices with the central panel. The model can include verifying link quality with each of the devices before registering the devices with the central panel by comparing signal quality between each device and a central panel with a pre-defined threshold level.

Owner:CARRIER CORP

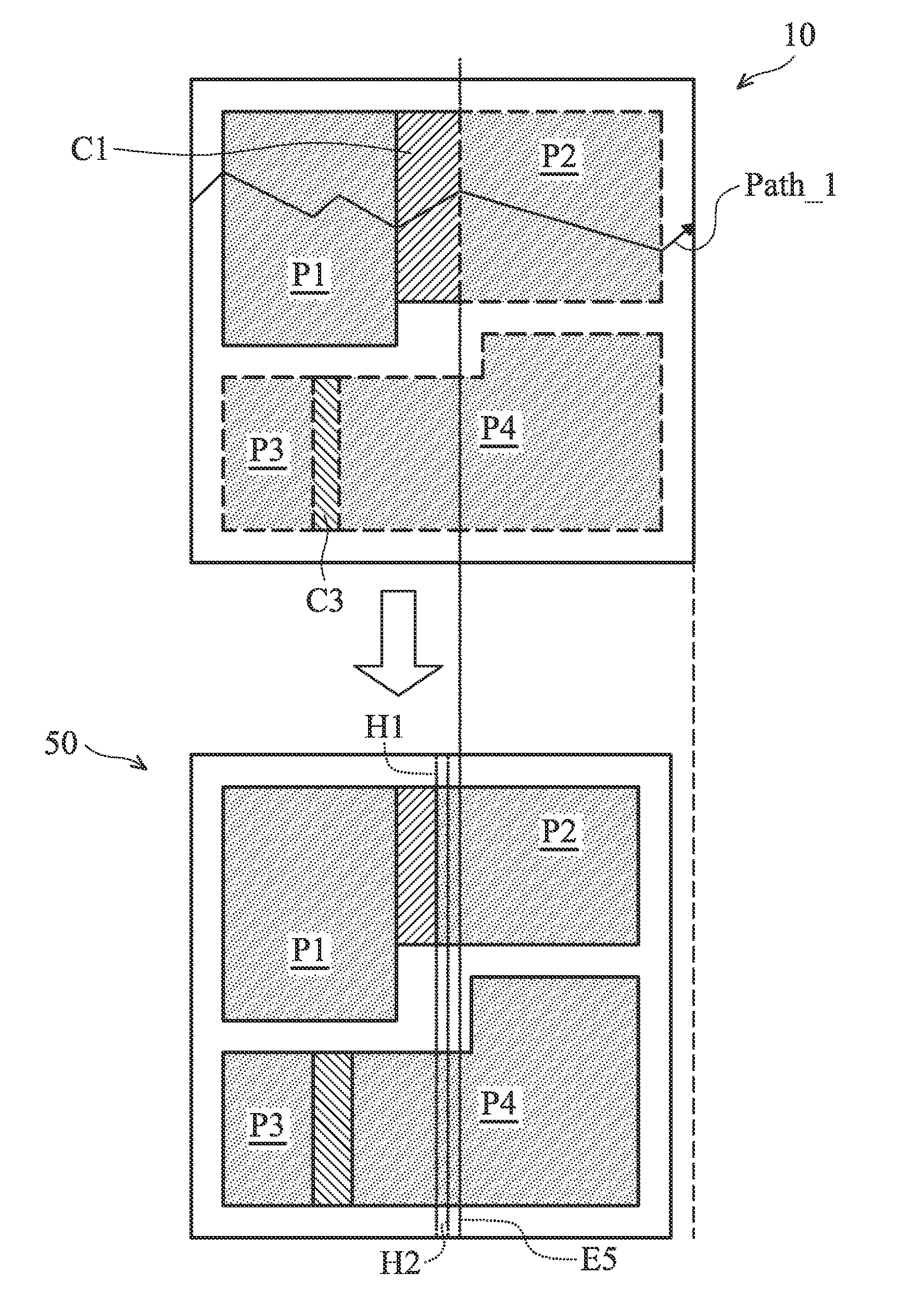

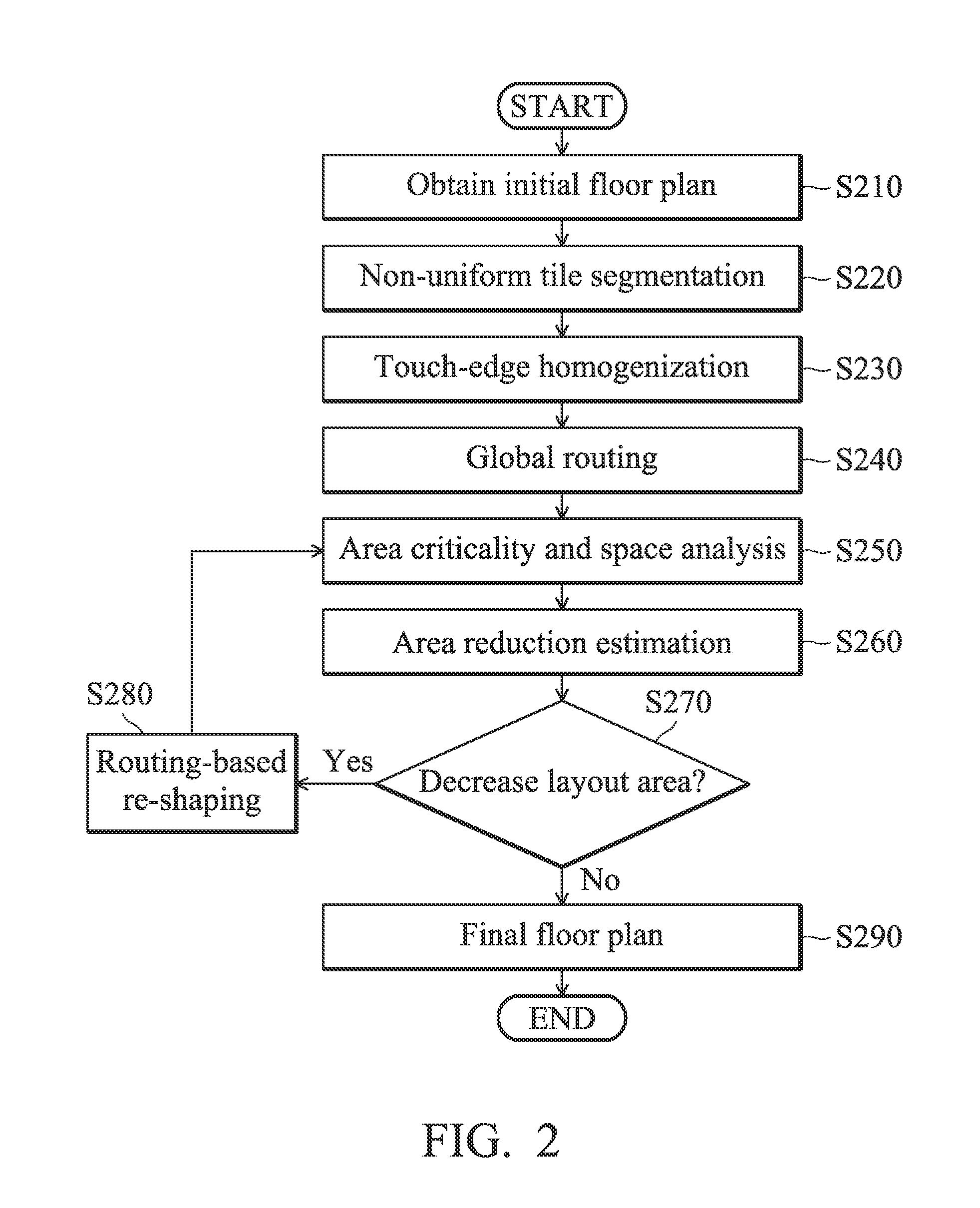

Methods for minimizing layout area of IC

ActiveUS20160171145A1Multi-objective optimisationSoftware simulation/interpretation/emulationFloor planEngineering

A method for minimizing layout area of IC is provided. A plurality of first tiles of an initial floor plan are obtained according to a plurality of partitions and channels of the initial floor plan. Each first tile between the partition and the channel has a fixed tile property being the partition or the channel. Each second tile between at least one of the partitions and at least one of the channels has a changeable tile property which can be changed between the at least one partition and the at least one channel. A specific area path of the layout area is obtained according to the partitions, the channels and the routing densities corresponding to the channels. The changeable tile properties of the second tiles are changed according to the specific area path, to re-shape the partitions and re-route the nets within the channels.

Owner:MEDIATEK INC

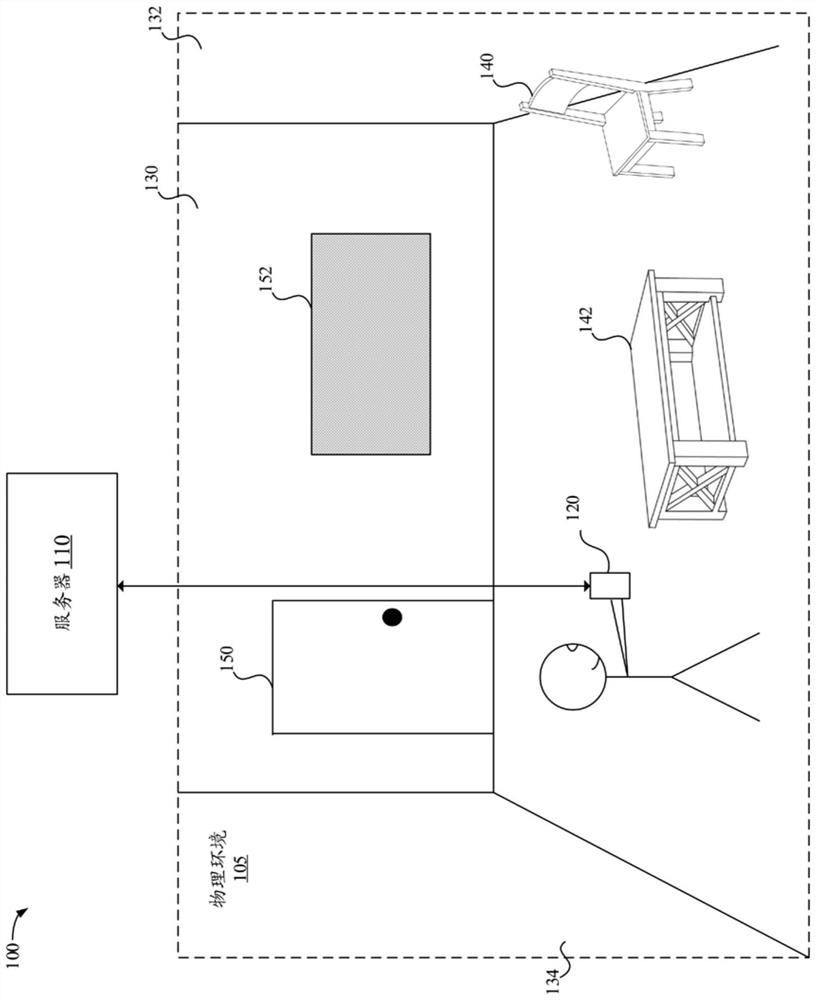

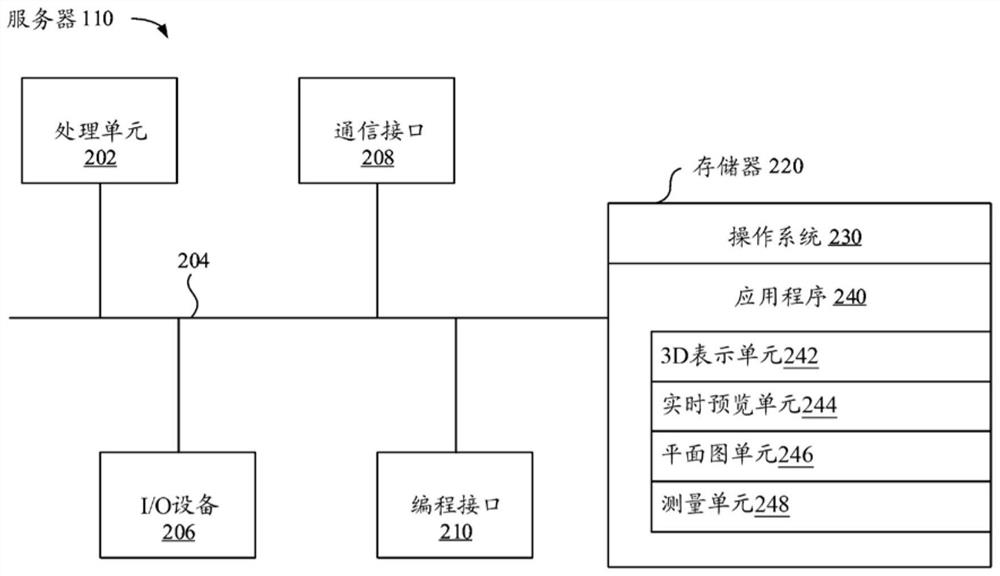

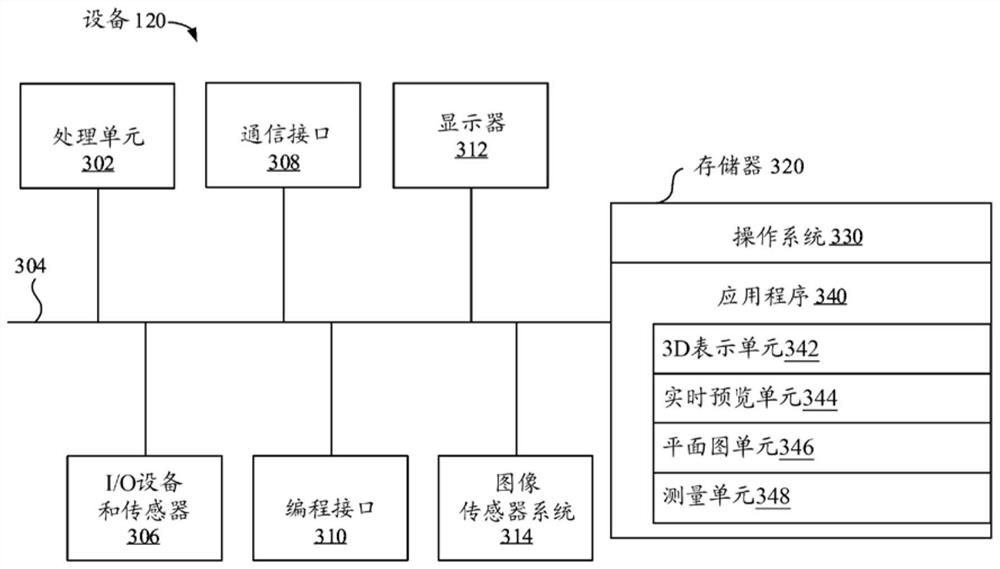

Floorplan generation based on room scanning

The invention relates to the floorplan generation based on room scanning. Various implementations disclosed herein include devices, systems, and methods that generate floorplans and measurements using a three-dimensional (3D) representation of a physical environment generated based on sensor data.

Owner:APPLE INC

System and method for synthesis of a network-on-chip for deadlock-free transformation

ActiveUS20210204360A1Reducing resource usageReduce congestionNetwork topologiesCAD circuit designComputer networkEngineering

Owner:ARTERIS

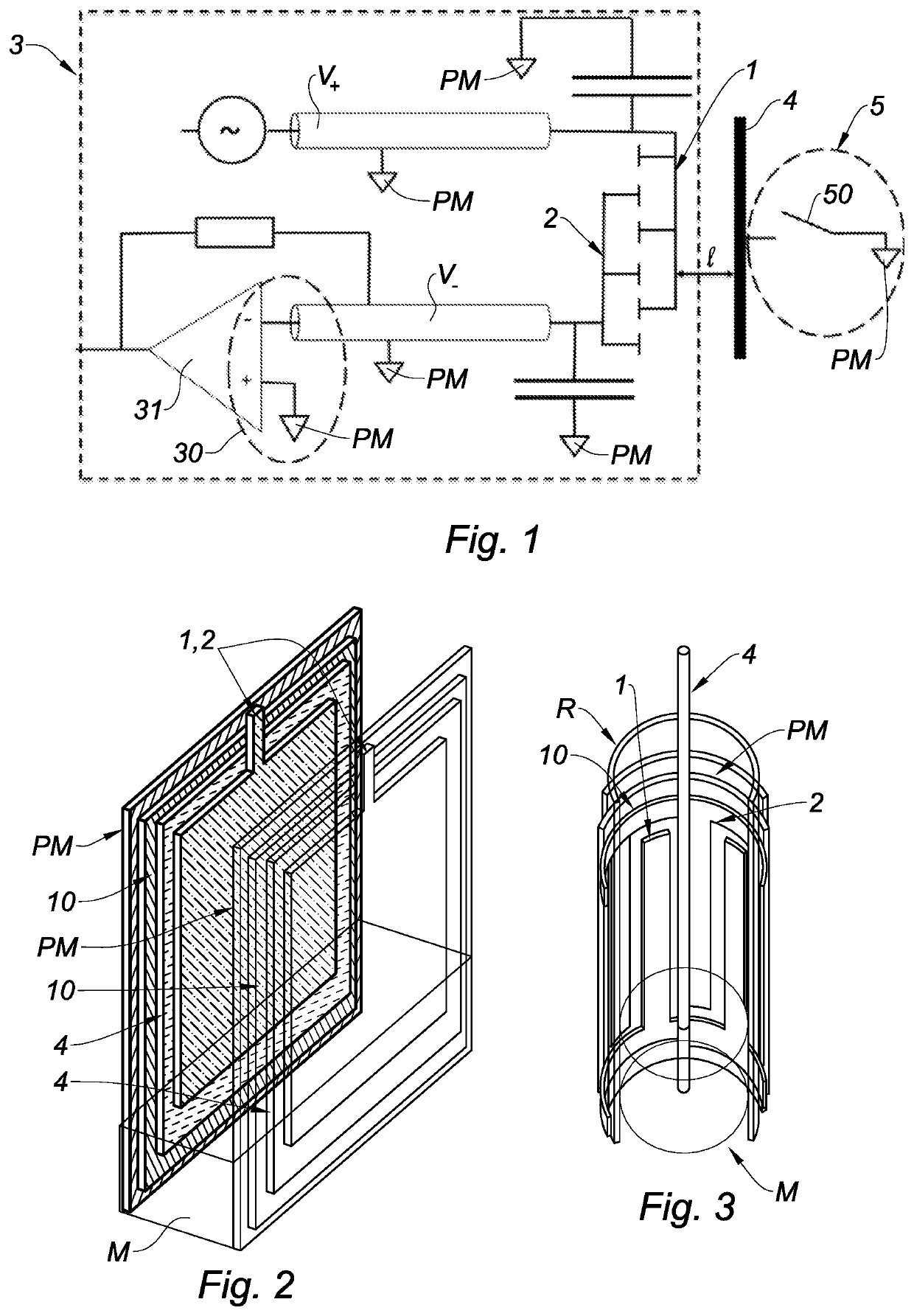

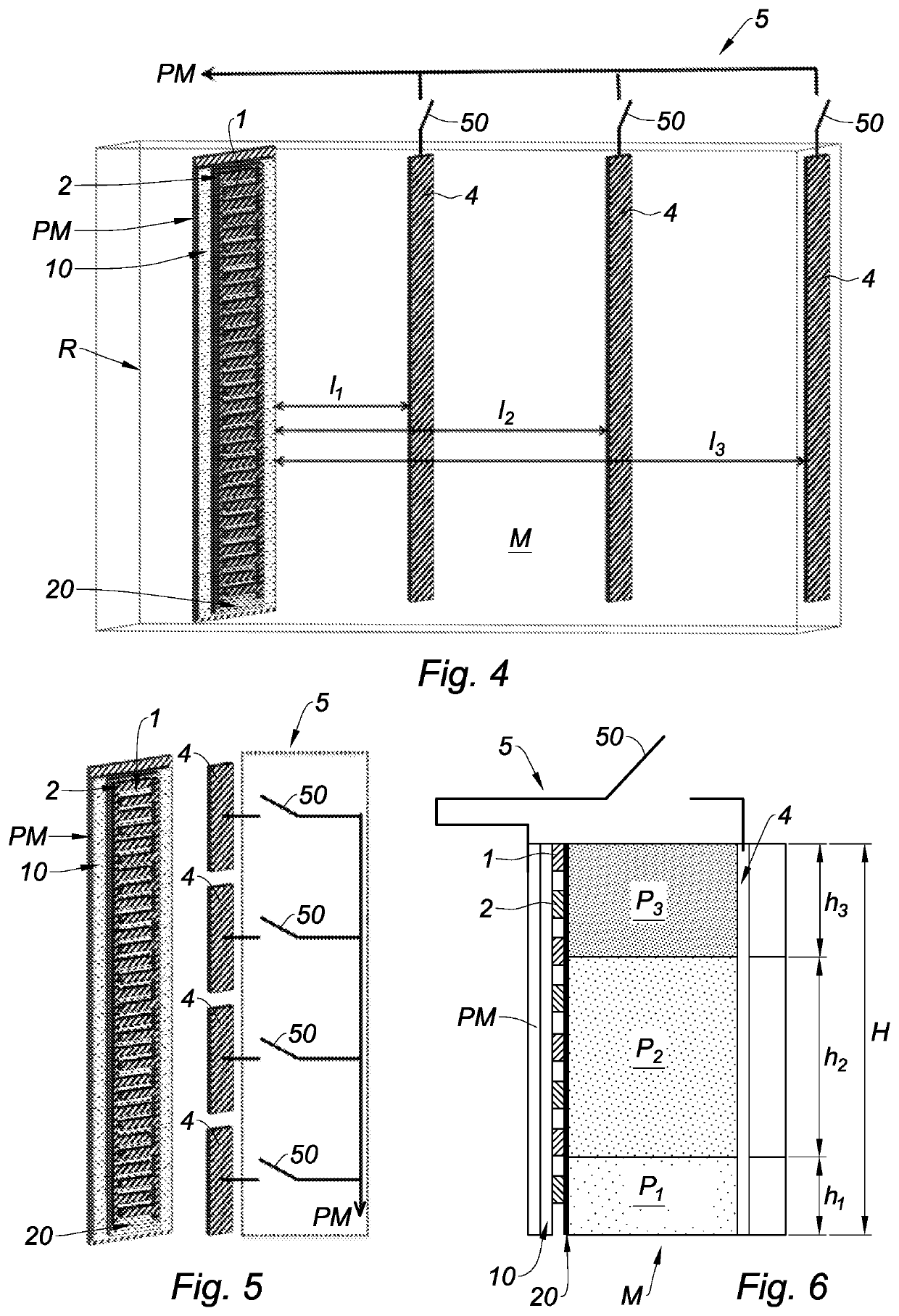

Device for capacitive measurements in a multi-phase medium

ActiveUS20200340844A1Improve equipment reliabilityHigh measurement accuracyCapacitance measurementsConverting sensor output electrically/magneticallyEngineeringComputational physics

A device comprises at least one pair of excitation electrodes forming a capacitor; a floorplan (e.g., a ground plane); and an electronic circuit. The device comprises at least one control electrode arranged at a distance from the capacitor. A switching circuit, of the device, comprises a switch having an open state and a closed state. The switching circuit is designed to apply, to the control electrode, an electric potential common to the floorplan when the switch is in the closed state. The switching circuit is also designed to leave a floating electrical potential for the control electrode when the switch is in the open state. The electronic circuit is designed to measure the mutual capacitance between the pair of excitation electrodes when the switch is in the open state and when it is in the closed state.

Owner:UNIV GRENOBLE ALPES