Patents

Literature

605results about How to "Improve equipment reliability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

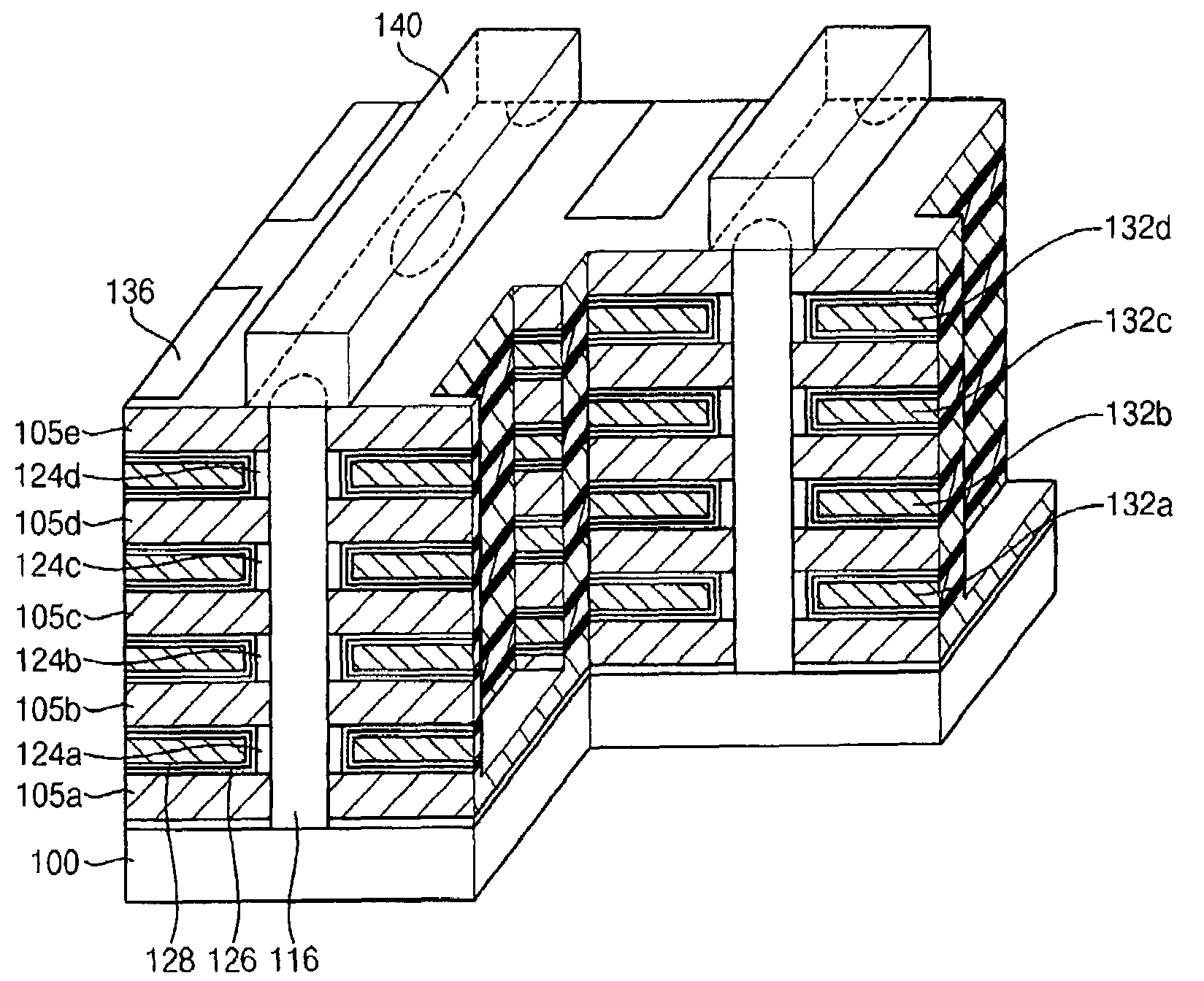

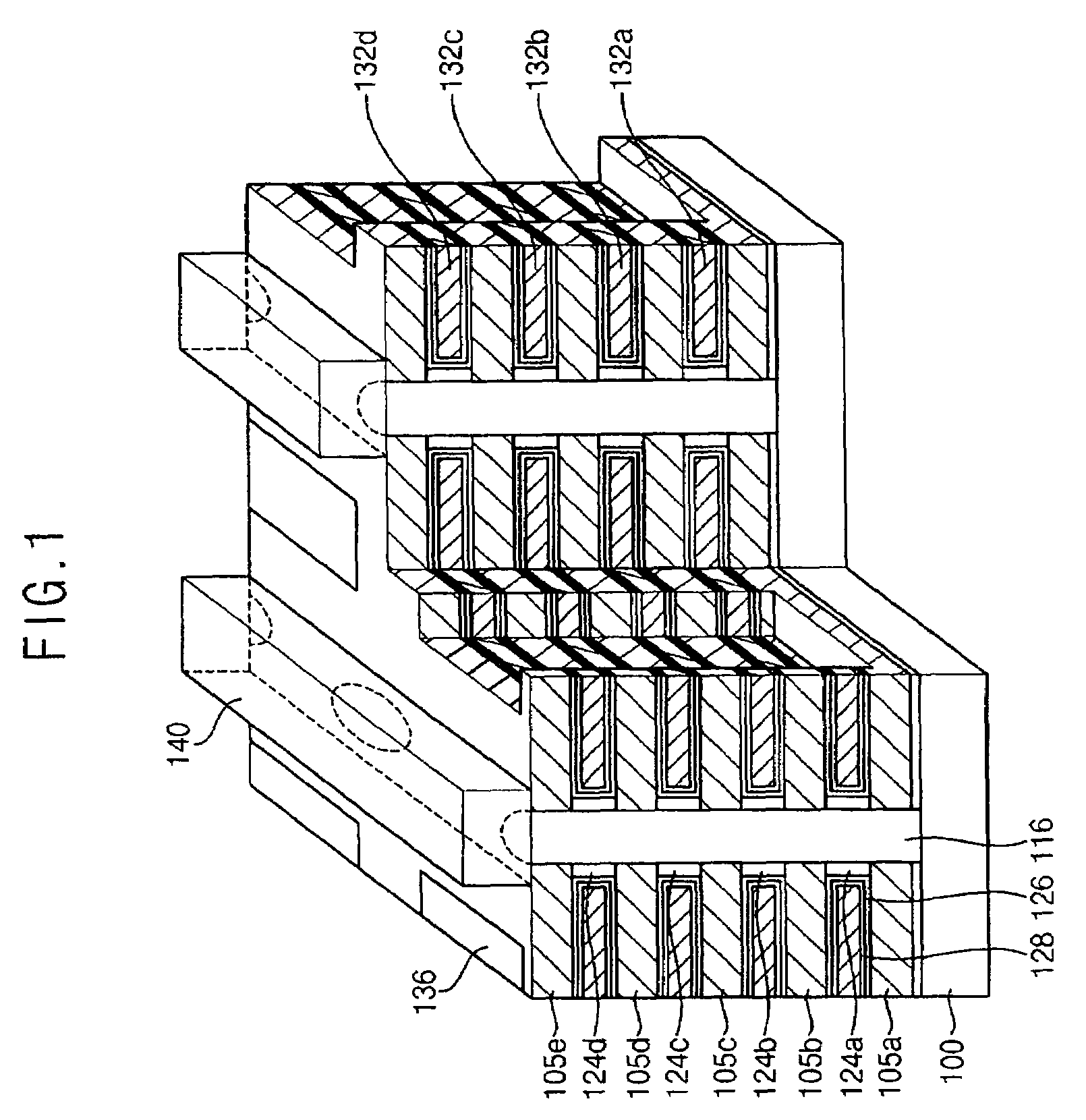

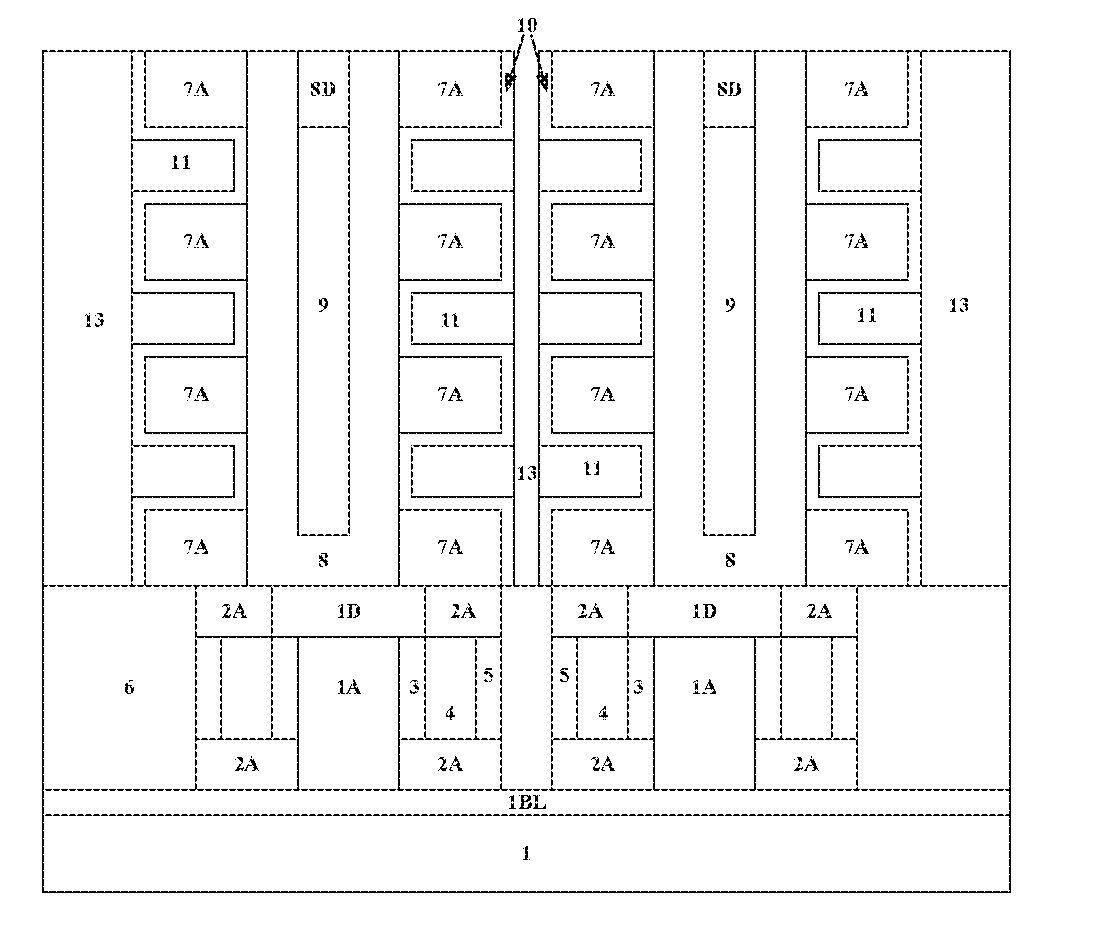

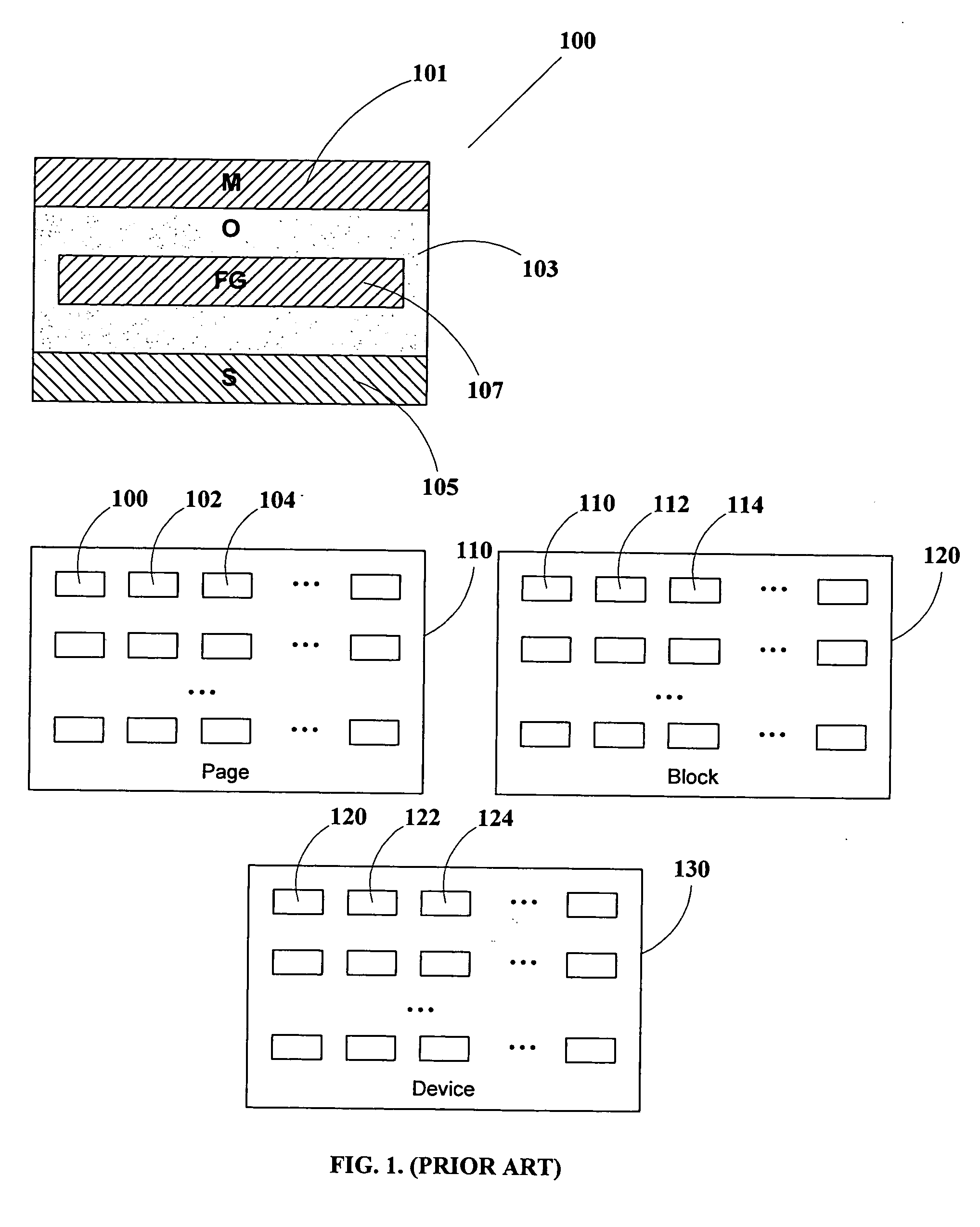

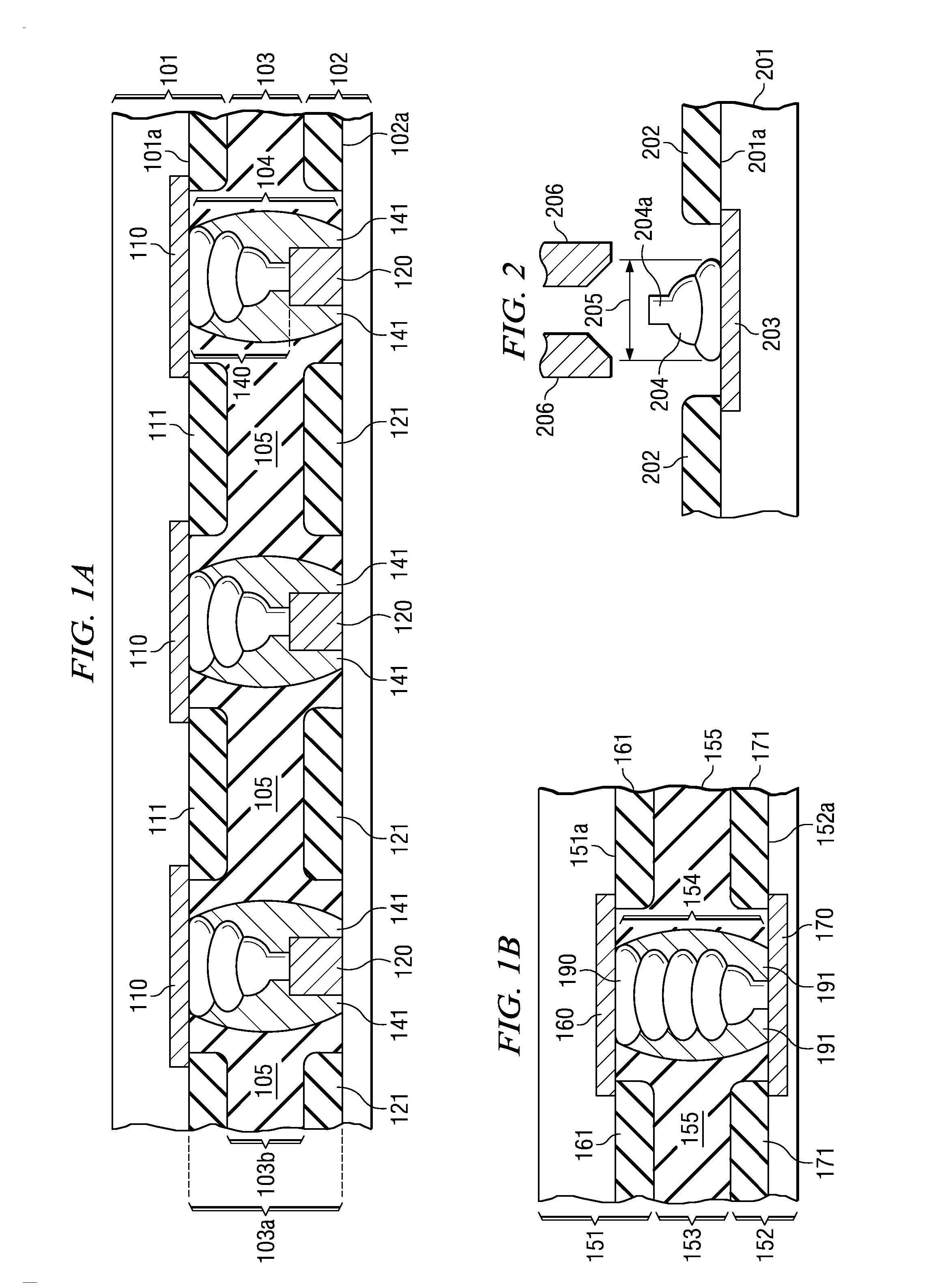

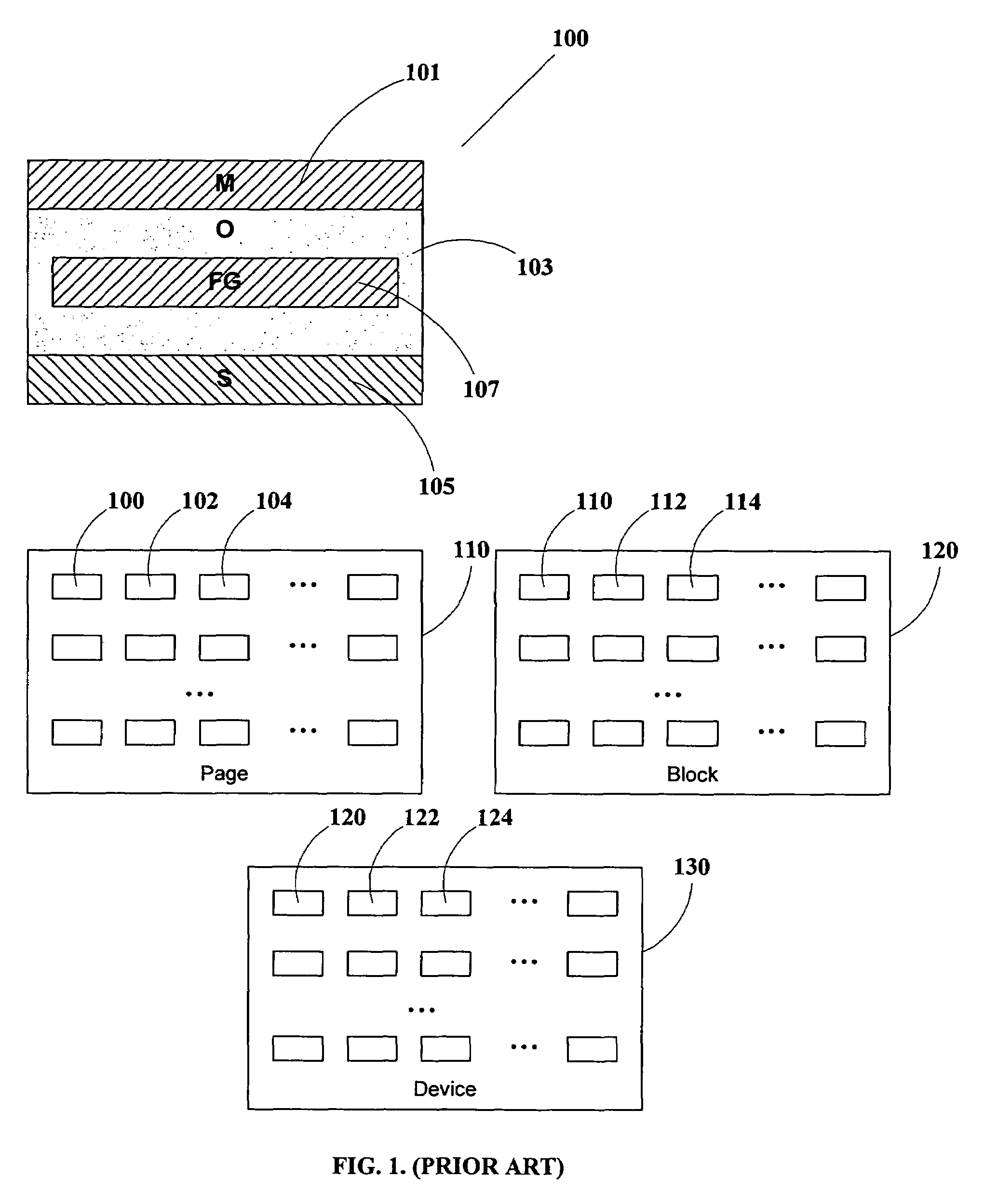

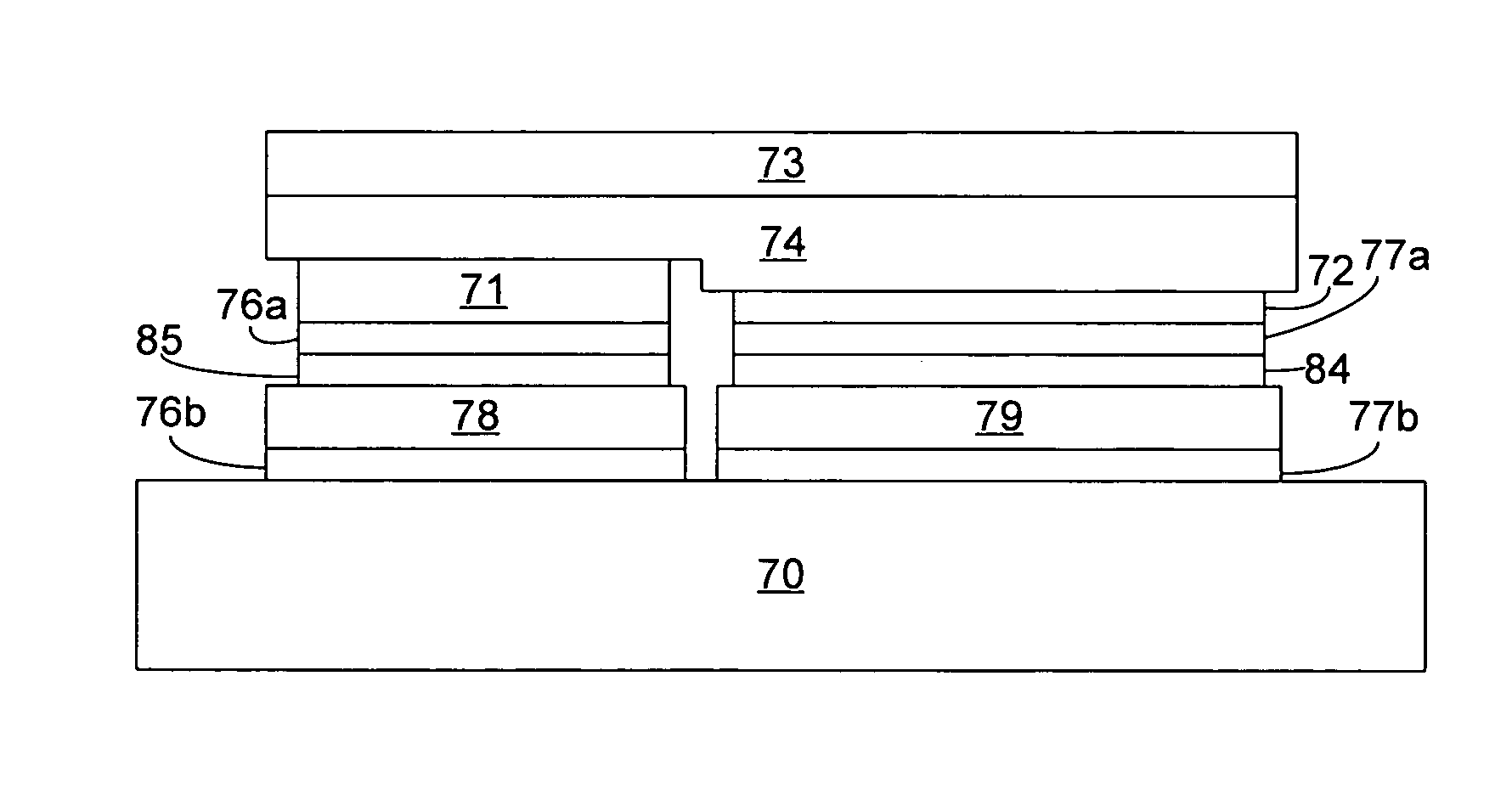

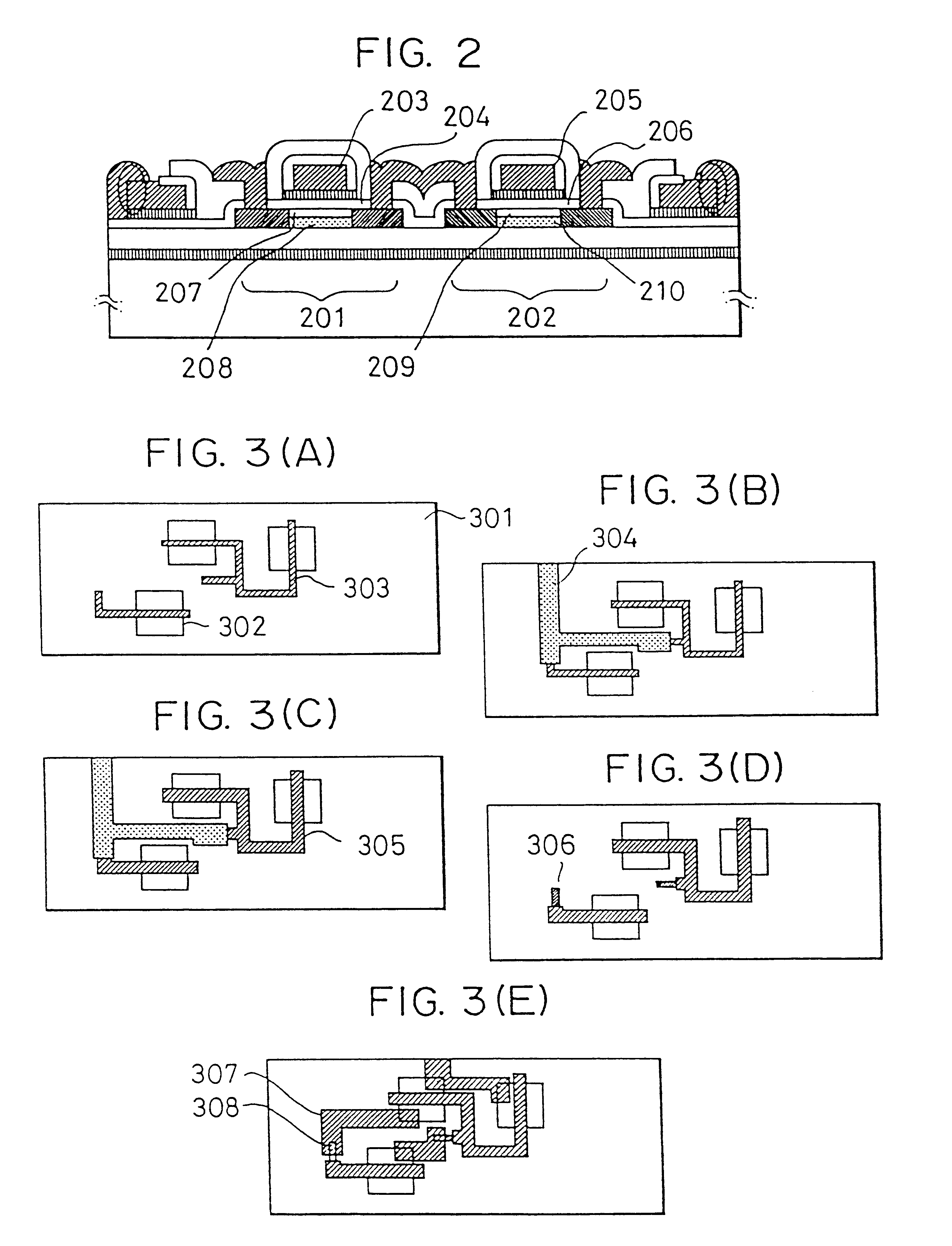

Vertical-type non-volatile memory devices

ActiveUS7679133B2Reduce the possibilityReduce in quantityTransistorSolid-state devicesSemiconductor materialsDevice material

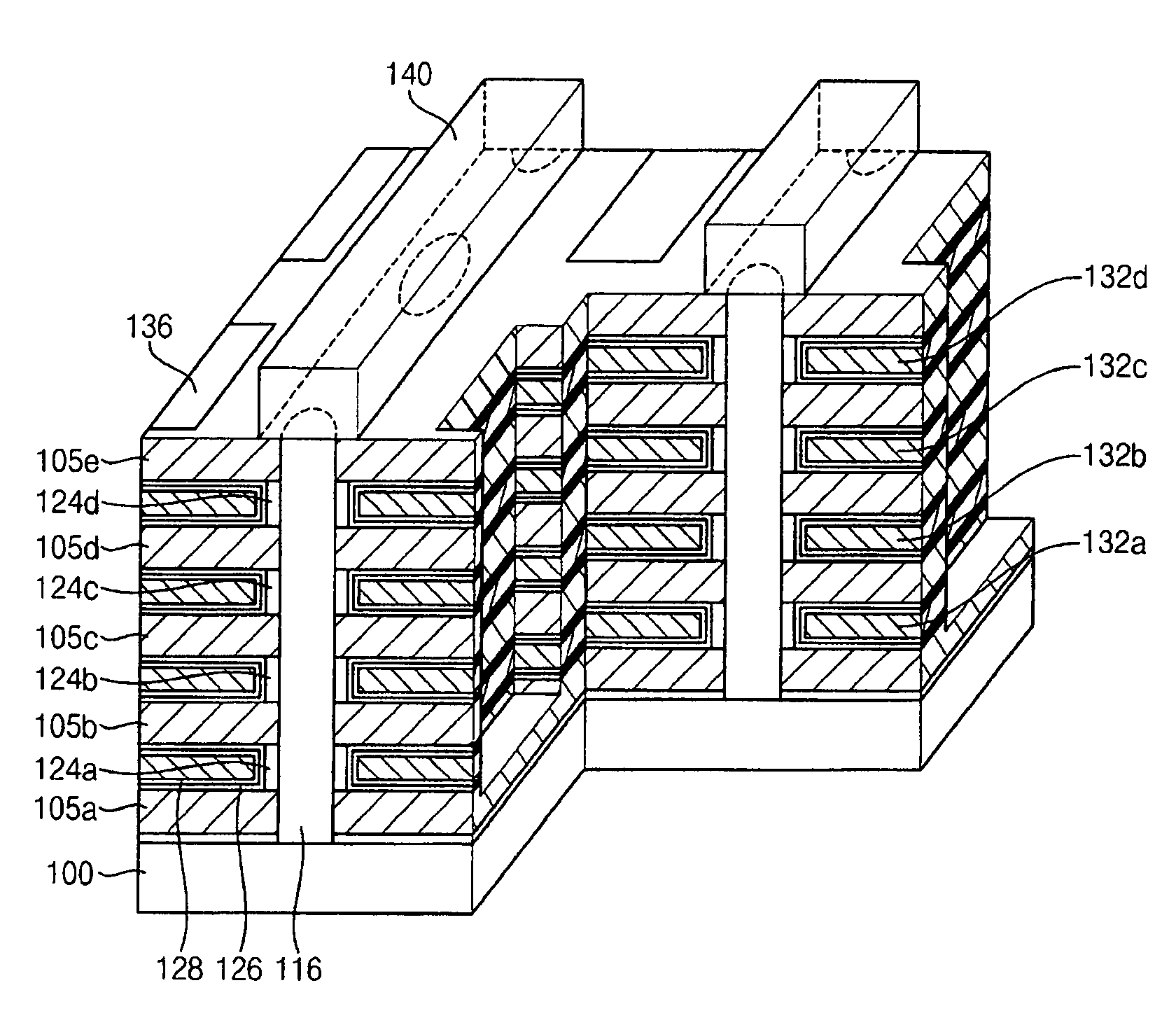

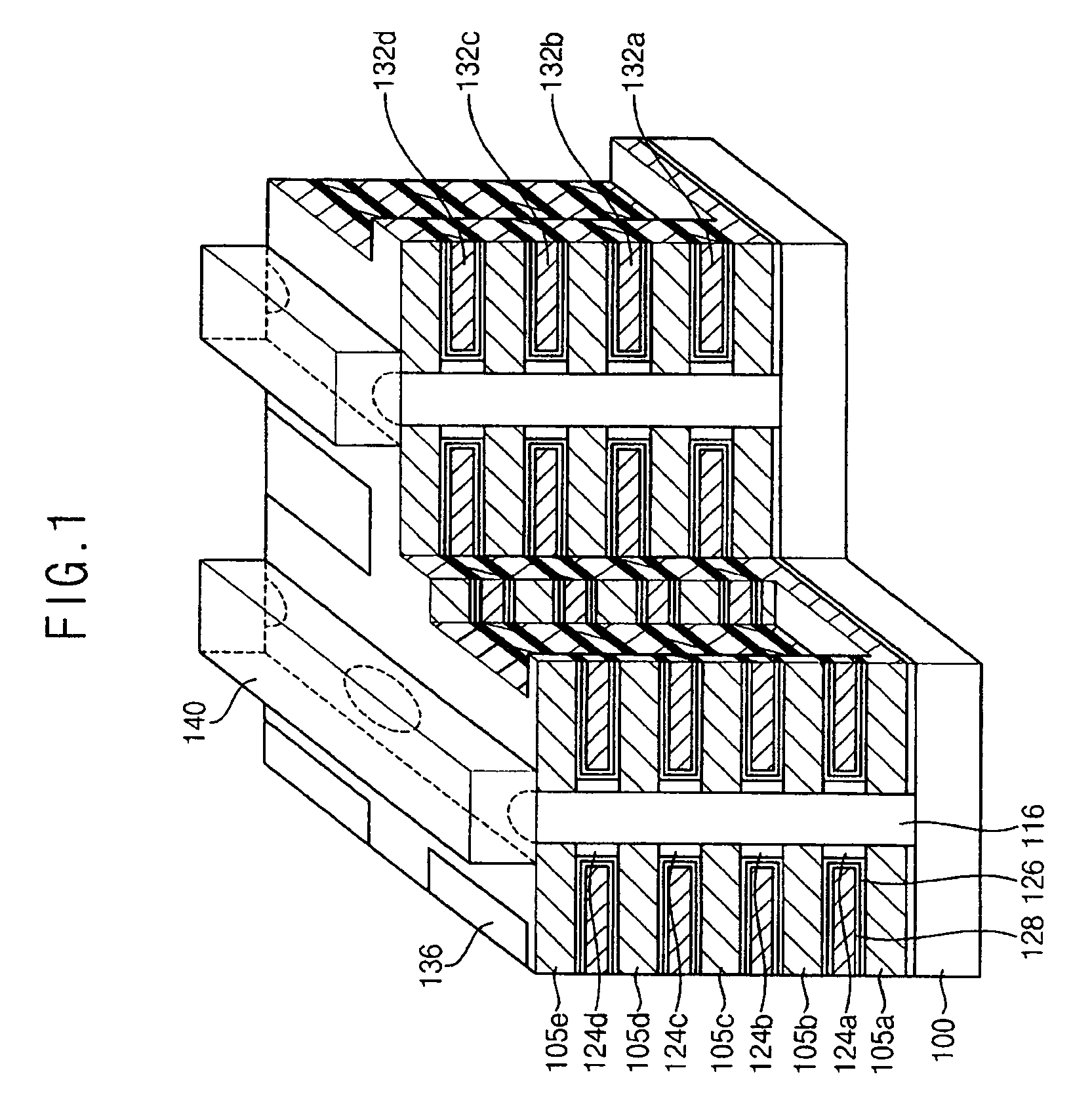

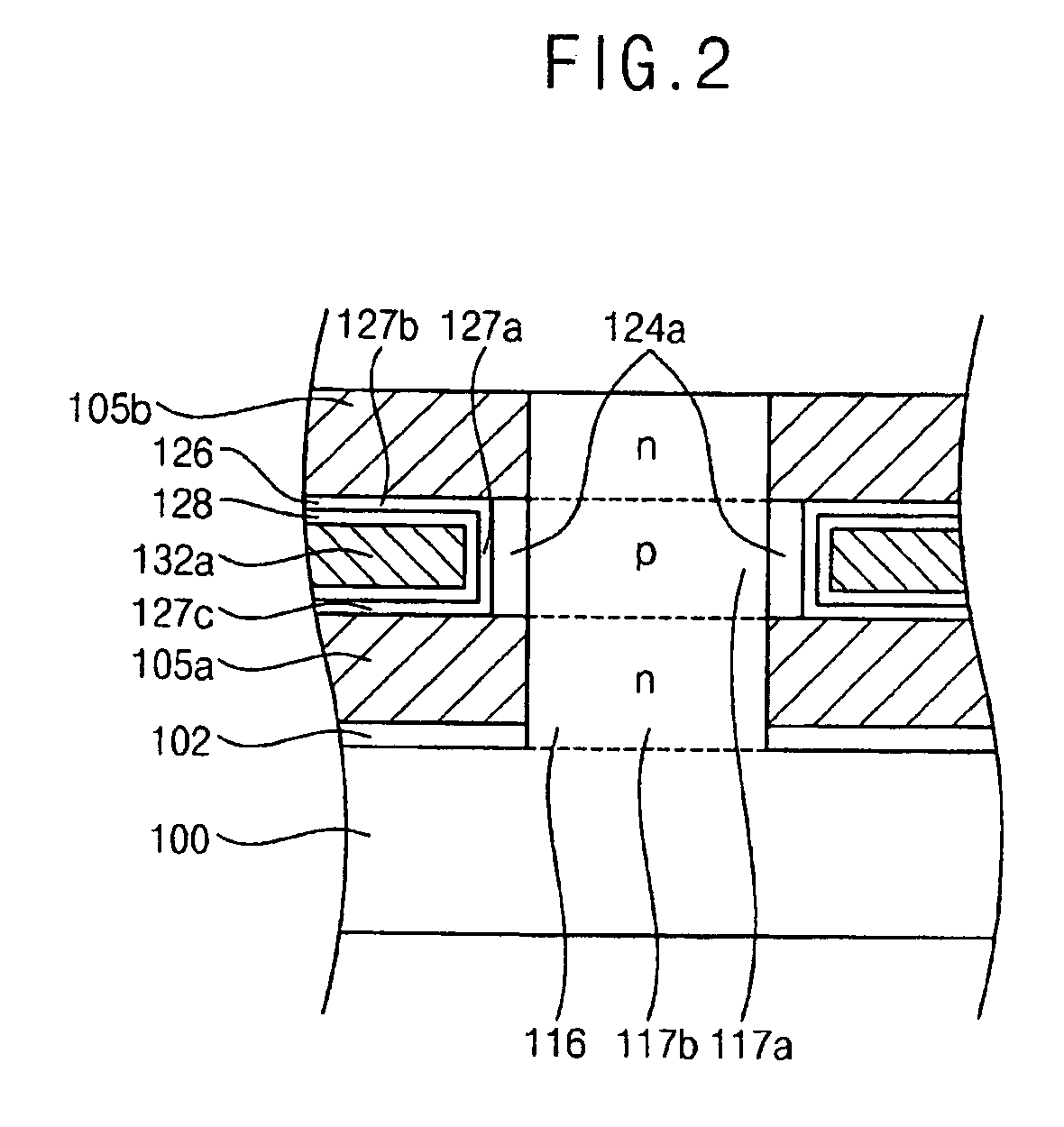

In a semiconductor device, and a method of manufacturing thereof, the device includes a substrate of single-crystal semiconductor material extending in a horizontal direction and a plurality of interlayer dielectric layers on the substrate. A plurality of gate patterns are provided, each gate pattern being between a neighboring lower interlayer dielectric layer and a neighboring upper interlayer dielectric layer. A vertical channel of single-crystal semiconductor material extends in a vertical direction through the plurality of interlayer dielectric layers and the plurality of gate patterns, a gate insulating layer being between each gate pattern and the vertical channel that insulates the gate pattern from the vertical channel.

Owner:SAMSUNG ELECTRONICS CO LTD

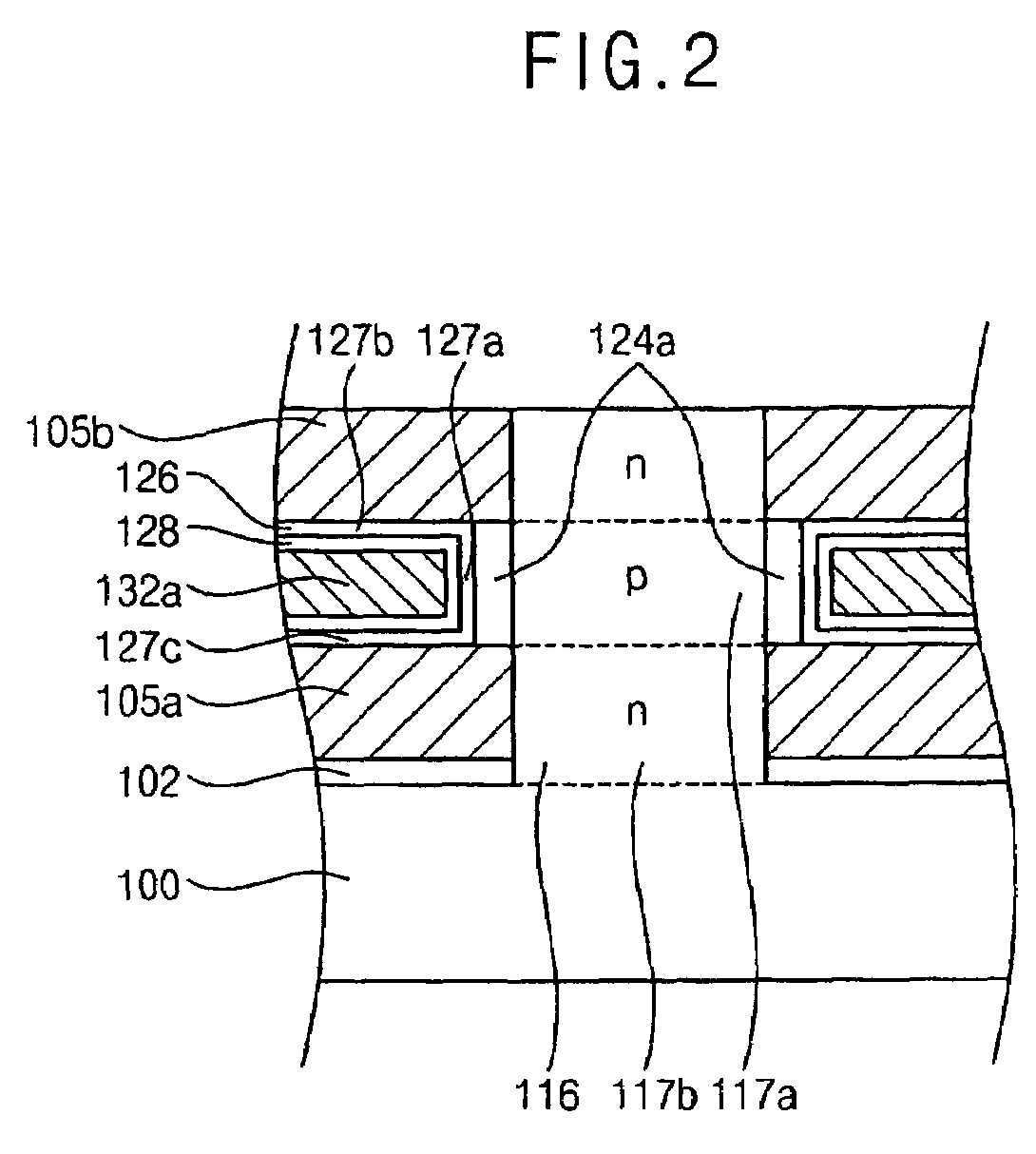

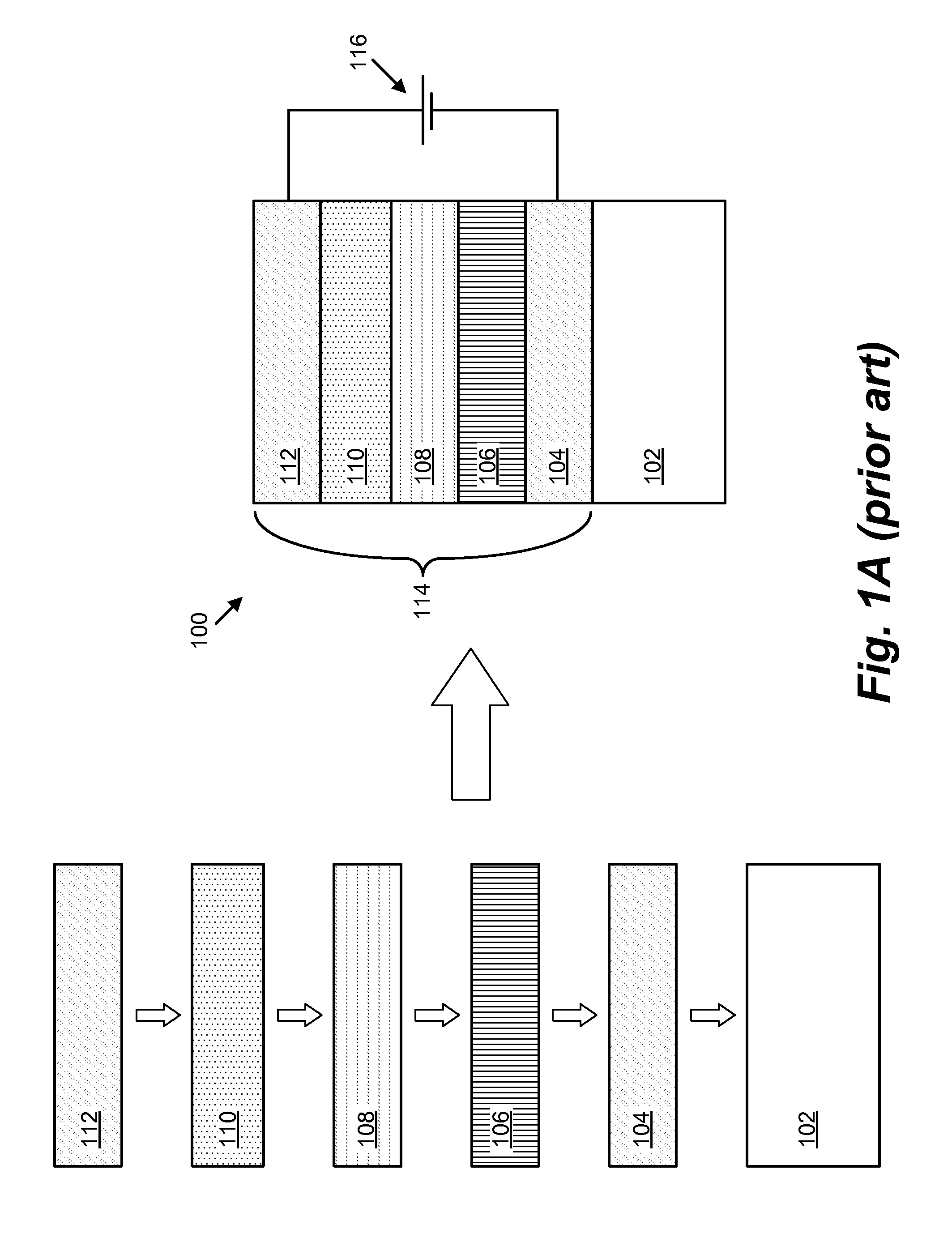

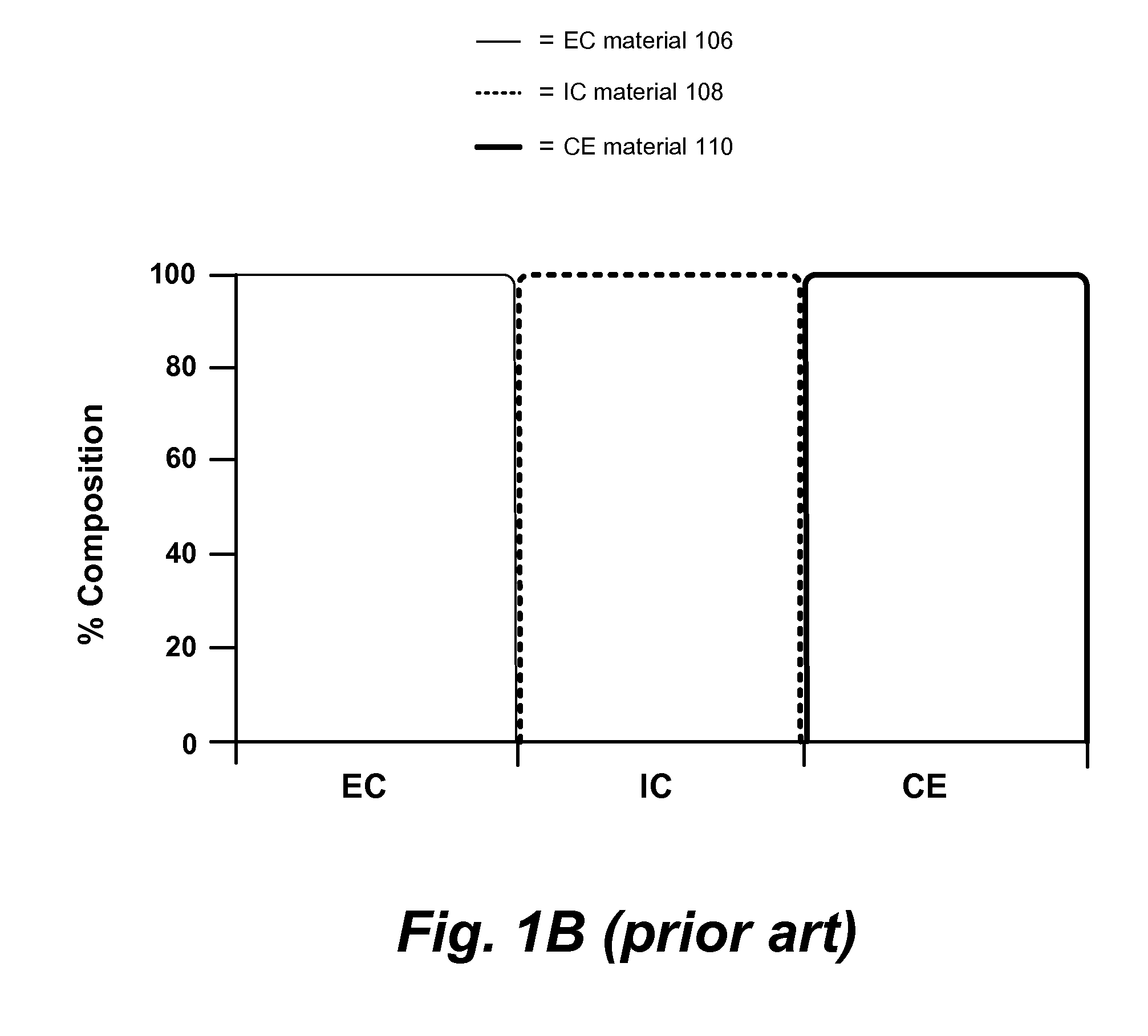

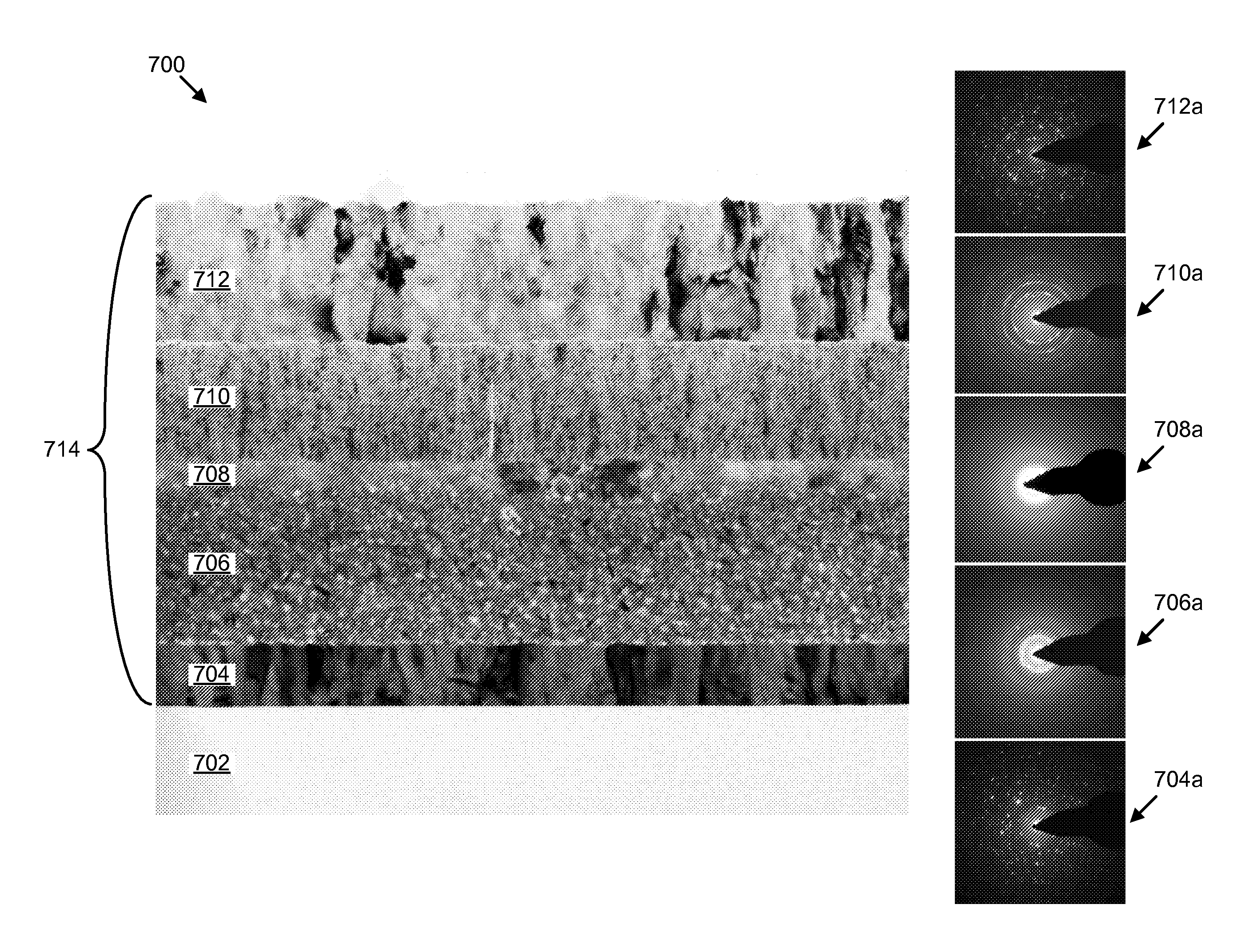

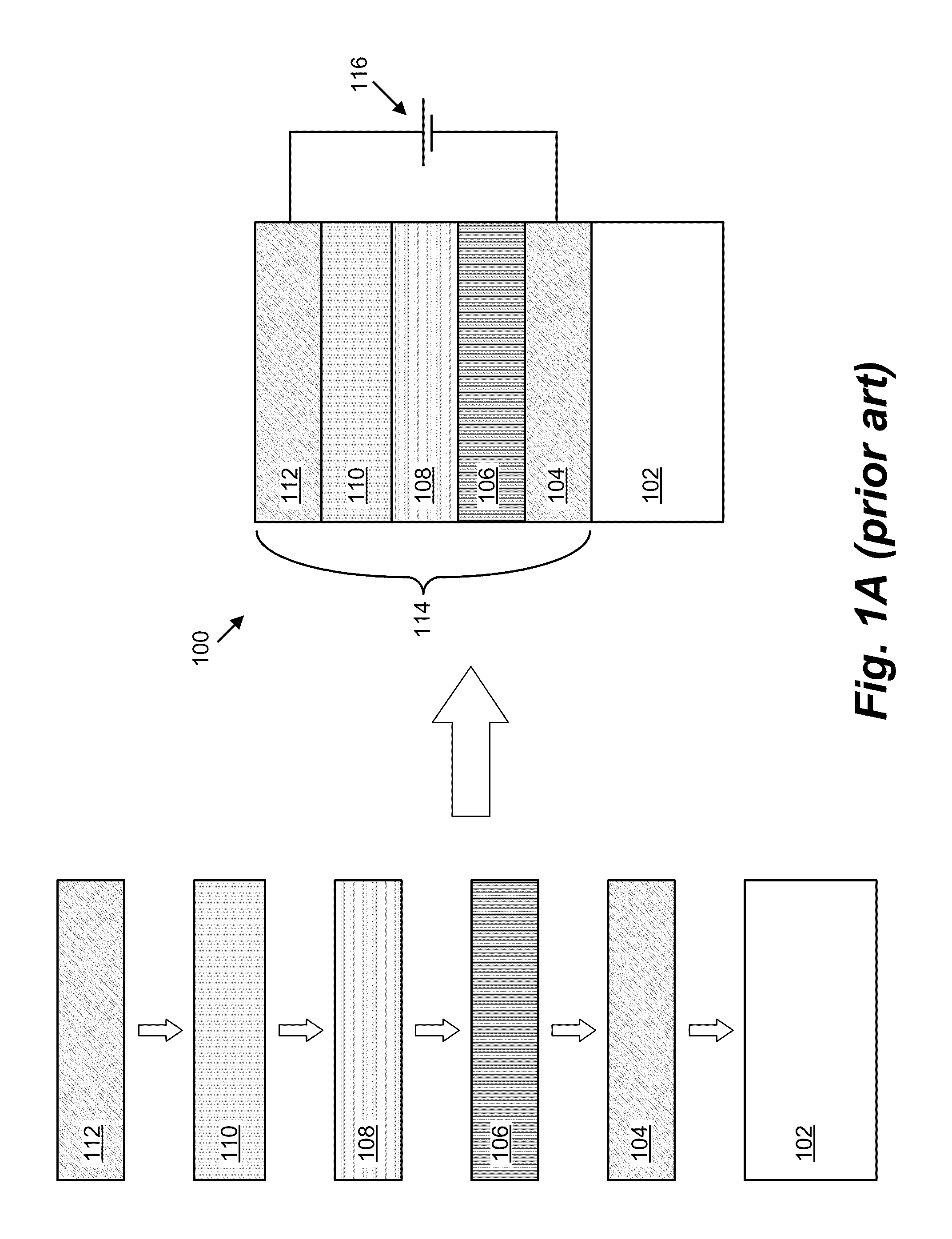

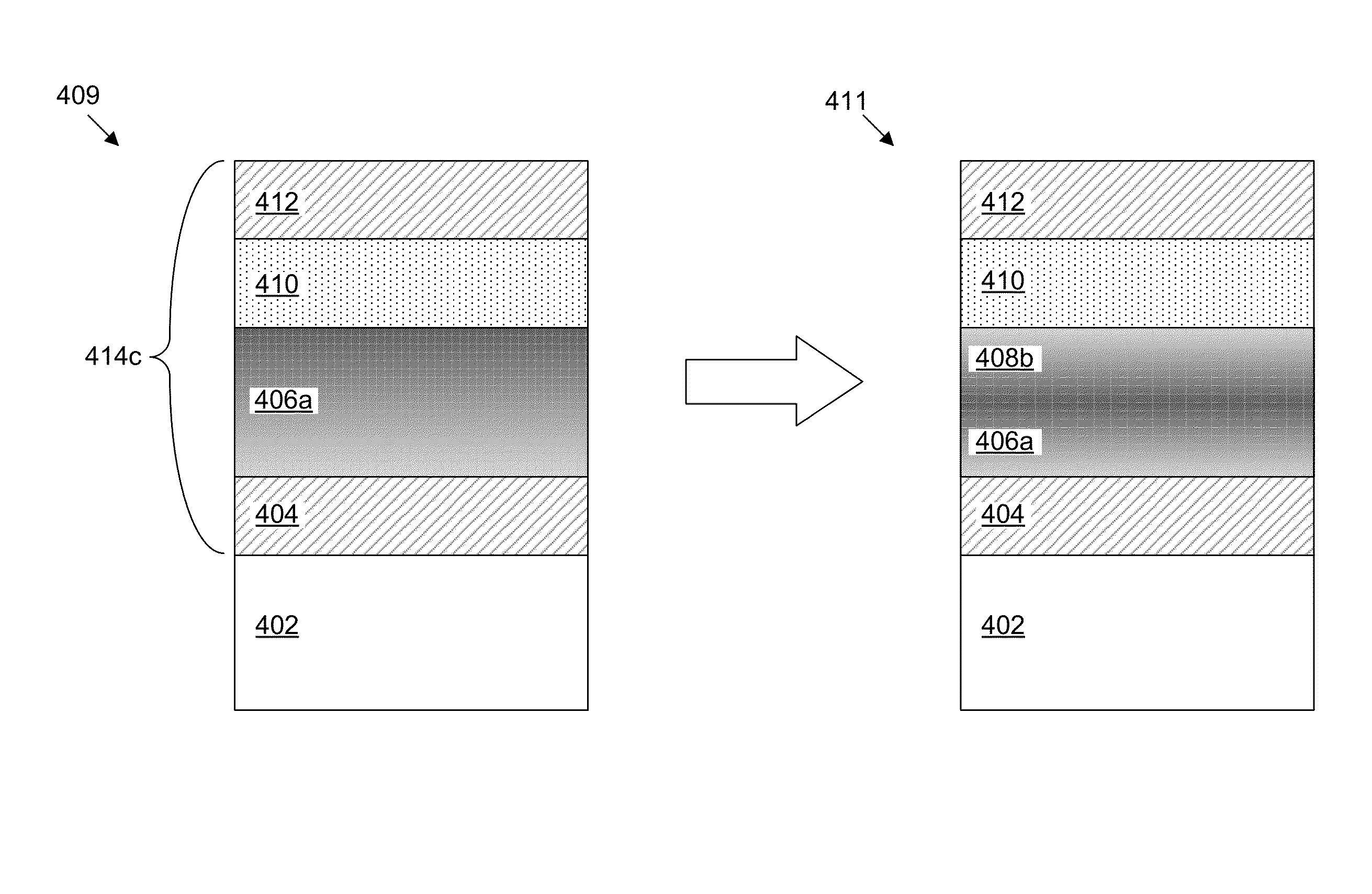

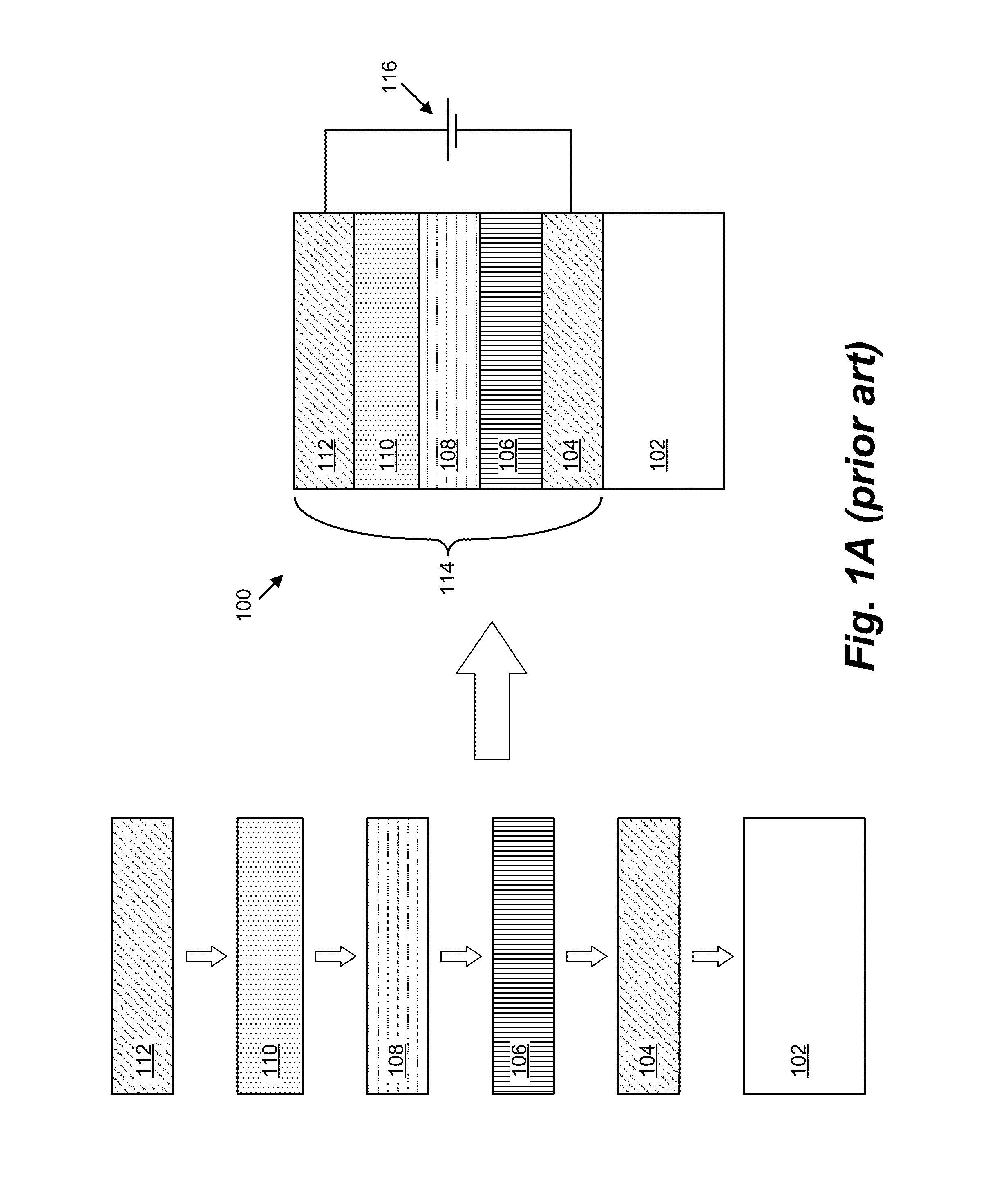

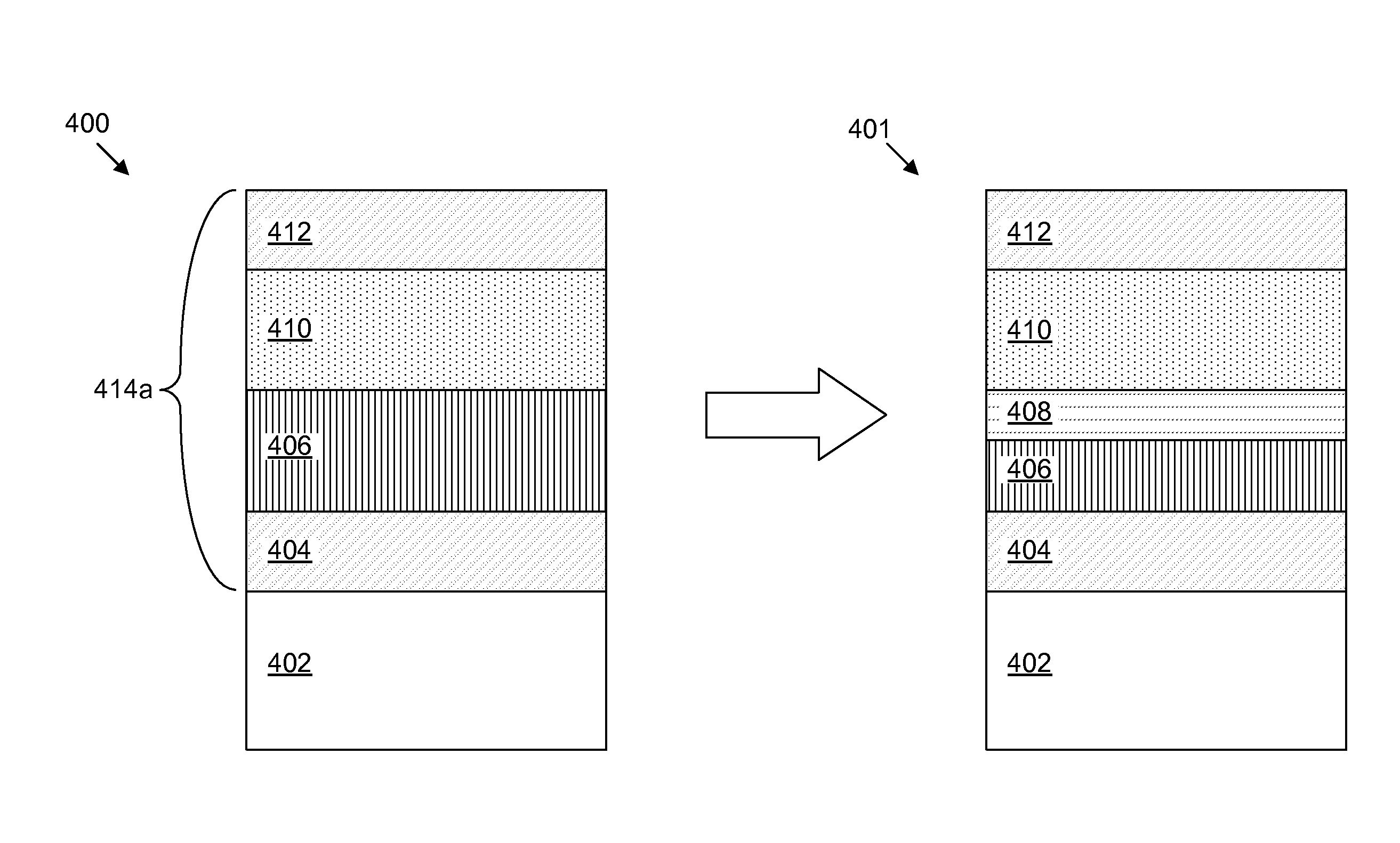

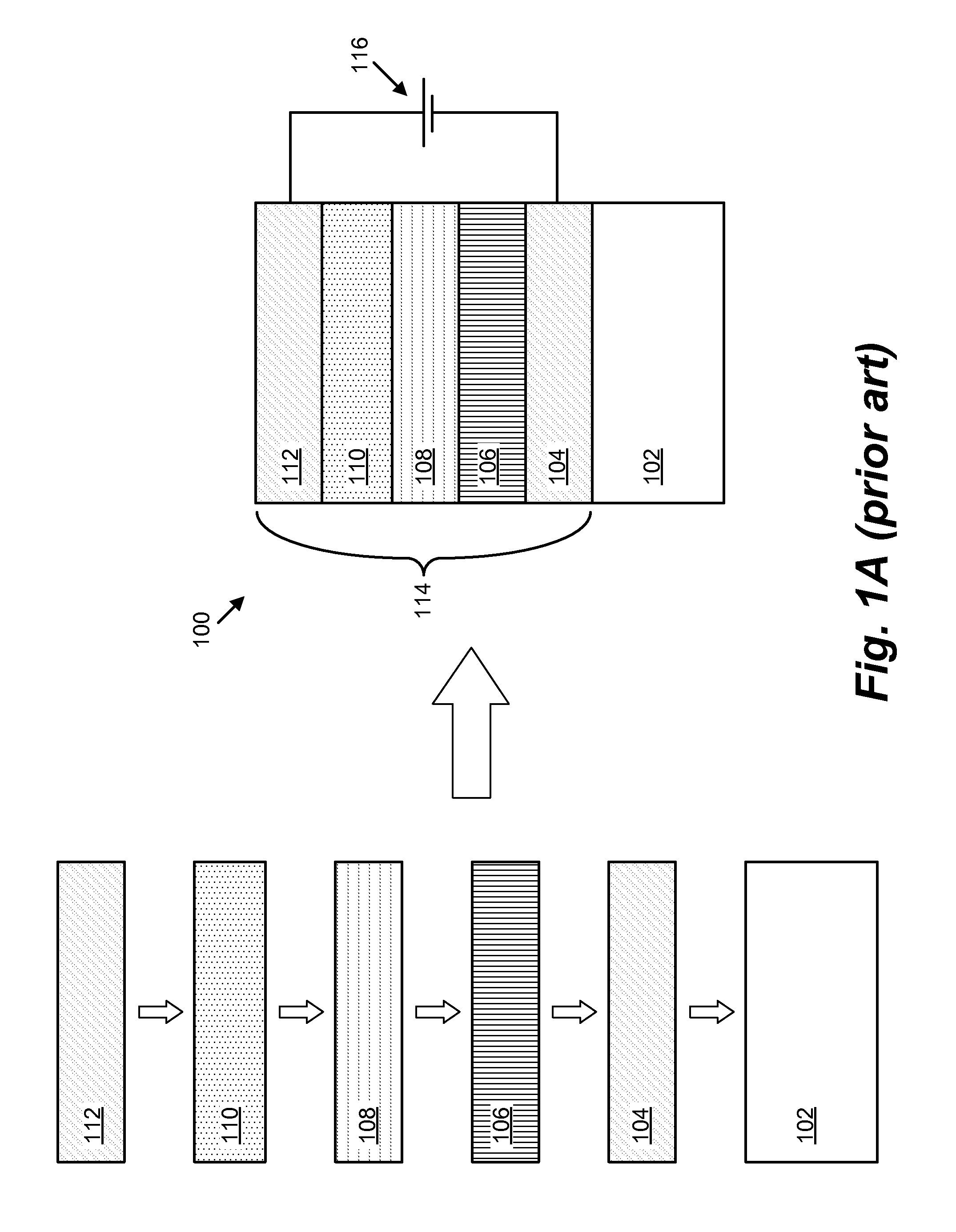

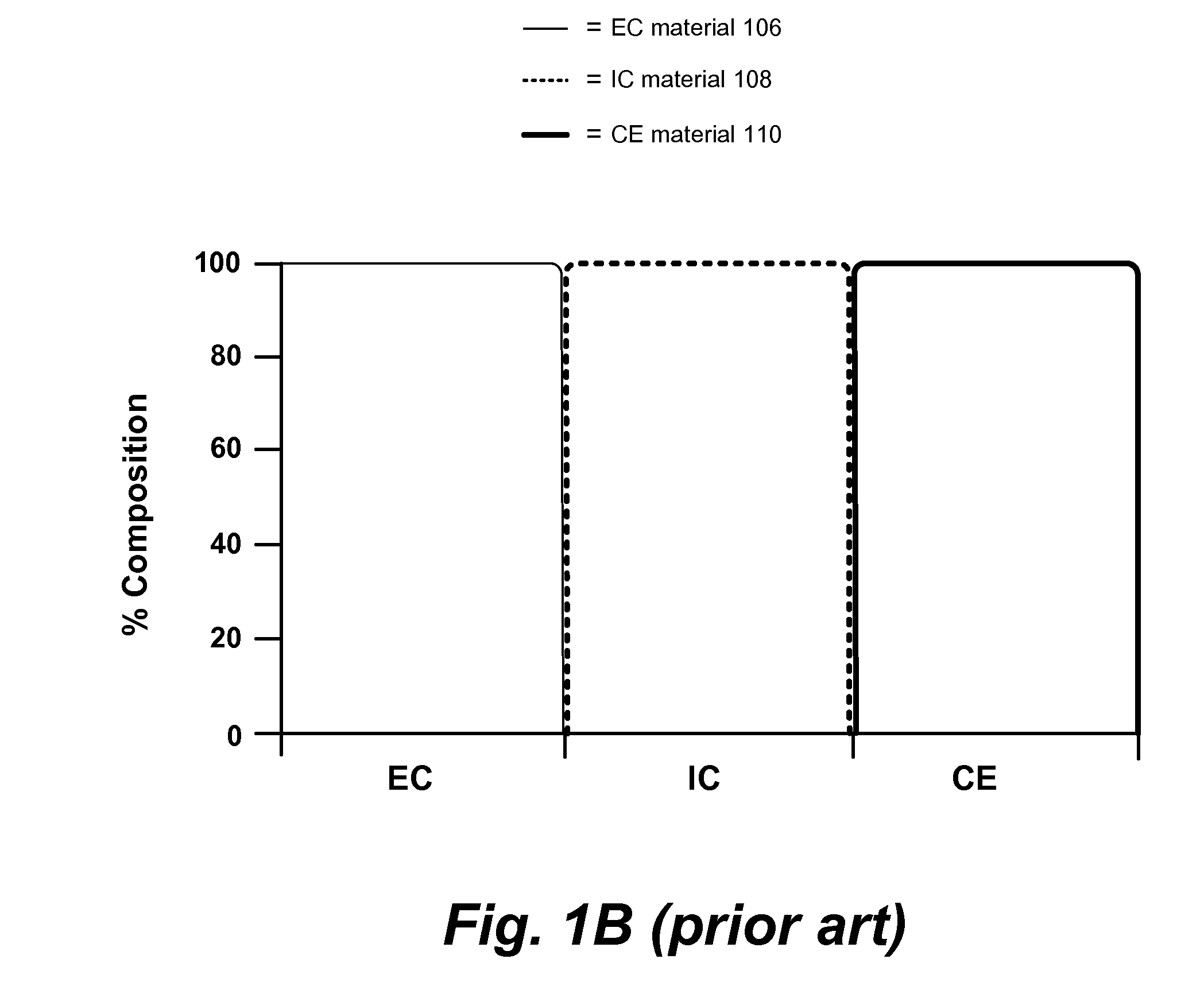

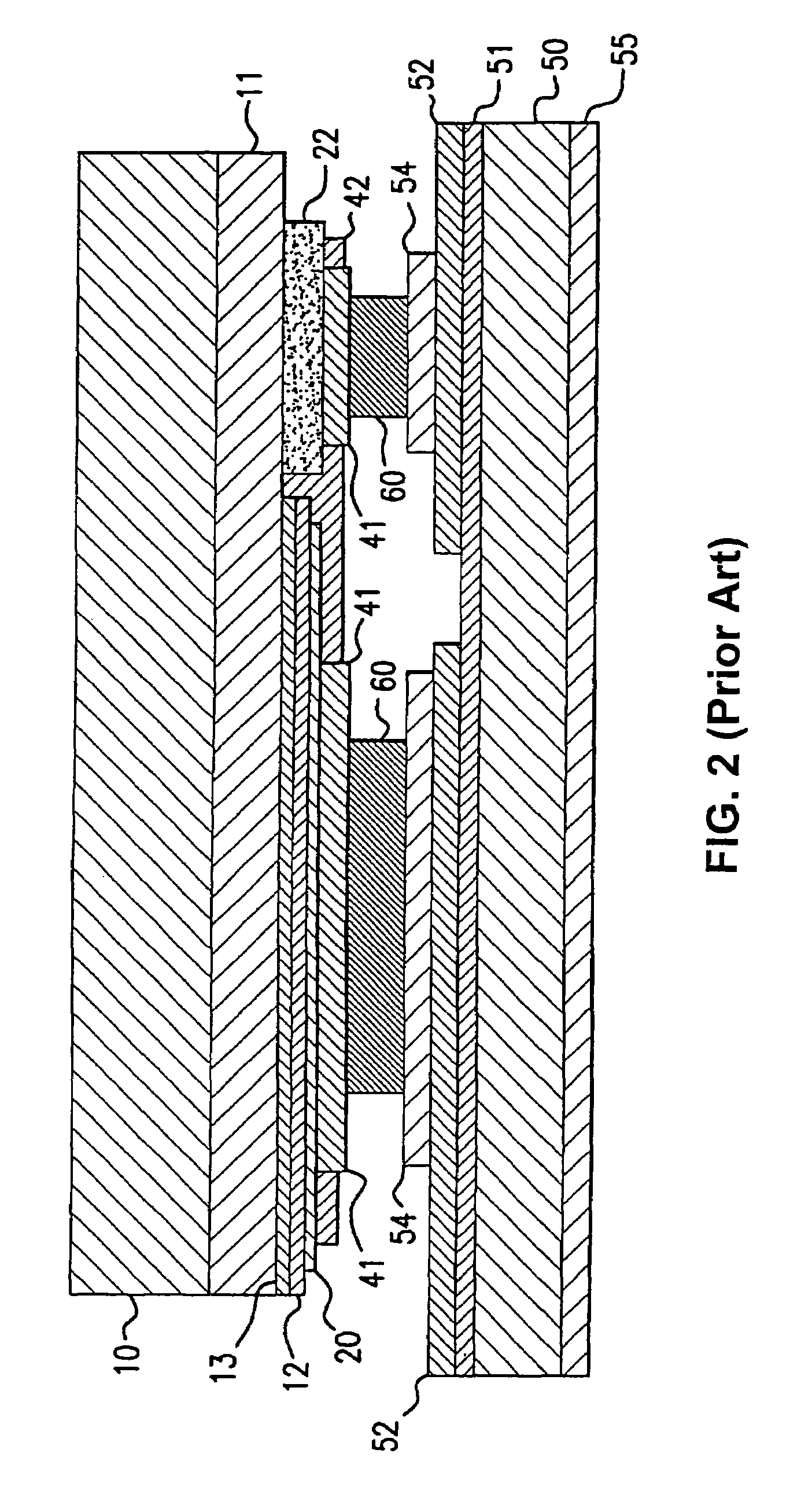

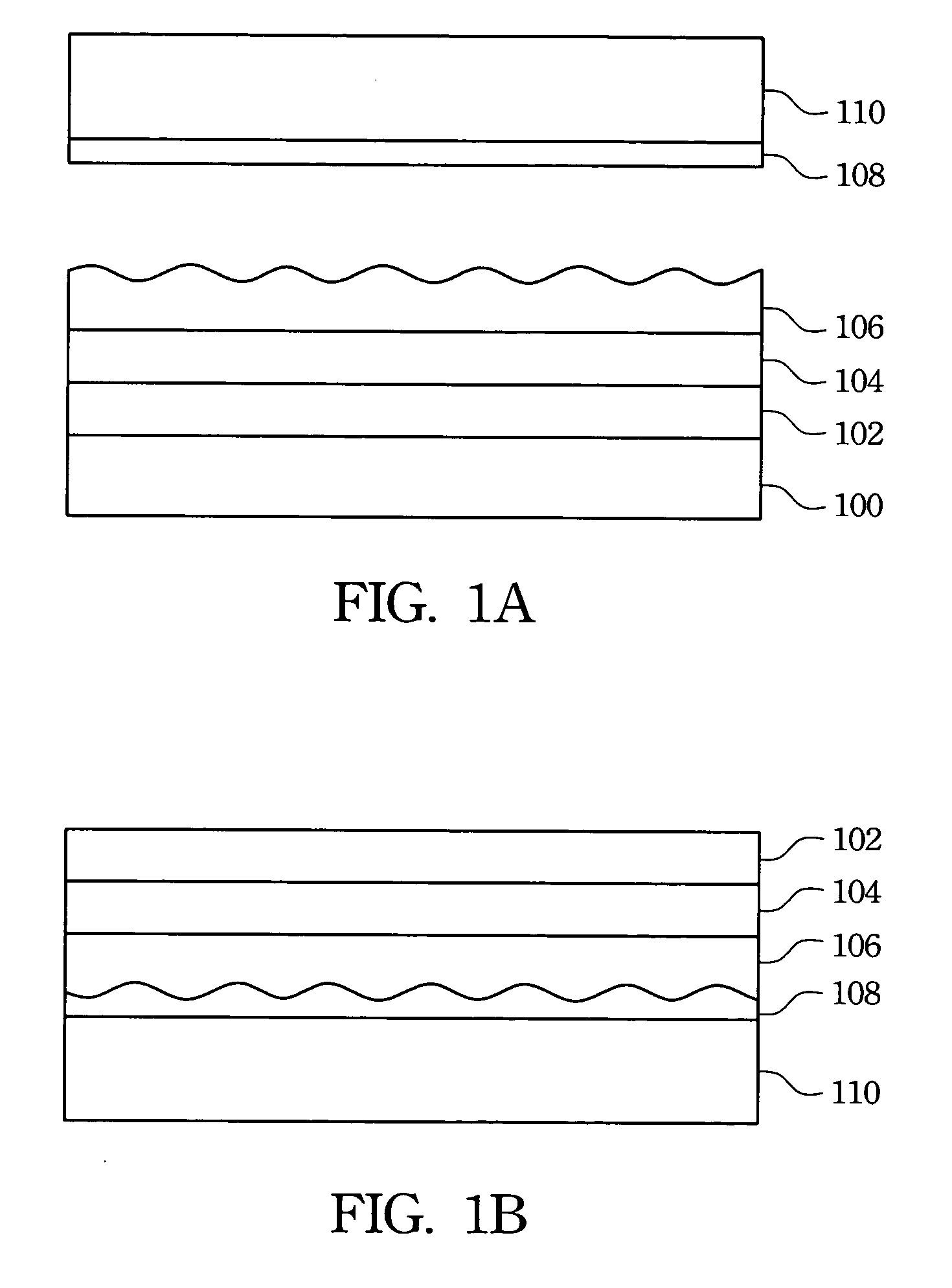

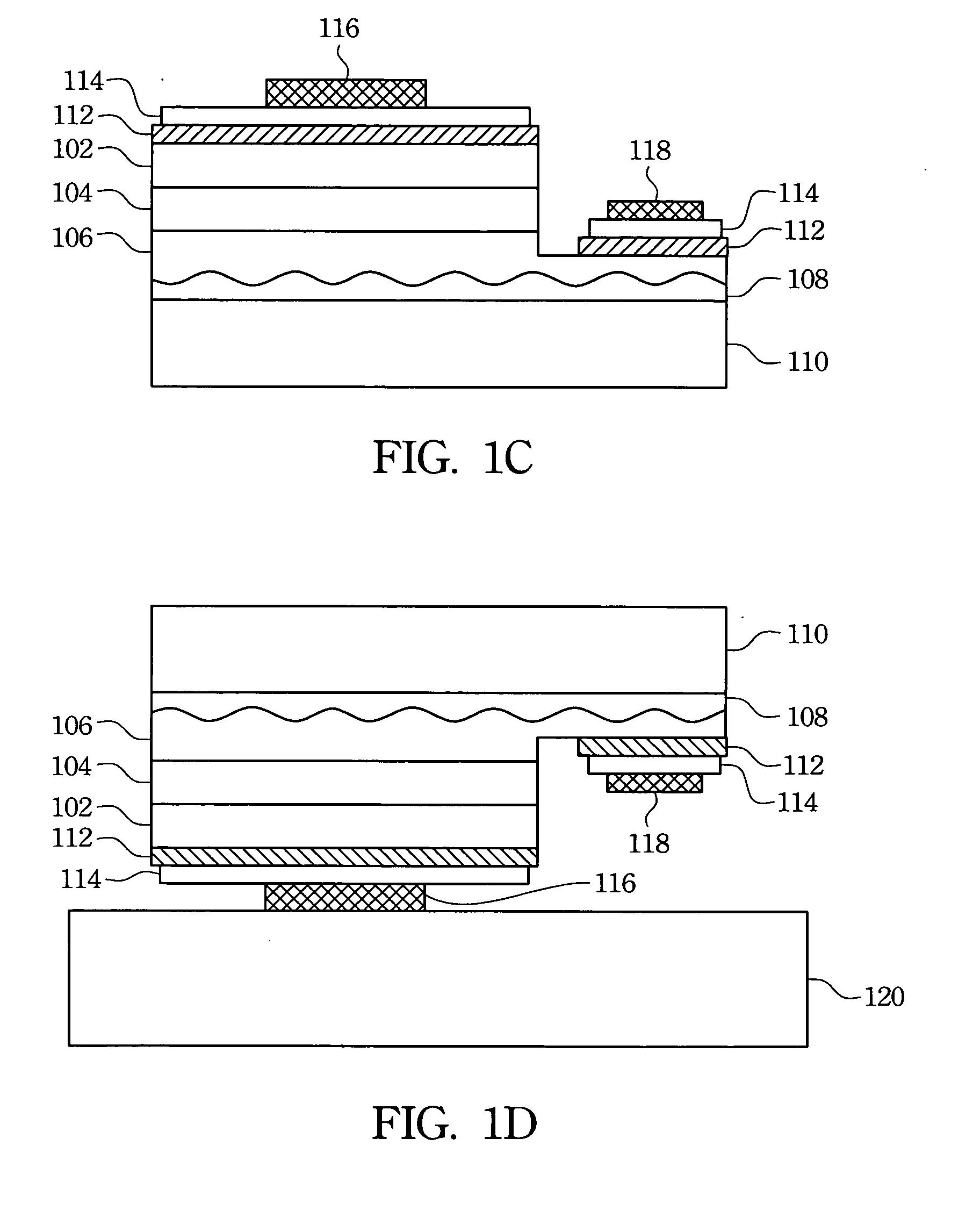

Electrochromic devices

ActiveUS20110266138A1Improve conductivityIncrease resistanceVacuum evaporation coatingSputtering coatingElectricityOptoelectronics

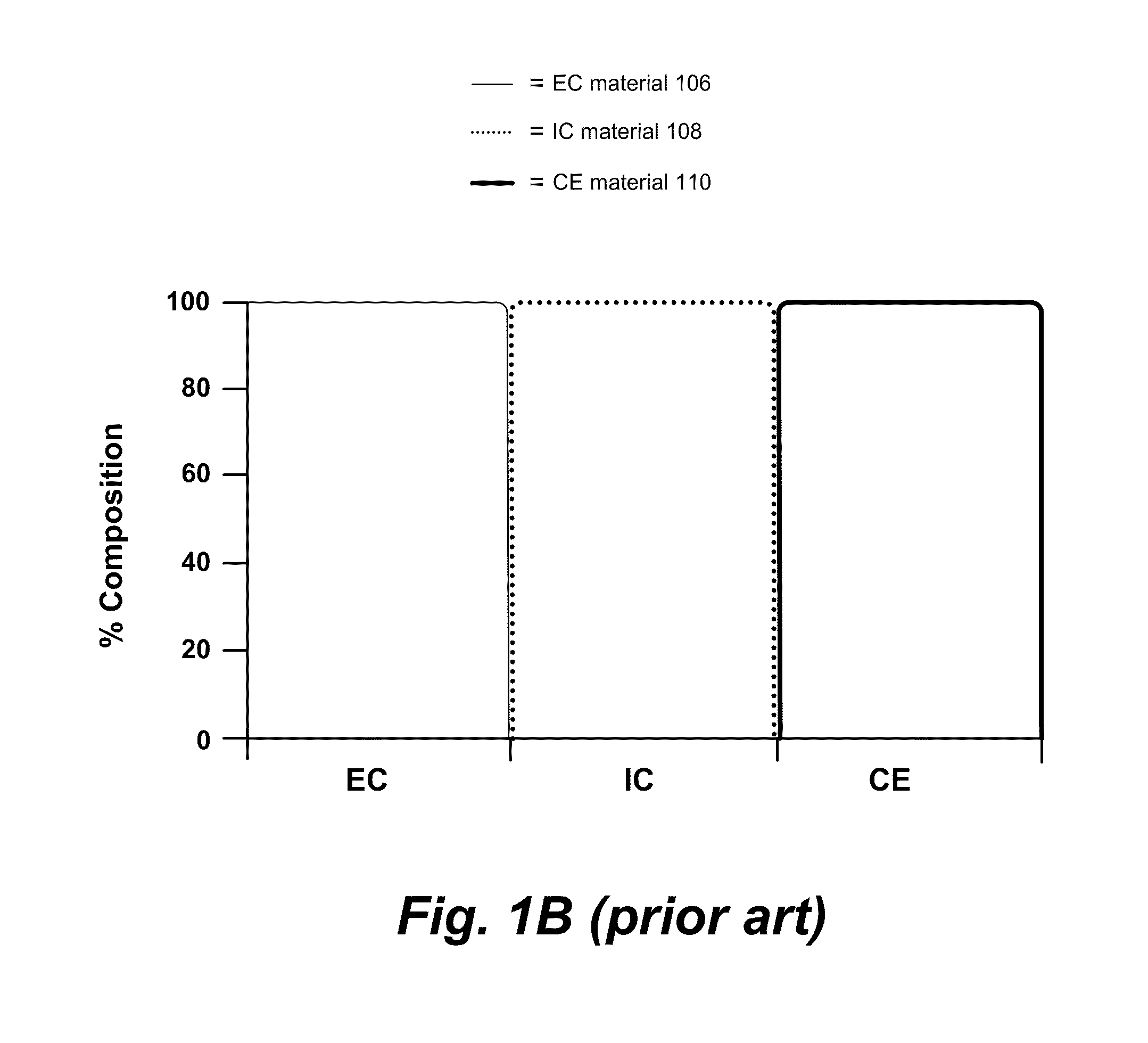

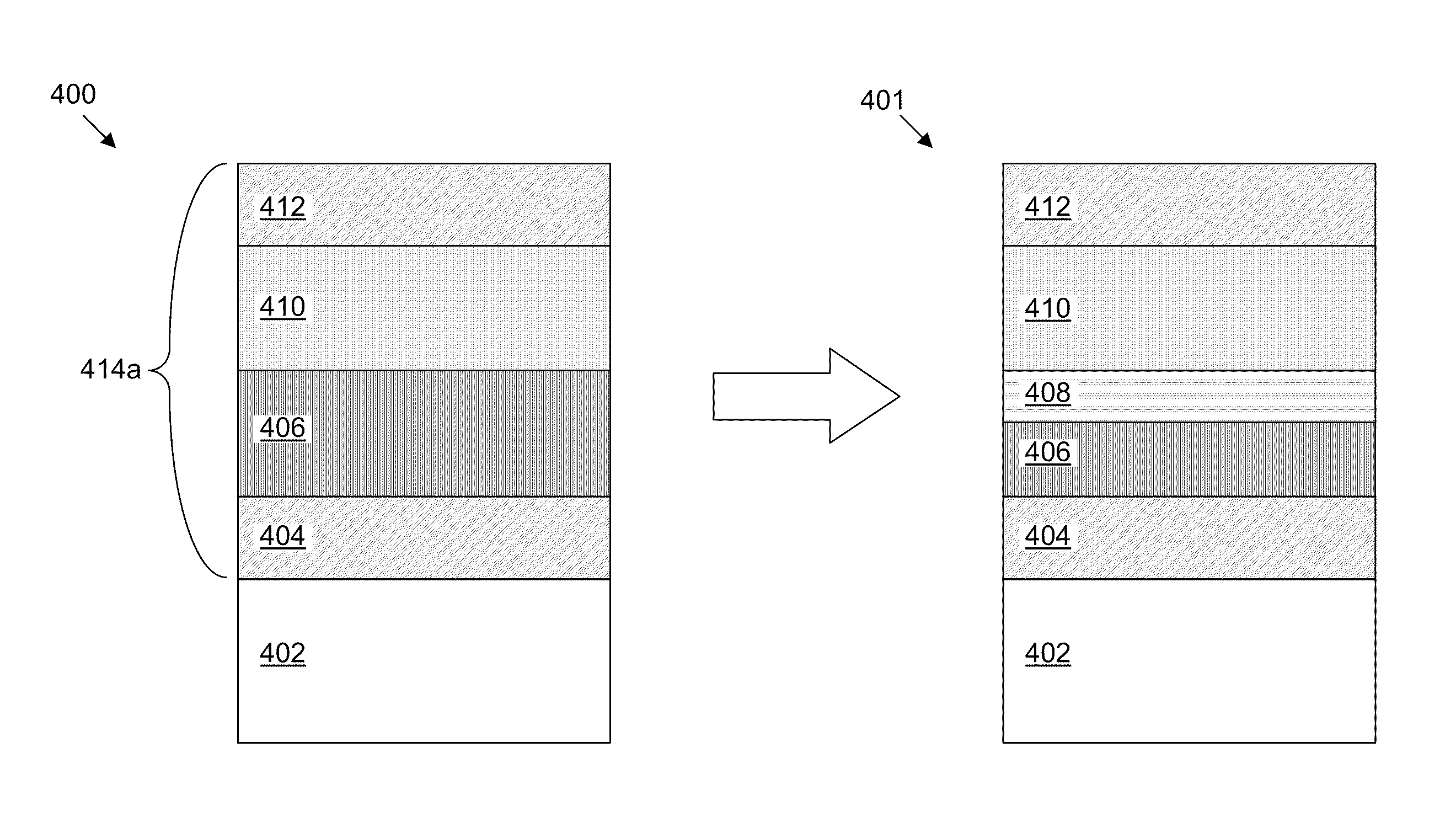

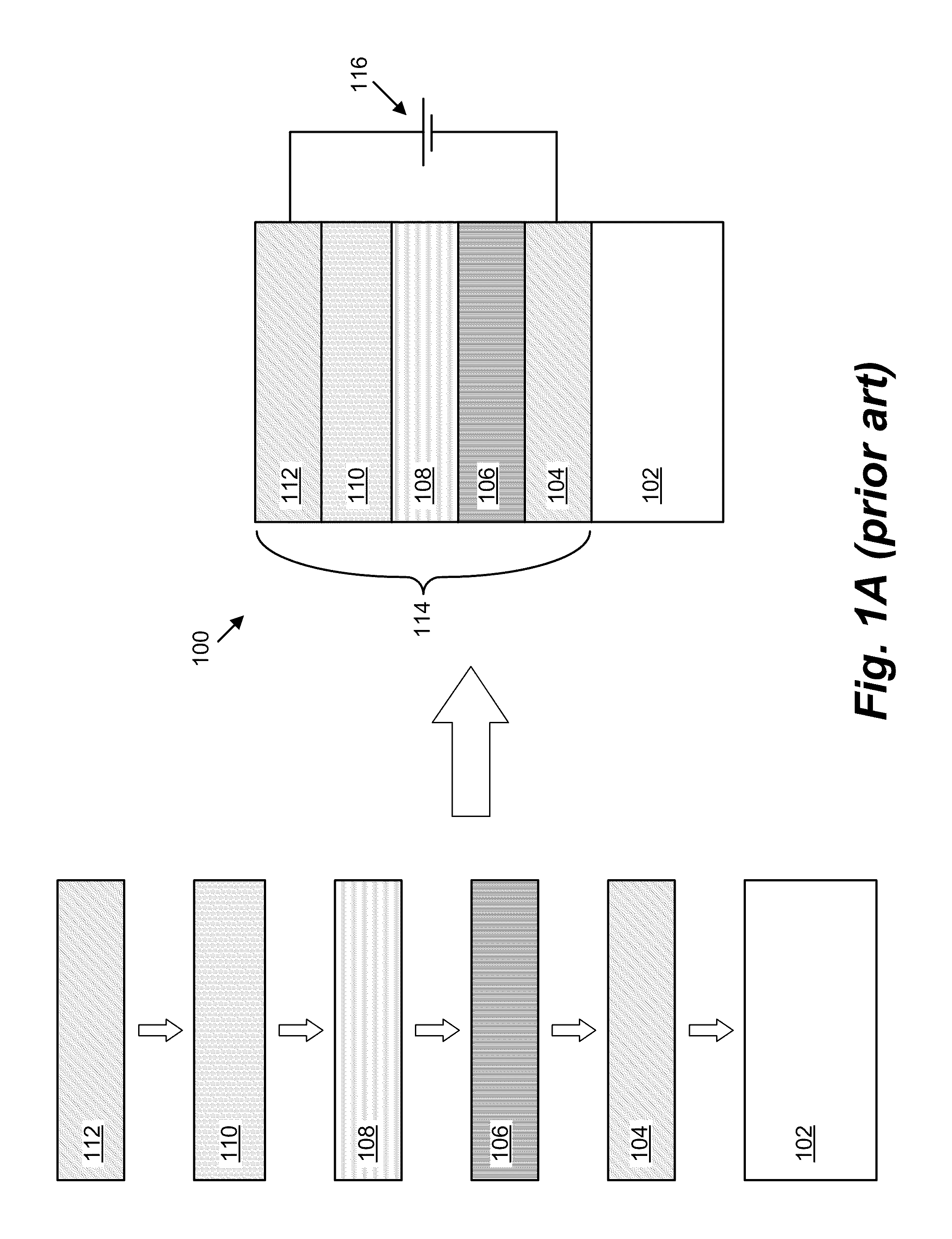

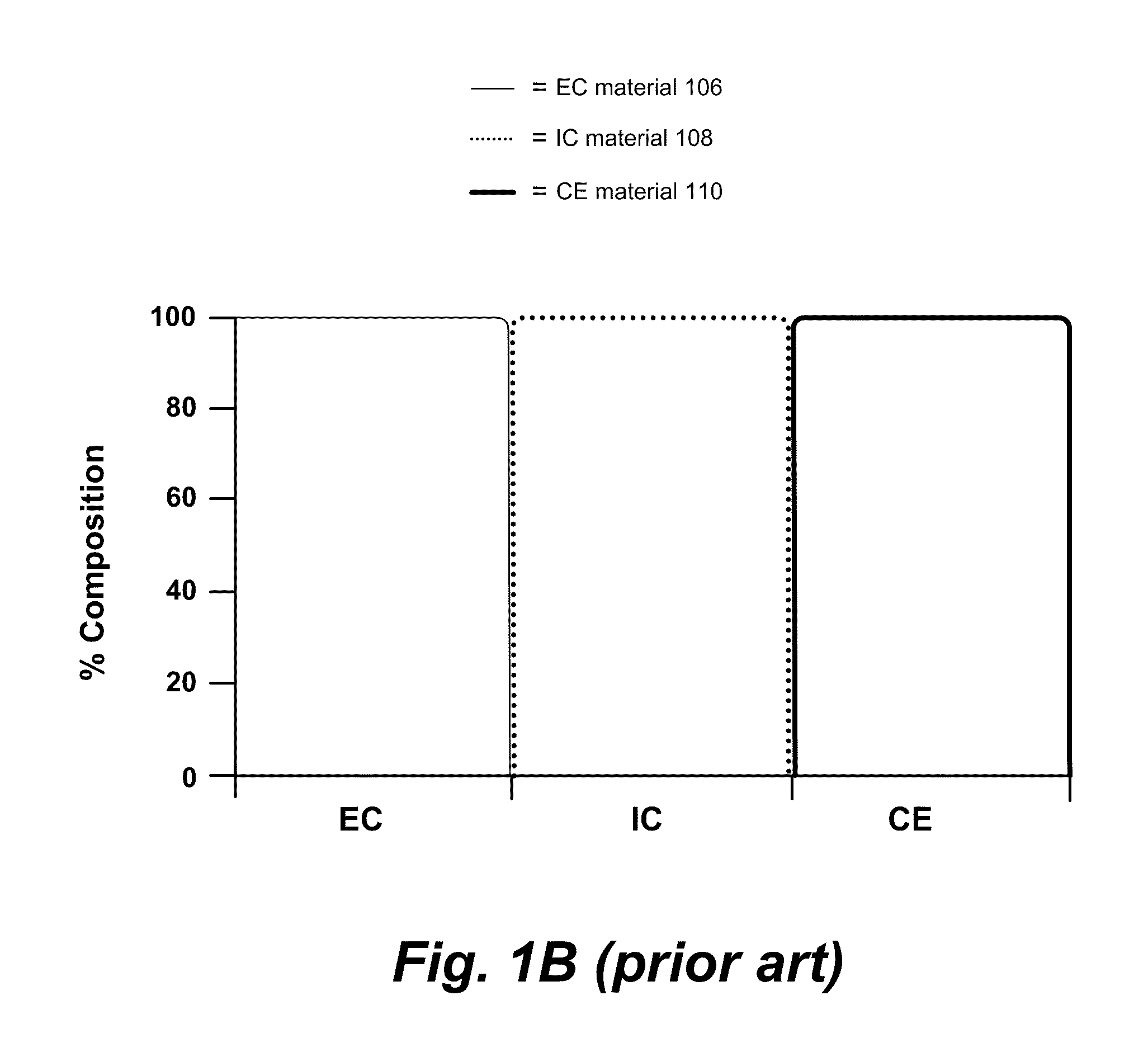

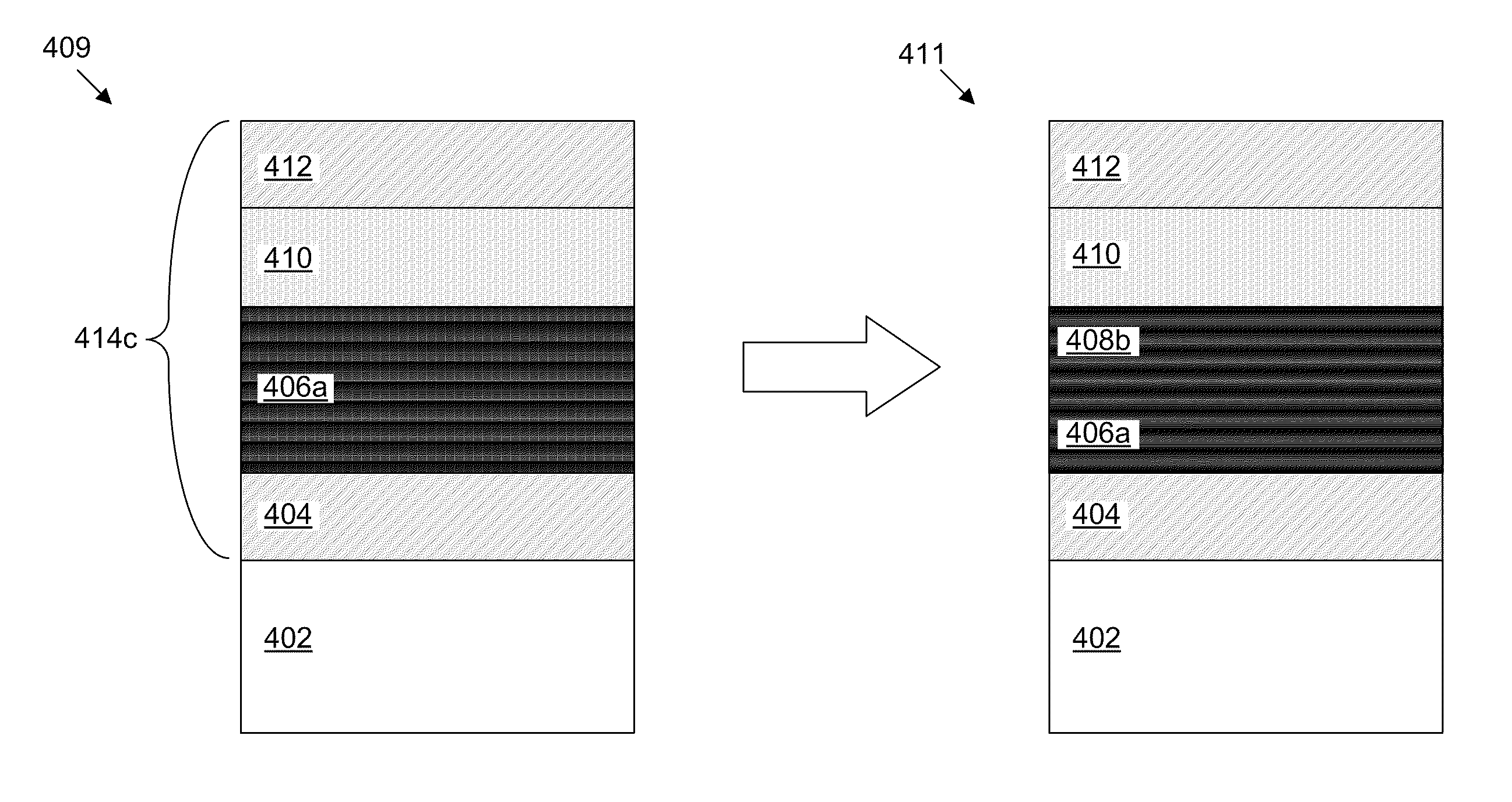

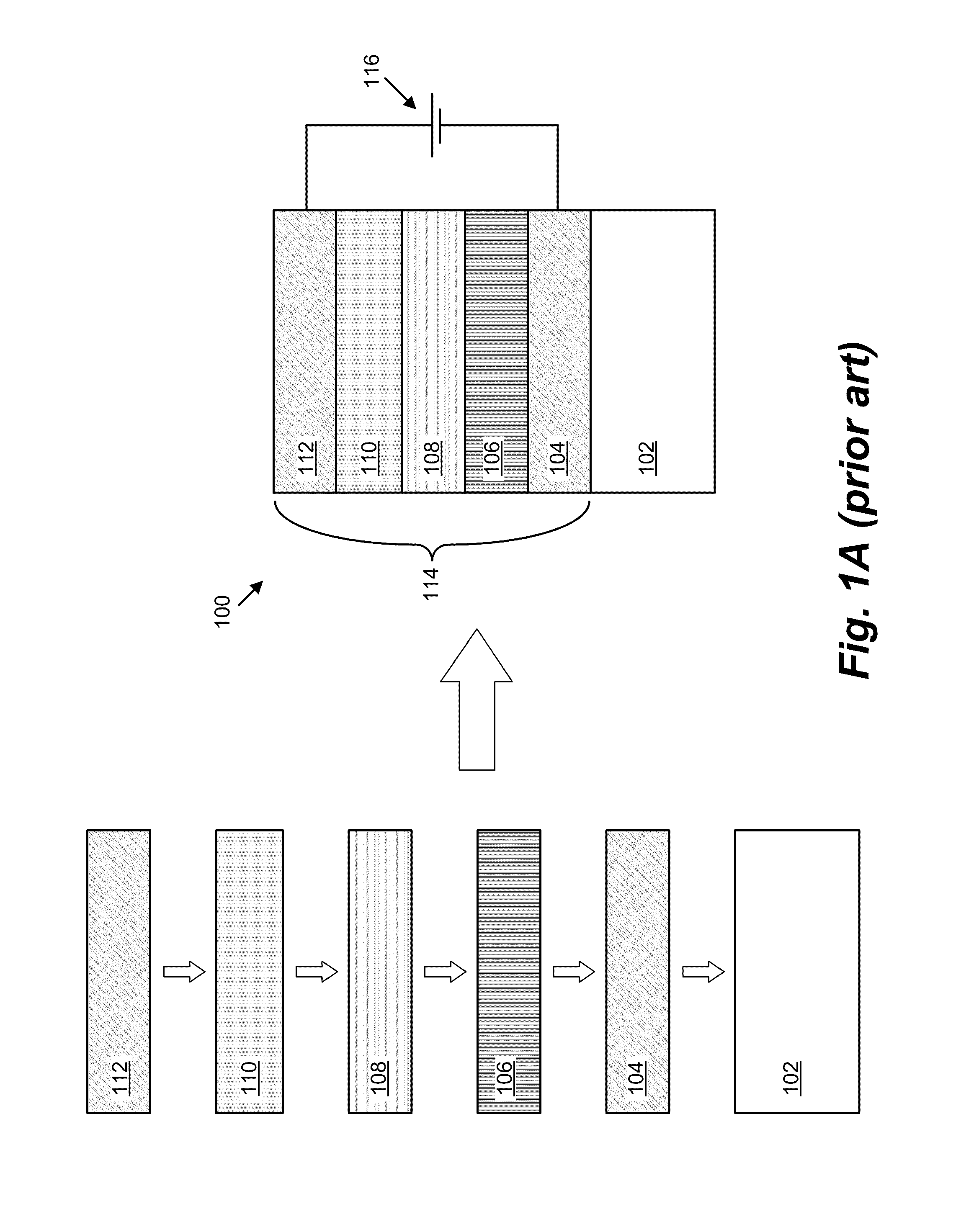

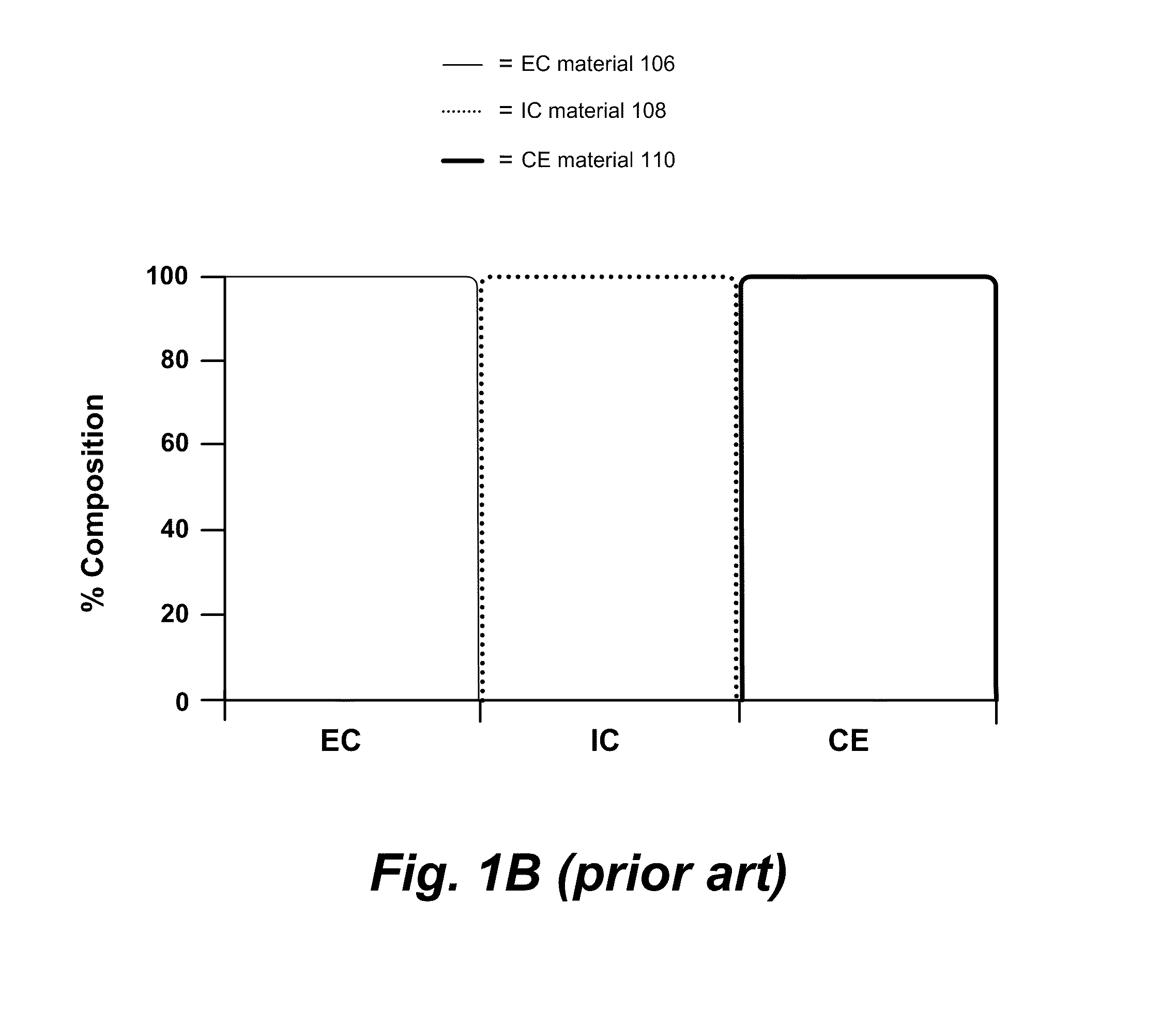

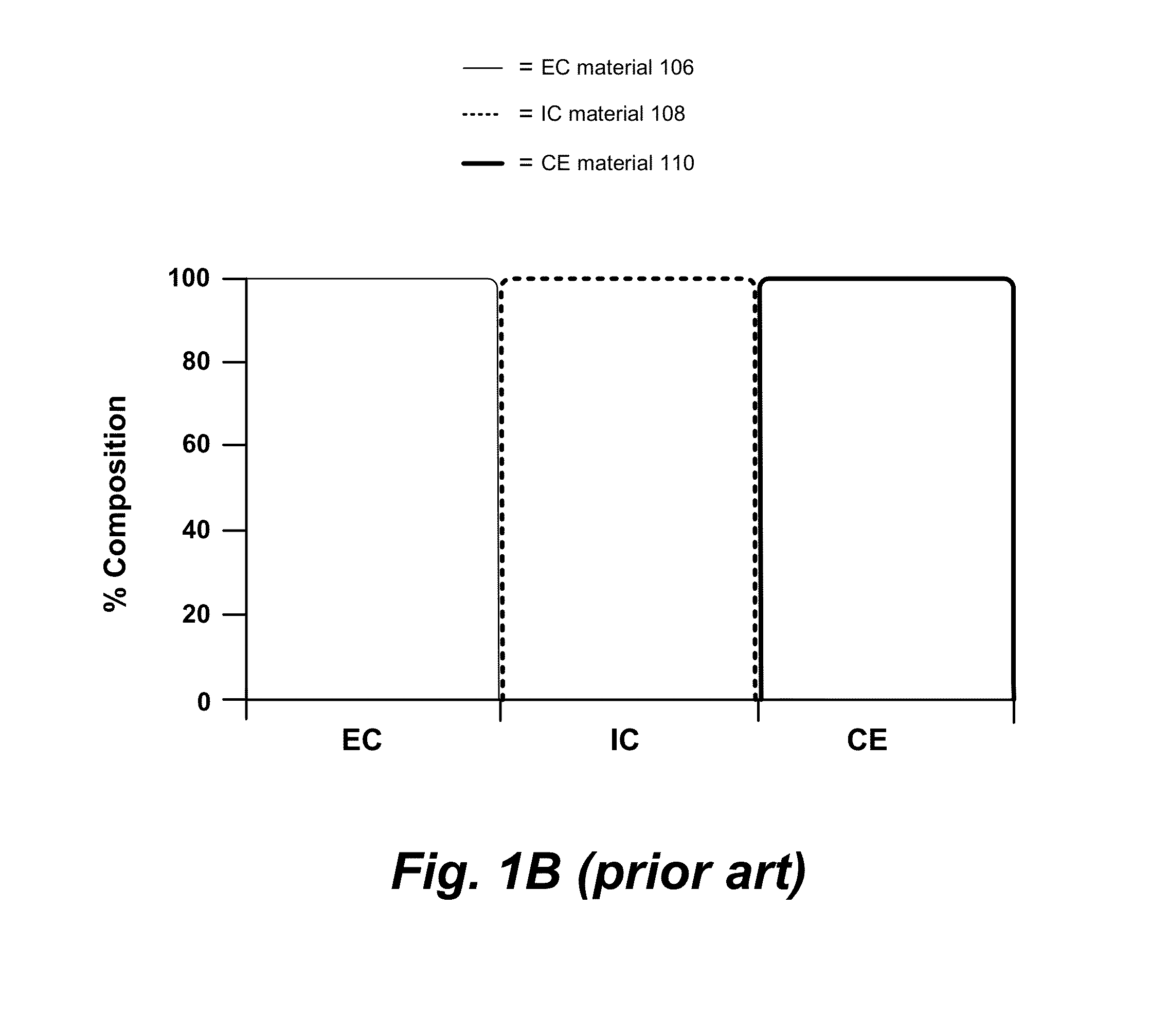

Conventional electrochromic devices frequently suffer from poor reliability and poor performance. Improvements are made using entirely solid and inorganic materials. Electrochromic devices are fabricated by forming an ion conducting electronically-insulating interfacial region that serves as an IC layer. In some methods, the interfacial region is formed after formation of an electrochromic and a counter electrode layer. The interfacial region contains an ion conducting electronically-insulating material along with components of the electrochromic and / or the counter electrode layer. Materials and microstructure of the electrochromic devices provide improvements in performance and reliability over conventional devices.

Owner:VIEW INC

Electrochromic devices

ActiveUS20110267674A1Highly conductiveHigh resistanceDoors/windowsVacuum evaporation coatingIonElectricity

Conventional electrochromic devices frequently suffer from poor reliability and poor performance. Improvements are made using entirely solid and inorganic materials. Electrochromic devices are fabricated by forming an ion conducting electronically insulating interfacial region that serves as an IC layer. In some methods, the interfacial region is formed after formation of an electrochromic and a counter electrode layer. The interfacial region contains an ion conducting electronically insulating material along with components of the electrochromic and / or the counter electrode layer. Materials and microstructure of the electrochromic devices provide improvements in performance and reliability over conventional devices.

Owner:VIEW INC

Vertical-type non-volatile memory devices

ActiveUS20090121271A1Reduce the possibilityReduce in quantityTransistorSolid-state devicesSemiconductor materialsDevice material

In a semiconductor device, and a method of manufacturing thereof, the device comprises a substrate of single-crystal semiconductor material extending in a horizontal direction and a plurality of interlayer dielectric layers on the substrate. A plurality of gate patterns are provided, each gate pattern being between a neighboring lower interlayer dielectric layer and a neighboring upper interlayer dielectric layer. A vertical channel of single-crystal semiconductor material extends in a vertical direction through the plurality of interlayer dielectric layers and the plurality of gate patterns, a gate insulating layer being between each gate pattern and the vertical channel that insulates the gate pattern from the vertical channel.

Owner:SAMSUNG ELECTRONICS CO LTD

Electrochromic devices

ActiveUS8300298B2Improve conductivityIncrease resistanceDoors/windowsVacuum evaporation coatingElectricityOptoelectronics

Conventional electrochromic devices frequently suffer from poor reliability and poor performance. Improvements are made using entirely solid and inorganic materials. Electrochromic devices are fabricated by forming an ion conducting electronically insulating interfacial region that serves as an IC layer. In some methods, the interfacial region is formed after formation of an electrochromic and a counter electrode layer. The interfacial region contains an ion conducting electronically insulating material along with components of the electrochromic and / or the counter electrode layer. Materials and microstructure of the electrochromic devices provide improvements in performance and reliability over conventional devices.

Owner:VIEW INC

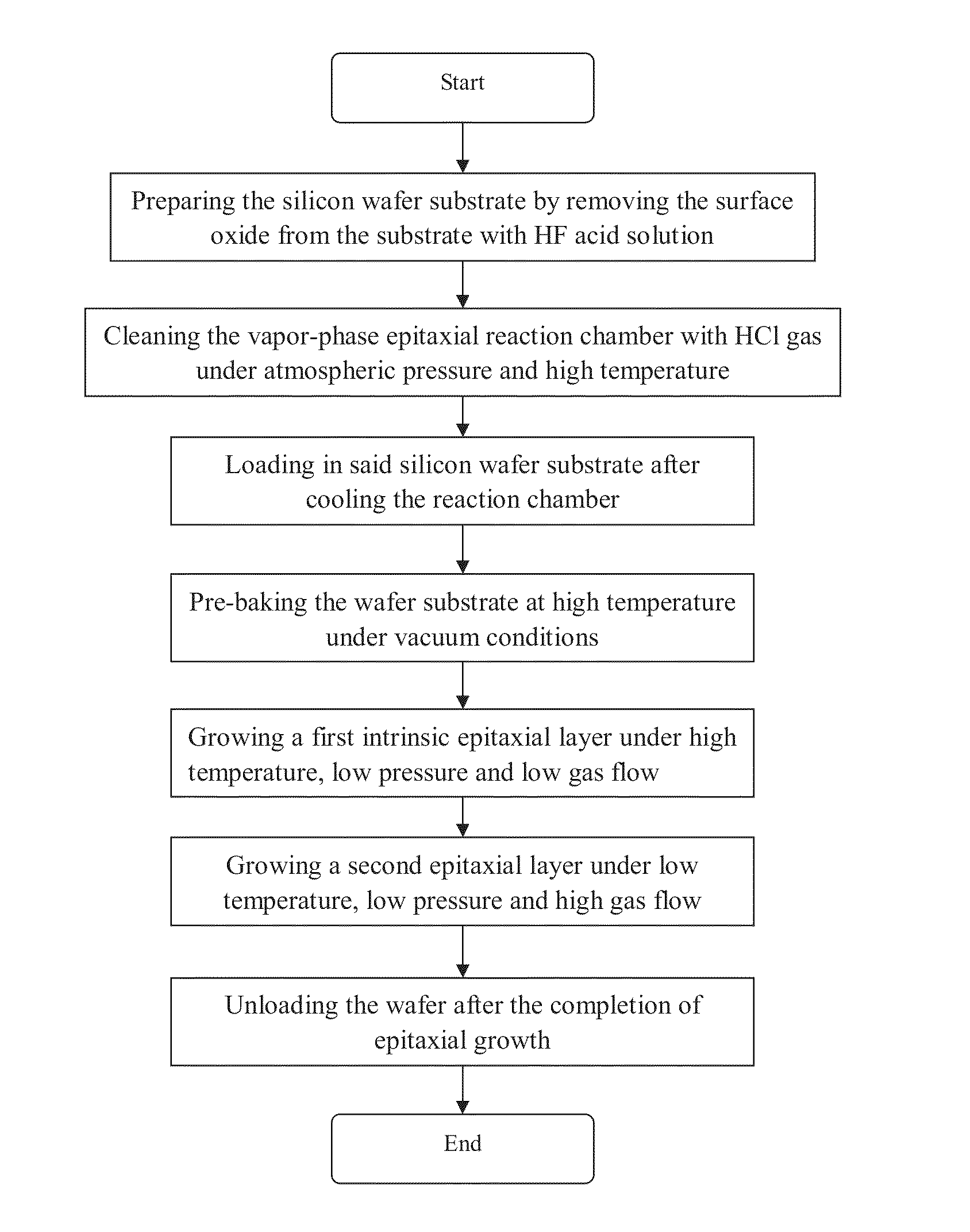

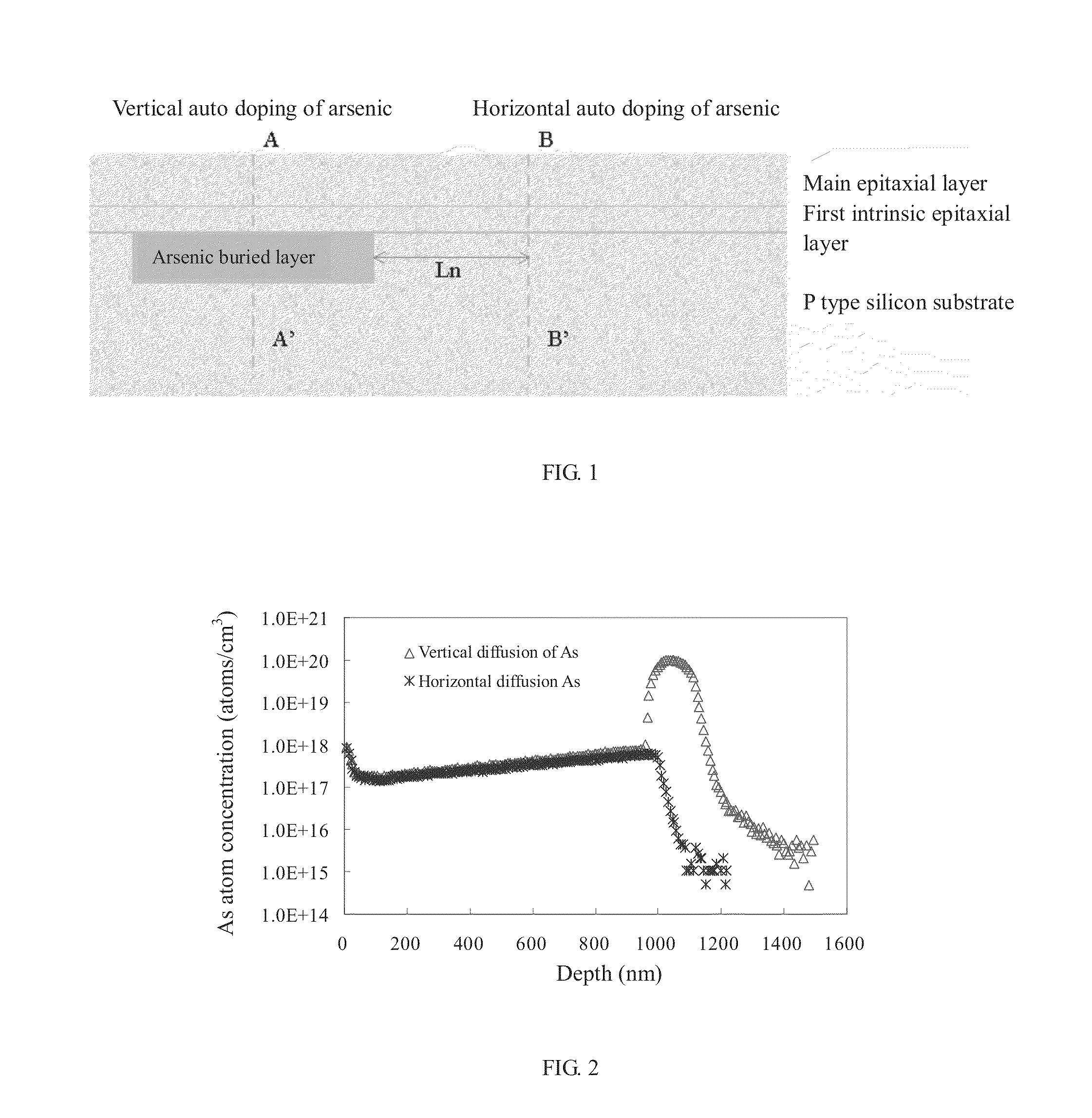

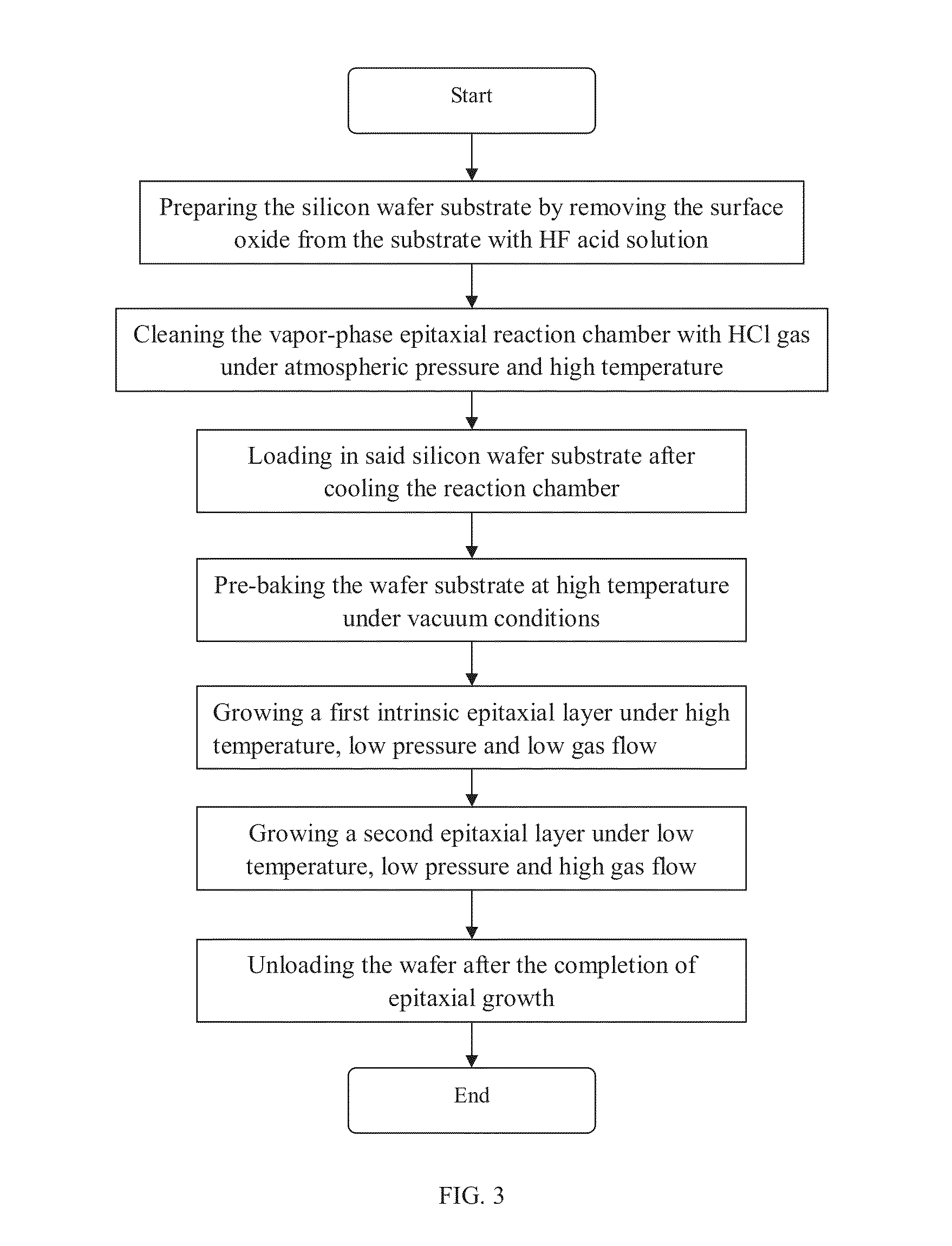

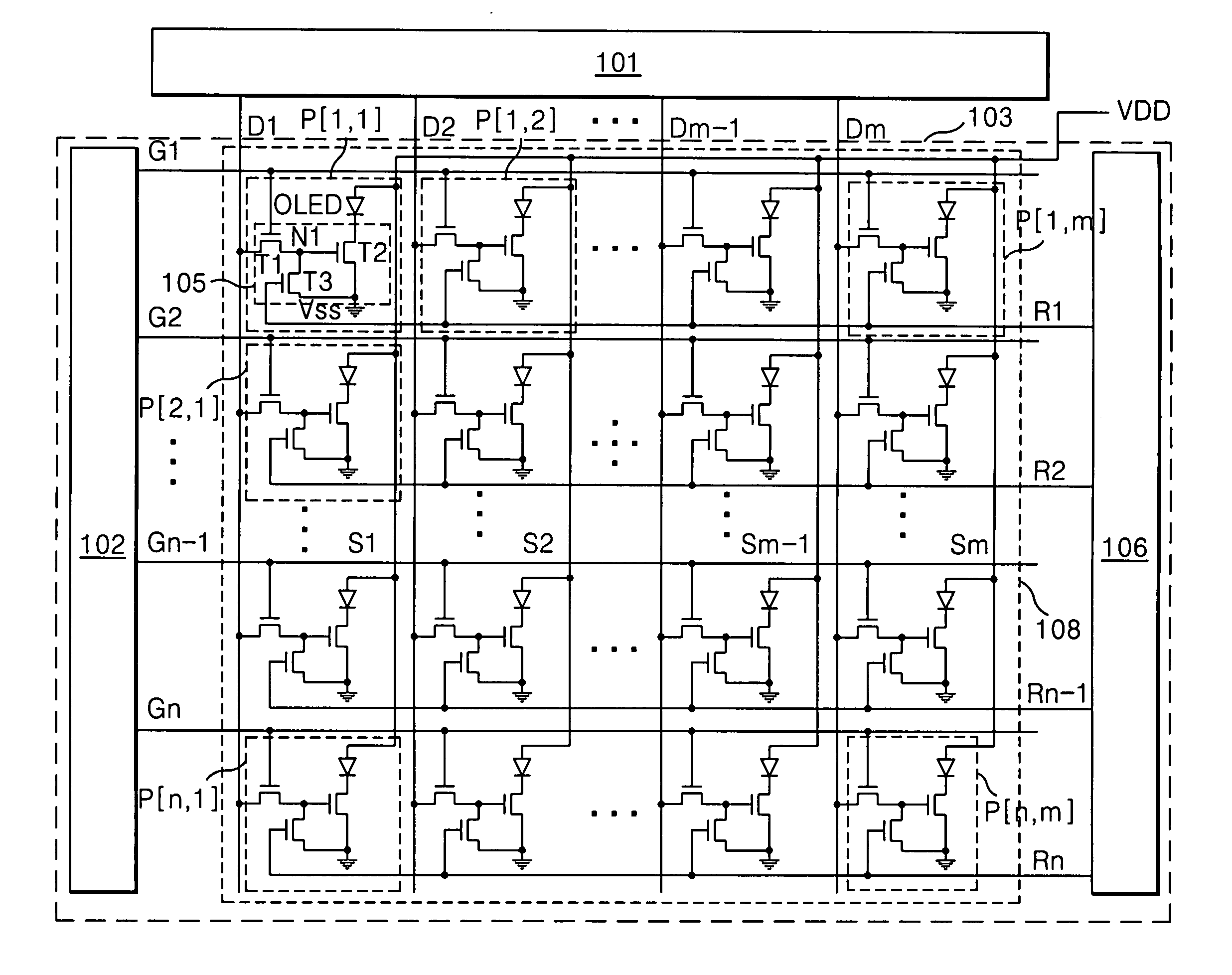

Method of epitaxial growth effectively preventing auto-doping effect

ActiveUS20130145984A1Improve equipment reliabilityInhibited DiffusionPolycrystalline material growthSemiconductor/solid-state device manufacturingDopantMoisture

This invention relates to a method of epitaxial growth effectively preventing auto-doping effect. This method starts with the removal of impurities from the semiconductor substrate having heavily-doped buried layer region and from the inner wall of reaction chamber to be used. Then the semiconductor substrate is loaded in the cleaned reaction chamber to be pre-baked under vacuum conditions so as to remove moisture and oxide from the surface of said semiconductor substrate before the extraction of the dopant atoms desorbed from the surface of the semiconductor substrate. Next, under high temperature and low gas flow conditions, a first intrinsic epitaxial layer is formed on the surface of said semiconductor substrate where the dopant atoms have been extracted out. Following this, under low temperature and high gas flow conditions, a second epitaxial layer of required thickness is formed on the structural surface of the grown intrinsic epitaxial layer. Last, silicon wafer is unloaded after cooling. This method can prevent auto-doping effect during the epitaxial growth on semiconductor substrate and thus ensure the performance and enhance the reliability of the devices in peripheral circuit region.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

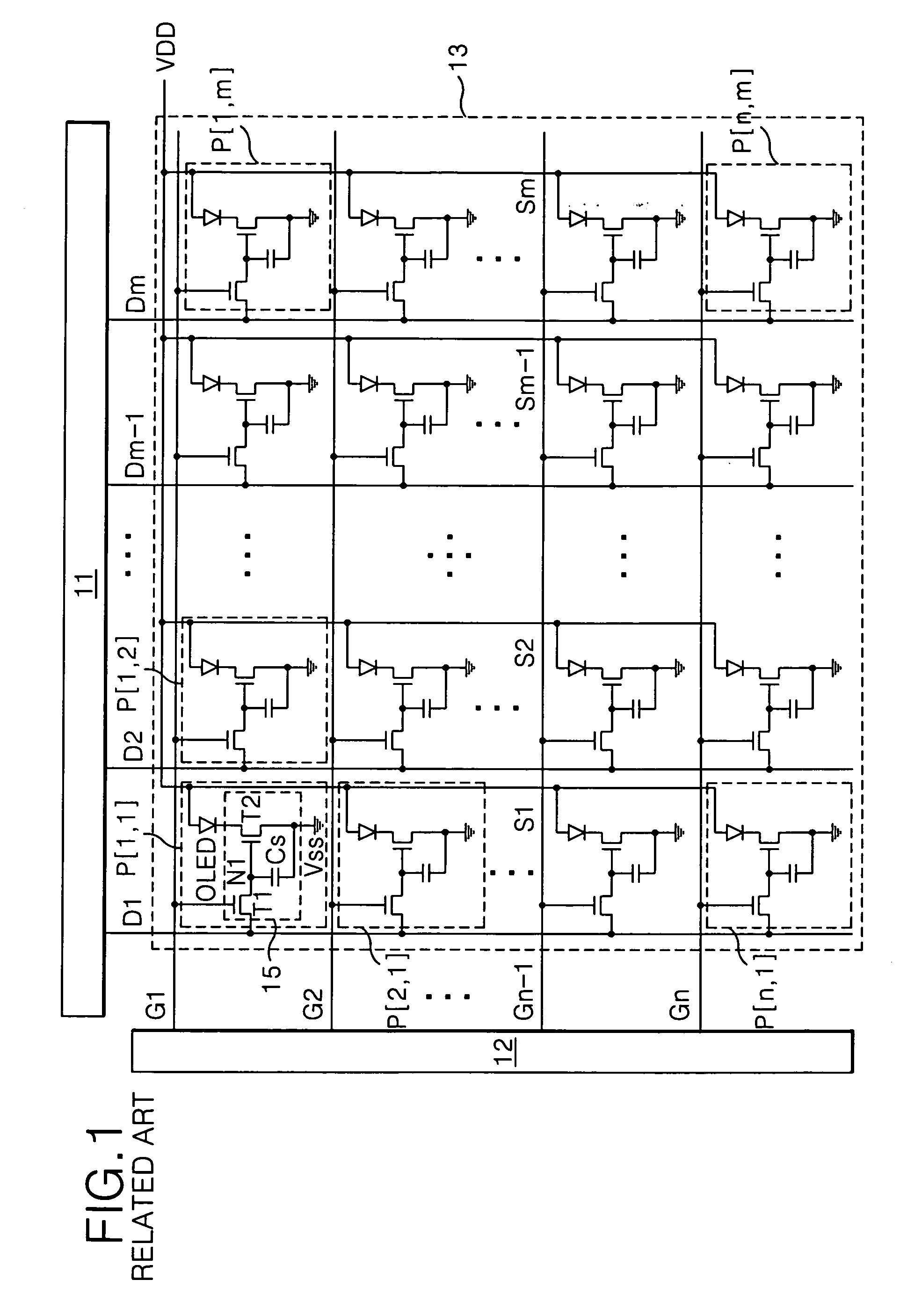

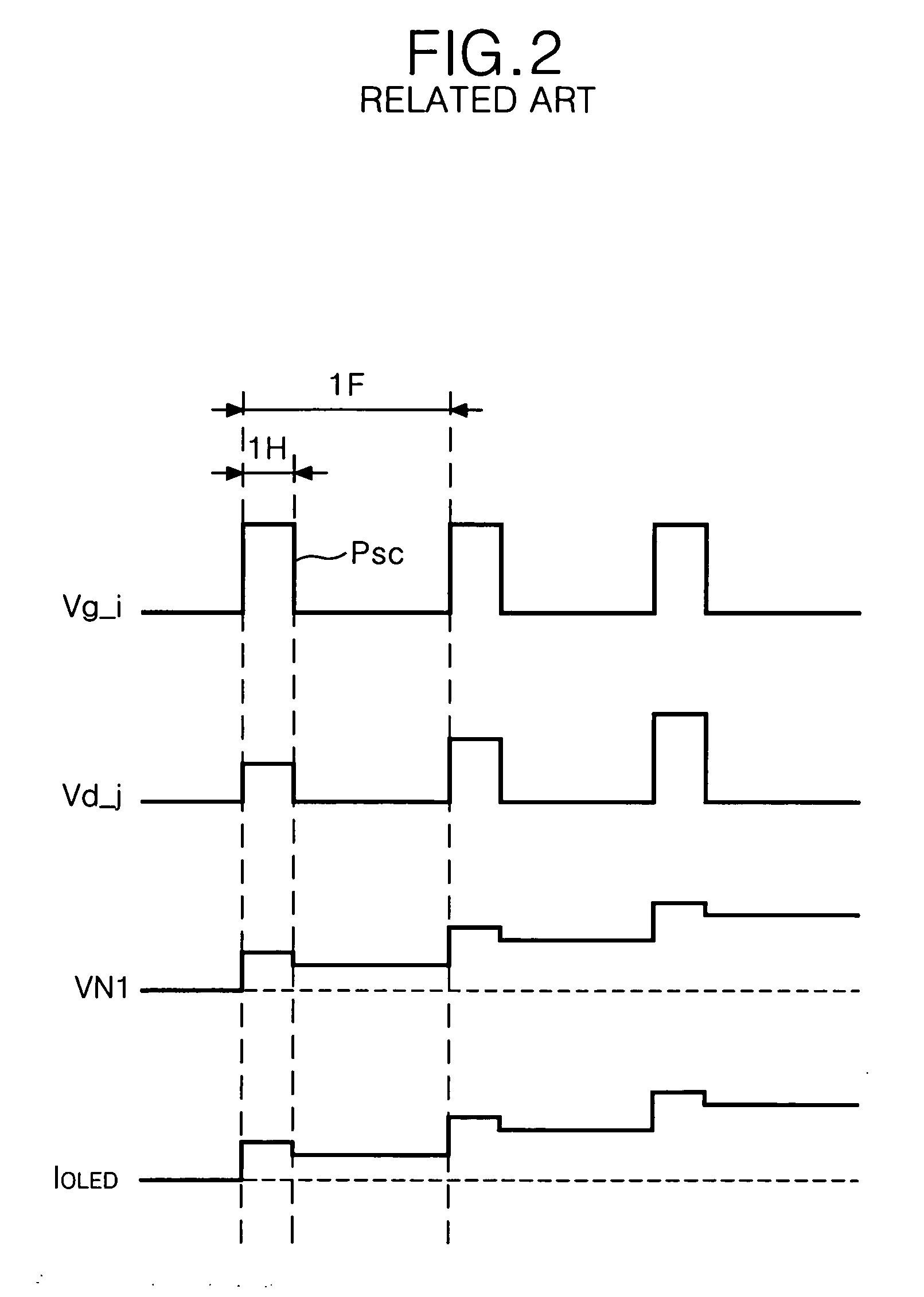

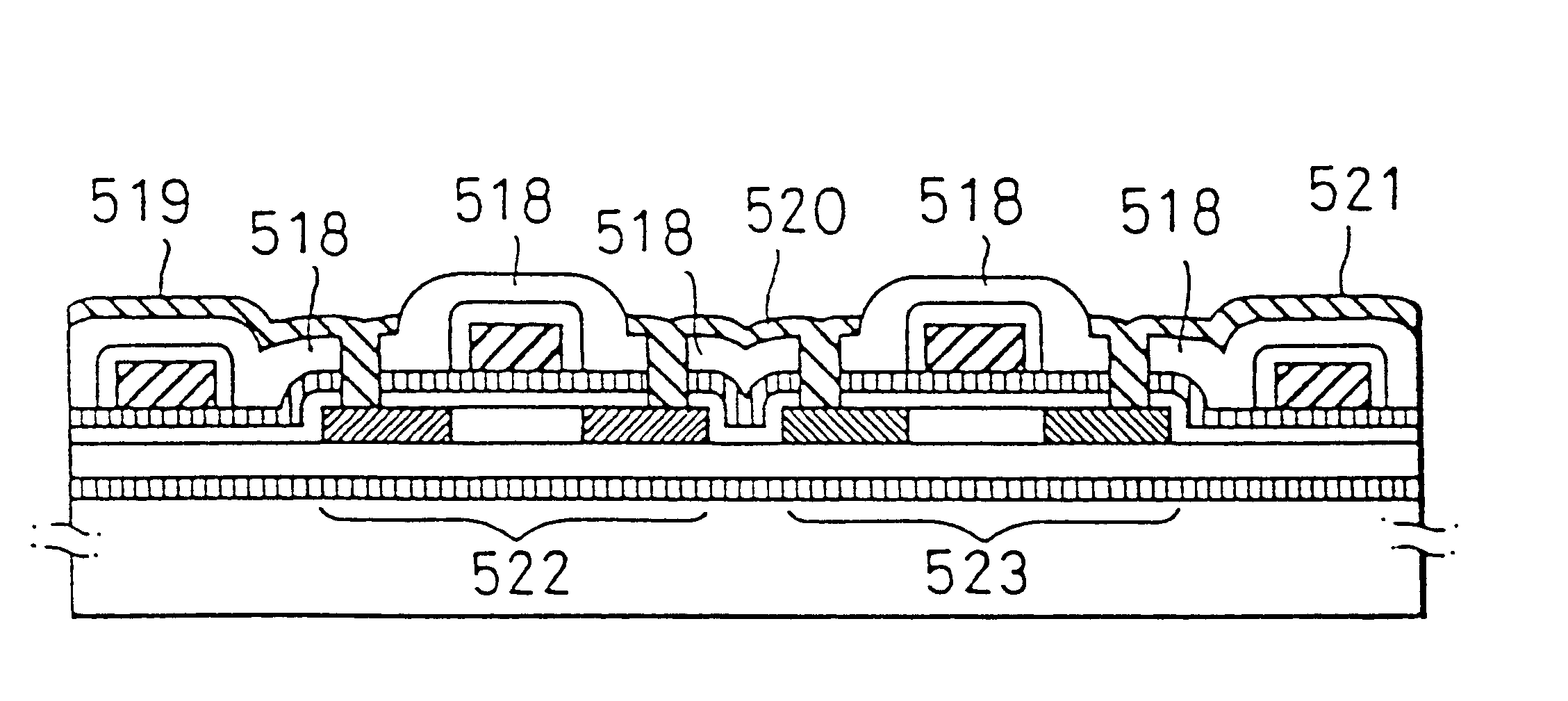

Organic light emitting diode display

ActiveUS20070008268A1Improve reliabilityImprove equipment reliabilityStatic indicating devicesDigital storagePixel arrayScan line

This invention relates to an organic light emitting diode display device that is adaptive for preventing a characteristic change of a device which drives the organic light emitting diode and for securing reliability of the device. The organic light emitting diode display device includes: a pixel array having a plurality of scan lines and a plurality of data lines that cross each other, a plurality of power voltage supply lines to which a high level power supply voltage is supplied and that are substantially parallel to the data lines, a plurality of reset lines substantially parallel to the scan lines, a plurality of organic light emitting diodes that emit light due to the high level power supply voltage from the power voltage supply line, and a plurality of organic light emitting diode drive circuits that drive the organic light emitting diode with data from the data line in response to a scan signal from the scan line and that is initialized in response to a reset signal from the reset line; a scan drive circuit that supplies the scan signal to the scan lines; a reset drive circuit that supplies the reset signal to the reset lines that initializes the organic light emitting diode drive circuit; and a data drive circuit that supplies the data to the data lines respectively, wherein the scan drive circuit and the reset drive circuit are on a substrate including the pixel array.

Owner:LG DISPLAY CO LTD

Three-Dimensional Semiconductor Device and Manufacturing Method Therefor

InactiveUS20170154895A1Improve control characteristicsReduce off-state leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETEtching

A three-dimensional semiconductor device, comprising a plurality of memory cell transistors and a plurality of select transistors at least partially overlapped in the vertical direction, wherein each select transistor comprises a first drain, an active region and a common source formed in the substrate, distributed along the vertical direction, as well as a metal gate distributed around the active region; wherein each memory cell transistor comprises a channel layer distributed perpendicularly to the substrate surface, a plurality of inter-layer insulating layers and a plurality of gate stack structures alternately stacked along the sidewalls of said channel layer, a second drain located on top of said channel layer; wherein said channel layer and said the first drain are electrically connected. In accordance with the three-dimensional semiconductor memory device and manufacturing method of the present invention, the multi-gate MOSFET is formed beneath the stack structure of the memory cell string including vertical channel to serve as the select transistor, this can improve the control characteristics of the gate threshold voltage, reduce the off-state leakage current, prevent the substrate from over-etching, and effectively improve the reliability of the device.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Electrochromic devices

ActiveUS8764950B2Improve conductivityIncrease resistanceVacuum evaporation coatingSputtering coatingElectricityOptoelectronics

Conventional electrochromic devices frequently suffer from poor reliability and poor performance. Improvements are made using entirely solid and inorganic materials. Electrochromic devices are fabricated by forming an ion conducting electronically-insulating interfacial region that serves as an IC layer. In some methods, the interfacial region is formed after formation of an electrochromic and a counter electrode layer. The interfacial region contains an ion conducting electronically-insulating material along with components of the electrochromic and / or the counter electrode layer. Materials and microstructure of the electrochromic devices provide improvements in performance and reliability over conventional devices.

Owner:VIEW INC

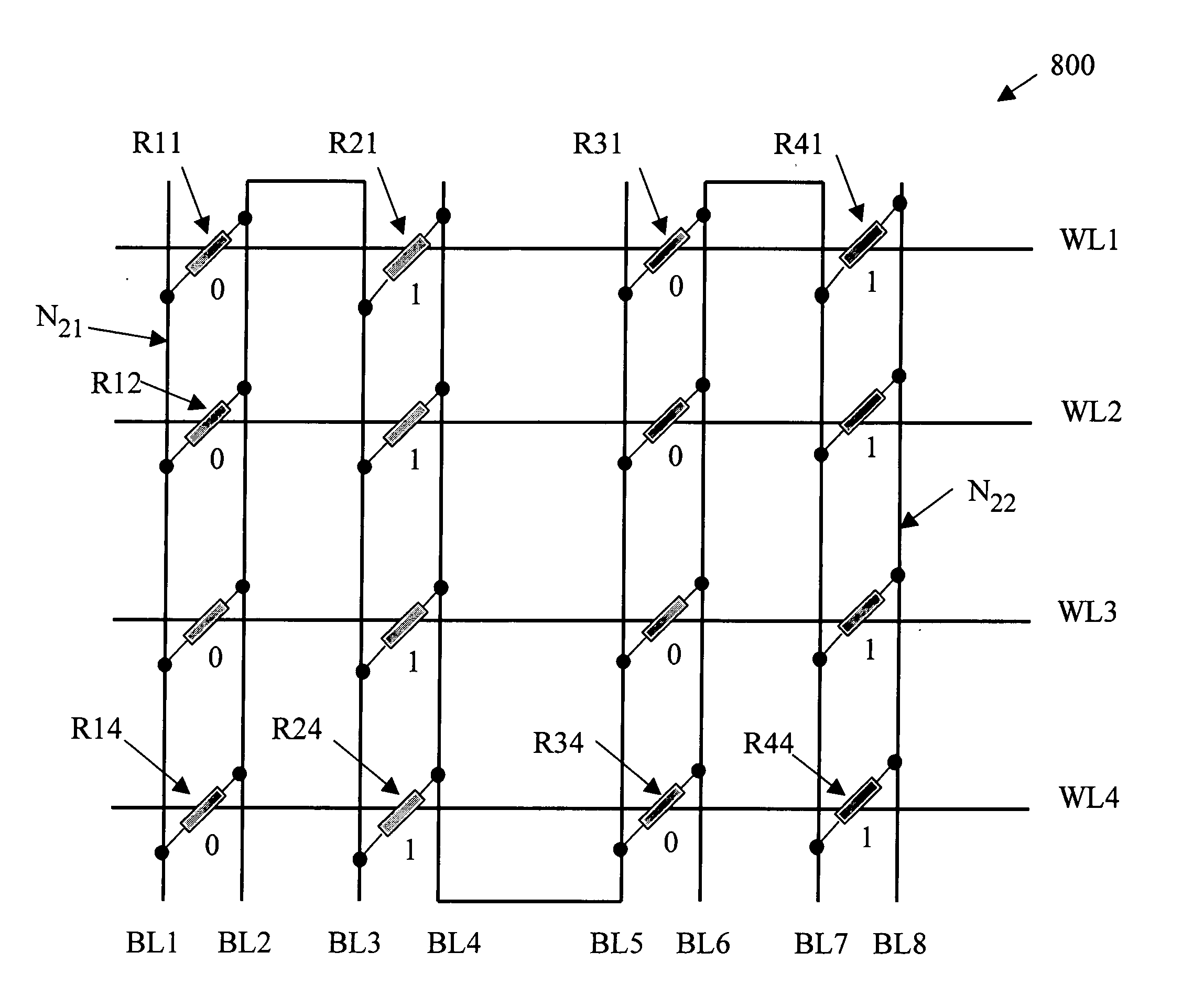

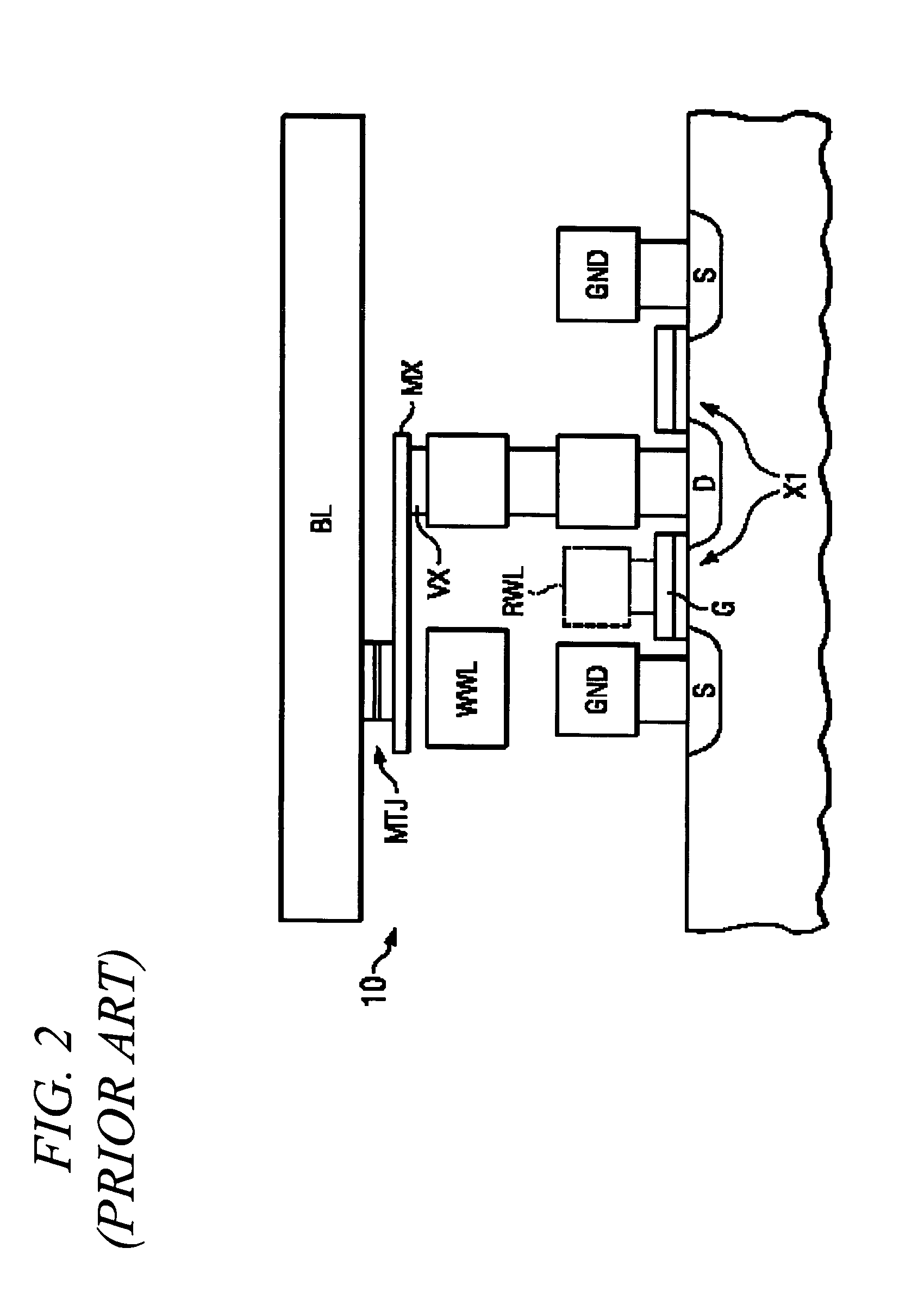

Reference current source for current sense amplifier and programmable resistor configured with magnetic tunnel junction cells

InactiveUS20060092689A1Improve reliabilityWithout compromising device design marginDigital storageAudio power amplifierReference current

A reference current source for a magnetic memory device is preferably configured with magnetic tunnel junction cells and includes more than four reference magnetic memory cells to improve reliability of the magnetic memory device and to reduce sensitivity at a device level to individual cell failures. The reference current source includes a large number of magnetic memory cells coupled in an array, and a current source provides a reference current dependent on the array resistance. In another embodiment a large number of magnetic memory cells are coupled to current sources that are summed and scaled to produce a reference current source. A current comparator senses the unknown state of a magnetic memory cell. In a further embodiment, an array of magnetic memory cells is configured to provide a non-volatile, adjustable resistance. In a further embodiment, the array of magnetic memory cells is configured with a tap to provide a non-volatile, adjustable potentiometer.

Owner:INFINEON TECH AG

Electrochromic devices

ActiveUS8764951B2Improve conductivityIncrease resistanceVacuum evaporation coatingSputtering coatingEngineeringInorganic materials

Conventional electrochromic devices frequently suffer from poor reliability and poor performance. Improvements are made using entirely solid and inorganic materials. Electrochromic devices are fabricated by forming an ion conducting electronically-insulating interfacial region that serves as an IC layer. In some methods, the interfacial region is formed after formation of an electrochromic and a counter electrode layer. The interfacial region contains an ion conducting electronically-insulating material along with components of the electrochromic and / or the counter electrode layer. Materials and microstructure of the electrochromic devices provide improvements in performance and reliability over conventional devices.

Owner:VIEW INC

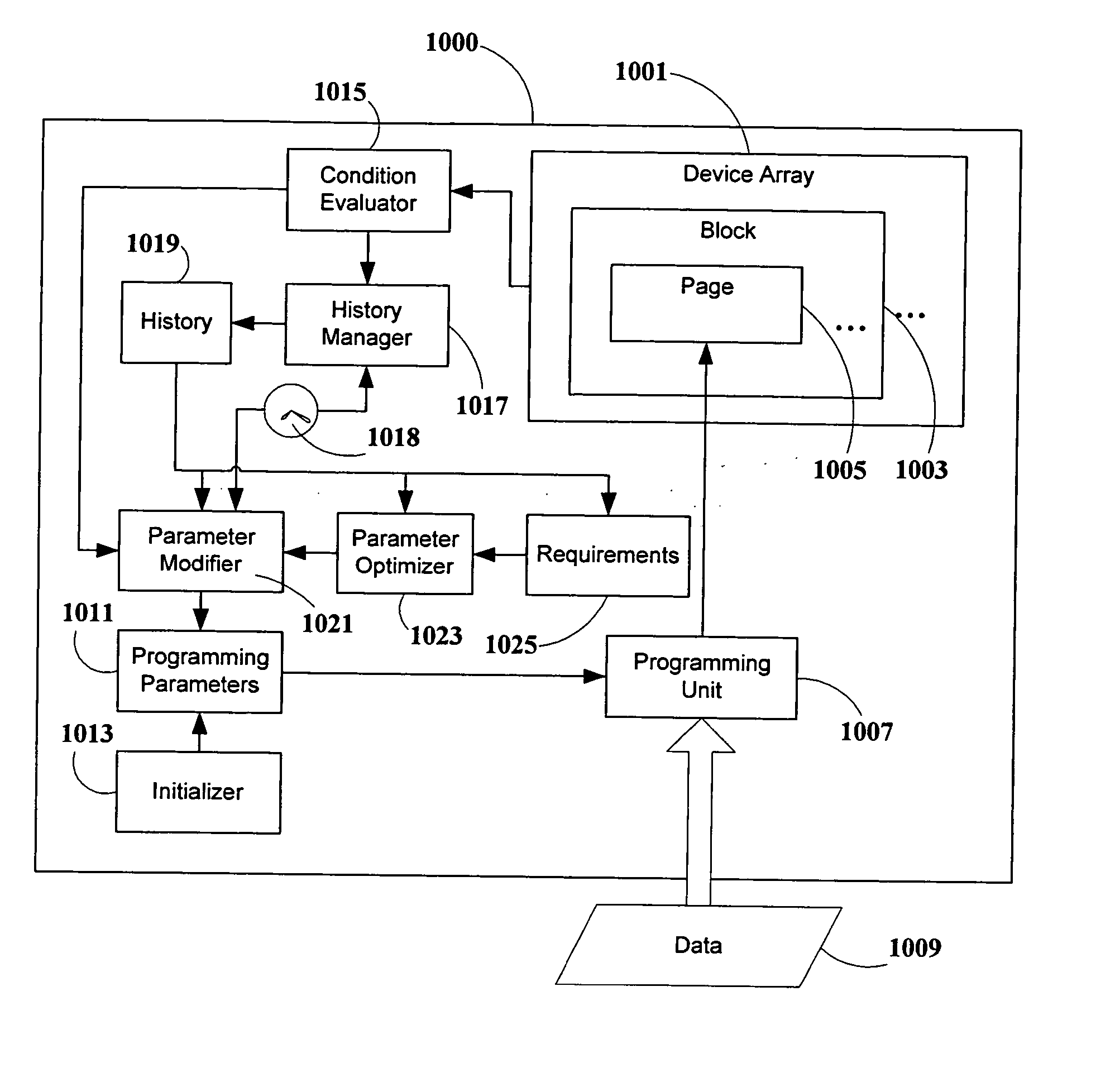

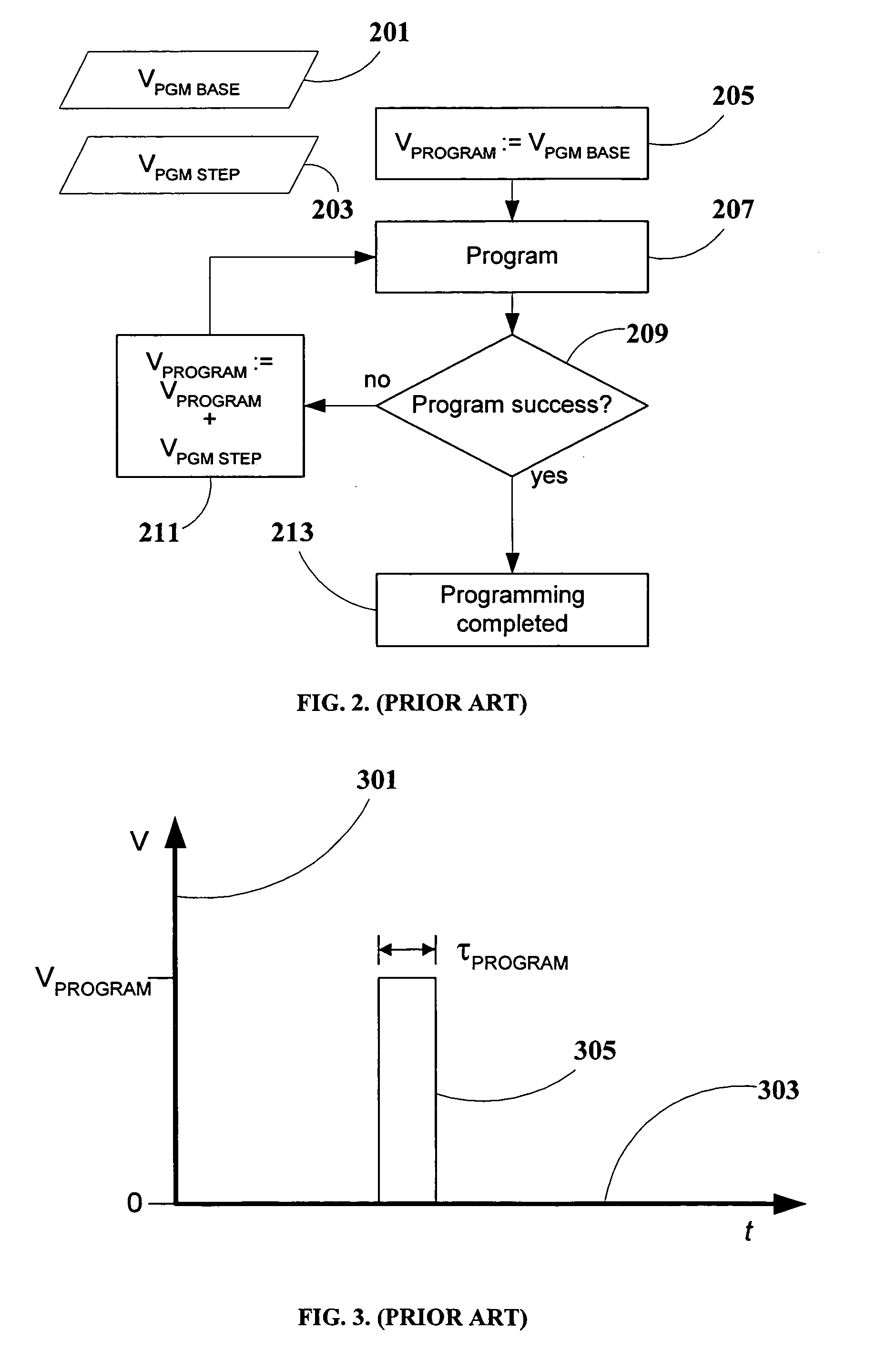

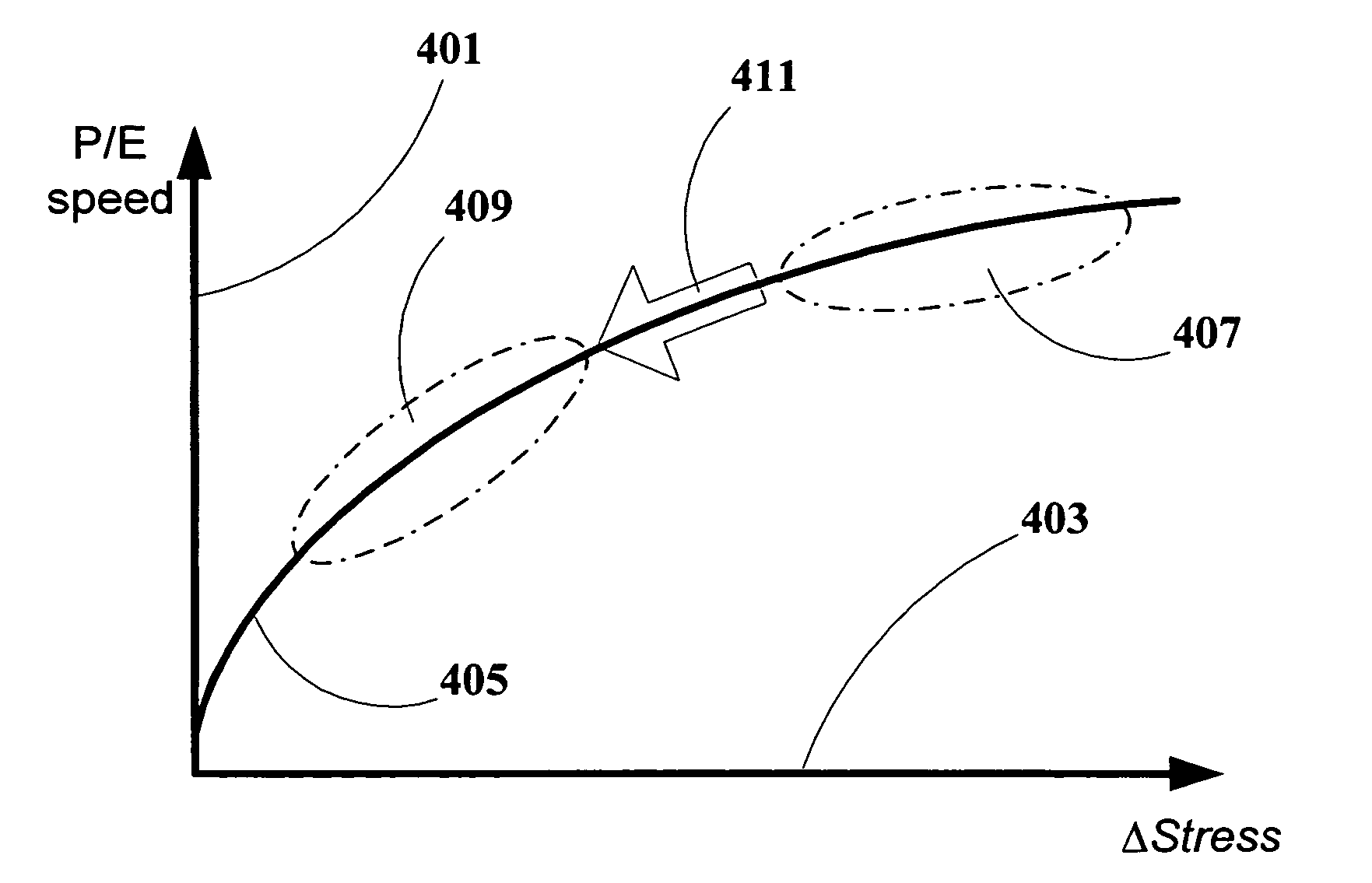

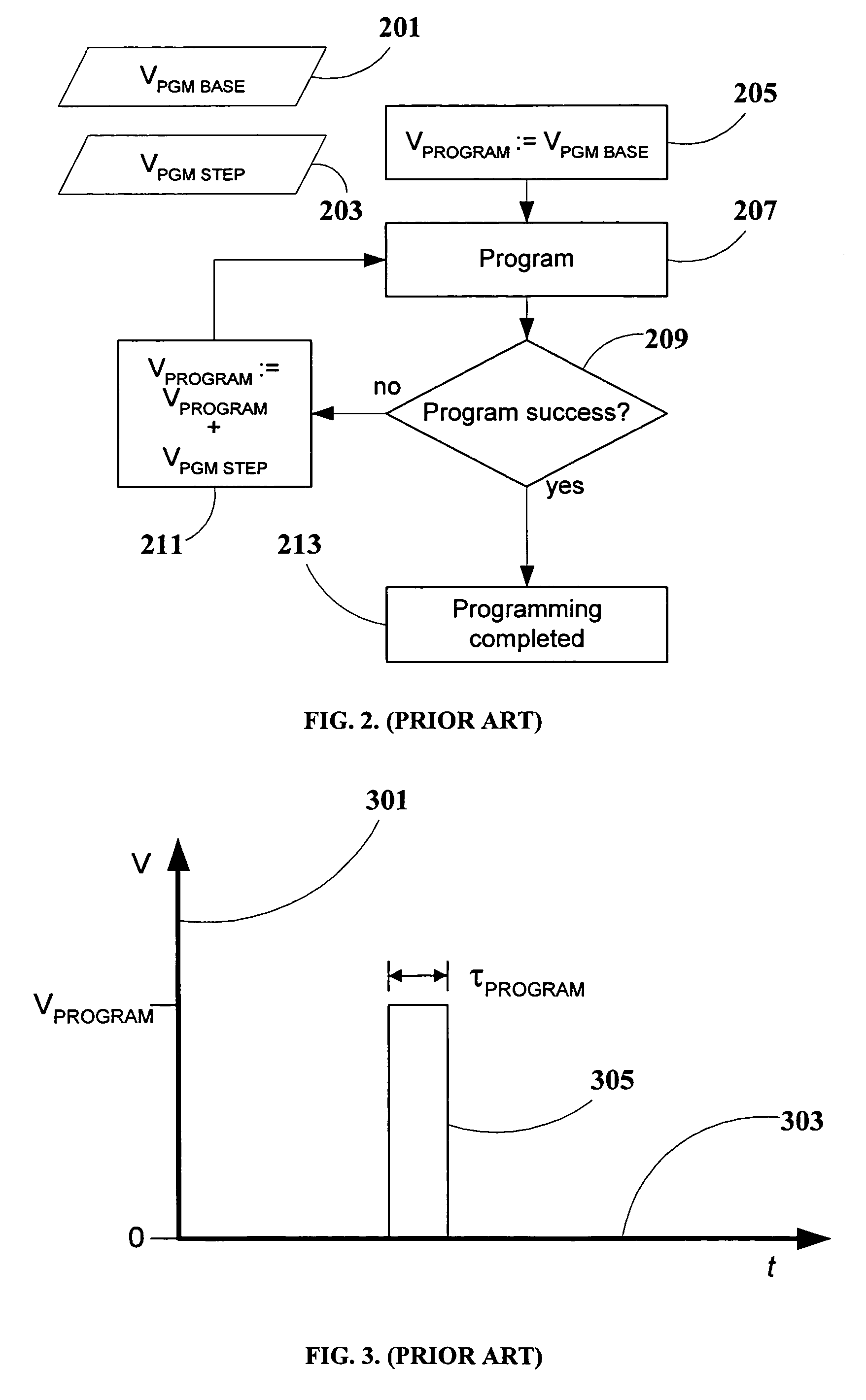

Method and system for optimizing reliability and performance of programming data in non-volatile memory devices

ActiveUS20050024978A1Improve reliabilityExtended service lifeRead-only memoriesDigital storageParallel computingVolatile memory

Methods of managing memory devices, and devices so managed. A value of a parameter, that is used to program one or more memory cells, is adapted to a monitored condition of the cell(s). Either the number of bits per cell is held fixed or the monitored condition is an intrinsic condition of the cell(s). The initial value of the parameter is optimized for those specific cells, relative to a pre-selected criterion, by programming the cell(s) in accordance with candidate values of the parameter.

Owner:WESTERN DIGITAL ISRAEL LTD

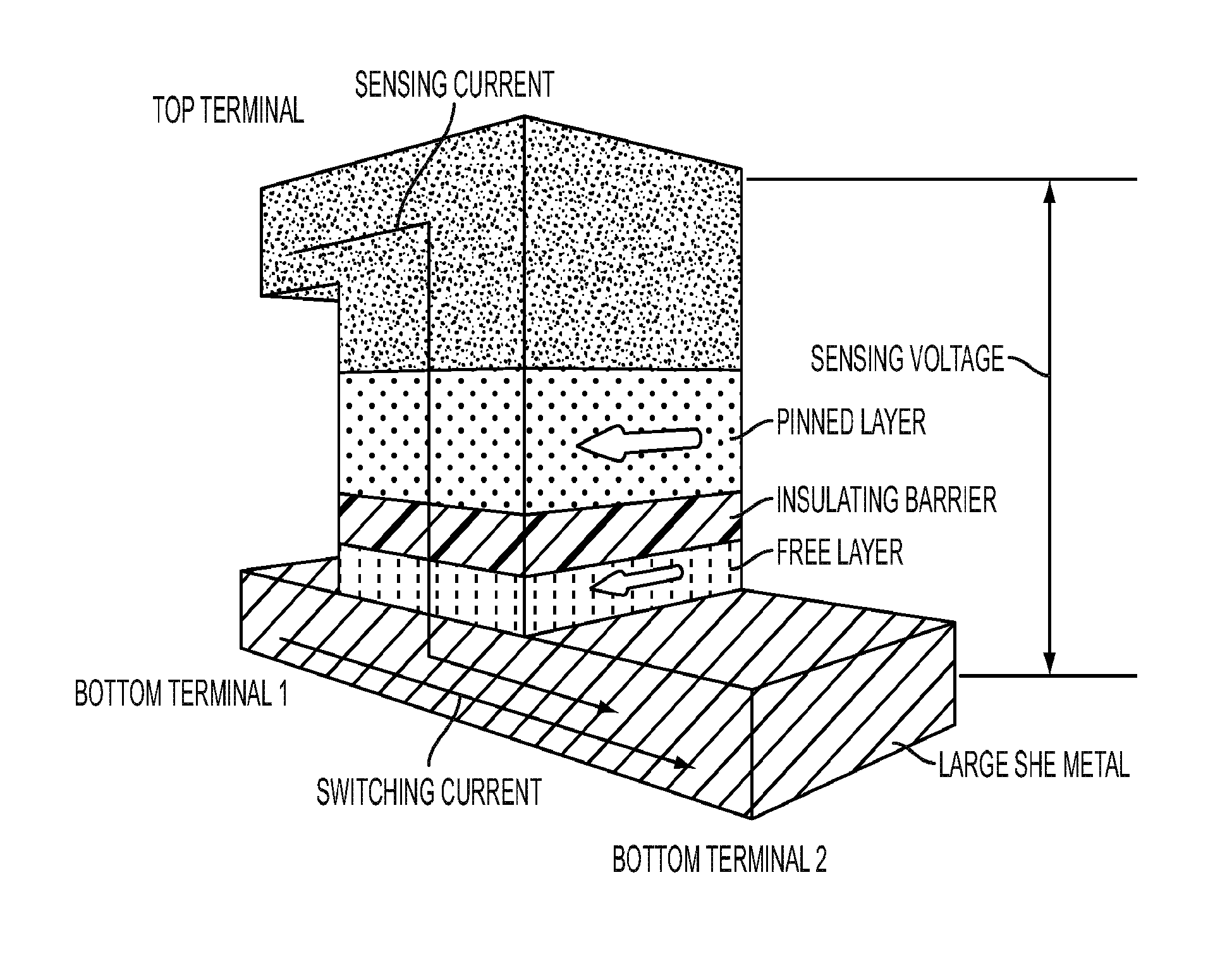

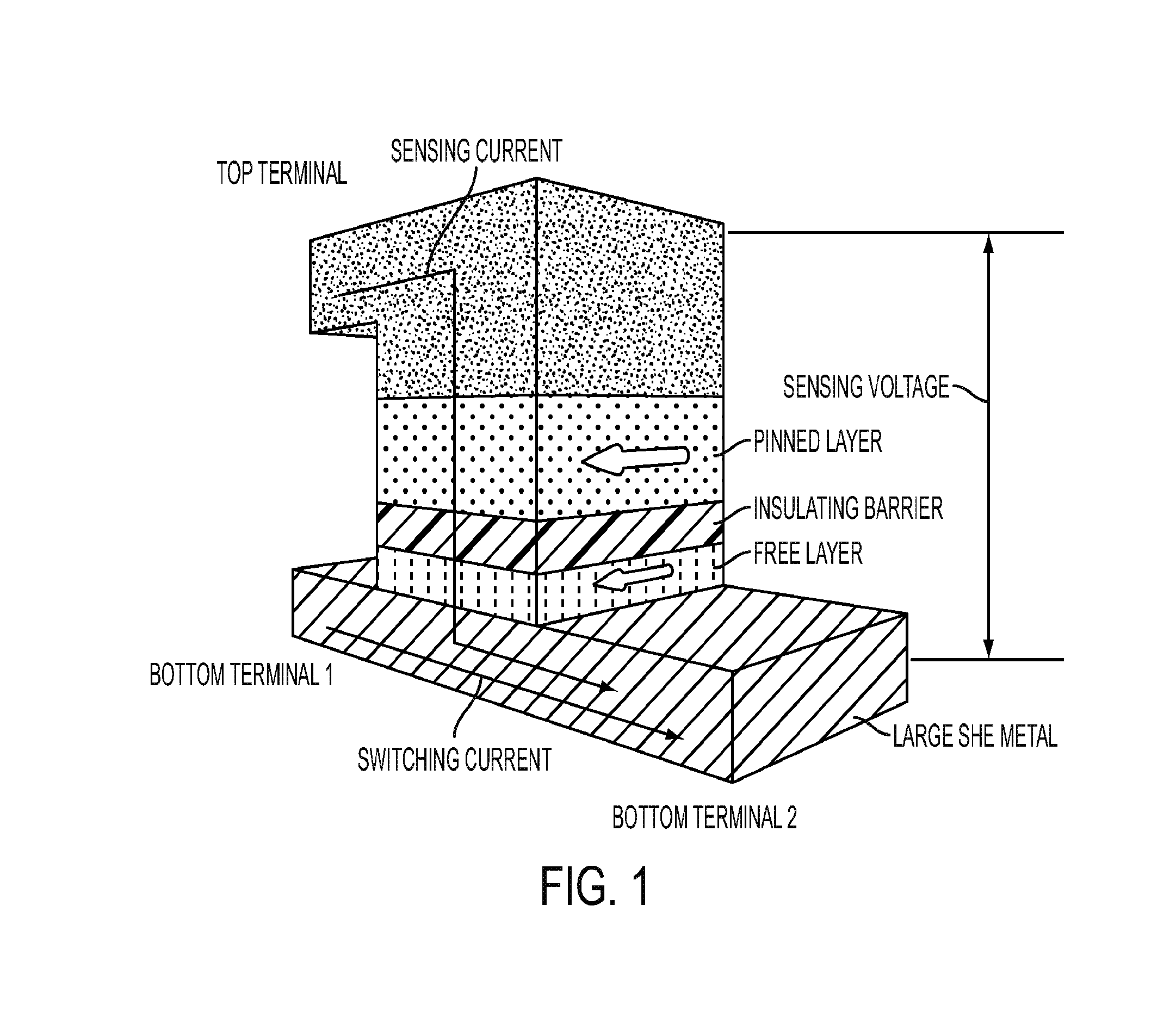

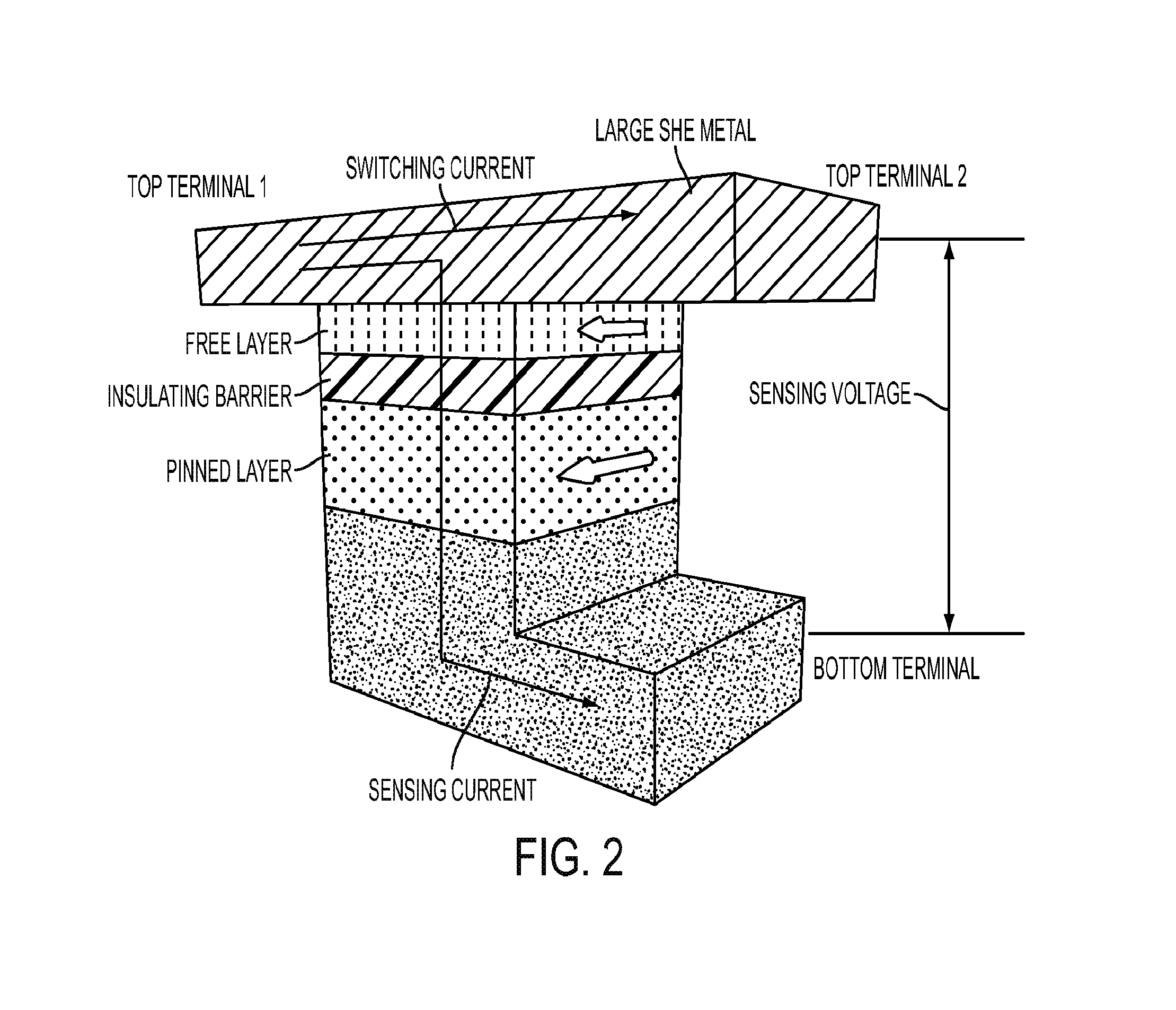

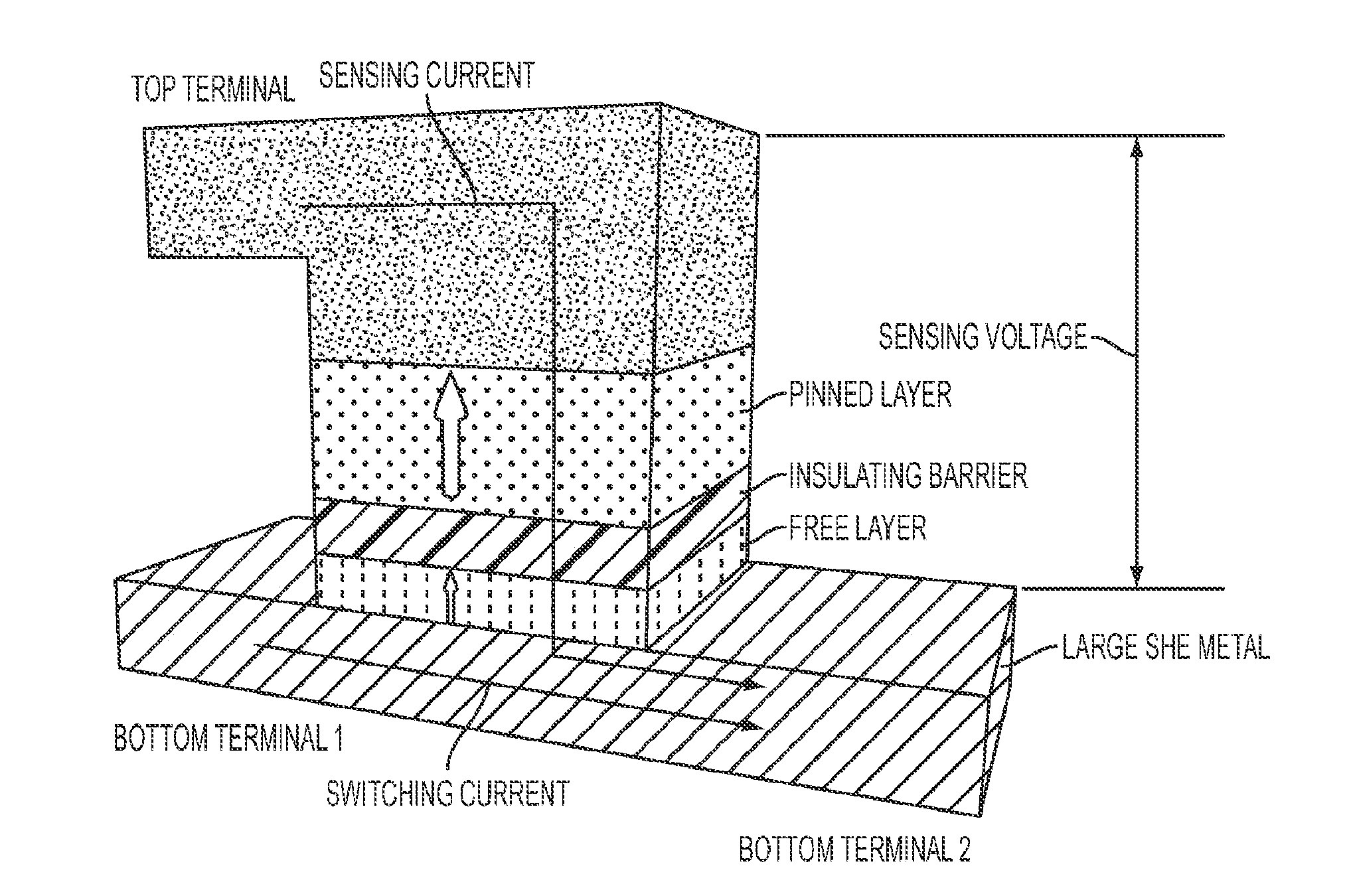

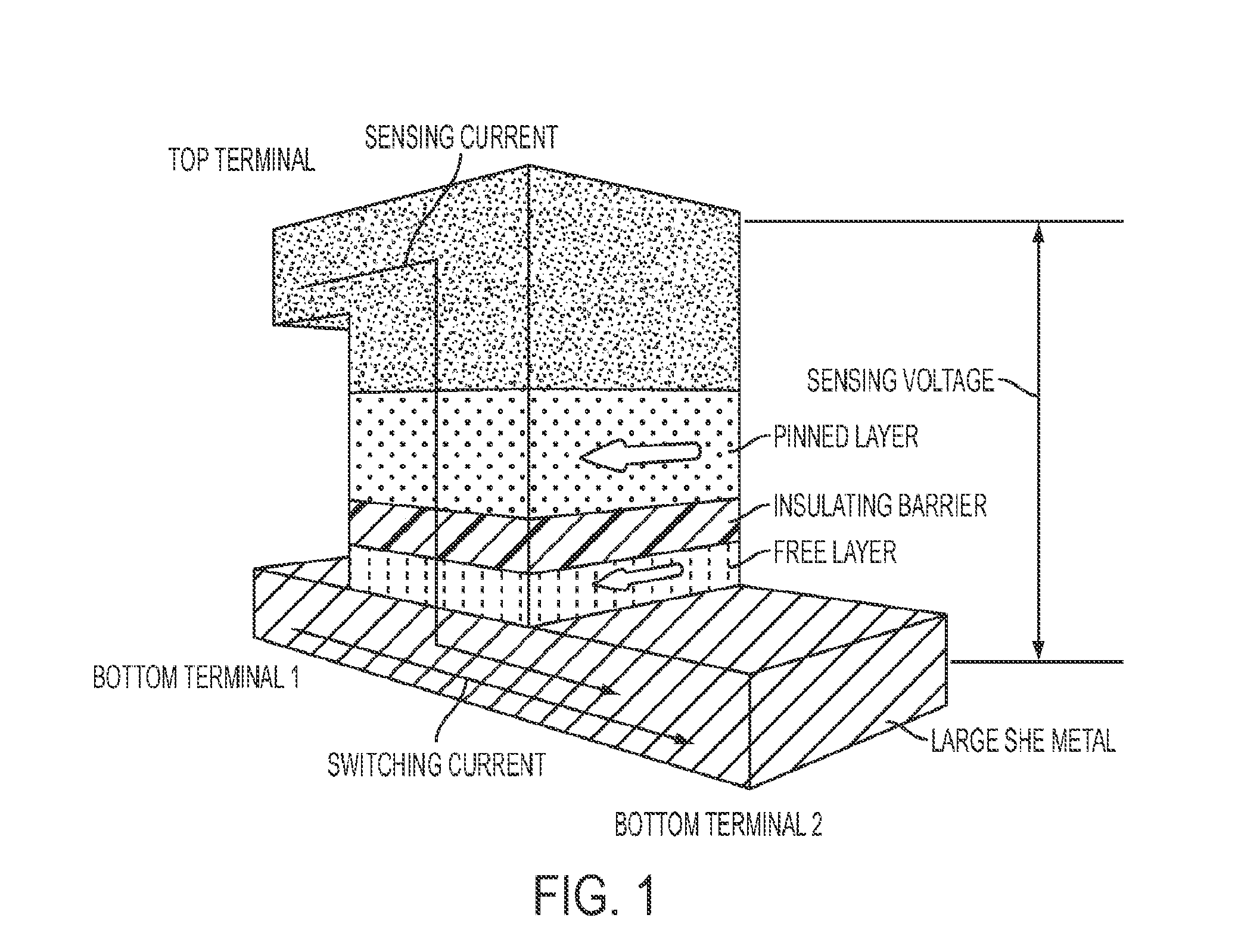

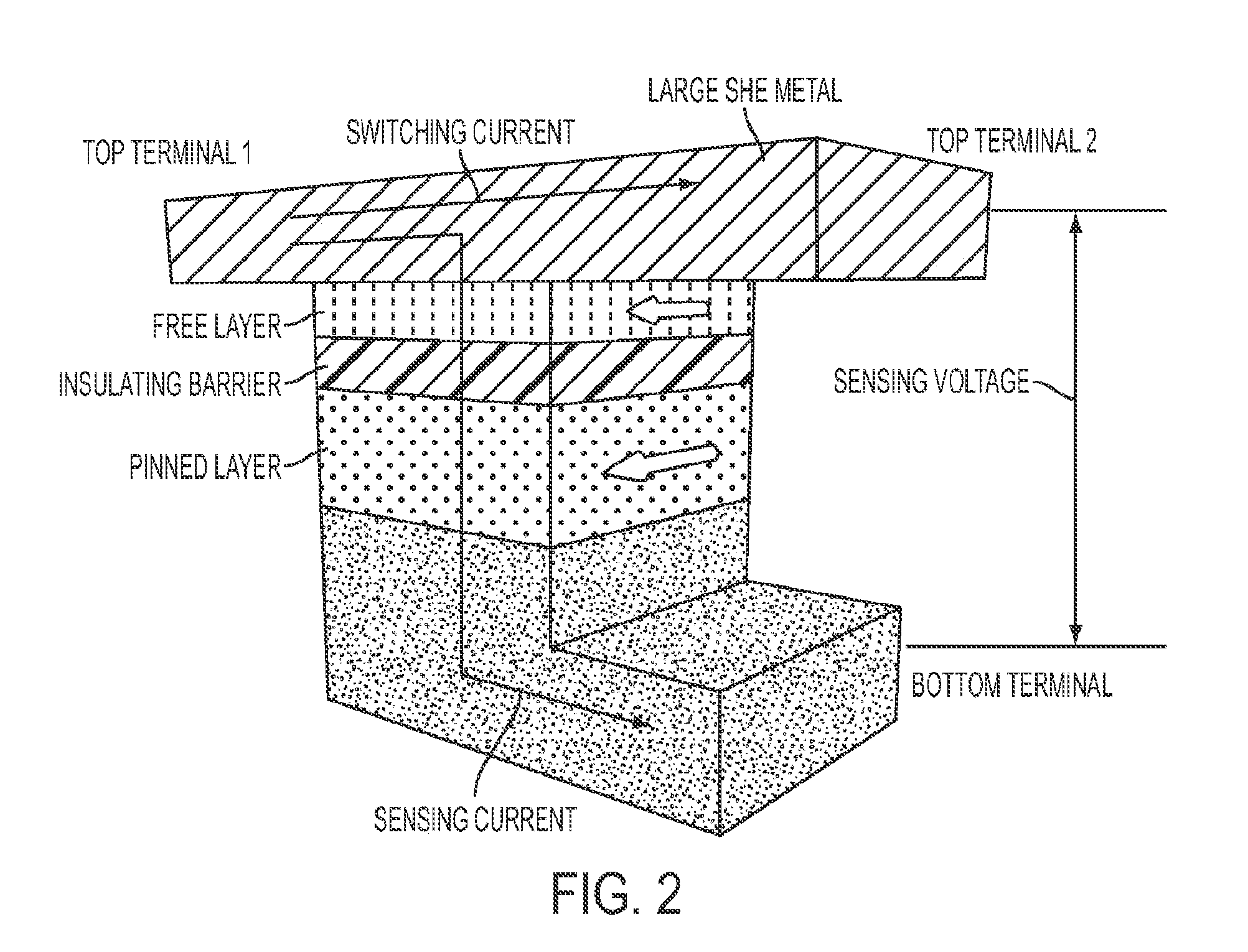

Spin hall effect magnetic apparatus, method and applications

ActiveUS20140169088A1Improve efficiencySmall costSolid-state devicesRead-only memoriesTungstenPower flow

An ST-MRAM structure, a method for fabricating the ST-MRAM structure and a method for operating an ST-MRAM device that results from the ST-MRAM structure each utilize a spin Hall effect base layer that contacts a magnetic free layer and effects a magnetic moment switching within the magnetic free layer as a result of a lateral switching current within the spin Hall effect base layer. This resulting ST-MRAM device uses an independent sense current and sense voltage through a magnetoresistive stack that includes a pinned layer, a non-magnetic spacer layer and the magnetic free layer which contacts the spin Hall effect base layer. Desirable non-magnetic conductor materials for the spin Hall effect base layer include certain types of tantalum materials and tungsten materials that have a spin diffusion length no greater than about five times the thickness of the spin Hall effect base layer and a spin Hall angle at least about 0.05.

Owner:CORNELL UNIVERSITY

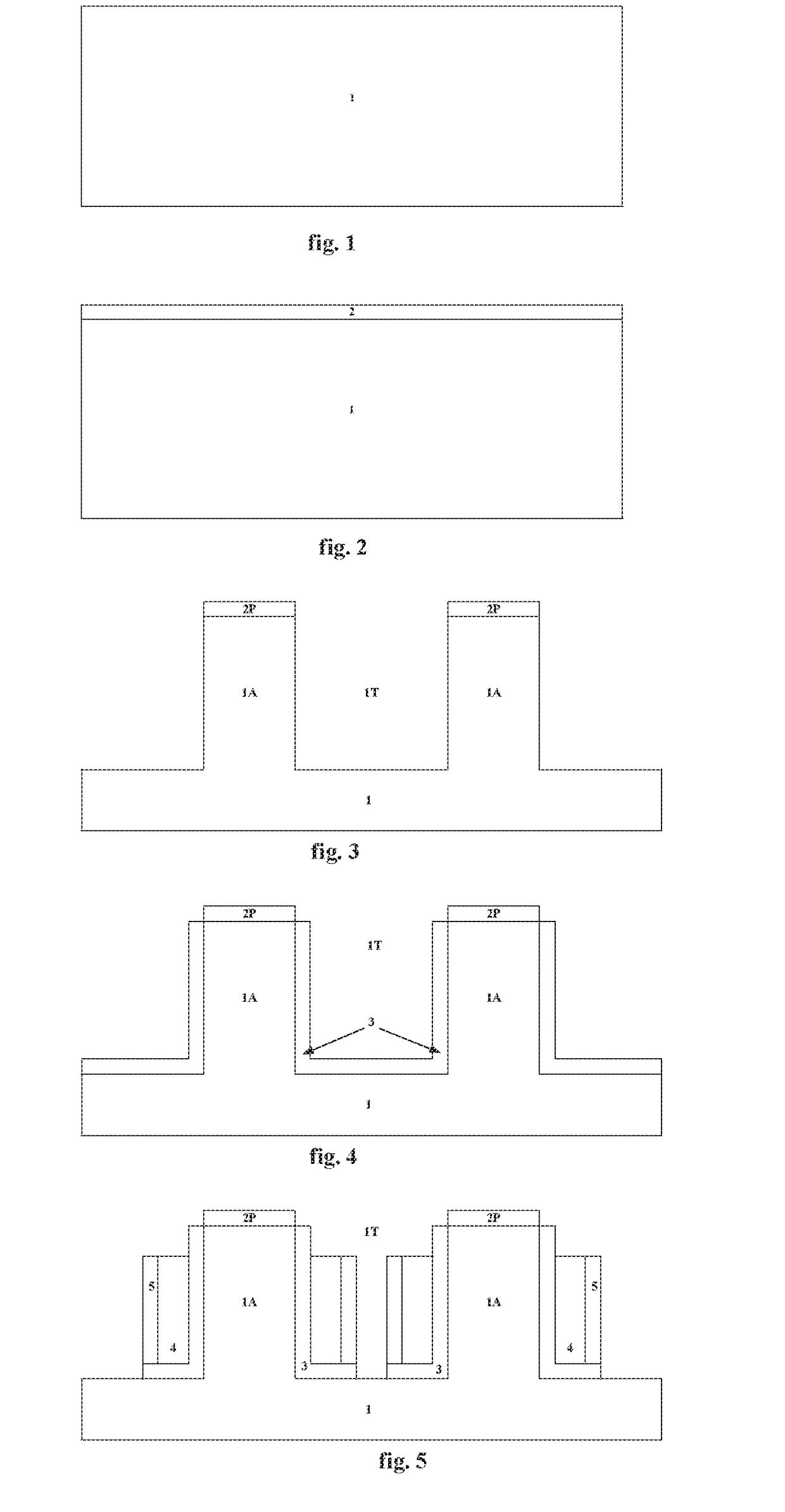

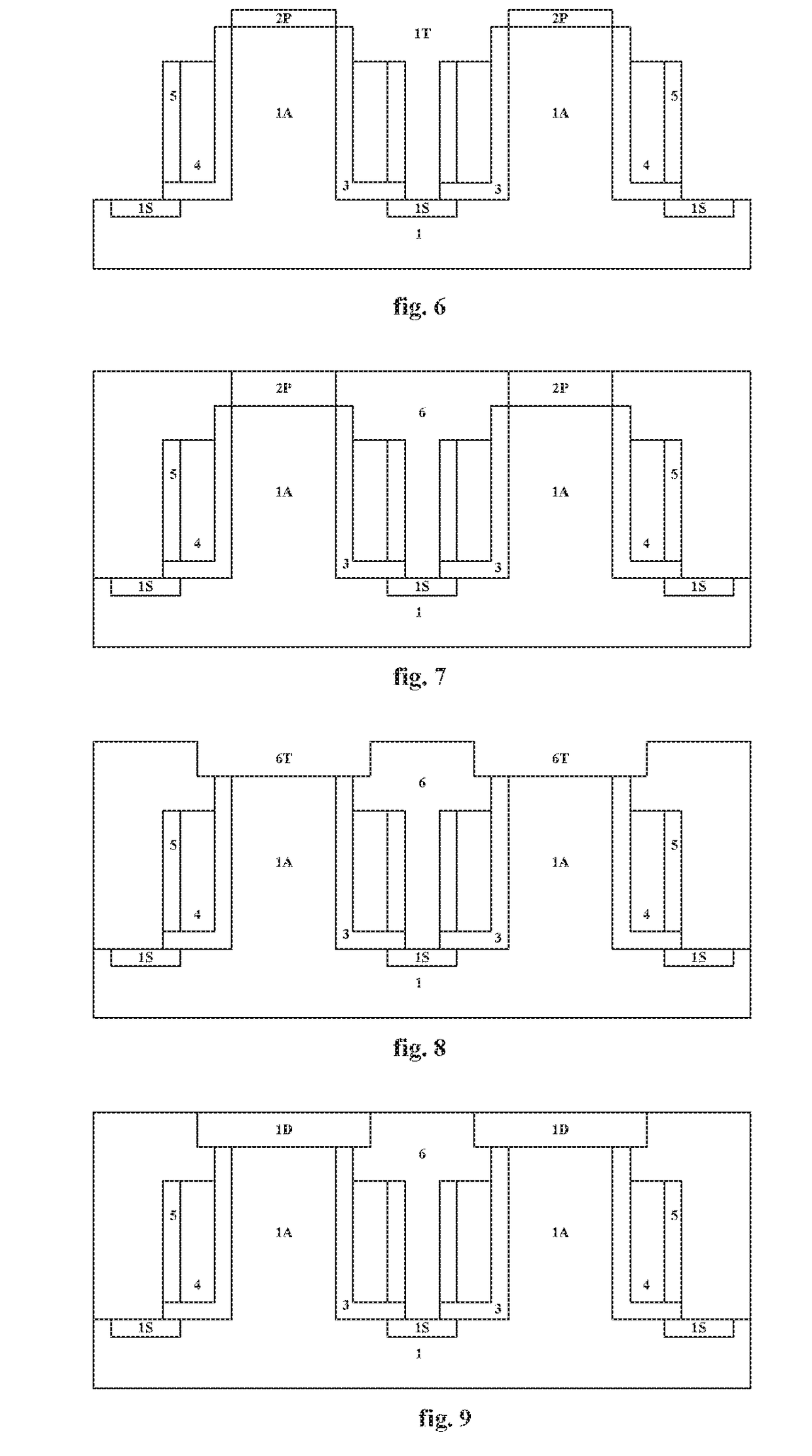

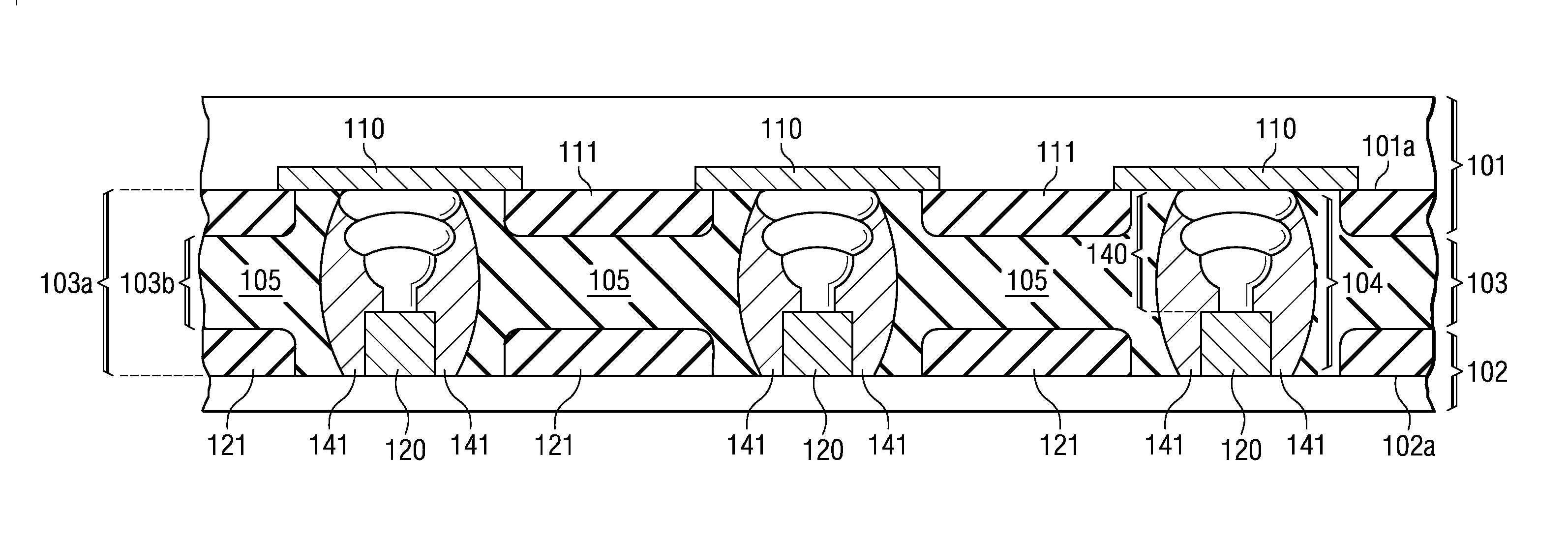

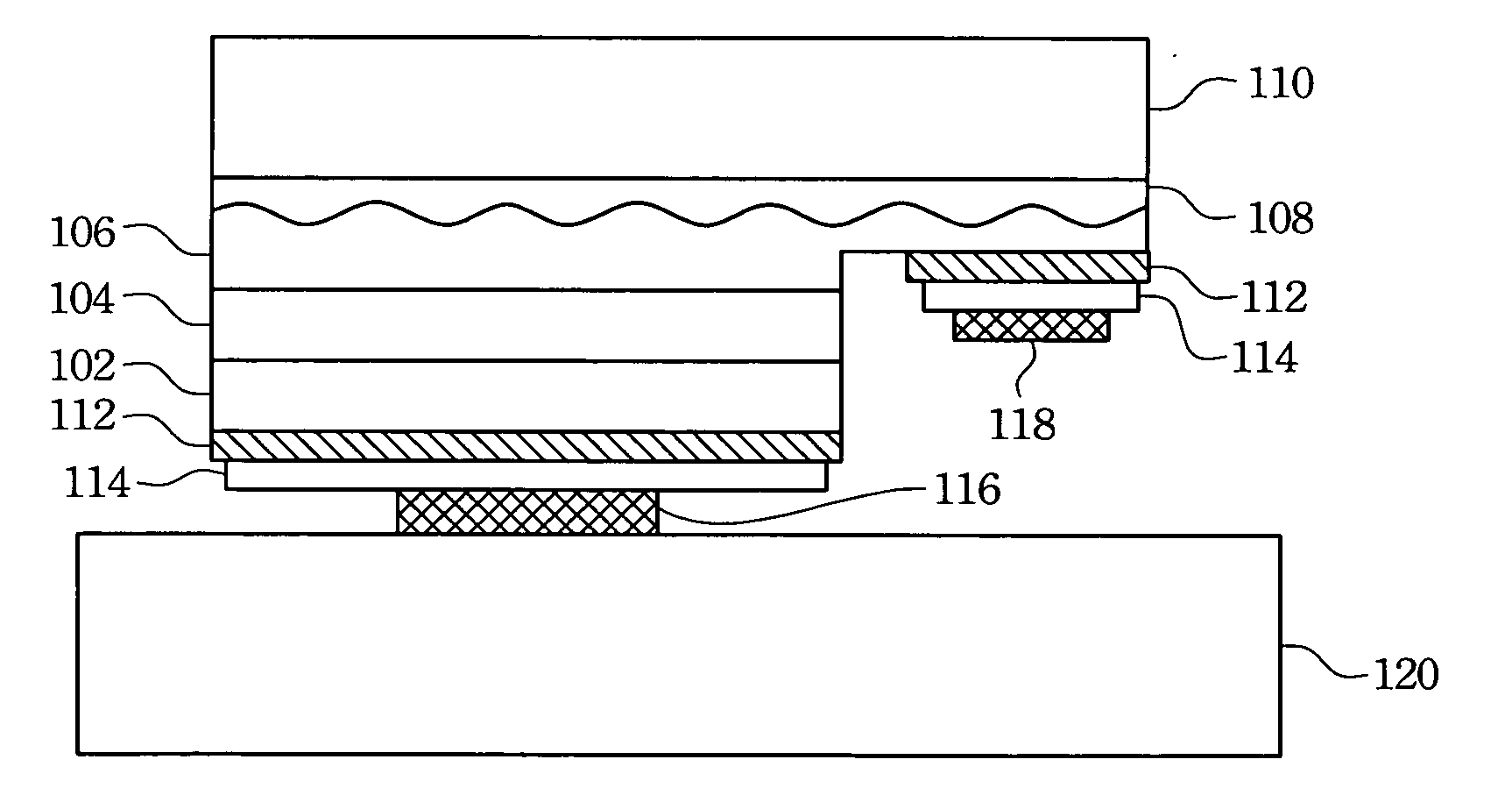

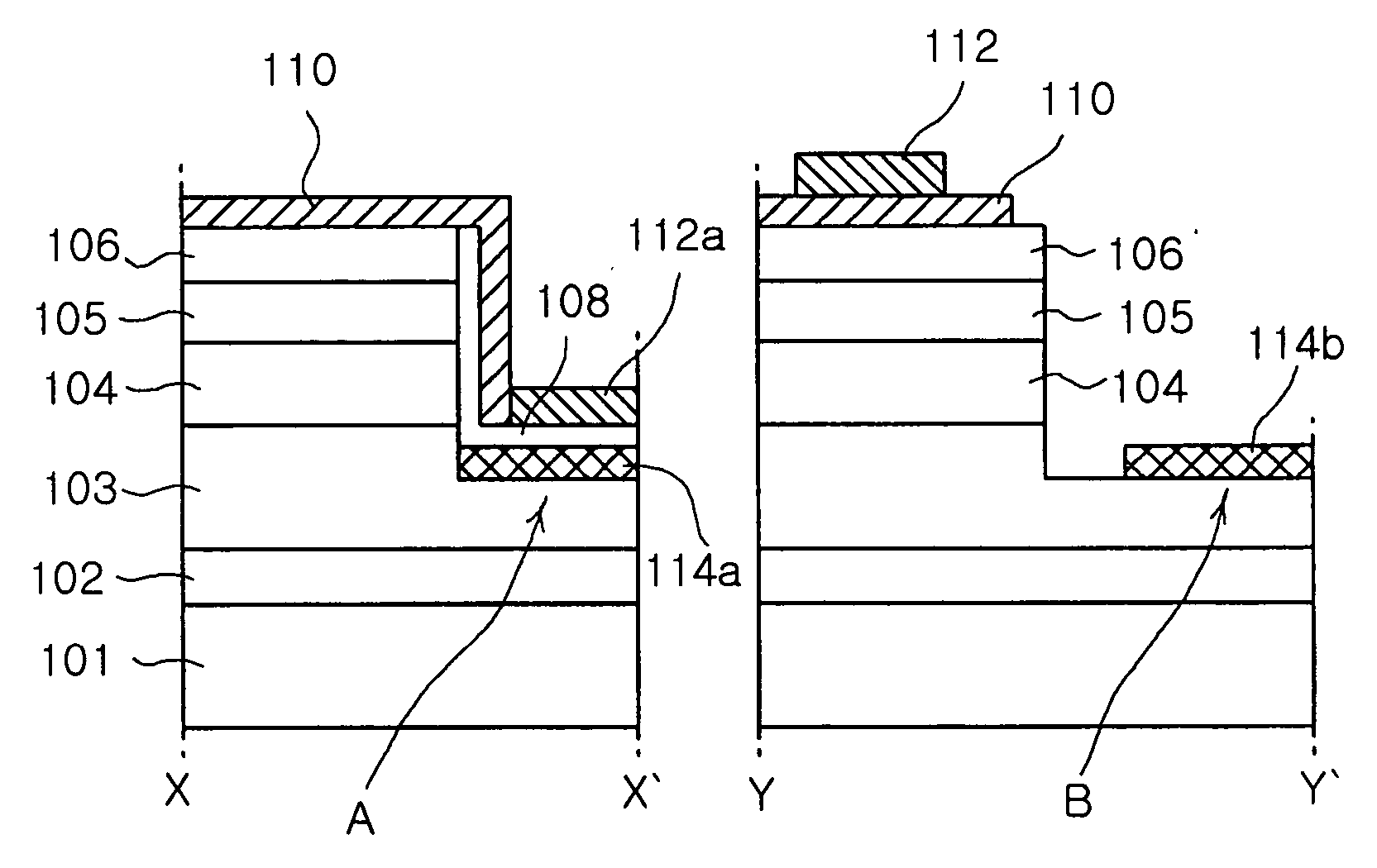

Flip-Chip Device Having Underfill in Controlled Gap

InactiveUS20070200234A1Improve equipment reliabilityUniform gapSemiconductor/solid-state device detailsSolid-state devicesContact padPolymer

A flip-chip and underfilled device, which includes a semiconductor chip (101) with contact pads and a workpiece (102) with contact pads in matching locations; the workpiece may be an insulating substrate or another semiconductor chip. The workpiece and the chip are spaced by a gap (103) of substantially uniform average width. Attached to each chip contact pad is a column-shaped spacer (140), which includes two or more deformed spheres of non-reflow metals, preferably gold, bonded together to a height about equal to the gap width. The spacer is attached to the contact pad (110) substantially normal to the chip surface and extends from the chip pad to the matching workpiece pad (120); it is bonded to the workpiece pad by reflow metals (141) such as tin or tin alloy, which covers at least portions of the workpiece pad and the spacer. The gap may be filled with a polymer material (105) surrounding the reflow metal and spacers.

Owner:TEXAS INSTR INC

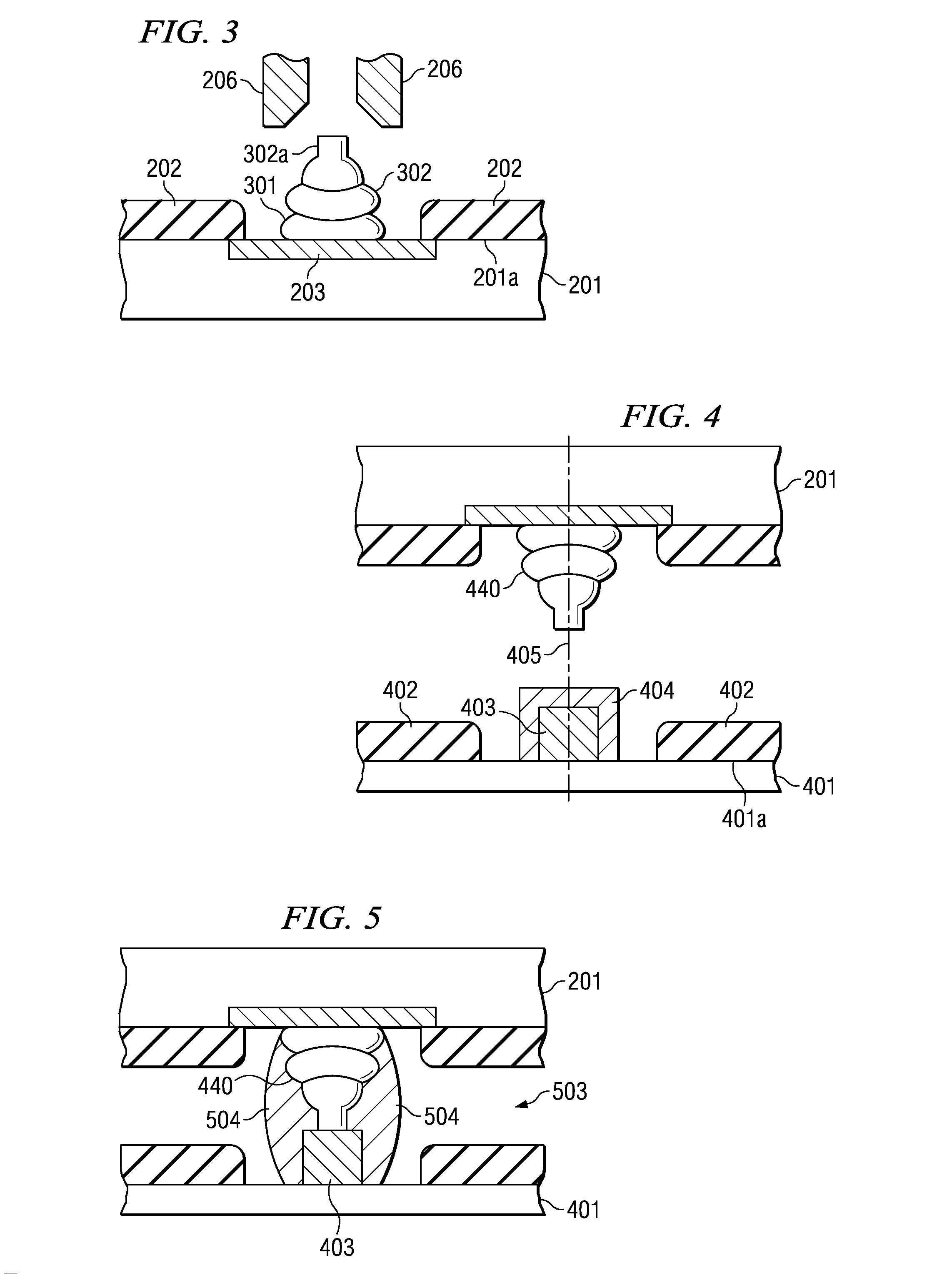

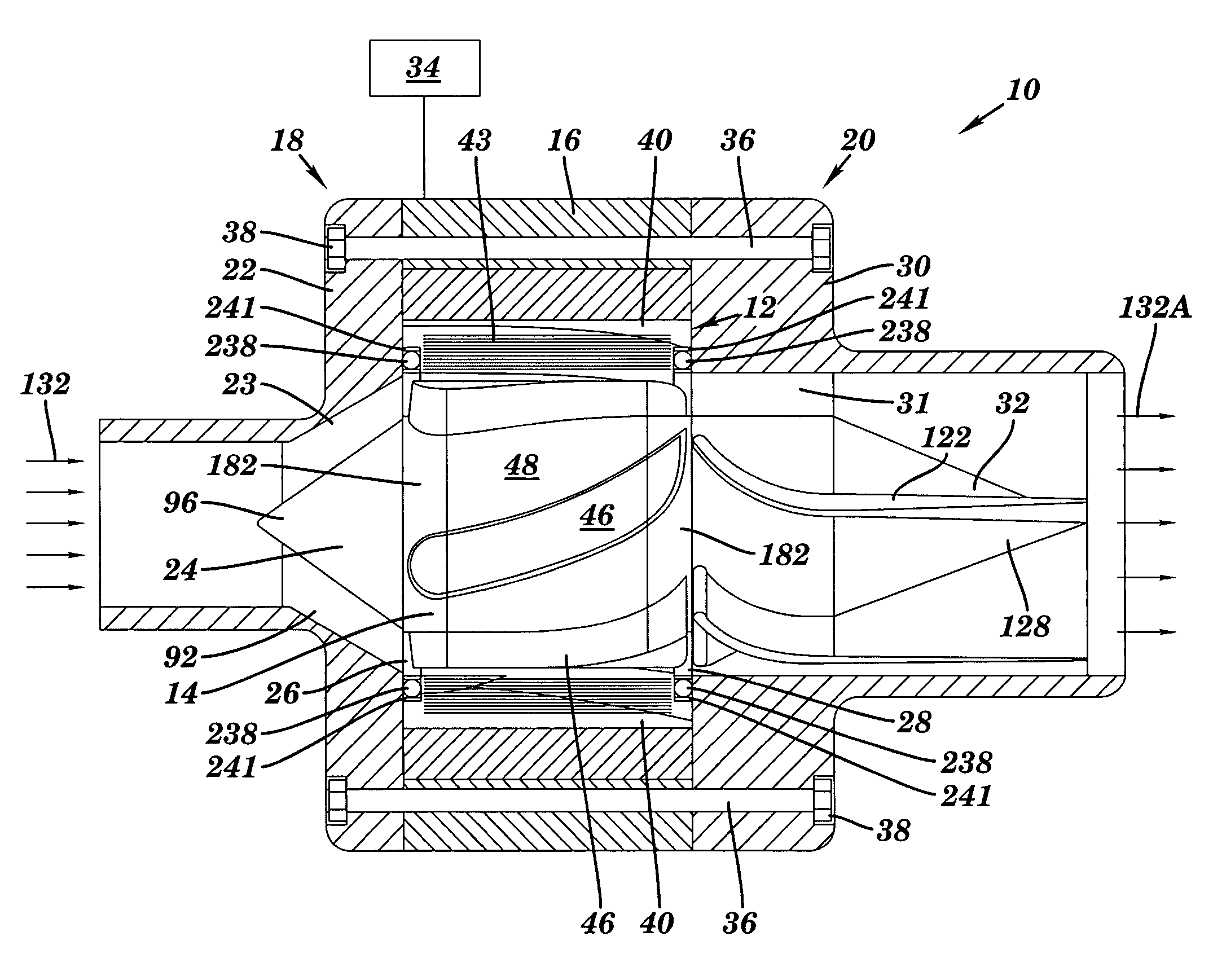

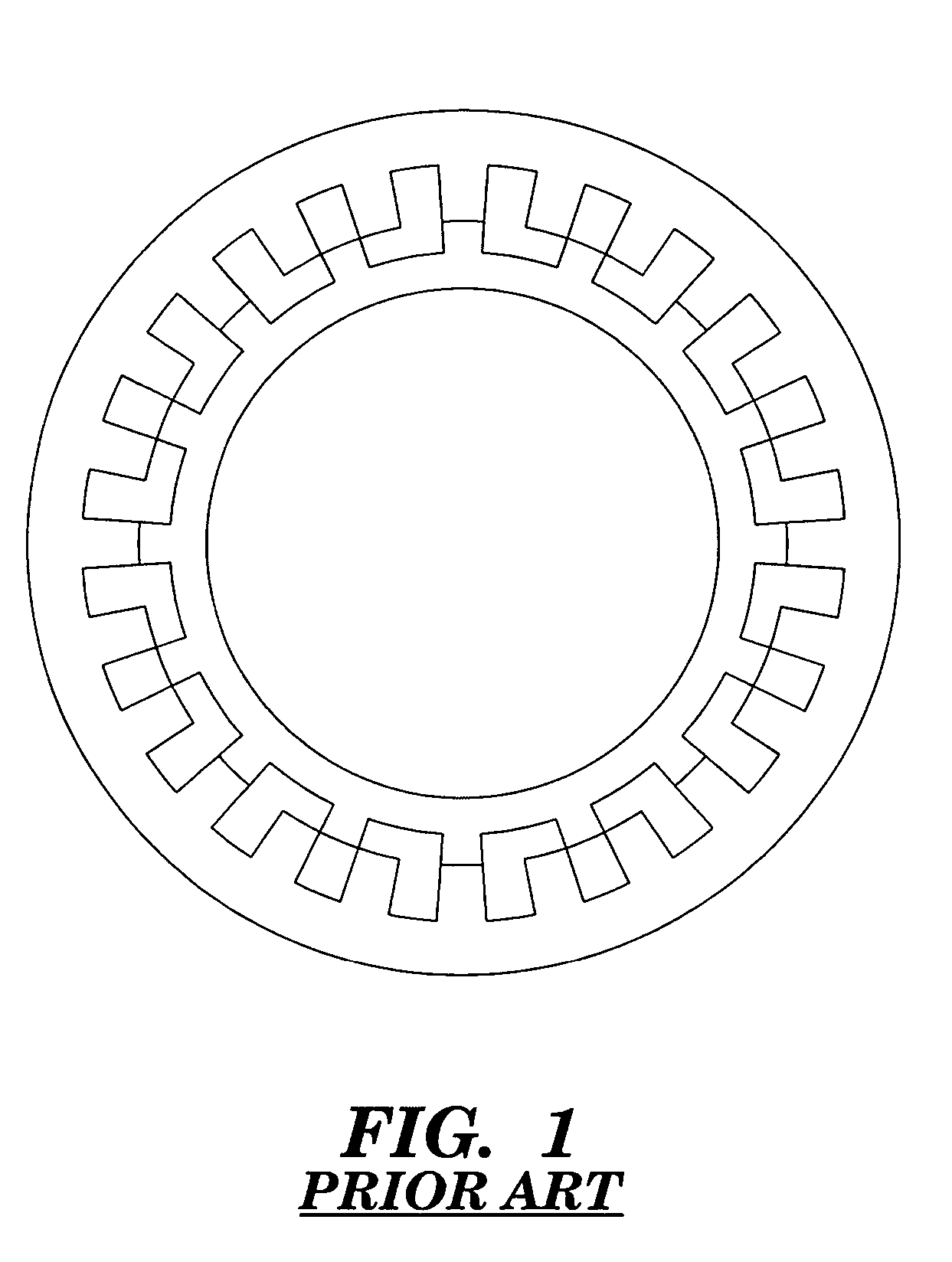

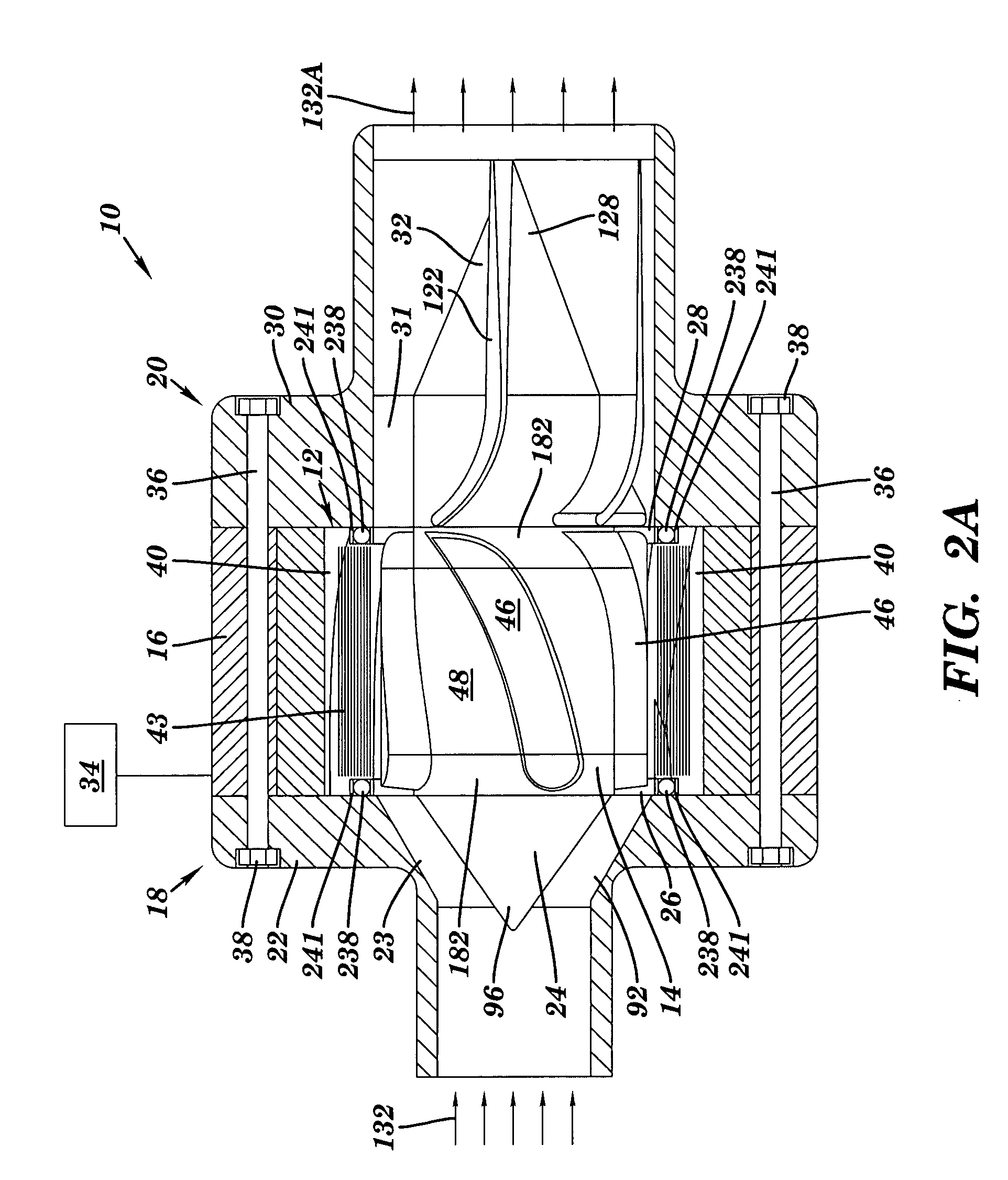

Fluid pump/generator with integrated motor and related stator and rotor and method of pumping fluid

InactiveUS7021905B2Small sizeReduce the number of partsGas turbine plantsRotary piston pumpsImpellerElectric machine

Owner:ADVANCED ENERGY CONVERSION

Electrochromic devices

ActiveUS20110249314A1Improve conductivityIncrease resistanceElectric discharge tubesVacuum evaporation coatingElectricityOptoelectronics

Conventional electrochromic devices frequently suffer from poor reliability and poor performance. Improvements are made using entirely solid and inorganic materials. Electrochromic devices are fabricated by forming an ion conducting electronically insulating interfacial region that serves as an IC layer. In some methods, the interfacial region is formed after formation of an electrochromic and a counter electrode layer. The interfacial region contains an ion conducting electronically insulating material along with components of the electrochromic and / or the counter electrode layer. Materials and microstructure of the electrochromic devices provide improvements in performance and reliability over conventional devices.

Owner:VIEW INC

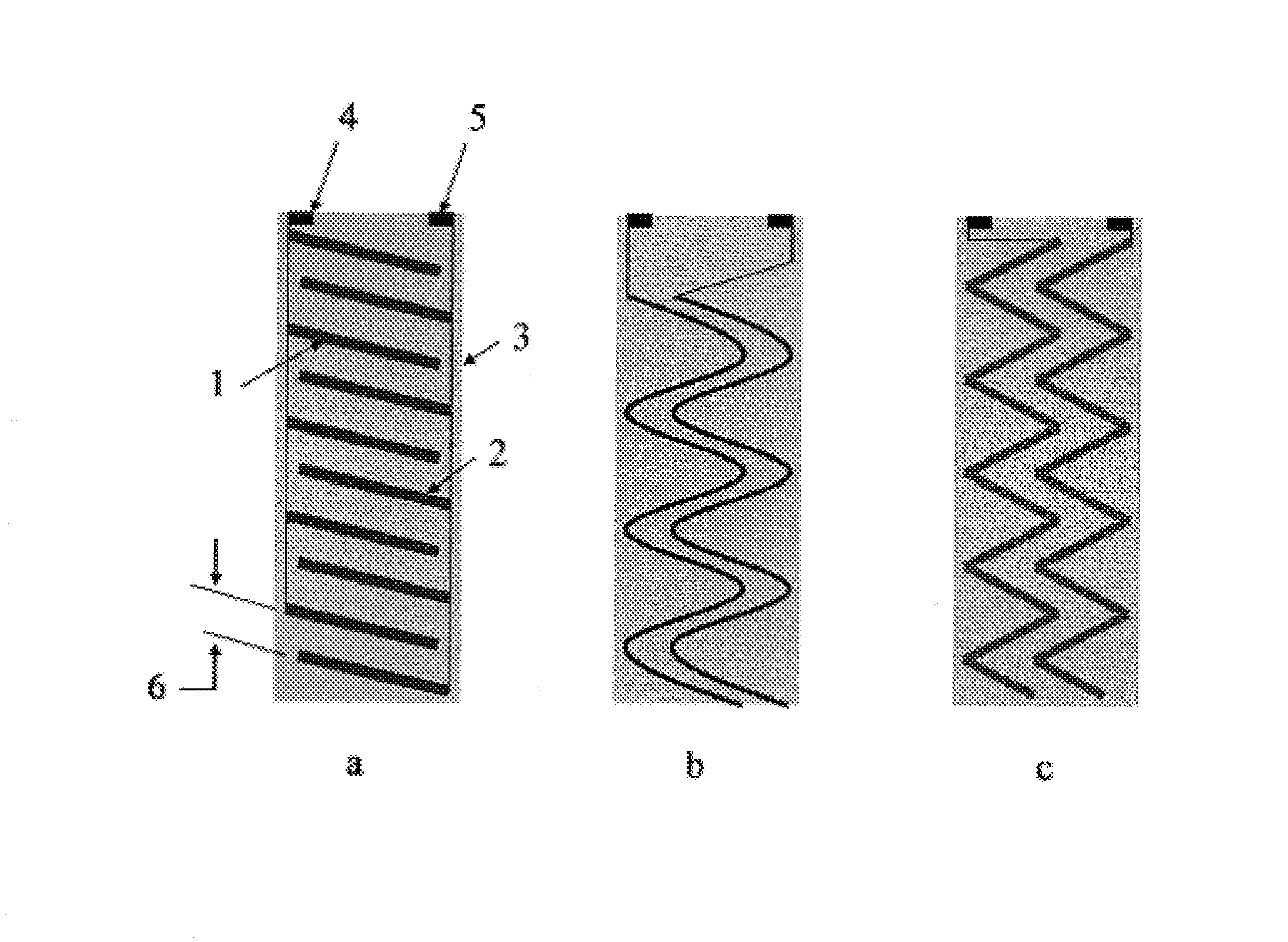

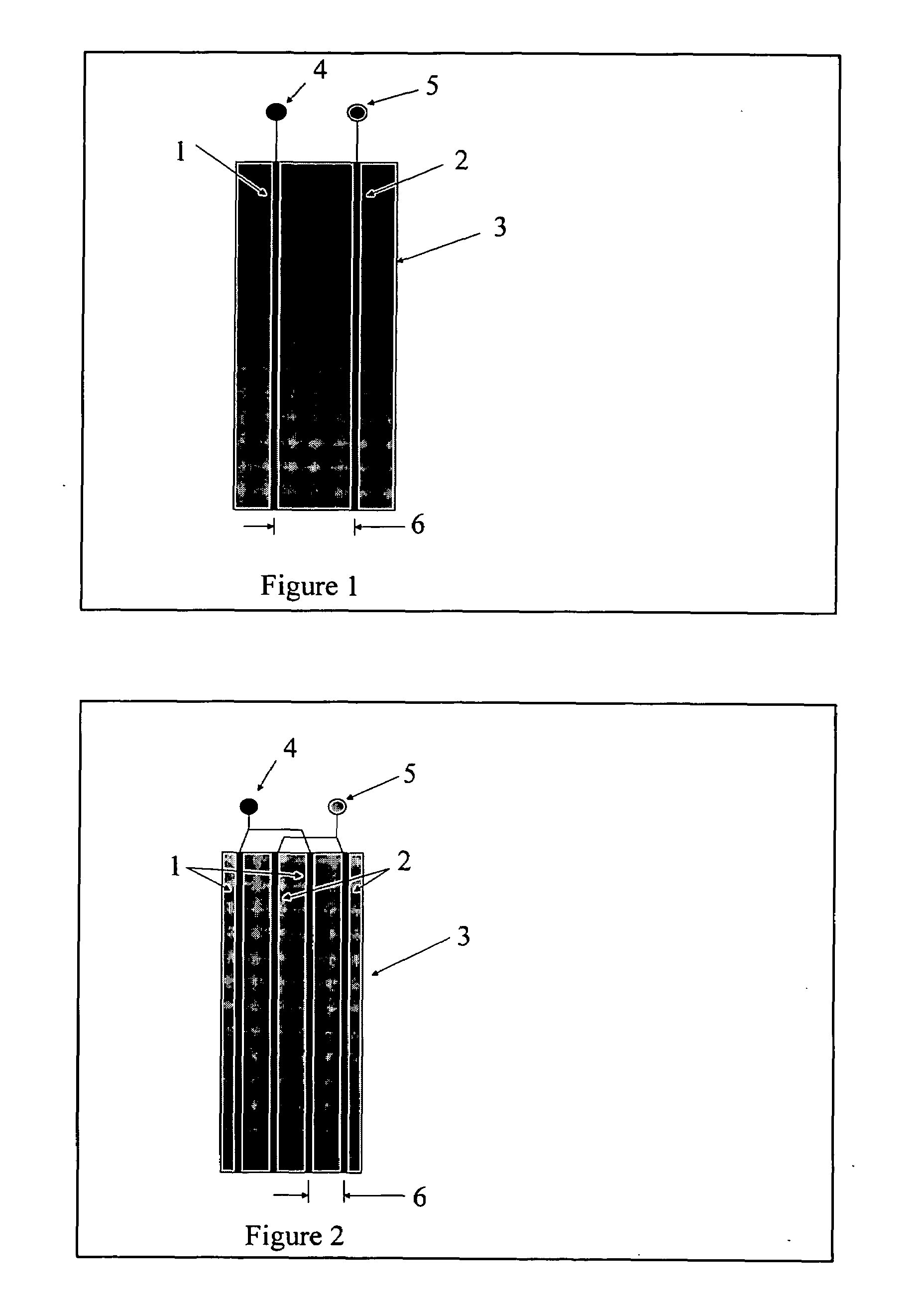

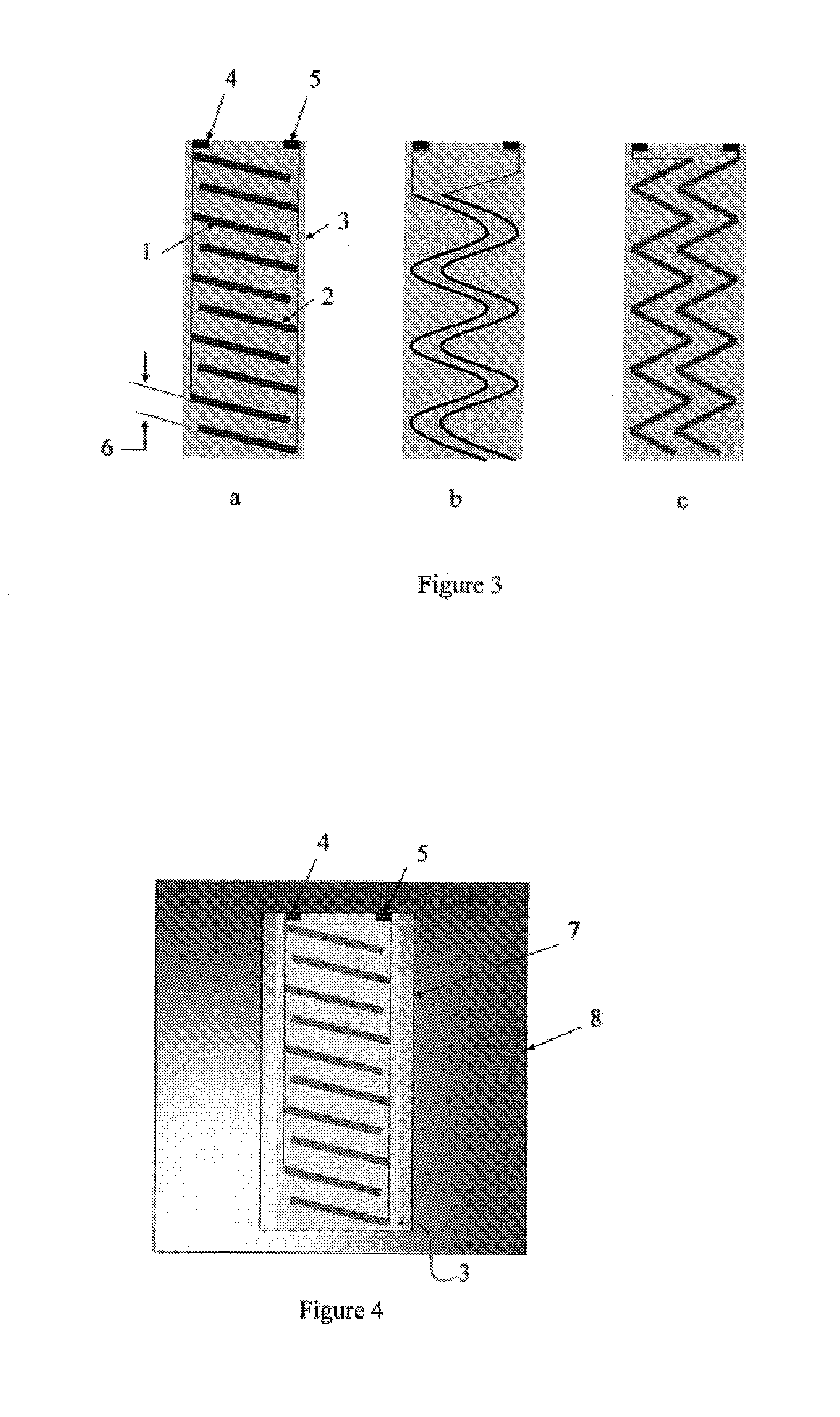

Isolated capacitive fluid level sensor

InactiveUS7258005B2Reliable separationEasy to addMachines/enginesLubrication indication devicesElectricityCapacitance

A capacitive fluid level sensor is disclosed that operates without the use of a float, wherein coplanar sensing electrodes disposed onto a dielectric substrate and positioned proximate a dielectric wall of a vessel containing a fluid, form a fringing field capacitance that changes in accordance with changes in the level of the fluid. The electrodes are electrically insulated from the measured fluid. The electrodes are sized and spaced to maximize response of the capacitance to changes in the level of the fluid, while minimizing the effects of the dielectric wall. The sensor is fabricated such that it can be positioned against the outside of a dielectric wall of a vessel, or embedded within a dielectric material. A low permitivity spacer and shield assembly are taught which reduces sensitivity to electric fields external to the vessel. An interdigital comb configuration of the electrodes is also disclosed in which depressions or gaps are formed into the dielectric substrate in an area of spacing of the electrodes.

Owner:NYCE DAVID SCOTT

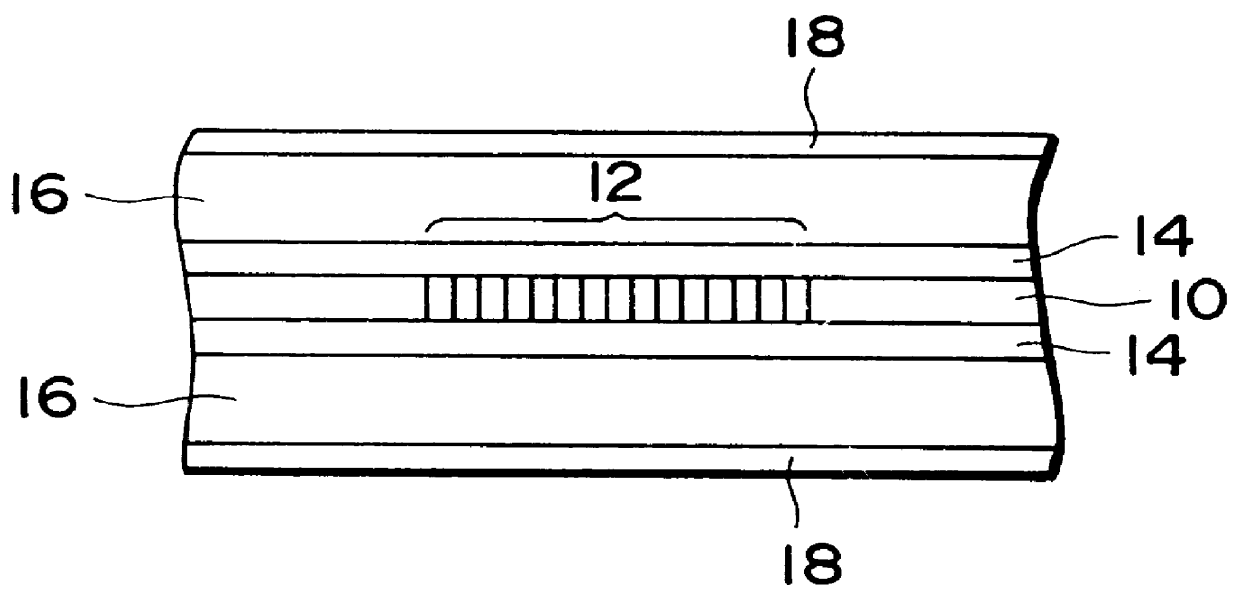

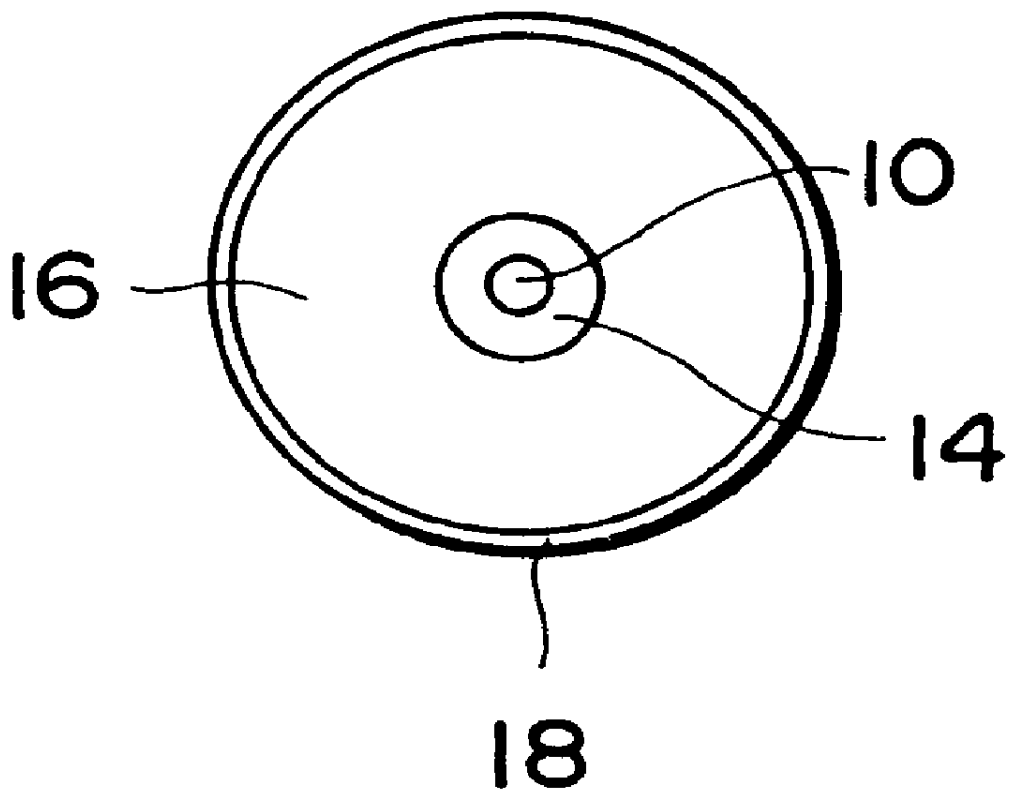

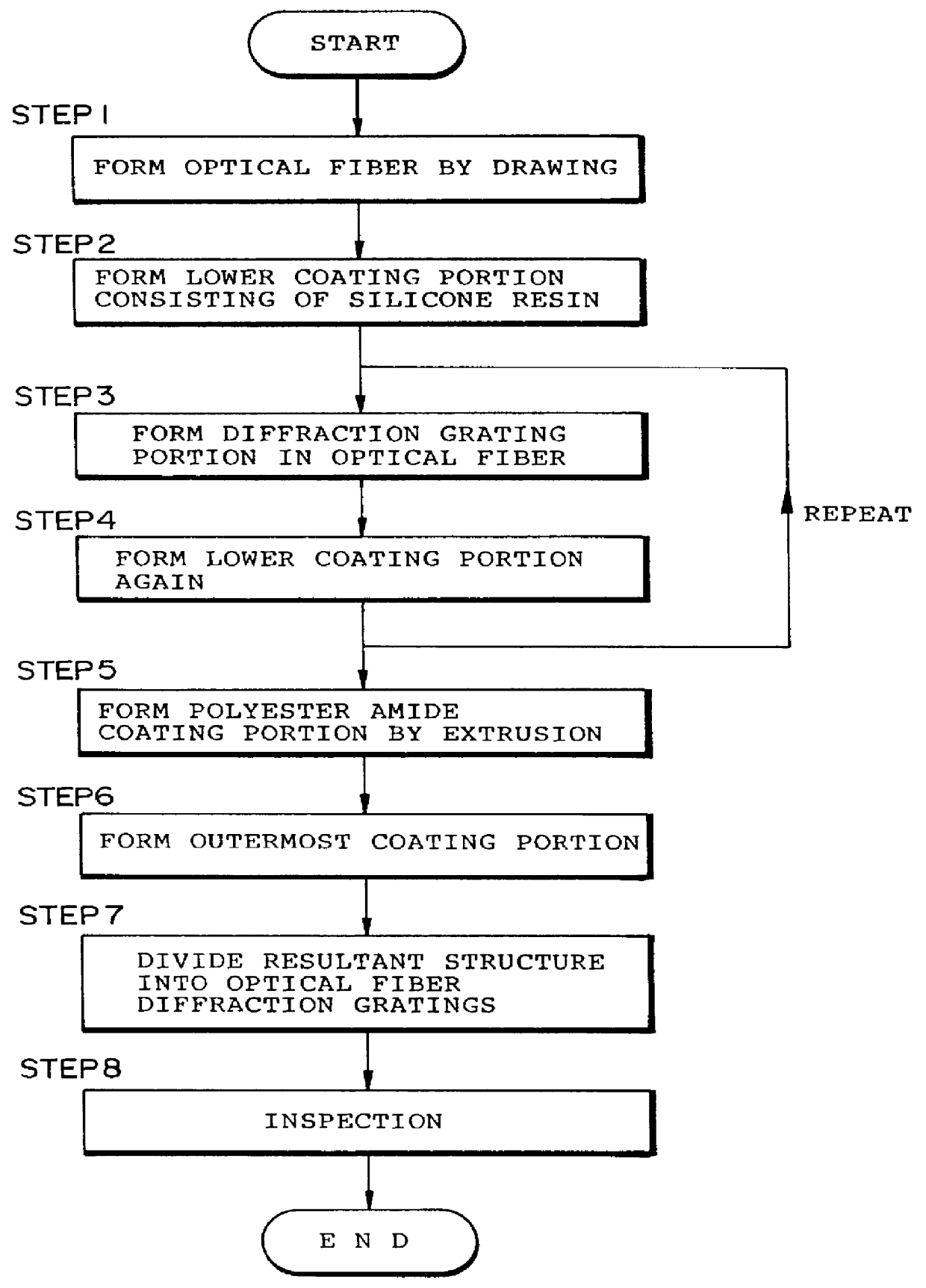

Optical fiber diffraction grating, a method of fabricating thereof and a laser light source

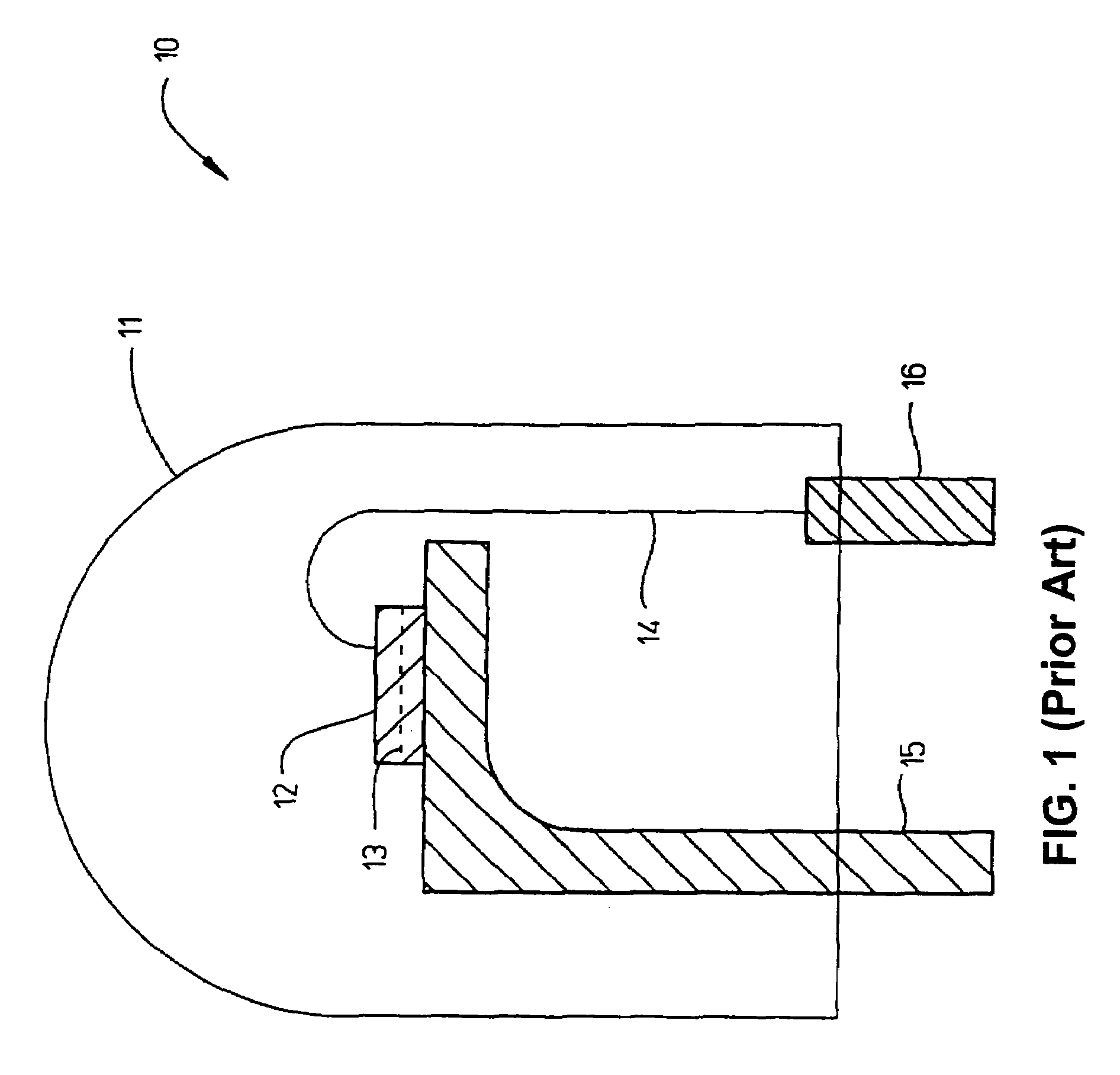

InactiveUS6067392ACanceled outPositive linear thermal expansion coefficientOptical fibre with multilayer core/claddingCoupling light guidesPolyesterLaser light

PCT No. PCT / JP96 / 03000 Sec. 371 Date Jun. 16, 1997 Sec. 102(e) Date Jun. 16, 1997 PCT Filed Oct. 16, 1996 PCT Pub. No. WO97 / 14983 PCT Pub. Date Apr. 24, 1997A diffraction grating portion (12) is formed in an optical fiber (10), having a diameter of 125 mu m and serving to transmit light, along its optical axis. The optical fiber is concentrically surrounded by a lower coating portion (14) having an outer diameter of 300 mu m and consisting of a silicone resin. The lower coating portion is concentrically surrounded by a coating portion (16) having an outer diameter of 900 mu m and consisting of a liquid crystal polymer, e.g., polyester amide. The coating portion is further surrounded by an outermost coating portion (18) having an outer diameter of 1 mm and consisting of a UV curing resin colored for identification. Both the optical fiber (10) and the lower coating portion (14) have positive thermal expansion coefficients. In contrast to this, the coating portion (16) consisting of the liquid crystal polymer has a negative thermal expansion coefficient.

Owner:SUMITOMO ELECTRIC IND LTD

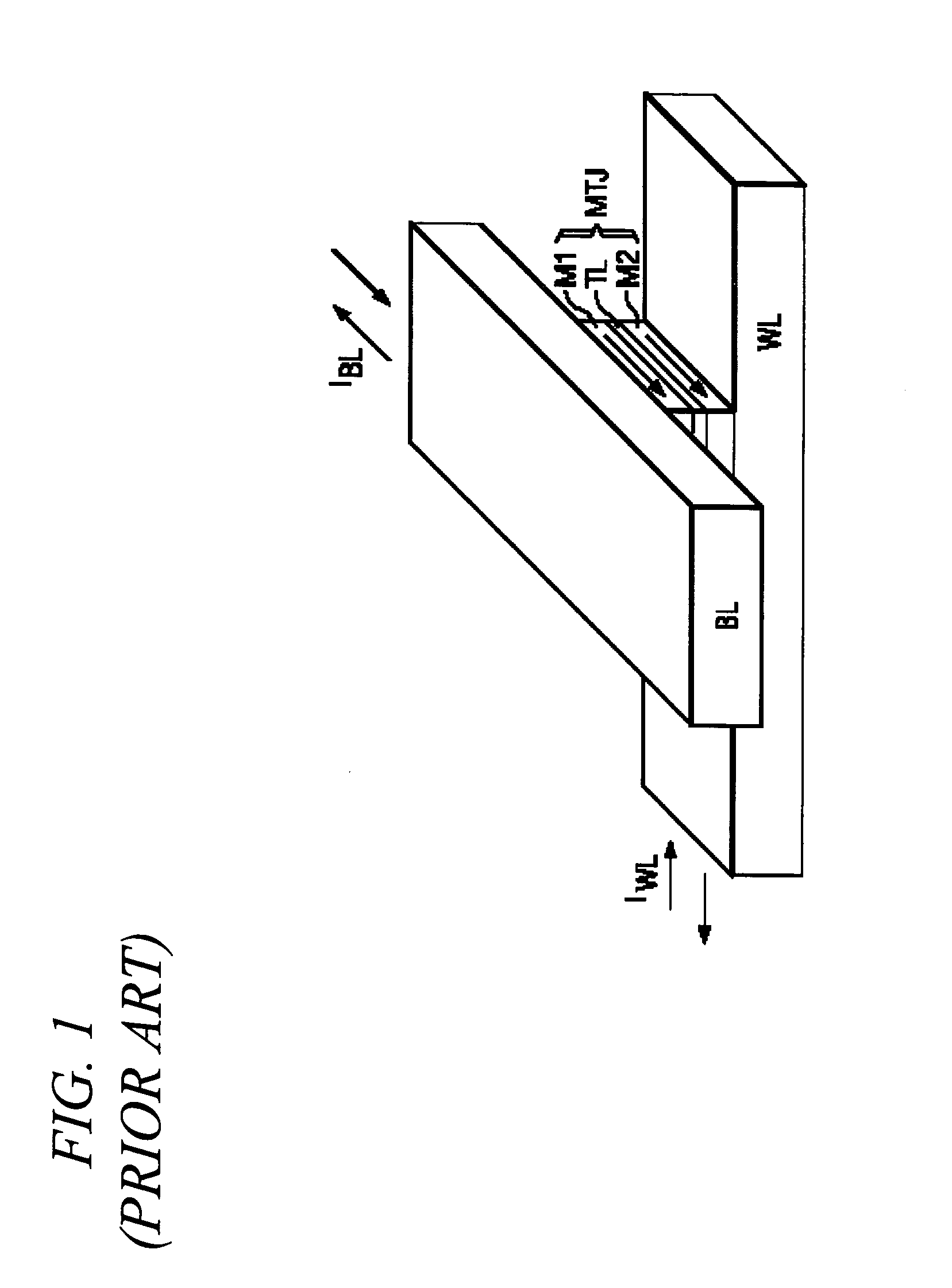

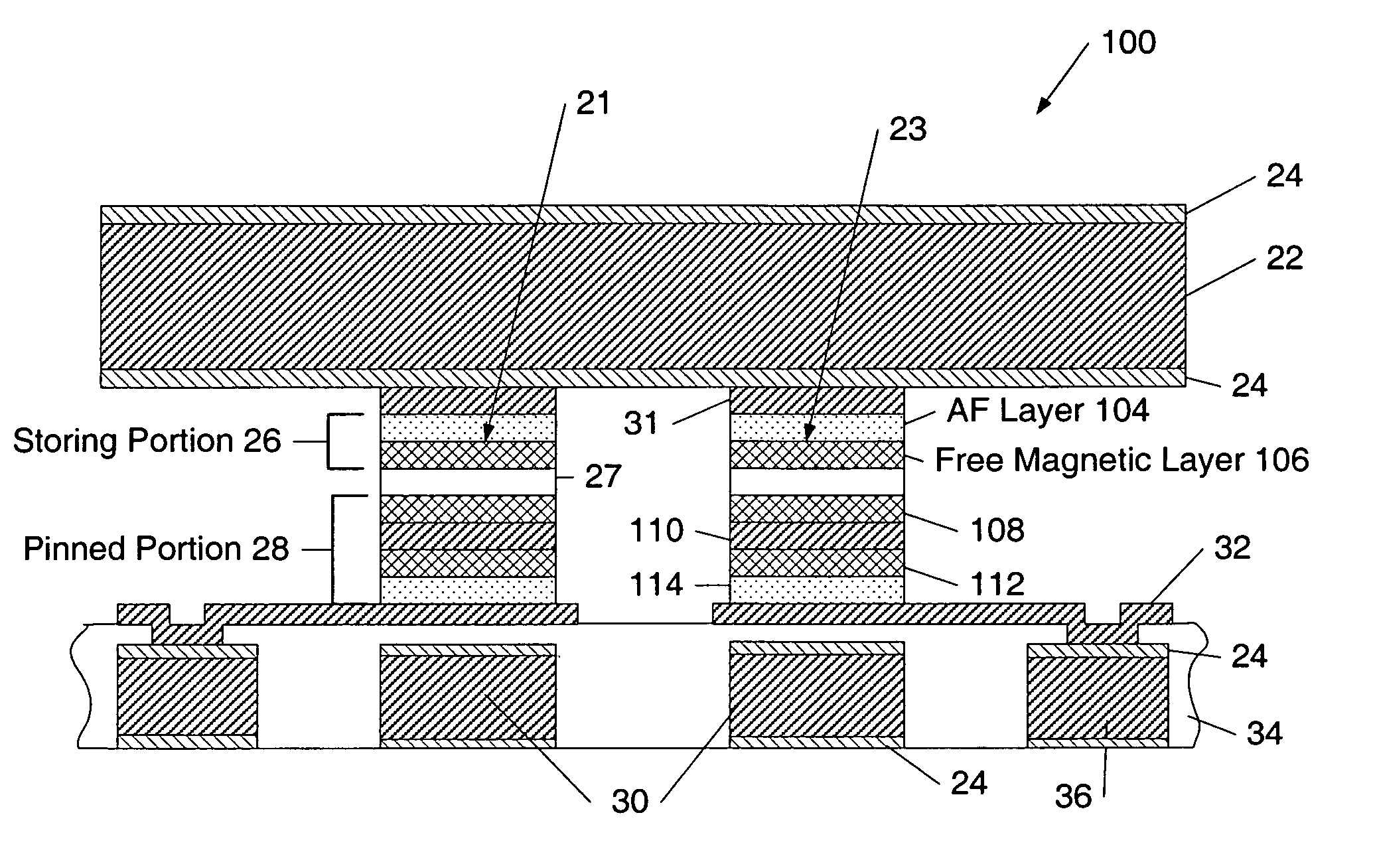

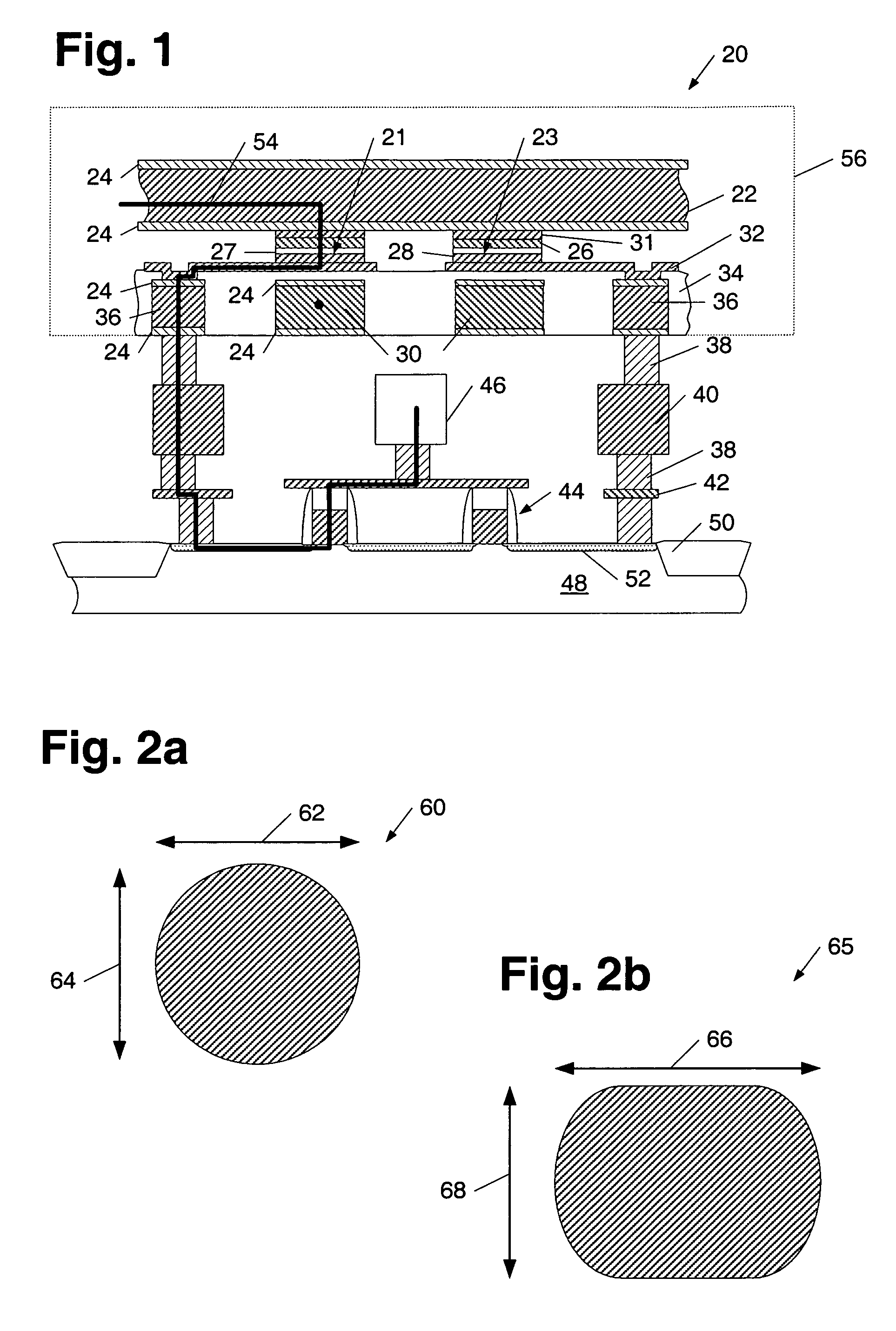

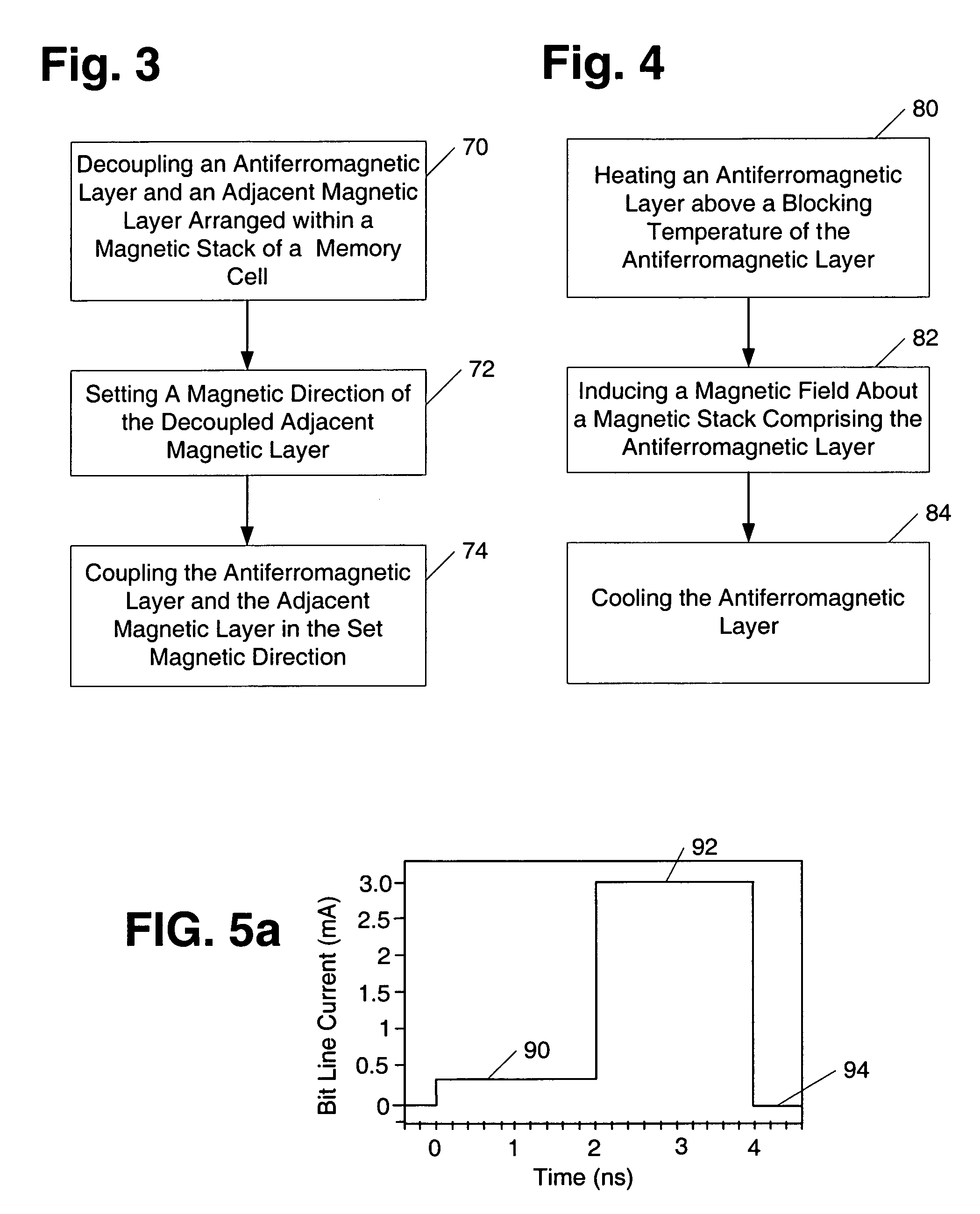

High density MRAM using thermal writing

ActiveUS6980468B1Reduce surface areaImprove reliability of deviceDigital storageAspect ratioMagnetic layer

A memory cell includes a magnetic cell junction having an antiferromagnetic layer within a portion of the cell junction that is adapted to characterize a logic state of a bit written to the junction. More specifically, a memory cell includes, an antiferromagnetic layer arranged in contact with an adjacent magnetic layer within a storing portion of a magnetic cell junction. Such a magnetic cell junction configuration and a method for programming a memory cell with such a cell junction configuration may be used to improve the write selectivity of a memory cell array and reduce the amount of current needed to write a bit to a memory cell. Moreover, a memory cell includes a magnetic cell junction having an aspect ratio less than 1.6. In addition, a memory cell includes at least two resistors.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES +1

Spin hall effect magnetic apparatus, method and applications

ActiveUS20150348606A1Improve efficiencySmall costRead-only memoriesDigital storageElectrical conductorSpin Hall effect

Owner:CORNELL UNIVERSITY

Method and system for optimizing reliability and performance of programming data in non-volatile memory devices

ActiveUS7437498B2Improve reliabilityExtended service lifeRead-only memoriesDigital storageParallel computingNon-volatile memory

Methods of managing memory devices, and devices so managed. A value of a parameter, that is used to program one or more memory cells, is adapted to a monitored condition of the cell(s). Either the number of bits per cell is held fixed or the monitored condition is an intrinsic condition of the cell(s). The initial value of the parameter is optimized for those specific cells, relative to a pre-selected criterion, by programming the cell(s) in accordance with candidate values of the parameter.

Owner:WESTERN DIGITAL ISRAEL LTD

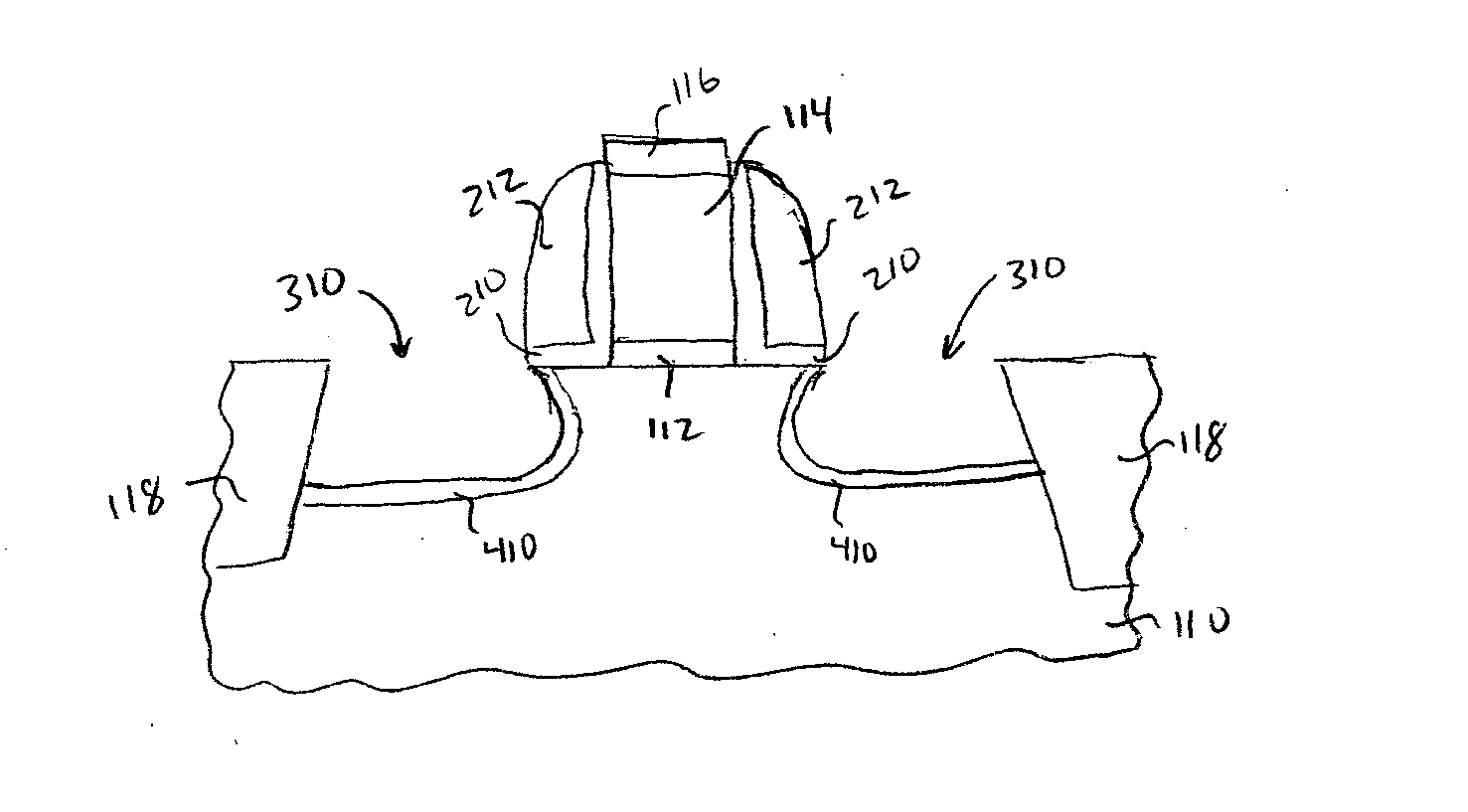

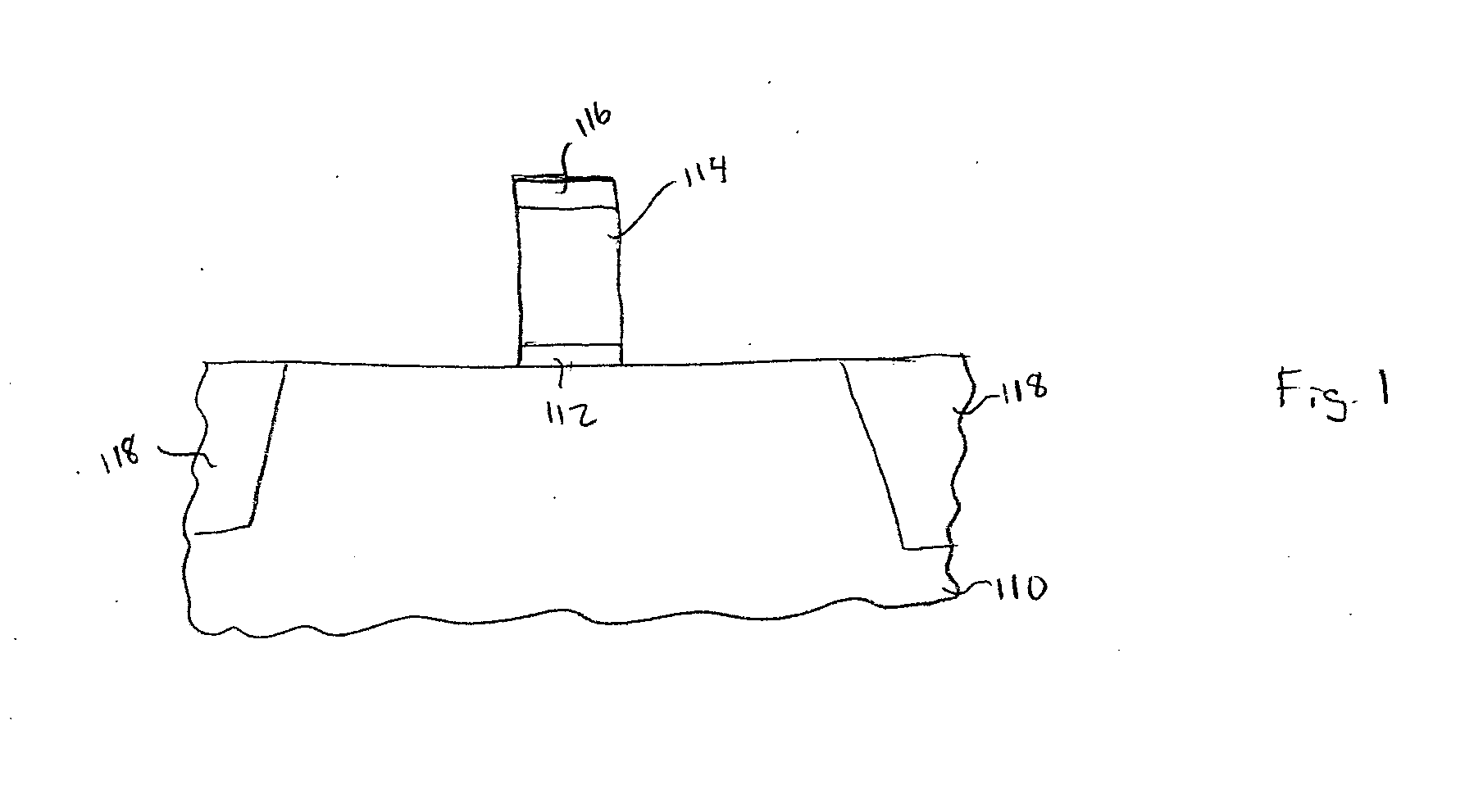

Interconnects for semiconductor light emitting devices

ActiveUS7348212B2Thermal and electrical resistanceImprove equipment reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingLight emitting deviceSemiconductor

A semiconductor light emitting device including a light emitting layer disposed between an n-type region and a p-type region and contacts electrically connected to the n-type region and the p-type region is connected to a mount. A metal layer arbitrarily patterned to cover at least 20% of the area of the semiconductor light emitting device is plated on either a metal layer formed on the mount or a metal layer formed on one of the contacts. The plated metal layer may replace other known interconnecting techniques such as stud bumps. The semiconductor light emitting device is physically connected to the mount by causing interdiffusion between the contact surfaces of the metal layers. In some embodiments, a layer of solder is formed over the plated metal layer, and then the semiconductor light emitting device is physically connected to the mount by heating the solder.

Owner:LUMILEDS

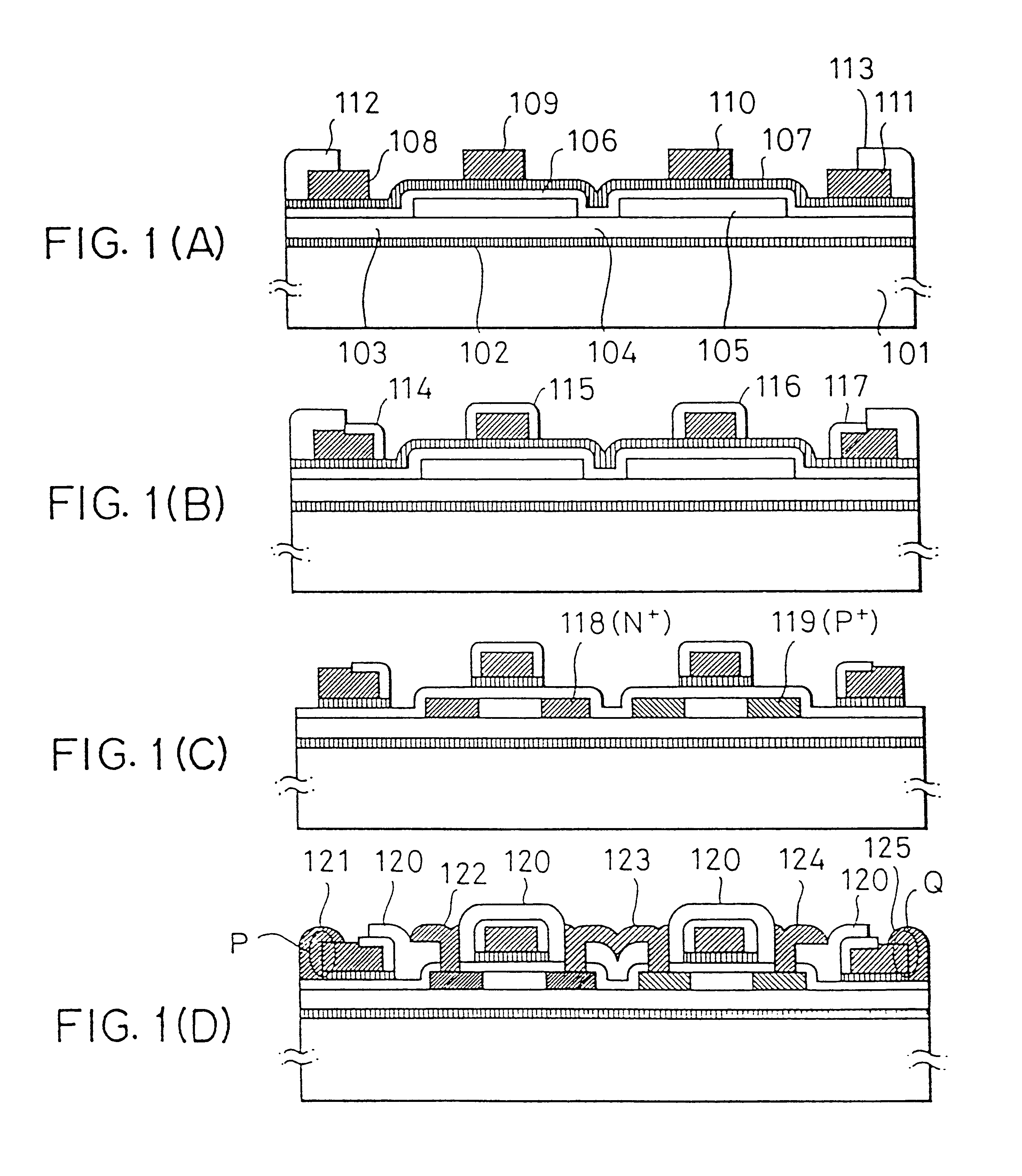

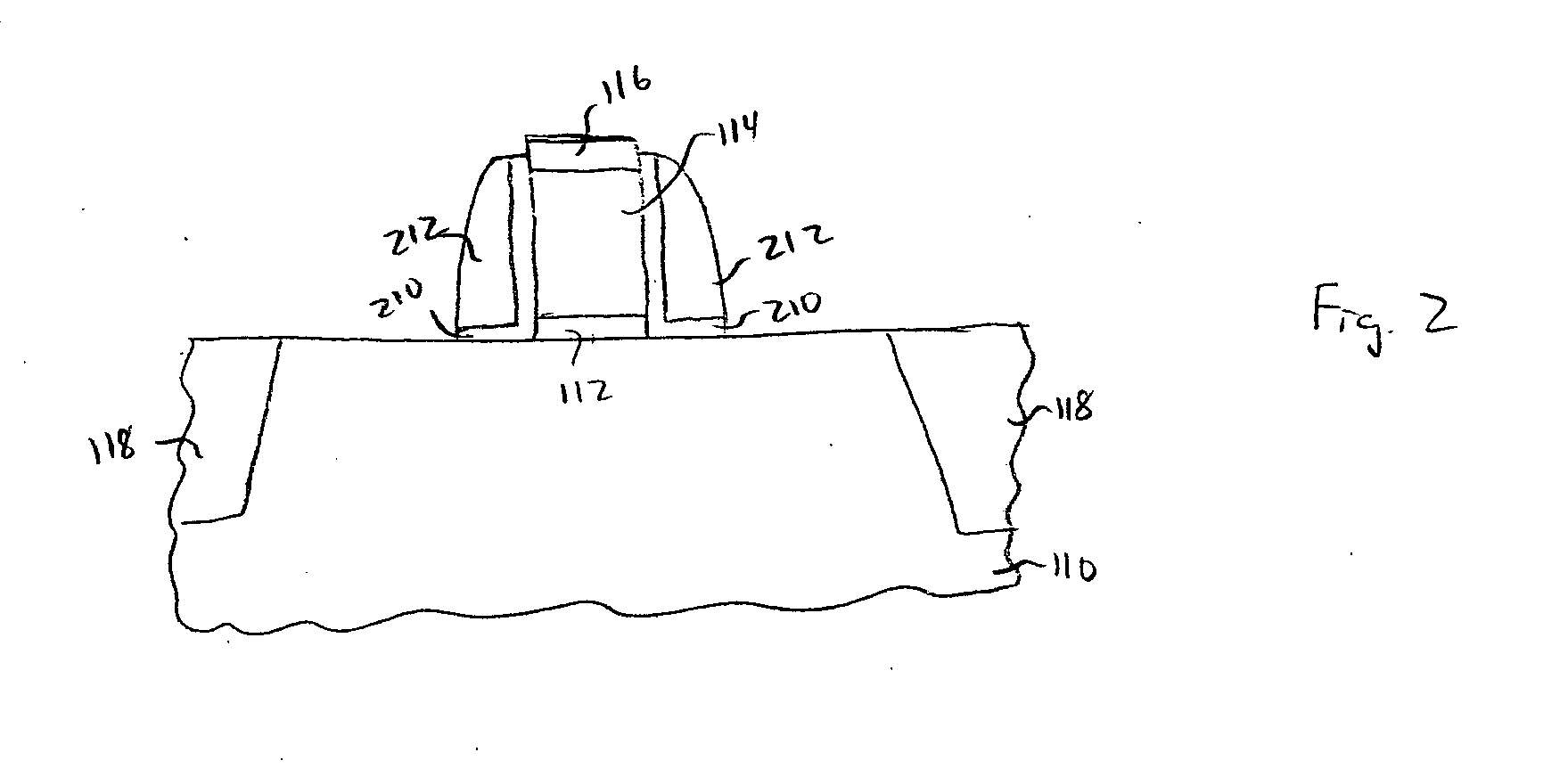

Semiconductor device and method for forming the same

InactiveUS6624450B1Improve flatnessImprove equipment reliabilityTransistorSolid-state devicesEtchingMetallic materials

In a thin-film insulated gate type field effect transistor having a metal gate in which the surface of the gate electrode is subjected to anodic oxidation, a silicon nitride film is provided so as to be interposed between the gate electrode and the gate insulating film to prevent invasion of movable ions into a channel, and also to prevent the breakdown of the gate insulating film due to a potential difference between the gate electrode and the channel region. By coating a specific portion of the gate electrode with metal material such as chrome or the like for the anodic oxidation, and then removing only the metal material such as chrome or the like together with the anodic oxide of the metal material such as chrome or the like, an exposed portion of metal gate (e.g. aluminum) is formed, and an upper wiring is connected to the exposed portion. Further, an aluminum oxide or silicon nitride is formed as an etching stopper between the gate electrode and the gate insulating film or between the substrate and the layer on the substrate, so that the over-etching can be prevented and the flatness of the element can be improved. In addition, a contact is formed in no consideration of the concept "contact hole".

Owner:SEMICON ENERGY LAB CO LTD

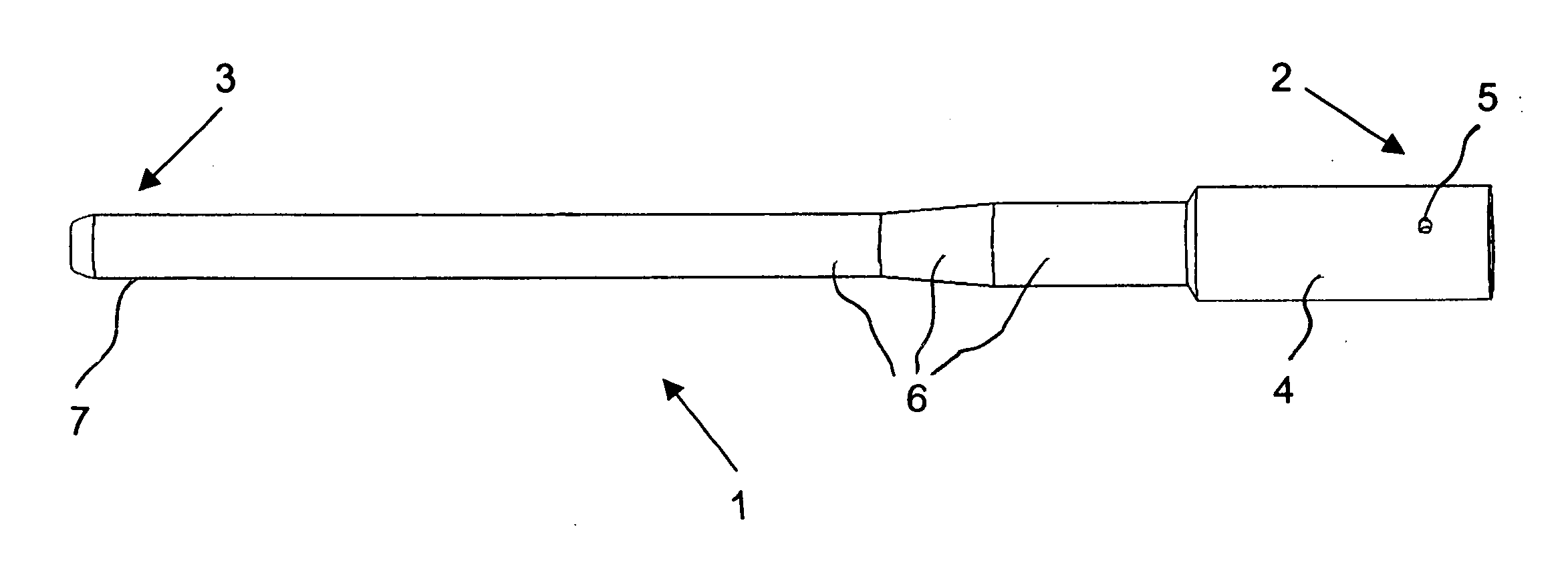

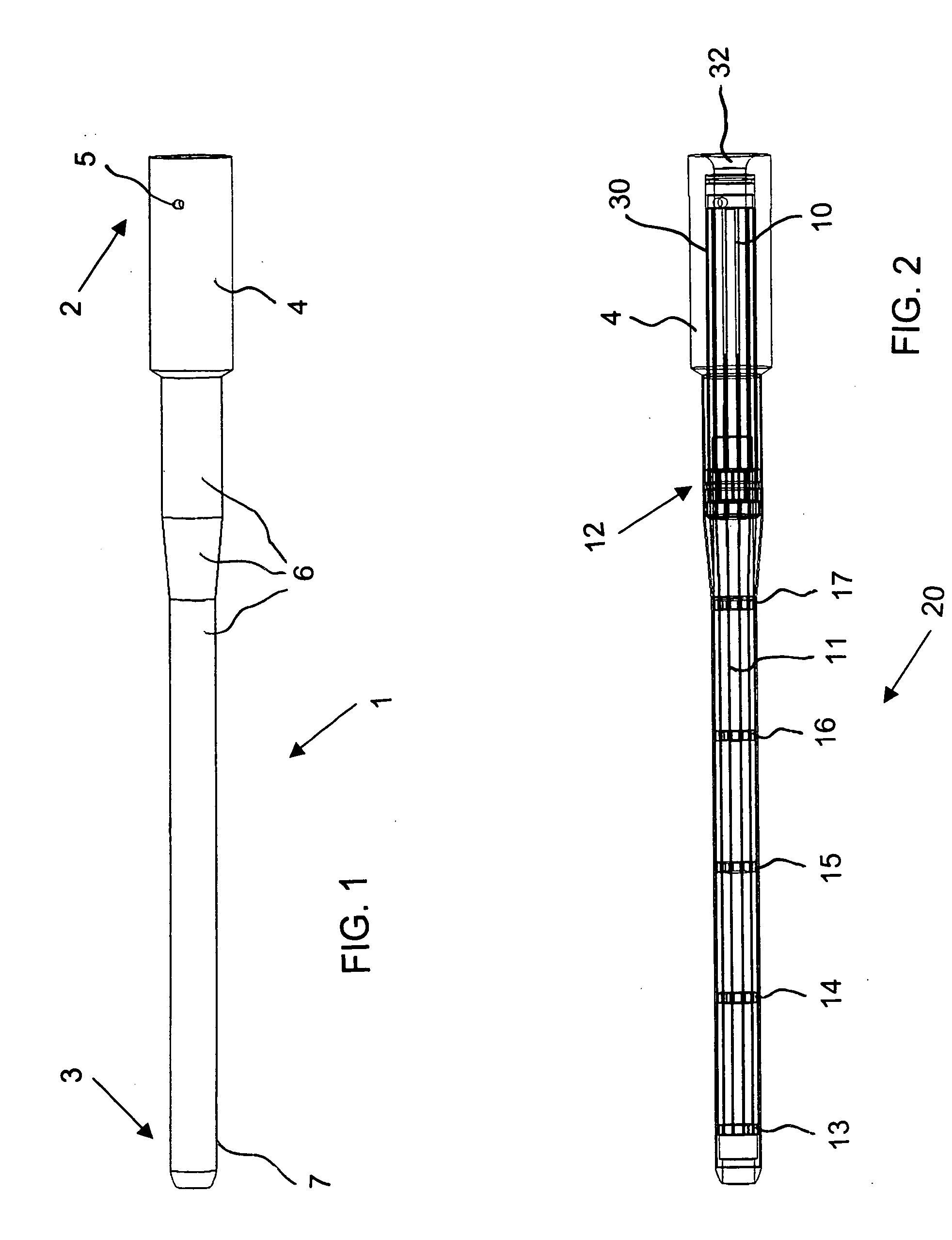

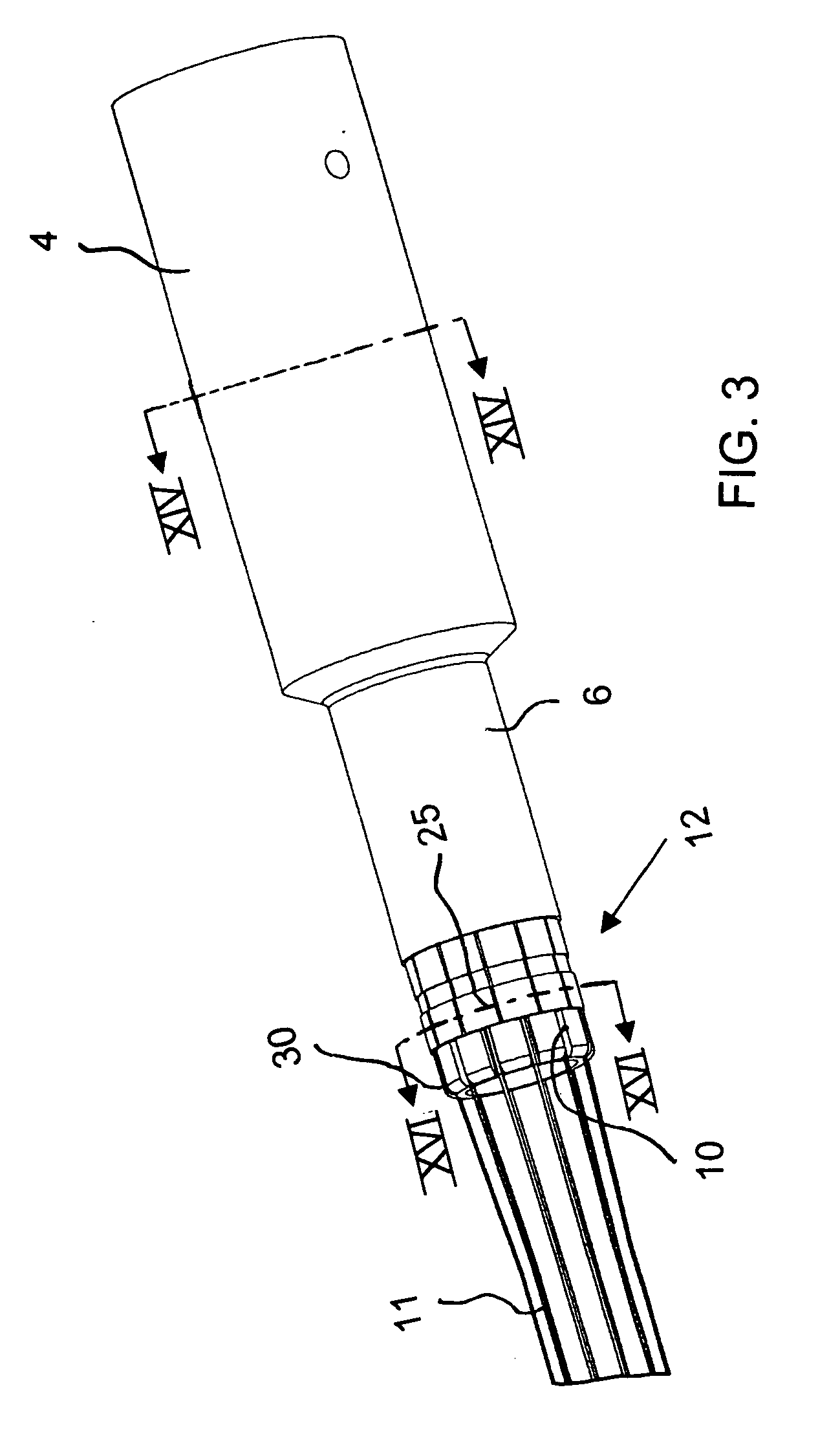

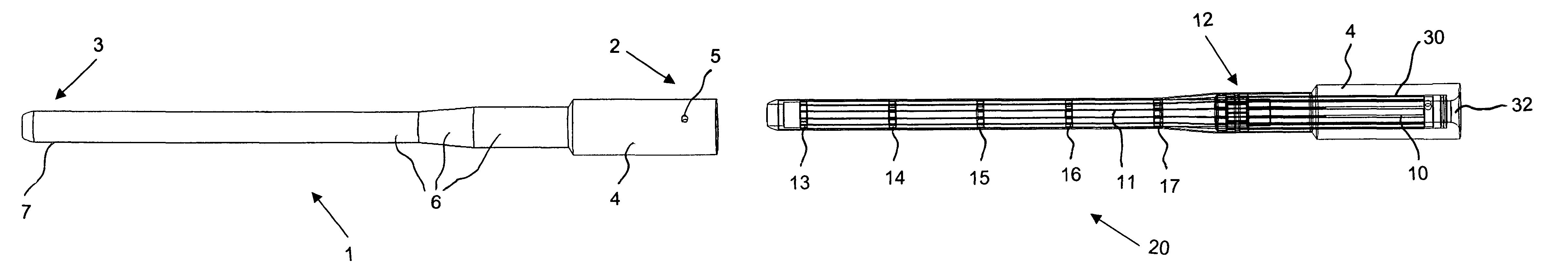

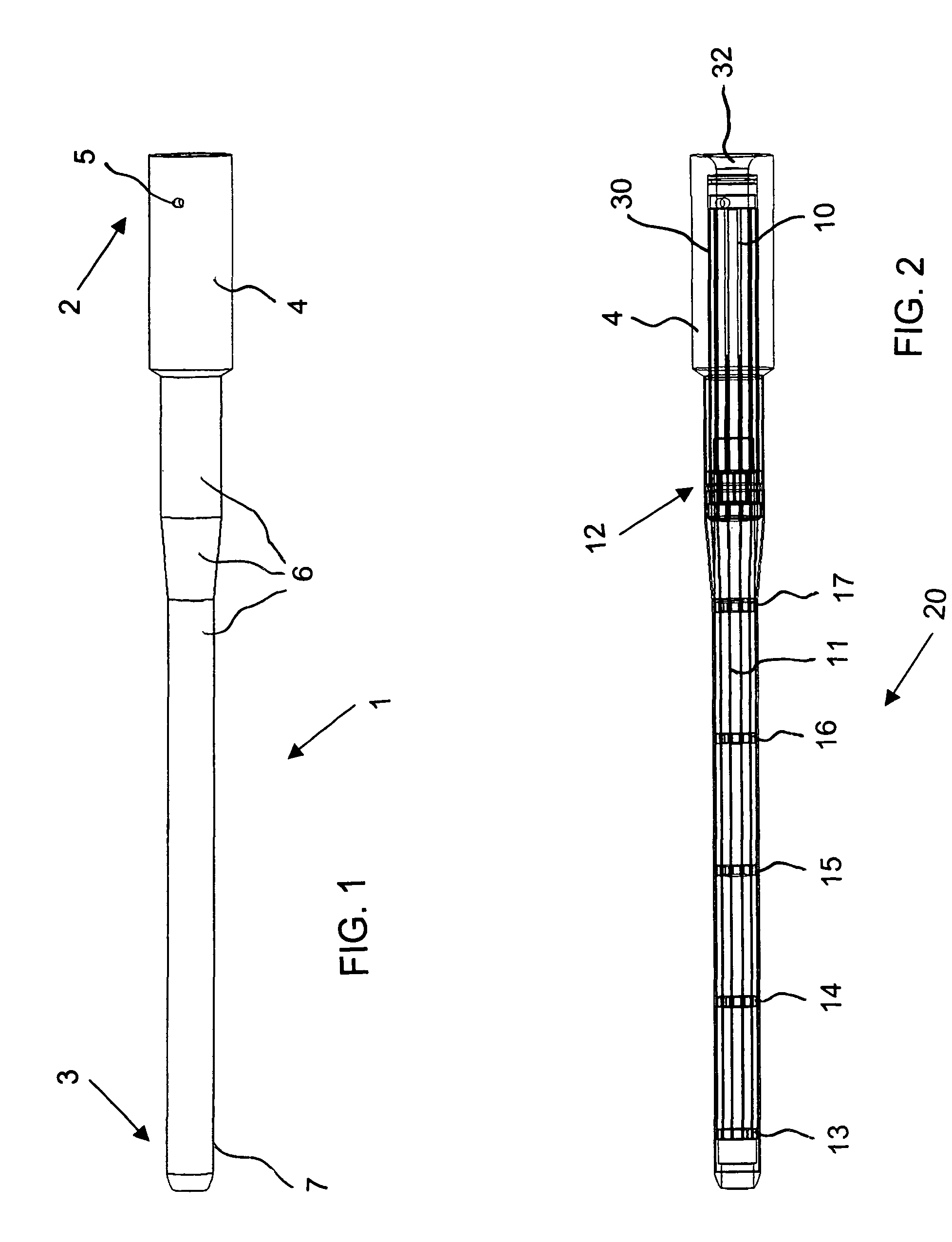

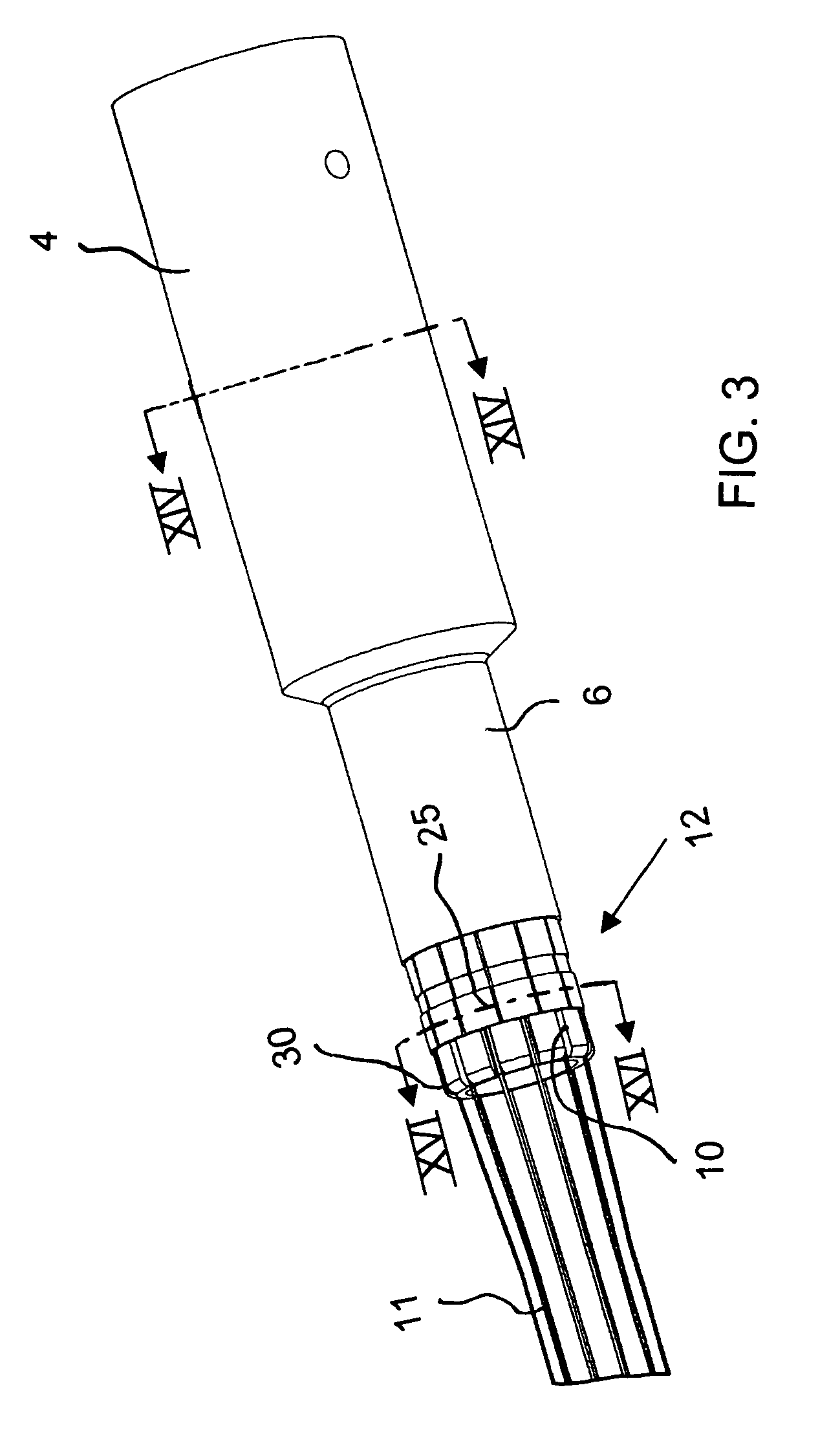

Variably flexible insertion device and method for variably flexing an insertion device

InactiveUS20070208364A1Enhance reliabilityImprove equipment reliabilitySurgeryDilatorsEngineeringInsertion device

A variably flexible insertion device includes a hollow body having a proximal end with an entrance for receiving an instrument and a distal end with a tip for protrusion of the instrument. A device transitions the hollow body between a relatively flexible condition and a relatively stiff condition. Tendons within the hollow body maintain the hollow body in the relatively flexible and relatively stiff conditions. A method for variably flexing an insertion device for receiving an instrument, includes providing a hollow body having inner and outer sleeves defining a space therebetween in which tendons are disposed. Suction is applied to create a vacuum in the space for frictionally locking the tendons in place between the sleeves in a relatively stiff condition of the hollow body. The vacuum is relieved to release the tendons in a relatively flexible condition of the hollow body.

Owner:SYNTHEON

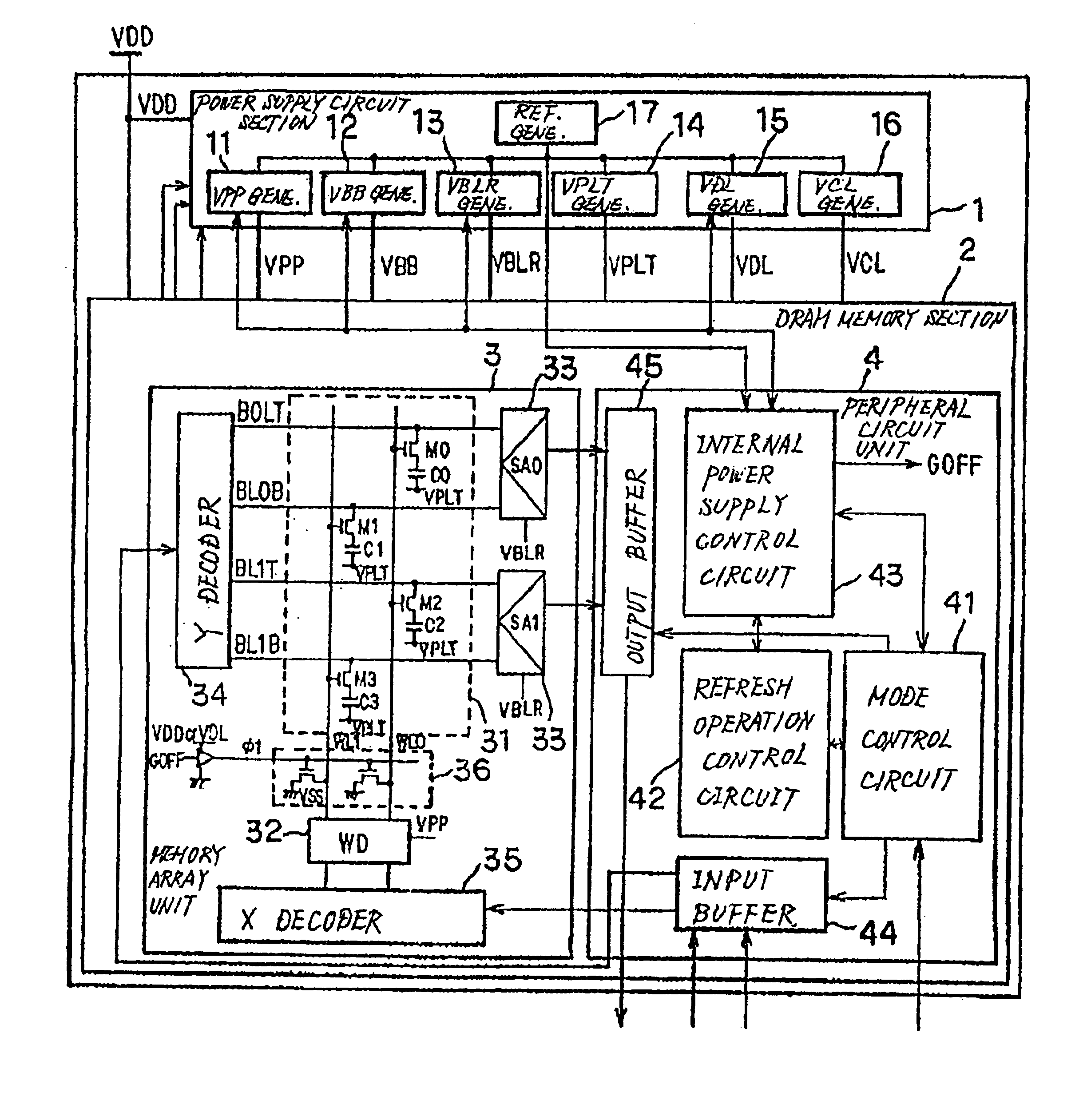

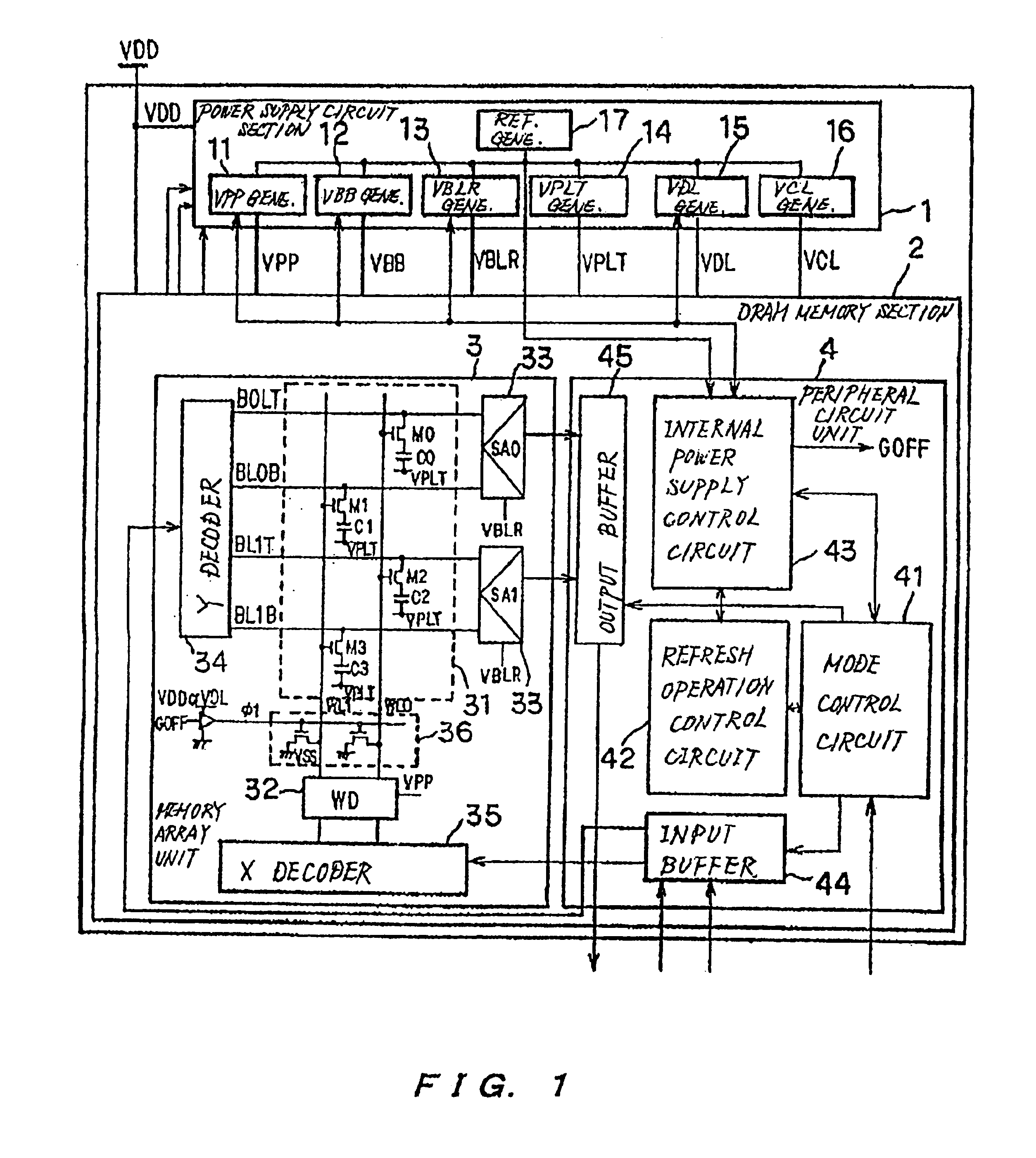

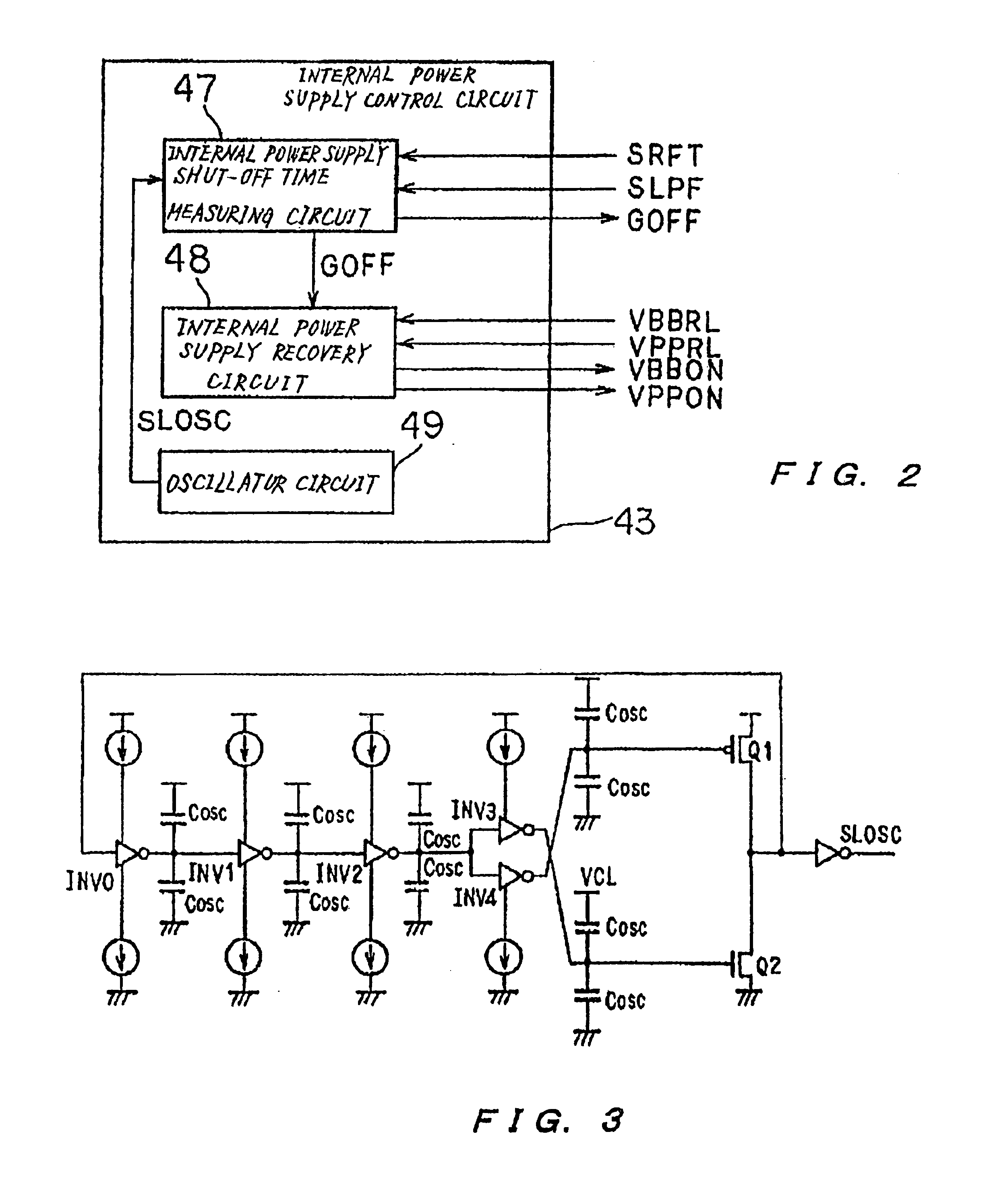

Semiconductor memory device control method and semiconductor memory device

ActiveUS6990031B2Reducing average current consumptionTotal current dropDigital storageBit lineEngineering

In a semiconductor memory device which requires a refresh operation, a control method stops supplying a word line voltage which is a boosted voltage higher than an external supply voltage, a memory array substrate voltage which is a negative voltage supplied to a semiconductor substrate, and a bit line precharge voltage for use in reproducing data held in memory cells for a predetermined period at the end of each refresh operation. In this event, voltage output terminals of the word line and memory array substrate voltages are respectively driven to a ground potential. For recovering these voltages, the delivery of the word line voltage is stopped until the memory array substrate voltage rises to some extent.

Owner:LONGITUDE LICENSING LTD

Method of fabricating algainp light-emitting diode and structure thereof

ActiveUS20050287687A1Increased light output intensityReduce reflectionSolid-state devicesSemiconductor/solid-state device manufacturingReflective layerLight-emitting diode

A soft transparent adhesive layer is utilized to bond a transparent substrate material onto an AlGaInP light-emitting diode epitaxy on a GaAs substrate, and the GaAs substrate is next removed entirely. Then, a mesa etching process is performed to form a first top surface and a second top surface on the AlGaInP light-emitting diode epitaxy for respectively exposing an n-type layer and a p-type layer in the AlGaInP light-emitting diode epitaxy. Next, a metal reflective layer and a barrier layer are formed on the AlGaInP light-emitting diode epitaxy in turn, and electrodes are finally fabricated on the barrier layer.

Owner:EPISTAR CORP

Diffusion layer for semiconductor devices

ActiveUS20070190731A1Improve equipment reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor alloysAlloy

A diffusion layer for semiconductor devices is provided. In accordance with embodiments of the present invention, a semiconductor device, such as a transistor, comprises doped regions surrounded by a diffusion barrier. The diffusion barrier may be formed by recessing regions of the substrate and implanting fluorine or carbon ions. A silicon layer may be epitaxially grown over the diffusion barrier in the recessed regions. Thereafter, the recessed regions may be filled and doped with a semiconductor or semiconductor alloy material. In an embodiment, a semiconductor alloy material, such as silicon carbon, is selected to induce a tensile stress in the channel region for an NMOS device, and a semiconductor alloy material, such as silicon germanium, is selected to induce a compressive stress in the channel region for a PMOS device.

Owner:TAIWAN SEMICON MFG CO LTD

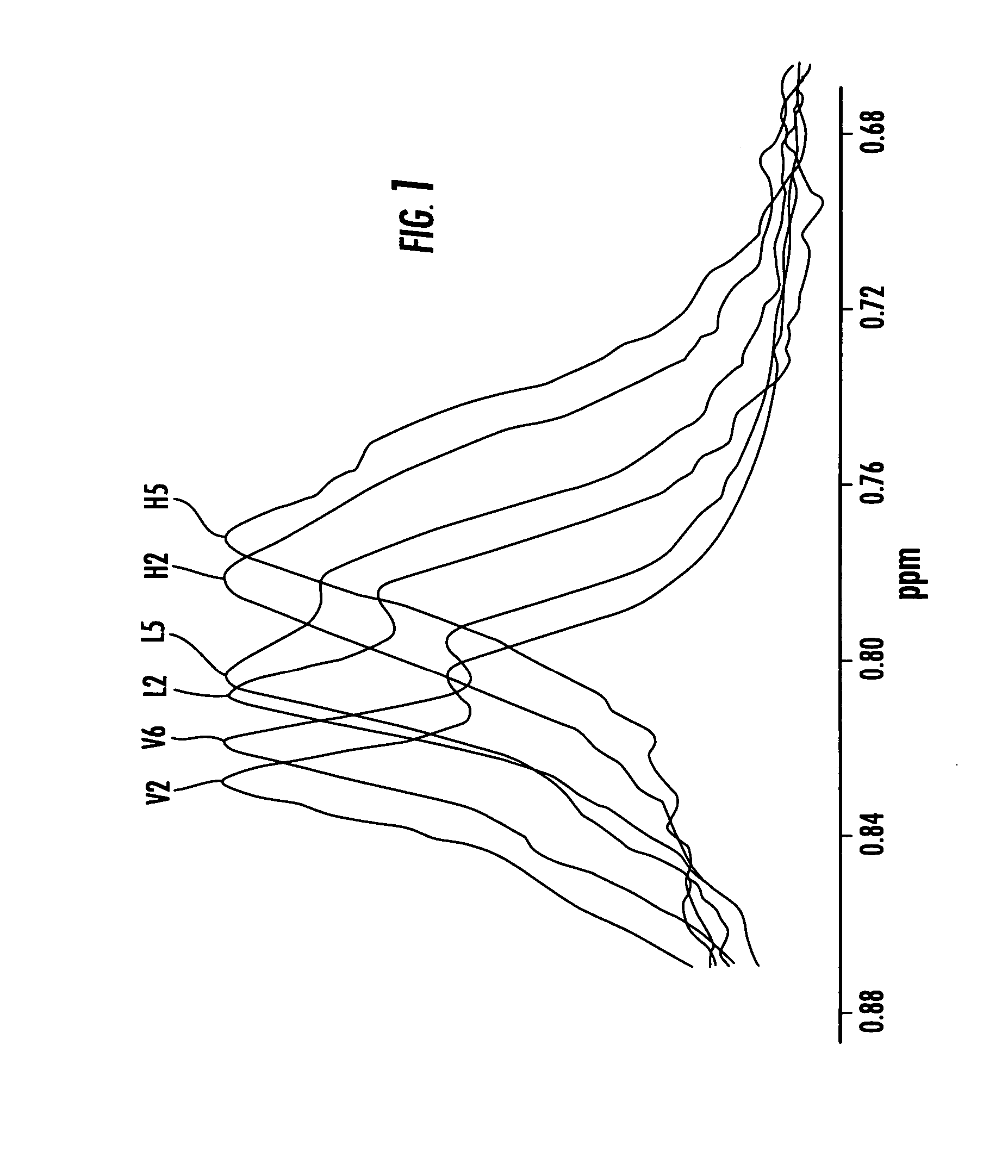

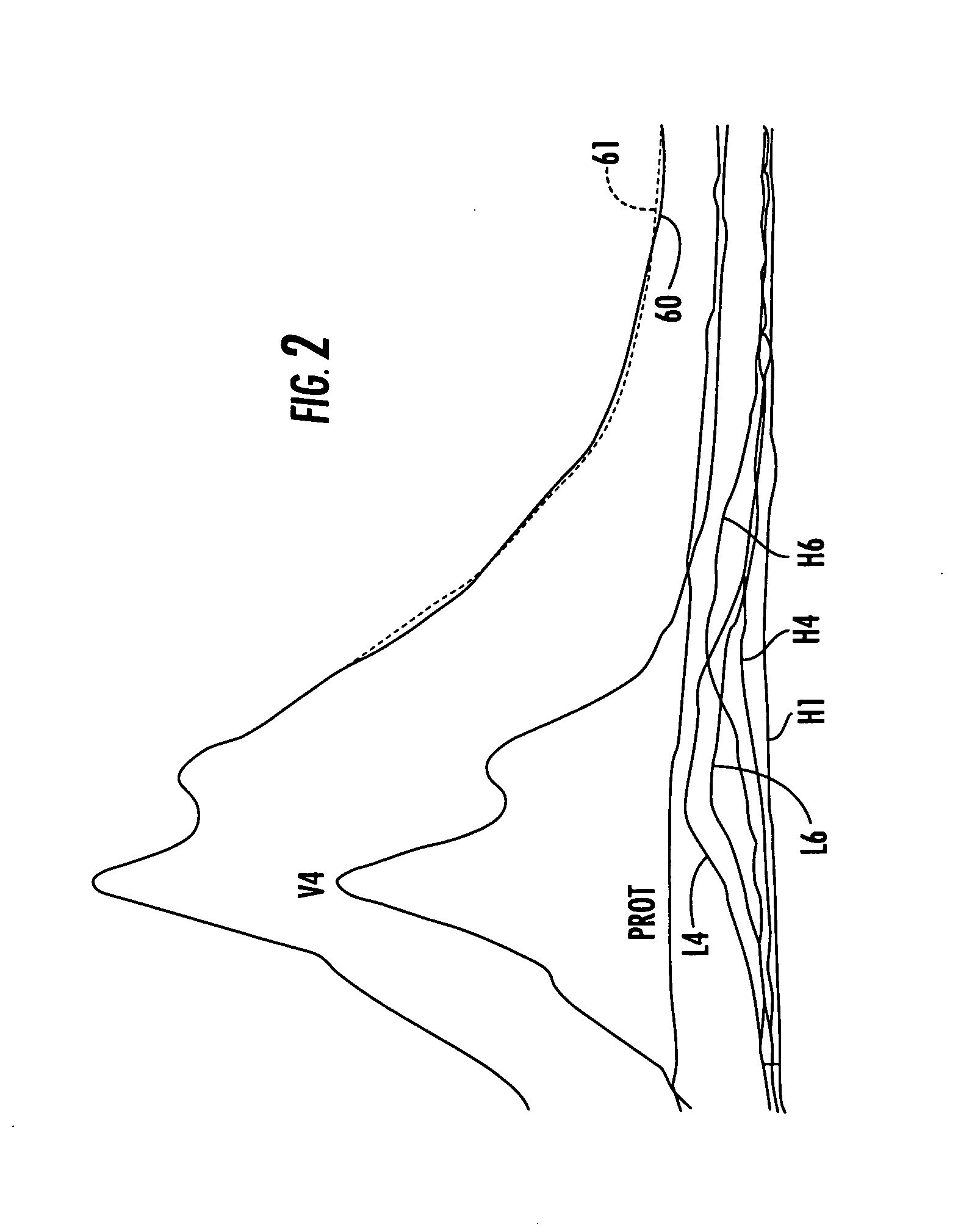

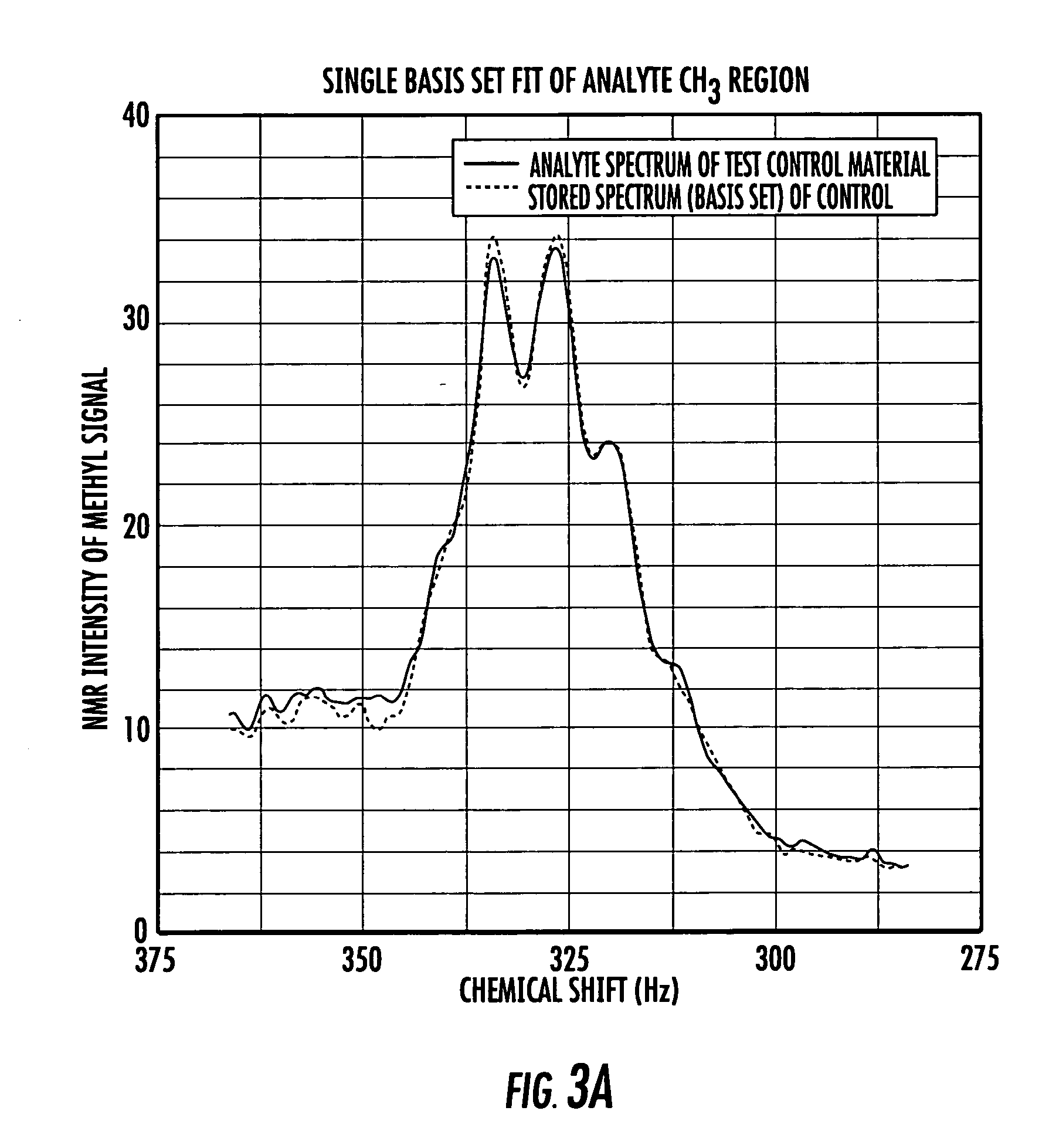

NMR clinical analyzers and related methods, systems, modules and computer program products for clinical evaluation of biosamples

ActiveUS20050222504A1Improve reliabilityAvoid downtimeMagnetic measurementsDiagnostic recording/measuringRemote systemRemote control

Methods, computer program products and apparatus automate clinical NMR in vitro diagnostic analyzers. The clinical analyzer can automatically electronically monitor selected parameters and automatically electronically adjust parameters to maintain the analyzer within desired operational ranges. The clinical NMR analyzers can be configured as a networked system with a plurality of clinical NMR analyzers located at different use sites; and at least one remote control system in communication with one or a plurality of clinical NMR analyzers, the at least one remote system configured to monitor selected local operating parameters associated with a respective clinical NMR analyzer.

Owner:LIPOSCI

Variably flexible insertion device and method for variably flexing an insertion device

A variably flexible insertion device includes a hollow body having a proximal end with an entrance for receiving an instrument and a distal end with a tip for protrusion of the instrument. A device transitions the hollow body between a relatively flexible condition and a relatively stiff condition. Tendons within the hollow body maintain the hollow body in the relatively flexible and relatively stiff conditions. A method for variably flexing an insertion device for receiving an instrument, includes providing a hollow body having inner and outer sleeves defining a space therebetween in which tendons are disposed. Suction is applied to create a vacuum in the space for frictionally locking the tendons in place between the sleeves in a relatively stiff condition of the hollow body. The vacuum is relieved to release the tendons in a relatively flexible condition of the hollow body.

Owner:SYNTHEON

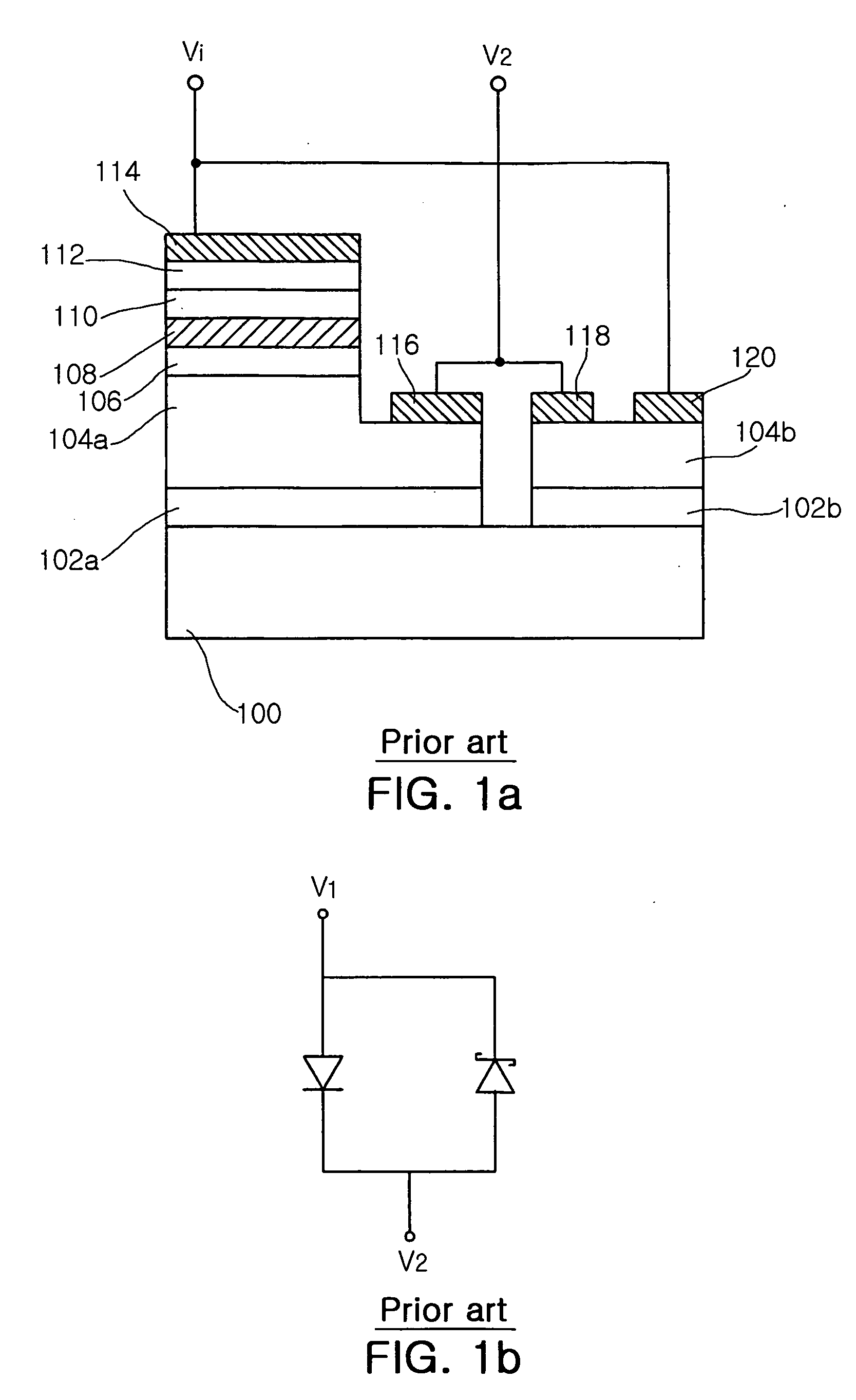

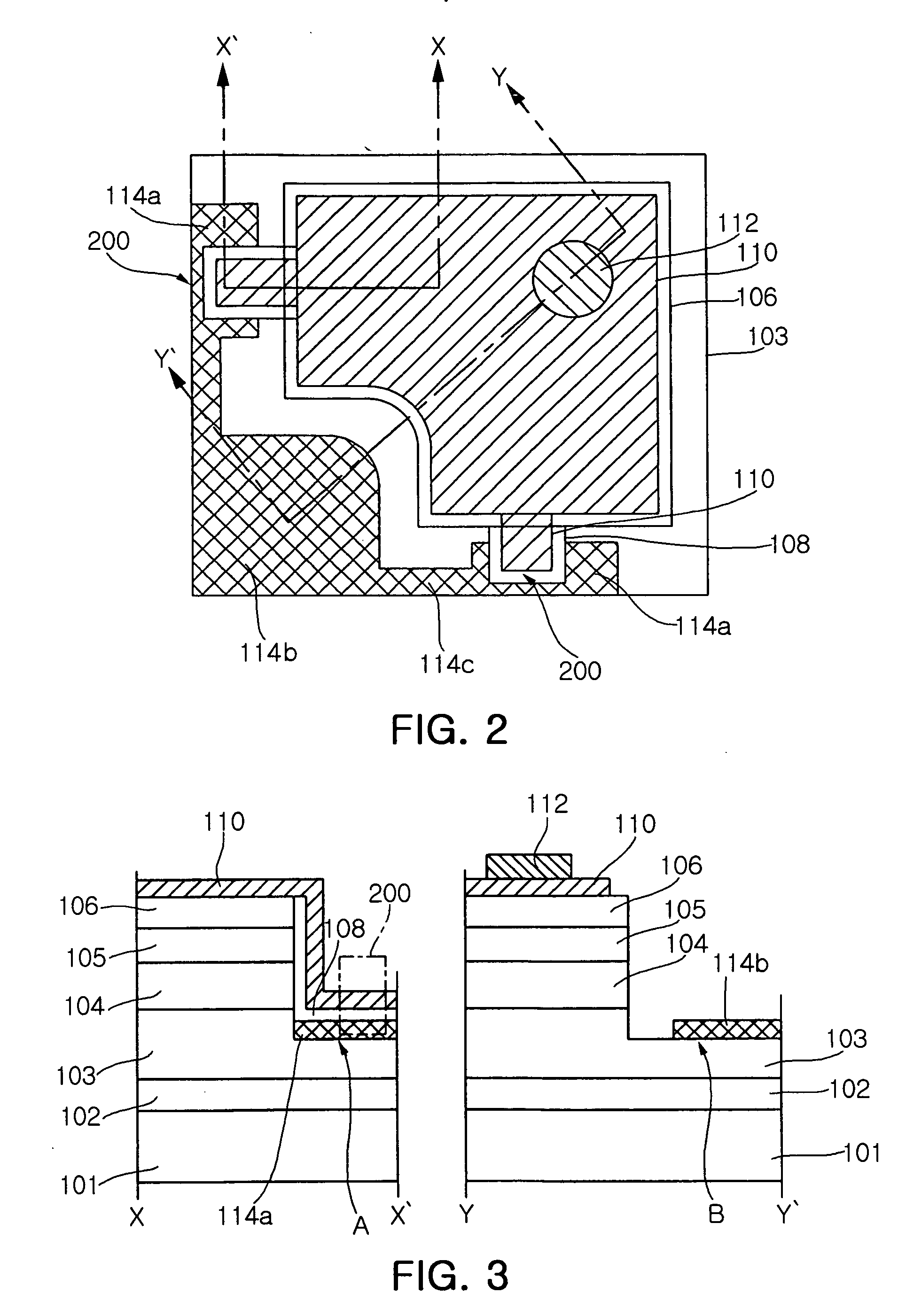

Gallium nitride-based light emitting device having ESD protection capacity and method for manufacturing the same

InactiveUS20060157718A1Improve toleranceImprove equipment reliabilitySidewalk pavingsSolid-state devicesGallium nitrideActive layer

A gallium nitride-based light emitting device, and a method for manufacturing the same are disclosed. The light emitting device comprises an n-type GaN-based clad layer, an active layer, a p-type GaN-based clad layer and a p-side electrode sequentially stacked on a substrate. The device further comprises an n-side electrode formed on one region of the n-type GaN-based clad layer, and two or more MIM type tunnel junctions formed on the other regions of the n-type GaN-based clad layer. Each of the MIM type tunnel junctions comprises a lower metal layer formed on the GaN-based clad layer so as to contact the n-type GaN-based clad layer, an insulating film formed on the lower metal layer, and an upper metal layer formed on the insulating film. The device is protected from reverse ESD voltage, so that tolerance to reverse ESD voltage can be enhanced, thereby improving reliability of the device.

Owner:SAMSUNG ELECTRONICS CO LTD