Patents

Literature

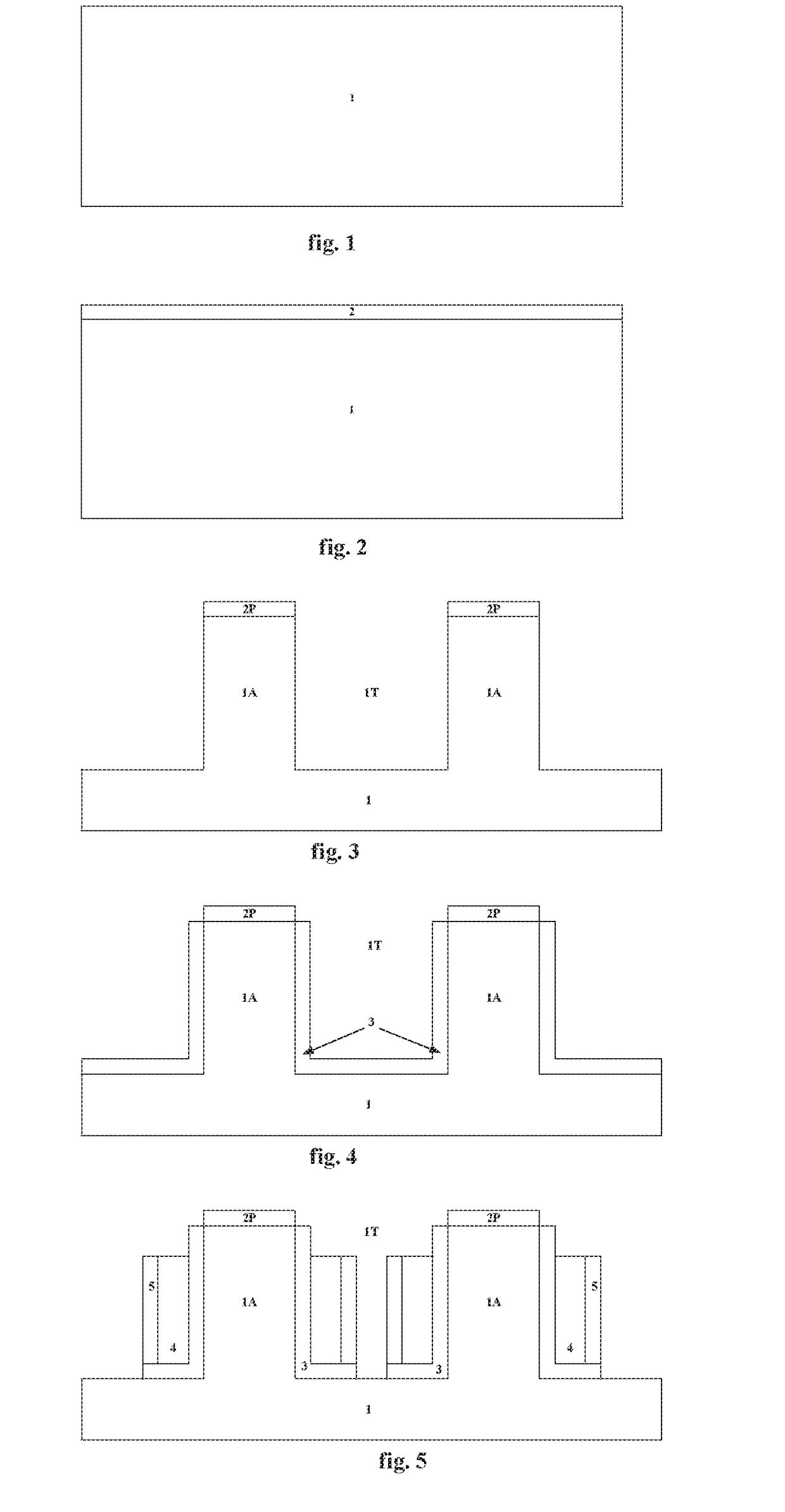

3563 results about "Metal gate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A metal gate, in the context of a lateral metal-oxide-semiconductor (MOS) stack, is just that—the gate material is made from a metal.

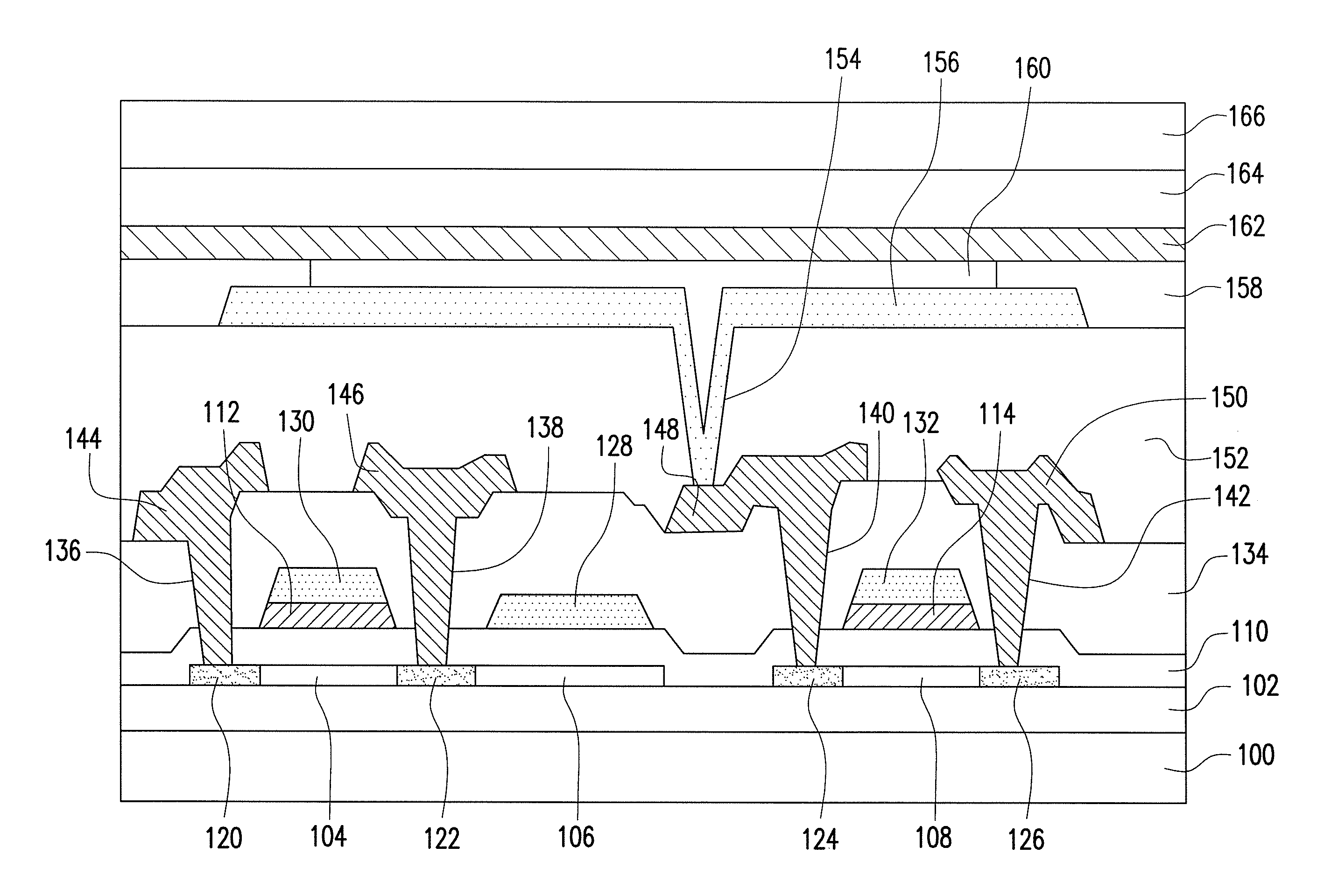

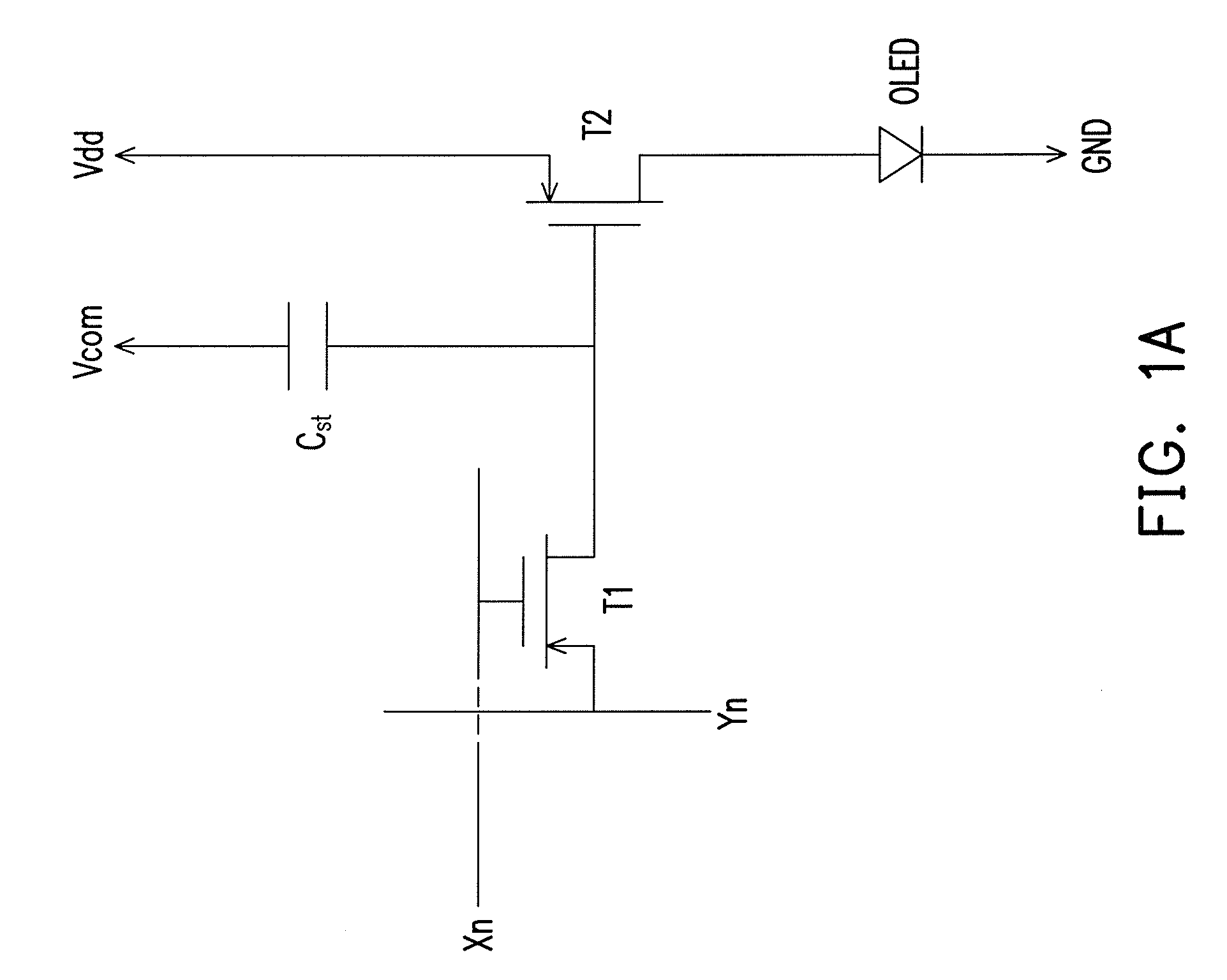

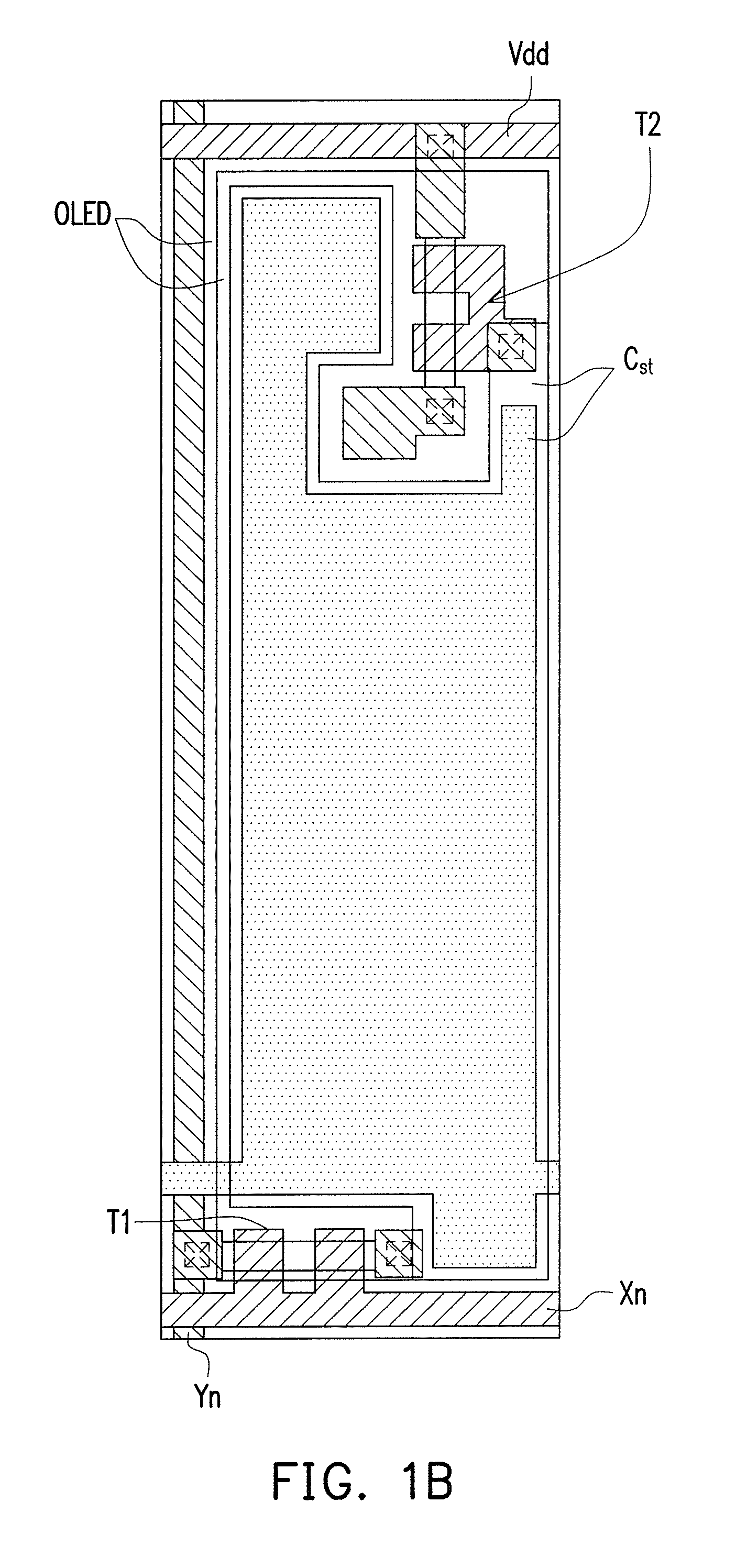

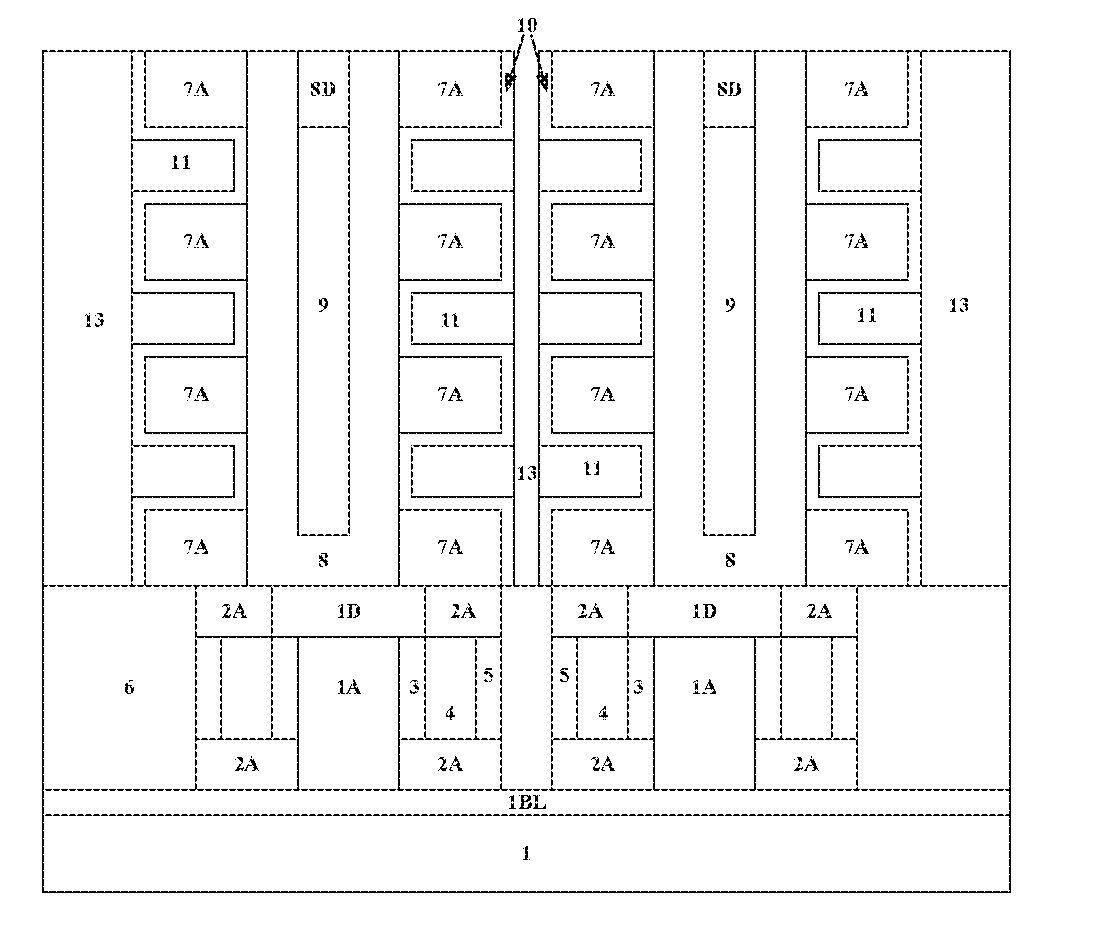

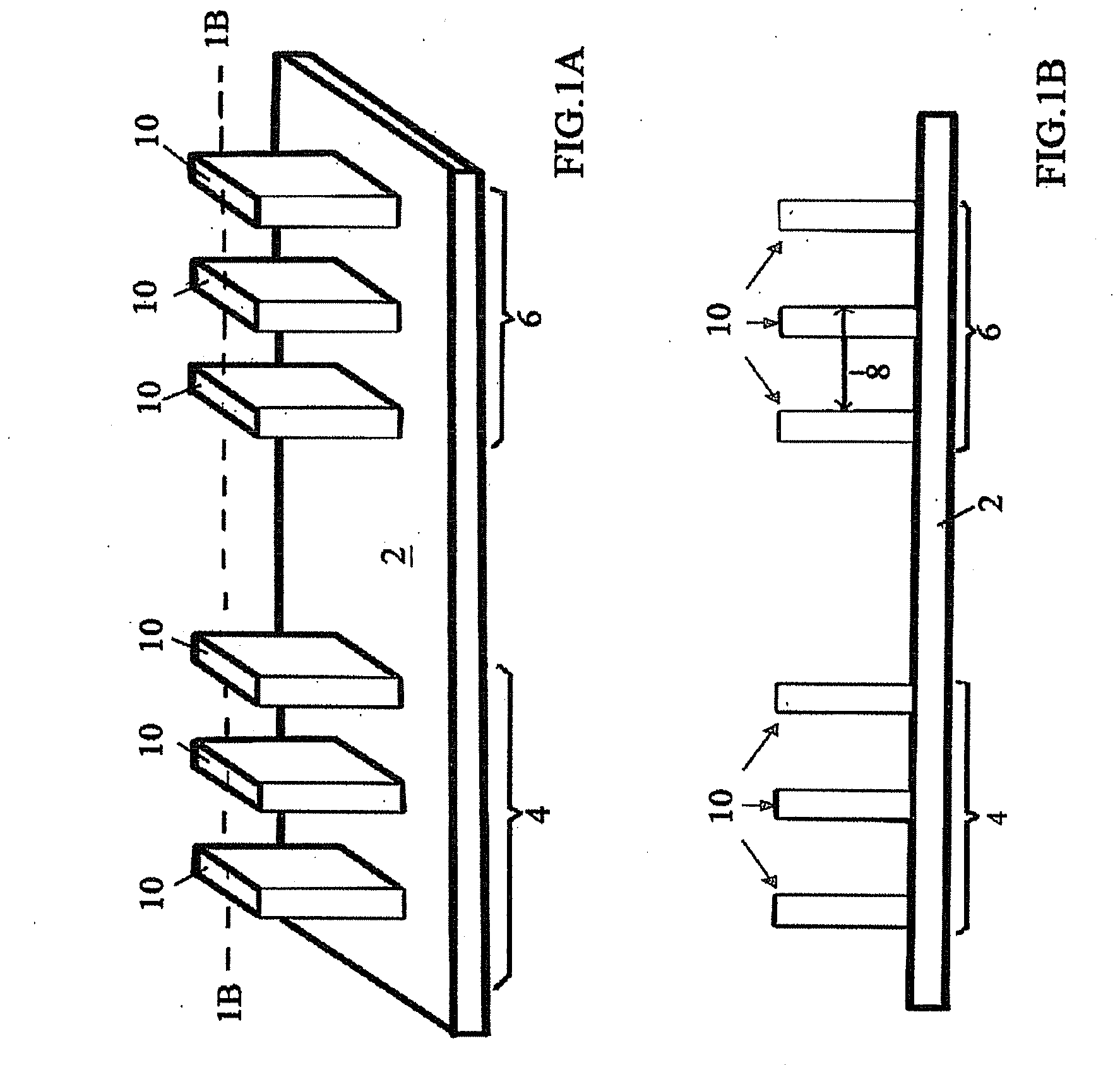

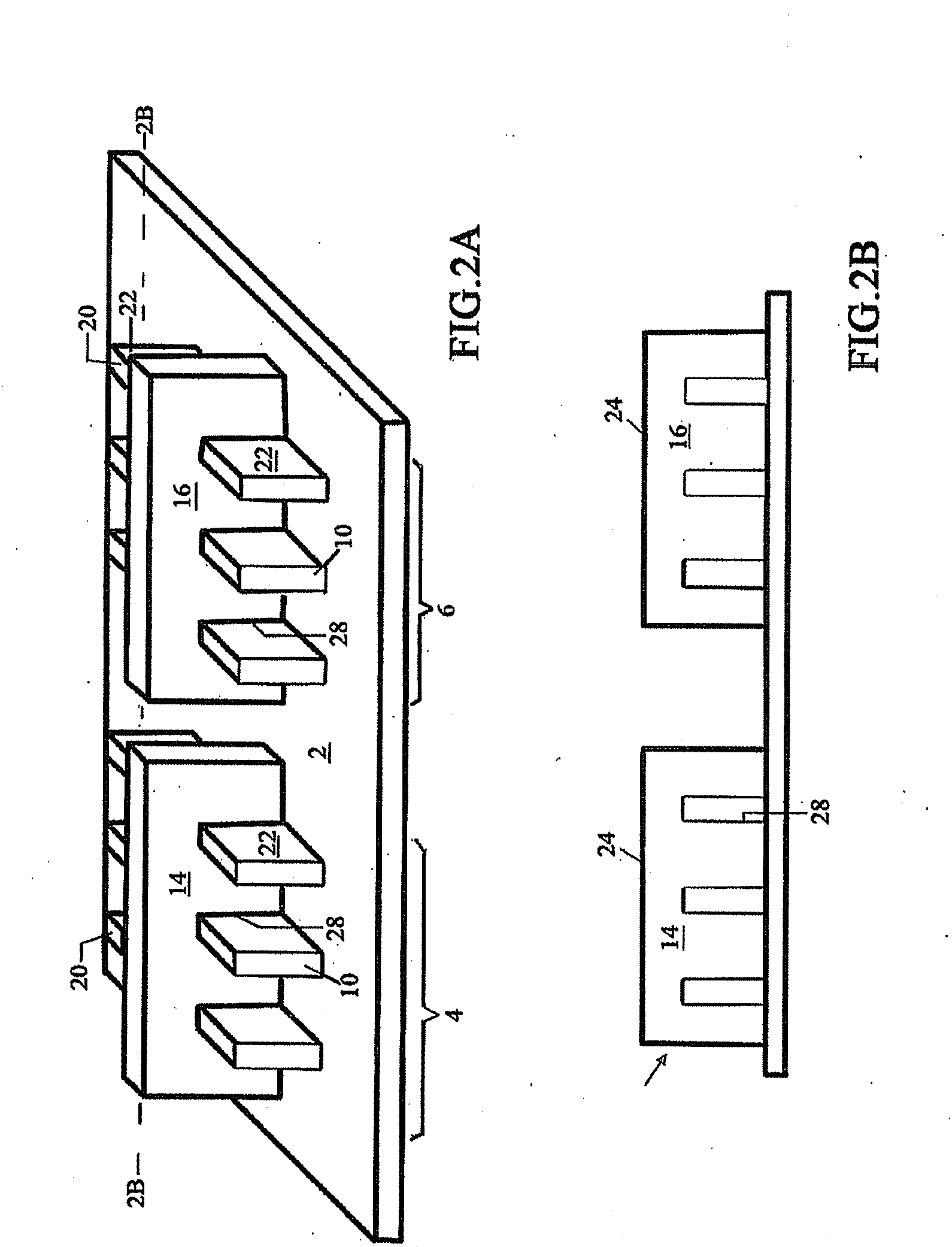

Method for fabricating pixel structure of active matrix organic light-emitting diode

ActiveUS20090068773A1Improve pixel aperture ratioIncrease the aperture ratioSolid-state devicesSemiconductor/solid-state device manufacturingActive matrixScan line

Owner:IND TECH RES INST

Method of depositing barrier layer for metal gates

InactiveUS6858524B2Eliminate the problemEasy to controlSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricRemote plasma

A method of manufacturing a high performance MOS device and transistor gate stacks comprises forming a gate dielectric layer over a semiconductor substrate; forming a barrier layer over the gate dielectric layer by an ALD type process; and forming a gate electrode layer over the barrier layer. The method enables the use of hydrogen plasma, high energy hydrogen radicals and ions, other reactive radicals, reactive oxygen and oxygen containing precursors in the processing steps subsequent to the deposition of the gate dielectric layer of the device. The ALD process for forming the barrier layer is performed essentially in the absence of plasma and reactive hydrogen radials and ions. This invention makes it possible to use oxygen as a precursor in the deposition of the metal gates. The barrier film also allows the use of hydrogen plasma in the form of either direct or remote plasma in the deposition of the gate electrode. Furthermore, the barrier film prevents the electrode material from reacting with the gate dielectric material. The barrier layer is ultra thin and, at the same time, it forms a uniform cover over the entire surface of the gate dielectric.

Owner:ASM INTERNATIONAL

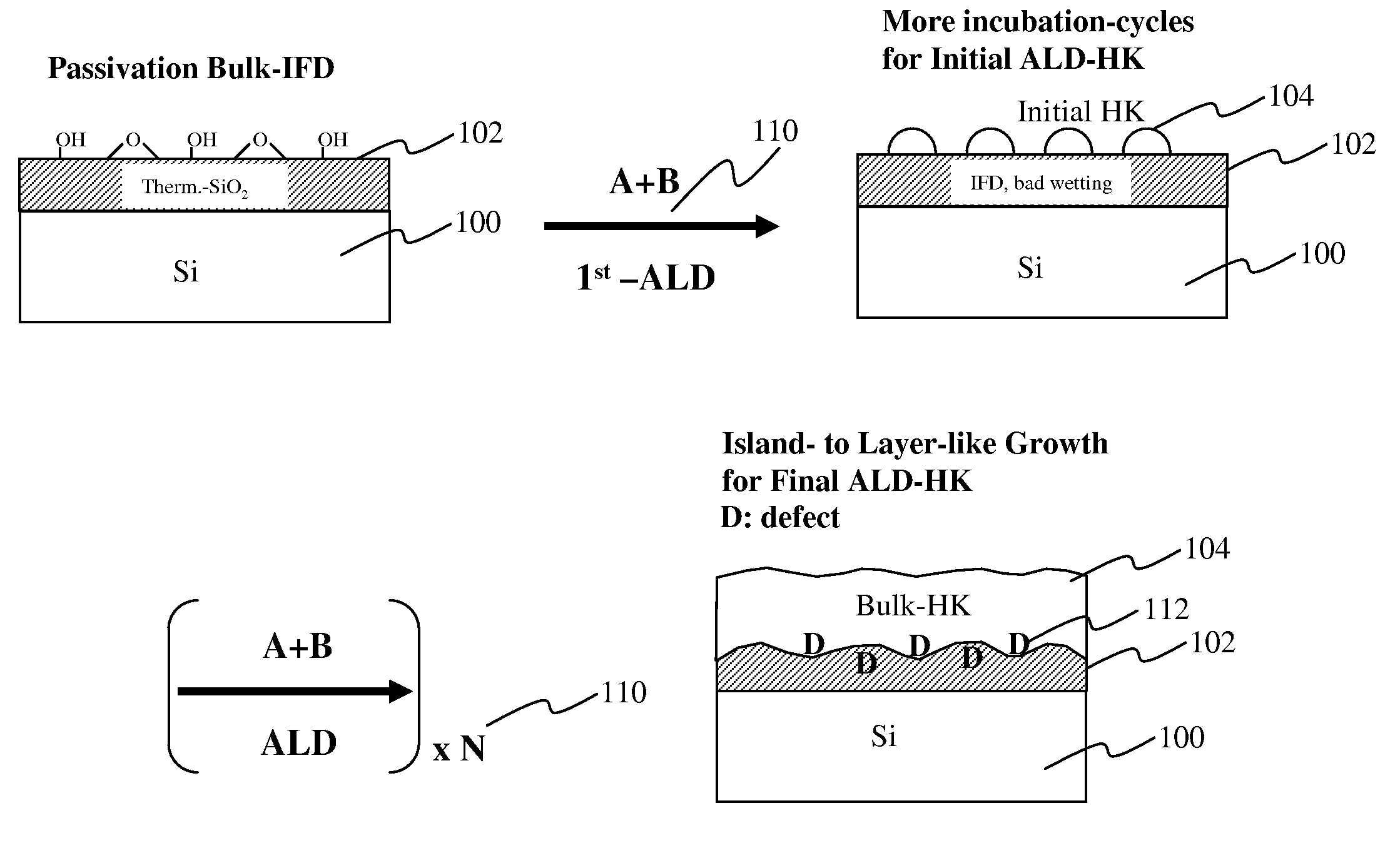

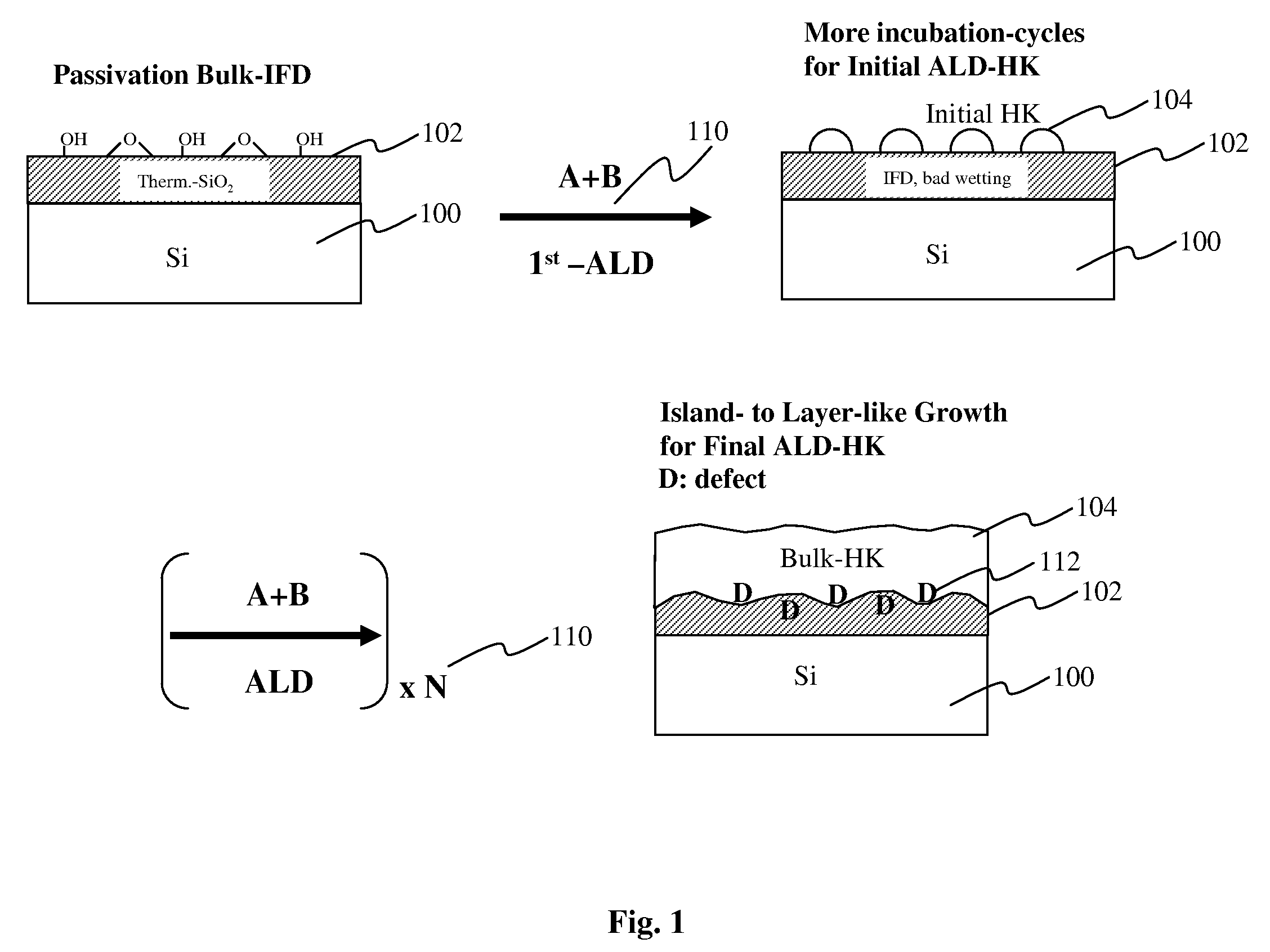

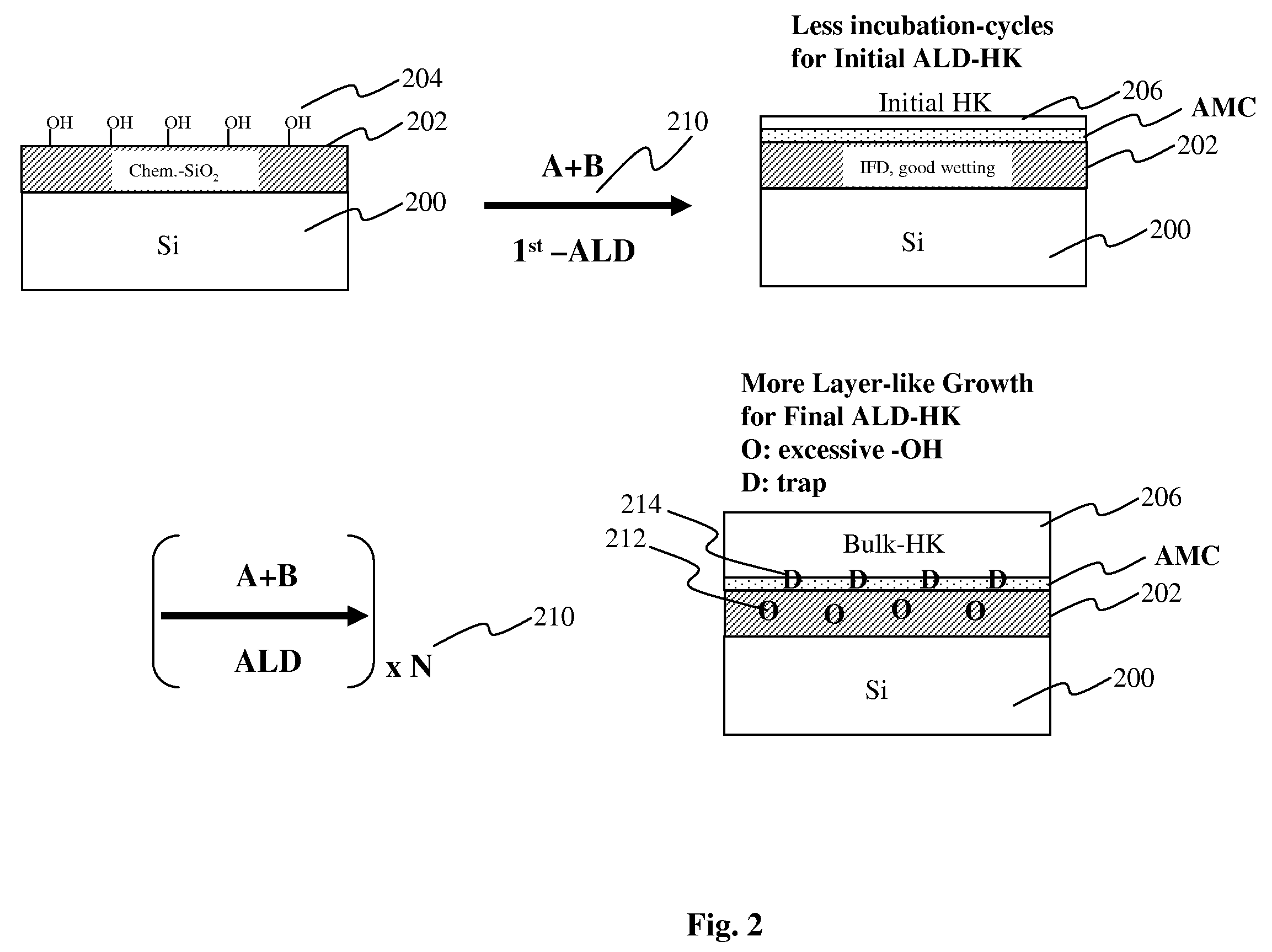

Method of Fabricating a Gate Dielectric for High-K Metal Gate Devices

ActiveUS20100075507A1Facilitate formation of the high-k dielectric layerImprove electrical performanceSemiconductor/solid-state device manufacturingChemical vapor deposition coatingGate dielectricSulfur

The present disclosure provides a method of fabricating a semiconductor device. The method includes providing a substrate, forming an interfacial layer on the substrate by treating the substrate with radicals, and forming a high-k dielectric layer on the interfacial layer. The radicals are selected from the group consisting of hydrous radicals, nitrogen / hydrogen radicals, and sulfur / hydrogen radicals.

Owner:TAIWAN SEMICON MFG CO LTD

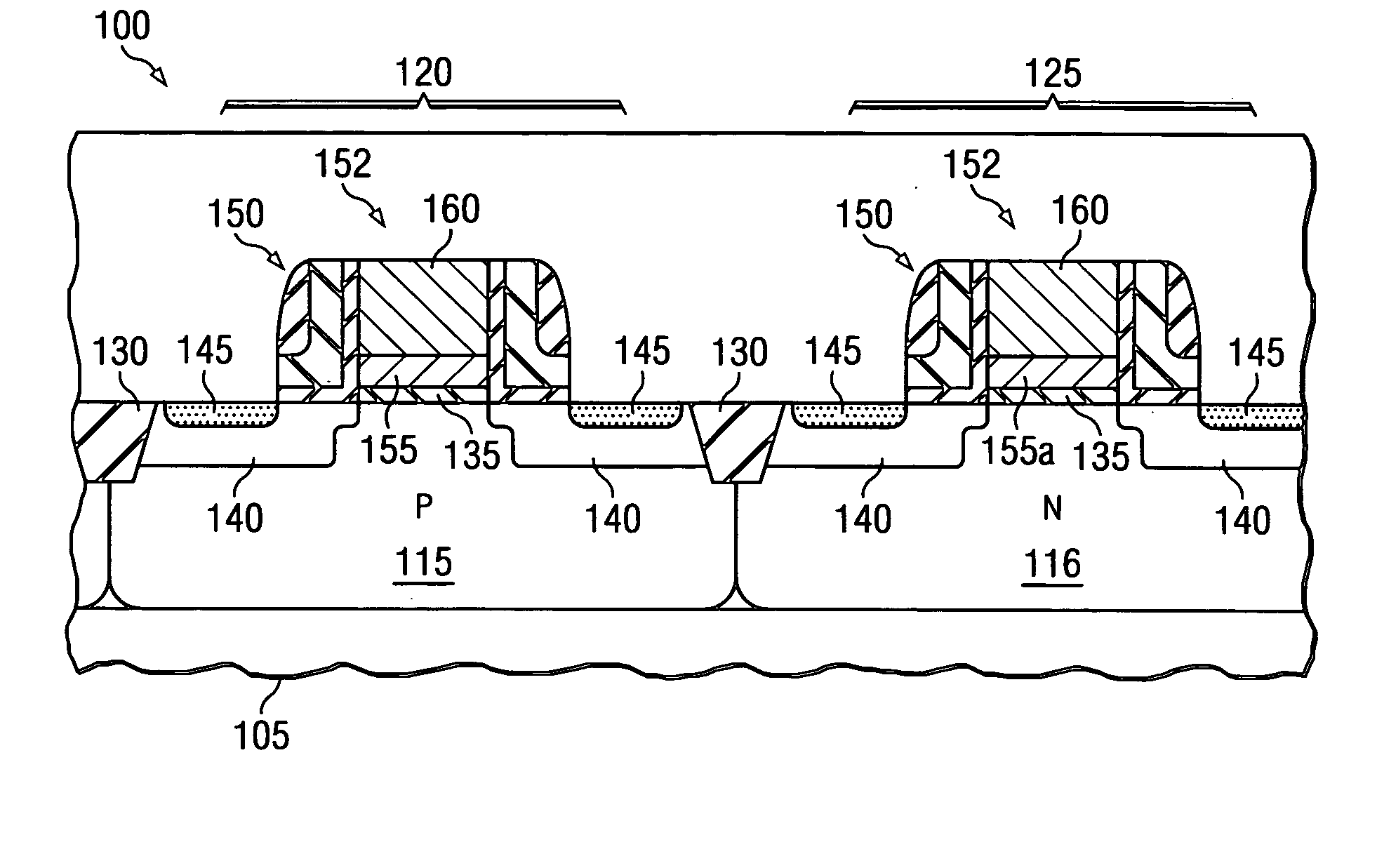

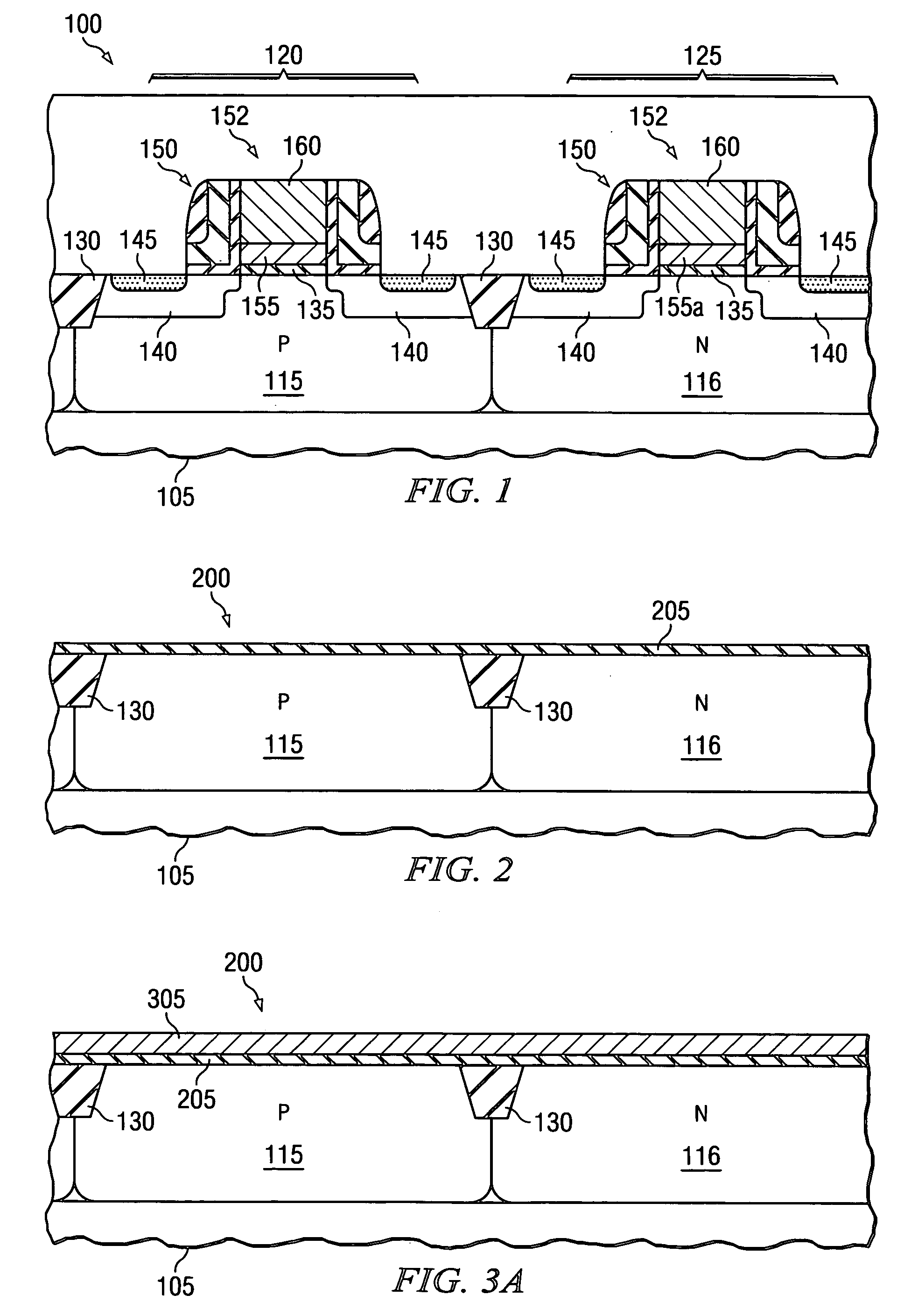

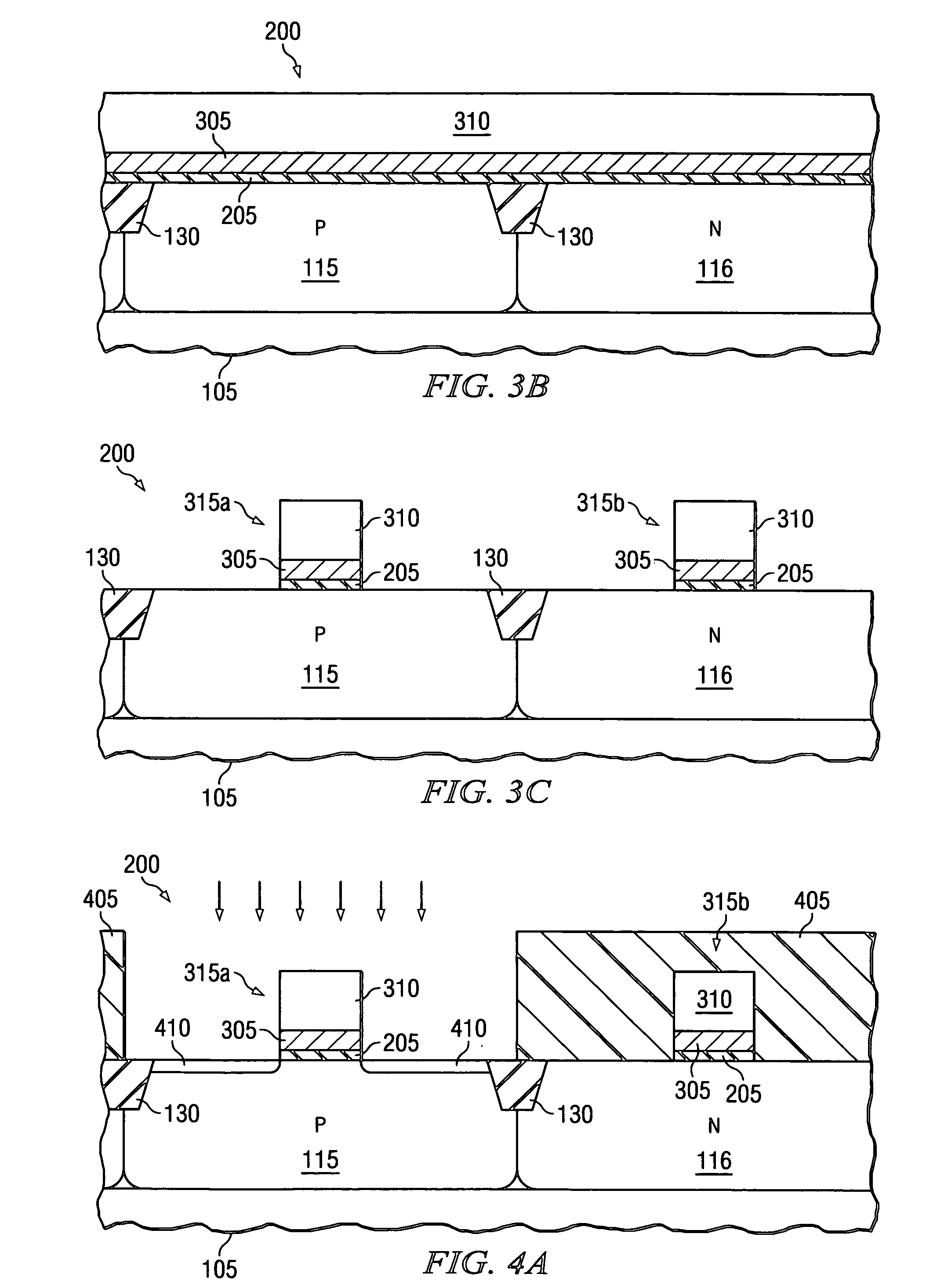

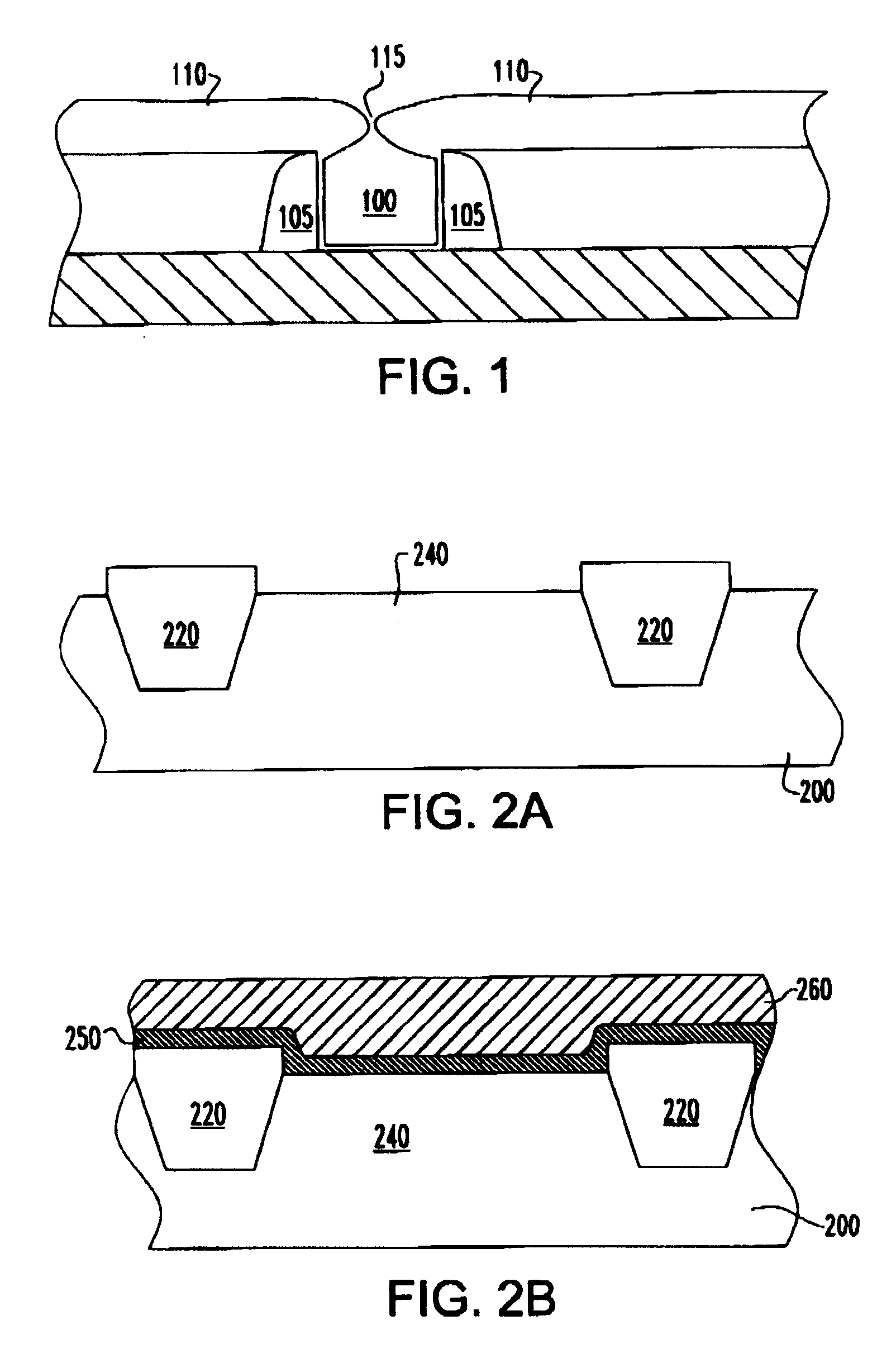

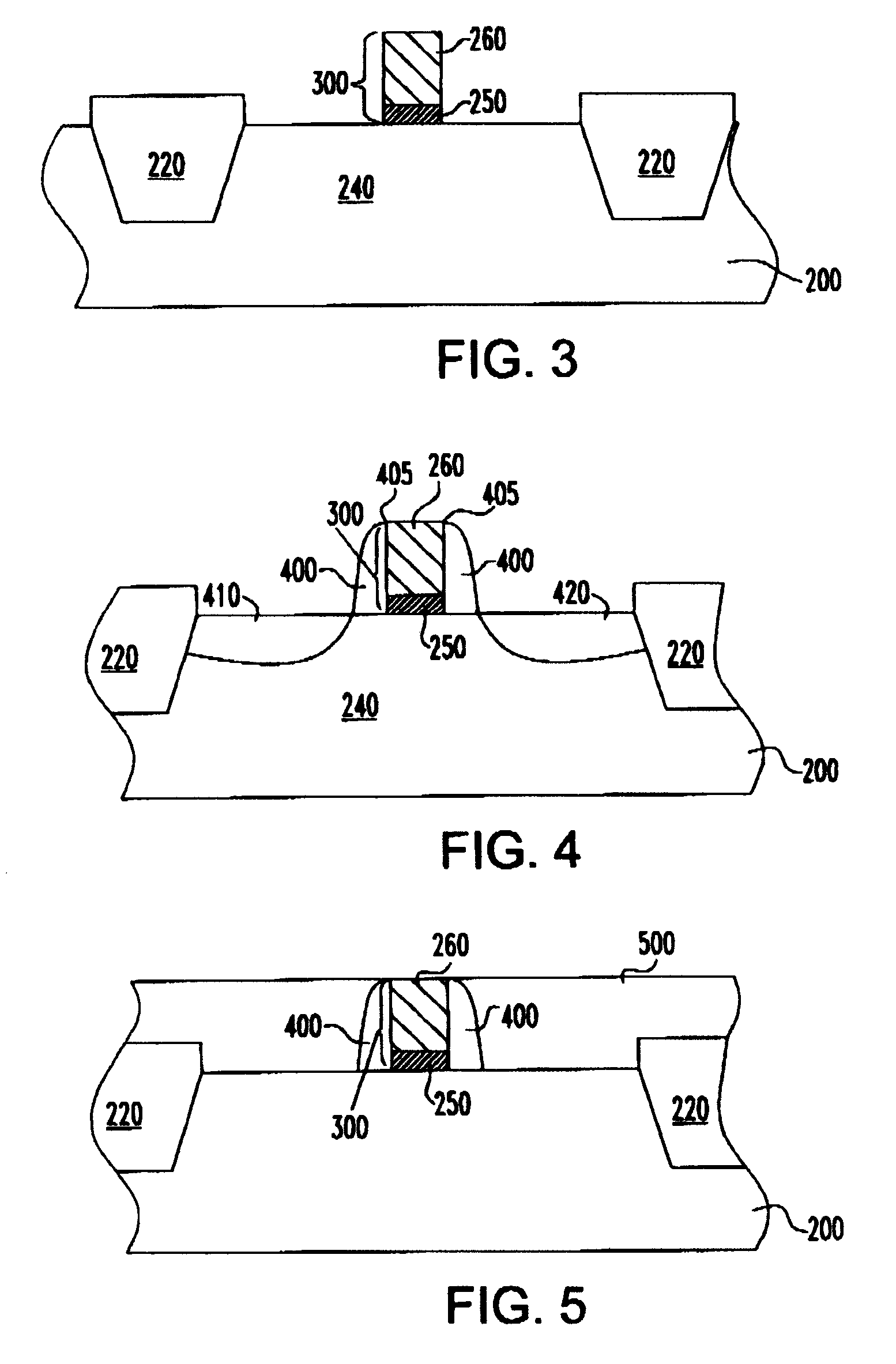

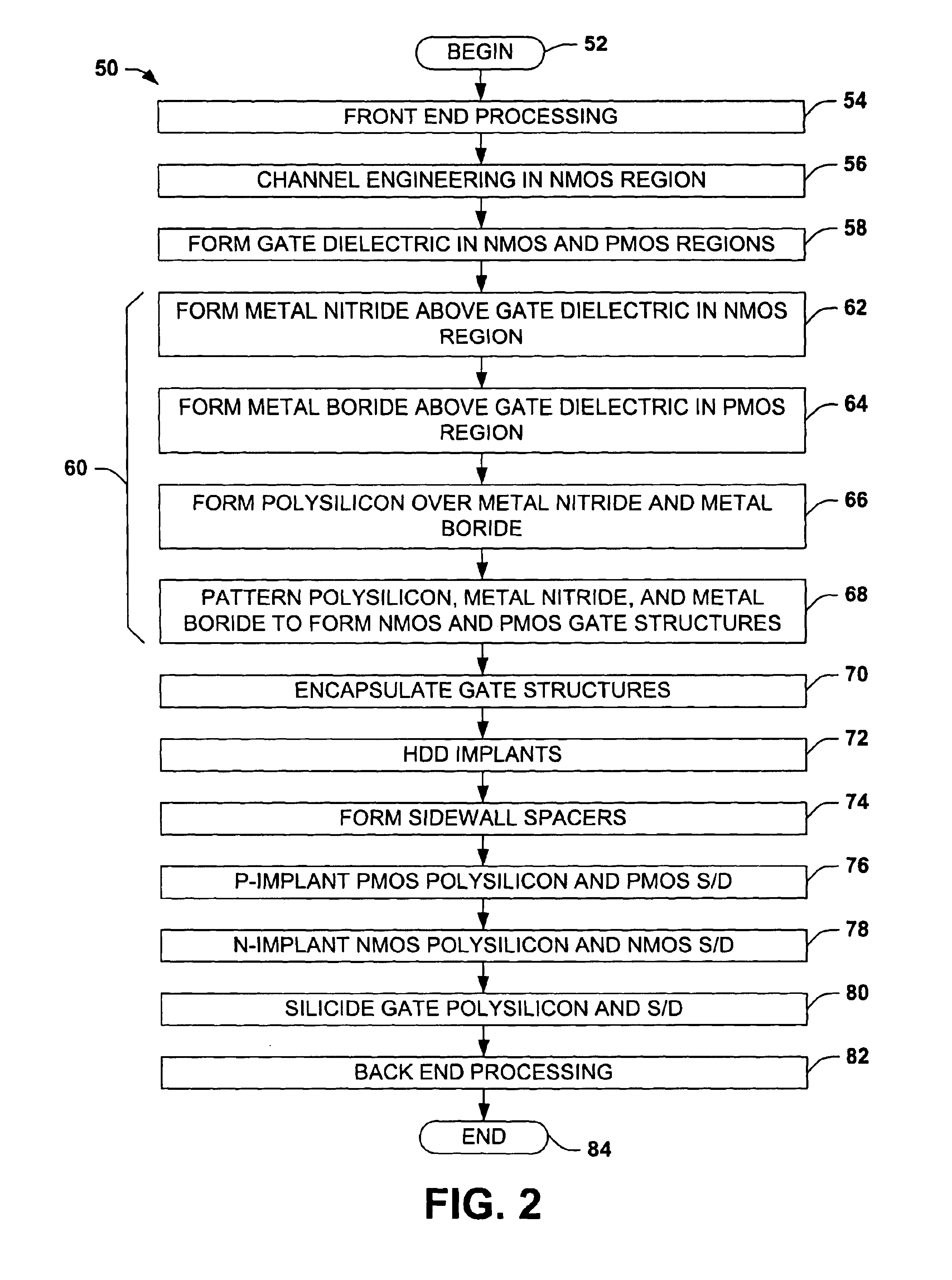

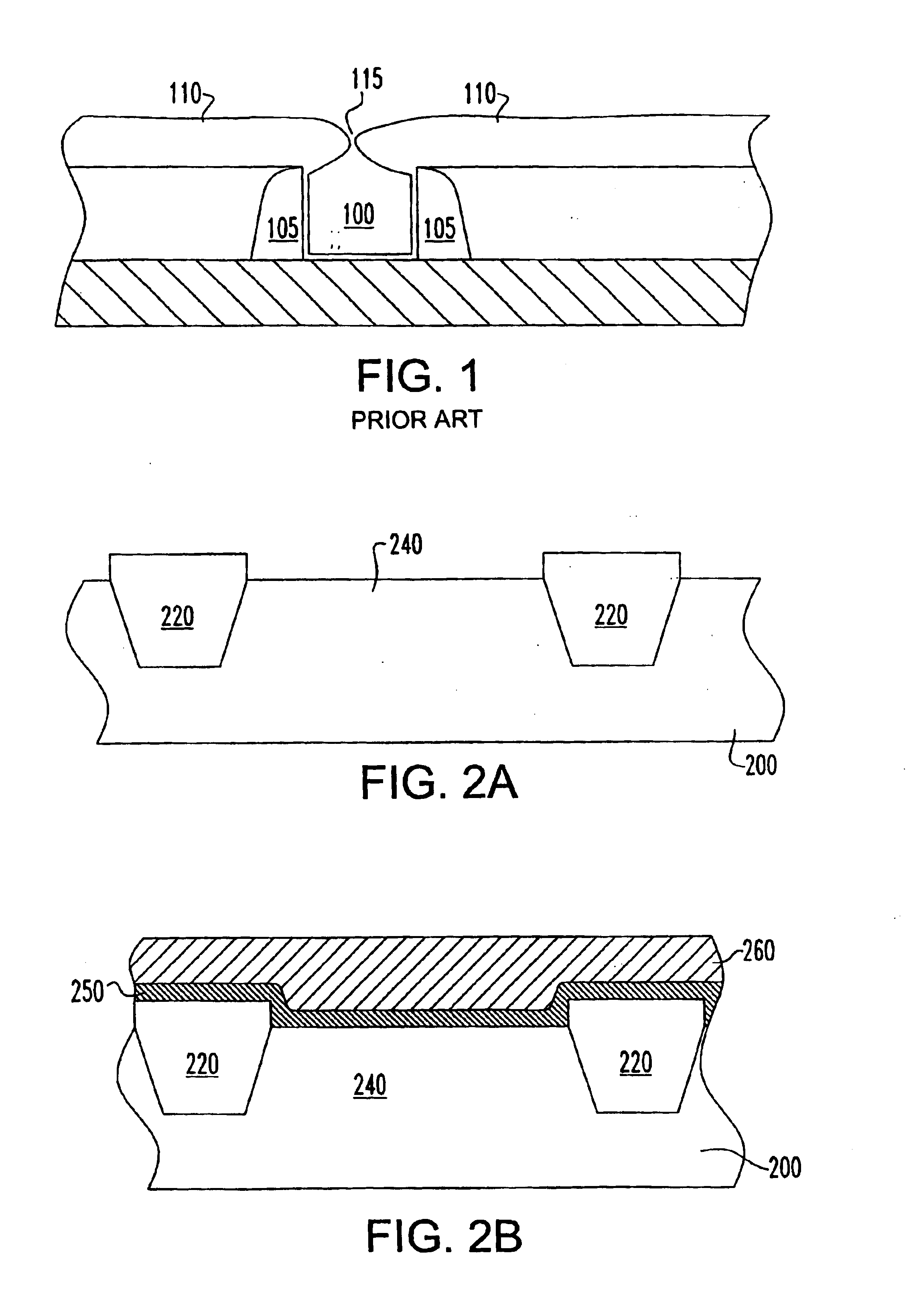

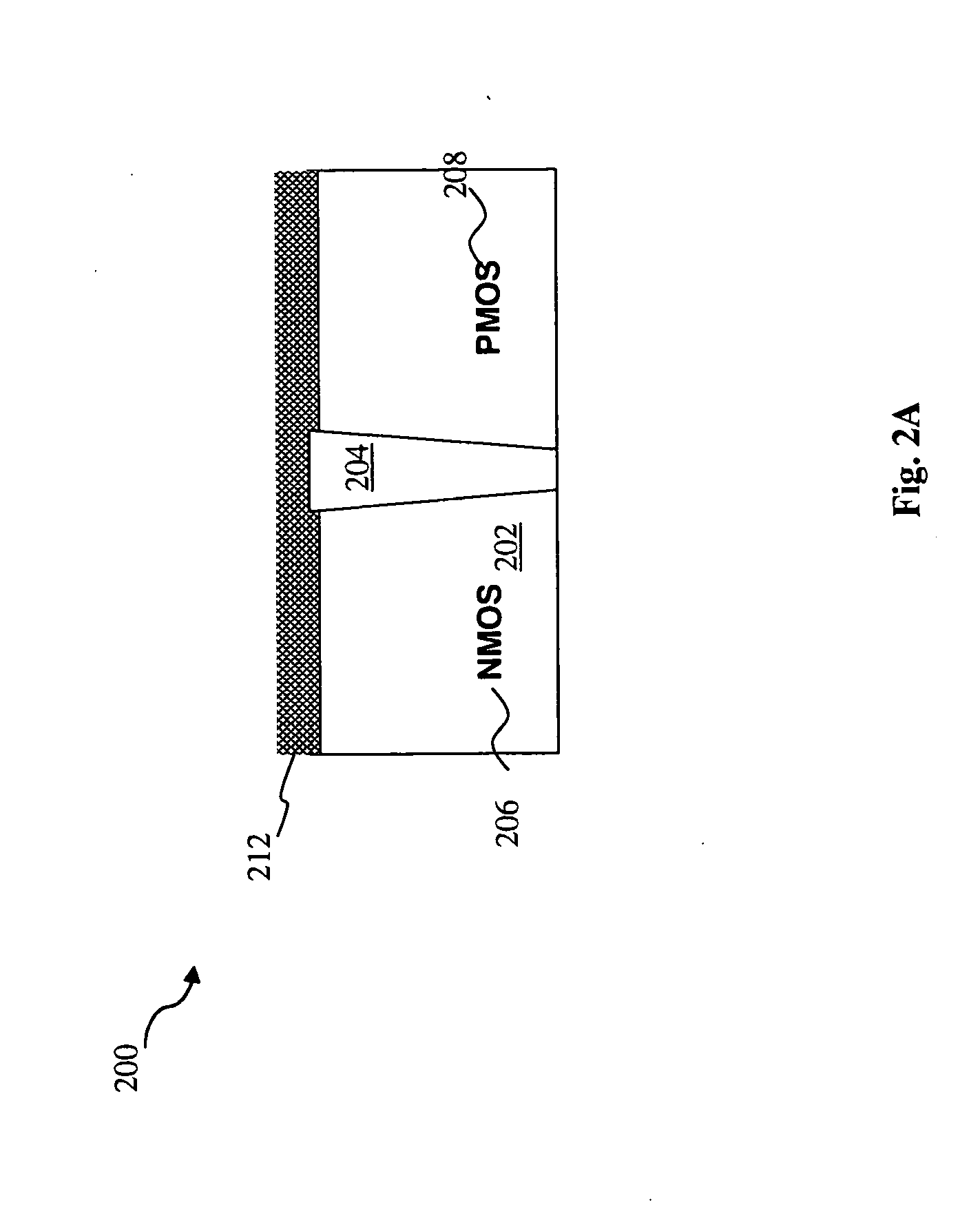

Process for manufacturing dual work function metal gates in a microelectronics device

ActiveUS20070037343A1Semiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricWork function

The present invention provides a method of forming a dual work function metal gate microelectronics device 200. In one aspect, the method includes forming nMOS and pMOS stacked gate structures 315a and 315b. The nMOS and pMOS stacked gate structures 315a and 315b each comprise a gate dielectric 205, a first metal layer, 305 located over the gate dielectric 205 and a sacrificial gate layer 310 located over the first metal layer 305. The method further includes removing the sacrificial gate layer 310 in at least one of the nMOS or pMOS stacked gate structures, thereby forming a gate opening 825 and modifying the first metal layer 305 within the gate opening 825 to form a gate electrode with a desired work function.

Owner:TEXAS INSTR INC

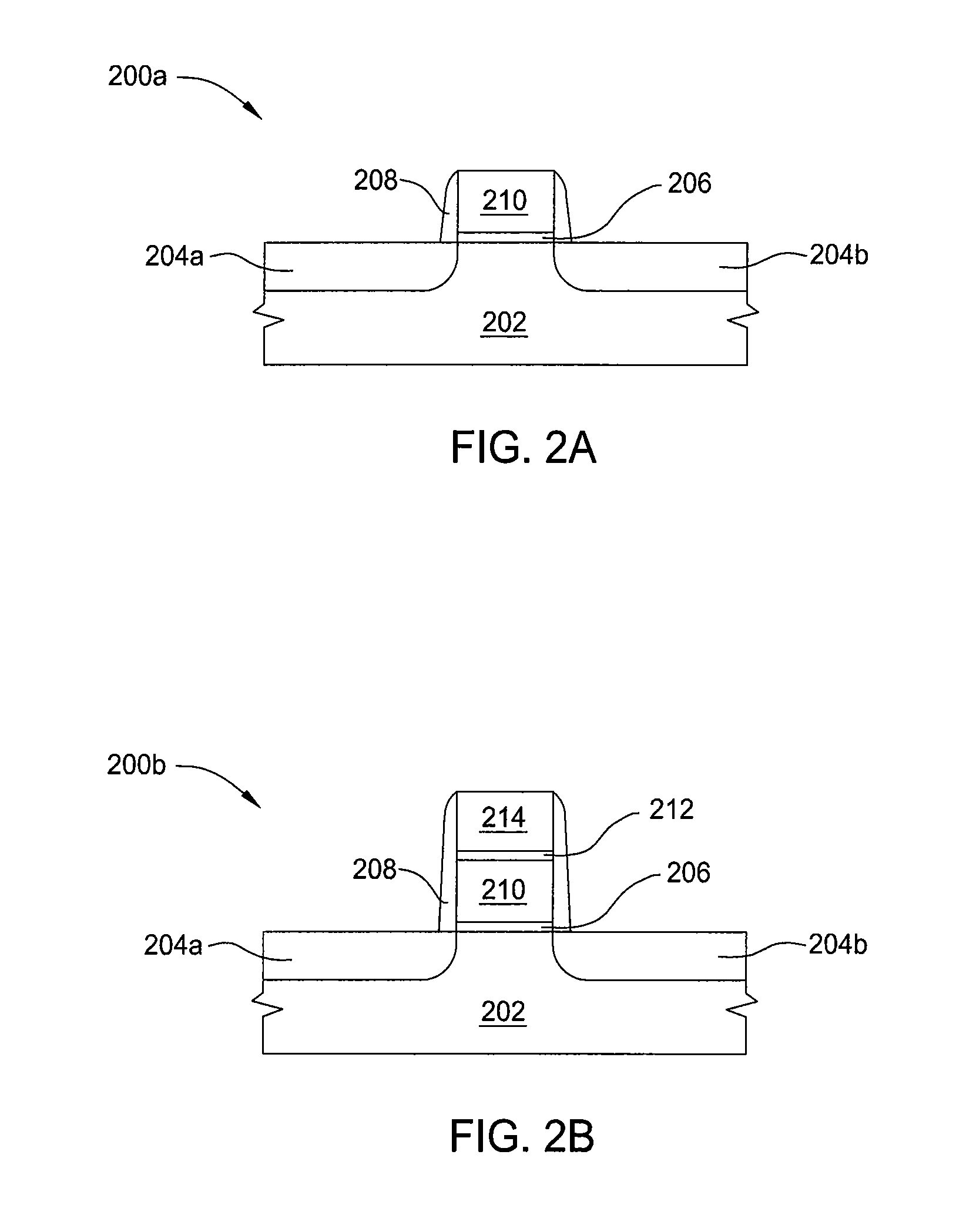

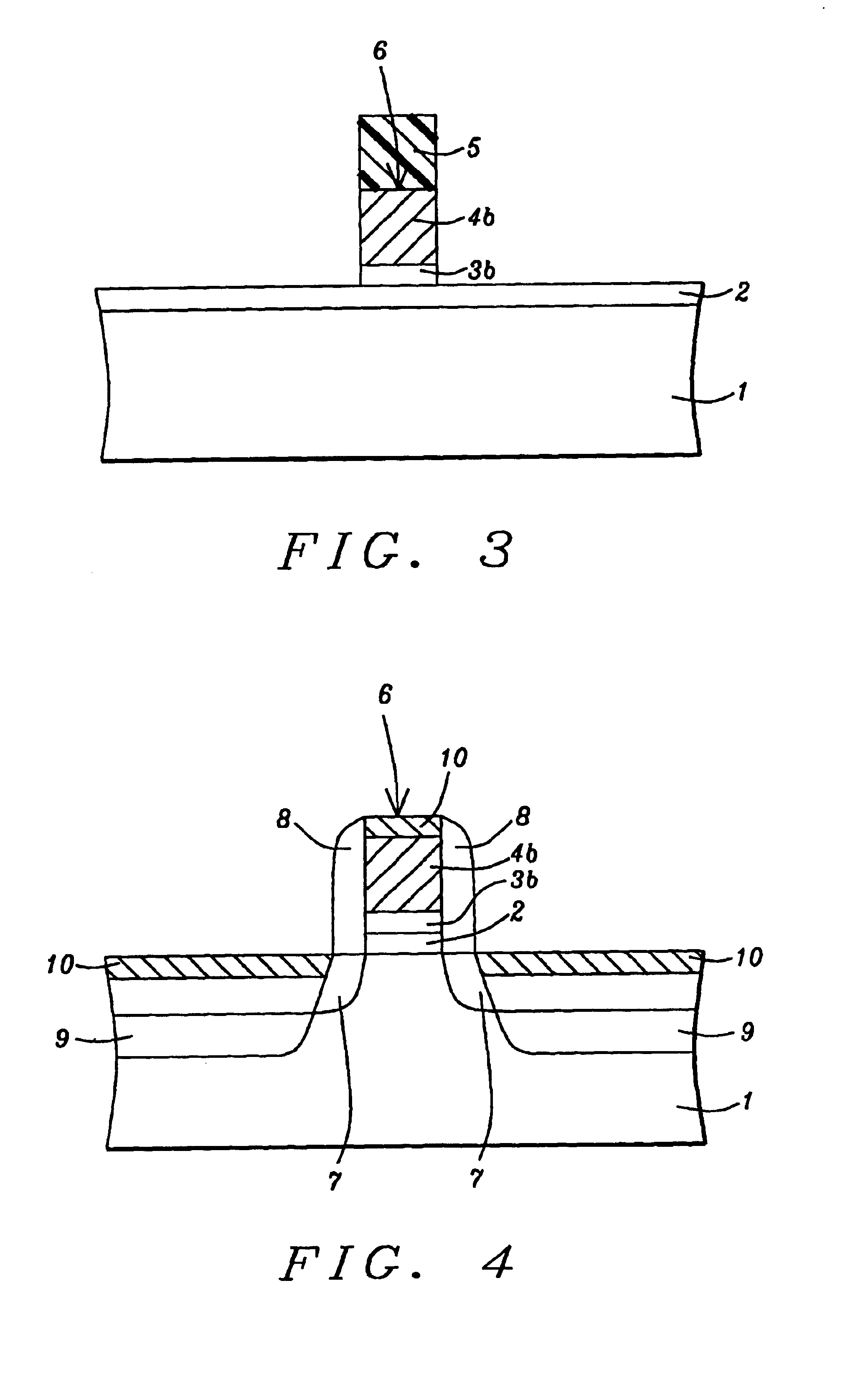

Opto-thermal annealing methods for forming metal gate and fully silicided gate field effect transistors

ActiveUS20070249131A1Avoid opto-thermal annealing damageAvoid damageSemiconductor/solid-state device manufacturingSemiconductor devicesSalicideGate dielectric

An opto-thermal annealing method for forming a field effect transistor uses a reflective metal gate so that electrical properties of the metal gate and also interface between the metal gate and a gate dielectric are not compromised when opto-thermal annealing a source / drain region adjacent the metal gate. Another opto-thermal annealing method may be used for simultaneously opto-thermally annealing: (1) a silicon layer and a silicide forming metal layer to form a fully silicided gate; and (2) a source / drain region to form an annealed source / drain region. An additional opto-thermal annealing method may use a thermal insulator layer in conjunction with a thermal absorber layer to selectively opto-thermally anneal a silicon layer and a silicide forming metal layer to form a fully silicide gate.

Owner:TAIWAN SEMICON MFG CO LTD

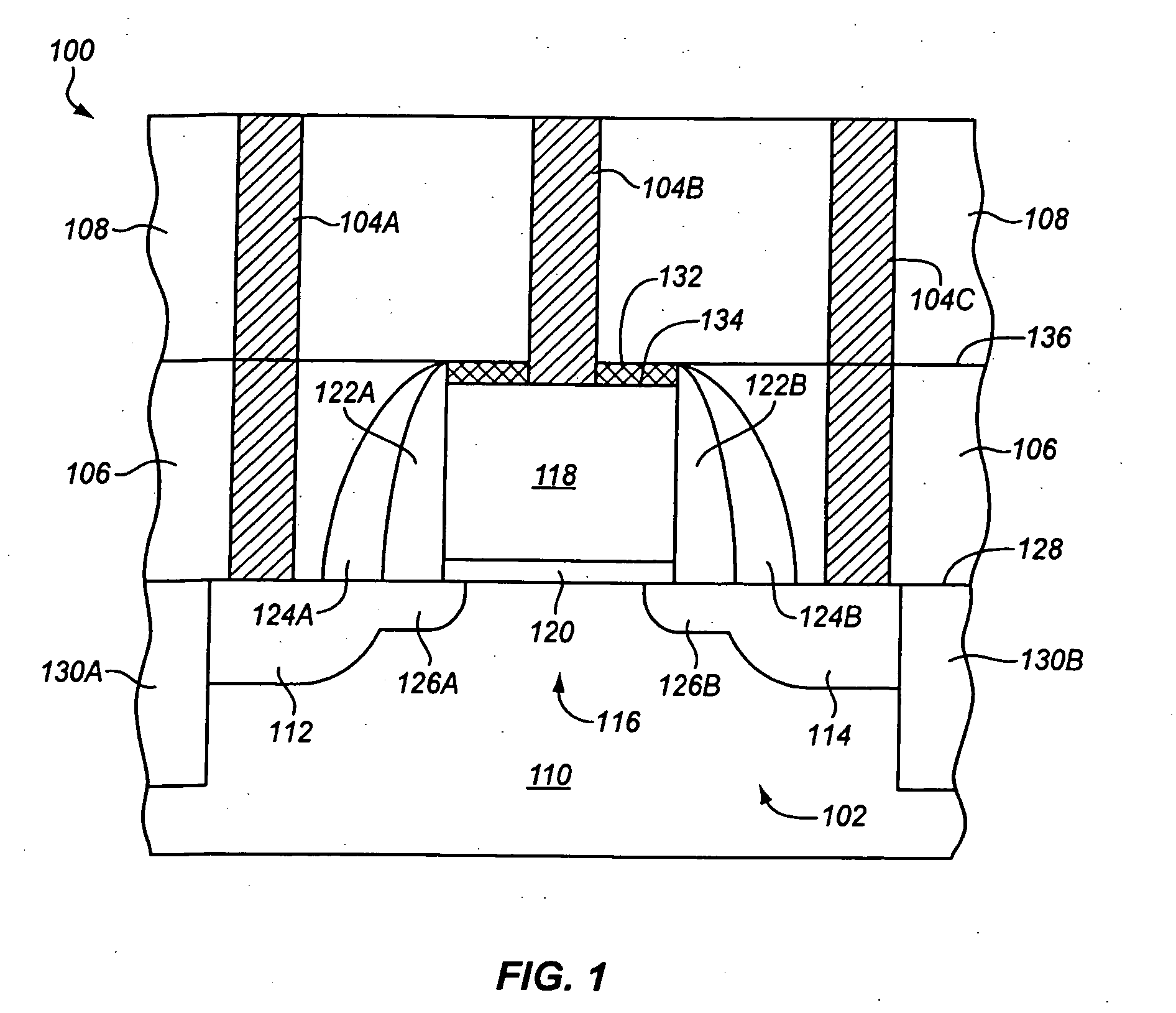

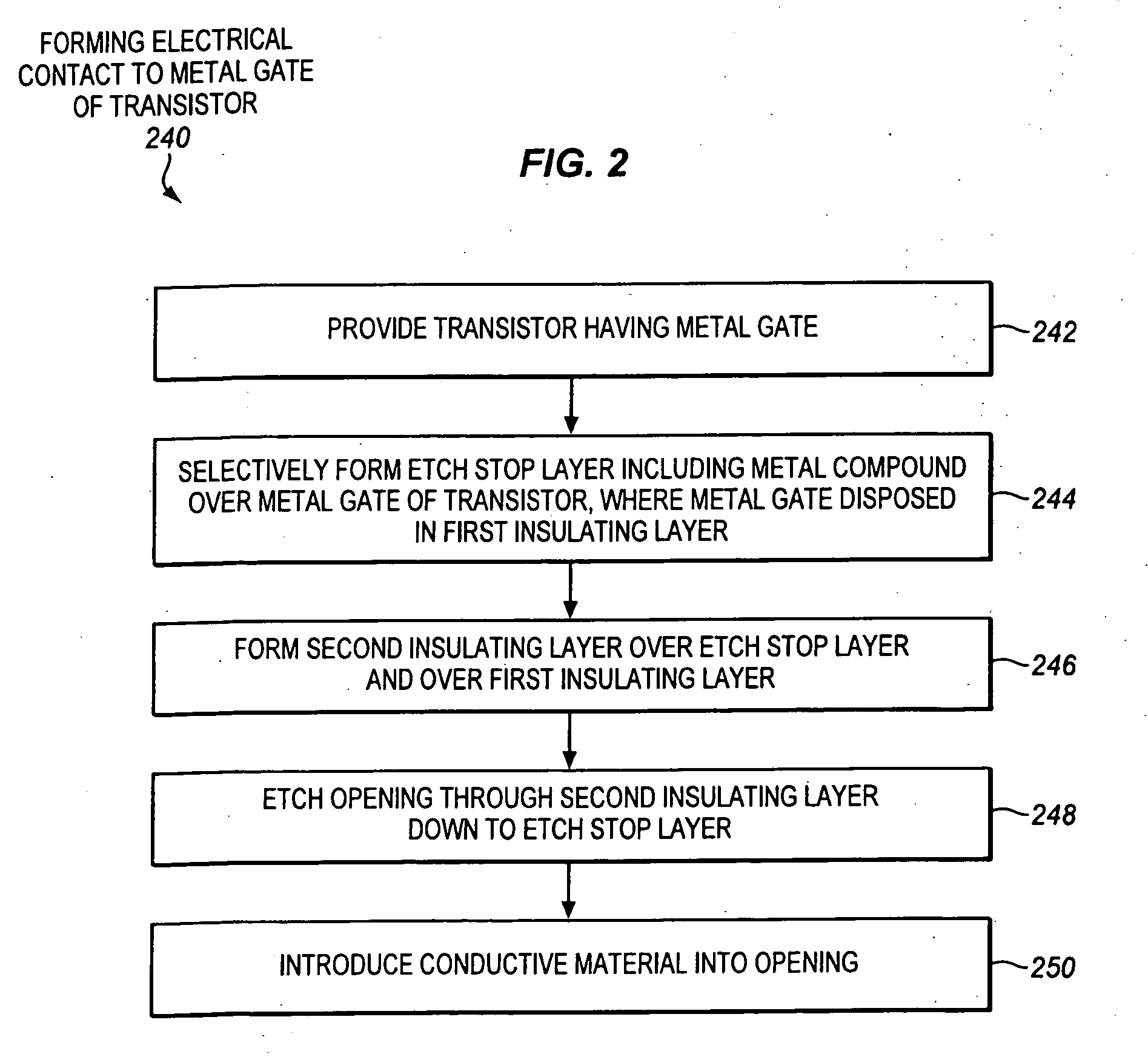

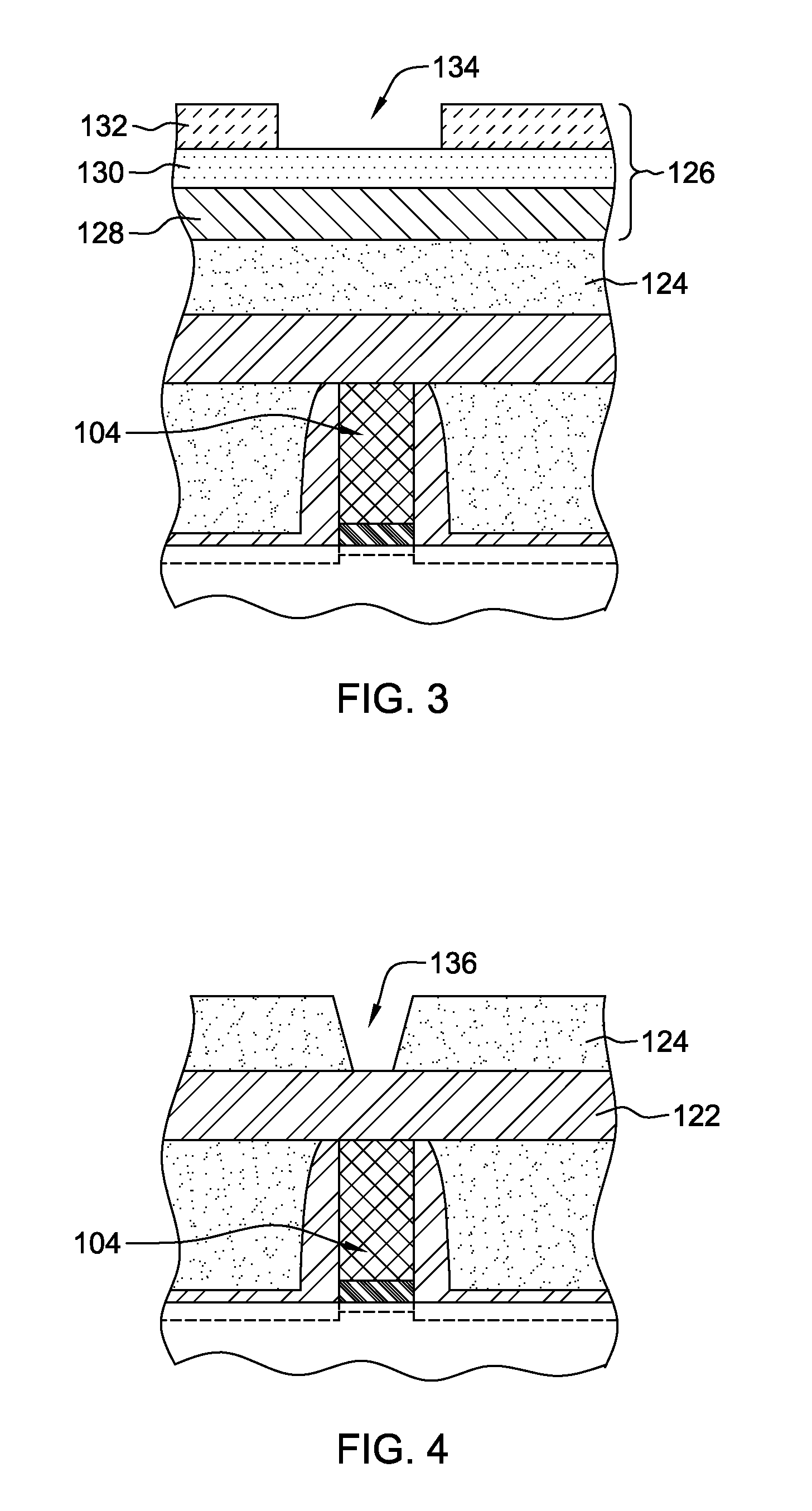

Transistor having an etch stop layer including a metal compound that is selectively formed over a metal gate, and method therefor

InactiveUS20080157365A1Semiconductor/solid-state device detailsSolid-state devicesOptoelectronicsMetal

In one aspect, an apparatus may include a metal gate of a transistor. An etch stop layer may be selectively formed over the metal gate. The etch stop layer may include a metal compound. An insulating layer may be over the etch stop layer. A conductive structure may be included through the insulating layer to the metal gate. Methods of making such transistors are also disclosed.

Owner:INTEL CORP

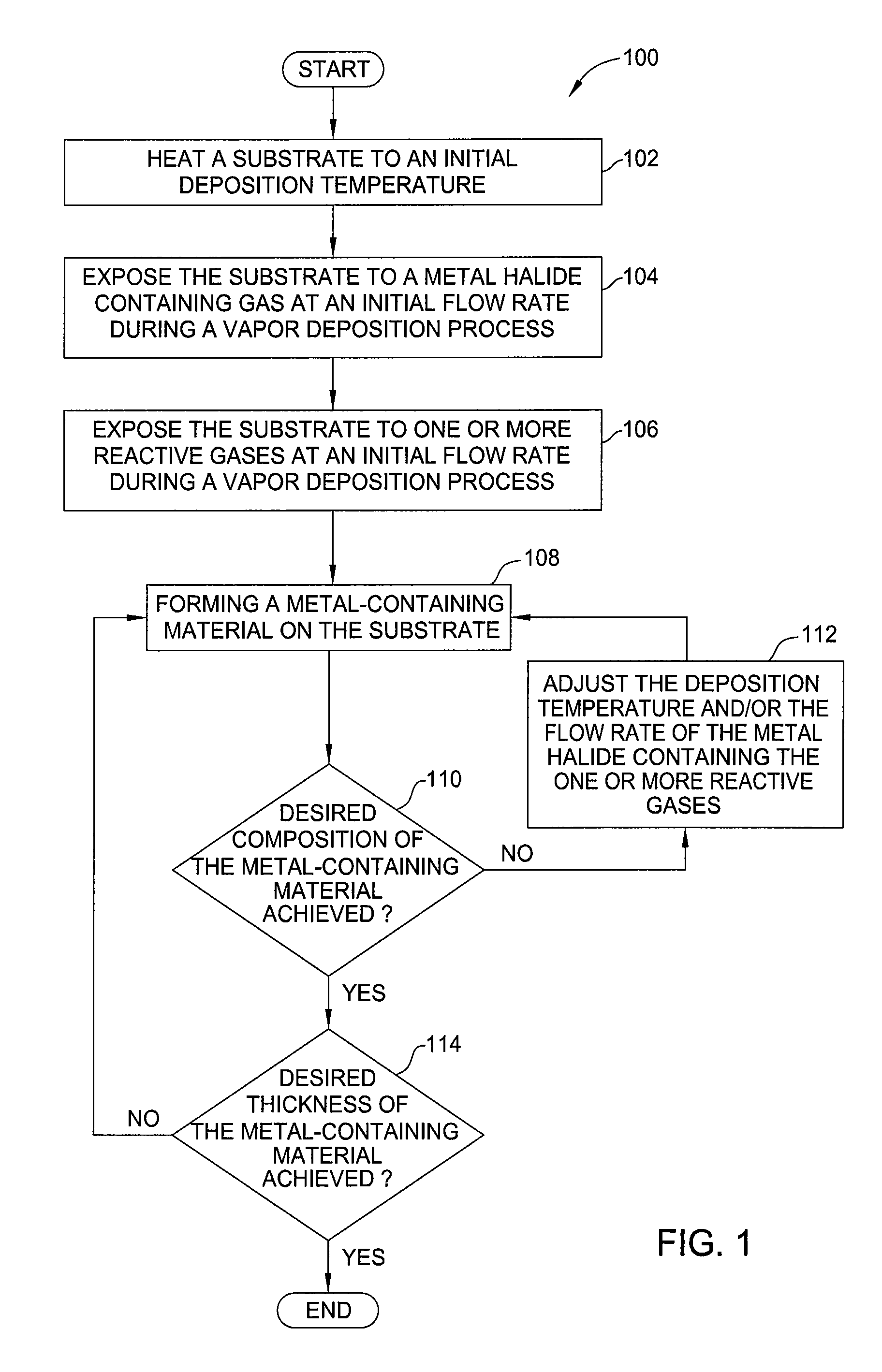

Nmos metal gate materials, manufacturing methods, and equipment using CVD and ald processes with metal based precursors

ActiveUS20110263115A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingGas phaseMetallic materials

Embodiments of the invention generally provide methods for depositing metal-containing materials and compositions thereof. The methods include deposition processes that form metal, metal carbide, metal silicide, metal nitride, and metal carbide derivatives by a vapor deposition process, including thermal decomposition, CVD, pulsed-CVD, or ALD. In one embodiment, a method for processing a substrate is provided which includes depositing a dielectric material having a dielectric constant greater than 10, forming a feature definition in the dielectric material, depositing a work function material conformally on the sidewalls and bottom of the feature definition, and depositing a metal gate fill material on the work function material to fill the feature definition, wherein the work function material is deposited by reacting at least one metal-halide precursor having the formula MXY, wherein M is tantalum, hafnium, titanium, and lanthanum, X is a halide selected from the group of fluorine, chlorine, bromine, or iodine, and y is from 3 to 5.

Owner:APPLIED MATERIALS INC

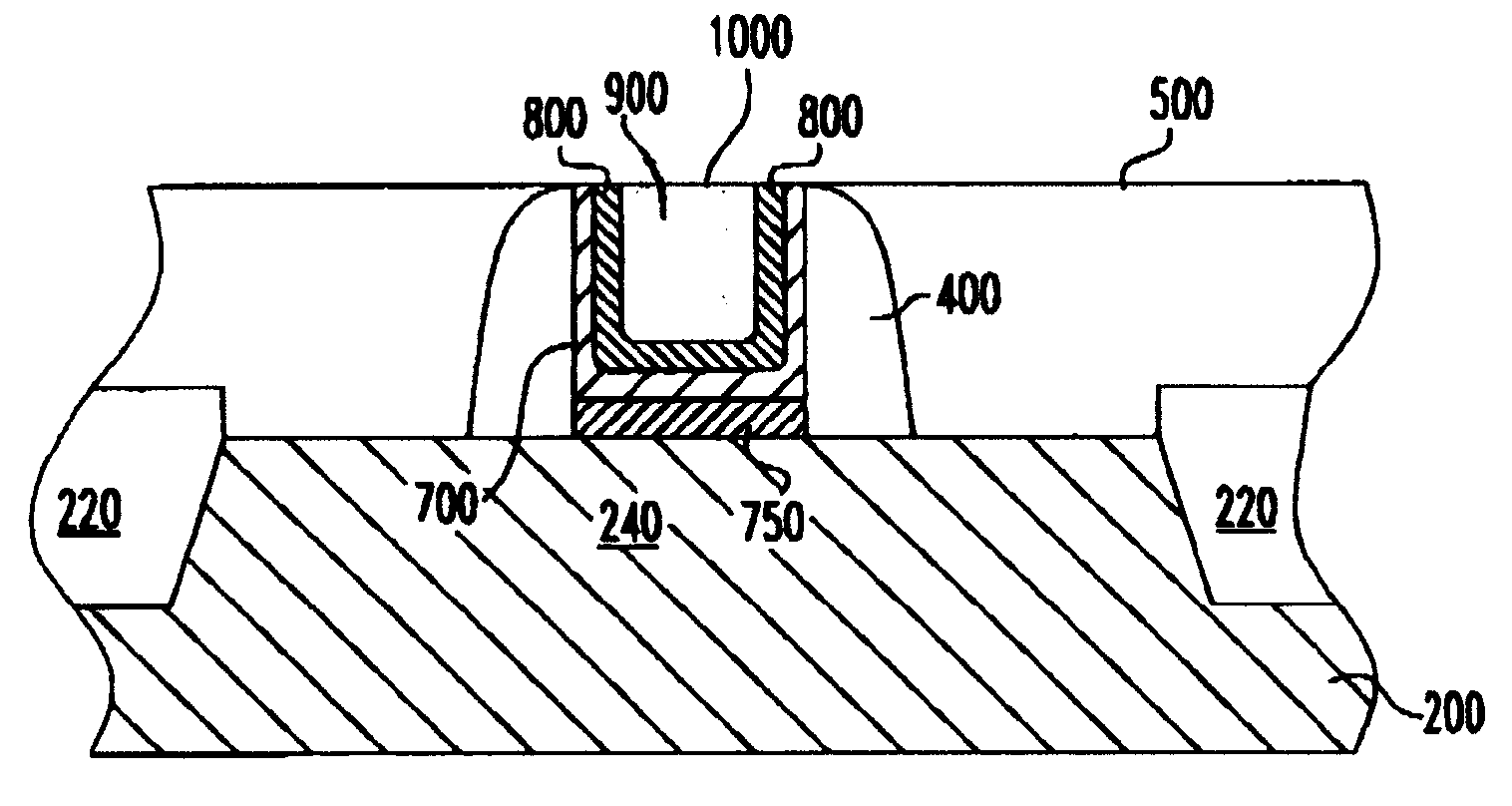

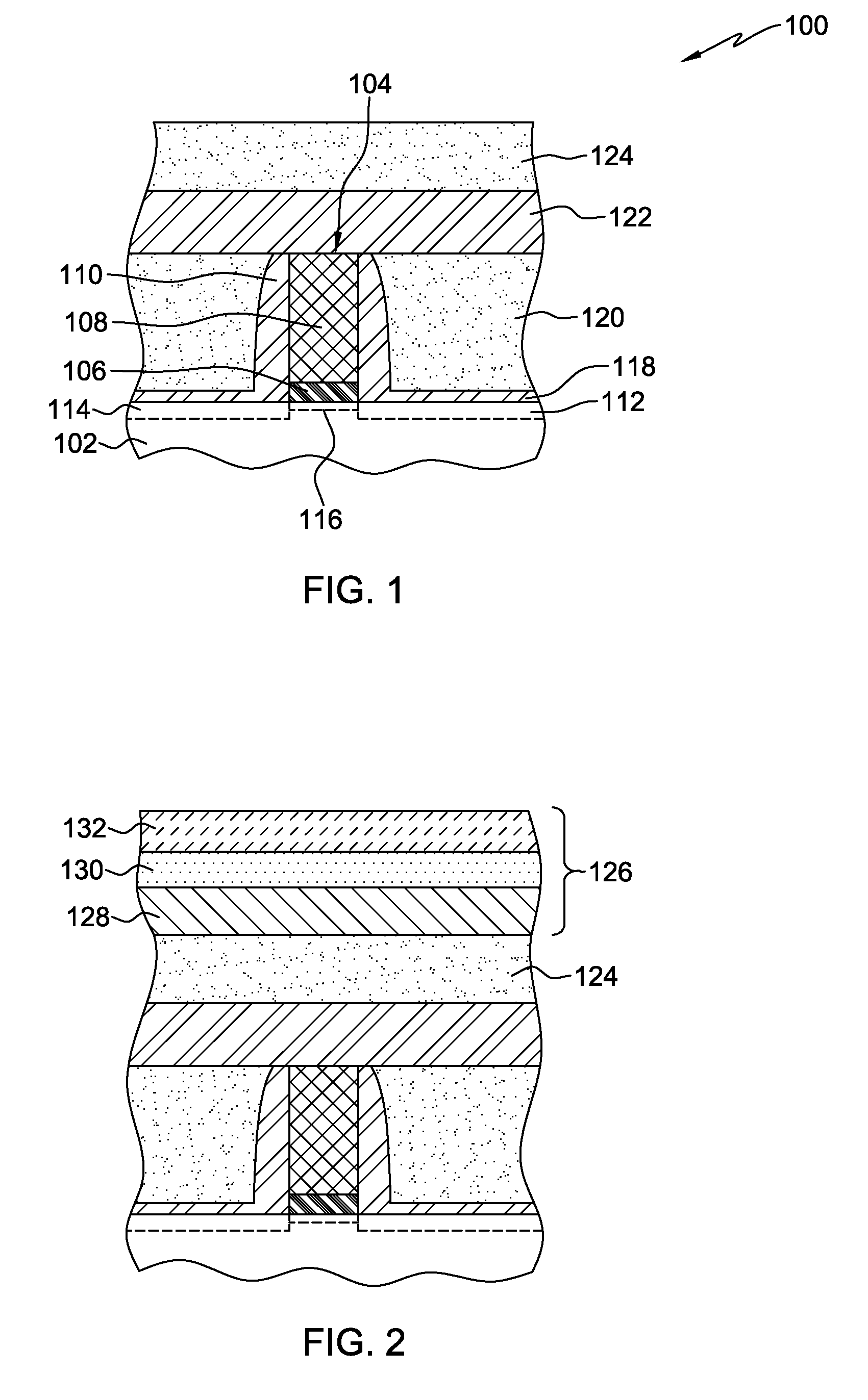

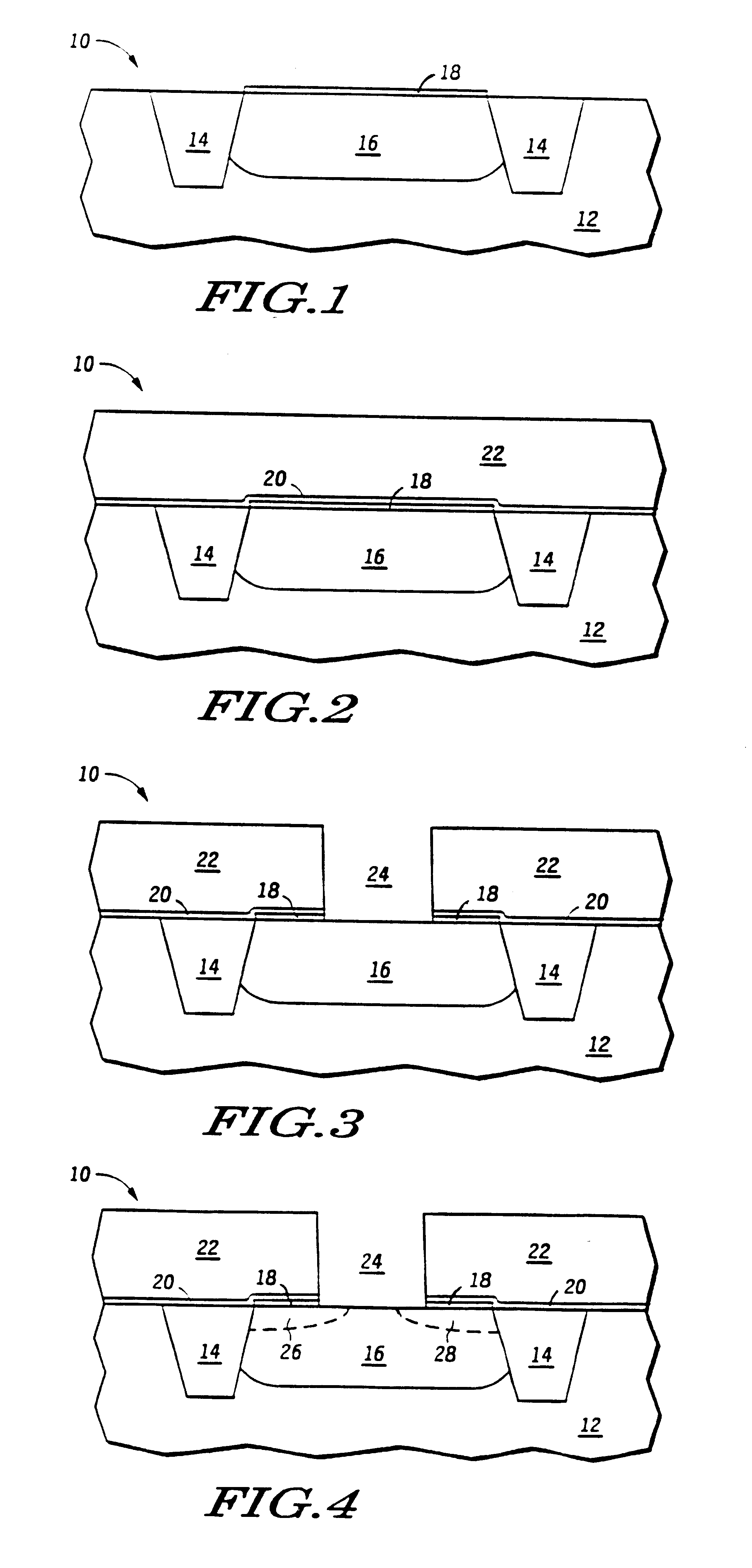

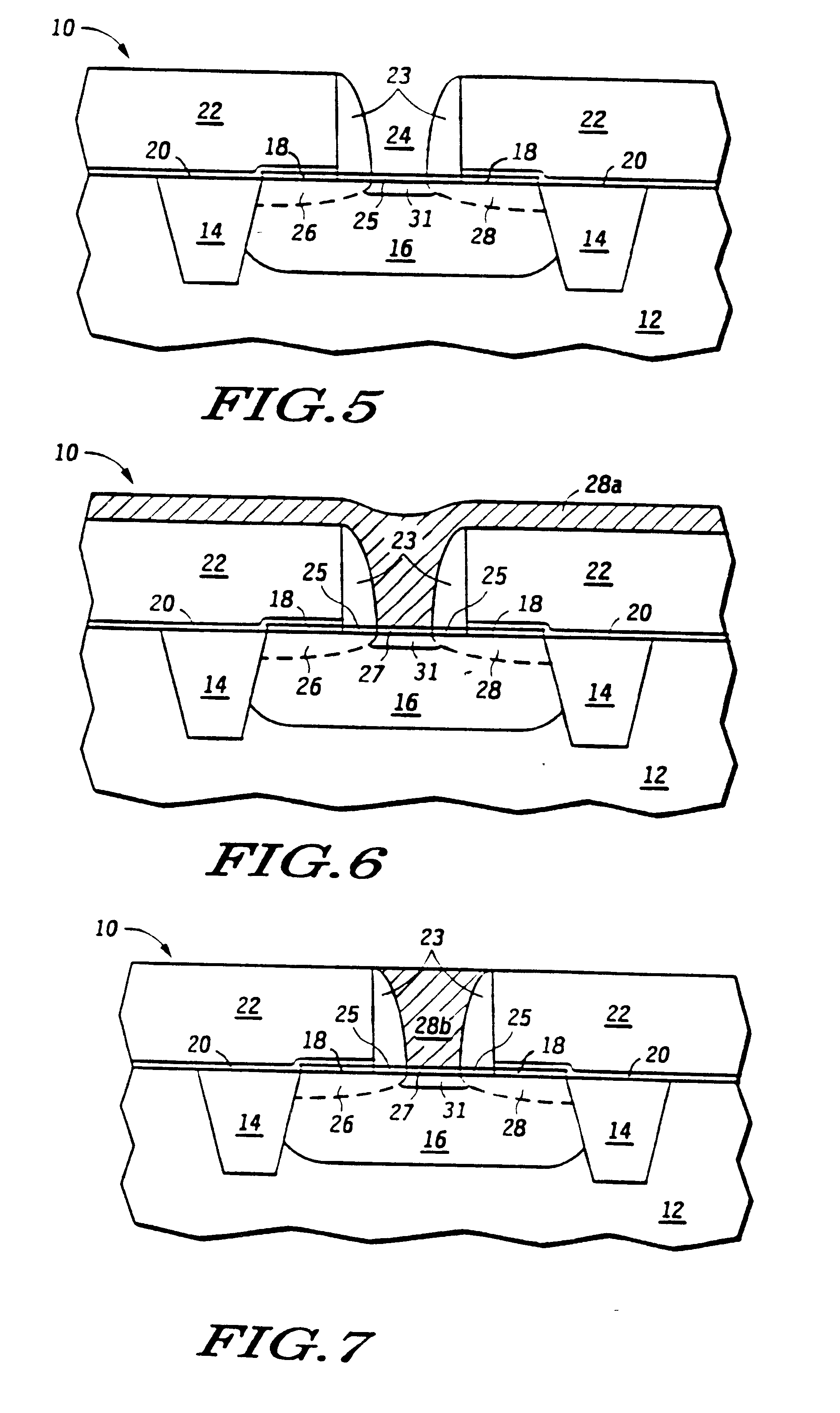

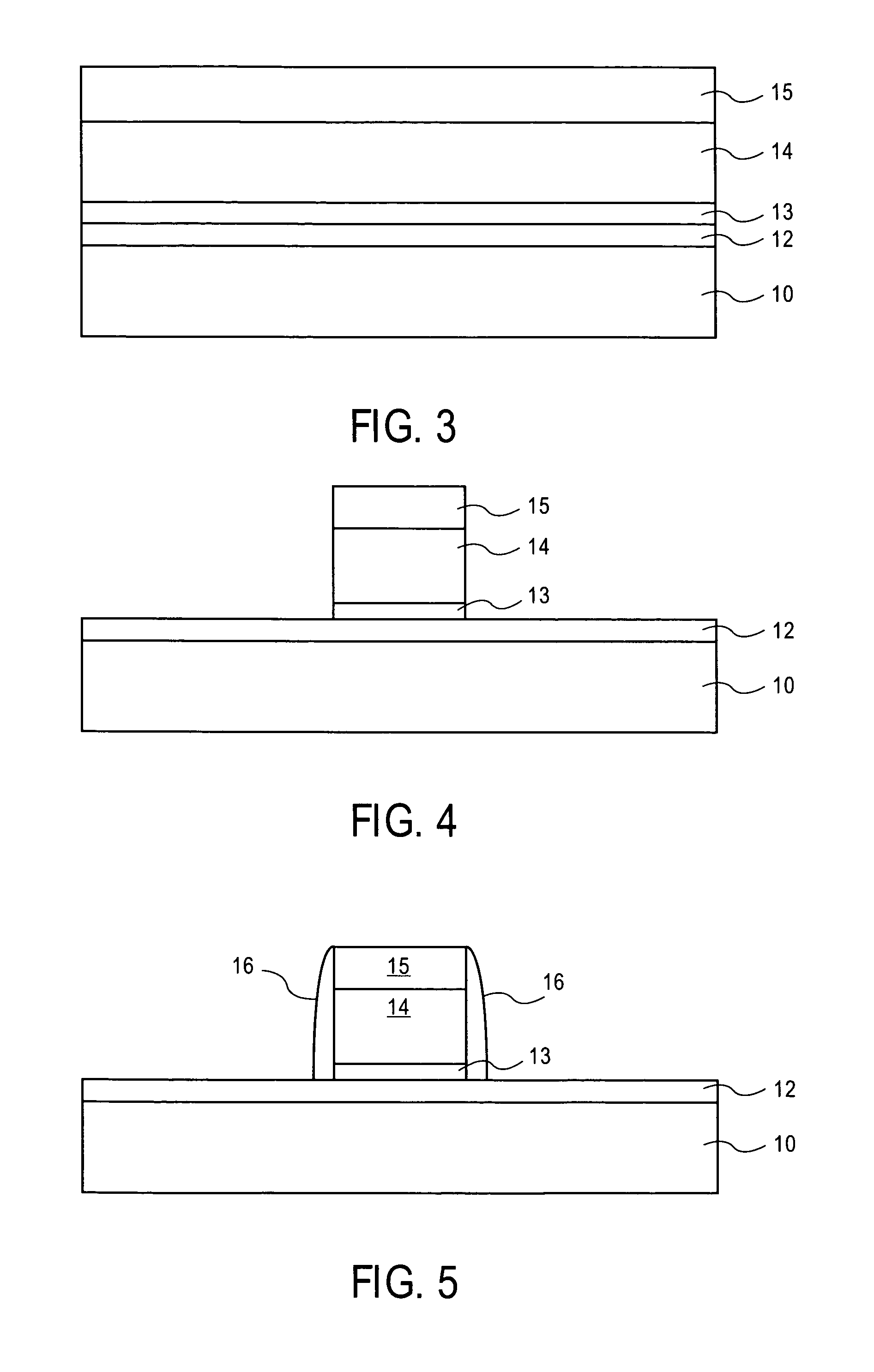

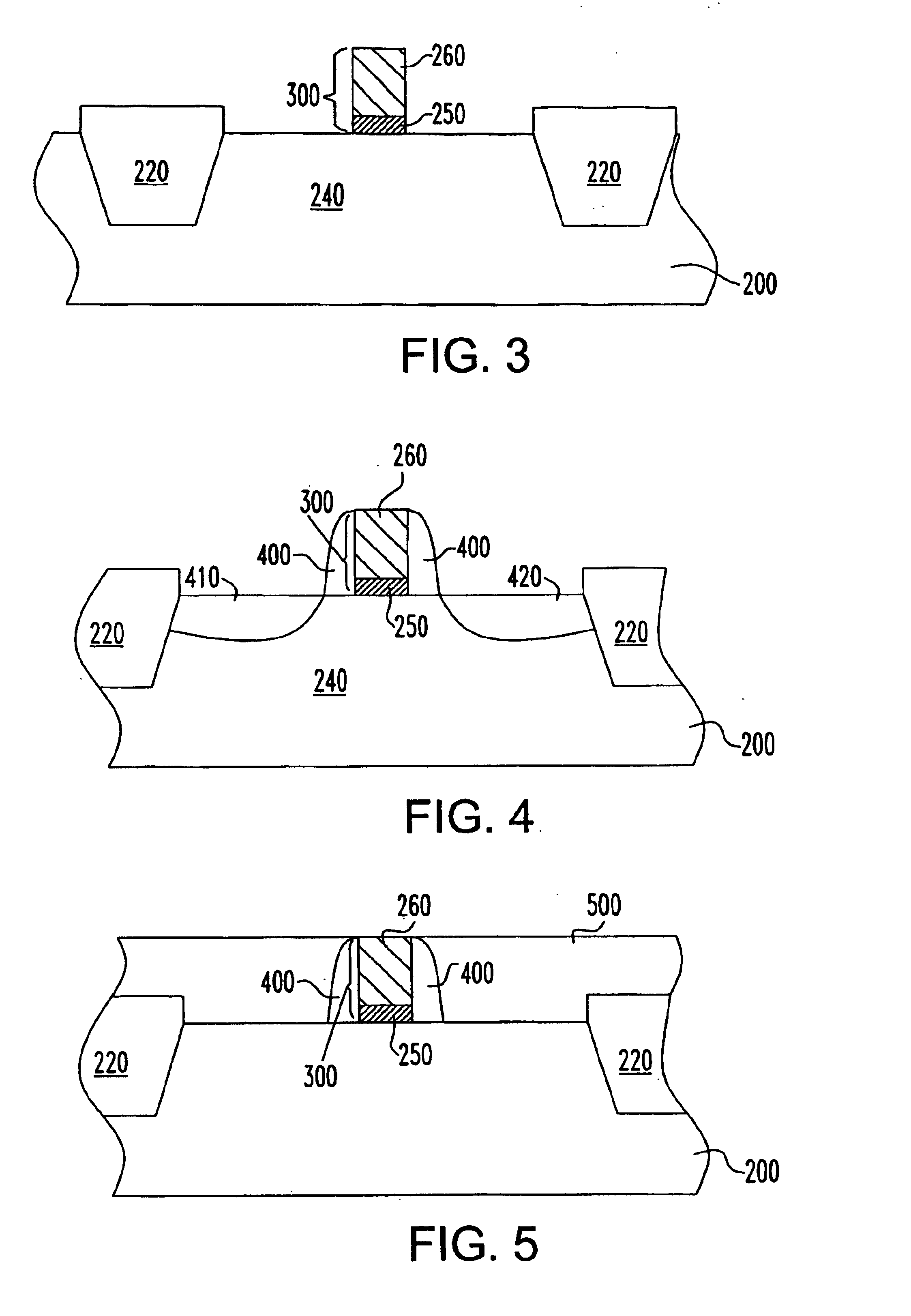

Structure and method for metal replacement gate of high performance

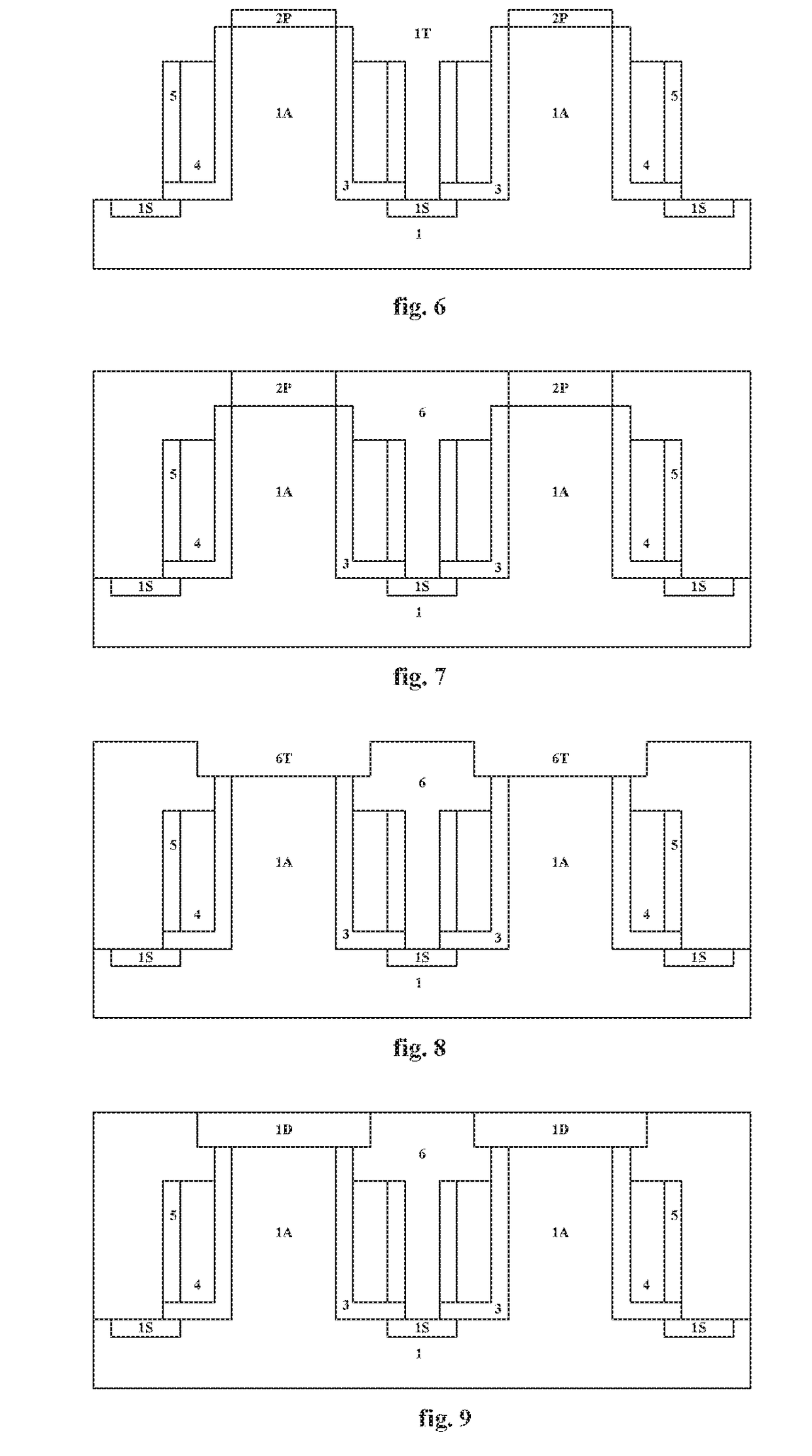

ActiveUS20050051854A1Improve performanceSemiconductor/solid-state device manufacturingSemiconductor devicesTitanium nitrideDiffusion barrier

A structure and method for a metal replacement gate of a high performance device is provided. A sacrificial gate structure is first formed on an etch stop layer provided on a semiconductor substrate. A pair of spacers is provided on sidewalls of the sacrificial gate structure. The sacrificial gate structure is then removed, forming an opening. Subsequently, a metal gate including an first layer of metal such as tungsten, a diffusion barrier such as titanium nitride, and a second layer of metal such as tungsten is formed in the opening between the spacers.

Owner:GLOBALFOUNDRIES US INC

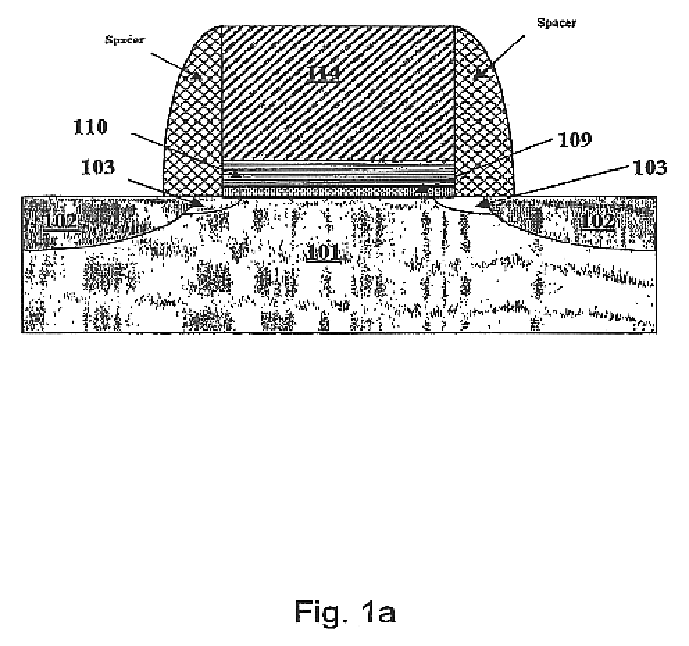

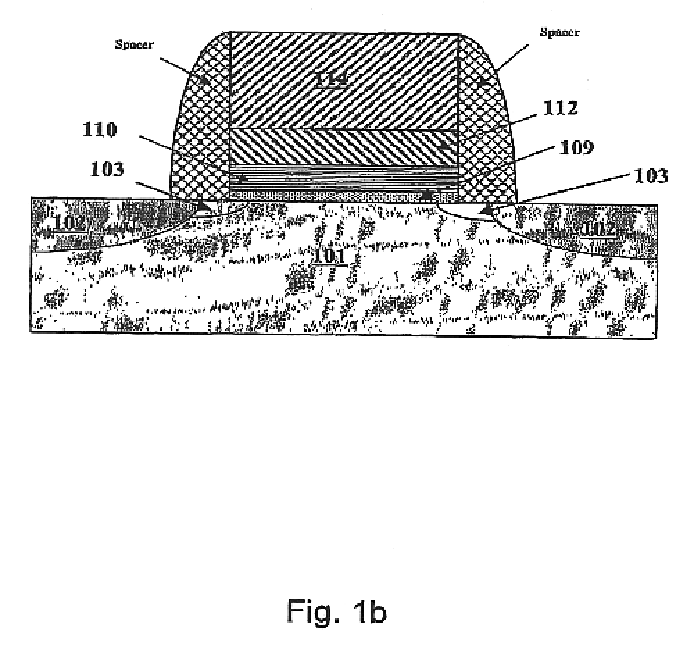

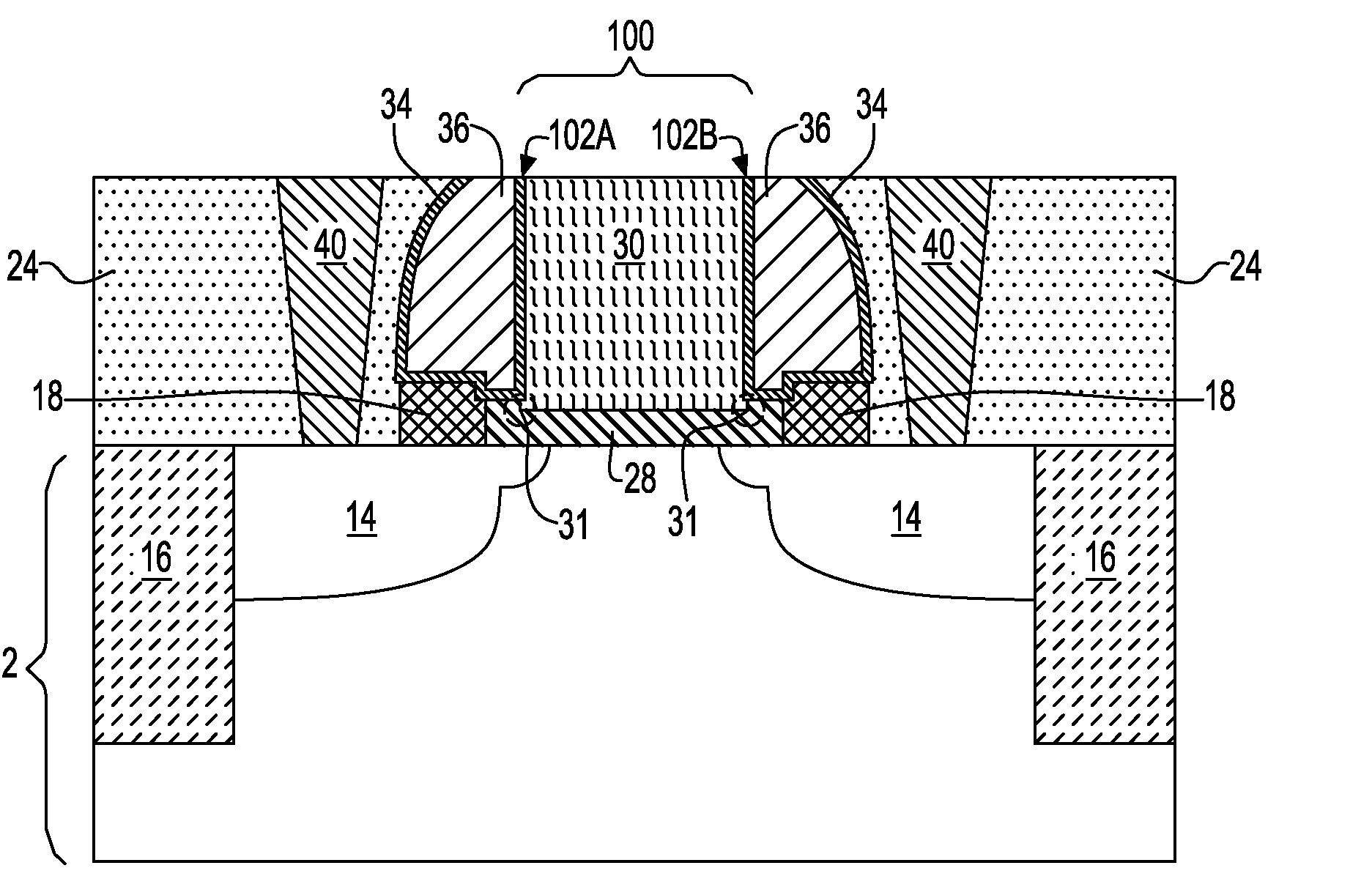

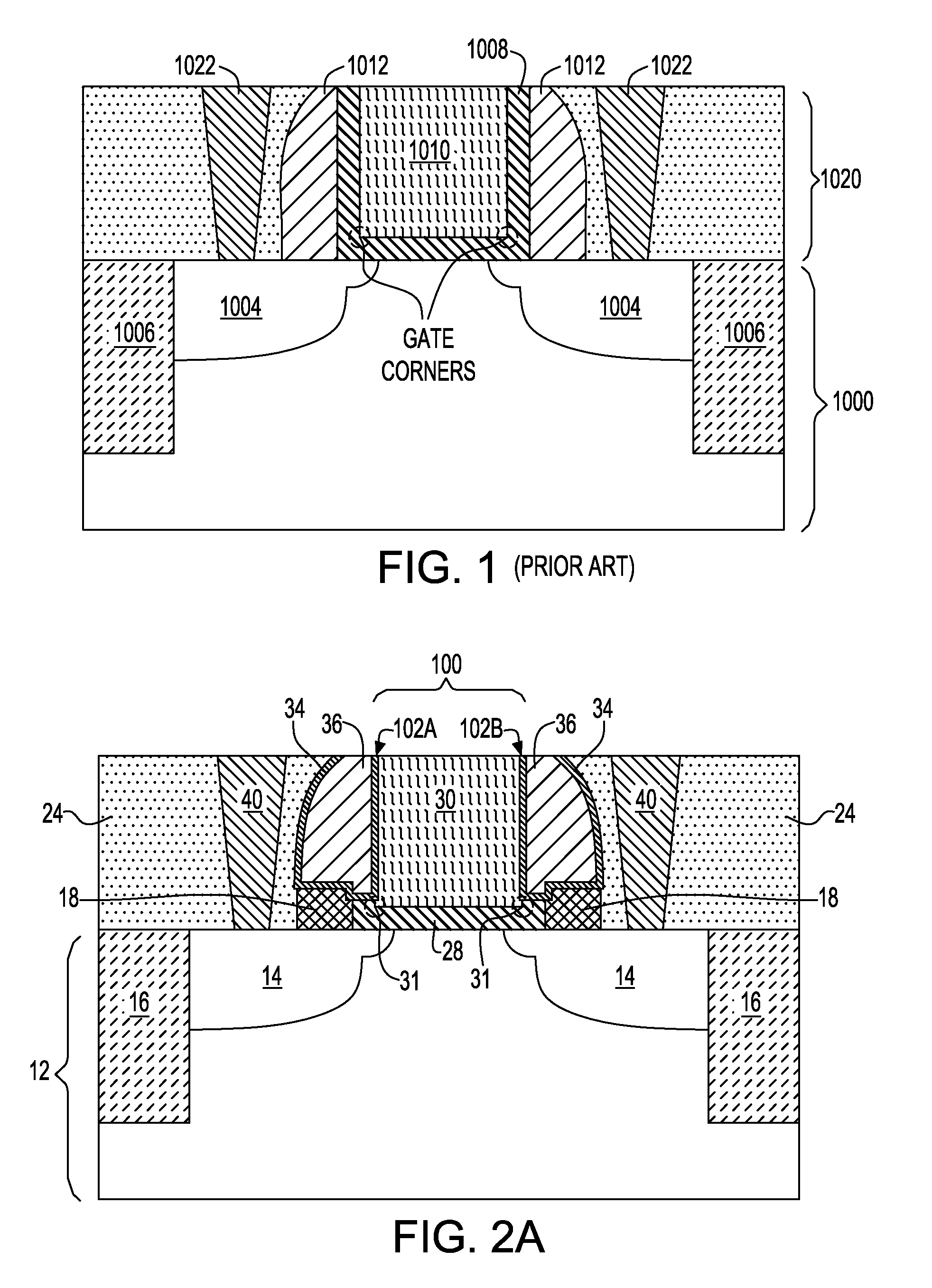

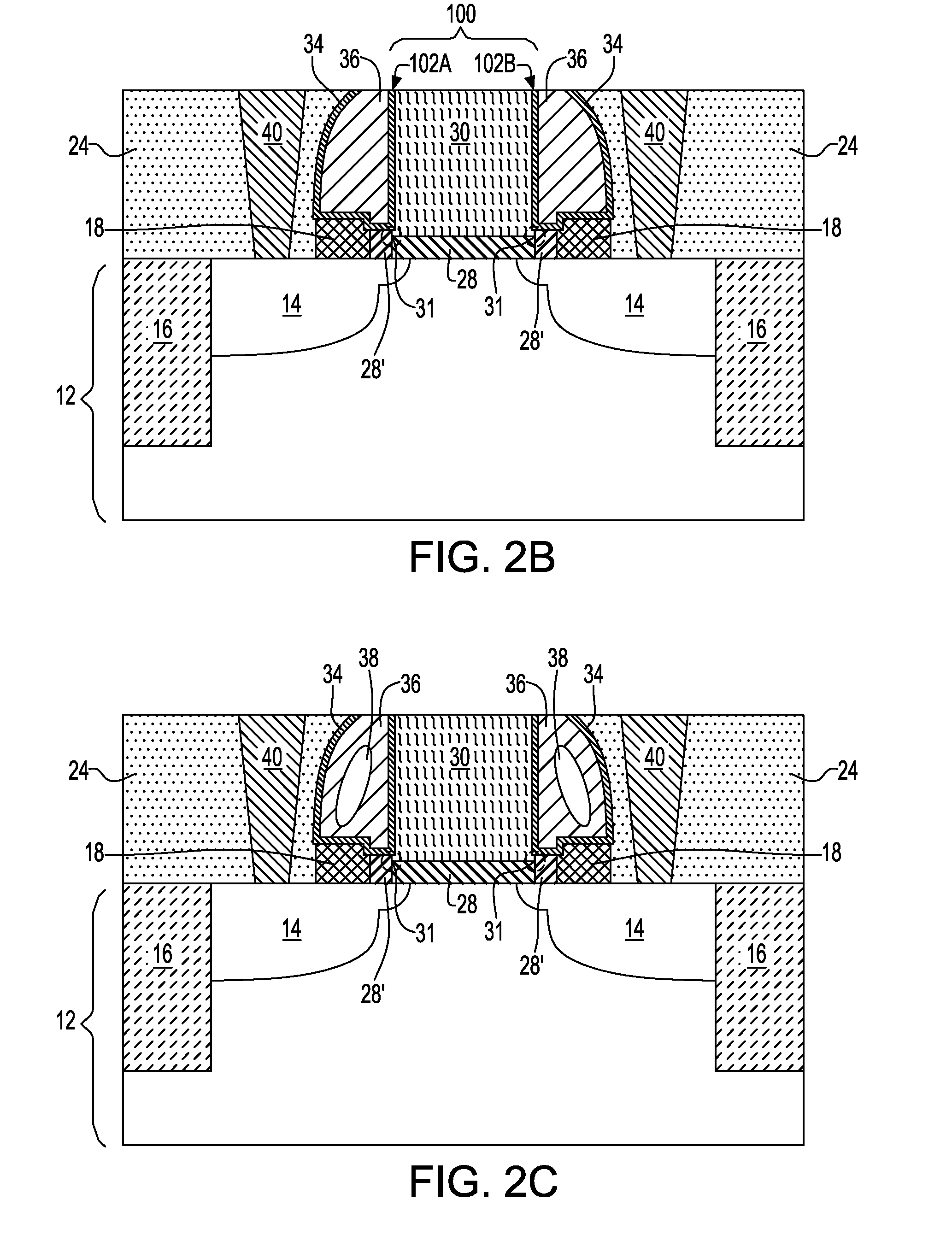

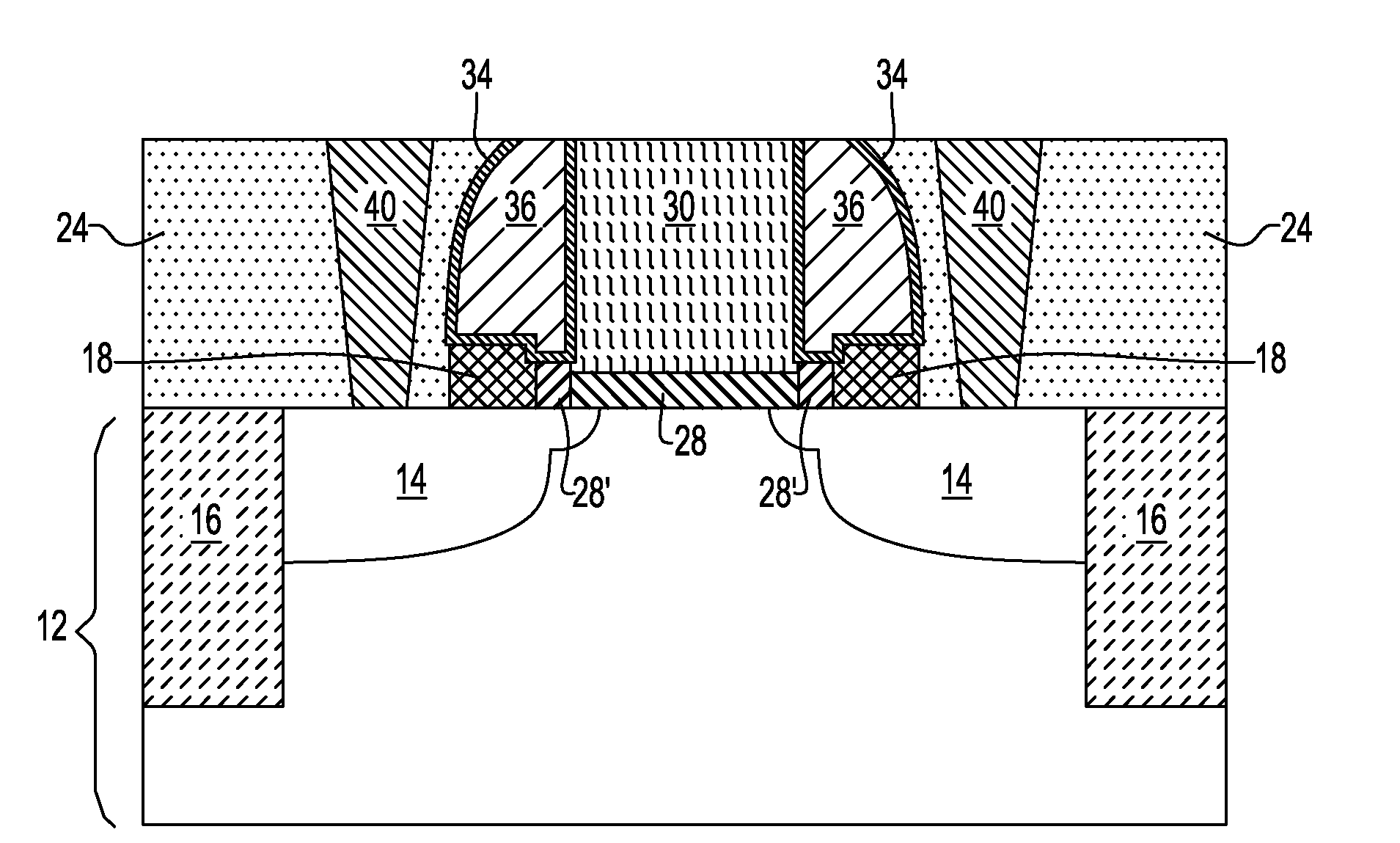

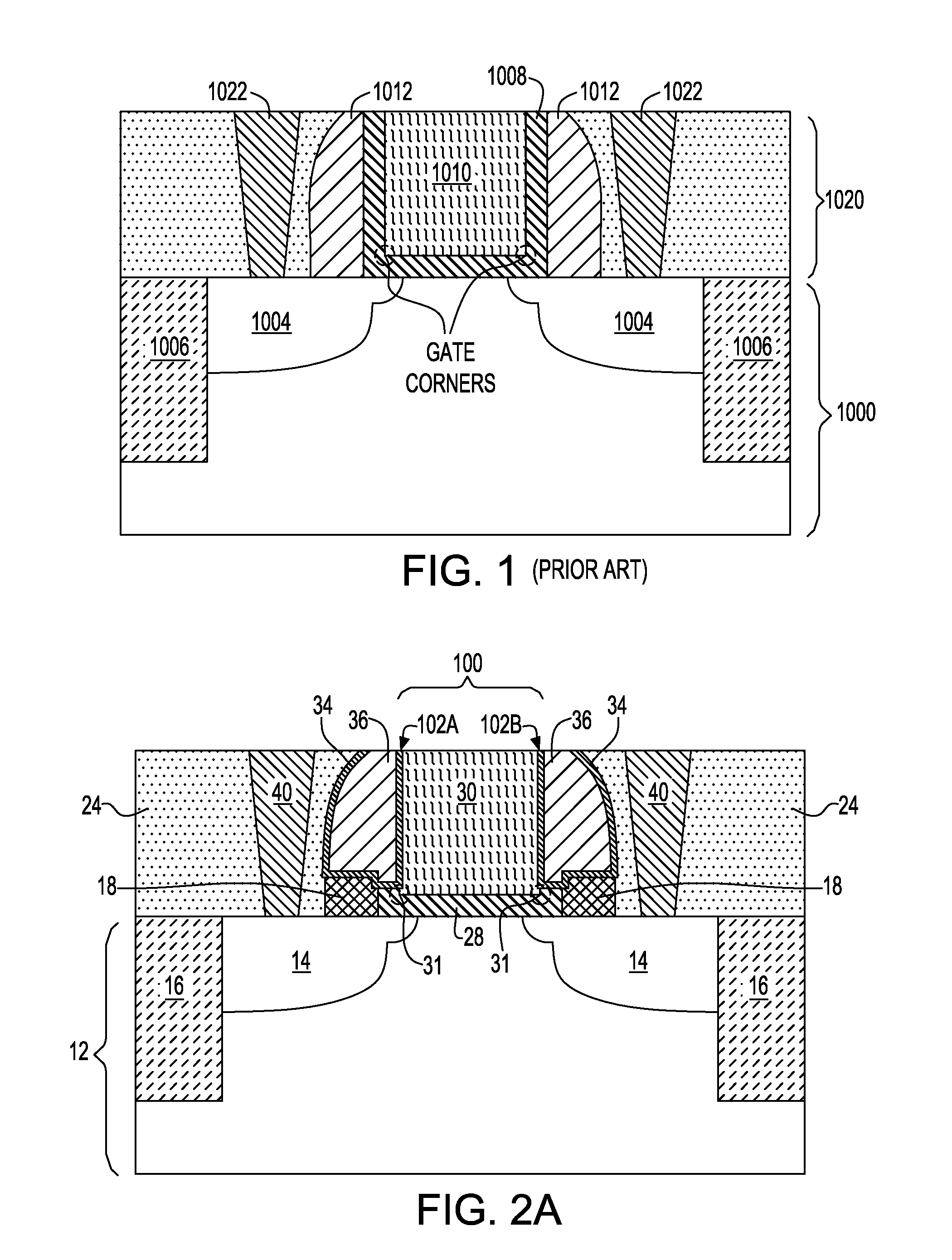

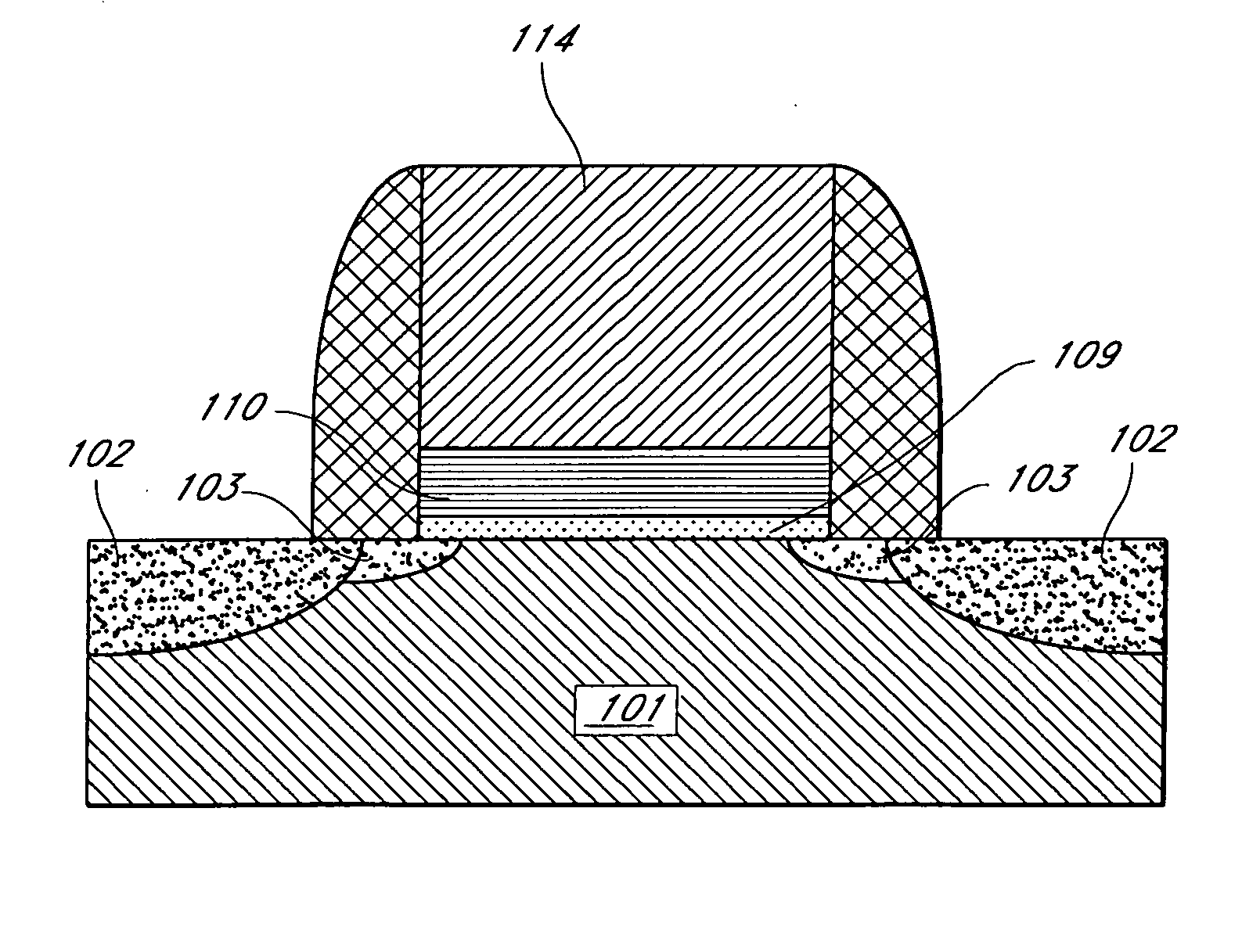

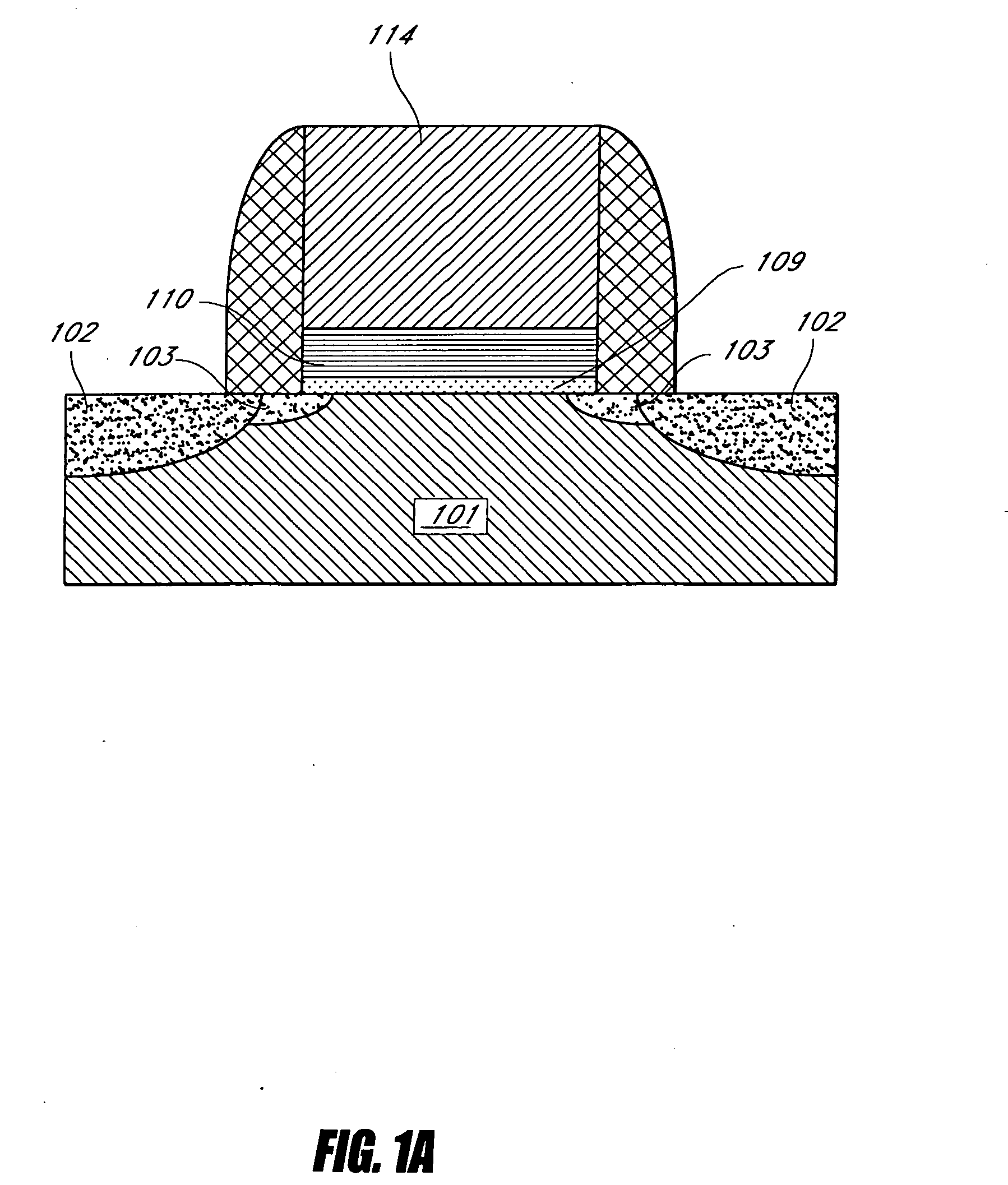

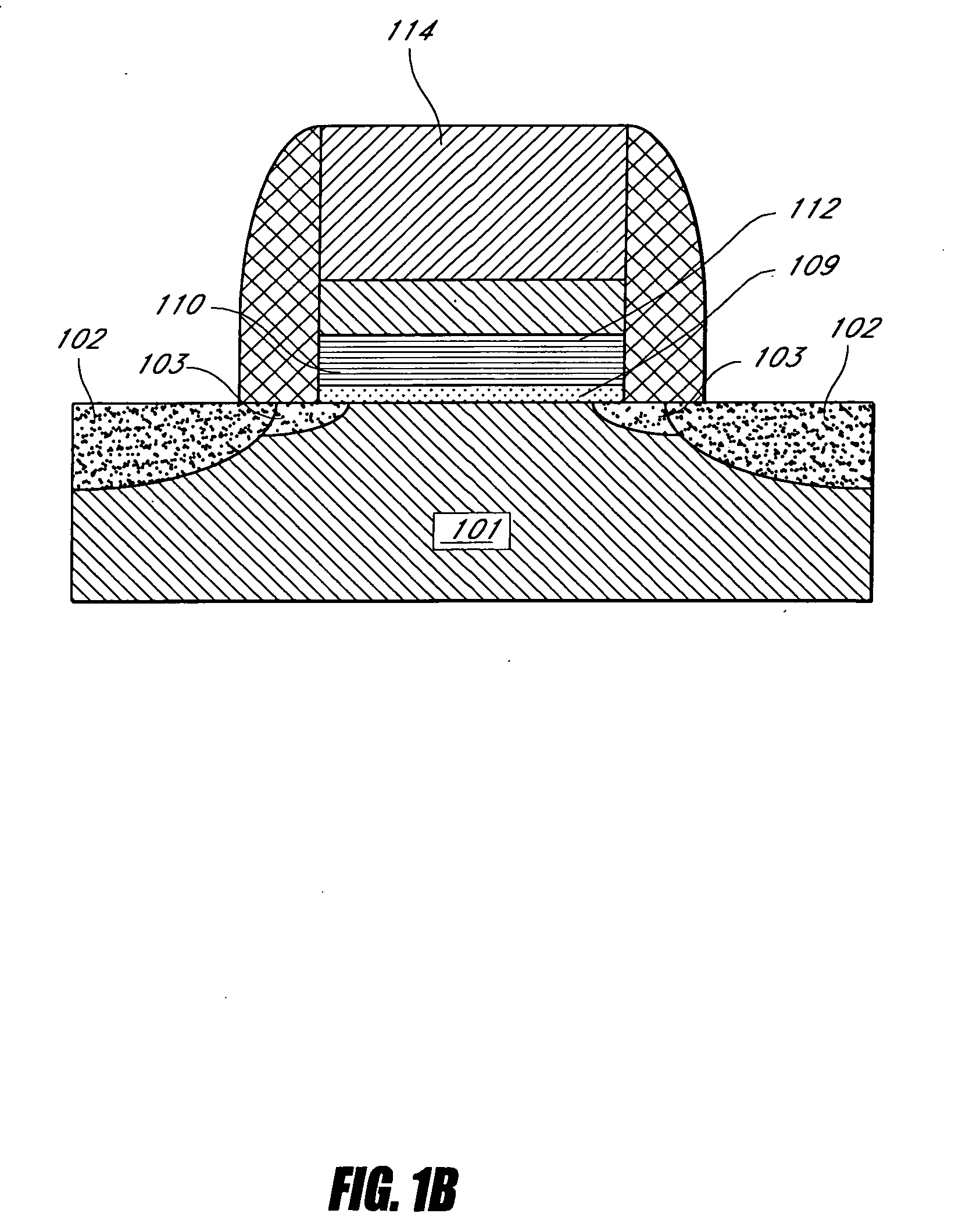

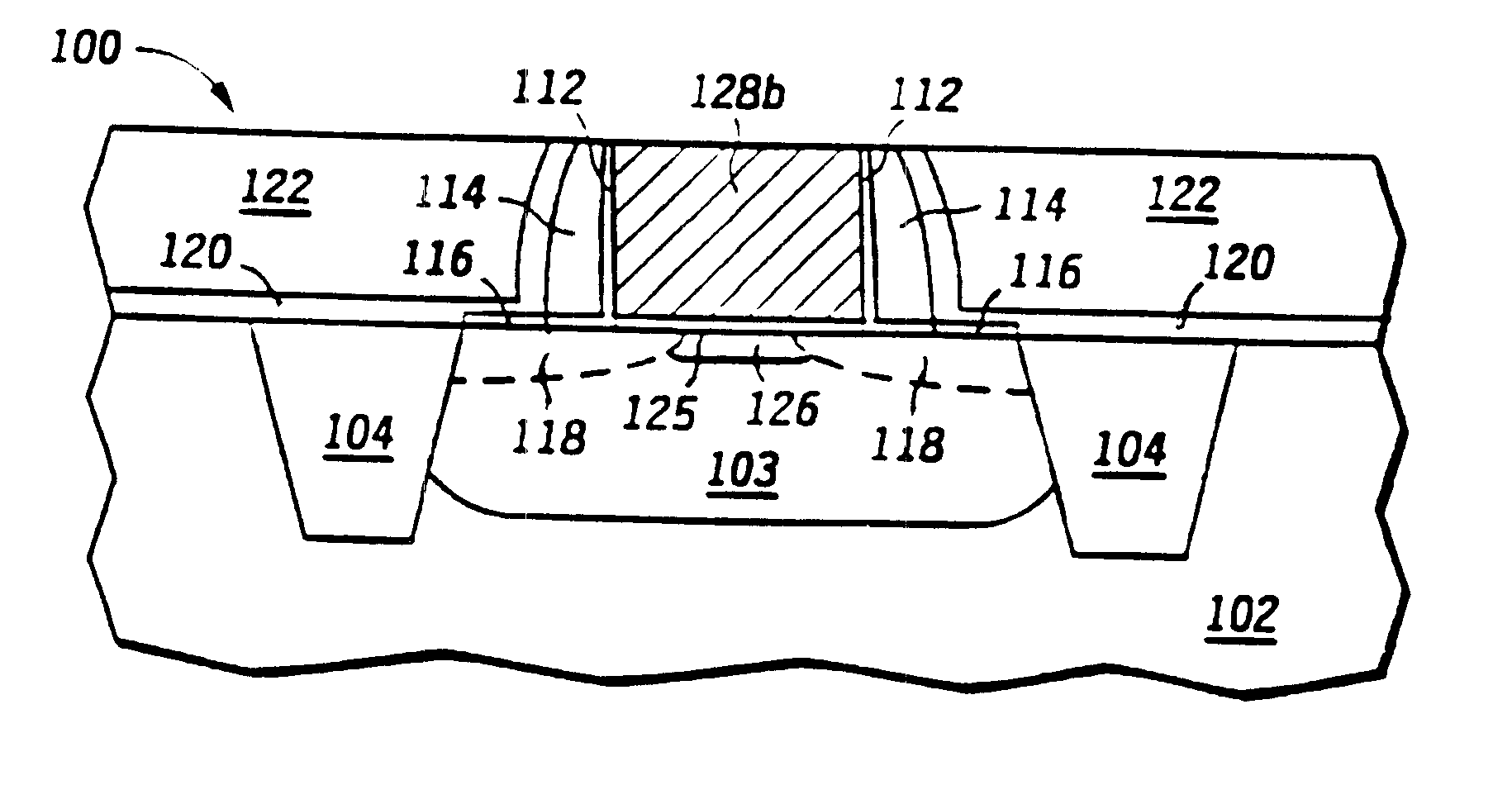

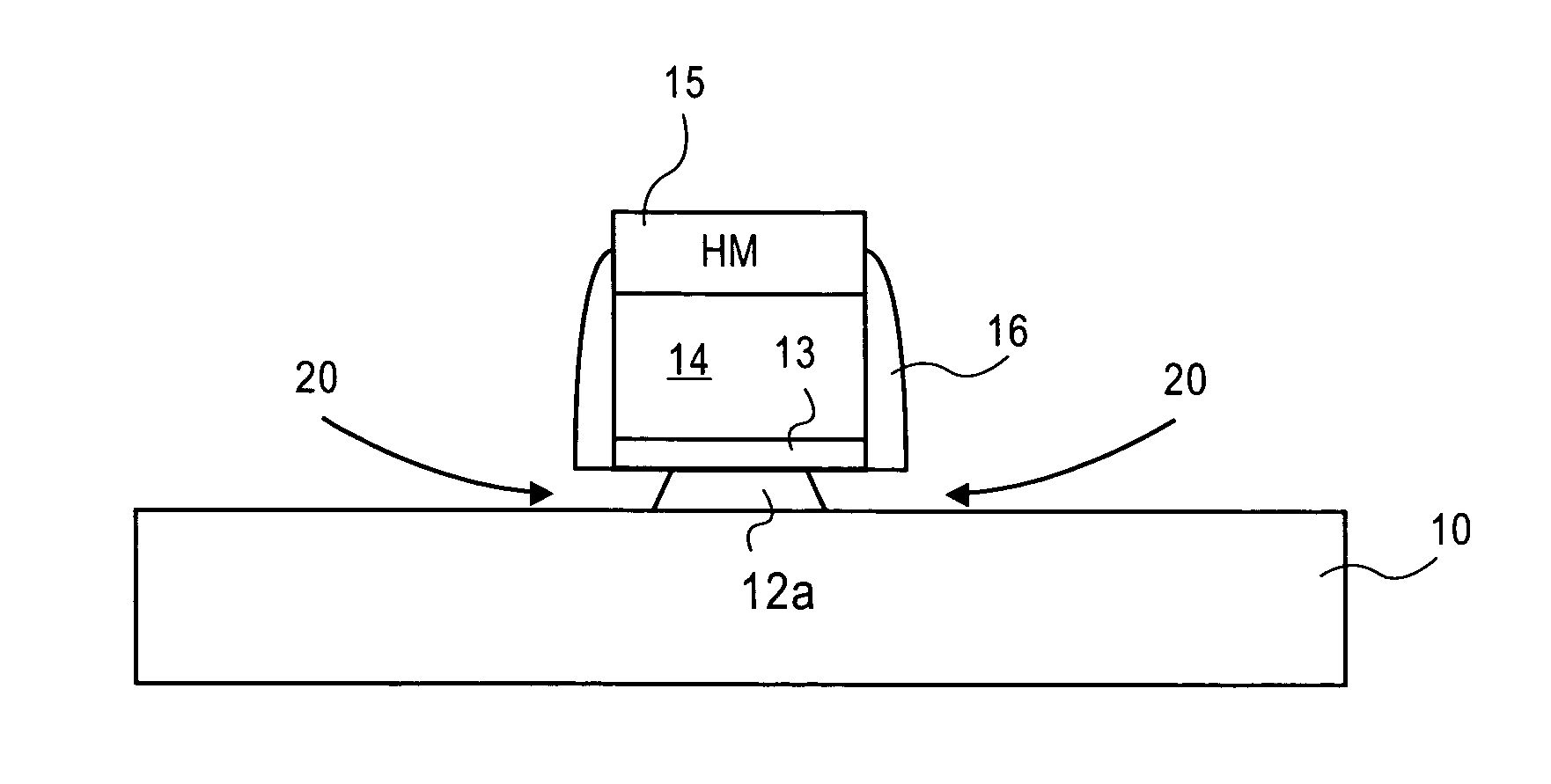

HIGH-k/METAL GATE MOSFET WITH REDUCED PARASITIC CAPACITANCE

InactiveUS20090001480A1Reduce parasitic capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETElectrical conductor

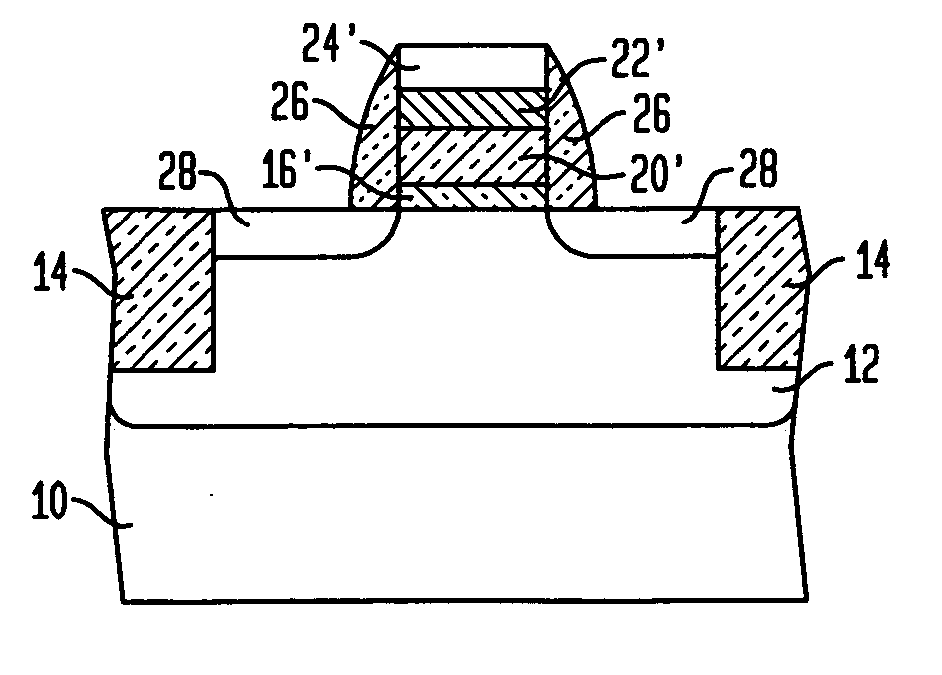

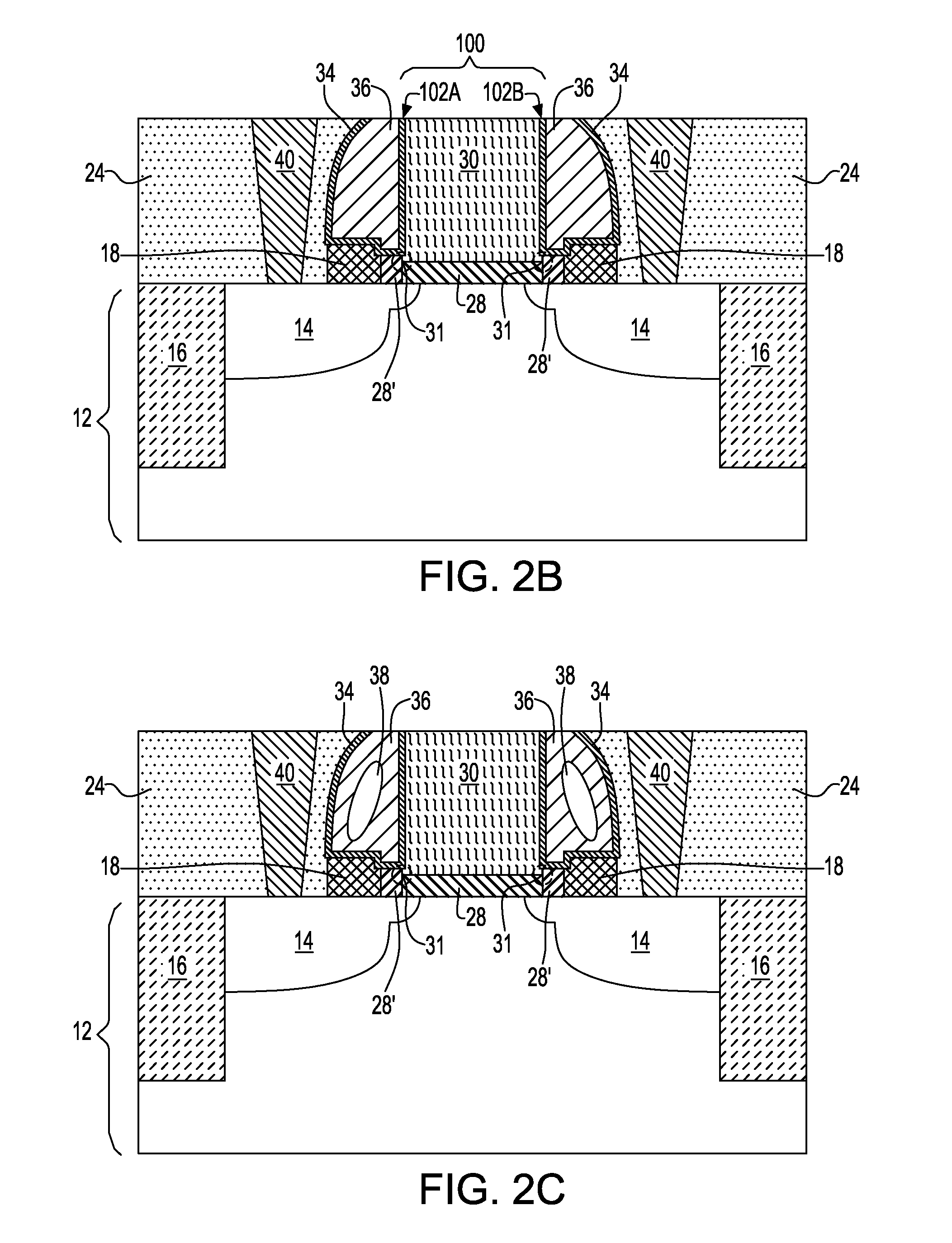

The present invention provides a high-k gate dielectric / metal gate MOSFET that has a reduced parasitic capacitance. The inventive structure includes at least one metal oxide semiconductor field effect transistor (MOSFET) 100 located on a surface of a semiconductor substrate 12. The least one MOSFET 100 includes a gate stack including, from bottom to top, a high-k gate dielectric 28 and a metal-containing gate conductor 30. The metal-containing gate conductor 30 has gate corners 31 located at a base segment of the metal-containing gate conductor. Moreover, the metal-containing gate conductor 30 has vertically sidewalls 102A and 102B devoid of the high-k gate dielectric 28 except at the gate corners 31. A gate dielectric 18 laterally abuts the high-k gate dielectric 28 present at the gate corners 31 and a gate spacer 36 laterally abuts the metal-containing gate conductor 30. The gate spacer 36 is located upon an upper surface of both the gate dielectric 18 and the high-k gate dielectric that is present at the gate corners 31.

Owner:TESSERA INC

HIGH-k/METAL GATE MOSFET WITH REDUCED PARASITIC CAPACITANCE

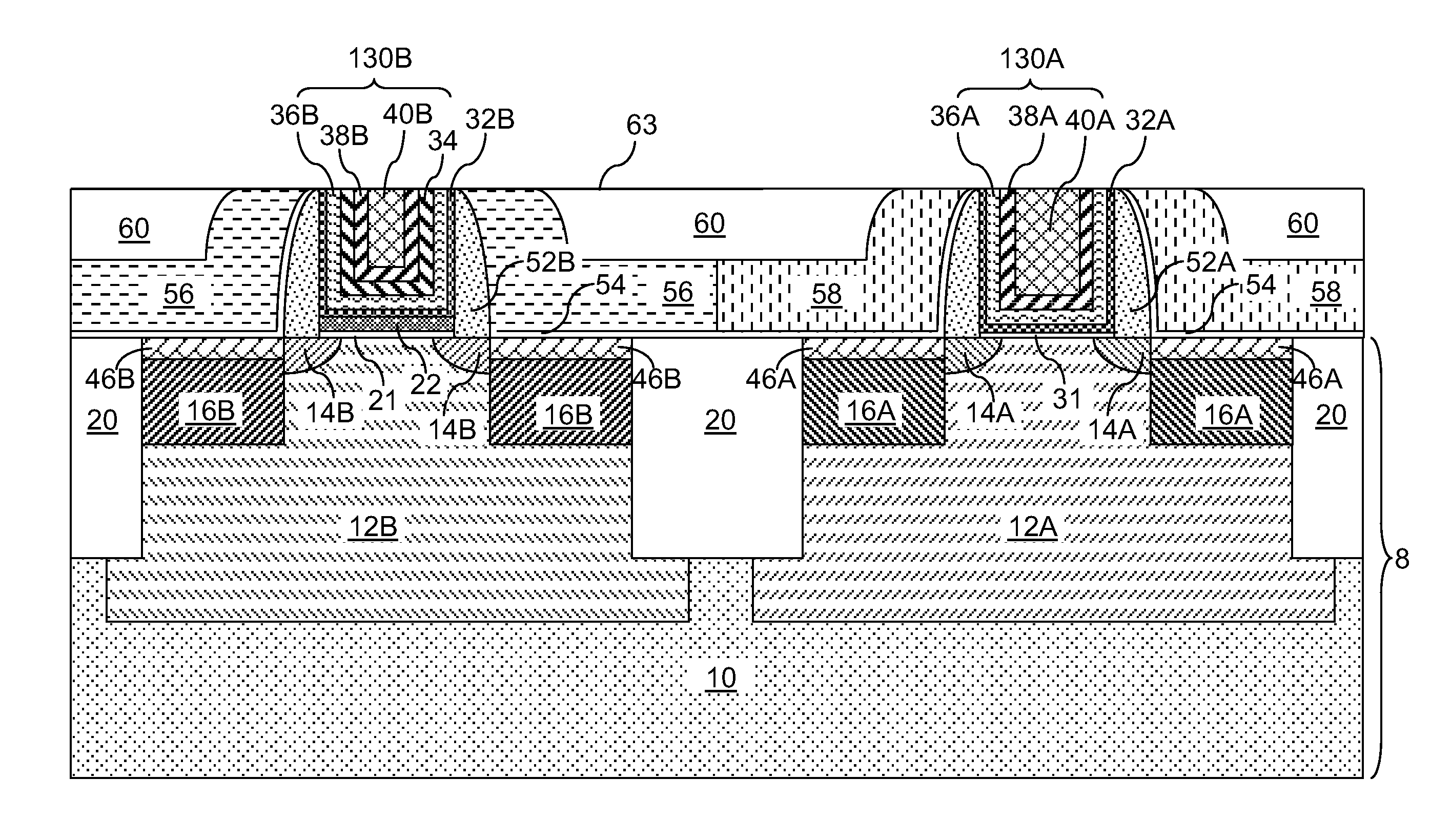

ActiveUS20090321853A1Reduce parasitic capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETGate dielectric

The present invention provides a high-k gate dielectric / metal gate MOSFET that has a reduced parasitic capacitance. The inventive structure includes at least one metal oxide semiconductor field effect transistor (MOSFET) 100 located on a surface of a semiconductor substrate 12. The least one MOSFET 100 includes a gate stack including, from bottom to top, a high-k gate dielectric 28 and a metal-containing gate conductor 30. The metal-containing gate conductor 30 has gate corners 31 located at a base segment of the metal-containing gate conductor. Moreover, the metal-containing gate conductor 30 has vertically sidewalls 102A and 102B devoid of the high-k gate dielectric 28 except at the gate corners 31. A gate dielectric 18 laterally abuts the high-k gate dielectric 28 present at the gate corners 31 and a gate spacer 36 laterally abuts the metal-containing gate conductor 30. The gate spacer 36 is located upon an upper surface of both the gate dielectric 18 and the high-k gate dielectric that is present at the gate corners 31.

Owner:TESSERA INC

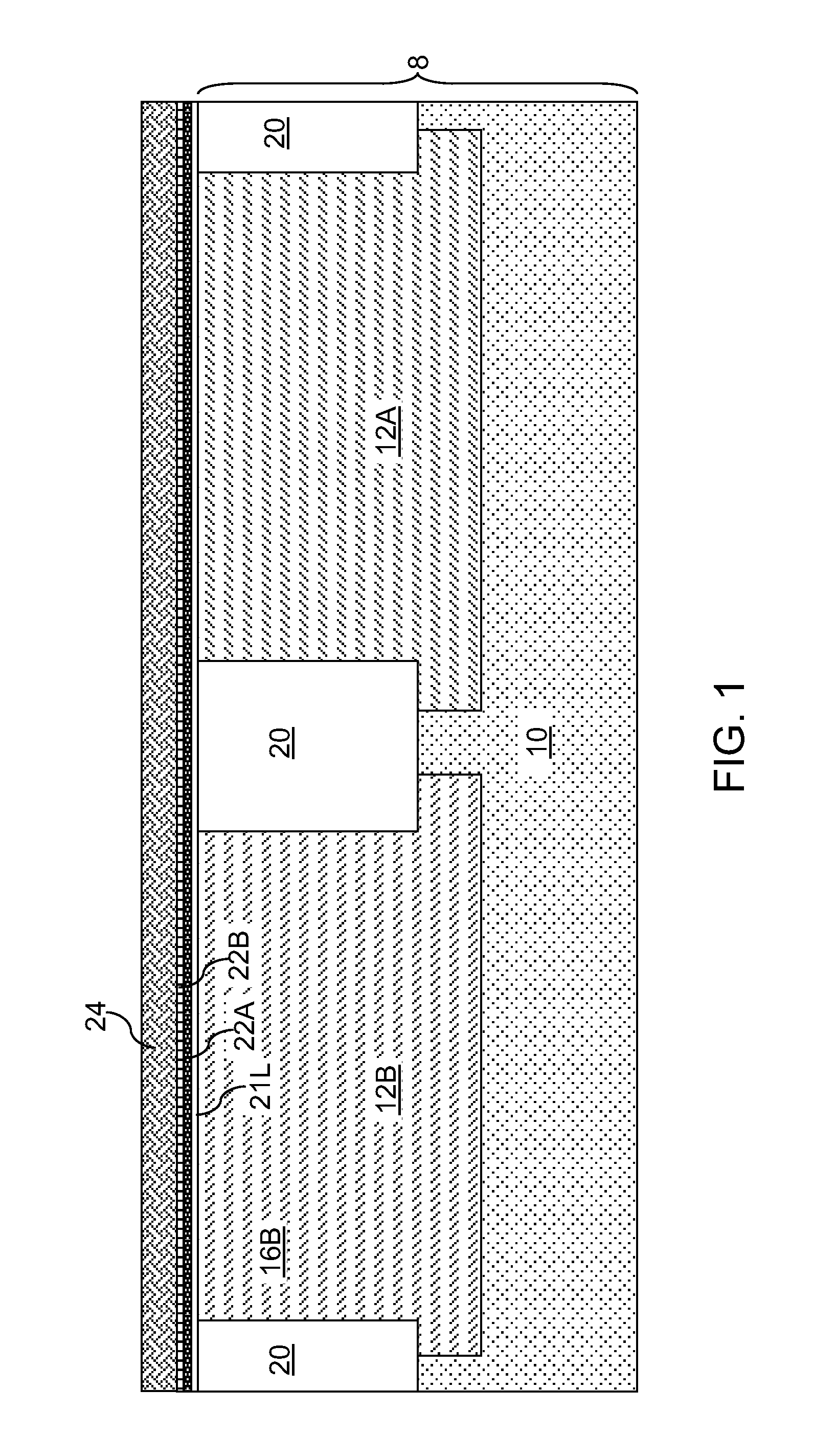

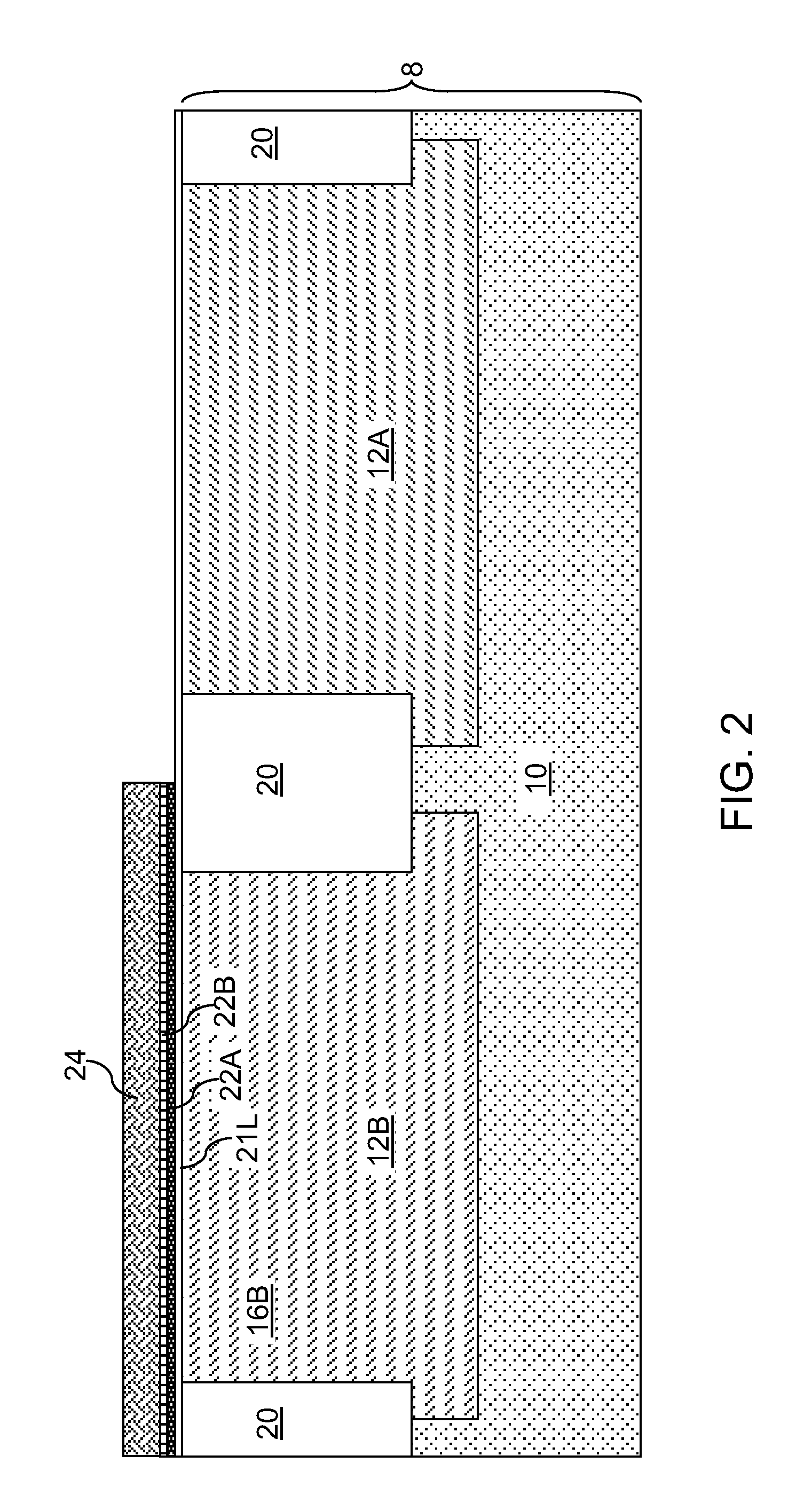

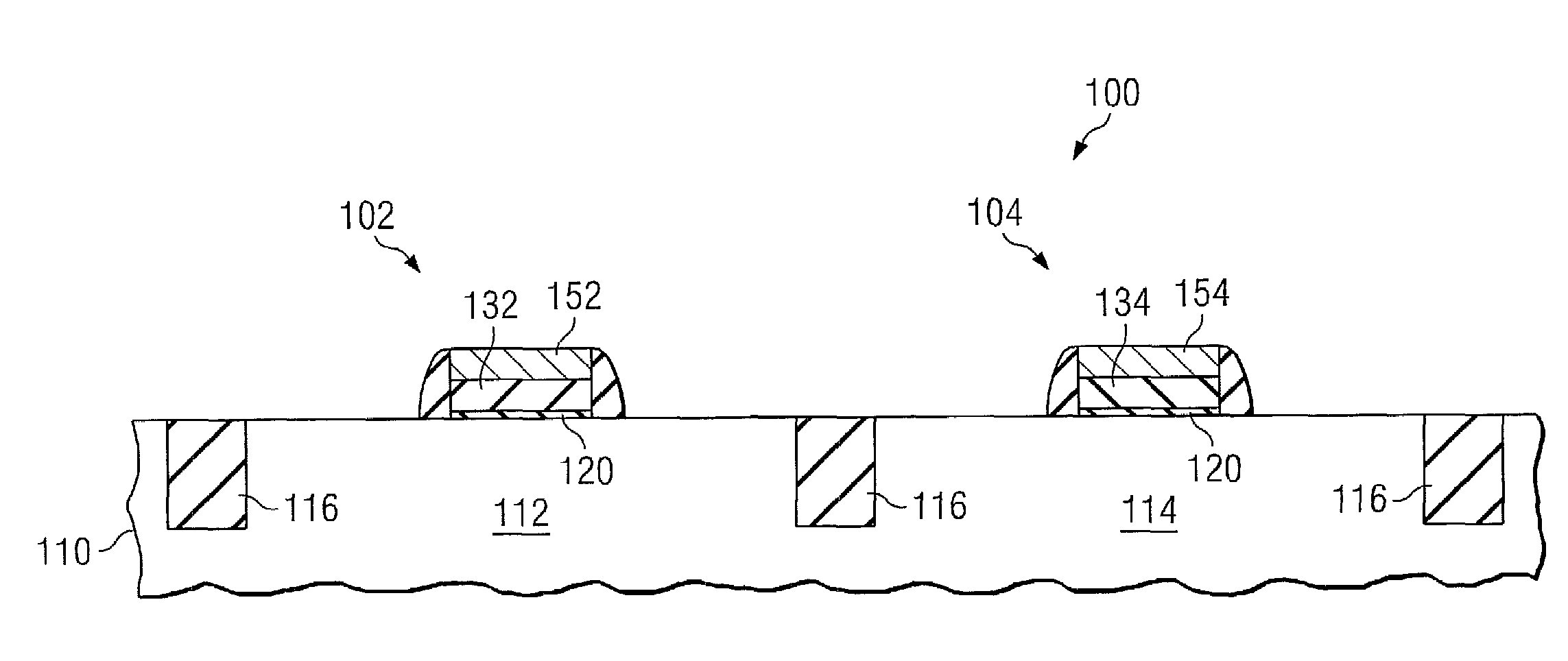

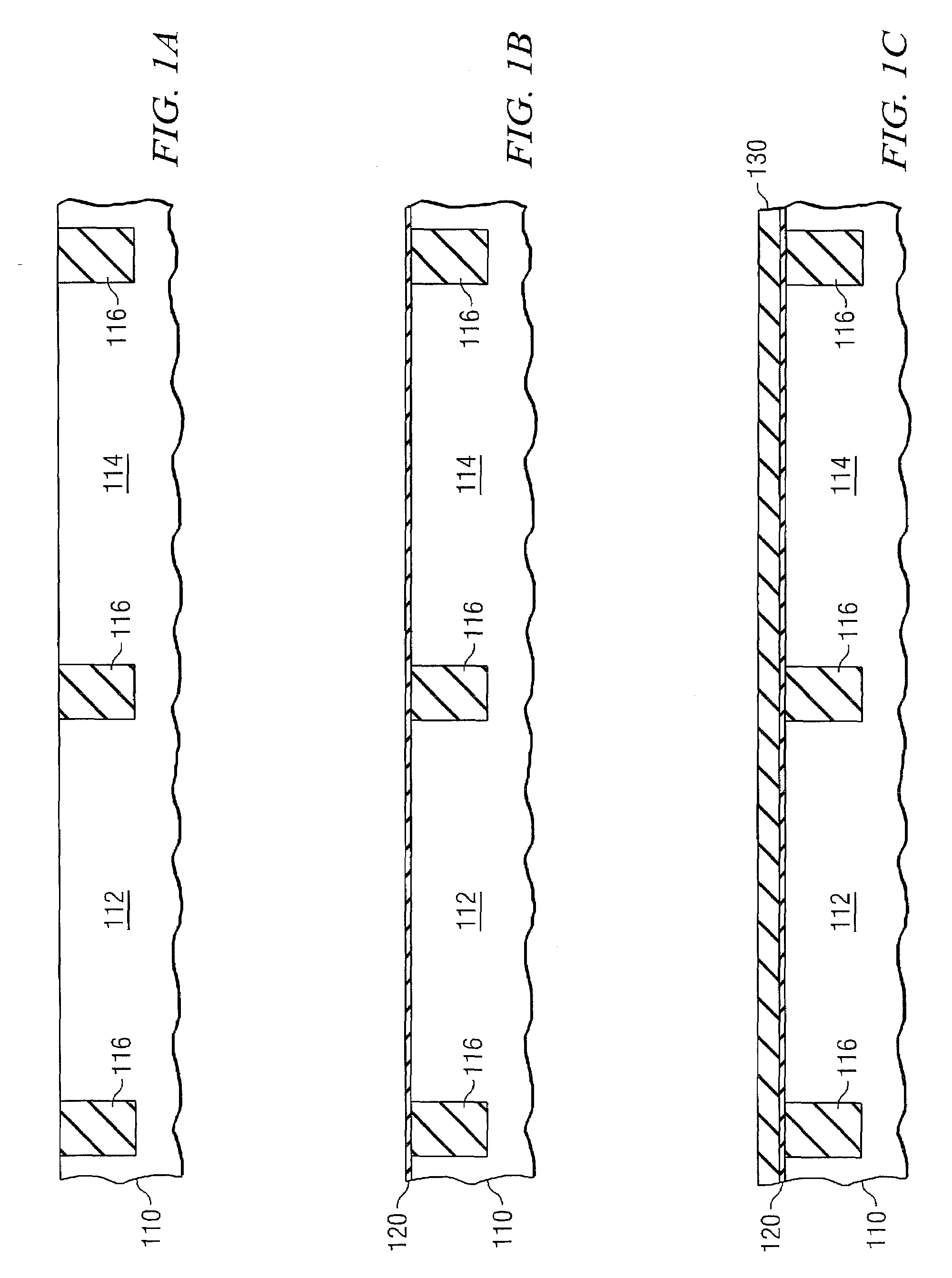

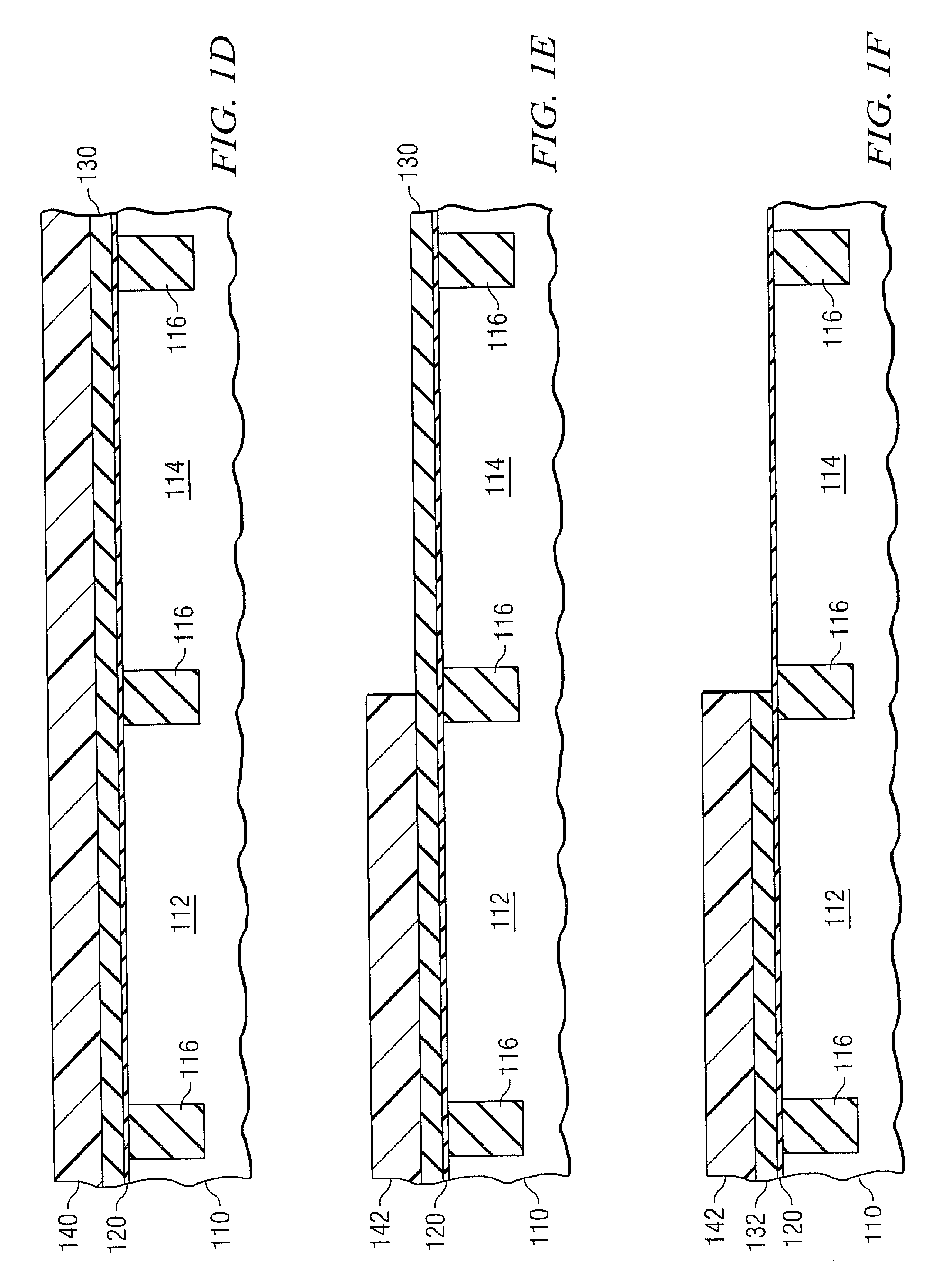

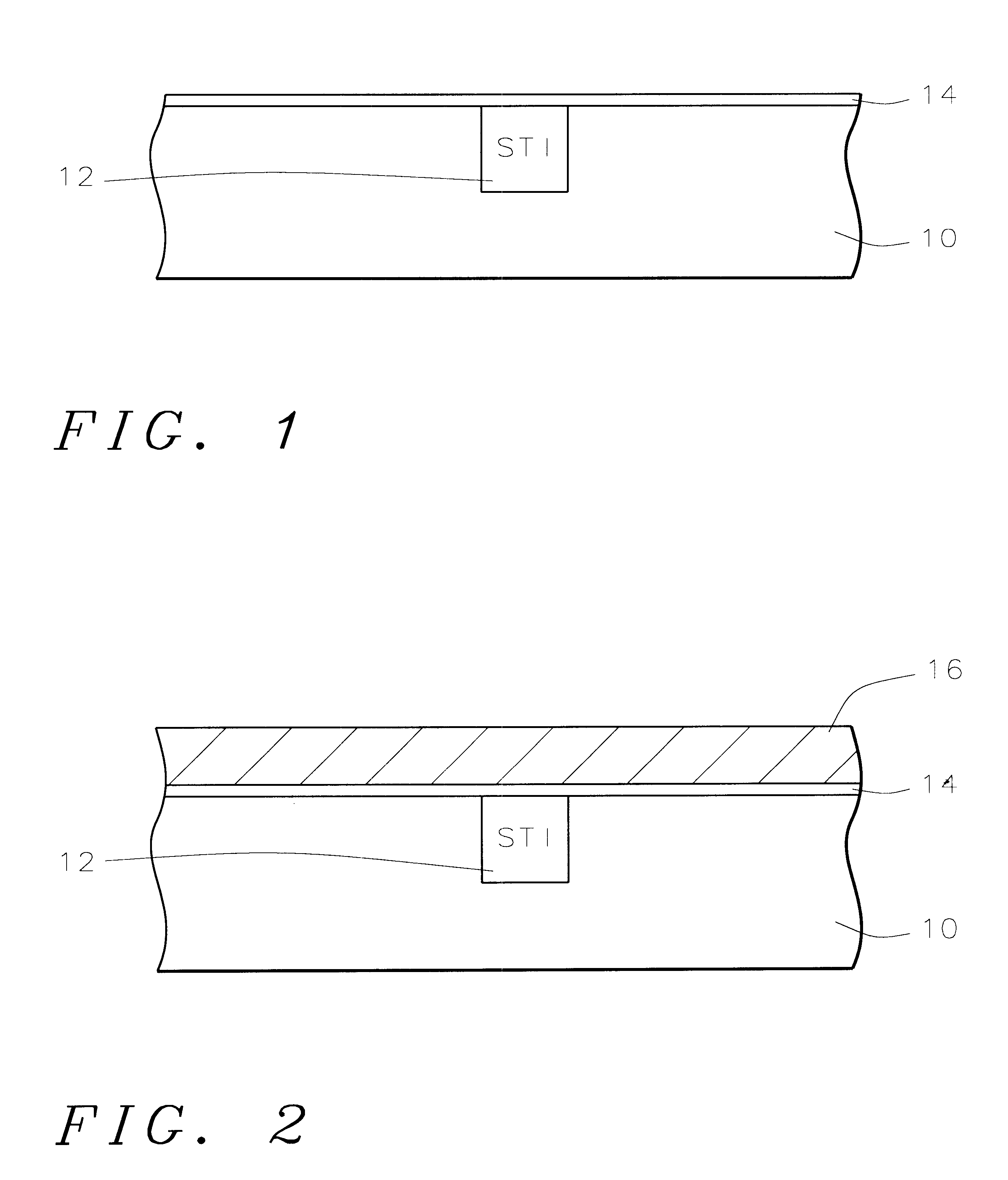

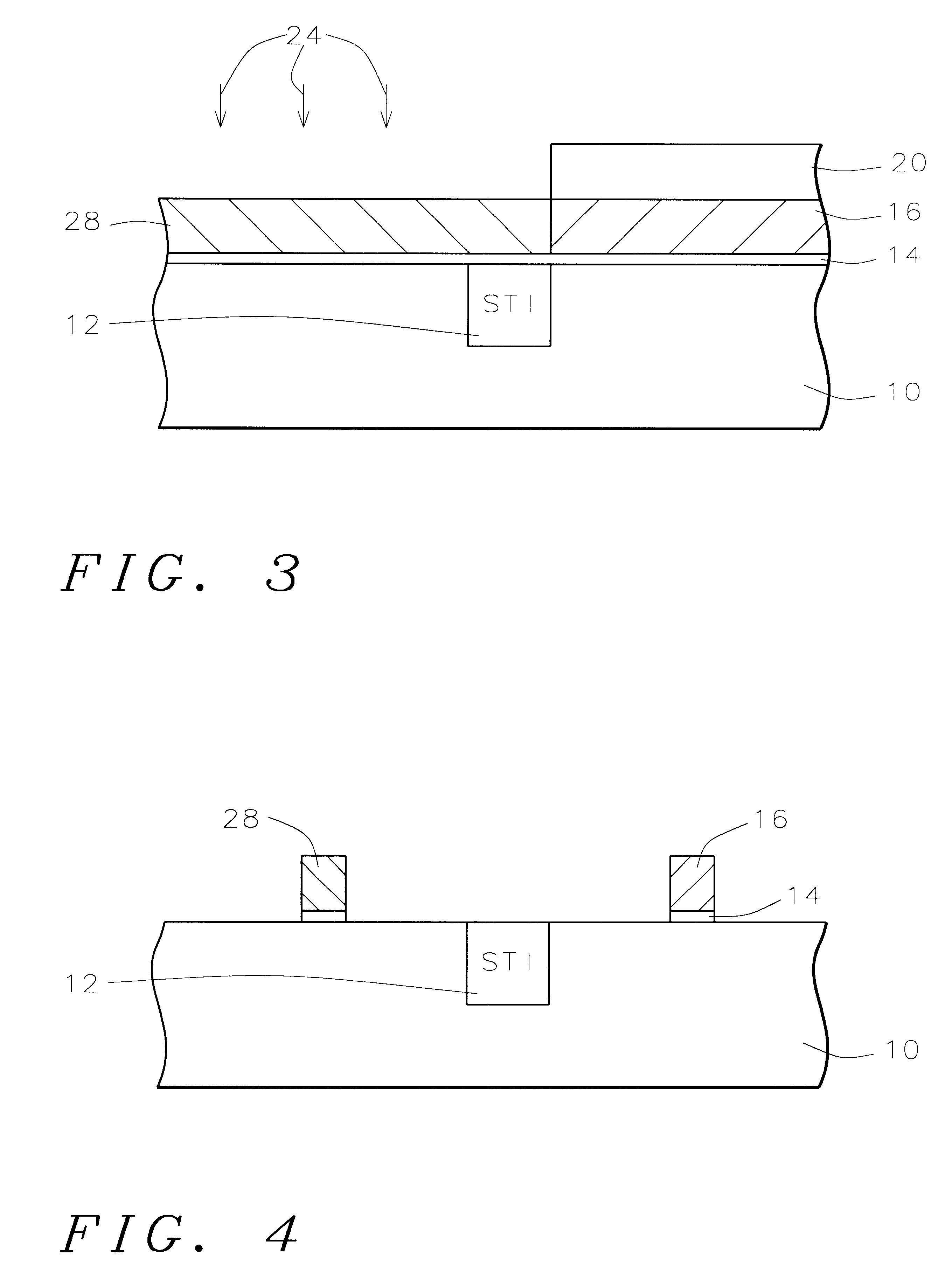

Integrated Circuit (IC) Chip Having Both Metal and Silicon Gate Field Effect Transistors (FETs) and Method of Manufacture

InactiveUS20120292664A1Suppression of short channel effectsWithout impairing performanceTransistorSemiconductor/solid-state device detailsField-effect transistorPolysilicon gate

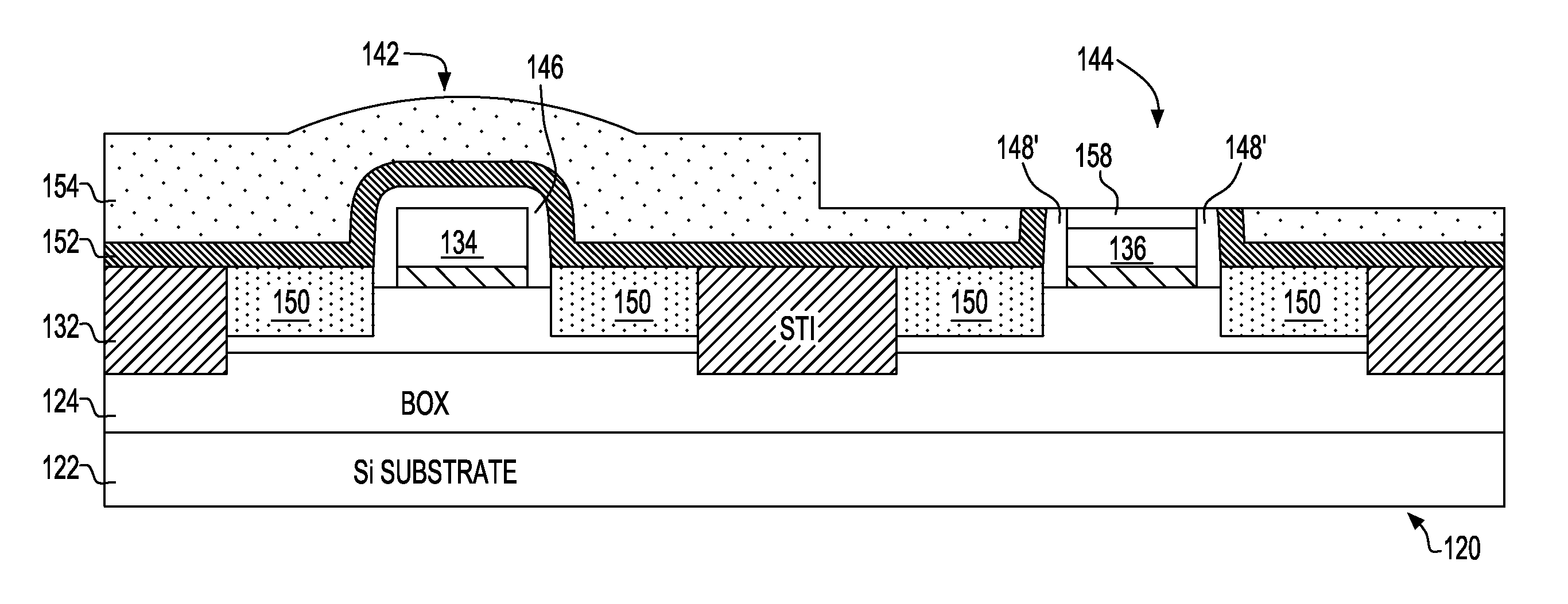

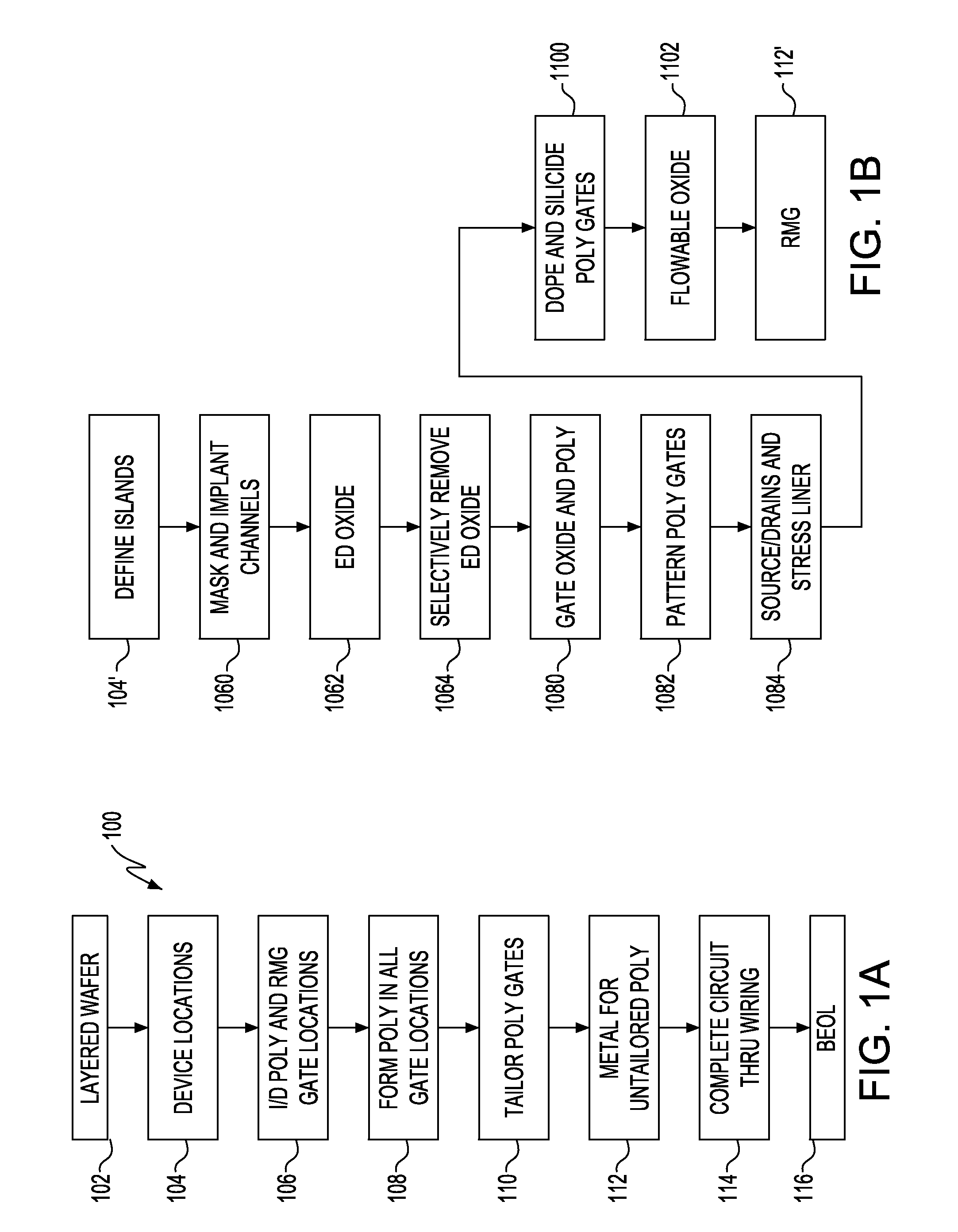

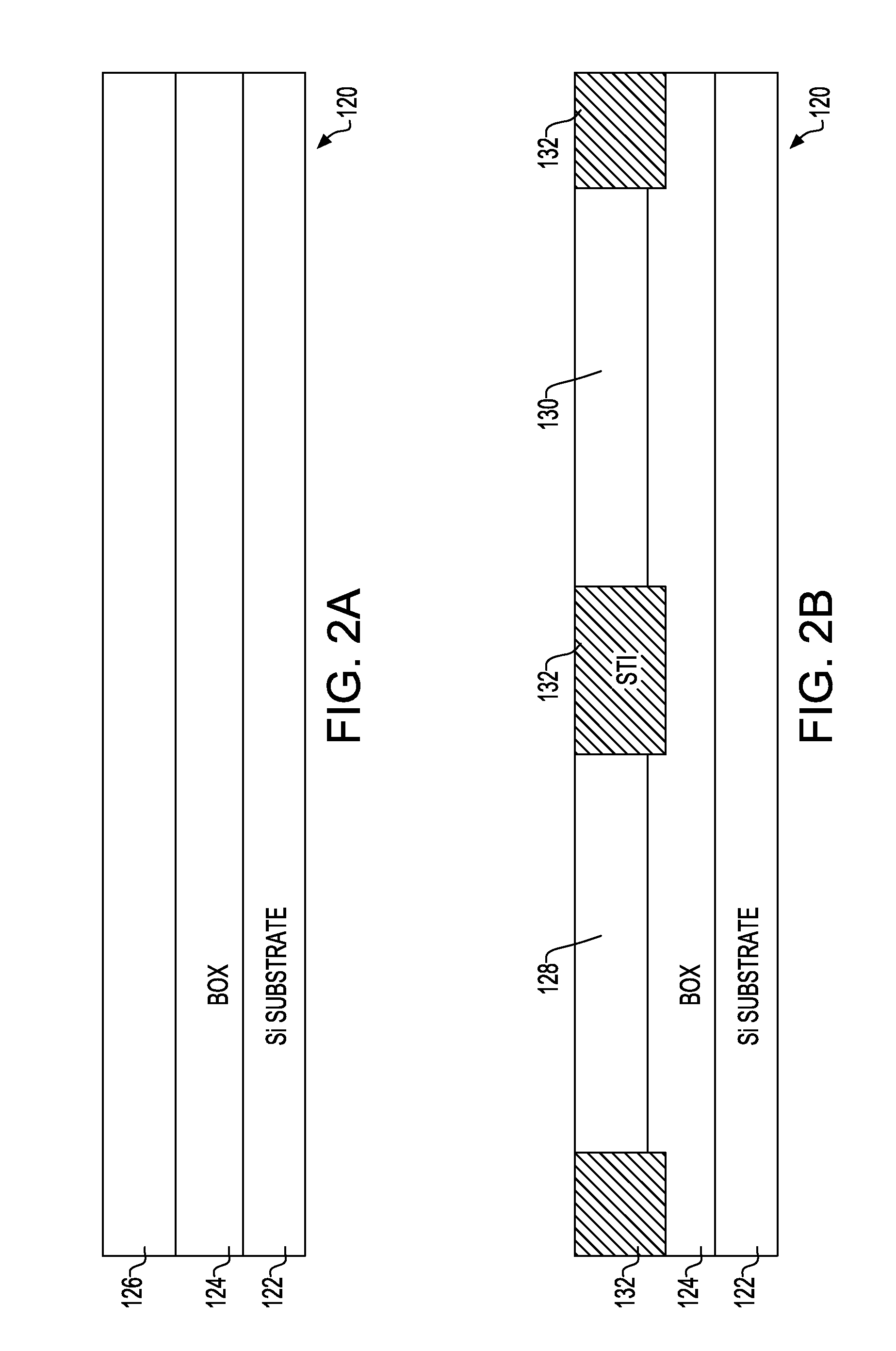

Field Effect Transistors (FETs), Integrated Circuit (IC) chips including the FETs, and a method of forming the FETs on ICs. FET locations are defined on a layered semiconductor wafer, preferably a Silicon On Insulator (SOI) wafer. One or more FET locations are defined as silicon gate locations and remaining as Replacement Metal Gate (RMG) FET locations with at least one of each on the IC. Polysilicon gates are formed in all FET locations. Gates in silicon gate locations are tailored, e.g., doped and silicided. Remaining polysilicon gates are replaced with metal in RMG FET locations. FETs are connected together into circuits with RMG FETs being connected to silicon gate FETs.

Owner:GLOBALFOUNDRIES INC

Method of depositing barrier layer from metal gates

InactiveUS20050104112A1Improve performanceEasy to useTransistorSolid-state devicesGate dielectricRemote plasma

A method of manufacturing a high performance MOS device and transistor gate stacks comprises forming a gate dielectric layer over a semiconductor substrate; forming a barrier layer over the gate dielectric layer by an ALD type process; and forming a gate electrode layer over the barrier layer. The method enables the use of hydrogen plasma, high energy hydrogen radicals and ions, other reactive radicals, reactive oxygen and oxygen containing precursors in the processing steps subsequent to the deposition of the gate dielectric layer of the device. The ALD process for forming the barrier layer is performed essentially in the absence of plasma and reactive hydrogen radials and ions. This invention makes it possible to use oxygen as a precursor in the deposition of the metal gates. The barrier film also allows the use of hydrogen plasma in the form of either direct or remote plasma in the deposition of the gate electrode. Furthermore, the barrier film prevents the electrode material from reacting with the gate dielectric material. The barrier layer is ultra thin and, at the same time, it forms a uniform cover over the entire surface of the gate dielectric.

Owner:HAUKKA SUVI +1

Three-Dimensional Semiconductor Device and Manufacturing Method Therefor

InactiveUS20170154895A1Improve control characteristicsReduce off-state leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETEtching

A three-dimensional semiconductor device, comprising a plurality of memory cell transistors and a plurality of select transistors at least partially overlapped in the vertical direction, wherein each select transistor comprises a first drain, an active region and a common source formed in the substrate, distributed along the vertical direction, as well as a metal gate distributed around the active region; wherein each memory cell transistor comprises a channel layer distributed perpendicularly to the substrate surface, a plurality of inter-layer insulating layers and a plurality of gate stack structures alternately stacked along the sidewalls of said channel layer, a second drain located on top of said channel layer; wherein said channel layer and said the first drain are electrically connected. In accordance with the three-dimensional semiconductor memory device and manufacturing method of the present invention, the multi-gate MOSFET is formed beneath the stack structure of the memory cell string including vertical channel to serve as the select transistor, this can improve the control characteristics of the gate threshold voltage, reduce the off-state leakage current, prevent the substrate from over-etching, and effectively improve the reliability of the device.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

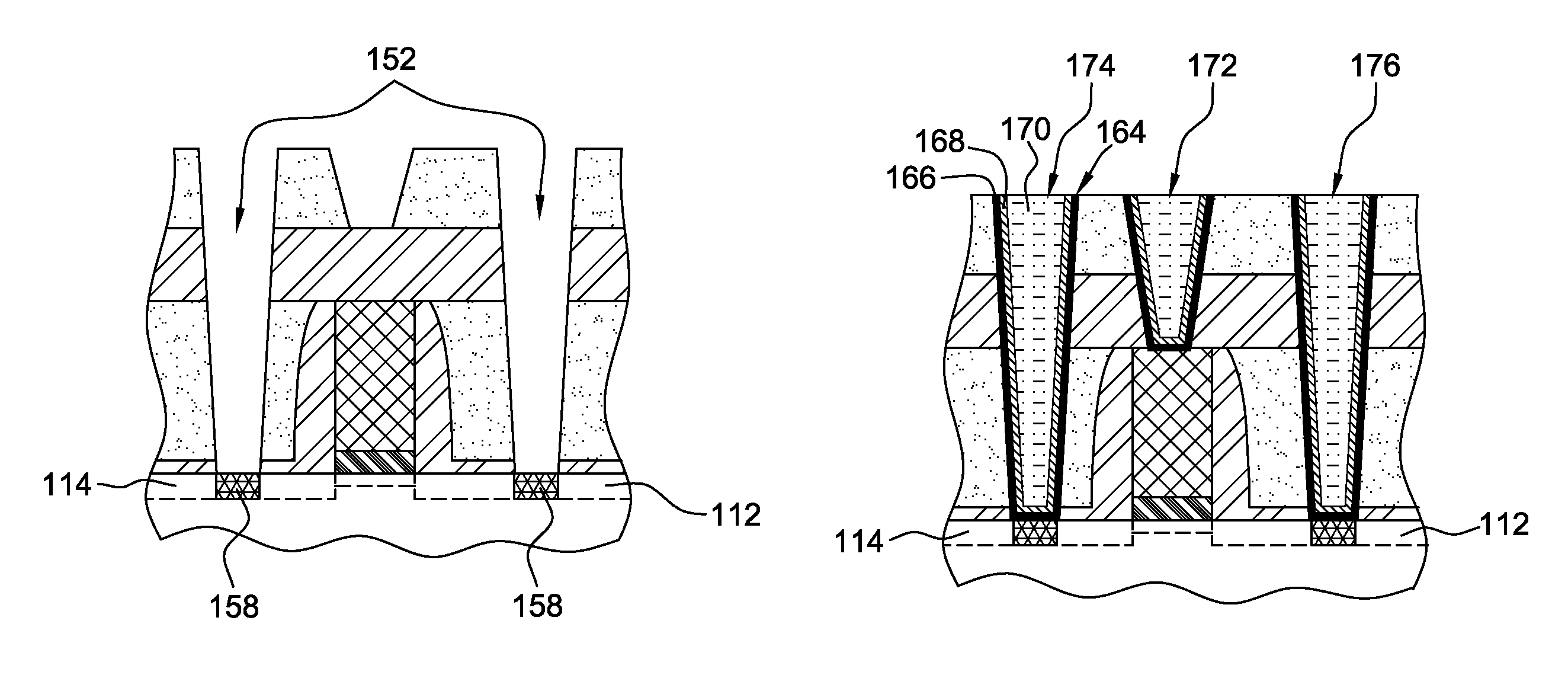

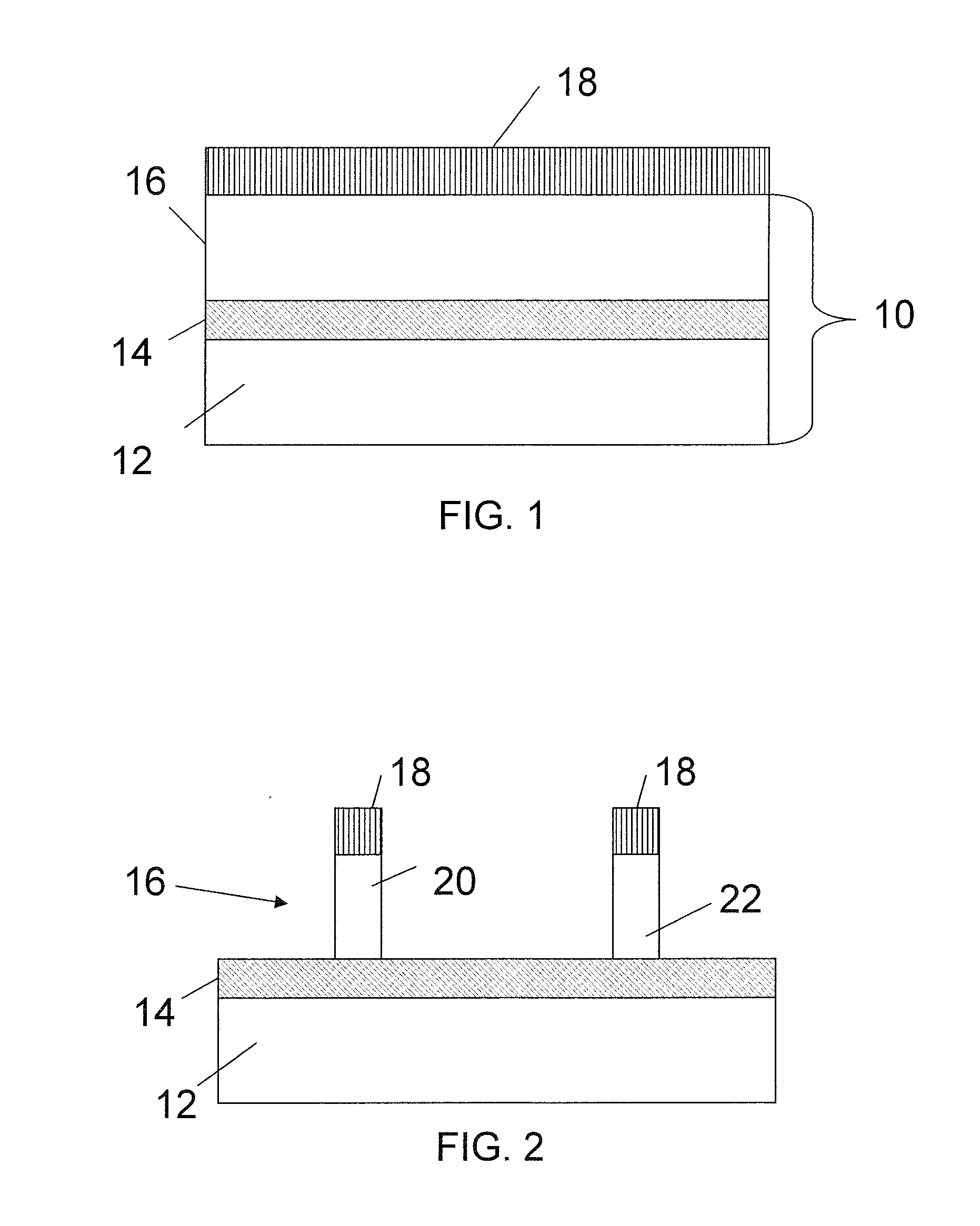

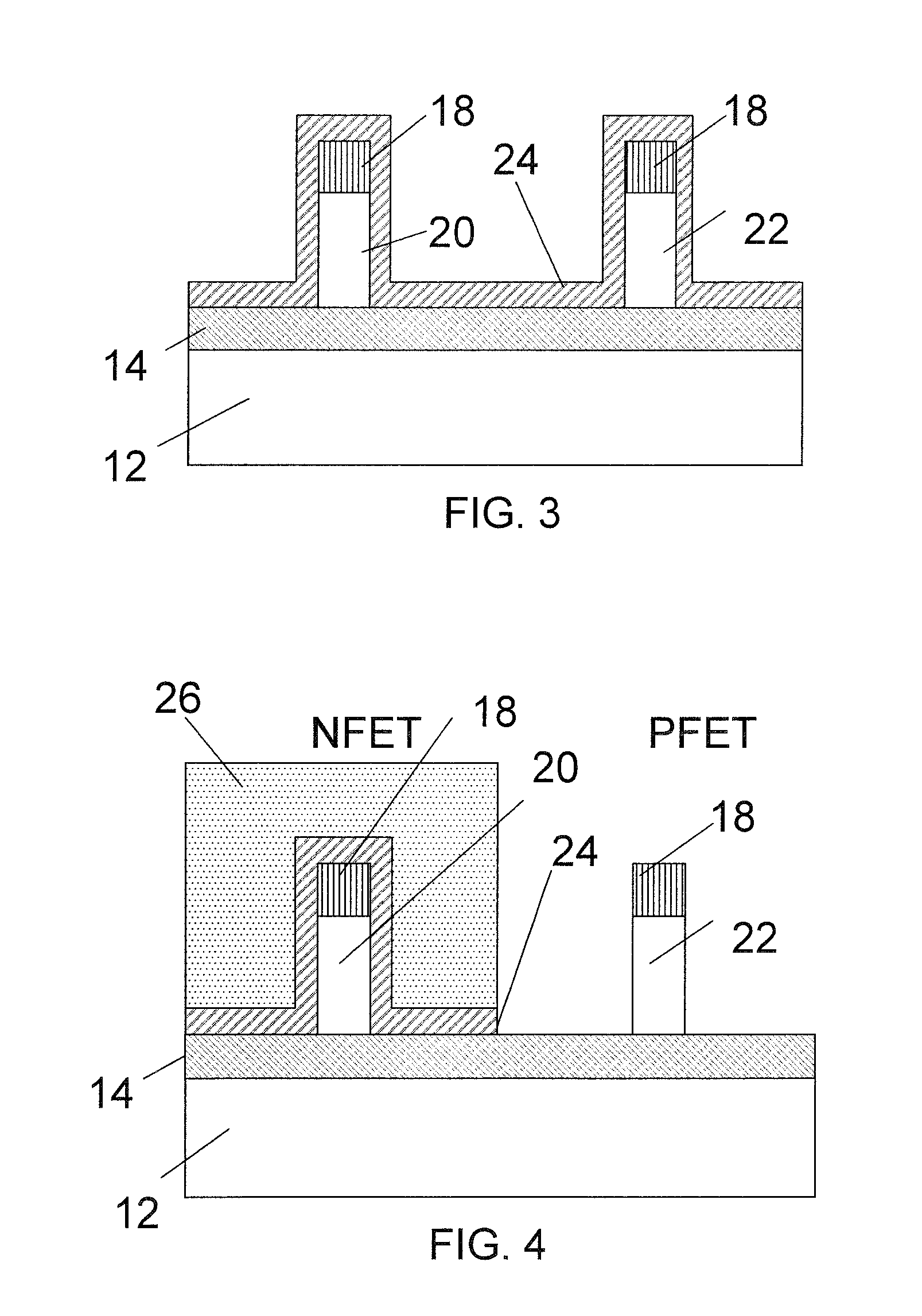

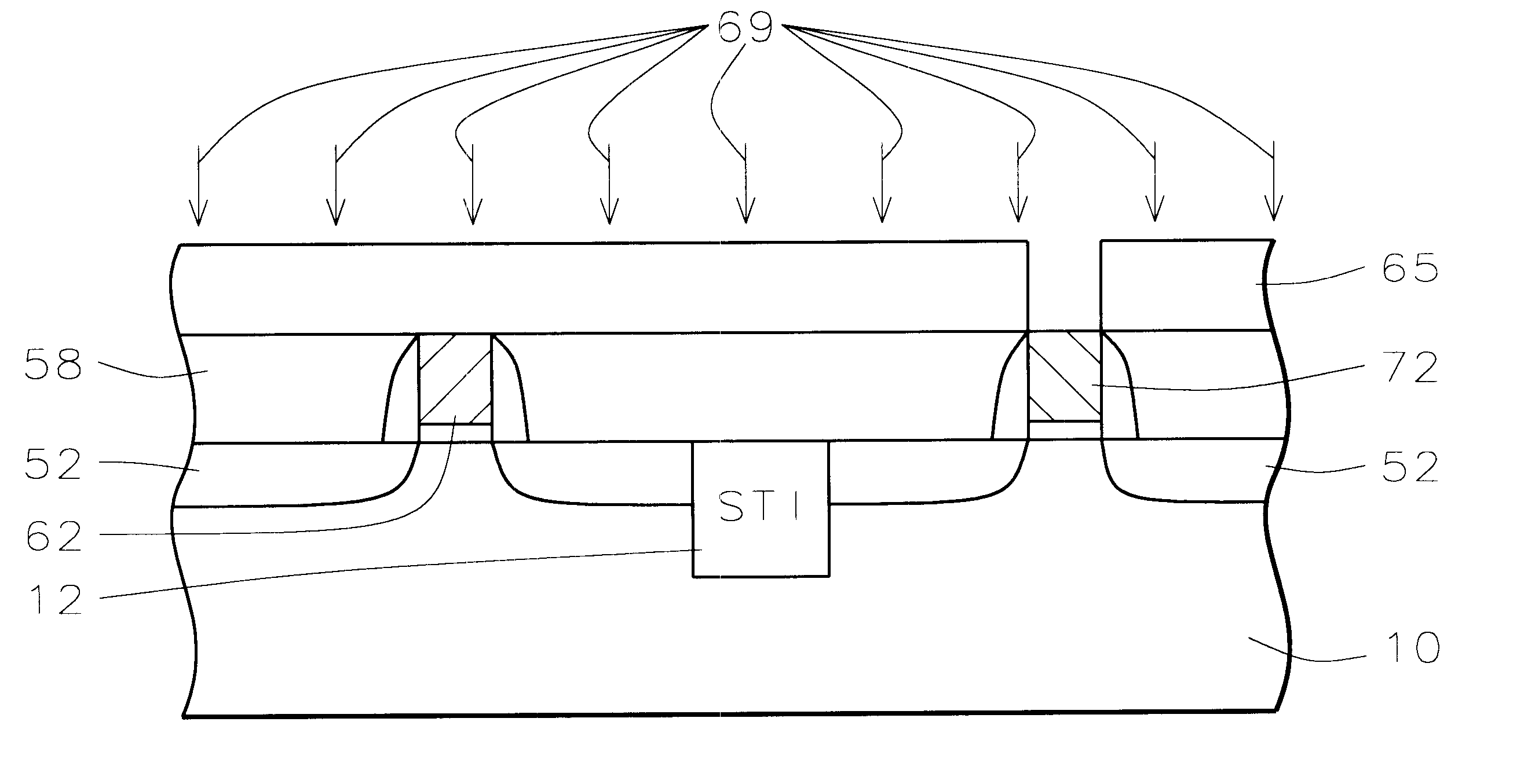

Metal gate MOS transistors and methods for making the same

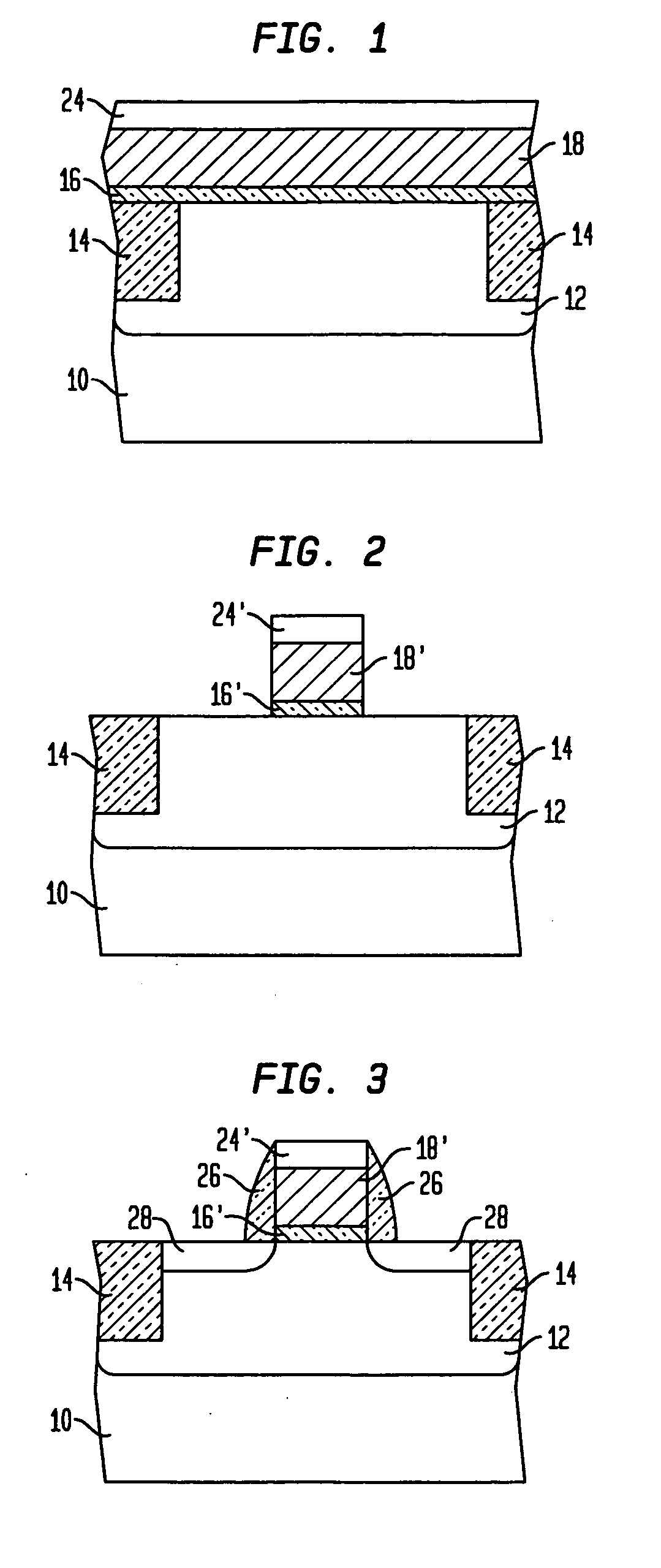

InactiveUS6936508B2Less dopantsReduce complexitySemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricNitrogen

Semiconductor devices and fabrication methods are provided, in which metal transistor gates are provided for MOS transistors. Metal boride is formed above a gate dielectric to create PMOS gate structures and metal nitride is formed over a gate dielectric to provide NMOS gate structures. The metal portions of the gate structures are formed from an initial starting material that is either a metal boride or a metal nitride, after which the starting material is provided with boron or nitrogen in one of the PMOS and NMOS regions through implantation, diffusion, or other techniques, either before or after formation of the conductive upper material, and before or after gate patterning. The change in the boron or nitrogen content of the starting material provides adjustment of the material work function, thereby tuning the threshold voltage of the resulting PMOS or NMOS transistors.

Owner:TEXAS INSTR INC

Silicide protection during contact metallization and resulting semiconductor structures

ActiveUS9111907B2Avoid damageOvercomes shortcomingSemiconductor/solid-state device detailsSolid-state devicesSalicideSemiconductor structure

Owner:GLOBALFOUNDRIES U S INC

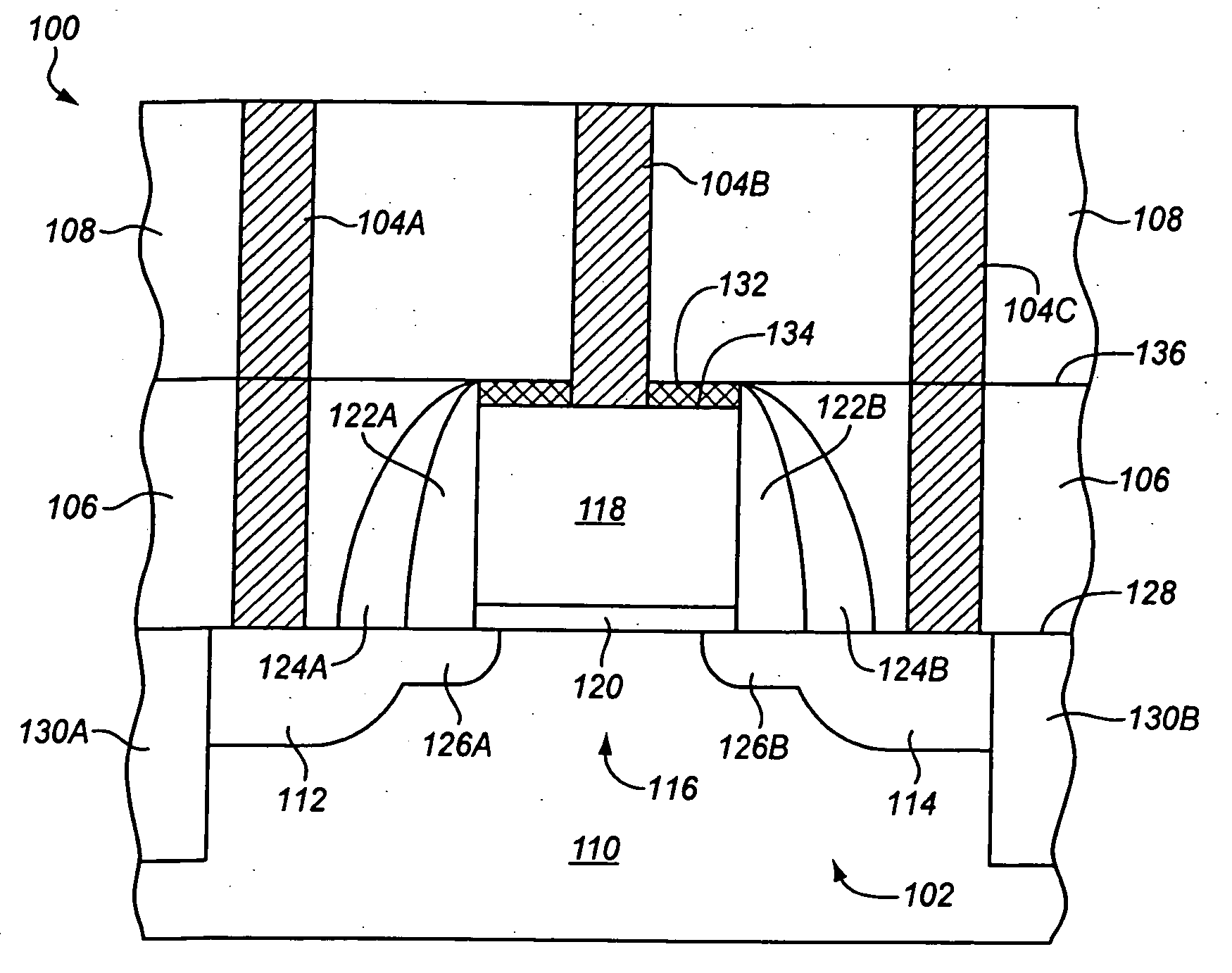

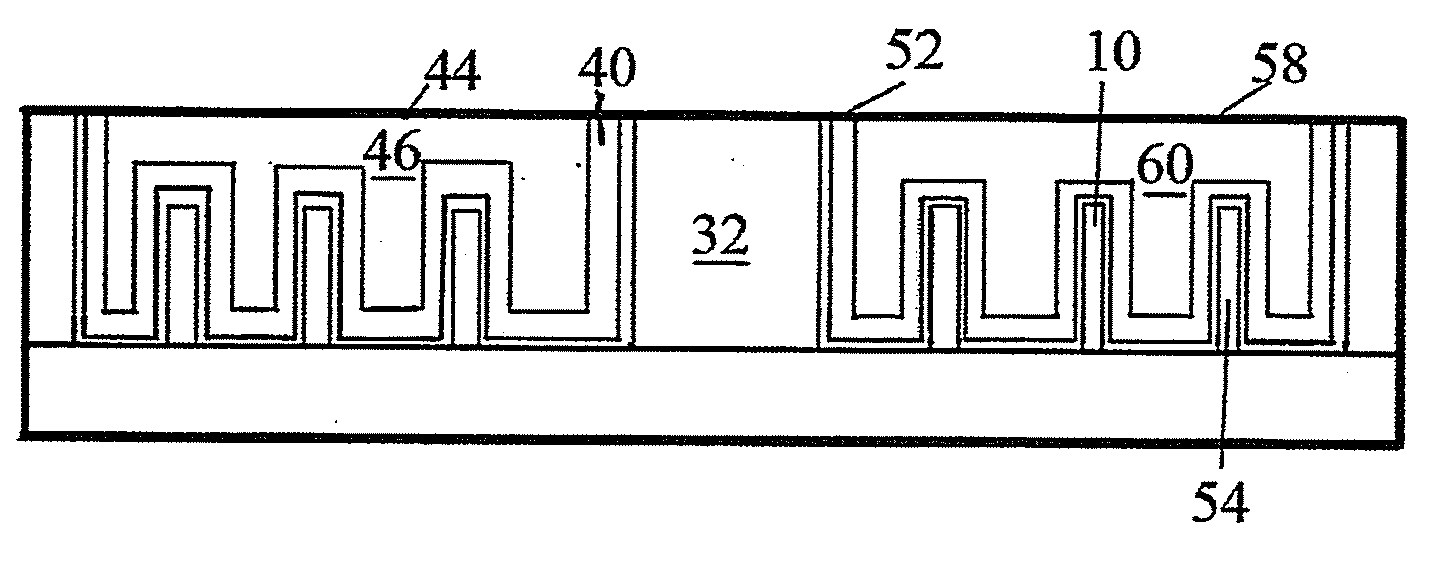

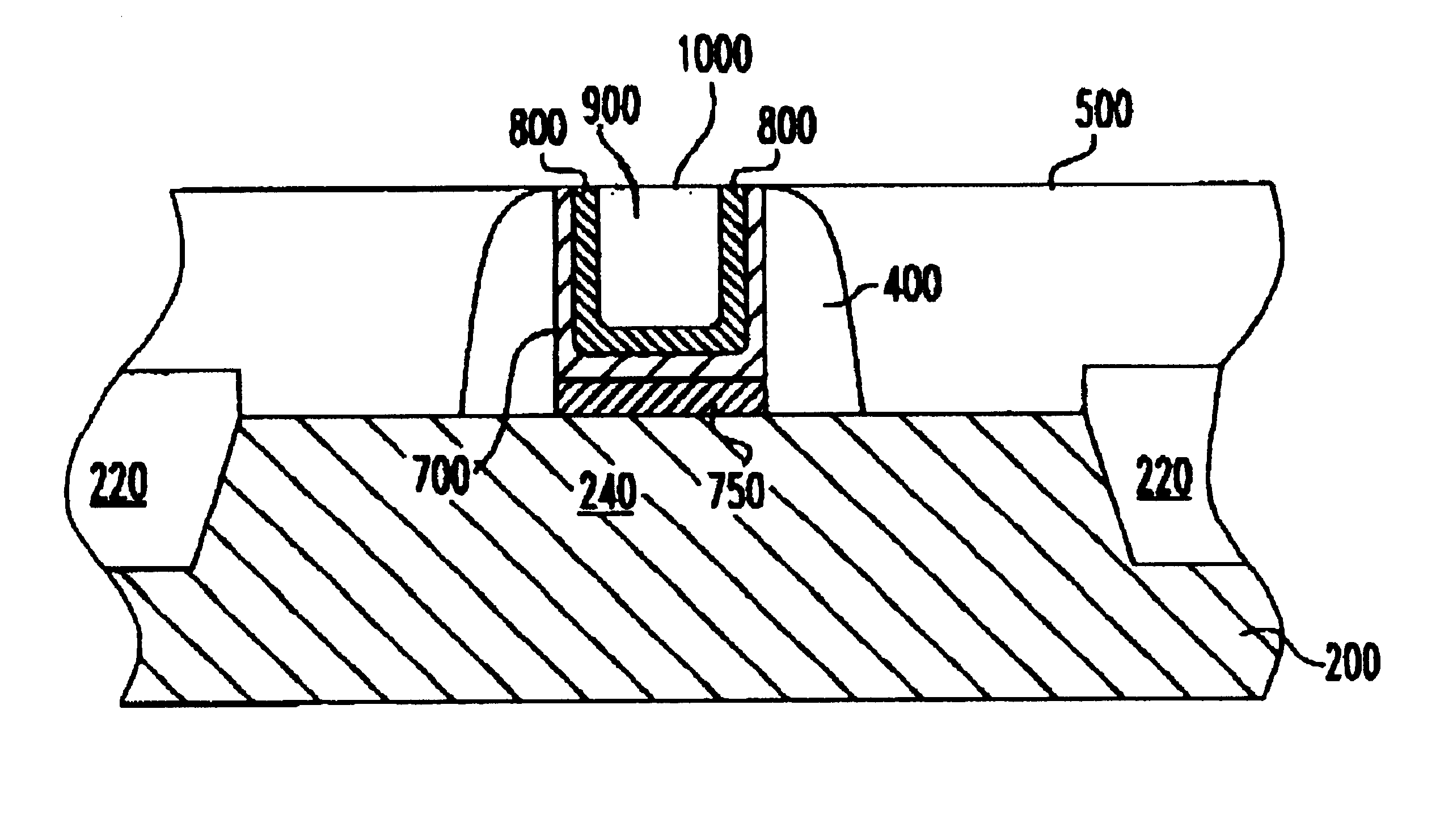

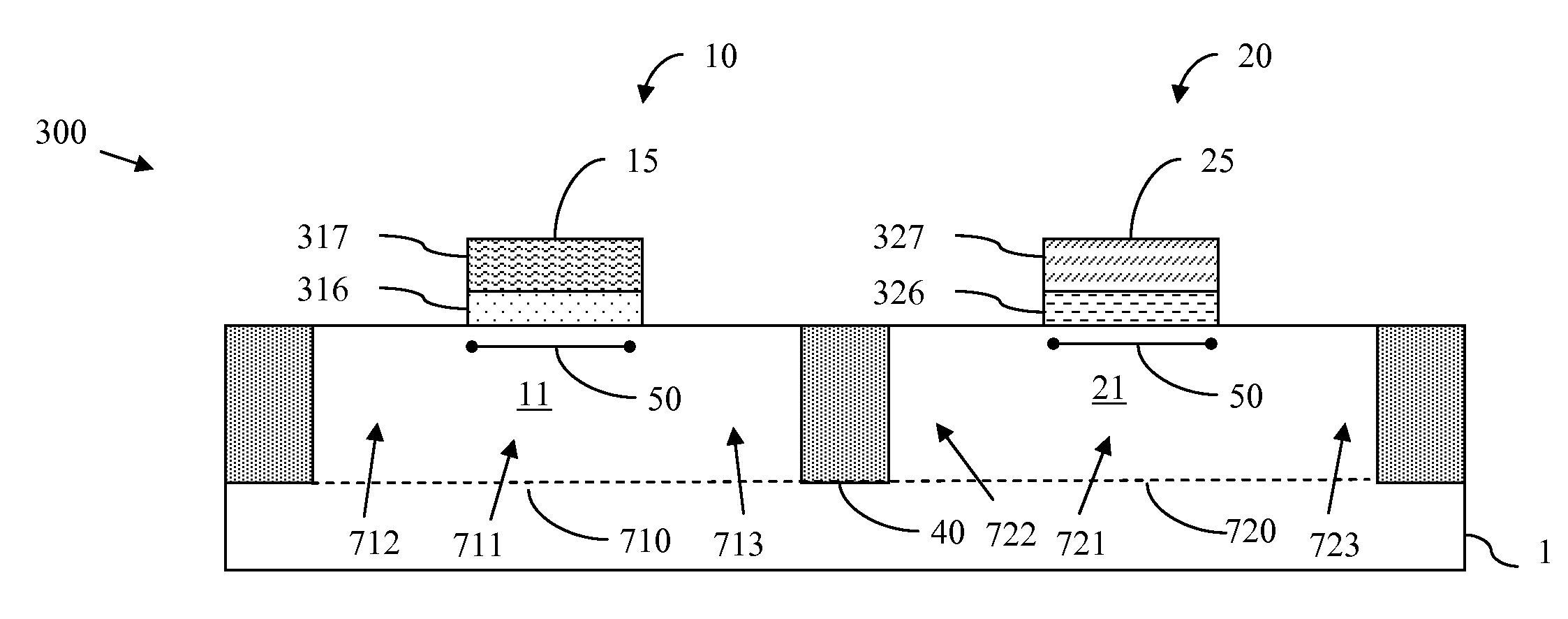

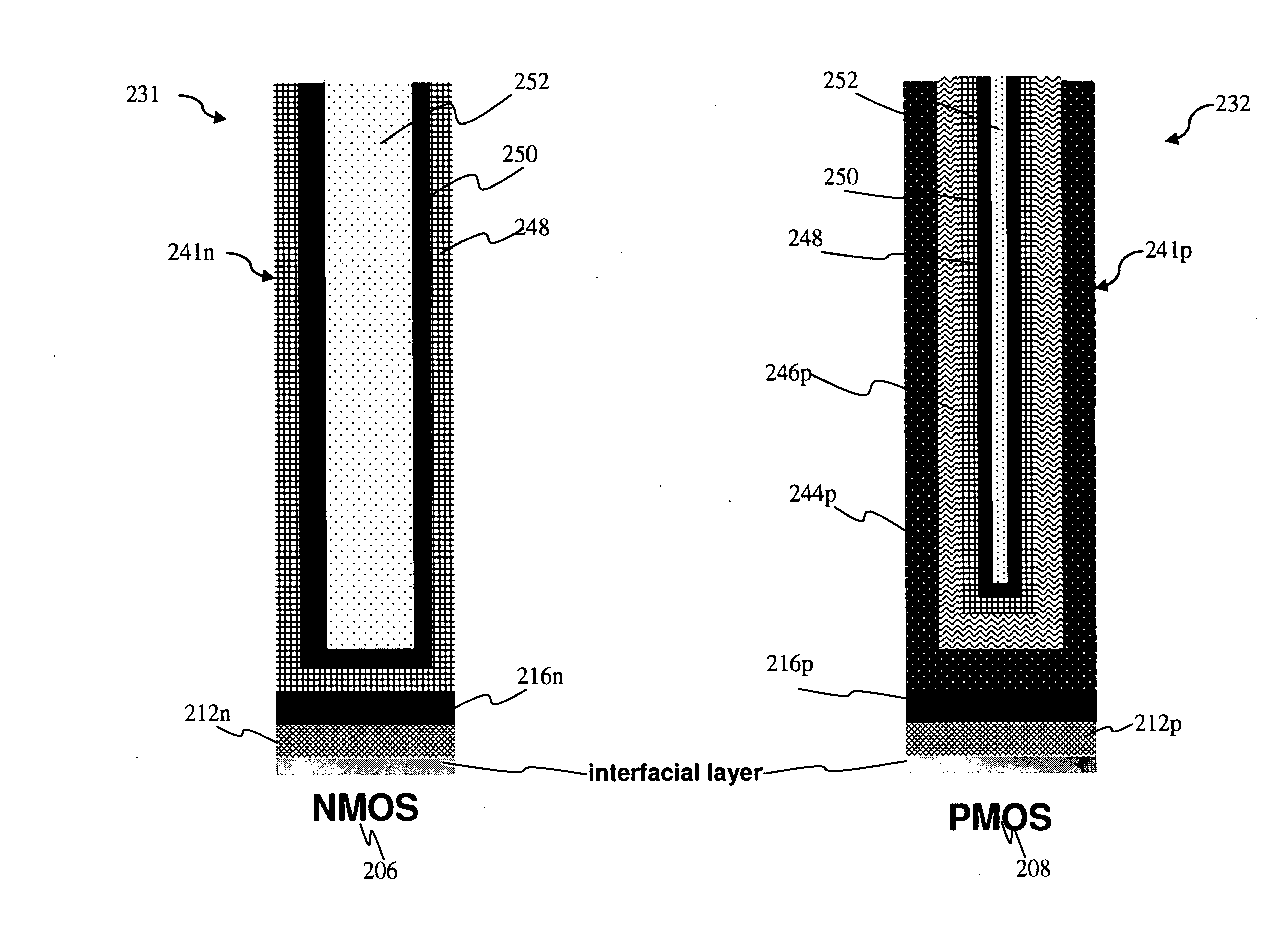

Replacement Metal Gate Structures Providing Independent Control On Work Function and Gate Leakage Current

The thickness and composition of a gate dielectric can be selected for different types of field effect transistors through a planar high dielectric constant material portion, which can be provided only for selected types of field effect transistors. Further, the work function of field effect transistors can be tuned independent of selection of the material stack for the gate dielectric. A stack of a barrier metal layer and a first-type work function metal layer is deposited on a gate dielectric layer within recessed gate cavities after removal of disposable gate material portions. After patterning the first-type work function metal layer, a second-type work function metal layer is deposited directly on the barrier metal layer in the regions of the second type field effect transistor. A conductive material fills the gate cavities, and a subsequent planarization process forms dual work function metal gate structures.

Owner:GLOBALFOUNDRIES INC

METAL GATE STRESS FILM FOR MOBILITY ENHANCEMENT IN FinFET DEVICE

A CMOS FinFET semiconductor device provides an NMOS FinFET device that includes a compressive stress metal gate layer over semiconductor fins and a PMOS FinFET device that includes a tensile stress metal gate layer over semiconductor fins. A process for forming the same includes a selective annealing process that selectively converts a compressive metal gate film formed over the PMOS device to the tensile stress metal gate film.

Owner:TAIWAN SEMICON MFG CO LTD

Enhanced electroless deposition of dielectric precursor materials for use in in-laid gate MOS transistors

InactiveUS6465334B1Semiconductor/solid-state device manufacturingSemiconductor devicesElectroless depositionOxygen

High quality dielectric layers, e.g., high-k dielectric layers comprised of at least one refractory or lanthanum series transition metal oxide or silicate, for use as gate insulator layers in in-laid metal gate MOS transistors and CMOS devices, are fabricated by forming an ultra-thin catalytic metal layer, e.g., a monolayer thick layer of Pd or Pd, on a Si-based semiconductor substrate, electrolessly plating on the catalytic layer comprising at least one refractory or lanthanum series transition metal or metal-based dielectric precursor layer, such as of Zr and / or Hf, and then reacting the precursor layer with oxygen or with oxygen and the semiconductor substrate to form the at least one high-k metal oxide or silicate. The inventive methodology prevents, or at least substantially reduces, oxygen access to the substrate surface during at least the initial stage(s) of formation of the gate insulator layer, thereby minimizing deleterious formation of oxygen-induced surface states at the semiconductor substrate / gate insulator interface.

Owner:GLOBALFOUNDRIES US INC

High-k/metal gate CMOS finfet with improved pfet threshold voltage

ActiveUS20110108920A1Solid-state devicesSemiconductor/solid-state device manufacturingCMOSCondensation process

A device and method for fabrication of fin devices for an integrated circuit includes forming fin structures in a semiconductor material of a semiconductor device wherein the semiconductor material is exposed on sidewalls of the fin structures. A donor material is epitaxially deposited on the exposed sidewalls of the fin structures. A condensation process is applied to move the donor material through the sidewalls into the semiconductor material such that accommodation of the donor material causes a strain in the semiconductor material of the fin structures. The donor material is removed, and a field effect transistor is formed from the fin structure.

Owner:GLOBALFOUNDRIES US INC

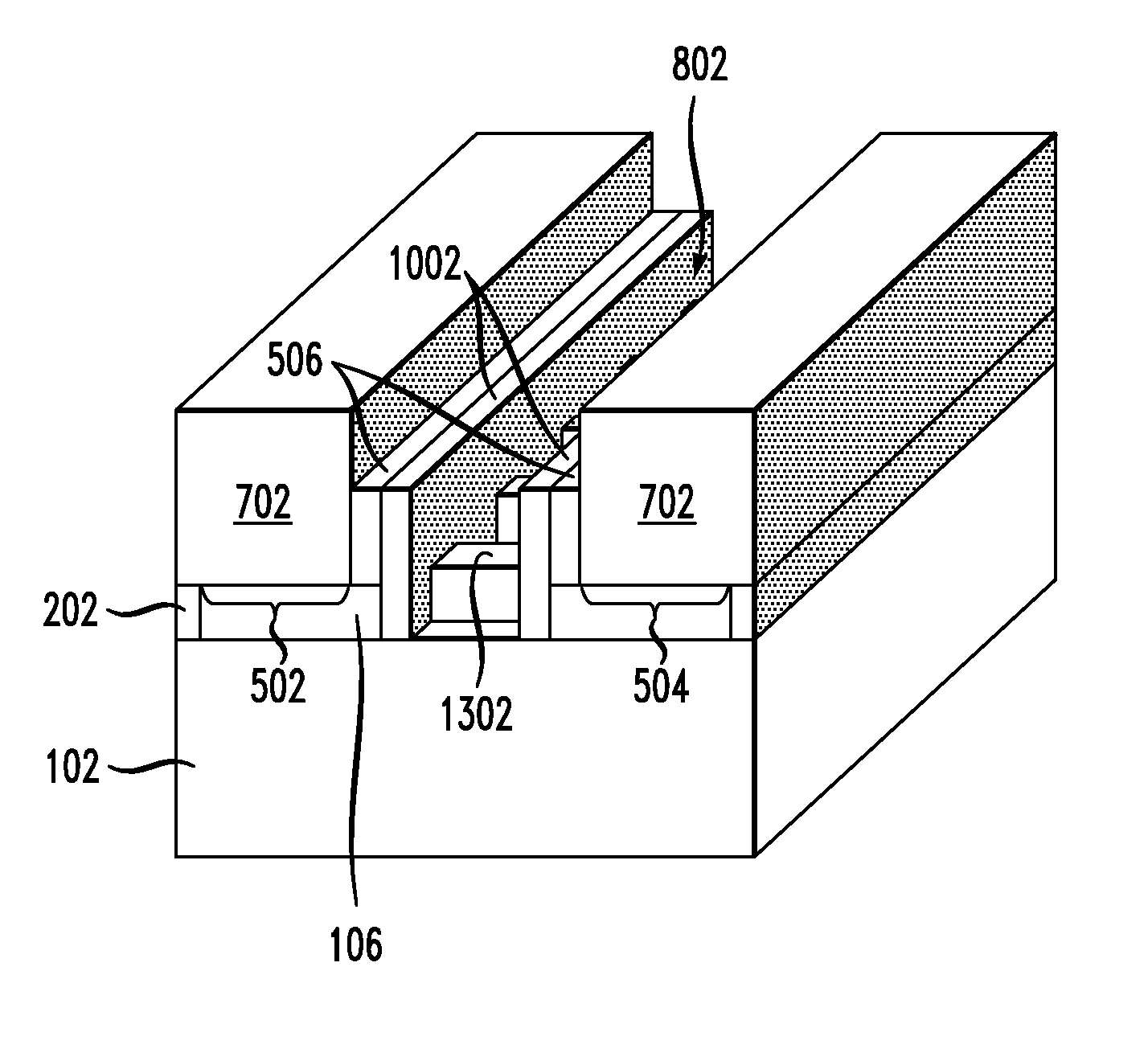

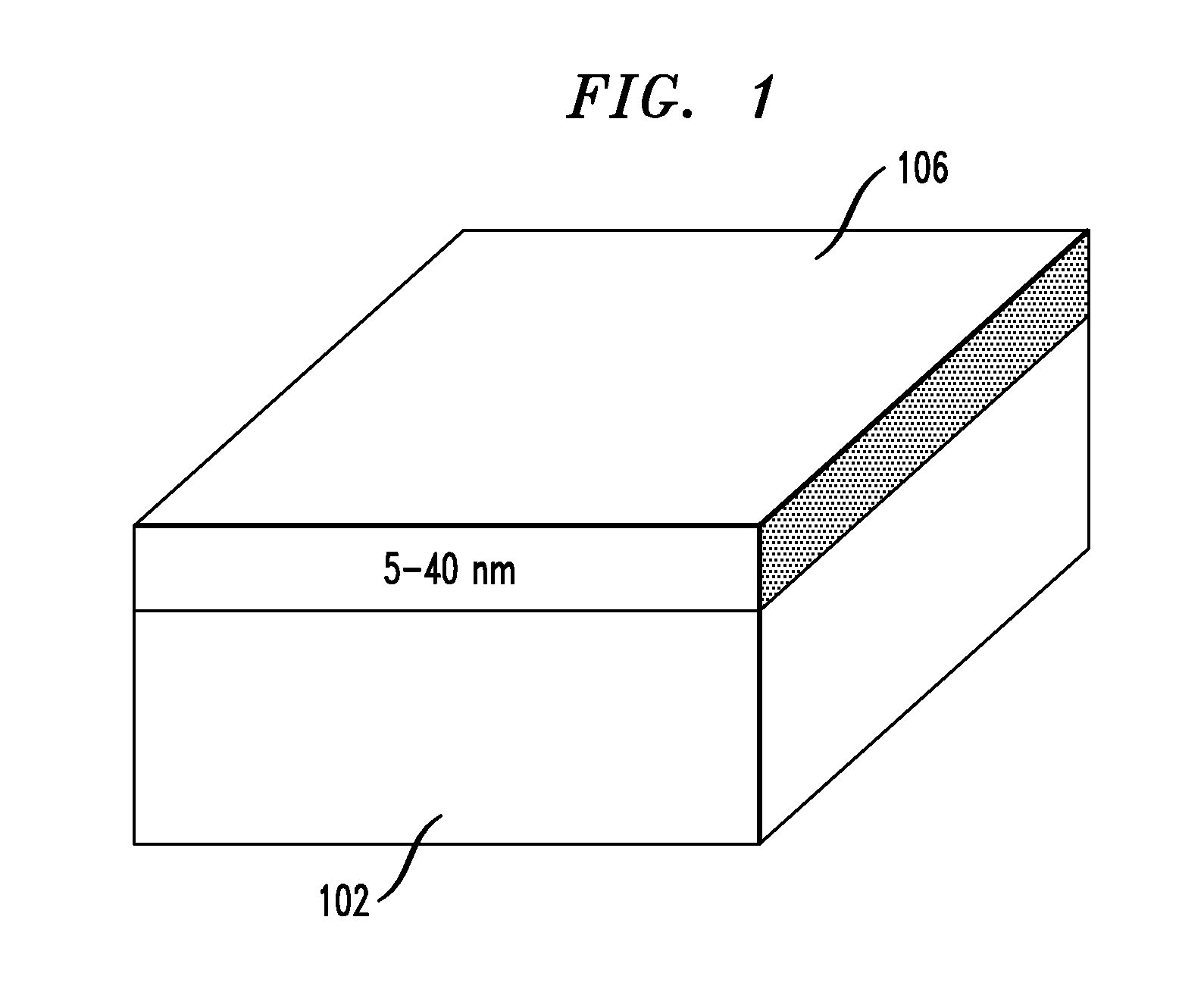

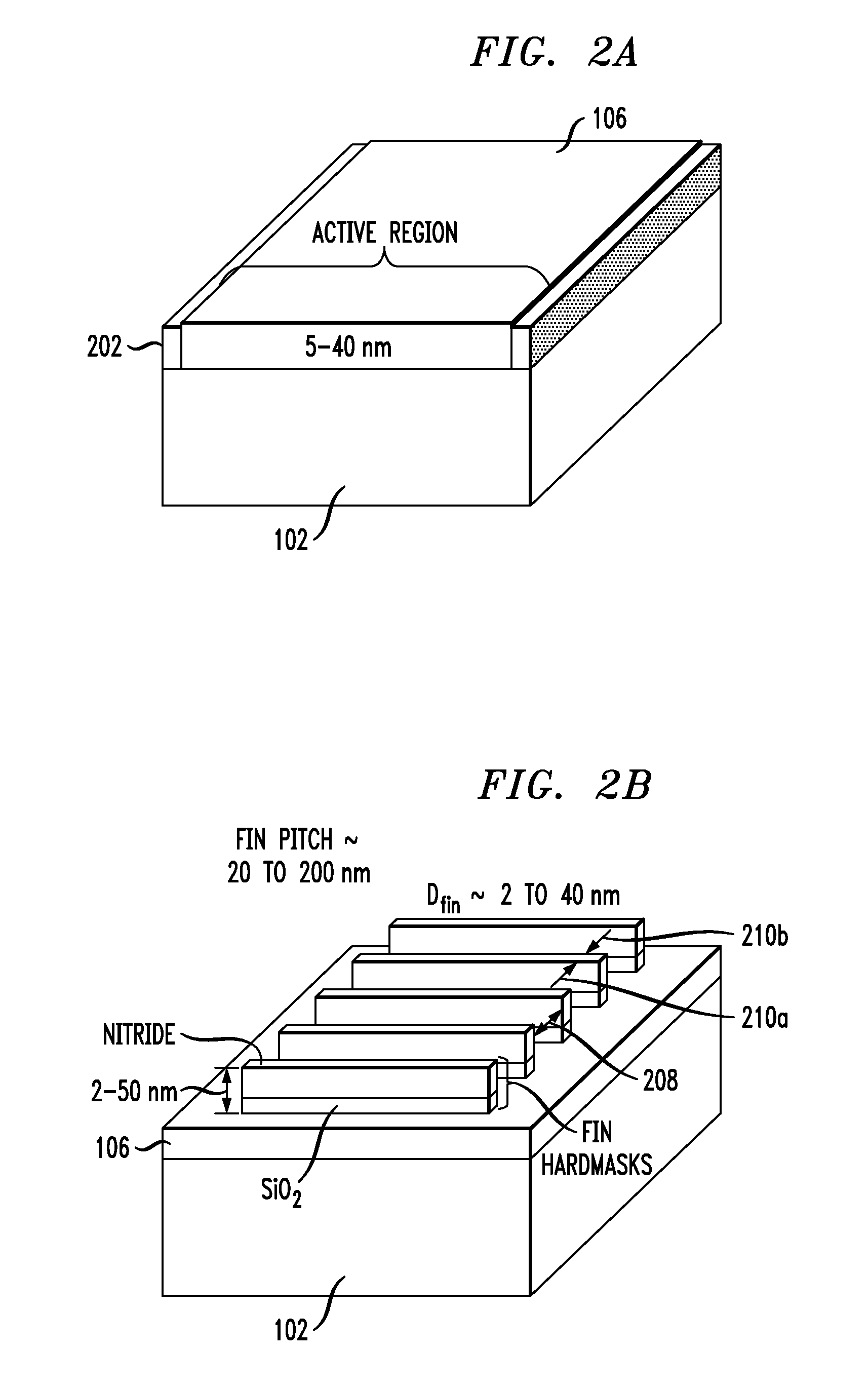

Fin-Last Replacement Metal Gate FinFET

InactiveUS20120313170A1Solid-state devicesSemiconductor/solid-state device manufacturingDopantEngineering

FinFET devices and methods for the fabrication thereof are provided. In one aspect, a method for fabricating a FET device includes the following steps. A wafer is provided having an active layer on an insulator. A plurality of fin hardmasks are patterned on the active layer. A dummy gate is placed over a central portion of the fin hardmasks. One or more doping agents are implanted into source and drain regions of the device. A dielectric filler layer is deposited around the dummy gate. The dummy gate is removed to form a trench in the dielectric filler layer. The fin hardmasks are used to etch a plurality of fins in the active layer within the trench. The doping agents are activated. A replacement gate is formed in the trench, wherein the step of activating the doping agents is performed before the step of forming the replacement gate.

Owner:AURIGA INNOVATIONS INC

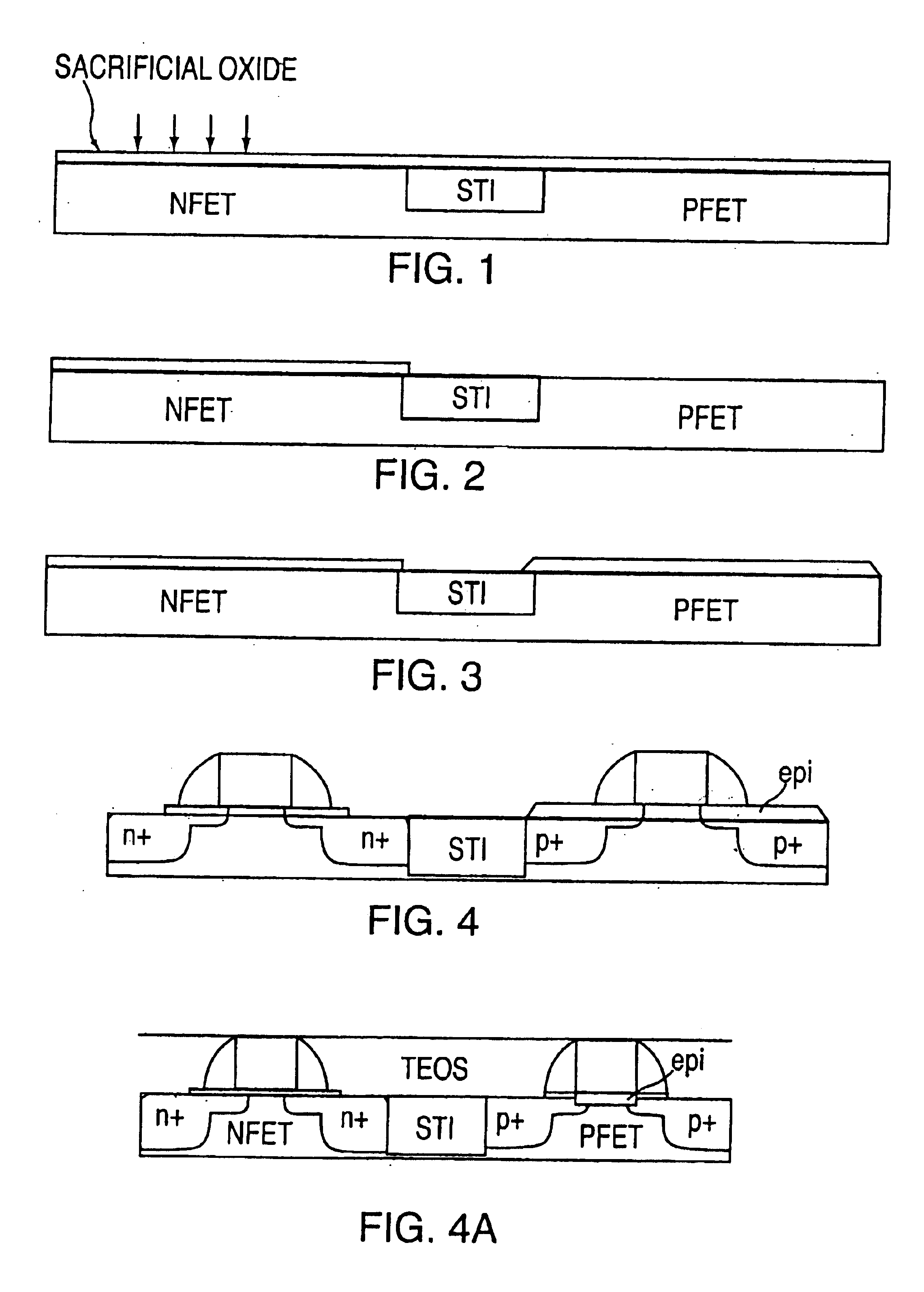

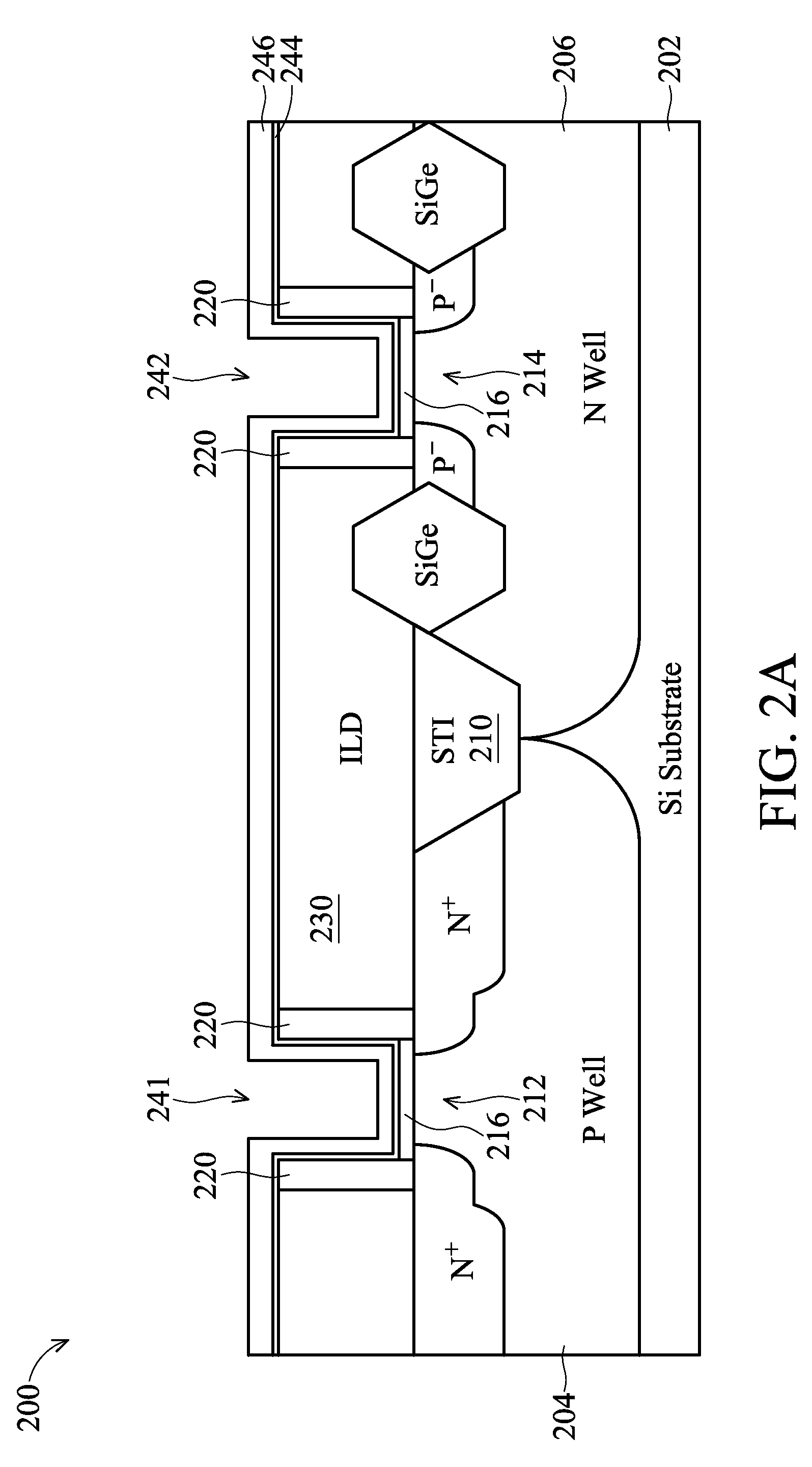

Metal gate transistors with epitaxial source and drain regions

ActiveUS7332439B2Decorative surface effectsSemiconductor/solid-state device manufacturingMetalTransistor

An MOS transistor formed on a heavily doped substrate is described. Metal gates are used in low temperature processing to prevent doping from the substrate from diffusing into the channel region of the transistor.

Owner:TAHOE RES LTD

Method for forming metal replacement gate of high performance

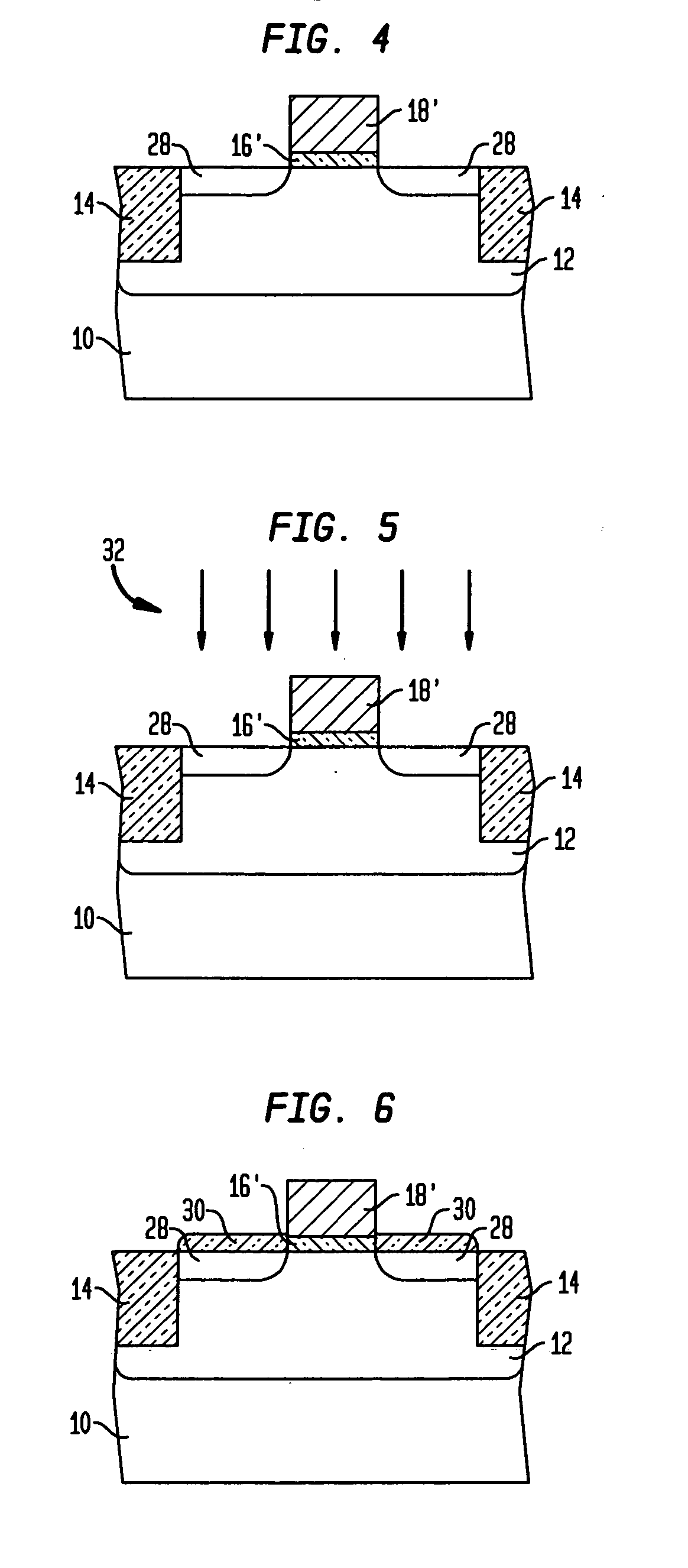

InactiveUS6921711B2Semiconductor/solid-state device manufacturingSemiconductor devicesTitanium nitrideDiffusion barrier

A structure and method for a metal replacement gate of a high performance device is provided. A sacrificial gate structure is first formed on an etch stop layer provided on a semiconductor substrate. A pair of spacers is provided on sidewalls of the sacrificial gate structure. The sacrificial gate structure is then removed, forming an opening. Subsequently, a metal gate including an first layer of metal such as tungsten, a diffusion barrier such as titanium nitride, and a second layer of metal such as tungsten is formed in the opening between the spacers.

Owner:GLOBALFOUNDRIES U S INC

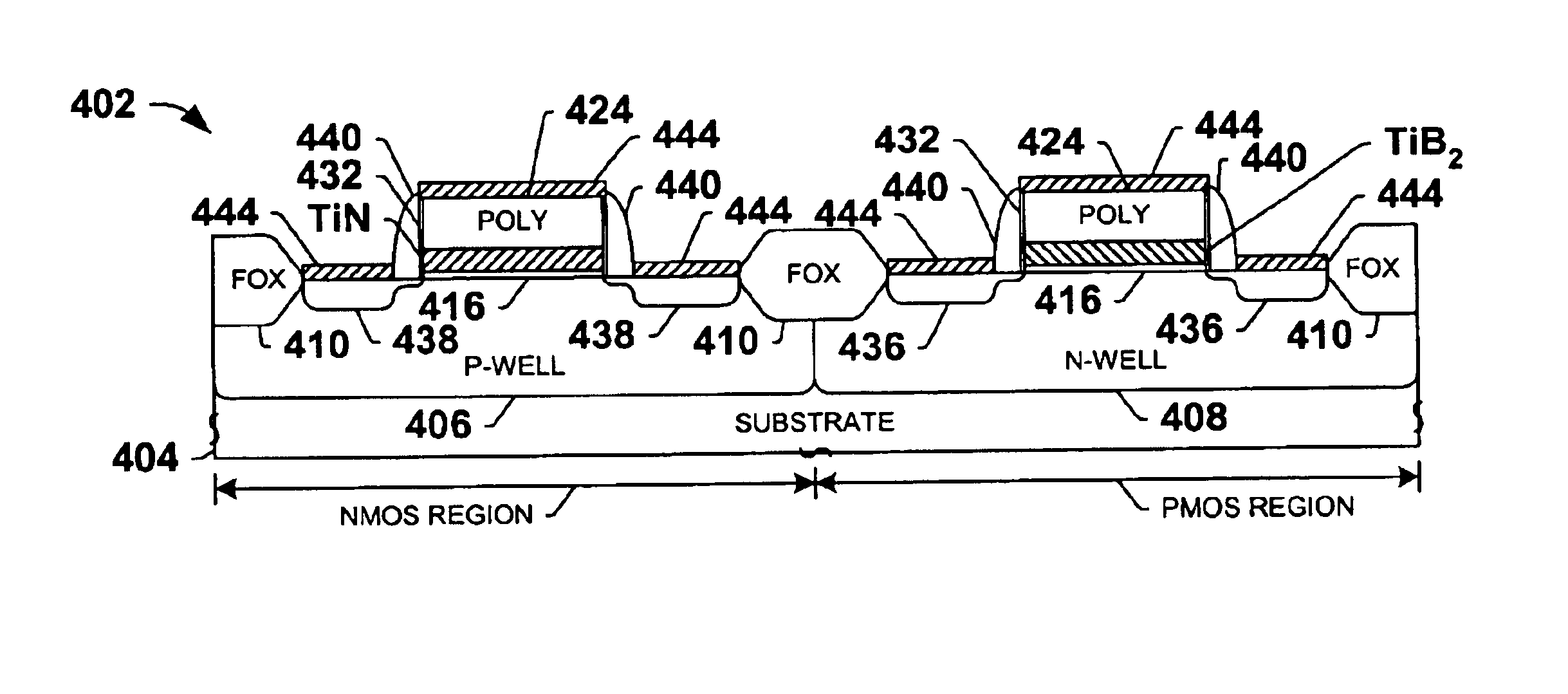

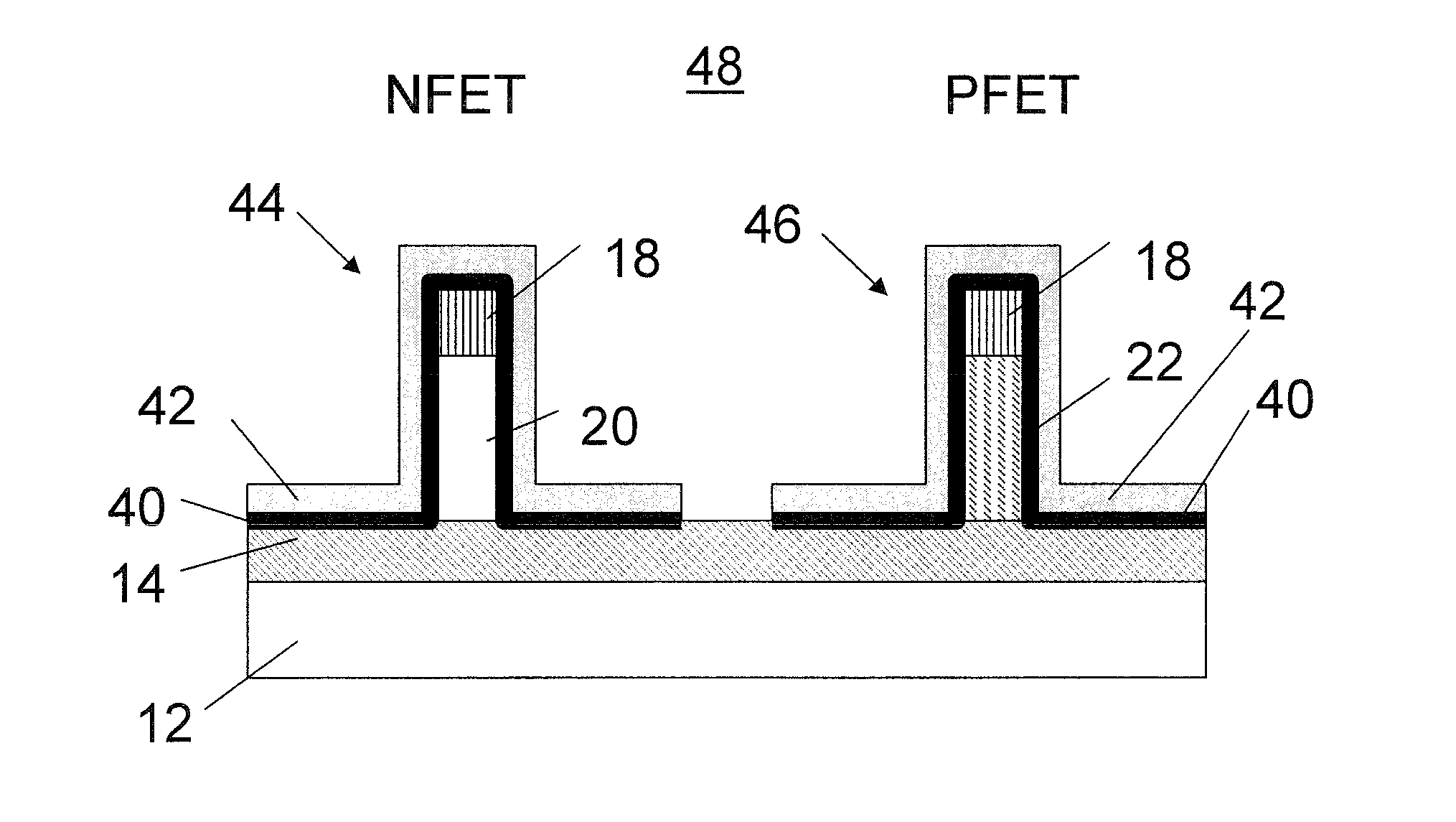

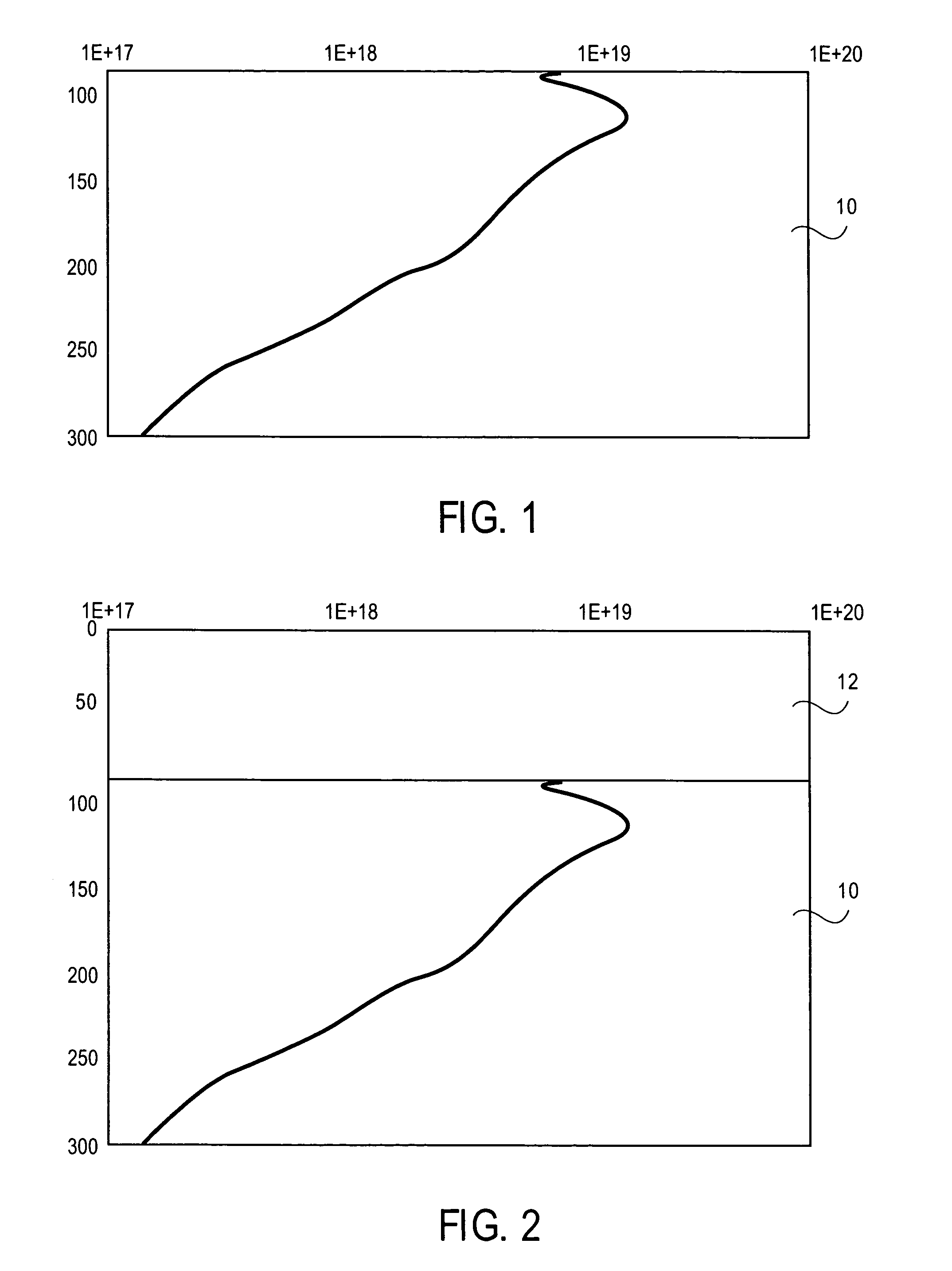

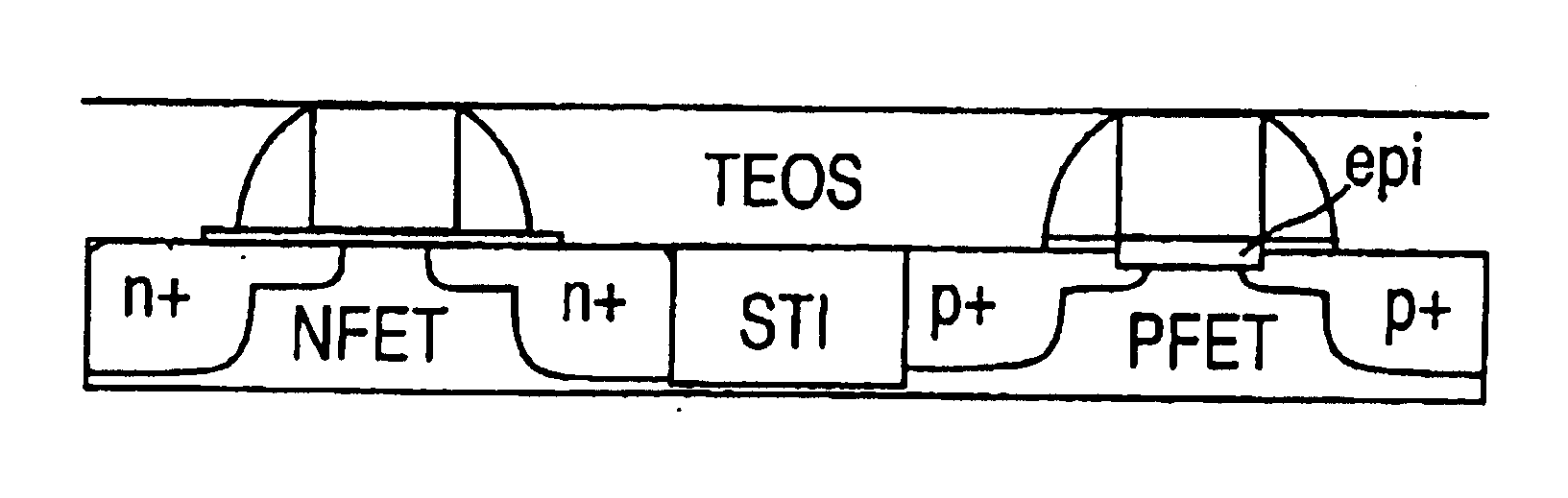

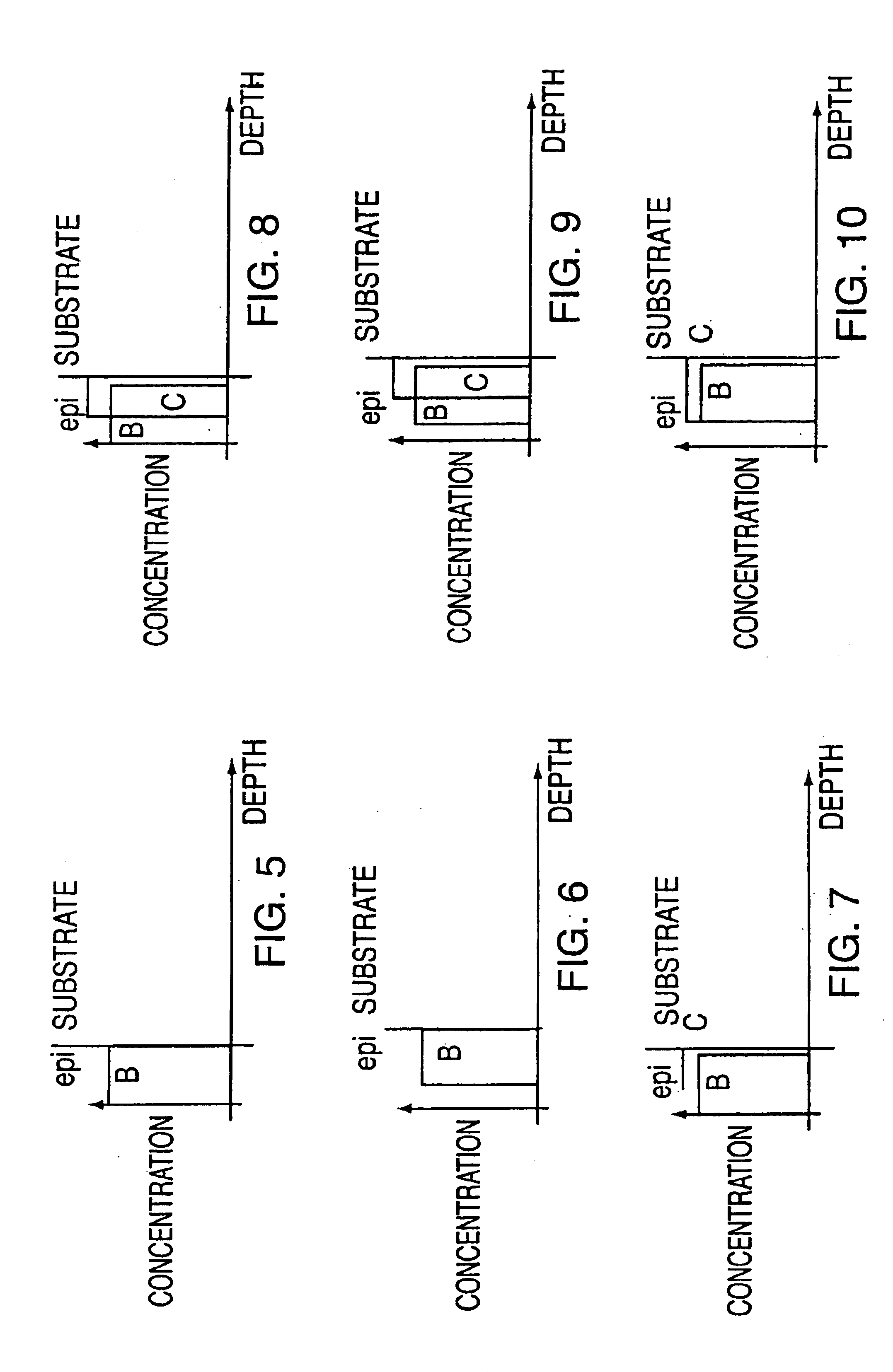

High performance CMOS device structure with mid-gap metal gate

InactiveUS6916698B2Improve performanceReduce diffuseTransistorSemiconductor/solid-state device manufacturingCMOSWork function

High performance (surface channel) CMOS devices with a mid-gap work function metal gate are disclosed wherein an epitaxial layer is used for a threshold voltage Vt adjust / decrease for the PFET area, for large Vt reductions (˜500 mV), as are required by CMOS devices with a mid-gap metal gate. The present invention provides counter doping using an in situ B doped epitaxial layer or a B and C co-doped epitaxial layer, wherein the C co-doping provides an additional degree of freedom to reduce the diffusion of B (also during subsequent activation thermal cycles) to maintain a shallow B profile, which is critical to provide a surface channel CMOS device with a mid-gap metal gate while maintaining good short channel effects. The B diffusion profiles are satisfactorily shallow, sharp and have a high B concentration for devices with mid-gap metal gates, to provide and maintain a thin, highly doped B layer under the gate oxide.

Owner:IBM CORP

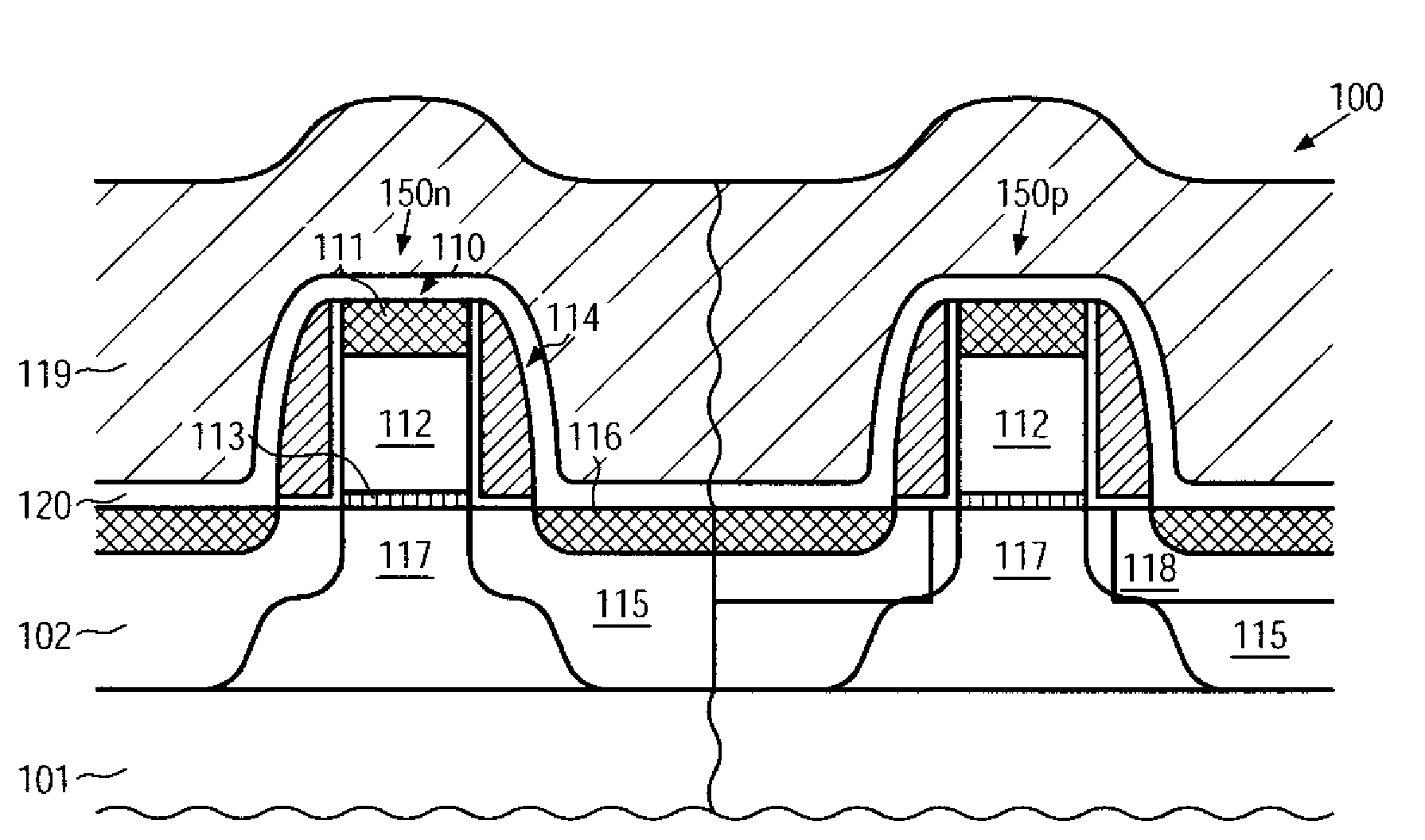

Plasma nitrided gate oxide, high-k metal gate based CMOS device

In accordance with the invention, there are CMOS devices and semiconductor devices and methods of fabricating them. The CMOS device can include a substrate including a first active region and a second active region and a first transistor device over the first active region, wherein the first transistor device includes a high-K layer over the first active region, a first dielectric capping layer on the high-K layer, and a first metal gate layer over the first dielectric capping layer. The CMOS device can also include a second transistor device over the second active region, wherein the second transistor device includes a high-K layer over the second active region, a second dielectric capping layer on the second high-K layer, and a second metal gate layer over the second dielectric capping layer.

Owner:TEXAS INSTR INC

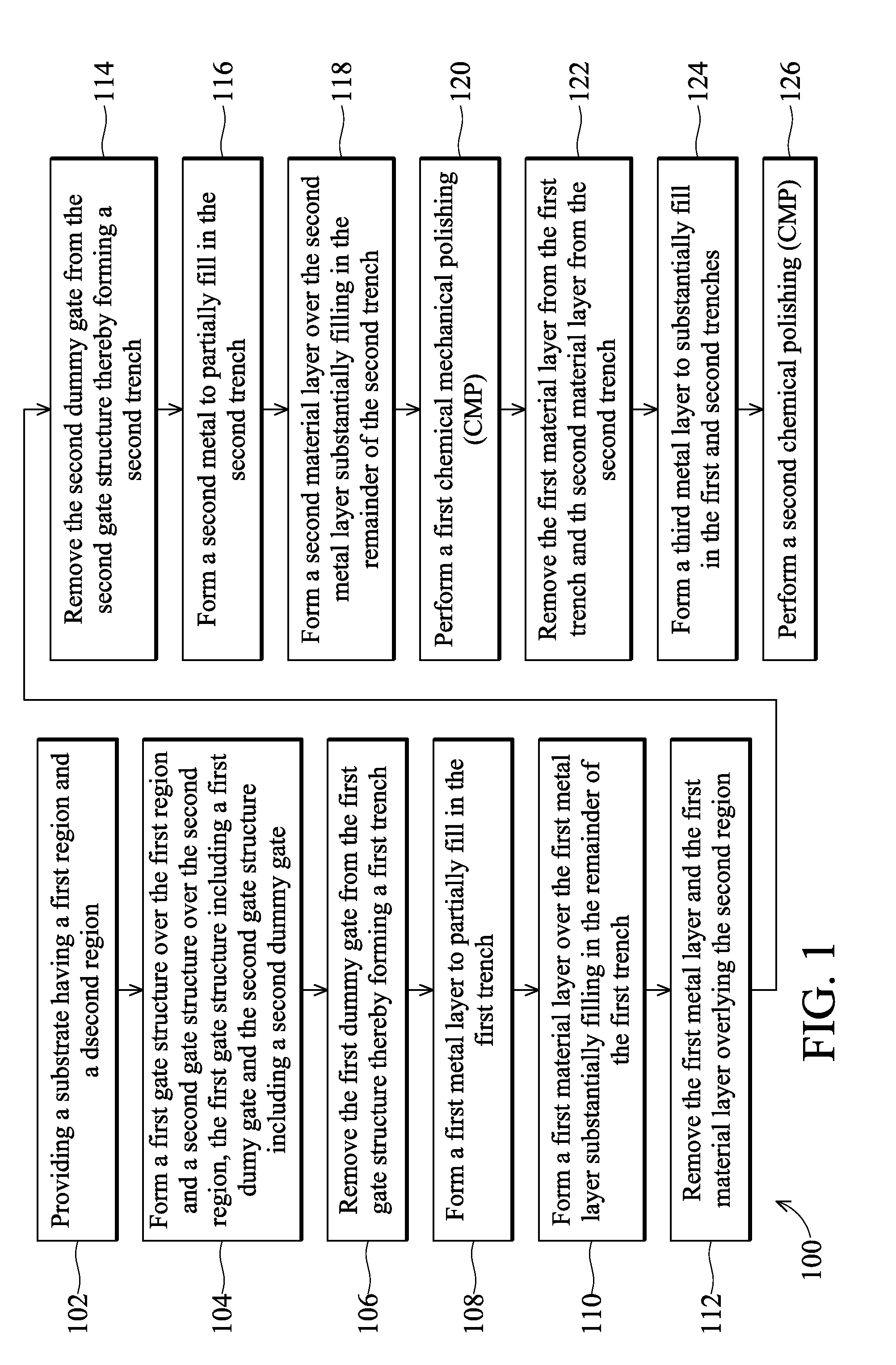

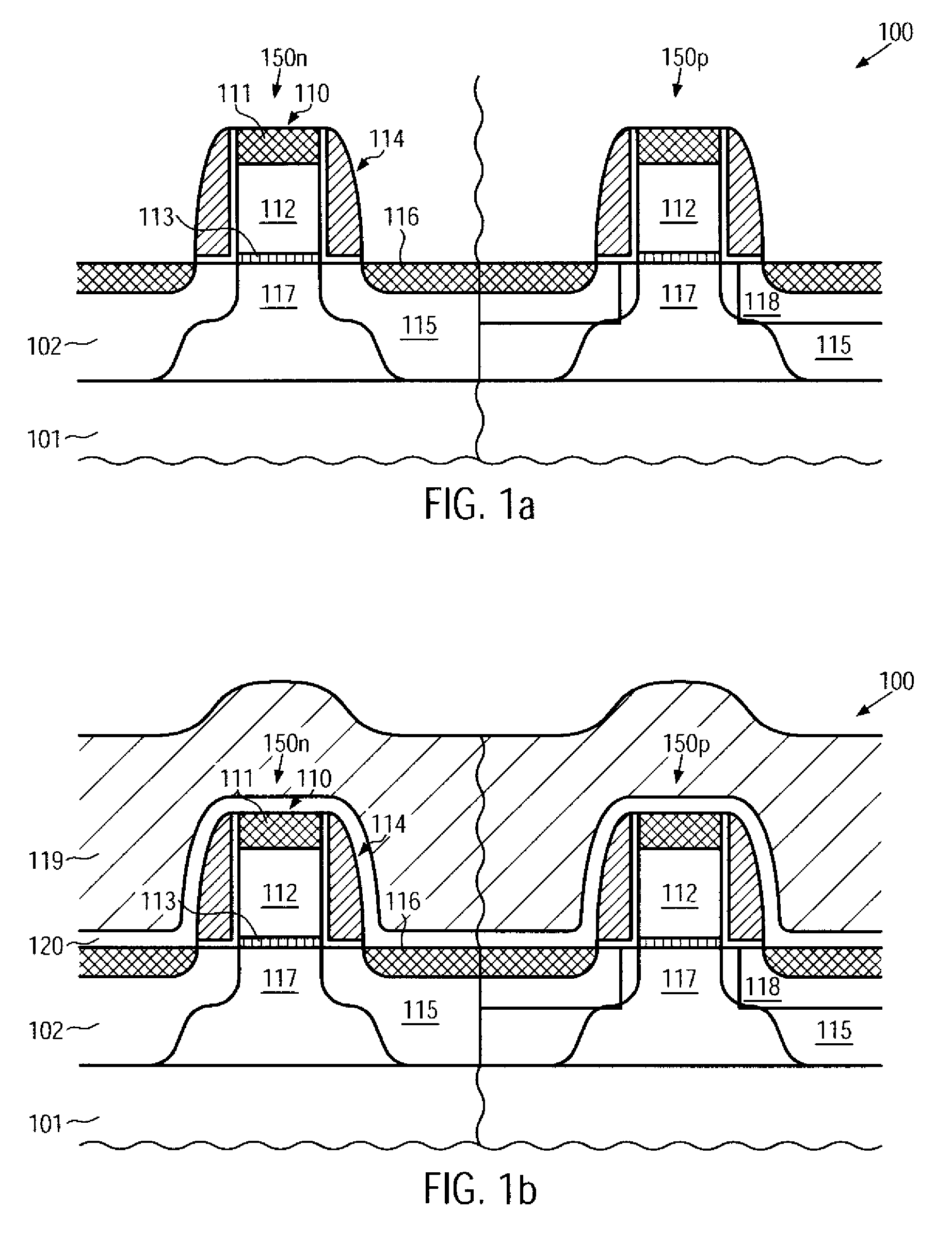

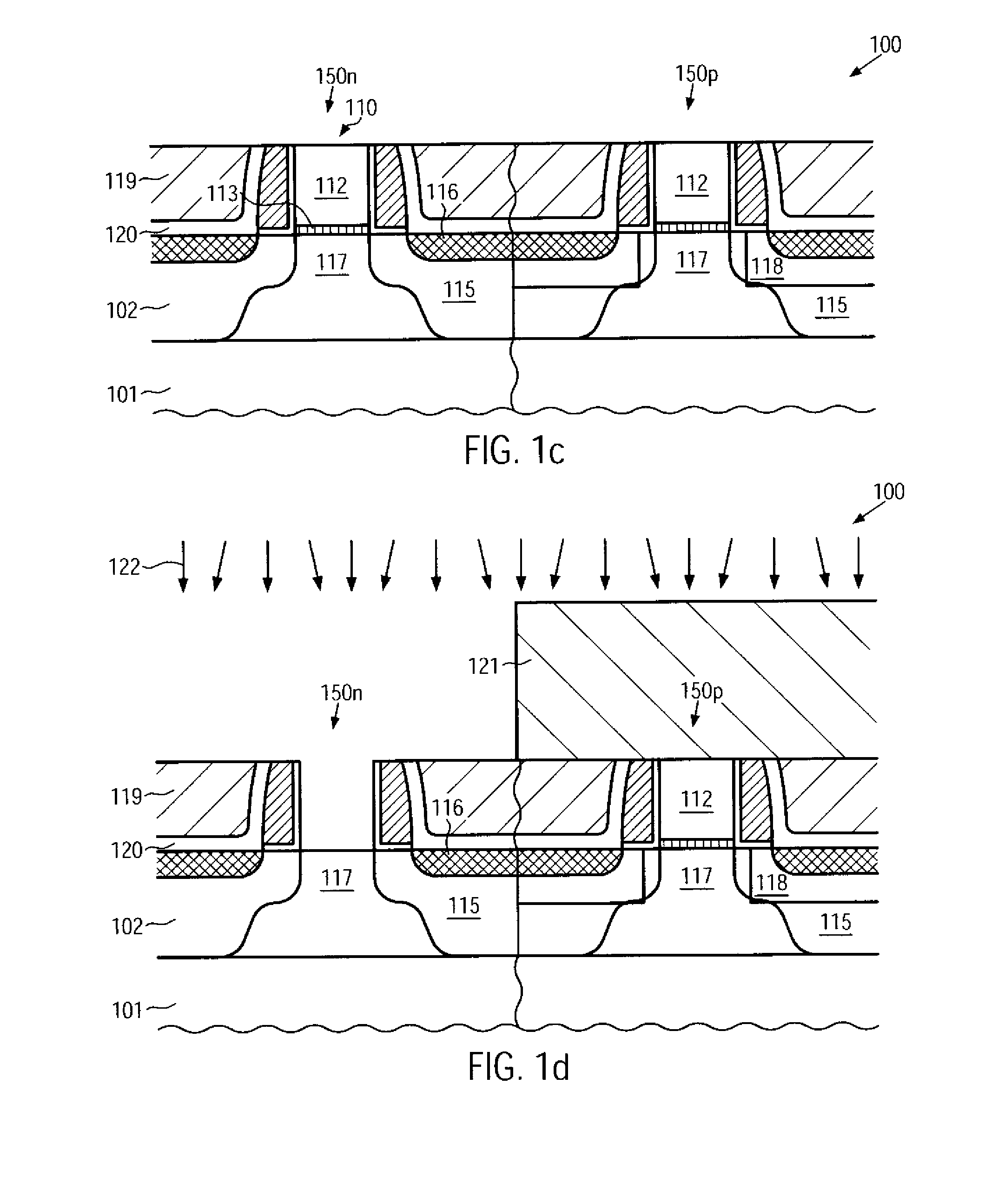

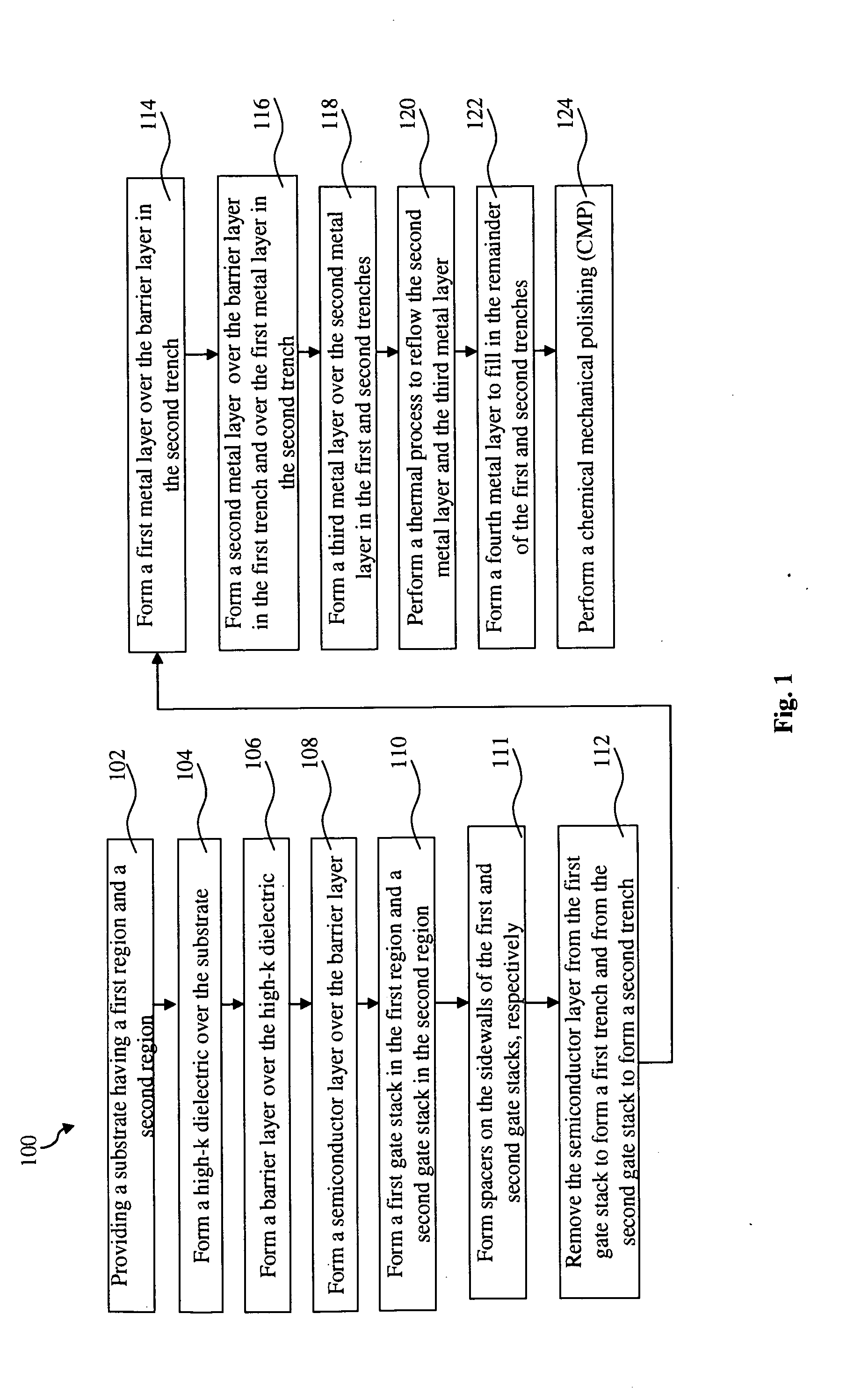

Method for forming metal gates in a gate last process

ActiveUS20100081262A1Semiconductor/solid-state device manufacturingSemiconductor devicesDevice materialEngineering

The present disclosure provides a method of fabricating a semiconductor device that includes providing a substrate having a first region and a second region, forming first and second gate stacks in the first and second regions, respectively, the first gate stack including a first dummy gate and the second gate stack including a second dummy gate, removing the first dummy gate in the first gate stack thereby forming a first trench and removing the second dummy gate in the second gate stack thereby forming a second trench, forming a first metal layer in the first trench and in the second trench, removing at least a portion of the first metal layer in the first trench, forming a second metal layer in the remainder of the first trench and in the remainder of the second trench, reflowing the second metal layer, and performing a chemical mechanical polishing (CMP).

Owner:TAIWAN SEMICON MFG CO LTD

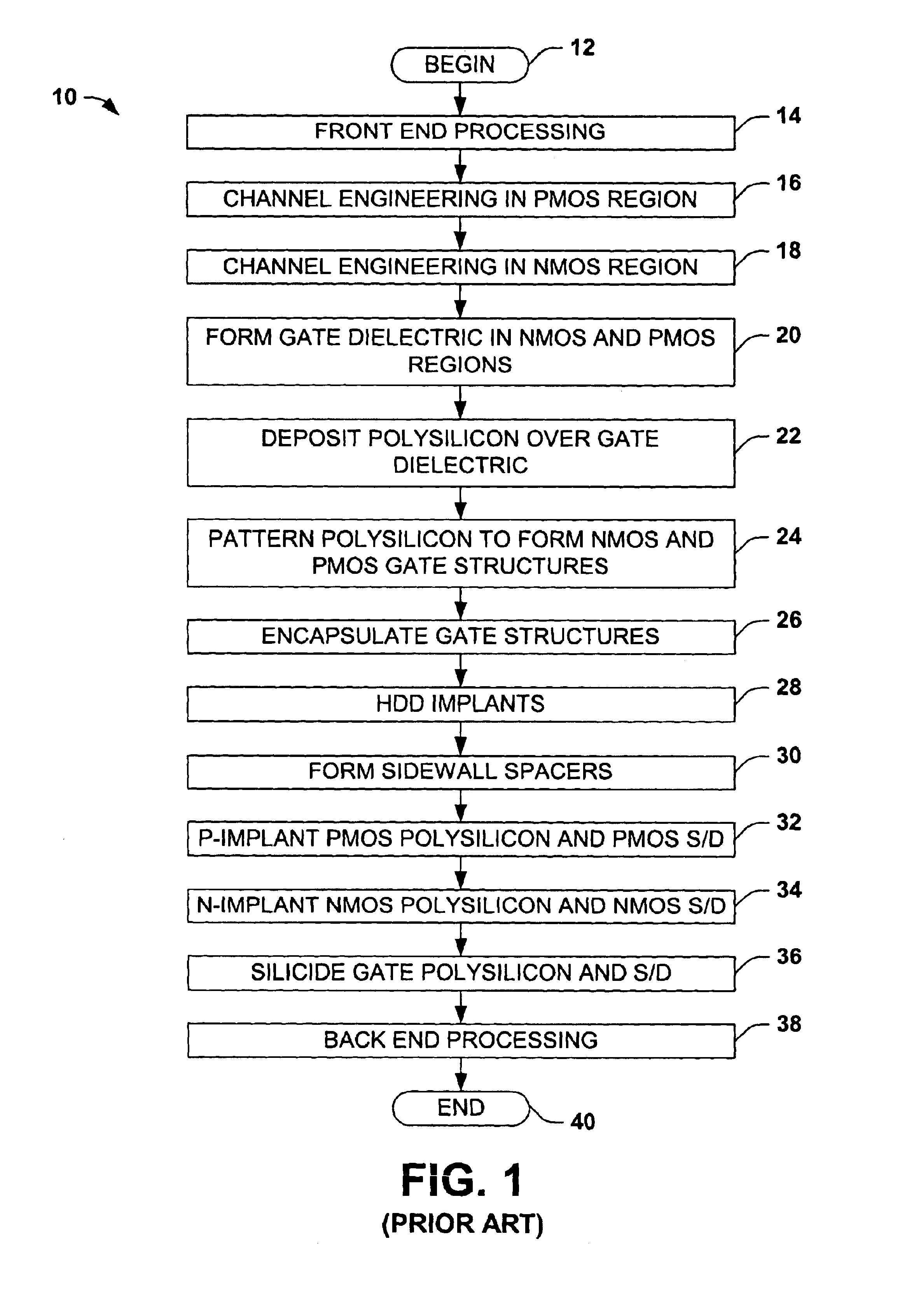

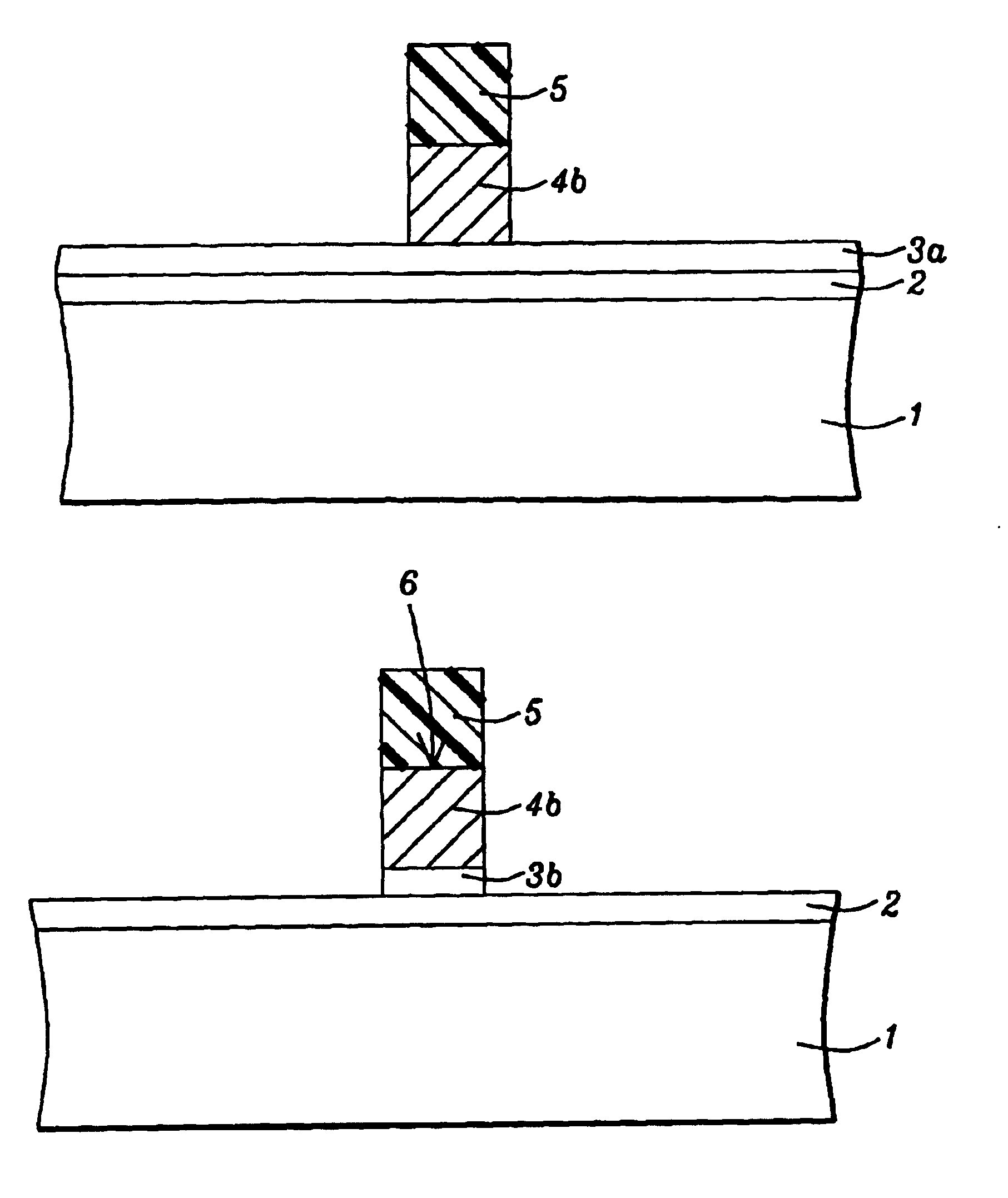

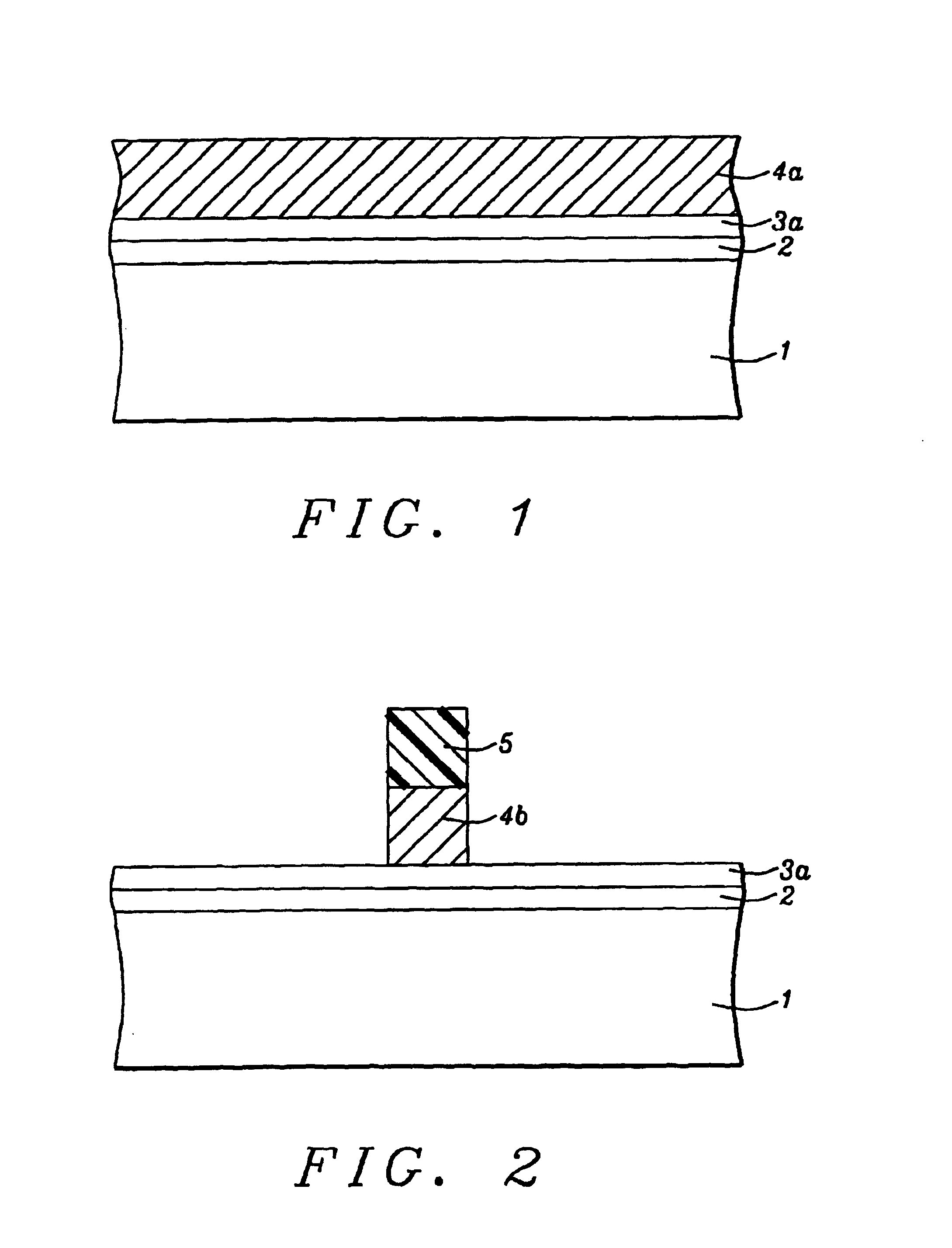

Method of fabricating a MOSFET device with metal containing gate structures

InactiveUS6869868B2Improve device performanceLow working voltageTransistorSemiconductor/solid-state device manufacturingTitanium nitrideTwo step

A method of forming a composite gate structure for a planar MOSFET device, as well as for vertical, double gate, FINFET device, has been developed. The method features a composite gate structure comprised of an overlying silicon gate structure shape, and an underlying titanium nitride gate structure shape. The titanium nitride component allows a lower work function, and thus lower device operating voltages to be realized when compared to counterpart gate structures formed with only polysilicon. A novel, two step gate structure definition procedure, featuring an anisotropic first etch procedure for definition of the polysilicon gate structure shape, followed by a wet or dry isotopic second etch procedure for definition of the titanium nitride gate structure shape, is employed.

Owner:TAIWAN SEMICON MFG CO LTD

Dual metal gate process: metals and their silicides

InactiveUS6475908B1High and work functionImprove work functionOperating chairsSemiconductor/solid-state device manufacturingSalicideCMOS

Methods for forming dual-metal gate CMOS transistors are described. An NMOS and a PMOS active area of a semiconductor substrate are separated by isolation regions. A metal layer is deposited over a gate dielectric layer in each active area. Silicon ions are implanted into the metal layer in one active area to form an implanted metal layer which is silicided to form a metal silicide layer. Thereafter, the metal layer and the metal silicide layer are patterned to form a metal gate in one active area and a metal silicide gate in the other active area wherein the active area having the gate with the higher work function is the PMOS active area. Alternatively, both gates may be metal silicide gates wherein the silicon concentrations of the two gates differ. Alternatively, a dummy gate may be formed in each of the active areas and covered with a dielectric layer. The dielectric layer is planarized thereby exposing the dummy gates. The dummy gates are removed leaving gate openings to the semiconductor substrate. A metal layer is deposited over a gate dielectric layer within the gate openings to form metal gates. One or both of the gates are silicon implanted and silicided. The PMOS gate has the higher work function.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

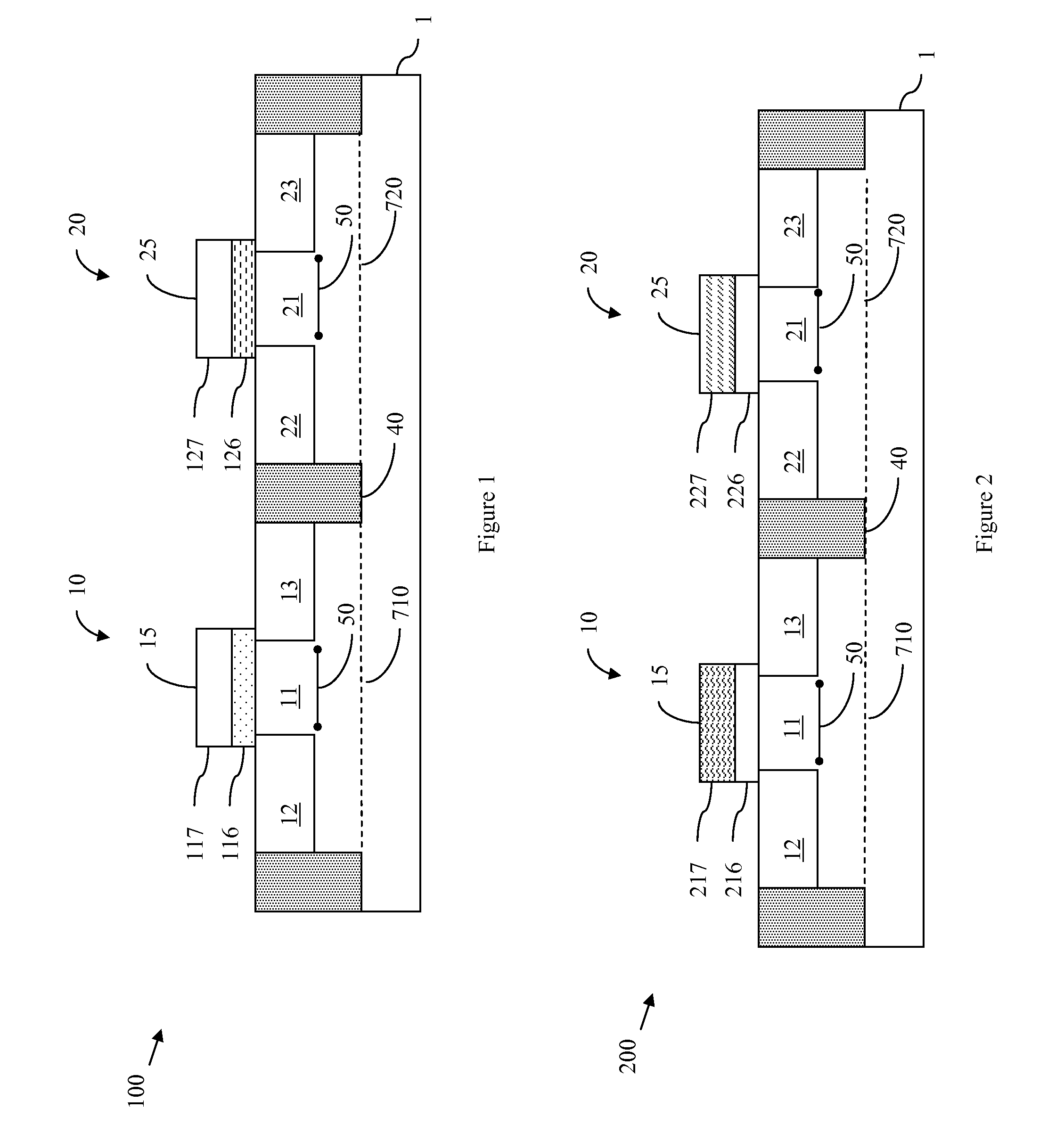

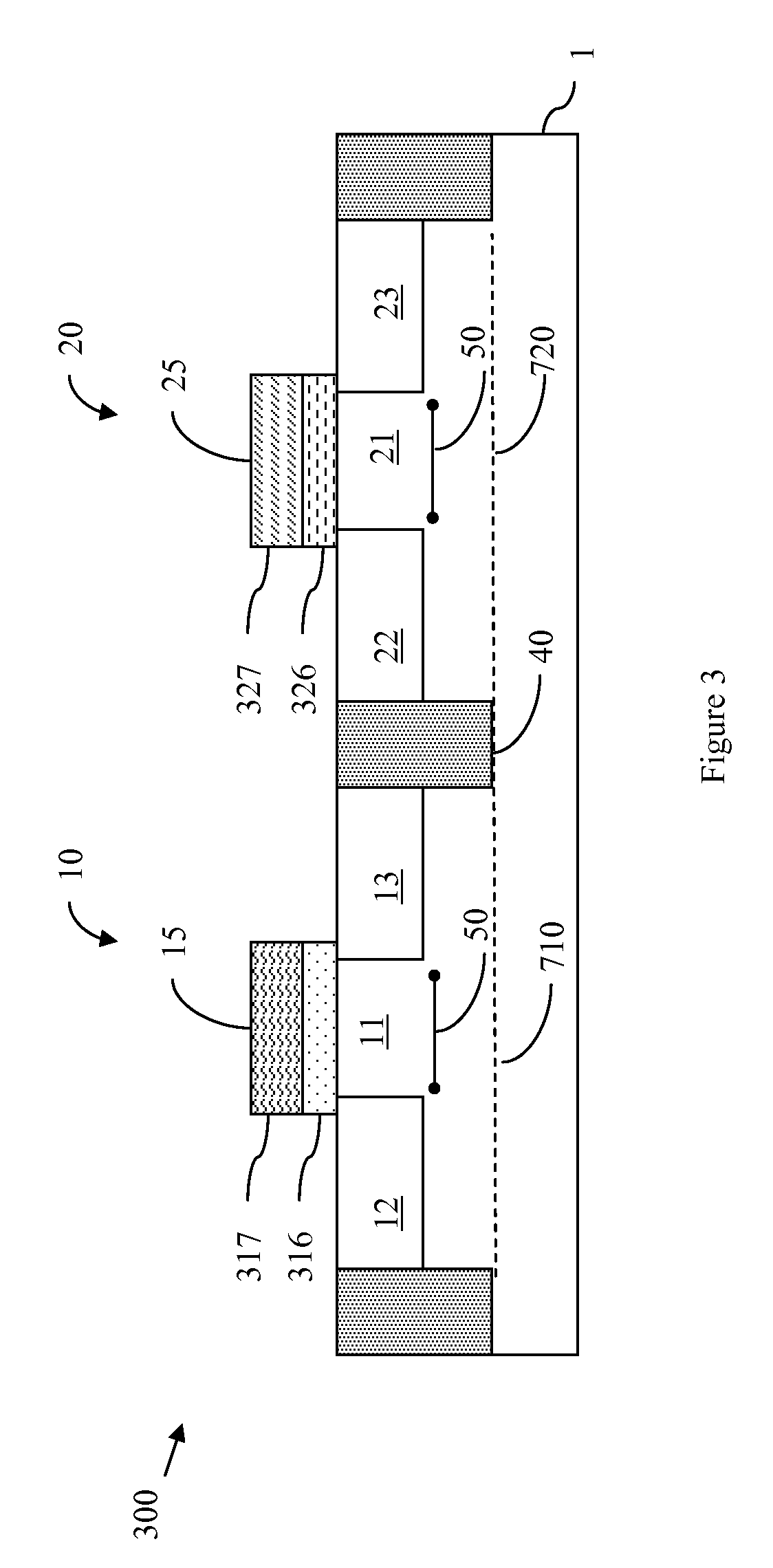

Metal-Gate High-K Reference Structure

Disclosed are embodiments of an integrated circuit structure that incorporates at least two field effect transistors (FETs) that have the same conductivity type and essentially identical semiconductor bodies (i.e., the same semiconductor material and, thereby the same conduction and valence band energies, the same source, drain, and channel dopant profiles, the same channel widths and lengths, etc.). However, due to different gate structures with different effective work functions, at least one of which is between the conduction and valence band energies of the semiconductor bodies, these FETs have selectively different threshold voltages, which are independent of process variables. Furthermore, through the use of different high-k dielectric materials and / or metal gate conductor materials, the embodiments allow threshold voltage differences of less than 700 mV to be achieved so that the integrated circuit structure can function at power supply voltages below 1.0V. Also disclosed are method embodiments for forming the integrated circuit structure.

Owner:TAIWAN SEMICON MFG CO LTD

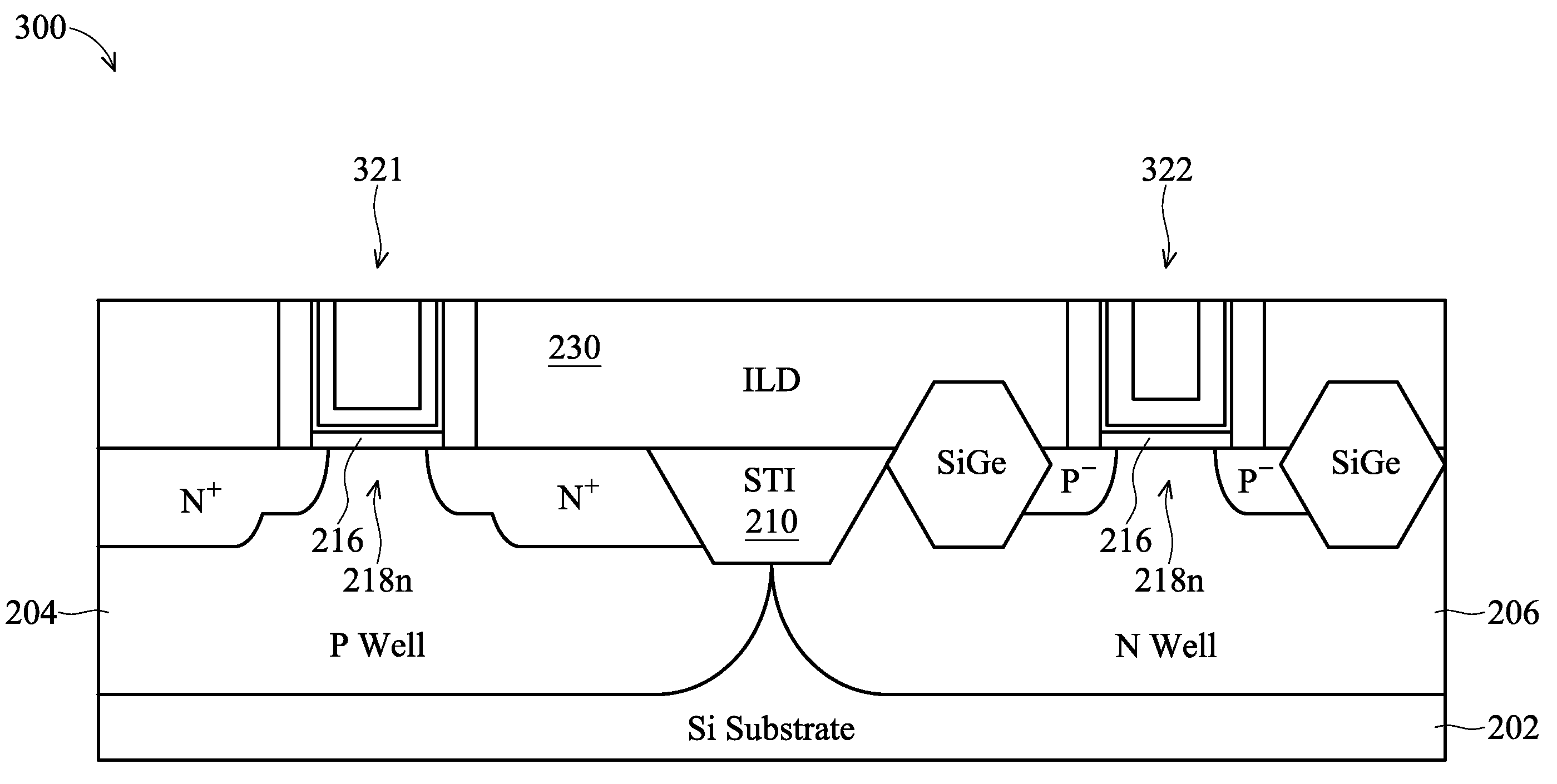

CMOS device having gate insulation layers of different type and thickness and a method of forming the same

ActiveUS20090057769A1Avoid normal workImprove compatibilityTransistorSolid-state devicesCMOSInsulation layer

In the process sequence for replacing conventional gate electrode structures by high-k metal gate structures, the number of additional masking steps may be maintained at a low level, for instance by using highly selective etch steps, thereby maintaining a high degree of compatibility with conventional CMOS techniques. Furthermore, the techniques disclosed herein enable compatibility to front-end process techniques and back-end process techniques, thereby allowing the integration of well-established strain-inducing mechanisms in the transistor level as well as in the contact level.

Owner:GLOBALFOUNDRIES US INC

Method for tuning a work function of high-k metal gate devices

InactiveUS20100068877A1Semiconductor/solid-state device manufacturingSemiconductor devicesWork functionEngineering

The present disclosure provides a method of fabricating a semiconductor device that includes providing a semiconductor substrate, forming first and second transistors in the substrate, the first transistor having a first gate structure that includes a first dummy gate, the second transistor having a second gate structure that includes a second dummy gate, removing the first and second dummy gates thereby forming a first trench and a second trench, respectively, forming a first metal layer to partially fill in the first and second trenches, removing the first metal layer within the first trench, forming a second metal layer to partially fill in the first and second trenches, forming a third metal layer to partially fill in the first and second trenches, reflowing the second metal layer and the third metal layer, and forming a fourth metal layer to fill in the remainder of the first and second trenches.

Owner:TAIWAN SEMICON MFG CO LTD