Method of depositing barrier layer from metal gates

a barrier layer and metal gate technology, applied in the field of semiconductor semiconductor manufacturing, can solve the problems of increasing the equivalent oxide thickness of the gate stack, difficult thickness control in this rather complicated process sequence, and increasing the exposure of the gate dielectric layer to detrimental circumstances, etc., to achieve easy control, the effect of elimination of polysilicon carrier depletion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

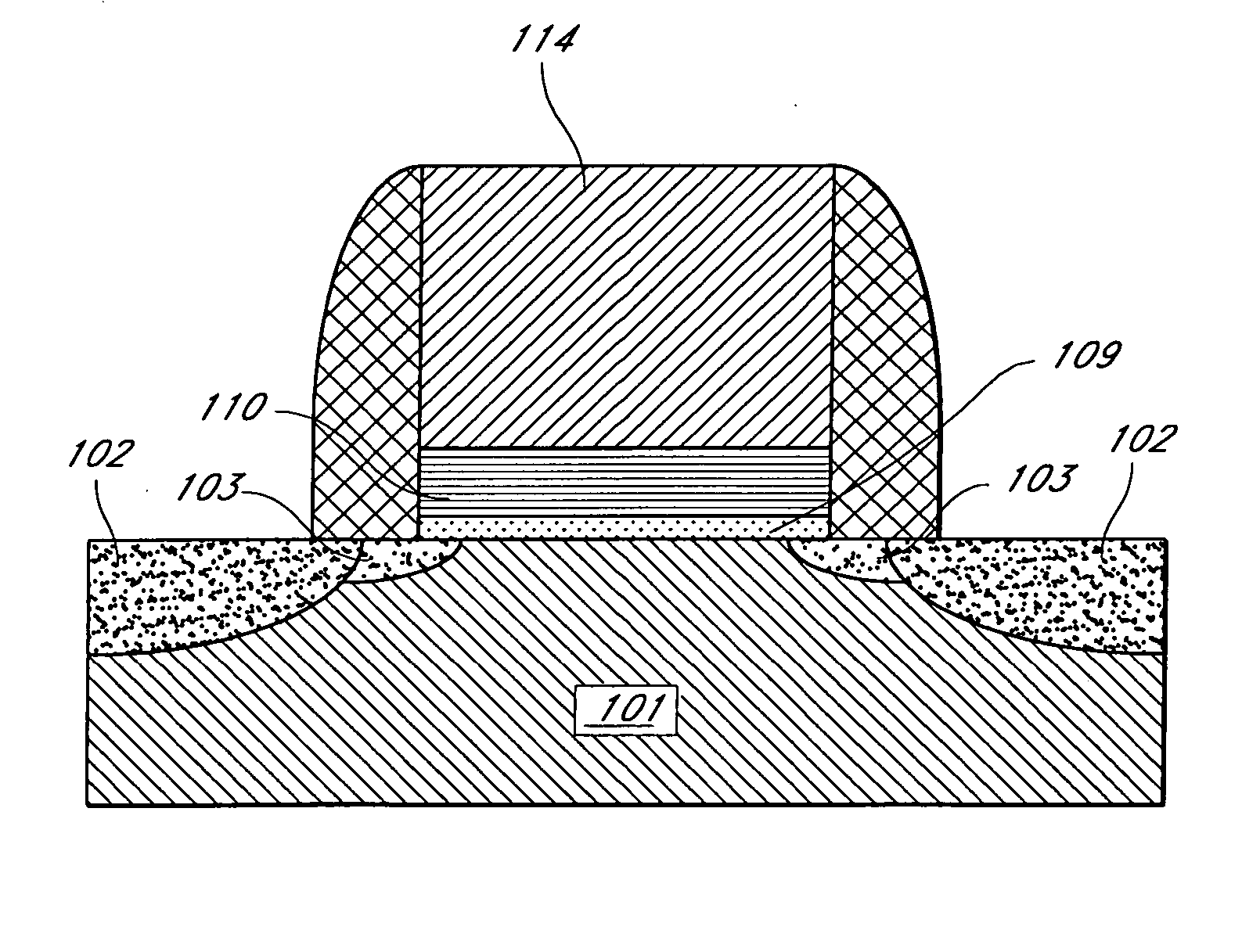

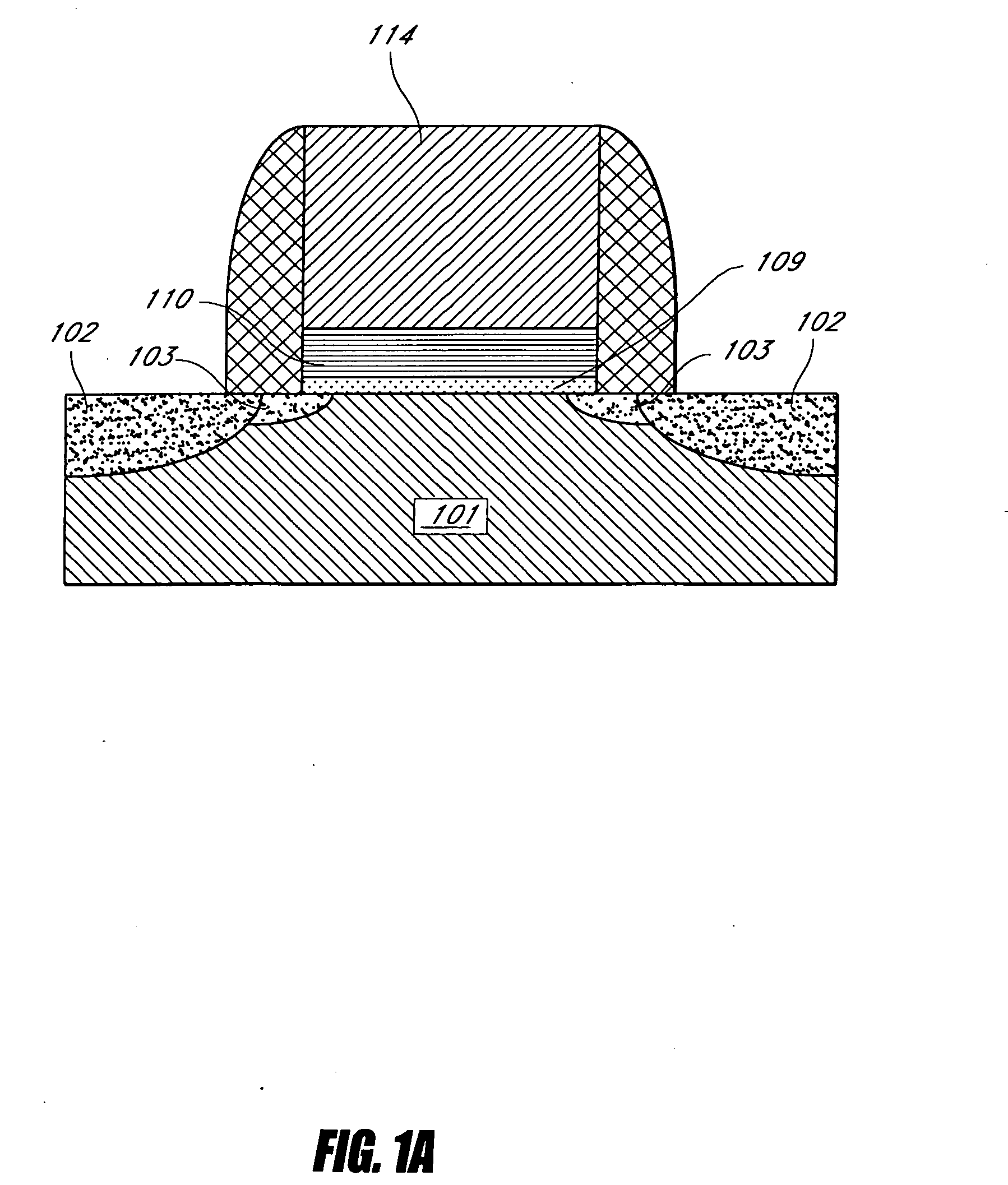

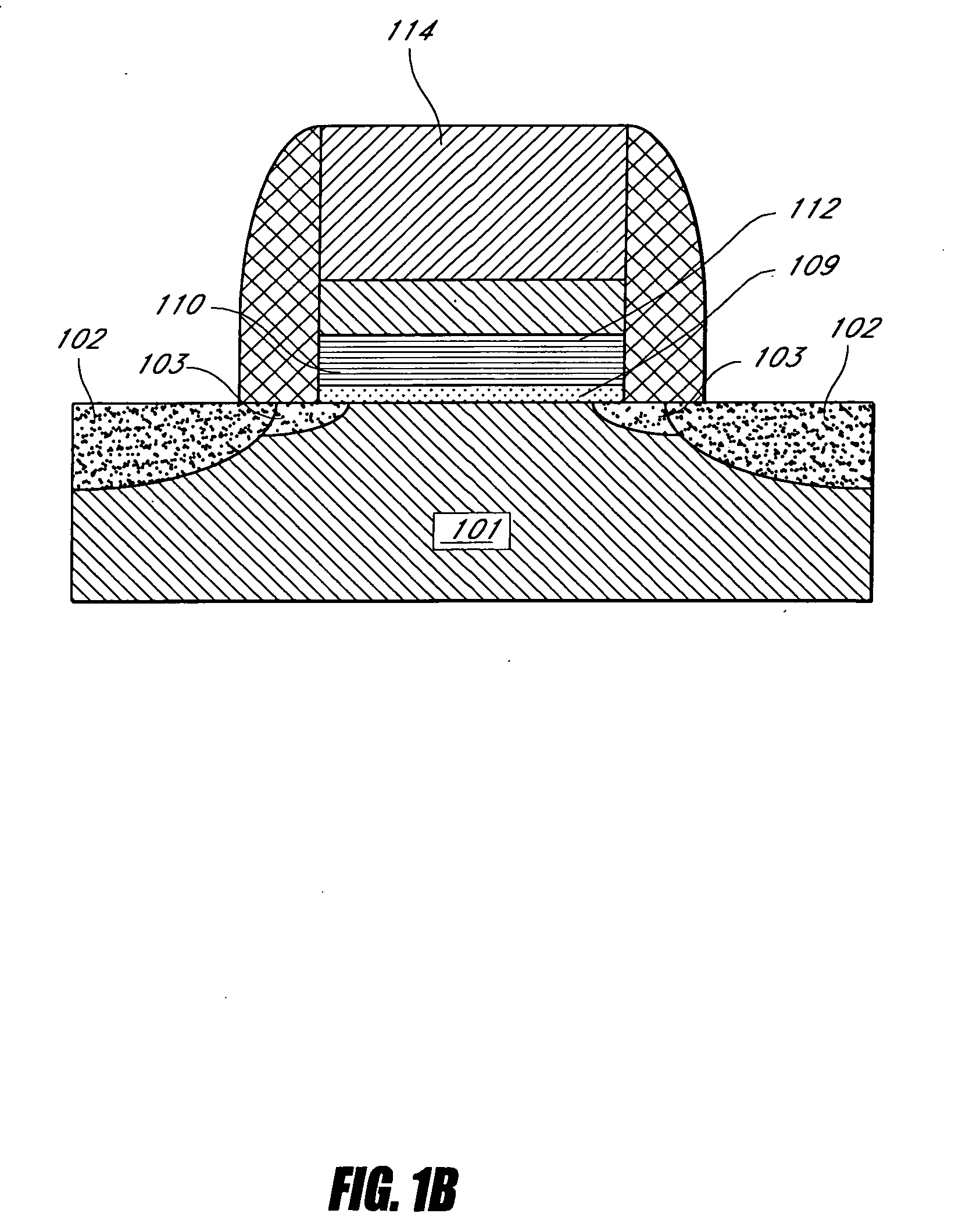

Image

Examples

example

[0057] Substrates consisted of wafers that had native oxide on the silicon surface, the native oxide comprising a thin chemical silicon oxide made with an IMEC-clean®. Hafnium dioxide thin films having thickness of 3-5 nm were deposited at 300° C. by thermal ALD on the substrates.

[0058] Titanium nitride (TiN) barrier thin films were deposited on top of the atomic layer deposited hafnium dioxide thin films (FIGS. 4-7). The TiN thin films were deposited in a Pulsar®2000 ALCVD™ reactor (ASM Microchemistry Oy of Espoo, Finland). In one set of experiments, TiN was deposited by thermal ALD from titanium tetrachloride (TiC4) and ammonia (NH3) at higher temperatures, preferably 350° C. In another set of experiment TiN was deposited by plasma enhanced ALD using TiCl4 and nitrogen / hydrogen remote plasma at lower temperatures. The thin films were characterized using standard techniques.

[0059] The average growth rate of titanium nitride deposited by thermal ALD was 0.02 nm / cycle. Films were v...

PUM

| Property | Measurement | Unit |

|---|---|---|

| dielectric constant | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| dielectric constant | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More