Patents

Literature

164 results about "Equivalent oxide thickness" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

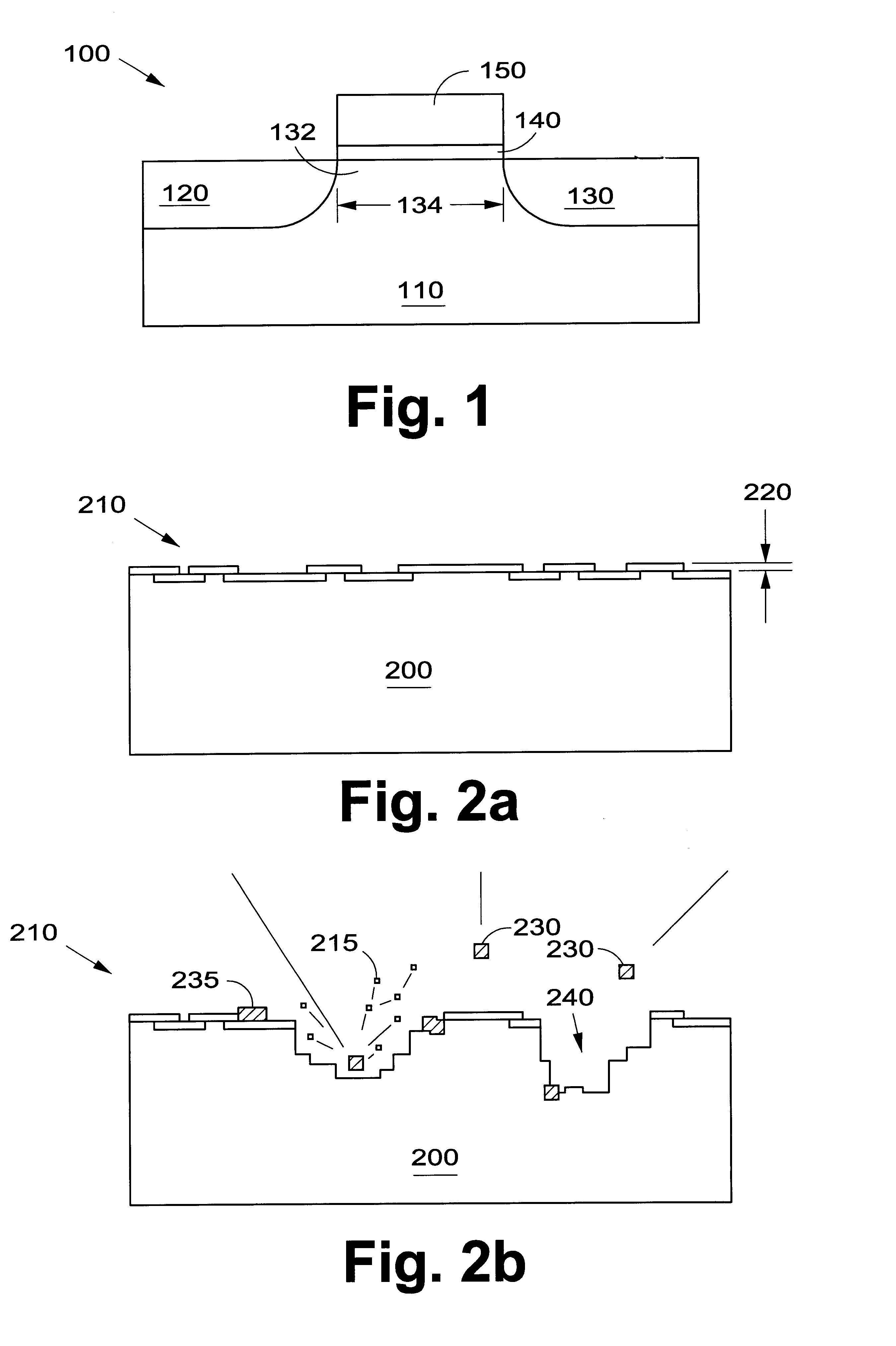

An Equivalent oxide thickness is a distance, usually given in nanometers (nm), which indicates how thick a silicon oxide film would need to be to produce the same effect as the high-κ material being used. The term is often used when describing field effect transistors which rely on an electrically insulating pad of material between a gate and a doped semiconducting region. Device performance has typically been improved by reducing the thickness of a silicon oxide insulating pad.

Gate oxides

InactiveUS6844203B2Improve surface roughnessSmooth surface roughnessSemiconductor/solid-state device manufacturingSemiconductor devicesEquivalent oxide thicknessGadolinium

A gate oxide and method of fabricating a gate oxide that produces a more reliable and thinner equivalent oxide thickness than conventional SiO2 gate oxides are provided. Also shown is a gate oxide with a conduction band offset of 2 eV or greater. Gate oxides formed from elements such as yttrium and gadolinium are thermodynamically stable such that the gate oxides formed will have minimal reactions with a silicon substrate or other structures during any later high temperature processing stages. The process shown is performed at lower temperatures than the prior art, which further inhibits reactions with the silicon substrate or other structures. Using a thermal evaporation technique to deposit the layer to be oxidized, the underlying substrate surface smoothness is preserved, thus providing improved and more consistent electrical properties in the resulting gate oxide.

Owner:HEWLETT PACKARD CO +1

Low-temperature grown high-quality ultra-thin praseodymium gate dielectrics

InactiveUS6900122B2Inhibition formationSave budgetVacuum evaporation coatingSputtering coatingEquivalent oxide thicknessGate dielectric

A praseodymium (Pr) gate oxide and method of fabricating same that produces a high-quality and ultra-thin equivalent oxide thickness as compared to conventional SiO2 gate oxides are provided. The Pr gate oxide is thermodynamically stable so that the oxide reacts minimally with a silicon substrate or other structures during any later high temperature processing stages. The process shown is performed at lower temperatures than the prior art, which further inhibits reactions with the silicon substrate or other structures. Using a thermal evaporation technique to deposit a Pr layer to be oxidized, the underlying substrate surface smoothness is preserved, thus providing improved and more consistent electrical properties in the resulting gate oxide.

Owner:MICRON TECH INC

Crystalline or amorphous medium-K gate oxides, Y2O3 and Gd2O3

InactiveUS20050032292A1Semiconductor/solid-state device manufacturingSemiconductor devicesEquivalent oxide thicknessGadolinium

A gate oxide and method of fabricating a gate oxide that produces a more reliable and thinner equivalent oxide thickness than conventional SiO2 gate oxides are provided. Also shown is a gate oxide with a conduction band offset of 2 eV or greater. Gate oxides formed from elements such as yttrium and gadolinium are thermodynamically stable such that the gate oxides formed will have minimal reactions with a silicon substrate or other structures during any later high temperature processing stages. The process shown is performed at lower temperatures than the prior art, which further inhibits reactions with the silicon substrate or other structures. Using a thermal evaporation technique to deposit the layer to be oxidized, the underlying substrate surface smoothness is preserved, thus providing improved and more consistent electrical properties in the resulting gate oxide.

Owner:MICRON TECH INC

Low-temperature grown high quality ultra-thin CoTiO3 gate dielectrics

InactiveUS6953730B2Solid-state devicesVacuum evaporation coatingEquivalent oxide thicknessGate dielectric

A gate oxide and method of fabricating a gate oxide that produces a more reliable and thinner equivalent oxide thickness than conventional SiO2 gate oxides are provided. Gate oxides formed from alloys such as cobalt-titanium are thermodynamically stable such that the gate oxides formed will have minimal reactions with a silicon substrate or other structures during any later high temperature processing stages. The process shown is performed at lower temperatures than the prior art, which inhibits unwanted species migration and unwanted reactions with the silicon substrate or other structures. Using a thermal evaporation technique to deposit the layer to be oxidized, the underlying substrate surface smoothness is preserved, thus providing improved and more consistent electrical properties in the resulting gate oxide.

Owner:MICRON TECH INC

Evaporated LaAlO3 films for gate dielectrics

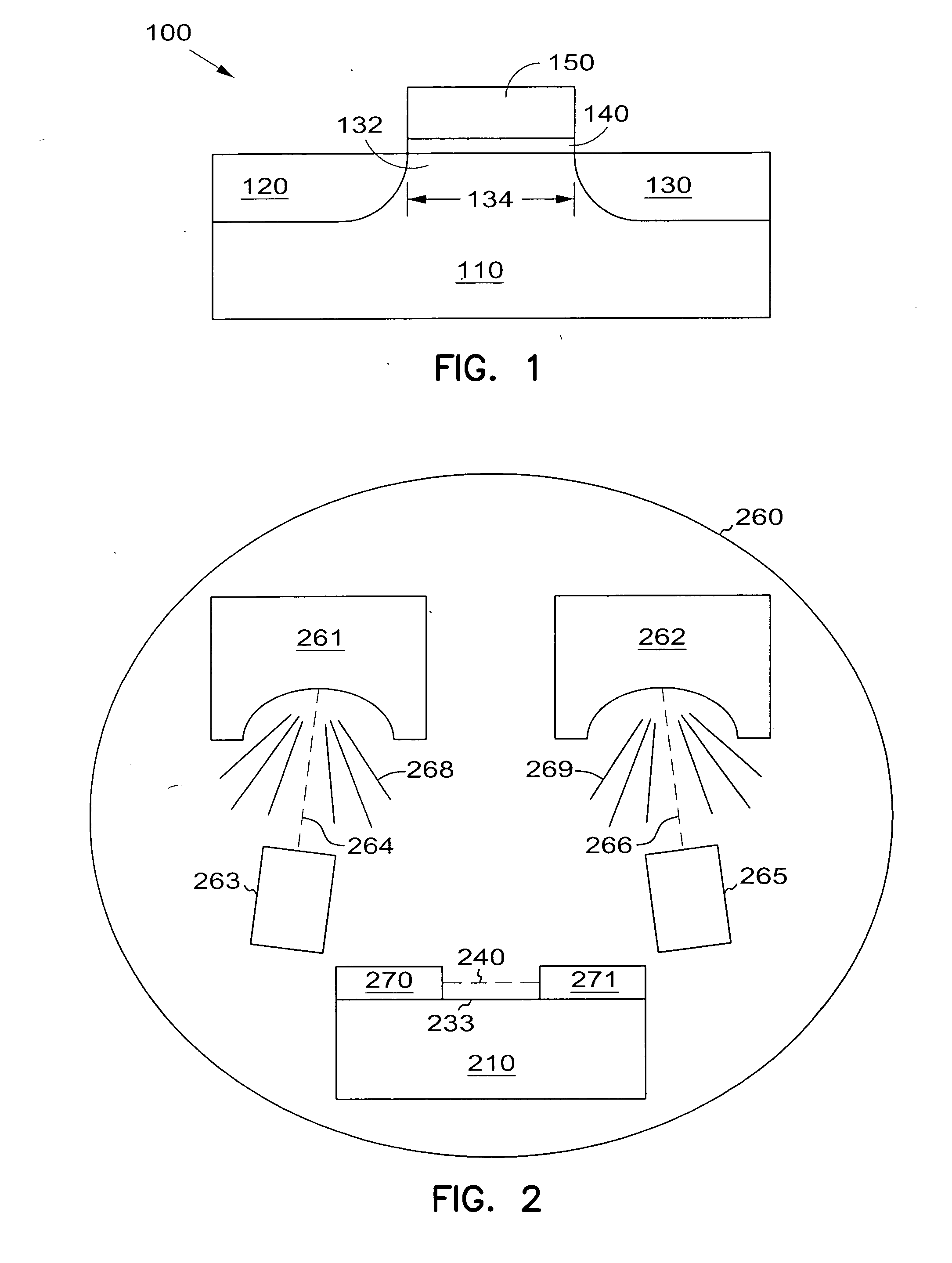

InactiveUS20050145957A1Semiconductor/solid-state device manufacturingSemiconductor devicesDielectricEquivalent oxide thickness

A gate dielectric containing LaAlO3 and method of fabricating a gate dielectric contained LaAlO3 produce a reliable gate dielectric having a thinner equivalent oxide thickness than attainable using SiO2. The LaAlO3 gate dielectrics formed are thermodynamically stable such that these gate dielectrics will have minimal reactions with a silicon substrate or other structures during processing. A LaAlO3 gate dielectric is formed by evaporating Al2O3 at a given rate, evaporating La2O3 at another rate, and controlling the two rates to provide an amorphous film containing LaAlO3 on a transistor body region. The evaporation deposition of the LaAlO3 film is performed using two electron guns to evaporate dry pellets of Al2O3 and La2O3. The two rates for evaporating the materials are selectively chosen to provide a dielectric film composition having a predetermined dielectric constant ranging from the dielectric constant of an Al2O3 film to the dielectric constant of a La2O3 film. In addition to forming a LaAlO3 gate dielectric for a transistor, memory devices, and information handling devices such as computers include elements having a LaAlO3 gate electric with a thin equivalent oxide thickness.

Owner:MICRON TECH INC

High-quality praseodymium gate dielectrics

InactiveUS6979855B2Inhibition formationSave budgetTransistorVacuum evaporation coatingEquivalent oxide thicknessGate dielectric

Owner:MICRON TECH INC

Evaporation of Y-Si-O films for medium-K dielectrics

InactiveUS20050026374A1Improve surface roughnessSmooth surface roughnessTransistorSolid-state devicesEquivalent oxide thicknessDielectric

A gate oxide and method of fabricating a gate oxide that produces a more reliable and thinner equivalent oxide thickness than conventional SiO2 gate oxides are provided. Gate oxides formed from yttrium, silicon, and oxygen are thermodynamically stable such that the gate oxides formed will have minimal reactions with a silicon substrate or other structures during any later high temperature processing stages. The process shown is performed at lower temperatures than the prior art, which inhibits unwanted species migration and unwanted reactions with the silicon substrate or other structures. Using a thermal evaporation technique to deposit the layer to be oxidized, the underlying substrate surface smoothness is preserved, thus providing improved and more consistent electrical properties in the resulting gate oxide.

Owner:MICRON TECH INC

Evaporation of Y-Si-O films for medium-K dielectrics

InactiveUS6930346B2Improve surface roughnessSmooth surface roughnessTransistorSolid-state devicesDielectricEquivalent oxide thickness

A gate oxide and method of fabricating a gate oxide that produces a more reliable and thinner equivalent oxide thickness than conventional SiO2 gate oxides are provided. Gate oxides formed from yttrium, silicon, and oxygen are thermodynamically stable such that the gate oxides formed will have minimal reactions with a silicon substrate or other structures during any later high temperature processing stages. The process shown is performed at lower temperatures than the prior art, which inhibits unwanted species migration and unwanted reactions with the silicon substrate or other structures. Using a thermal evaporation technique to deposit the layer to be oxidized, the underlying substrate surface smoothness is preserved, thus providing improved and more consistent electrical properties in the resulting gate oxide.

Owner:MICRON TECH INC

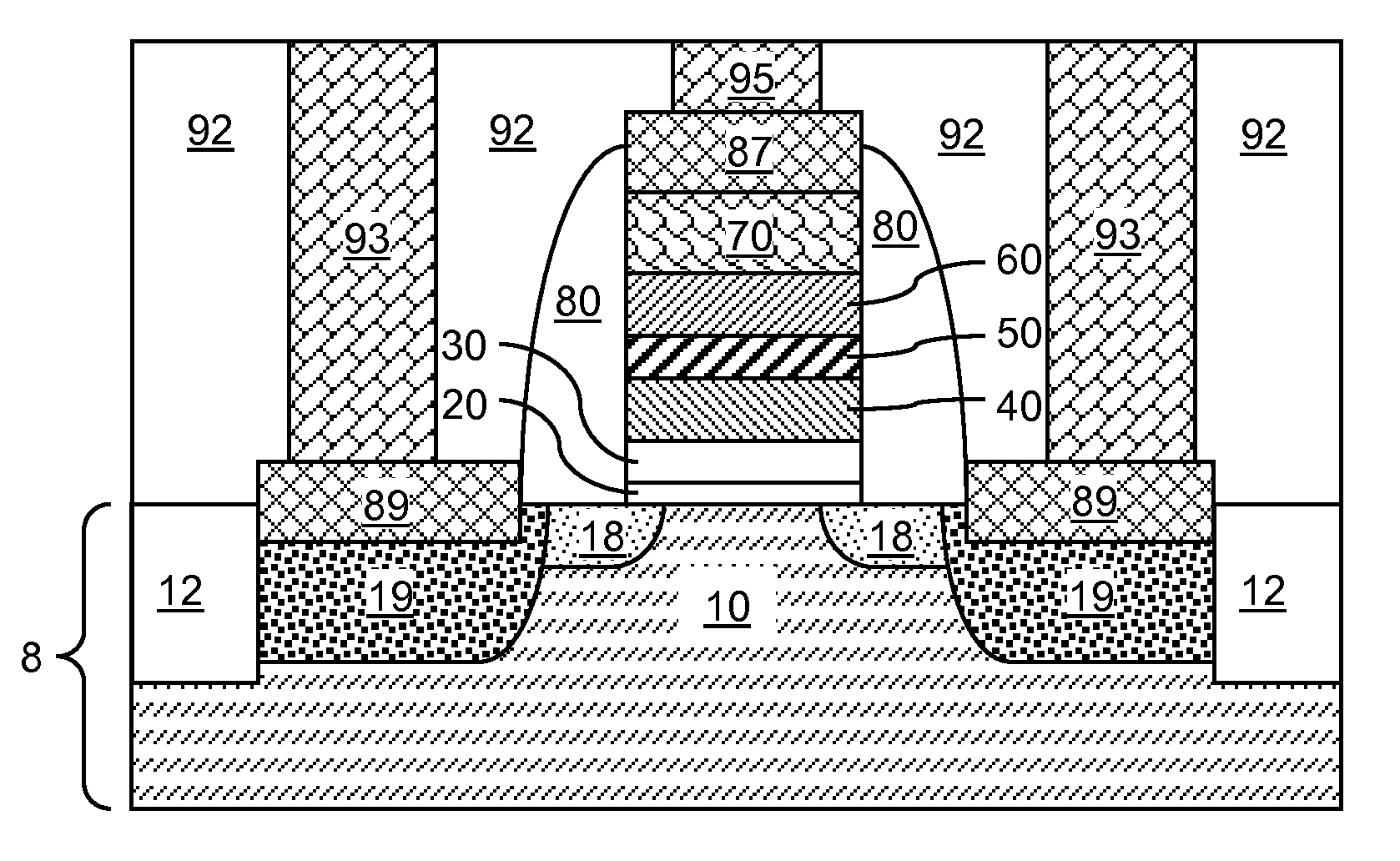

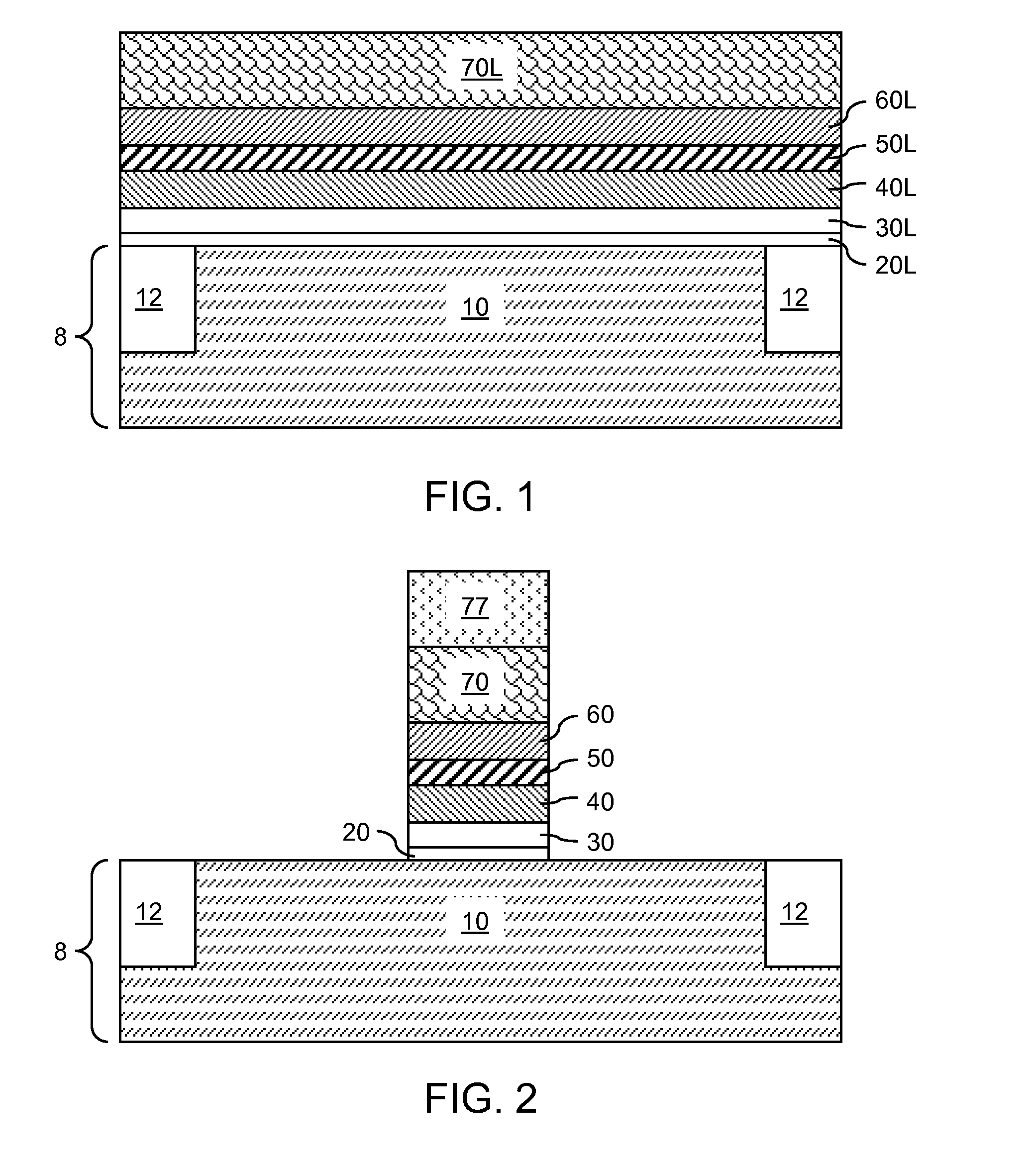

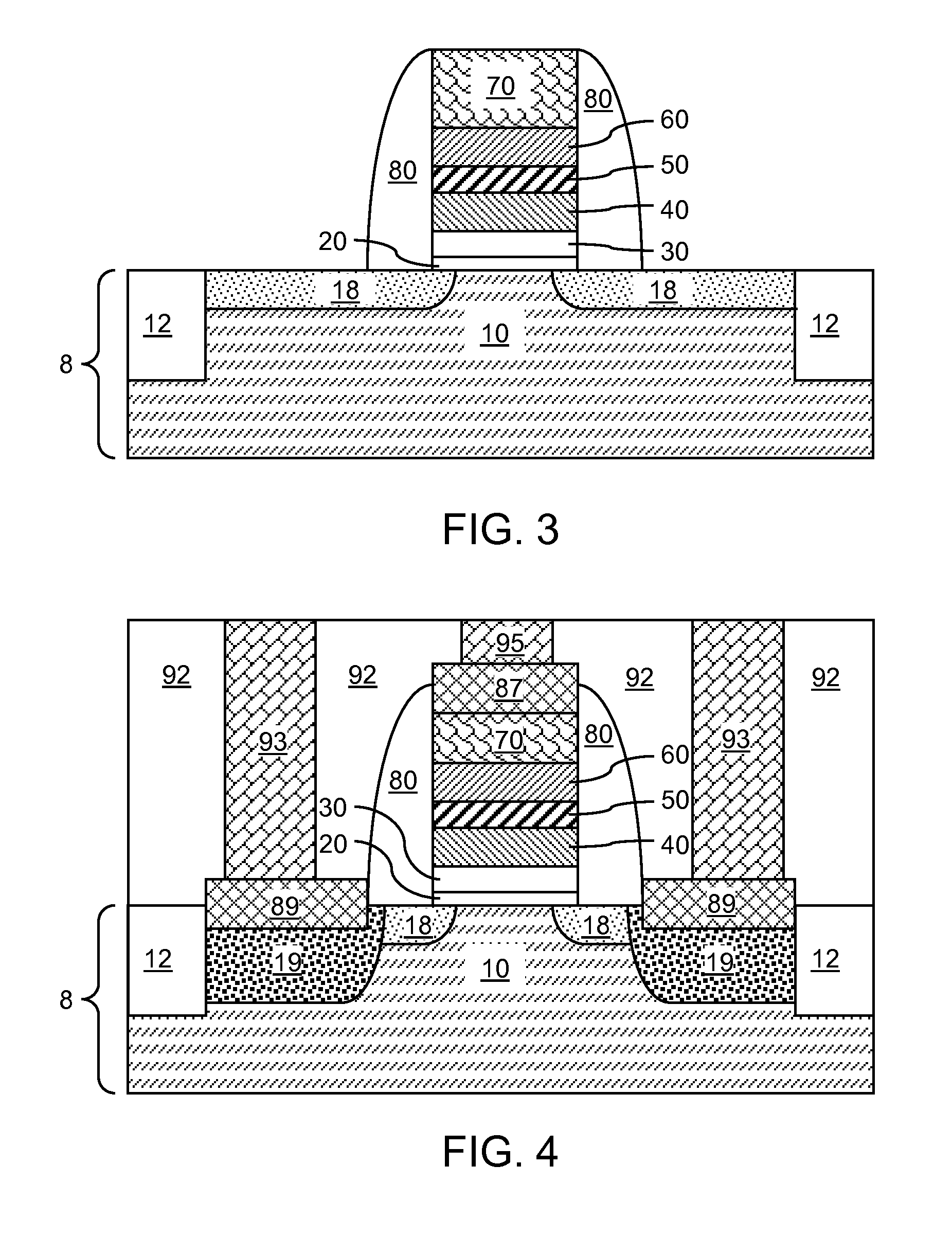

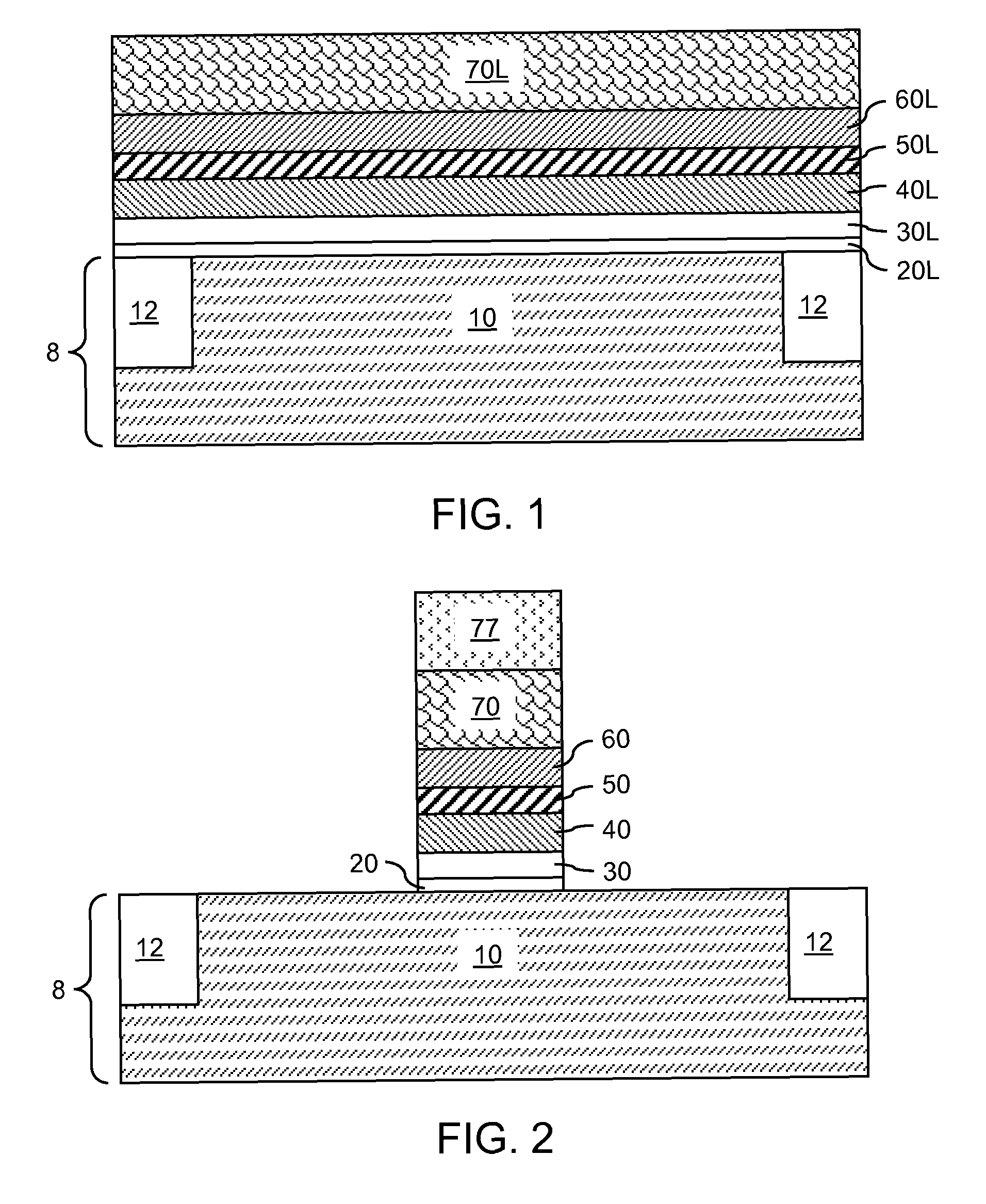

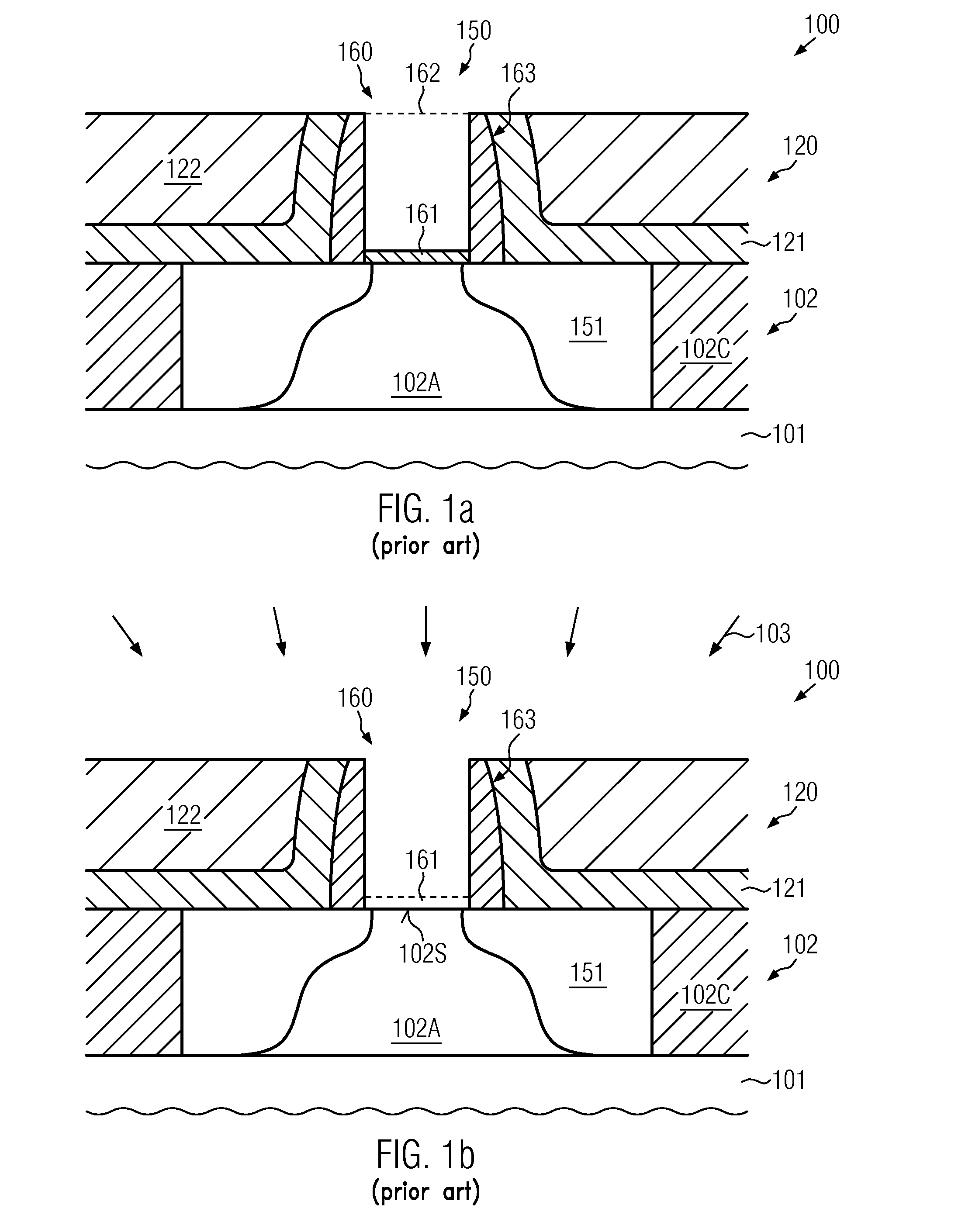

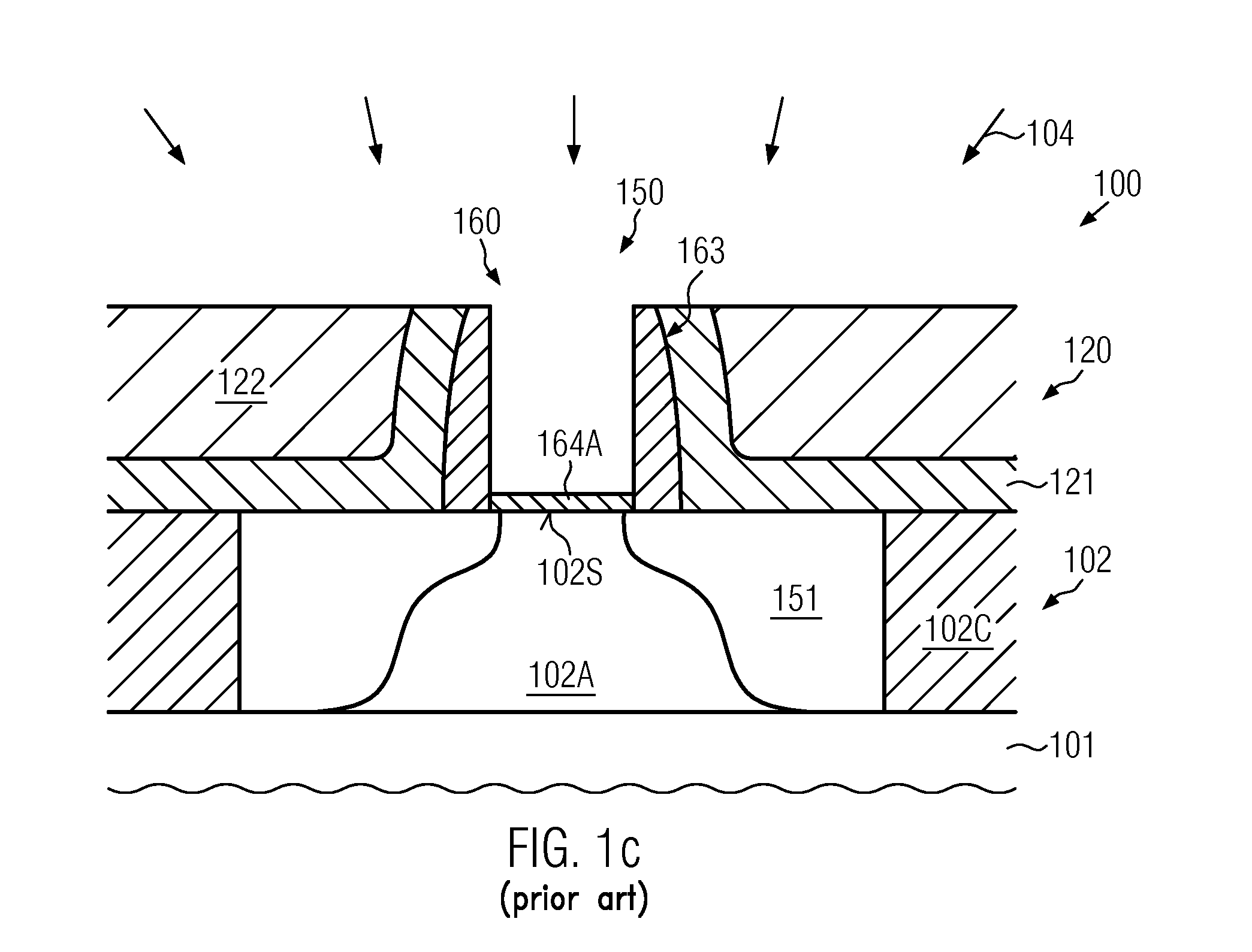

Scavanging metal stack for a high-k gate dielectric

ActiveUS20100320547A1Constant threshold voltageReduce equivalent oxide thicknessTransistorSemiconductor/solid-state device manufacturingDielectricEquivalent oxide thickness

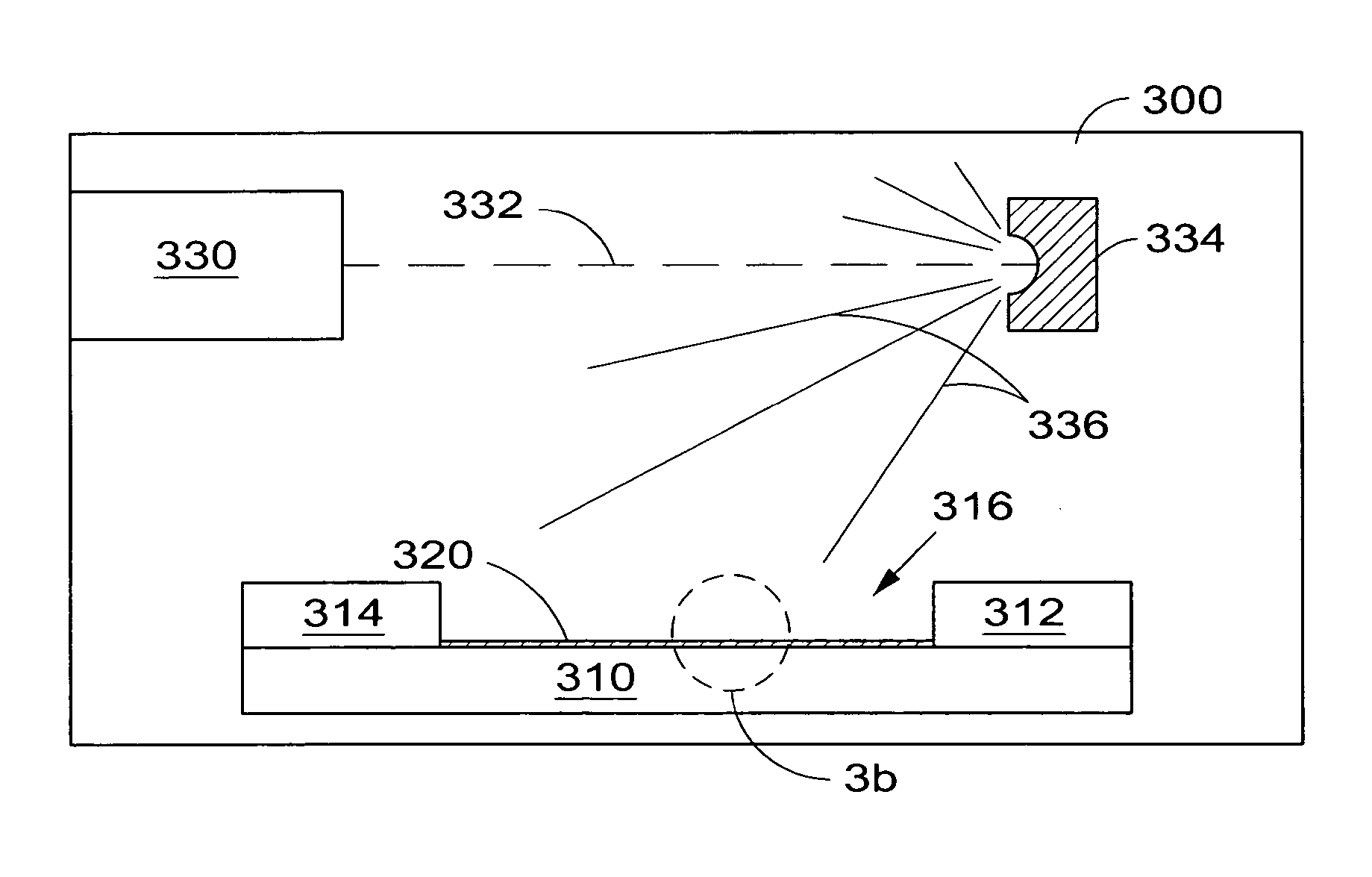

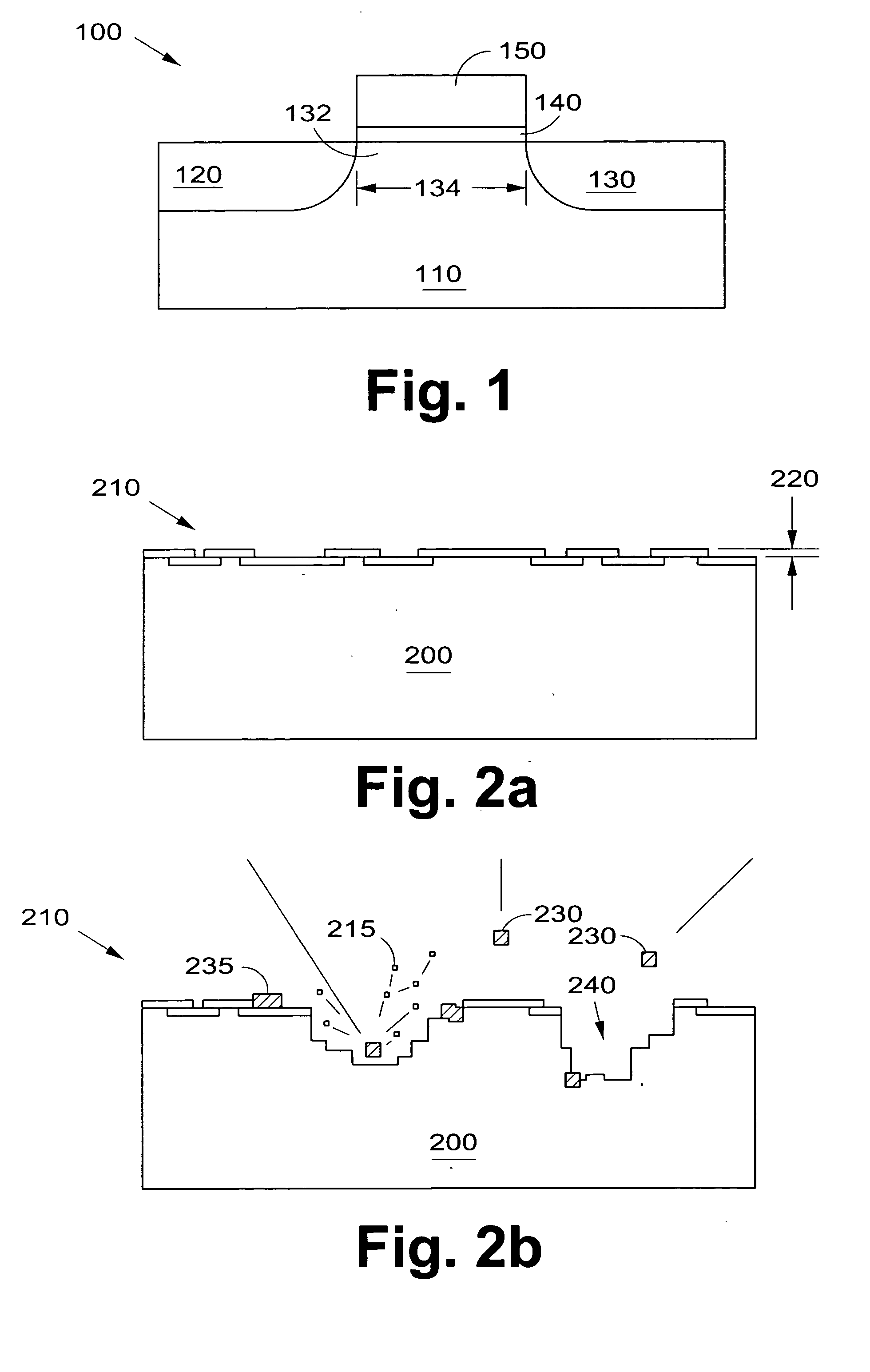

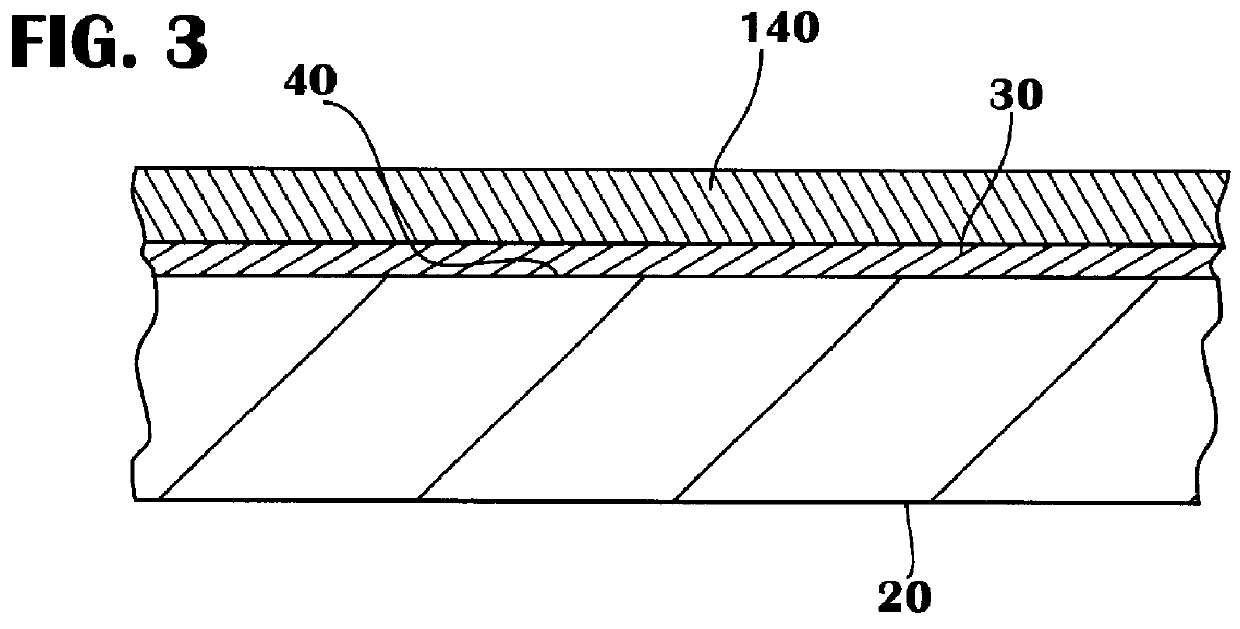

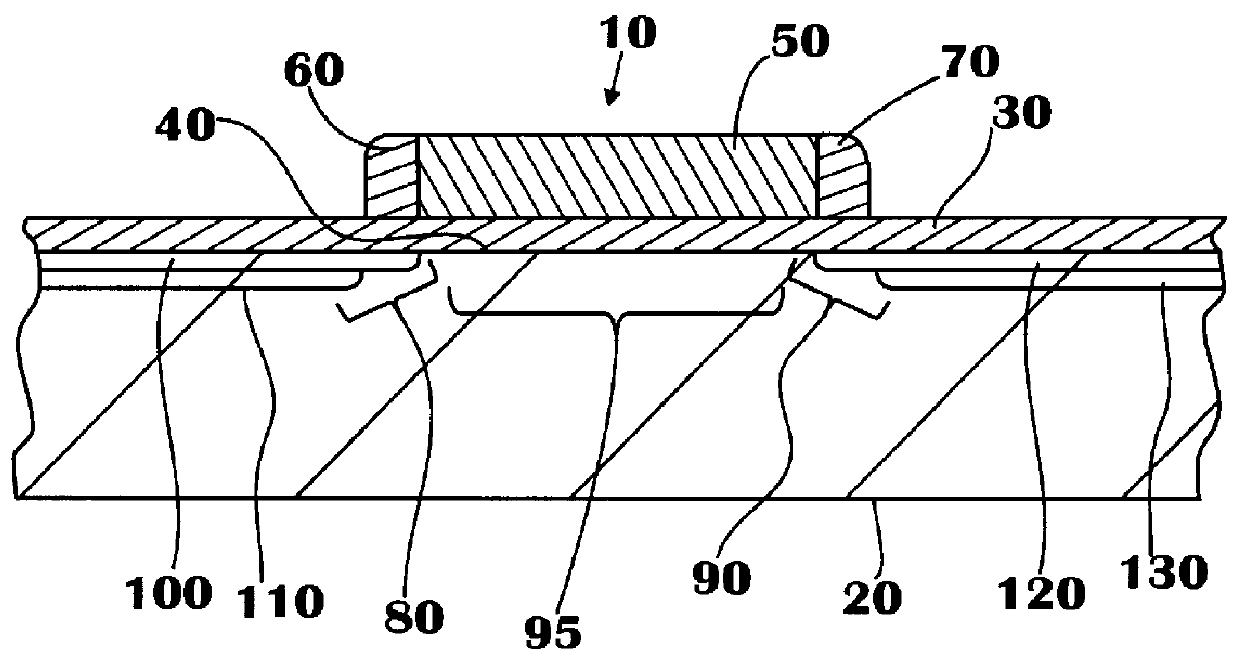

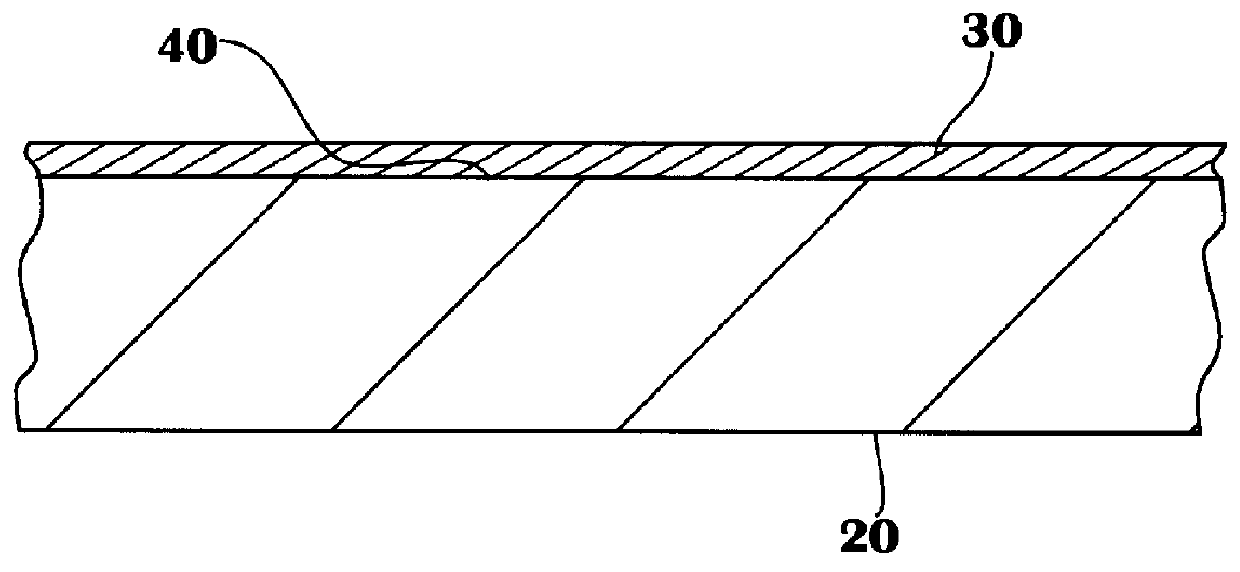

A stack of a high-k gate dielectric and a metal gate structure includes a lower metal layer, a scavenging metal layer, and an upper metal layer. The scavenging metal layer meets the following two criteria 1) a metal (M) for which the Gibbs free energy change of the reaction Si+2 / y MxOy→2x / y M+SiO2 is positive 2) a metal that has a more negative Gibbs free energy per oxygen atom for formation of oxide than the material of the lower metal layer and the material of the upper metal layer. The scavenging metal layer meeting these criteria captures oxygen atoms as the oxygen atoms diffuse through the gate electrode toward the high-k gate dielectric. In addition, the scavenging metal layer remotely reduces the thickness of a silicon oxide interfacial layer underneath the high-k dielectric. As a result, the equivalent oxide thickness (EOT) of the total gate dielectric is reduced and the field effect transistor maintains a constant threshold voltage even after high temperature processes during CMOS integration.

Owner:GLOBALFOUNDRIES US INC

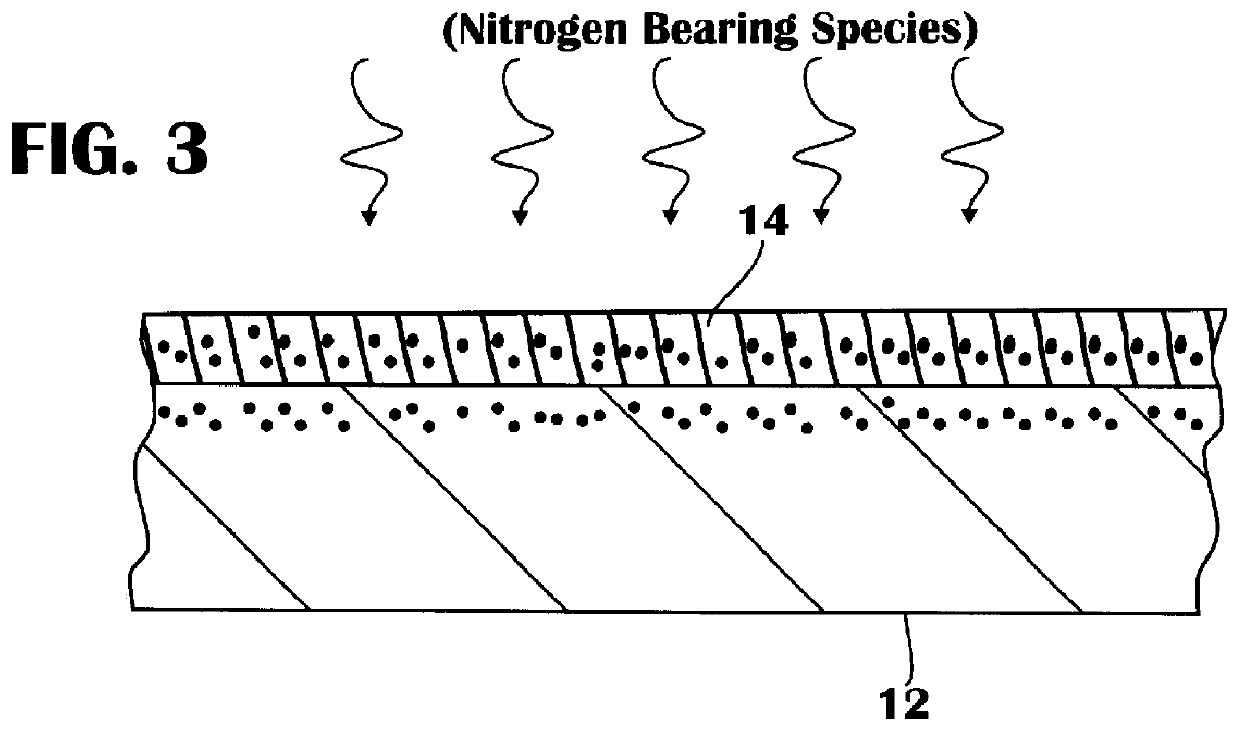

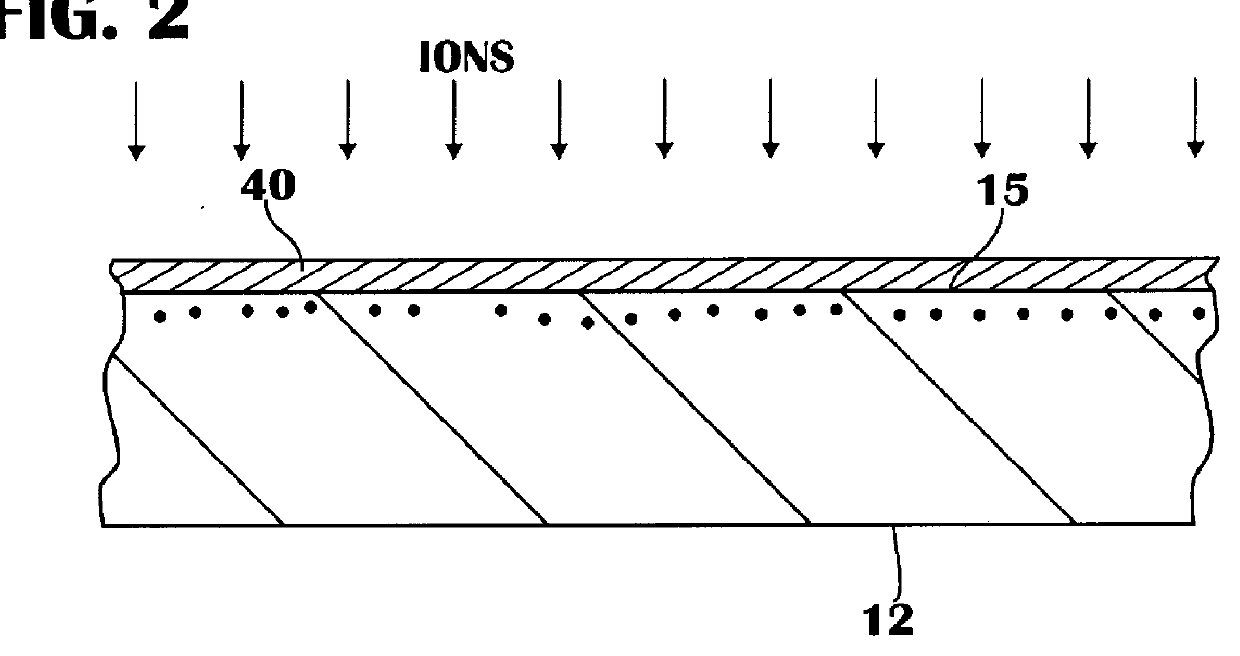

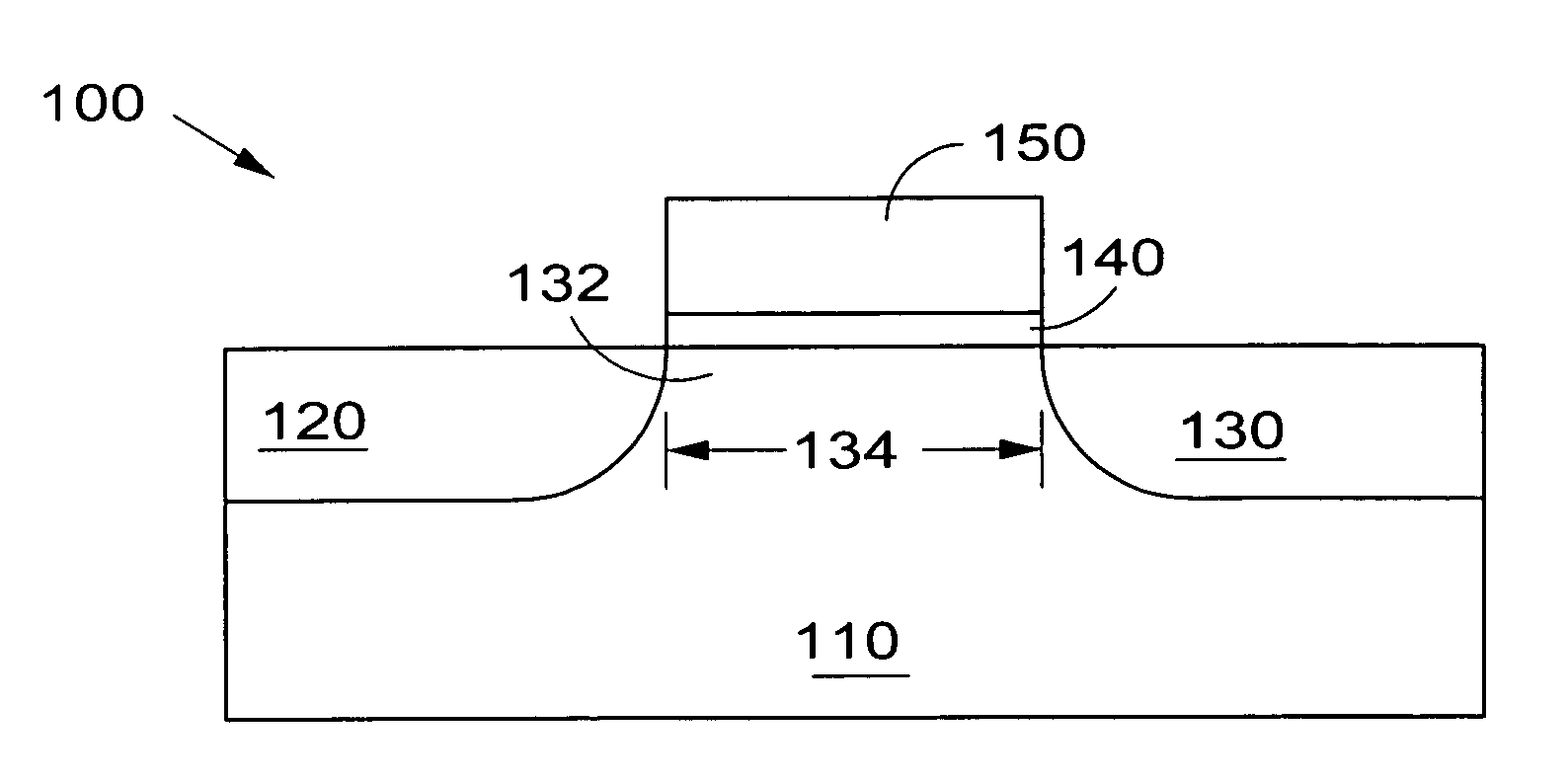

Method of integration of nitrogen bearing high K film

InactiveUS6110784ATransistorSemiconductor/solid-state device detailsEquivalent oxide thicknessGate dielectric

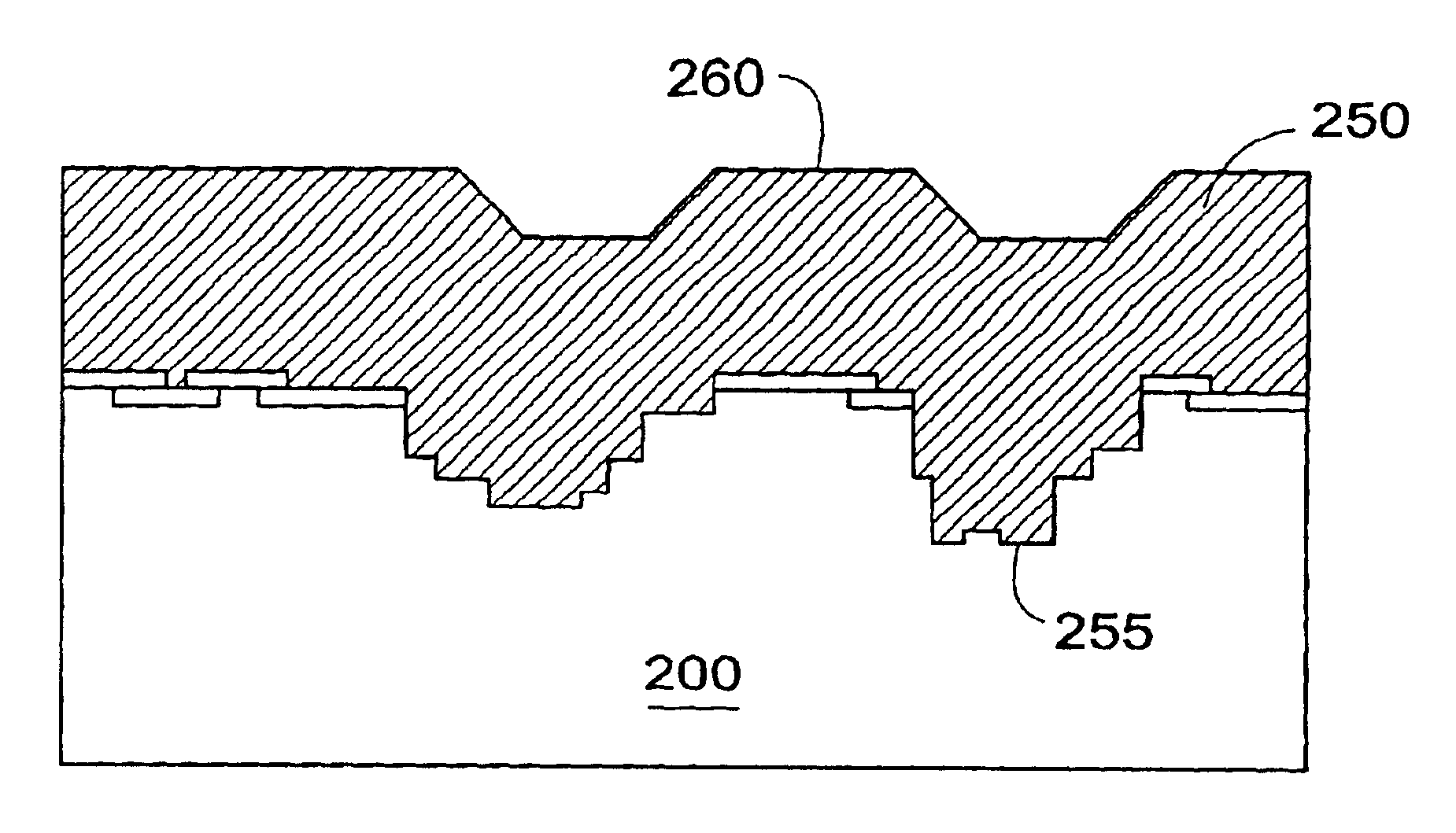

A transistor and a method of making the same are provided. The transistor includes a substrate that has an upper surface and a gate dielectric layer positioned on the substrate that has a first quantity of nitrogen therein. A gate electrode is positioned on the gate dielectric layer. First and second source / drain regions are positioned in the substrate and laterally separated to define a channel region beneath the gate dielectric layer. The gate dielectric layer may be composed of a high K material with a thin equivalent thickness of oxide, such as TiO2, Ta2O5, CrO2 or SrO2. The nitrogen suppresses later oxide formation which may otherwise increase the equivalent thickness of oxide of the gate dielectric layer. Nitrogen may also be incorporated into the substrate and the gate electrode.

Owner:GLOBALFOUNDRIES INC

Highly reliable amorphous high-k gate dielectric ZrOxNy

InactiveUS7205620B2Improve surface roughnessSmooth surface roughnessVacuum evaporation coatingSemiconductor/solid-state device manufacturingEquivalent oxide thicknessGate dielectric

A gate dielectric and method of fabricating a gate dielectric that produces a more reliable and thinner equivalent oxide thickness than conventional SiO2 gate oxides are provided. Gate dielectrics formed from metals such as zirconium are thermodynamically stable such that the gate dielectrics formed will have minimal reactions with a silicon substrate or other structures during any later high temperature processing stages. The addition of nitrogen to the microstructure of the gate dielectric promotes an amorphous phase that further improves the electrical properties of the gate dielectric. The process shown is performed at lower temperatures than the prior art, which inhibits unwanted species migration and unwanted reactions with the silicon substrate or other structures. By using a thermal evaporation technique to first deposit a metal layer, the underlying substrate surface smoothness is preserved, thus providing improved and more consistent electrical properties in the resulting gate dielectric.

Owner:MICRON TECH INC

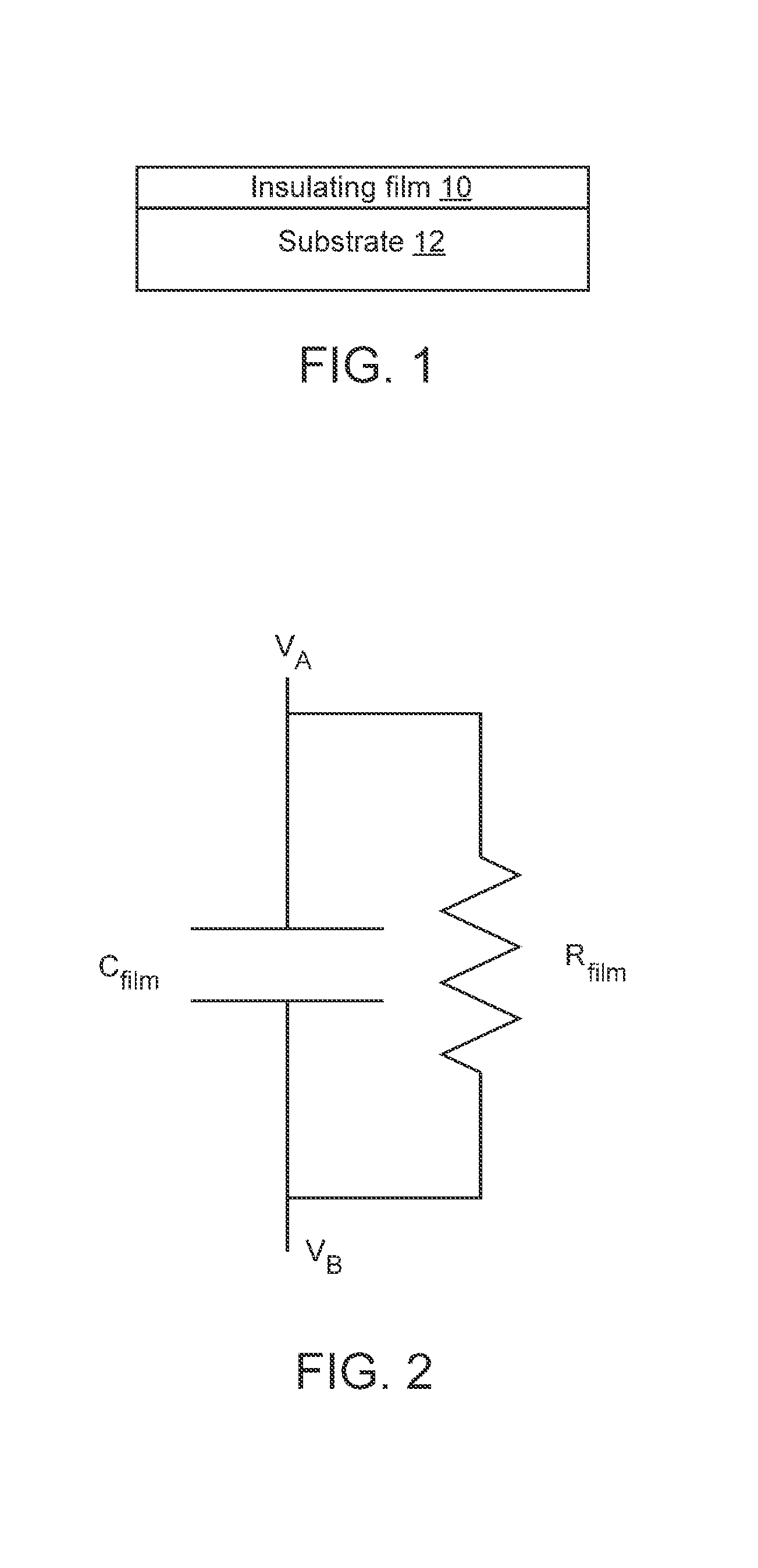

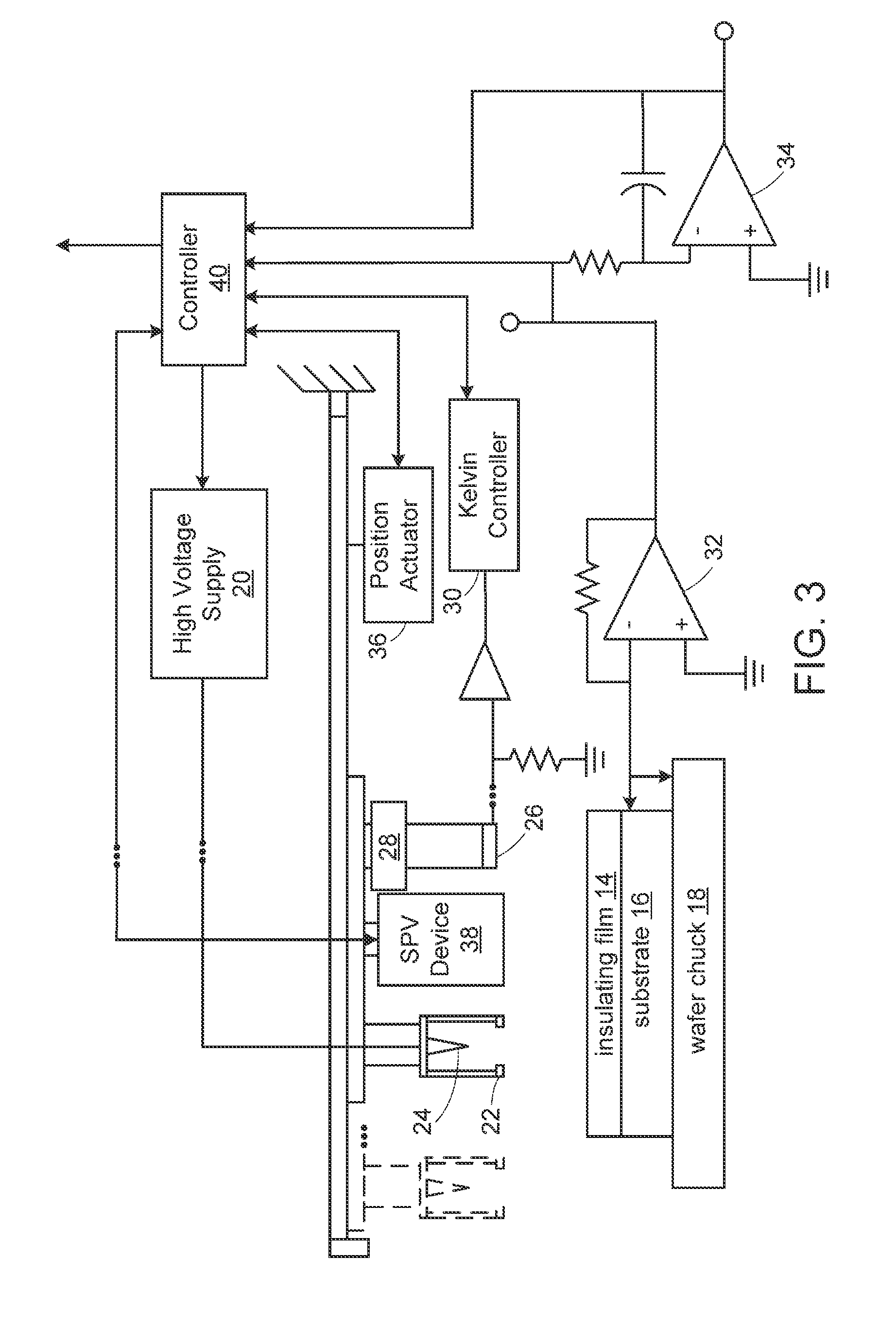

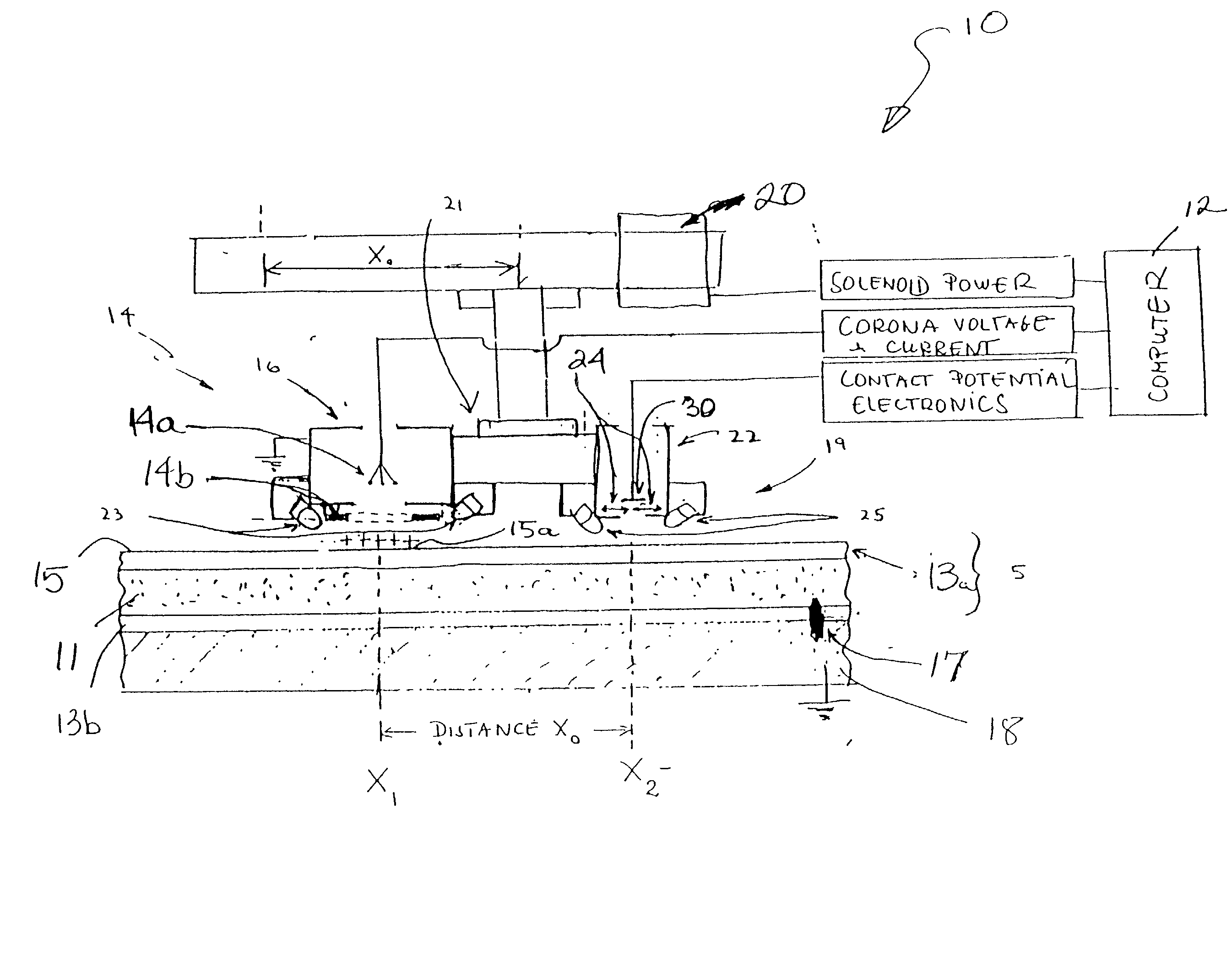

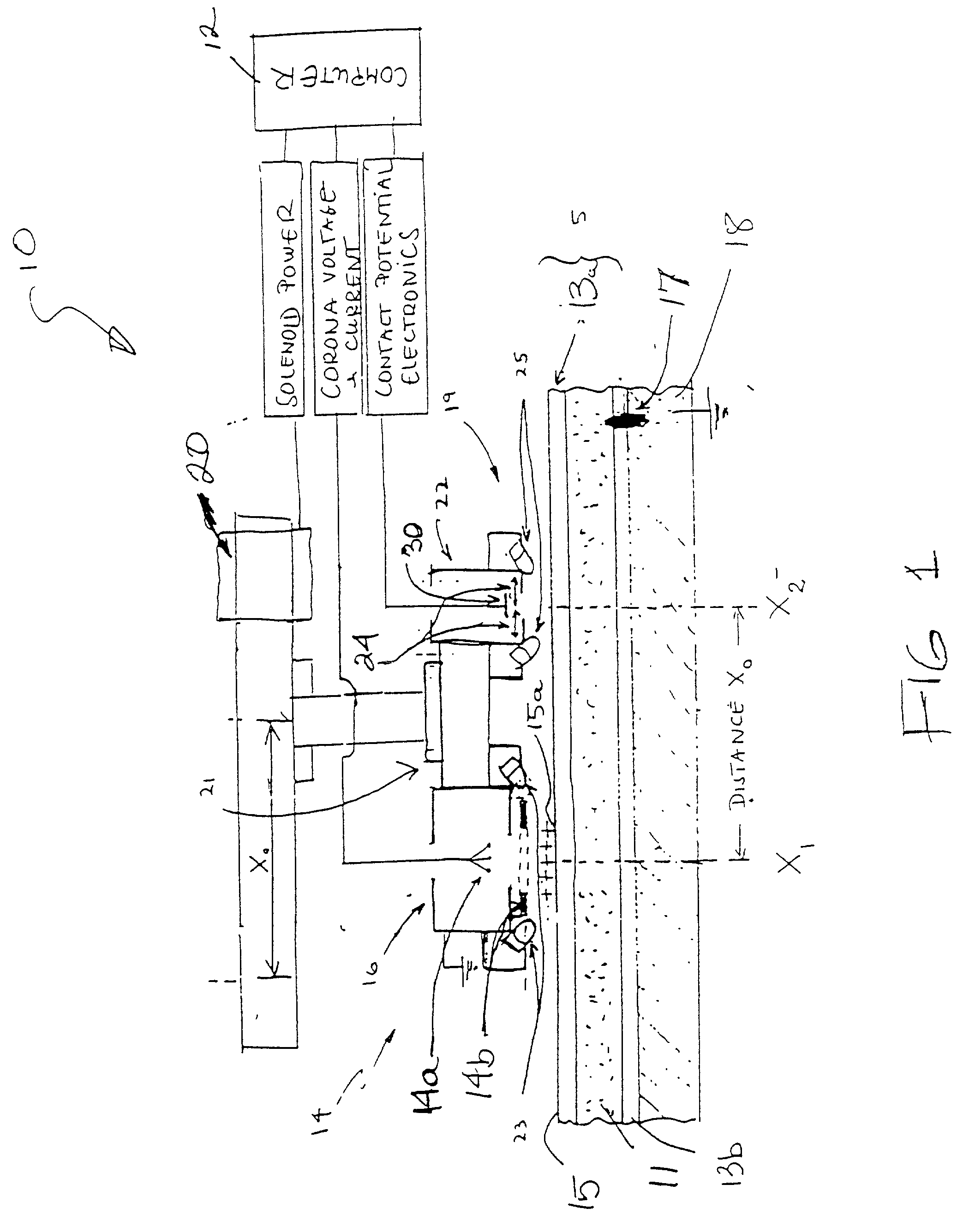

Non-contact methods for measuring electrical thickness and determining nitrogen content of insulating films

InactiveUS7103484B1Not decreaseSemiconductor/solid-state device testing/measurementSolid-state devicesEquivalent oxide thicknessNitrogen

Non-contact methods for determining a parameter of an insulating film are provided. One method includes measuring at least two surface voltages of the insulating film. The surface voltages are measured after different charge depositions. Measuring the surface voltages is performed in two or more sequences. The method also includes determining individual parameters for the two or more sequences from the surface voltages and the charge depositions. In addition, the method includes determining the parameter of the insulating film as an average of the individual parameters. The parameter is substantially independent of leakage in the insulating film. Another method includes determining a characteristic of nitrogen in an insulating film using two parameters of the insulating film selected from equivalent oxide thickness, optical thickness, and a measure of leakage through the insulating film. The characteristic may be a nitrogen dose, a nitrogen percentage, or a presence of nitrogen in the insulating film.

Owner:KLA TENCOR TECH CORP

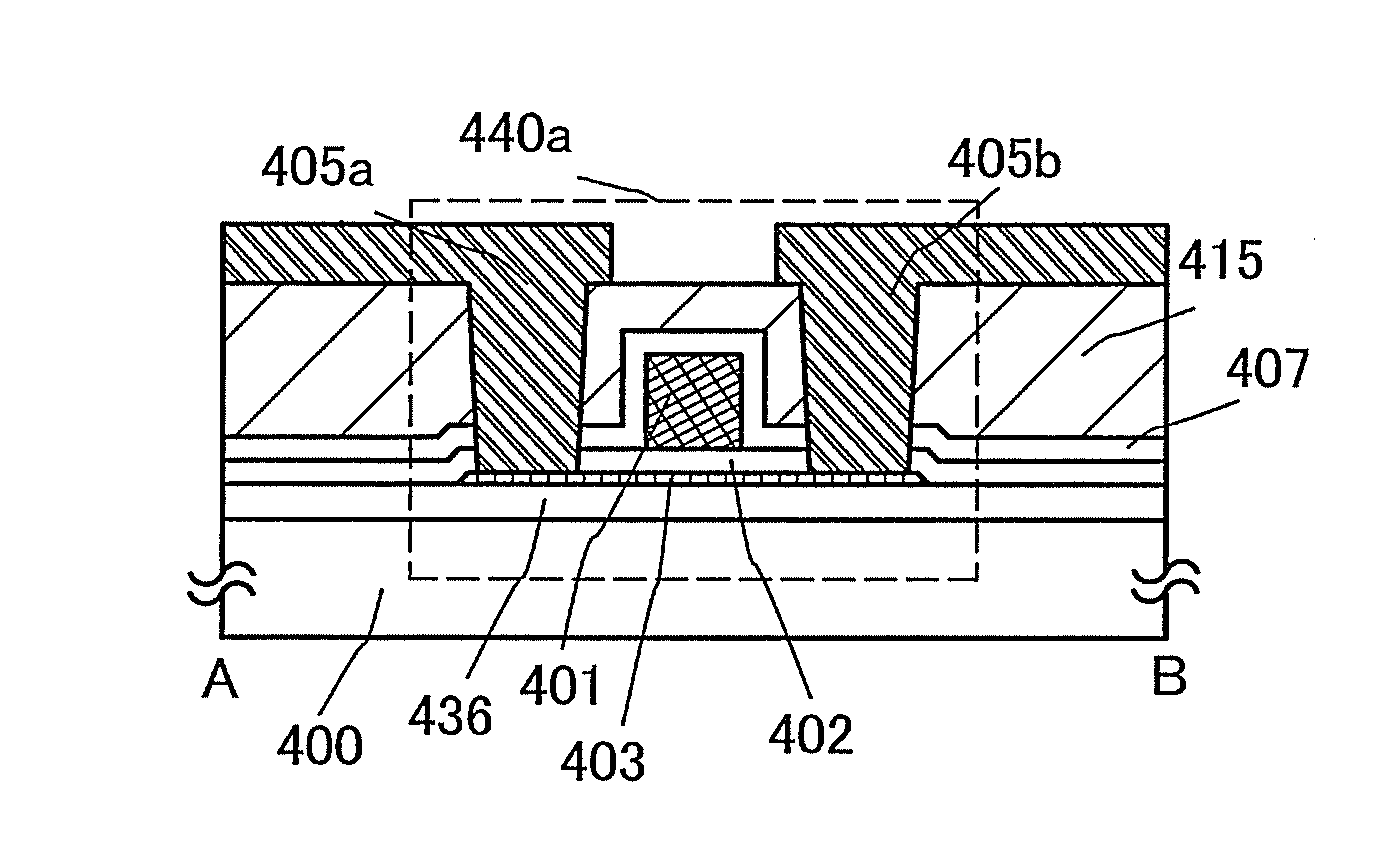

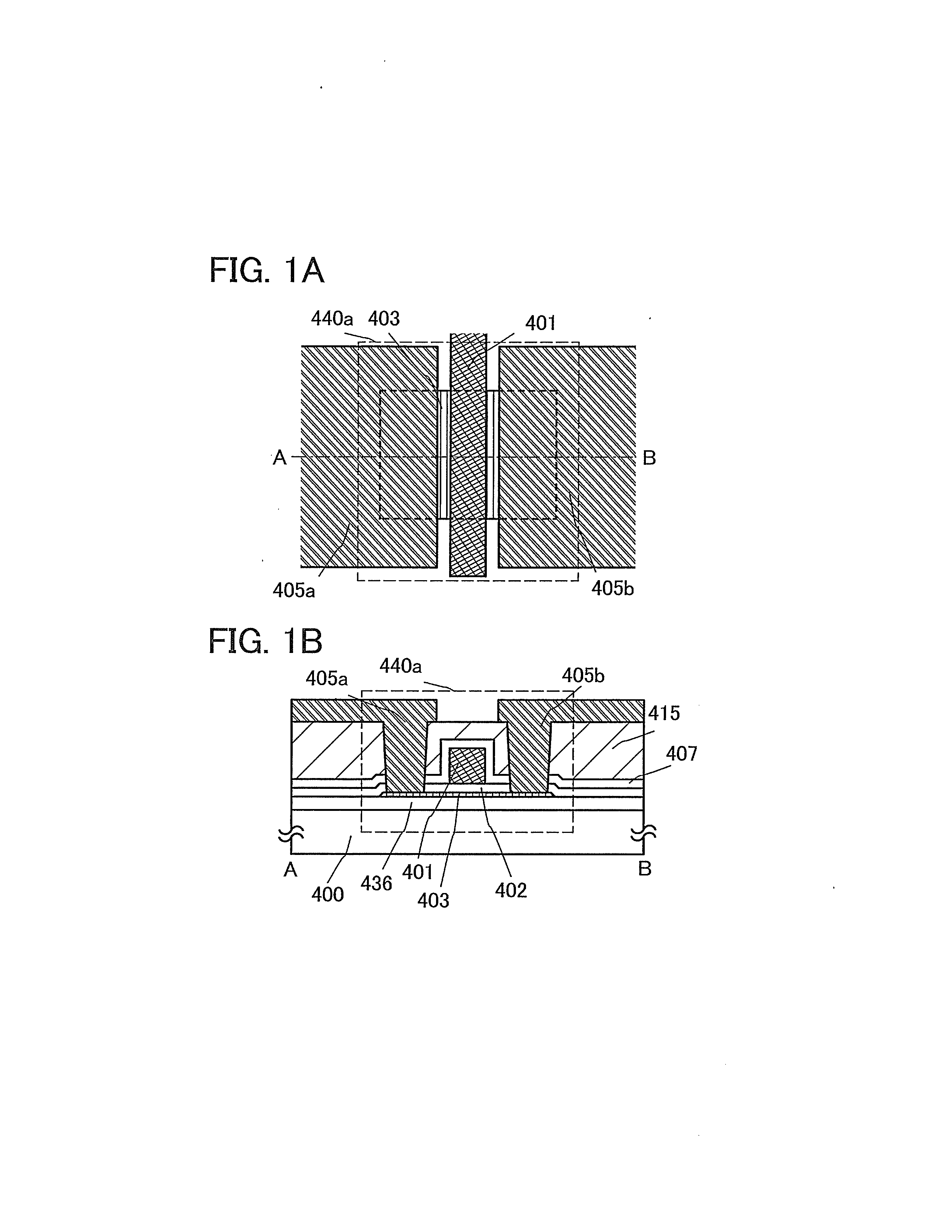

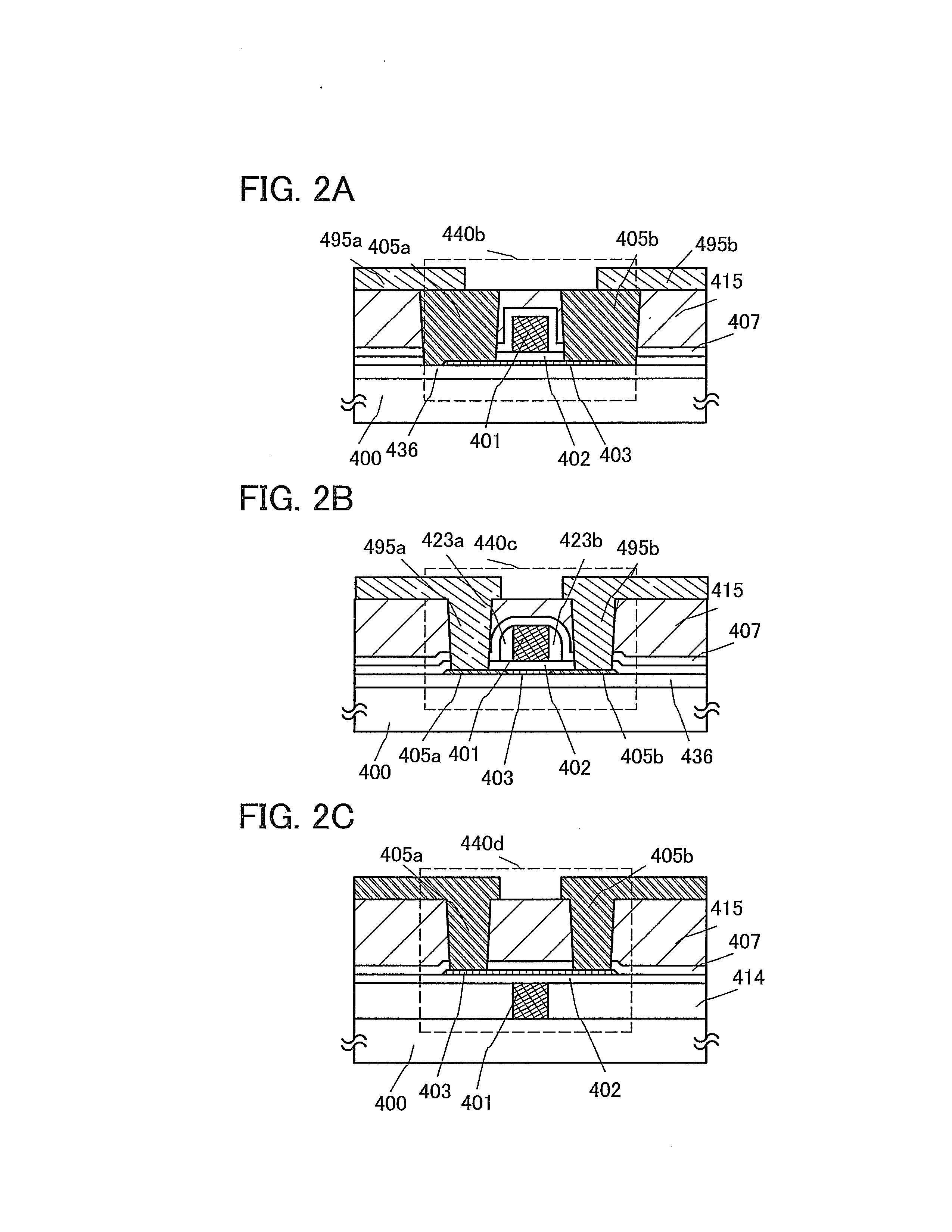

Semiconductor device

InactiveUS20130181214A1Lower on-state resistanceShort channel lengthTransistorEquivalent oxide thicknessNitrogen

Owner:SEMICON ENERGY LAB CO LTD

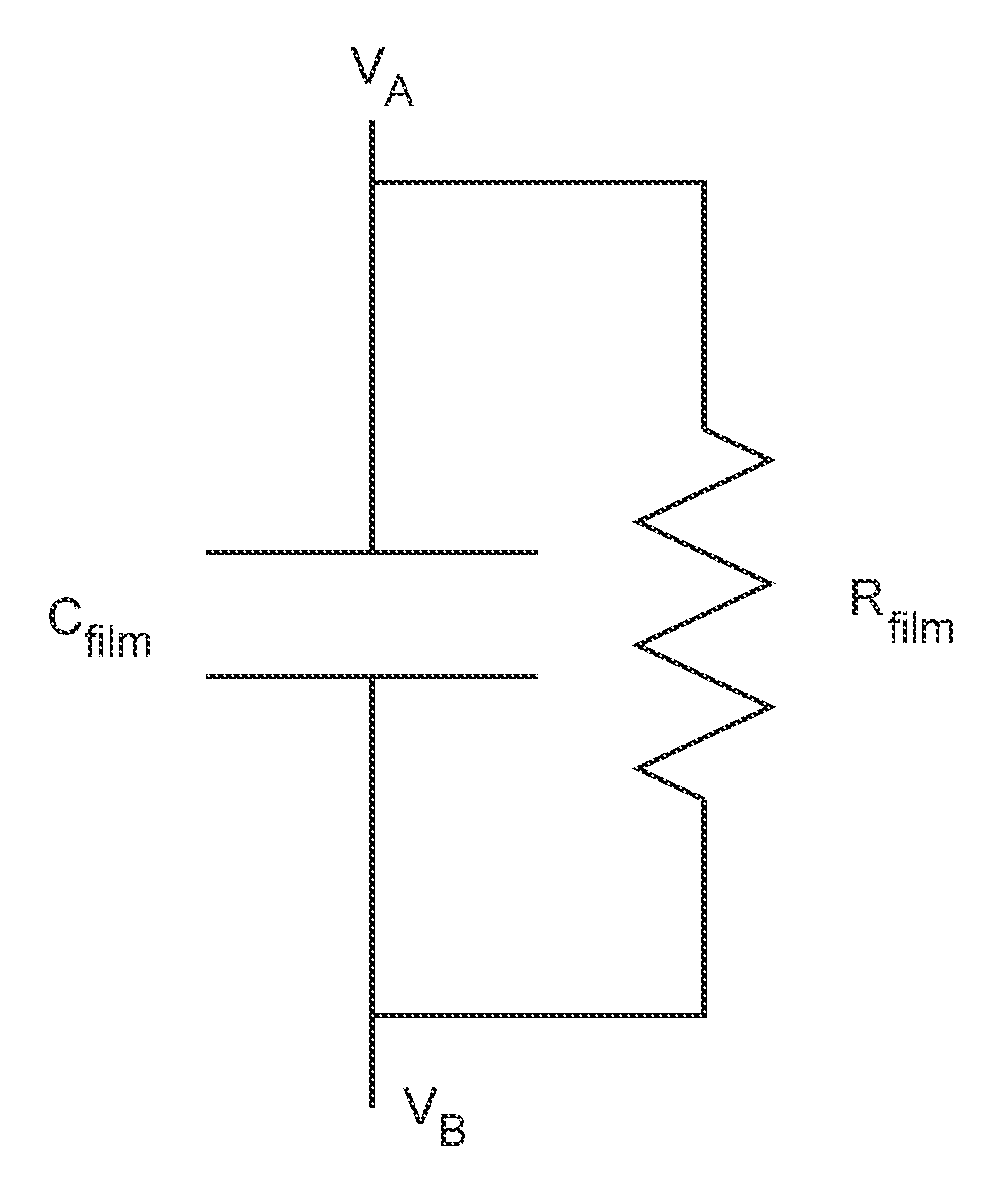

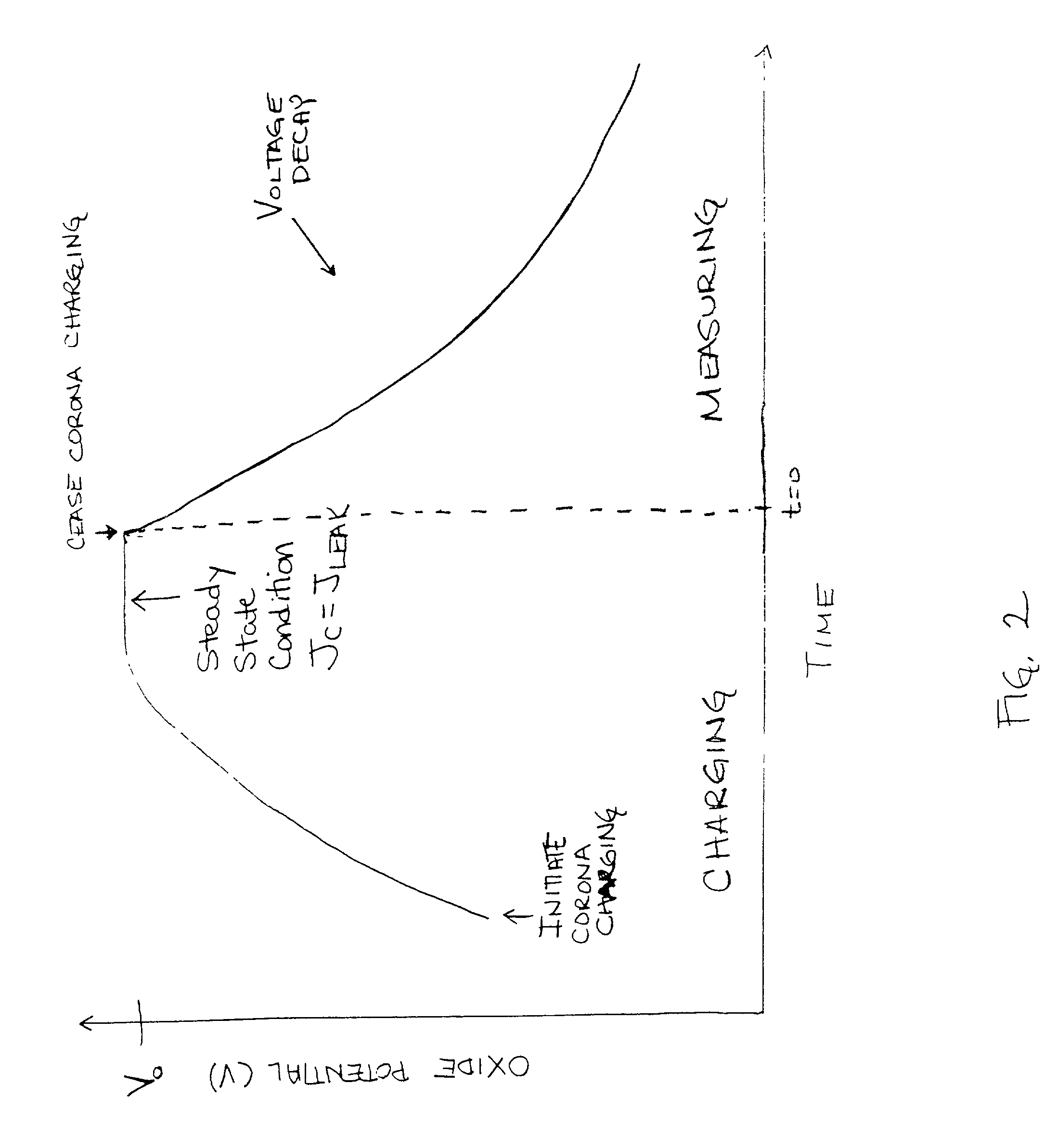

Steady state method for measuring the thickness and the capacitance of ultra thin dielectric in the presence of substantial leakage current

InactiveUS20020125900A1Effective and accurate measurementMaterial analysis by electric/magnetic meansUsing electrical meansEquivalent oxide thicknessCapacitance

A method is described for measuring the capacitance and the equivalent oxide thickness of an ultra thin dielectric layer on a silicon substrate in which the dielectric layer is uniform or patterned. The surface of a dielectric layer is electrically charged by a flux on ions from a corona discharge source until a steady state is reached when the corona flux is balanced by the leakage current across a dielectric. The flux is abruptly terminated and the surface potential of a dielectric is measured versus time. The steady state value of the surface potential is obtained by extrapolation of the potential decay curve to the initial moment of ceasing the corona flux. The thickness of a dielectric layer is determined by using the steady state potential or by using the value of the surface potential after a predetermined time.

Owner:SEMICON DIAGNOSTICS

Highly reliable amorphous high-k gate oxide ZrO2

InactiveUS7259434B2Solid-state devicesSemiconductor/solid-state device manufacturingState of artEquivalent oxide thickness

A gate oxide and method of fabricating a gate oxide that produces a more reliable and thinner equivalent oxide thickness than conventional SiO2 gate oxides are provided. Also shown is a gate oxide with a conduction band offset in a range of approximately 5.16 eV to 7.8 eV. Gate oxides formed from elements such as zirconium are thermodynamically stable such that the gate oxides formed will have minimal reactions with a silicon substrate or other structures during any later high temperature processing stages. The process shown is performed at lower temperatures than the prior art, which further inhibits reactions with the silicon substrate or other structures. Using a thermal evaporation technique to deposit the layer to be oxidized, the underlying substrate surface smoothness is preserved, thus providing improved and more consistent electrical properties in the resulting gate oxide.

Owner:MICRON TECH INC

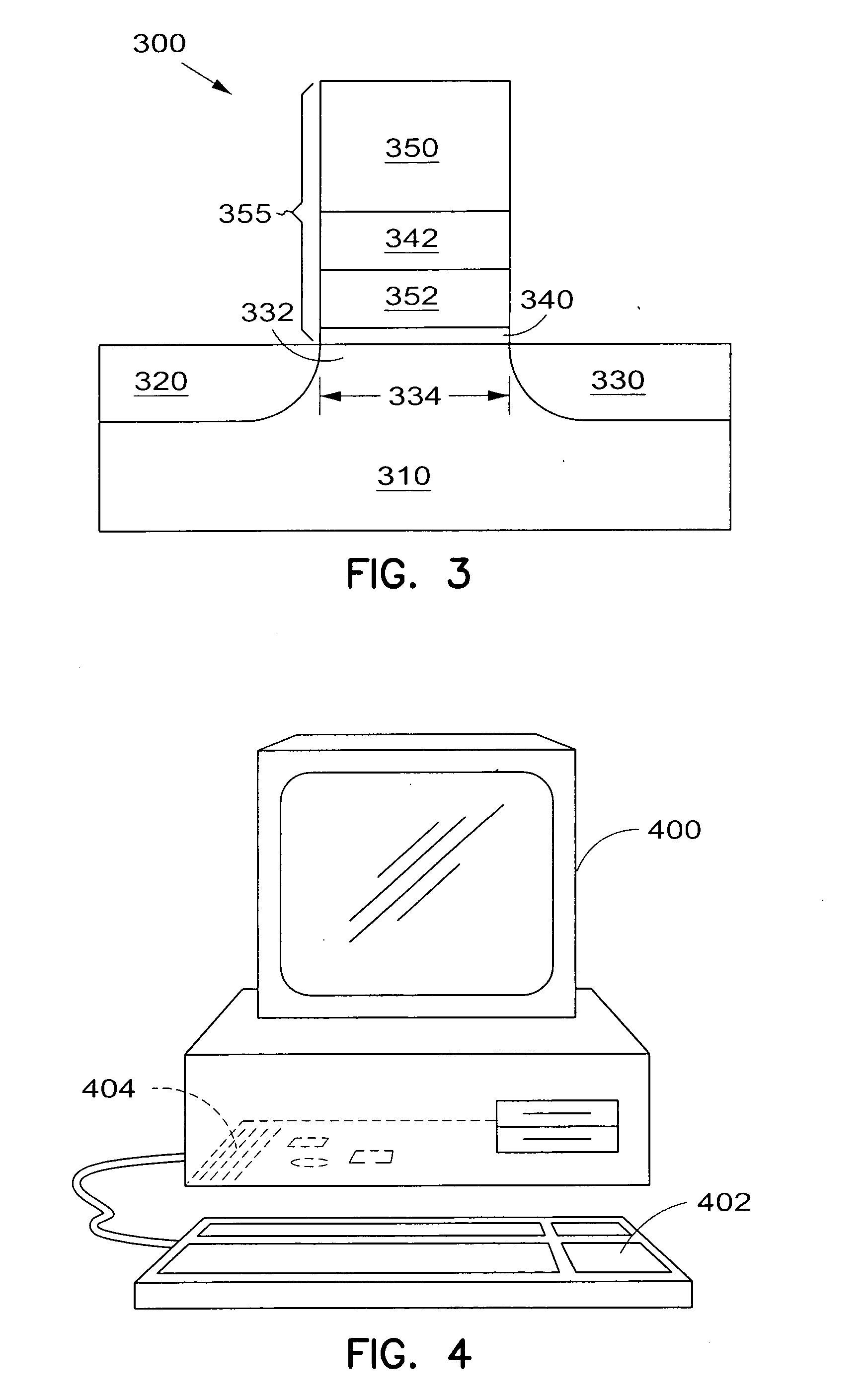

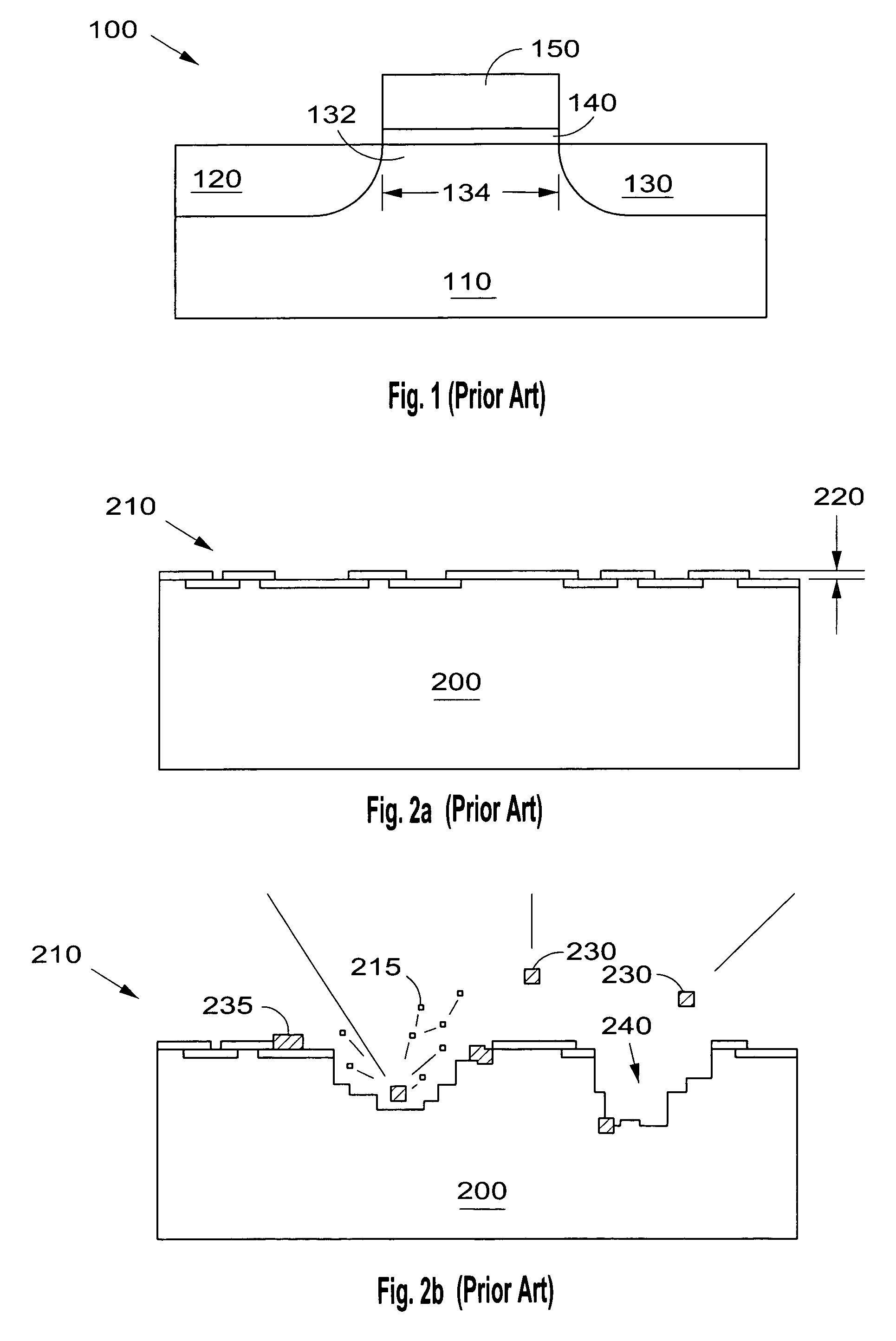

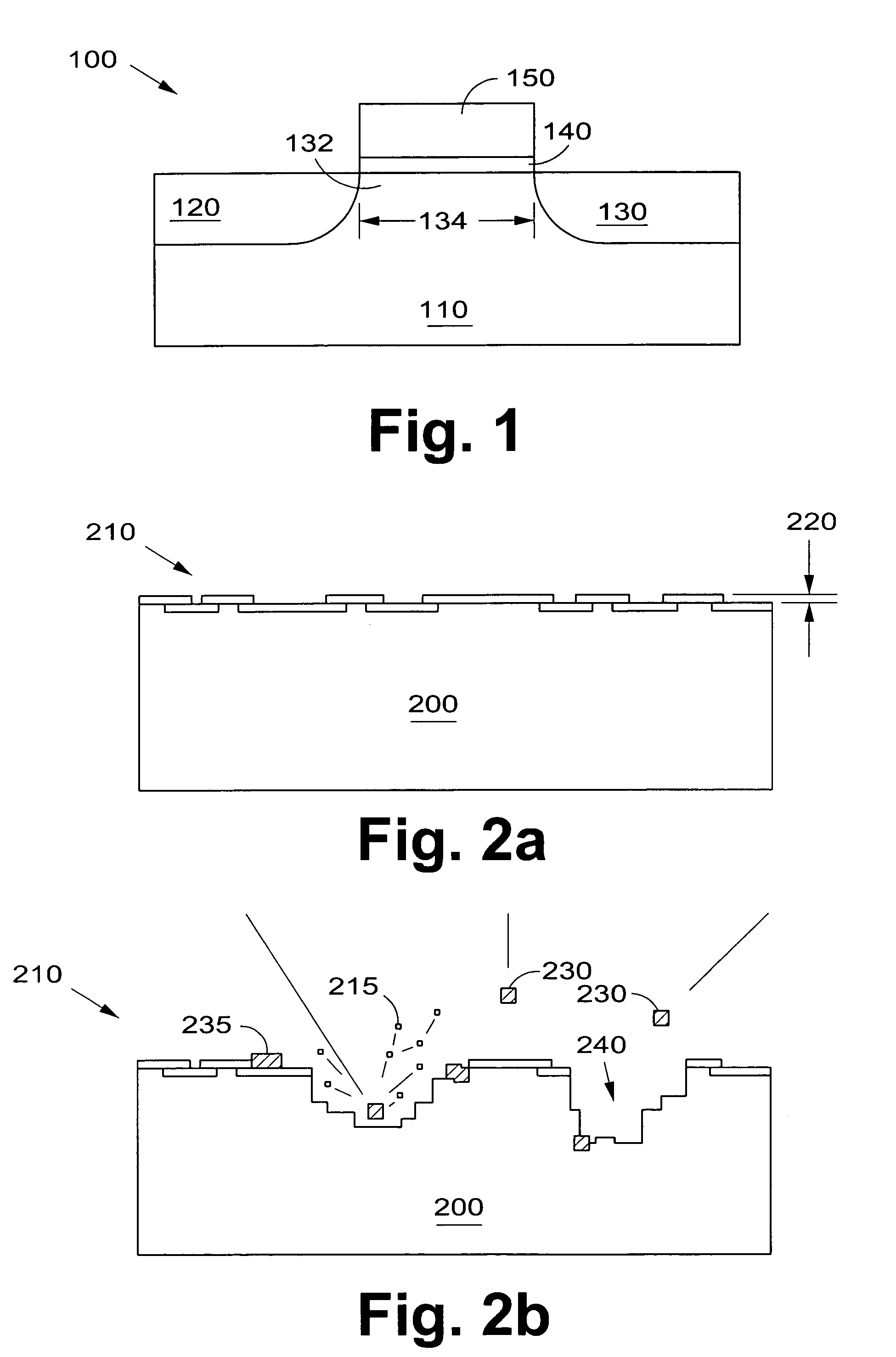

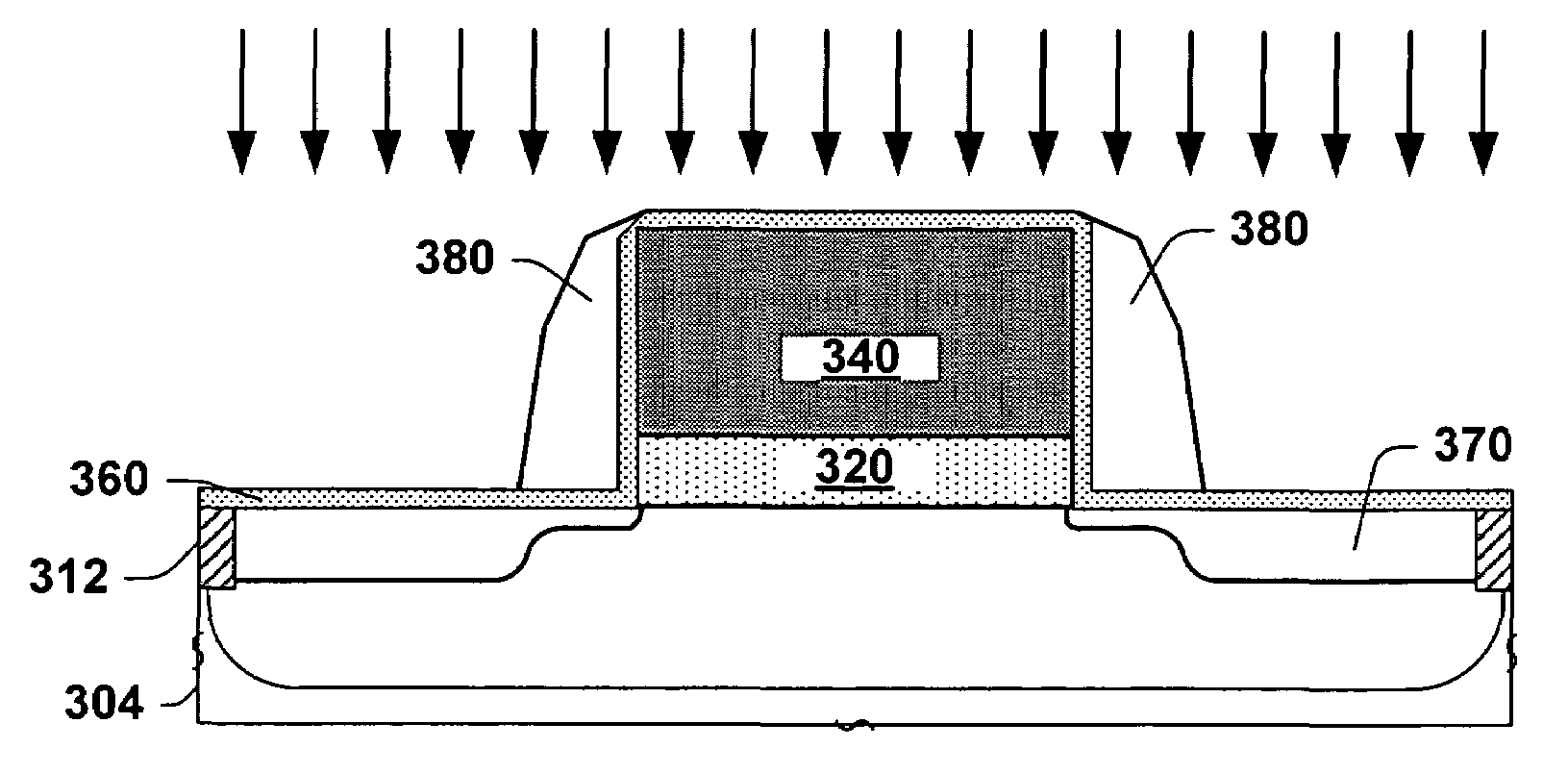

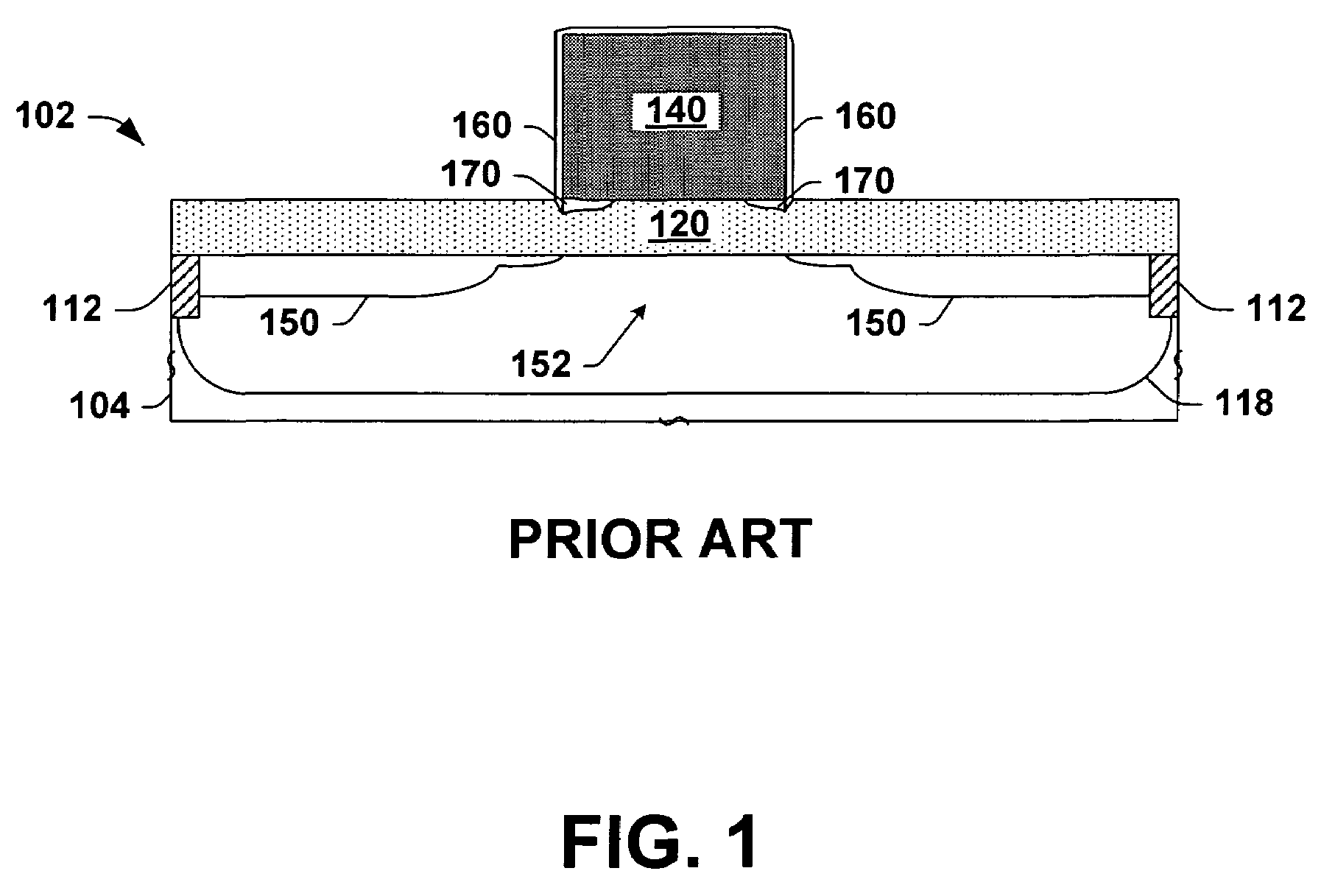

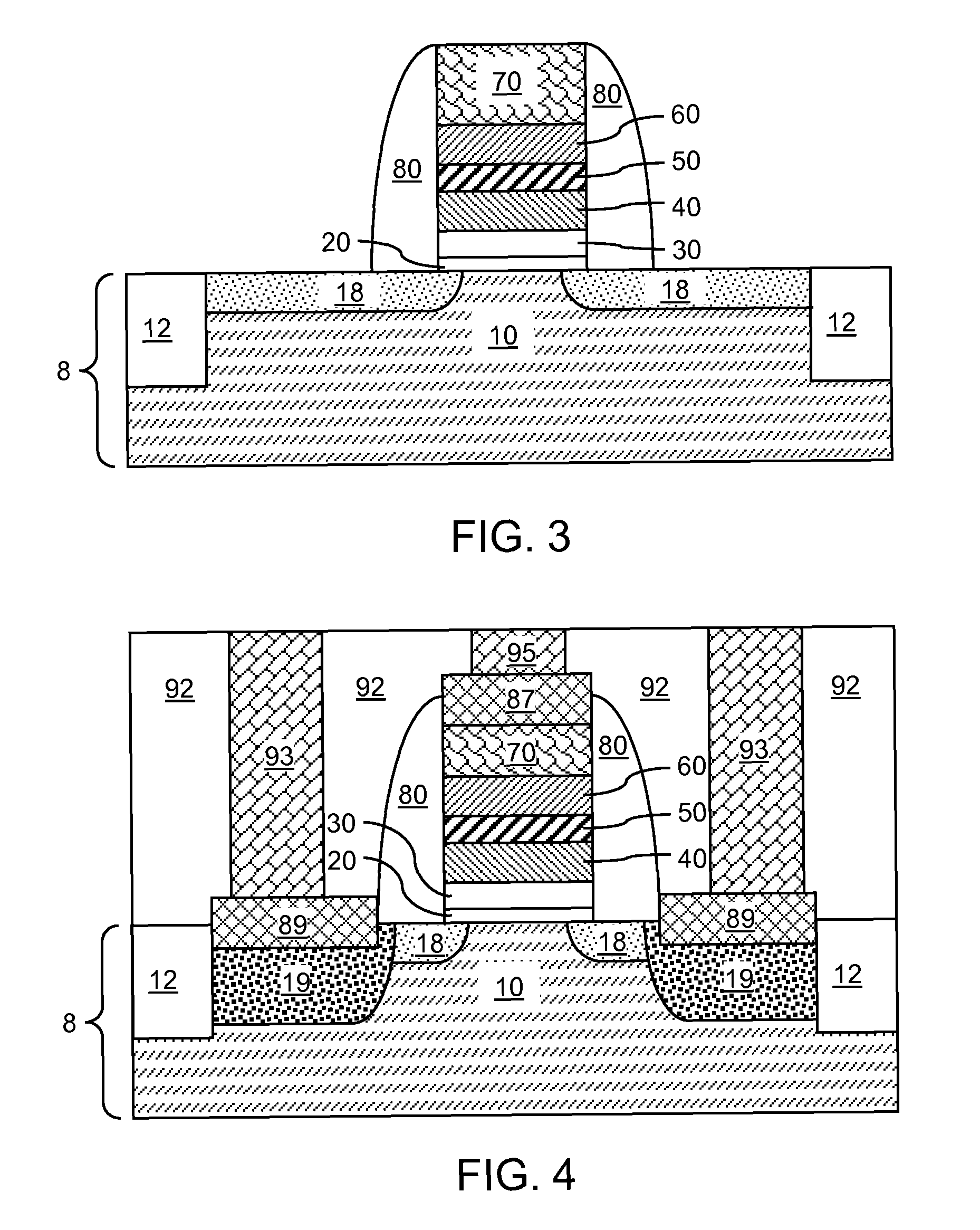

Method for integrating high-k dielectrics in transistor devices

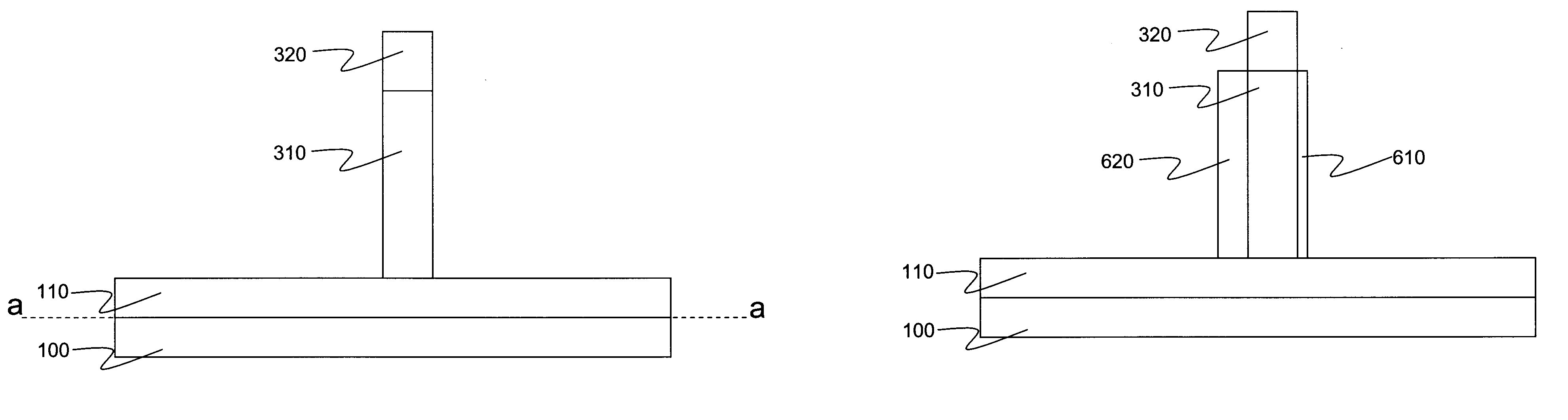

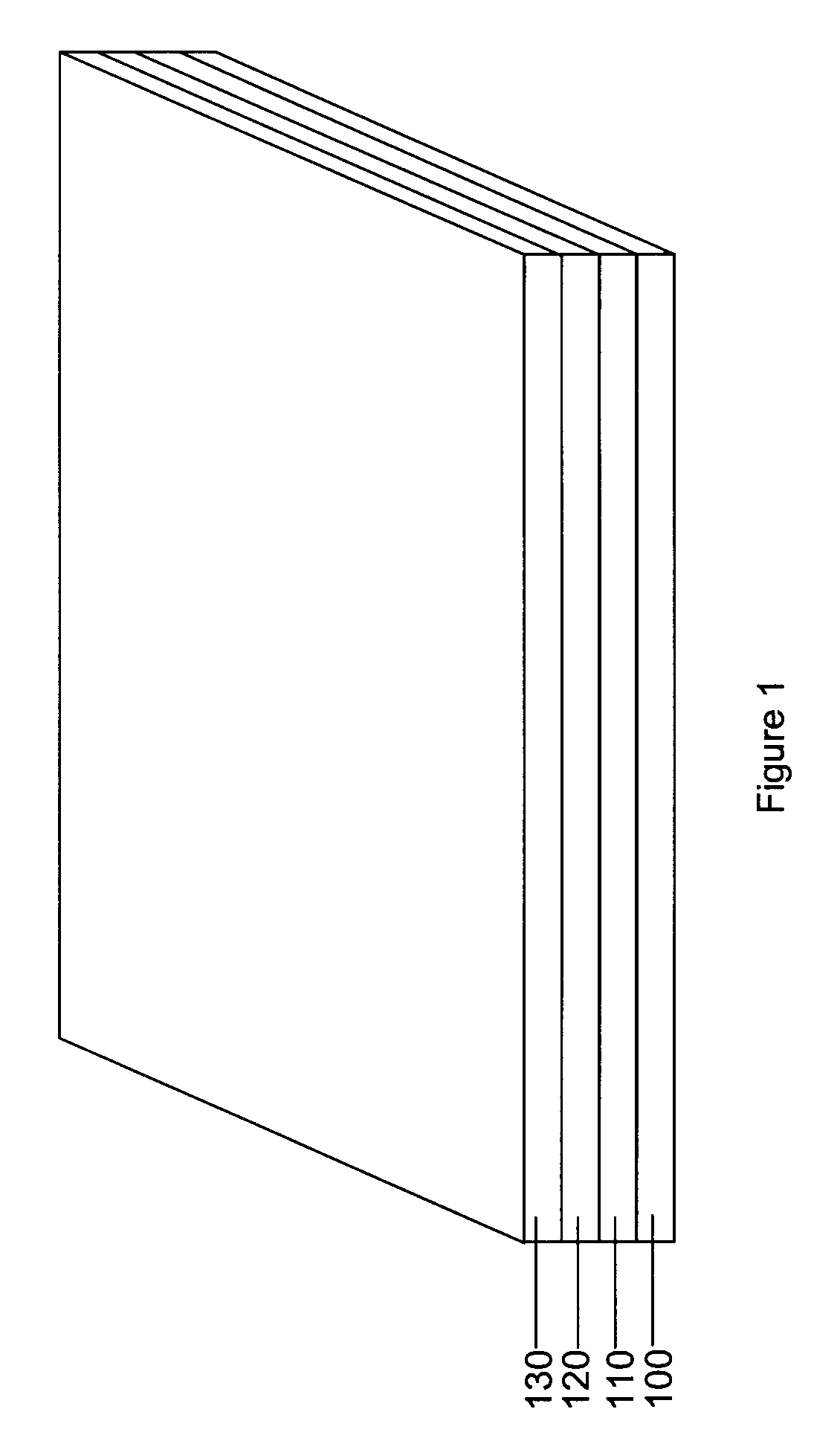

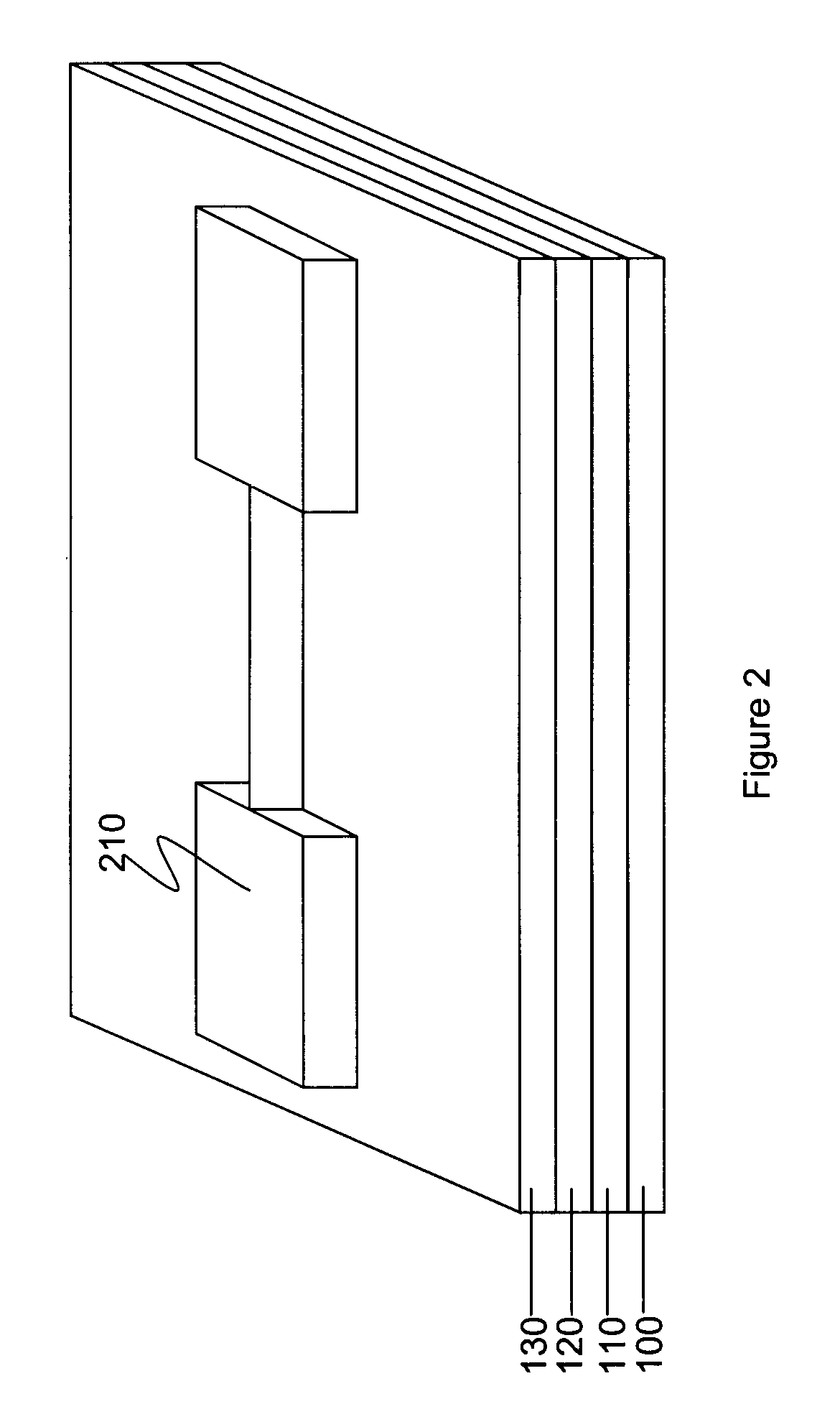

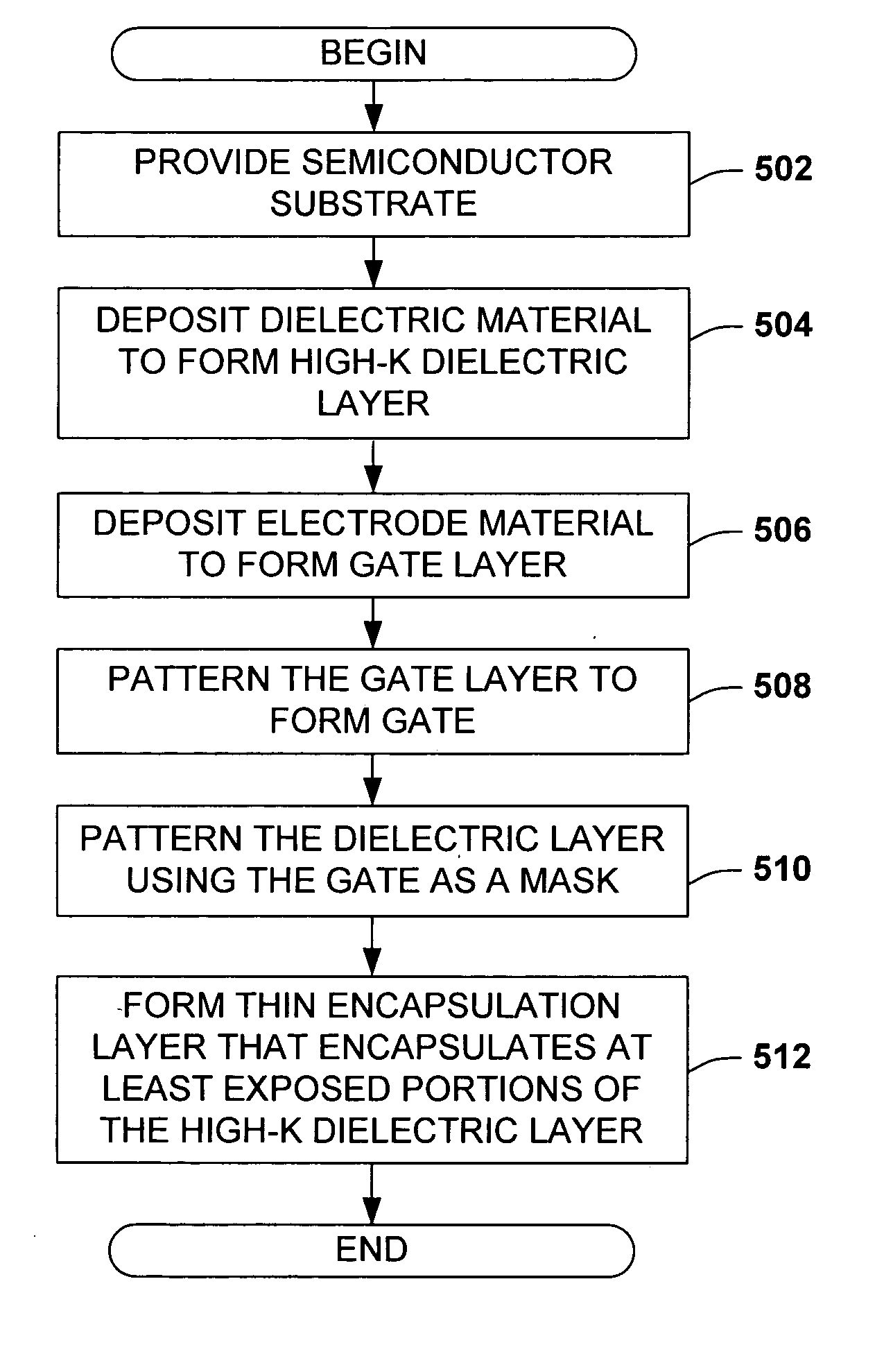

ActiveUS7045431B2Reduce defectsEasy to manufactureTransistorSemiconductor/solid-state device manufacturingEquivalent oxide thicknessDielectric layer

Owner:TEXAS INSTR INC

Backgated finfet having diferent oxide thicknesses

InactiveUS20050245009A1TransistorSemiconductor/solid-state device manufacturingEquivalent oxide thicknessEngineering

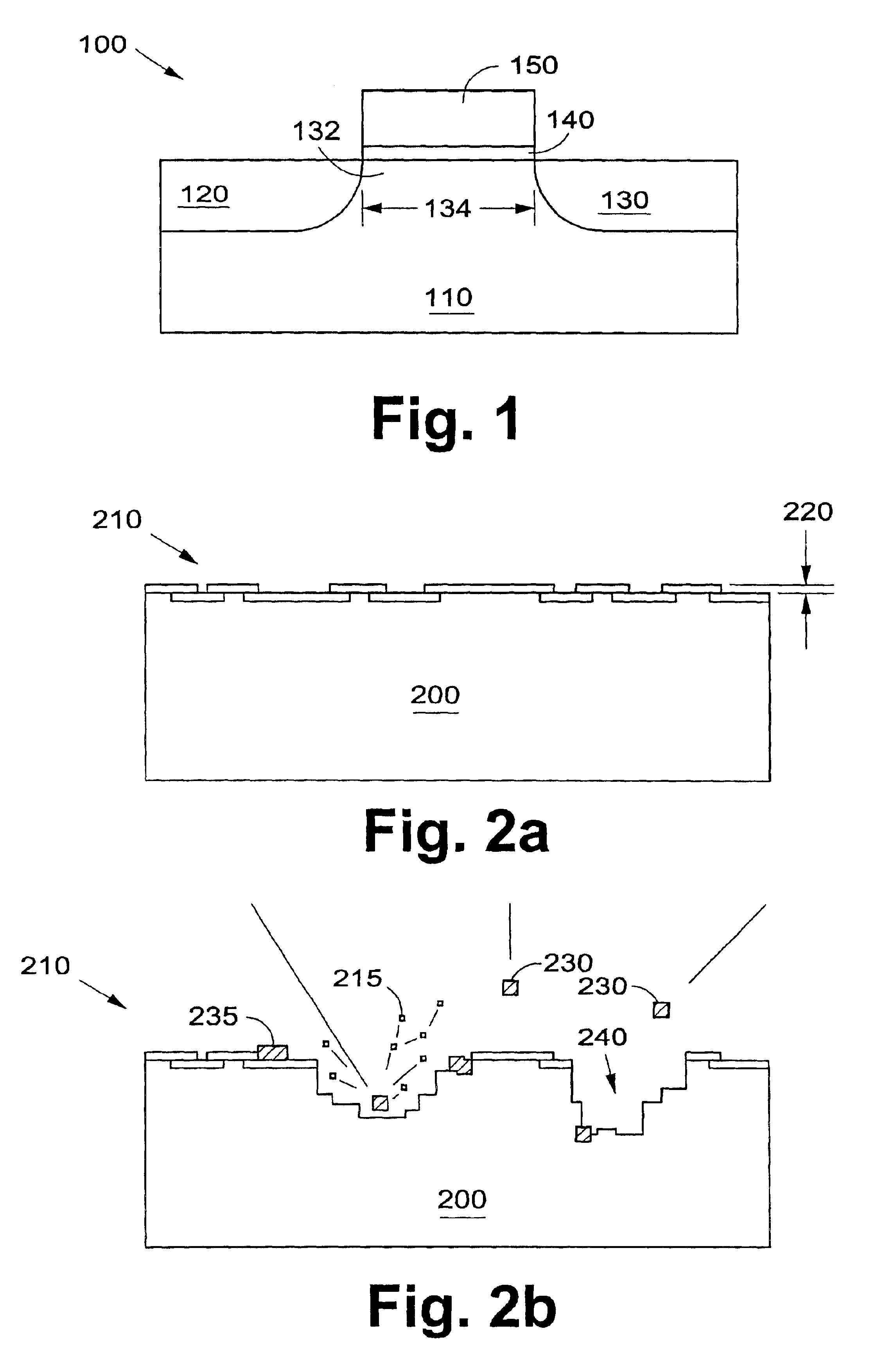

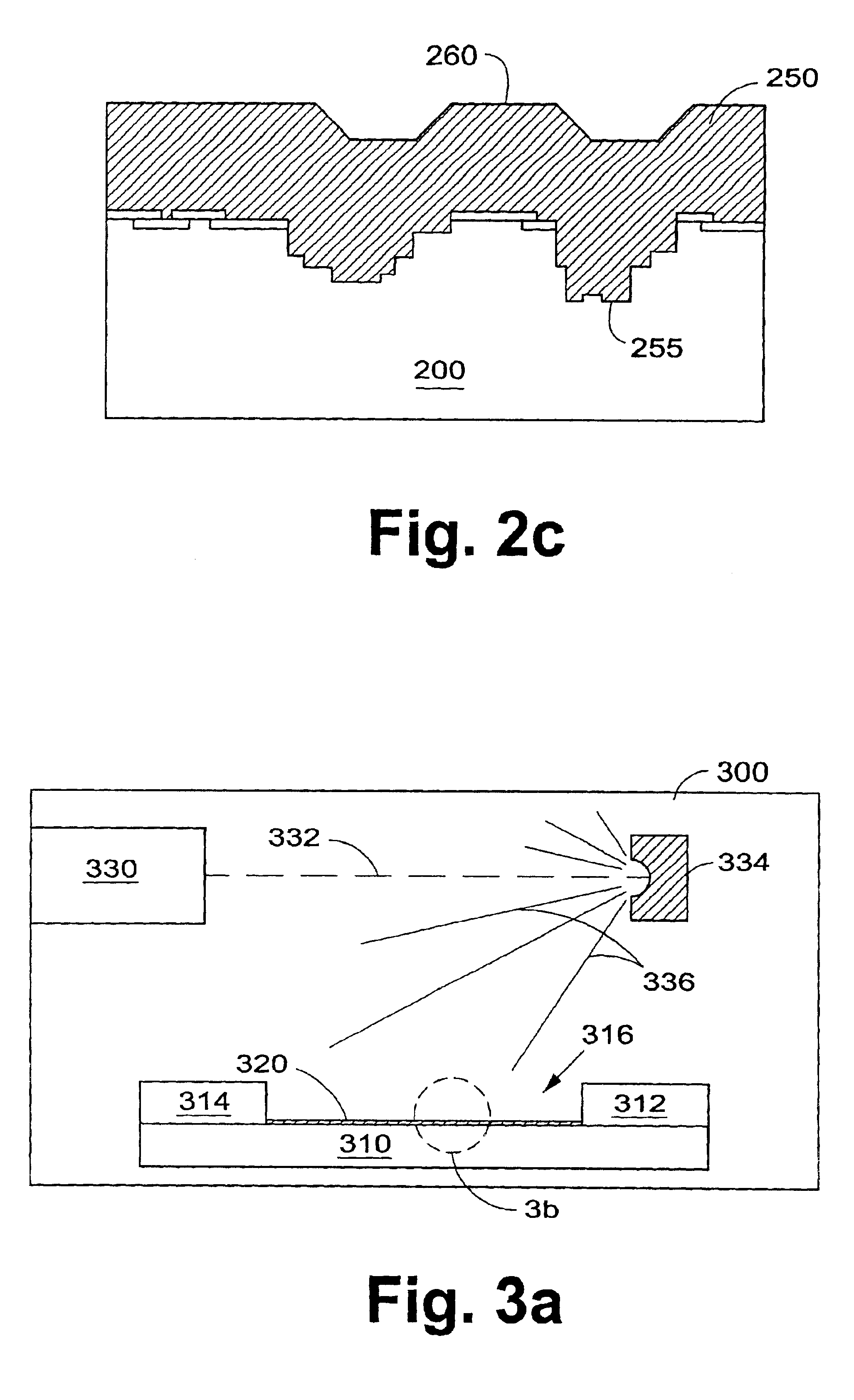

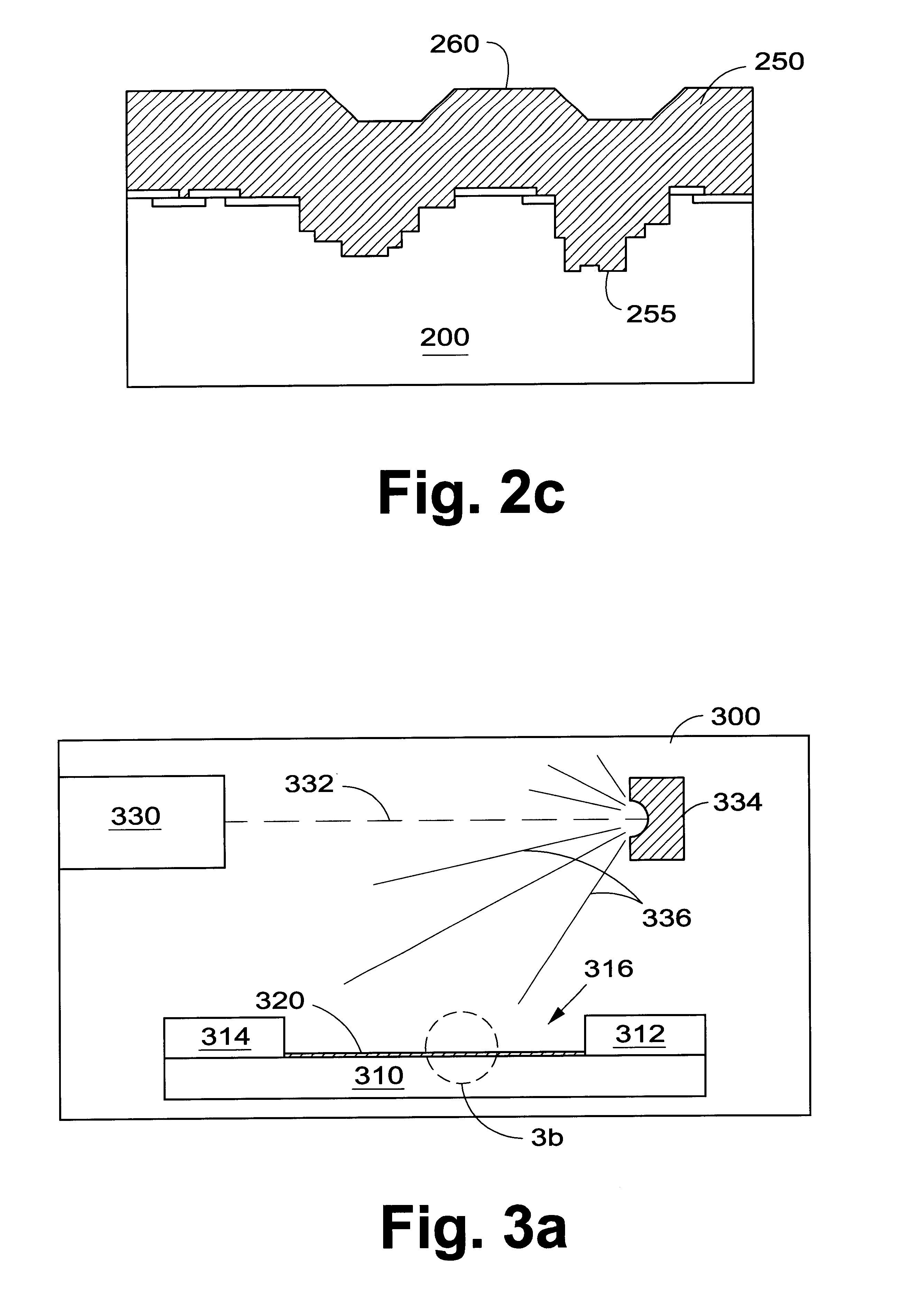

A method of producing a backgated FinFET having different dielectric layer thickness on the front and back gate sides includes steps of introducing impurities into at least one side of a fin of a FinFET to enable formation of dielectric layers with different thicknesses. The impurity, which may be introduced by implantation, either enhances or retards dielectric formation.

Owner:GLOBALFOUNDRIES INC

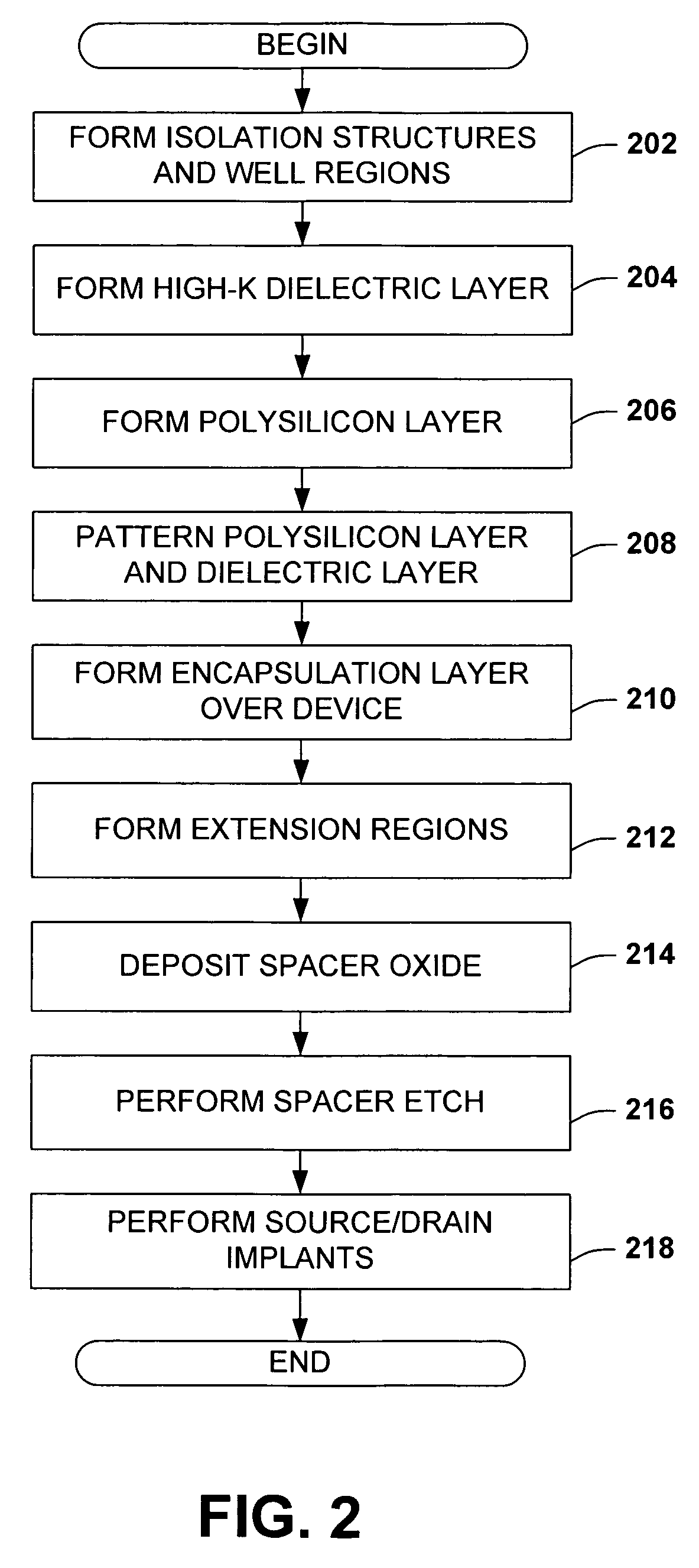

Method for integrating high-k dielectrics in transistor devices

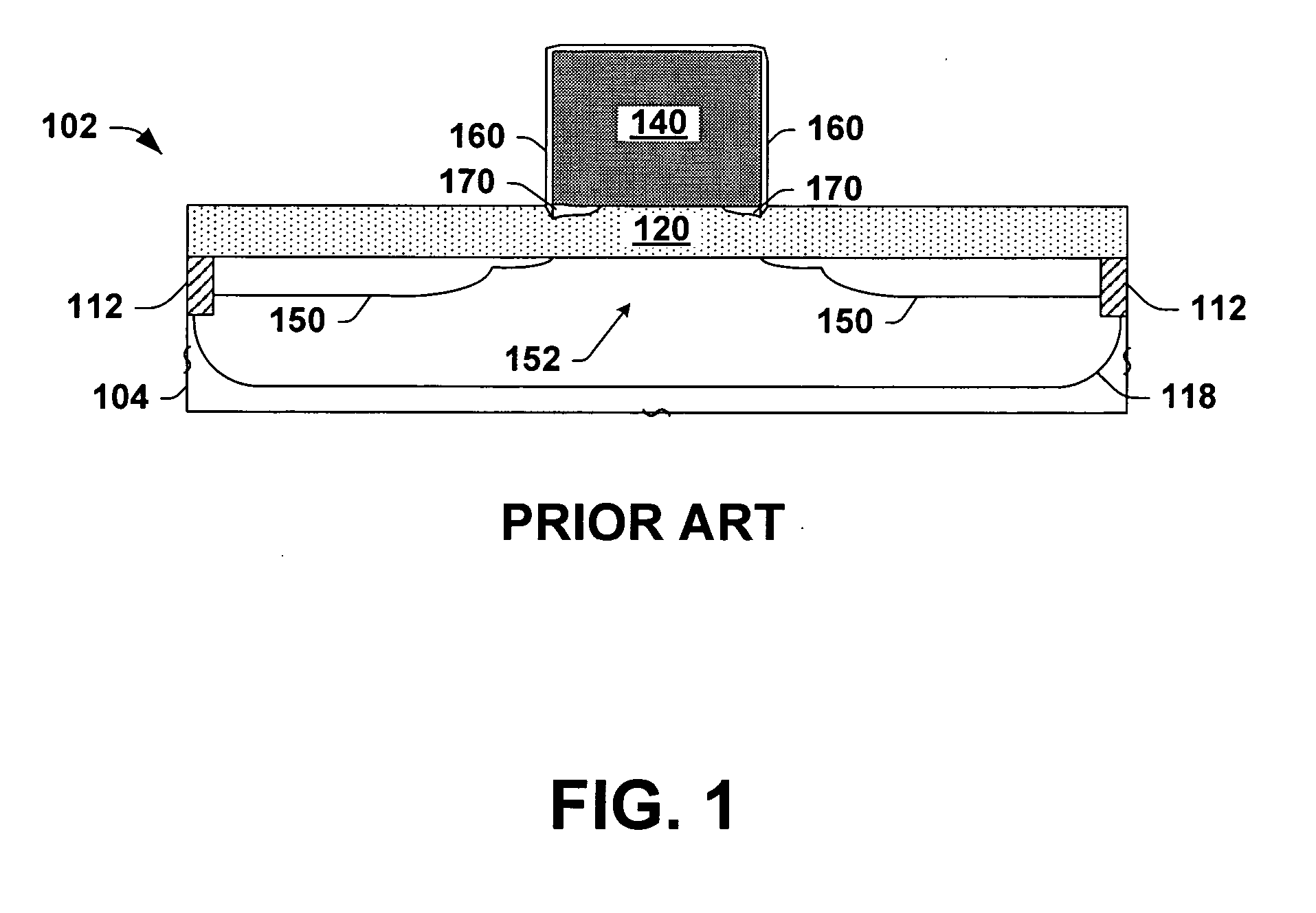

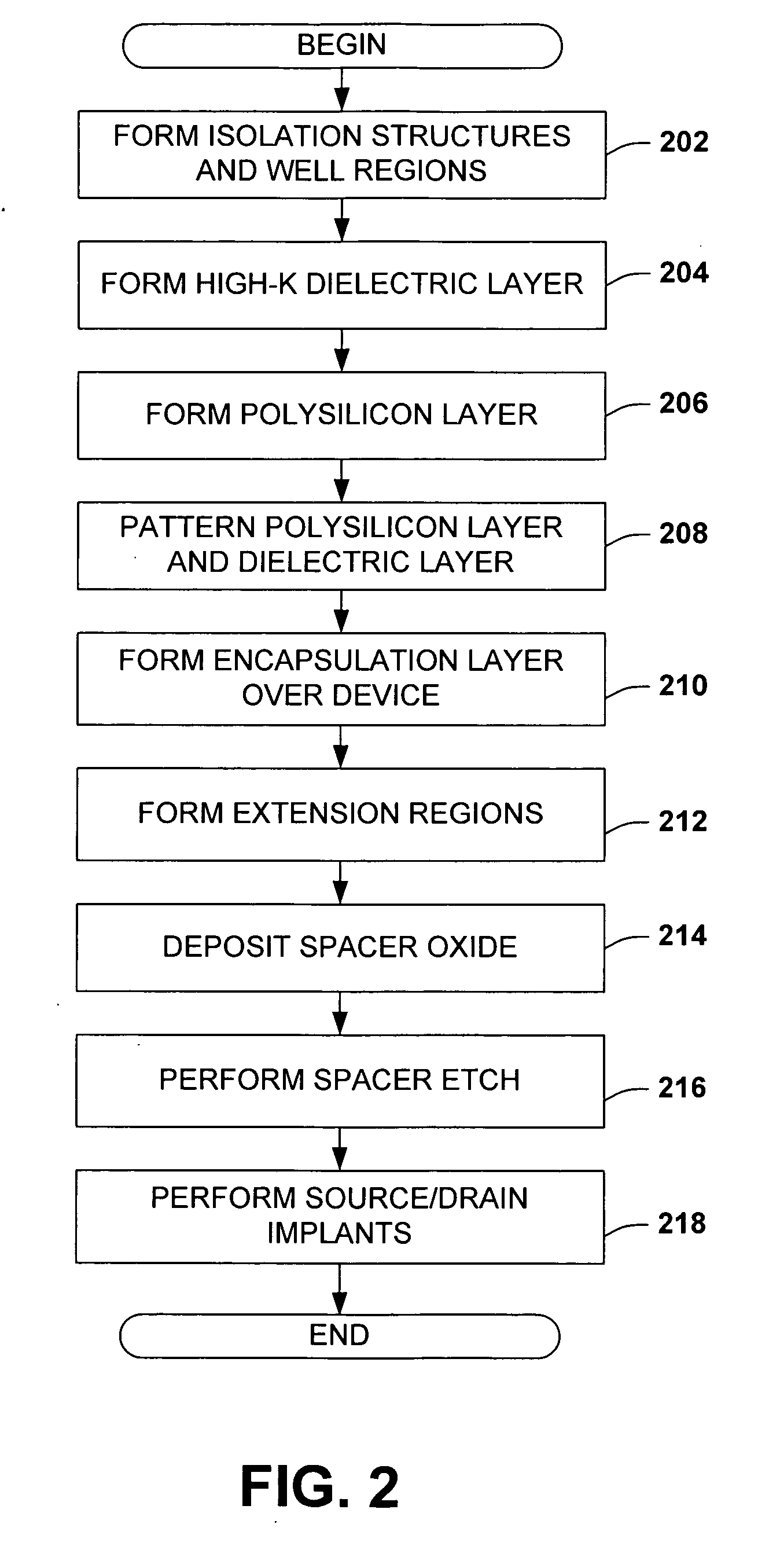

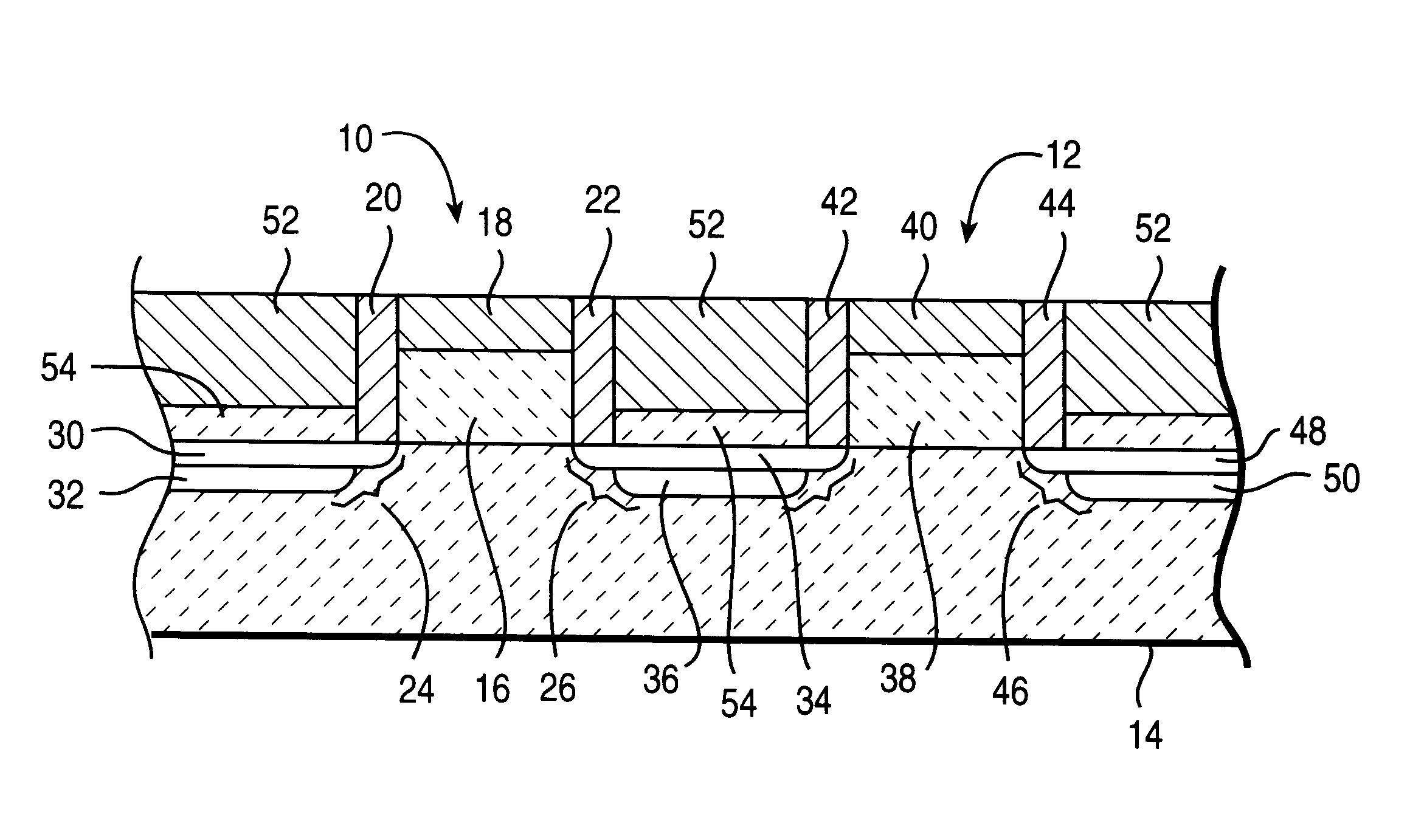

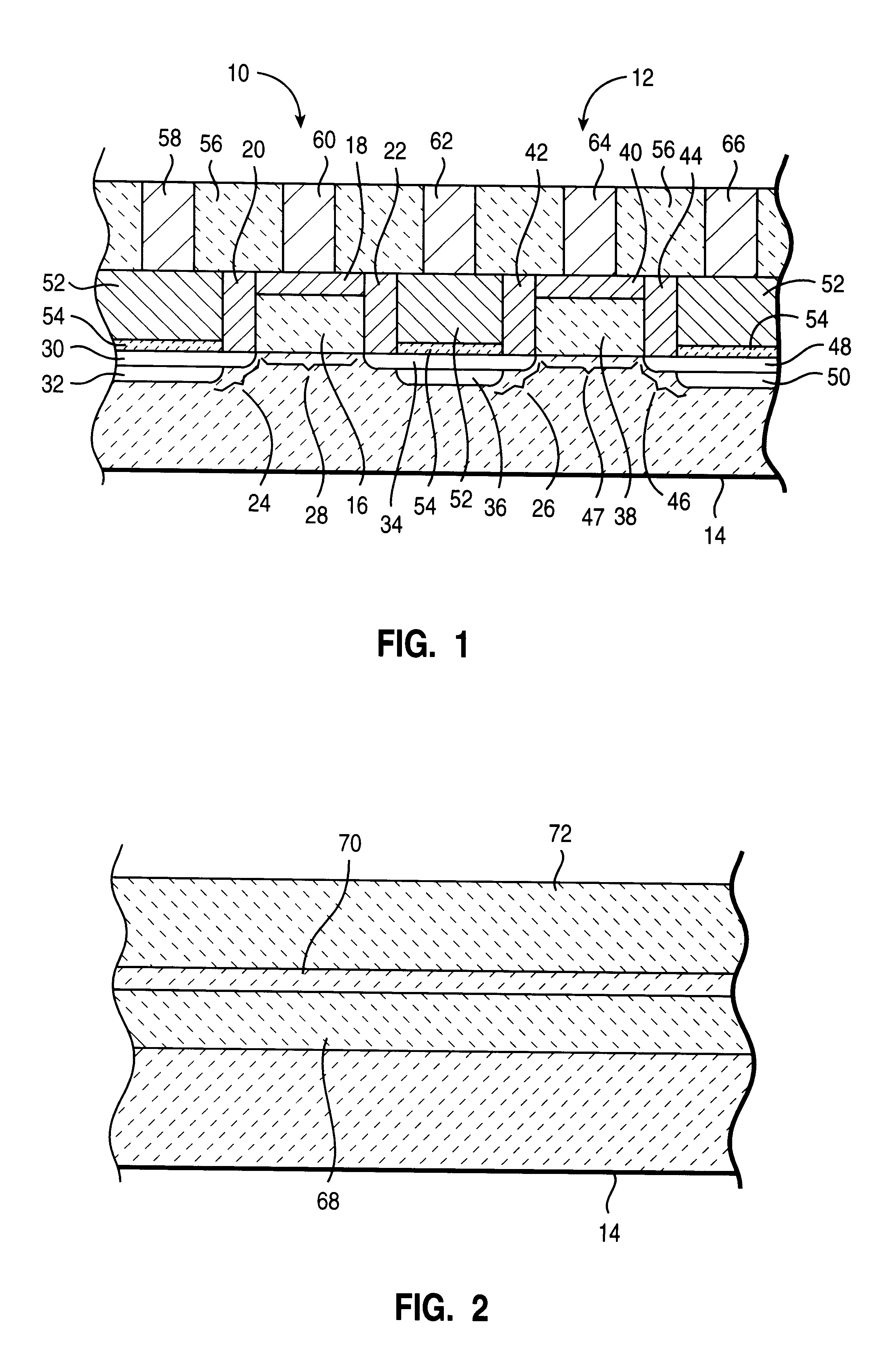

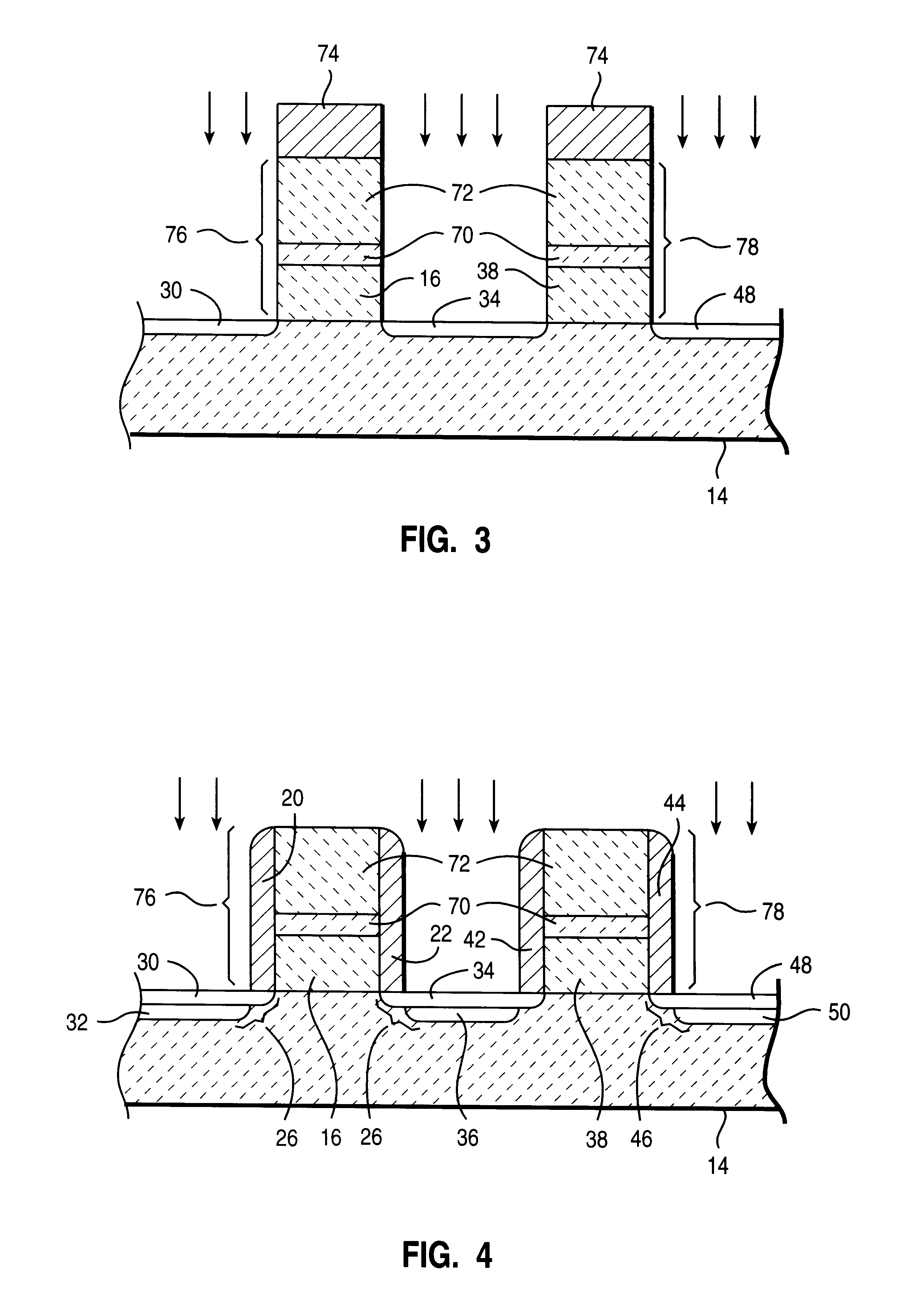

ActiveUS20050136589A1Facilitate semiconductor fabricationReduce defectsTransistorSemiconductor/solid-state device manufacturingEquivalent oxide thicknessDevice material

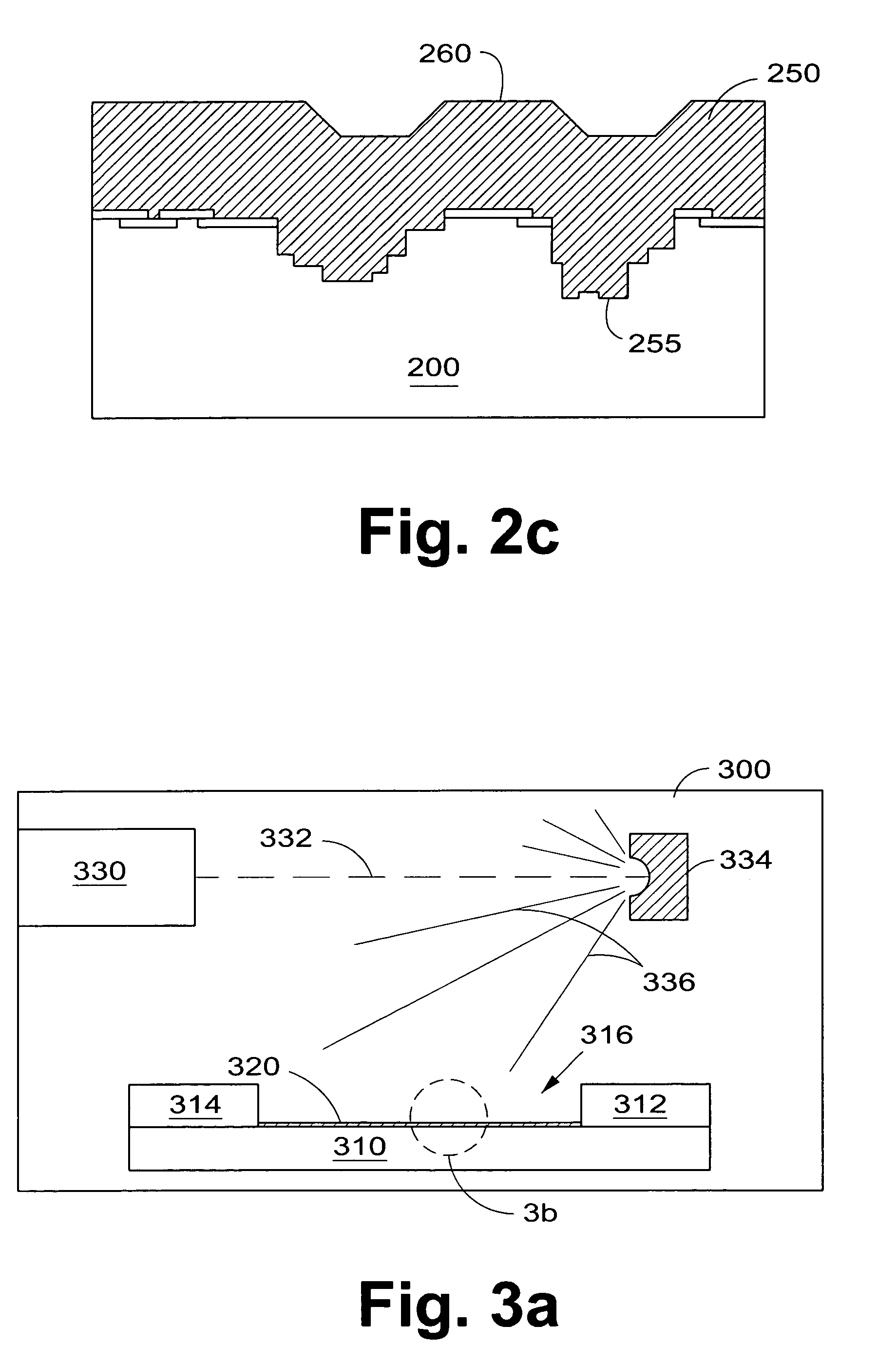

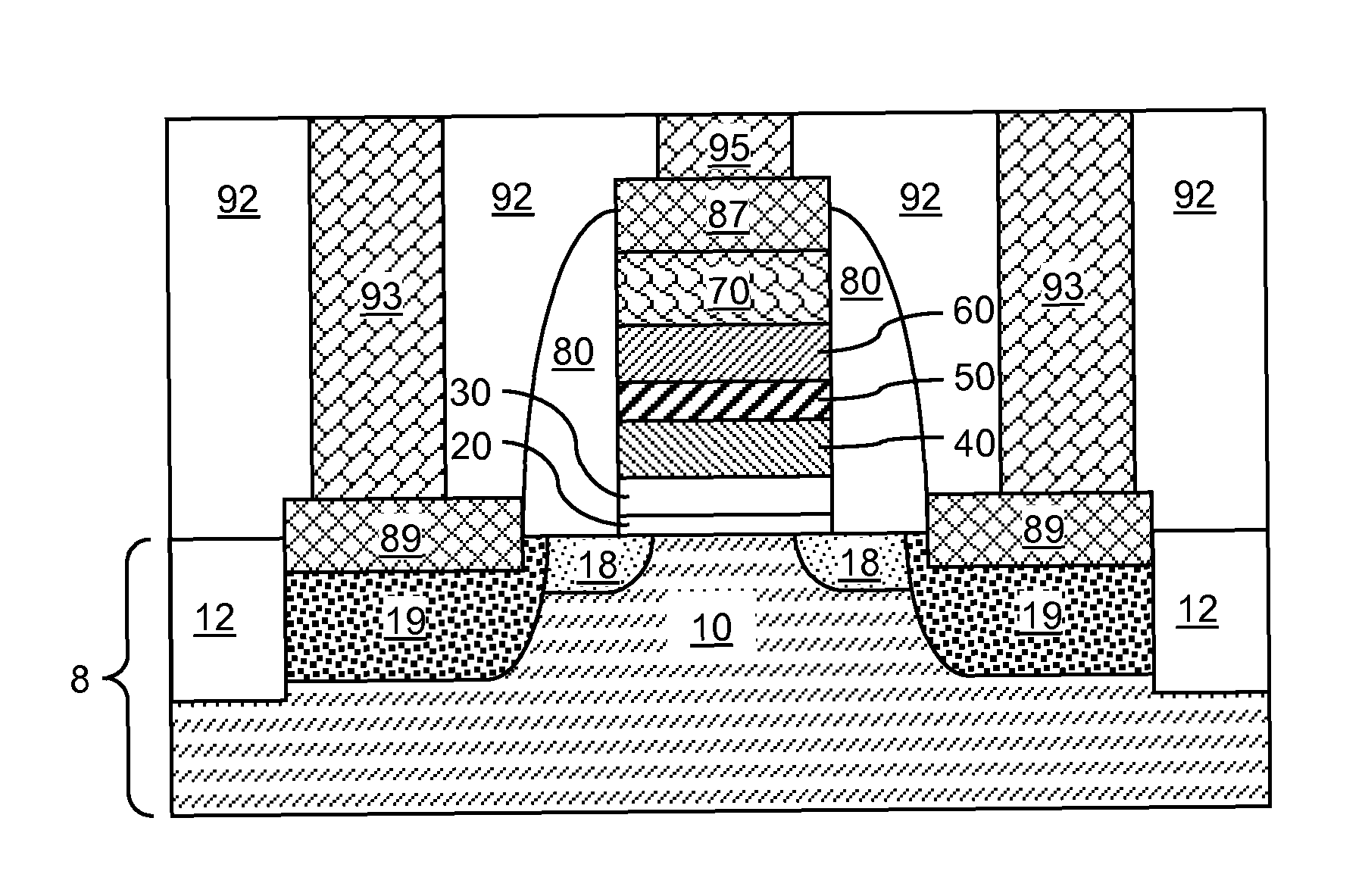

Methods are disclosed that fabricating semiconductor devices with high-k dielectric layers. The invention removes portions of deposited high-k dielectric layers not below gates and covers exposed portions (e.g., sidewalls) of high-k dielectric layers during fabrication with an encapsulation layer, which mitigates defects in the high-k dielectric layers and contamination of process tools. The encapsulation layer can also be employed as an etch stop layer and, at least partially, in comprising sidewall spacers. As a result, a semiconductor device can be fabricated with a substantially uniform equivalent oxide thickness.

Owner:TEXAS INSTR INC

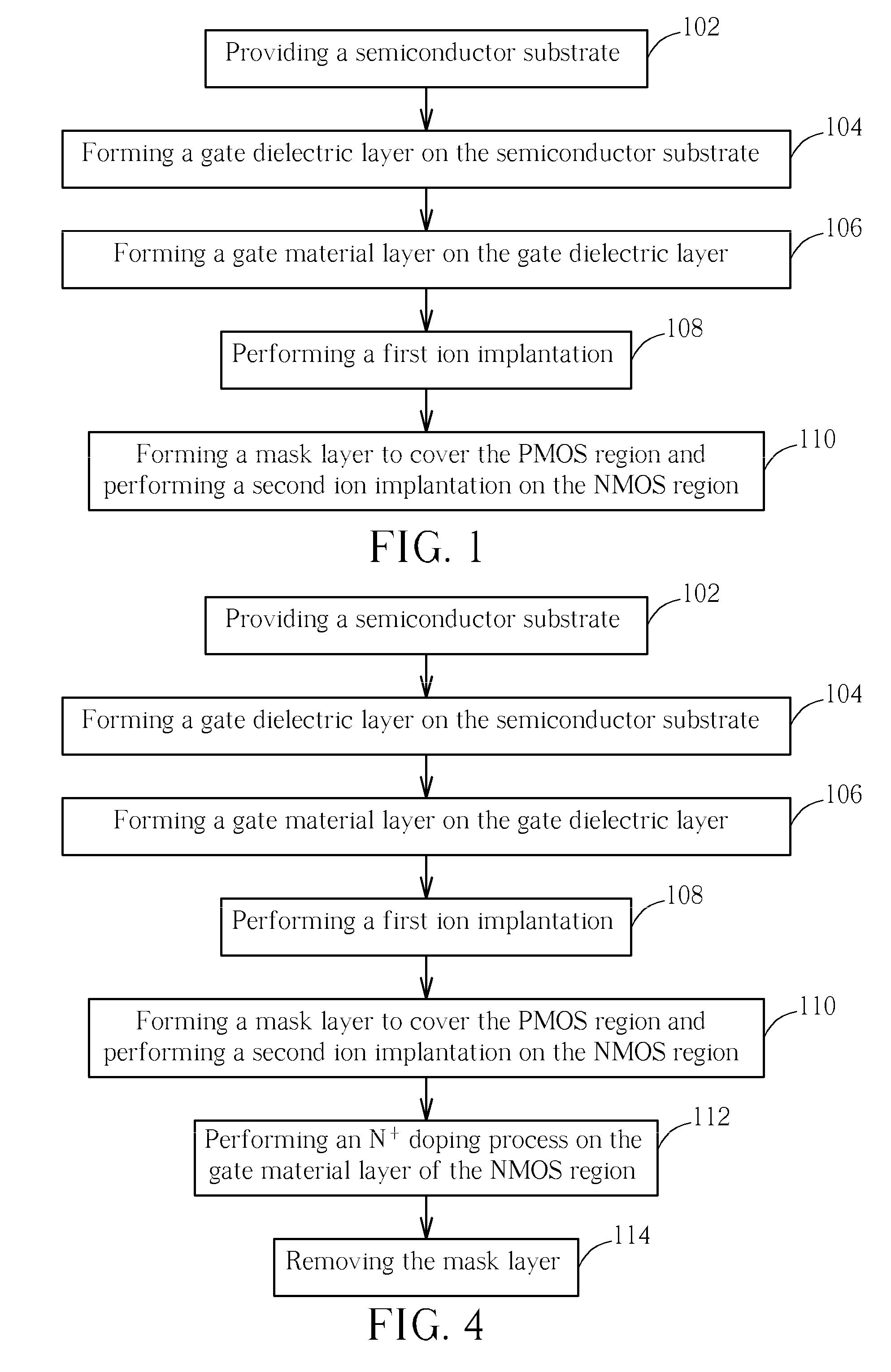

Manufacturing method for semiconductor element

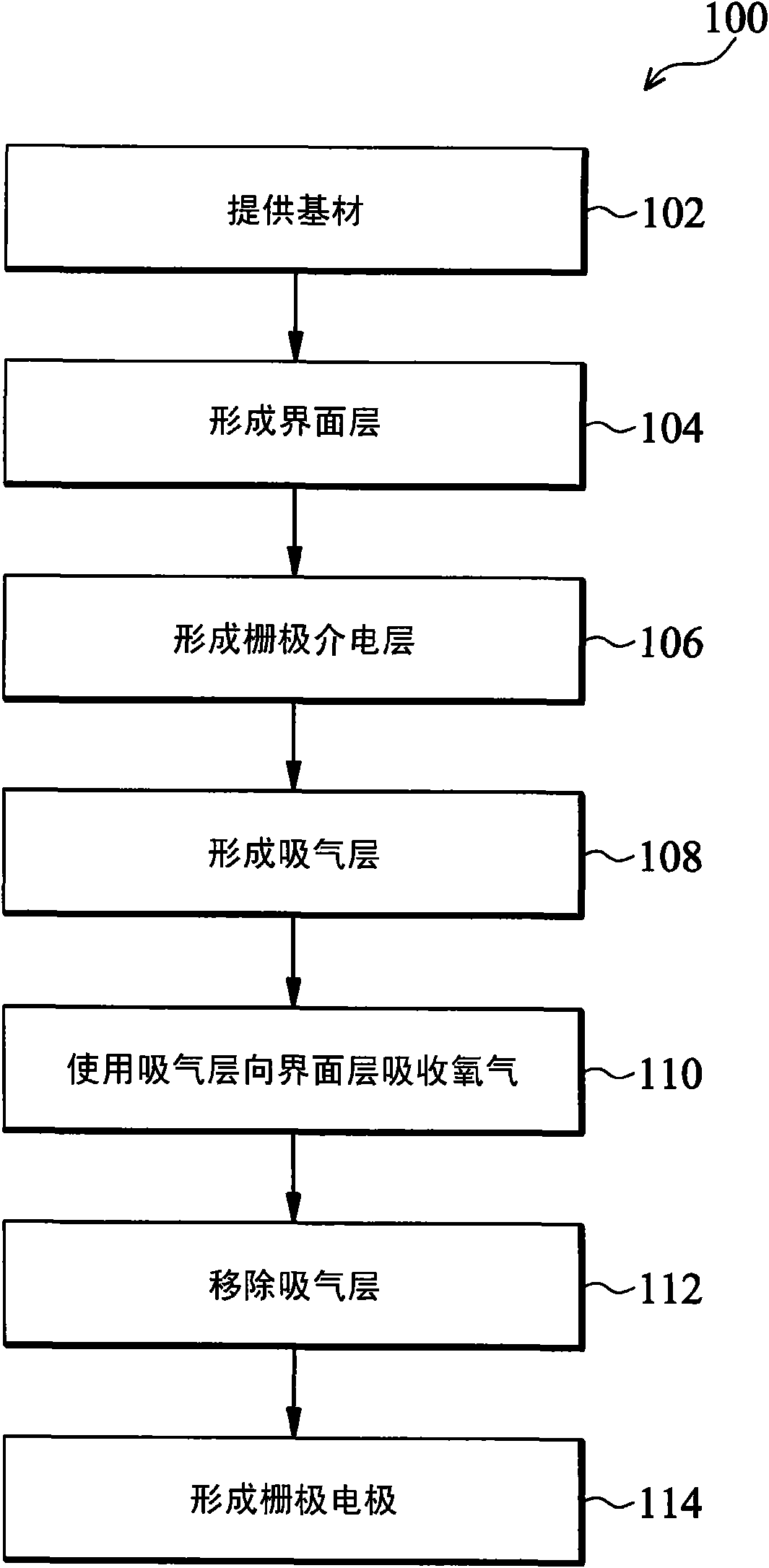

ActiveCN101661883AReduce thicknessControl thicknessSemiconductor/solid-state device manufacturingSemiconductor devicesEquivalent oxide thicknessGate dielectric

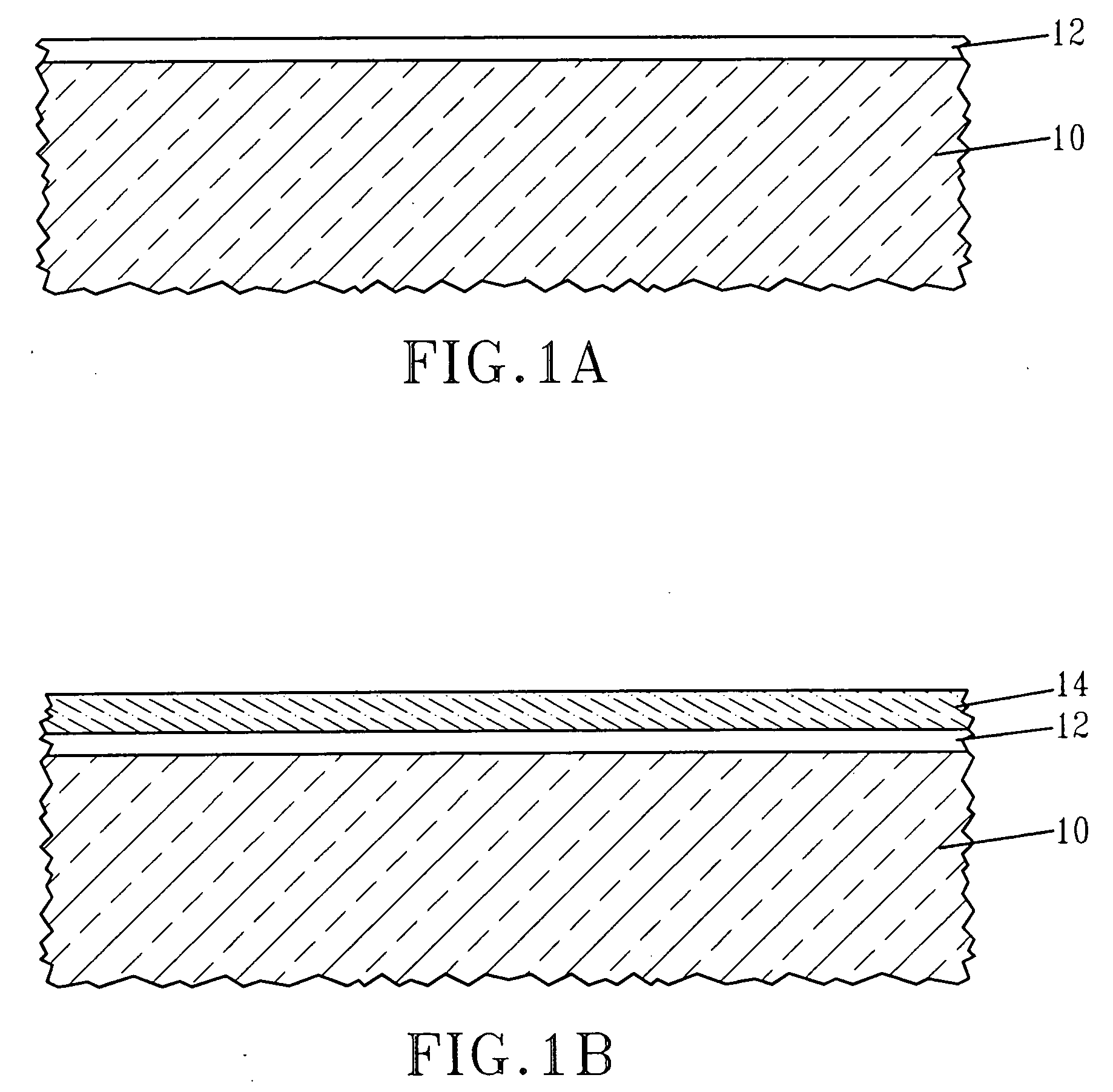

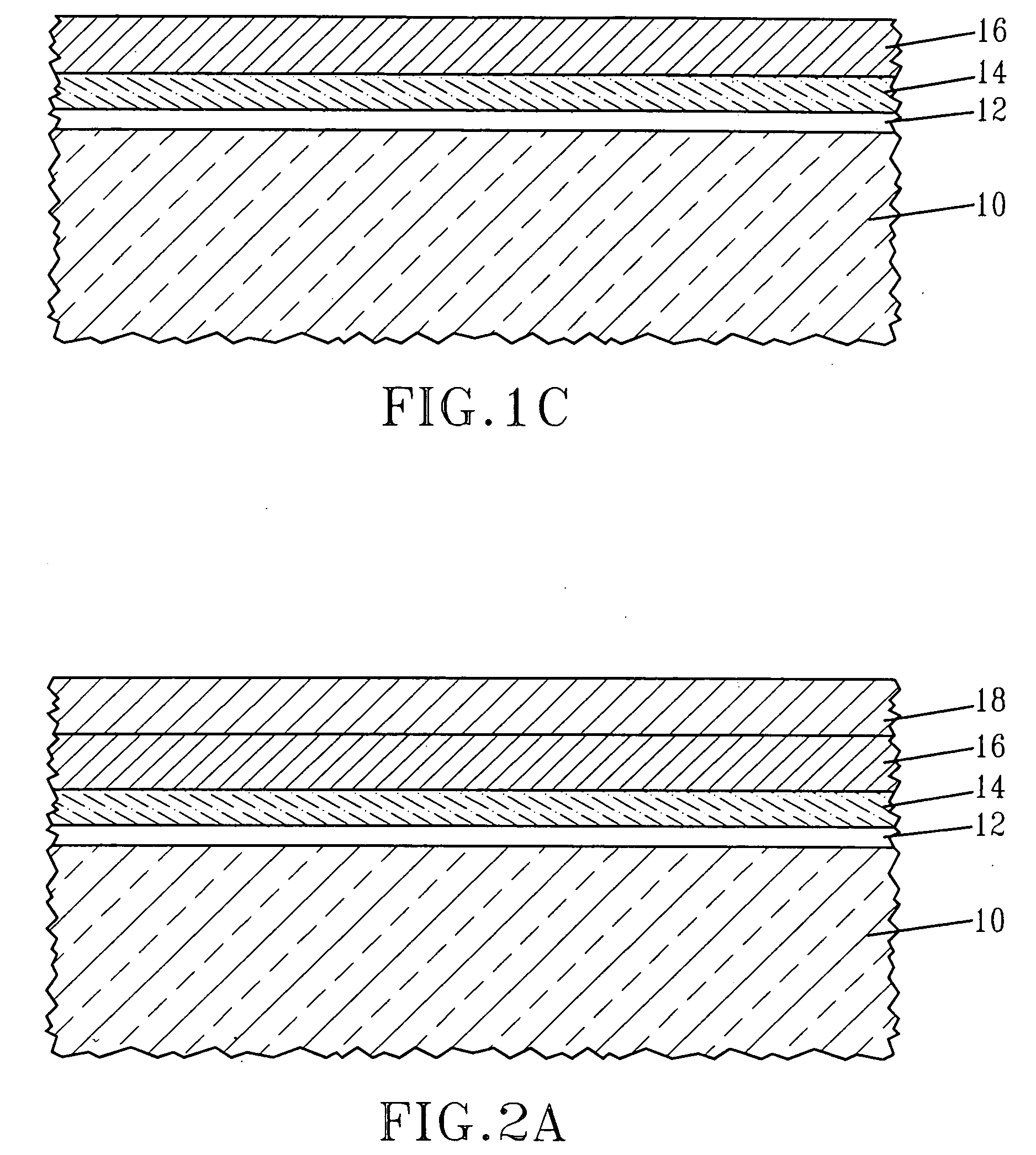

A method is provided that allows for maintaining a desired equivalent oxide thickness (EOT) by reducing the thickness of an interfacial layer in a gate structure. An interfacial layer is formed on a substrate, a gate dielectric layer such as, a high-k gate dielectric, is formed on the interfacial layer. A gettering layer is formed on the substrate overlying the interfacial layer. The gettering layer may function to getter oxygen from the interfacial layer such that the interfacial layer thickness is decreased and / or restricted from growth. The invention is beneficial to controlling the equivalent oxide thickness of the gate structure. The gettering layer includes a dielectric layer and / or a metal layer, thus the gettering layer is able to be removed from the gate stack or retained in the structure.

Owner:TAIWAN SEMICON MFG CO LTD

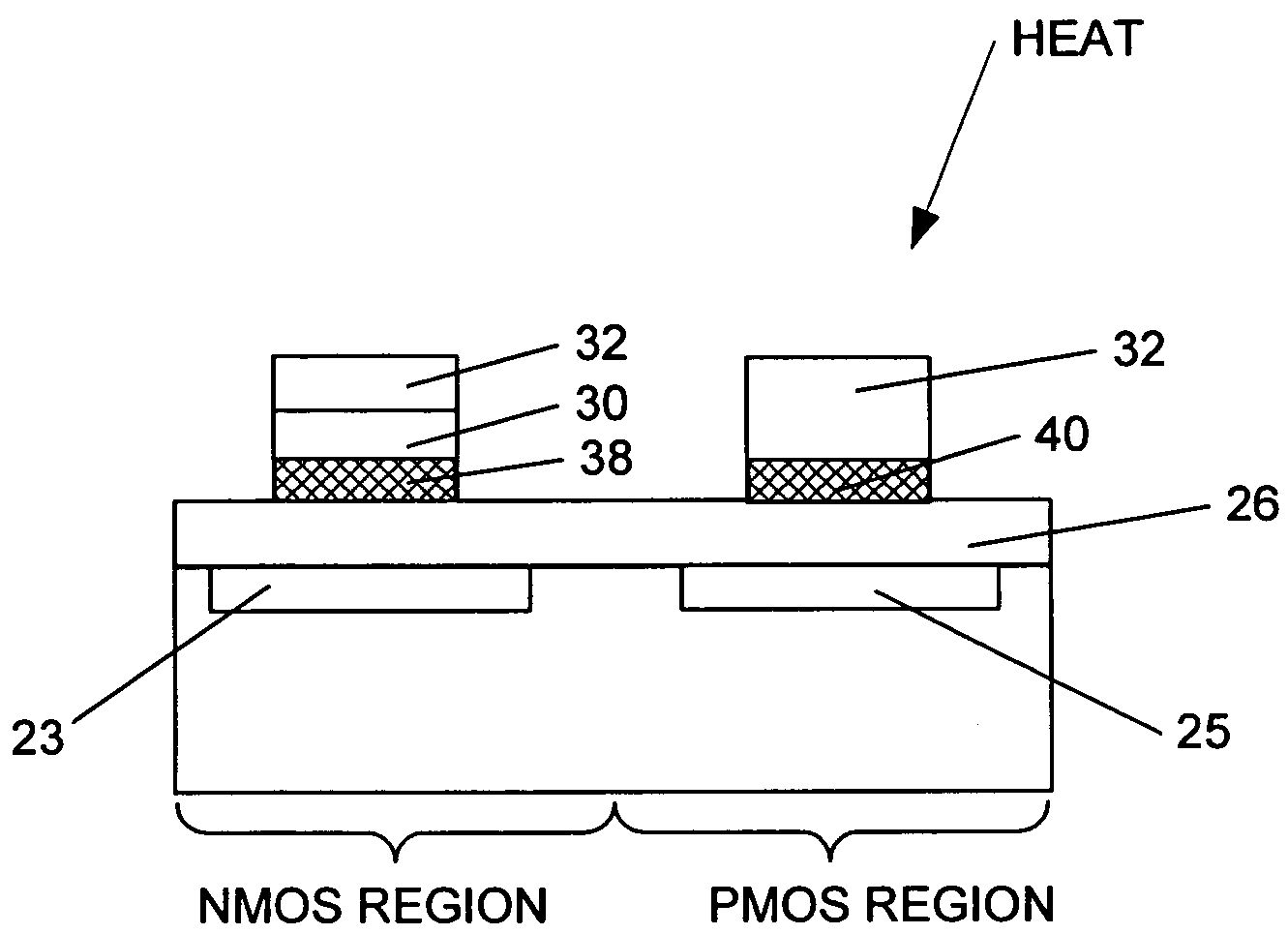

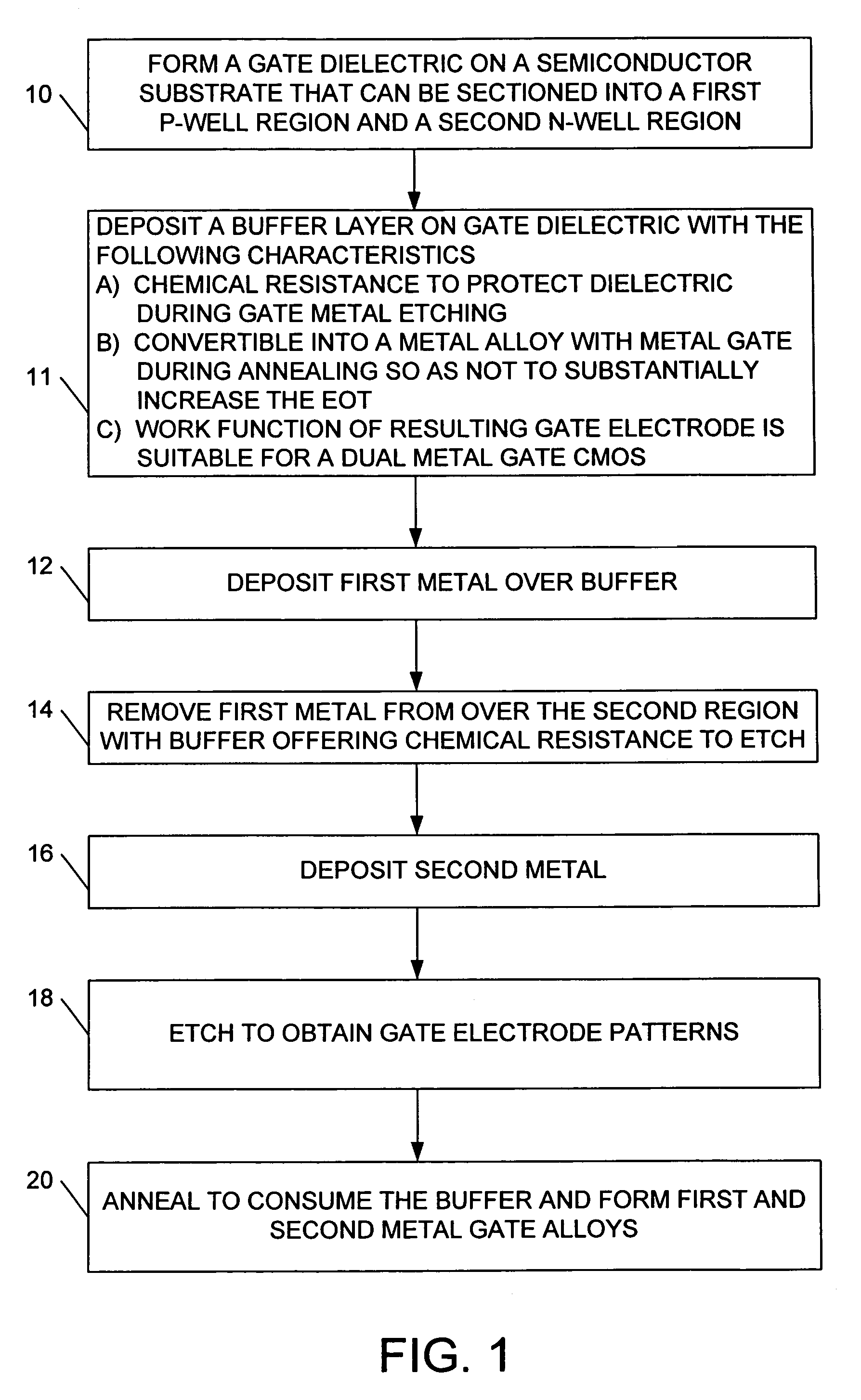

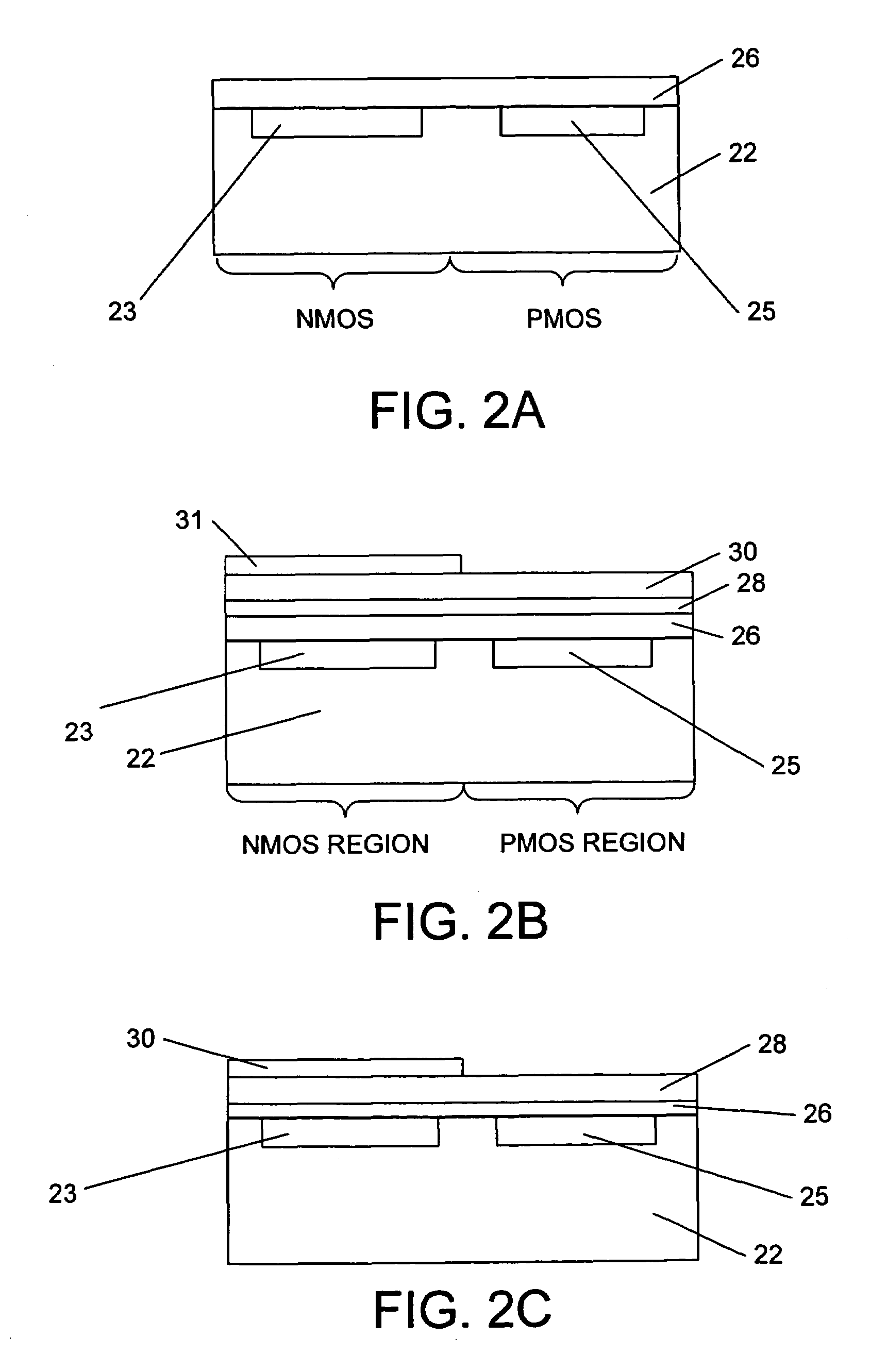

Method of fabricating a CMOS device with dual metal gate electrodes

InactiveUS7316950B2Semiconductor/solid-state device manufacturingSemiconductor devicesDielectricEquivalent oxide thickness

A method of constructing a dual metal gate CMOS structure that uses an ultra thin aluminum nitride (AINx) buffer layer between the metal gate and gate dielectric during processing for preventing the gate dielectric from being exposed in the metal etching process. After the unwanted gate metal is etched away, the CMOS structure is annealed. During the annealing, the buffer layer is completely consumed through reaction with the metal gate and a new metal alloy is formed, resulting in only a minimal increase in the equivalent oxide thickness. The buffer layer and gate metals play a key role in determining the work functions of the metal / dielectric interface, since the work functions of the original gate metals are modified as a result of the annealing process.

Owner:AGENCY FOR SCI TECH & RES +1

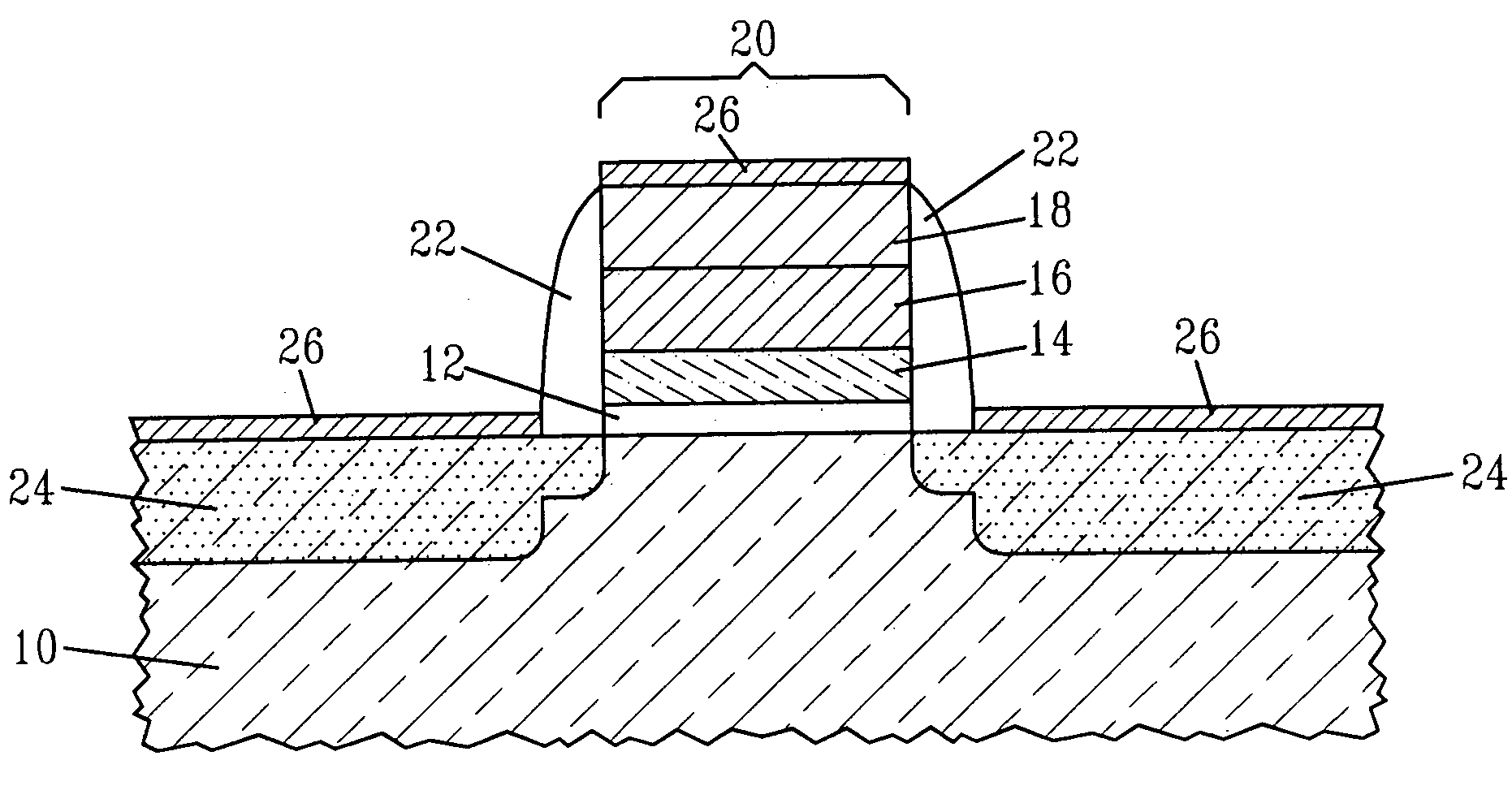

Method of making ultra thin gate oxide using aluminum oxide

InactiveUS6100204ATransistorSemiconductor/solid-state device manufacturingEquivalent oxide thicknessGate dielectric

A transistor and a method of making the same are provided. The method includes the step of forming a gate dielectric layer on the substrate where the gate dielectric layer is composed of an aluminum oxide containing material. A gate electrode is formed on the gate dielectric layer and first and second source / drain regions are formed in the substrate laterally separated to define a channel region beneath the gate electrode. The aluminum oxide containing material may be, for example, Al2O3. Aluminum oxide provides for a gate dielectric with a thin equivalent thickness of oxide in a potentially single crystal form.

Owner:GLOBALFOUNDRIES INC

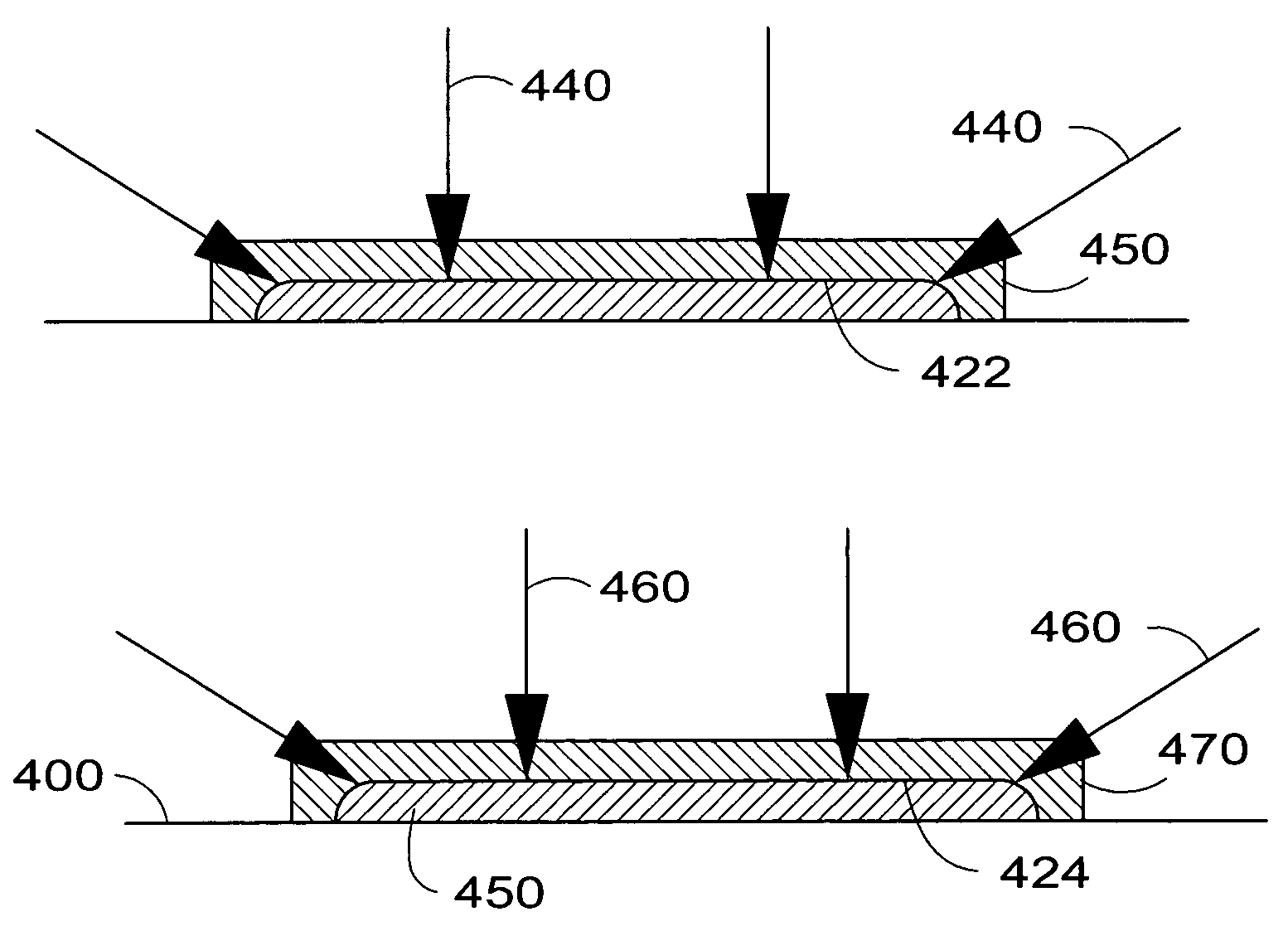

Scavenging metal stack for a high-k gate dielectric

ActiveUS7989902B2Constant voltageReduce thicknessTransistorSemiconductor/solid-state device manufacturingDielectricEquivalent oxide thickness

A stack of a high-k gate dielectric and a metal gate structure includes a lower metal layer, a scavenging metal layer, and an upper metal layer. The scavenging metal layer meets the following two criteria 1) a metal (M) for which the Gibbs free energy change of the reaction Si+2 / y MxOy→2x / y M+SiO2 is positive 2) a metal that has a more negative Gibbs free energy per oxygen atom for formation of oxide than the material of the lower metal layer and the material of the upper metal layer. The scavenging metal layer meeting these criteria captures oxygen atoms as the oxygen atoms diffuse through the gate electrode toward the high-k gate dielectric. In addition, the scavenging metal layer remotely reduces the thickness of a silicon oxide interfacial layer underneath the high-k dielectric. As a result, the equivalent oxide thickness (EOT) of the total gate dielectric is reduced and the field effect transistor maintains a constant threshold voltage even after high temperature processes during CMOS integration.

Owner:GLOBALFOUNDRIES US INC

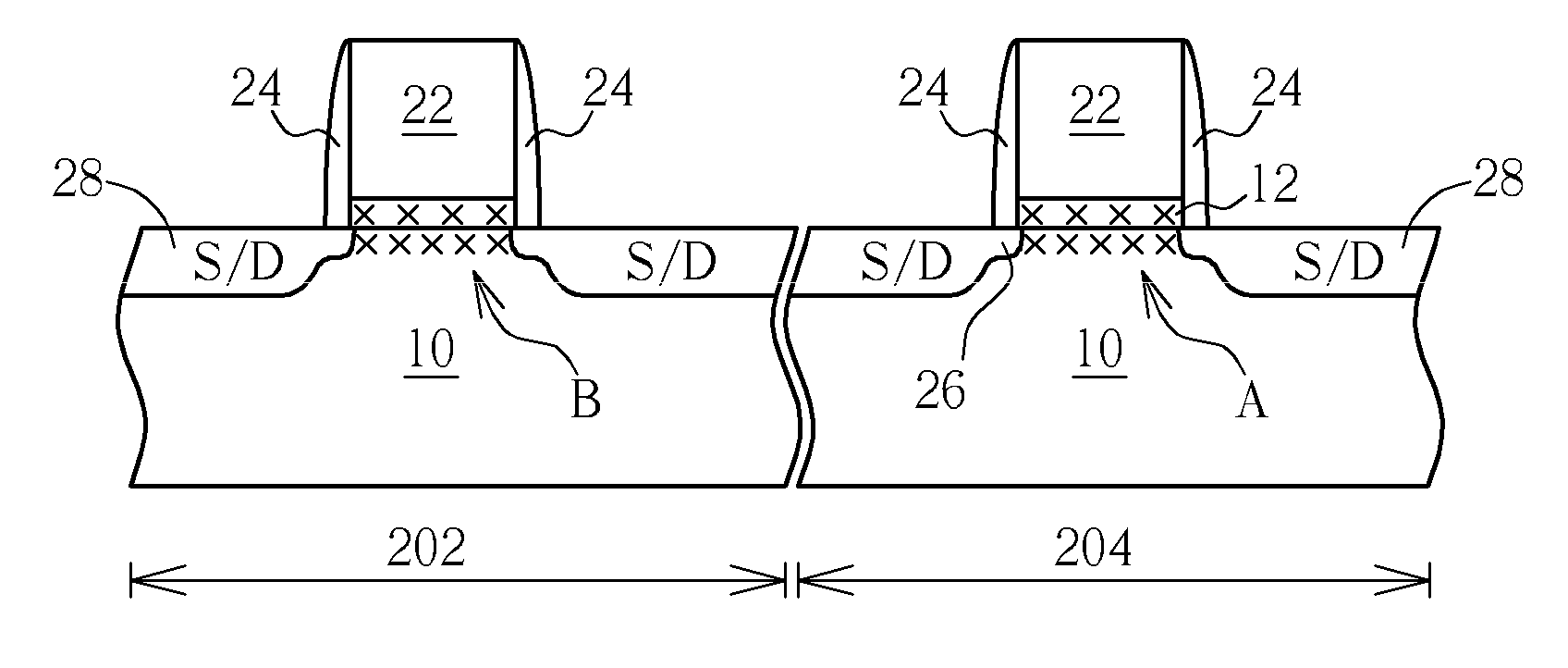

Method for gate leakage reduction and Vt shift control and complementary metal-oxide-semiconductor device

ActiveUS20100148271A1Efficient reductionSuppress Vt shiftTransistorSolid-state devicesEquivalent oxide thicknessGate dielectric

The present invention relates to a method for gate leakage reduction and Vt shift control, in which a first ion implantation is performed on PMOS region and NMOS region of a substrate to implant fluorine ions, carbon ions, or both in the gate dielectric or the semiconductor substrate, and a second ion implantation is performed only on the NMOS region of the substrate to implant fluorine ions, carbon ions, or both in the gate dielectric or the semiconductor substrate in the NMOS region, with the PMOS region being covered by a mask layer. Thus, the doping concentrations obtained by the PMOS region and the NMOS region are different to compensate the side effect caused by the different equivalent oxide thickness and to avoid the Vt shift.

Owner:UNITED MICROELECTRONICS CORP

Semiconductor device

ActiveCN102104042AHigh electron mobilityImprove performanceTransistorSemiconductor/solid-state device manufacturingEquivalent oxide thicknessCMOS

The invention relates to a semiconductor device, in particular to an interface optimized high-k gate dielectric complementary metal oxide semiconductor (CMOS) device. Interface layers with different thicknesses and different materials are adopted on a semiconductor substrate in an N-channel metal oxide semiconductor (NMOS) region and a semiconductor substrate of a P-channel metal oxide semiconductor (PMOS) region, the equivalent oxide thickness (EOT) of a device, in particular the EOT of a PMOS device, is effectively reduced, and the electron mobility of the device, in particular the electronmobility of an NMOS device is improved, so that the overall performance of the device is effectively improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

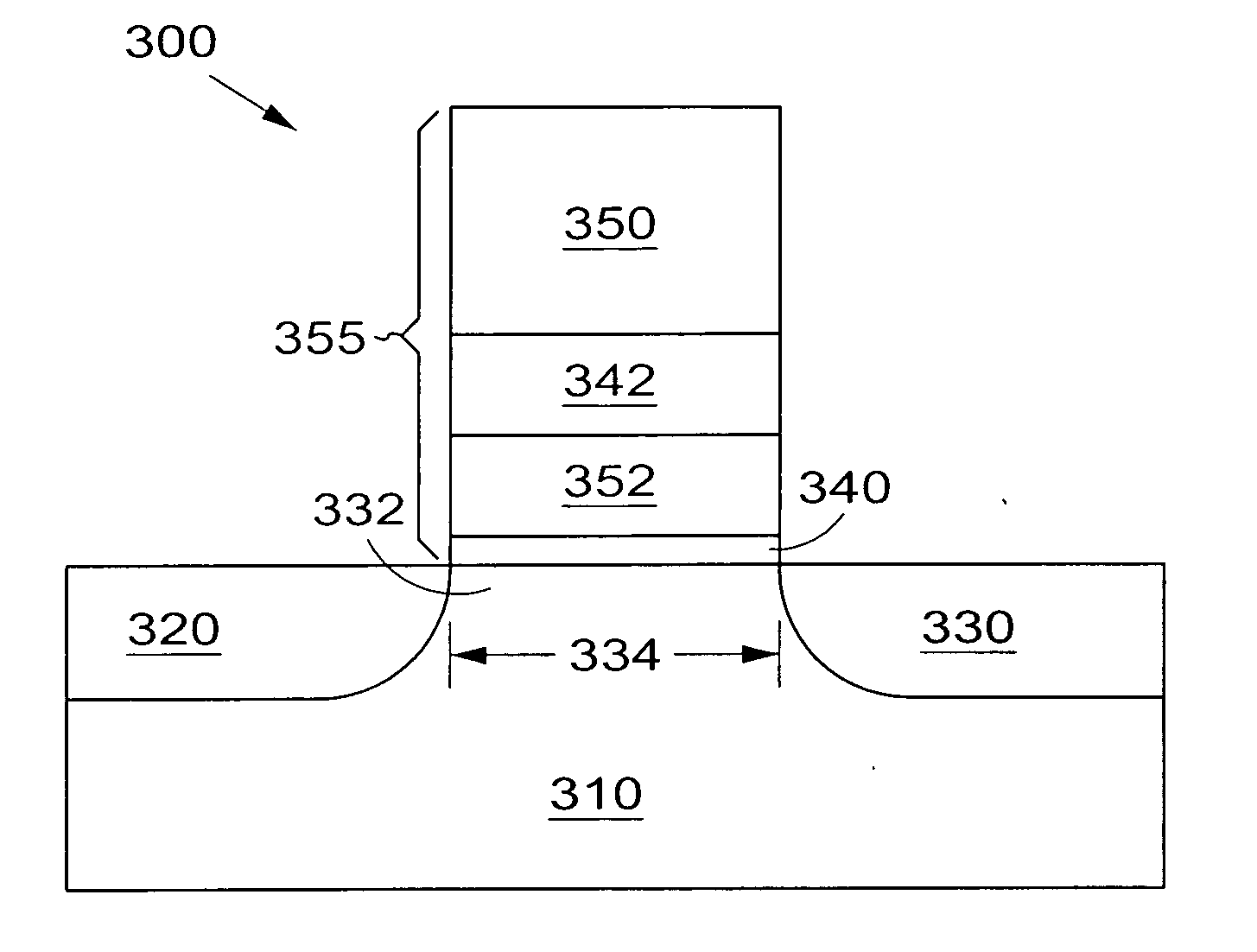

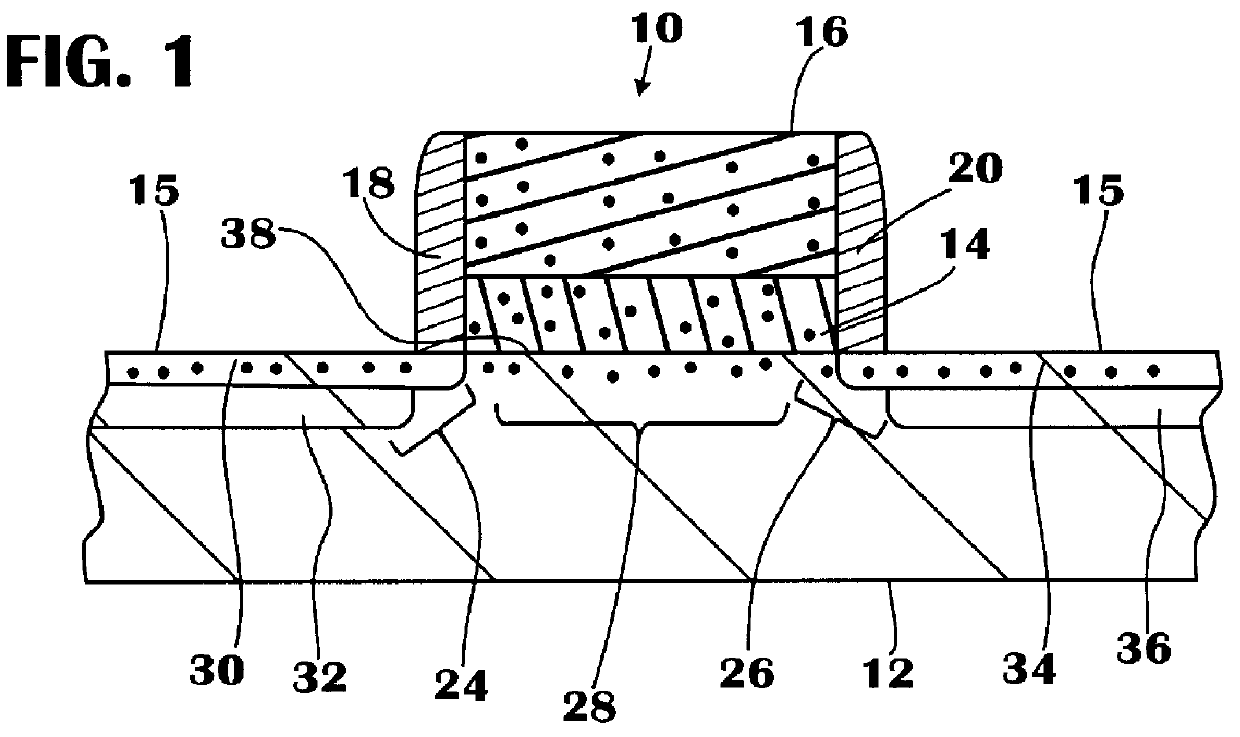

Method of making high performance MOSFET with polished gate and source/drain feature

InactiveUS6174794B1TransistorSemiconductor/solid-state device manufacturingMOSFETEquivalent oxide thickness

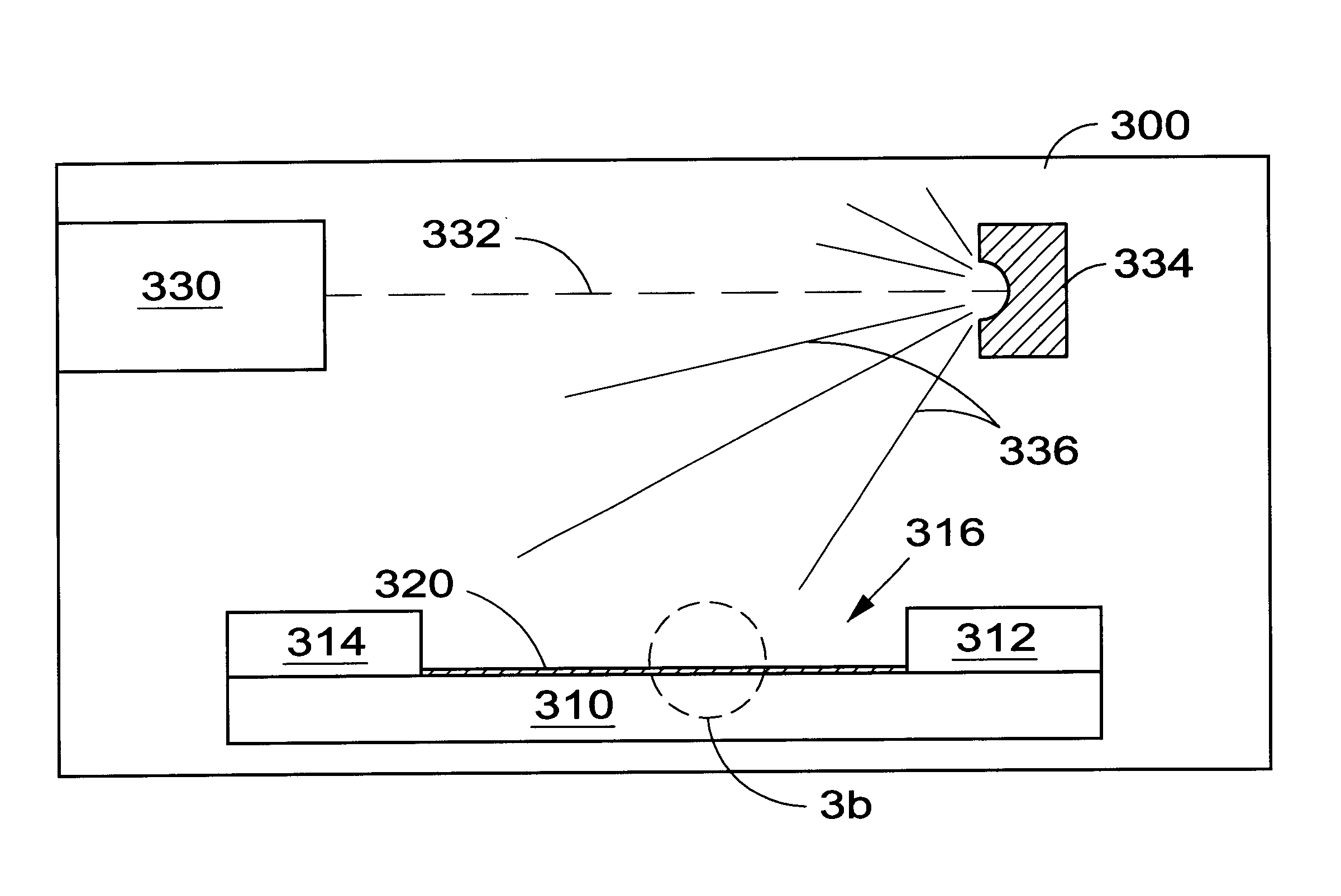

A transistor and a method of making the same are provided. The method includes the steps of forming a gate dielectric stack on the substrate that has a gate dielectric layer and forming first and second sidewall spacers adjacent the gate dielectric stack. A first portion of the gate dielectric stack is removed while a second portion thereof is left in place. First and second source / drain regions are formed in the substrate, and a conductor layer is formed over the first and second source / drain regions and on the second portion of the gate dielectric stack. The gate dielectric may be composed of a high dielectric constant material with a thin equivalent thickness of oxide. The method enables integrated processing of the gate electrode and source / drain metallization.

Owner:GLOBALFOUNDRIES INC

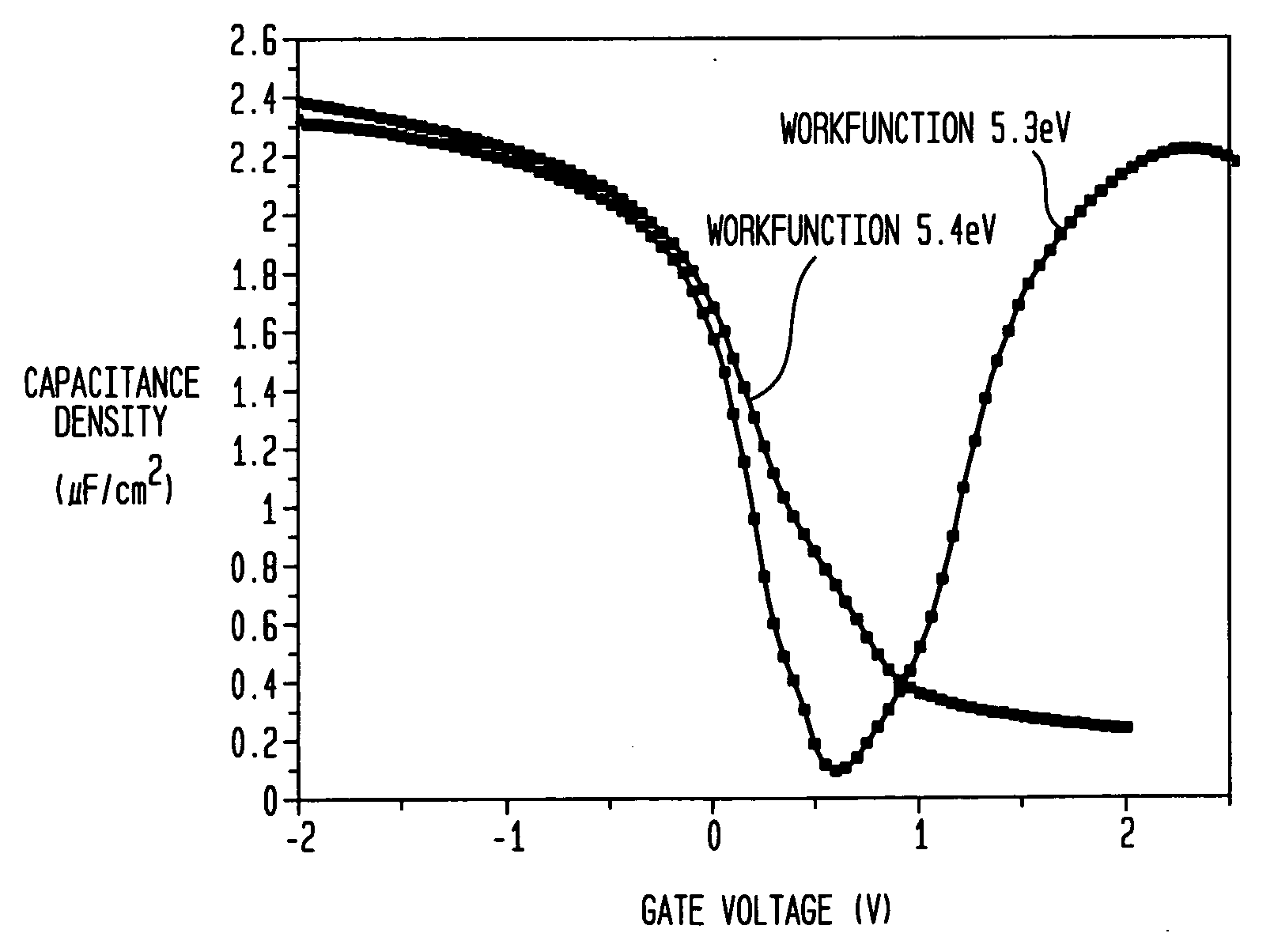

Metal oxynitride as a pFET material

ActiveUS20070138578A1Semiconductor/solid-state device manufacturingSemiconductor devicesDielectricEquivalent oxide thickness

A compound metal comprising MOxNy which is a p-type metal having a workfunction of about 4.75 to about 5.3, preferably about 5, eV that is thermally stable on a gate stack comprising a high k dielectric and an interfacial layer is provided as well as a method of fabricating the MOxNy compound metal. Furthermore, the MOxNy metal compound of the present invention is a very efficient oxygen diffusion barrier at 1000° C. allowing very aggressive equivalent oxide thickness (EOT) and inversion layer thickness scaling below 14 Å in a p-metal oxide semiconductor (PMOS) device. In the above formula, M is a metal selected from Group IVB, VB, VIB or VIIB of the Periodic Table of Elements, x is from about 5 to about 40 atomic % and y is from about 5 to about 40 atomic %.

Owner:GLOBALFOUNDRIES US INC

Capacitor and methods of manufacturing the same

InactiveUS20060267019A1Sufficient equivalent oxide thicknessLeakage currentTransistorSolid-state devicesEquivalent oxide thicknessDielectric layer

In a capacitor having a semiconductor-insulator-metal (SIM) structure, an upper electrode may be formed into a multilayer structure including a polycrystalline semiconductor Group IV material. A dielectric layer may include a metal oxide, and a lower electrode may include a metal-based material. Therefore, a capacitor may have a sufficiently small equivalent oxide thickness (EOT) and / or may have improved current leakage characteristics.

Owner:SAMSUNG ELECTRONICS CO LTD

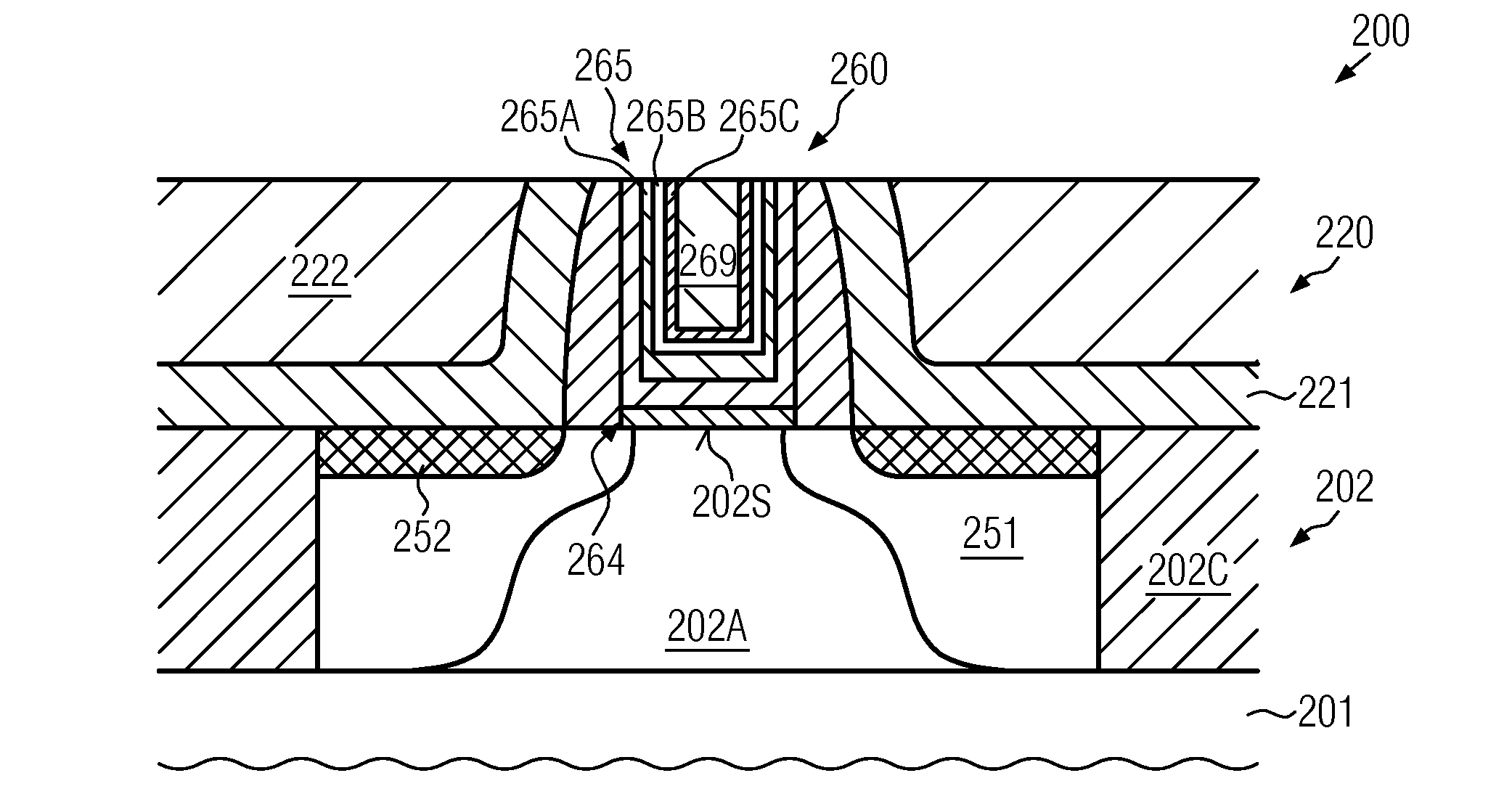

Reducing equivalent thickness of high-k dielectrics in field effect transistors by performing a low temperature anneal

InactiveUS20120238086A1Excellent interface characteristicEquivalent Thickness ReductionSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricEquivalent oxide thickness

When forming sophisticated high-k metal gate electrode structures, for instance on the basis of a replacement gate approach, superior interface characteristics may be obtained on the basis of using a thermally grown base material, wherein the electrically effective thickness may be reduced on the basis of a low temperature anneal process. Consequently, the superior interface characteristics of a thermally grown base material may be provided without requiring high temperature anneal processes, as are typically applied in conventional strategies using a very thin oxide layer formed on the basis of a wet oxidation chemistry.

Owner:GLOBALFOUNDRIES INC

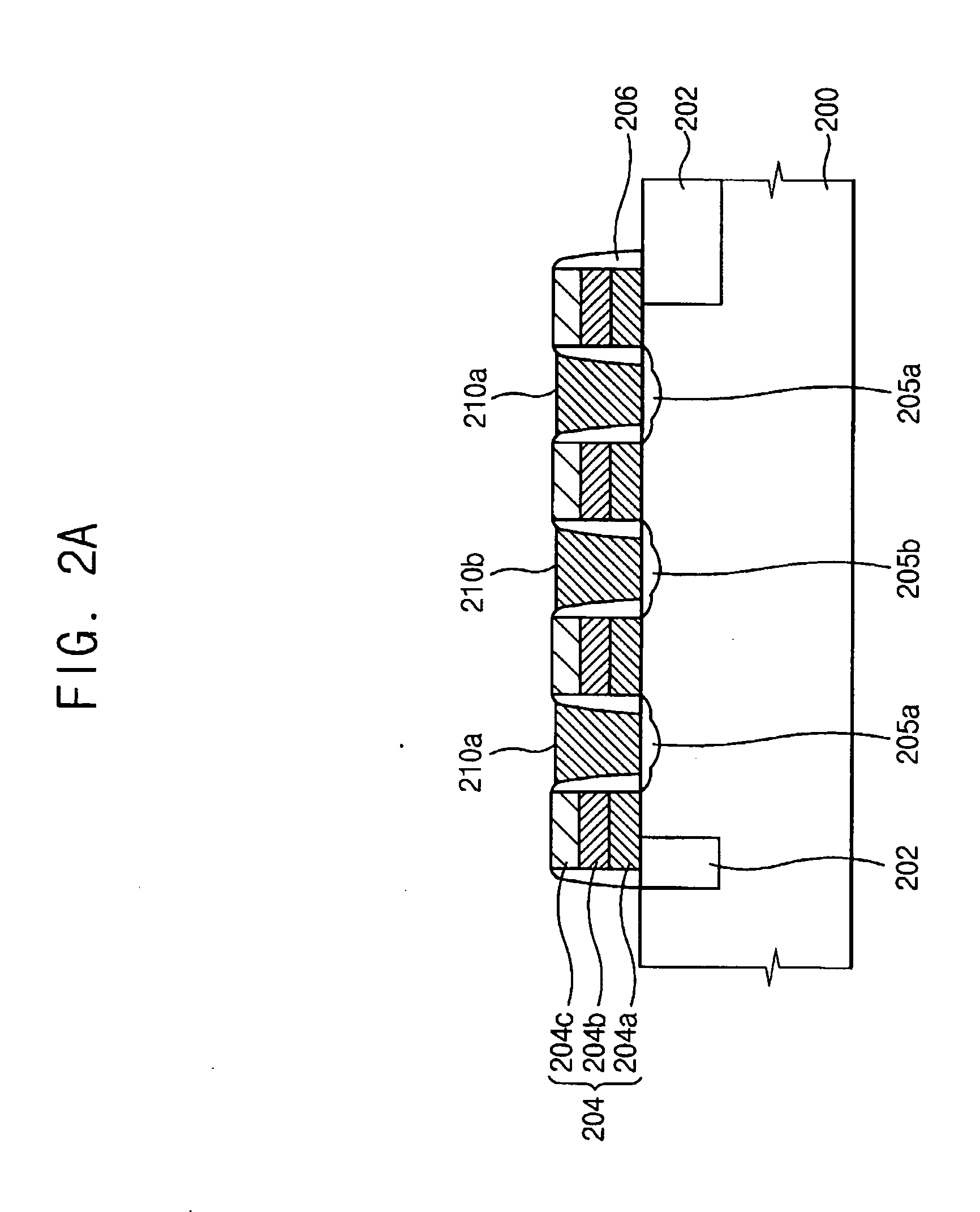

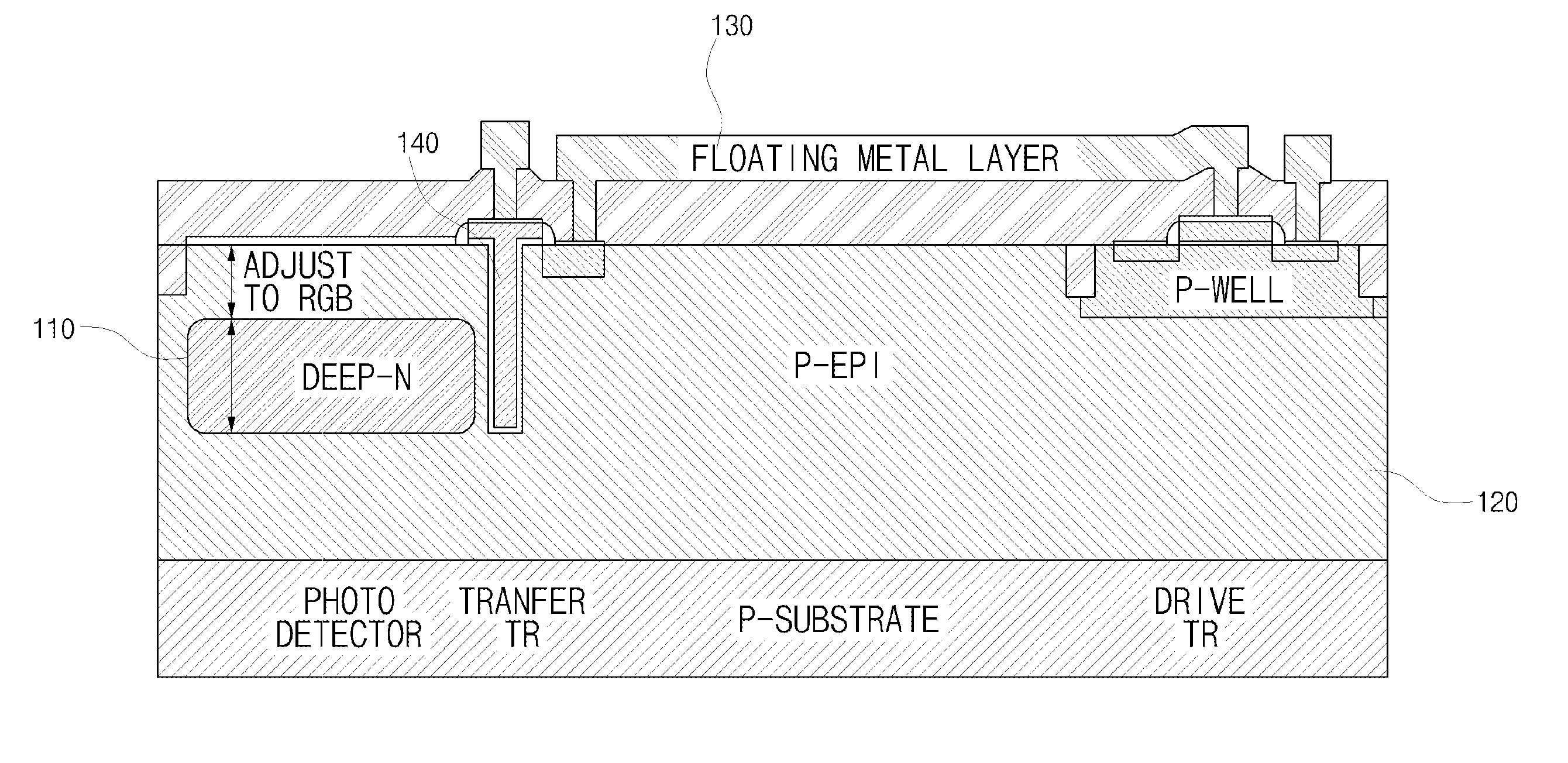

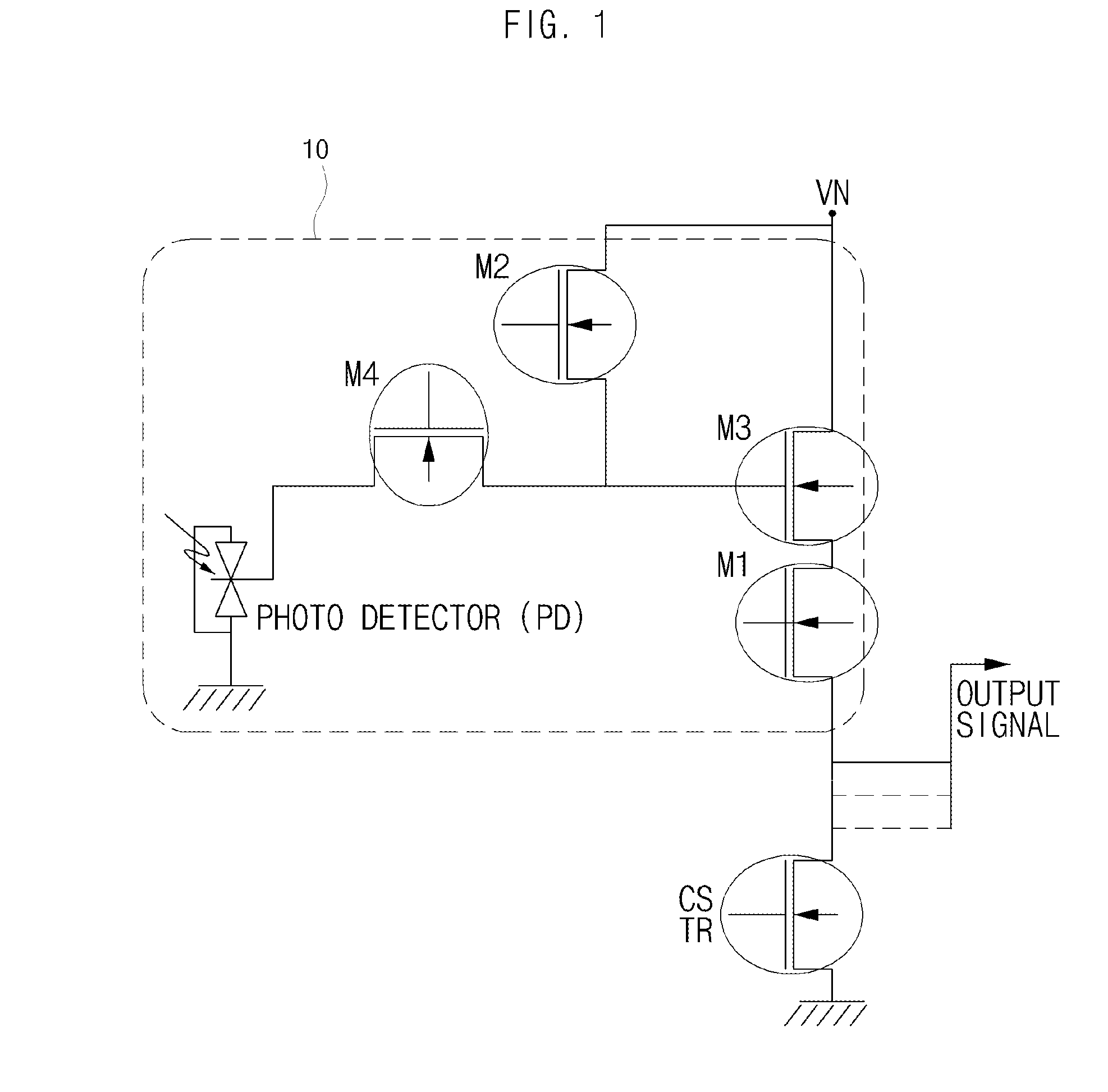

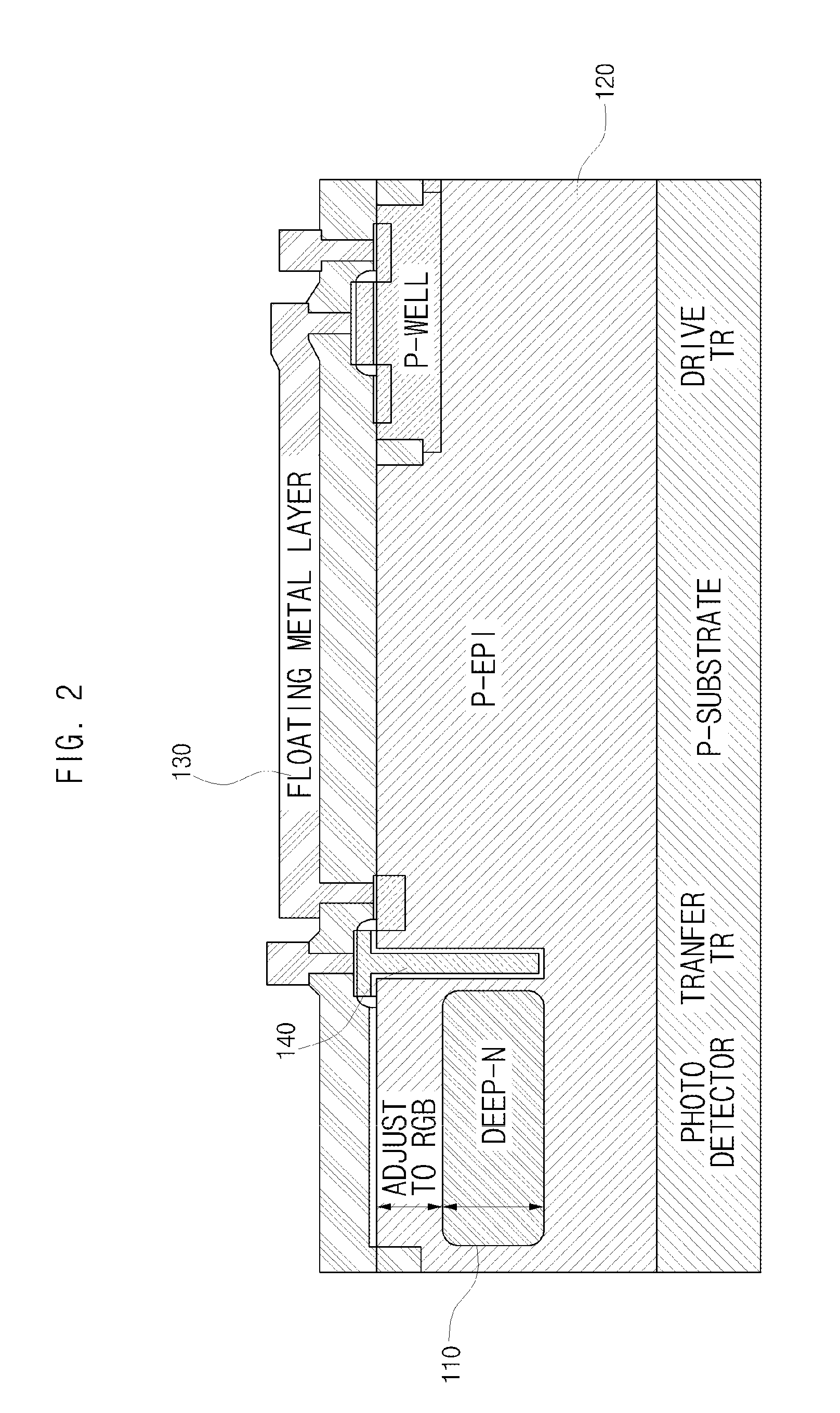

CMOS image sensor and manufacturing method thereof

InactiveUS20110084322A1Improving low exposureIncrease exposureSolid-state devicesSemiconductor/solid-state device manufacturingCMOSEquivalent oxide thickness

Disclosed is a CMOS image sensor and a manufacturing method thereof. According to an aspect of the present invention, each pixel of CMOS image sensor includes a photo detector that includes an electon Collection layer doped with a concentration of 5×1015 / cm3 to 2×1016 / cm3; and a transfer transistor that is connected to the photo detector and is formed of a vertical type trench gate of which the equivalent oxide thickness is 120 Å or more.

Owner:ELECTRONICS & TELECOMM RES INST

Method of forming HfSiN metal for n-FET applications

InactiveUS20060151846A1Improve film qualityHigh resistivityTransistorSemiconductor/solid-state device manufacturingDielectricEquivalent oxide thickness

A compound metal comprising HfSiN which is a n-type metal having a workfunction of about 4.0 to about 4.5, preferably about 4.3, eV which is thermally stable on a gate stack comprising a high k dielectric and an interfacial layer. Furthermore, after annealing the stack of HfSiN / high k dielectric / interfacial layer at a high temperature (on the order of about 1000° C.), there is a reduction of the interfacial layer, thus the gate stack produces a very small equivalent oxide thickness (12 Å classical), which cannot be achieved using TaSiN.

Owner:GLOBALFOUNDRIES INC