Manufacturing method for semiconductor element

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as severe interface layer thickness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The process of forming a semiconductor device on a substrate will be first described below, especially the description about forming a gate structure. In various examples in this specification, repeated reference numerals may appear to simplify the description, but this does not mean that there is any specific relationship between the various embodiments and / or the drawings. Furthermore, when it is mentioned that a certain layer is “on” or “over” another layer, it may mean that the two layers are in direct contact or that other elements or film layers are interposed therebetween.

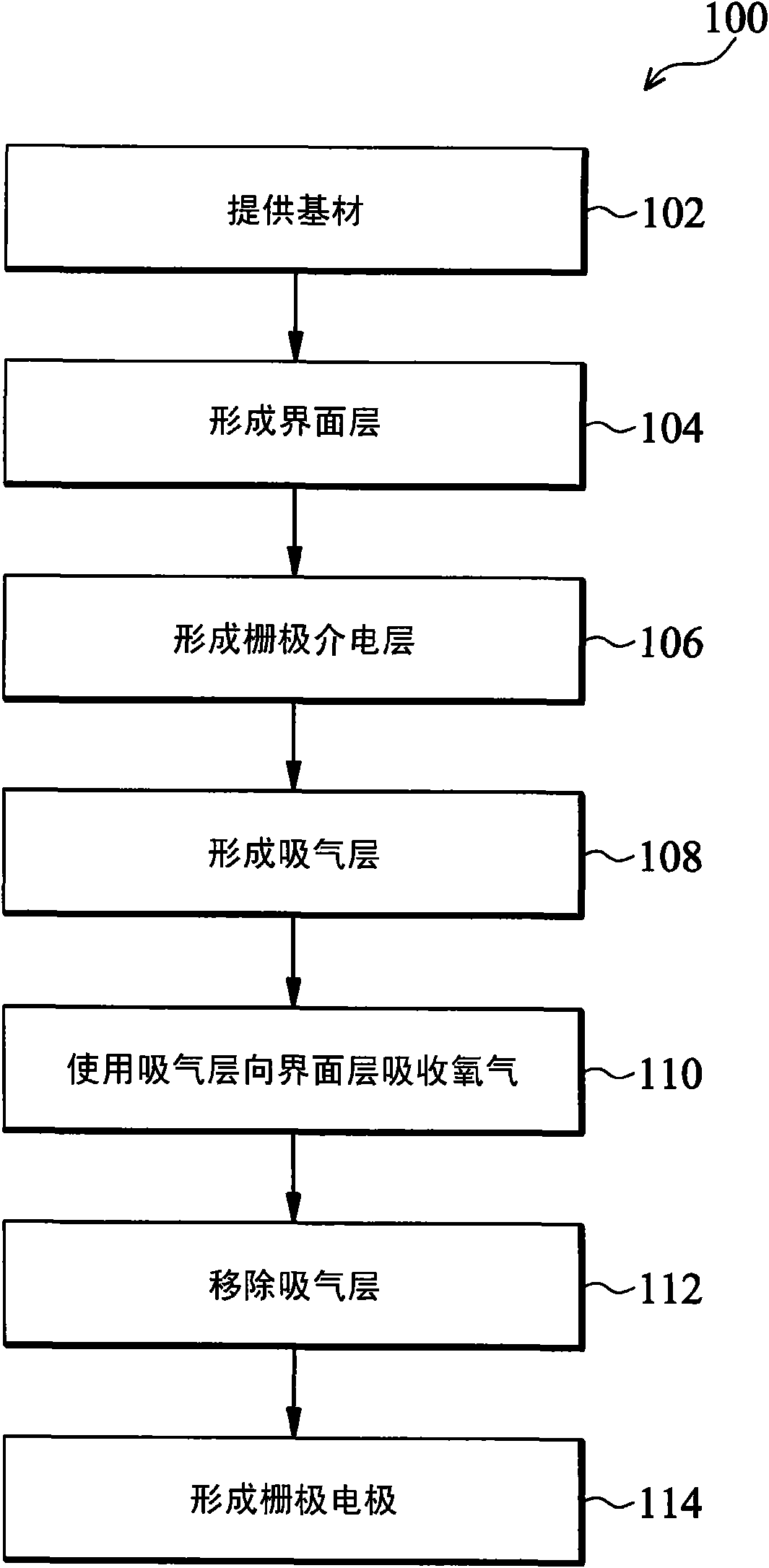

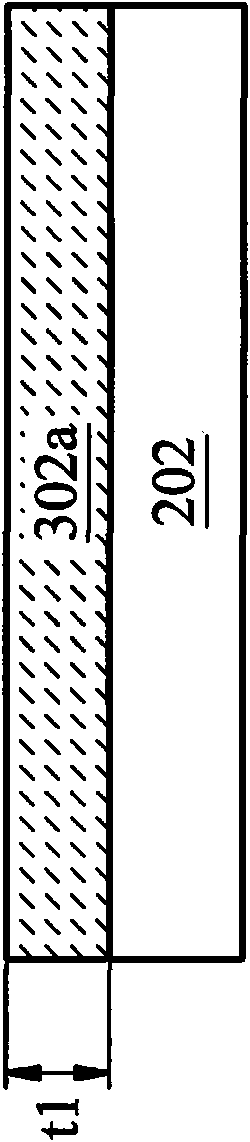

[0018] figure 1 A method 100 for forming a gate electrode according to an embodiment of the present invention is shown. Figure 2 to Figure 9 in accordance with figure 1 The process cross-sectional schematic diagram corresponding to the manufacturing steps. The method 100 may include a partial or complete integrated circuit process, including static random access memory (Static Random Acce...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More