Method of forming HfSiN metal for n-FET applications

a technology of hfsin metal and nfet, which is applied in the field of forming hfsin metal for nfet applications, complementary metal oxide semiconductors (cmos), can solve the problems of further degradation of device performance, limiting the choice of materials, and using a polysilicon gate, so as to improve the quality of the film and the effect of higher resistivity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

example

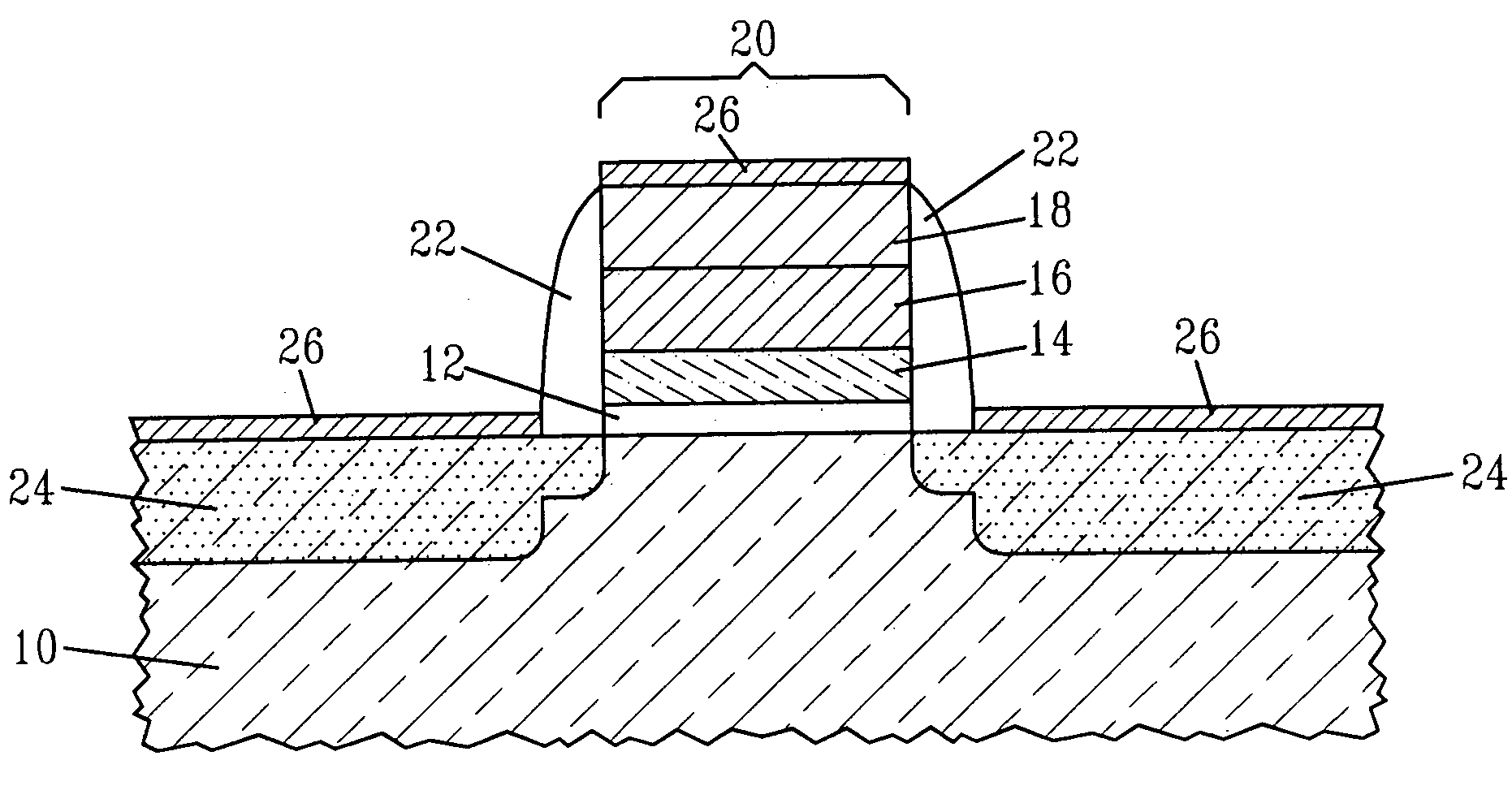

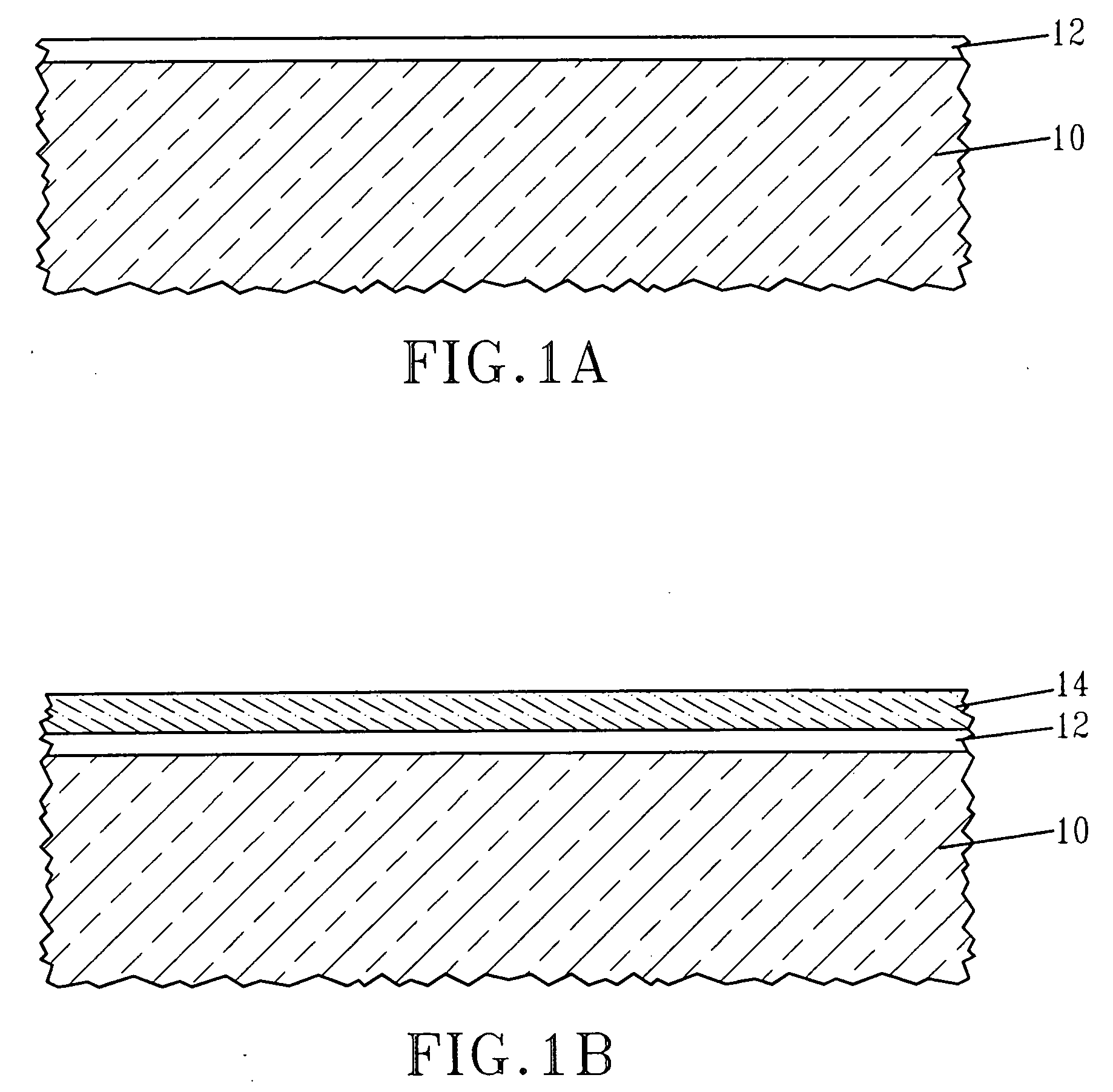

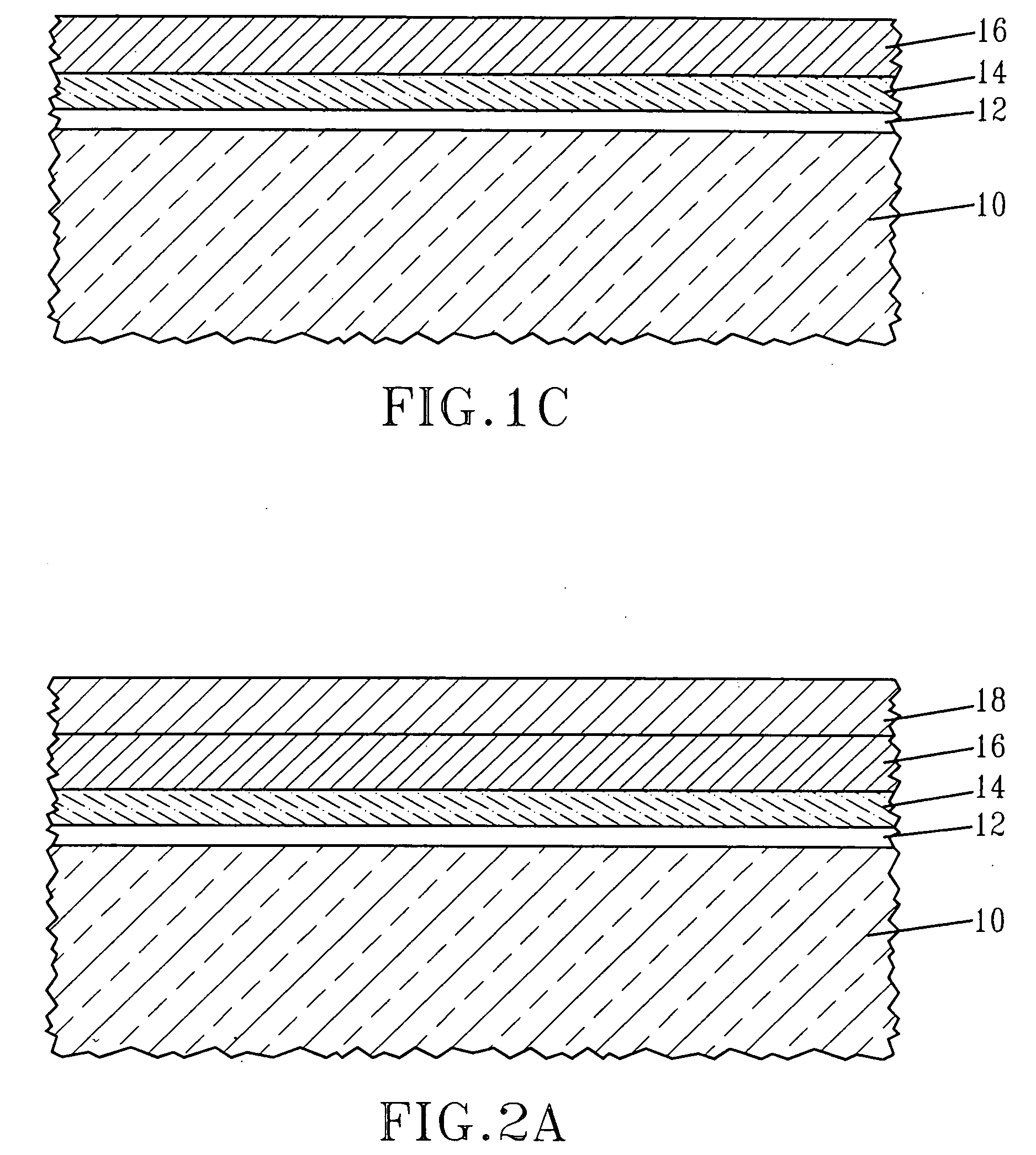

[0062] In this example, a HfSiN / HfO2 / SiO2 stack was formed on a surface of a Si wafer. The SiO2 interfacial layer was formed by oxidation of the Si wafer. The thickness of the SiO2 interfacial layer was about 1 nm. A HfO2 dielectric having a thickness of about 3 nm was then formed on the SiO2 interfacial layer by ALD. The HfSiN layer was then formed by providing a Hf target and an atmosphere comprising Ar / N2 / SiH4 (2% in He) in which flow ratio of Ar:N2:SiH4 (2% in He) was 20:10:20 sccm, respectively. The HfSiN layer had a thickness of about 40 nm. After providing the stack, the stack was subjected to a 1000° C. anneal, followed by a forming gas anneal that was performed at 450° C. For comparison, a TaSiN compound metal was formed about a similar HfO2 / SiO2 stack. FIG. 3 shows the CV characteristics at 10 kHz of these stacks on a n-substate. Note that the workfunction for the stack containing HfSiN was about 4.3 eV which is typical for a NMOS device, while the TaSiN-containing stack h...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| dielectric constant | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More