Semiconductor device

A semiconductor and device technology, applied in the field of high-k gate dielectric CMOS devices, can solve the problems of carrier mobility degradation, degradation, high interface state, etc., and achieve the effect of improving electron mobility, improving overall performance and reducing EOT

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

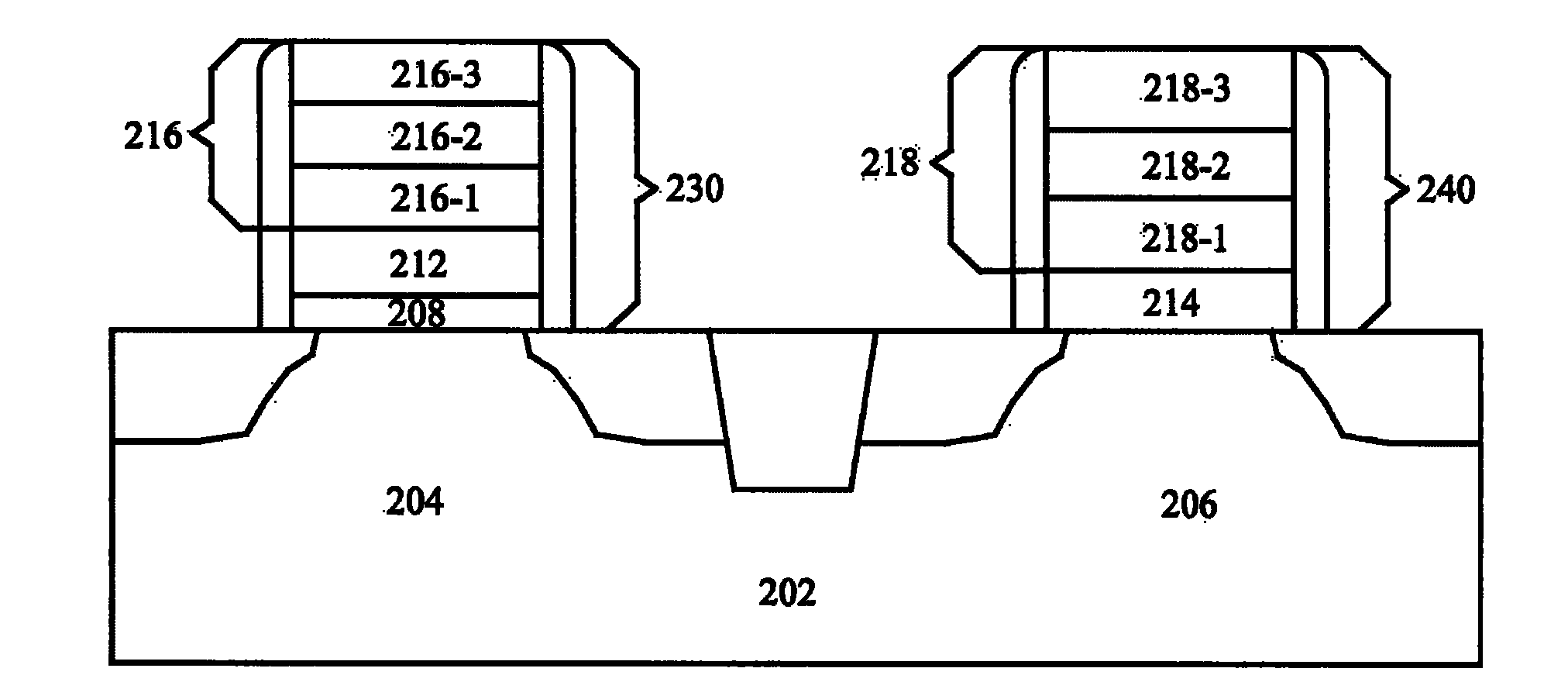

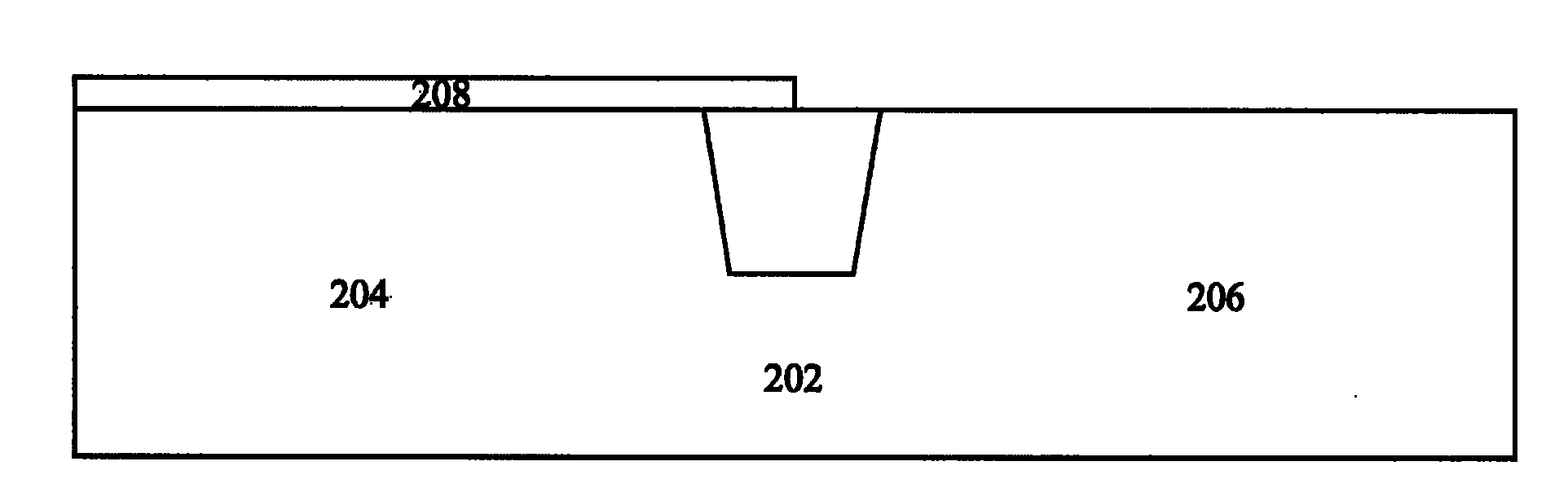

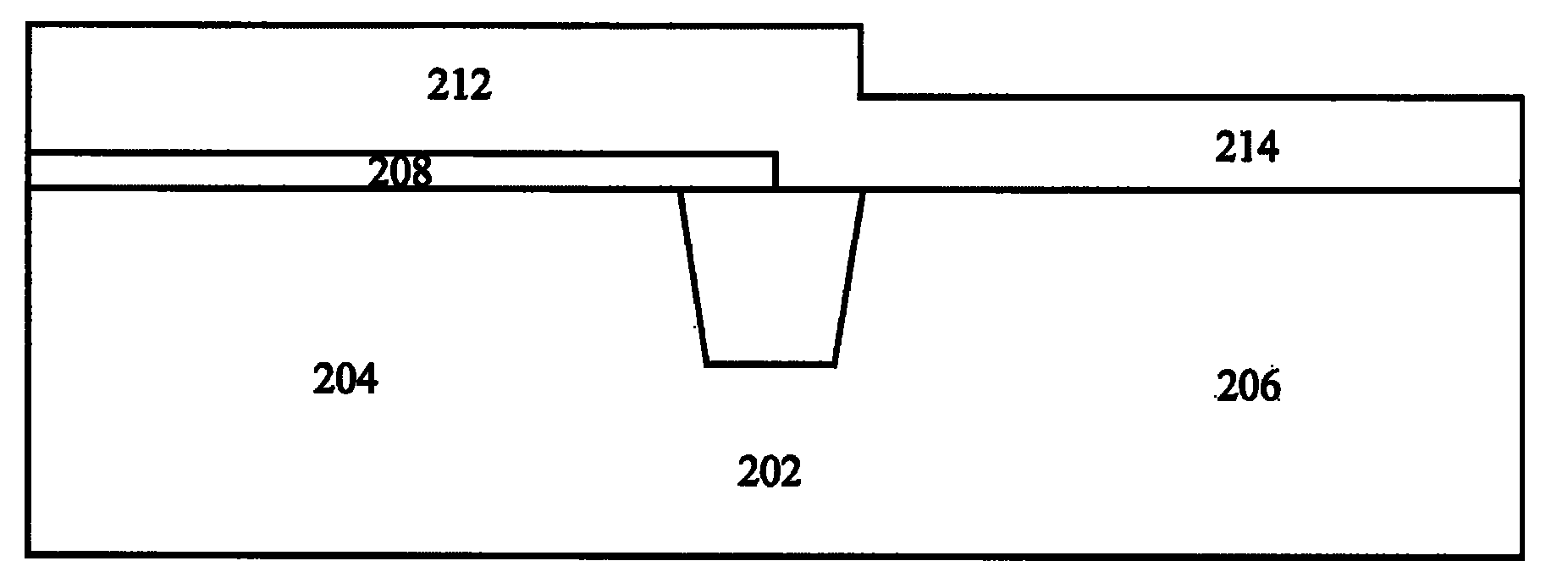

[0014] refer to figure 1 , figure 1 A schematic structural diagram of a semiconductor device according to an embodiment of the present invention is shown. like figure 1 As shown, the device includes: a semiconductor substrate 202 having an NMOS region 204 and a PMOS region 206, the NMOS region 204 is isolated from the PMOS region 206; the semiconductor substrate 202 formed on the NMOS region 204 The first gate stack 230 and the second gate stack 240 formed on the semiconductor substrate 202 of the PMOS region 206, the first gate stack 230 includes: a first interface layer 208; formed on the first interface layer 208 The first high-k gate dielectric layer 212 on the first high-k gate dielectric layer; the first gate layer 216 formed on the first high-k gate dielectric layer, wherein the first gate layer 216 is one or more layers; the first The second gate stack 240 includes: a second high-k gate dielectric layer 214; a second gate layer 218 formed on the second high-k gate d...

no. 2 example

[0024] A second embodiment of the present invention will be described below. In the second embodiment, different interfacial layers are provided for the NMOS device and the PMOS device, so as to adjust the carrier mobility of the NMOS device and the PMOS device respectively.

[0025] refer to Figure 10 , Figure 10 A schematic structural diagram of a semiconductor device according to a second embodiment of the present invention is shown. like Figure 10 As shown, the device includes: a semiconductor substrate 202 having an NMOS region 204 and a PMOS region 206, the NMOS region 204 is isolated from the PMOS region 206; the semiconductor substrate 202 formed on the NMOS region 204 The first gate stack 230 and the second gate stack 240 formed on the semiconductor substrate 202 of the PMOS region 206; wherein the first gate stack 230 includes: a first interface layer 208; formed on the first interface layer The first high-k gate dielectric layer 212 on 208; the first gate lay...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More