Dual metal gate process: metals and their silicides

a metal gate and metal silicide technology, applied in the direction of seat furniture, vehicle safety belts, applications, etc., can solve the problems of buried channel effects, threshold voltage becomes too high for both types of transistors, and single metal gate work function values that are not suitable for cmos applications, etc., to achieve and higher or lower work functions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

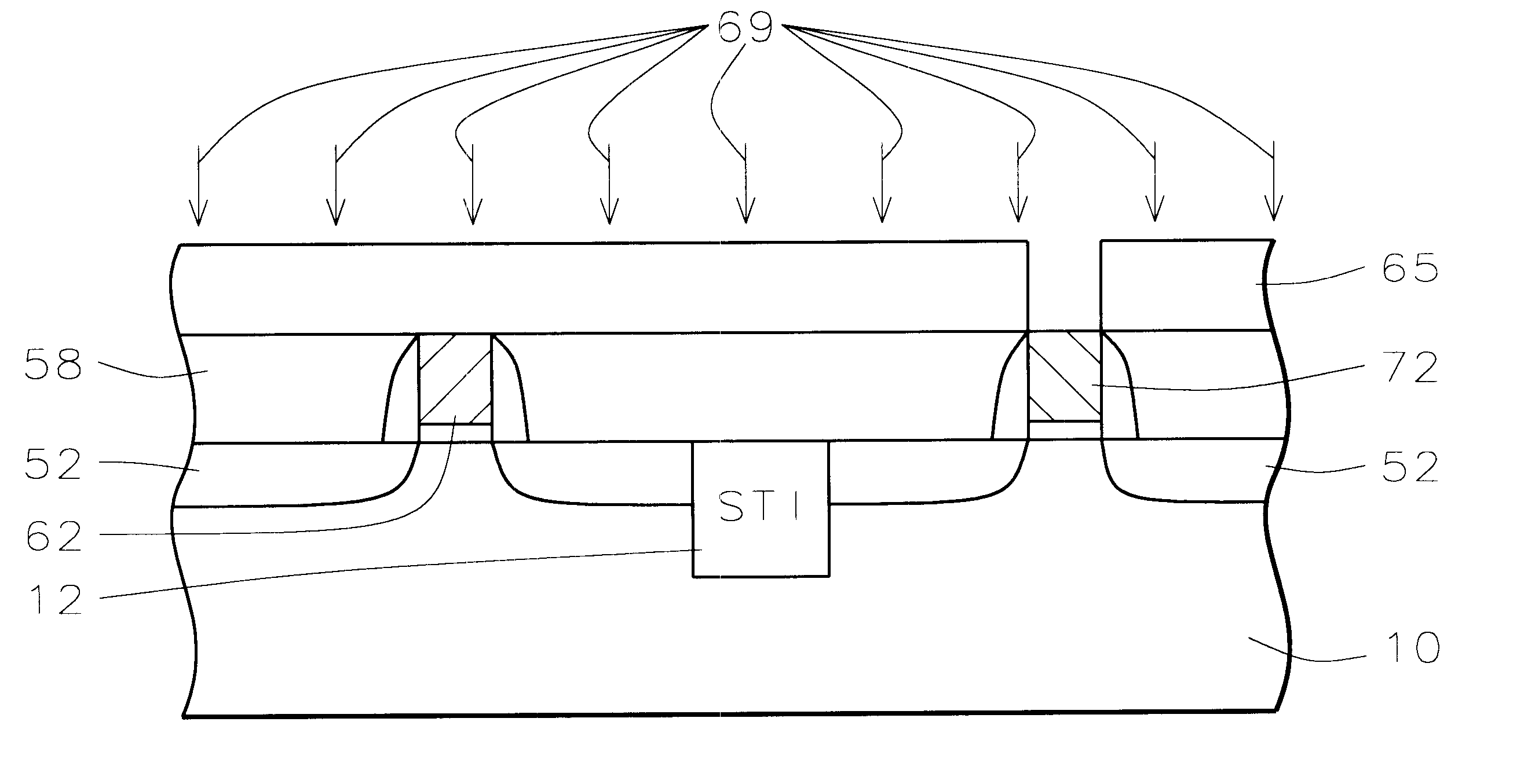

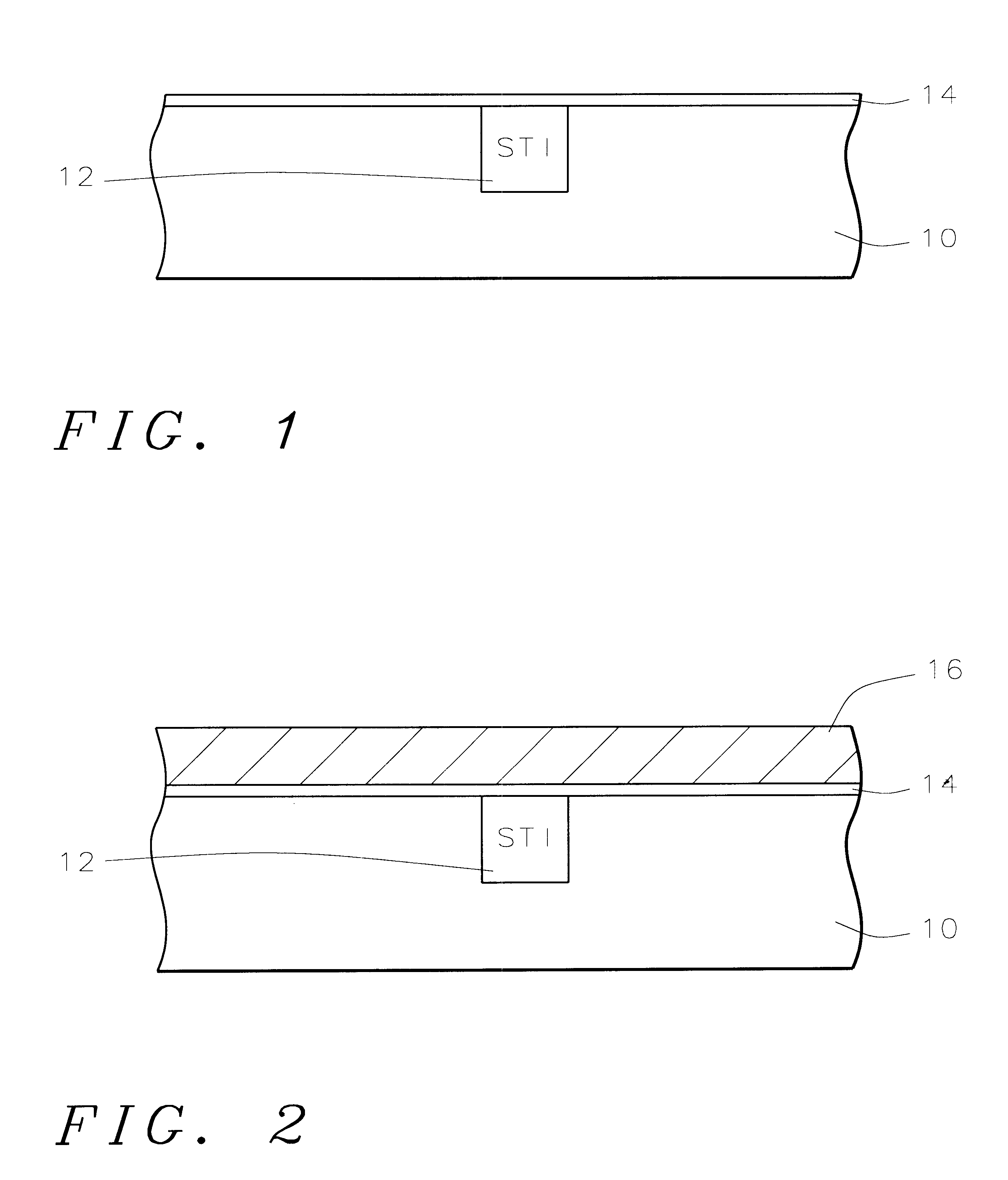

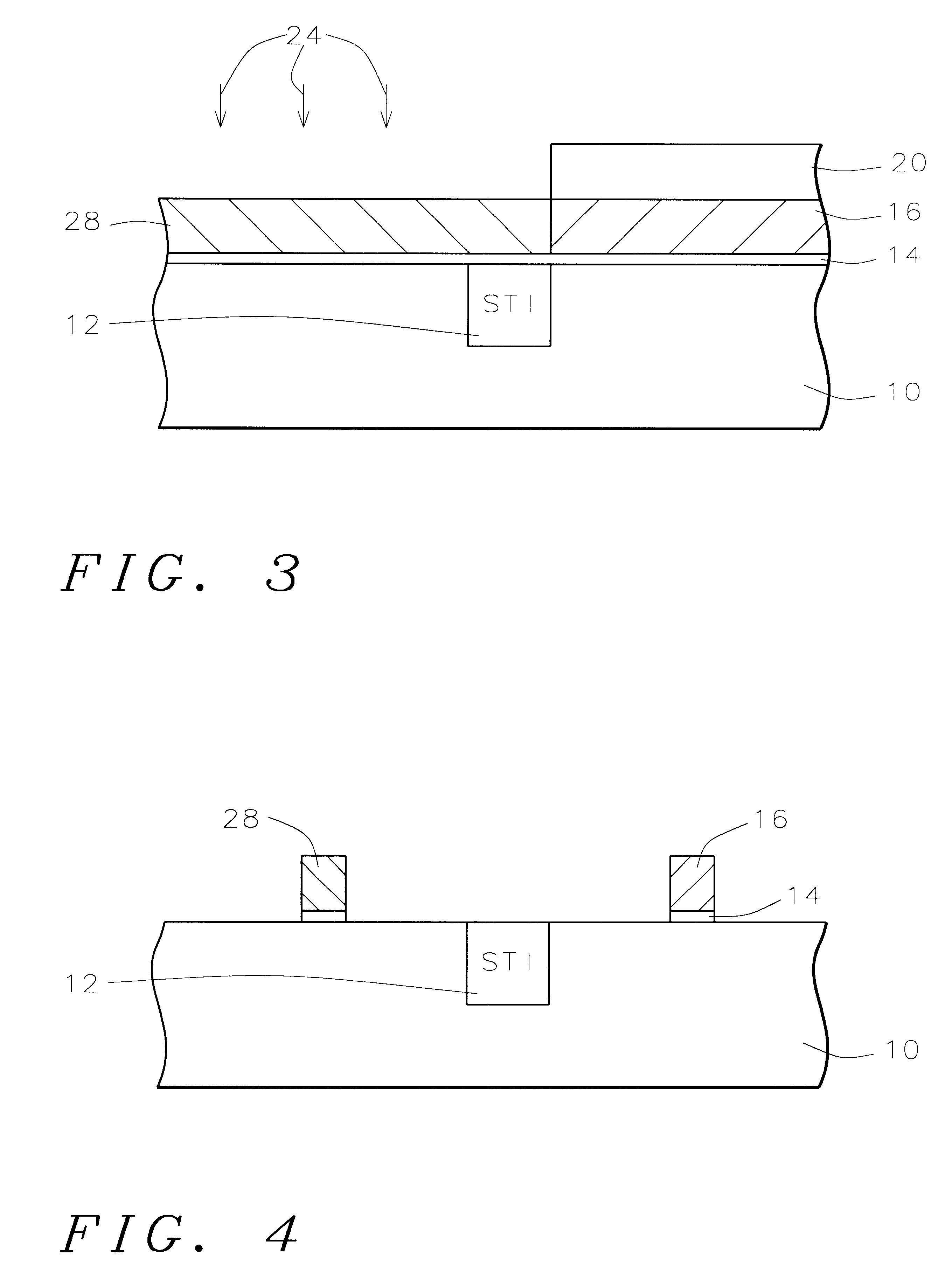

The present invention uses a metal and its metal silicide to form dual-metal gates having different work functions. In one embodiment, two different silicides of the metal are used as the dual-metal gates. It will be understood by those skilled in the art that the invention should not be limited to the embodiments described herein, but can be extended and applied to any application in which it is desired to have metal gates having differing work functions. The first embodiment of the invention will be described with reference to FIGS. 1-5. The second embodiment of the invention will be described with reference to FIGS. 6-11. The third embodiment of the invention will be described with reference to FIGS. 12 and 13.

Referring now to FIGS. 1-5, the first preferred embodiment of the present invention will be described. Referring now more particularly to FIG. 1, there is shown a semiconductor substrate 10. This is preferably monocrystalline silicon. Isolation regions, such as shallow tren...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More