Patents

Literature

1256 results about "Very large scale integrated" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Definition of very large scale integration. : the process of placing a very large number (as thousands) of circuits on a small semiconductor chip —abbreviation VLSI.

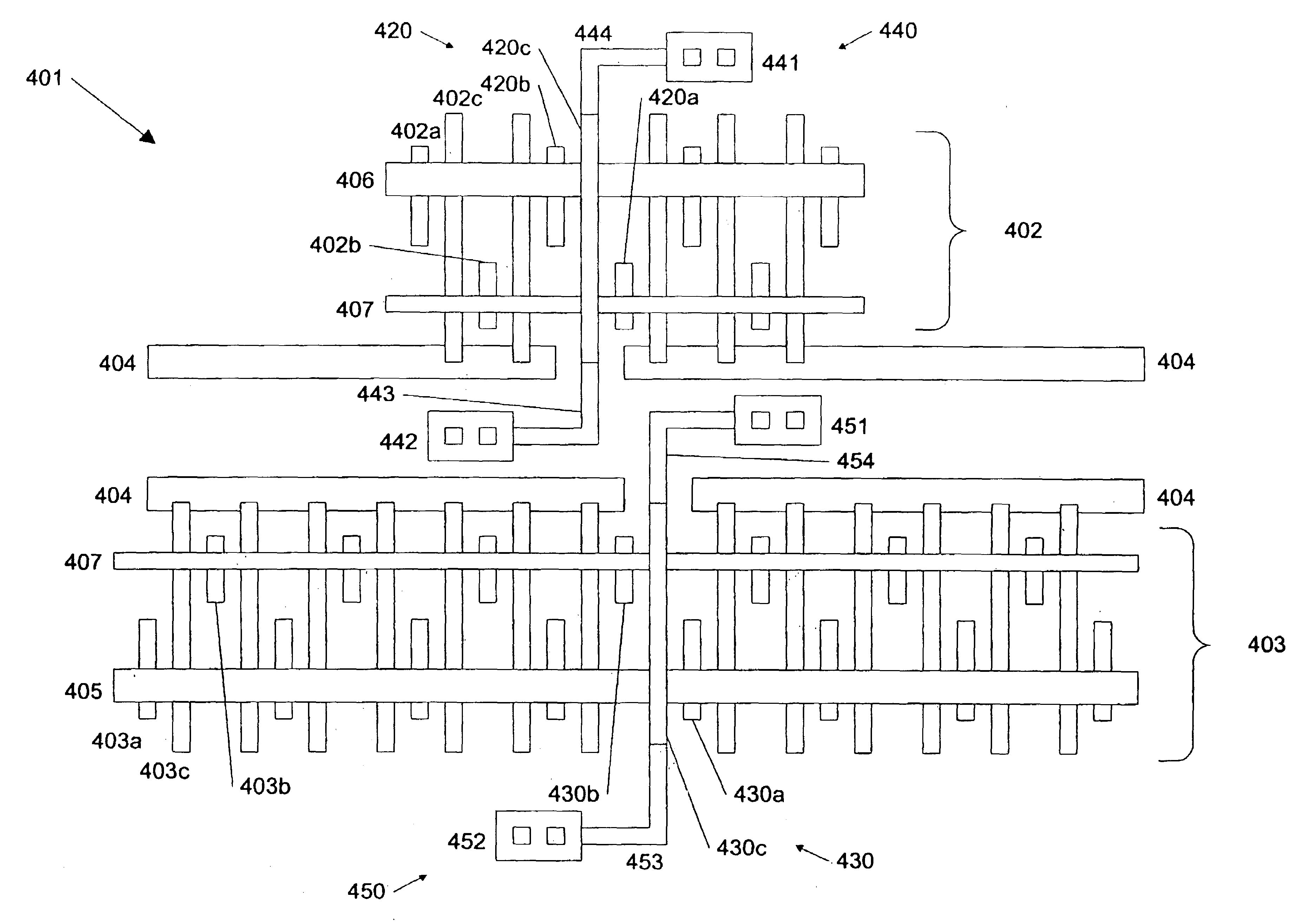

Microfluidic large scale integration

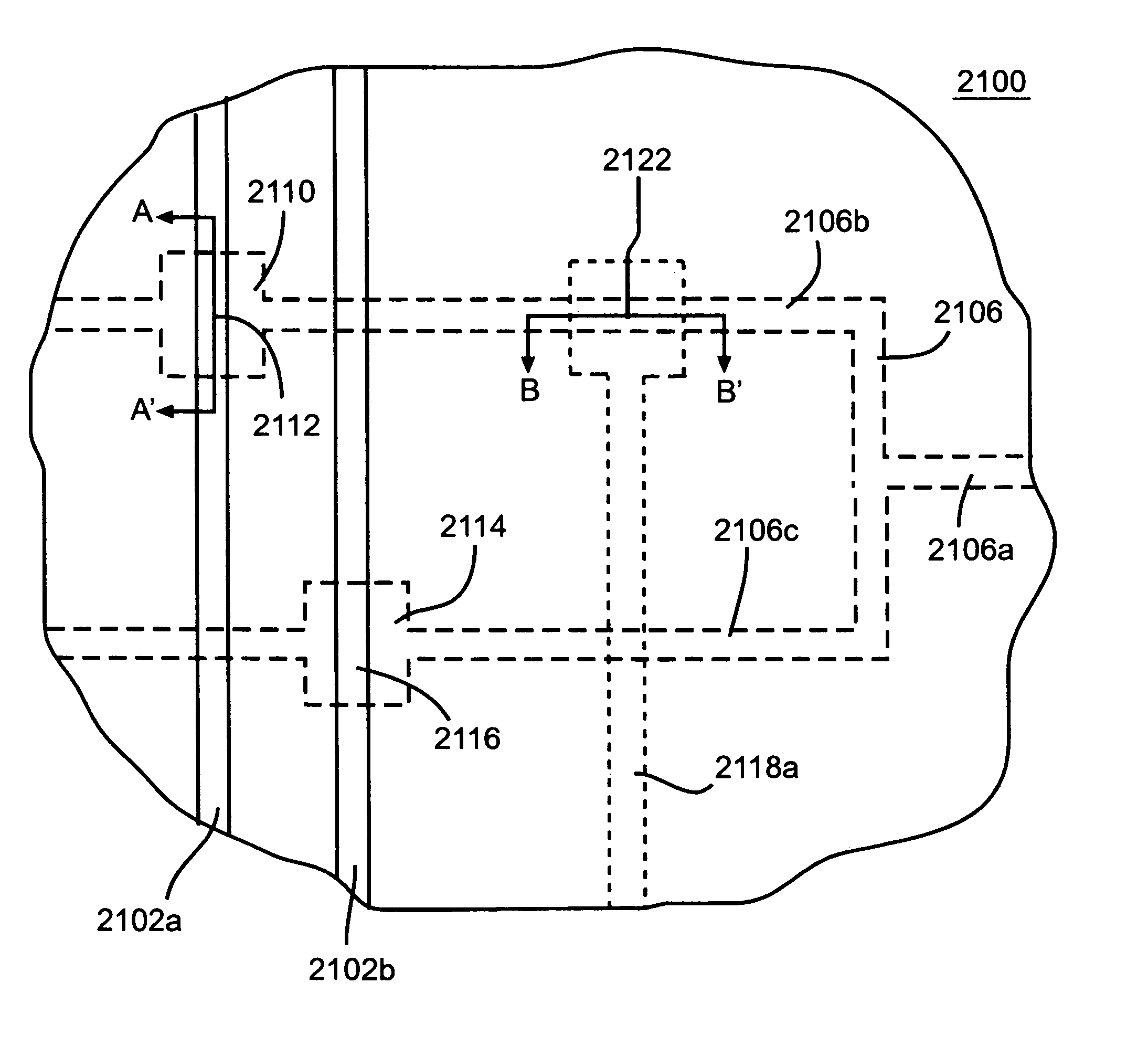

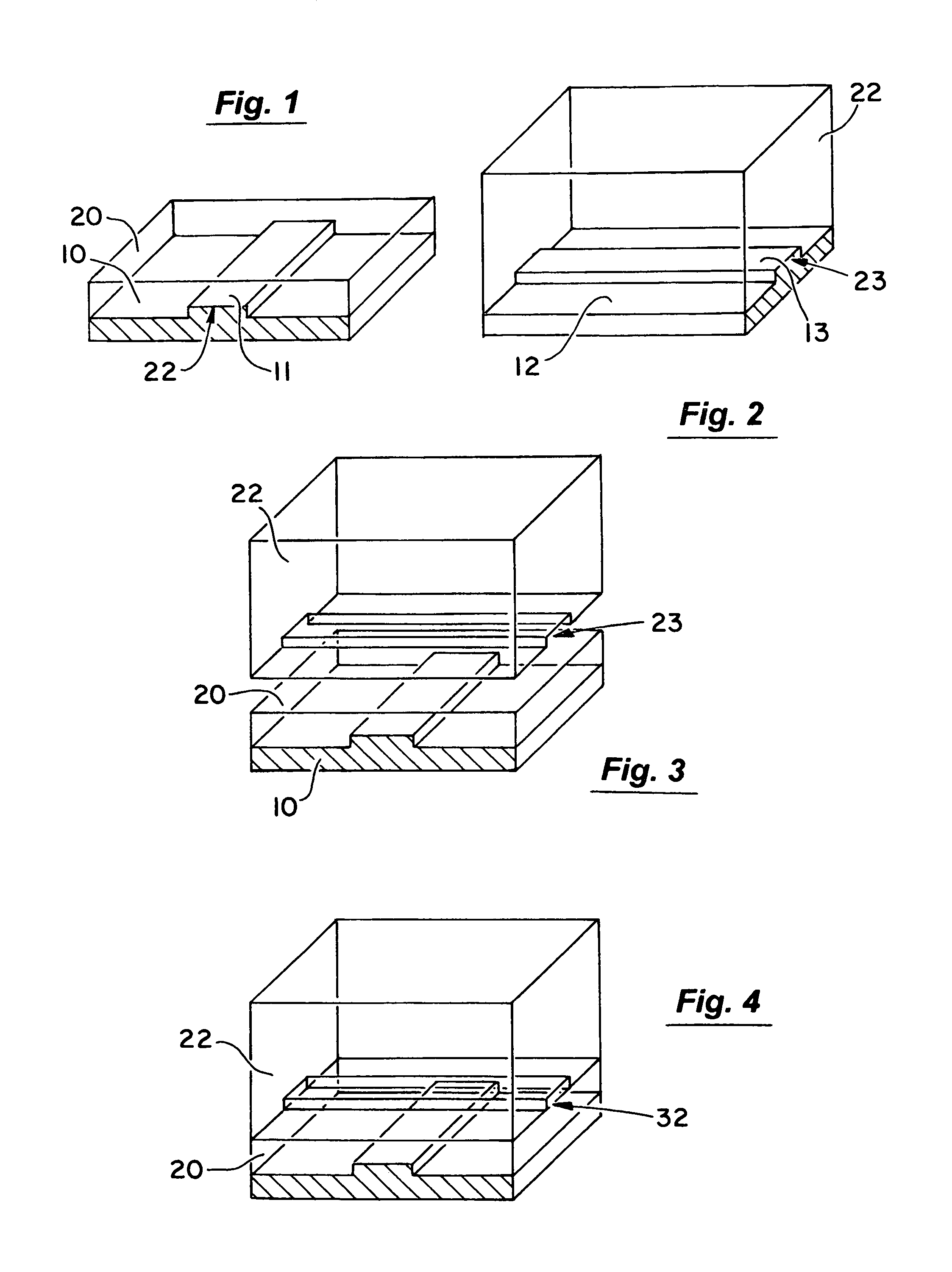

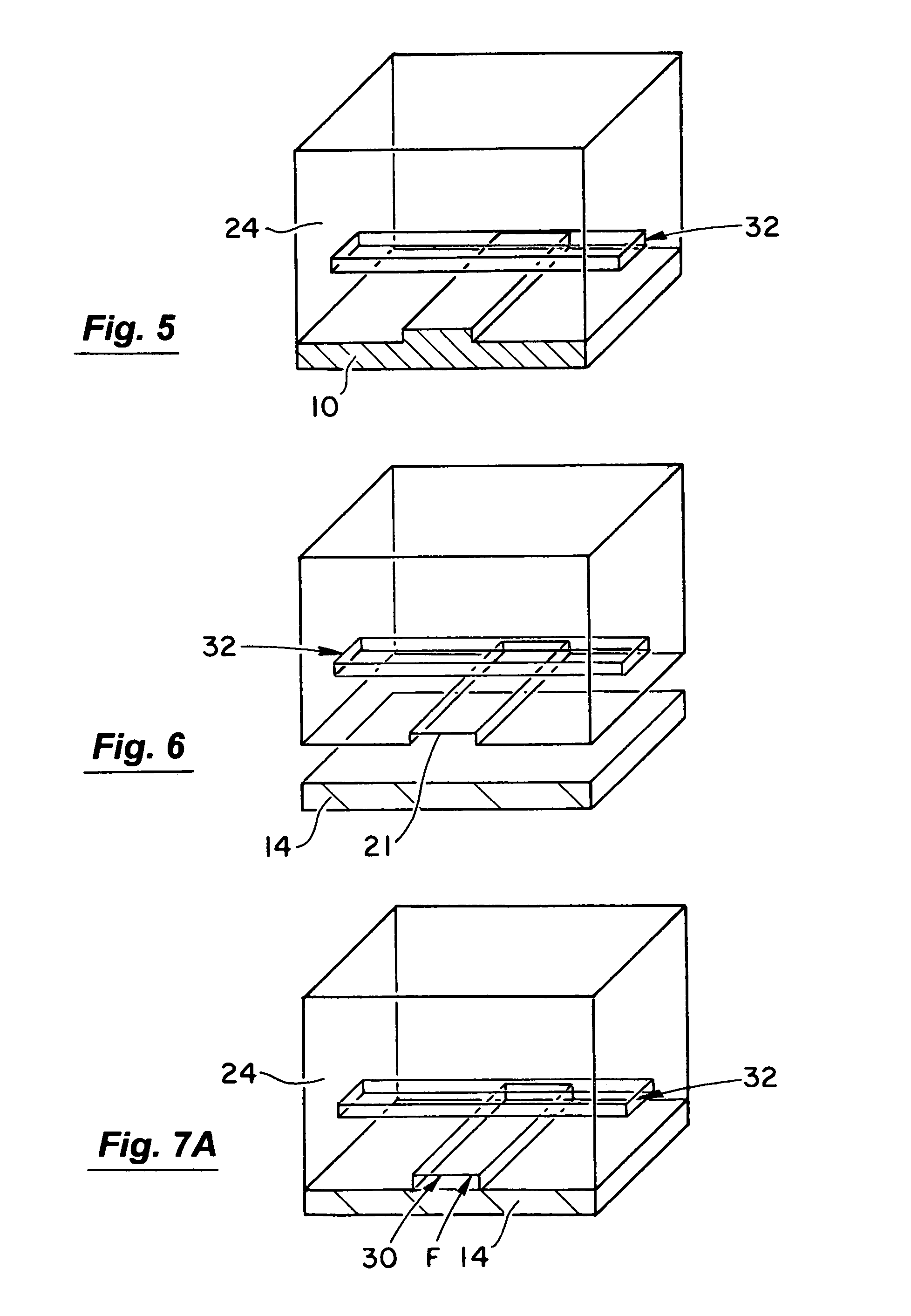

ActiveUS7143785B2Easy to handleDiaphragm valvesOperating means/releasing devices for valvesHigh densityRandom access memory

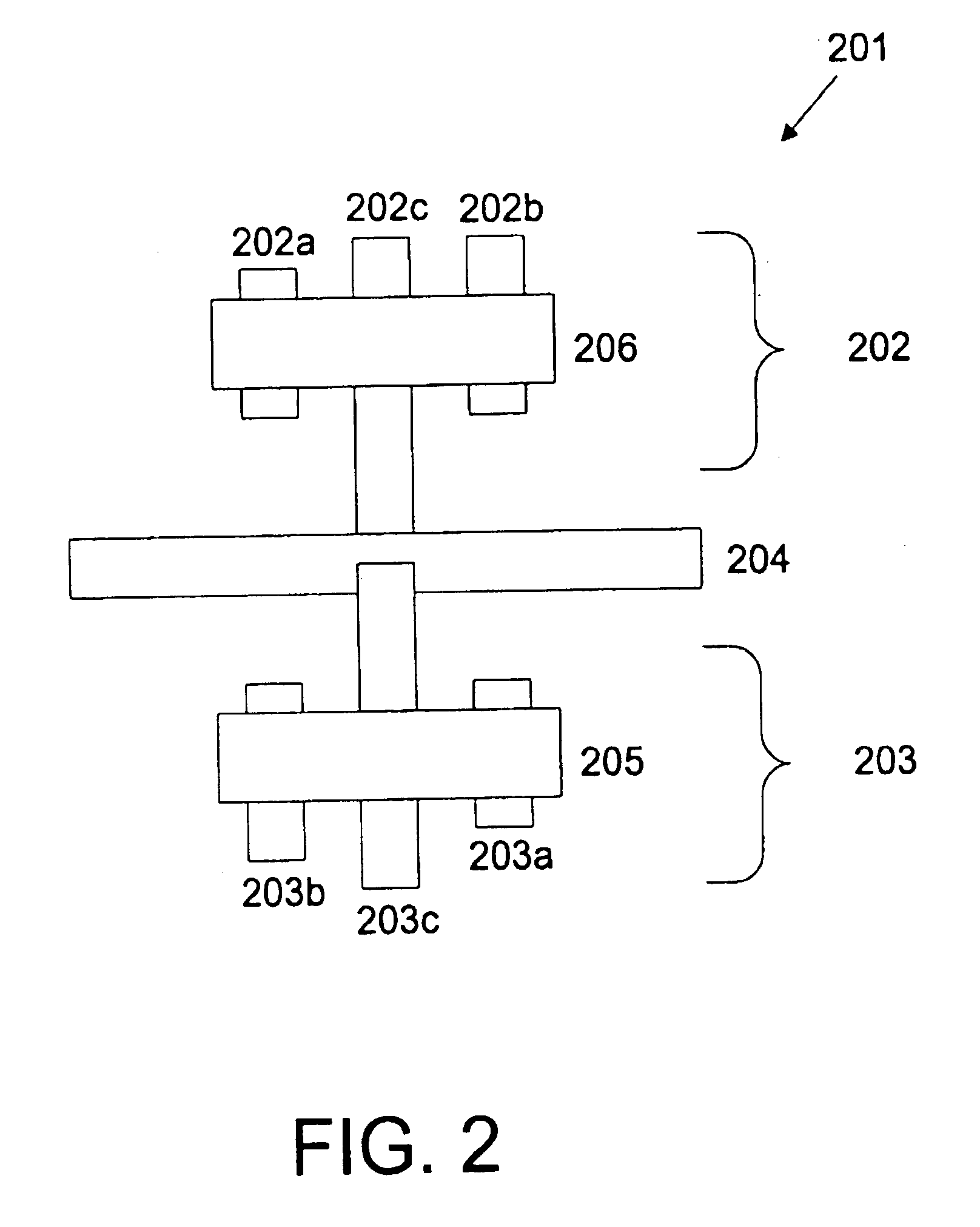

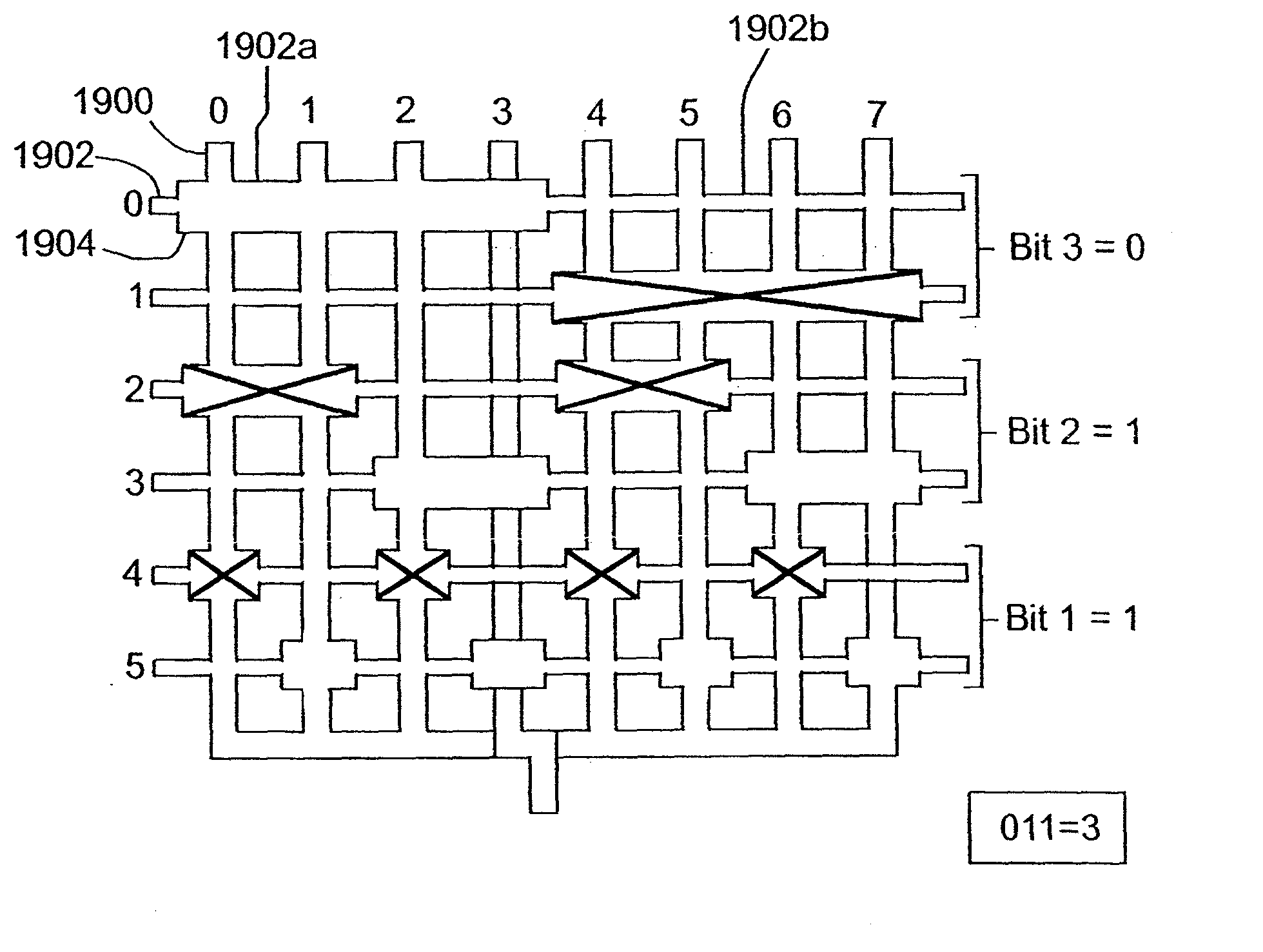

High-density microfluidic chips contain plumbing networks with thousands of micromechanical valves and hundreds of individually addressable chambers. These fluidic devices are analogous to electronic integrated circuits fabricated using large scale integration (LSI). A component of these networks is the fluidic multiplexor, which is a combinatorial array of binary valve patterns that exponentially increases the processing power of a network by allowing complex fluid manipulations with a minimal number of inputs. These integrated microfluidic networks can be used to construct a variety of highly complex microfluidic devices, for example the microfluidic analog of a comparator array, and a microfluidic memory storage device resembling electronic random access memories.

Owner:MOTOROLA INC +1

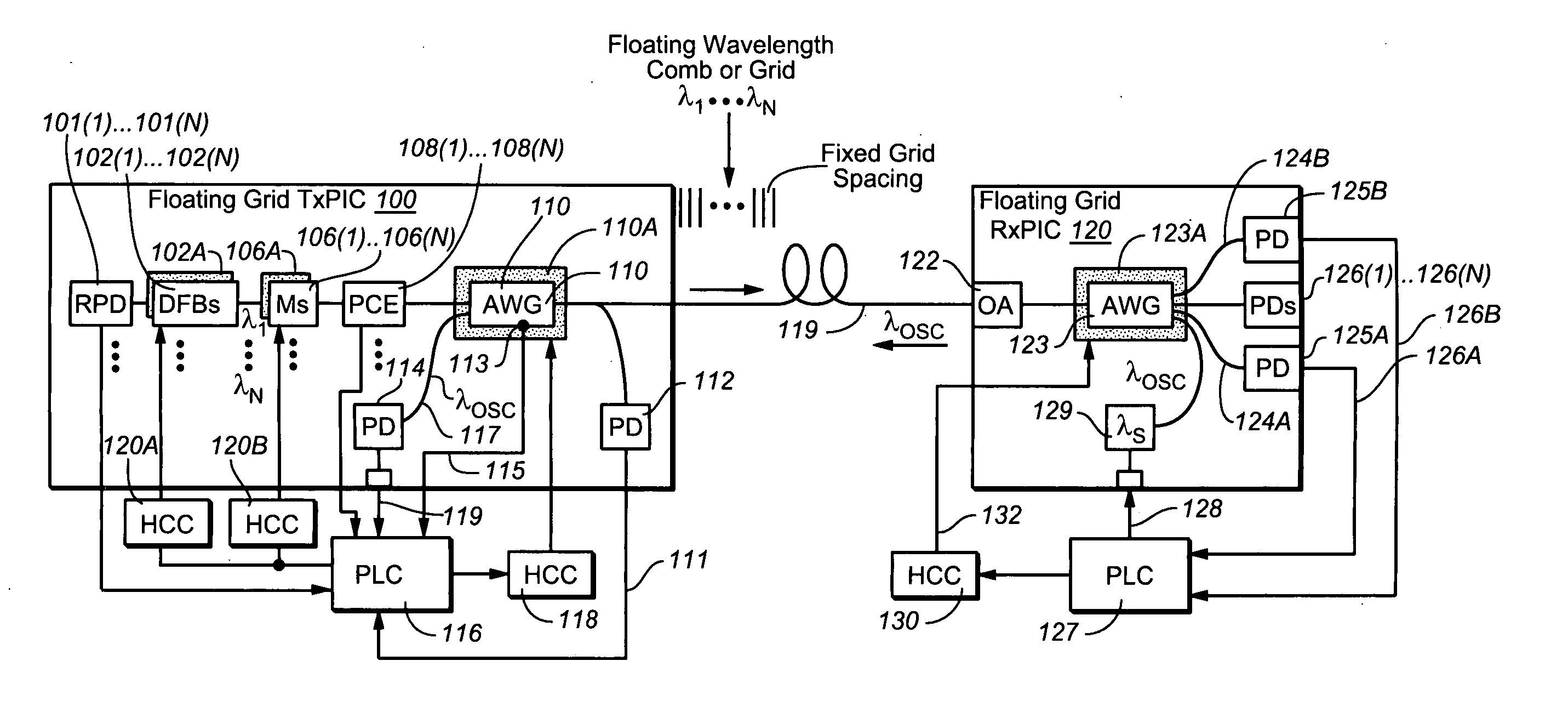

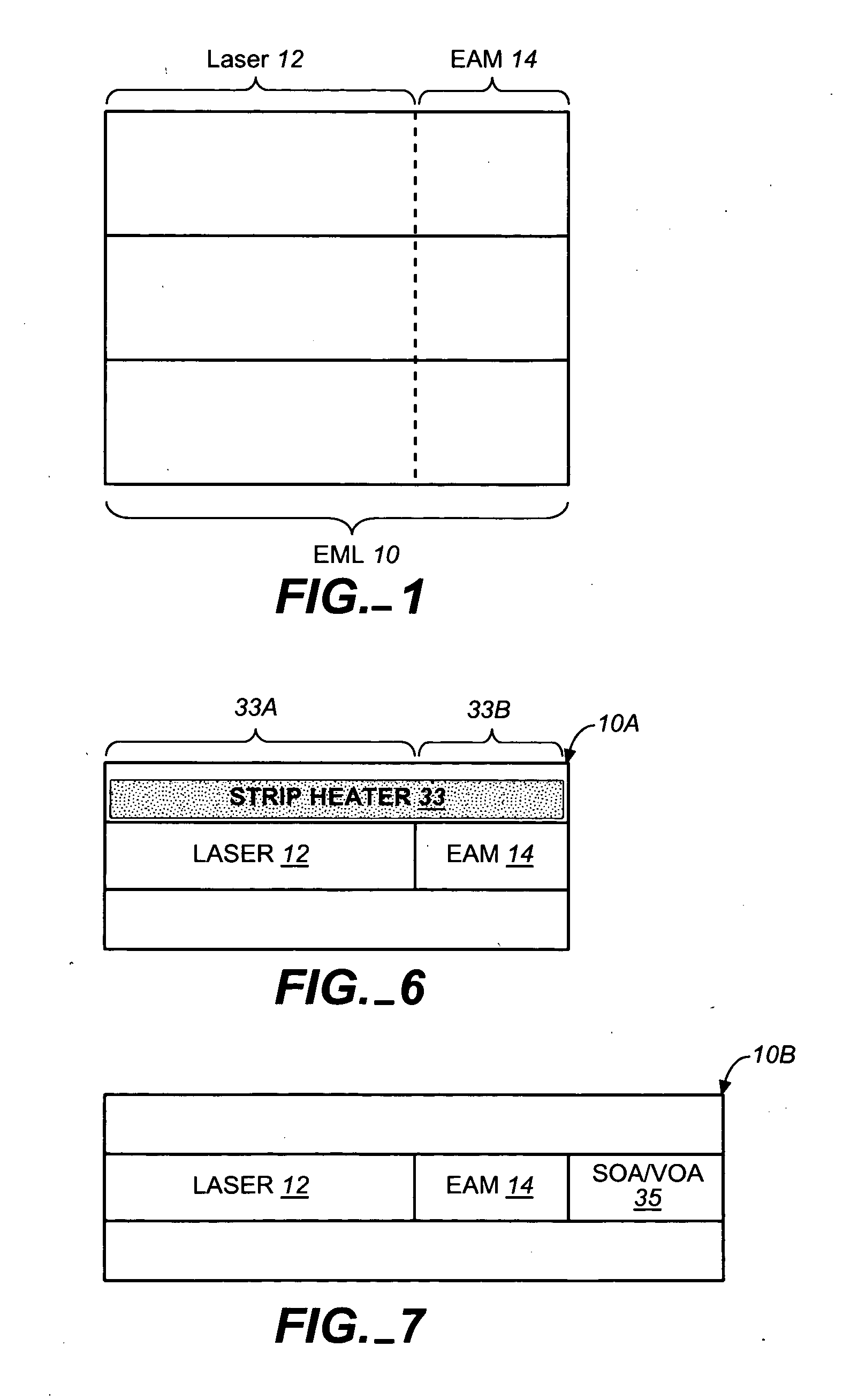

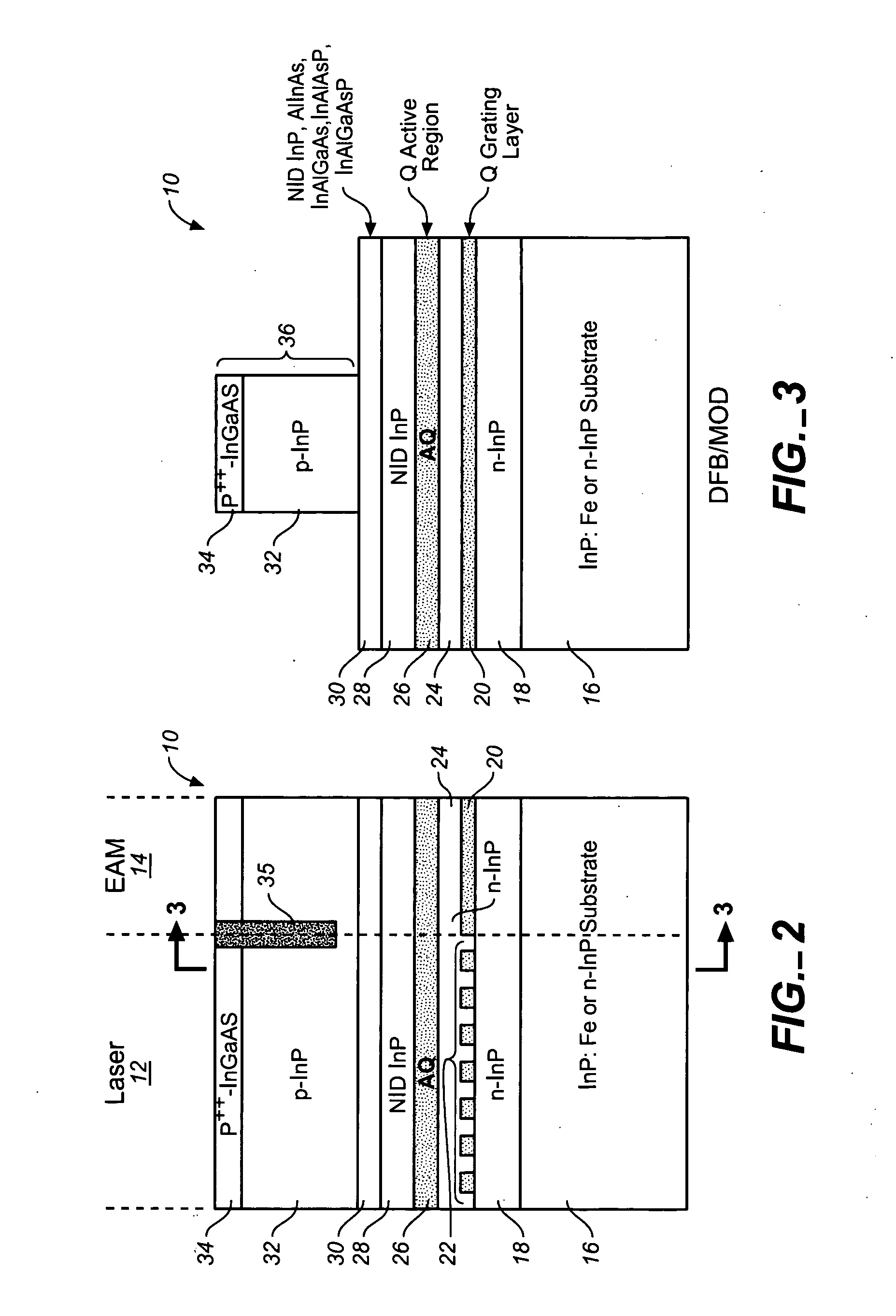

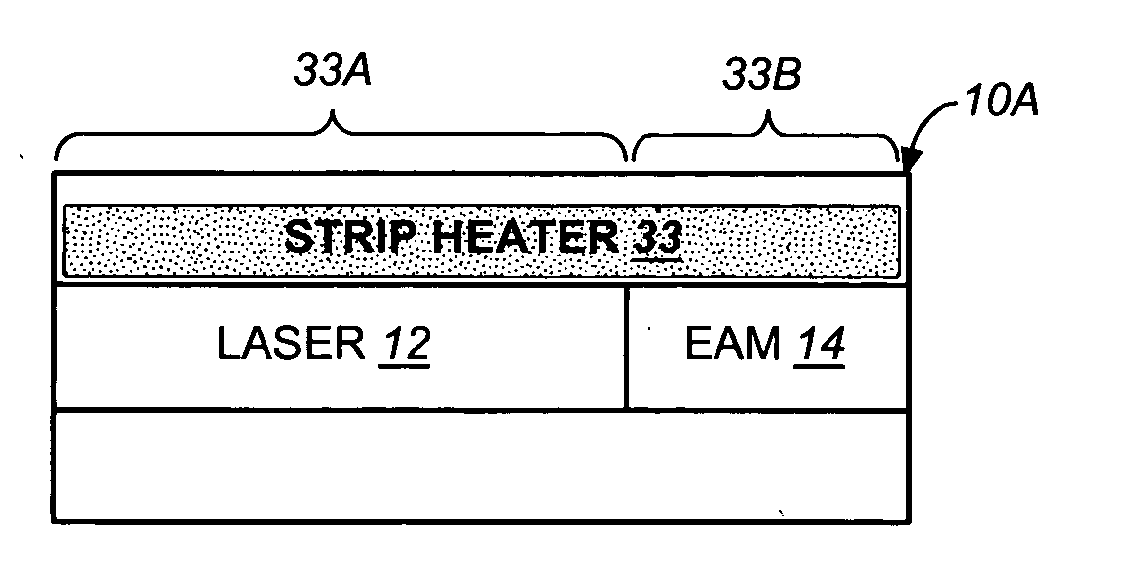

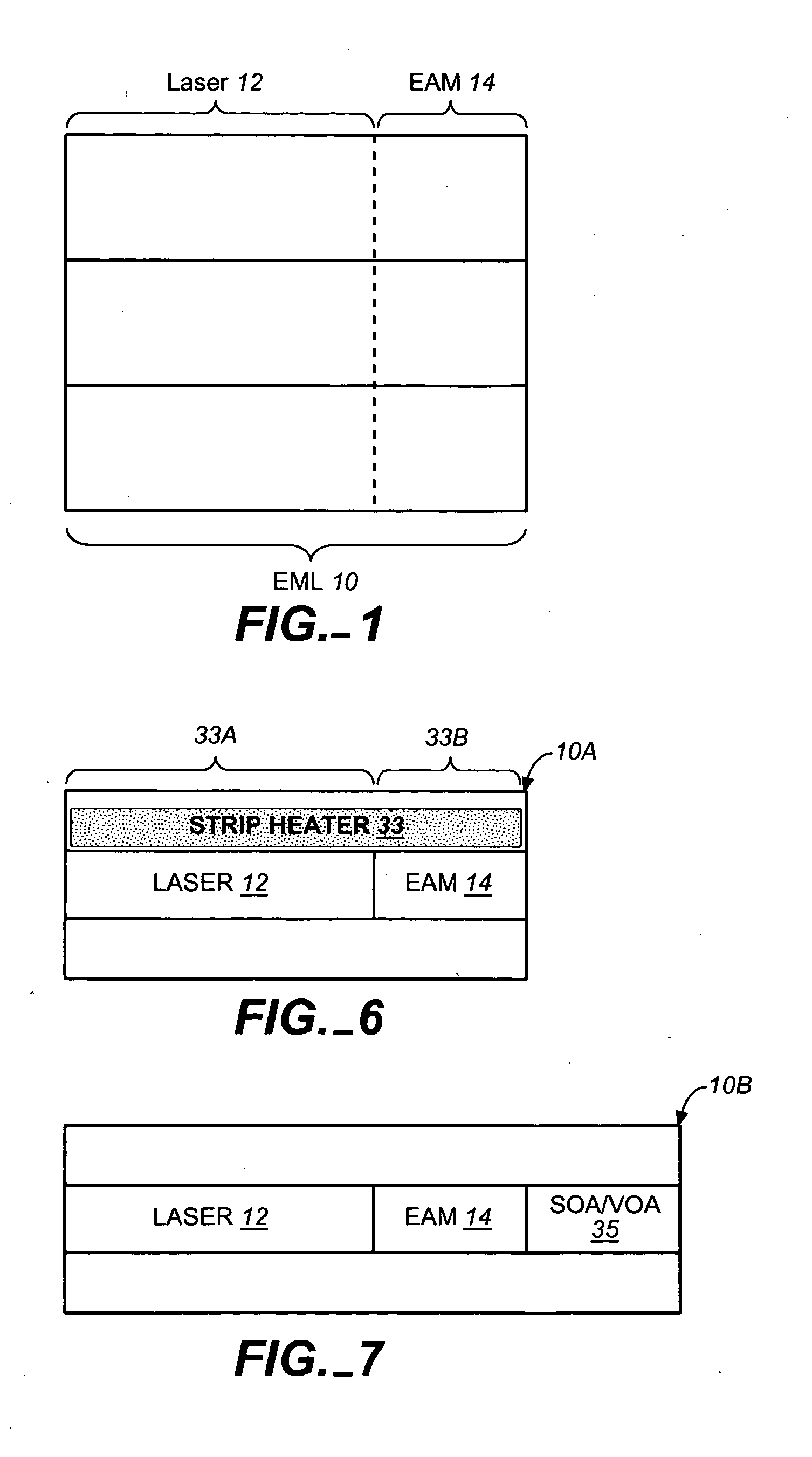

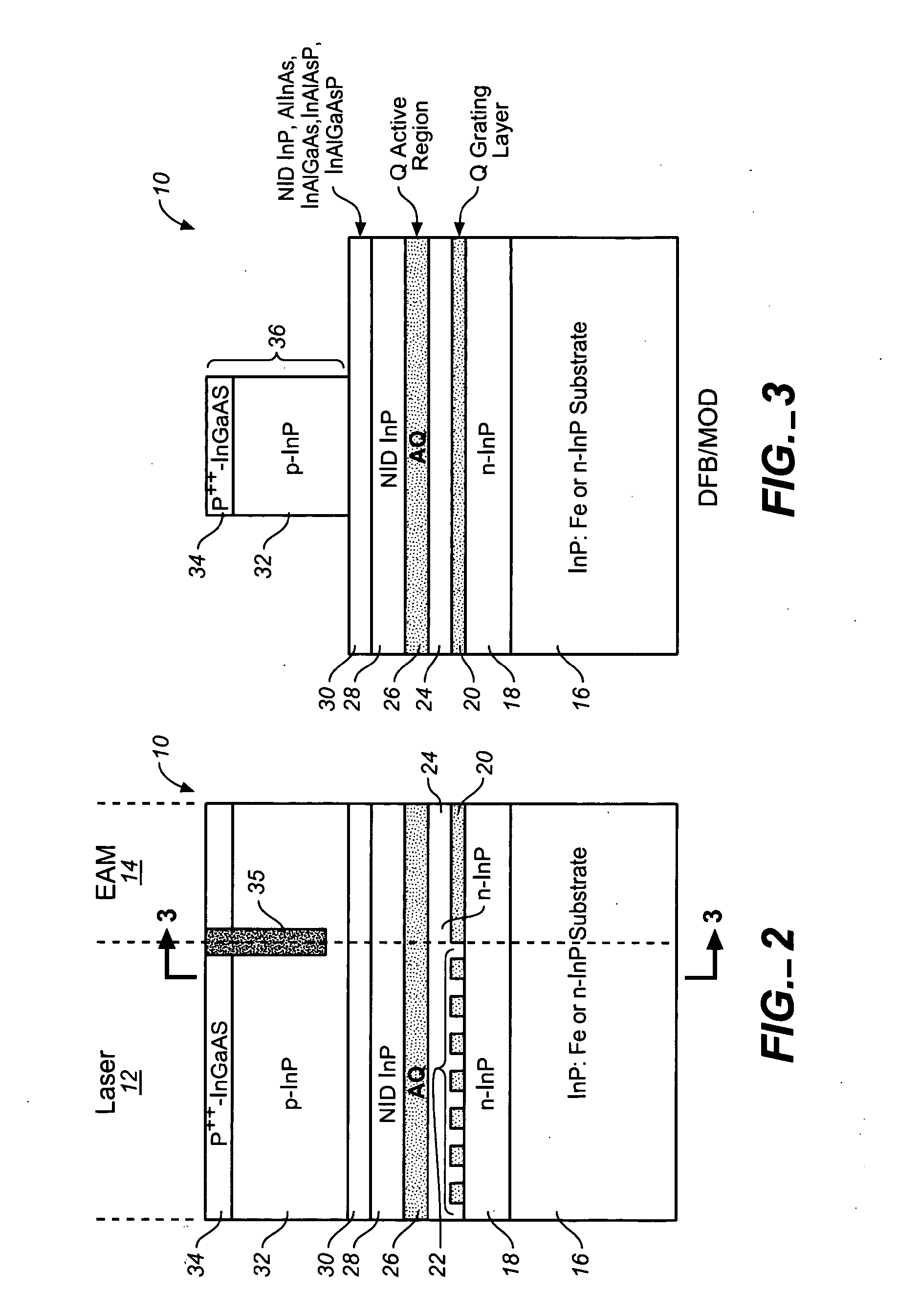

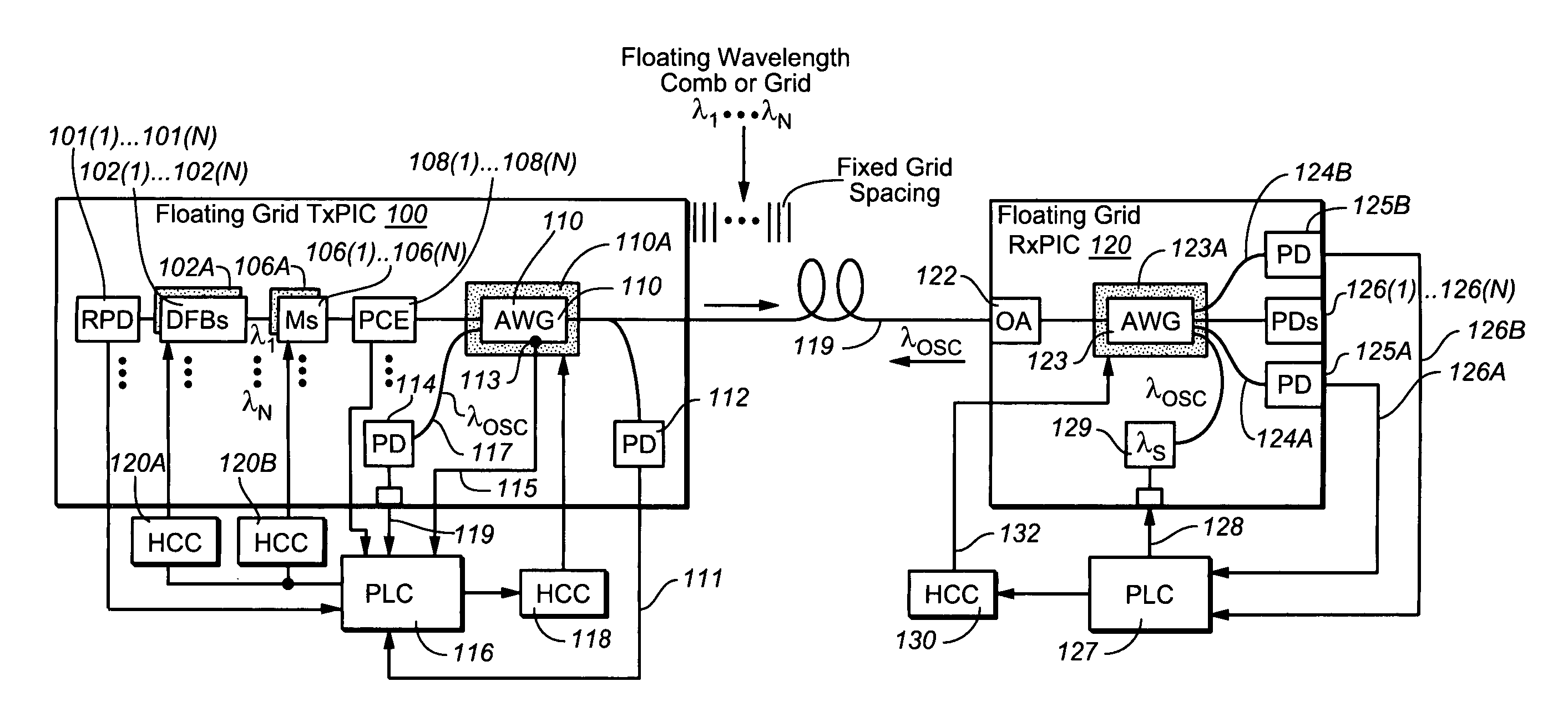

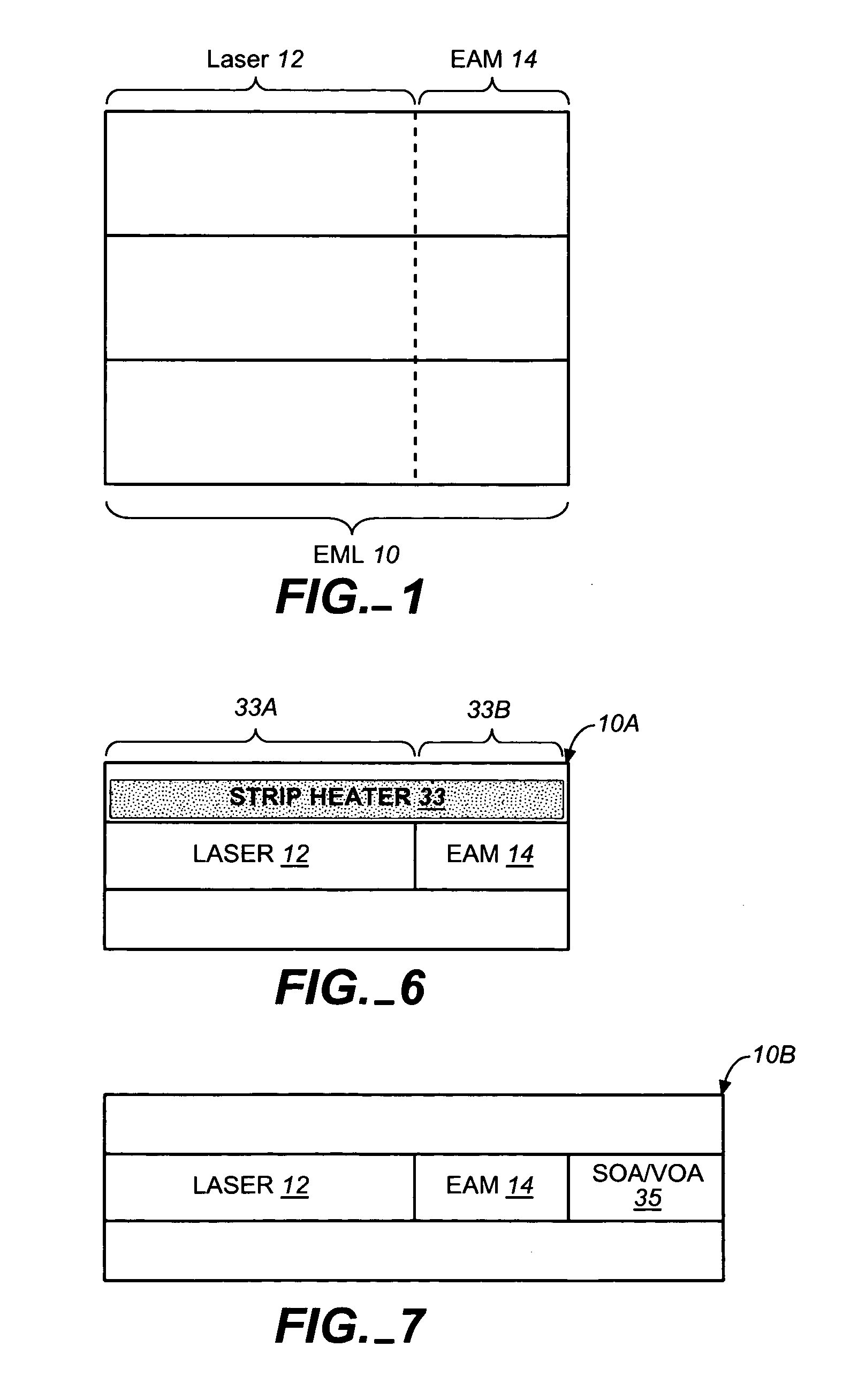

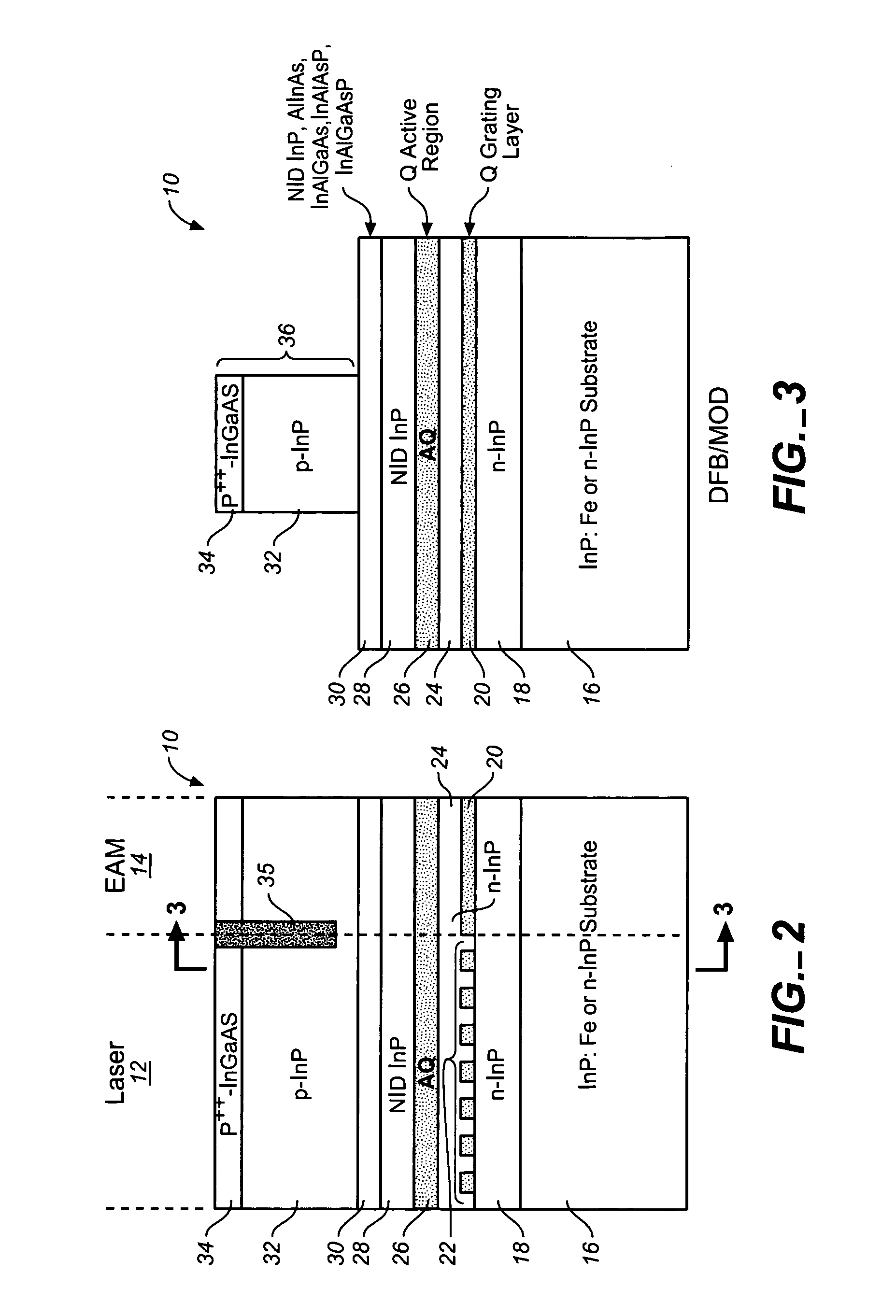

Coolerless photonic integrated circuits (PICs) for WDM transmission networks and PICs operable with a floating signal channel grid changing with temperature but with fixed channel spacing in the floating grid

ActiveUS20050249509A1Requirements for a hermetically sealed package are substantially relievedEasy to controlLaser optical resonator constructionSemiconductor laser arrangementsElectro-absorption modulatorHermetic packaging

A coolerless photonic integrated circuit (PIC), such as a semiconductor electro-absorption modulator / laser (EML) or a coolerless optical transmitter photonic integrated circuit (TxPIC), may be operated over a wide temperature range at temperatures higher then room temperature without the need for ambient cooling or hermetic packaging. Since there is large scale integration of N optical transmission signal WDM channels on a TxPIC chip, a new DWDM system approach with novel sensing schemes and adaptive algorithms provides intelligent control of the PIC to optimize its performance and to allow optical transmitter and receiver modules in DWDM systems to operate uncooled. Moreover, the wavelength grid of the on-chip channel laser sources may thermally float within a WDM wavelength band where the individual emission wavelengths of the laser sources are not fixed to wavelength peaks along a standardized wavelength grid but rather may move about with changes in ambient temperature. However, control is maintained such that the channel spectral spacing between channels across multiple signal channels, whether such spacing is periodic or aperiodic, between adjacent laser sources in the thermally floating wavelength grid are maintained in a fixed relationship. Means are then provided at an optical receiver to discover and lock onto floating wavelength grid of transmitted WDM signals and thereafter demultiplex the transmitted WDM signals for OE conversion.

Owner:INFINERA CORP

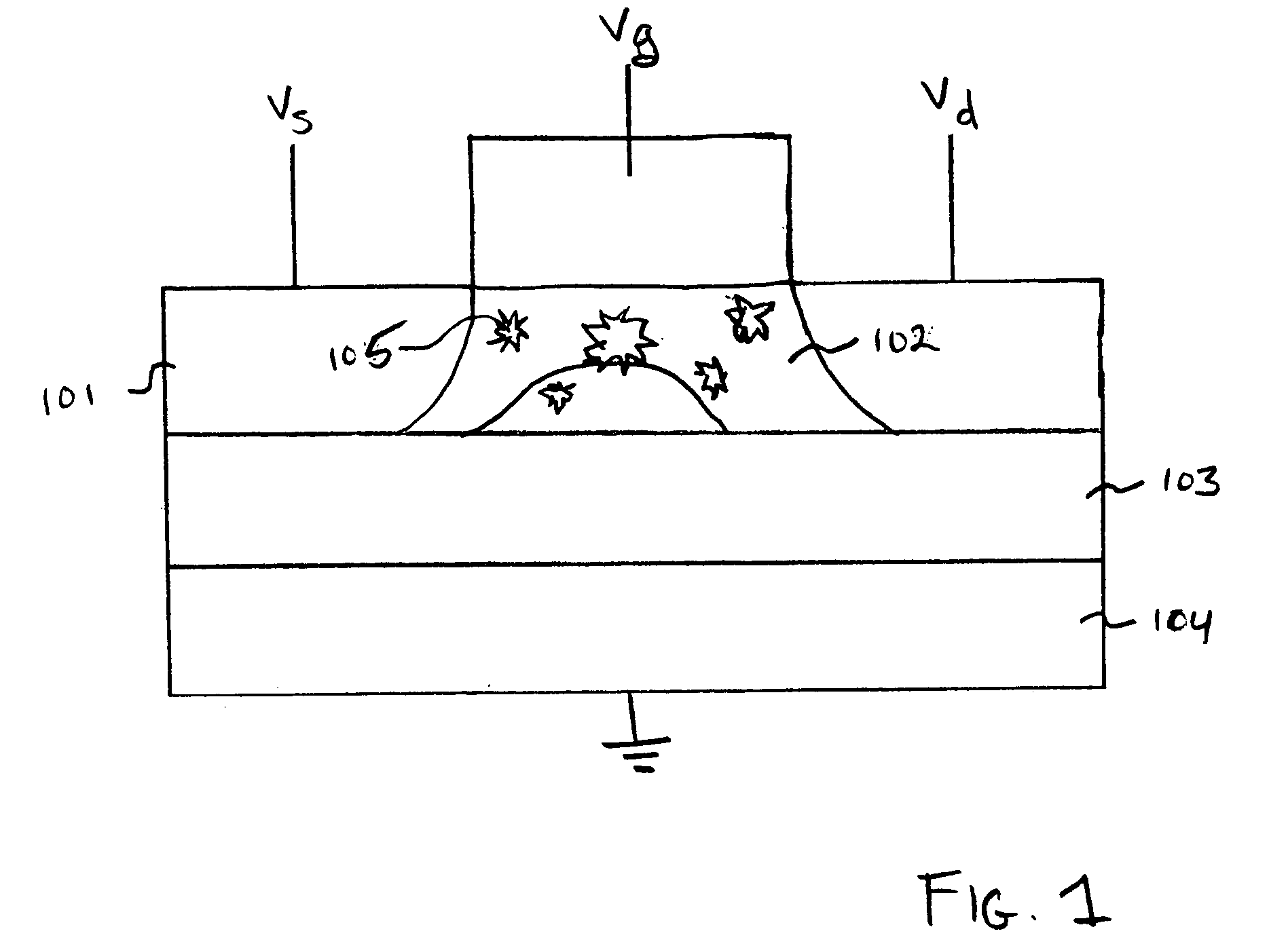

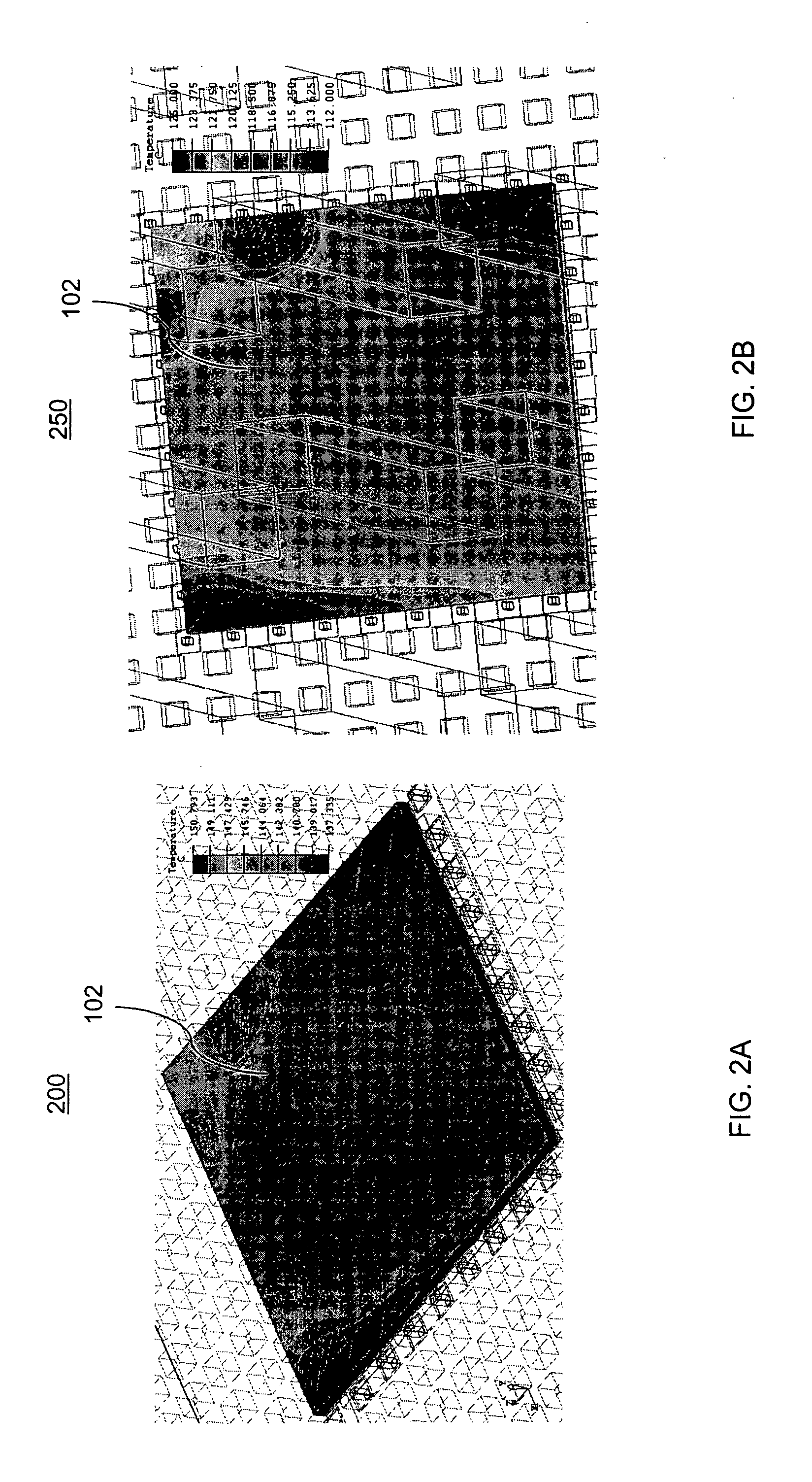

Temperature sensor for high power very large scale integration circuits

ActiveUS7176508B2Improve thermal model-to-hardware correlationSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsElectrical resistance and conductanceEngineering

Disclosed is a temperature sensor for an integrated circuit having at least one field effect transistor (FET) having a polysilicon gate, in which a current and a voltage is supplied to the polysilicon gate, changes in the current and the voltage of the polysilicon gate are monitored, wherein the polysilicon gate of the at least one FET is electrically isolated from other components of the integrated circuit, and the changes in the current or voltage are used to calculate a change in resistance of the polysilicon gate, and the change in resistance of the polysilicon gate is used to calculate a temperature change within the integrated circuit.

Owner:GLOBALFOUNDRIES US INC

Microfluidic Large Scale Integration

InactiveUS20100154890A1Easy to handleMicrobiological testing/measurementCircuit elementsHigh densityRandom access memory

High-density microfluidic chips contain plumbing networks with thousands of micromechanical valves and hundreds of individually addressable chambers. These fluidic devices are analogous to electronic integrated circuits fabricated using large scale integration (LSI). A component of these networks is the fluidic multiplexor, which is a combinatorial array of binary valve patterns that exponentially increases the processing power of a network by allowing complex fluid manipulations with a minimal number of inputs. These integrated microfluidic networks can be used to construct a variety of highly complex microfluidic devices, for example the microfluidic analog of a comparator array, and a microfluidic memory storage device resembling electronic random access memories.

Owner:CALIFORNIA INST OF TECH

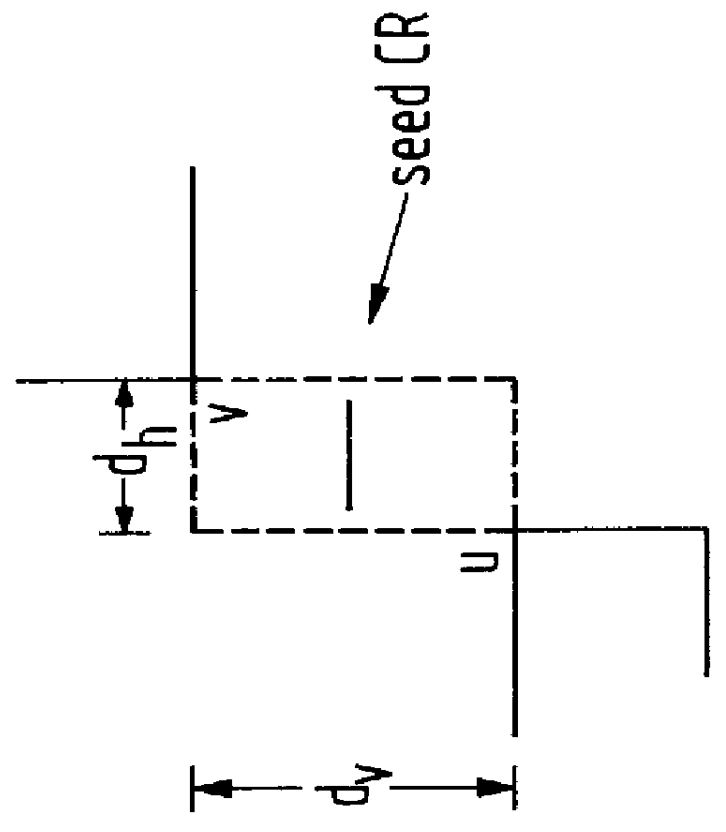

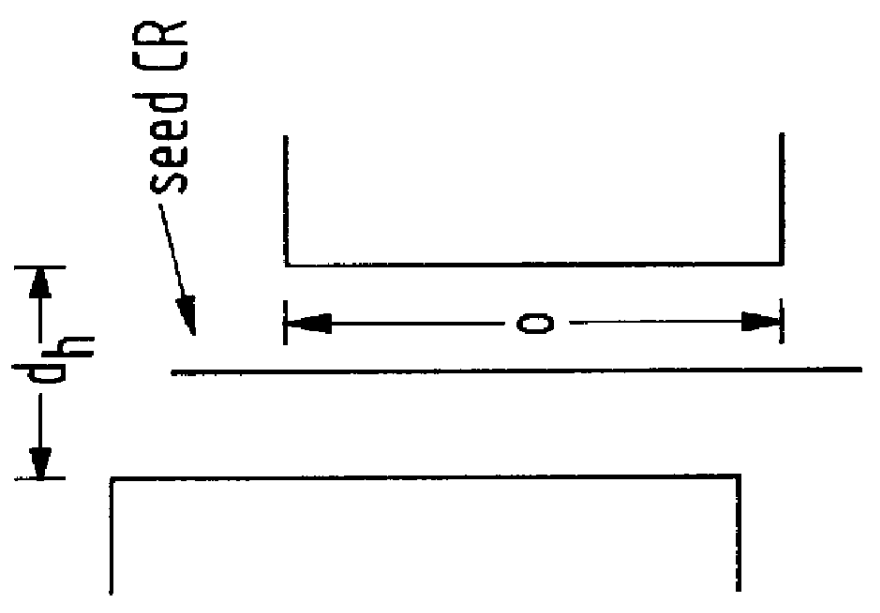

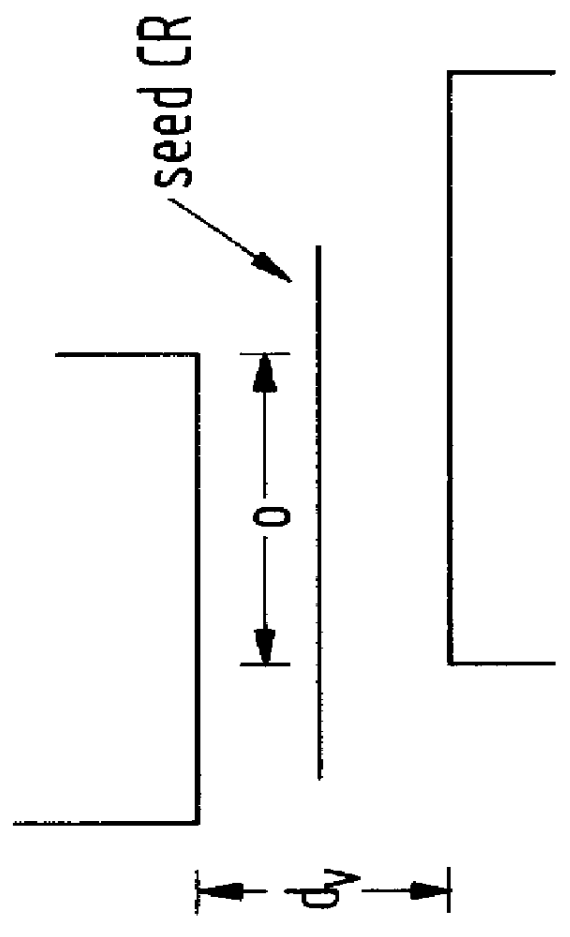

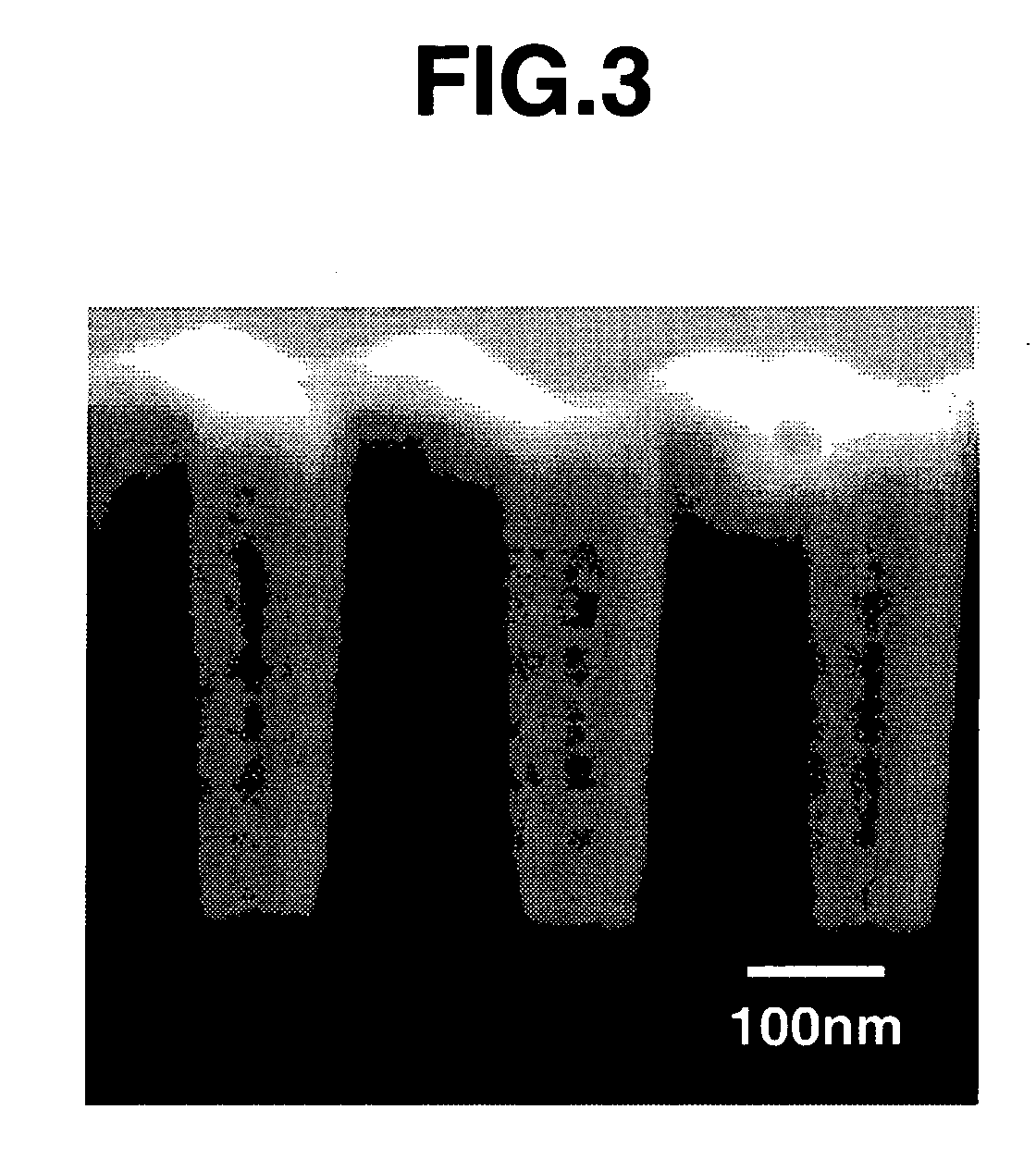

Methods for nanoscale structures from optical lithography and subsequent lateral growth

InactiveUS20070029643A1Reduce defect densityReduce dislocationMaterial nanotechnologyDecorative surface effectsLithographic artistPhotonics

Methods, and structures formed thereby, are disclosed for forming laterally grown structures with nanoscale dimensions from nanoscale arrays which can be patterned from nanoscale lithography. The structures and methods disclosed herein have applications with electronic, photonic, molecular electronic, spintronic, microfluidic or nano-mechanical (NEMS) technologies. The spacing between laterally grown structures can be a nanoscale measurement, for example with a spacing distance which can be approximately 1-50 nm, and more particularly can be from approximately 3-5 nm. This spacing is appropriate for integration of molecular electronic devices. The pitch between posts can be less than the average distance characteristic between dislocation defects for example in GaN (ρ=1010 / cm2→d=0.1 μm) resulting an overall reduction in defect density. Large-scale integration of nanoscale devices can be achieved using lithographic equipment that is orders of magnitude less expensive that that used for advanced lithographic techniques, such as electron beam lithography.

Owner:NORTH CAROLINA STATE UNIV

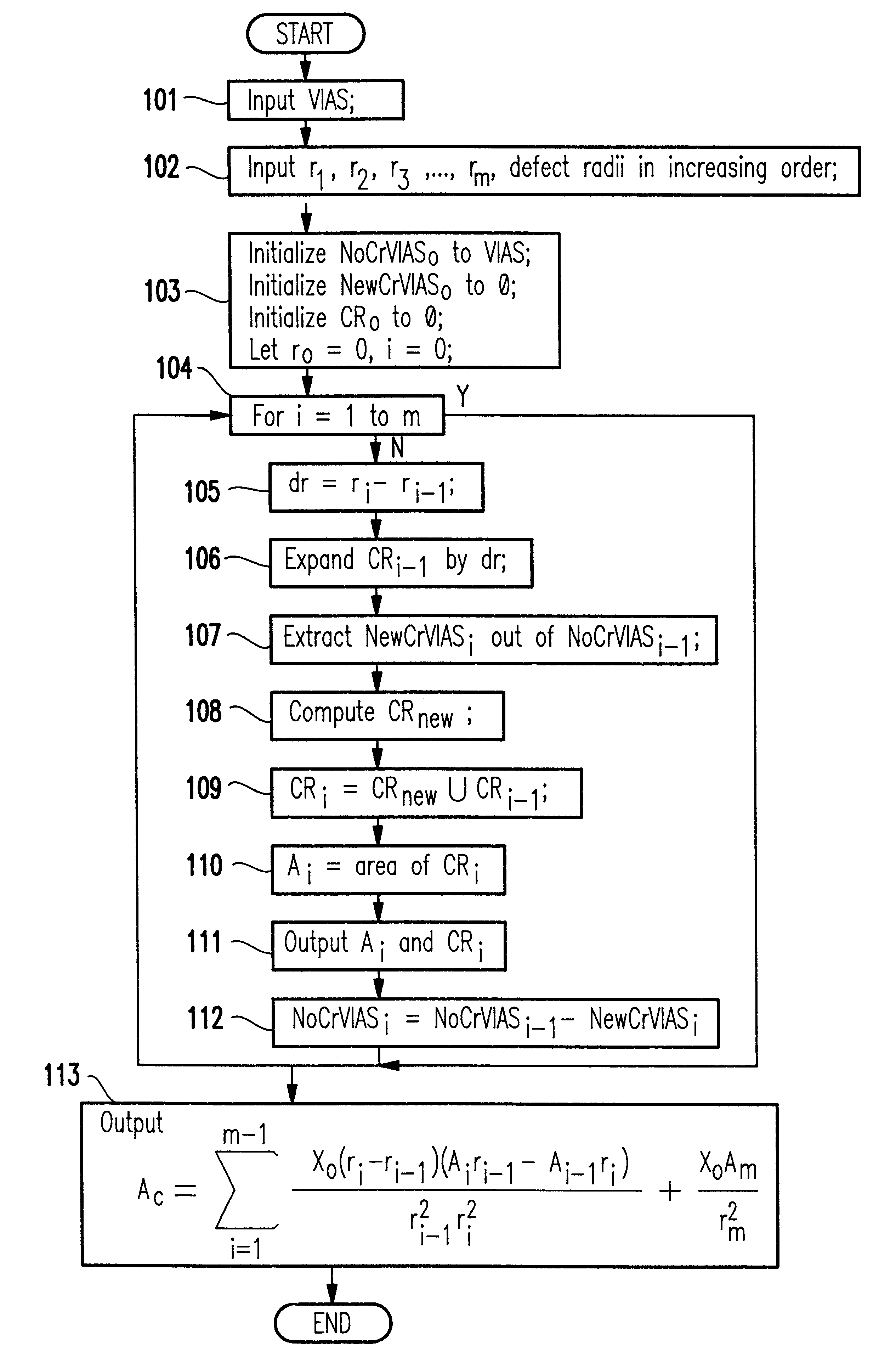

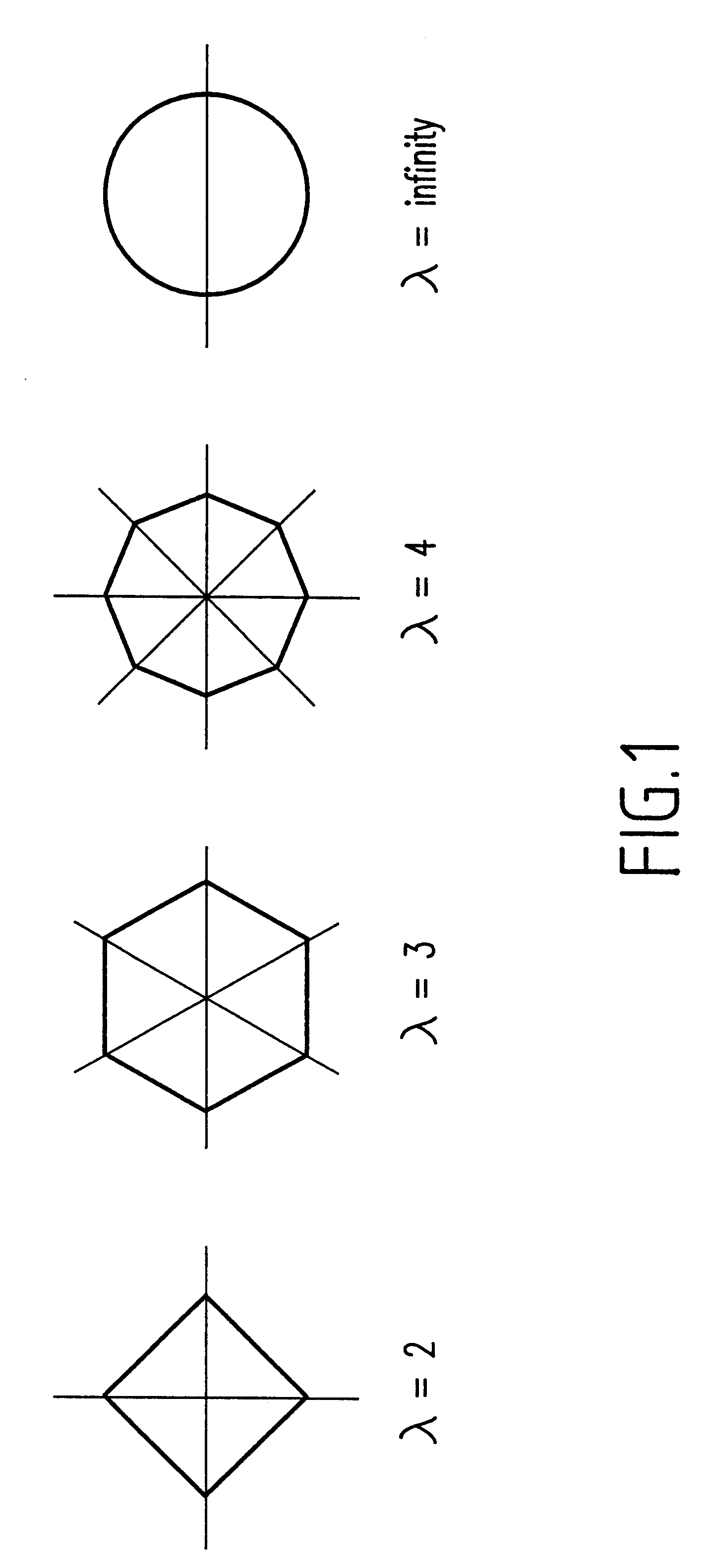

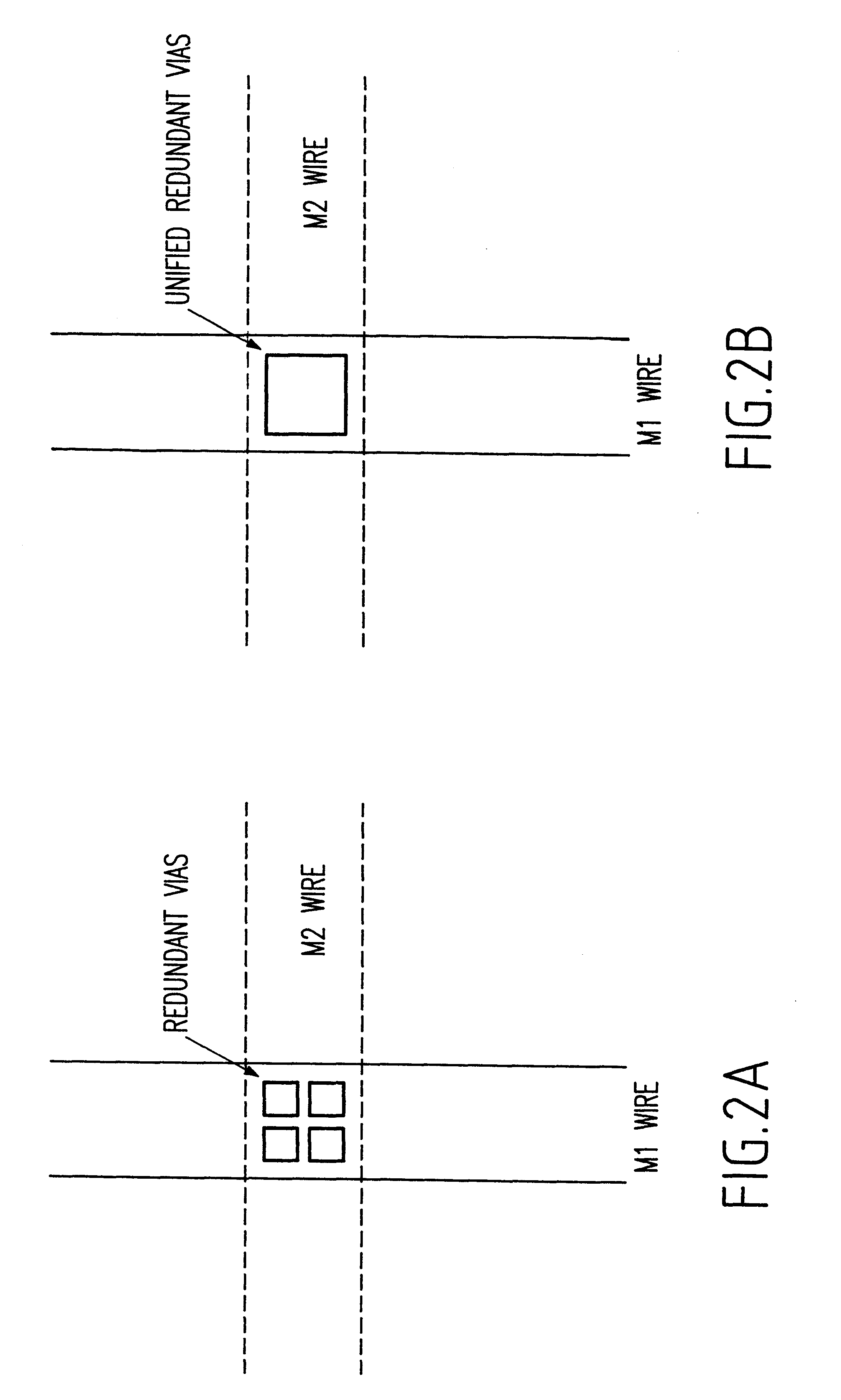

Incremental method for critical area and critical region computation of via blocks

InactiveUS6247853B1Reduce manufacturing costSemiconductor/solid-state device testing/measurementSpecial data processing applicationsData miningIncremental methods

An efficient computer implemented method computes critical area for via blocks in Very Large Scale Integrated (VLSI) circuits. The method is incremental and takes advantage of the hierarchy in the design. In order to increase the efficiency further we use the Linfin or the L1 metric instead of the Euclidean geometry.

Owner:GLOBALFOUNDRIES INC

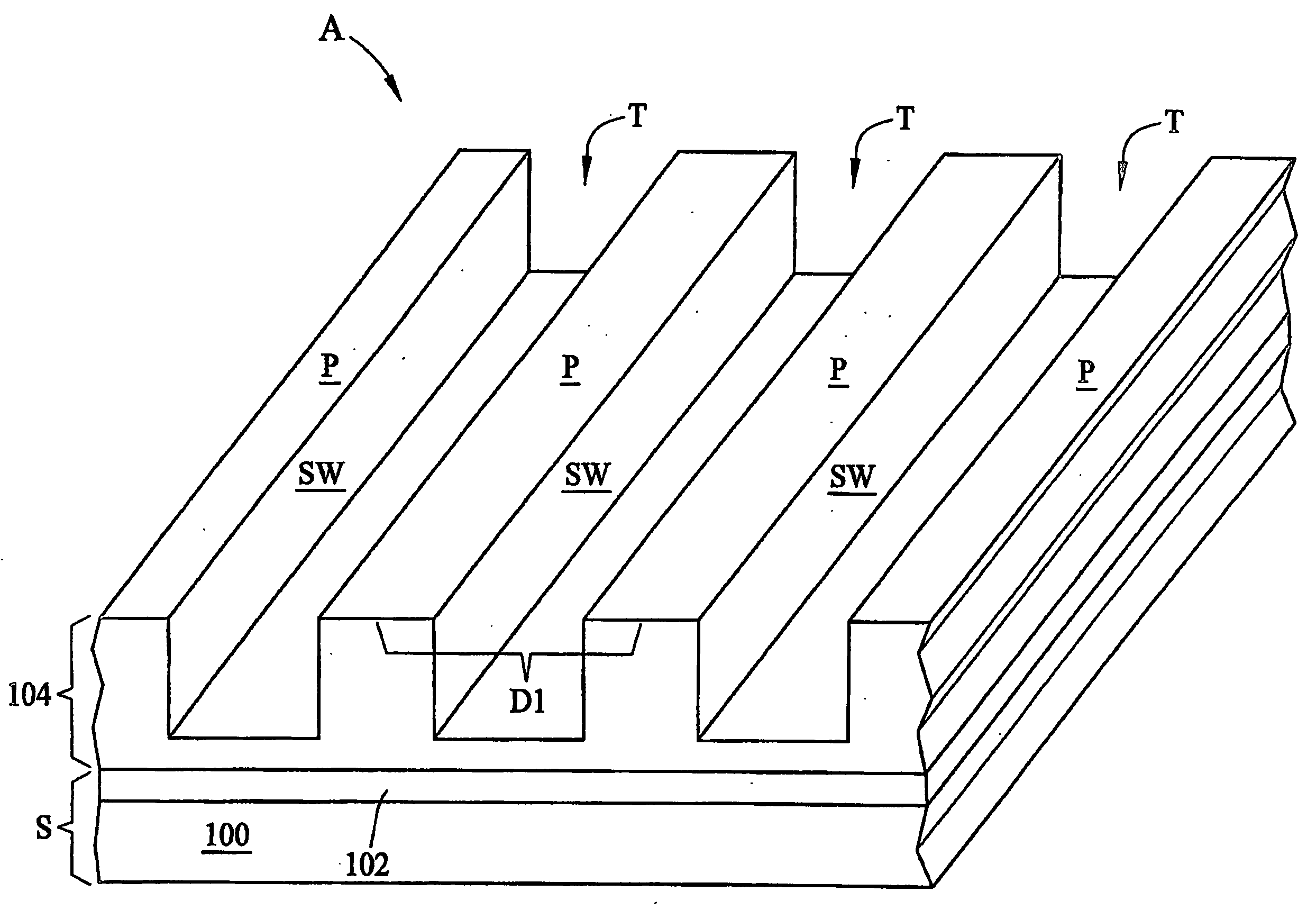

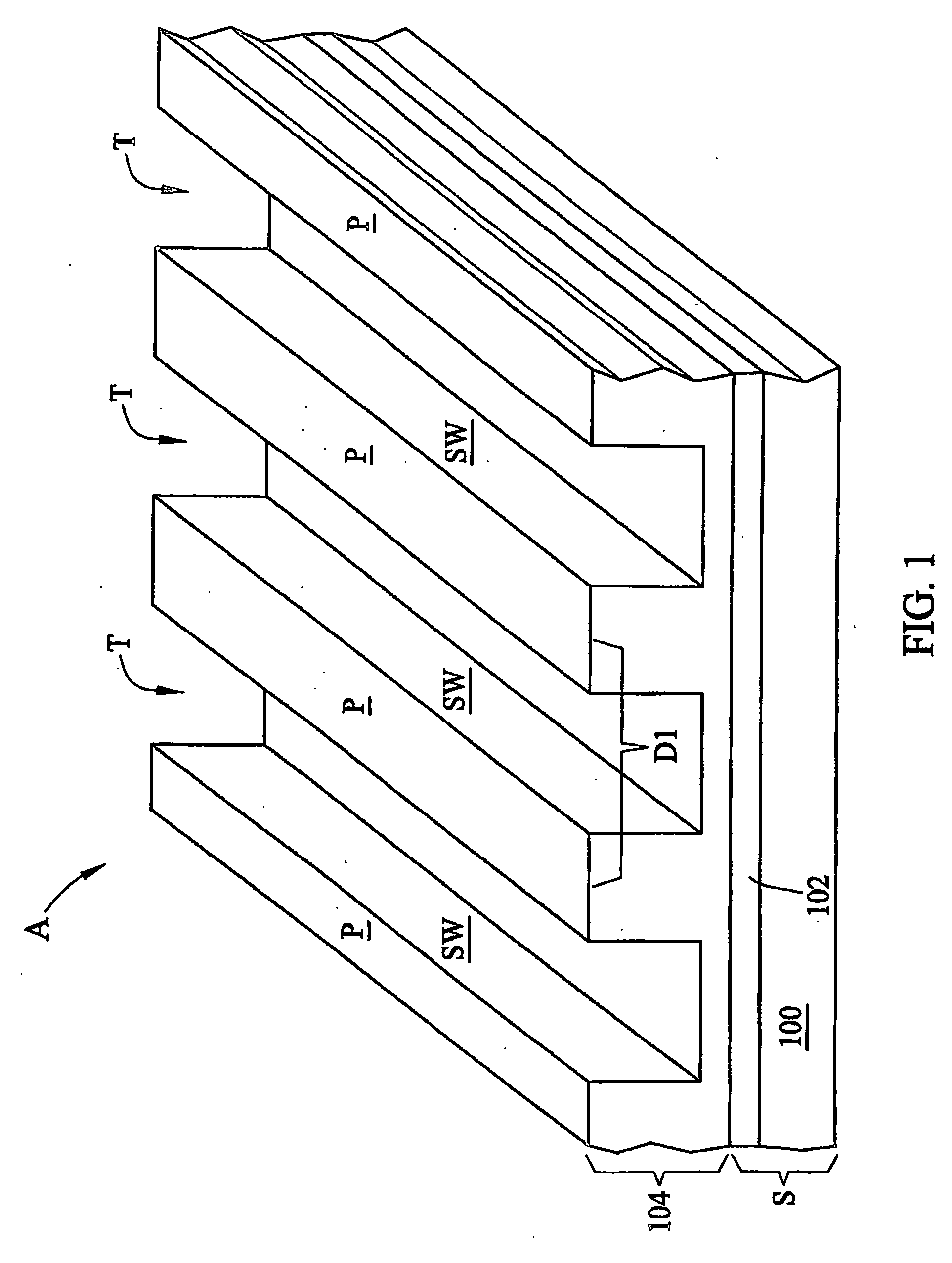

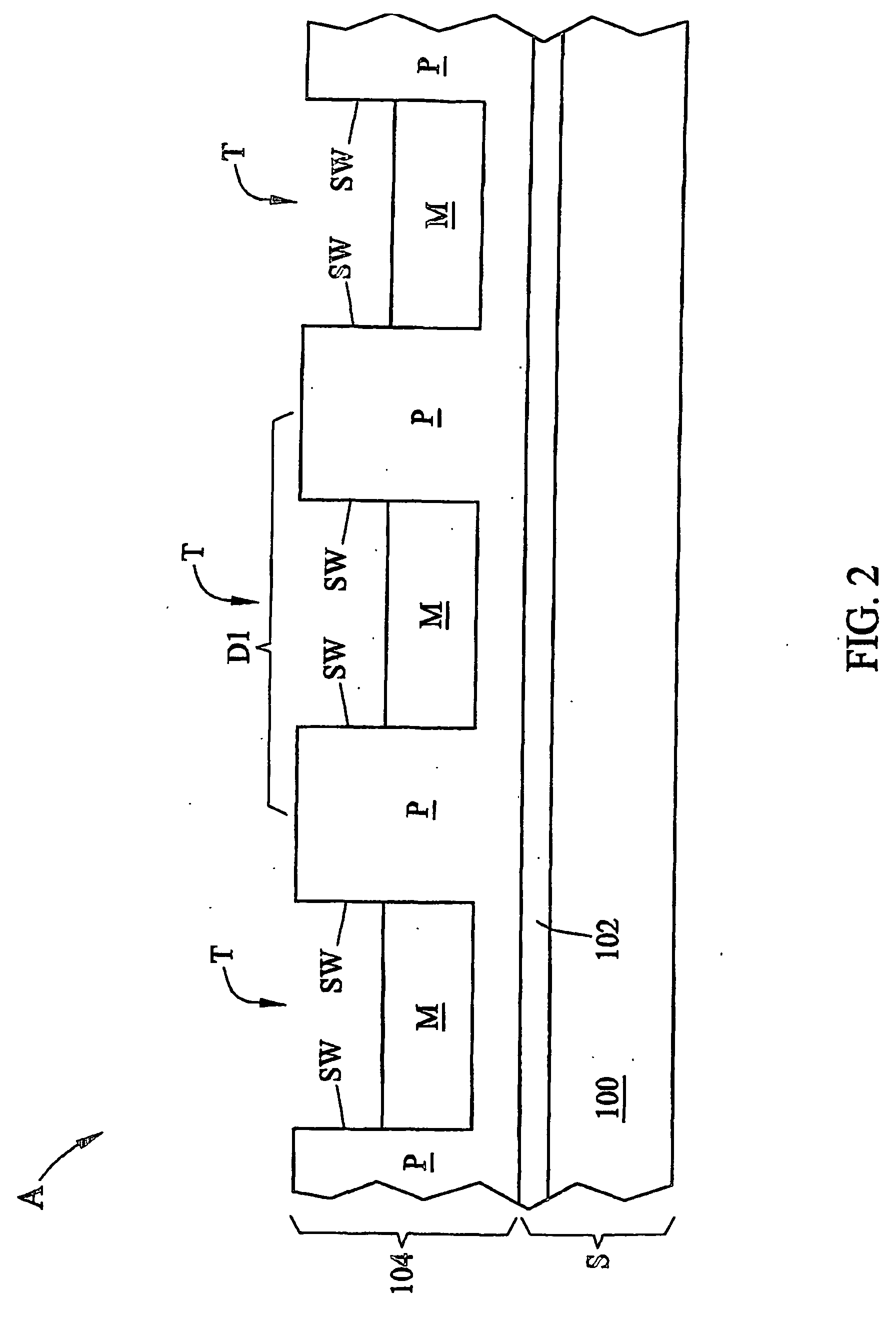

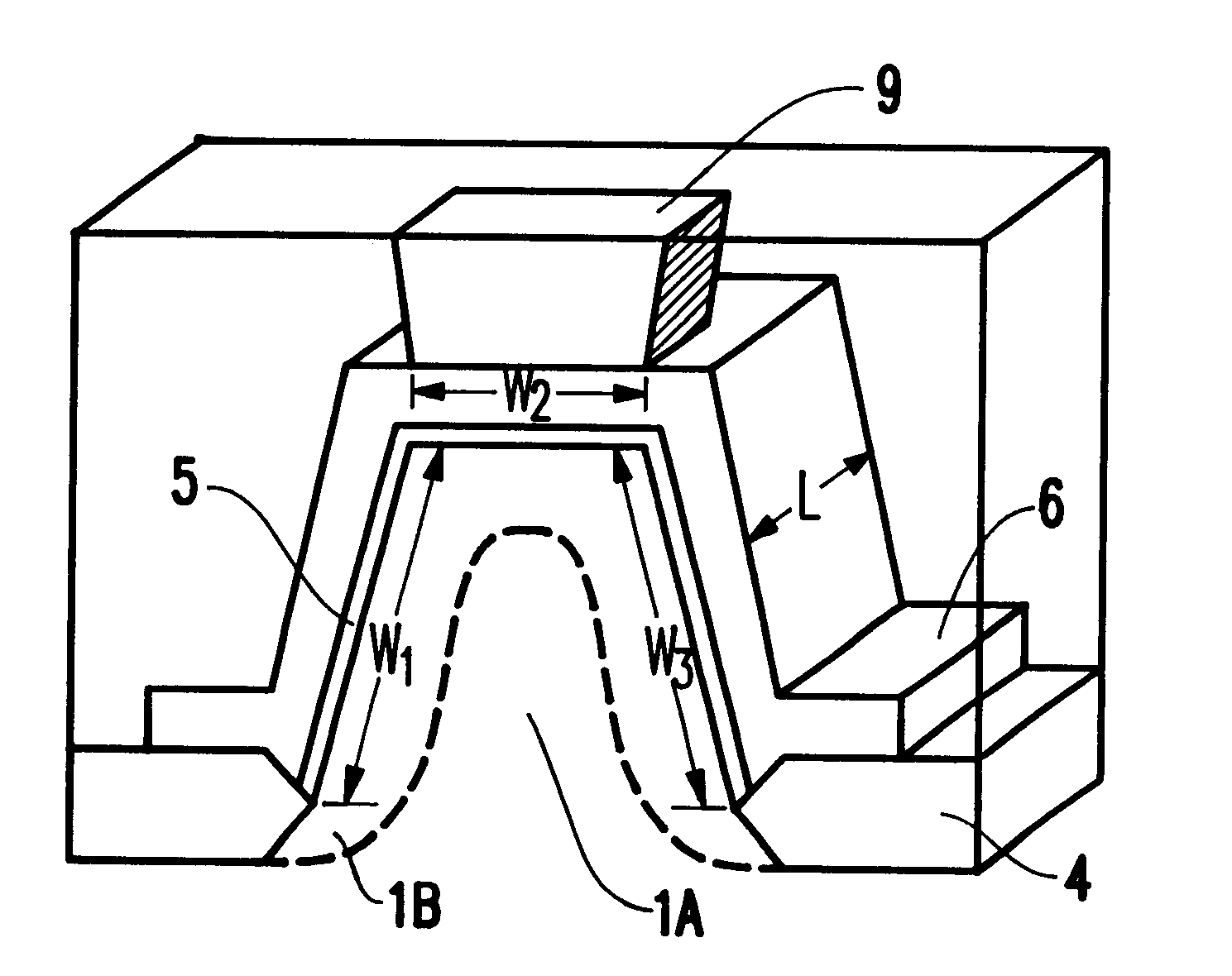

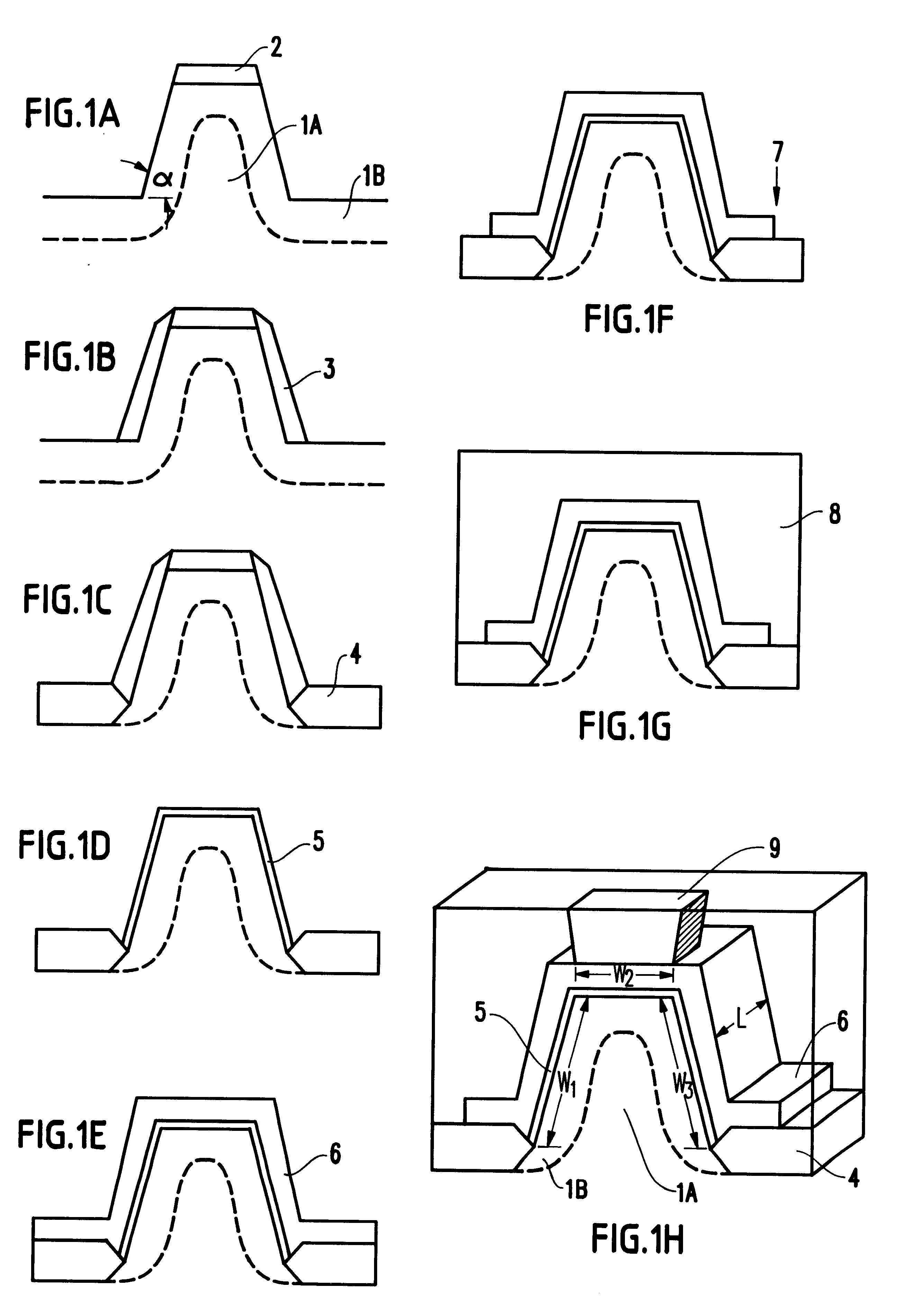

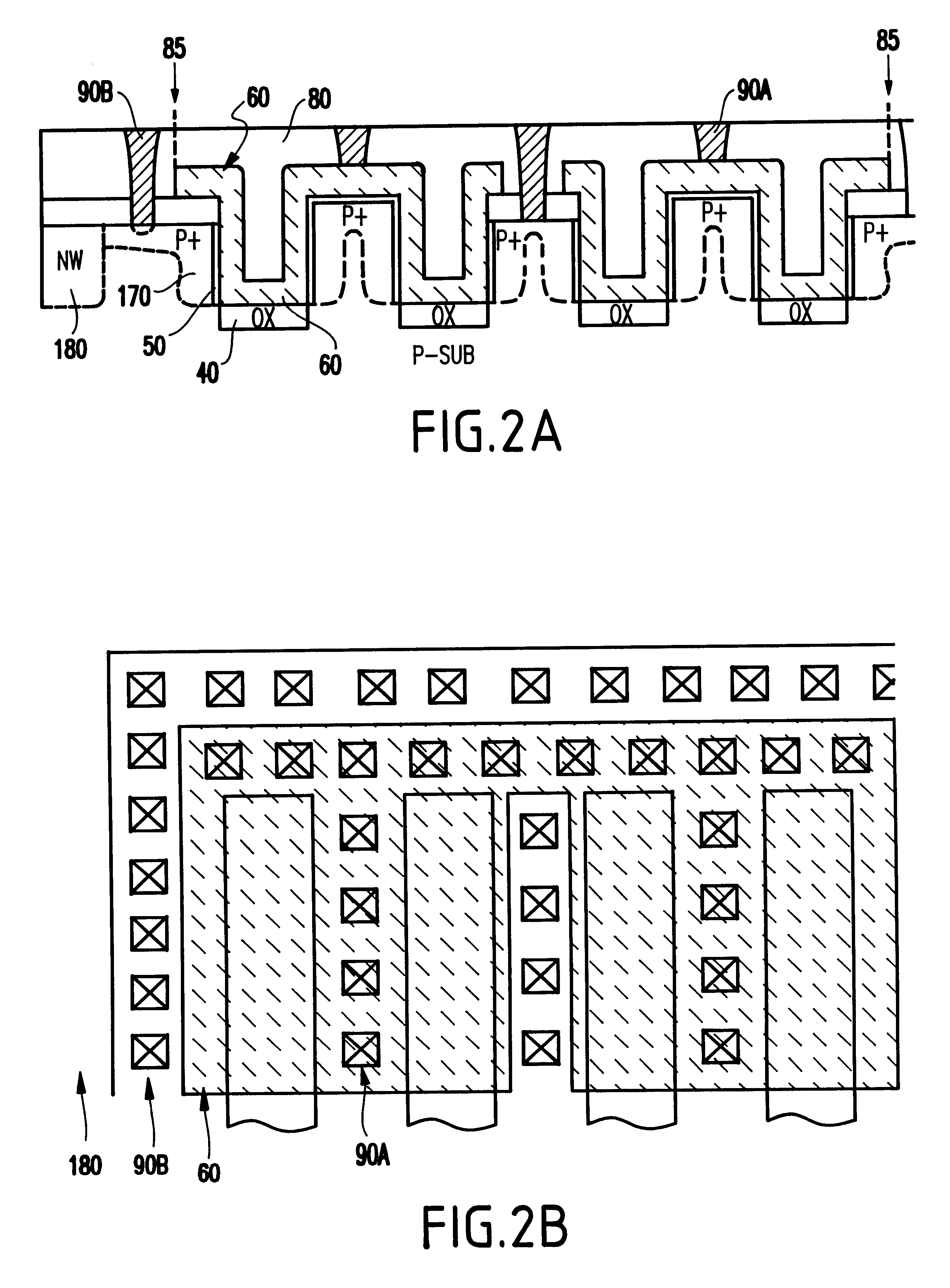

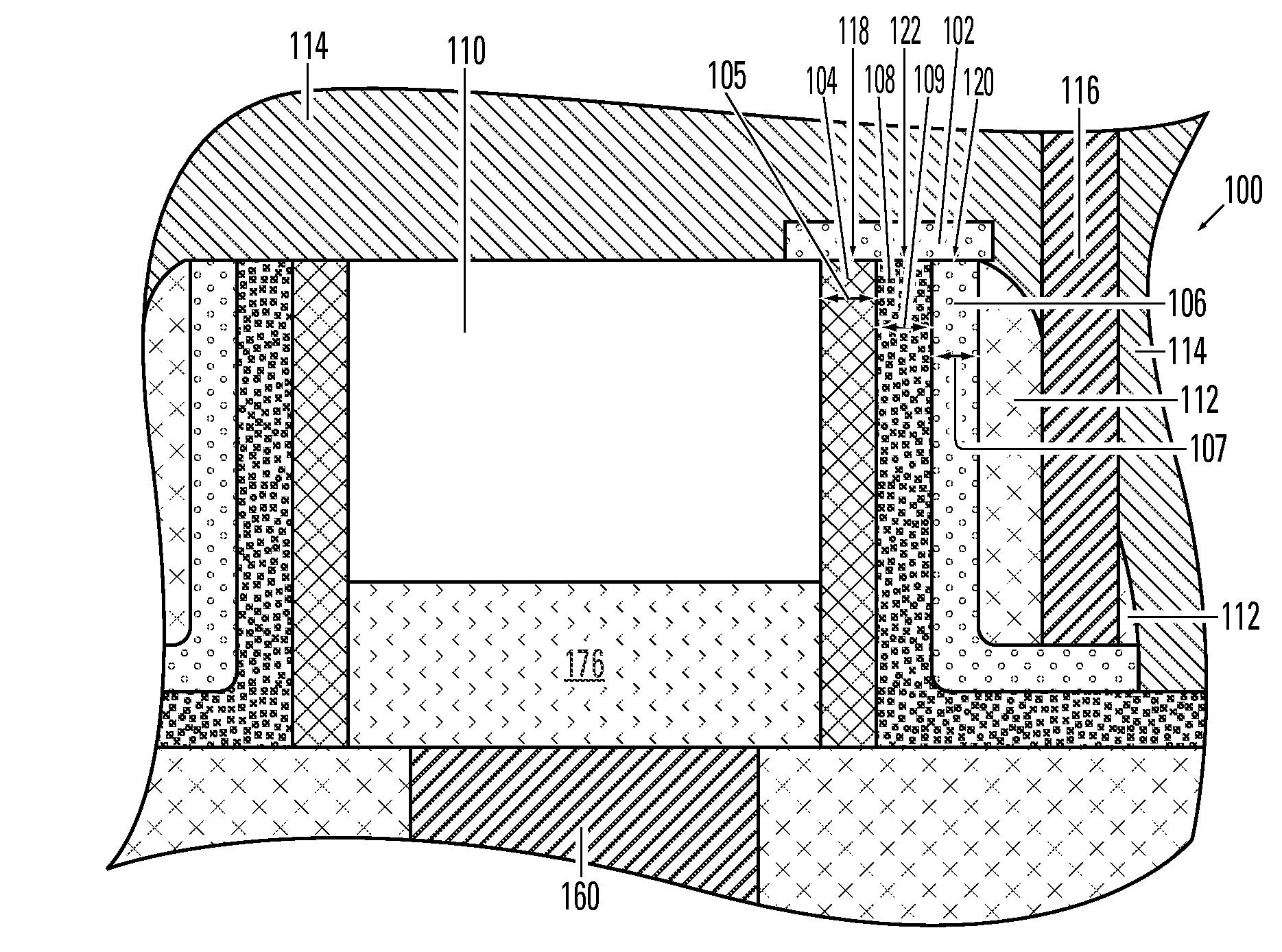

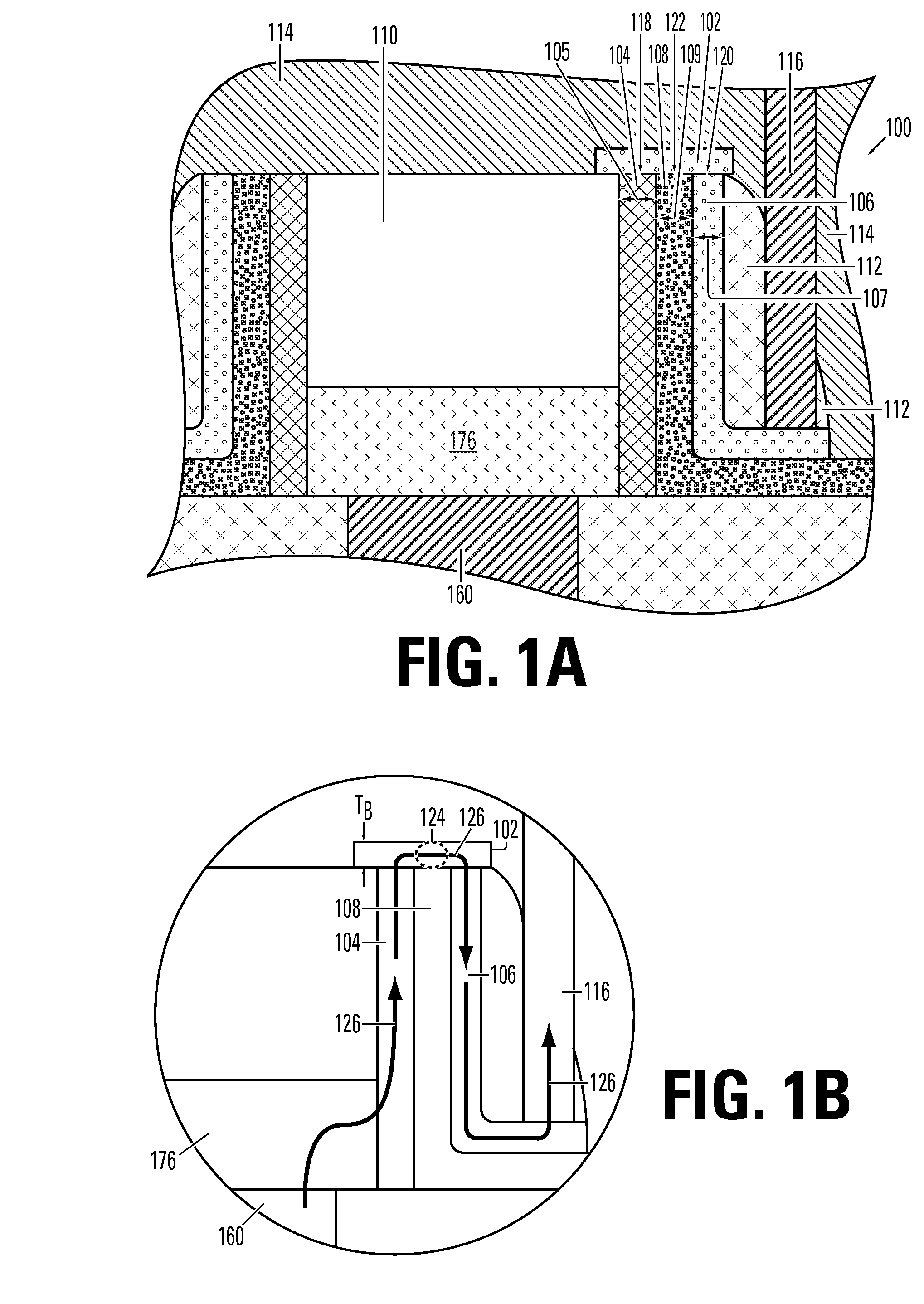

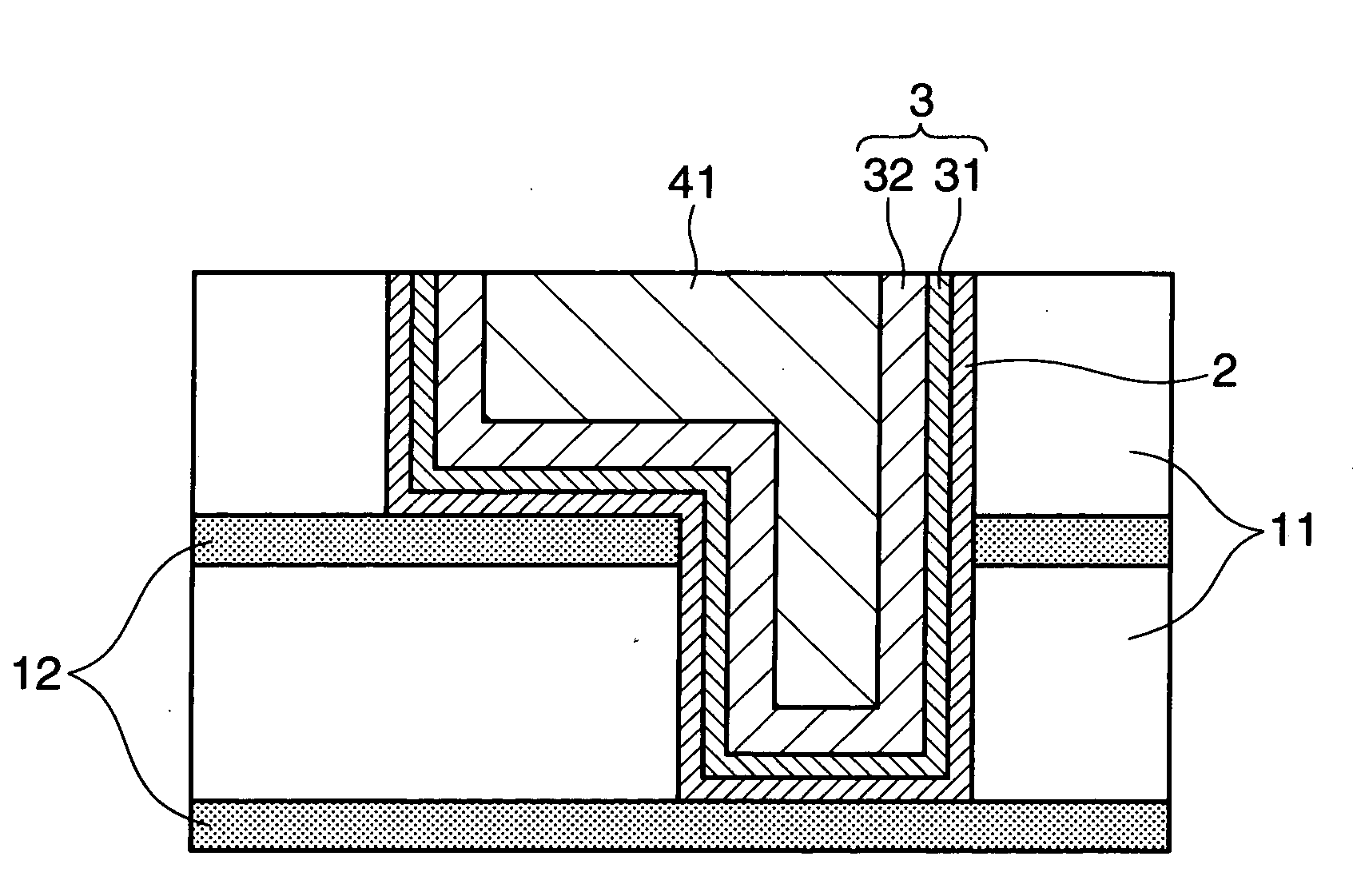

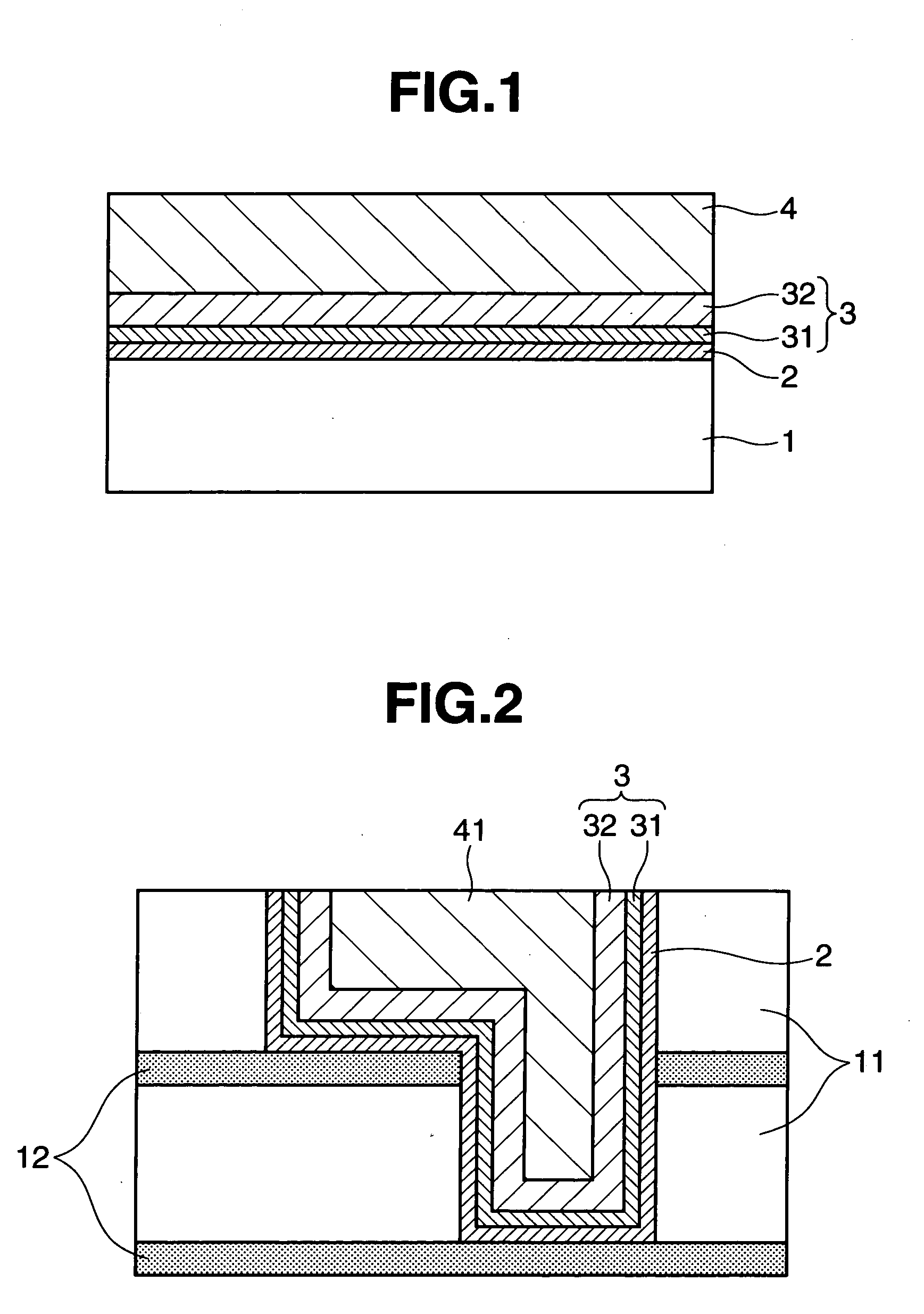

Method for increasing a very-large-scale-integrated (VLSI) capacitor size on bulk silicon and silicon-on-insulator (SOI) wafers and structure formed thereby

InactiveUS6358791B1Without processing costHigh densitySolid-state devicesSemiconductor/solid-state device manufacturingConductive materialsCapacitor

A method of forming a semiconductor device, includes forming at least one conductive island having a predetermined sidewall angle in a conductive substrate, forming a dielectric material over the at least one island, forming a conductive material over the dielectric material, and forming a contact to the conductive material and the at least one island.

Owner:GLOBALFOUNDRIES INC

Interconnect Structures Incorporating Air-Gap Spacers

InactiveUS20090072409A1Avoid depositionFacilitates a quick pinchVibration measurement in fluidSubsonic/sonic/ultrasonic wave measurementEngineeringMetal

A dual damascene article of manufacture comprises a trench containing a conductive metal column where the trench and the conductive metal column extend down into and are contiguous with a via. The trench and the conductive metal column and the via have a common axis. These articles comprise interconnect structures incorporating air-gap spacers containing metal / insulator structures for Very Large Scale Integrated (VLSI) and Ultra Large Scale Integrated (ULSI) devices and packaging. The trench in this regard comprises a sidewall air-gap immediately adjacent the side walls of the trench and the conductive metal column, the sidewall air-gap extending down to the via to a depth below a line fixed by the bottom of the trench, and continues downward in the via for a distance of from about 1 Angstrom below the line to the full depth of the via. In another aspect, the article of manufacture comprises a capped dual damascene structure.

Owner:TESSERA INC

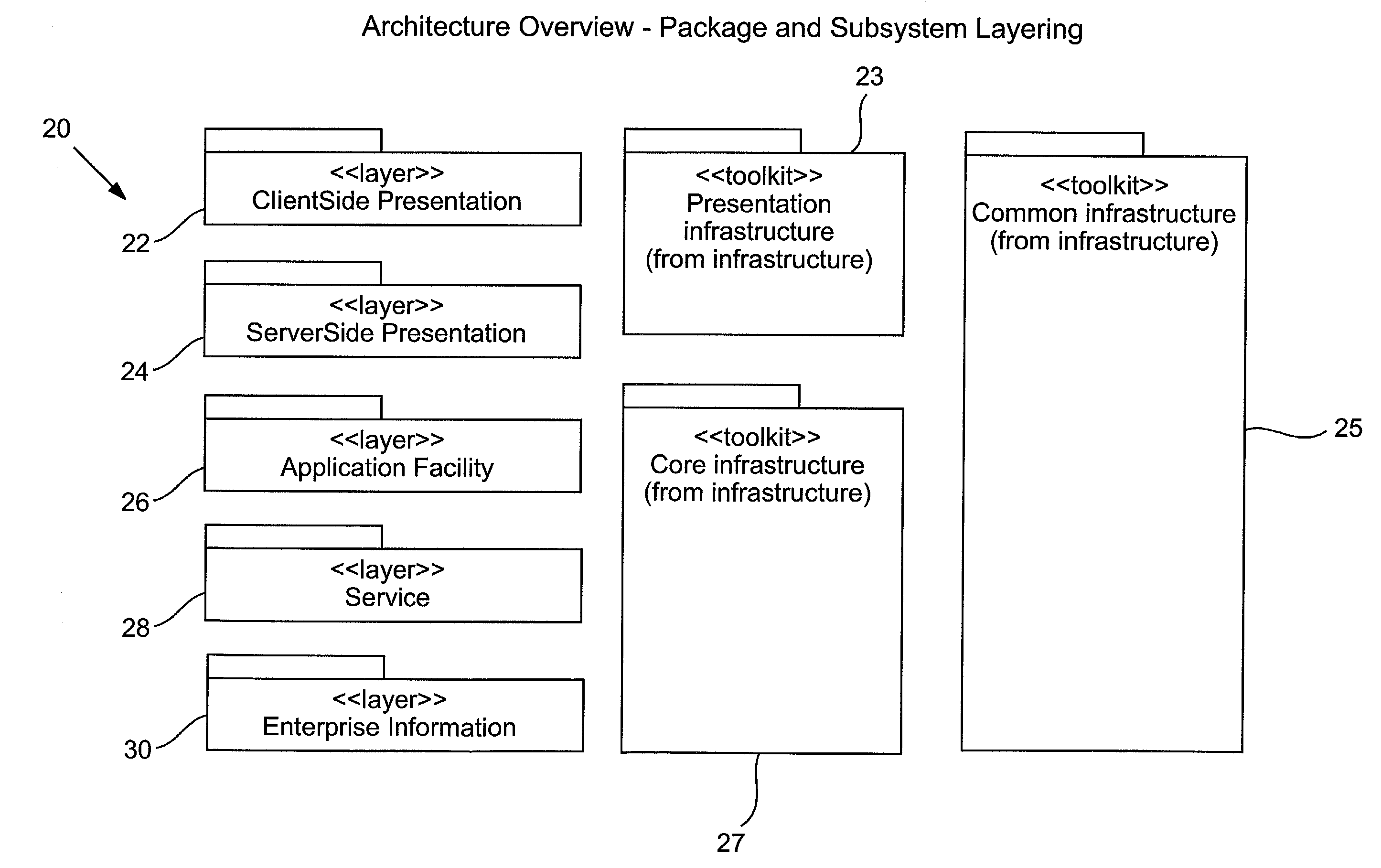

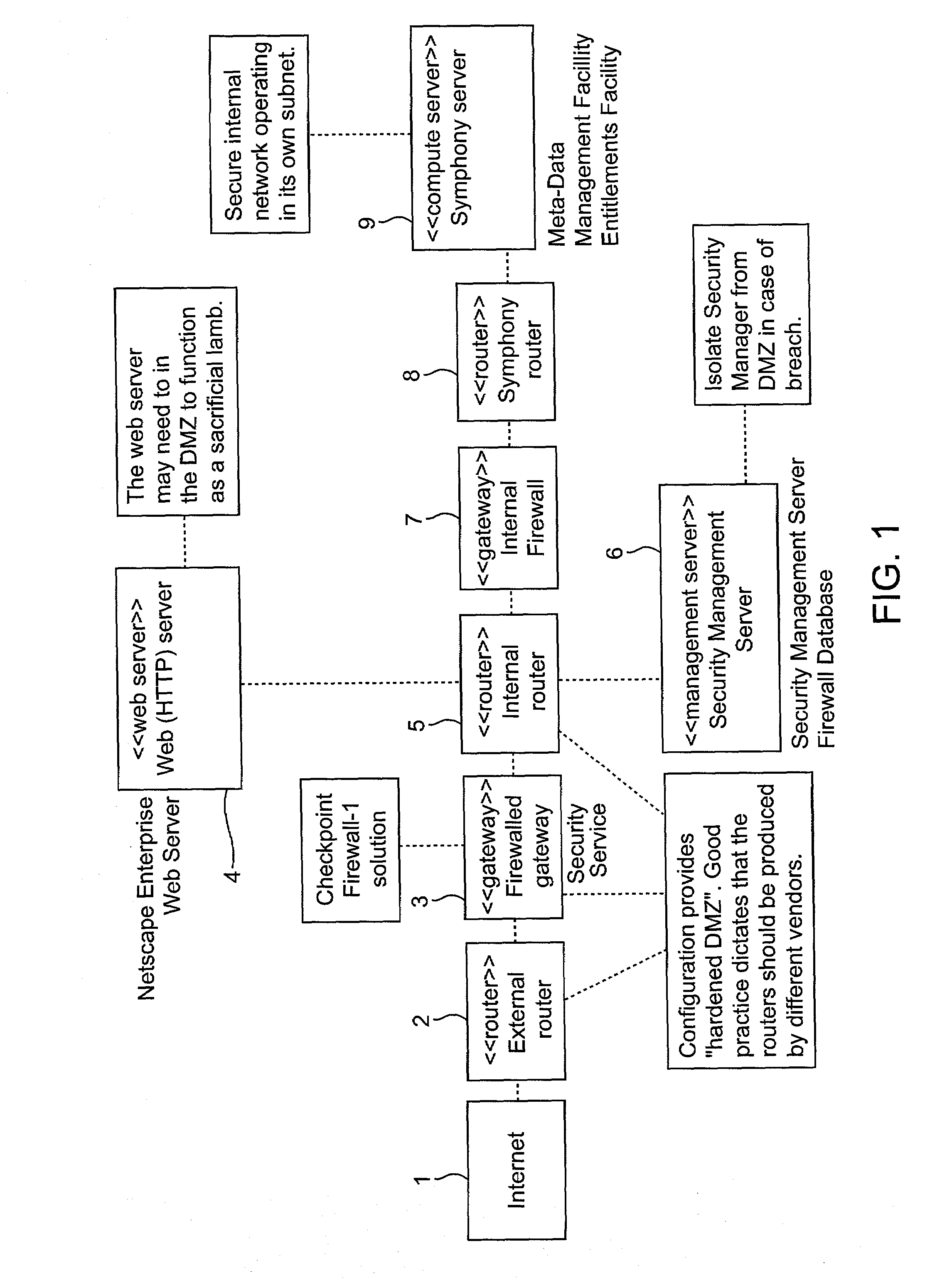

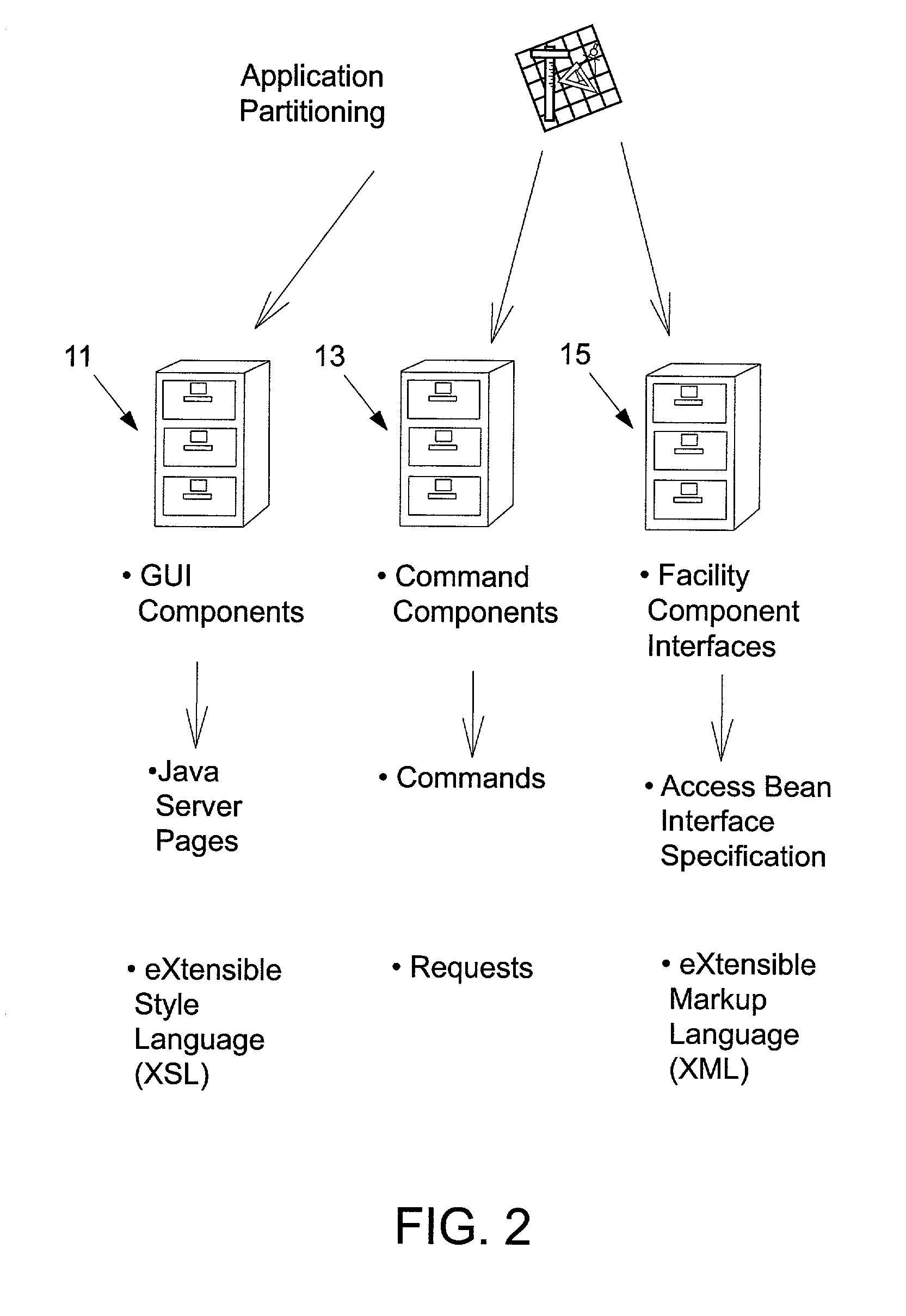

Enterprise framework and applications supporting meta-data and data traceability requirements

InactiveUS7016919B2Anchor value chainSignificant richnessDigital data processing detailsOffice automationMetadata managementData source

An application adapted to run within an enterprise wide, web-based framework which provides reusable services and facilities such as security, meta-data management and traceability of data and a framework supporting the same. The framework supports decision making across the value chain, with an emphasis on the meta-data needed for decision making. The framework can support the activities of a virtual organization (internal or external) and the inevitable variations in data types, file formats etc. without requiring massive integration between the various sources of data involved.

Owner:AGILENT TECH INC

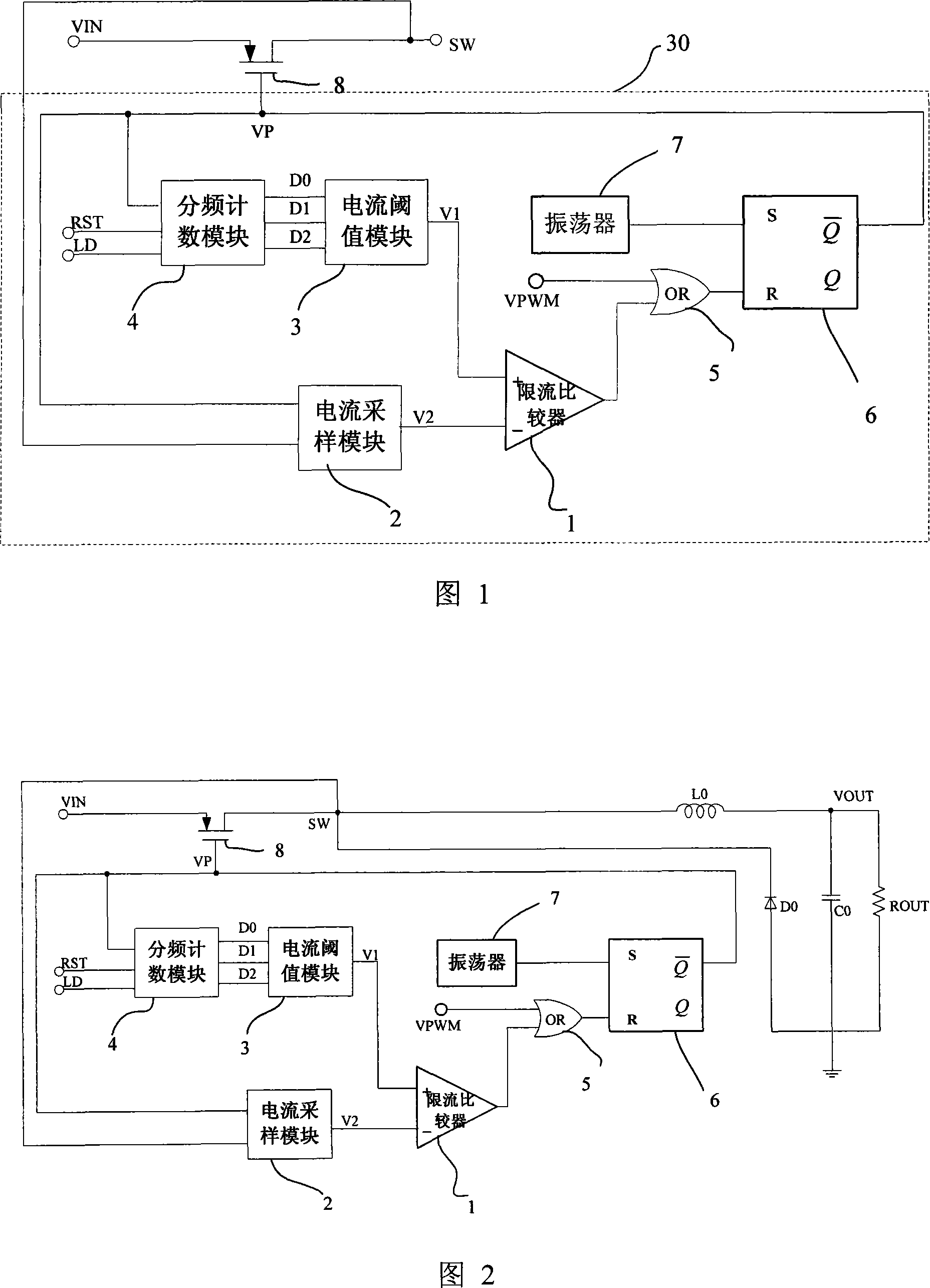

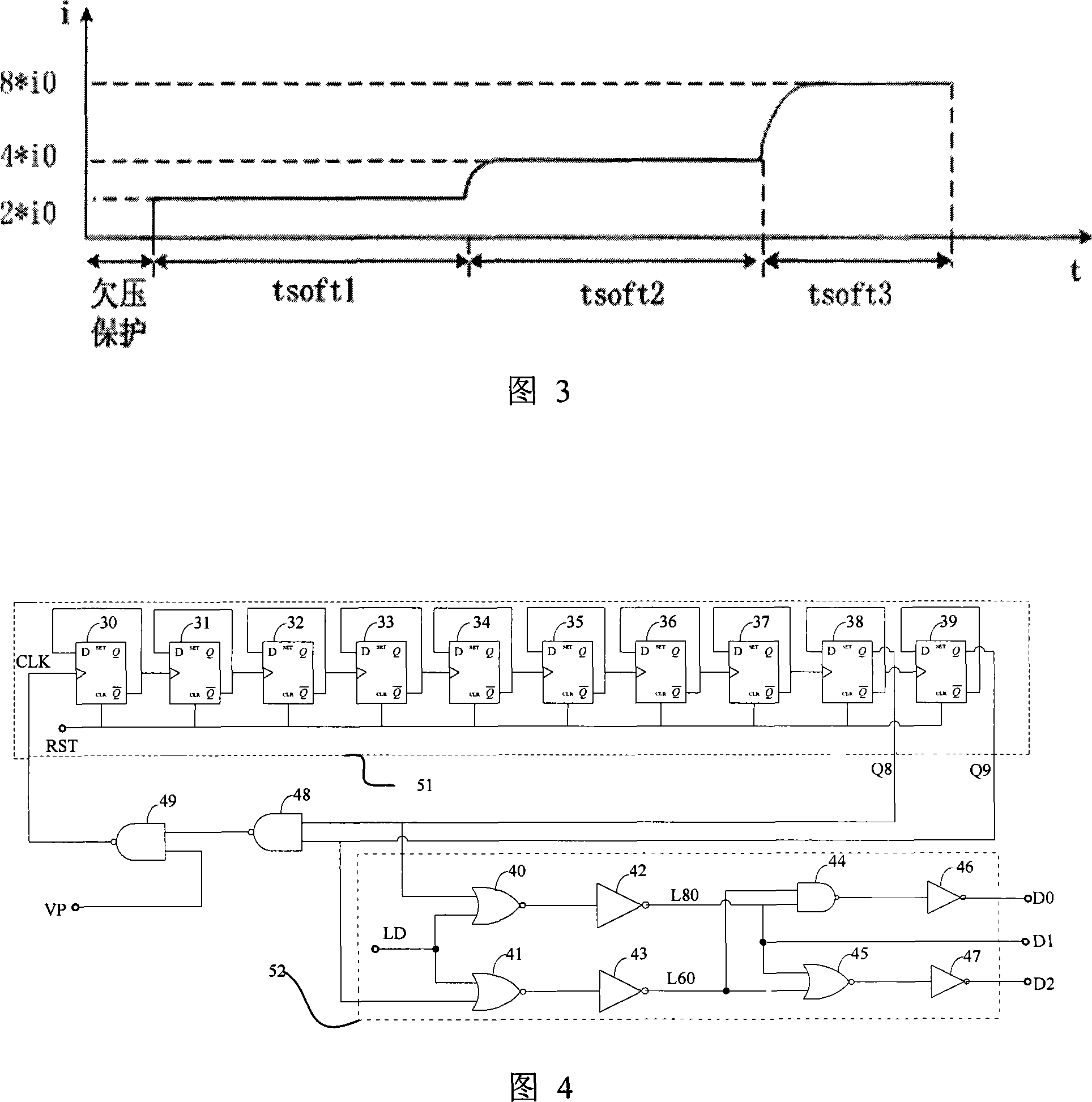

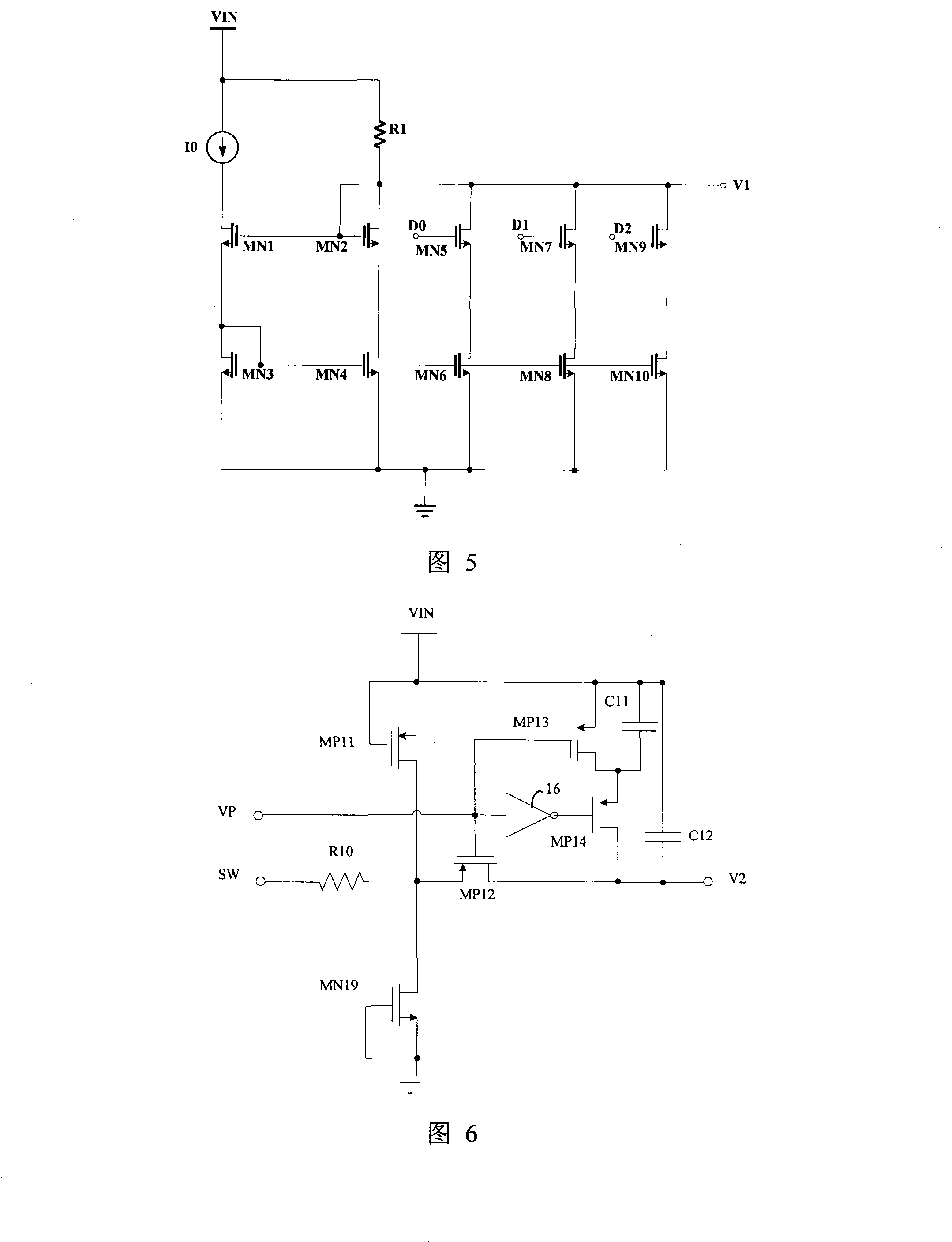

A soft start circuit for PDM DC-DC switching power supply

InactiveCN101217252AGood soft start effectAvoid Inrush CurrentDc-dc conversionElectric variable regulationCapacitanceMicrocontroller

The invention discloses a soft starting circuit for a pulse width modulation DC-DC switch power, comprising a frequency splitting count module, a current threshold module, a current sampling module, a current limiting comparator, a two input or-gate, an oscillator and an RS trigger. The current in a power inductance is sampled when an external switch rectifier is conducted, and the current changes from small to big by stage by limiting the peak value of the current so as to control the step change of the duty ratio, thus leading the output voltage to increase by stage gradually, avoiding surge current in starting procedure and realizing the soft starting function. The invention has the advantages of integrating to the inside of large scale integrated circuit without high capacitance in the outside or a microcontroller to control, limiting the load current directly with good soft starting effect and being suitable for a voltage control mode and a current control mode; the circuit is simple correspondingly by adopting a current gating network; the soft starting time can be regulated automatically according to different loads.

Owner:HUAZHONG UNIV OF SCI & TECH

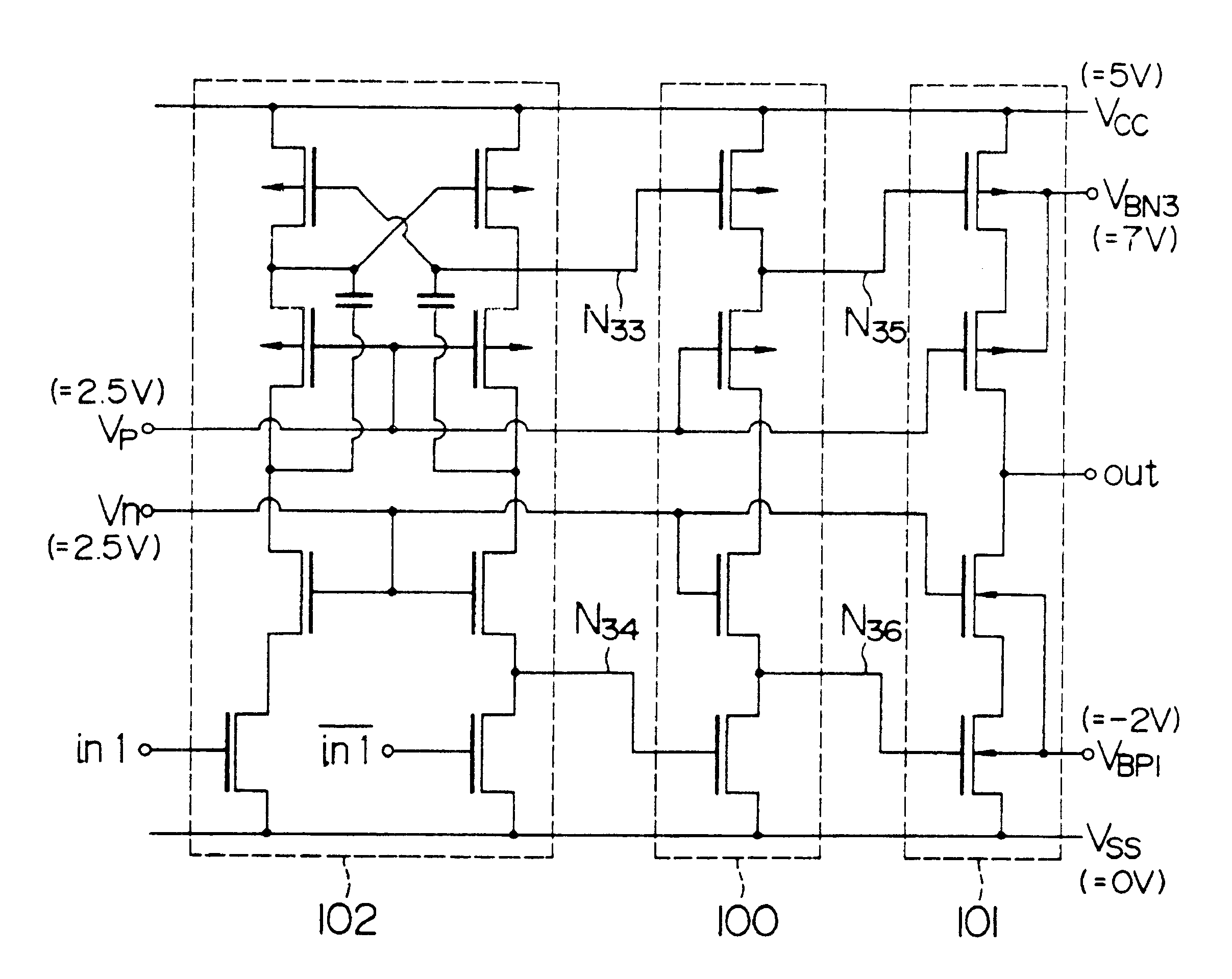

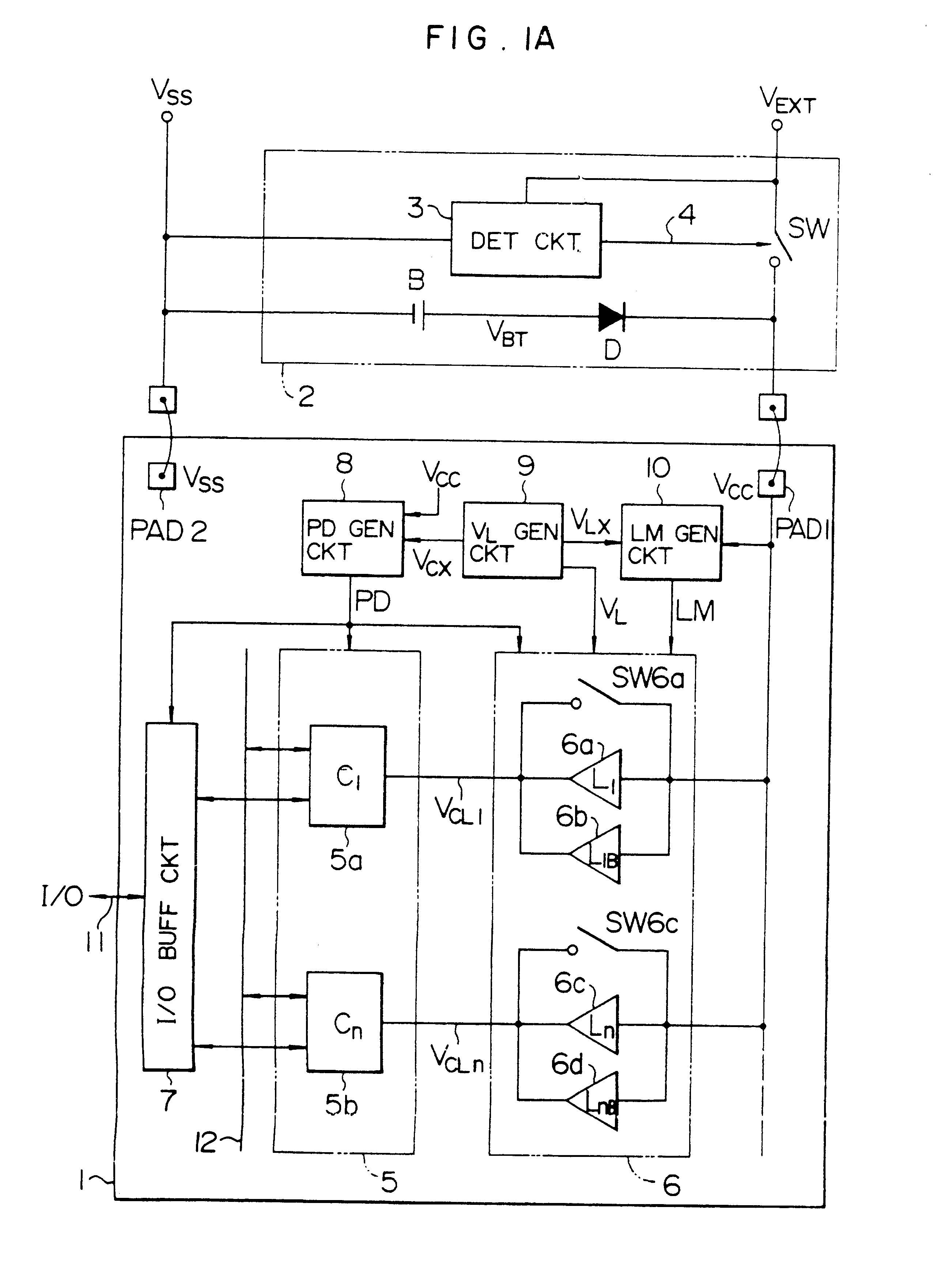

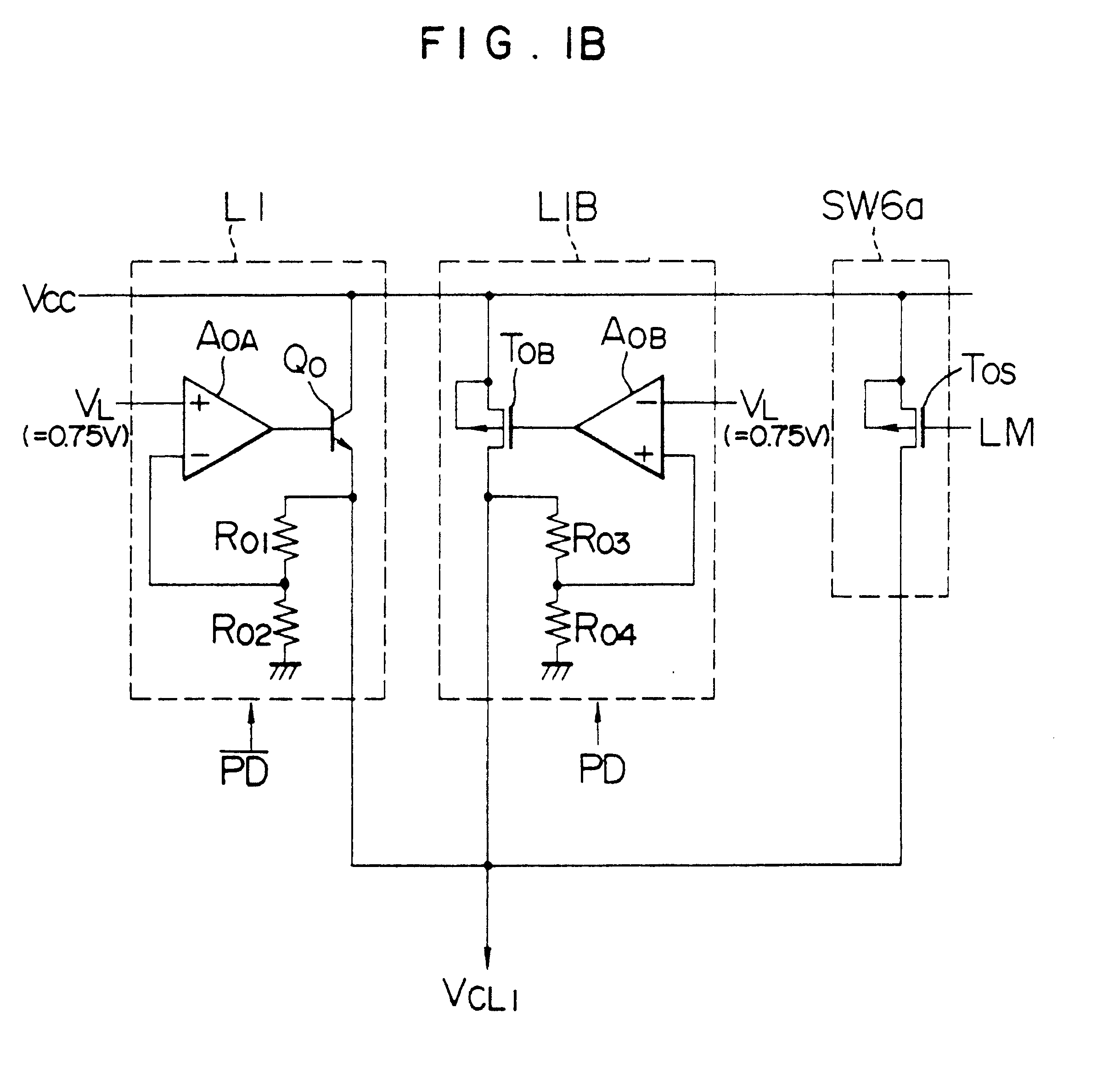

Large scale integrated circuit with sense amplifier circuits for low voltage operation

InactiveUSRE37593E1Low working voltageEasy to operateSingle network parallel feeding arrangementsDigital storageLow voltageHemt circuits

Disclosed is a one-chip ULSI which can carry out the fixed operation in a wide range of power supply voltage (1 V to 5.5 V). This one-chip ULSI is composed of a voltage converter circuit(s) which serves to a fixed internal voltage for a wide range of power supply voltage, an input / output buffer which can be adapted to several input / output levels, a dynamid RAM(s) which can operate at a power supply voltage of 2 V or less, etc. This one-chip ULSI can be applied to compact and portable electronic devices such as a lap-top type personal computer, an electronic pocket note book, a solid-state camera, etc.

Owner:PS4 LUXCO SARL

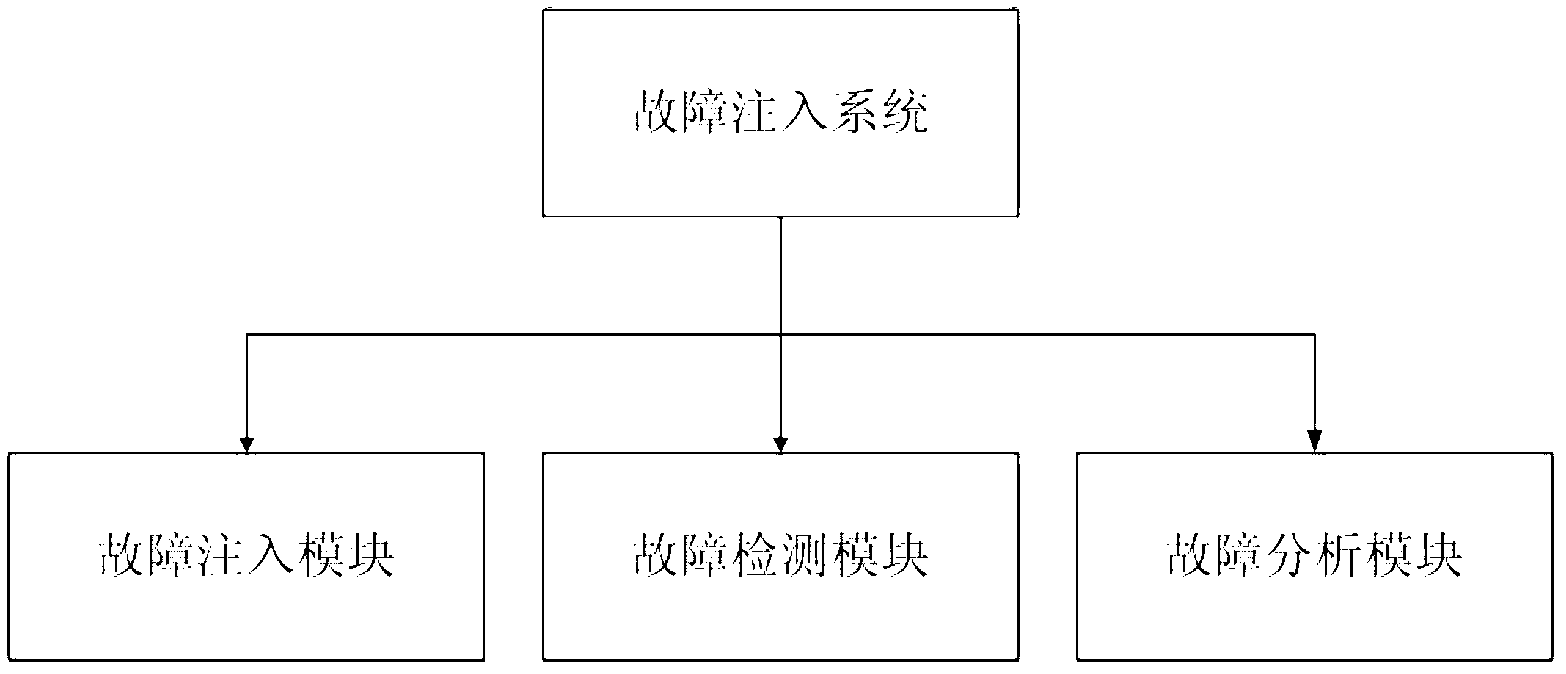

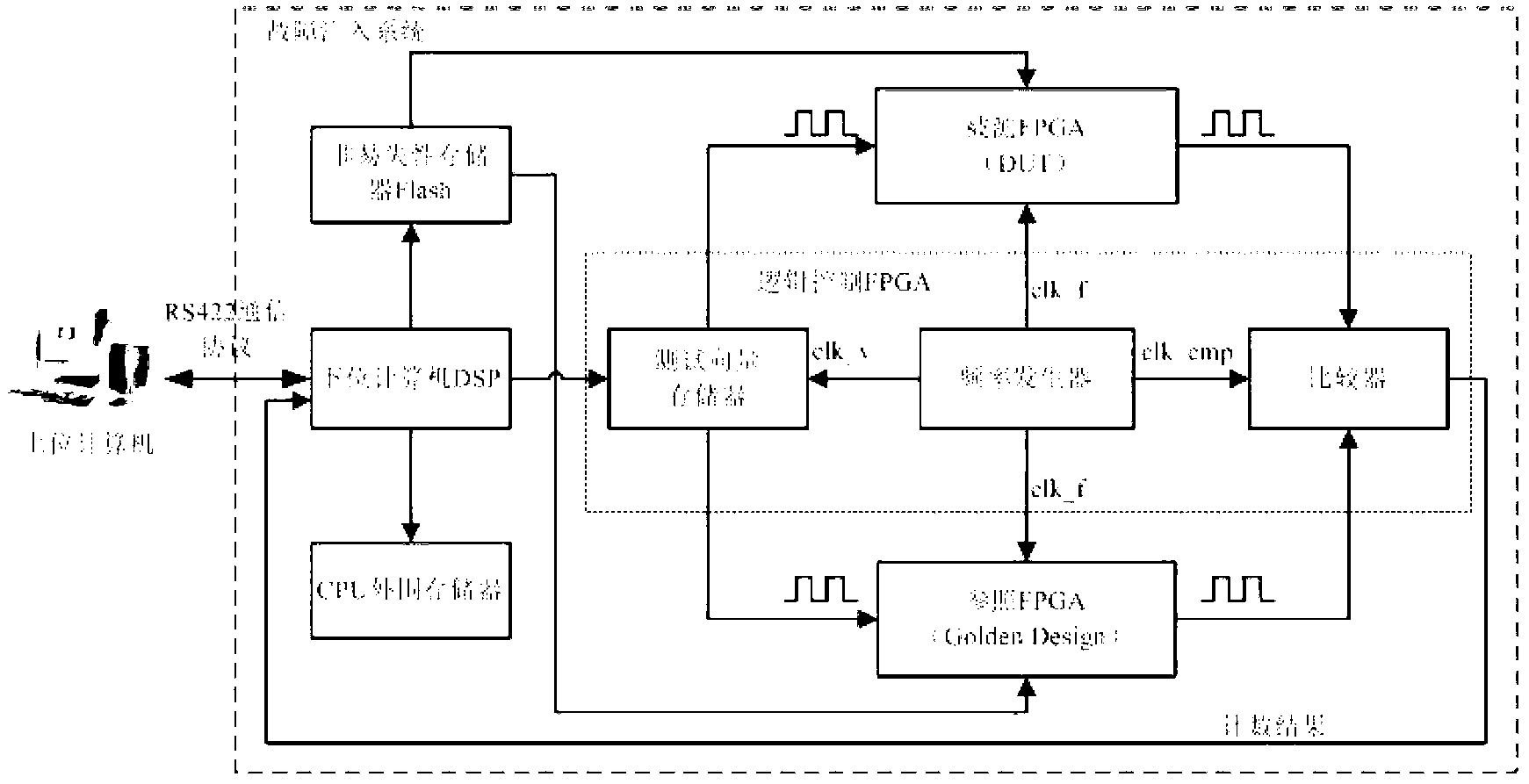

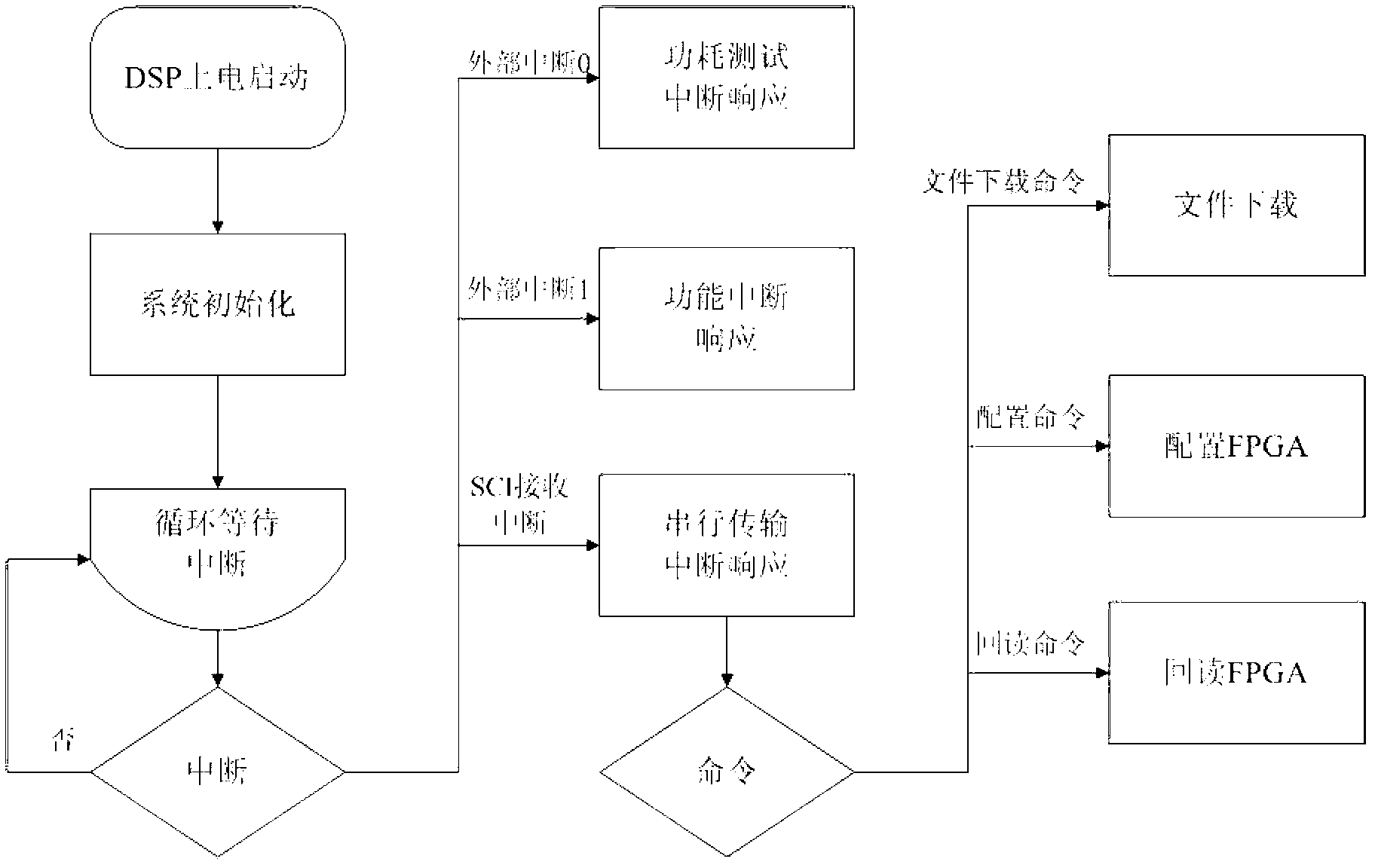

Fault simulation system and fault analysis method for single event upset

InactiveCN103198868ANo damageThrottling flow timeStatic storageSpecial data processing applicationsComputer moduleFault analysis

The invention relates to a fault simulation system and a fault analysis method for single event upset in a large scale integrated circuit SRAM-type FPGA (Field Programmable Gate Array). The fault simulation system comprises a host computer and a control board, wherein the control board comprises a fault injection module, a fault detecting module and a fault analyzing module. The fault simulation system and the fault analysis method provided by the invention are flexible to use, low in cost, high in simulation precision, fast in simulation speed and free from any physical damage to a chip.

Owner:NORTHWEST INST OF NUCLEAR TECH

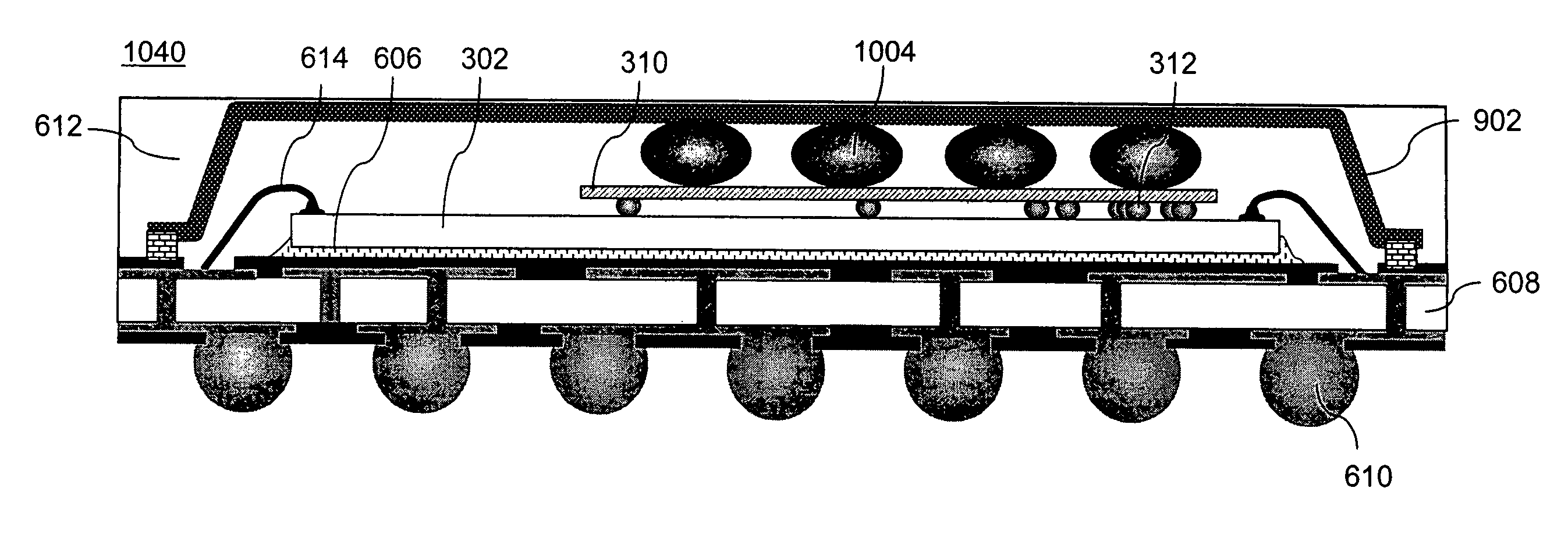

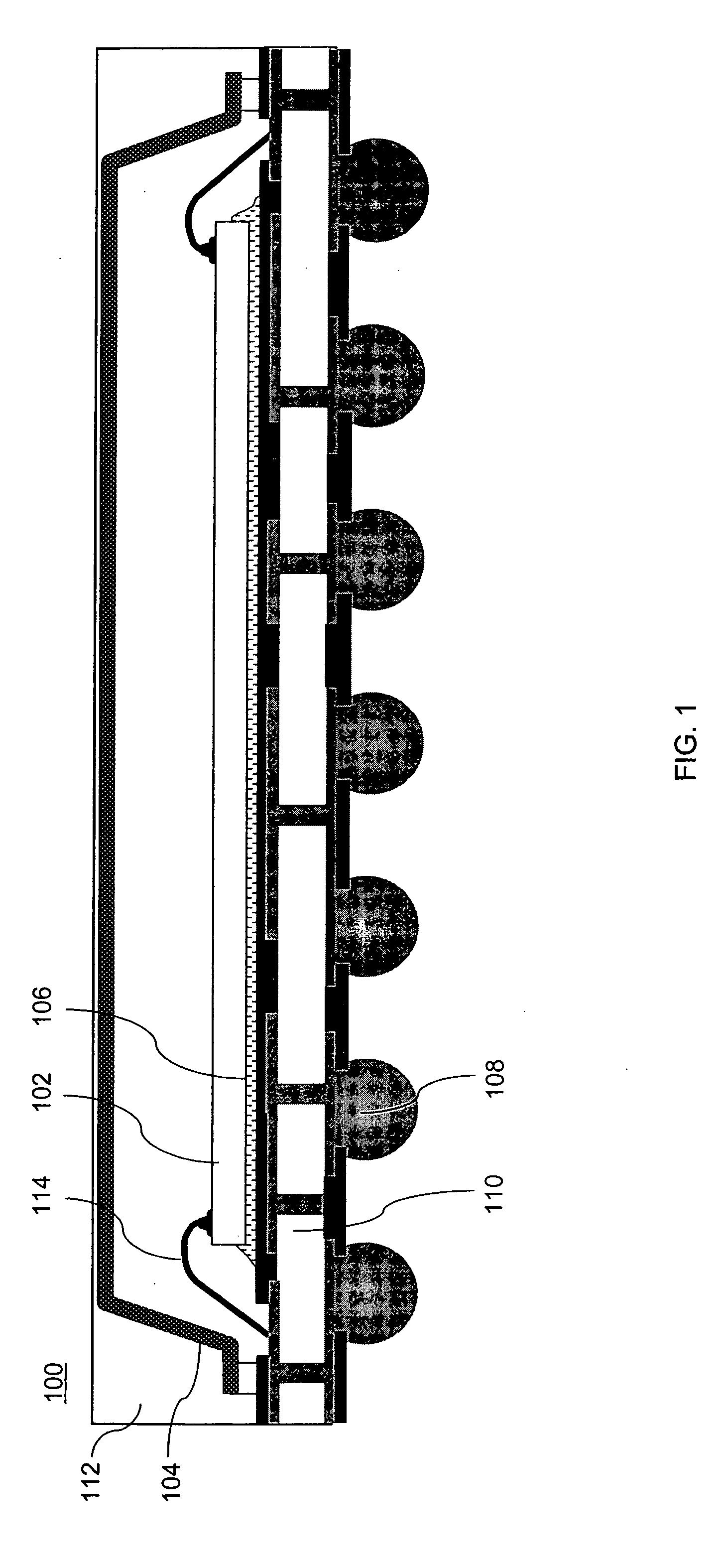

Method and apparatus for cooling semiconductor device hot blocks and large scale integrated circuit (IC) using integrated interposer for IC packages

ActiveUS20070267740A1Semiconductor/solid-state device detailsSolid-state devicesContact padFilling materials

A method, system, and apparatus for improved IC device packaging is described. In an aspect, an (IC) device package includes an IC die having at one or more contact pads, each contact pad located at a corresponding hotspot on a surface of the IC die. The package also includes a thermally conductive interposer which is thermally coupled to the IC die at the contact pads. In another aspect, an underfill material fills a space between the IC die and the interposer. The interposer may also be electrically coupled to the IC die. In an aspect, the interposer and the IC die are coupled through thermal interconnects or “nodules.”

Owner:AVAGO TECH INT SALES PTE LTD

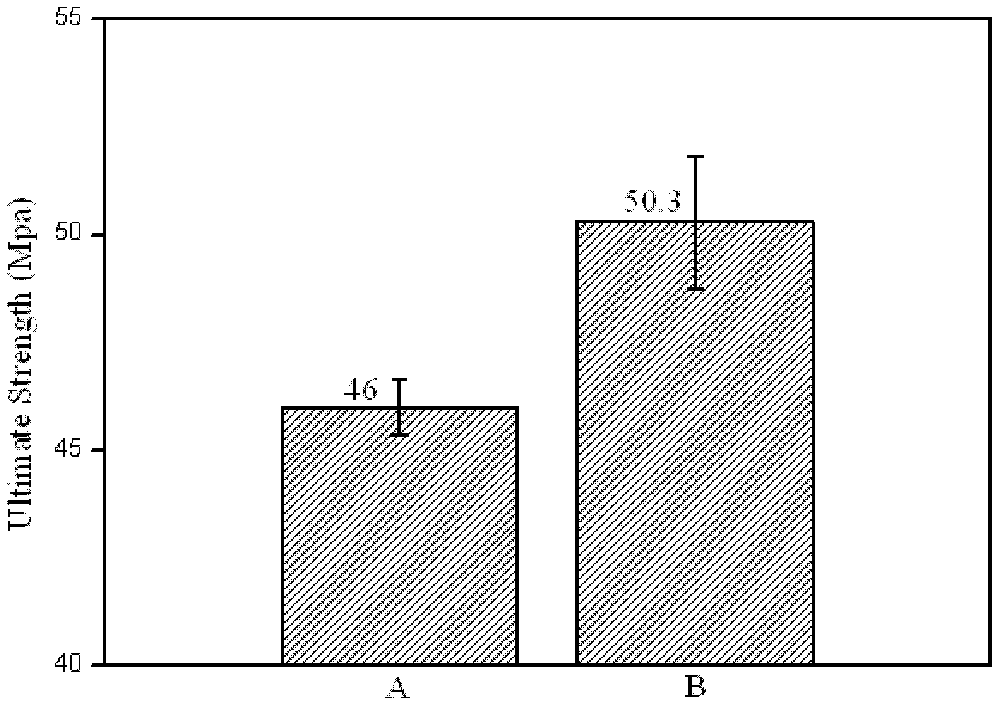

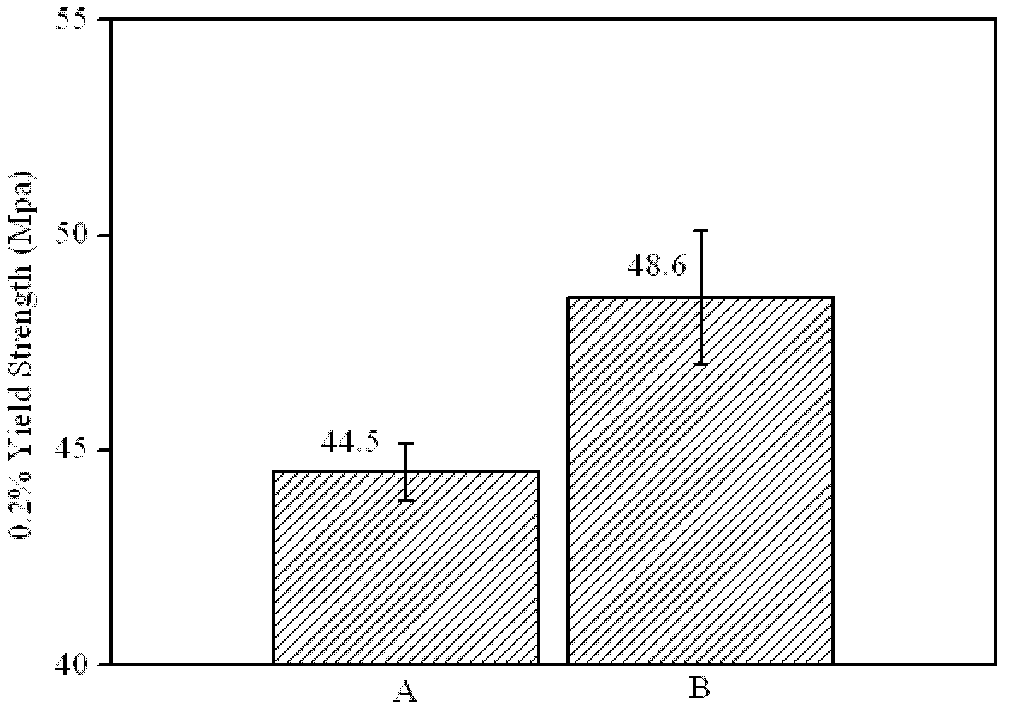

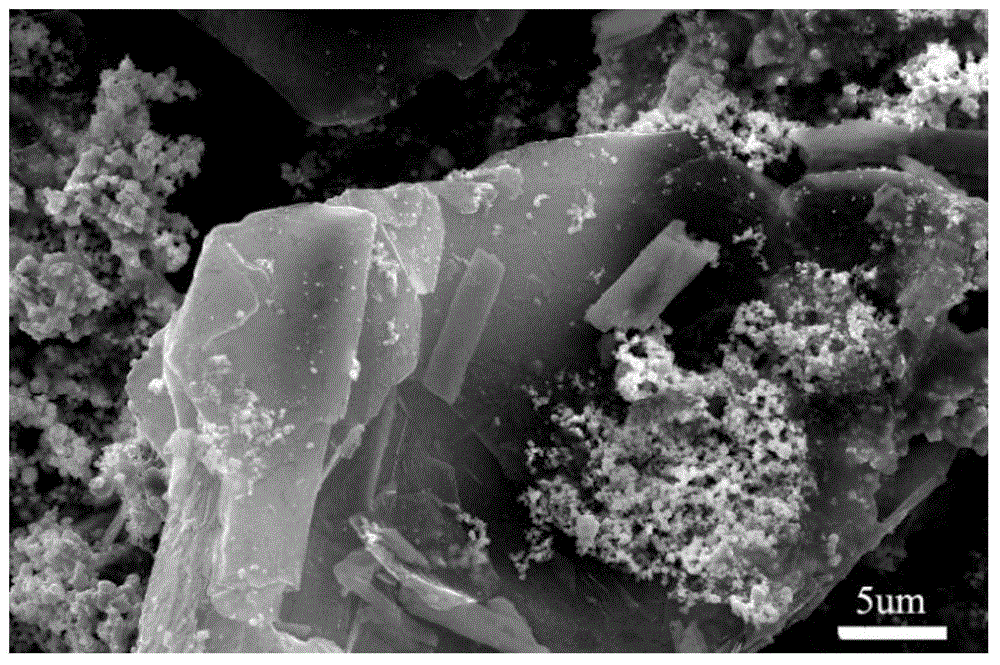

Cu-Al2O3 nano strengthened dispersion alloy and preparation method thereof

The invention relates to a Cu-Al2O3 nanometer dispersion strengthening alloy and preparation thereof. The preparation includes the steps of Cu-Al alloy vacuum smelting, pulverizing, screening, internal oxidizing, hydrogen reducing, vacuum hot pressing, canned hot extruding, etc. Comparing with oxygen-free copper, sigma of the alloy of the invention is 2 to 6 times higher that of the oxygen-free copper, the anti-annealing softening temperature is up to over 900 DEG C, the conductivity is up to 96% IACA and more. The process of the invention is simple, the prepared Cu-Al2O3 nanometer dispersion strengthening alloy has high strength, high conductivity, electrical conductivity higher than 96% IACA, and is anti-annealing and antimagnetic. The alloy can not only used for large-scale integrated circuit lead frame, manufacturing of controlled thermonuclear reaction heat sink components, and is expecially suitable for manufacturing of microwave tube grid mesh, inertial instrument sensor, particle accelerator and other high-precise parts.

Owner:CENT SOUTH UNIV

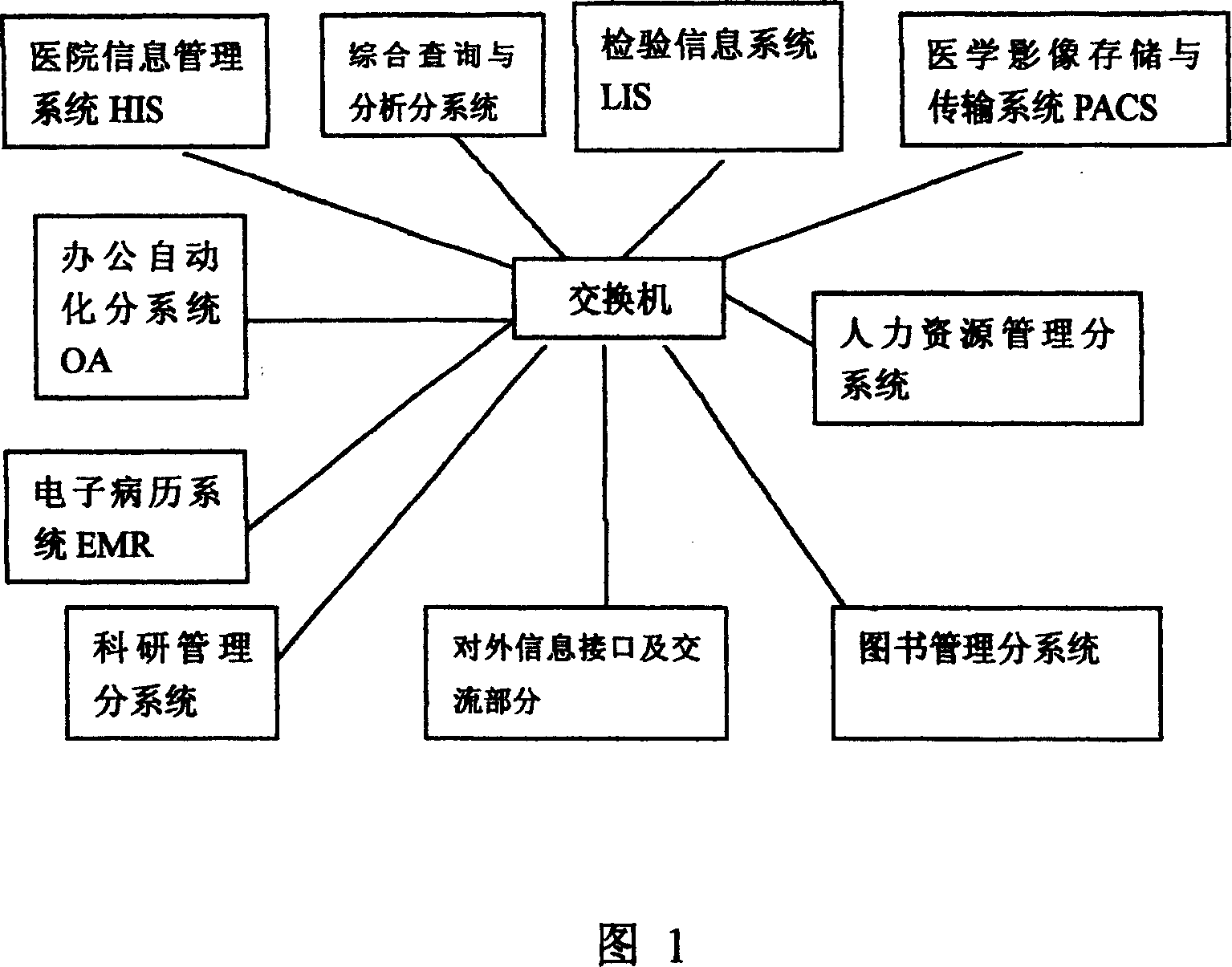

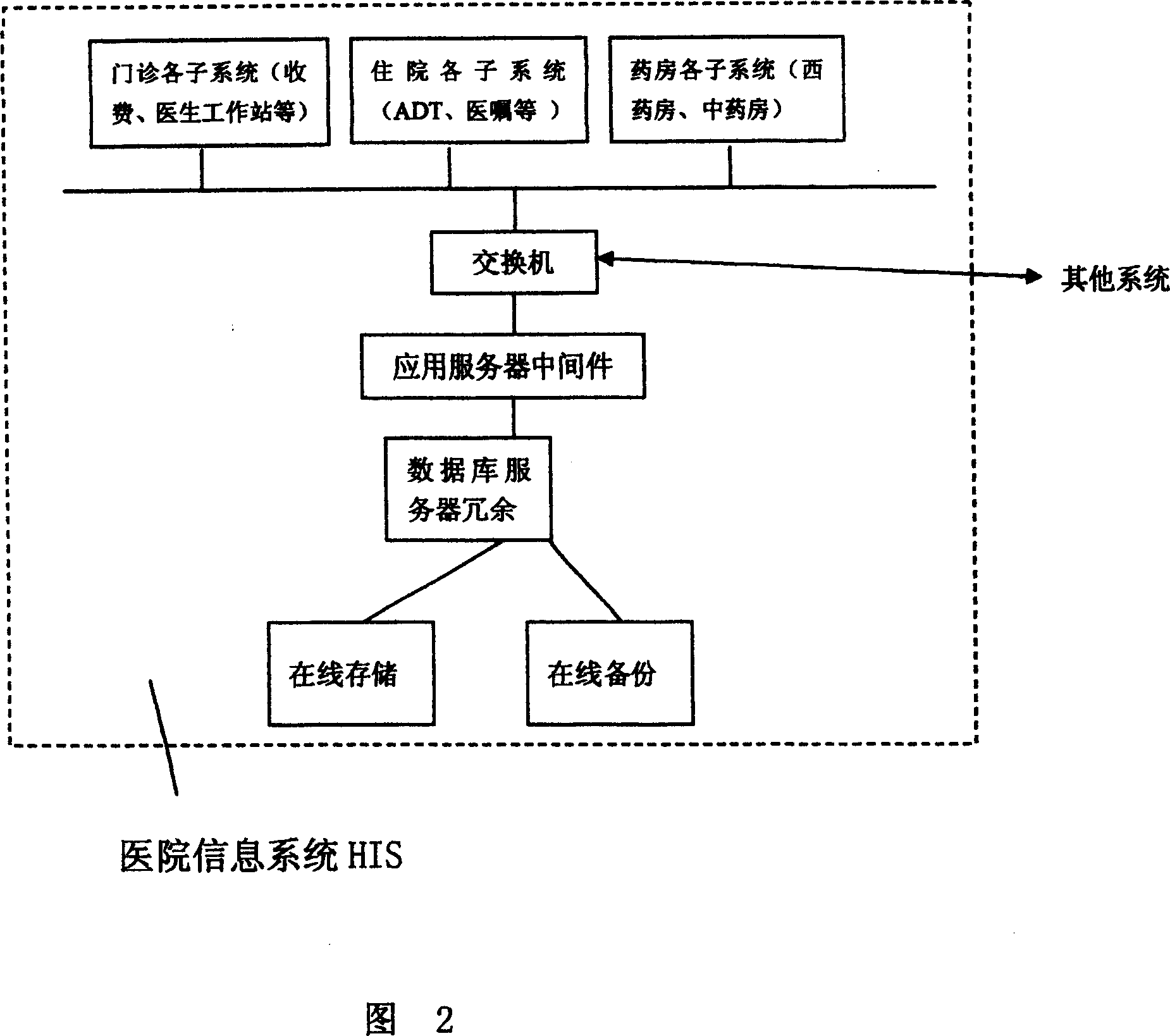

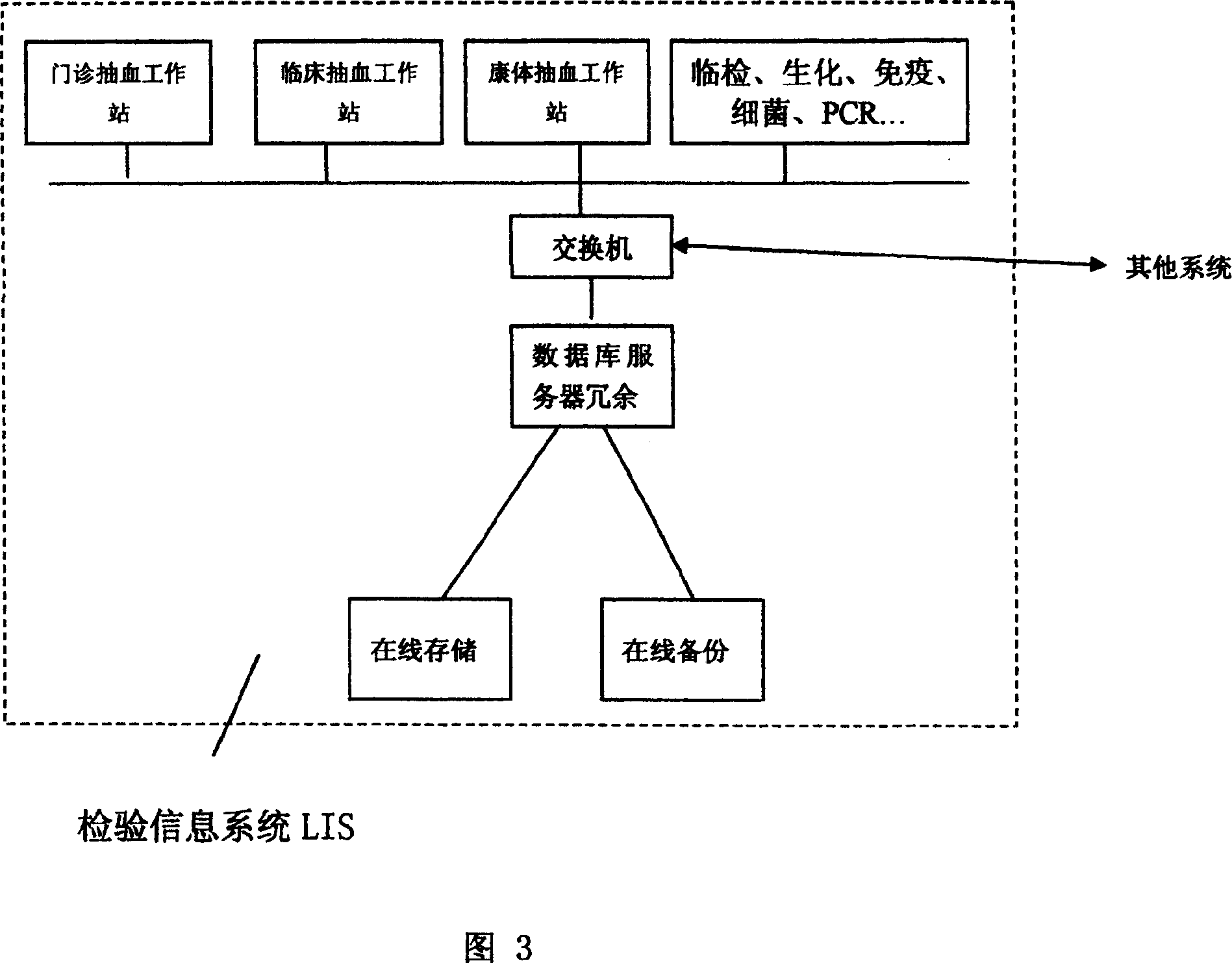

Large scale integrated hospital information system and equipment thereof

InactiveCN101021910AImprove performanceImprove reliabilityData processing applicationsSpecial data processing applicationsMedical recordLife quality

This invention discloses a large scale integrated hospital information system including a hospital information management system HIS, an electronic case history system EMR, an image transmission and storage system PACS, a check network information system LIS and an office automation system HOS, a combined enquiry and analysis system, a manpower resource management sub-system and a foreign information interface and exchange part, in which, all systems are connected by exchanges to transmit information. This invented device applies at least two stages of exchange structure and a server cluster mode fiber to connect to the floors, and the server includes an IBM520 optical channel disc array small computer, an IBM365 optical channel disc array double heat-standby server, an IBM 440 disc array double motor heat-standby server, a PACS cluster load balance server set and a WEB server.

Owner:ZHONG SHAN PEOPLES HOSPITAL

COOLERLESS PHOTONIC INTEGRATED CIRCUITS (PICs) FOR WDM TRANSMISSION NETWORKS AND PICs OPERABLE WITH A FLOATING SIGNAL CHANNEL GRID CHANGING WITH TEMPERATURE BUT WITH FIXED CHANNEL SPACING IN THE FLOATING GRID

ActiveUS20100166424A1Requirements for a hermetically sealed package are substantially relievedLaser optical resonator constructionSemiconductor laser arrangementsElectro-absorption modulatorPeak value

A coolerless photonic integrated circuit (PIC), such as a semiconductor electro-absorption modulator / laser (EML) or a coolerless optical transmitter photonic integrated circuit (TxPIC), may be operated over a wide temperature range at temperatures higher then room temperature without the need for ambient cooling or hermetic packaging. Since there is large scale integration of N optical transmission signal WDM channels on a TxPIC chip, a new DWDM system approach with novel sensing schemes and adaptive algorithms provides intelligent control of the PIC to optimize its performance and to allow optical transmitter and receiver modules in DWDM systems to operate uncooled. Moreover, the wavelength grid of the on-chip channel laser sources may thermally float within a WDM wavelength band where the individual emission wavelengths of the laser sources are not fixed to wavelength peaks along a standardized wavelength grid but rather may move about with changes in ambient temperature. However, control is maintained such that the channel spectral spacing between channels across multiple signal channels, whether such spacing is periodic or aperiodic, between adjacent laser sources in the thermally floating wavelength grid are maintained in a fixed relationship. Means are then provided at an optical receiver to discover and lock onto floating wavelength grid of transmitted WDM signals and thereafter demultiplex the transmitted WDM signals for OE conversion.

Owner:INFINERA CORP

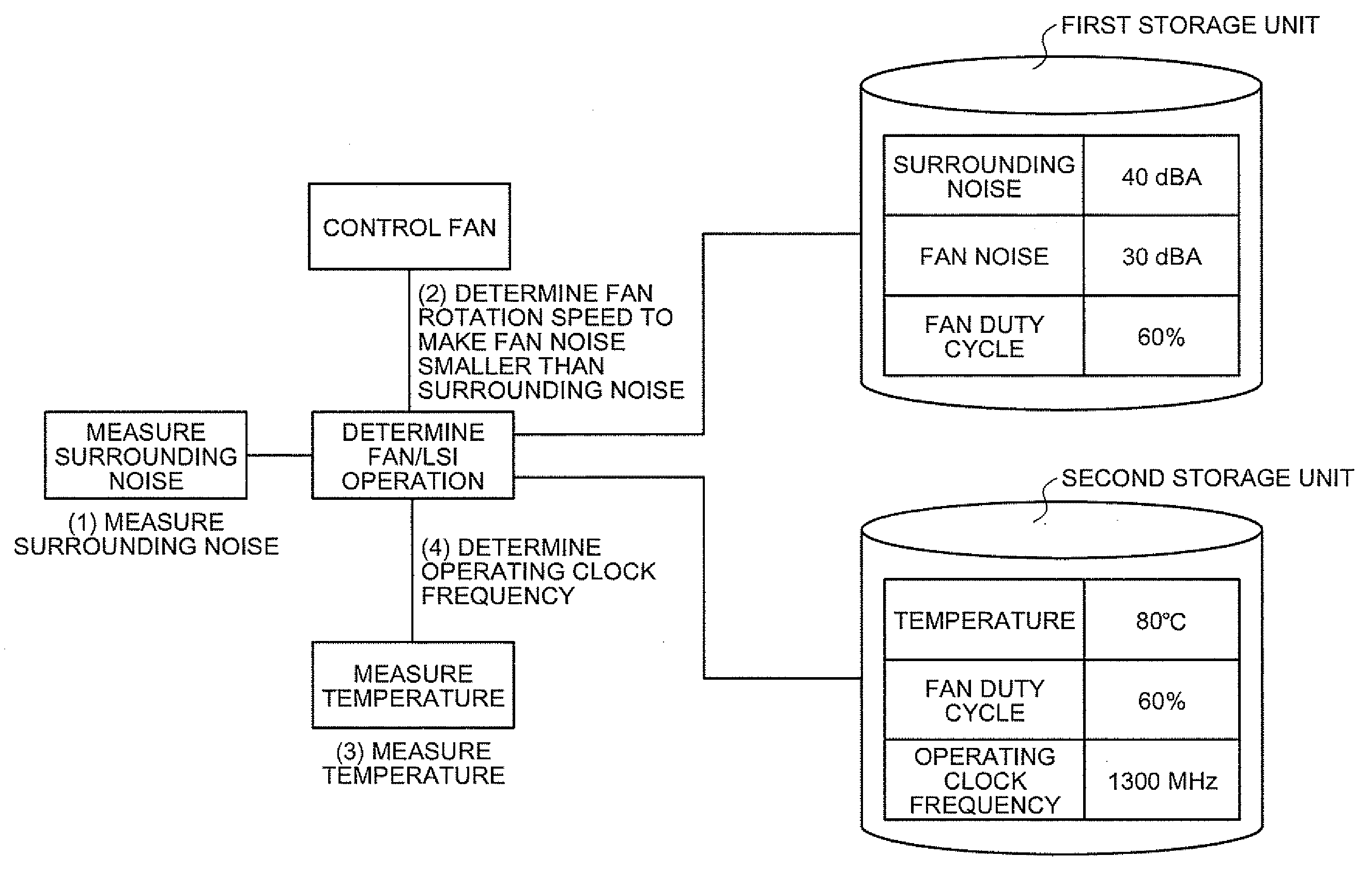

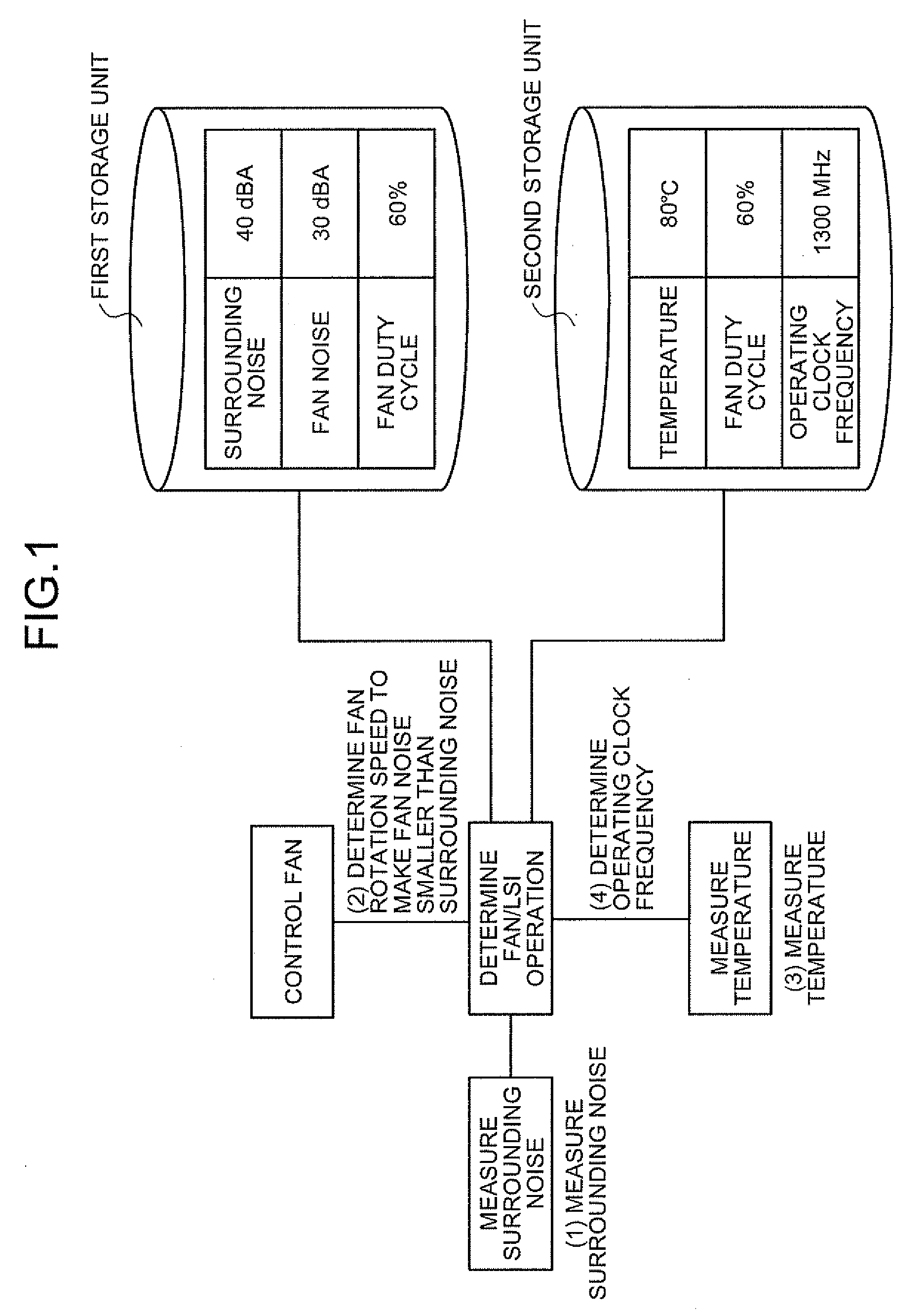

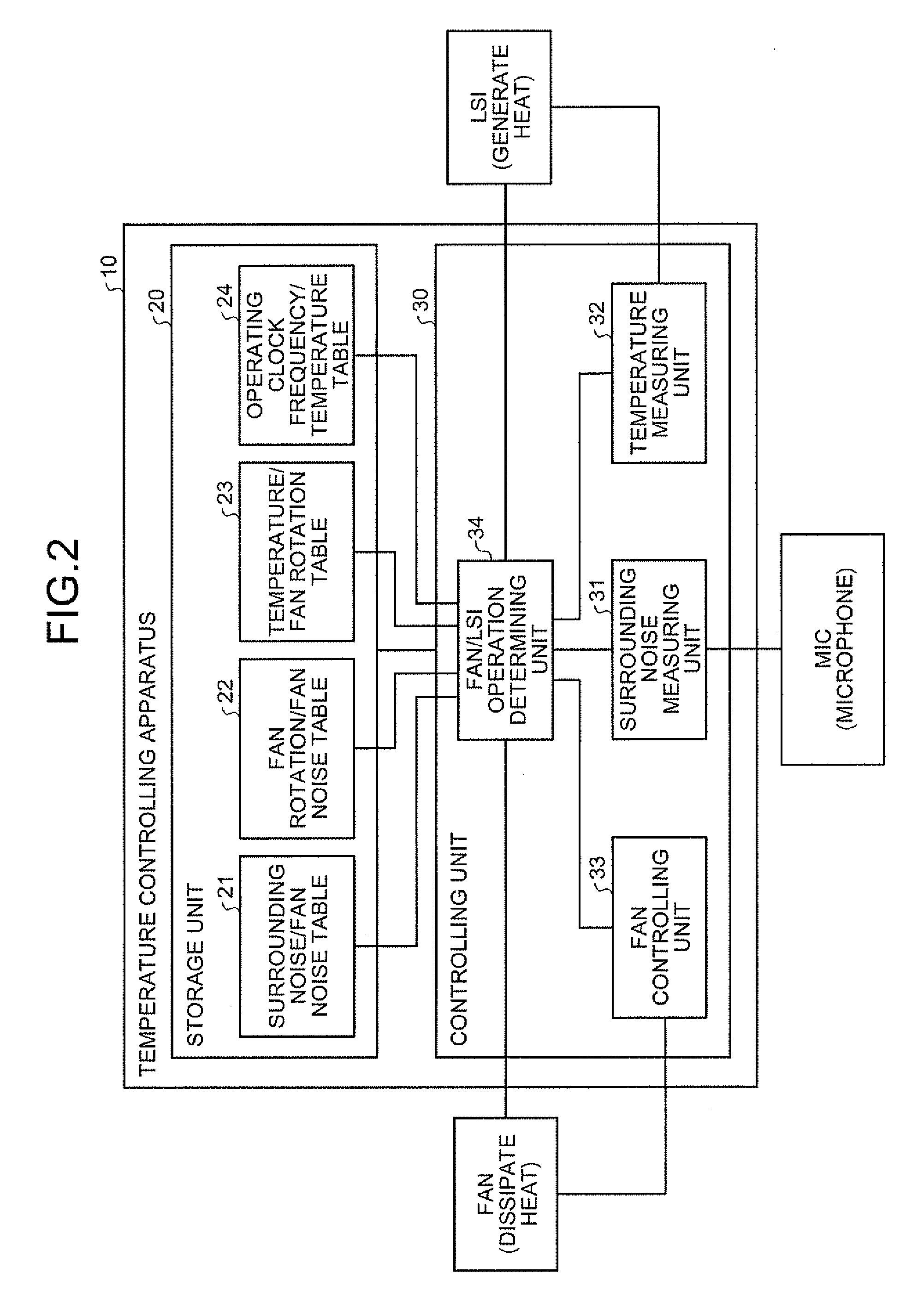

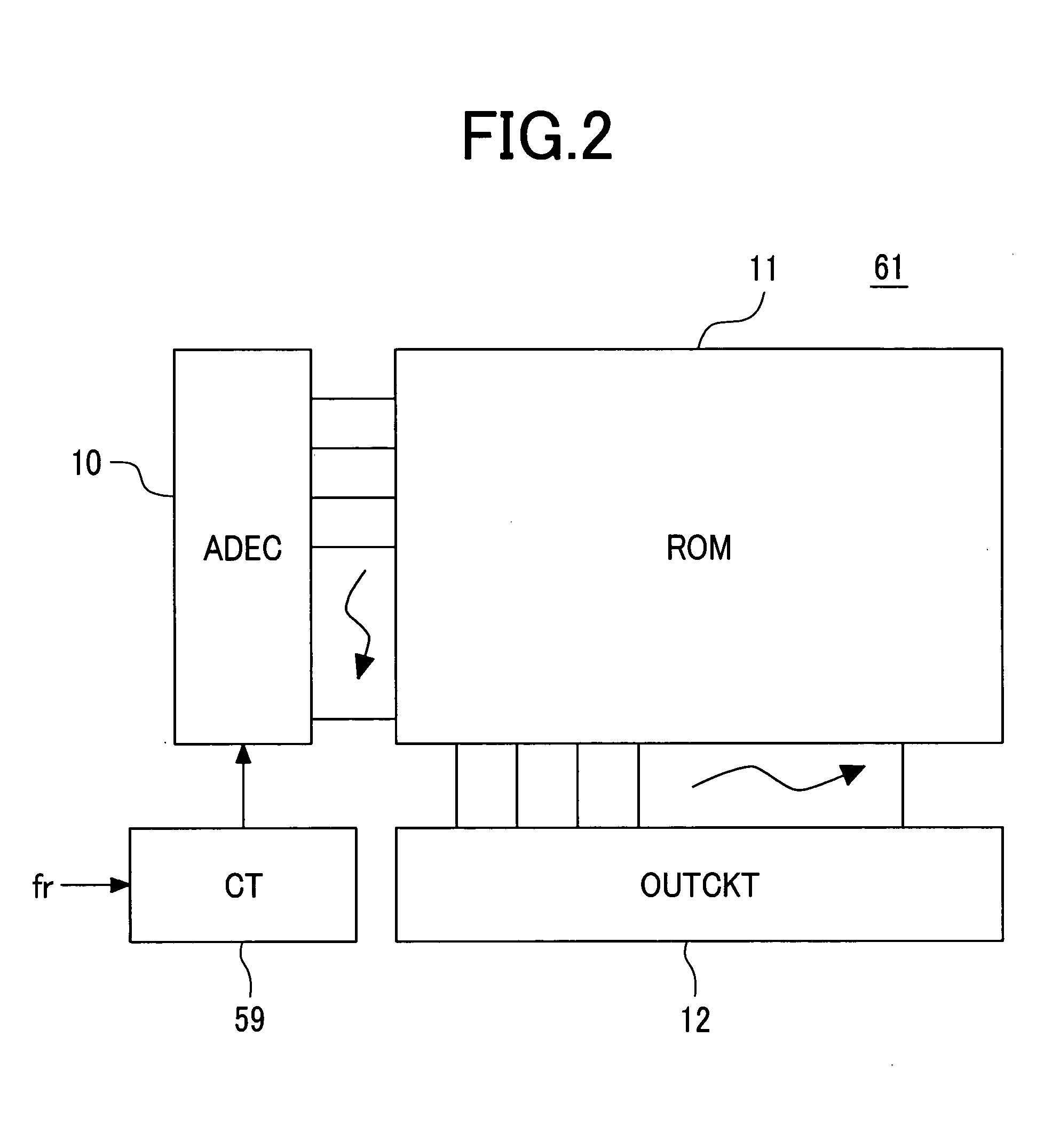

Temperature controlling apparatus, information processing apparatus, and recording medium

InactiveUS20090222147A1Solve problemsTemperatue controlGenerating/distributing signalsInformation processingTemperature control

A temperature controlling apparatus determines a fan rotation speed from a surrounding noise and a fan noise, measures a temperature of a large scale integration (LSI) device or the like that is a controlled object, determines, in a cooling capacity range of the determined fan rotation speed, an operating clock frequency that falls within an allowable temperature range, and controls the LSI to be connected.

Owner:FUJITSU LTD

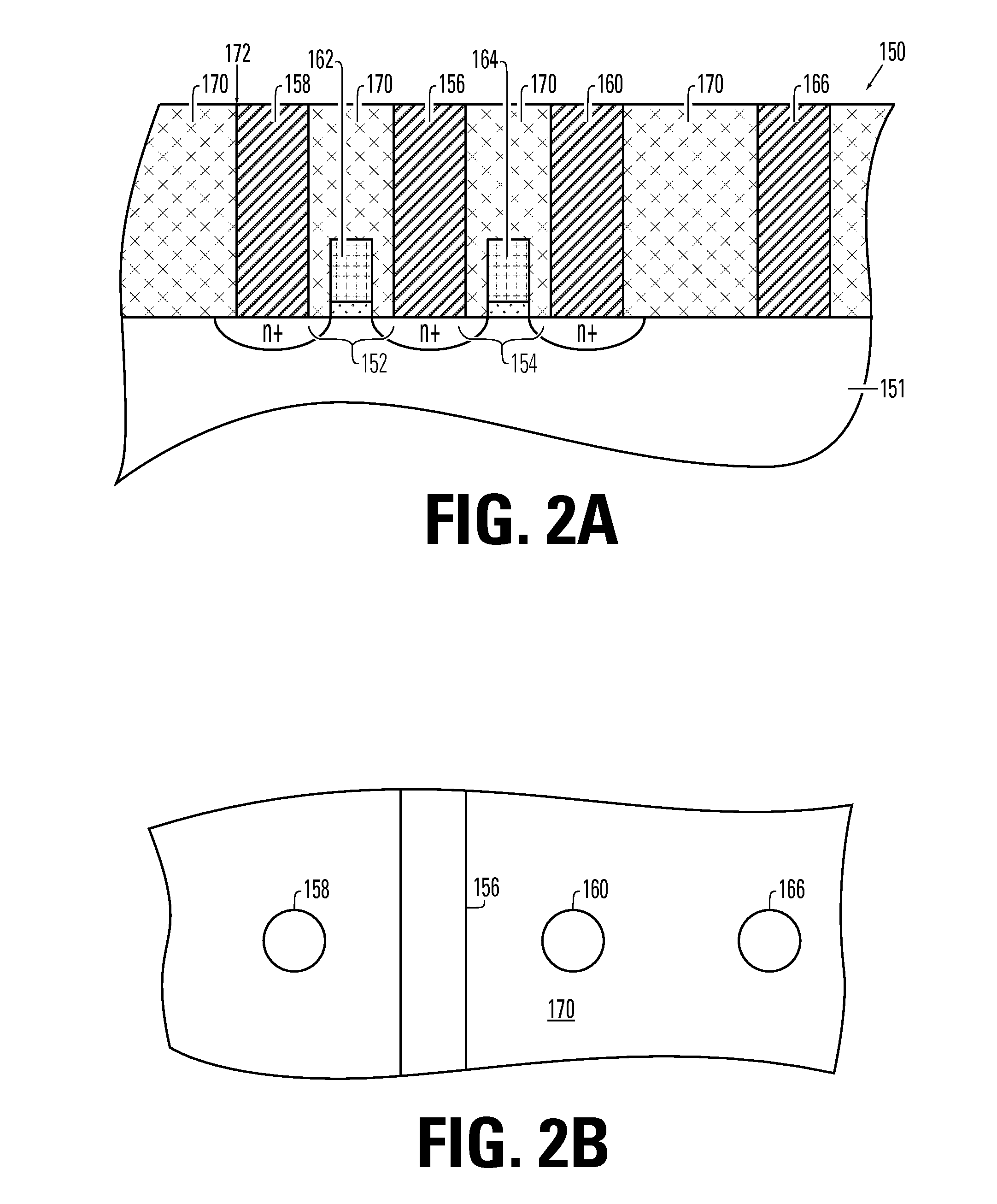

Resistor random access memory cell with l-shaped electrode

ActiveUS20070278529A1Improve insulation performanceIncrease current densitySemiconductor/solid-state device detailsSolid-state devicesRandom access memoryEngineering

A phase change random access memory PCRAM device is described suitable for use in large-scale integrated circuits. An exemplary memory device has a pipe-shaped first electrode formed from a first electrode layer on a sidewall of a sidewall support structure. A sidewall spacer insulating member is formed from a first oxide layer and a second, “L-shaped,” electrode is formed on the insulating member. An electrical contact is connected to the horizontal portion of the second electrode. A bridge of memory material extends from a top surface of the first electrode to a top surface of the second electrode across a top surface of the sidewall spacer insulating member.

Owner:MACRONIX INT CO LTD

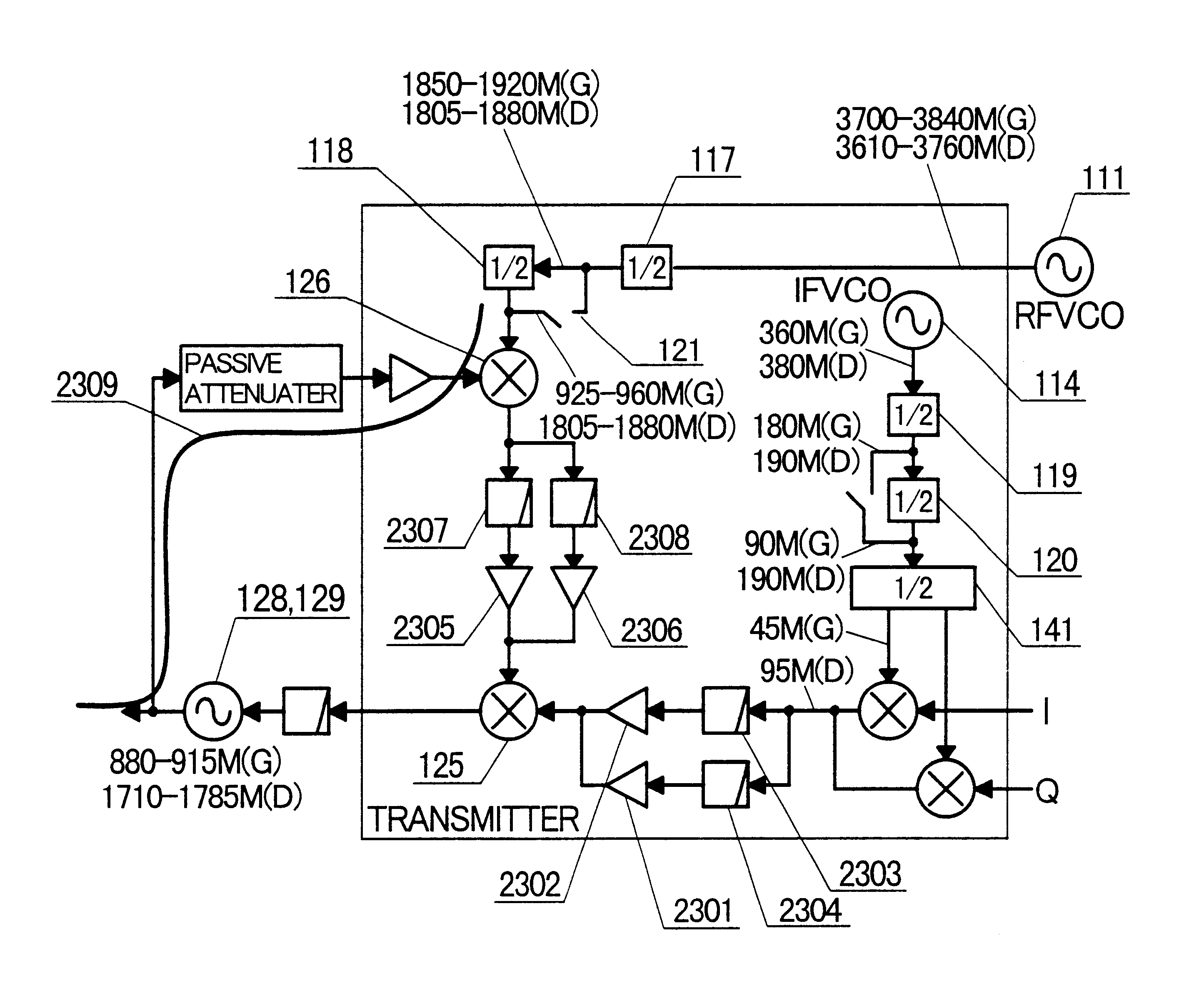

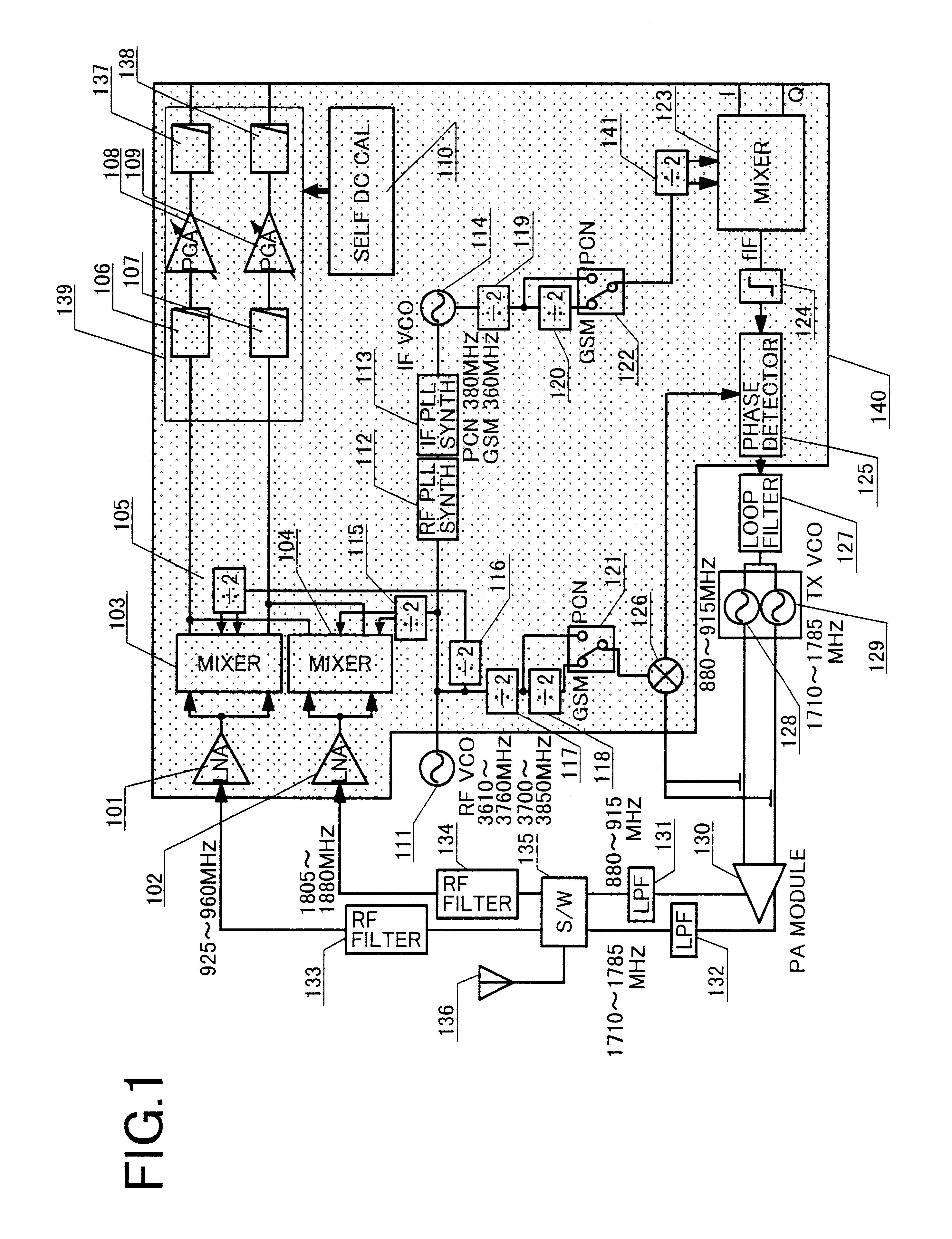

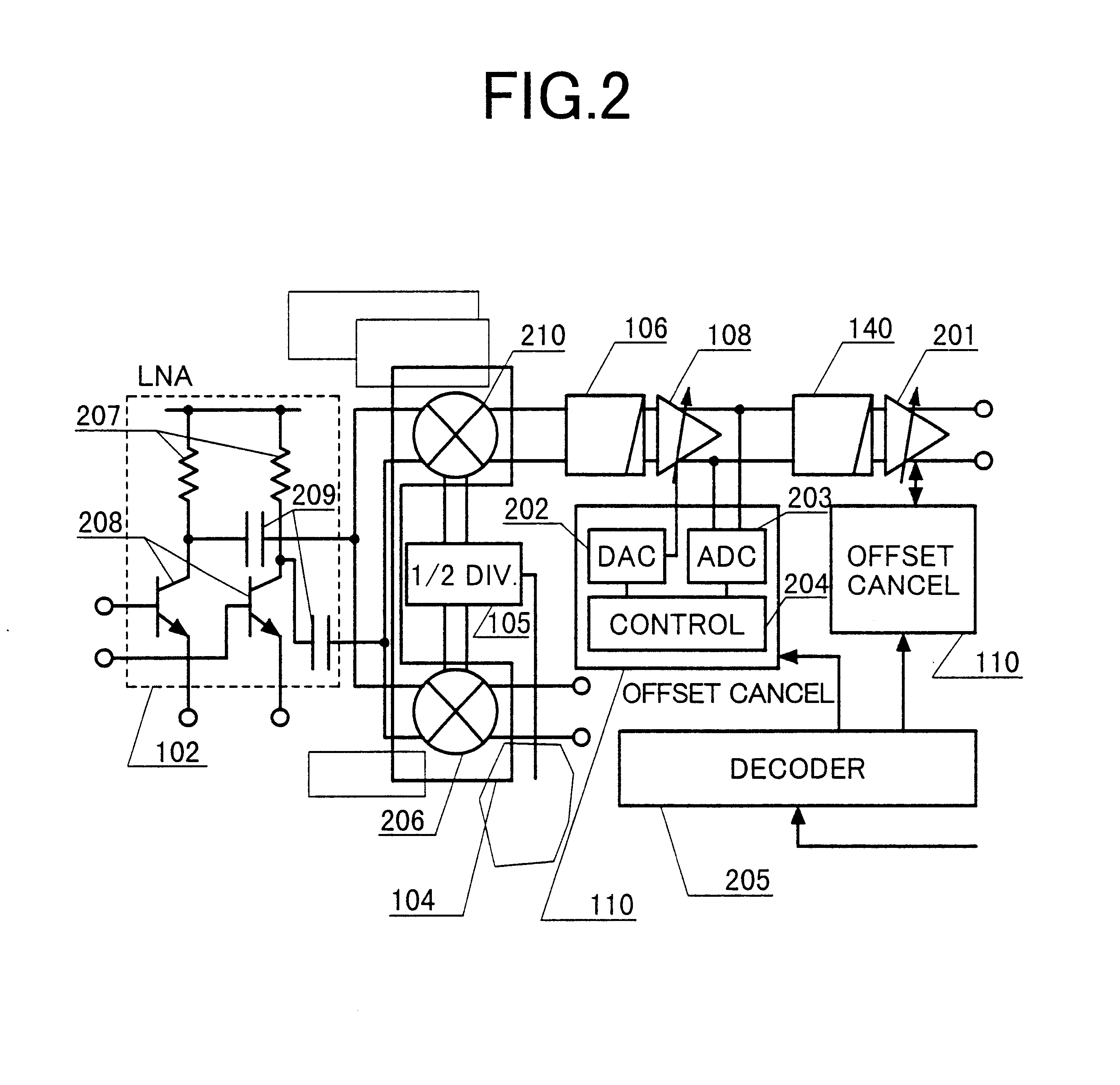

Mobile communication apparatus including dividers in transmitter and receiver

A transceiver suitable for larger scale of integration employs direct conversion reception for reducing the number of filters. Also, the number of VCOs is reduced by utilizing dividers to supply a receiver and a transmitter with locally oscillated signals at an RF band. Dividers each having a fixed division ratio are used for generating locally oscillated signals for the receiver, while a divider having a switchable division ratio are used for generating the locally oscillated signal for the transmitter. In addition, a variable gain amplifier for baseband signal is provided with a DC offset voltage detector and a DC offset canceling circuit for supporting high speed data communications to accomplish fast cancellation of a DC offset by eliminating intervention of a filter within a feedback loop for offset cancellation.

Owner:TTPCOM

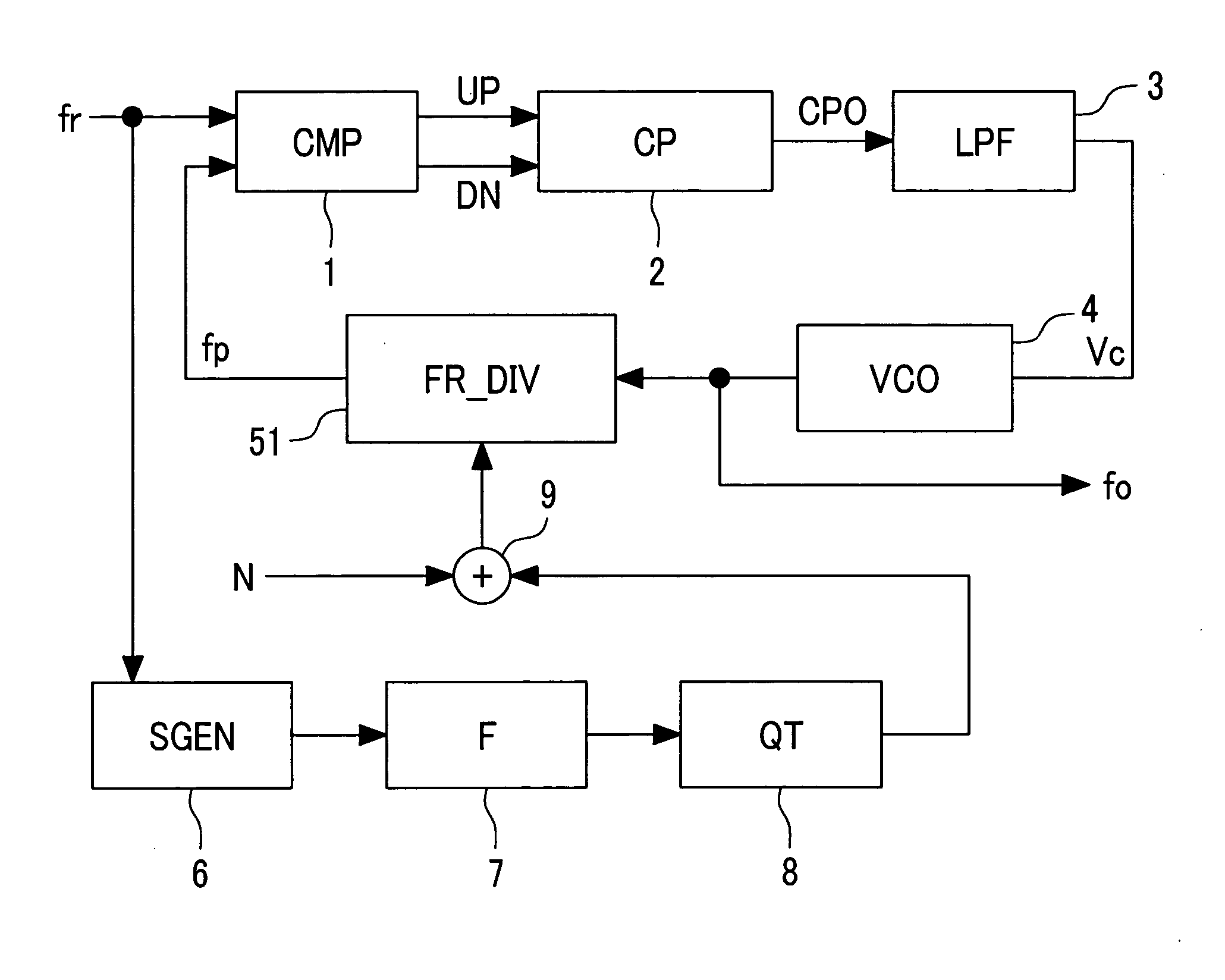

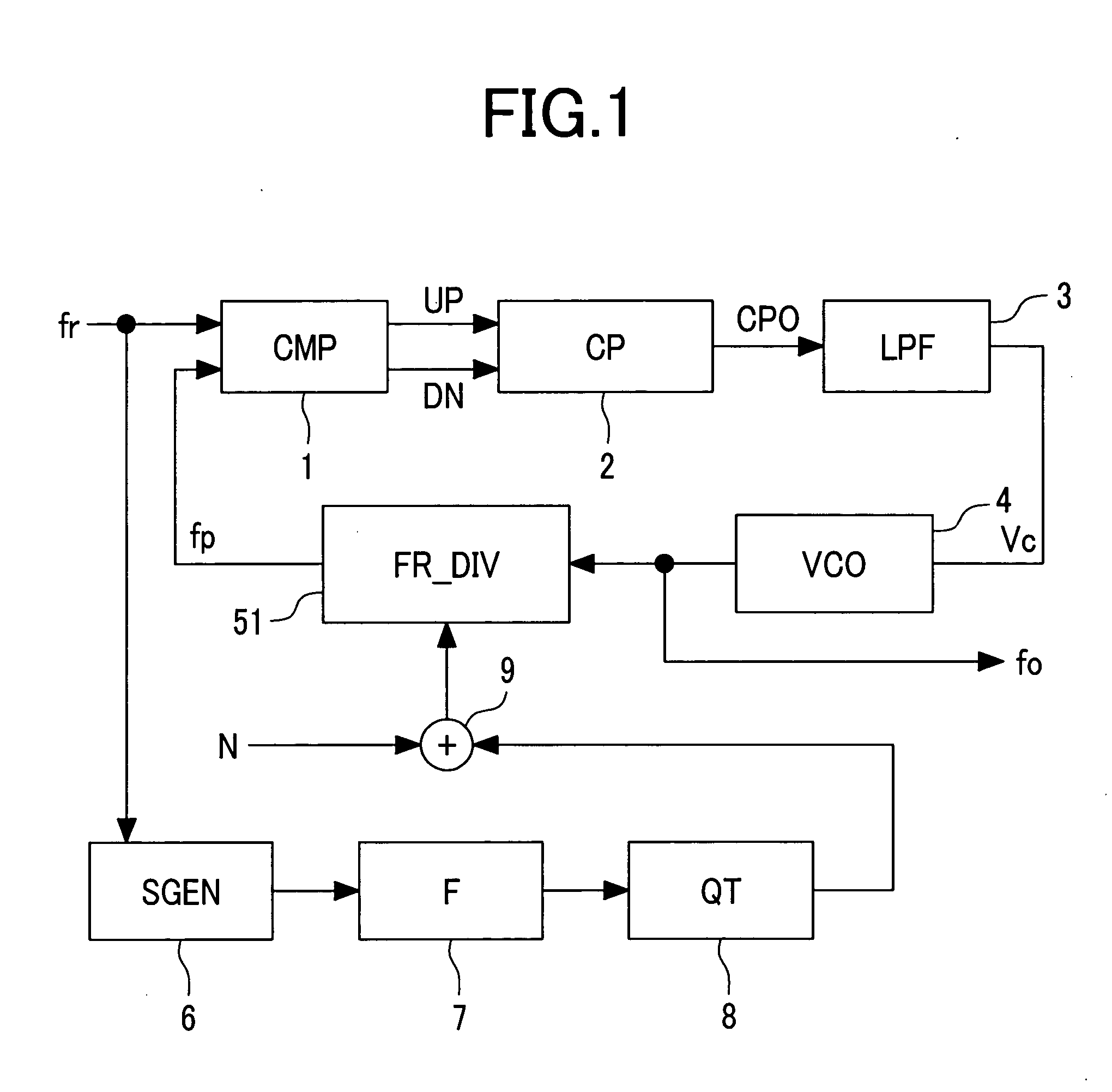

Spread spectrum clock generator and integrated circuit device using the spread spectrum clock generators

ActiveUS20050008113A1Prevents precipitous phase variationInhibitionPulse automatic controlGenerating/distributing signalsPhase variationElectromagnetic interference

The present invention provides a spread spectrum clock generator that is capable of preventing phase jumps and jitters and suppressing the occurrence of Electro Magnetic Interference components and that can easily be applied to large scale integrated circuits. The spread spectrum clock generator can be configured with a filter, quantizer, fractional divider, and other elements. Also, this clock generator circuitry can be configured by combination of a delta-sigma ΔΣ quantizer and factional divider so that sine wave modulation and random number modulation can be realized. Thereby, control with digital values can be performed. This clock generator prevents precipitous phase variations in the output high frequency clock and makes fine phase control possible. Consequently, EMI reduction by 20-30 dB can be expected.

Owner:RENESAS ELECTRONICS CORP

Coolerless photonic integrated circuits (PICs) for WDM transmission networks and PICs operable with a floating signal channel grid changing with temperature but with fixed channel spacing in the floating grid

ActiveUS7636522B2Requirements for a hermetically sealed package are substantially relievedLaser optical resonator constructionSemiconductor laser arrangementsElectro-absorption modulatorPeak value

Owner:INFINERA CORP

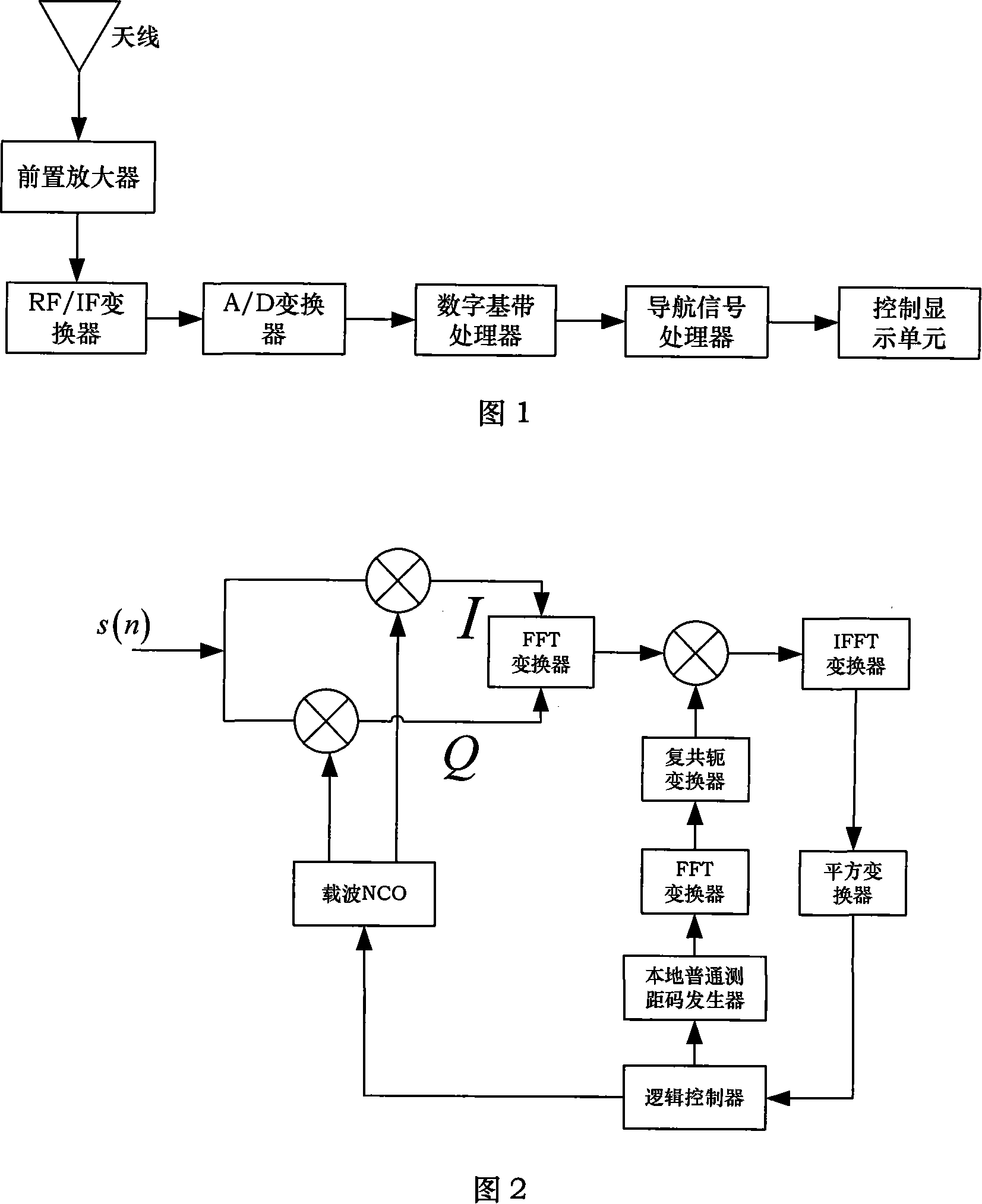

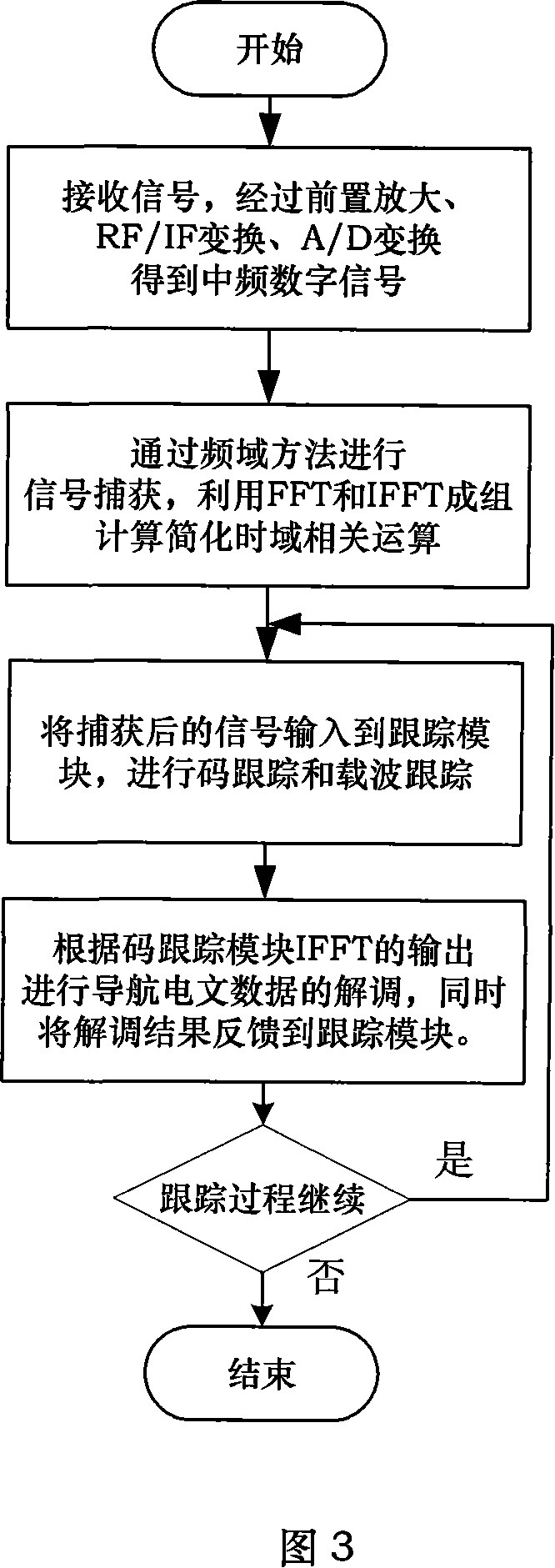

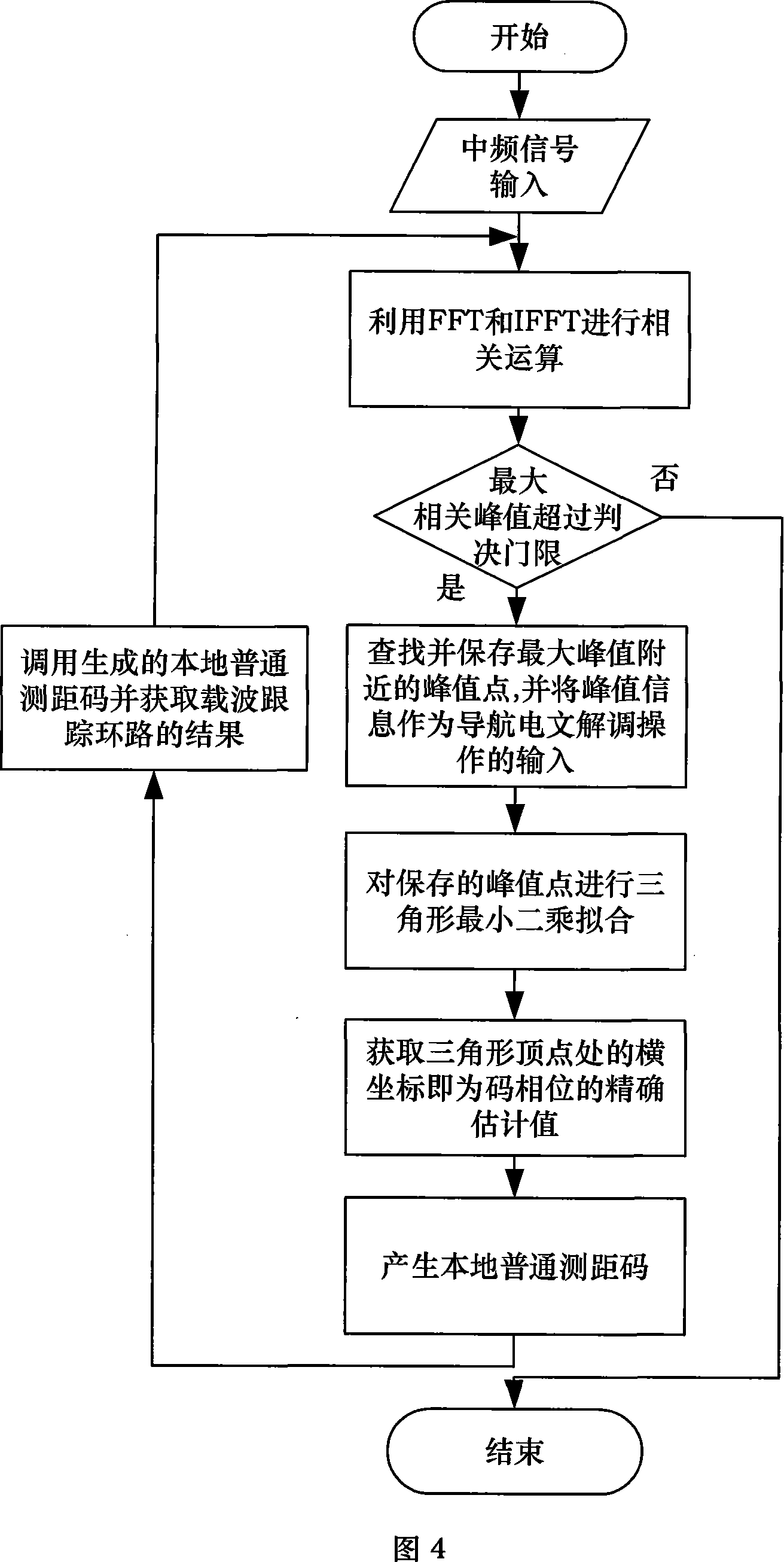

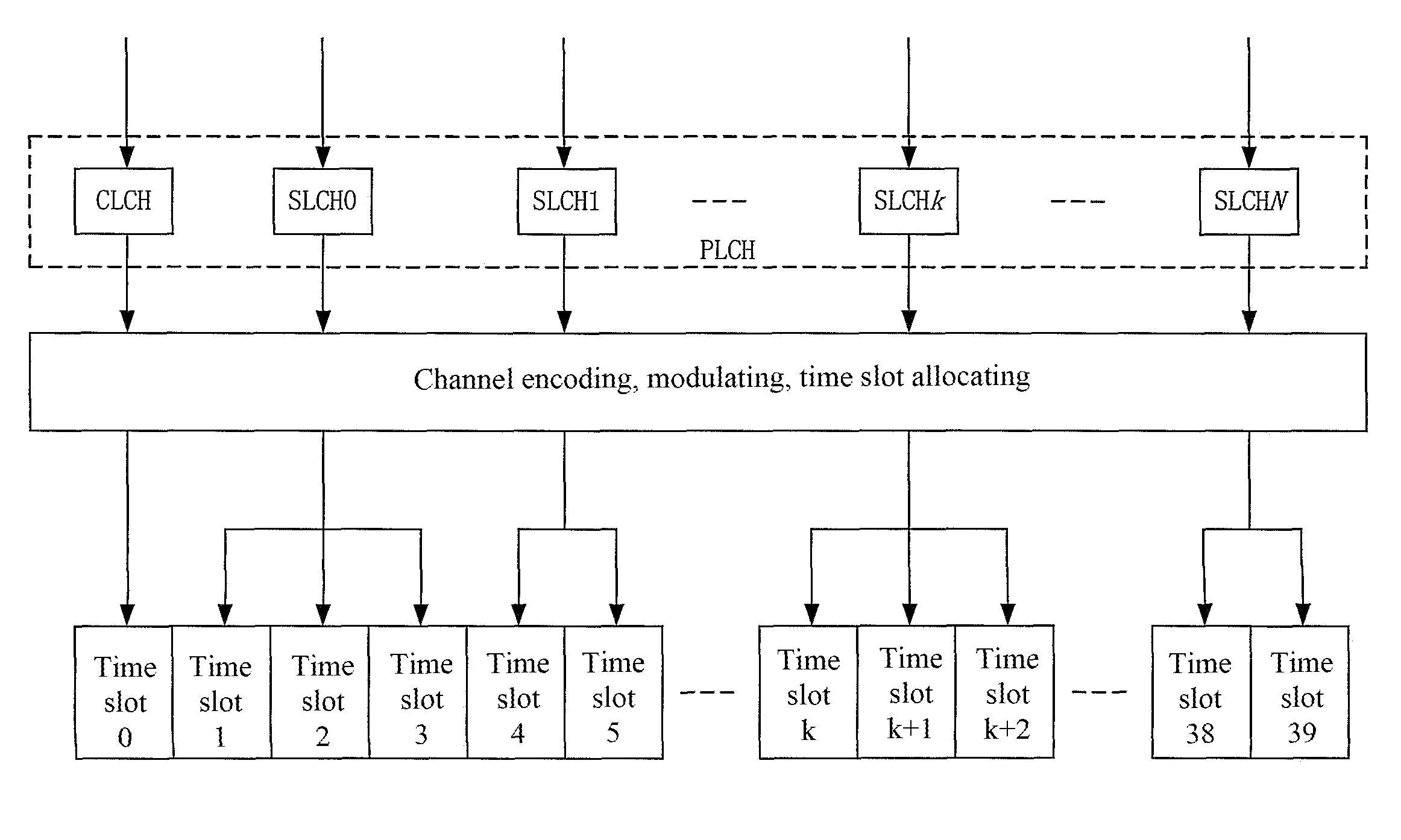

Baseband signal processing method for GNSS receiver

InactiveCN101132191AQuick captureFast recaptureMulti-frequency code systemsTransmitter/receiver shaping networksTime domainCurve fitting

This invention discloses a baseband signal processing method for GNSS receivers, particularly for common ranging-code signal for GNSS receiver, completing: the baseband signal catching, the tracking processing within frequency domain, easily for realization in large scale integrated circuit. During the signal catching step, FFT and IFFT calculation method is used for grouped calculation to simplify the time-domain related calculation. During the code-tracking, thus obtained related peak positions are found, then precision est1 mate of code phase is fulfilled by utilizing curve-fitting method. During the carrier tracking, DFT values of these points is calculated by using sliding DFT method, after the DFT point values ranges are determined based on rough carrier frequency estimate, and then proceeding estimate of carrier frequency, data demodulation by using IFFT output result.

Owner:BEIHANG UNIV

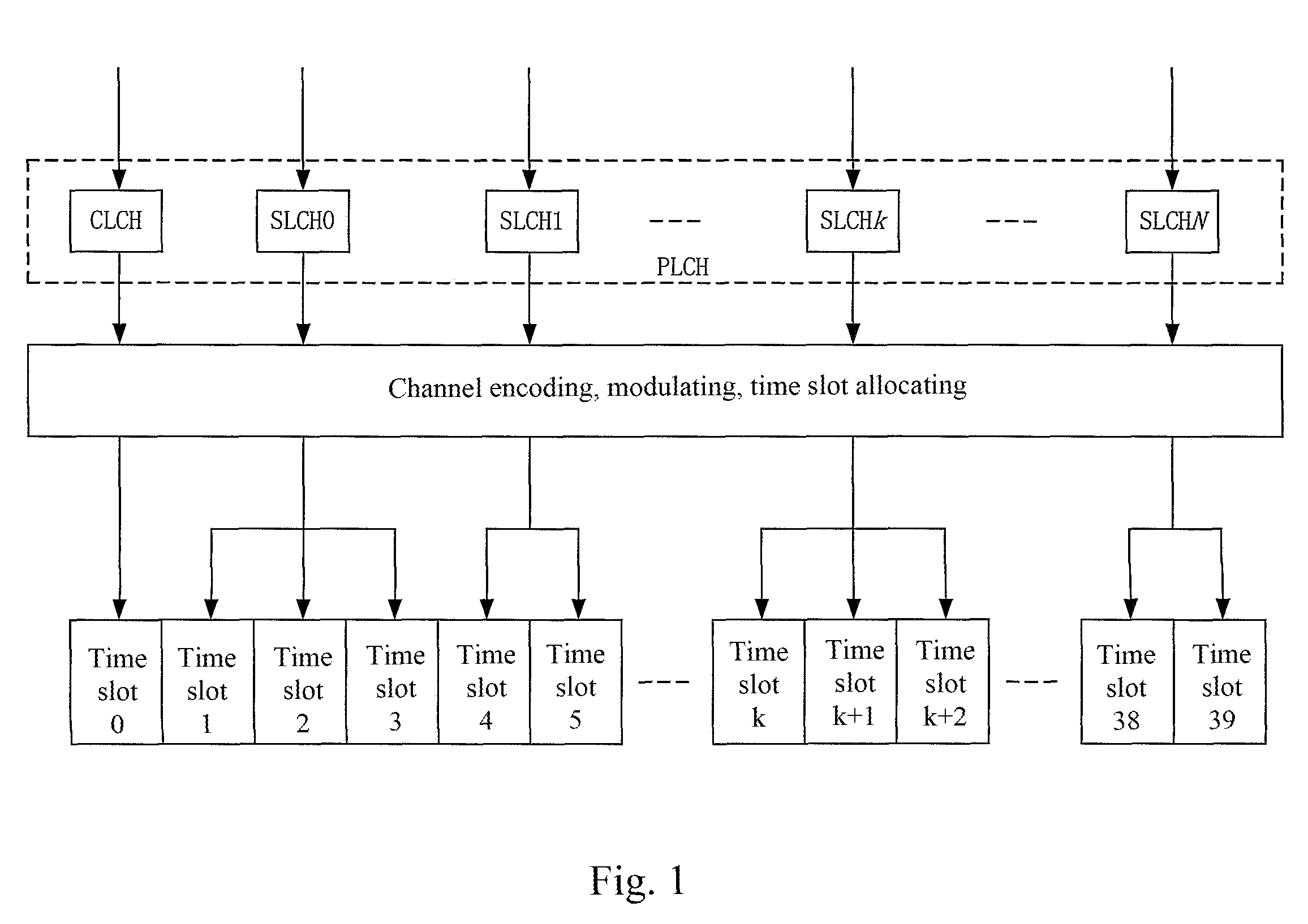

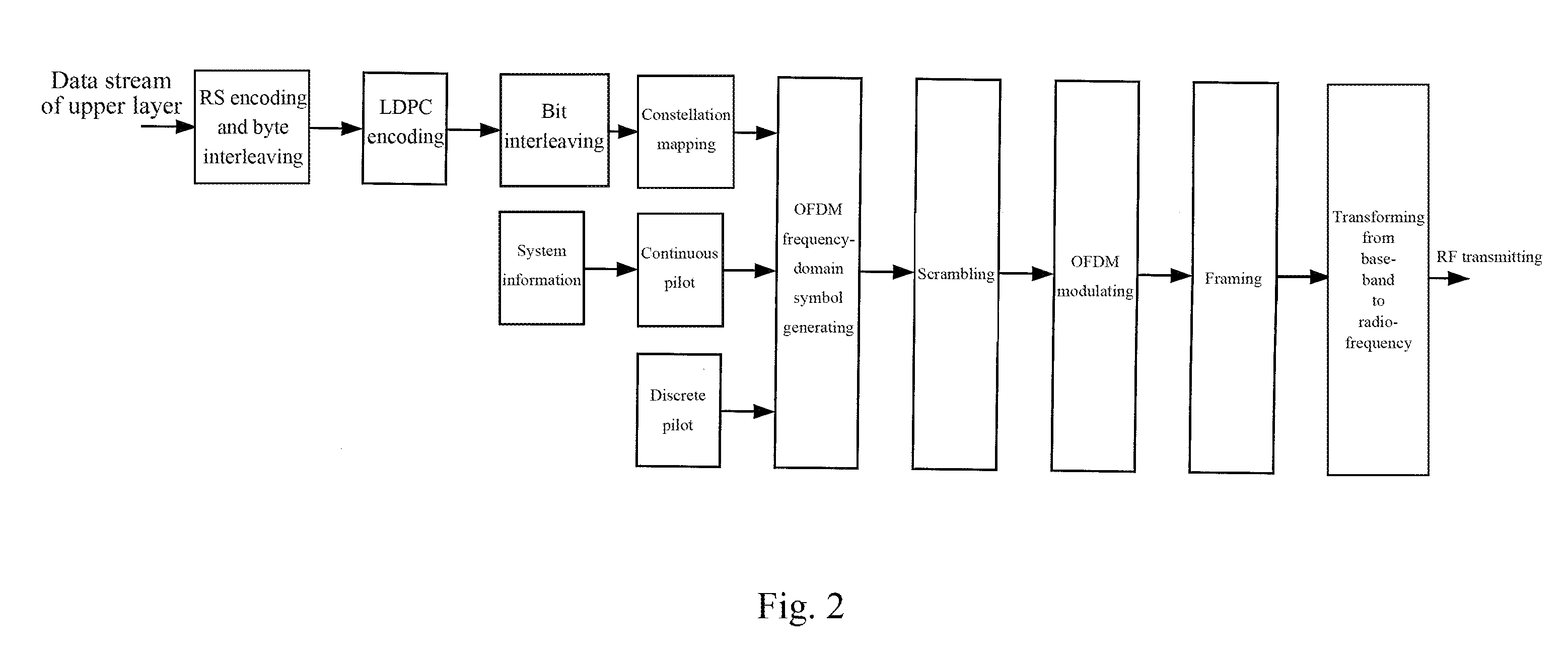

A multi-carrier digital mobile multimedia broadcast system and the digital information transmission method thereof

InactiveUS20110051825A1Low costImprove performanceBroadcast with distributionSecret communicationData streamLow-pass filter

The present invention discloses a multi-carrier digital multimedia broadcast system and the digital information transmission method thereof. After RS encoding and byte interleaving, LDPC encoding, bit interleaving and constellation mapping to an upper layer of data streams in turn, the obtained data symbol is multiplexed with scattered pilots and continual pilots which include the system information to form an OFDM frequency domain symbol and scrambled; an OFDM time domain symbol is generated by IFFT transforming, and after inserted with the frame head to build a time slot, it is connected to form a signal frame of the physical layer; the signal frame of the physical layer is transmitted after being low-pass filtered and orthogonal upconverted. The system and method thereof provide wireless broadcast with high quality such as audio, video and multimedia data and the like for mobile, fixed and portable receivers, and can use the satellite transmission and terrestrial transmission method for transmitting. The method utilizes the LDPC OFDM scheme, and the system applies the microwave and large scale integrated circuit technologies while fulfills the needs for low cast and high performance.

Owner:TIMI TECH

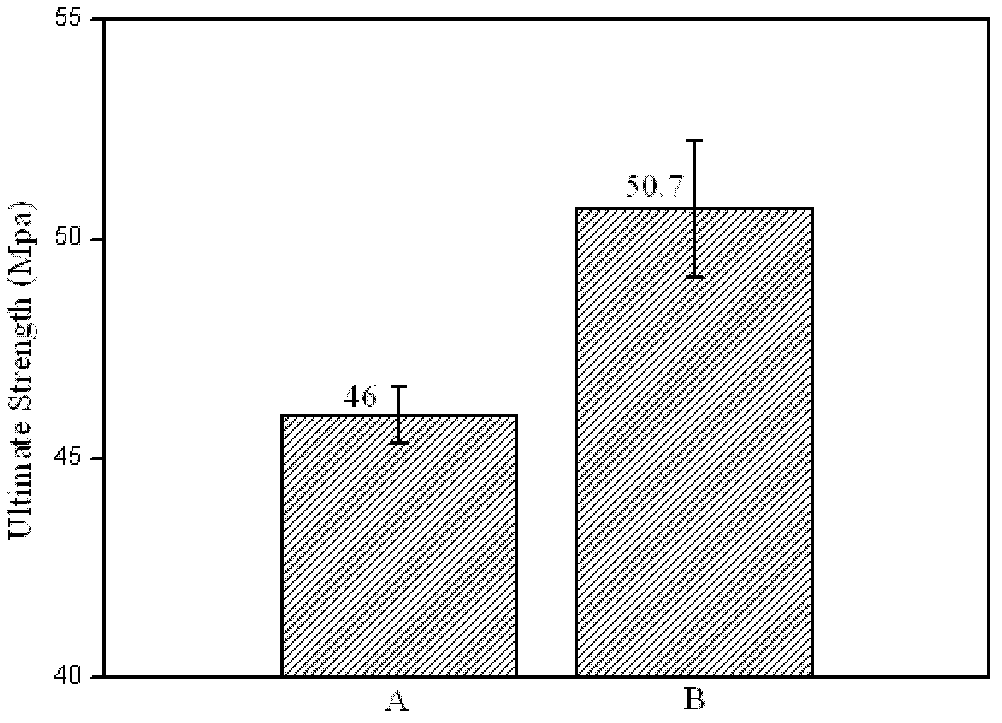

Graphene reinforced lead-free solder and preparation method thereof

ActiveCN102581504ADoes not damage the structureGood dispersionWelding/cutting media/materialsSoldering mediaGrapheneElectronic industry

The invention discloses a graphene reinforced lead-free solder, which comprises, by weight parts, graphene and lead-free solder base body of the ratio of 0.75-1.75:50000. The preparation method includes: by means of process of powder metallurgy, disposing the graphene into absolute ethyl alcohol according to proportion, vibrating ultrasonically, milling and drying the absolute ethyl alcohol with the graphene, mixing and stirring the absolute ethyl alcohol and the lead-free solder base body, pressing the same into a blank, sintering the blank at the temperature of 175 DEG C under the protective atmosphere of high-purity argon, extruding the same into a bar with the diameter of 6mm, and preparing the graphene reinforced lead-free solder. The graphene reinforced lead-free solder can meet the requirements of environmental protection and reliable welding, substitutes for conventional stannum-lead solder, has higher and more reliable mechanical performance than lead-free solder in the prior art, can be used as connection materials for oversized integrated circuits and is a composite material according with development trends of the modern electronic industry.

Owner:TIANJIN UNIV

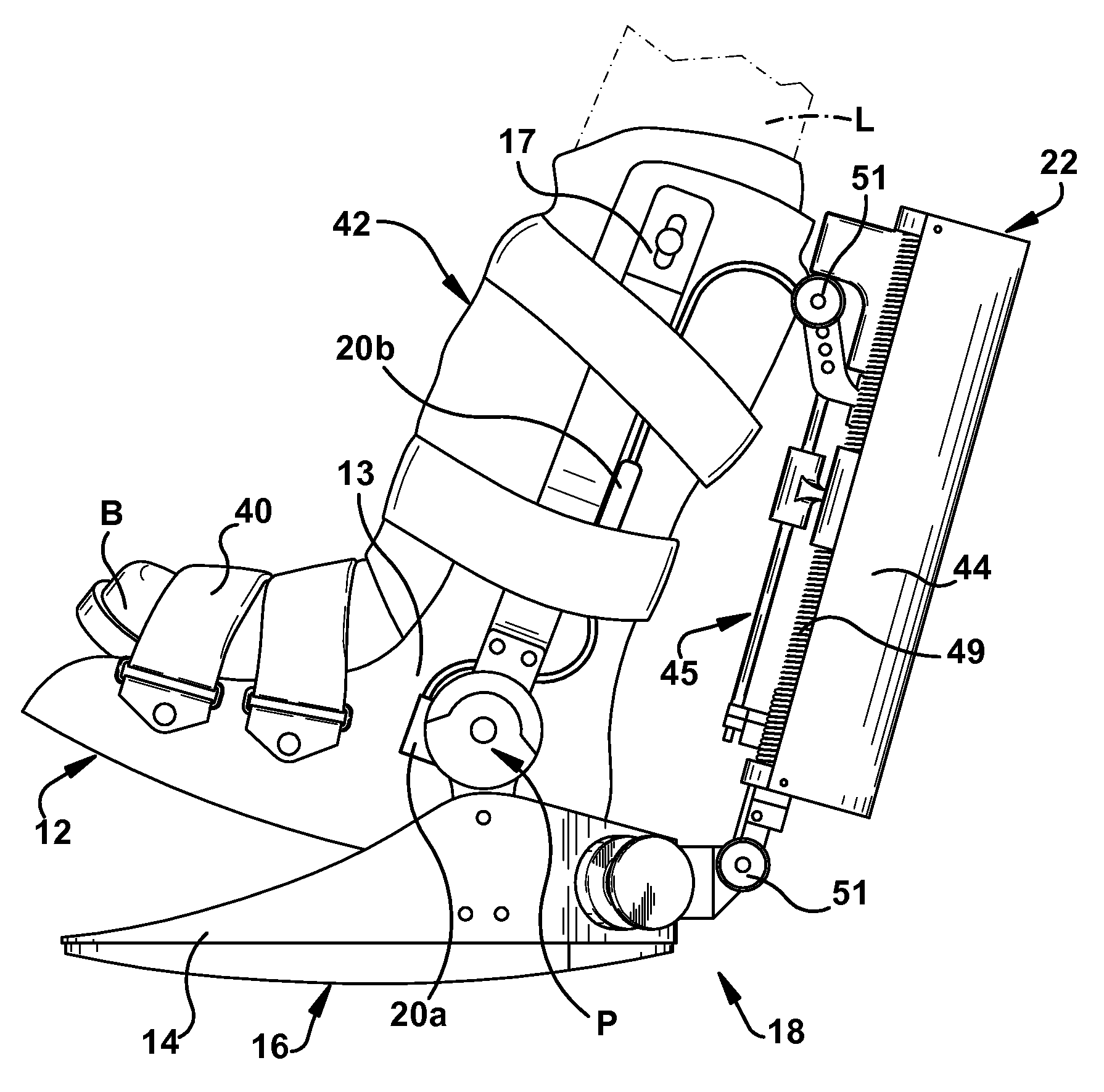

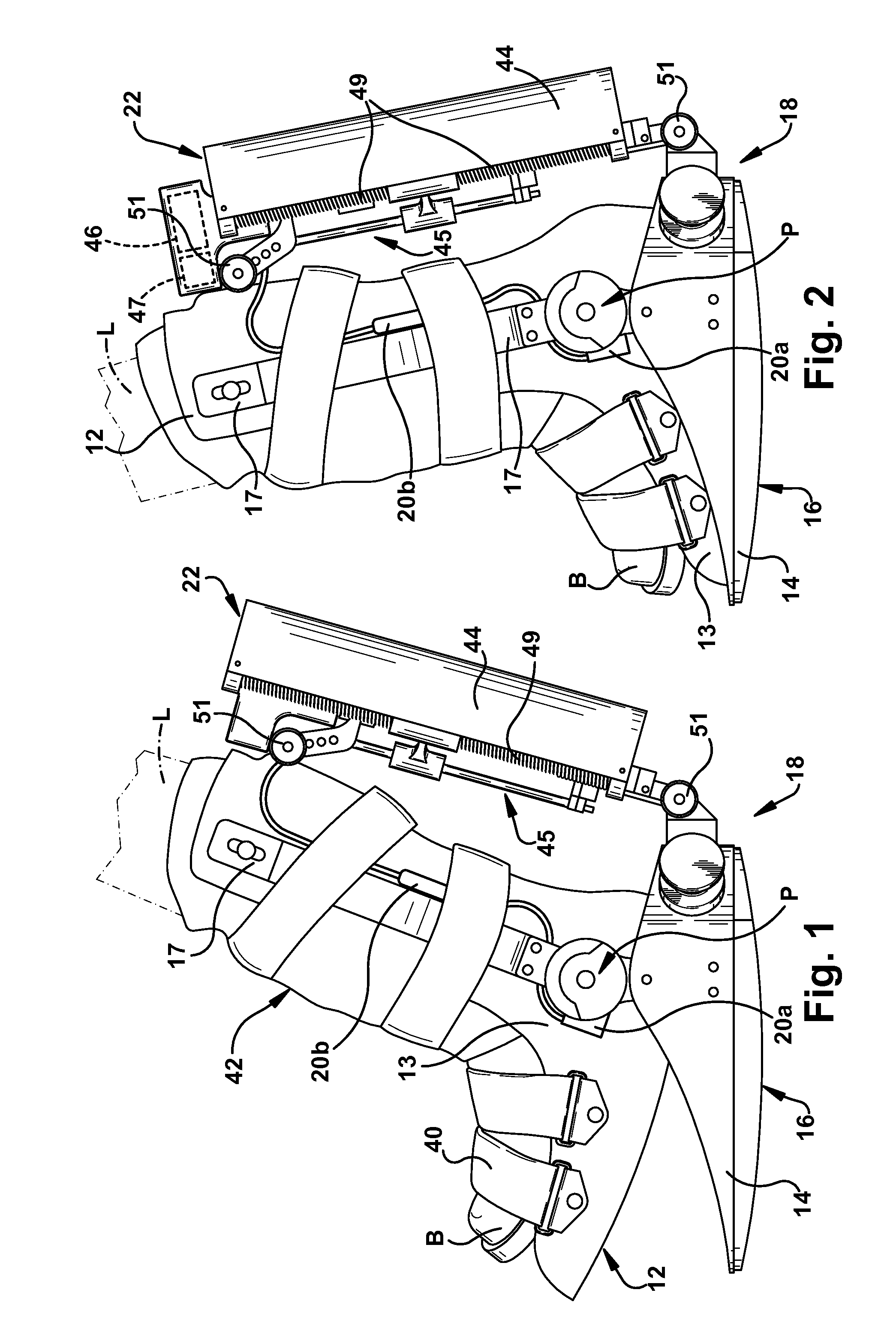

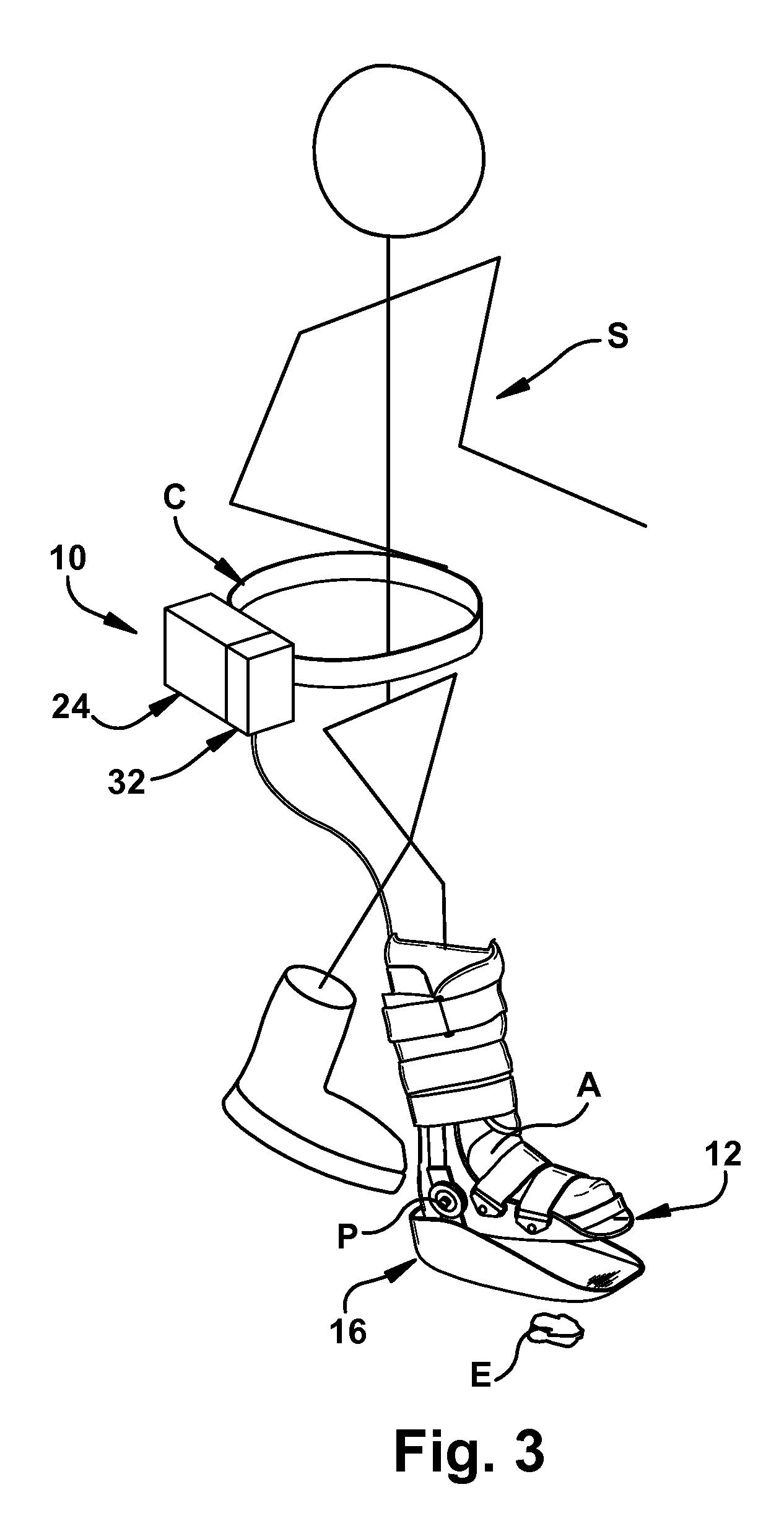

Neuromorphic controlled powered orthotic and prosthetic system

ActiveUS8790282B2Advanced technologyImprove motor functionDiagnosticsChiropractic devicesRange of motionSpinal cord

A neuromorphic controlled powered orthotic and prosthetic system and device including a custom or universal fit fixed-ankle orthosis, to stabilize or immobilize an injured lower limb or act as an ankle prosthesis, and an actuated or powered articulated false-foot connected to the fixed-ankle orthosis or the prosthesis to form an actuated articulated false-foot orthosis. Associated with or mounted on the actuated articulated false-foot, or in or on the body, are sensors for sensing the intent of the subject to move, and the movement range of the articulating false-foot or AAFO and an environmental perturbation. An actuator is used to drive the articulated false-foot orthosis. The system and device further include a controller having an electronic circuit with a biomimetic design based on knowledge of connectivity of neurons within the spinal cord of a primitive vertebrate. The system and device include an electronic circuit made from analog very large scale integrated components and discrete electronic components capable of autonomously generating cyclic voltage output. An integral power supply serves the portable controller and AAFO.

Owner:ADVENSYS

Incremental critical area computation for VLSI yield prediction

InactiveUS6044208ASemiconductor/solid-state device testing/measurementSolid-state devicesMaterial defectLinear approximation

An efficient method to compute critical area for shorts and breaks in rectilinear layouts in Very Large Scale Integrated (VLSI) circuits. The method is incremental and works in the L INFINITY geometry and has three major steps: Compute critical area for rectilinear layouts for both extra material and missing material defects (i.e., shorts and opens) by modeling defects as squares (which corresponds to the L INFINITY metric) instead of circles (Euclidean geometry). Treat the critical region for shorts and opens between any two edges or corners of the layout as a rectangle that grows uniformly as the defect radius increases. This is valid for rectilinear layouts and square defects (L INFINITY metric) . Use an incremental critical area algorithm for shorts and opens, which are computed for rectilinear layouts assuming square defects. Non-rectilinear layouts are approximated, first, by a rectilinear layout using a shape processing tool. The critical area for the rectilinear approximation is computed using the preferred incremental method.

Owner:GLOBALFOUNDRIES INC

Preparation method of high-thermal conductivity graphene-Sn-Ag composite brazing filler metal

ActiveCN104400247AImprove performanceSolve reunionWelding/cutting media/materialsSoldering mediaDensity differenceCvd graphene

The invention discloses a preparation method of a high-thermal conductivity graphene-Sn-Ag composite brazing filler metal, ad relates to a preparation method of a high-thermal conductivity composite brazing filler metal. The preparation method has the following purposes: the problem of graphene floating and agglomeration in the preparation and application process of the composite brazing filler metal is solved by reducing a greater density difference between graphene and an Sn-Ag brazing filler metal matrix through plating a metal on the graphene; meanwhile, the graphene is dispersed more uniformly in the brazing filler metal matrix; and the reliability of sealing and brazing is improved by improving the heat conductivity of the composite brazing filler metal through adding the graphene. The method comprises the following steps: (1) the metal is plated on the graphene; and (2) the ball milling, the mixing and the medium-temperature smelting are performed for the metal-plated graphene and the Sn-Ag brazing filler metal to obtain the high-thermal conductivity composite brazing filler metal. The prepared composite brazing filler metal is high in thermal conductivity, has a higher wettability compared with a traditional Sn-Ag brazing filler metal, and is a composite brazing filler metal accordant with the present development tendency of an electronic industry as a connecting material of traditional large-scale integrated circuits.

Owner:HARBIN INST OF TECH

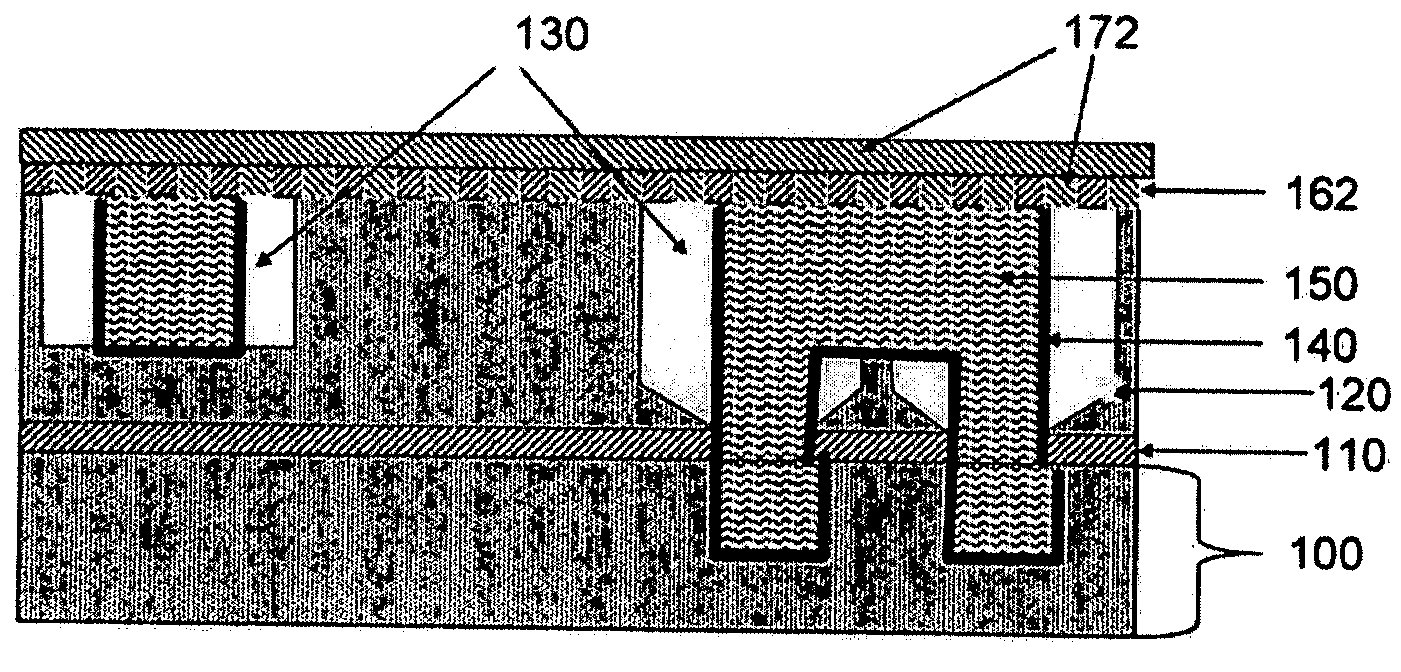

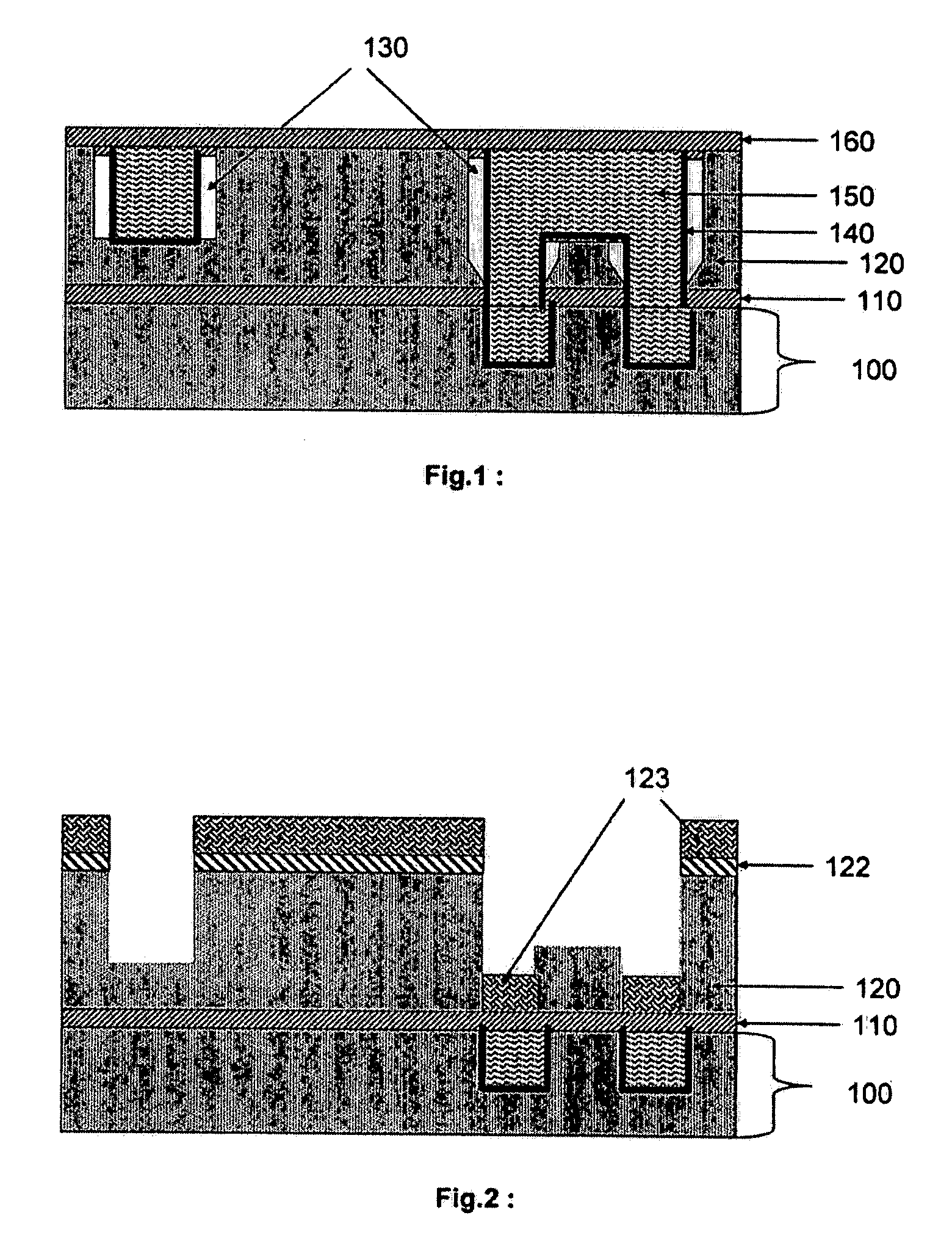

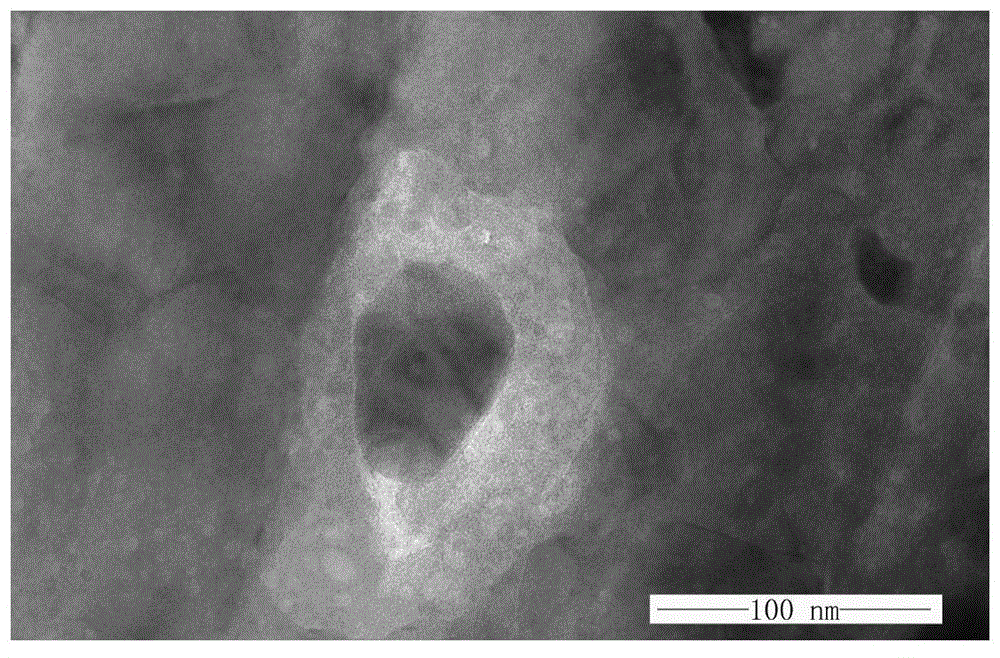

Laminated structure, very-large-scale integrated circuit wiring board, and method of formation thereof

InactiveUS20080079154A1Prevent peelingEfficient manufacturingSemiconductor/solid-state device detailsSolid-state devicesVery large scale integrated circuitsCopper plating

The laminated structure includes a substrate of low dielectric constant material of silicon compound and an electroless copper plating layer laminated thereon with a barrier layer. The barrier layer is interposed between the substrate and the copper layer, and the barrier layer is formed by electroless plating. And the laminated structure is characterized in that the barrier layer is formed on the substrate with a monomolecular layer of organosilane compound and a palladium catalyst which are interposed between the substrate and the barrier layer, the palladium catalyst modifies the terminal, adjacent to the barrier layer, of the monomolecular layer, and the barrier layer includes an electroless NiB plating layer which is disposed on the substrate side, and a electroless CoWP plating layer.The present invention makes it possible to coat the low dielectric constant material of silicon compound in a simple all-wet process with a firmly adhering barrier layer and an electroless copper plating layer as the wiring layer. the advantage of requiring. Thus, the laminated structure formed in this way includes a substrate of low dielectric constant material of silicon compound, a barrier layer, and a copper layer as the wiring layer formed by electroless plating, which firmly adhere to one another. In addition, the laminated structure is suitable for the copper wiring in a ULSI, particularly the one which is to be formed in a narrower trench than conventional one.

Owner:WASEDA UNIV

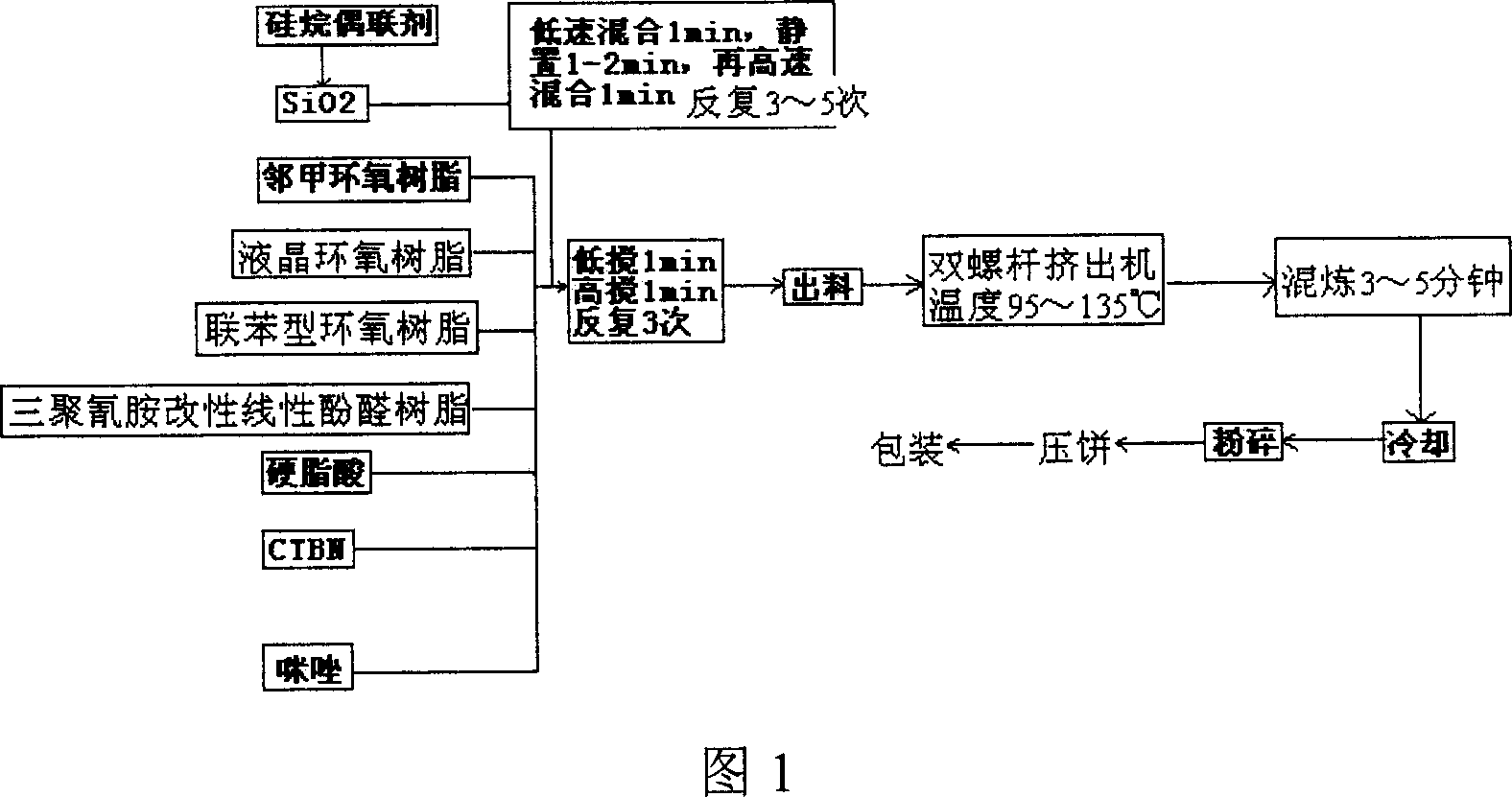

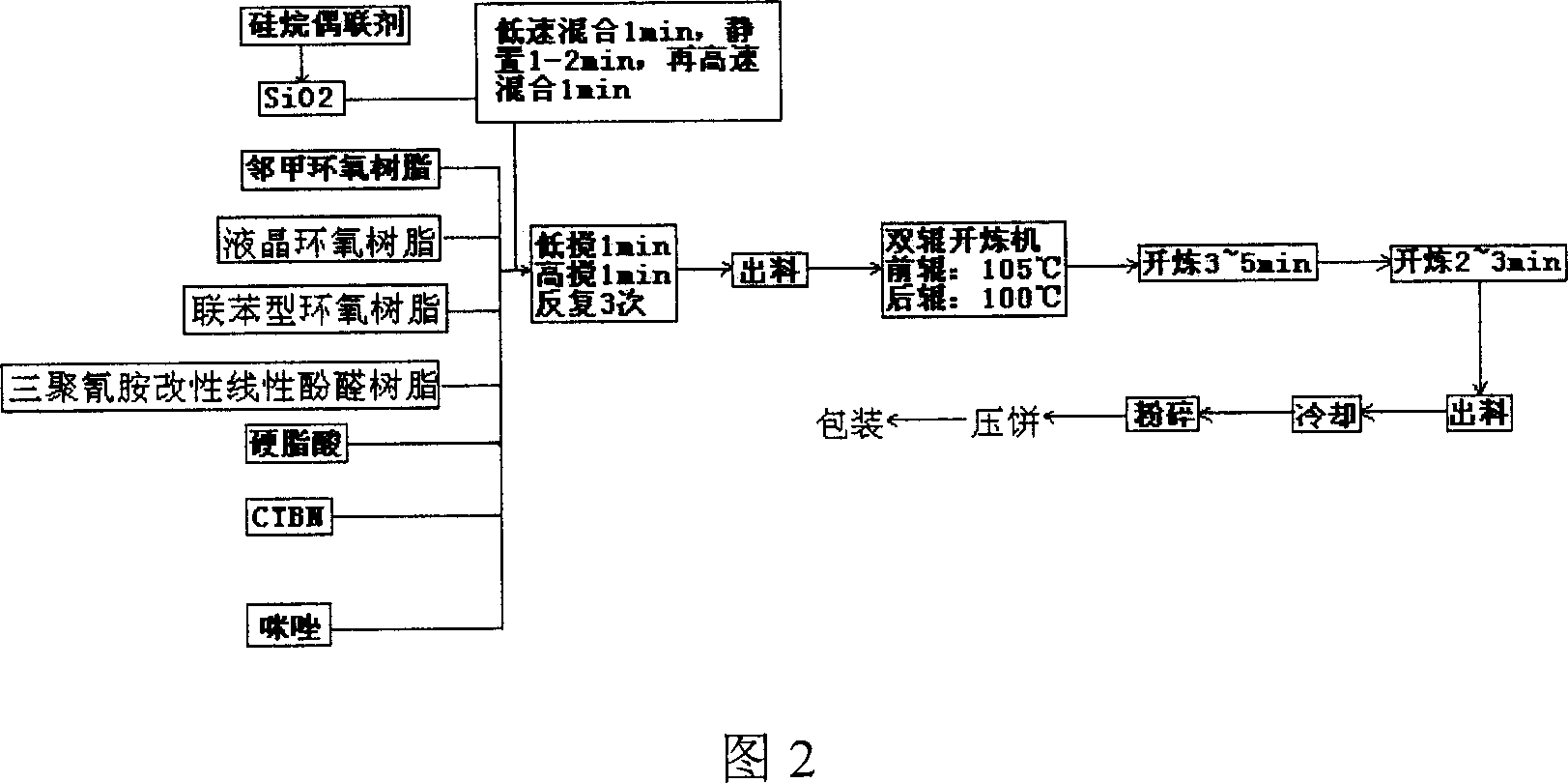

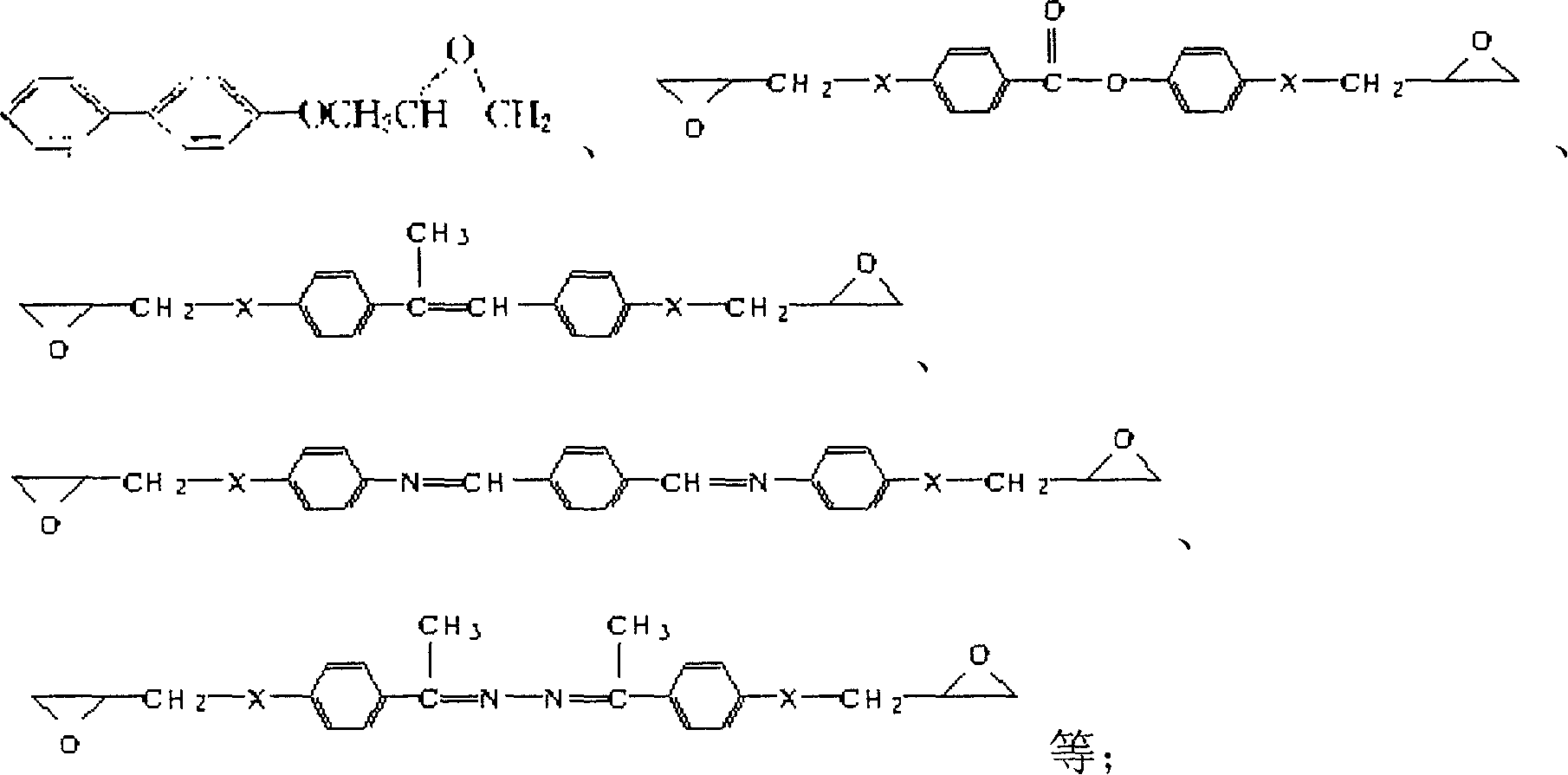

Epoxy-resin mould plastic for packing IC circuit and its production

InactiveCN101029165AHigh glass transition temperatureReduce melt viscositySemiconductor/solid-state device detailsSolid-state devicesEpoxyThermal expansion

An epoxy resin mold plastic and its production are disclosed. The mold plastic consists of liquid-crystal epoxy resin, methyl-phenolic epoxy resin, epoxy resin containing biphenyl unit structure, melamine modified linear phenolic resin, silicone micro-powder, imidazo curing improver, toughening agent and silane coupling agent. The process is carried out by treating silicone micro-powder in mixer by coupling agent for 2-5mins, adding into other components, mixing for 3-5mins, melt milling at 95-135 degree for 3-5mins, cooling, crushing, mesh screening, pressing into material cake and storing below 6degree. Its advantages include low thermal expansion coefficient, excellent heat and fire resistances, better toughness and fluidity, no phosphor, no antimony and environmental pollution. It can be used to pack large-scale circuit and electronic devices.

Owner:GUANGDONG RONGTAI IND

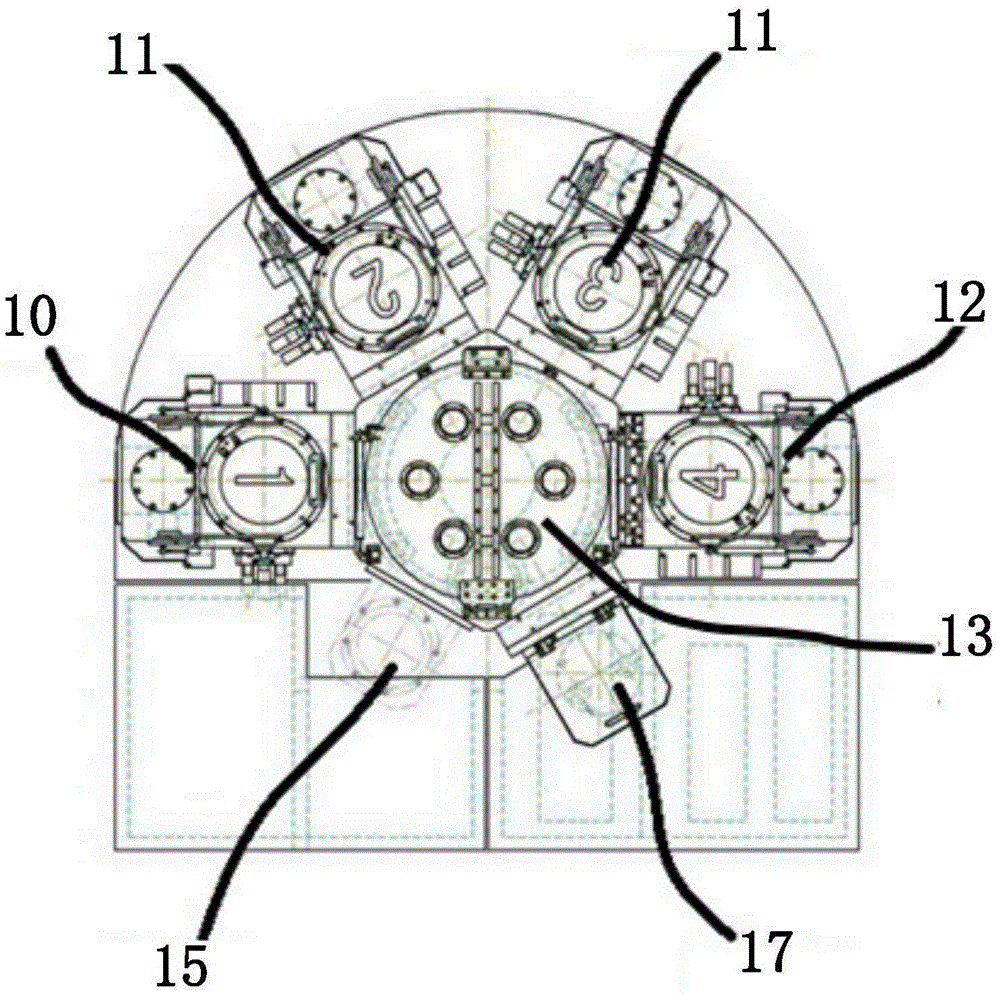

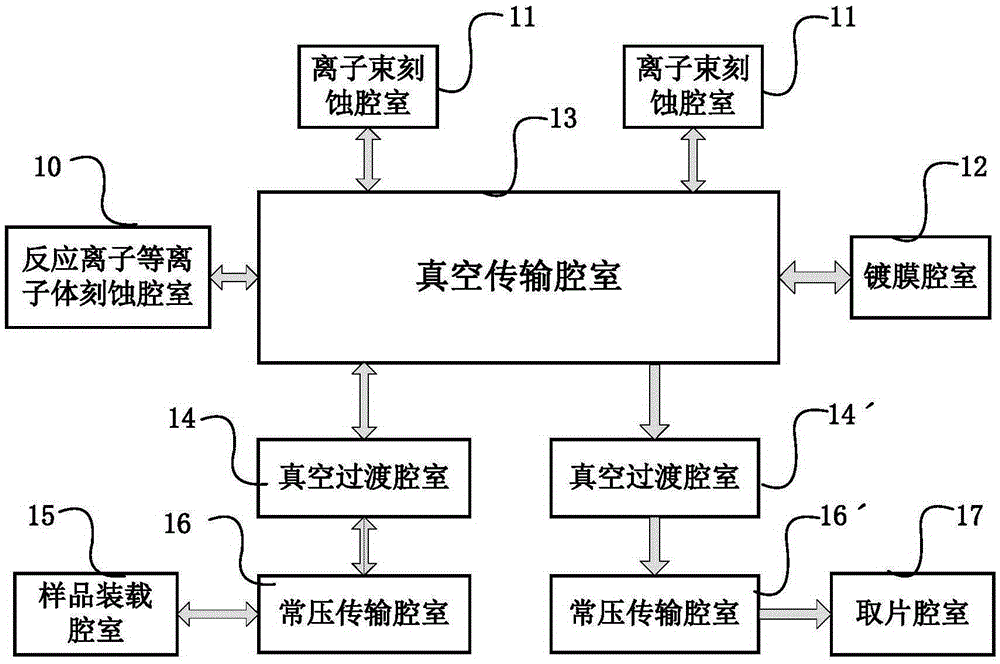

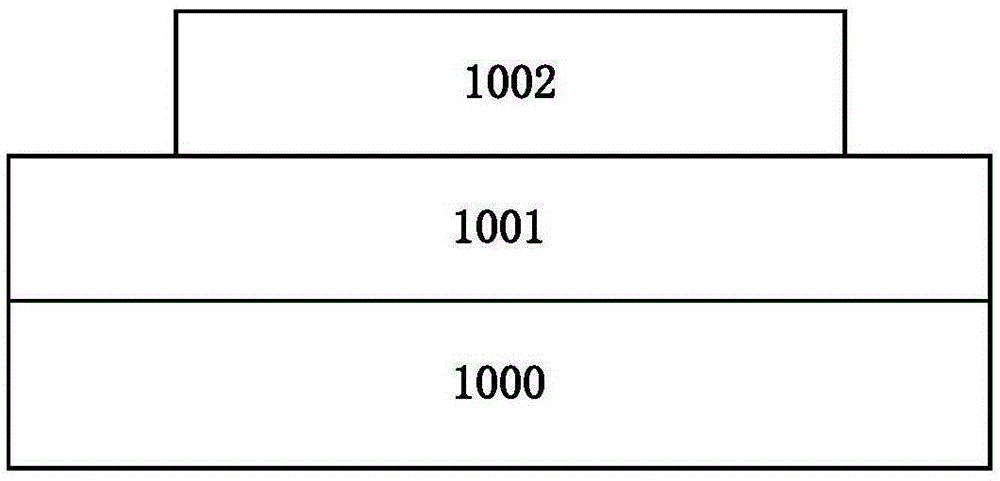

Metal etching device and method

ActiveCN106676532AImprove yieldUndamagedGalvano-magnetic device manufacture/treatmentMetal contaminationTunnel junction

The invention discloses a metal etching device and method which can be used in a large-scale integrated circuit industrial manufacturing environment. Particularly, by means of the metal etching device and method, in a vacuum uninterrupted environment, magnetic tunnel junctions of a magnetic random access memory (MRAM) are subjected to etching and etching post-processing in a reactive-ion plasma etching chamber and an ion beam etching chamber and then subjected to coating surface protection in a coating chamber, so that the side wall of the magnetic tunnel junctions are free of metal contamination after being etched, the chemical and physical structures of the magnetic tunnel junctions are consistent with the chemical and physical structures before etching, the magnetic tunnel junctions can be taken out from etching equipment and not destroyed by the air environment, and the yield of MRAM devices is effectively increased. In addition, the metal etching device and method are also applicable to etching of resistive random access memories and other metals.

Owner:江苏鲁汶仪器股份有限公司