Patents

Literature

2553 results about "Copper-wiring" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Copper is the electrical conductor in many categories of electrical wiring. Copper wire is used in power generation, power transmission, power distribution, telecommunications, electronics circuitry, and countless types of electrical equipment.

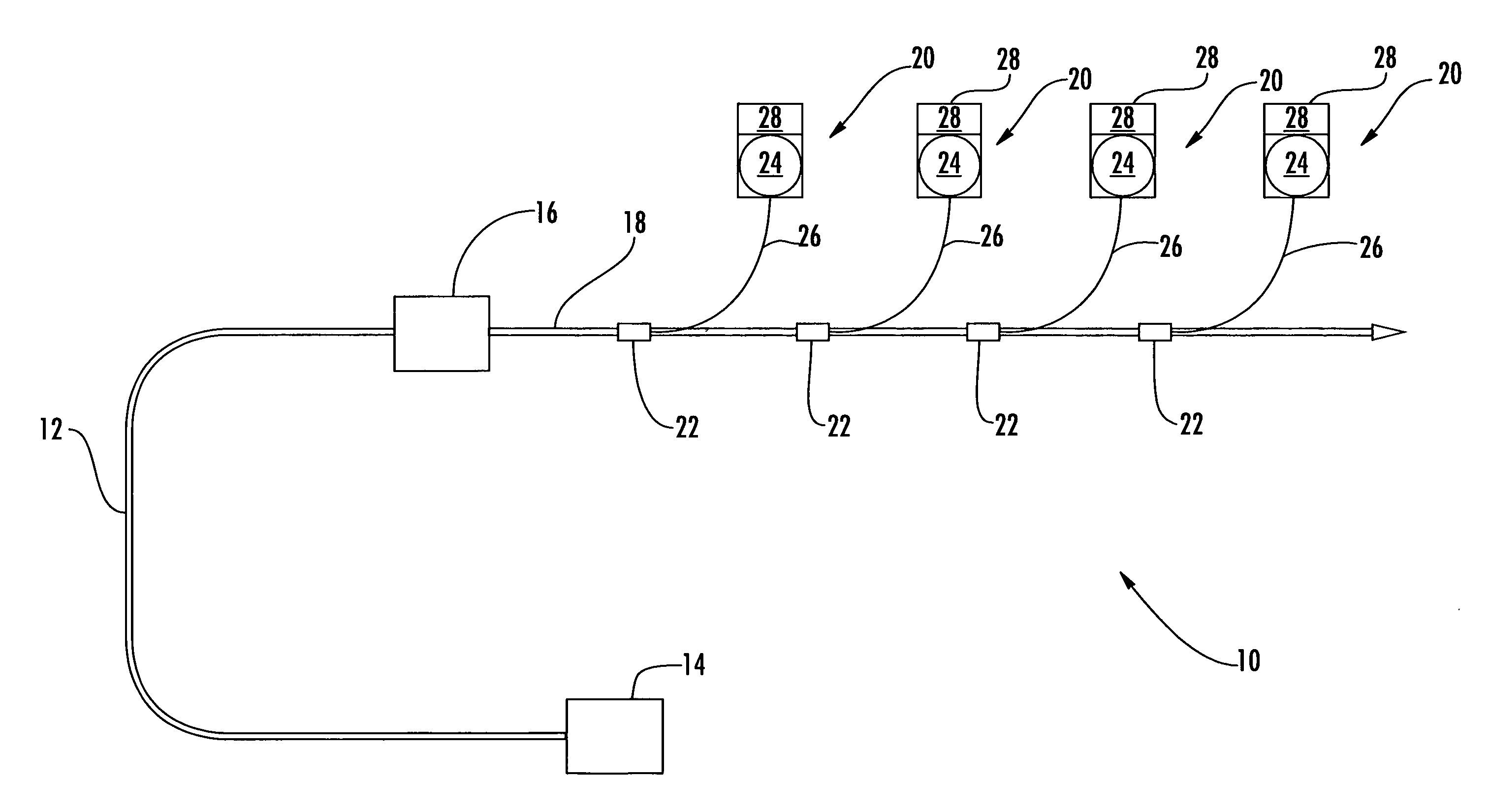

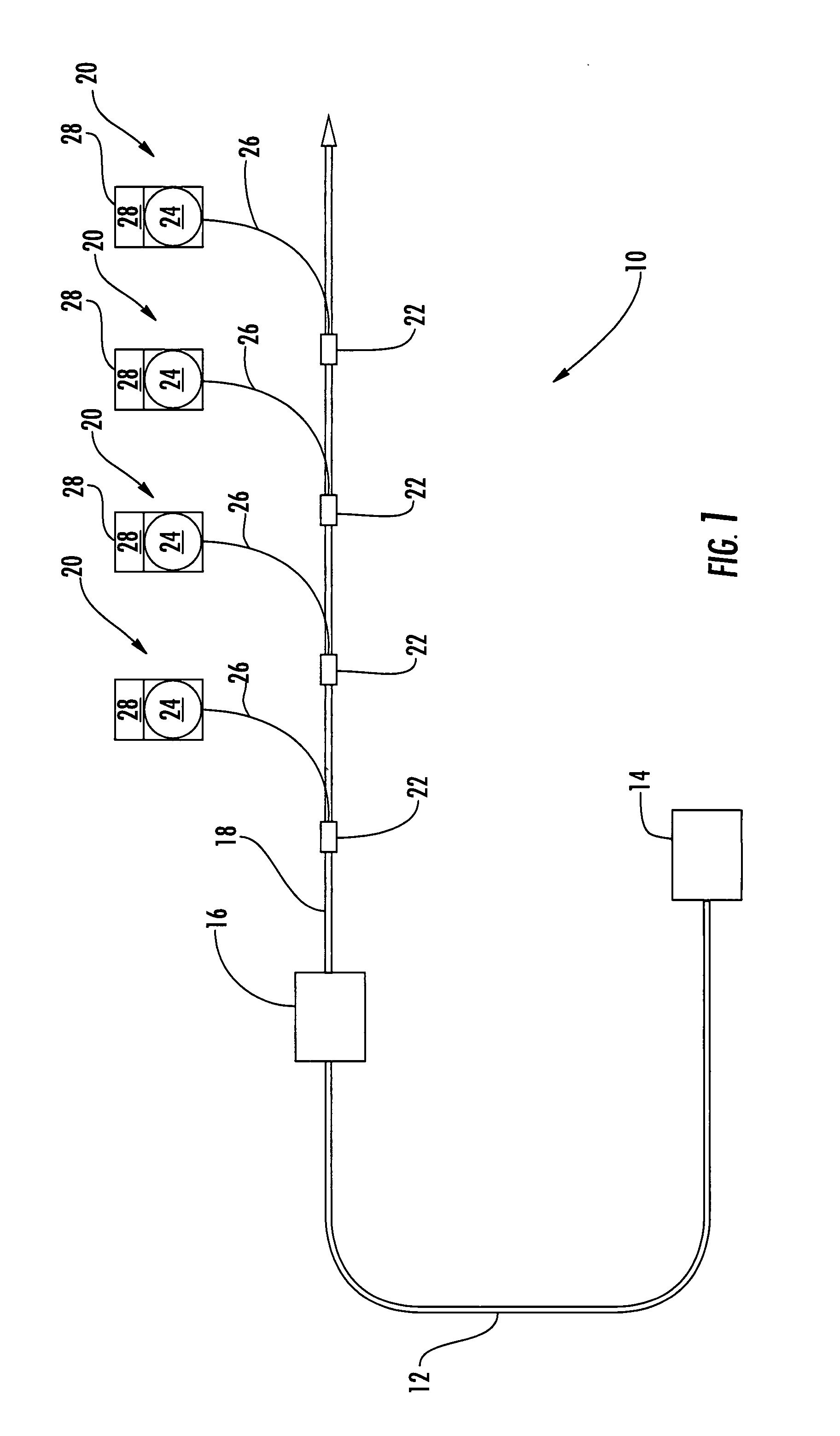

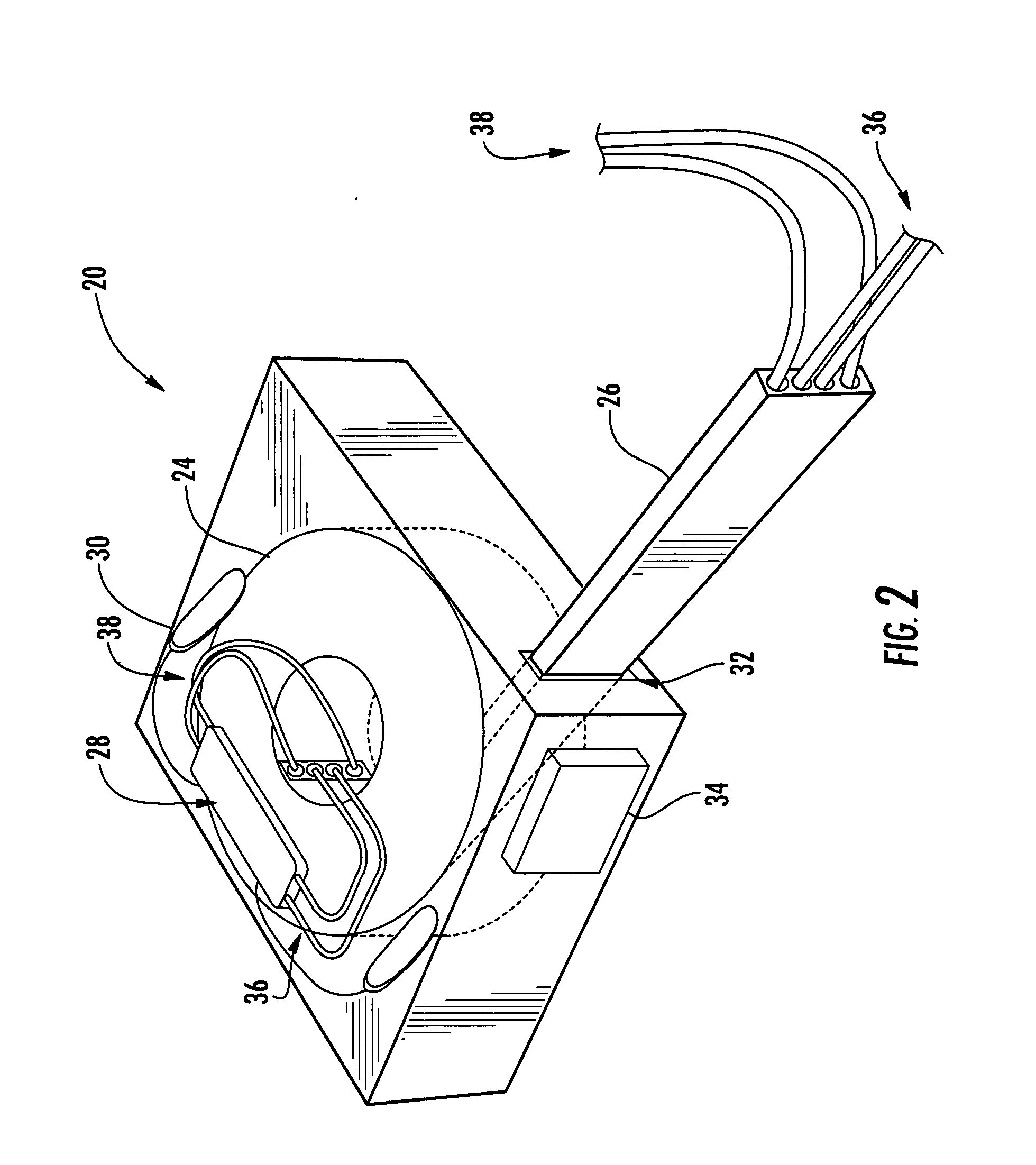

Retractable optical fiber tether assembly and associated fiber optic cable

The present invention provides an optical system that allows for the flexible location of an optical device that is coupled to a patch panel in a wiring closet or other optical signal source through a series of fiber optic cables and optical connections, or the flexible location of an array of such optical devices. The optical system includes, in part, one or more retractable optical fiber tether assemblies that each allow varying lengths of tether cable to be pulled and used. The retraction device of each of the optical tether assemblies may be disposed mid-tether cable, or may terminate the respective tether cable and incorporate the given optical device. In an exemplary wireless local area network (WLAN) application, each of the retractable optical fiber tether assemblies includes an integral transceiver and associated software. Thus, each of the retractable optical fiber tether assemblies functions as an antenna. The associated fiber optic cable carries both optical fiber to provide optical continuity and copper wire to provide electrical conductivity to the antenna array.

Owner:CORNING OPTICAL COMM LLC

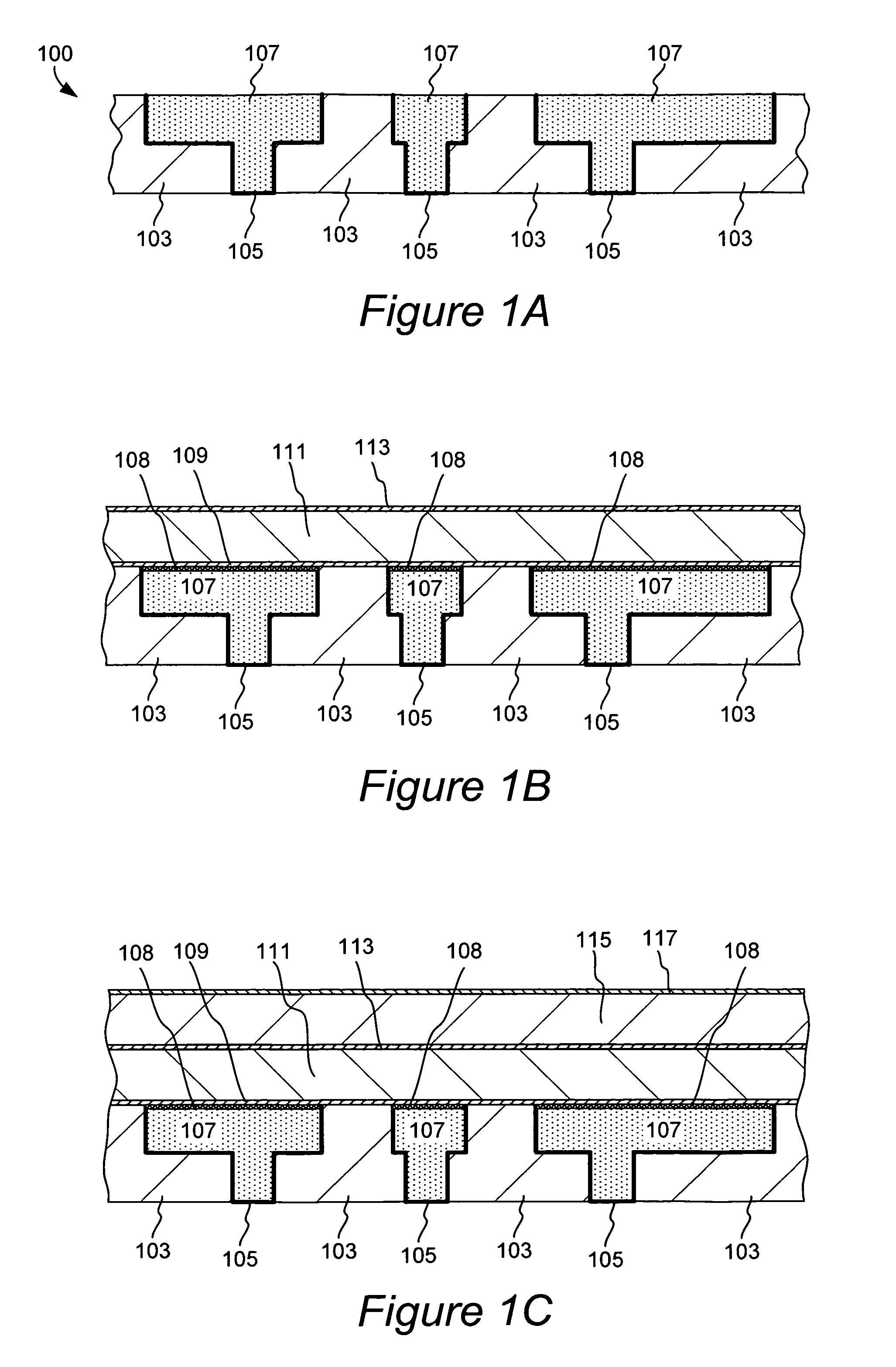

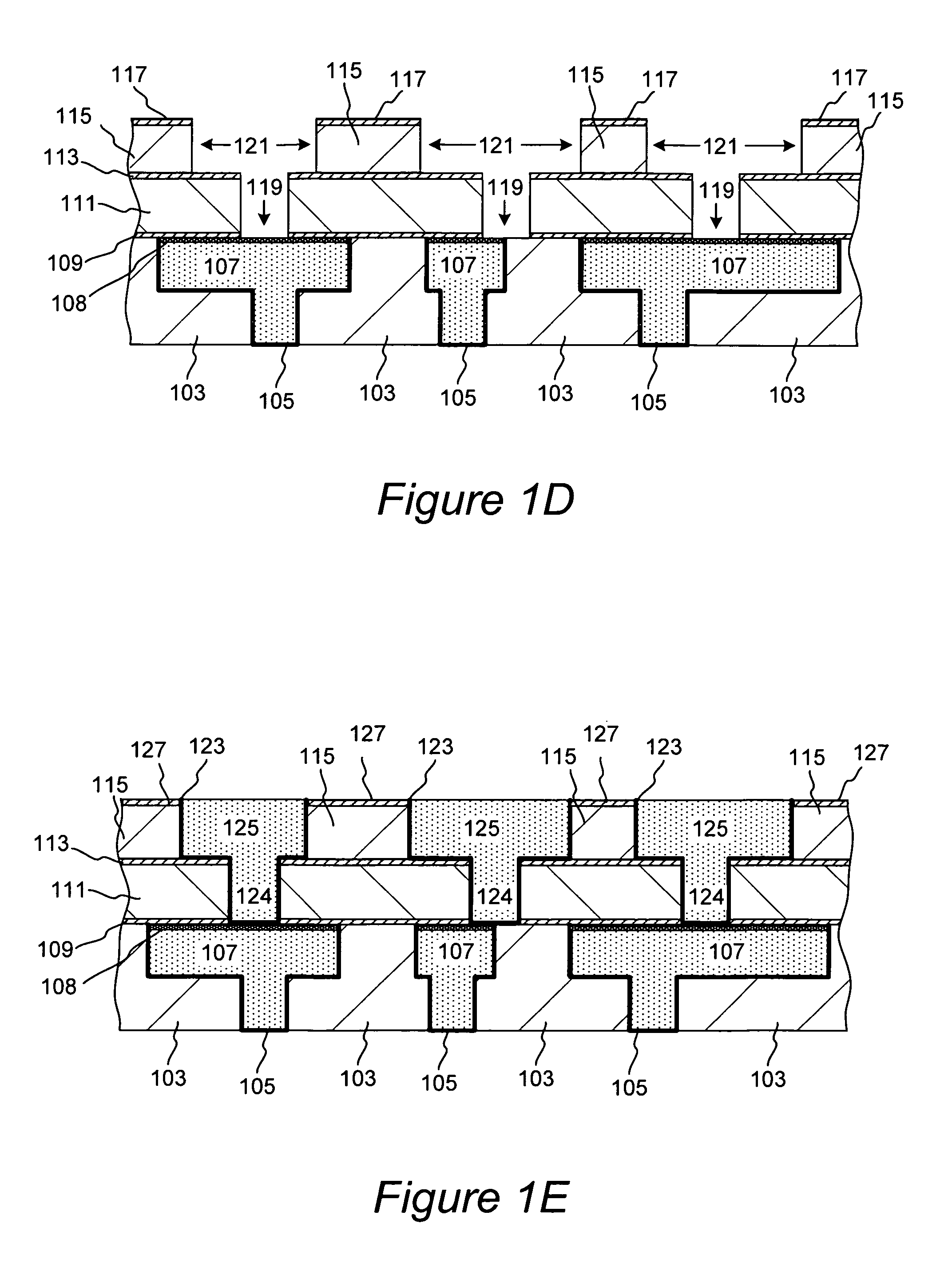

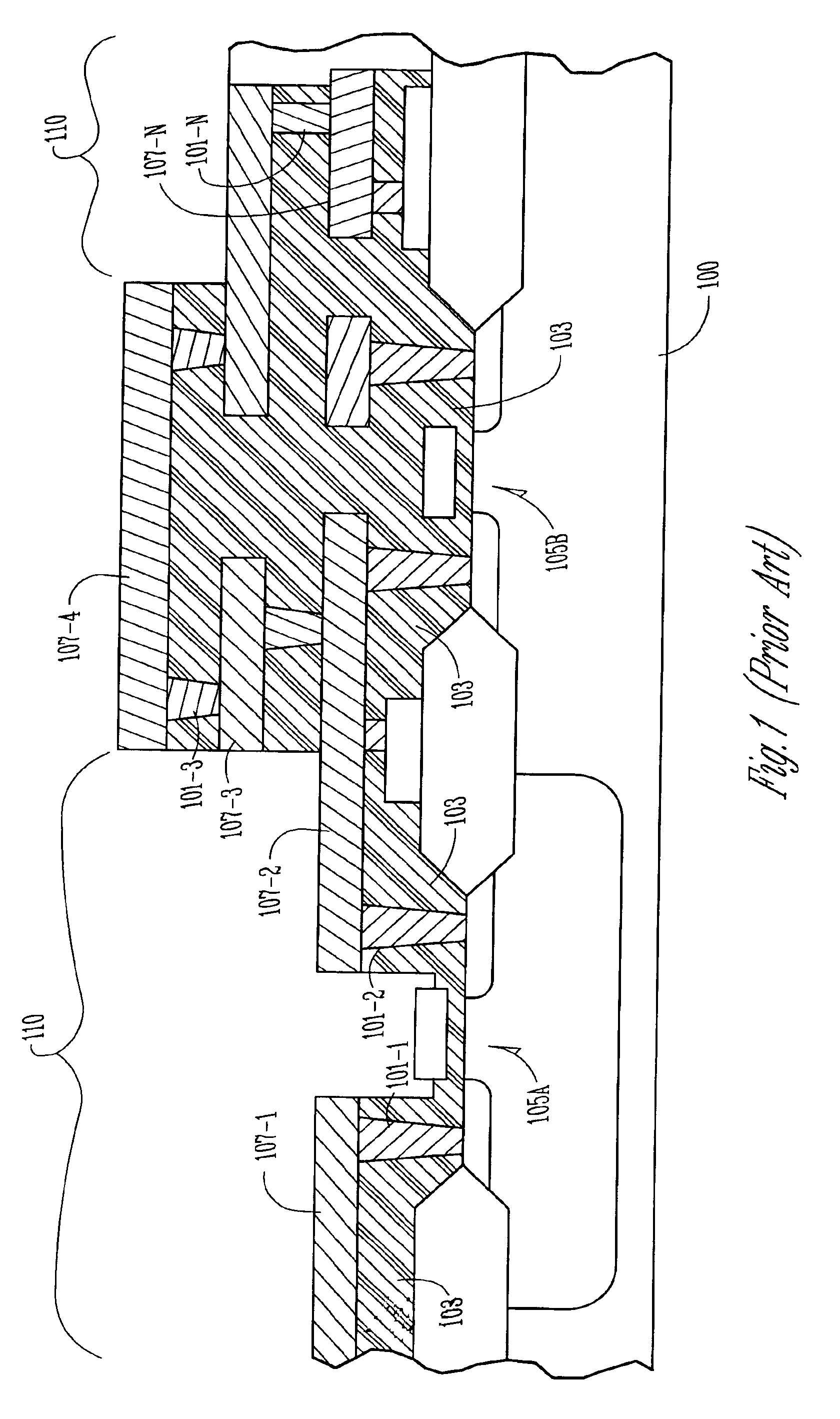

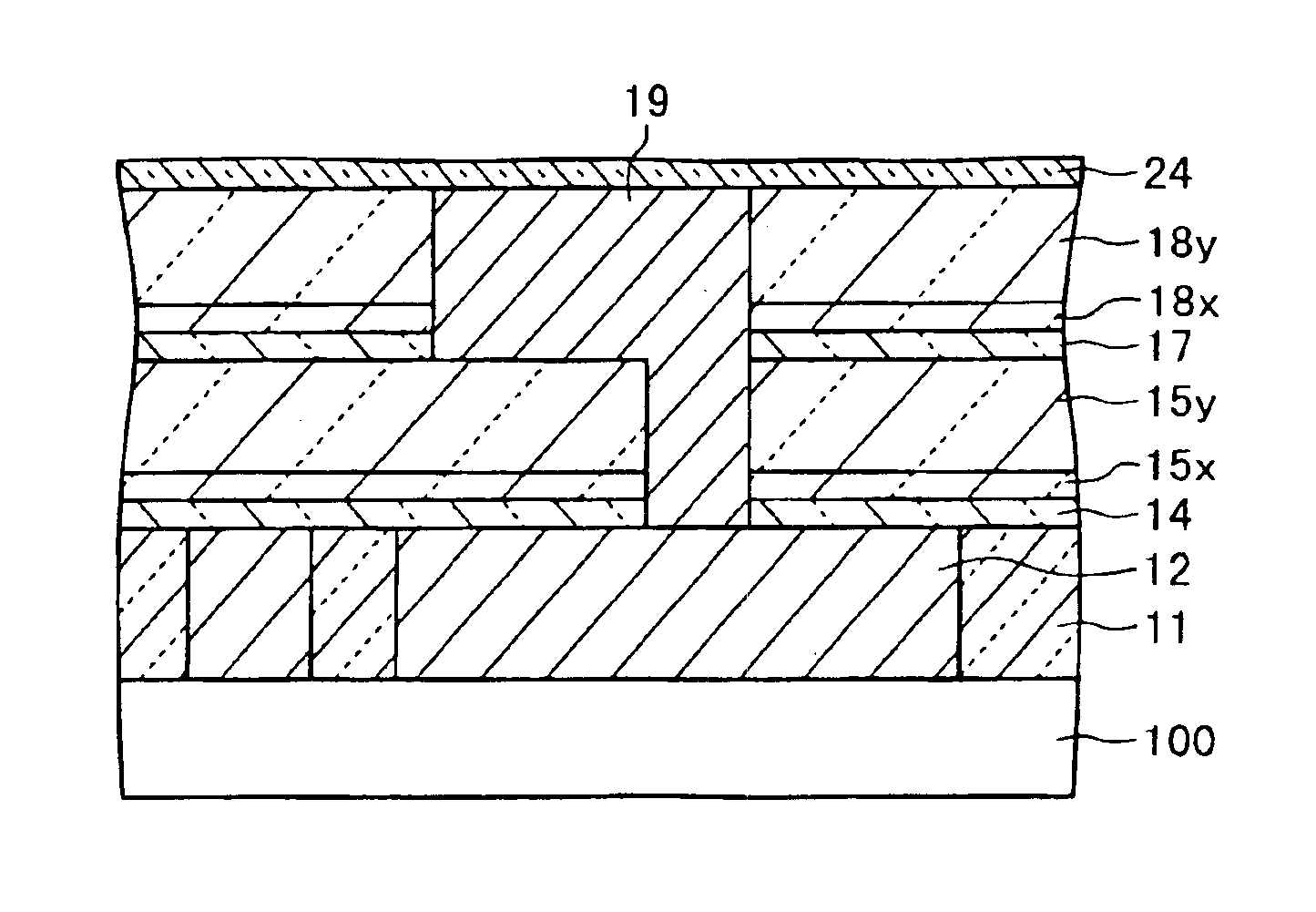

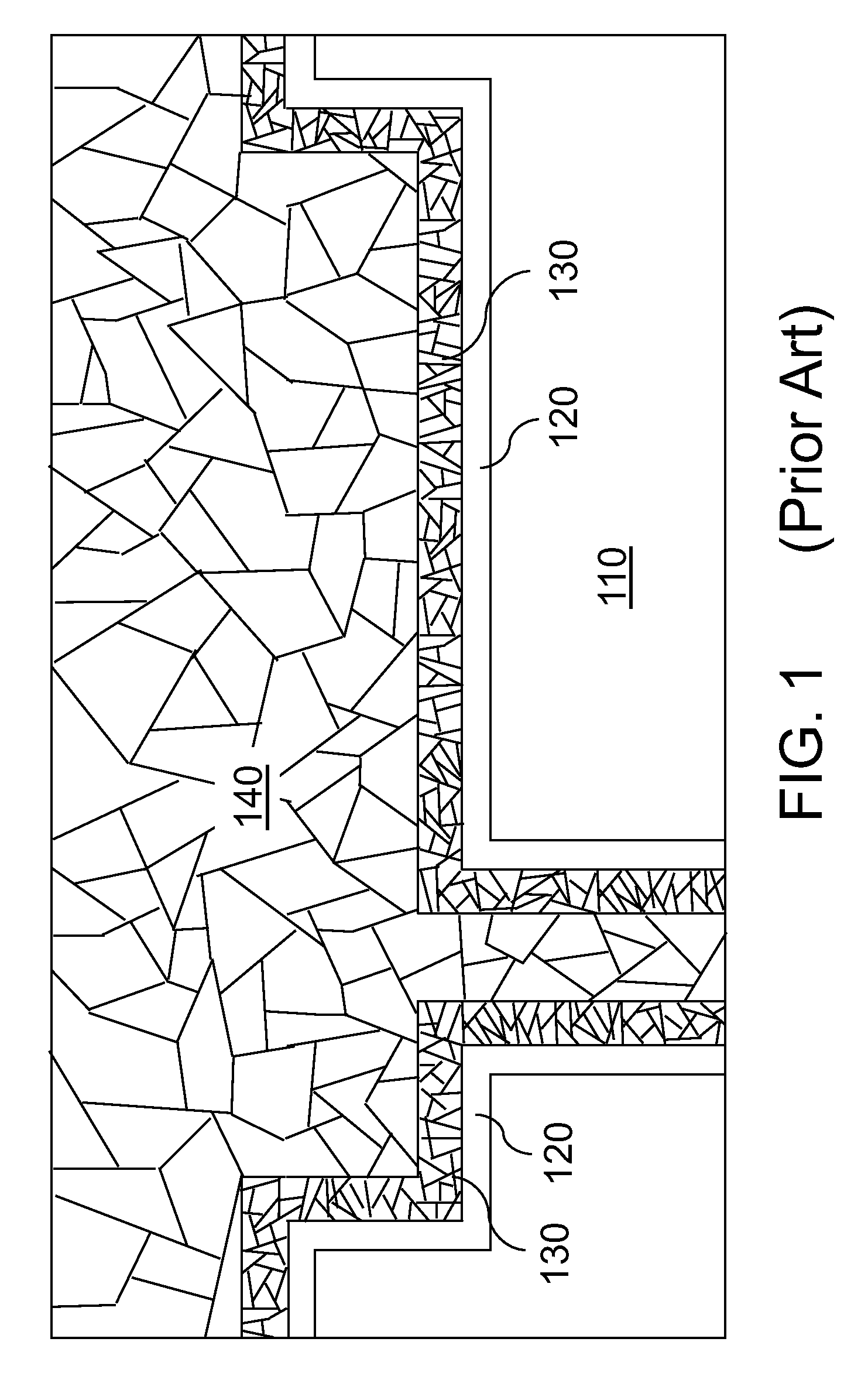

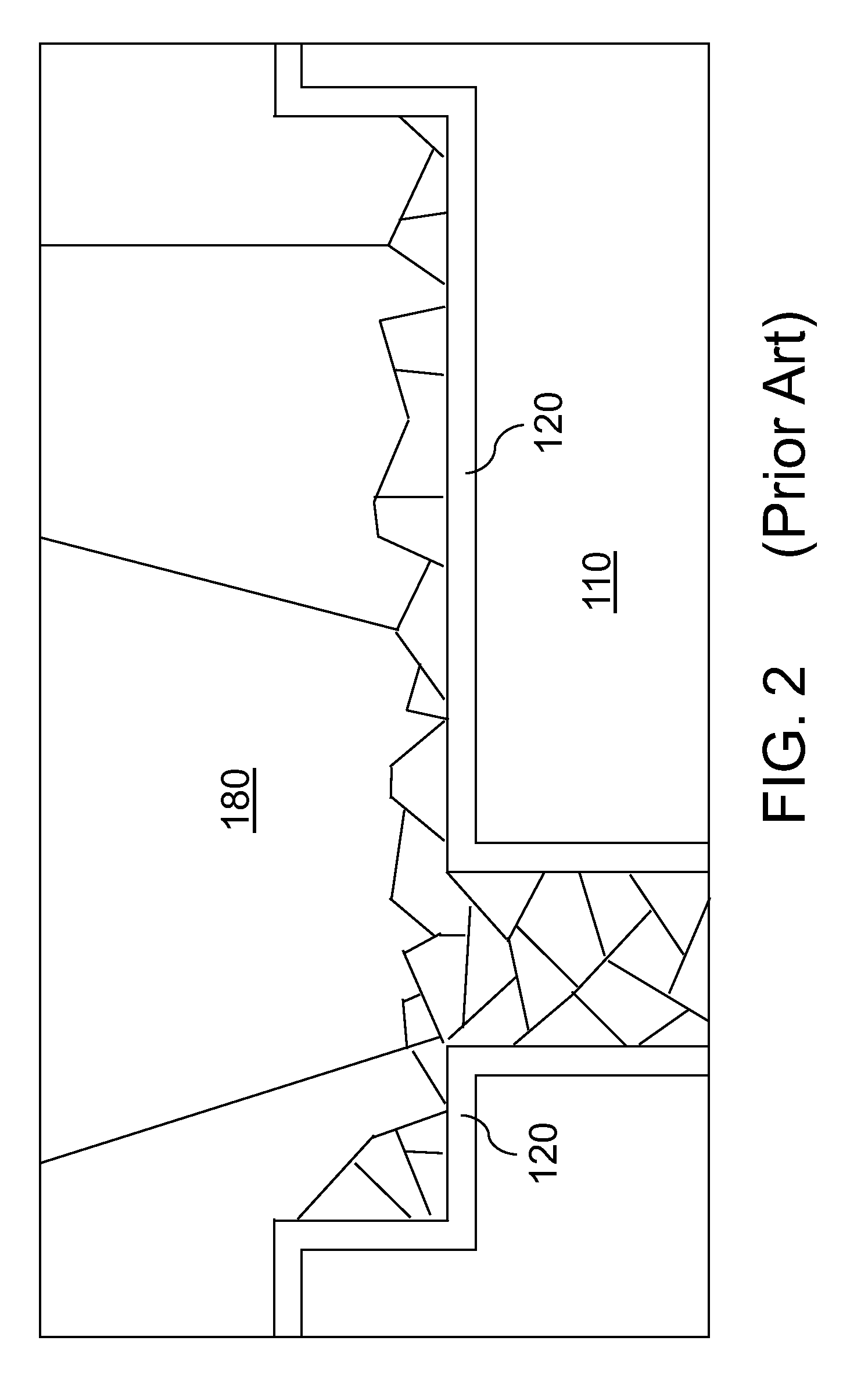

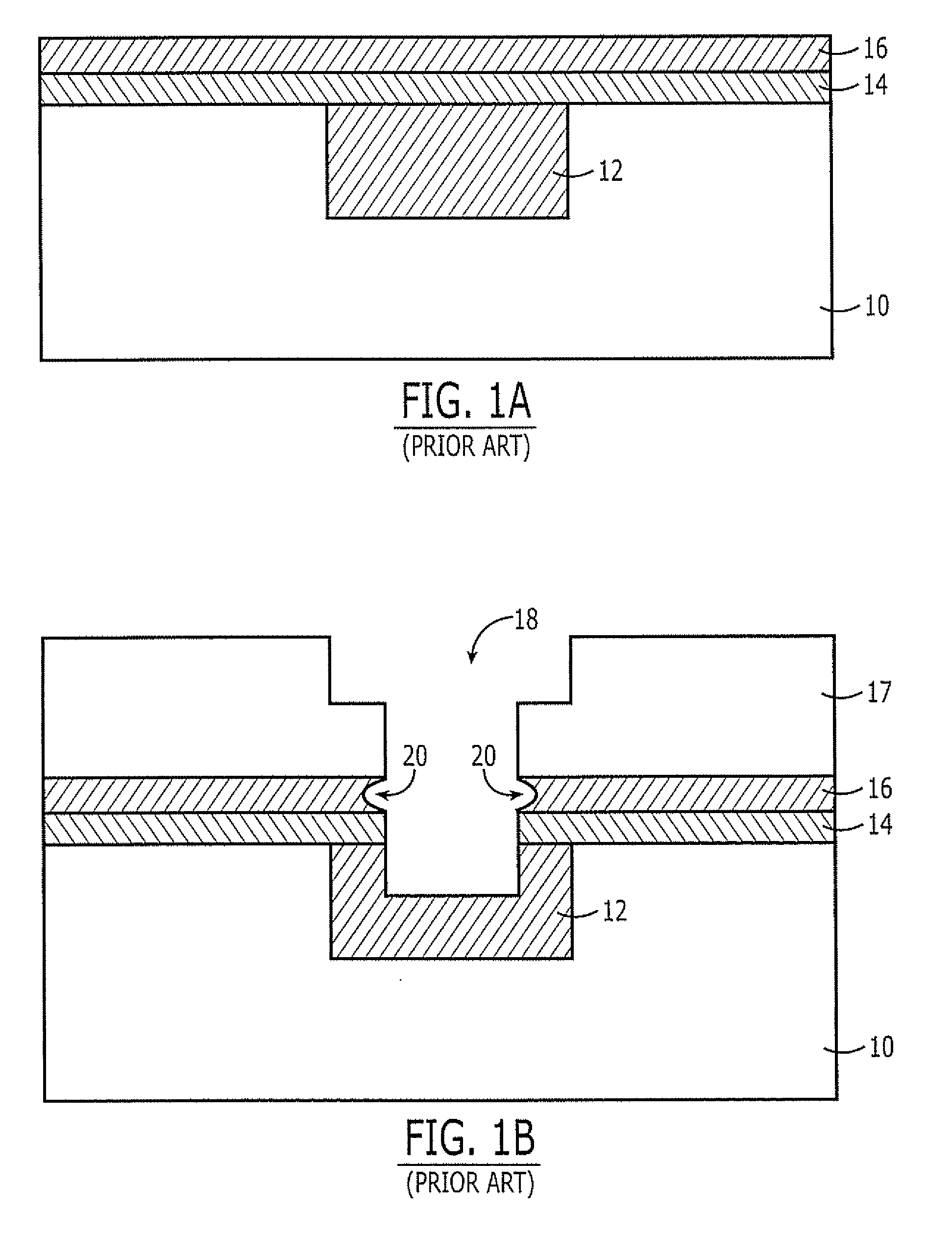

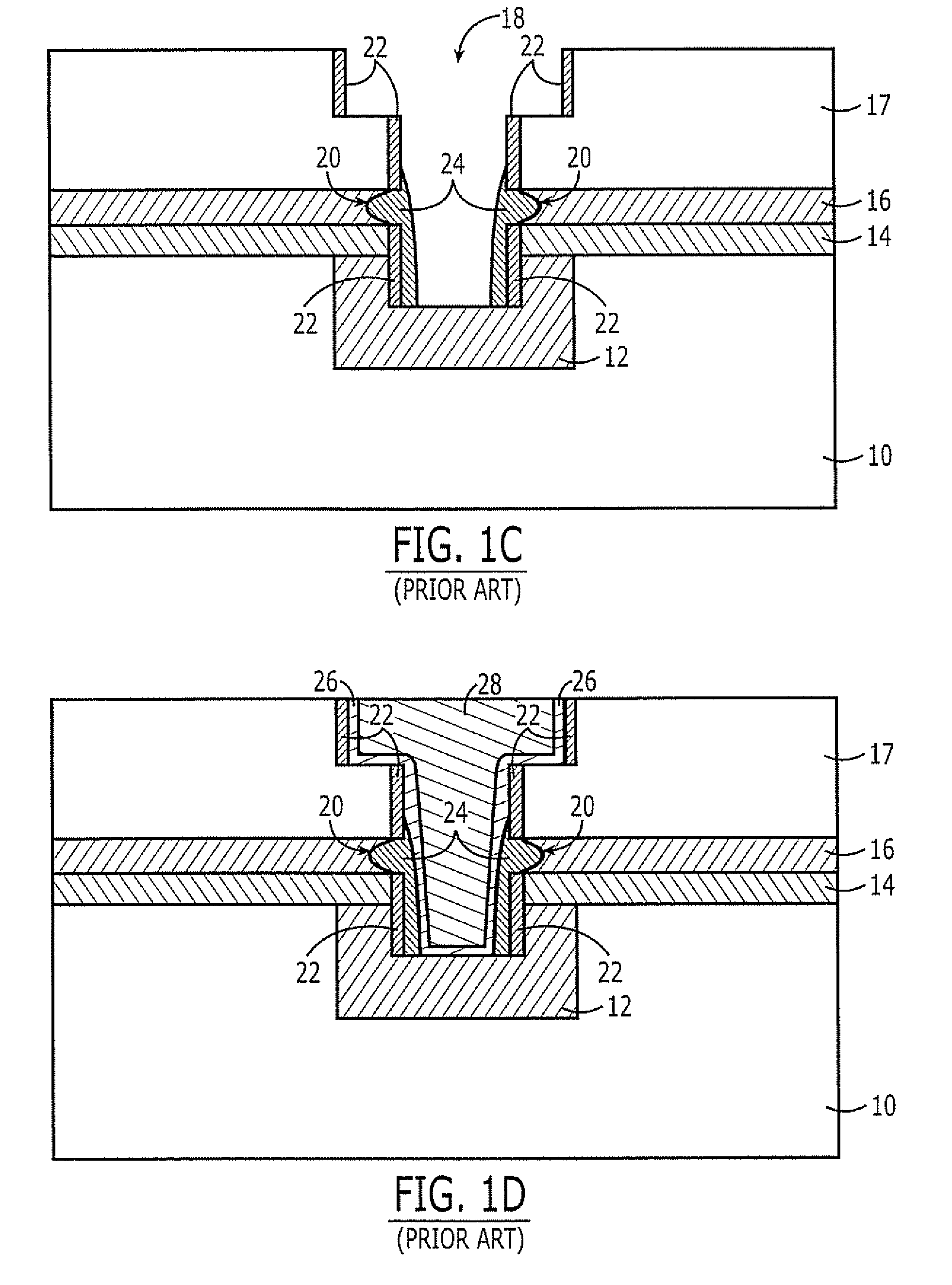

Very low effective dielectric constant interconnect Structures and methods for fabricating the same

InactiveUS7023093B2Low structural requirementsHigh mechanical strengthSemiconductor/solid-state device detailsSolid-state devicesCopper-wiringElectrical performance

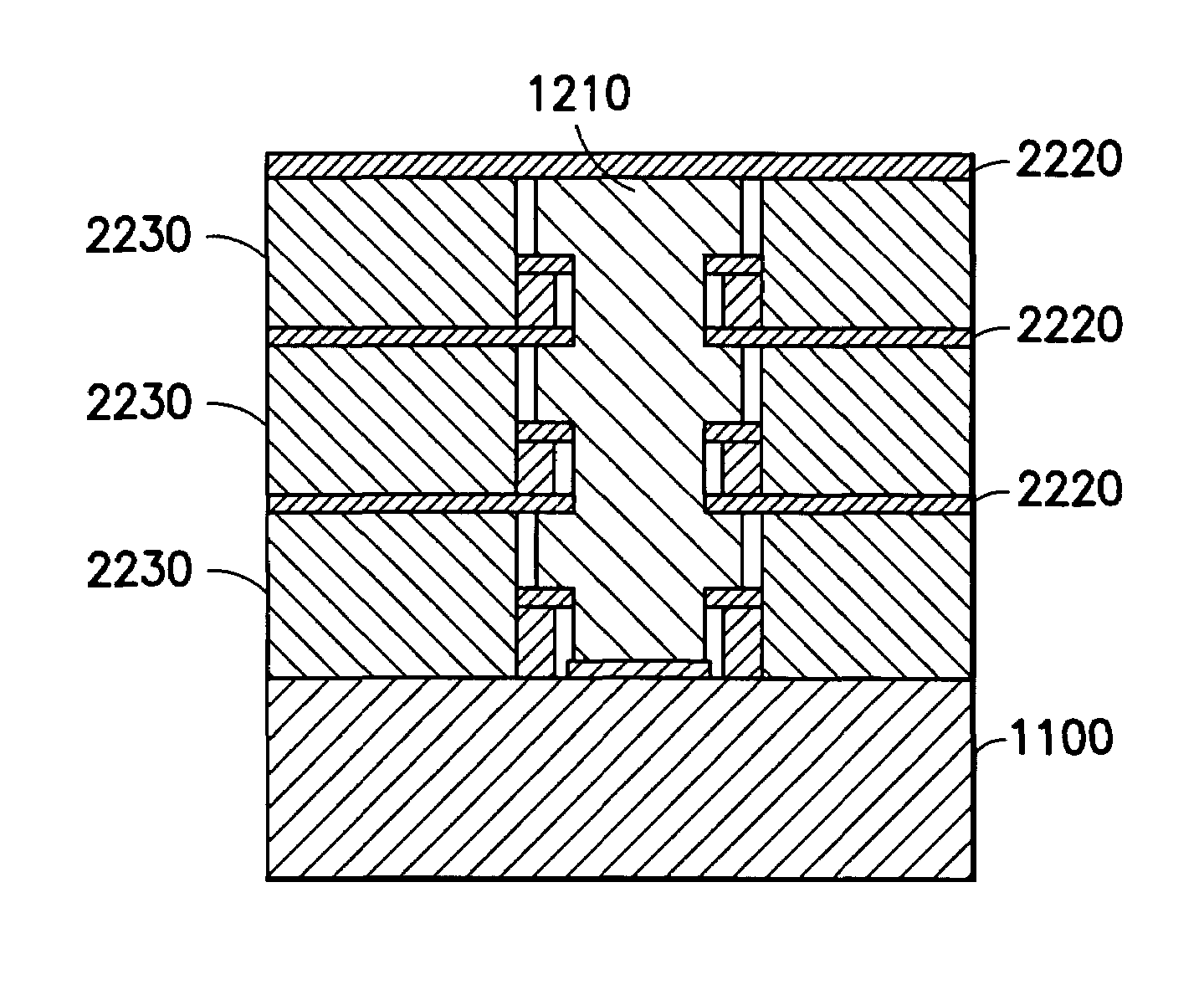

A structure incorporates very low dielectric constant (k) insulators with copper wiring to achieve high performance interconnects. The wiring is supported by a relatively durable low k dielectric such as SiLk or SiO2 and a very low k and less robust gap fill dielectric is disposed in the remainder of the structure, so that the structure combines a durable layer for strength with a very low k dielectric for interconnect electrical performance.

Owner:GLOBALFOUNDRIES US INC

Selective capping of copper wiring

InactiveUS7008871B2Semiconductor/solid-state device detailsSolid-state devicesCopper-wiringElectroplating

Patterned copper structures are fabricated by selectively capping the copper employing selective etching and / or selective electroplating in the presence of a liner material. Apparatus for addressing the problem of an increased resistive path as electrolyte during electroetching and / or electroplating flows from the wafer edge inwards is provided.

Owner:TWITTER INC

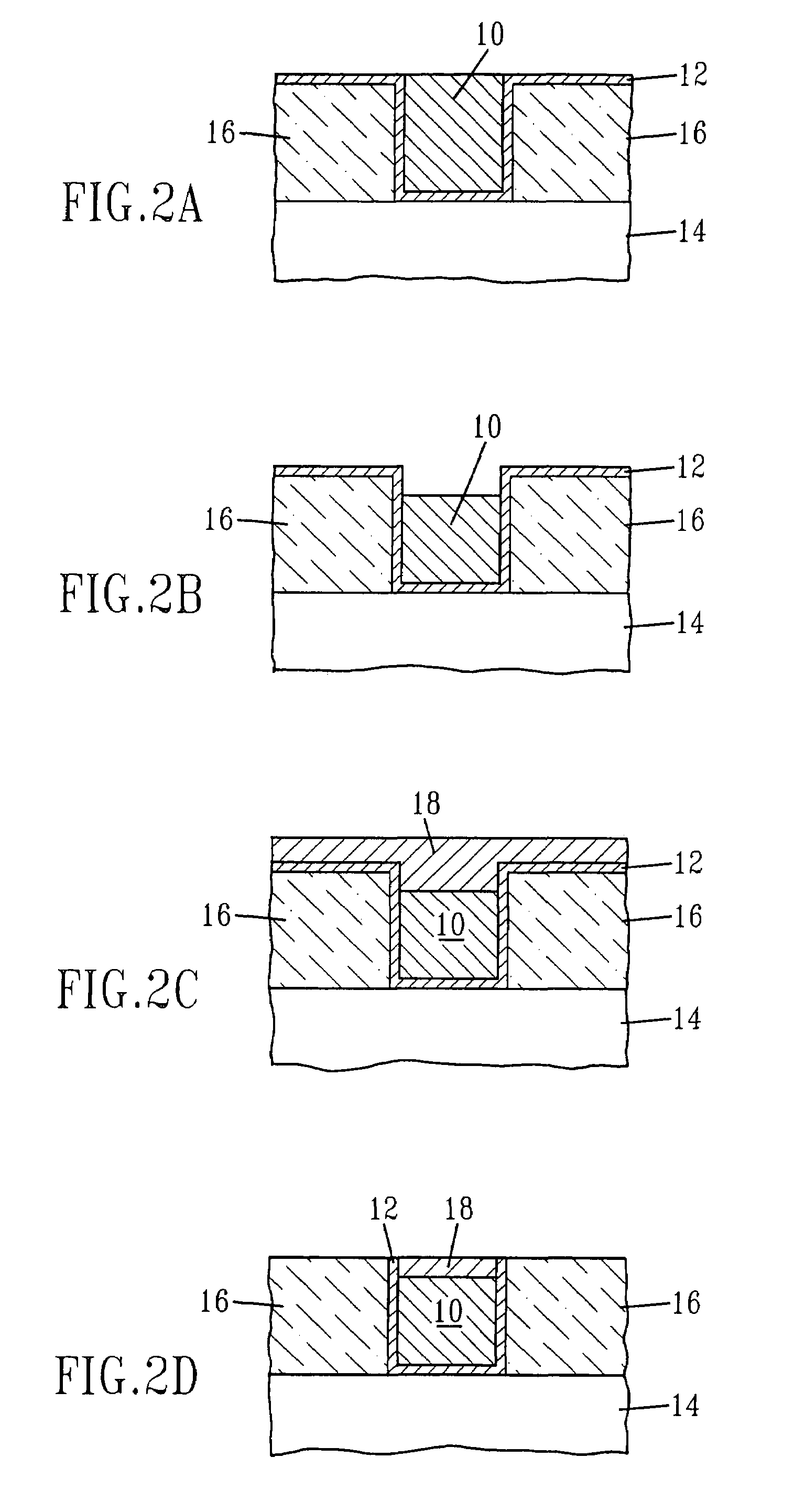

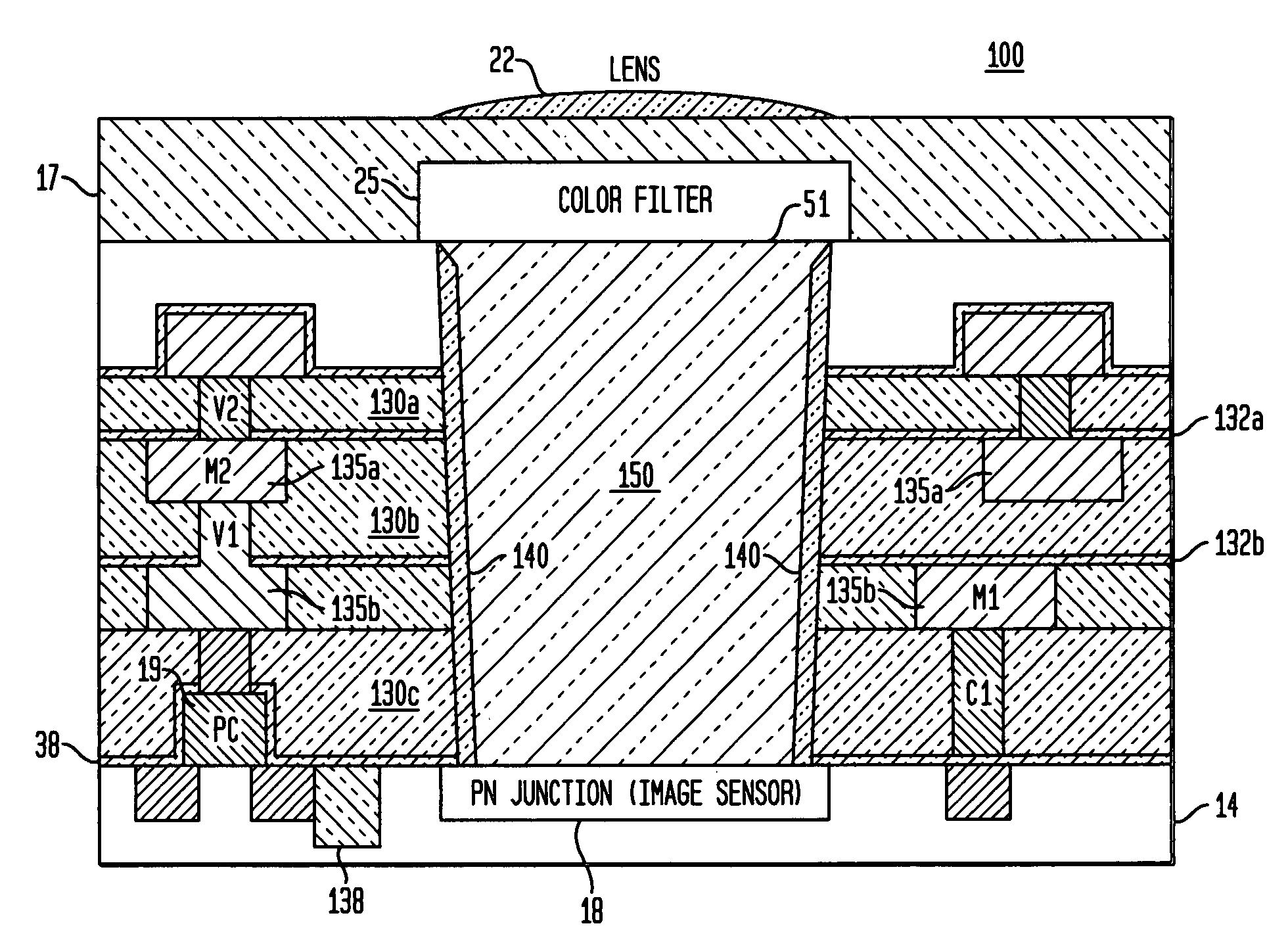

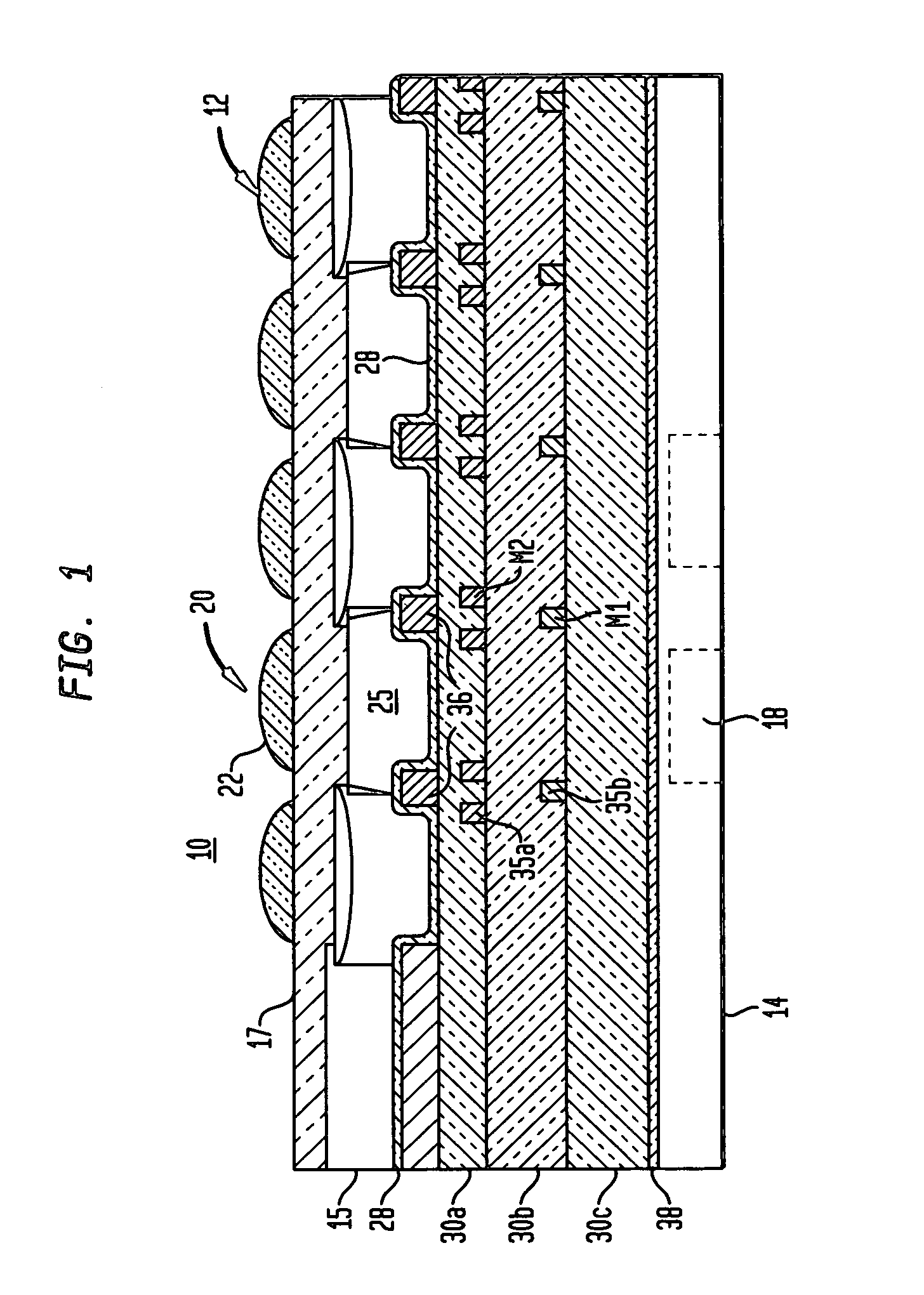

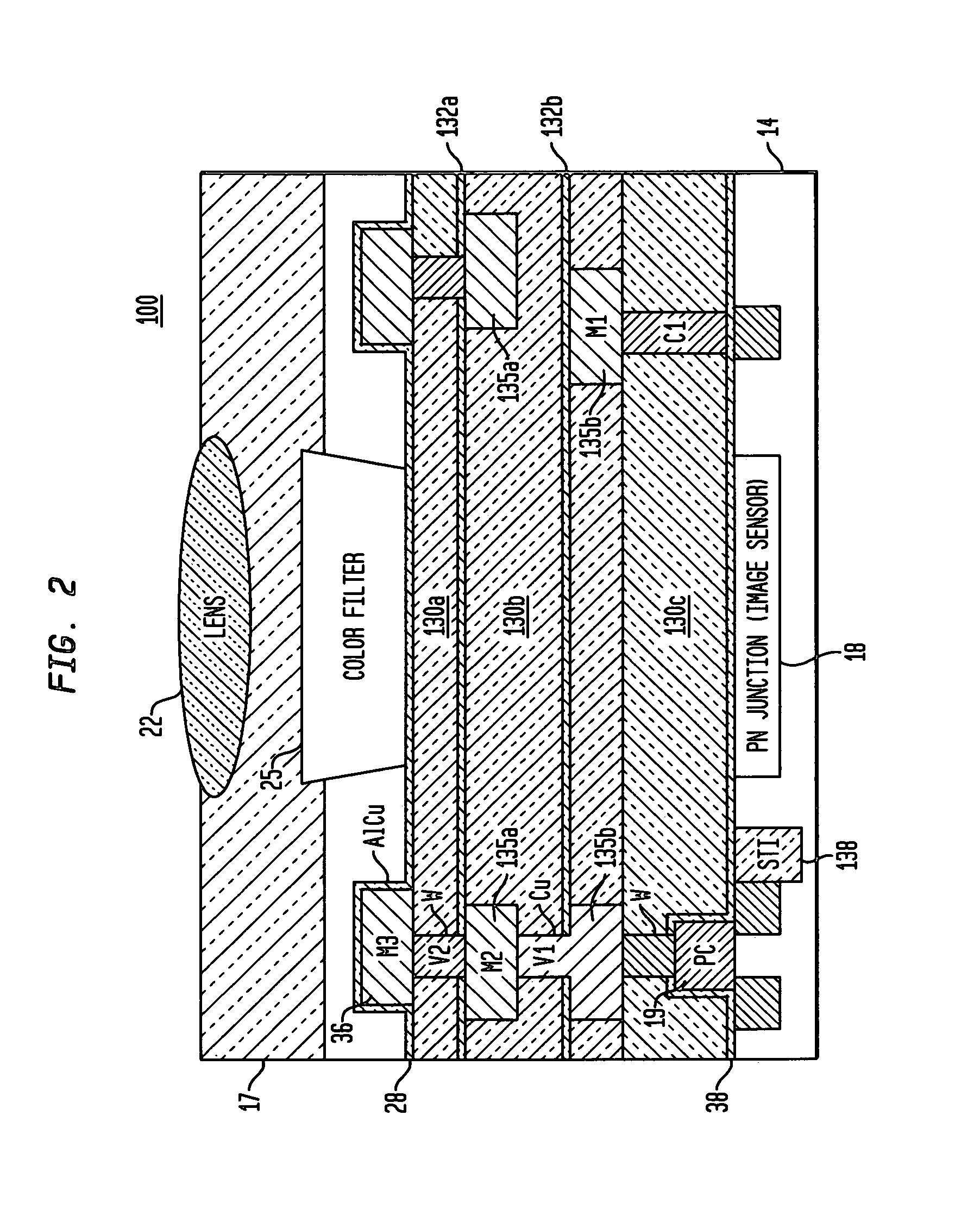

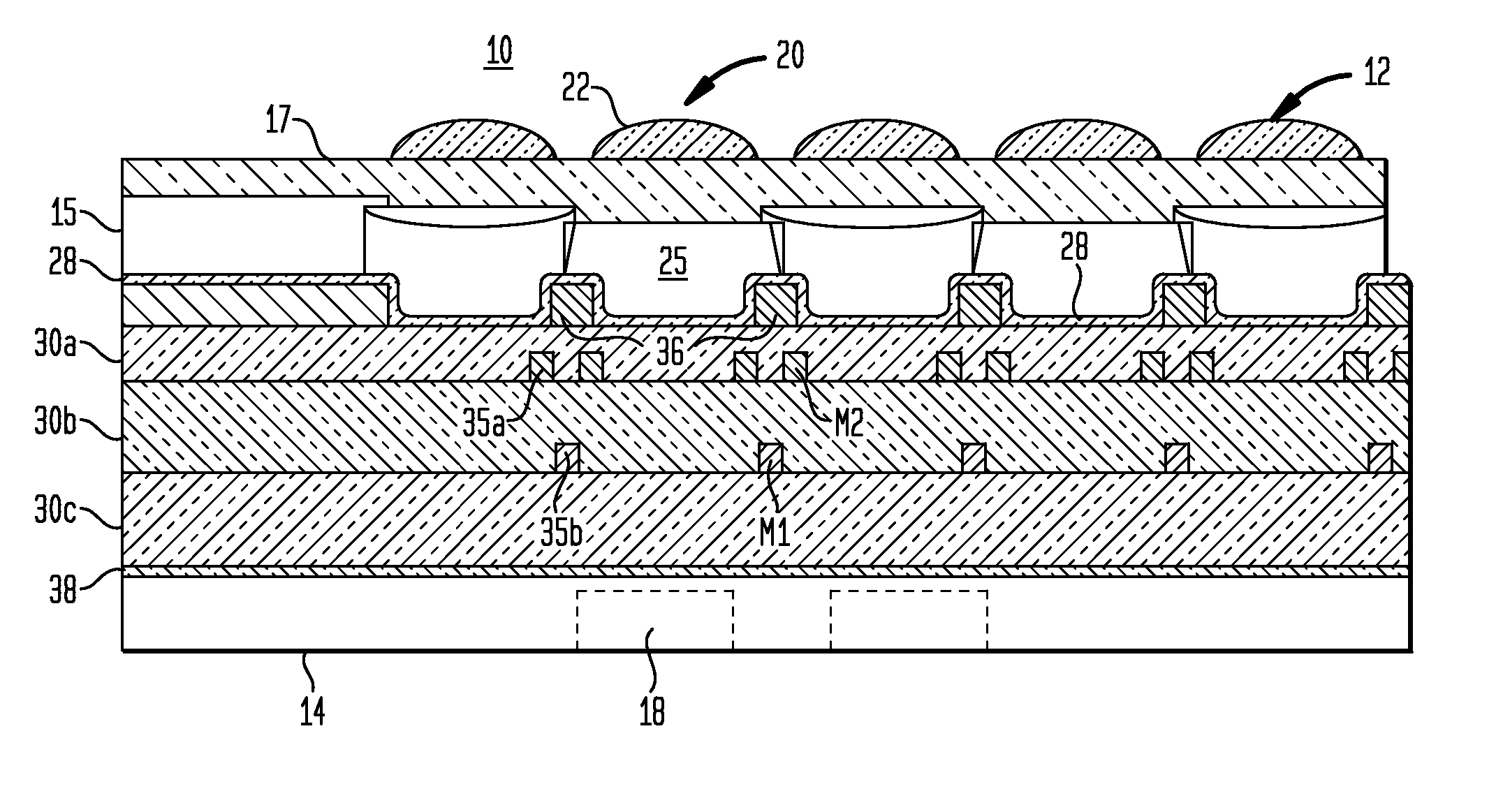

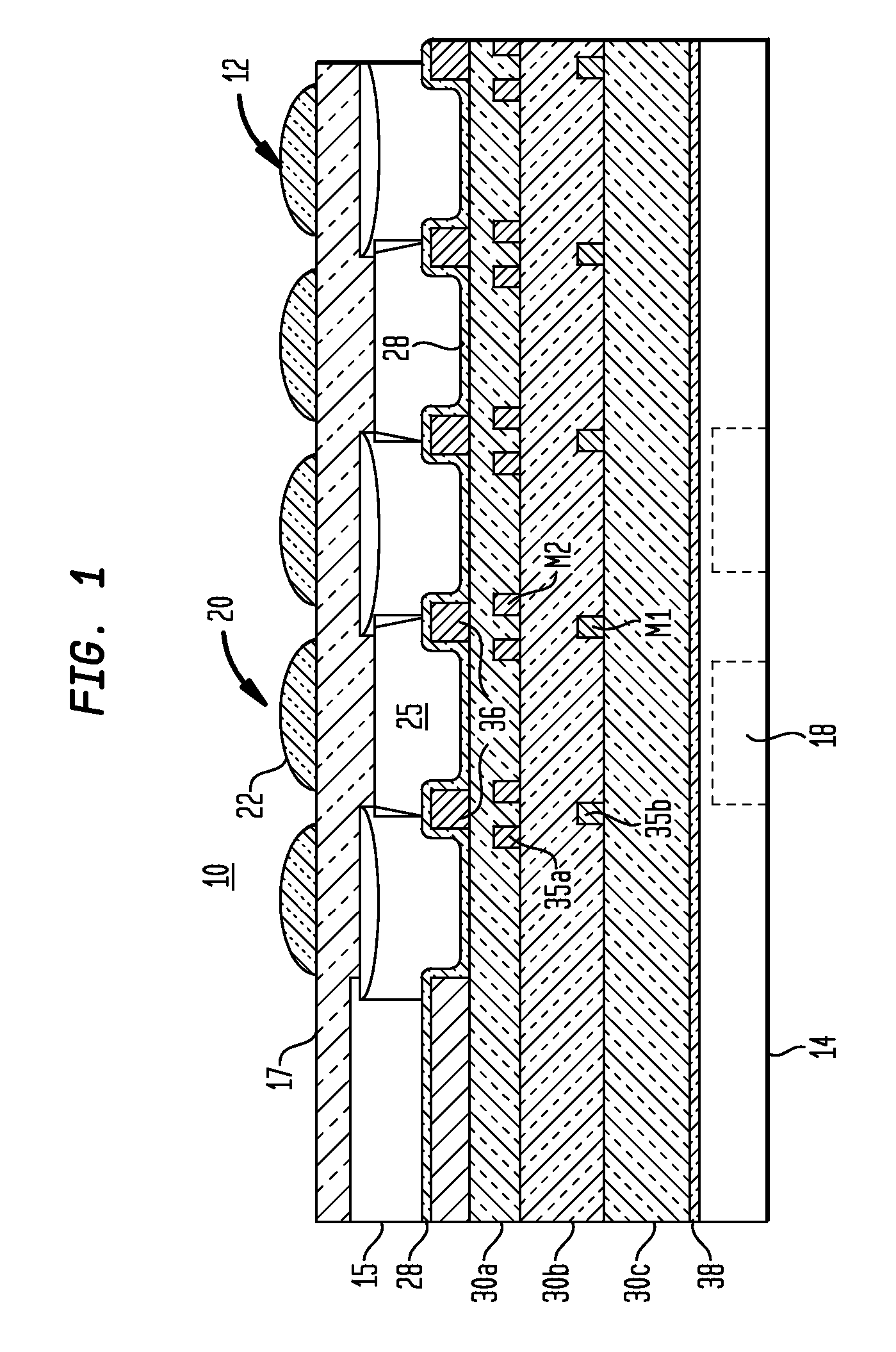

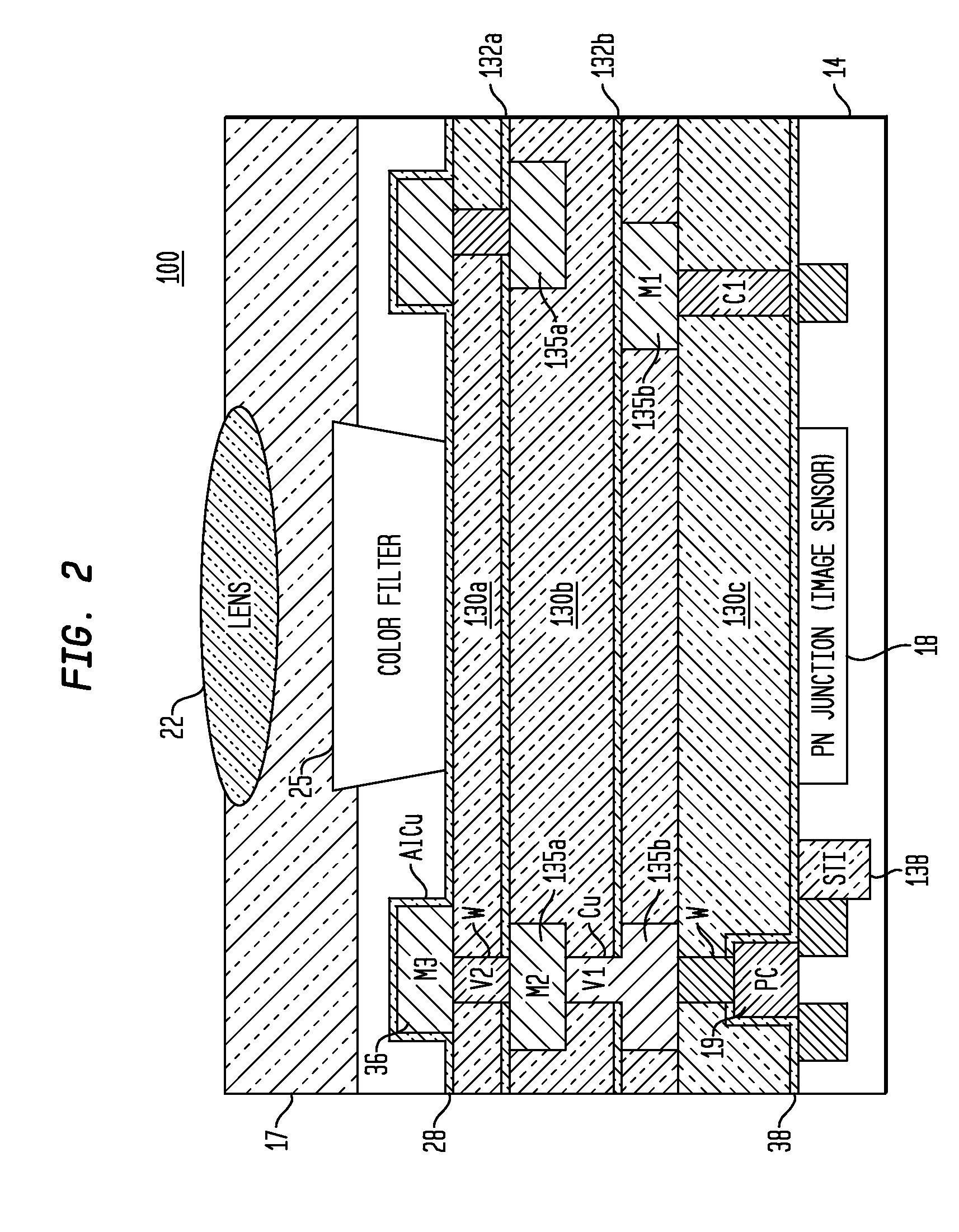

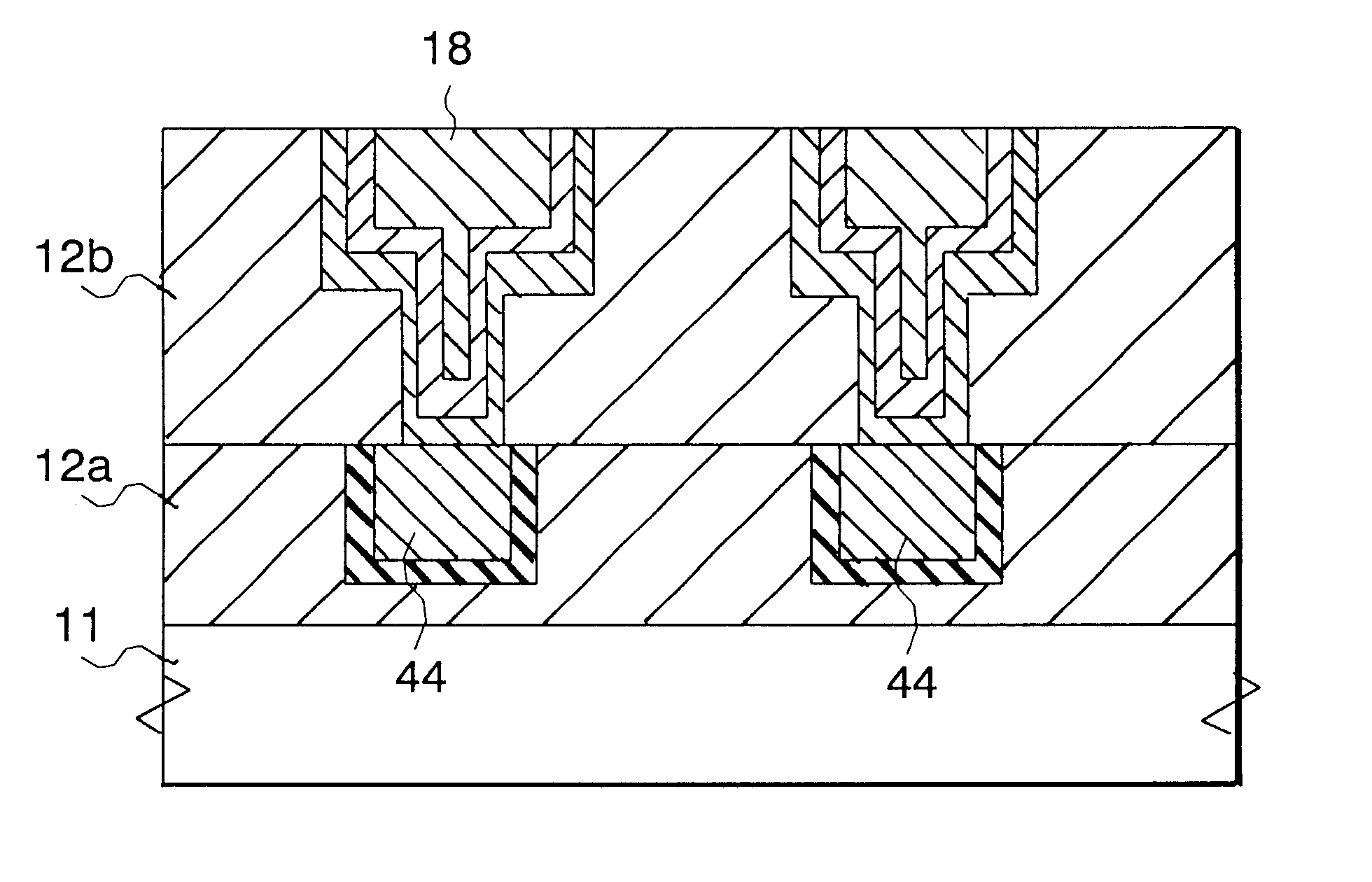

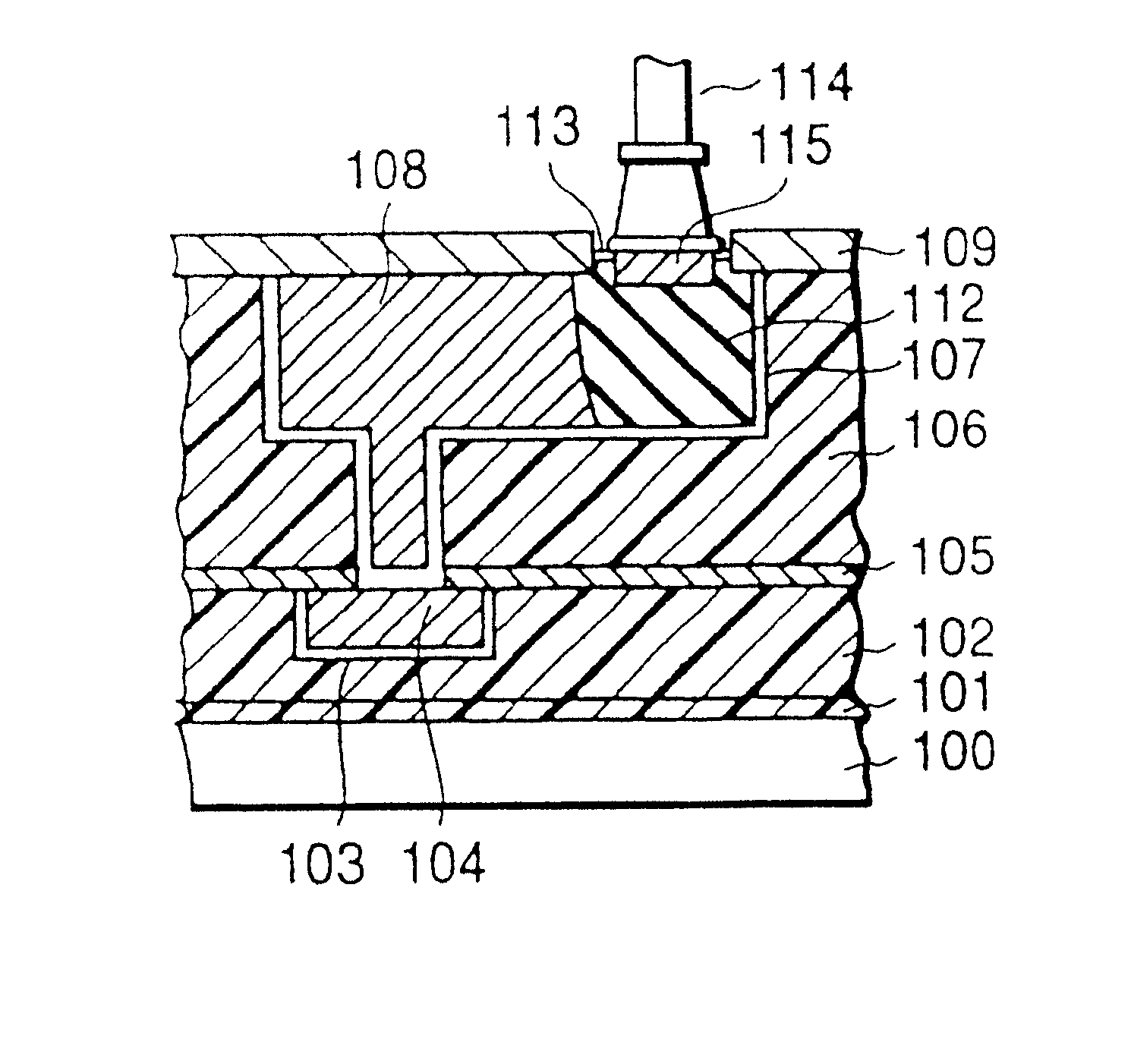

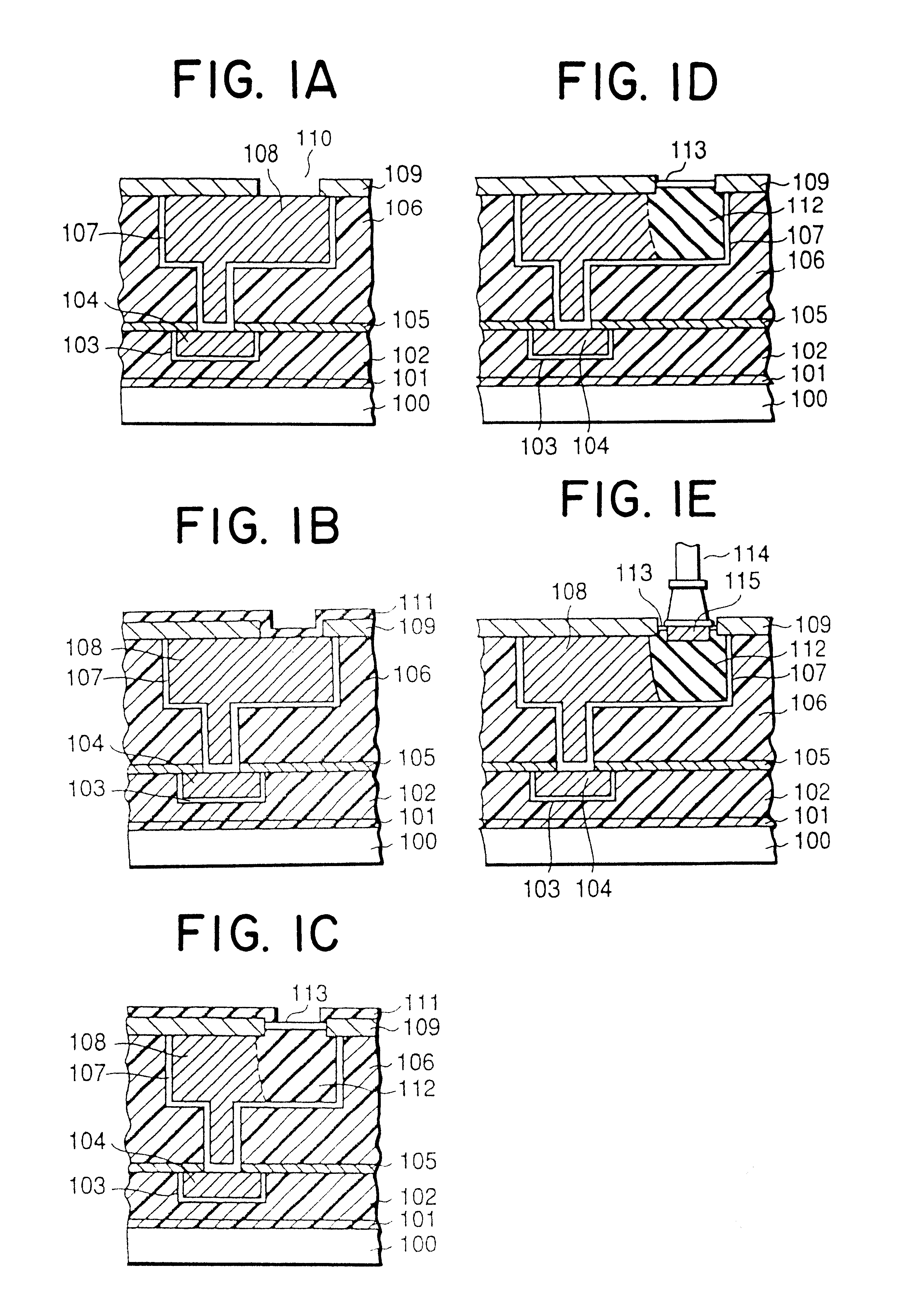

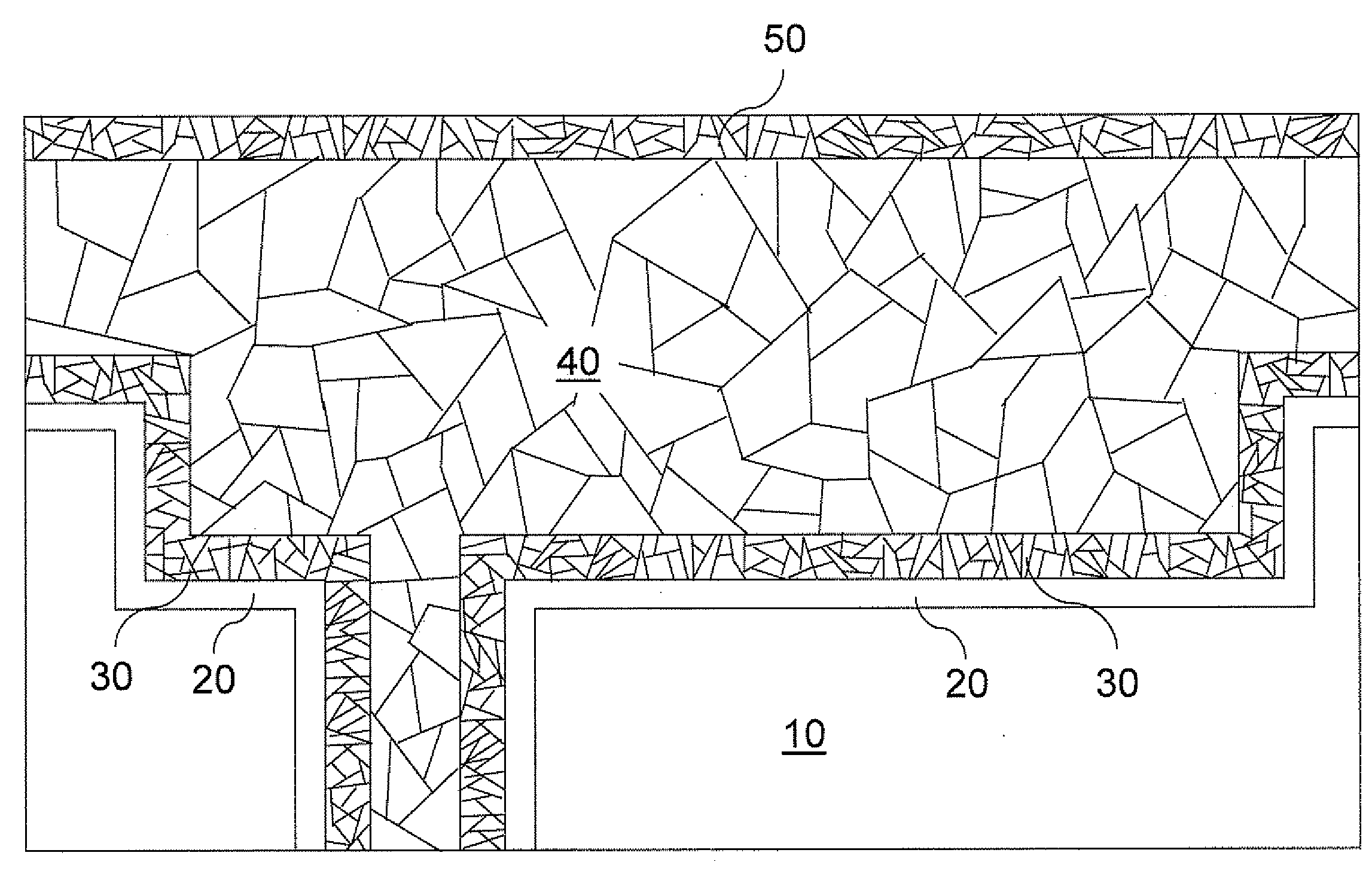

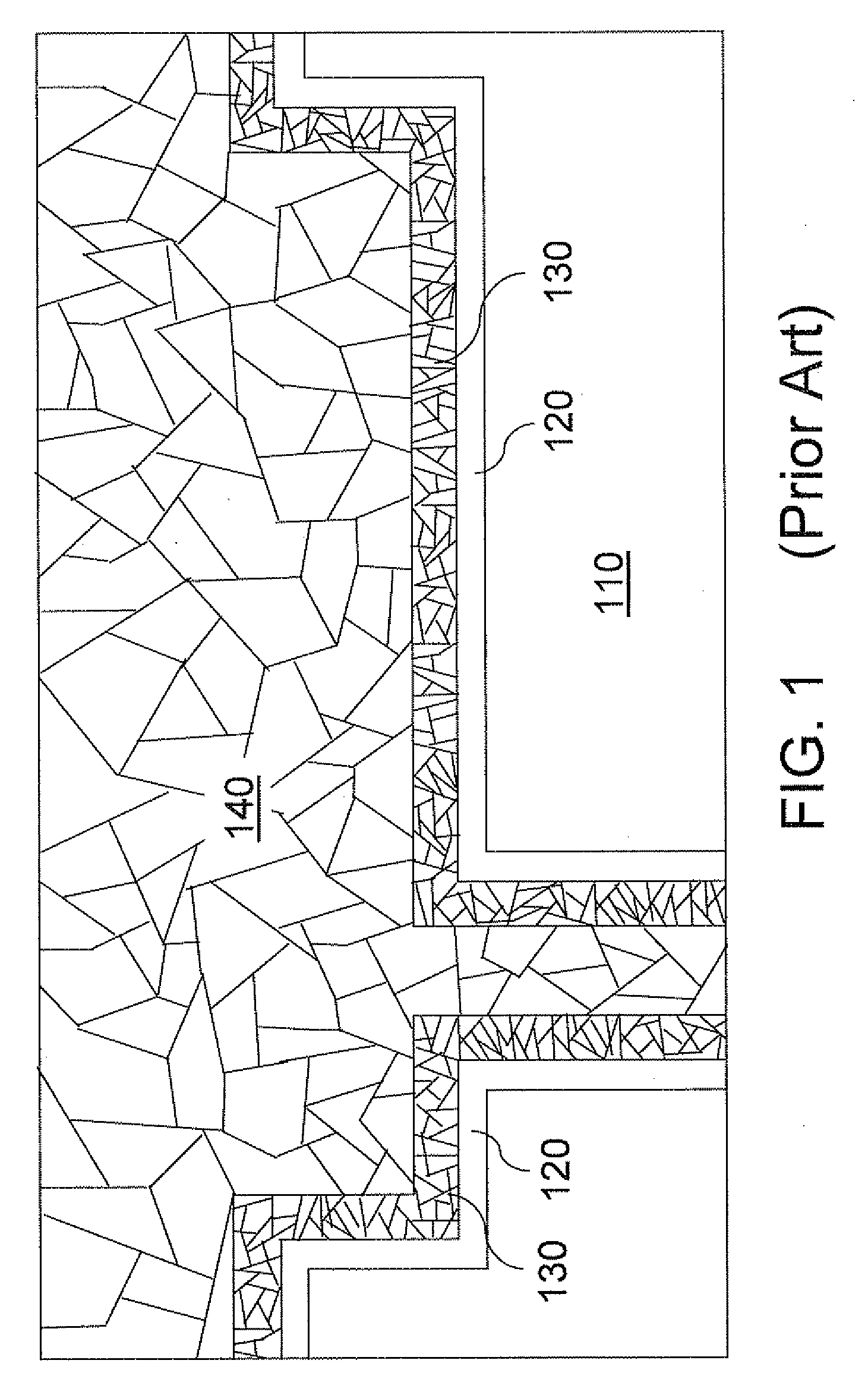

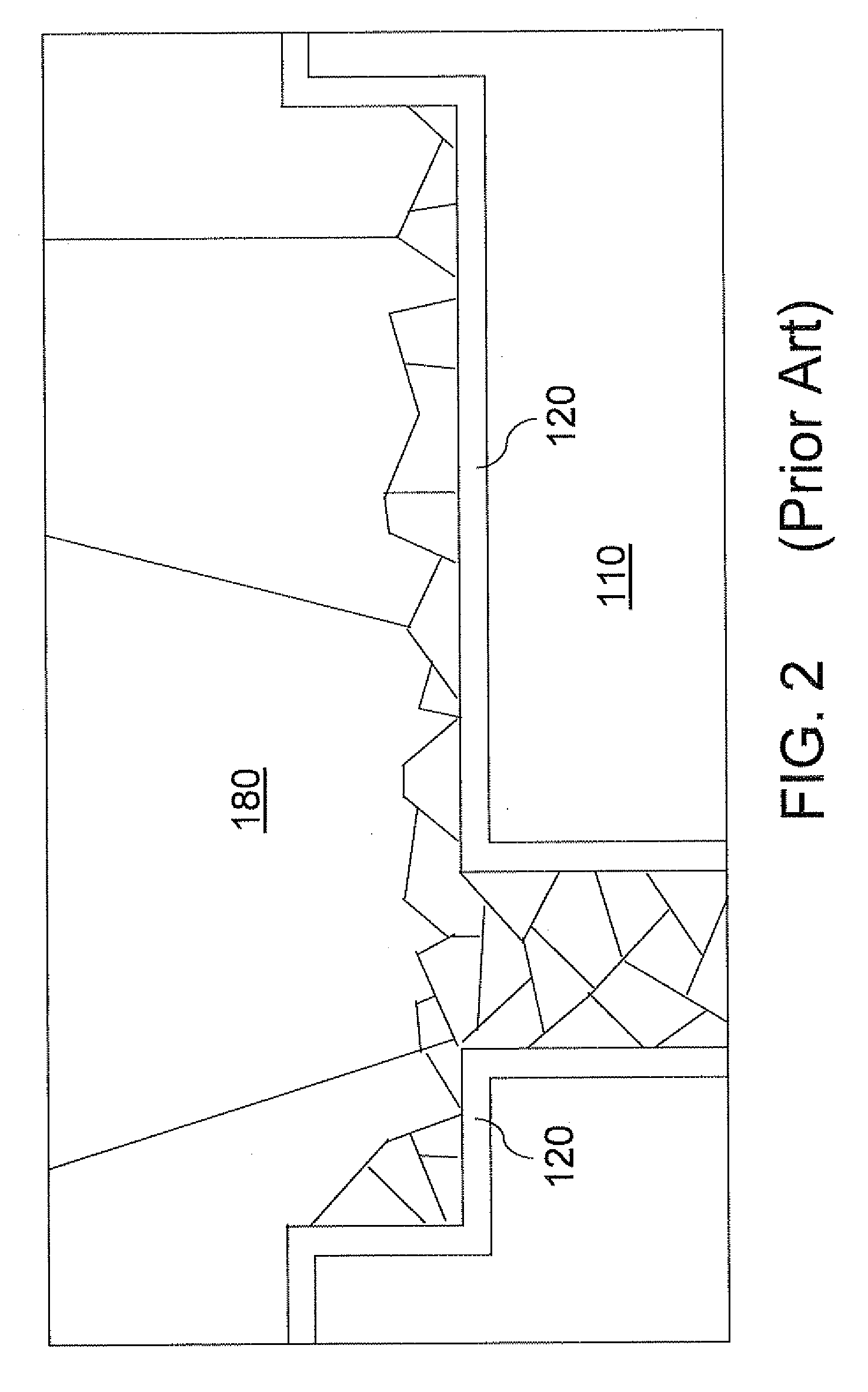

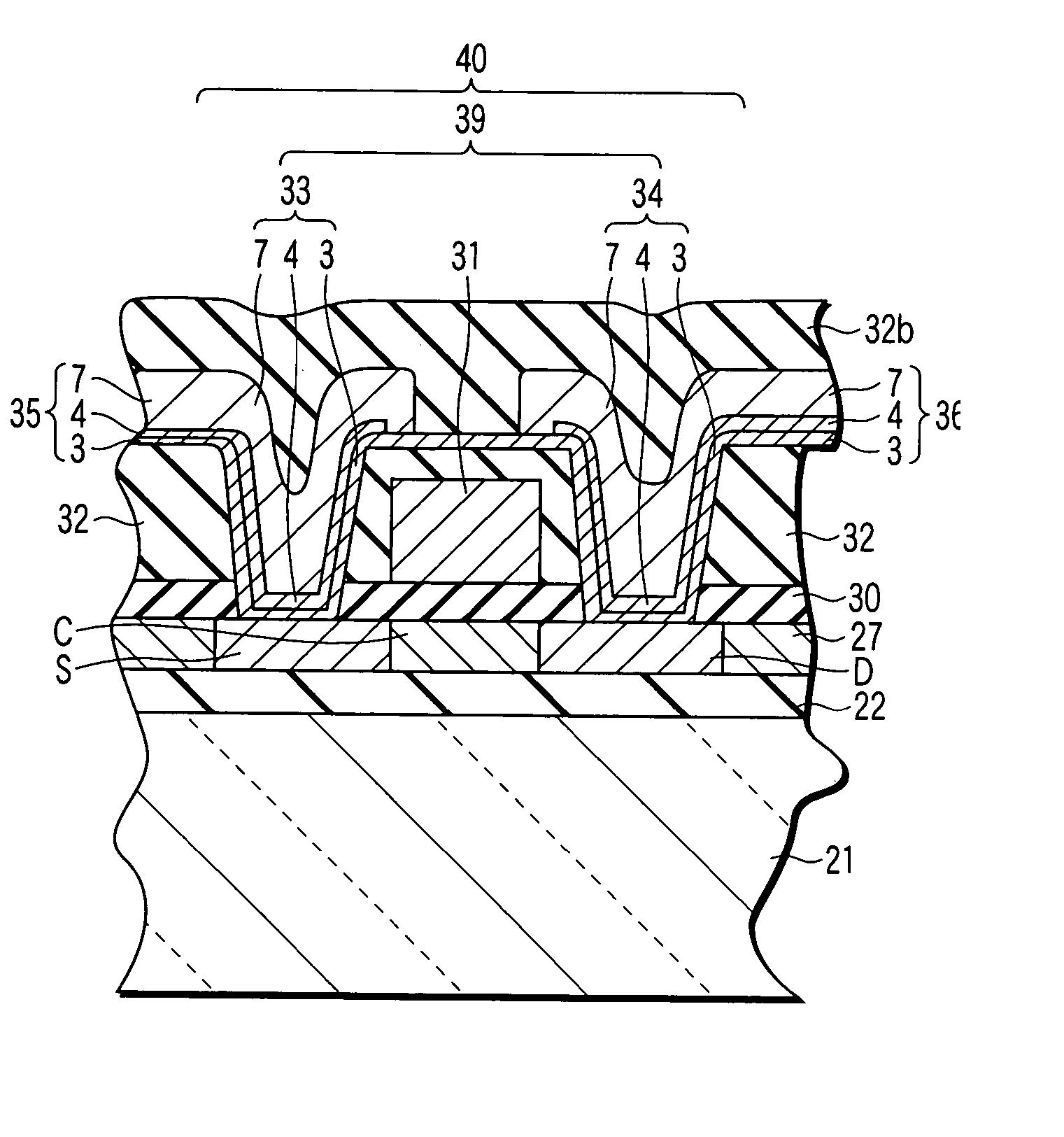

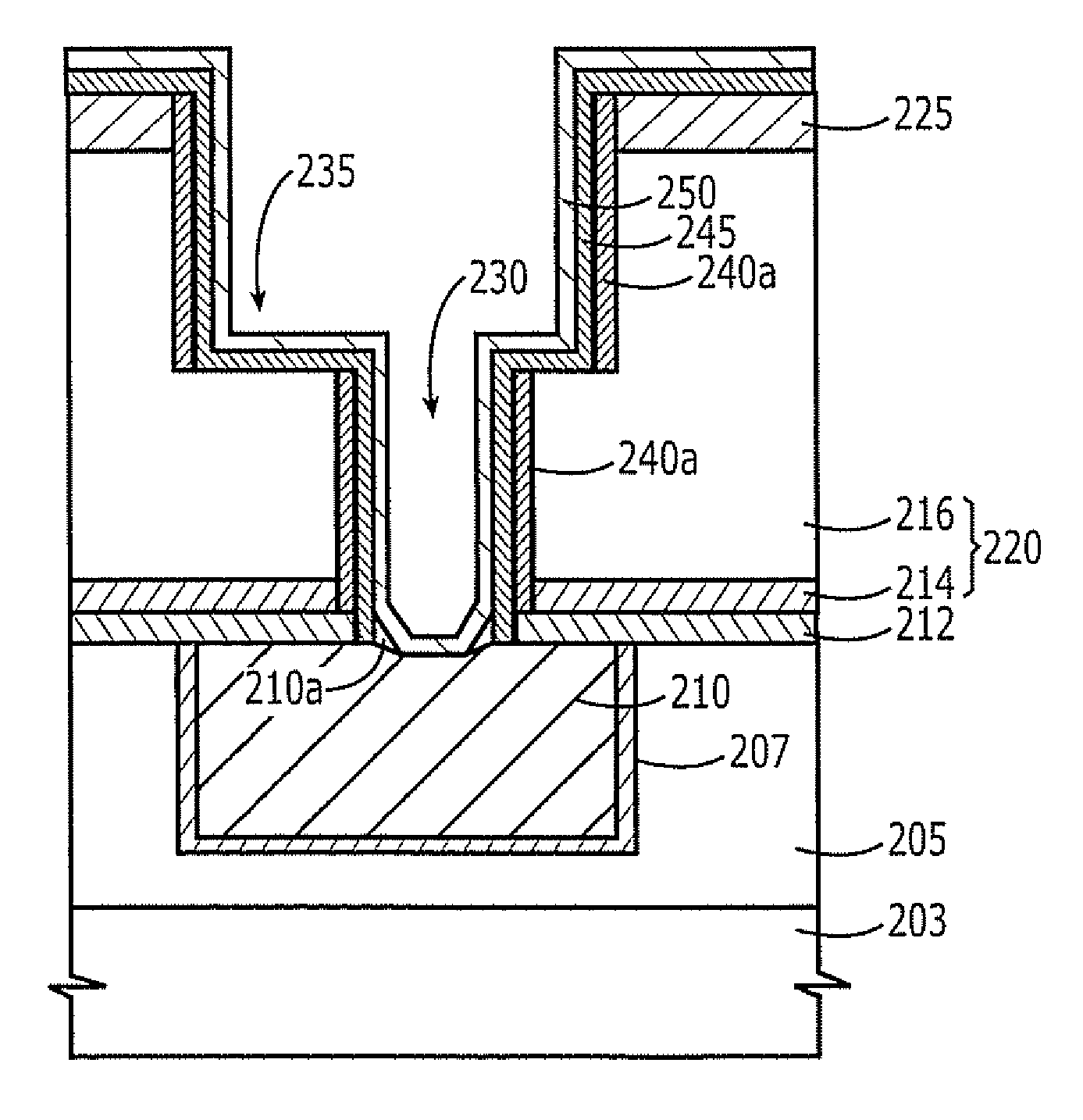

Damascene copper wiring image sensor

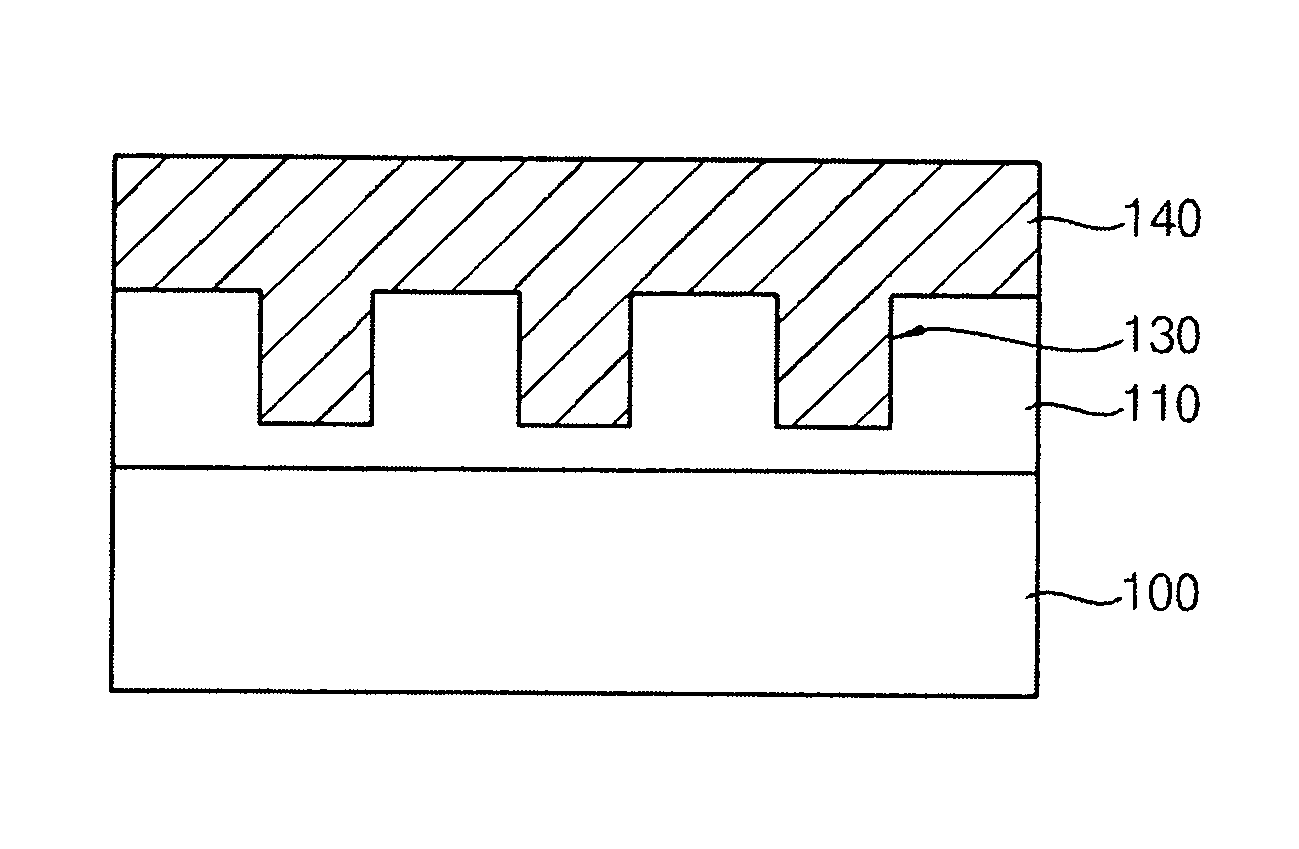

ActiveUS7193289B2Eliminate contaminationHigh light sensitivitySolid-state devicesSemiconductor/solid-state device manufacturingSensor arrayLight reflection

An image sensor array and method of fabrication wherein the sensor includes Copper (Cu) metallization levels allowing for incorporation of a thinner interlevel dielectric stack with improved thickness uniformity to result in a pixel array exhibiting increased light sensitivity. In the sensor array, each Cu metallization level includes a Cu metal wire structure formed at locations between each array pixel and, a barrier material layer is formed on top each Cu metal wire structure that traverses the pixel optical path. By implementing a single mask or self-aligned mask methodology, a single etch is conducted to completely remove the interlevel dielectric and barrier layers that traverse the optical path. The etched opening is then refilled with dielectric material. Prior to depositing the refill dielectric, a layer of either reflective or absorptive material is formed along the sidewalls of the etched opening to improve sensitivity of the pixels by either reflecting light to the underlying photodiode or by eliminating light reflections.

Owner:SMARTSENS TECH (HK) CO LTD

Damascene copper wiring optical image sensor

ActiveUS20070114622A1Eliminate contaminationHigh light sensitivitySolid-state devicesSemiconductor/solid-state device manufacturingDielectricCopper-wiring

A CMOS image sensor array and method of fabrication wherein the sensor includes Copper (Cu) metallization levels allowing for incorporation of a inner interlevel dielectric stack with improved thickness uniformity to result in a pixel array exhibiting increased light sensitivity. In the sensor array, each Cu metallization level includes a Cu metal wire structure formed at locations between each array pixel and, a barrier material layer is formed on top each Cu metal wire structure that traverses the pixel optical path. By implementing a single mask or self-aligned mask methodology, a single etch is conducted to completely remove the interlevel dielectric and barrier layers that traverse the optical path. The etched opening is then refilled with dielectric material. Prior to depositing the refill dielectric, a layer of either reflective or absorptive material is formed along the sidewalls of the etched opening to improve sensitivity of the pixels by either reflecting light to the underlying photodiode or by eliminating light reflections.

Owner:SMARTSENS TECH (HK) CO LTD

Interfacial layers for electromigration resistance improvement in damascene interconnects

ActiveUS7648899B1Improve performanceIncrease resistanceSemiconductor/solid-state device detailsSolid-state devicesDielectricDopant

Protective caps residing at an interface between metal lines and dielectric diffusion barrier (or etch stop) layers are used to improve electromigration performance of interconnects. Protective caps are formed by depositing a source layer of dopant-generating material (e.g., material generating B, Al, Ti, etc.) over an exposed copper line, converting the upper portion of the source layer to a passivated layer (e.g., nitride or oxide) while allowing an unmodified portion of a dopant-generating source layer to remain in contact with copper, and, subsequently, allowing the dopant from the unmodified portion of source layer to controllably diffuse into and / or react with copper, thereby forming a thin protective cap within copper line. The cap may contain a solid solution or an alloy of copper with the dopant.

Owner:NOVELLUS SYSTEMS

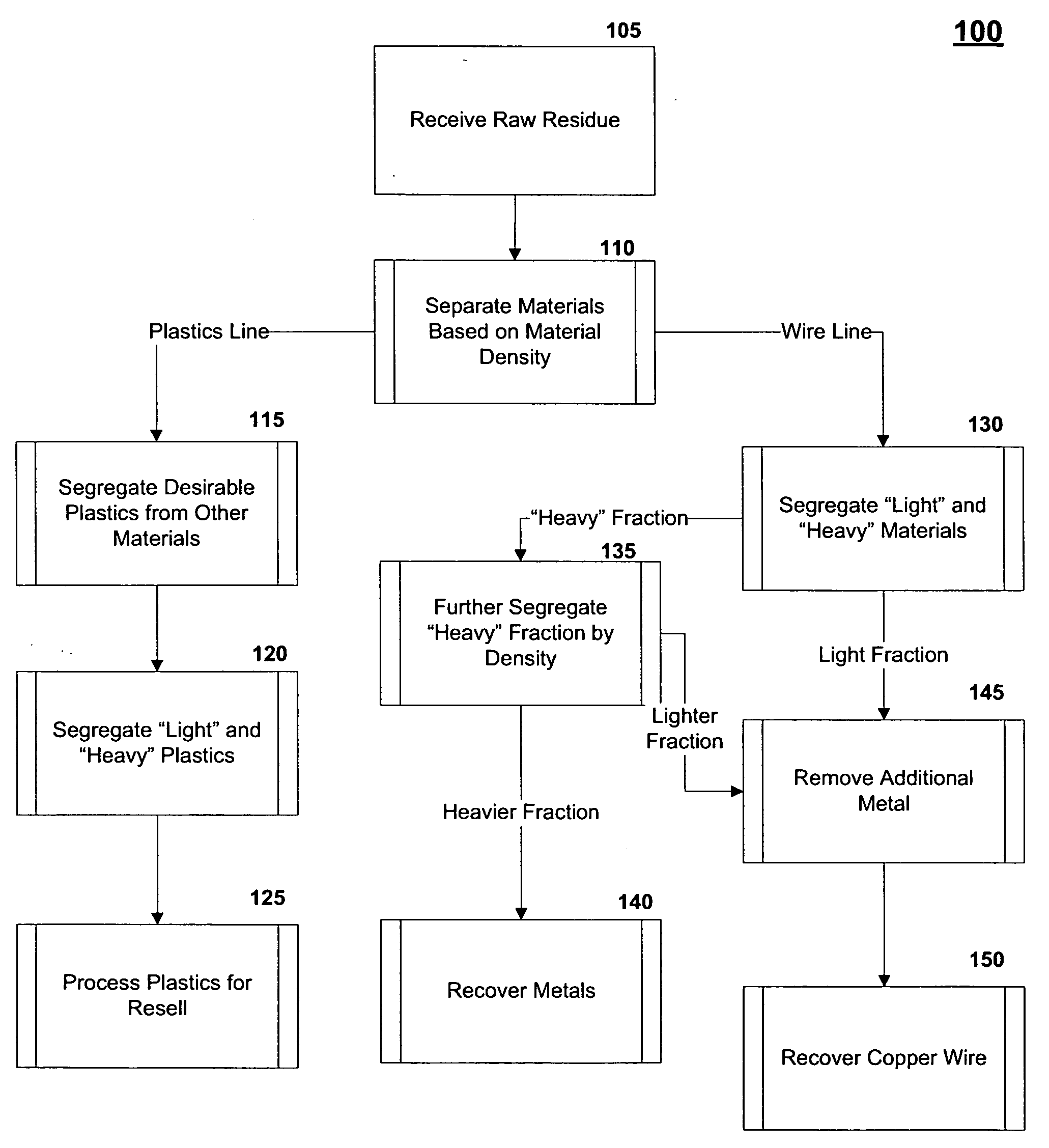

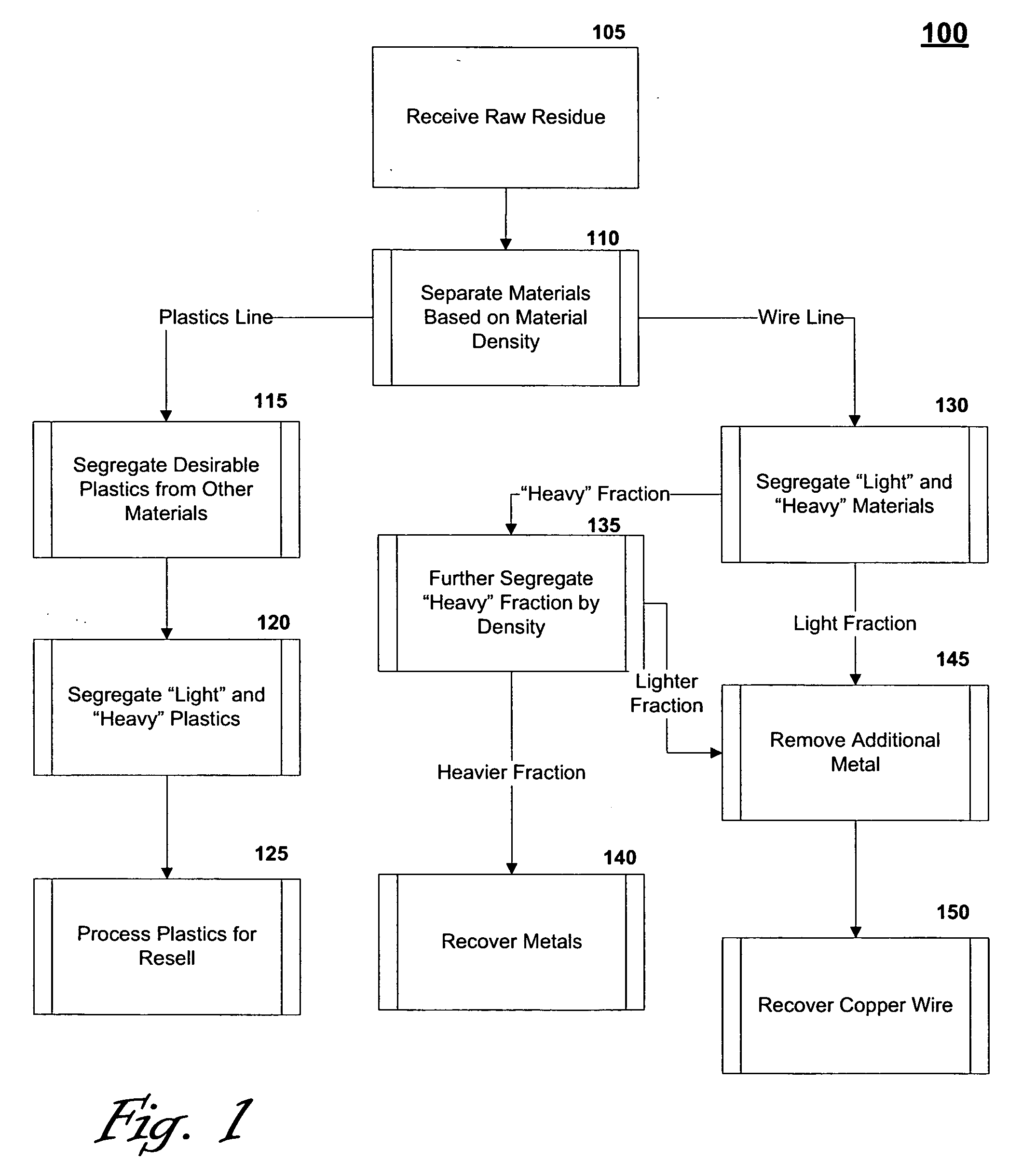

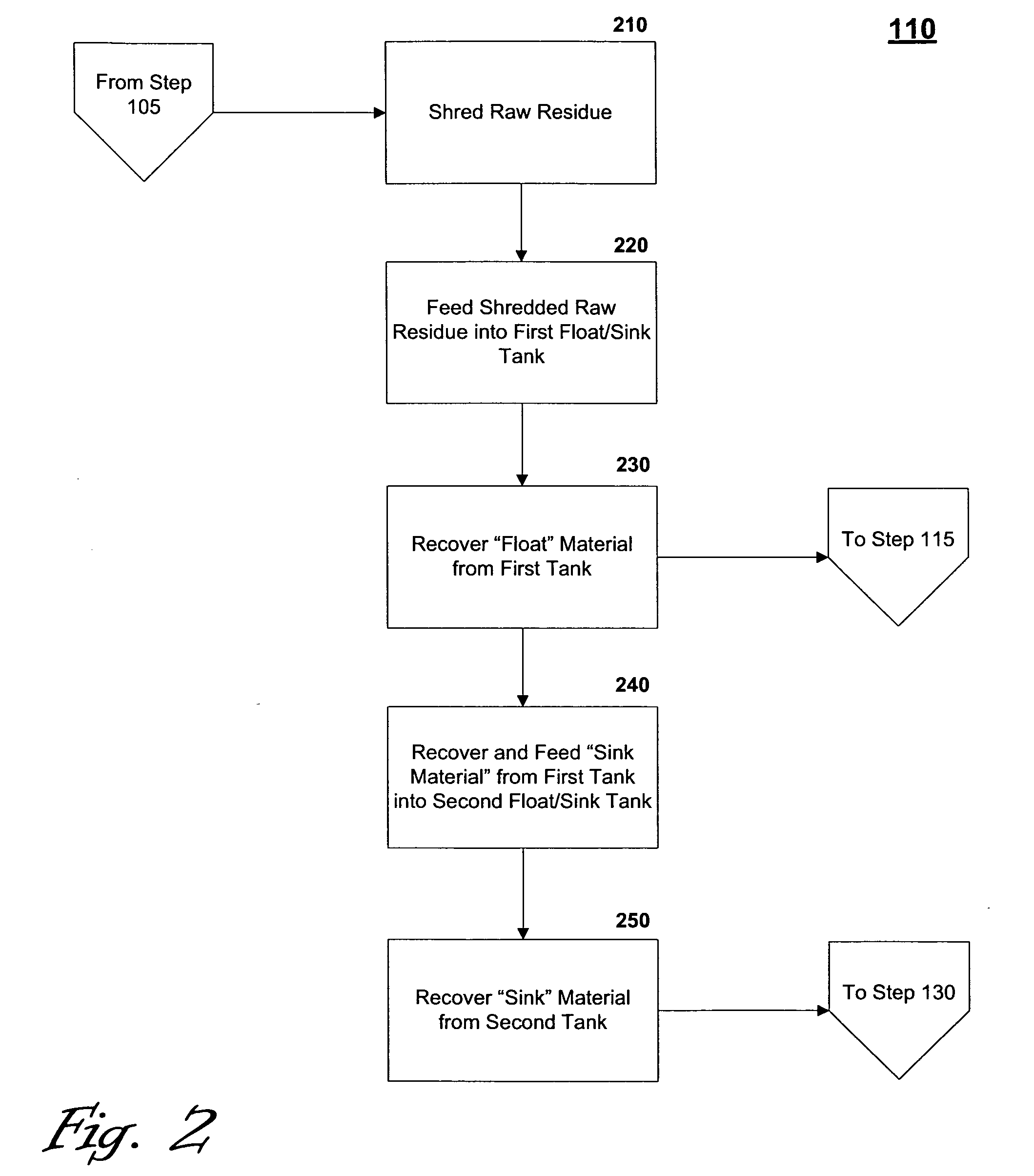

Method and system for sorting and processing recycled materials

InactiveUS20080257794A1Small sizePlastic recyclingAuxillary shaping apparatusCopper wireNonferrous metal

Processing recycled materials to recover plastics, copper wire, and other non-ferrous metals. Aspects of the invention employ density separation to separate plastic-bearing materials from copper-bearing materials. Plastic-bearing materials are further separated to separate light plastics from heavy plastics. Plastics are concentrated, extruded, and palletized. Copper and other valuable metals are recovered from copper-bearing materials using a water separation table.

Owner:VALERIO THOMAS A

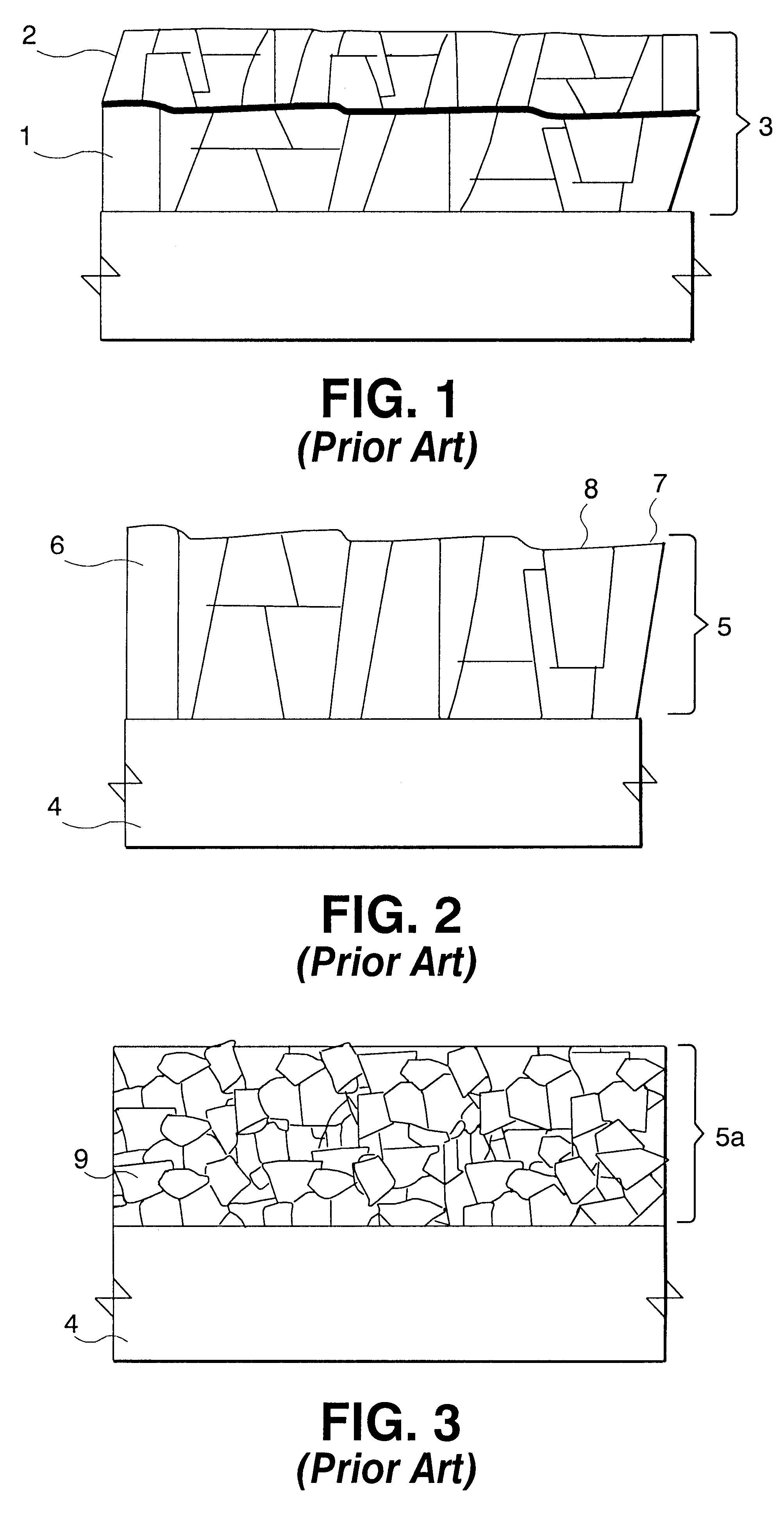

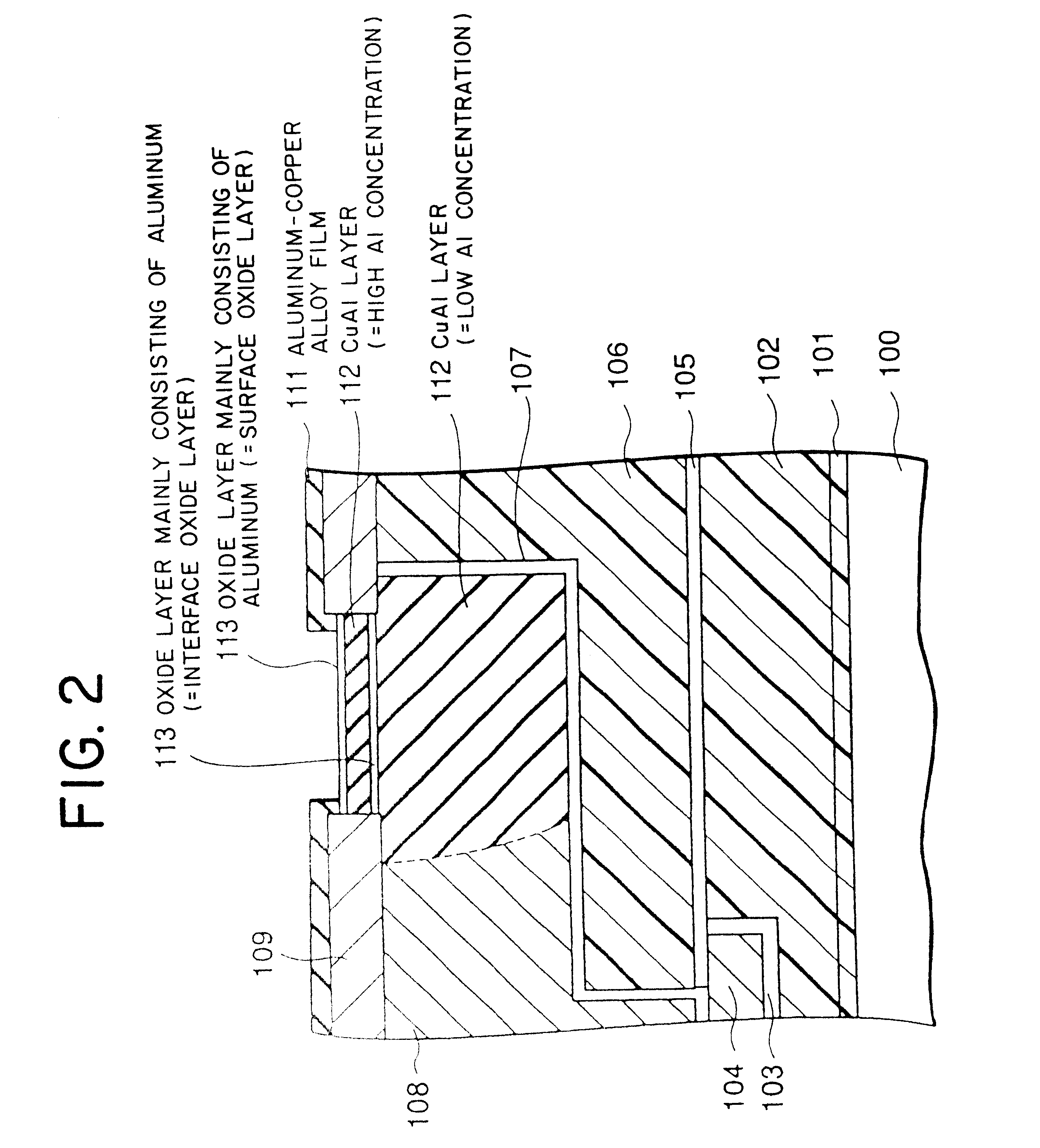

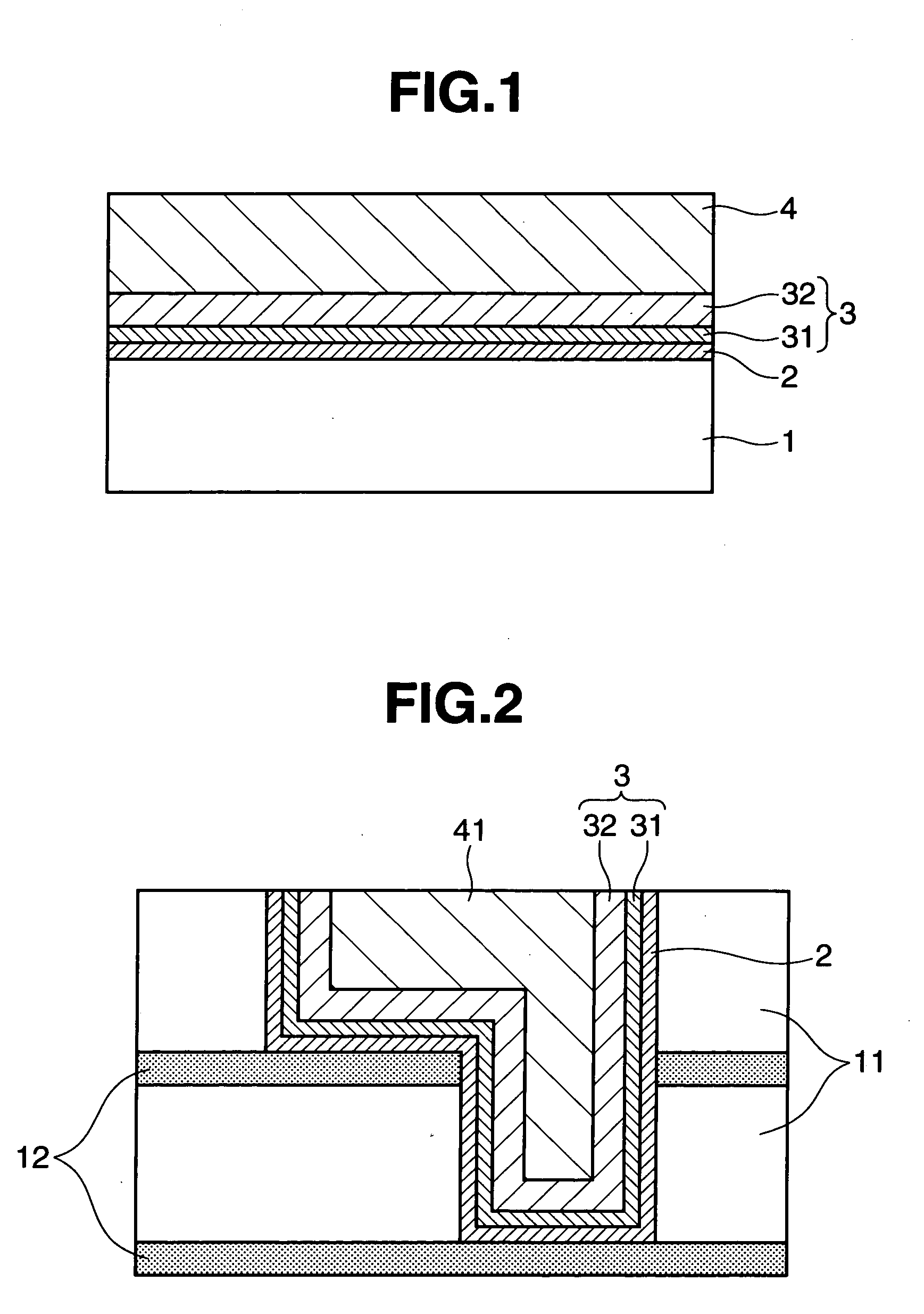

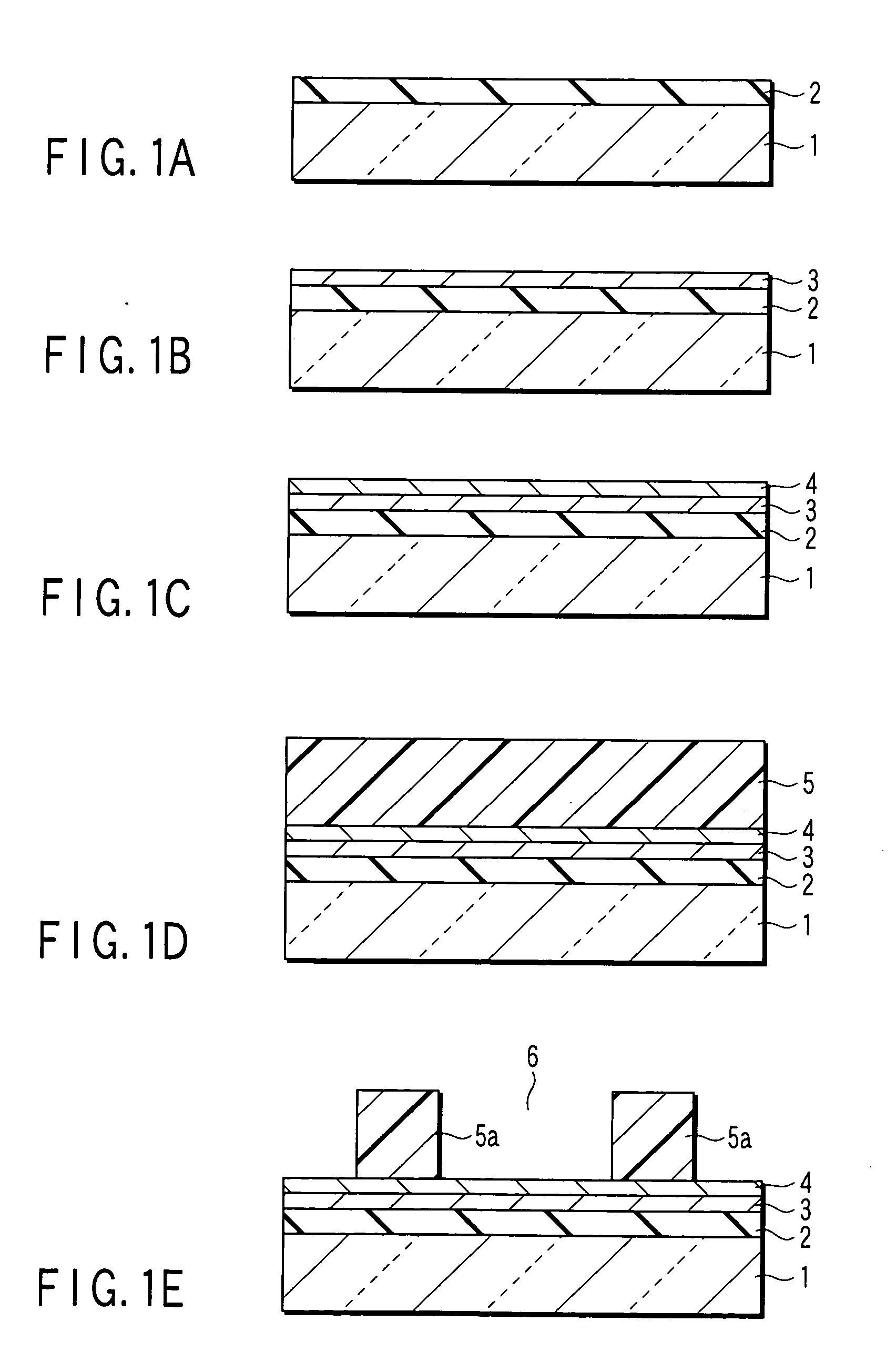

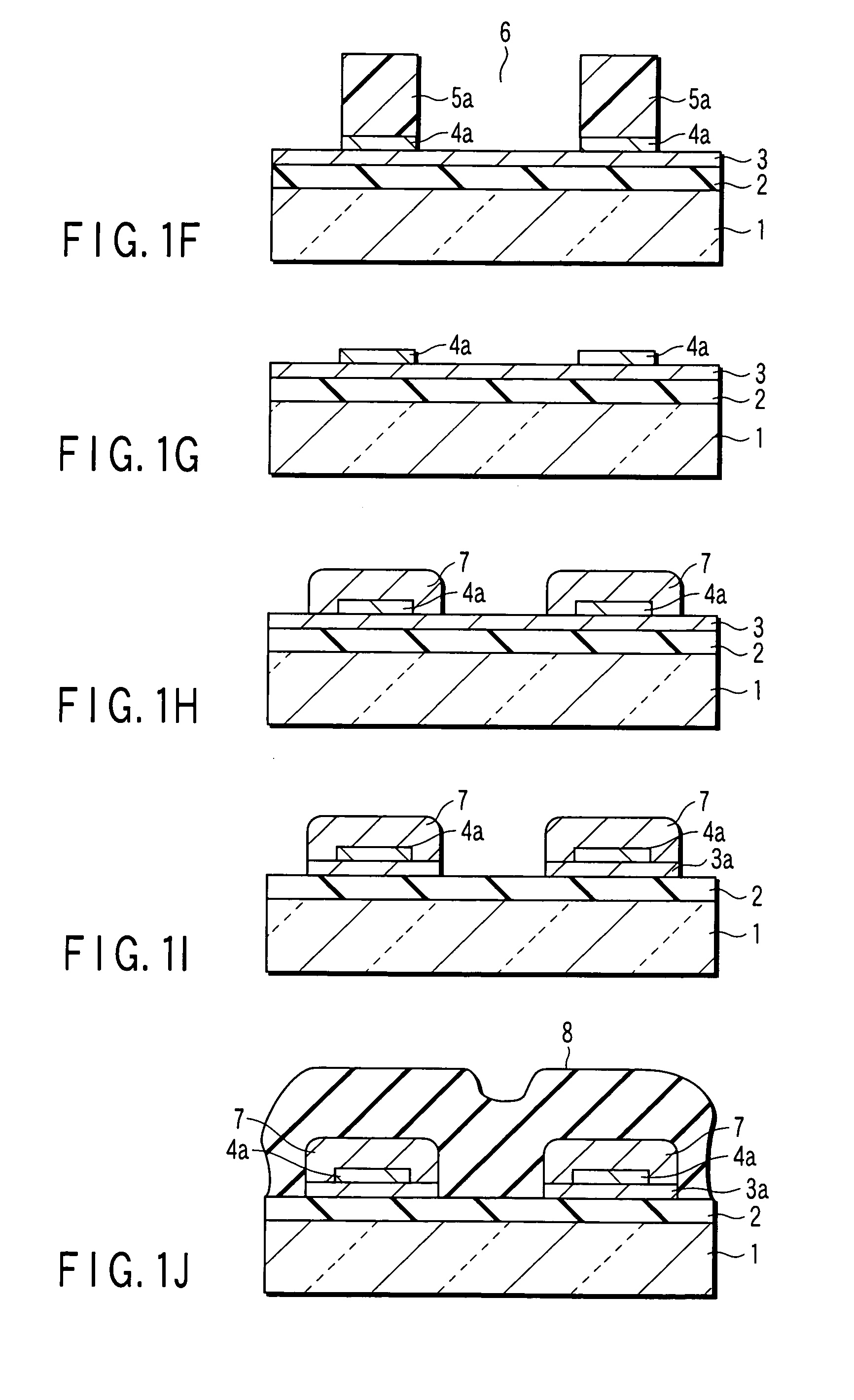

Multi-layered wiring layer and method of fabricating the same

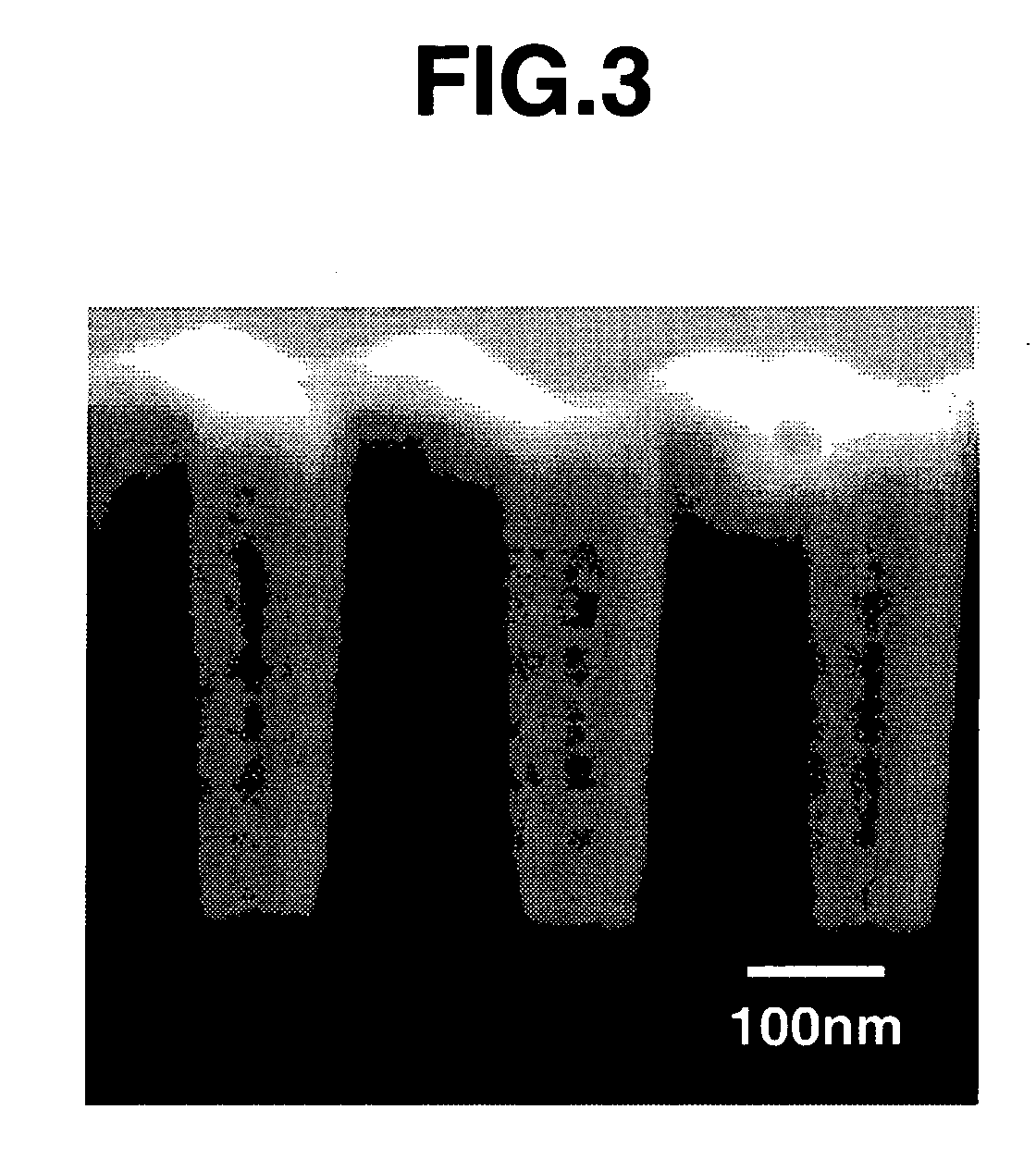

InactiveUS6538324B1Semiconductor/solid-state device detailsSolid-state devicesDevice materialNitrogen

There is provided a barrier film preventing diffusion of copper from a copper wiring layer formed on a semiconductor substrate. The barrier film has a multi-layered structure of first and second films wherein the first film is composed of crystalline metal containing nitrogen therein, and the second film is composed of amorphous metal nitride. The barrier film is constituted of common metal atomic species. The barrier film prevents copper diffusion from a copper wiring layer into a semiconductor device, and has sufficient adhesion characteristic to both a copper film and an interlayer insulating film.

Owner:GK BRIDGE 1

Method and structure for creating ultra low resistance damascene copper wiring

InactiveUS6987059B1Lower resistanceSimple and available process techniqueSemiconductor/solid-state device manufacturingDielectricCopper-wiring

A low resistance copper damascene interconnect structure is formed by providing a thin dielectric film such as SiC or SiOC formed on the sidewalls of the via and trench structures to function as a copper diffusion barrier layer. The dielectric copper diffusion barrier formed on the bottom of the trench structure is removed by anisotropic etching to expose patterned metal areas. The residual dielectric thus forms a dielectric diffusion barrier film on the sidewalls of the structure, and coupled with the metal diffusion barrier subsequently formed in the trench, creates a copper diffusion barrier to protect the bulk dielectric from copper leakage.

Owner:BELL SEMICON LLC

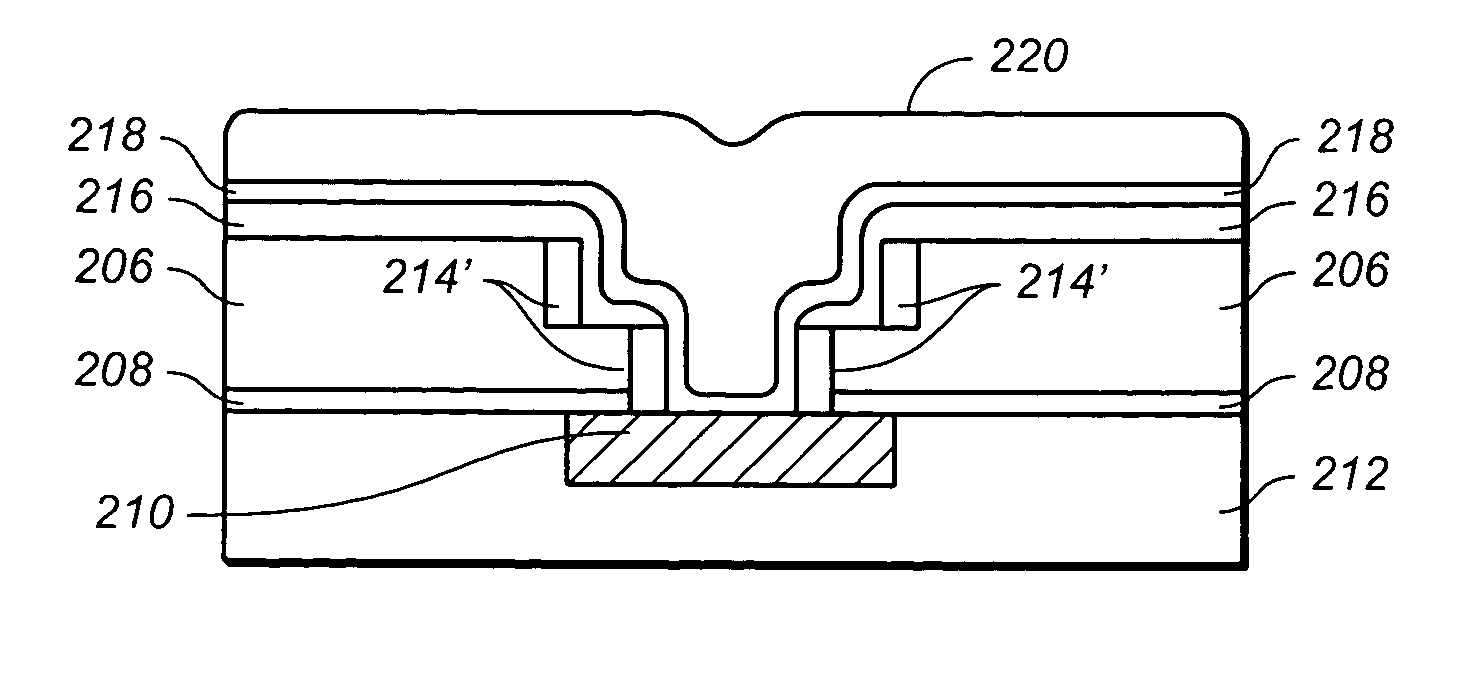

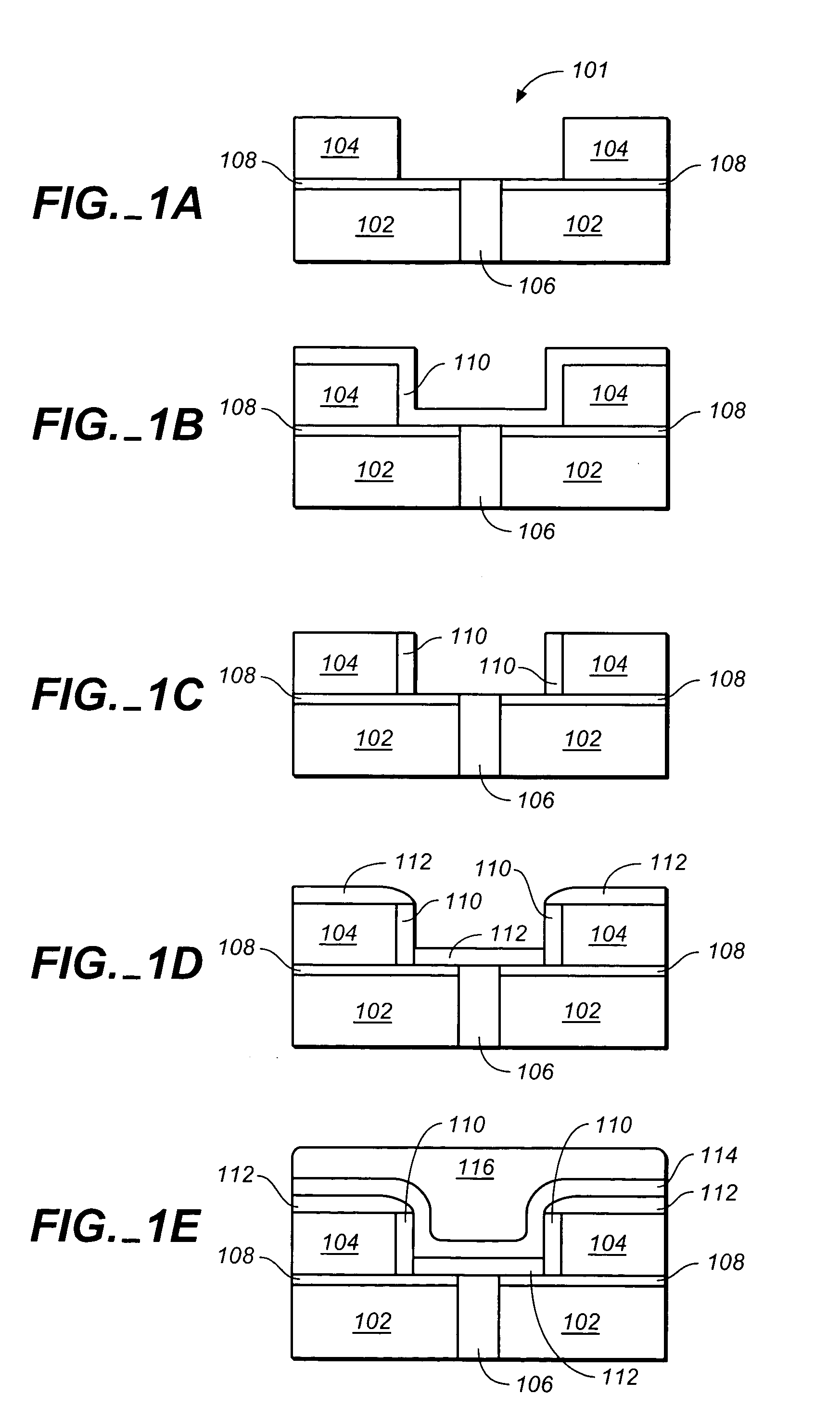

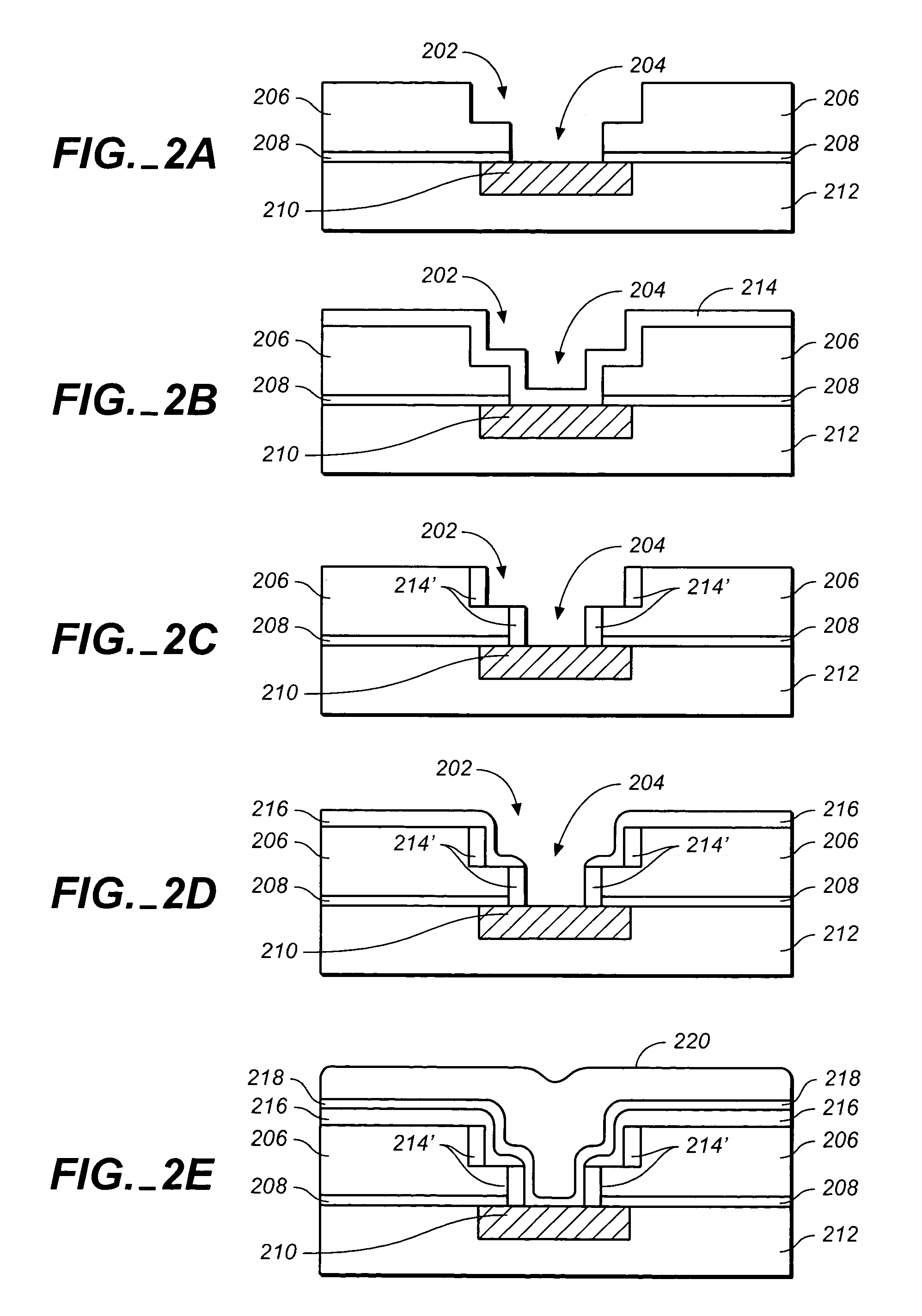

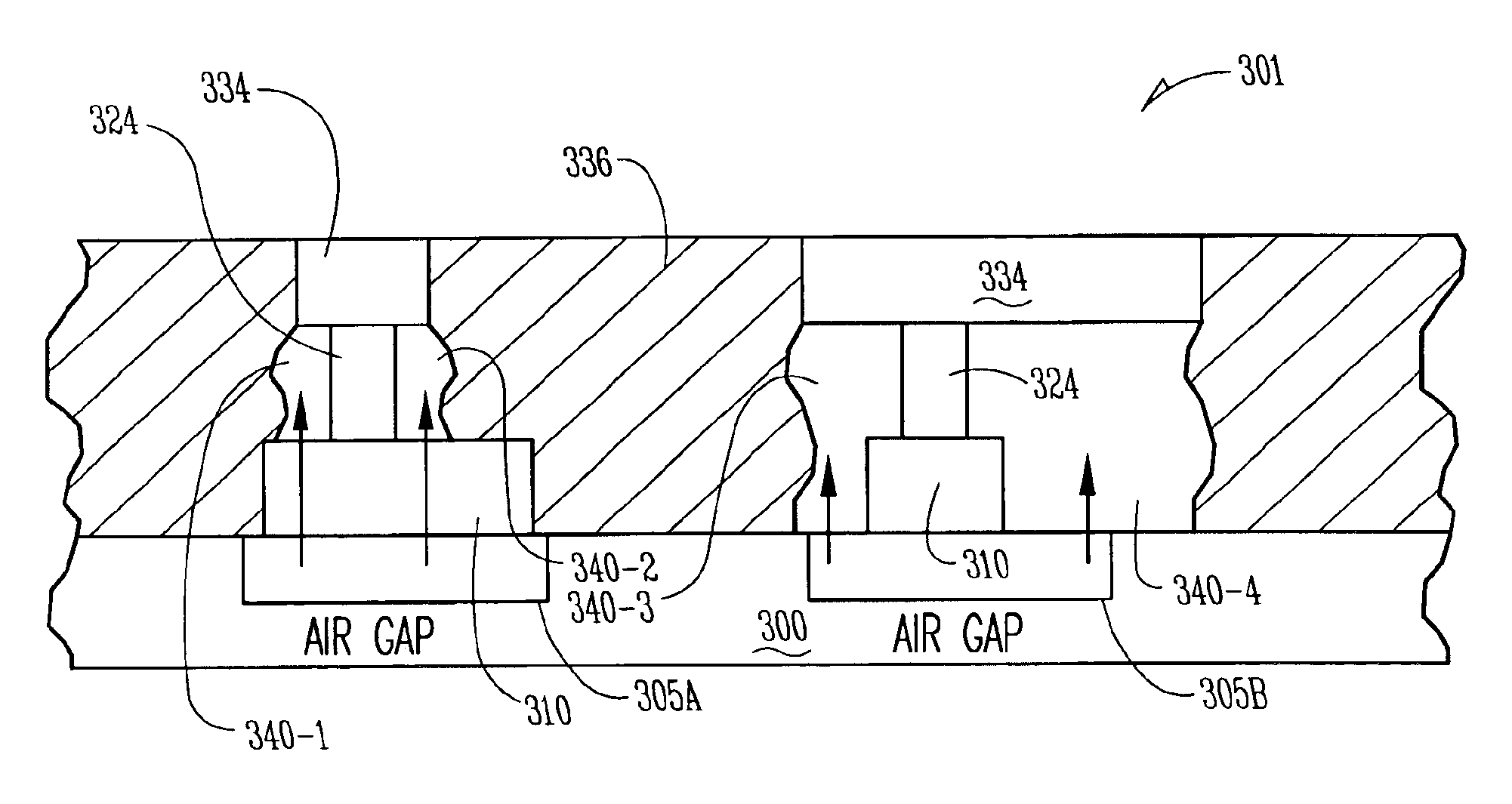

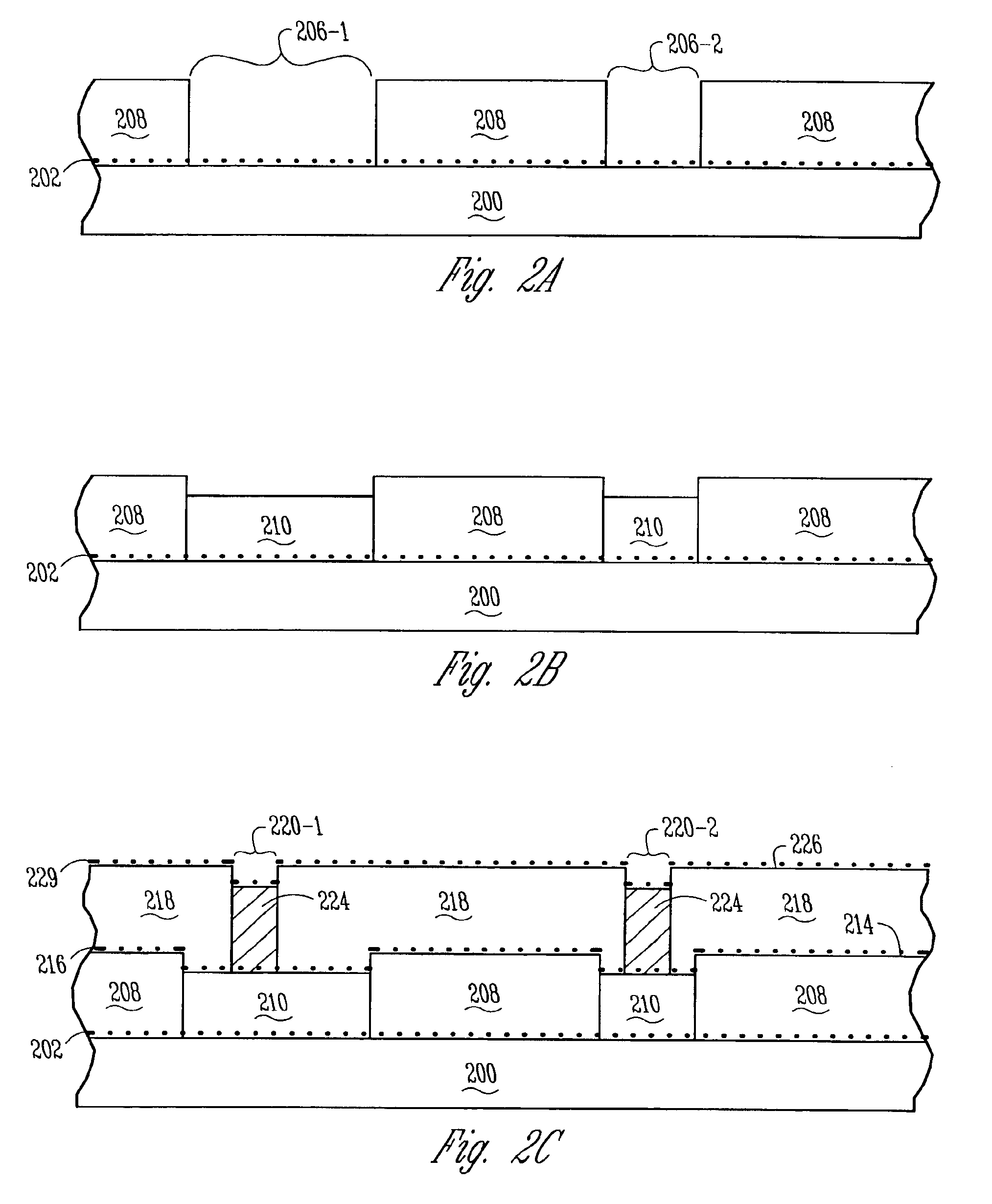

Multilevel copper interconnects with low-k dielectrics and air gaps

InactiveUS7091611B2Semiconductor/solid-state device detailsSolid-state devicesCapacitanceCopper interconnect

Structures and methods are provided for an improved multilevel wiring interconnect in an integrated circuit assembly. The present invention provides for a multilayer copper wiring structure by electroless, selectively deposited copper in a streamlined process which further reduces both intra-level line to line capacitance and the inter-level capacitance.In particular, an illustrative embodiment of the present invention includes a novel methodology for forming multilevel wiring interconnects in an integrated circuit assembly. The method includes forming a number of multilayer metal lines, e.g. copper lines formed by selective electroless plating, separated by air gaps above a substrate. A low dielectric constant material is deposited between the number of metal lines and the substrate using a directional process. According to the teachings of the present invention, using a directional process includes maintaining a number of air gaps in the low dielectric constant material. Structures and systems are similarly included in the present invention.

Owner:ROUND ROCK RES LLC

Photoresist stripper composition

InactiveUS20050287480A1Improve high-speed performanceLower resistanceSemiconductor/solid-state device manufacturingDetergent compounding agentsResistDevice material

(Problem) It is to provide a stripper having excellent ability to suppress corrosion or damage to the copper wiring or the low-k film, and having excellent photoresist residue removability after ashing. (Solution) The invention provides a photoresist stripper composition characterized in containing salts of at least two different inorganic acids, surfactants and a corrosion inhibitor for metal, and having a pH in the range of 3-10; and a process for preparation of semiconductor devices characterized in that the photoresist residues generated during the preparation of semiconductor devices which employs copper or a copper-dominant alloy as the material for wiring is stripped using said photoresist stripper.

Owner:DONGWOO FINE CHEM CO LTD

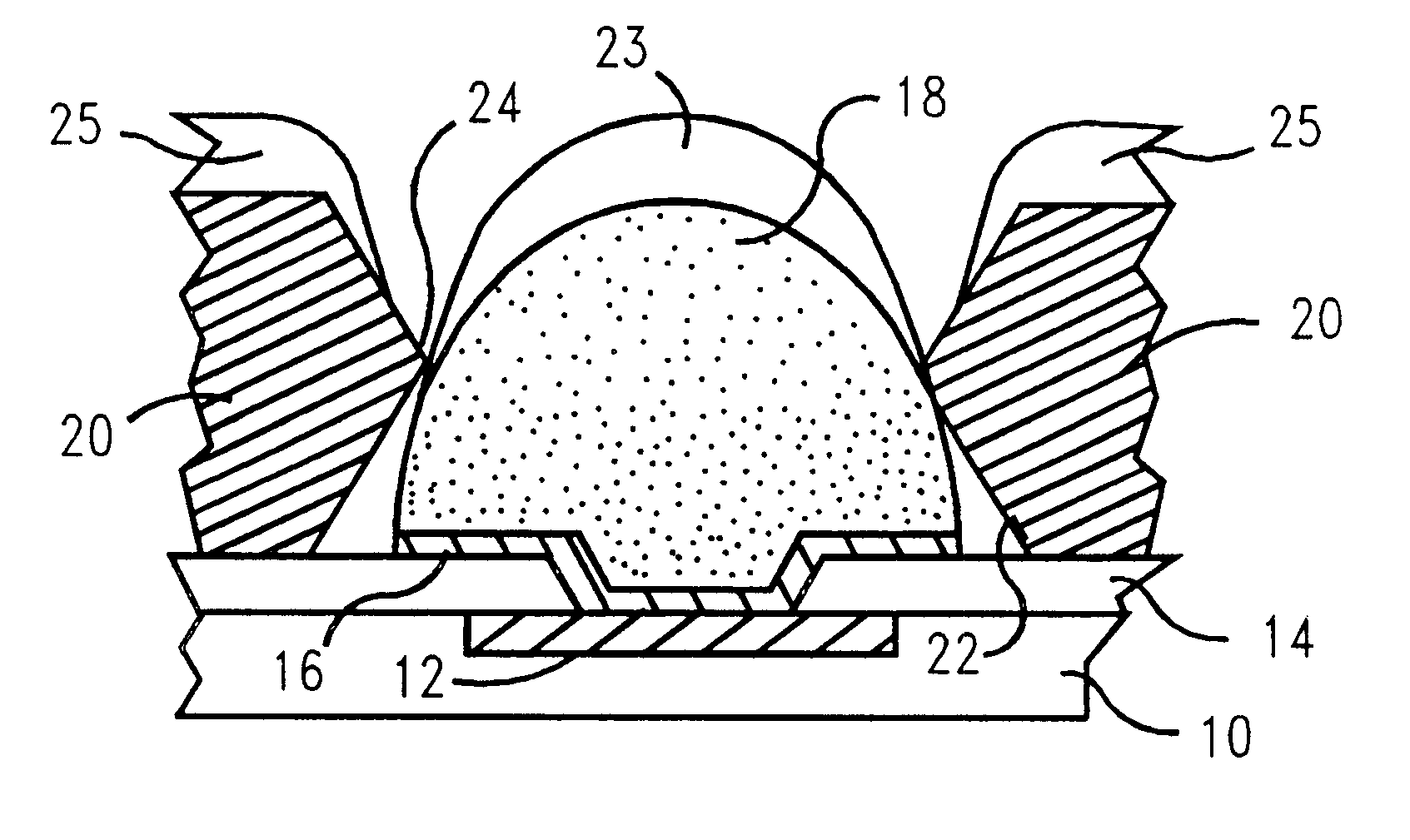

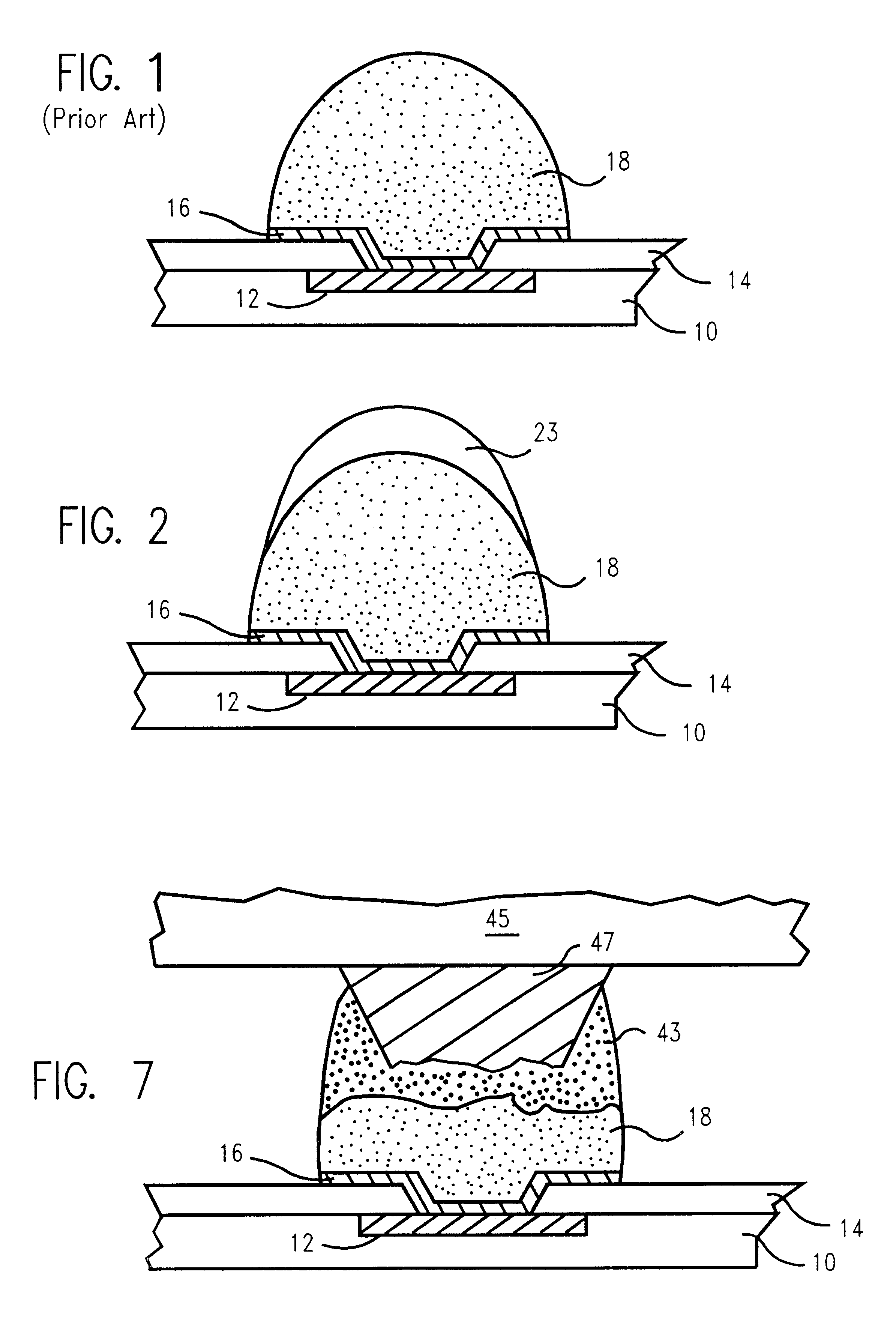

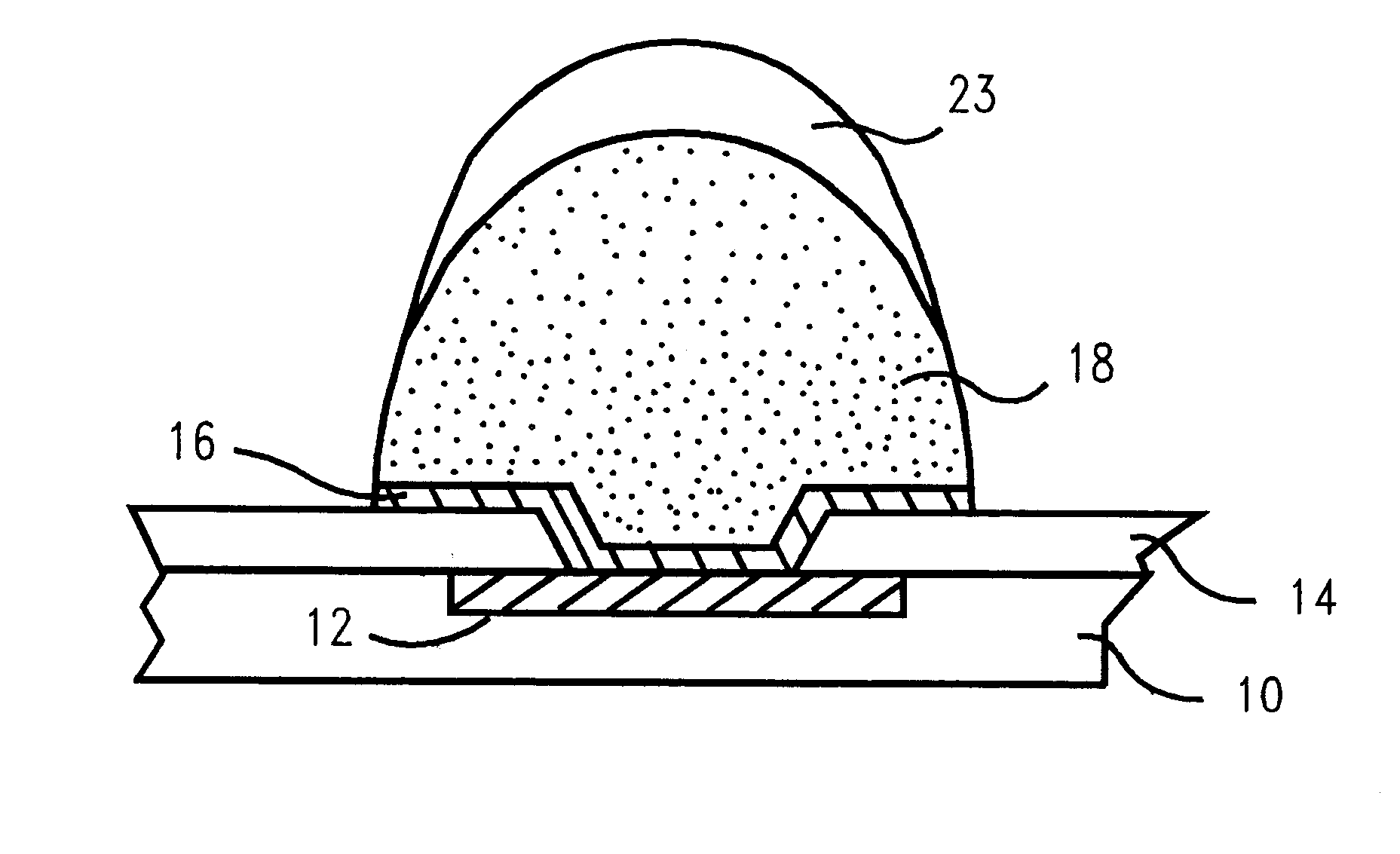

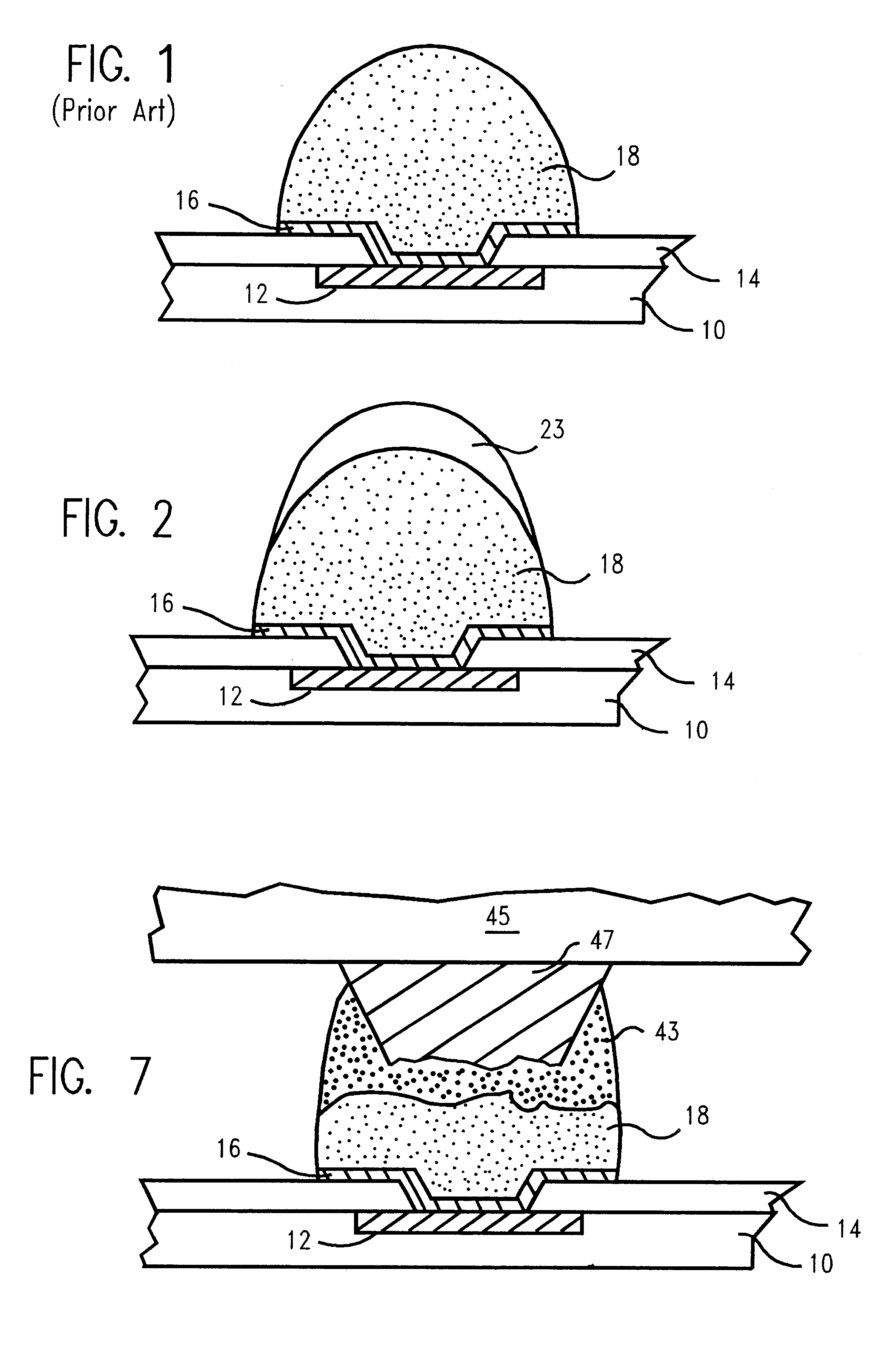

Method for forming reflowed solder ball with low melting point metal cap

InactiveUS6344234B1Reduce the hole diameterMinimal diameterFinal product manufactureSemiconductor/solid-state device detailsTinningIndium

A method and structure for a solder interconnection, using solder balls for making a low temperature chip attachment directly to any of the higher levels of packaging substrate is disclosed. After a solder ball has been formed using standard methods it is reflowed to give the solder ball a smooth surface. A layer of low melting point metal, such as, bismuth, indium or tin, preferably, pure tin, is deposited on the top of the solder balls. This structure results in localizing of the eutectic alloy, formed upon subsequent low temperature joining cycle, to the top of the high melting solder ball even after multiple low temperature reflow cycles. This method does not need tinning of the substrate to which the chip is to be joined, which makes this method economical. It has also been noticed that whenever temperature is raised slightly above the eutectic temperature, the structure always forms a liquid fillet around the joint with copper wires. This liquid fillet formation results in substantial thermal fatigue life improvement for reduced stress at interface; and secondly, provides an easy means to remove chip for the purpose of chip burn-in, replacement or field repairs.

Owner:ULTRATECH INT INC

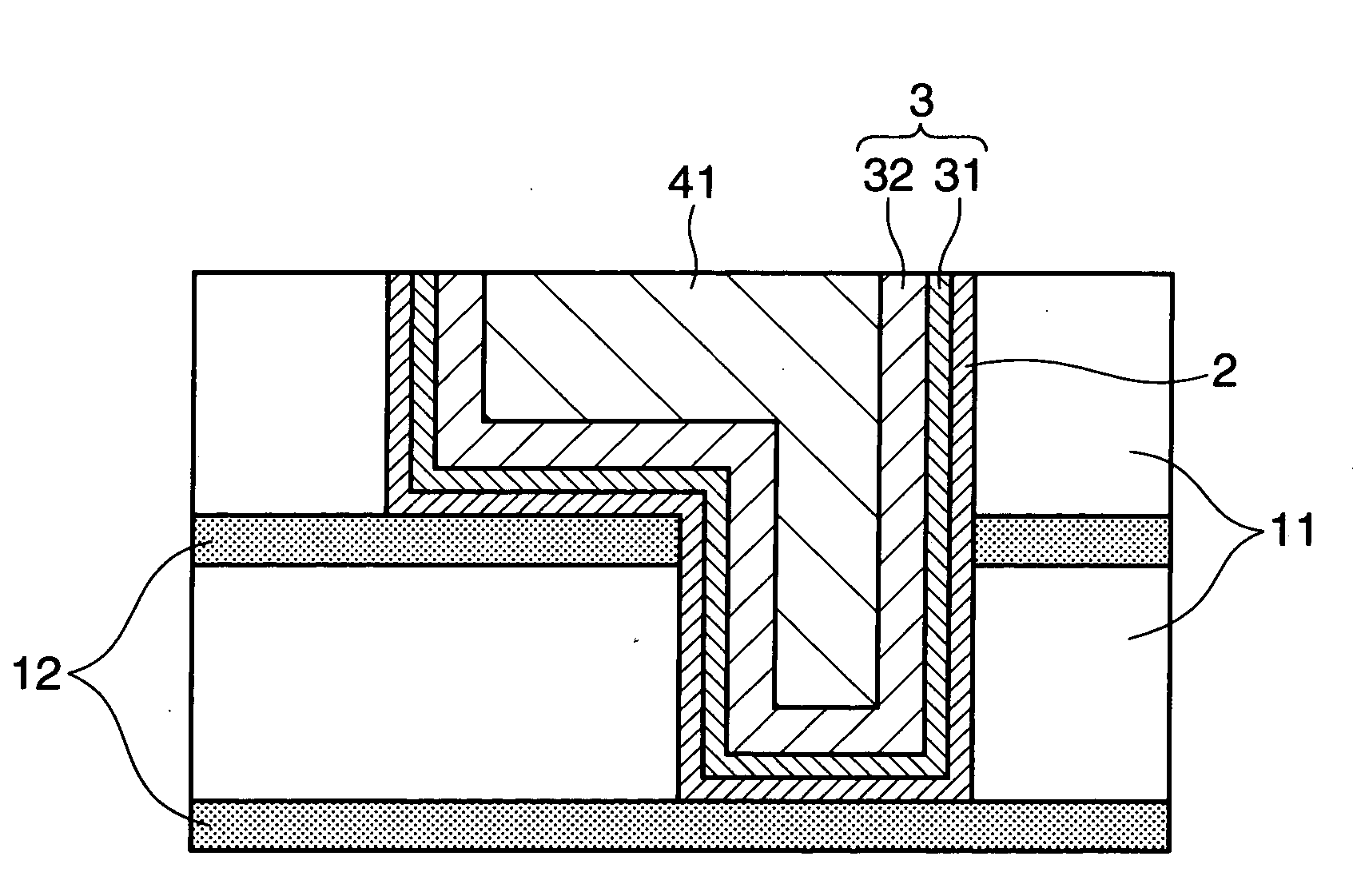

Method for forming barrier layer for copper metallization

A method comprises forming a barrier layer for copper metallization, selectively forming a silicon film on a surface of copper wiring formed on the main surface of a semiconductor substrate, and reacting the silicon film with a non-copper metal and / or nitrogen to form a barrier layer in a self-aligned manner relative to the copper wiring. In the method, the capacitance increase in the copper wirings formed is prevented, and the barrier layer formed has a satisfactory barrier property of protecting the copper wirings.

Owner:TOSHIBA MEMORY CORP

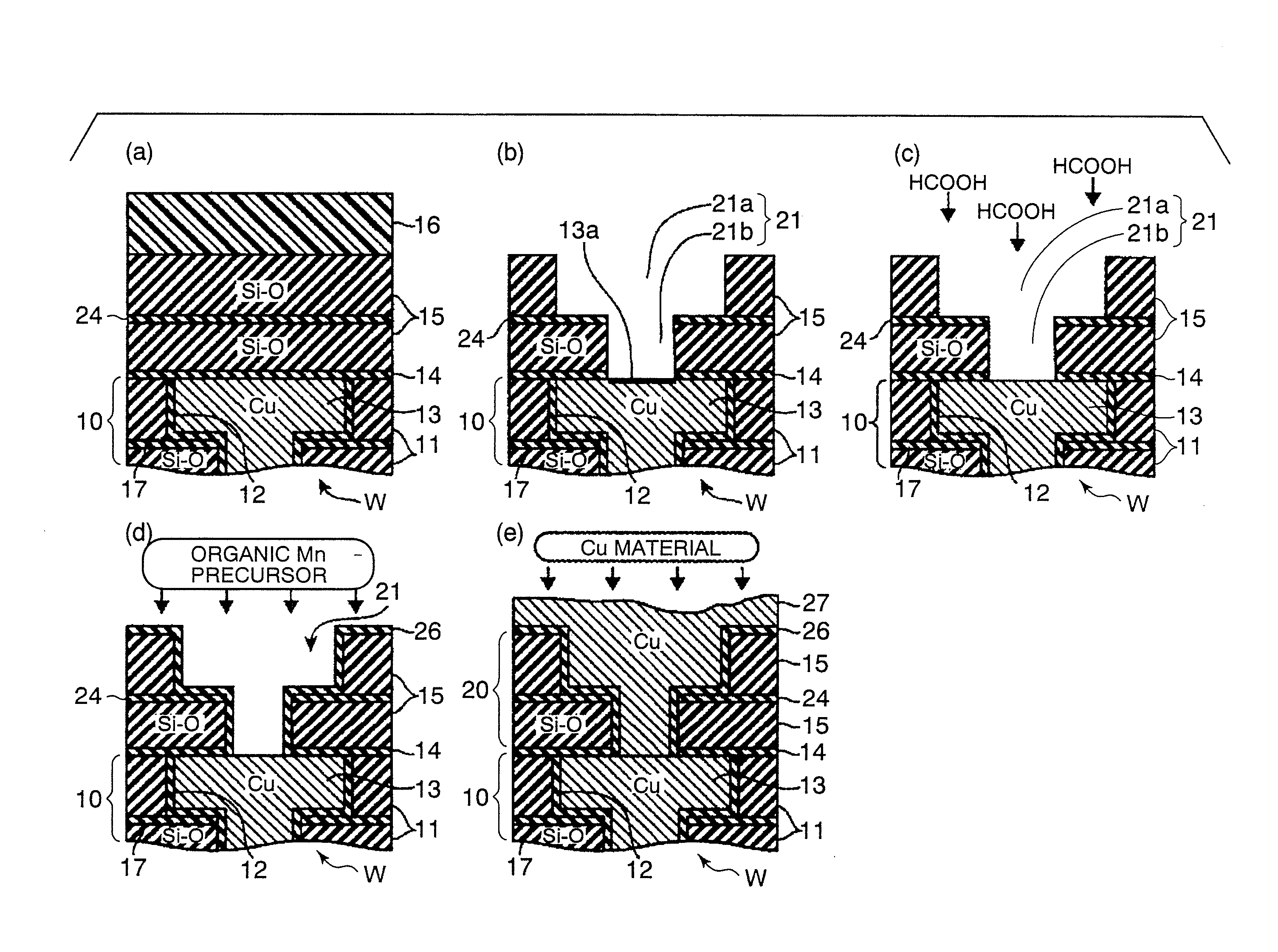

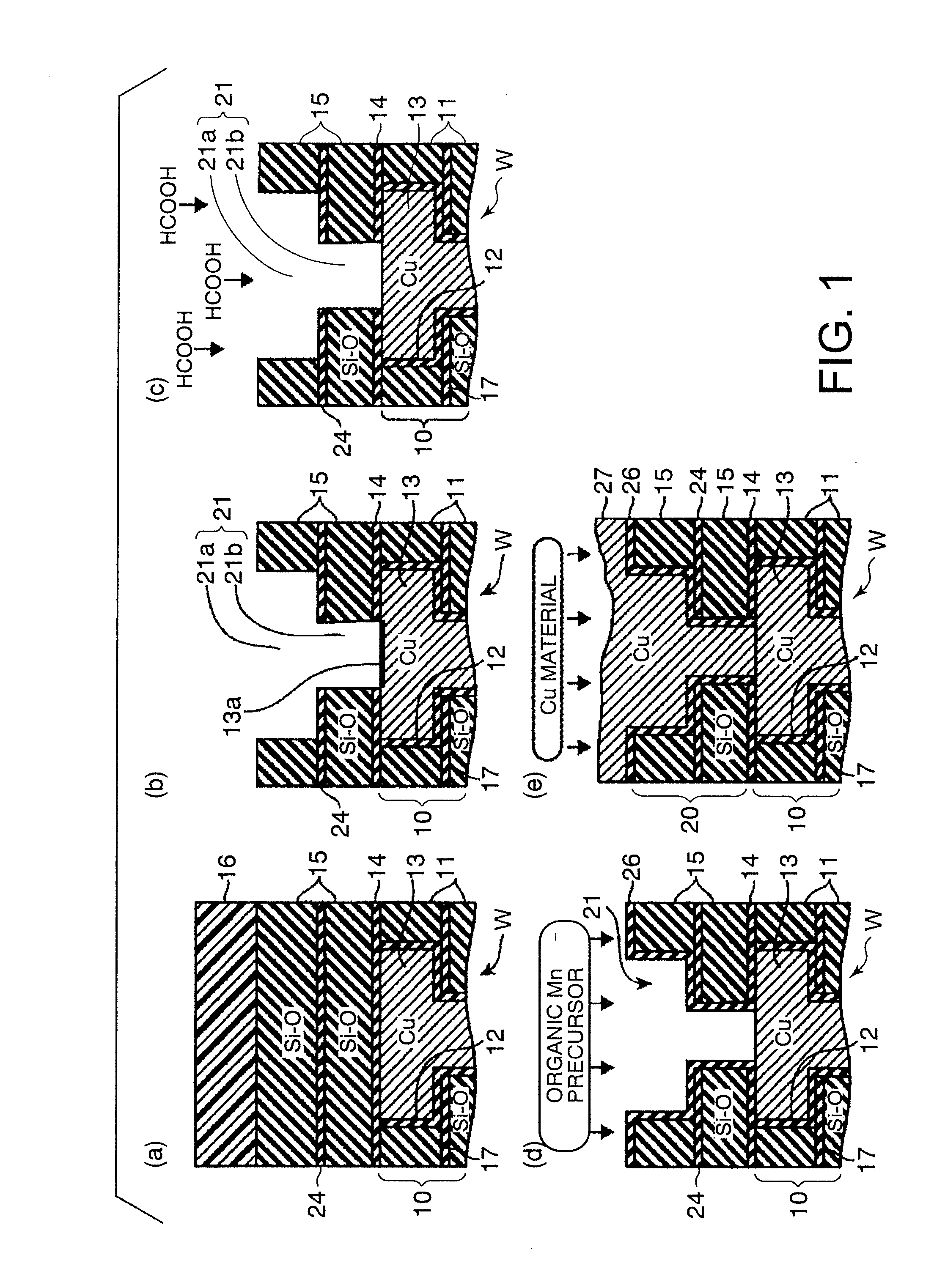

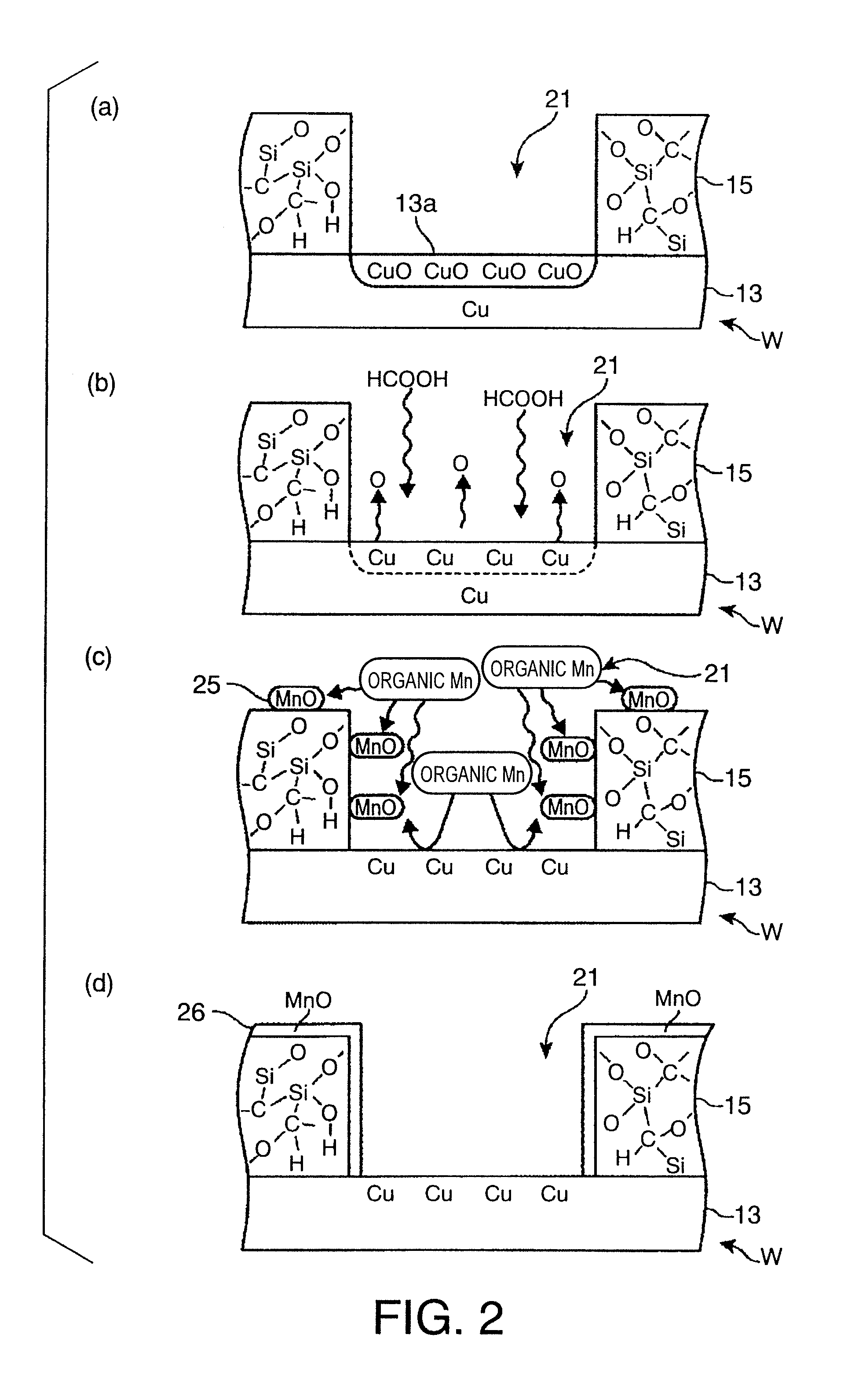

Method of manufacturing semiconductor device, semiconductor device, electronic instrument, semiconductor manufacturing apparatus, and storage medium

InactiveUS20110049718A1Low costGood step coverageLiquid surface applicatorsSemiconductor/solid-state device detailsDevice materialCopper-wiring

When a barrier film is formed on an exposed surface of an interlayer insulation film on a substrate, the interlayer insulation film having a recess formed therein, and a metal wiring to be electrically connected to a metal wiring in a lower layer is formed in the recess, a barrier film having an excellent step coverage can be formed and increase of a wiring resistance can be restrained. An oxide film on a surface of the lower copper wiring exposed to a bottom surface of the interlayer insulation film is reduced or edged so as to remove oxygen on the surface of the copper wiring. Then, by supplying an organic metal compound containing manganese and containing no oxygen, generation of manganese oxide as a self-forming barrier film is selectively allowed on an area containing oxygen, such as a sidewall of the recess and a surface of the interlayer insulation film, while generation of the manganese oxide is not allowed on the surface of the copper wiring. Thereafter, copper is embedded in the recess.

Owner:TOKYO ELECTRON LTD +1

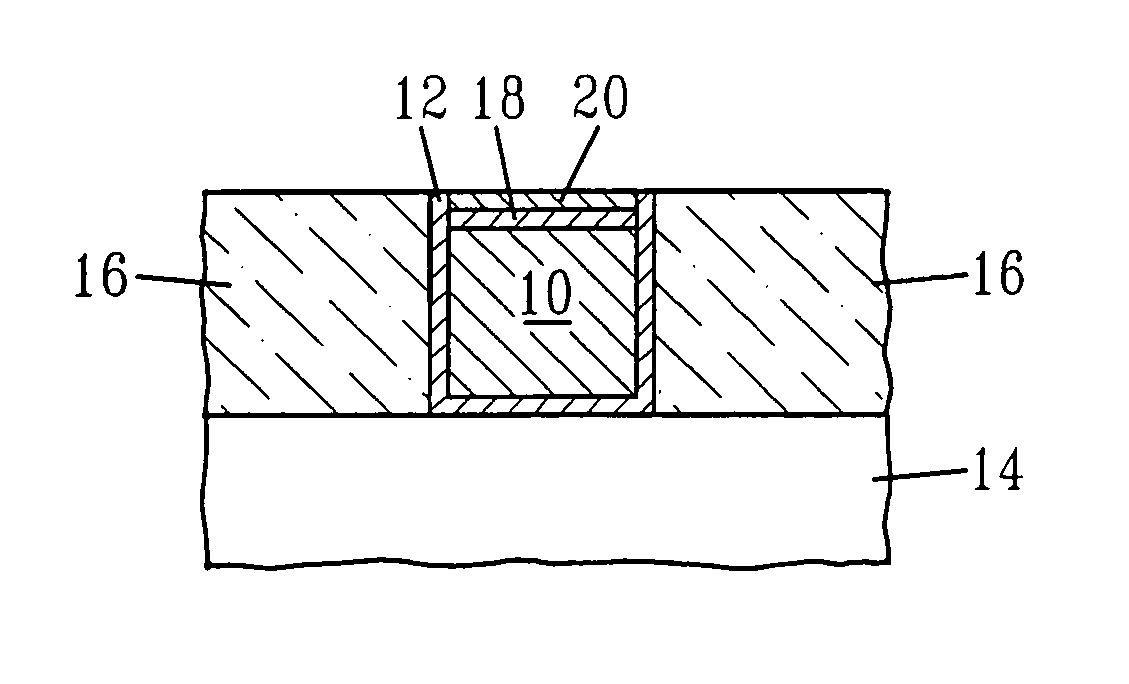

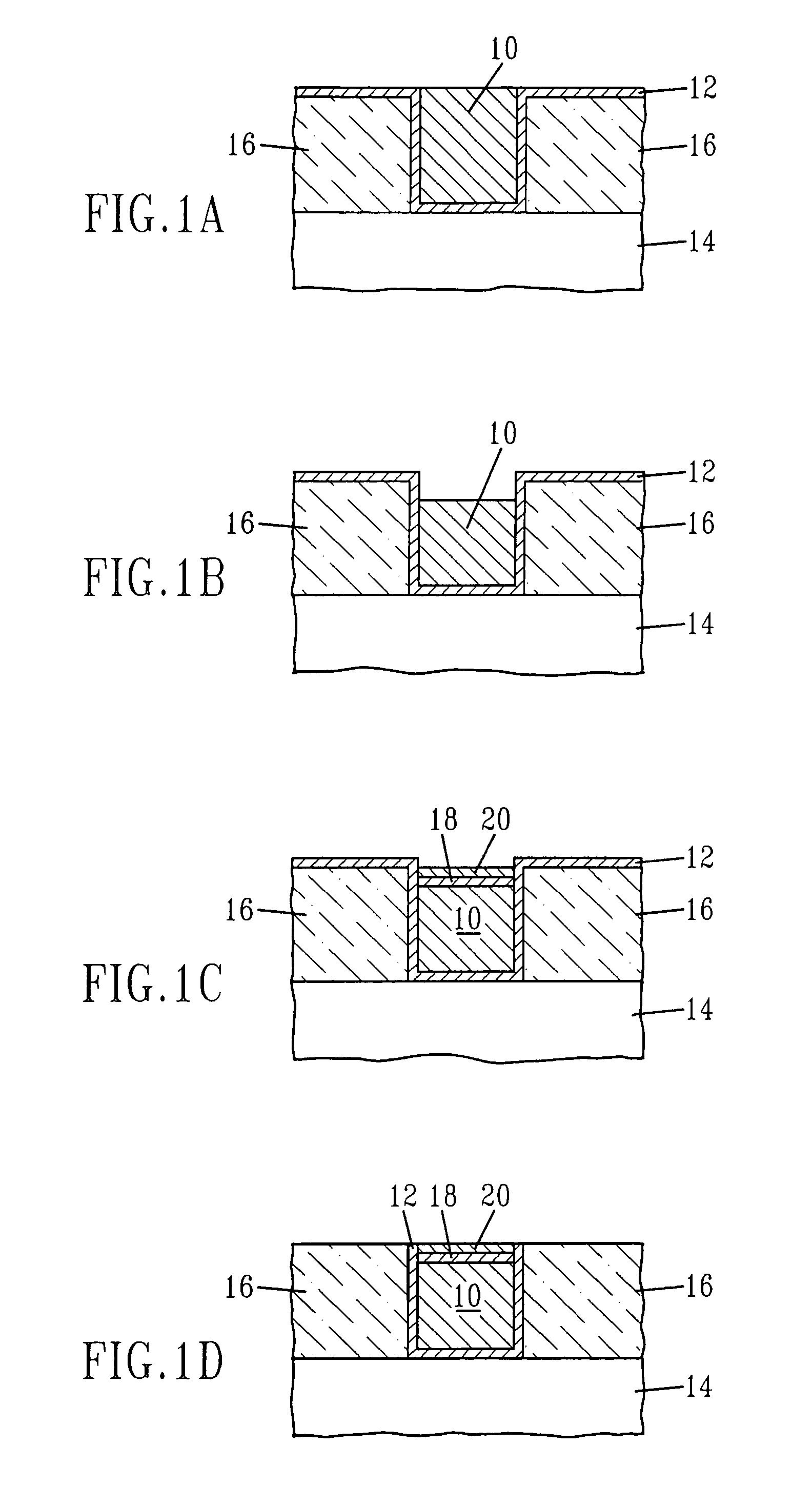

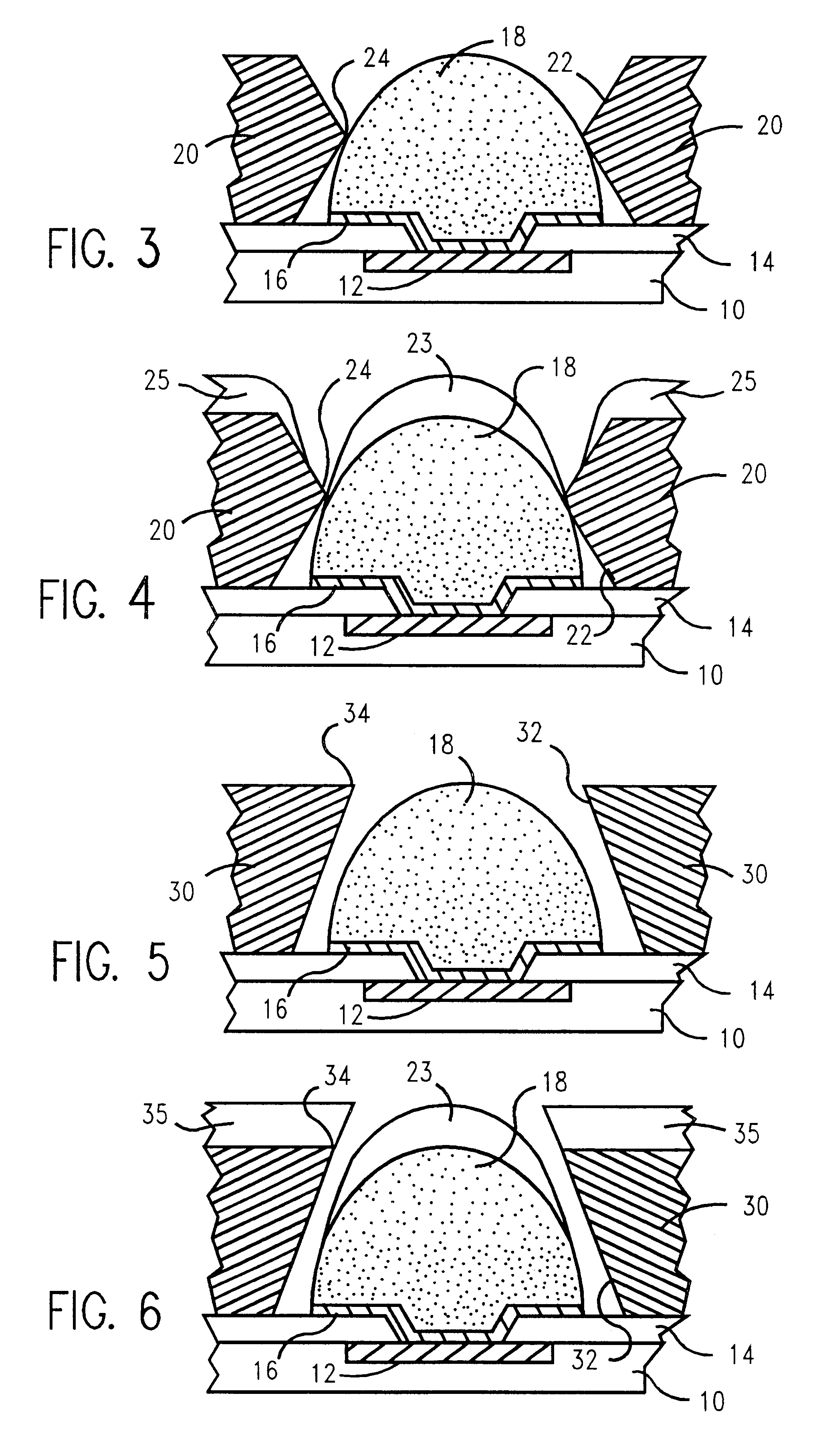

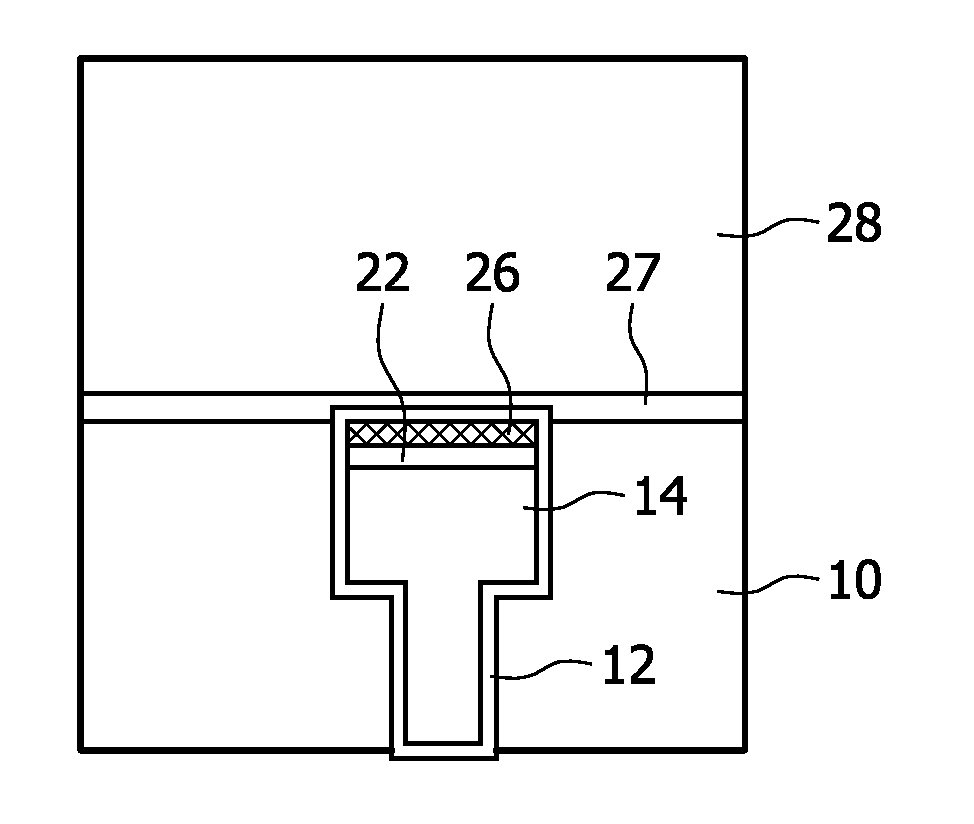

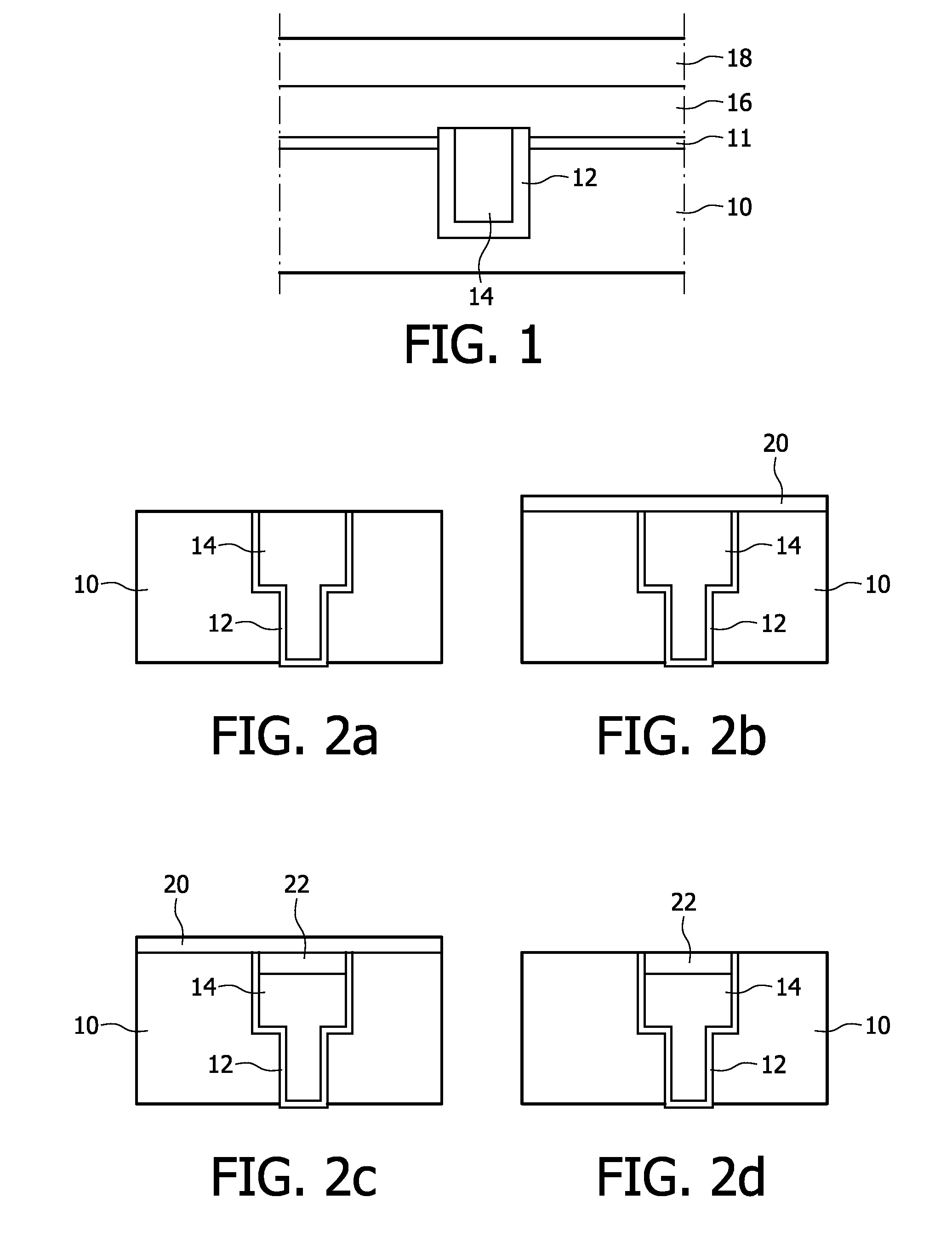

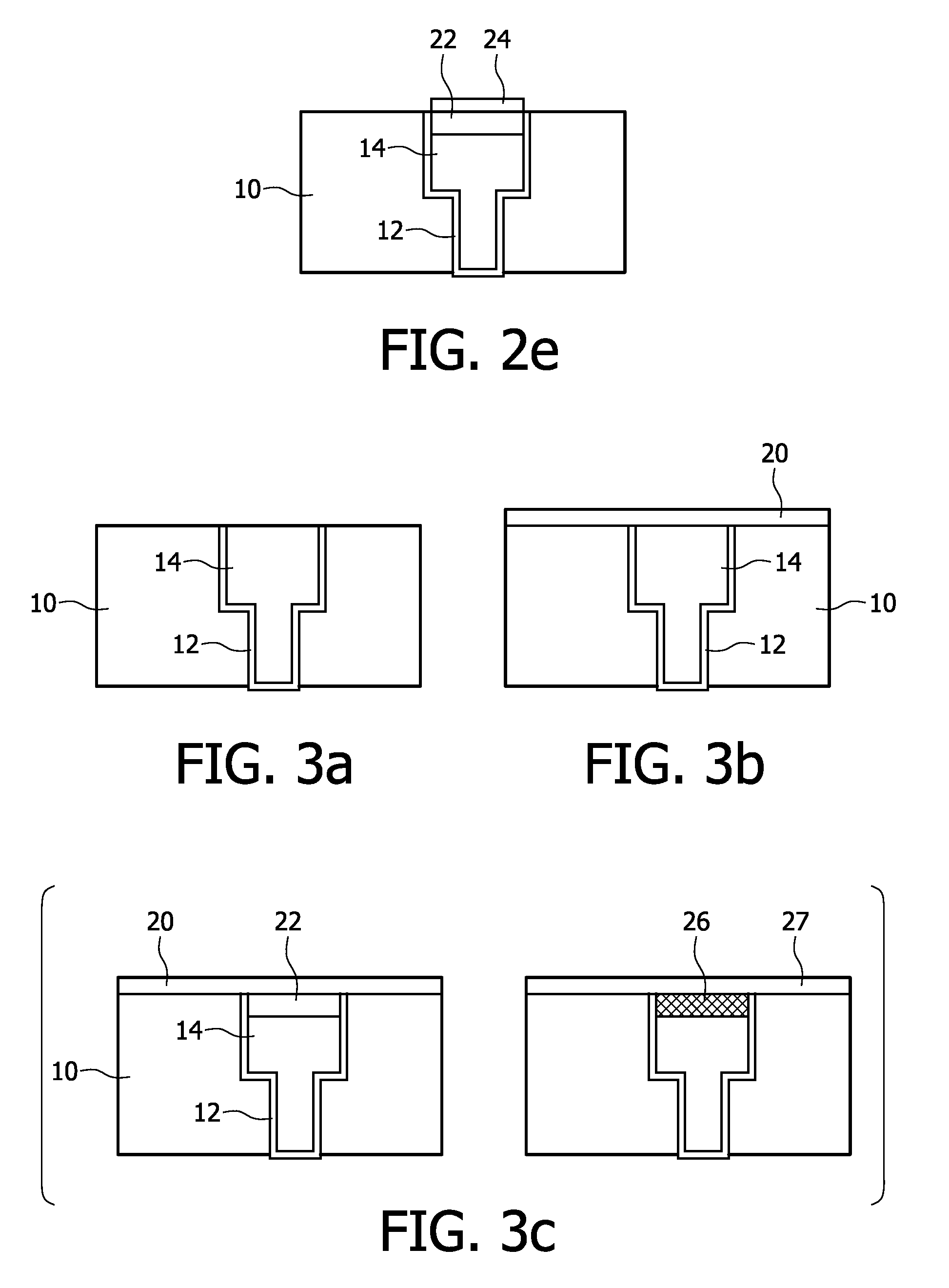

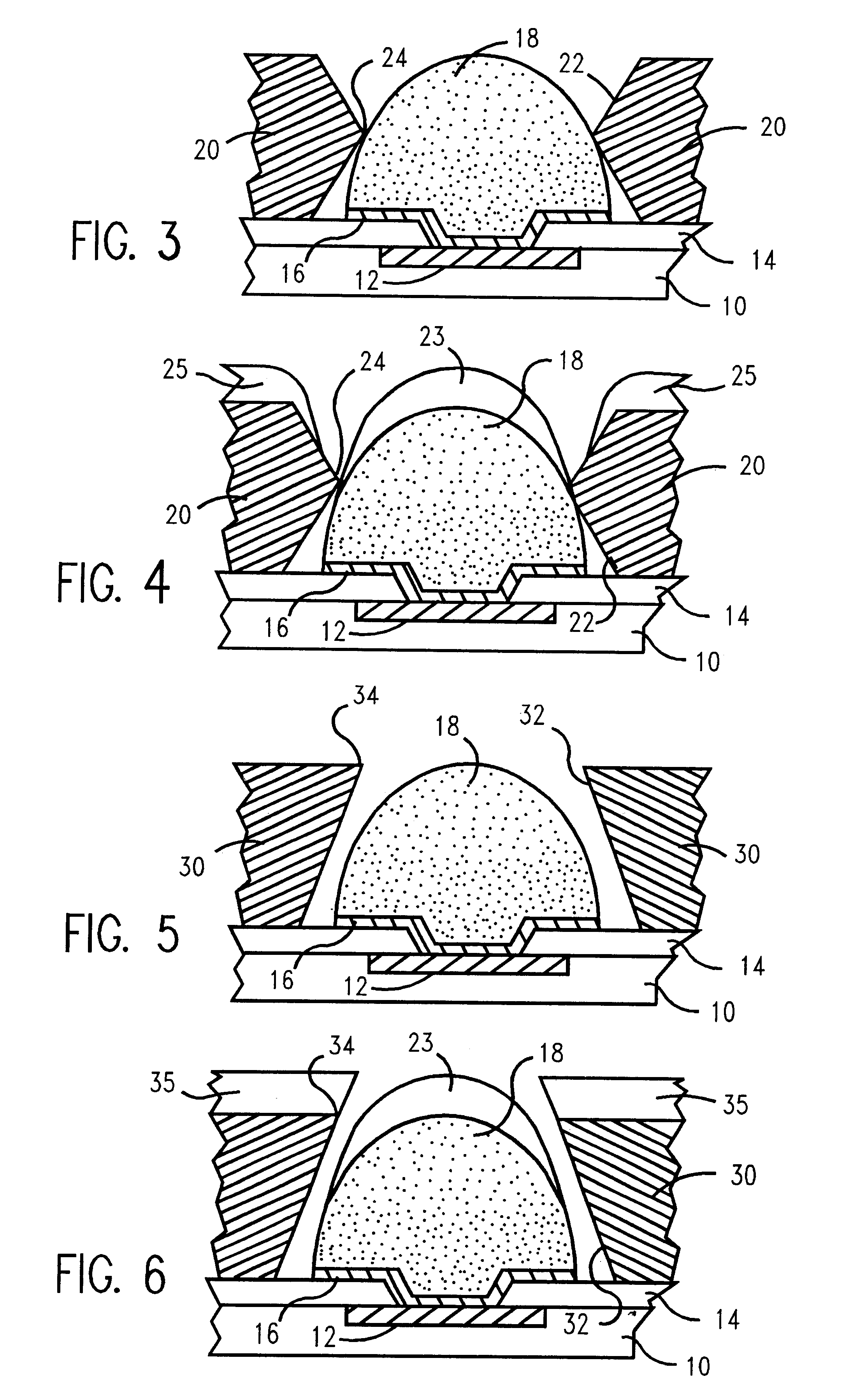

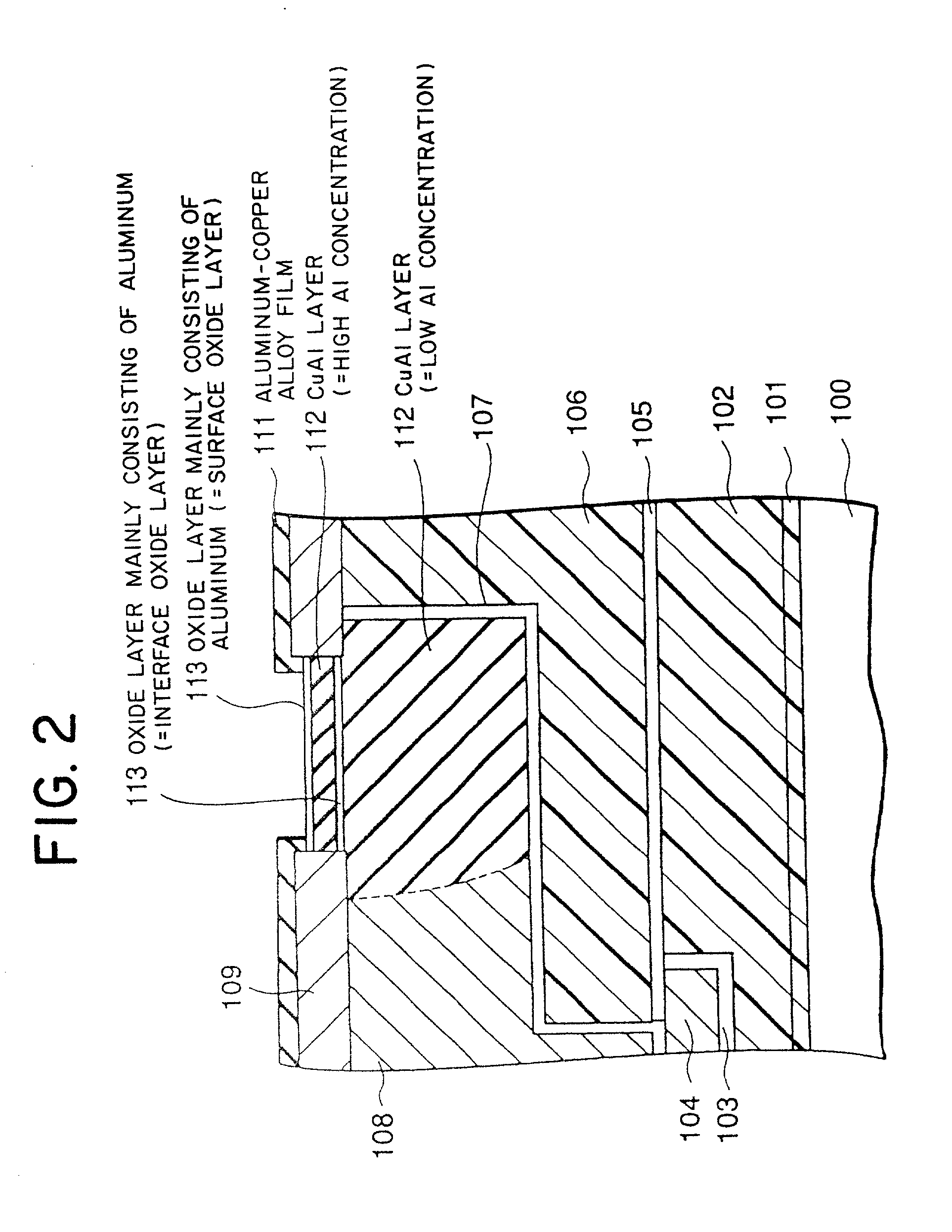

Method of Forming a Self Aligned Copper Capping Layer

InactiveUS20080311739A1Prevent further spreadPreventing inter-metal line leakageSemiconductor/solid-state device detailsSolid-state devicesCopper interconnectChemical exposure

A method of forming a capping layer on a copper interconnect line (14). The method comprises providing a layer (20) of Aluminium over the interconnect line (14) and the dielectric layer (10) in which it is embedded. This may be achieved by deposition or chemical exposure. The structure is then subjected to a process, such as annealing or further chemical exposure, in an environment containing, for example, Nitrogen atoms, so as to cause indiffusion of Al into the copper line (14) and nitridation to form a diffusion barrier 26 of the intermetallic compound CuAlN.

Owner:NXP BV

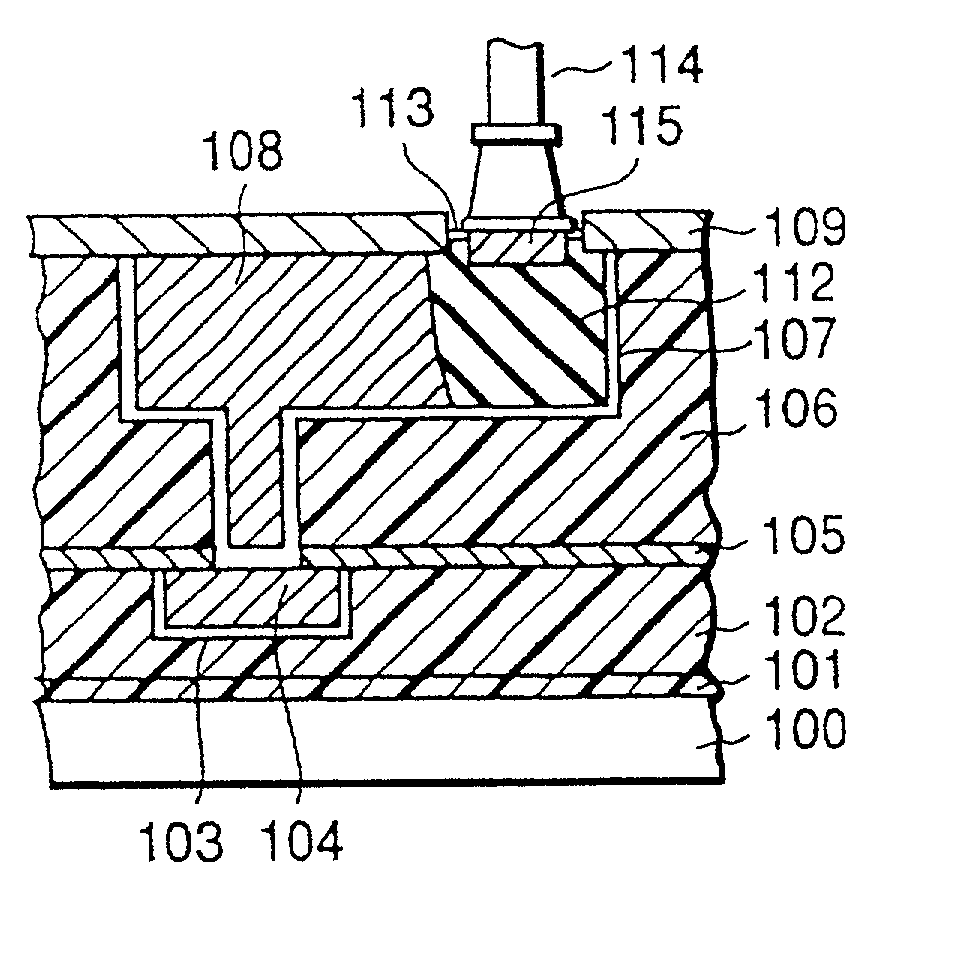

Semiconductor device with improved bonding

InactiveUS6727593B2Dust could be greatly decreasedSolution value is not highSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsDevice materialCopper-wiring

A semiconductor device, which is comprised of a copper wiring layer which is formed above a semiconductor substrate, a pad electrode layer which conducts electrically to the copper wiring layer and has an alloy, which contains copper and a metal whose oxidation tendency is higher than copper, formed to extend to the bottom surface, and an insulating protective film which has an opening extended to the pad electrode layer, is provided.

Owner:KIOXIA CORP

Reflowed solder ball with low melting point metal cap

InactiveUS6259159B1Low costEasy to buildPrinted circuit assemblingFinal product manufactureTinningIndium

A method and structure for a solder interconnection, using solder balls for making a low temperature chip attachment directly to any of the higher levels of packaging substrate is disclosed. After a solder ball has been formed using standard methods it is reflowed to give the solder ball a smooth surface. A layer of low melting point metal, such as, bismuth, indium or tin, preferably, pure tin, is deposited on the top of the solder balls. This structure results in localizing of the eutectic alloy, formed upon subsequent low temperature joining cycle, to the top of the high melting solder ball even after multiple low temperature reflow cycles. This method does not need tinning of the substrate to which the chip is to be joined, which makes this method economical. It has also been noticed that whenever temperature is raised slightly above the eutectic temperature, the structure always forms a liquid fillet around the joint with copper wires. This liquid fillet formation results in substantial thermal fatigue life improvement for reduced stress at interface; and secondly, provides an easy means to remove chip for the purpose of chip burn-in, replacement or field repairs.

Owner:IBM CORP

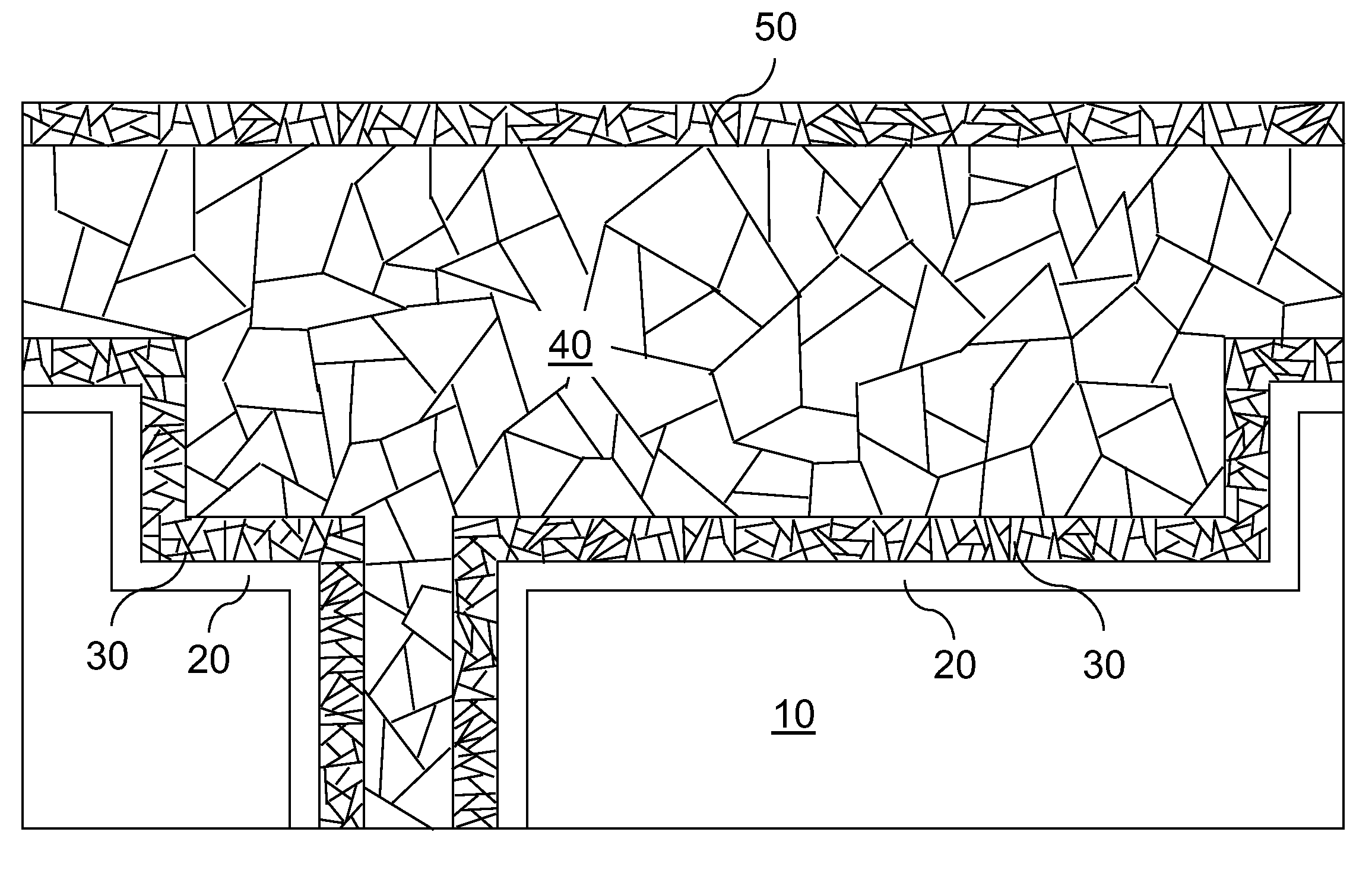

Microstructure modification in copper interconnect structure

ActiveUS20090206484A1Preventing diffusion of copperFaster rateSemiconductor/solid-state device detailsSolid-state devicesCopper platingMetal interconnect

Cobalt is added to a copper seed layer, a copper plating layer, or a copper capping layer in order to modify the microstructure of copper lines and vias. The cobalt can be in the form of a copper-cobalt alloy or as a very thin cobalt layer. The grain boundaries configured in bamboo microstructure in the inventive metal interconnect structure shut down copper grain boundary diffusion. The composition of the metal interconnect structure after grain growth contains from about 1 ppm to about 10% of cobalt in atomic concentration. Grain boundaries extend from a top surface of a copper-cobalt alloy line to a bottom surface of the copper-cobalt alloy line, and are separated from any other grain boundary by a distance greater than a width of the copper-cobalt alloy line.

Owner:TESSERA INC

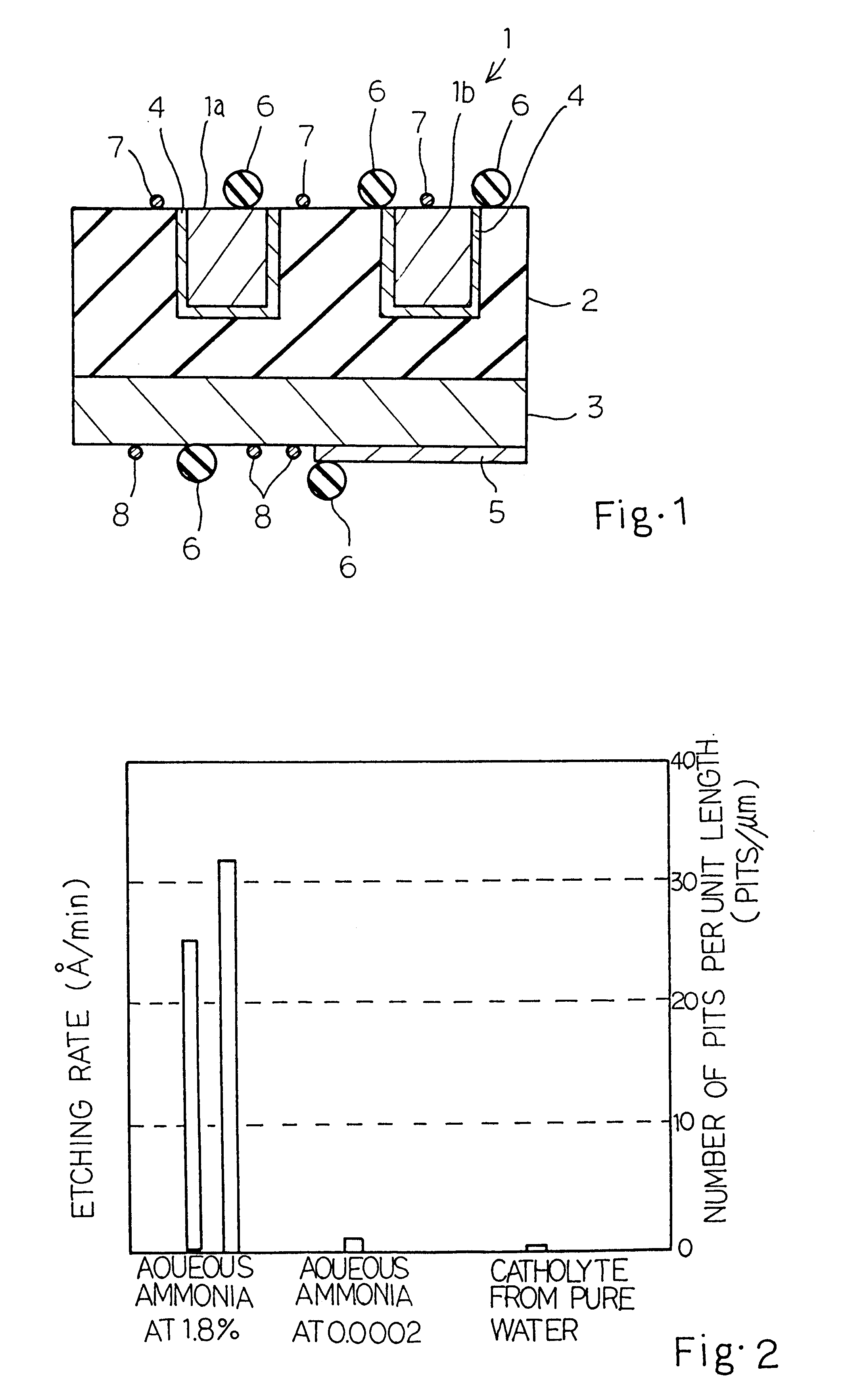

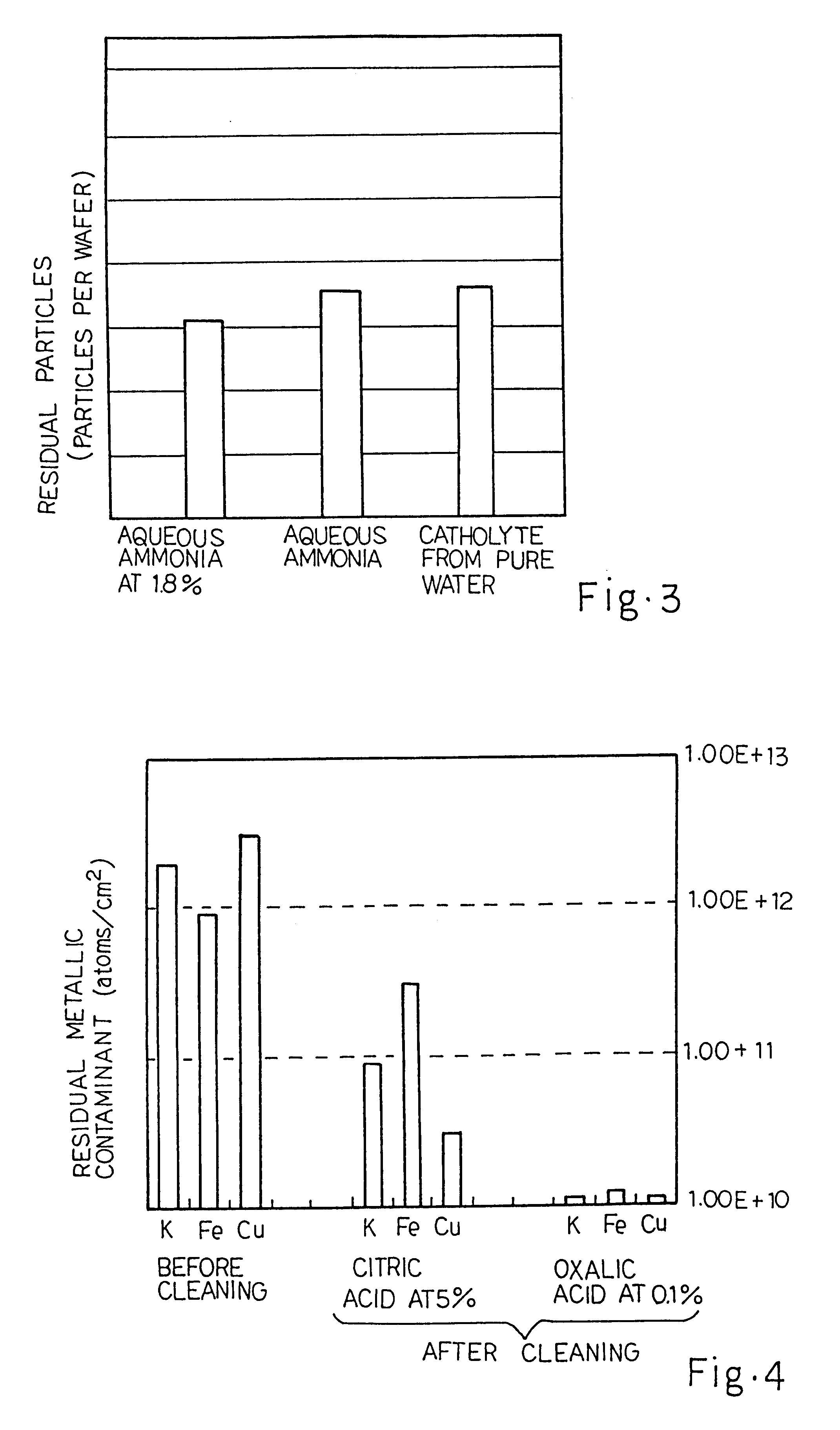

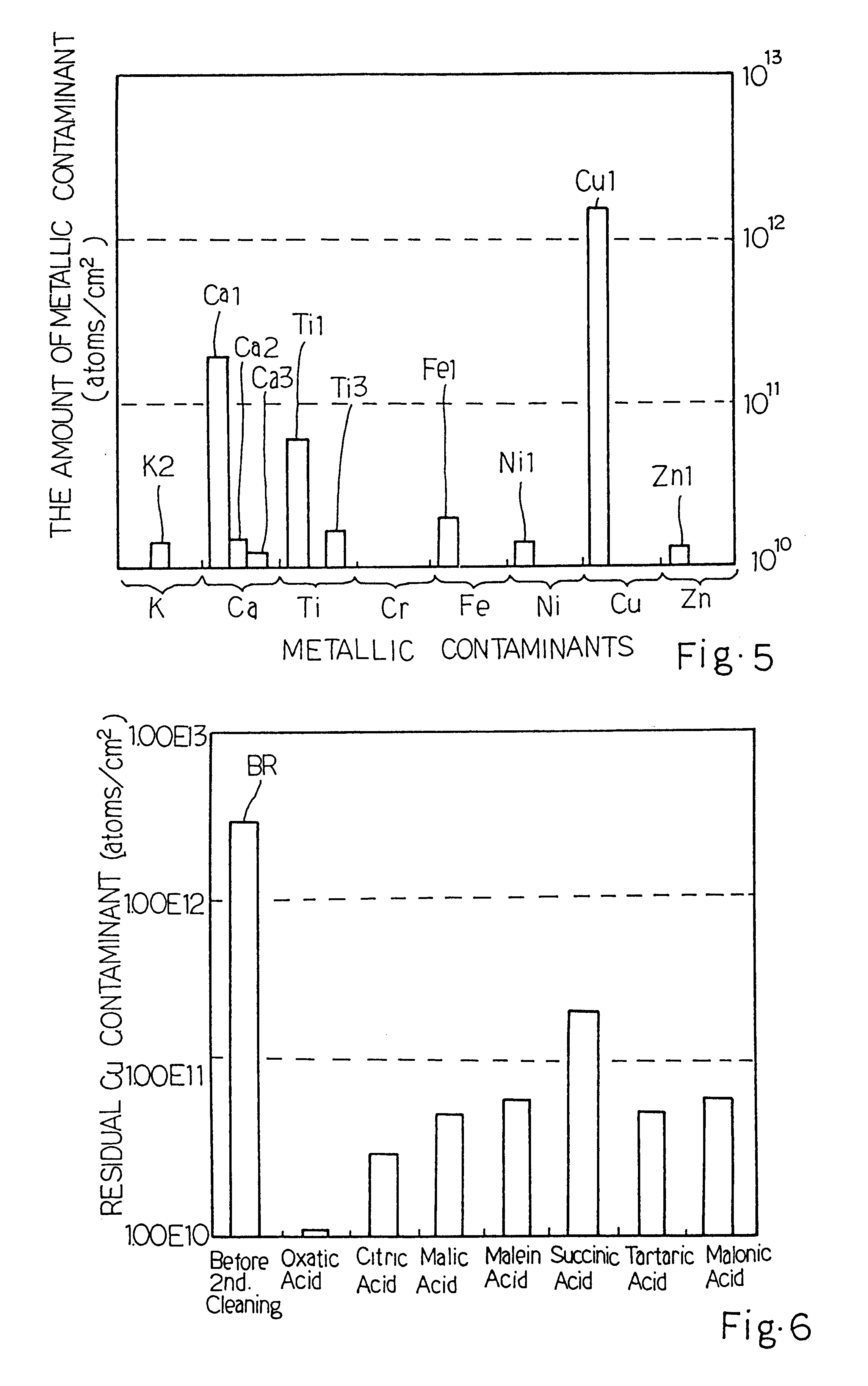

Method for cleaning semiconductor wafer after chemical mechanical polishing on copper wiring

InactiveUS6387190B1Semiconductor/solid-state device detailsSolid-state devicesHydrogenSemiconductor structure

A copper wiring is desirable for a high-speed logic circuit integrated on a semiconductor substrate, and is patterned through a chemical mechanical polishing, wherein polishing particles are brushed away from the major surface of the resultant semiconductor structure by using hydrogen-containing water without damage to the copper wiring, and, thereafter, metallic contaminants such as copper is removed by using washer containing decontaminating agent selected from polycarboxylic acid, ammonium salts thereof and polyaminocarboxylic acid also without damage to the copper wiring.

Owner:RENESAS ELECTRONICS CORP

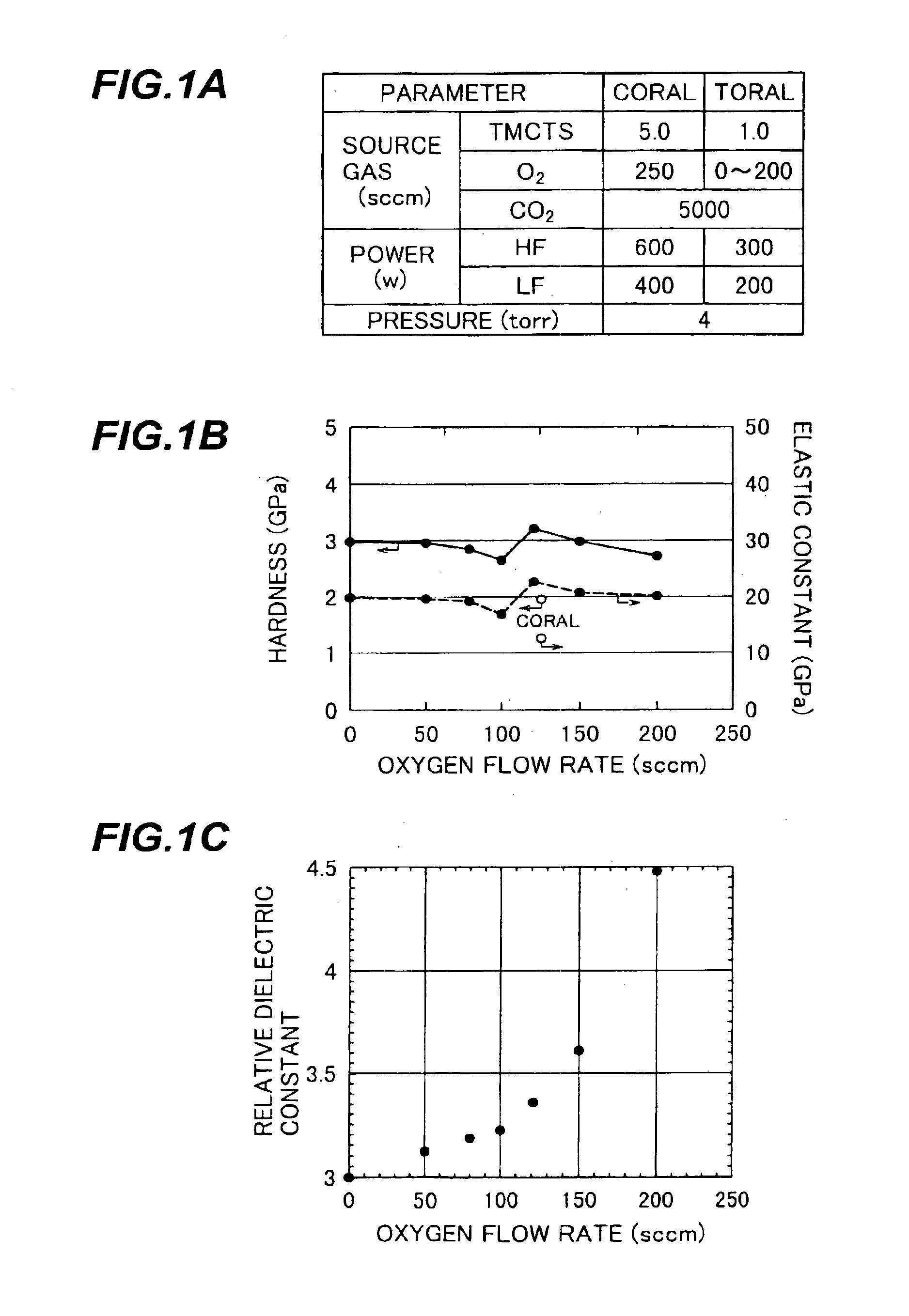

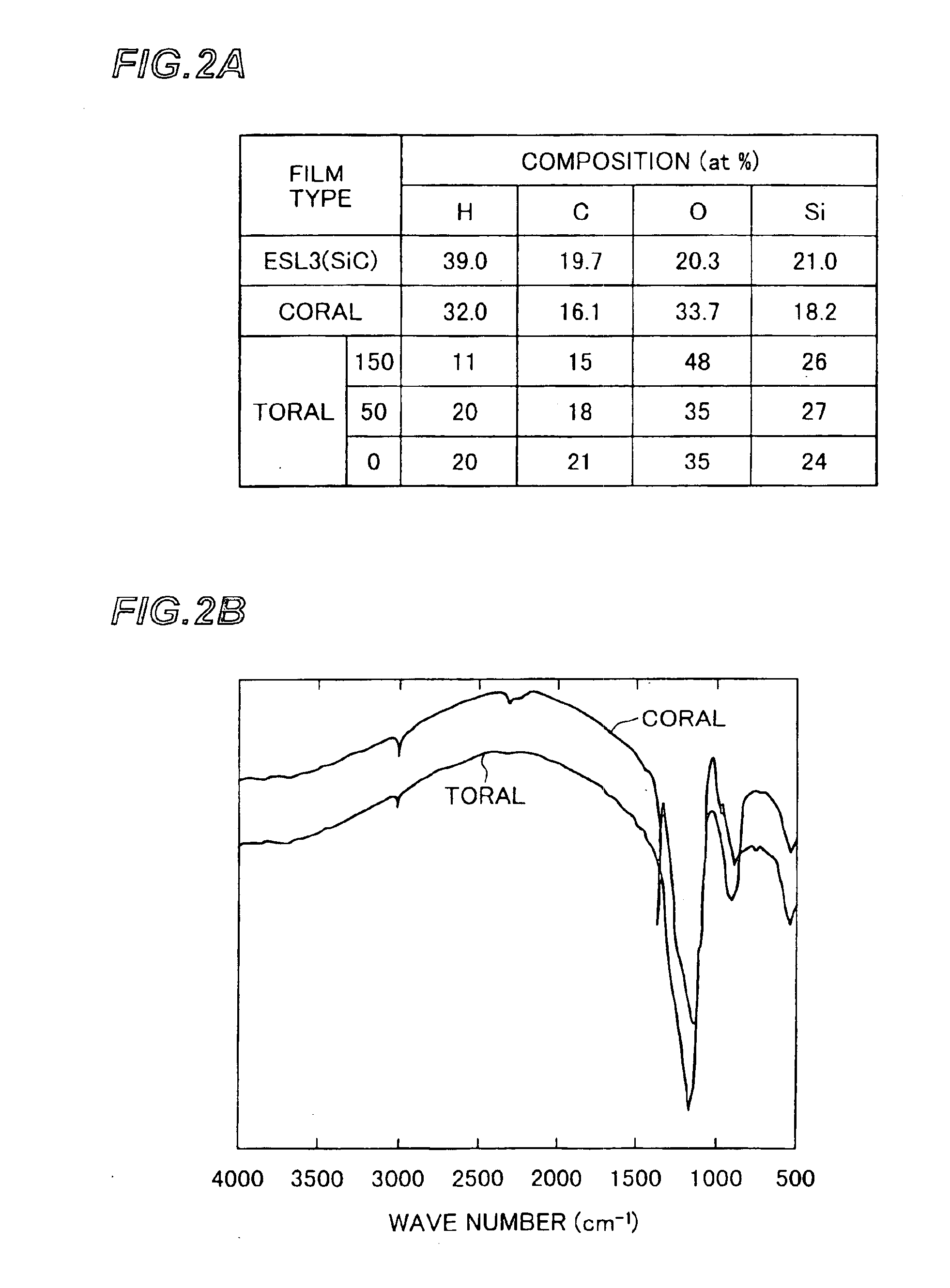

Silicon oxycarbide, growth method of silicon oxycarbide layer, semiconductor device and manufacture method for semiconductor device

ActiveUS6949830B2Prevent peel-offAvoid crackingSemiconductor/solid-state device detailsSolid-state devicesDevice materialGas phase

Owner:FUJITSU LTD

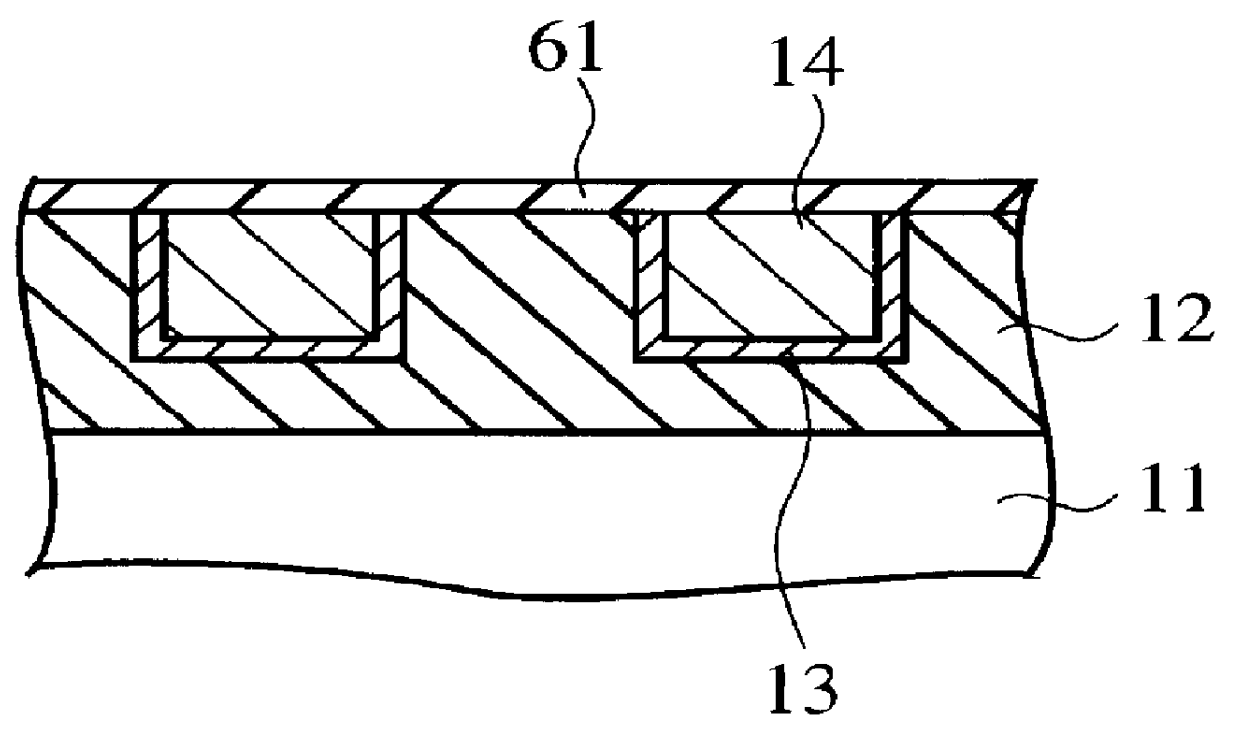

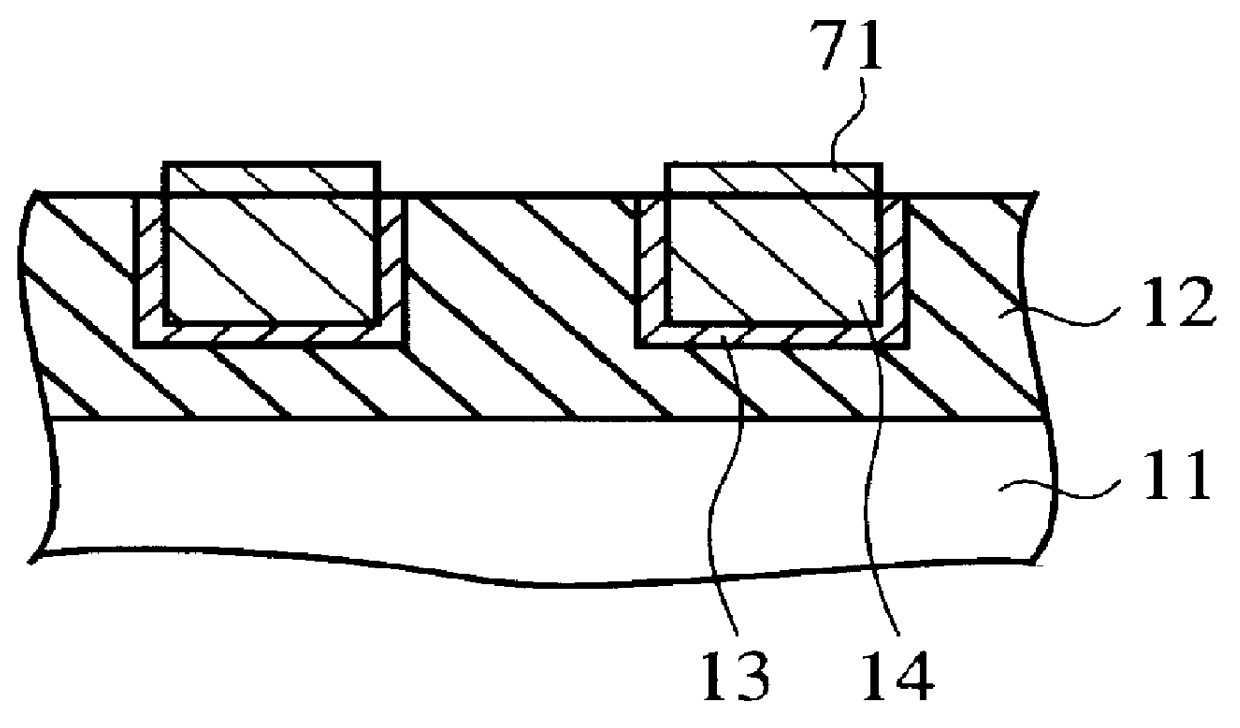

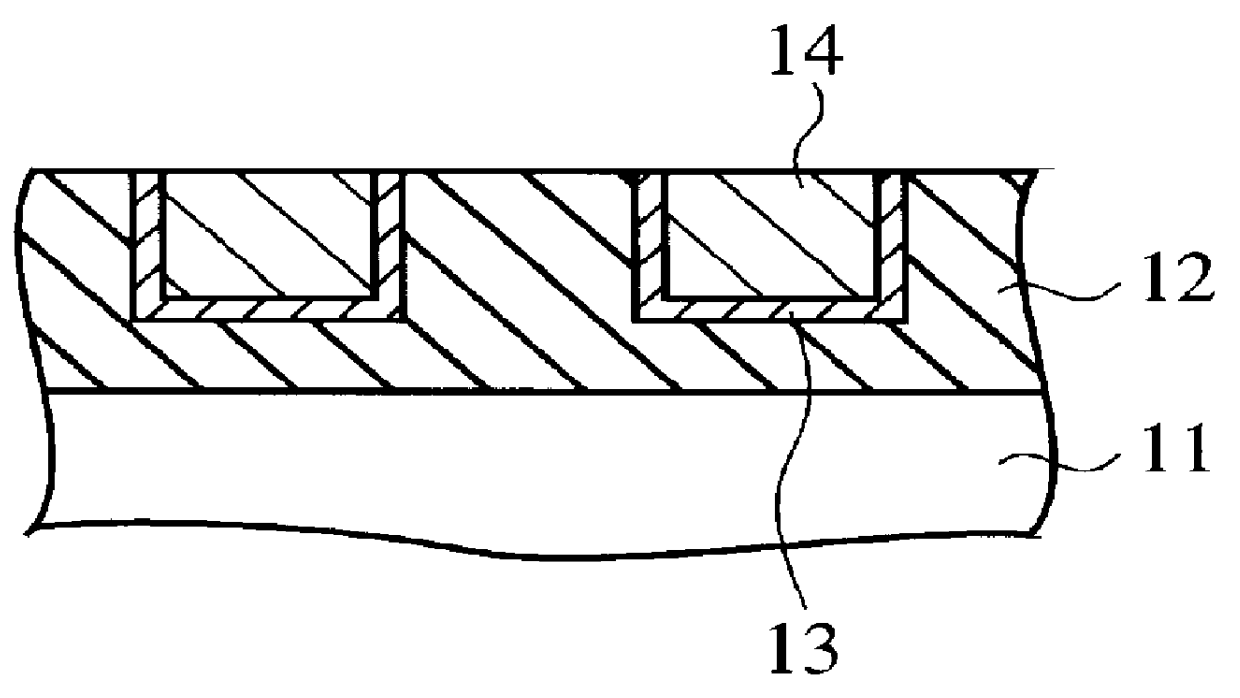

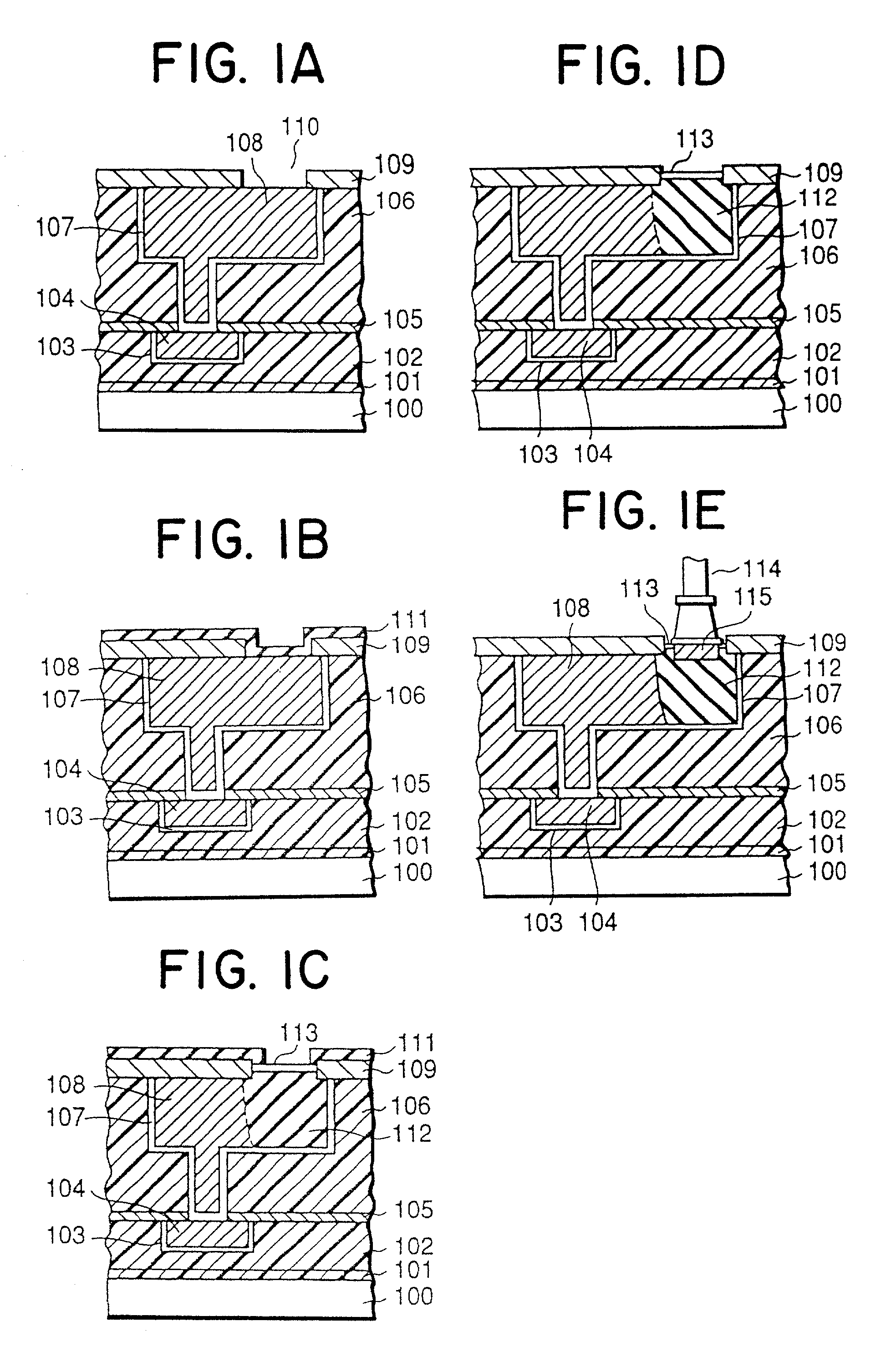

Semiconductor device featuring copper wiring layers of different widths having metal capping layers of different thickness formed thereon, and method for manufacturing the same

InactiveUS20060157854A1Avoid it happening againImprove featuresSemiconductor/solid-state device detailsSolid-state devicesDevice materialCopper-wiring

In a semiconductor device, an insulating interlayer is provided above a semiconductor substrate, and a plurality of first wiring layers and a plurality of second wiring layers are formed in the insulating interlayer. The first wiring layers are substantially composed of copper, and are arranged in parallel at a large pitch. The second wiring layers are substantially composed of copper, and are arranged in parallel at a small pitch. A first metal capping layer is formed on each of the first wiring layers, and a second metal capping layer is formed on each of the second wiring layers. The second metal capping layer has a smaller thickness than that of the first metal capping layer.

Owner:RENESAS ELECTRONICS CORP

Semiconductor device and manufacturing method of semiconductor device

InactiveUS20020121703A1Dust could be greatly decreasedSolution value is not highSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsDevice materialCopper-wiring

A semiconductor device, which is comprised of a copper wiring layer which is formed above a semiconductor substrate, a pad electrode layer which conducts electrically to the copper wiring layer and has an alloy, which contains copper and a metal whose oxidation tendency is higher than copper, formed to extend to the bottom surface, and an insulating protective film which has an opening extended to the pad electrode layer, is provided.

Owner:KIOXIA CORP

Microstructure modification in copper interconnect structure

InactiveUS20100323517A1Inhibited DiffusionFaster rateSemiconductor/solid-state device detailsSolid-state devicesCopper platingMetal interconnect

Cobalt is added to a copper seed layer, a copper plating layer, or a copper capping layer in order to modify the microstructure of copper lines and vias. The cobalt can be in the form of a copper-cobalt alloy or as a very thin cobalt layer. The grain boundaries configured in bamboo microstructure in the inventive metal interconnect structure shut down copper grain boundary diffusion. The composition of the metal interconnect structure after grain growth contains from about 1 ppm to about 10% of cobalt in atomic concentration. Grain boundaries extend from a top surface of a copper-cobalt alloy line to a bottom surface of the copper-cobalt alloy line, and are separated from any other grain boundary by a distance greater than a width of the copper-cobalt alloy line.

Owner:TESSERA INC

Laminated structure, very-large-scale integrated circuit wiring board, and method of formation thereof

InactiveUS20080079154A1Prevent peelingEfficient manufacturingSemiconductor/solid-state device detailsSolid-state devicesVery large scale integrated circuitsCopper plating

The laminated structure includes a substrate of low dielectric constant material of silicon compound and an electroless copper plating layer laminated thereon with a barrier layer. The barrier layer is interposed between the substrate and the copper layer, and the barrier layer is formed by electroless plating. And the laminated structure is characterized in that the barrier layer is formed on the substrate with a monomolecular layer of organosilane compound and a palladium catalyst which are interposed between the substrate and the barrier layer, the palladium catalyst modifies the terminal, adjacent to the barrier layer, of the monomolecular layer, and the barrier layer includes an electroless NiB plating layer which is disposed on the substrate side, and a electroless CoWP plating layer.The present invention makes it possible to coat the low dielectric constant material of silicon compound in a simple all-wet process with a firmly adhering barrier layer and an electroless copper plating layer as the wiring layer. the advantage of requiring. Thus, the laminated structure formed in this way includes a substrate of low dielectric constant material of silicon compound, a barrier layer, and a copper layer as the wiring layer formed by electroless plating, which firmly adhere to one another. In addition, the laminated structure is suitable for the copper wiring in a ULSI, particularly the one which is to be formed in a narrower trench than conventional one.

Owner:WASEDA UNIV

Method of forming copper wiring layer

InactiveUS20060178007A1Solid-state devicesSemiconductor/solid-state device manufacturingDevice materialCopper-wiring

A method of forming a copper wiring layer, which includes forming a pattern of copper seed layer on a substrate, and forming a copper wiring pattern on the pattern of copper seed layer by means of electroless plating. At least one component of semiconductor device selected from the group consisting of the gate electrode, the source electrode, the drain electrode, and a wiring connected with at least one of these electrodes is formed by a method comprising forming a pattern of copper seed layer, and forming a copper wiring pattern on the pattern of copper seed layer by means of electroless plating.

Owner:TOSHIBA MOBILE DISPLAY CO LTD

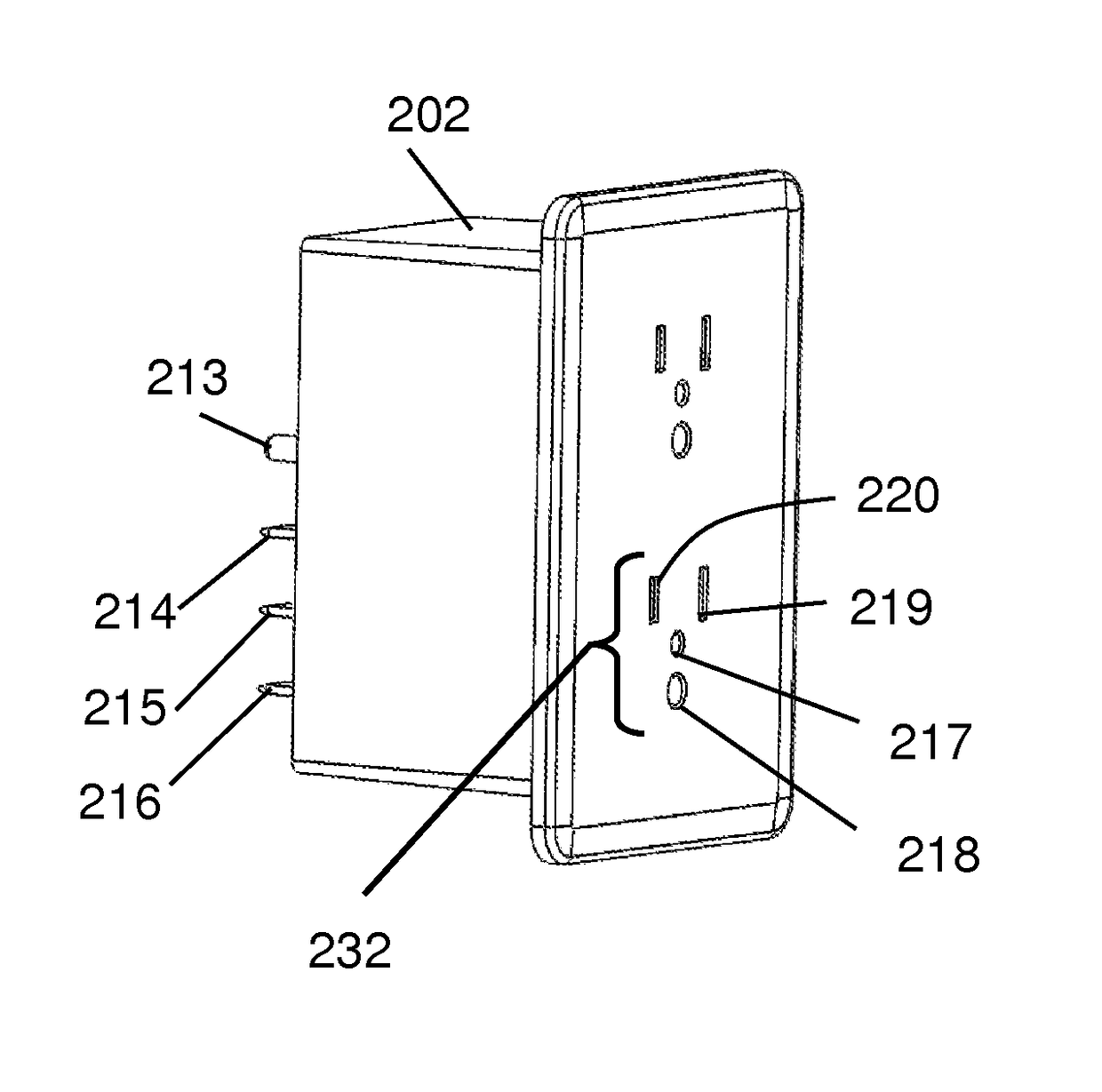

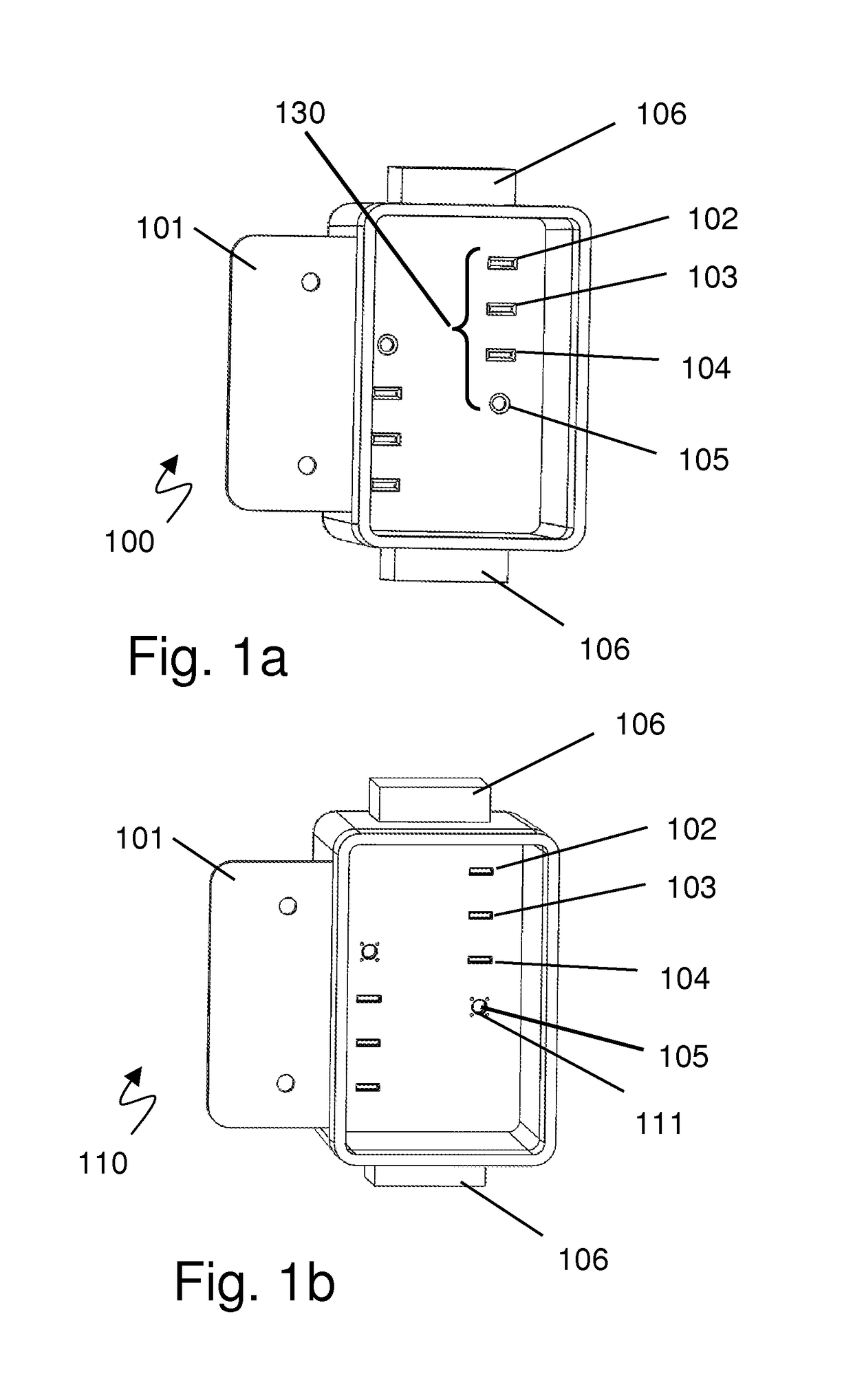

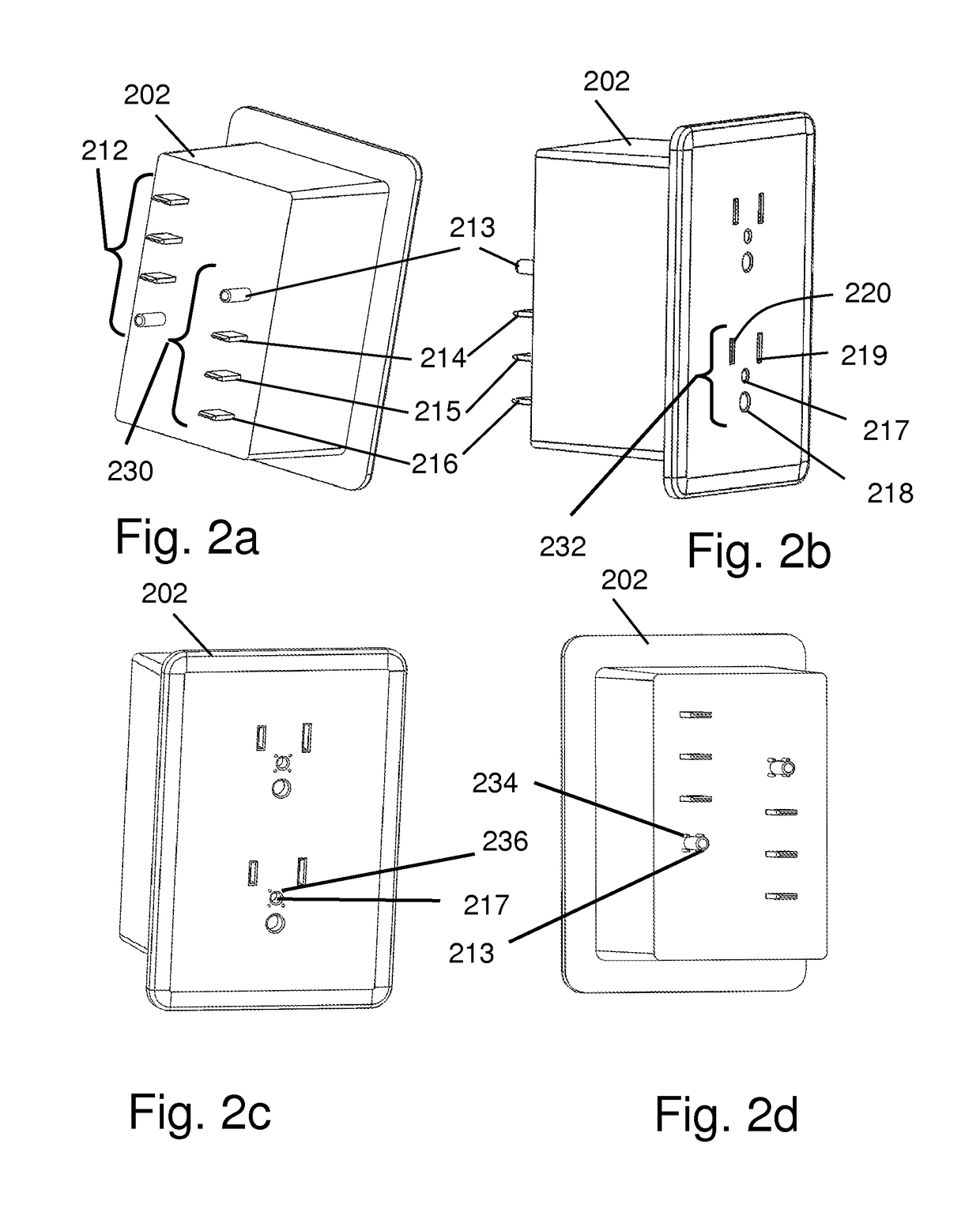

Optical wiring systems and methods

ActiveUS9618714B2Simplifies all the other devicesImprove uniformityTwo-part coupling devicesCoupling light guidesFiberElectric force

An architected system of distribution of power and information using copper wire for power distribution and fiber optic for communication of information. The architected system is comprehensive for connections and upgrades related to the function, installation, terminations at every junction of a 3 wire plus light system. The archetected system enables each powered device in a smart home, smart office, or smart industrial installation with respect to a permanent and adaptable framework for an network foundation and structure. The architected system may include: wire, connectors, housings, devices, extension cords, appliance termination points, central processing, central power distribution, and a software methods for reliable data distribution.

Owner:MURRAY DAVID W

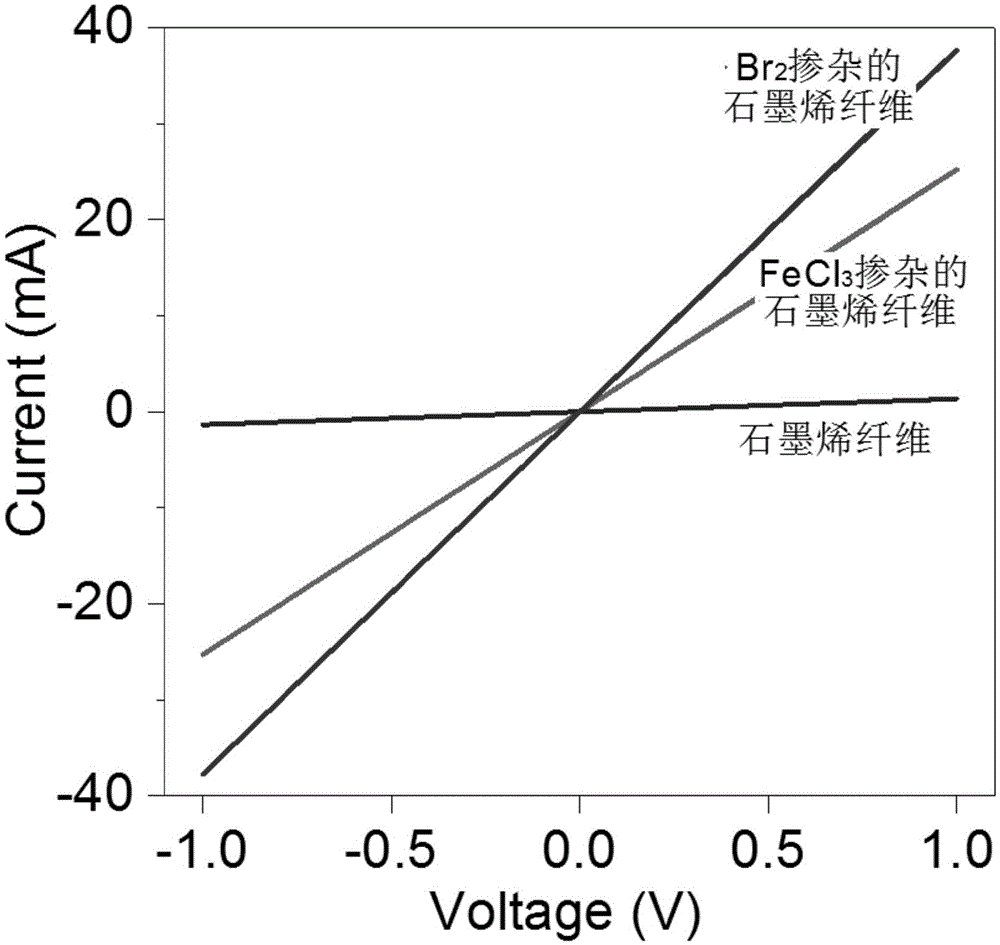

High-conductivity graphene fiber and preparation method thereof

ActiveCN105544017AWide variety of sourcesLow costWet spinning methodsArtificial filament chemical after-treatmentFiberElectric power transmission

The invention discloses a high-conductivity graphene fiber and a preparation method thereof. By the adoption of the wet spinning technology, oxidized graphene spinning liquid with the mass percentage being 1-10% is extruded from a spinning head into a coagulating bath to obtain an oxidized graphene gel fiber, the oxidized graphene gel fiber is collected on a graphite rolling shaft after being fully solidified, the oxidized graphene fiber is obtained, and the oxidized graphene fiber is sequentially subjected to chemical reduction, high-temperature thermal treatment and chemical doping. The prepared graphene fiber has high conductivity, and the conductivity of the prepared graphene fiber is one magnitude order higher than that of a common graphene fiber. The whole process is simple and controllable in technology, and conductivity of the graphene fiber is improved. The obtained graphene fiber has excellent mechanical property and excellent electrical conductivity and thermal conductivity. The high-conductivity graphene fiber can be used for preparing soft solar batteries, supercapacitors and wearable devices and can serve as a light wire to be used in ultra-light wires and cables, and it is hopeful to replace a metal copper wire with the graphene fiber for new-generation power transmission.

Owner:杭州德烯科技集团有限公司

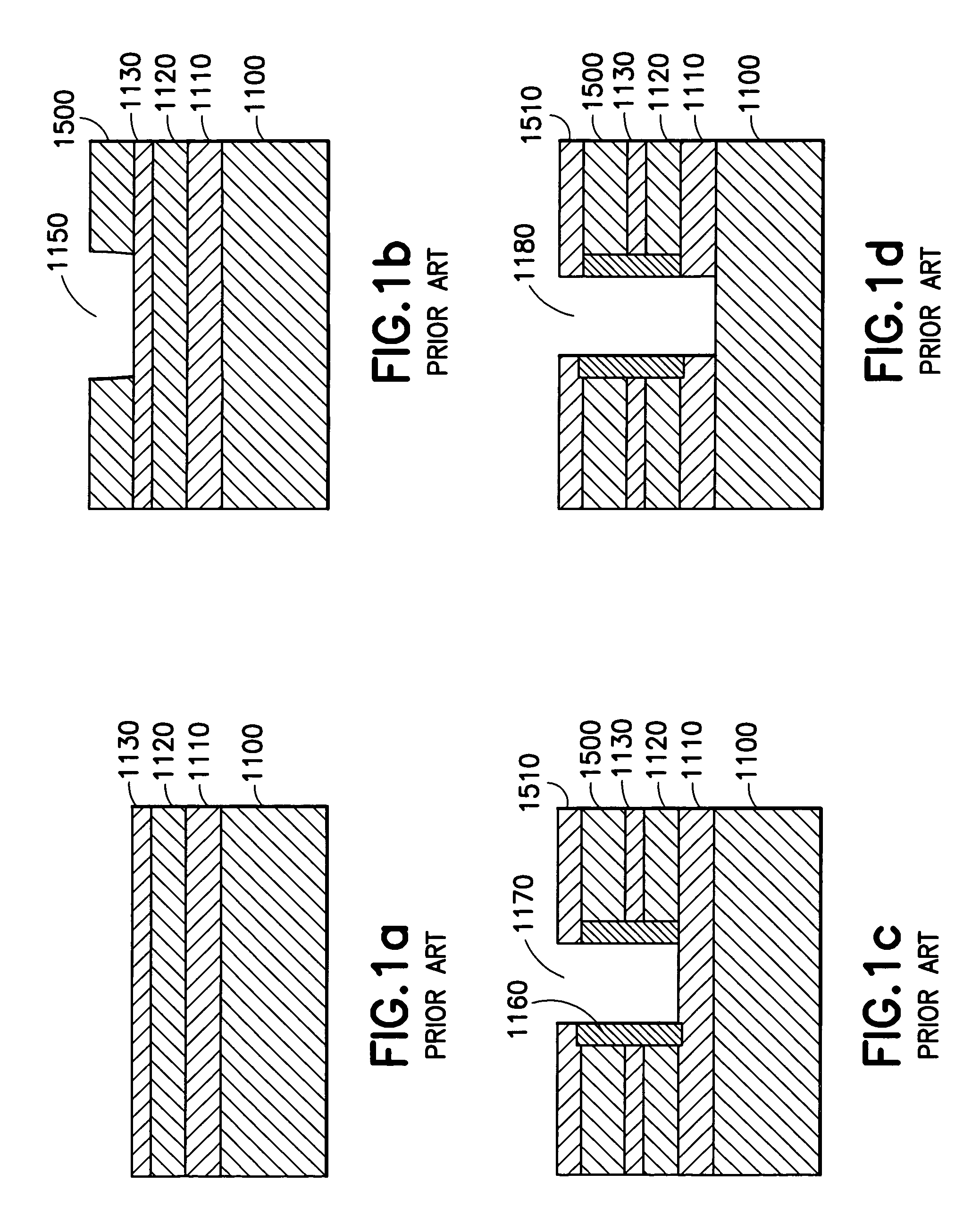

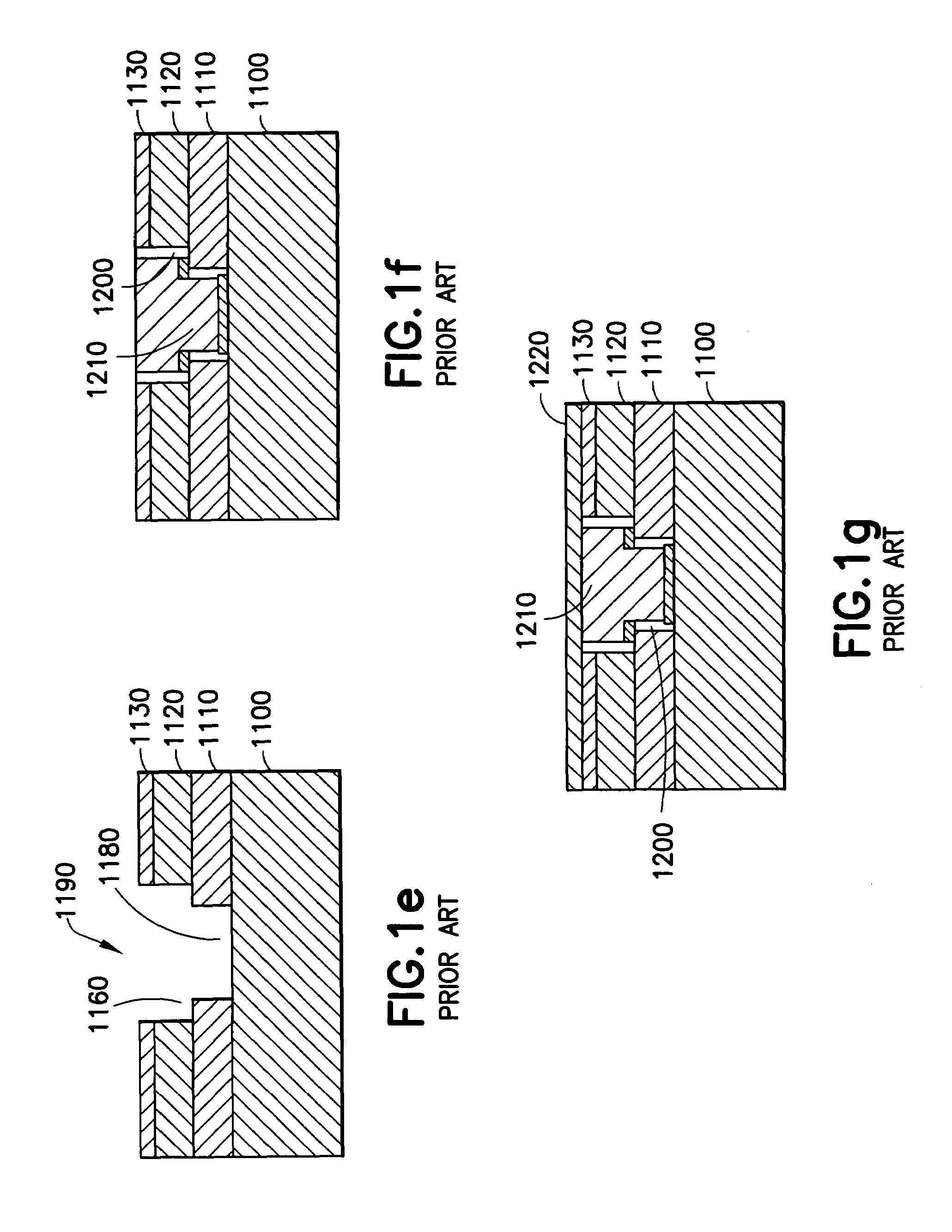

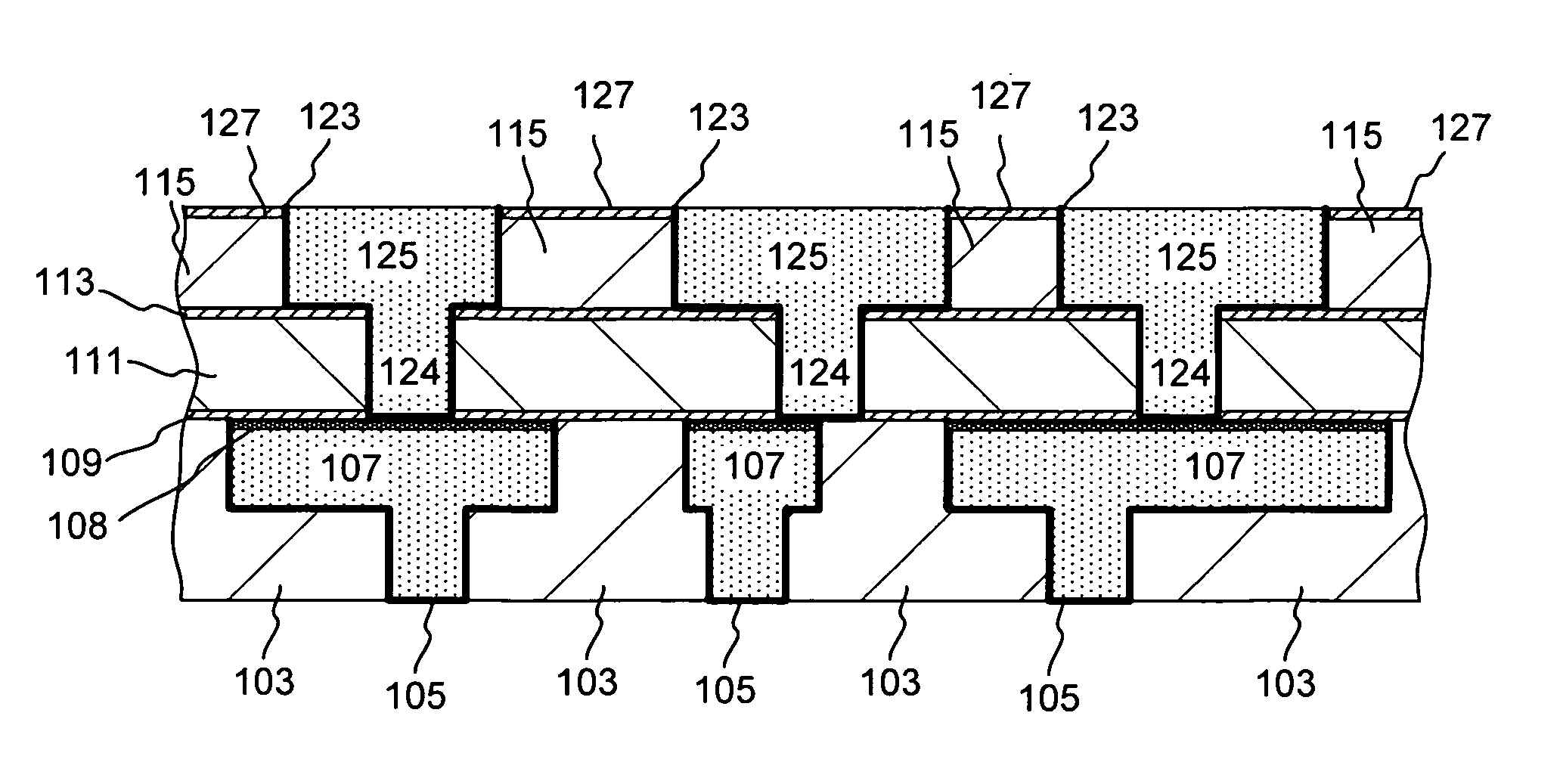

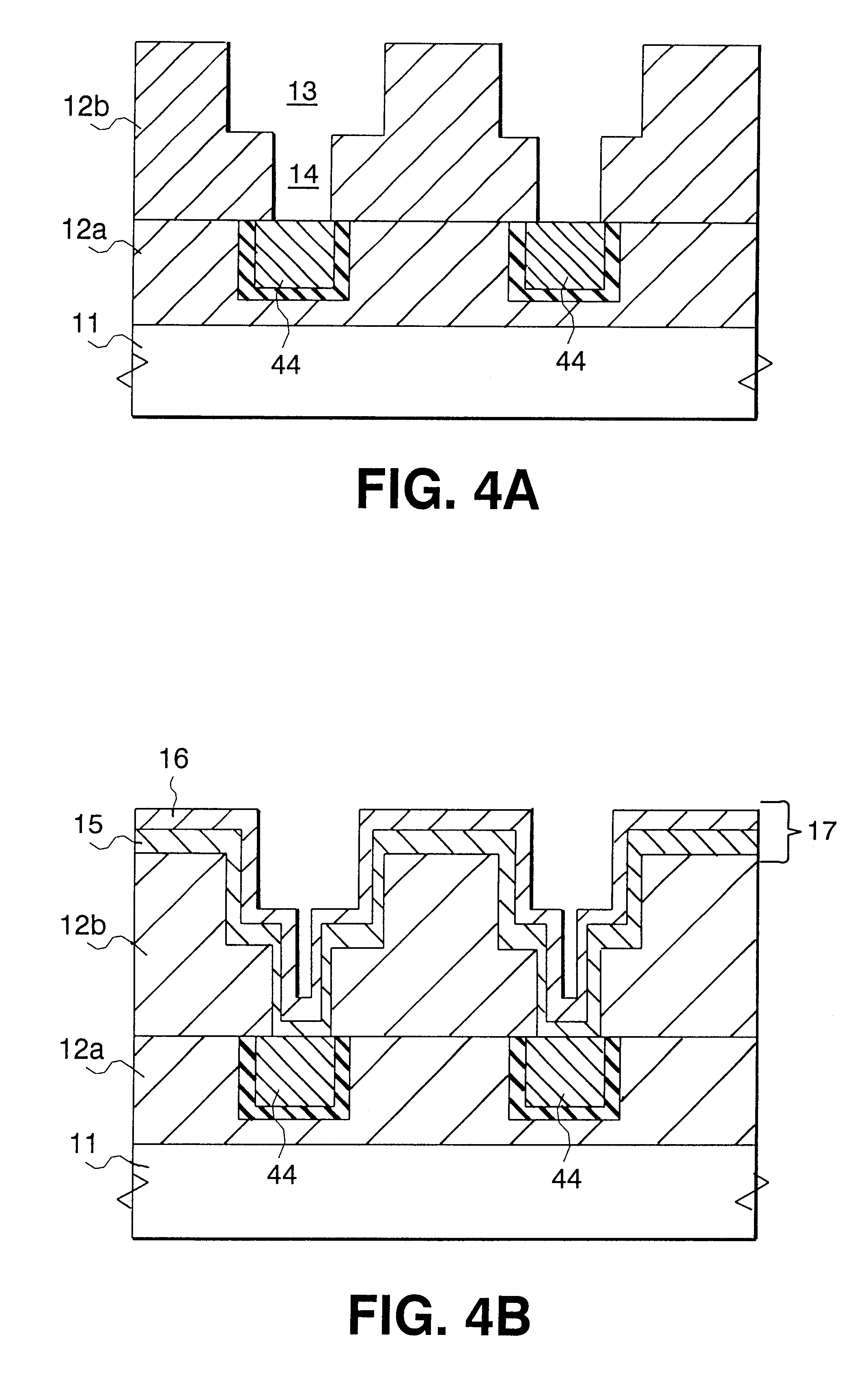

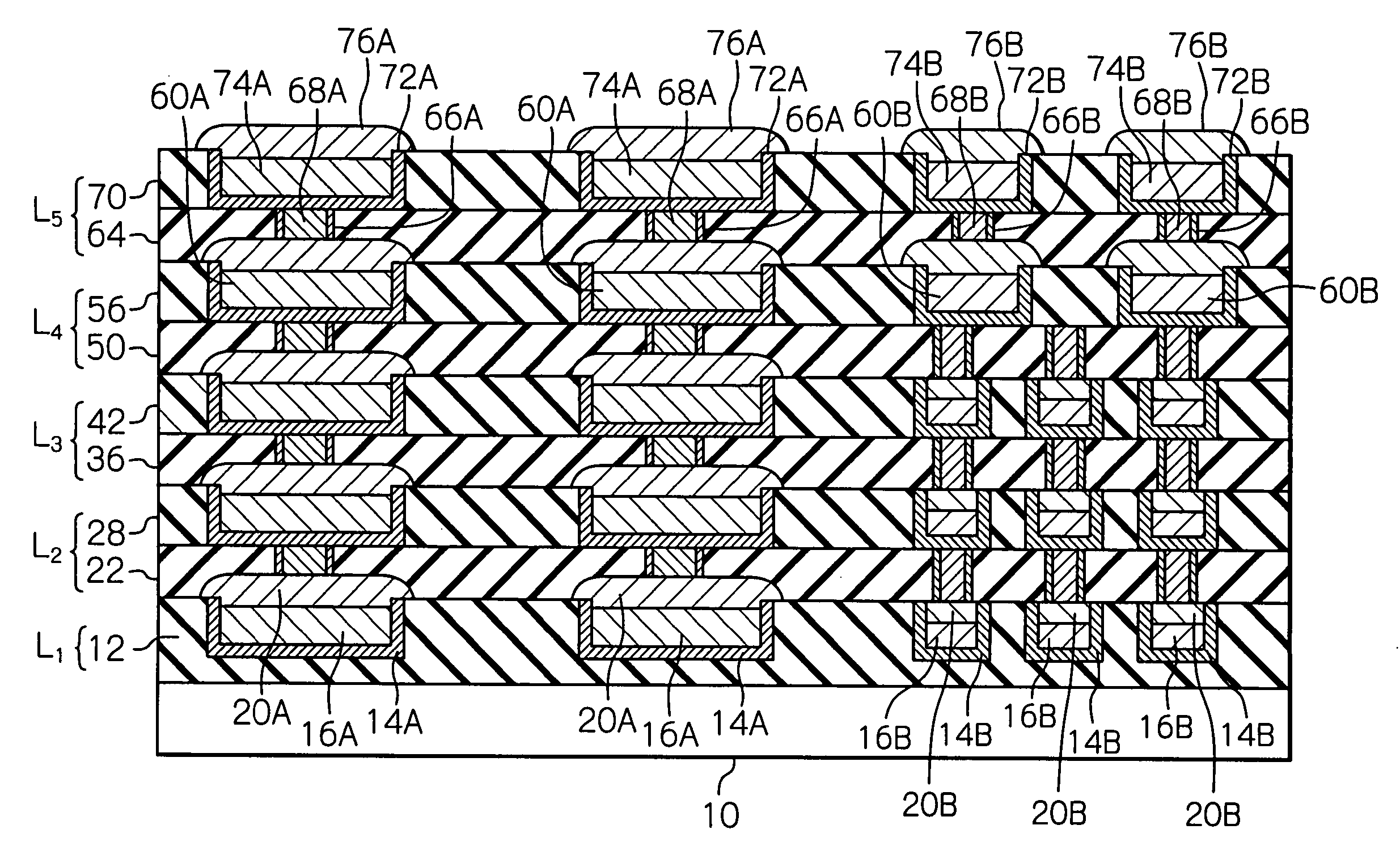

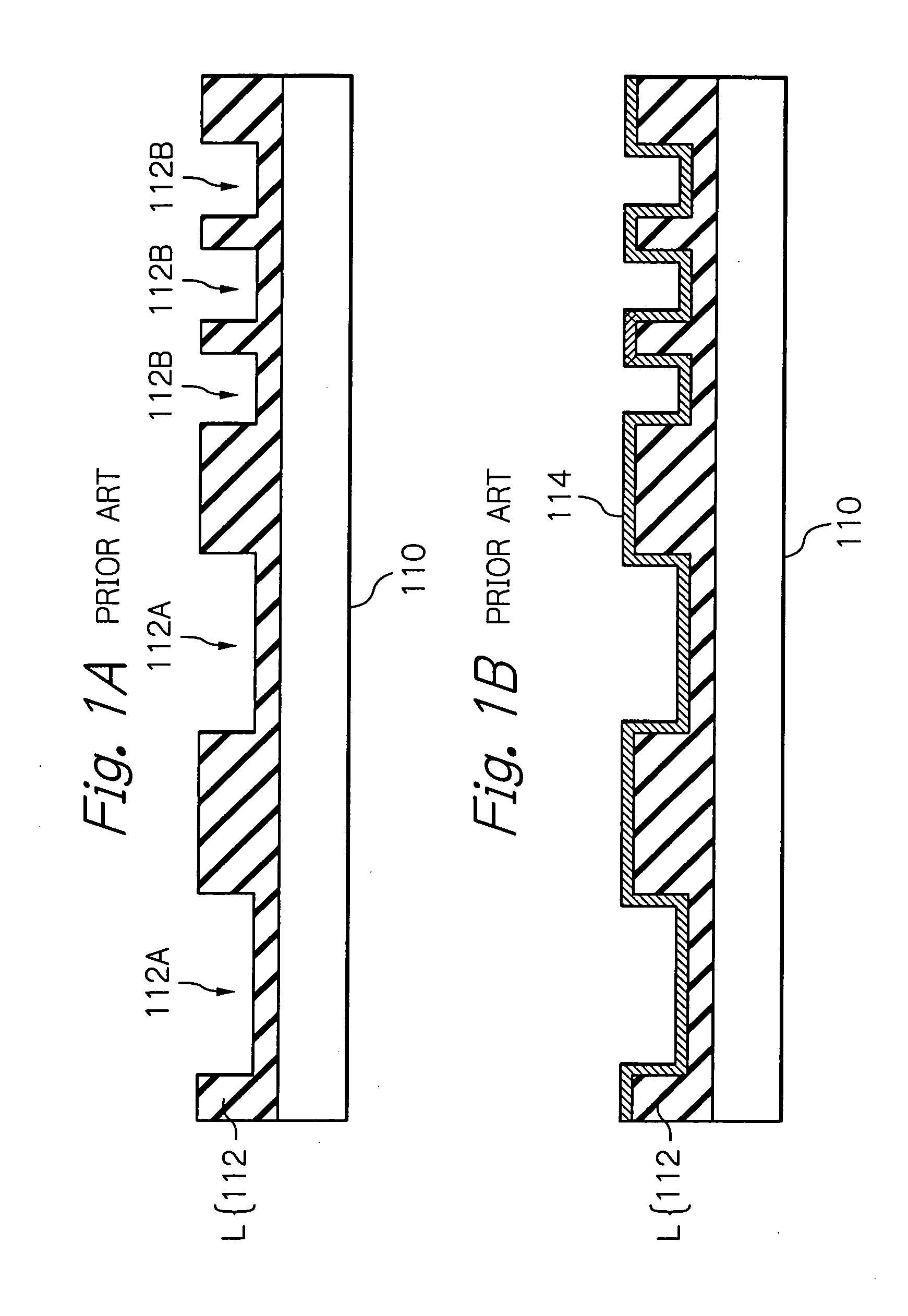

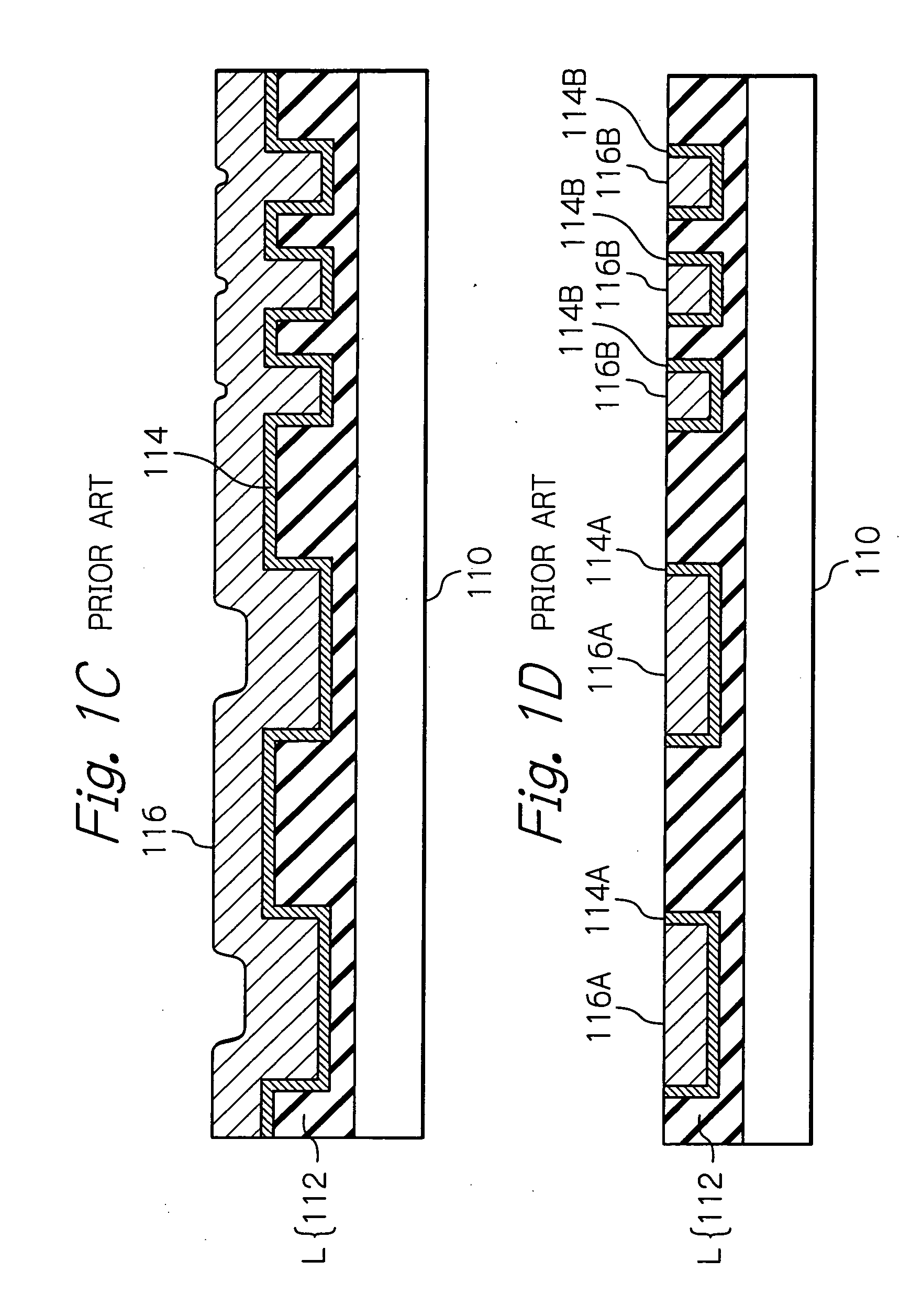

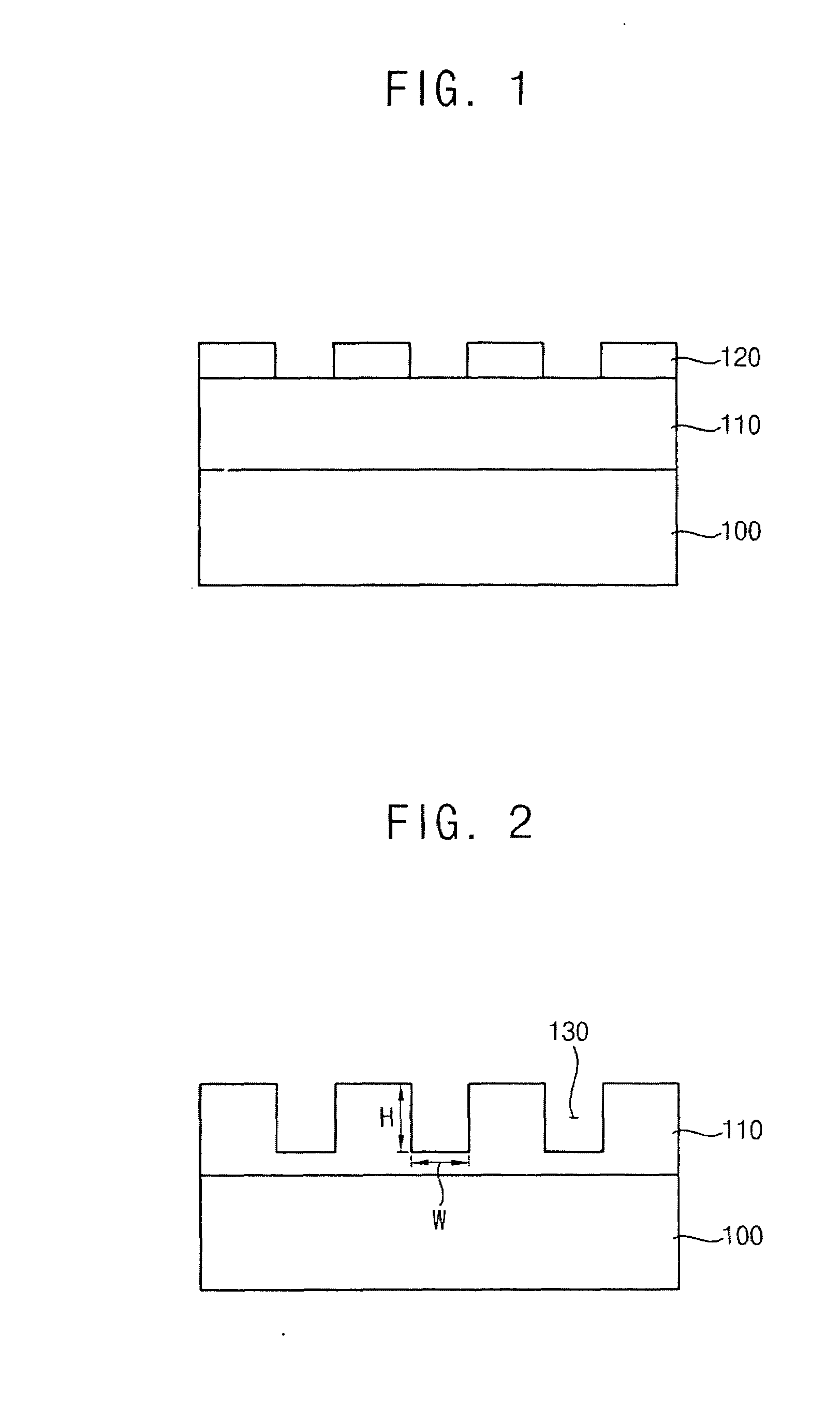

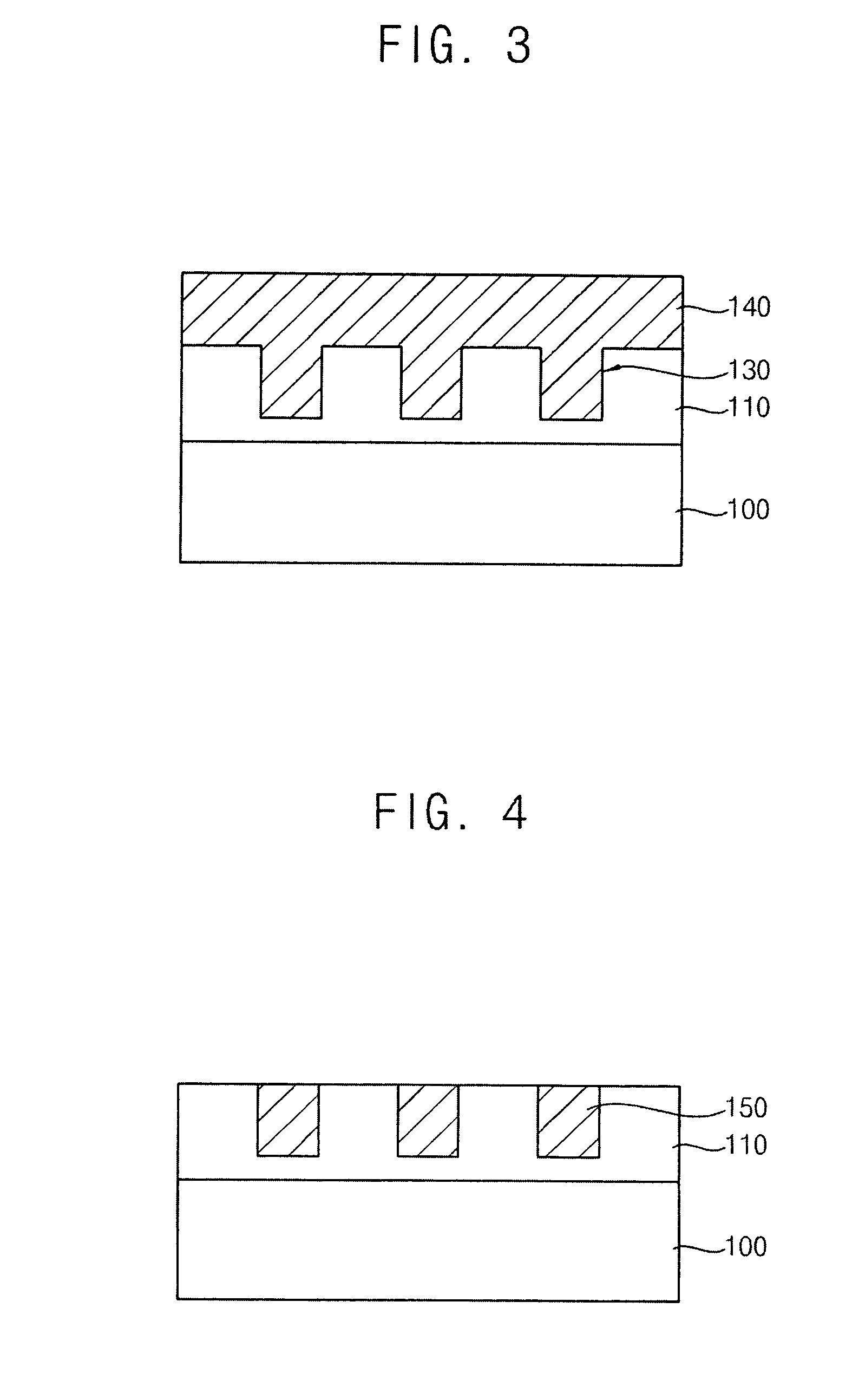

Methods of Forming Dual-Damascene Metal Wiring Patterns for Integrated Circuit Devices and Wiring Patterns Formed Thereby

ActiveUS20070032062A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringCopper-wiring

Methods of forming dual-damascene metal wiring patterns include forming a first metal wiring pattern (e.g., copper wiring pattern) on an integrated circuit substrate and forming an etch-stop layer on the first metal wiring pattern. These steps are followed by the steps of forming an electrically insulating layer on the etch-stop layer and forming an inter-metal dielectric layer on the electrically insulating layer. The inter-metal dielectric layer and the electrically insulating layer are selectively etched in sequence to define an opening therein that exposes a first portion of the etch-stop layer. This opening may include a trench and a via hole extending downward from a bottom of the trench. A first barrier metal layer is formed on a sidewall of the opening and directly on the first portion of the etch-stop layer. A portion of the first barrier metal layer is selectively removed from the first portion of the etch-stop layer. The first portion of the etch-stop layer is then selectively etched for a sufficient duration to expose a portion of the first metal wiring pattern. A second metal wiring pattern is formed in the opening in order to complete a dual-damascene structure.

Owner:SAMSUNG ELECTRONICS CO LTD

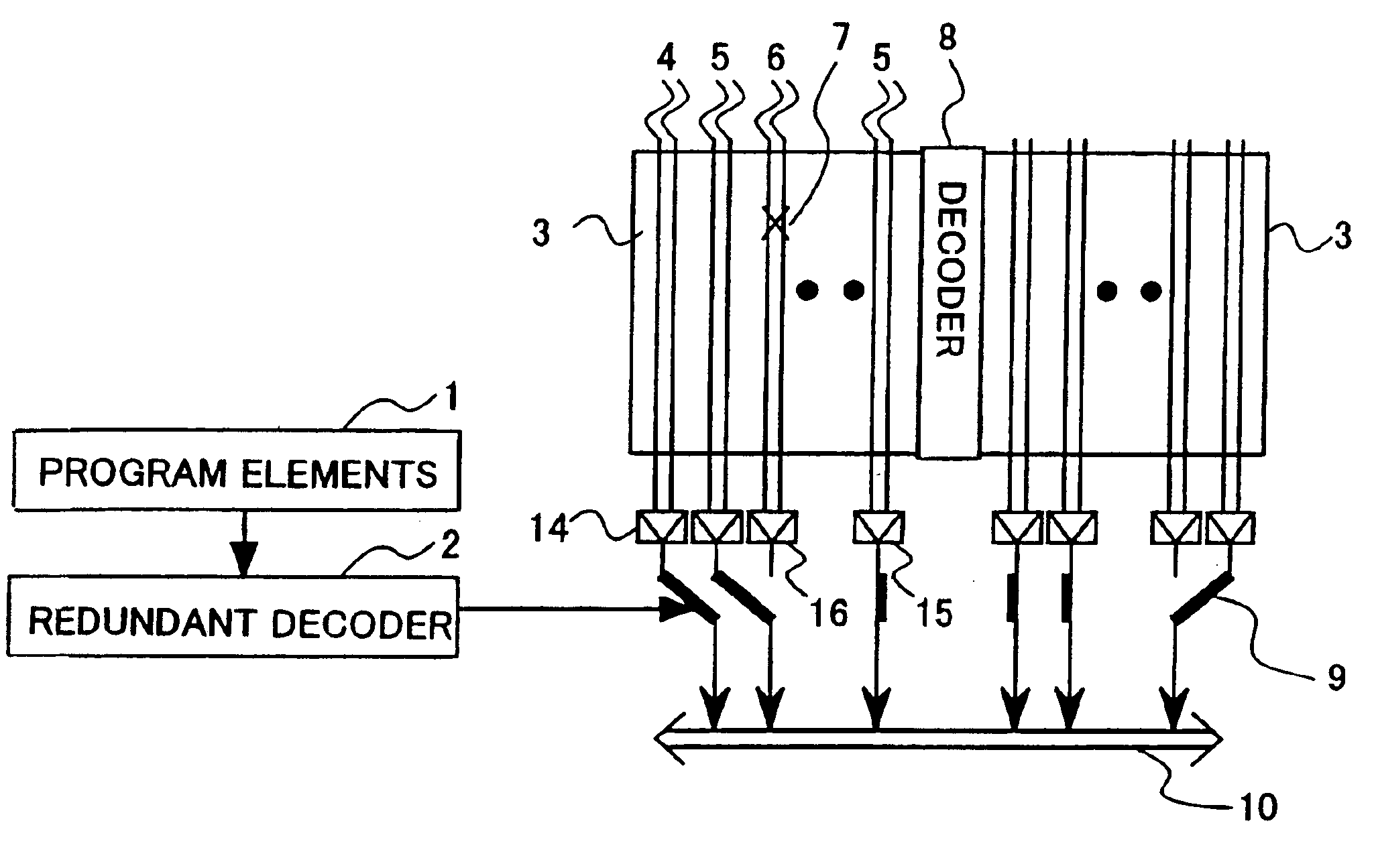

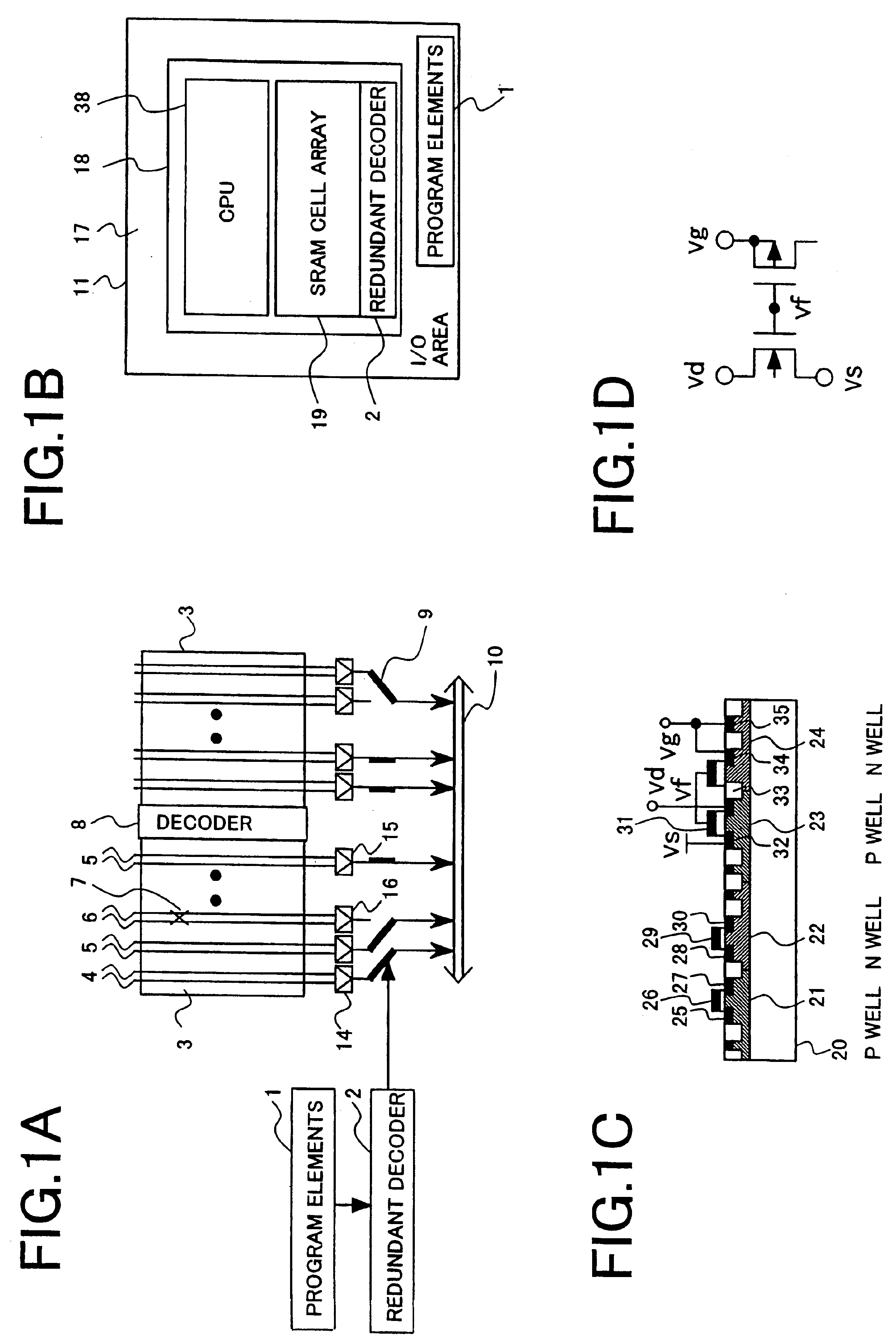

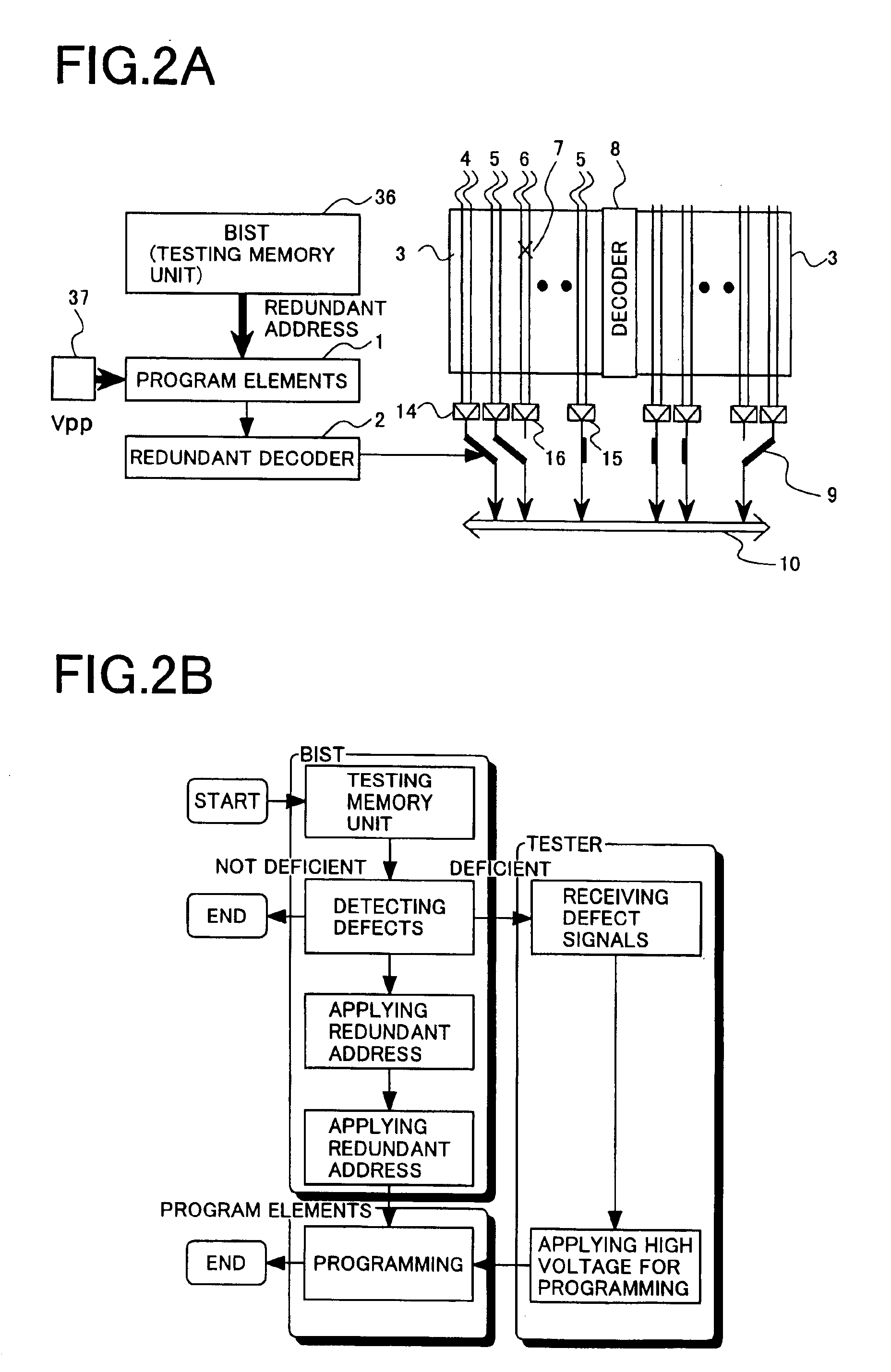

Semiconductor integrated circuit device

InactiveUS6894944B2Avoid breakingImprove reliabilityTransistorSemiconductor/solid-state device testing/measurementCMOSCopper-wiring

To reduce cost of defect redundancy and trimming in a semiconductor integrated circuit having multiple layer wirings and copper wirings, an address for salvaging a defect of a memory cell array in a semiconductor is stored by using a nonvolatile memory element constituting a floating electrode by a first layer of polysilicon, or the nonvolatile memory element is programmed in testing the semiconductor integrated circuit. As a result, a special process is not needed in forming the nonvolatile memory element. In other words, the nonvolatile memory element can be formed in a process of forming a CMOS device and an apparatus of a laser beam for programming is not needed since the programming is carried out in testing. Thus, the time necessary for programming can be shortened, and, therefore, testing costs can be reduced.

Owner:RENESAS ELECTRONICS CORP

Composition for copper plating and associated methods

InactiveUS20100084277A1High aspect ratioReducing generation voidSemiconductor/solid-state device manufacturingSemiconductor devicesBetaine compoundCopper plating

A composition for copper plating and associated methods, a method of forming a copper wiring including forming an insulation layer having a recessed portion on a substrate, and forming a copper layer on the insulation layer to fill the recessed portion by performing an electroplating process using a composition that includes an aqueous electrolyte solution containing a copper ion and at least one of a disulfide compound represented by Formula 1, a betaine compound represented by at least one of Formulae 3 and 4, and a triblock copolymer of polyethylene oxide-polypropylene oxide-polyethylene oxide (PEO-PPO-PEO) having a weight average molecular weight of about 2,500 to about 5,000 g / mol and an ethylene oxide content (EO %, w / w) of about 30% to about 60%.

Owner:SAMSUNG ELECTRONICS CO LTD