Patents

Literature

1073results about How to "Reduce defect density" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

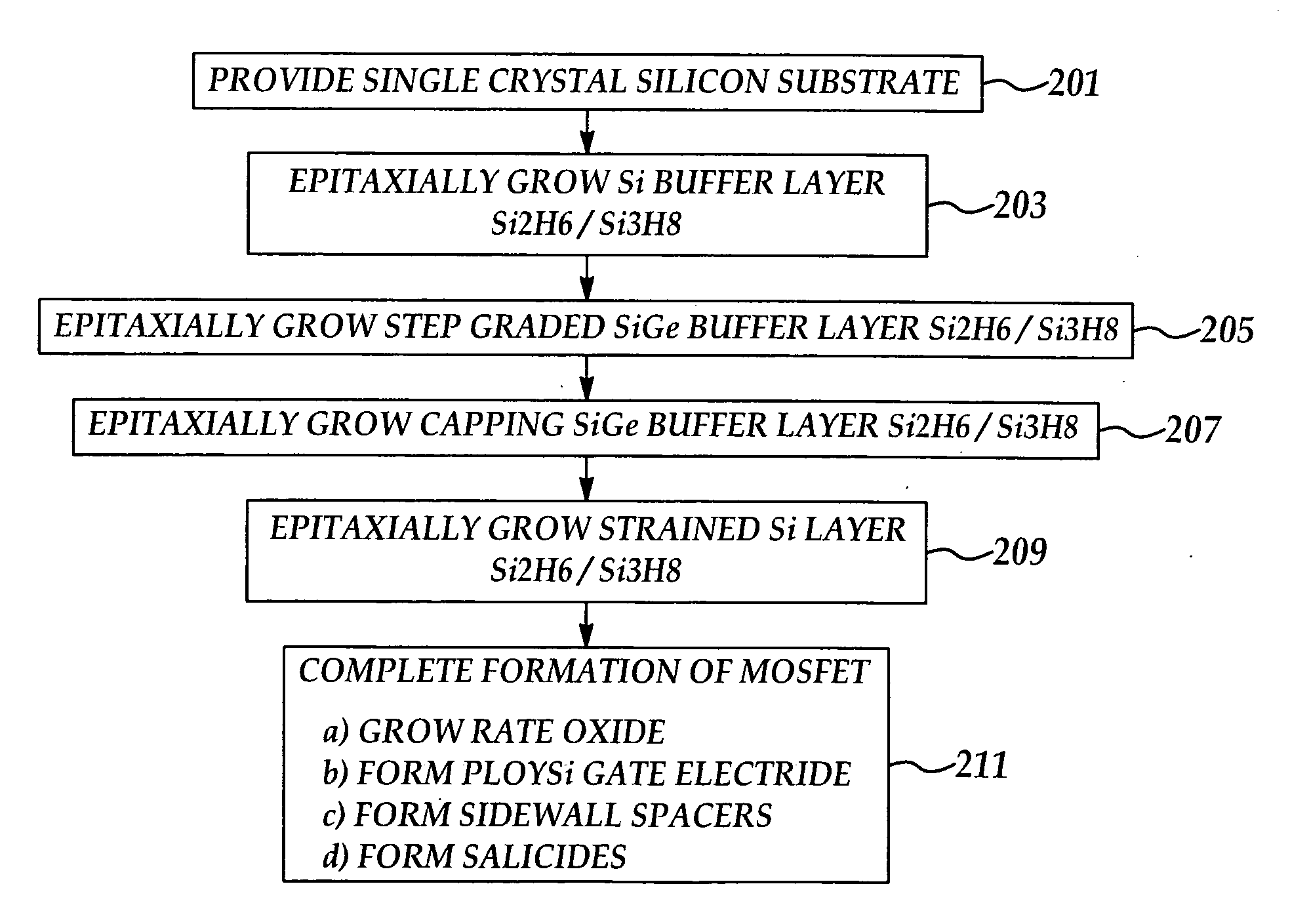

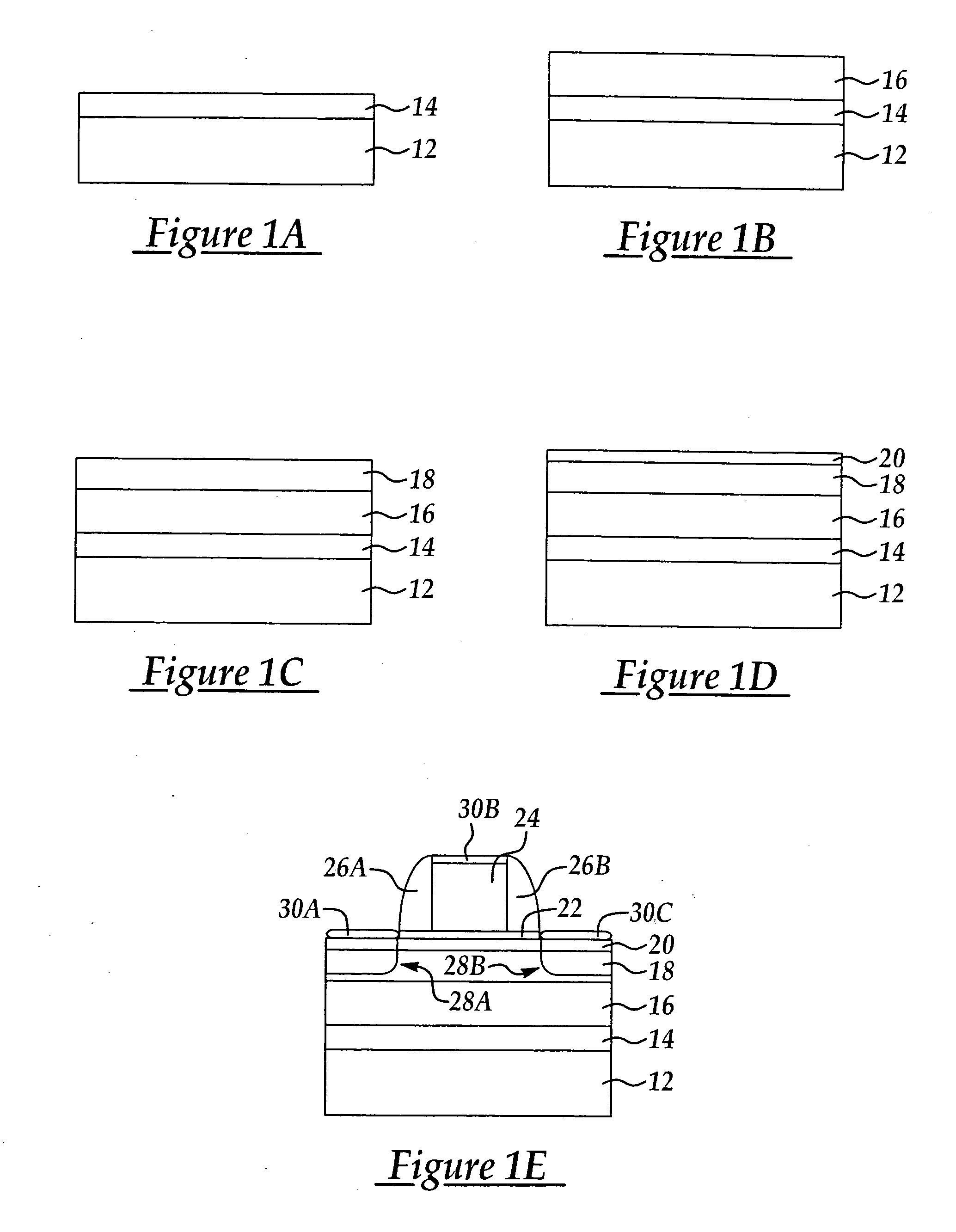

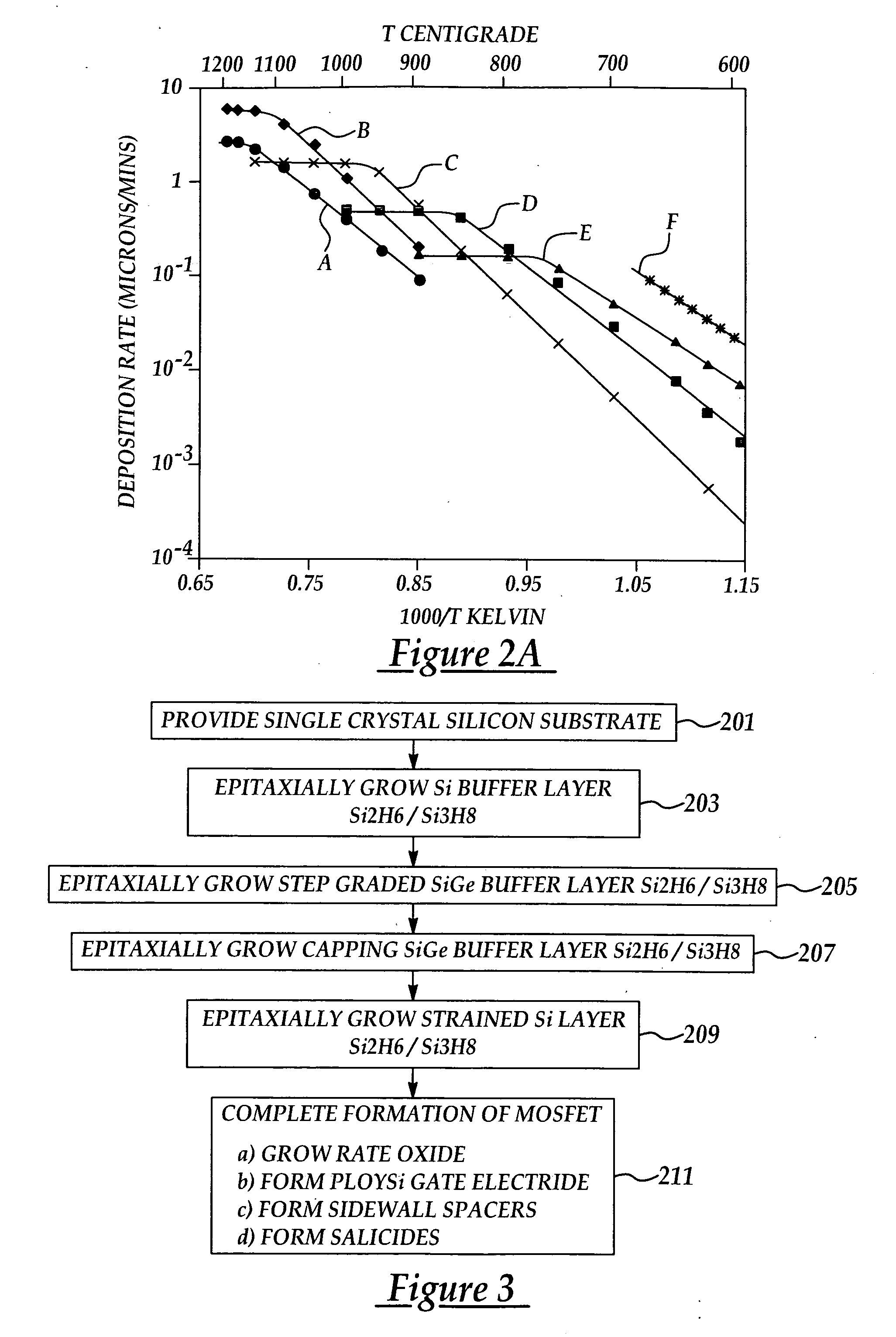

Method for producing high throughput strained-si channel mosfets

InactiveUS20050245058A1Improve throughputReduce defect densityPolycrystalline material growthFrom solid stateSilanesMaterials science

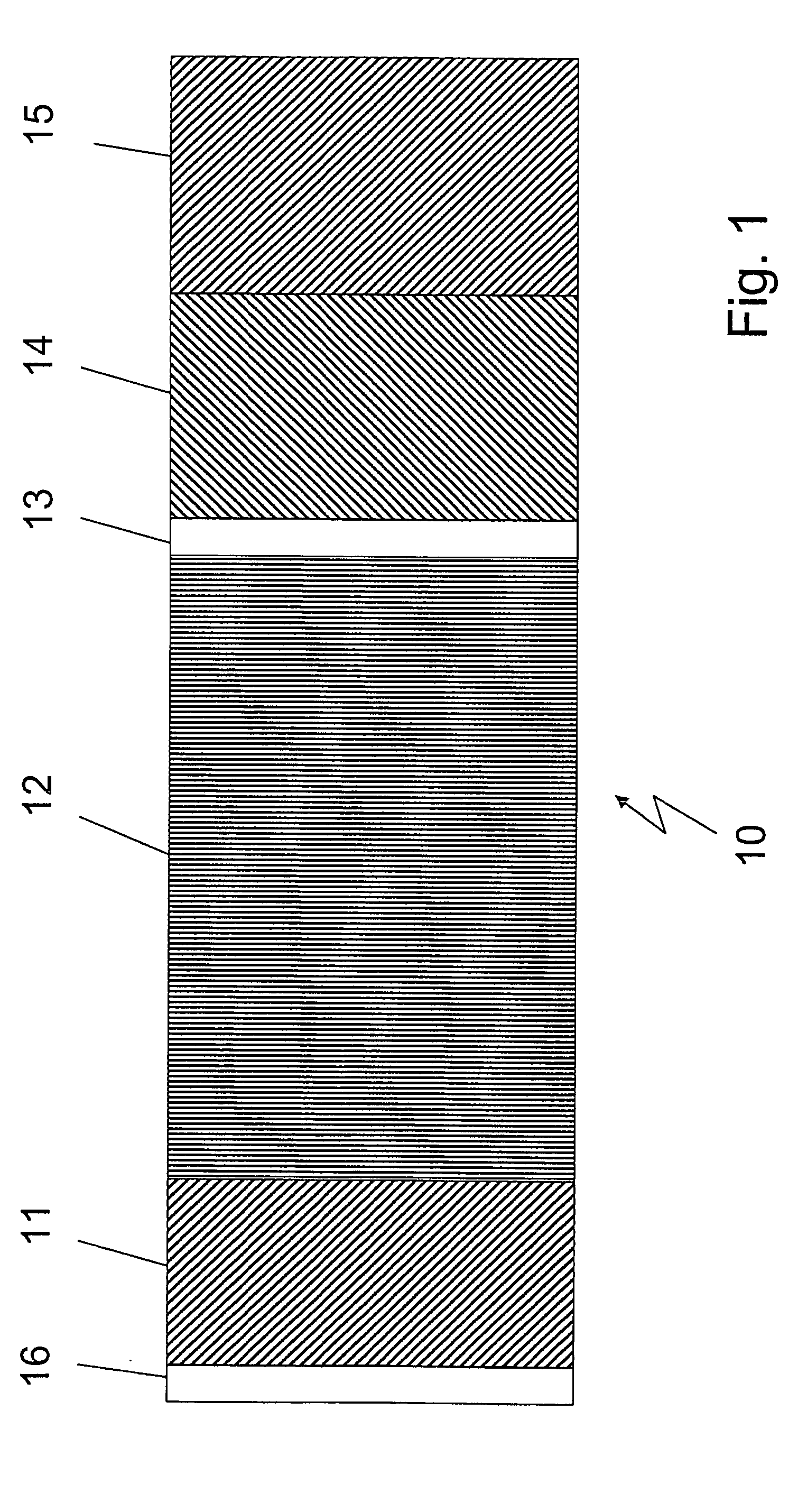

A method for forming a strained silicon layer device with improved wafer throughput and low defect density including providing a silicon substrate; epitaxially growing a first silicon layer using at least one deposition precursor selected from the group consisting of disilane and trisilane; epitaxially growing a step-grade SiGe buffer layer over and contacting the first silicon layer using at least one deposition precursor selected from the group consisting of disilane and trisilane; epitaxially growing a SiGe capping layer over and contacting the step-grade SiGe buffer layer using at least one deposition precursor selected from the group consisting of disilane and trisilane; and, epitaxially growing a second silicon layer using at least one deposition precursor selected from the group consisting of disilane and silane.

Owner:TAIWAN SEMICON MFG CO LTD

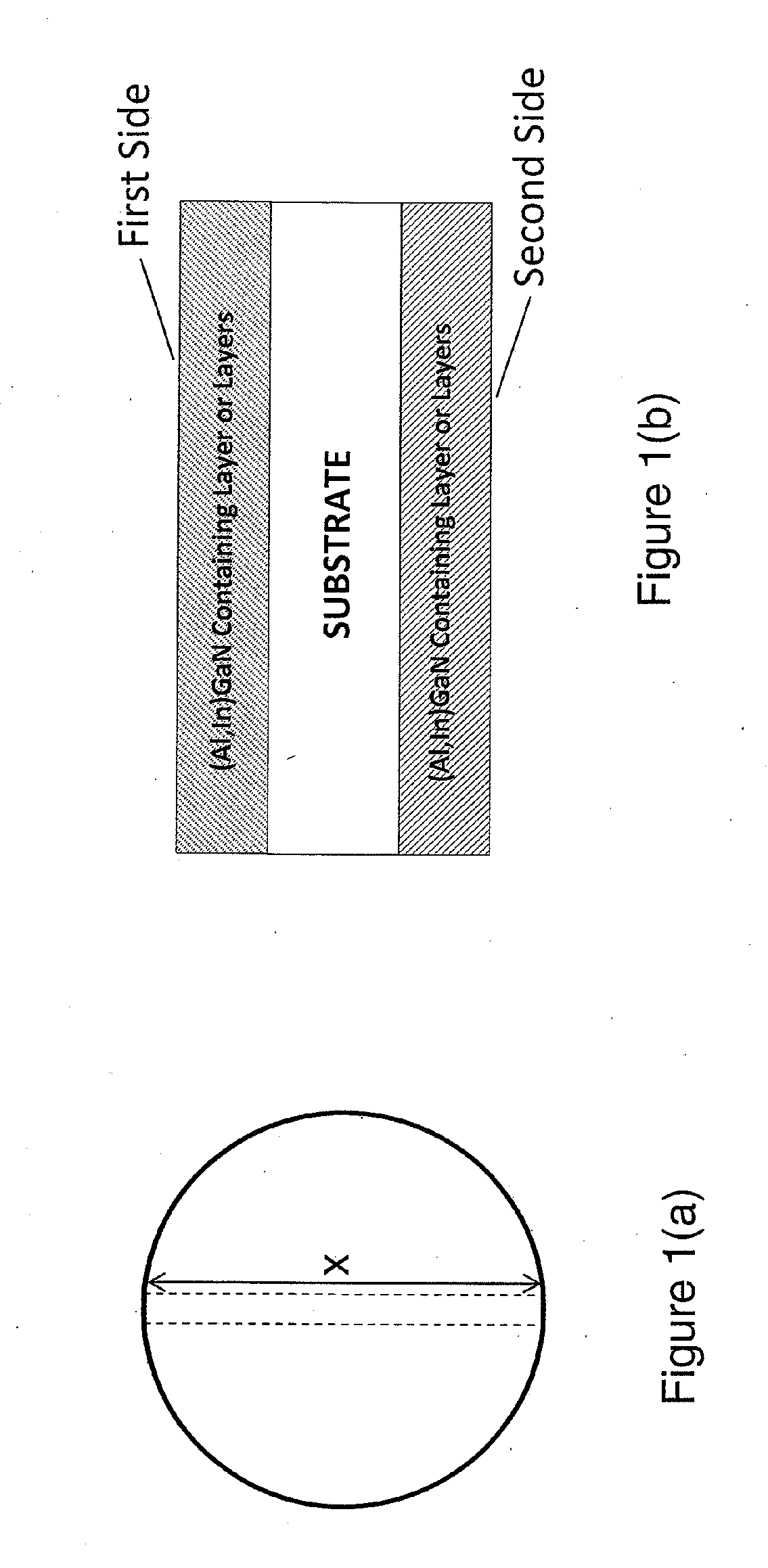

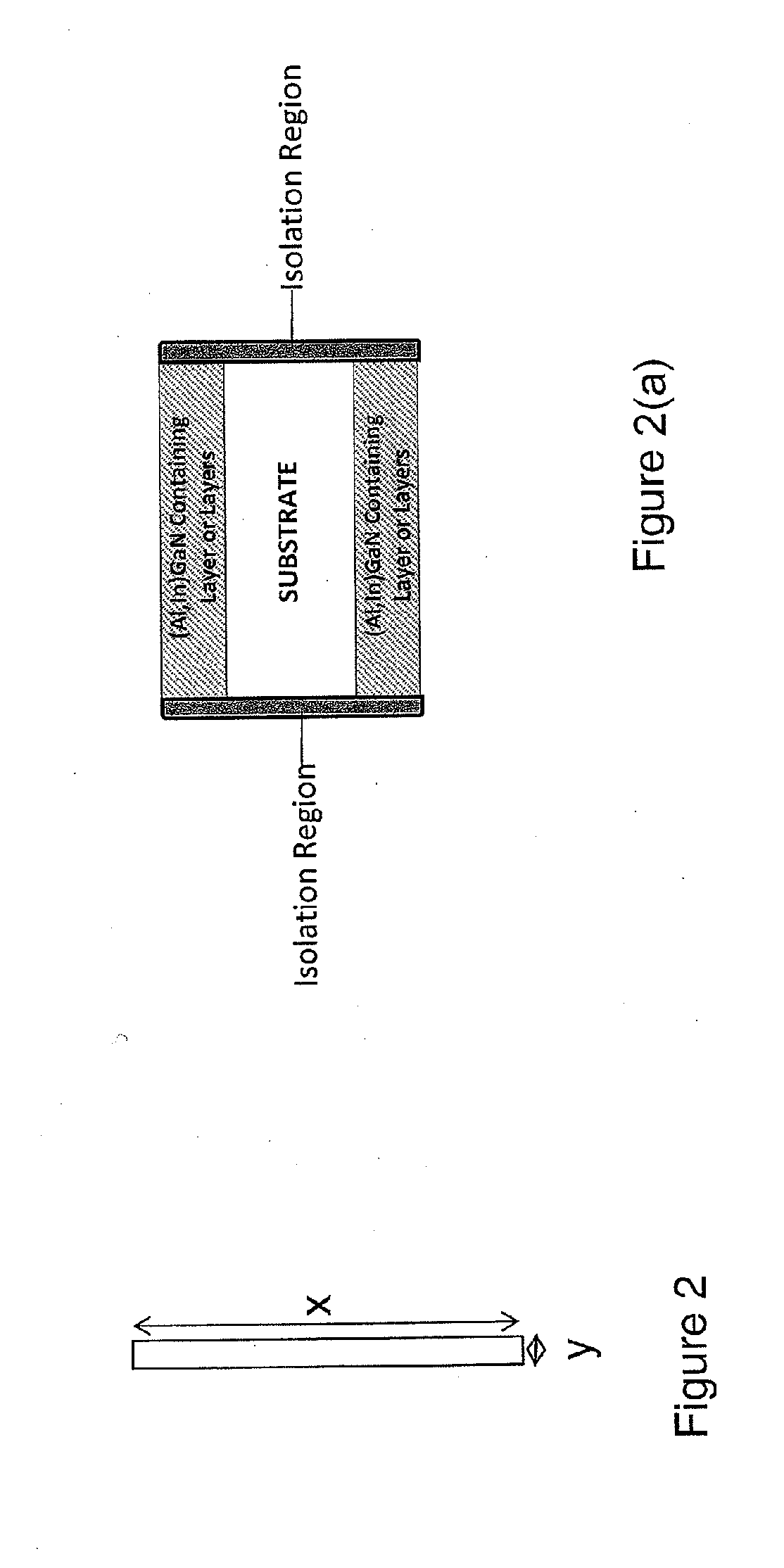

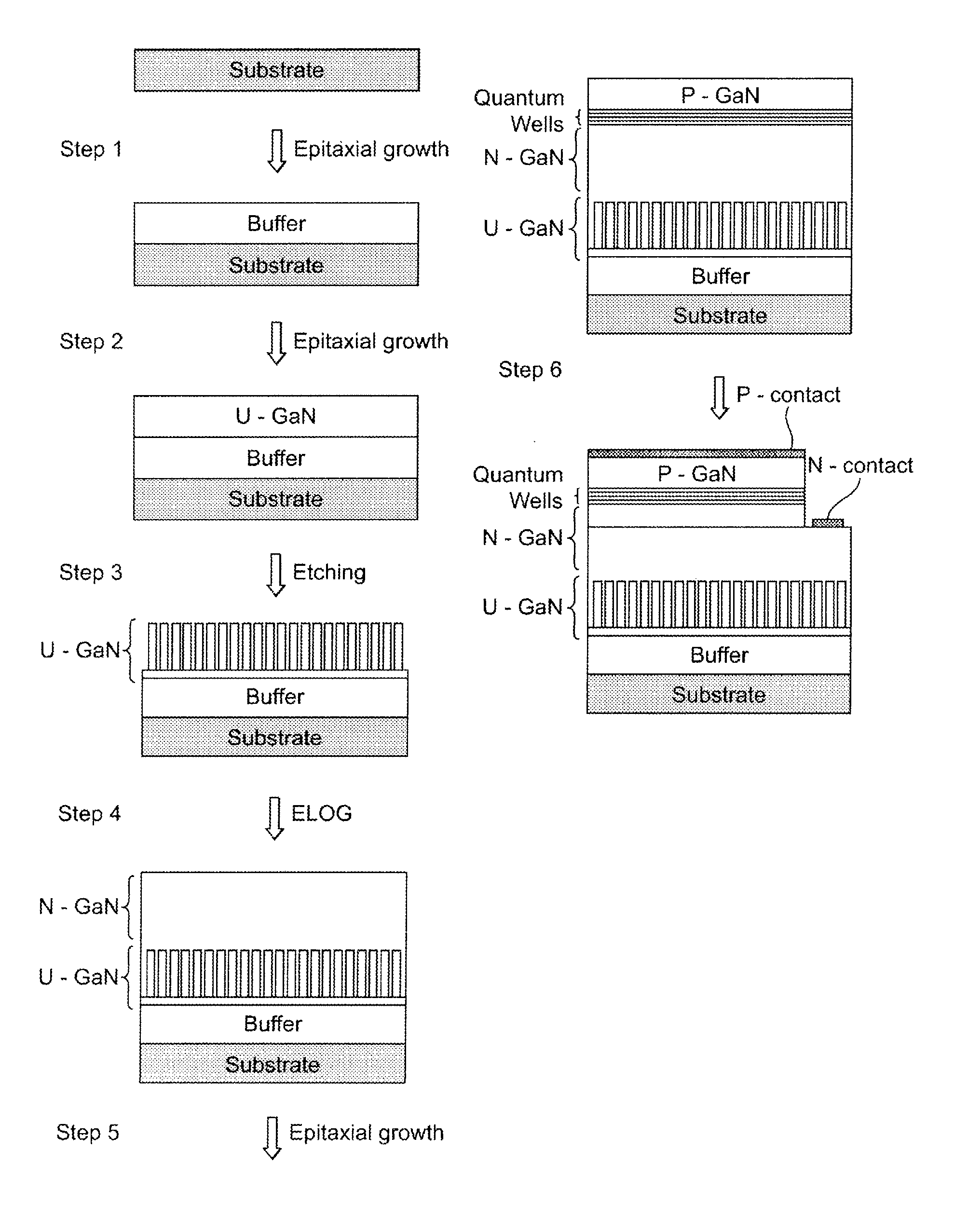

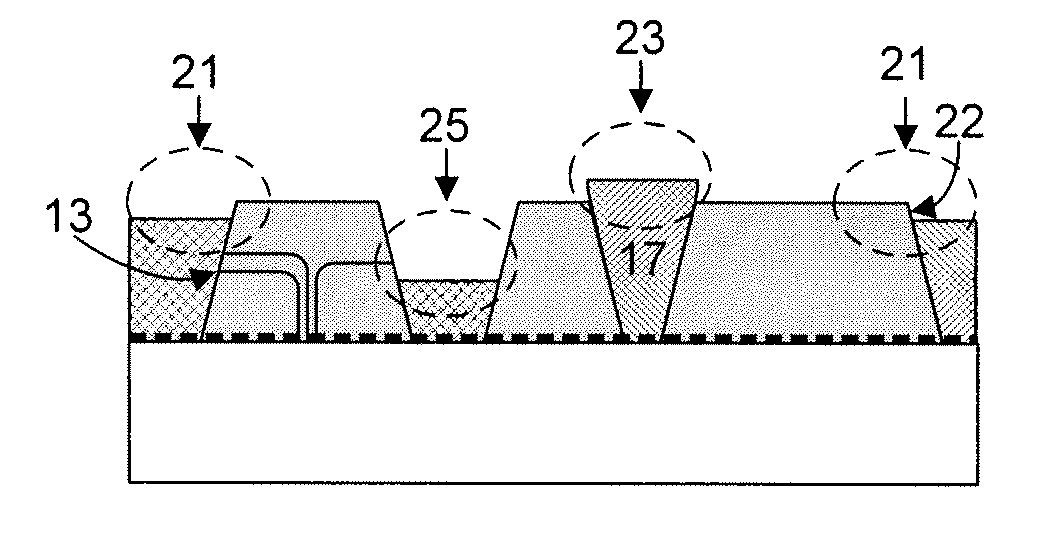

Method for producing a gallium nitride epitaxial layer

InactiveUS6325850B1GaN crystal qualityImprove crystal qualityPolycrystalline material growthLaser detailsEtchingGallium nitride

The invention concerns a method for producing a gallium nitride (GaN) epitaxial layer characterised in that it consists in depositing on a substrate a dielectric layer acting as a mask and depositing on the masked gallium nitride, by epitaxial deposit, so as to induce the deposit of gallium nitride patterns and the anisotropic lateral growth of said patterns, the lateral growth being pursued until the different patterns coalesce. The deposit of the gallium nitride patterns can be carried out ex-situ by dielectric etching or in-situ by treating the substrate for coating it with a dielectric film whereof the thickness is of the order of one angstrom. The invention also concerns the gallium nitride layers obtained by said method.

Owner:SAINT GOBAIN CRISTAUX & DETECTEURS

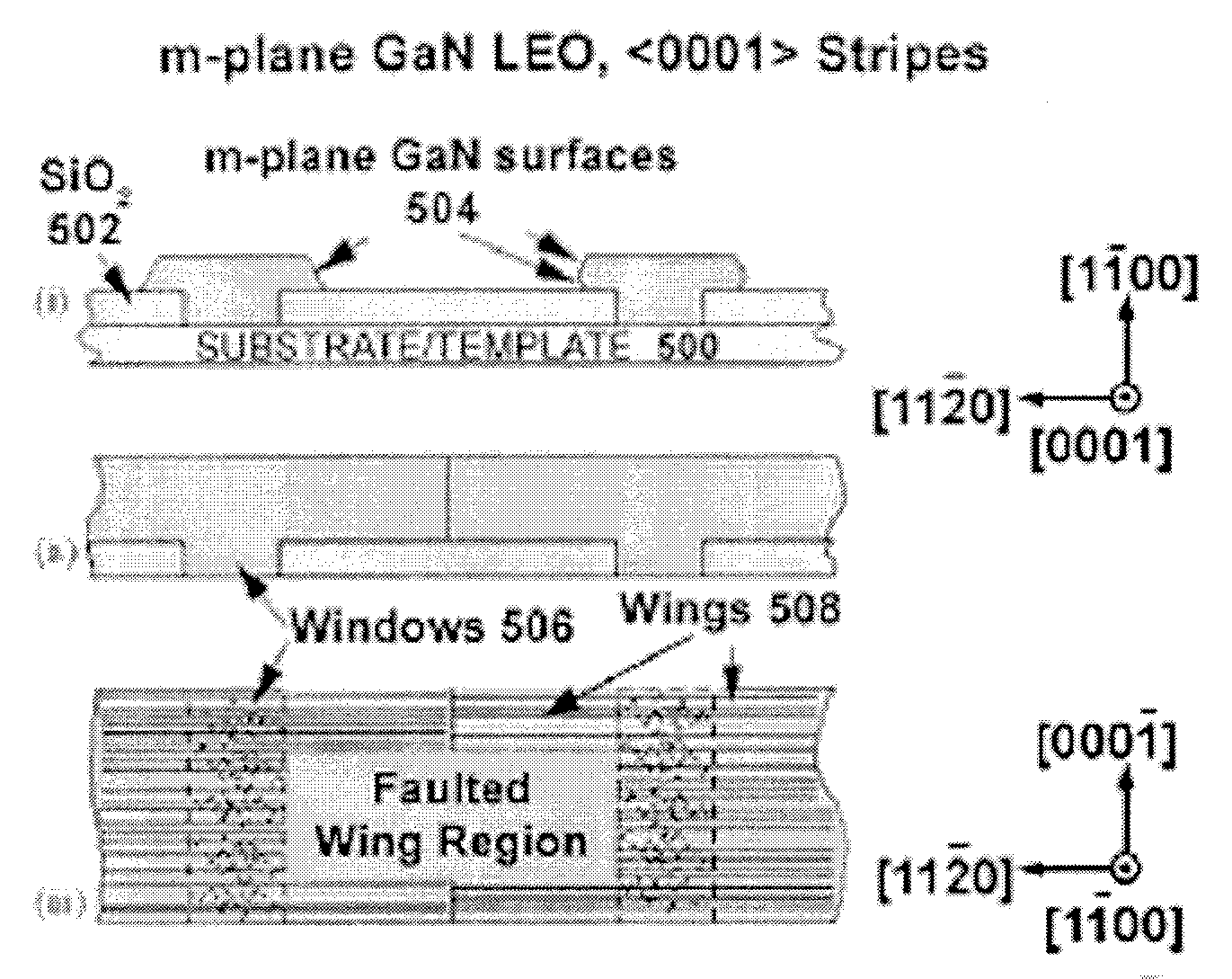

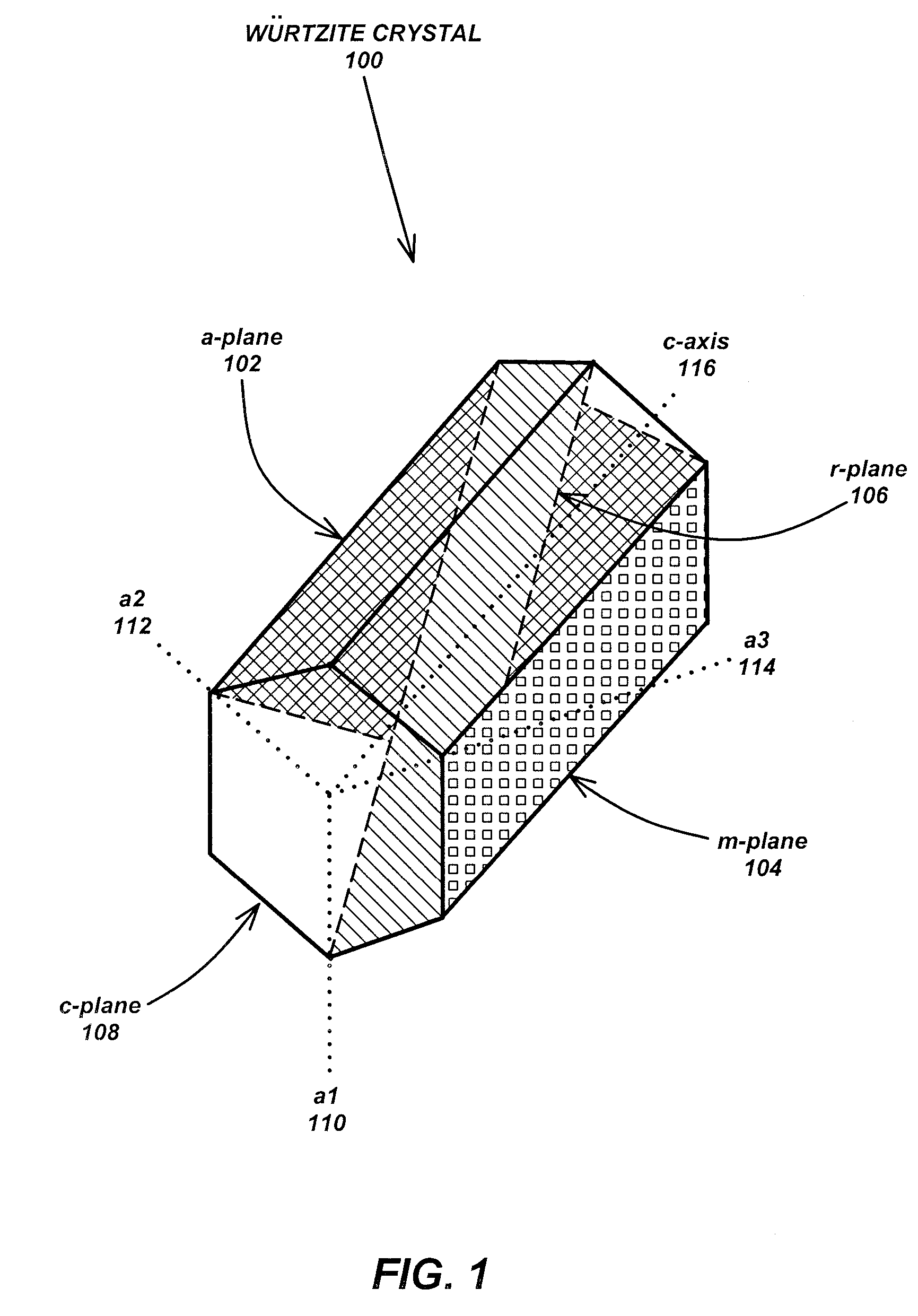

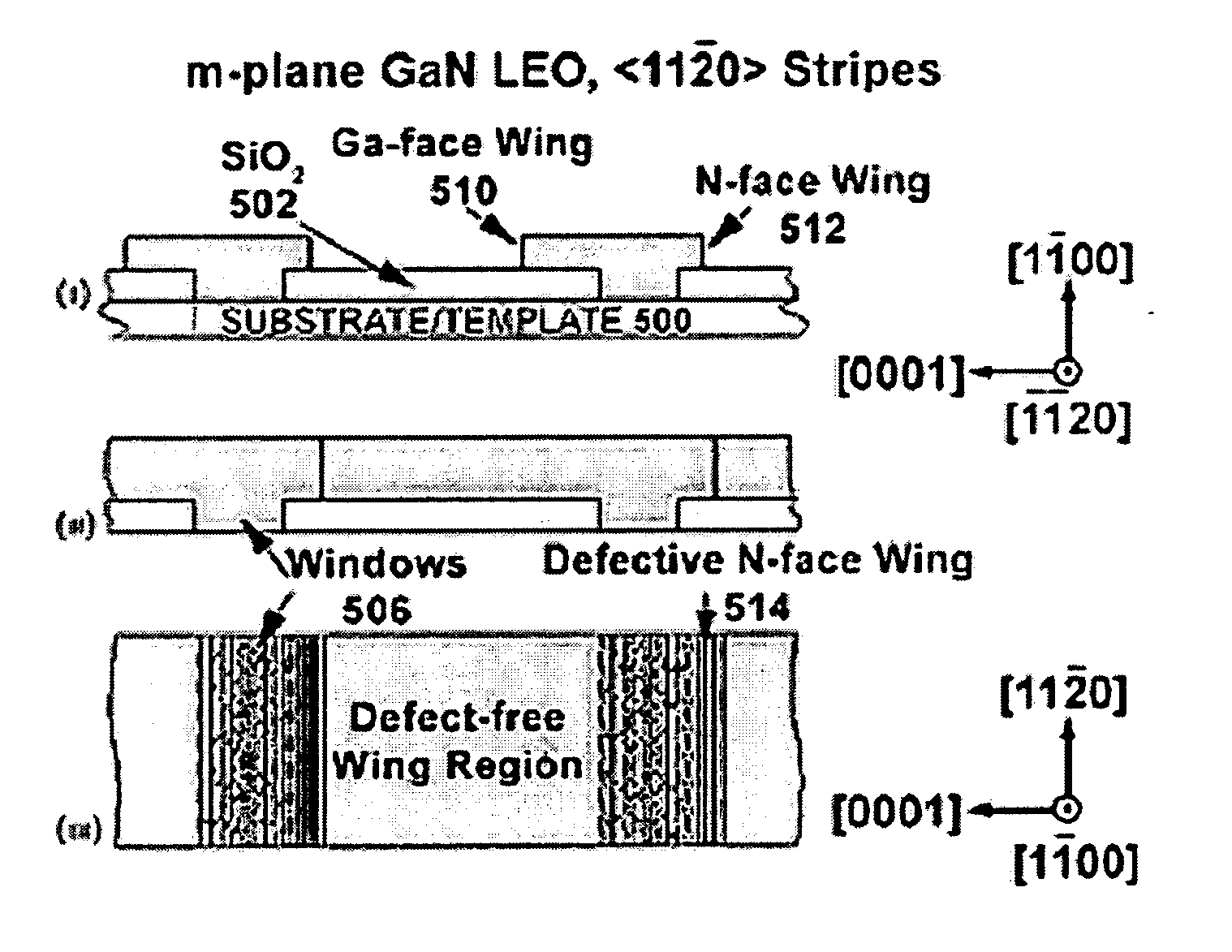

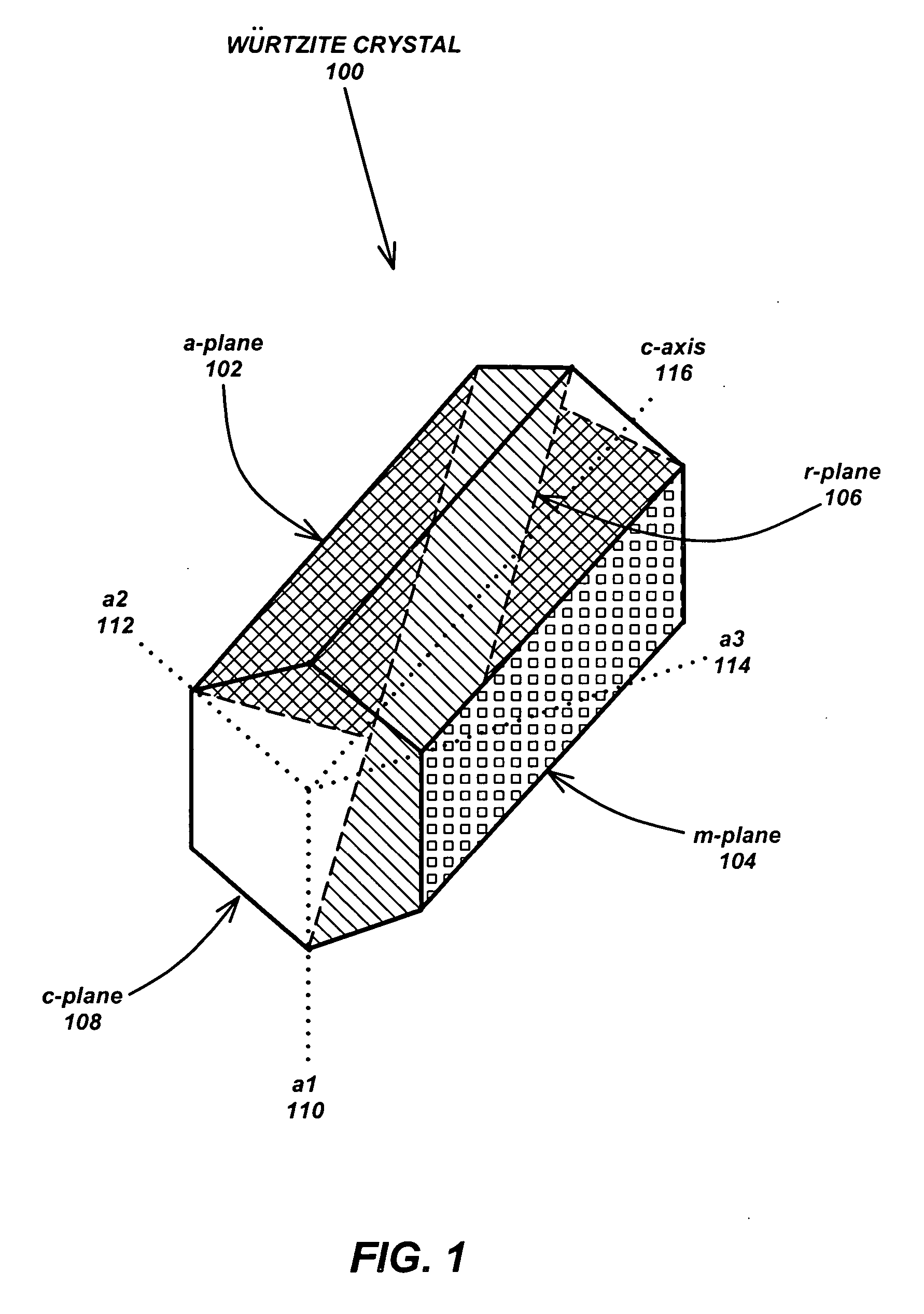

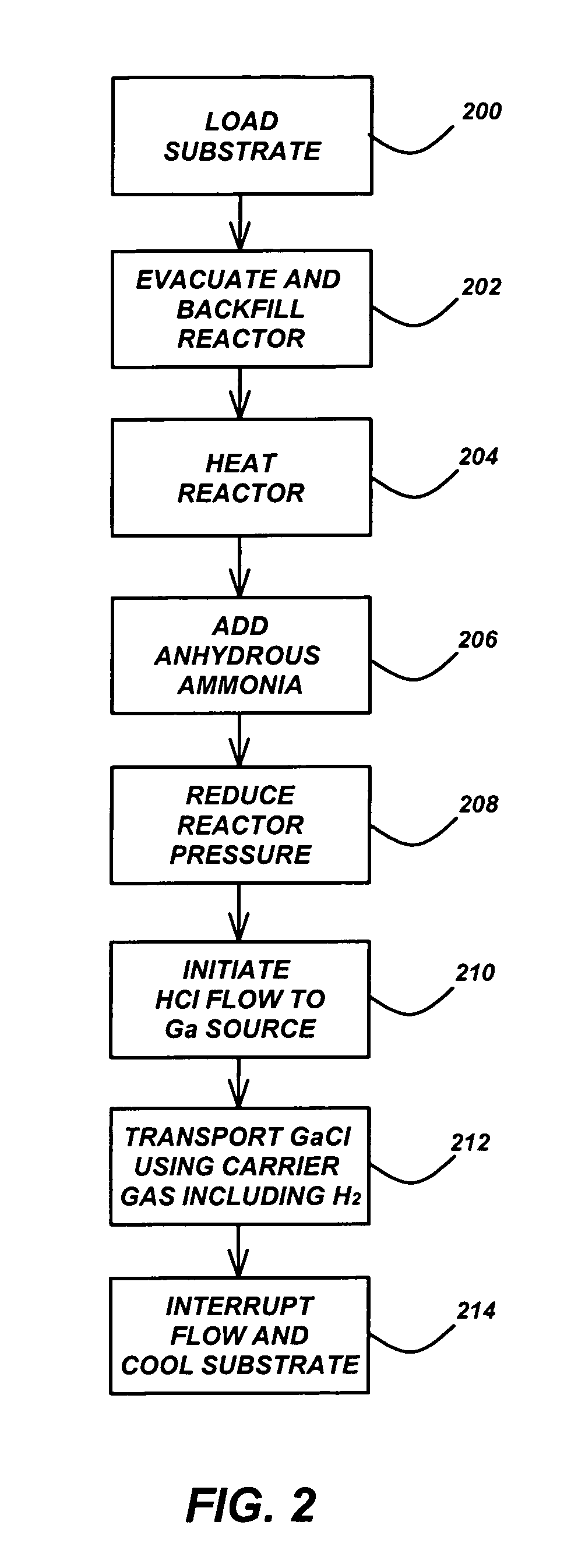

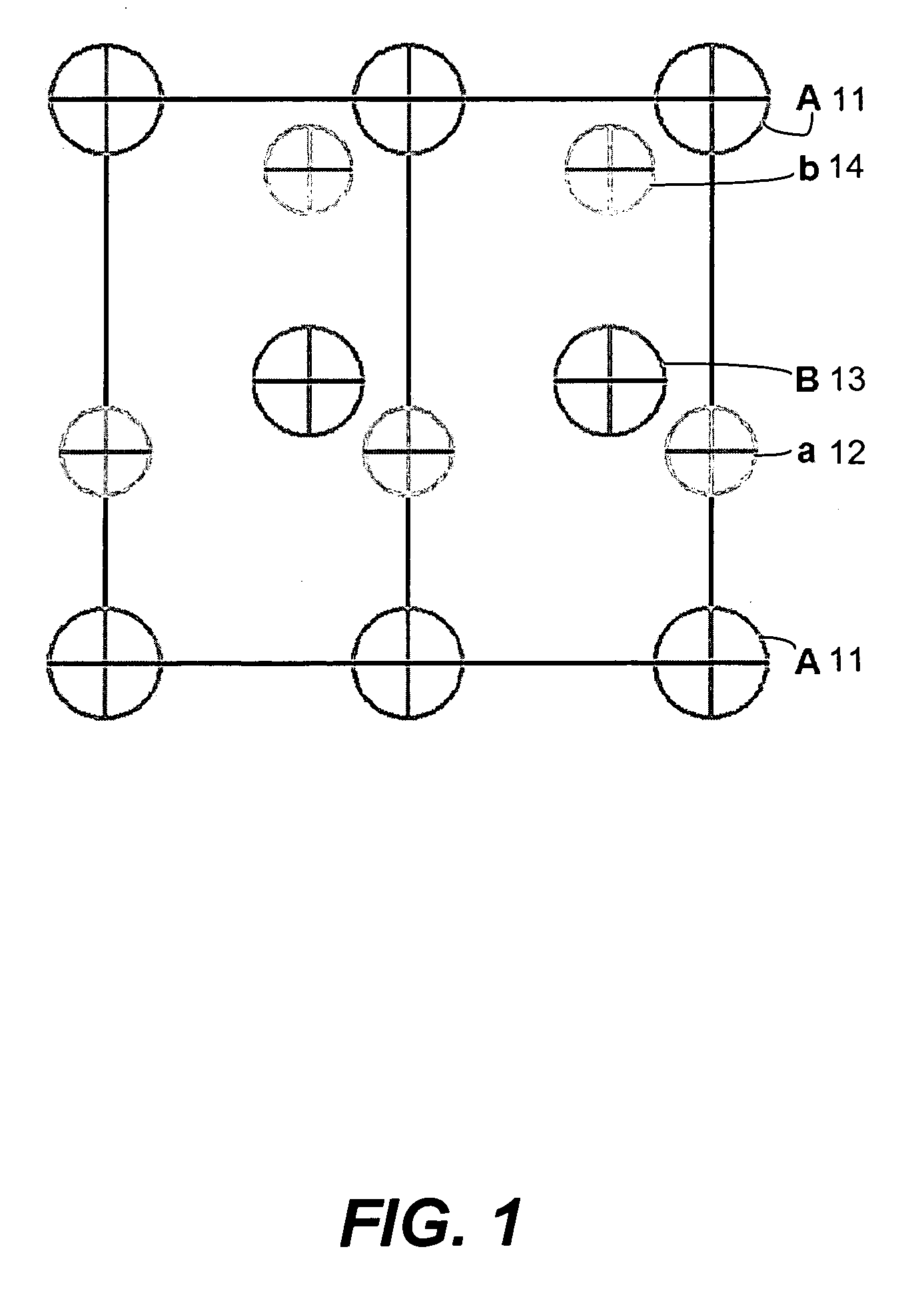

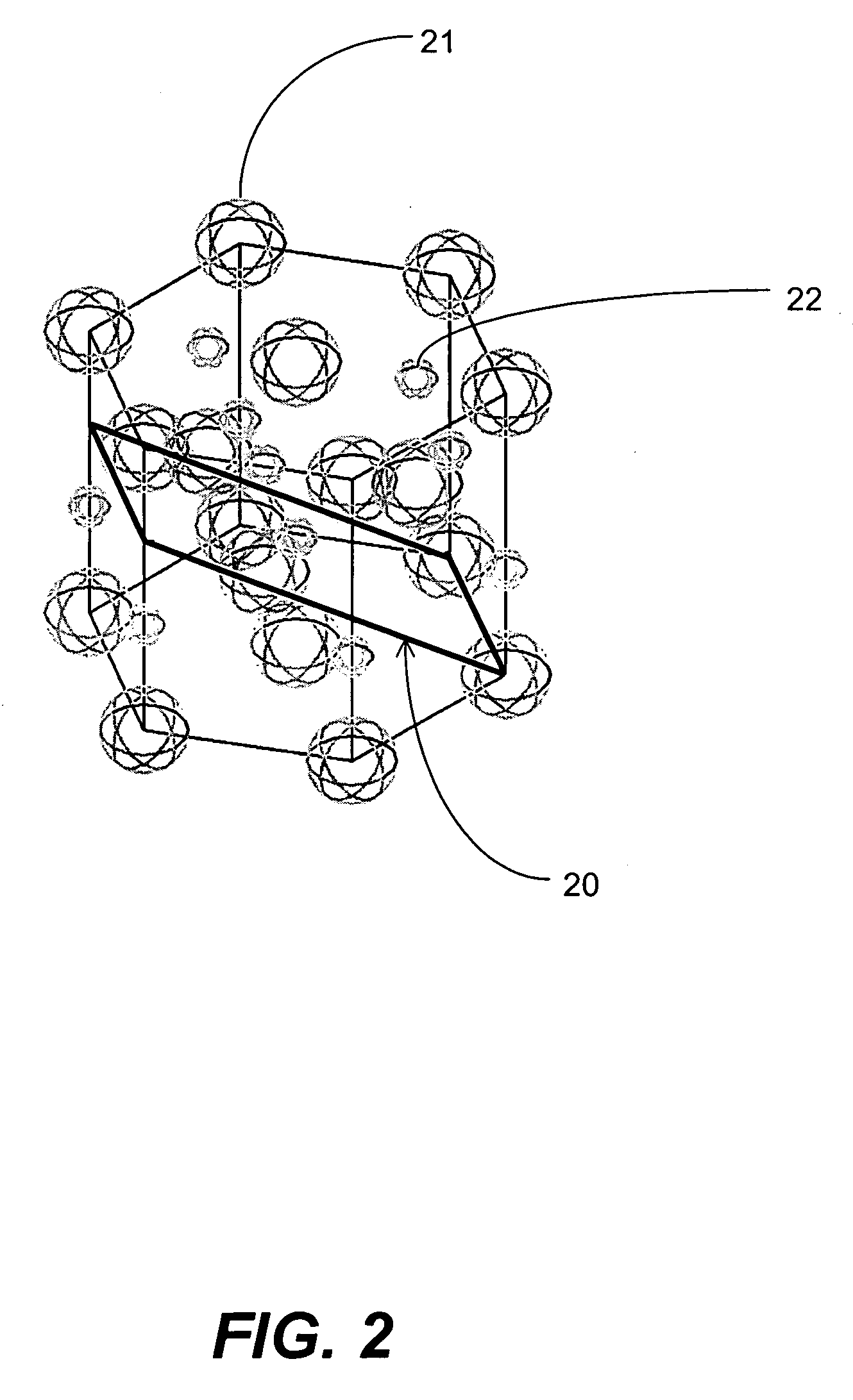

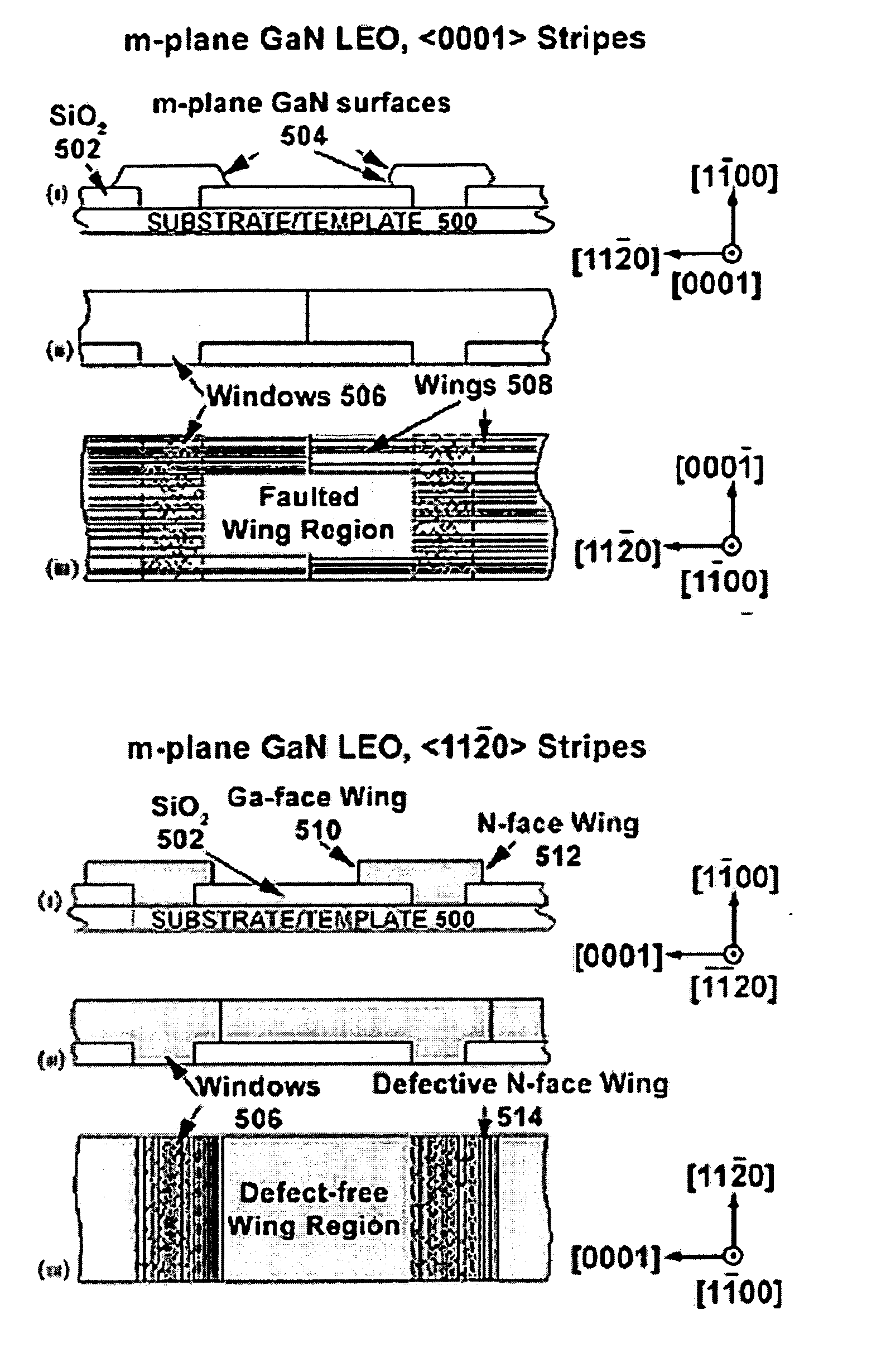

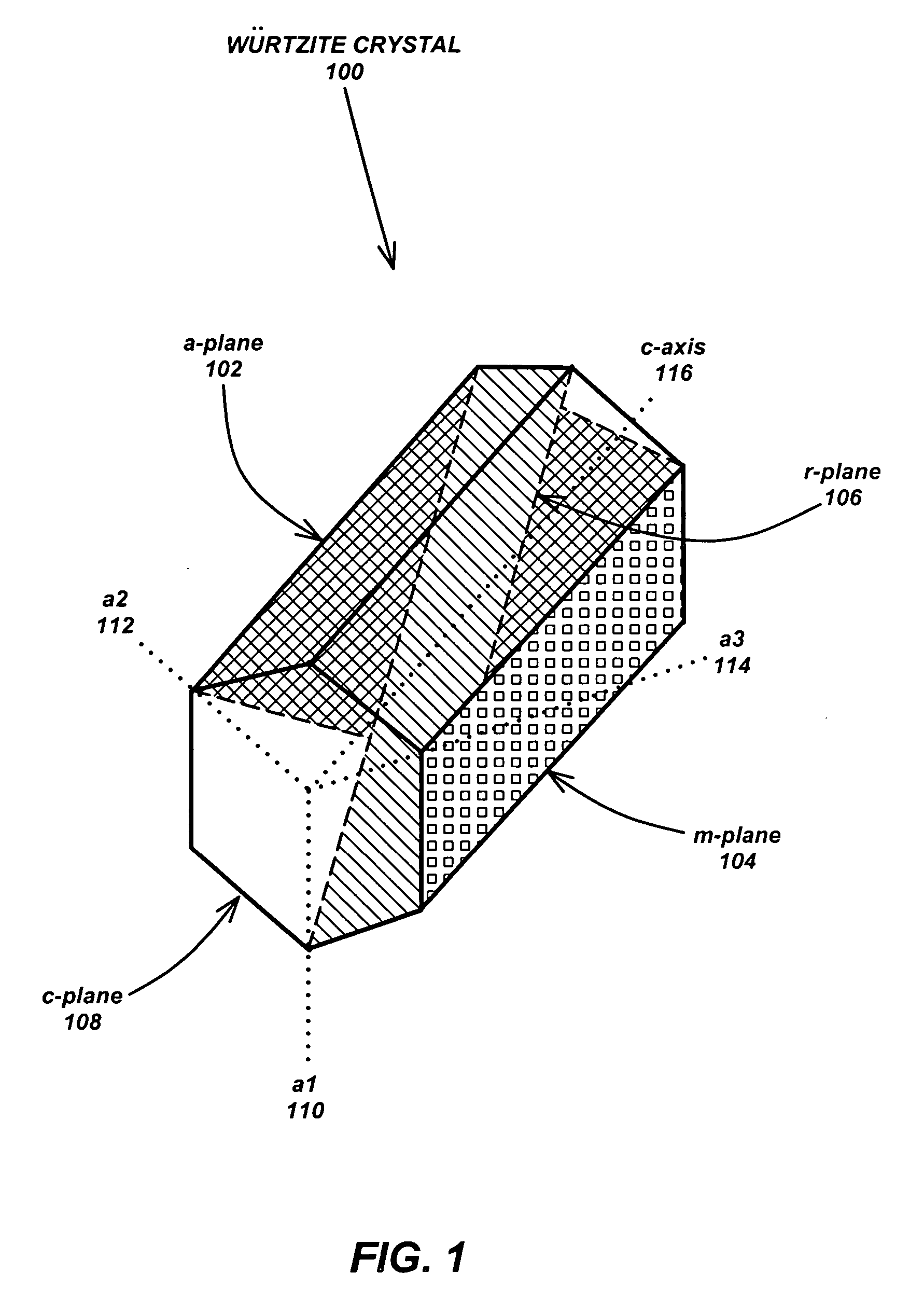

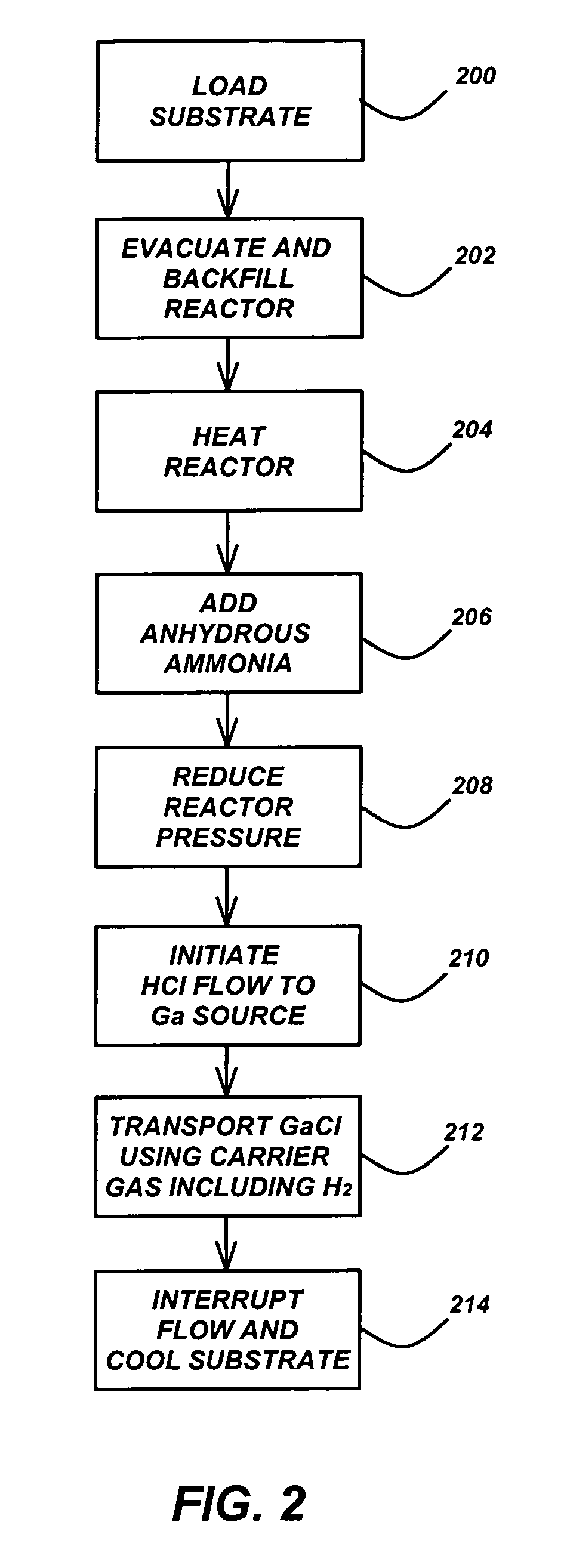

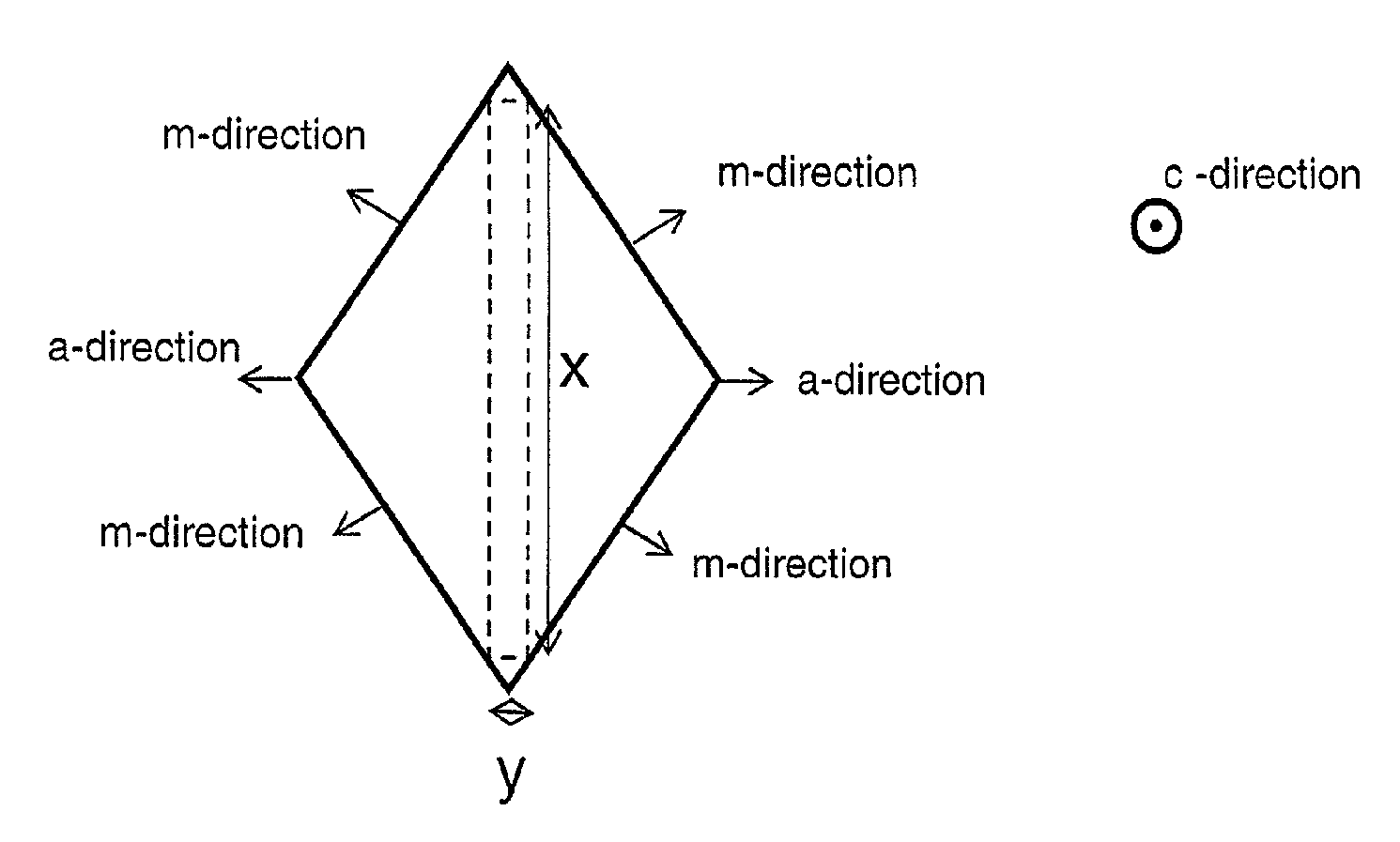

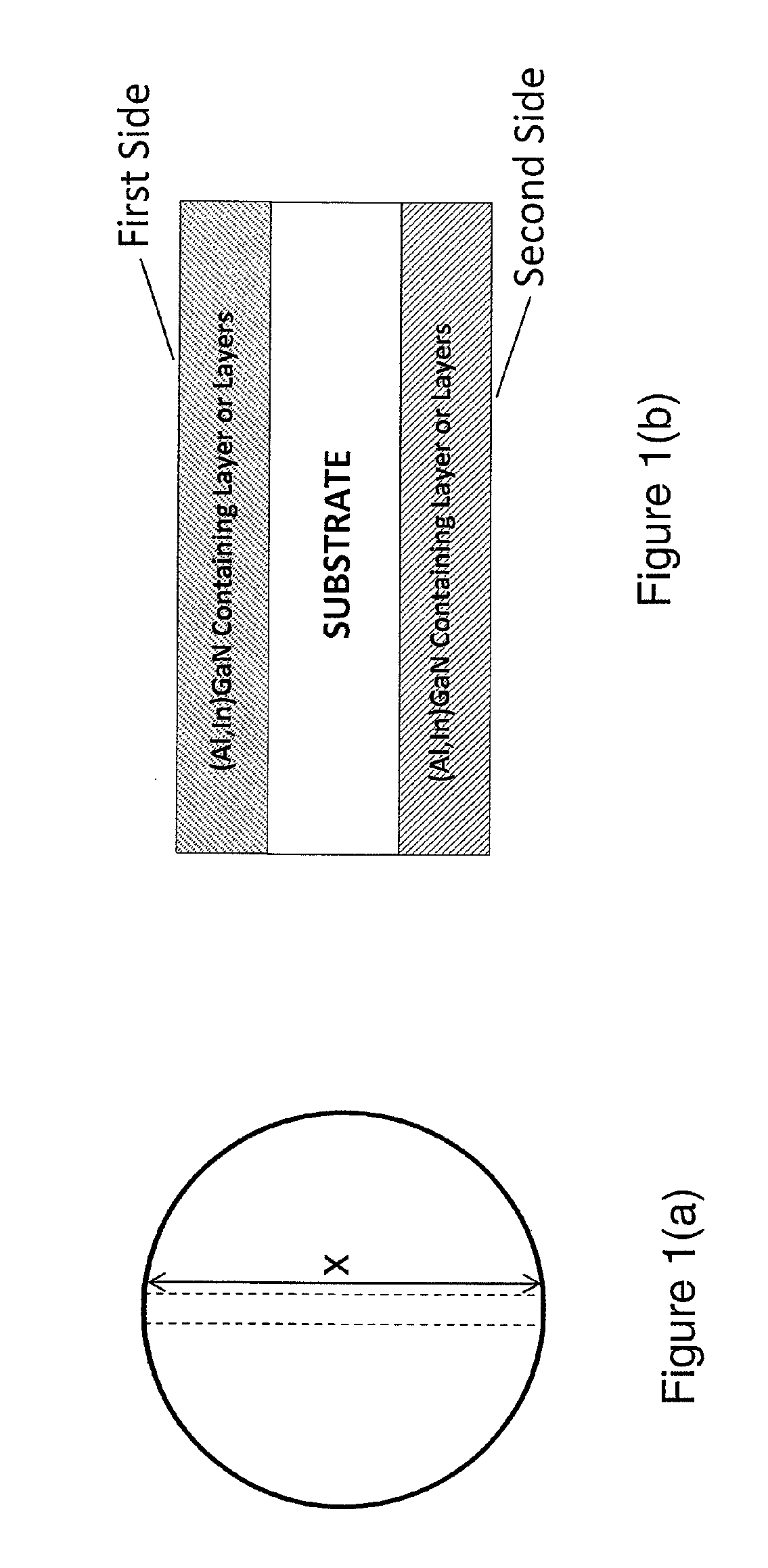

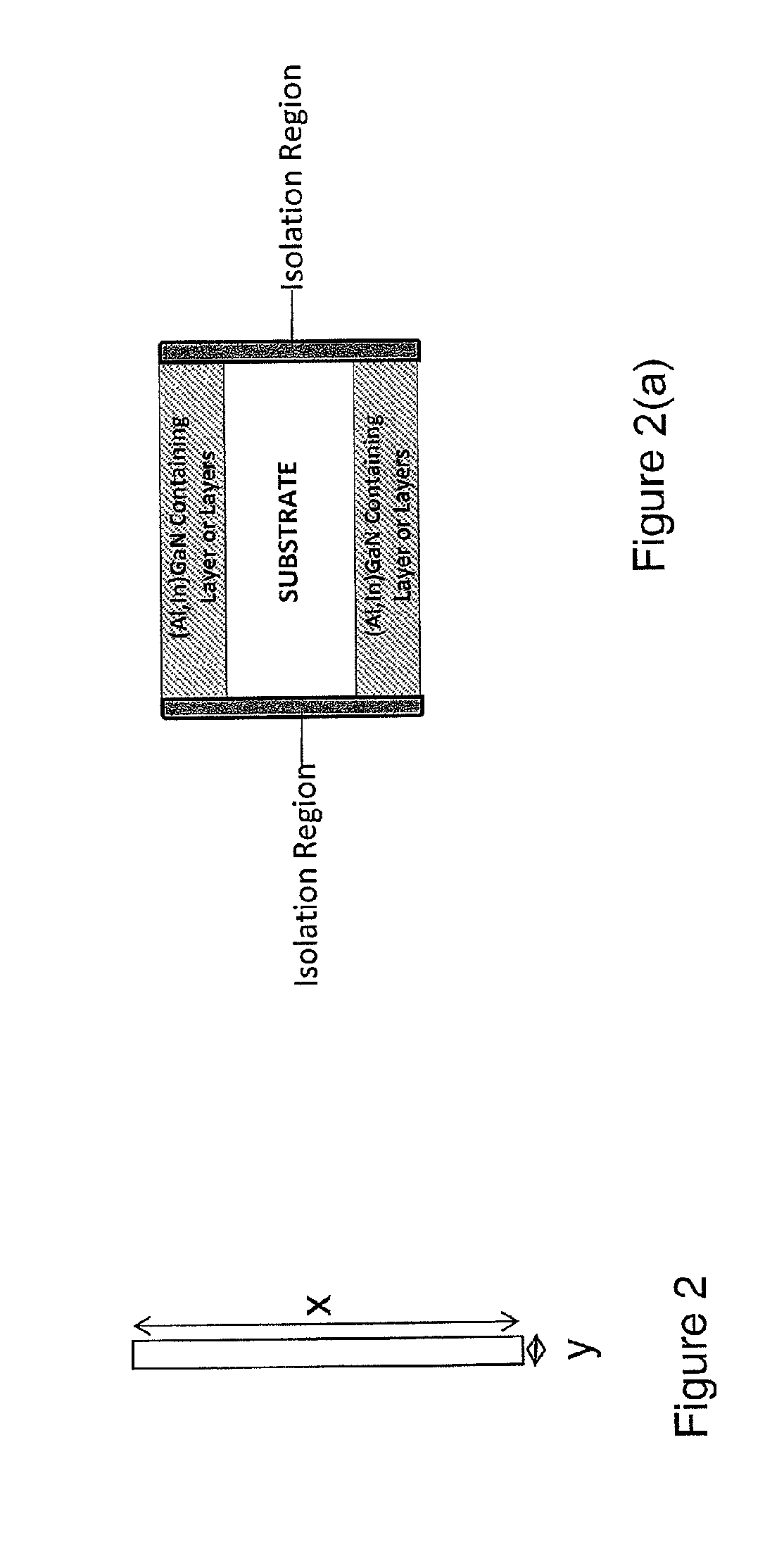

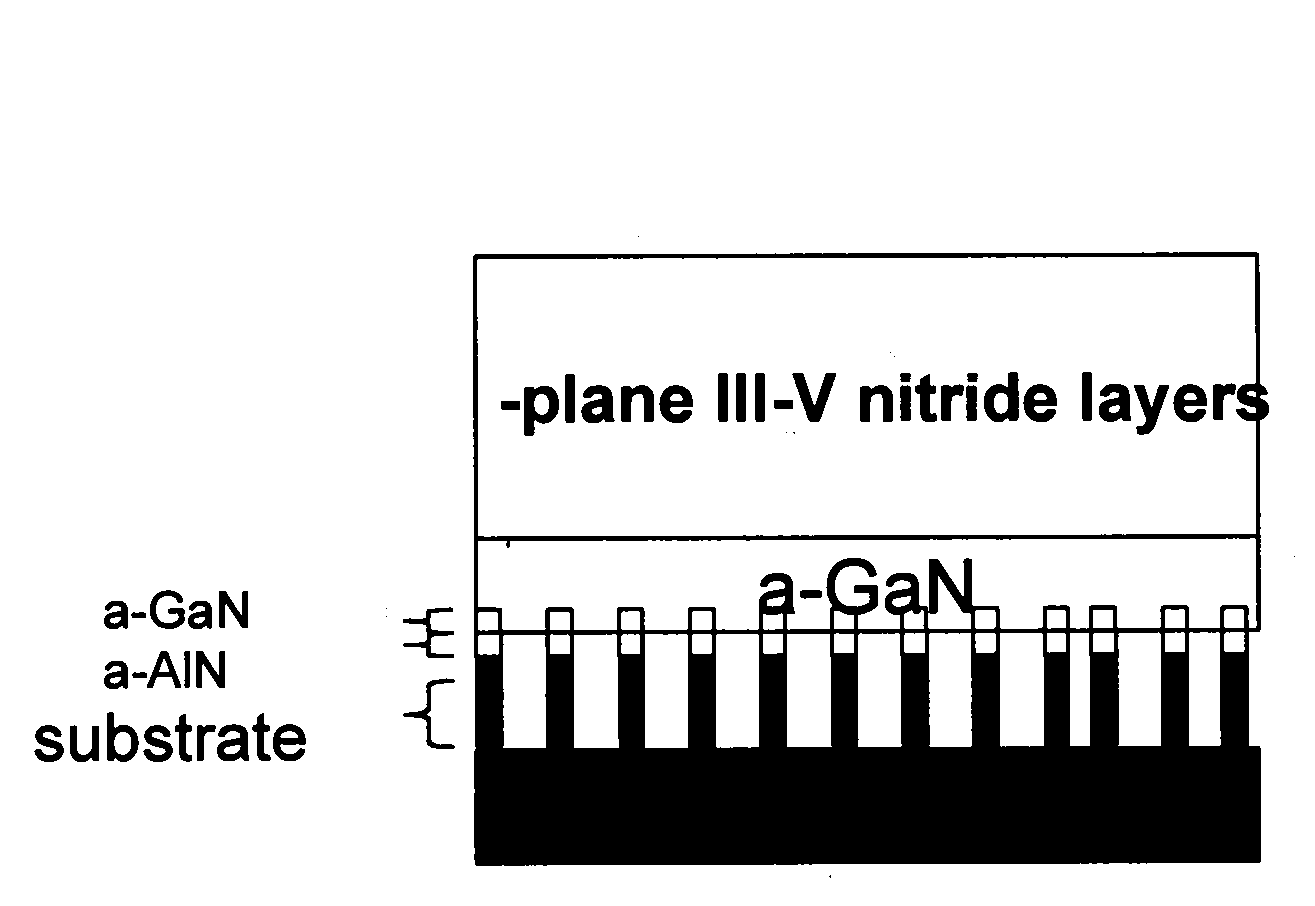

Growth of planar reduced dislocation density m-plane gallium nitride by hydride vapor phase epitaxy

ActiveUS20070184637A1Reduction in structural defect densityReduce defect densitySemiconductor/solid-state device manufacturingSemiconductor devicesLateral overgrowthVolumetric Mass Density

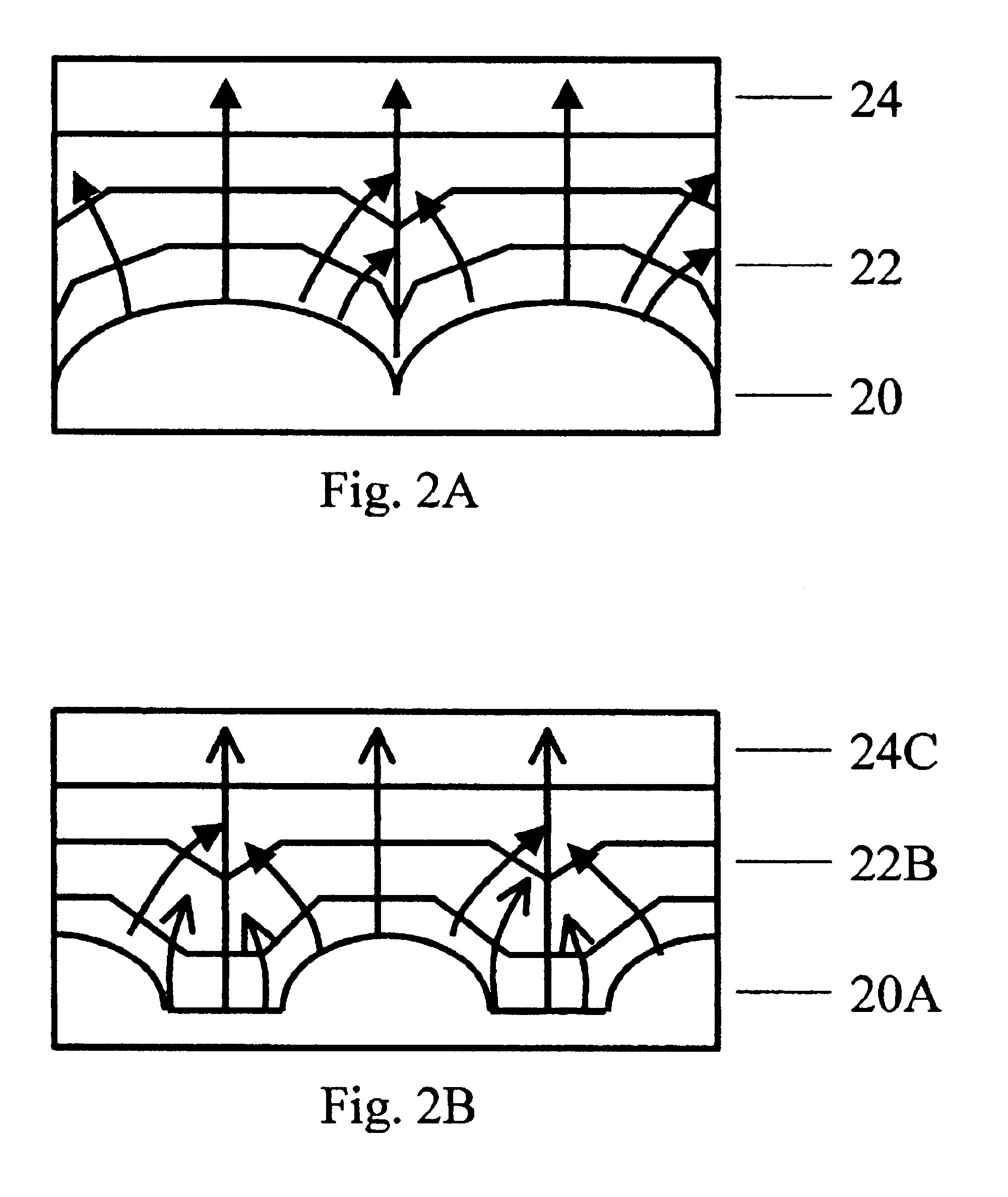

A method of growing highly planar, fully transparent and specular m-plane gallium nitride (GaN) films. The method provides for a significant reduction in structural defect densities via a lateral overgrowth technique. High quality, uniform, thick m-plane GaN films are produced for use as substrates for polarization-free device growth.

Owner:JAPAN SCI & TECH CORP

Growth of planar reduced dislocation density m-plane gallium nitride by hydride vapor phase epitaxy

InactiveUS20050245095A1Reduction in structural defect densityReduce defect densityPolycrystalline material growthSemiconductor/solid-state device manufacturingLateral overgrowthGallium nitride

A method of growing highly planar, fully transparent and specular m-plane gallium nitride (GaN) films. The method provides for a significant reduction in structural defect densities via a lateral overgrowth technique. High quality, uniform, thick m-plane GaN films are produced for use as substrates for polarization-free device growth.

Owner:JAPAN SCI & TECH CORP

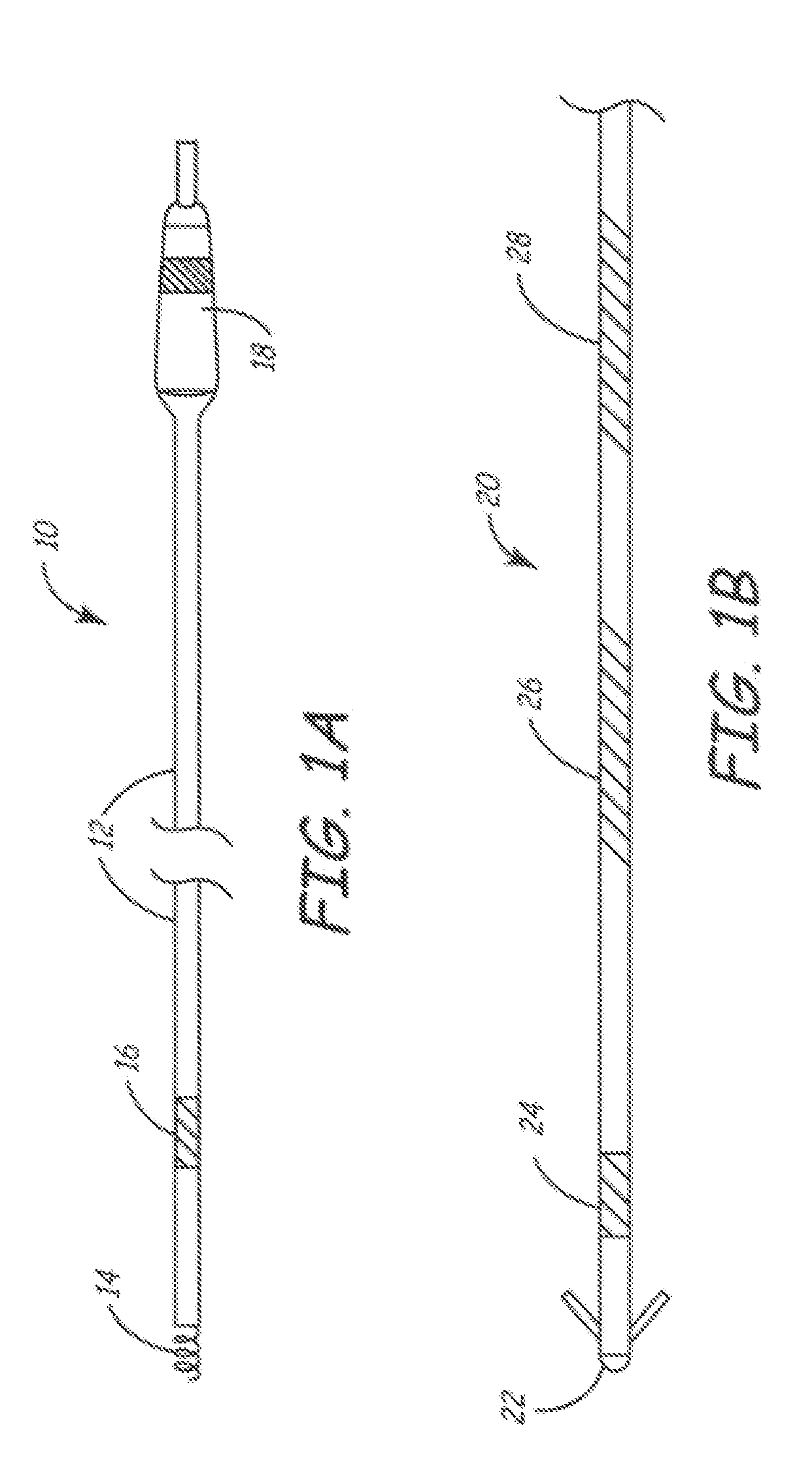

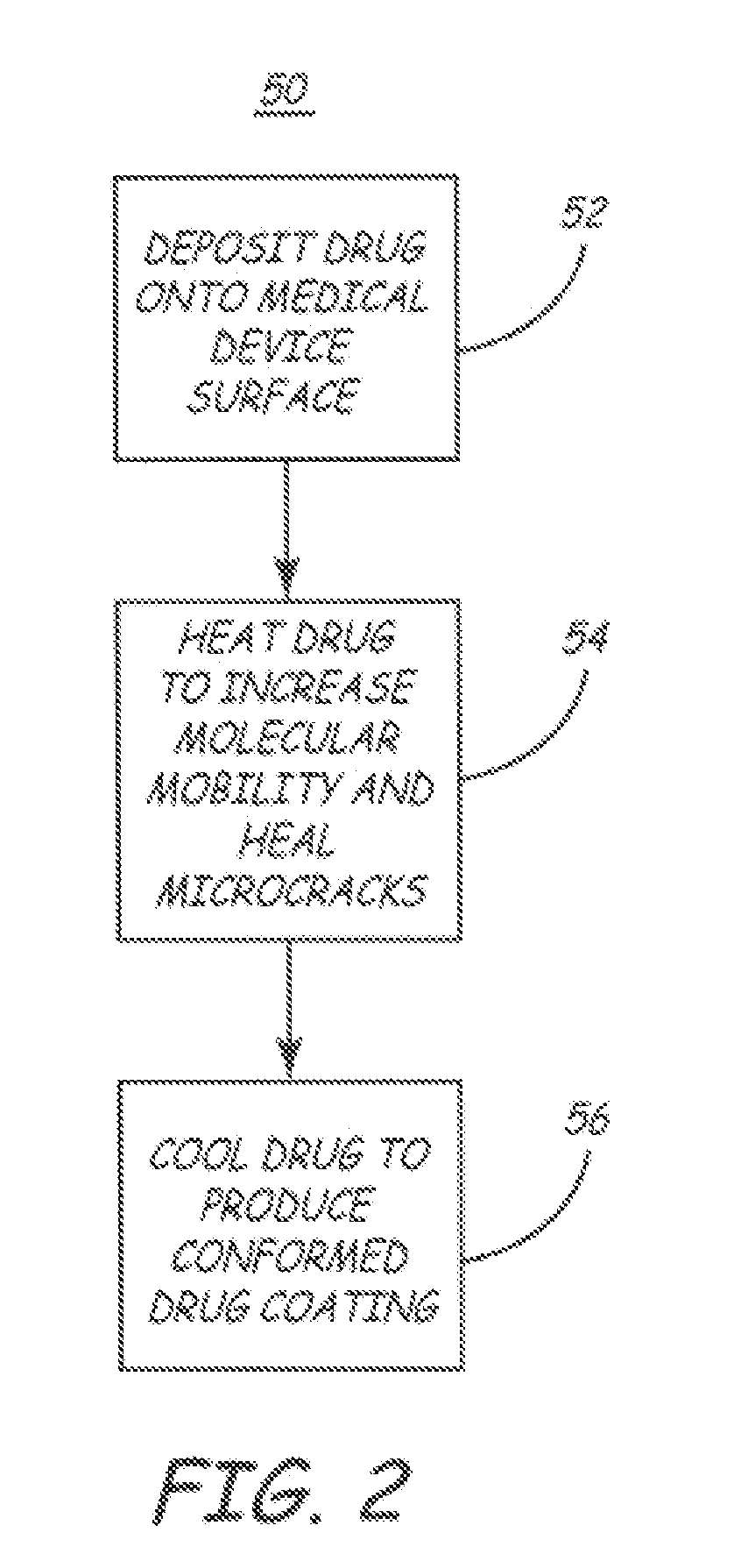

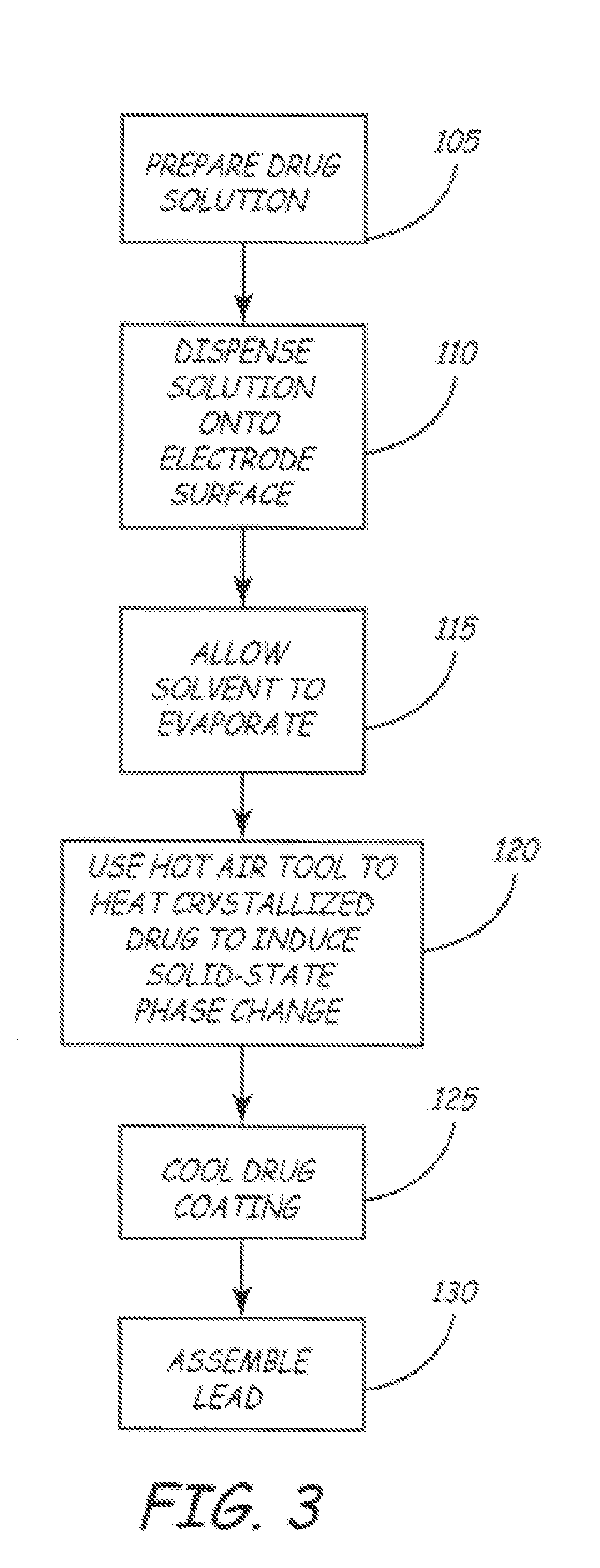

Method for applying a drug coating to a medical device

A method for coating a medical device with a drug is provided. Energy, preferably thermal energy, is applied to a crystalline deposit of a drug on the surface of a medical device to increase the molecular mobility and form a conformable drug coating with a low density of micro-cracks and other mechanical defects that can degrade the coating toughness and effective adhesion to the device surface. In a preferred embodiment, solution evaporation methods are used to deposit a crystalline coating of an anti-inflammatory steroid on a medical electrode. Heat applied at a controlled temperature, for a predetermined amount of time, induces a solid-state phase change of the drug coating providing a smooth, uniform, well-attached, conformable coating to form a layer that will elute from the electrode over time when implanted in a patient's body.

Owner:MEDTRONIC INC

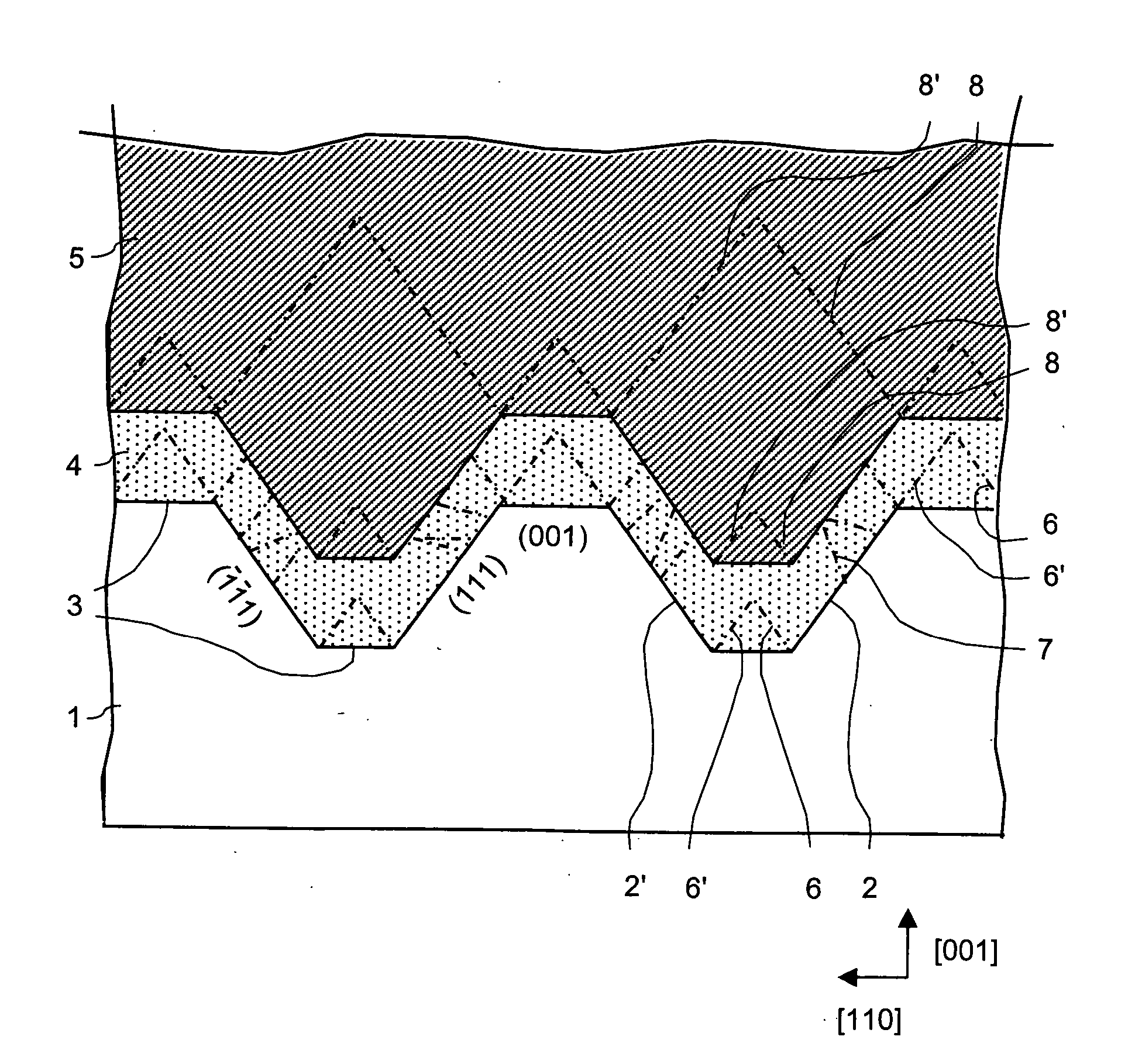

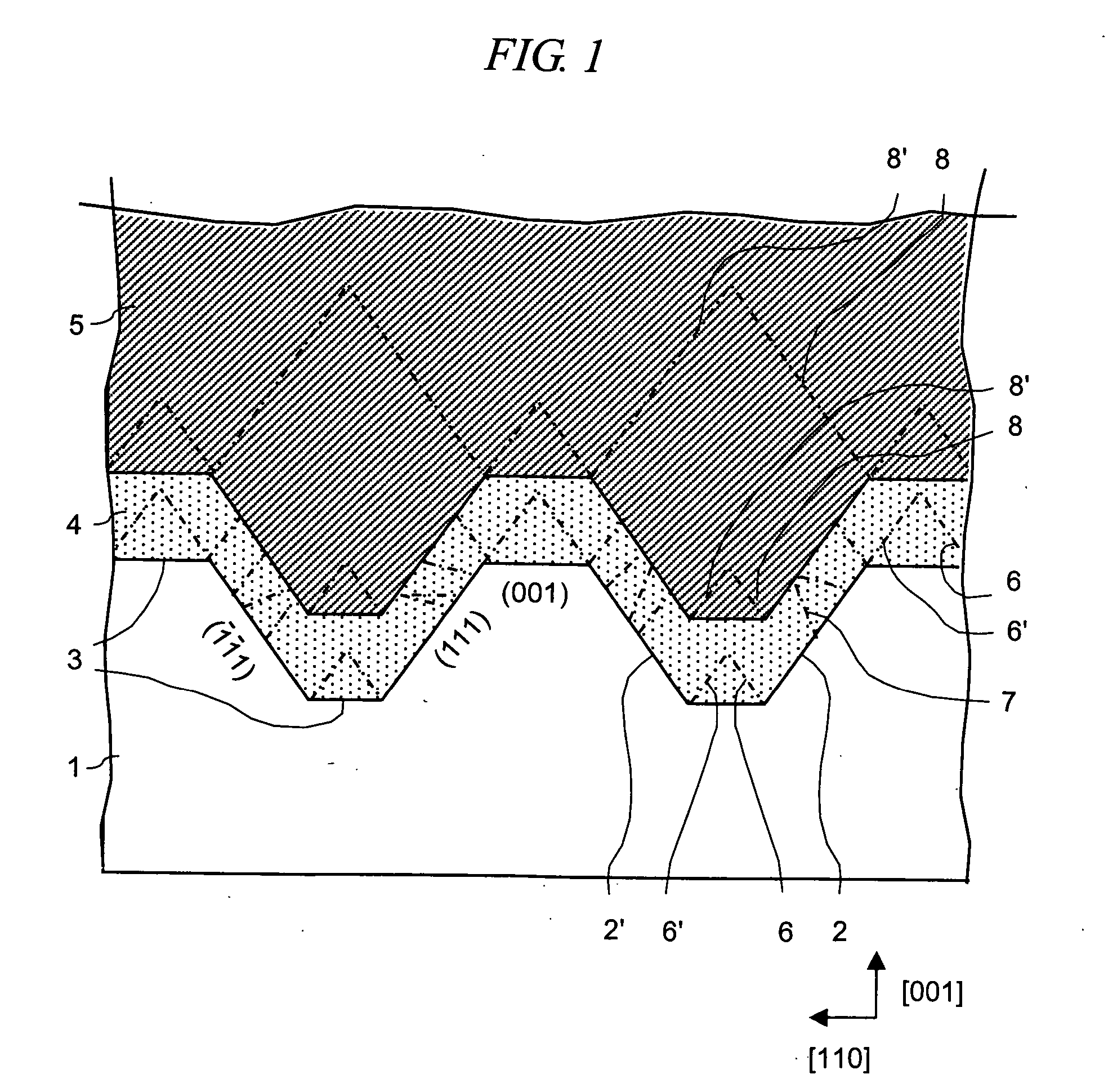

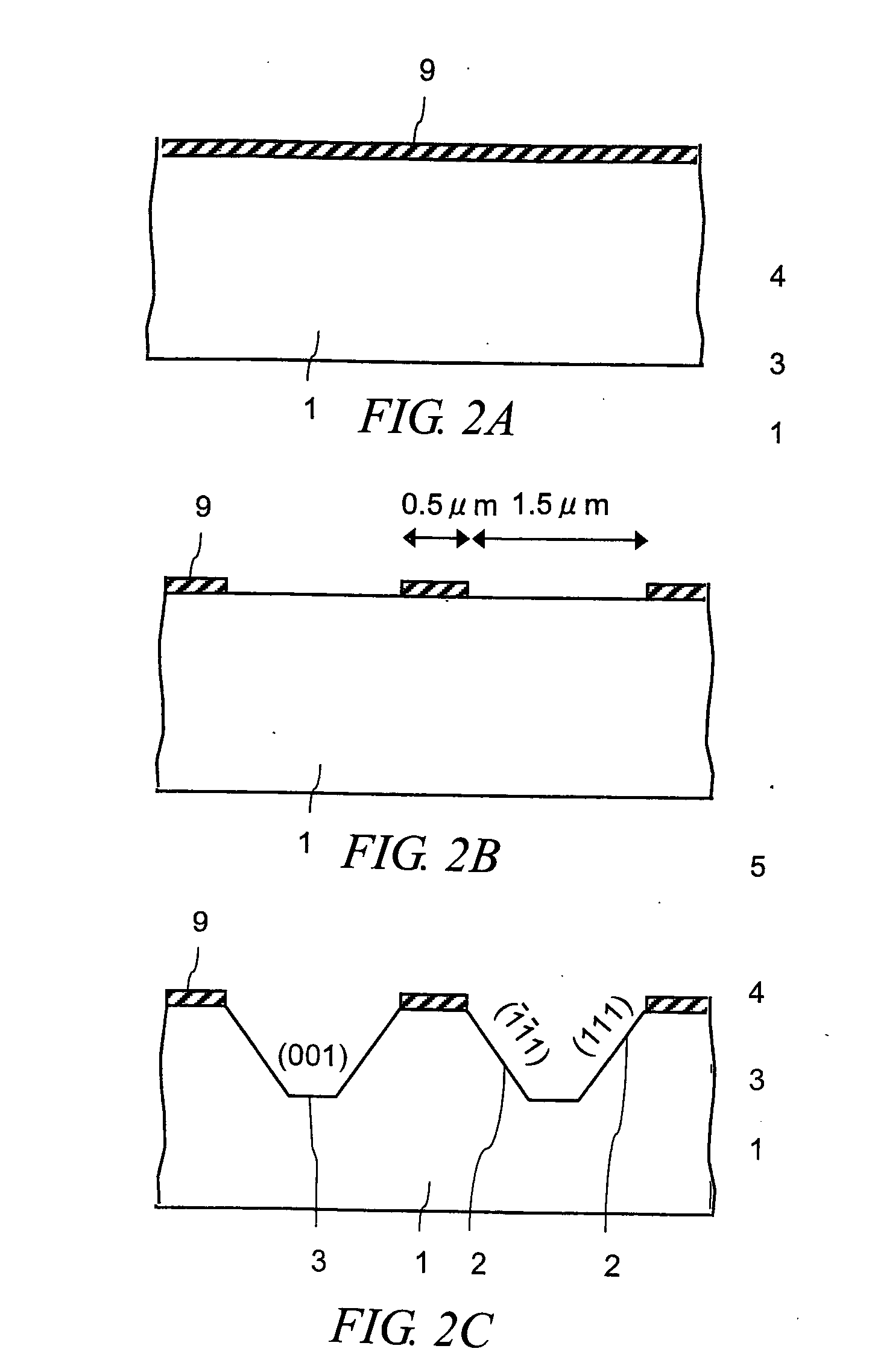

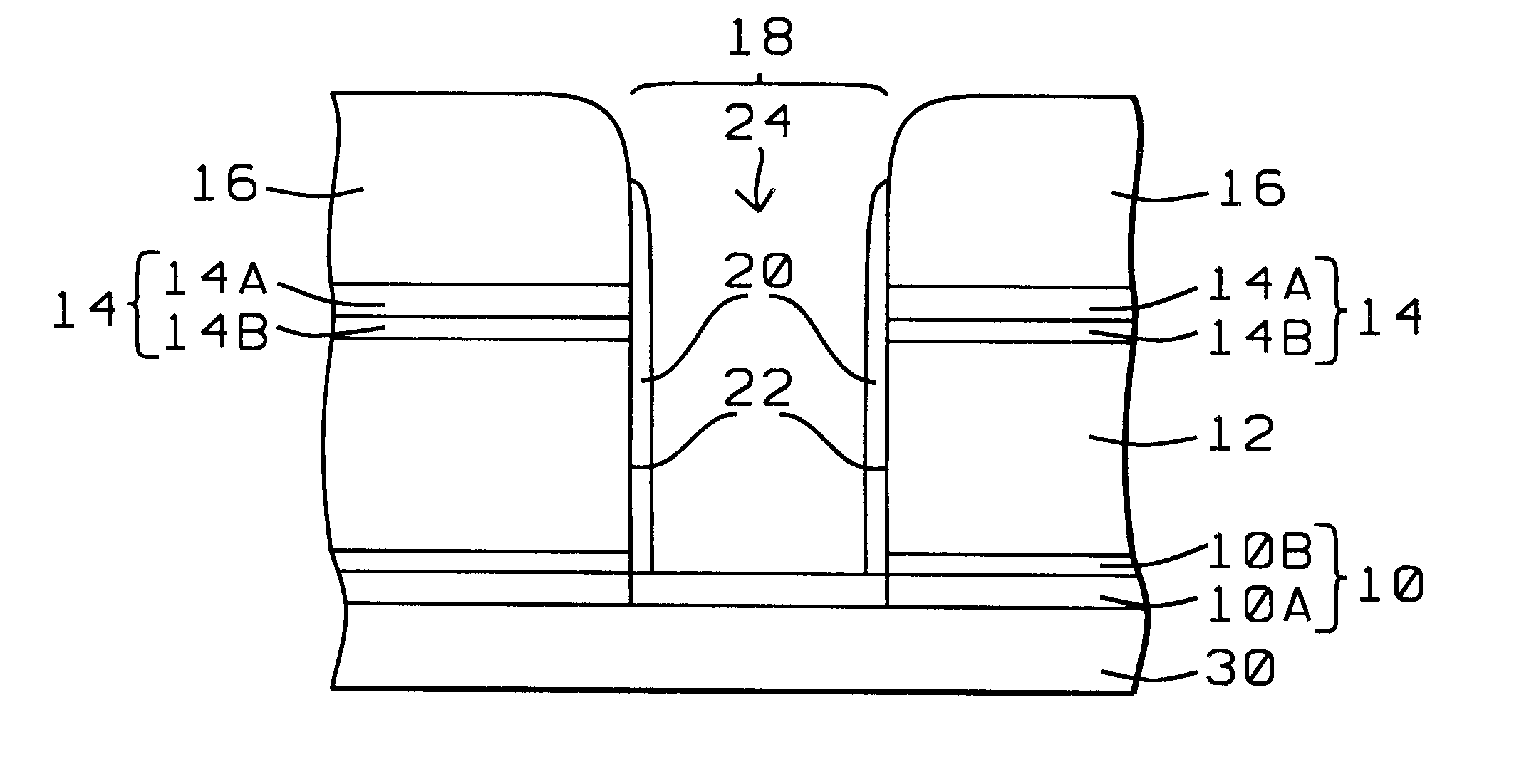

Semiconductor device and manufacturing method thereof

InactiveUS20060169987A1Quality improvementReduce defect densityOptical wave guidanceLaser detailsThreading dislocationsDevice material

A high quality silicon carbide (SiC) layer being substantially lower in threading dislocation density than a prior layer is formed on silicon (Si) substrate. A semiconductor device is fabricated in such a way that a semiconductor buffer layer containing Si in part and being higher in defect density than a Si substrate is formed on the Si substrate on the upper portion of which are formed a plurality of pairs of facets being mirror-symmetrical to the surface orientation of a semiconductor substrate, further on the top of the layer a SiC layer is sequentially formed.

Owner:HITACHI LTD

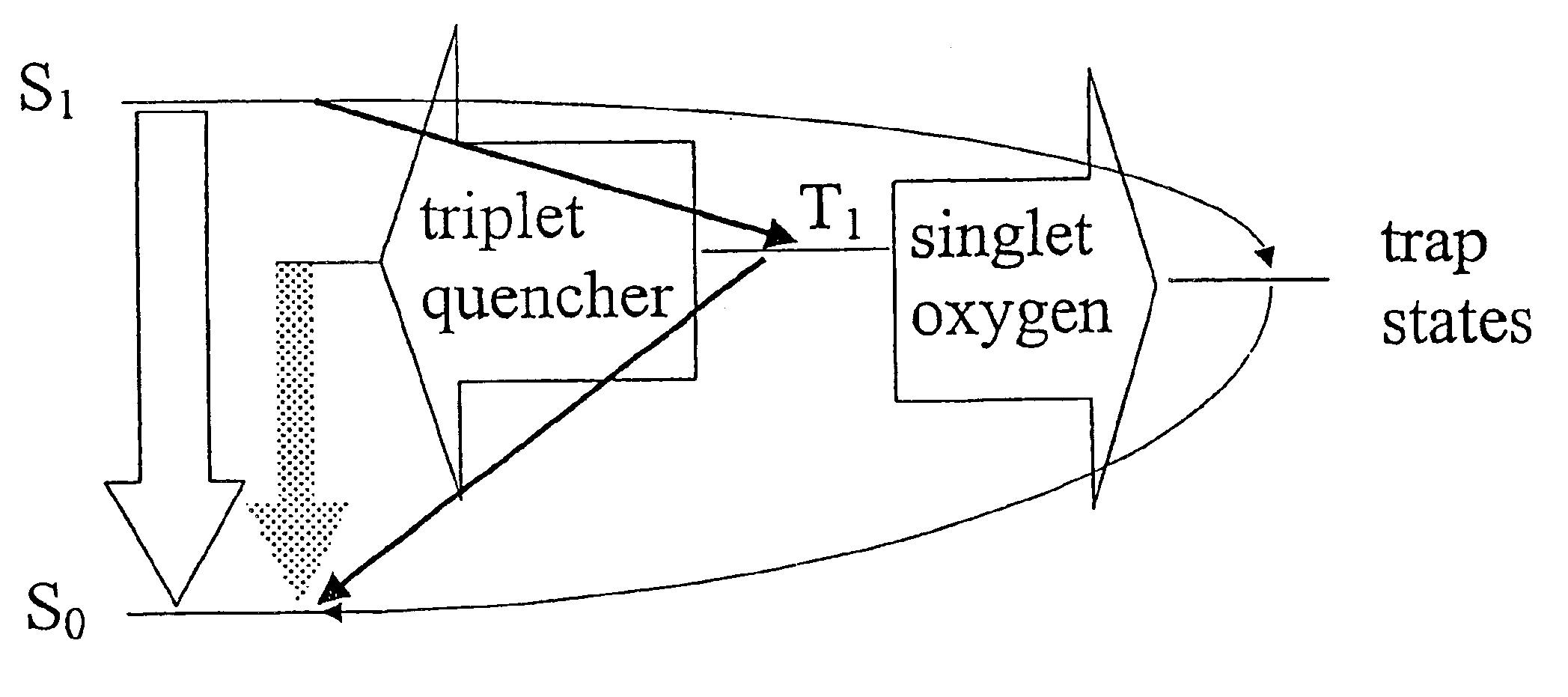

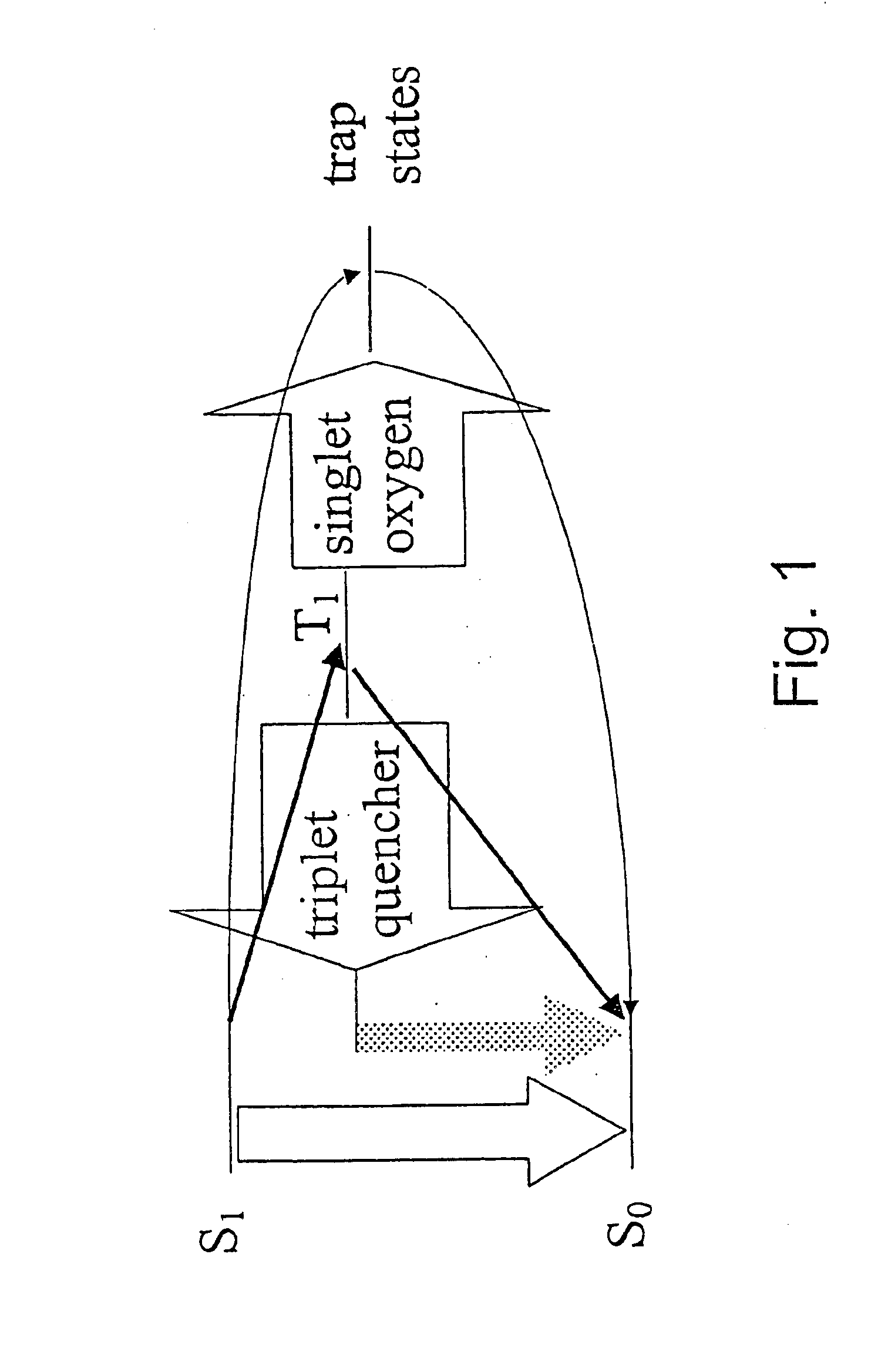

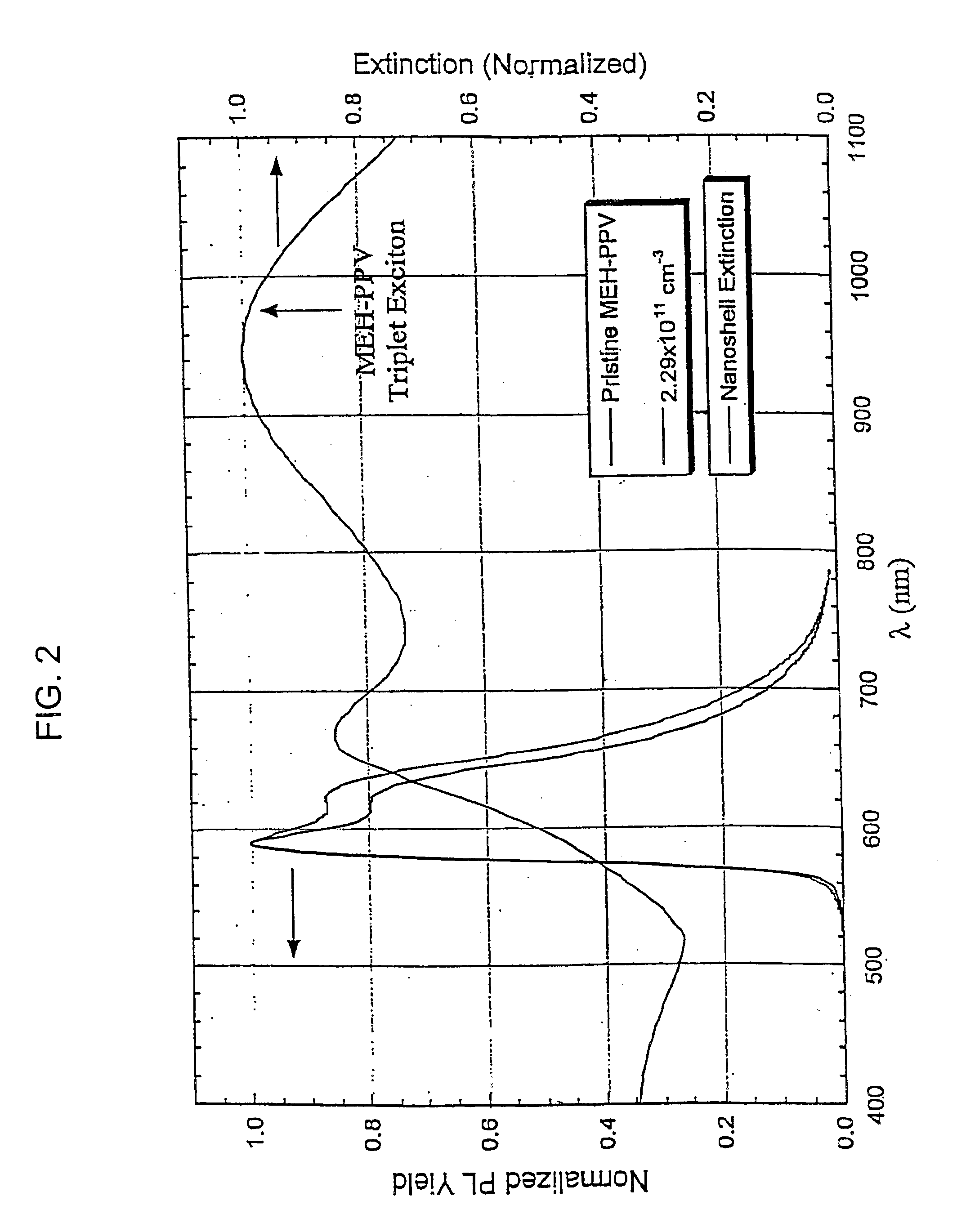

Use of metalnanoshells to impede the photo-oxidation of conjugated polymer

InactiveUS6852252B2Impede photo-oxidation processReduce degradationMaterial nanotechnologyDiffusing elementsPhoto-oxidation of polymersVolumetric Mass Density

The present invention relates to incorporating metal nanoshells specifically designed to interact with triplet excitons in polymers. By interacting with triplet excitons, the rate of photo-oxidation can be slowed and the density of luminescence-quenching traps can be reduced.

Owner:RICE UNIV

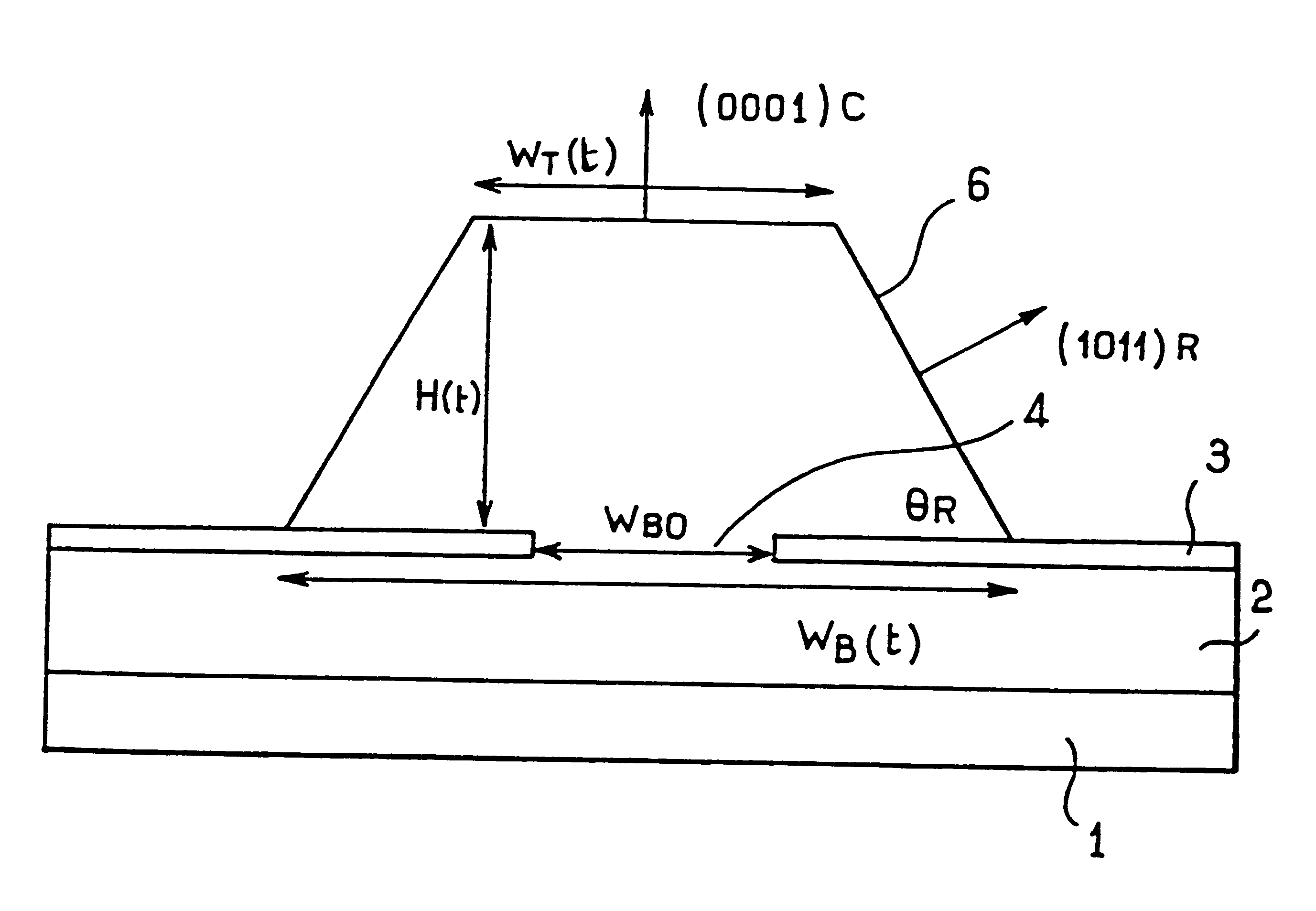

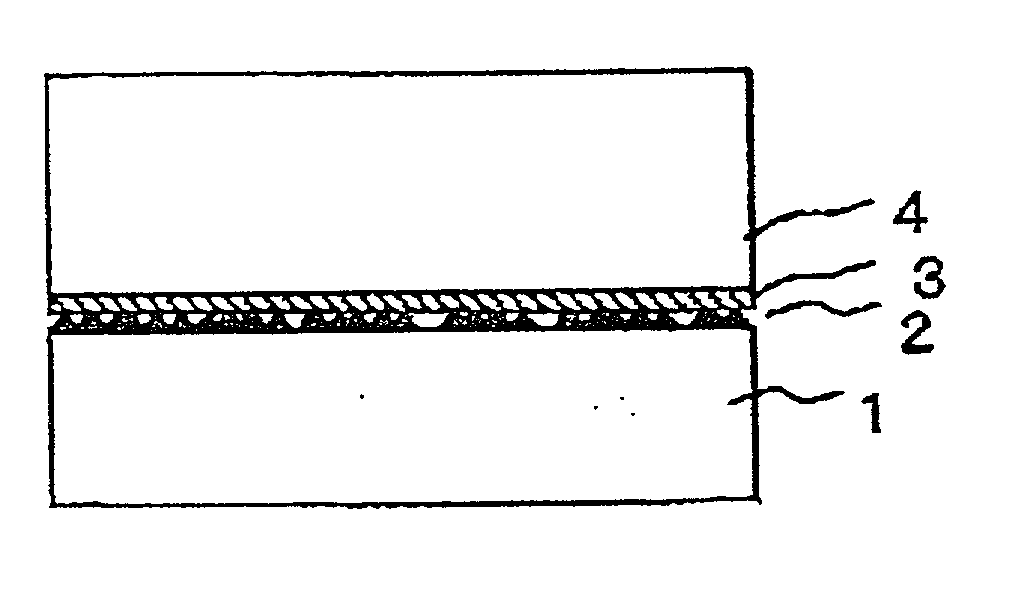

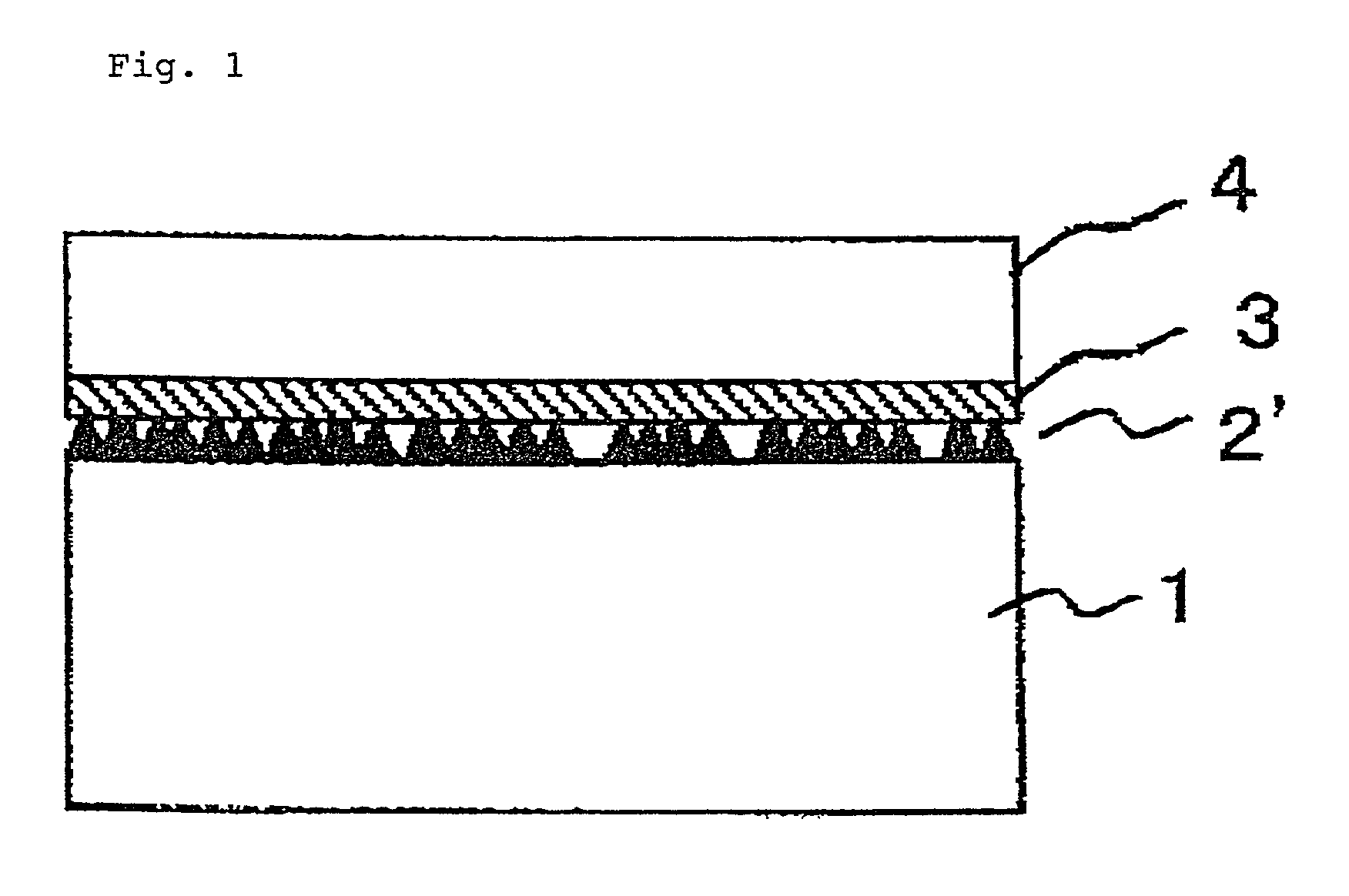

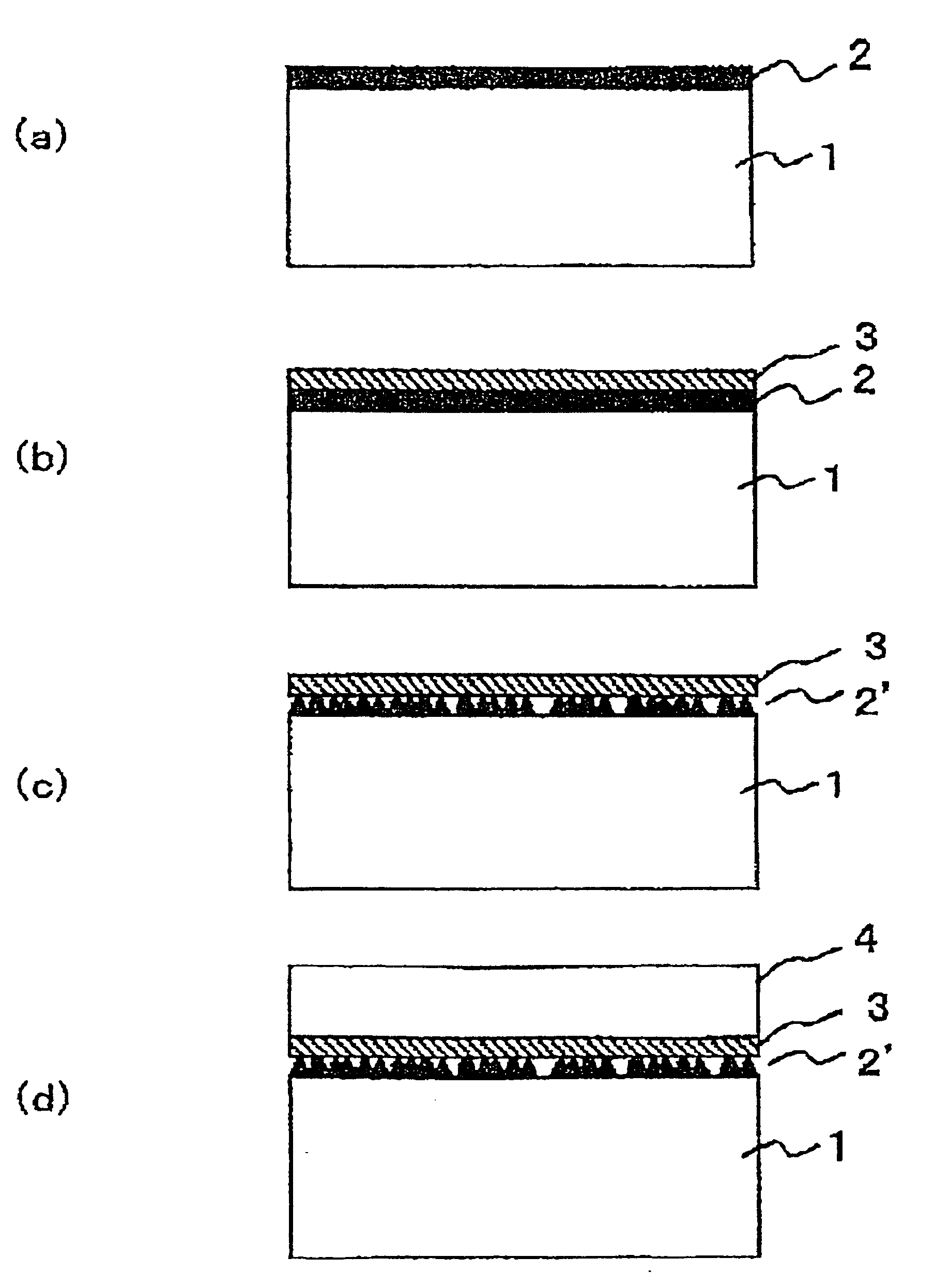

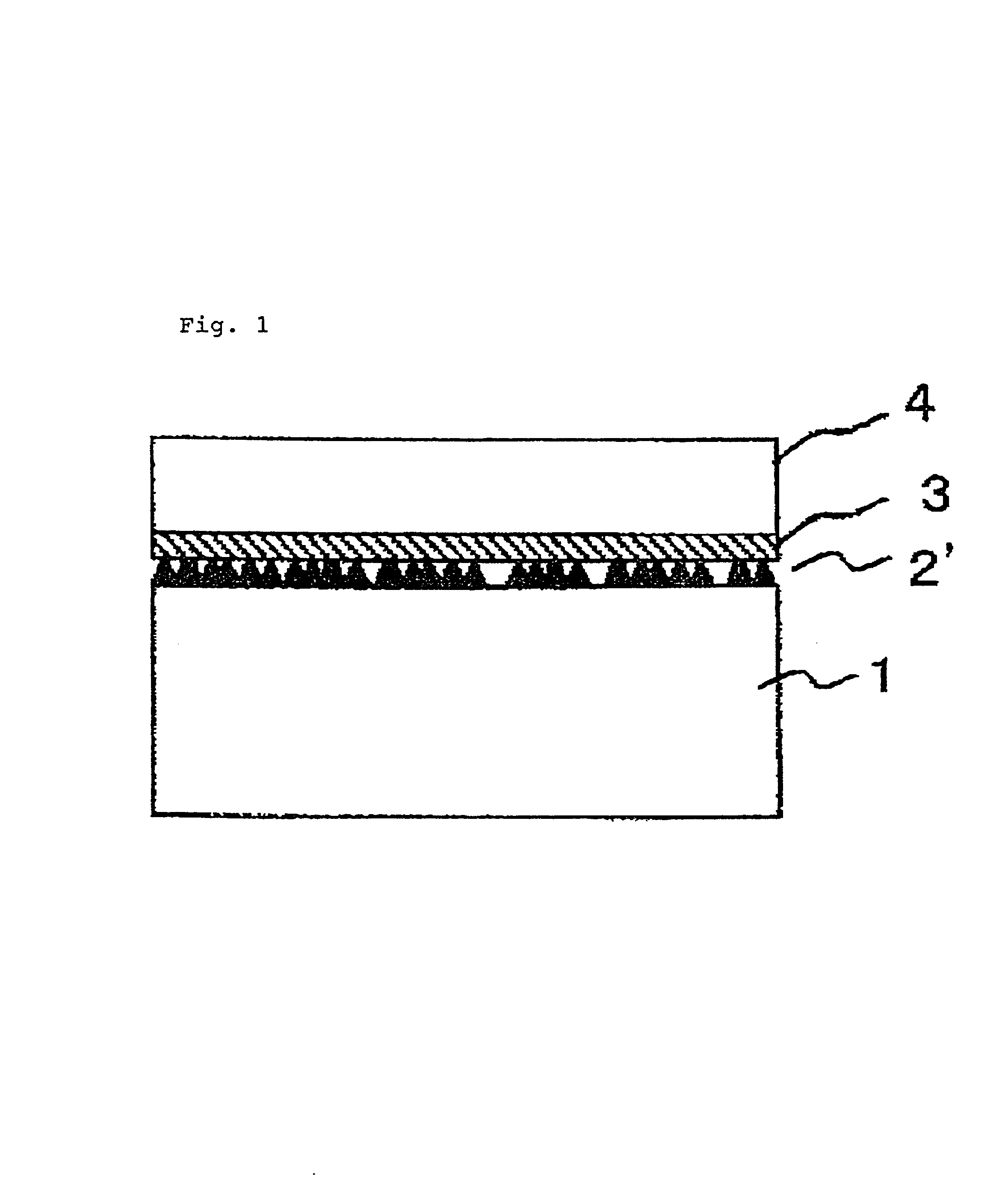

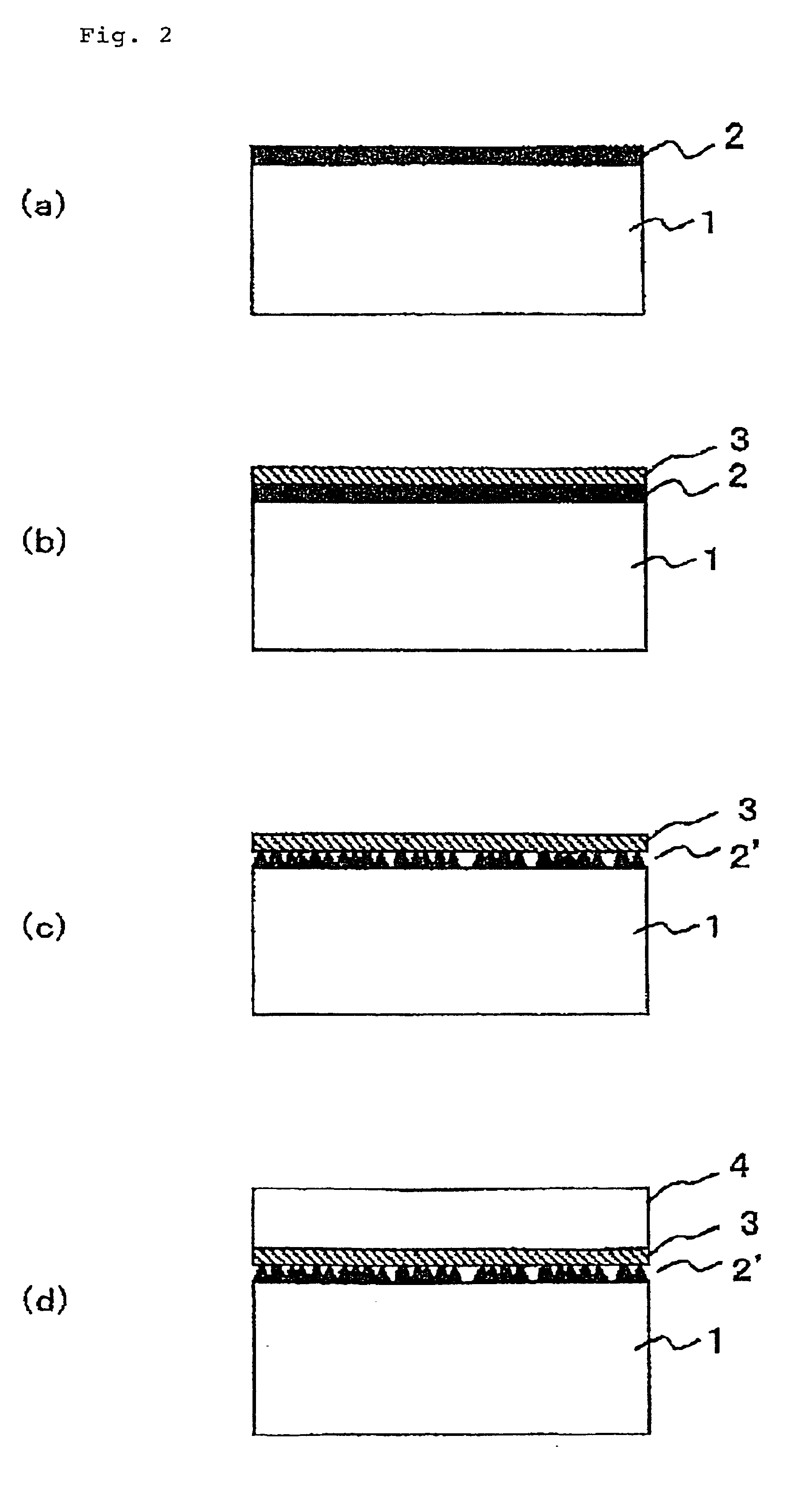

Semiconductor substrate made of group III nitride, and process for manufacture thereof

InactiveUS20020197825A1Reduce defect densityImprove crystal qualityPolycrystalline material growthSemiconductor/solid-state device manufacturingHydrogen compoundsTitanium

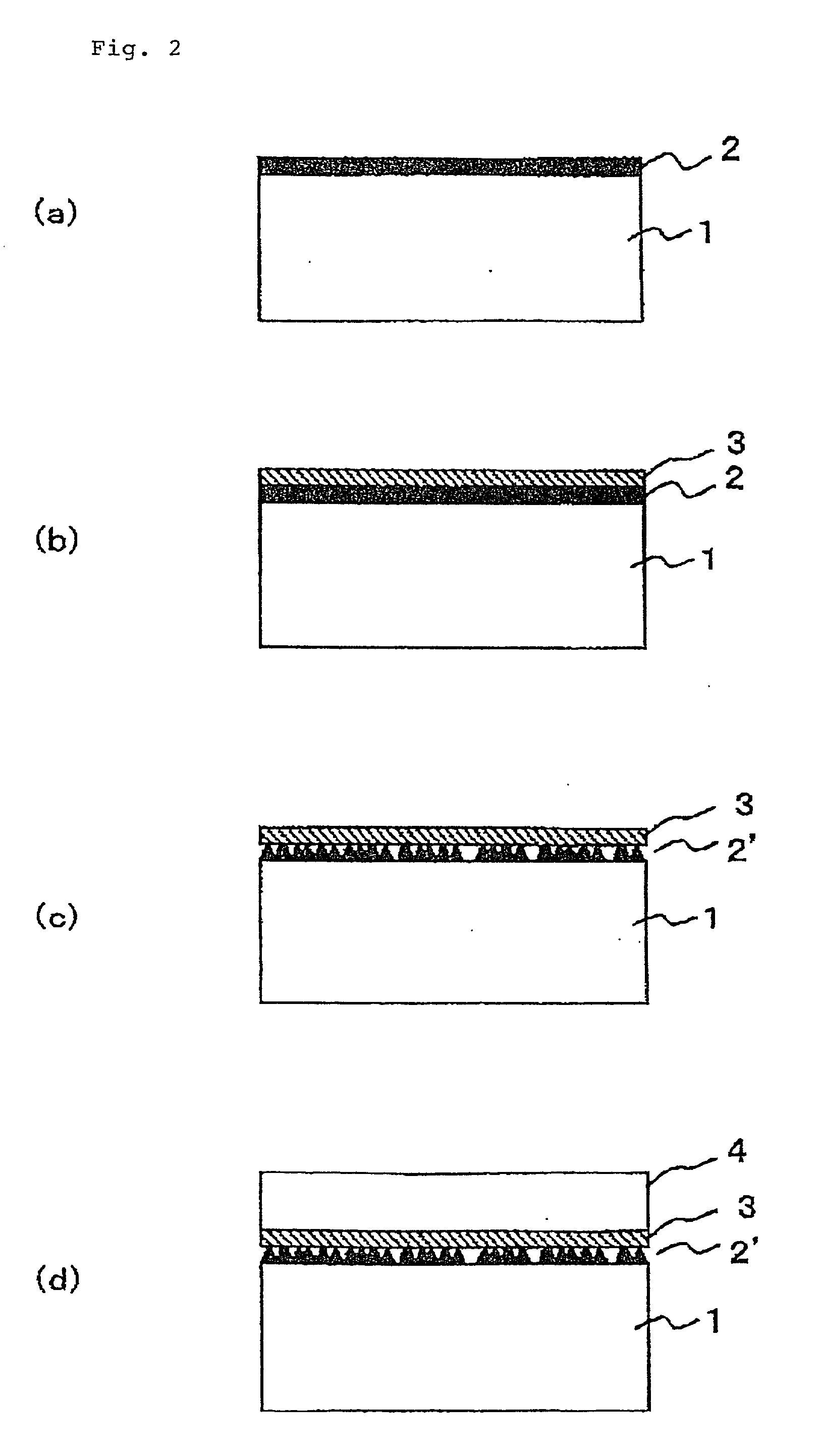

To provide a semiconductor substrate of a group III nitride with low defect density and little warp, this invention provides a process comprising such steps of: forming a GaN layer 2 on a sapphire substrate 1 of the C face ((0001) face); forming a titanium film 3 thereon; heat-treating the substrate in an atmosphere containing hydrogen gas or a gas of a compound containing hydrogen to form voids in the GaN layer 2; and thereafter forming a GaN layer 4 on the GaN layer 2'.

Owner:SUMITOMO CHEM CO LTD

Low defect Si:C layer with retrograde carbon profile

ActiveUS7696000B2High bulk carbon concentrationReduce defect densitySolid-state devicesSemiconductor/solid-state device manufacturingHigh concentrationSemiconductor structure

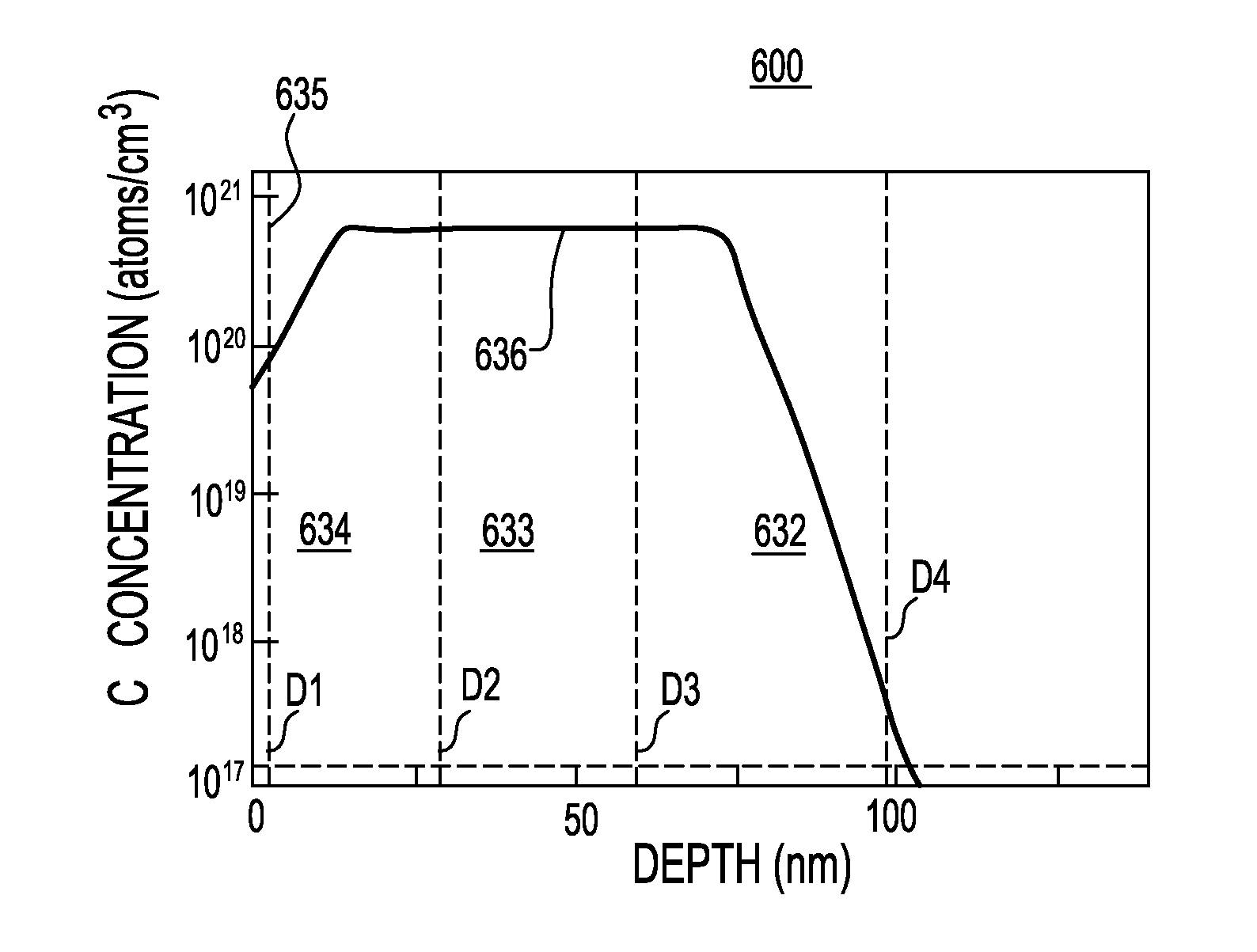

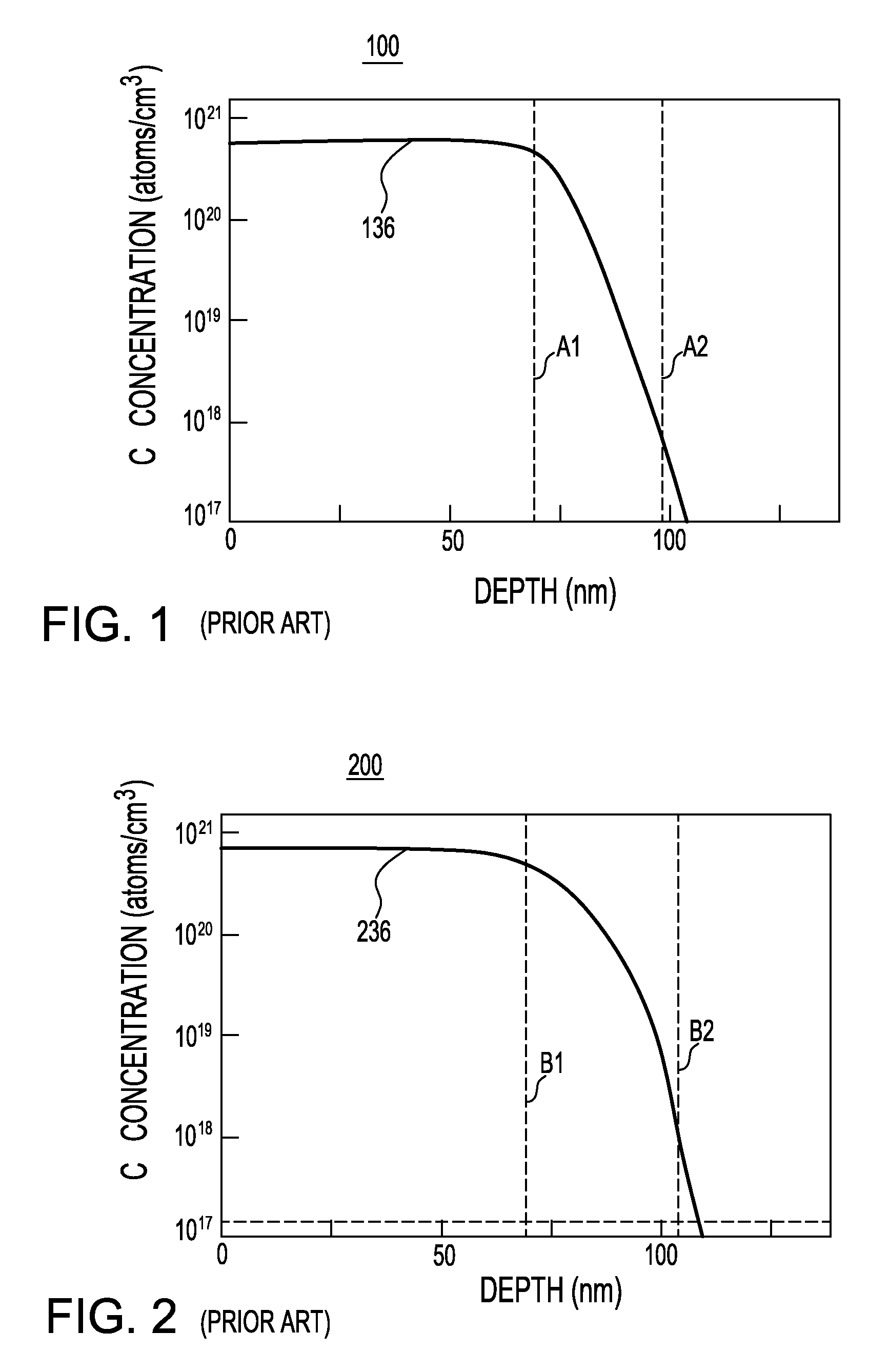

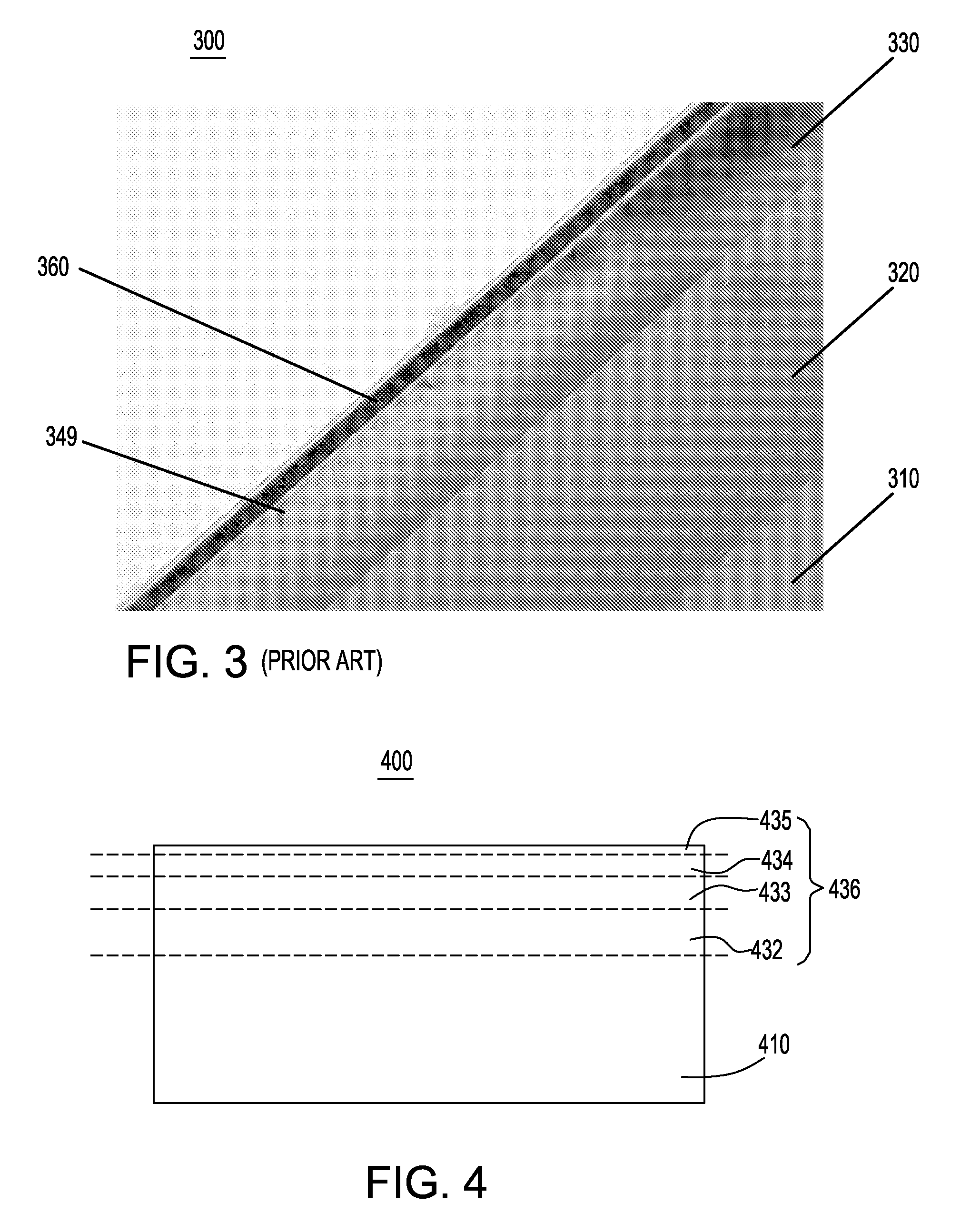

Formation of carbon-substituted single crystal silicon layer is prone to generation of large number of defects especially at high carbon concentration. The present invention provides structures and methods for providing low defect carbon-substituted single crystal silicon layer even for high concentration of carbon in the silicon. According to the present invention, the active retrograde profile in the carbon implantation reduces the defect density in the carbon-substituted single crystal silicon layer obtained after a solid phase epitaxy. This enables the formation of semiconductor structures with compressive stress and low defect density. When applied to semiconductor transistors, the present invention enables N-type field effect transistors with enhanced electron mobility through the tensile stress that is present into the channel.

Owner:GLOBALFOUNDRIES U S INC

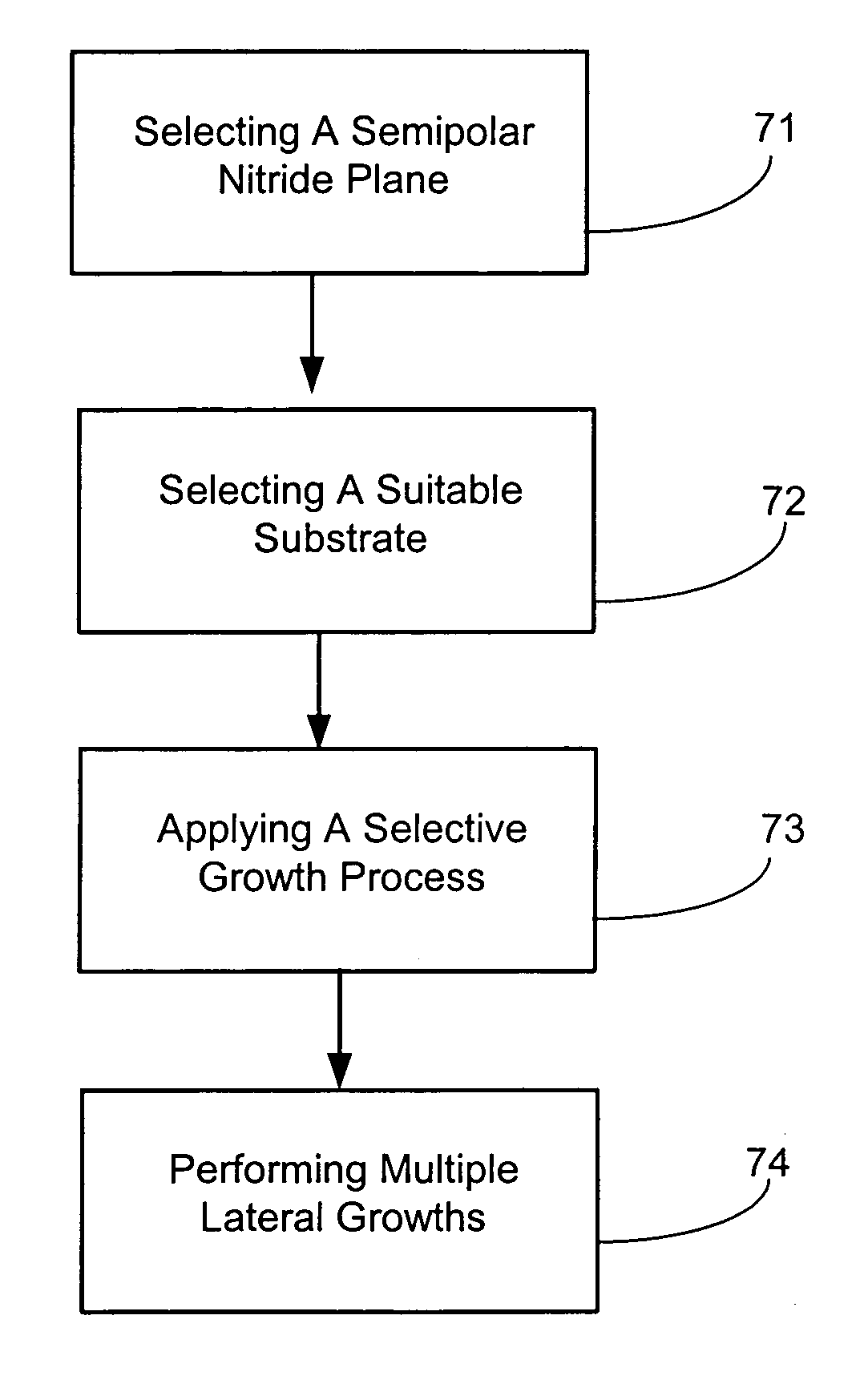

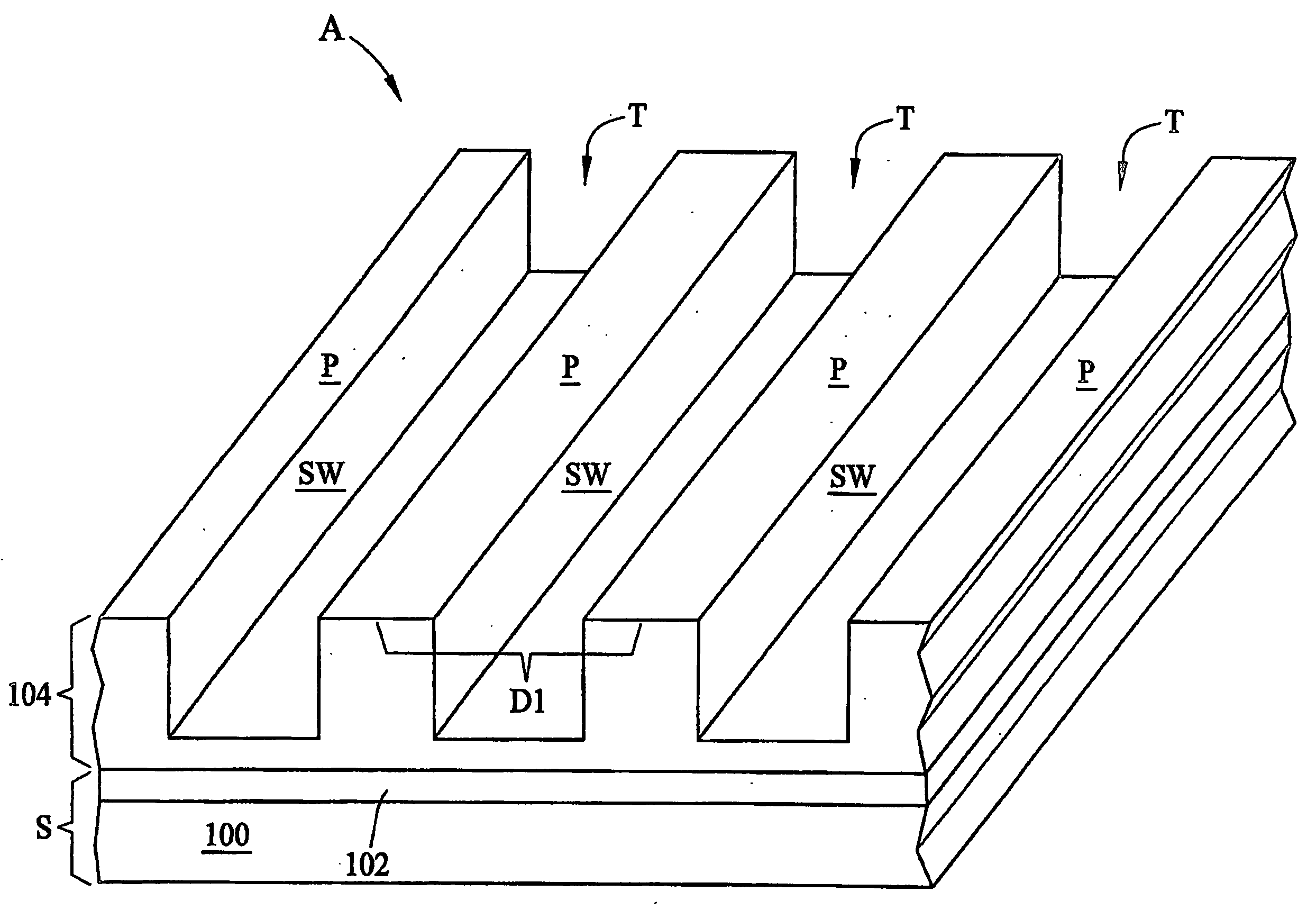

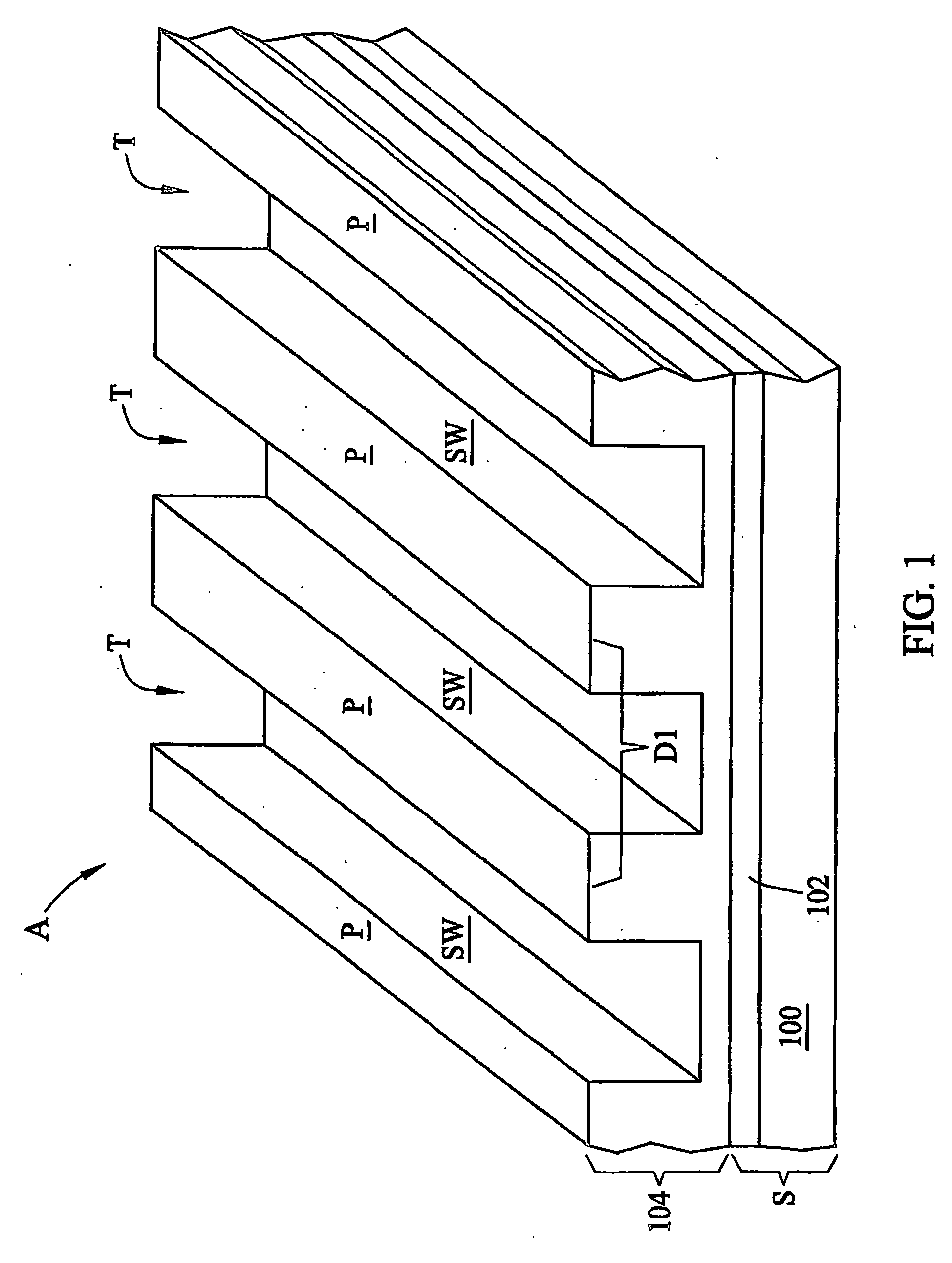

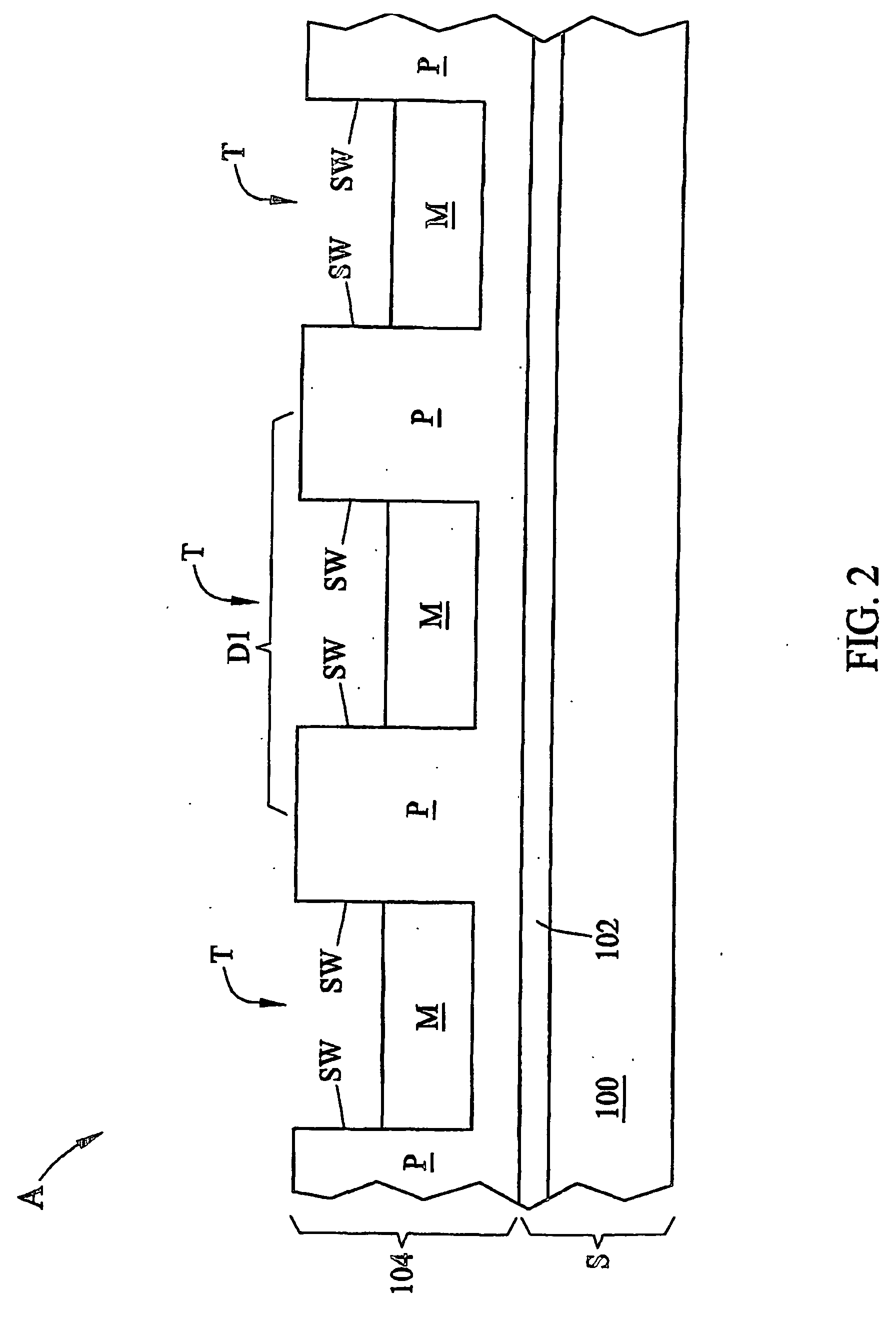

Lateral growth method for defect reduction of semipolar nitride films

ActiveUS20070015345A1Reduce defect densityHigh performancePolycrystalline material growthSemiconductor/solid-state device manufacturingCantileverEpitaxy

A lateral growth method for defect reduction of semipolar nitride films. The process steps include selecting a semipolar nitride plane and composition, selecting a suitable substrate for growth of the semipolar nitride plane and composition, and applying a selective growth process in which the semipolar nitride nucleates on some areas of the substrate at the exclusion of other areas of the substrate, wherein the selective growth process includes lateral growth of nitride material by a lateral epitaxial overgrowth (LEO), sidewall lateral epitaxial overgrowth (SLEO), cantilever epitaxy or nanomasking.

Owner:JAPAN SCI & TECH CORP

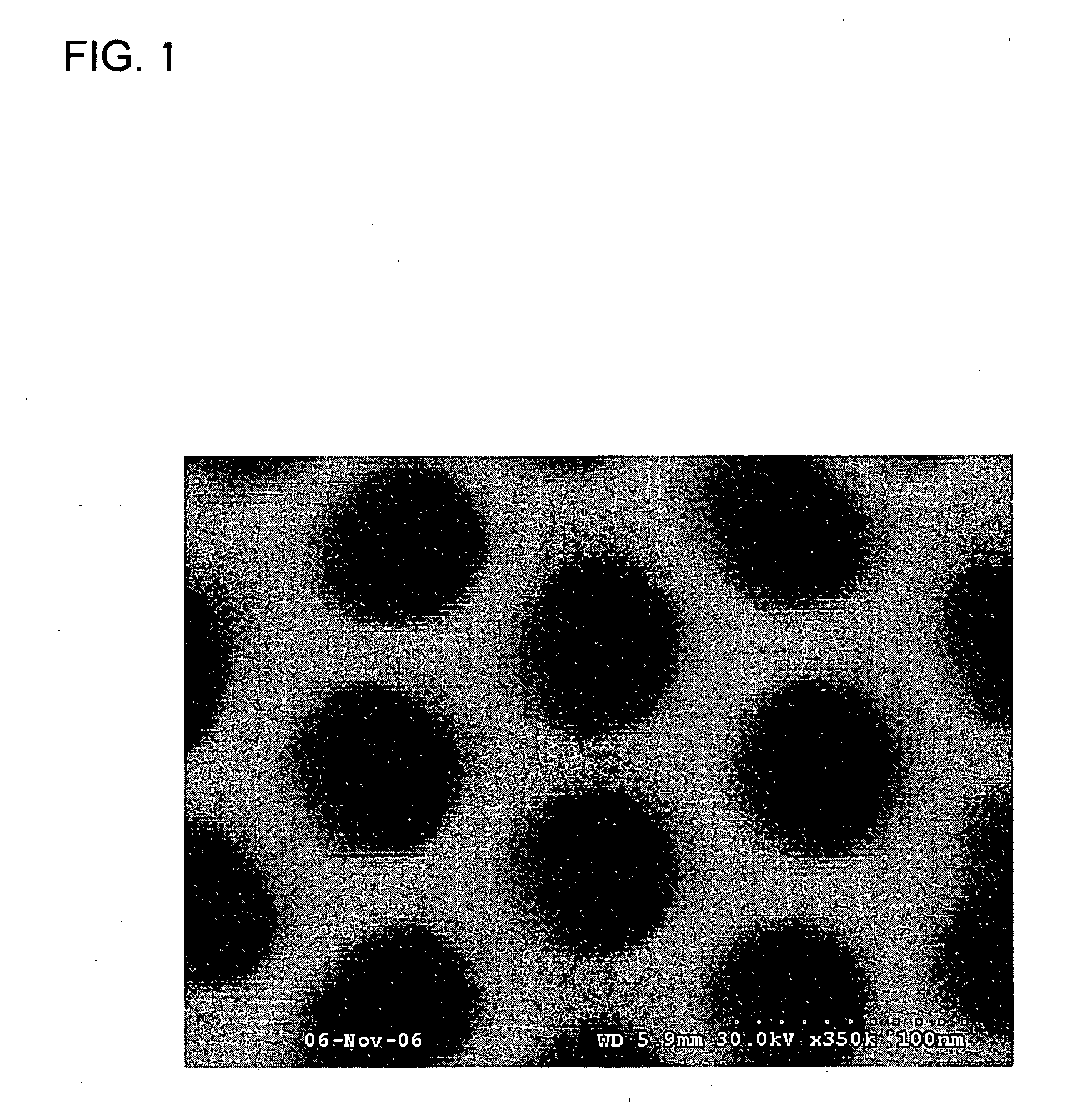

Methods for nanoscale structures from optical lithography and subsequent lateral growth

InactiveUS20070029643A1Reduce defect densityReduce dislocationMaterial nanotechnologyDecorative surface effectsLithographic artistPhotonics

Methods, and structures formed thereby, are disclosed for forming laterally grown structures with nanoscale dimensions from nanoscale arrays which can be patterned from nanoscale lithography. The structures and methods disclosed herein have applications with electronic, photonic, molecular electronic, spintronic, microfluidic or nano-mechanical (NEMS) technologies. The spacing between laterally grown structures can be a nanoscale measurement, for example with a spacing distance which can be approximately 1-50 nm, and more particularly can be from approximately 3-5 nm. This spacing is appropriate for integration of molecular electronic devices. The pitch between posts can be less than the average distance characteristic between dislocation defects for example in GaN (ρ=1010 / cm2→d=0.1 μm) resulting an overall reduction in defect density. Large-scale integration of nanoscale devices can be achieved using lithographic equipment that is orders of magnitude less expensive that that used for advanced lithographic techniques, such as electron beam lithography.

Owner:NORTH CAROLINA STATE UNIV

Semiconductor substrate made of group III nitride, and process for manufacture thereof

InactiveUS6924159B2Reduce defect densityImprove crystal qualityPolycrystalline material growthSemiconductor/solid-state device manufacturingNitride semiconductorsSapphire substrate

To provide a semiconductor substrate of a group III nitride with low defect density and little warp, this invention provides a process comprising such steps of:forming a GaN layer 2 on a sapphire substrate 1 of the C face ((0001) face); forming a titanium film 3 thereon; heat-treating the substrate in an atmosphere containing hydrogen gas or a gas of a compound containing hydrogen to form voids in the GaN layer 2; and thereafter forming a GaN layer 4 on the GaN layer 2′.

Owner:SUMITOMO CHEM CO LTD

Growth of planar reduced dislocation density m-plane gallium nitride by hydride vapor phase epitaxy

InactiveUS7208393B2Reduce defect densityPolycrystalline material growthSemiconductor/solid-state device manufacturingLateral overgrowthGallium nitride

A method of growing highly planar, fully transparent and specular m-plane gallium nitride (GaN) films. The method provides for a significant reduction in structural defect densities via a lateral overgrowth technique. High quality, uniform, thick m-plane GaN films are produced for use as substrates for polarization-free device growth.

Owner:JAPAN SCI & TECH CORP

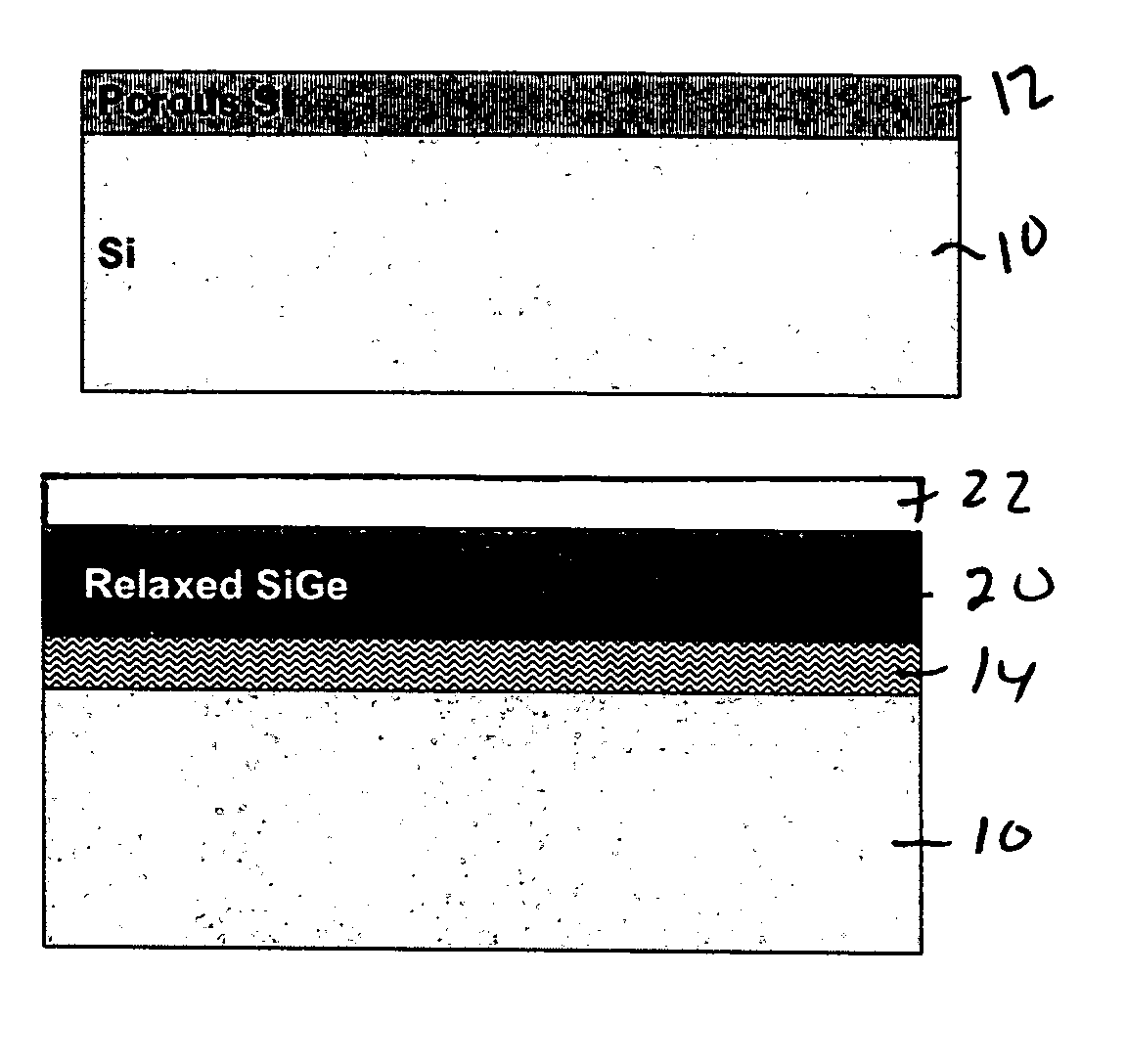

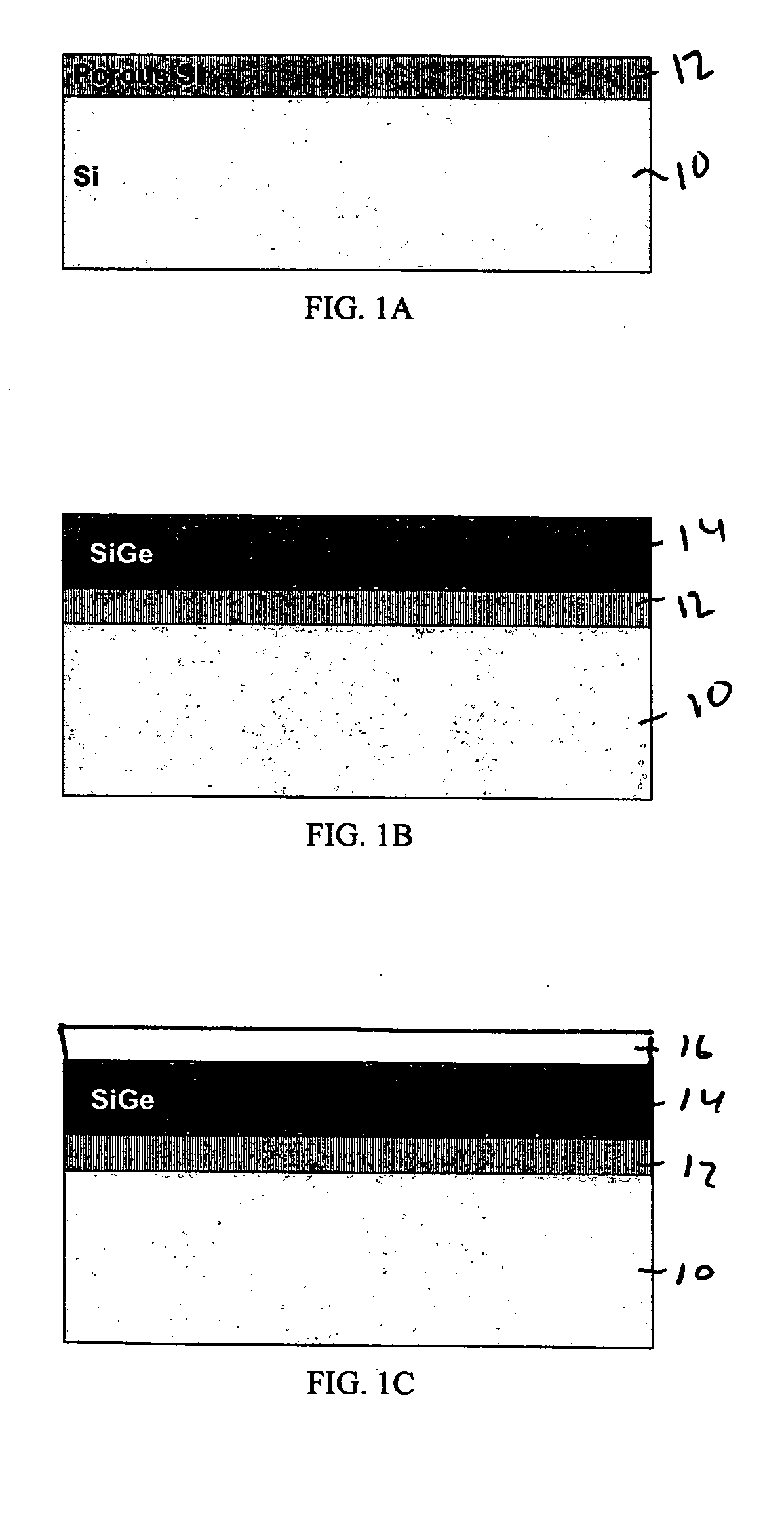

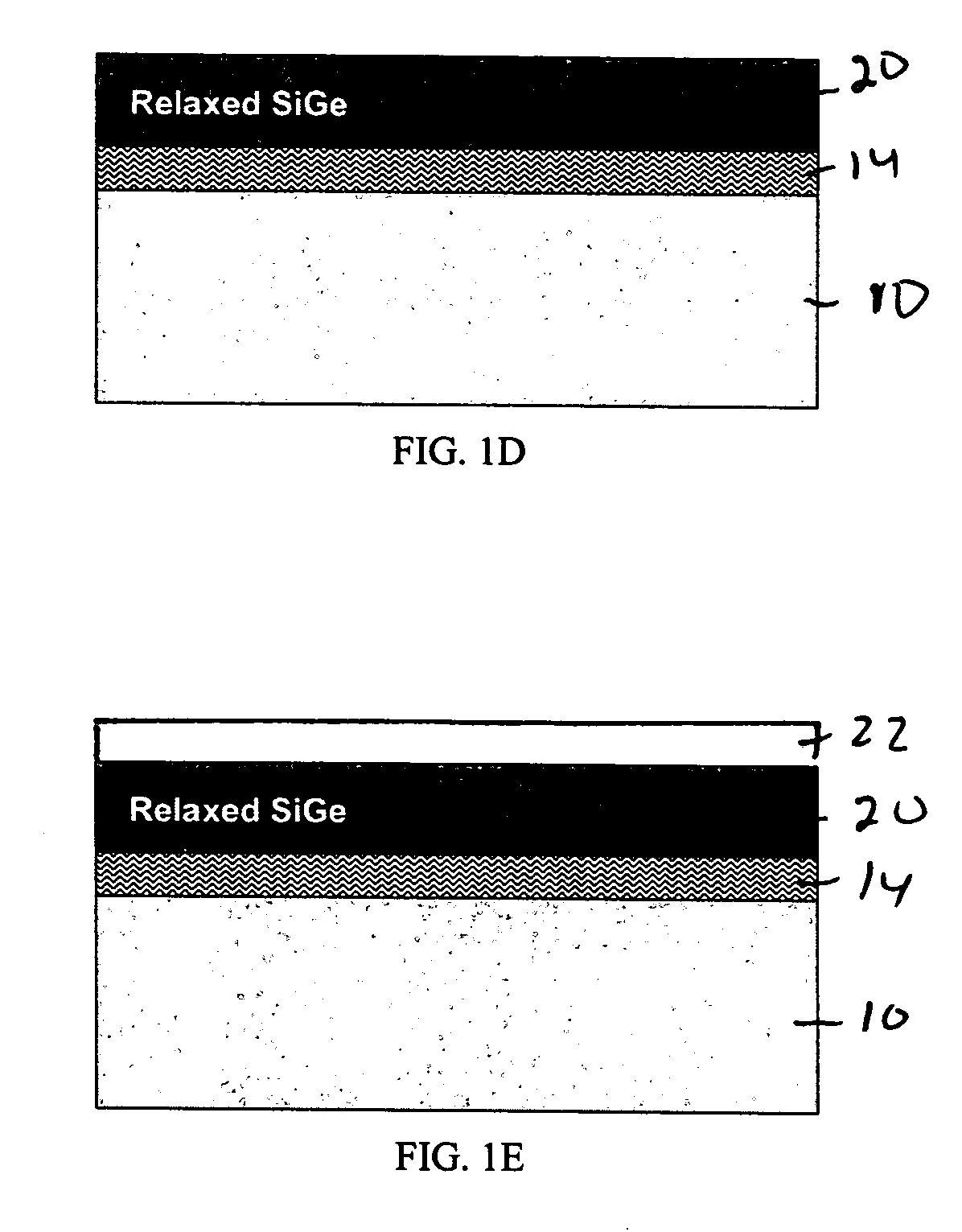

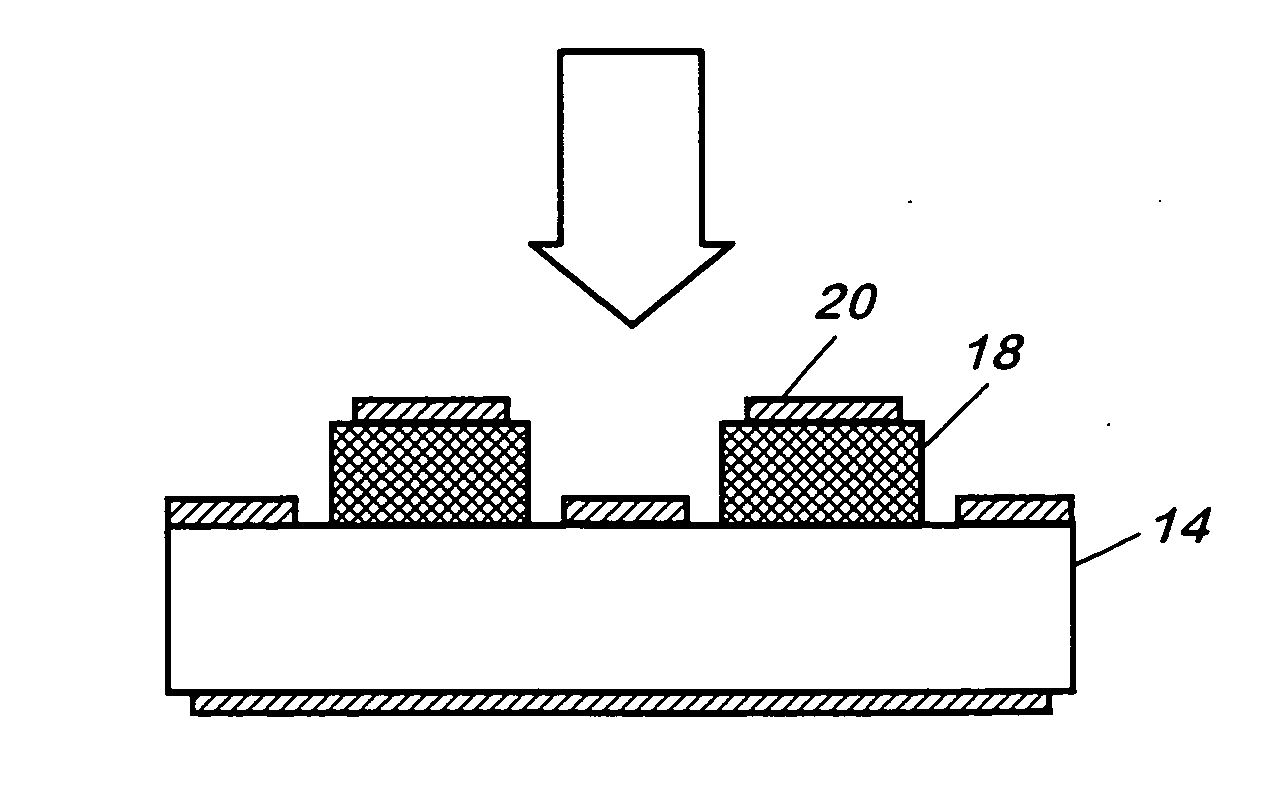

Method of forming high-quality relaxed SiGe alloy layers on bulk Si substrates

InactiveUS20050221591A1Easy to relaxQuality improvementFrom solid stateSemiconductor/solid-state device manufacturingPorous layerAlloy

A method of forming a high-quality relaxed SiGe alloy layer on a bulk Si-containing substrate is provided. The method of the present invention includes growing a strained SiGe alloy layer on a Si-containing substrate that has a porous Si-containing layer at or near the surface of the Si-containing substrate. The porous layer is formed by an electrolytic anodization process. The pores create free volume below the strained SiGe layer which can serve to accommodate strain relaxation during SiGe deposition or a subsequent heating step. The subsequent heating step is optional and is performed to further increase the relaxation of the SiGe alloy layer. The buried porous structure allows for a unique relaxation mechanism compared to prior art methods.

Owner:GLOBALFOUNDRIES INC

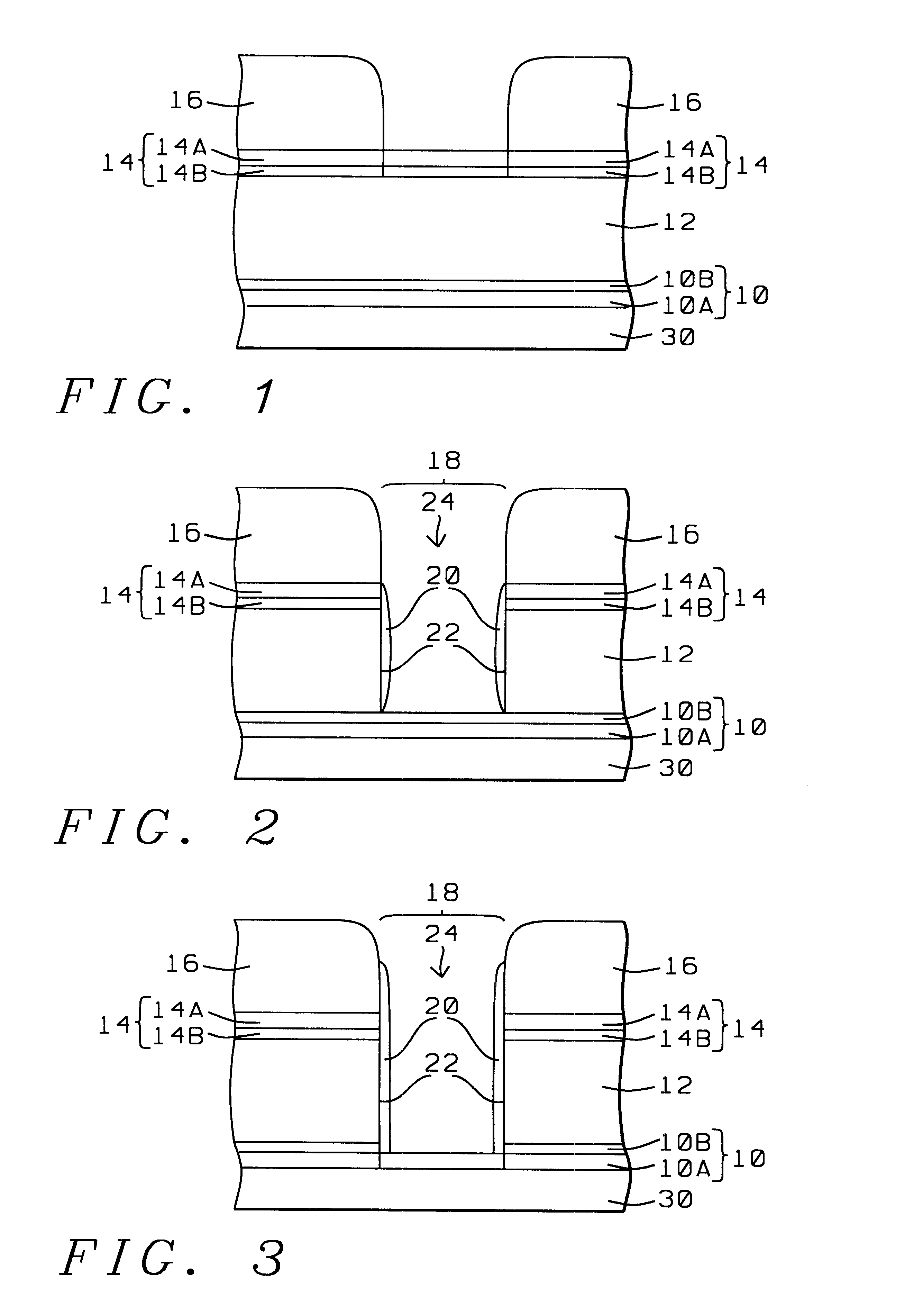

Technique for perfecting the active regions of wide bandgap semiconductor nitride devices

InactiveUS20050164475A1Enhanced thicknessLow reverse bias leakage currentPolycrystalline material growthFrom solid stateEngineeringWideband

This invention pertains to e lectronic / optoelectronic devices with reduced extended defects and to a method for making it. The method includes the steps of depositing a dielectric thin film mask material on a semiconductor substrate surface; patterning the mask material to form openings therein extending to the substrate surface; growing active material in the openings; removing the mask material to form the device with reduced extended defect density; and depositing electrical contacts on the device.

Owner:THE UNITED STATES OF AMERICA AS REPRESENTED BY THE SECRETARY OF THE NAVY

Group III nitride semiconductor substrate and its manufacturing method

InactiveUS20060046325A1Reduce defect densityLittle warpingPolycrystalline material growthSemiconductor/solid-state device manufacturingNitrationTitanium

The present invention provides a group III nitride semiconductor substrate with low defect density as well as small warp and a process for producing the same; for instance, the process according to the present invention comprises the following series of steps of: forming a metallic Ti film 63 on a sapphire substrate 61, followed by treatment of nitration to convert it into a TiN film 64 having fine pores; thereafter growing a HVPE-GaN layer 66 thereon; forming voids 65 in the HVPE-GaN layer 66 by means of effects of the metallic Ti film 63 and the TiN film 64; and peeling the sapphire substrate 61 from the region of the voids 65 to remove it therefrom.

Owner:SUMITOMO CHEM CO LTD

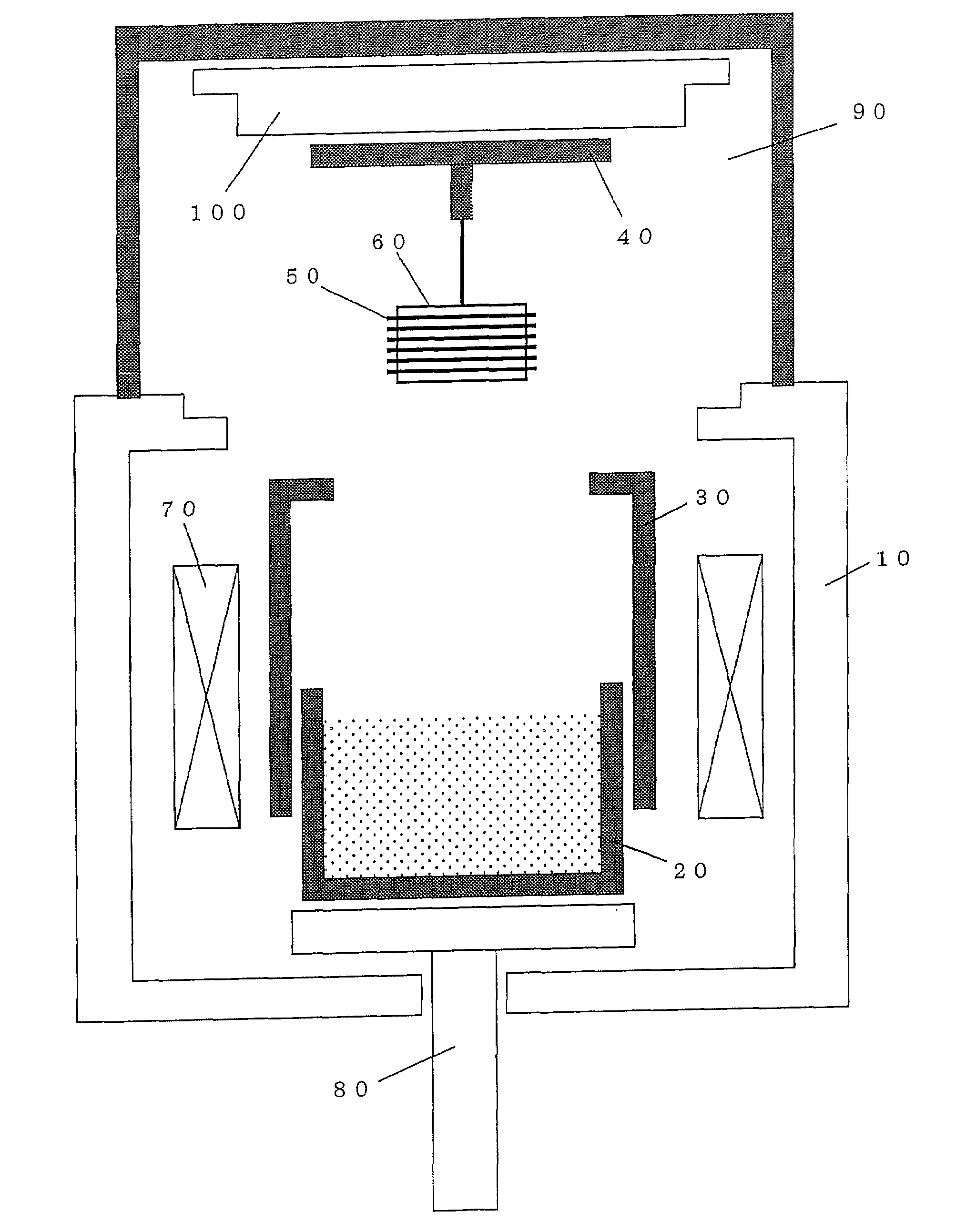

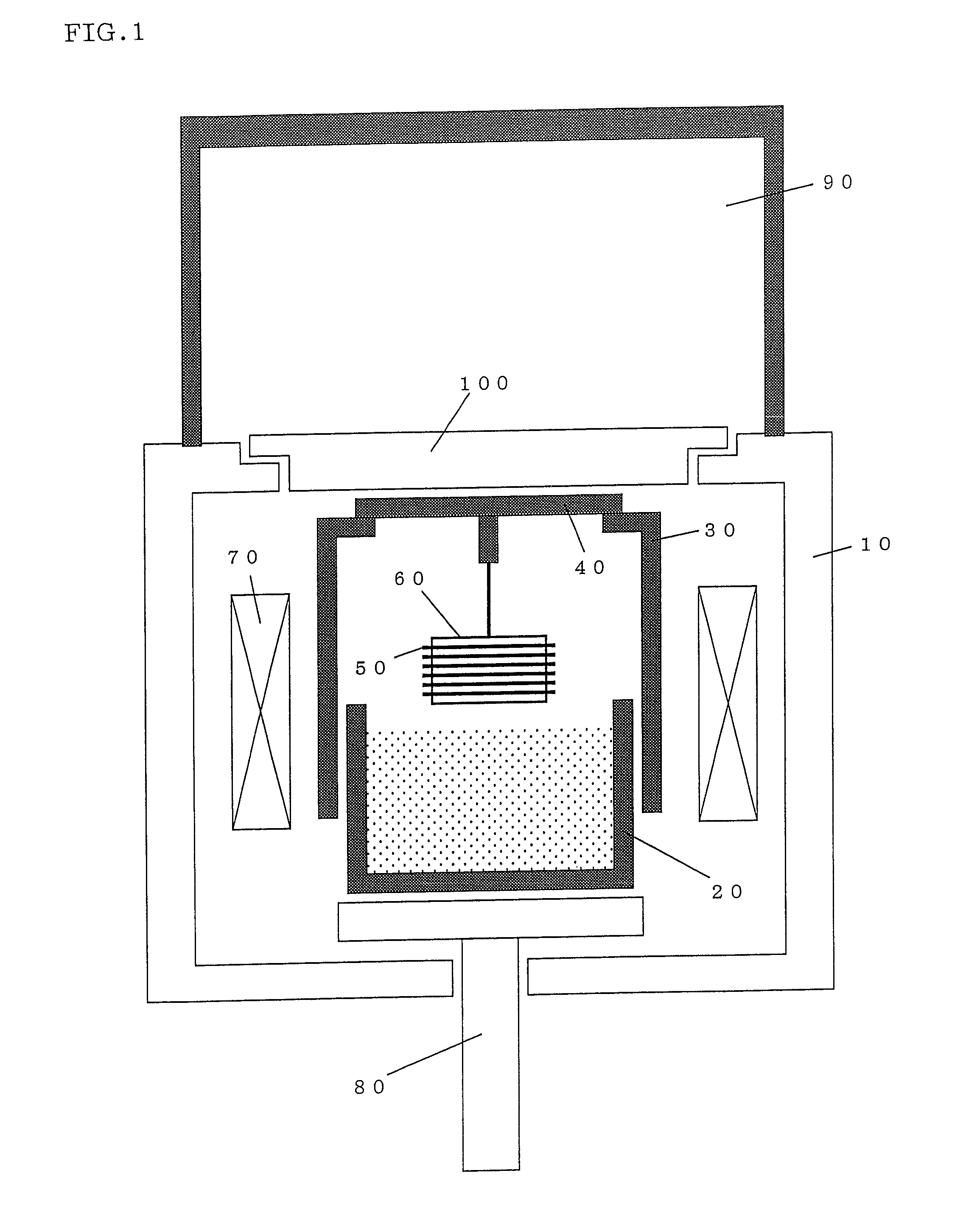

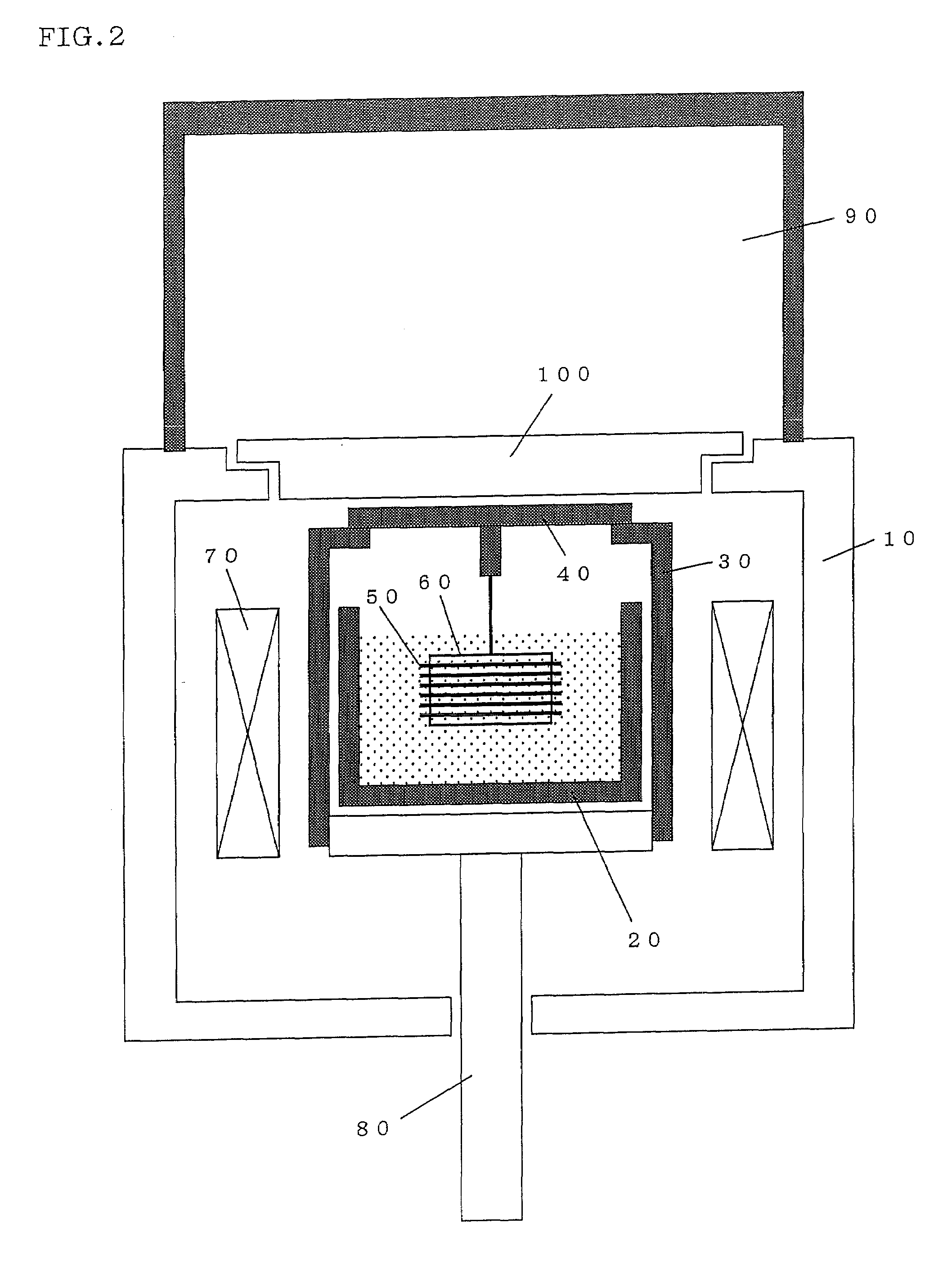

Method and apparatus for manufacturing group iii nitride crystals

InactiveUS20070215033A1Reduce defect densityAchieve mass productionPolycrystalline material growthFrom normal temperature solutionsAlkaline earth metalNitrogen

There is provided a group III nitride crystal growth method capable of obtaining a material which is a GaN substrate of low defect density capable of being used as a power semiconductor substrate and in which characteristics of n-type and p-type requested for formation of transistor or the like. A growth method of group III nitride crystals includes: forming a mixed melt containing at least group III element and a flux formed of at least one selected from the group consisting of-alkaline metal and alkaline earth metal, in a reaction vessel; and growing group III nitride crystals from the mixed melt and a substance containing at least nitrogen, wherein after immersing a plurality of seed crystal substrates placed in an upper part of the reaction vessel in which the mixed melt is formed, into the mixed melt to cause crystal growth, the plurality of seed crystal substrates are pulled up above the mixed melt.

Owner:NGK INSULATORS LTD

Dry clean method instead of traditional wet clean after metal etch

InactiveUS6526996B1Increase plasma densityIncrease ion accelerationDecorative surface effectsSemiconductor/solid-state device manufacturingChemistryMicrowave

A dry cleaning method for use in semiconductor fabrication, including the following steps. An etched metallization structure is provided and placed in a processing chamber. The etched metallization structure is cleaned by introducing a fluorine containing gas / oxygen containing gas mixture into the processing chamber proximate the etched metallization structure without the use of a downstream microwave while applying a magnetic field proximate the etched metallization structure and maintaining a pressure of less than about 50 millitorr within the processing chamber for a predetermined time.

Owner:PROMOS TECH INC +2

Non-polar iii-v nitride semiconductor and growth method

ActiveUS20090079034A1Low defect densityLow stressPolycrystalline material growthSemiconductor/solid-state device manufacturingEtchingNanopillar

A method for growing flat, low defect density, and strain-free thick non-polar III-V nitride materials and devices on any suitable foreign substrates using a fabricated nanocolumns compliant layer with an HVPE growth process is provided. The method uses a combination of dry and wet etching to create nanocolumns consisting of layers of non-polar III nitride material and other insulating materials or materials used to grow the non-polar III-V nitride materials.

Owner:IQE

Method of fabricating silicon devices on sapphire with wafer bonding at low temperature

InactiveUS6911375B2Avoid process stepsCost effectiveSolid-state devicesSemiconductor/solid-state device manufacturingWaferingWafer bonding

Described is a method for making silicon on sapphire structures, and devices therefrom. The inventive method of forming integrated circuits on a sapphire substrate comprises the steps of providing a device layer on an oxide layer of a temporary substrate; bonding the device layer to a handling substrate; removing the temporary substrate to provide a structure containing the device layer between the oxide layer and the handling substrate; bonding a sapphire substrate to the oxide layer; removing the handling substrate from the structure; and annealing the final structure to provide a substrate comprising the oxide layer between the device layer and the sapphire substrate. The sapphire substrate may comprise bulk sapphire or may be a conventional substrate material with an uppermost sapphire layer.

Owner:IBM CORP

Large-area bulk gallium nitride wafer and method of manufacture

ActiveUS20100189981A1Quality improvementReduce defect densityPolycrystalline material growthSynthetic resin layered productsWaferingGallium nitride

The present invention includes a high-quality, large-area bulk GaN seed crystal for ammonothermal GaN growth and method for fabricating. The seed crystal is of ultra-low defect density, has flat surfaces free of bowing, and is free of foreign substrate material. The seed crystal is useful for producing large-volume, high-quality bulk GaN crystals by ammonothermal growth methods for eventual wafering into large-area GaN substrates for device fabrication.

Owner:SLT TECH

Production of semiconductor devices

ActiveUS20100276665A1Large growth rateReduce defect densityNanostructure manufactureSemiconductor/solid-state device manufacturingNanometreNano structuring

A method of producing a layered semiconductor device comprises the steps of: (a) providing a base comprising a plurality of semiconductor nano-structures, (b) growing a semiconductor material onto the nano-structures using an epitaxial 5 growth process, and (c) growing a layer of the semiconductor material using an epitaxial growth process.

Owner:QUANTUM NIL LTD +1

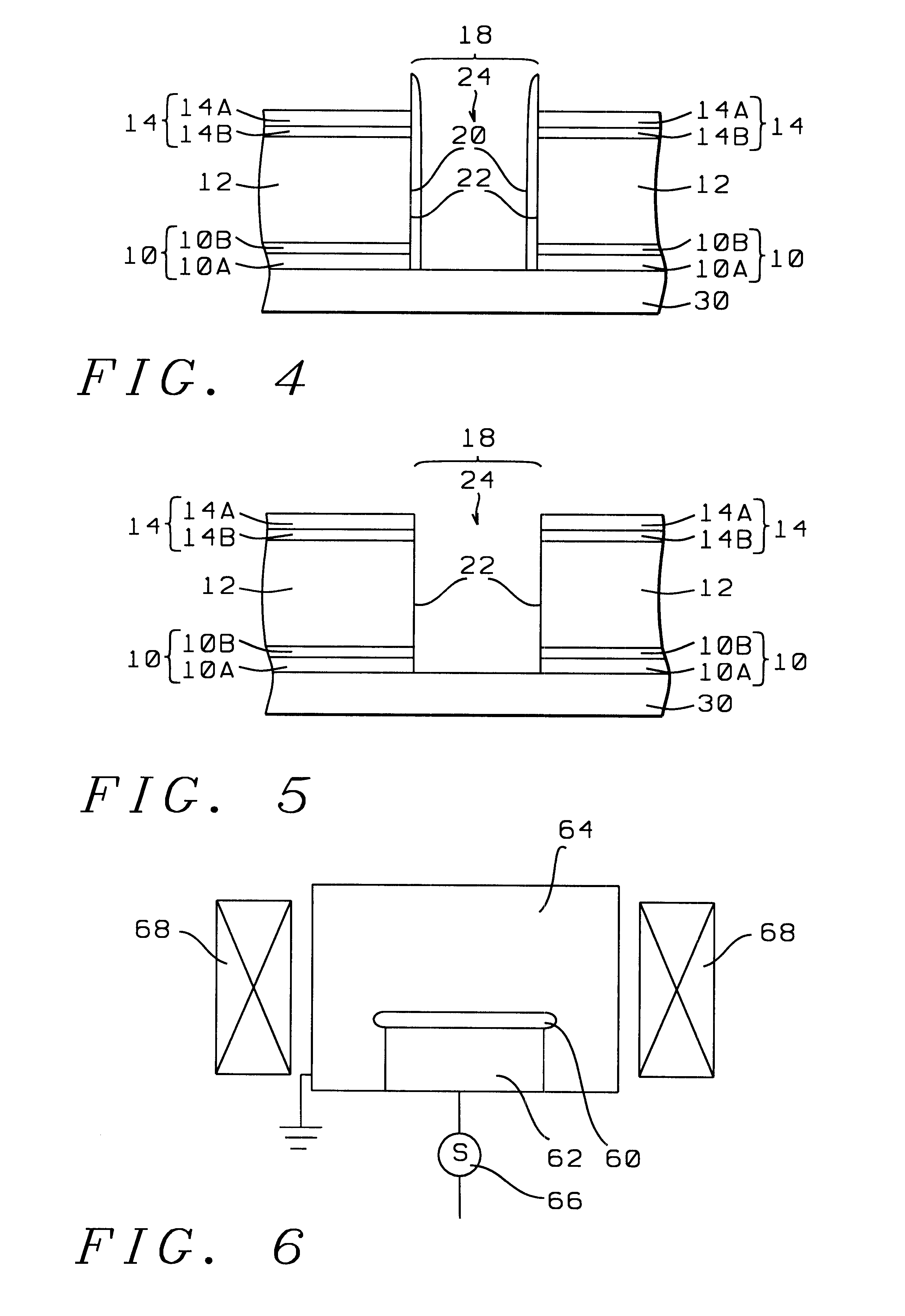

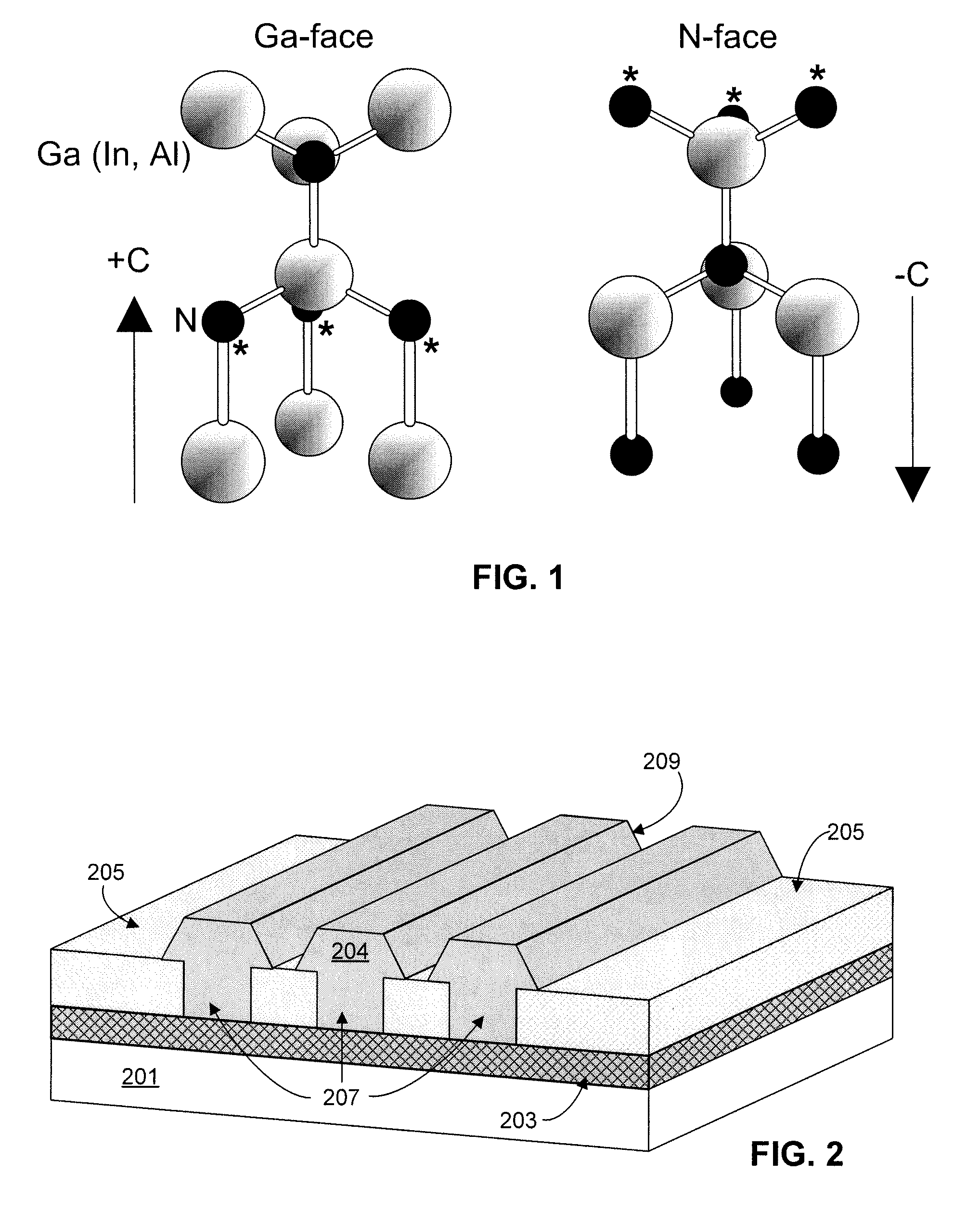

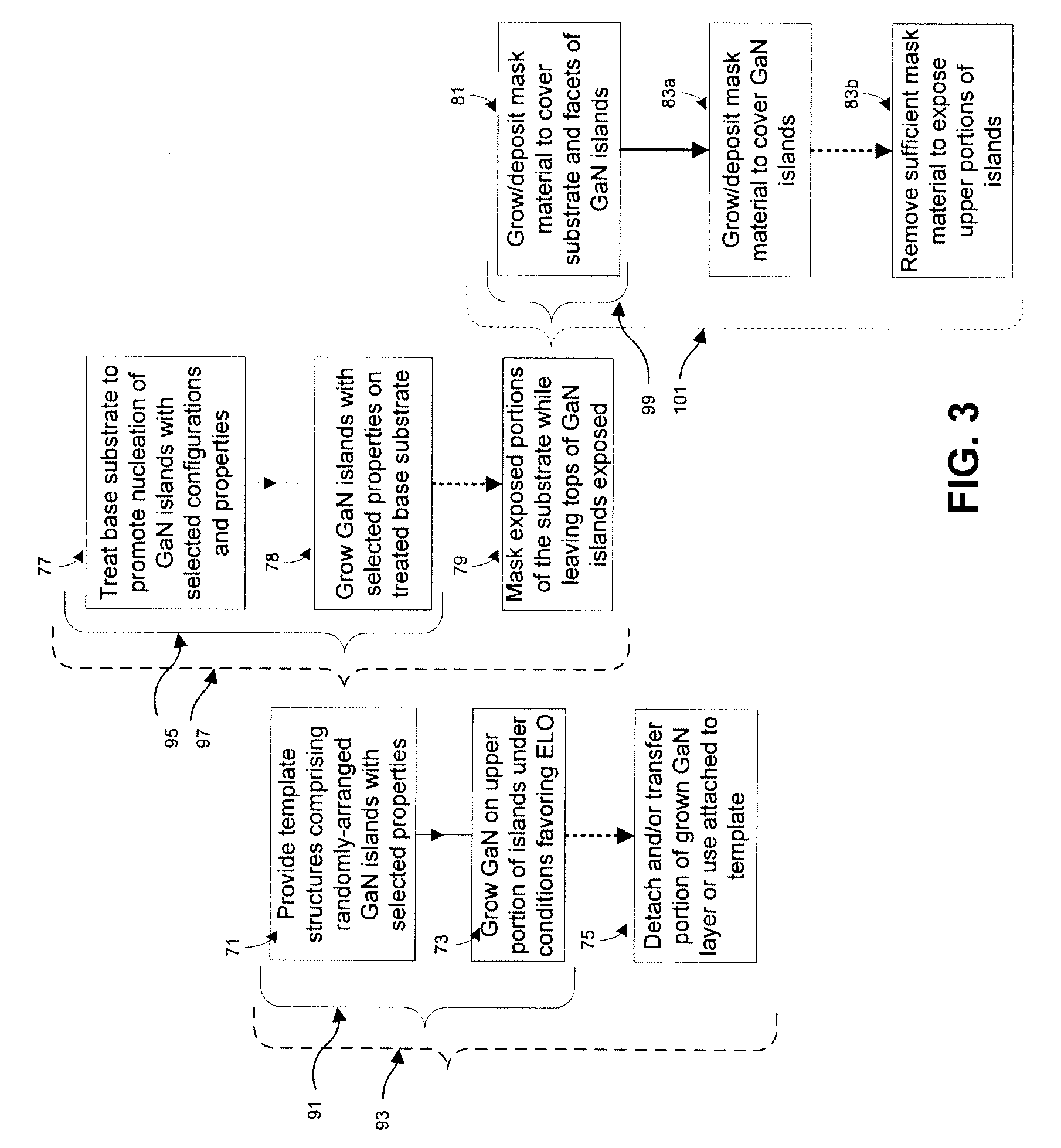

Epitaxial methods and templates grown by the methods

ActiveUS20090098343A1Relieve lattice strainReduce lattice strainLayered productsSemiconductor/solid-state device manufacturingSemiconductor materialsElectrical polarity

This invention provides methods for fabricating substantially continuous layers of a group III nitride semiconductor material having low defect densities and optionally having a selected crystal polarity. The methods include epitaxial growth nucleating and / or seeding on the upper portions of a plurality of pillars / islands of a group III nitride material that are irregularly arranged on a template structure. The upper portions of the islands have low defect densities and optionally have a selected crystal polarity. The invention also includes template structures having a substantially continuous layer of a masking material through which emerge upper portions of the pillars / islands. The invention also includes such template structures. The invention can be applied to a wide range of semiconductor materials, both elemental semiconductors, e.g., combinations of Si (silicon) with strained Si (sSi) and / or Ge (germanium), and compound semiconductors, e.g., group II-VI and group III-V compound semiconductor materials.

Owner:S O I TEC SILICON ON INSULATOR THECHNOLOGIES +1

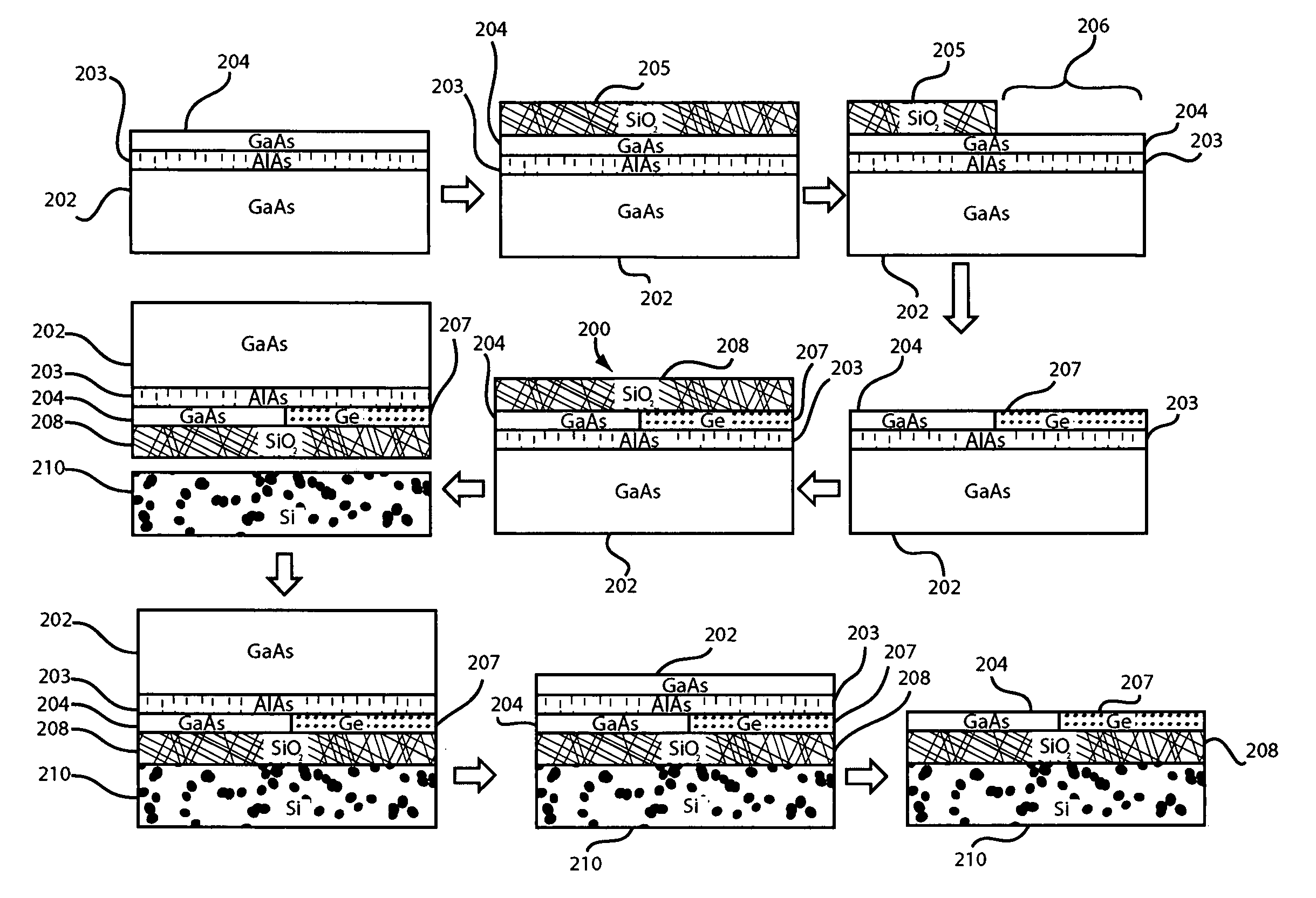

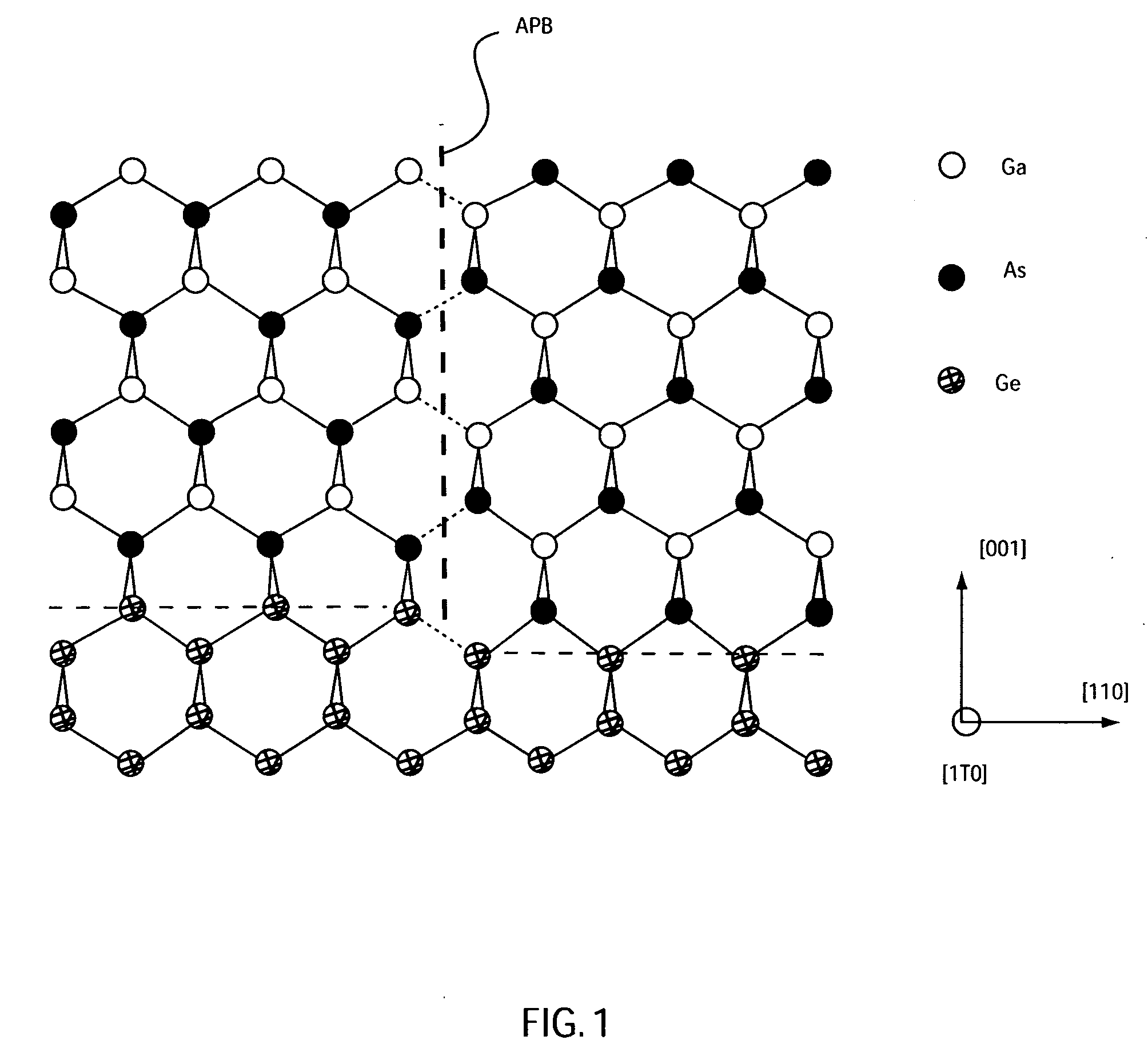

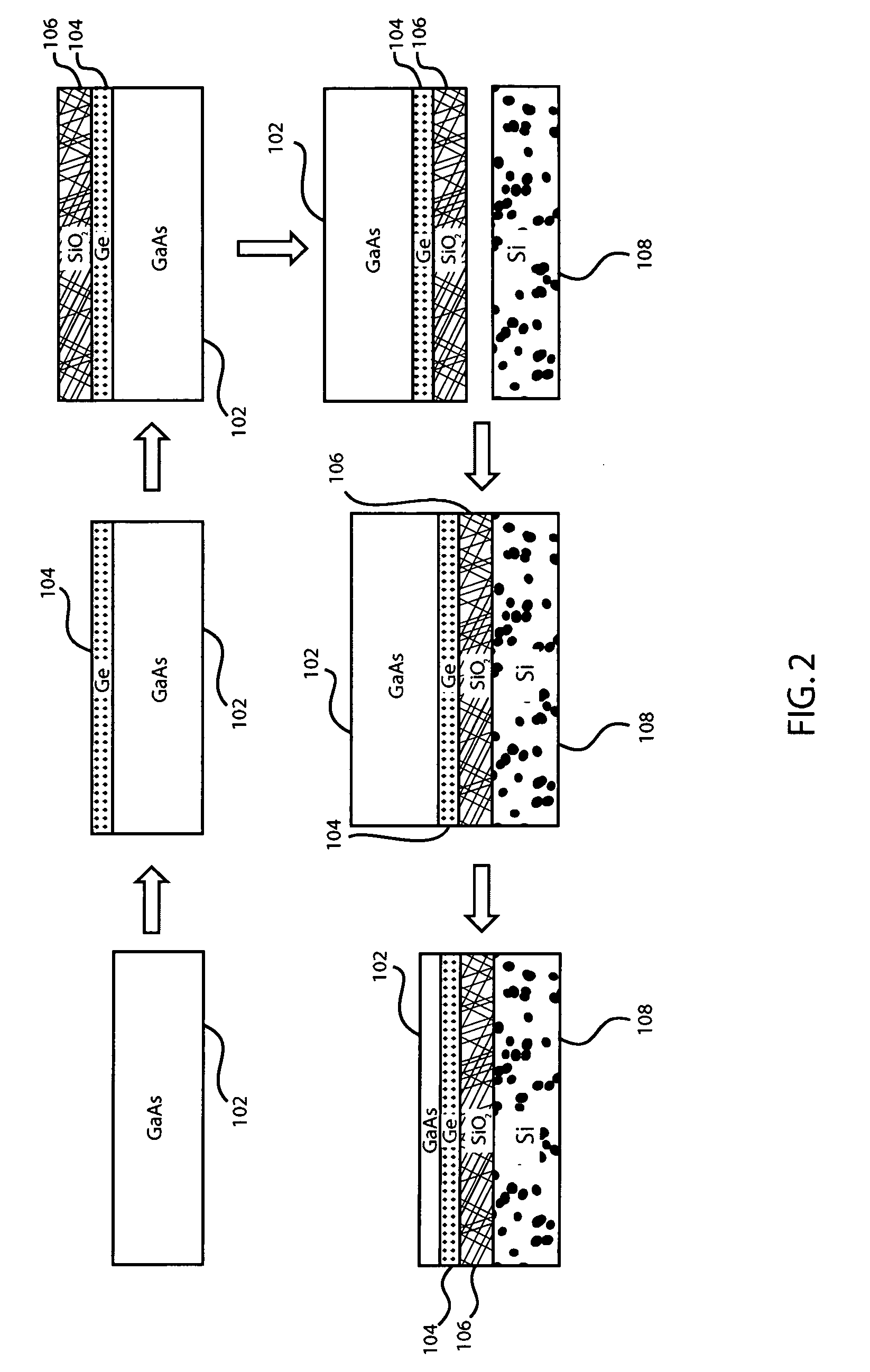

Structure and method of integrating compound and elemental semiconductors for high-performace CMOS

InactiveUS20060172505A1Reduce defect densityHigh-quality materialSolid-state devicesSemiconductor/solid-state device manufacturingCMOSSemiconductor materials

A method for fabricating a semiconductor substrate includes epitaxially growing an elemental semiconductor layer on a compound semiconductor substrate. An insulating layer is deposited on top of the elemental semiconductor layer, so as to form a first substrate. The first substrate is wafer bonded onto a monocrystalline Si substrate, such that the insulating layer bonds with the monocrystalline Si substrate. A semiconductor device includes a monocrystalline substrate, and a dielectric layer formed on the monocrystalline substrate. A semiconductor compound is formed on the dielectric layer and an elemental semiconductor material formed in proximity of the semiconductor compound and lattice-matched to the semiconductor compound.

Owner:ALSEPHINA INNOVATIONS INC

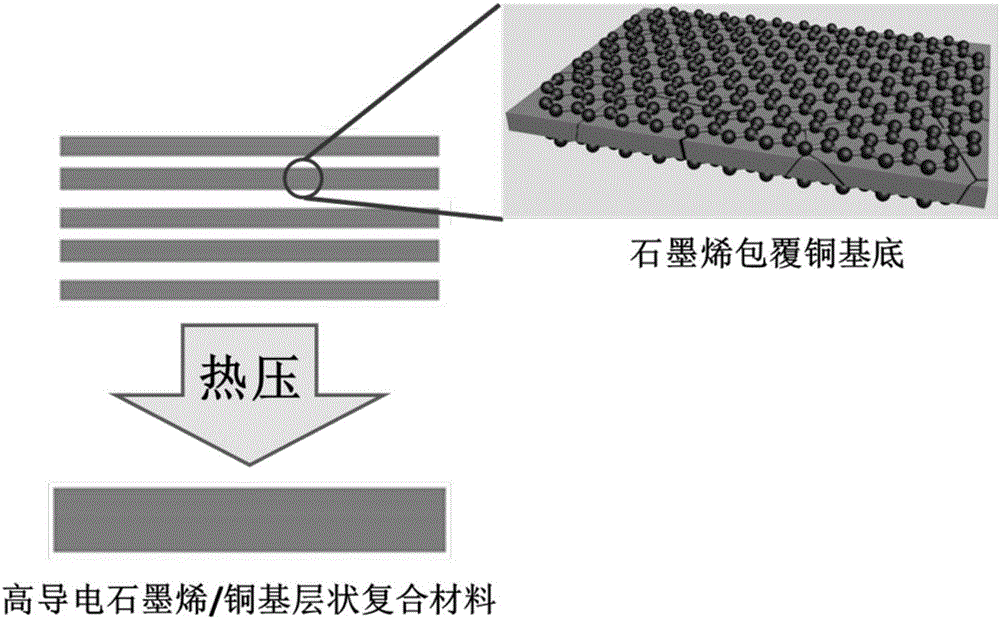

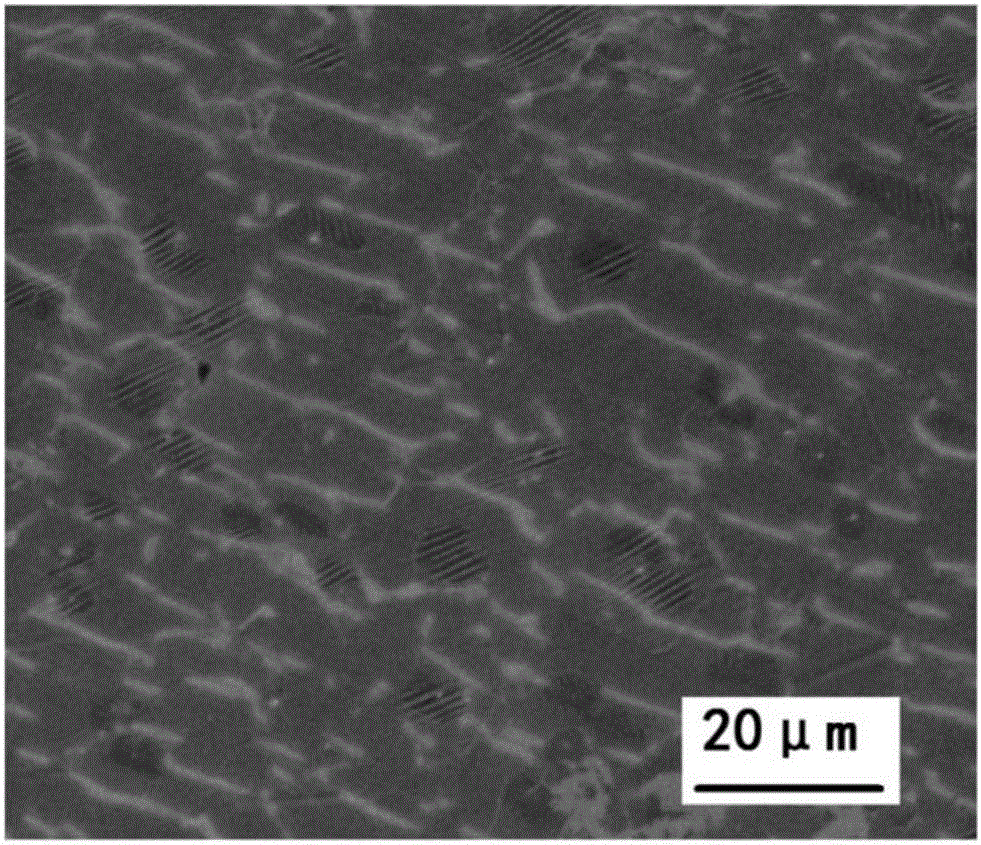

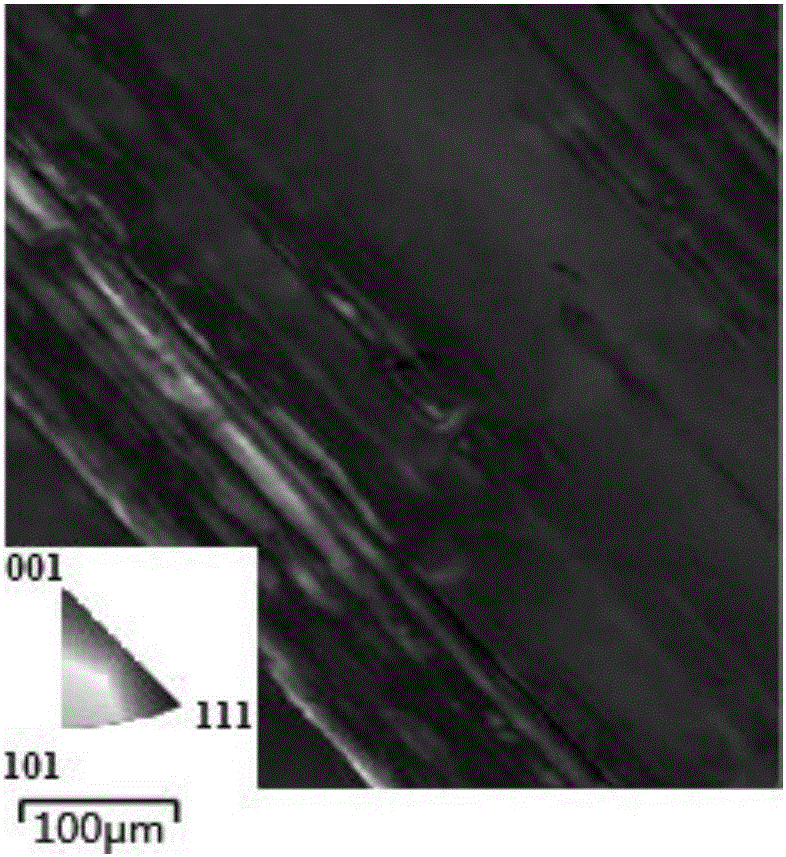

High-conductivity graphene/copper-based layered composite material and preparation method thereof

InactiveCN106584976AImprove utilization efficiencyTo overcome the deficiency of reducing resistanceLaminationLamination apparatusSingle crystalCvd graphene

The invention discloses a high-conductivity graphene / copper-based layered composite material and a preparation method thereof. The composite material is characterized in that the composite material is of a layered structure formed by alternate combination of chemical vapor deposition (CVD) graphene and a copper substrate, the copper substrate is in a single-crystal state in the thickness direction in layers, and the (111) crystal face high-orientation effect is achieved. The method includes the following steps that (1) graphene is grown on the upper surface and the lower surface of the platy copper substrate through a CVD technology and the copper substrate is induced to achieve preferred orientation along a (111) crystal face, and the sandwich-shaped graphene-cladding copper substrate is obtained through preparation; and (2) multiple pieces of graphene-cladding copper substrates are subjected to hot pressed sintering densification to form the high-conductivity graphene / copper-based layered composite material. The layered composite material prepared by the method is high in conductivity, higher than pure silver in conduction level and easy to produce and can be used as various conduction materials.

Owner:SHANGHAI JIAO TONG UNIV

Large-area bulk gallium nitride wafer and method of manufacture

ActiveUS8048225B2Quality improvementReduce defect densityPolycrystalline material growthSynthetic resin layered productsWaferingGallium nitride

The present invention includes a high-quality, large-area bulk GaN seed crystal for ammonothermal GaN growth and method for fabricating. The seed crystal is of ultra-low defect density, has flat surfaces free of bowing, and is free of foreign substrate material. The seed crystal is useful for producing large-volume, high-quality bulk GaN crystals by ammonothermal growth methods for eventual wafering into large-area GaN substrates for device fabrication.

Owner:SLT TECH

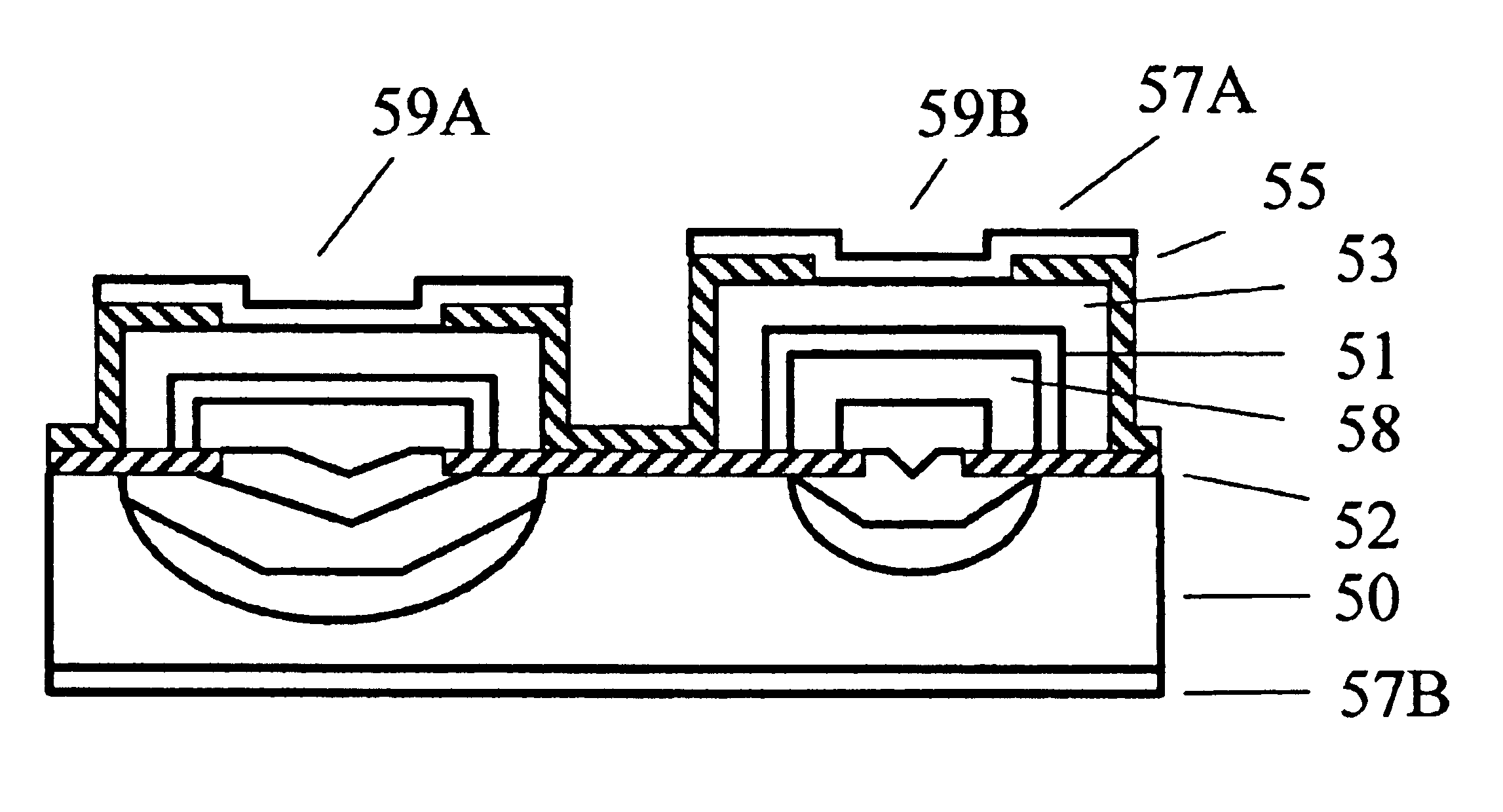

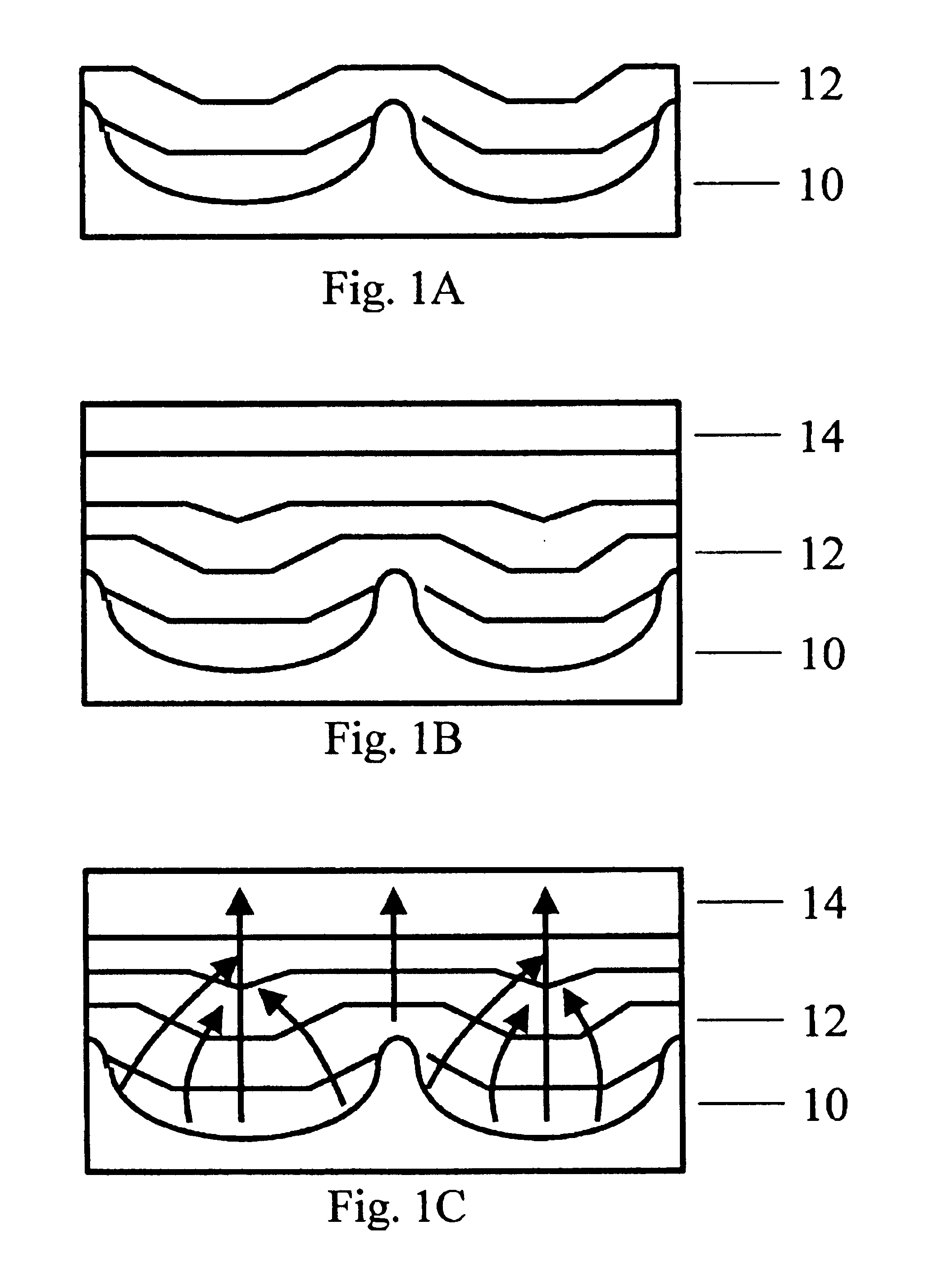

Semiconductor light-emitting device and method for manufacturing the same

ActiveUS6936851B2Reduce defect densityRestrict propagationLaser detailsSolid-state devicesActive layerLight emitting device

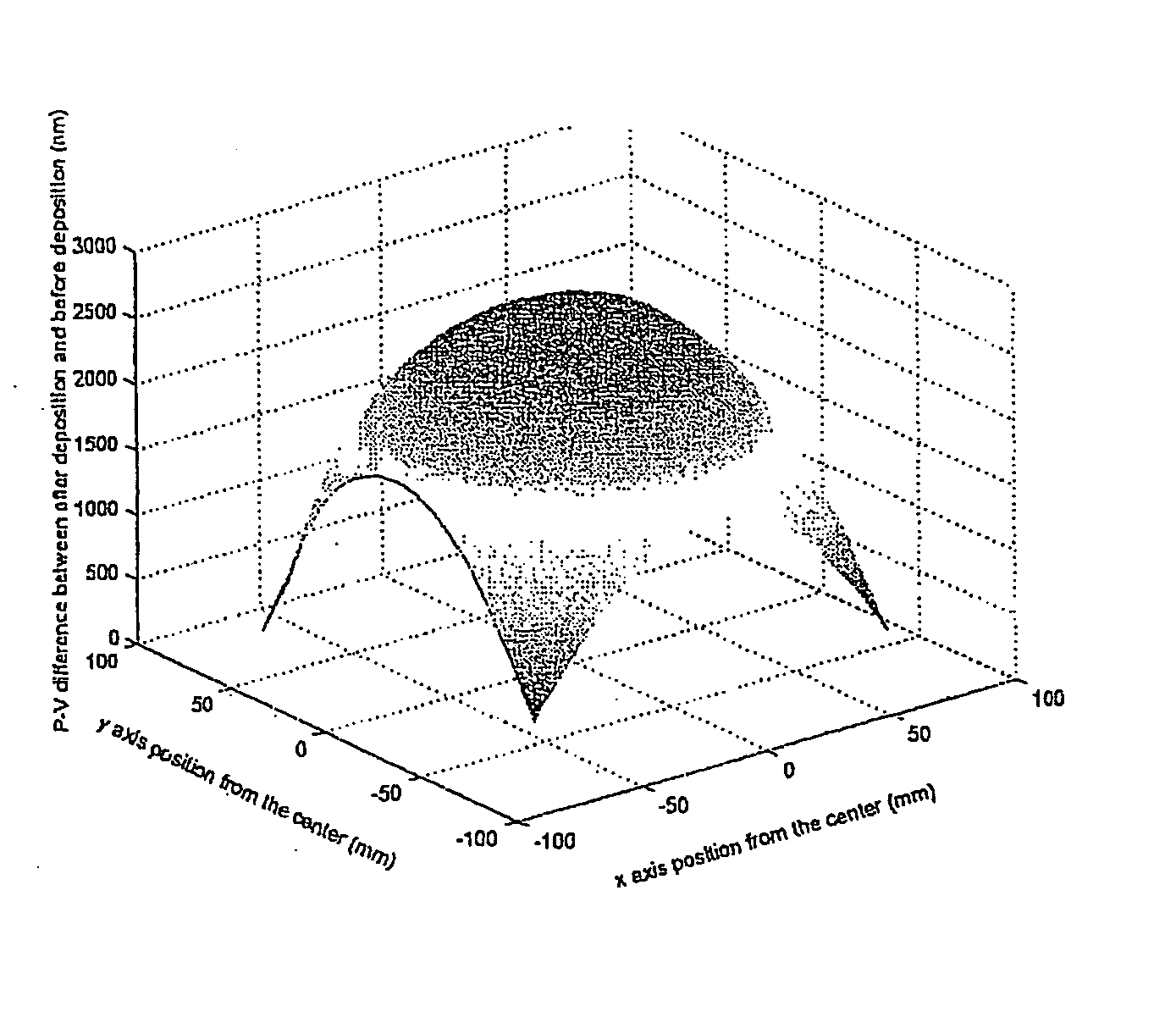

Semiconductor light emitting device and methods for its manufacture comprises a plurality of textured district defined on the surface of the substrate. The initial inclined layer deposition serves to guide the extended defects to designated gettering centers in the trench region where the defects combine with each other. As a result, the defect density in the upper section of the structure is much reduced. By incorporating a blocking mask in the structure, the free propagation of extended defects into the active layer is further restricted. The present invention is useful in the fabrication of semiconductor light emitting devices in misfit systems.

Owner:LEXINGTON LUMINANCE

Method for manufacturing of a mask blank for EUV photolithography and mask blank

InactiveUS20060008749A1Difficult and costly to produceGenerate and manipulate easilyNanoinformaticsVacuum evaporation coatingExtreme ultravioletConductive coating

The invention relates to a method for manufacturing of a mask blank for extreme ultraviolet (EUV) photolithography, comprising the steps of: providing a substrate having a front surface and a back surface; depositing a film comprising tantalum nitride (TaN) on said front surface of said substrate for absorbing EUV light used during a photolithographic process; and depositing a conductive coating on said back surface of said substrate. Preferably, ion beam sputtering is used for depositing the film comprising tantalum nitride (TaN) and / or the conductive coating on the back surface of the substrate. Preferably, Xenon is used as a sputter gas for ion beam sputtering. Another aspect of the present invention relates to a mask blank for extreme ultraviolet (EUV) photolithography.

Owner:SCHOTT AG

Non-polar iii-v nitride material and production method

ActiveUS20090079035A1Reduce defect densityReduce stressMaterial nanotechnologyPolycrystalline material growthNitrideNanometre

A method for growing flat, low defect density, and strain-free thick non-polar III-V nitride materials and devices on any suitable foreign substrates using a fabricated nano-pores and nano-network compliant layer with an HVPE, MOCVD, and integrated HVPE / MOCVD growth process in a manner that minimum growth will occur in the nano-pores is provided. The method produces nano-networks made of the non-polar III-V nitride material and the substrate used to grow it where the network is continuous along the surface of the template, and where the nano-pores can be of any shape.

Owner:QUANTUM NIL LTD +1

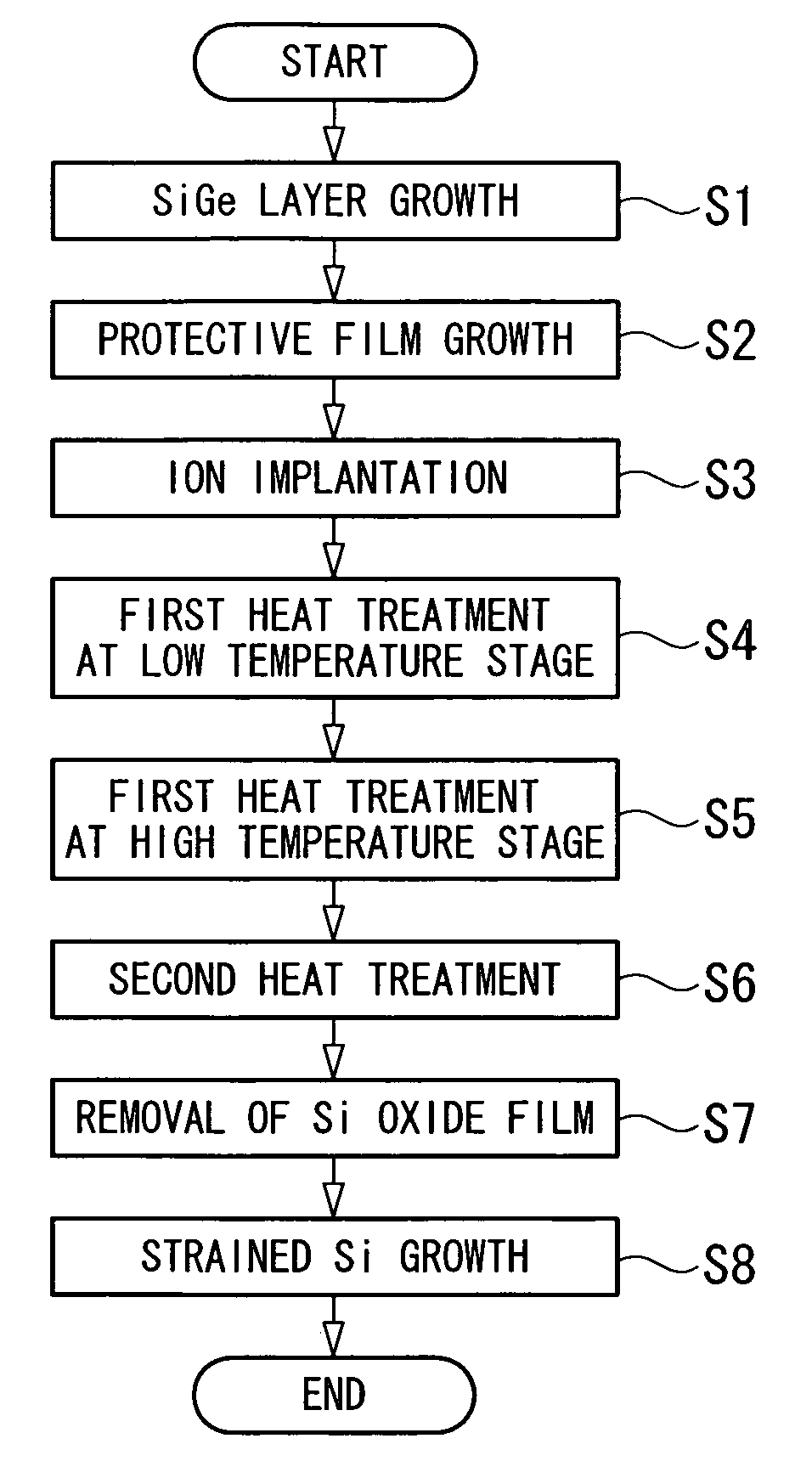

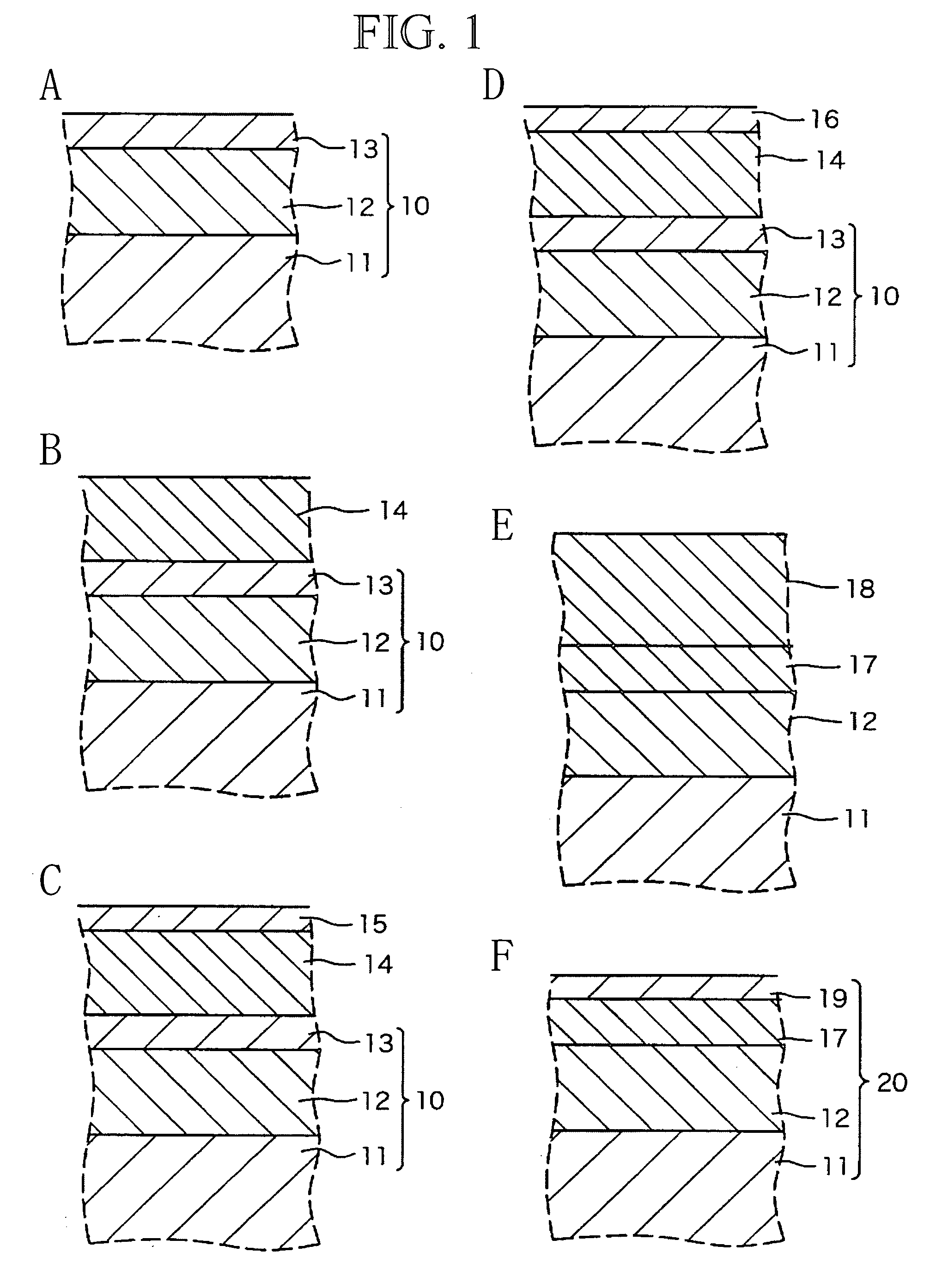

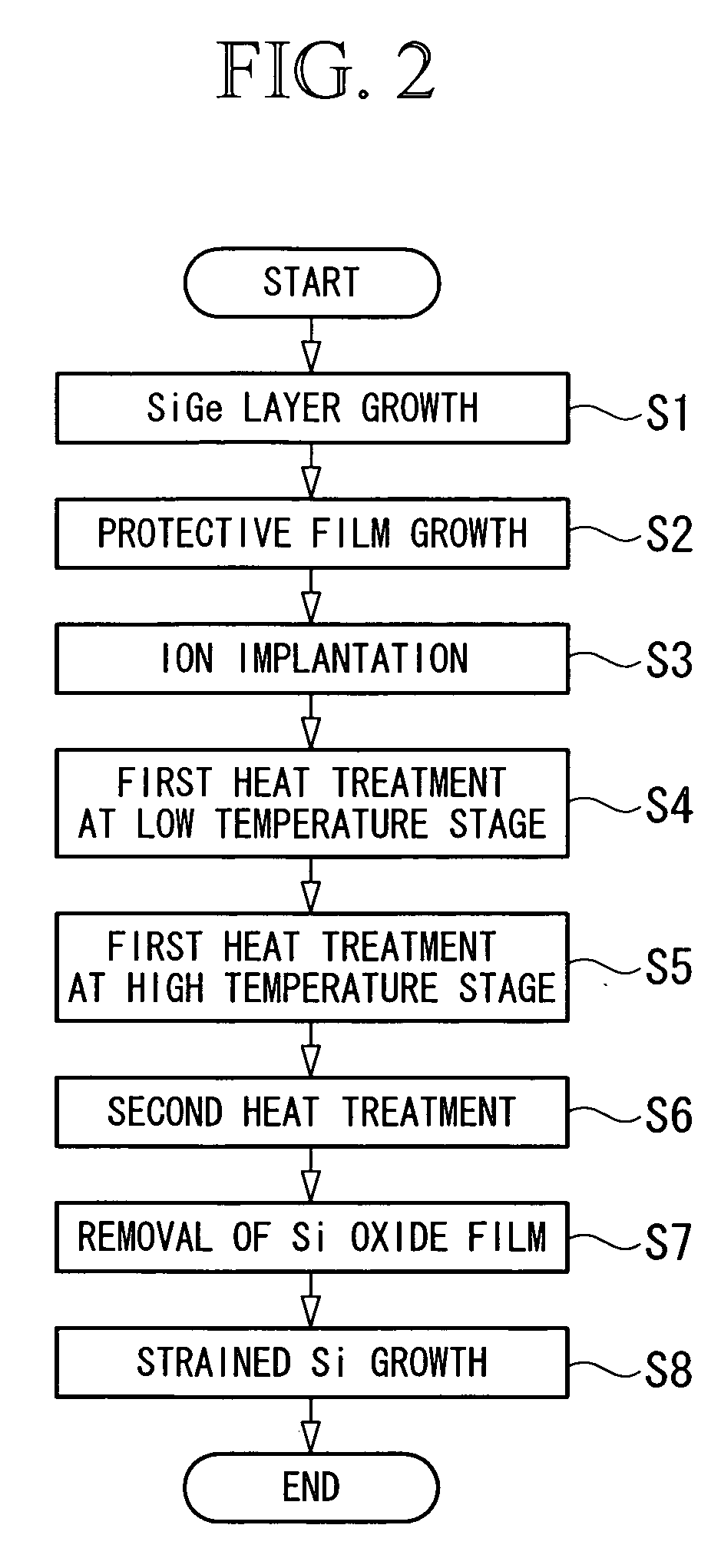

Production method of strained silicon-SOI substrate and strained silicon-SOI substrate produced by same

InactiveUS20060214257A1Reduce bond strengthEnhances strain relaxationSolid-state devicesSemiconductor/solid-state device manufacturingSoi substrateMixed crystal

A strained Si-SOI substrate is produced by a method comprising: growing a SiGe mixed crystal layer on an SOI substrate having a Si layer of not less than 5 nm in thickness and a buried oxide layer; forming a protective film on the SiGe mixed crystal layer; implanting light element ions into a vicinity of an interface between the silicon layer and the buried oxide layer; a first heat treatment for heat treating the substrate at a temperature of 400 to 1000° C. in an inert gas atmosphere; a second heat treatment for heat treating the substrate at a temperature not lower than 1050° C. in an oxidizing atmosphere containing chlorine; removing an oxide film from the surface of the substrate, and forming a strained silicon layer on the surface of the substrate.

Owner:SUMCO CORP +1