Patents

Literature

166 results about "Threading dislocations" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A threading dislocation is one that extends from the surface of a strained layer system, goes through the layer and penetrates the substrate or bends at the interface into a misfit dislocation.

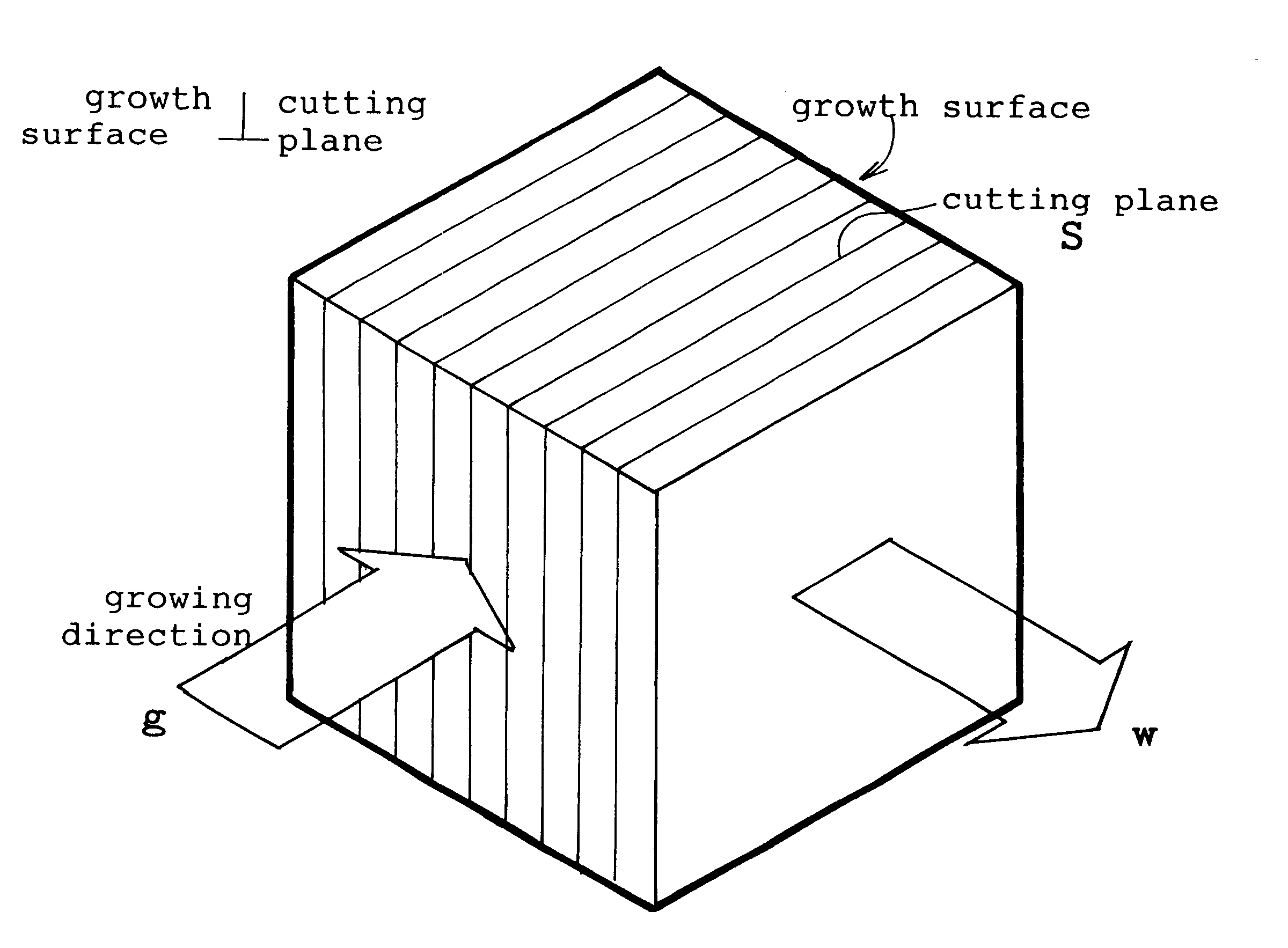

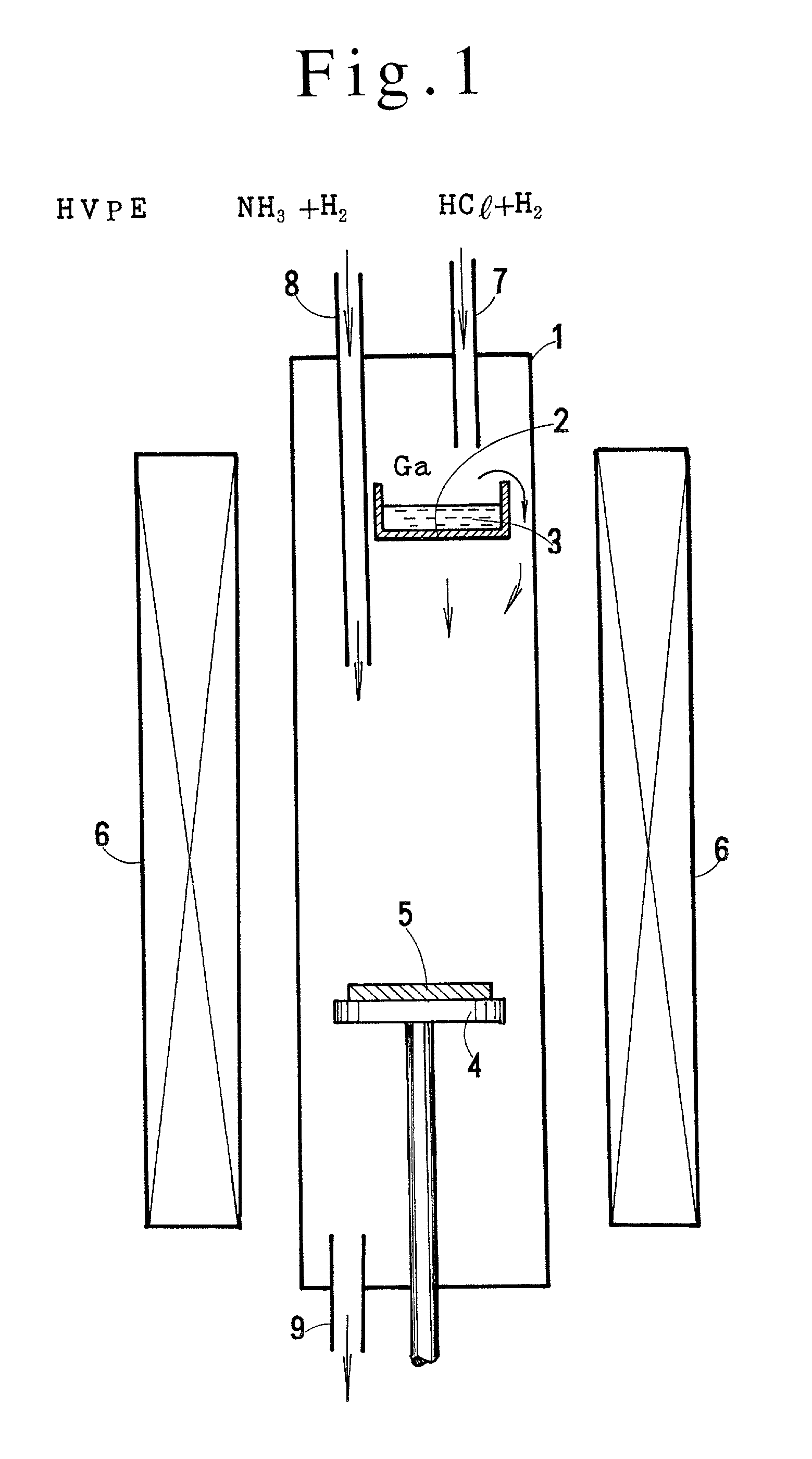

Method of producing a single crystal gallium nitride substrate and single crystal gallium nitride substrate

InactiveUS6468882B2Increase the number ofPolycrystalline material growthLaser detailsThreading dislocationsSingle crystal substrate

GaN single crystal substrates are produced by slicing a GaN single crystal ingot in the planes parallel to the growing direction. Penetration dislocations which have been generated in the growing direction extend mainly in the bulk of the GaN substrate. A few of the threading dislocations appear on the surface of the GaN substrate. GaN substrates of low-dislocation density are obtained.

Owner:SUMITOMO ELECTRIC IND LTD

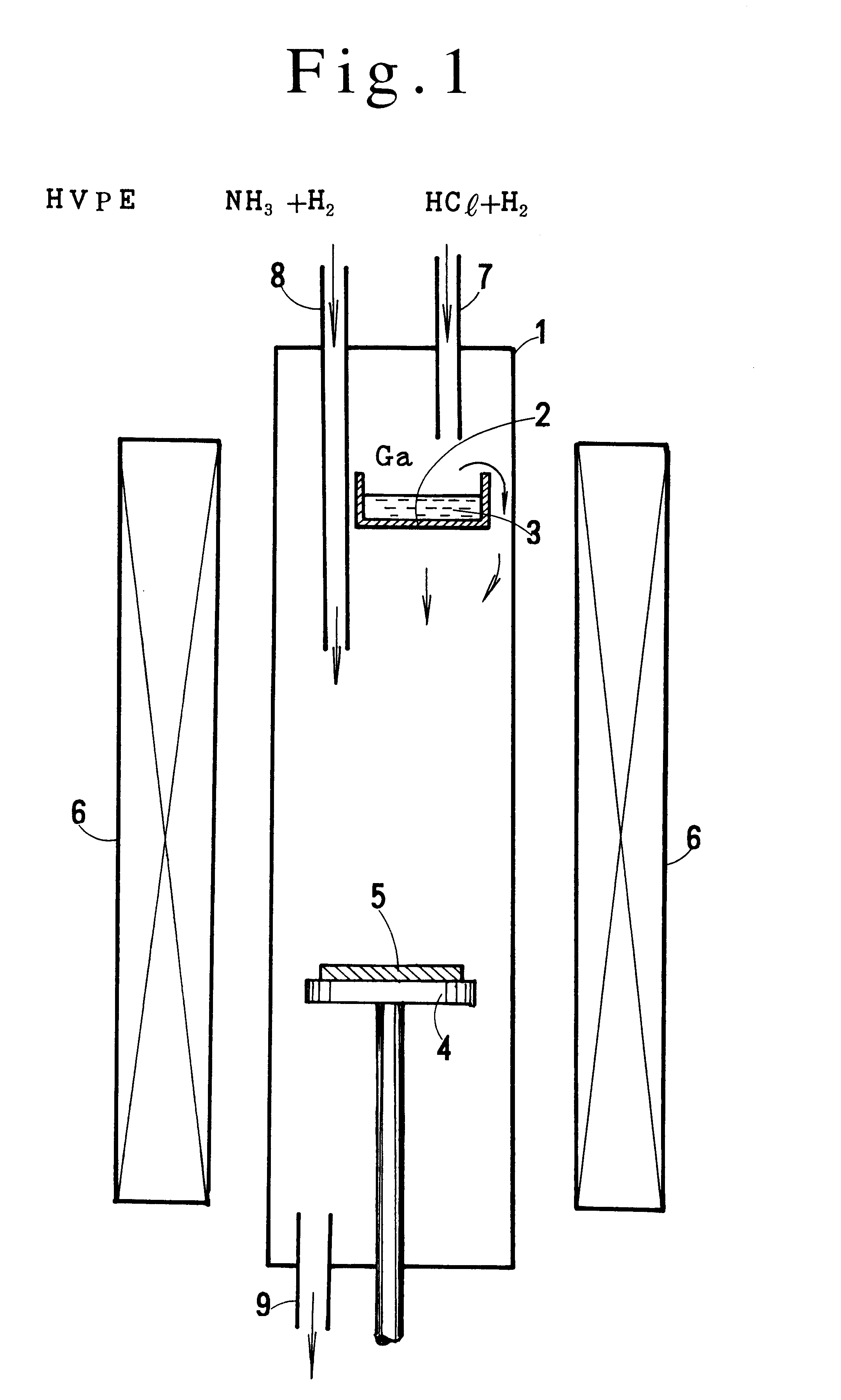

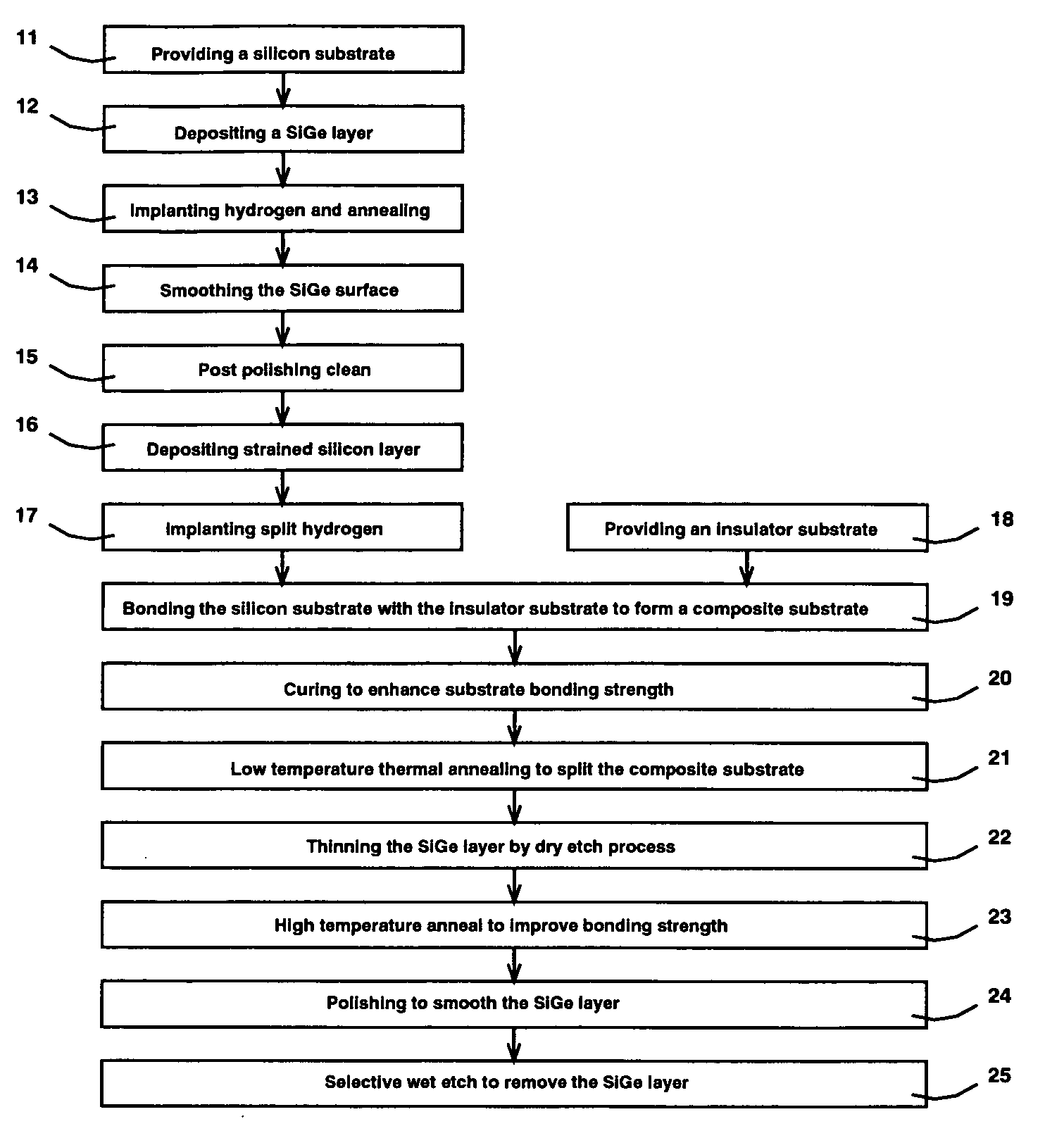

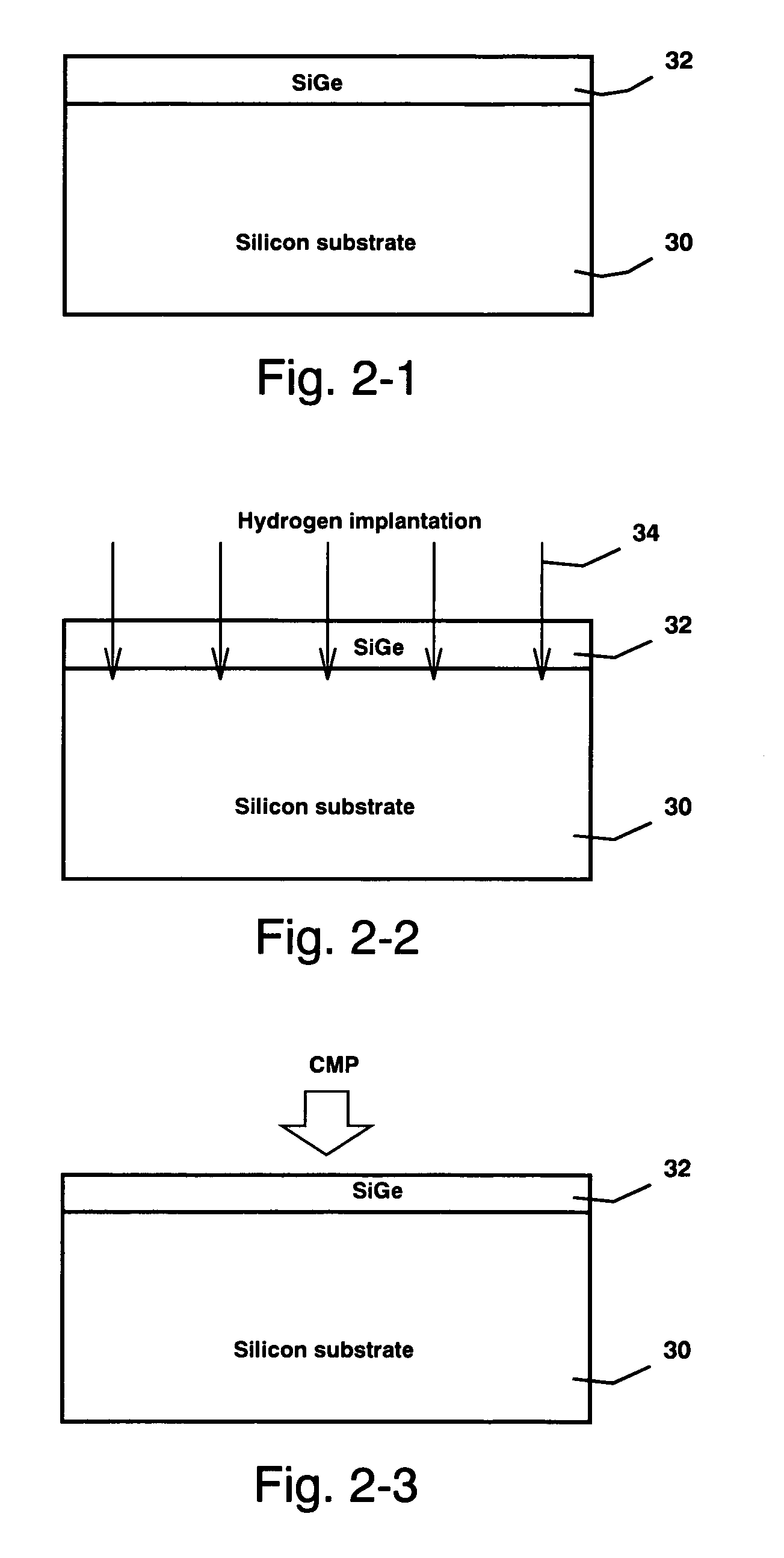

Strained silicon on insulator from film transfer and relaxation by hydrogen implantation

ActiveUS20050153524A1Easy to relaxEasy to integrateSolid-state devicesSemiconductor/solid-state device manufacturingThreading dislocationsHydrogen

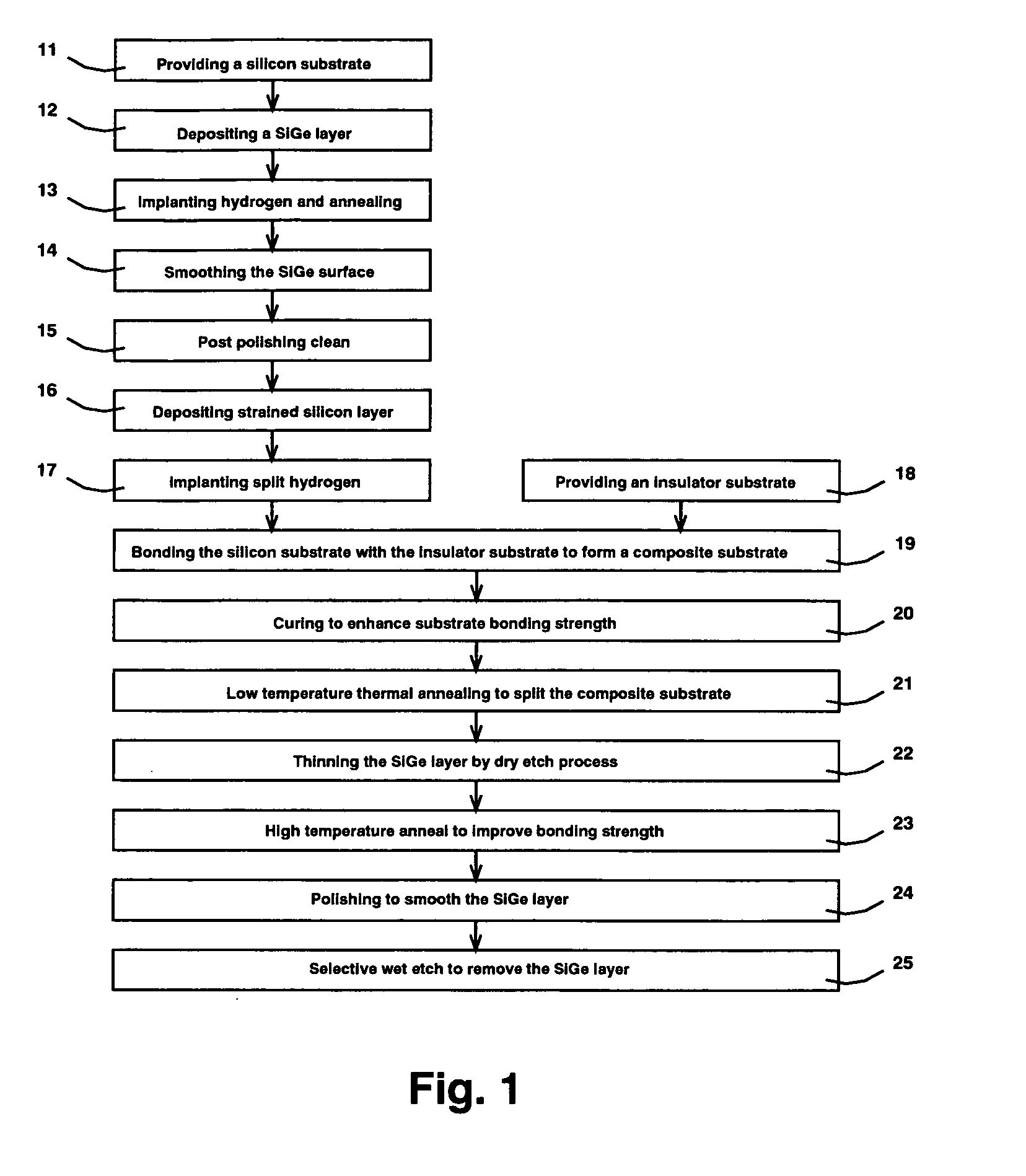

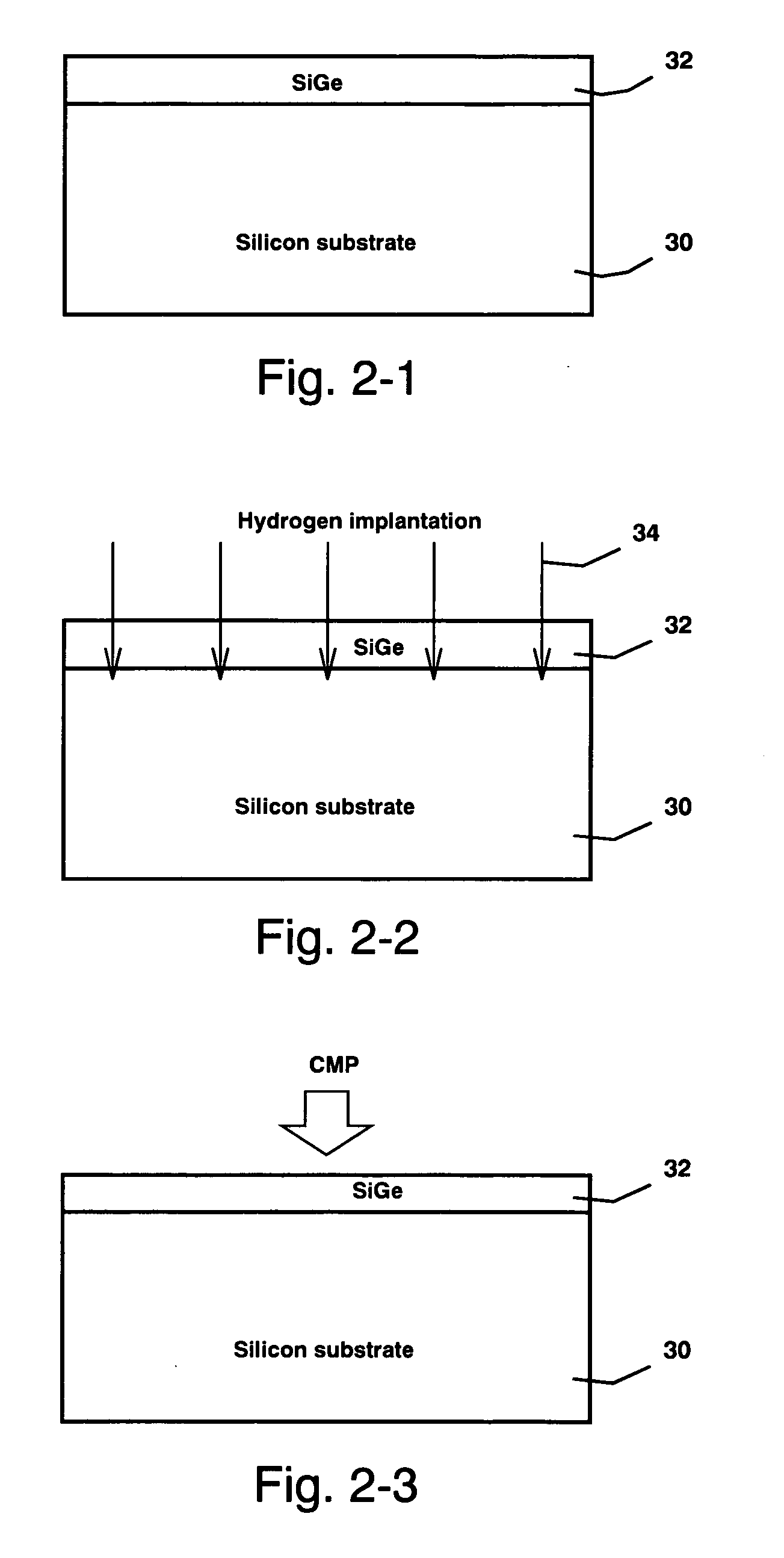

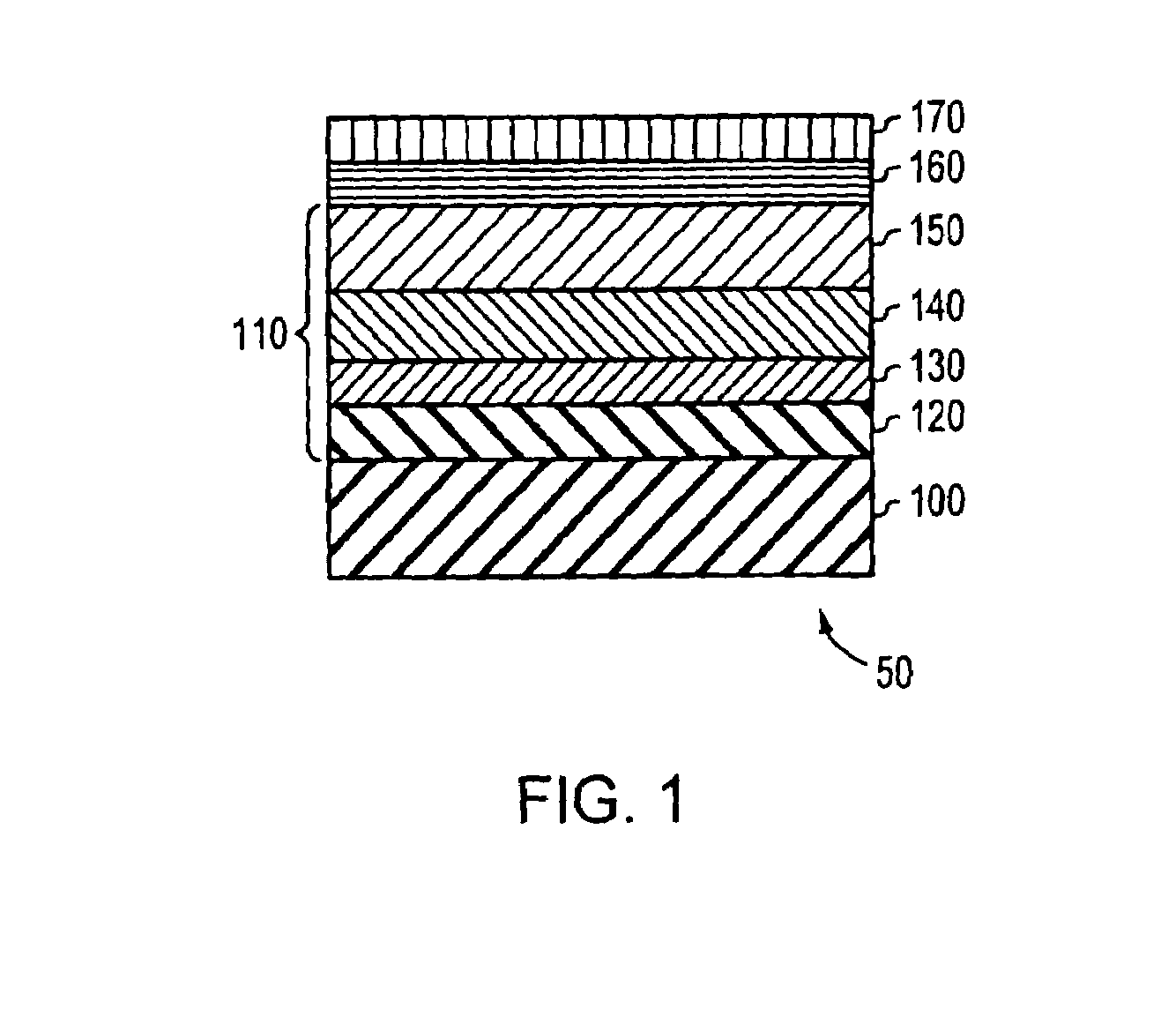

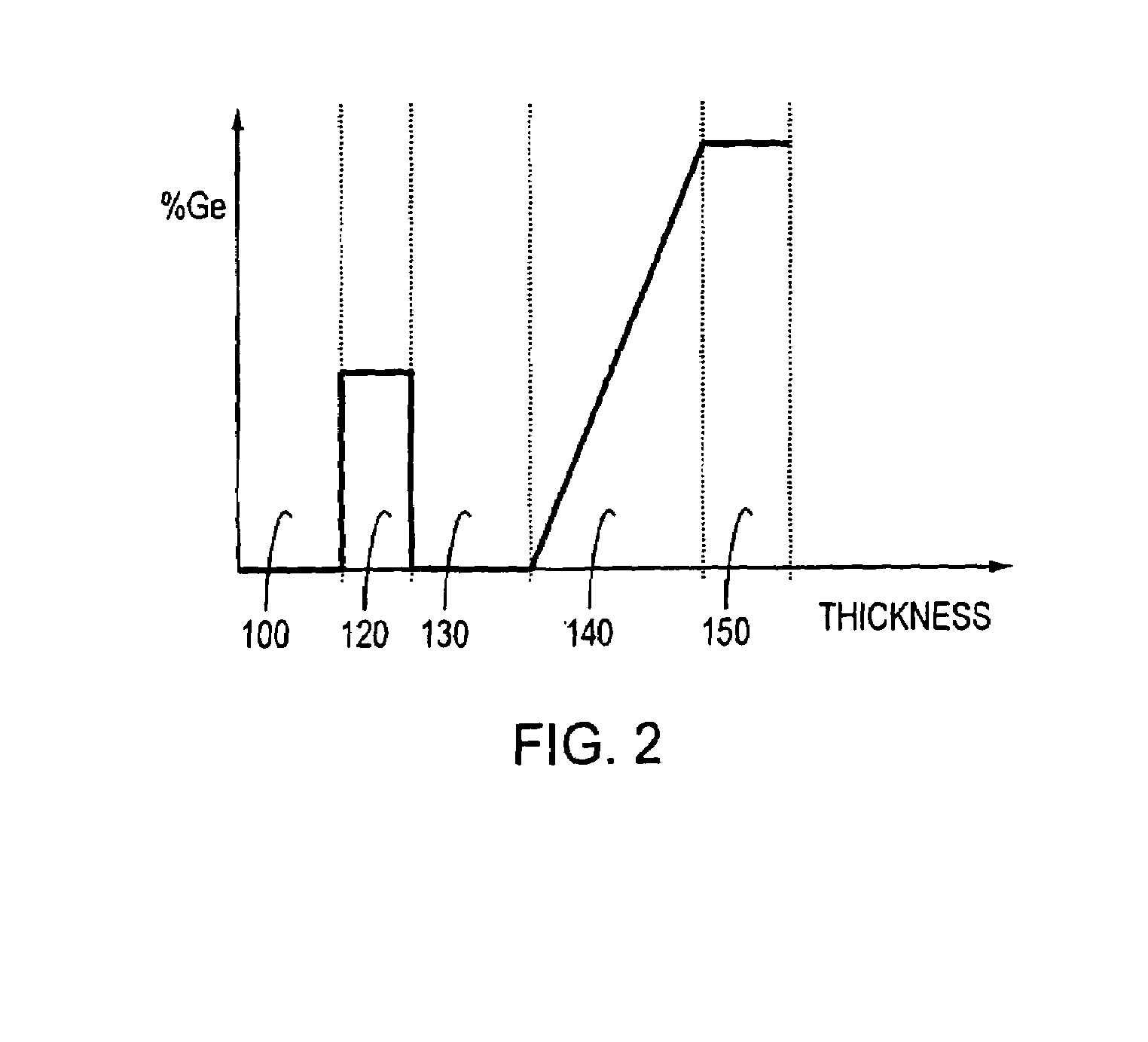

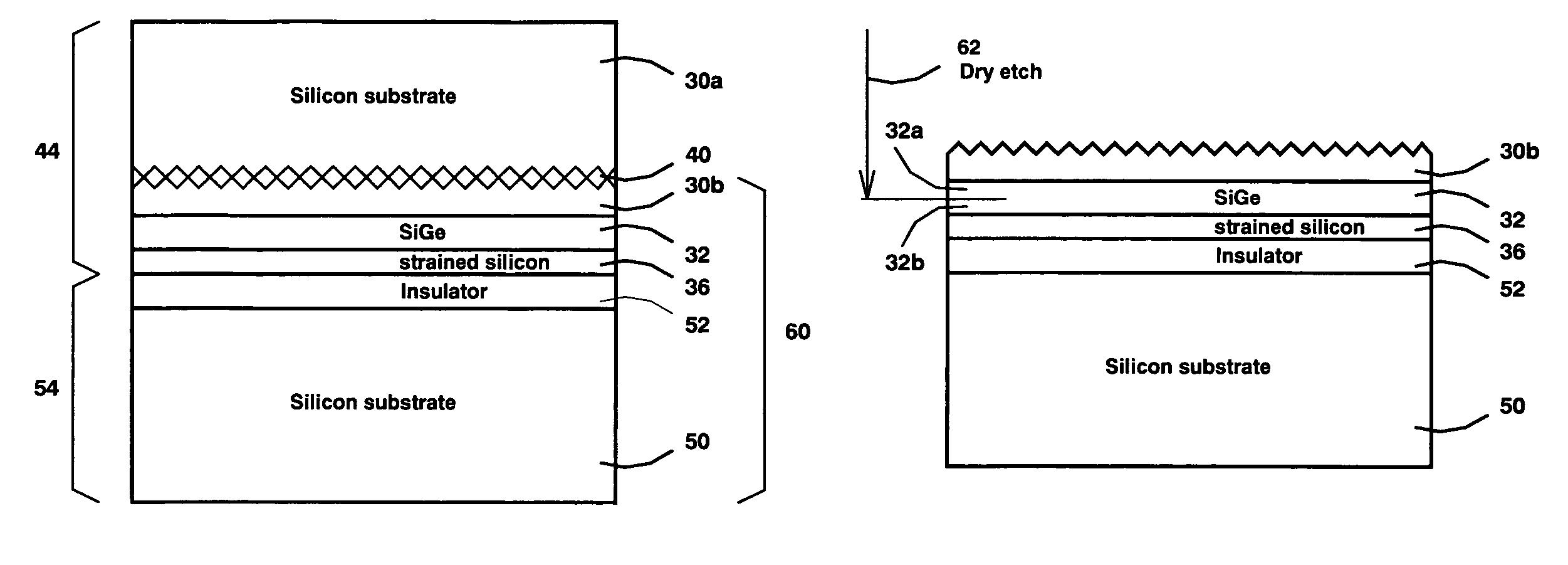

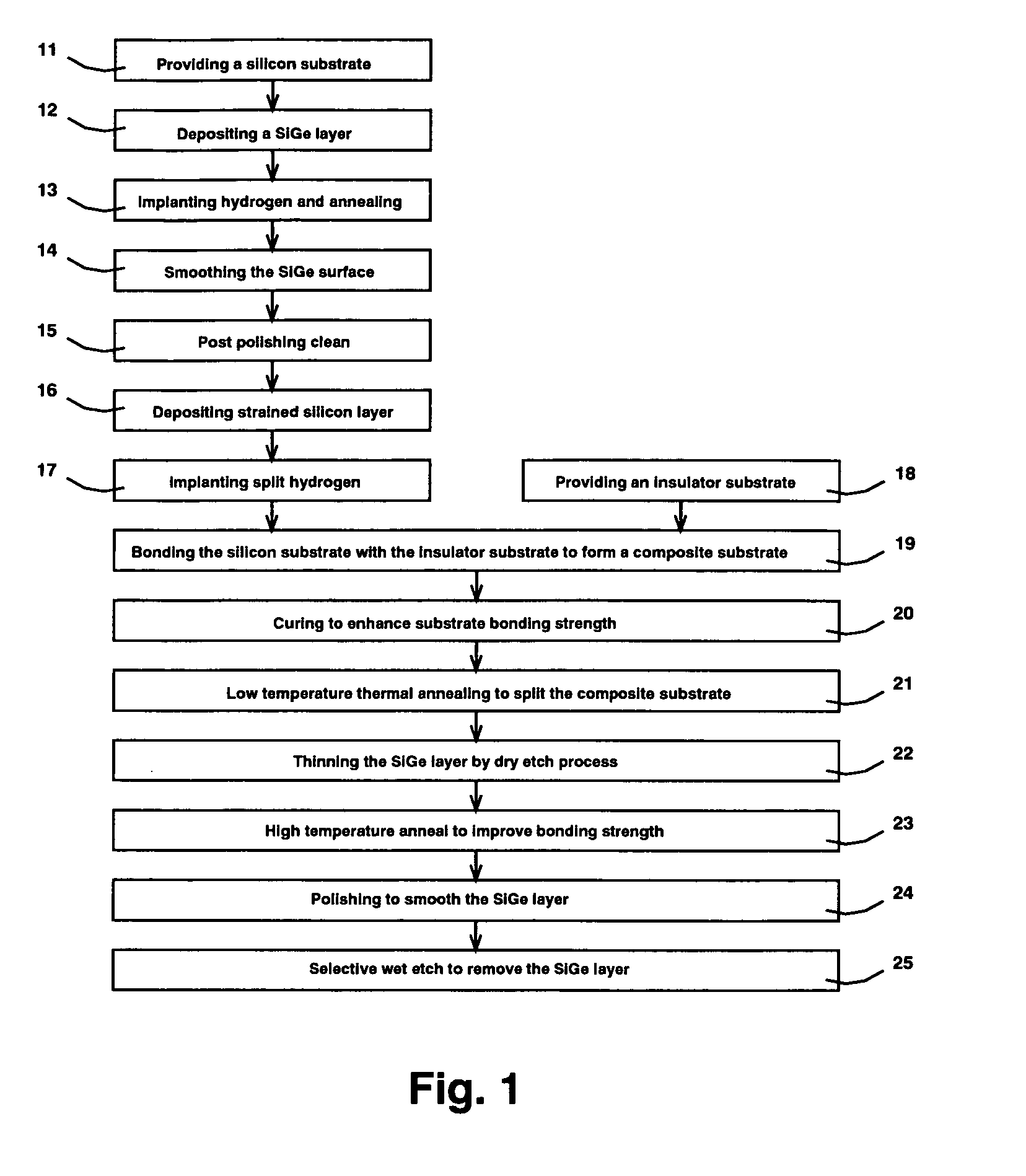

Transistors fabricated on SSOI (Strained Silicon On Insulator) substrate, which comprises a strained silicon layer disposed directly on an insulator layer, have enhanced device performance due to the strain-induced band modification of the strained silicon device channel and the limited silicon volume because of the insulator layer. The present invention discloses a SSOI substrate fabrication process comprising various novel approaches. One is the use of a thin relaxed SiGe layer as the strain-induced seed layer to facilitate integration and reduce processing cost. Another is the formation of split implant microcracks deep in the silicon substrate to reduce the number of threading dislocations reaching the strained silicon layer. And lastly is the two step annealing / thinning process for the strained silicon / SiGe multilayer film transfer without blister or flaking formation.

Owner:SHARP KK

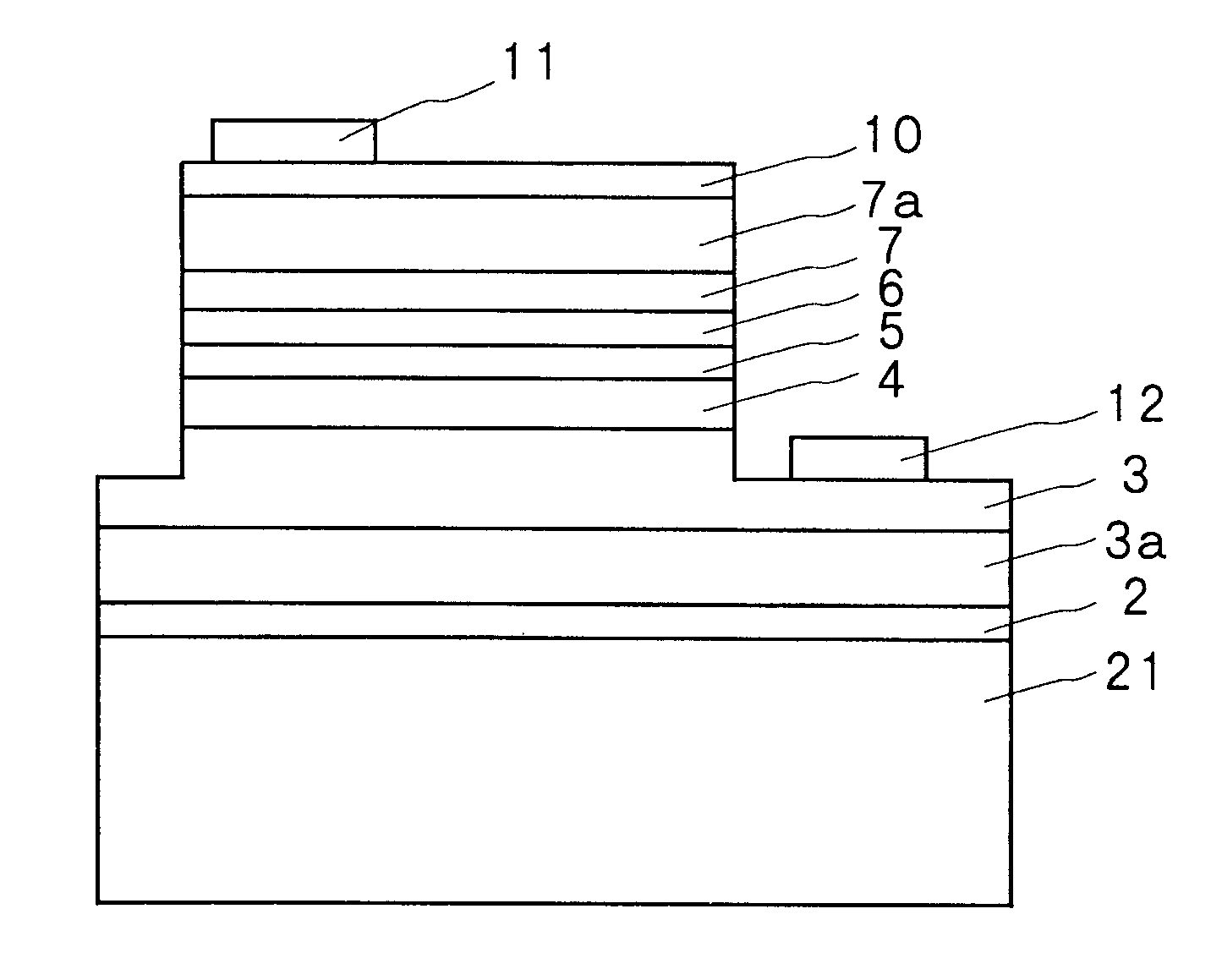

Semiconductor device and manufacturing method thereof

InactiveUS20060169987A1Quality improvementReduce defect densityOptical wave guidanceLaser detailsThreading dislocationsDevice material

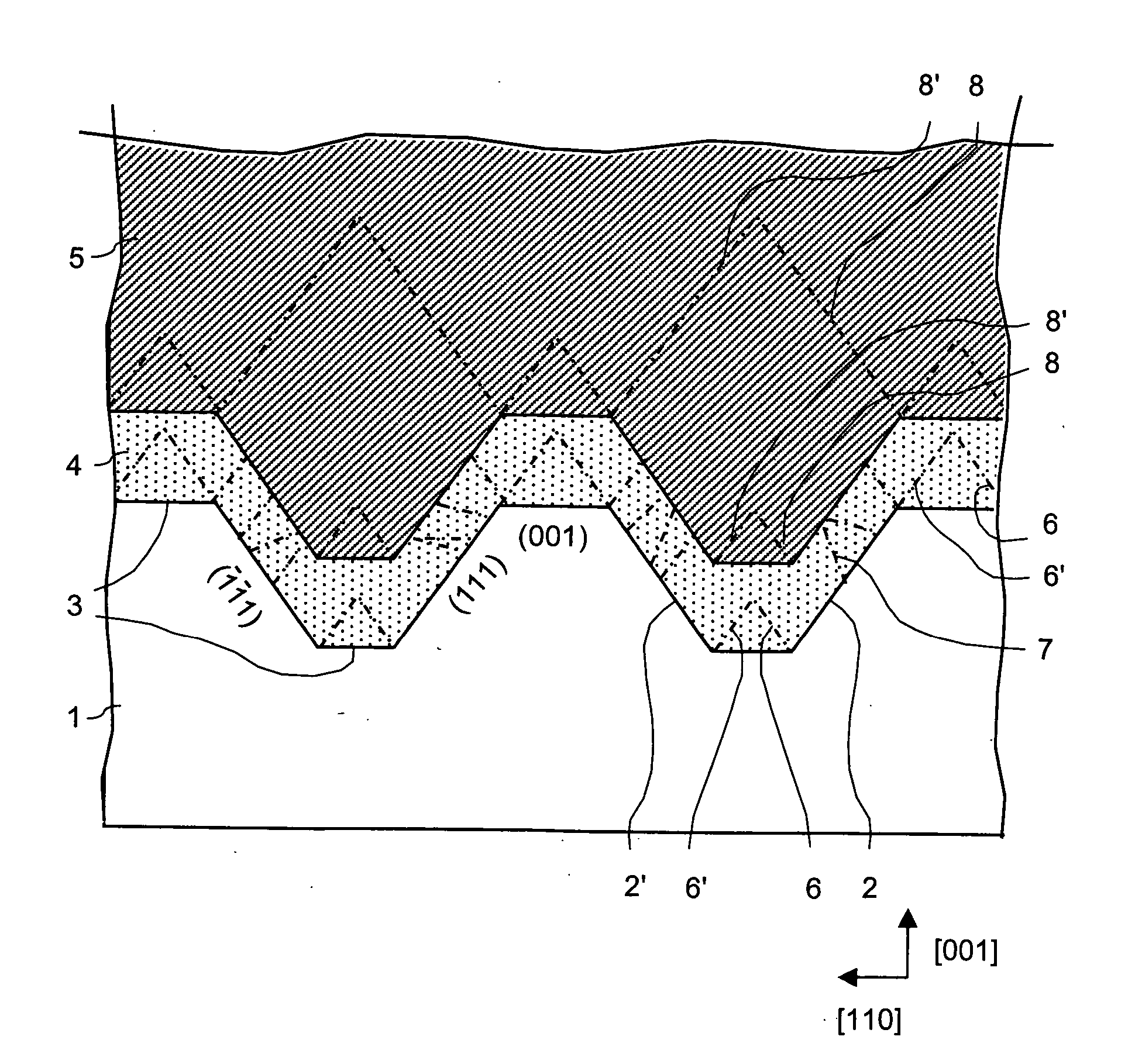

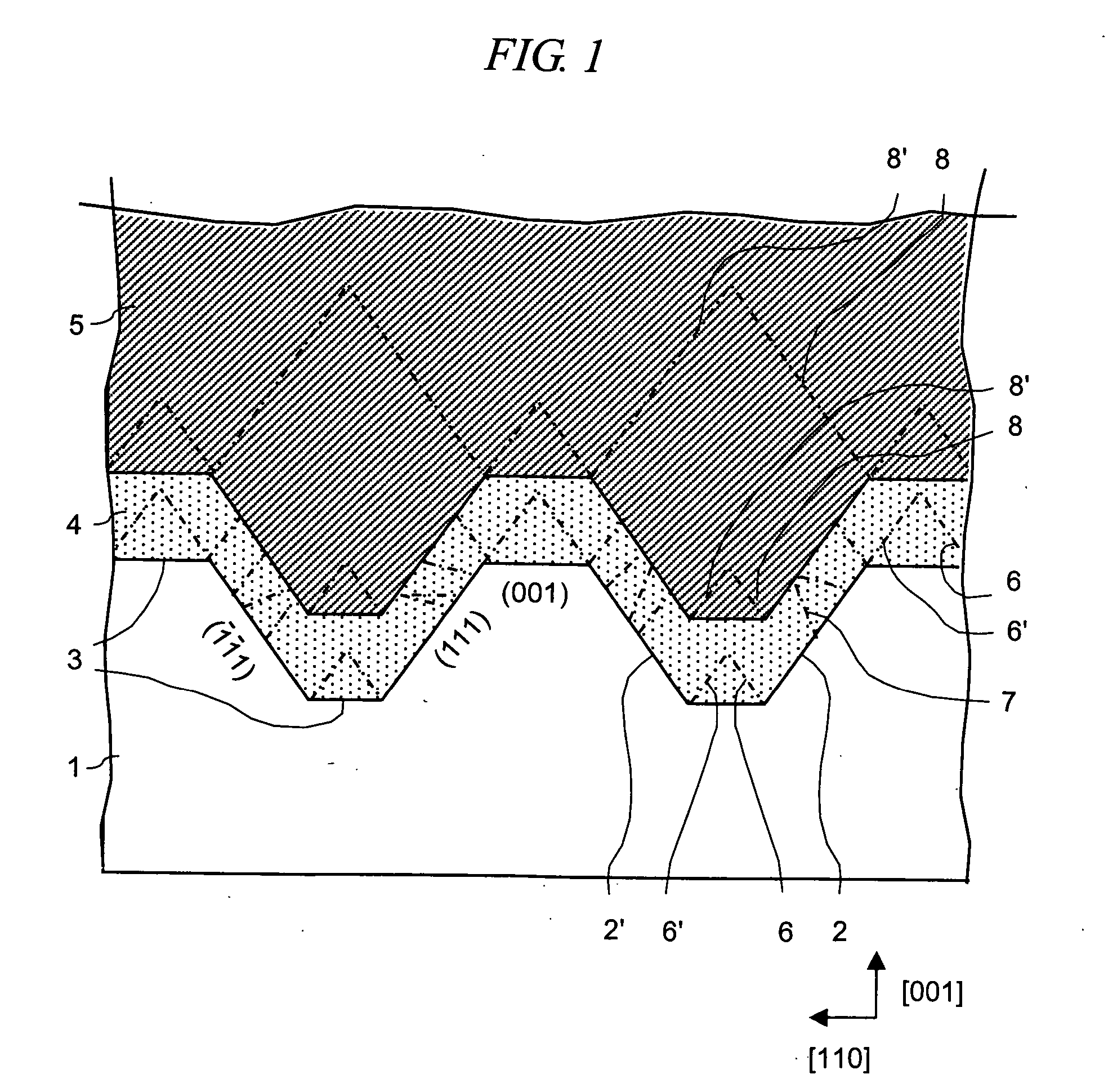

A high quality silicon carbide (SiC) layer being substantially lower in threading dislocation density than a prior layer is formed on silicon (Si) substrate. A semiconductor device is fabricated in such a way that a semiconductor buffer layer containing Si in part and being higher in defect density than a Si substrate is formed on the Si substrate on the upper portion of which are formed a plurality of pairs of facets being mirror-symmetrical to the surface orientation of a semiconductor substrate, further on the top of the layer a SiC layer is sequentially formed.

Owner:HITACHI LTD

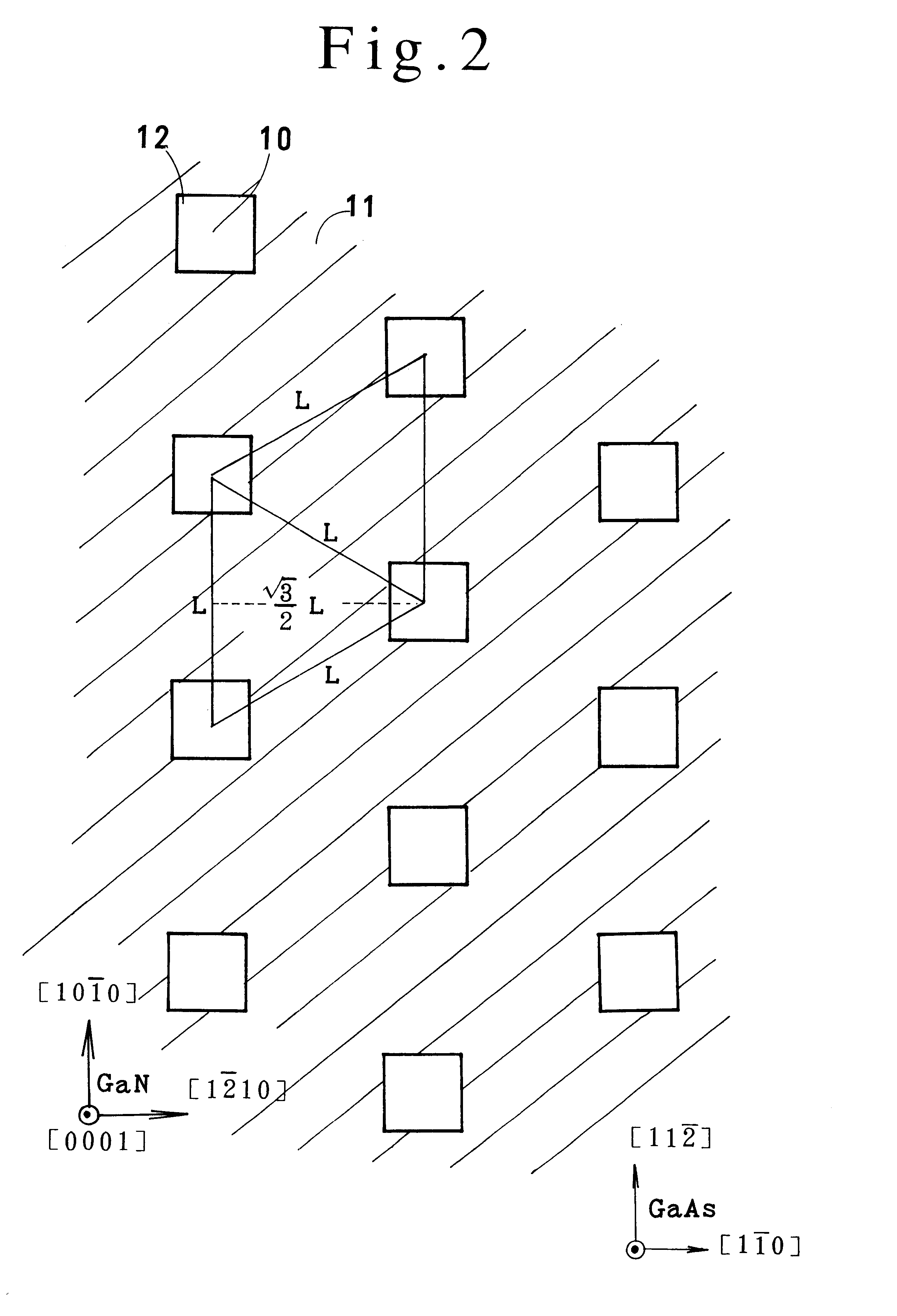

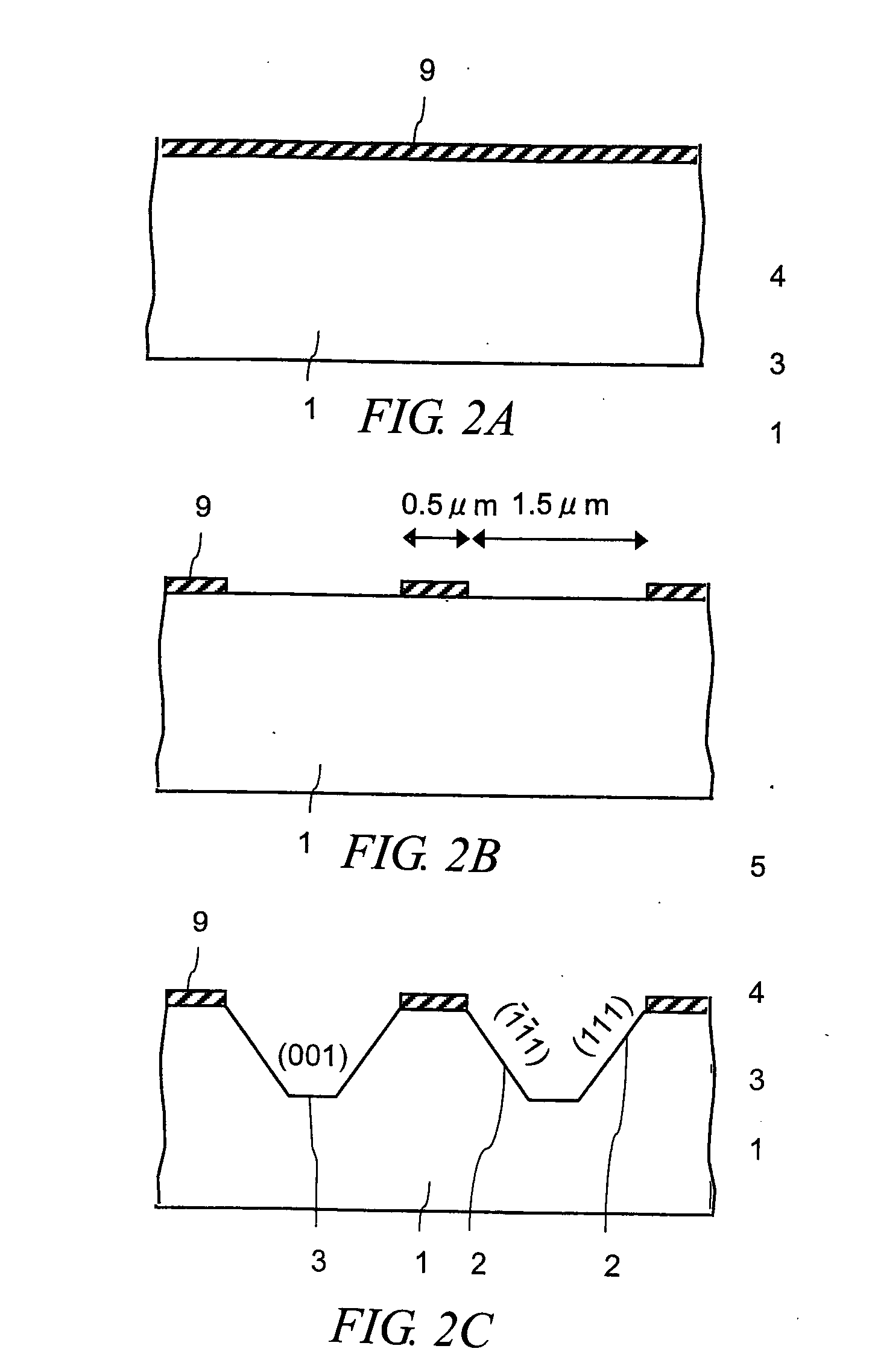

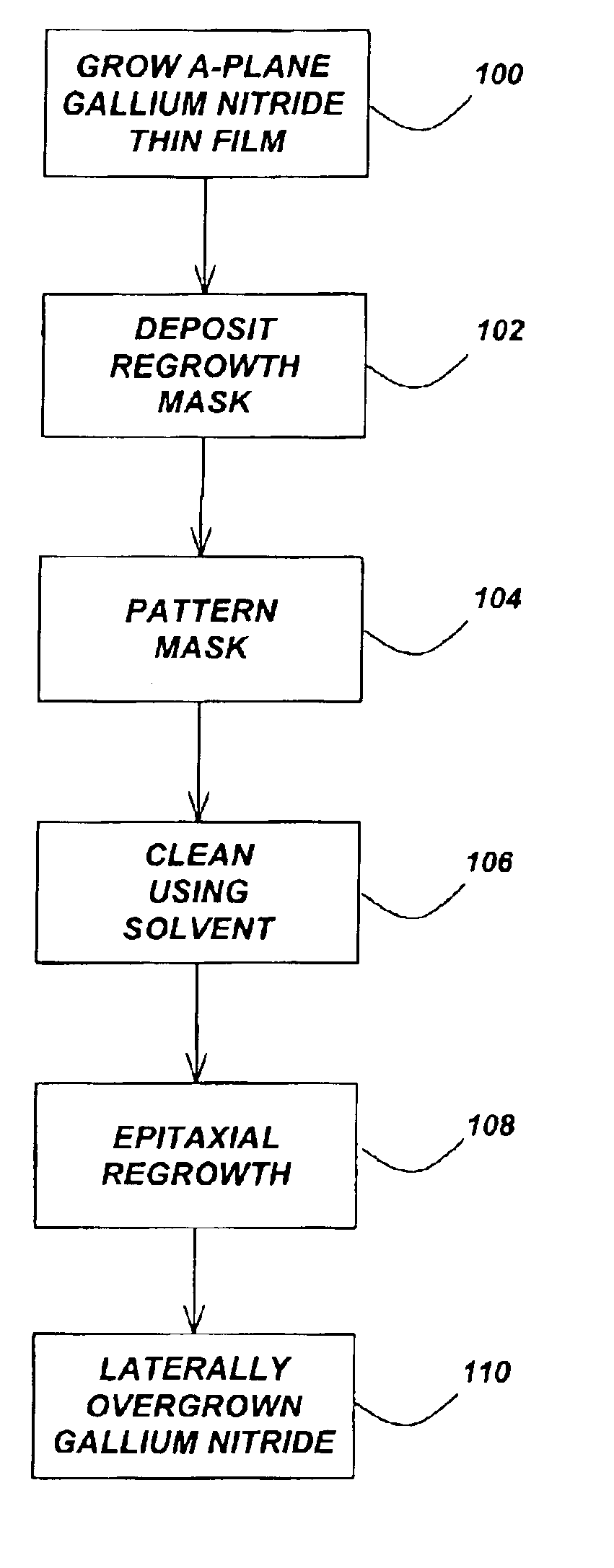

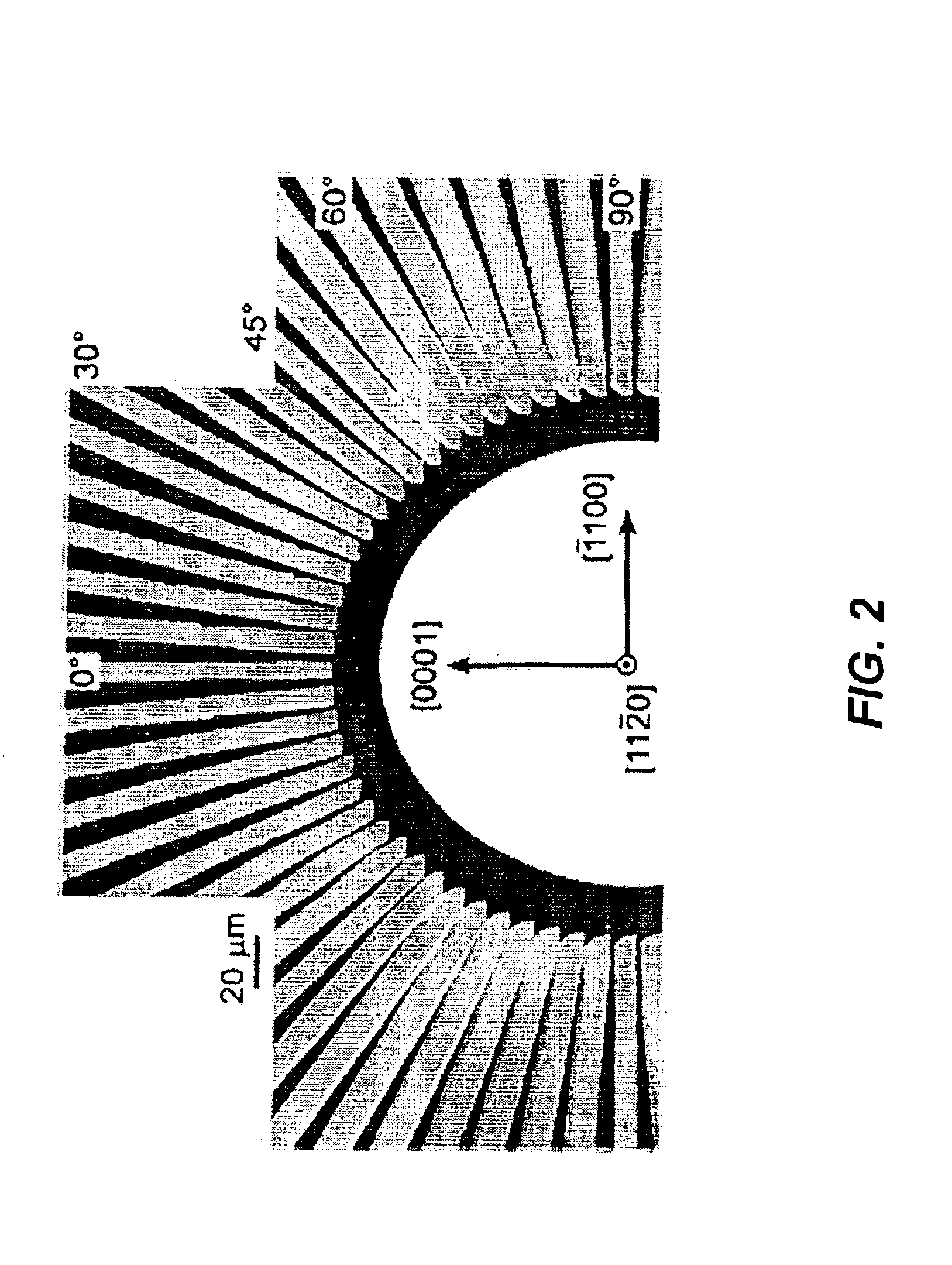

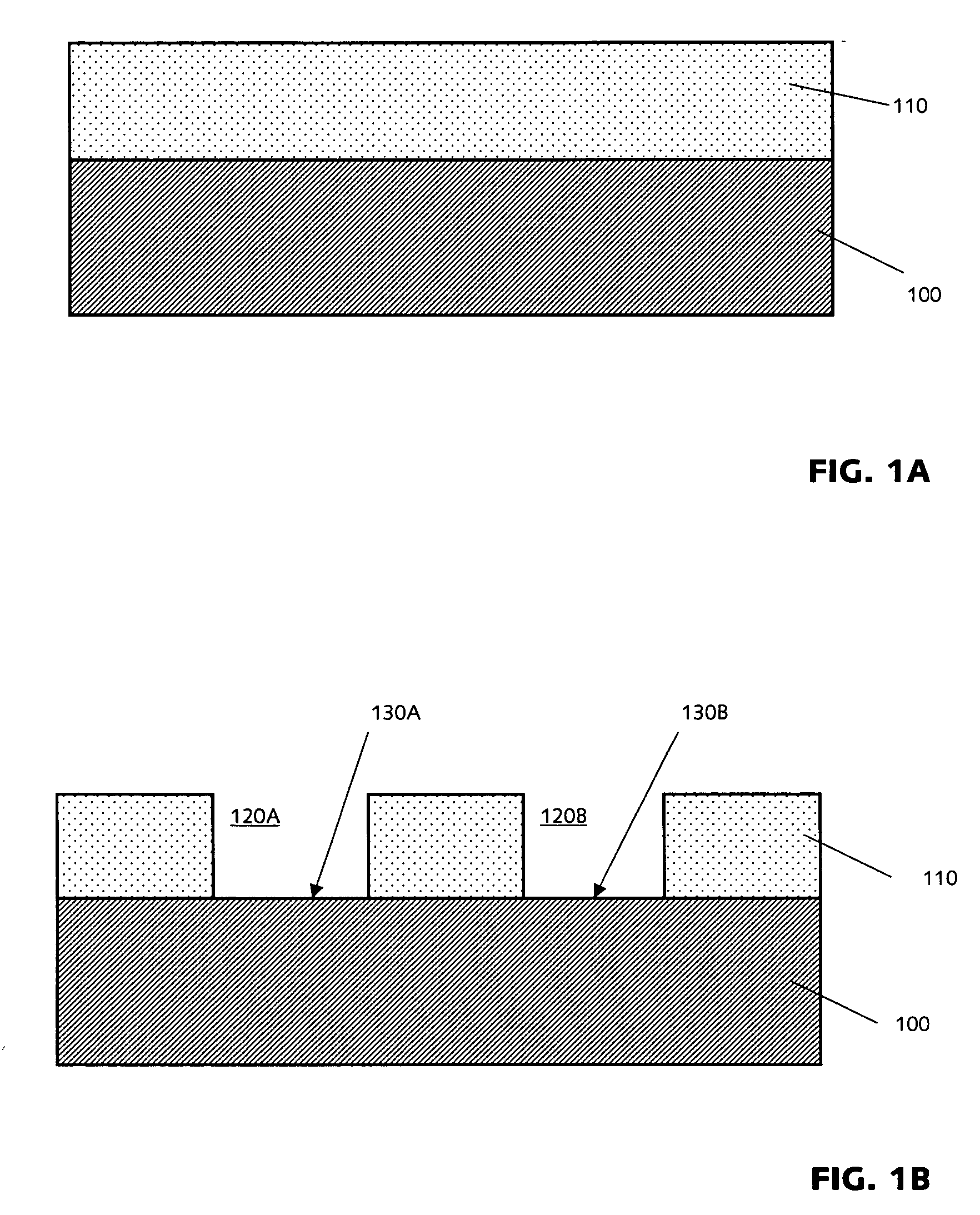

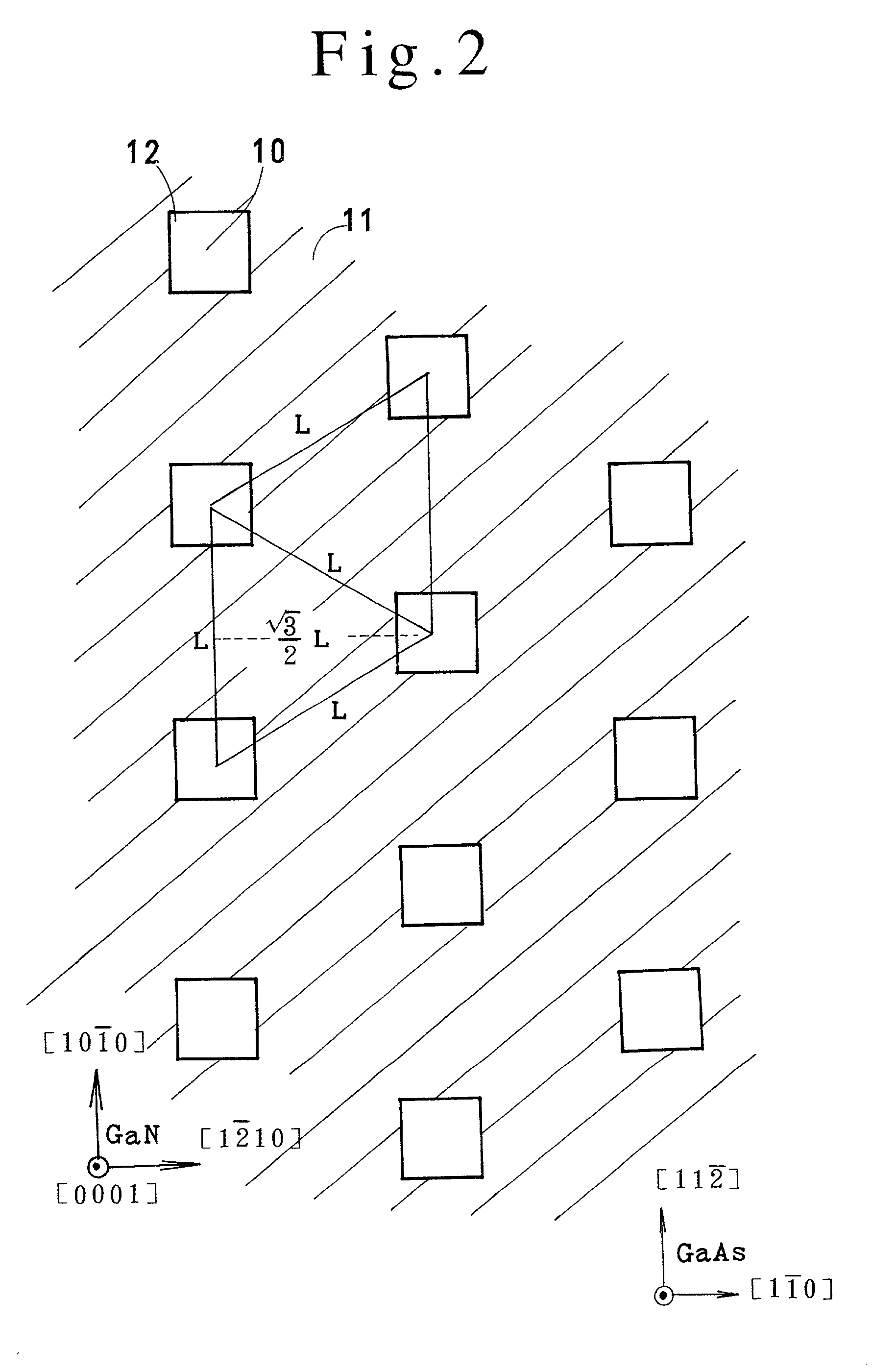

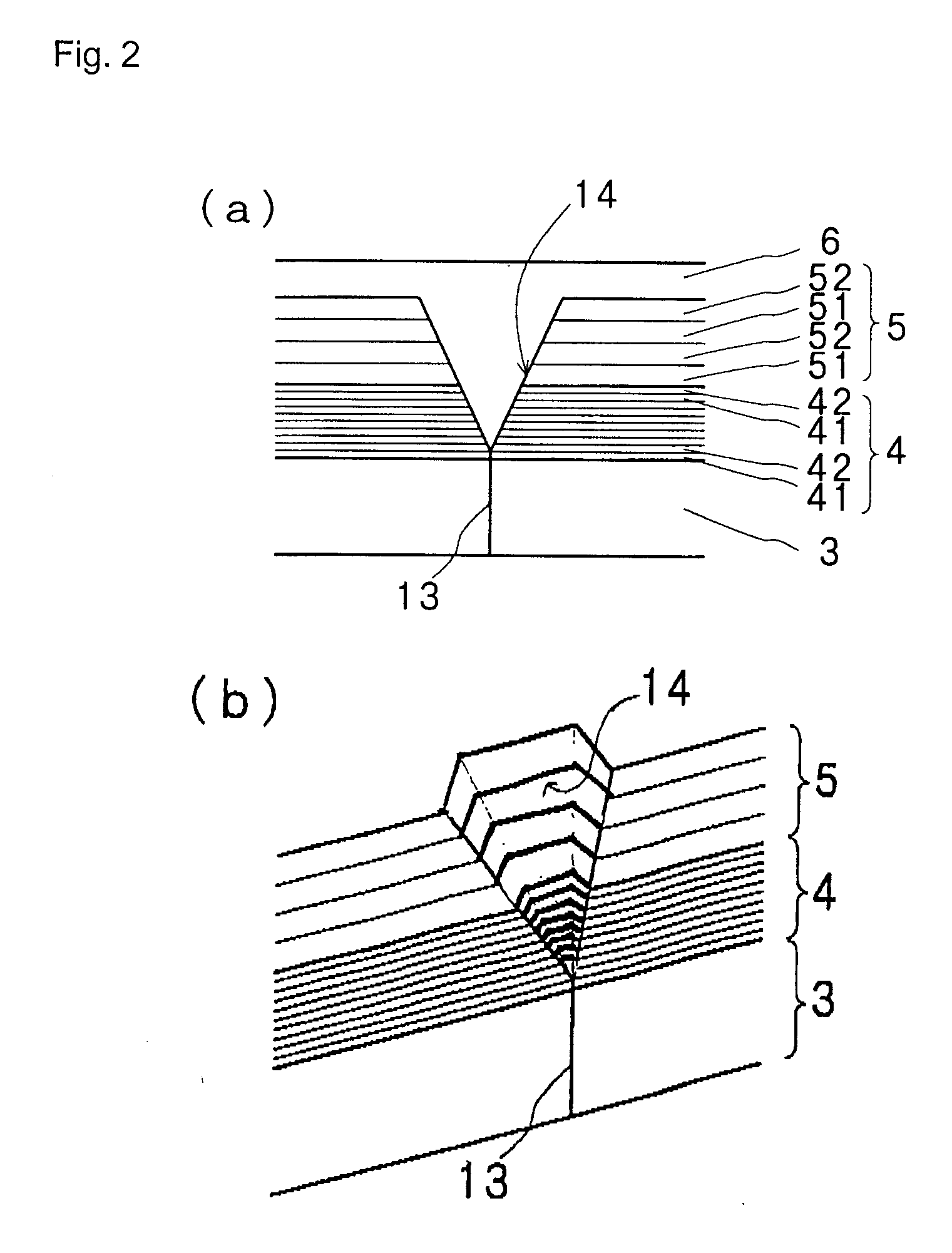

Dislocation reduction in non-polar gallium nitride thin films

InactiveUS6900070B2Reduce threading dislocationReduce misalignmentPolycrystalline material growthLaser detailsThreading dislocationsDielectric

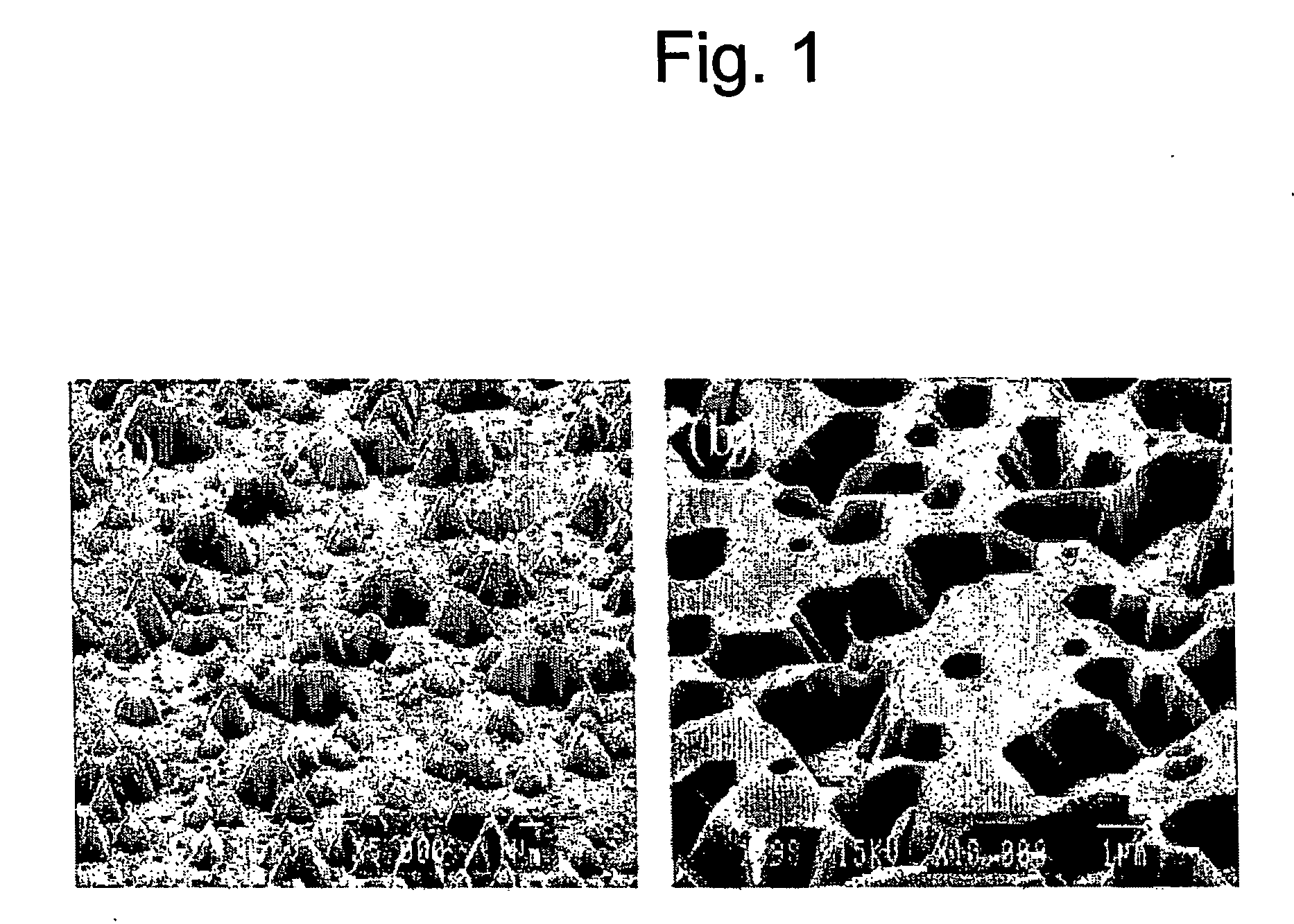

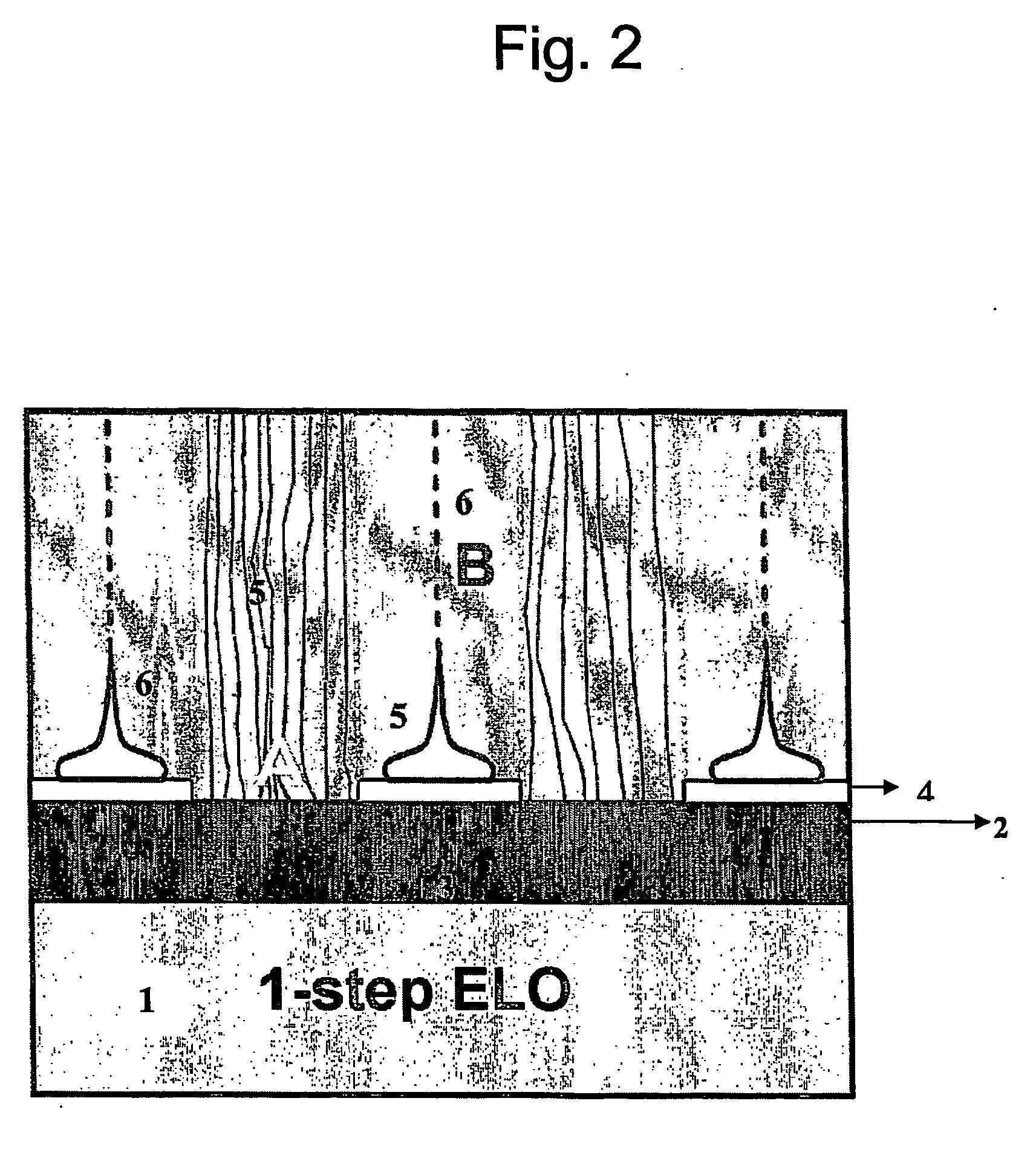

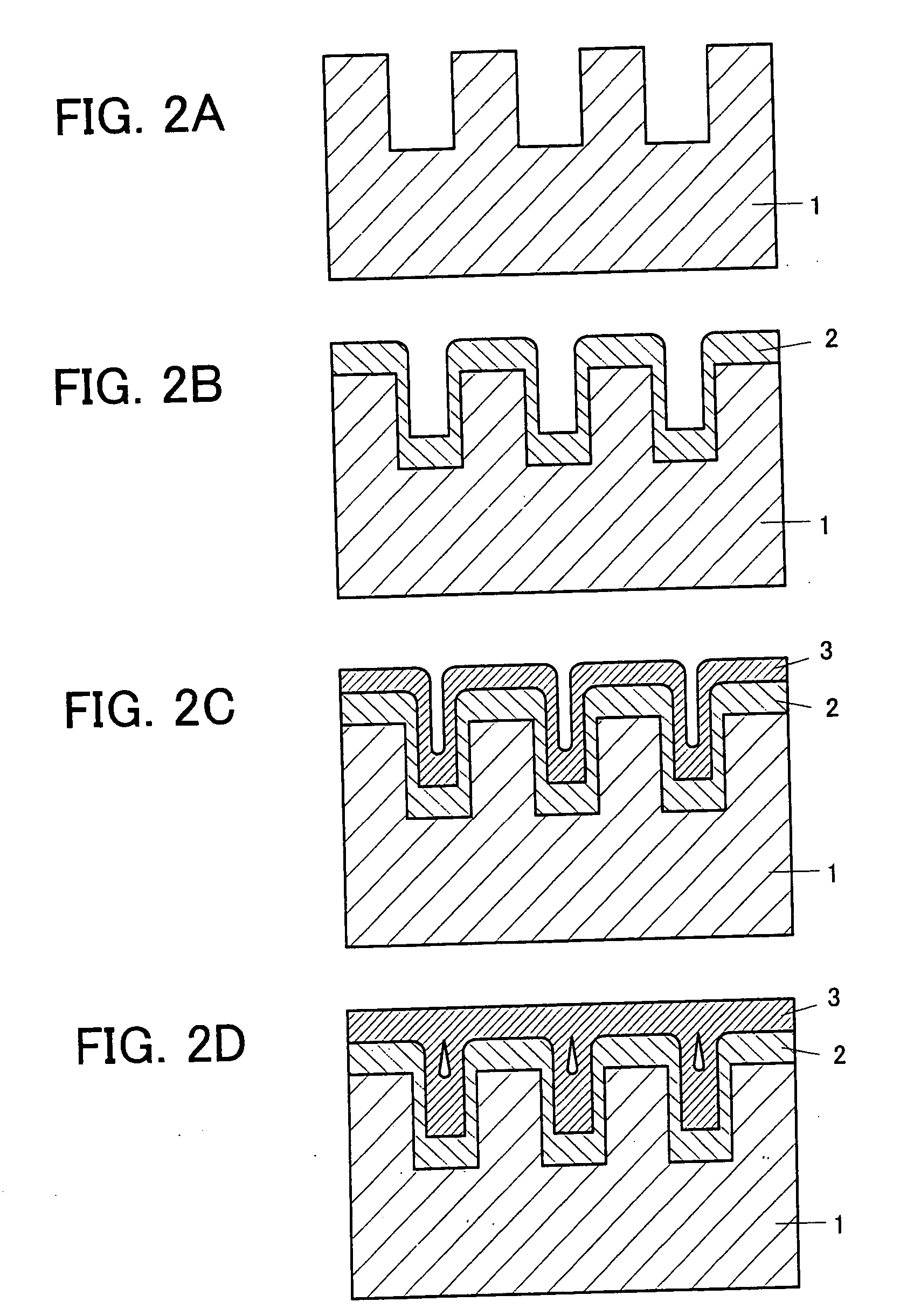

Lateral epitaxial overgrowth of non-polar (11{overscore (2)}0) a-plane GaN seed layers reduces threading dislocations in the GaN films. First, a thin patterned dielectric mask is applied to the seed layer. Second, a selective epitaxial regrowth is performed to achieve a lateral overgrowth based on the patterned mask. Upon regrowth, the GaN films initially grow vertically through openings in the dielectric mask before laterally overgrowing the mask in directions perpendicular to the vertical growth direction. Threading dislocations are reduced in the overgrown regions by (1) the mask blocking the propagation of dislocations vertically into the growing film and (2) the bending of dislocations through the transition from vertical to lateral growth.

Owner:RGT UNIV OF CALIFORNIA

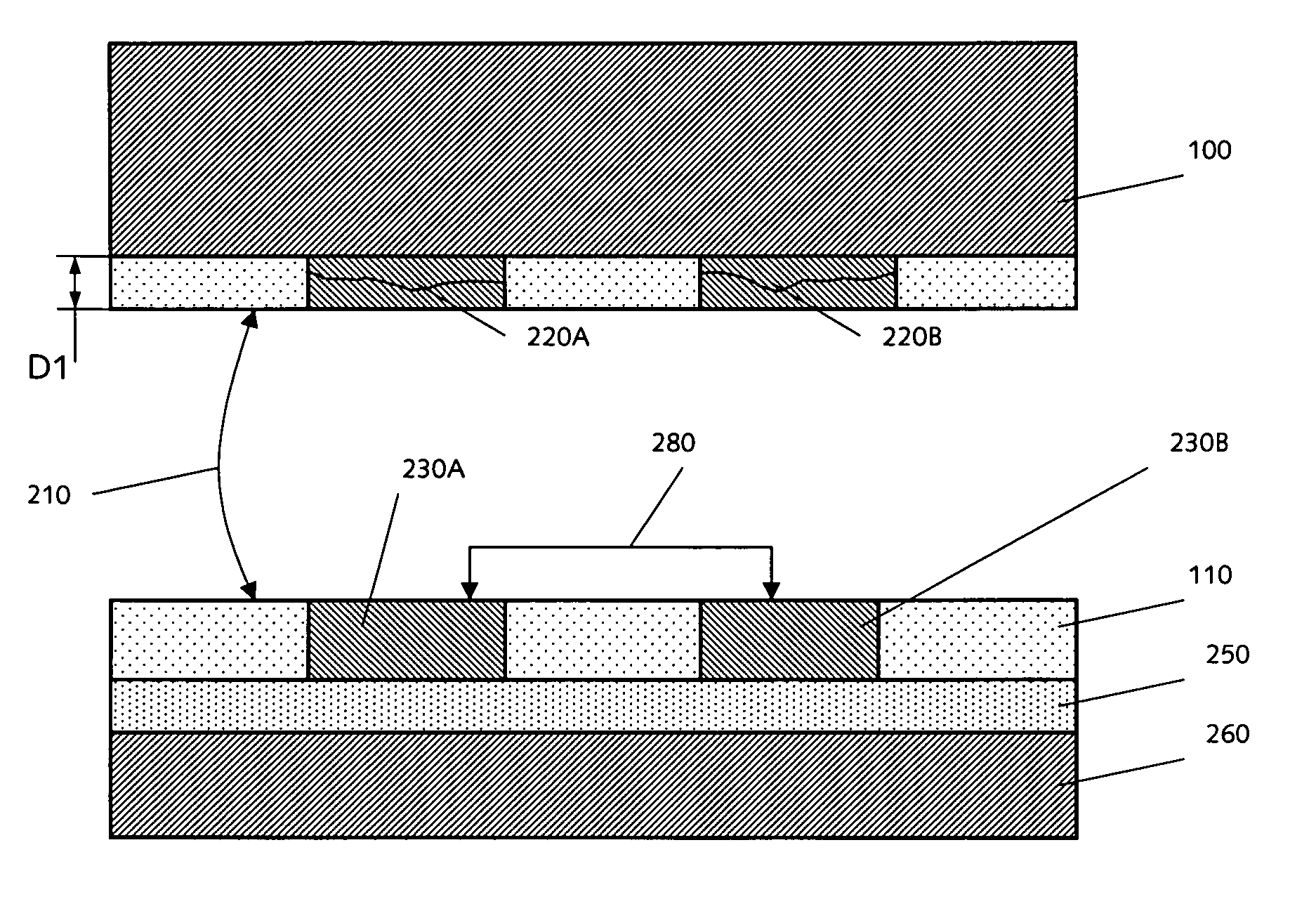

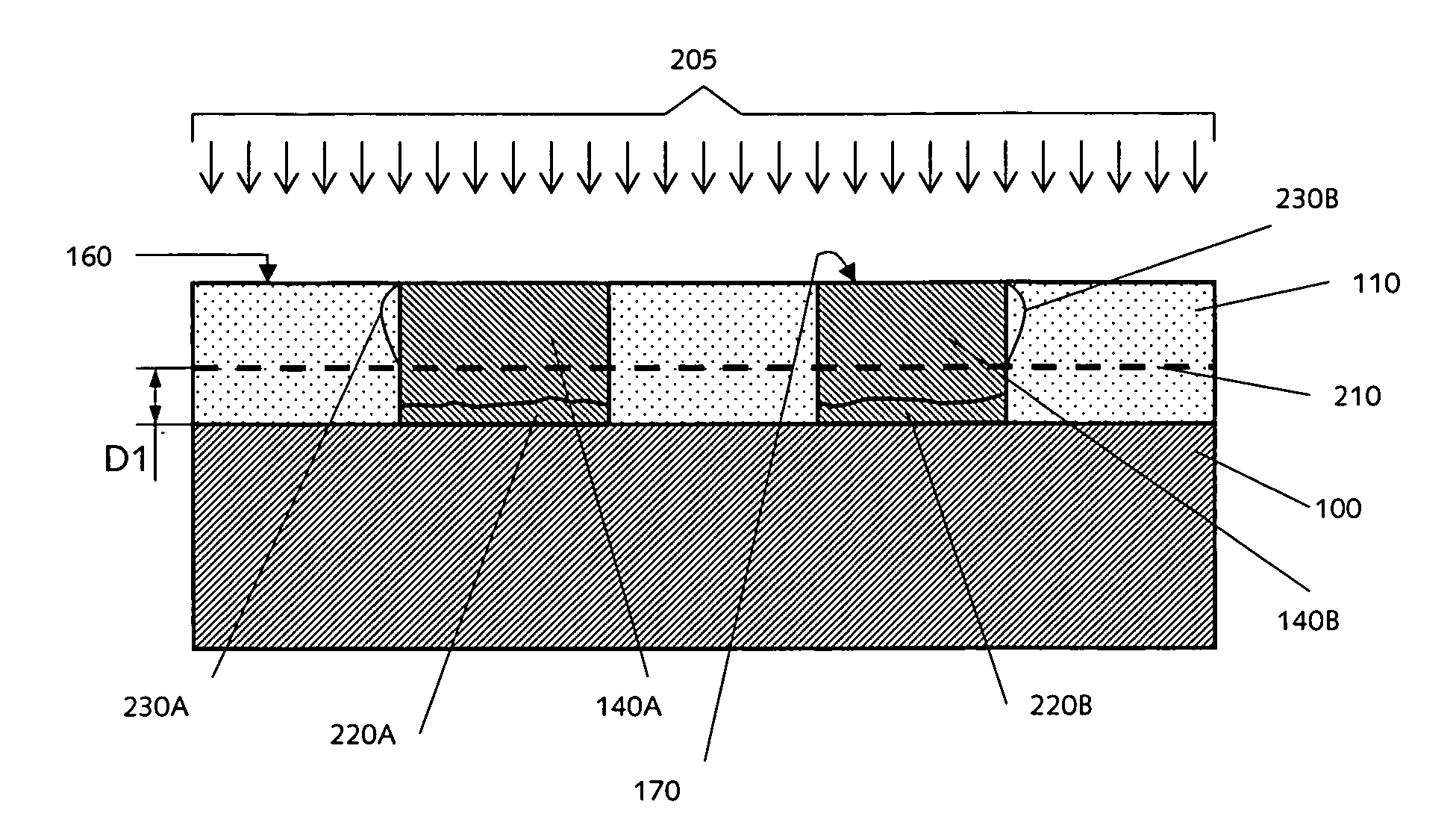

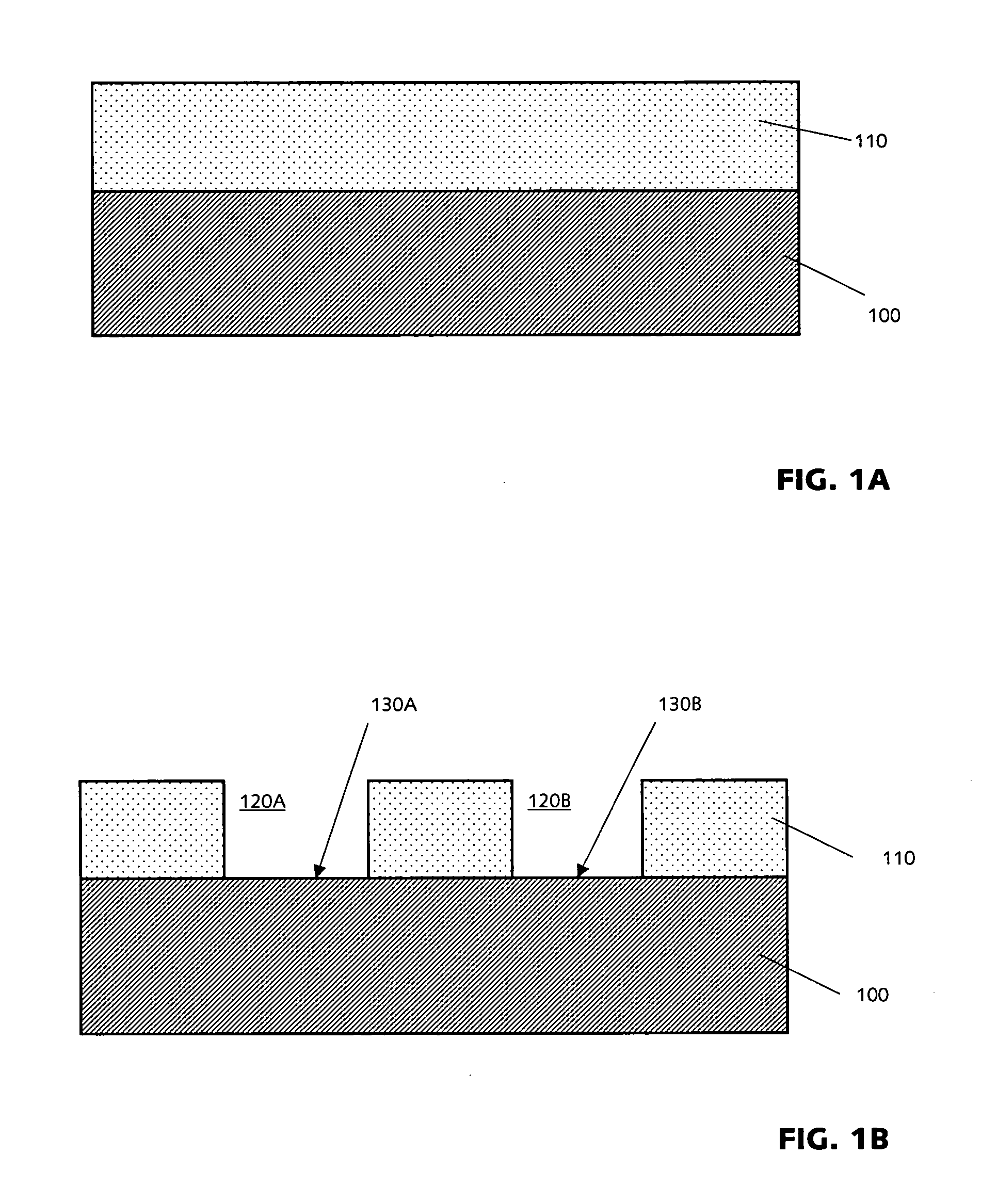

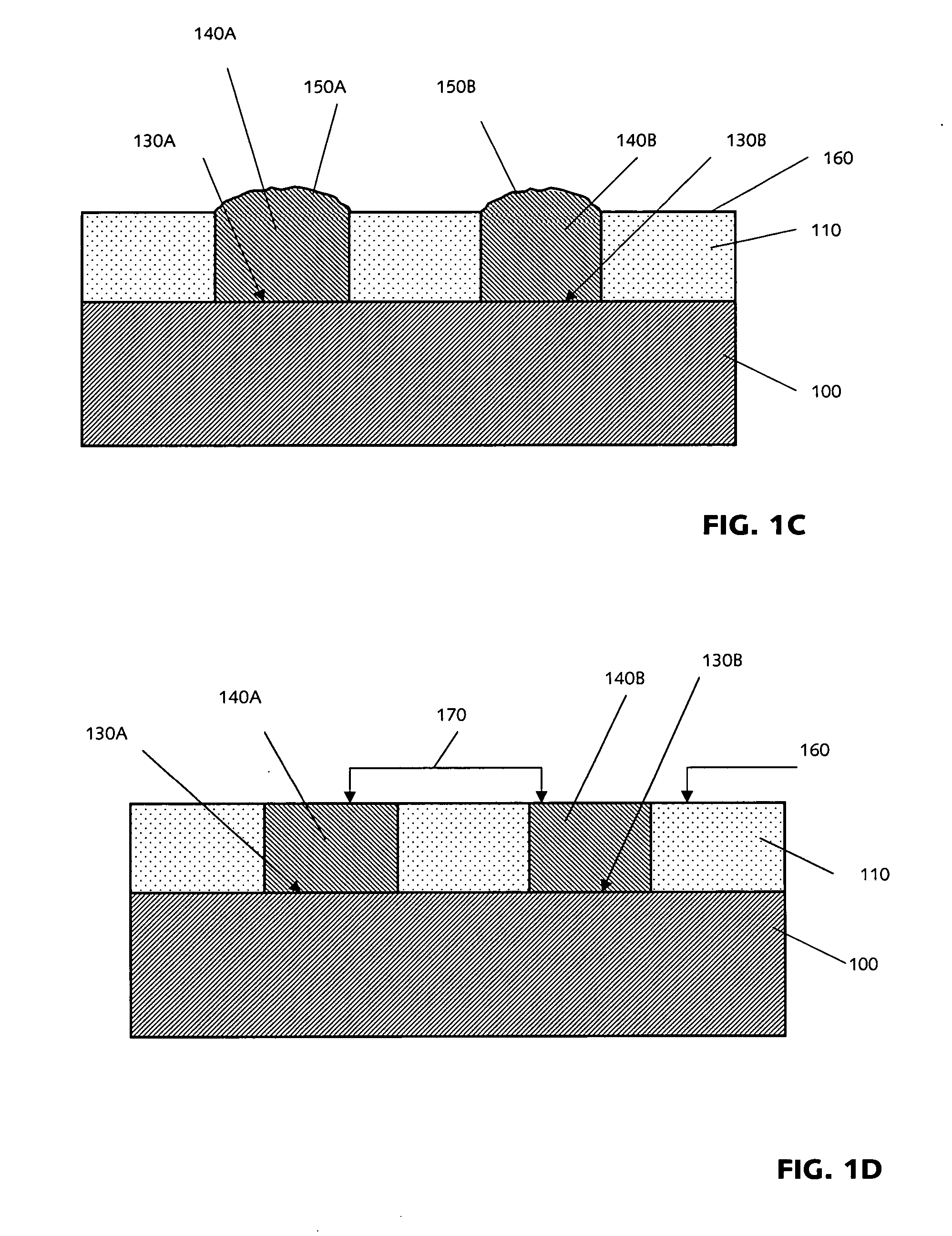

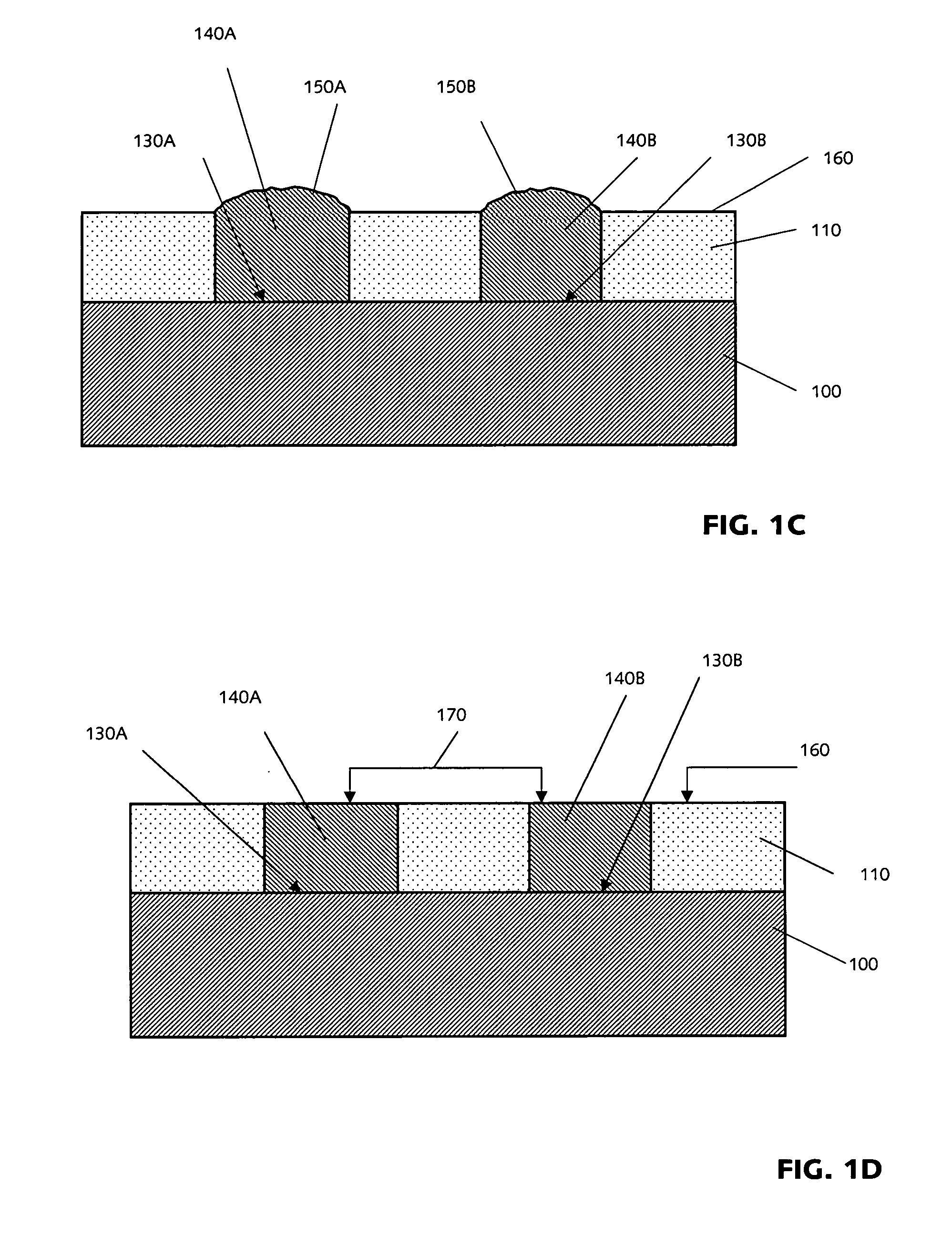

Methods for integrating lattice-mismatched semiconductor structure on insulators

InactiveUS20070054467A1Improve functionalityImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingThreading dislocationsSemiconductor structure

Monolithic lattice-mismatched semiconductor heterostructures are fabricated by bonding patterned substrates with alternative active-area materials formed thereon to a rigid dielectric platform and then removing the highly-defective interface areas along with the underlying substrates to produce alternative active-area regions disposed over the insulator and substantially exhausted of misfit and threading dislocations.

Owner:AMBERWAVE SYST

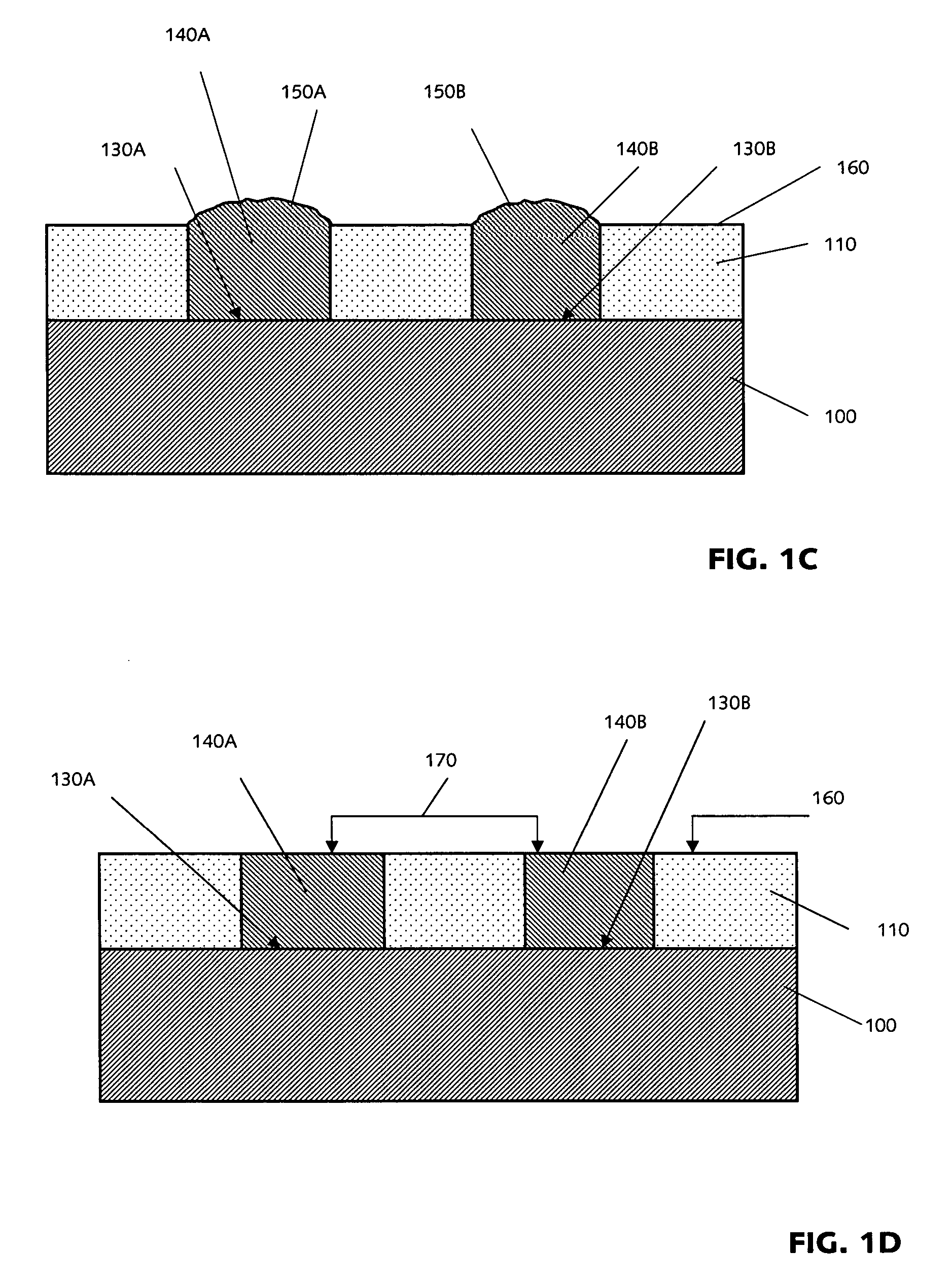

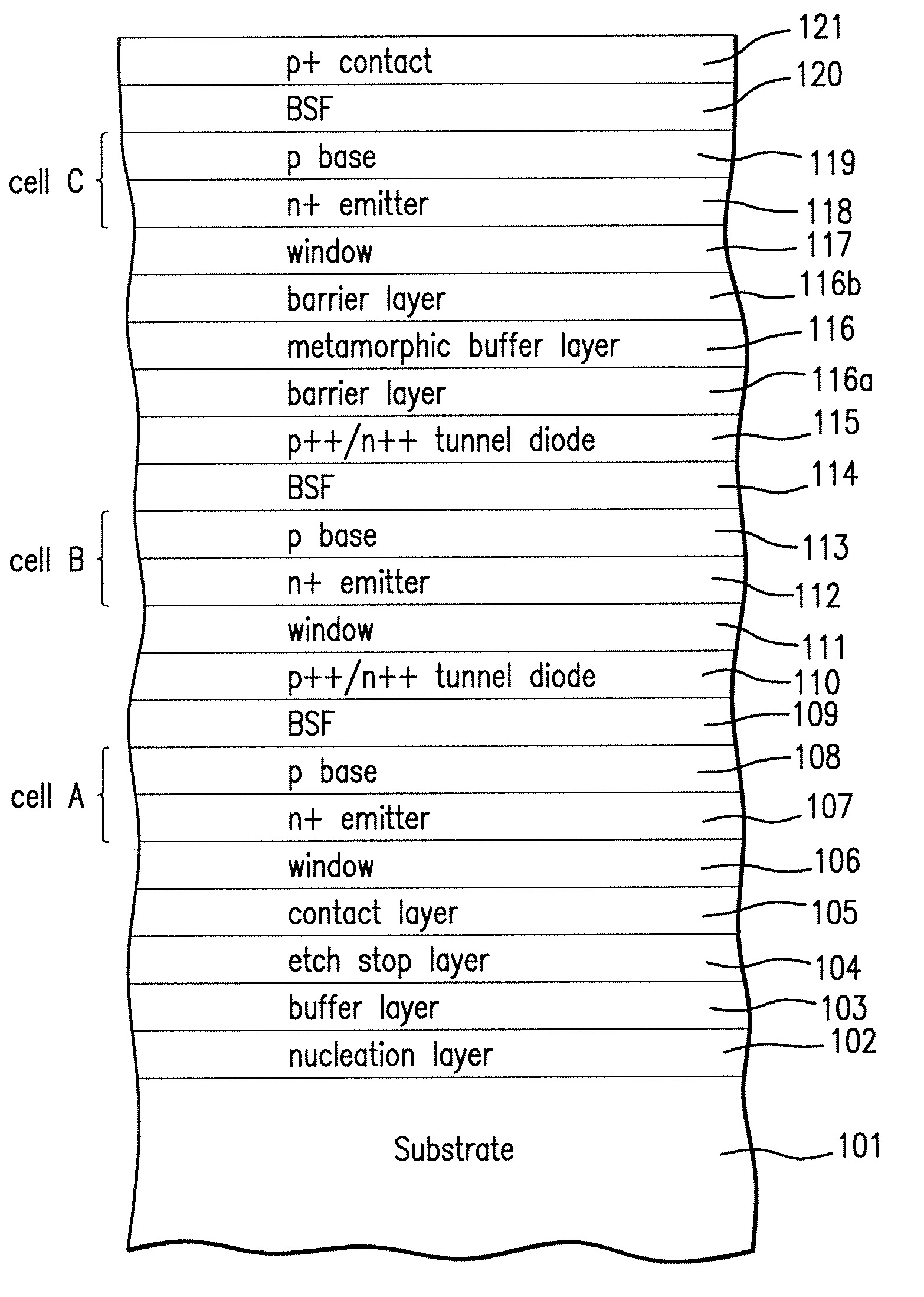

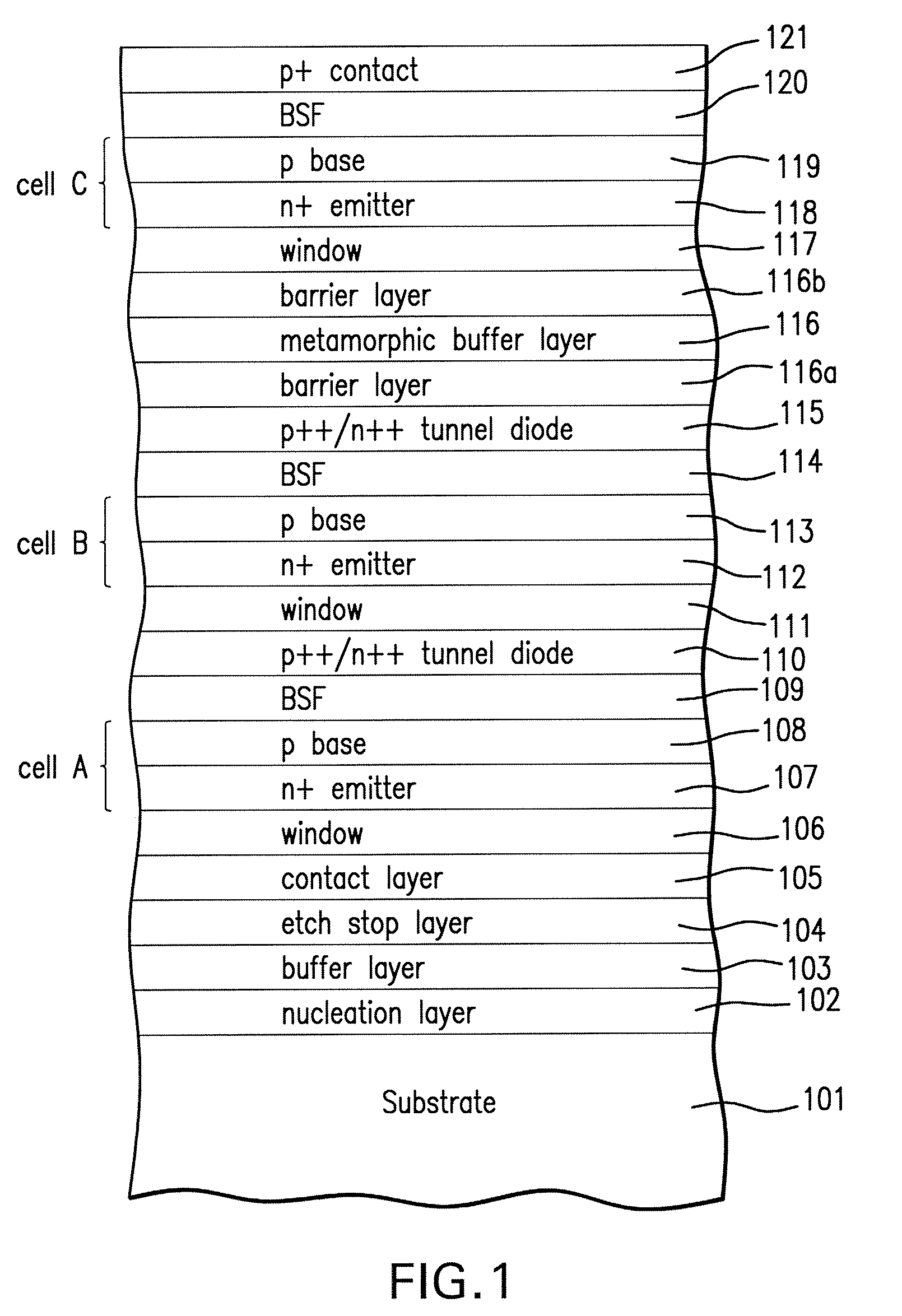

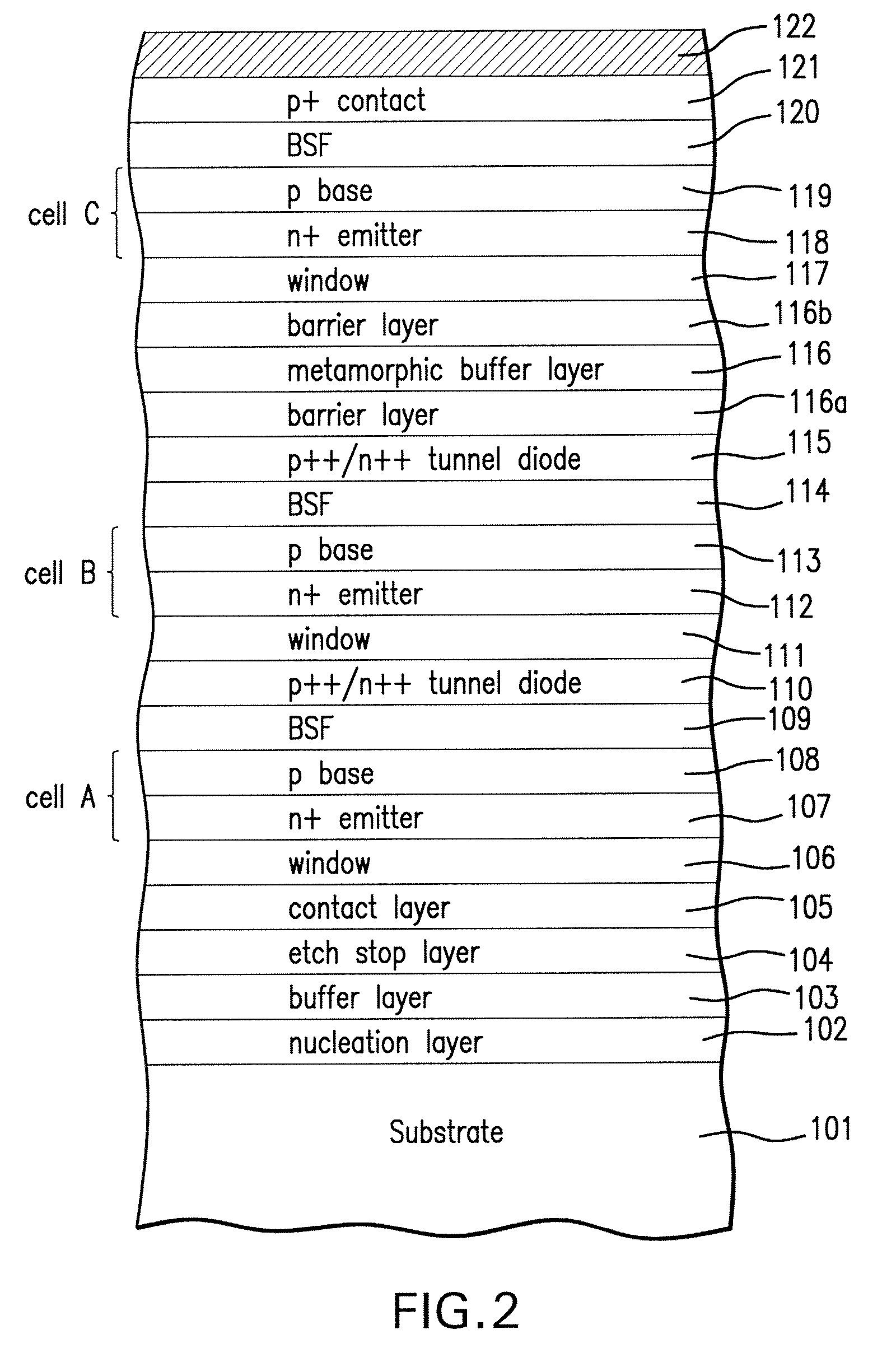

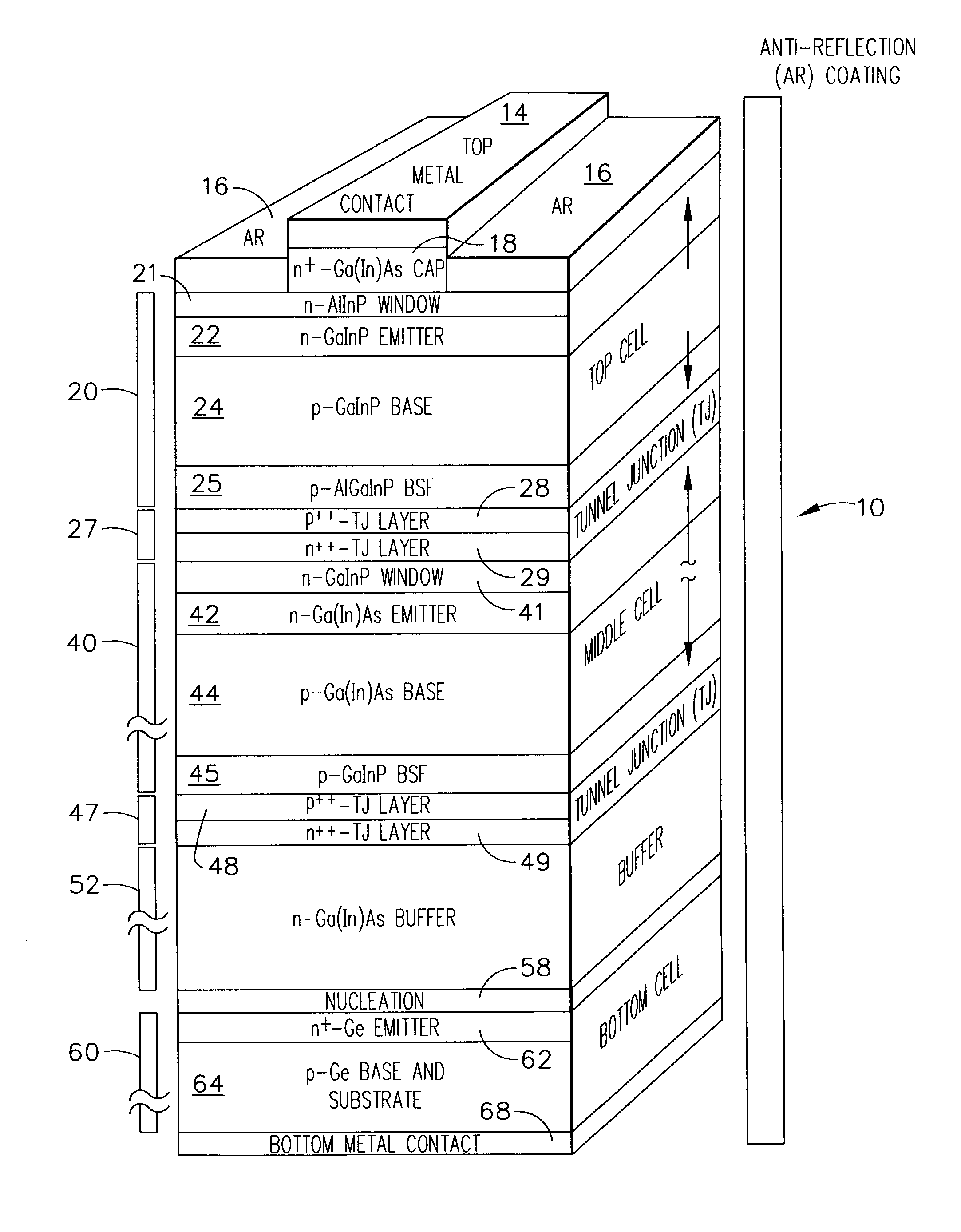

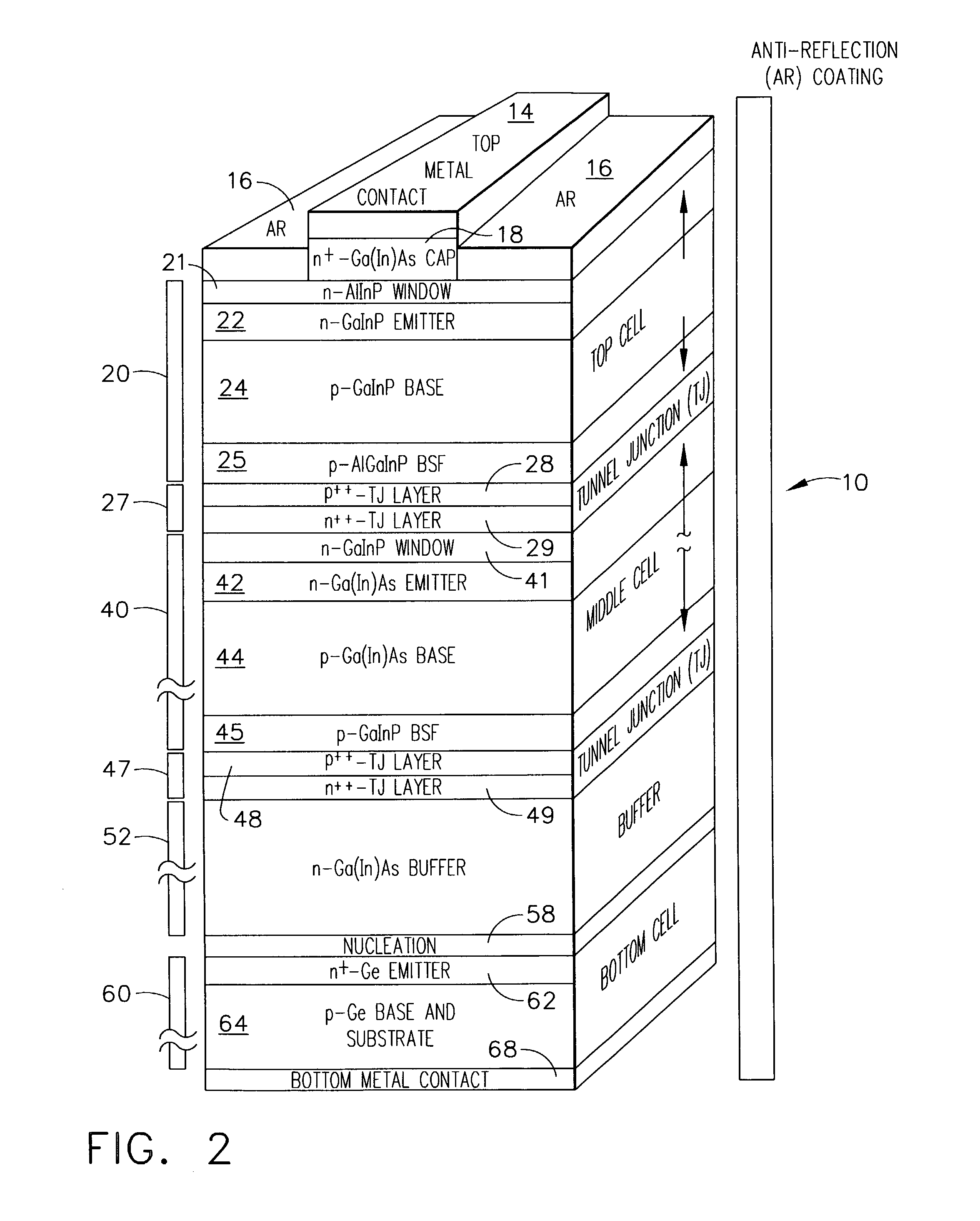

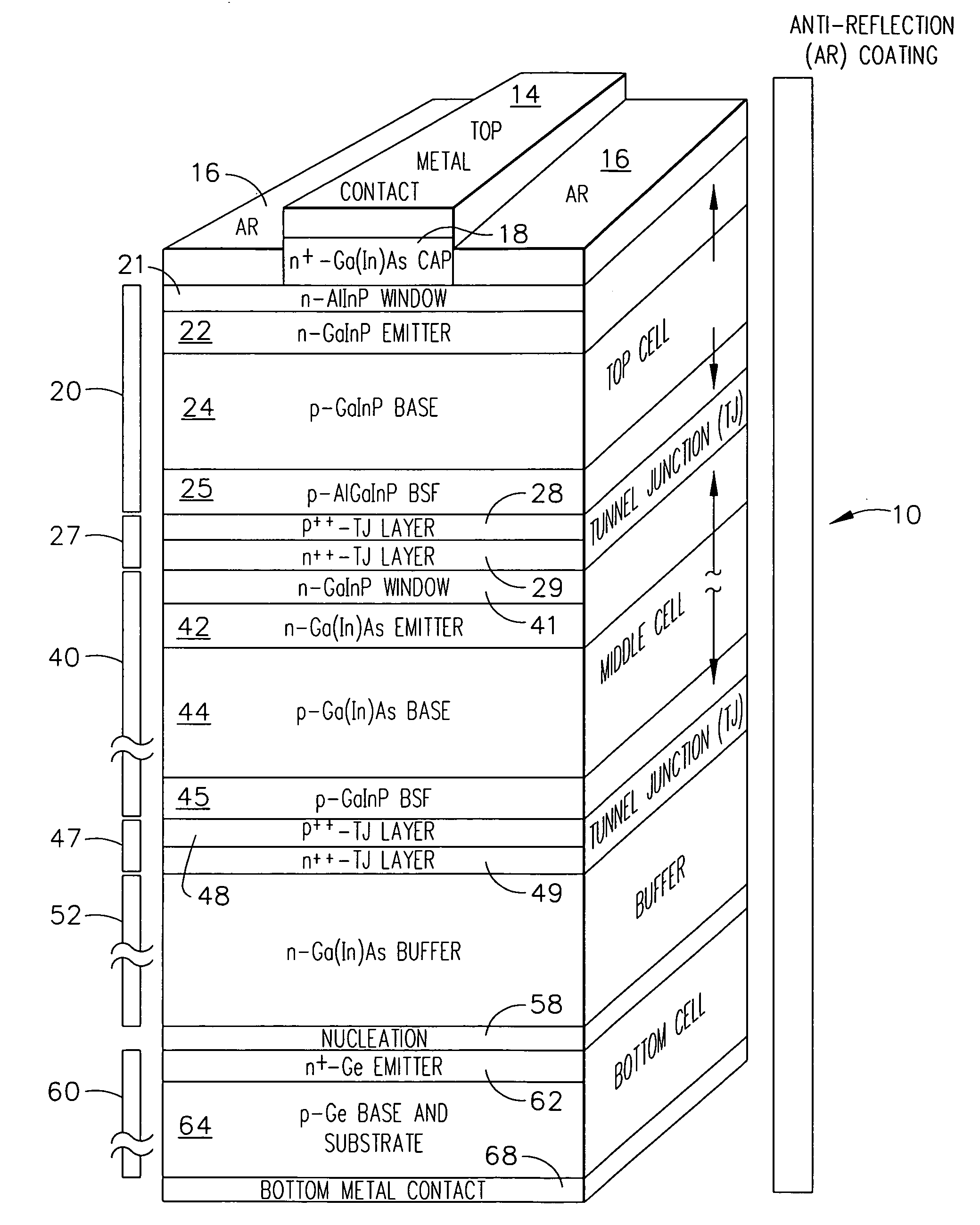

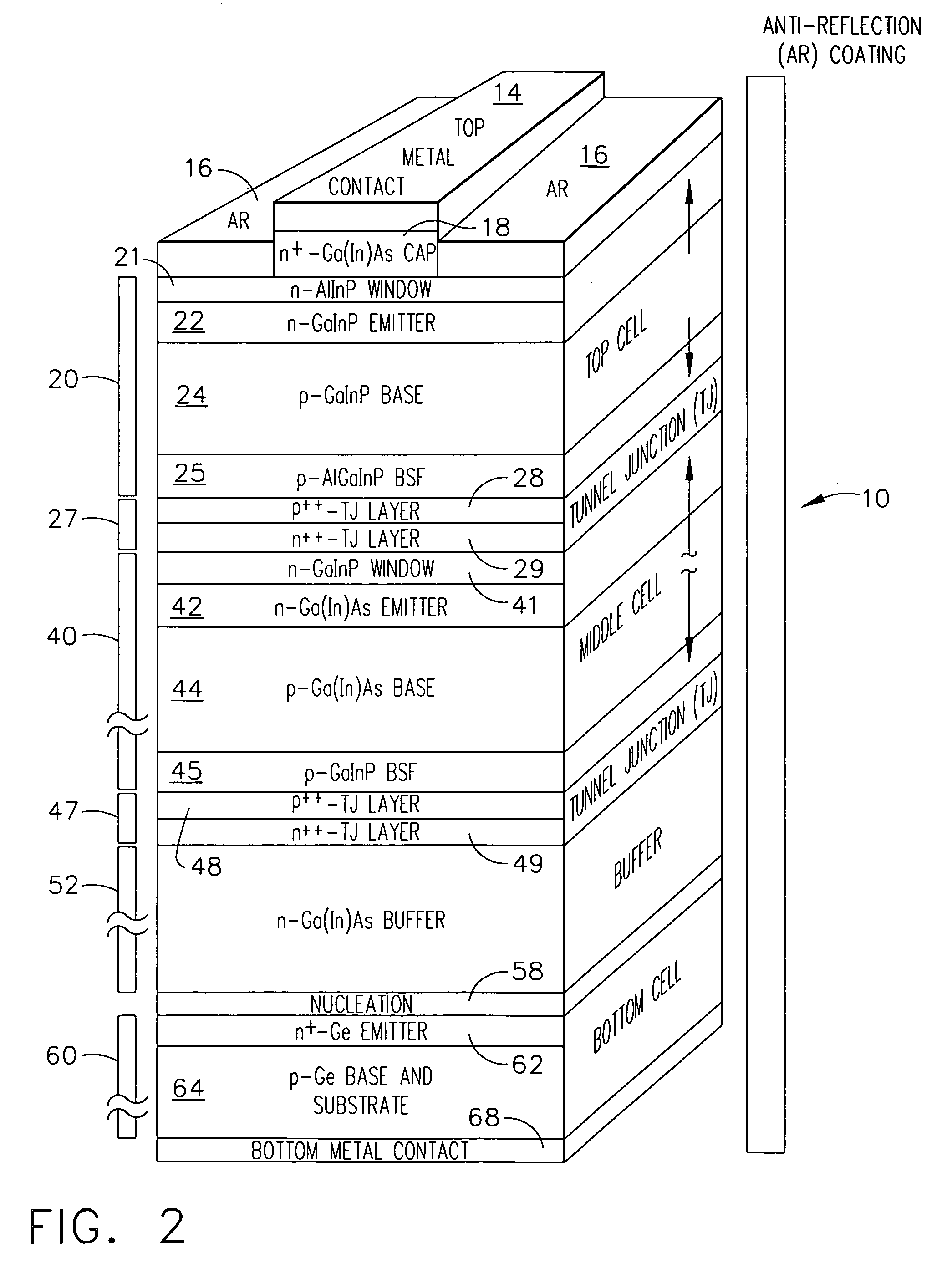

Barrier Layers In Inverted Metamorphic Multijunction Solar Cells

InactiveUS20090078309A1Semiconductor/solid-state device manufacturingPhotovoltaic energy generationThreading dislocationsSemiconductor materials

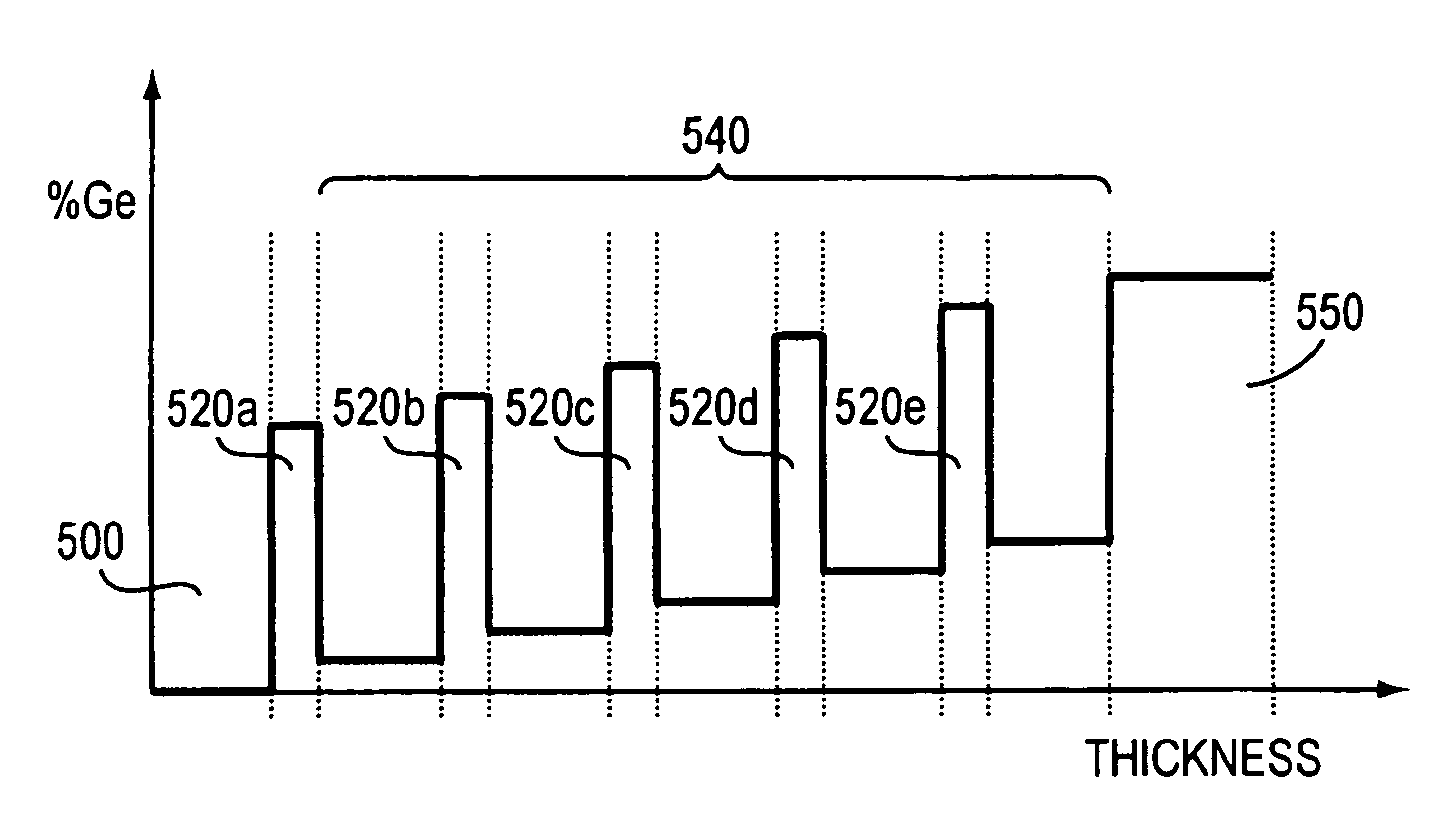

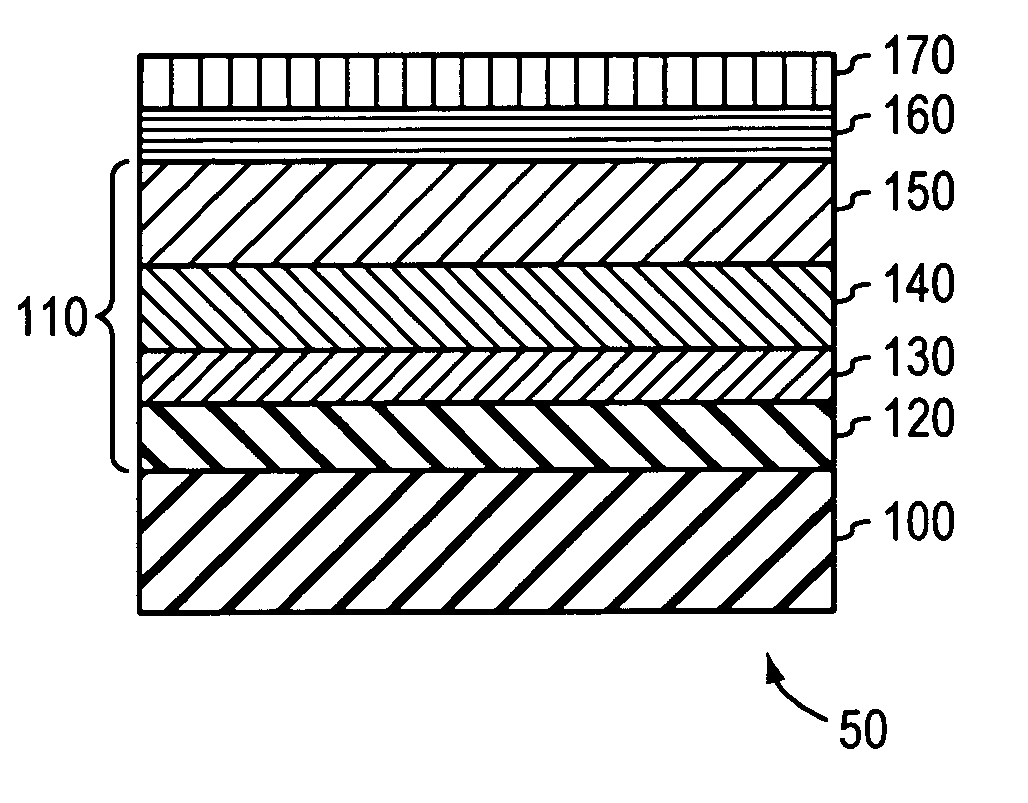

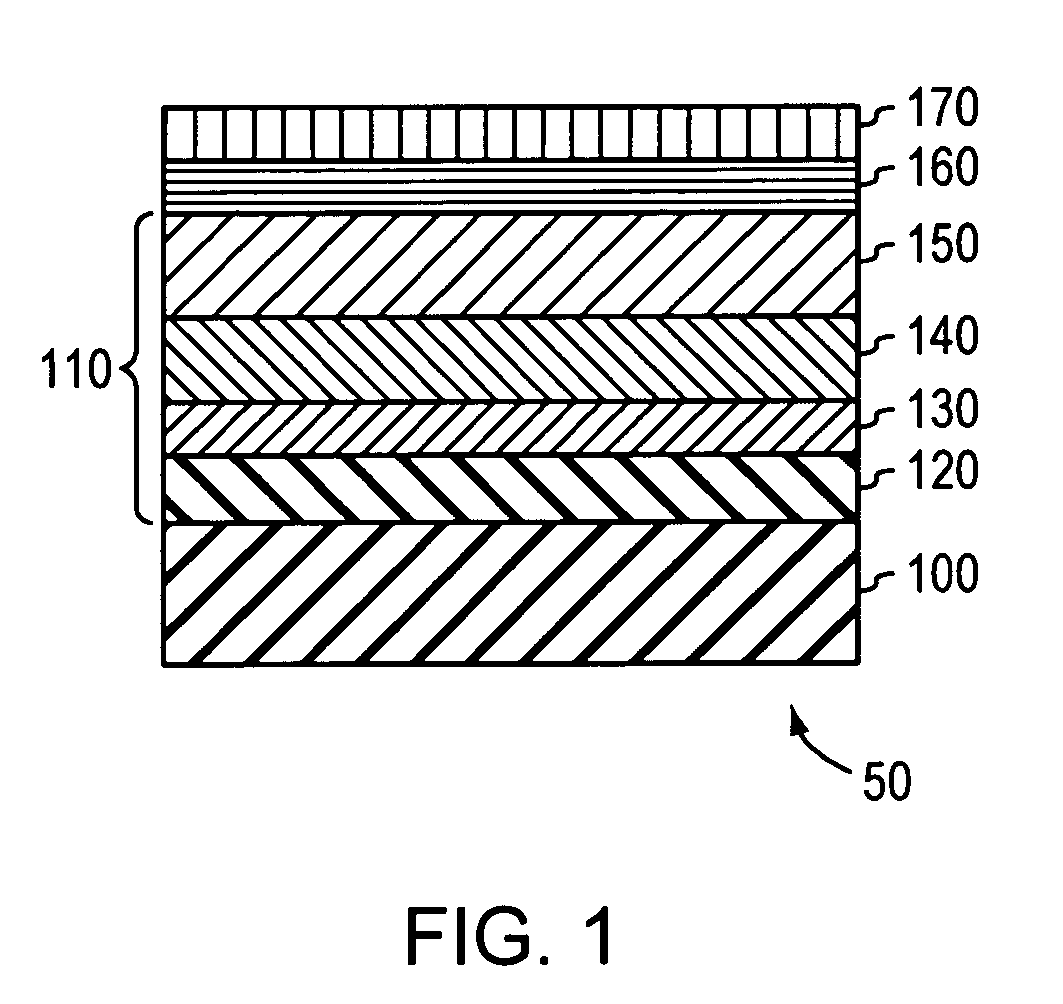

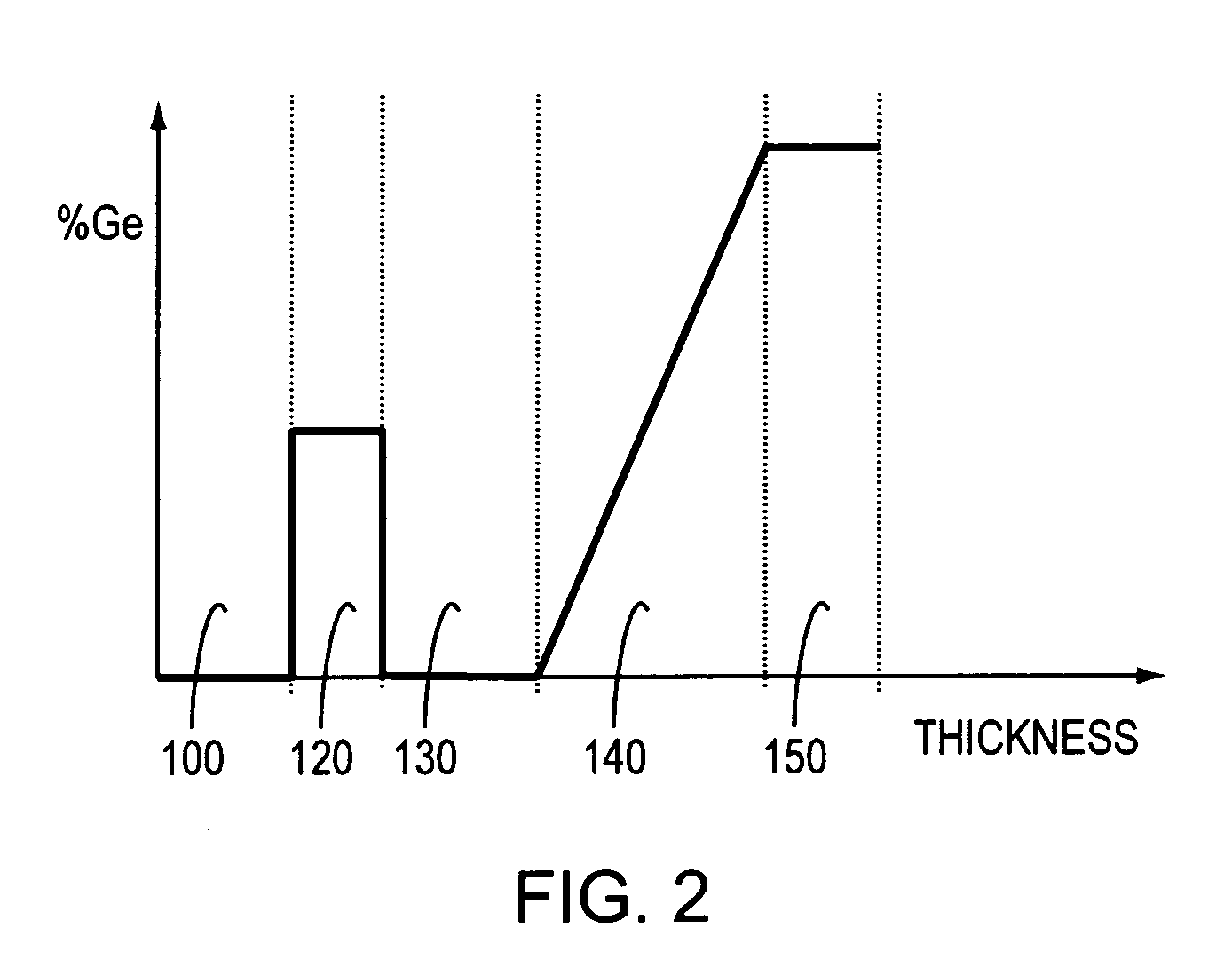

A method of forming a multijunction solar cell including an upper subcell, a middle subcell, and a lower subcell, the method including: providing first substrate for the epitaxial growth of semiconductor material; forming a first solar subcell on the substrate having a first band gap; forming a second solar subcell over the first solar subcell having a second band gap smaller than the first band gap; forming a barrier layer over the second subcell to reduce threading dislocations; forming a grading interlayer over the barrier layer, the grading interlayer having a third band gap greater than the second band gap; and forming a third solar subcell over the grading interlayer having a fourth band gap smaller than the second band gap such that the third subcell is lattice mismatched with respect to the second subcell.

Owner:SOLAERO TECH CORP

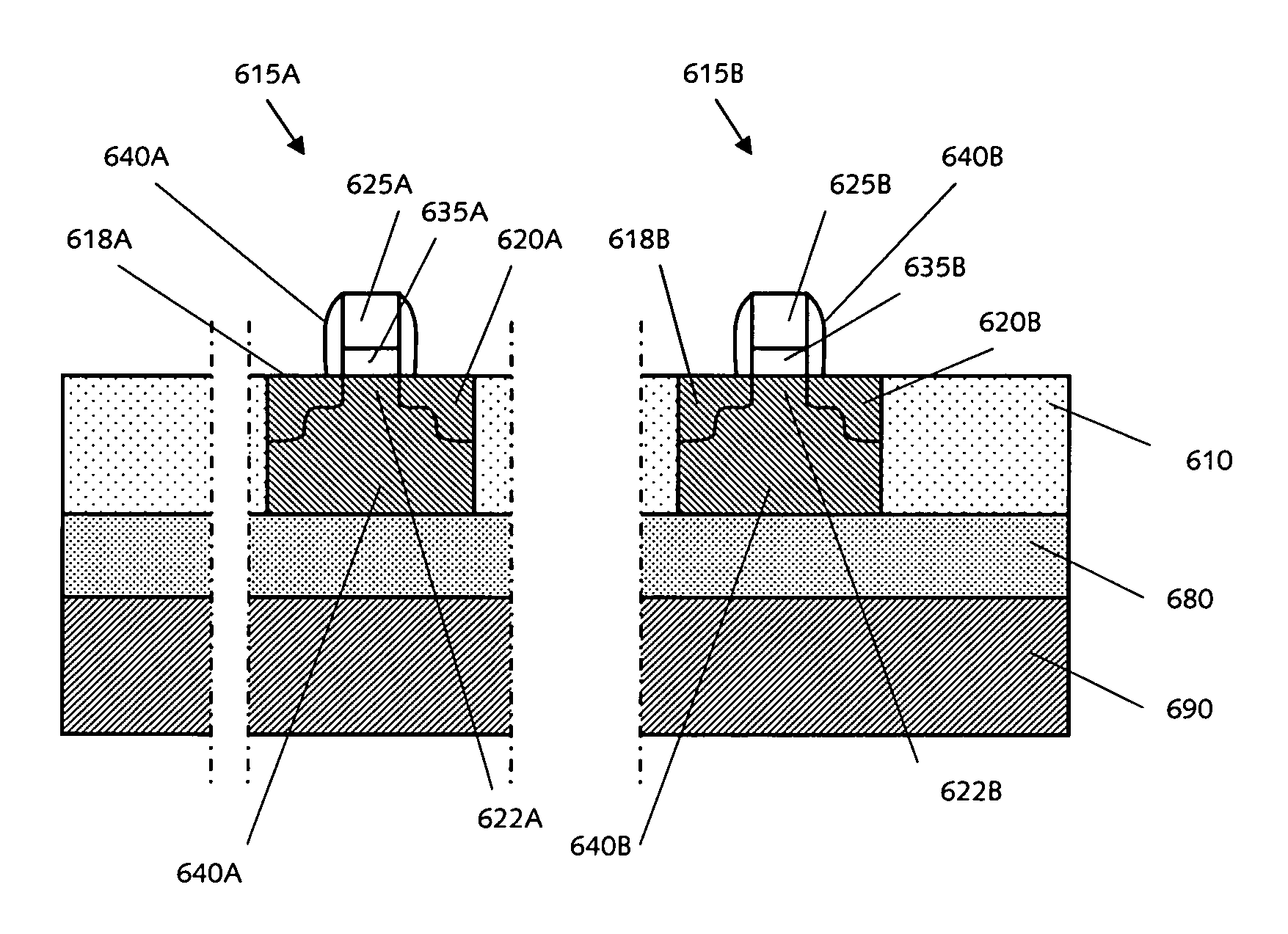

Lattice-mismatched semiconductor structures on insulators

ActiveUS20070054465A1Improve functionalityImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingThreading dislocationsLattice mismatch

Monolithic lattice-mismatched semiconductor heterostructures are fabricated by bonding patterned substrates with alternative active-area materials formed thereon to a rigid dielectric platform and then removing the highly-defective interface areas along with the underlying substrates to produce alternative active-area regions disposed over the insulator and substantially exhausted of misfit and threading dislocations.

Owner:TAIWAN SEMICON MFG CO LTD

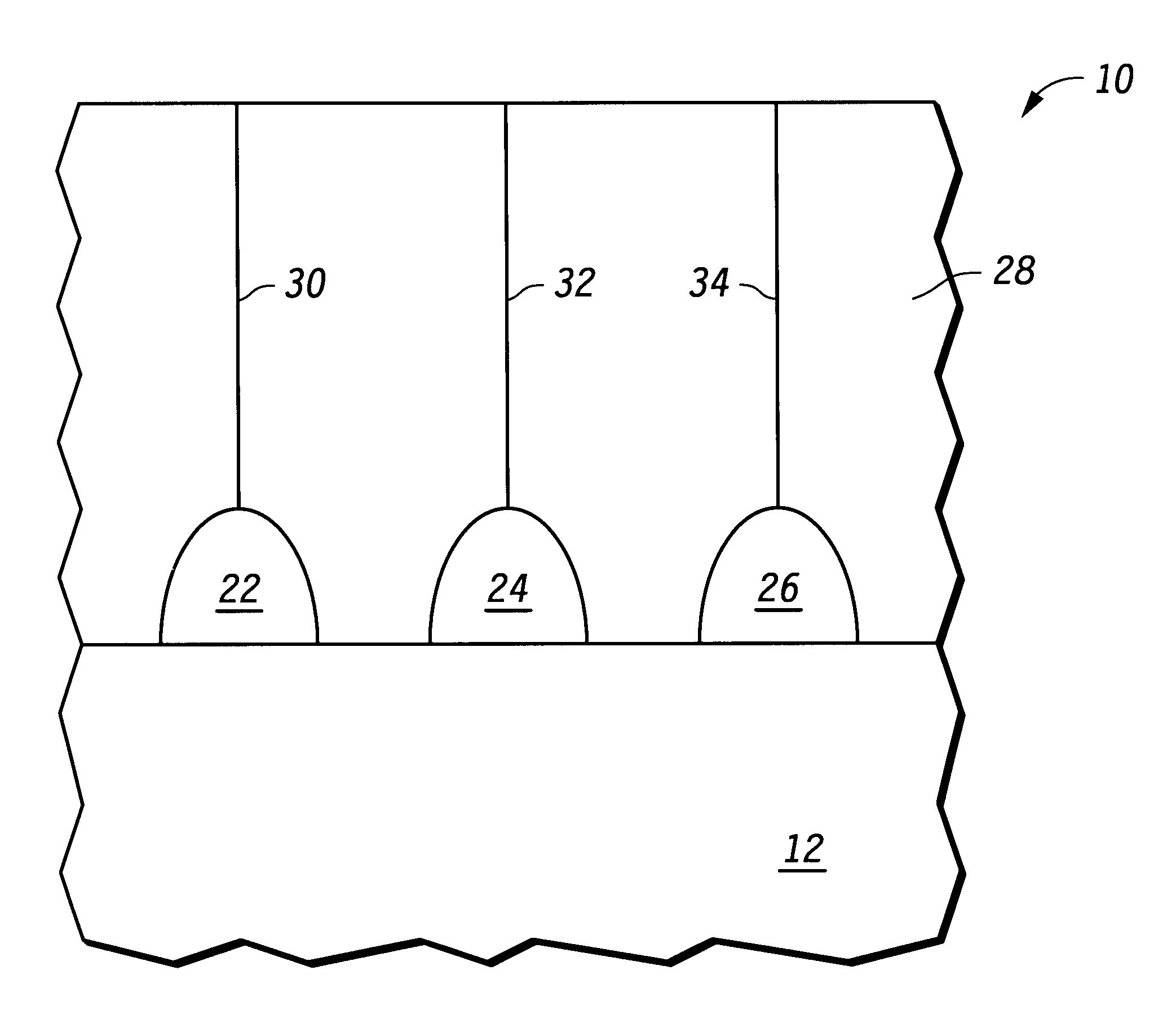

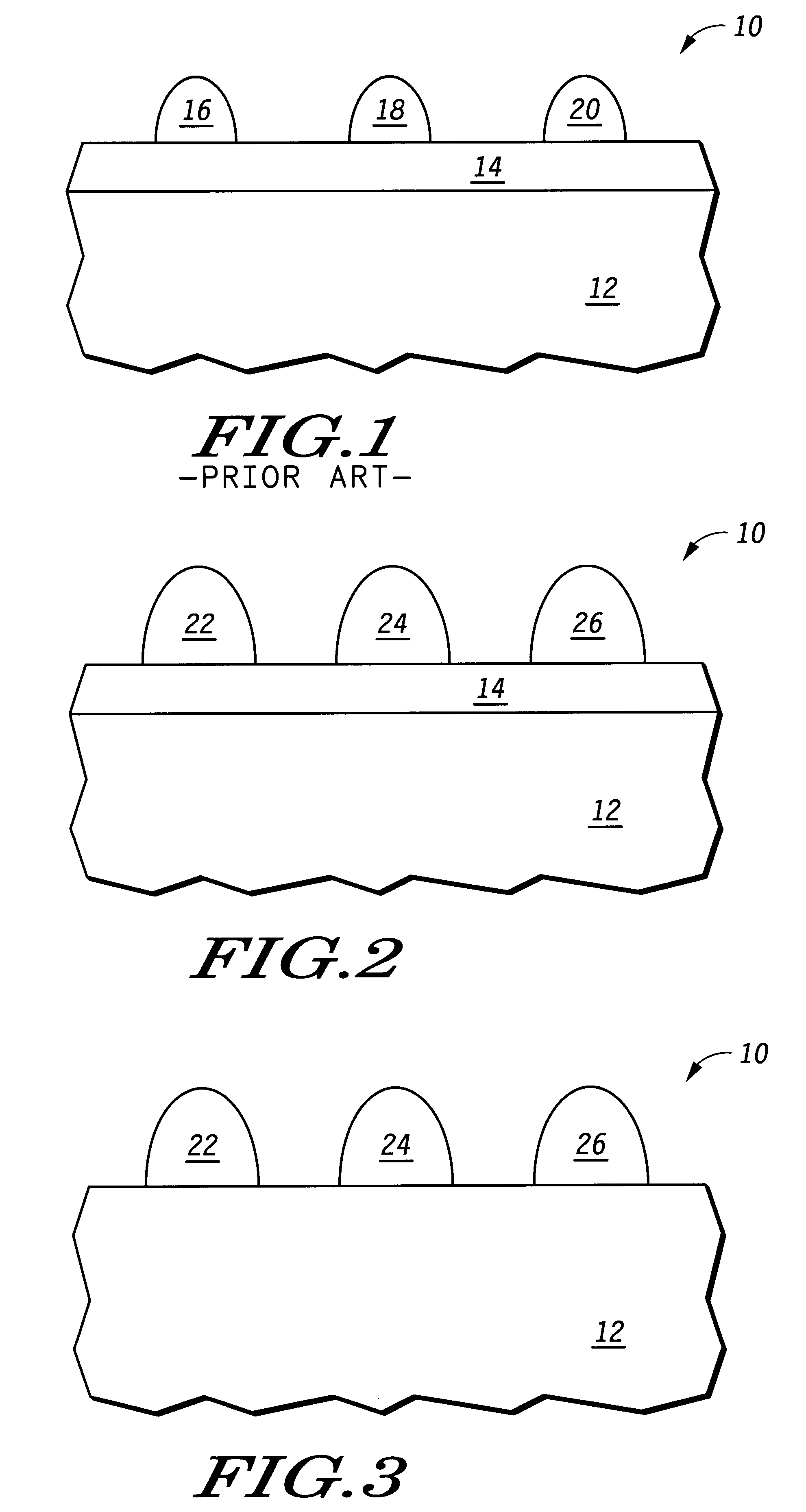

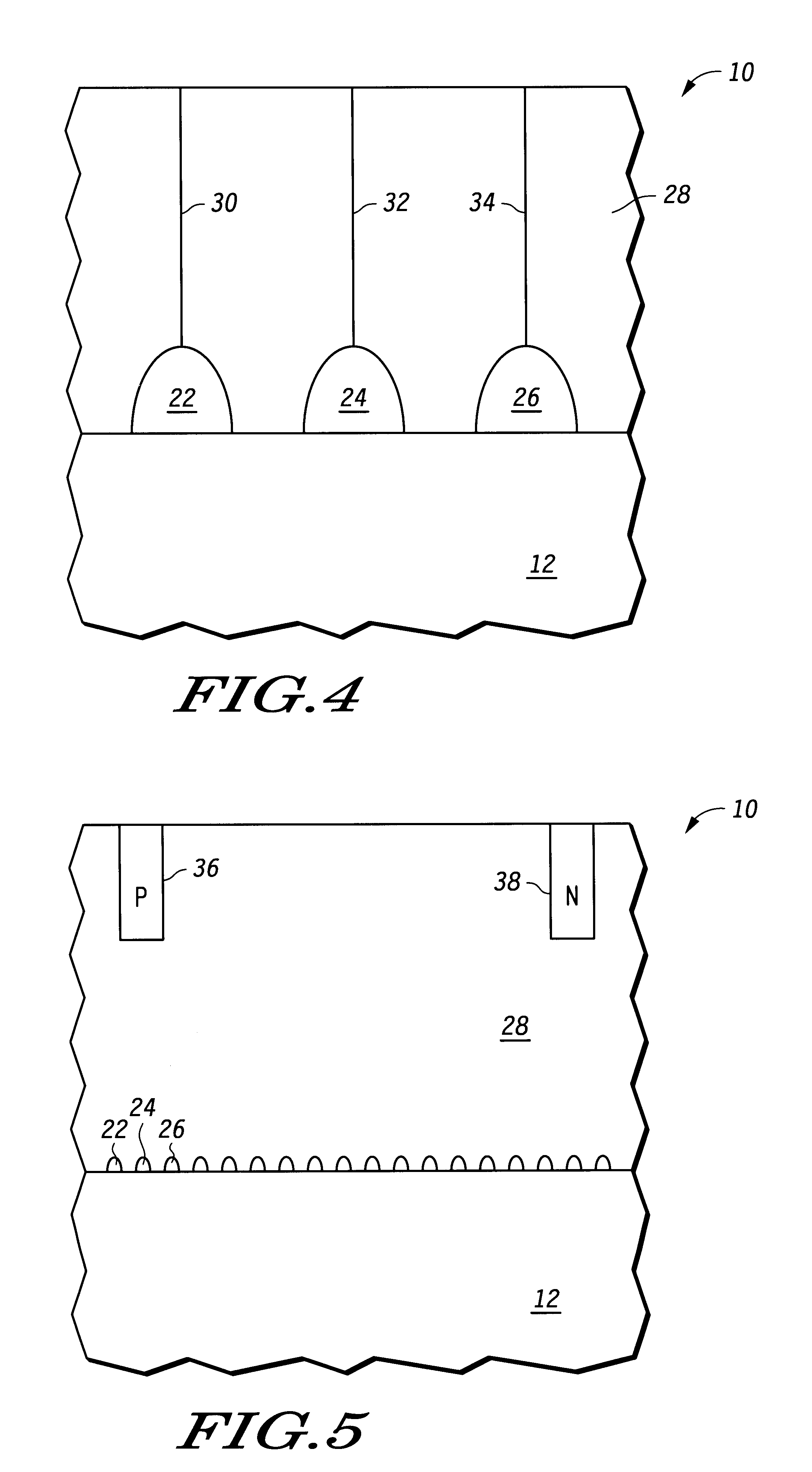

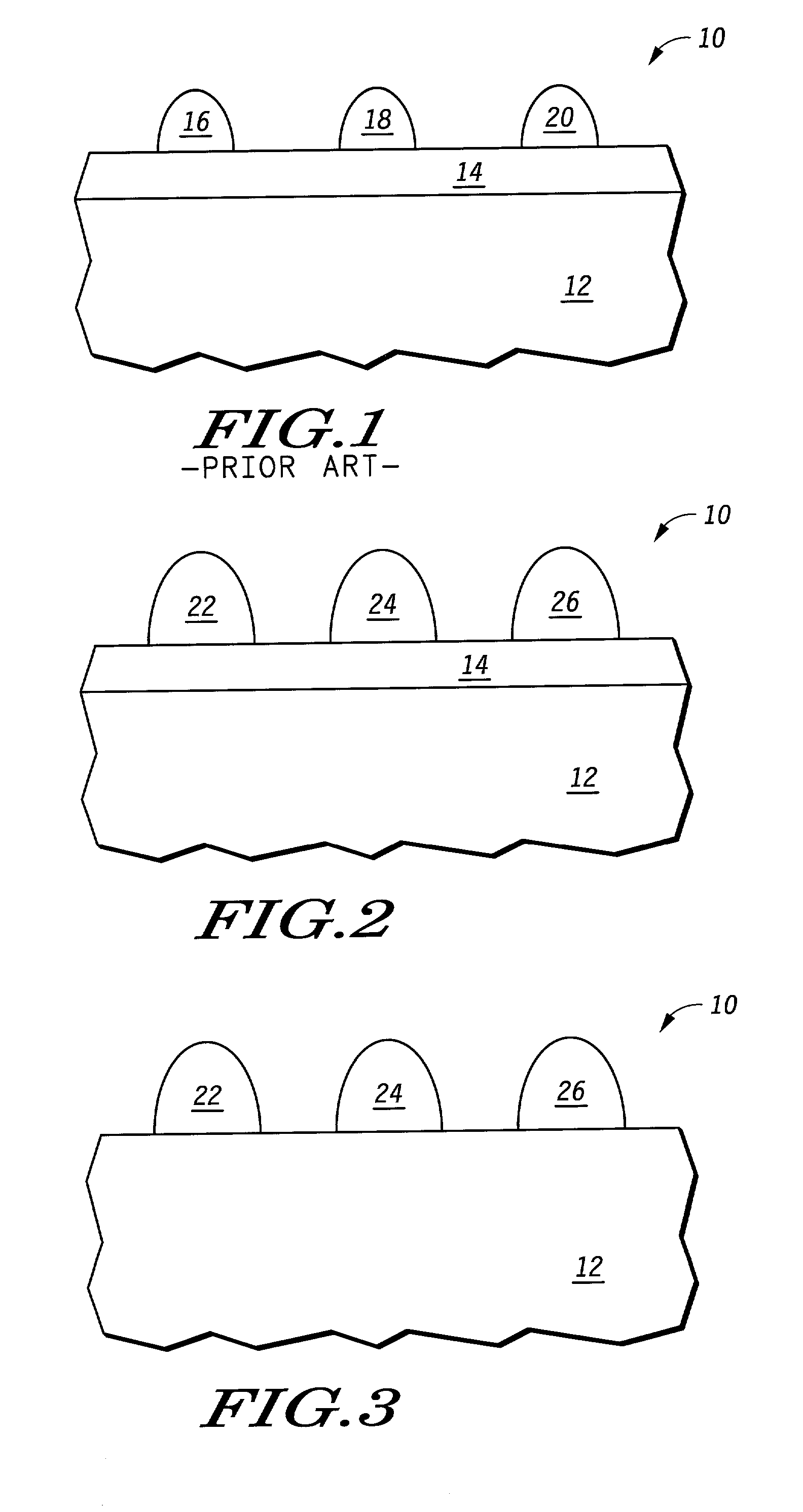

Semiconductor device and method therefor

InactiveUS6576532B1Final product manufactureSemiconductor/solid-state device manufacturingThreading dislocationsLithographic artist

A heteroepitaxial structure is made using nanocrystals that are formed closer together than normal lithography patterning would allow. The nanocrystals are oxidized and thus selectively etchable with respect to the substrate and surrounding material. In one case the oxidized nanocrystals are removed to expose the substrate at those locations and selective epitaxial germanium is then grown at those exposed substrate locations. The inevitable formation of the misfit dislocations does minimal harm because they are terminated at the surrounding material. In another case the surrounding material is removed and the germanium is epitaxially grown at the exposed substrate where the surrounding material is removed. The resulting misfit dislocations in the germanium terminate at the oxidized nanocrystals. By using nanocrystals that are able to be formed much closer together than is available for other features through lithography, the misfits are prevented from extending so far as to create harmful threading dislocations.

Owner:NORTH STAR INNOVATIONS

Manufacturing method of strained si substrate

InactiveUS20100003803A1Low densityLow roughness requirementsPolycrystalline material growthSolid-state devicesThreading dislocationsHydrogen

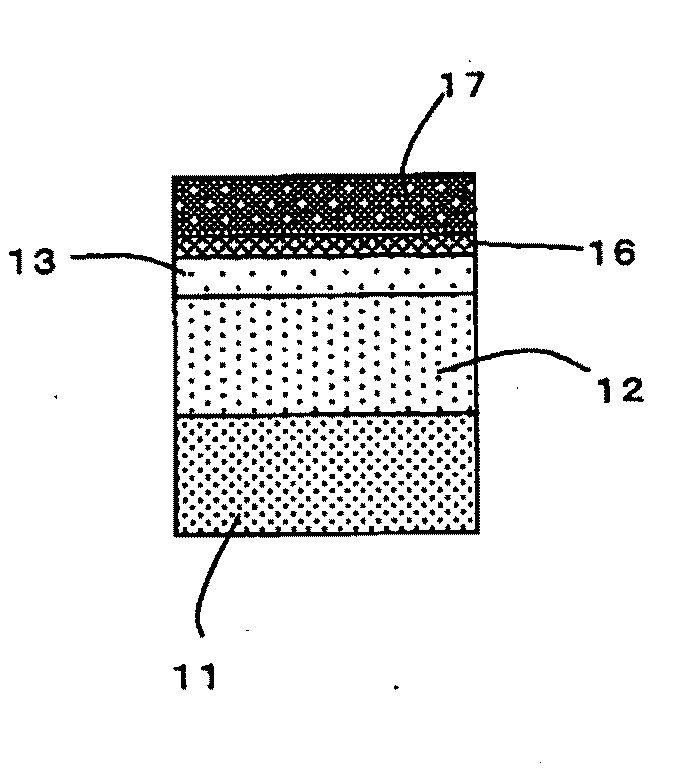

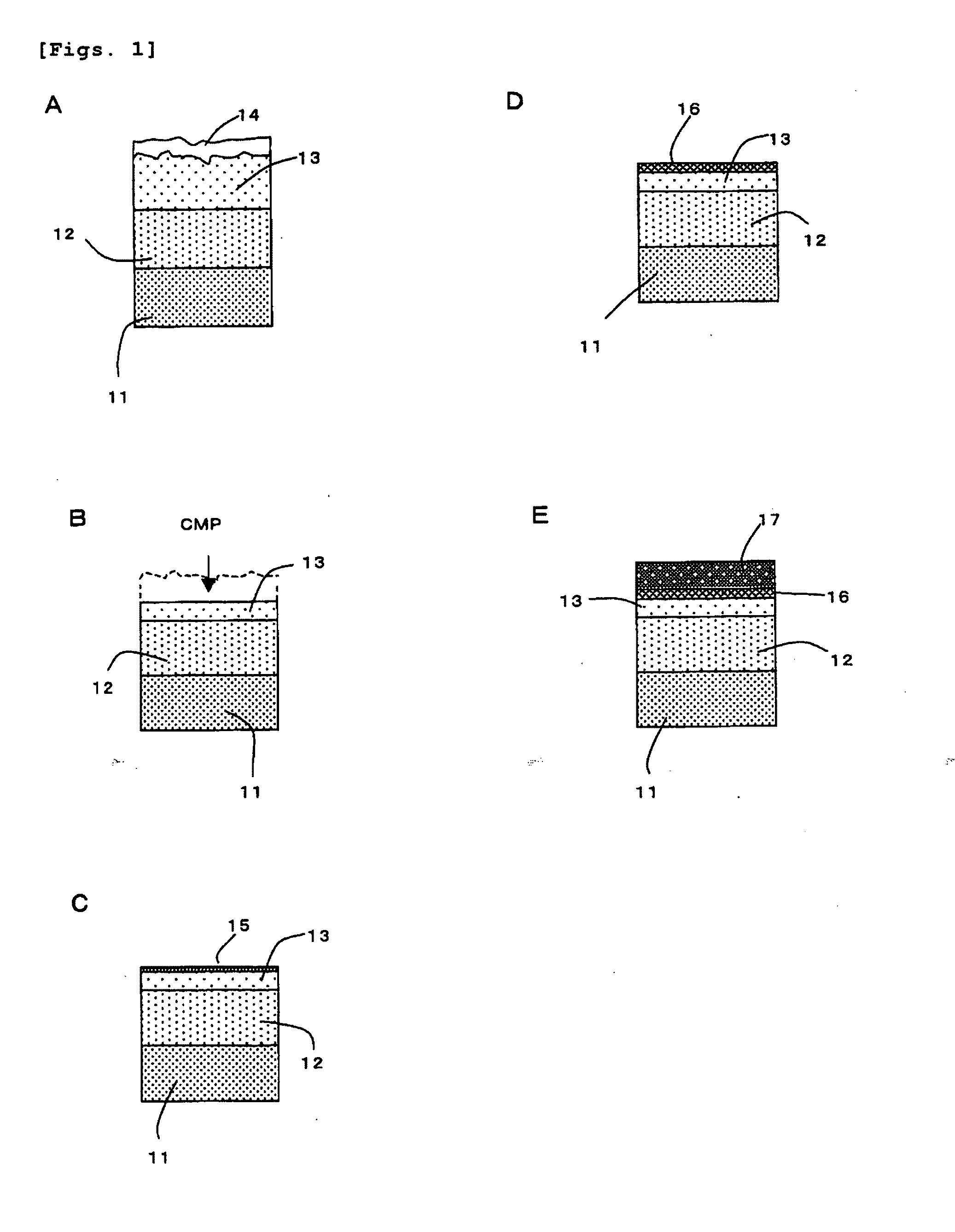

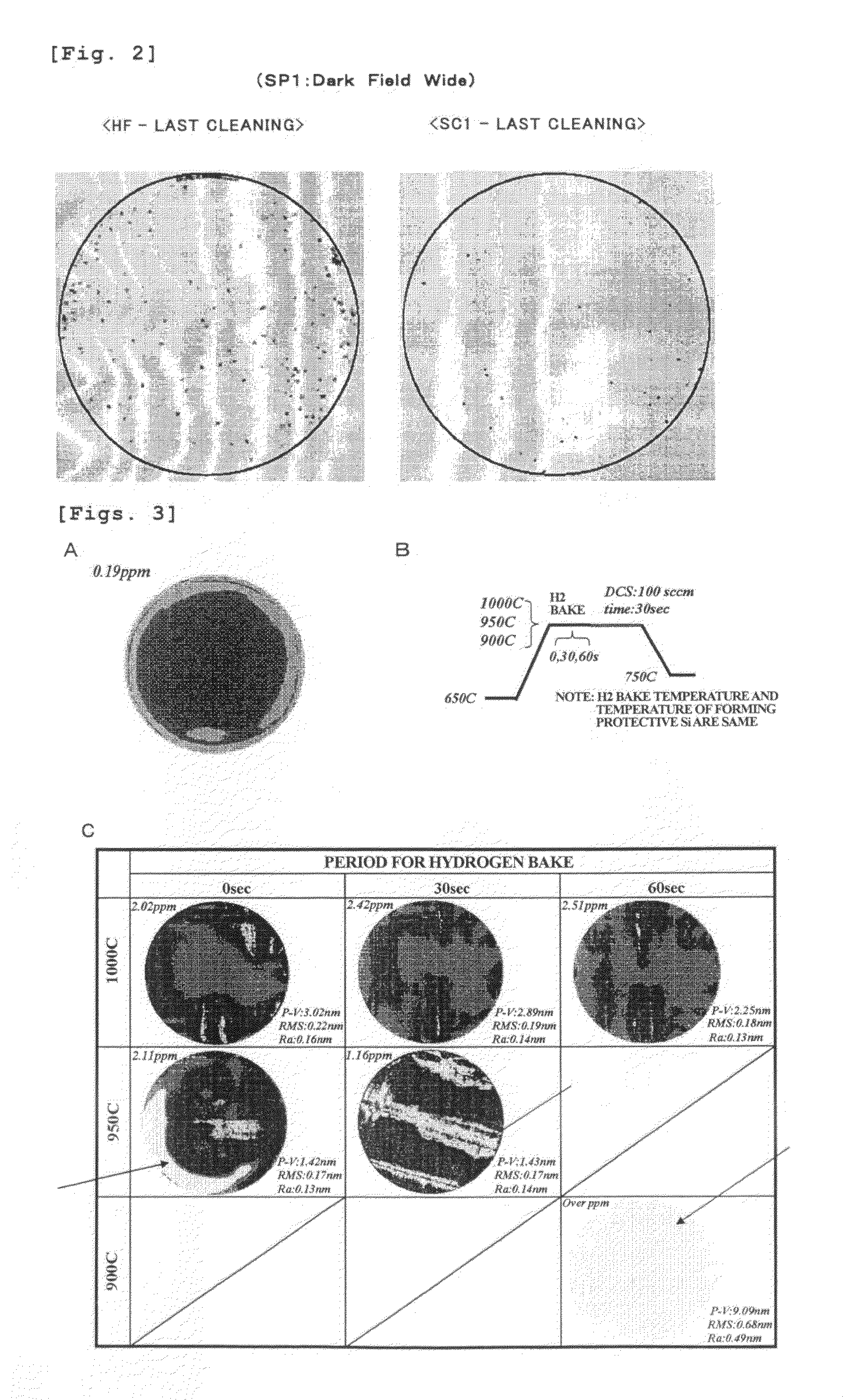

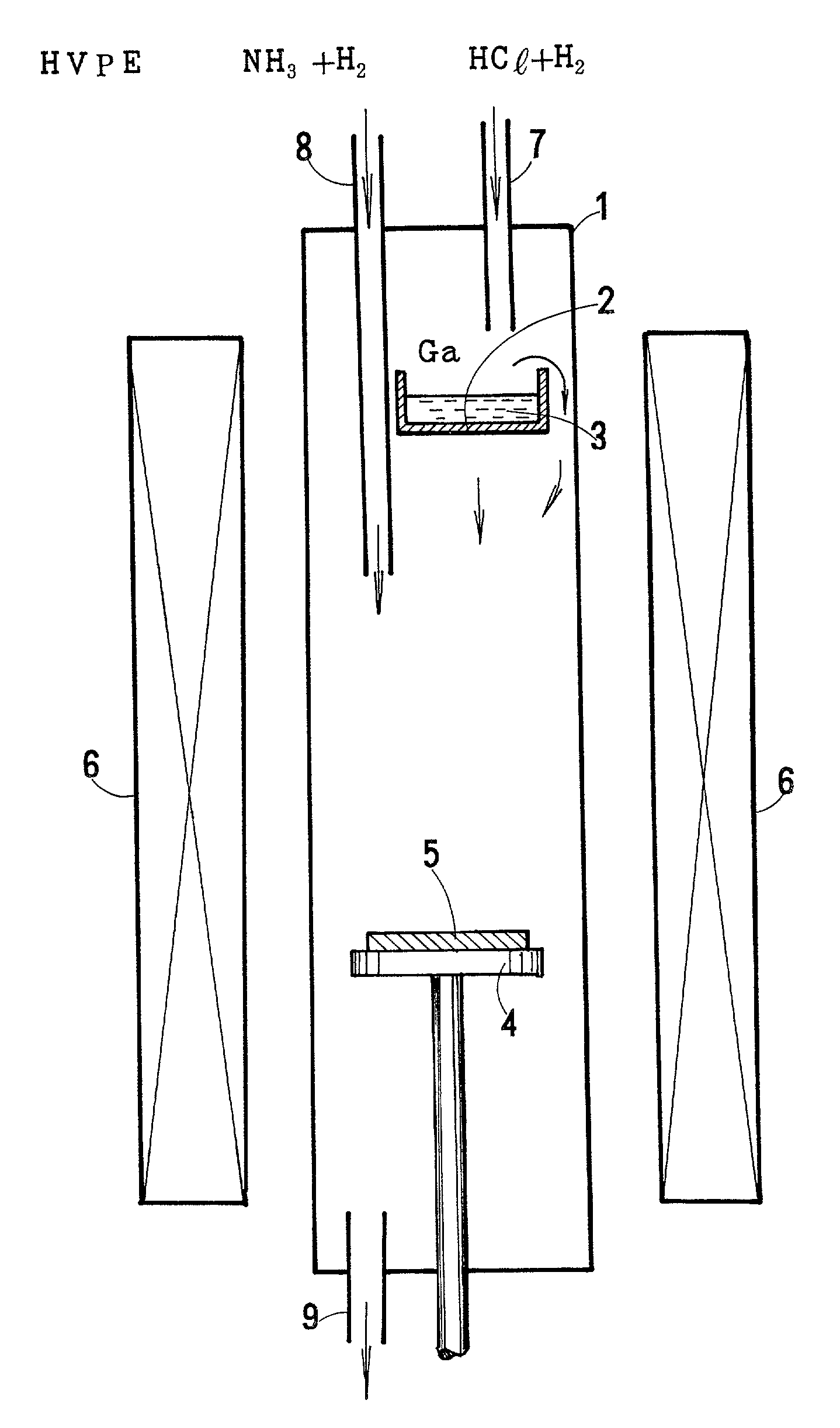

According to the present invention, there is provided a manufacturing method of a strained Si substrate including at least steps of: forming a lattice-relaxed SiGe layer on a silicon single crystal substrate; flattening a surface of the SiGe layer by CMP; and forming a strained Si layer on the surface of the flattened SiGe layer, wherein the method comprises steps of: subjecting the surface of the SiGe layer to SC1 cleaning, before forming the strained Si layer on the lattice-relaxed SiGe layer surface that is flattened; heat-treating the substrate having the SiGe layer after being subjected to SC1 cleaning in a hydrogen-containing atmosphere at 800° C. or higher; immediately forming a protective Si layer on the SiGe layer surface on the heat-treated substrate, without lowering the temperature below 800° C. after the heat treatment; and forming the strained Si layer on the surface of the protective Si layer at a temperature lower than the temperature of forming the protective Si layer. Thereby, a manufacturing method of a strained Si substrate having low surface roughness, threading dislocation density and low particle level can be provided.

Owner:SHIN-ETSU HANDOTAI CO LTD

Method of producing a single crystal gallium nitride substrate and single crystal gallium nitride substrate

InactiveUS20020028564A1Reduce misalignmentIncrease the number ofPolycrystalline material growthLaser detailsThreading dislocationsSingle crystal substrate

GaN single crystal substrates are produced by slicing a GaN single crystal ingot in the planes parallel to the growing direction. Penetration dislocations which have been generated in the growing direction extend mainly in the bulk of the GaN substrate. A few of the threading dislocations appear on the surface of the GaN substrate. GaN substrates of low-dislocation density are obtained.

Owner:SUMITOMO ELECTRIC IND LTD

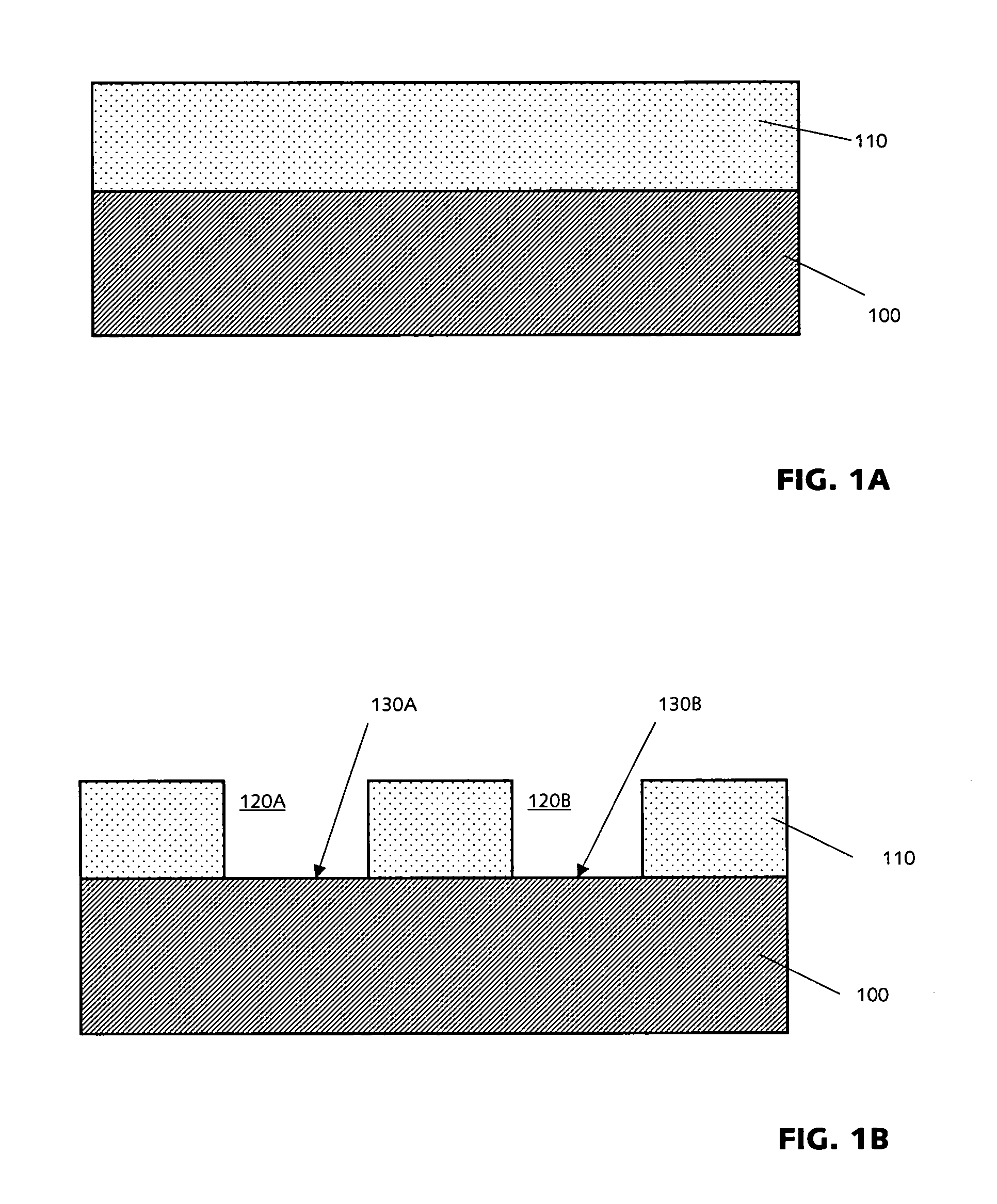

Threading-dislocation-free nanoheteroepitaxy of Ge on Si using self-directed touch-down of Ge through a thin SiO2 layer

ActiveUS20050054180A1Polycrystalline material growthSolid-state devicesThreading dislocationsDirect touch

A method of forming a virtually defect free lattice mismatched nanoheteroepitaxial layer is disclosed. The method includes forming an interface layer on a portion of a substrate. A plurality of seed pads are then formed by self-directed touchdown by exposing the interface layer to a material comprising a semiconductor material. The plurality of seed pads, having an average width of about 1 nm to 10 nm, are interspersed within the interface layer and contact the substrate. An epitaxial layer is then formed by lateral growth of the seed pads over the interface layer.

Owner:STC UNM

Semiconductor heterostructures and related methods

InactiveUS7049627B2Overcome limitationsImprove manufacturabilityPolycrystalline material growthSemiconductor/solid-state device manufacturingThreading dislocationsInter layer

Dislocation pile-ups in compositionally graded semiconductor layers are reduced or eliminated, thereby leading to increased semiconductor device yield and manufacturability. This is accomplished by introducing a semiconductor layer having a plurality of threading dislocations distributed substantially uniformly across its surface as a starting layer and / or at least one intermediate layer during growth and relaxation of the compositionally graded layer. The semiconductor layer may include a seed layer disposed proximal to the surface of the semiconductor layer and having the threading dislocations uniformly distributed therein.

Owner:TAIWAN SEMICON MFG CO LTD

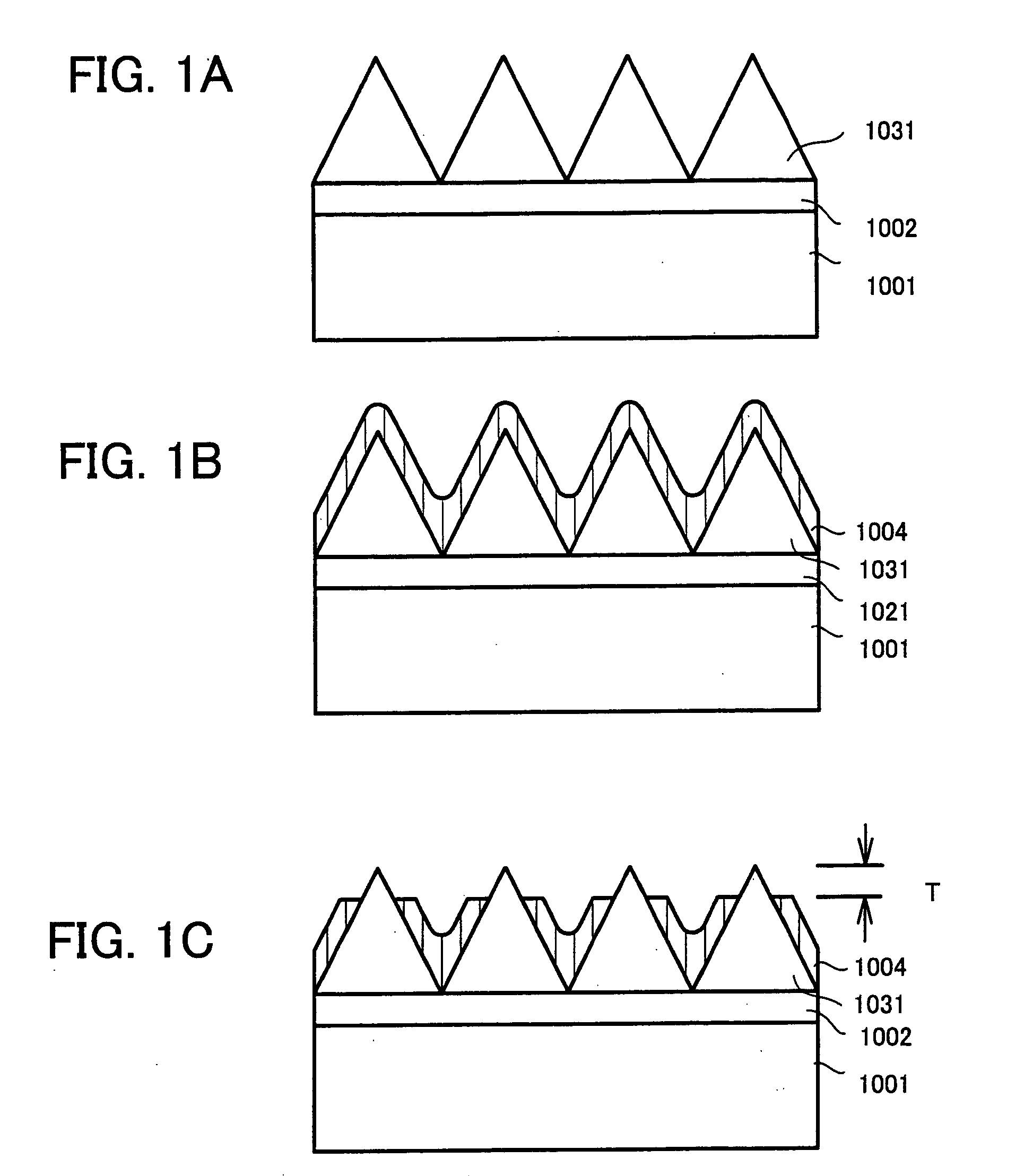

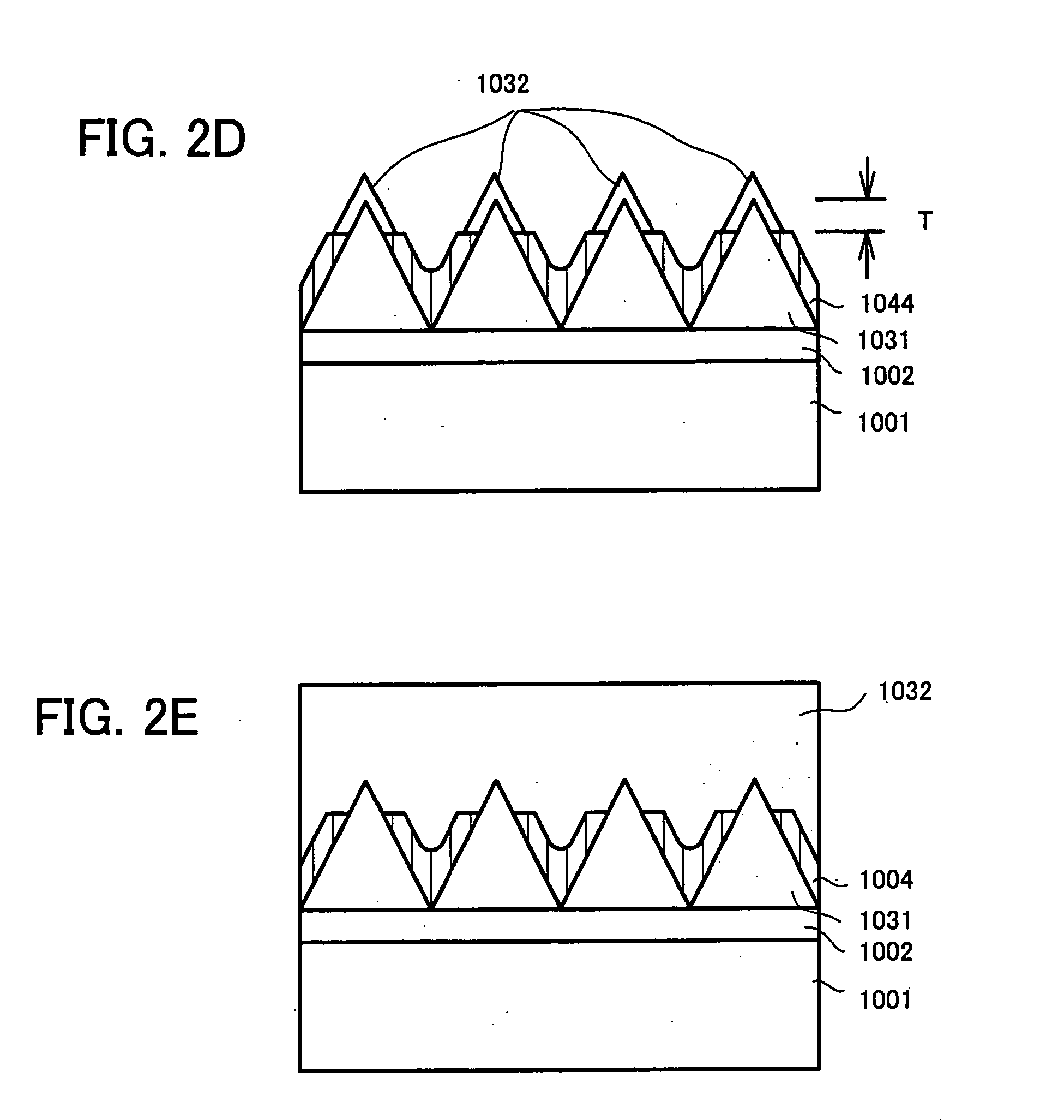

Manufacturing gallium nitride substrates by lateral overgrowth through masks and devices fabricated thereof

ActiveUS20060266281A1Polycrystalline material growthSemiconductor/solid-state device manufacturingThreading dislocationsLateral overgrowth

Gallium nitride substrates are grown by epitaxial lateral overgrowth using multiple steps. On a masked substrate having openings areas, selective growth produces first triangular stripes in which most of the threading dislocations are bent at 90°. In a second step, growth conditions are changed to increase the lateral growth rate and produce a flat (0001) surface. At this stage the density of dislocations on the surface is <5×107 cm 2. Dislocations are primarily located at the coalescence region between two laterally grown facets pinching off together. To further decrease the dislocation density a second masking step is achieved, with the openings exactly located above the first ones. Threading dislocations (TDs) of the coalescence region do not propagate in the top layer. Therefore the density of dislocations is lowered below <1×107 cm lover the entire surface.

Owner:IV WORKS

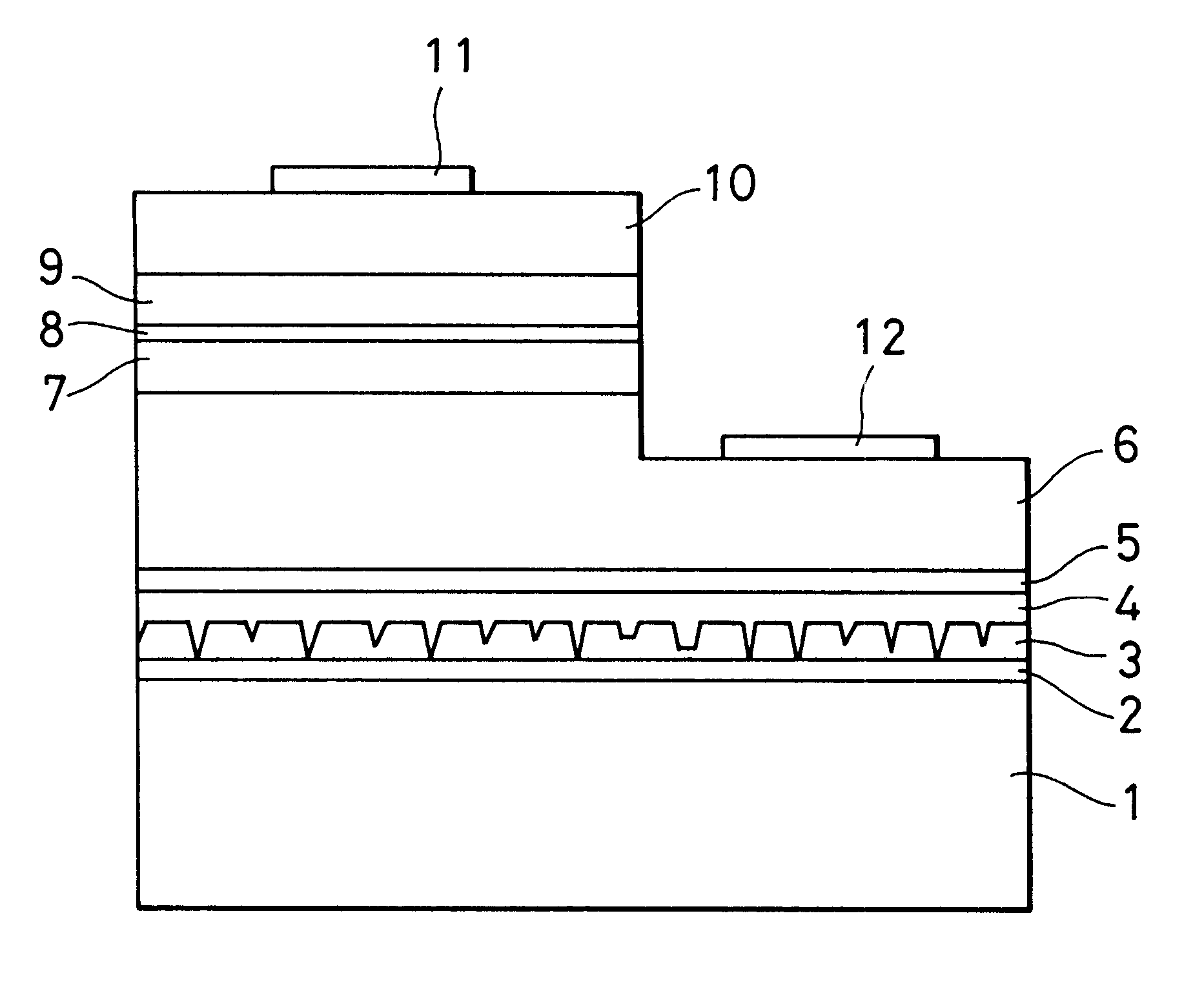

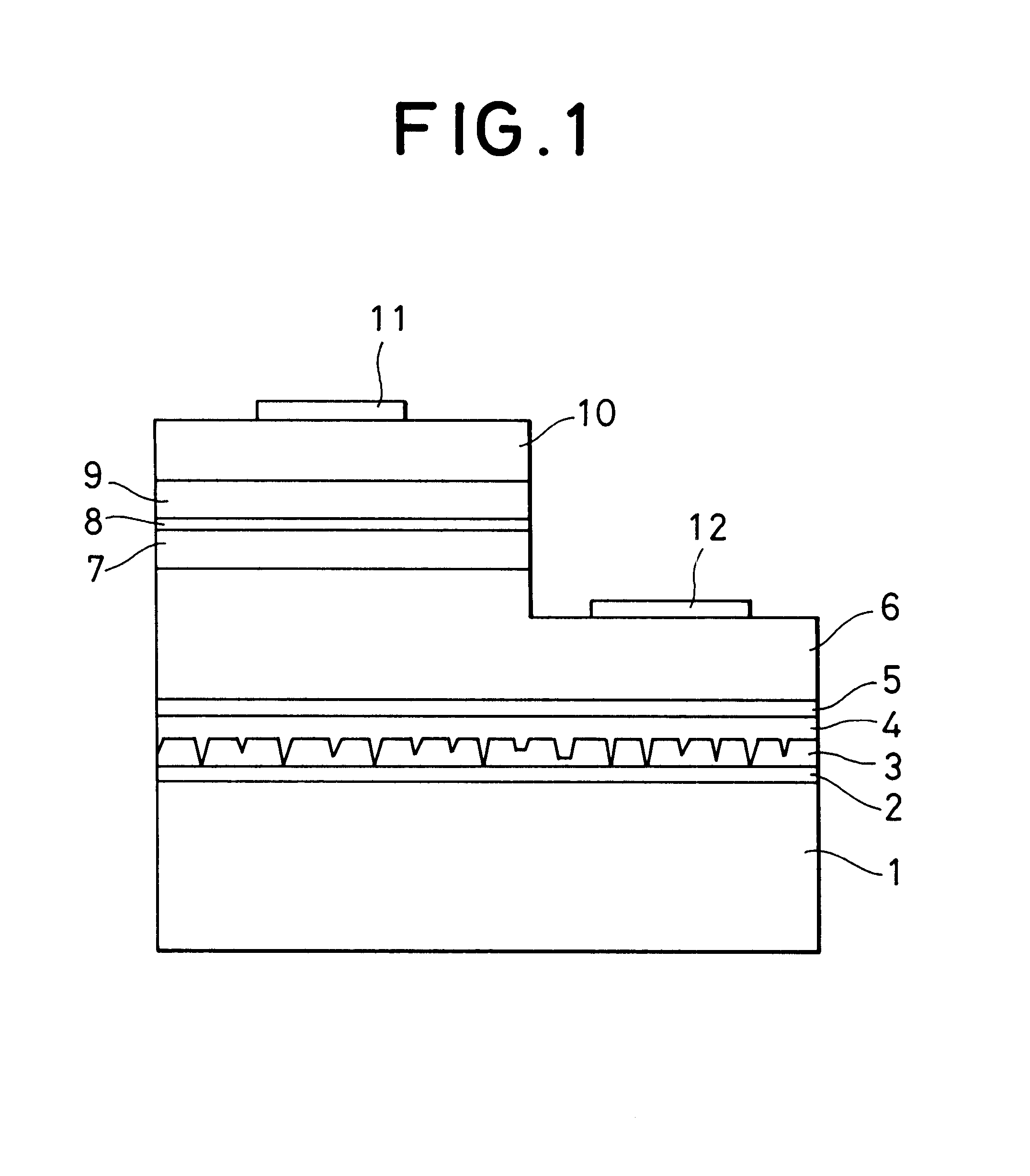

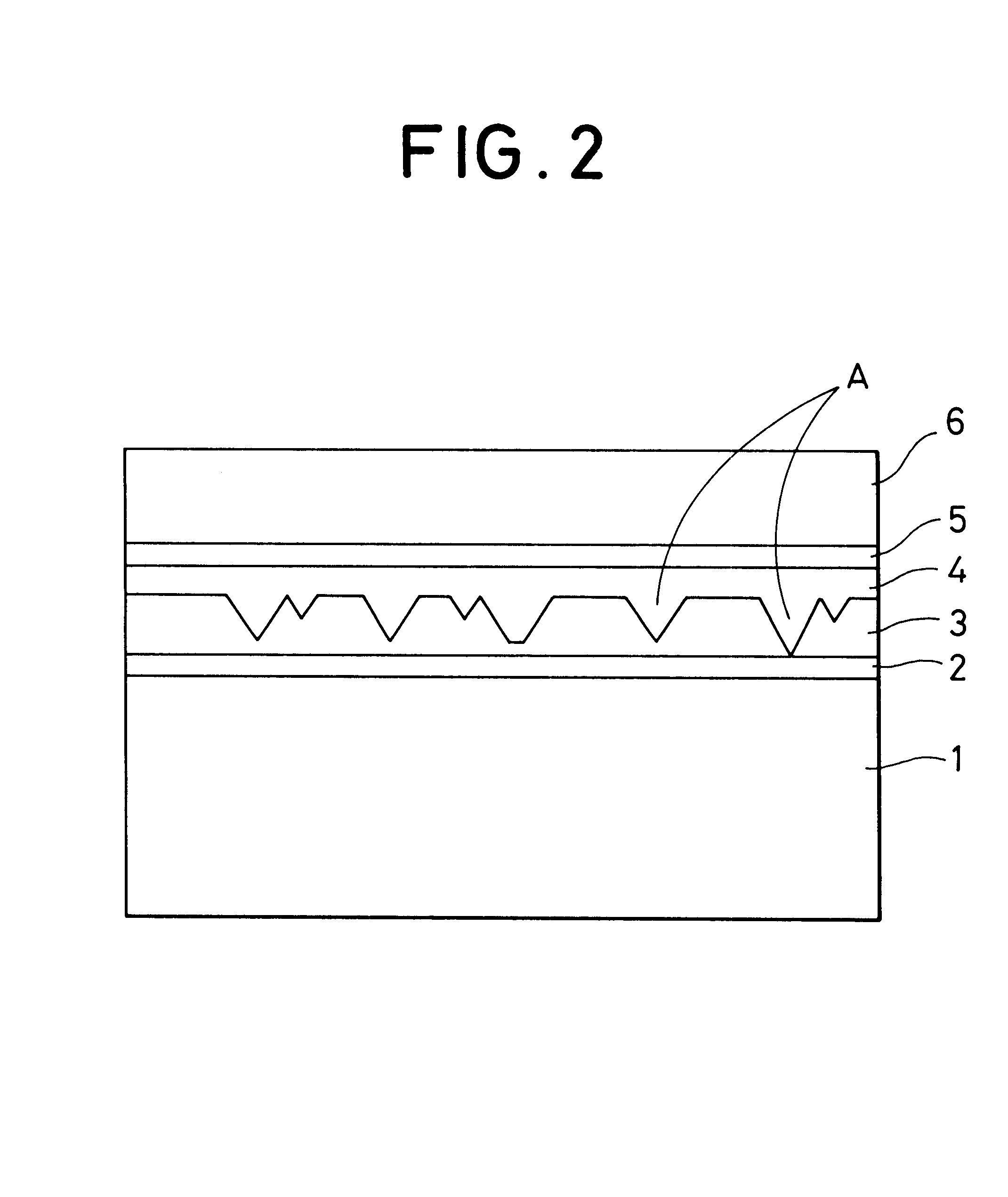

Group III nitride compound semiconductor devices and method for fabricating the same

InactiveUS20060060866A1Avoid problemsQuality improvementLaser detailsSemiconductor laser structural detailsThreading dislocationsDislocation

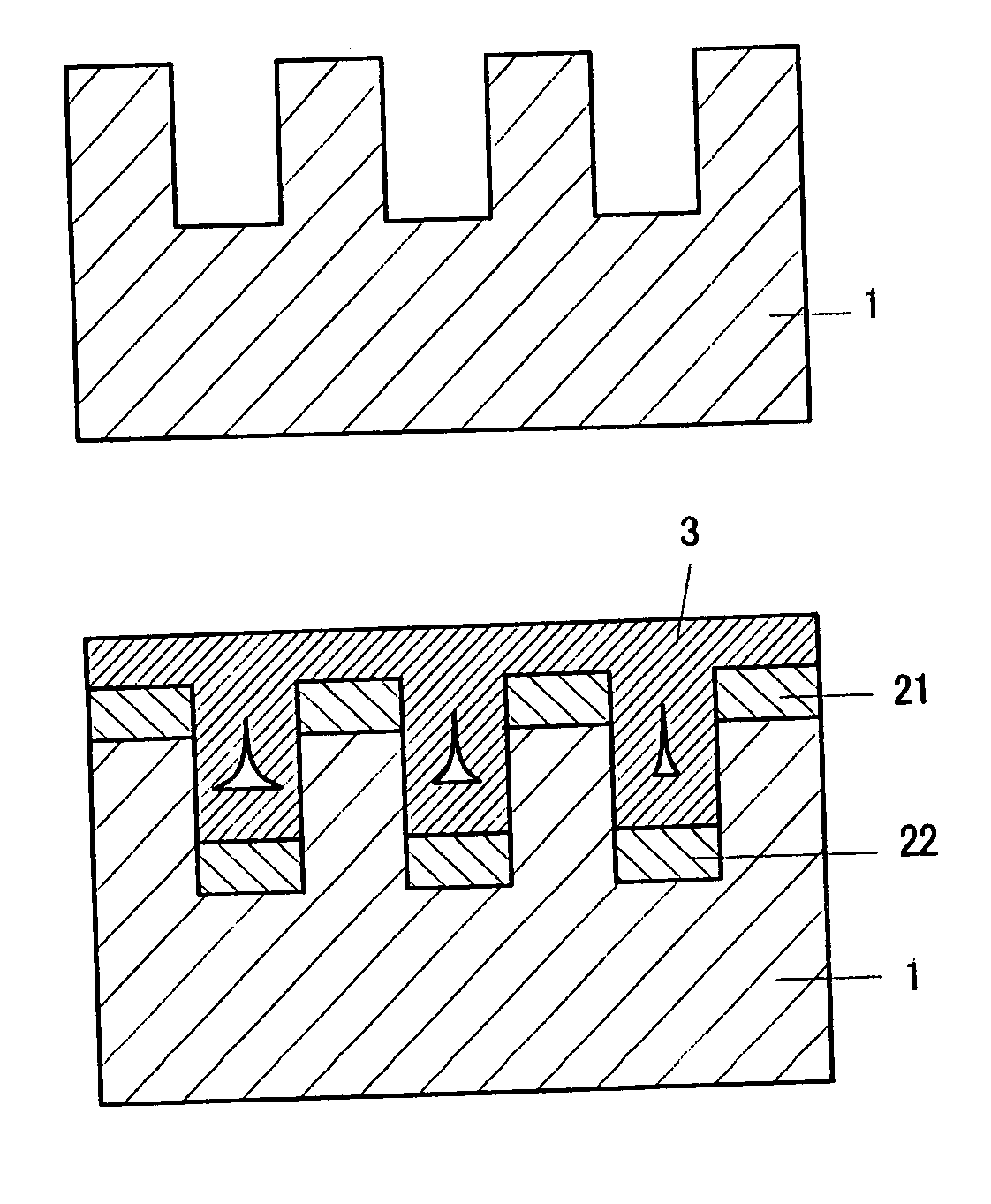

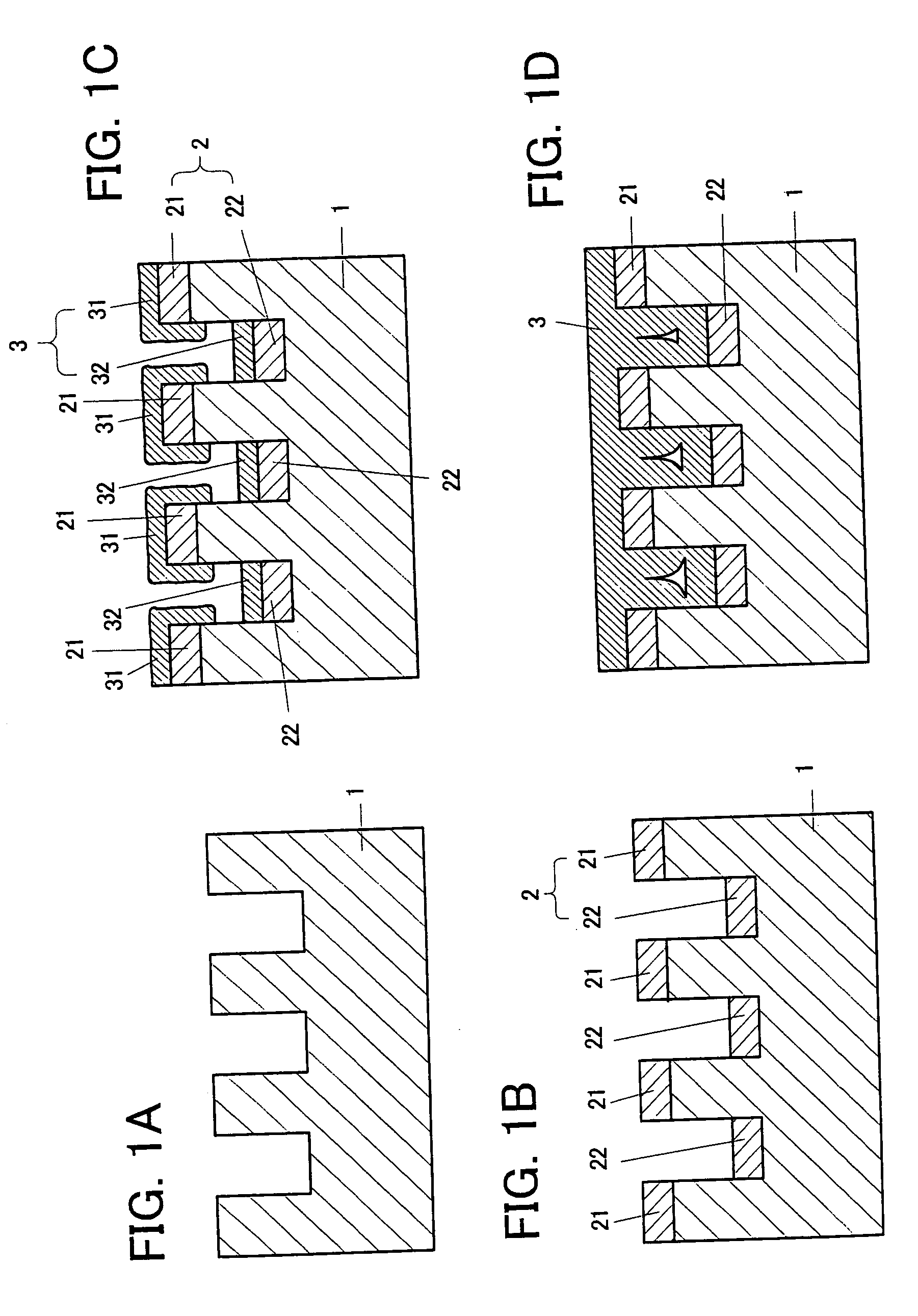

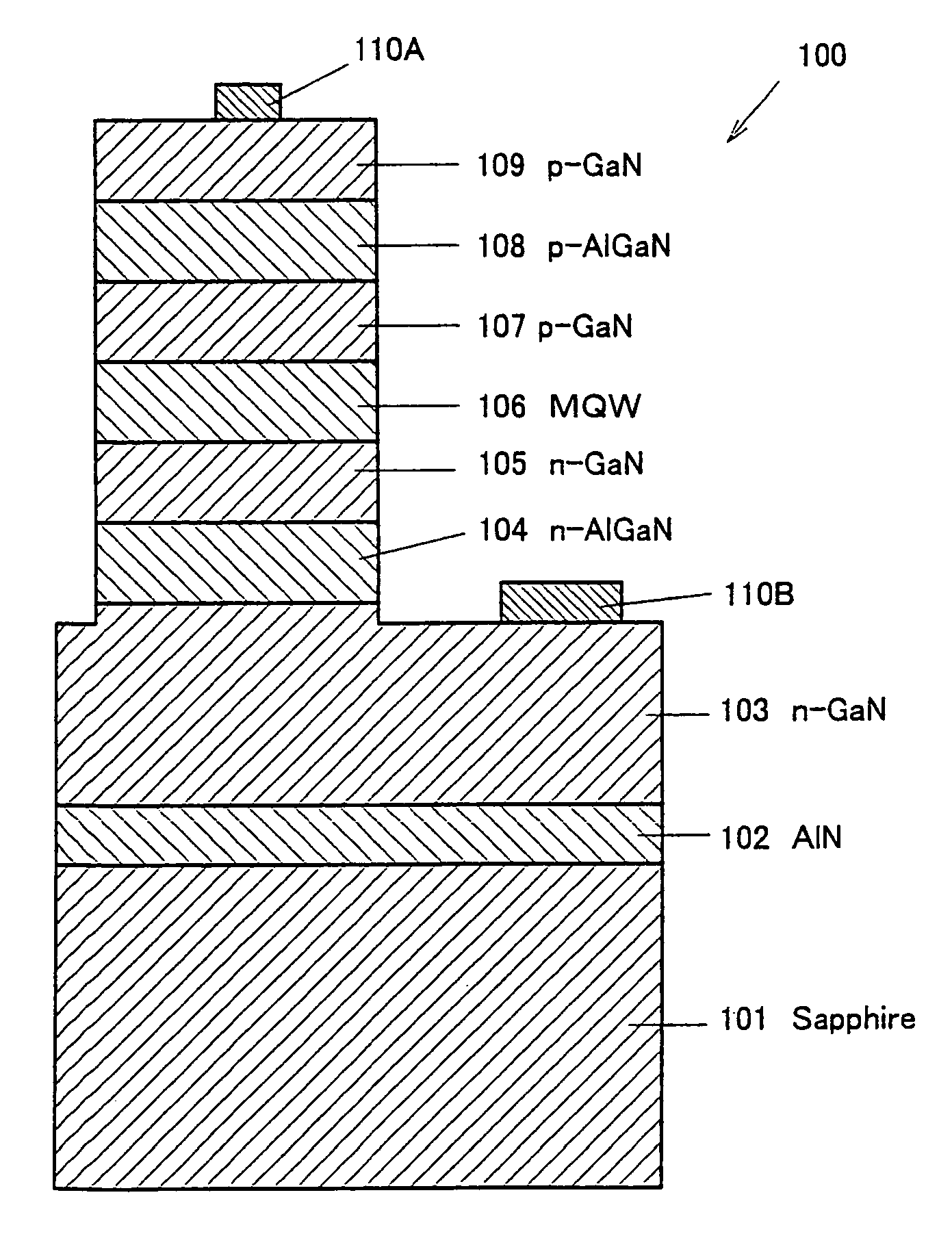

A sapphire substrate 1 is etched so that each trench has a width of 10 μm and a depth of 10 μm were formed at 10 μm of intervals in a stripe pattern. Next, an AlN buffer layer 2 having a thickness of approximately 40 nm is formed mainly on the upper surface and the bottom surface of the trenches of the substrate 1. Then a GaN layer 3 is formed through vertical and lateral epitaxial growth. At this time, lateral epitaxial growth of the buffer layer 21, which was mainly formed on the upper surface of the trenches, filled the trenches and thus establishing a flat top surface. The portions of the GaN layer 3 formed above the top surfaces of the mesas having a depth of 10 μm exhibited significant suppression of threading dislocation in contrast to the portions formed above the bottoms of the trenches.

Owner:TOYODA GOSEI CO LTD

Methods of fabricating semiconductor heterostructures

InactiveUS20060009012A1Overcome limitationsImprove manufacturabilityPolycrystalline material growthSemiconductor/solid-state device manufacturingThreading dislocationsDevice material

Dislocation pile-ups in compositionally graded semiconductor layers are reduced or eliminated, thereby leading to increased semiconductor device yield and manufacturability. This is accomplished by introducing a semiconductor layer having a plurality of threading dislocations distributed substantially uniformly across its surface as a starting layer and / or at least one intermediate layer during growth and relaxation of the compositionally graded layer. The semiconductor layer may include a seed layer disposed proximal to the surface of the semiconductor layer and having the threading dislocations uniformly distributed therein.

Owner:TAIWAN SEMICON MFG CO LTD

Group iii nitride semiconductor epitaxial substrate and method for manufacturing the same

InactiveUS20100327228A1Improve crystal qualitySuppressed dislocationPolycrystalline material growthFinal product manufactureThreading dislocationsDislocation

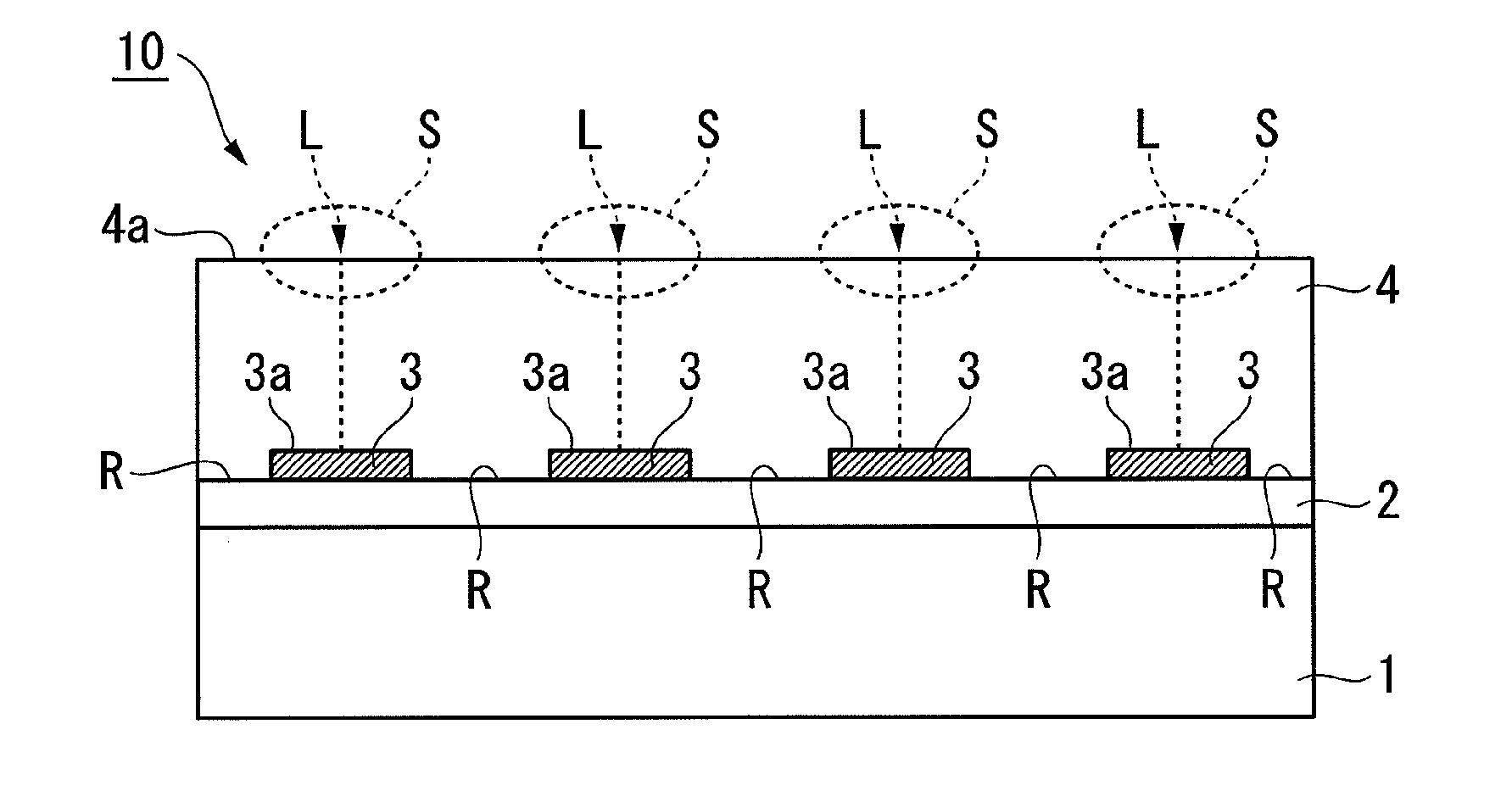

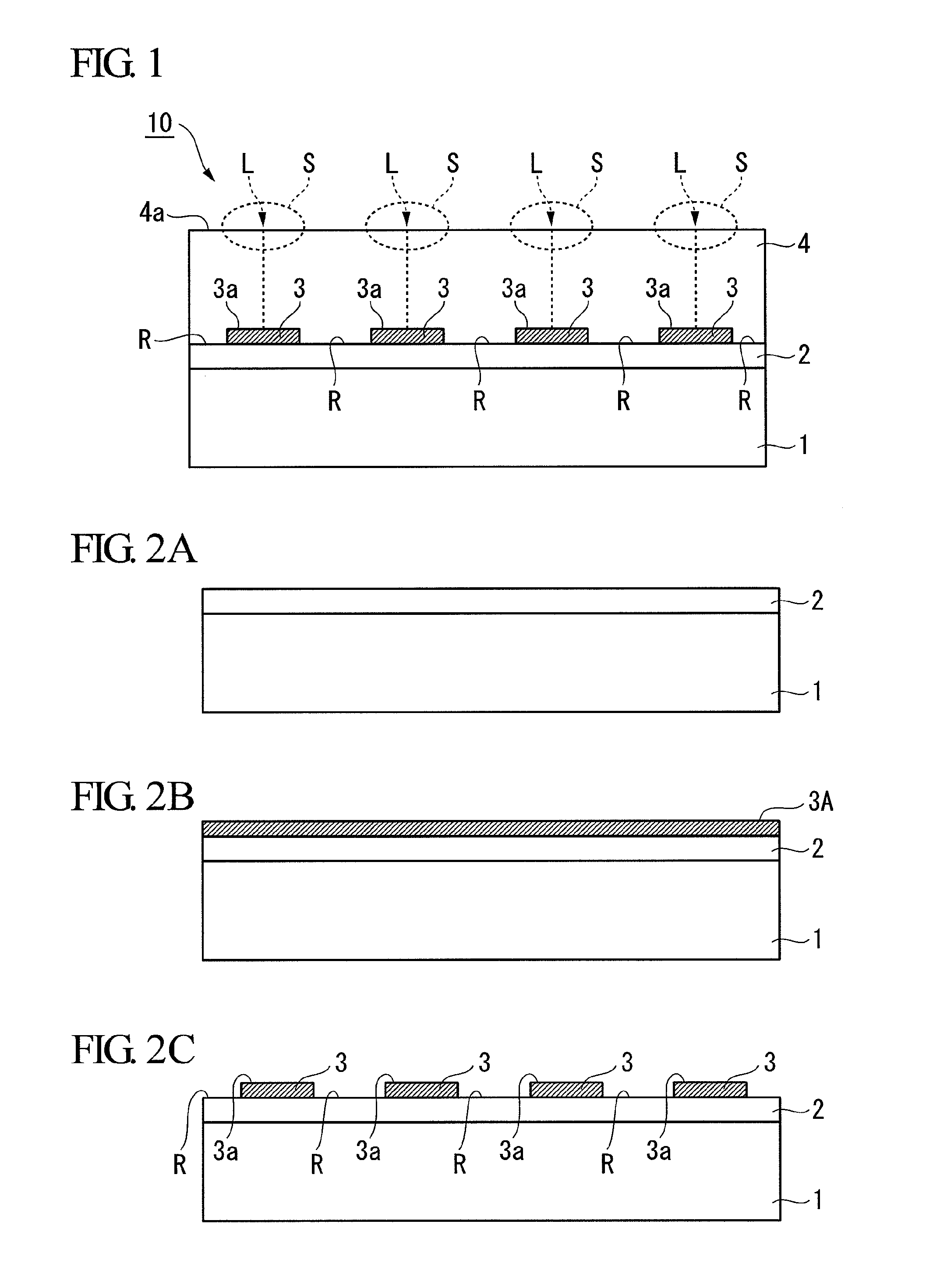

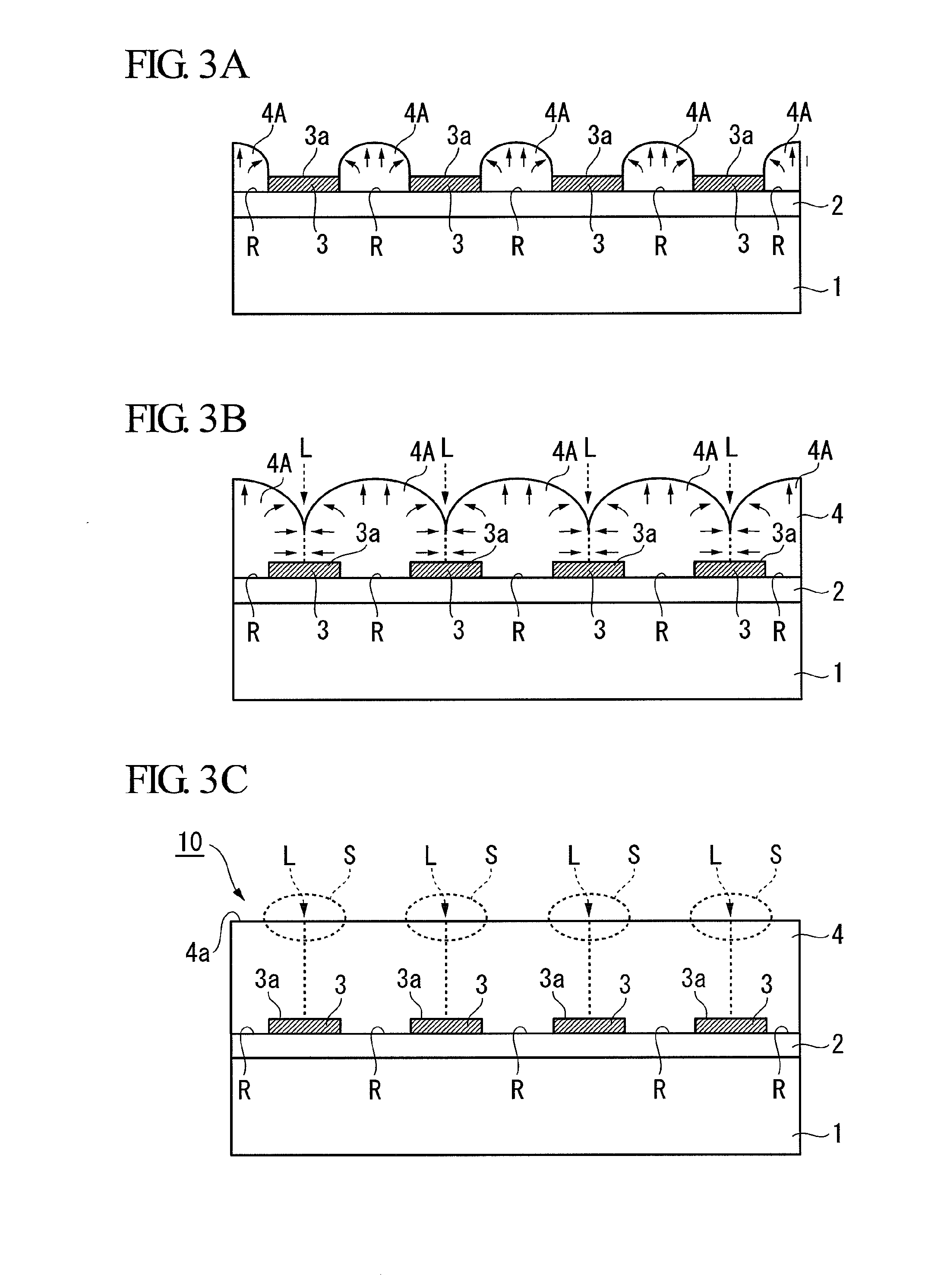

There is provided a group III nitride semiconductor epitaxial substrate which has a suppressed level of threading dislocation in the vertical direction and excellent crystal quality, the group III nitride semiconductor epitaxial substrate including a substrate (1) for growing an epitaxial film; and an ELO layer (4) having a composition of AlxGa1-xN (0≦x≦1) formed either on top of the substrate (1) or on top of a group III nitride layer (2) formed on top of the substrate (1), wherein the ELO layer (4) is a layer formed by using a mask pattern (3), which is composed of carbon and is formed either on top of the substrate (1) or on top of the group III nitride layer (2).

Owner:SHOWA DENKO KK

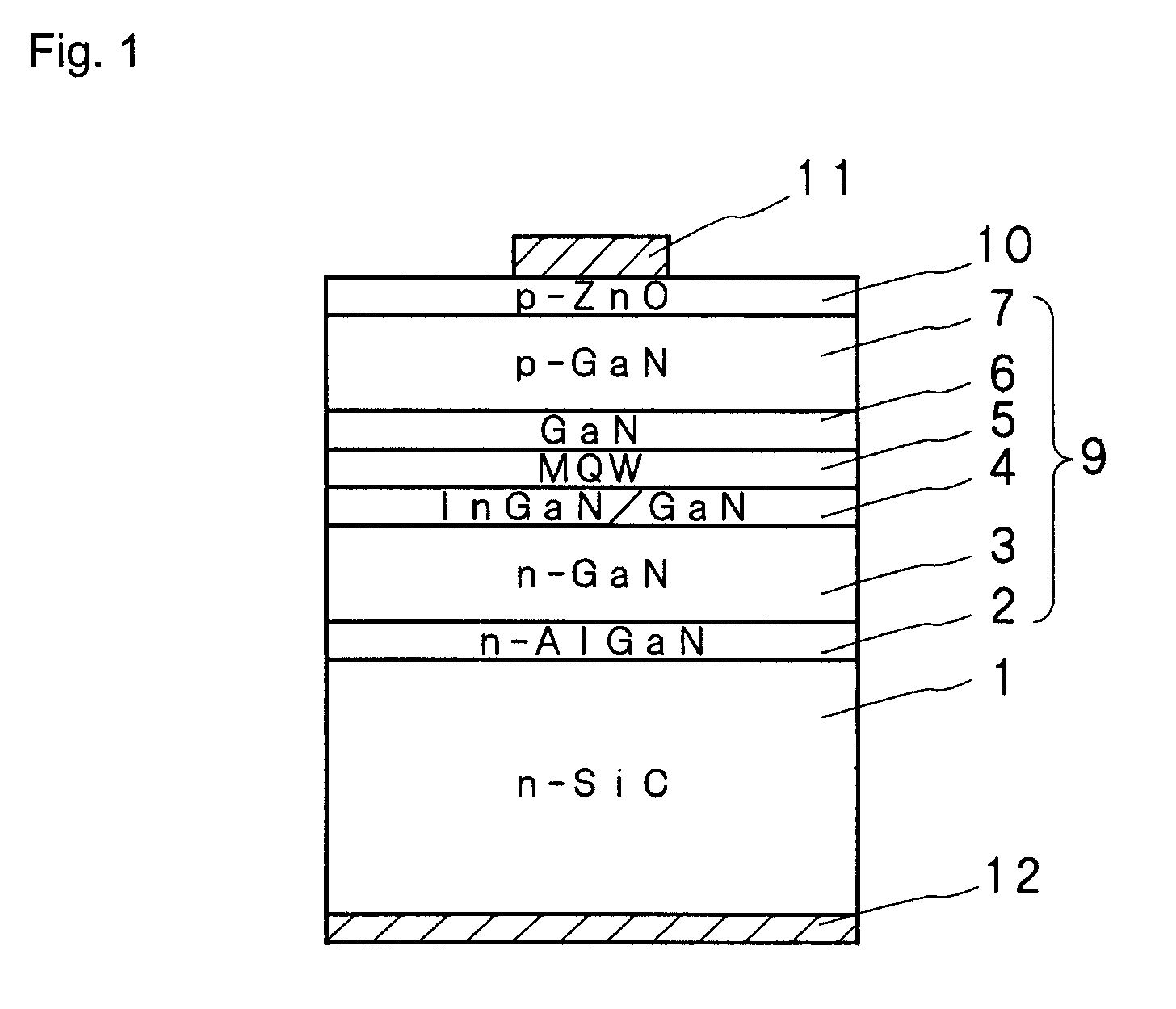

Nitride semiconductor light emitting element

InactiveUS20070122994A1Suppresses minimizesImprove film qualityLaser detailsSolid-state devicesThreading dislocationsQuantum efficiency

A nitride semiconductor light-emitting element suppresses leakage currents and non-radiative recombination centers by providing, as an underlying layer of the active layer, a pit formation layer that reliably generates pits, while maintaining a good film quality, so that the internal quantum efficiency is improved, and the light-emitting characteristics are also improved. A nitride semiconductor lamination portion including at least an active layer for forming a light-emitting portion is present on a substrate, and a pit formation layer is formed as a superlattice layer of nitride semiconductor on the side of the substrate of the active layer. The pit formation layer generates pits in the end portions of threading dislocations that are generated in the nitride semiconductor layer on the side of the substrate.

Owner:ROHM CO LTD

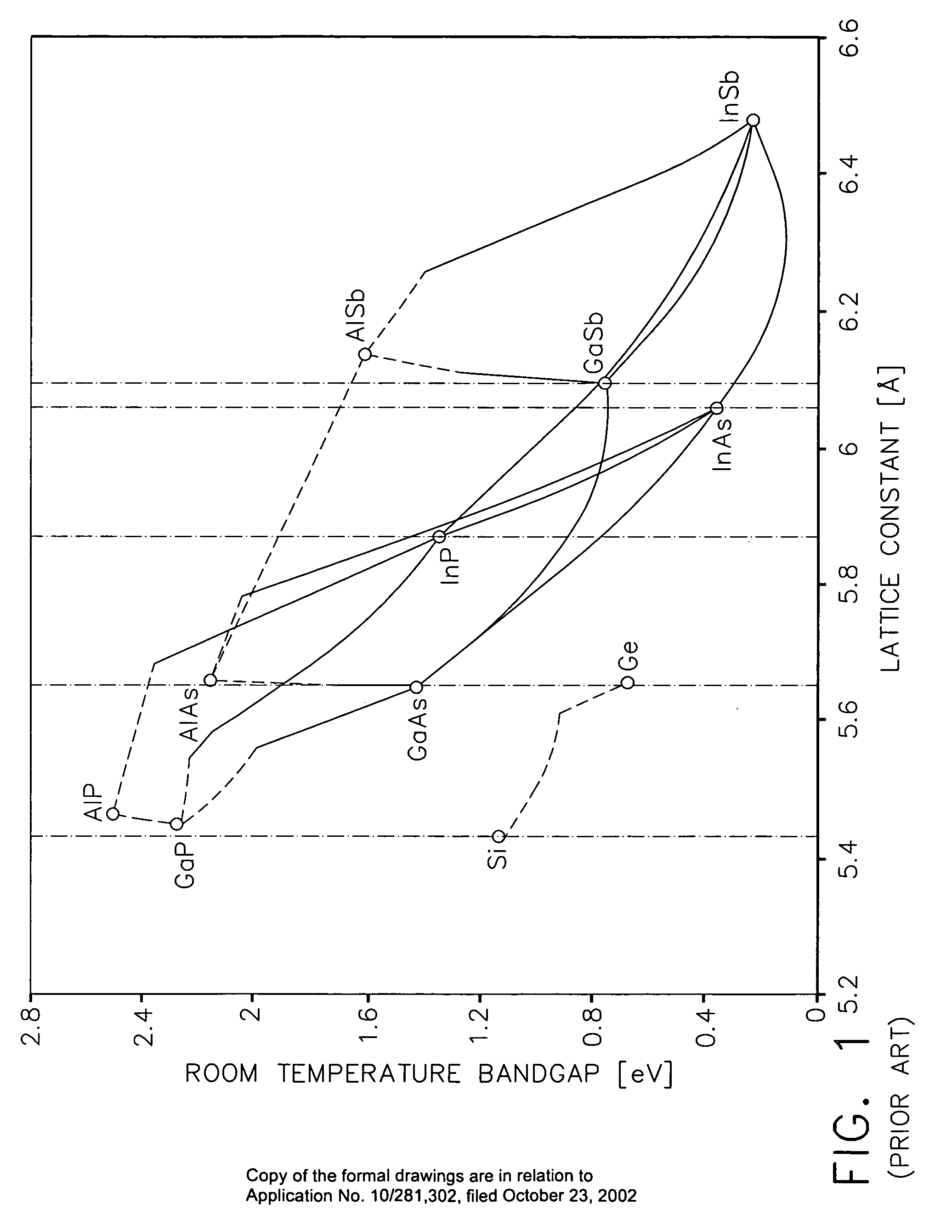

Isoelectronic surfactant suppression of threading dislocations in metamorphic epitaxial layers

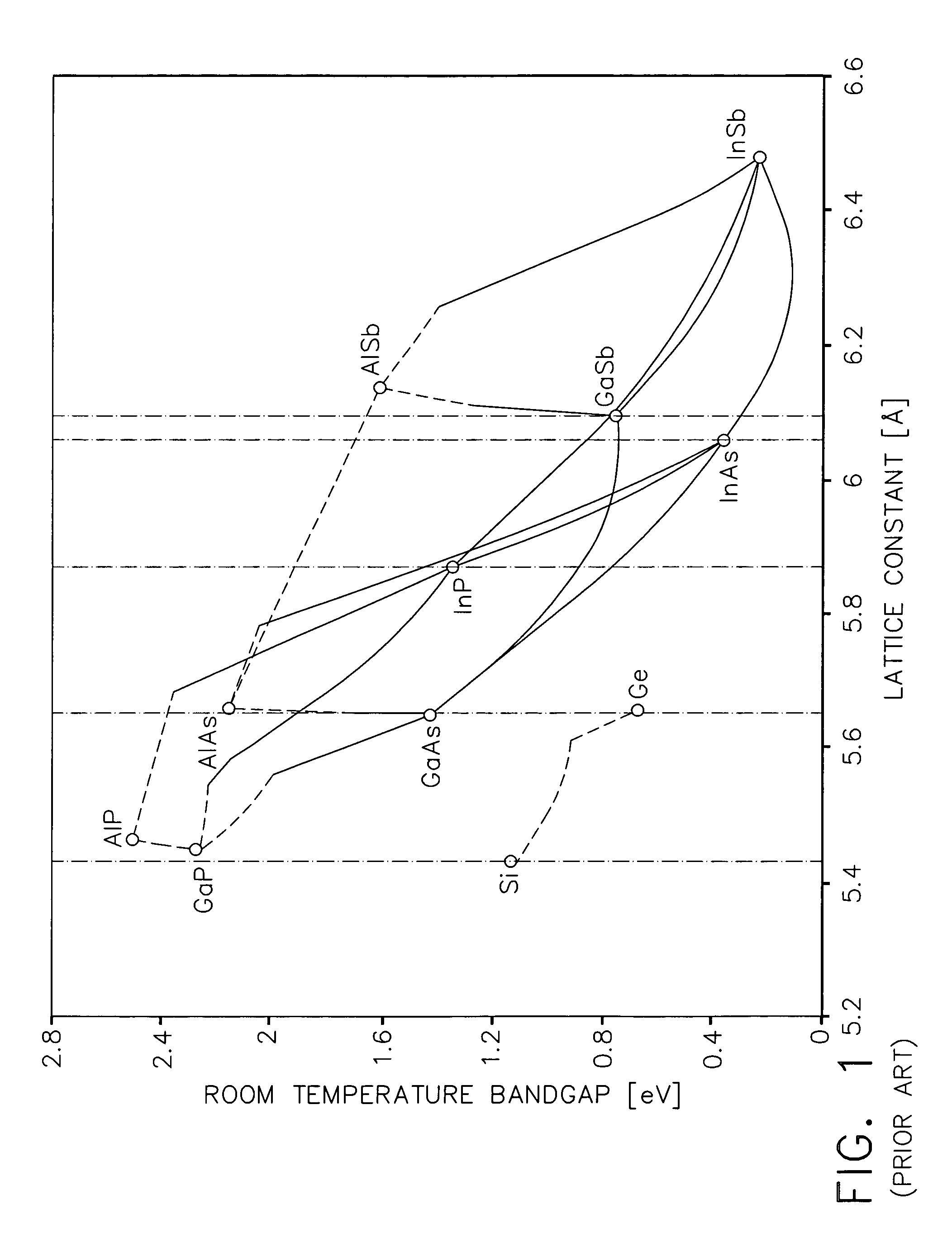

ActiveUS7122734B2Decrease their propagationCosmonautic vehiclesCosmonautic power supply systemsThreading dislocationsLattice constant

A method of reducing propagation of threading dislocations into active areas of an optoelectronic device having a III–V material system includes growing a metamorphic buffer region in the presence of an isoelectronic surfactant. A first buffer layer may be lattice matched to an adjacent substrate and a second buffer layer may be lattice matched to device layers disposed upon the second buffer layer. Moreover, multiple metamorphic buffer layers fabricated in this manner may be used in a single given device allowing multiple layers to have their band gaps and lattice constants independently selected from those of the rest of the device.

Owner:THE BOEING CO

Lattice-mismatched semiconductor structures on insulators

ActiveUS7638842B2Functionality and performance improvementsLower channel resistanceSemiconductor/solid-state device detailsSolid-state devicesThreading dislocationsSemiconductor structure

Monolithic lattice-mismatched semiconductor heterostructures are fabricated by bonding patterned substrates with alternative active-area materials formed thereon to a rigid dielectric platform and then removing the highly-defective interface areas along with the underlying substrates to produce alternative active-area regions disposed over the insulator and substantially exhausted of misfit and threading dislocations.

Owner:TAIWAN SEMICON MFG CO LTD

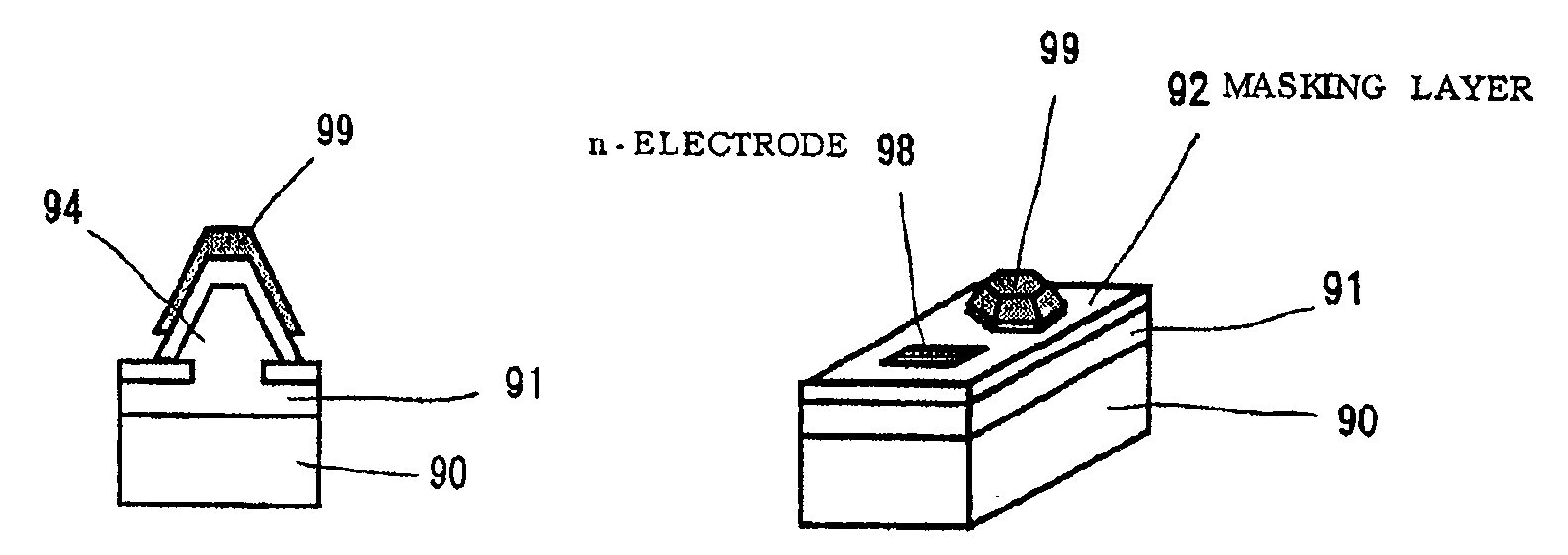

Method for manufacturing a nitride semiconductor device and device manufactured by the method

InactiveUS6555846B1Laser detailsSemiconductor/solid-state device manufacturingThreading dislocationsDopant

A group III nitride semiconductor device is disclosed which has a reduced number of threading dislocations adversely affecting characteristics of the group III nitride semiconductor device. A method for manufacturing the group III nitride semiconductor device controls pit formation in a GaN layer formed on a sapphire substrate.First, a low temperature buffer layer is formed on a sapphire substrate by MOCVD. An undoped GaN layer having a predetermined thickness is then grown on the low temperature buffer layer. Next, a GaN layer containing magnesium as a dopant is formed on the layer at a lower pressure than that of depositing the GaN layer, which results in filling pits generated on the GaN layer to flatten the surface of another GaN layer.

Owner:SHOWA DENKO KK

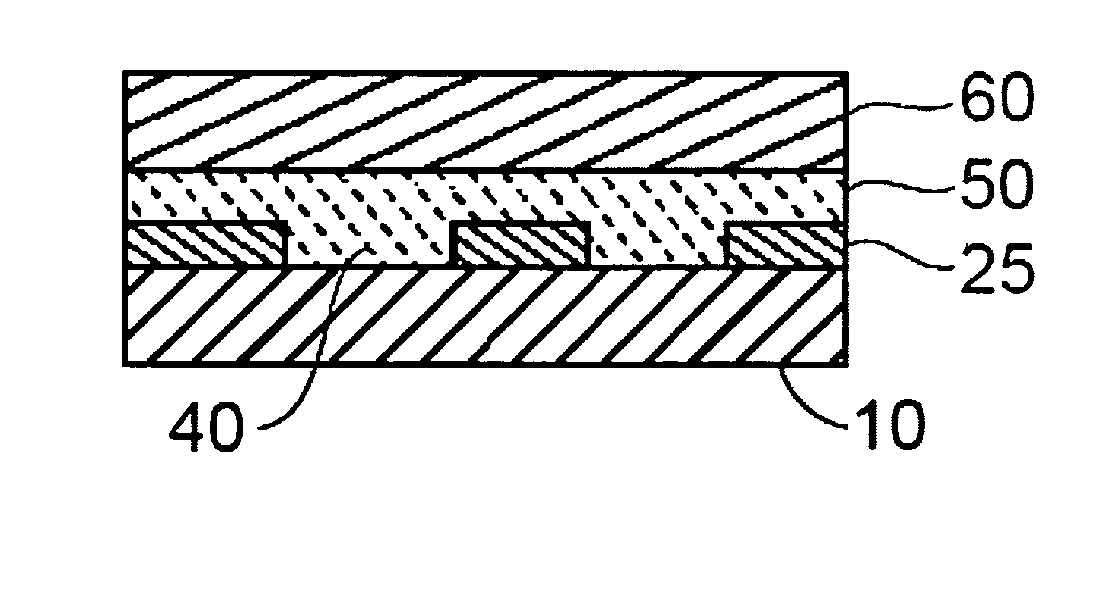

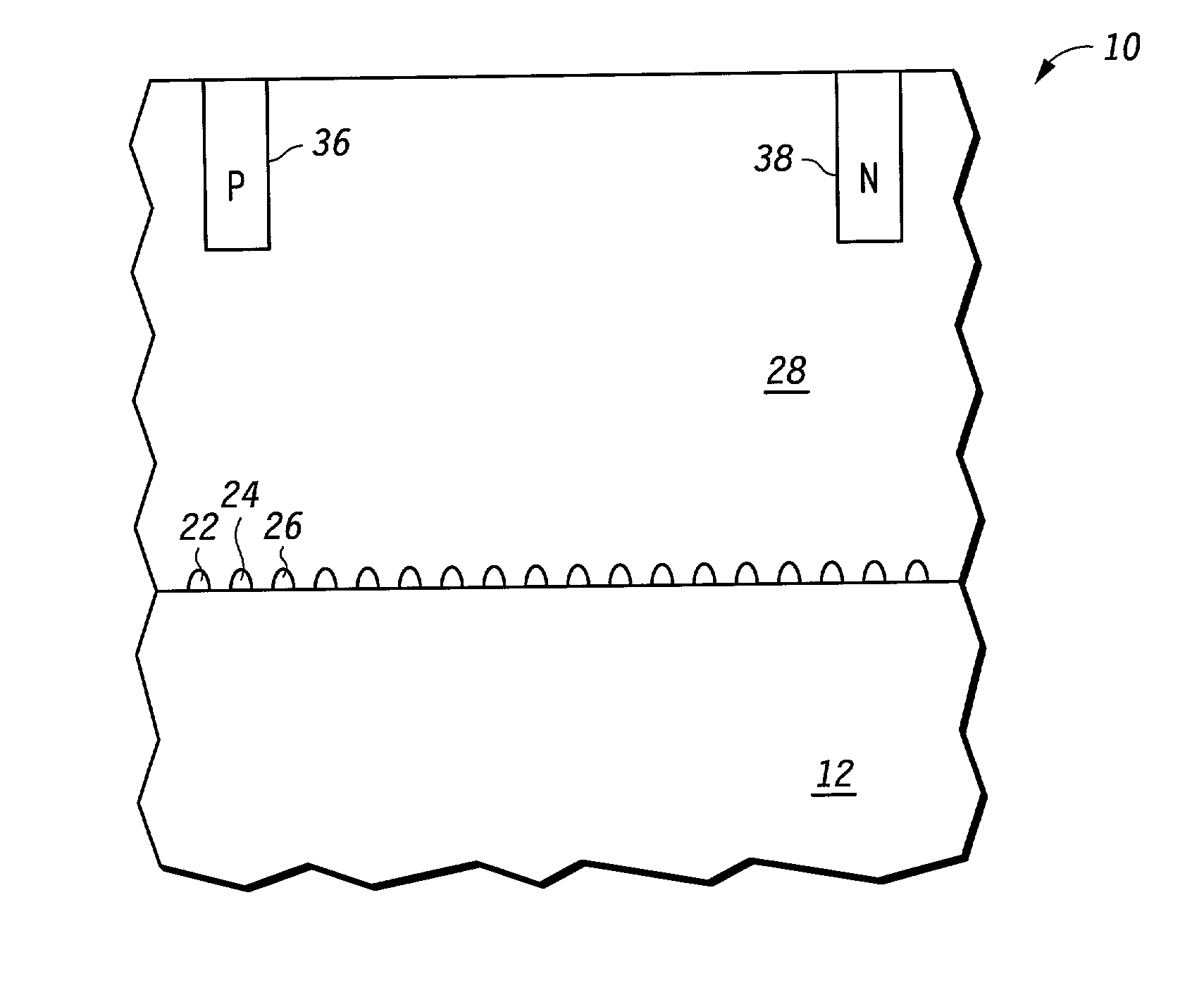

Method for manufacturing semiconductor substrate

ActiveUS20080194078A1Simple technologyQuality improvementSemiconductor/solid-state device manufacturingSemiconductor devicesThreading dislocationsHigh density

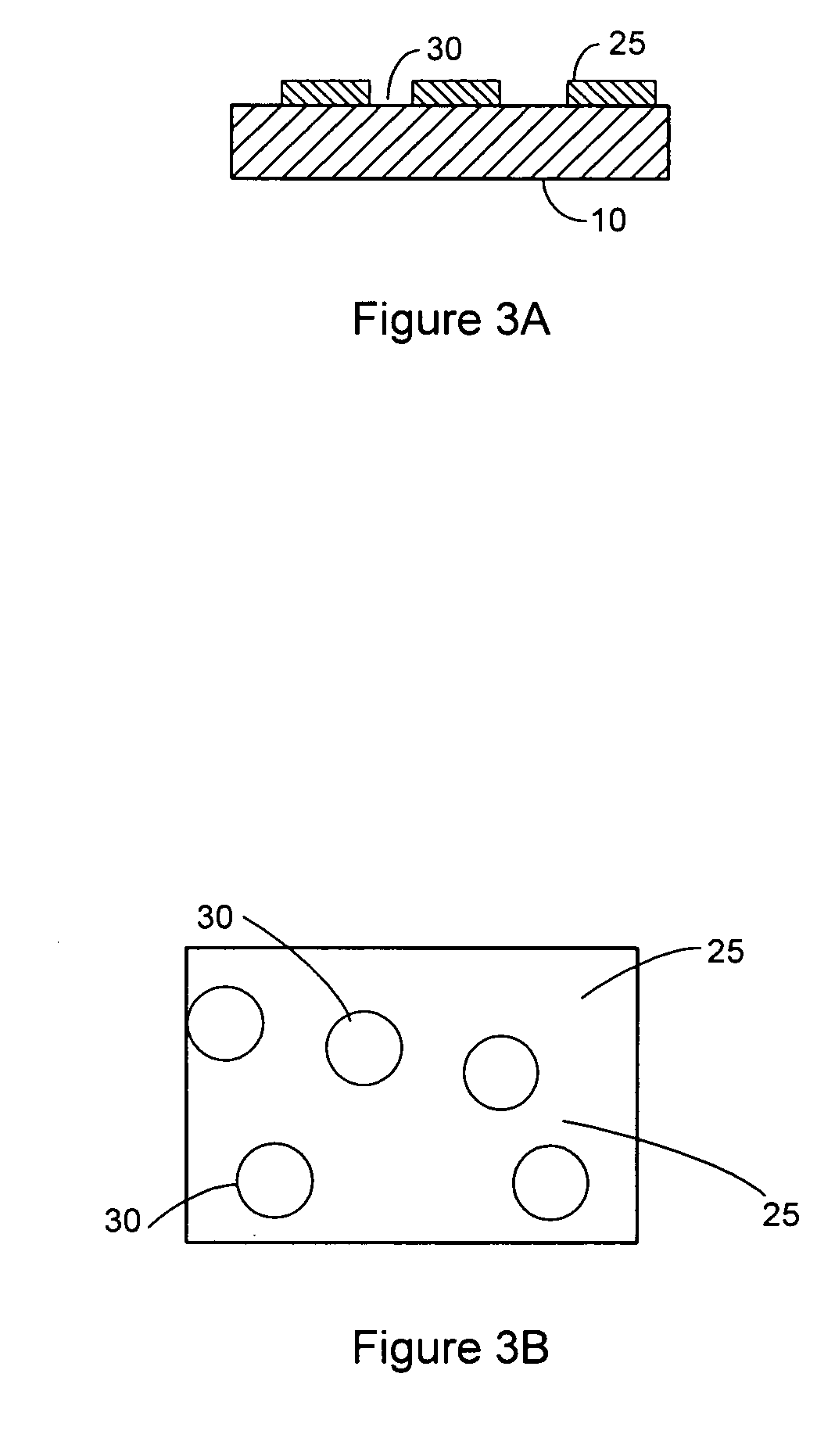

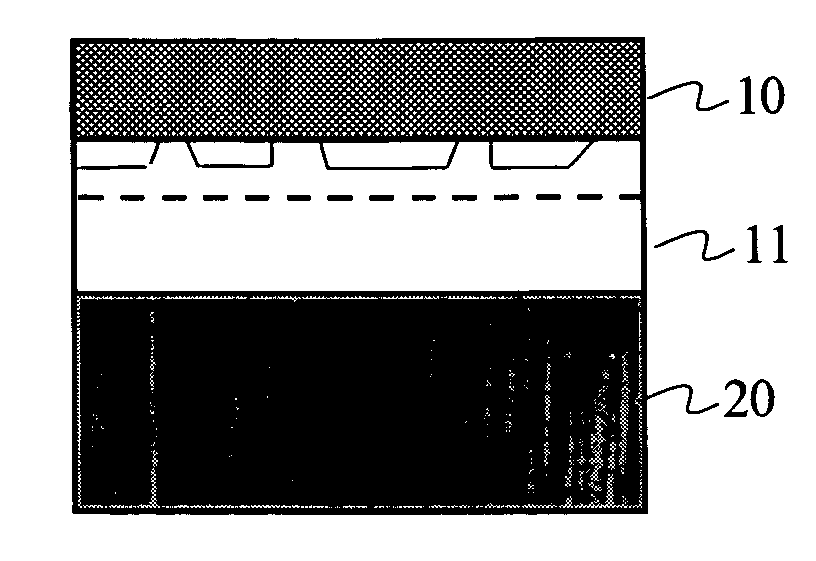

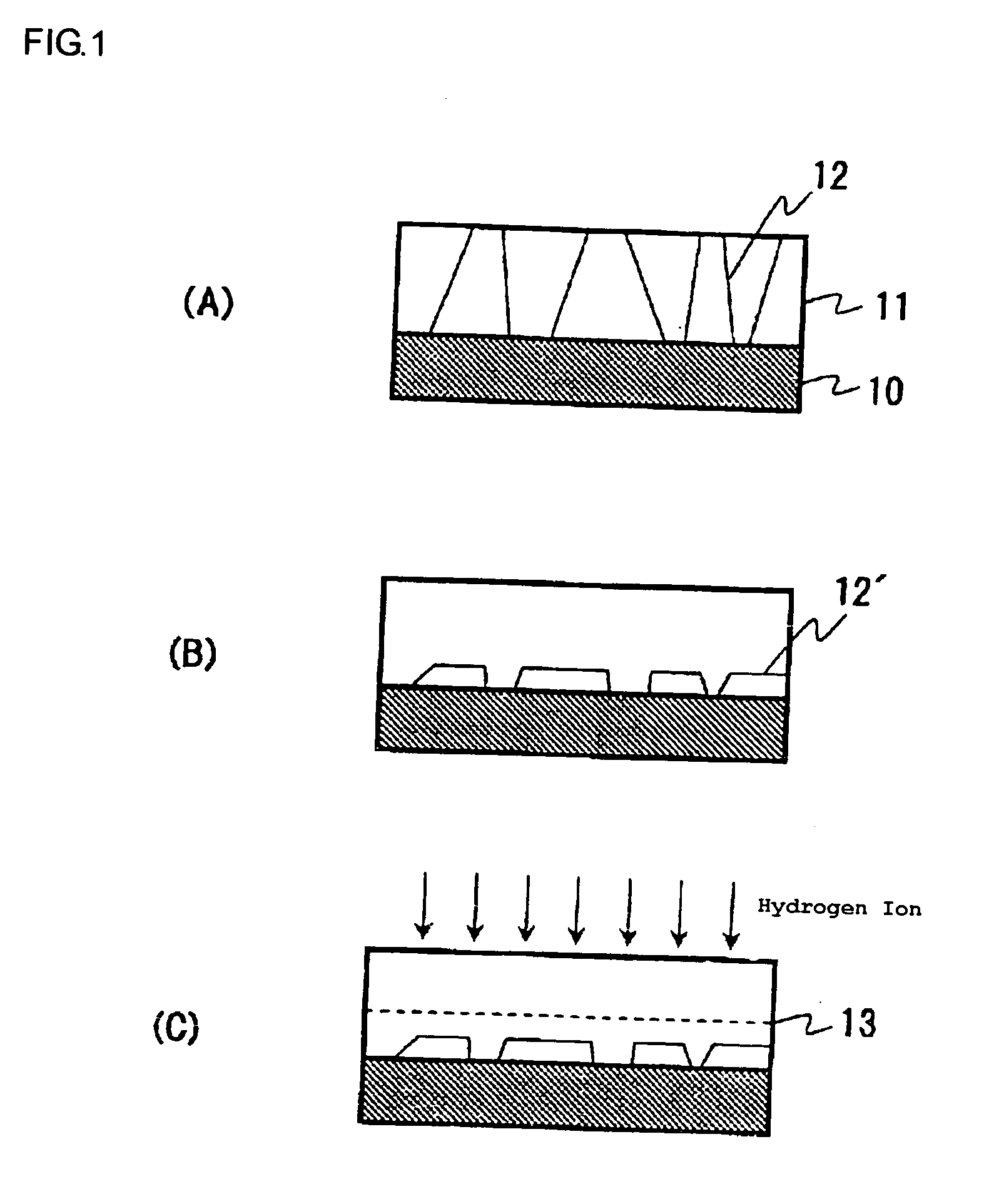

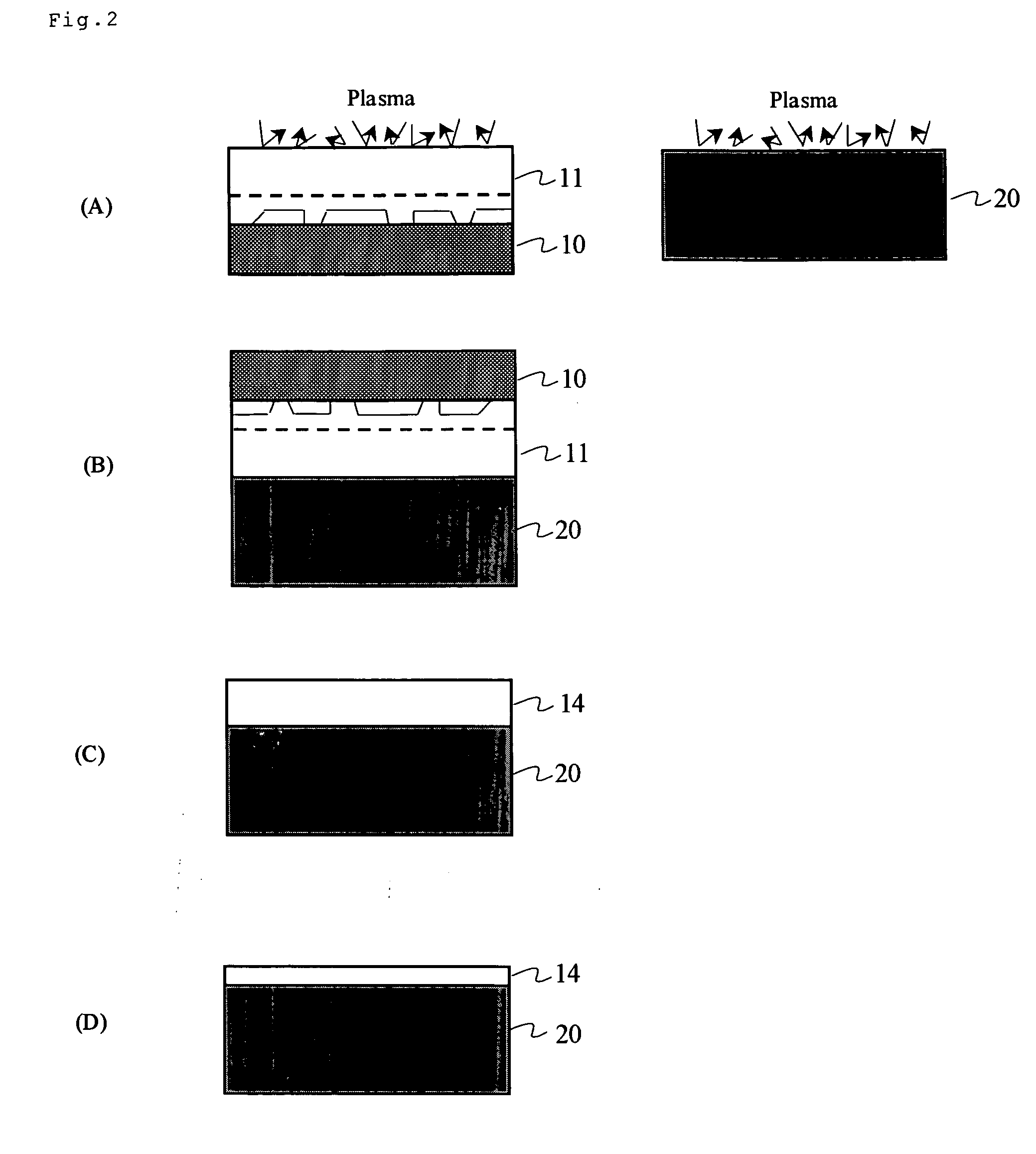

To obtain a semiconductor substrate having a high-quality Ge-based epitaxial film in a large area, a SiGe mixed crystal buffer layer and a Ge epitaxial film is grown on a main surface of a Si substrate 10. Although high-density defects are introduced in the Ge epitaxial film 11 from an interface between the Ge epitaxial film 11 and the Si substrate 10, the Ge epitaxial film is subjected to a heat treatment at a temperature of not less than 700° C. and not more than 900° C. to cause threading dislocations 12 to change into dislocation-loop defects 12′ near the interface between the Ge epitaxial film 11 and the Si substrate. A main surface of at least one of the Ge epitaxial film 11 with an ion implanted layer and a support substrate 20 is then subjected to a plasma treatment or ozone treatment for the purpose of surface cleaning, surface activation, and the like, after which the main surfaces of the Ge epitaxial film 11 and the support substrate 20 are appressed against and bonded to each other with their surfaces being determined as the joint surfaces. An external impact is then applied to the bonding interface, causing the Ge epitaxial film to be delaminated along a hydrogen ion implanted interface 13, thus obtaining a Ge thin film 14. A surface of the Ge thin film 14 is subsequently subjected to a final surface treatment (for example, CMP) to remove the damage caused by the hydrogen ion implantation, thus resulting in a GeOI substrate having the Ge thin film 14 on the surface thereof.

Owner:SHIN ETSU CHEM IND CO LTD

Method for fabricating Group III nitride compound semiconductors and Group III nitride compound semiconductor devices

InactiveUS20060027831A1Avoid problemsExtended service lifePolycrystalline material growthLaser detailsThreading dislocationsNitride

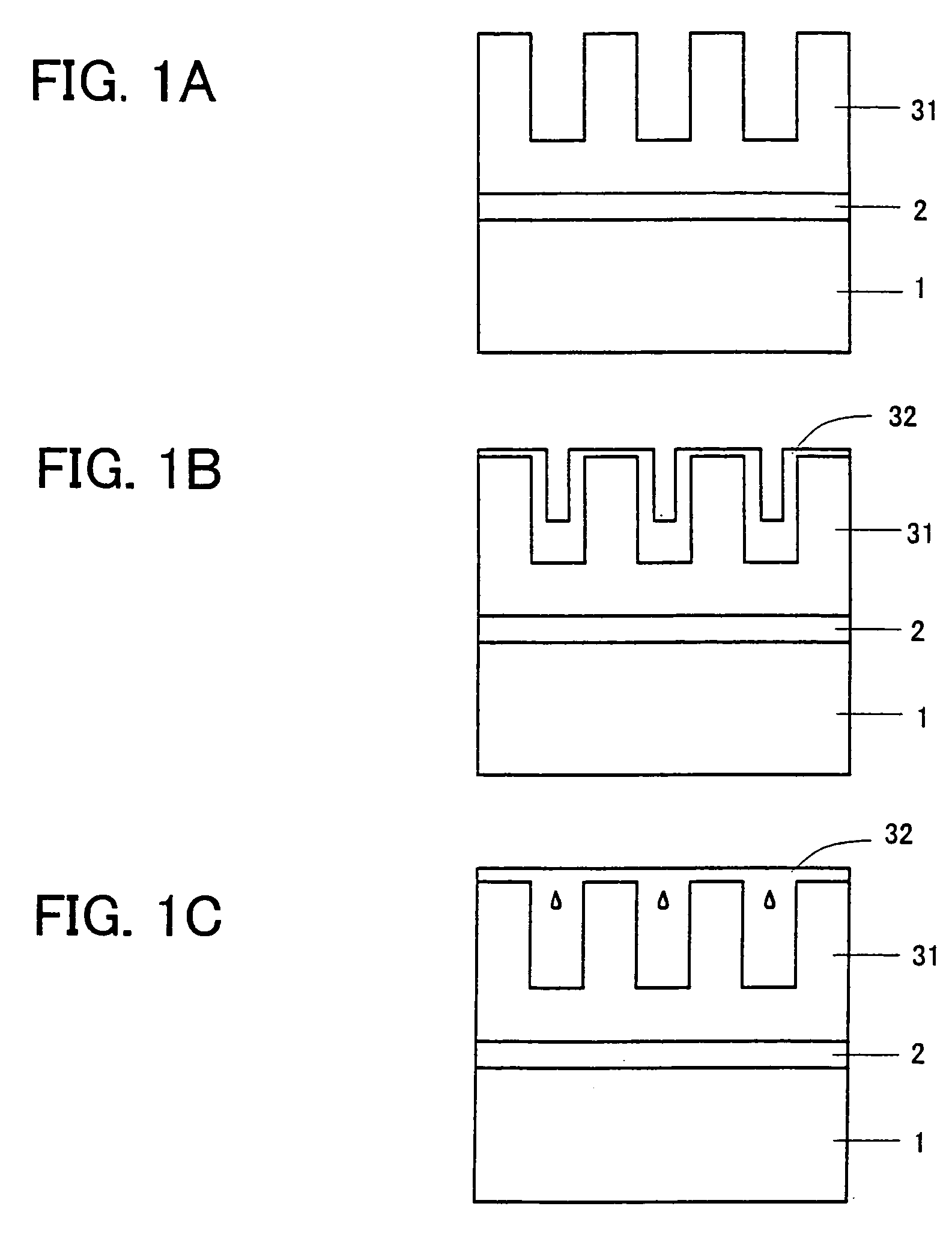

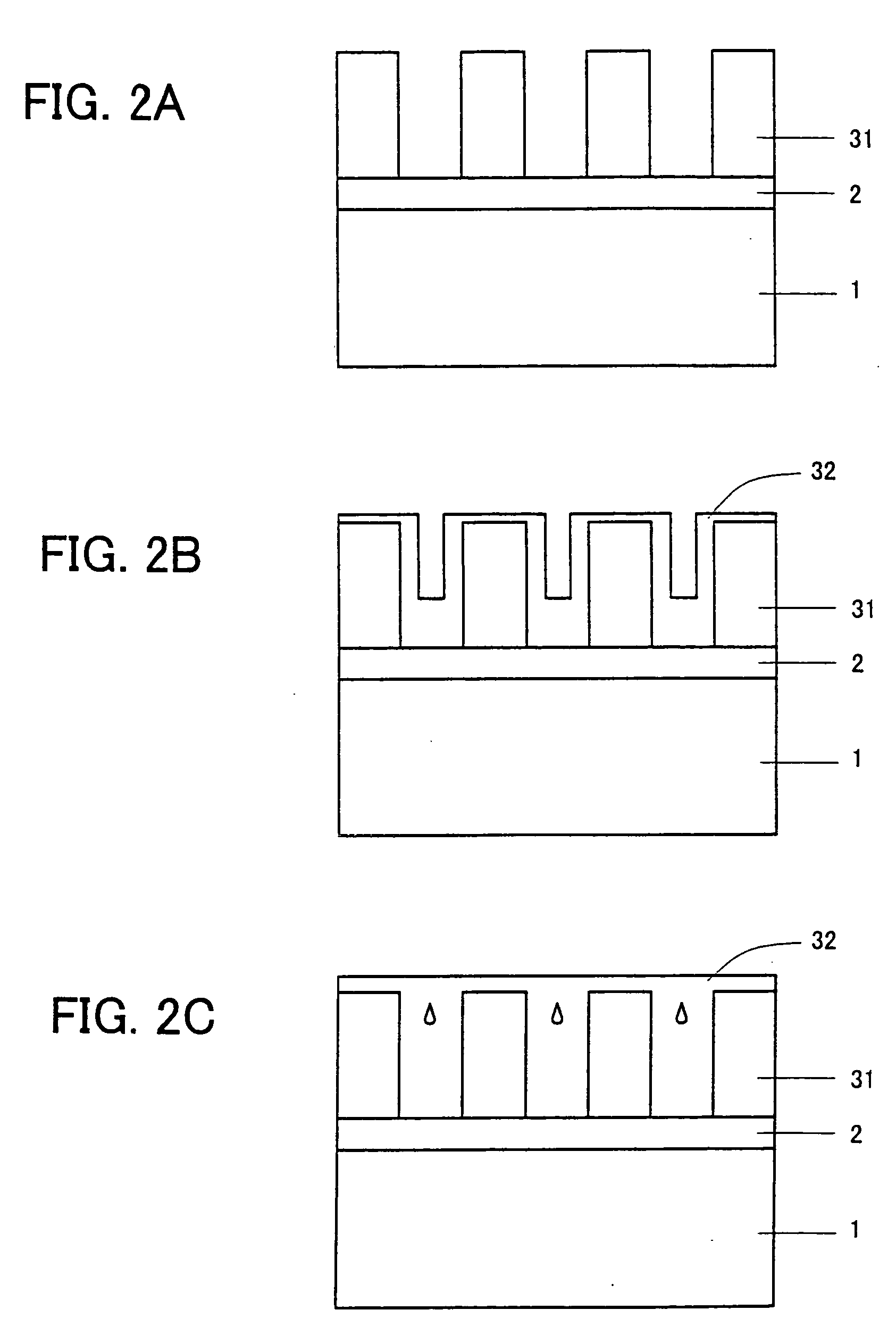

A first Group III nitride compound semiconductor layer 31 is etched, to thereby form an island-like structure such as a dot-like, stripe-shaped, or grid-like structure, so as to provide a trench / post. Thus, a second Group III nitride compound layer 32 can be epitaxially grown, vertically and laterally, from a top surface of the post and a sidewall / sidewalls of the trench serving as a nucleus for epitaxial growth, to thereby bury the trench and also grow the layer in the vertical direction. In this case, propagation of threading dislocations contained in the first Group III nitride compound semiconductor layer 31 can be prevented in the upper portion of the second Group III nitride compound semiconductor 32 that is formed through lateral epitaxial growth. As a result, a region having less threading dislocations is formed at the buried trench.

Owner:TOYODA GOSEI CO LTD

Strained silicon on insulator from film transfer and relaxation by hydrogen implantation

ActiveUS6992025B2Easy to relaxEasy to integrateSolid-state devicesSemiconductor/solid-state device manufacturingThreading dislocationsPhysical chemistry

Owner:SHARP KK

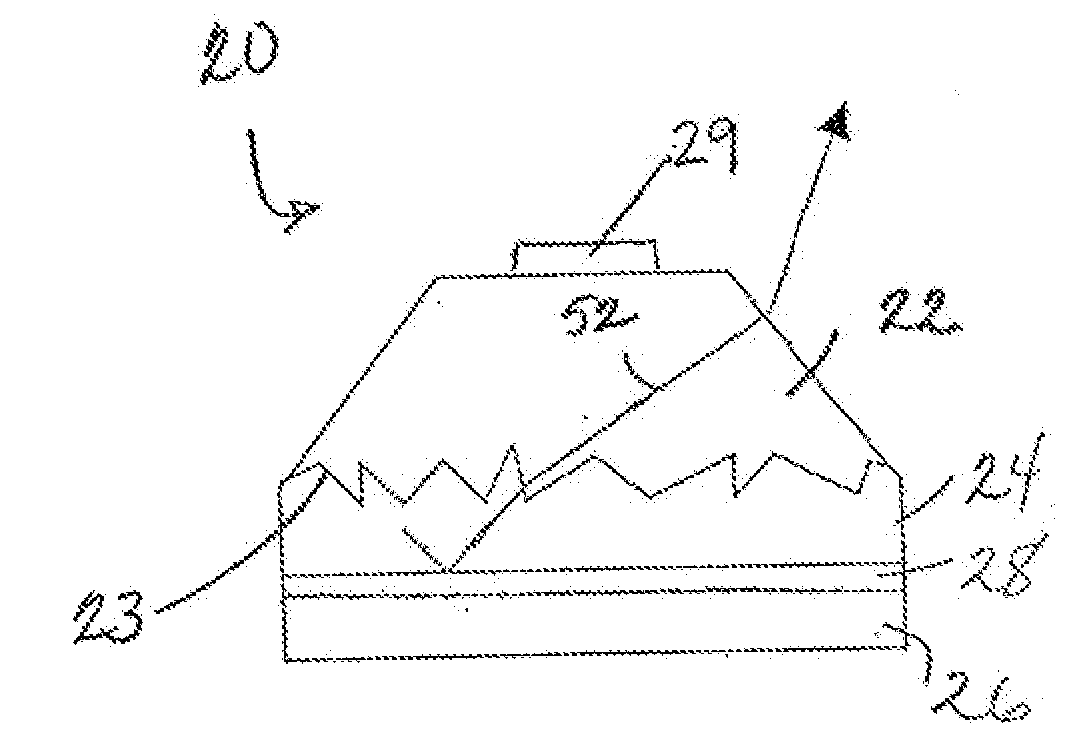

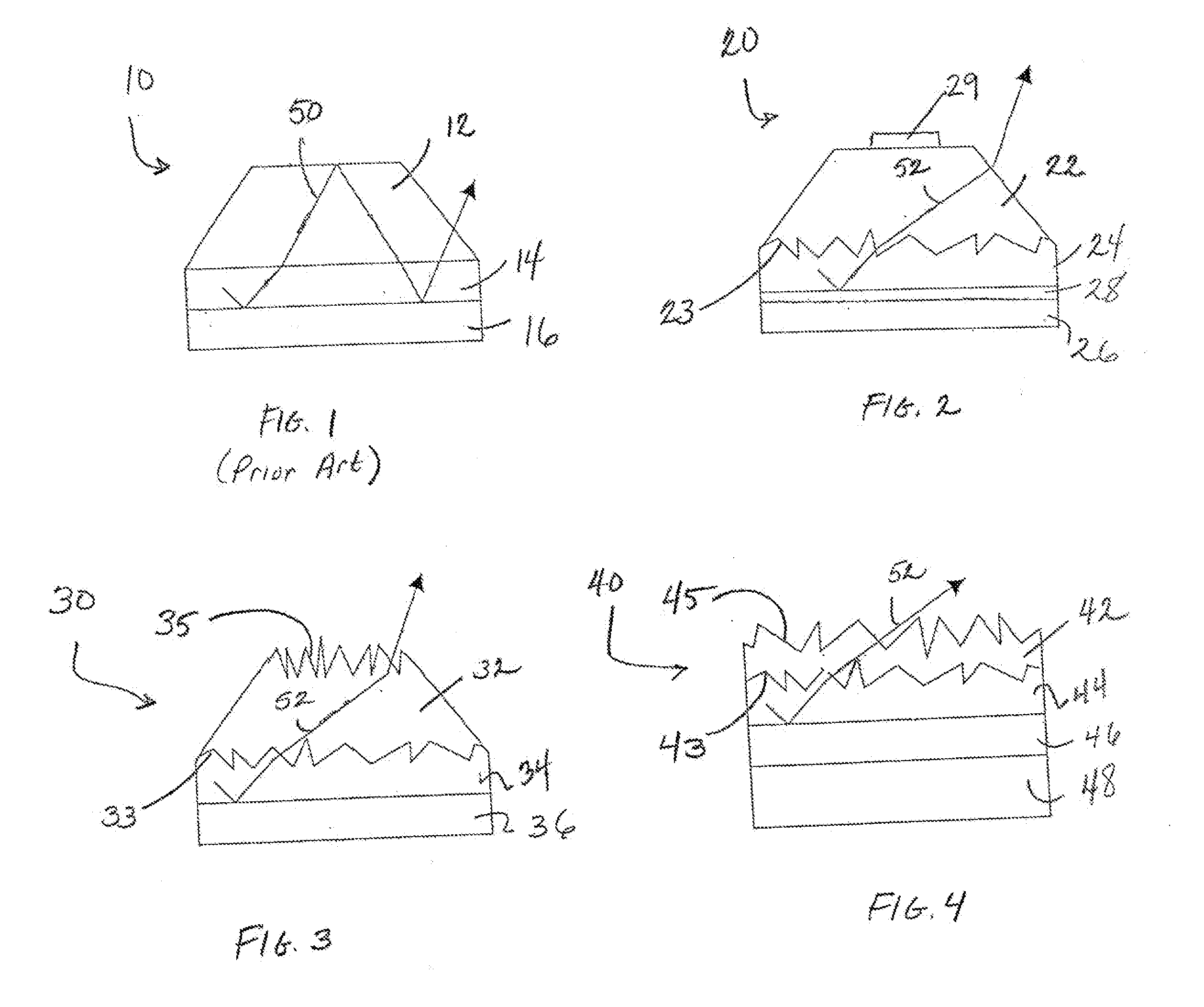

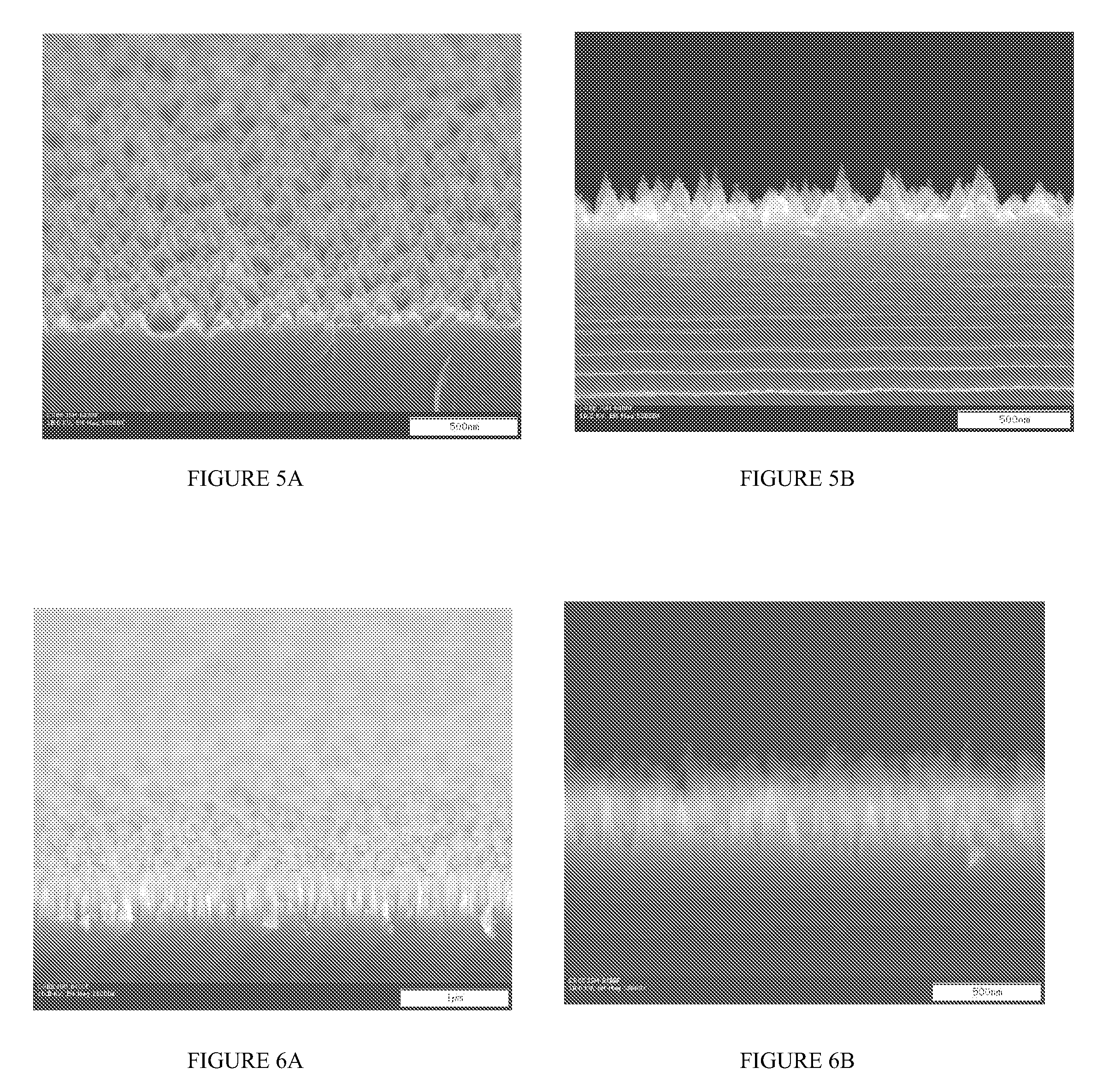

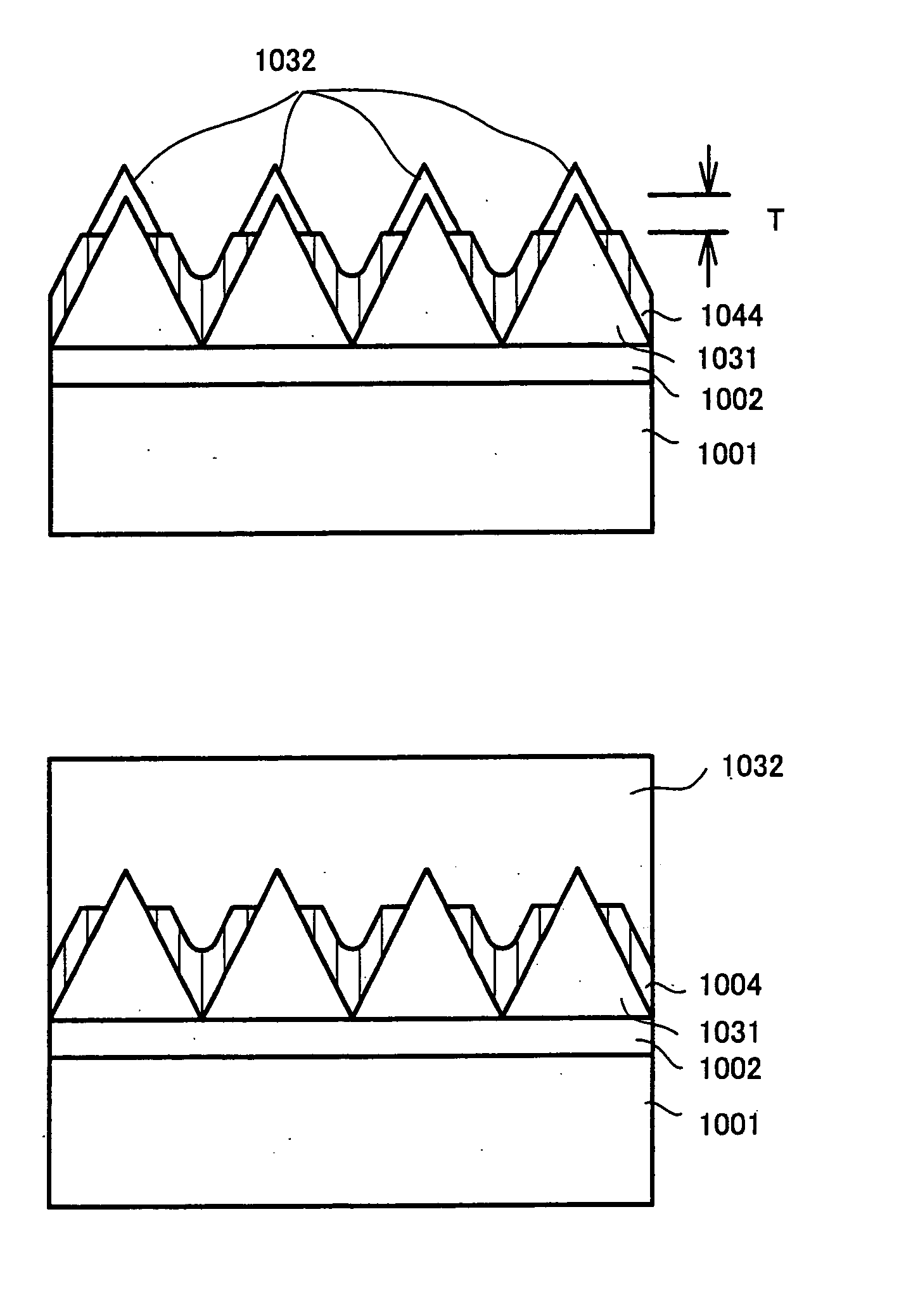

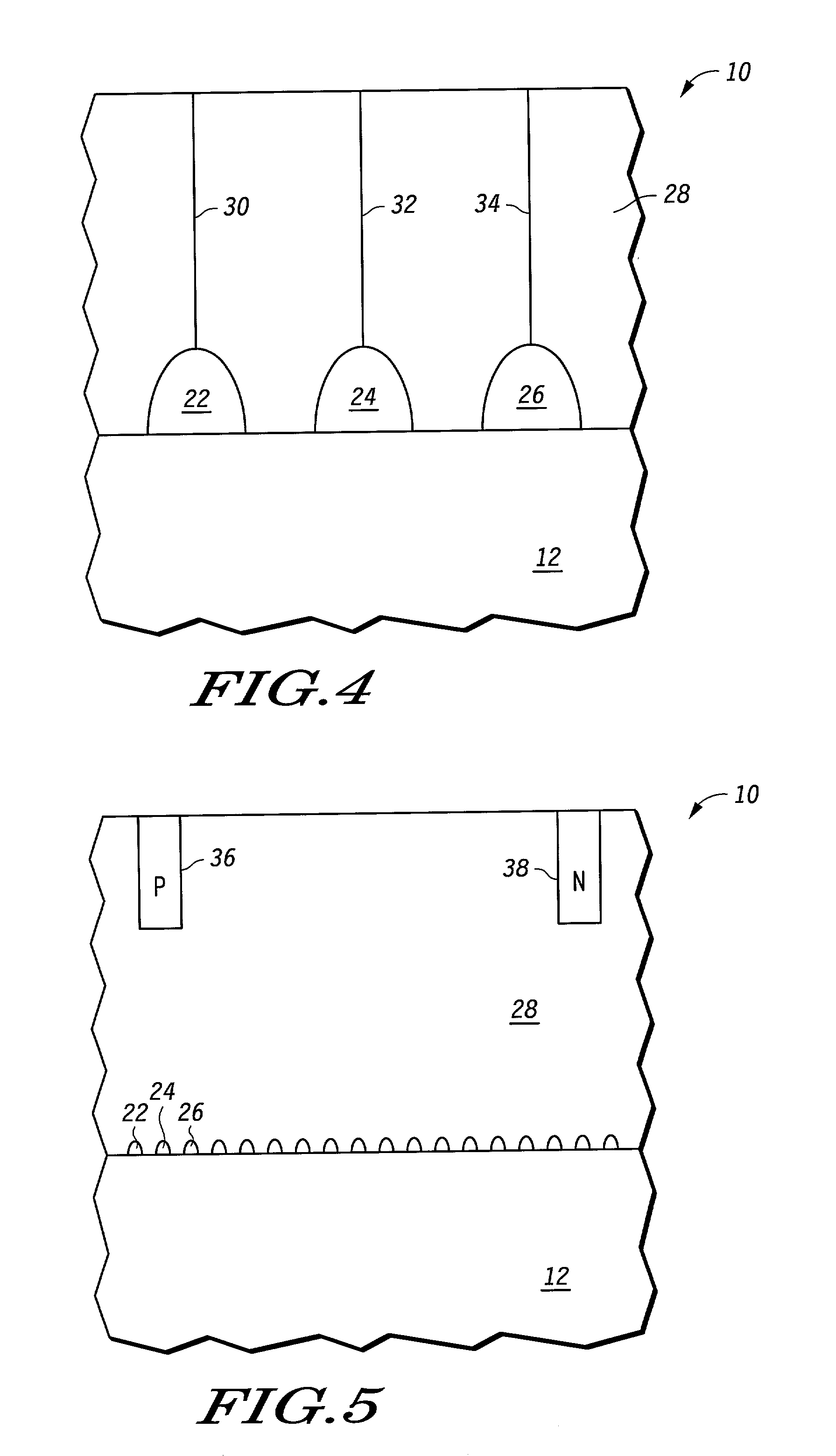

Semiconductor Devices Having Low Threading Dislocations and Improved Light Extraction and Methods of Making the Same

ActiveUS20080121910A1Reduce defectsImproved radiation extraction efficiencySemiconductor/solid-state device manufacturingPhotovoltaic energy generationThreading dislocationsDislocation

Semiconductor device structures are provided that are suitable for use in the fabrication of electronic devices such as light emitting diodes. The semiconductor device structures include a substrate having a roughened growth surface suitable for supporting the growth of an epitaxial region thereon. The device structure can include an epitaxial region having reduced defects and / or improved radiation extraction efficiency on the roughened growth surface of the substrate. The roughened growth surface of the substrate can have an average roughness Ra of at least about 1 nanometer (nm) and an average peak to valley height Rz of at least about 10 nanometers (nm).

Owner:CREELED INC

Isoelectronic surfactant suppression of threading dislocations in metamorphic epitaxial layers

InactiveUS20090145476A1Cosmonautic vehiclesCosmonautic power supply systemsThreading dislocationsLattice constant

Owner:THE BOEING CO

Method for fabricating group III nitride compound semiconductors and group III nitride compound semiconductor devices

InactiveUS20050093099A1Avoid problemsExtended service lifeFrom solid stateSolid-state devicesThreading dislocationsDislocation

The present invention provides a Group III nitride compound semiconductor with suppressed generation of threading dislocations. A GaN layer 31 is subjected to etching, so as to form an island-like structure having a shape of, for example, dot, stripe, or grid, thereby providing a trench / mesa structure, and a mask 4 is formed at the bottom of the trench such that the upper surface of the mask 4 is positioned below the top surface of the GaN layer 31. A GaN layer 32 is lateral-epitaxially grown with the top surface 31a of the mesa and sidewalls 31b of the trench serving as nuclei, to thereby bury the trench, and then epitaxial growth is effected in the vertical direction. In the upper region of the GaN layer 32 formed above the mask 4 through lateral epitaxial growth, propagation of threading dislocations contained in the GaN layer 31 can be prevented.

Owner:TOYODA GOSEI CO LTD

Semiconductor device and method therefor

InactiveUS20030102469A1From solid stateFinal product manufactureThreading dislocationsLithographic artist

A heteroepitaxial structure is made using nanocrystals that are formed closer together than normal lithography patterning would allow. The nanocrystals are oxidized and thus selectively etchable with respect to the substrate and surrounding material. In one case the oxidized nanocrystals are removed to expose the substrate at those locations and selective epitaxial germanium is then grown at those exposed substrate locations. The inevitable formation of the misfit dislocations does minimal harm because they are terminated at the surrounding material. In another case the surrounding material is removed and the germanium is epitaxially grown at the exposed substrate where the surrounding material is removed. The resulting misfit dislocations in the germanium terminate at the oxidized nanocrystals. By using nanocrystals that are able to be formed much closer together than is available for other features through lithography, the misfits are prevented from extending so far as to create harmful threading dislocations.

Owner:NORTH STAR INNOVATIONS

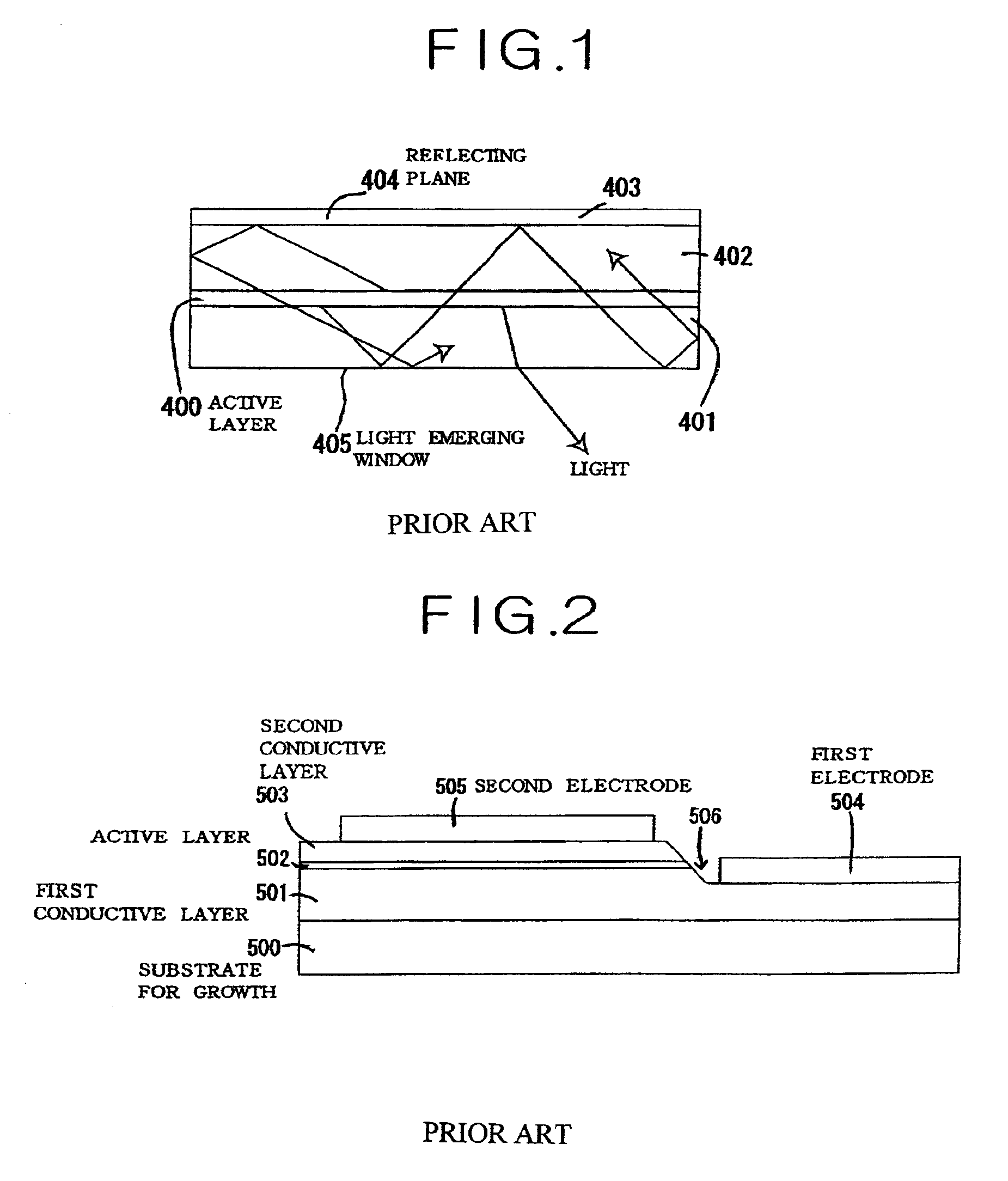

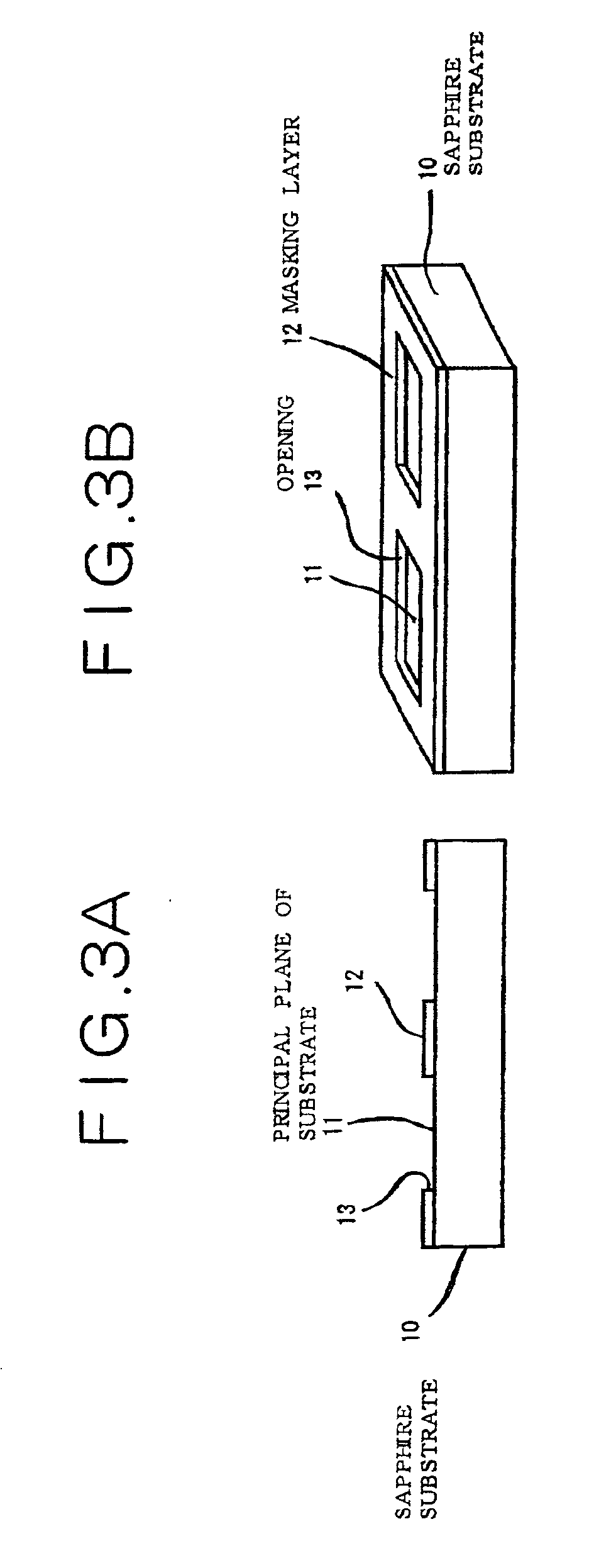

Semiconductor light-emitting device and process for producing the same

InactiveUS6924500B2Improve propertiesLayer deterioratesSolid-state devicesSemiconductor/solid-state device manufacturingThreading dislocationsMiniaturization

Semiconductor light-emitting devices are provided. The semiconductor light-emitting devices include a substrate and a crystal layer selectively grown thereon at least a portion of the crystal layer is oriented along a plane that slants to or diagonally intersect a principal plane of orientation associated with the substrate thereby for example, enhancing crystal properties, preventing threading dislocations, and facilitating device miniaturization and separation during manufacturing and use thereof.

Owner:SONY CORP

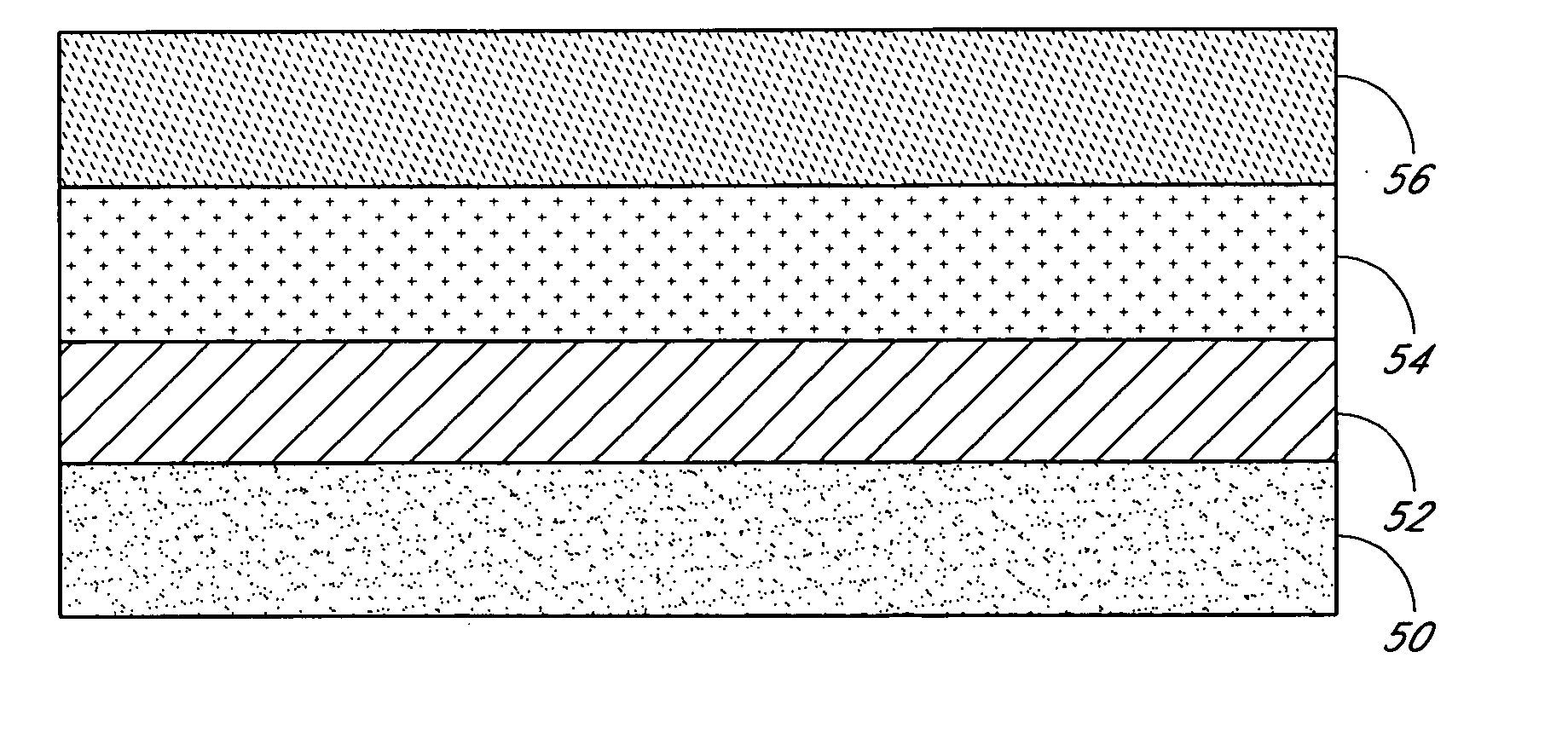

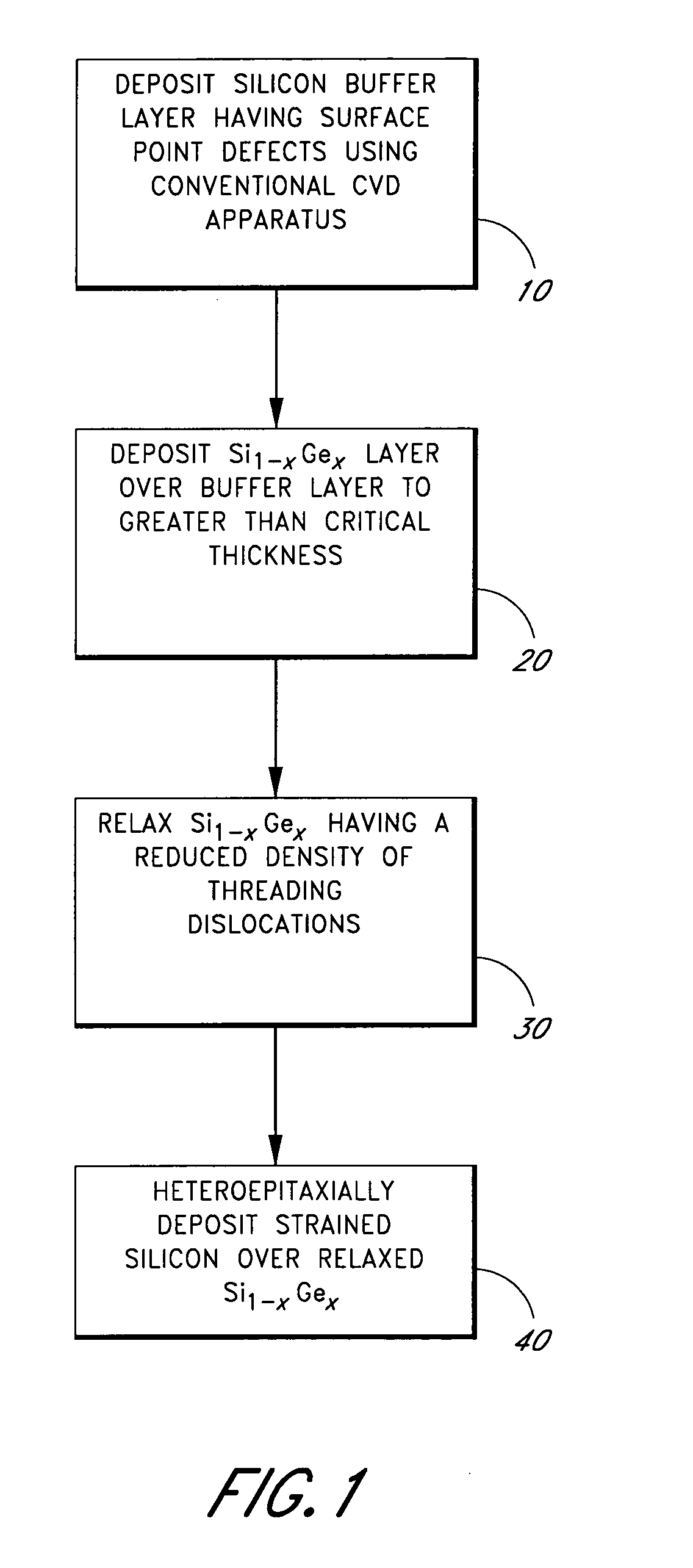

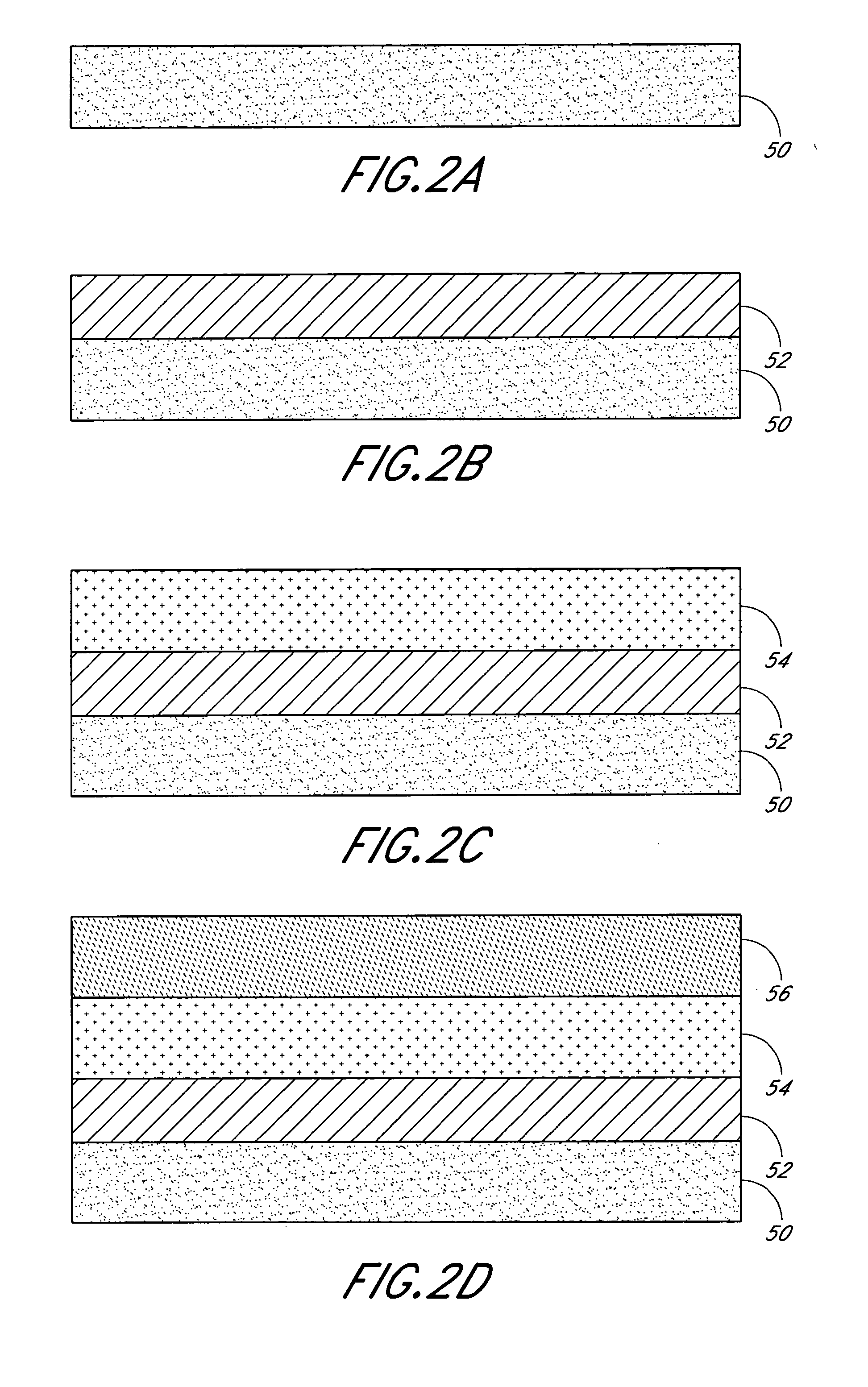

Epitaxial growth of relaxed silicon germanium layers

ActiveUS20050051795A1Polycrystalline material growthSemiconductor/solid-state device manufacturingThreading dislocationsGas phase

A relaxed silicon germanium structure comprises a silicon buffer layer produced using a chemical vapor deposition process with an operational pressure greater than approximately 1 torr. The relaxed silicon germanium structure further comprises a silicon germanium layer deposited over the silicon buffer layer. The silicon germanium layer has less than about 107 threading dislocations per square centimeter. By depositing the silicon buffer layer at a reduced deposition rate, the overlying silicon germanium layer can be provided with a “crosshatch free” surface.

Owner:ASM IP HLDG BV

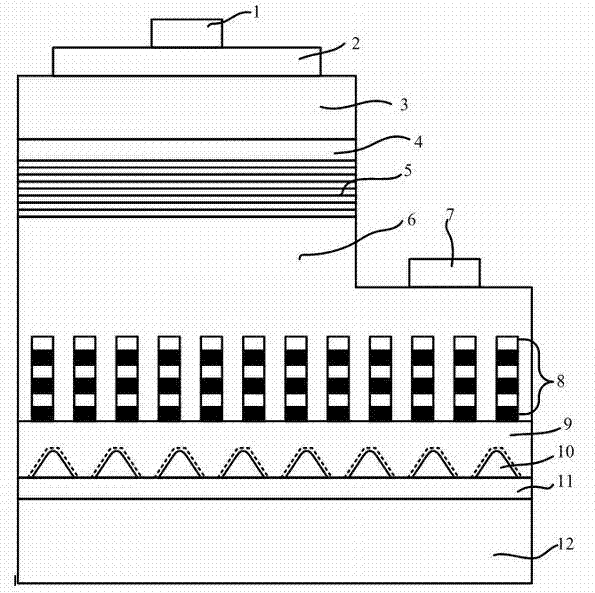

Manufacturing method for near ultraviolet LED device

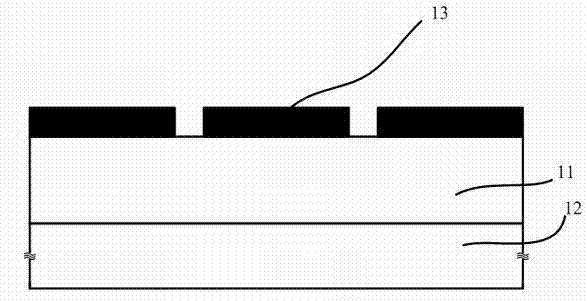

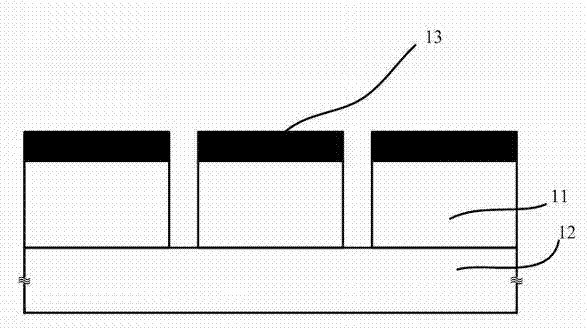

InactiveCN102368526APrevent escapeImprove light extraction efficiencySemiconductor devicesThreading dislocationsEngineering

The invention discloses a manufacturing method for an InGaN / AlGaN-based near ultraviolet LED device. The device is mainly characterized in that: technologies including an embedded tapered air clearance structure and a patterning built-in DBR and the like are employed in a substructure of the device; the patterning built-in DBR is capable of blocking extension of threading dislocation, thereby substantially reducing a density of extended dislocation in an epitaxial layer and improving a crystal quality of an epitaxial film; meanwhile, because the structure of the DBR reflecting layer especially has a property of high reflectivity and an air clearance structure is especially designed on the bottom, reflection at many times and scattering on an upper surface can be carried out on lights emitted to a substrate, so that a light extraction efficiency of the LED can be substantially enhanced.

Owner:HC SEMITEK CORP