Patents

Literature

2262 results about "Soi substrate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

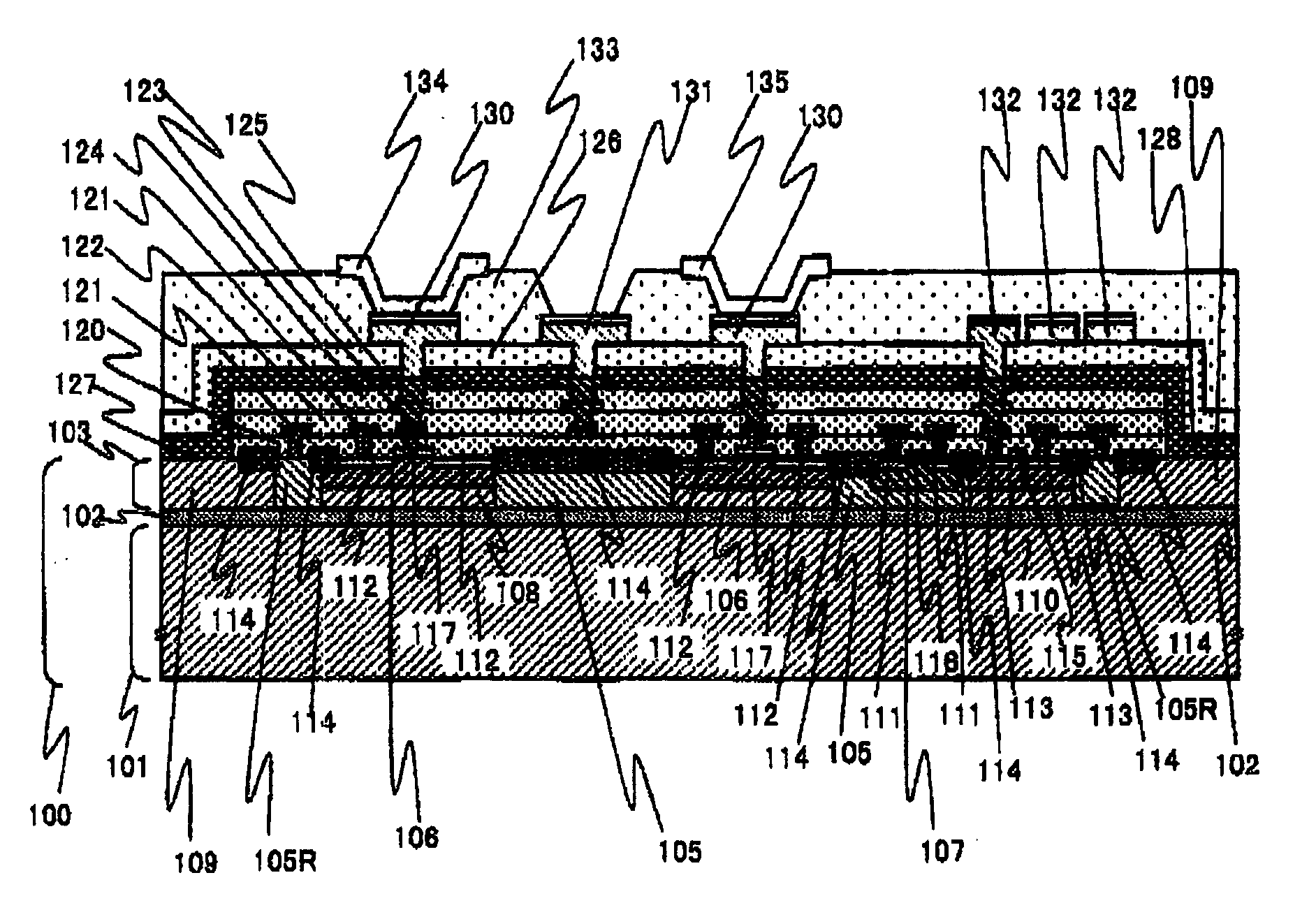

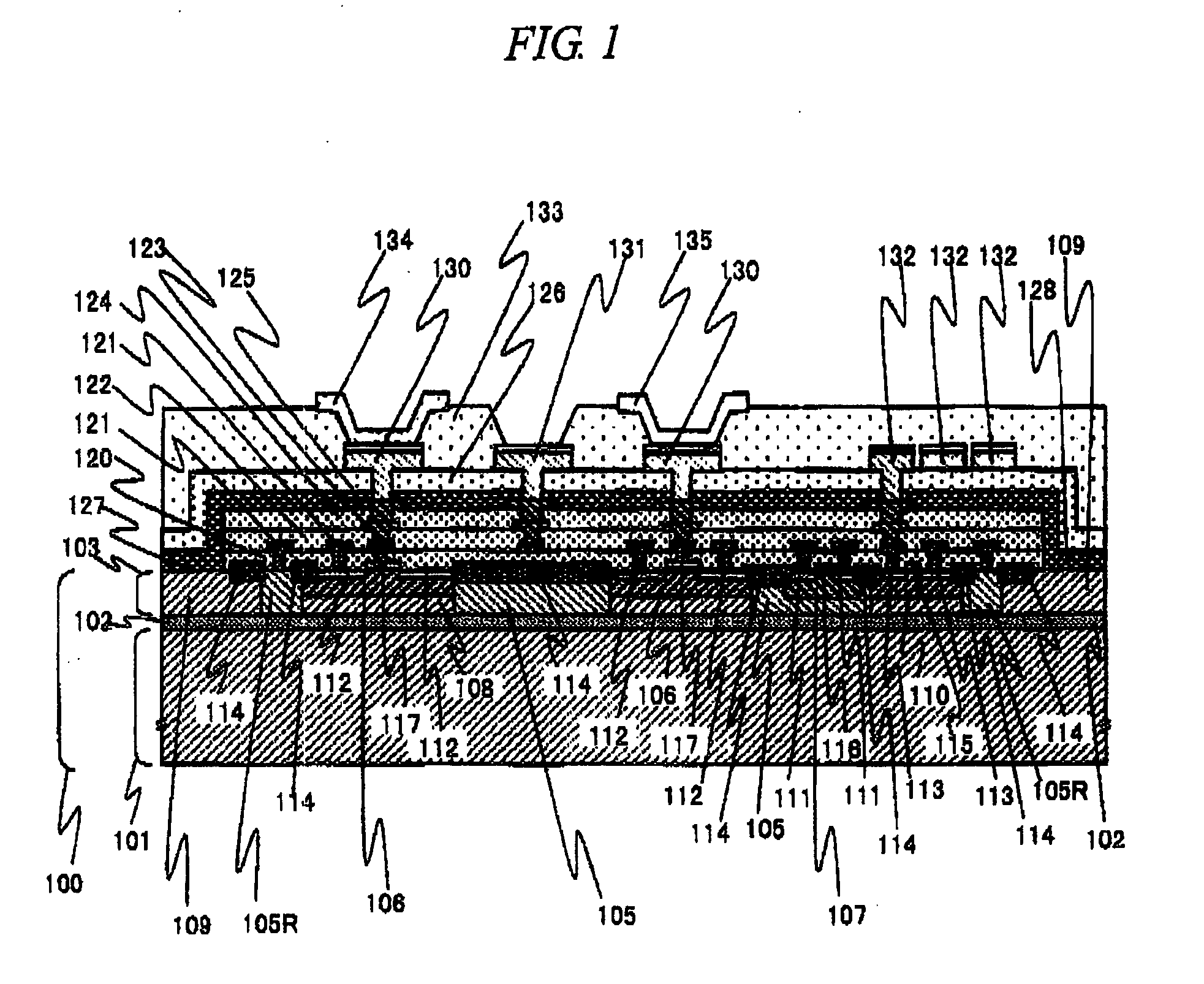

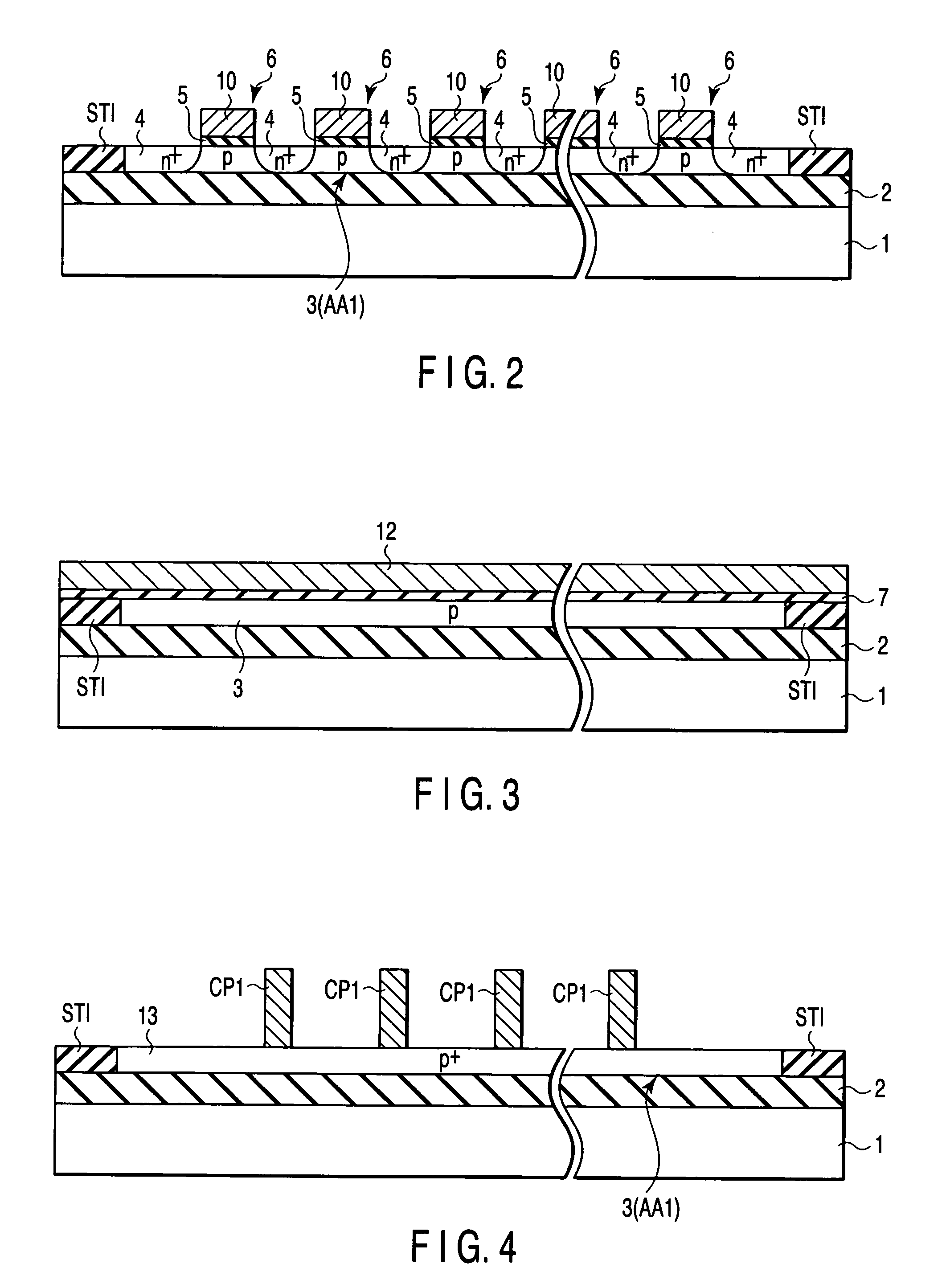

Power IC having SOI structure

The present invention relates in general to power ICs, etc. having the SOI structure, and more specifically to the structure in which an SOI substrate comprises a base substrate, an SOI oxide film formed on the base substrate, and active layers formed on the SOI oxide film, and also integrates on itself power devices and the corresponding control elements monolithically. Between this base substrate and this SOI oxide film is formed heavily-doped semiconductor regions having a conductivity type opposite to that of this base substrate. Hence, the junction capacitance between the base substrate and the heavily-doped semiconductor regions decreases an actual capacitance between the base substrate and the active layer so that to inhibit or prevent inversion layers from being formed at the bottom of the active layers.

Owner:KK TOSHIBA

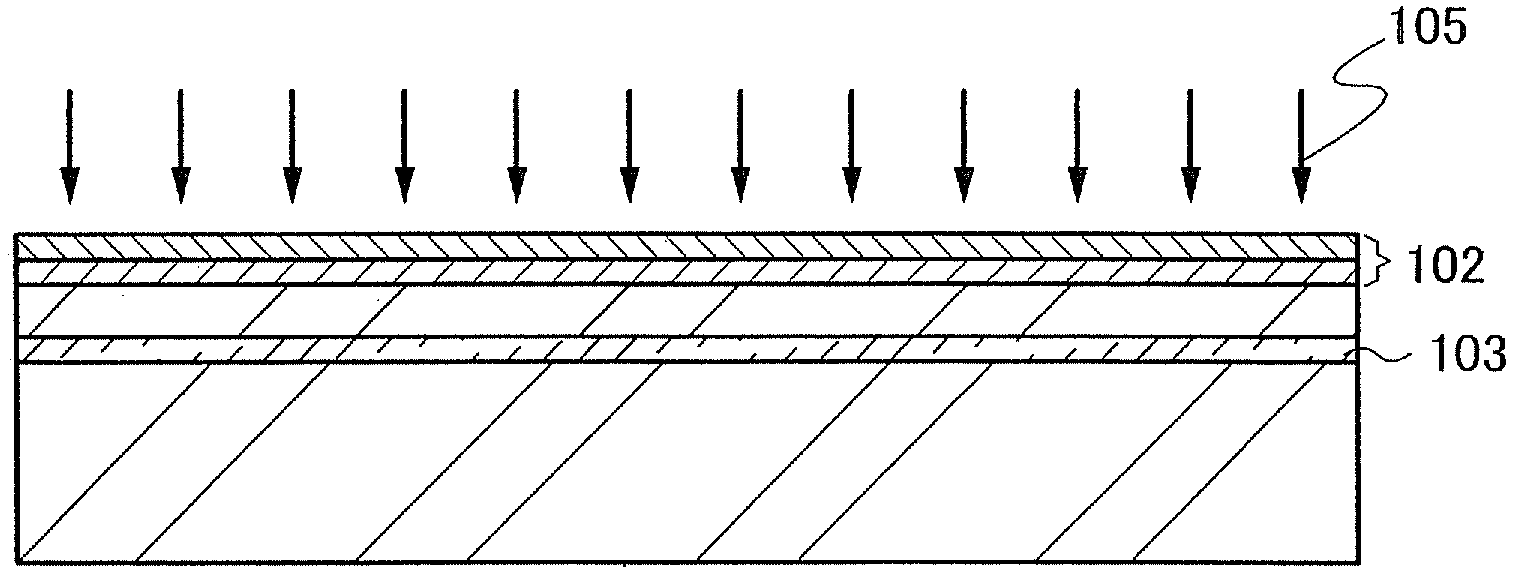

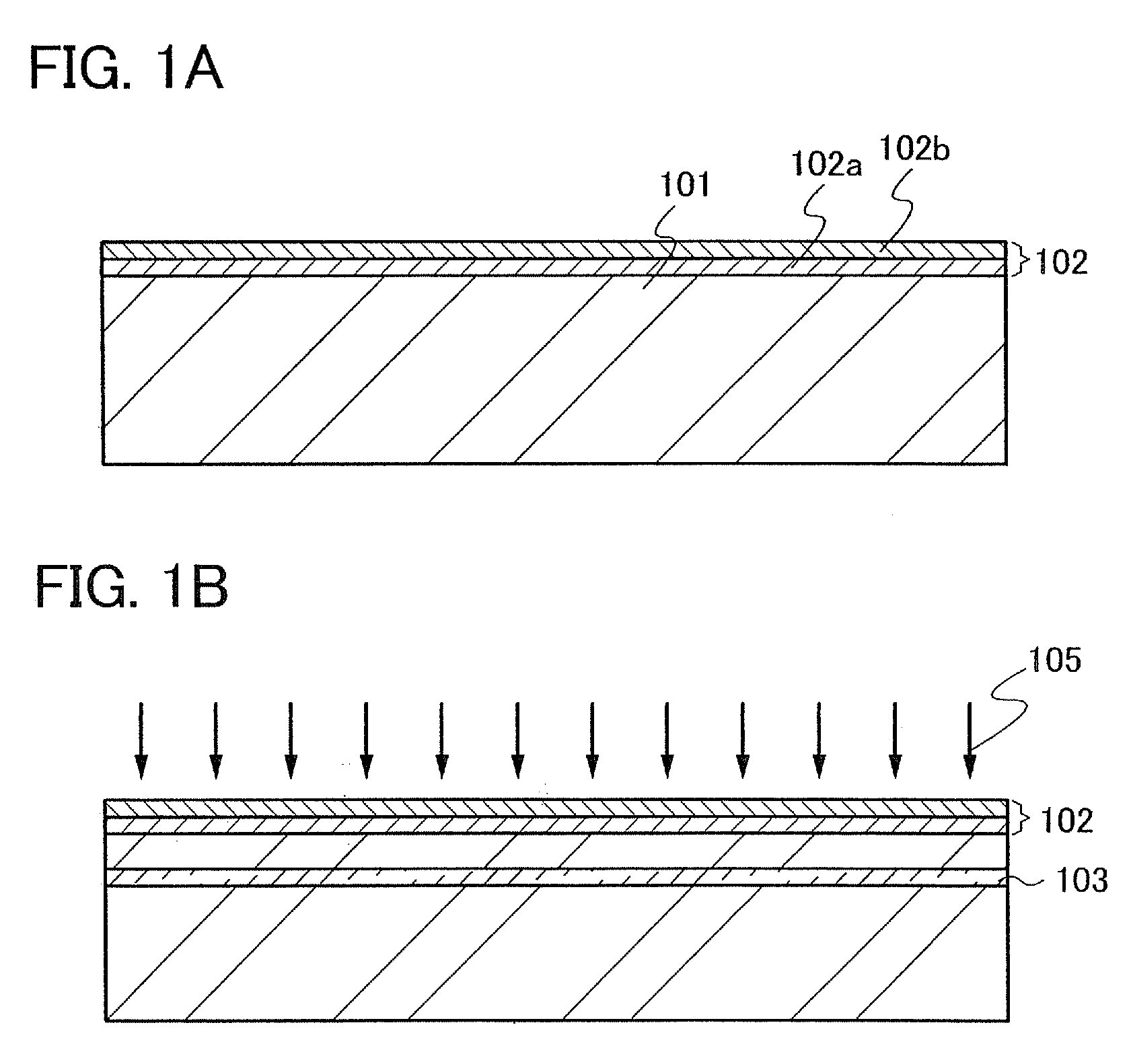

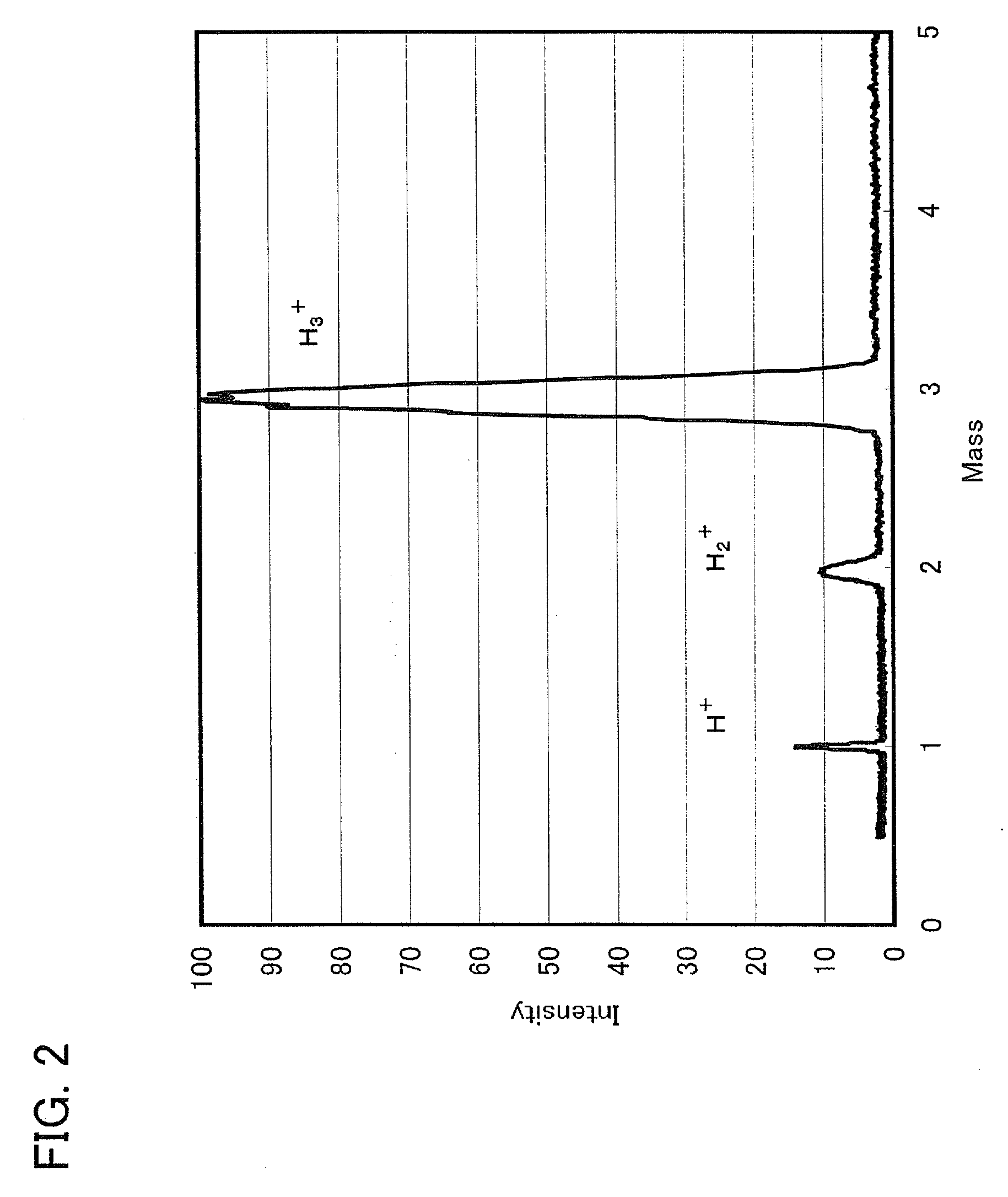

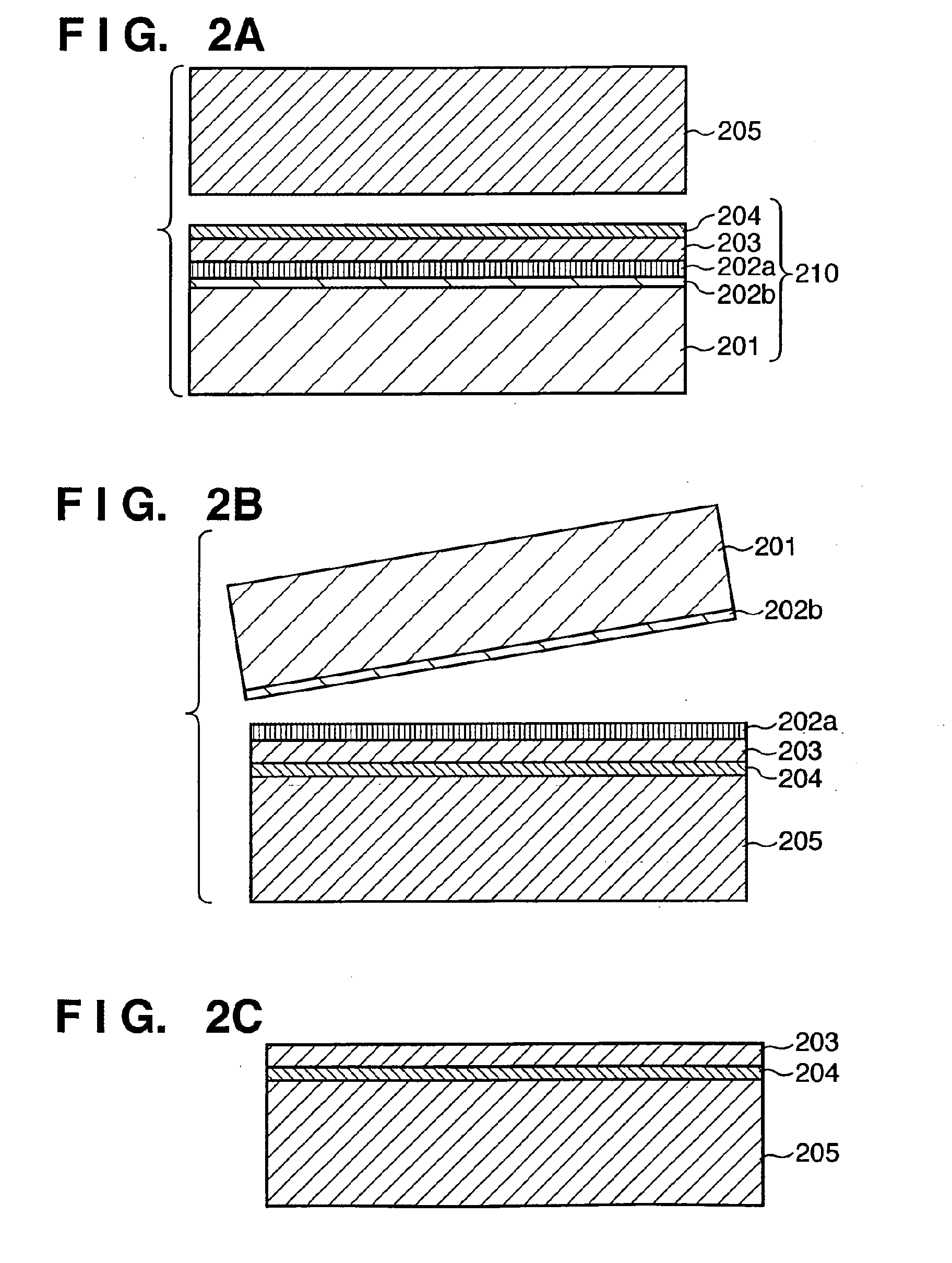

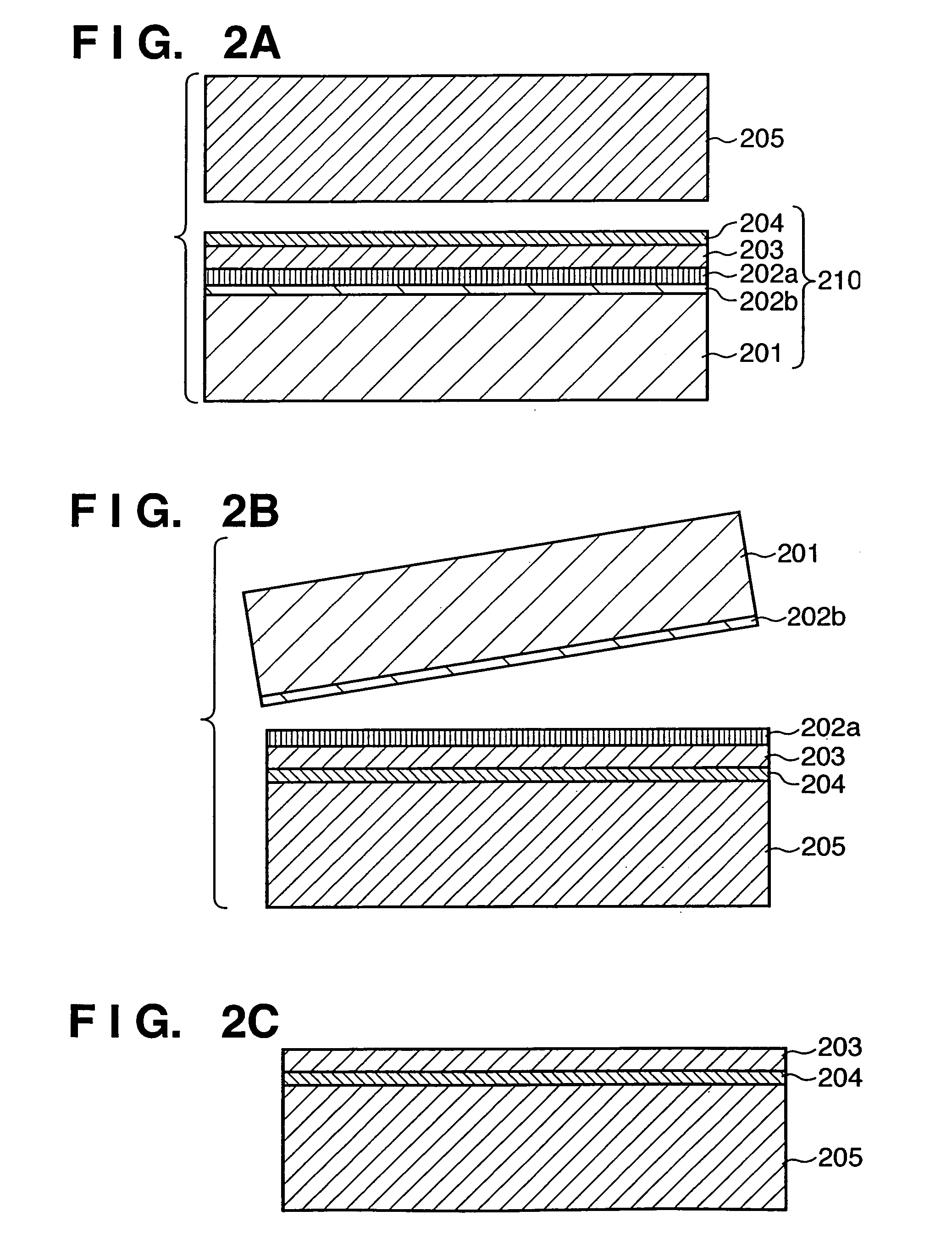

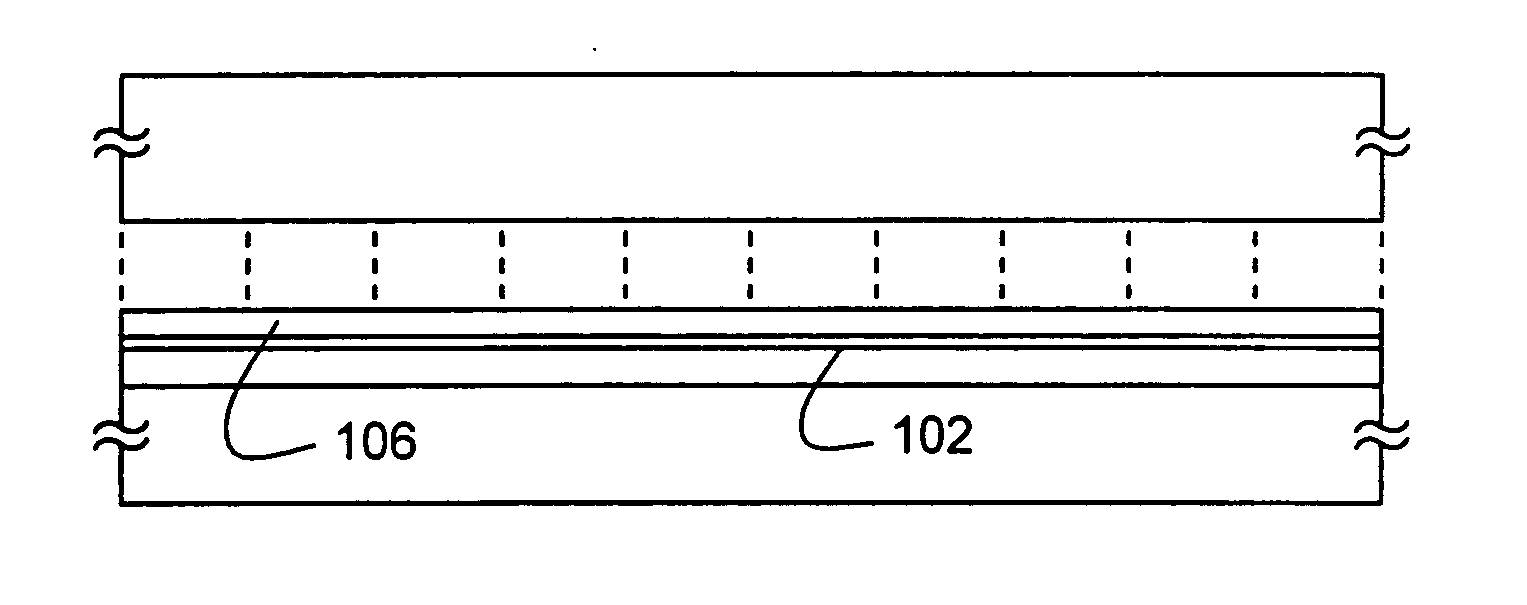

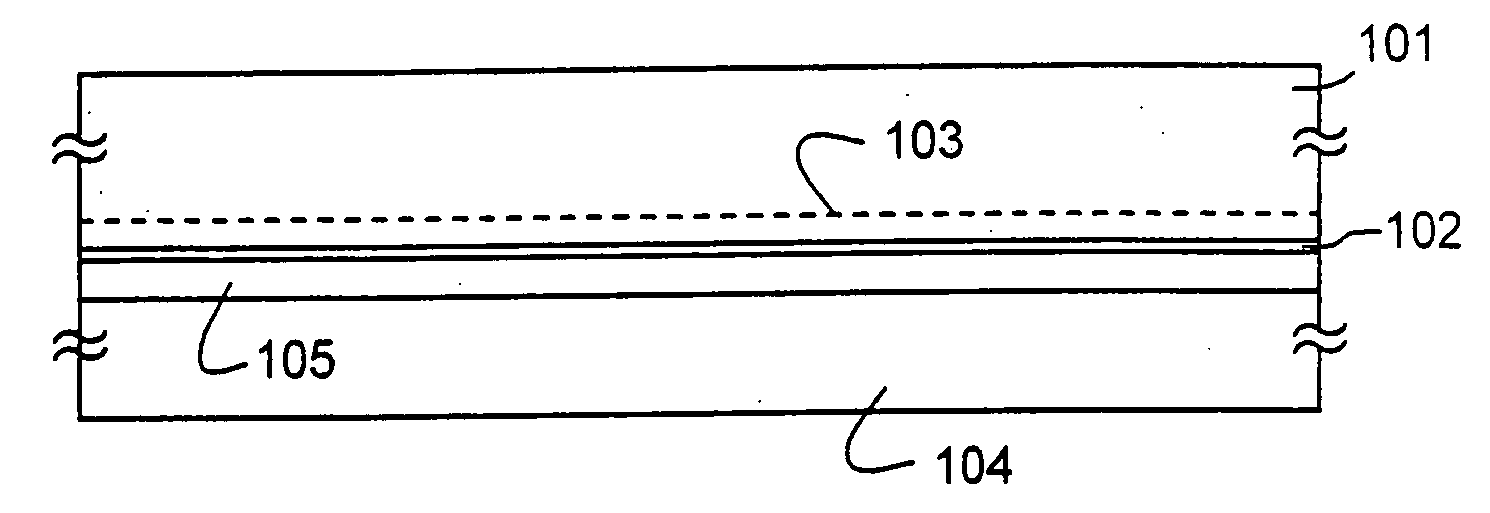

Method for manufacturing soi substrate

InactiveUS20090142905A1High bonding strengthImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesOptoelectronicsSingle crystal

Owner:SEMICON ENERGY LAB CO LTD

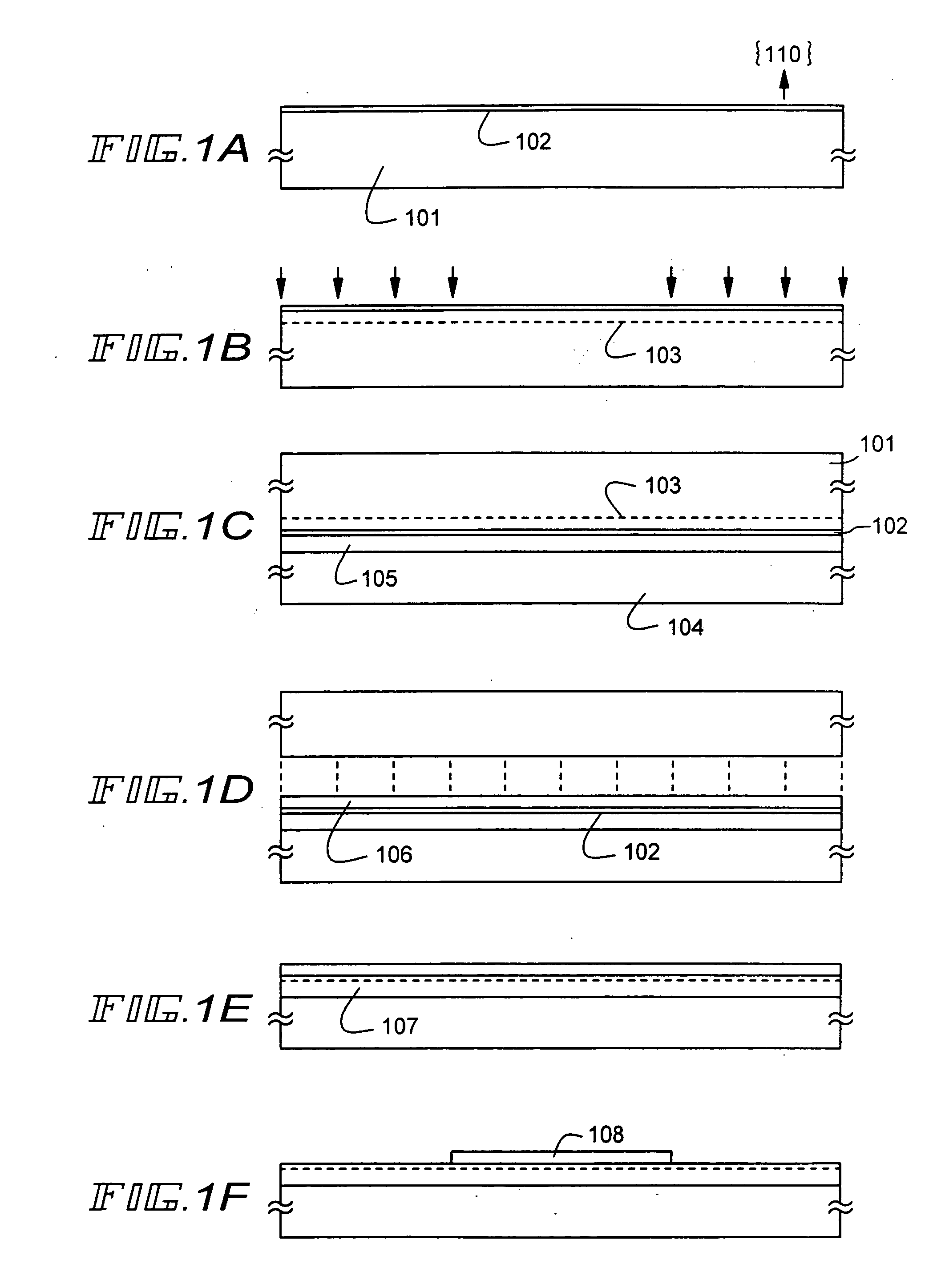

Three dimensional CMOS integrated circuits having device layers built on different crystal oriented wafers

InactiveUS20050067620A1High bulk densityReduce chip footprintTransistorSemiconductor/solid-state device details3d integrated circuitCMOS

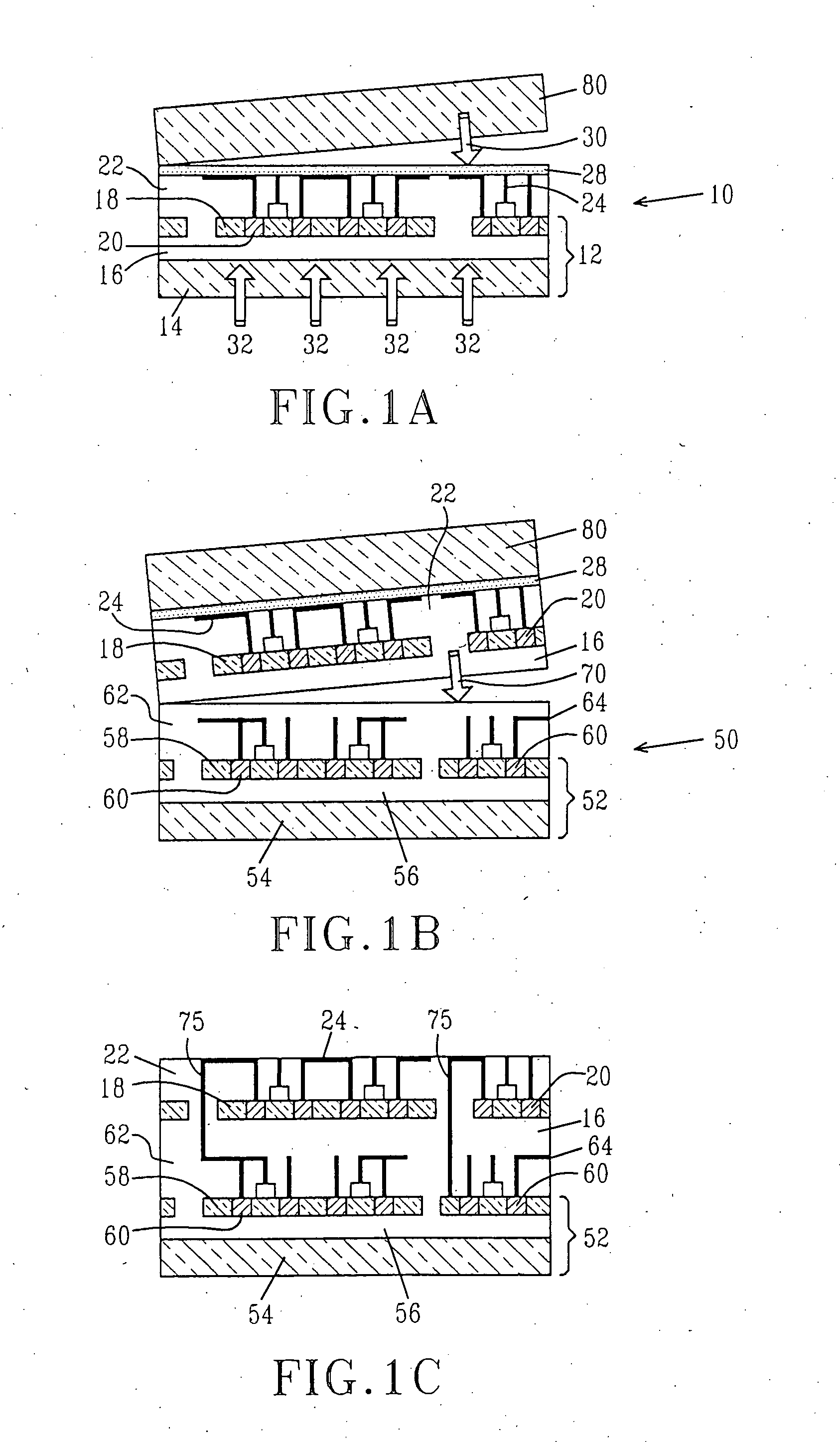

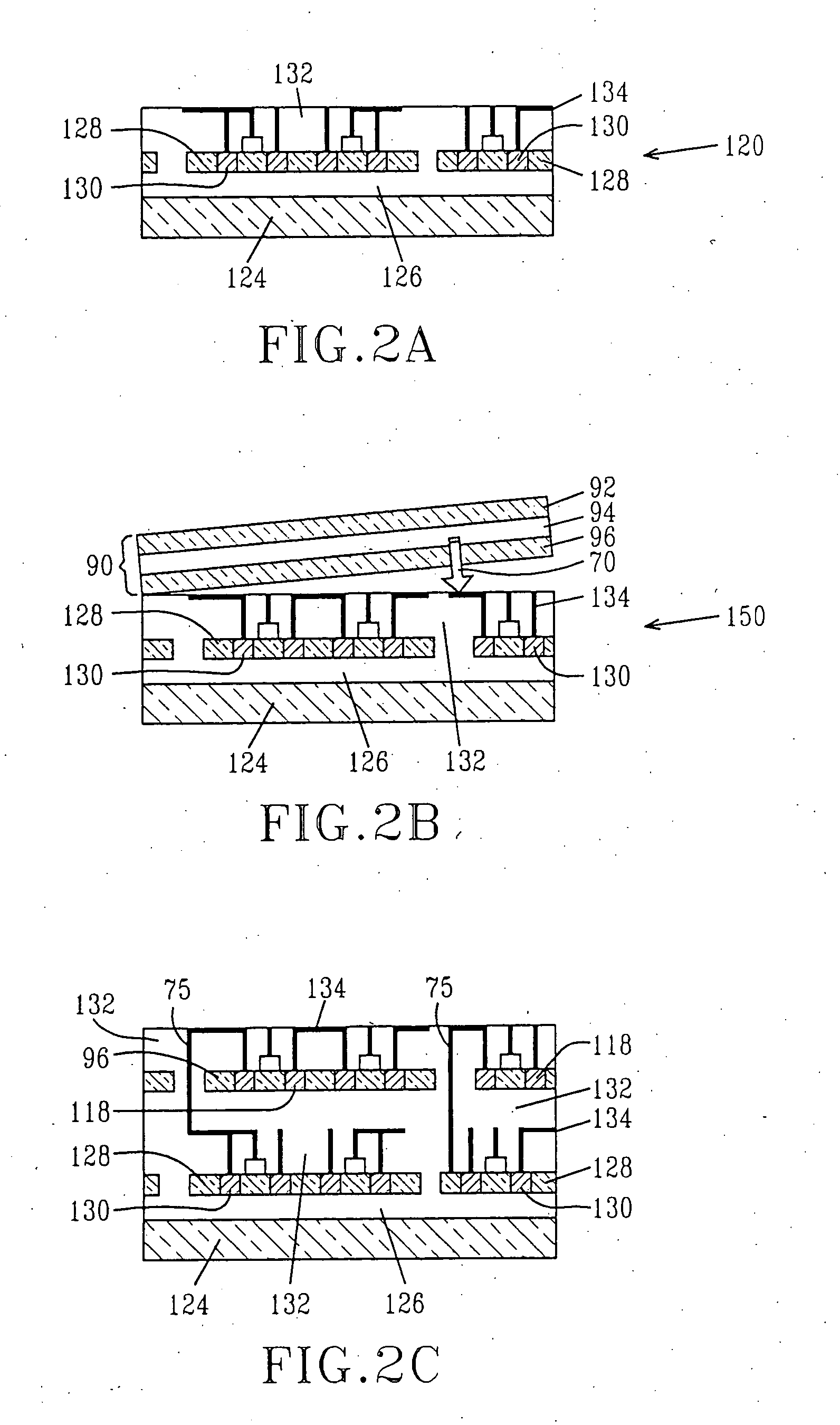

Three-dimensional (3D) integration schemes of fabricating a 3D integrated circuit in which the pFETs are located on an optimal crystallographic surface for that device and the nFETs are located on a optimal crystallographic surface for that type of device are provided. In accordance with a first 3D integration scheme of the present invention, first semiconductor devices are pre-built on a semiconductor surface of a first silicon-on-insulator (SOI) substrate and second semiconductor devices are pre-built on a semiconductor surface of a second SOI substrate. After pre-building those two structures, the structure are bonded together and interconnect through wafer-via through vias. In a second 3D integration scheme, a blanket silicon-on-insulator (SOI) substrate having a first SOI layer of a first crystallographic orientation is bonded to a surface of a pre-fabricating wafer having second semiconductor devices on a second SOI layer that has a different crystallographic orientation than the first SOI layer; and forming first semiconductor device on the first SOI layer.

Owner:GLOBALFOUNDRIES INC

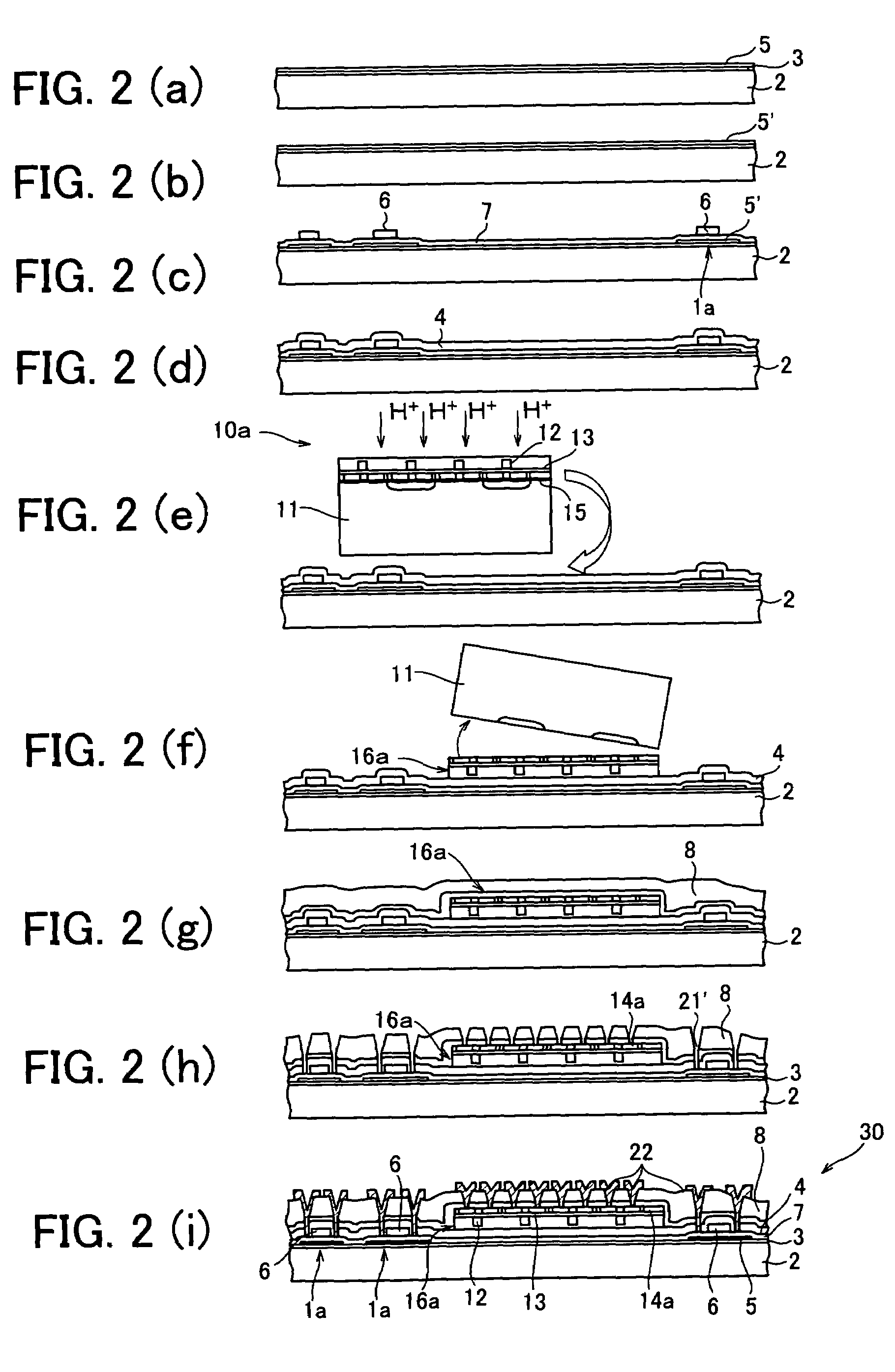

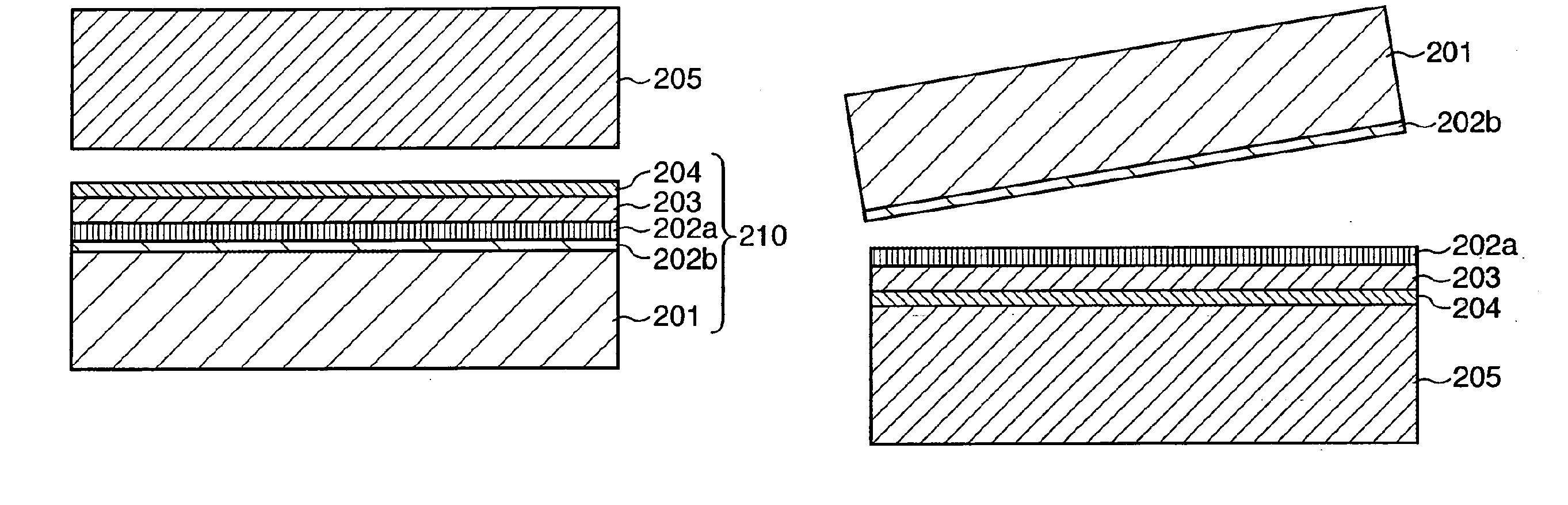

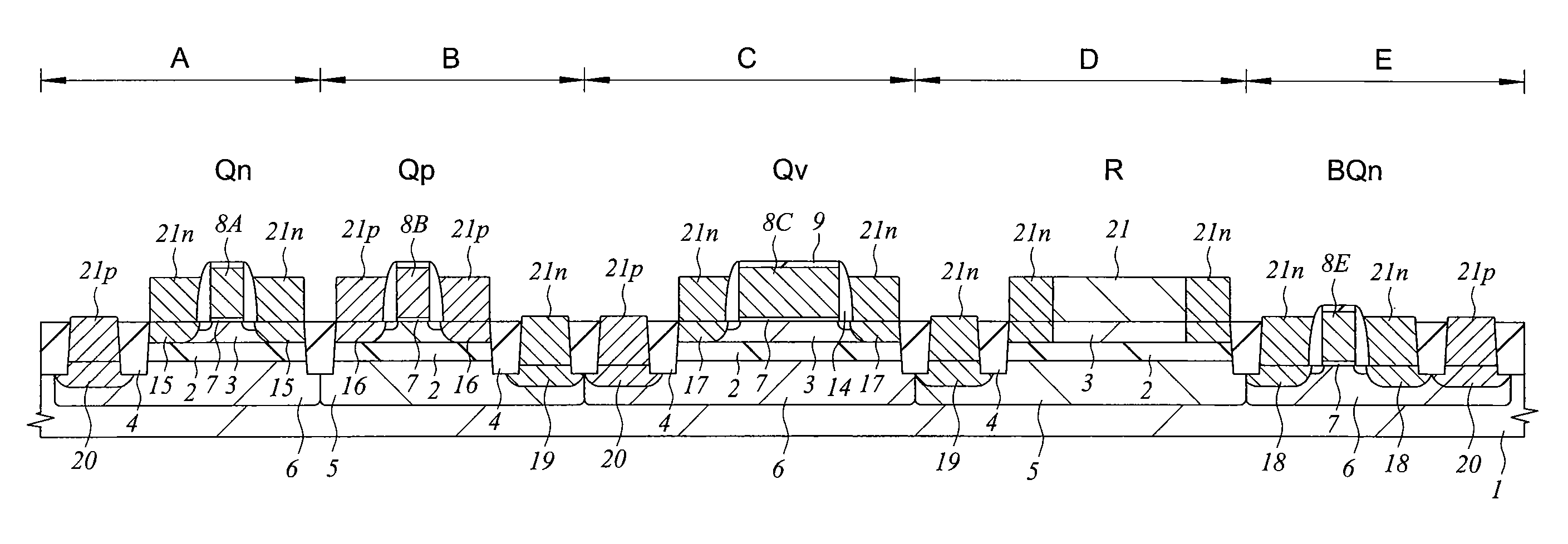

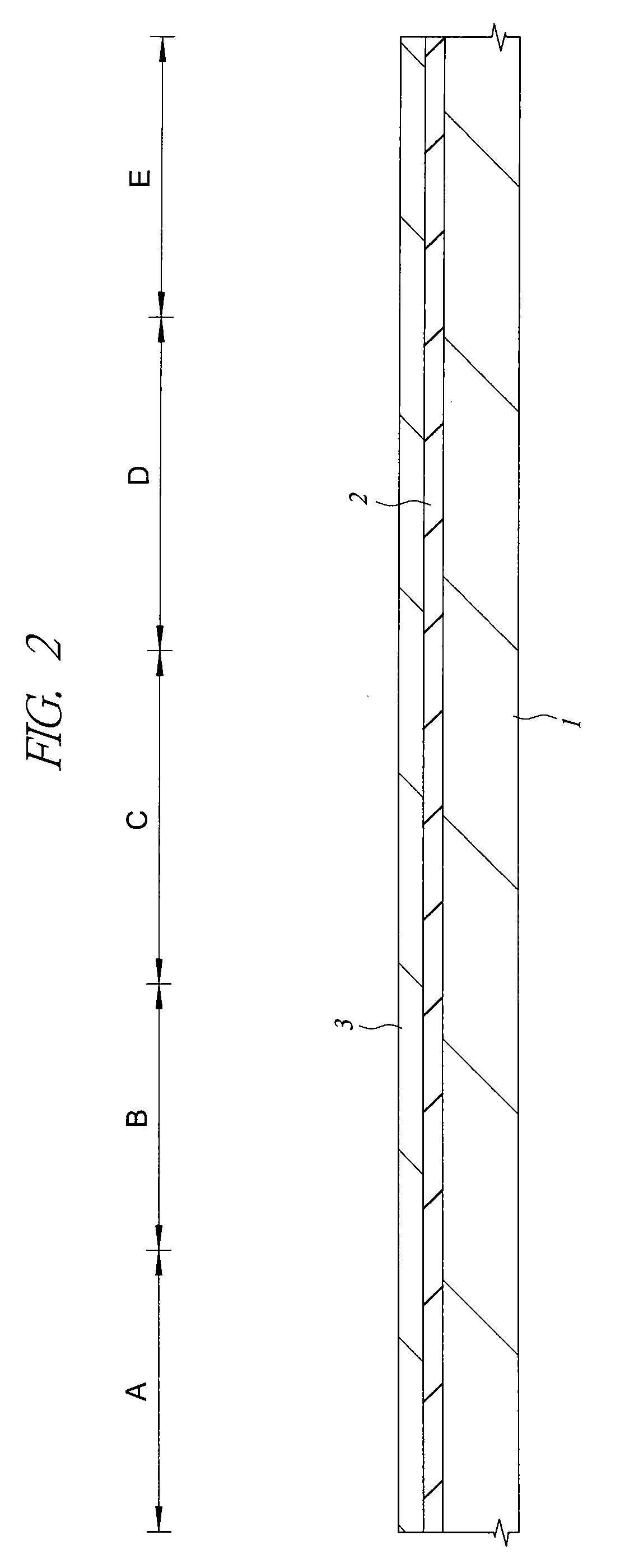

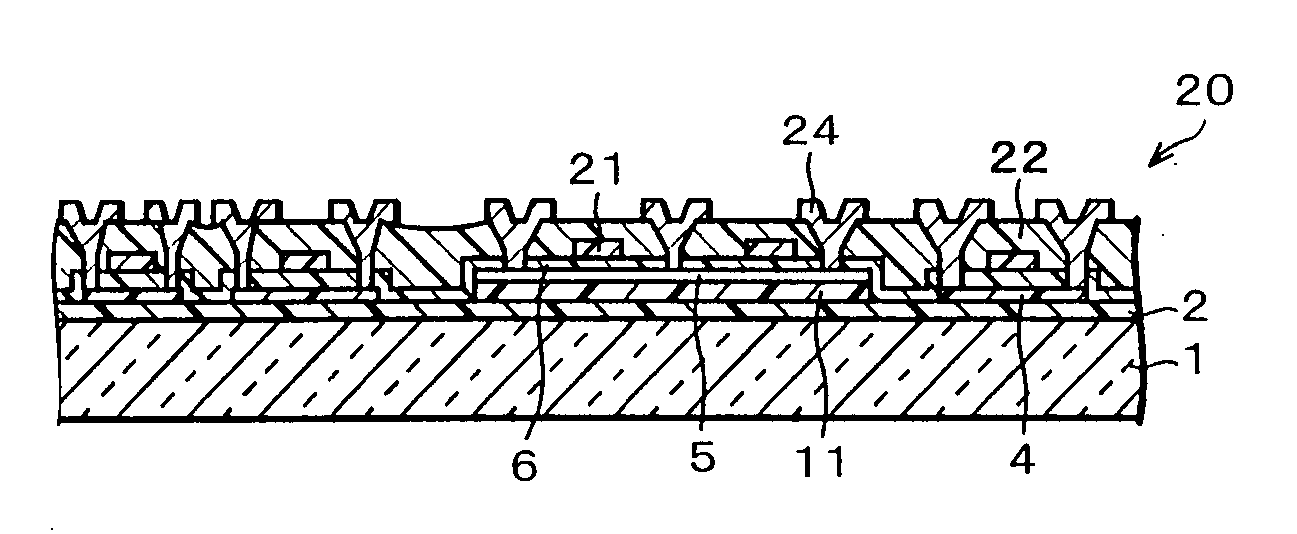

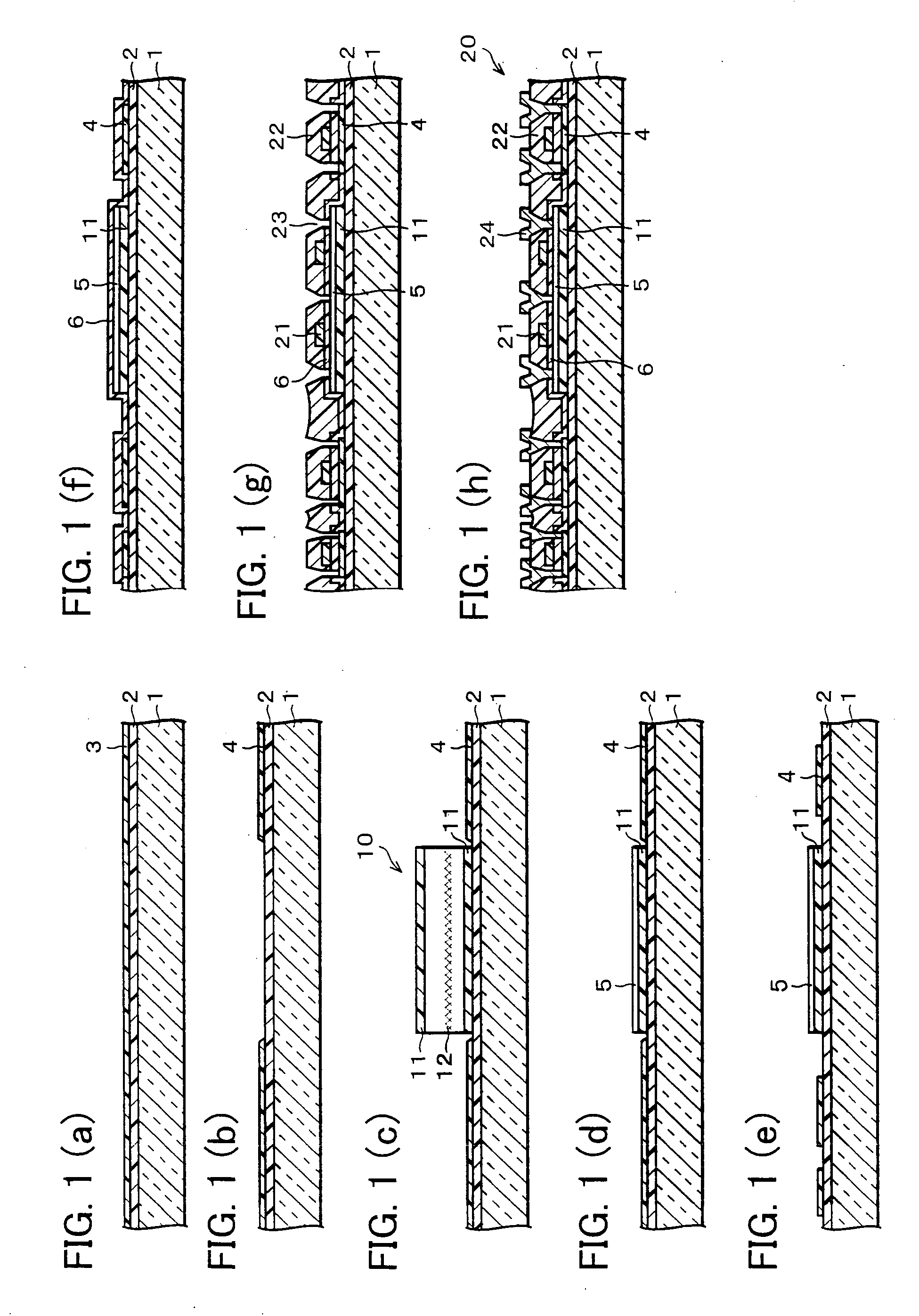

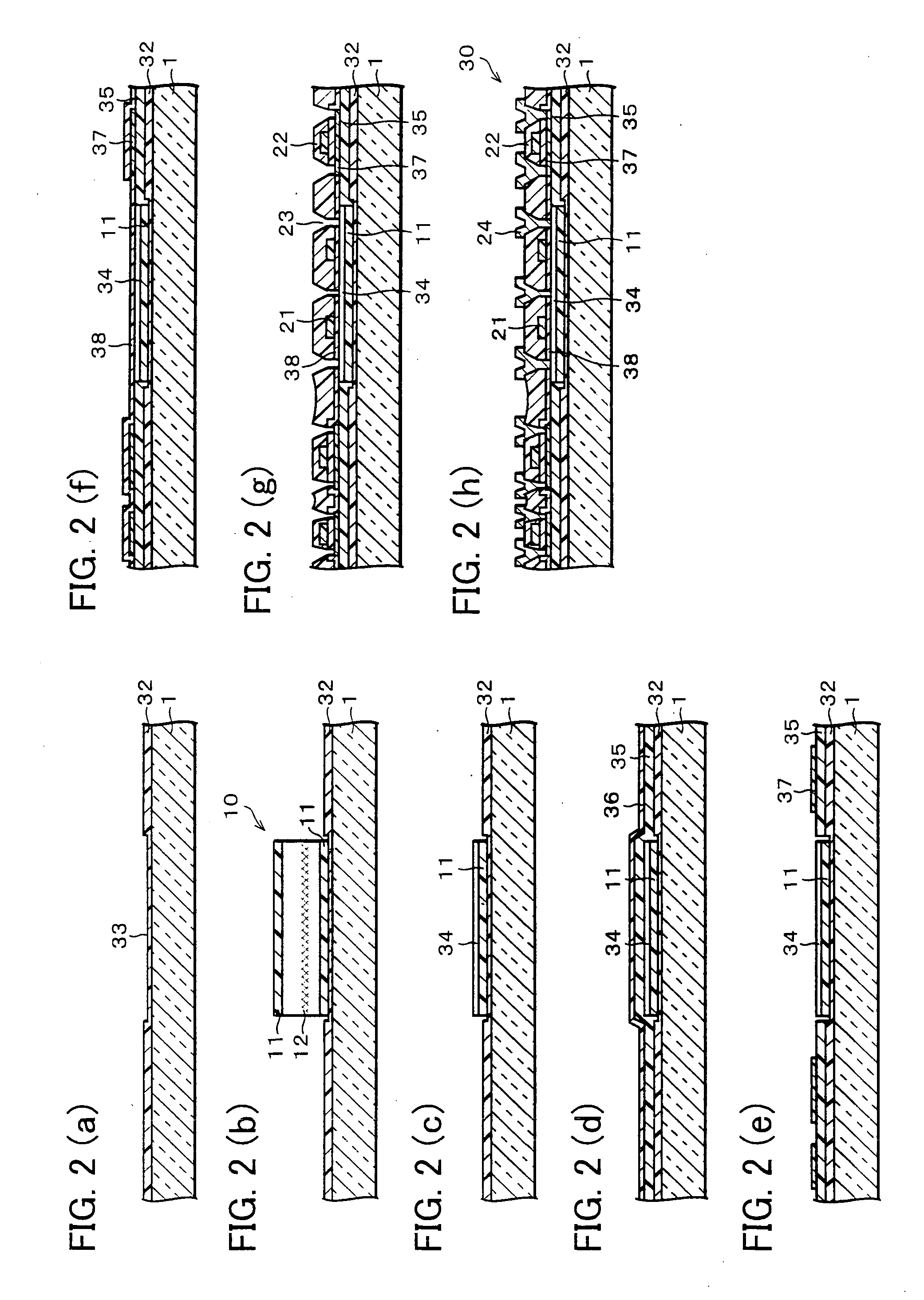

Single-crystal silicon substrate, SOI substrate, semiconductor device, display device, and manufacturing method of semiconductor device

InactiveUS7508034B2Well formedHigh bonding strengthTransistorSolid-state devicesDisplay deviceSoi substrate

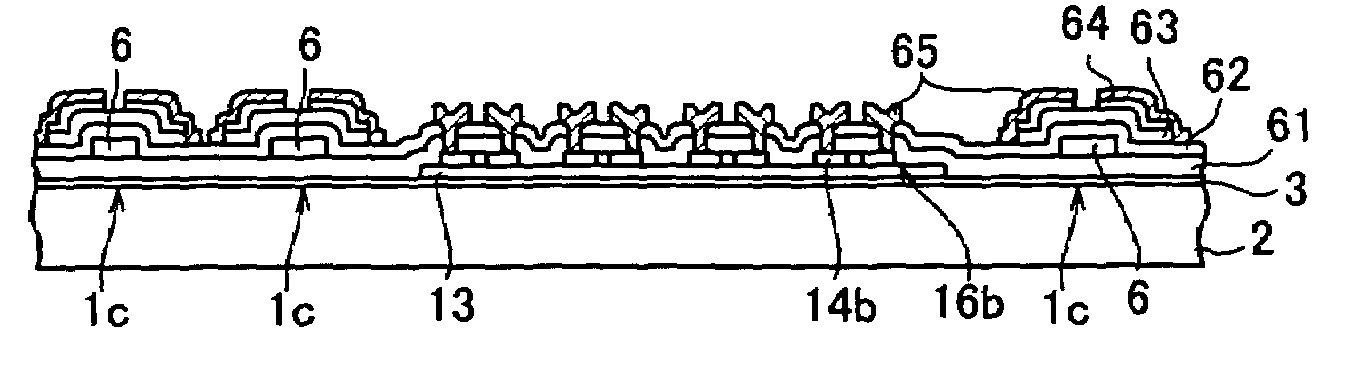

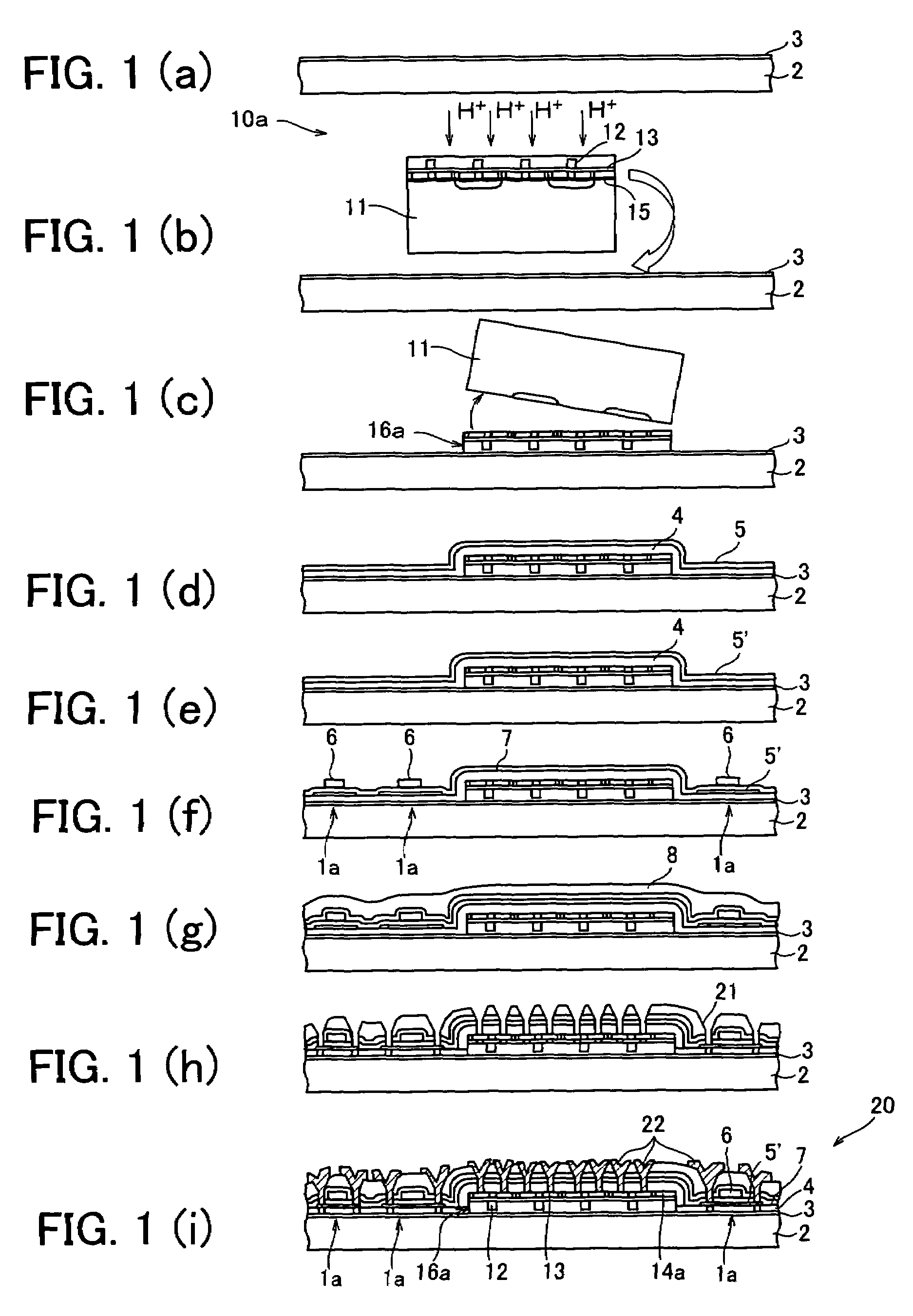

A semiconductor device of the present invention is arranged in such a manner that a MOS non-single-crystal silicon thin-film transistor including a non-single-crystal silicon thin film made of polycrystalline silicon, a MOS single-crystal silicon thin-film transistor including a single-crystal silicon thin film, and a metal wiring are provided on an insulating substrate. With this arrangement, (i) a semiconductor device in which a non-single-crystal silicon thin film and a single-crystal silicon thin-film device are formed and high-performance systems are integrated, (ii) a method of manufacturing the semiconductor device, and (iii) a single-crystal silicon substrate for forming the single-crystal silicon thin-film device of the semiconductor device are obtained.

Owner:SHARP KK

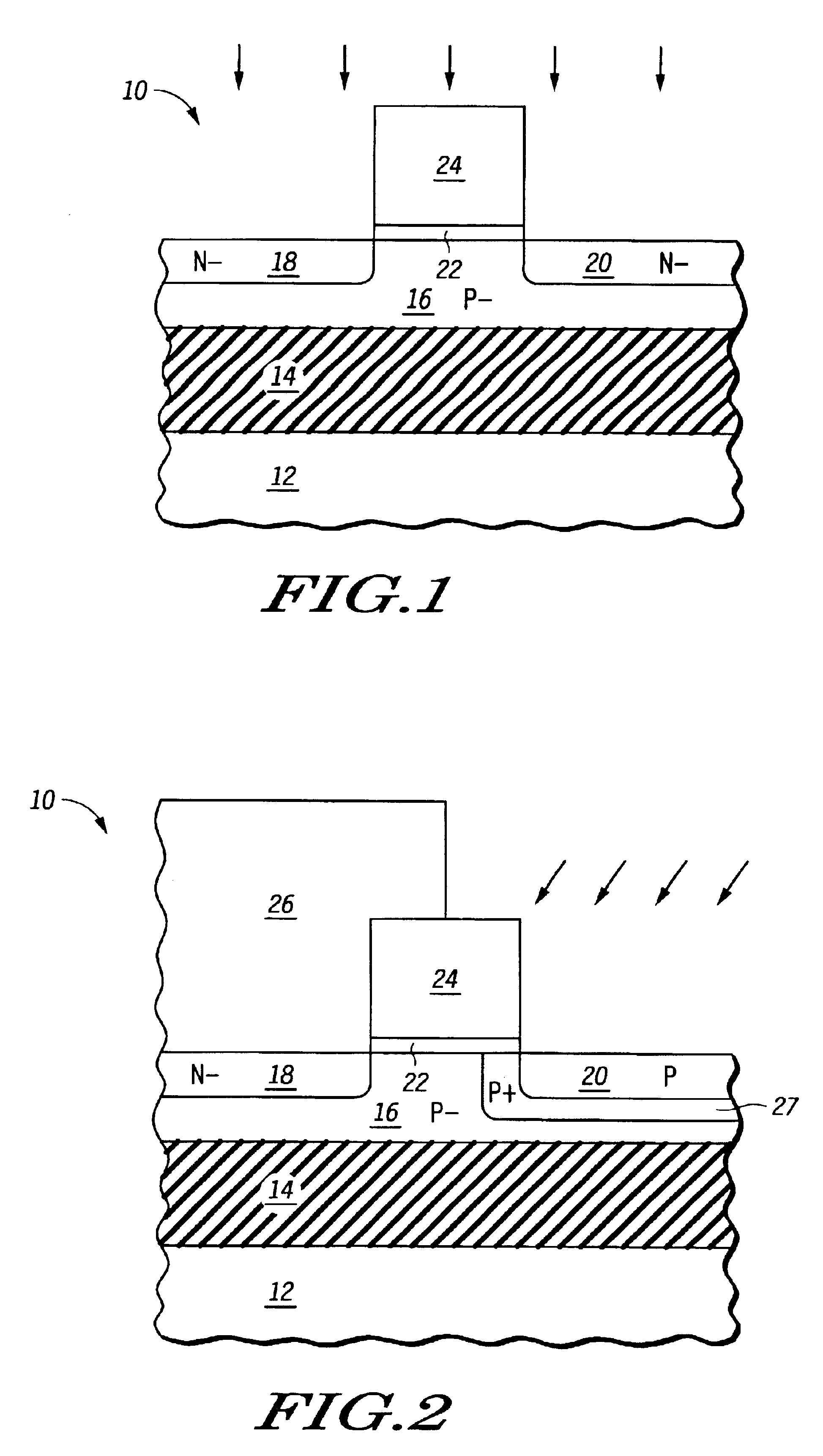

One transistor DRAM cell structure and method for forming

A single transistor DRAM cell is formed in a SOI substrate so that the DRAM cells are formed in bodies that are electrically isolated from each other. Each cell has doped regions that act as source and drain contacts. Between the drain contact and the body is a region, which aids in impact ionization and thus electron / hole formation during programming that is the same conductivity type as the body but of a higher concentration than the body. Adjacent to the source contact and to the body is a region, which aids in diode current during erase, that is the same conductivity type as the source contact but of a lower concentration than the source contact.

Owner:III HLDG 12 LLC

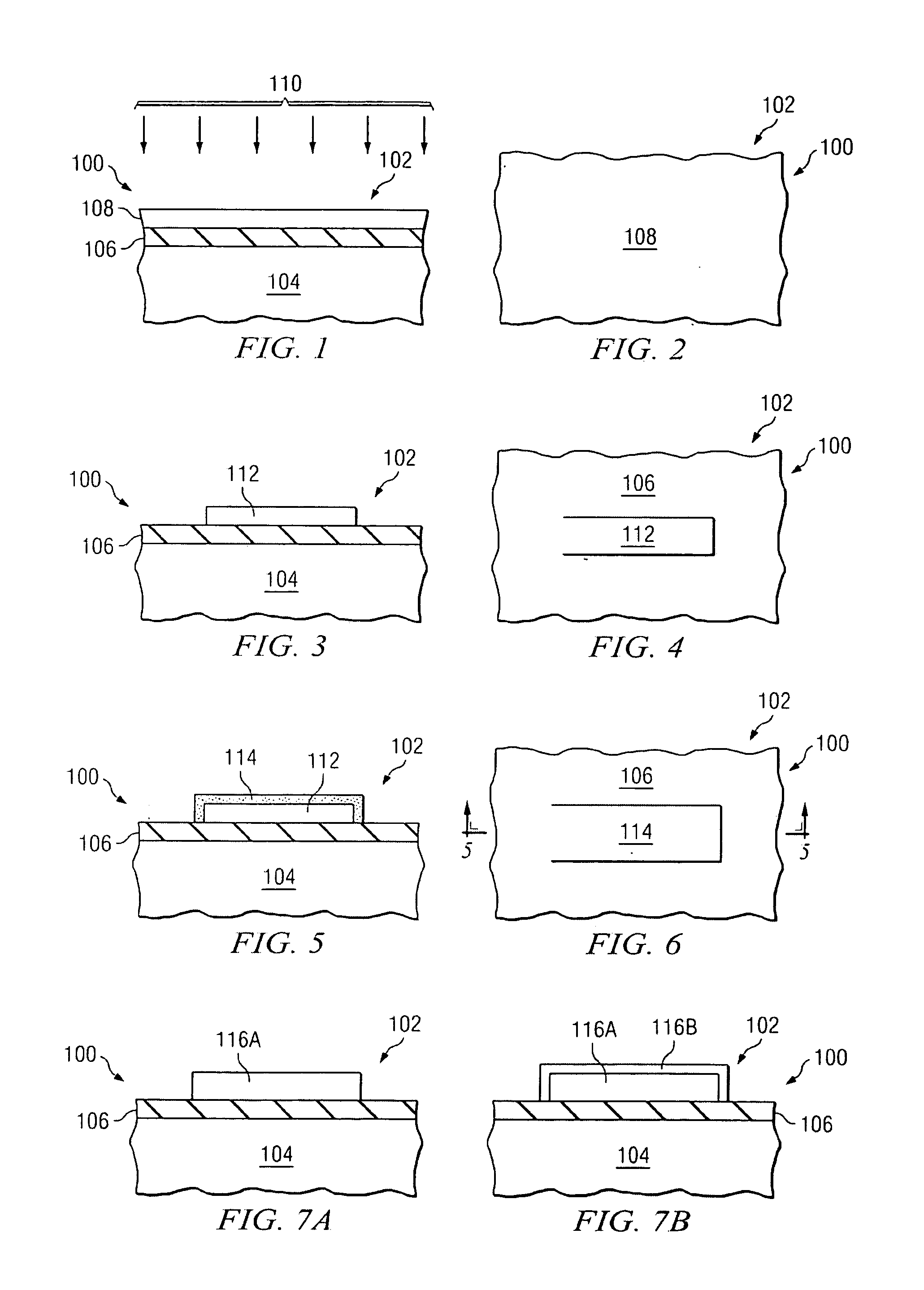

Methods of forming wiring to transistor and related transistor

InactiveUS7666723B2Semiconductor/solid-state device detailsSolid-state devicesEngineeringSoi substrate

Methods of wiring to a transistor and a related transistor are disclosed. In one embodiment, the method includes a method of forming wiring to a transistor, the method comprising: forming a transistor on a semiconductor-on-insulator (SOI) substrate using masks that are mirror images of an intended layout, the forming including forming a gate and a source / drain region for each and a channel, the SOI substrate including a semiconductor-on-insulator (SOI) layer, a buried insulator layer and a silicon substrate; forming a dielectric layer over the transistor; bonding the dielectric layer to another substrate; removing the silicon substrate from the SOI substrate to the buried insulator layer; forming a contact to each of the source / drain region and the gate from a channel side of the gate; and forming at least one wiring to the contacts on the channel side of the gate.

Owner:GLOBALFOUNDRIES INC

Substrate processing apparatus

InactiveUS20070190746A1Easy thickness controlIncrease flexibilitySemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingChemical solutionSoi substrate

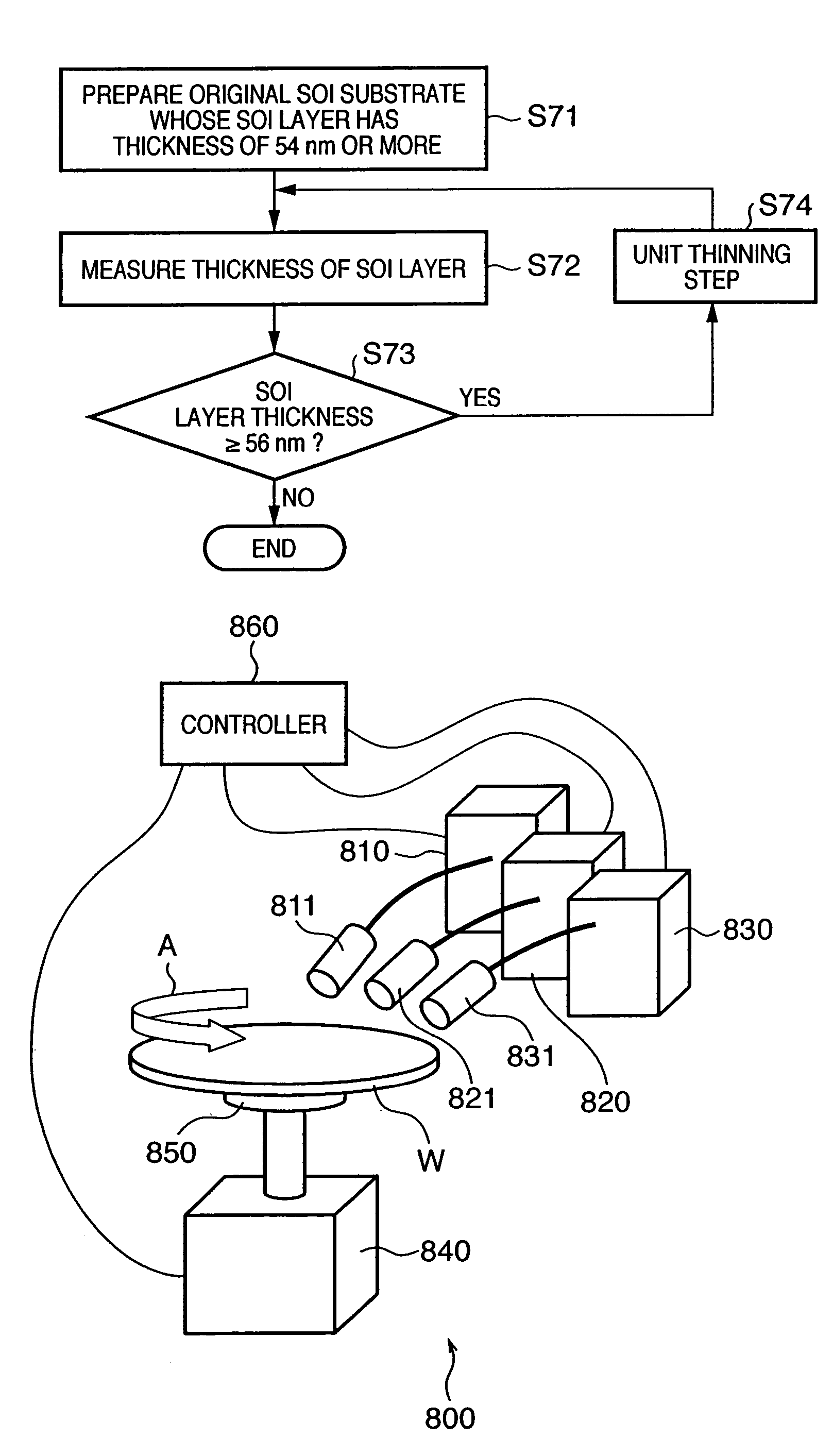

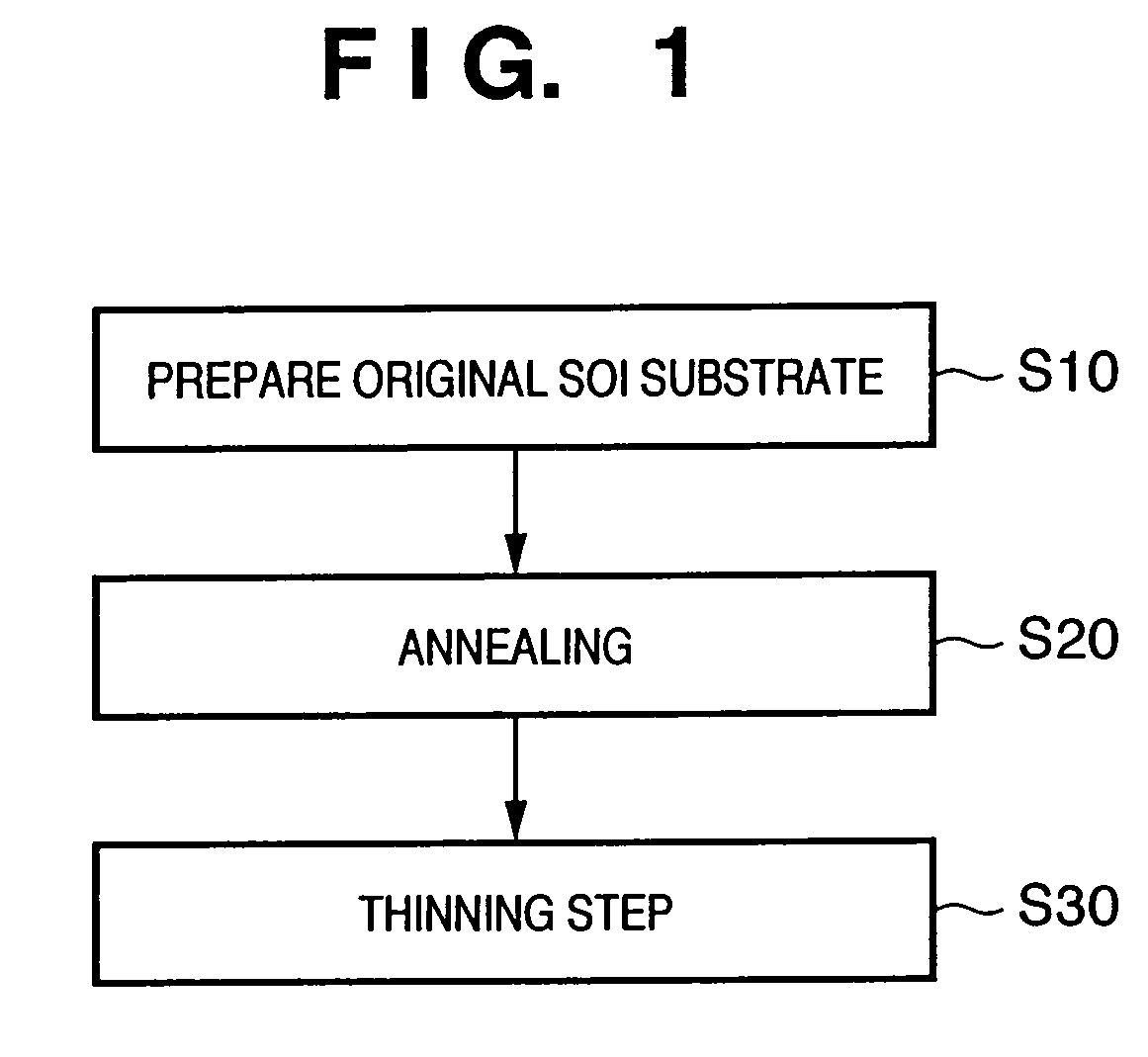

An SOI substrate which has a thick SOI layer is first prepared. Then, the SOI layer is thinned to a target film thickness using as a unit a predetermined thickness not more than that of one lattice. This thinning is performed by repeating a unit thinning step which includes an oxidation step of oxidizing the surface of the SOI layer by the predetermined thickness not more than that of one lattice and a removal step of selectively removing silicon oxide formed by the oxidation. The SOI layer of the SOI substrate is chemically etched by supplying a chemical solution to the SOI layer, and the film thickness of the etched SOI layer is measured. When the measured film thickness of the SOI layer has a predetermined value, a process of chemically etching the SOI layer ends.

Owner:CANON KK

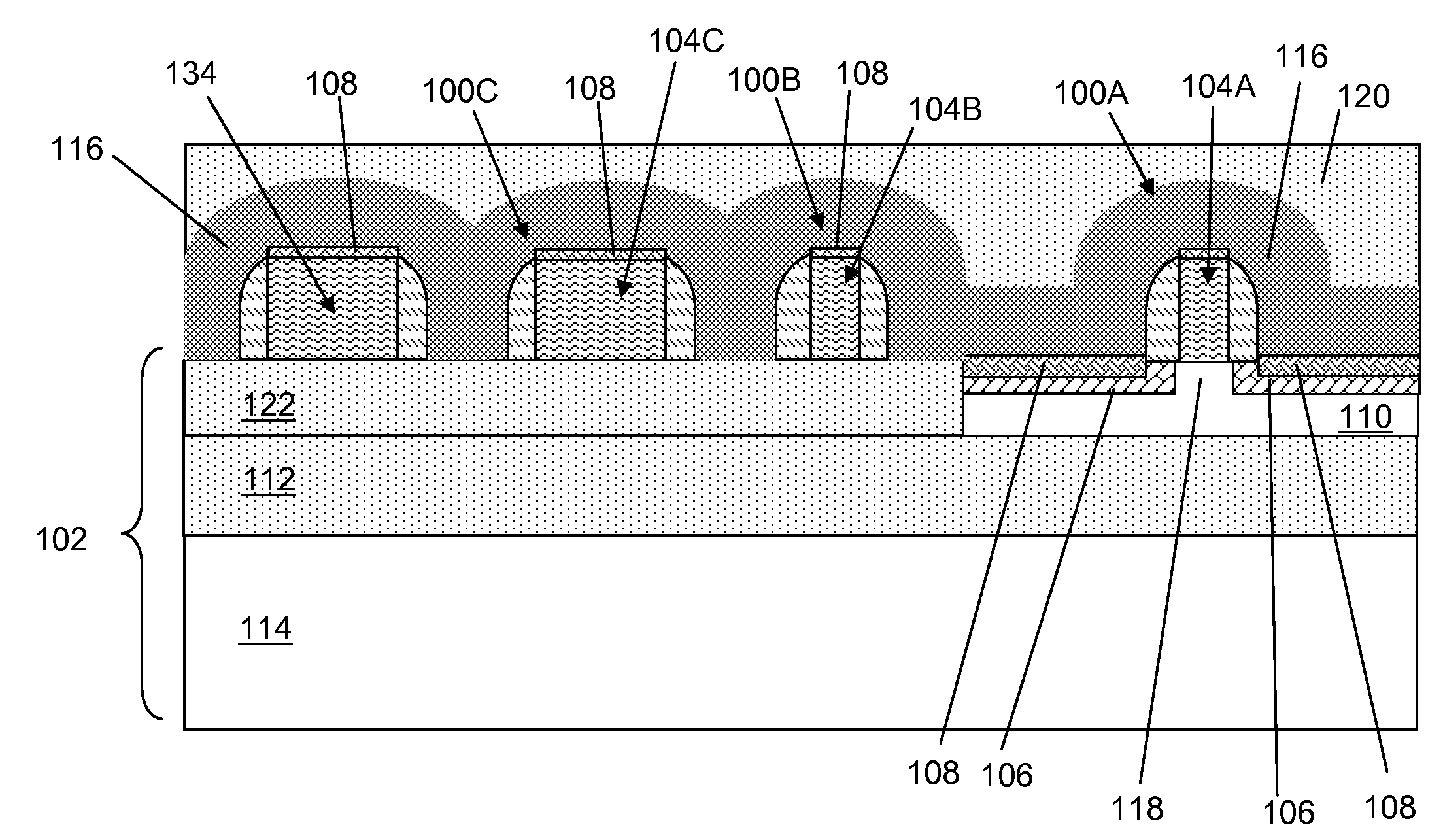

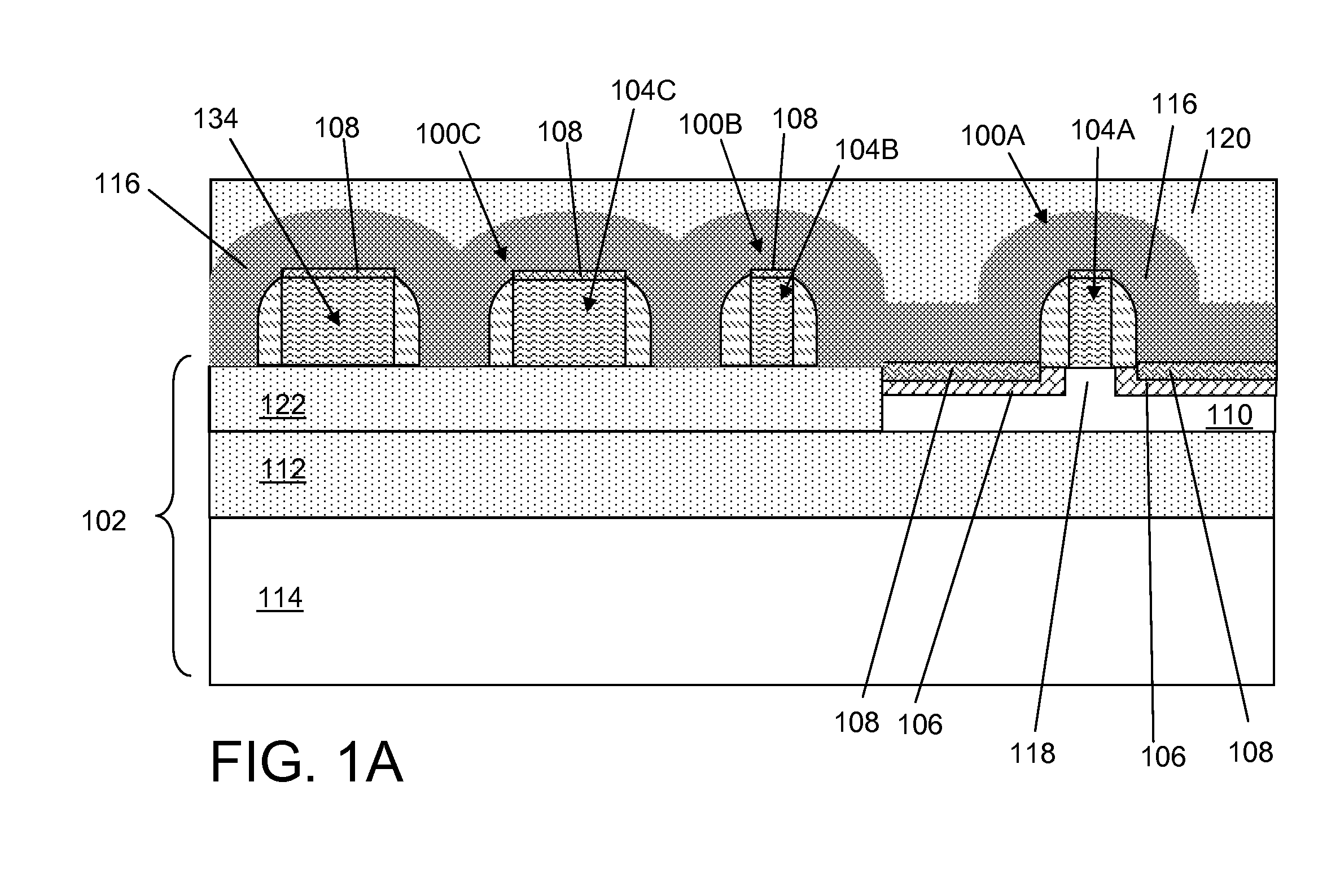

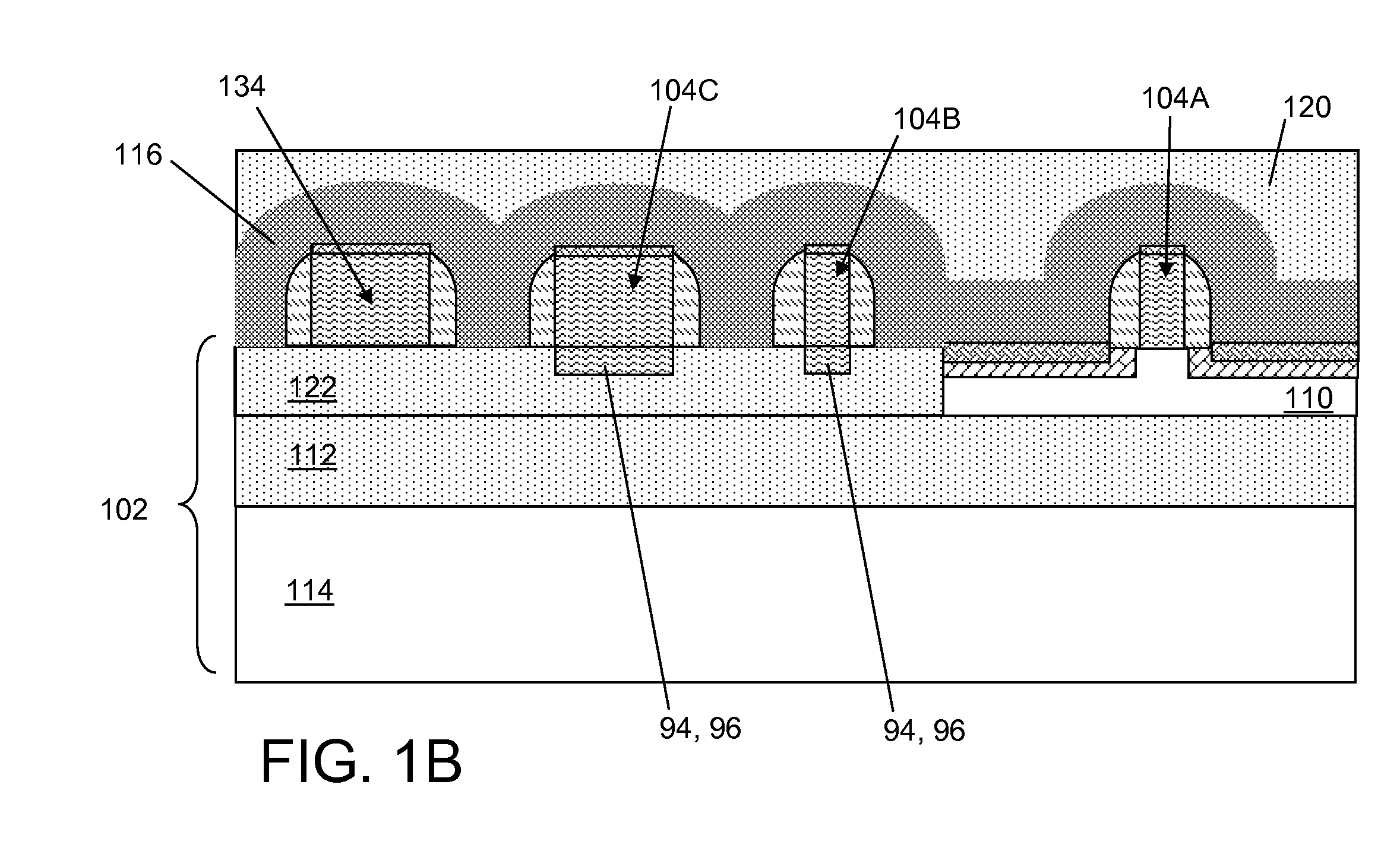

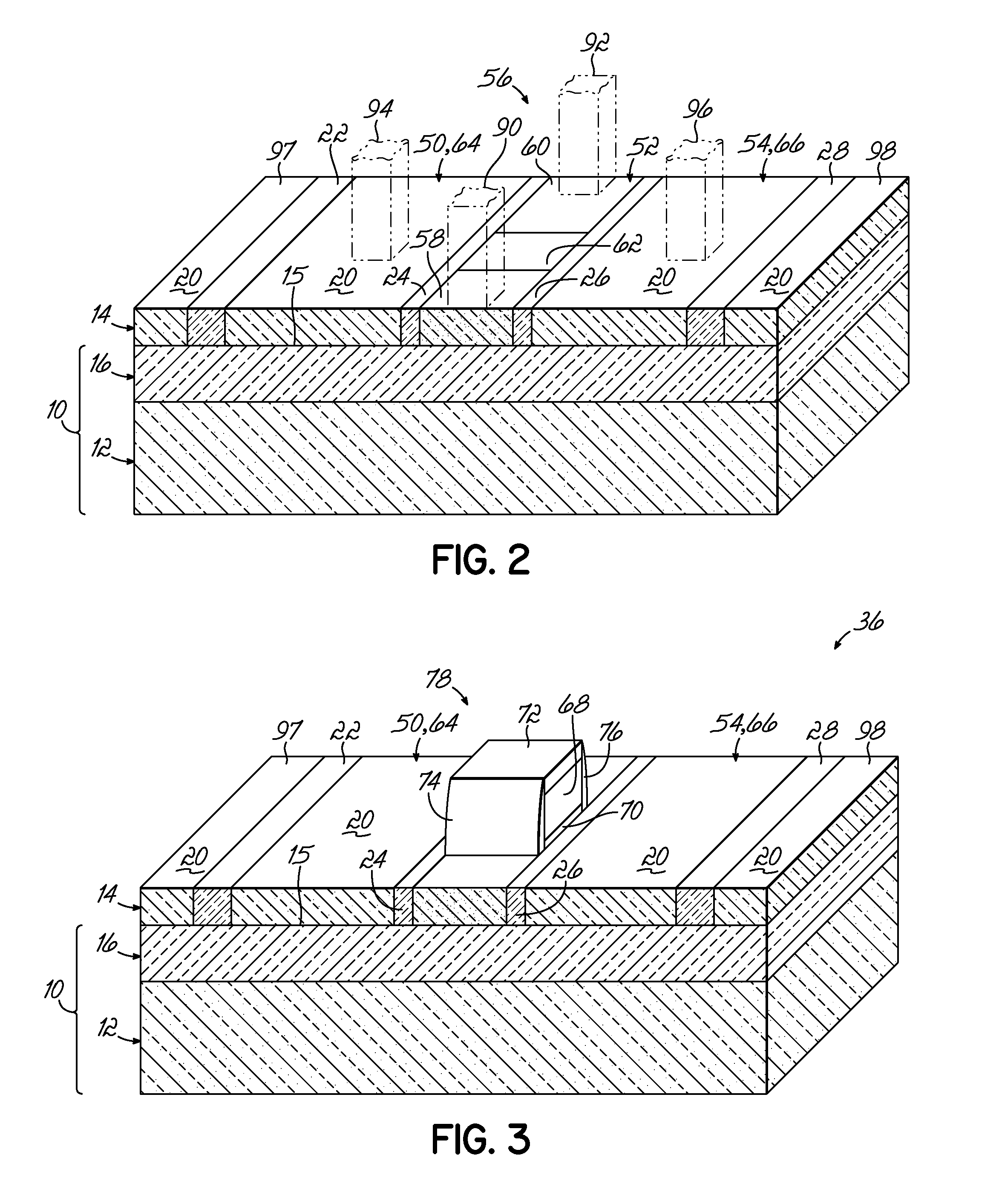

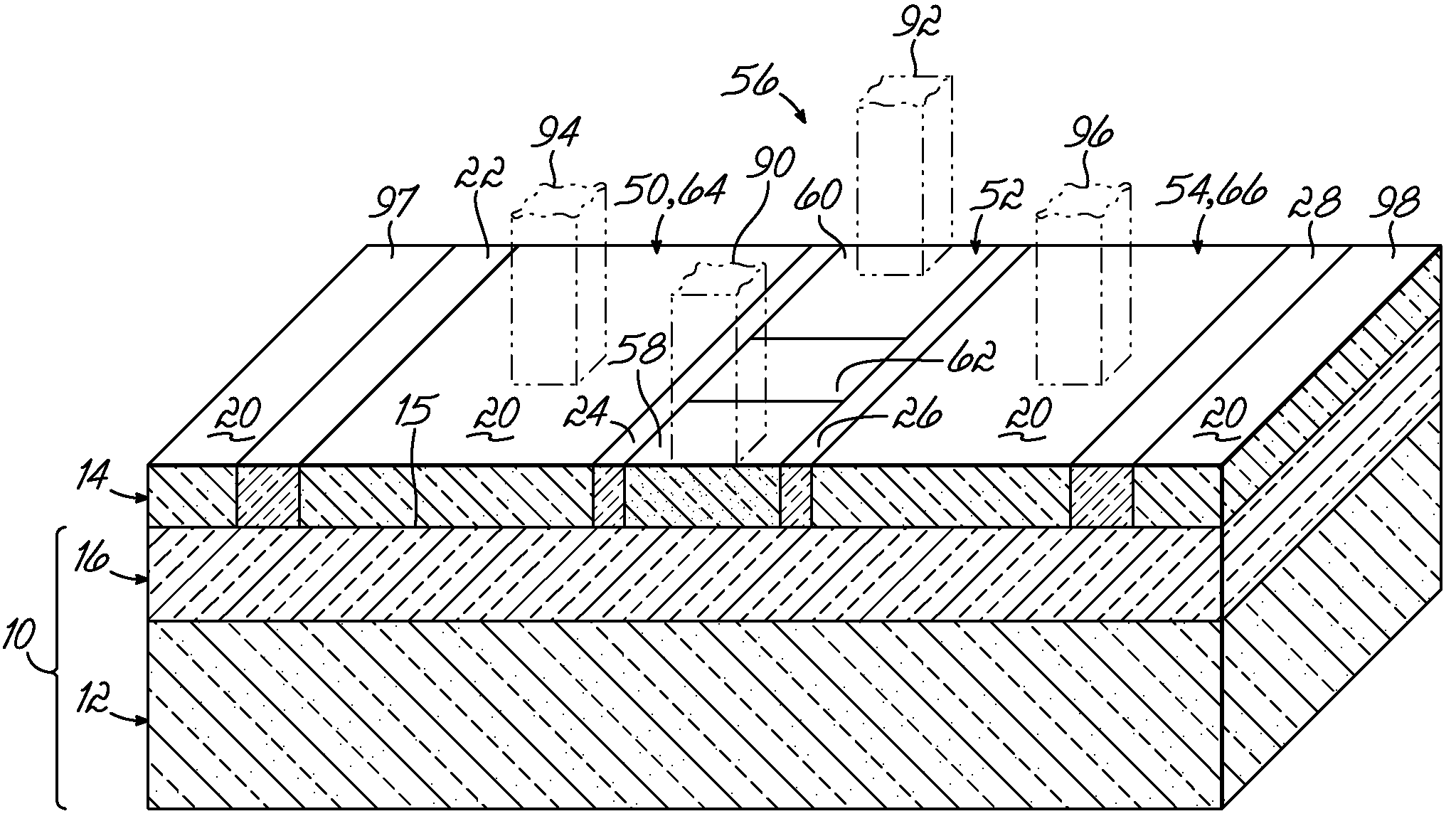

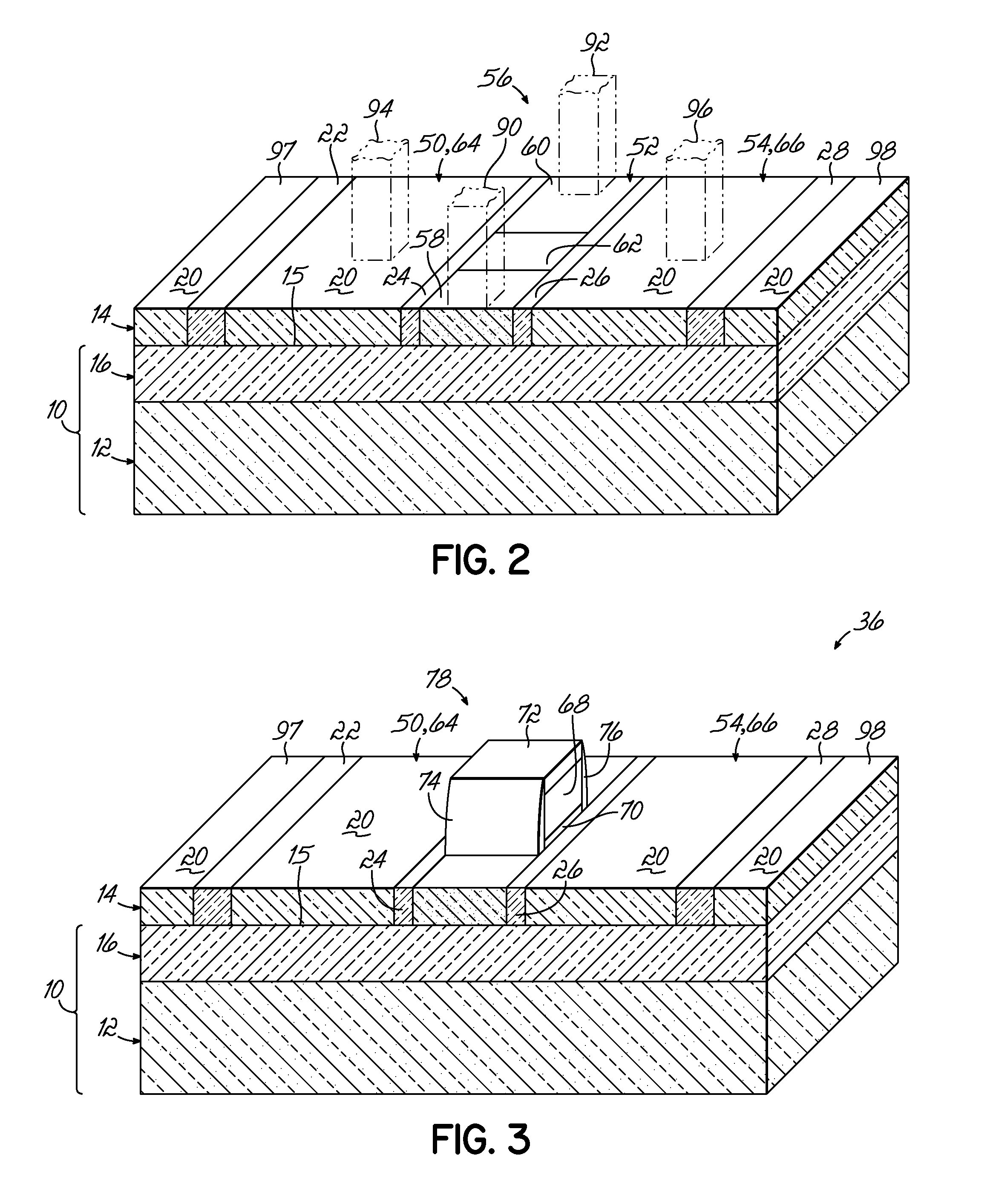

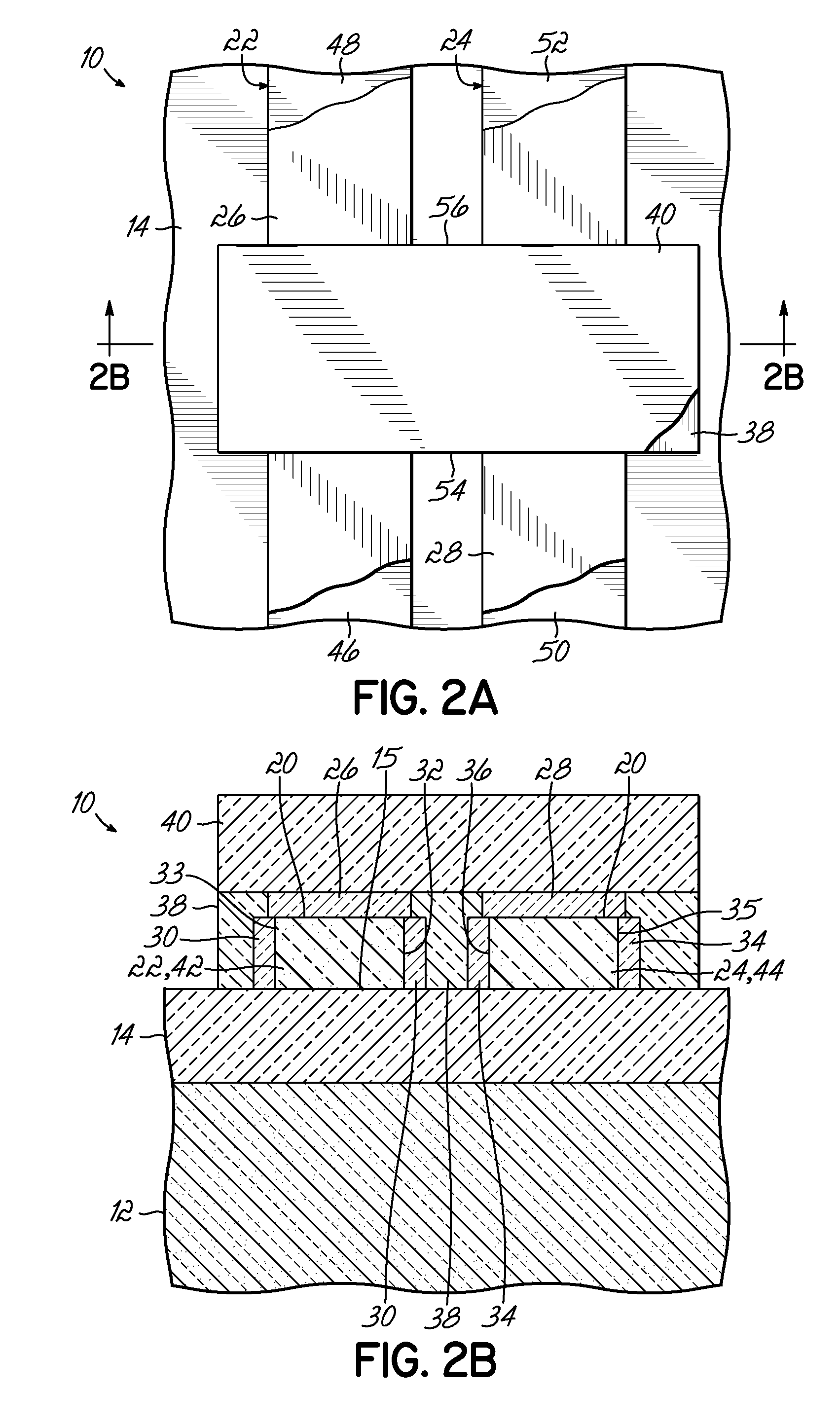

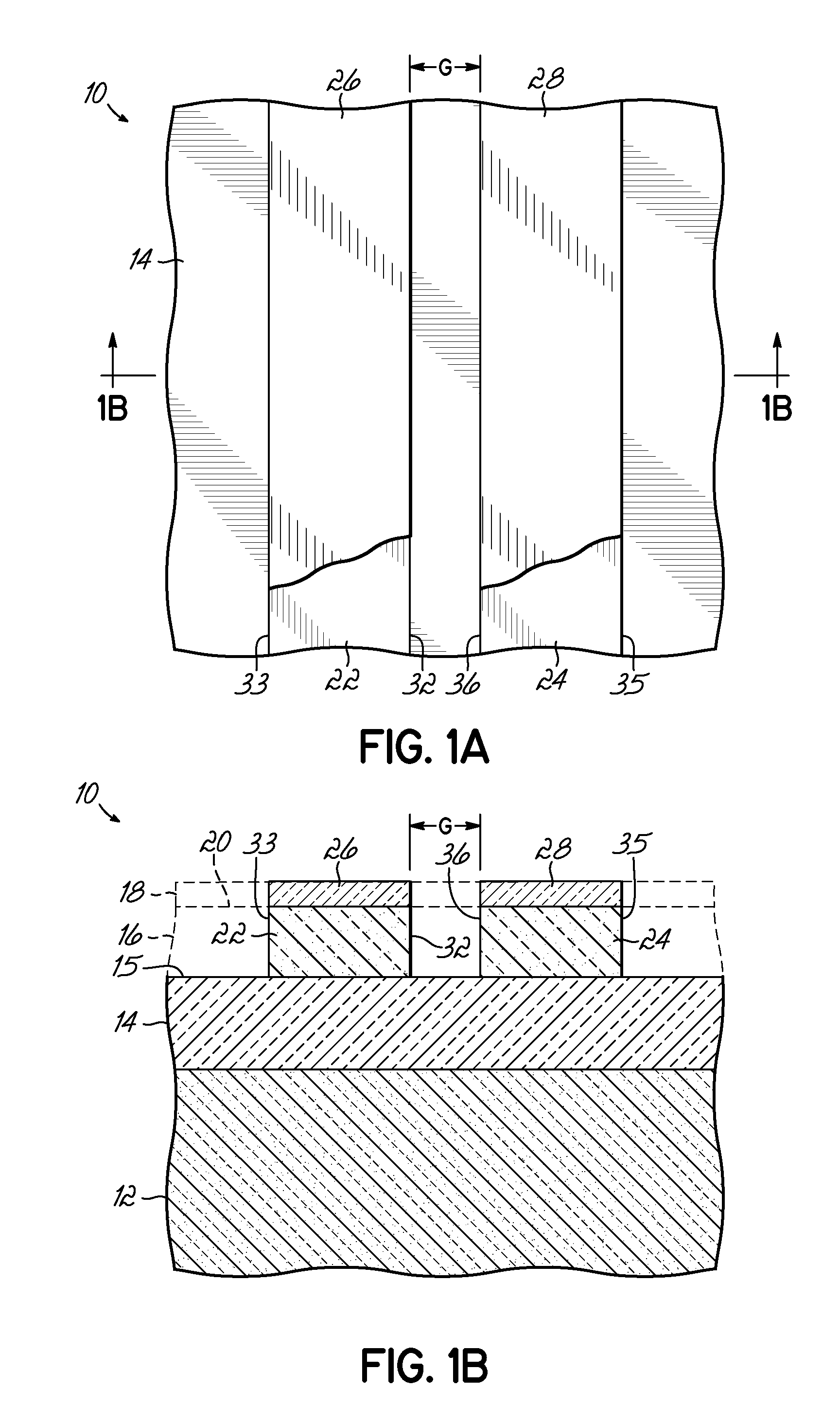

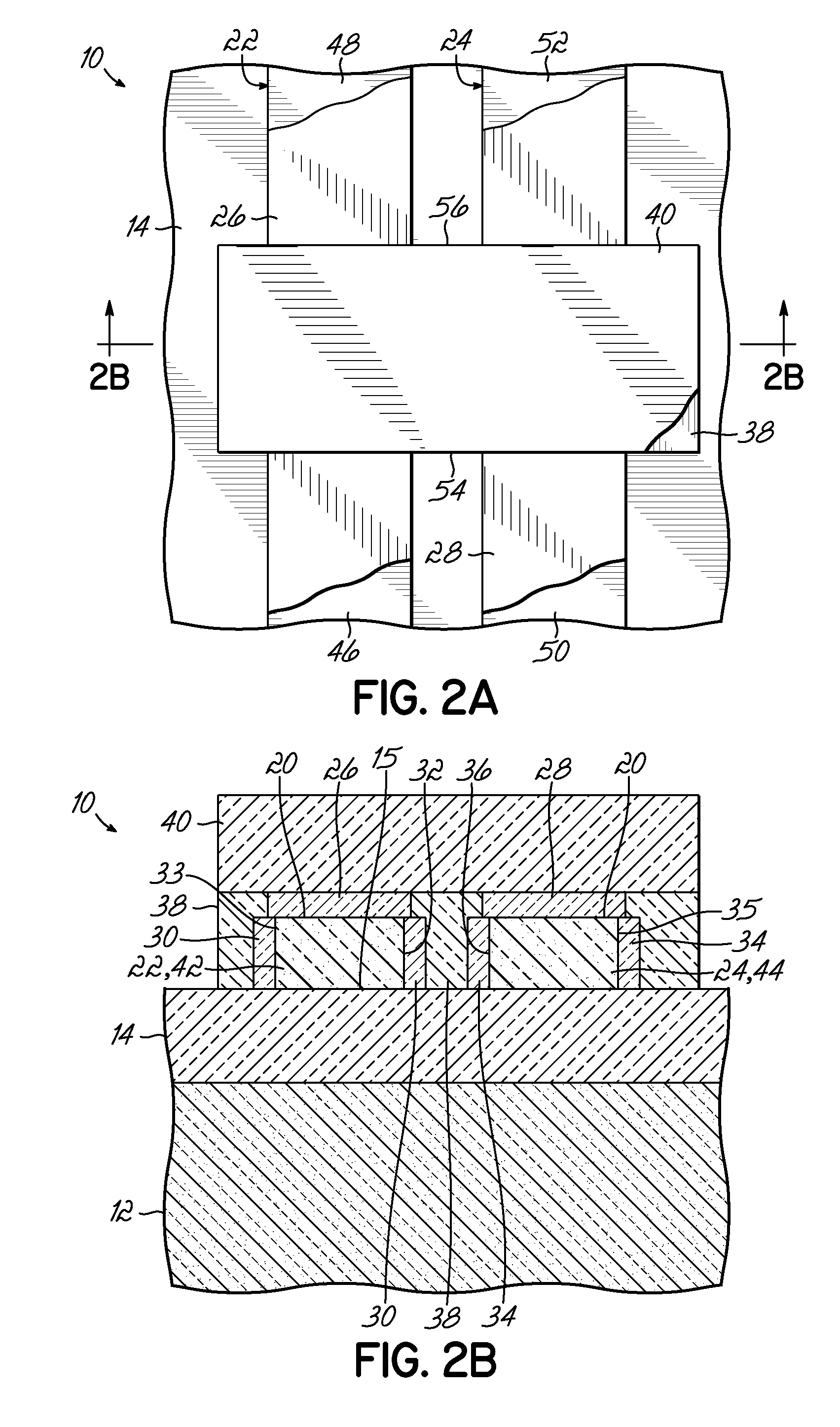

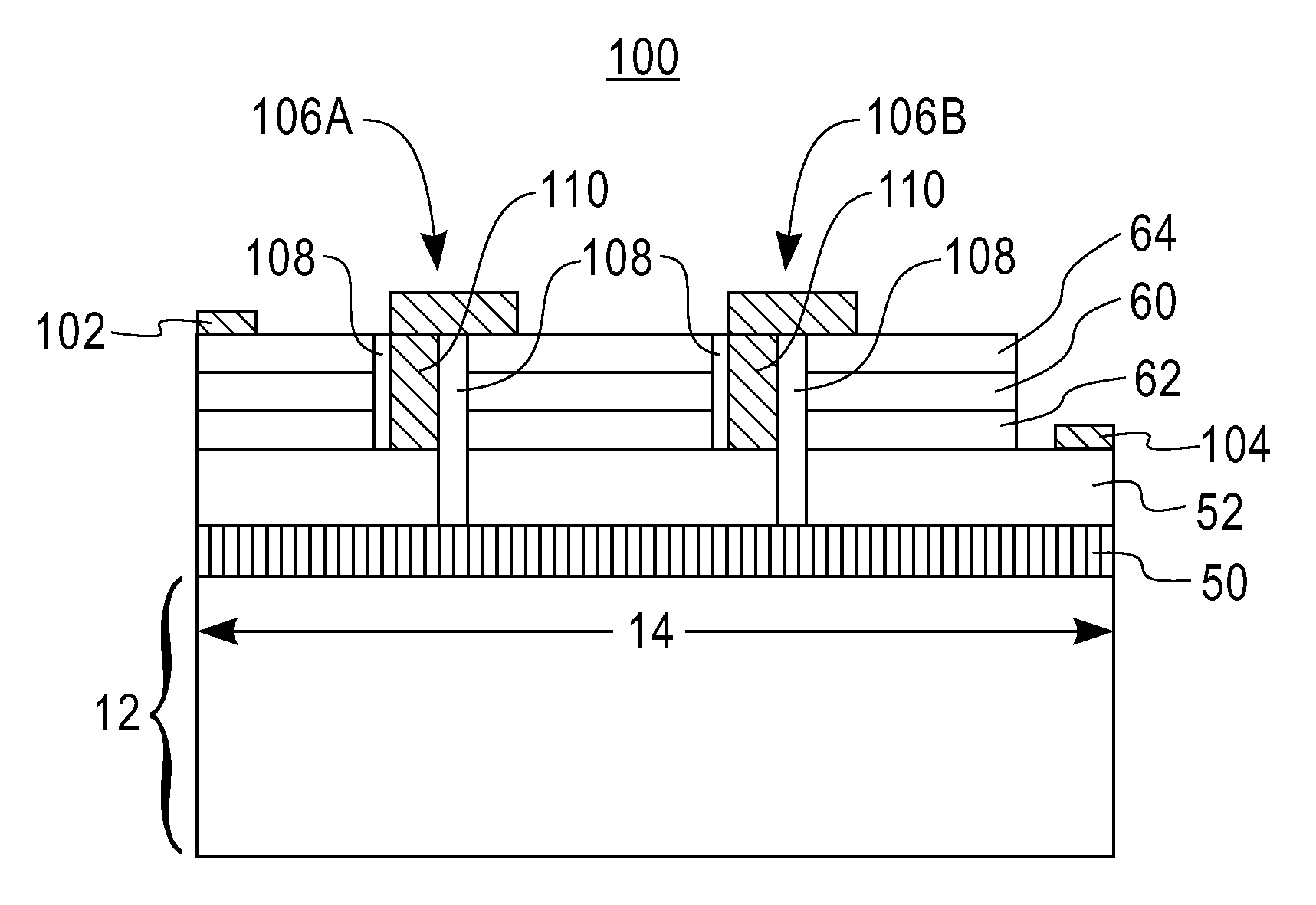

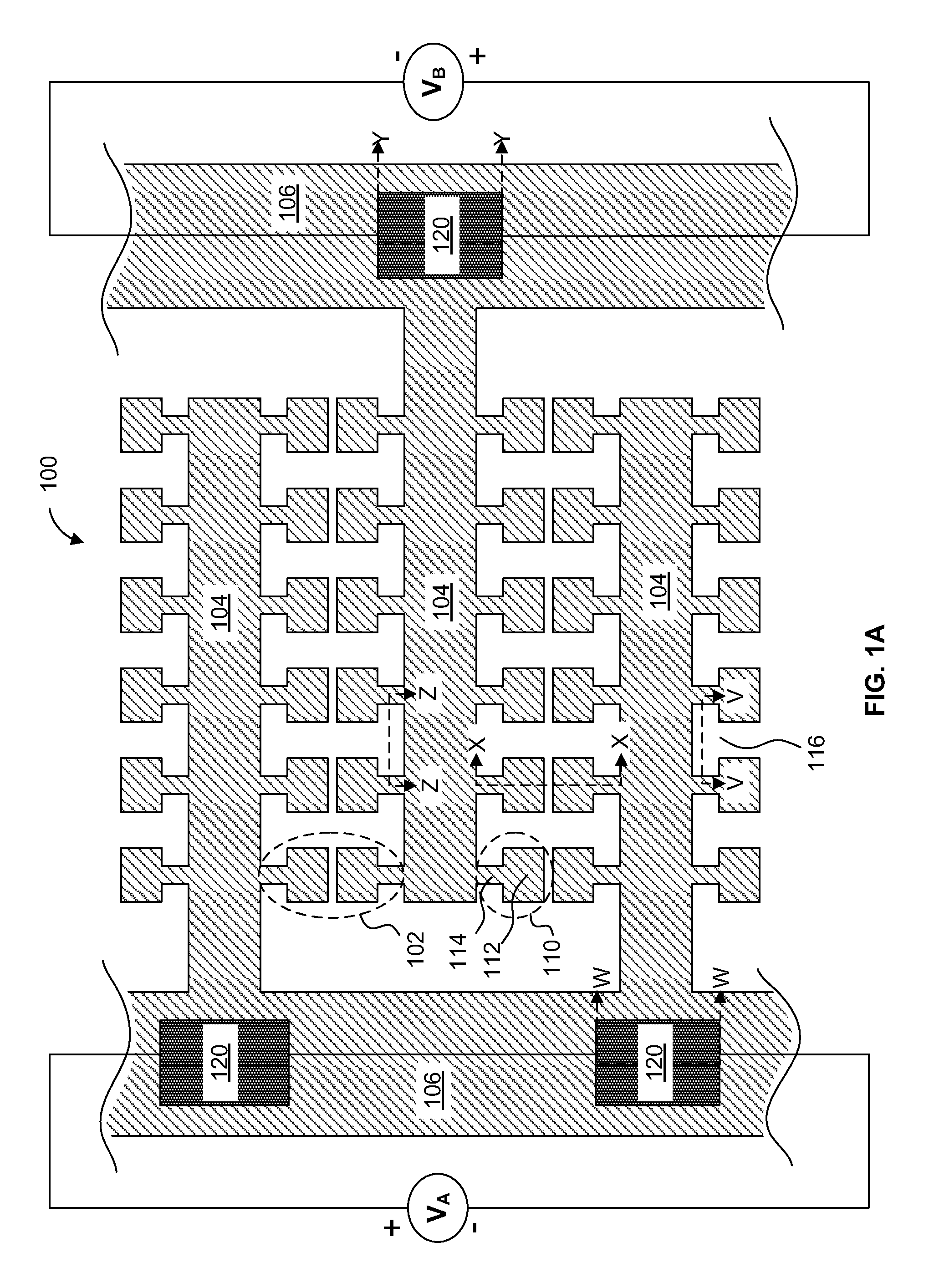

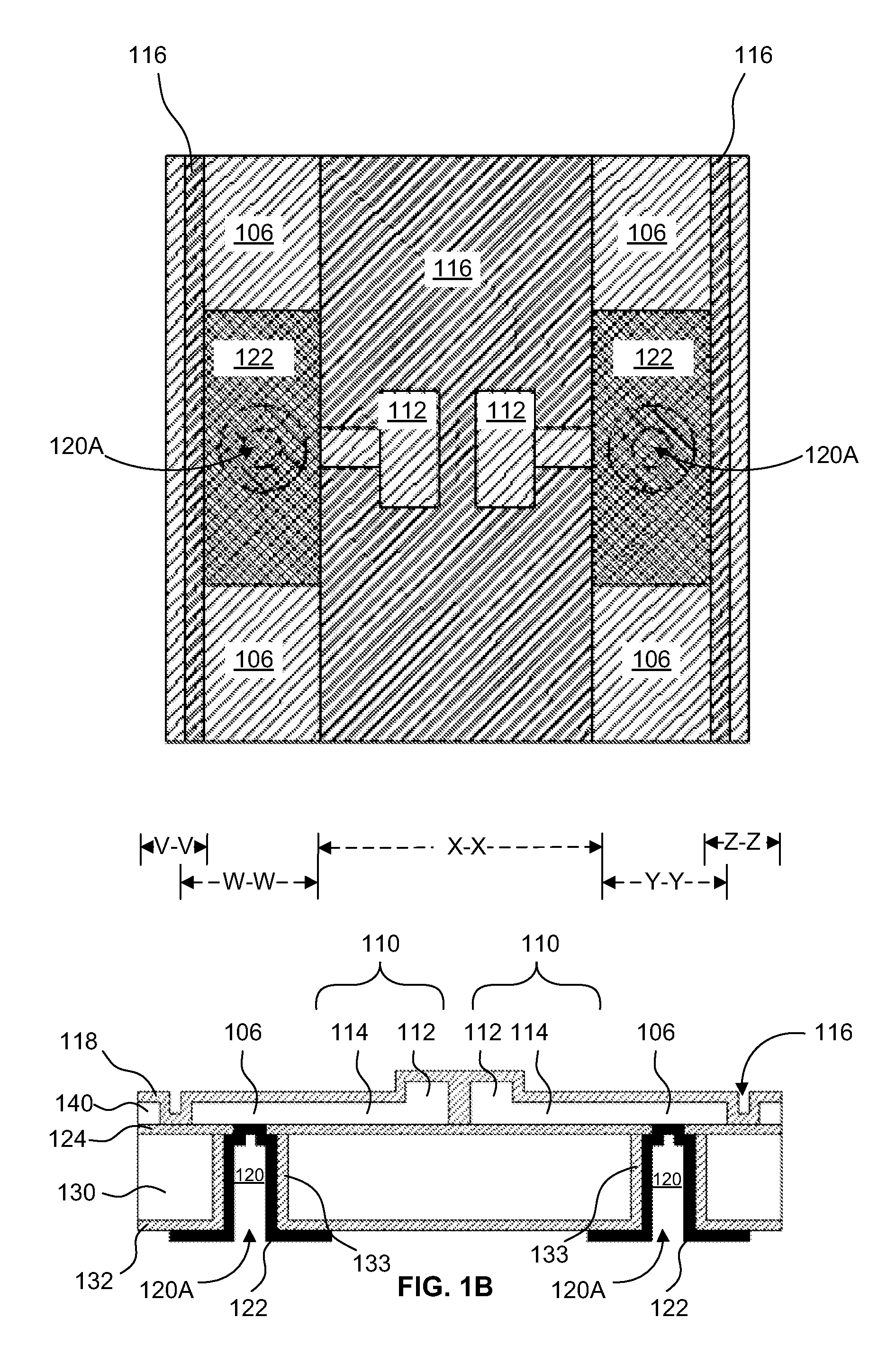

Design structures for high-voltage integrated circuits

Design structures for high-voltage integrated circuits. The design structure, which is formed using a semiconductor-on-insulator (SOI) substrate, may include device structure with a semiconductor body positioned between first and second gate electrodes. The first and second gate electrodes and the semiconductor body may be formed from the monocrystalline SOI layer of the SOI substrate. A dielectric layer separates each of the first and second gate electrodes from the semiconductor body. These dielectric layers are formed by defining trenches in the SOI layer and filling the trenches with a dielectric material, which may occur concurrently with a process forming other device isolation regions.

Owner:GLOBALFOUNDRIES INC

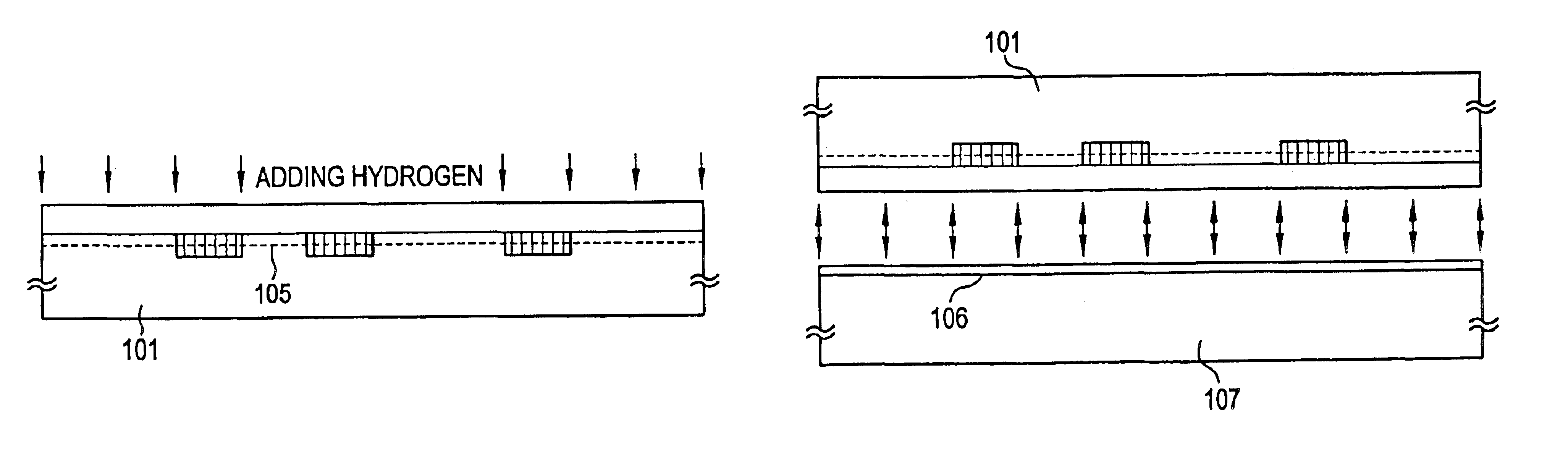

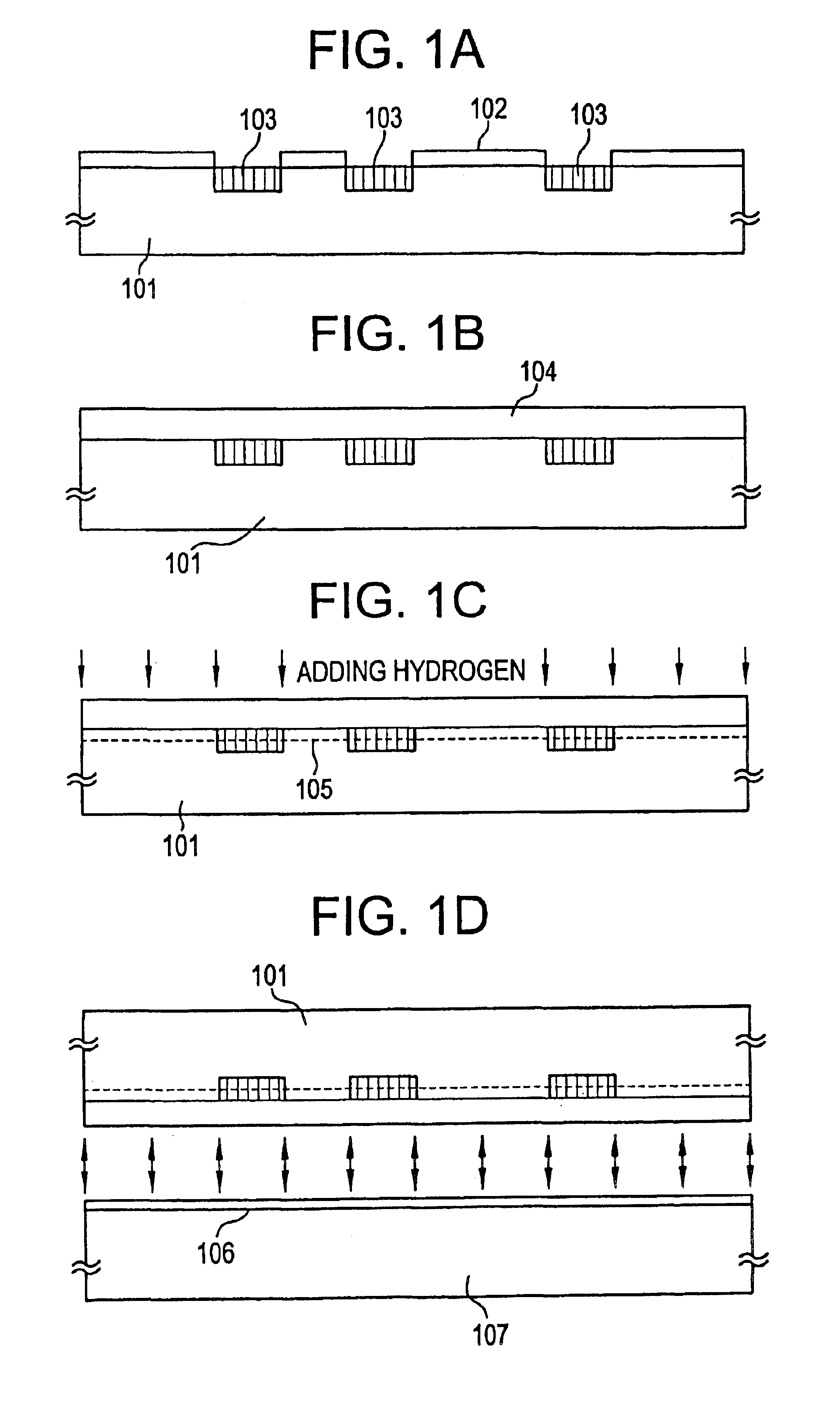

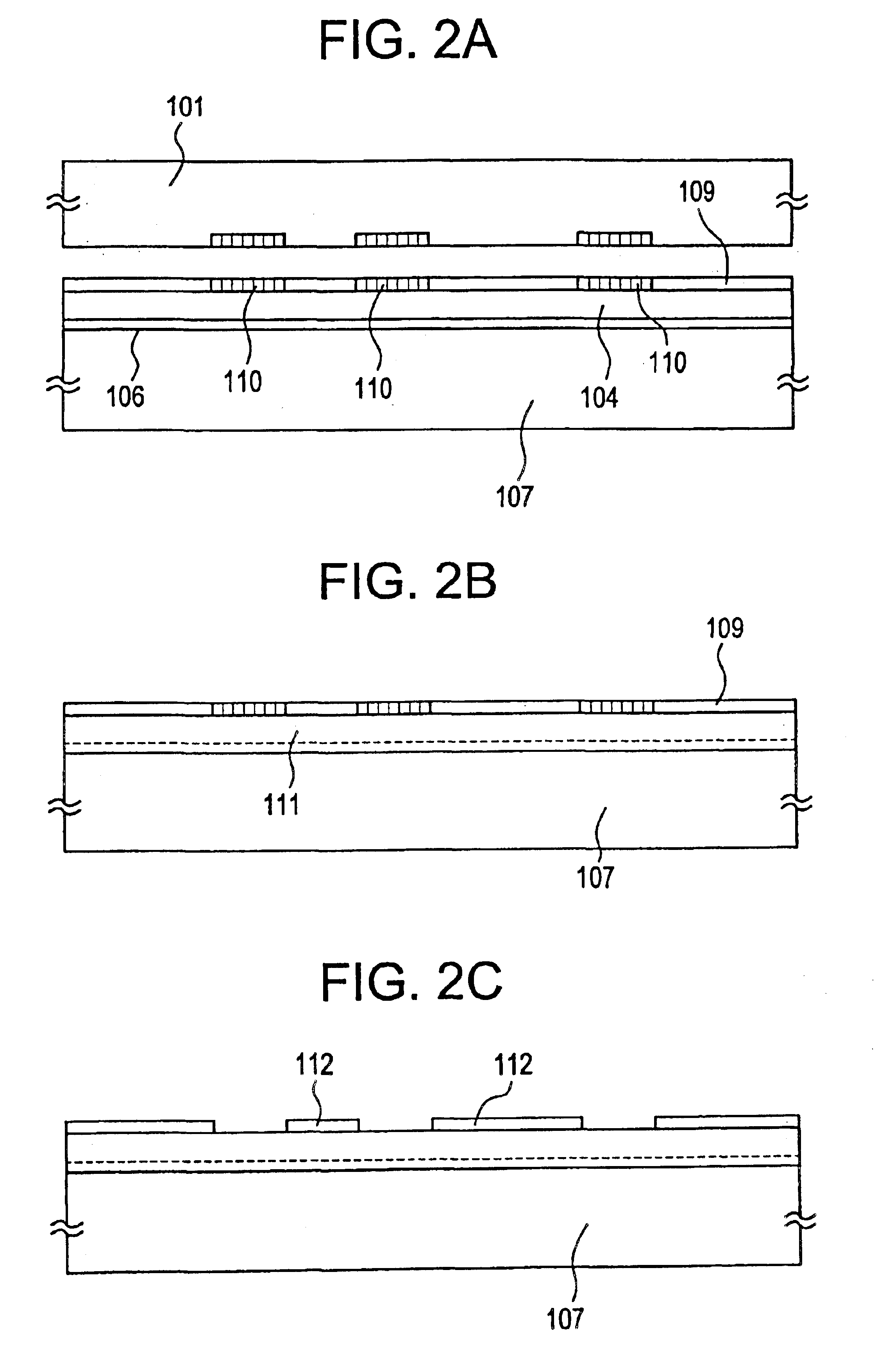

Process for production of SOI substrate and process for production of semiconductor device

A process for producing an adhered SOI substrate without causing cracking and peeling of a single-crystal silicon thin film. The process consists of selectively forming a porous silicon layer in a single-crystal semiconductor substrate, adding hydrogen into the single-crystal semiconductor substrate to form a hydrogen-added layer, adhering the single-crystal semiconductor substrate to a supporting substrate, separating the single-crystal semiconductor substrate at the hydrogen-added layer by thermal annealing, performing thermal annealing again to stabilize the adhering interface, and selectively removing the porous silicon layer to give single-crystal silicon layer divided into islands.

Owner:SEMICON ENERGY LAB CO LTD

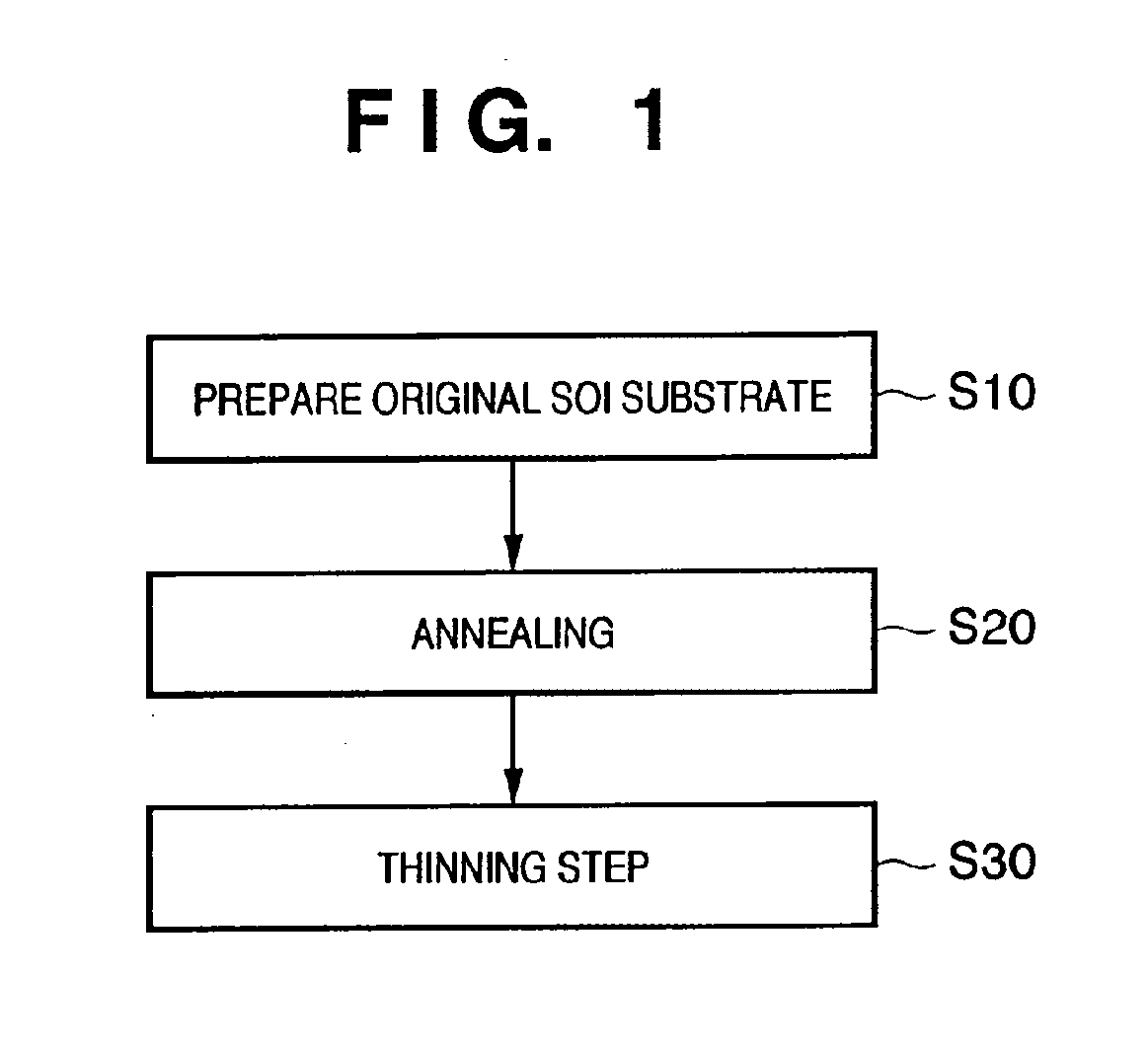

Substrate manufacturing method and substrate processing apparatus

InactiveUS7256104B2Easy thickness controlIncrease flexibilitySemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingChemical solutionSoi substrate

An SOI substrate which has a thick SOI layer is first prepared. Then, the SOI layer is thinned to a target film thickness using as a unit a predetermined thickness not more than that of one lattice. This thinning is performed by repeating a unit thinning step which includes an oxidation step of oxidizing the surface of the SOI layer by the predetermined thickness not more than that of one lattice and a removal step of selectively removing silicon oxide formed by the oxidation. The SOI layer of the SOI substrate is chemically etched by supplying a chemical solution to the SOI layer, and the film thickness of the etched SOI layer is measured. When the measured film thickness of the SOI layer has a predetermined value, a process of chemically etching the SOI layer ends.

Owner:CANON KK

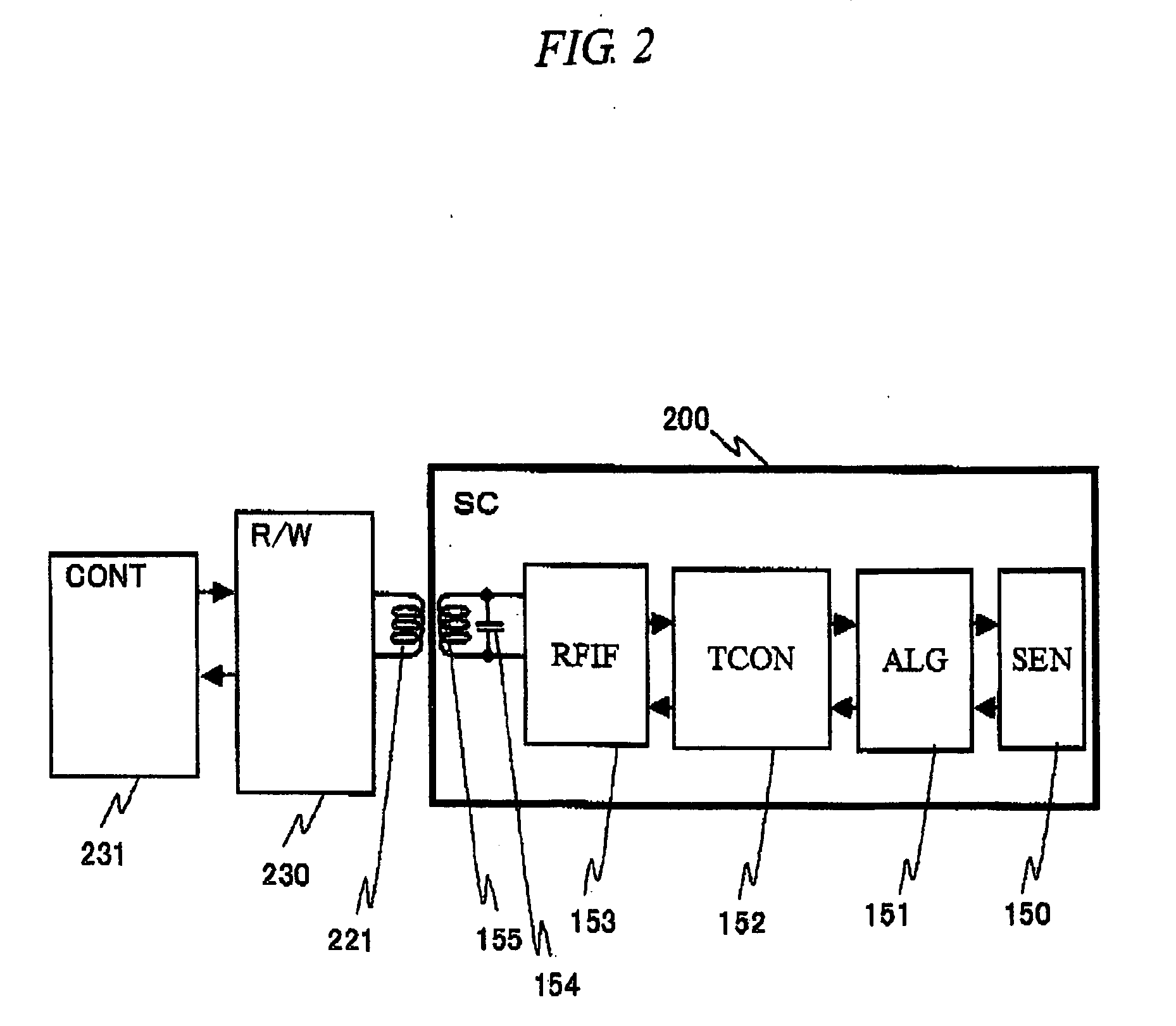

Examination apparatus for biological sample and chemical sample

InactiveUS20050156207A1Easy to measureLow costTransistorSemiconductor/solid-state device detailsCompound (substance)Soi substrate

A wireless sensor chip suitable for the compact, high-sensitive, and low-cost examination apparatus for easily examining a biological material such as gene at low cost is provided. A sensor chip is formed on an SOI substrate, and an n type semiconductor layer on which a pMOS transistor is formed and a p type semiconductor layer on which an nMOS transistor is formed are isolated by a pn junction. Therefore, the p type semiconductor layer at the outermost portion (chip edge portion to be in contact with solution) is set to floating, and the maximum potential and the minimum potential of the chip are supplied to an n type semiconductor layer and a p type semiconductor layer inside the outermost portion, respectively. Also, the chip is covered with an ion impermeable insulating film for reducing the penetration of positive ions through the oxide layer.

Owner:HITACHI LTD

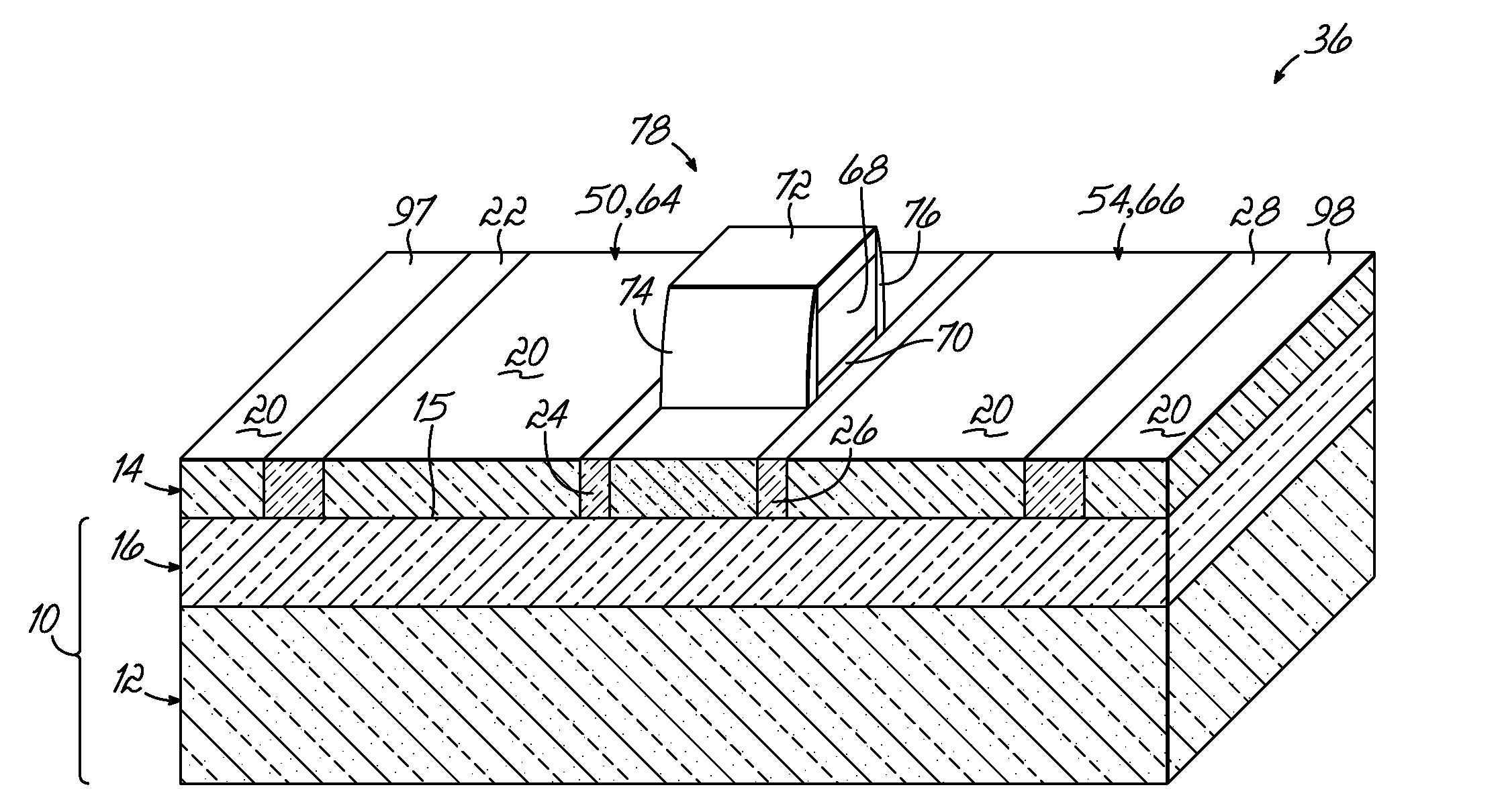

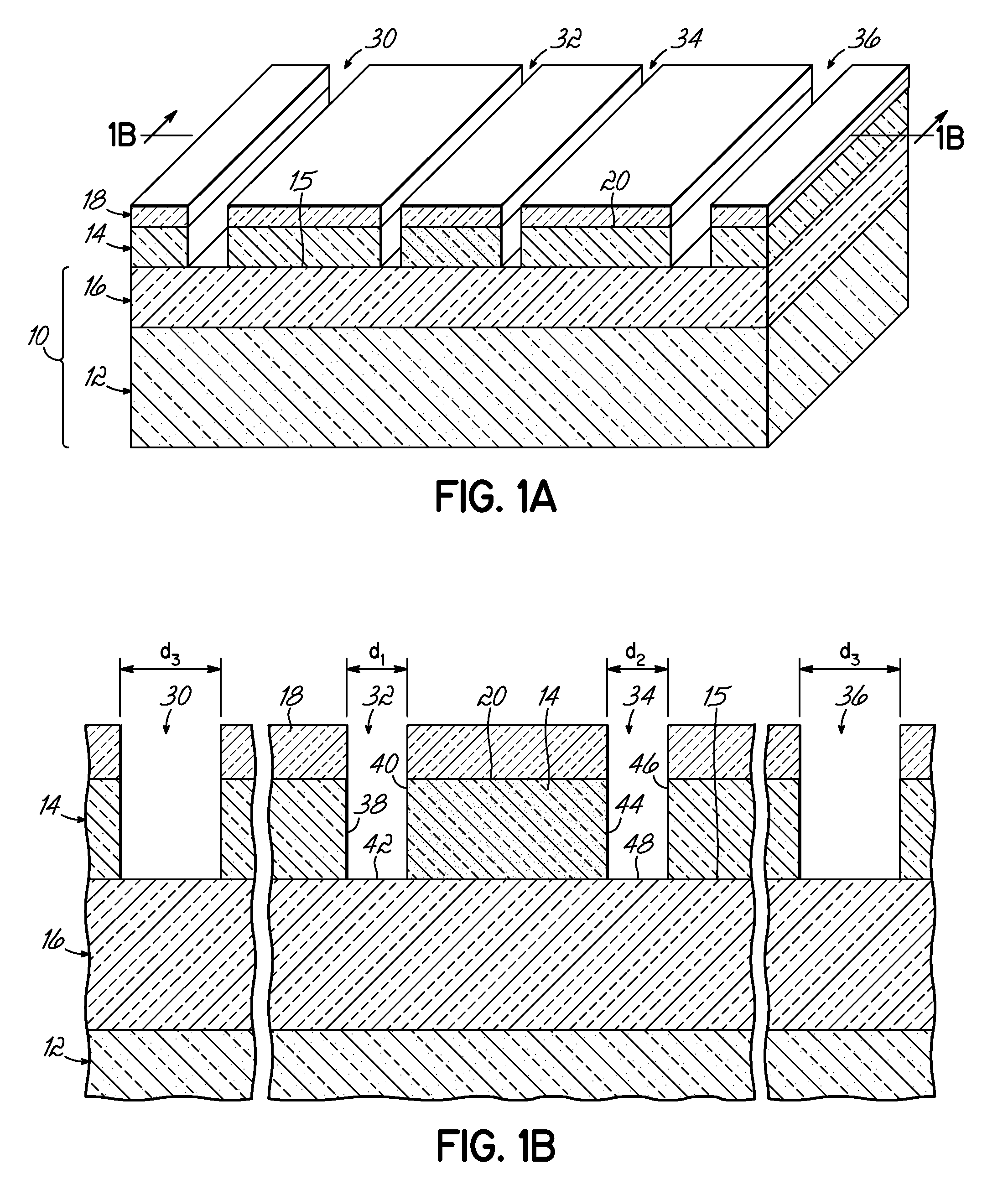

Design structures for high-voltage integrated circuits

InactiveUS7786535B2Solid-state devicesSoftware simulation/interpretation/emulationBody positionsSoi substrate

Design structures for high-voltage integrated circuits. The design structure, which is formed using a semiconductor-on-insulator (SOI) substrate, may include device structure with a semiconductor body positioned between first and second gate electrodes. The first and second gate electrodes and the semiconductor body may be formed from the monocrystalline SOI layer of the SOI substrate. A dielectric layer separates each of the first and second gate electrodes from the semiconductor body. These dielectric layers are formed by defining trenches in the SOI layer and filling the trenches with a dielectric material, which may occur concurrently with a process forming other device isolation regions.

Owner:GLOBALFOUNDRIES INC

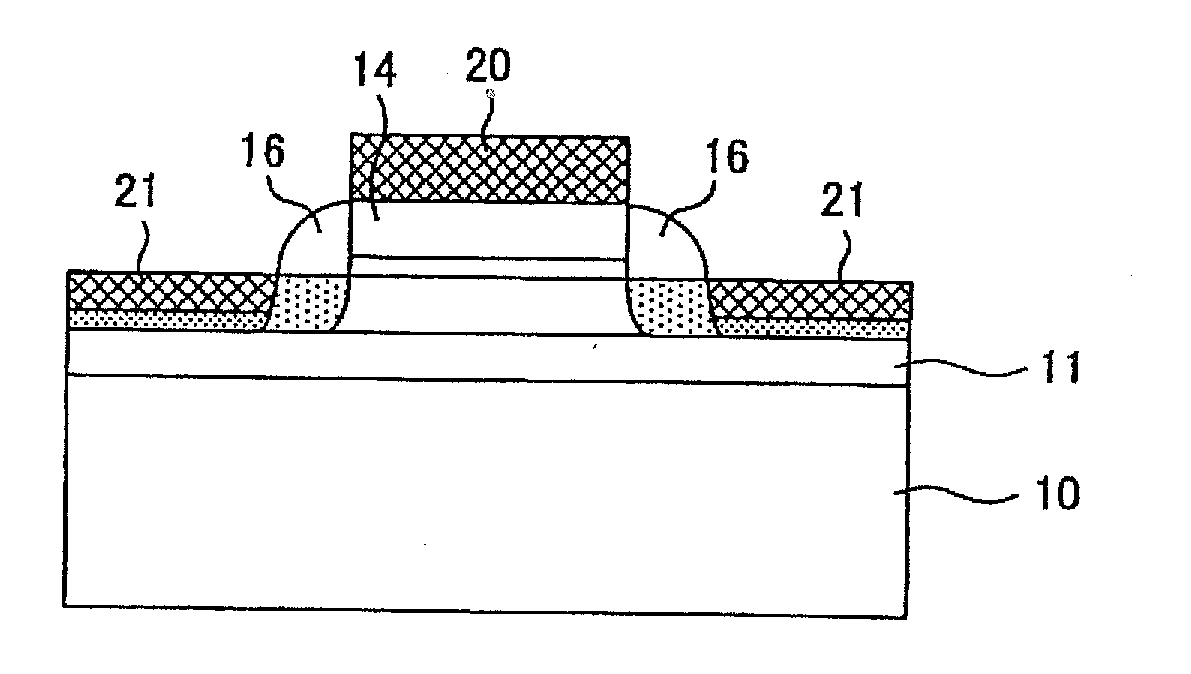

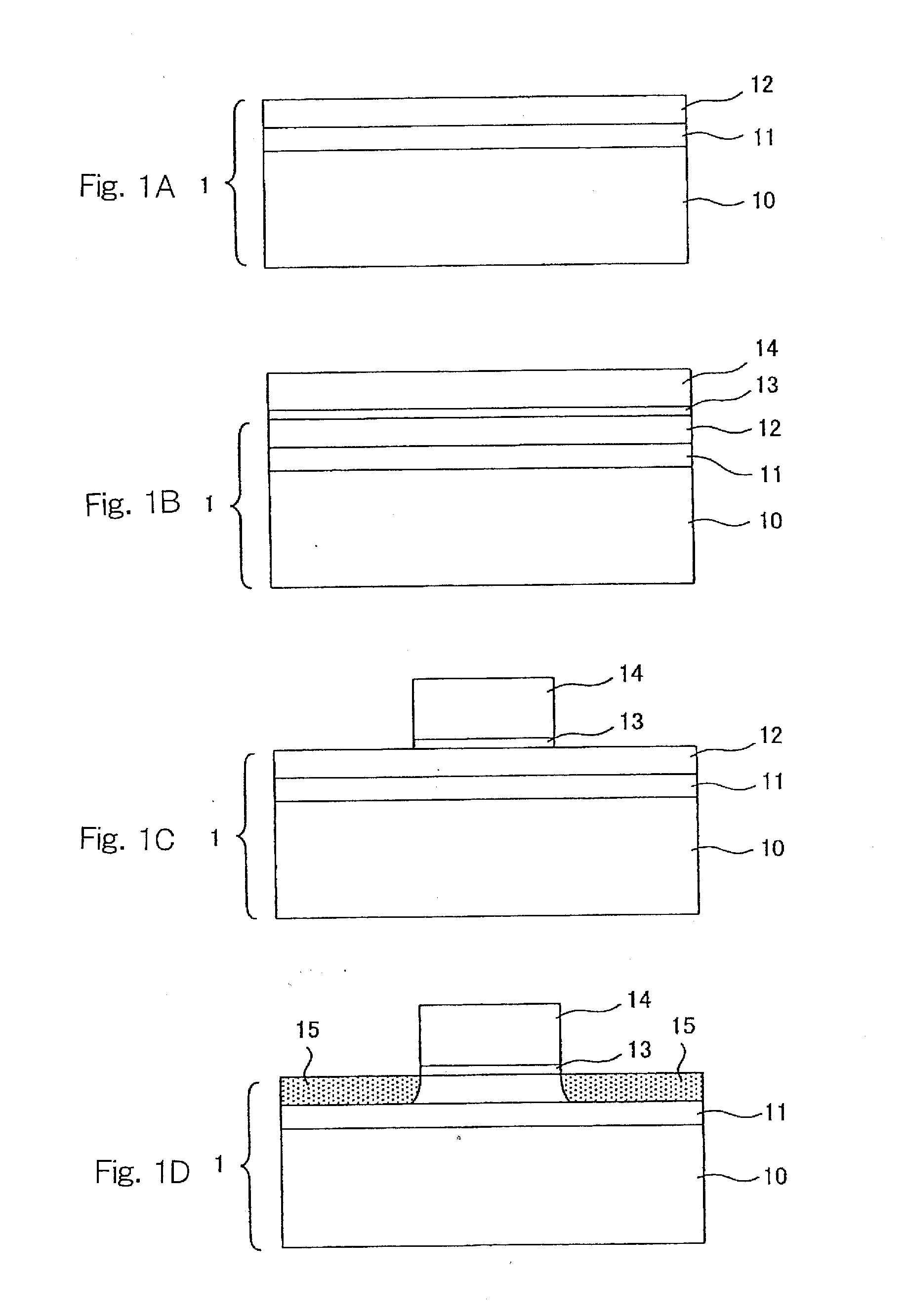

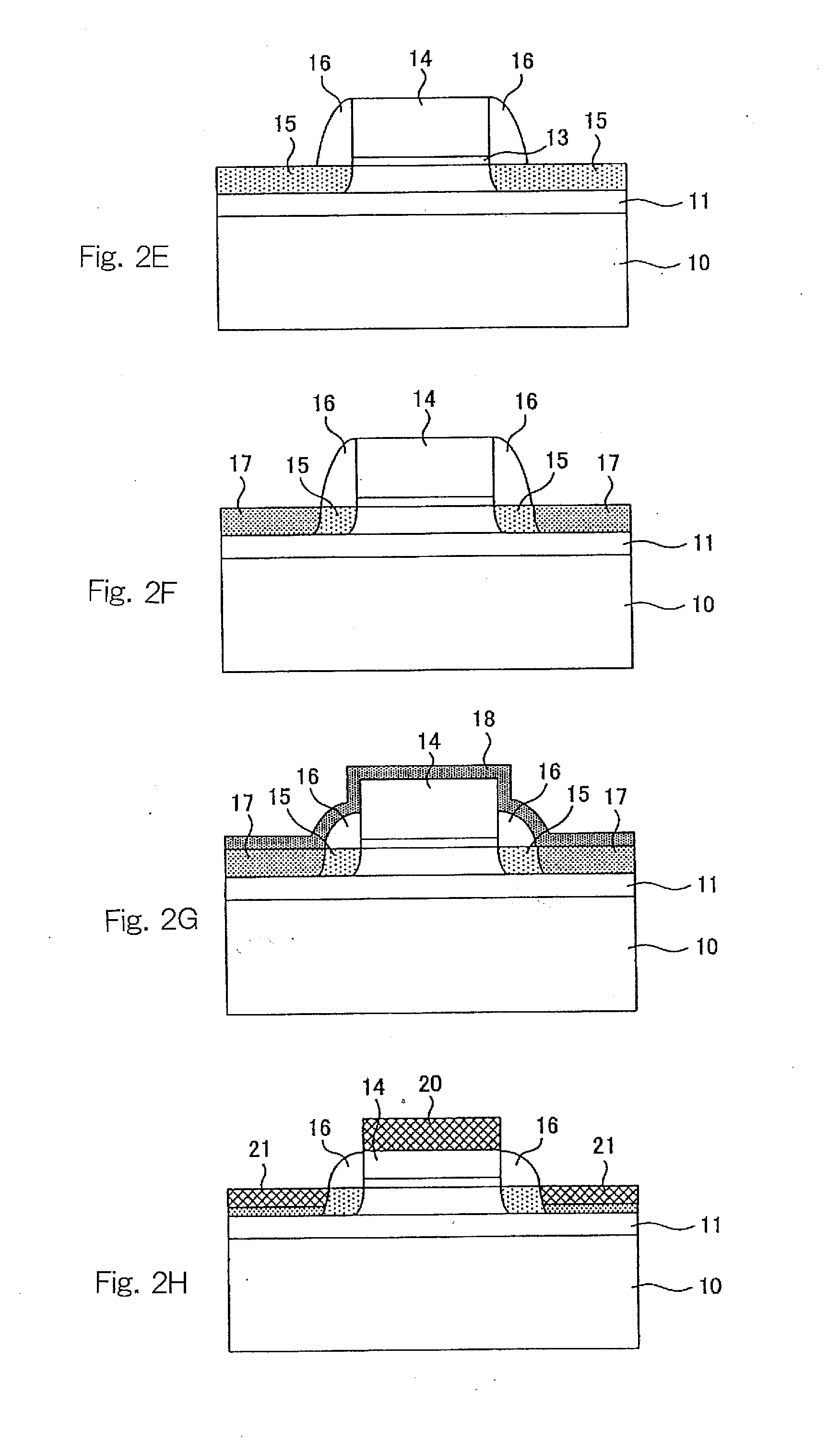

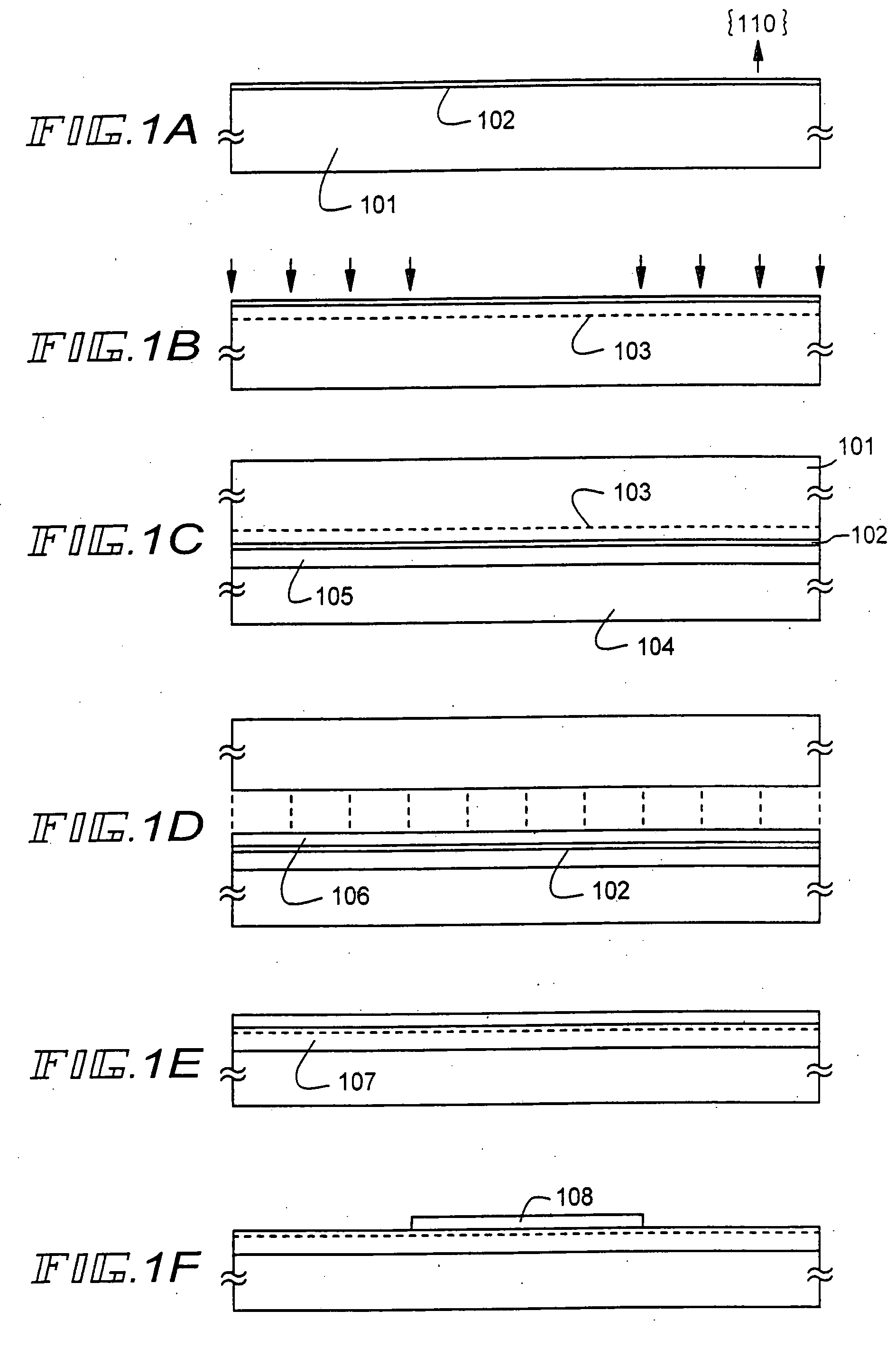

Method of manufacturing semiconductor device

InactiveUS20090317950A1Reduce parasitic resistanceImprove leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor packageSoi substrate

A semiconductor device manufacturing method which sequentially forms a gate oxide film and gate electrode material over a semiconductor layer of an SOI substrate and patterns the material into gate electrodes. The method further comprises the steps of forming sidewalls made of an insulator to cover side surfaces of the gate electrode; ion-implanting into the semiconductor layer on both sides of the gate electrode to form drain / source regions; partially etching the sidewalls to expose upper parts of the side surfaces of the gate electrode; depositing a metal film to cover the tops of the drain / source regions and of the gate electrode and the exposed upper parts of the side surfaces of the gate electrode; and performing heat treatment on the SOI substrate to form silicide layers respectively in the surfaces of the gate electrode and of the drain / source regions.

Owner:LAPIS SEMICON CO LTD

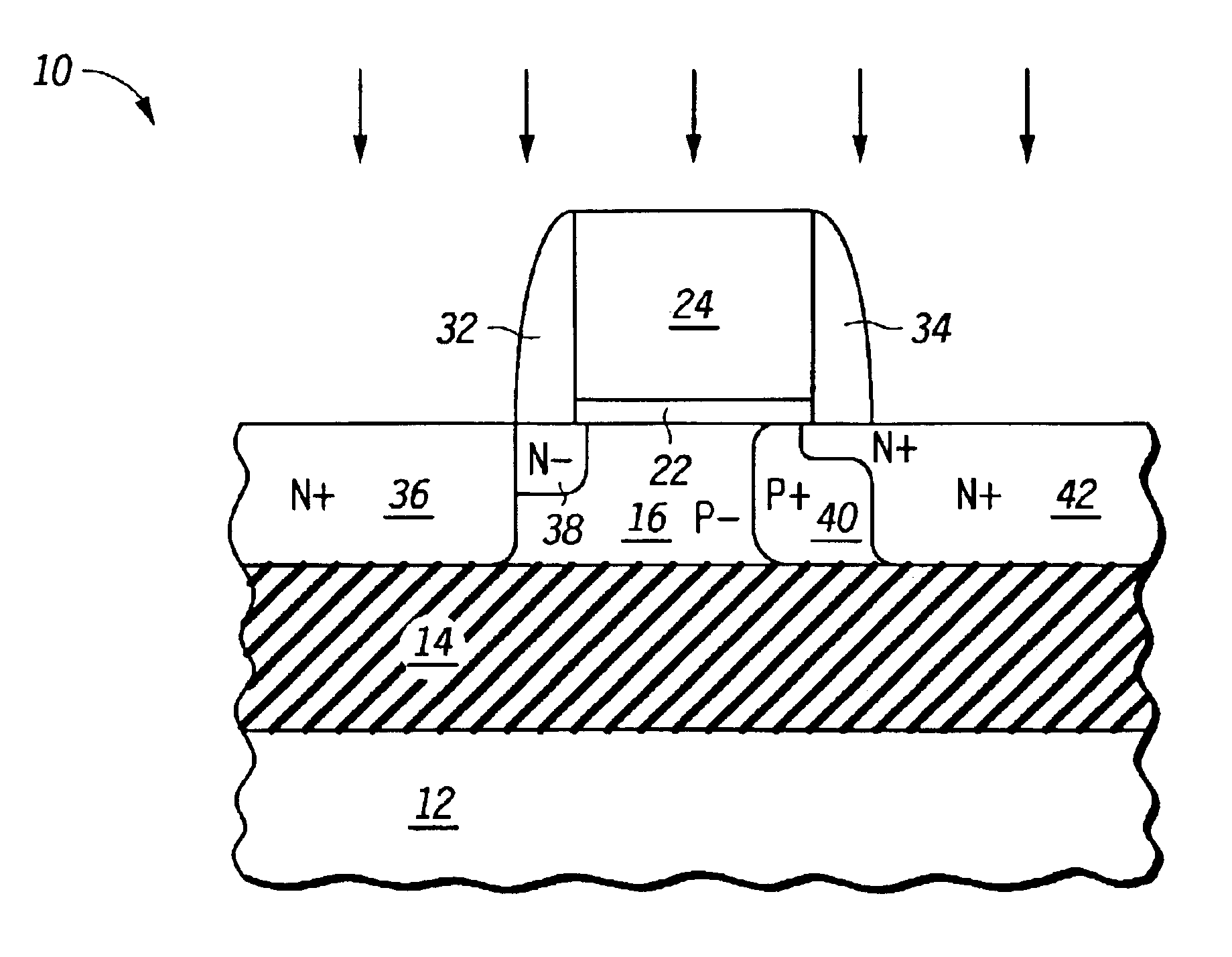

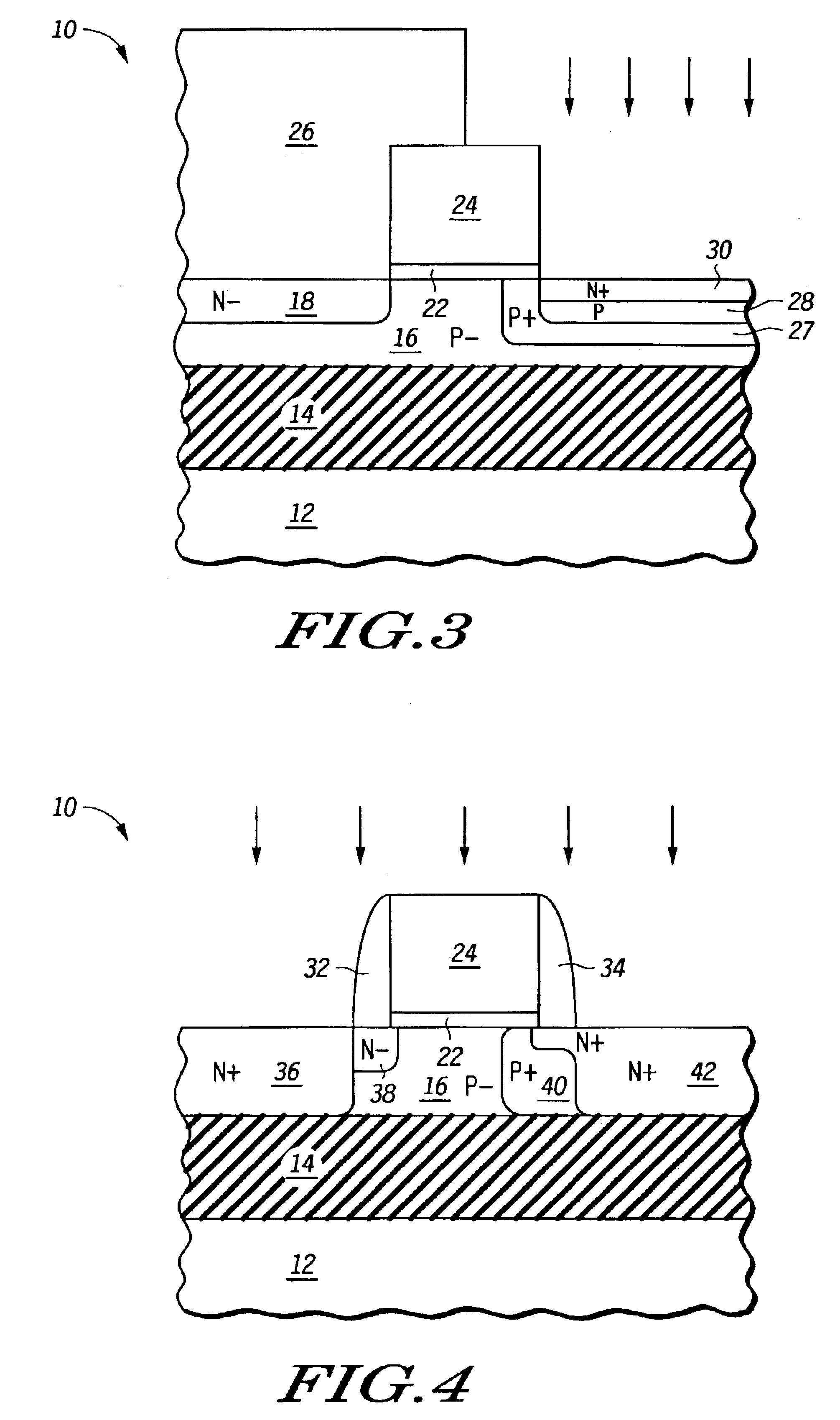

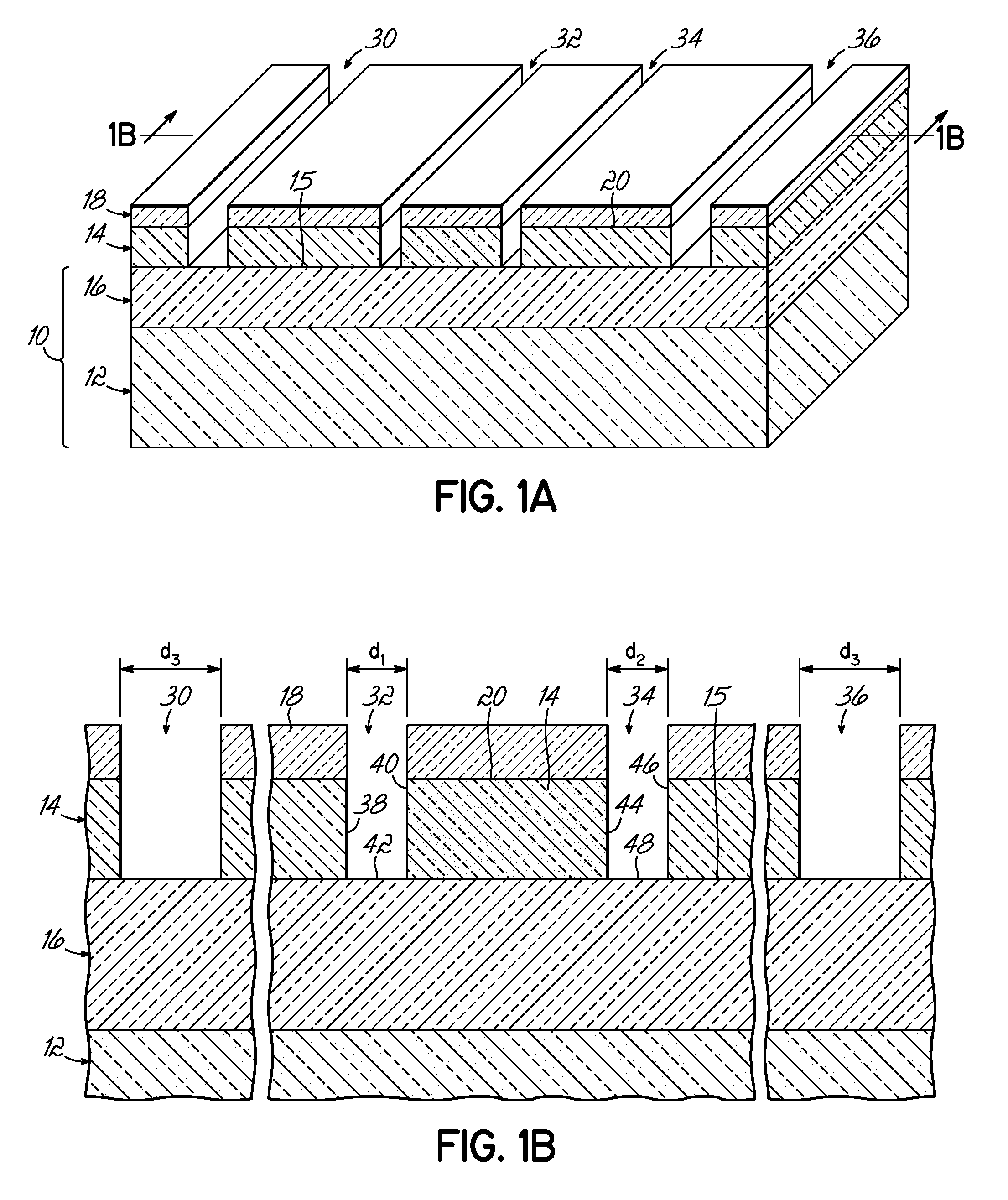

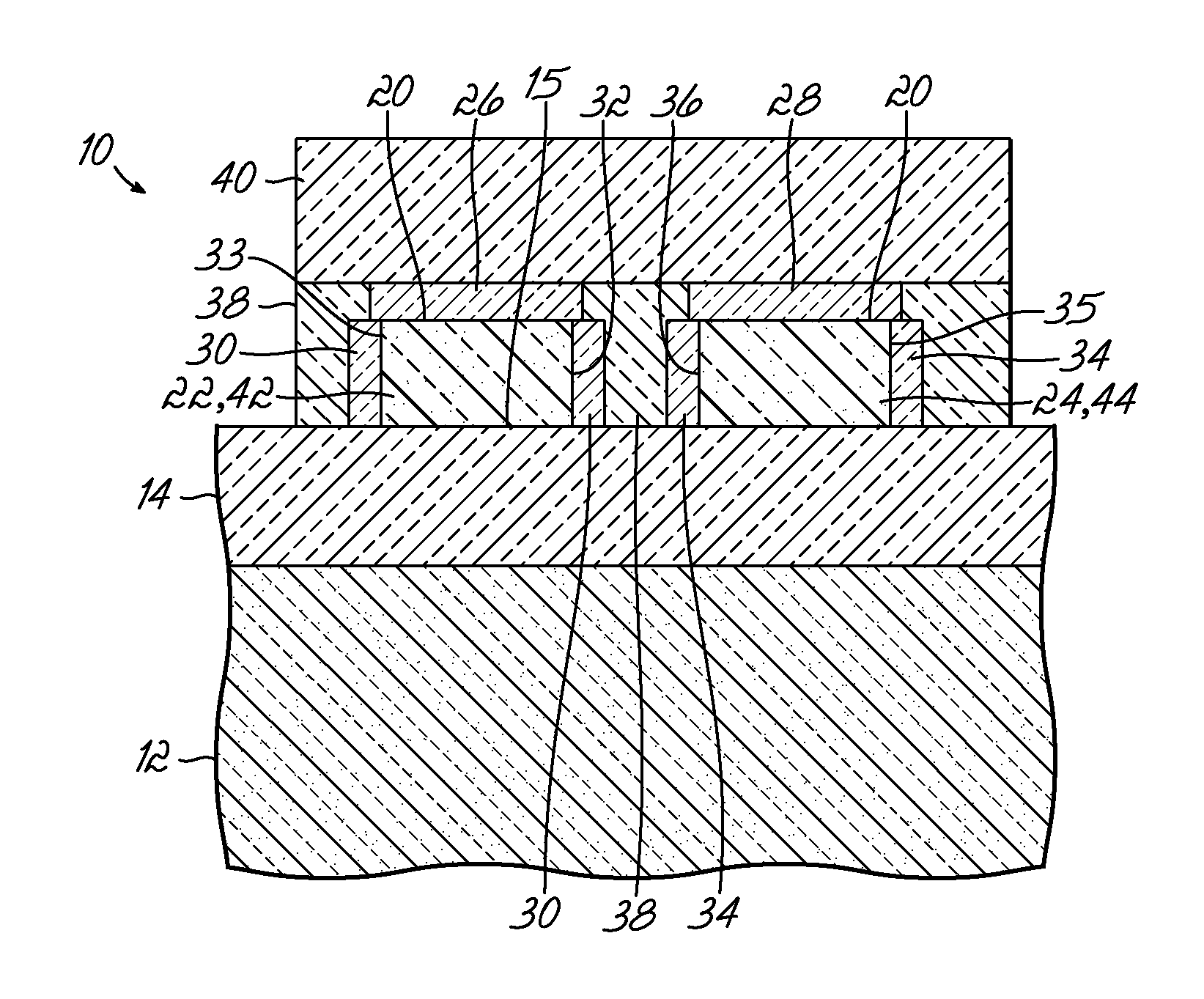

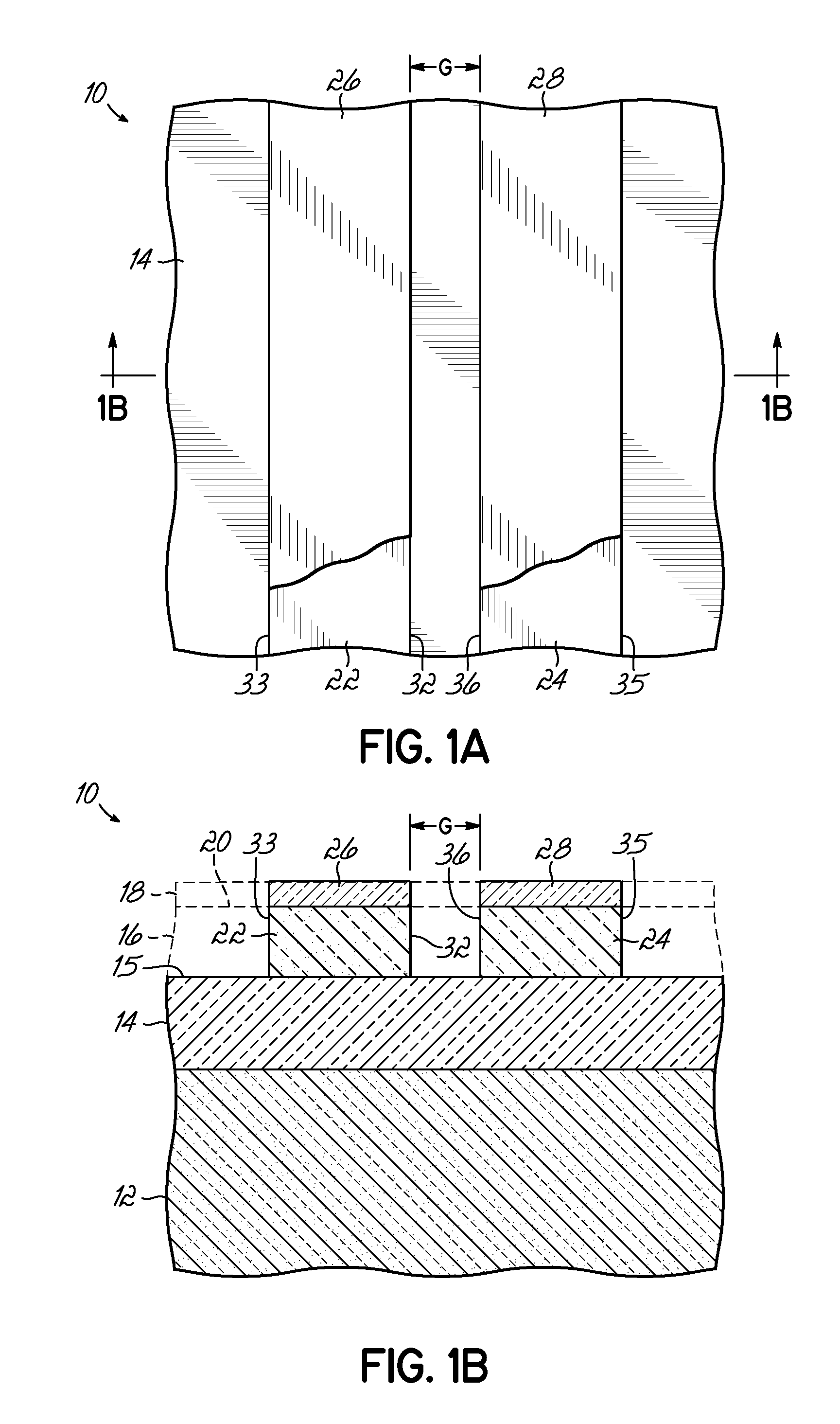

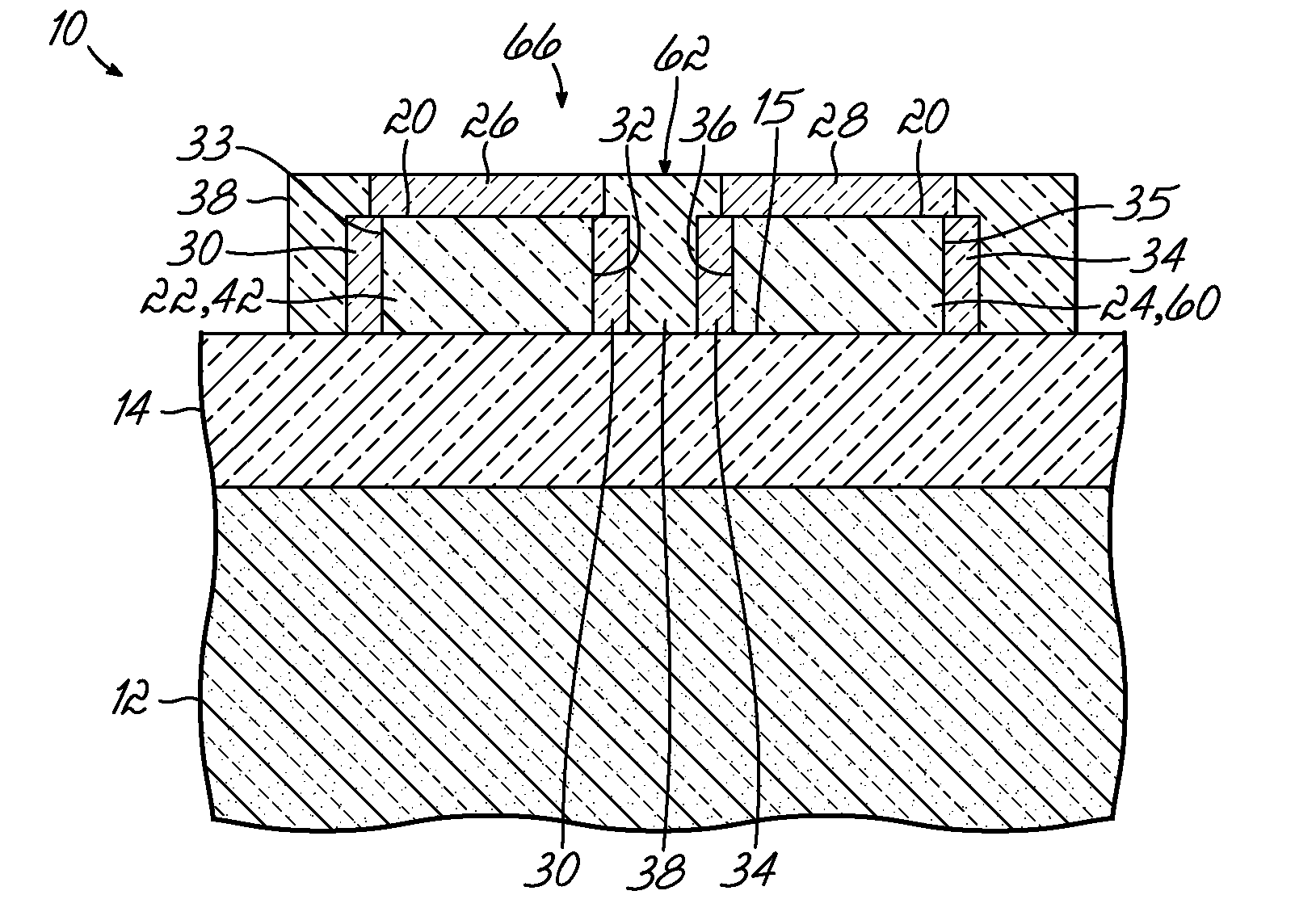

Device structures for a metal-oxide-semiconductor field effect transistor and methods of fabricating such device structures

InactiveUS7790543B2Solid-state devicesSemiconductor/solid-state device manufacturingMOSFETGate dielectric

Device structures for a metal-oxide-semiconductor field effect transistor (MOSFET) that is suitable for operation at relatively high voltages and methods of forming same. The MOSFET, which is formed using a semiconductor-on-insulator (SOI) substrate, includes a channel in a semiconductor body that is self-aligned with a gate electrode. The gate electrode and semiconductor body, which are both formed from the monocrystalline SOI layer of the SOI substrate, are separated by a gap that is filled by a gate dielectric layer. The gate dielectric layer may be composed of thermal oxide layers grown on adjacent sidewalls of the semiconductor body and gate electrode, in combination with an optional deposited dielectric material that fills the remaining gap between the thermal oxide layers.

Owner:GLOBALFOUNDRIES INC

Device structures for a metal-oxide-semiconductor field effect transistor and methods of fabricating such device structures

InactiveUS20090179266A1Solid-state devicesSemiconductor/solid-state device manufacturingMOSFETGate dielectric

Device structures for a metal-oxide-semiconductor field effect transistor (MOSFET) that is suitable for operation at relatively high voltages and methods of forming same. The MOSFET, which is formed using a semiconductor-on-insulator (SOI) substrate, includes a channel in a semiconductor body that is self-aligned with a gate electrode. The gate electrode and semiconductor body, which are both formed from the monocrystalline SOI layer of the SOI substrate, are separated by a gap that is filled by a gate dielectric layer. The gate dielectric layer may be composed of thermal oxide layers grown on adjacent sidewalls of the semiconductor body and gate electrode, in combination with an optional deposited dielectric material that fills the remaining gap between the thermal oxide layers.

Owner:GLOBALFOUNDRIES INC

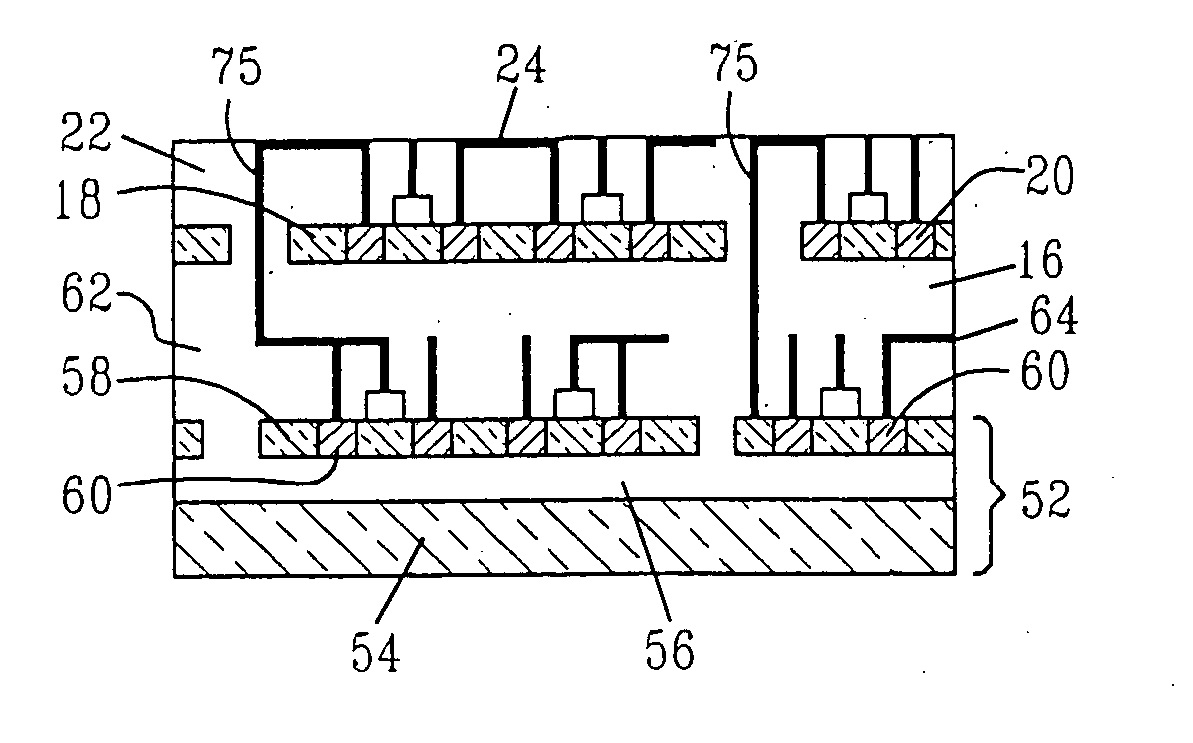

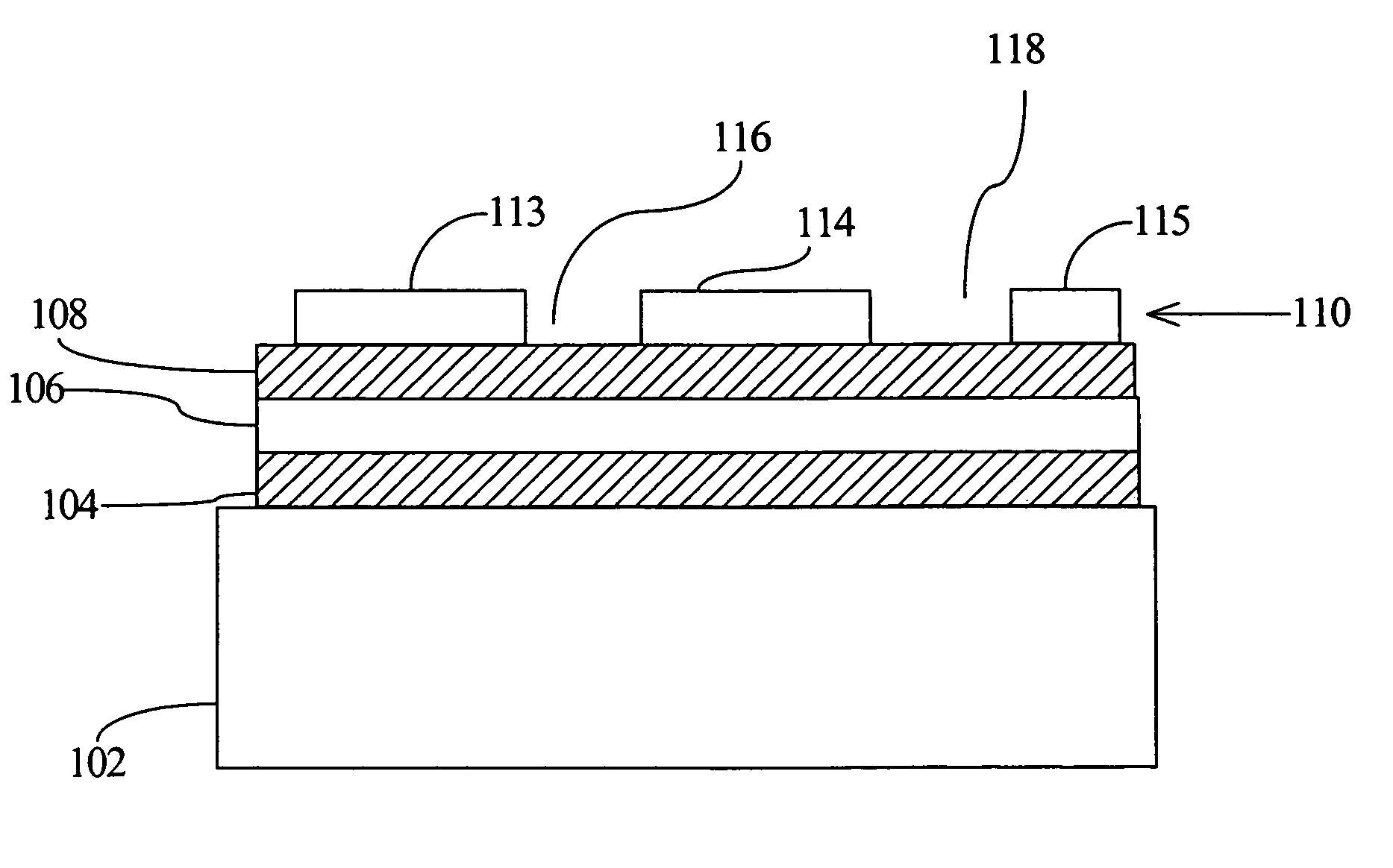

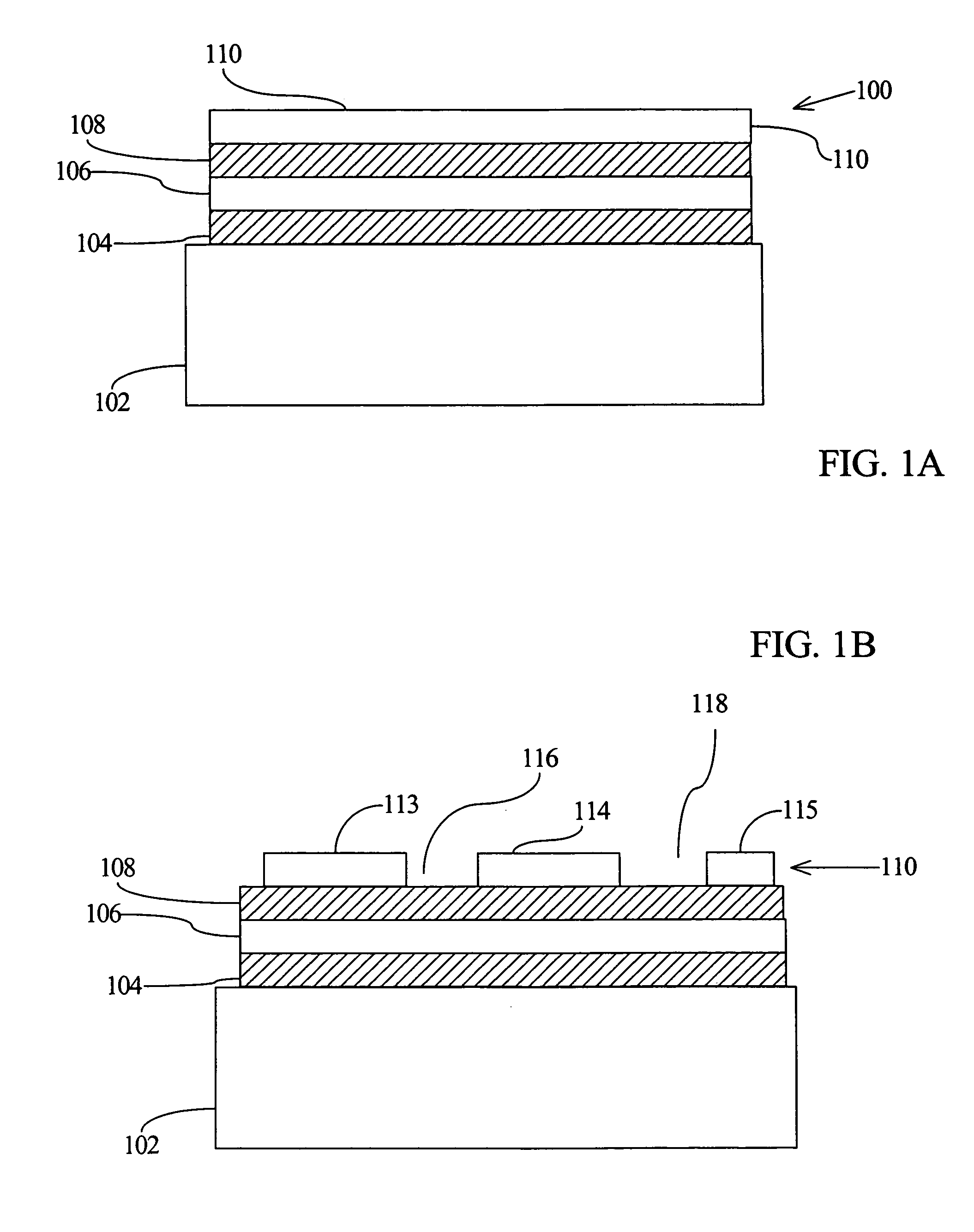

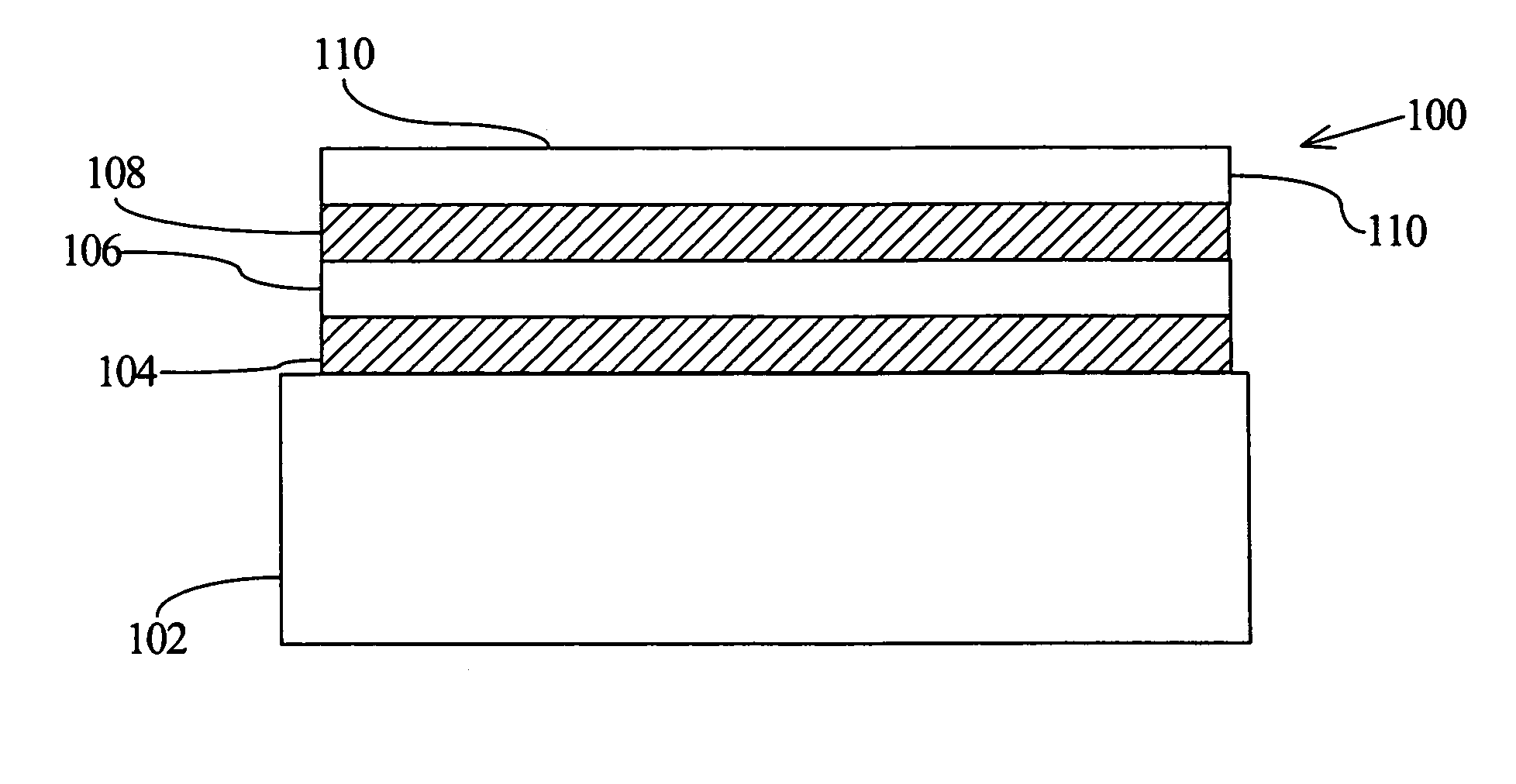

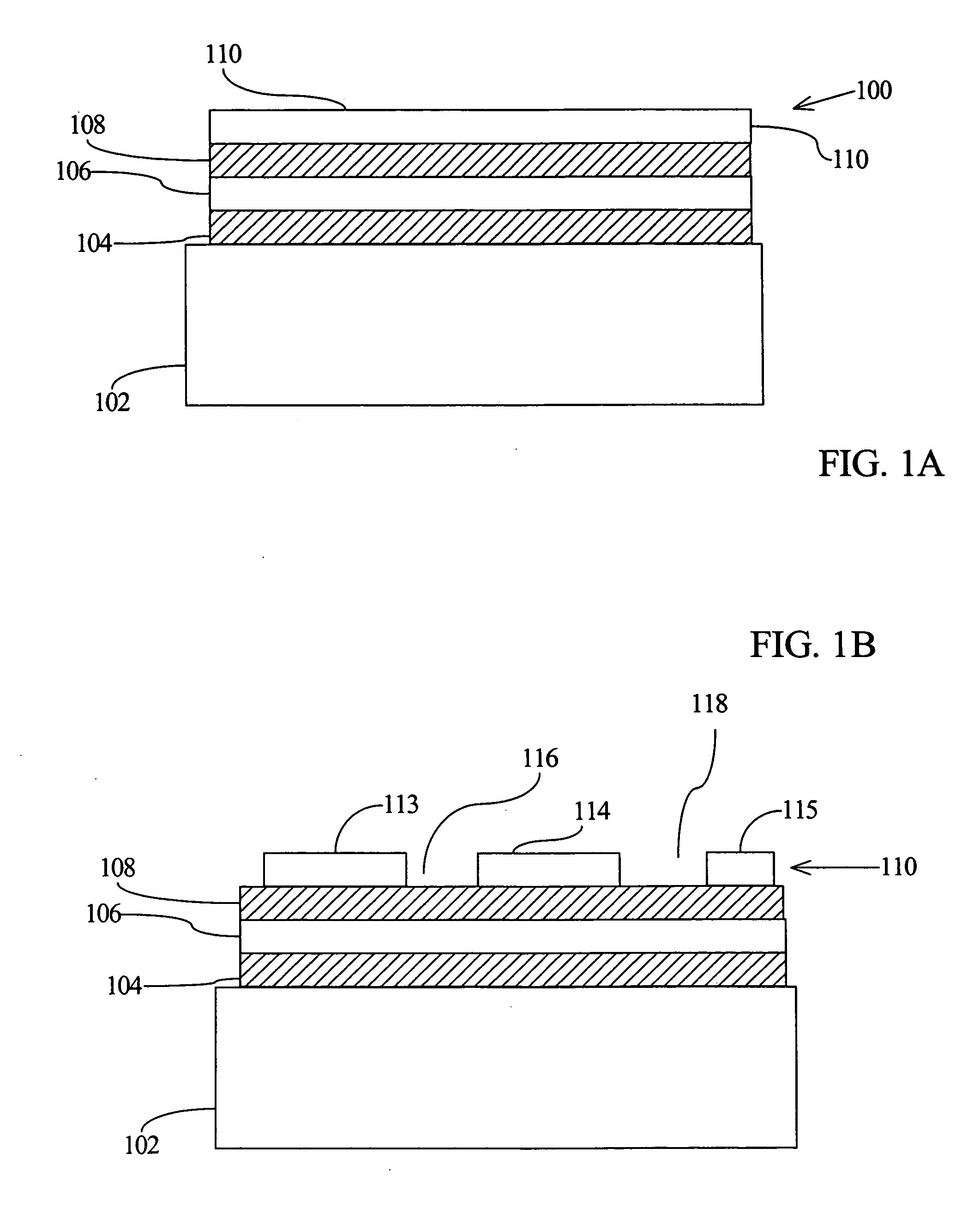

Silicon-on-insulator active pixel sensors

ActiveUS7160753B2Improve performanceEasy to manufactureSolid-state devicesSemiconductor/solid-state device manufacturingCMOS sensorSoi substrate

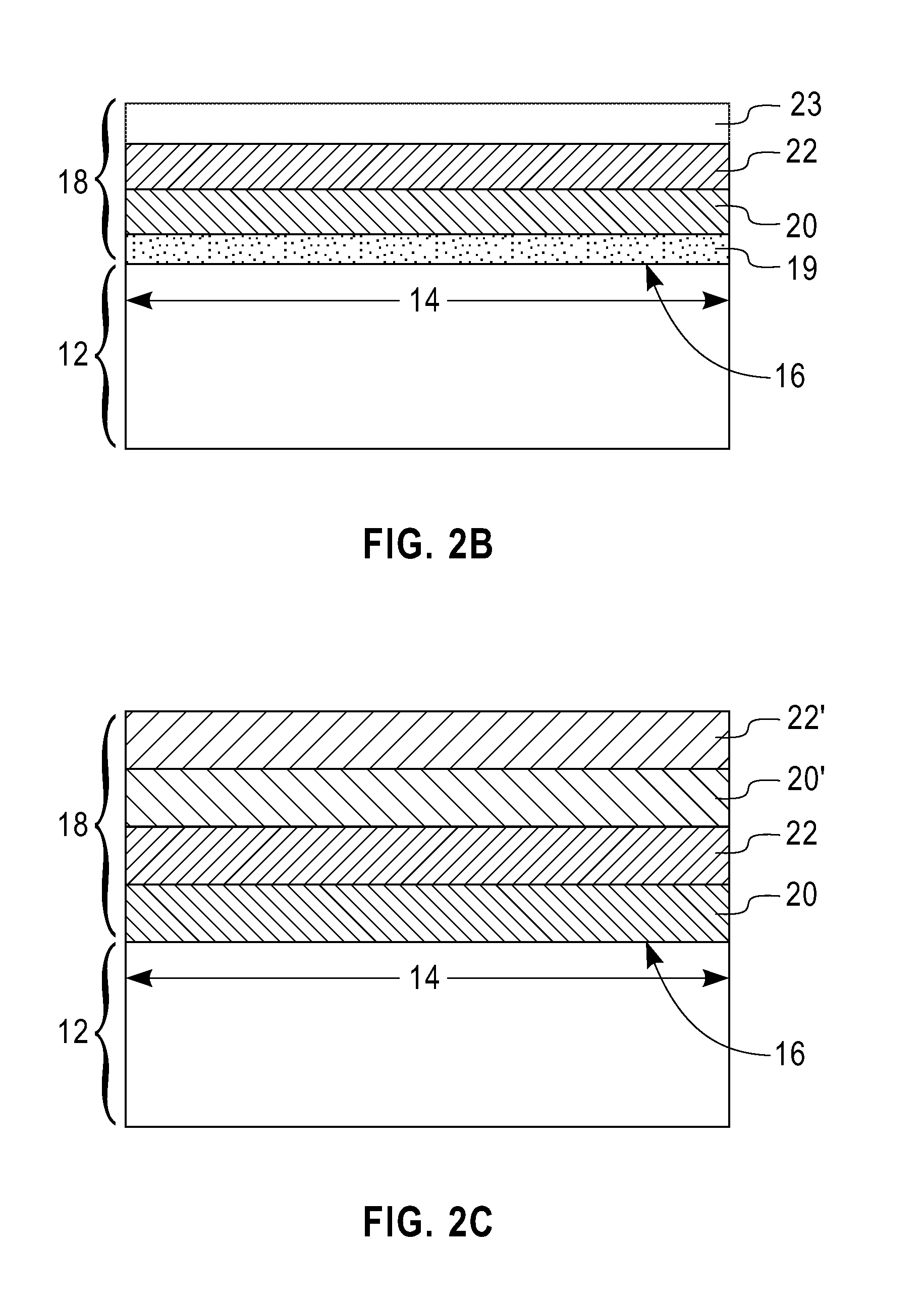

Active pixel sensors are defined on double silicon on insulator (SOI) substrates such that a first silicon layer is selected to define radiation detection regions, and a second silicon layer is selected to define readout circuitry. The first and second silicon layers are separated by an insulator layer, typically an oxide layer, and the layers can be independently doped. Doping can be provided in the silicon layers of the SOI substrate during assembly of the SOI substrate, or later during device processing. A semiconductor substrate that supports the first and second layers can be removed for, for example, back side radiation detection, using a second insulator layer (typically an oxide layer) as an etch stop.

Owner:LADARSYST INC

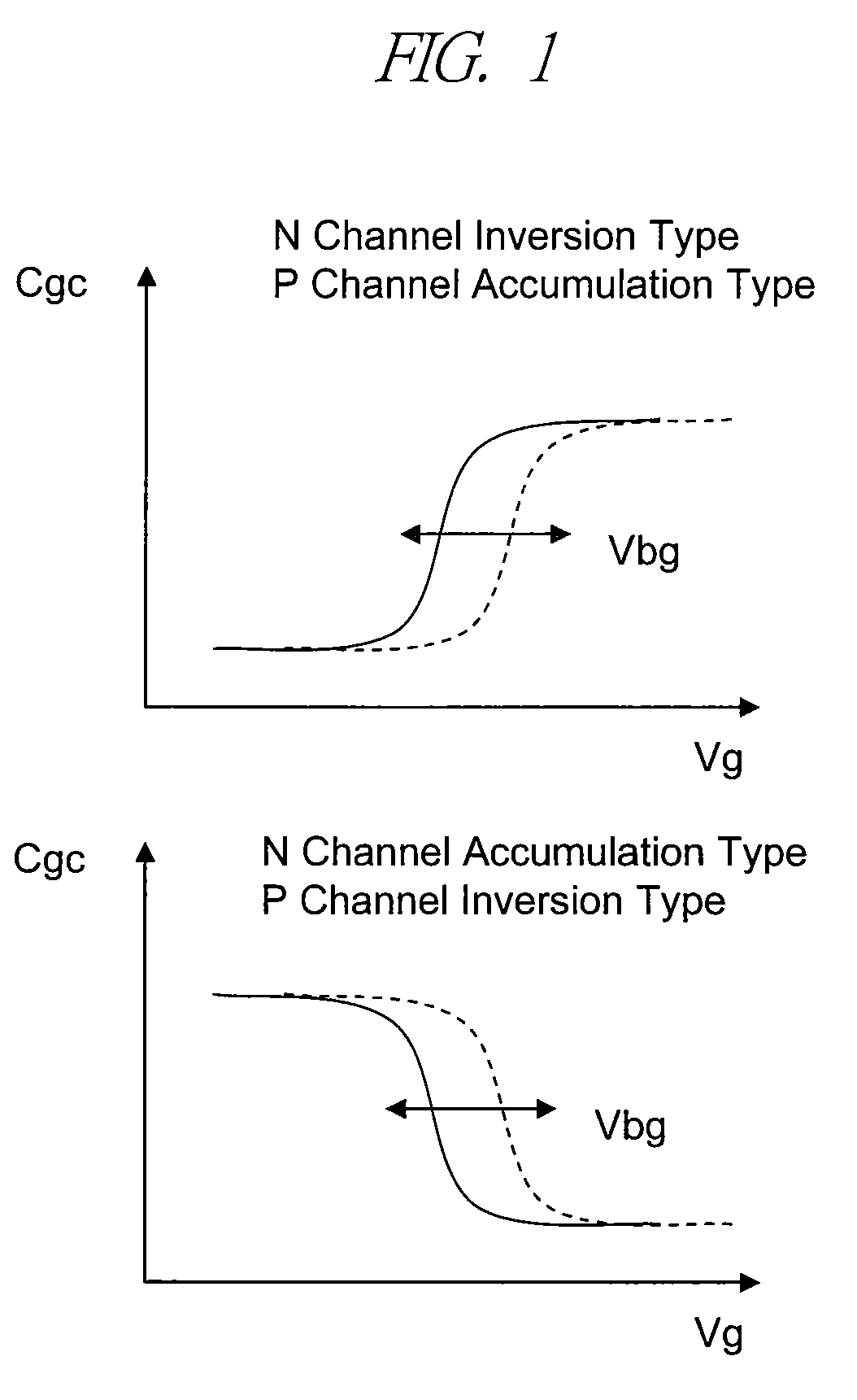

Semiconductor device

InactiveUS20090057746A1High Q valueSmall parasitic capacitanceTransistorSolid-state devicesCapacitanceGate dielectric

A semiconductor device having a passive element whose characteristic is adjustable even after manufacture by applying back bias voltage is provided. Formed on a main surface of a SOI substrate comprising a supporting substrate, a BOX layer, and an SOI layer is a MOS varactor comprising a gate dielectric formed on a surface of the SOI layer, a gate electrode formed on the gate dielectric, and a n+ type semiconductor region formed in the SOI layer located on both sides of the gate electrode. The MOS varactor, is configured so that capacitance formed by the SOI layer, gate dielectric, and gate electrode is varied by applying bias voltage to the supporting substrate (p type well) under the gate electrode.

Owner:RENESAS TECH CORP

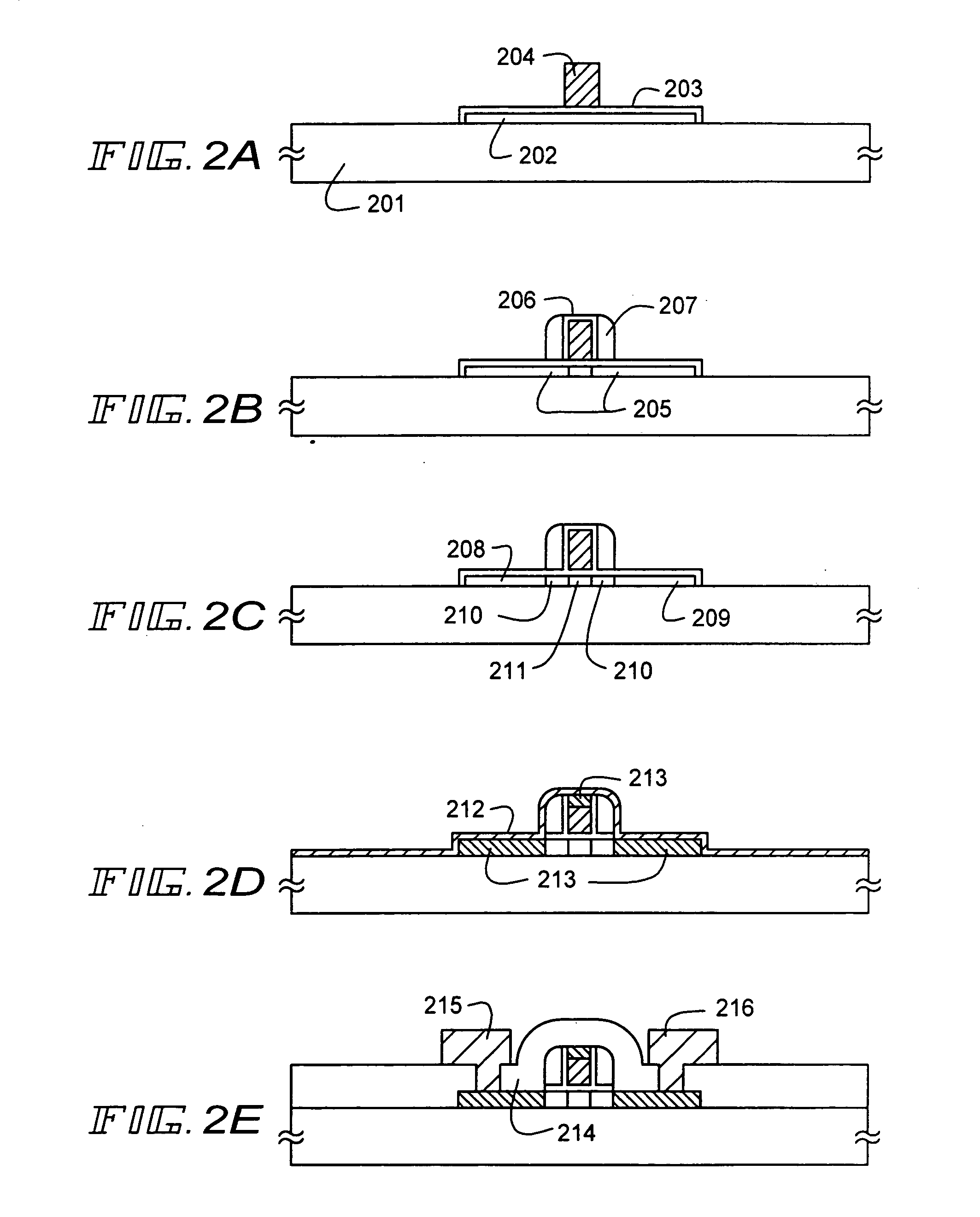

Method of fabricating a semiconductor device

A semiconductor device with high reliability is provided using an SOI substrate. When the SOI substrate is fabricated by using a technique typified by SIMOX, ELTRAN, or Smart-Cut, a single crystal semiconductor substrate having a main surface (crystal face) of a {110} plane is used. In such an SOI substrate, adhesion between a buried insulating layer as an under layer and a single crystal silicon layer is high, and it becomes possible to realize a semiconductor device with high reliability.

Owner:SEMICON ENERGY LAB CO LTD

Low cost soi substrates for monolithic solar cells

InactiveUS20100221867A1Reduce defect densityFinal product manufactureSemiconductor/solid-state device manufacturingSoi substrateSingle crystal

A lost cost method for fabricating SOI substrates is provided. The method includes forming a stack of p-type doped amorphous Si-containing layers on a semiconductor region of a substrate by utilizing an evaporation deposition process. A solid phase recrystallization step is then performed to convert the amorphous Si-containing layers within the stack into a stack of p-type doped single crystalline Si-containing layers. After recrystallization, the single crystalline Si-containing layers are subjected to anodization and at least an oxidation step to form an SOI substrate. Solar cells and / or other semiconductor devices can be formed on the upper surface of the inventive SOI substrate.

Owner:GLOBALFOUNDRIES INC

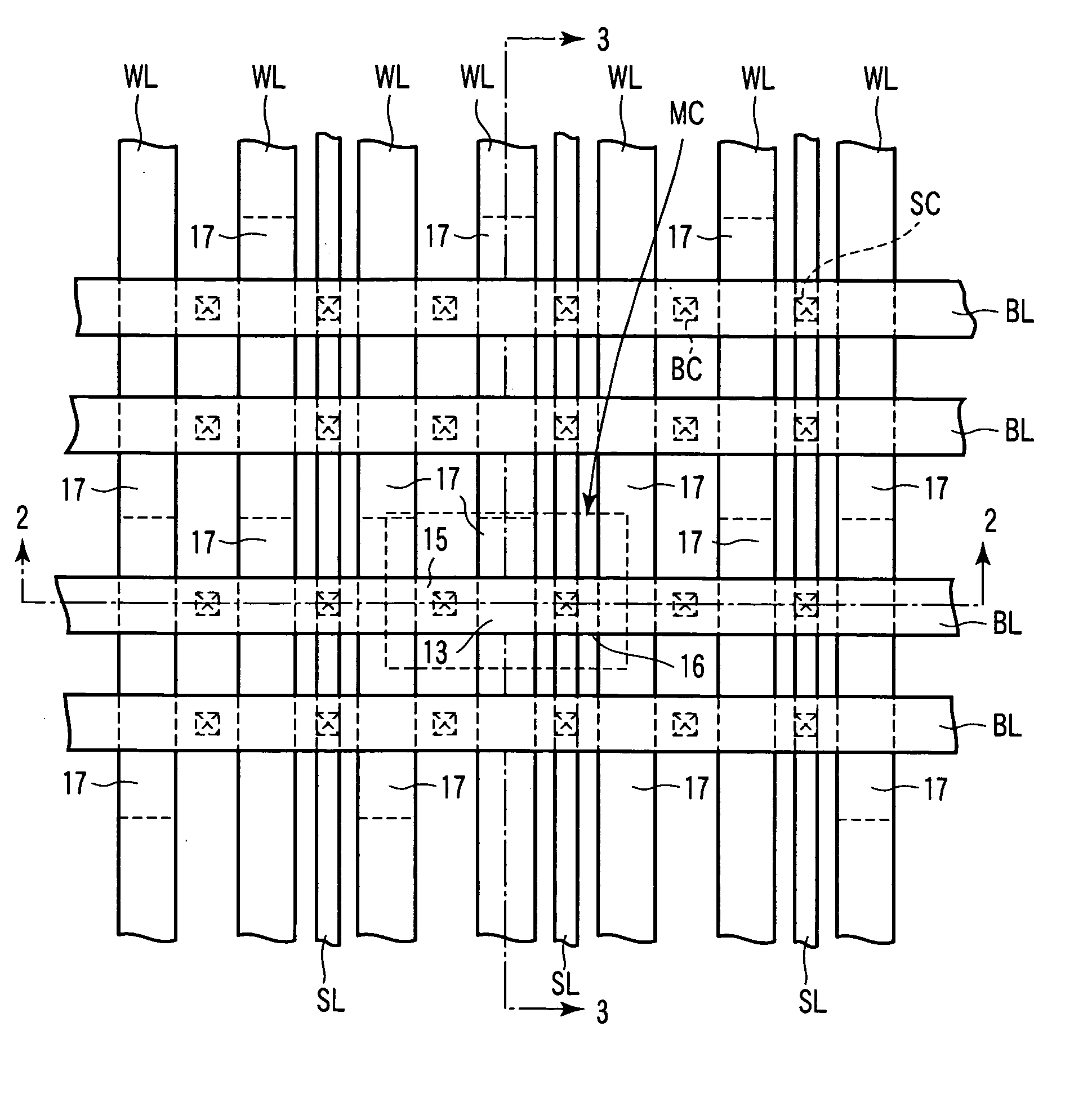

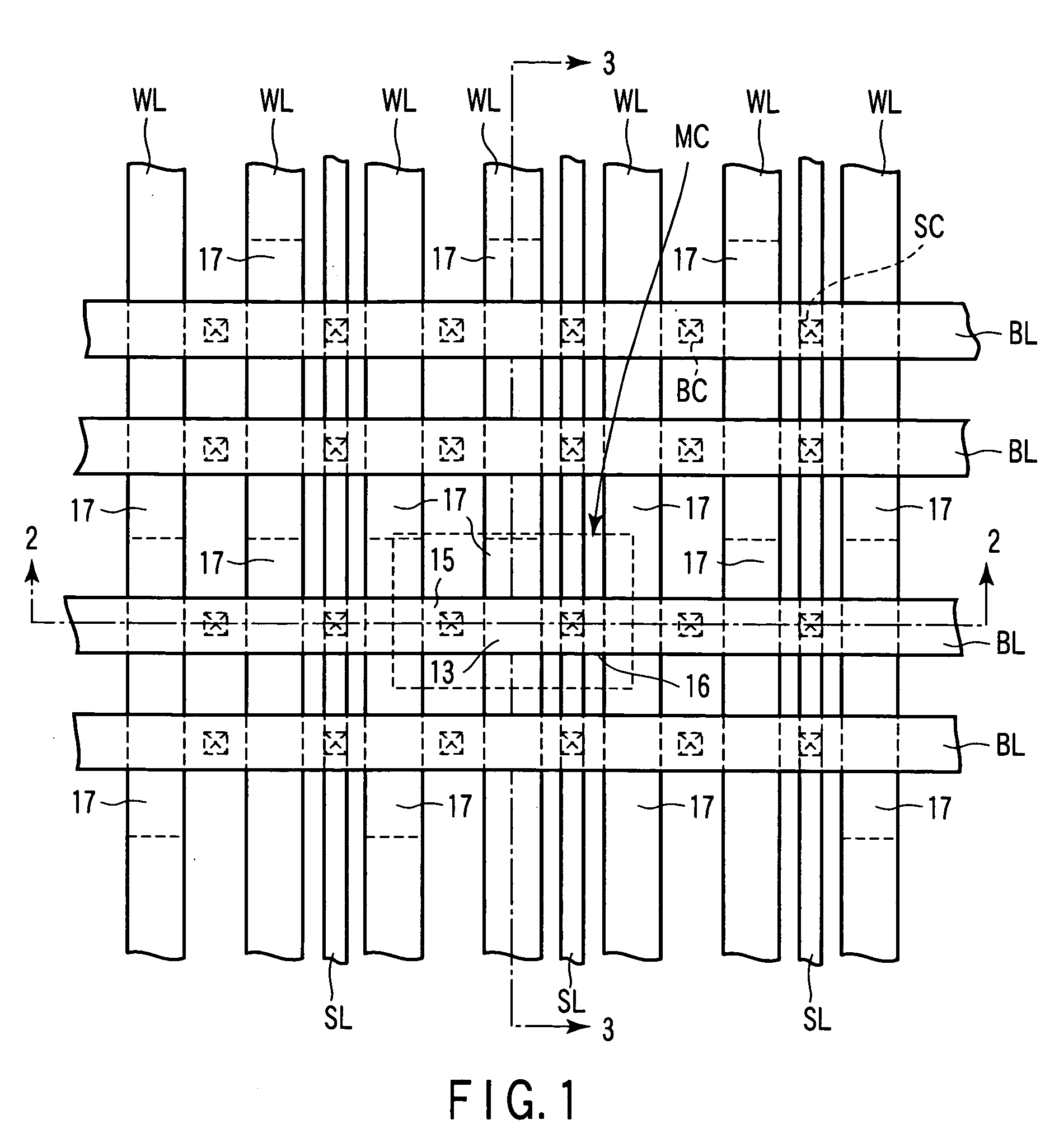

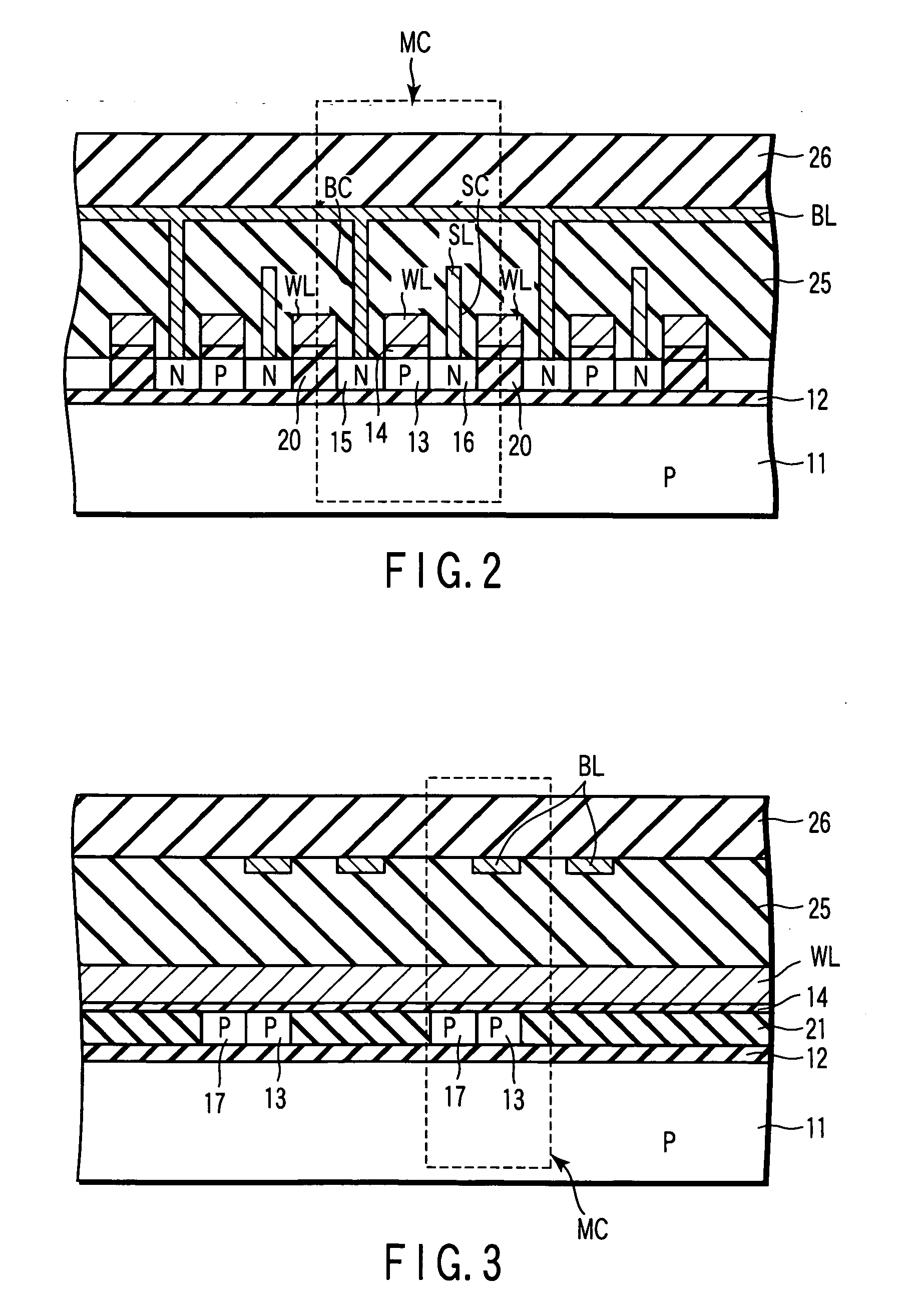

Semiconductor memory device for dynamically storing data with channel body of transistor used as storage node

A semiconductor memory device includes a plurality of MIS transistors arranged at intersections of first word lines and bit lines formed on an SOI substrate and each configuring a memory cell. Each of the plurality of MIS transistors includes a channel body formed in a semiconductor layer on an insulating film and set in an electrically floating state, a first extension region formed in contact with the channel body in the semiconductor layer and arranged in a first word line direction, a gate insulating film formed on the channel body, a gate electrode formed on the gate insulating film and electrically connected to a corresponding one of the first word lines, and source and drain regions separately formed in a bit line direction in the semiconductor layer to sandwich the channel body.

Owner:KK TOSHIBA

Silicon-on-insulator active pixel sensors

ActiveUS20050205930A1Reduce sensitivityImprove radiation hardnessSolid-state devicesSemiconductor/solid-state device manufacturingCMOS sensorSoi substrate

Active pixel sensors are defined on double silicon on insulator (SOI) substrates such that a first silicon layer is selected to define radiation detection regions, and a second silicon layer is selected to define readout circuitry. The first and second silicon layers are separated by an insulator layer, typically an oxide layer, and the layers can be independently doped. Doping can be provided in the silicon layers of the SOI substrate during assembly of the SOI substrate, or later during device processing. A semiconductor substrate that supports the first and second layers can be removed for, for example, back side radiation detection, using a second insulator layer (typically an oxide layer) as an etch stop.

Owner:LADARSYST INC

Method of fabricating a semiconductor device

A semiconductor device with high reliability is provided using an SOI substrate. When the SOI substrate is fabricated by using a technique typified by SIMOX, ELTRAN, or Smart-Cut, a single crystal semiconductor substrate having a main surface (crystal face) of a {110} plane is used. In such an SOI substrate, adhesion between a buried insulating layer as an under layer and a single crystal silicon layer is high, and it becomes possible to realize a semiconductor device with high reliability.

Owner:SEMICON ENERGY LAB CO LTD

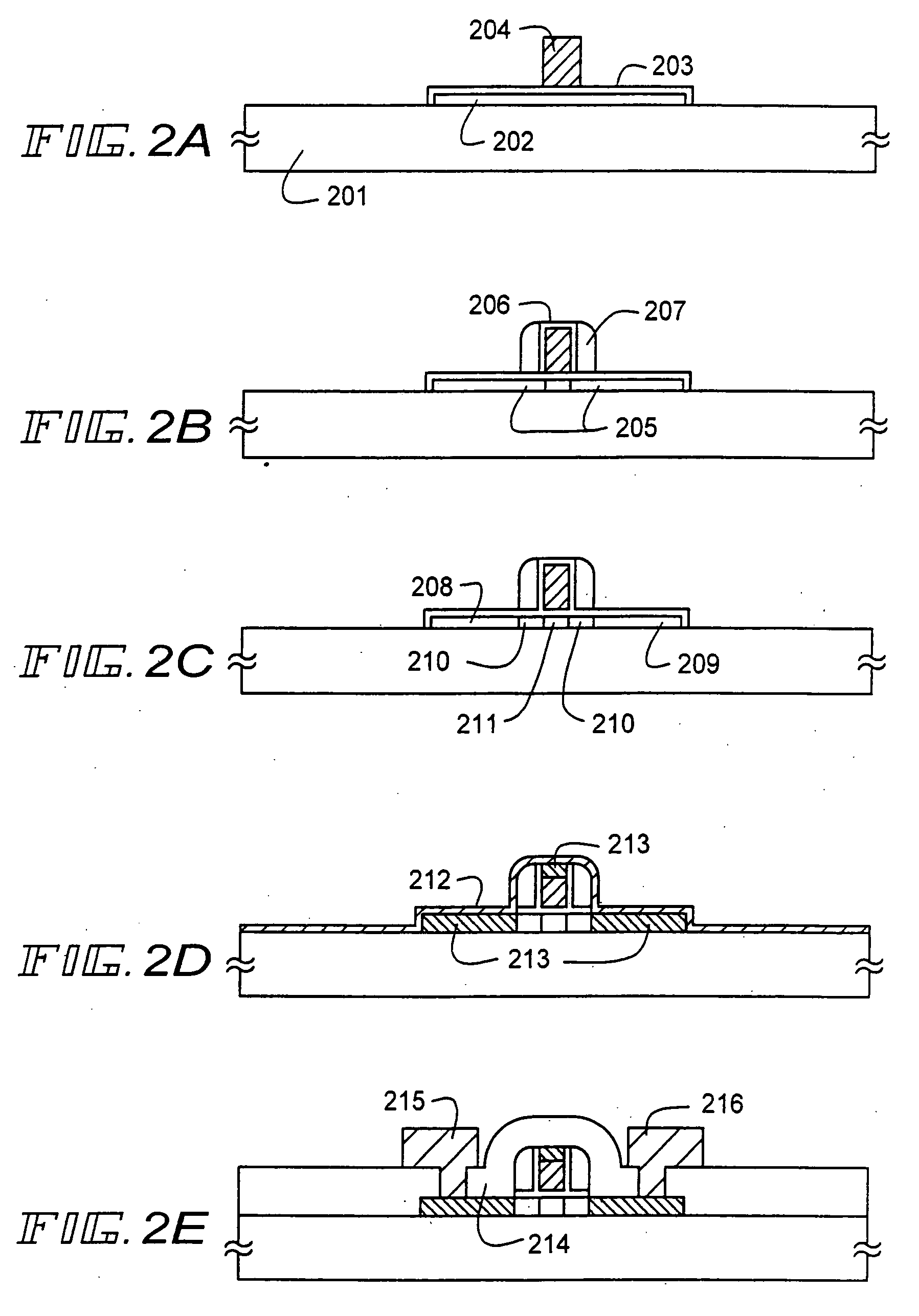

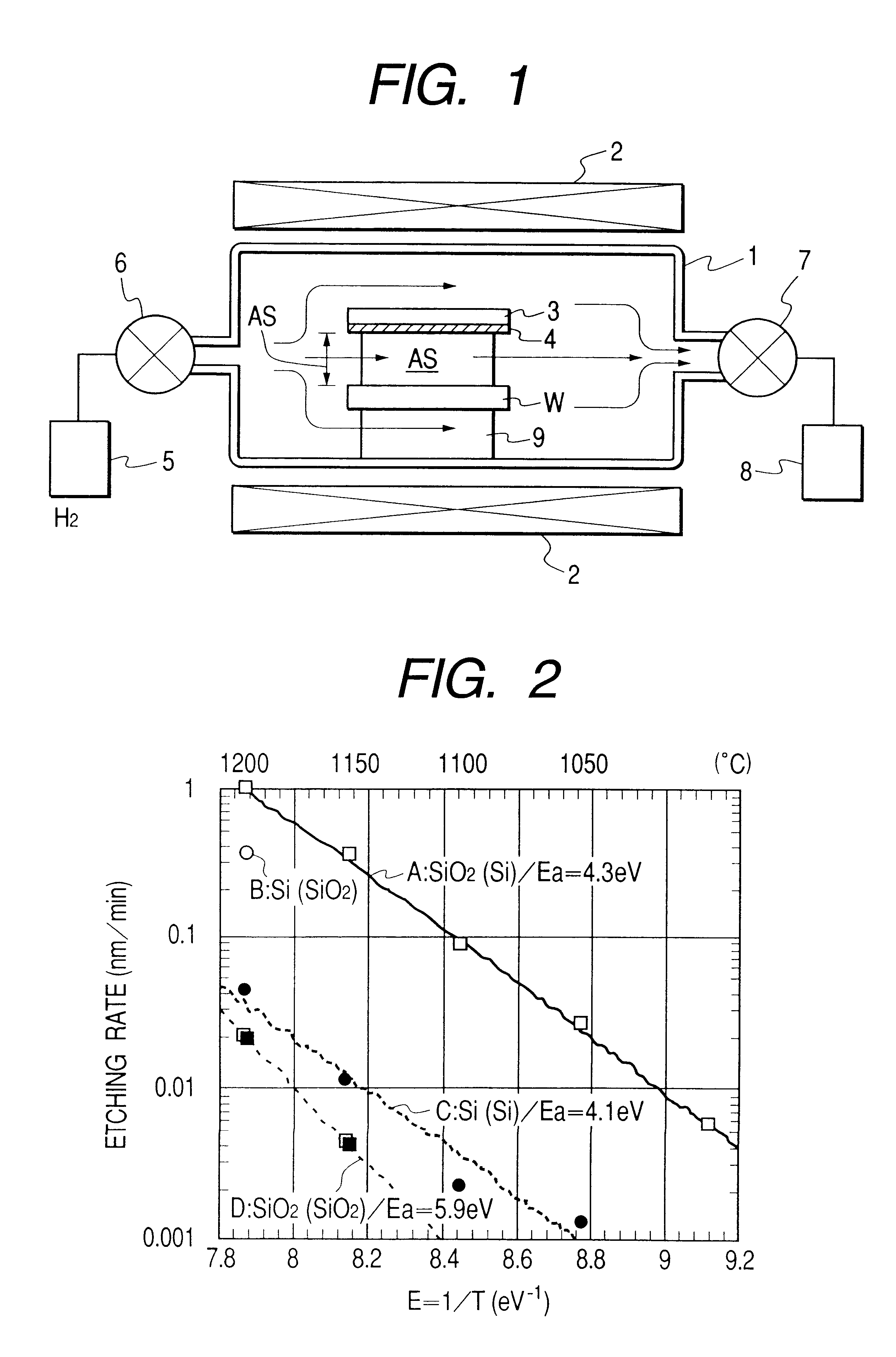

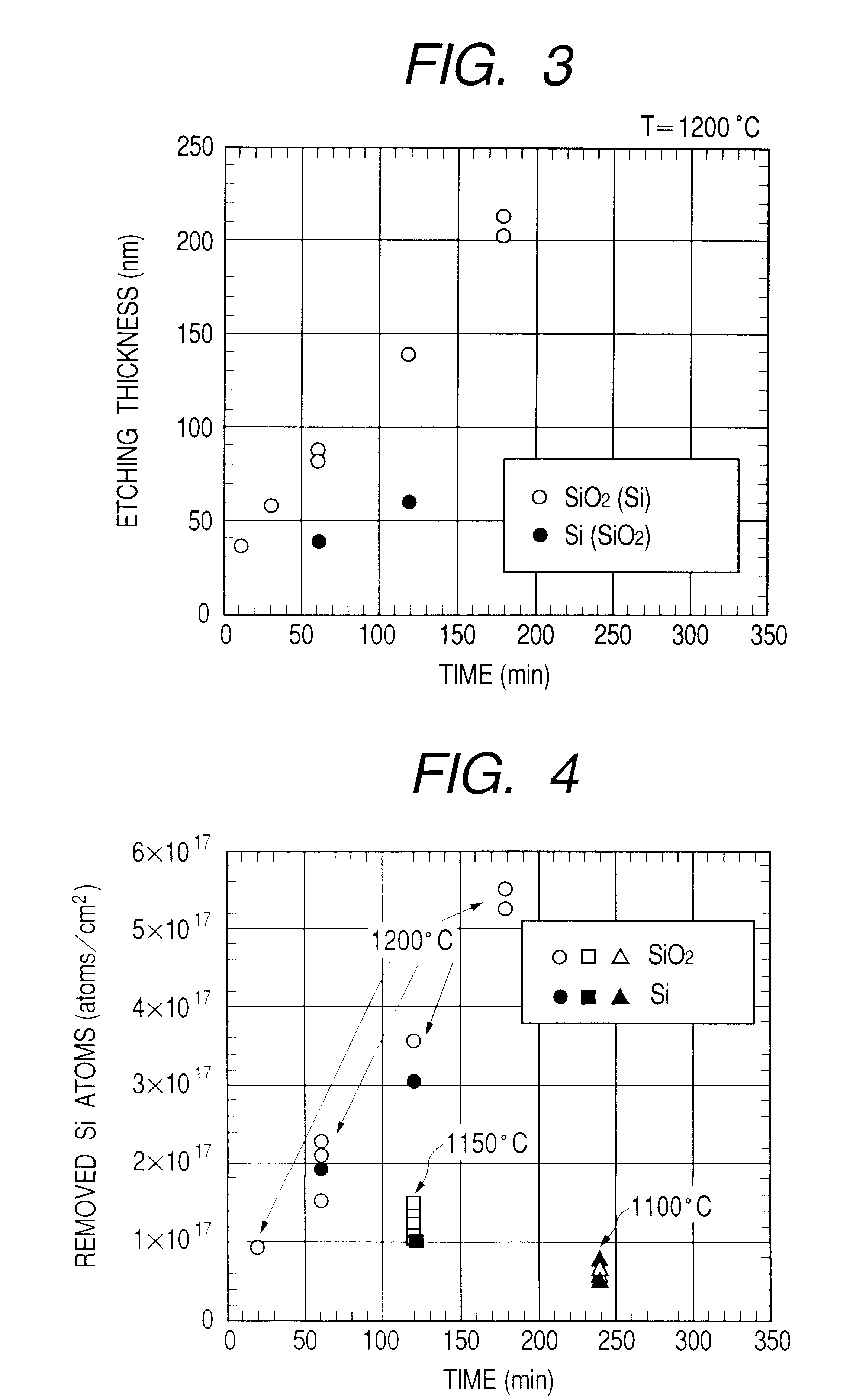

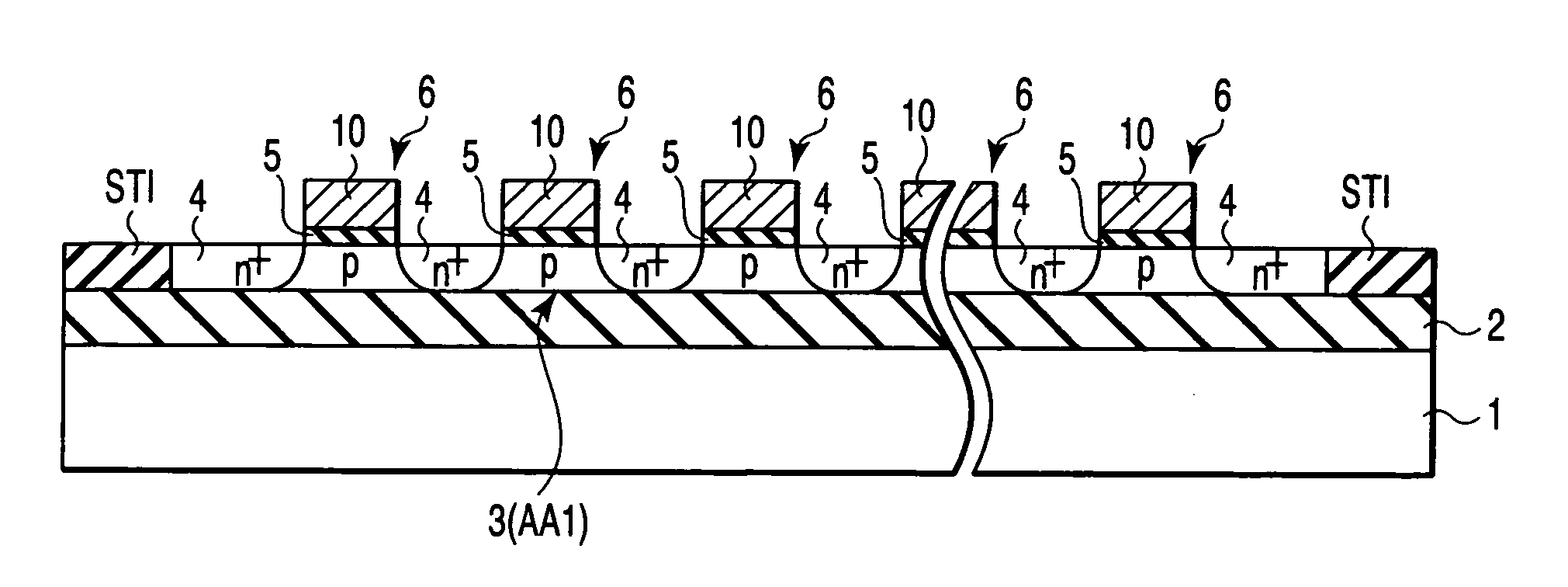

Method and apparatus for heat-treating an SOI substrate and method of preparing an SOI substrate by using the same

InactiveUS6171982B1Reduce the presence of impuritiesMaintain consistencyMuffle furnacesSolid-state devicesWaferingHydrogen

An SOI substrate having on the surface thereof a single crystal silicon film formed on an insulator is heat-treated in a hydrogen-containing reducing atmosphere in order to smooth the surface and reduce the boron concentration without damaging the film thickness uniformity in a single wafer and among different wafers. The method is characterized in that the single crystal silicon film is arranged opposite to a member of non-oxidized silicon for heat treatment.

Owner:CANON KK

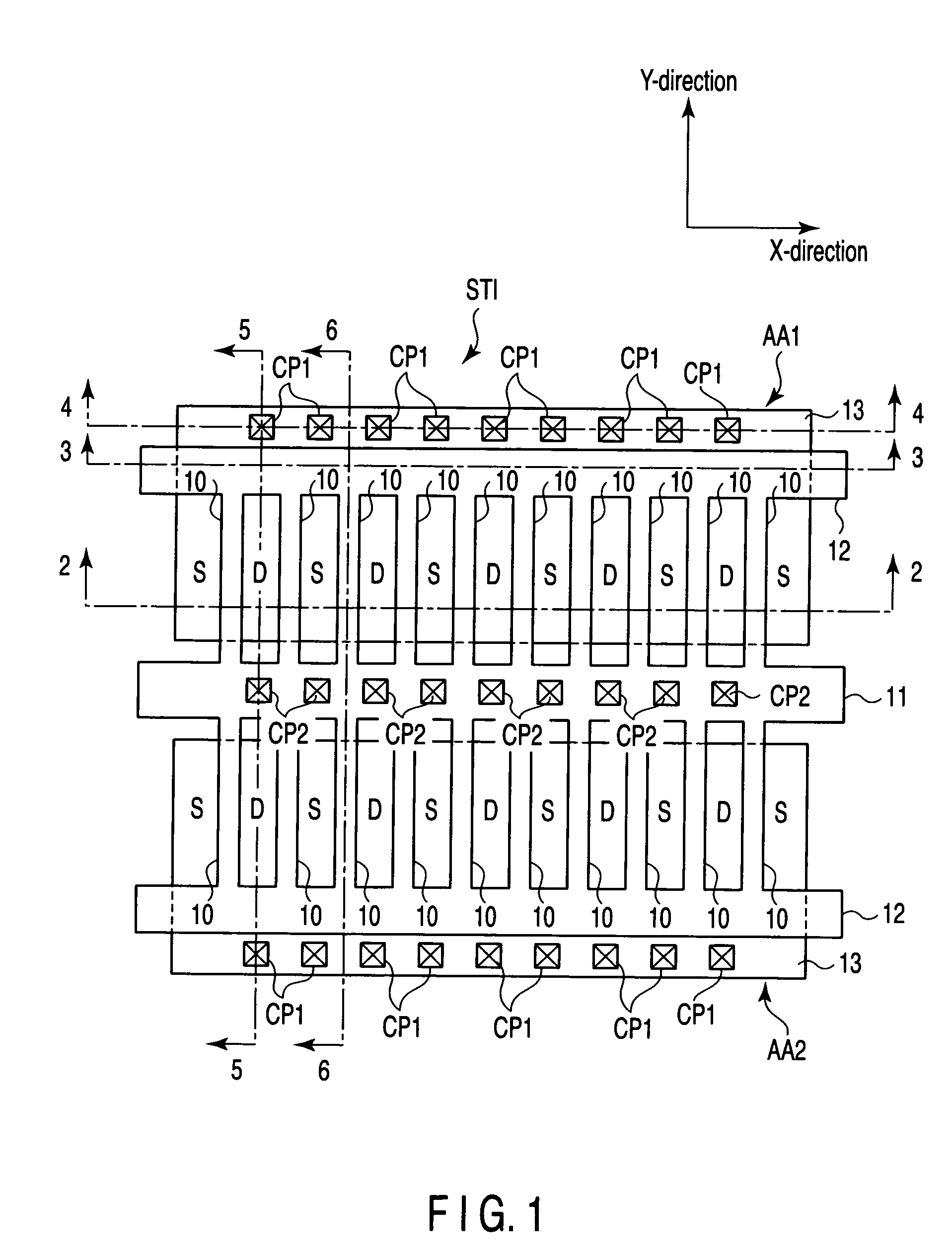

Semiconductor device having SOI substrate

A semiconductor device includes first semiconductor layers with a first conductivity, second to fifth semiconductor layers with a second conductivity, gate electrodes, and a first wiring layer. The second semiconductor layers are each disposed between adjacent ones of the first semiconductor layers. The third semiconductor layer is in contact with the second semiconductor layers. The gate electrodes are formed on the second semiconductor layers. The fourth semiconductor layer is in contact with the third semiconductor layer. The first wiring layer is formed on the third semiconductor layer and commonly connects the gate electrodes. The length of the fourth semiconductor layer in the lengthwise direction is smaller than the length of the third semiconductor layer in the lengthwise direction. The fifth semiconductor layer is in contact with the fourth semiconductor layer and isolated from the first semiconductor layers by the fourth semiconductor layer.

Owner:KK TOSHIBA

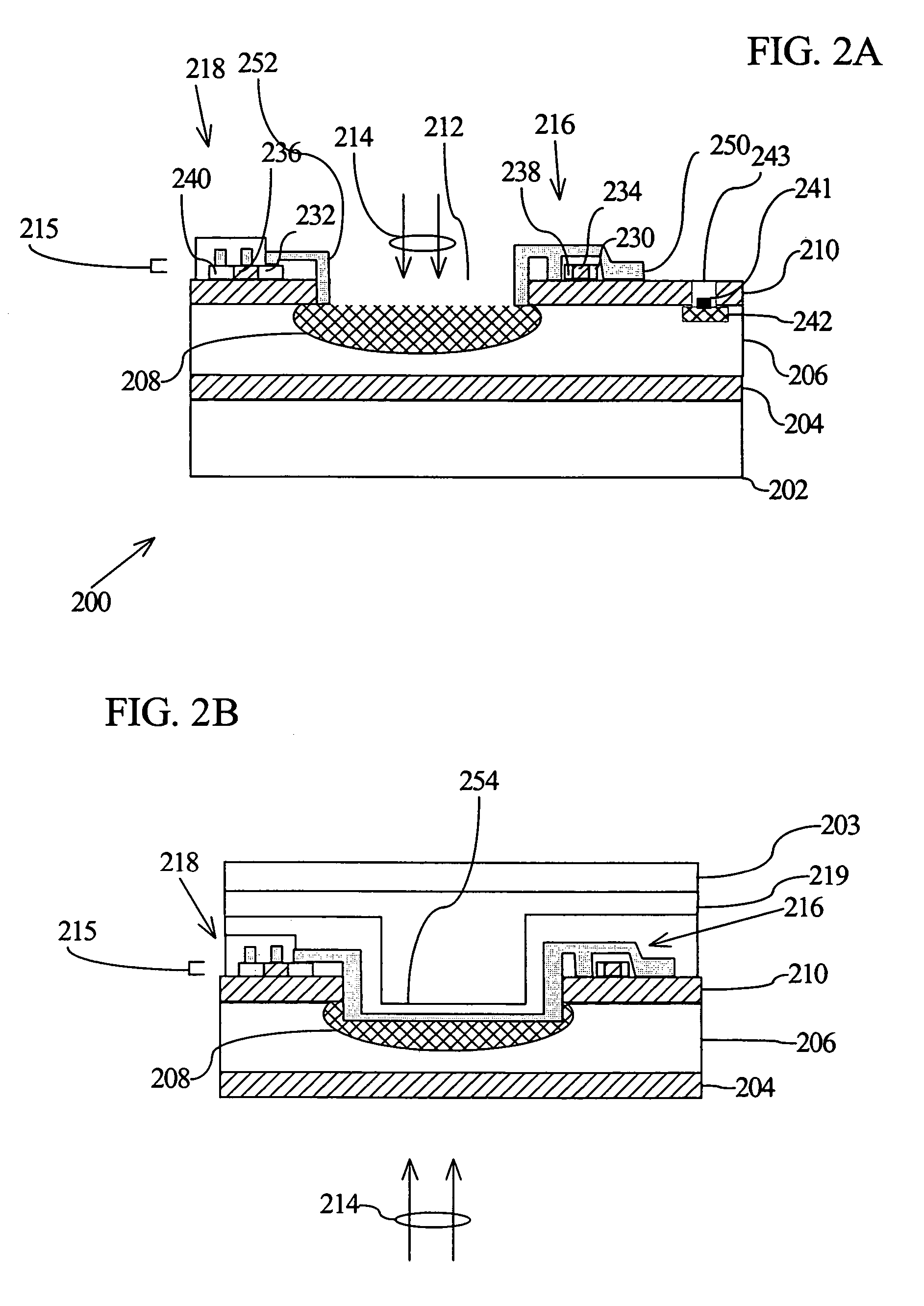

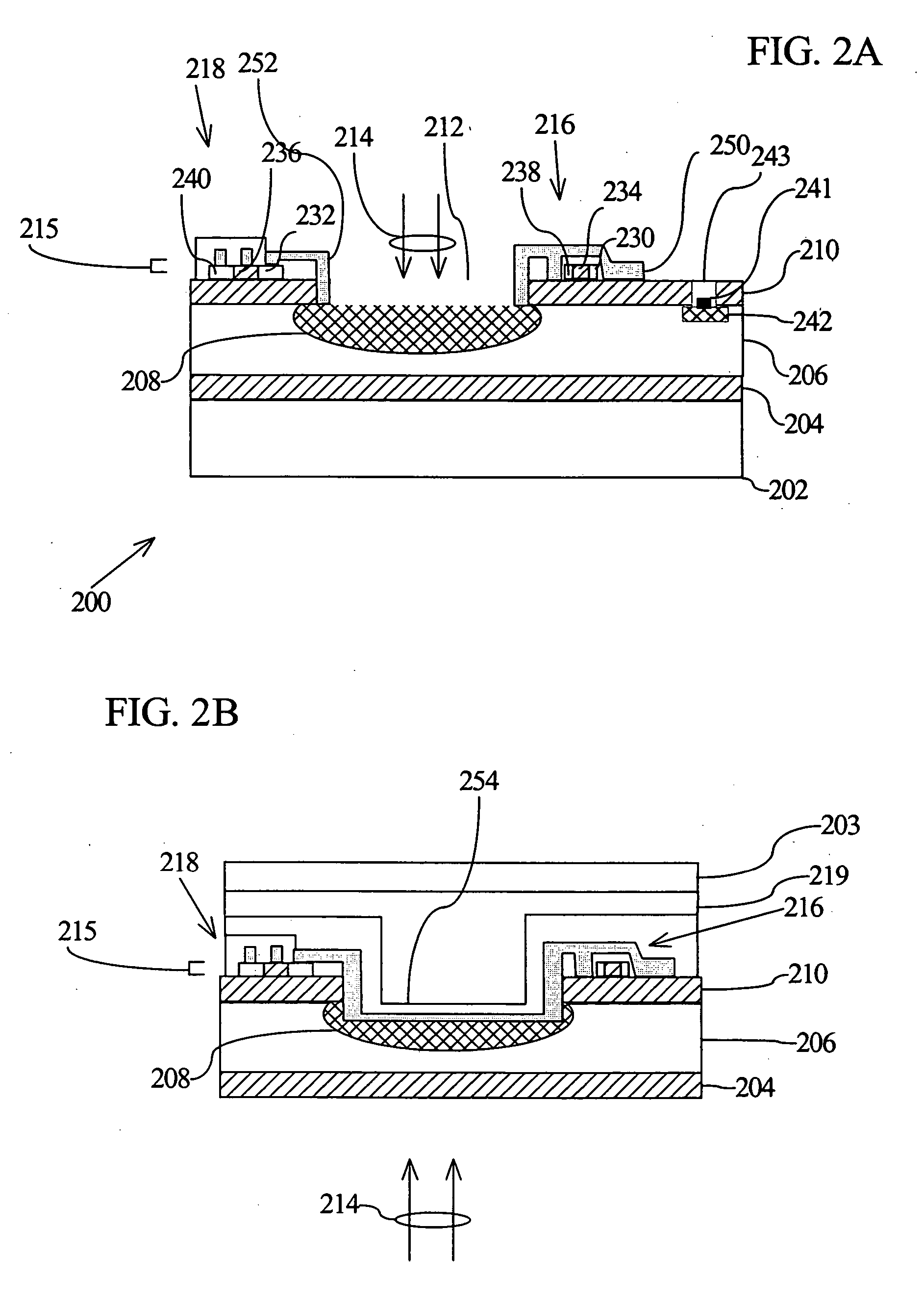

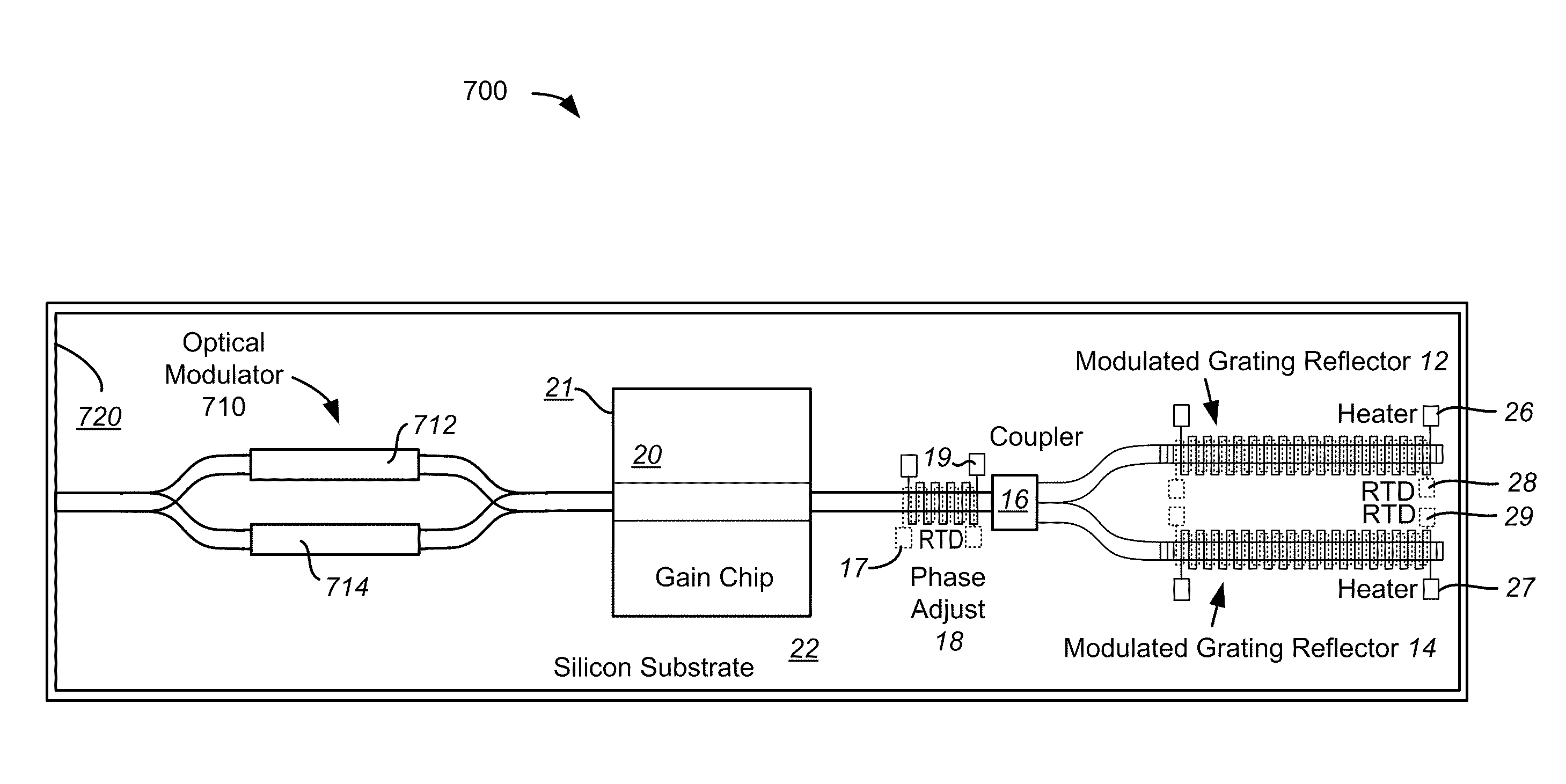

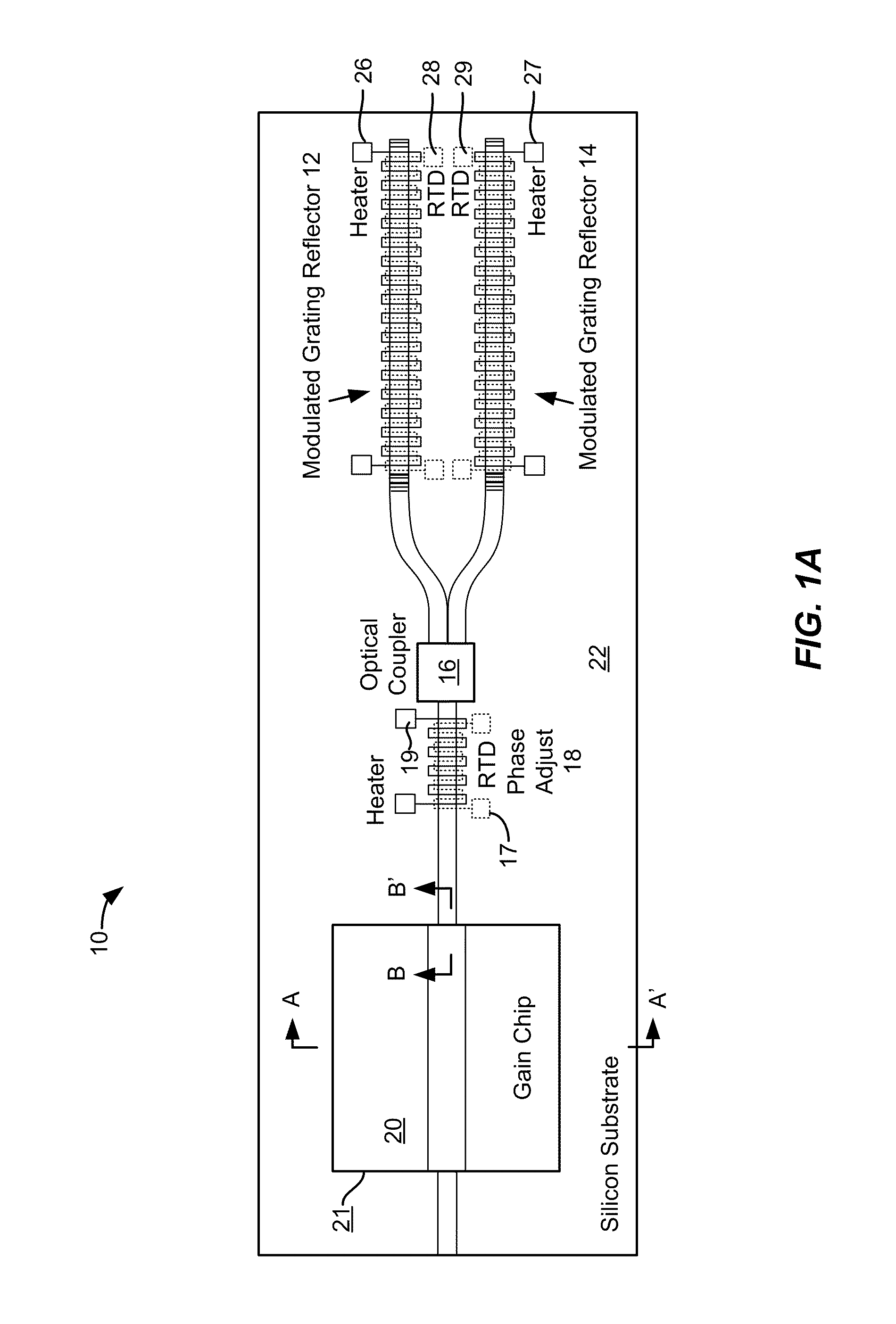

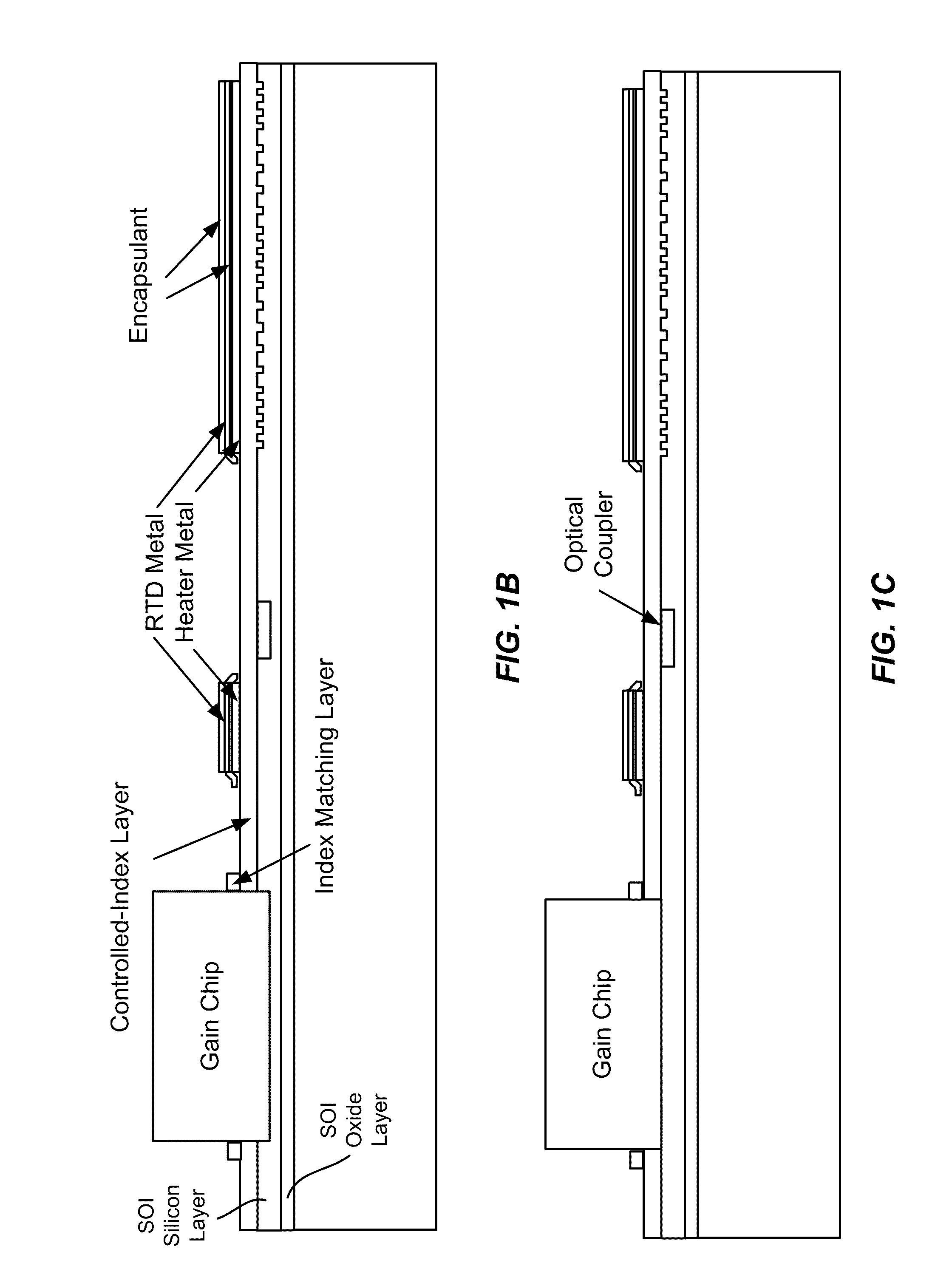

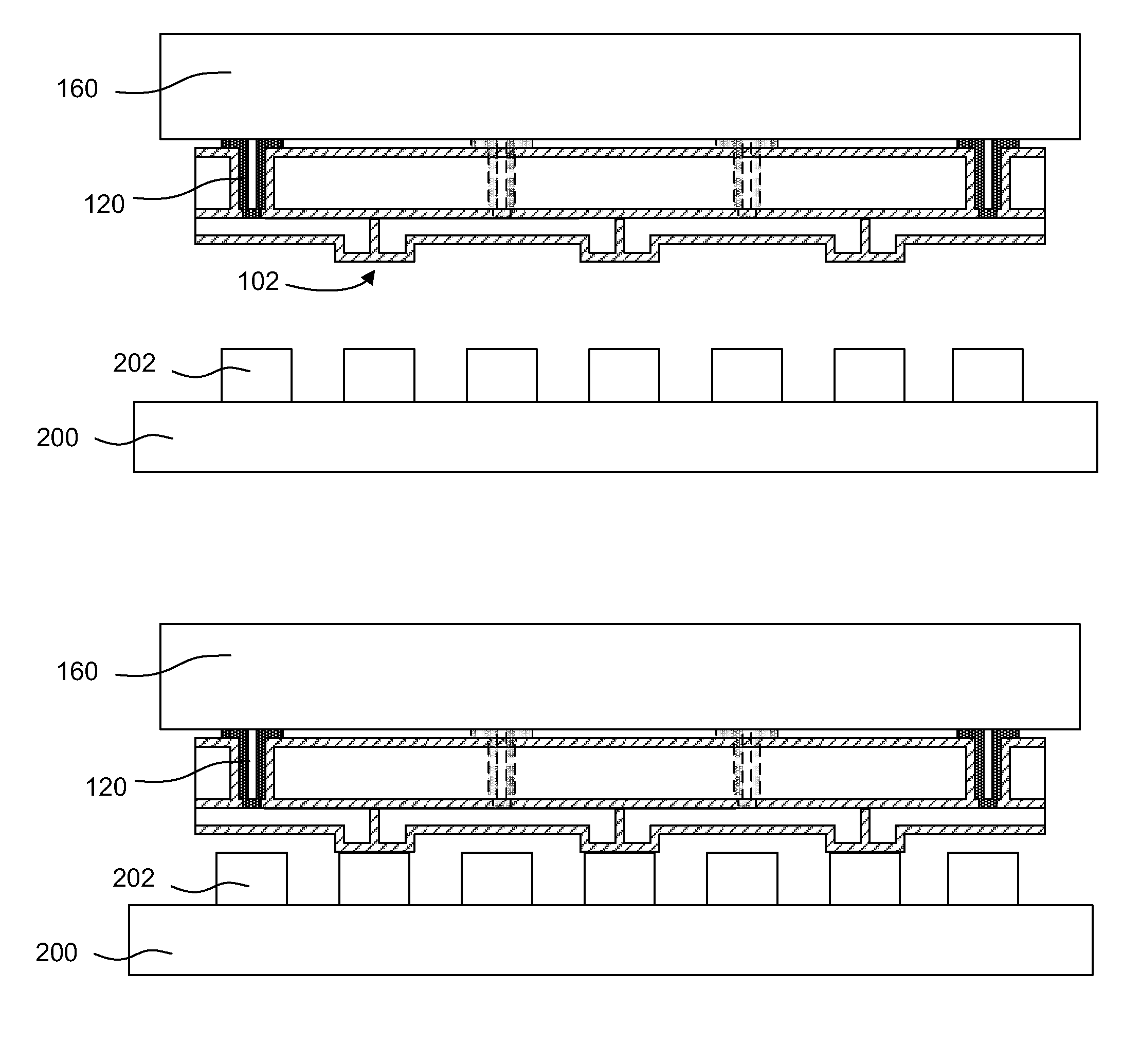

Method and system for hybrid integration of an opto-electronic integrated circuit

ActiveUS20110267676A1Reduce power consumptionSmall sizeCoupling light guidesSemiconductor lasersEngineeringOpto electronic

An opto-electronic integrated circuit (OEIC) includes an SOI substrate, a set of composite optical transmitters, a set of composite optical receivers, and control electronics disposed in the substrate and electrically coupled to the set of composite optical transmitters and receivers. Each of the composite optical transmitters includes a gain medium including a compound semiconductor material and an optical modulator. Each of the composite optical receivers includes a waveguide disposed in the SOI substrate, an optical detector bonded to the SOI substrate, and a bonding region disposed between the SOI substrate and the optical detector. The bonding region includes a metal-assisted bond at a first portion of the bonding region and a direct semiconductor-semiconductor bond at a second portion of the bonding region. The OEIC also includes control electronics disposed in the SOI substrate and electrically coupled to the set of composite optical transmitters and the set of composite optical receivers.

Owner:SKORPIOS TECH

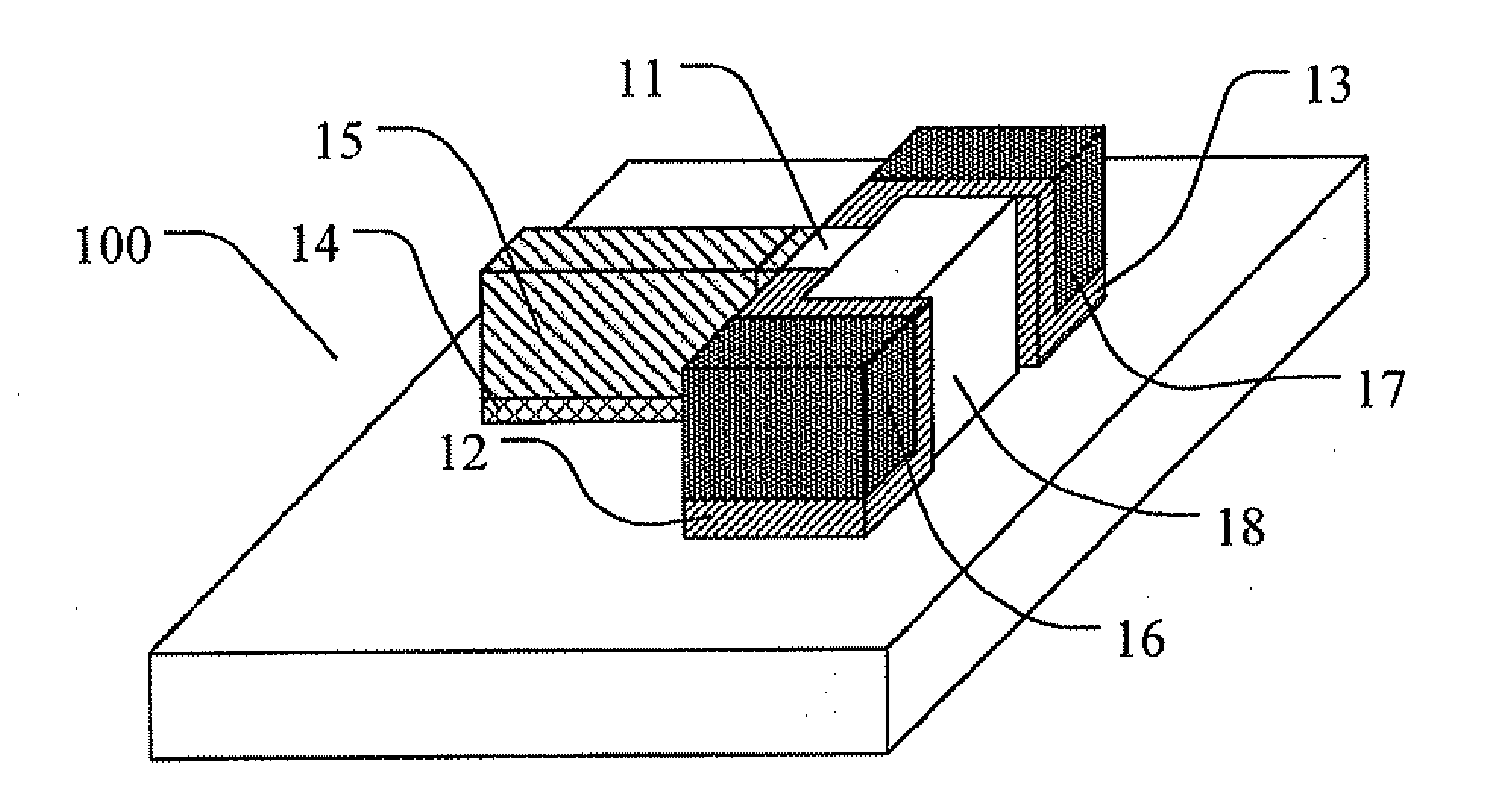

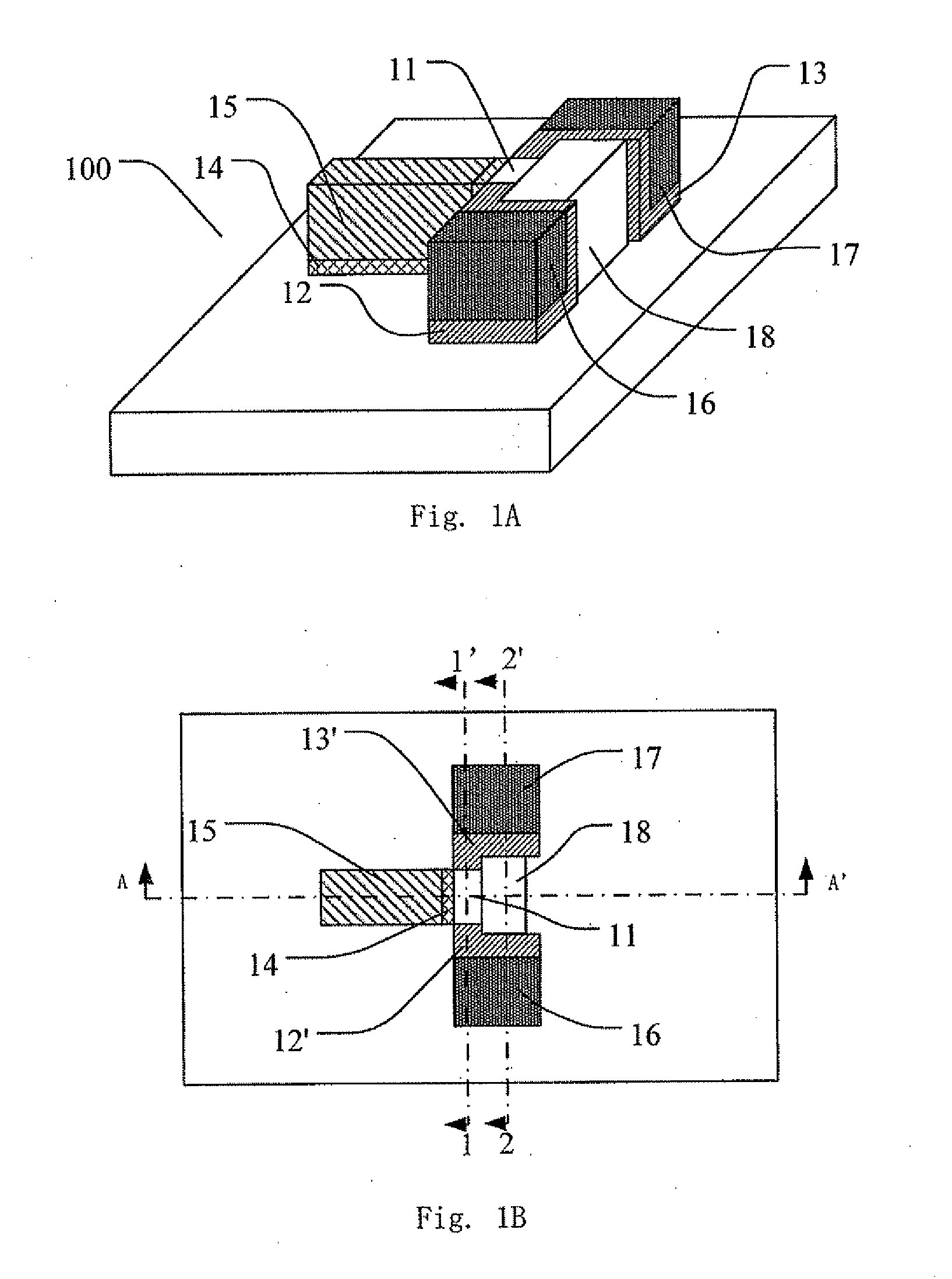

Semiconductor device and method for manufacturing the same

ActiveUS20110193164A1Reduce parasitic capacitanceLarge thicknessSolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceGate dielectric

The present application discloses a semiconductor device formed on a SOI substrate which comprises a buried insulating layer and a semiconductor layer on the buried insulating layer and a method for manufacturing the same, wherein a fin of semiconductive material having two opposing sides perpendicular to a main surface of the SOI substrate is provided in the semiconductor layer, said semiconductor device comprising: a source region and a drain region provided at two ends of the fin respectively; a channel region provided at a central portion of the fin; and a stack of gate dielectric and gate conductor provided at one side of the fin, where the gate conductor is isolated from the channel region by the gate dielectric, wherein the gate conductor extends away from the one side of the fin in a direction parallel to the main surface of the SOI substrate. The semiconductor device has an improved short channel effect and a reduced parasitic capacitance and resistance, which contributes to an improved electrical property and facilitates scaling down of the transistor.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Method for fabricating graphene transistors on a silicon or soi substrate

ActiveUS20090181502A1Well formedSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricSoi substrate

A method of fabricating graphene transistors, comprising providing an SOI substrate, performing an optional threshold implant on the SOI substrate, forming an upper silicon layer mesa island, carbonizing the silicon layer into SiC utilizing a gaseous source, converting the SiC into graphene, forming source / drain regions on opposite longitudinal ends of the graphene, forming gate oxide between the source / drain regions on the graphene, forming gate material over the gate oxide, creating a transistor edge, depositing dielectric onto the transistor edge and performing back end processing.

Owner:TEXAS INSTR INC

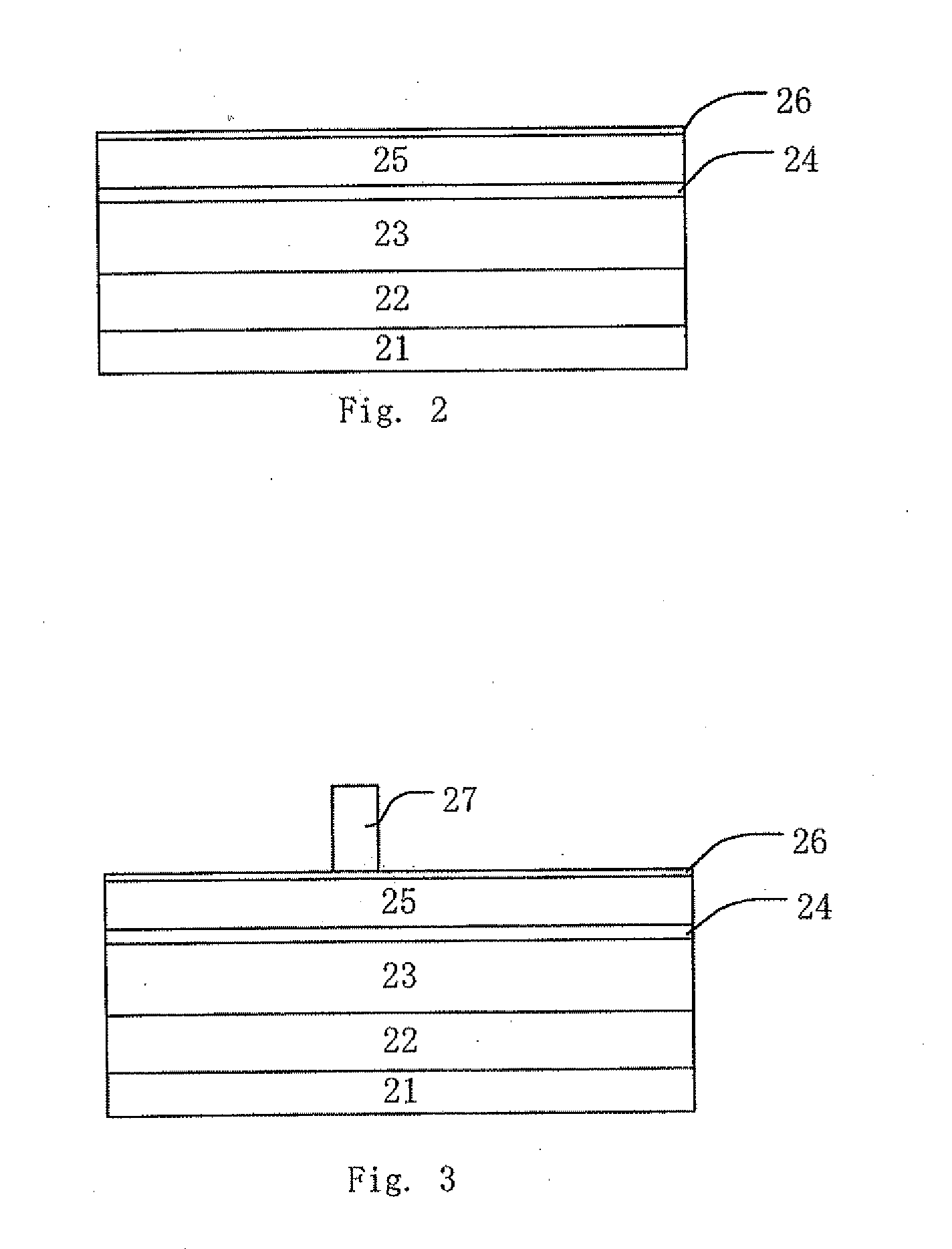

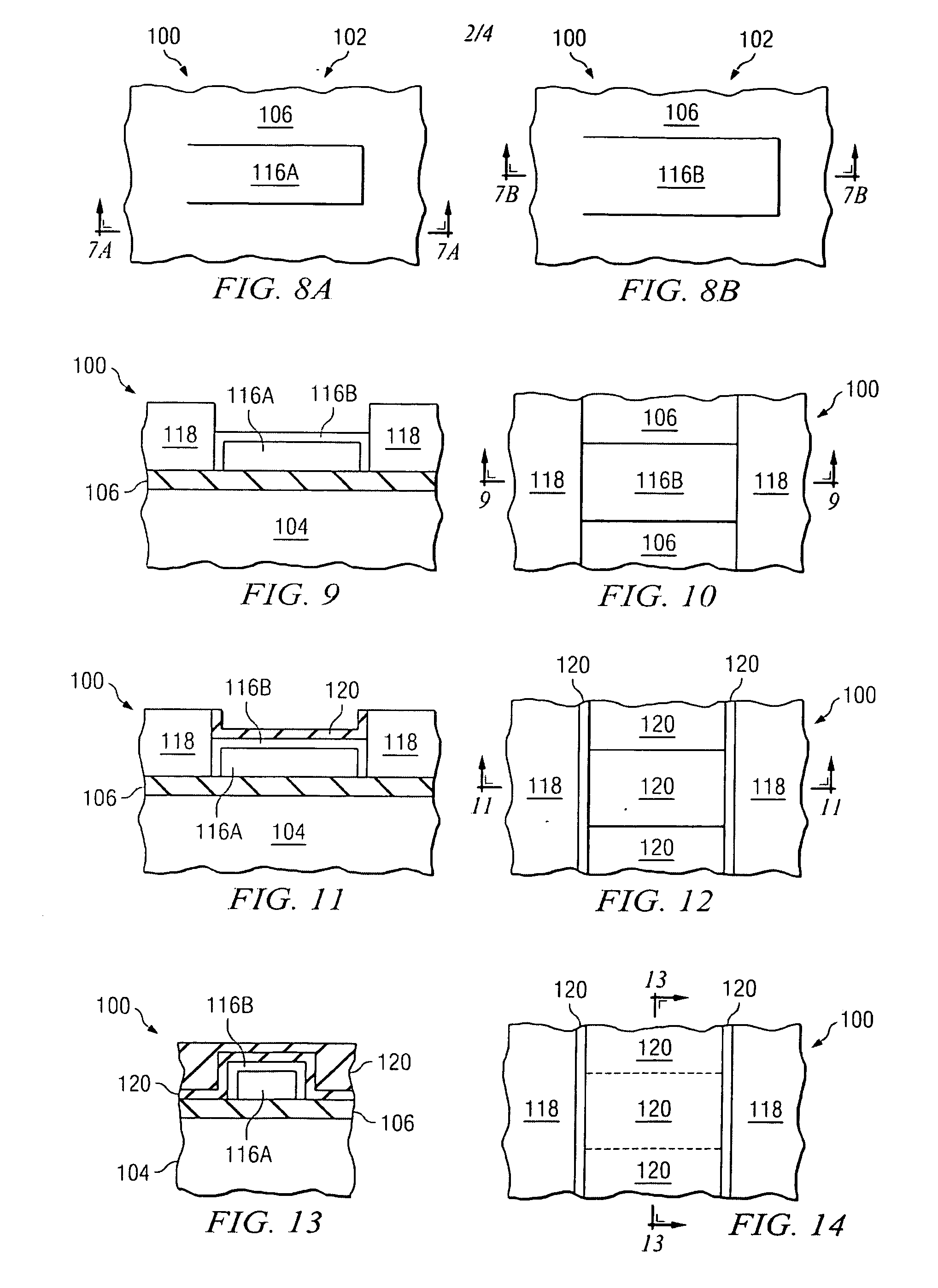

Micro device transfer head with silicon electrode

ActiveUS8415771B1Solid-state devicesSemiconductor/solid-state device manufacturingSilicon electrodeSoi substrate

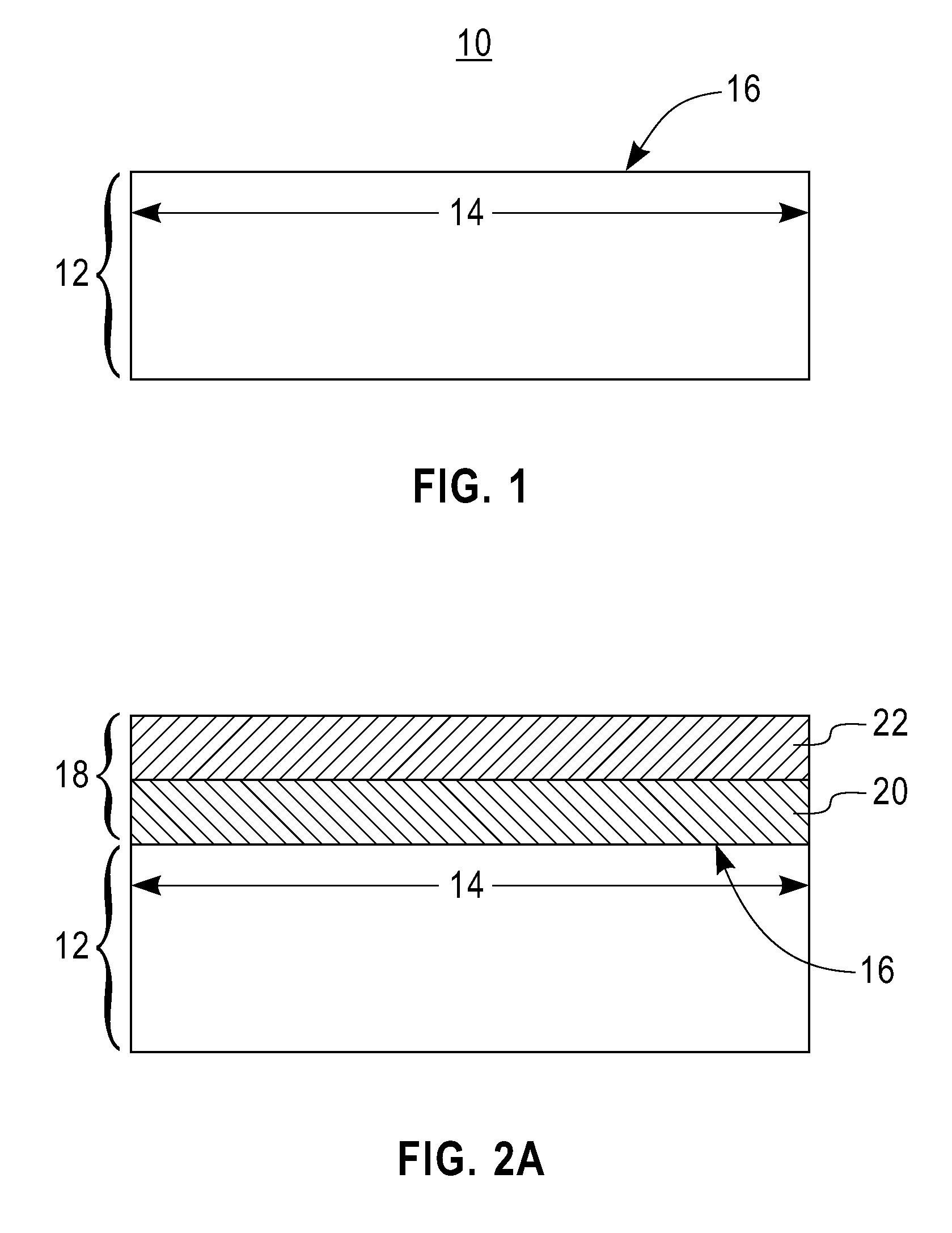

A micro device transfer head array and method of forming a micro device transfer array from an SOI substrate are described. In an embodiment, the micro device transfer head array includes a base substrate and a patterned silicon layer over the base substrate. The patterned silicon layer may include a silicon interconnect and an array of silicon electrodes electrically connected with the silicon interconnect. Each silicon electrode includes a mesa structure protruding above the silicon interconnect. A dielectric layer covers a top surface of each mesa structure.

Owner:APPLE INC

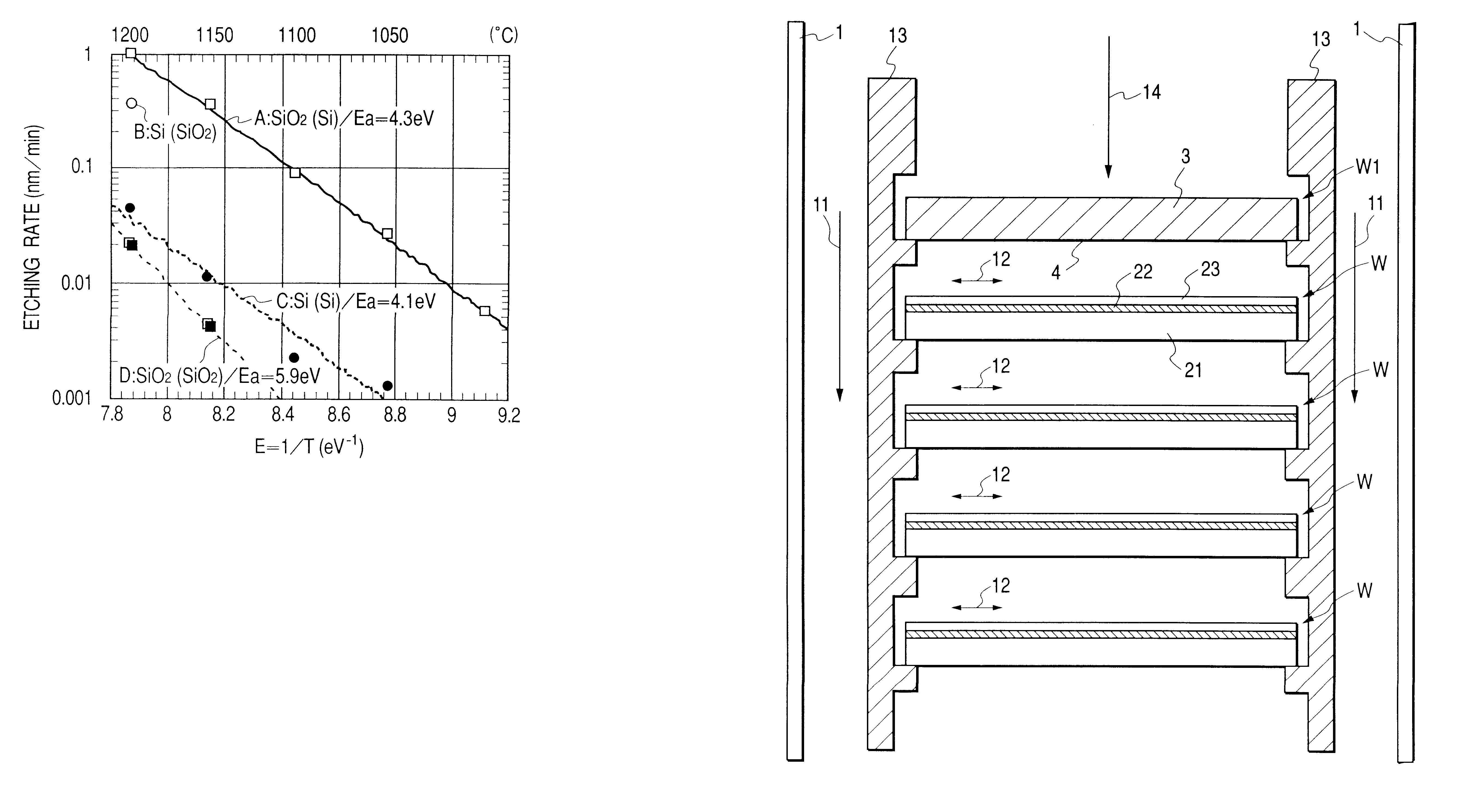

Semiconductor device and manufacturing method thereof, SOI substrate and display device using the same, and manufacturing method of the SOI substrate

A polycrystalline Si thin film and a single crystal Si thin film are formed on an SiO2 film deposited on an insulating substrate. A polycrystalline Si layer is grown by thermally crystallizing an amorphous Si thin film so as to form the polycrystalline Si thin film. A single crystal Si substrate, having (a) an SiO2 film thereon and (b) a hydrogen ion implantation portion therein, is bonded to an area of the polycrystalline Si thin film that has been subjected to etching removal, and is subjected to a heating process. Then, the single crystal Si substrate is divided at the hydrogen ion implantation portion in an exfoliating manner, so as to form the single crystal Si thin film. As a result, it is possible to provide a large-size semiconductor device, having the single crystal Si thin film, whose property is stable, at a low cost.

Owner:SHARP KK

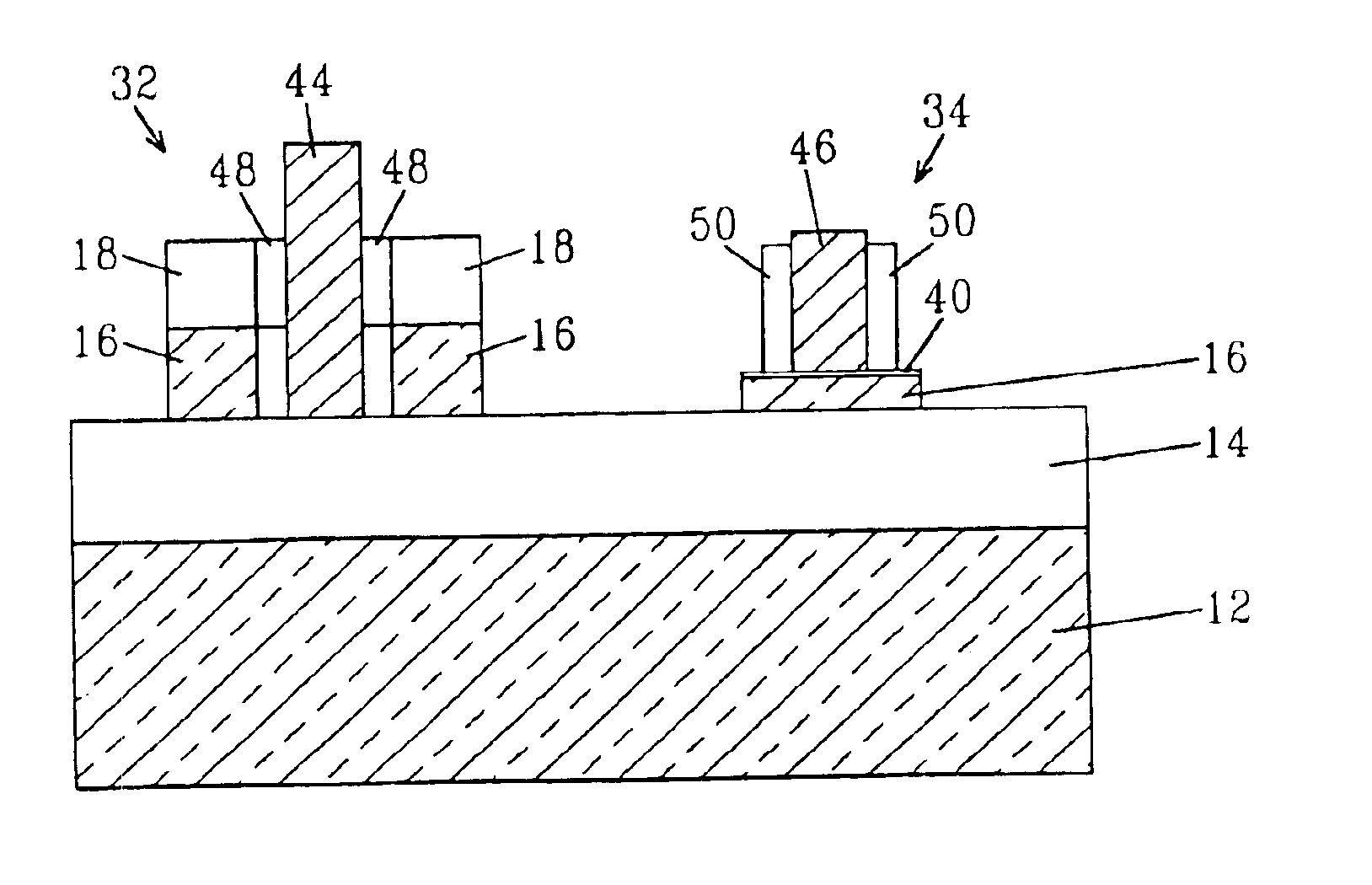

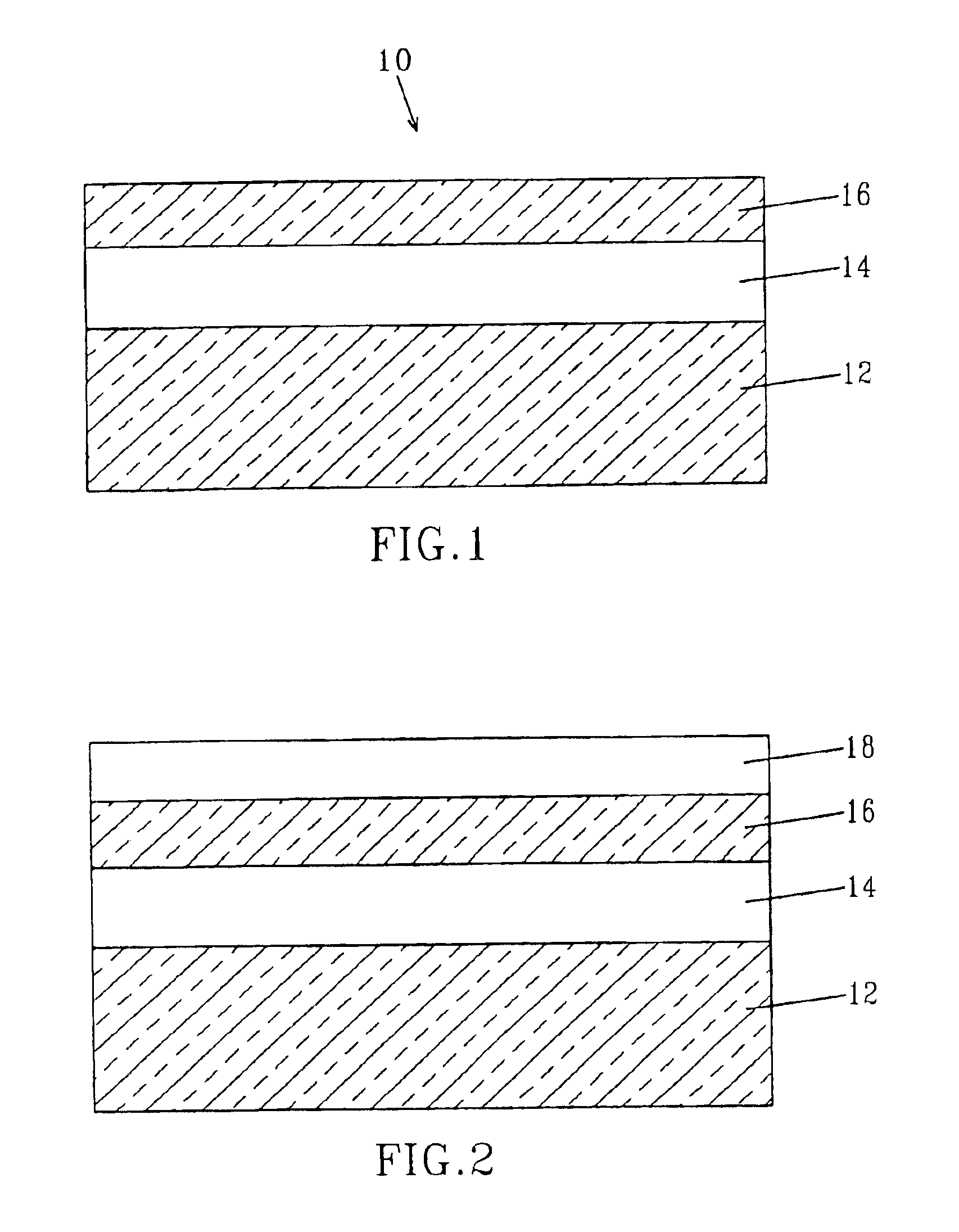

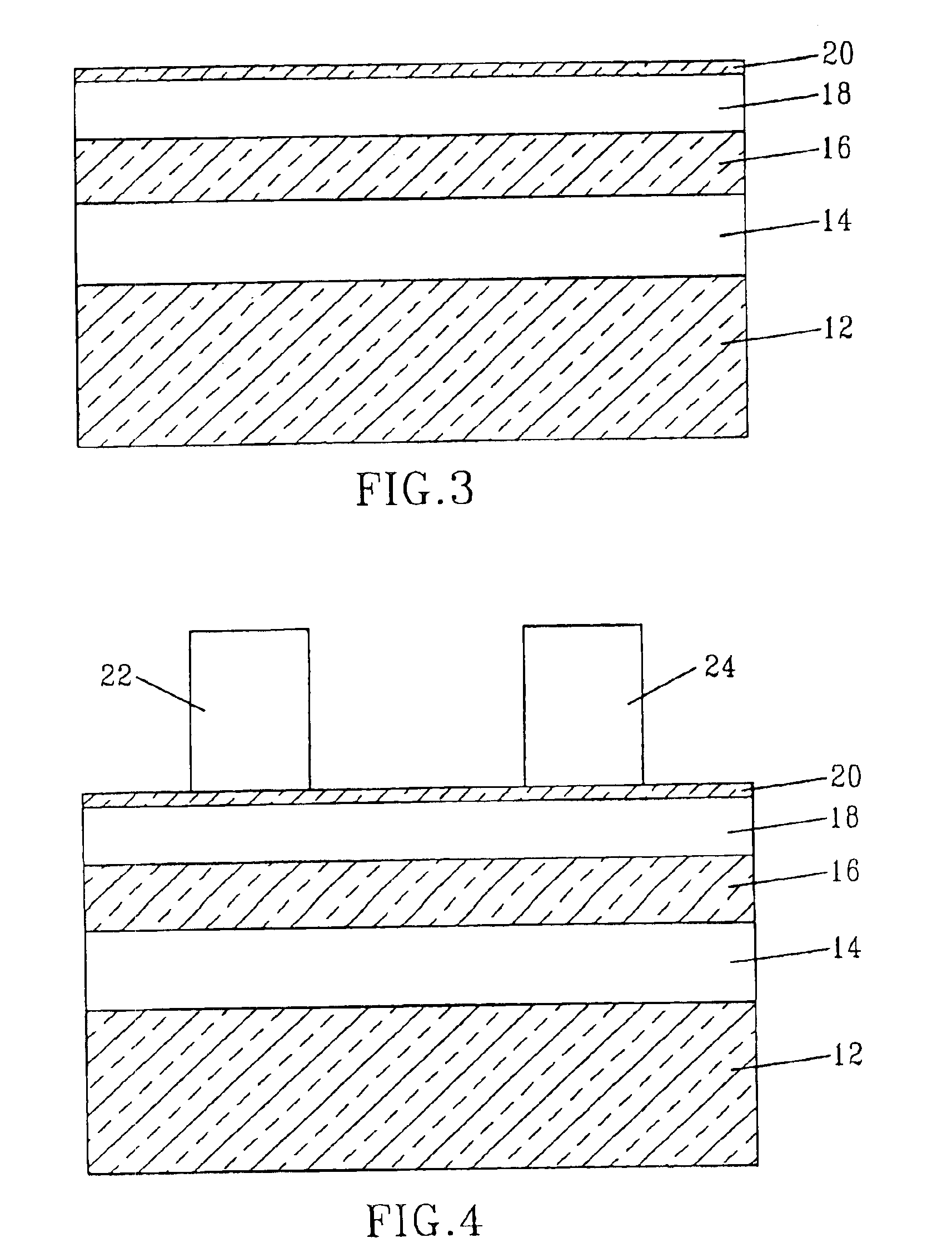

Hybrid planar and finFET CMOS devices

The present invention provides an integrated semiconductor circuit containing a planar single gated FET and a FinFET located on the same SOI substrate. Specifically, the integrated semiconductor circuit includes a FinFET and a planar single gated FET located atop a buried insulating layer of an silicon-on-insulator substrate, the planar single gated FET is located on a surface of a patterned top semiconductor layer of the silicon-on-insulator substrate and the FinFET has a vertical channel that is perpendicular to the planar single gated FET. A method of forming a method such an integrated circuit is also provided. In the method, resist imaging and a patterned hard mask are used in trimming the width of the FinFET active device region and subsequent resist imaging and etching are used in thinning the thickness of the FET device area. The trimmed active FinFET device region is formed such that it lies perpendicular to the thinned planar single gated FET device region.

Owner:AURIGA INNOVATIONS INC