Patents

Literature

179 results about "3d integrated circuit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Three dimensional CMOS integrated circuits having device layers built on different crystal oriented wafers

InactiveUS20050067620A1High bulk densityReduce chip footprintTransistorSemiconductor/solid-state device details3d integrated circuitCMOS

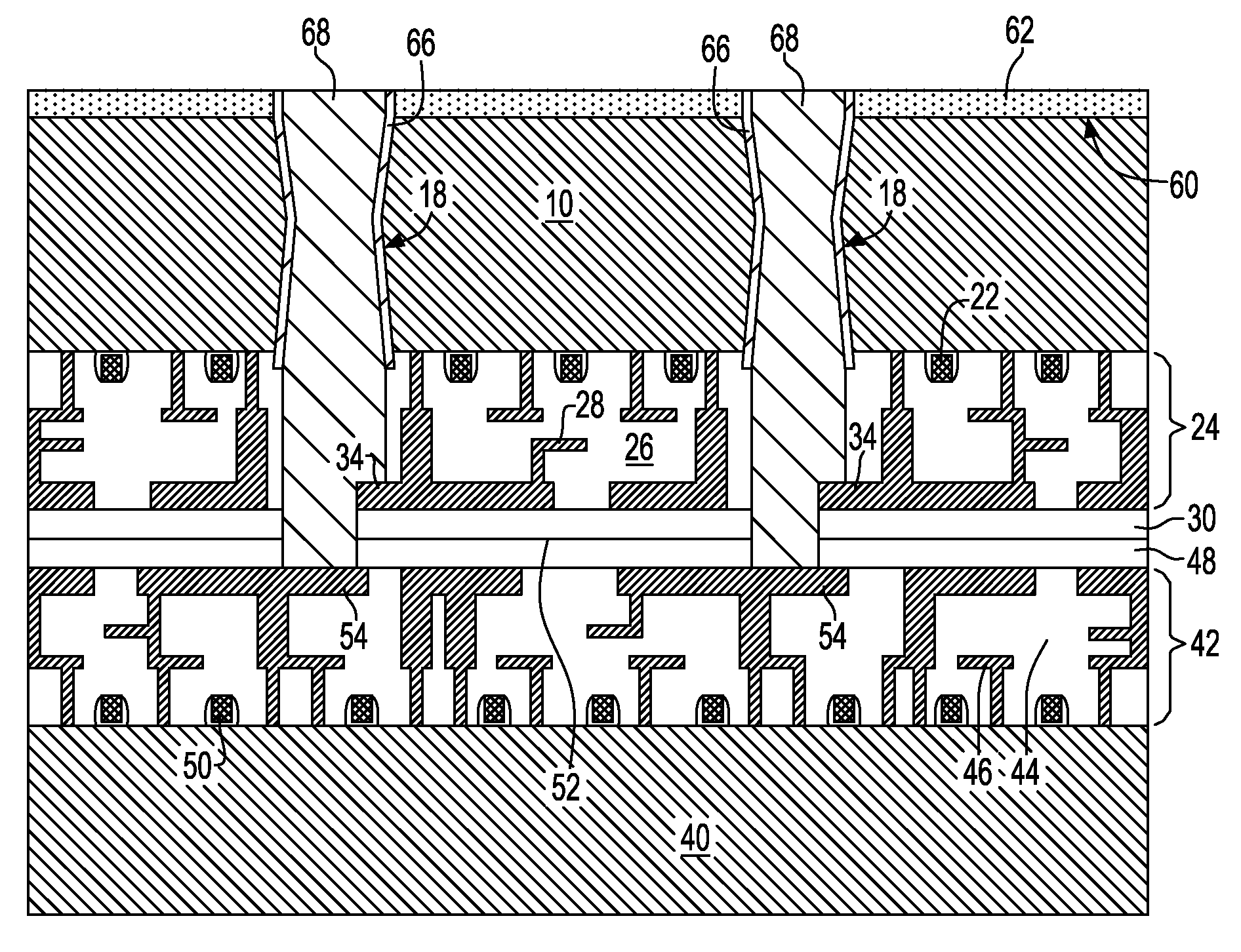

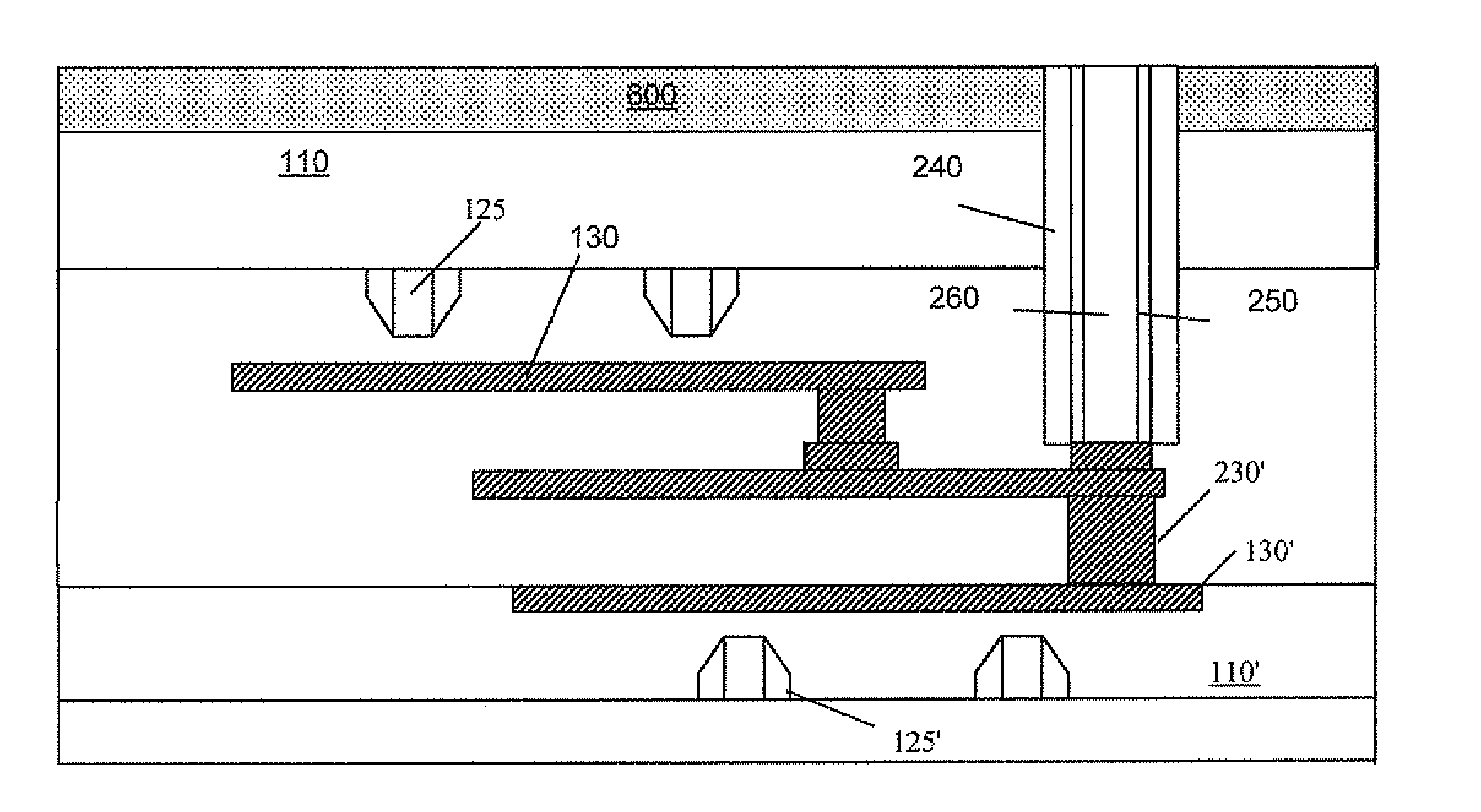

Three-dimensional (3D) integration schemes of fabricating a 3D integrated circuit in which the pFETs are located on an optimal crystallographic surface for that device and the nFETs are located on a optimal crystallographic surface for that type of device are provided. In accordance with a first 3D integration scheme of the present invention, first semiconductor devices are pre-built on a semiconductor surface of a first silicon-on-insulator (SOI) substrate and second semiconductor devices are pre-built on a semiconductor surface of a second SOI substrate. After pre-building those two structures, the structure are bonded together and interconnect through wafer-via through vias. In a second 3D integration scheme, a blanket silicon-on-insulator (SOI) substrate having a first SOI layer of a first crystallographic orientation is bonded to a surface of a pre-fabricating wafer having second semiconductor devices on a second SOI layer that has a different crystallographic orientation than the first SOI layer; and forming first semiconductor device on the first SOI layer.

Owner:GLOBALFOUNDRIES INC

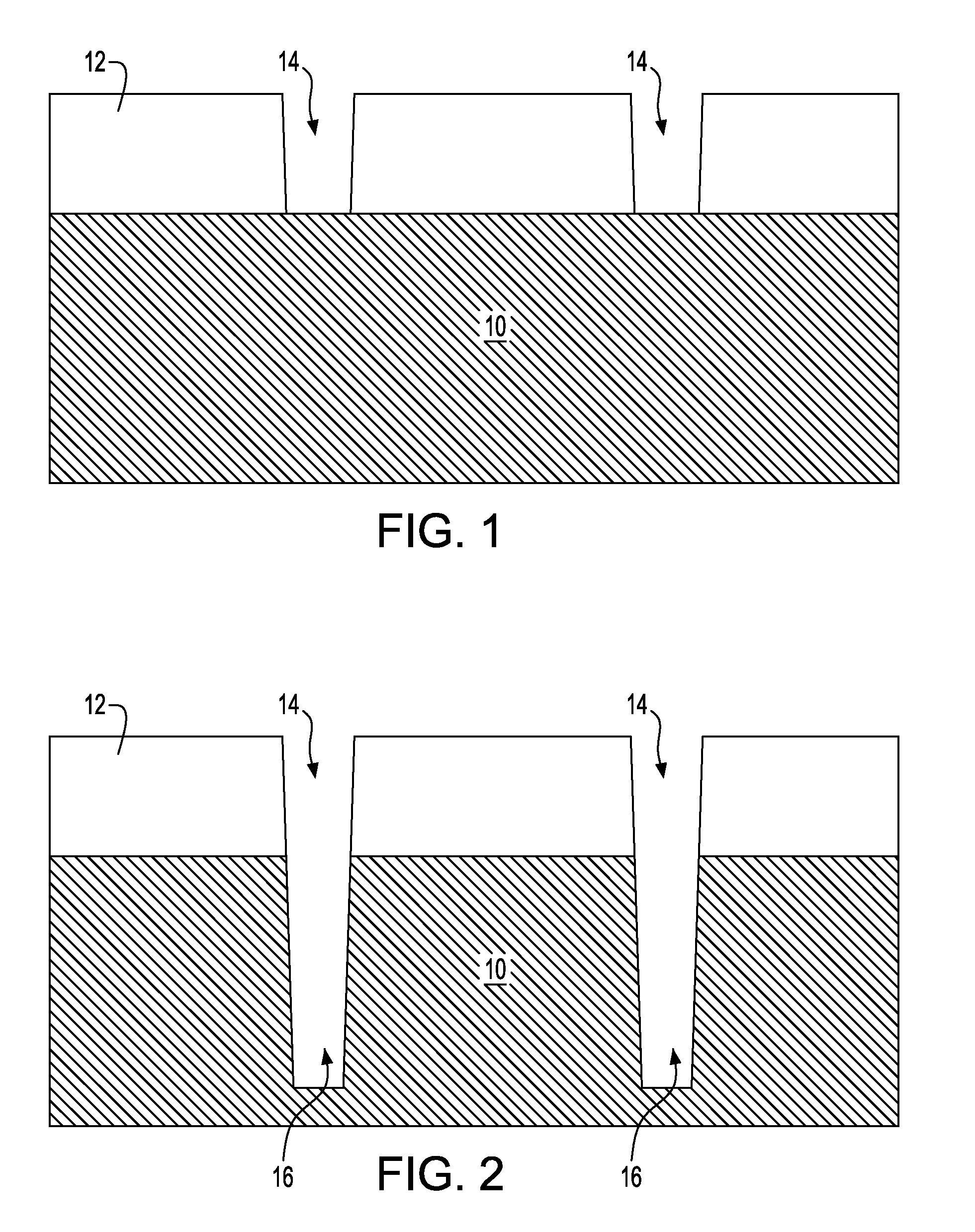

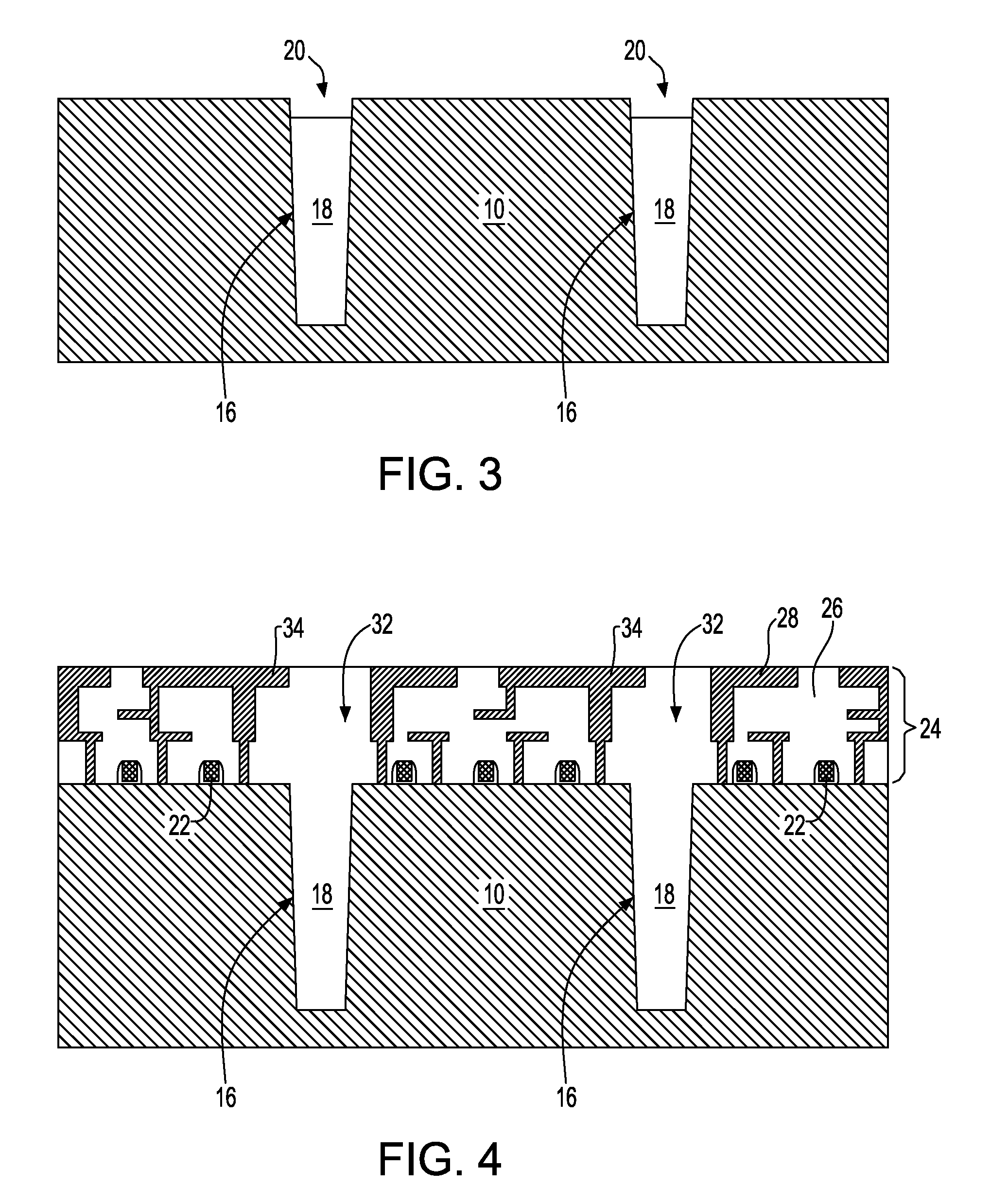

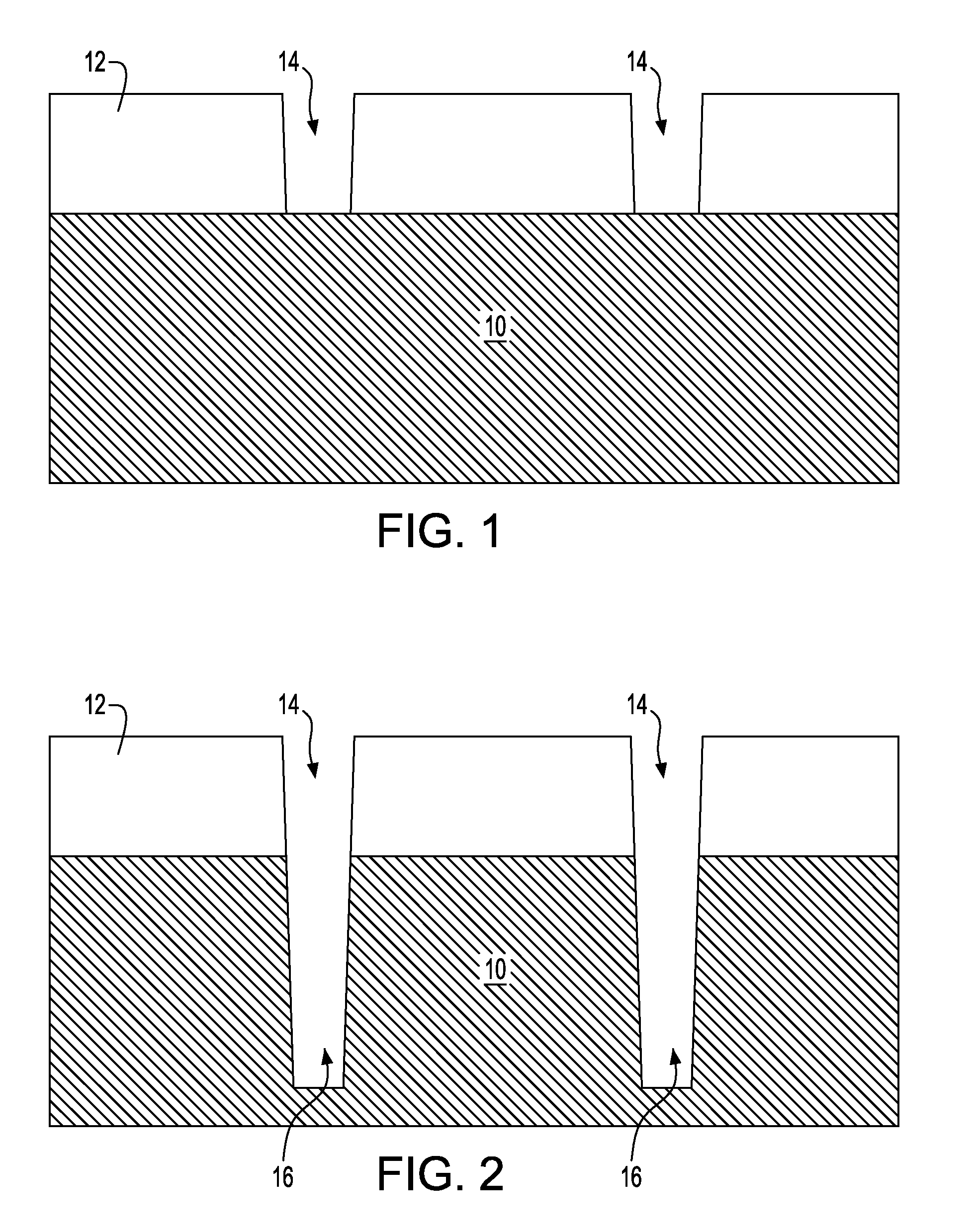

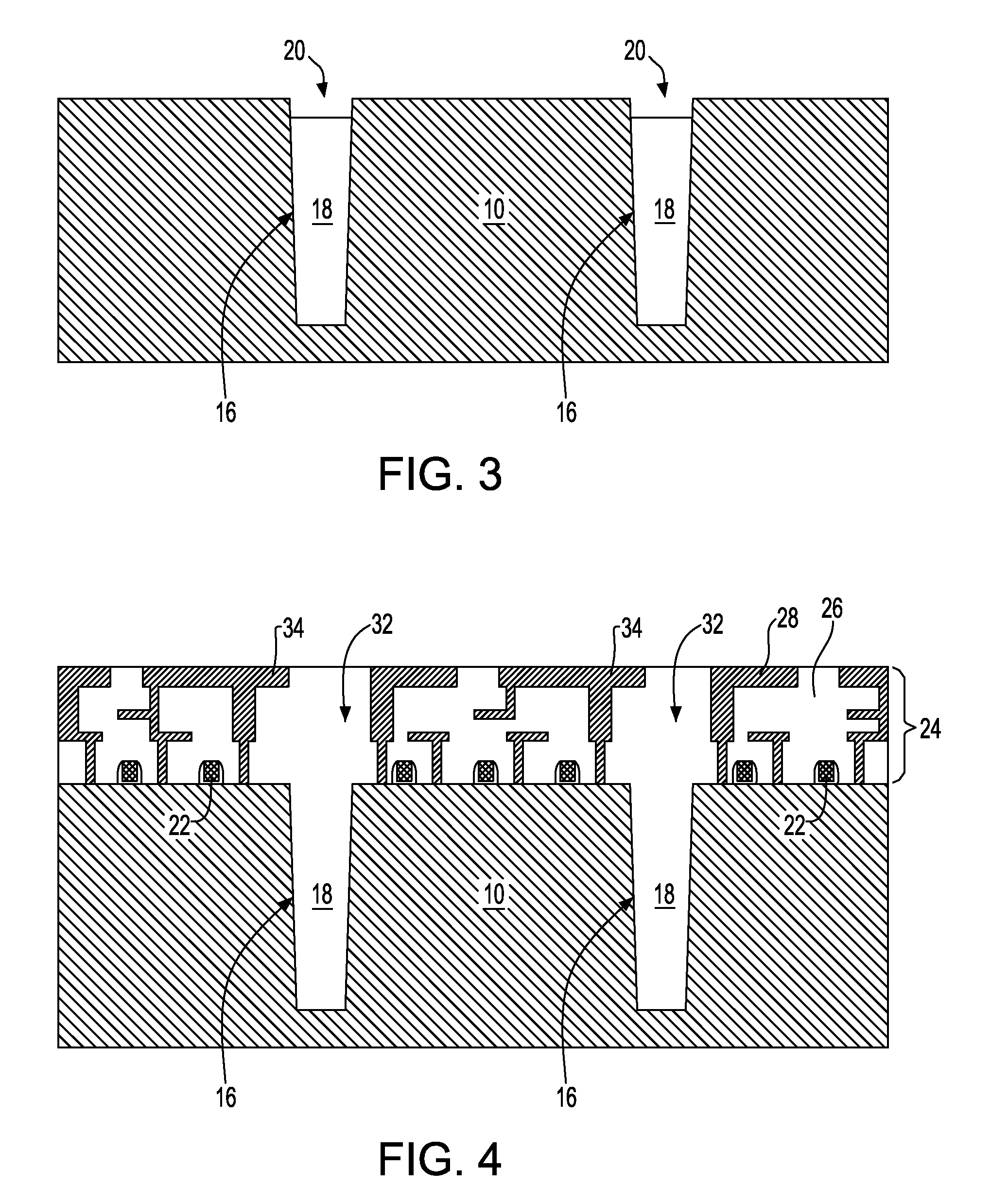

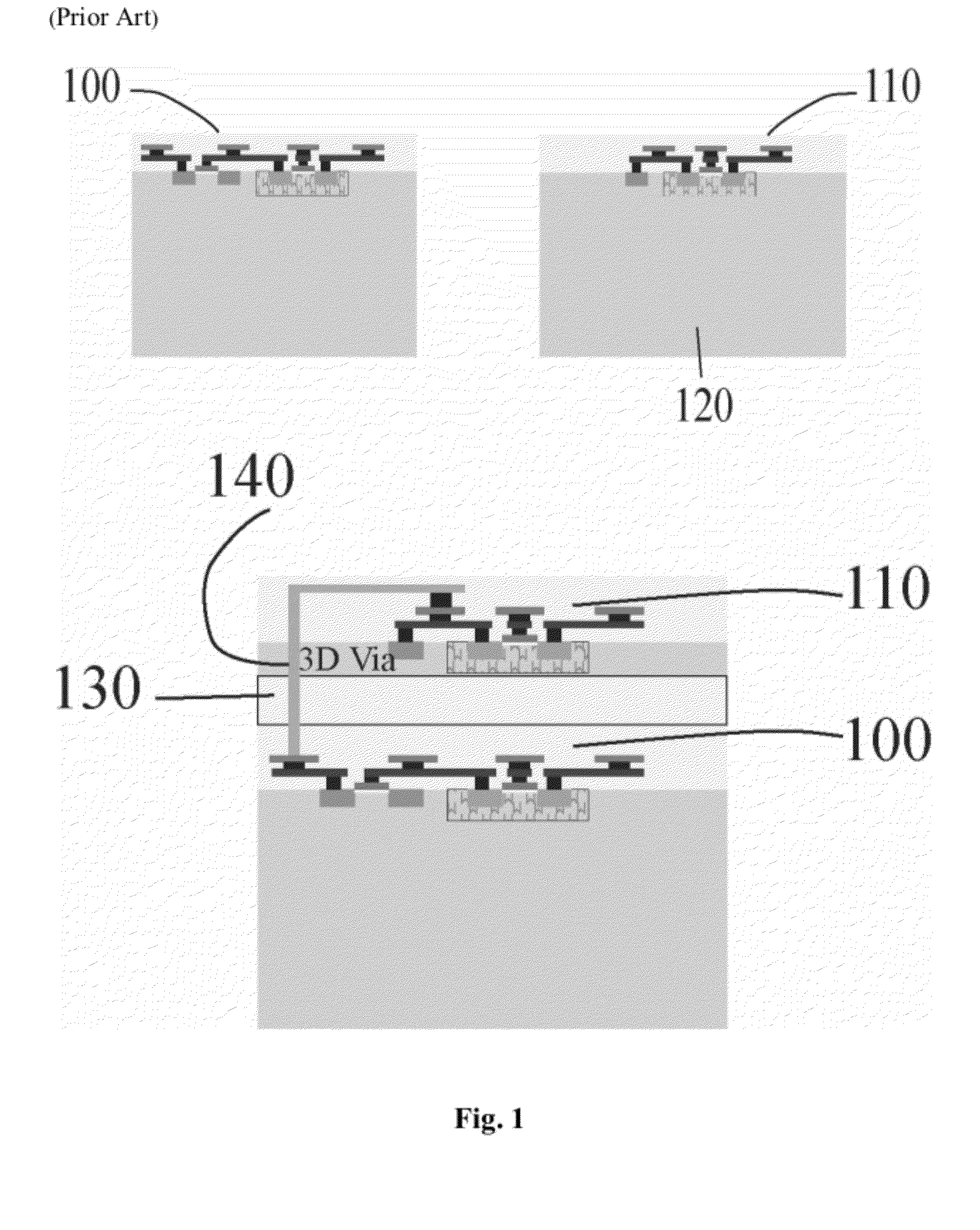

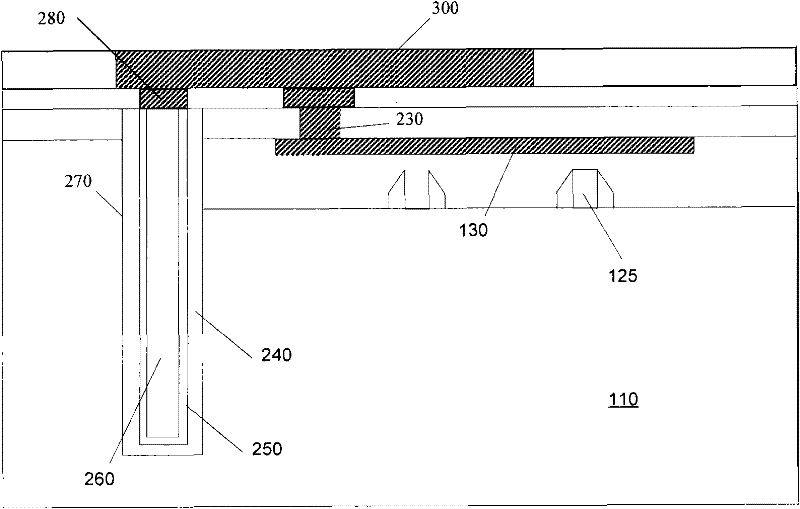

Method of making 3D integrated circuits and structures formed thereby

ActiveUS20100193964A1Semiconductor/solid-state device detailsSolid-state devices3d integrated circuitEngineering

A method and structure of connecting at least two integrated circuits in a 3D arrangement by a through silicon via which simultaneously connects a connection pad in a first integrated circuit and a connection pad in a second integrated circuit.

Owner:GLOBALFOUNDRIES US INC

Method of making 3D integrated circuits

ActiveUS8158515B2Semiconductor/solid-state device detailsSolid-state devices3d integrated circuitEngineering

A method and structure of connecting at least two integrated circuits in a 3D arrangement by a through silicon via which simultaneously connects a connection pad in a first integrated circuit and a connection pad in a second integrated circuit.

Owner:GLOBALFOUNDRIES US INC

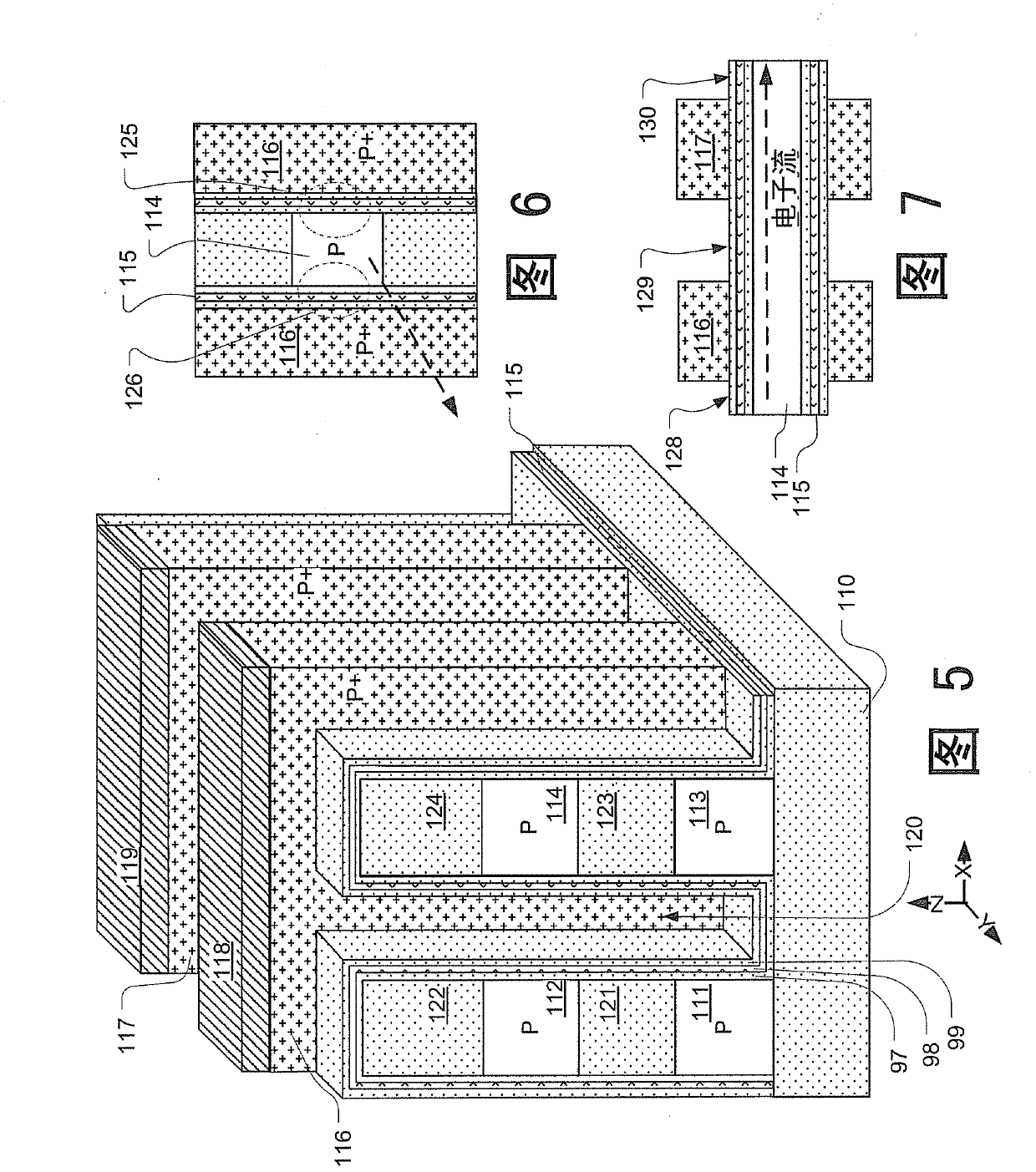

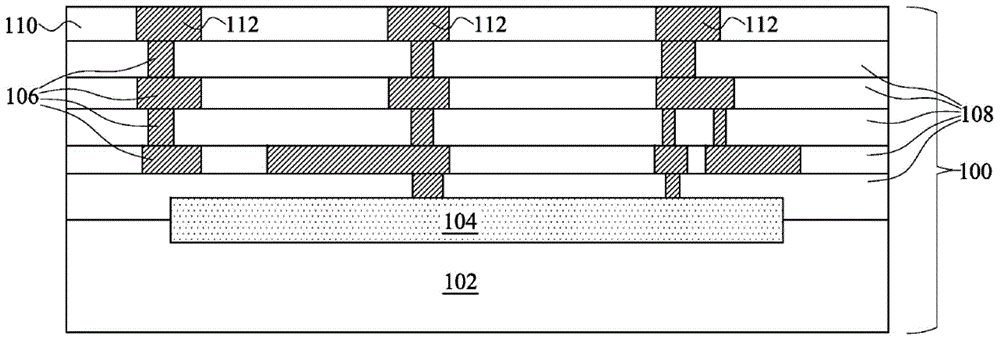

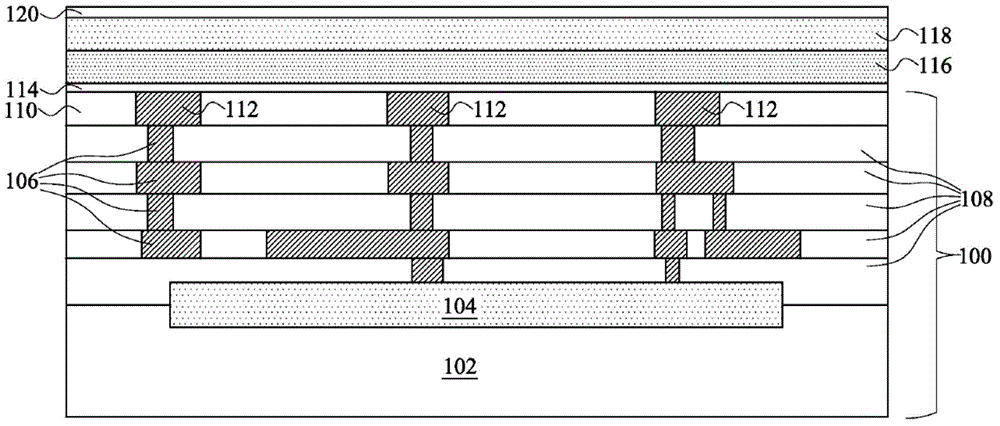

3D integrated circuit structure, semiconductor device and method of manufacturing same

ActiveUS20110227158A1Improve performanceSemiconductor/solid-state device detailsSolid-state devicesMOSFETPower semiconductor device

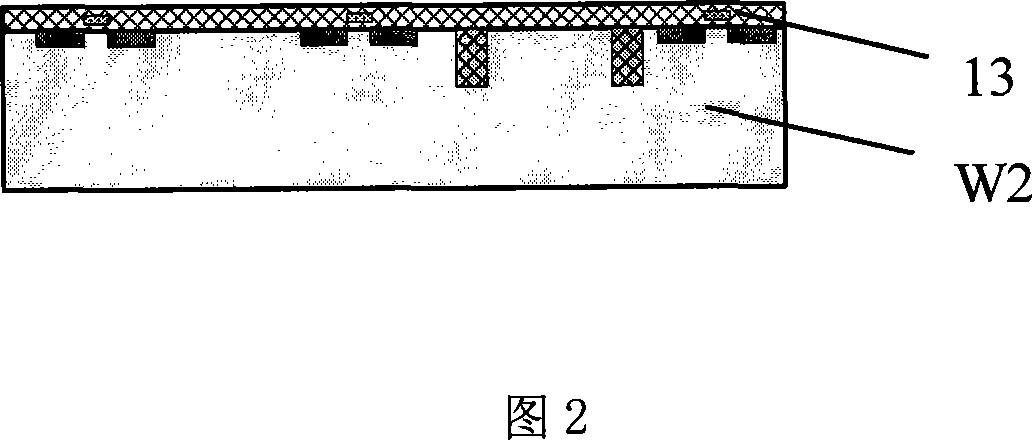

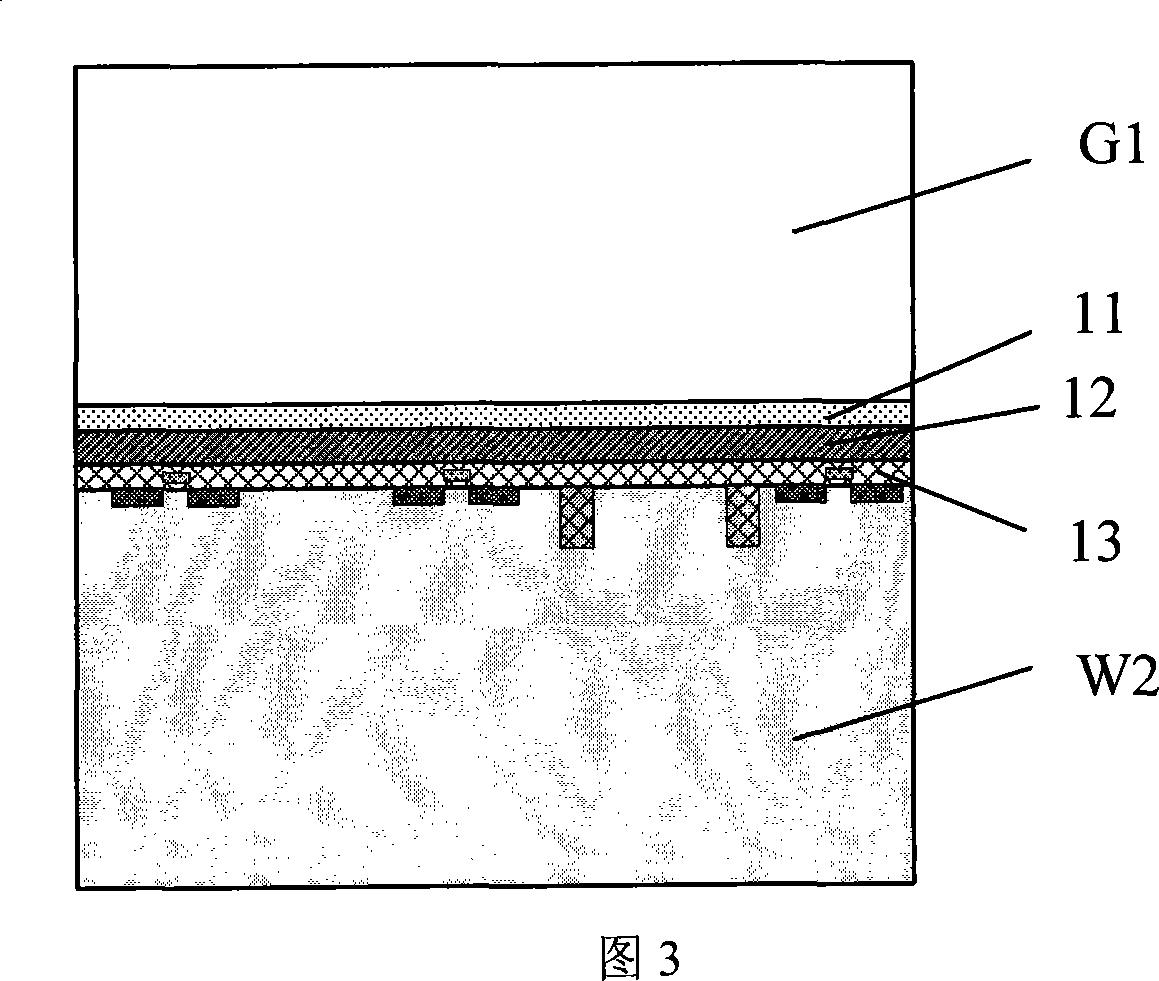

The present invention discloses a semiconductor device. In one embodiment, the semiconductor device comprises a substrate, a diffusion stop layer formed on the substrate, an SOI layer formed on the diffusion stop layer, an MOSFET transistor formed on the SOI layer, and a TSV formed in a manner of penetrating through the substrate, the diffusion stop layer, the SOI layer, and a layer where the MOSFET transistor is located; and an interconnect structure connecting the MOSFET transistor and the TSV.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Chip having thermal vias and spreaders of CVD diamond

InactiveUS20100140790A1Minimize and preferably eliminate localized hot spotHeat dissipationSemiconductor/solid-state device detailsPrinted circuit aspects3d integrated circuitHeat spreader

An integrated circuit chip having a heat spreader comprising CVD diamond extending along the chip support body and thermal vias extending through the support body in regions free of active devices or functional elements. The thermal vias may thermally conductive and electrically conductive or may be thermally conductive and electrically resistive. The integrated circuit chips may be 3D integrated circuit chips.

Owner:SEAGATE TECH LLC

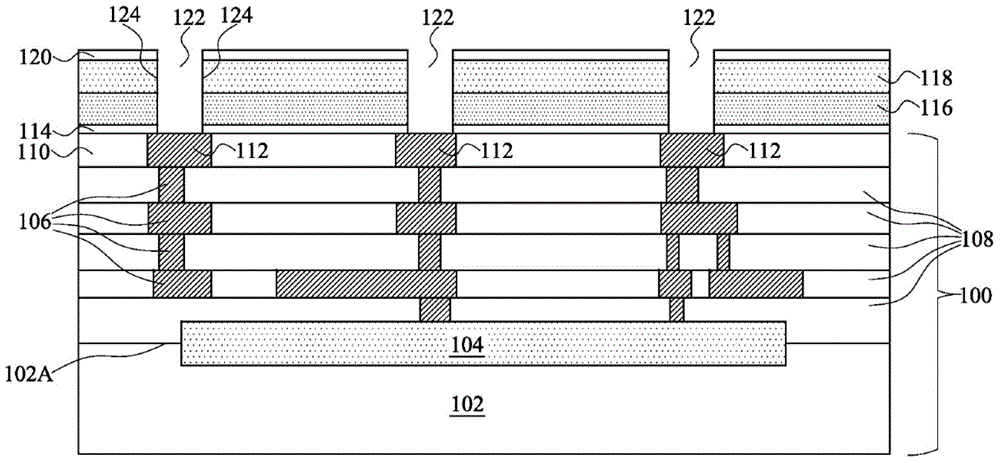

3D integrated circuit and method of manufacturing the same

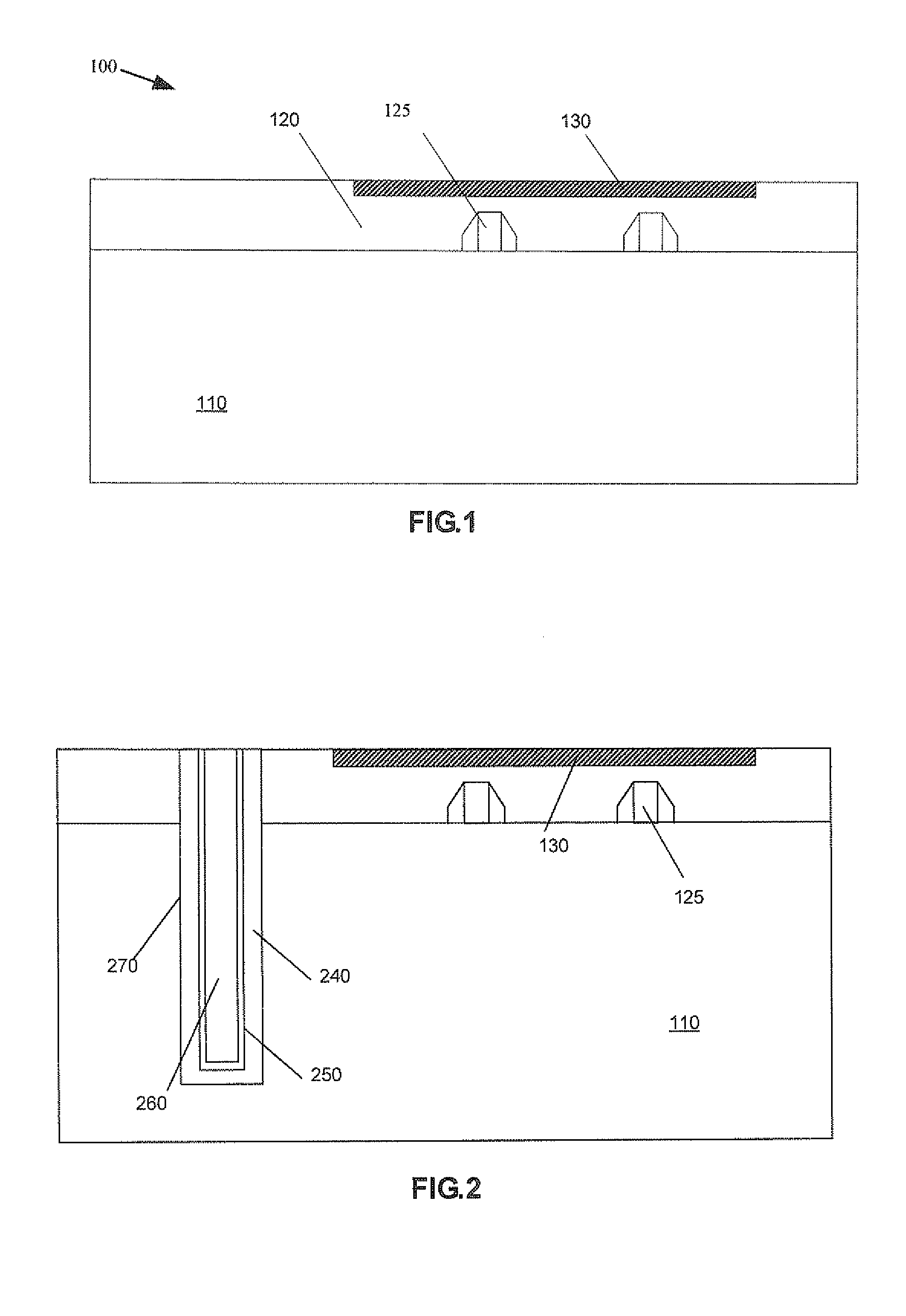

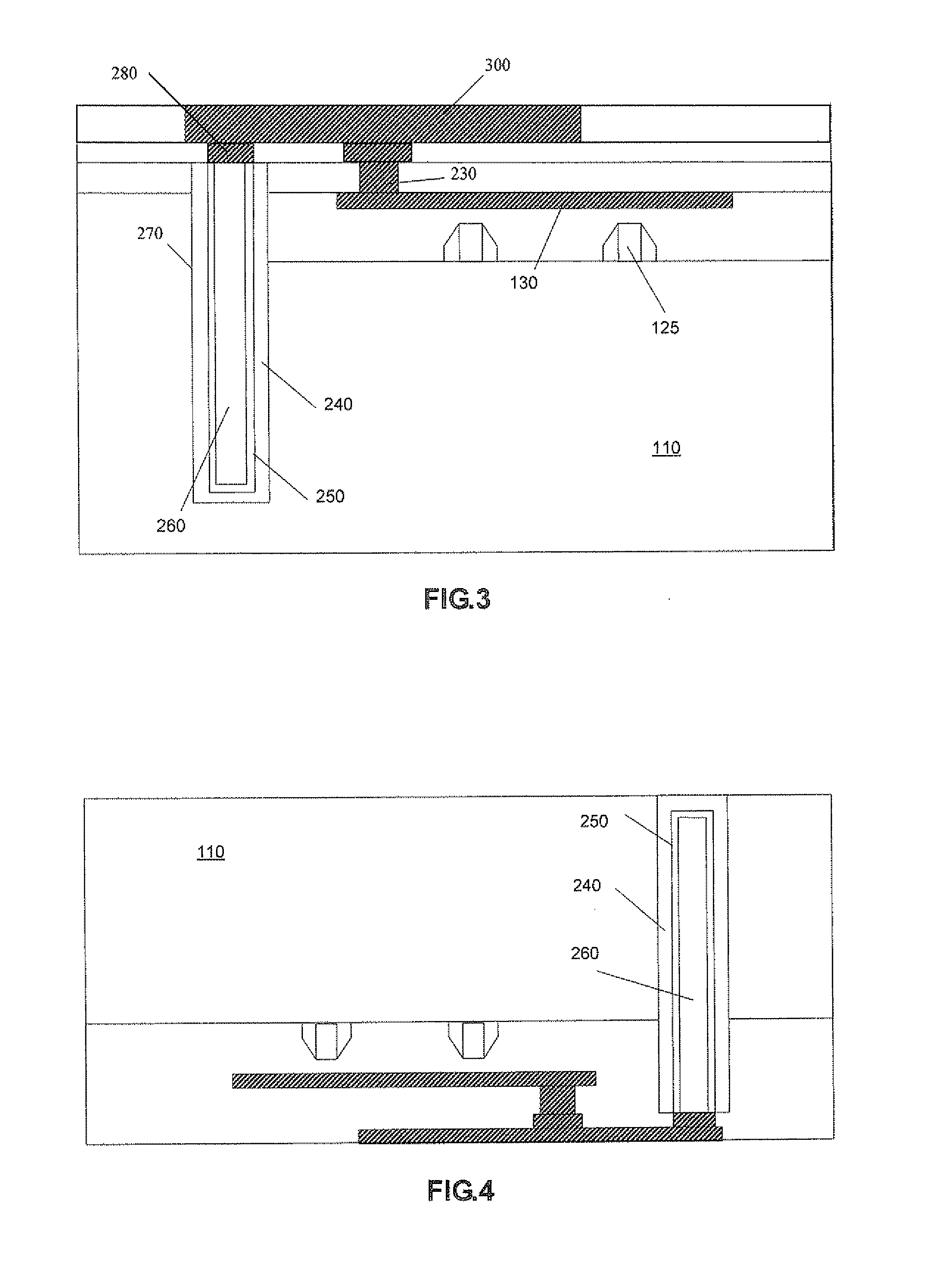

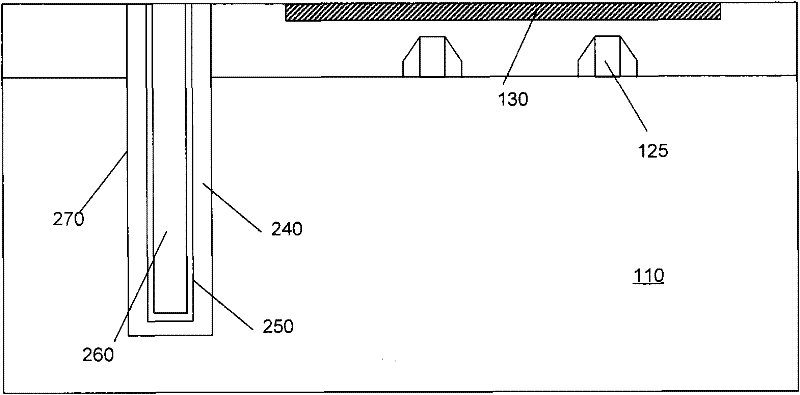

ActiveUS20110284992A1Avoid damageSemiconductor/solid-state device detailsSolid-state devices3d integrated circuitInterconnection

The present invention provides a 3D integrated circuit and a manufacturing method thereof. The circuit structure comprises: a semiconductor substrate; at least one semiconductor device formed on the upper surface of the semiconductor substrate; a through-Si-via through the semiconductor substrate and comprising an insulating layer covering sidewalls of the through-Si-via and conductive material filled in the insulating layer; an interconnection structure connecting the at least one semiconductor device and the through-Si-via; and a diffusion trapping region formed on the lower surface of the semiconductor substrate. The present invention is applicable in manufacture of the 3D integrated circuit.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

3D integrated circuit device fabrication with precisely controllable substrate removal

ActiveUS8129256B2Solid-state devicesSemiconductor/solid-state device manufacturing3d integrated circuitEngineering

Owner:TAIWAN SEMICON MFG CO LTD

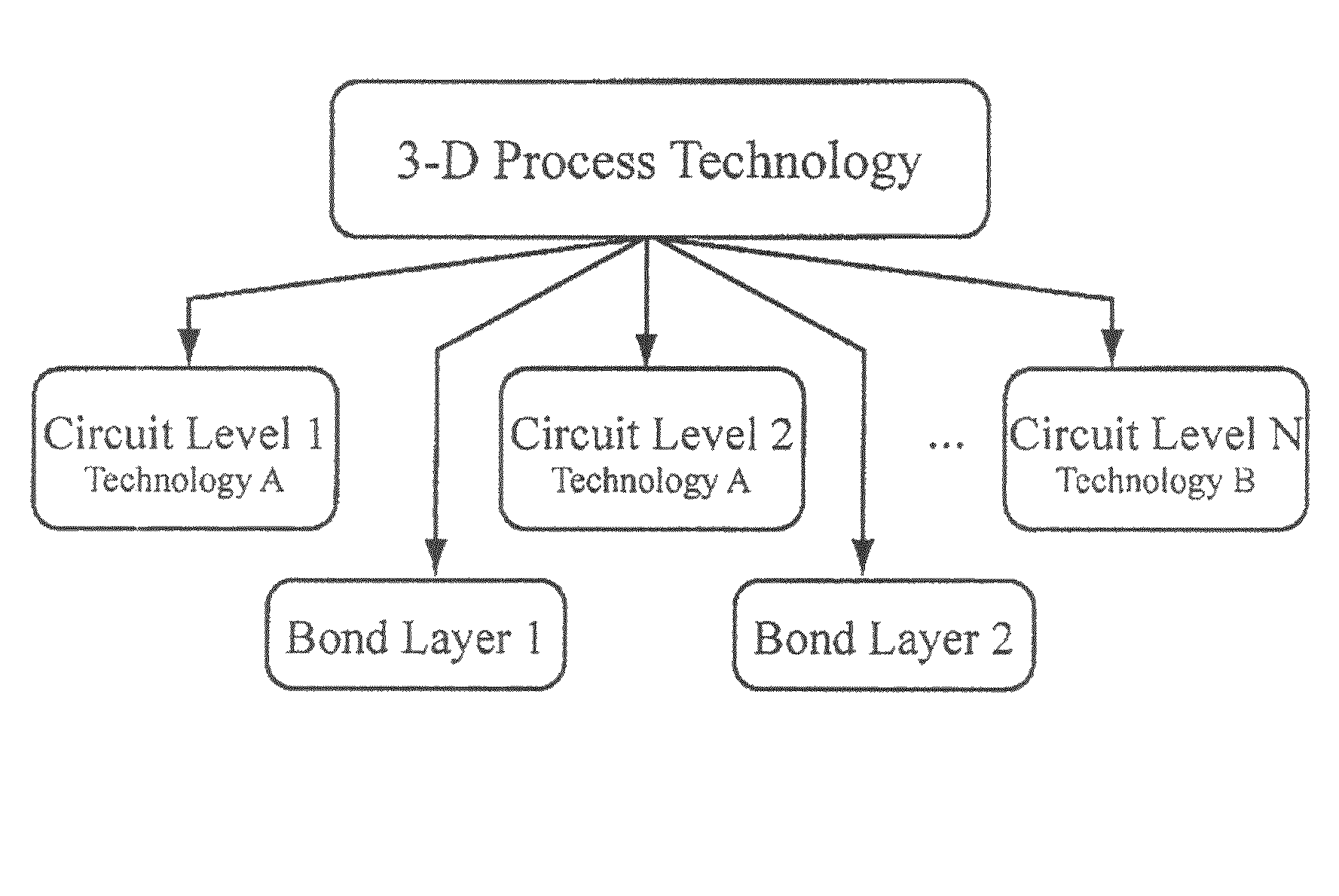

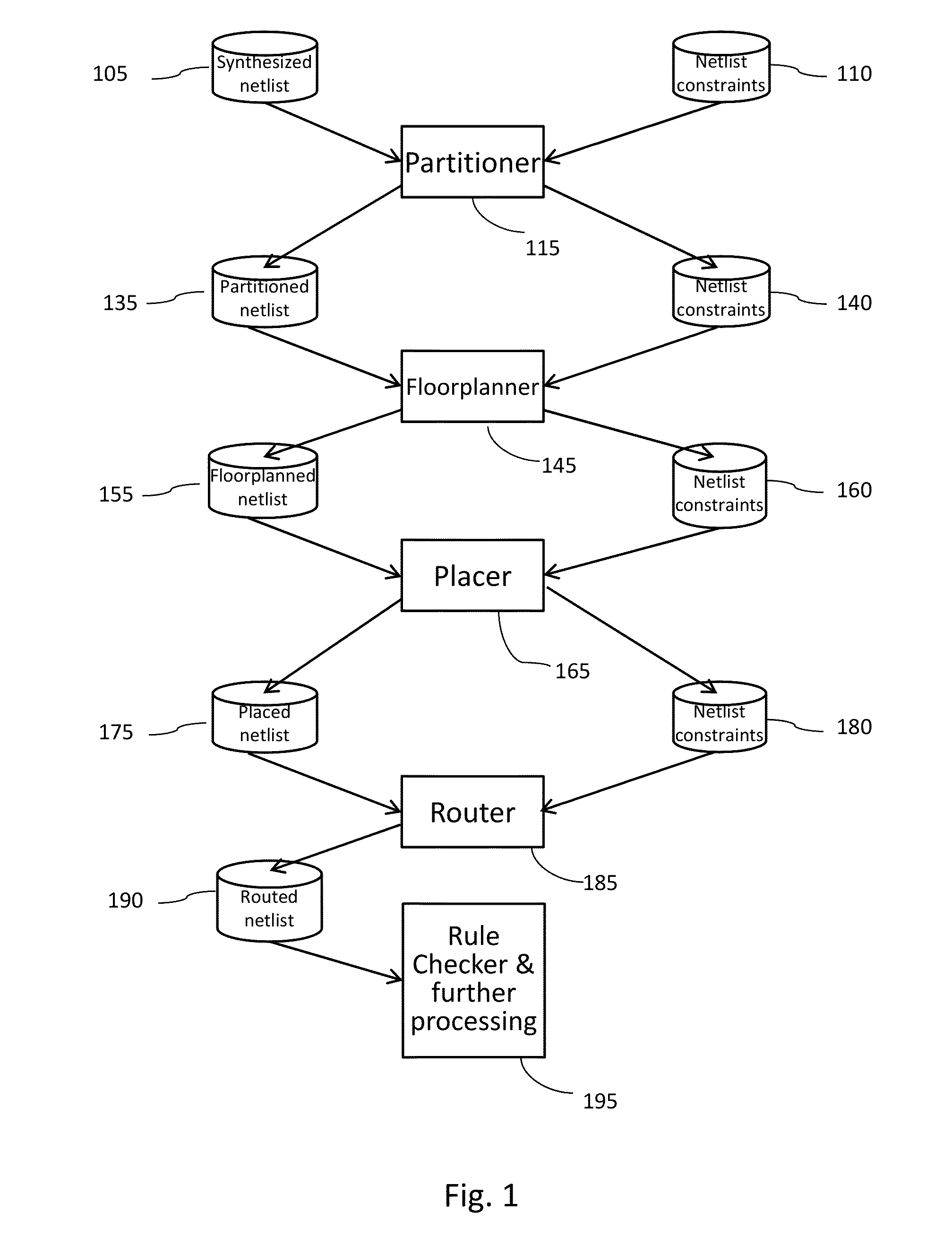

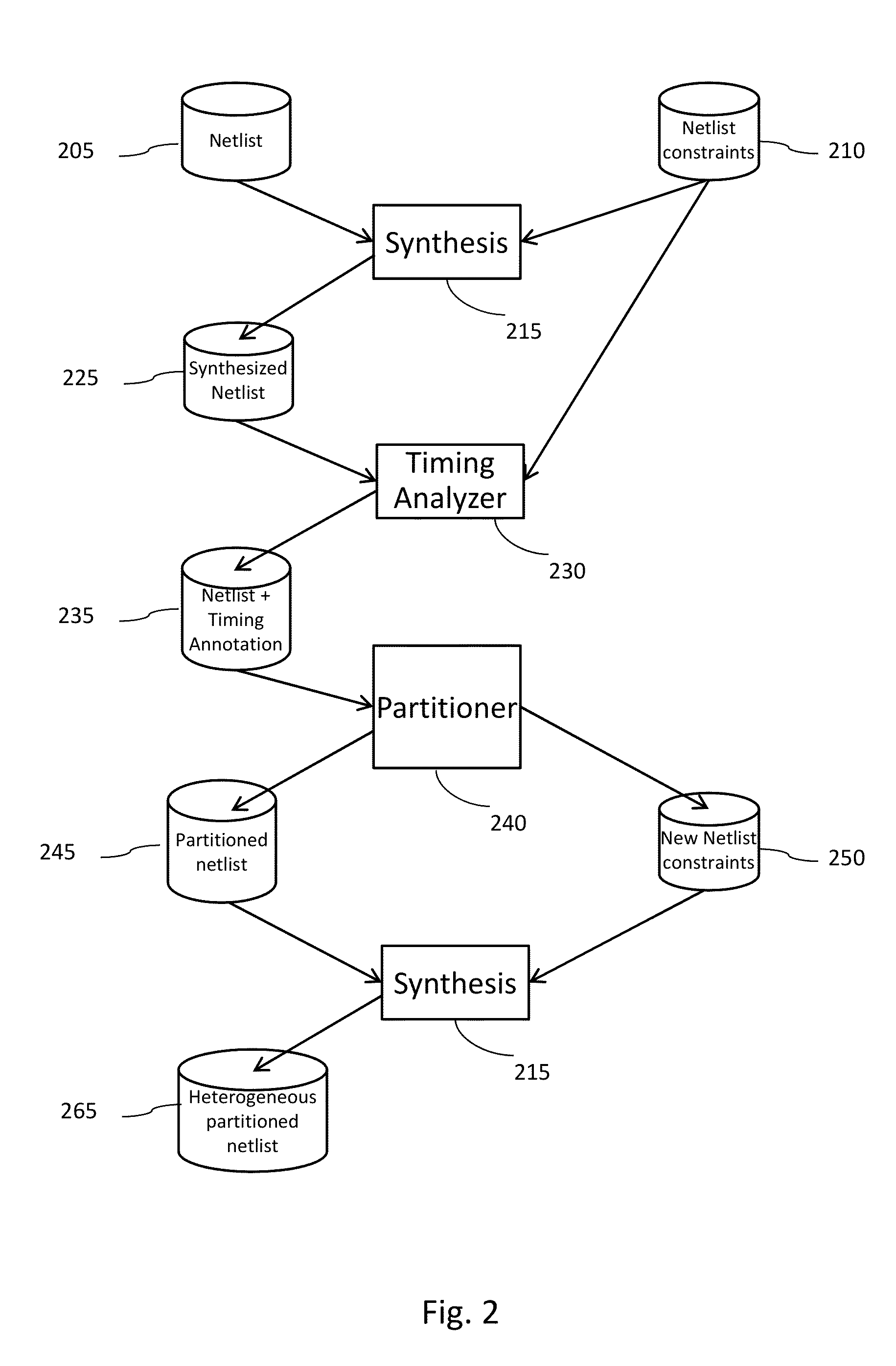

Methods and systems for computer aided design of 3D integrated circuits

ActiveUS8209649B2Computer programmed simultaneously with data introductionCAD circuit design3d integrated circuitComputer Aided Design

Owner:R3 LOGIC

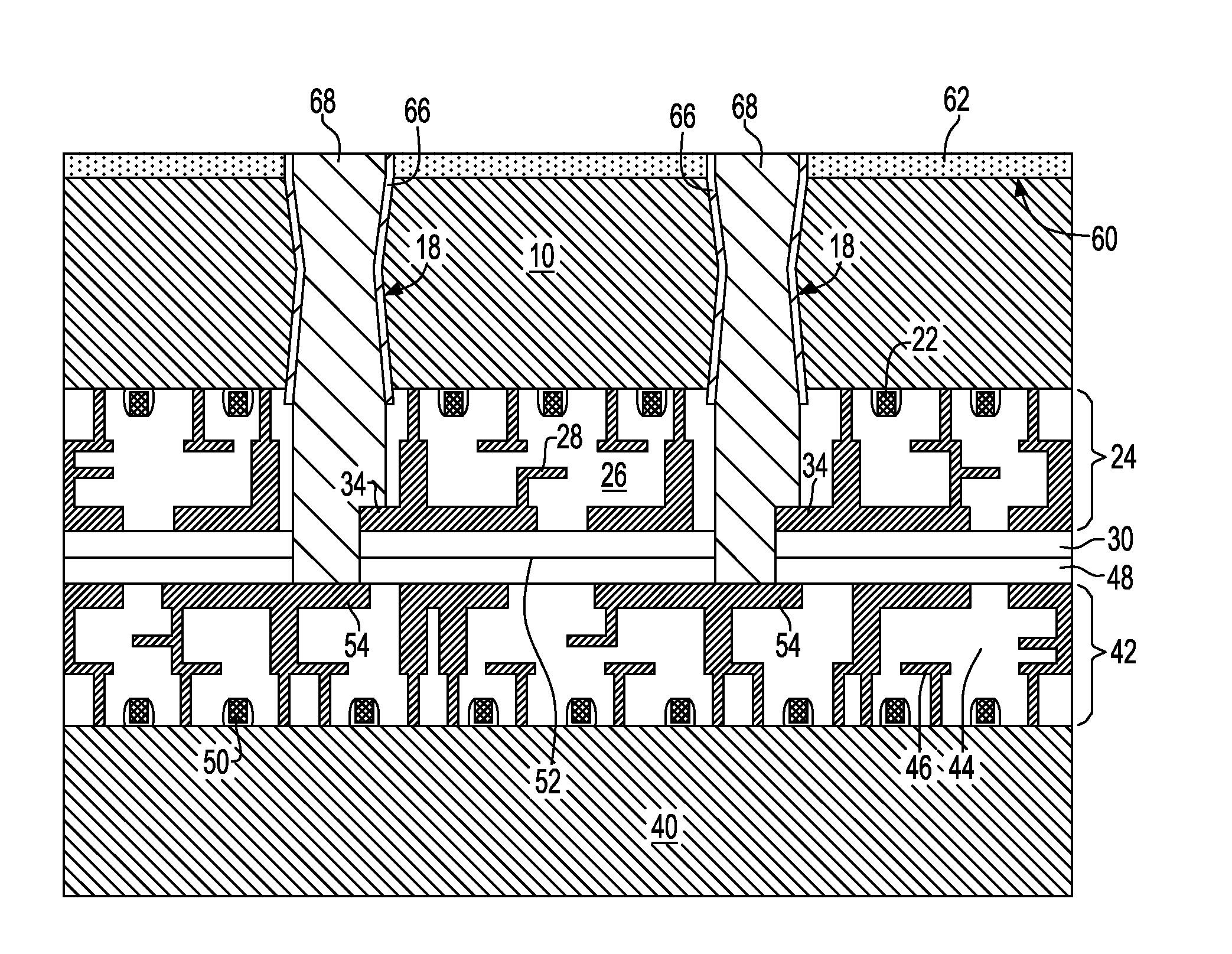

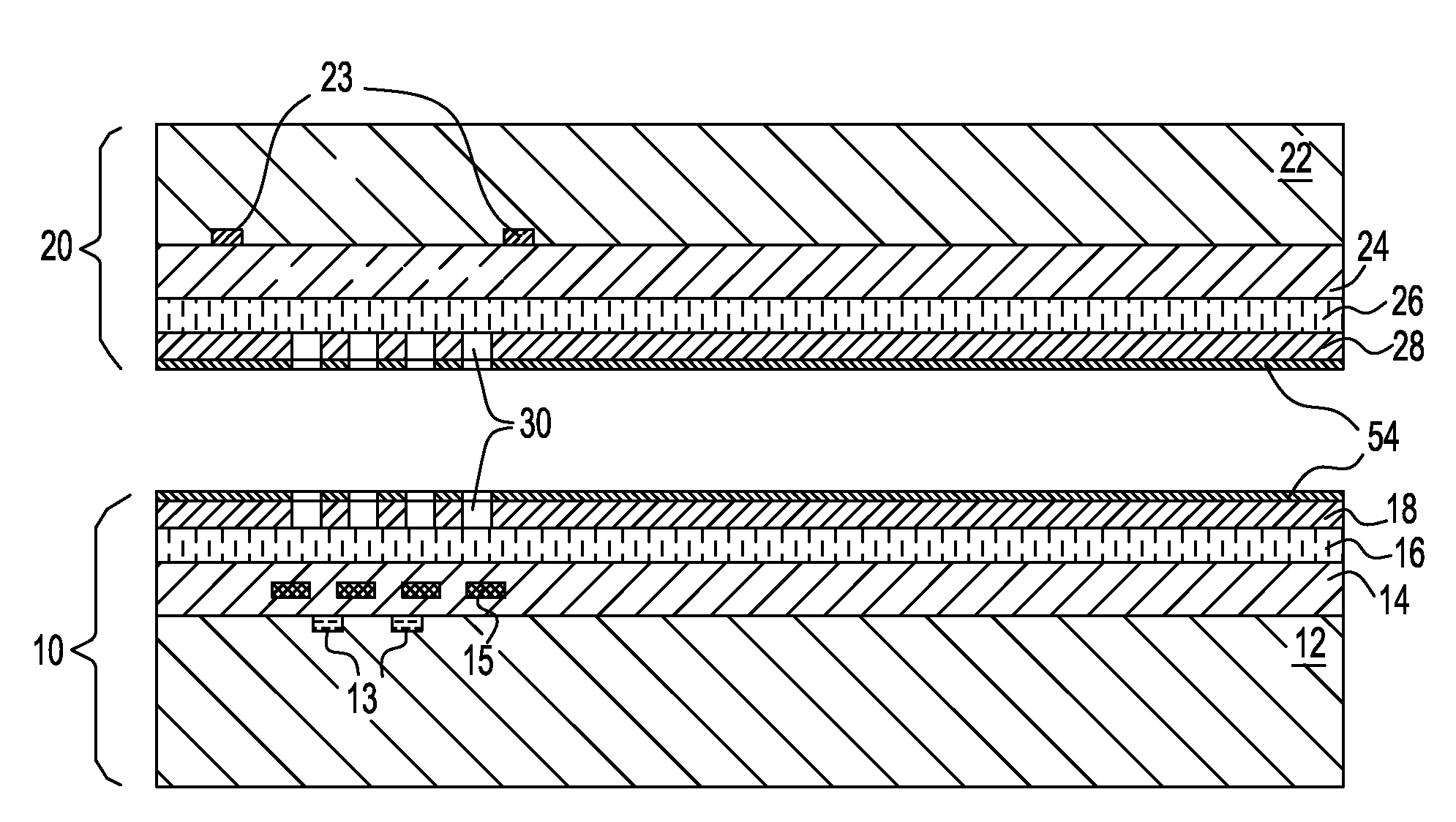

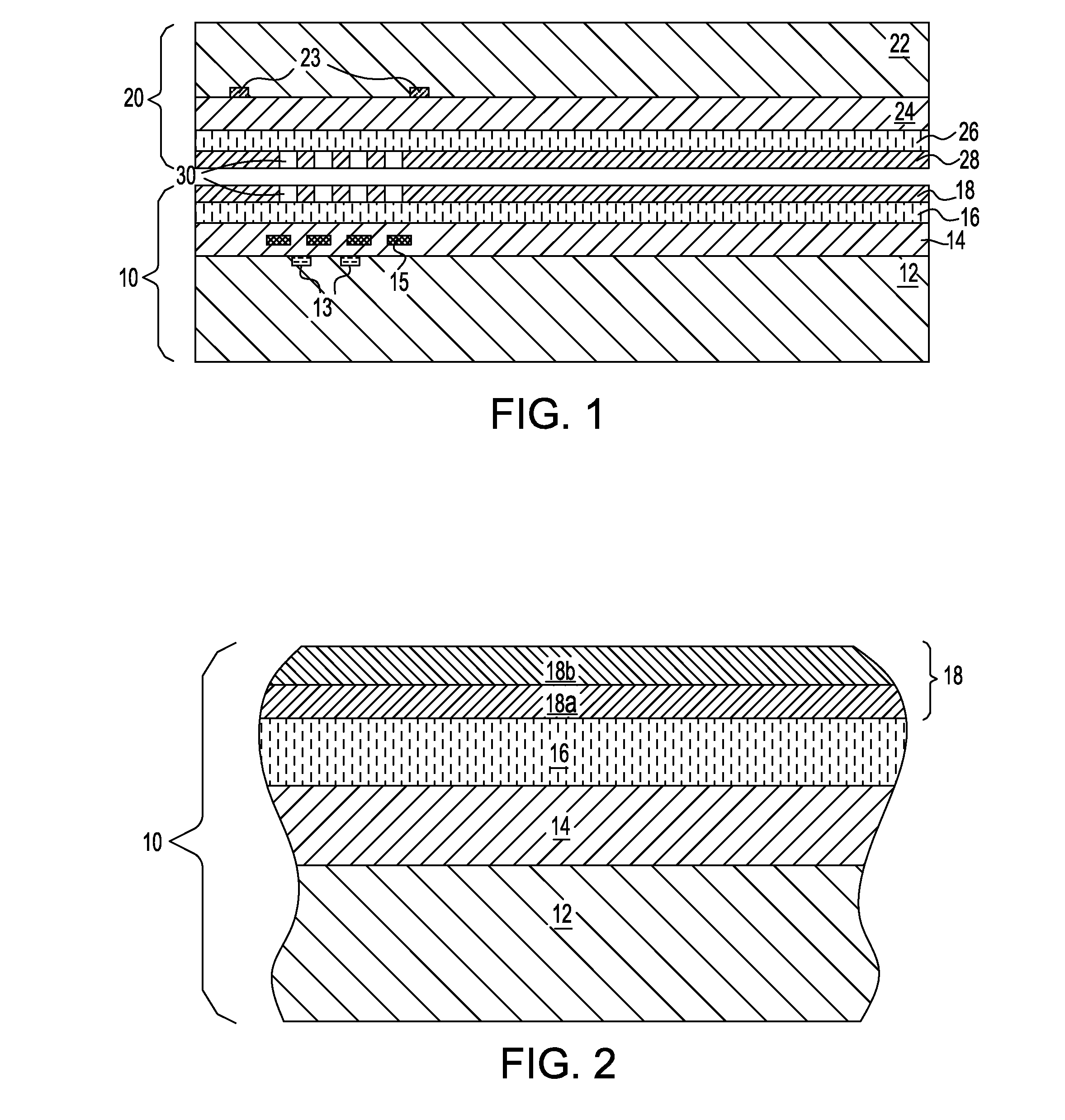

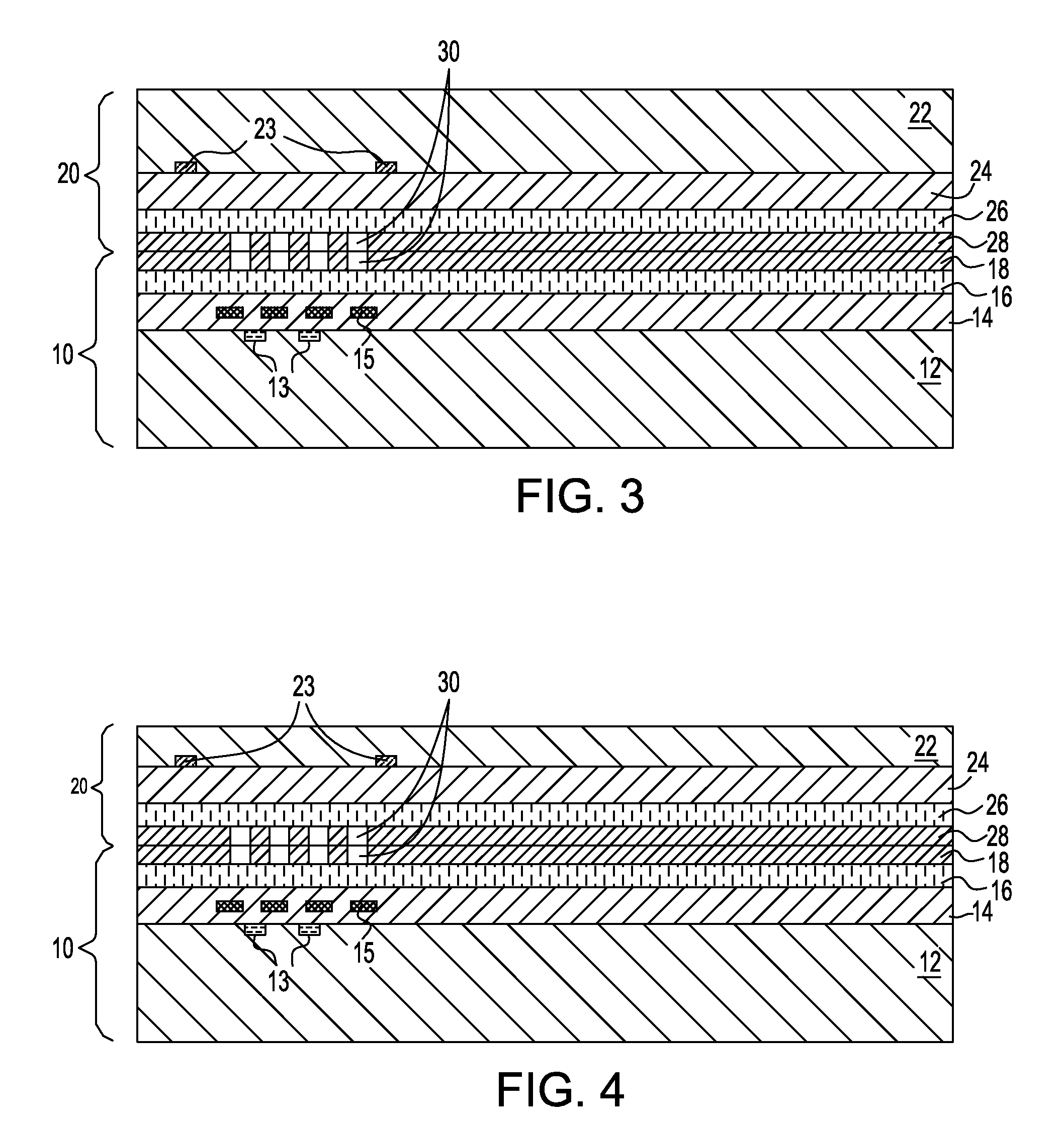

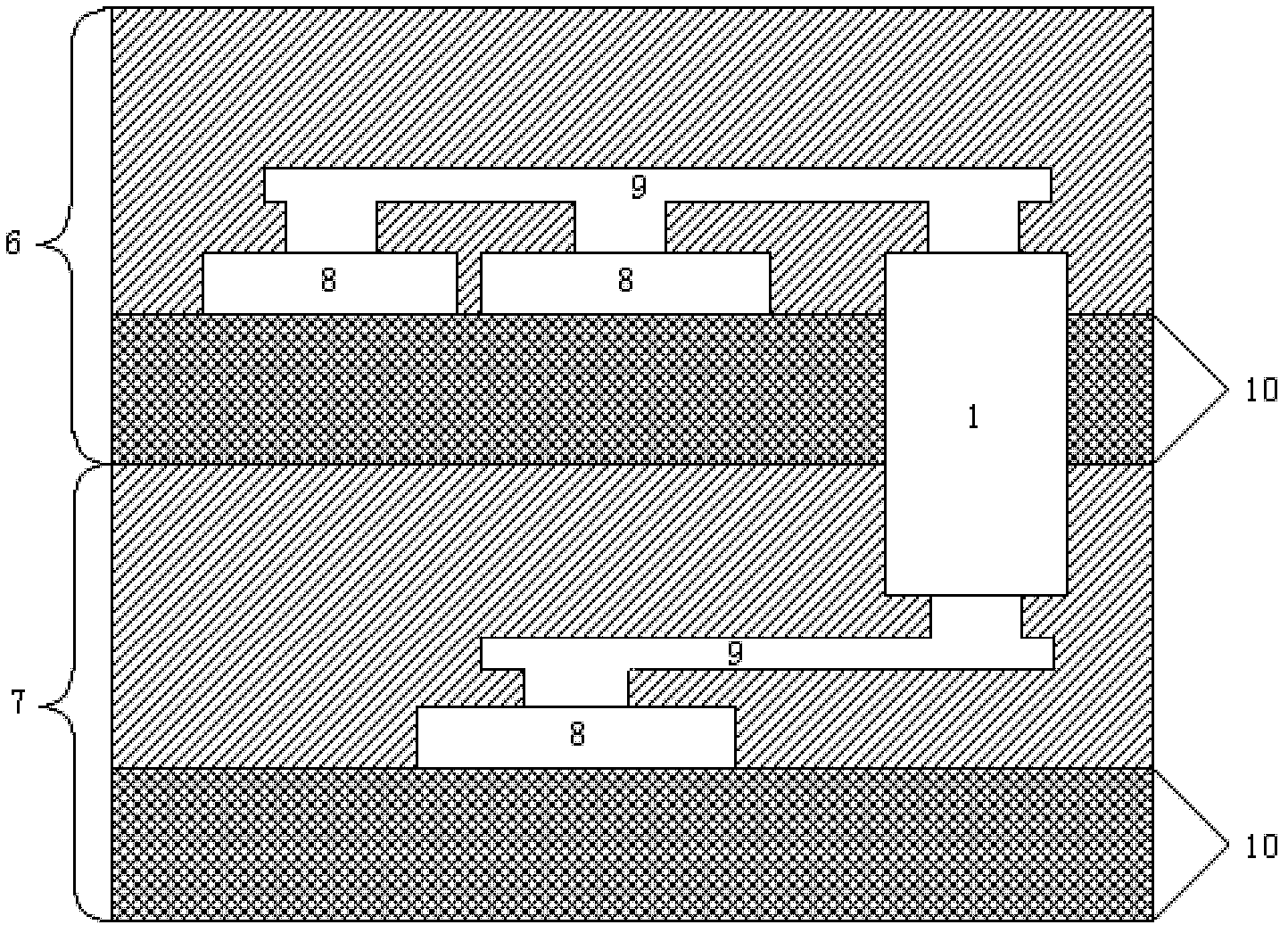

3D integration structure and method using bonded metal planes

ActiveUS20100289144A1Less thicknessSemiconductor/solid-state device detailsSolid-state devices3d integrated circuitSemiconductor structure

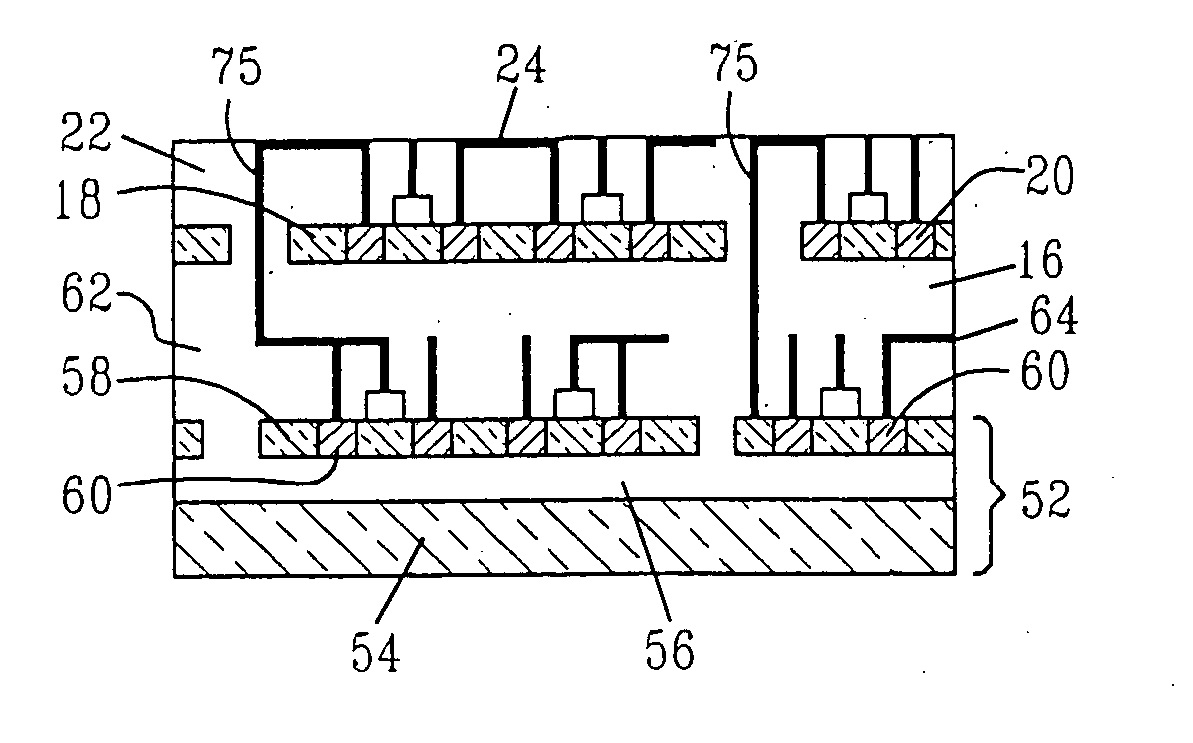

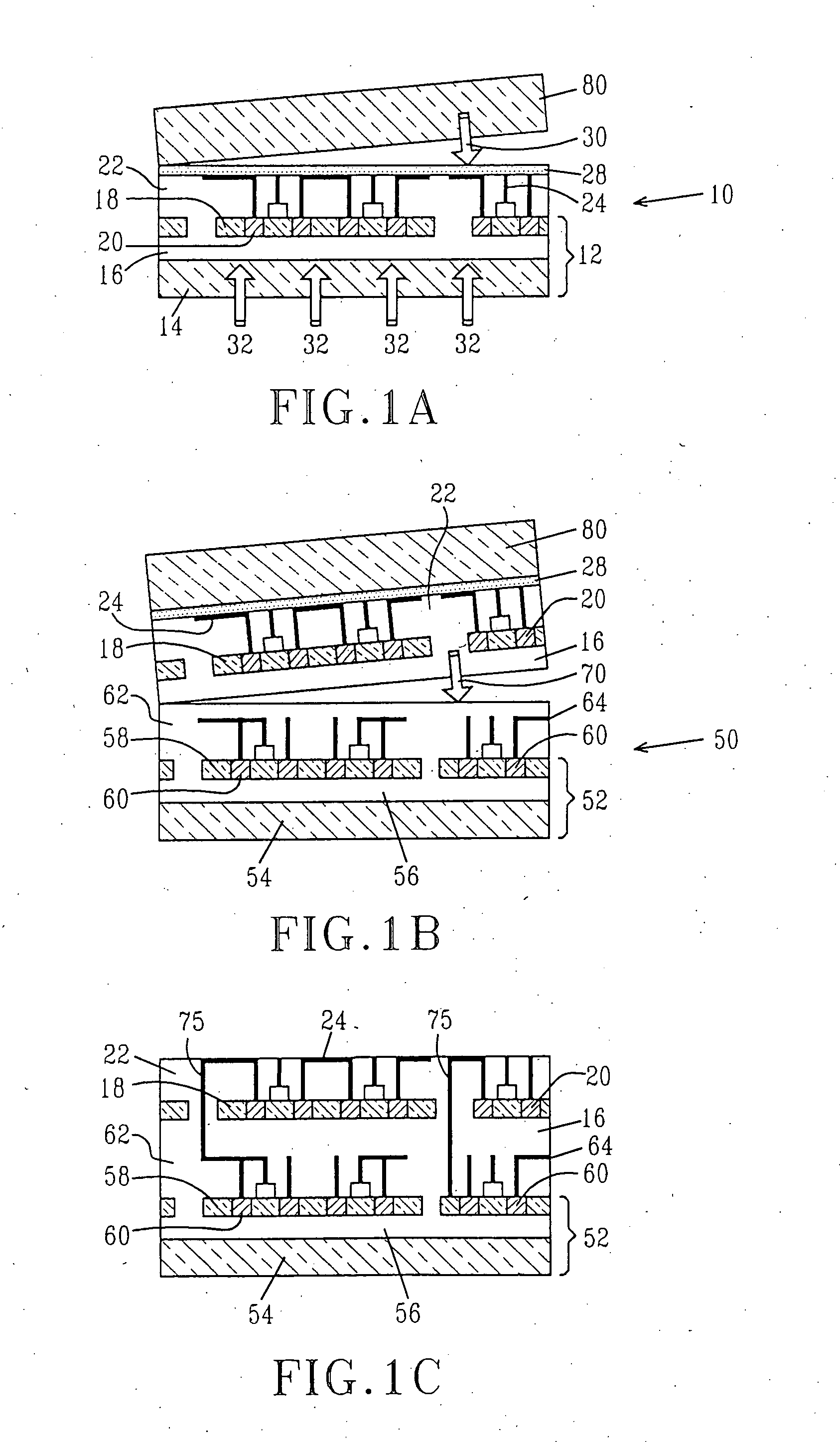

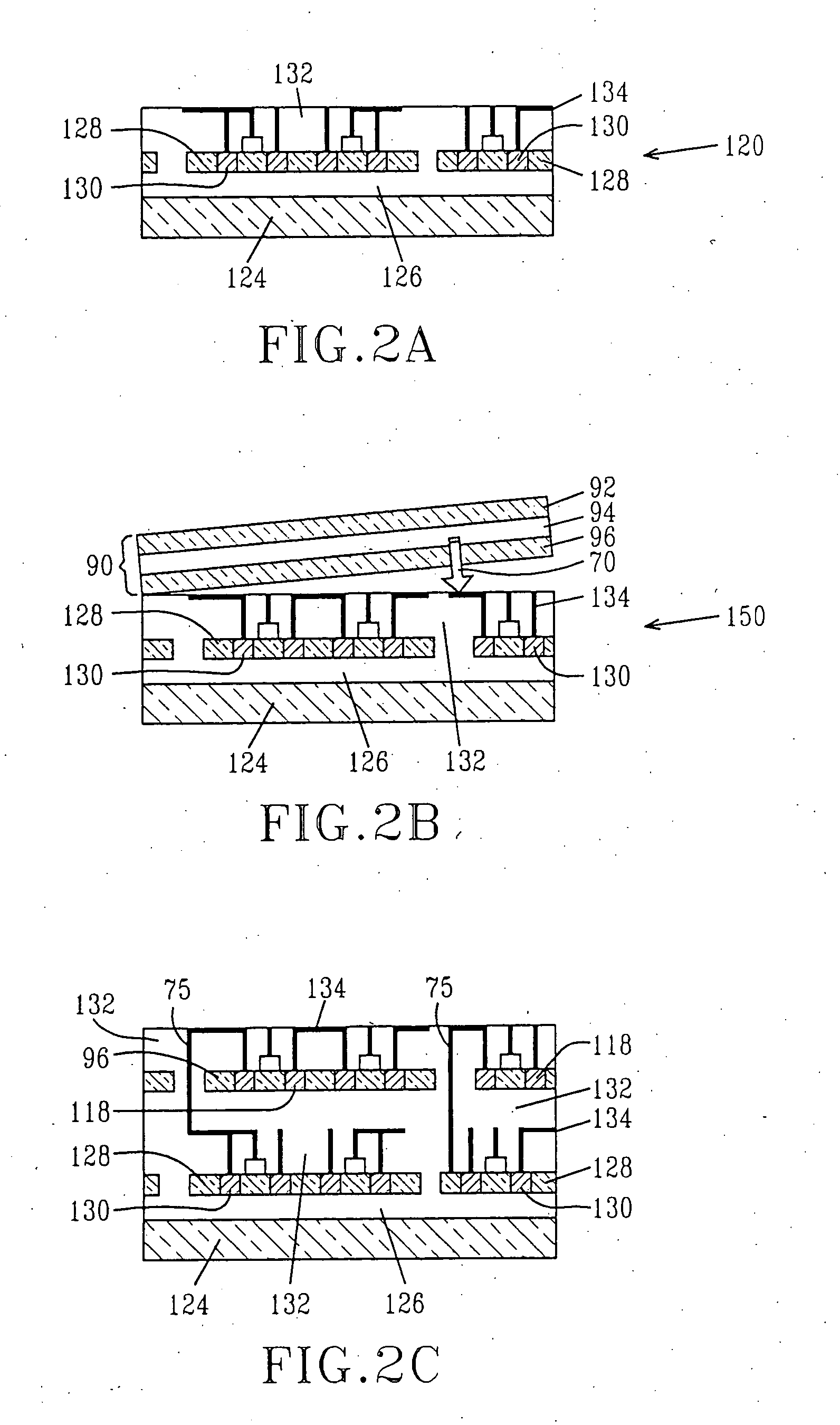

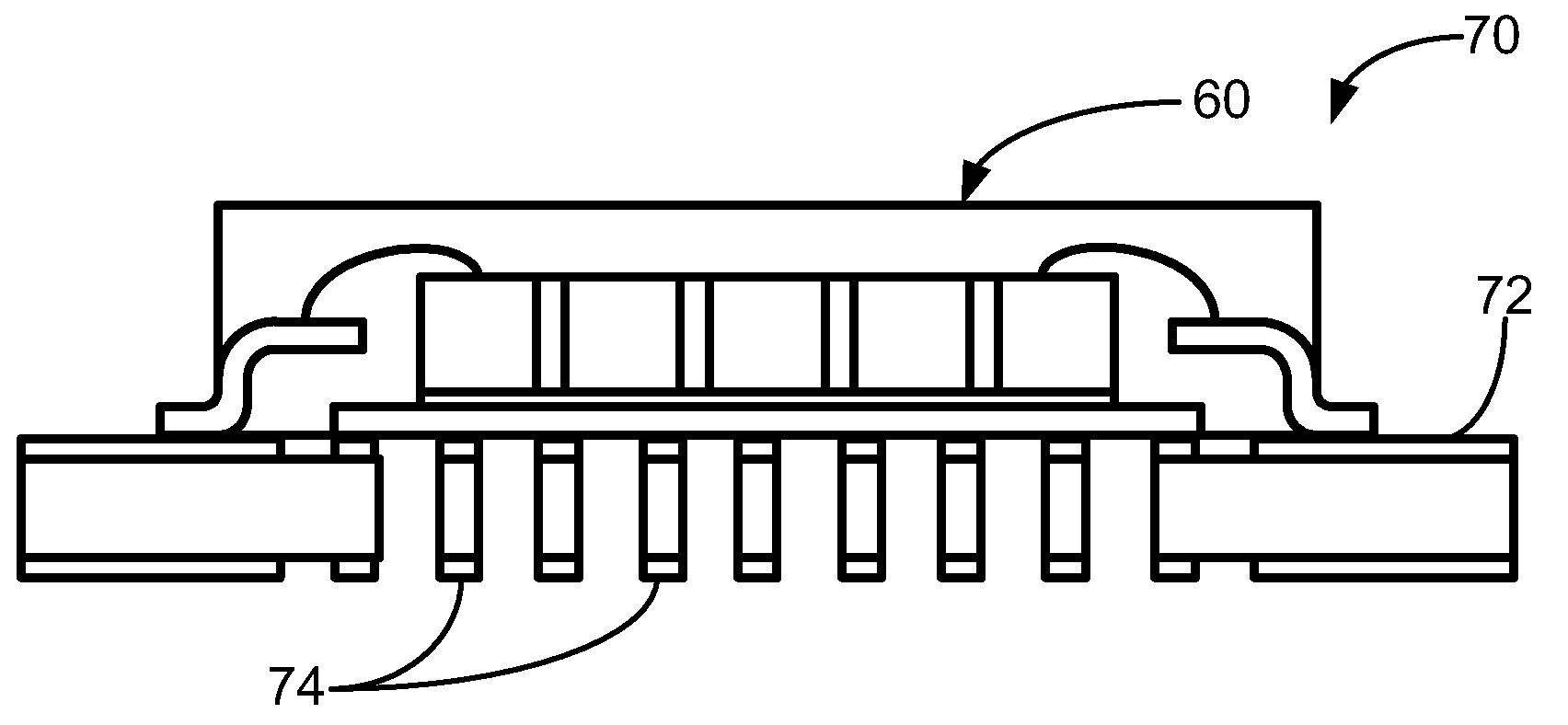

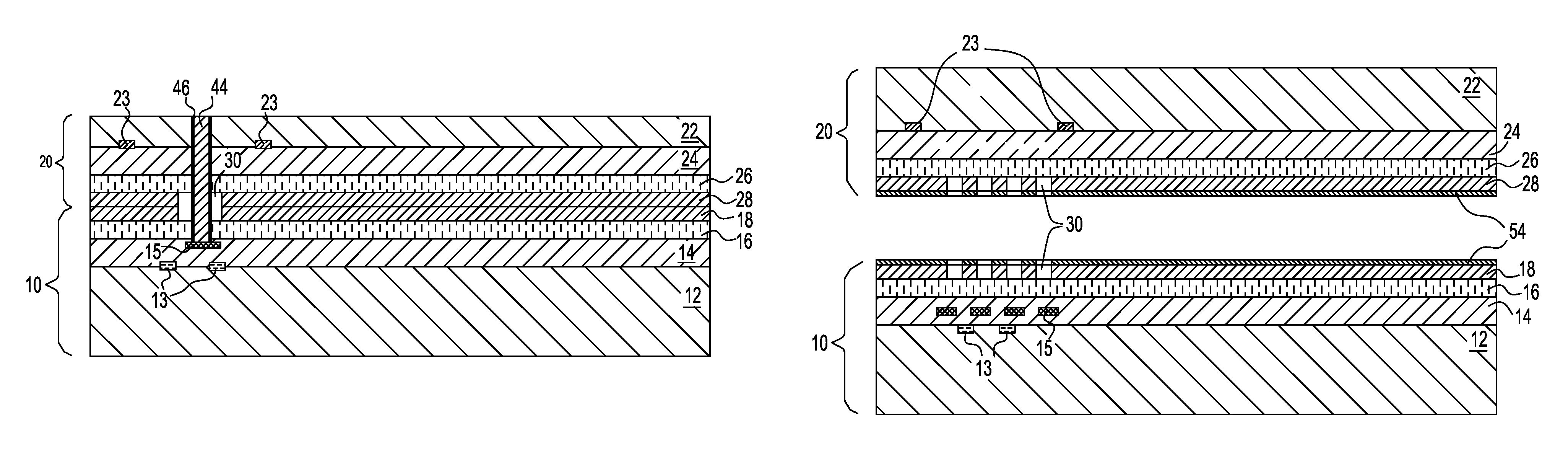

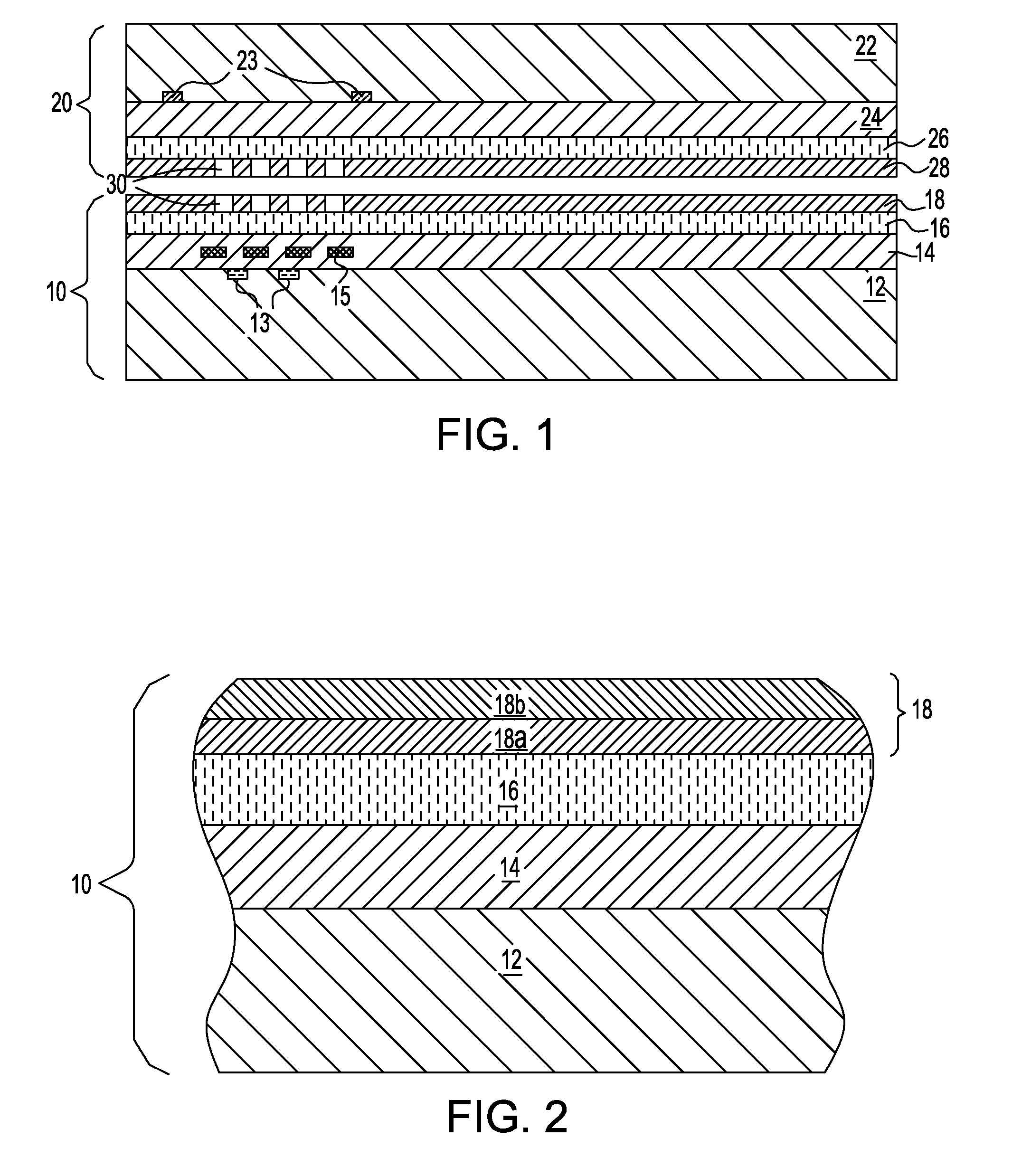

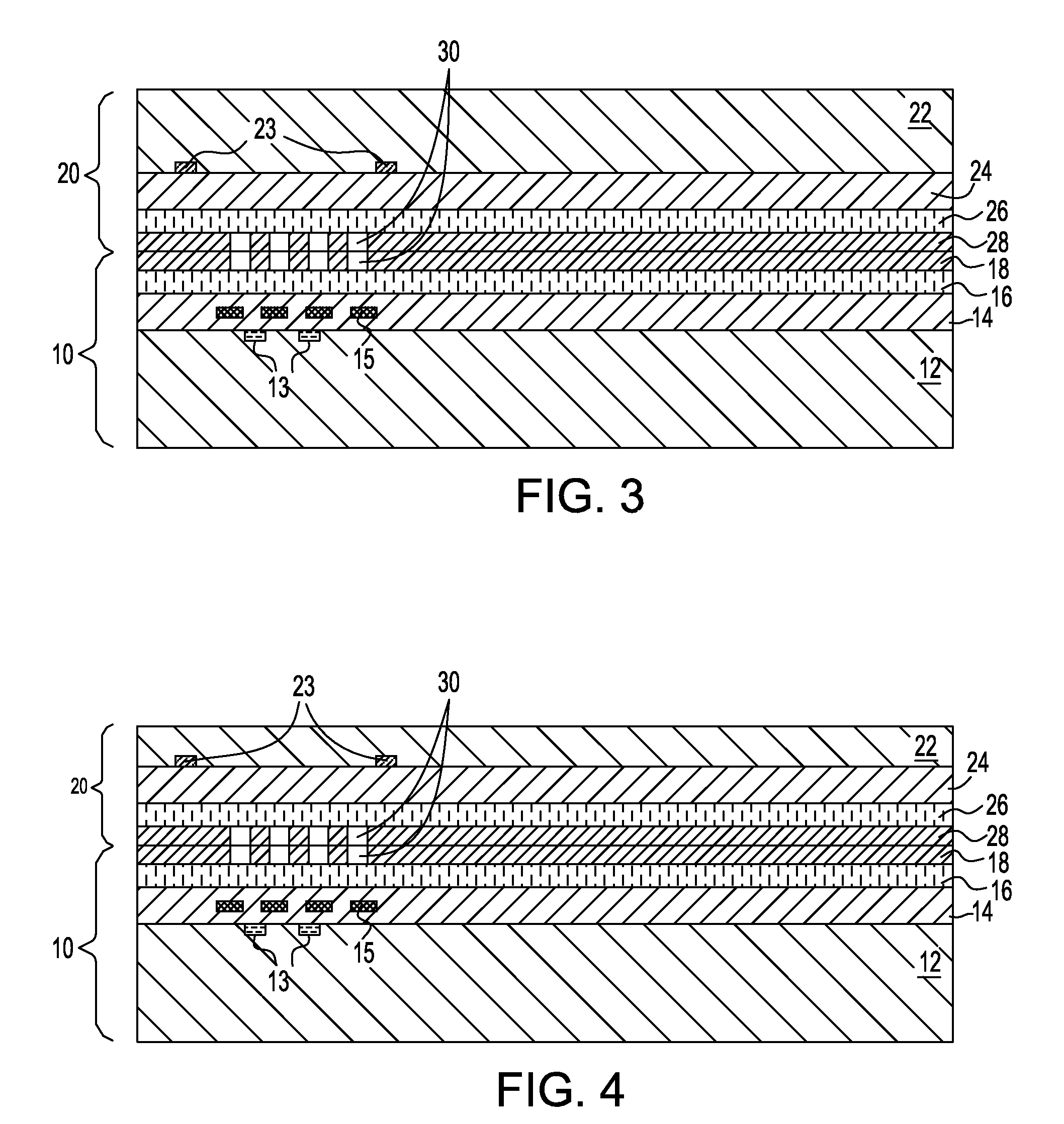

A method of making 3D integrated circuits and a 3D integrated circuit structure. There is a first semiconductor structure joined to a second semiconductor structure. Each semiconductor structure includes a semiconductor wafer, a front end of the line (FEOL) wiring on the semiconductor wafer, a back end of the line (BEOL) wiring on the FEOL wiring, an insulator layer on the BEOL wiring and a metallic layer on the insulator layer. The first semiconductor structure is aligned with the second semiconductor structure such that the metallic layers of each of the semiconductor structures face each other. The metallic layers of each of the semiconductor structures are in contact with and bonded to each other by a metal to metal bond wherein the bonded metallic layers form an electrically isolated layer.

Owner:TESSERA INC

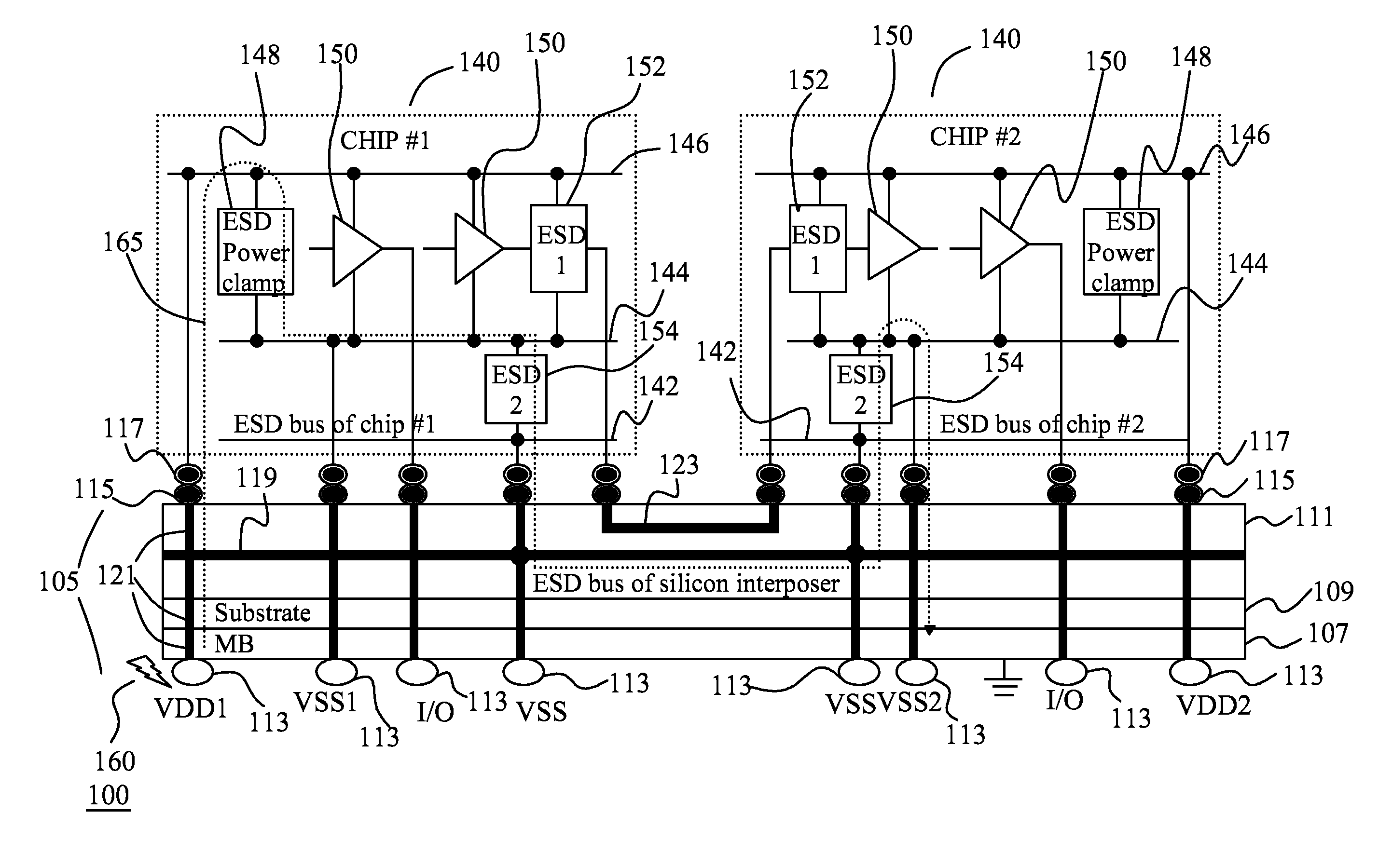

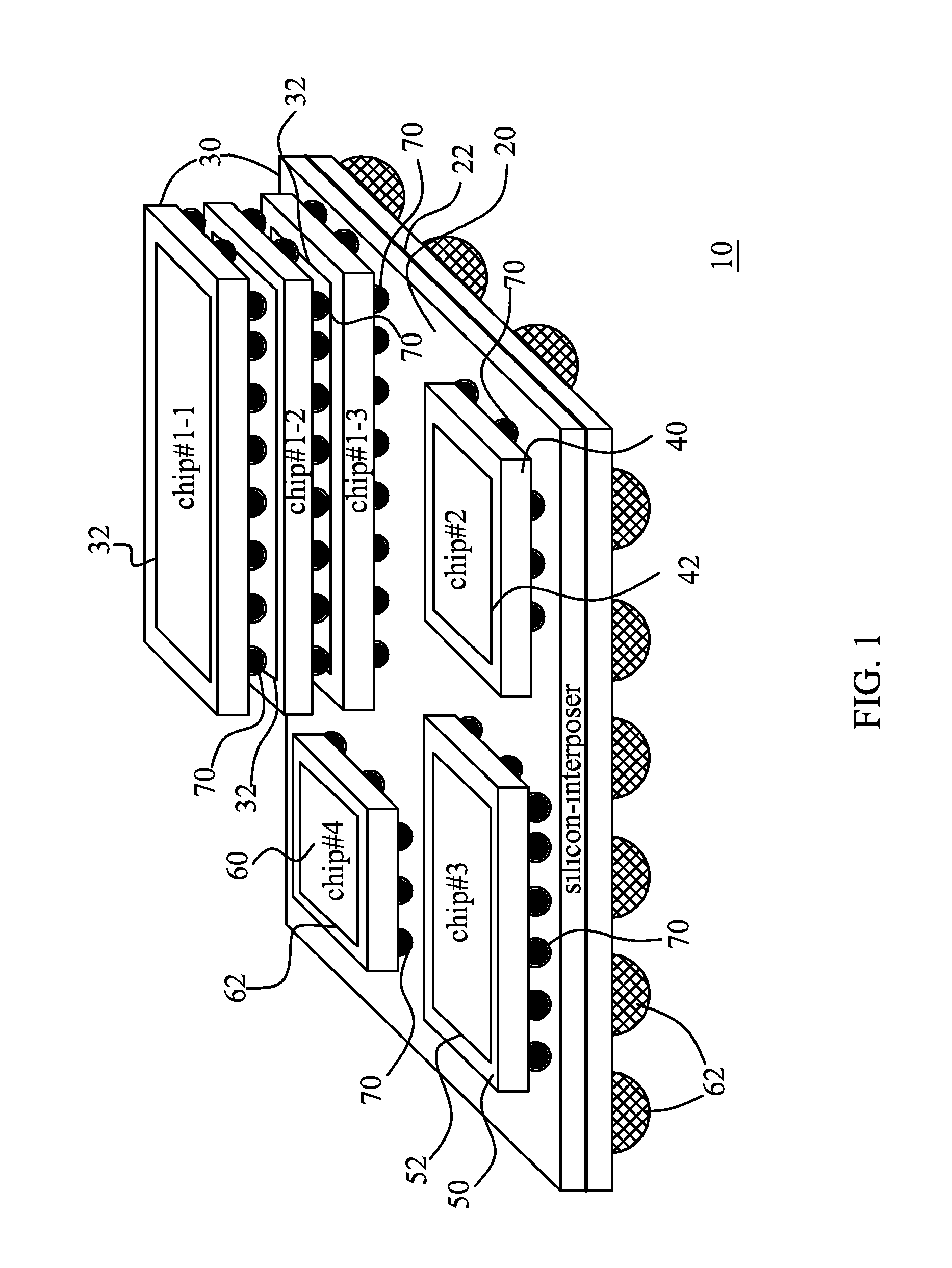

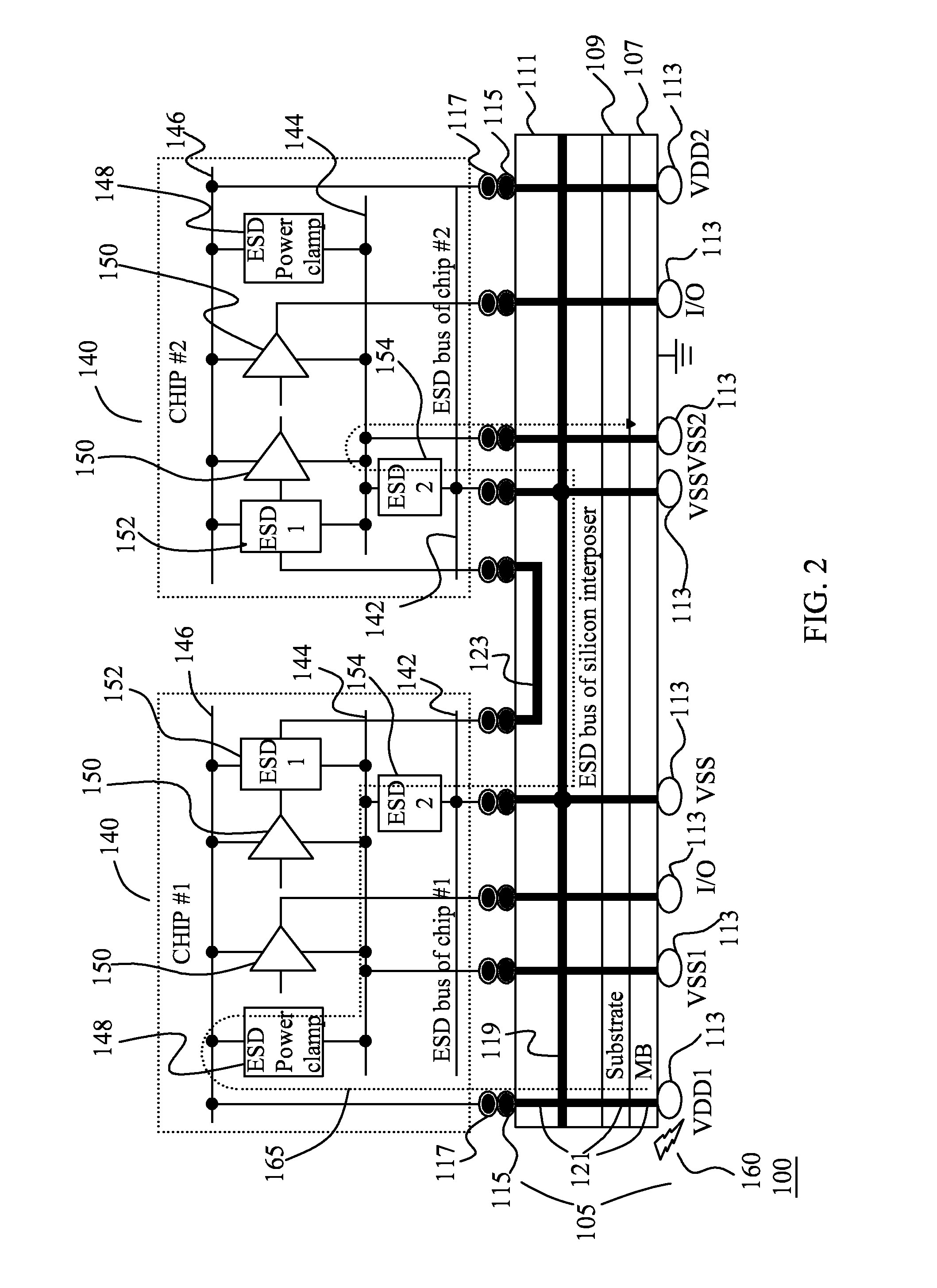

ESD protection for 2.5d/3d integrated circuit systems

ActiveUS20130063843A1Semiconductor/solid-state device detailsSolid-state devices3d integrated circuitInterposer

An integrated circuit structure includes first and second integrated circuit devices disposed on a interposer. Each integrated circuit device has electrostatic discharge (ESD) protection circuitry therein connected to an internal ESD bus. The first and second integrated circuit devices communicate with one another through the interposer. The interposer includes an ESD bus electrically connected to the ESD busses of the first and second integrated circuit devices for providing cross-device ESD protection for the integrated circuit devices.

Owner:TAIWAN SEMICON MFG CO LTD

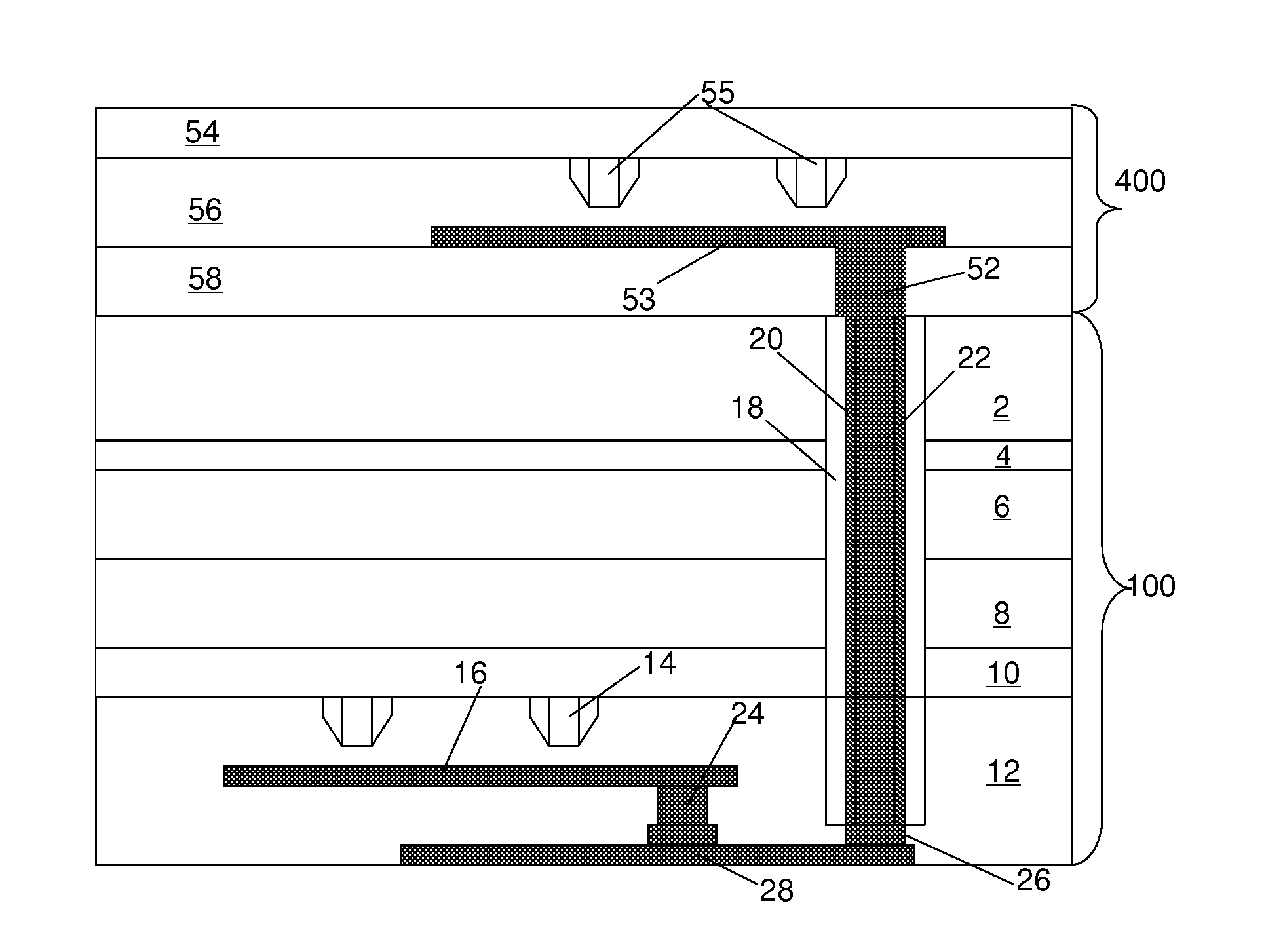

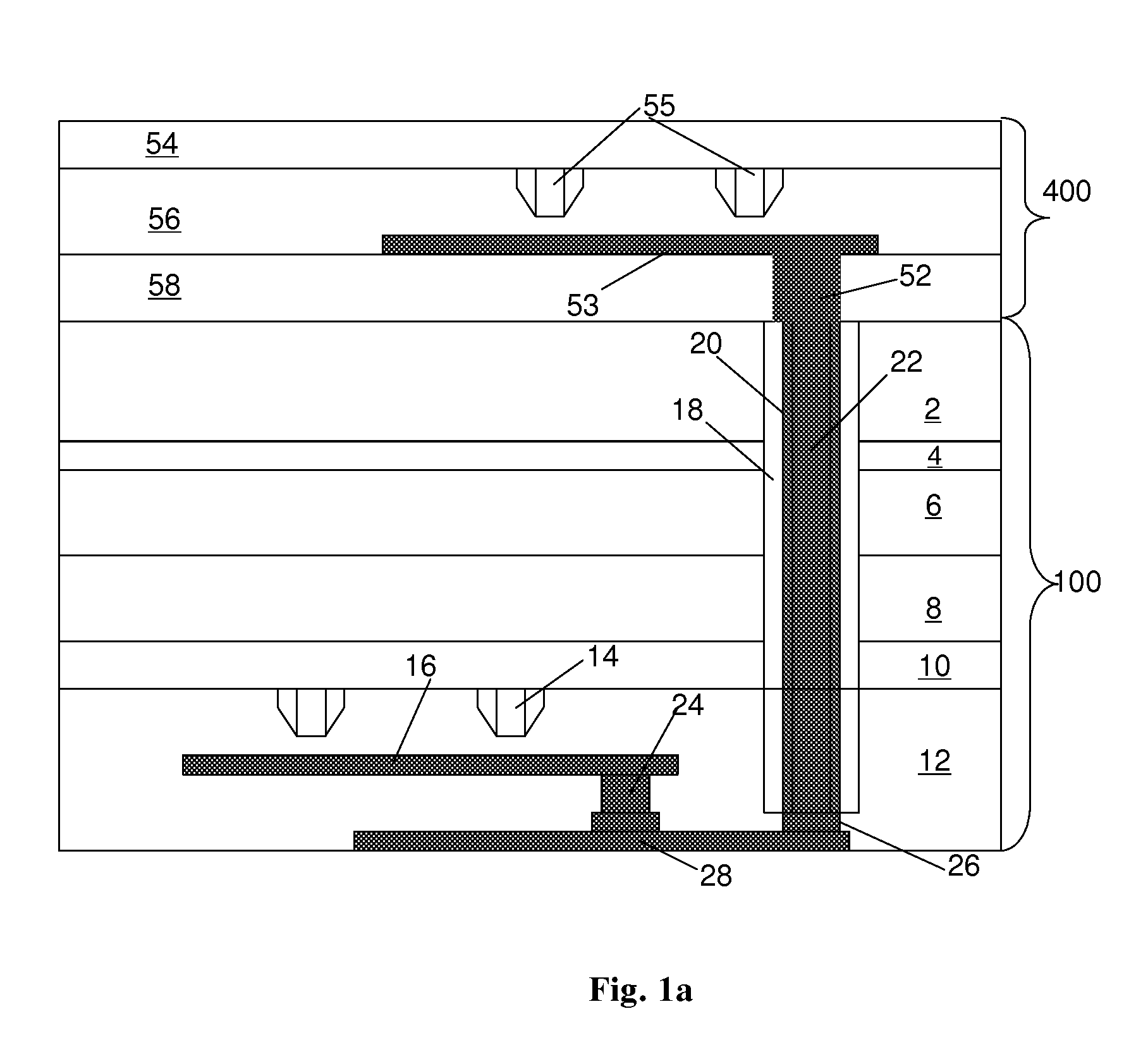

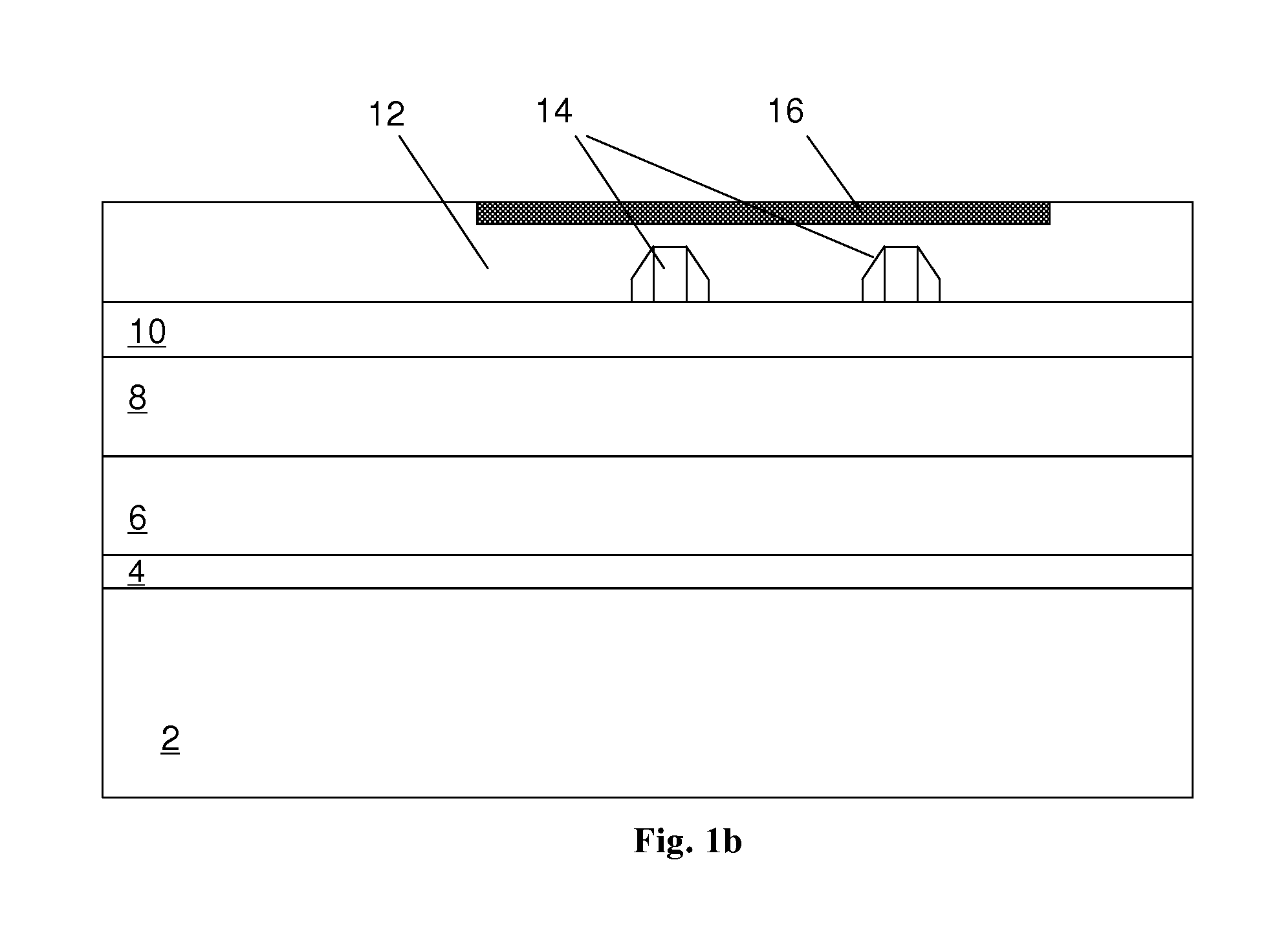

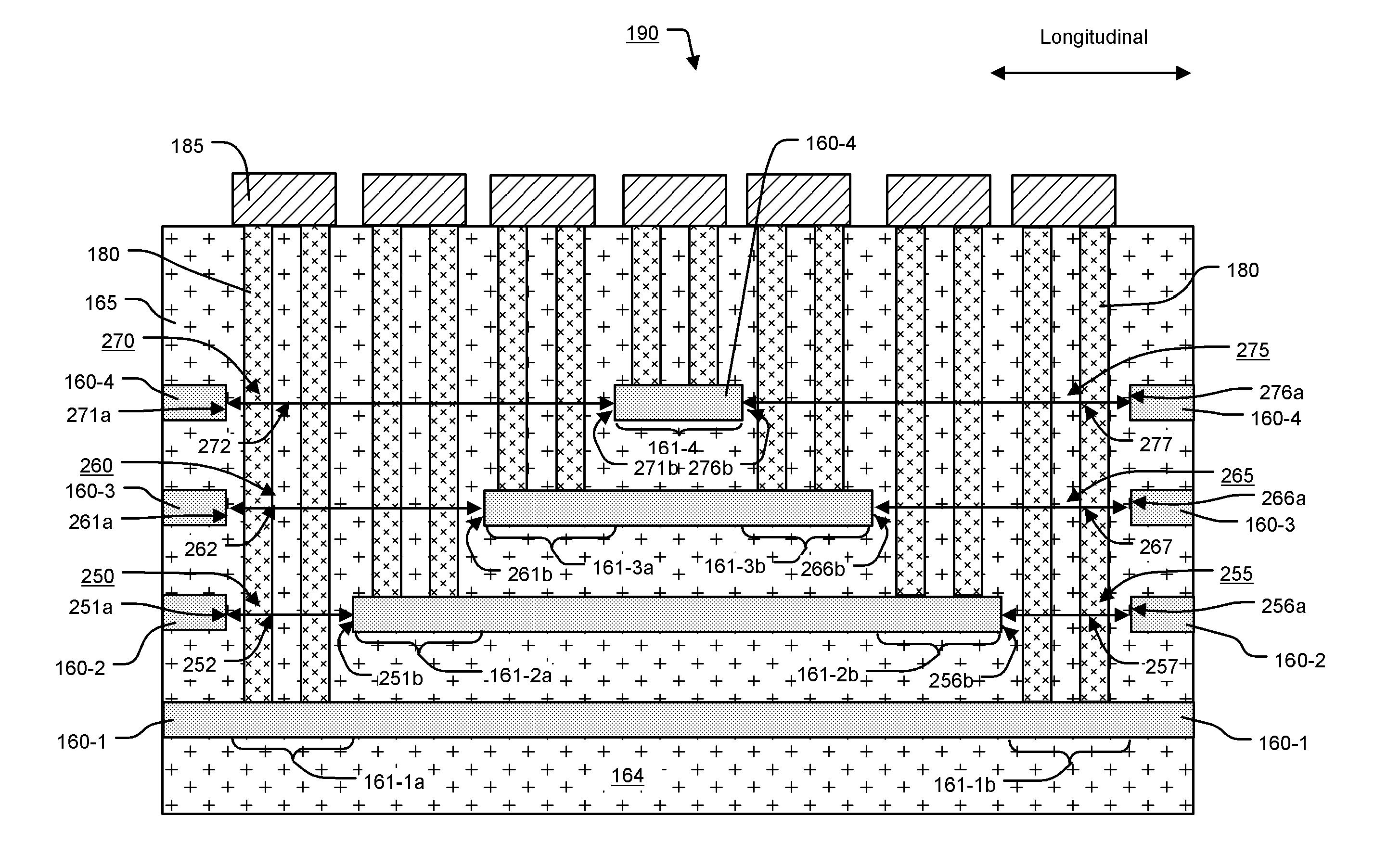

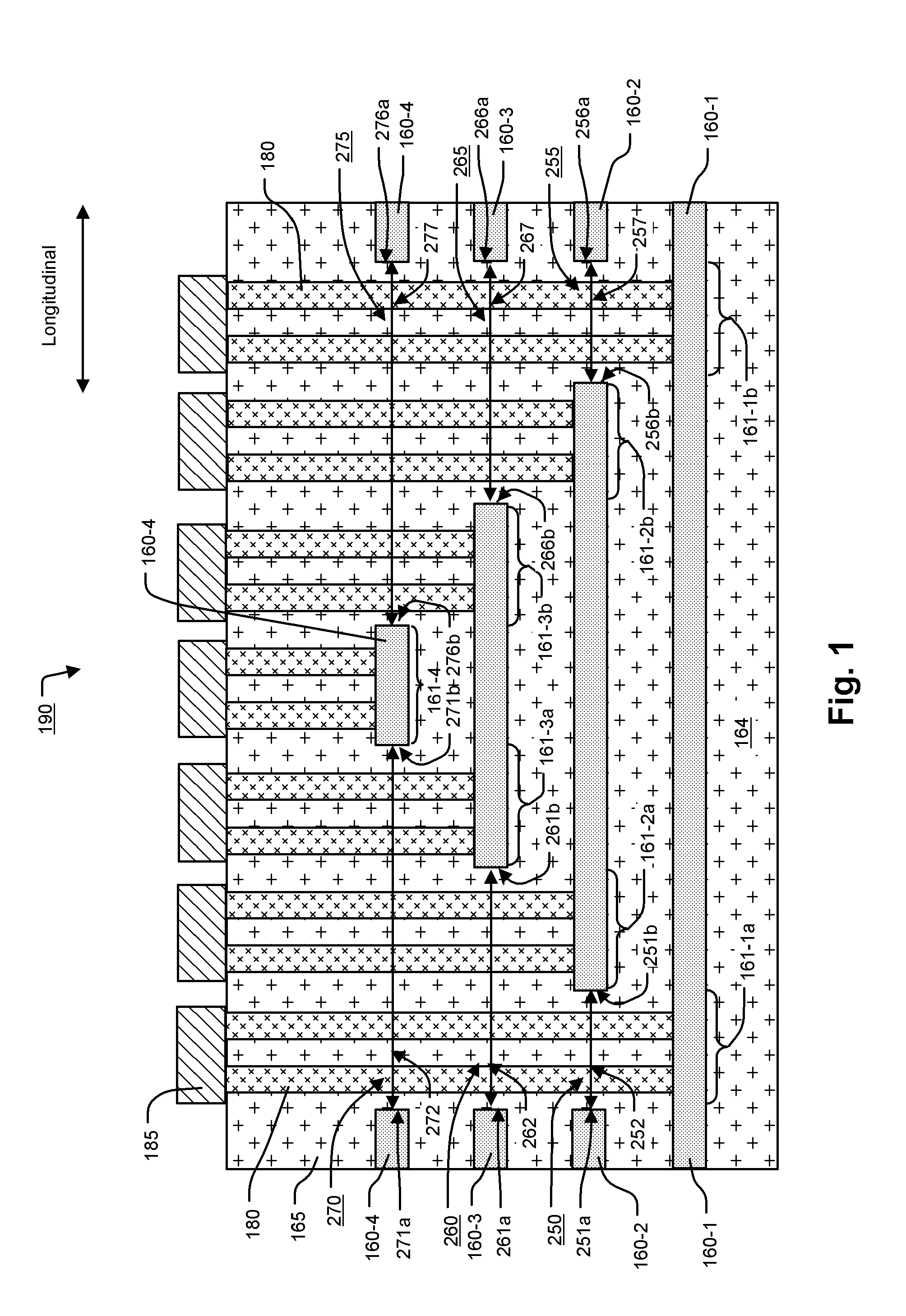

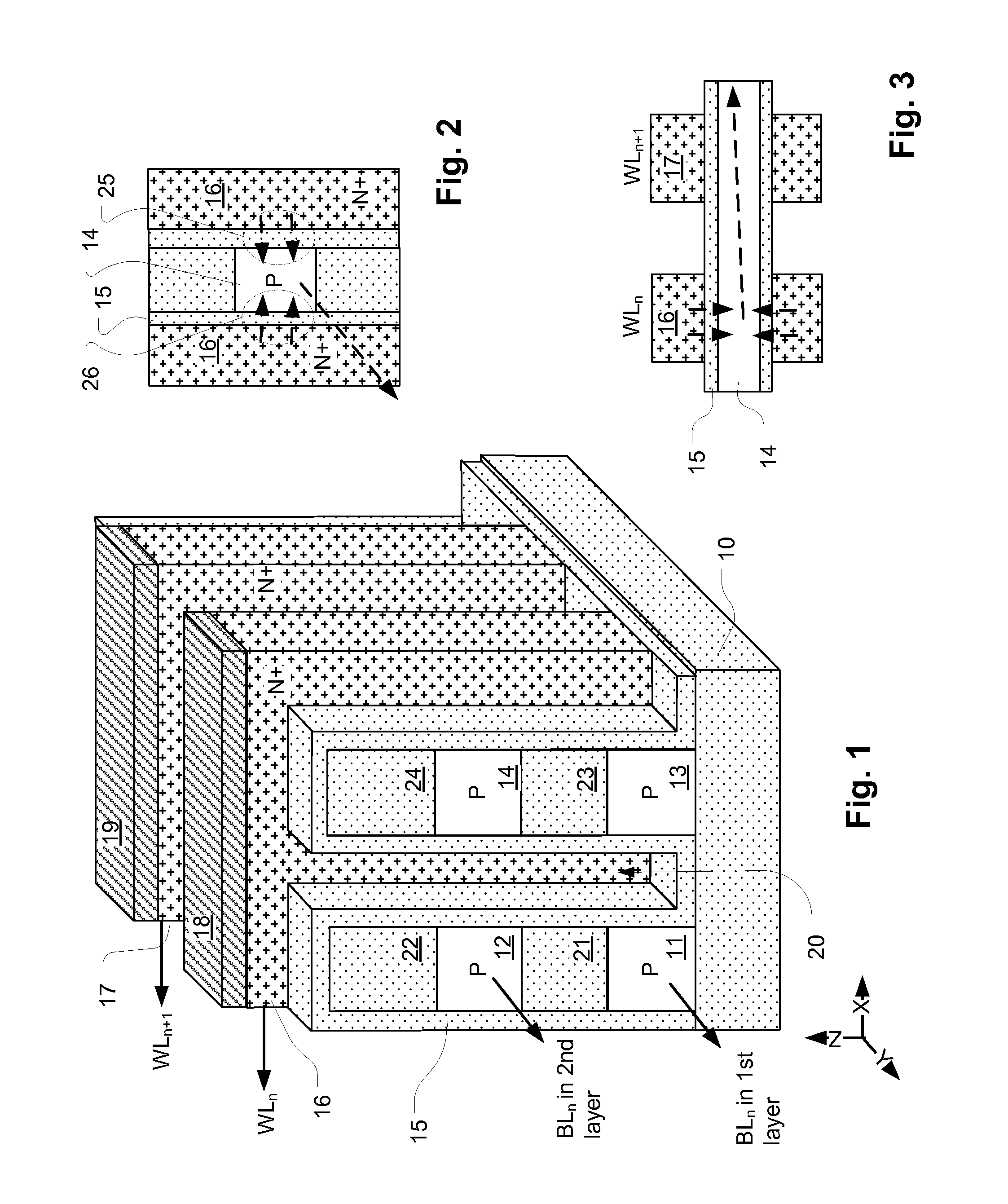

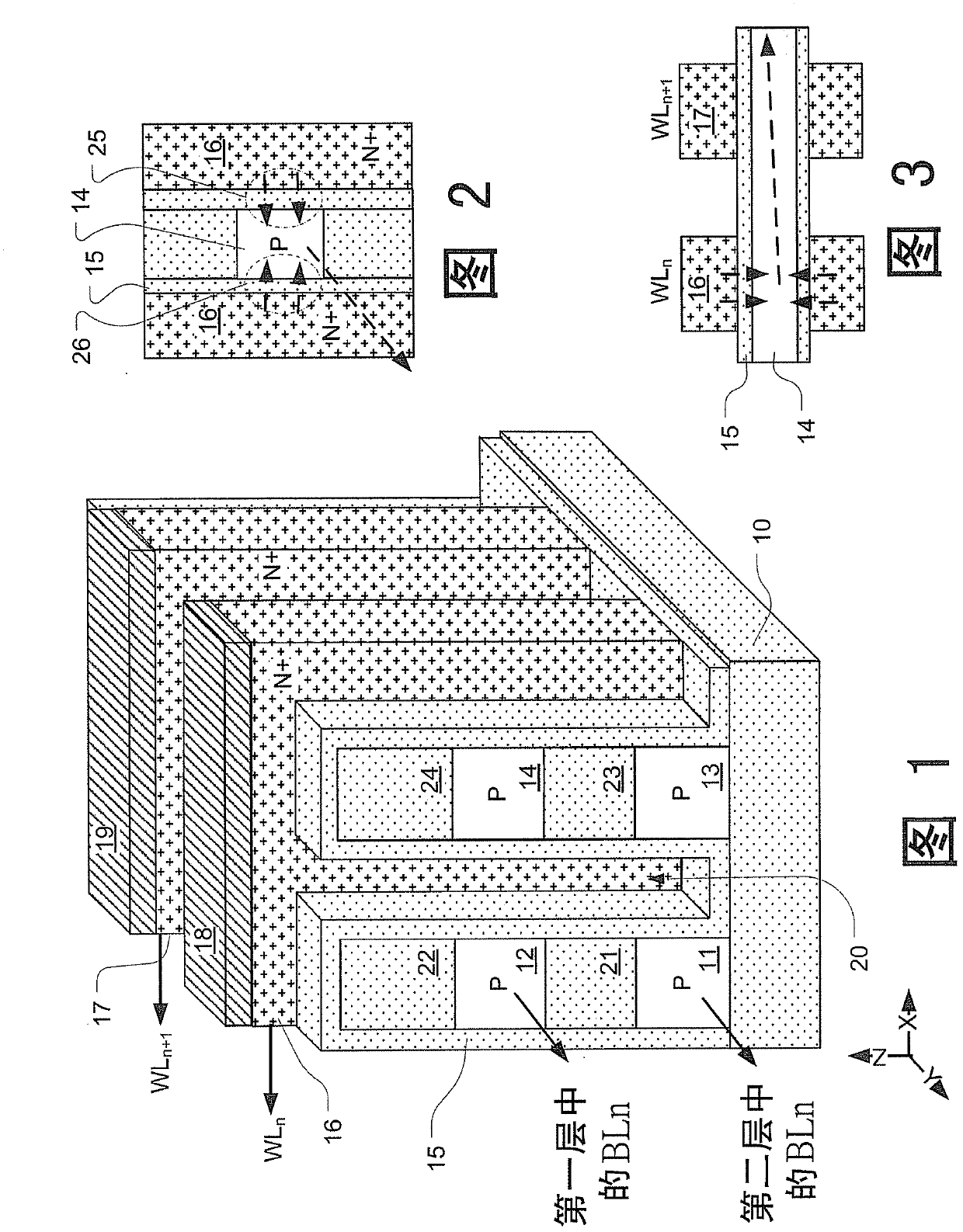

3D integrated circuit layer interconnect

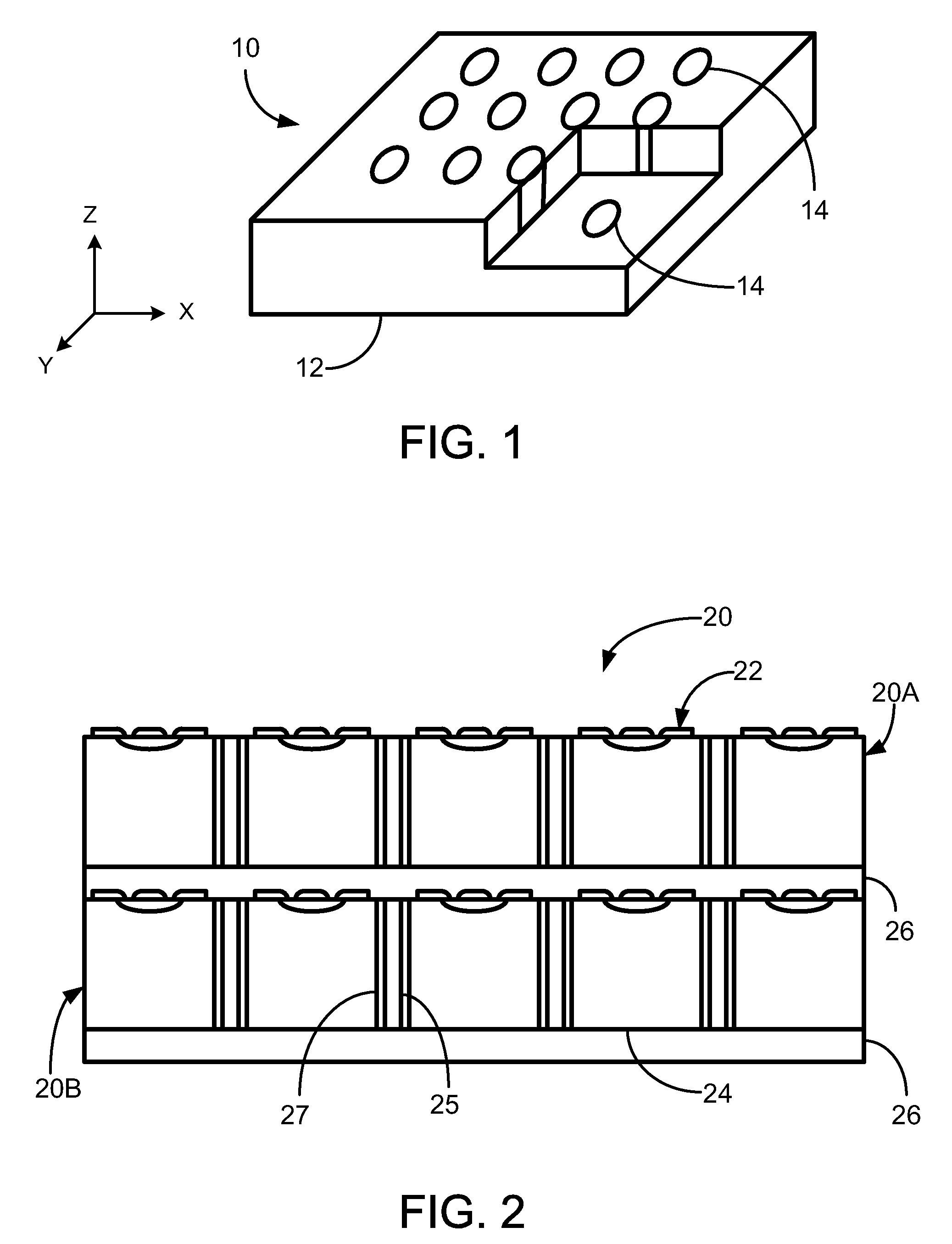

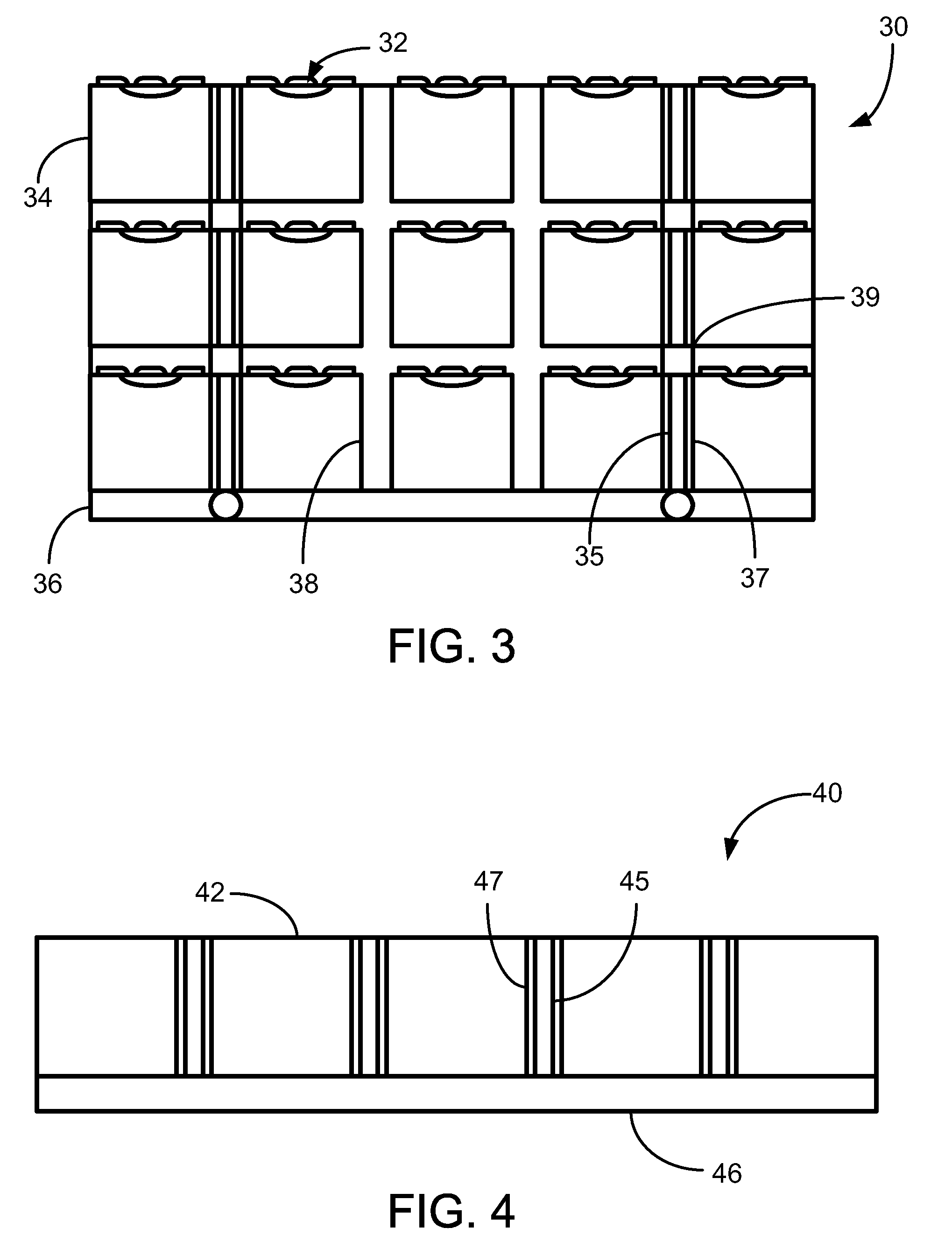

ActiveUS20110084397A1Efficient and low methodSmall footprintTransistorSemiconductor/solid-state device details3d integrated circuitSmall footprint

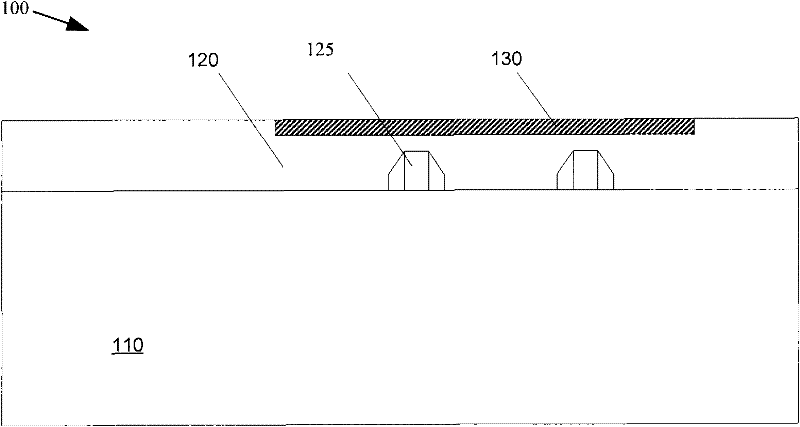

A three-dimensional 3D interconnect structure with a small footprint is described, useful for connection from above to levels of circuit structures in a multi-level device. Also, an efficient and low cost method for manufacturing the 3D interconnect structure is provided.

Owner:MACRONIX INT CO LTD

3D semiconductor device and structure

ActiveUS20170213821A1TransistorSemiconductor/solid-state device detailsPower semiconductor device3d integrated circuit

A 3D integrated circuit device, including: a first layer including first transistors, overlaid by a second layer including second transistors, overlaid by a third layer including third transistors, where the first layer, the second layer and the third layer are each thinner than 2 microns, where the first layer includes first circuits including at least one of the first transistors, where the second layer includes second circuits including at least one of the second transistors, and where the third layer includes a charge pump circuit and control circuits to control the first circuits and the second circuits

Owner:MONOLITHIC 3D

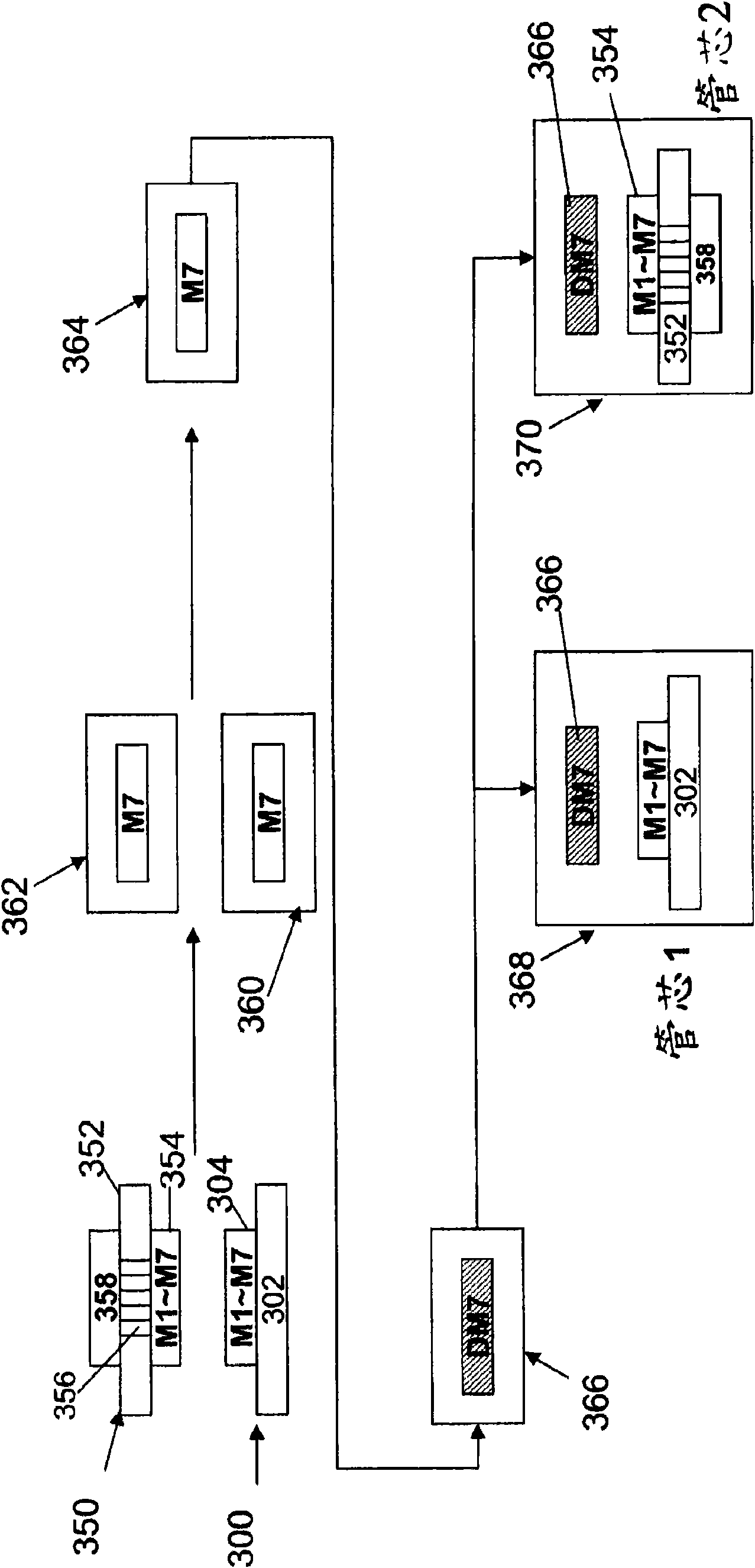

3D integrated circuit device having lower-cost active circuitry layers stacked before higher-cost active circuitry layer

ActiveUS20100314711A1Low costLower-costSolid-state devicesSemiconductor/solid-state device manufacturing3d integrated circuitIntegrated circuit design

A method is provided for fabricating a 3D integrated circuit structure. According to the method, a first active circuitry layer wafer that includes active circuitry is provided, and a first portion of the first active circuitry layer wafer is removed such that a second portion of the first active circuitry layer wafer remains. Another wafer that includes active circuitry is provided, and the other wafer is bonded to the second portion of the first active circuitry layer wafer. The first active circuitry layer wafer is lower-cost than the other wafer. Also provided are a tangible computer readable medium encoded with a program for fabricating a 3D integrated circuit structure, and a 3D integrated circuit structure.

Owner:GLOBALFOUNDRIES US INC

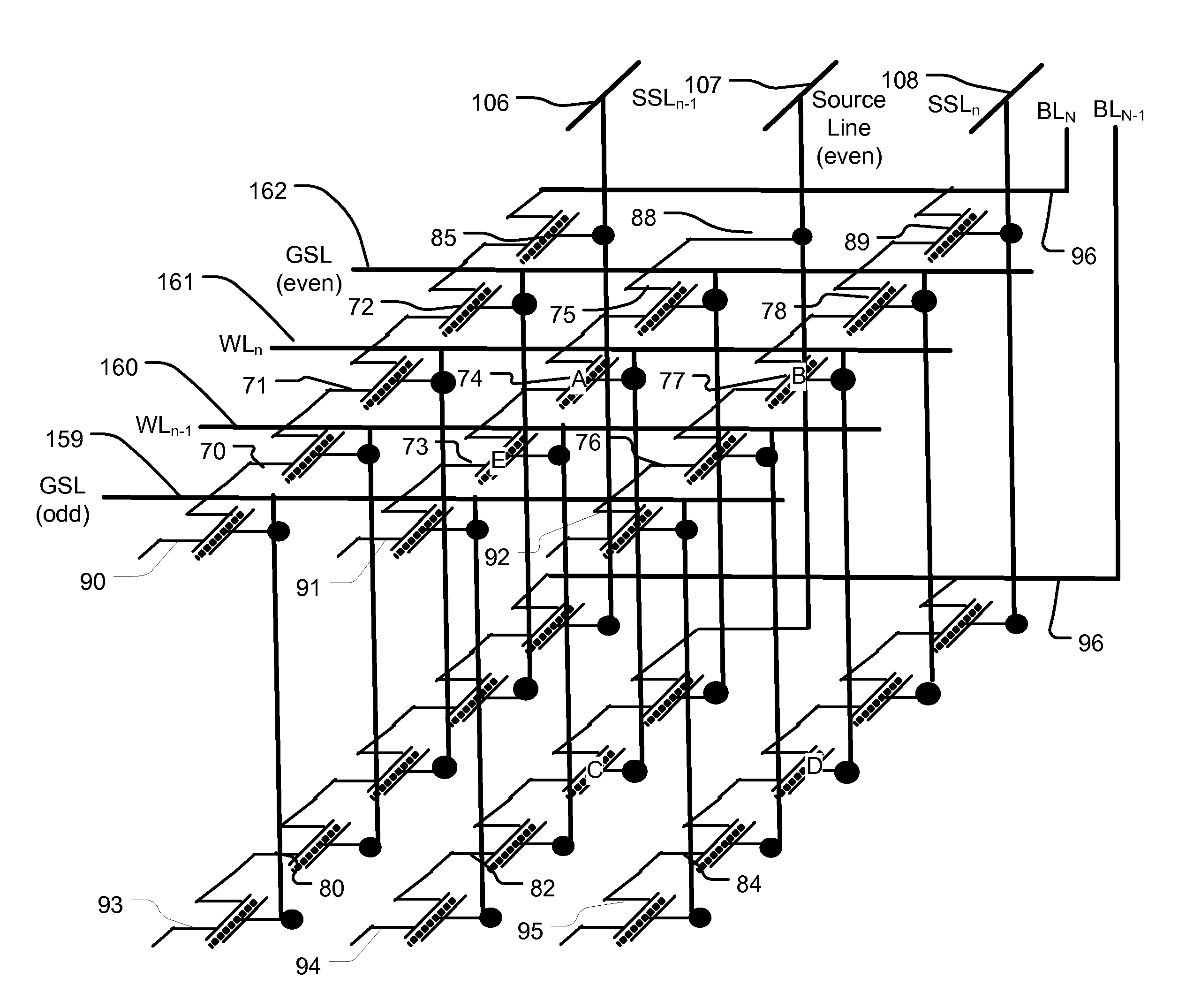

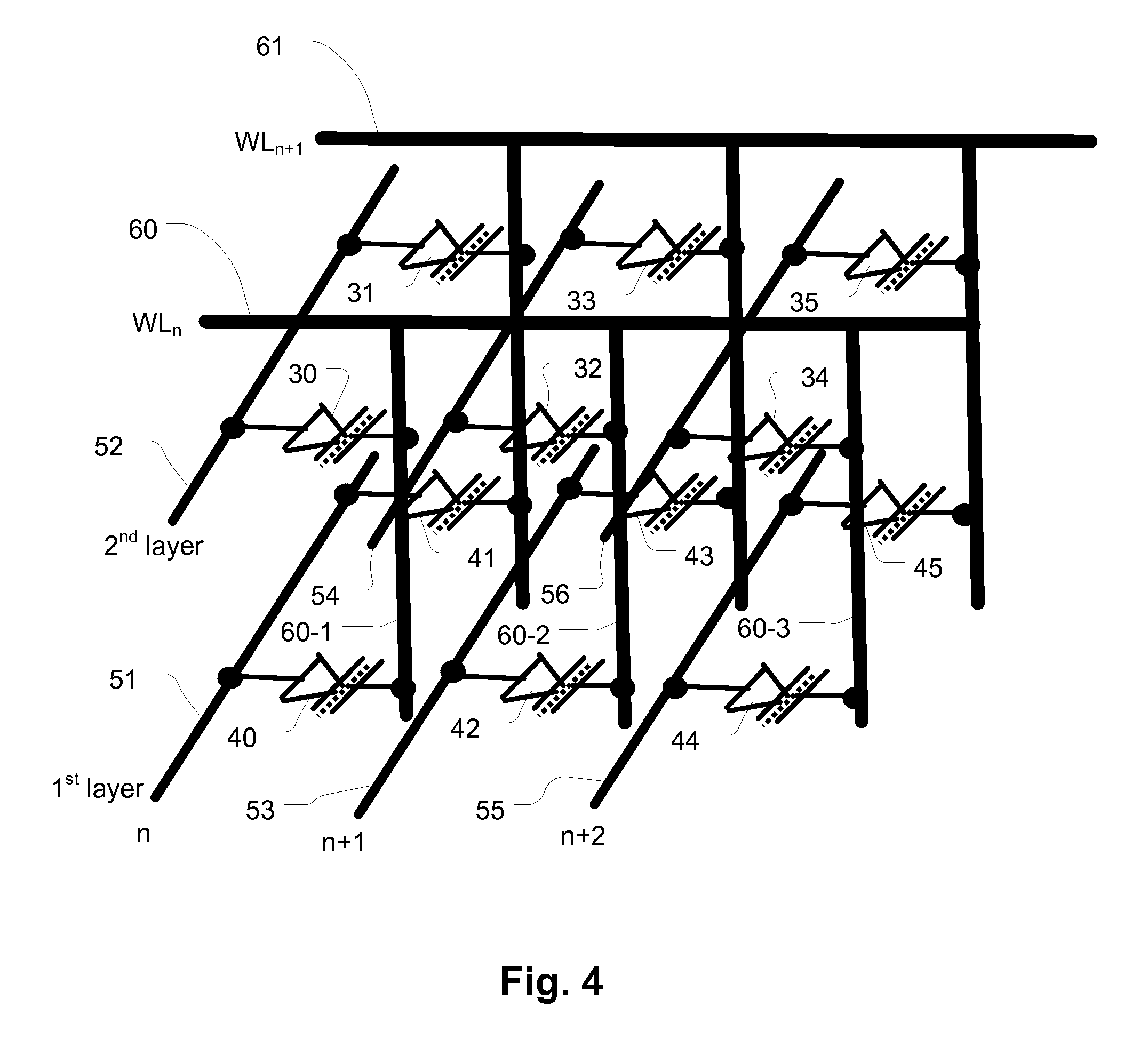

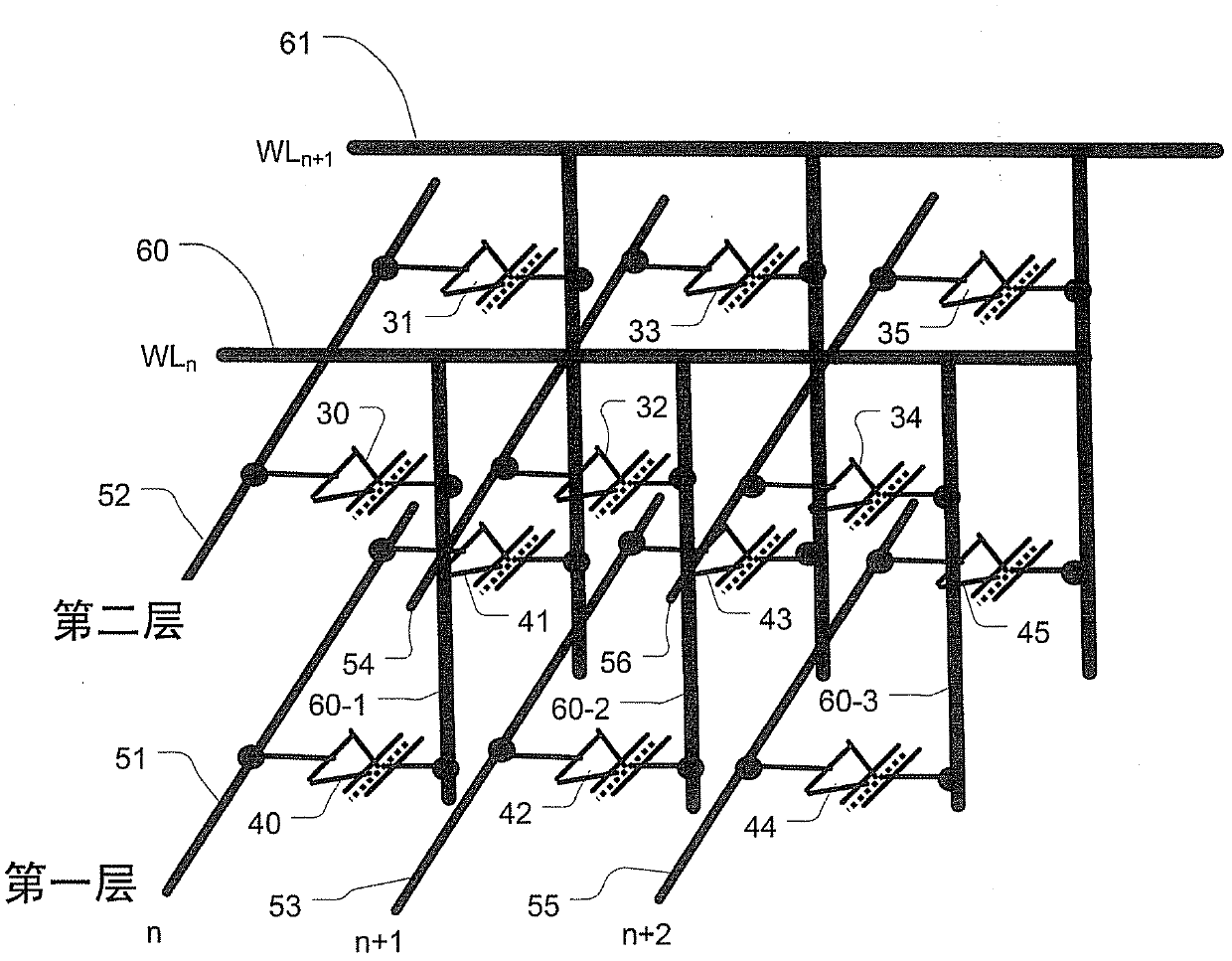

Memory Architecture of 3D Array With Improved Uniformity of Bit Line Capacitances

ActiveUS20120182802A1Good senseMinimize capacitanceTransistorSolid-state devicesCapacitance3d integrated circuit

A 3D integrated circuit memory array has a plurality of plane positions. Multiple bit line structures have a multiple sequences of multiple plane positions. Each sequence characterizes an order in which a bit line structure couples the plane positions to bit lines. Each bit line is coupled to at least two different plane positions to access memory cells at two or more different plane positions.

Owner:MACRONIX INT CO LTD

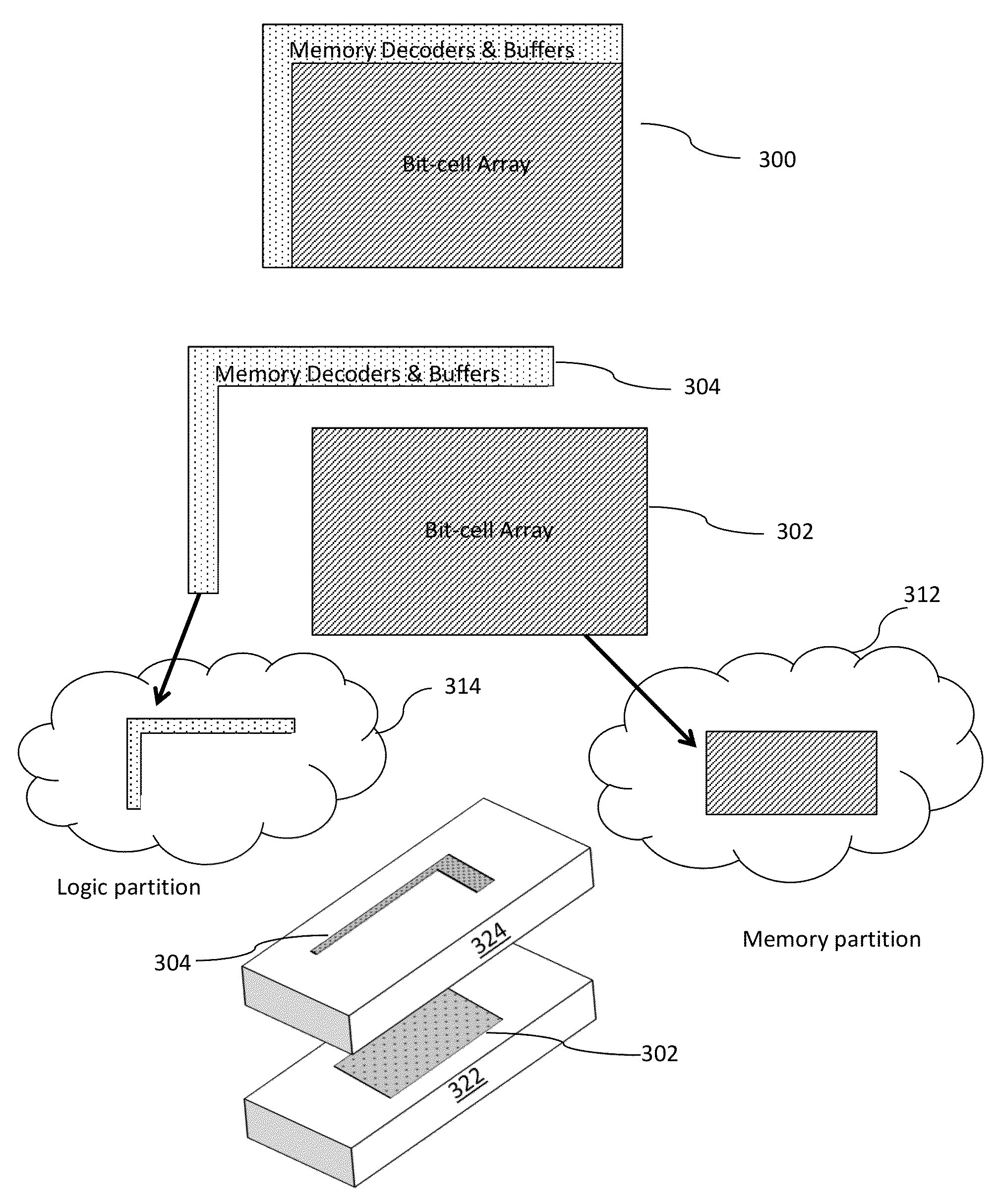

Automation for monolithic 3D devices

ActiveUS9021414B1Increase physical distanceMinimize the numberComputer aided designSpecial data processing applications3d integrated circuitEngineering

A method of designing a 3D Integrated Circuit, the method including: performing placement using a 2D placer, performing placement for at least a first strata and a second strata, and then performing routing and completing the physical design of said 3D Integrated Circuit.

Owner:MONOLITHIC 3D

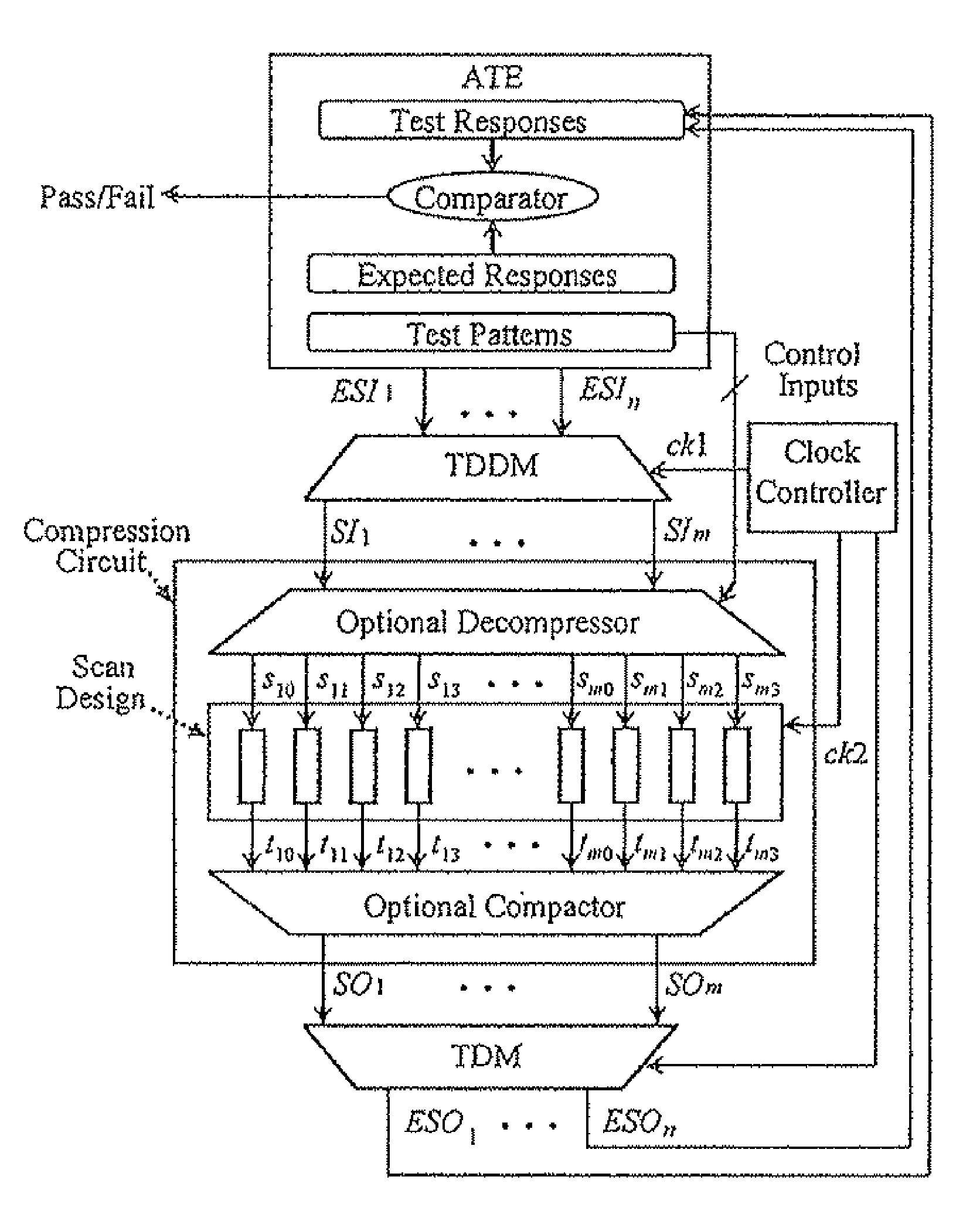

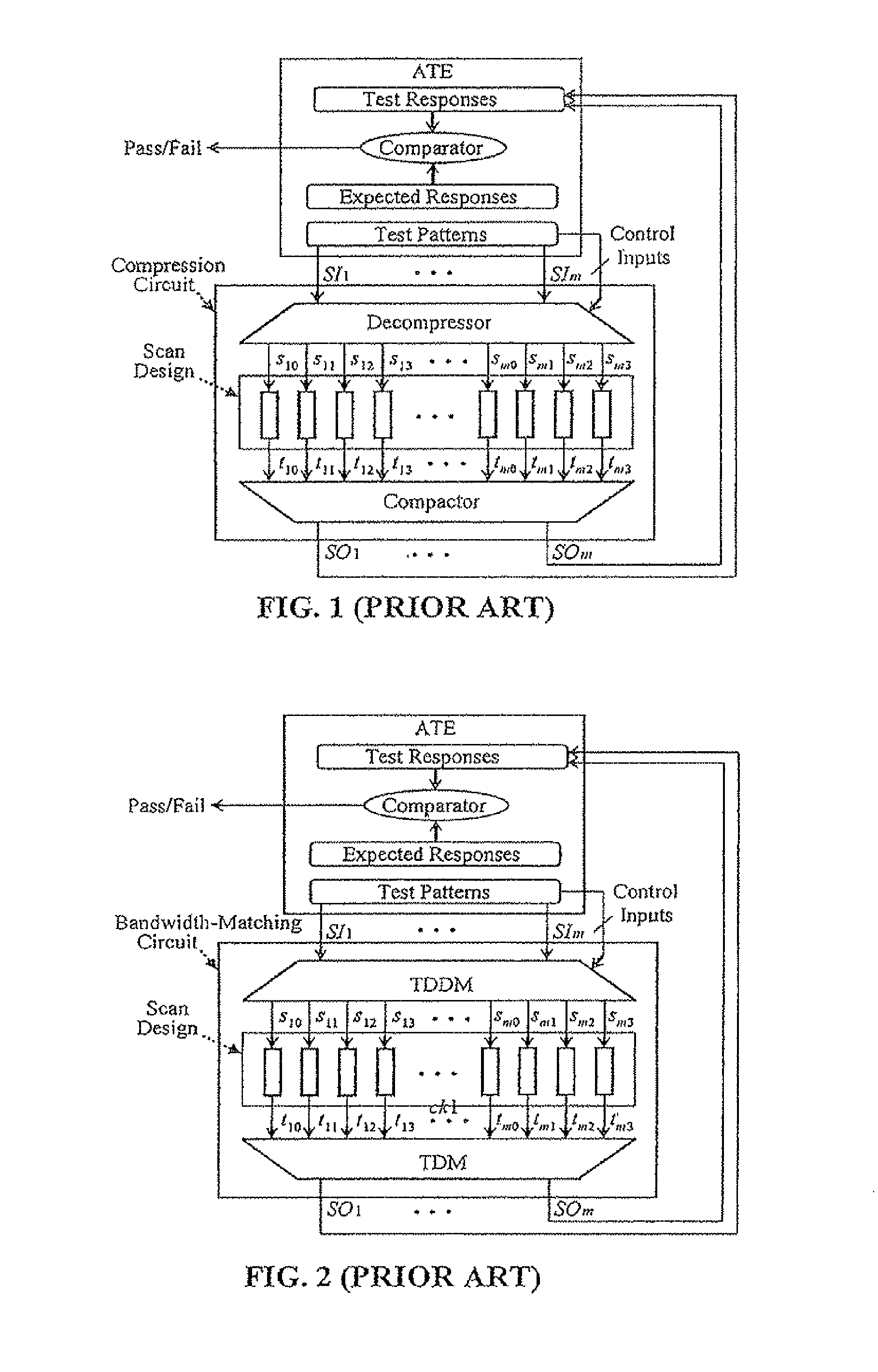

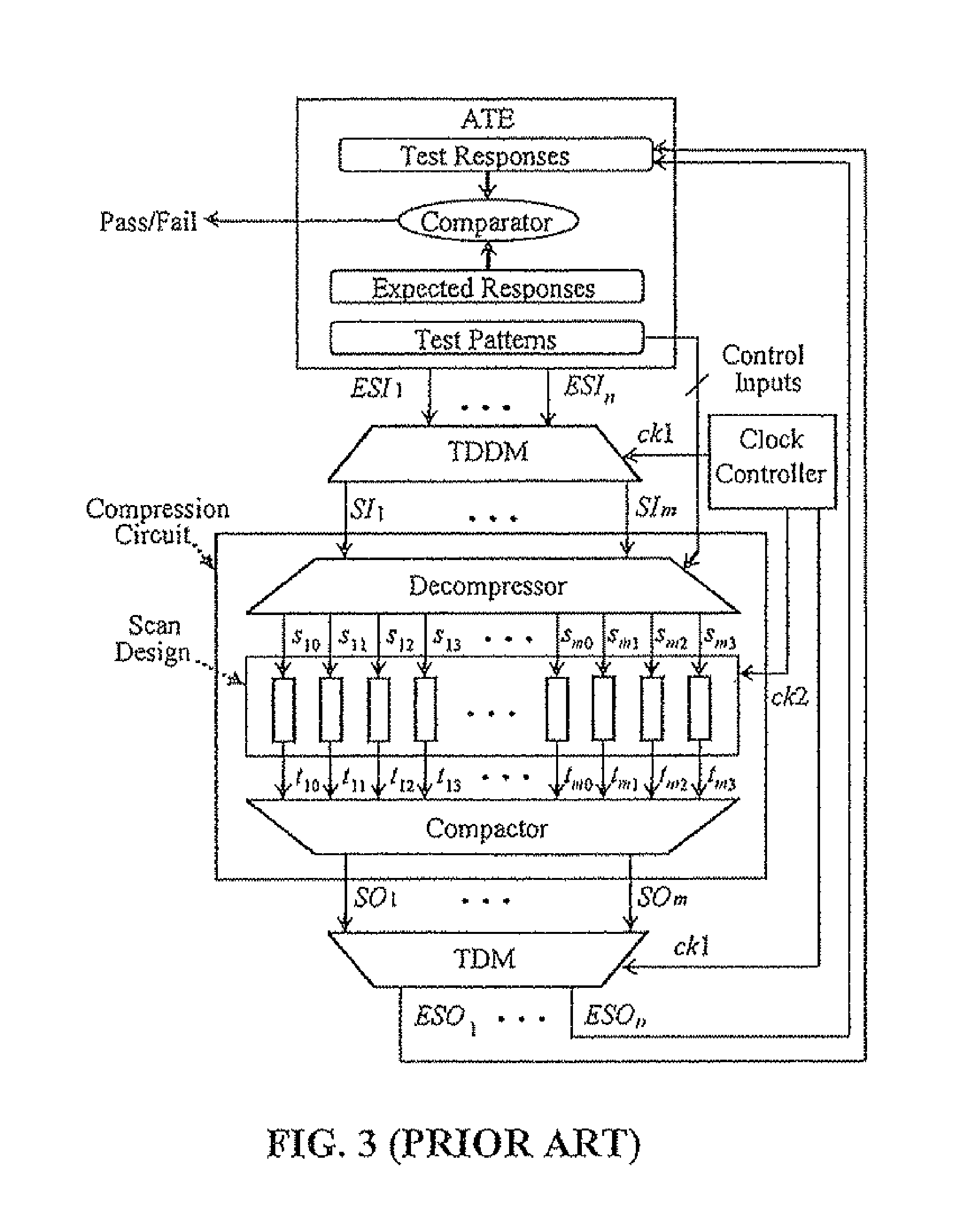

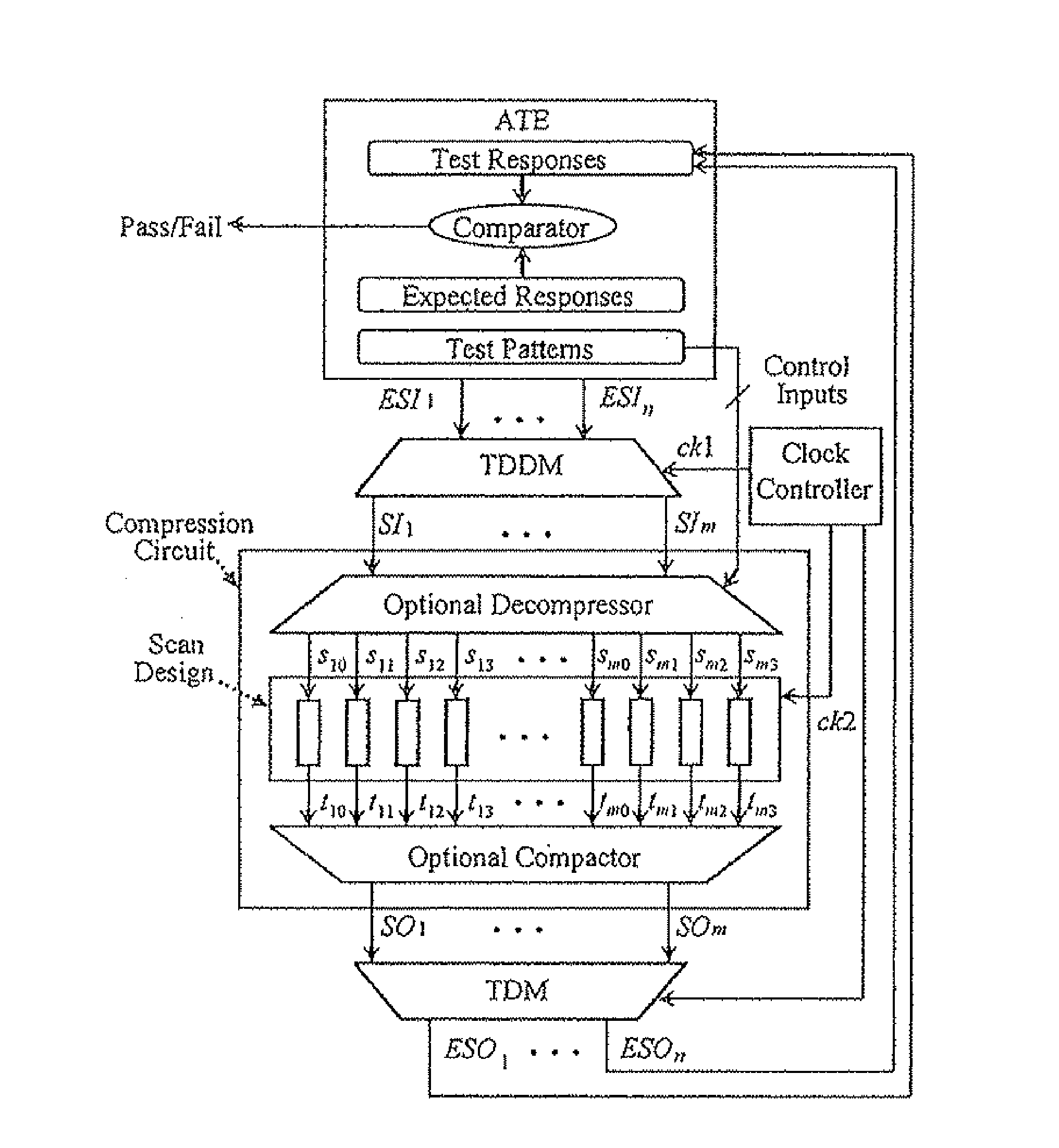

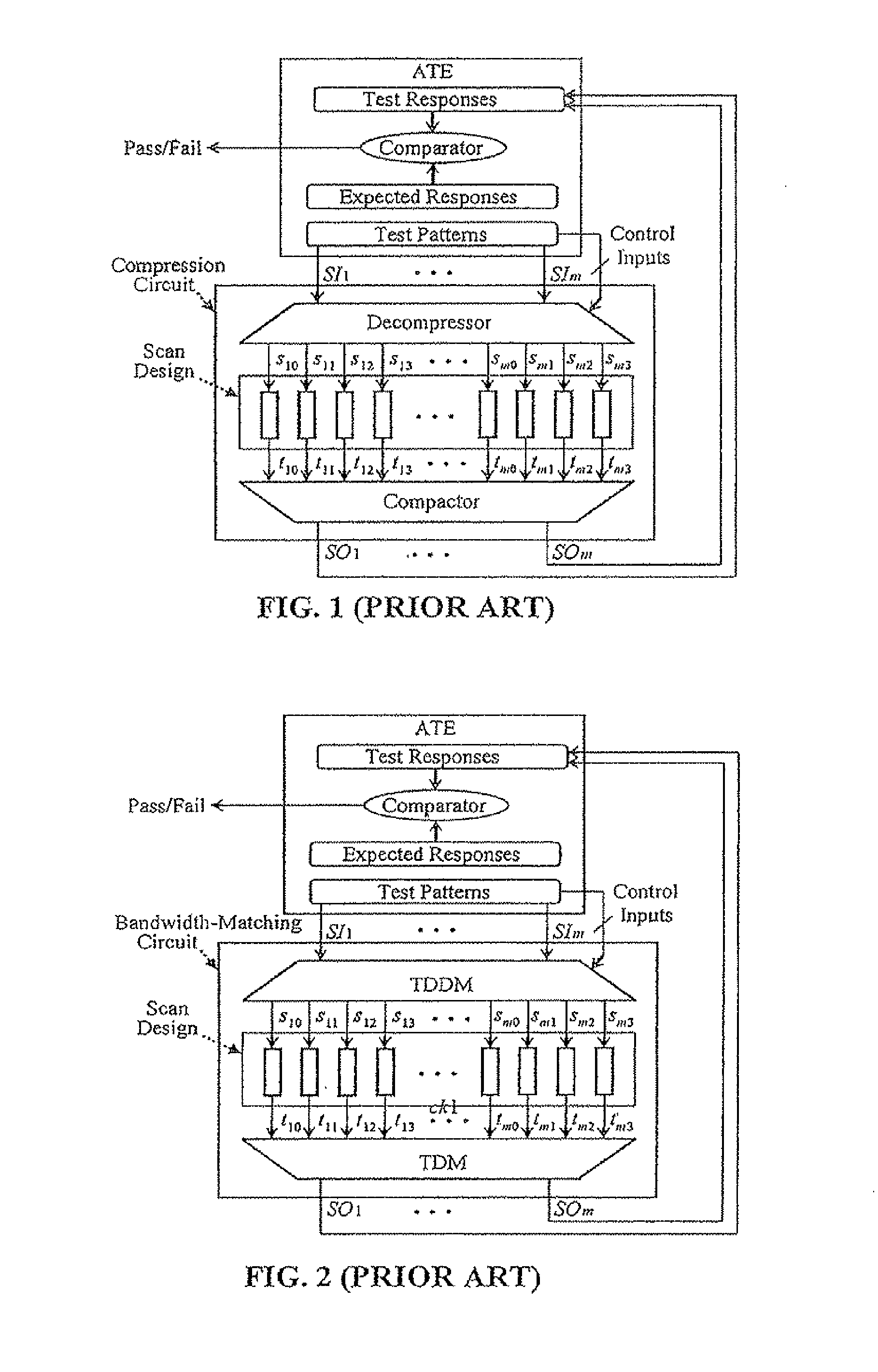

Method and apparatus for testing 3D integrated circuits

InactiveUS8522096B2Reduce testing costsIncrease data rateElectronic circuit testingFault coverageEngineering

A method and apparatus for testing a scan-based 3D integrated circuit (3DIC) using time-division demultiplexing / multiplexing allowing for high-data-rate scan patterns applied at input / output pads converting into low-data-rate scan patterns applied to each embeddded module in the 3DIC. A set of 3D design guidelines is proposed to reduce the number of test times and the number of through-silicon vias (TSVs) required for both pre-bond testing and post-bond testing. The technique allows reuse of scan patterns developed for pre-bond testing of each die (layer) for post-bond testing of the whole 3DIC. It further reduces test application time without concerns for I / O pad count limit and risks for fault coverage loss.

Owner:SYNTEST TECH

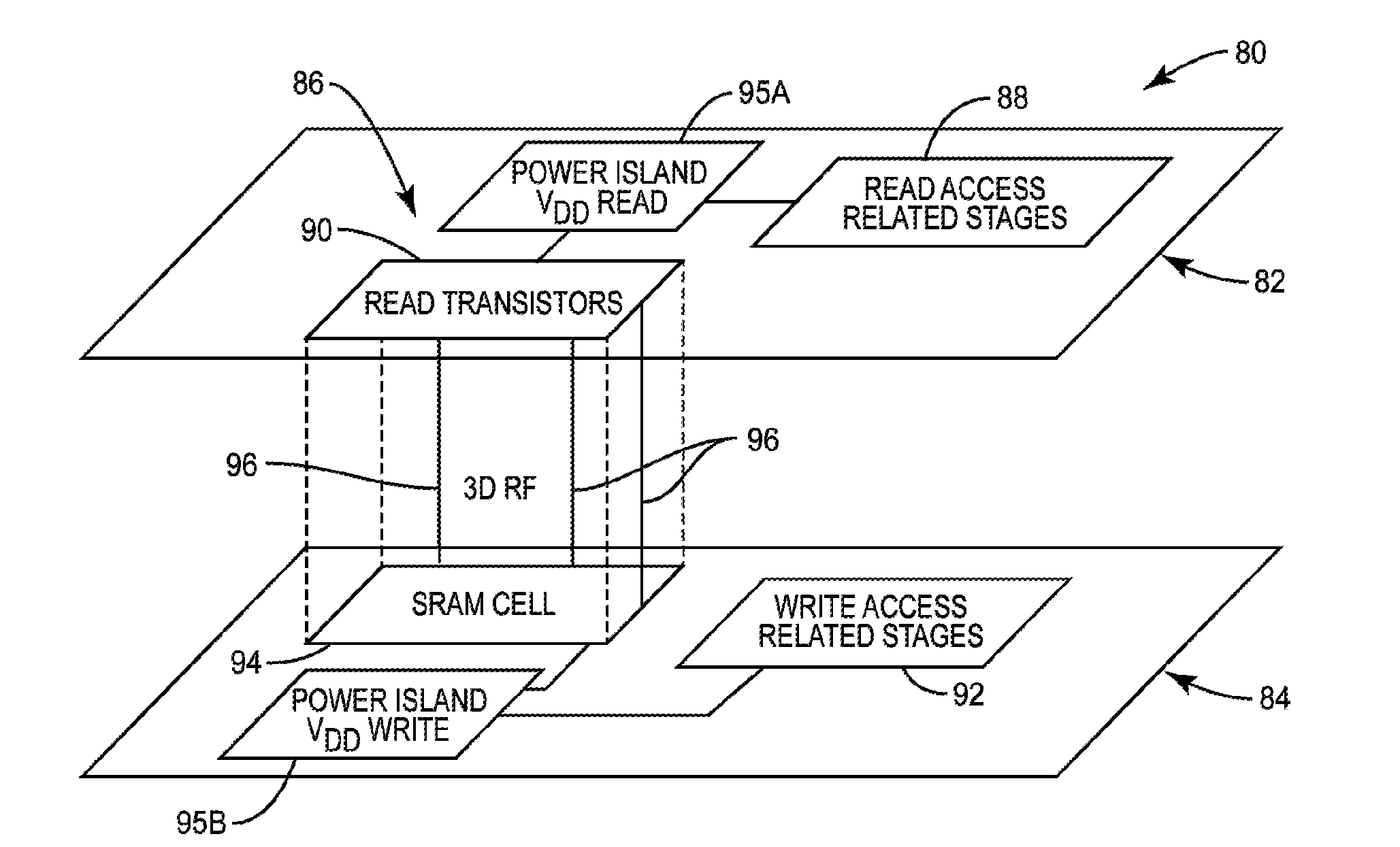

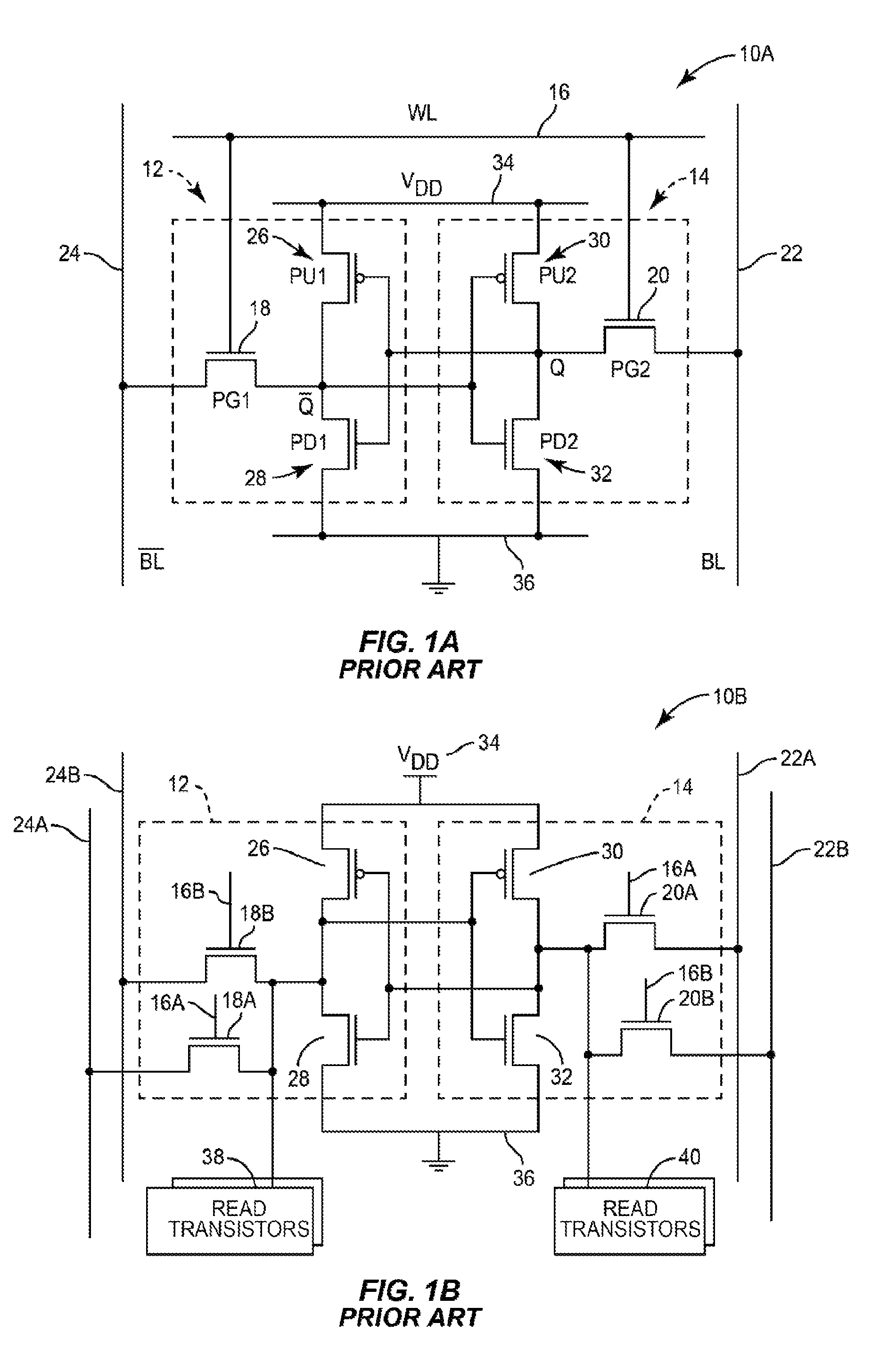

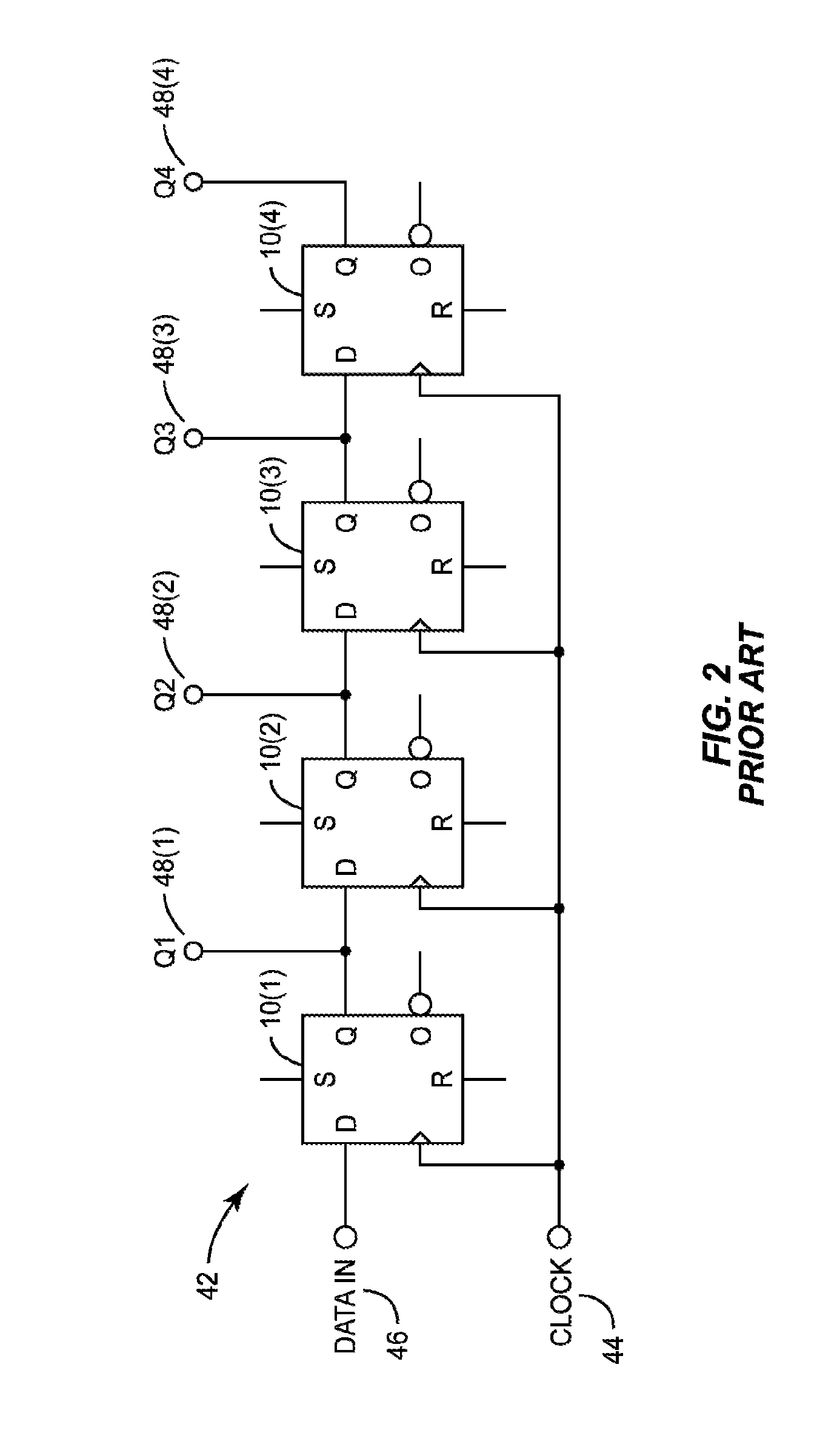

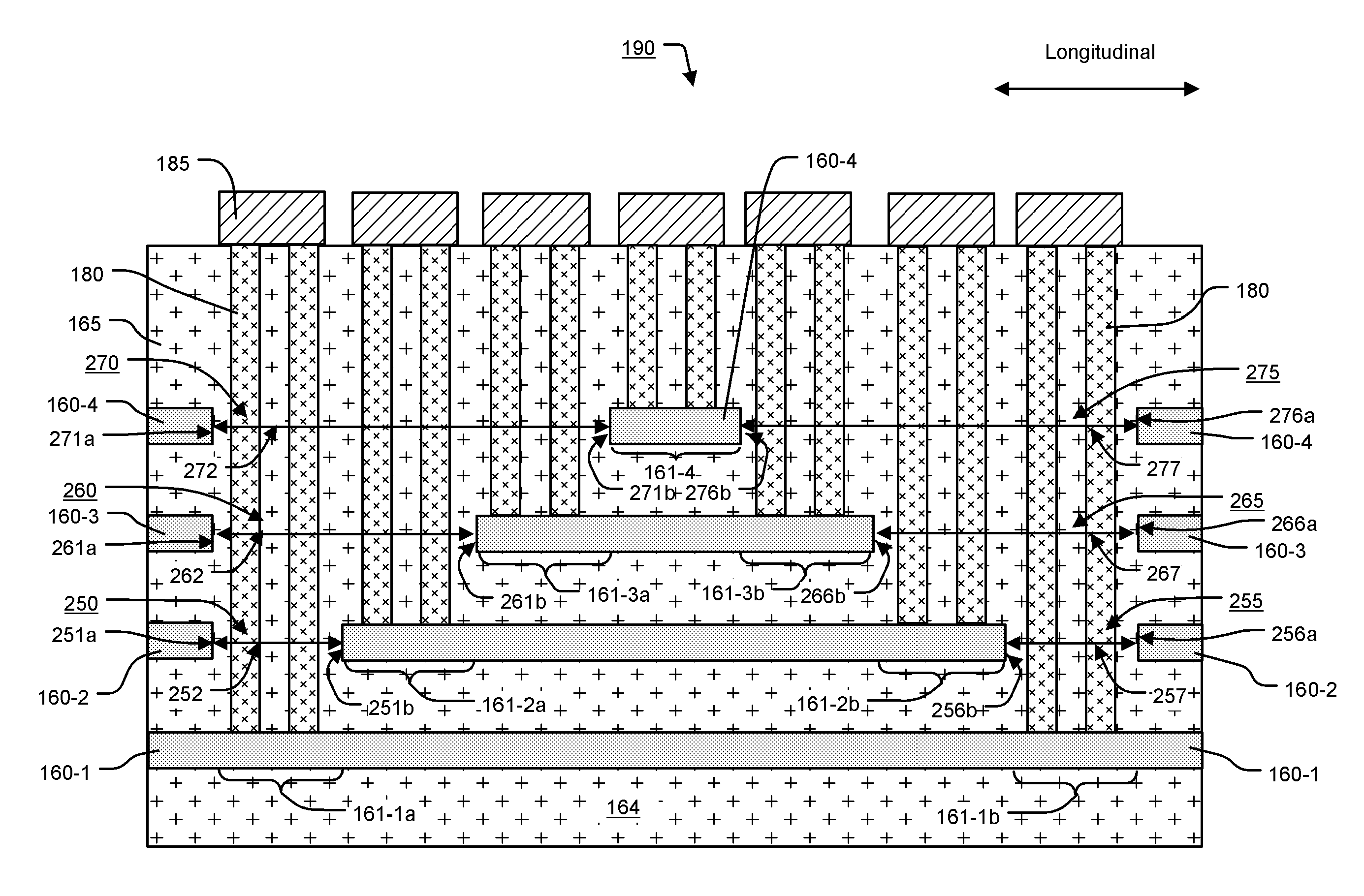

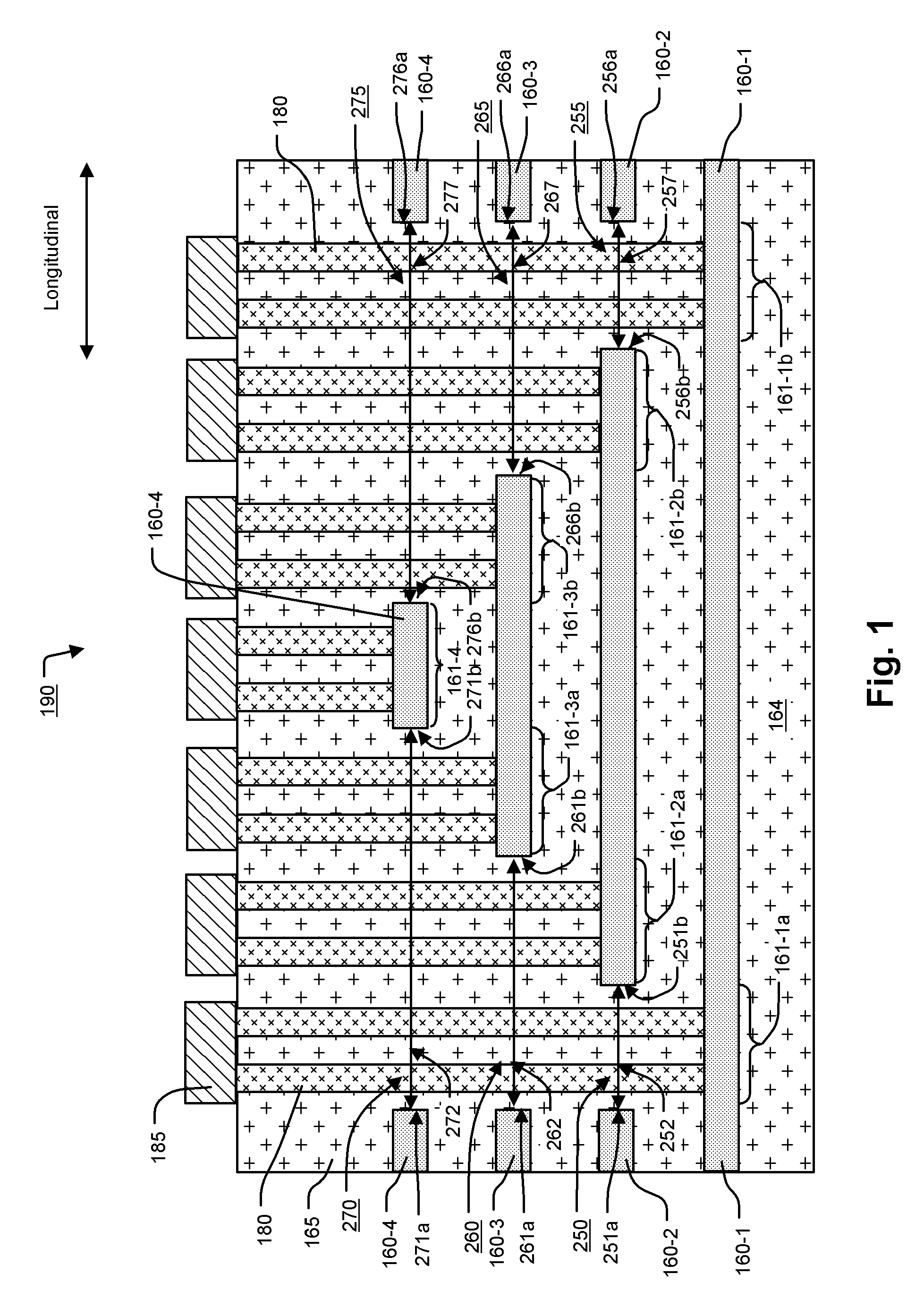

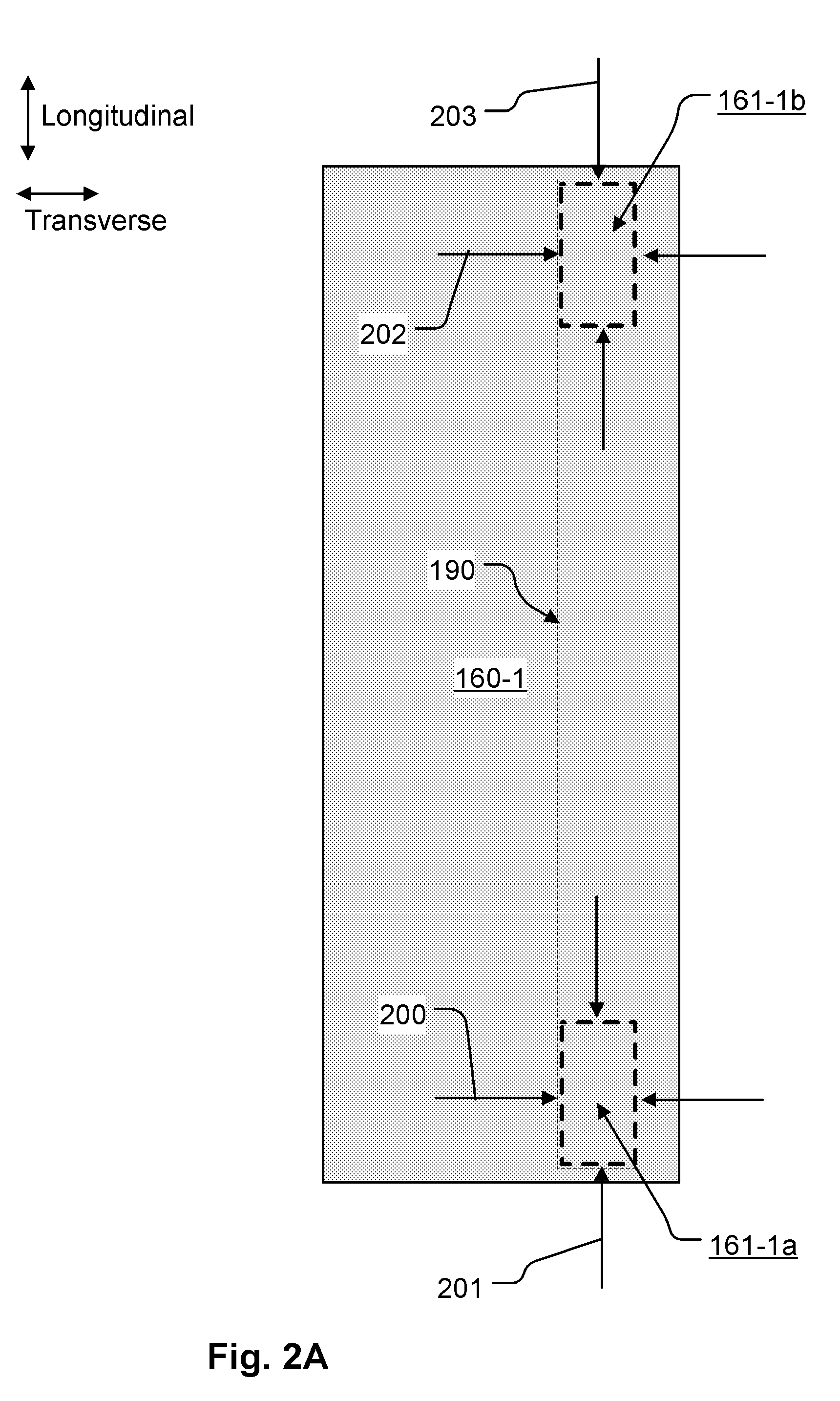

Three-dimensional (3D) memory cell separation among 3D integrated circuit (IC) tiers, and related 3D integrated circuits (3DICS), 3Dic processor cores, and methods

ActiveUS20140269022A1High device packing densityLower latencyTransistorSemiconductor/solid-state device details3d integrated circuitComputer architecture

A three-dimensional (3D) memory cell separation among 3D integrated circuit (IC) (3DIC) tiers is disclosed. Related 3DICs, 3DIC processor cores, and methods are also disclosed. In embodiments disclosed herein, memory read access ports of a memory block are separated from a memory cell in different tiers of a 3DIC. 3DICs achieve higher device packing density, lower interconnect delays, and lower costs. In this manner, different supply voltages can be provided for the read access ports and the memory cell to be able to lower supply voltage for the read access ports. Static noise margins and read / write noise margins in the memory cell may be provided as a result. Providing multiple power supply rails inside a non-separated memory block that increases area can also be avoided.

Owner:QUALCOMM INC

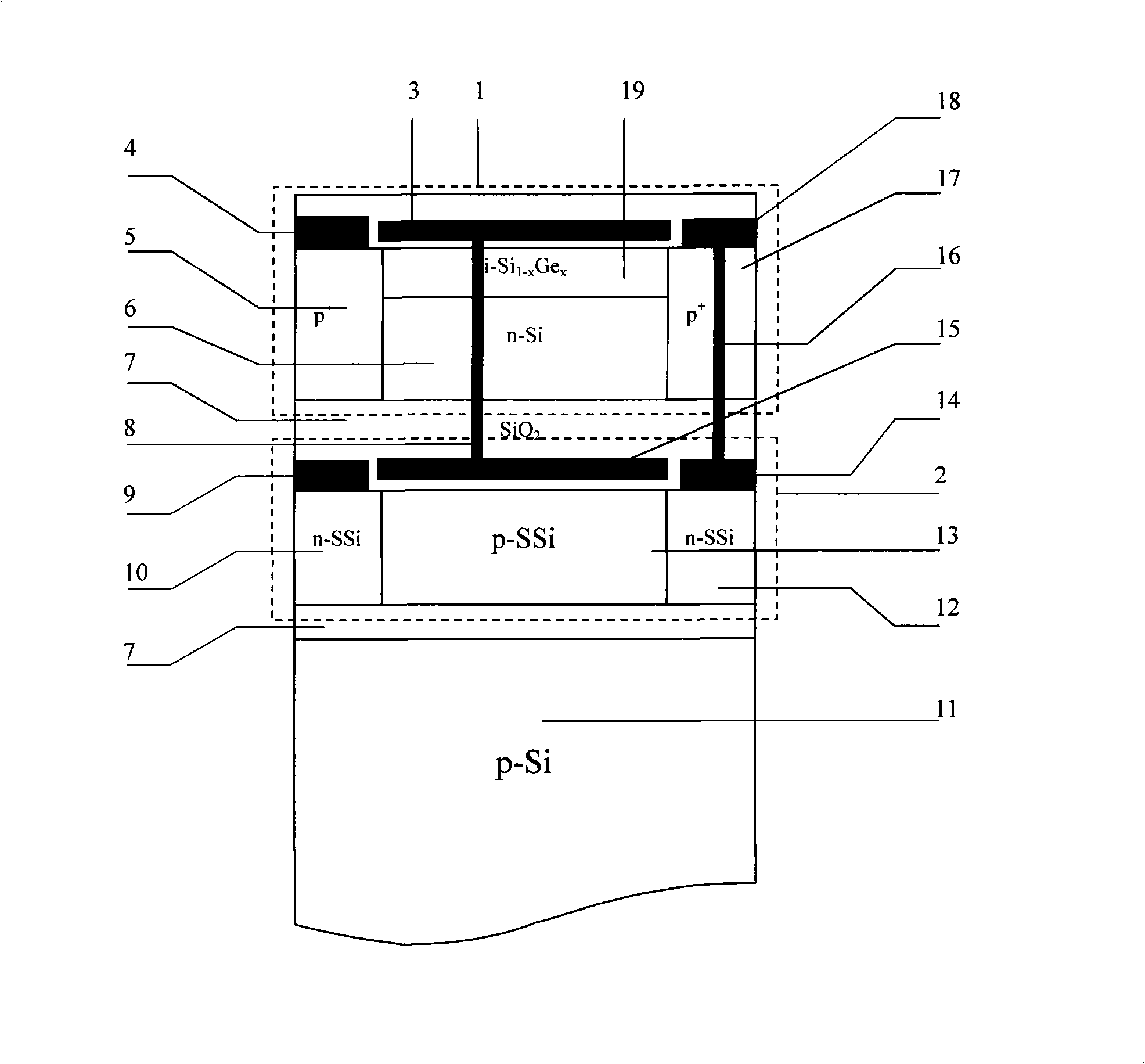

SOI three-dimensional CMOS integrated component and preparation method thereof

InactiveCN101409292AHigh hole mobilityImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingSoi cmosLow speed

The invention discloses a 3D SOI CMOS integrated device and a manufacturing method thereof, relates to the technical field of microelectronics, and mainly solves the problem of low speed of the existing 3D integrated circuits. The proposal is that an SSOI substrate and an SSGOI substrate are employed to construct two active layers of a new 3D CMOS integrated device; wherein, the lower active layer is the SSOI substrate and is made into a strained Si nMOSFET device by utilizing the characteristic of high electron mobility of a strained Si material in the SSOI substrate; the upper active layer is the SSGOI substrate and is made into a strained SiGe surface channel pMOSFET device by utilizing the characteristic of high hole mobility of the strained Si material in the SSGOI substrate; the upper active layer and the lower active layer form a 3D active layer structure by a bonding process, and are connected by an interconnection line to form the 3D CMOS integrated device with a conducting channel of 65nm to 130nm. Compared with the existing 3D integrated devices, the 3D SOI CMOS integrated device manufactured by the manufacturing method has the advantages of high speed and good performance, and can be applied to manufacturing large-scale and high-speed 3D CMOS integrated circuits.

Owner:XIDIAN UNIV

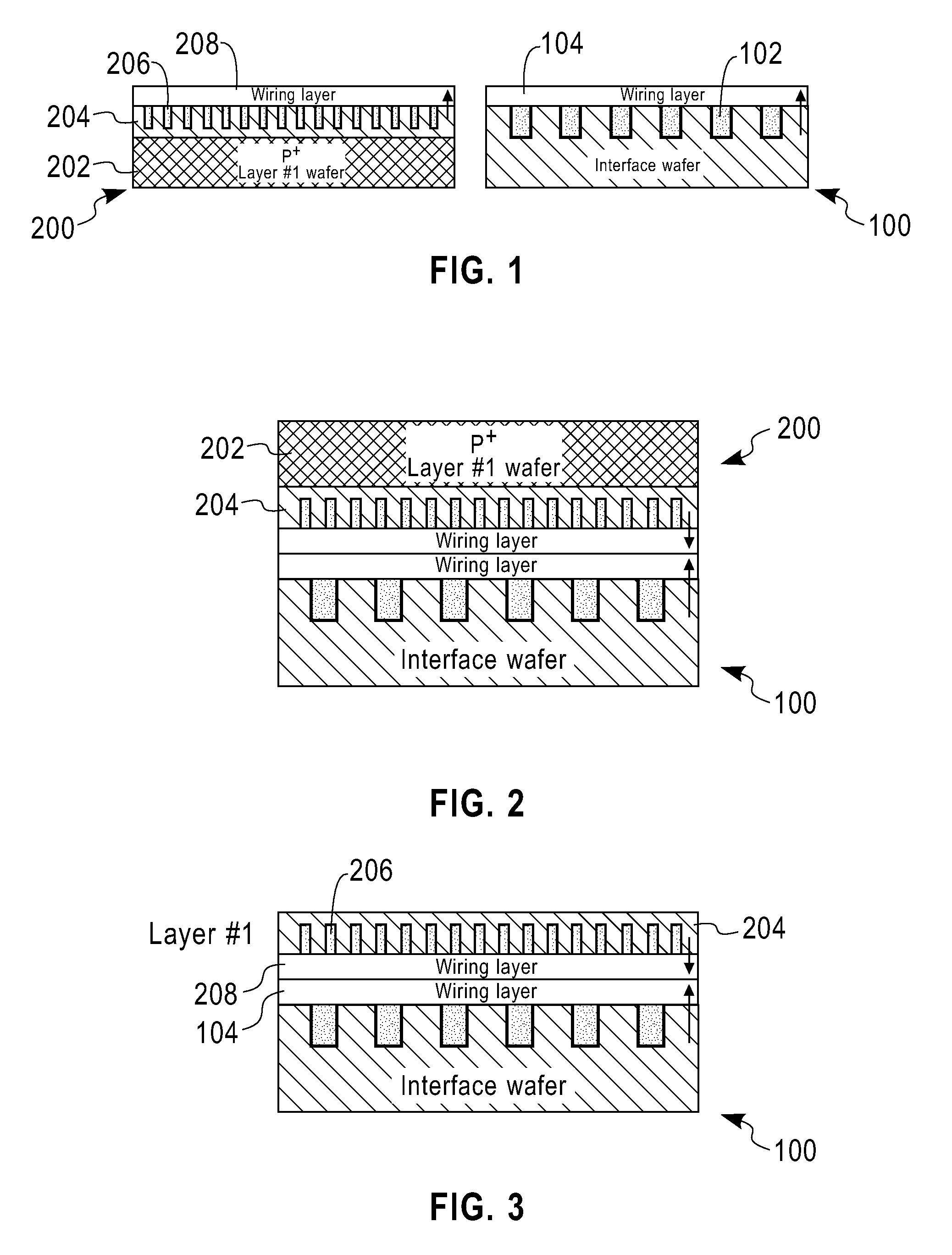

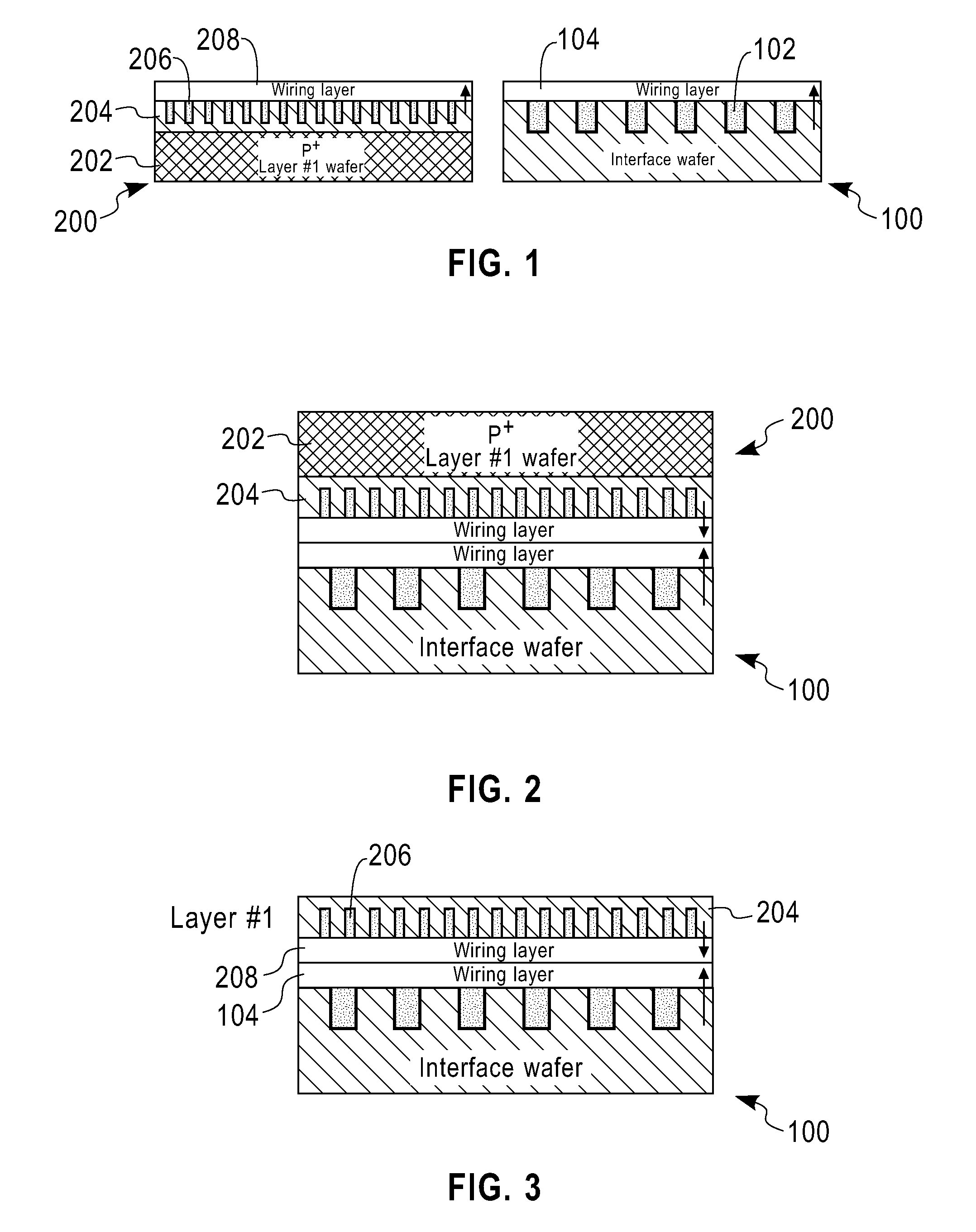

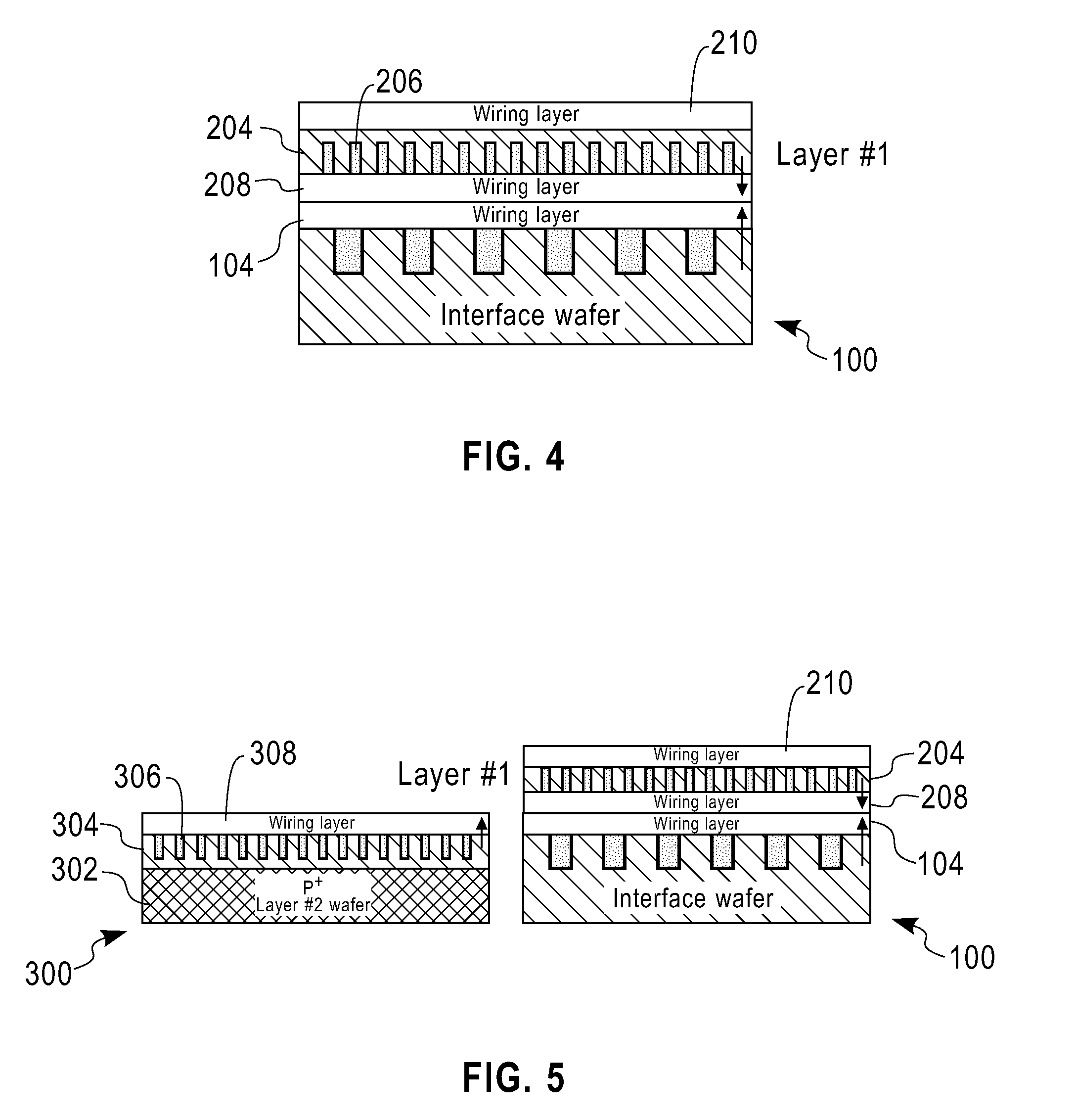

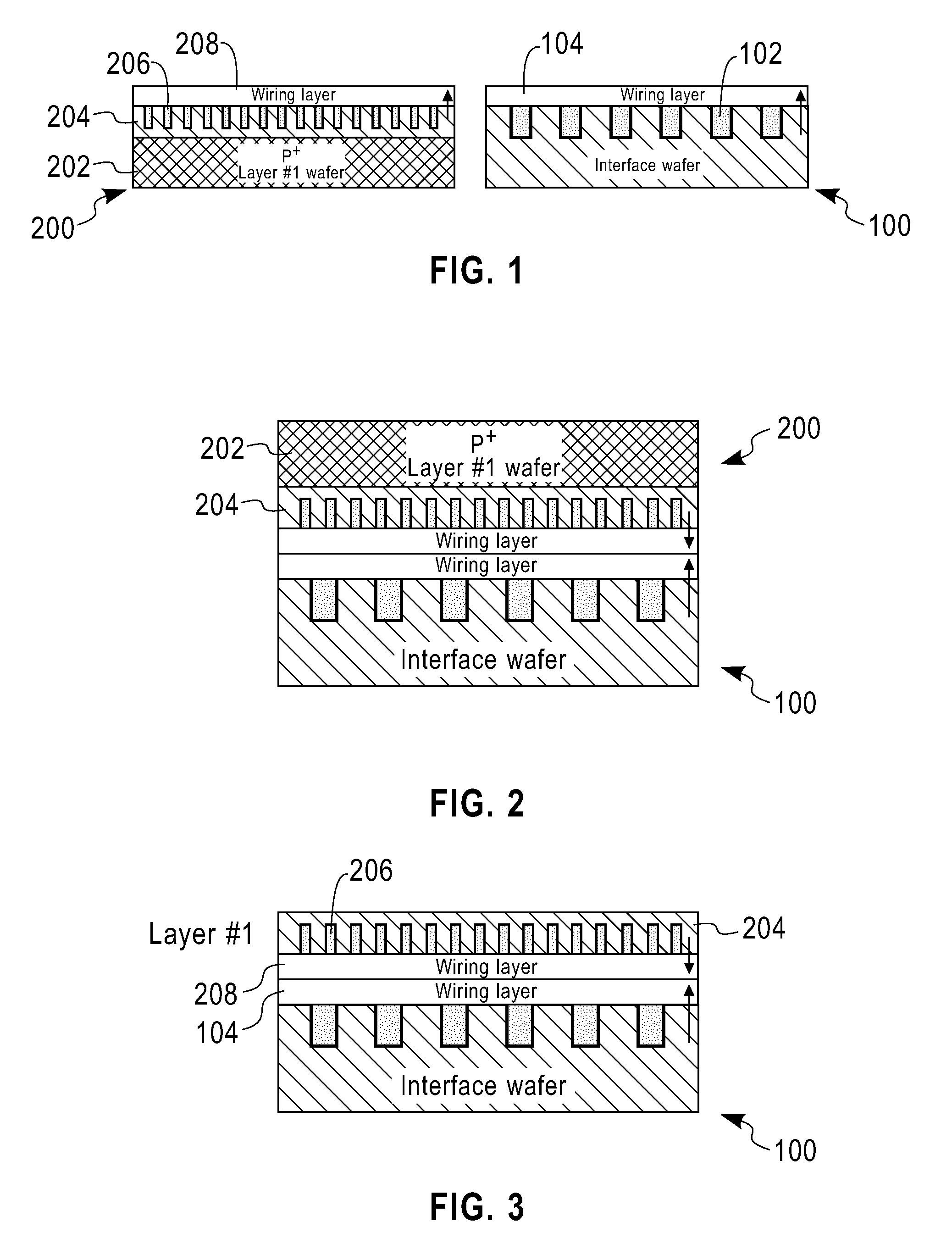

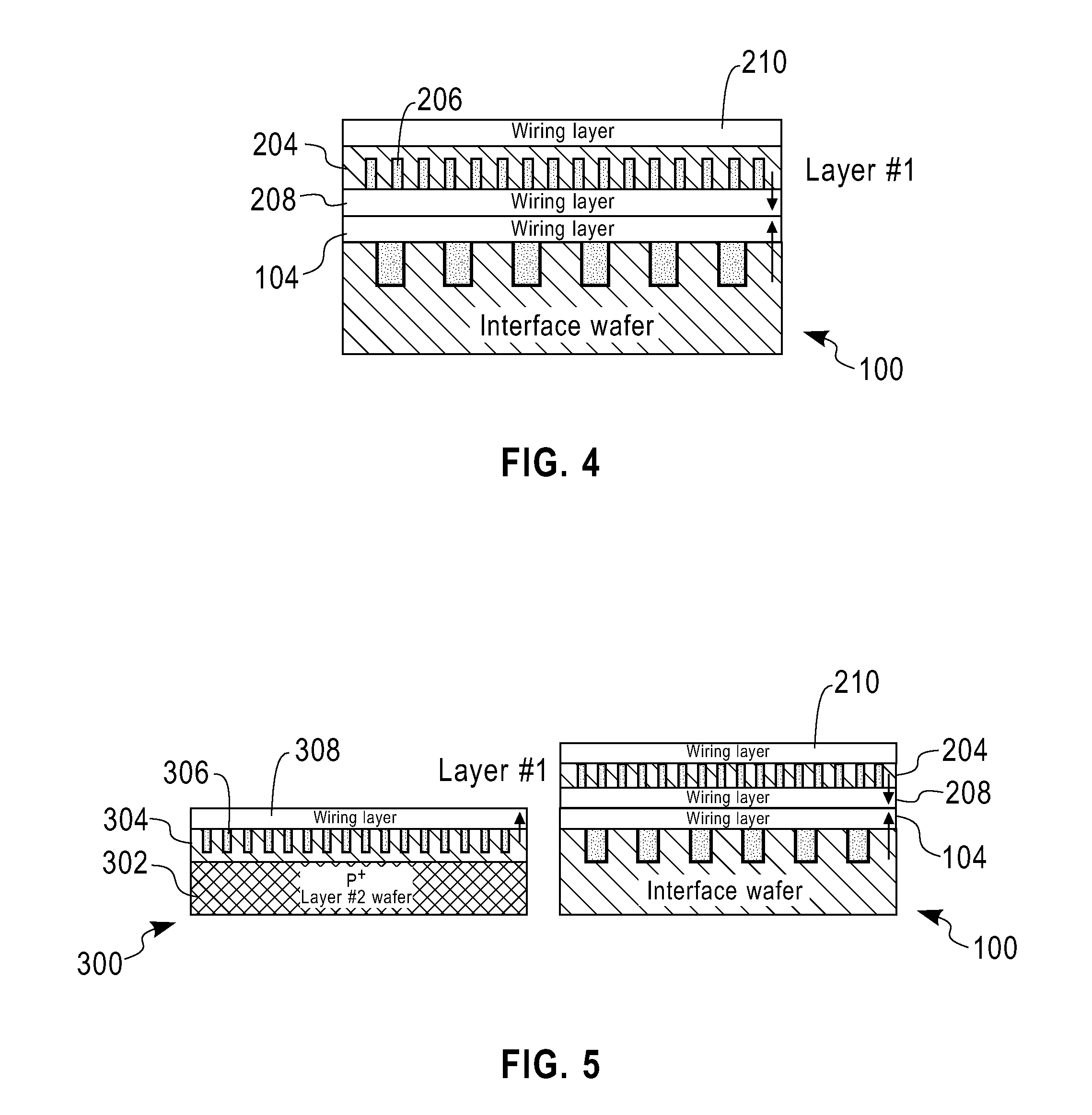

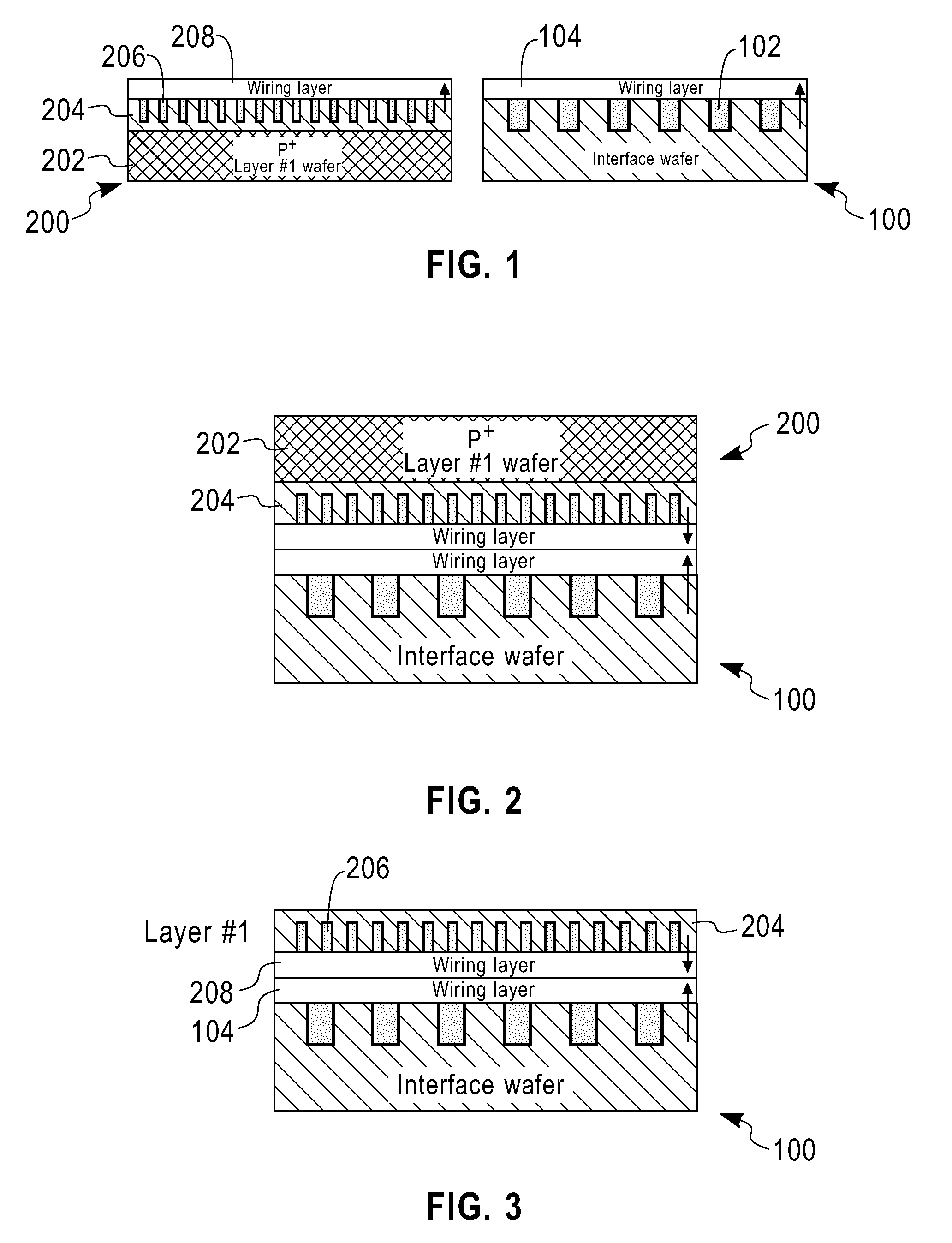

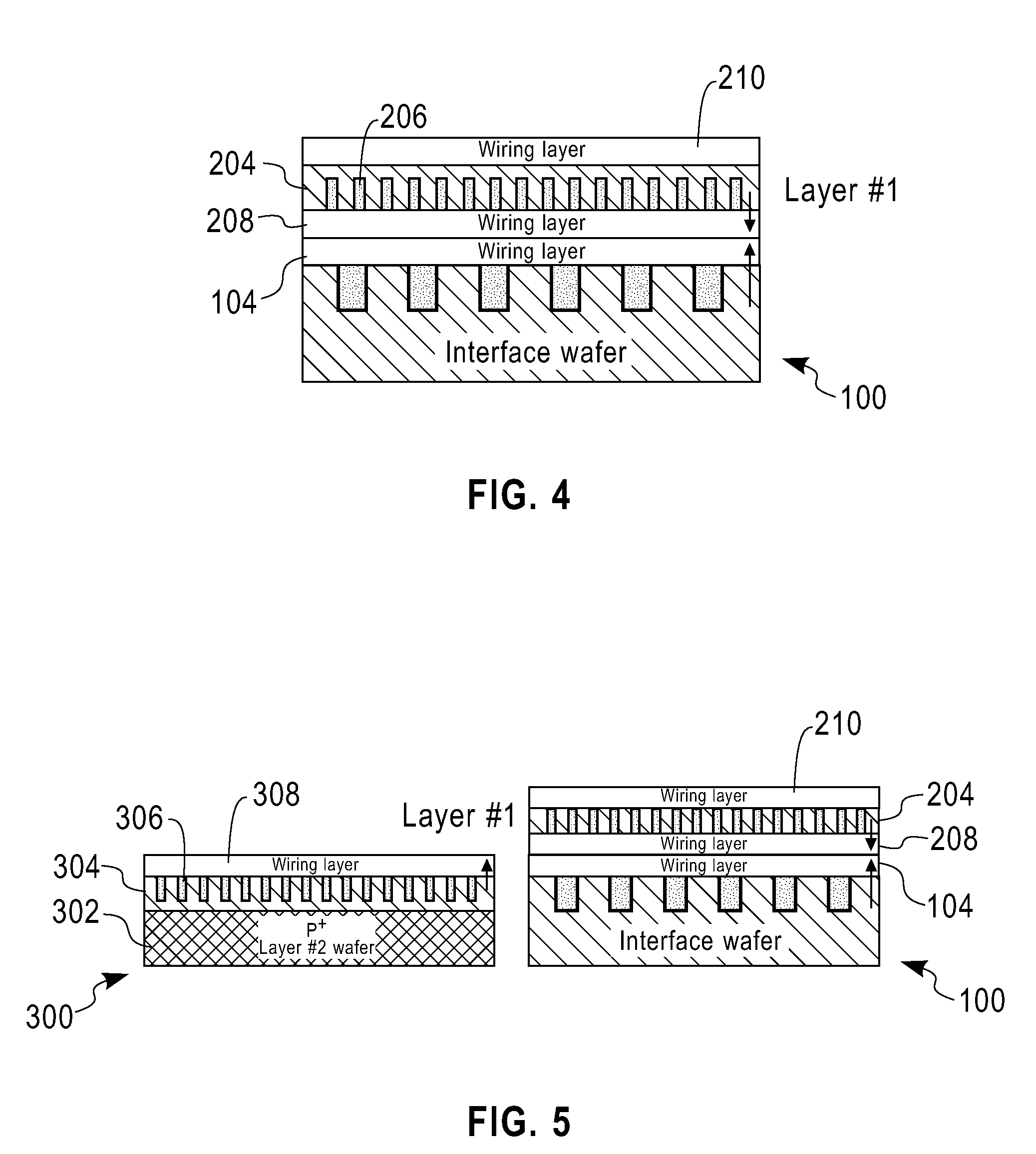

3D integrated circuit device fabrication with precisely controllable substrate removal

ActiveUS20100044826A1Solid-state devicesSemiconductor/solid-state device manufacturing3d integrated circuitEngineering

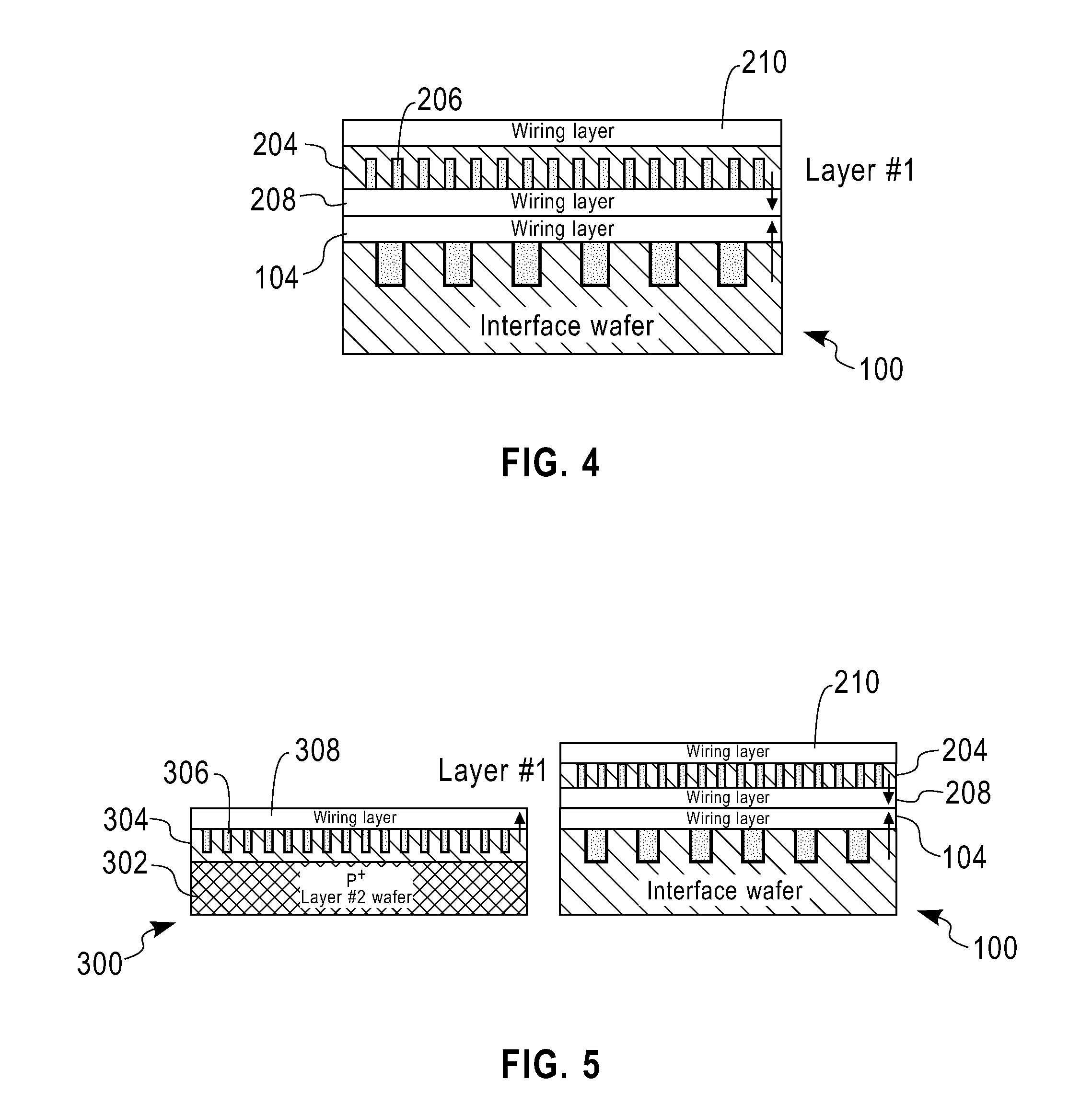

A method is provided for fabricating a 3D integrated circuit structure. According to the method, a first active circuitry layer wafer is provided. The first active circuitry layer wafer comprises a P+ portion covered by a P− layer, and the P− layer includes active circuitry. The first active circuitry layer wafer is bonded face down to an interface wafer that includes a first wiring layer, and then the P+ portion of the first active circuitry layer wafer is selectively removed with respect to the P− layer of the first active circuitry layer wafer. Next, a wiring layer is fabricated on the backside of the P− layer. Also provided are a tangible computer readable medium encoded with a program for fabricating a 3D integrated circuit structure, and a 3D integrated circuit structure.

Owner:TAIWAN SEMICON MFG CO LTD

3D integrated circuit layer interconnect

ActiveUS8154128B2Small footprintEfficient and low methodTransistorSemiconductor/solid-state device details3d integrated circuitSmall footprint

A three-dimensional 3D interconnect structure with a small footprint is described, useful for connection from above to levels of circuit structures in a multi-level device. Also, an efficient and low cost method for manufacturing the 3D interconnect structure is provided.

Owner:MACRONIX INT CO LTD

Method and apparatus for testing 3D integrated circuits

InactiveUS20120110402A1Reduce testing costsIncrease data rateElectronic circuit testingLogical operation testingFault coverageEngineering

A method and apparatus for testing a scan-based 3D integrated circuit (3DIC) using time-division demultiplexing / multiplexing allowing for high-data-rate scan patterns applied at input / output pads converting into low-data-rate scan patterns applied to each embeddded module in the 3DIC. A set of 3D design guidelines is proposed to reduce the number of test times and the number of through-silicon vias (TSVs) required for both pre-bond testing and post-bond testing. The technique allows reuse of scan patterns developed for pre-bond testing of each die (layer) for post-bond testing of the whole 3DIC. It further reduces test application time without concerns for I / O pad count limit and risks for fault coverage loss.

Owner:SYNTEST TECH

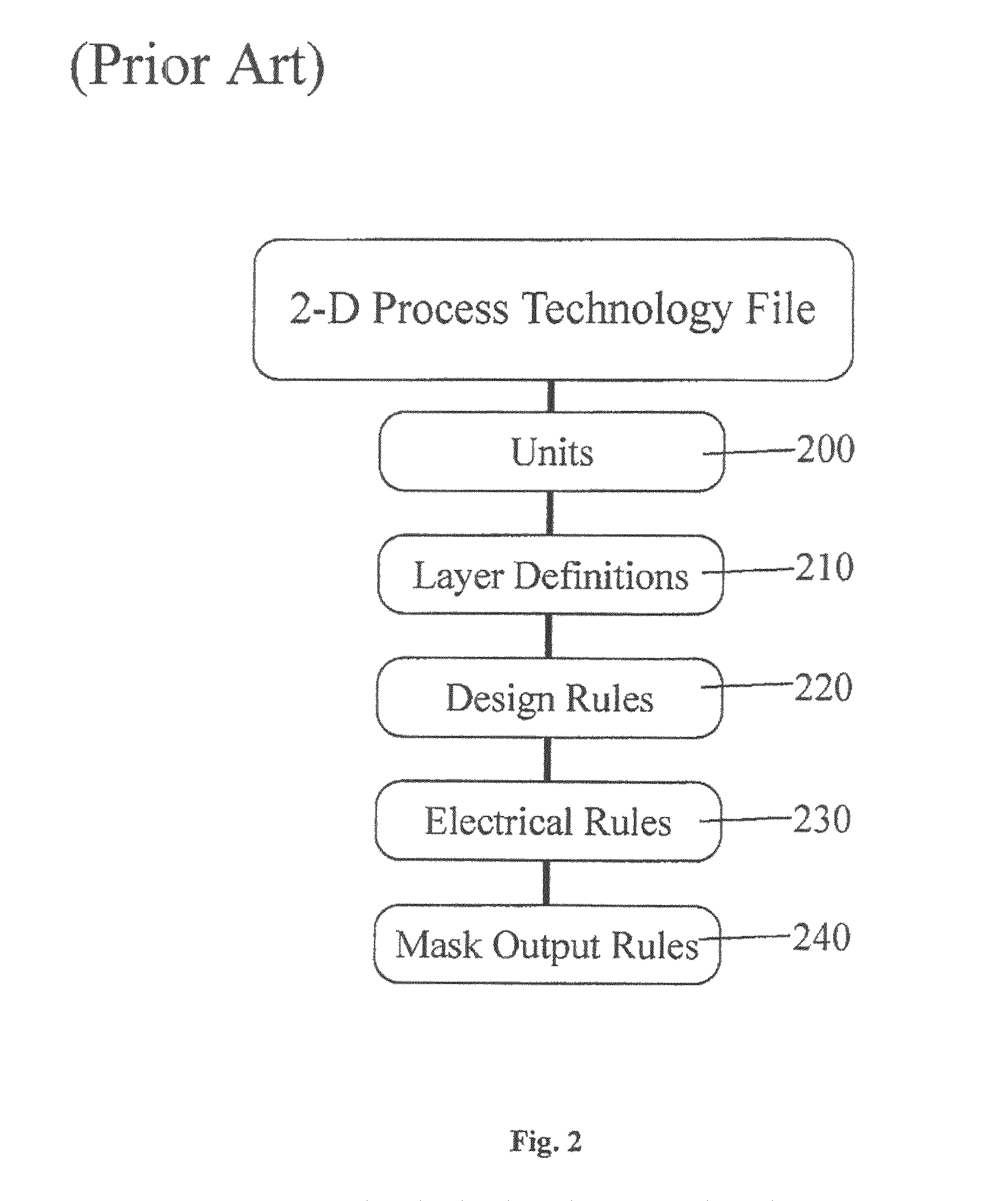

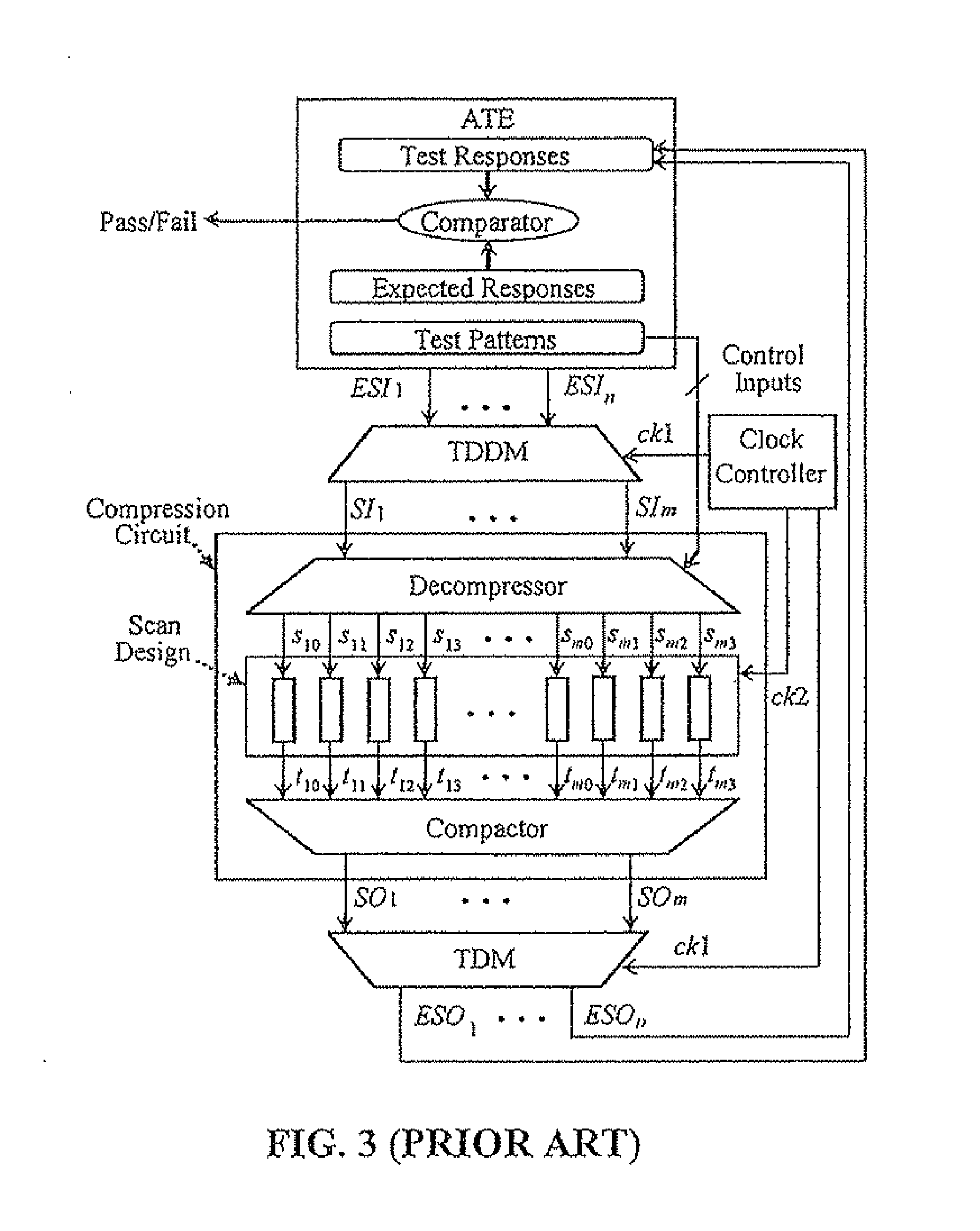

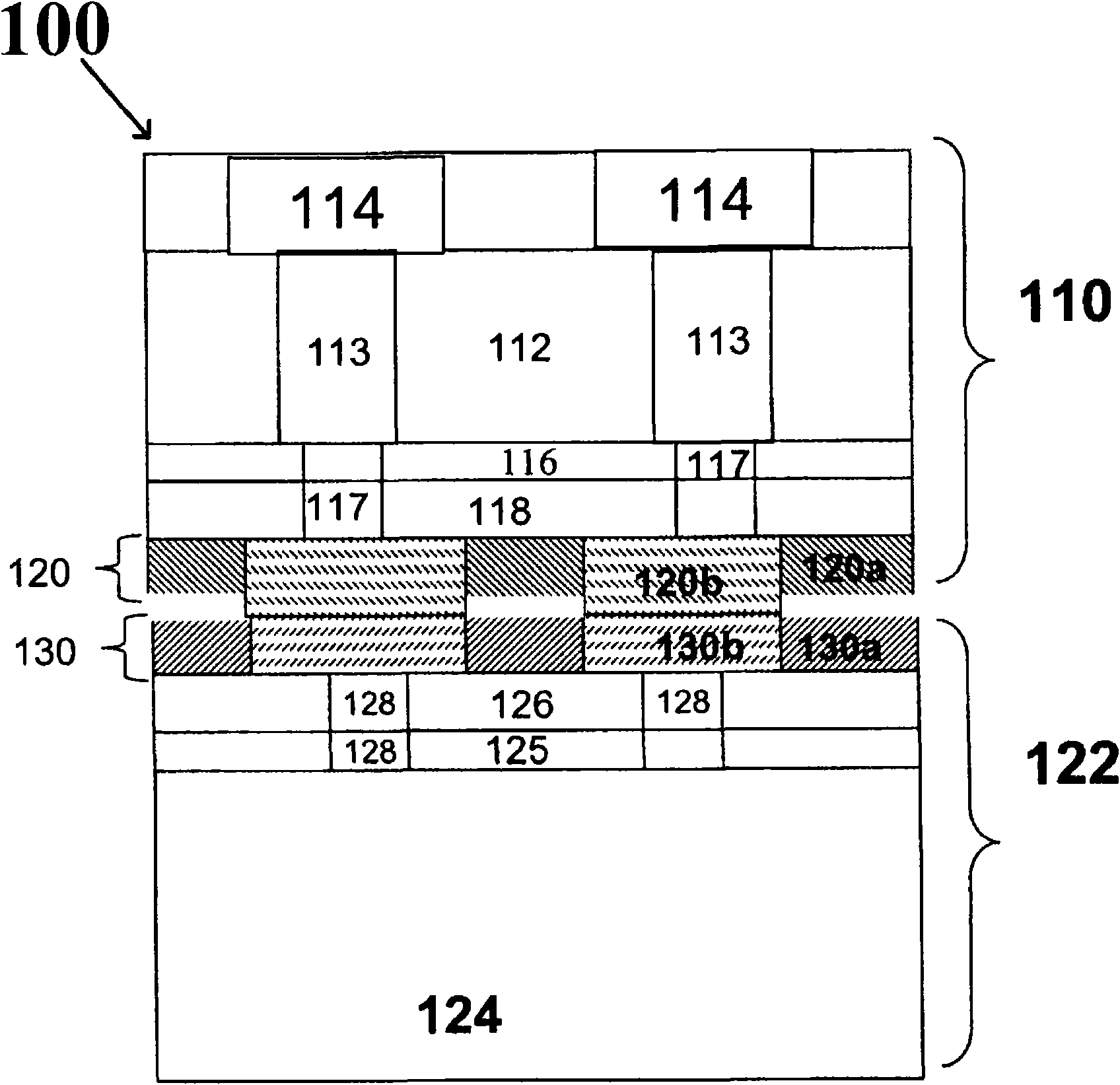

Design and verification of 3d integrated circuits

ActiveCN101609482ACAD circuit designSpecial data processing applications3d integrated circuitComputer architecture

A method of designing a 3D integrated circuit (3D IC) including providing a first layout corresponding to a first device of a 3D IC and a second layout corresponding to a second device of a 3D IC is provided. A verification, such as LVS or DRC, may be performed not only on each device separately, but may also be performed to ensure proper connectivity between devices. The verification may be performed on a single layout file (e.g., GDS II file) including the interface layer of the first and second die. Dummy feature pattern may be determined for the 3D IC using a layout including the interface layers of the first and second devices.

Owner:TAIWAN SEMICON MFG CO LTD

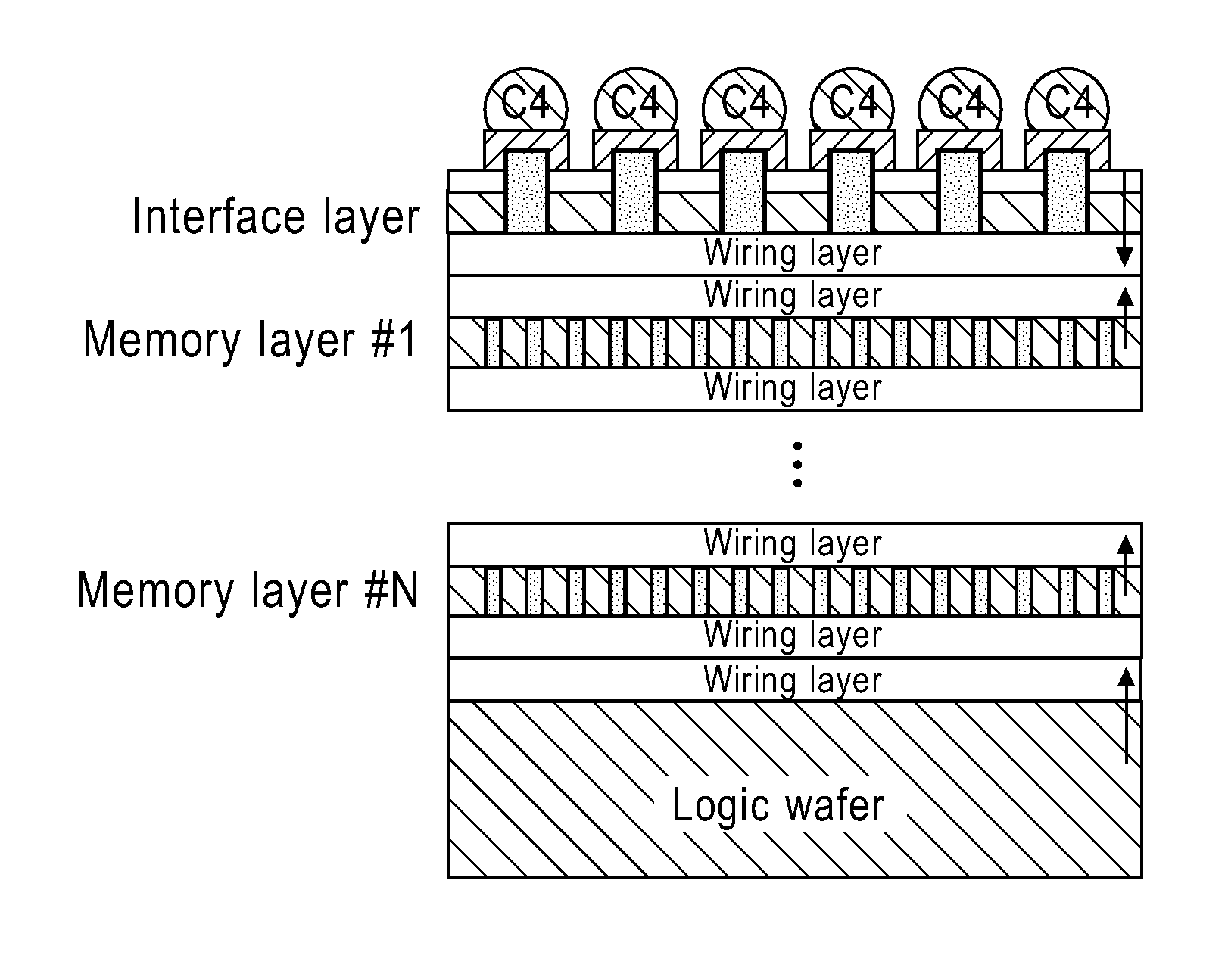

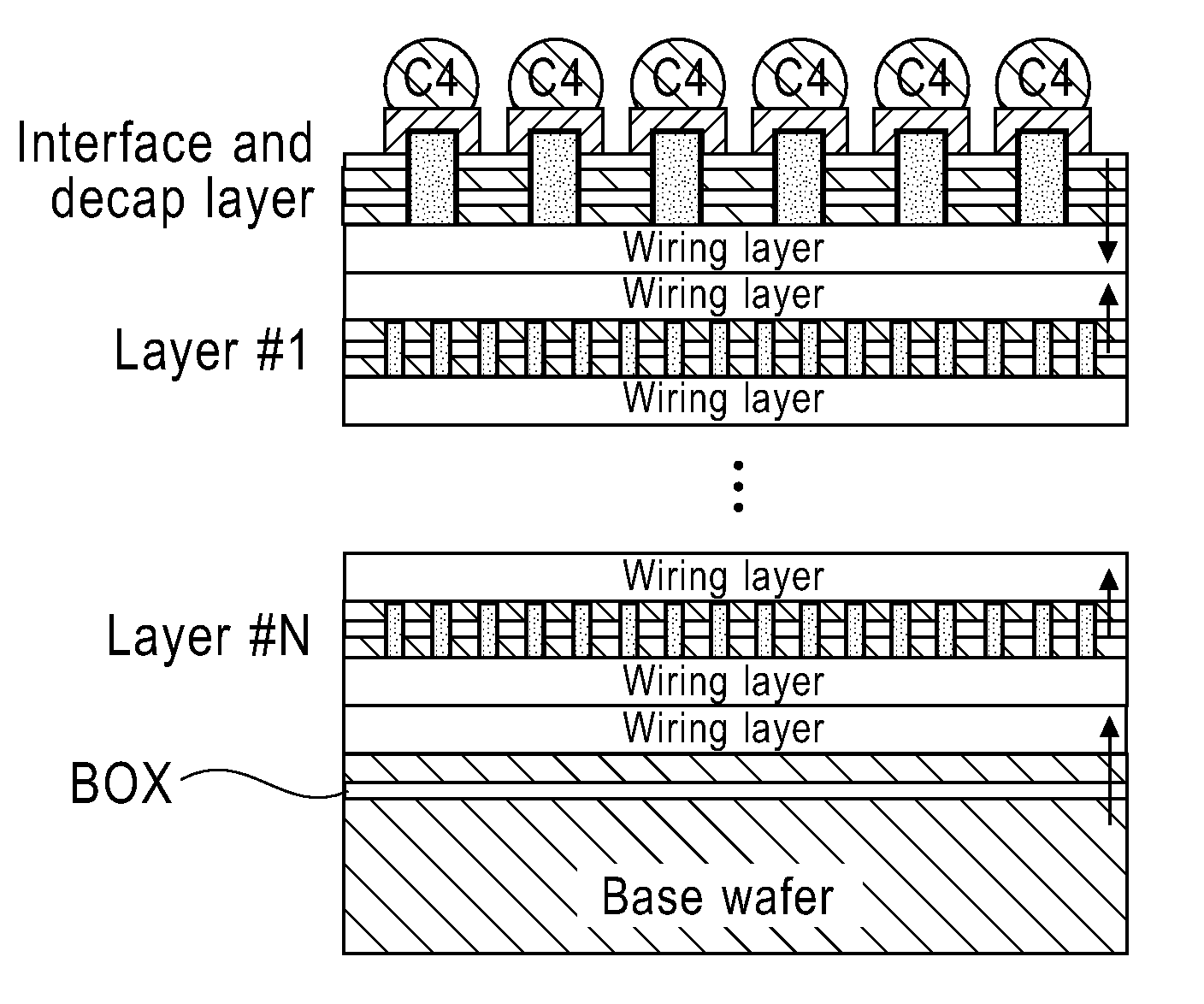

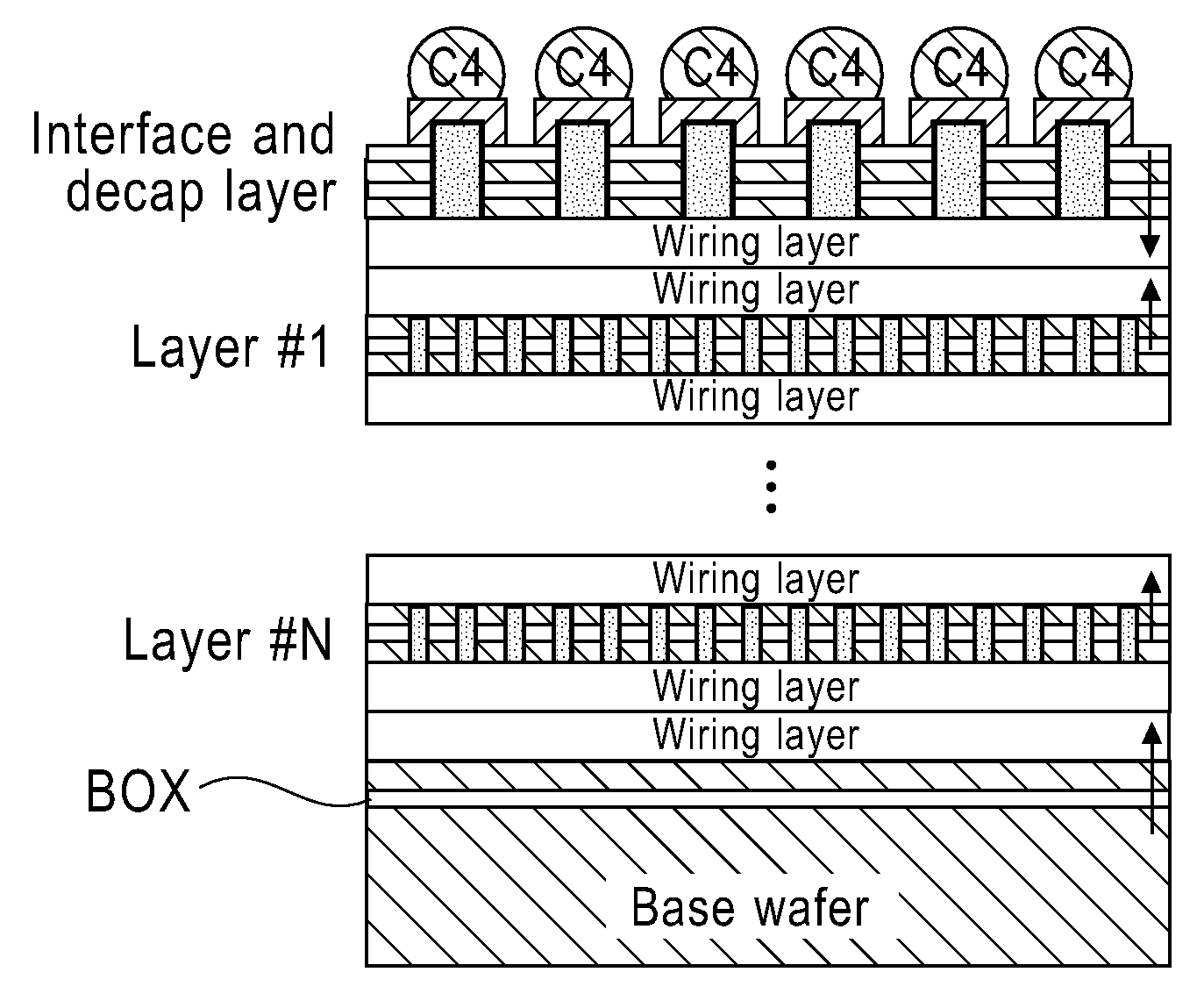

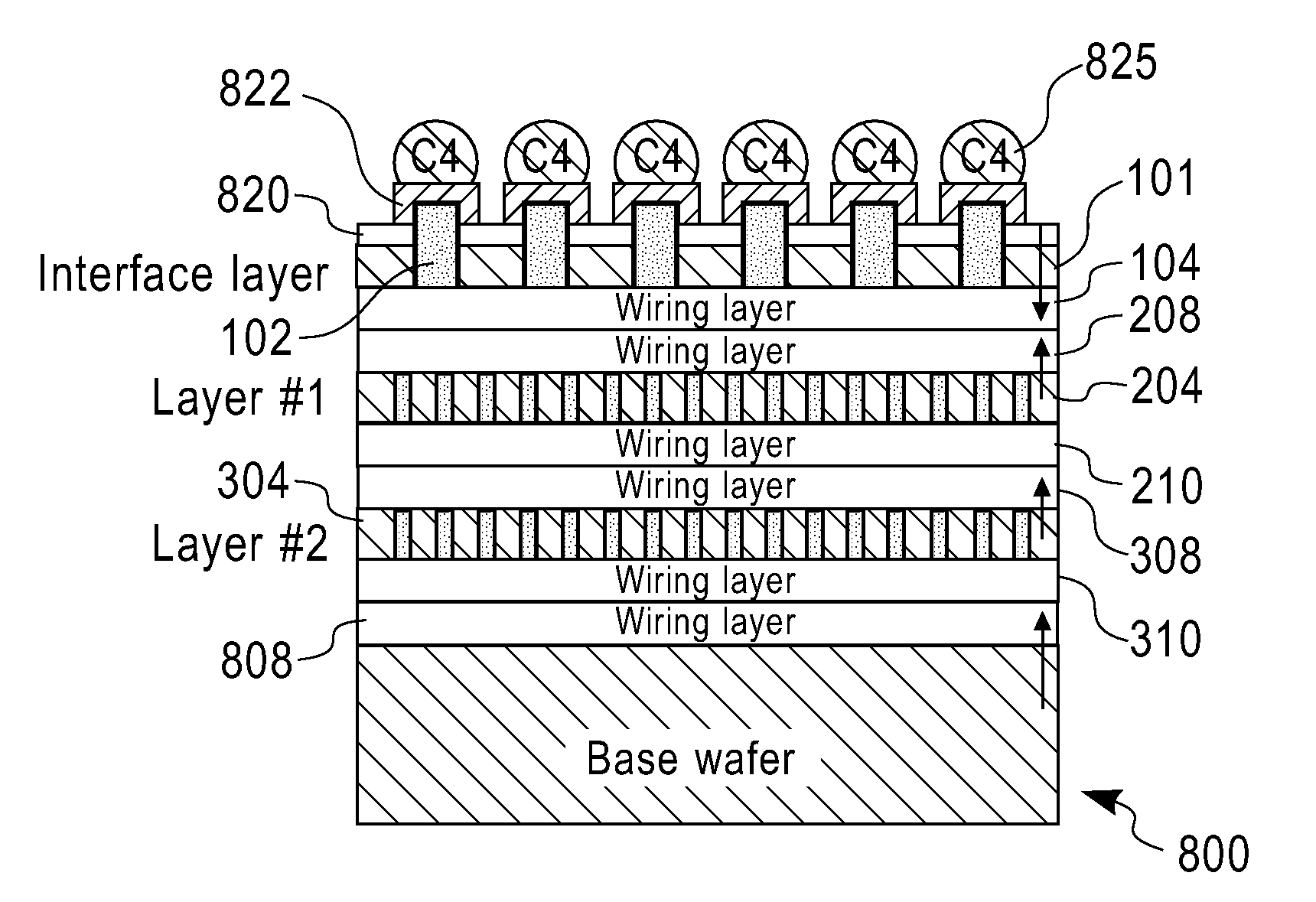

3D integrated circuit device fabrication using interface wafer as permanent carrier

ActiveUS20100047964A1Semiconductor/solid-state device detailsSolid-state devices3d integrated circuitInterface layer

A method is provided for fabricating a 3D integrated circuit structure. Provided are an interface wafer including a first wiring layer and through-silicon vias, and a first active circuitry layer wafer including active circuitry. The first active circuitry layer wafer is bonded to the interface wafer. Then, a first portion of the first active circuitry layer wafer is removed such that a second portion remains attached to the interface wafer. A stack structure including the interface wafer and the second portion of the first active circuitry layer wafer is bonded to a base wafer. Next, the interface wafer is thinned so as to form an interface layer, and metallizations coupled through the through-silicon vias in the interface layer to the first wiring layer are formed on the interface layer. Also provided is a tangible computer readable medium encoded with a program that comprises instructions for performing such a method.

Owner:GLOBALFOUNDRIES US INC

Memory architecture of 3d array with improved uniformity of bit line capacitances

ActiveCN102709269ASemiconductor/solid-state device detailsSolid-state devices3d integrated circuitCapacitance

A 3D integrated circuit memory array has a plurality of plane positions. Multiple bit line structures have a multiple sequences of multiple plane positions. Each sequence characterizes an order in which a bit line structure couples the plane positions to bit lines. Each bit line is coupled to at least two different plane positions to access memory cells at two or more different plane positions.

Owner:MACRONIX INT CO LTD

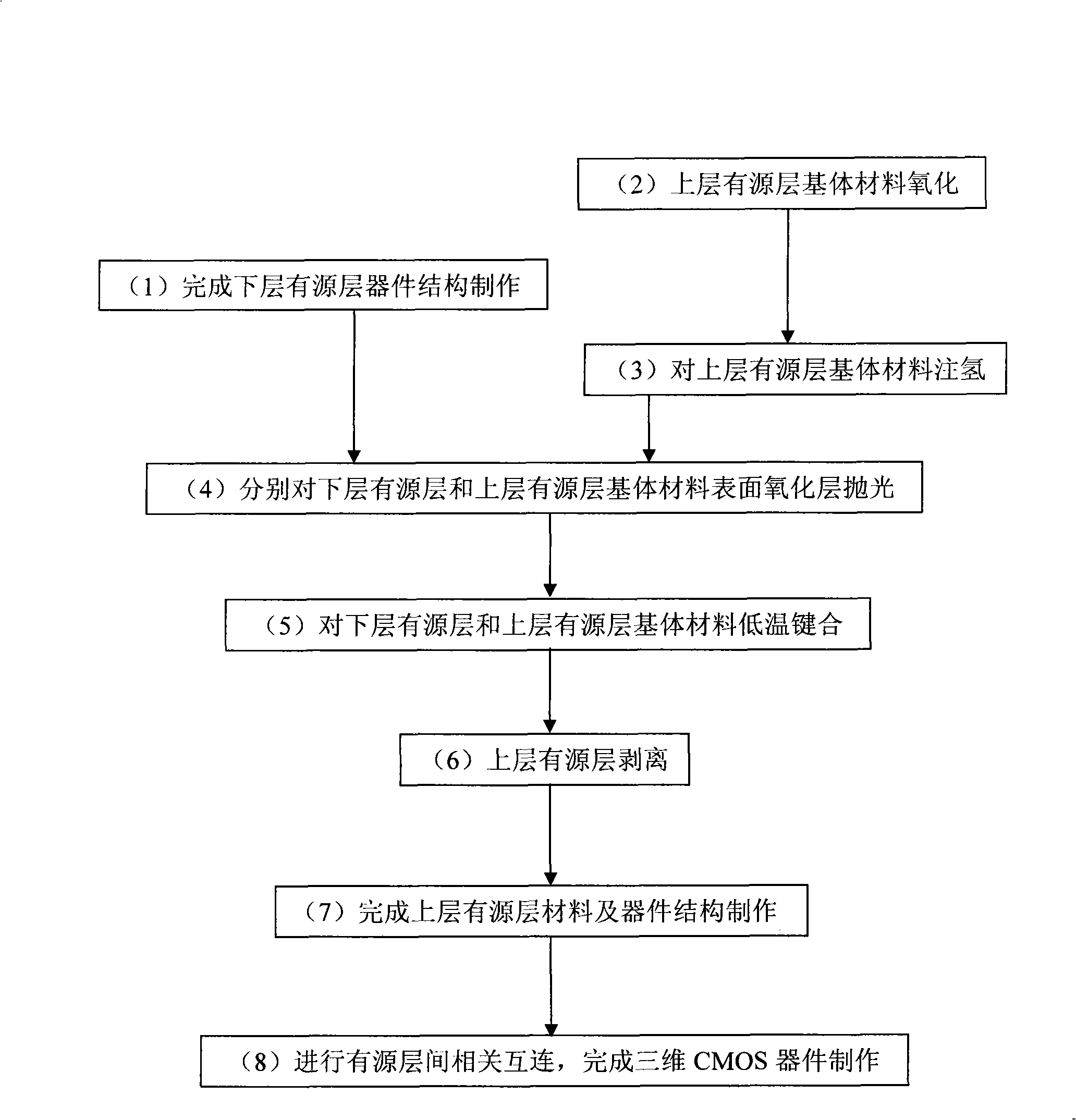

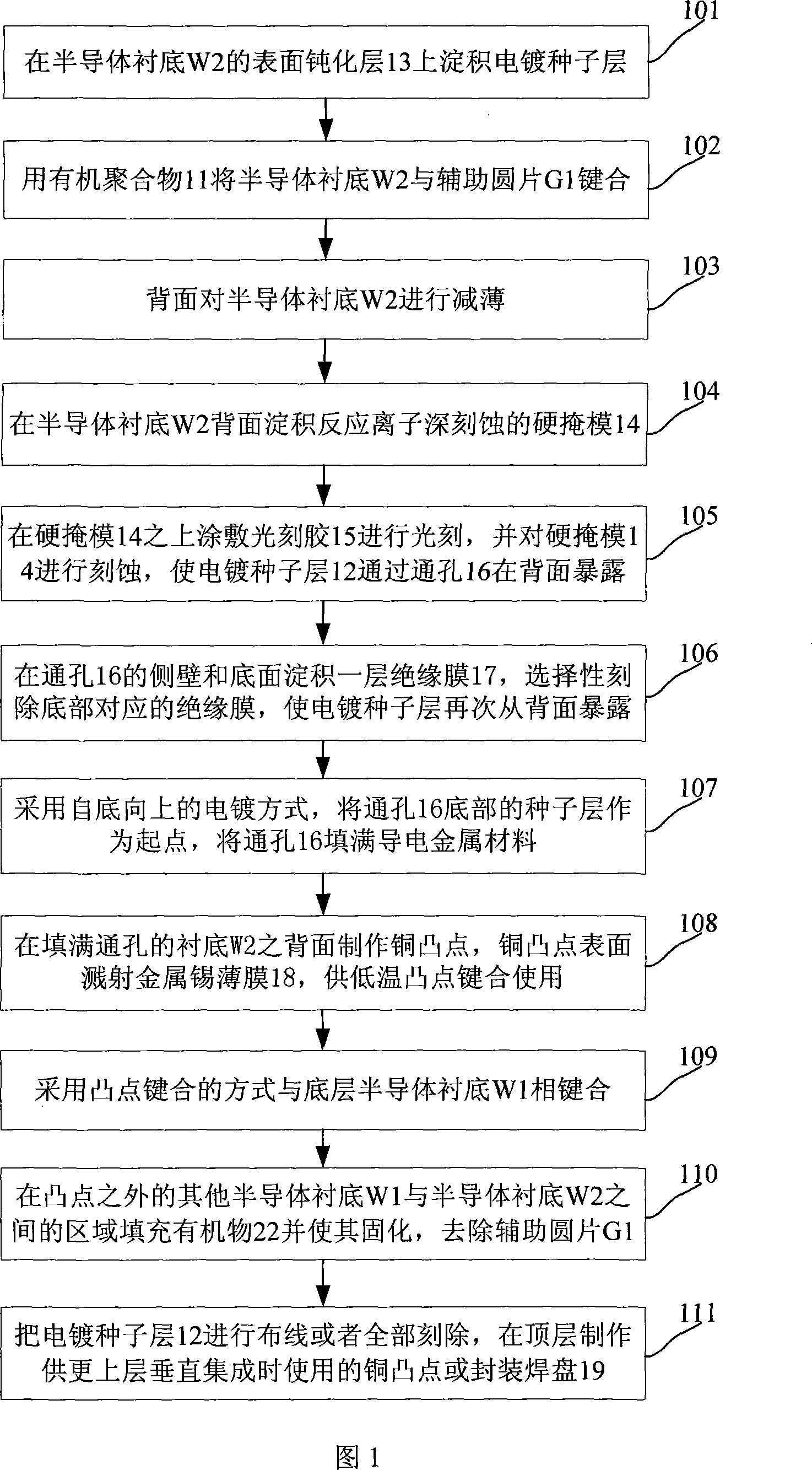

Implementation method for 3D integrated circuit

InactiveCN101079386AReduce thicknessSolid-state devicesSemiconductor/solid-state device manufacturing3d integrated circuitEngineering

The invention discloses a realizng method of three-dimensional integrated circuit in the semiconductor making technique and three-dimensional integrated technical domain, which comprises the following steps: sedimenting plating seed layer on the bonding face of the first circuit disc or auxiliary disc; making the auxiliary disc as the through-hole to reduce the back to support the first layer of circuit disc and etch the disc; exposing the plating seed layer through the through-hole; using plating technique from bottom to top; adopting the plating seed layer as original; plating to fill the through-hole; making projection on the filled through-hole; adopting bonding pattern to connect the first layer of circuit disc and the second layer of circuit disc. The invention reduces the technical difficulty to realize three-dimensional integration on the silicon substrate, which has good versatility.

Owner:TSINGHUA UNIV

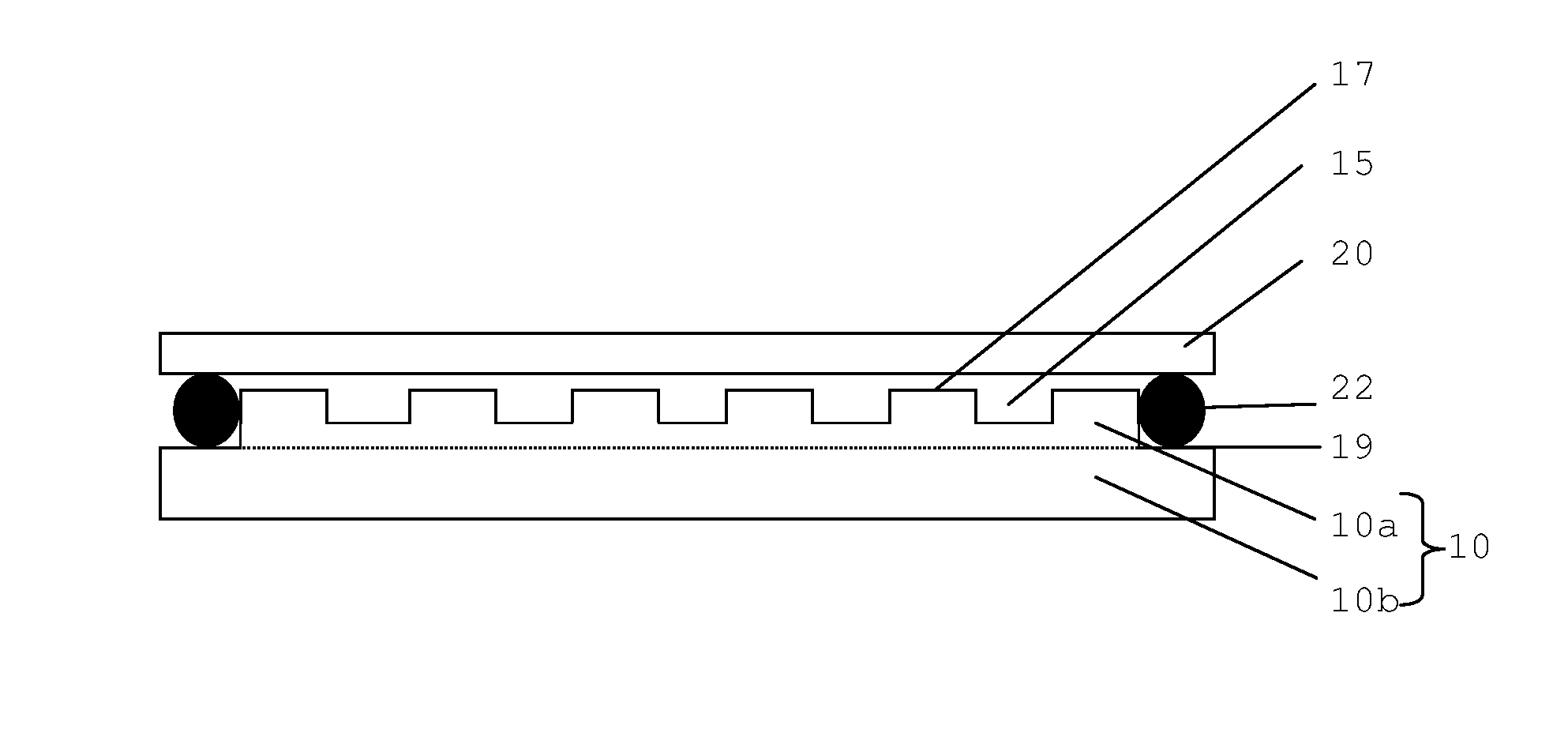

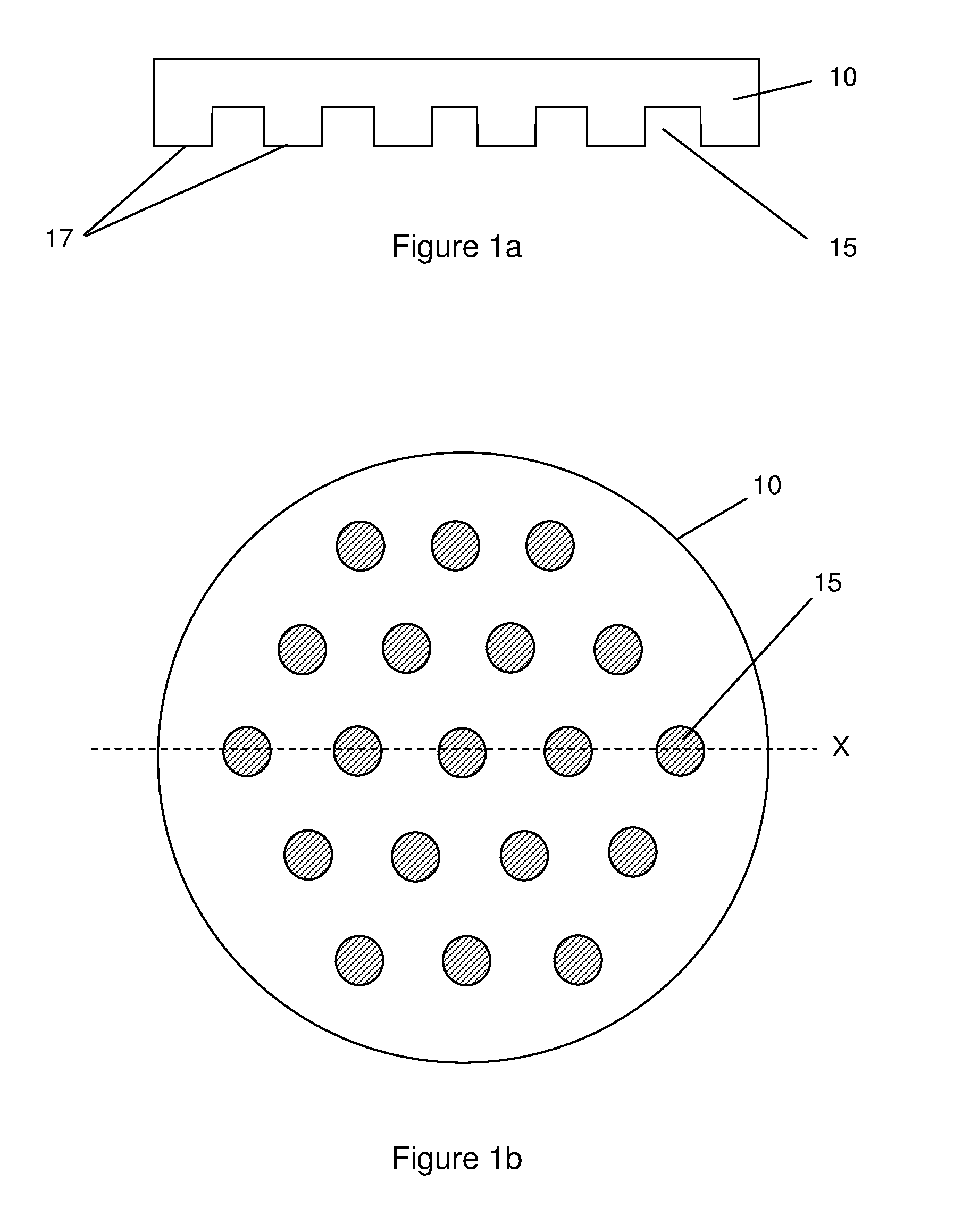

Method and carrier for handling a substrate

InactiveUS20150086301A1Increase temperatureIncrease pressureSemiconductor/solid-state device manufacturingConveyor parts3d integrated circuitEngineering

There is disclosed a carrier and method for handling and / or transport of a substrate, such as during processing of the substrate, for example, back-thinning. The carrier and method provide support for the substrate. The process is particularly suited to thinning of substrates for use in 3D integrated circuits. The carrier comprises: a contact surface with one or more recesses therein for trapping a volume when the contact surface is brought towards the substrate, the contact surface for supporting the substrate; a sealing surface at the periphery of the contact surface and offset from the contact surface; and the sealing member seating on the sealing surface and arranged to be compressed to form a seal to the substrate when a substrate is in contact with the contact surface, the seal sealing the trapped volume between the substrate and carrier.

Owner:APPLIED MICROENG

3D Integrated Circuit and Methods of Forming Same

ActiveCN104576637ASemiconductor/solid-state device detailsSolid-state devicesPorosity3d integrated circuit

An integrated circuit structure includes a package component, which further includes a non-porous dielectric layer having a first porosity, and a porous dielectric layer over and contacting the non-porous dielectric layer, wherein the porous dielectric layer has a second porosity higher than the first porosity. A bond pad penetrates through the non-porous dielectric layer and the porous dielectric layer. A dielectric barrier layer is overlying, and in contact with, the porous dielectric layer. The bond pad is exposed through the dielectric barrier layer. The dielectric barrier layer has a planar top surface. The bond pad has a planar top surface higher than a bottom surface of the dielectric barrier layer.

Owner:TAIWAN SEMICON MFG CO LTD

3D integration structure and method using bonded metal planes

ActiveUS7939369B2Semiconductor/solid-state device detailsSolid-state devices3d integrated circuitSemiconductor structure

A method of making 3D integrated circuits and a 3D integrated circuit structure. There is a first semiconductor structure joined to a second semiconductor structure. Each semiconductor structure includes a semiconductor wafer, a front end of the line (FEOL) wiring on the semiconductor wafer, a back end of the line (BEOL) wiring on the FEOL wiring, an insulator layer on the BEOL wiring and a metallic layer on the insulator layer. The first semiconductor structure is aligned with the second semiconductor structure such that the metallic layers of each of the semiconductor structures face each other. The metallic layers of each of the semiconductor structures are in contact with and bonded to each other by a metal to metal bond wherein the bonded metallic layers form an electrically isolated layer.

Owner:TESSERA INC

3D integrated circuit and its manufacturing method

ActiveCN102263099AAvoid damageSemiconductor/solid-state device detailsSolid-state devices3d integrated circuitInterconnection

The invention provides a 3D (three-dimensional) IC (integrated circuit) and a manufacturing method thereof. The circuit comprises a semiconductor substrate, a semiconductor device, a silicon through hole, an interconnection structure and a diffusion trapping region, wherein the semiconductor device is formed on the upper surface of the semiconductor substrate; the silicon through hole penetrates through the semiconductor substrate and comprises an insulating layer for covering the side walls of the silicon through hole and a conducting material filled in the insulating layer; the interconnection structure is used for connecting the semiconductor device with the silicon through hole; and the diffusion trapping region is formed on the lower surface of the semiconductor substrate. The manufacturing method is applicable to manufacturing of 3D integrated circuits.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

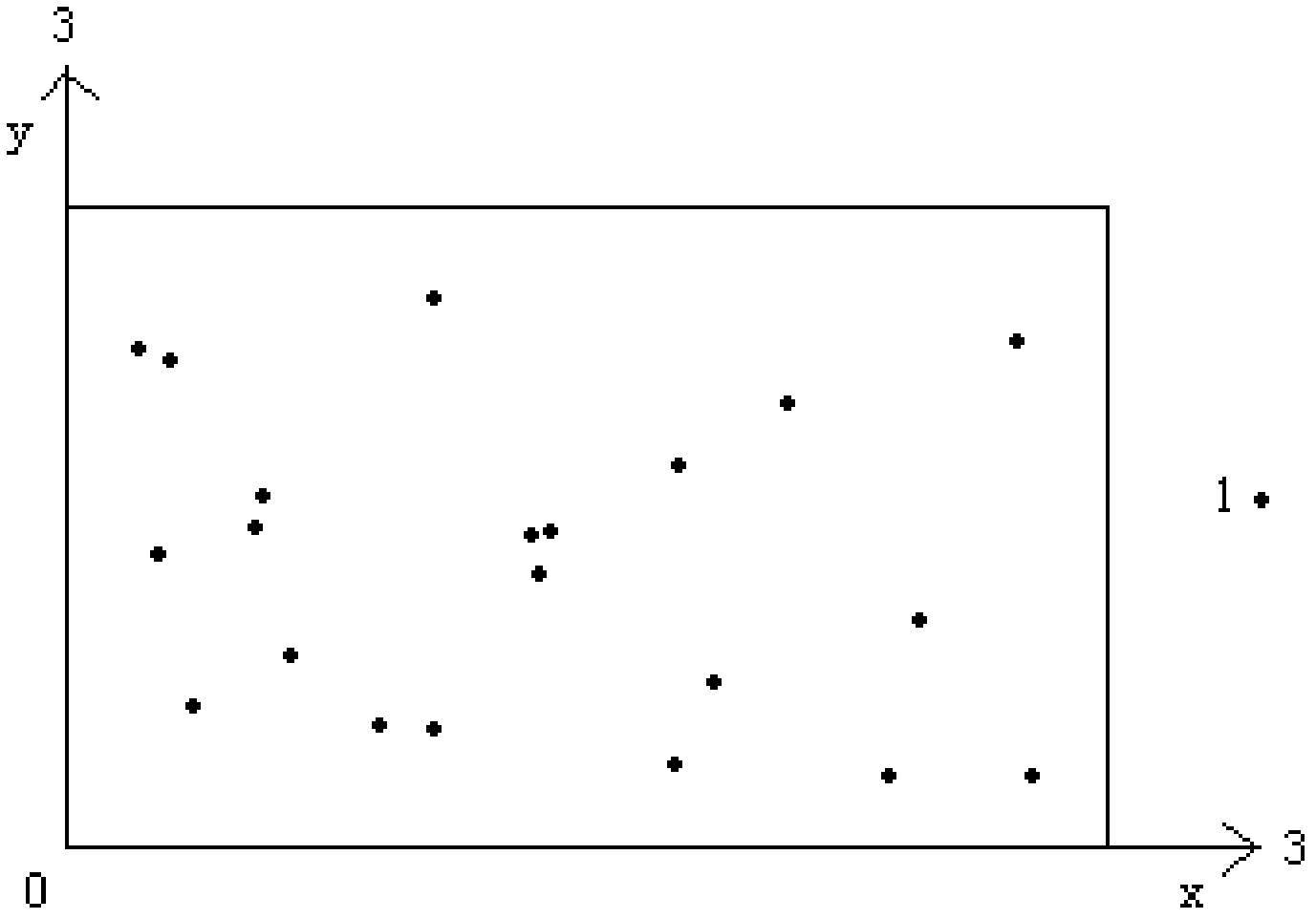

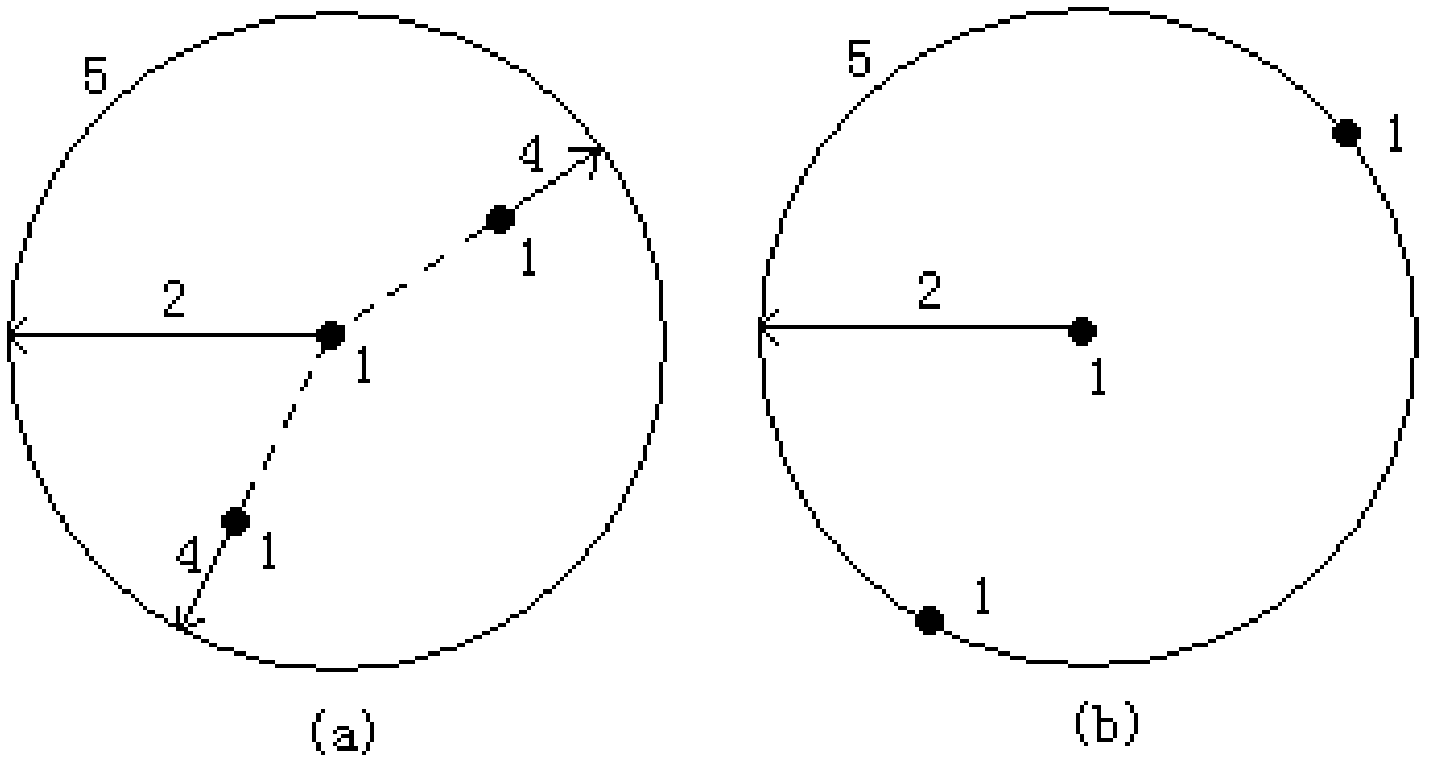

Distance optimizing method of through silicon via (TSV) positions in three-dimensional (3D) integrated circuit automatic layout

InactiveCN102663204ATo achieve the purpose of dredging the crowded TSVMeet the process requirementsSpecial data processing applications3d integrated circuitIntegrated circuit layout

The invention discloses a distance optimizing method of through silicon via (TSV) positions in a three-dimensional (3D) integrated circuit automatic layout. The distance optimizing method has wide application to the field of design and manufacture of 3D integrated circuits. In a layout formed after initial locating of common 3D integrated circuit TSVs, the number of the TSVs is big, and distribution of the TSVs in the layout is dense, therefore a problem that the positions of the TSVs are too close occurs. When the 3D integrated circuit is manufactured and produced, manufacturers can not manufacture the layout where gaps of the TSVs are smaller than gap restrain of manufacture process. The method uses a distance method to optimize the gaps of the TSVs, an optimized layout is obtained so as to enable the gaps of the TSVs to meet process manufacture requirements, and manufacture can be finished. In the optimized TSV layout, distance of the TSVs is appropriate, working speed of the circuit can be increased, and crosstalk is reduced.

Owner:BEIJING UNIV OF TECH