Design and verification of 3d integrated circuits

An integrated circuit, 3D technology, used in CAD circuit design, computer-aided design, calculation, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

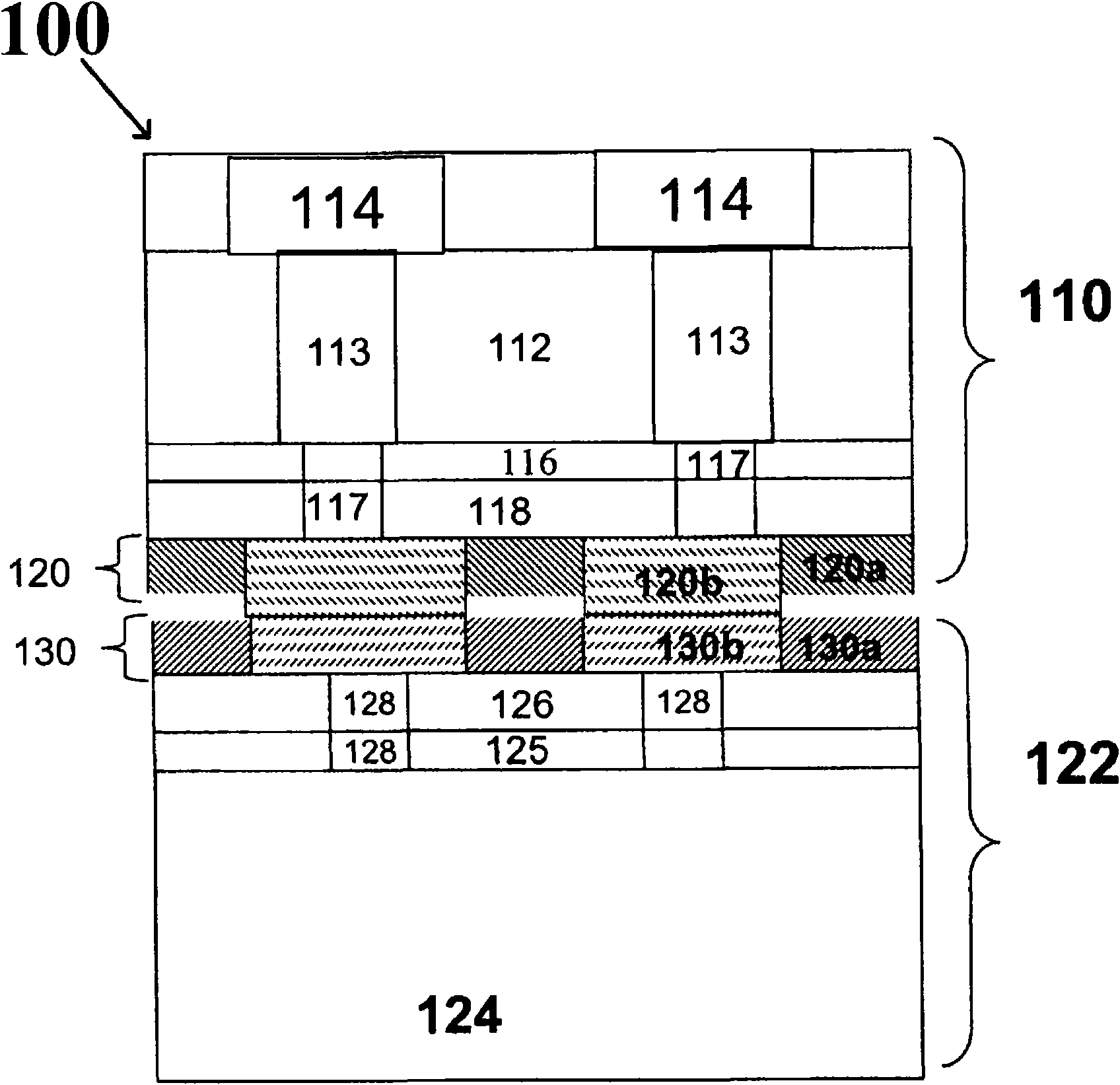

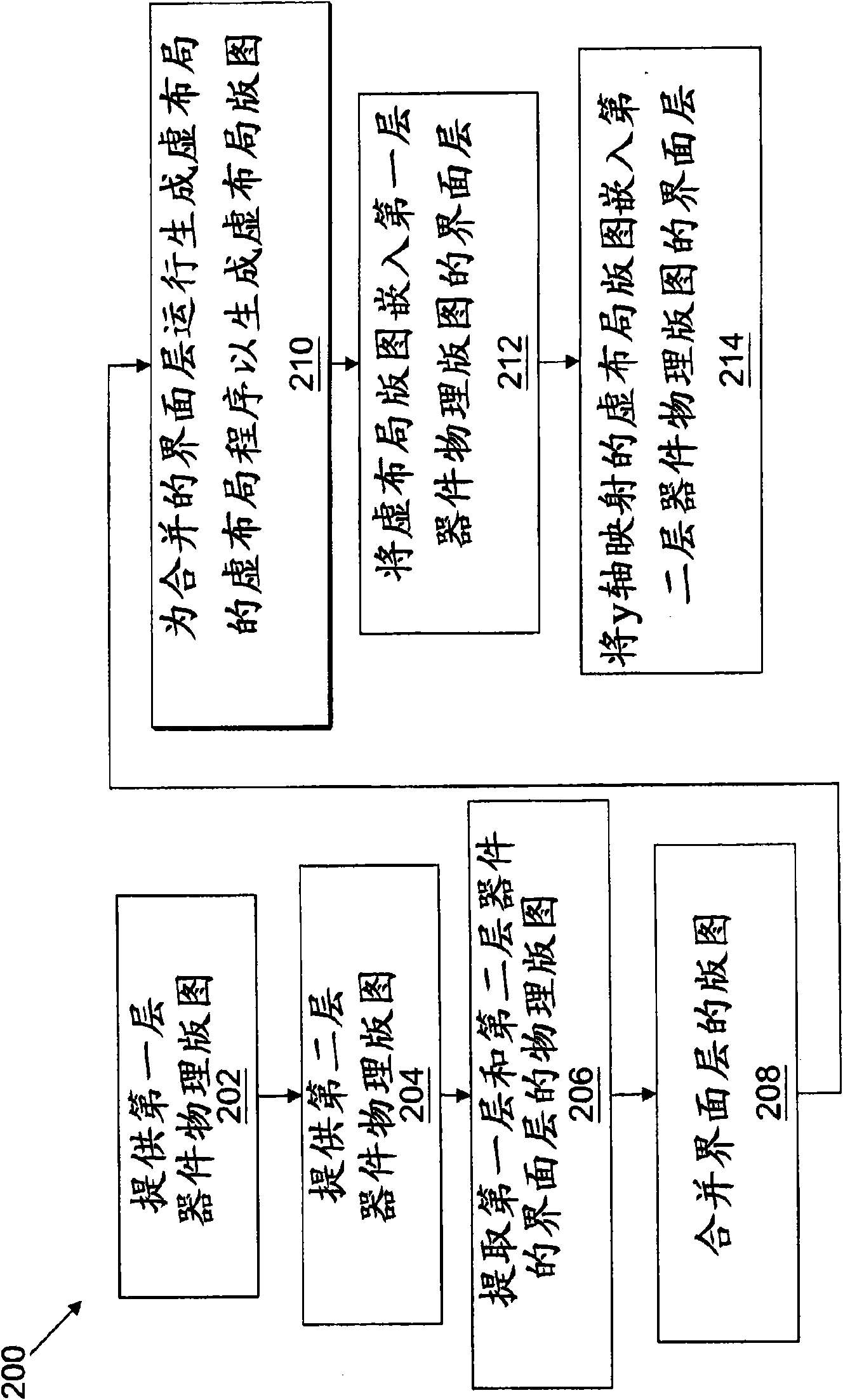

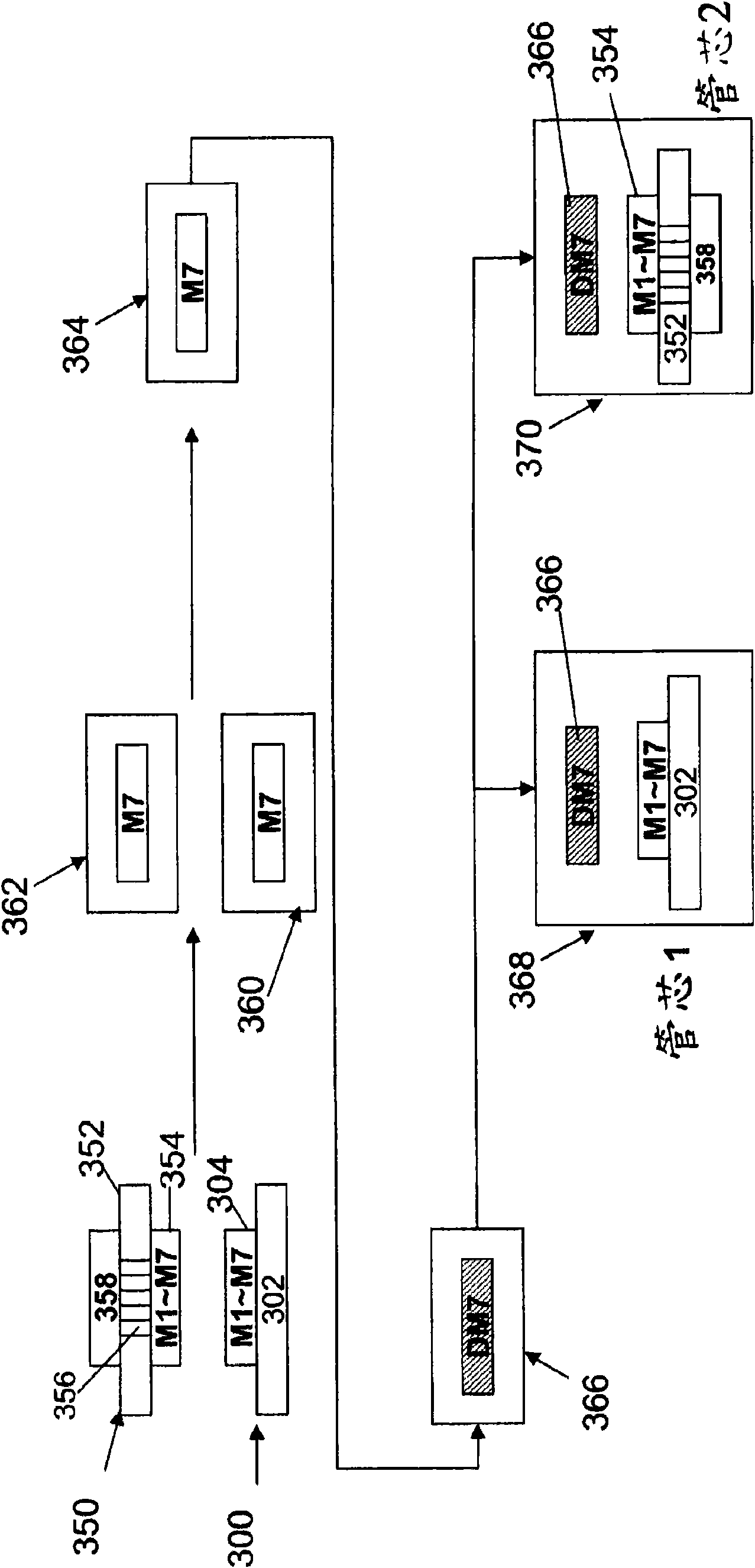

[0019] It will be appreciated that the specific embodiments provided herein are examples to teach the broader inventive concepts, and those skilled in the art can readily apply the teachings of the present invention to other methods and systems. Additionally, it is to be understood that the methods and systems discussed herein include some general structures and / or processes. Because these structures and processes are well known in the art, they will be discussed in general detail only. Reference numerals in the drawings may be repeated for convenience and illustration, and such repetition does not represent any necessary combination of features or steps in the drawings. Additionally, although methods for the design and verification of 3D ICs are described herein, those skilled in the art will recognize that other design processes may also benefit from the present disclosure. Verification methods including Layout Schematic Verification (LVS) and Design Rule Checking (DRC) for...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More