Distance optimizing method of through silicon via (TSV) positions in three-dimensional (3D) integrated circuit automatic layout

An integrated circuit, automatic layout technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as inability to process, and achieve the effect of avoiding too dense

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

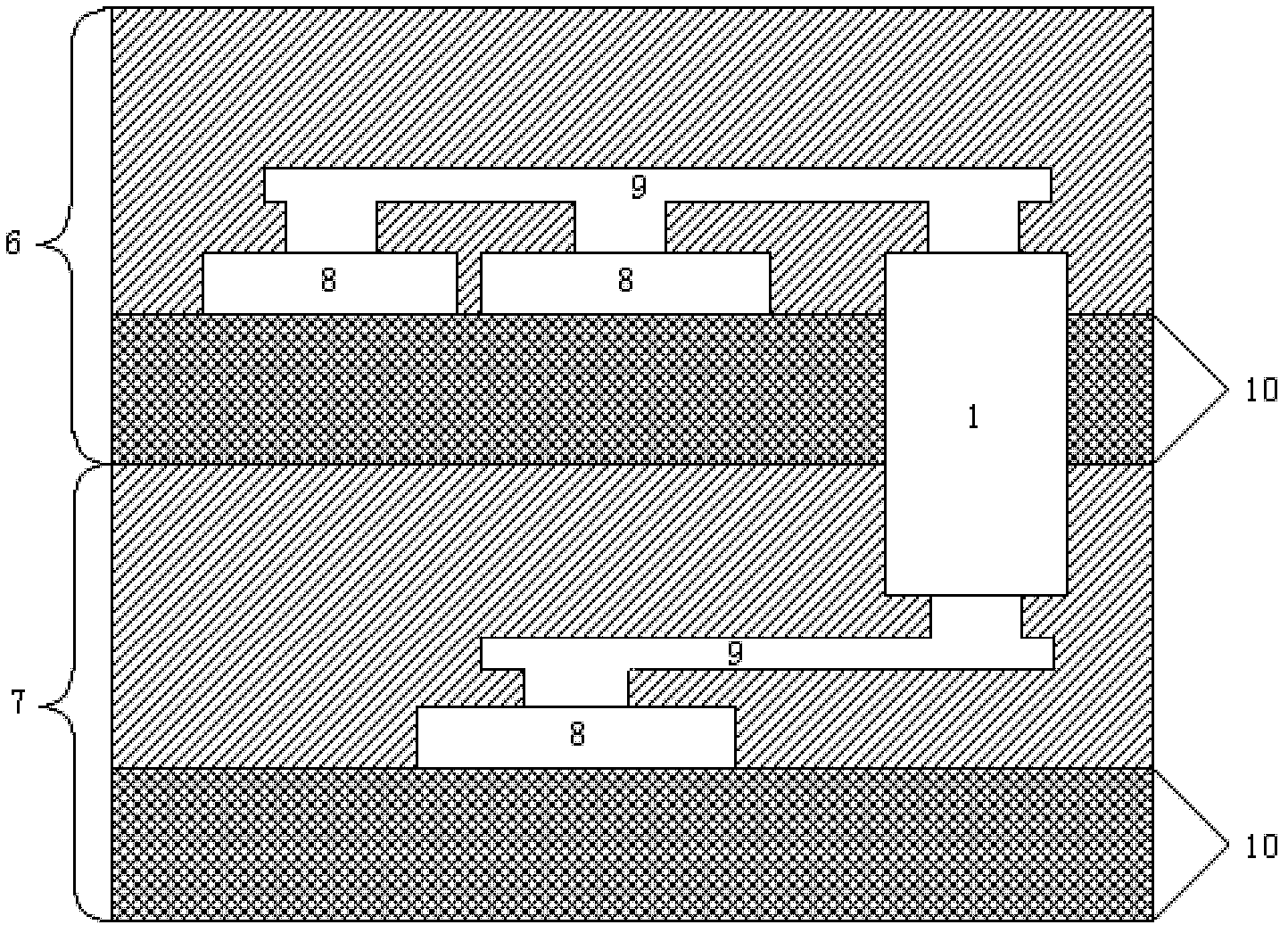

[0036] A 3D integrated circuit is a three-dimensional chip structure, each layer of which is a 2D chip, and the structure between any two layers is as follows: figure 1 As shown, the units 8 in the chip are arranged horizontally in the chip, and the units are the basic structure for signal communication in the circuit, and are connected by metal interconnection lines in the chip. The units in the adjacent two-layer chips need to be connected through TSV1. TSV1 is a via hole passing through the chip in the circuit, so that the upper and lower two-layer chips are connected. Therefore, TSV1 is a structure different from 2D circuits for 3D integrated circuits. Among them, in the 3D circuit, the upper chip is called the top chip, and the lower chip is called the bottom chip. These two layers of chips can be any two layers of adjacent chips in the 3D circuit.

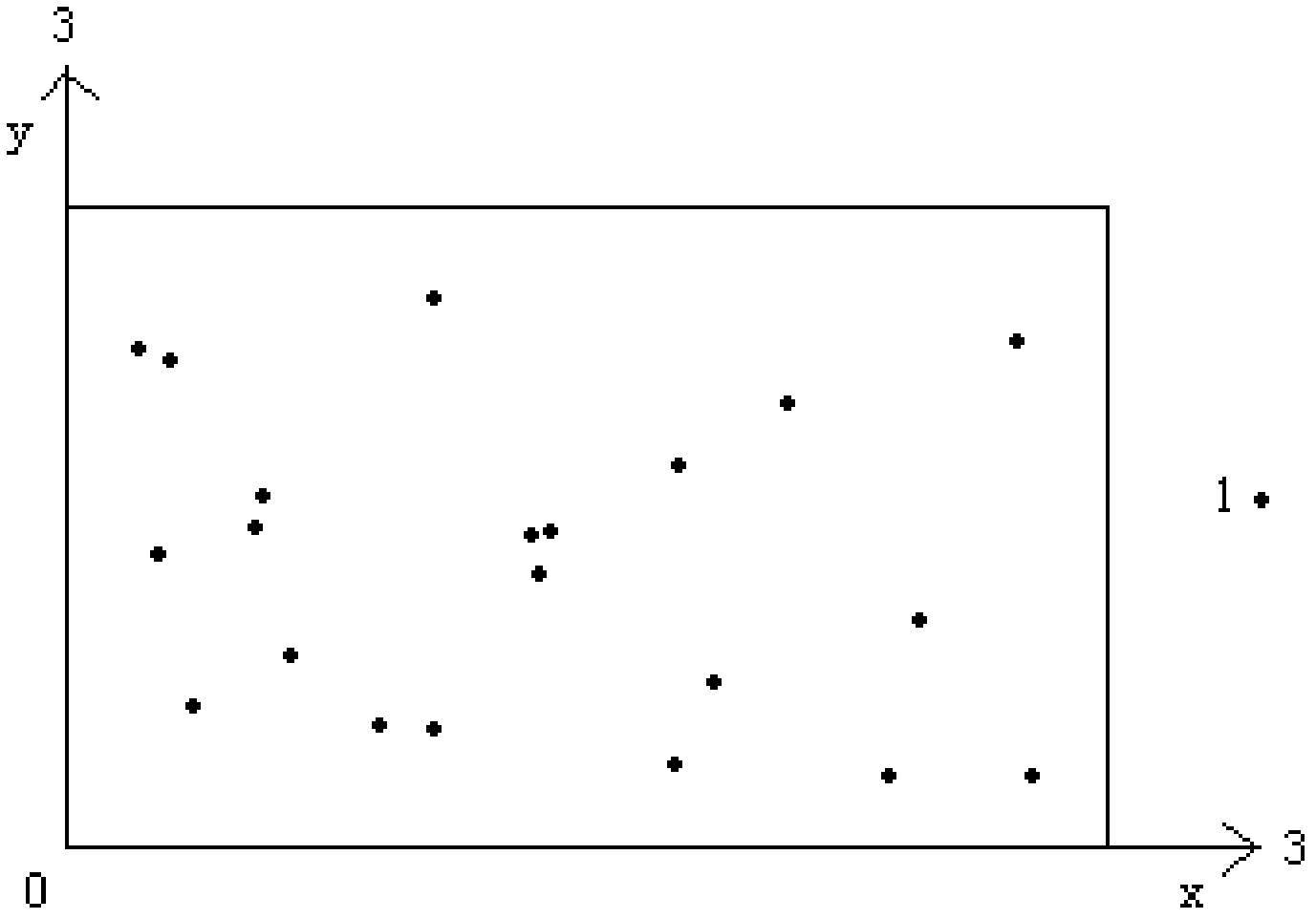

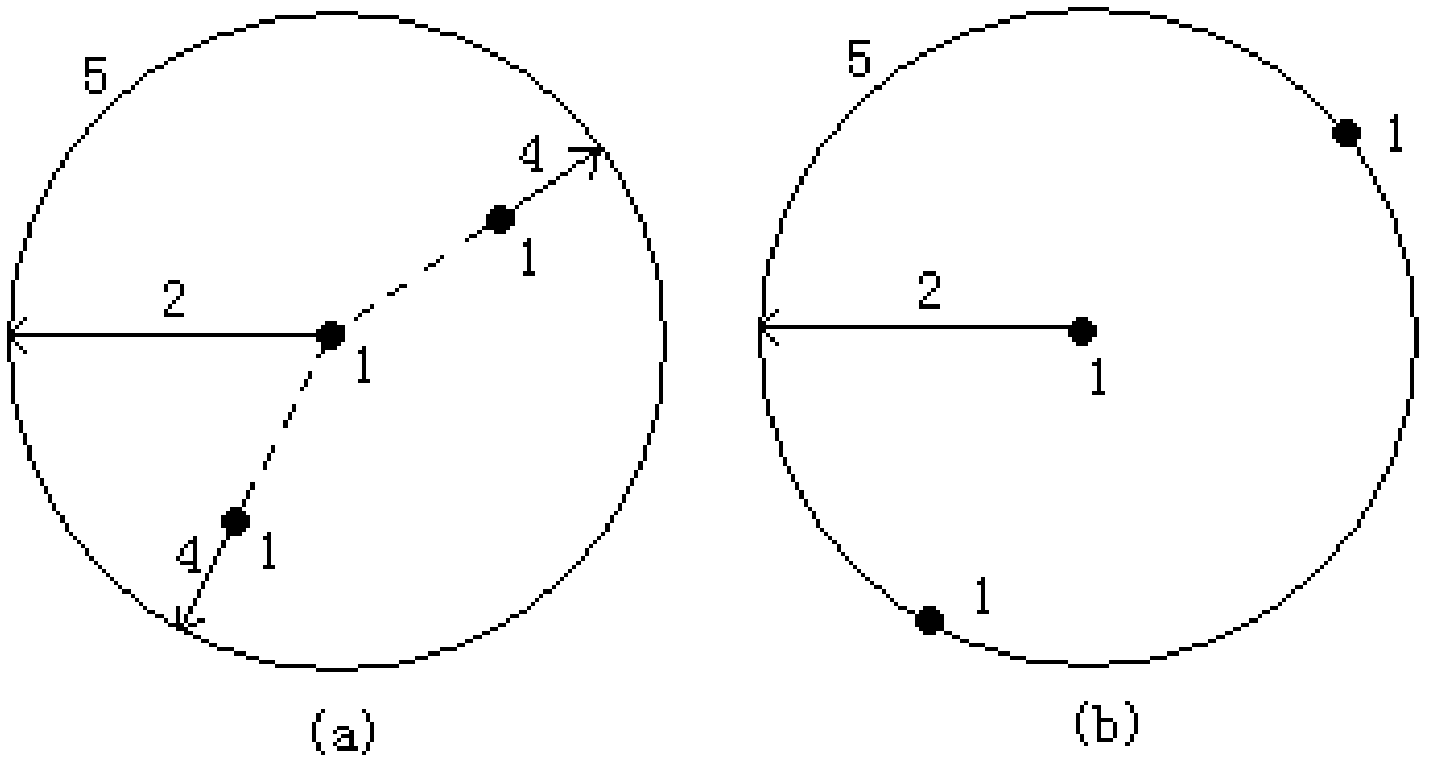

[0037] The present invention is dedicated to optimizing the 3D integrated circuit layout whose TSV1 coordinates have been ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More