Patents

Literature

886 results about "Line length" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In typography, line length is the width of a block of typeset text, usually measured in units of length like inches or points or in characters per line (in which case it is a measure).

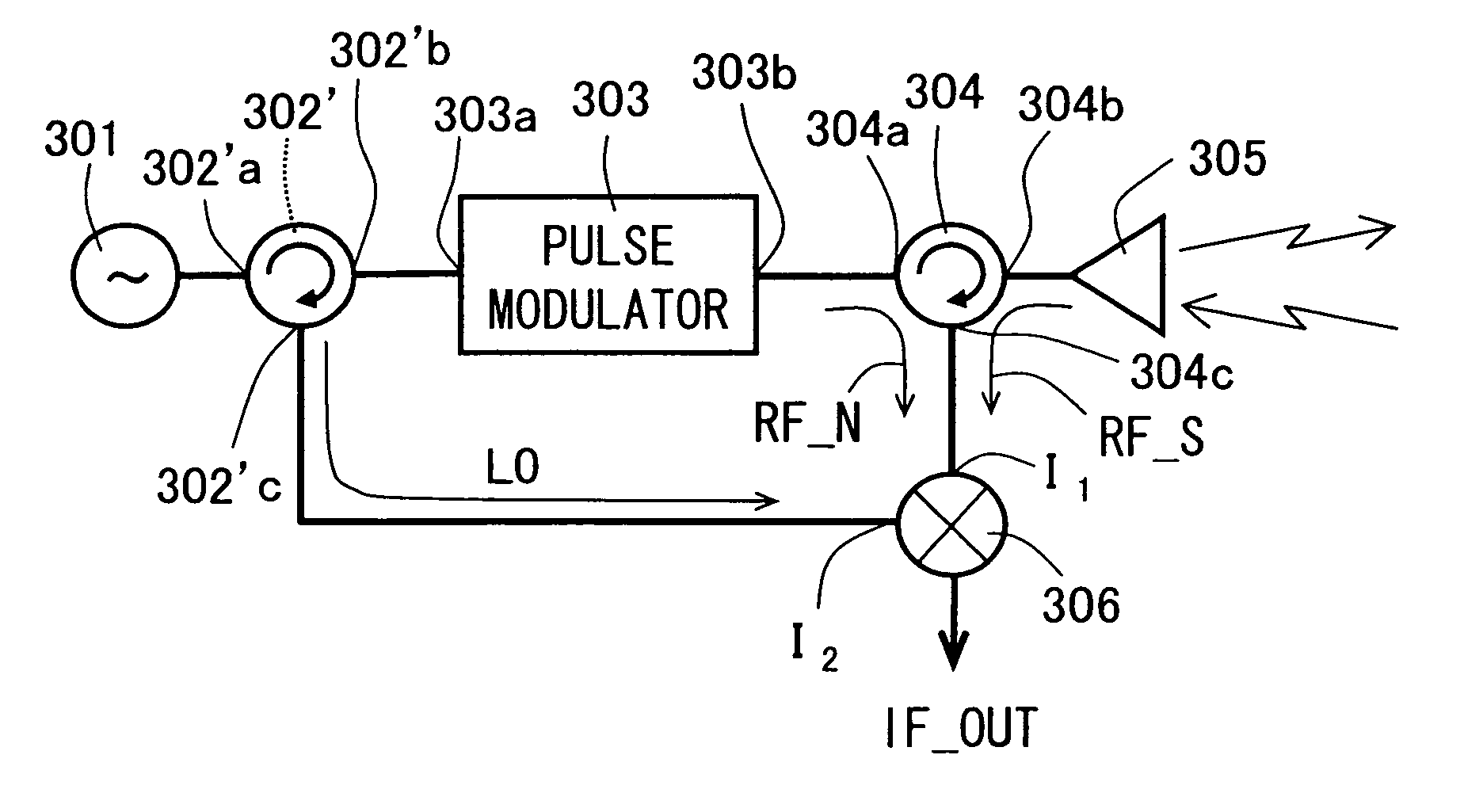

Transmitting/receiving antenna, isolator, high-frequency oscillator, and high-frequency transmitter-receiver using the same

InactiveUS20050190101A1Satisfactory characteristicOscillation stabilityWaveguide type devicesRadio wave reradiation/reflectionDielectricPhase difference

A millimeter-wave transmitter-receiver uses an NRD guide as a fundamental configuration and includes a millimeter-wave signal oscillator, a pulse modulator, a circulator, an antenna and a mixer. In the millimeter-wave transmitter-receiver, a line length of a third dielectric guide is set so that δ=±π in which δ is a phase difference at a center frequency between a portion of a transmission millimeter-wave signal, which is reflected via a third dielectric guide on the leading end portion of the third dielectric guide and returned to leak to a third connecting portion of the circulator, and another portion of the millimeter-wave signal, which leaks from a first connecting portion to the third connecting portion of the circulator. It is possible to reduce the change in the mixer output and enhance the millimeter-wave transmission / reception performance.

Owner:KYOCERA CORP

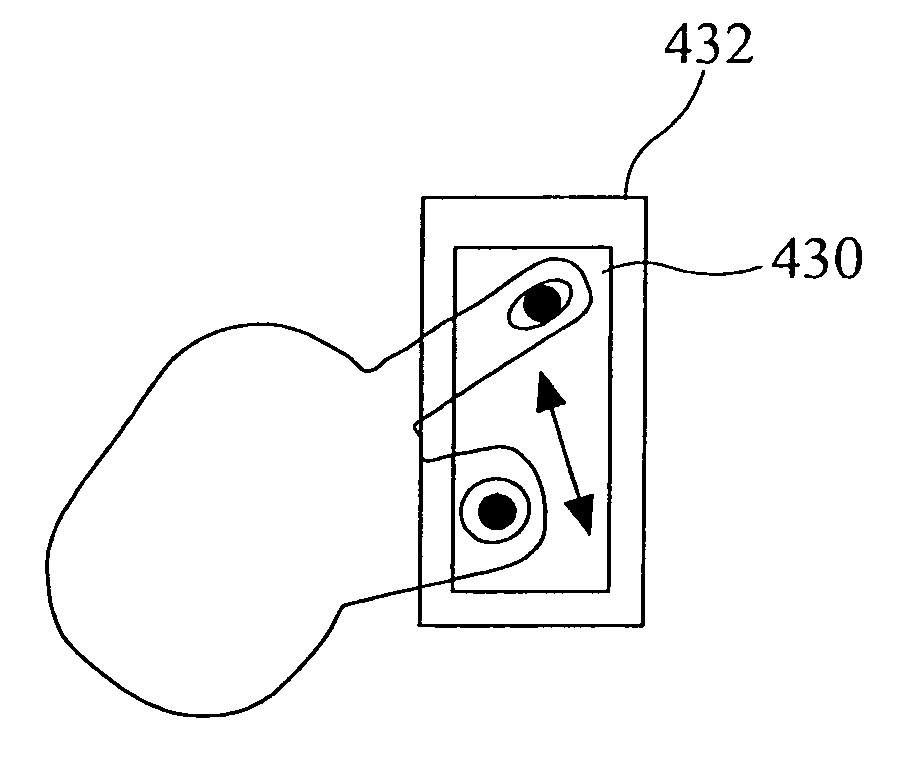

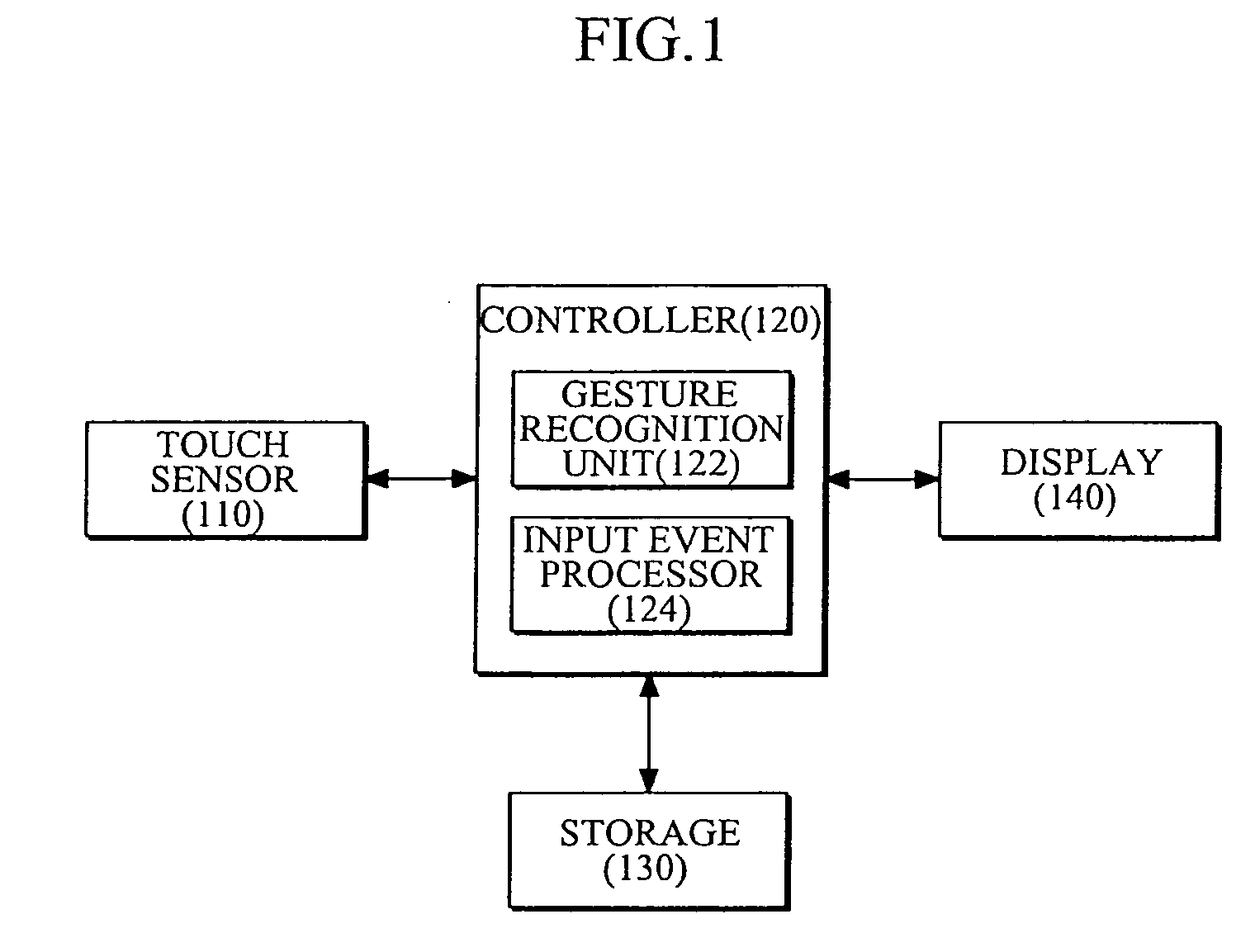

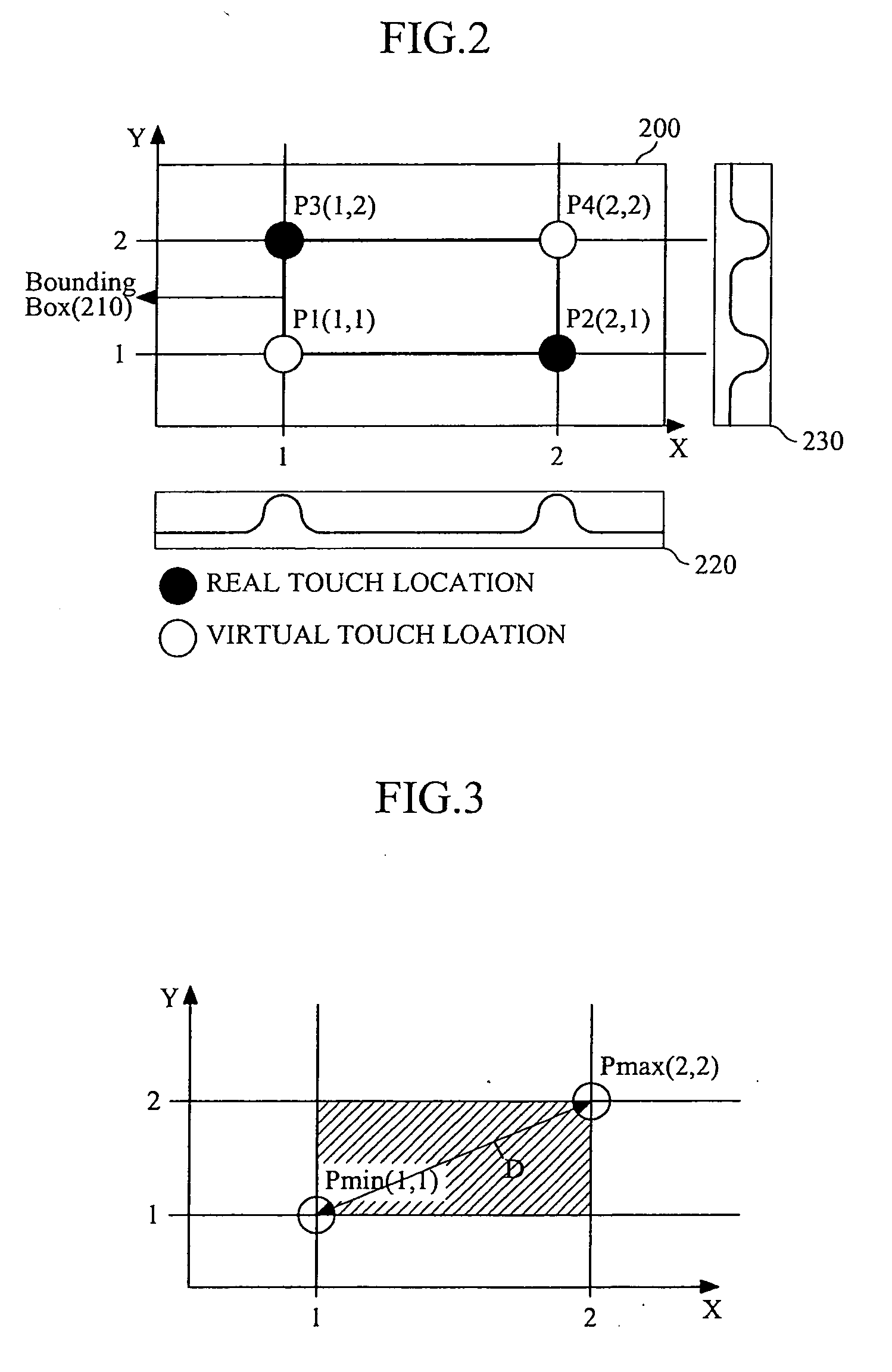

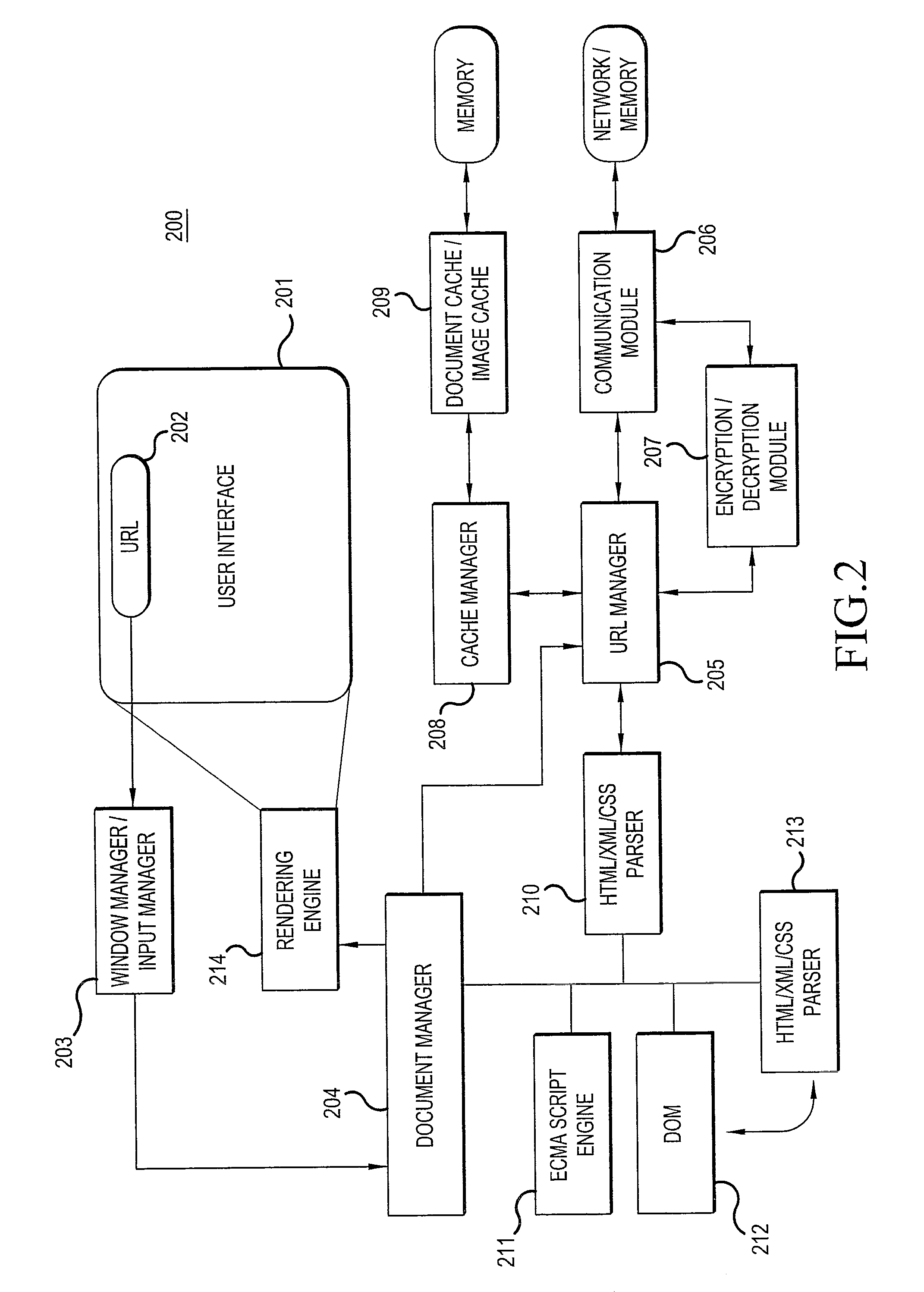

Apparatus and method recognizing touch gesture

ActiveUS20100259493A1Reduce the amount requiredInput/output processes for data processingUser inputLine length

Disclosed are a touch gesture recognition apparatus and method that can be, or applied to, both a single-touch system and a multi-touch system. The touch gesture recognition method recognizes touch gestures using the diagonal-line length of a bounding box created based on touch location information and variations in the diagonal-line length. After a gesture is recognized, the recognized gesture is mapped to an input event of a user input device and feedback according to the input event is provided.

Owner:SAMSUNG ELECTRONICS CO LTD

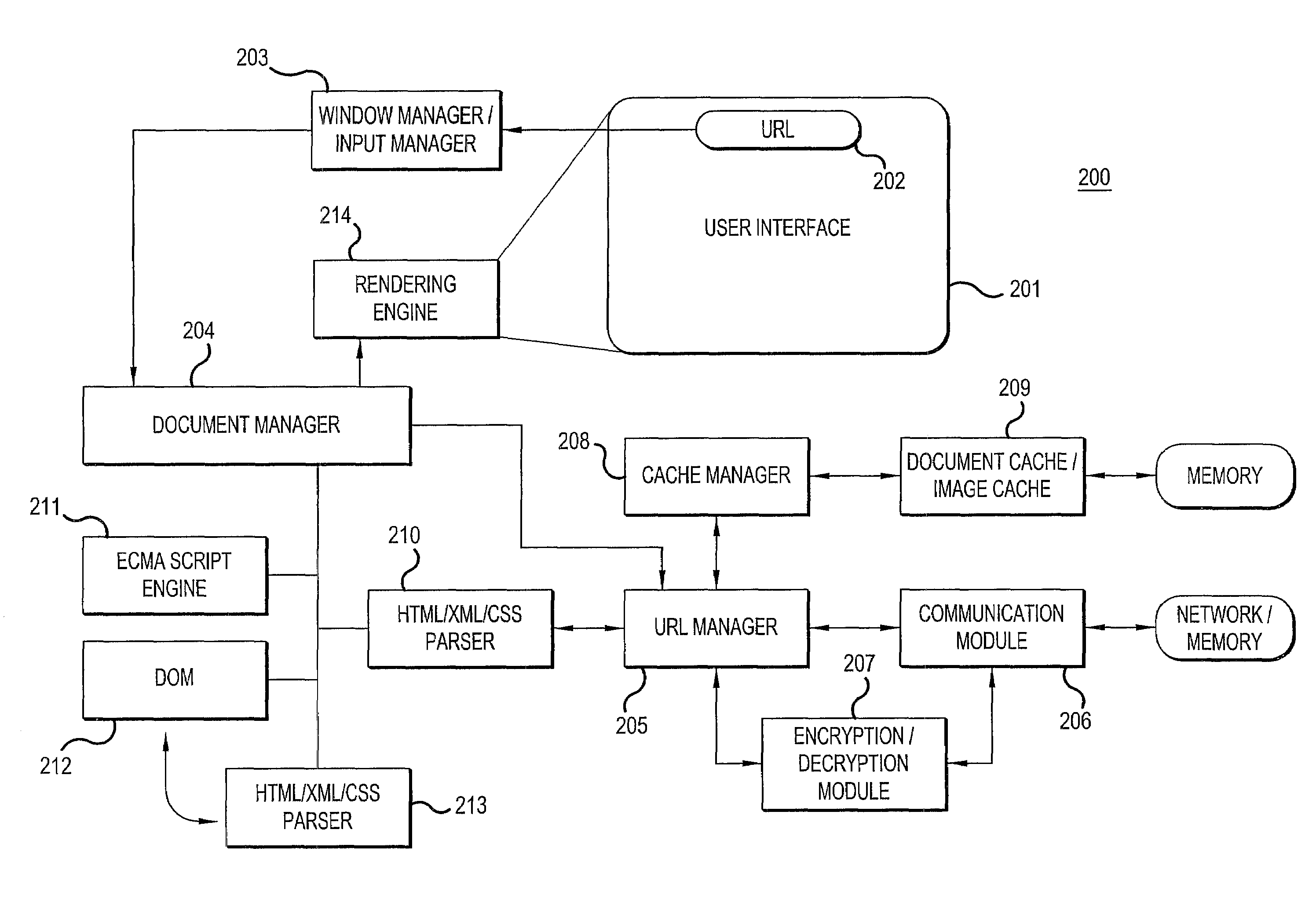

Method and device for dynamically wrapping text when displaying a selected region of an electronic document

ActiveUS20090319888A1High resolutionReduce rateDigital data information retrievalNatural language data processingElectronic documentAlgorithm

A method is provided for rewrapping text when changing from a first to a second zoom level when displaying an electronic document. The line length at which to rewrap the text is chosen such that no horizontal scrolling becomes necessary. Since the rewrapping may result in a change to the layout of the document, the method may further include s identifying an element in the electronic document and ensuring that the element is included in the display after a zooming-in or zooming-out operation. Also described is a device configured to perform the method and a computer program including instructions for performing the method when executed by a computing device.

Owner:OPERA SOFTVEAR AS

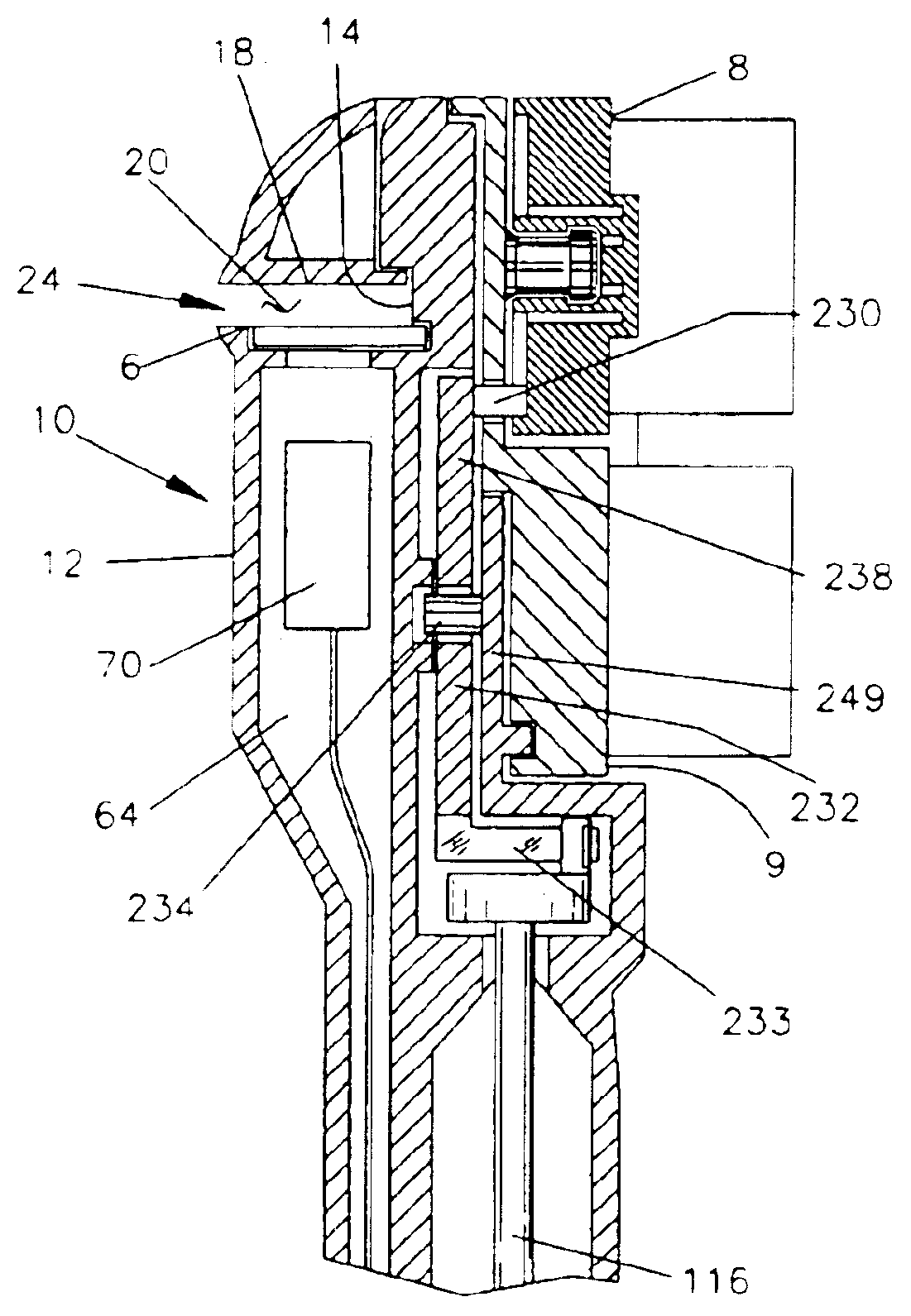

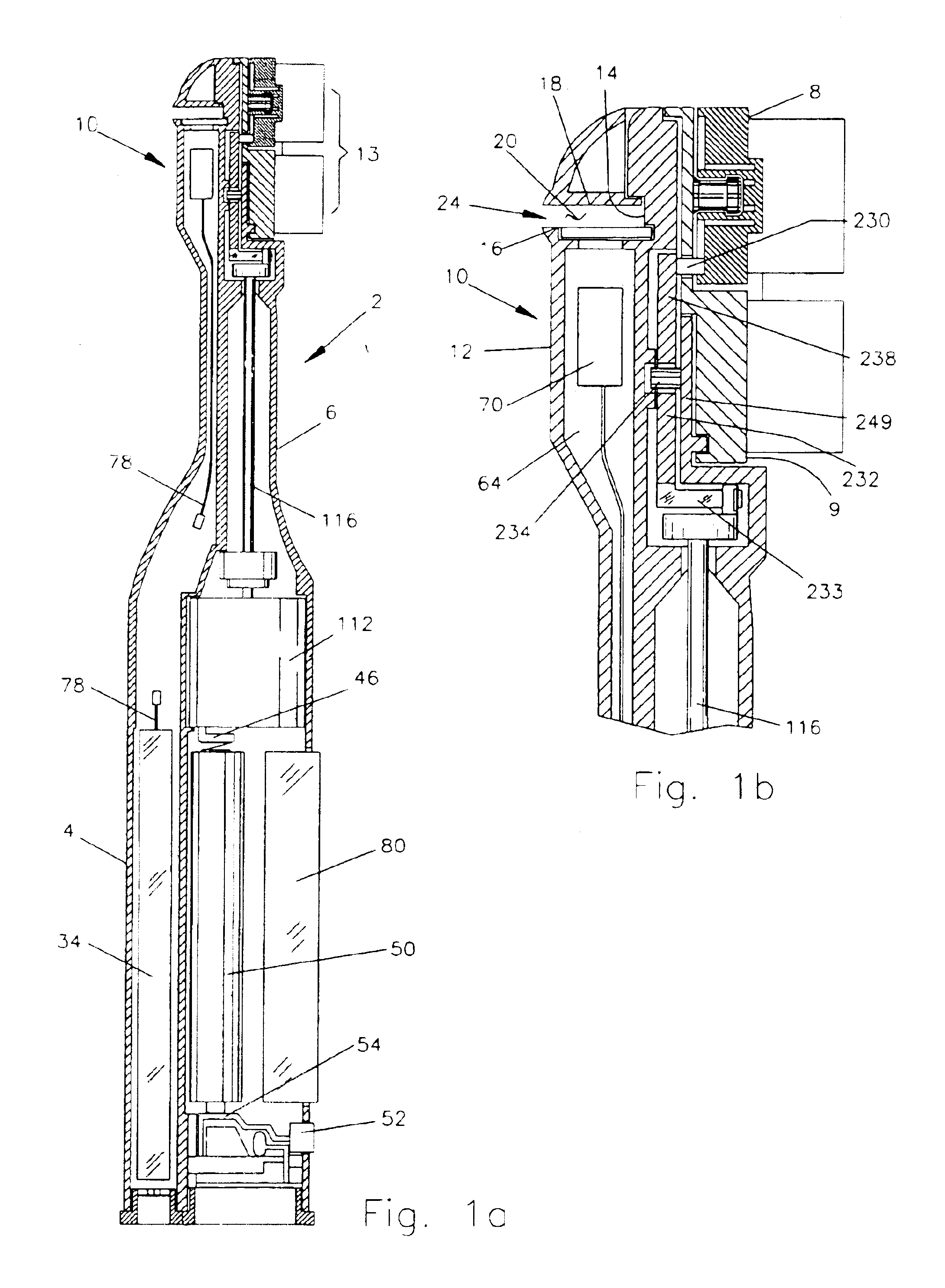

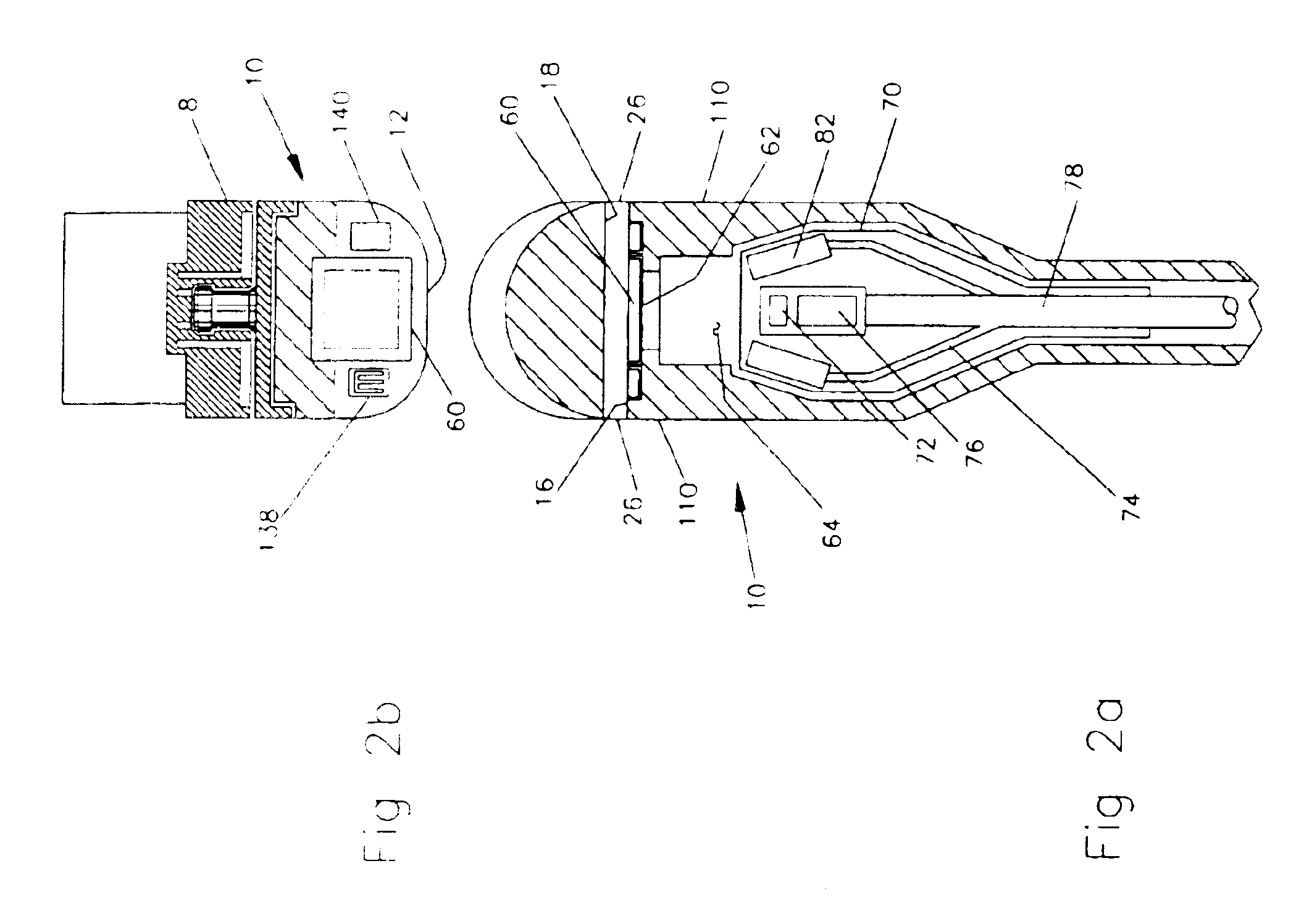

Image processing system for predicting ovulation

InactiveUS6960170B2Stimulates saliva productionAnalysis using chemical indicatorsSurgerySaliva sampleBristle

An image processing system for predicting ovulation using a test channel for collecting saliva sample and a miniature camera for capturing the image of the saliva at dried state for analyzing the crystalline patterns for ovulation prediction. A rotary bristle element is attached to the drive head and a notch-like test channel traverses the width of the drive head. A conductivity sensor is mounted on a wall of the test channel for detecting filling and drying of the saliva sample. An algorithm in the microprocessor analyzes the image of the dried saliva and calculates the characteristic line length of line segments of connected saliva dots. A ferning index is also defined and calculated based on the percentage of area coverage of line segments which are exceeding the threshold line length. Trend curves are established based on the daily saliva analysis in a woman's menstrual cycle for predicting days from the ovulation.

Owner:KUO YOUTI

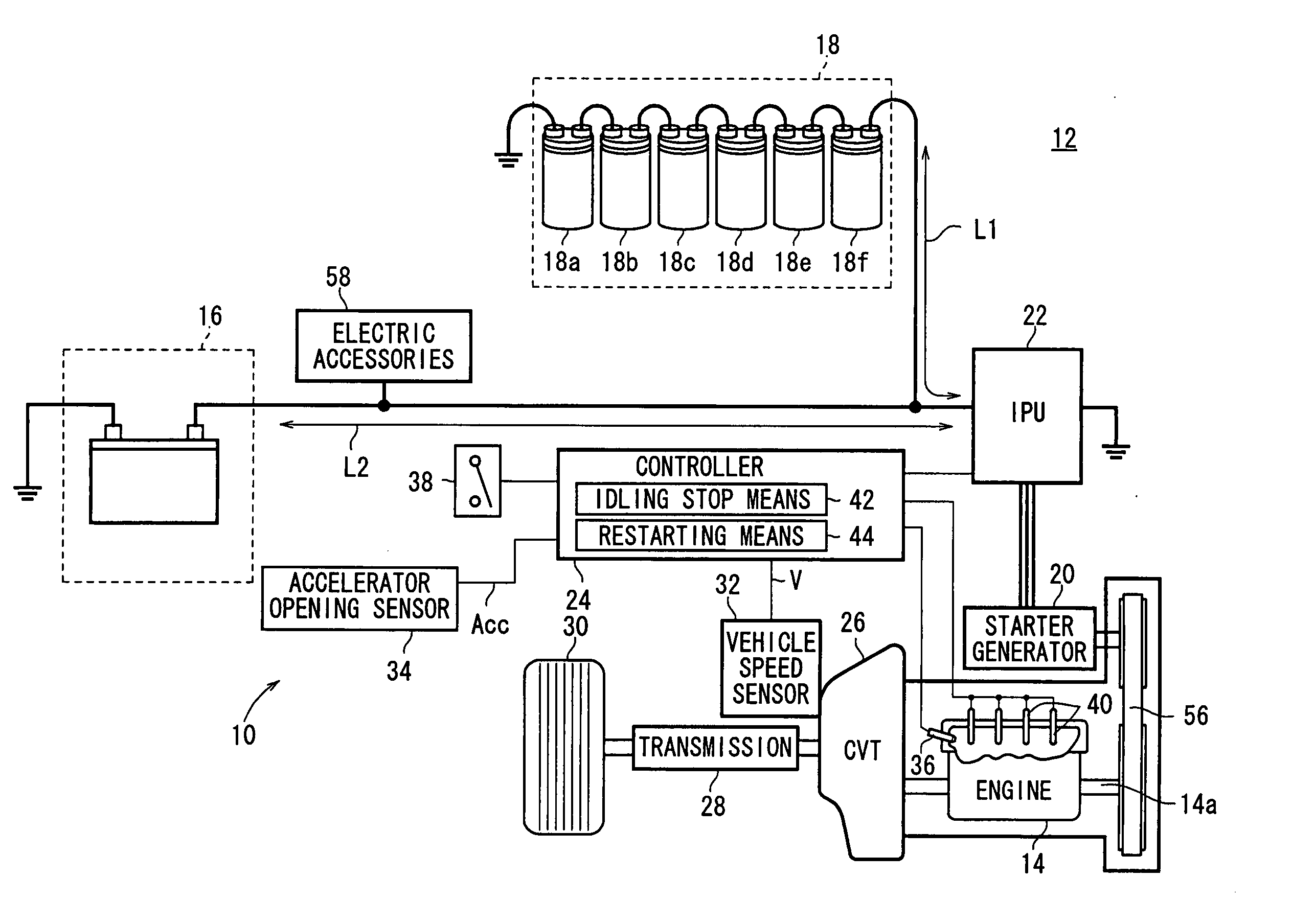

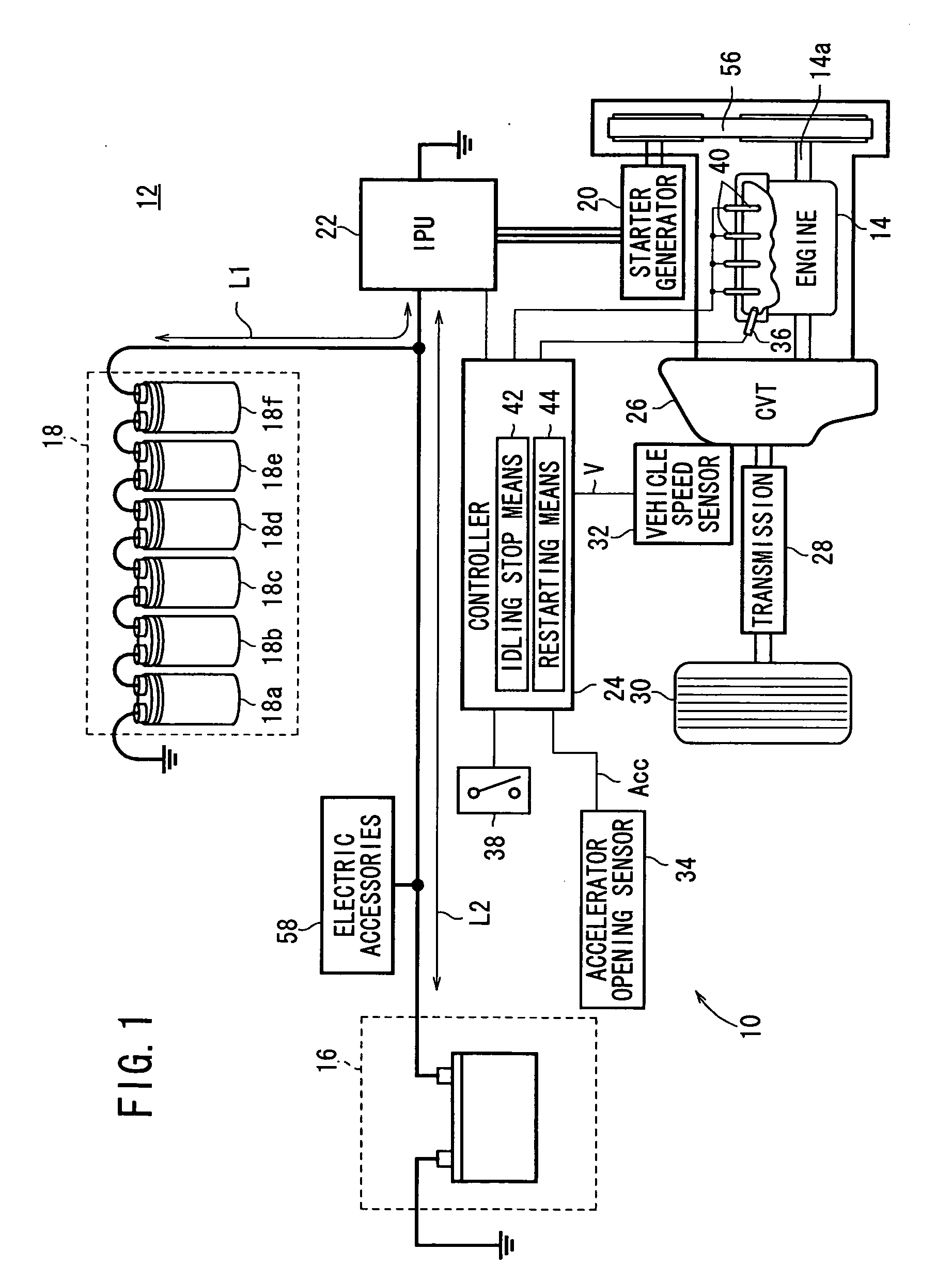

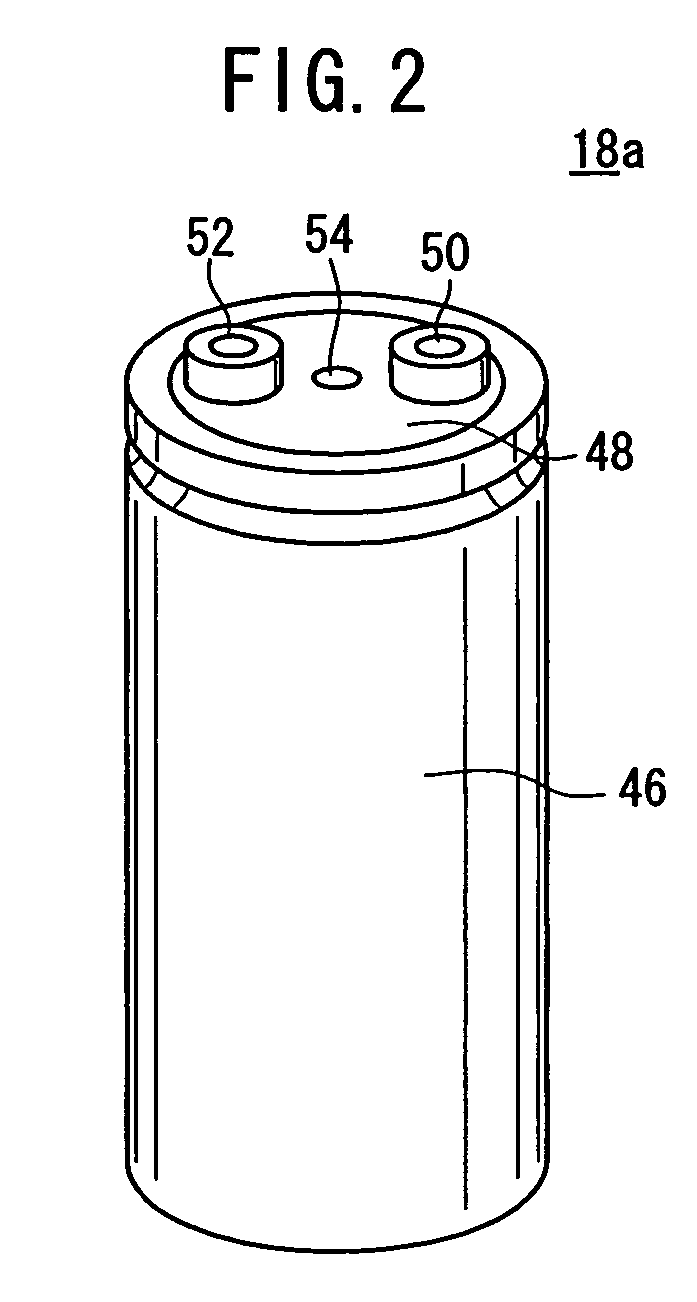

Method of supplying electric current, method of starting internal combustion engine, power supply apparatus, and vehicle

InactiveUS20060186738A1Extended service lifeSimple and inexpensive procedurePower operated startersBatteries circuit arrangementsStarter generatorInternal combustion engine

A power supply apparatus has a lead storage battery and an electric double-layer capacitor which are connected in parallel to each other, and a starter generator for being supplied with electric power discharged from the storage battery and the electric double-layer capacitor and for operating as an electric generator after an engine is started. Electric power generated by the starter generator is supplied to charge the storage battery and the electric double-layer capacitor. An IPU as a connection switching device is connected between the storage battery and the electric double-layer capacitor, and the starter generator. A line length between the electric double-layer capacitor and the starter generator is shorter than a line length between the lead storage battery and the starter generator.

Owner:HONDA MOTOR CO LTD

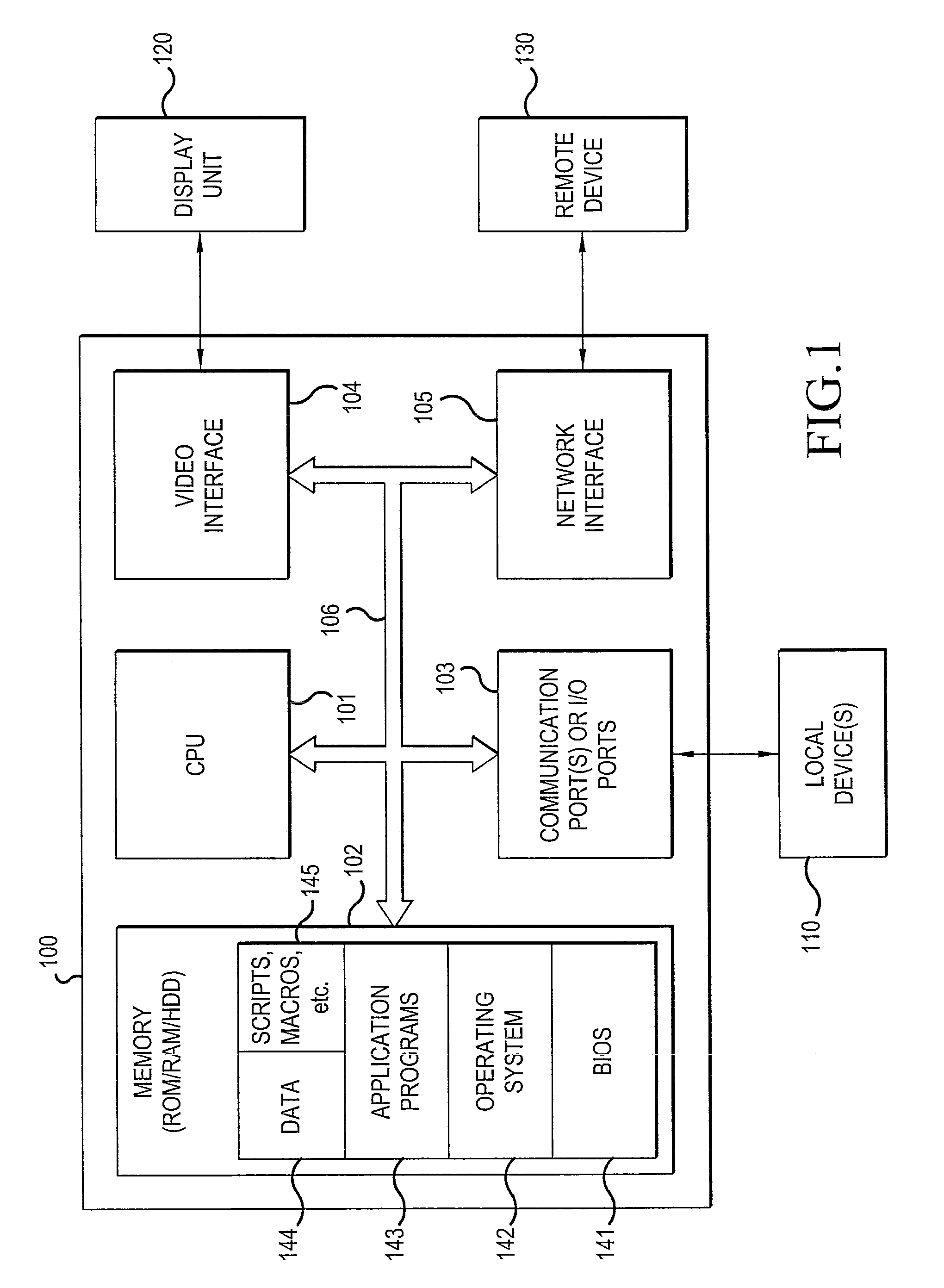

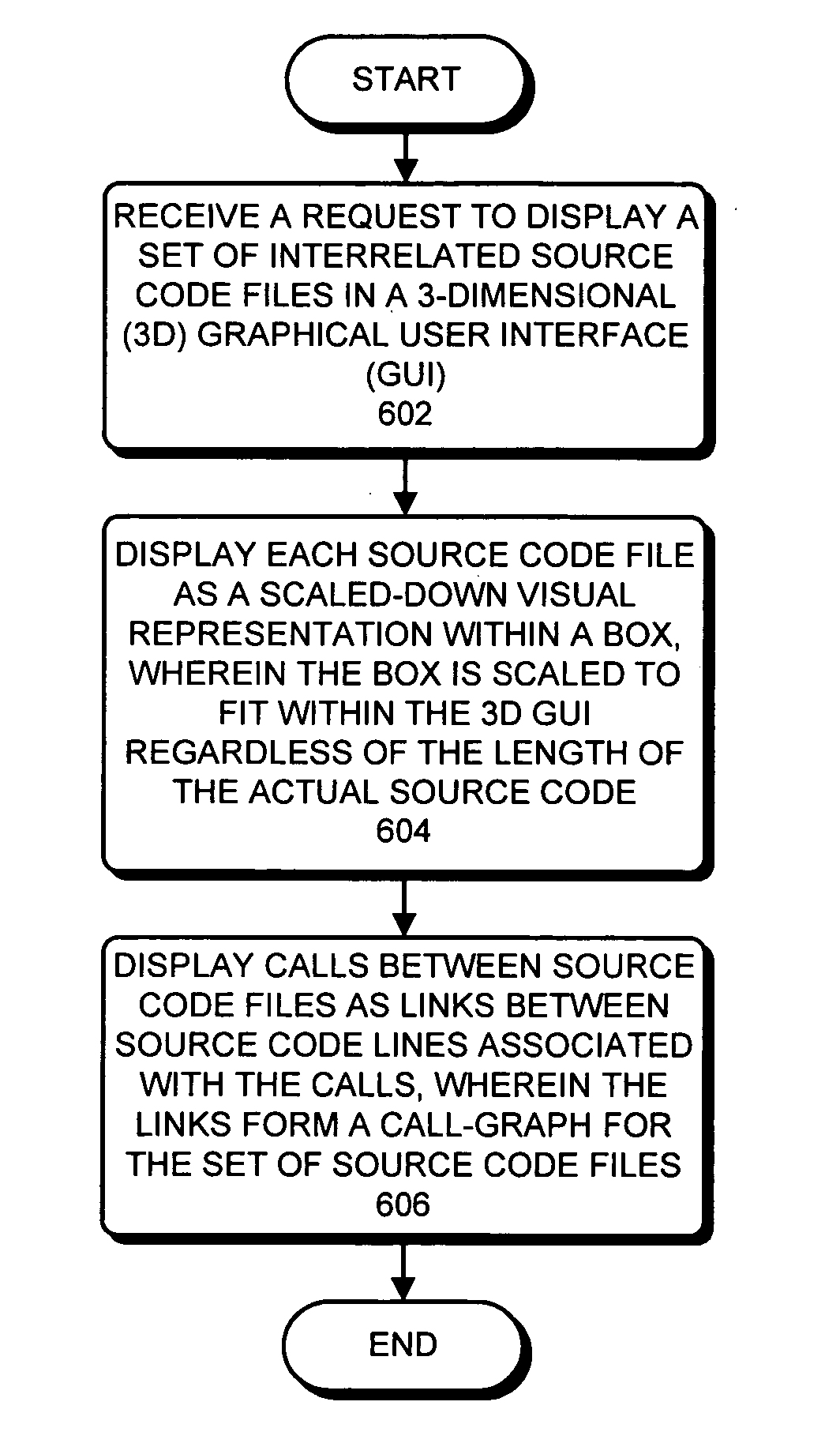

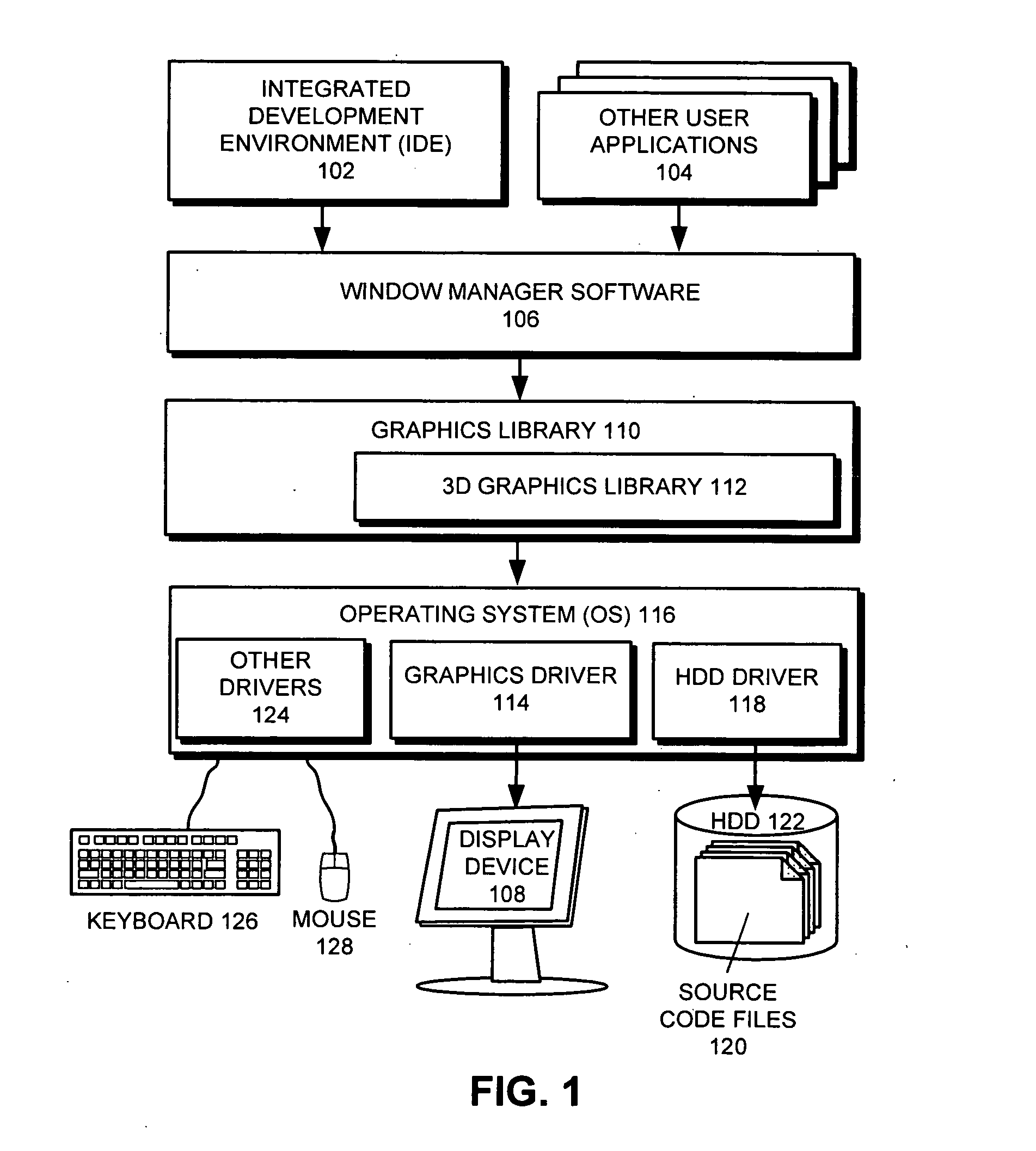

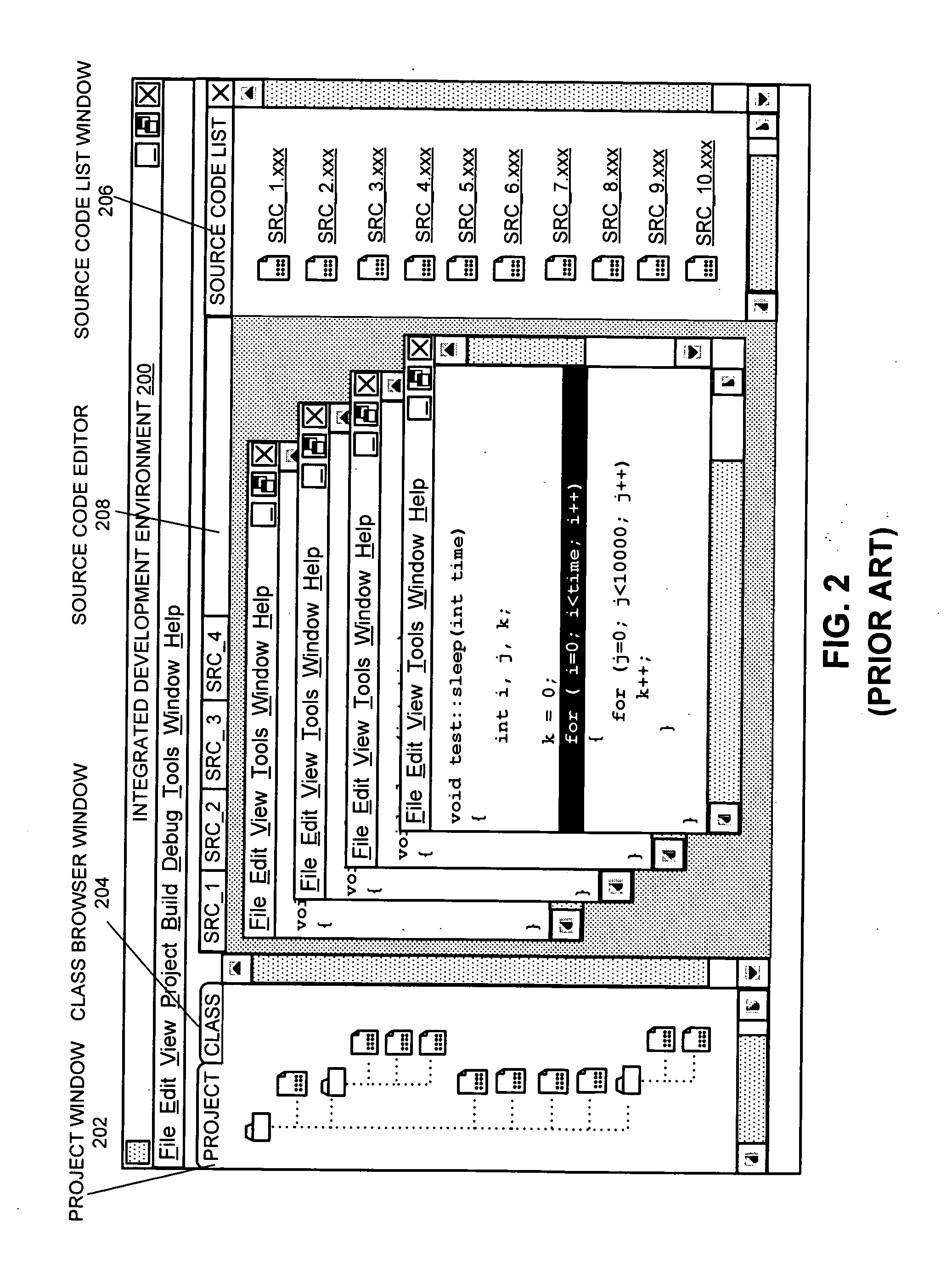

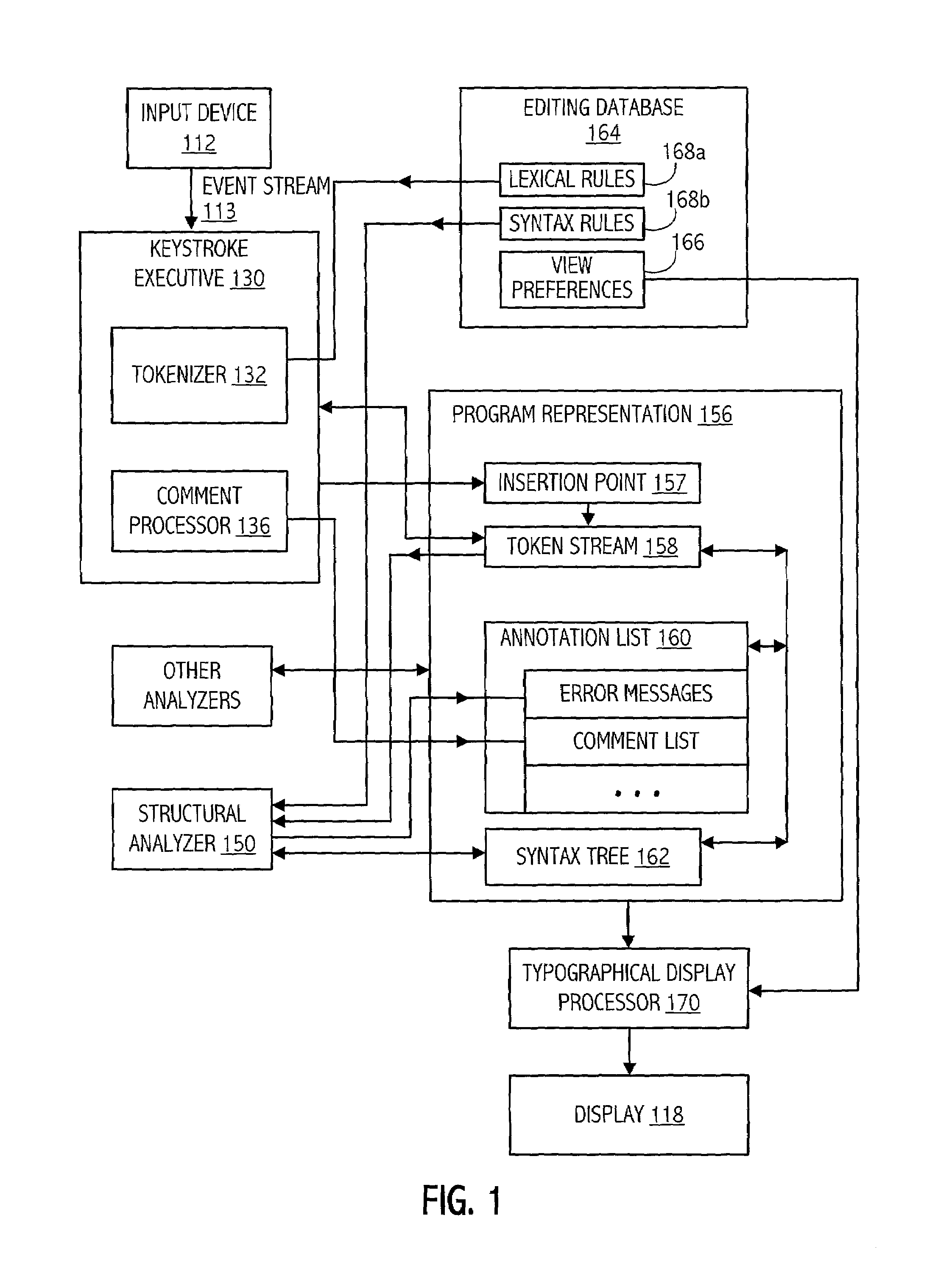

Using 3-dimensional rendering effects to facilitate visualization of complex source code structures

InactiveUS20070256054A1Facilitates displaying debugging toolIncrease and decrease visual resolutionProgram documentationSpecific program execution arrangementsLine lengthGraphical user interface

One embodiment of the present invention provides a system that uses three-dimensional (3D) rendering effects within a 3D graphical user interface (GUI) to enable a user to efficiently visualize and navigate through complex source code structures. During operation, the system receives a request to display a set of source code files in a 3D GUI. Next, in response to the request, the system displays each source code file as a scaled-down version of the actual source code within a box in the 3D GUI, wherein the box is scaled to fit within a viewing window of the 3D GUI regardless of the length of the source code in the file. Note that the scaled-down source code within the box preserves the structure of the actual source code file, including line lengths and indentations. The system also displays calls between source code files as links between source code lines associated with the calls, wherein the links form a call-graph between the set of source code files.

Owner:SUN MICROSYSTEMS INC

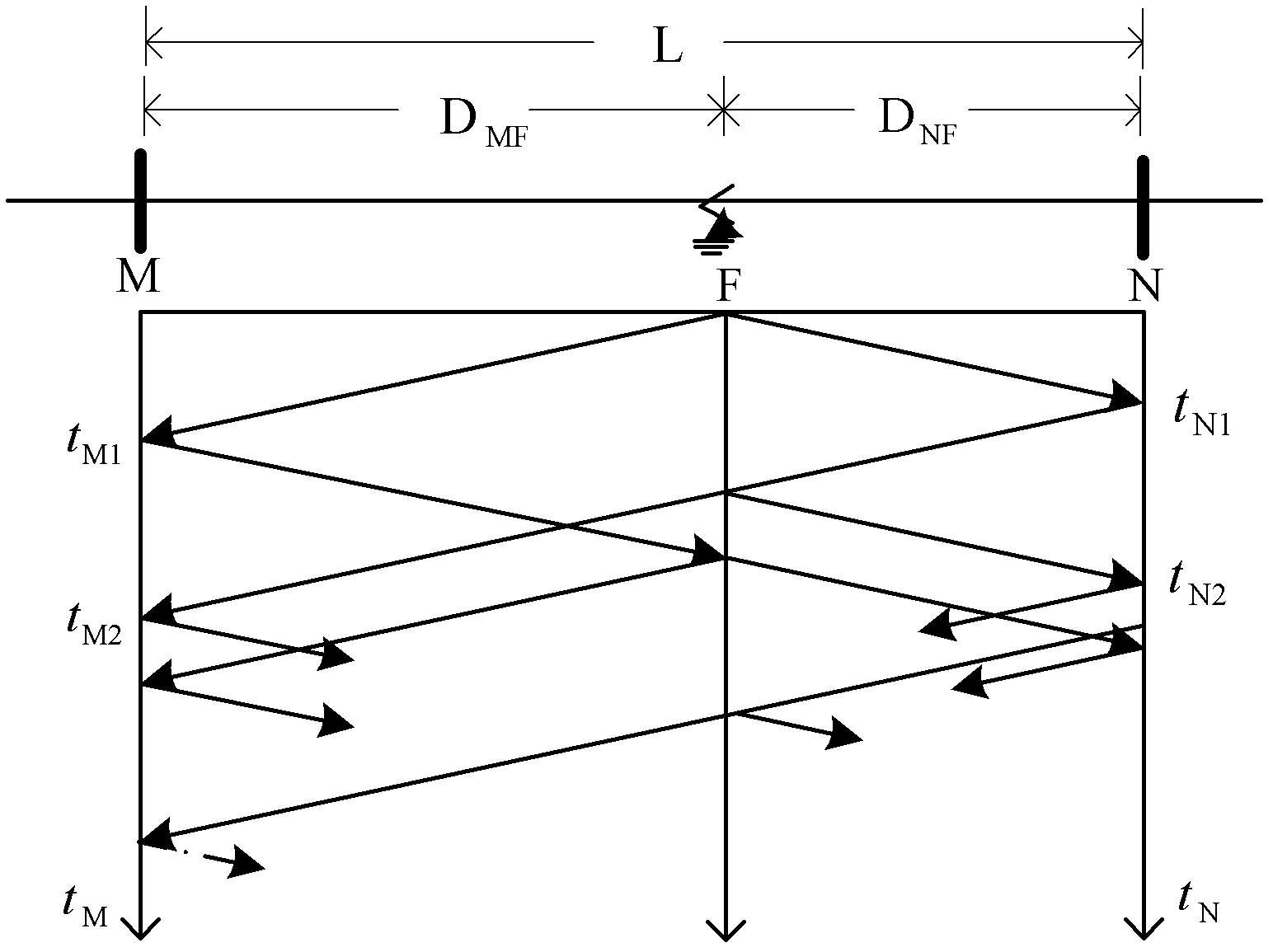

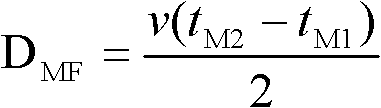

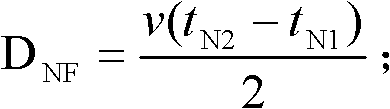

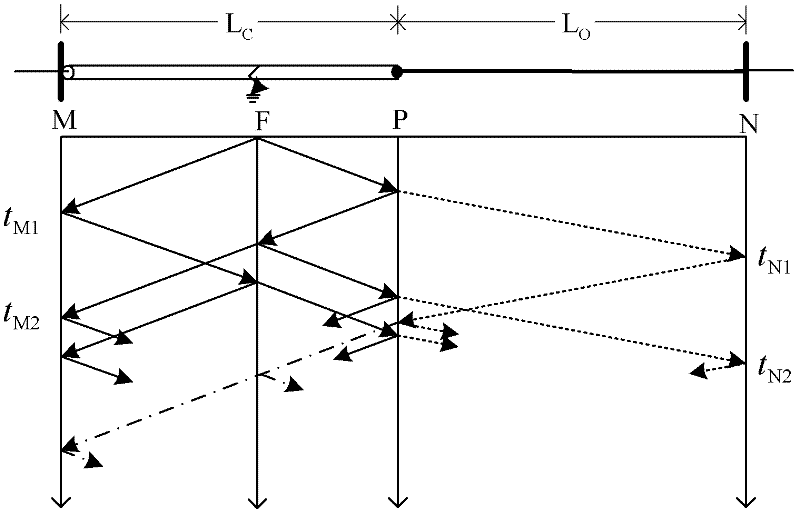

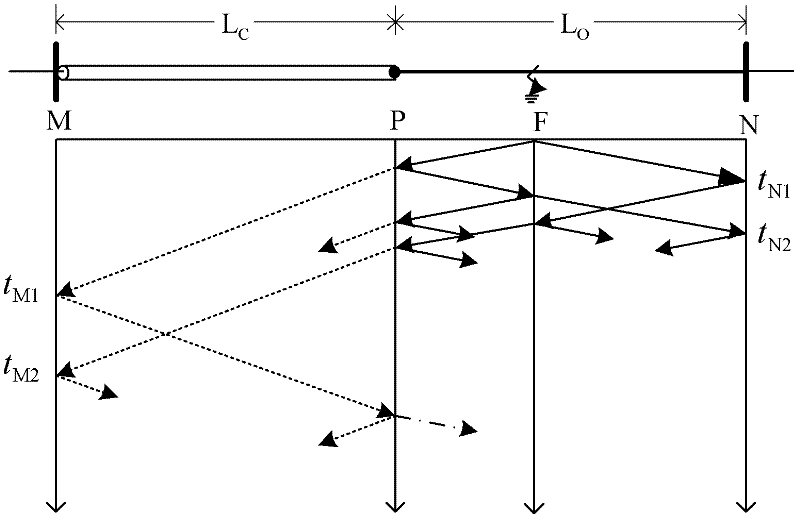

Fault distance measuring method for combined travelling wave of power transmission line

InactiveCN102353875AImprove reliabilityImprove accuracyPosition fixationFault locationCable fault locationTime difference

The invention provides a fault distance measuring method for a combined travelling wave of a power transmission line. The method comprises the following steps of: firstly, performing primary fault distance measurement with the single-end principle to obtain two possible fault positions; and then, comparing the time difference of the fault initial travelling wave arriving at the two sides of the line with the time difference of the fault travelling wave arriving at the two ends of the line after the possible fault points fail, so as to obtain the real fault point determined by the single-end travelling wave principle. The method has the advantages that: as the obtained distance measurement result is obtained by the single-end principle, the influence of the mixed line length error caused by the distance measurement adopting the double-end principle and the accurate time synchronization problem between the two sides of the line on the distance measurement accuracy is eliminated, thus the accuracy and reliability of the distance measurement are improved. Through the method, the fault distance measurement for the travelling wave of the power line is realized, and the reliability and accuracy of the travelling wave distance measurement are improved; and after the line fails, the fault point can be found without taking much time, the power supply reliability is improved, and the method has wide application prospects.

Owner:SHANDONG UNIV OF TECH

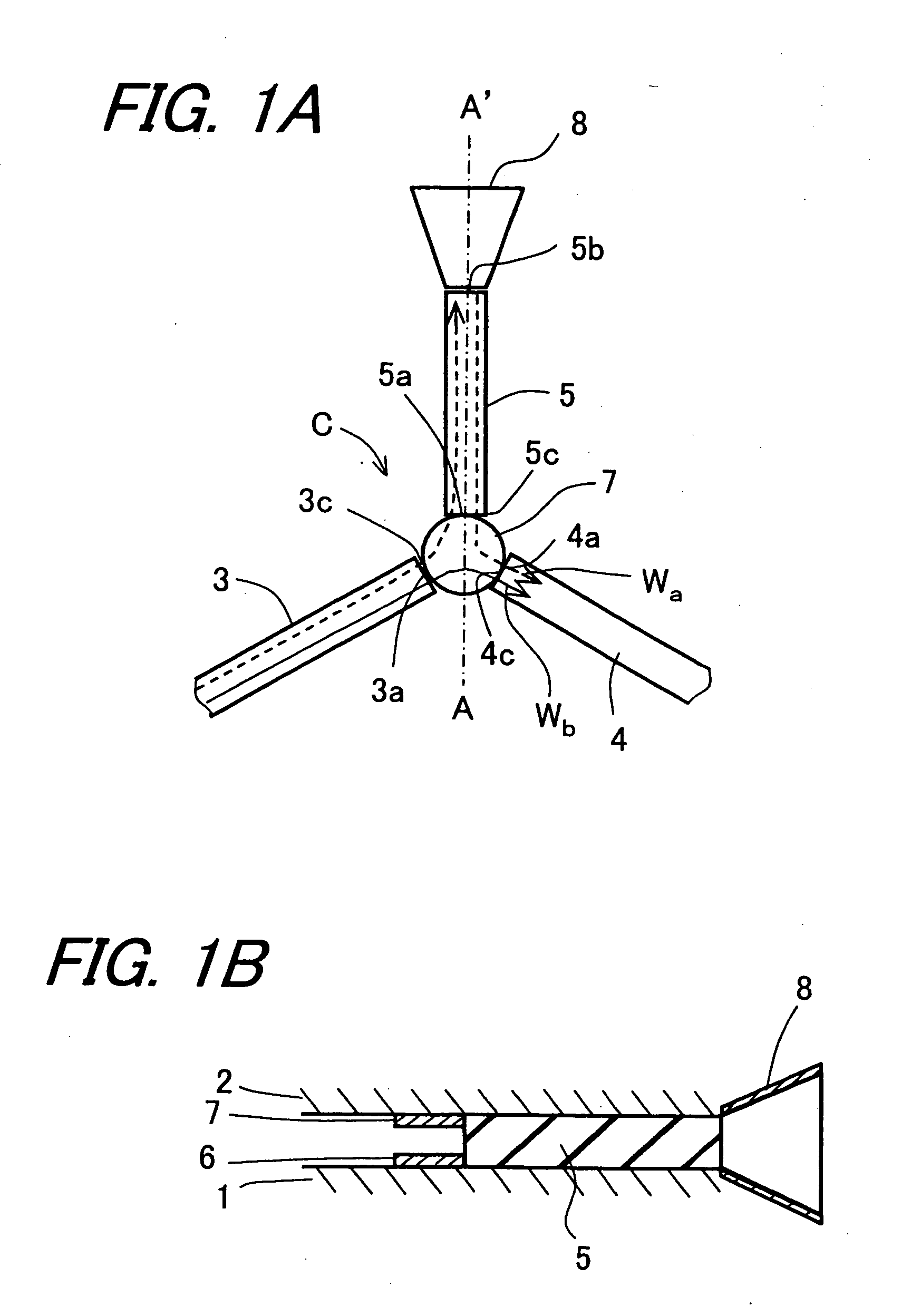

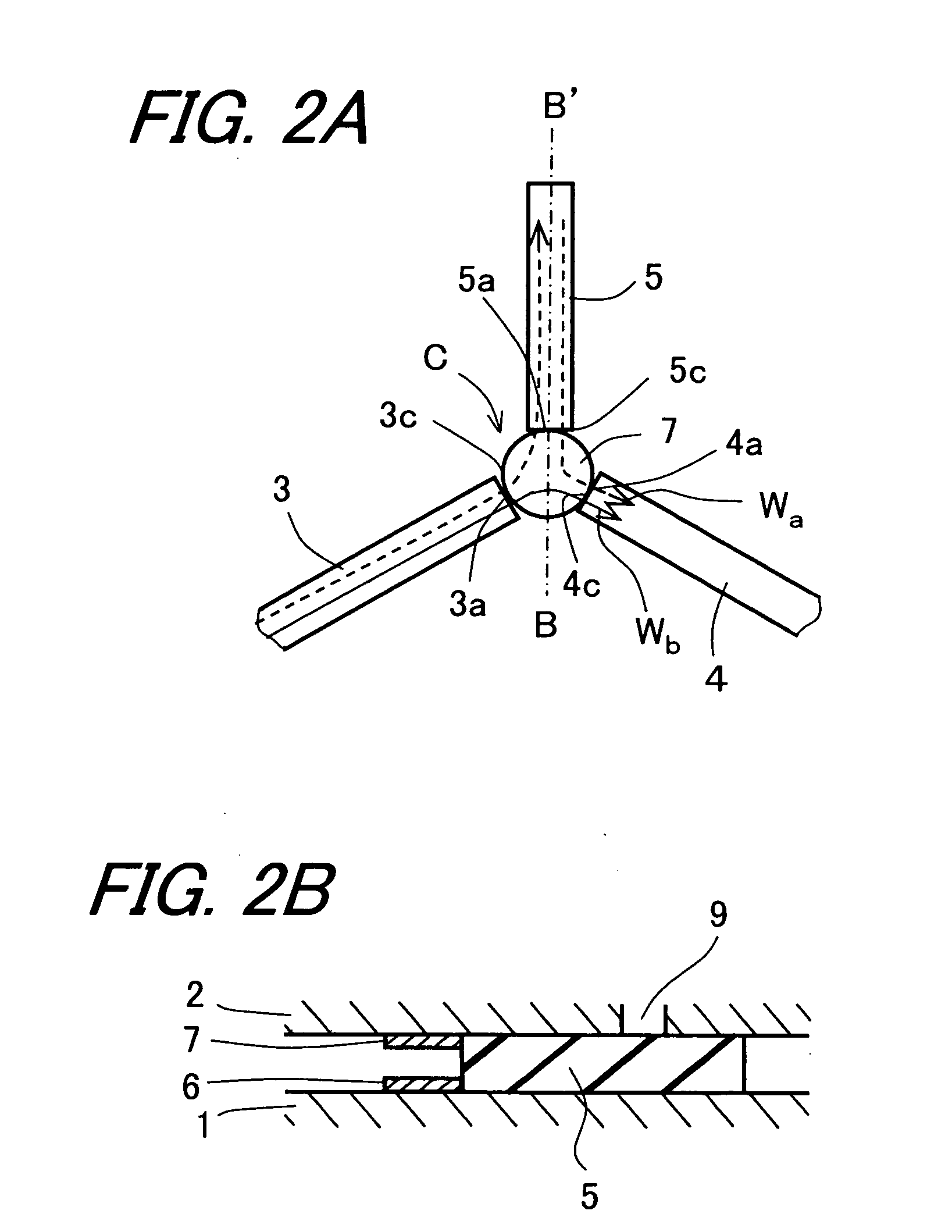

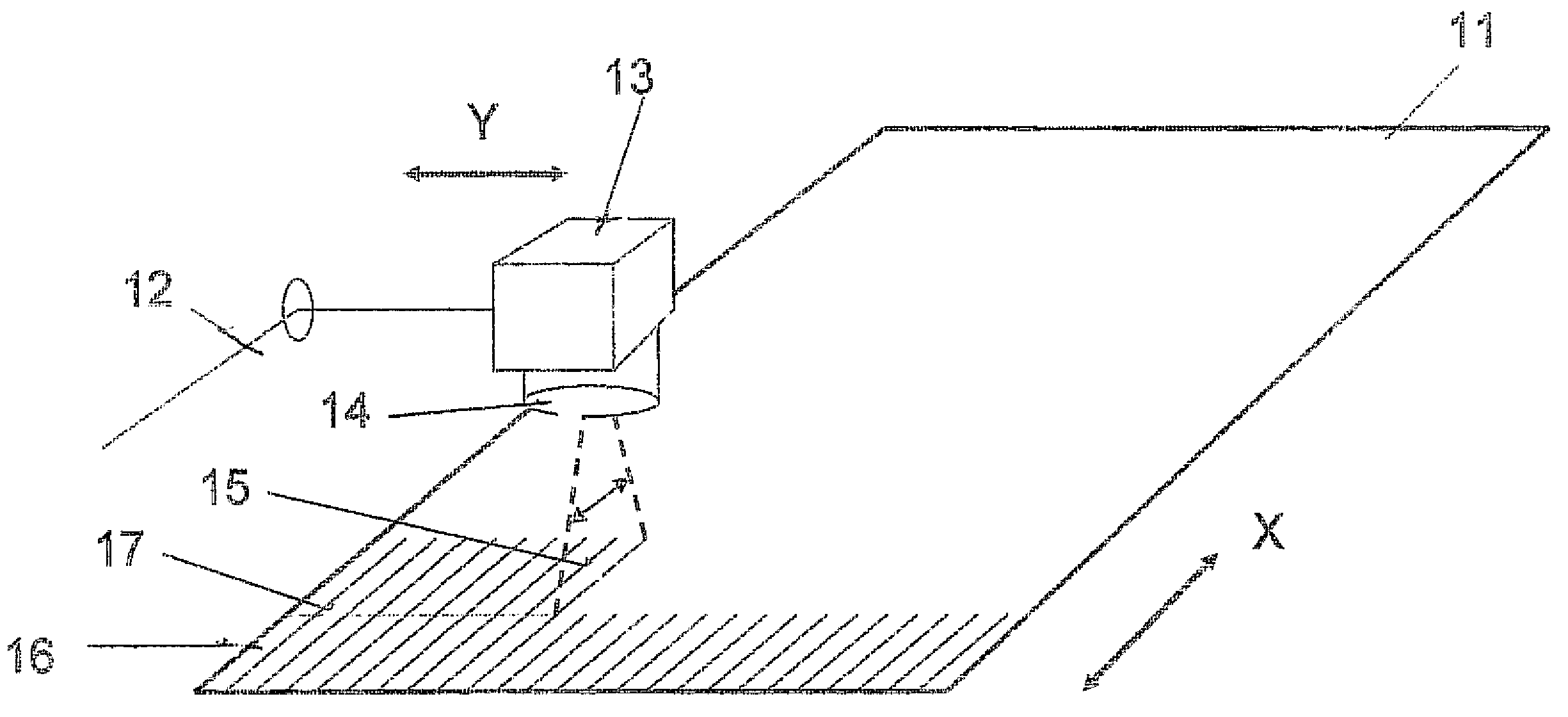

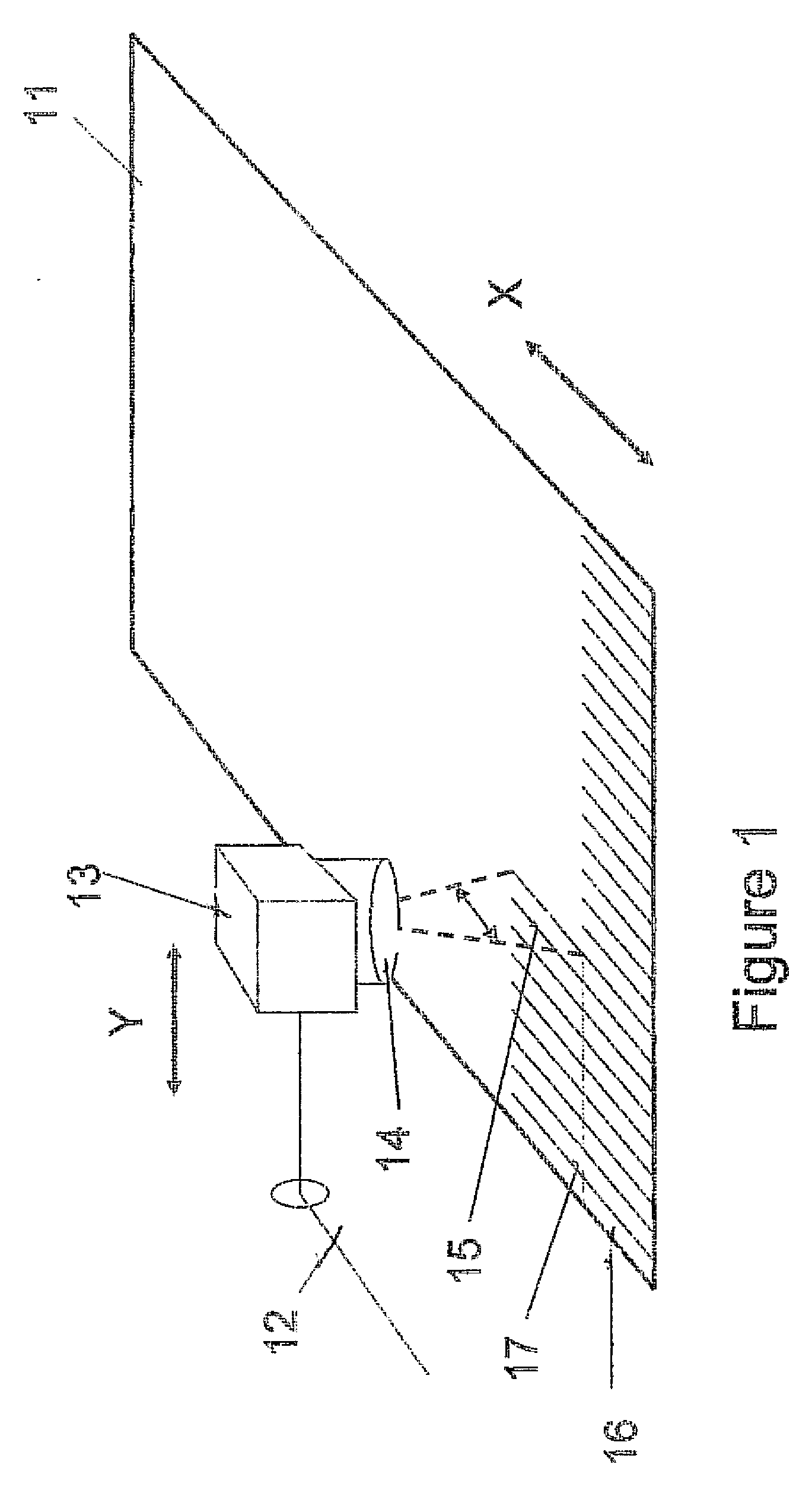

Process for laser scribing

InactiveUS20090188543A1Easy to controlEasy to implementPV power plantsLaser beam welding apparatusOptoelectronicsLaser scribing

A method for accurately laser scribing lines on a panel utilising a laser beam scanner unit (13) including an optical system and a scanner lens. The unit (13) moves a laser beam (12) in a first direction (X), to scribe sections of lines (15) on the panel (11) that are a fraction of the total line length required and then moving the unit (13) continuously with respect to the panel (11) in a second direction (Y), perpendicular to the first direction (X), to form a band (16) of scribe lines. The scanner unit (13) is positioned so that the starting position of scribe lines in each band next to be processed overlap exactly the finishing position ends of scribe lines in the last band that has been processed so that all scribe lines interconnect. The method repeats the using and moving steps to form a plurality of parallel bands of scribe lines which cover the area of the panel.

Owner:OERLIKON SOLAR AG (TRUEBBACH)

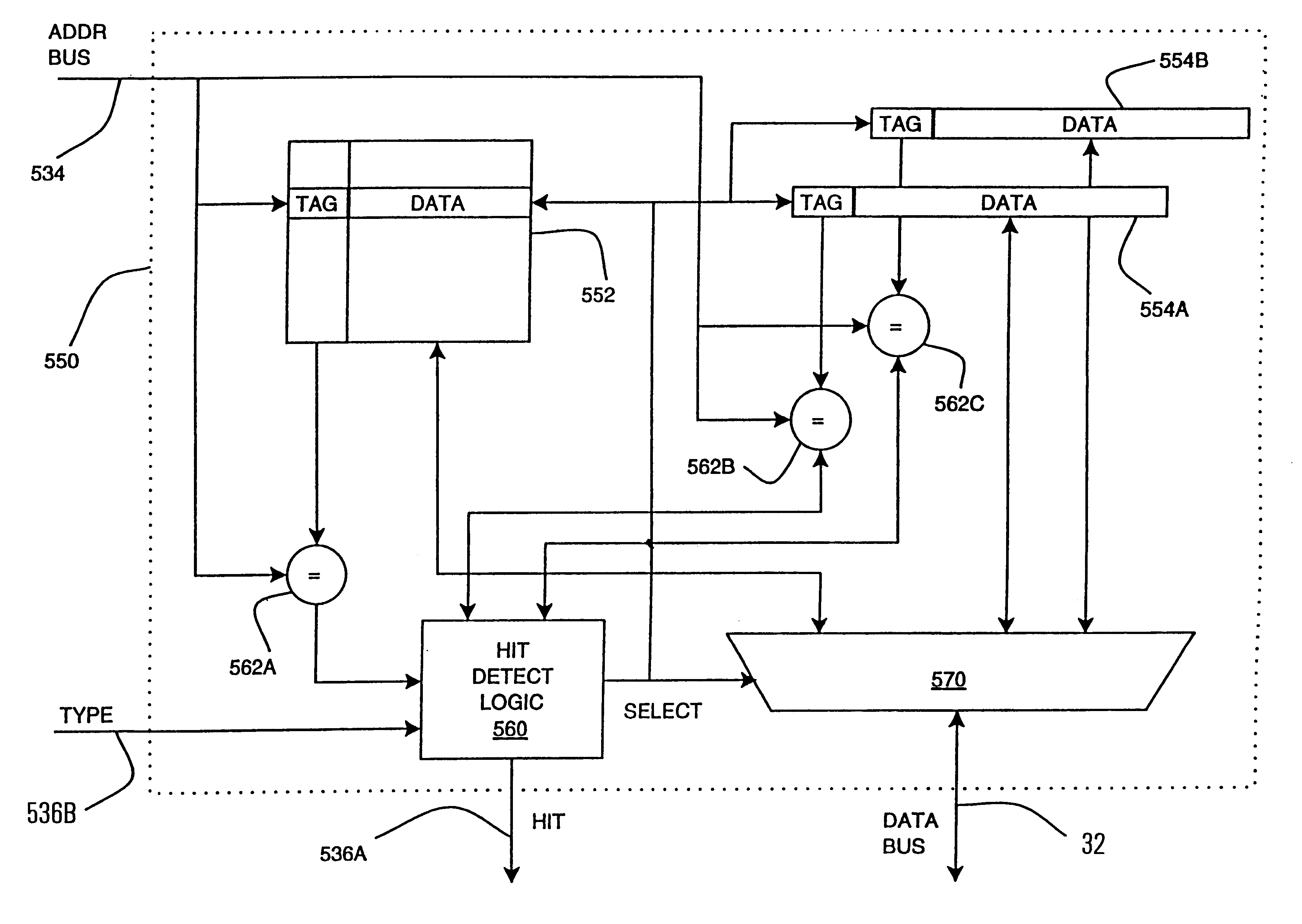

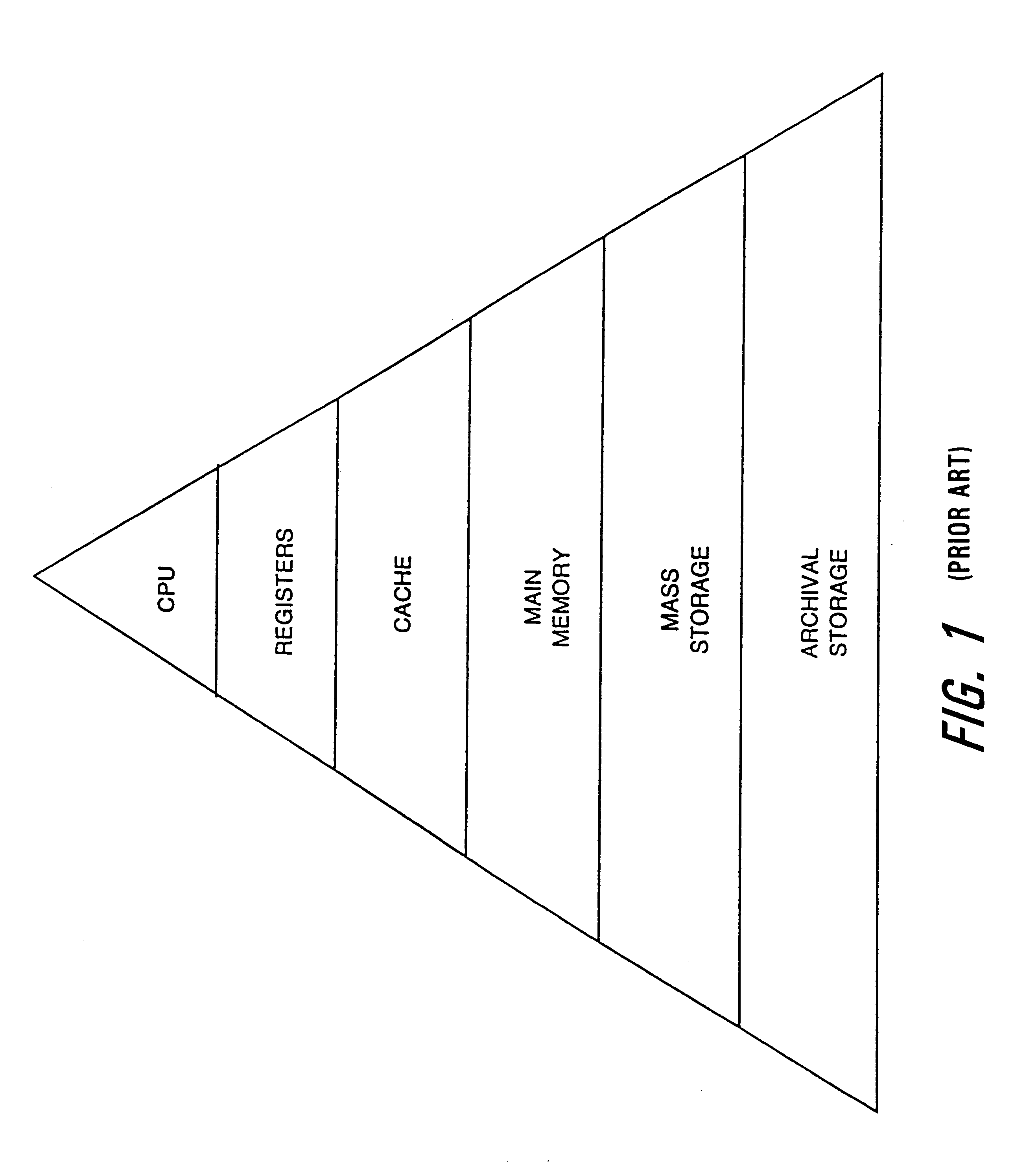

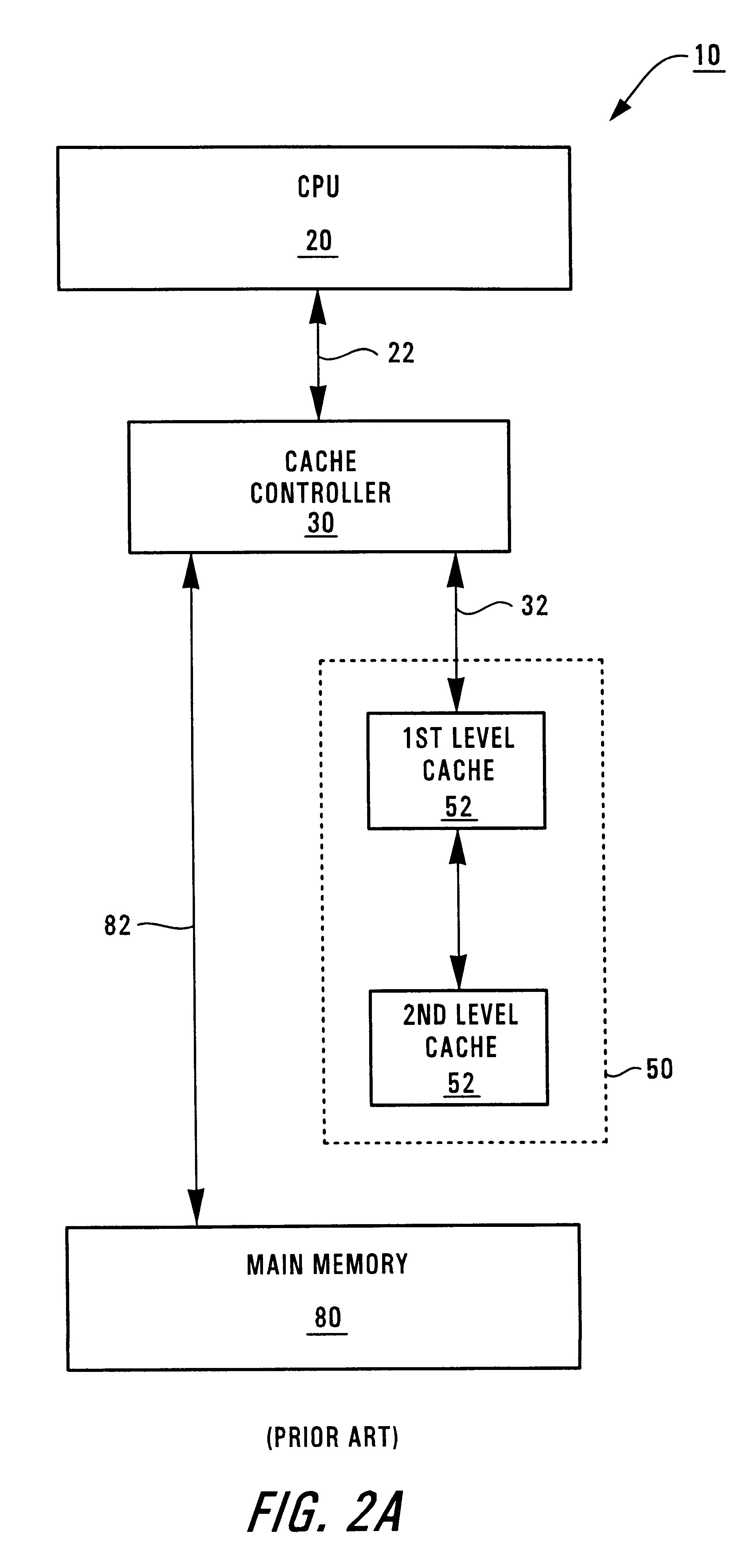

Method and architecture for data coherency in set-associative caches including heterogeneous cache sets having different characteristics

A processor architecture and method are shown which involve a cache having heterogeneous cache sets. An address value of a data access request from a CPU is compared to all cache sets within the cache regardless of the type of data and the type of data access indicated by the CPU to create a unitary interface to the memory hierarchy of the architecture. Data is returned to the CPU from the cache set having the shortest line length of the cache sets containing the data corresponding to the address value of the data request. Modified data replaced in a cache set having a line length that is shorter than other cache sets is checked for matching data resident in the cache sets having longer lines and the matching data is replaced with the modified data. All the cache sets at the cache level of the memory hierarchy are accessed in parallel resulting in data being retrieved from the fastest memory source available, thereby improving memory performance. The unitary interface to a memory hierarchy having multiple cache sets maintains data coherency, simplifies code design and increases resilience to coding errors.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

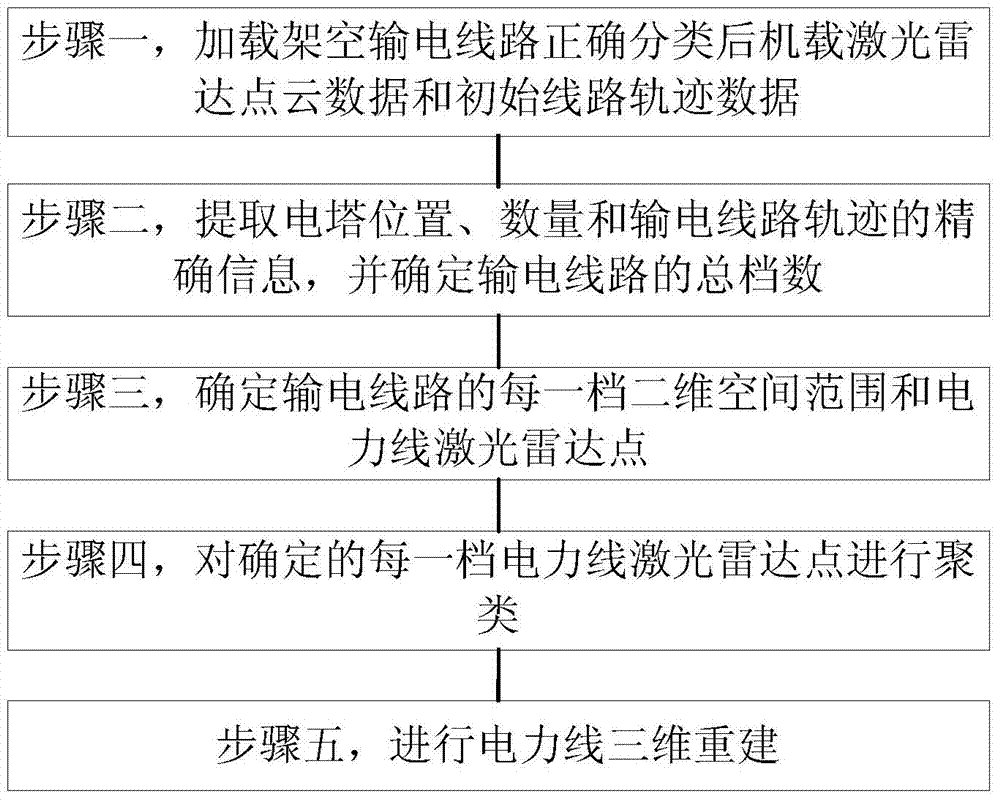

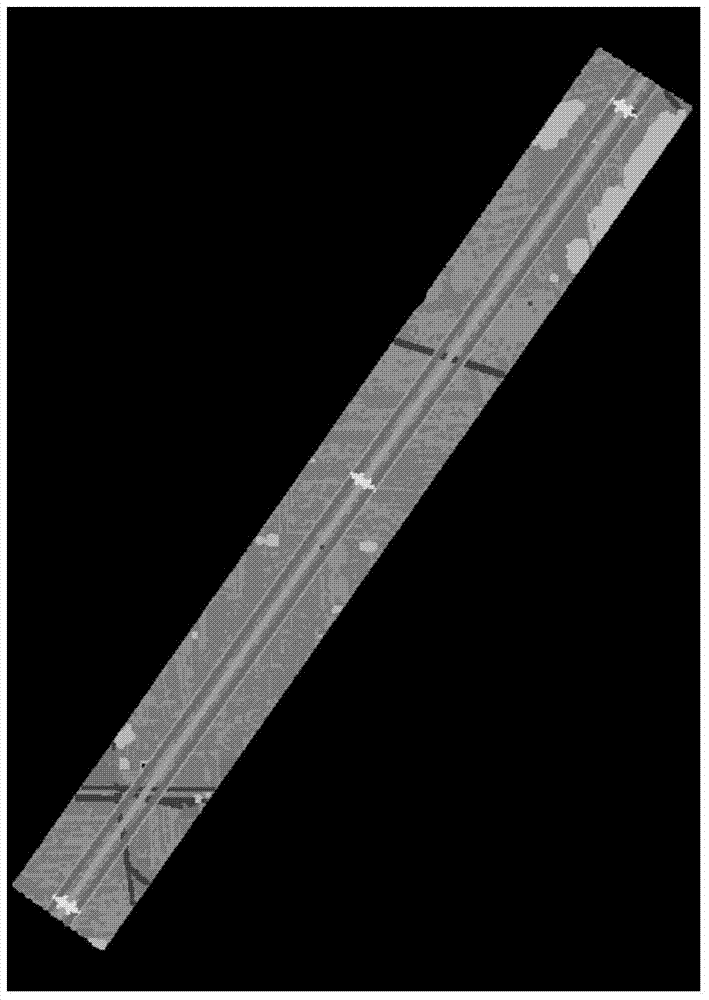

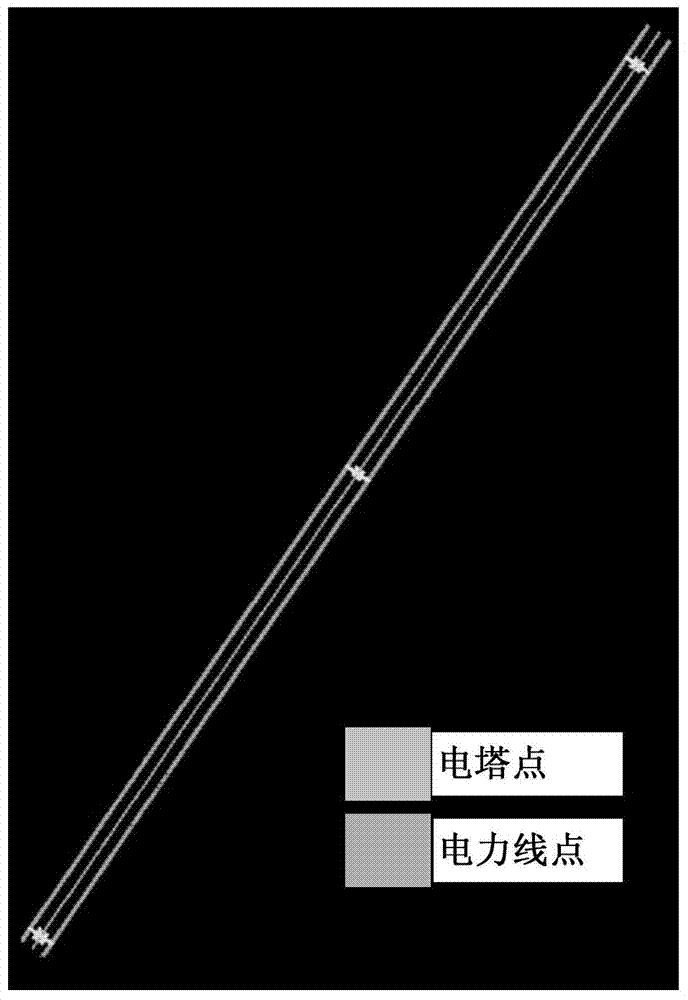

Power line three-dimensional reconstructing method based on airborne laser radar point cloud

InactiveCN104732588AHigh precisionImprove reconstruction accuracyElectromagnetic wave reradiation3D modellingElectric powerLine length

The invention discloses a power line three-dimensional reconstructing method based on airborne laser radar point cloud. Data of the airborne laser radar point cloud have been correctly classified. The method includes the following steps: 1, loading the correctly-classified data of the airborne laser radar point cloud and initial line track data of an overhead transmission line; 2, extracting accurate information of the positions and the number of electric towers and the track of the power transmission line, and determining the total number of spans of the power transmission line; 3, determining the two-dimensional space range and power line laser radar points of each span of the power transmission line; 4, clustering the determined power line laser radar points of the spans; 5, carrying out power line three-dimensional reconstruction. According to the power line three-dimensional reconstructing method, the number of required parameters is small, the automation degree is high, robustness and universality are better, and the power line three-dimensional reconstructing method has the advantage of being insensitive to the factors such as the number of power lines, the types of the power lines, the power line space arrangement structure, gross error points, point-cloud irregular breaking and the line length; in addition, a reconstruction model has the high reconstruction accuracy.

Owner:CHINESE ACAD OF SURVEYING & MAPPING

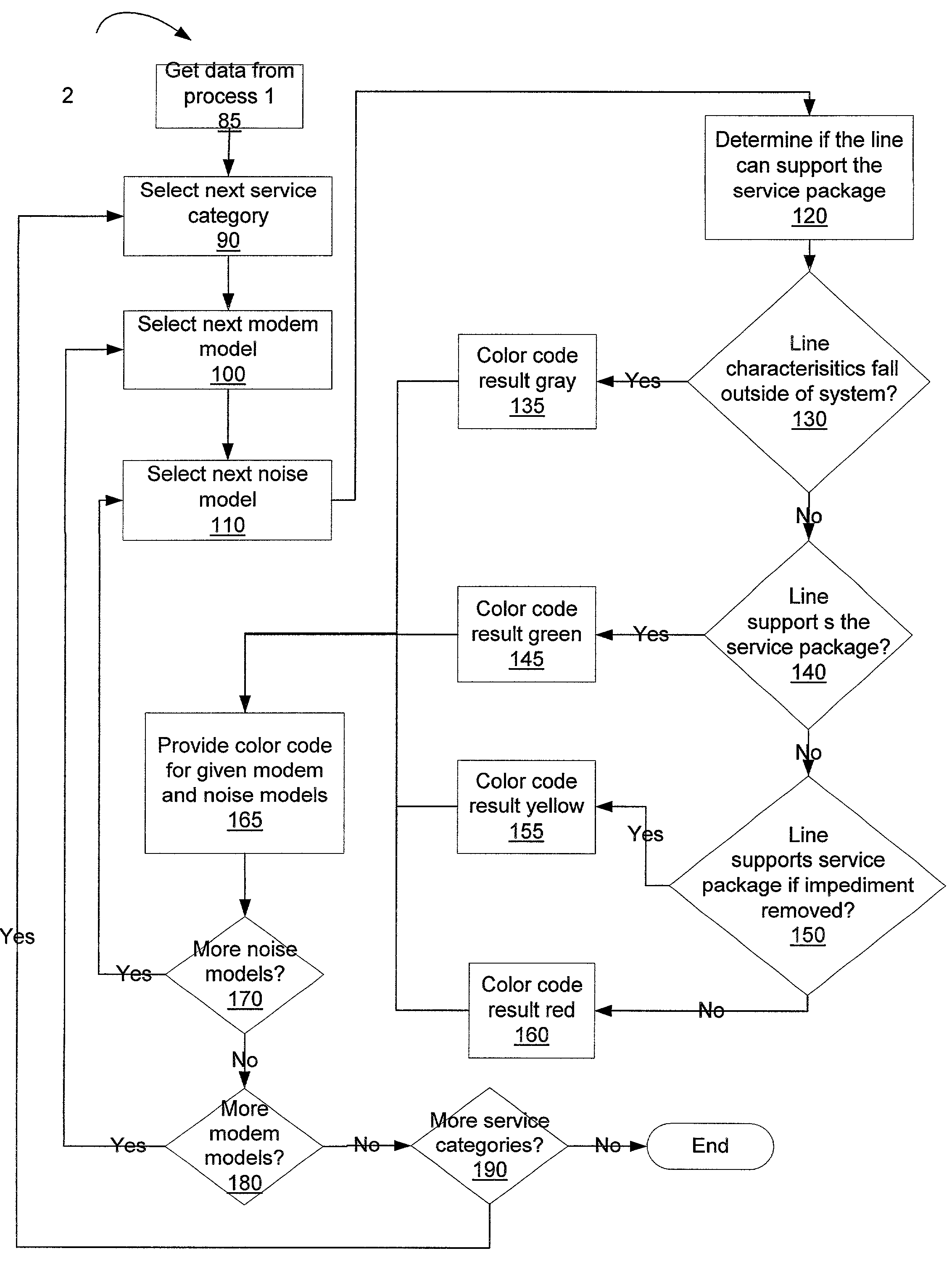

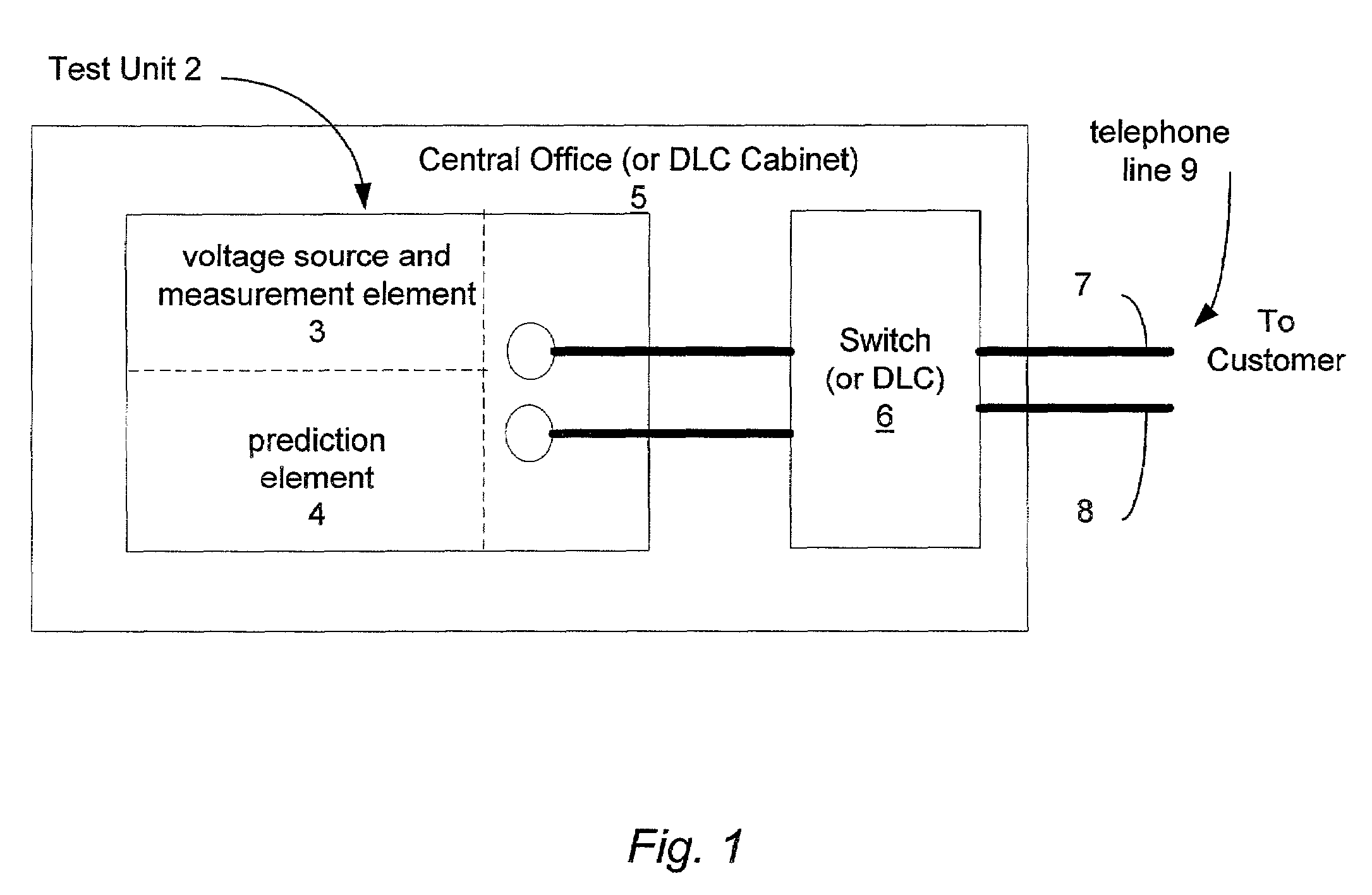

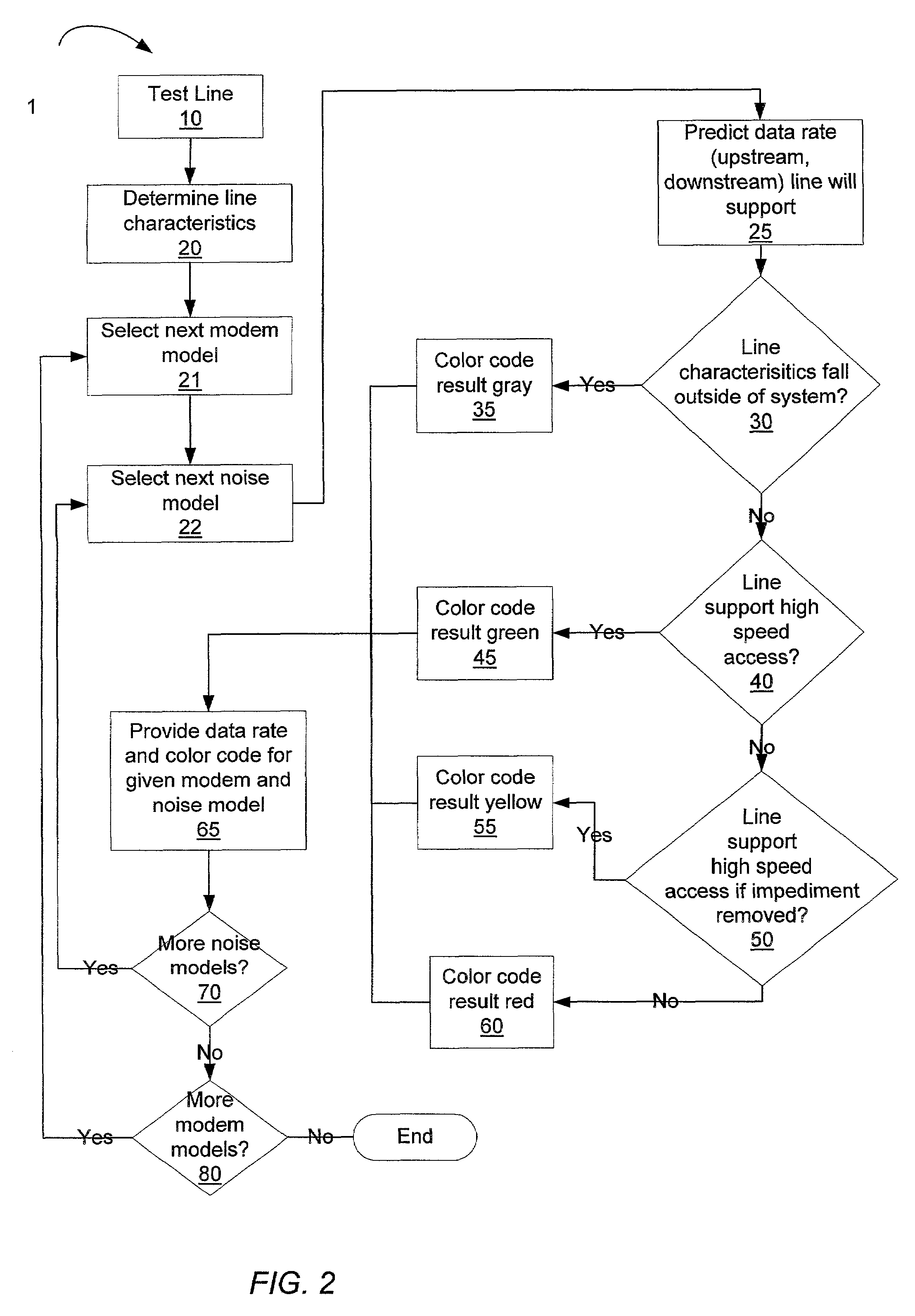

Binning of results from loop qualification tests

InactiveUS6985444B1Easily discernable statusError preventionFrequency-division multiplex detailsData rateSoftware design

The present invention provides a method and apparatus for performing line qualification tests, and binning the results of such testing. The lines are tested to determine or estimate various characteristics of the line. Physical characteristics of the line may be estimated (e.g. line length, line gauge, insertion loss). The presence of devices on the line such as load coils, bridged taps, terminations and the like may also be determined. A prediction of the data rate the loop can support is made from the measured and estimated line conditions. The results are binned according to certain criteria and to provide an easily discernable status of the line. The binning can be performed by a computer using software designed specifically for this purpose. The binned results may include a first category indicating the line cannot support a certain level of high speed access. The binned results may also include a second category indicating the line can support a certain level of high speed access. The results may also include a third category indicating the line cannot currently support a certain level of high speed access but would be able to upon removal of an impediment. A fourth category indicating the characteristics of the selected line fall outside the area of coverage of the test system may also be included. Each category may be assigned a respective color in order to make the status of the line easily discernable. The testing and binning may be performed for a variety of different high speed access levels. Customers can be charged different rates dependent upon the level of service made available to them.

Owner:TOLLGRADE COMM INC

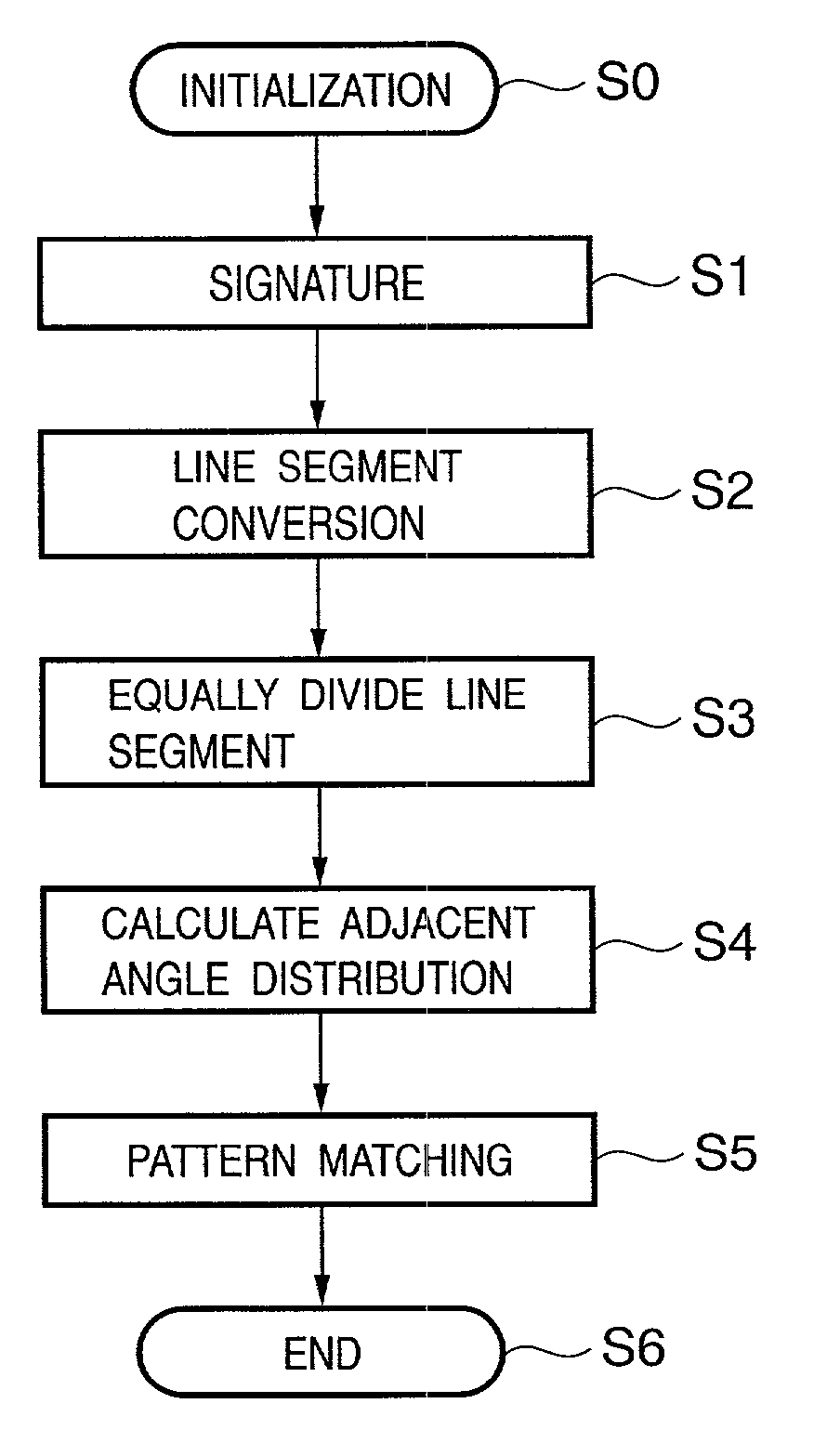

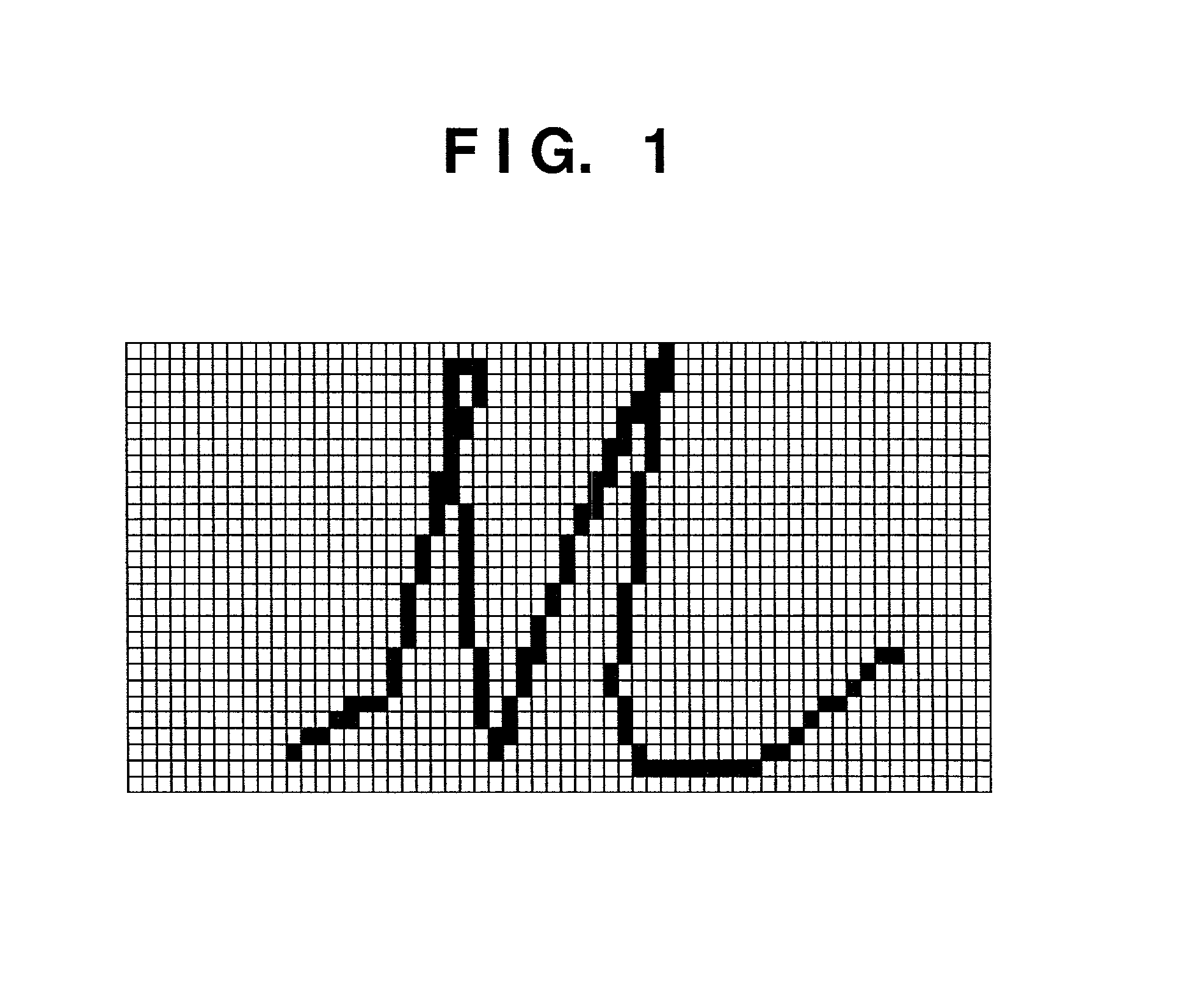

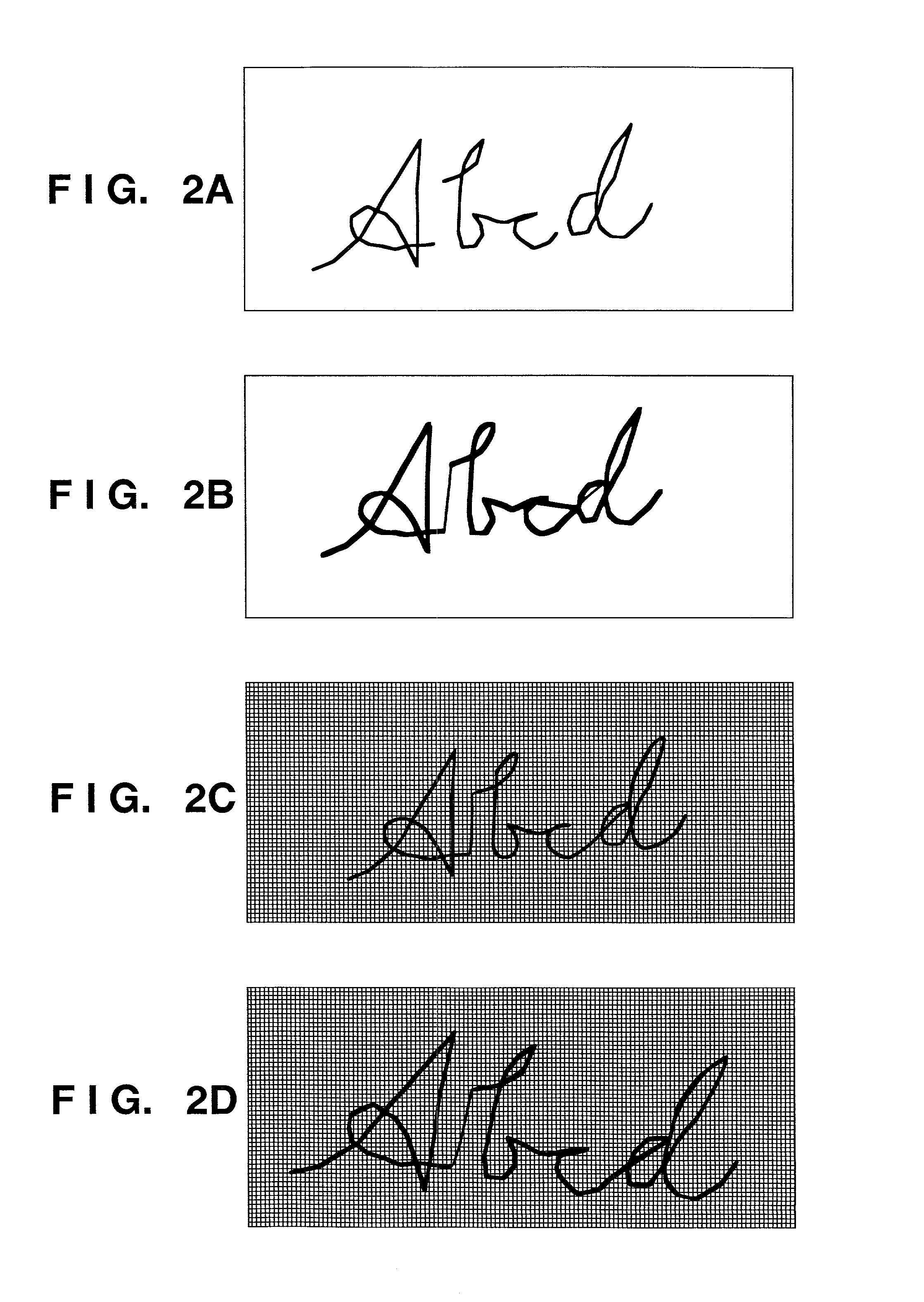

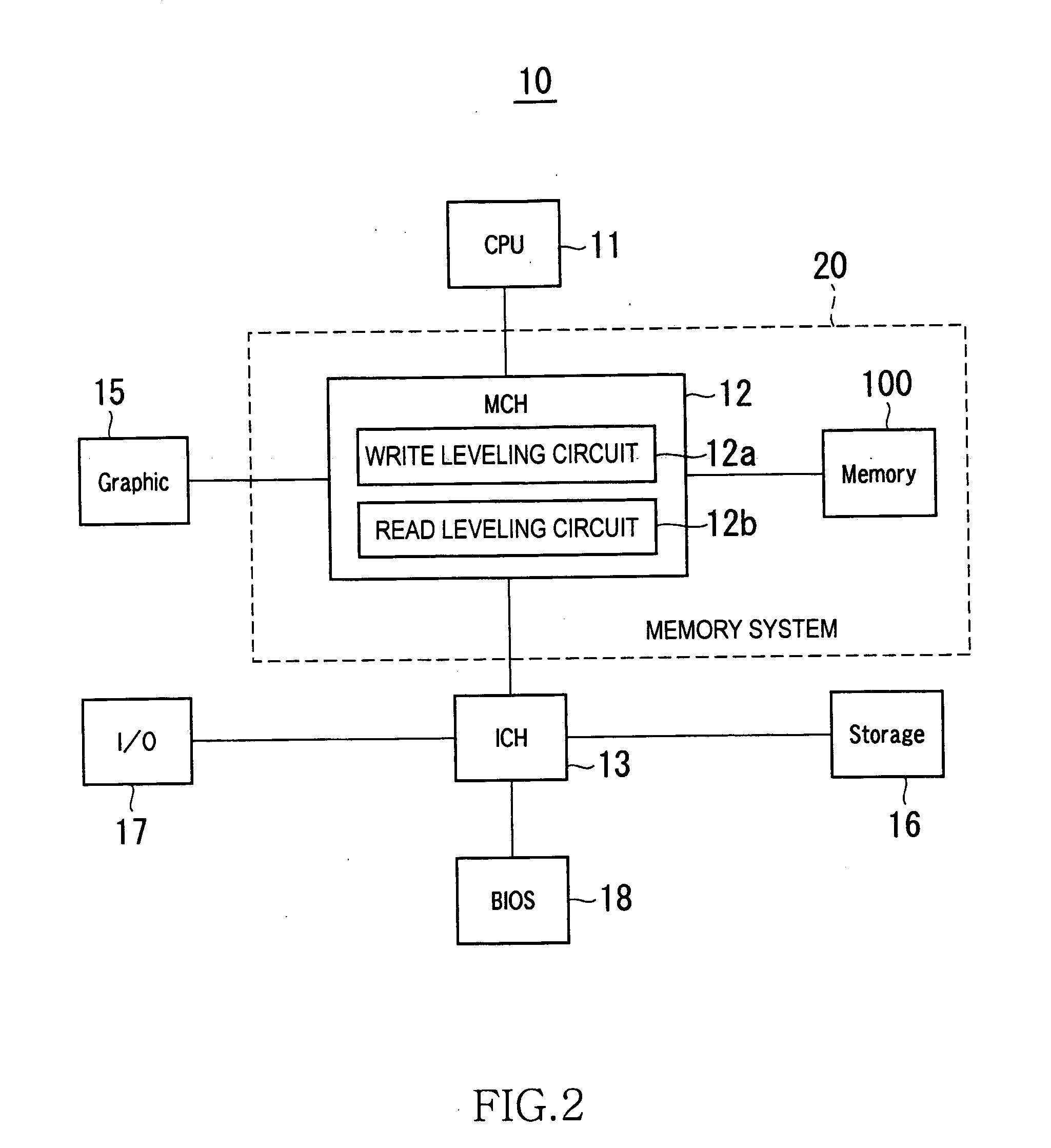

Information processing method and apparatus

InactiveUS7068821B2Exact matchReduce impactImage analysisTransmission systemsInformation processingPattern matching

An input coordinate sequence is acquired by sampling a handwritten input pattern at predetermined intervals, and a pattern expressed by this input coordinate sequence is approximated by coupling a plurality of line segments to attain line segment conversion. Adjacent angle data φ[i] is generated based on the directions of the respective line segments. At this time, the segment line length along line segments of all the line segments is divided by a predetermined value at equal intervals, and the angles obtained from the directions of the line segments at respective division positions are defined as φ[i]. This φ[i] is compared with a standard pattern (adjacent angle distribution data) prepared in advance to obtain a matching level. In this way, more accurate pattern matching for a handwritten input, which is approximately invariant to affine transformation and can reduce the influence of discretization errors can be implemented.

Owner:CANON KK

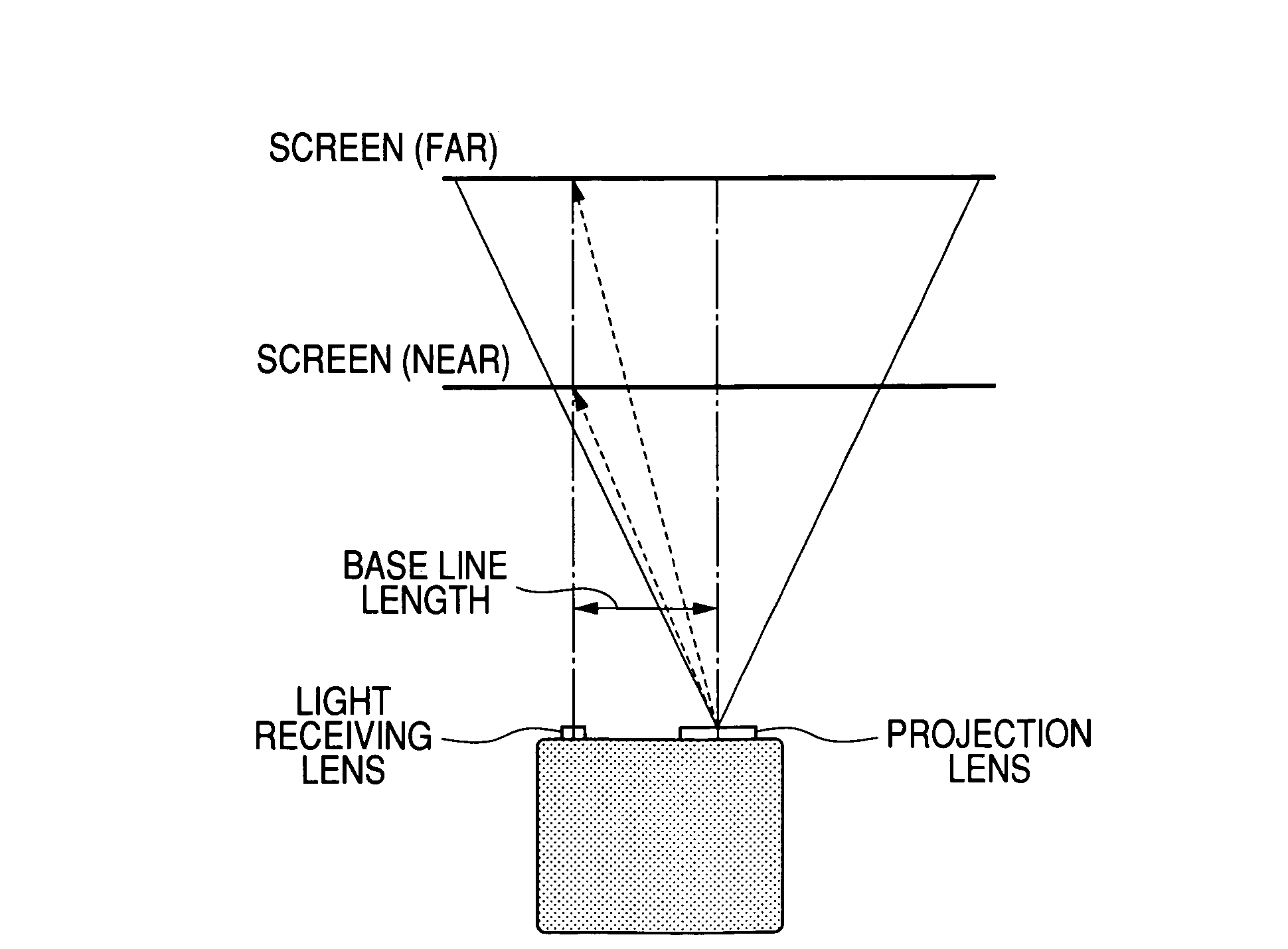

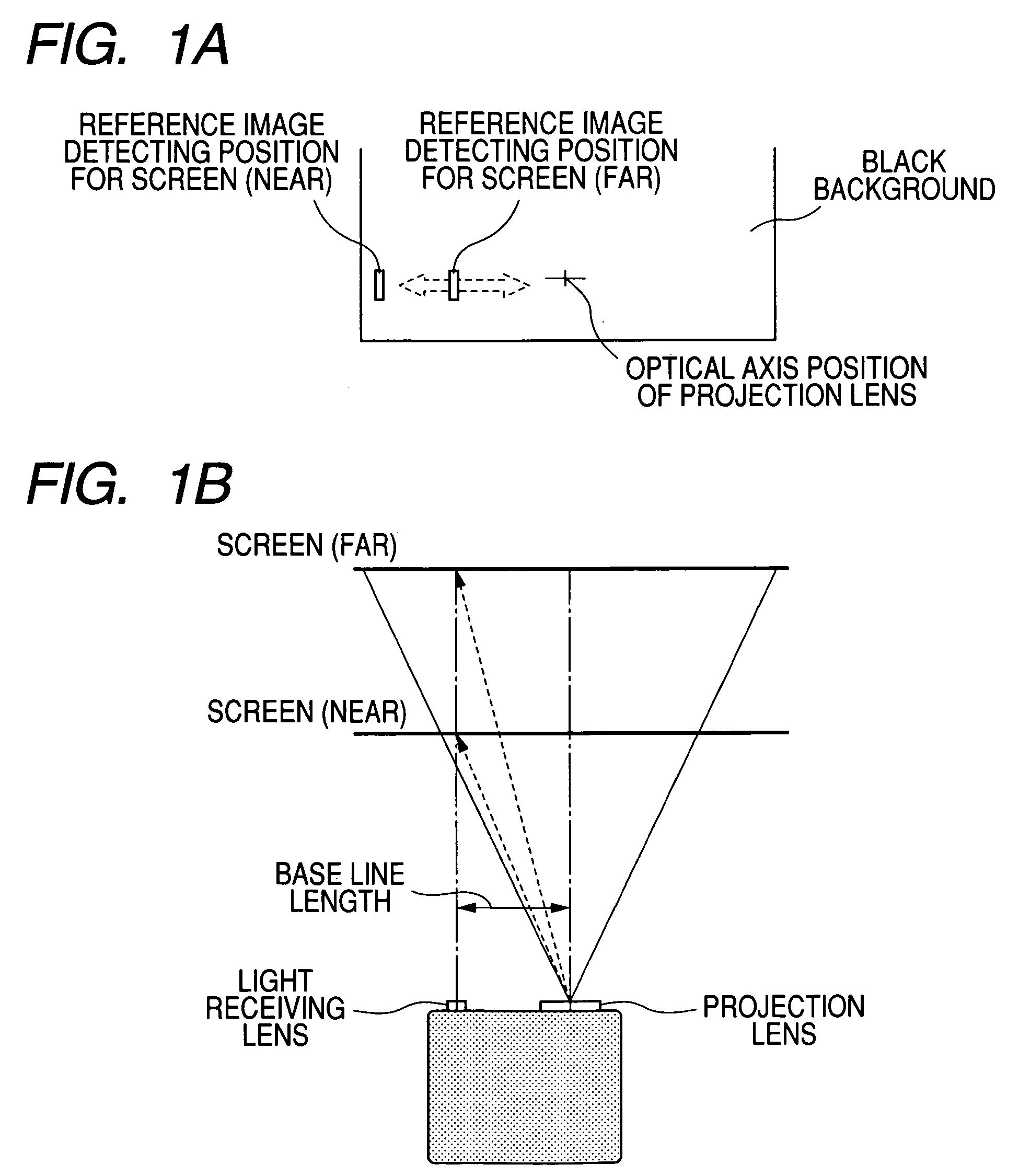

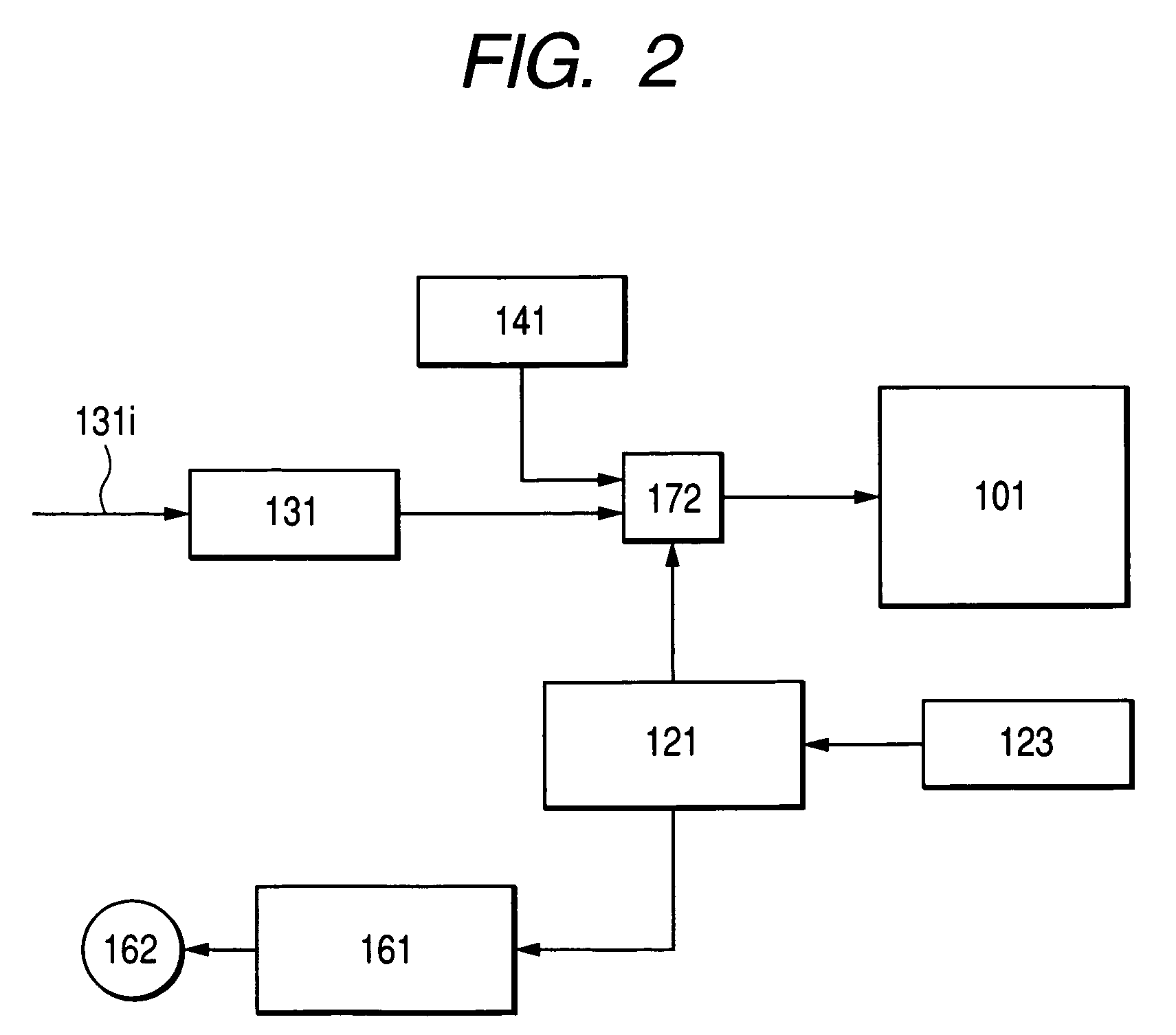

Projection type display apparatus

InactiveUS7303289B2Low costProjector focusing arrangementCamera focusing arrangementComputer graphics (images)Reference image

A projection type display apparatus includes a projection portion for projecting an image onto a surface to be projected, a light receiving portion disposed apart from the projection portion by a base line length and used for detecting a reference image projected onto the surface to be projected, and a scanning portion for scanning the reference image on the surface to be projected in a direction of the base line length, in which the projection portion is focused based on information about a scanning position of the reference image upon predetermined detection with the light receiving portion. With the projection type display apparatus, a system can be configured with a simple processing circuit, and cost reduction can be realized.

Owner:CANON KK

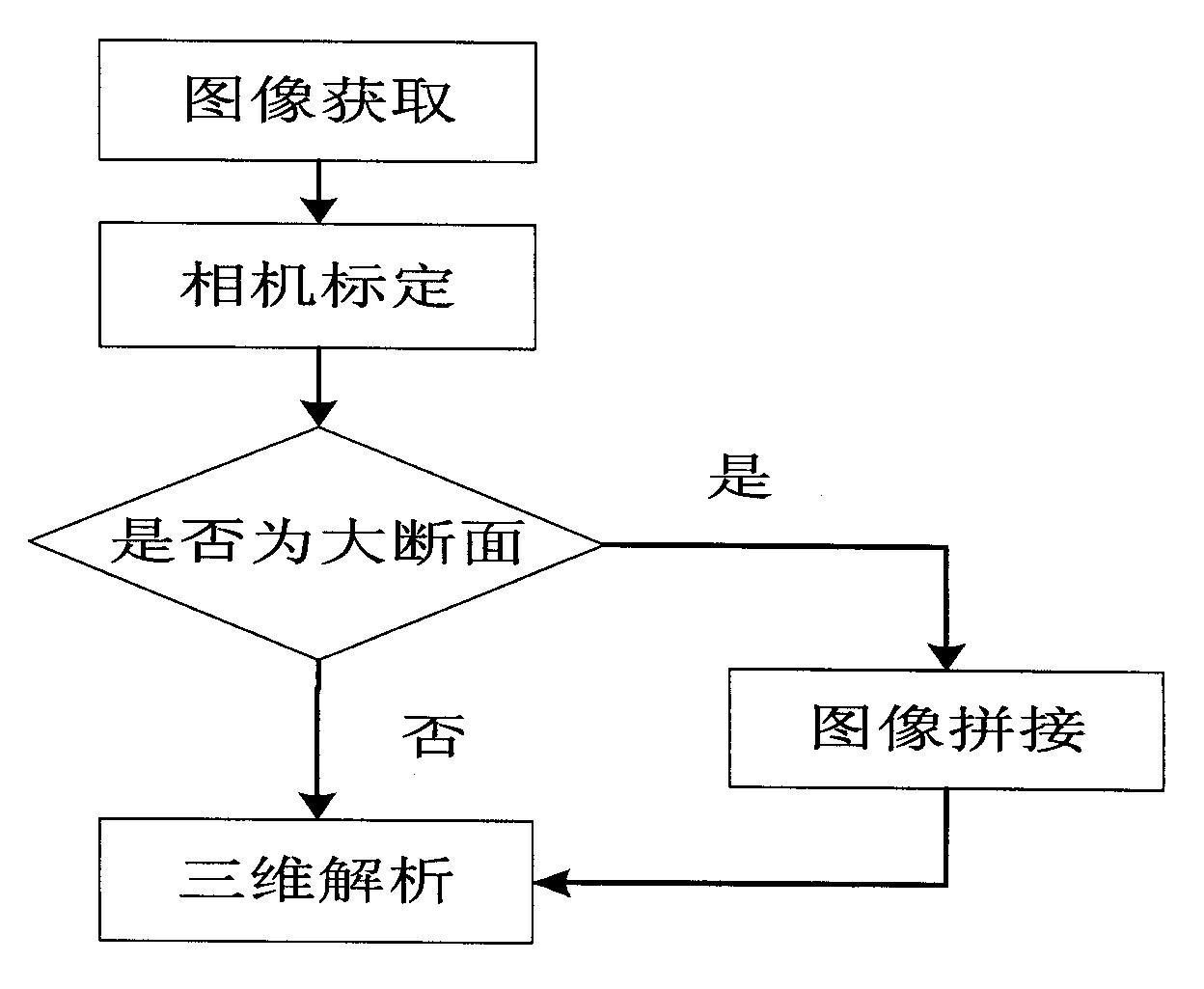

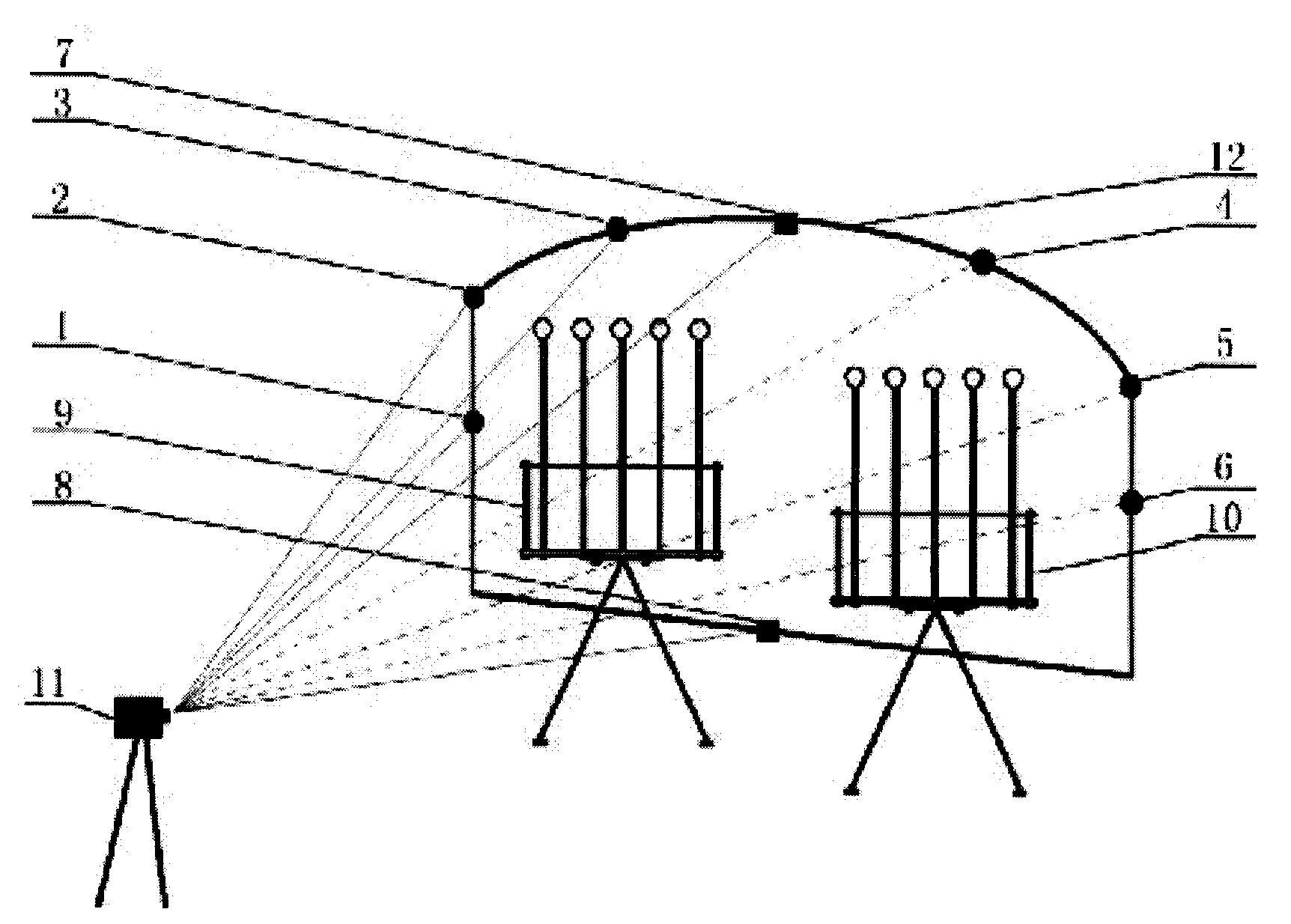

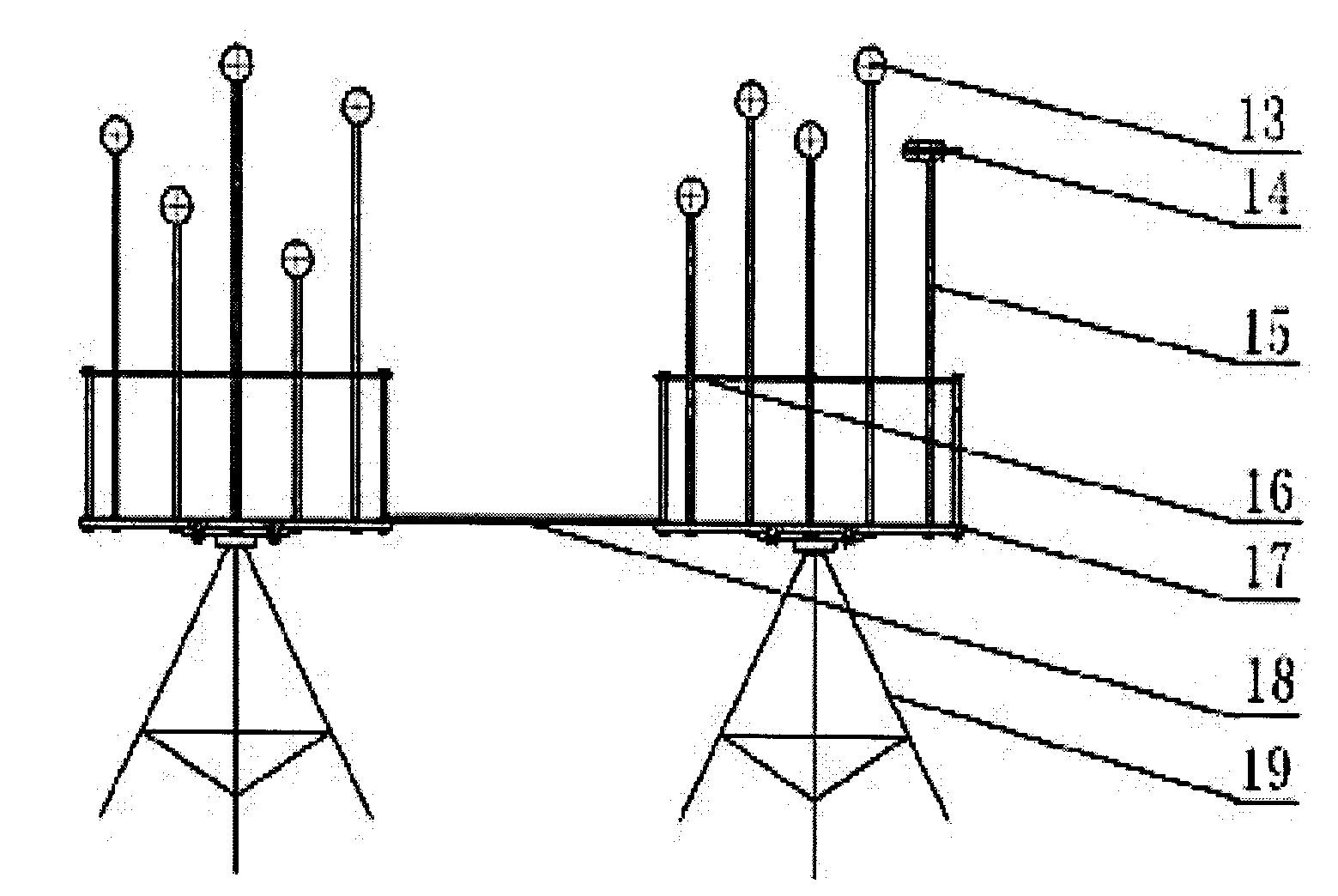

Application of image mosaic technology in tunnel surrounding rock deformation noncontact measurement

The invention relates to an application of the image mosaic technology in tunnel surrounding rock deformation noncontact measurement, in particular to an application in noncontact measurement of tunnel large-size section surrounding rock deformation. The measurement method includes firstly, arranging points to be measured and image mosaic mark points on a large-size monitoring section, placing portable precise three-dimensional controlling fields in front of the large-size monitoring section, performing convergent photography by an ordinary digital camera to capture monitored section overlapping sub-image groups of the points to be measured, the image mosaic mark points and the controlling fields included during different periods, then carrying out distortion correction and high-precision mosaic to the images to acquire a panorama of the monitoring section; secondly, extracting image point coordinates of the points to be measured and the controlling points in the panorama by using the sub-pixel location technology, analyzing the spatial three-dimensional coordinates of the points to be measured by a direct linear transformation method, calculating the measuring line lengths among the points to be measured during the same period and the changes of the measuring line lengths among the points to be measured during different periods so as to acquire the displacement information. Accordingly, the accurate results of the tunnel large-size section surrounding rock deformation noncontact measurement can be realized.

Owner:63653 FORCES PLA

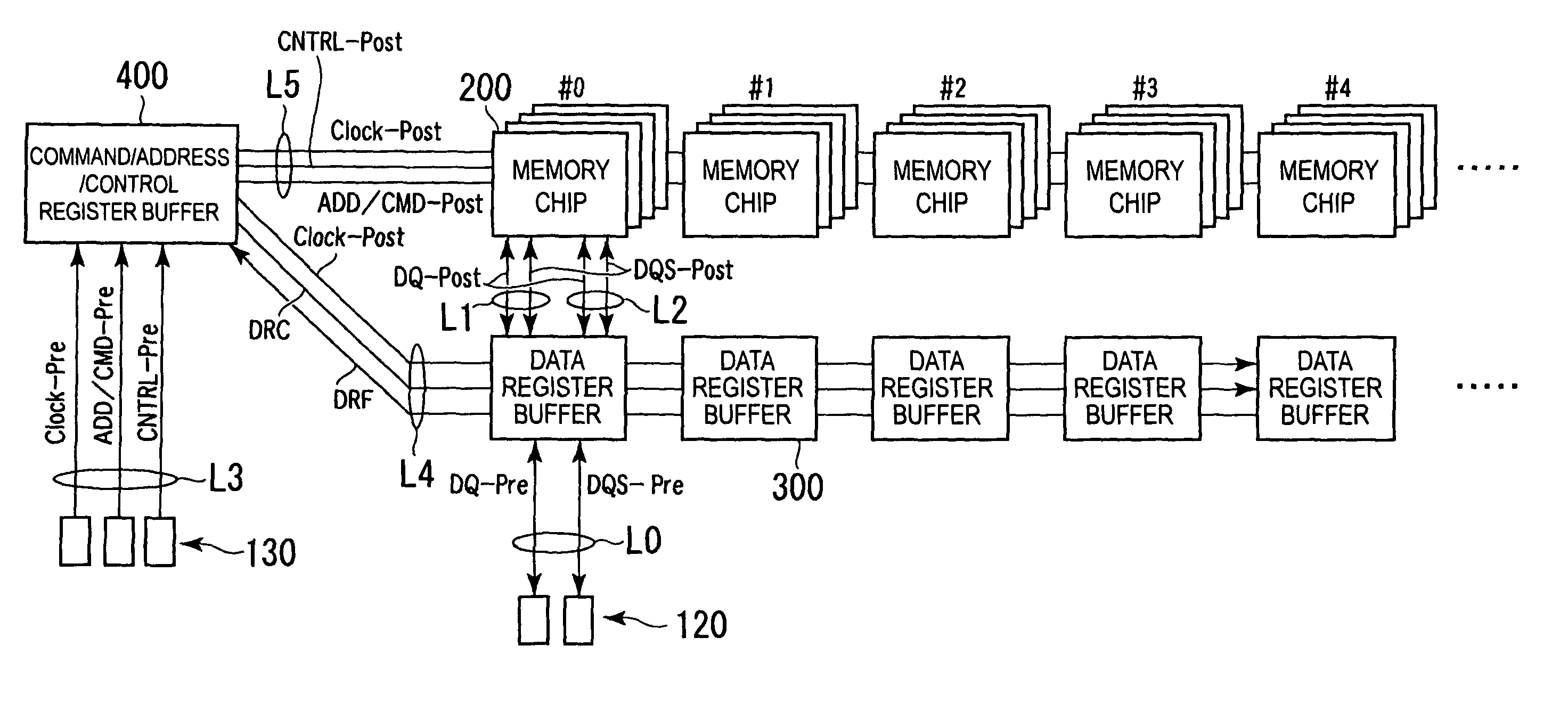

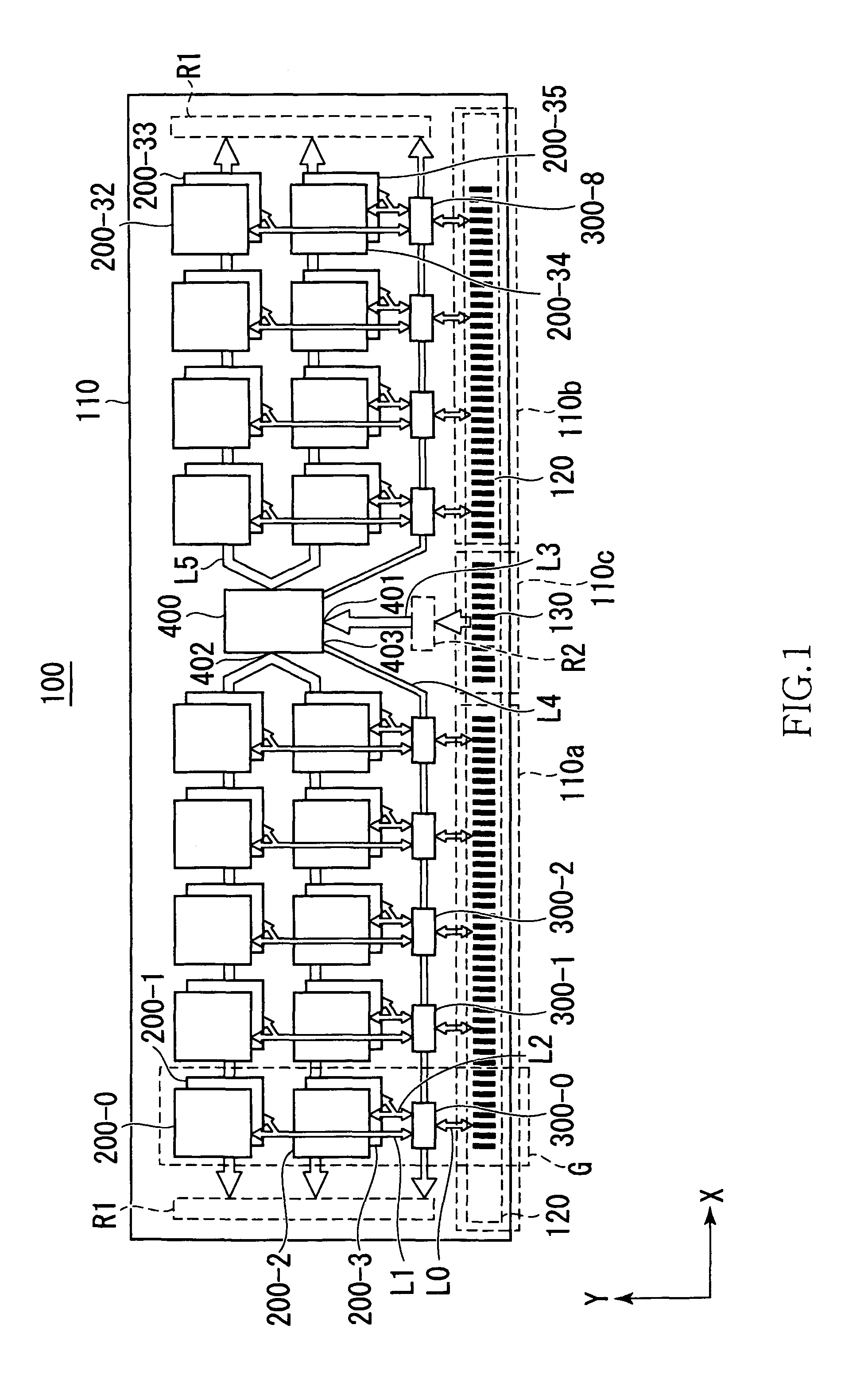

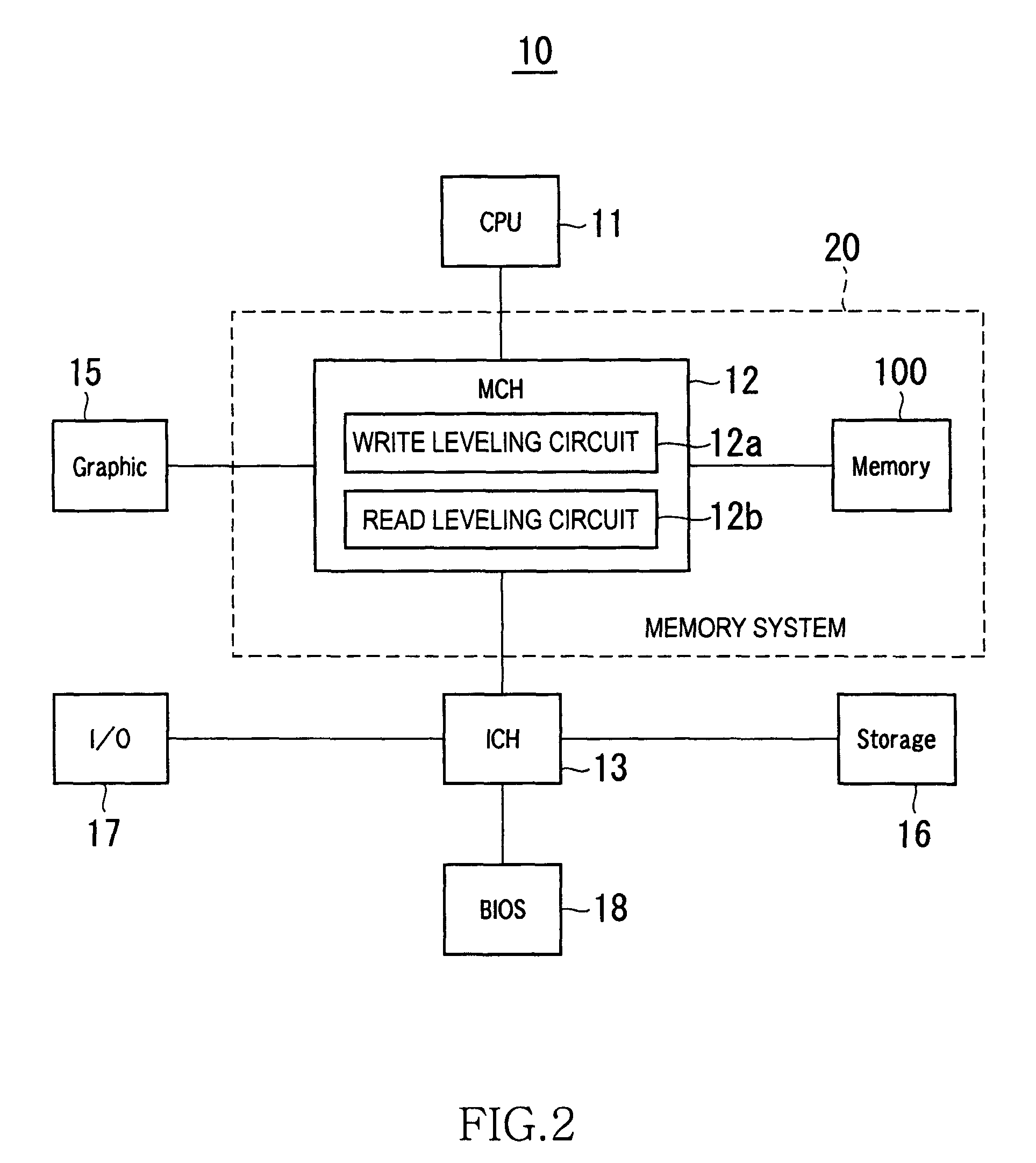

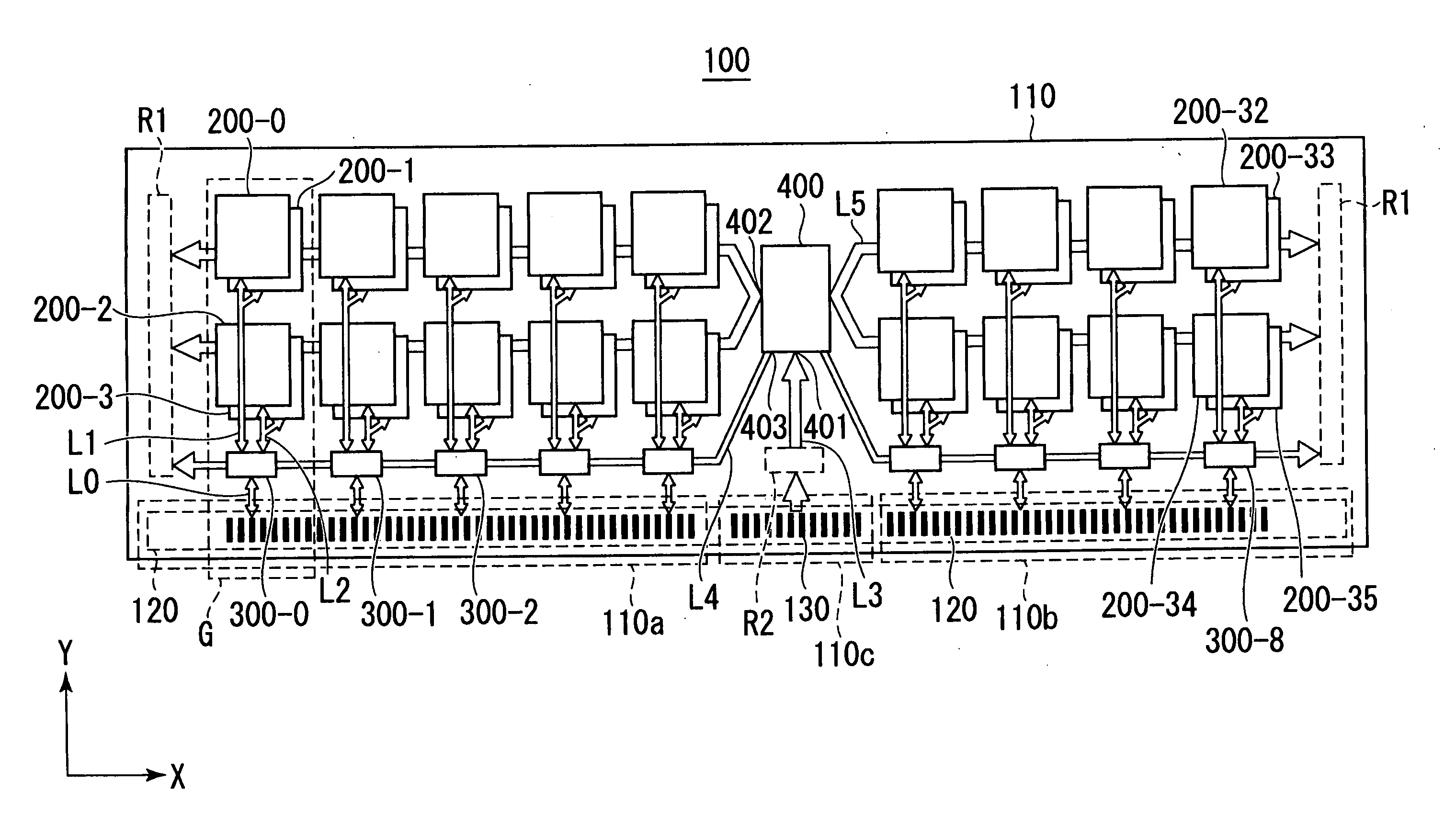

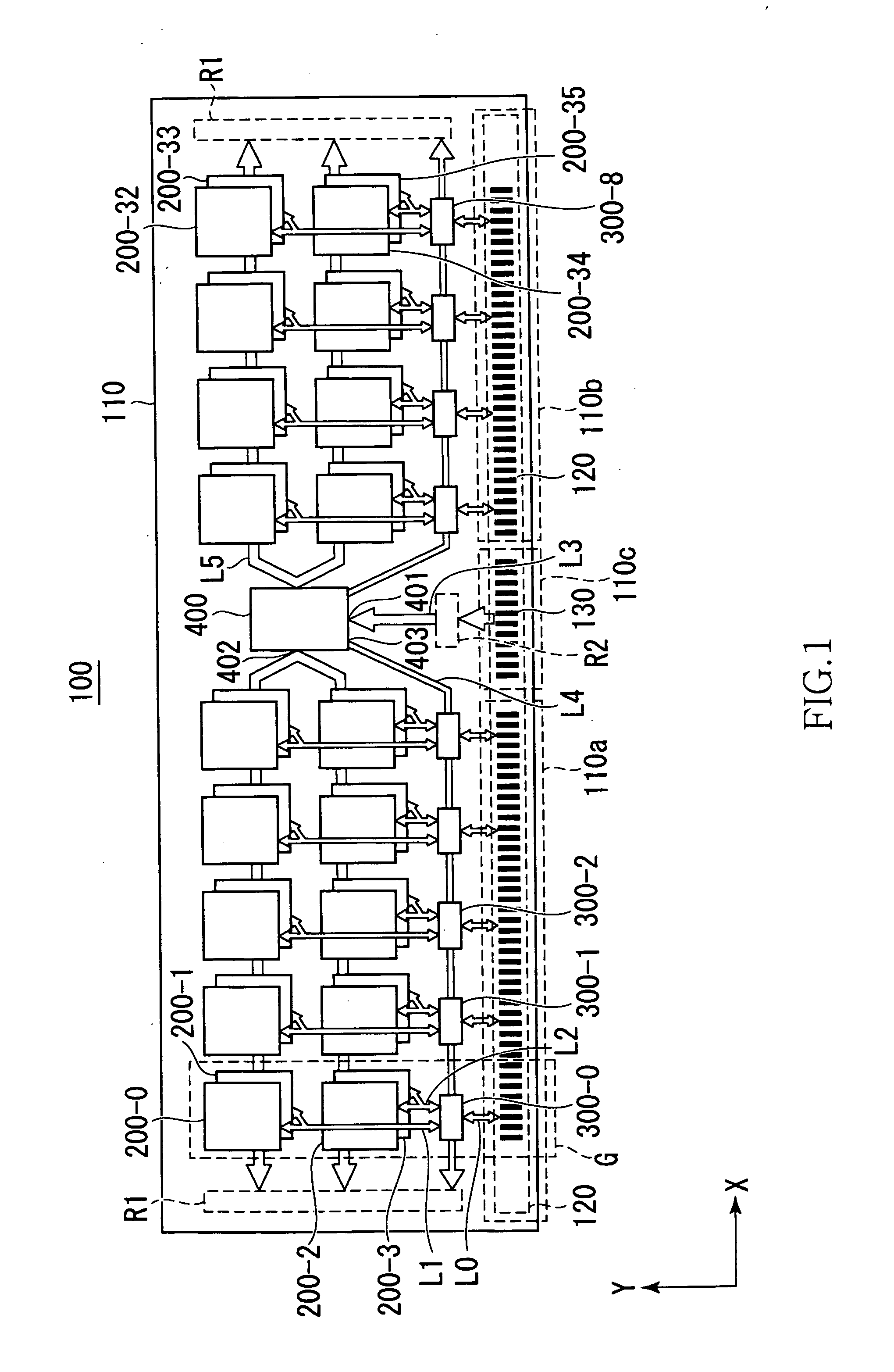

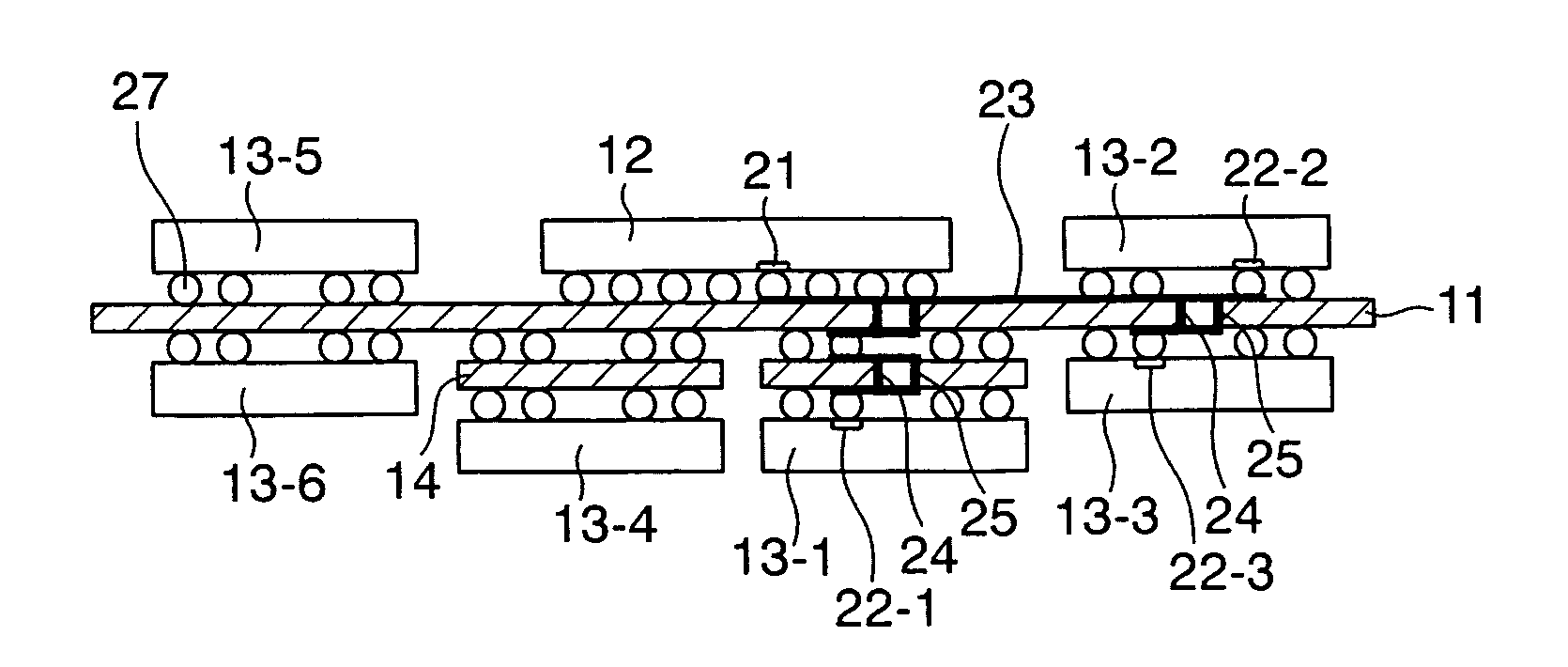

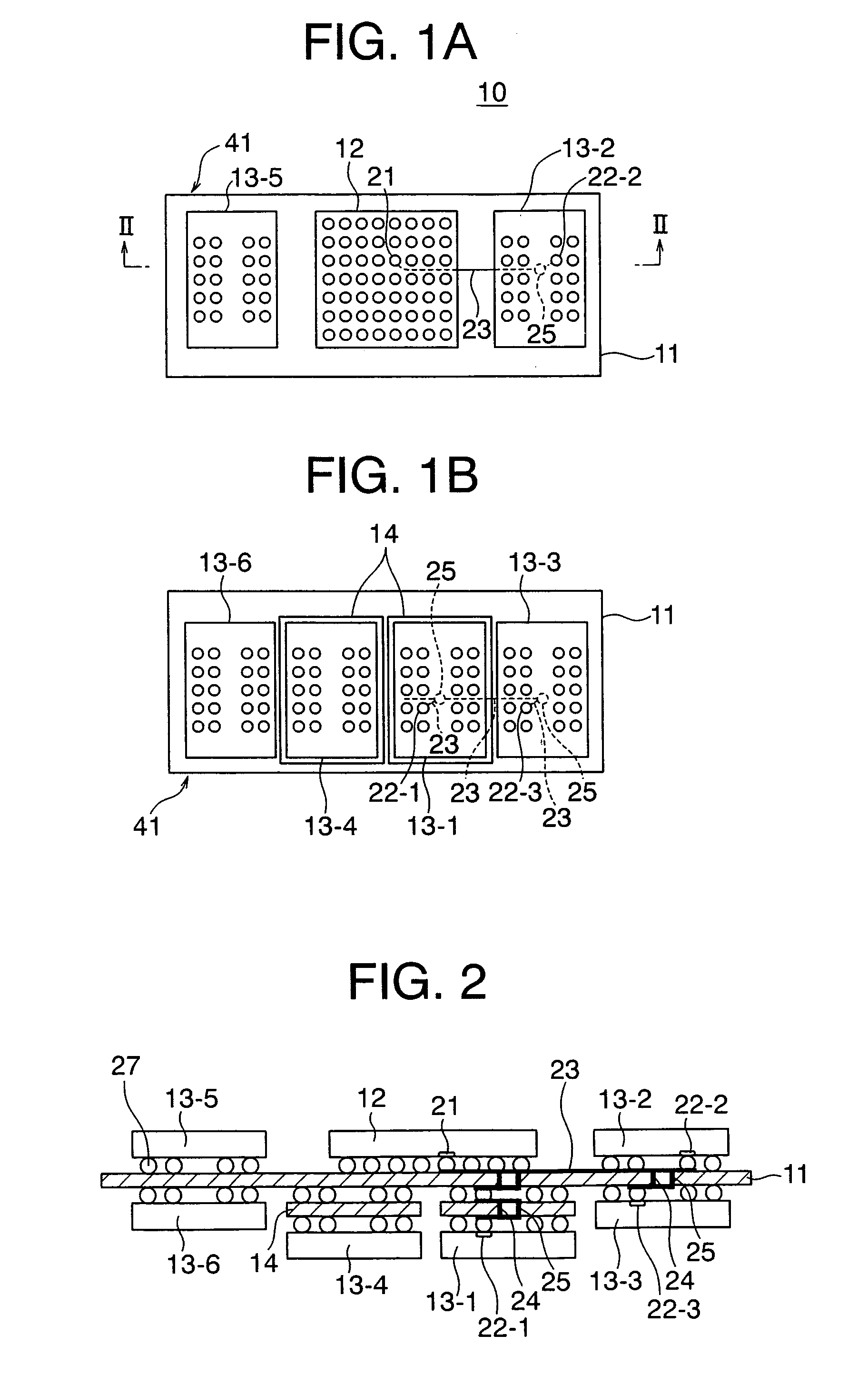

Load reduced memory module and memory system including the same

ActiveUS8422263B2Improve signal qualityLine lengthSolid-state devicesDigital storageMemory chipControl signal

A memory module includes a plurality of memory chips, a plurality of data register buffers, and a command / address / control register buffer mounted on a module PCB. The data register buffers perform data transfers with the memory chips. The command / address / control register buffer performs buffering of a command / address / control signal and generates a control signal. The buffered command / address / control signal is supplied to the memory chips, and the control signal is supplied to the data register buffers. According to the present invention, because line lengths between the data register buffers and the memory chips are shortened, it is possible to realize a considerably high data transfer rate.

Owner:LONGITUDE LICENSING LTD

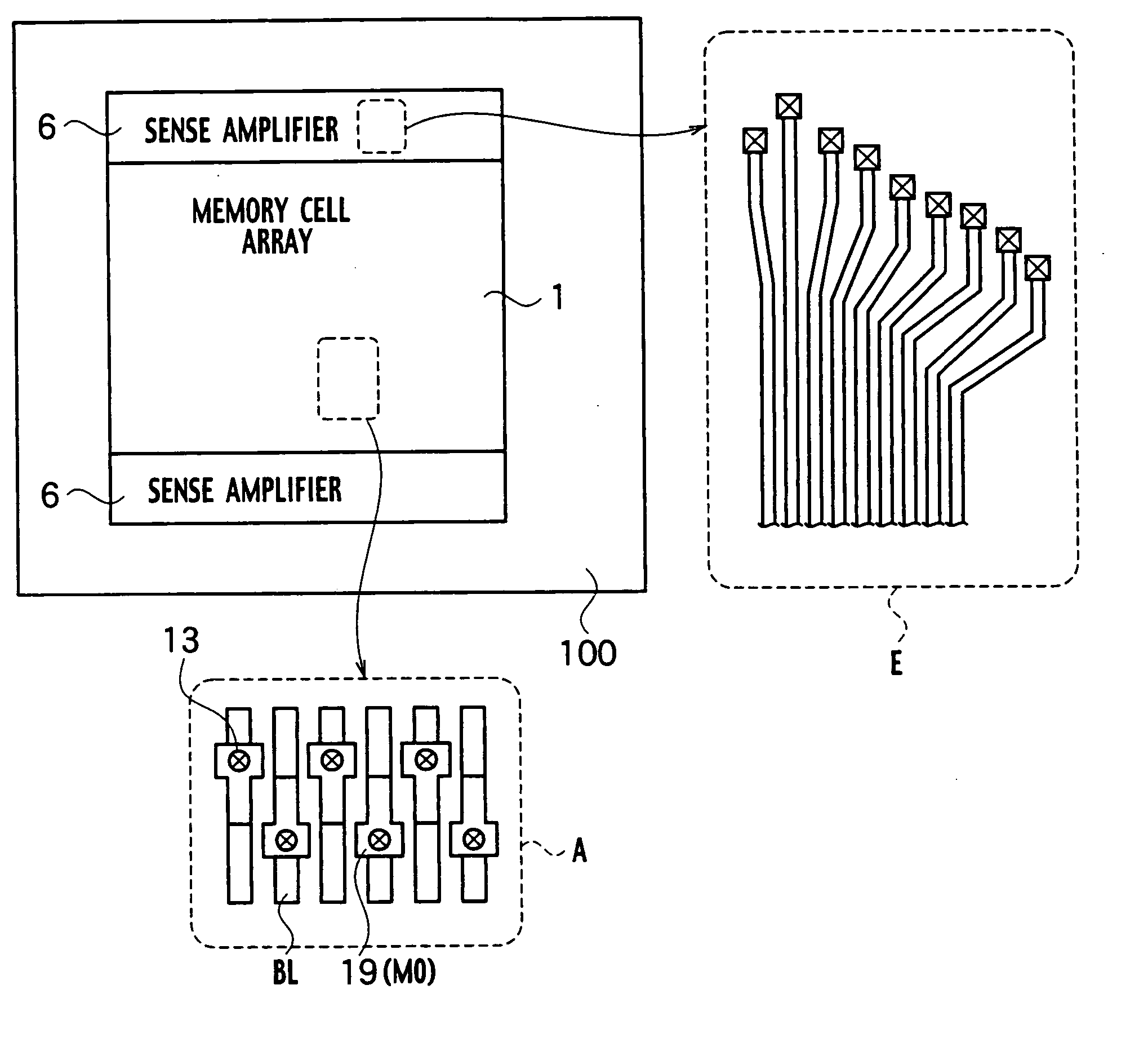

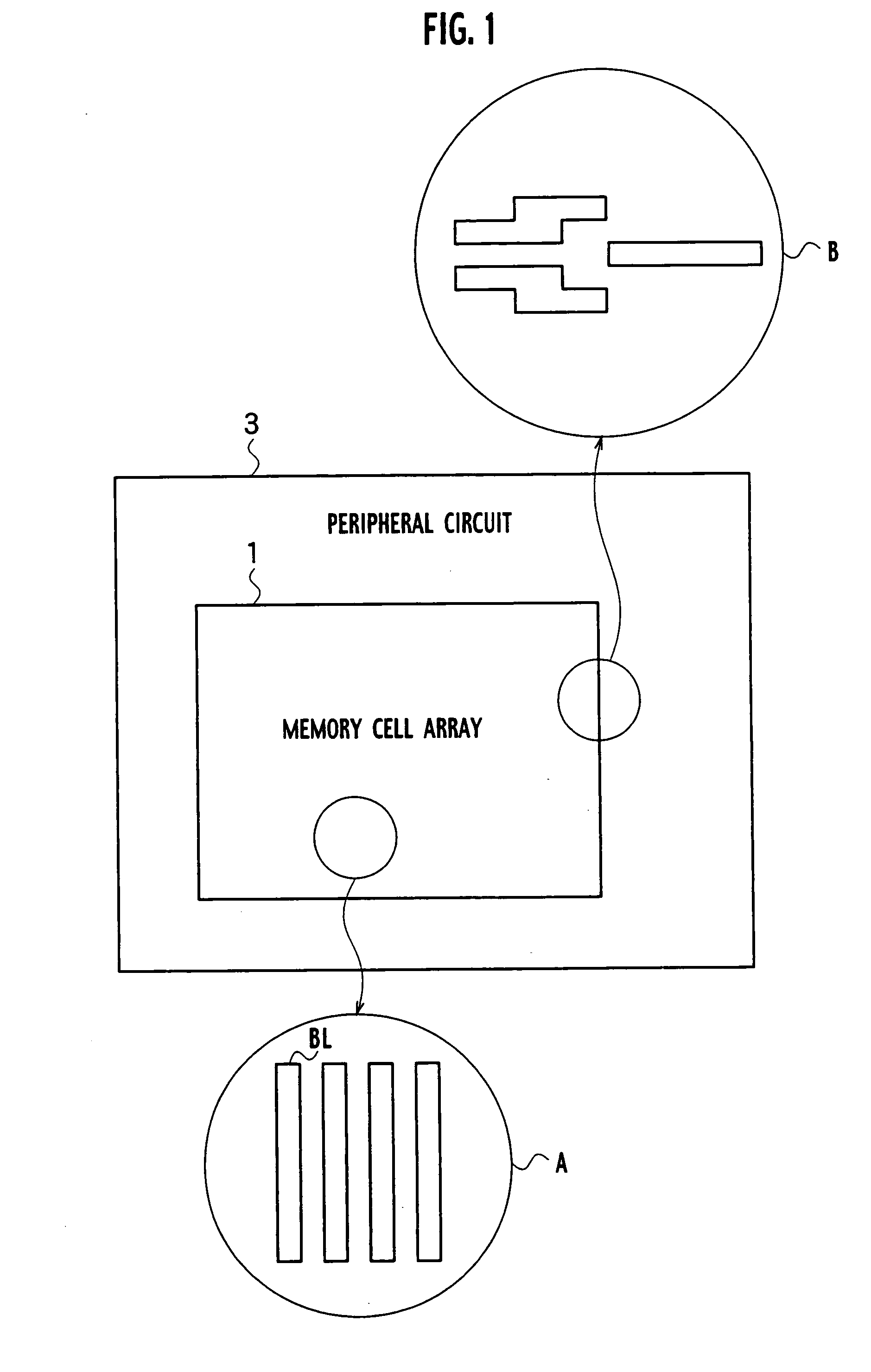

Semiconductor memory

Borderless contacts for word lines or via contacts for bit lines are formed using interconnect patterns, a part of which is removed. A semiconductor memory includes: a plurality of active regions AAi, AAi+1, . . . , AAn, which extend on a memory cell array along the column length; a plurality of word line patterns WL1, WL2, . . . , extend along the row length and are non-uniformly arranged; a plurality of select gate line patterns SG1, SG2, . . . , are arranged parallel to the plurality of word line patterns; borderless contacts are formed near the ends of the word line patterns on the memory cell array, and are in contact with part of an interconnect extended from the end of the memory cell array, but are not in contact with interconnects adjacent to that interconnect; and bit line contacts are formed within contact forming regions provided by removing part of the plurality of word line patterns and select gate line patterns through double exposure.

Owner:KATANA SILICON TECH LLC

Load reduced memory module and memory system including the same

ActiveUS20100309706A1Improve signal qualityImprove data transfer rateSolid-state devicesDigital storageMemory chipProcessor register

A memory module includes a plurality of memory chips, a plurality of data register buffers, and a command / address / control register buffer mounted on a module PCB. The data register buffers perform data transfers with the memory chips. The command / address / control register buffer performs buffering of a command / address / control signal and generates a control signal. The buffered command / address / control signal is supplied to the memory chips, and the control signal is supplied to the data register buffers. According to the present invention, because line lengths between the data register buffers and the memory chips are shortened, it is possible to realize a considerably high data transfer rate.

Owner:LONGITUDE LICENSING LTD

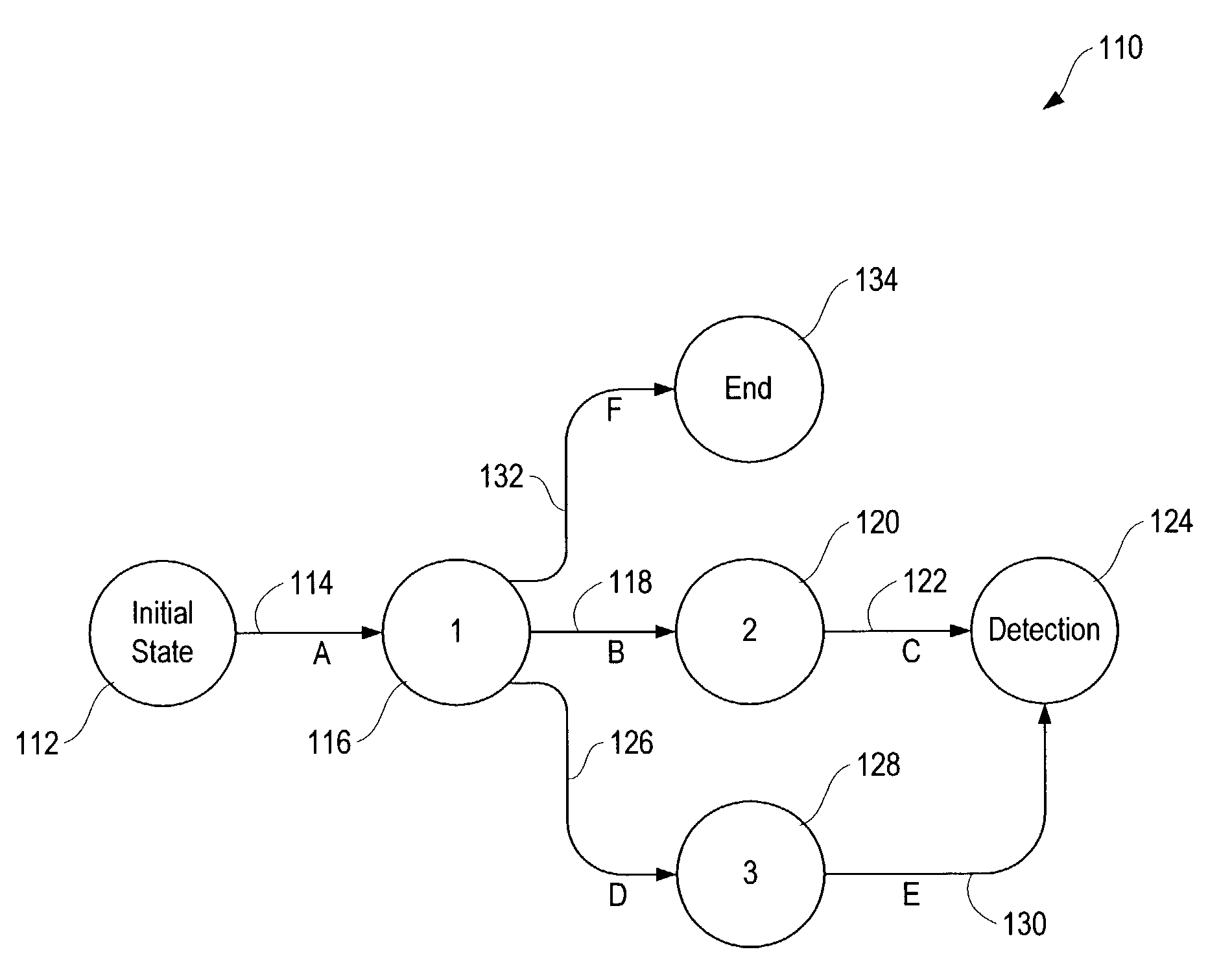

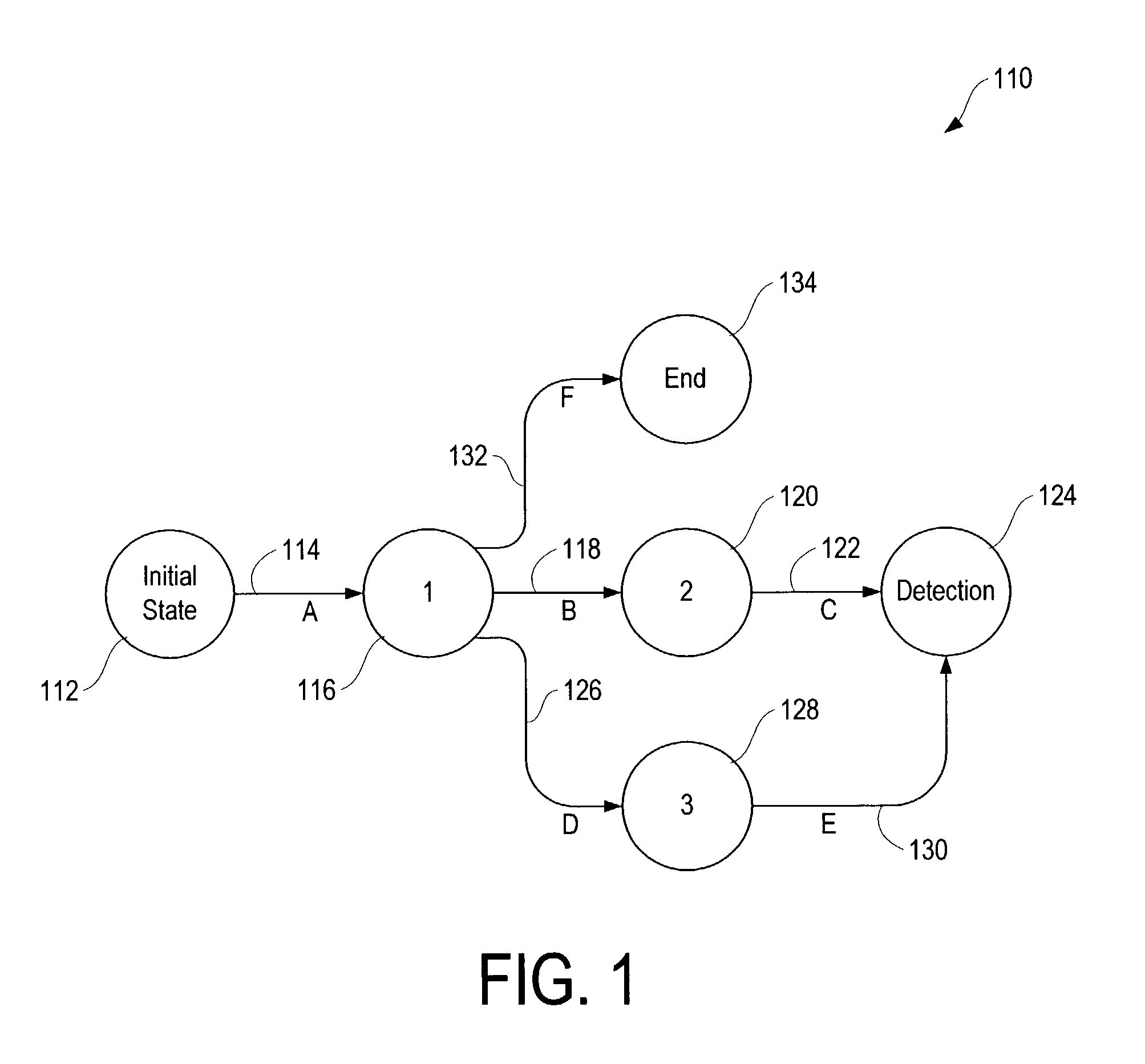

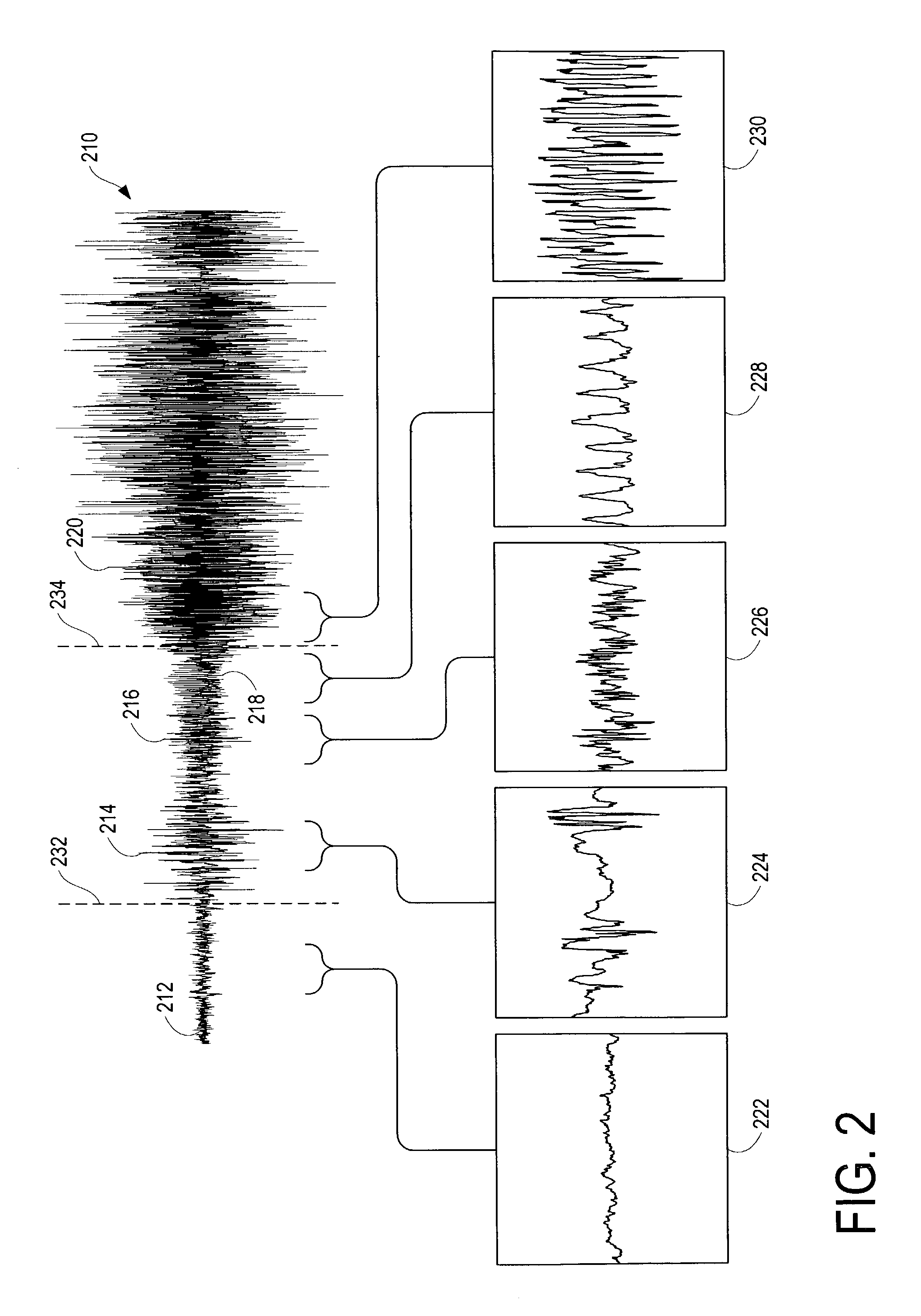

Spatiotemporal pattern recognition for neurological event detection and prediction in an implantable device

ActiveUS7277748B2Reduce the amount requiredAccurate and reliable seizure detectionElectroencephalographyEndoradiosondesSignal processing circuitsFinite-state machine

A system and method for detecting and predicting neurological events with an implantable device uses a relatively low-power central processing unit in connection with signal processing circuitry to identify features (including half waves) and calculate window-based characteristics (including line lengths and areas under the curve of the waveform) in one or more electrographic signals received from a patient's brain. The features and window-based characteristics are employed within the framework of a programmable finite state machine to identify patterns and sequences in and across the electrographic signals, facilitating early and reliable detection and prediction of complex spatiotemporal neurological events in real time, and enabling responsive action by the implantable device.

Owner:NEUROPACE

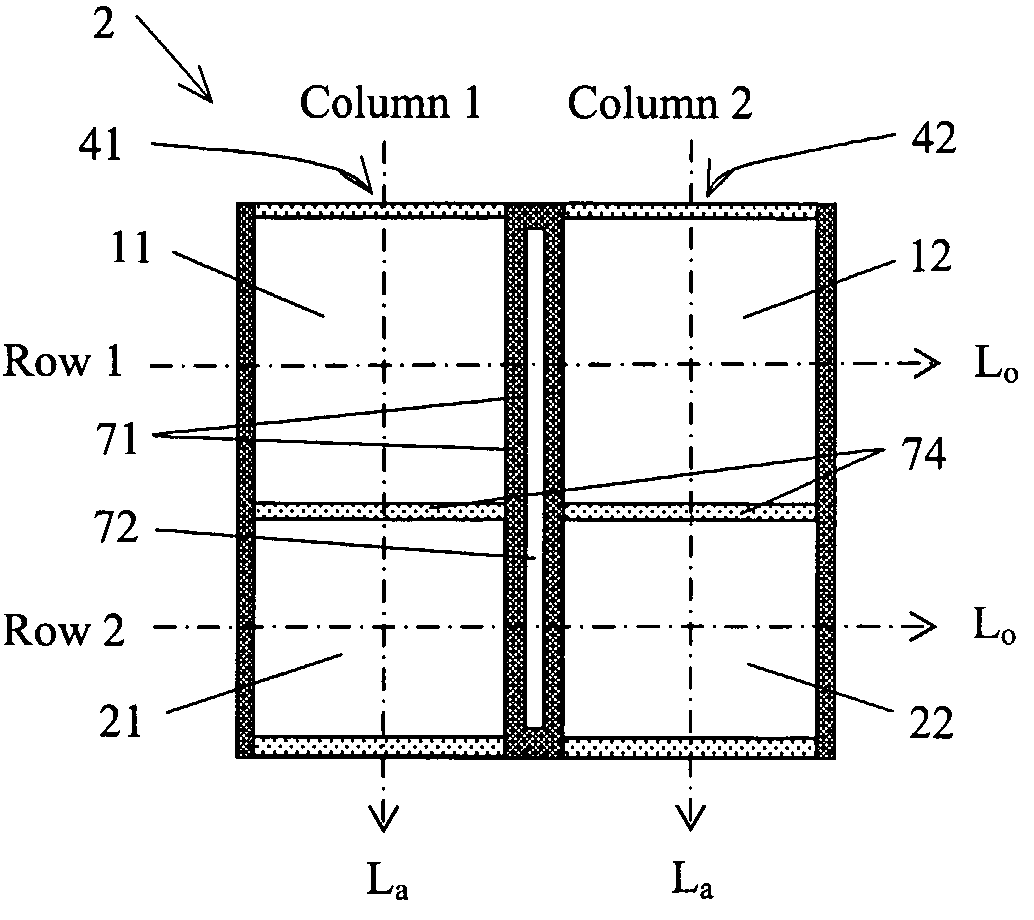

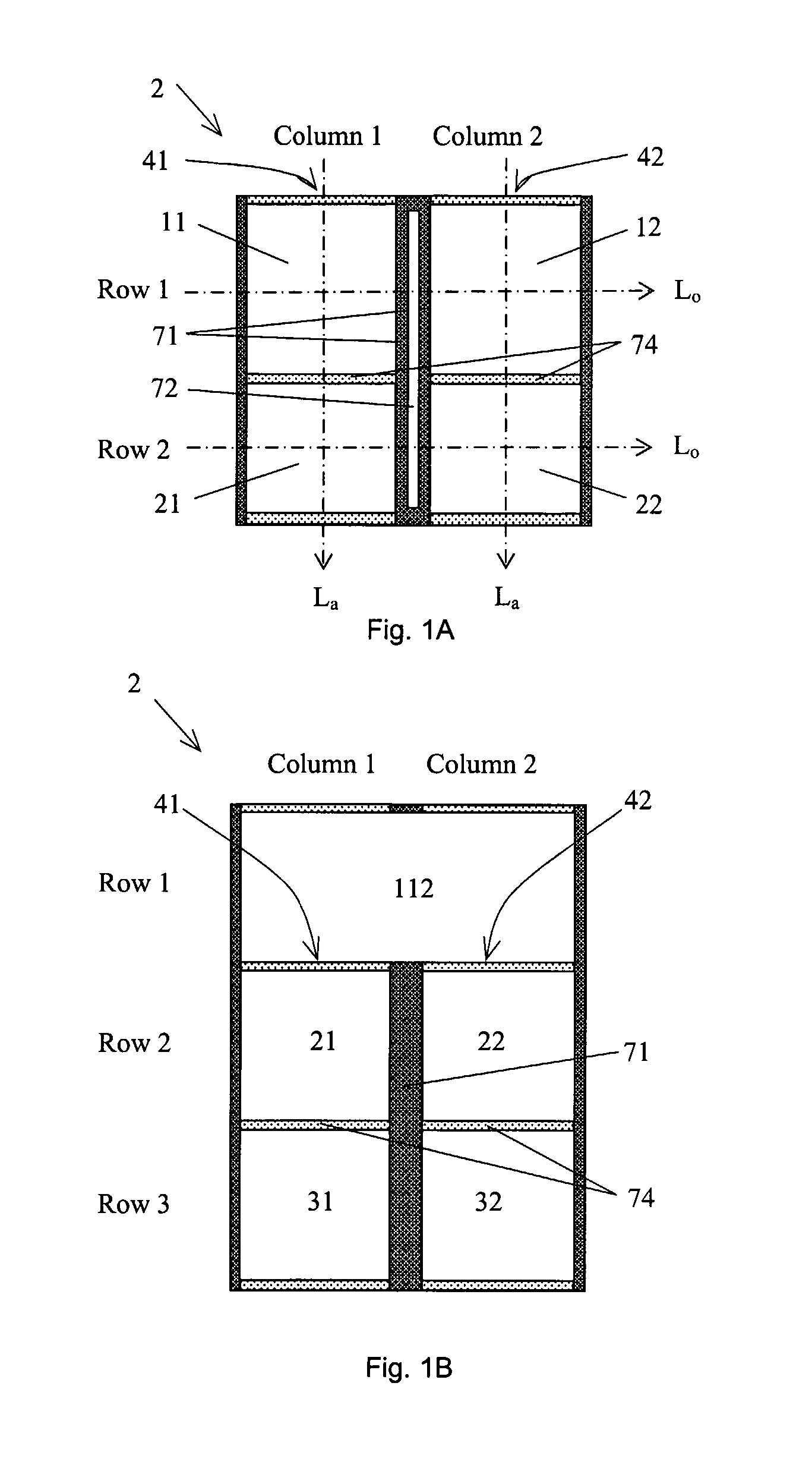

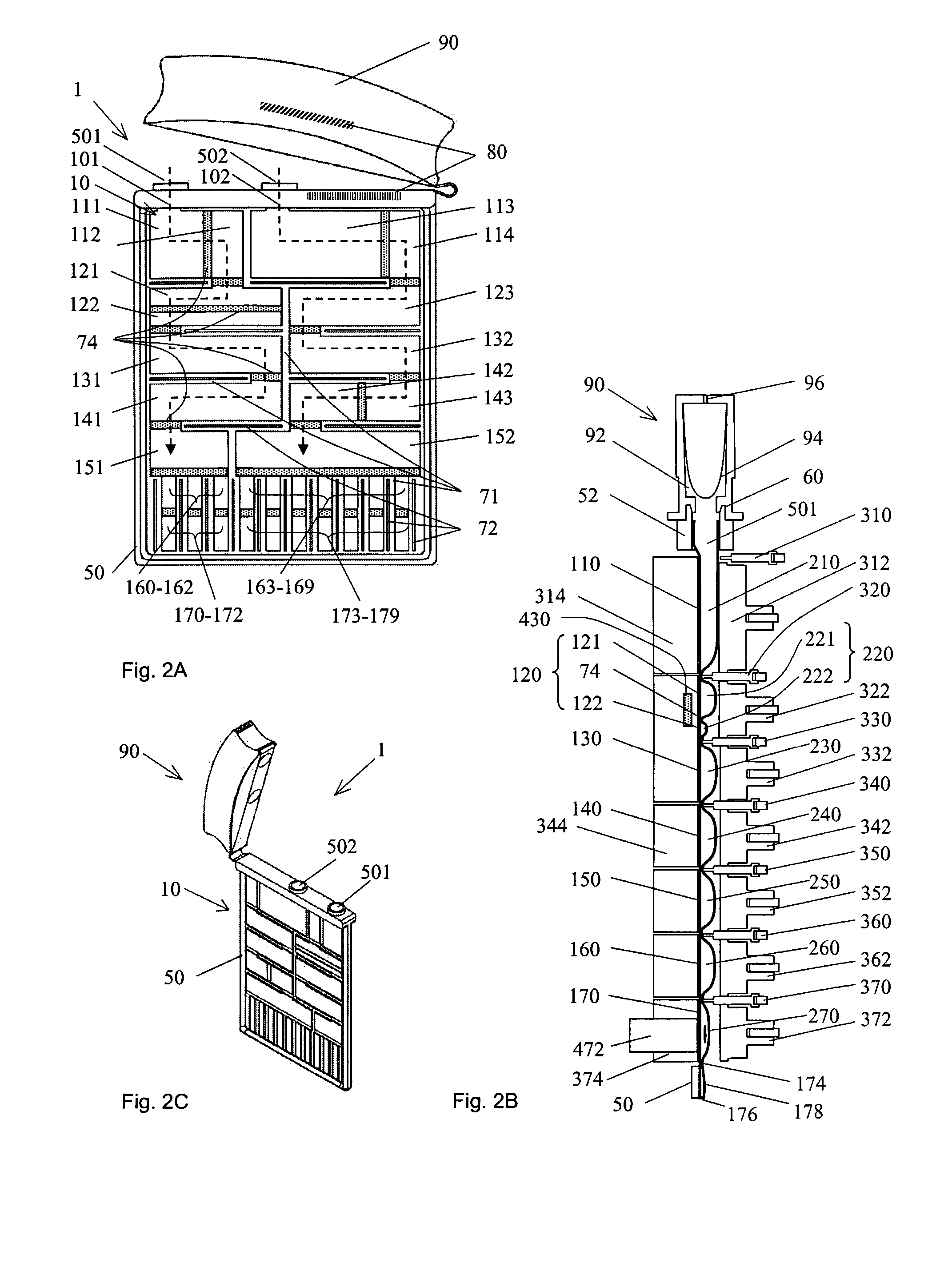

Sample multiprocessing

ActiveUS7785535B2Easy to prepareBioreactor/fermenter combinationsHeating or cooling apparatusEngineeringMultiprocessing

A sample processing cartridge may include a plurality of segments arranged in an array at least two rows long and two columns wide. Each segment may be defined by at least one wall of the sample cartridge, fluidly isolated from adjacent segments at least in part by at least one breakable seal or by at least one permanent seal, so expandable as to receive a volume of fluid expelled from another segment, and so compressible as to contain substantially no fluid when so compressed. At least two adjacent segments of at least one row of the array may be aligned along a longitudinal axis of the row and have substantially the same height along a latitudinal axis of the row. At least two adjacent segments in at least one row may be separated by a permanent seal to form at least two tracks. At least one segment, or at least two adjacent segments separated by a breakable seal, may be in fluid communication with the at least two tracks. At least one segment may contain at least one reagent.

Owner:IQUUM

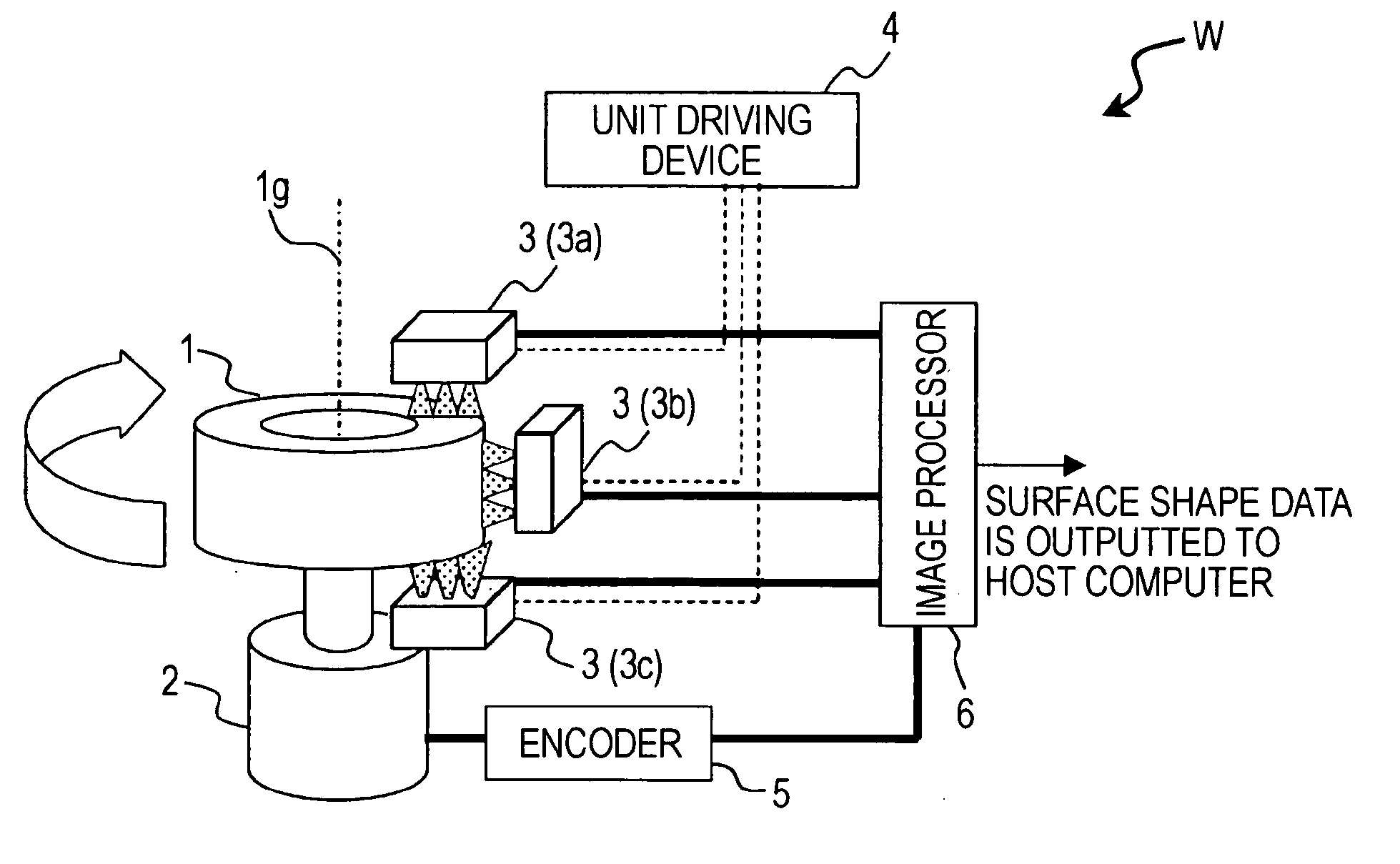

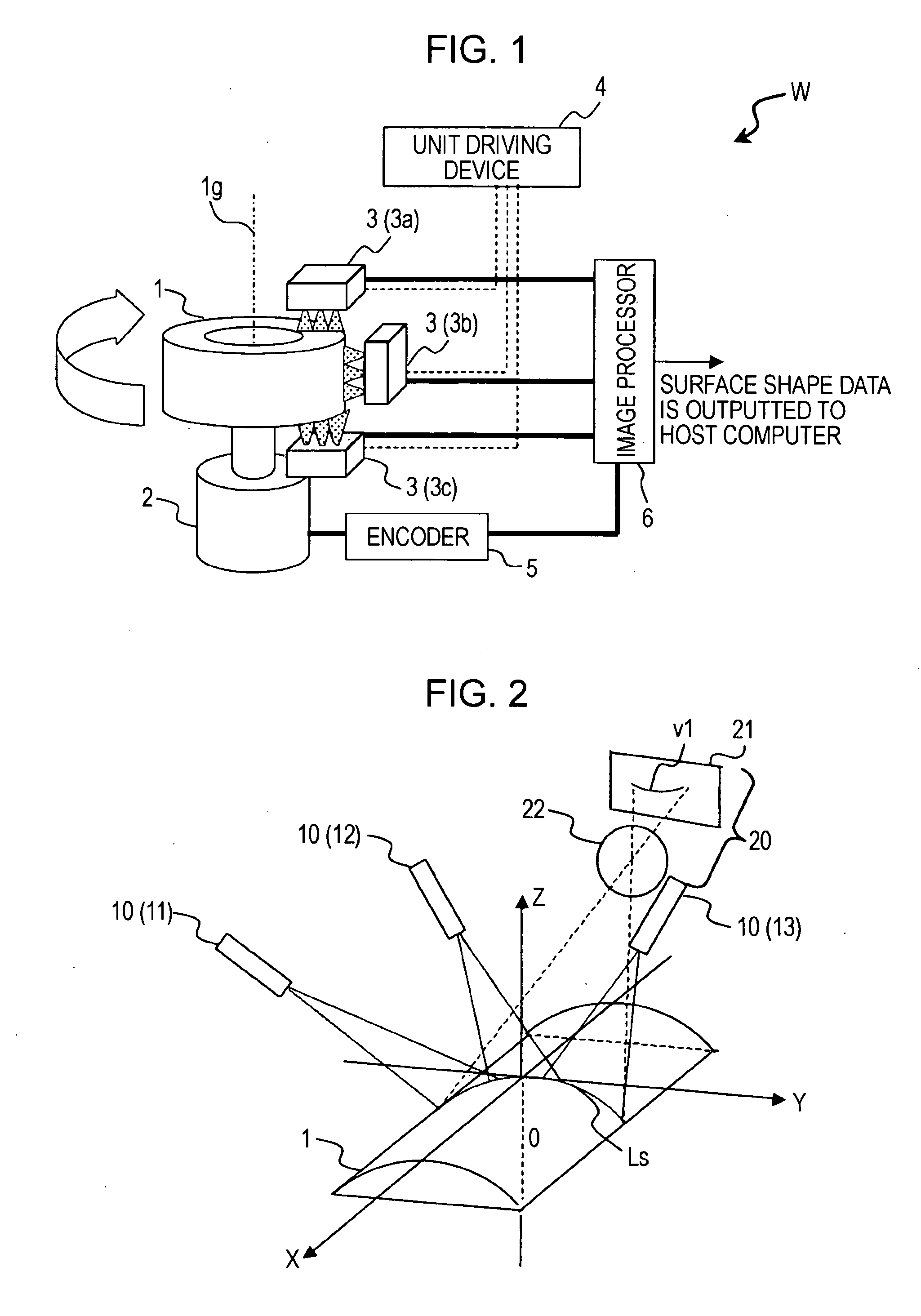

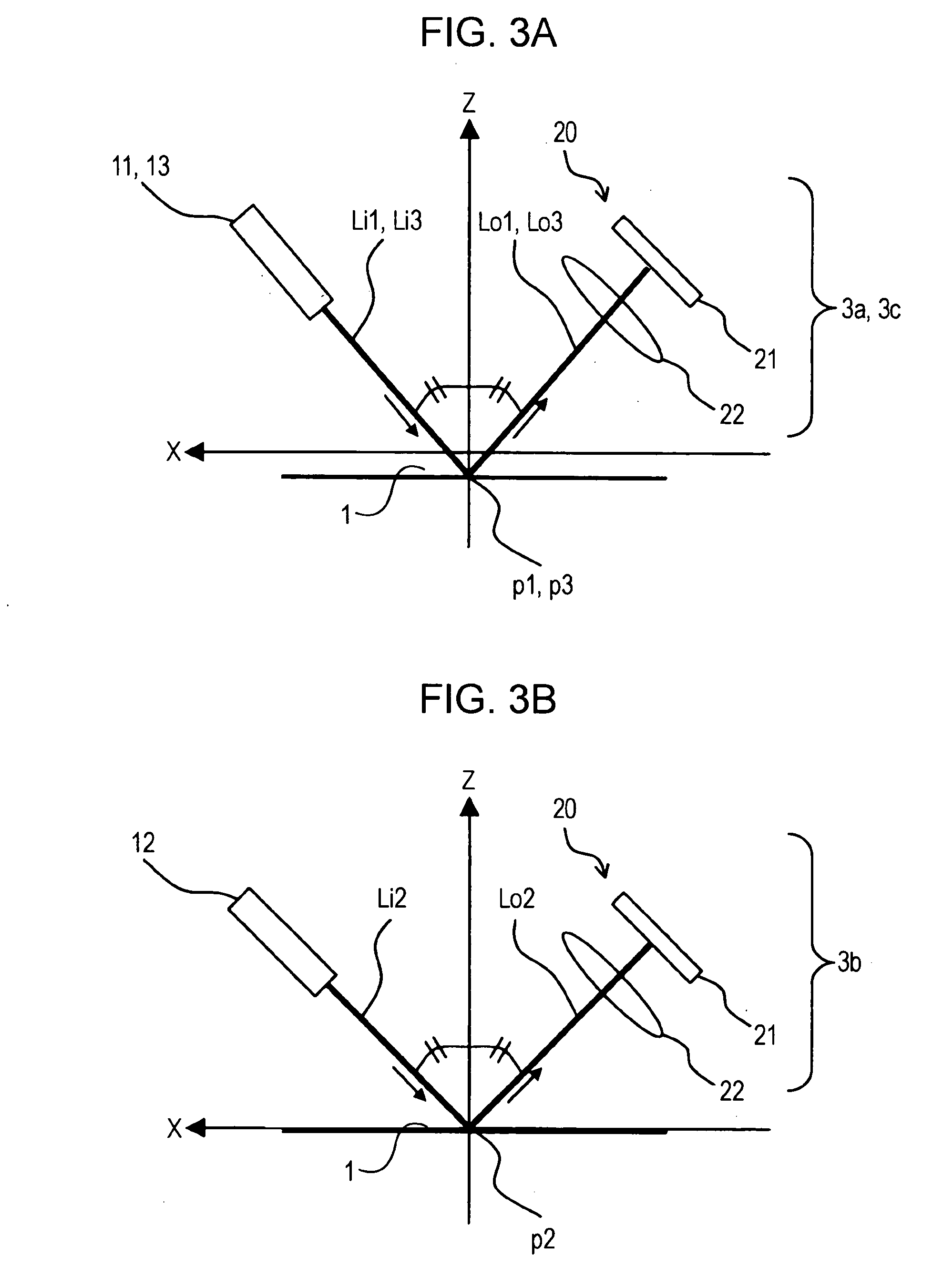

Apparatus and method for detecting tire shape

A tire shape detecting apparatus includes a projector that applies a plurality line light beams in a continuously joined manner, from a direction different from the detection height direction (Z-axis direction) in one light section line, or that applies one line light beam in a condensed manner in the line length direction thereof in order that the one light section line may be formed on the one line Ls on the surface of the tire; and a camera for picking up images of the plurality of line light beams applied to the tire surface in the direction in which the principal ray of each of the plurality of line light beams performs specular reflection with respect to the tire surface, or in the direction in which the principal ray of the condensed one line light beam performs specular reflection with respect to the tire surface.

Owner:KOBE STEEL LTD

Combined traveling wave fault location method of high-voltage overhead line and cable hybrid line

InactiveCN102508109AEliminate the impact of ranging accuracyImprove ranging accuracyFault locationInformation technology support systemCable fault locationHigh pressure

The invention provides a combined traveling wave fault location method of a high-voltage overhead line and cable hybrid line. The method comprises the following steps of: firstly, carrying out fault section selection by using a double-ended principle according to time difference generated when a fault initial traveling wave of the hybrid line arrives at two ends, then carrying out initial fault location by using a single-ended principle, and finally working out an accurate result via the single-ended principle by combining with the time difference generated when the fault initial traveling wave arrives at two sides of the line. The method has the advantages that: the obtained fault location result is the result of the single-ended fault location principle, and the effects of hybrid line length error and accurate time synchronization problem of two sides of the line to the fault location accuracy are eliminated in the fault location by using the double-ended principle so that the accuracy and reliability of the fault location are improved. Therefore, the traveling wave fault location of the high-voltage overhead line and cable hybrid line is realized by using the method, the problem on how to accurately search a fault point position after the hybrid line is in the fault can be reliably solved and the traveling wave fault location method has a good application prospect.

Owner:SHANDONG UNIV OF TECH

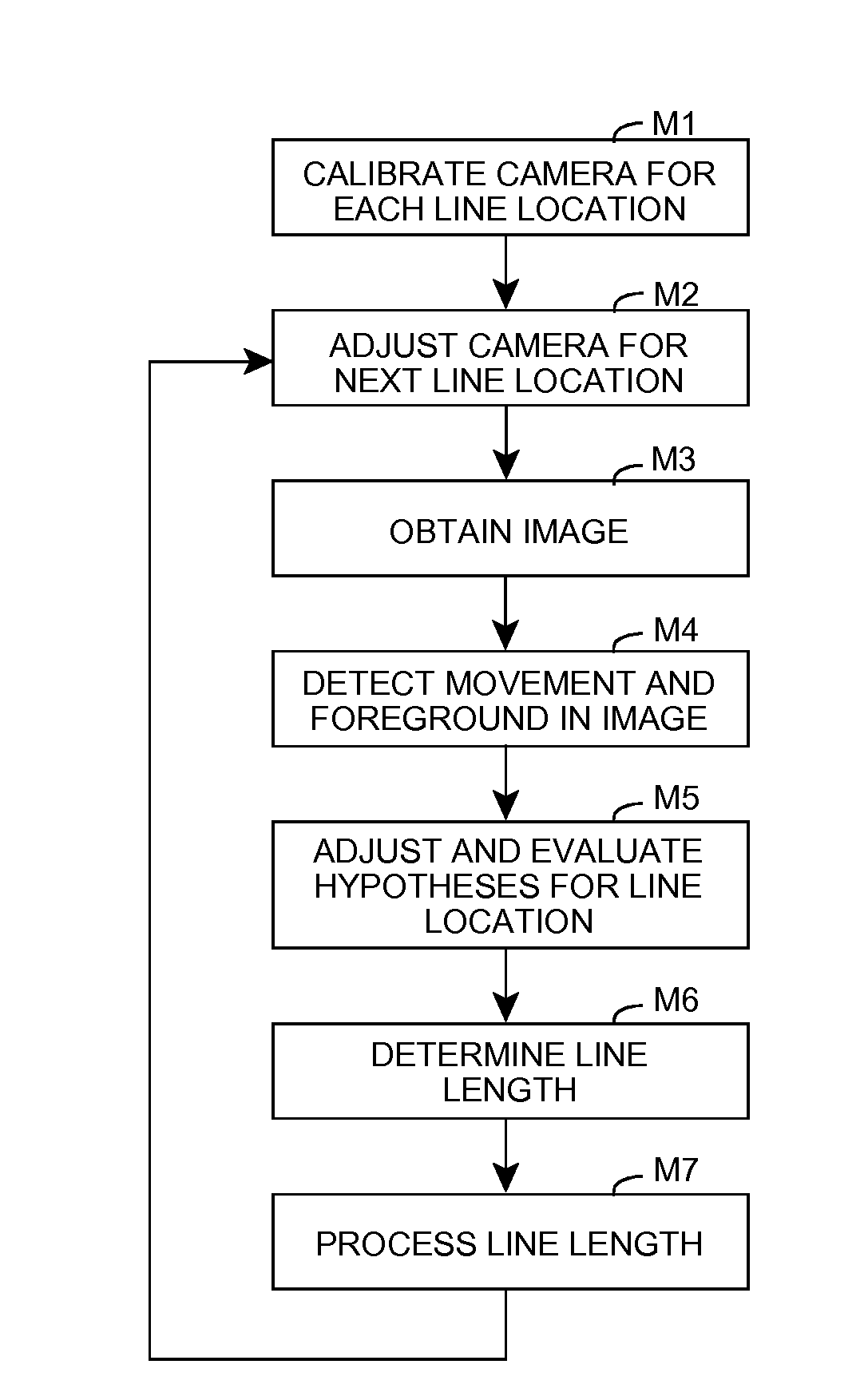

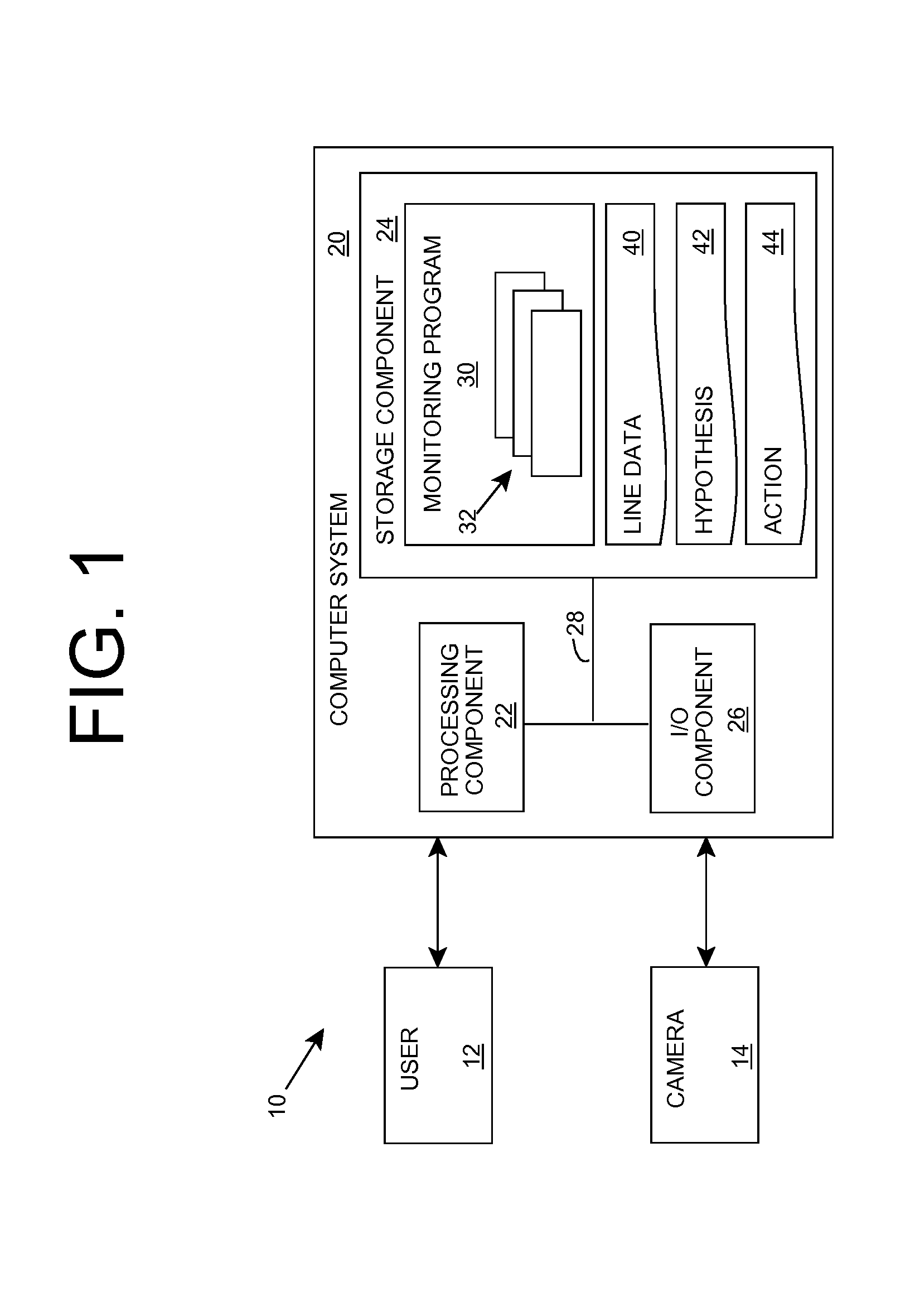

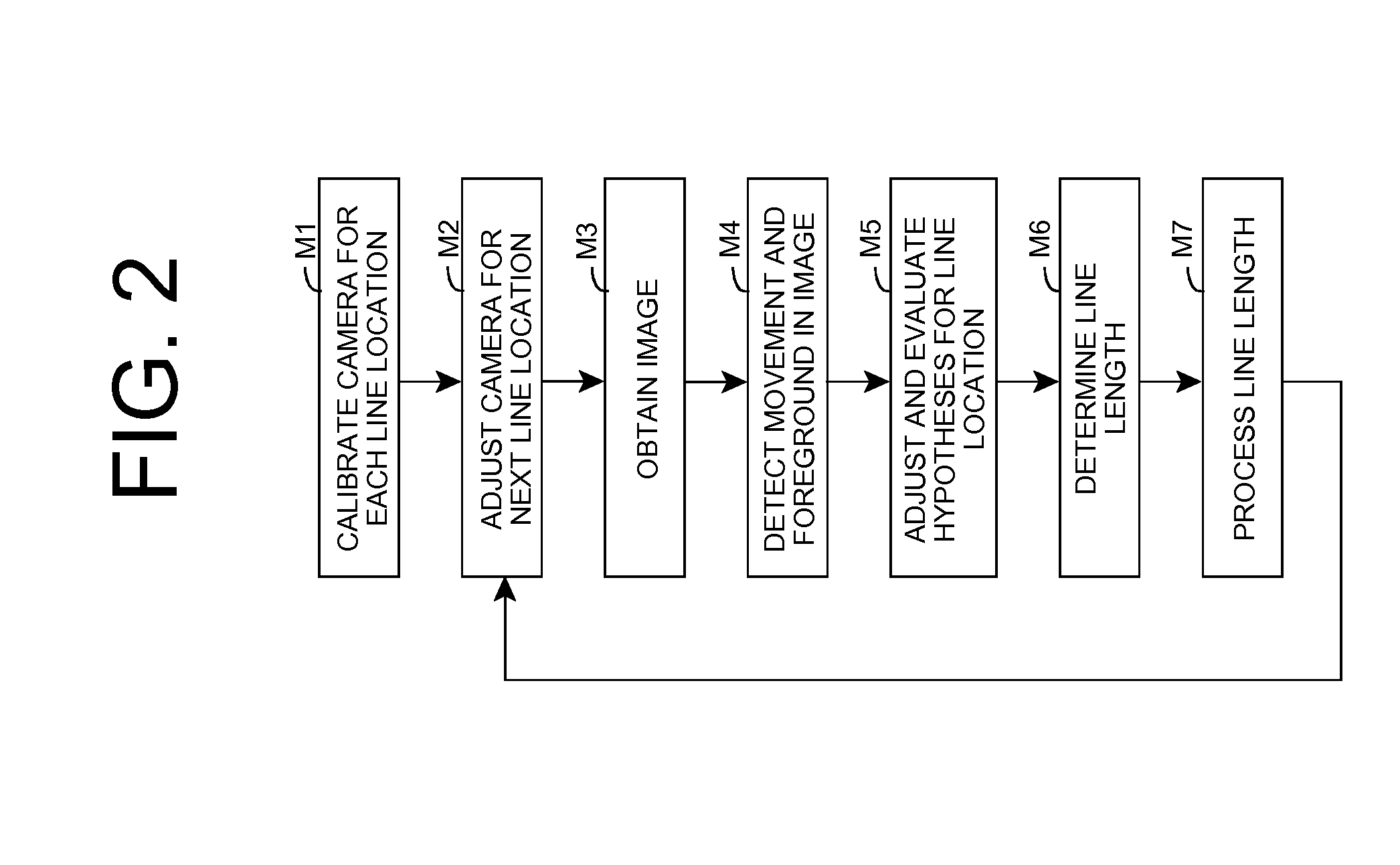

Line length estimation

A solution for monitoring an area is provided. At least one image of a physical area corresponding to a line is obtained and a set of hypotheses are evaluated based on the image(s). For one or more hypotheses, an estimated length of the line is extracted, and an estimated line length is generated based on the estimated length(s) and the corresponding evaluation(s) of the set of hypotheses. In this manner, a length of a line of people, customers, vehicles, and / or the like, can be estimated. The estimation can be stored for later use, utilized to generate one or more alerts, and / or the like. The invention also provides for the use of a single camera to monitor multiple lines and / or perform other monitoring functions.

Owner:TERRACE LICENSING LLC

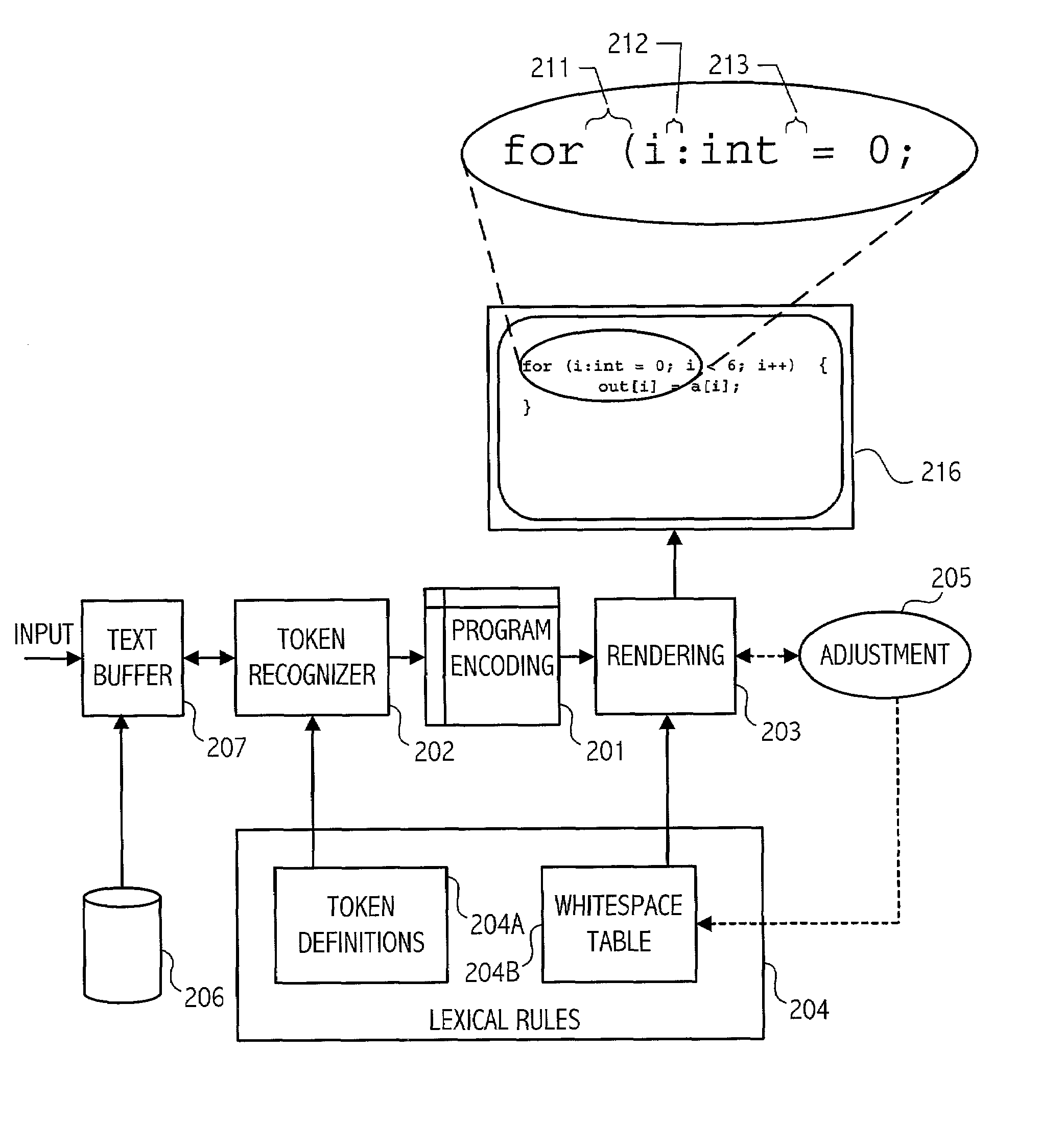

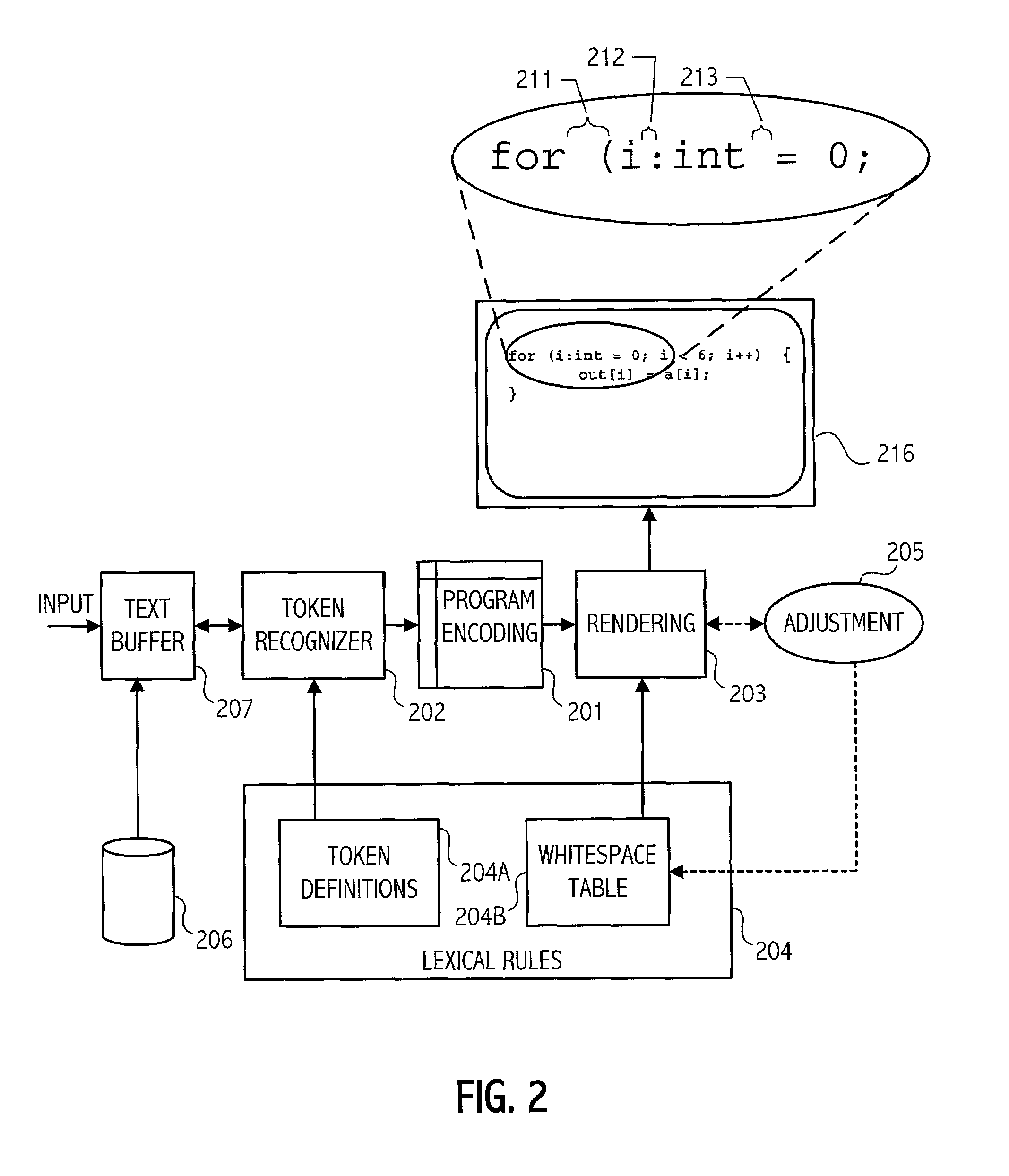

Language-sensitive whitespace adjustment in a software engineering tool

InactiveUS7117479B2Intelligent editorsSpecific program execution arrangementsAlgorithmEngineering tool

An editor or software engineering tool may be configured to render whitespace between adjacent tokens, wherein the amount of whitespace between any two adjacent tokens is determined according to language-specific style rules and scaled in accordance with display considerations. In some realizations, the operative scaling is selected or defined by a user according to the user's visual preferences. In some realizations, the operative scaling relates to requirements or constraints of an automated layout mechanism. For example, a particular scaling may be calculated to adjust line length in conformance with a desired margin alignment or to optimize layout when long lines are automatically wrapped (or folded) in some automatic way.

Owner:ORACLE INT CORP

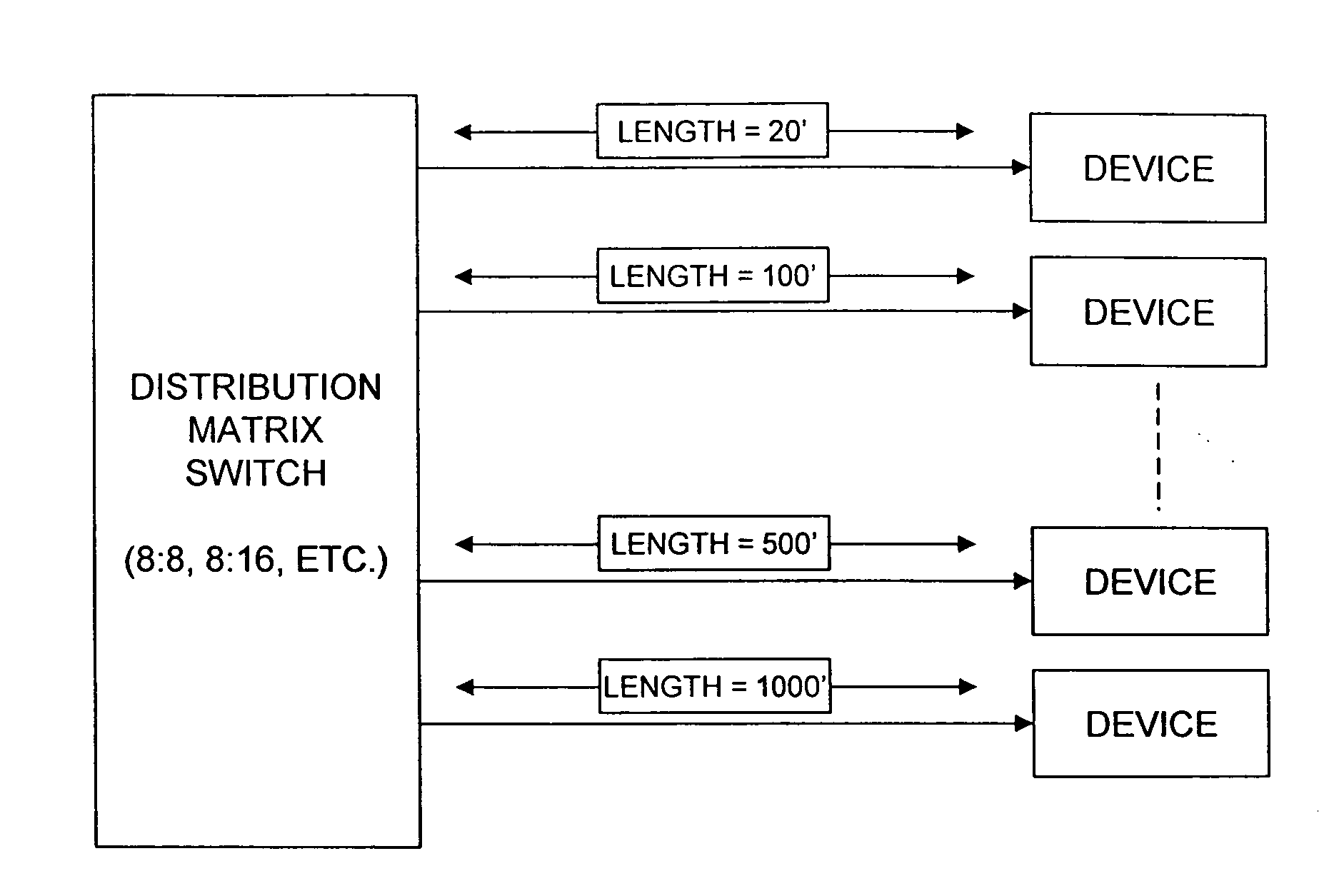

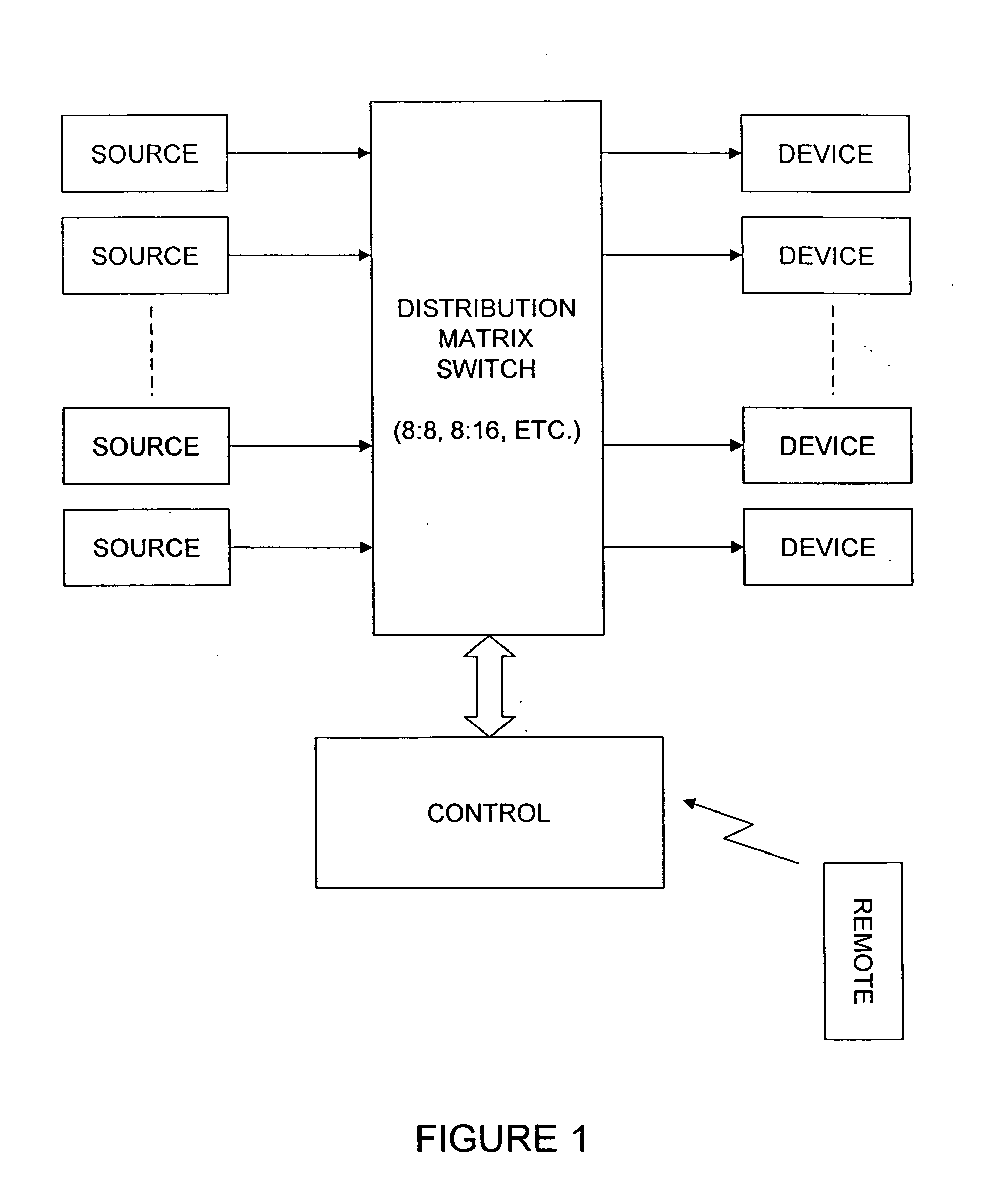

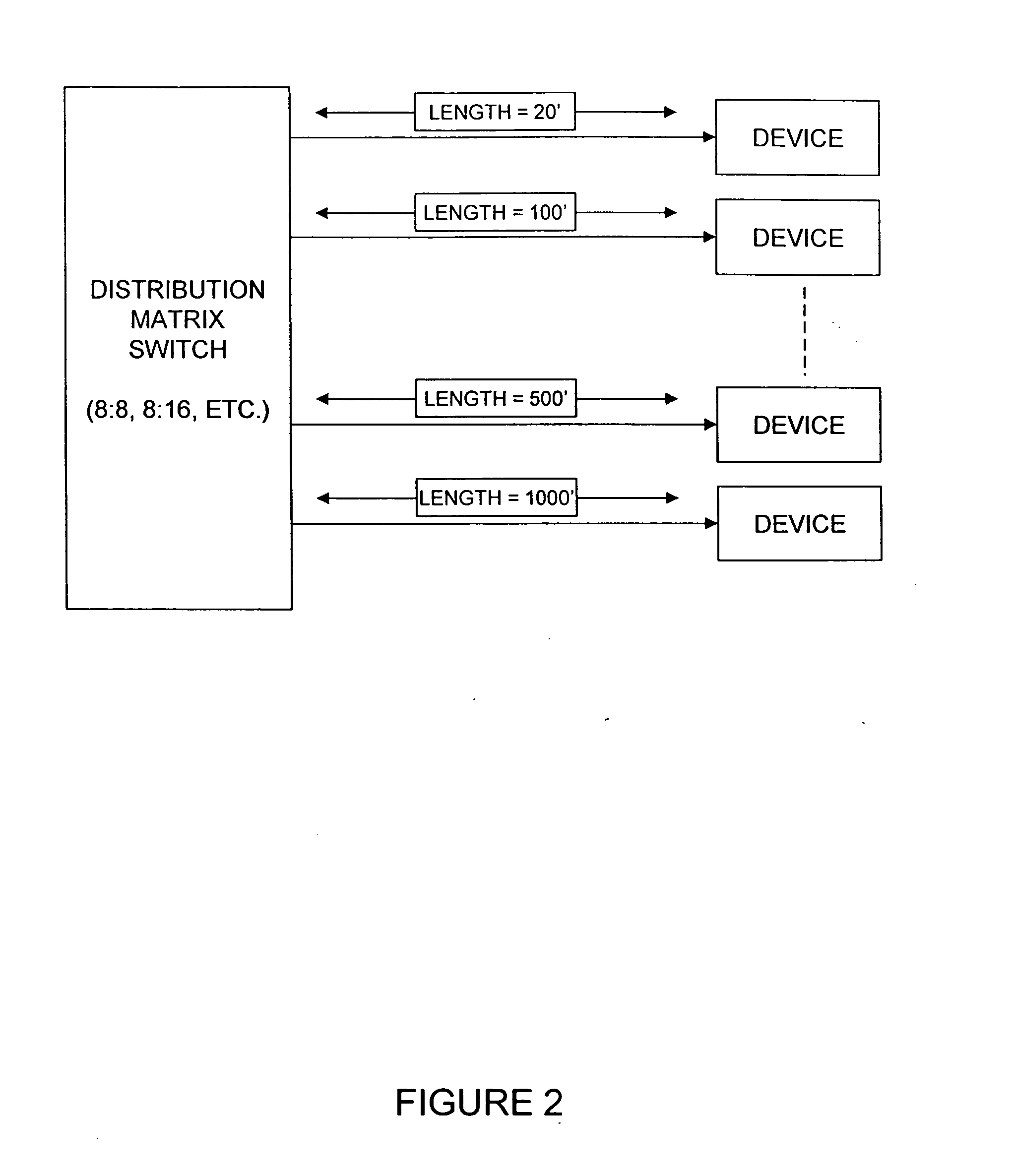

Audio video matrix switch with automatic line length signal compensator

InactiveUS20110277010A1Quality improvementTelevision system detailsTransmission control/equlisationDifferential signalingEngineering

An audio video matrix switch with automatic line length signal compensator provides for the determination of the line length and an automatic compensation signal to be generated, and for that compensation signal to be used to provide an equalizing gain to the transmitted signal thereby providing a higher quality signal to the output device. A system of the present invention includes a matrix switch assembly receiving inputs from a plurality of audio and video signal sources, and a plurality of audio and video output device. Each of the video output devices is equipped with a differential signal receiver and equalizer module which receives a routed signal from the matrix switch, determines the cable length, and provides a compensation signal to the audio and video signals to compensate for the cable length, and provides that compensated signal to an output device.

Owner:PAUL BILL

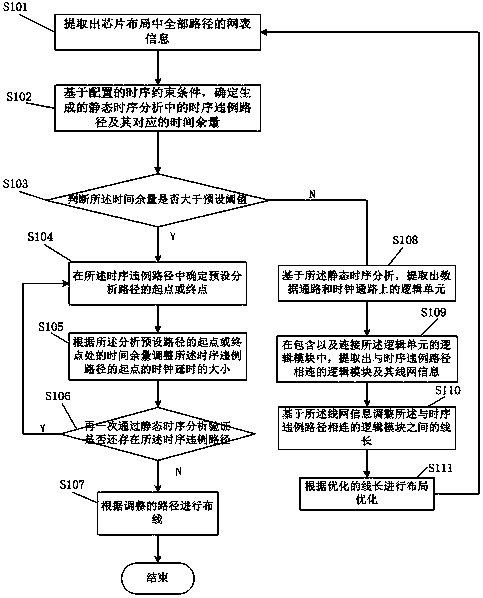

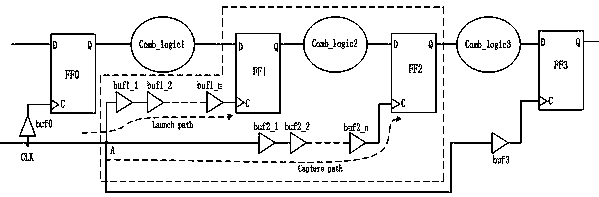

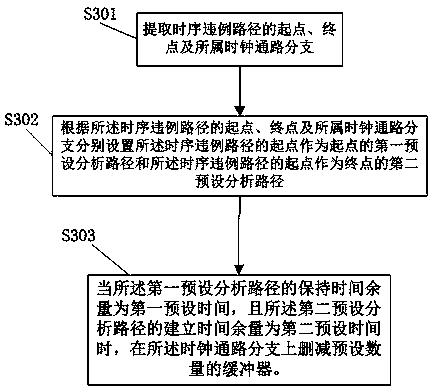

A time sequence repairing method based on time headroom

ActiveCN109583103ASmall design areaIncrease working frequencySpecial data processing applicationsTiming marginStatic timing analysis

The invention provides a time sequence repairing method based on time headroom, which comprises the following steps: step 1, extracting netlist information of all paths in a chip layout, and then entering a step 2; Step 2, determining a time sequence violation path in the generated static time sequence analysis and a corresponding time margin based on the configured time sequence constraint condition, and then entering a step 3; Step 3, judging whether the time margin is greater than a preset threshold value or not, if so, determining a starting point or an end point of a preset analysis pathin the time sequence violation path, and adjusting the magnitude of the clock delay of the time sequence violation path; Otherwise, analyzing based on the static time sequence; The method comprises the following steps: firstly, extracting logic units on a data path and a clock path according to a preset time sequence violation path, further extracting logic modules connected with the time sequenceviolation path and line network information of the logic modules, adjusting the line length between the logic modules connected with the time sequence violation path, performing optimized layout according to the optimized line length, and then returning to the step 1. The design area of the chip is reduced, and the working frequency of the chip is improved.

Owner:AMICRO SEMICON CORP

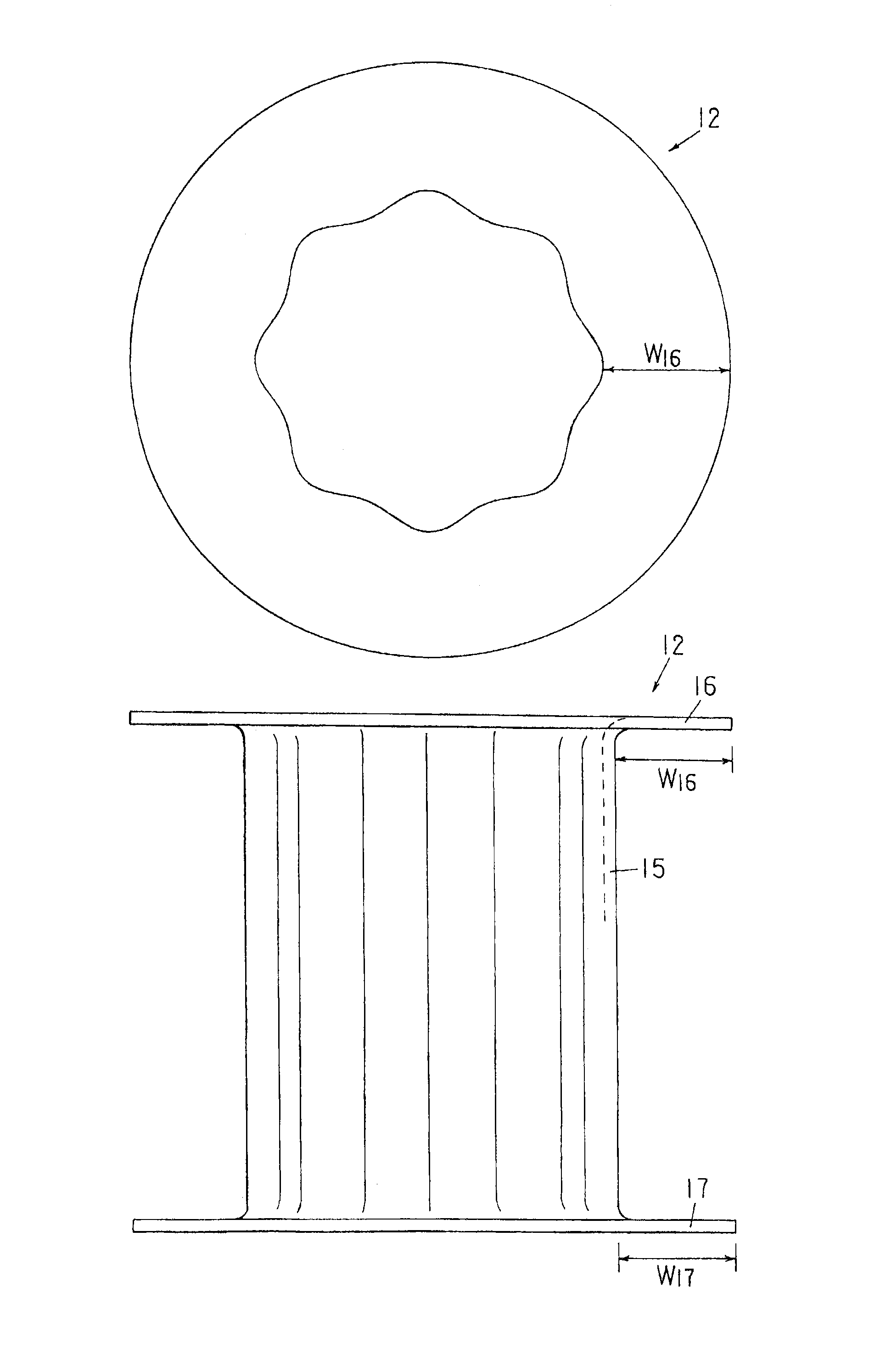

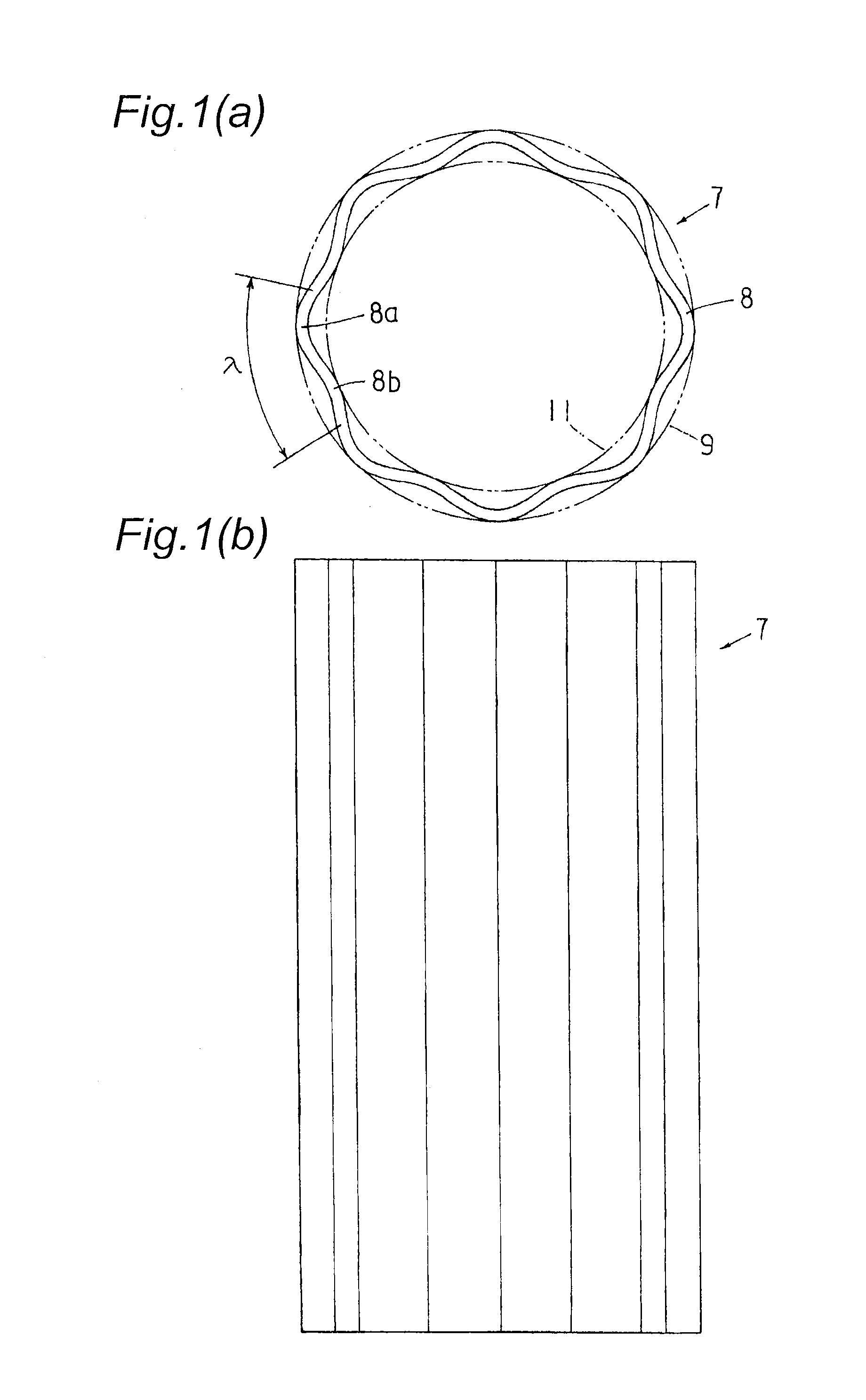

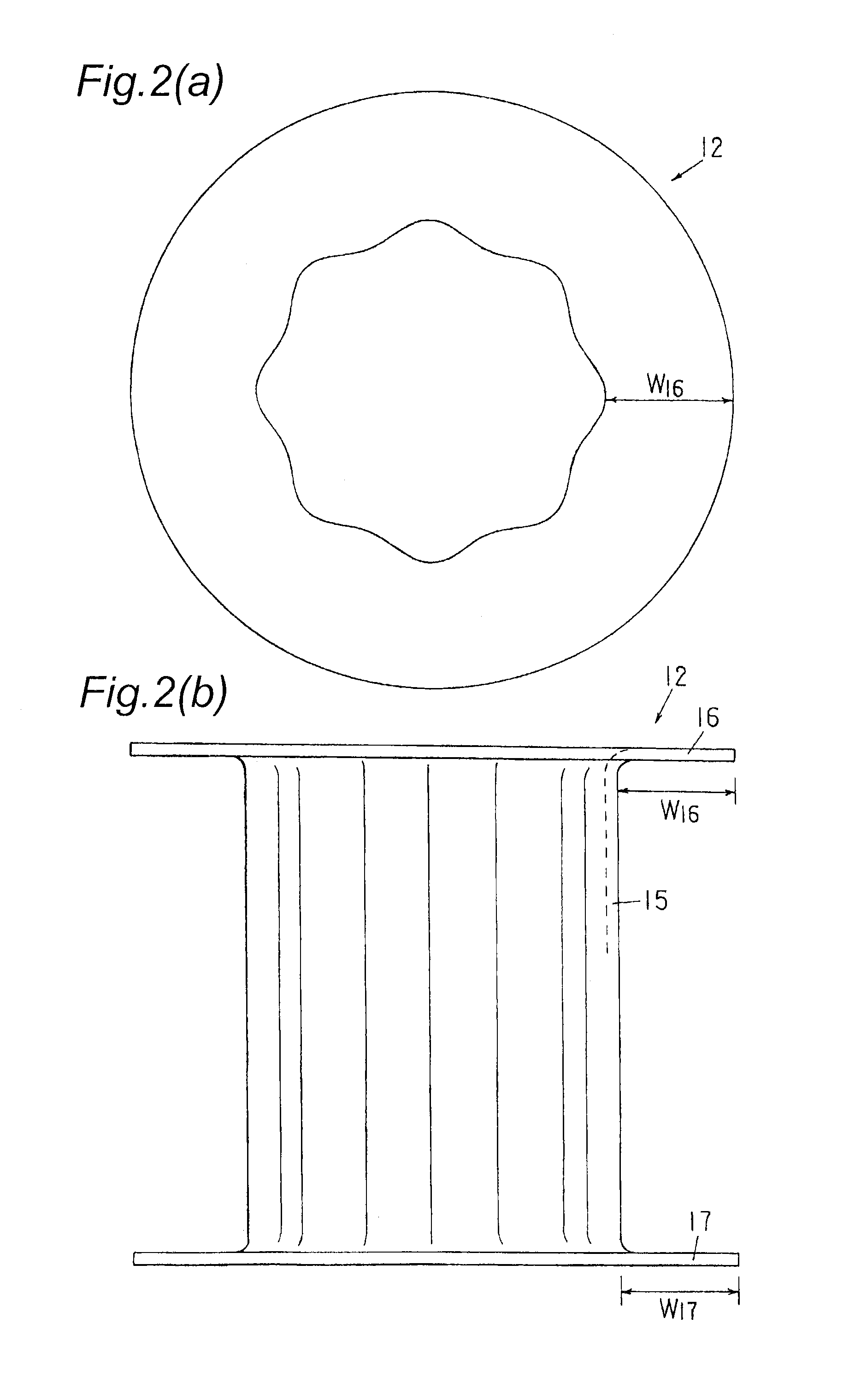

Energy absorbing member, method for producing same, and electromagnetic tube expansion method for rectangular cross-section member and polygon cross-section member

ActiveUS20140353990A1Increase freedomLarge widthMetal-working apparatusElastic dampersMaterials scienceFlange

An end of a stay material made of a tubular aluminum alloy extruded material is expanded by electromagnetic molding to form a flange for producing a bumper stay. The flange width is increased without cracking and a decrease in the thickness. A stay material having a circumferential wall undulating in a waveform pattern is used. A circumferential length L (one round length along waveform pattern) of the outer periphery wall along the circumferential direction of the stay material is longer than a circumferential length L0 of a simple cylindrical circumferential wall having the same outer diameter (circumscribed circle) (L>L0). L−L0 is an excessive line length. Since the circumferential wall has the excessive line length, when the end of the circumferential wall is expanded to form the flange, the flange having a large diameter can be formed.

Owner:KOBE STEEL LTD

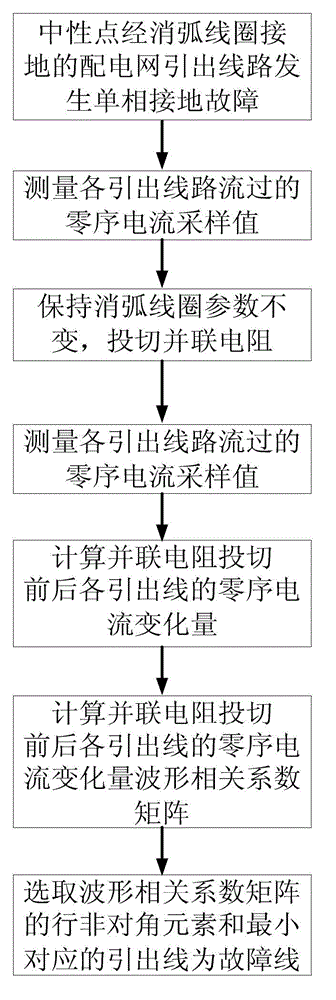

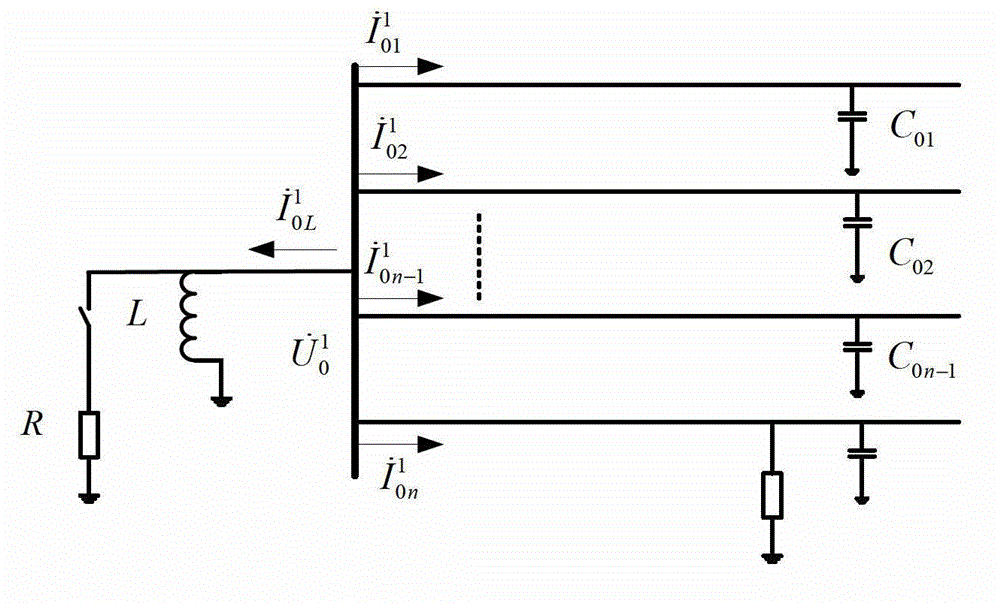

Distribution network fault line selection method based on zero sequence current variable quantity waveform correlation coefficient matrix

The invention discloses a distribution network fault line selection method based on a zero sequence current variable quantity waveform correlation coefficient matrix. According to the distribution network fault line selection method disclosed by the invention, a row off-diagonal element of each feeder zero sequence current variable quantity waveform correlation coefficient matrix and feeders in minimum corresponding before and after switching of a parallel resistance are utilized to carry out line selection for a fault line principle; and zero sequence voltage of a distribution network bus is larger than 15% phase voltage, the parallel resistance is switched by keeping arc suppression coil parameters invariable, a zero sequence current sampling value of each feeder flowing before and after switching of the parallel resistance is measured, the zero sequence current variable quantity waveform correlation coefficient matrix is further calculated, and the row off-diagonal element of each feeder zero sequence current variable quantity waveform correlation coefficient matrix and the feeders in minimum corresponding are selected as fault lines. With the adoption of the method, a line selection result is not influenced by factors such as transition resistance, line parameters, line length, distribution network running mode and fault position, the line selection principle is simple, and the line selection result is high in reliability and strong in practicability.

Owner:STATE GRID CORP OF CHINA +2

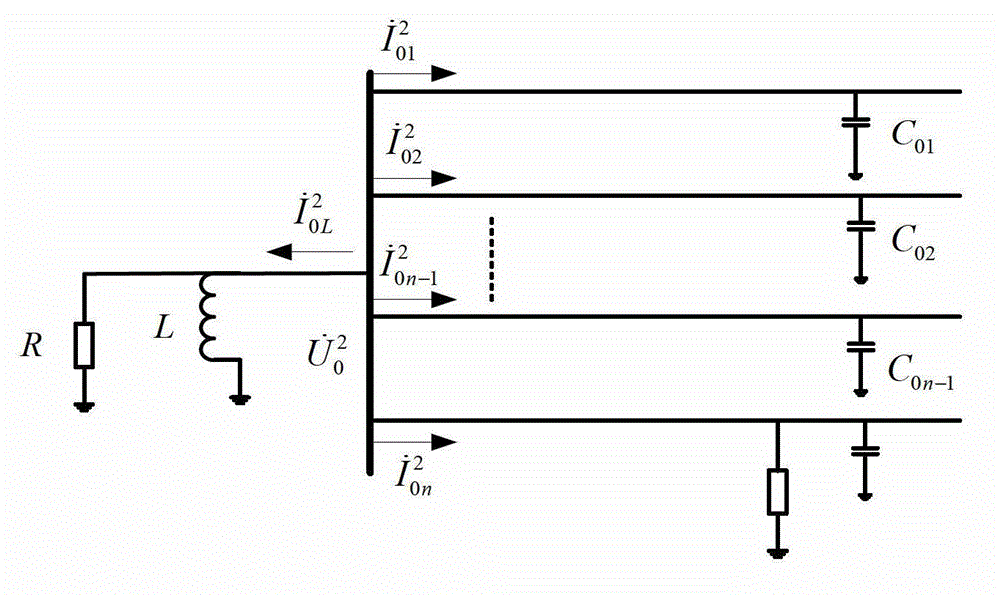

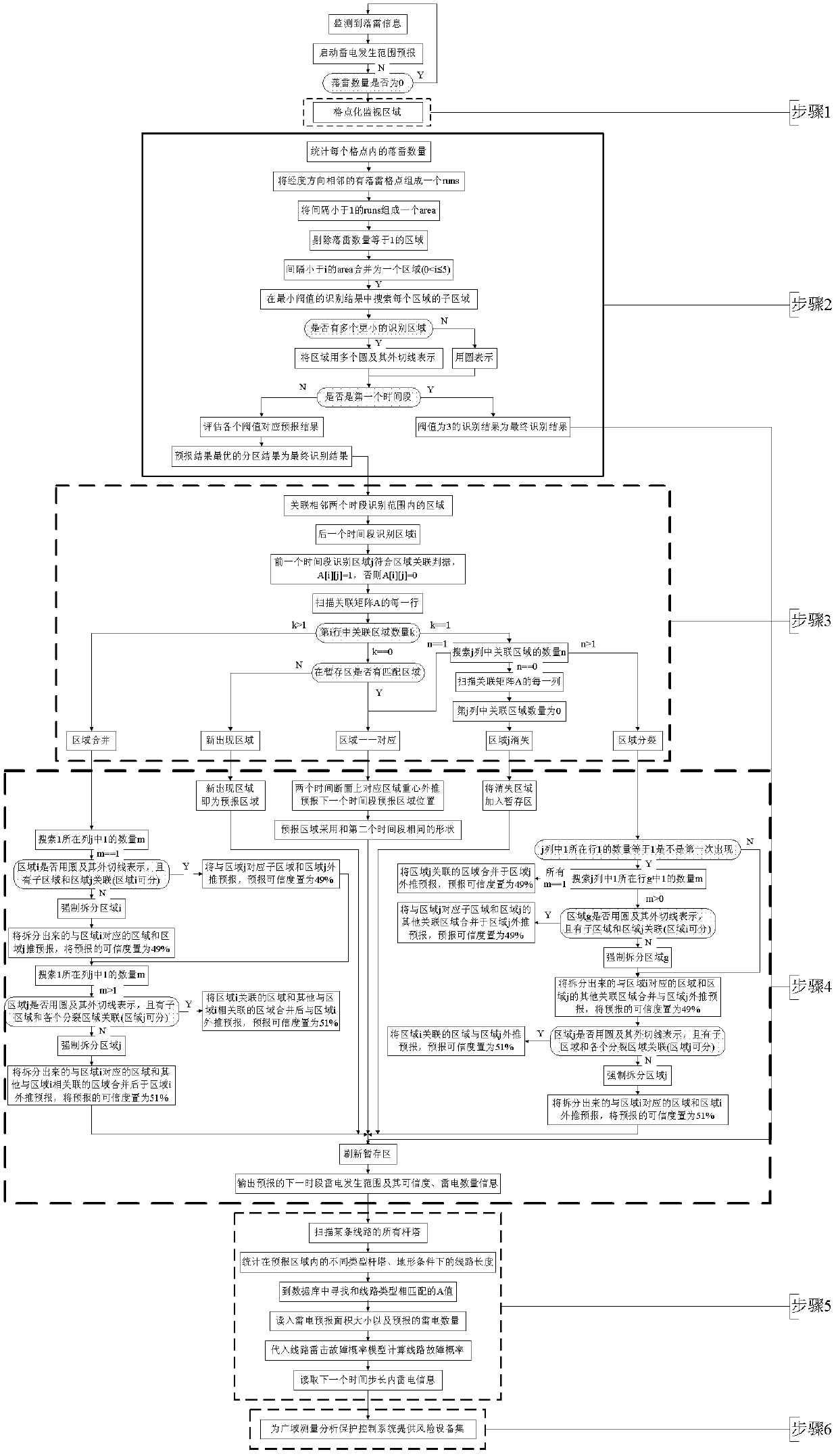

Measured lightning data-based transmission line failure probability evaluation method

The invention discloses a measured lightning data-based transmission line failure probability evaluation method, and belongs to the technical field of power systems and automation thereof. The method comprises the following two steps of: (1) identifying a lightning occurrence range within a certain time period according to the measured lightning data of lightning occurrence time, occurrence positions, strength and the like which are measured, and predicting a lightning occurrence region in the next time step length and credibility thereof; and (2) calculating the lightning failure probability of each line by using a lightning failure probability formula according to real-time parameters of a line length in the predicted lightning occurrence region, the area of the predicted lighting occurrence region, thunderbolt density and the like. By the method, the line failure probability can be dynamically and adaptively evaluated according to changes in external weather conditions, so that the risks of lightning disasters can be early warned for the system; and the method is combined with a wide-area measurement analysis protection control system, so that the capability of the power system in withstanding the lightning disasters can be improved.

Owner:NARI TECH CO LTD +1

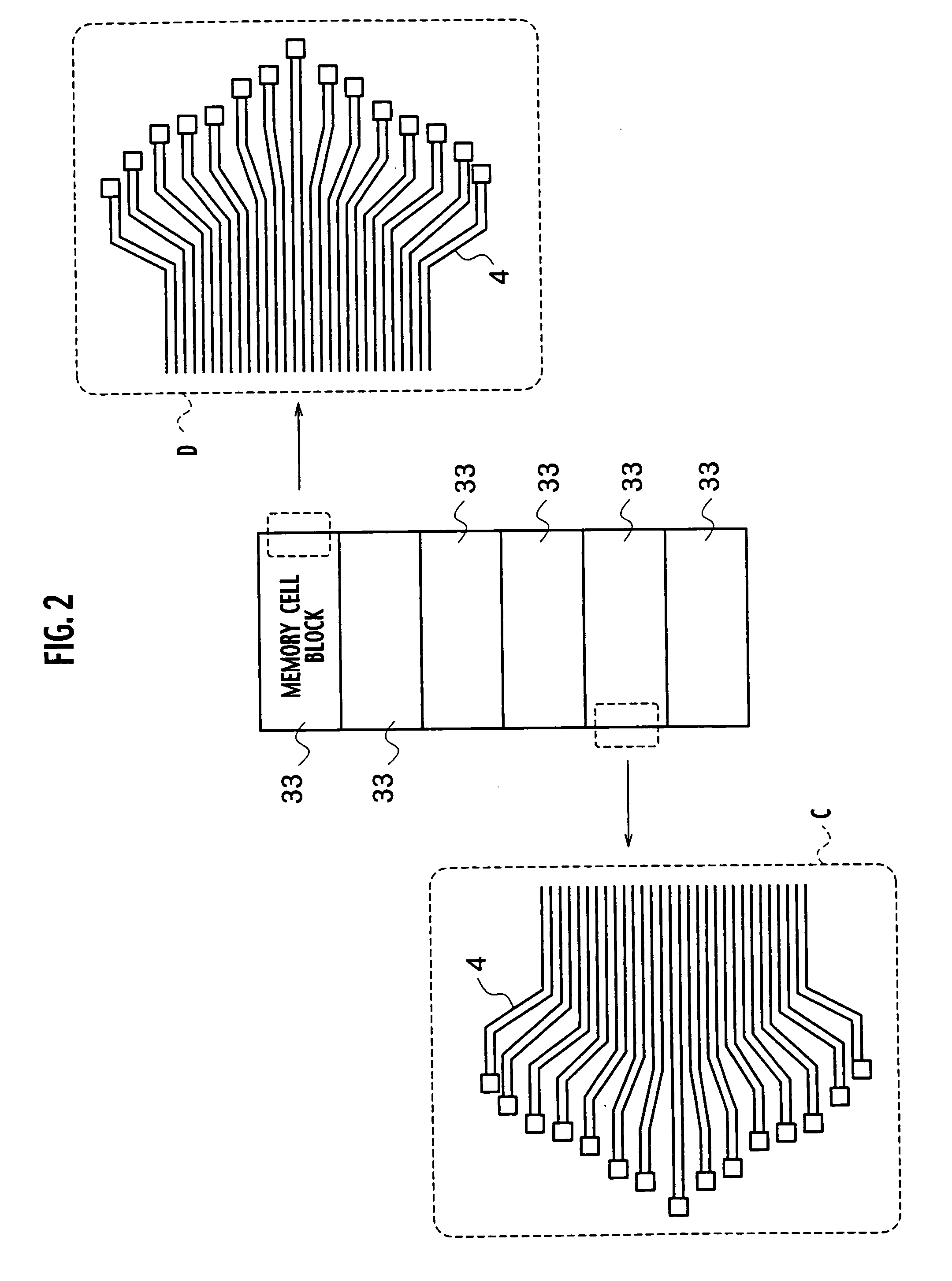

Semiconductor module including a plurality of IC chips therein

InactiveUS20070090534A1Adjustable lengthIncreasing thickness and costFinal product manufactureSemiconductor/solid-state device detailsMemory chipSemiconductor

A semiconductor module includes a driver IC chip and a plurality of memory IC chips on a common wiring board. Some of the memory IC chips nearer to the driver IC chip than the other memory IC chips are mounted on an interposer substrate mounted on the wiring board, providing a uniform line length among a species of signal lines for the memory IC chips.

Owner:RENESAS TECH CORP +2

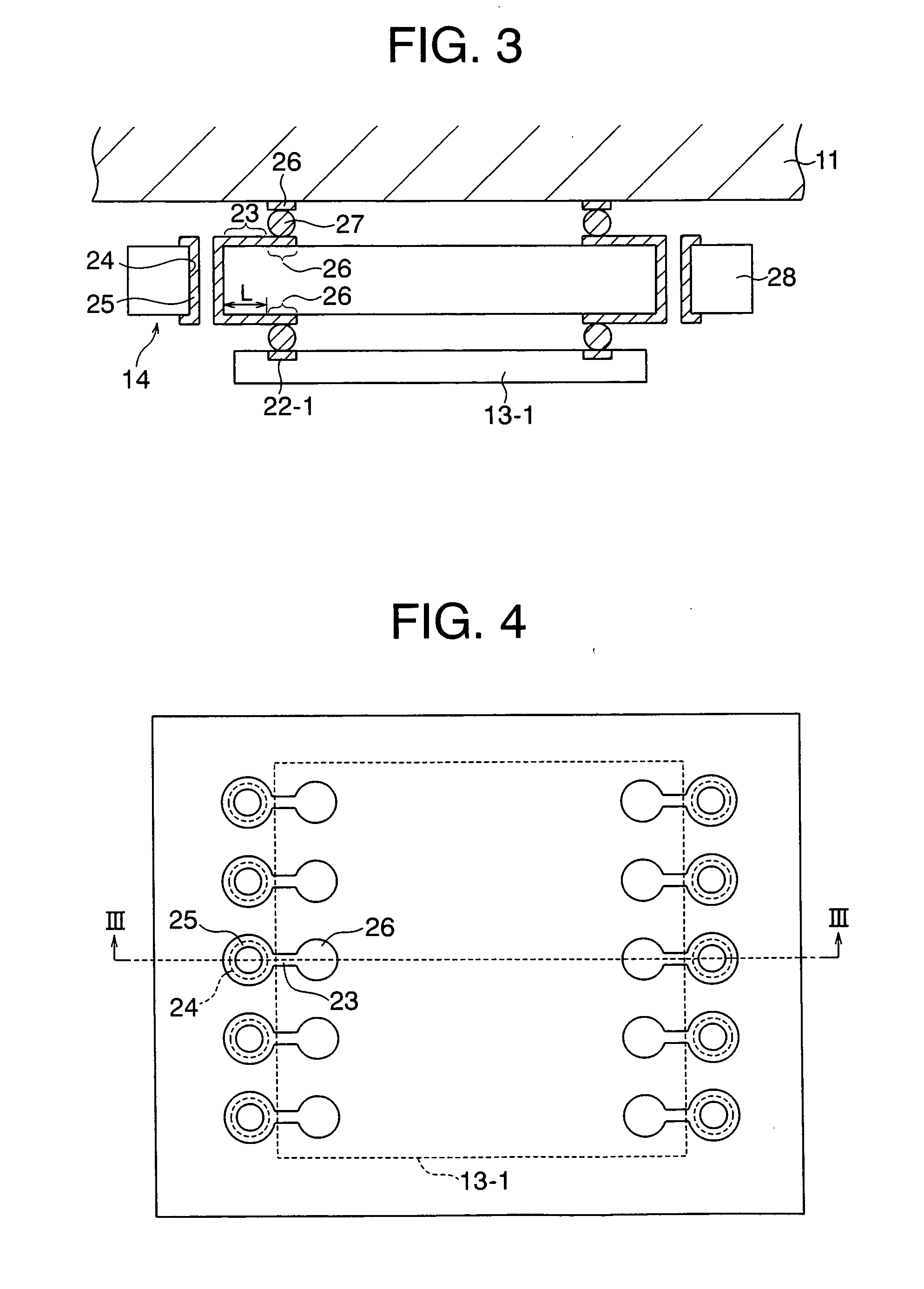

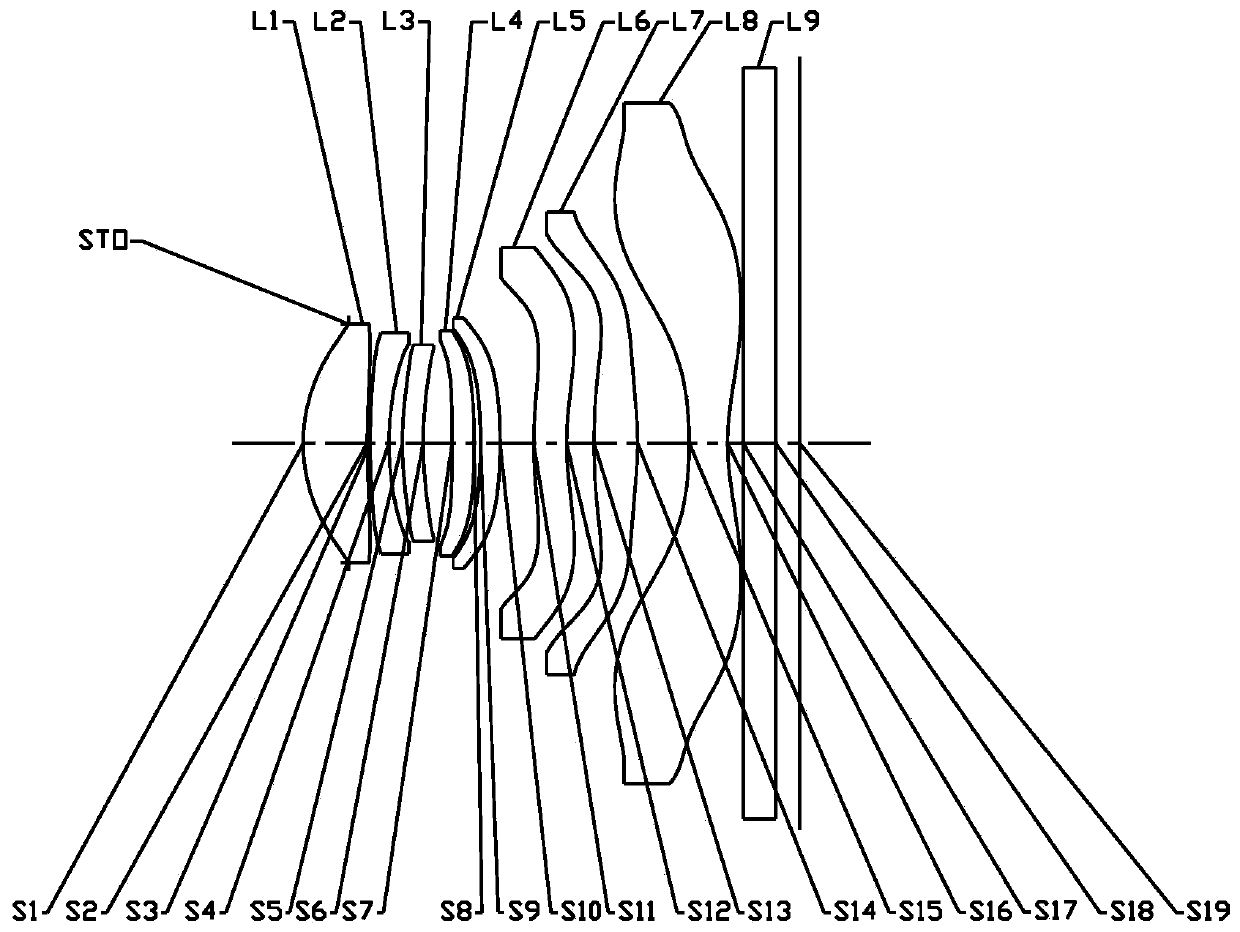

Camera lens group

The invention discloses a camera lens group. The camera lens group comprises a first lens with positive focal power, a second lens with focal power, a third lens with focal power, a fourth lens with focal power, a fifth lens with focal power, a sixth lens with focal power, a seventh lens with focal power and an eighth lens with focal power along the optical axis from the object side to the image side in sequence, wherein the image side surface of the sixth lens is a concave surface; the image side surface of the seventh lens is a convex surface. A half of diagonal line length ImgH in the effective pixel region on the imaging surface of the camera lens group and F number Fno of the camera lens group meet the condition that ImgH / Fno is larger than 3.5 mm.

Owner:ZHEJIANG SUNNY OPTICAL CO LTD