A time sequence repairing method based on time headroom

A repair method and timing technology, applied in the direction of instrumentation, calculation, electrical digital data processing, etc., can solve unreasonable problems, achieve the effect of reducing design area, increasing operating frequency, and optimizing line network delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The technical solutions in the embodiments of the present invention will be described in detail below with reference to the drawings in the embodiments of the present invention. It should be understood that the specific embodiments described below are only used to explain the present invention, not to limit the present invention.

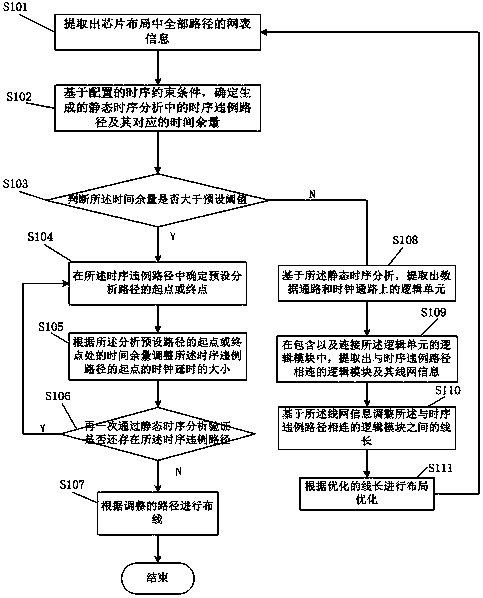

[0024] The principle of the solution of the present invention is to implement corresponding processing methods according to different time margin slack, because when the absolute value of time margin slack exceeds a certain threshold, it is no longer possible to repair the timing by constraining the clock path, only by modifying The layout of the chip is to reduce the absolute value of the time margin slack, and then the timing is repaired by constraining the clock path. To this end, an embodiment of the present invention provides a timing repair method based on a time margin, such as figure 1 As shown, the detailed steps are as follows:

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More