Patents

Literature

711results about How to "High hole mobility" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

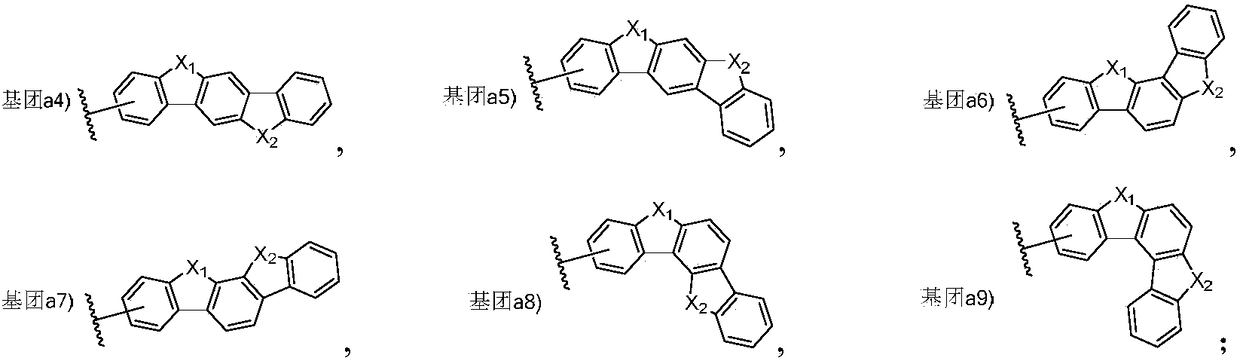

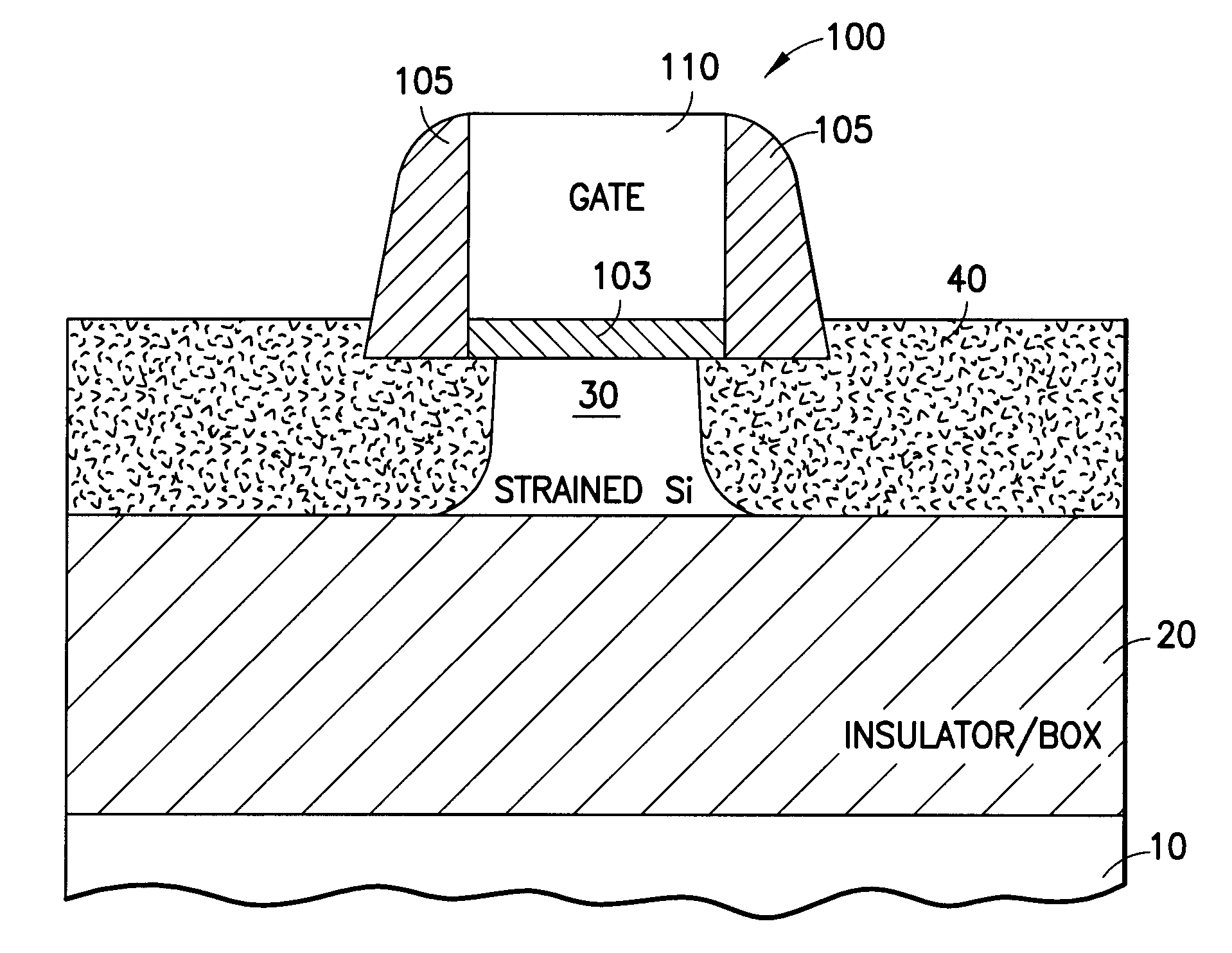

High mobility heterojunction complementary field effect transistors and methods thereof

ActiveUS20050093021A1Minimal toleranceHigh hole mobilityTransistorSolid-state devicesHeterojunctionCMOS

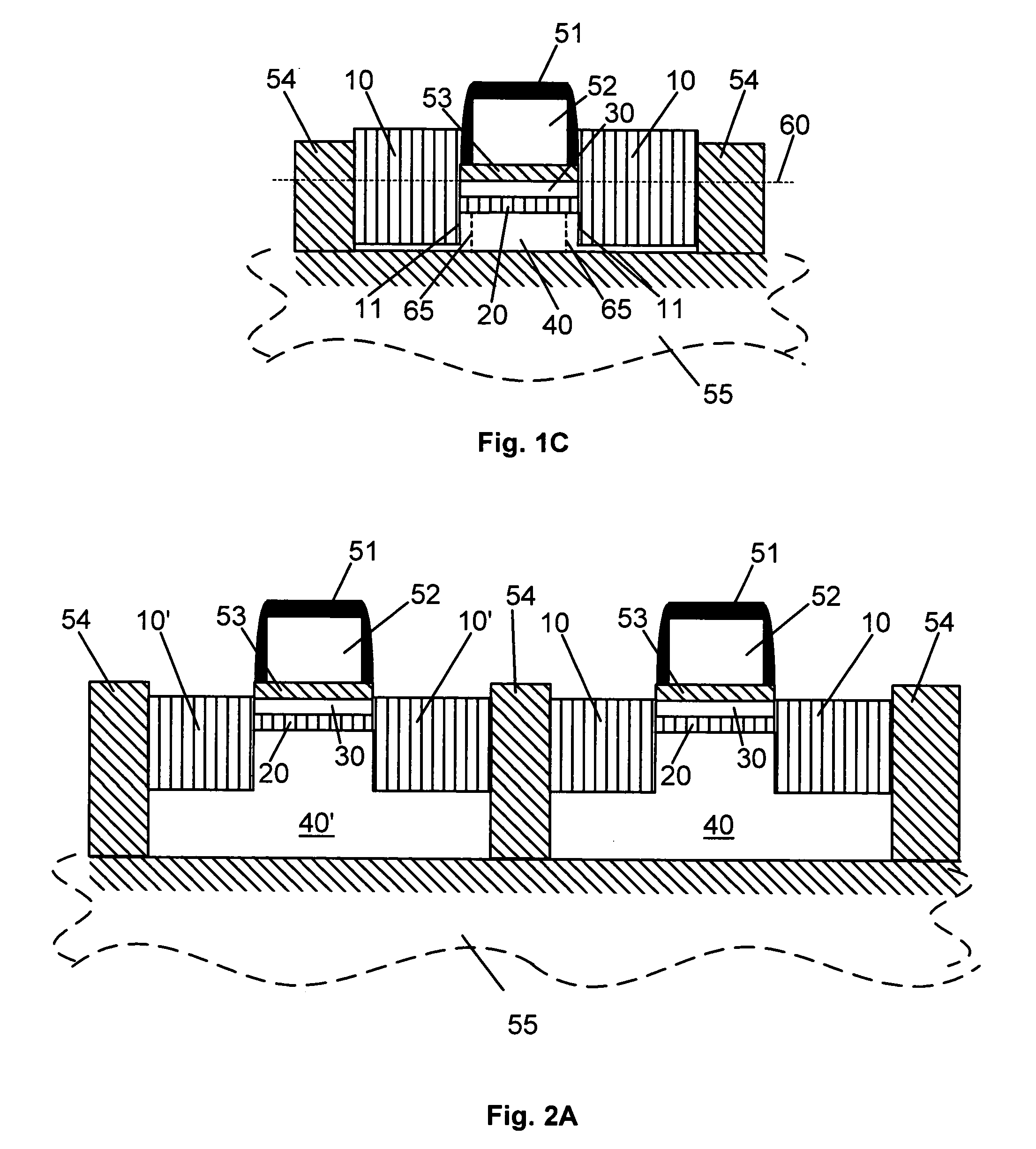

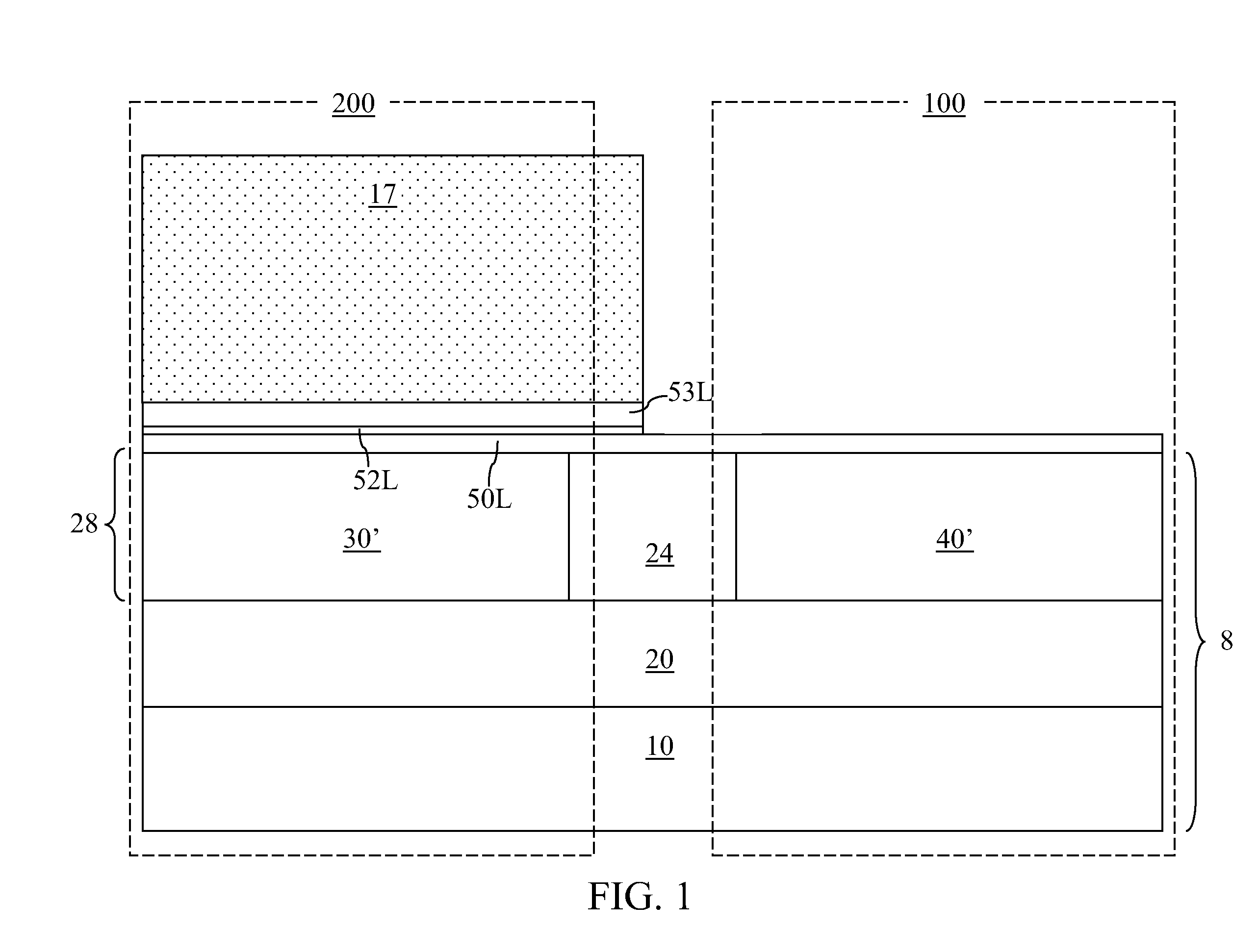

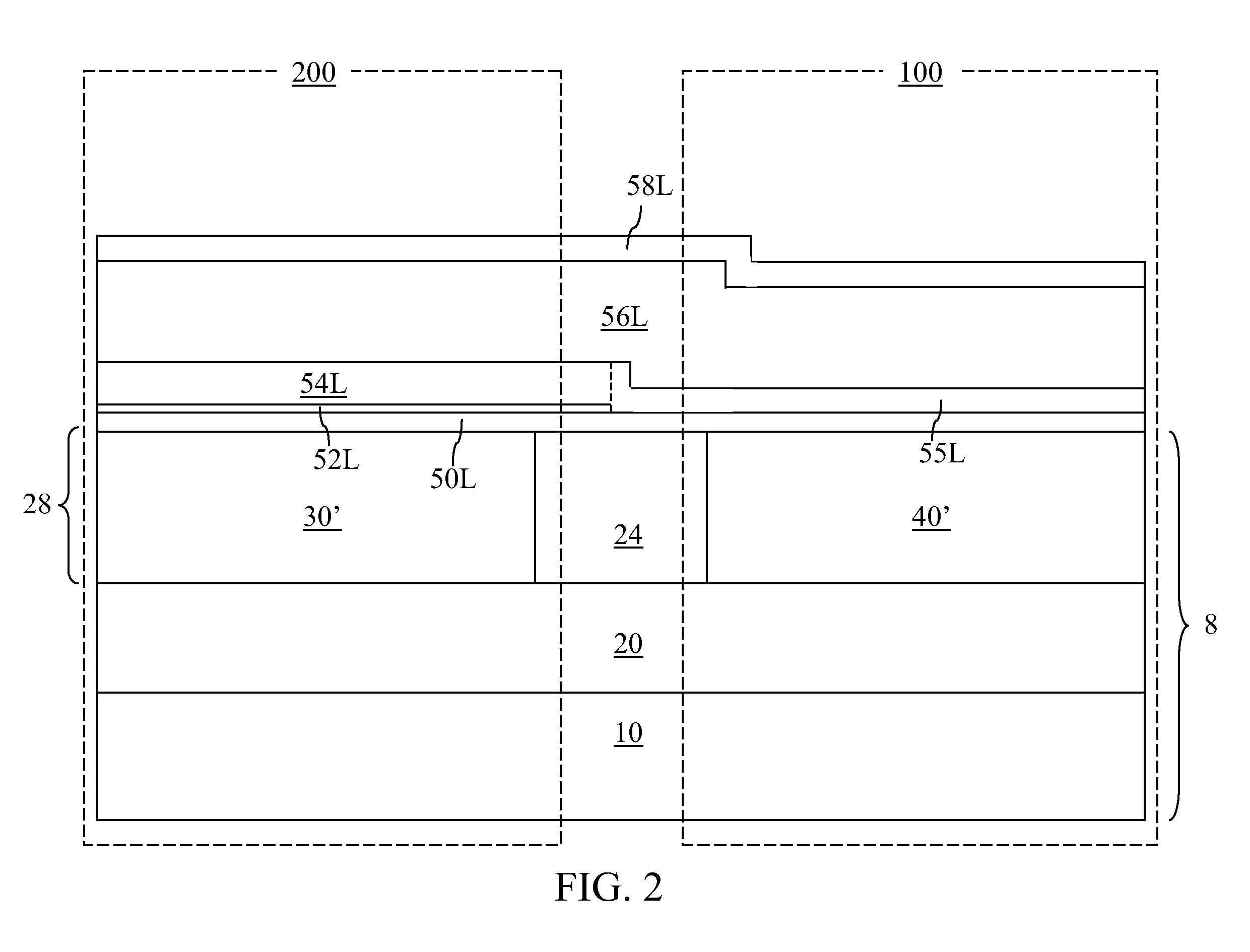

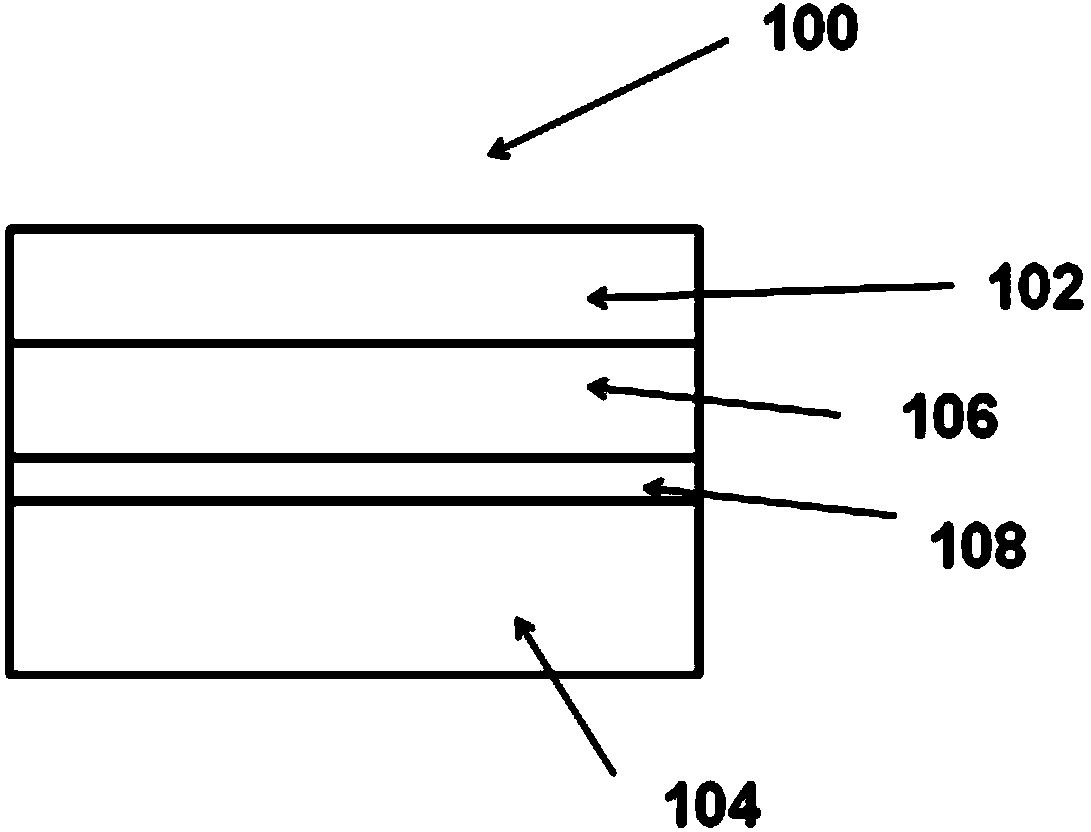

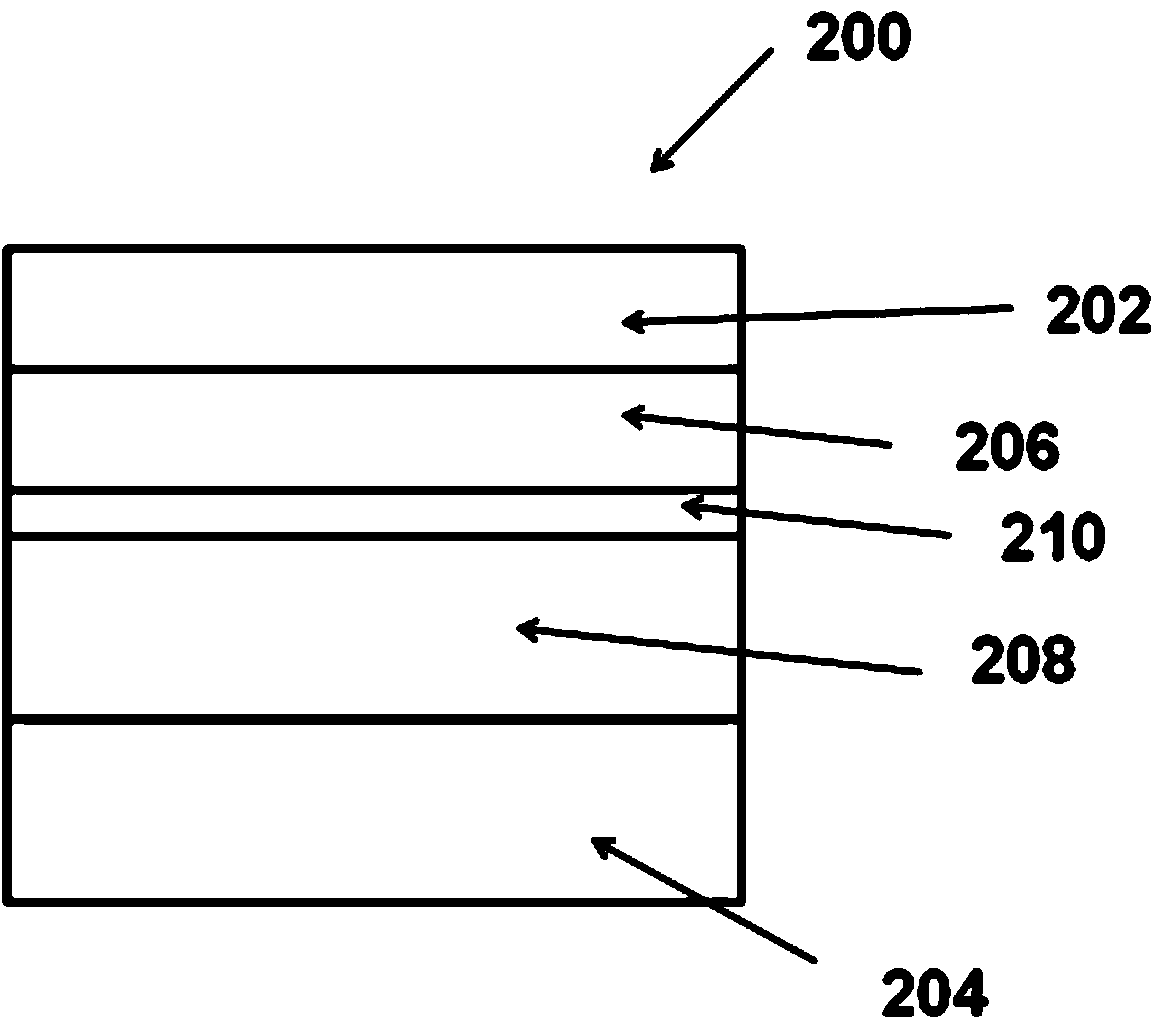

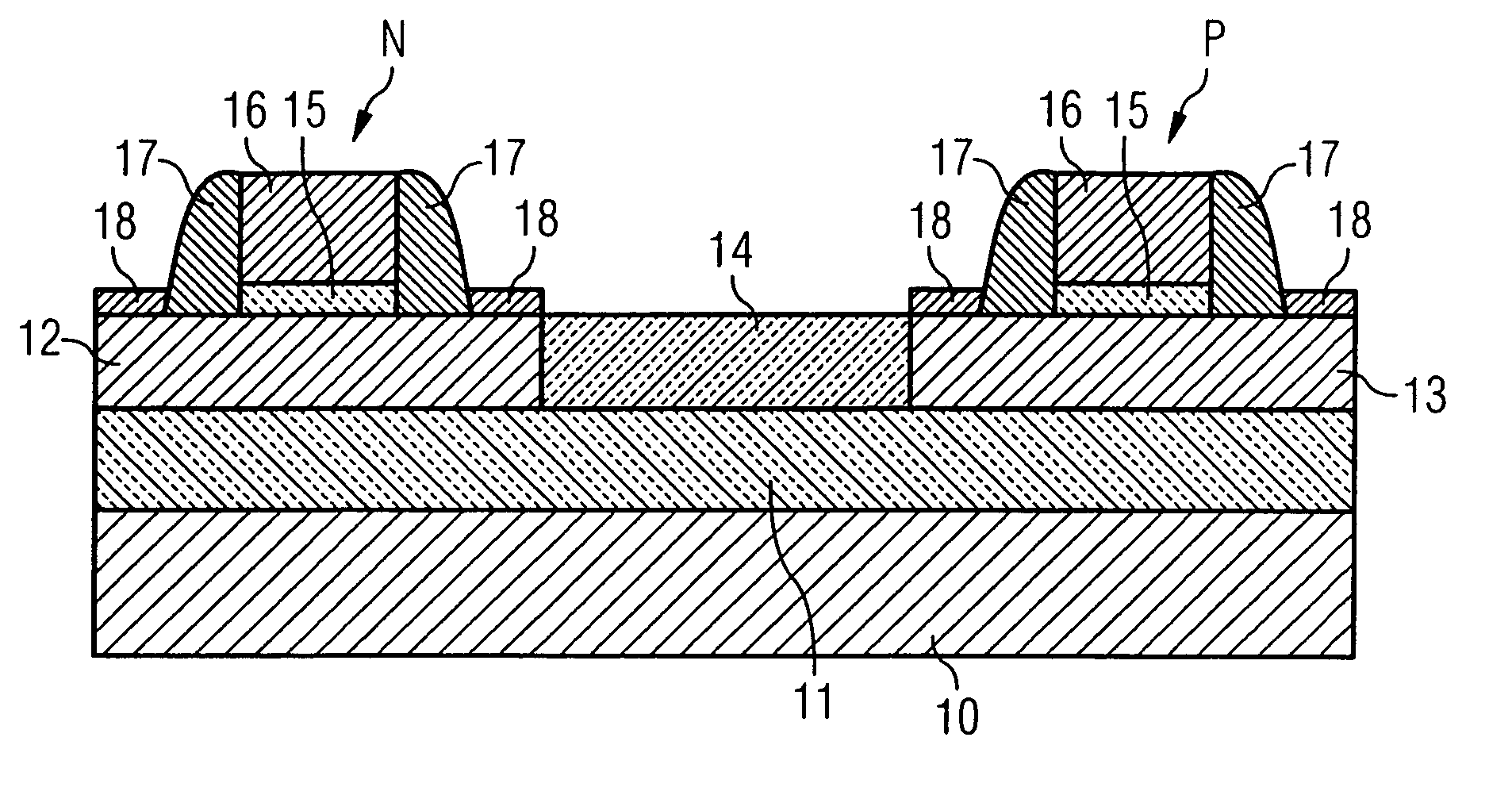

A structure, and method of fabrication, for high performance field effect devices is disclosed. The MOS structures include a crystalline Si body of one conductivity type, a strained SiGe layer epitaxially grown on the Si body serving as a buried channel for holes, a Si layer epitaxially grown on the SiGe layer serving as a surface channel for electrons, and a source and a drain containing an epitaxially deposited, strained SiGe of opposing conductivity type than the Si body. The SiGe source / drain forms a heterojunction and a metallurgical junction with the Si body that coincide with each other with a tolerance of less than about 10 nm, and preferably less than about 5 nm. The heterostructure source / drain is instrumental in reducing short channel effects. These structures are especially advantageous for PMOS due to increased hole mobility in the compressively strained SiGe channel. Representative embodiments include CMOS structures on bulk and on SOI.

Owner:GLOBALFOUNDRIES US INC

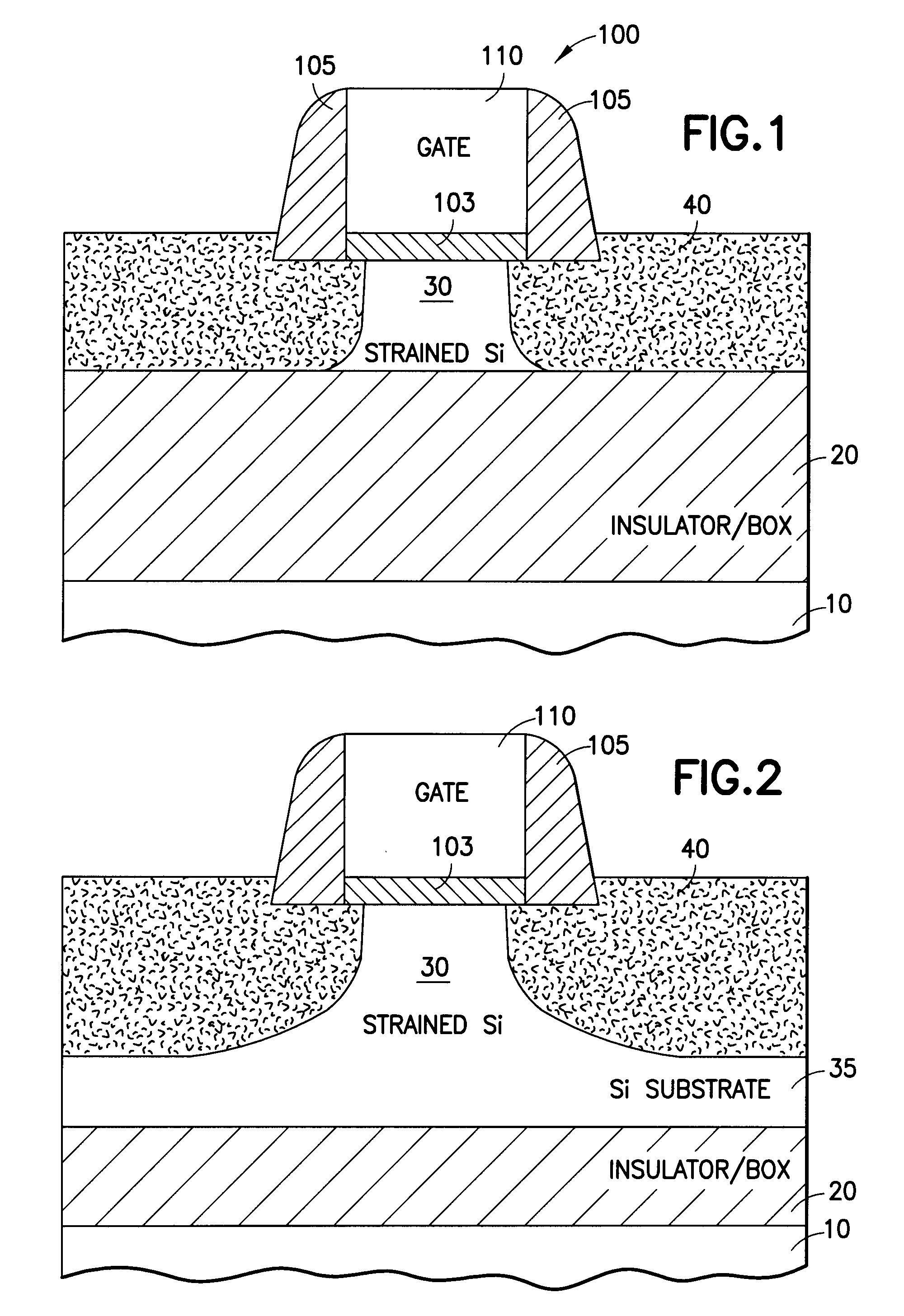

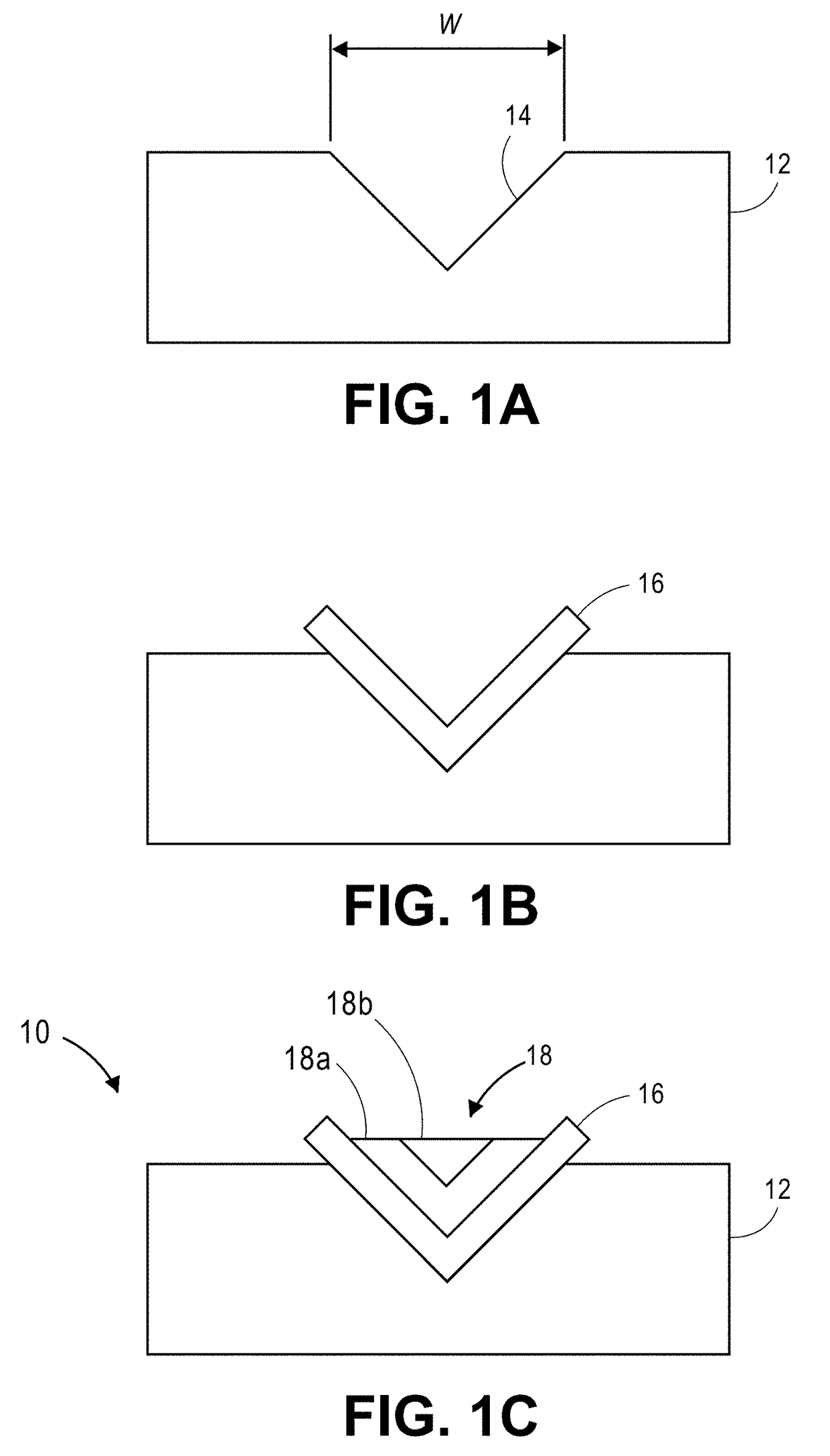

High mobility heterojunction complementary field effect transistors and methods thereof

InactiveUS7057216B2High hole mobilitySimilar current carrying capabilityTransistorSolid-state devicesHeterojunctionPresent day

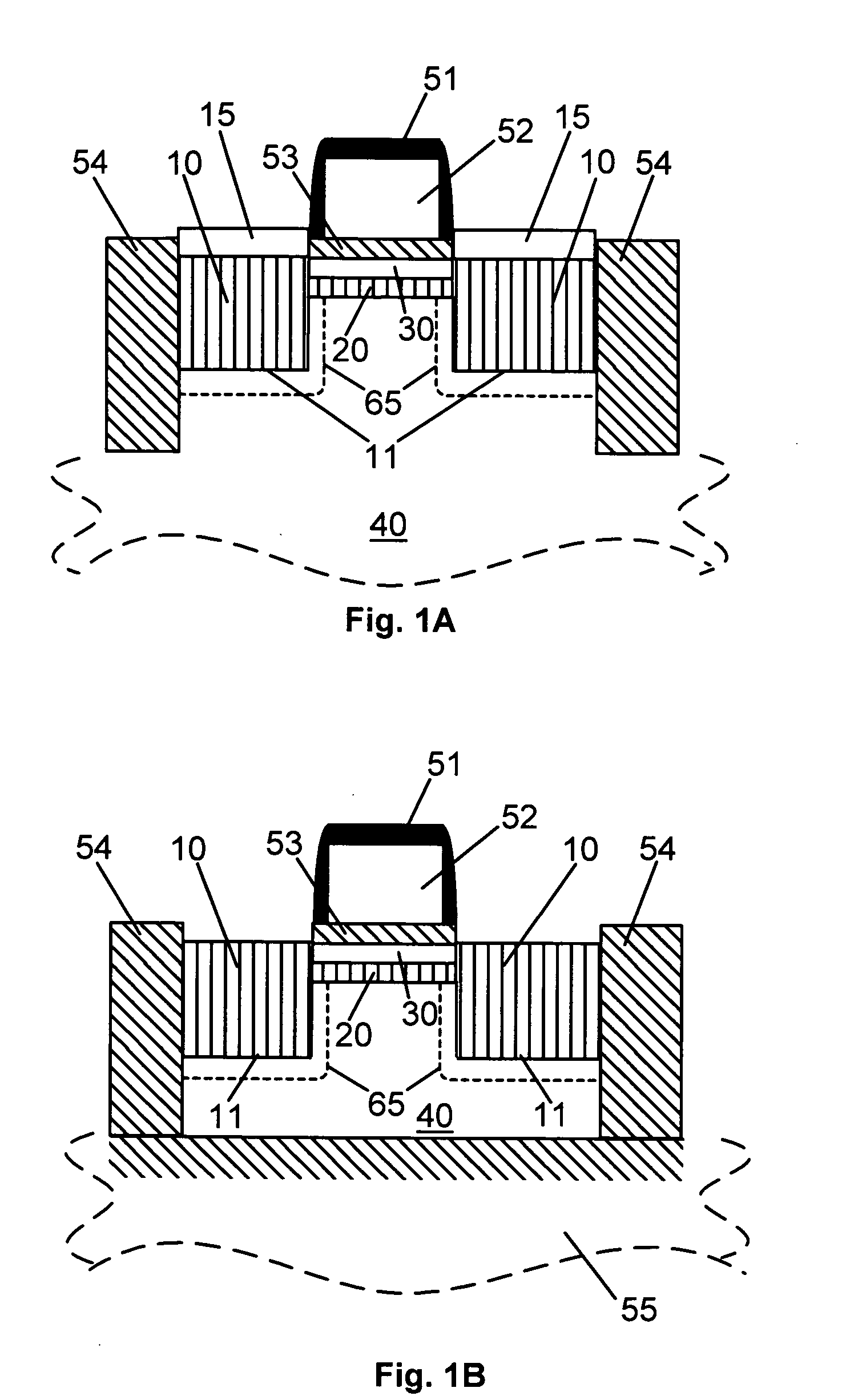

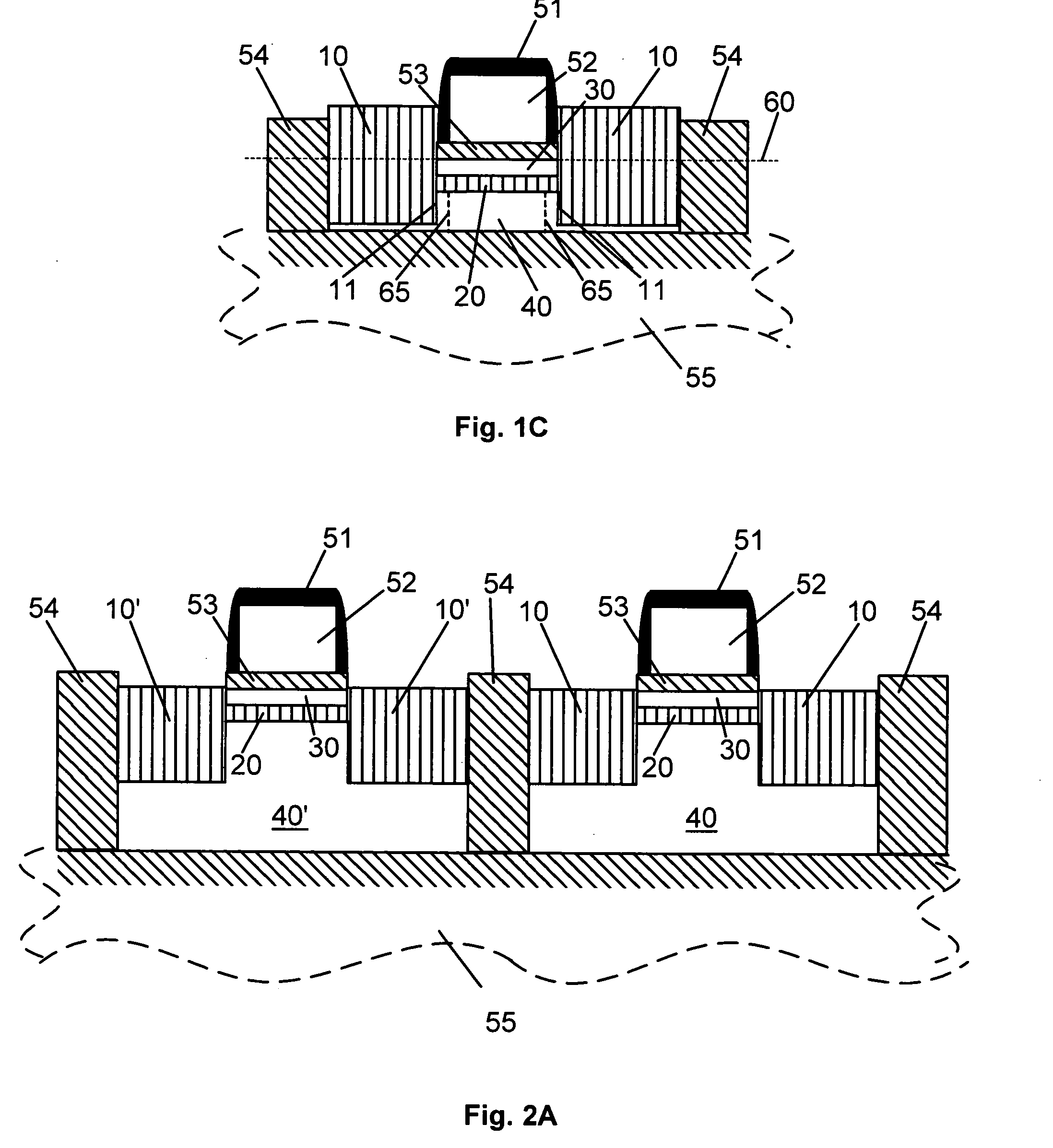

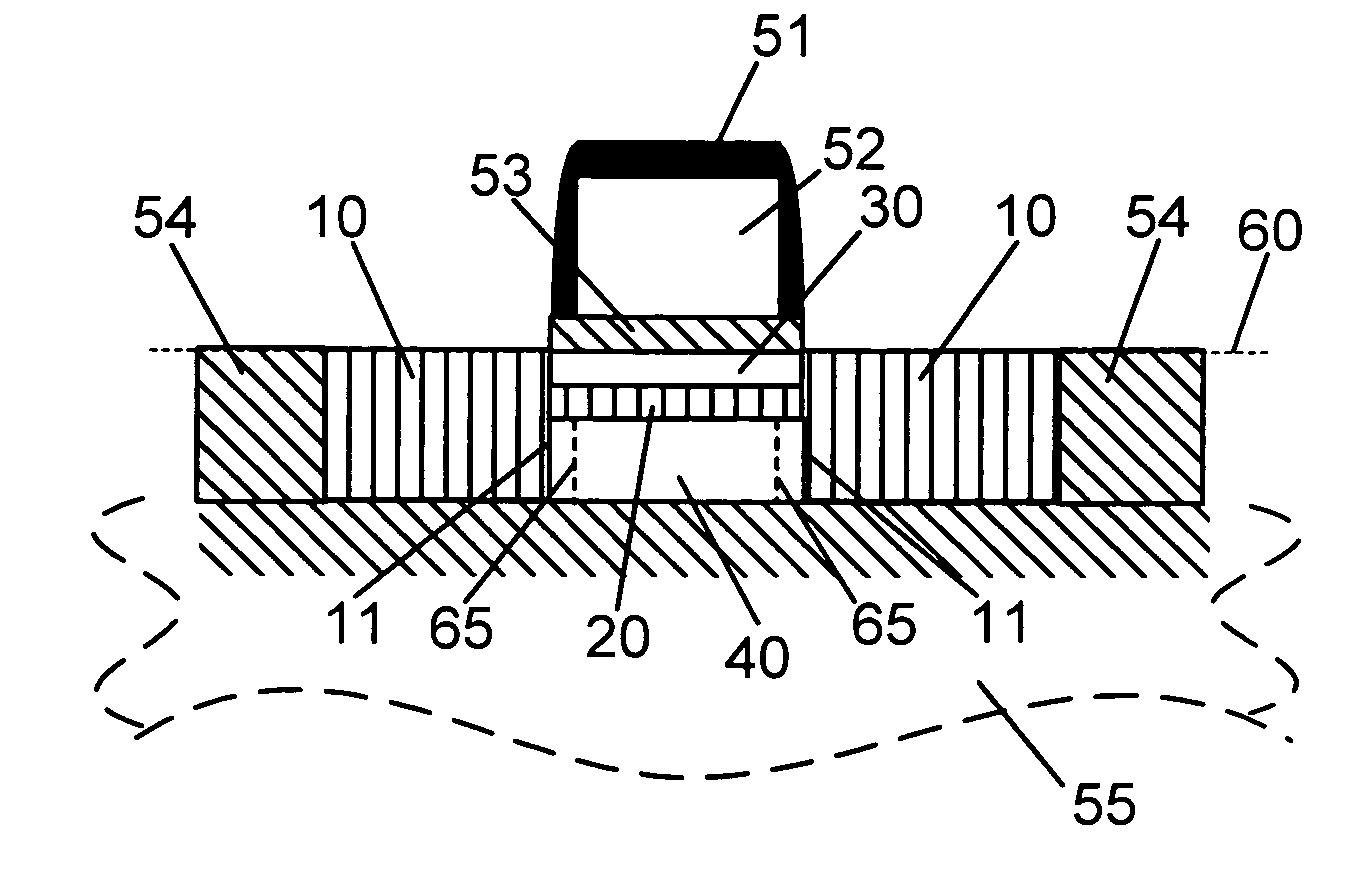

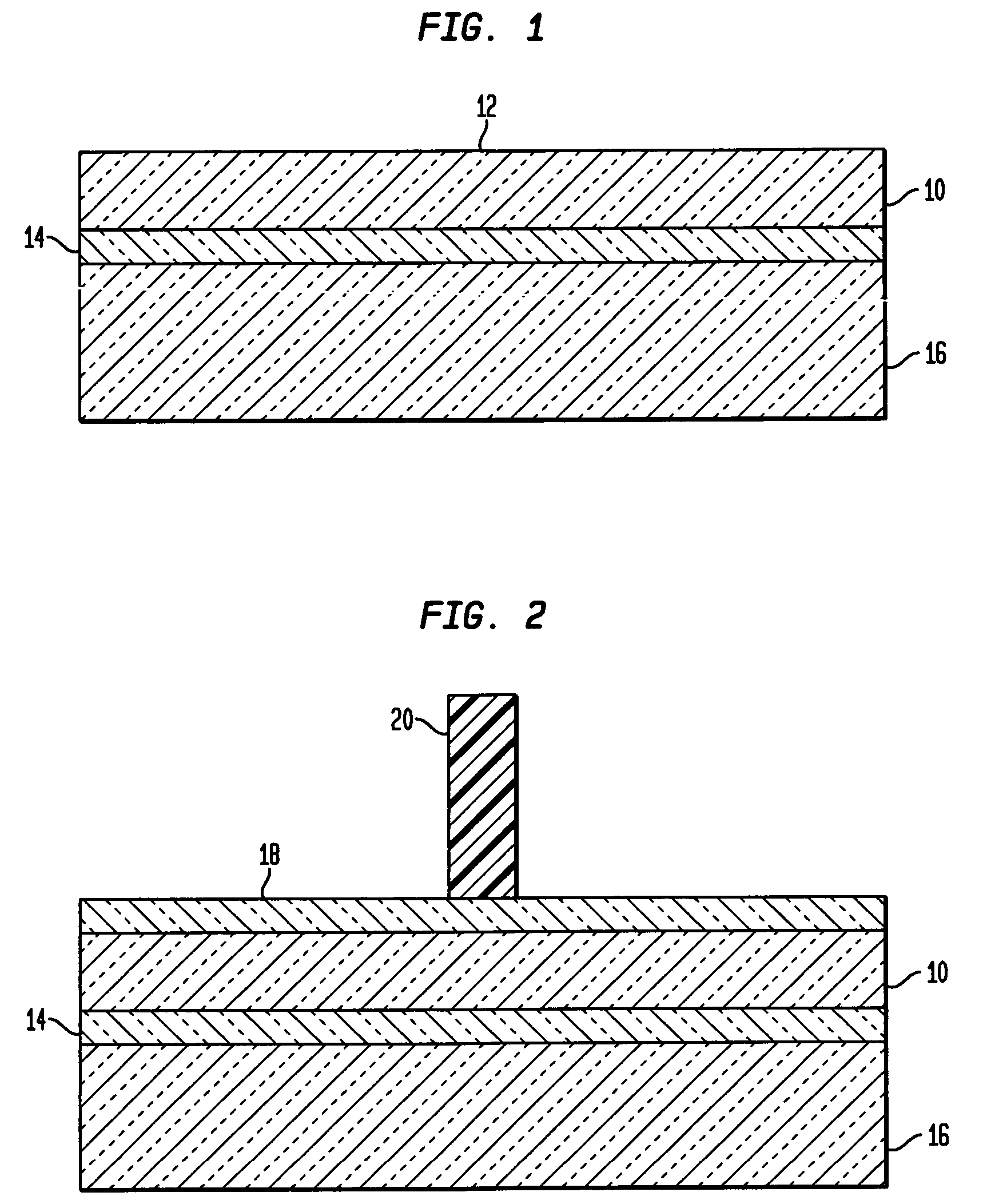

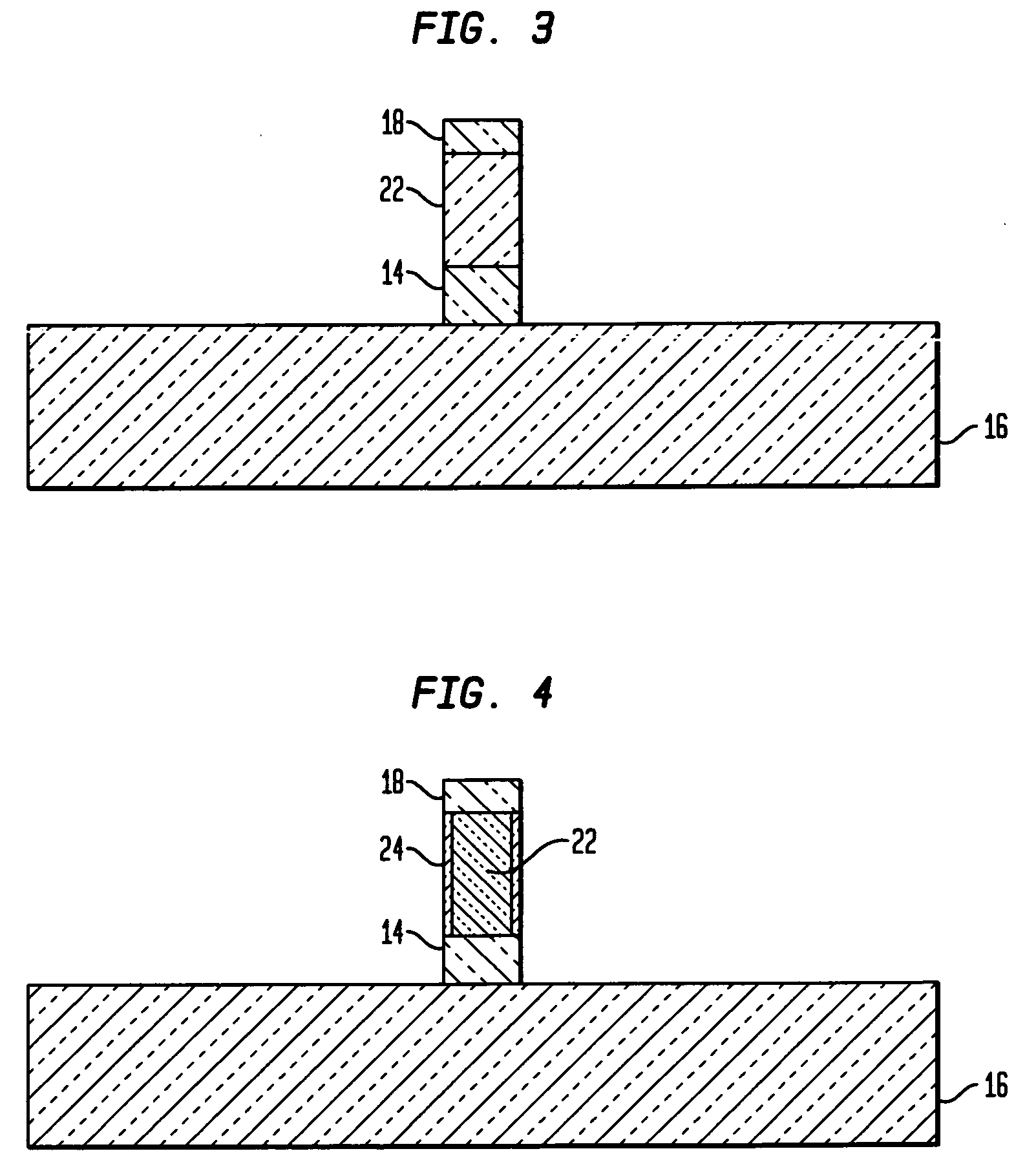

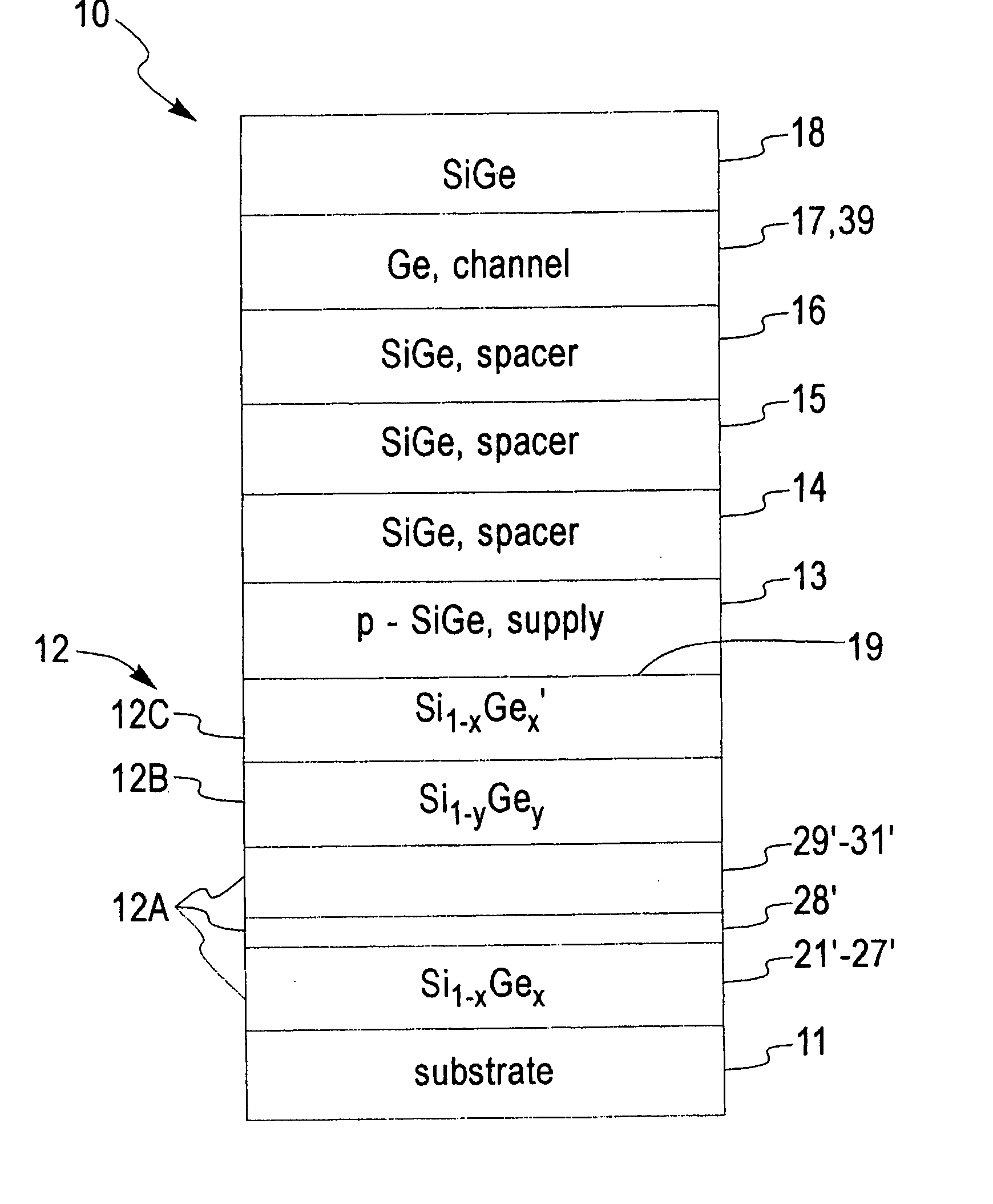

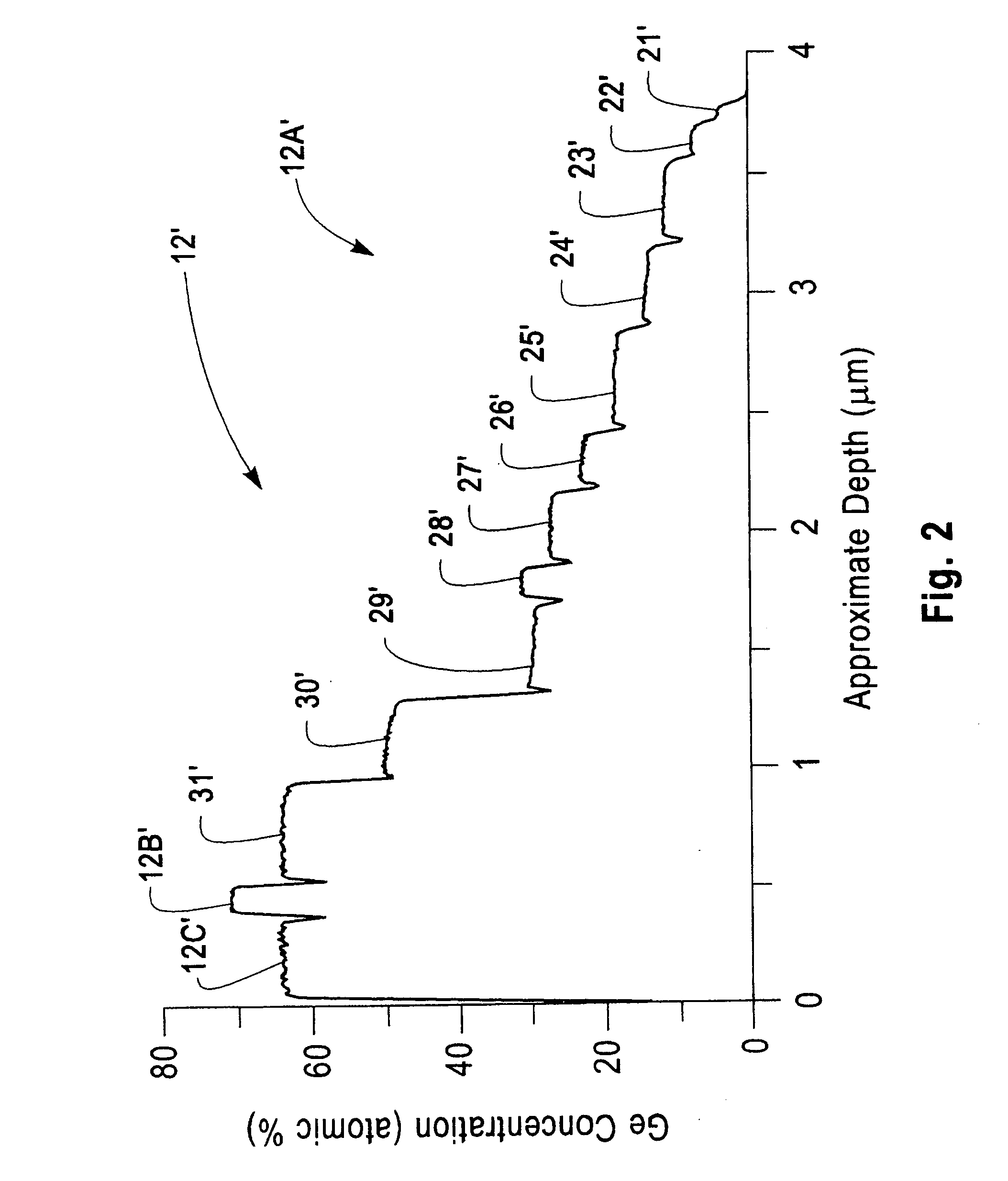

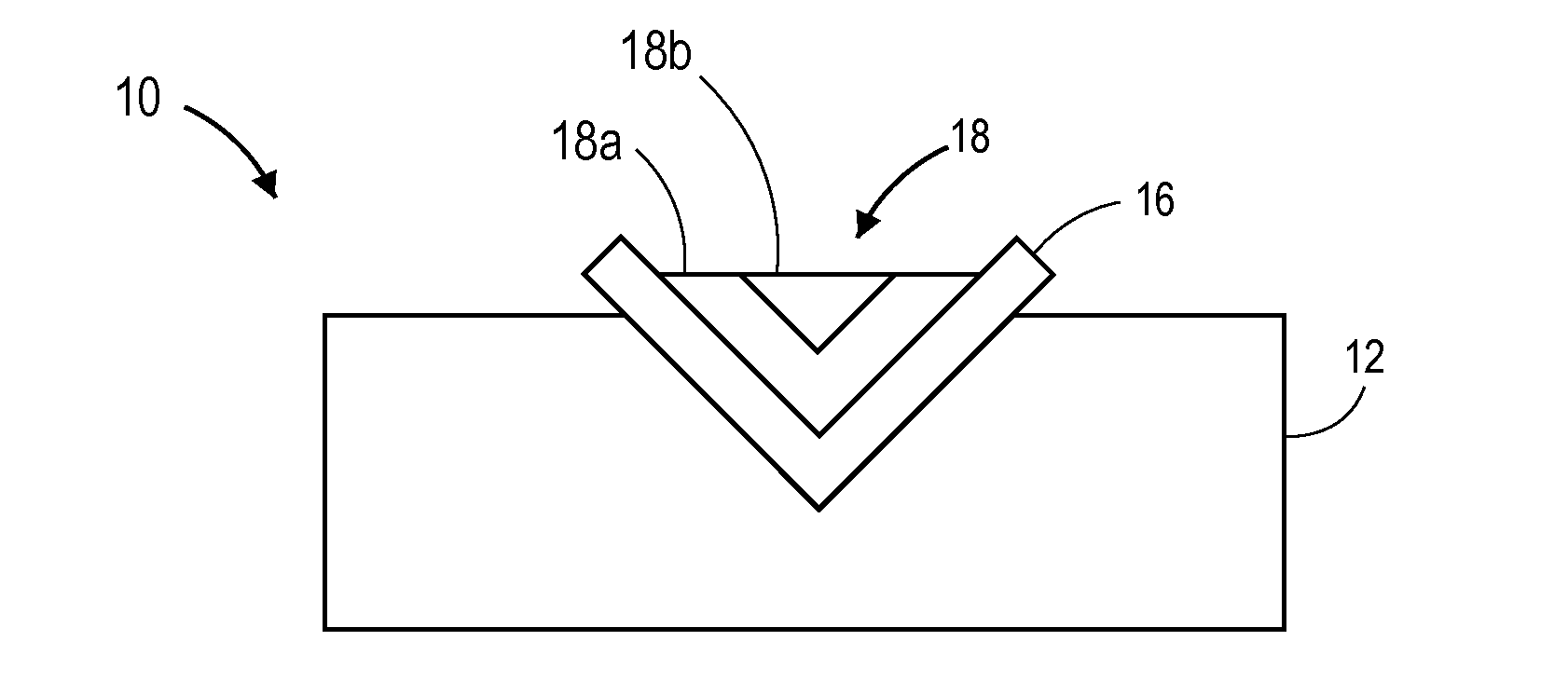

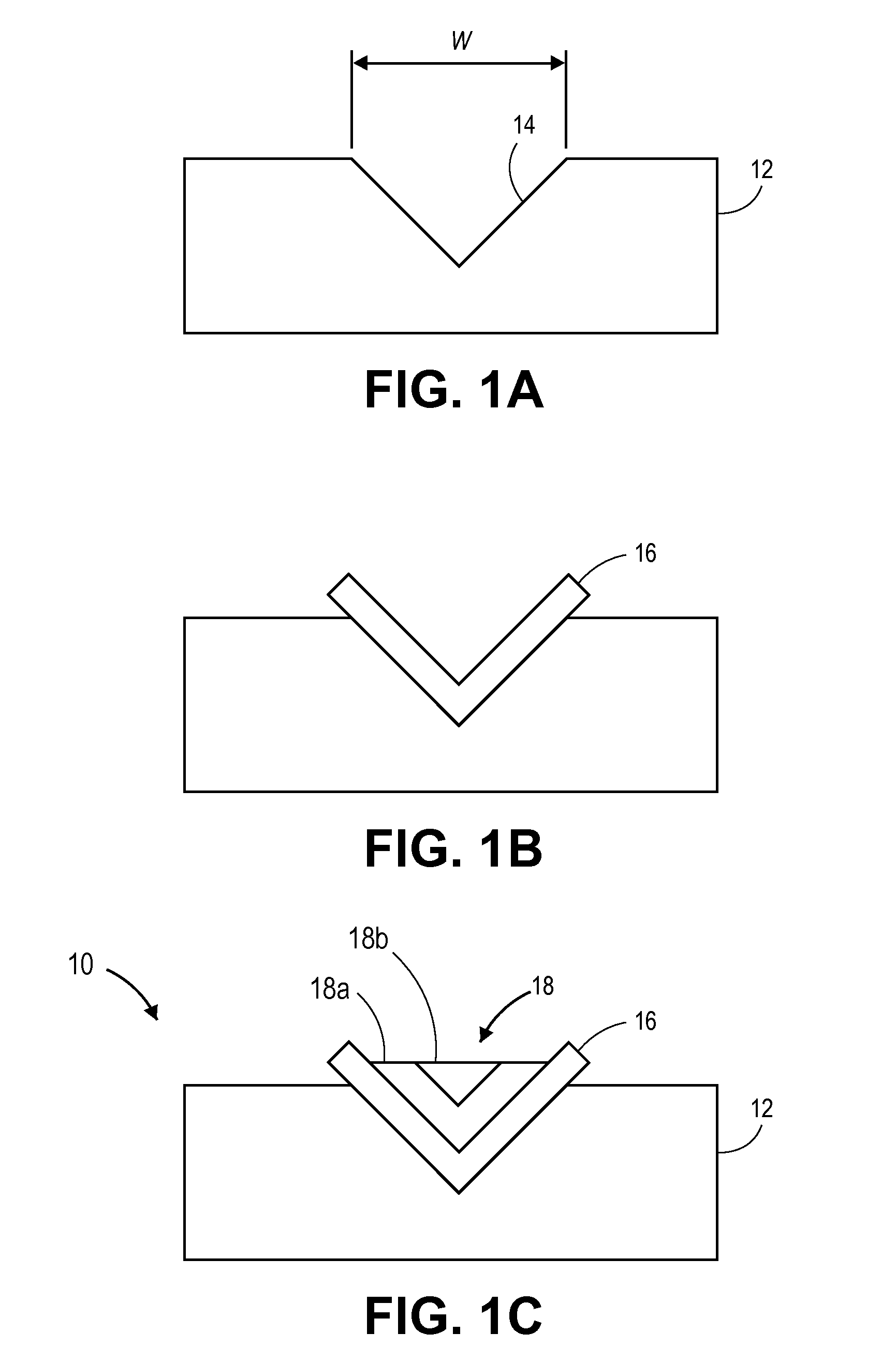

In all representative embodiments presented, the Ge concentration in the source and drain 10 and the SiGe epitaxial channel layer 20 is in the 15% to 50% range, preferably between about 20% to 40%. The SiGe thicknesses in the source / drain 10 are staying below the critical thickness for the given Ge concentration. The critical thickness is defined such that above it the SiGe will relax and defects and dislocations will form. The thickness of the SiGe epitaxial layer 20 typically is between about 5nm and 15nm. The thickness of the epitaxial Si layer 30 is typically between about 5nm and 15nm. FIG. 1A shows an embodiment where the body is bulk Si. These type of devices are the most common devices in present day microelectronics. FIGS. 1B and 1C show representative embodiment of the heterojunction source / drain FET device when the Si body 40 is disposed on top of an insulating material 55. This type of technology is commonly referred to as silicon on insulator (SOI) technology. The insulator material 55 usually, and preferably, is SiO2. FIG. 1B shows an SOI embodiment where the body 40 has enough volume to contain mobile charges. Such SOI devices are called partially depleted devices. FIG. 1C shows an SOI embodiment where the volume of the body 40 is insufficient to contain mobile charges. Such SOI devices are called fully depleted devices. For devices shown in FIG. 1B and 1C there is, at least a thin, layer of body underneath the source and drain 10. This body material serves as the seed material onto which the epitaxial SiGe source and drain 10 are grown. In an alternate embodiment, shown in FIG. 1D. for extremely thin fully depleted SOI devices, one could grow the source and drain 10 laterally, from a lateral seeding, in which case the source and drain 10 would penetrate all the way down to the insulating layer 55.

Owner:GLOBALFOUNDRIES US INC

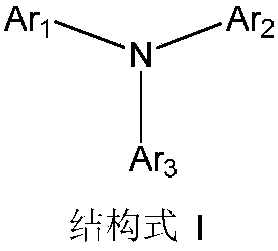

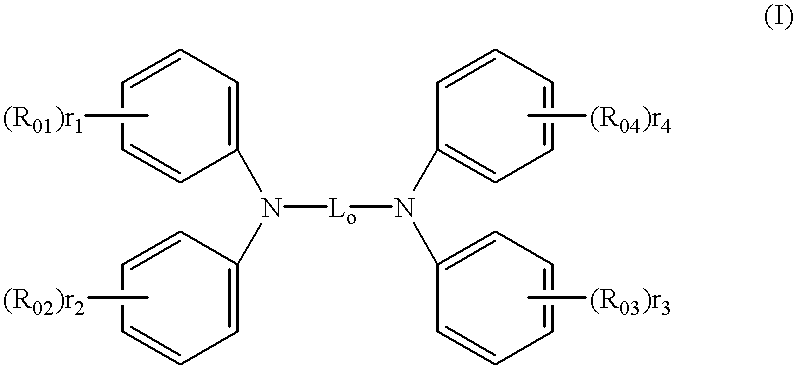

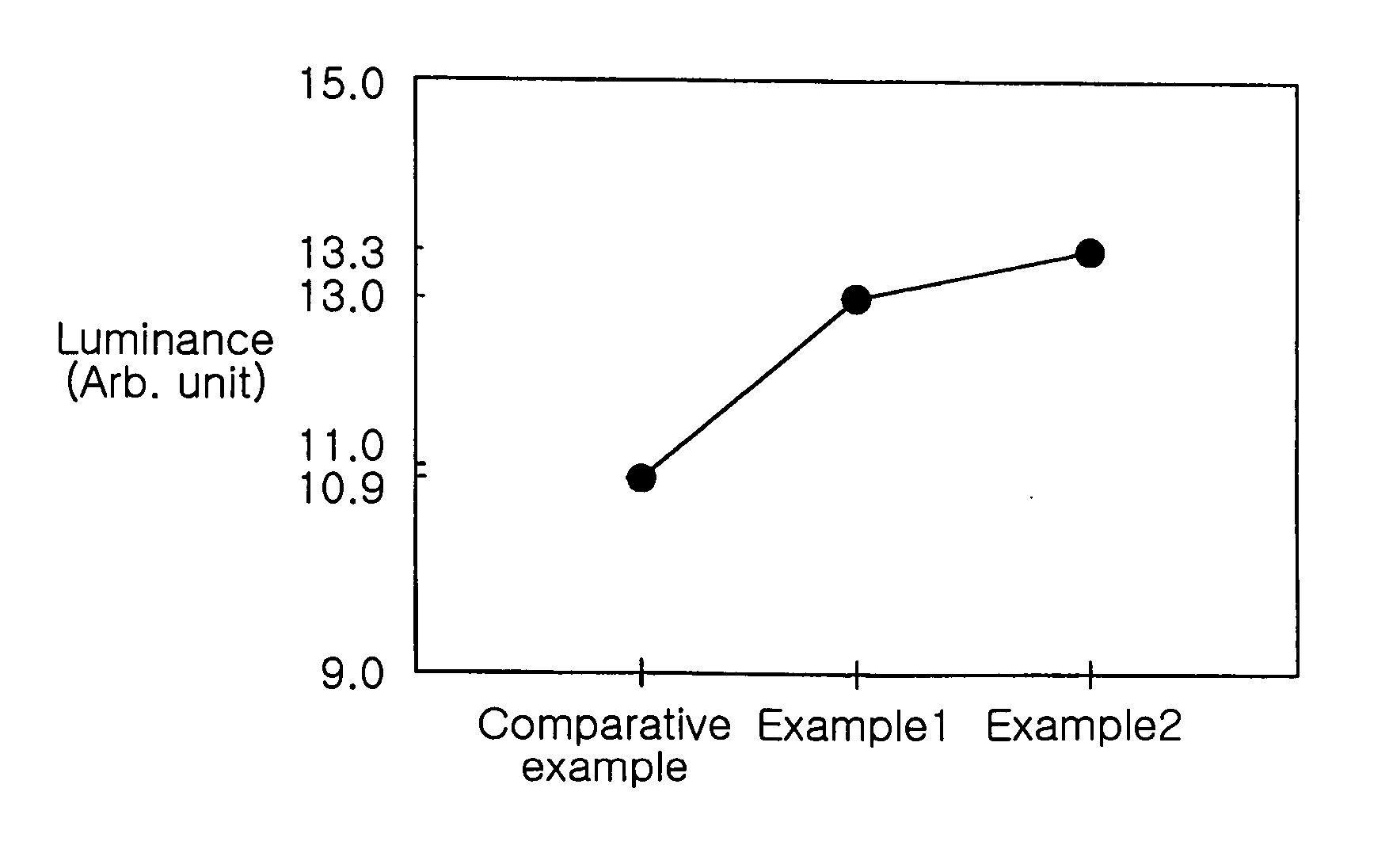

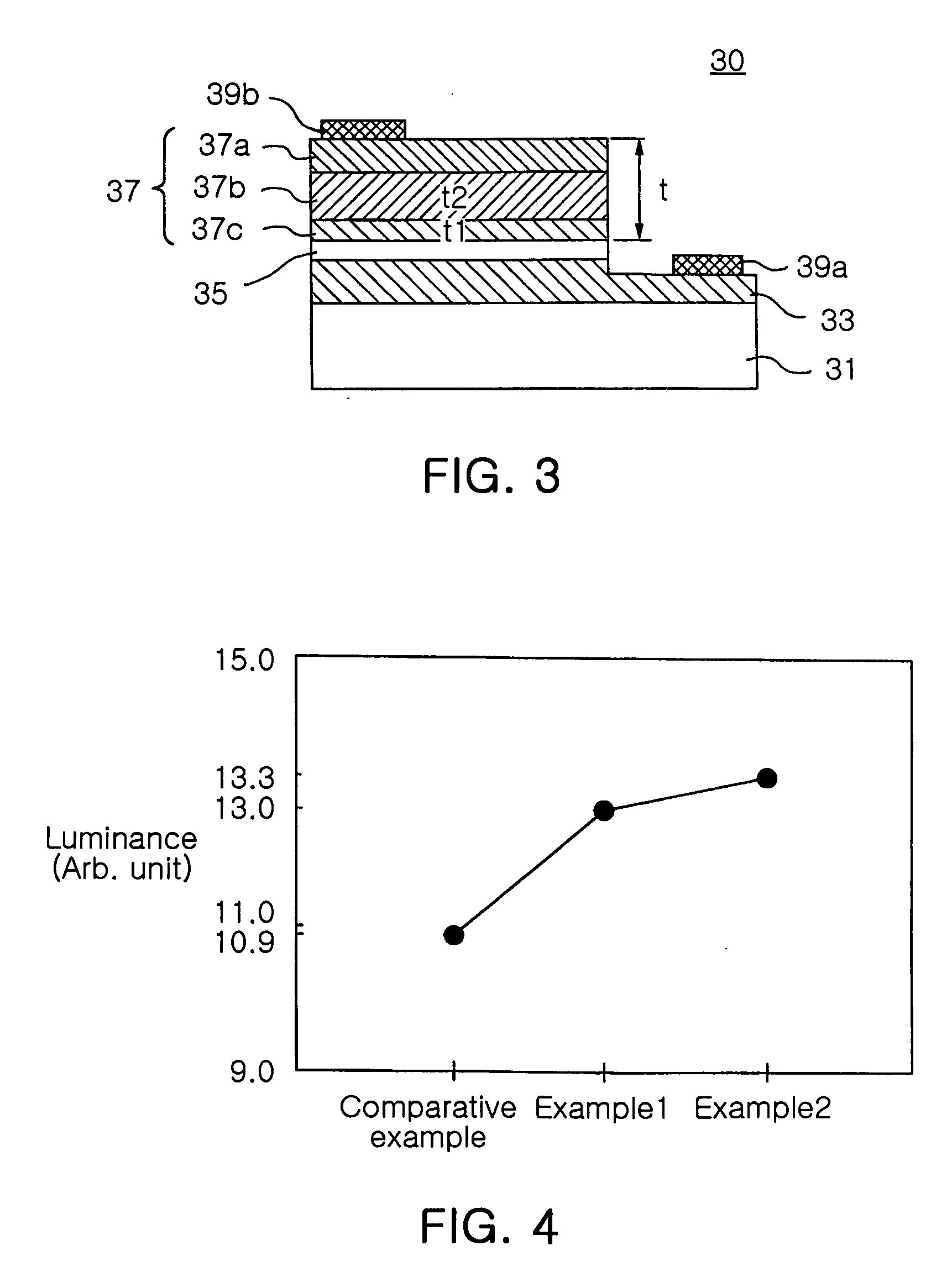

Organic electroluminescence device and phenylenediamine derivative

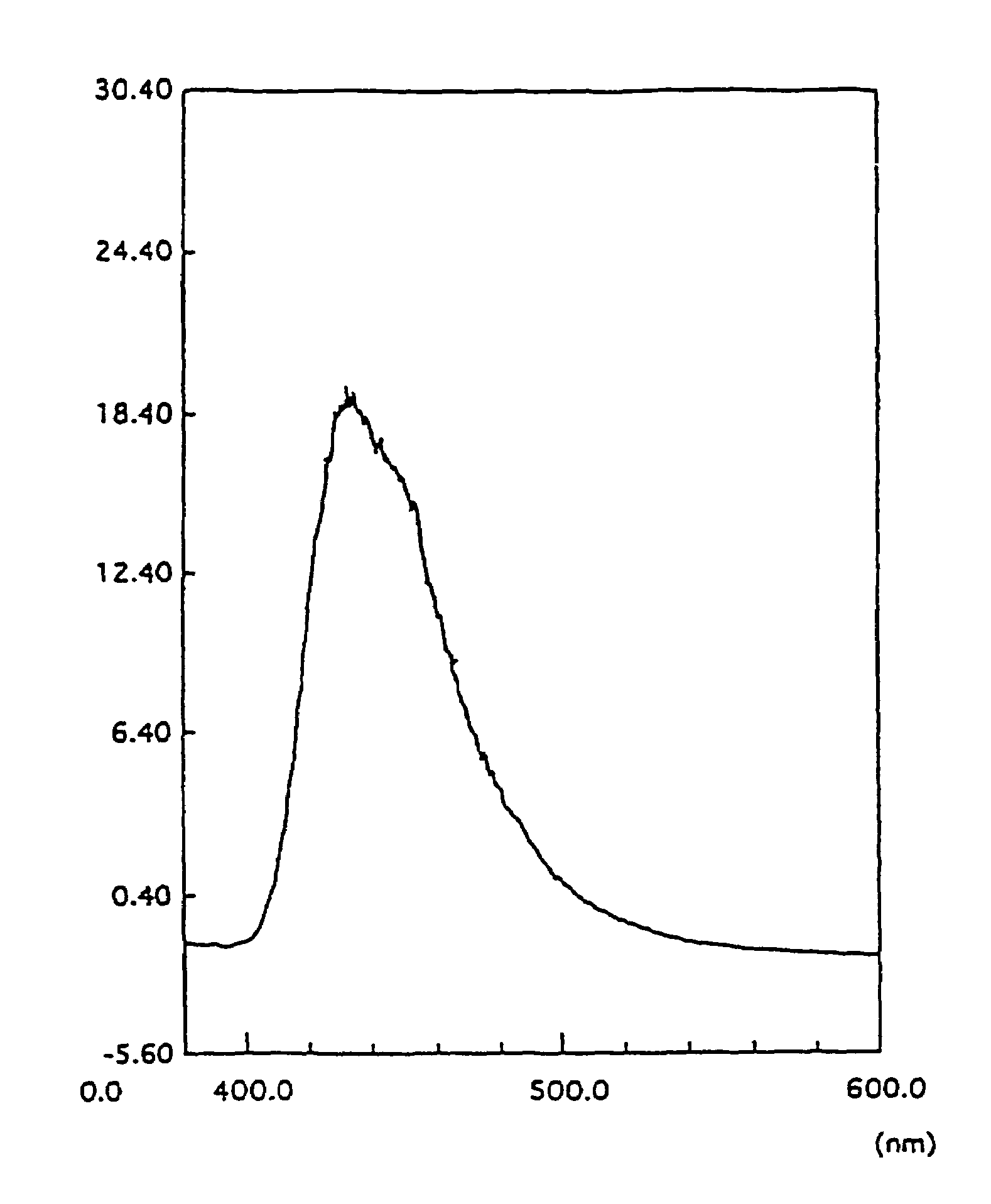

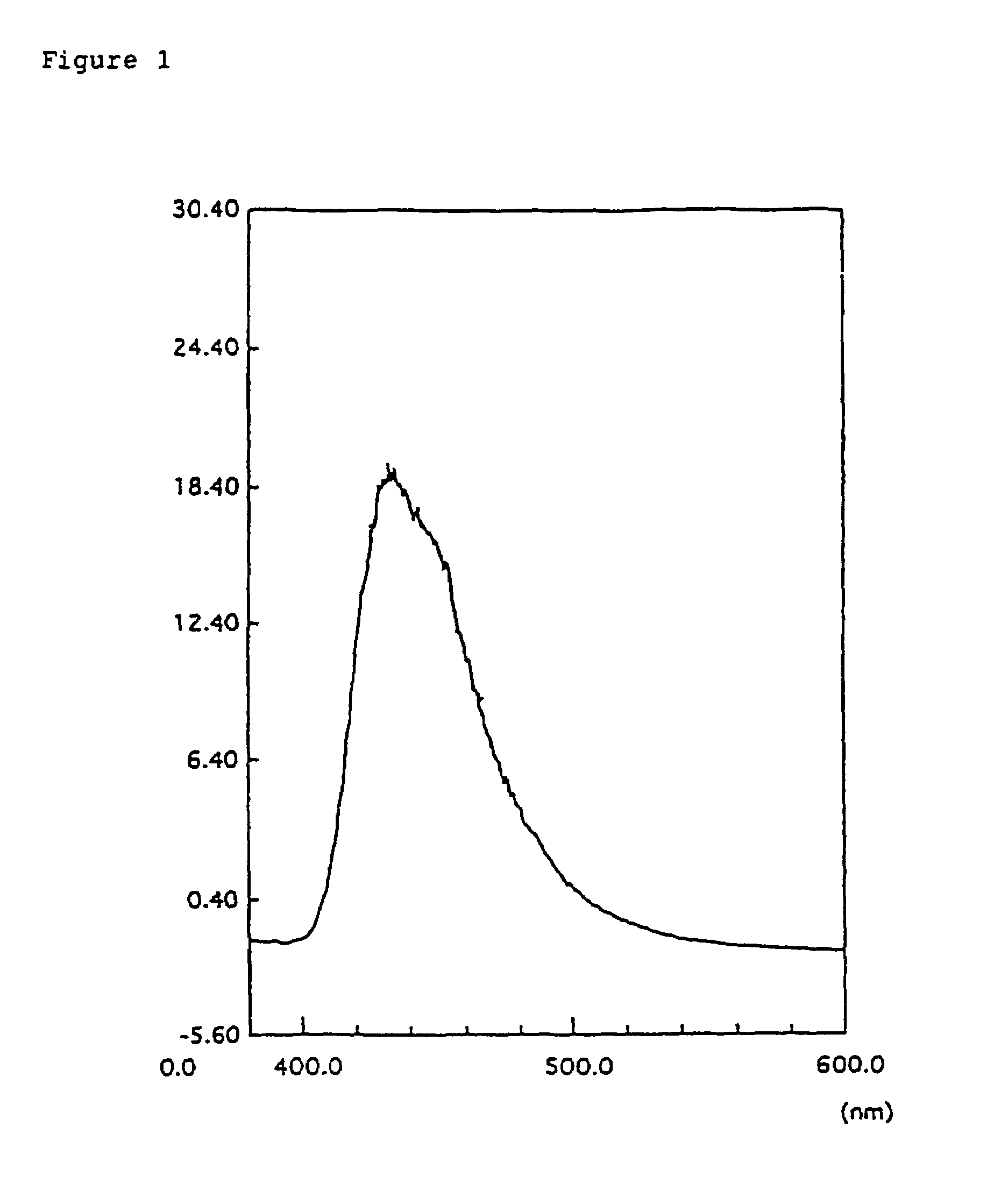

InactiveUS7399537B2Reduce the driving voltageSmall ionization potentialOrganic chemistryDischarge tube luminescnet screensElectron holeCharge injection

The invention is to provide an organic EL device having a long life time that can reduce the driving voltage of the organic EL device, and to provide a material having a small ionization potential and exhibiting a large hole mobility by using as a layer or a zone. The organic electroluminescence device comprises a pair of electrodes and an organic light emitting layer sandwiched in the electrodes, characterized in that a hole transporting zone provided between the electrodes comprises the phenylenediamine derivative represented by the specific structural formulae, and the phenylenediamine derivative has a hole mobility of 10−4 cm2 / V·s or more upon using as a layer or a zone, with the organic light emitting layer containing a charge injection auxiliary.

Owner:IDEMITSU KOSAN CO LTD

High speed Ge channel heterostructures for field effect devices

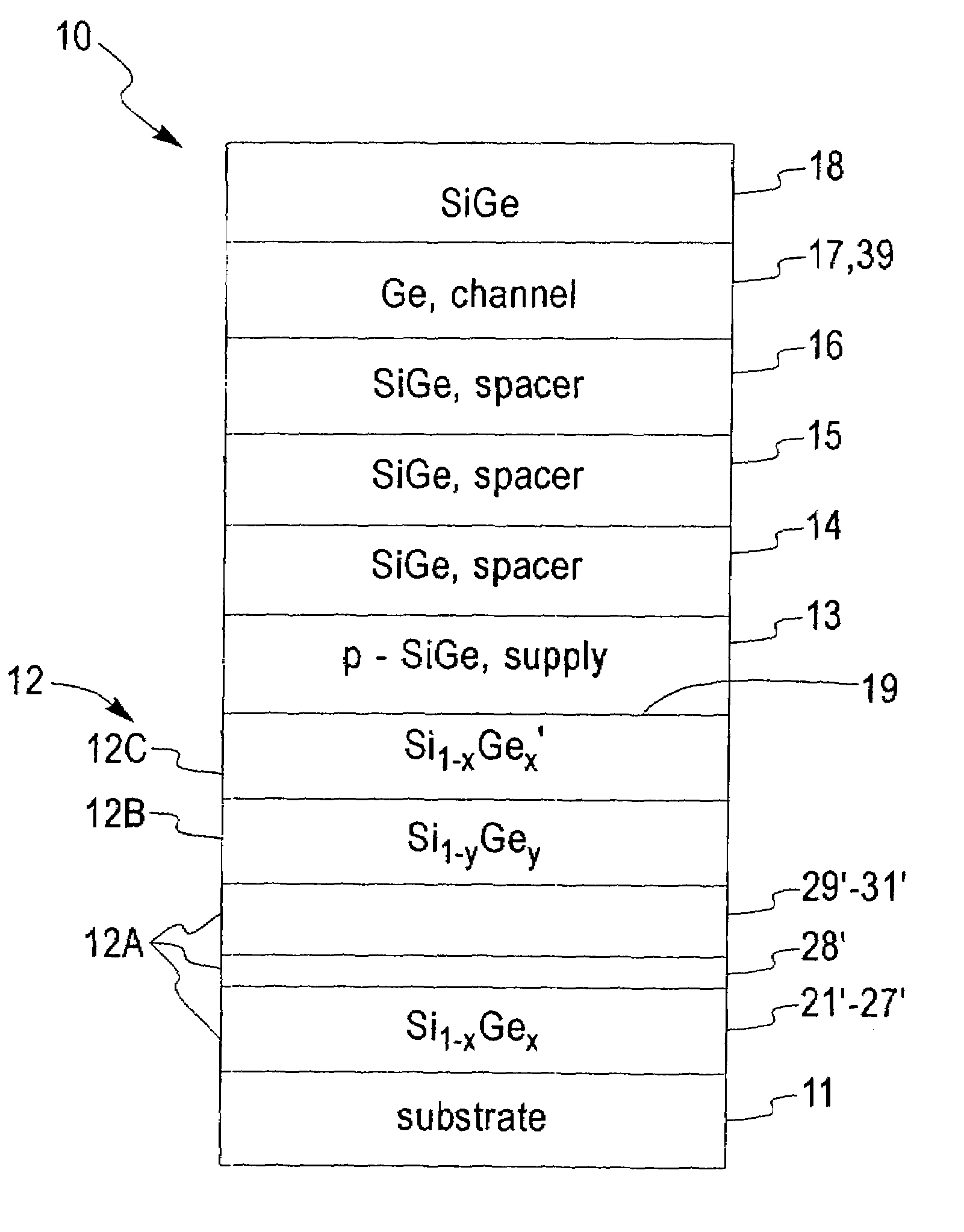

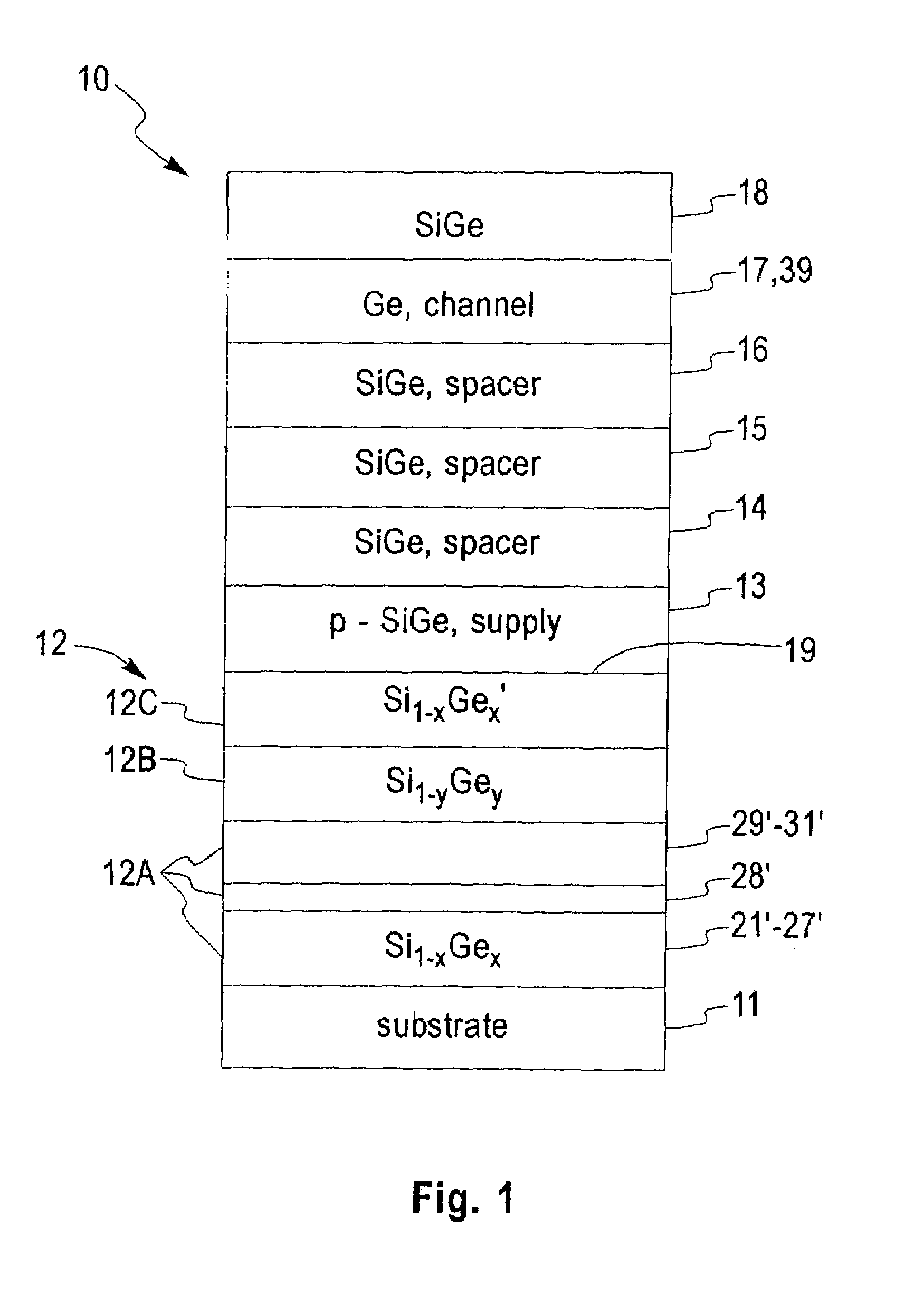

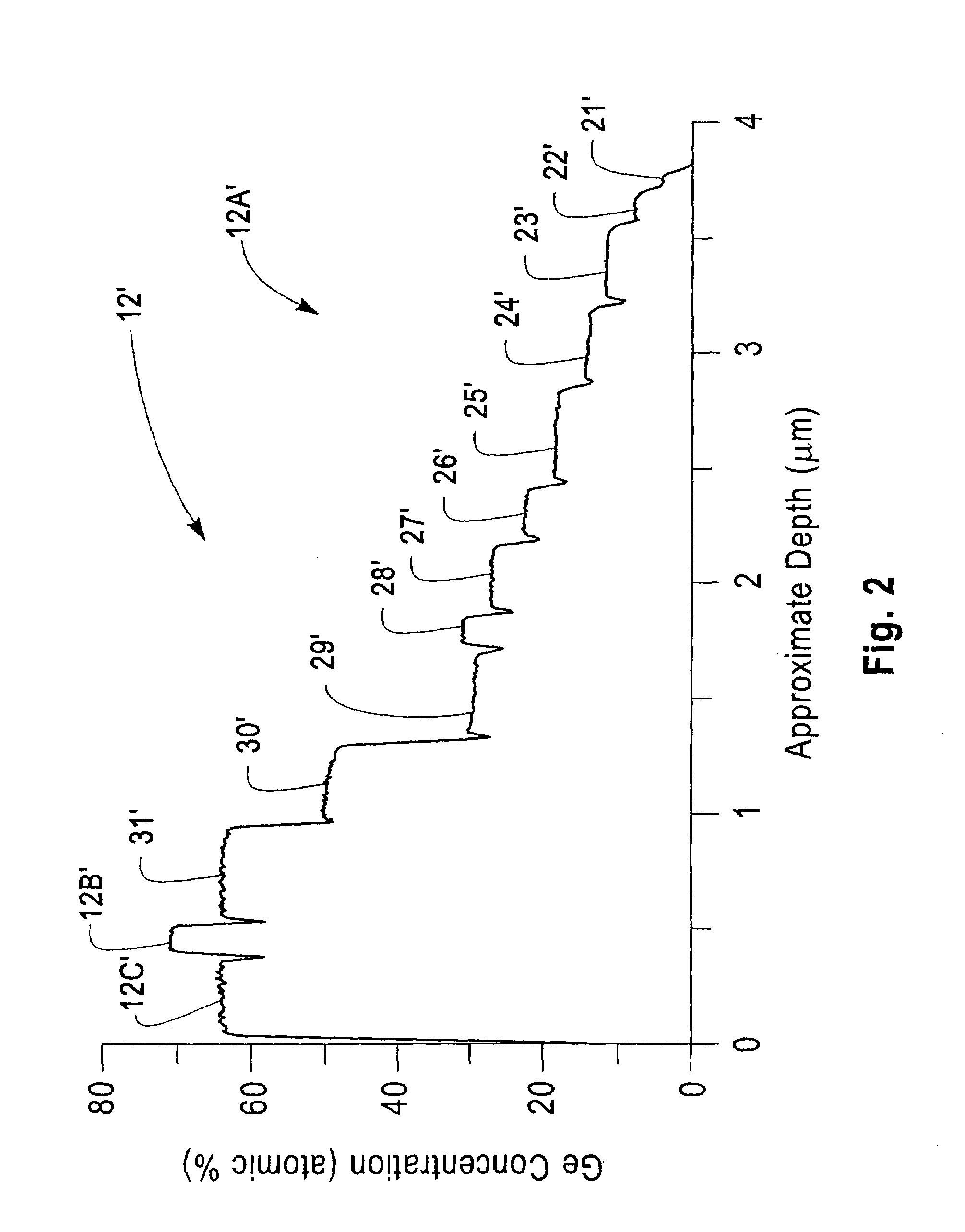

InactiveUS7145167B1High hole mobilityHigh compressive strainTransistorSemiconductor/solid-state device manufacturingMOSFETAlloy scattering

A method and a layered heterostructure for forming high mobility Ge channel field effect transistors is described incorporating a plurality of semiconductor layers on a semiconductor substrate, and a channel structure of a compressively strained epitaxial Ge layer having a higher barrier or a deeper confining quantum well and having extremely high hole mobility for complementary MODFETs and MOSFETs. The invention overcomes the problem of a limited hole mobility due to alloy scattering for a p-channel device with only a single compressively strained SiGe channel layer. This invention further provides improvements in mobility and transconductance over deep submicron state-of-the art Si pMOSFETs in addition to having a broad temperature operation regime from above room temperature (425 K) down to cryogenic low temperatures (0.4 K) where at low temperatures even high device performances are achievable.

Owner:ELPIS TECH INC

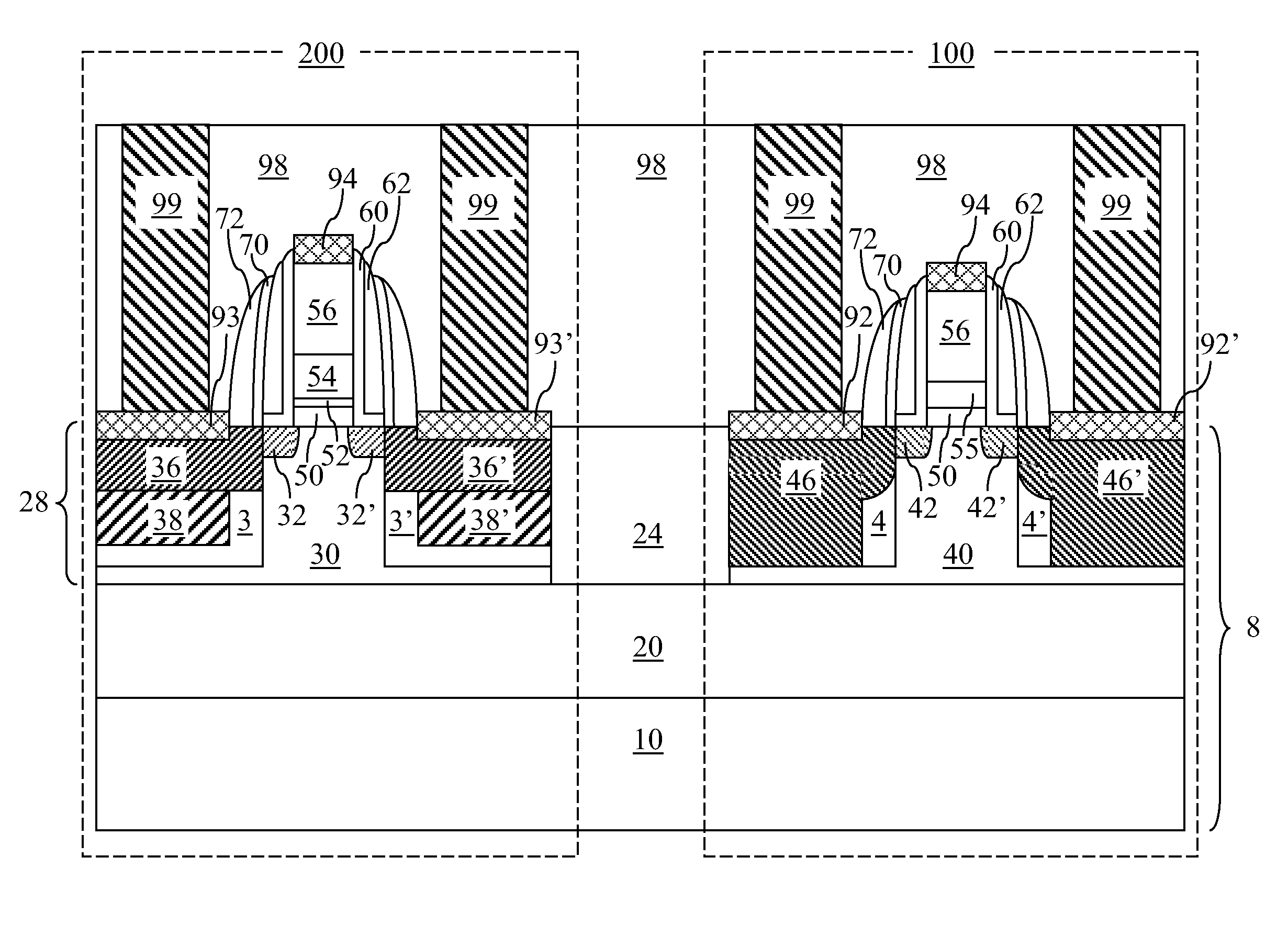

CMOS Transistors With Silicon Germanium Channel and Dual Embedded Stressors

ActiveUS20100224938A1High hole mobilityHigh electron mobilityTransistorSolid-state devicesHigh concentrationMOSFET

A p-type MOSFET of a CMOS structure has a silicon-germanium alloy channel to which a longitudinal compressive stress is applied by embedded epitaxial silicon-germanium alloy source and drain regions comprising a silicon-germanium alloy having a higher concentration of germanium than the channel of the p-type MOSFET. An n-type MOSFET of the CMOS structure has a silicon-germanium alloy channel to which a longitudinal tensile stress is applied by embedded epitaxial silicon source and drain regions comprising silicon. The silicon-germanium alloy channel in the p-type MOSFET provides enhanced hole mobility, while the silicon-germanium alloy channel in the n-type MOSFET provides enhanced electron mobility, thereby providing performance improvement to both the p-type MOSFET and the n-type MOSFET.

Owner:GLOBALFOUNDRIES US INC

Organic electroluminescent elements

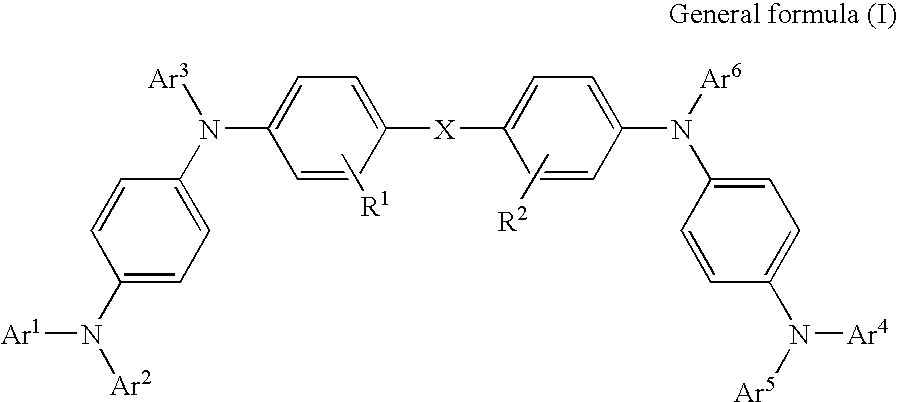

InactiveUS6344283B1Improve film propertiesImprove hole injection efficiencyDischarge tube luminescnet screensLayered productsArylOrganic electroluminescence

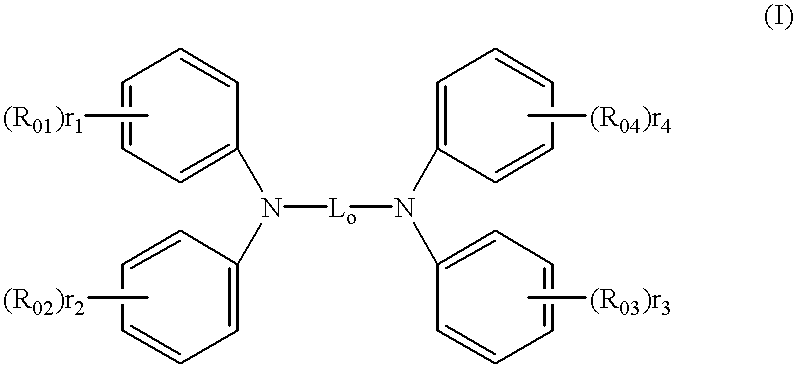

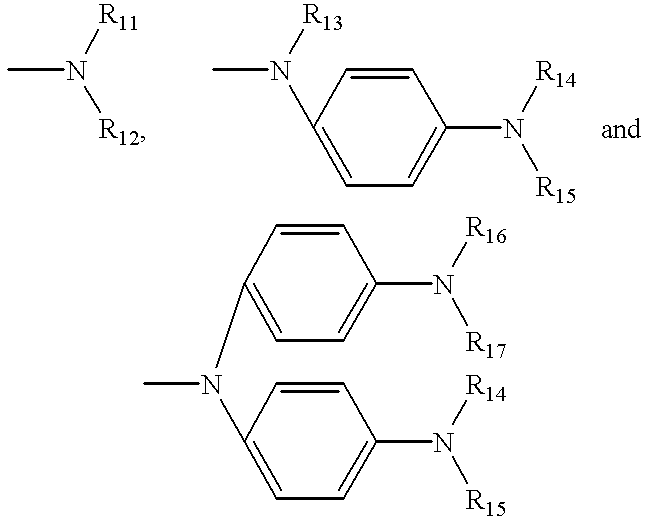

An organic EL device comprising a cathode, an anode, and at least one organic compound layer containing an organic compound represented by formula (I):where L0 is any one of o-, p-, and m-phenylene groups which have two, three or four rings and which have a substituent with the proviso that when L0 is a phenylene group having four rings, the phenylene group may have an unsubstituted or substituted aminophenyl group somewhere therein, and at least one of R01, R02, R03 and R04 is any one of the following groups:where R1, R12, R13, R14, R15, R16 and R17 are each a substituted or unsubstituted aryl group, and r1, r2, r3 and r4 are each an integer of 0 to 5 with the proviso that r1+r2+r3+r4>=1.

Owner:FUTABA CORPORATION

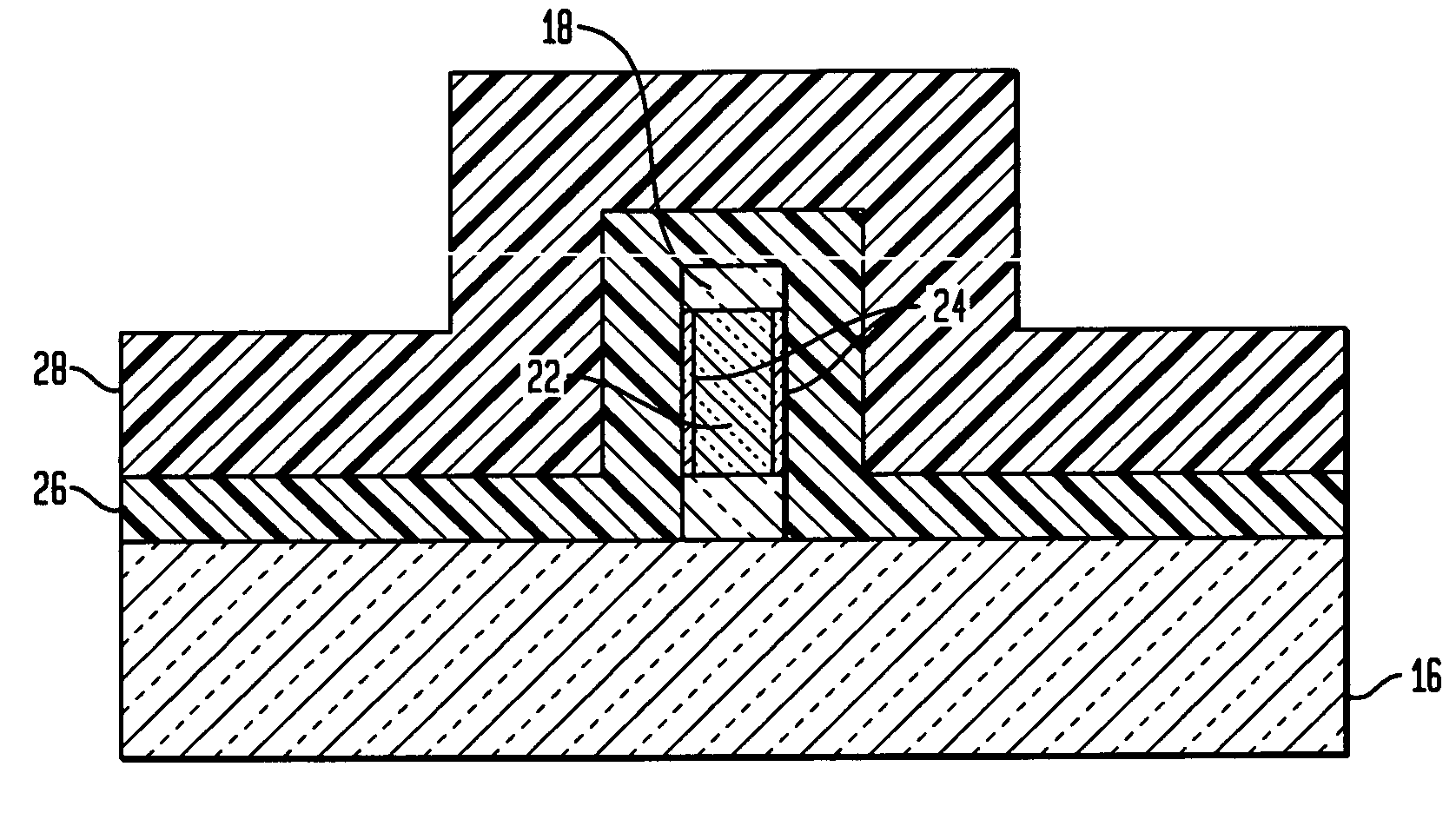

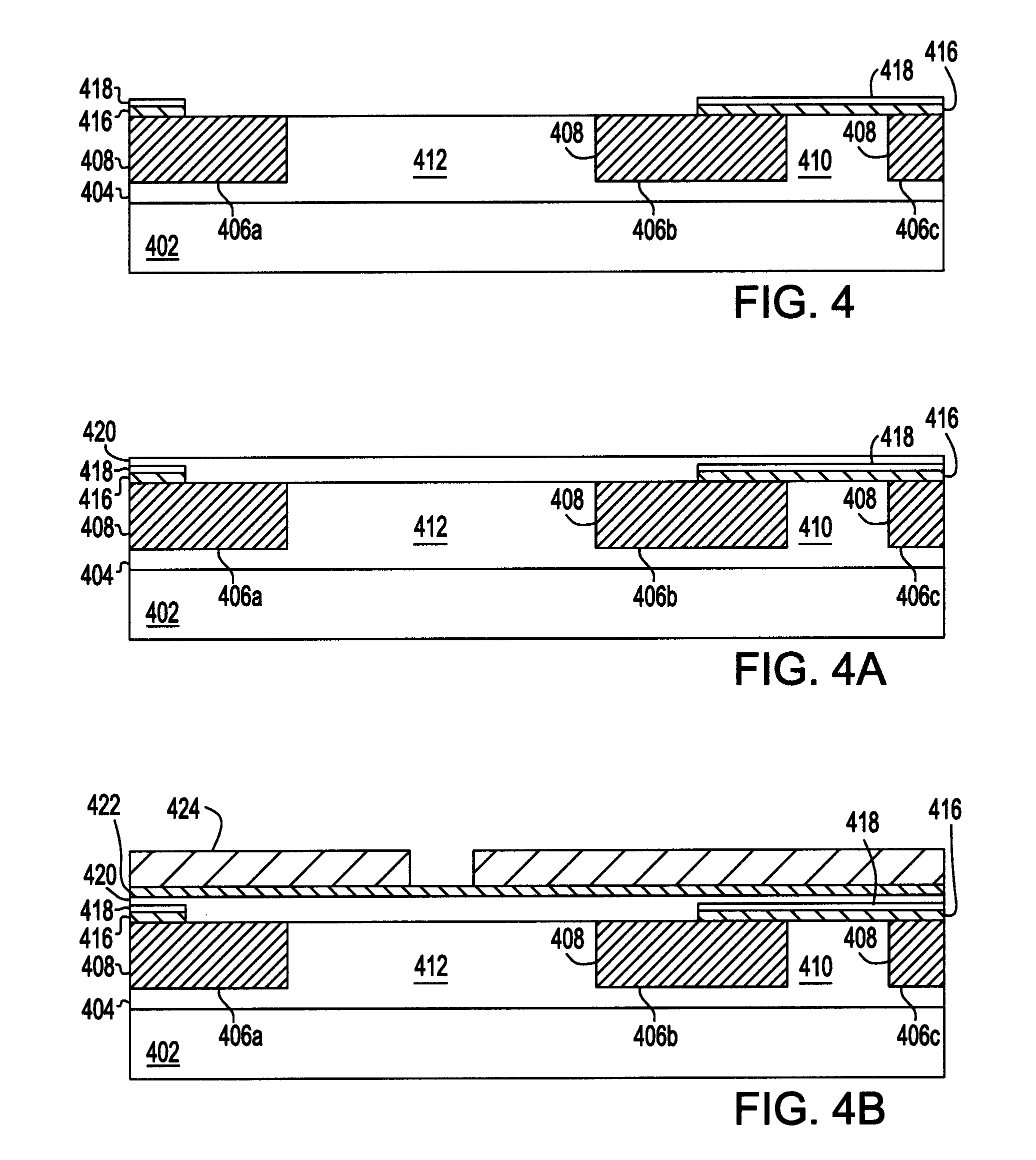

Structures and methods for manufacturing p-type mosfet withgraded embedded silicon-germanium source-drain and/or extension

InactiveUS20050285192A1High hole mobilityImprove mobilityTransistorSolid-state devicesMOSFETGate dielectric

P-type MOSFETs (PMOSFETs) are formed by encapsulating the gate with an insulator and depositing a germanium containing layer outside the sidewalls, then diffusing the germanium into the silicon-on-insulator layer or bulk silicon by annealing or by oxidizing to form graded embedded silicon-germanium source-drain and / or Extension (geSiGe-SDE). For SOI devices, the geSiGe-SDE is allowed to reach the buried insulator to maximize the stress in the channel of SOI devices, which is beneficial for ultra-thin SOI devices. Graded germanium profiles provide a method to optimize stress in order to enhance device performance. The geSiGe-SDE creates a compressive stress in the horizontal direction (parallel to the gate dielectric surface) and tensile stress in the vertical direction (normal to the gate dielectric surface) in the channel of the PMOSFET, therebyforming a structure that enhances PMOSFET performance.

Owner:GLOBALFOUNDRIES INC

Structure and method for manufacturing strained finfet

ActiveUS20060180866A1High electron mobilityHigh hole mobilityTransistorSolid-state devicesNitrideElectrical and Electronics engineering

A part of the gate of a FINFET is replaced with a stress material to apply stress to the channel of the FINFET to enhance electron and hole mobility and improve performance. The FINFET has a SiGe / Si stacked gate, and before silicidation the SiGe part of the gate is selectively etched to form a gate gap that makes the gate thin enough to be fully silicidated. After silicidation, the gate-gap is filled with a stress nitride film to create stress in the channel and enhance the performance of the FINFET.

Owner:GLOBALFOUNDRIES US INC

High speed ge channel heterostructures for field effect devices

InactiveUS20070187716A1High hole mobilityHigh compressive strainTransistorSemiconductor/solid-state device manufacturingMOSFETAlloy scattering

A method and a layered heterostructure for forming high mobility Ge channel field effect transistors is described incorporating a plurality of semiconductor layers on a semiconductor substrate, and a channel structure of a compressively strained epitaxial Ge layer having a higher barrier or a deeper confining quantum well and having extremely high hole mobility for complementary MODFETs and MOSFETs. The invention overcomes the problem of a limited hole mobility due to alloy scattering for a p-channel device with only a single compressively strained SiGe channel layer. This invention further provides improvements in mobility and transconductance over deep submicron state-of-the art Si pMOSFETs in addition to having a broad temperature operation regime from above room temperature (425 K) down to cryogenic low temperatures (0.4 K) where at low temperatures even high device performances are achievable.

Owner:ELPIS TECH INC

Transistor design and layout for performance improvement with strain

ActiveUS20050139929A1Improve performanceFacilitate fabricationSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialEngineering

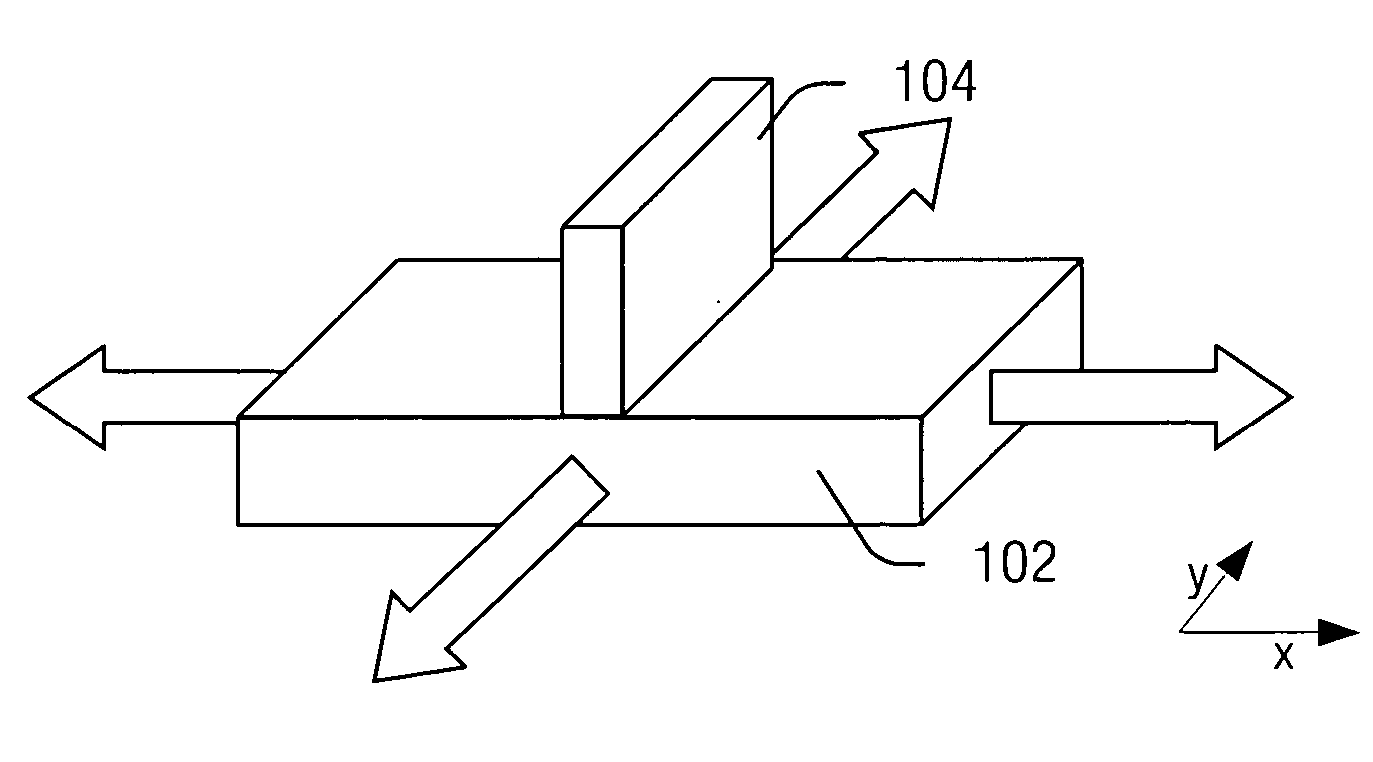

The present invention facilitates semiconductor device fabrication and performance by providing a semiconductor device that can improve channel mobility for both N type and P type transistor devices. The semiconductor device of the present invention is fabricated on a semiconductor substrate 802 that has a first and second crystallographic orientation axes (e.g., <110>, <100>) 804 and 806. Source to drain channel regions for P type devices are formed 904 and aligned along the first crystallographic orientation axis. Source to drain channel regions for N type devices are formed 906 rotated from the channel regions of the P type devices by an offset angle so that the source to drain channel regions for the N type devices are aligned with the second crystallographic orientation axis. Subsequently, a uniaxial or biaxial tensile stress 908 is applied to the source to drain channel regions of the N type devices and a uniaxial or biaxial compressive stress 910 is applied to the source to drain channel regions of the P type devices.

Owner:TEXAS INSTR INC

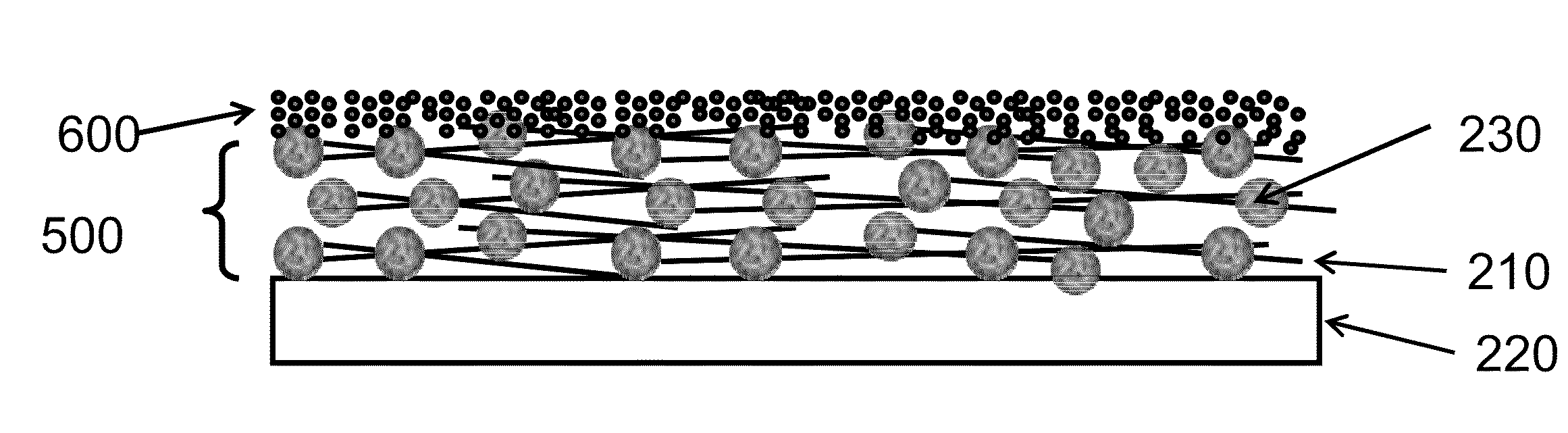

Carbon nanotube-transparent conductive inorganic nanoparticles hybrid thin films for transparent conductive applications

ActiveUS20100047522A1Low mechanical strengthHigh mechanical strengthNanostructure manufactureConductive layers on insulating-supportsCarbon nanotubeNanometre

An optically transparent, electrically conductive hybrid film includes a carbon nanotubes network deposited on a substrate, and a population of transparent conductive inorganic nanoparticles distributed throughout the carbon nanotubes network to provide a conductive transparent hybrid film.

Owner:NANO C INC

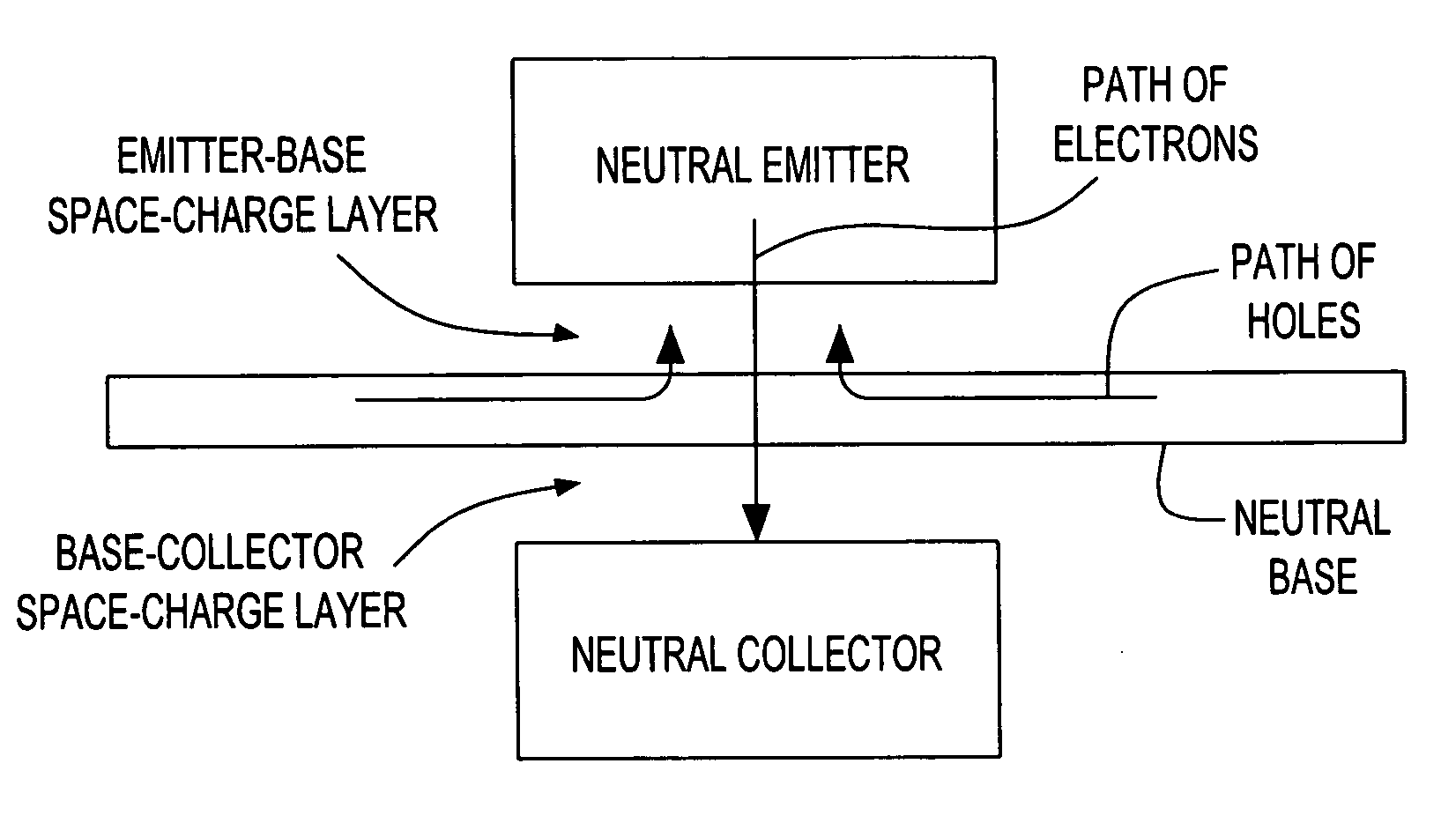

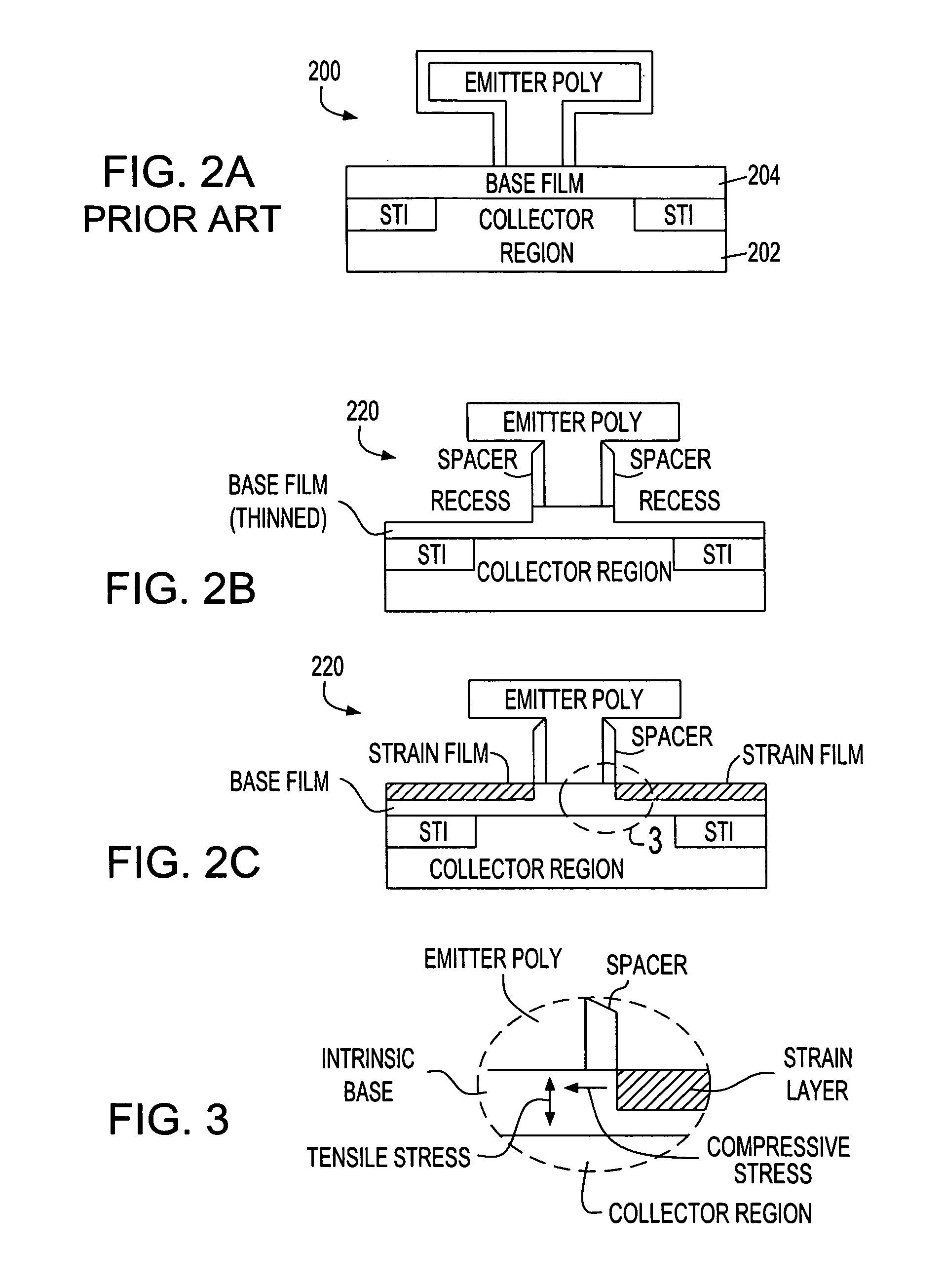

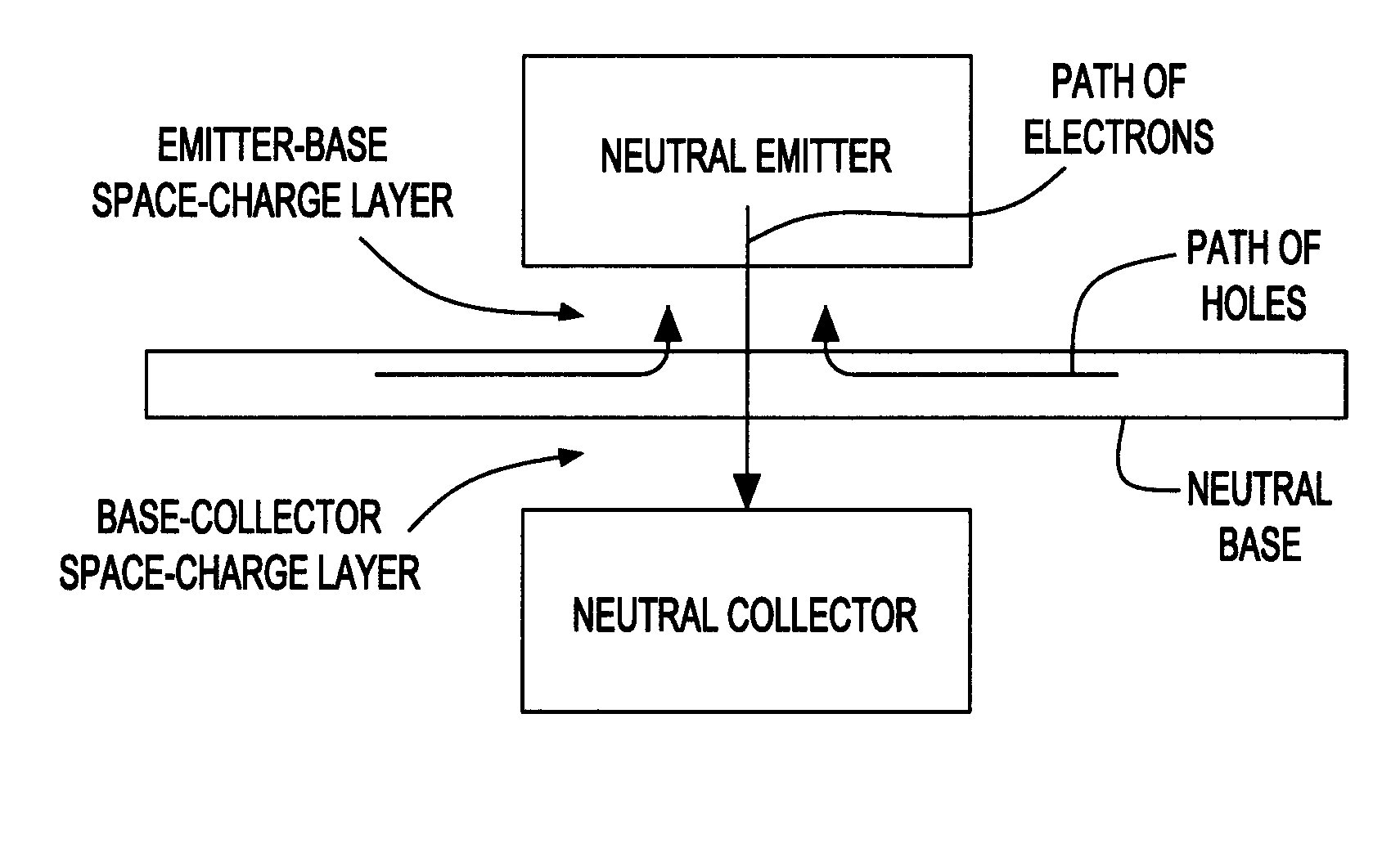

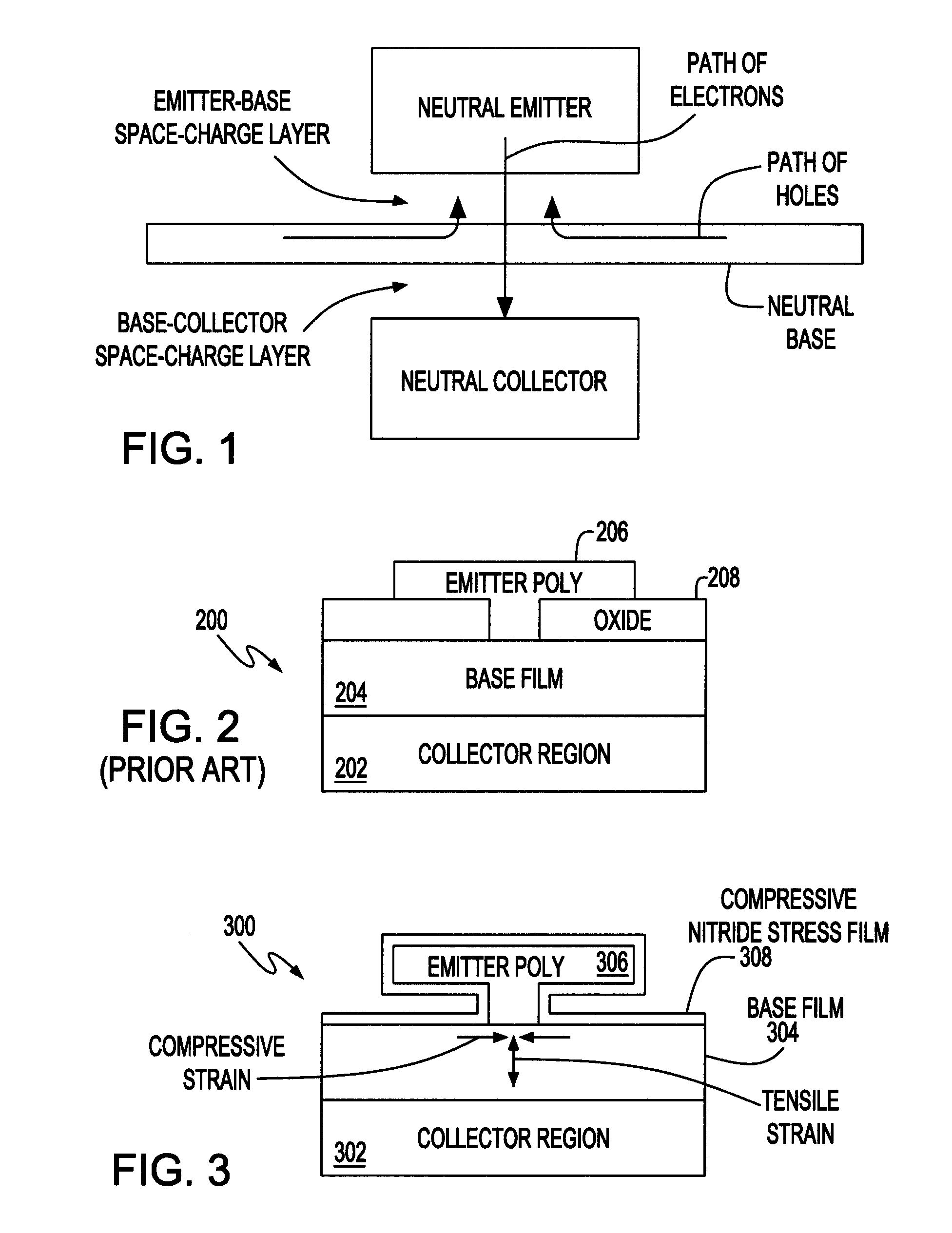

Bipolar transistor with extrinsic stress layer

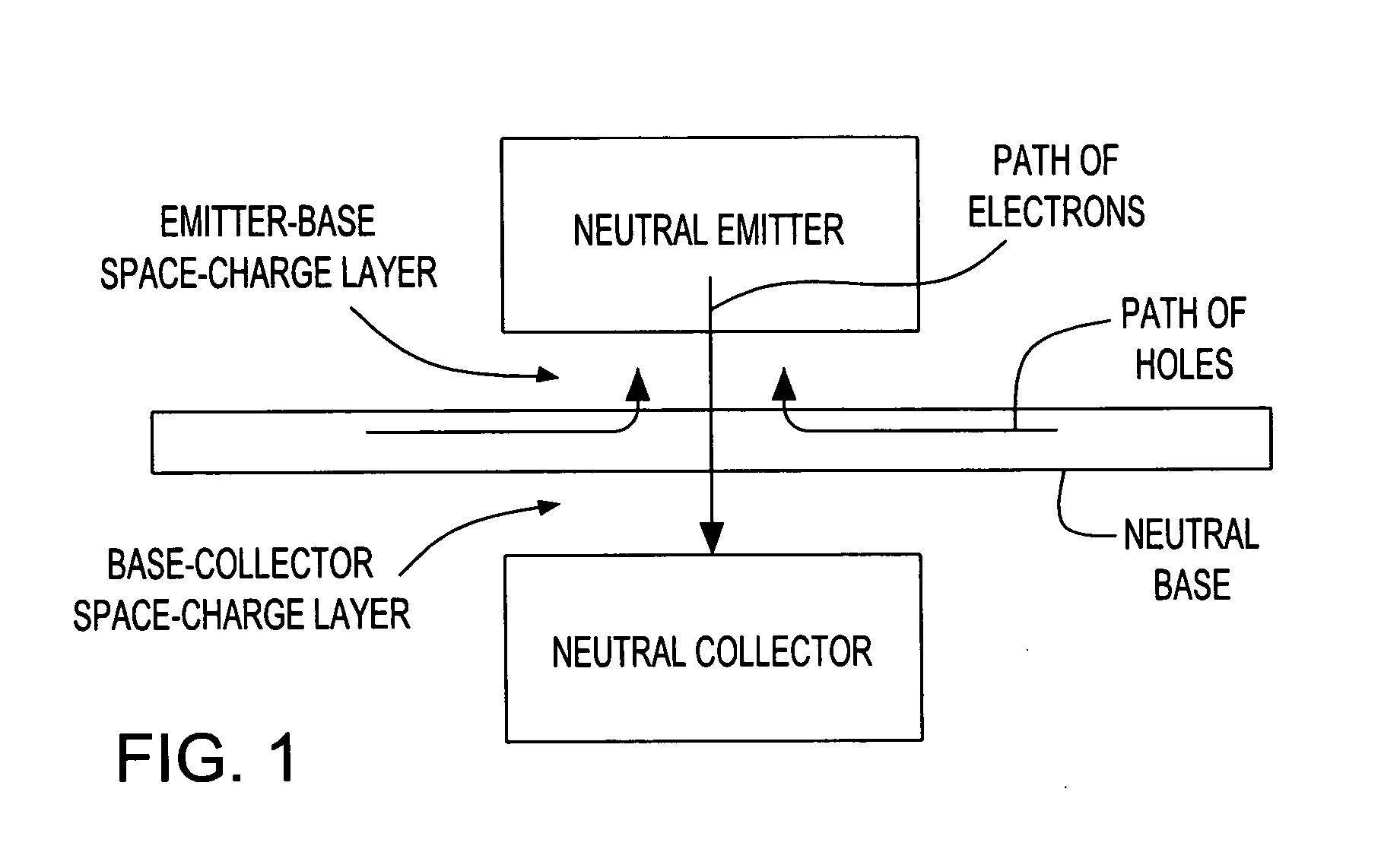

ActiveUS20060043529A1Improve performanceLow field mobilityTransistorSemiconductor/solid-state device manufacturingTensile strainCharge carrier

A method of increasing mobility of charge carriers in a bipolar device comprises the steps of: creating compressive strain in the device to increase mobility of holes in an intrinsic base of the device; and creating tensile strain in the device to increase mobility of electrons in the intrinsic base of the device. The compressive and tensile strains are created by forming a stress layer in close proximity to the intrinsic base of the device. The stress layer is at least partially embedded in a base layer of the device, adjacent an emitter structure of the device. The stress layer has different lattice constant than the intrinsic base. Method and apparatus are described.

Owner:GLOBALFOUNDRIES US INC

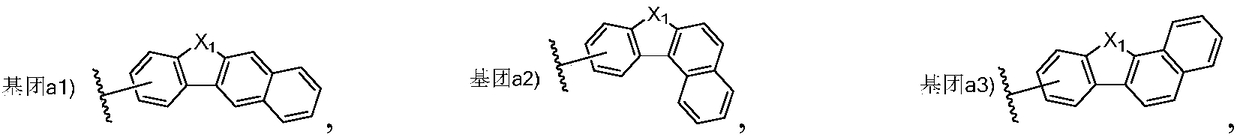

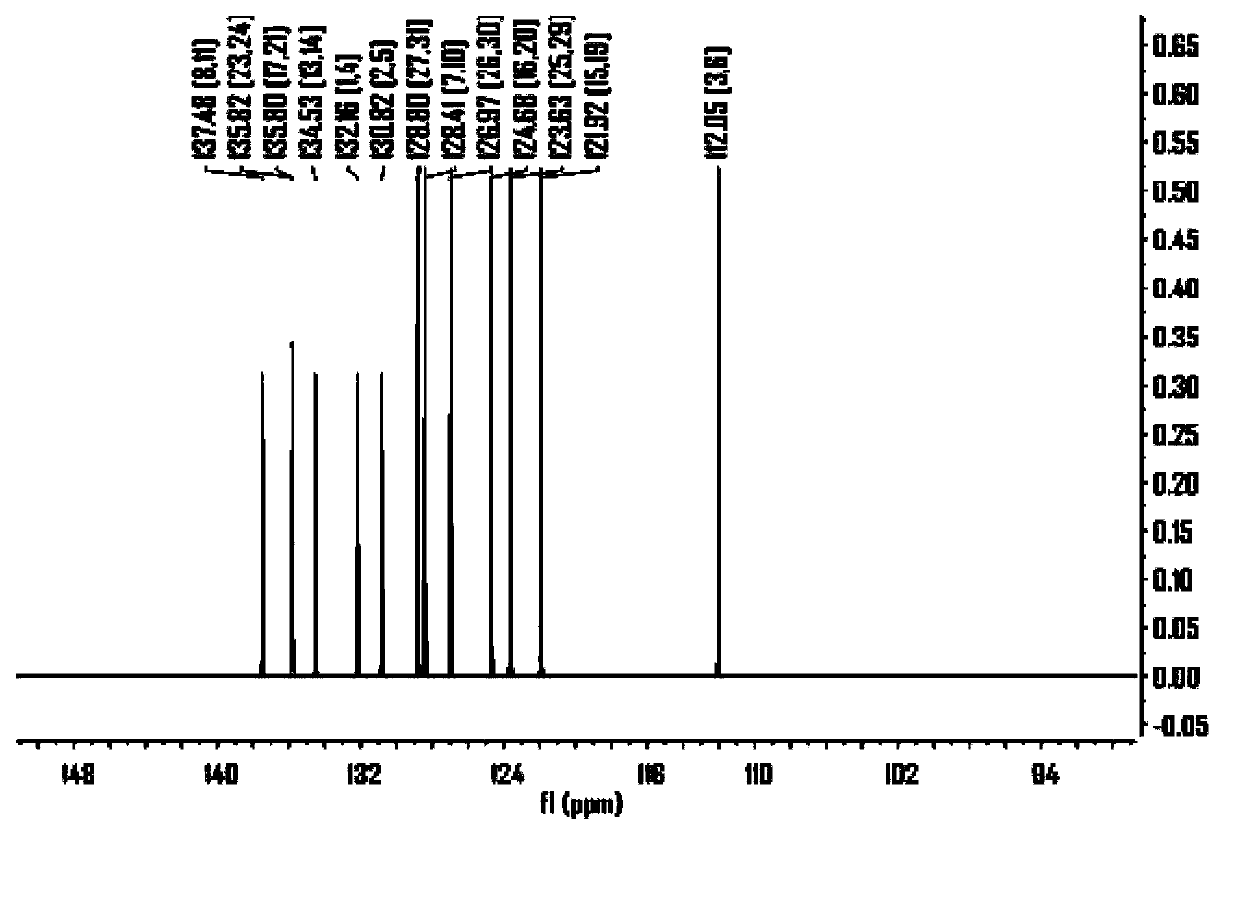

Organic compound, electronic element comprising same, and electronic device

ActiveCN111018797AIncrease space volumeHigh glass transition temperatureOrganic chemistrySolid-state devicesArylSimple Organic Compounds

The invention relates to the technical field of organic photoelectric materials, and in particular, relates to an organic compound, an electronic element containing the same and an electronic device.The compound has a structure represented by a chemical formula 1', wherein one of R1, R2, R3 and R4 is a group defined in the specification, and the other three are selected from substituents such asalkyl, halogen and cyano; one of R5, R6, R7 and R8 is a group defined in the specification, the other three are selected from substituents such as alkyl, halogen and cyano, Y and Y1 are respectively and independently a group defined in the specification, and L and L1 are single bonds, aryl, heteroaryl and the like. By using the organic compound in an electronic component, the driving voltage, luminous efficiency, and life of the electronic component are improved.

Owner:SHAANXI LIGHTE OPTOELECTRONICS MATERIAL CO LTD

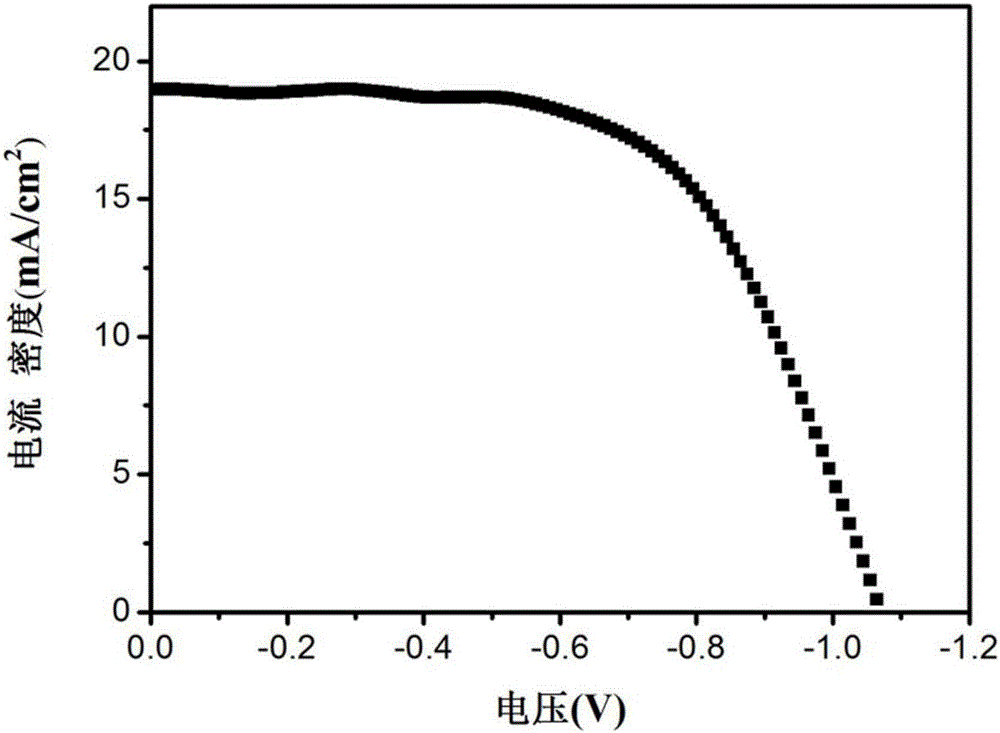

P-type doped perovskite-based photoelectric functional material and application thereof

InactiveCN105405974AHigh hole mobilityImprove conductivitySolid-state devicesSemiconductor/solid-state device manufacturingDopantElectrical battery

The invention discloses a P-type doped perovskite-based photoelectric functional material, prepared by taking a perovskite-based photoelectric functional material ABX3 as a substrate and organic or inorganic doping agent as a P-type doping agent for doping purpose. The chemical formula of the obtained perovskite-based photoelectric functional material is (A1)<x>(A2)<1-x>B(X1)<y>(X2)<3-y>, wherein 0<=x<=1, 0<=y<=3, A1 is a monovalent organic or inorganic cation, A2 is a monovalent organic or inorganic cation, B is a divalent metal cation, and X1 or X2 is a monovalent anion. The invention further discloses a corresponding preparation method and a solar cell and the like comprising the photoelectric functional material. The P-type doped perovskite-based photoelectric functional material has the advantages that carrier concentration, hole mobility and conductivity can be improved; the perovskite-based photoelectric functional material with excellent electrical property can be obtained; and the preparation method is simple and low in cost.

Owner:HUAZHONG UNIV OF SCI & TECH

High carrier concentration p-type transparent conducting oxide films

InactiveUS6908782B2Suppress formationHigh hole mobilityZinc oxides/hydroxidesSolid-state devicesPhysical chemistryElectrically conductive

Owner:ALLIANCE FOR SUSTAINABLE ENERGY

Triarylamine compound and organic electroluminescent device thereof

ActiveCN111808042AHigh triplet energy levelHigh glass transition temperatureOrganic chemistrySolid-state devicesBenzoxazoleRefractive index

The invention provides a triarylamine compound and an organic electroluminescent device thereof, and relates to the technical field of organic photoelectric materials. According to the invention, a substituted or unsubstituted 9-phenyl-fluorene group and a triarylamine group containing benzoxazole / benzothiazole / benzimidazole / benzotriazole undergoes a reaction to obtain the triarylamine compound by9-position (tertiary C) connection of fluorene. The triarylamine compound has a good hole transport capability, is high in glass transition temperature, good in thermal stability, good in film-forming property, high in refractive index and simple to synthesize, can be applied to an organic electroluminescent device to serve as a hole transport layer and / or a covering layer, can effectively solvethe problems of low luminous efficiency and short service life of the organic electroluminescent device, and has the advantages of high luminous efficiency and long service life.

Owner:CHANGCHUN HYPERIONS TECH CO LTD

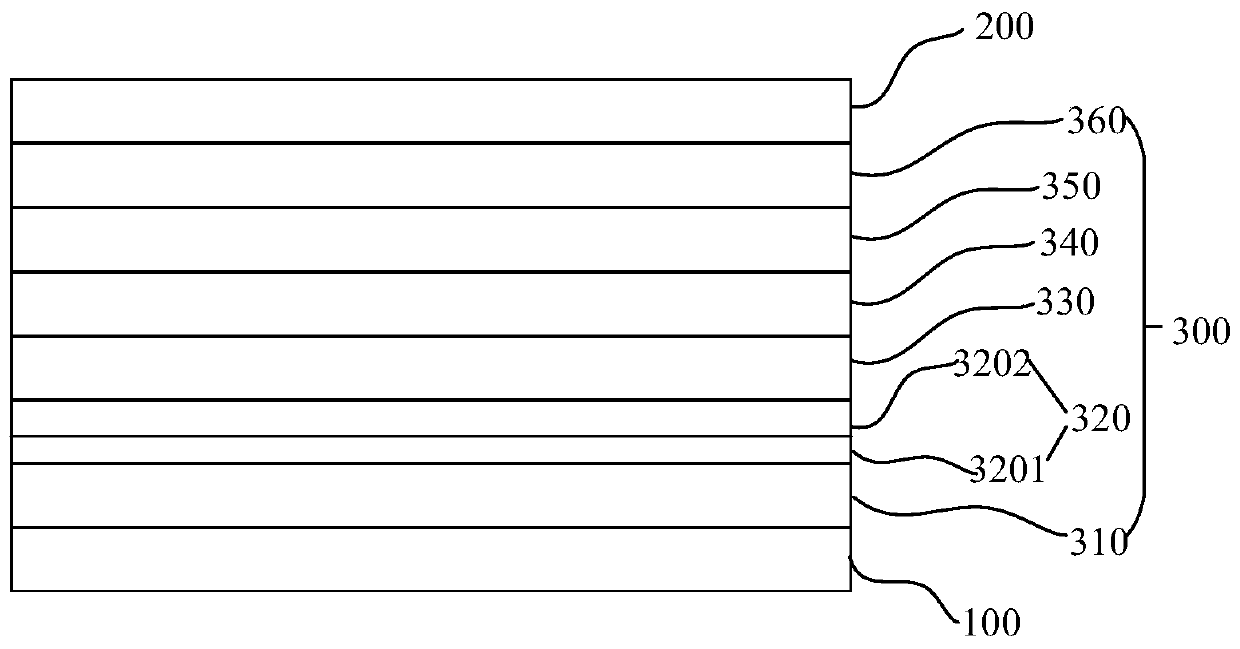

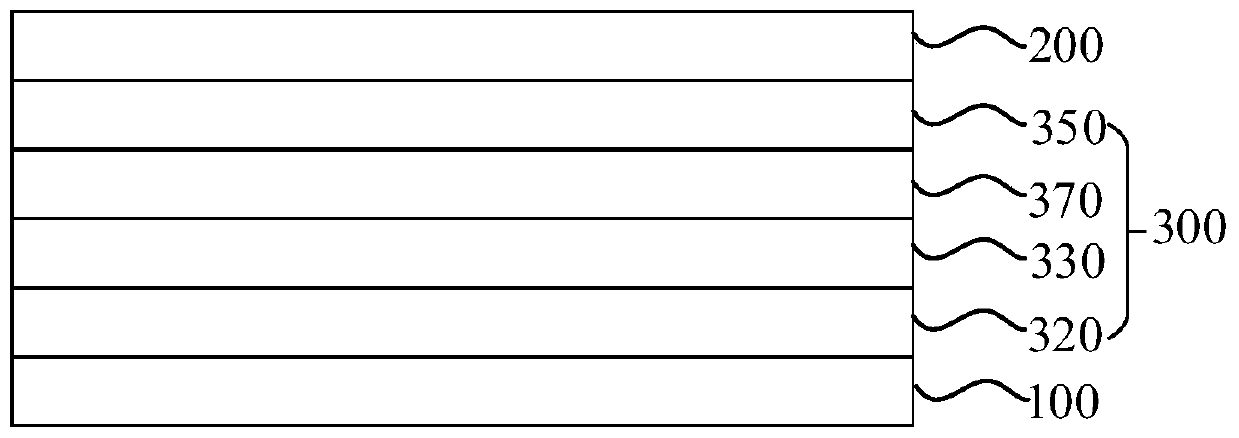

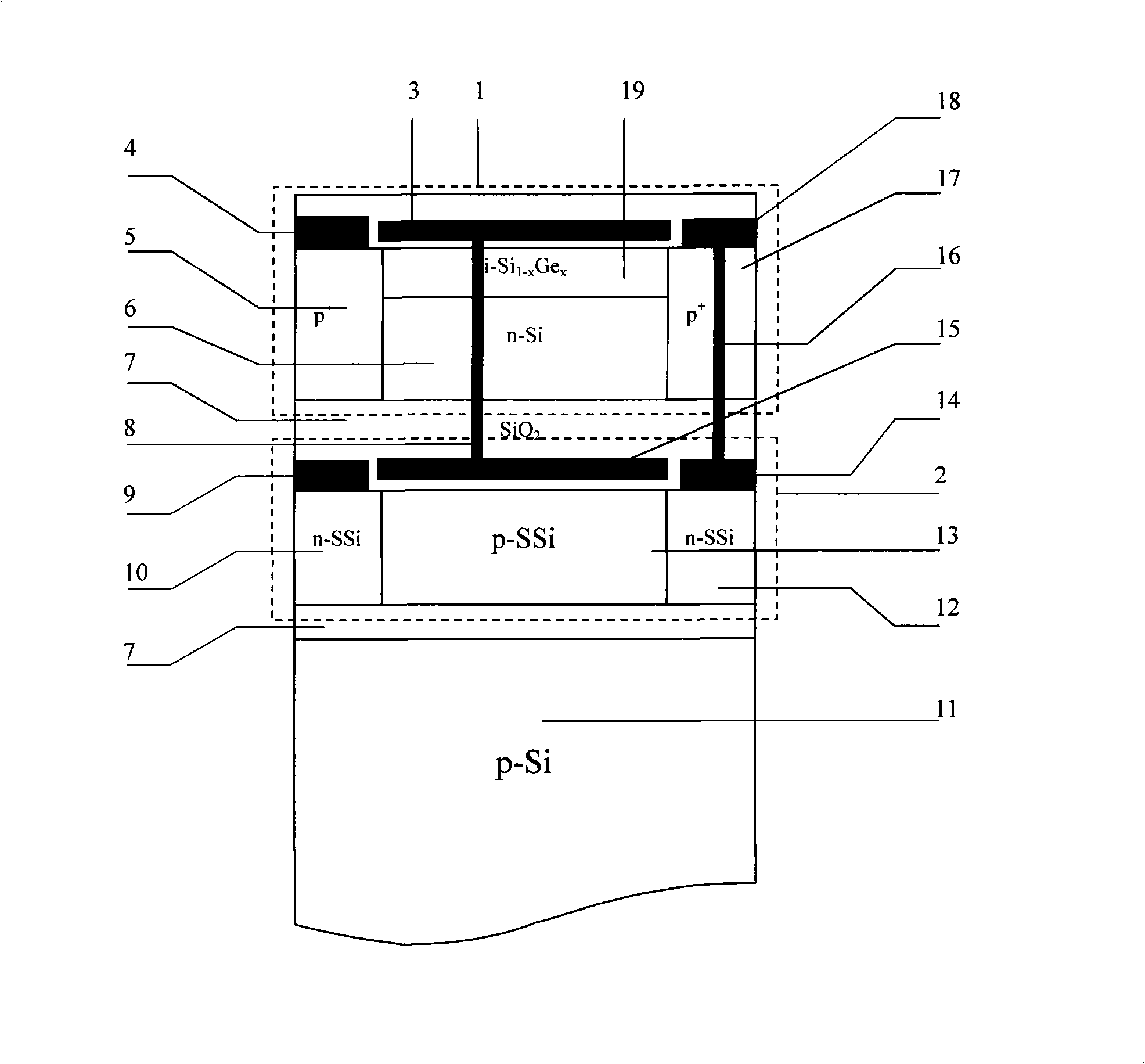

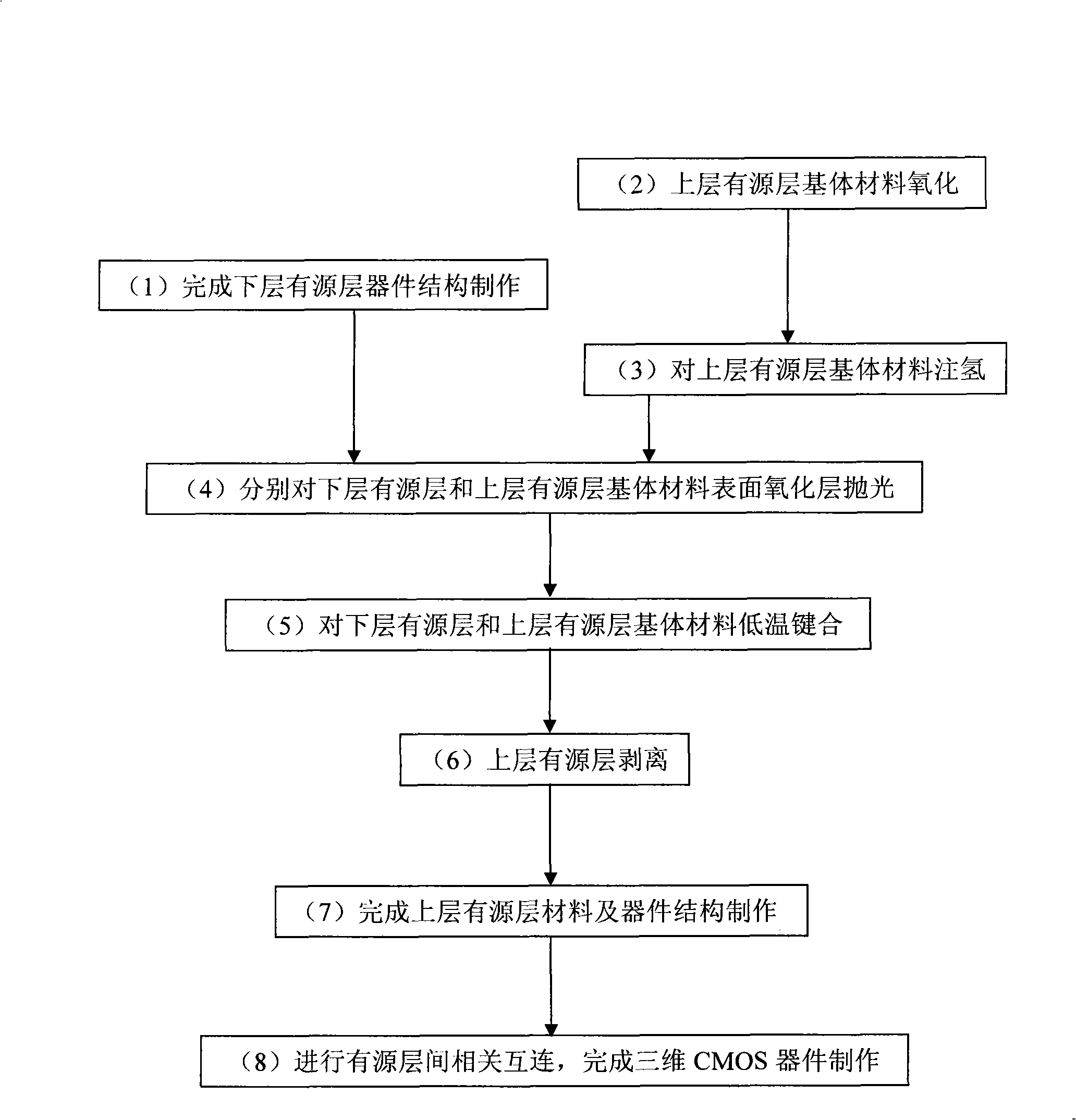

SOI three-dimensional CMOS integrated component and preparation method thereof

InactiveCN101409292AHigh hole mobilityImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingSoi cmosLow speed

The invention discloses a 3D SOI CMOS integrated device and a manufacturing method thereof, relates to the technical field of microelectronics, and mainly solves the problem of low speed of the existing 3D integrated circuits. The proposal is that an SSOI substrate and an SSGOI substrate are employed to construct two active layers of a new 3D CMOS integrated device; wherein, the lower active layer is the SSOI substrate and is made into a strained Si nMOSFET device by utilizing the characteristic of high electron mobility of a strained Si material in the SSOI substrate; the upper active layer is the SSGOI substrate and is made into a strained SiGe surface channel pMOSFET device by utilizing the characteristic of high hole mobility of the strained Si material in the SSGOI substrate; the upper active layer and the lower active layer form a 3D active layer structure by a bonding process, and are connected by an interconnection line to form the 3D CMOS integrated device with a conducting channel of 65nm to 130nm. Compared with the existing 3D integrated devices, the 3D SOI CMOS integrated device manufactured by the manufacturing method has the advantages of high speed and good performance, and can be applied to manufacturing large-scale and high-speed 3D CMOS integrated circuits.

Owner:XIDIAN UNIV

Spiro-OMeTAD/PbS composite hole transport layer based perovskite solar cell and preparation method therefor

ActiveCN106129252AImprove photoelectric conversion efficiencyImprove stabilitySolid-state devicesSemiconductor/solid-state device manufacturingSolar lightEvaporation

The invention discloses a Spiro-OMeTAD / PbS composite hole transport layer based perovskite solar cell and a preparation method therefor. The perovskite solar cell comprises a transparent conductive substrate, an oxide electron transport layer, a perovskite solar light absorption layer, the Spiro-OMeTAD / PbS composite hole transport layer and a metal electrode. The perovskite thin film solar cell adopts a simple process; a lead sulfide thin film can be prepared by a large-area evaporation method; and the lead sulfide thin film can be inserted between the Spiro-OMeTAD and the metal electrode layer to be used as a buffer layer. The Spiro-OMeTAD / PbS composite hole transport layer based perovskite solar cell achieves a high photoelectric conversion efficiency which is as high as 15.11%; the lead sulfide, which is used as the buffer layer between the hole transport layer and the metal electrode, has higher hole mobility, and higher humidity stability and light and heat stability, so that the recombination of electron-hole pairs can be reduced; meanwhile, the stability of the cell can be improved; compared with other buffer layer materials, the lead sulfide can protect a device and improve the performance of the device as well; and therefore, a positive promotion effect is realized on the industrial development of the solar cell.

Owner:WUHAN UNIV

High carrier concentration p-type transparent conducting oxide films

InactiveUS20040061114A1Increase hole concentrationHigh hole mobilityZinc oxides/hydroxidesSolid-state devicesPhysical chemistryElectrically conductive

Owner:ALLIANCE FOR SUSTAINABLE ENERGY

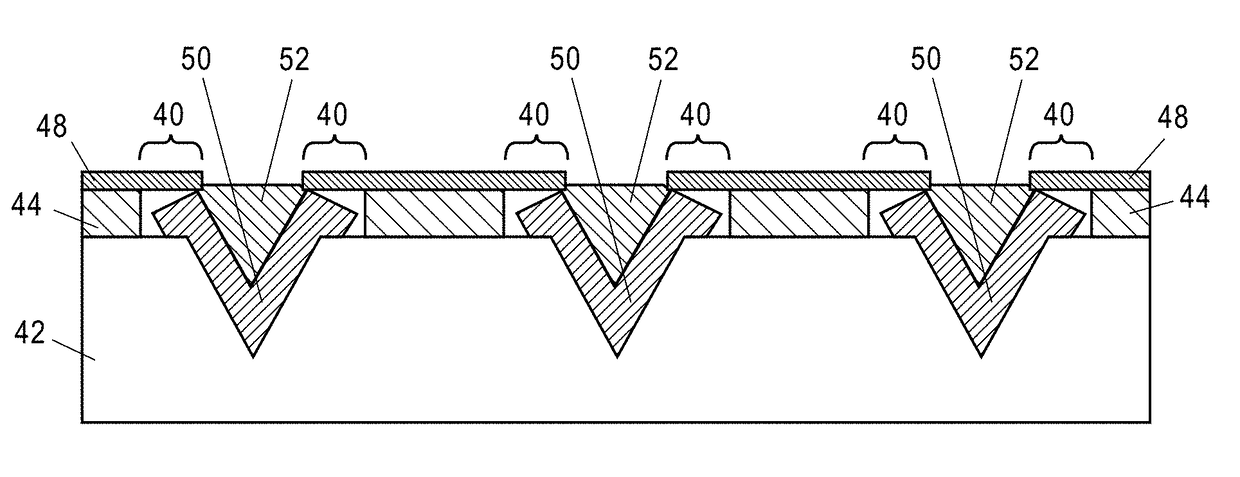

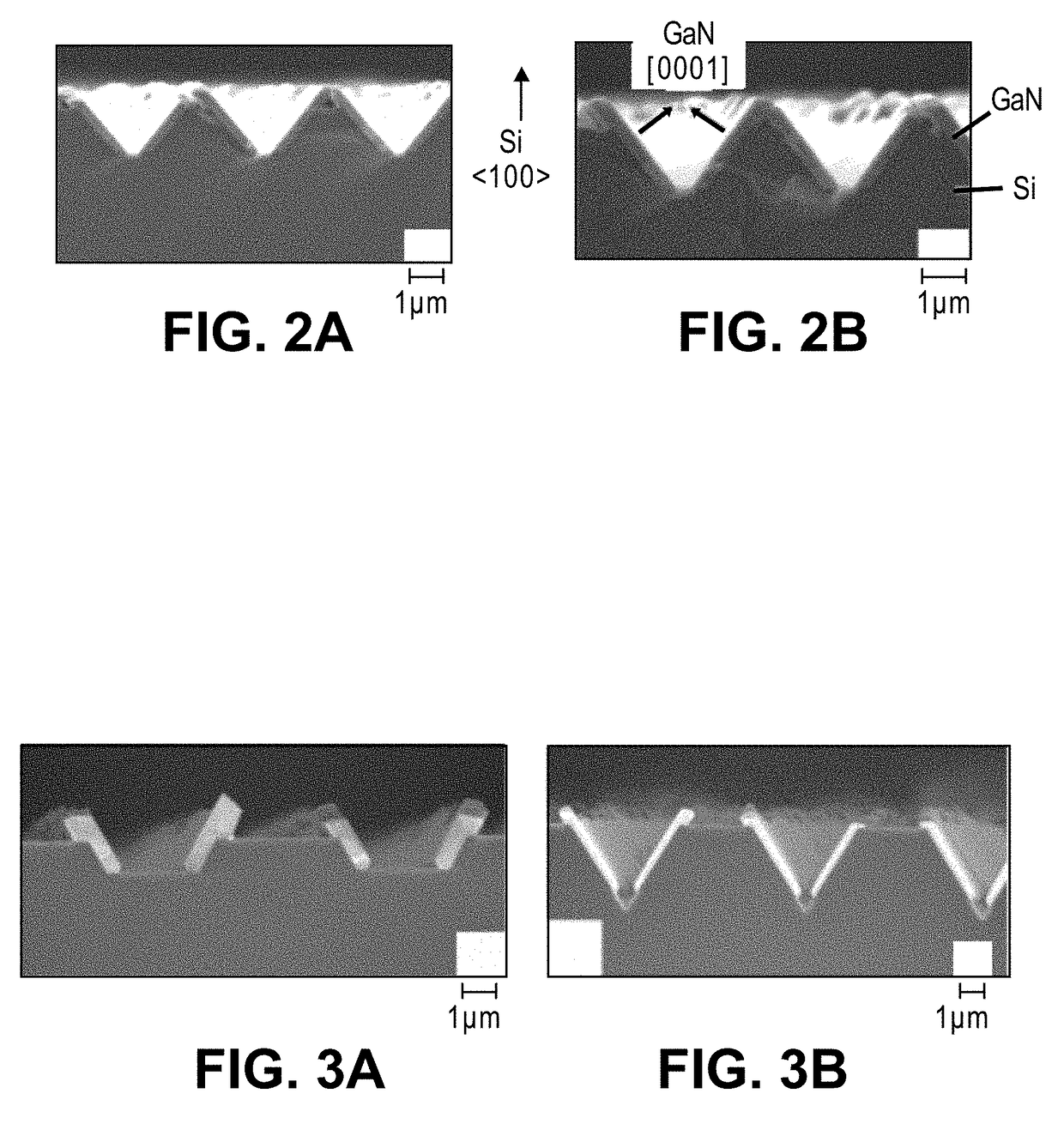

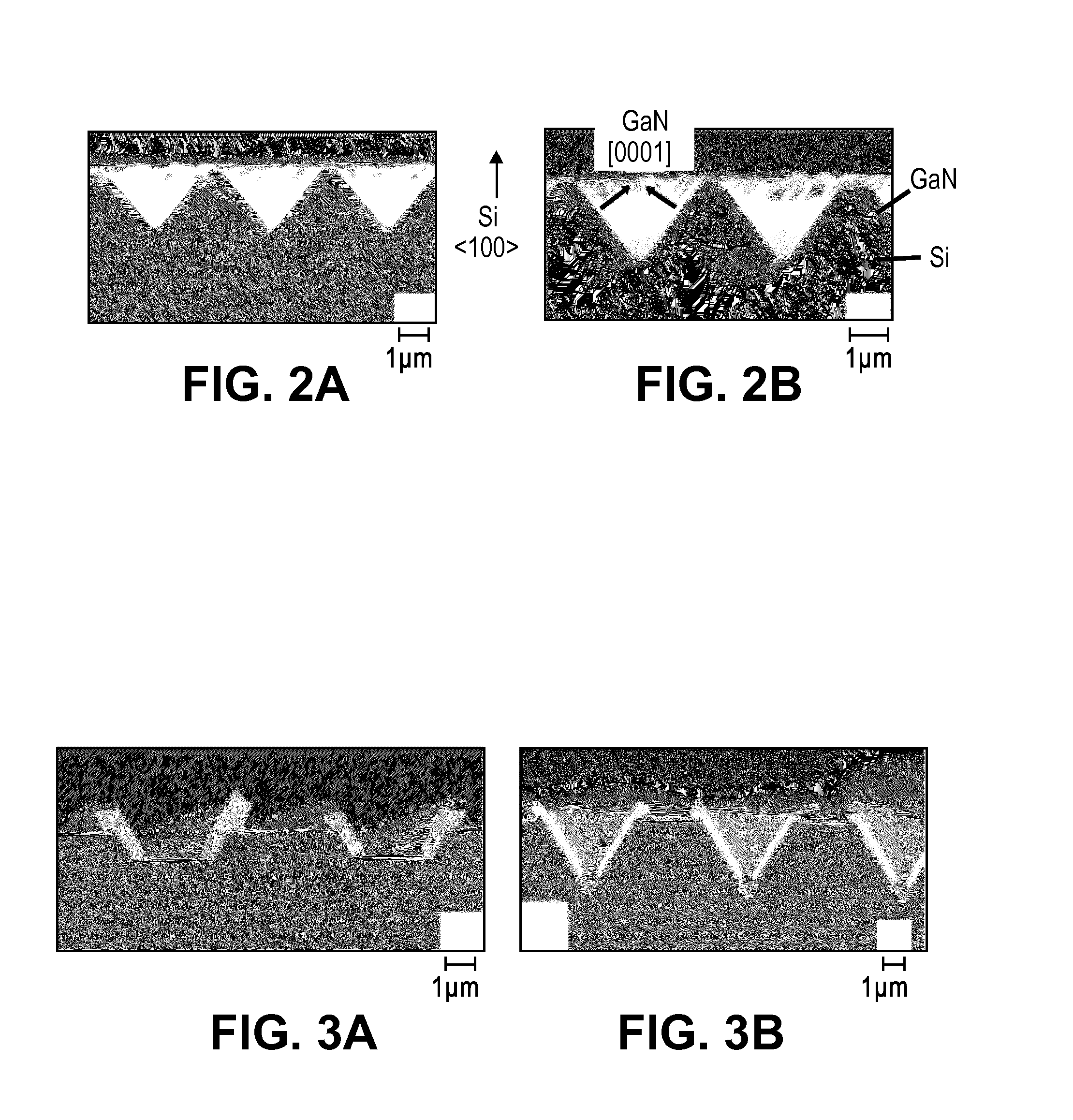

Growth of cubic crystalline phase structure on silicon substrates and devices comprising the cubic crystalline phase structure

ActiveUS20170194476A1Eliminate redshiftHigh hole mobilityOptical wave guidanceSemiconductor/solid-state device manufacturingPhysicsCompound semiconductor

A transistor comprises a substrate comprising a Group III / V compound semiconductor material having a cubic crystalline phase structure positioned on a hexagonal crystalline phase layer having a first region and a second region, the cubic crystalline phase structure being positioned between the first region and the second region of the hexagonal crystalline phase layer. A source region and a drain region are both positioned in the Group III / V compound semiconductor material. A channel region is in the Group III / V compound semiconductor material. A gate is over the channel region. An optional backside contact can also be formed. A source contact and electrode are positioned to provide electrical contact to the source region. A drain contact and electrode are positioned to provide electrical contact to the drain region. Methods of forming transistors are also disclosed.

Owner:RENESSELAER POLYTECHNIC INST +1

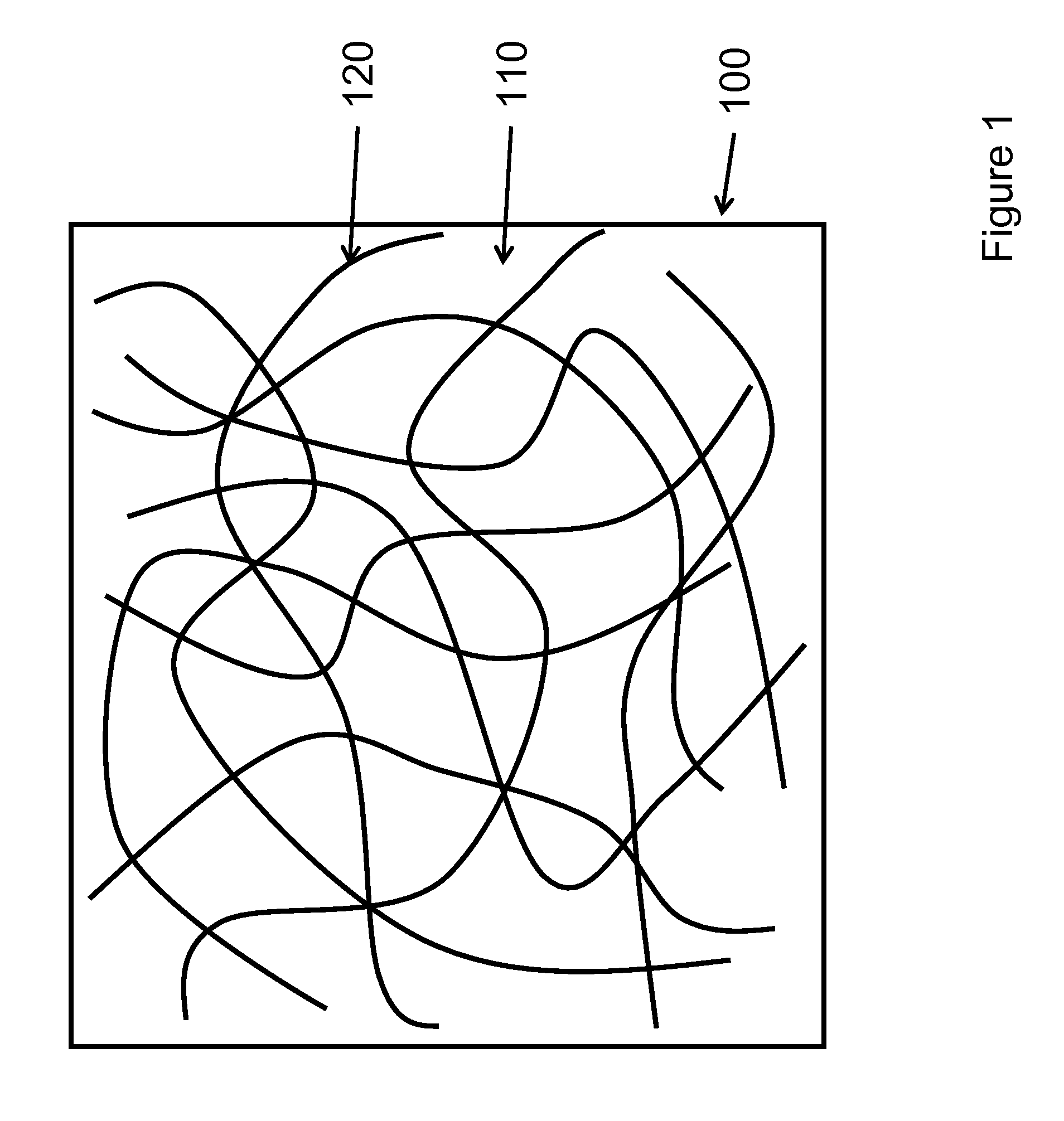

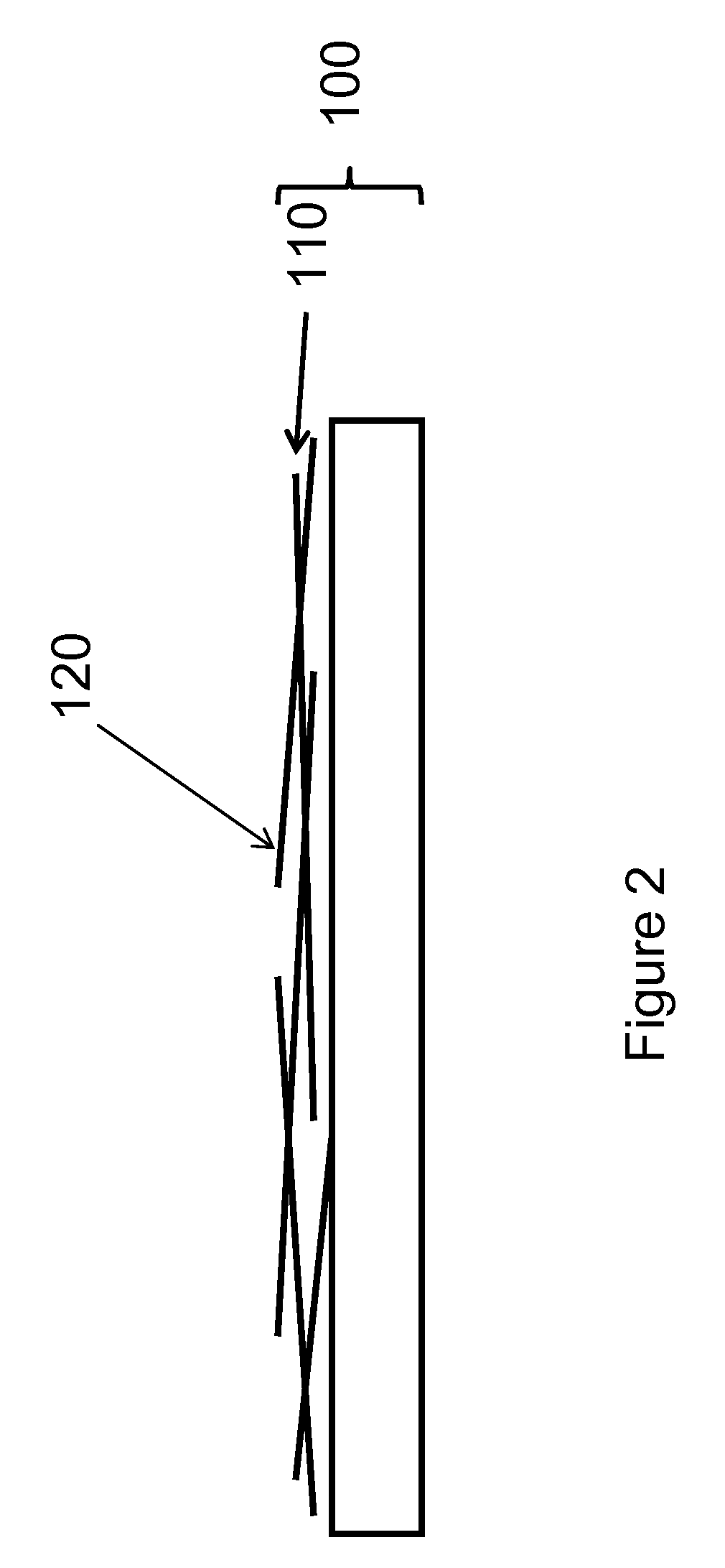

Creating increased mobility in a bipolar device

InactiveUS20060019458A1Improve performanceLow field mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesTensile strainCharge carrier

The mobility of charge carriers in a bipolar (BJT) device is increased by creating compressive strain in the device to increase mobility of electrons in the device, and creating tensile strain in the device to increase mobility of holes in the device. The compressive and tensile strain are created by applying a stress film adjacent an emitter structure of the device and atop a base film of the device. In this manner, the compressive and tensile strain are located in close proximity to an intrinsic portion of the device. A suitable material for the stress film is nitride. The emitter structure may be “T-shaped”, having a lateral portion atop an upright portion, a bottom of the upright portion forms a contact to the base film, and the lateral portion overhangs the base film.

Owner:IBM CORP

Method for preparing diamond substrate for high-heat-conductivity integrated circuit

ActiveCN102157353AHigh hole mobilityImprove performancePolycrystalline material growthSemiconductor/solid-state device manufacturingSurface grindingIntegrated circuit

The invention belongs to the technical field of preparation of substrate materials for semiconductor basic circuits and particularly provides a method for preparing a composite doped diamond-film substrate for a high-heat-conductivity electronic device. The method comprises the following steps of: firstly carrying out high-density diamond nucleation growth on a metal substrate or a graphite transition layer substrate, depositing an element-doped diamond film, and carrying out the growth of the diamond film to reach a required thickness; carrying out vacuum heat treatment on a diamond gradient composite substrate after demoulding for homogenizing and destressing; and carrying out double-surface grinding and polishing on the doped diamond gradient composite substrate and meeting the requirements on the surface finish quality and the thickness of a substrate for a semiconductor integrated circuit. The invention has the advantages that a boron-doped diamond film has high electron and hole mobility; a boron-undoped diamond film is taken as a substrate support of the doped diamond film; and the heat conductivity of the relatively thicker boron-undoped diamond film is five times of that of copper, thus the heat can be transferred to a radiator in time.

Owner:UNIV OF SCI & TECH BEIJING

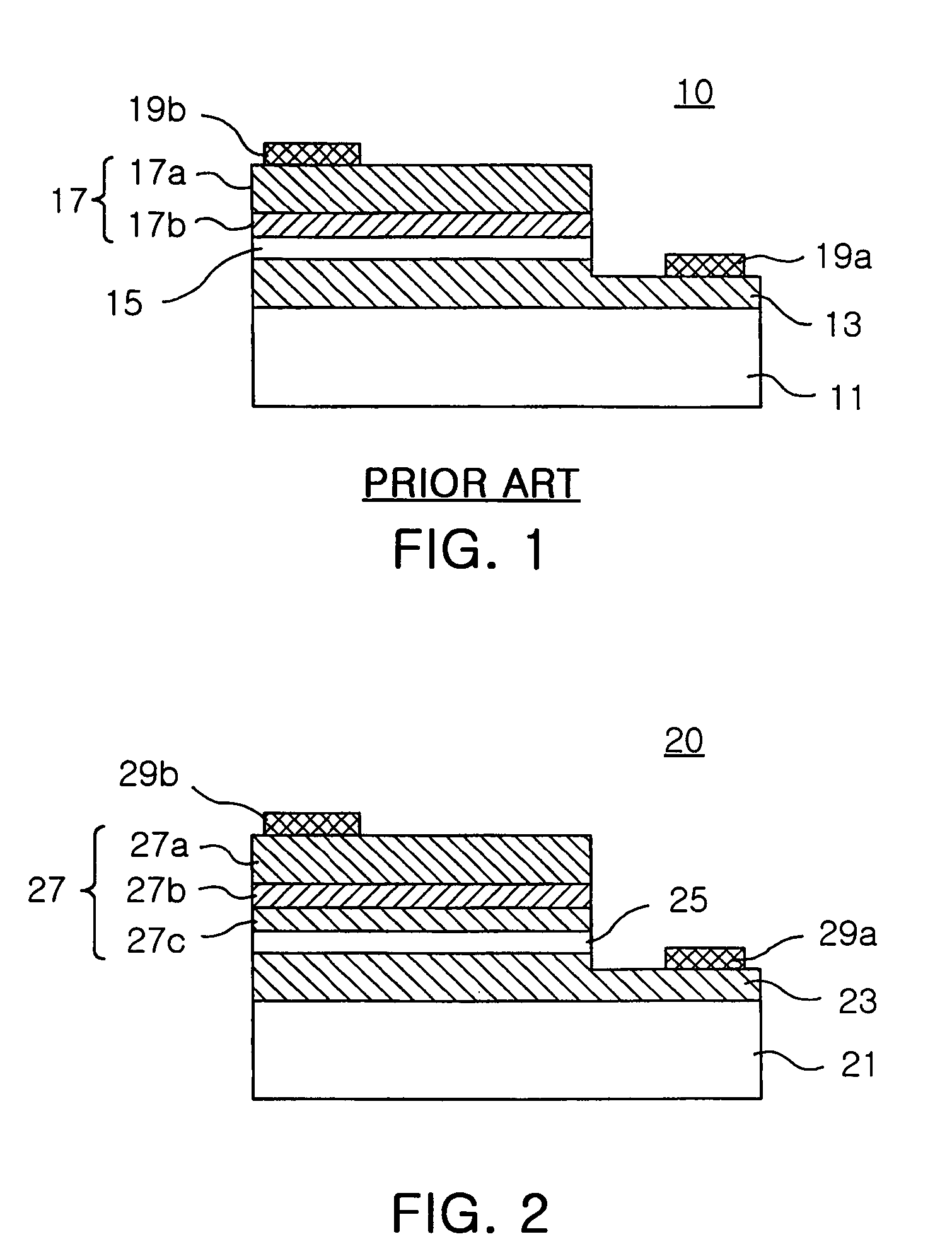

Nitride based semiconductor light-emitting device

InactiveUS20050179027A1Improve hole injection efficiencyImprove injection efficiencyNanoopticsPackagingGalliumActive layer

Disclosed herein is a nitride-based semiconductor light-emitting device. The nitride-based semiconductor light-emitting device comprises an n-type clad layer made of n-type Alx1Iny1Ga(1−x1−y1)N (where 0≦x1≦1, 0≦y1≦1, and 0≦x1+y1≦1), a multiple quantum well-structured active layer made of undoped InAGa1−AN (where 0<A<1) formed on the n-type clad layer, and a p-type clad layer formed on the active layer wherein the p-type clad layer includes at least a first layer made of p-type Iny2Ga1−y2N (where 0≦y2<1) formed on the active layer and a second layer made of p-type Alx3Iny3Ga(1−x3−y3)N (where 0<x3≦1, 0≦y3≦1, and 0<x3+y3≦1) formed on the first layer.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

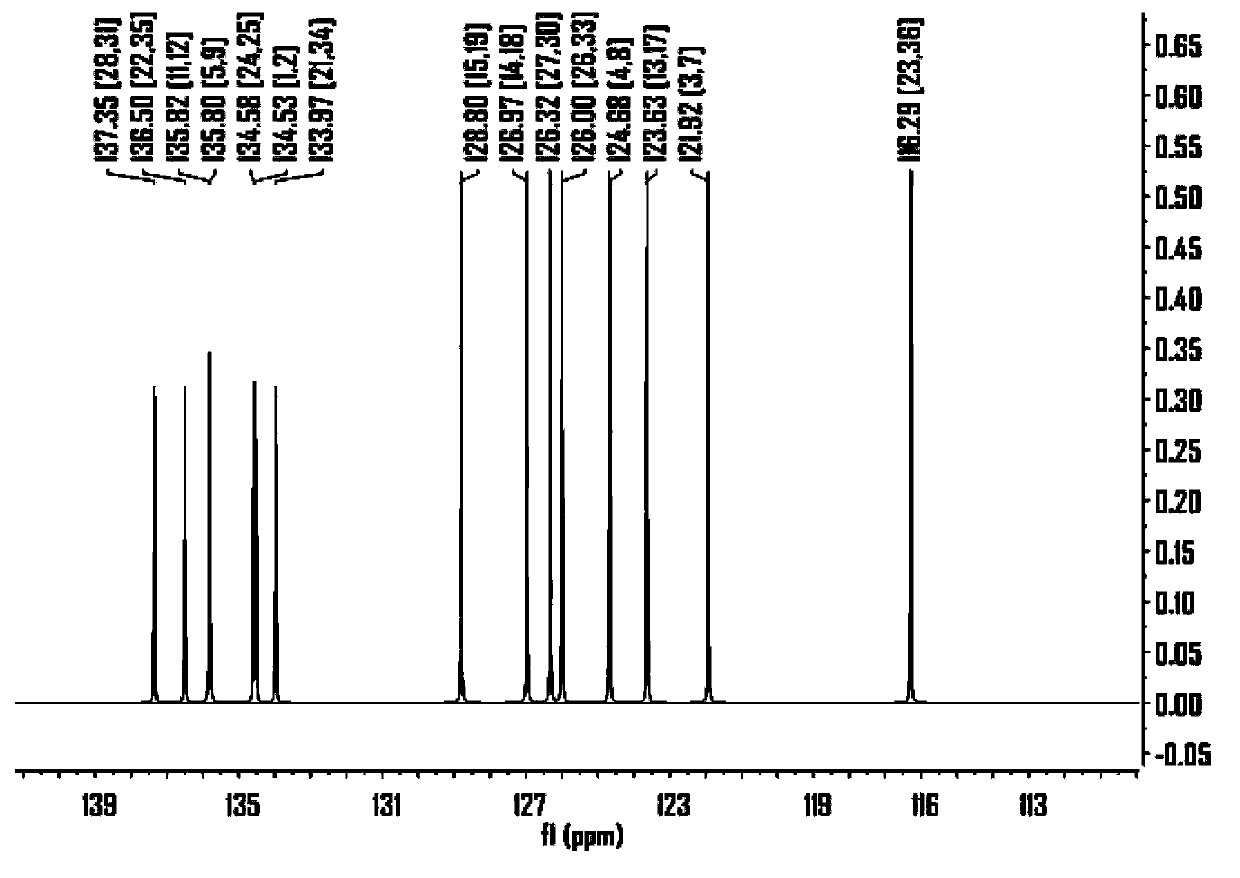

Naphthodithiophene derivative organic electroluminescent material and application thereof

ActiveCN103664995AHigh hole mobilityOrganic chemistrySolid-state devicesFluorescenceOrganic electroluminescence

The invention provides novel compounds, of which the structures are represented as Formula (I), Formula (II), Formula (III) and Formula (IV), wherein Ar1-Ar6 are selected from C1-C20 aliphatic alkyl groups, C4-C30 aromatic rings, C4-C30 aromatic heterocyclic rings, C4-C30 condensed heterocyclic ring aromatics, C4-C30 arylamino or triarylamino groups or C4-C30 aryloxy groups. The compounds are used as a hole injection material, hole transmission material or fluorescence body material in organic electroluminescent devices.

Owner:KUNSHAN VISIONOX DISPLAY TECH +2

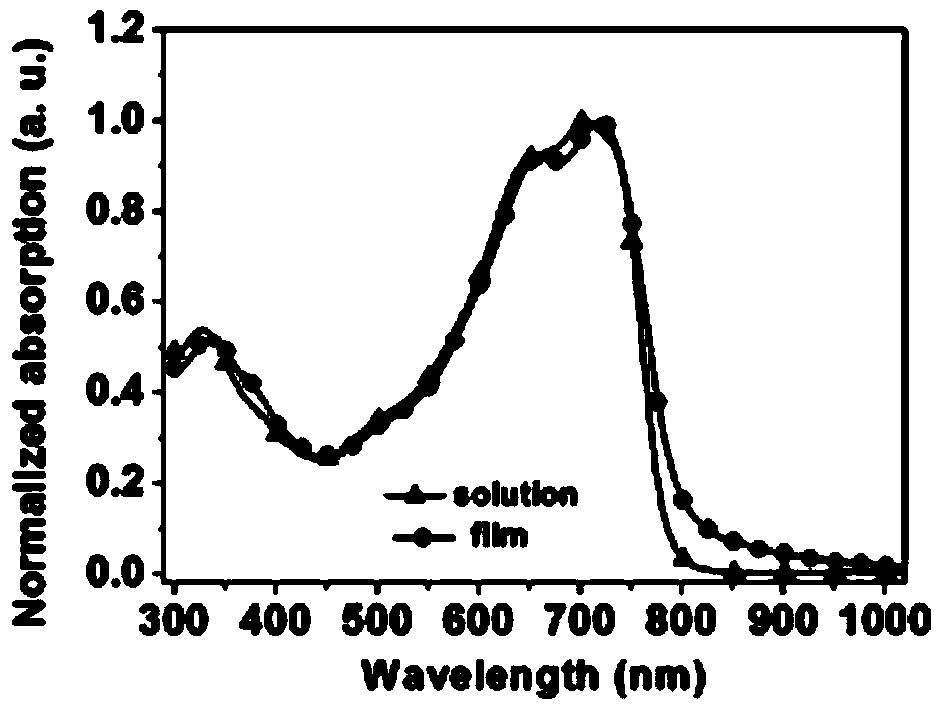

Sulfur-containing substituted two-dimensional conjugated polymer as well as preparation method and application thereof

ActiveCN103833991AHigh hole mobilityImprove photoelectric conversion efficiencySolid-state devicesSemiconductor/solid-state device manufacturingPolymer scienceSulfur containing

The invention provides a two-dimensional conjugated polymer as shown in a formula (I). The invention also provides a polymer-containing semi-conductor blend, a preparation method of the polymer and an application of the polymer in organic photoelectric fields such as polymer solar cells and polymer field-effect tubes. The energy conversion efficiency of the two-dimensional conjugated polymer provided by the invention is greatly improved, so that the application of the two-dimensional conjugated polymer in the organic photoelectric fields is expanded.

Owner:INST OF CHEM CHINESE ACAD OF SCI

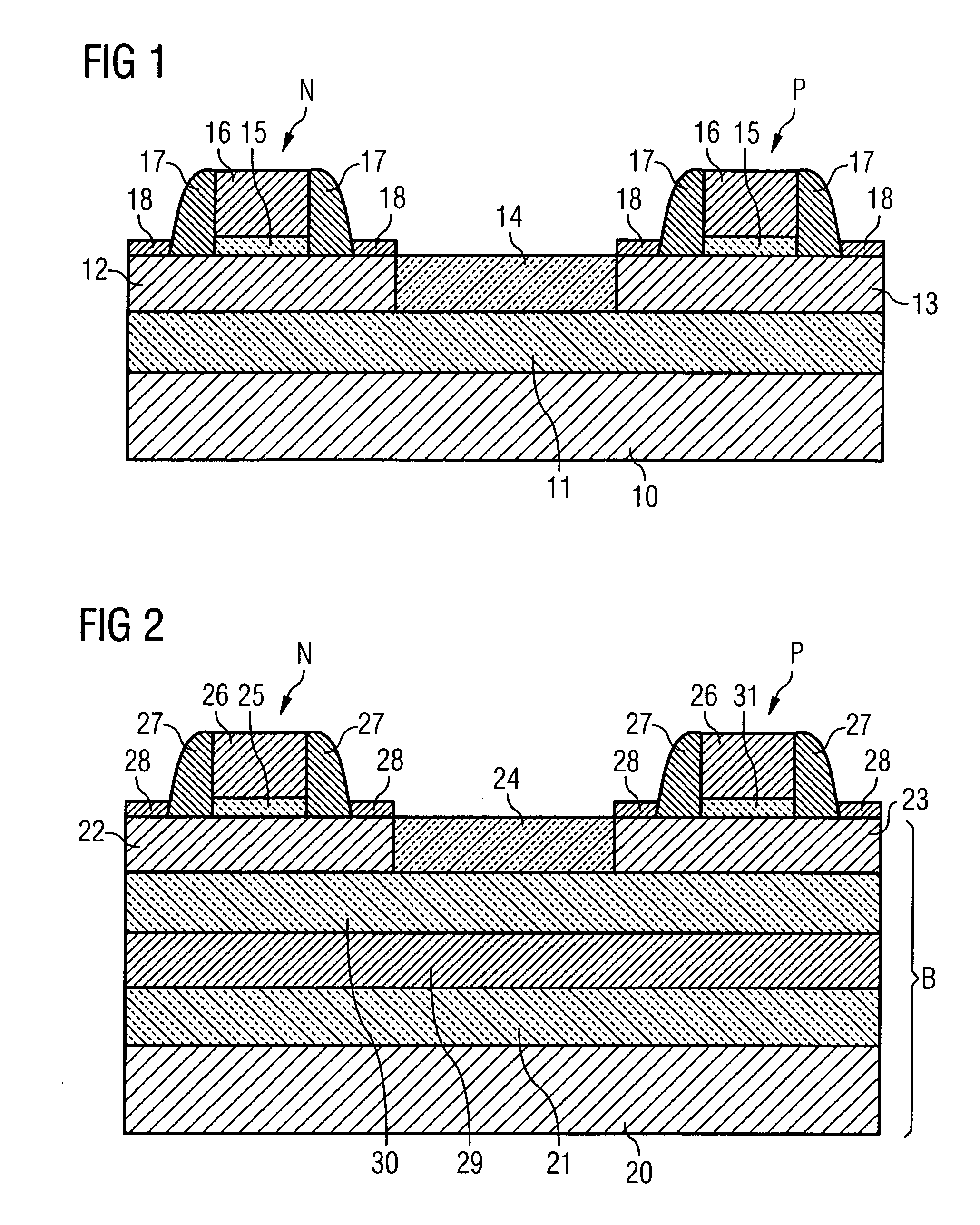

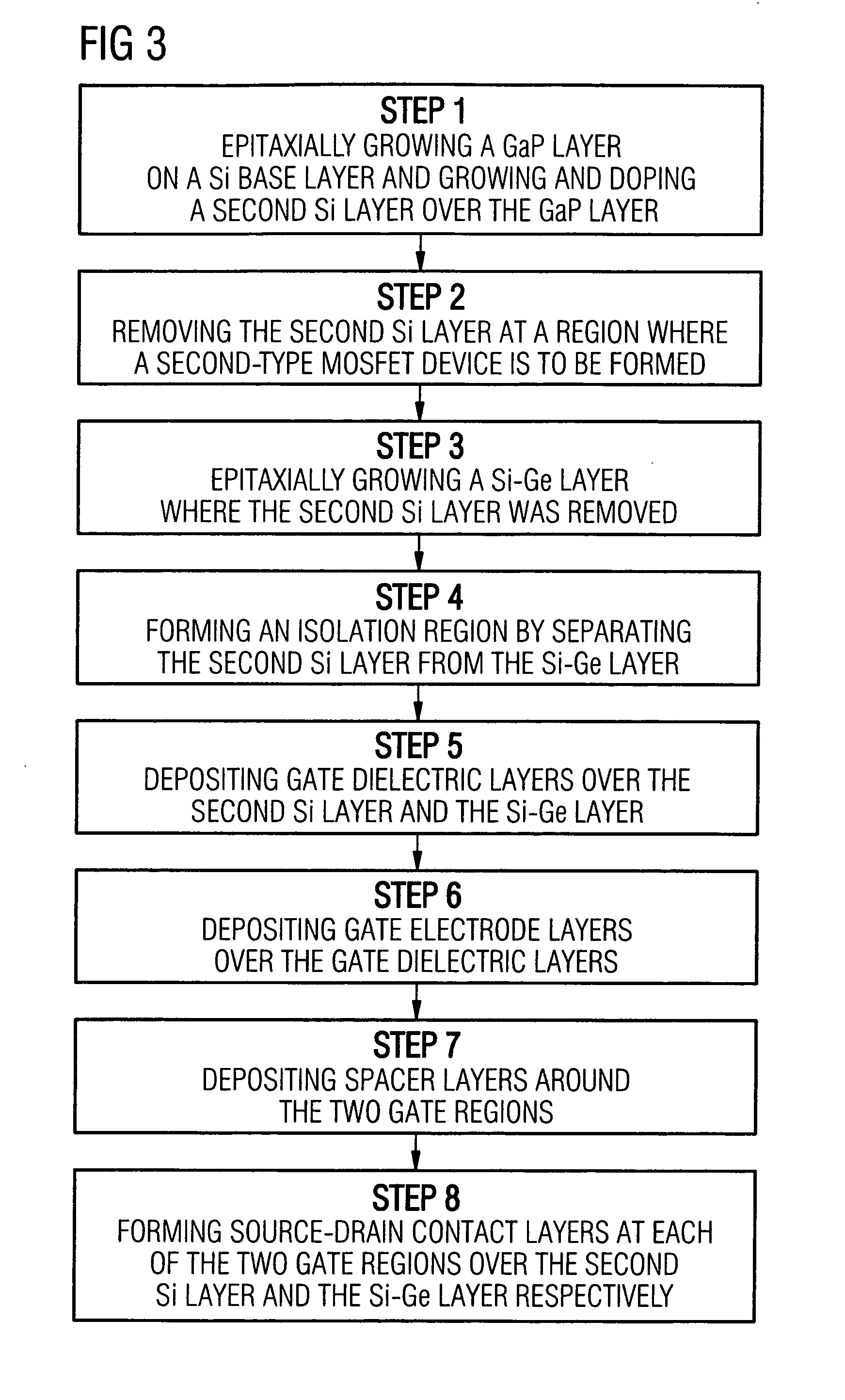

Semiconductor device and a method of manufacturing such a semiconductor device

InactiveUS20070252216A1Improve performanceImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesCMOSSemiconductor materials

A semiconductor device, specifically a Complementary Metal Oxide Semiconductor (CMOS) device, has a substrate on which are formed first and second field effect transistors. Each of the field effect transistors comprises a source-drain region, a channel of either an n-type or a p-type conductivity semiconductor material formed on the substrate, a first gate region, and a first dielectric region that separates the first channel from the first gate region. However, dissimilar semiconductor materials are used to form the channel regions of the first and second field effect transistors so that high electron and hole mobility can be achieved.

Owner:INFINEON TECH AG

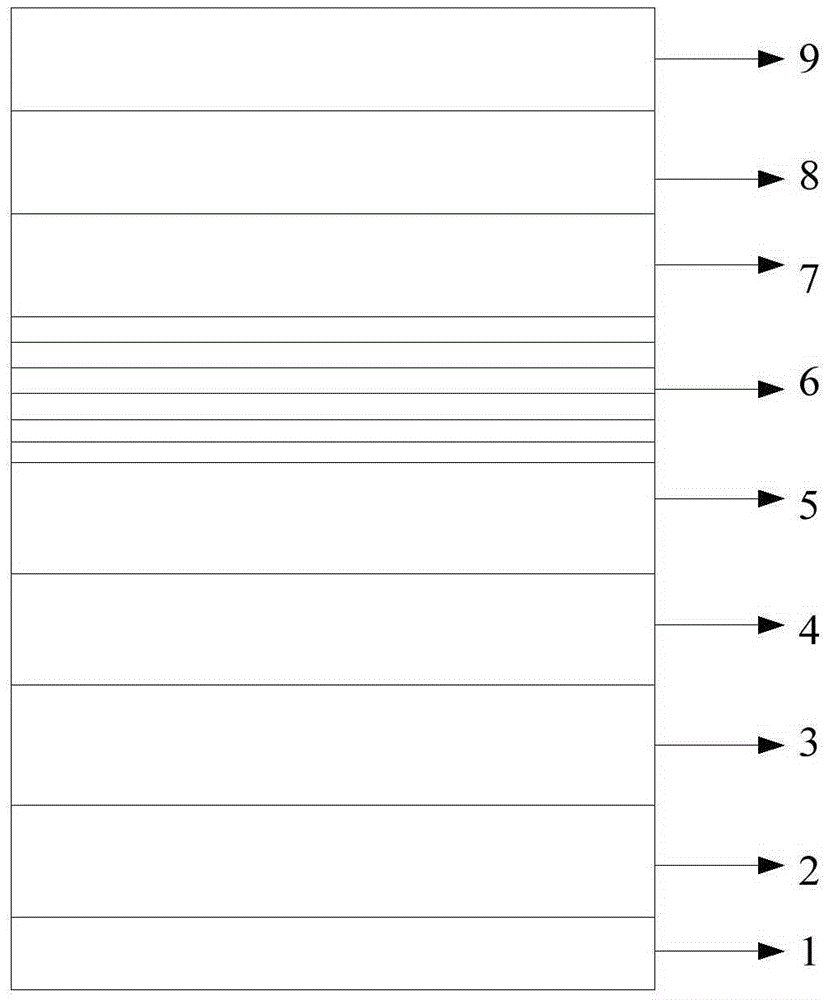

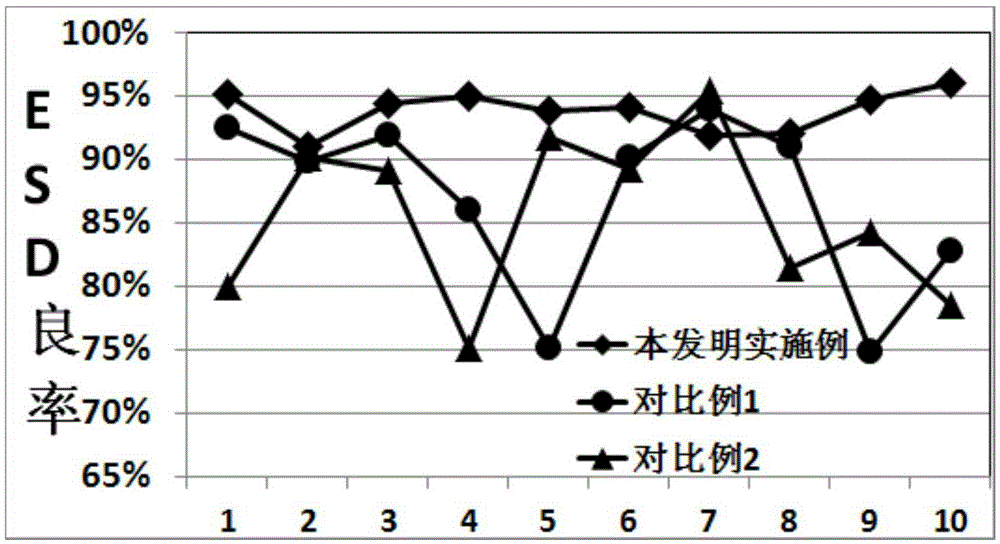

LED epitaxial layer growth method and LED chip acquired in method

ActiveCN105390574AImprove antistatic performanceHigh hole mobilityPolycrystalline material growthFrom chemically reactive gasesOptoelectronicsElectron blocking layer

The invention discloses an LED epitaxial layer growth method and an LED chip acquired in the method. To grow a Mg-doped P-type GaN layer, at an N2 atmosphere, a first Mg-doped P-type GaN layer with a thickness of 40nm to 80nm grows on an electron blocking layer; temperature of a reaction chamber rises to 1070 to 1140 DEG C, the reaction chamber has a pressure of 400mbar to 700mbar, and at an H2 and N2 mixed atmosphere, a second Mg-doped P-type GaN layer grows on the first P-type GaN layer; temperature of the reaction chamber rises to 1070 to 1140 DEG C, the reaction chamber has a pressure of 200mbar to 400mbar, and at an H2 and N2 mixed atmosphere, a third Mg-doped P-type GaN layer grows on the second P-type GaN layer. Thus, the antistatic performance and the light emitting efficiency of the LED device are improved.

Owner:XIANGNENG HUALEI OPTOELECTRONICS

Growth of cubic crystalline phase strucure on silicon substrates and devices comprising the cubic crystalline phase structure

ActiveUS20150108427A1Eliminate redshiftHigh hole mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesCrystallographySemiconductor materials

A semiconductor device is disclosed. The semiconductor device includes a substrate comprising a groove. A buffer layer is formed on a surface of the groove. The buffer layer comprising at least one material chosen from AIN, GaN or AlxGa1-xN, where x is between zero and one. An epitaxially grown semiconductor material is disposed over the buffer layer, at least a portion of the epitaxially grown semiconductor material having a cubic crystalline phase structure. Methods of forming the semiconductor devices are also taught.

Owner:STC UNM +1

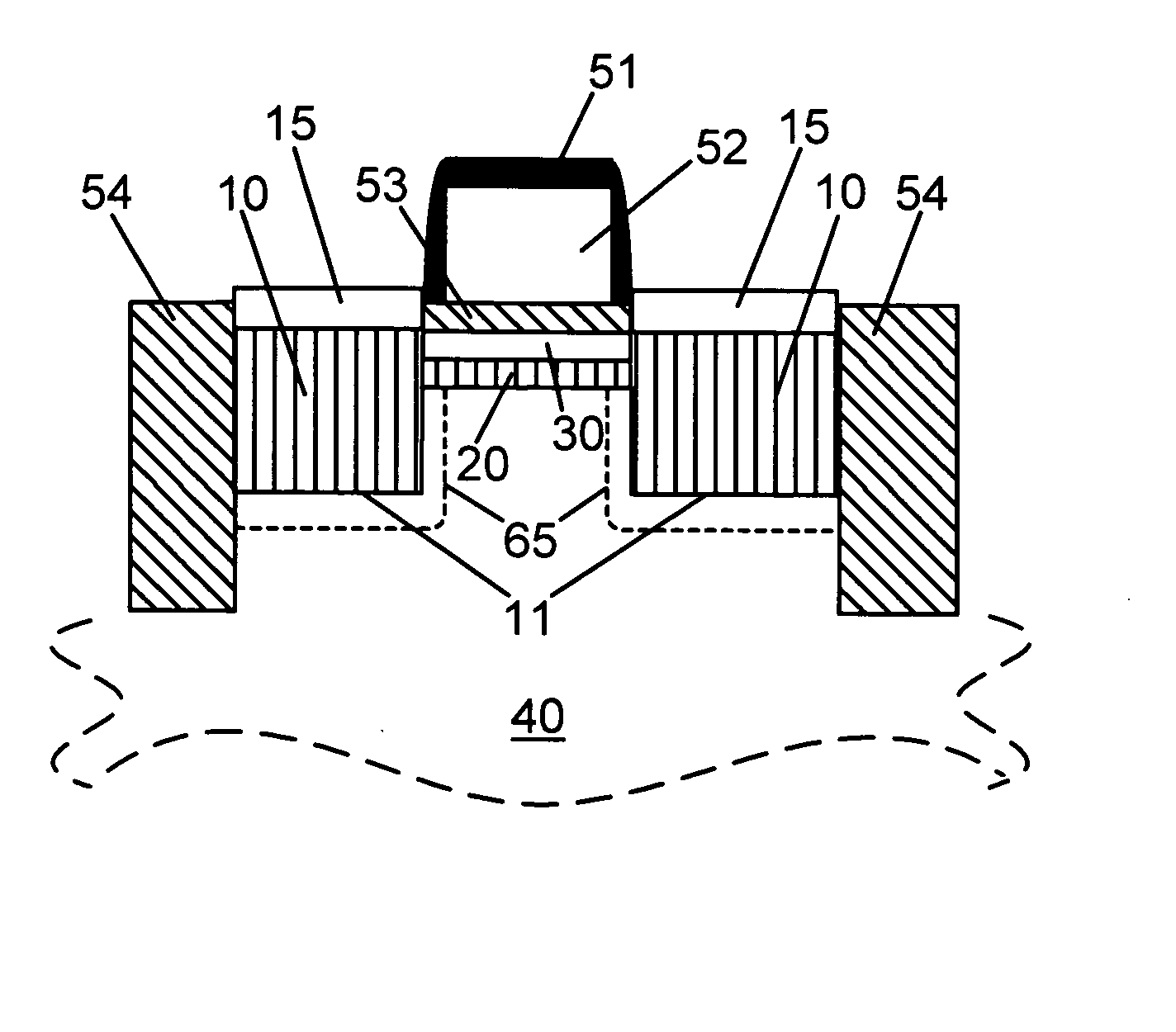

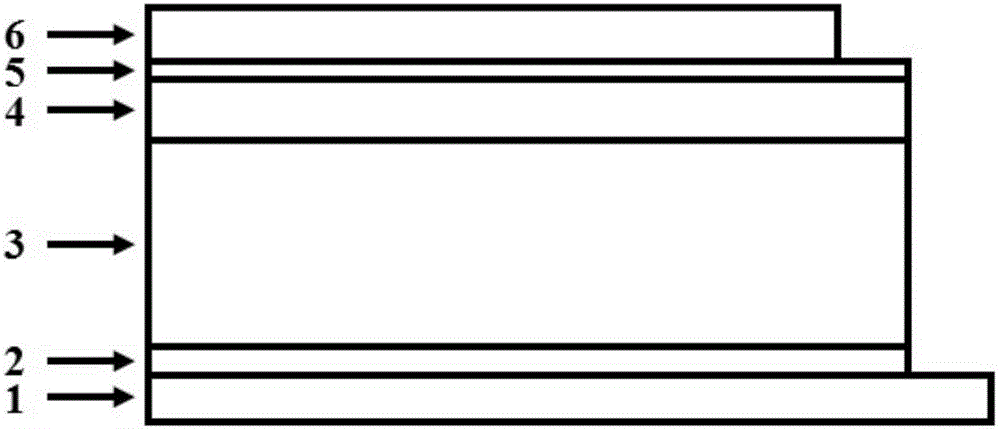

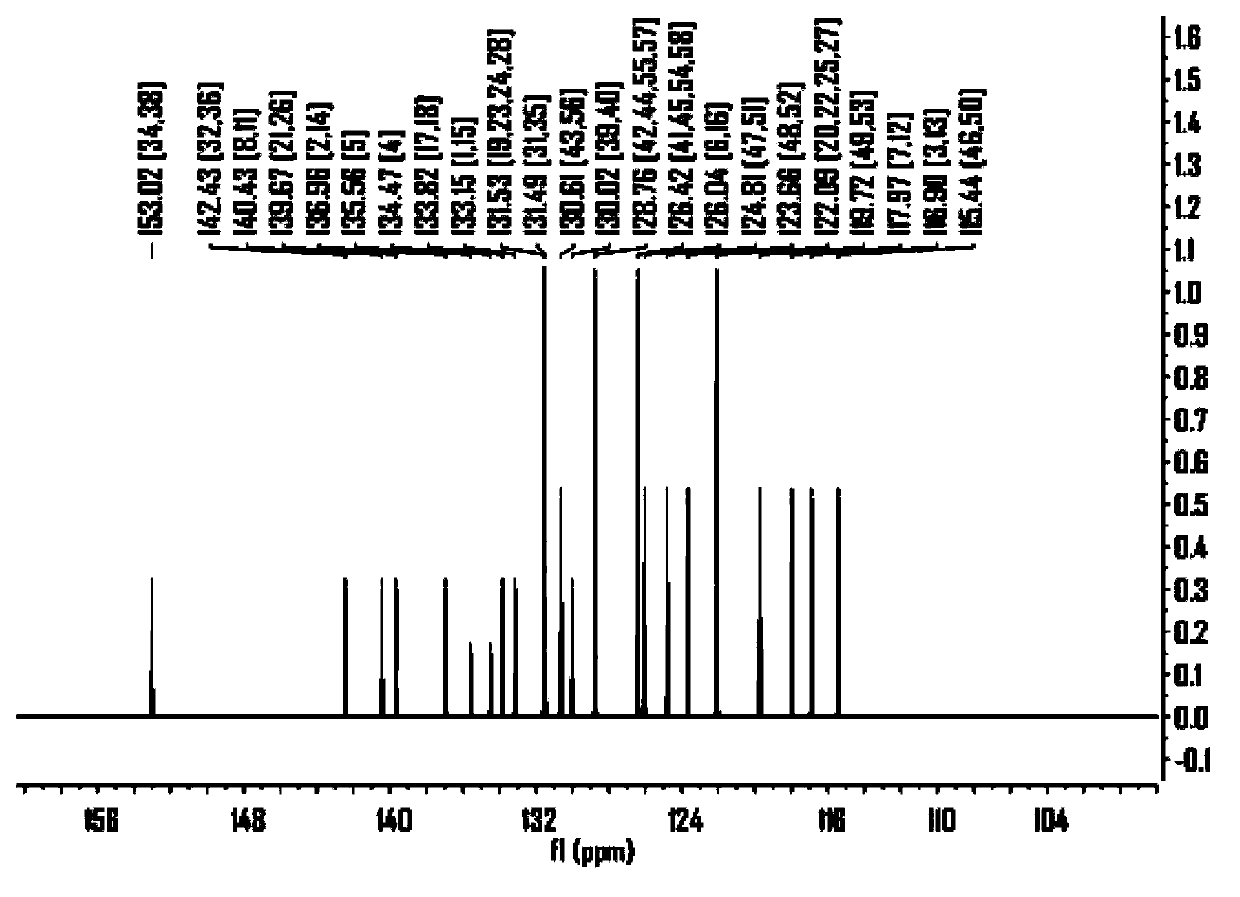

Spiro [fluorene-9, 9-xanthene]-class hole transport material and application thereof

InactiveCN106977491AEasy to separateGuaranteed normal transmissionOrganic chemistrySolid-state devicesPerovskite solar cellRedox

A spiro [fluorene-9, 9-xanthene]-class hole transport material and application thereof are disclosed, the spiro [fluorene-9, 9-xanthene]-class hole transport material is an aromatic-amine compound using spiro [fluorene-9, 9-xanthene] as a core-shell structure, the aromatic-amine compound has one or more than 1 N nuclear structure unit, two adjacent N nuclear structure units are connected by a connecting group, the N nuclear structure unit meets the general formula F, and Rx, Ry and Rz are substitutes or connecting groups. Compared with similar products in the prior art, the spiro [fluorene-9, 9-xanthene]-class hole transport material is the aromatic-amine compound using the spiro [fluorene-9, 9-xanthene] as the core-shell structure, has higher glass transition temperature and thermal decomposition temperature, higher redox potential, and higher hole mobility and conductivity, and has great application value and broad application prospects in the field of perovskite solar cells and other organic electronic devices.

Owner:孙立成 +1

Triarylated amine derivative and organic electroluminescence device with same

InactiveCN108341795AIncreased conjugated systemHigh hole mobilityOrganic chemistrySolid-state devicesOrganic electroluminescencePerylene derivatives

The invention discloses a triarylated amine derivative and an organic electroluminescence device with the same, and relates to the technical field of organic photoelectric materials. The triarylated amine derivative has a large conjugated system, thereby having high hole mobility and presenting good hole transmissibility; in addition, the triarylated amine derivative has high thermal stability anddissolubility and is beneficial for material film forming. The organic electroluminescence device comprises a cathode, an anode and one or more organic matter layers. The organic matter layers are located between the cathode and the anode. At least one of the organic matter layers contains the triarylated amine derivative. The organic electroluminescence device has low driving voltages, high light-emitting efficiency, light-emitting luminance and long service life.

Owner:CHANGCHUN HYPERIONS TECH CO LTD

![Spiro [fluorene-9, 9-xanthene]-class hole transport material and application thereof Spiro [fluorene-9, 9-xanthene]-class hole transport material and application thereof](https://images-eureka.patsnap.com/patent_img/91946f2e-150a-41eb-a46c-681761800a90/HDA0001219050130000011.png)

![Spiro [fluorene-9, 9-xanthene]-class hole transport material and application thereof Spiro [fluorene-9, 9-xanthene]-class hole transport material and application thereof](https://images-eureka.patsnap.com/patent_img/91946f2e-150a-41eb-a46c-681761800a90/HDA0001219050130000012.png)

![Spiro [fluorene-9, 9-xanthene]-class hole transport material and application thereof Spiro [fluorene-9, 9-xanthene]-class hole transport material and application thereof](https://images-eureka.patsnap.com/patent_img/91946f2e-150a-41eb-a46c-681761800a90/HDA0001219050130000021.png)