Patents

Literature

557results about How to "Improve leakage current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

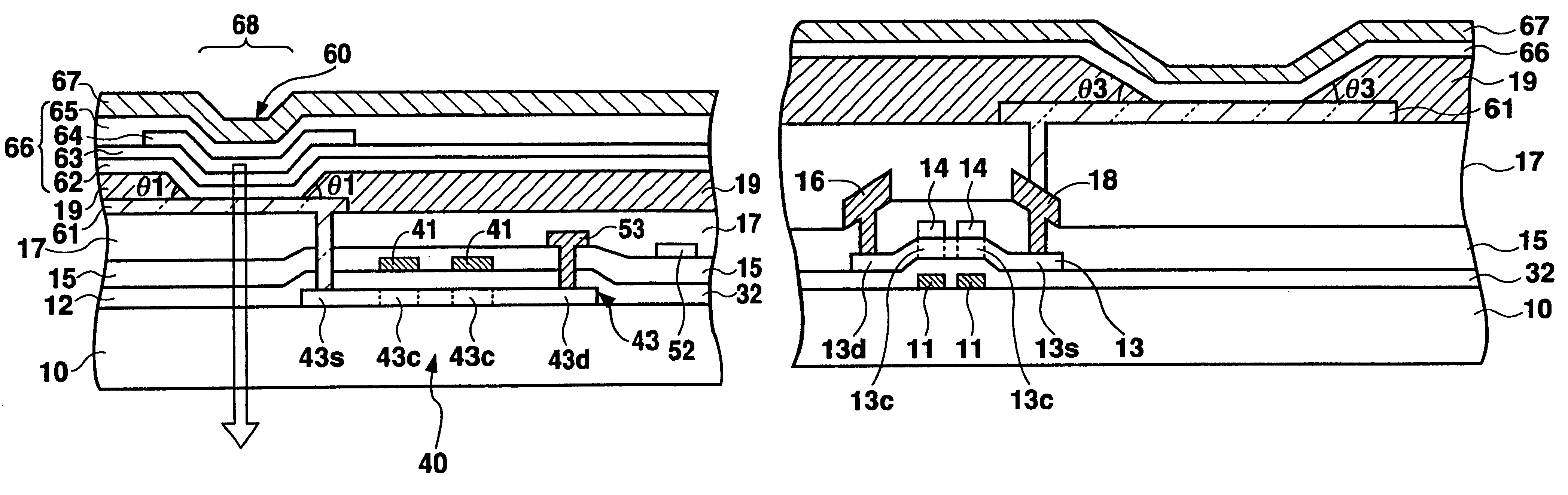

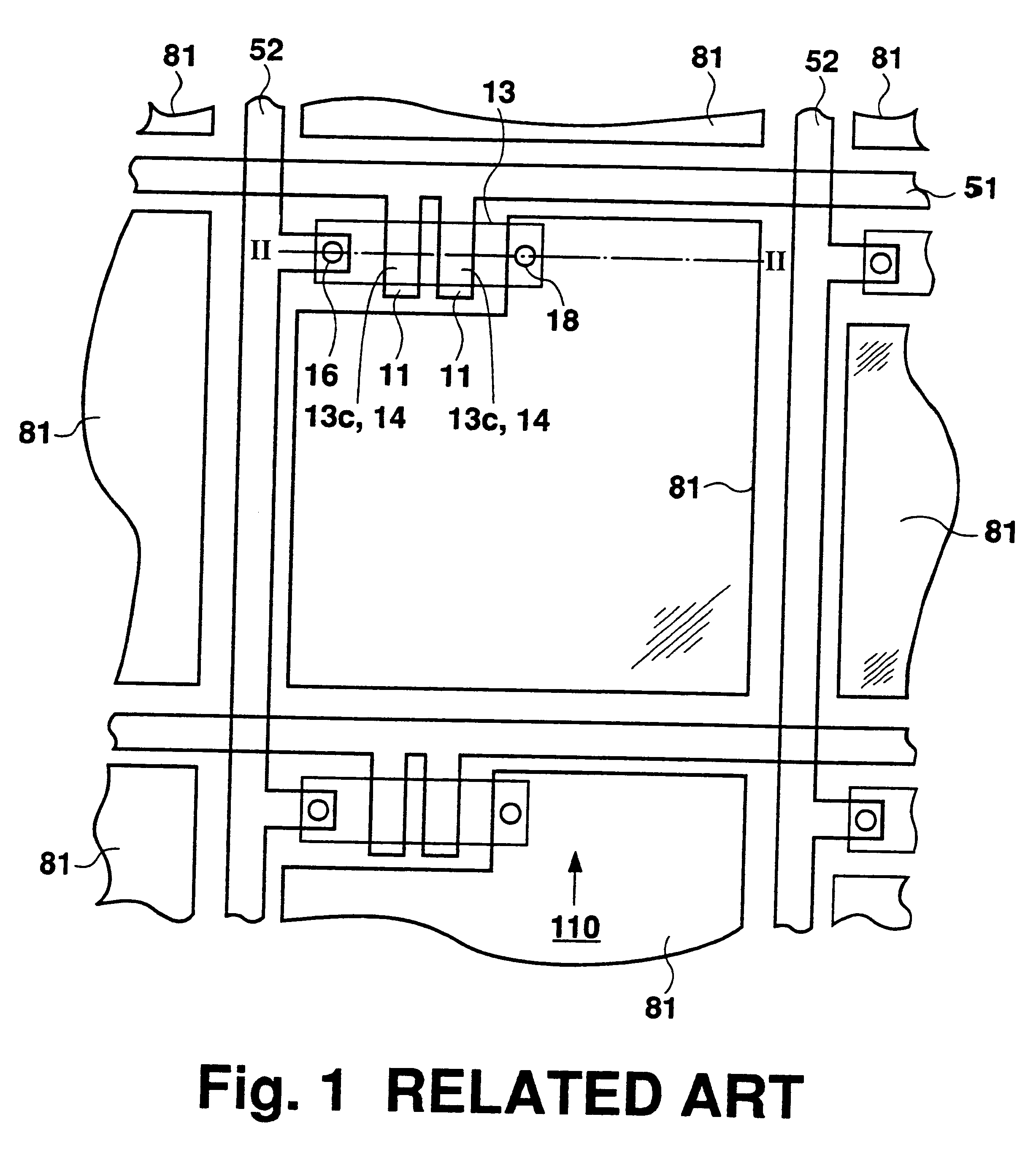

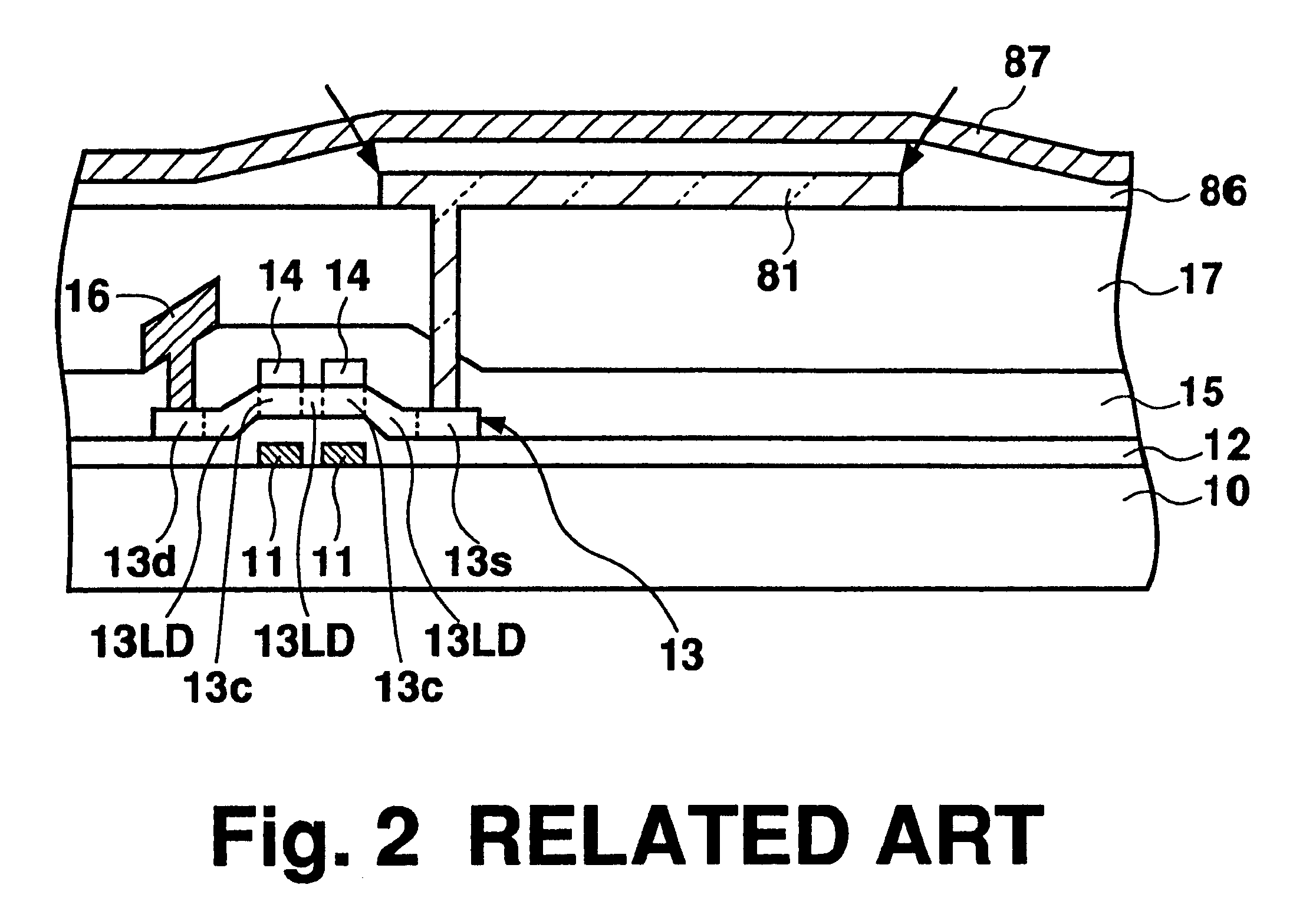

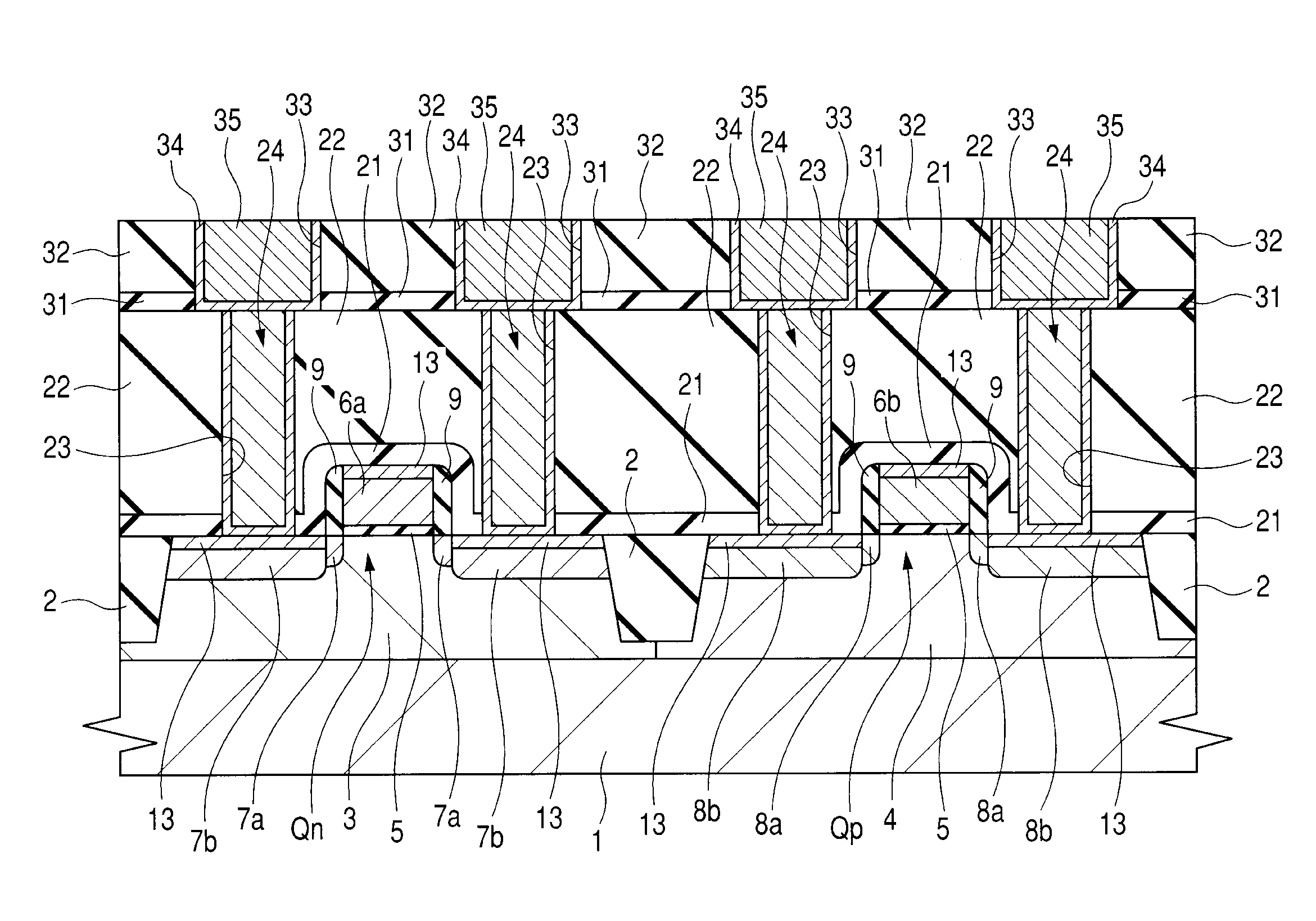

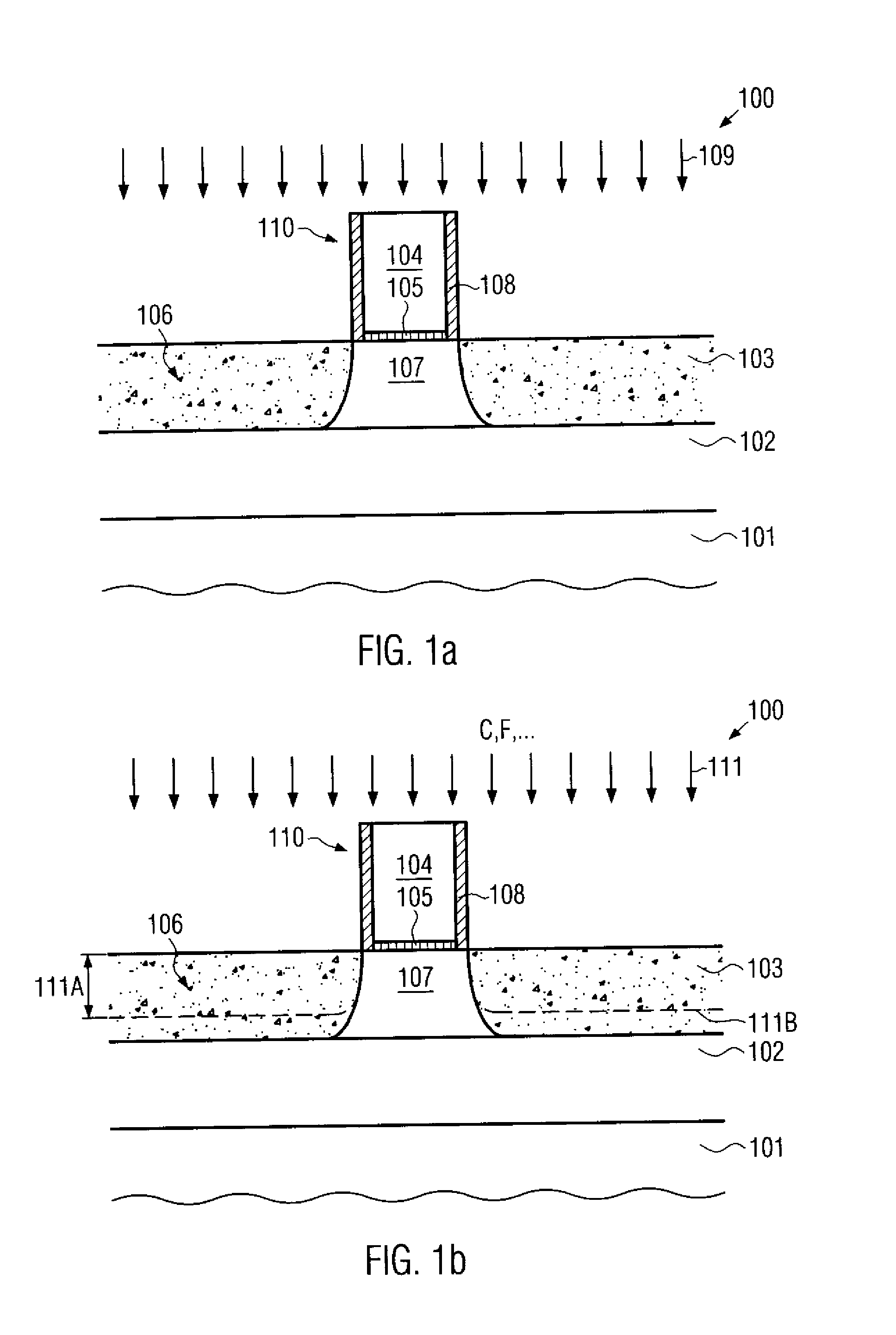

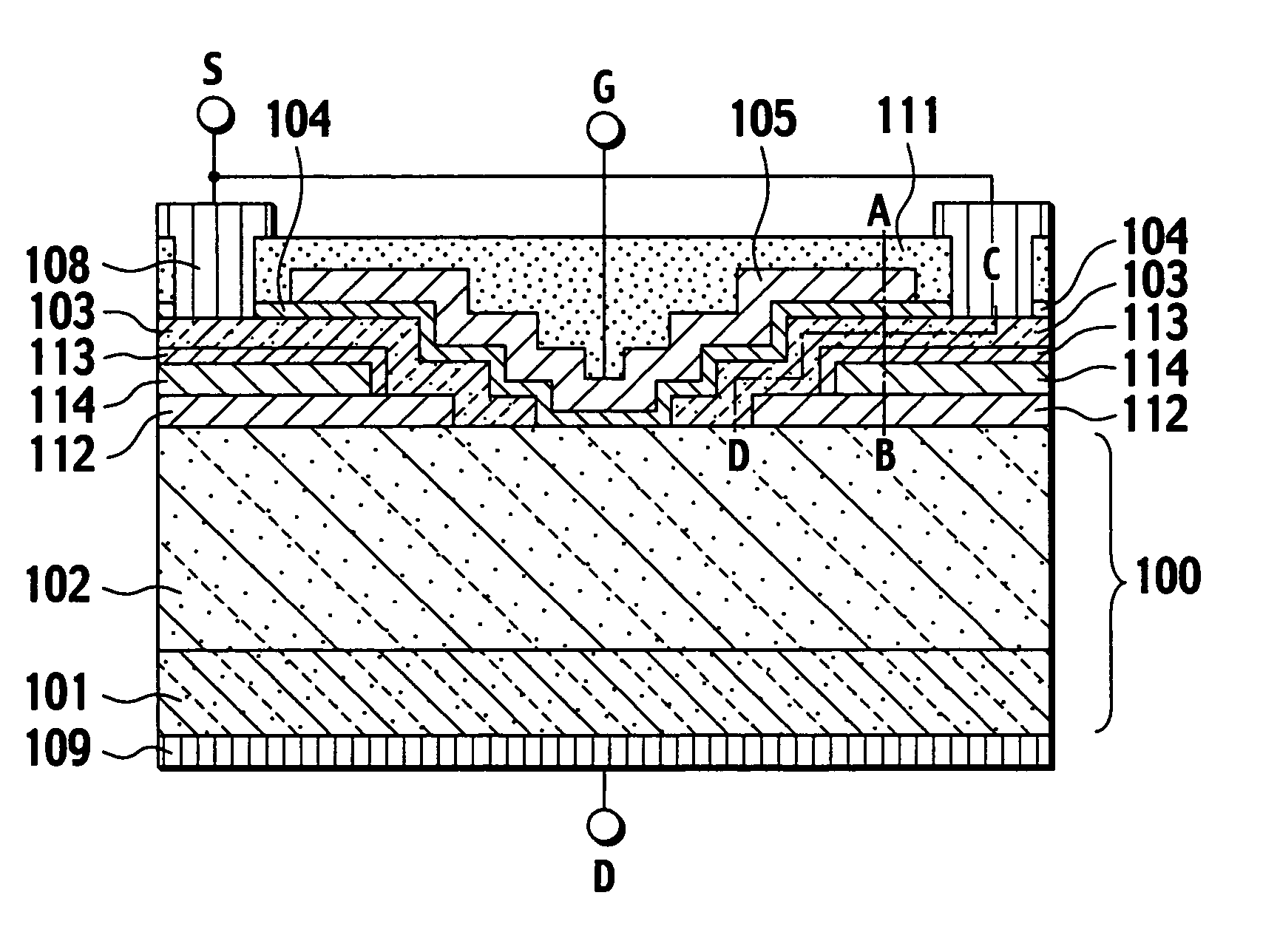

Emissive element and display device using such element

InactiveUS6246179B1Avoid it happening againLayer deterioratesDischarge tube luminescnet screensStatic indicating devicesDisplay deviceOptoelectronics

An EL element (60) comprises an anode (61), a cathode (67), and an emissive element layer (66) interposed between the two electrodes. A TFT is connected to the anode (61) at its source electrode (33s). The peripheral portion of the anode (61) and the entire region over the TFT are covered with a planarizing insulating film (17), and a part of the exposed portion of the anode (61) is connected to the emissive element layer (66). According to the above arrangement, it is possible to prevent disconnection of the emissive element layer (66) which may be caused by an uneven surface created by the thickness of the anode (61), and to avoid formation of a short circuit between the anode (61) and the cathode (67).

Owner:SANYO ELECTRIC CO LTD

Methods of atomic layer deposition of hafnium oxide / erbium oxide bi-layer as advanced gate dielectrics

InactiveUS20130313656A1Improve electrical performanceFew defectSemiconductor/solid-state device manufacturingChemical vapor deposition coatingGate dielectricHafnium

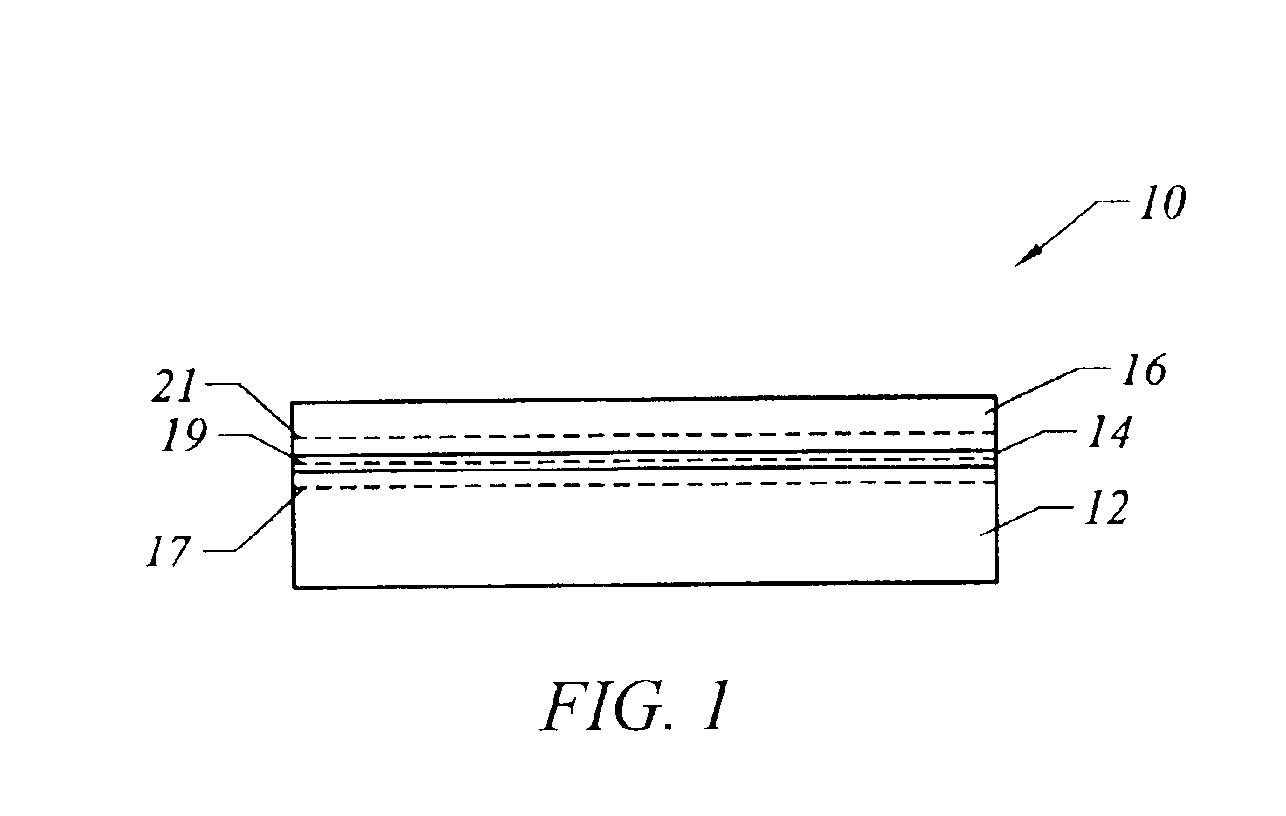

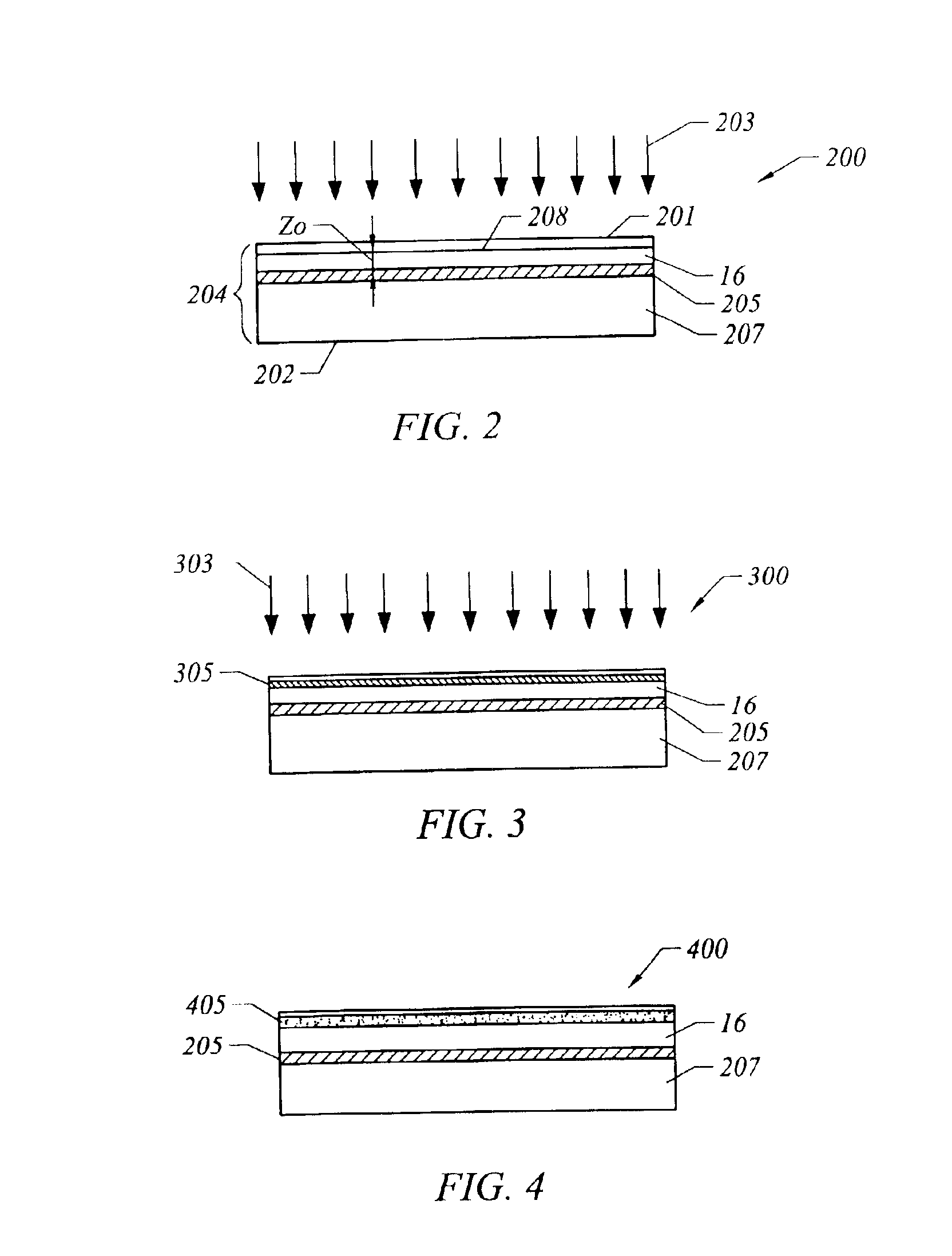

Provided is a two-step ALD deposition process for forming a gate dielectric involving an erbium oxide layer deposition followed by a hafnium oxide layer deposition. Hafnium oxide can provide a high dielectric constant, high density, large bandgap and good thermal stability. Erbium oxide can act as a barrier against oxygen diffusion, which can lead to increasing an effective oxide thickness of the gate dielectric and preventing hafnium-silicon reactions that may lead to higher leakage current.

Owner:INTERMOLECULAR

Method for forming aluminum nitride-based film by PEALD

ActiveUS9711345B2Improve leakage currentSemiconductor/solid-state device detailsSolid-state devicesPhysical chemistryThin membrane

Owner:ASM IP HLDG BV

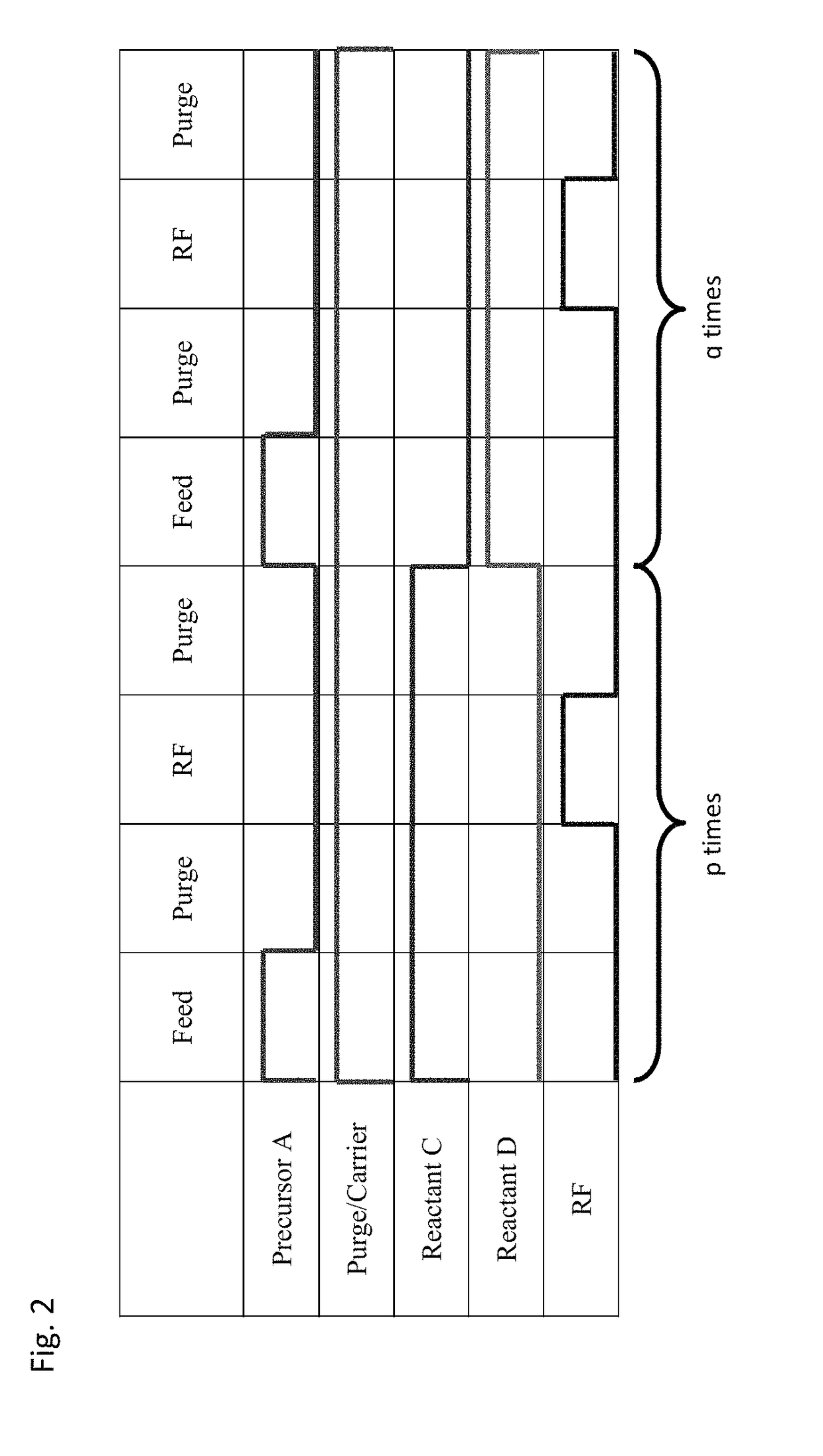

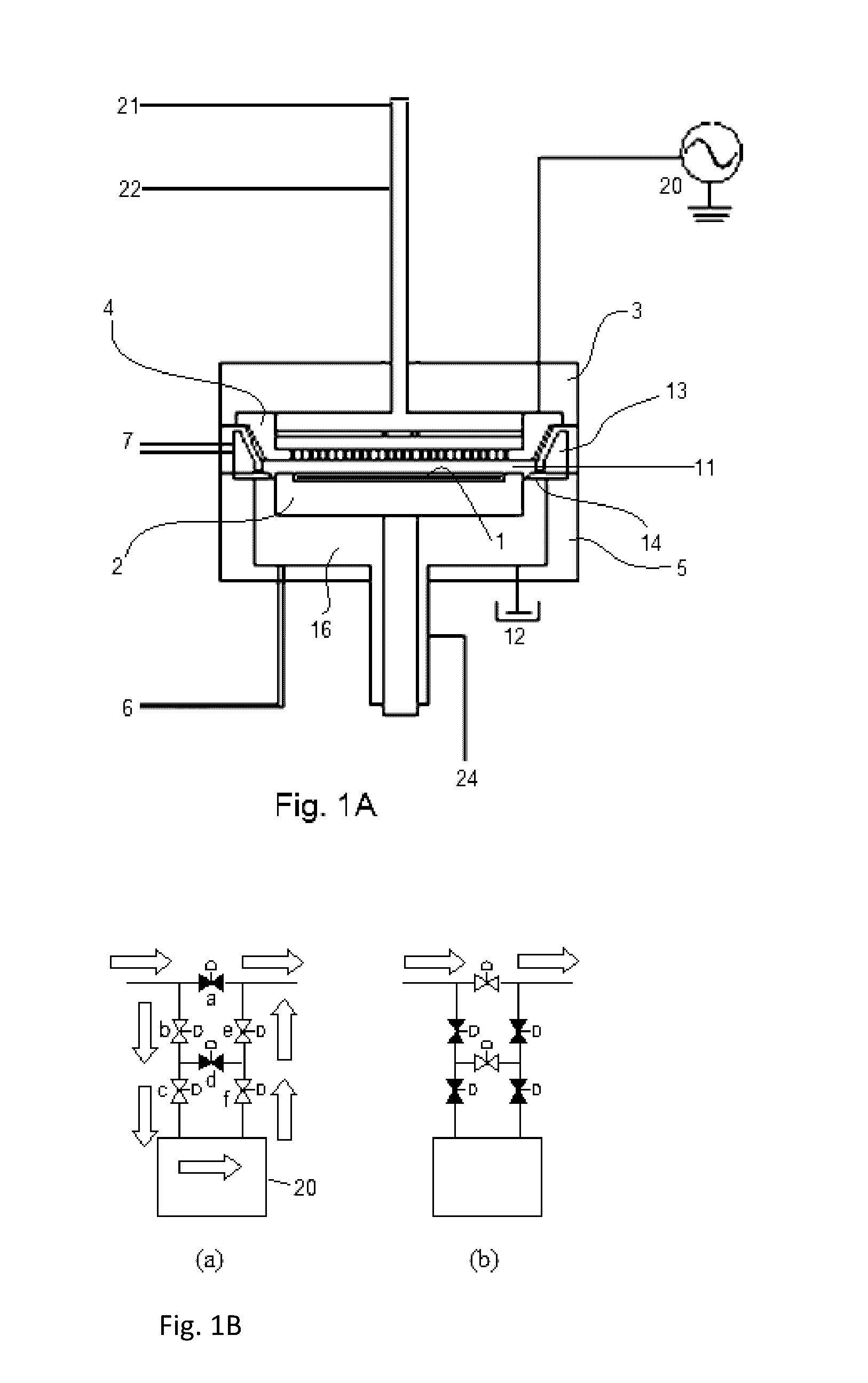

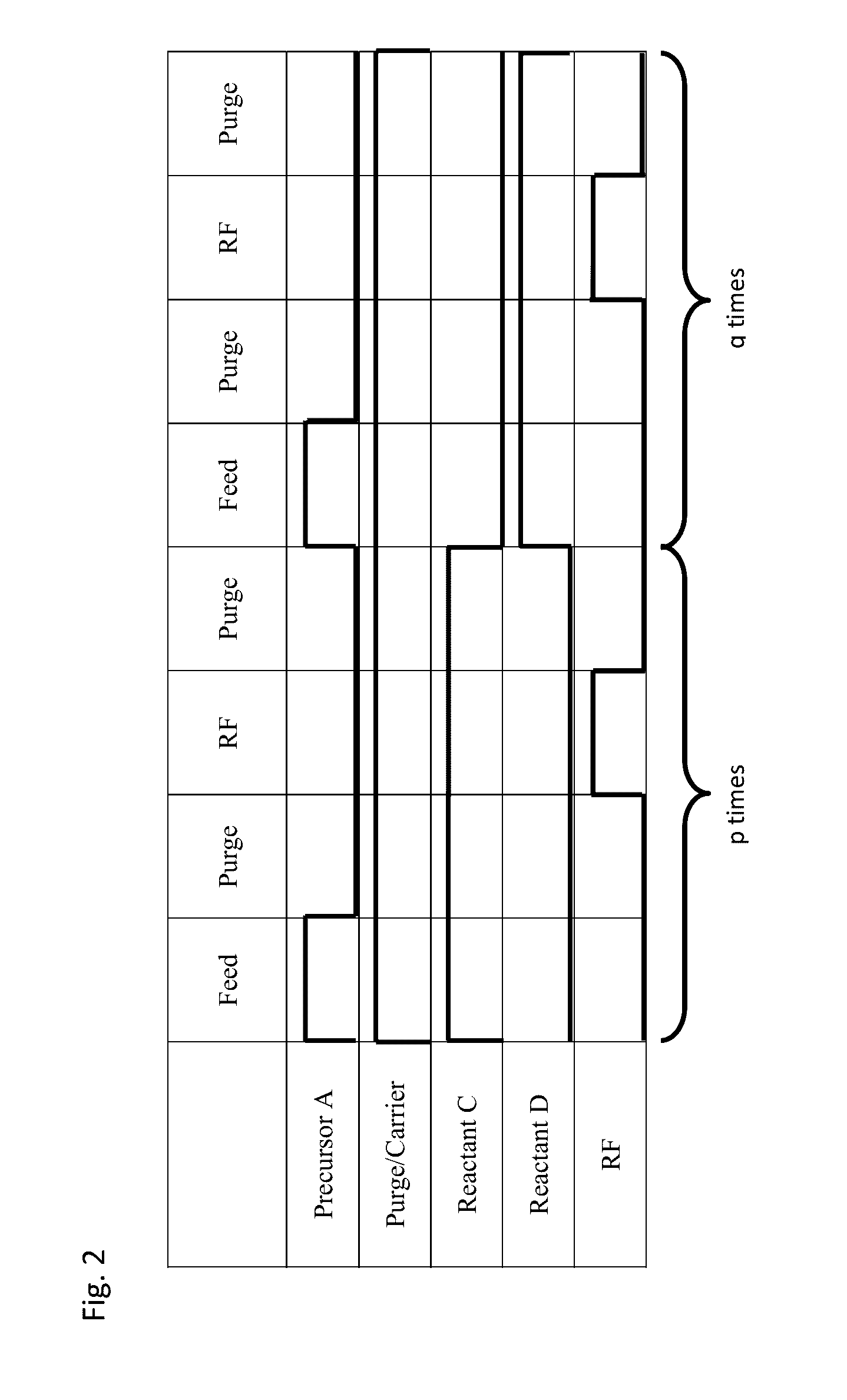

Method for forming aluminum nitride-based film by peald

ActiveUS20170062209A1Improve leakage currentSemiconductor/solid-state device detailsSolid-state devicesPhysical chemistryThin membrane

A method for forming an aluminum nitride-based film on a substrate by plasma-enhanced atomic layer deposition (PEALD) includes: (a) forming at least one aluminum nitride (AlN) monolayer and (b) forming at least one aluminum oxide (AlO) monolayer, wherein steps (a) and (b) are alternately conducted continuously to form a laminate. Steps (a) and (b) are discontinued before a total thickness of the laminate exceeds 10 nm, preferably 5 nm.

Owner:ASM IP HLDG BV

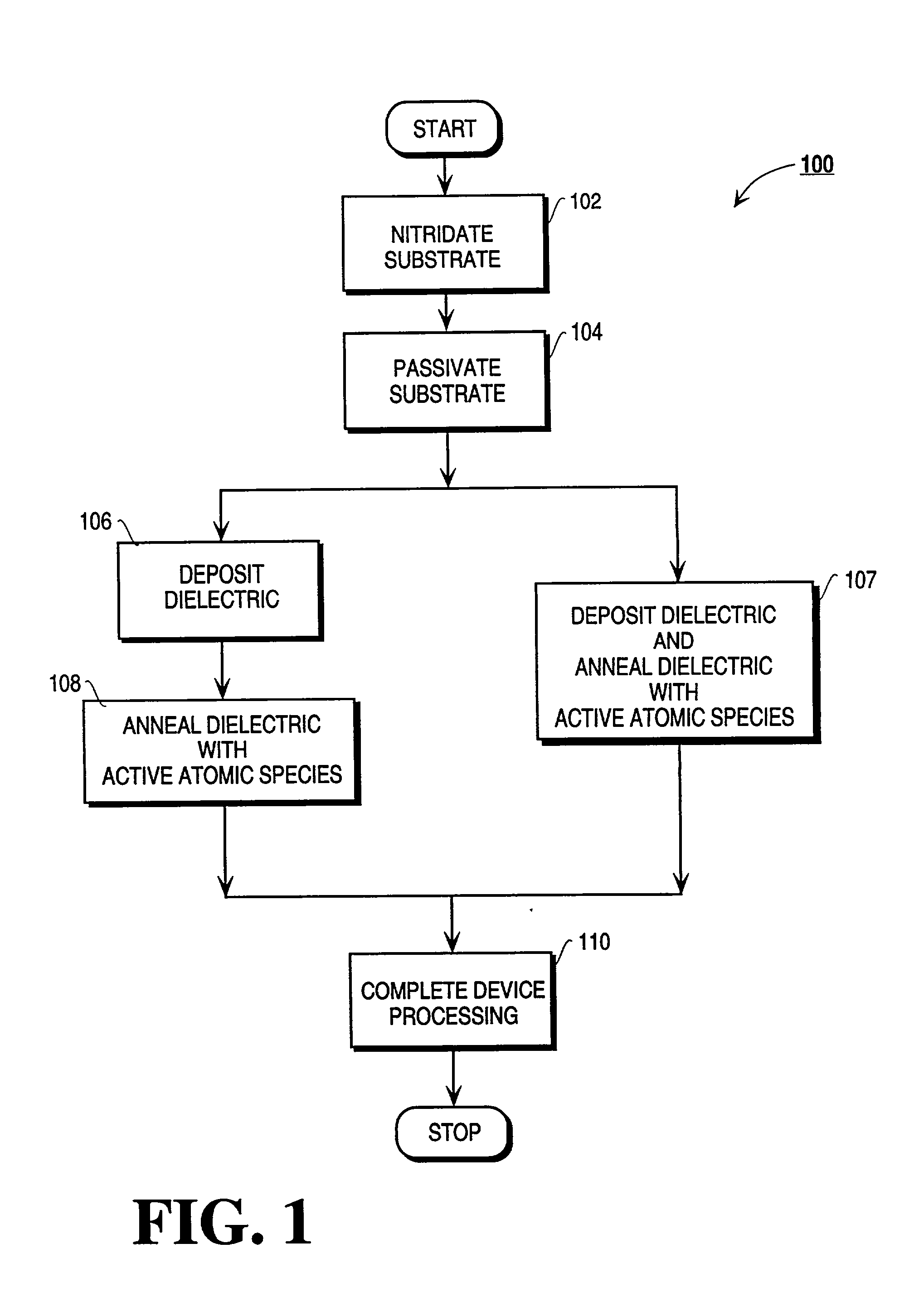

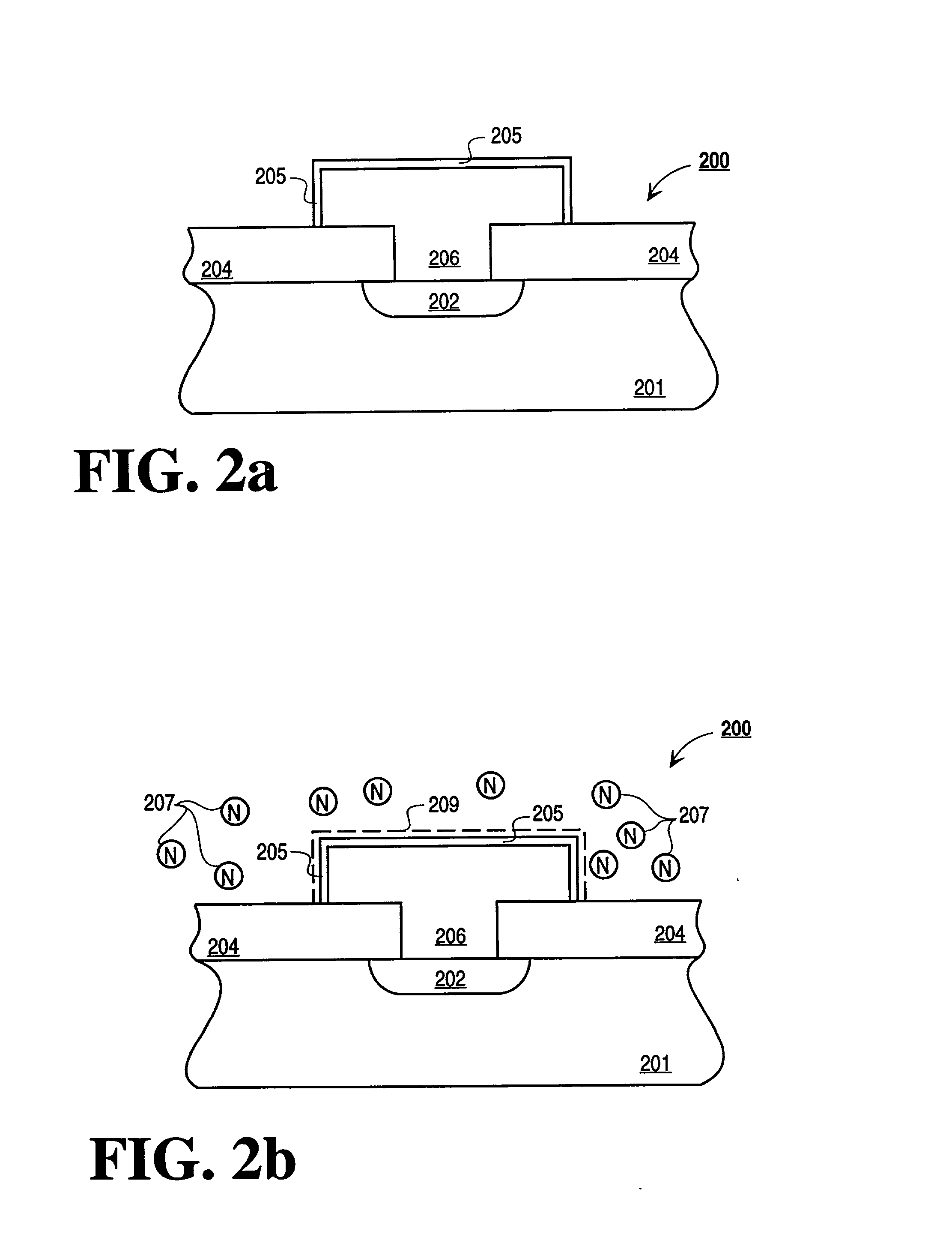

Method and apparatus for the formation of dielectric layers

InactiveUS20020009861A1Simple interfaceImprove performanceTransistorVacuum evaporation coatingAtomic speciesDielectric layer

A method and apparatus for forming and annealing a dielectric layer. According to the present invention an active atomic species is generated in a first chamber. A dielectric layer formed on a substrate is then exposed to the active atomic species in a second chamber, wherein the second chamber is remote from the first chamber.

Owner:APPLIED MATERIALS INC

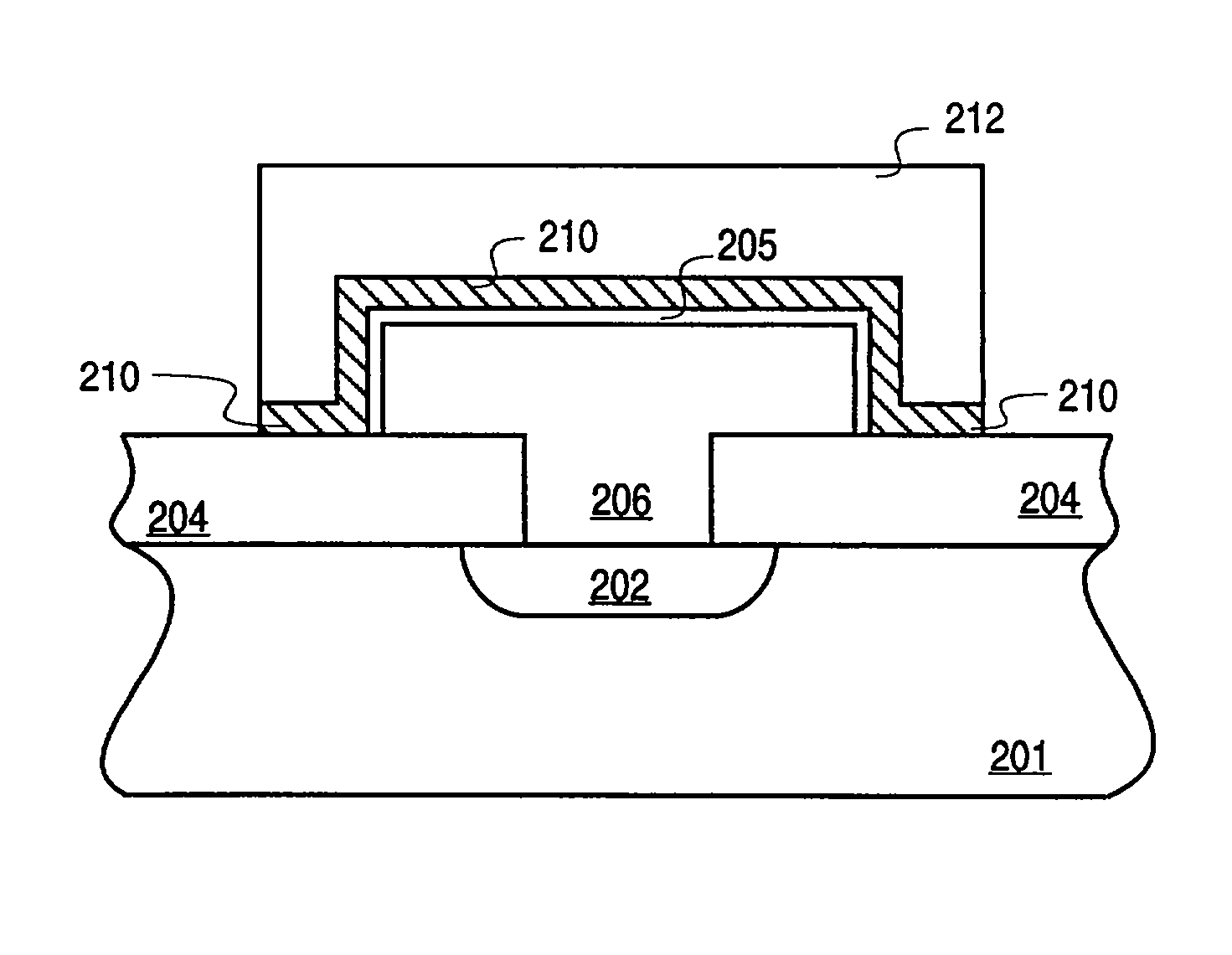

Method for manufacturing a semiconductor integrated circuit device circuit device

ActiveUS20100129974A1Increased integration scaleLower gate resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesMetal silicideField-effect transistor

When a natural oxide film is left at the interface between a metal silicide layer and a silicon nitride film, in various heating steps (steps involving heating of a semiconductor substrate, such as various insulation film and conductive film deposition steps) after deposition of the silicon nitride film, the metal silicide layer partially abnormally grows due to oxygen of the natural oxide film occurring on the metal silicide layer surface. A substantially non-bias (including low bias) plasma treatment is performed in a gas atmosphere containing an inert gas as a main component on the top surface of a metal silicide film of nickel silicide or the like over source / drain of a field-effect transistor forming an integrated circuit. Then, a silicon nitride film serving as an etching stop film of a contact process is deposited. As a result, without causing undesirable cutting of the metal silicide film, the natural oxide film over the top surface of the metal silicide film can be removed.

Owner:RENESAS ELECTRONICS CORP

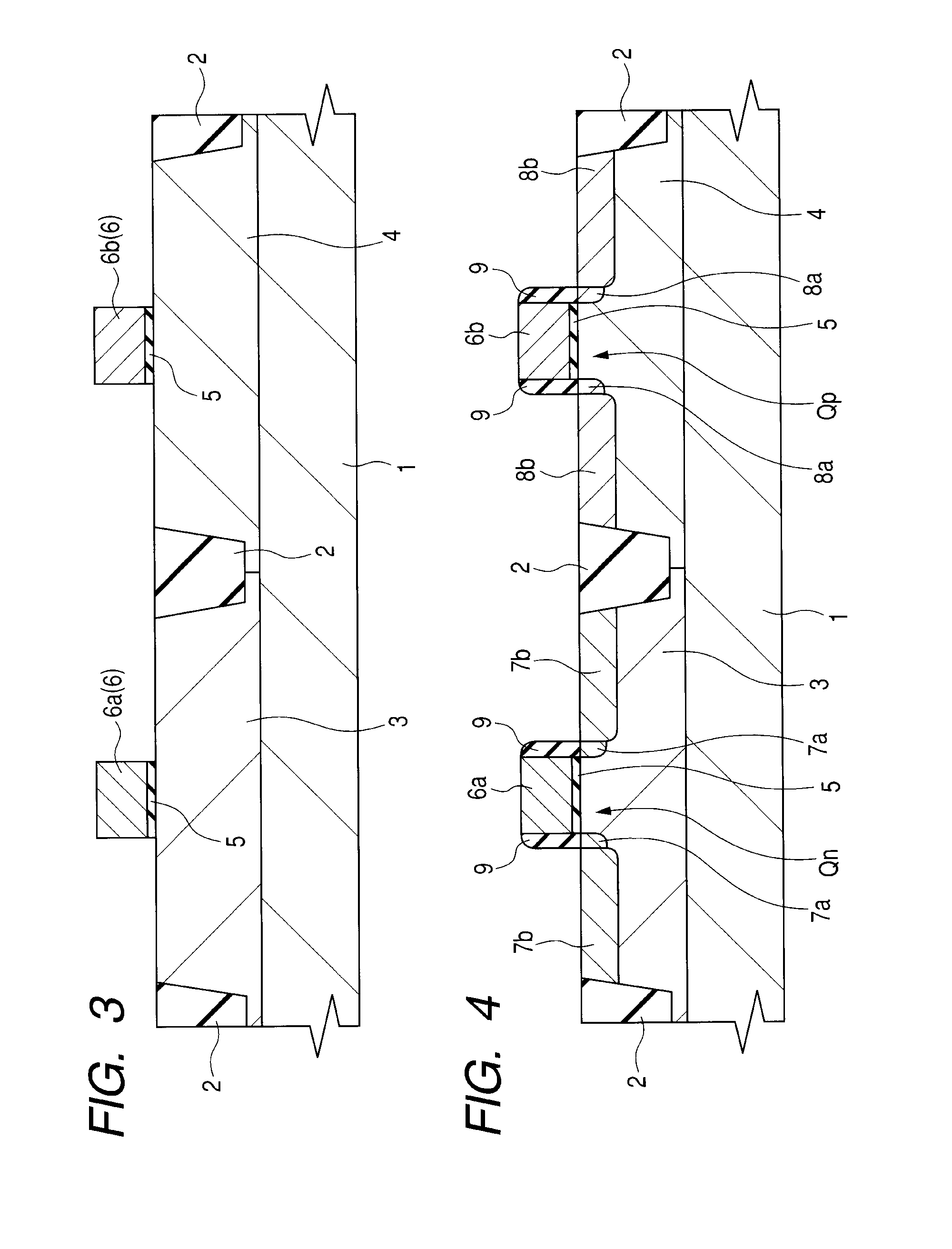

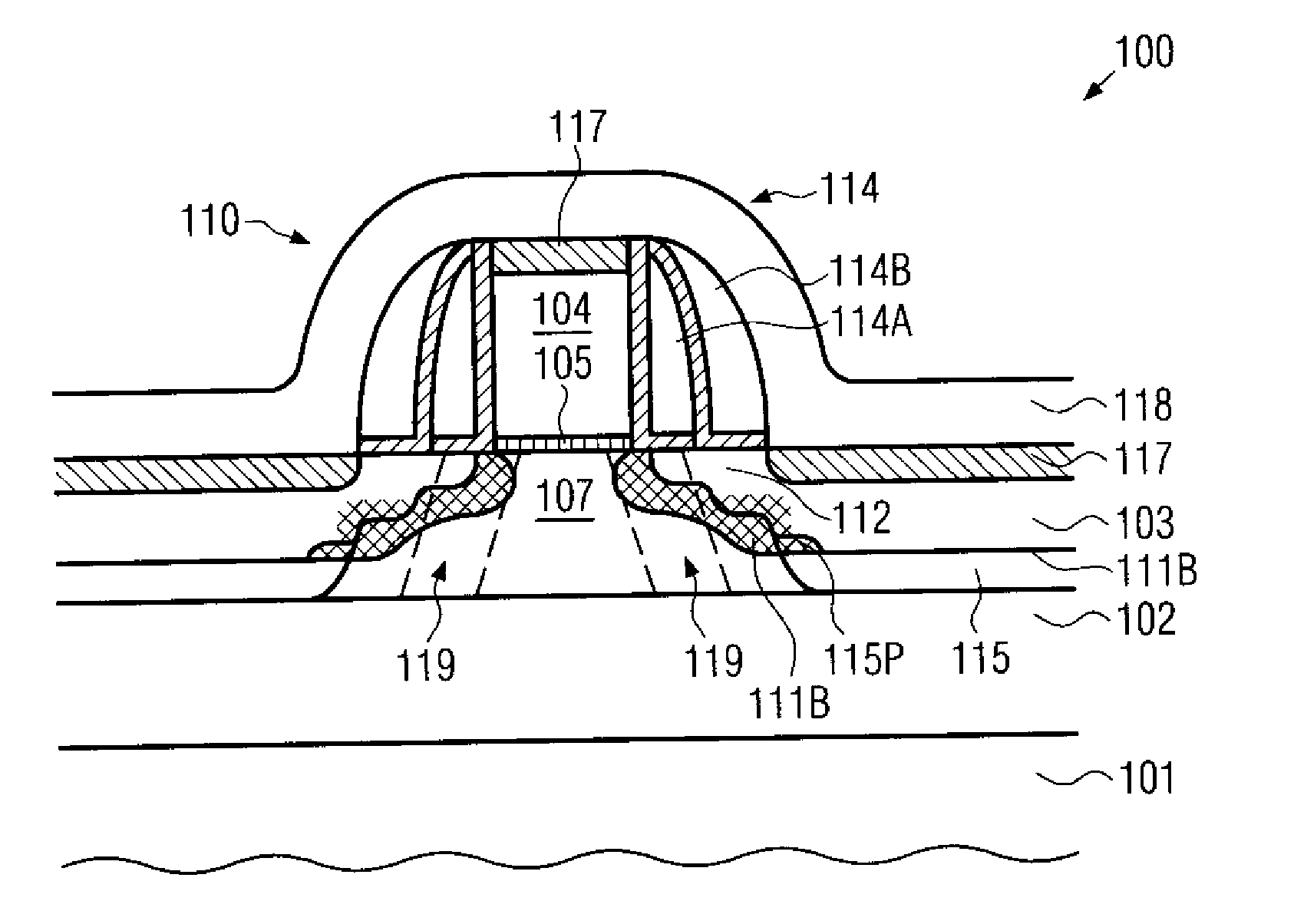

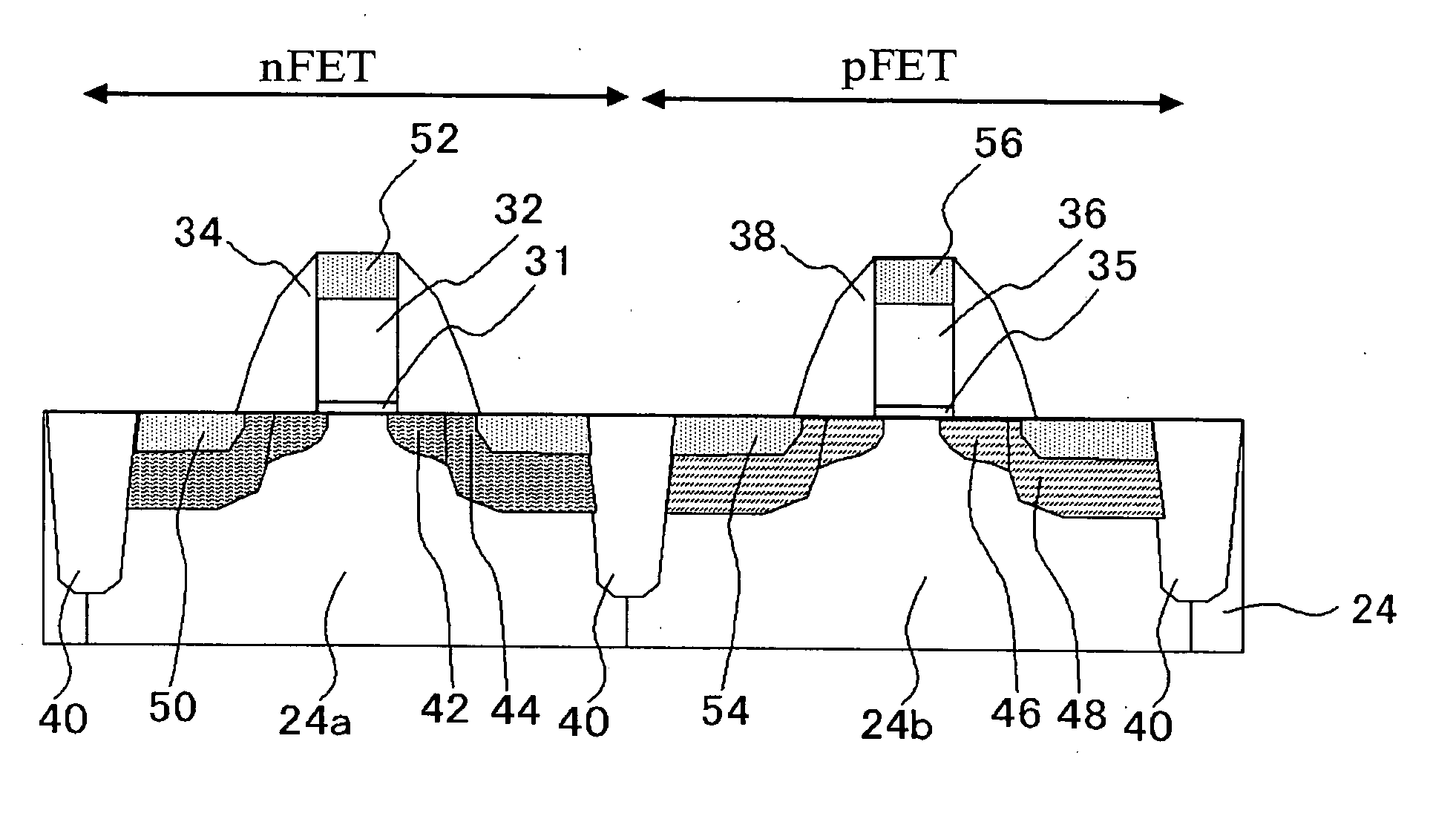

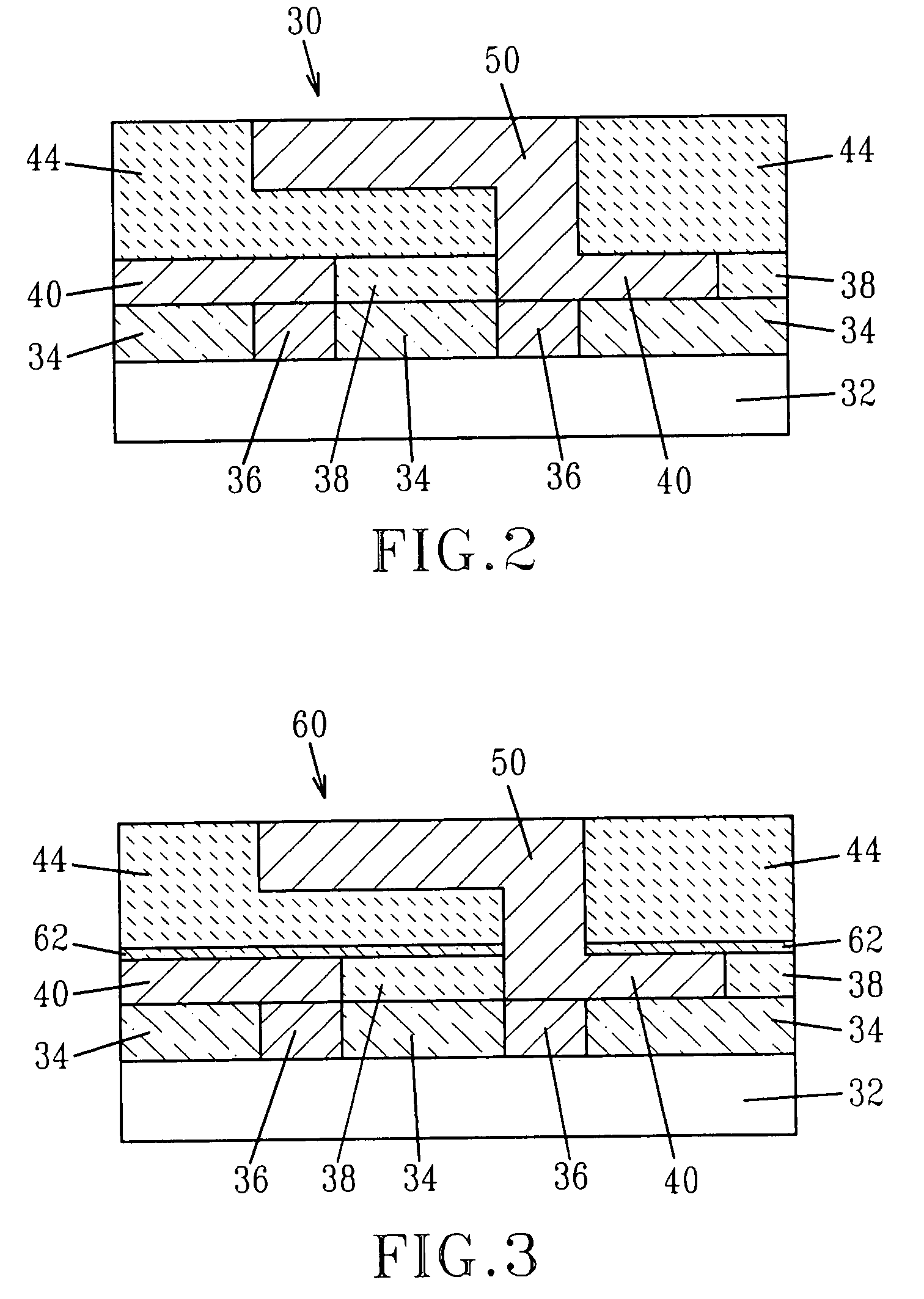

Soi transistor having a reduced body potential and a method of forming the same

ActiveUS20070252205A1Reduce hysteresis effectsImprove compatibilitySolid-state devicesSemiconductor/solid-state device manufacturingJunction leakageCharge carrier

By introducing a atomic species, such as carbon, fluorine and the like, into the drain and source regions, as well as in the body region, the junction leakage of SOI transistors may be significantly increased, thereby providing an enhanced leakage path for accumulated minority charge carriers. Consequently, fluctuations of the body potential may be significantly reduced, thereby improving the overall performance of advanced SOI devices. In particular embodiments, the mechanism may be selectively applied to threshold voltage sensitive device areas, such as static RAM areas.

Owner:ADVANCED MICRO DEVICES INC

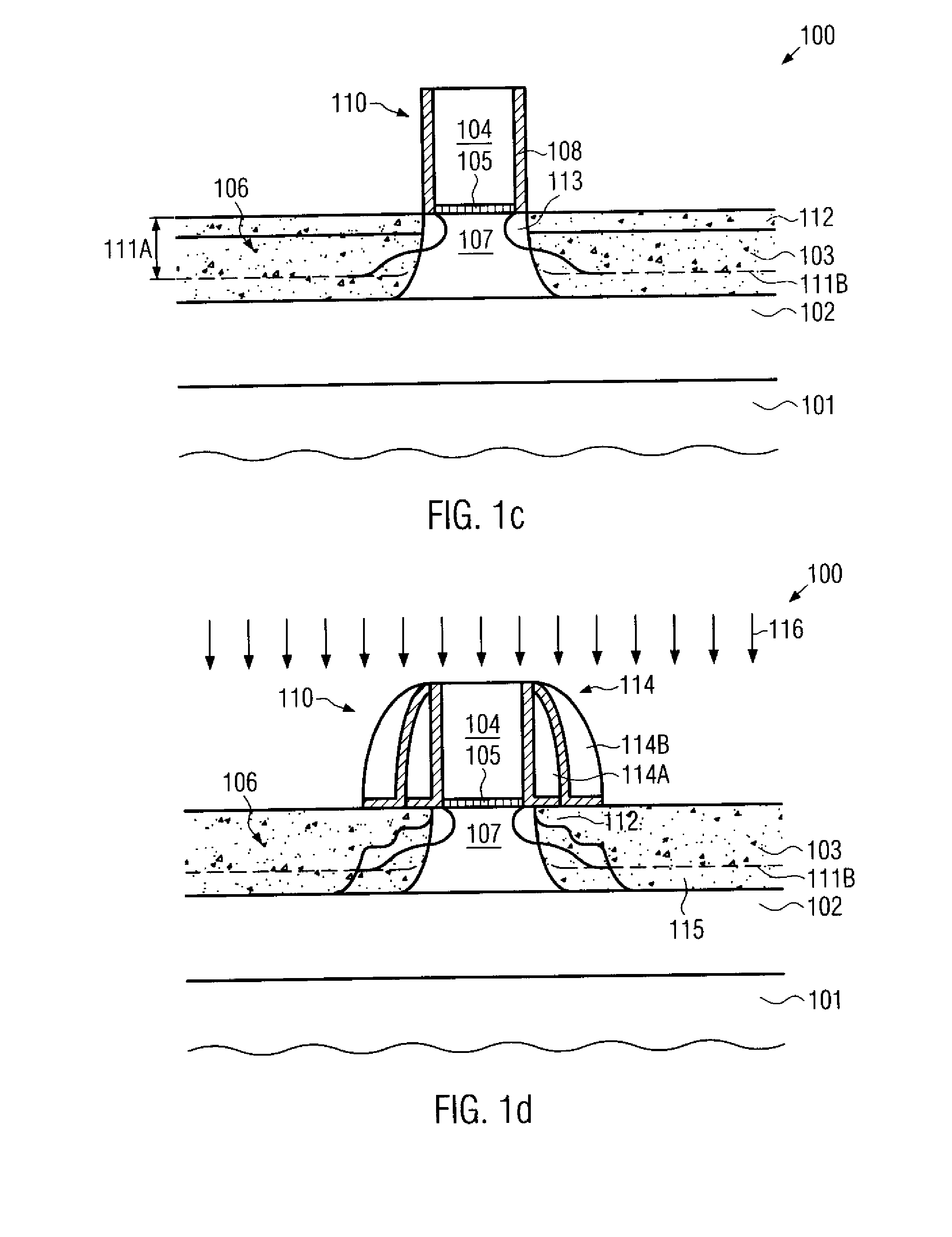

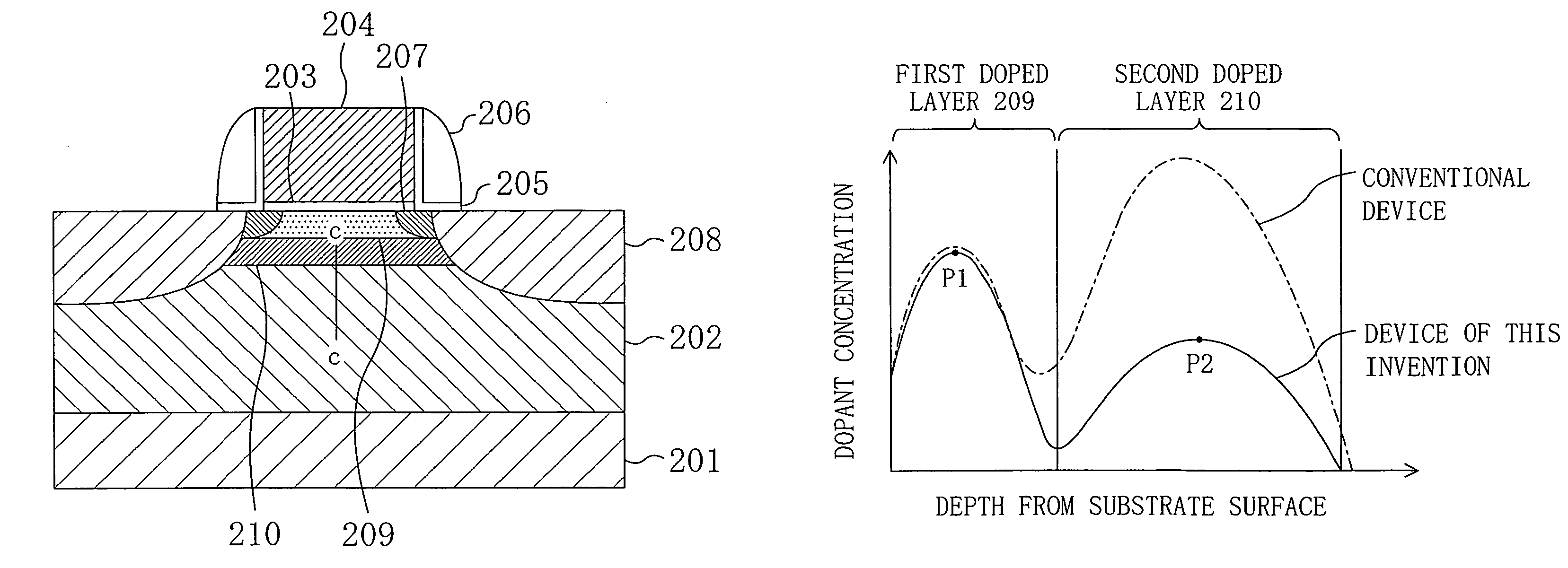

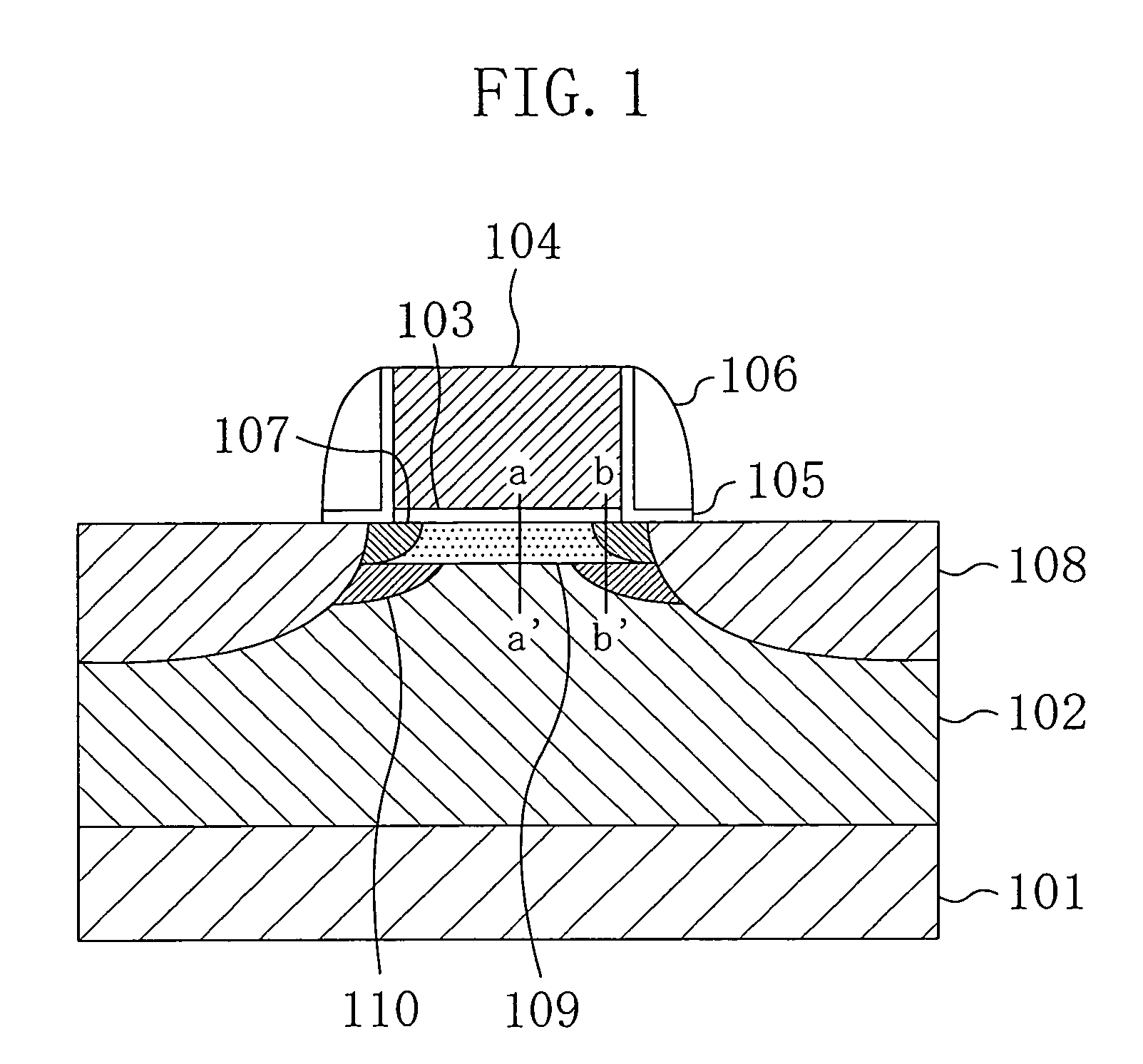

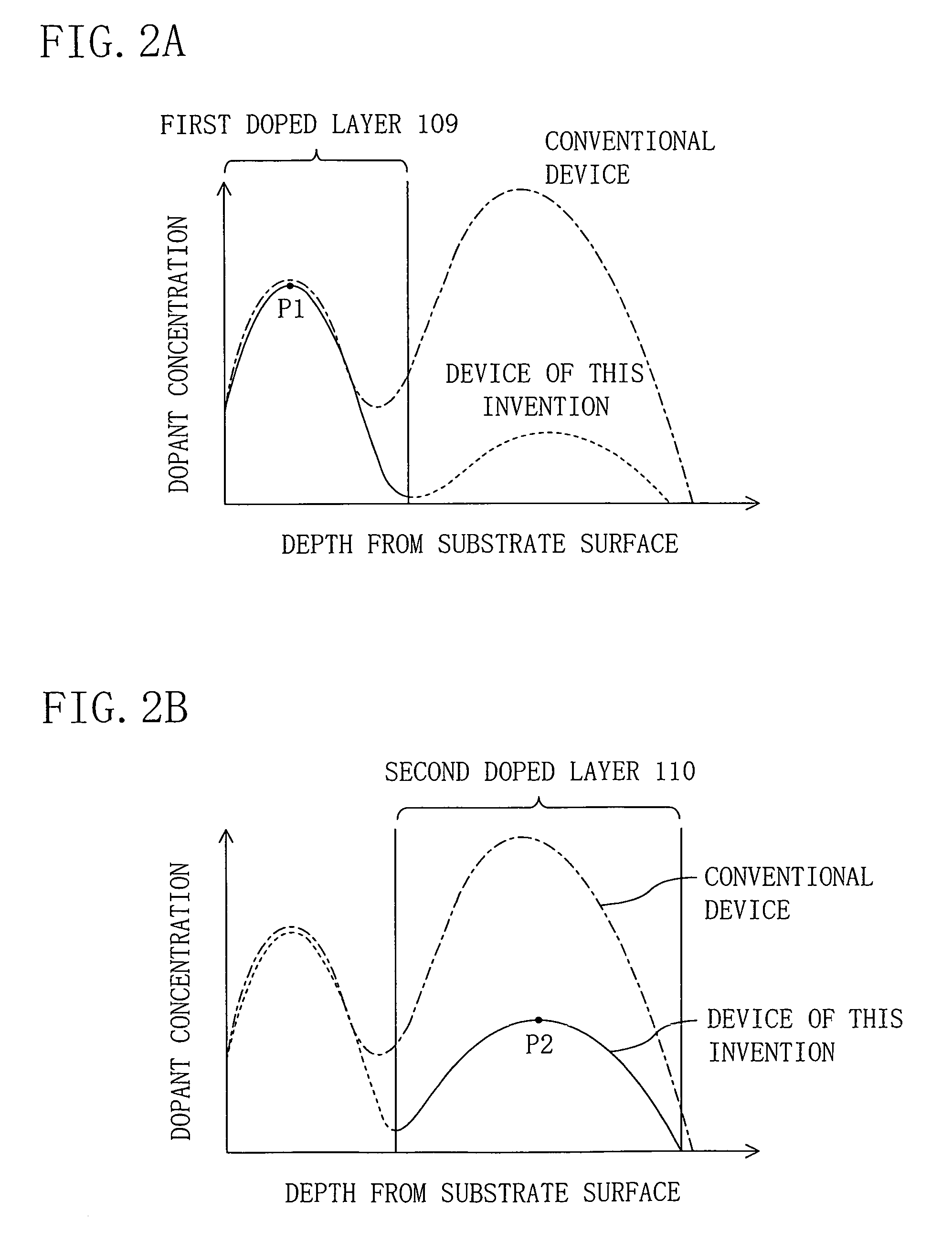

Semiconductor device and method for fabricating the same

ActiveUS7301208B2Increase powerImprove leakage currentTransistorSemiconductor/solid-state device manufacturingDopantPeak value

A first doped layer of a conductivity type opposite to that of source / drain regions is formed in a semiconductor substrate under a gate electrode. A second doped layer of the conductivity type opposite to that of the source / drain regions is formed in the semiconductor substrate below the first doped layer. The first doped layer has a first peak in dopant concentration distribution in the depth direction. The first peak is located at a position shallower than the junction depth of the source / drain regions. The second doped layer has a second peak in dopant concentration distribution in the depth direction. The second peak is located at a position deeper than the first peak and shallower than the junction depth of the source / drain regions. The dopant concentration at the first peak is higher than that at the second peak.

Owner:GK BRIDGE 1

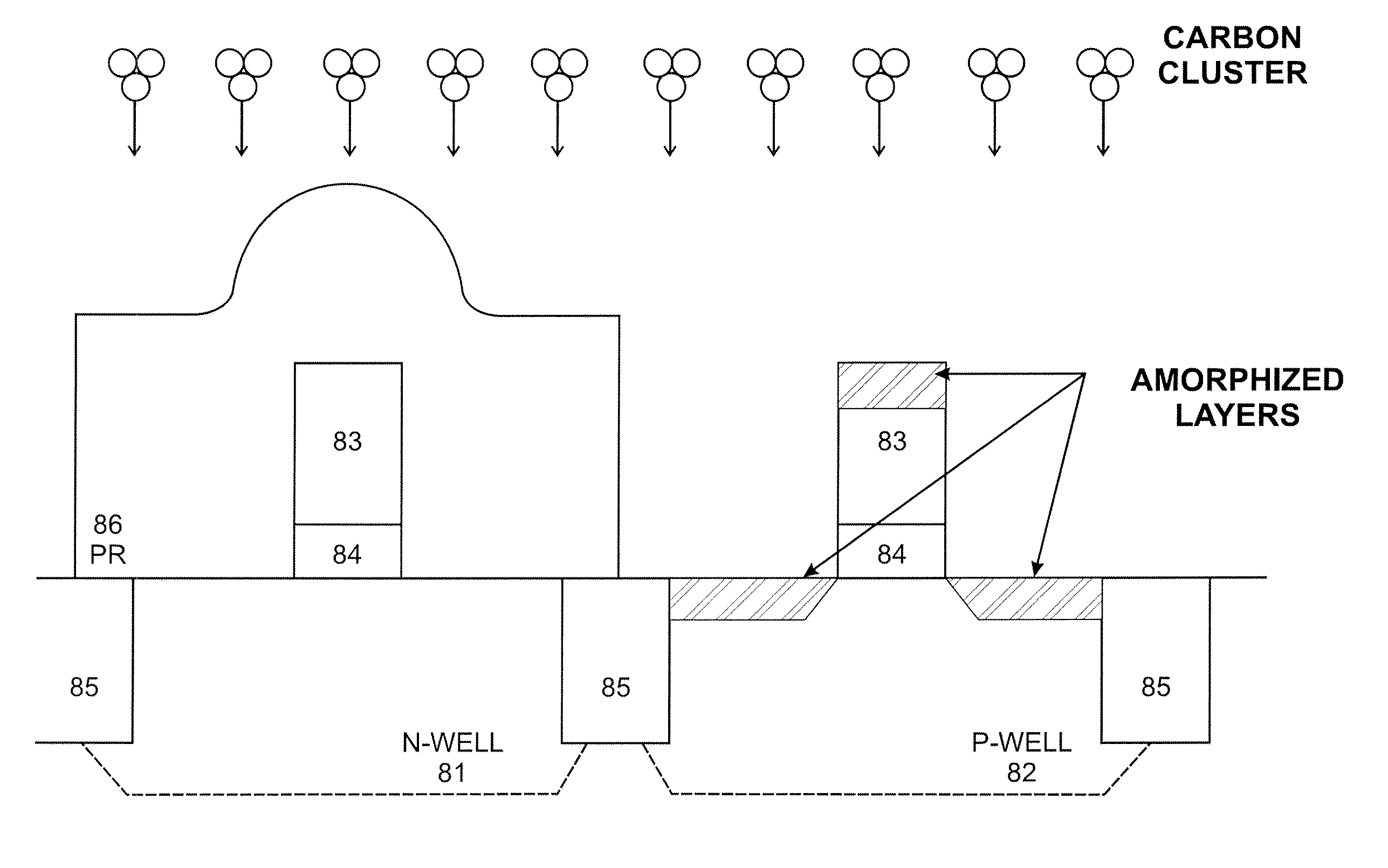

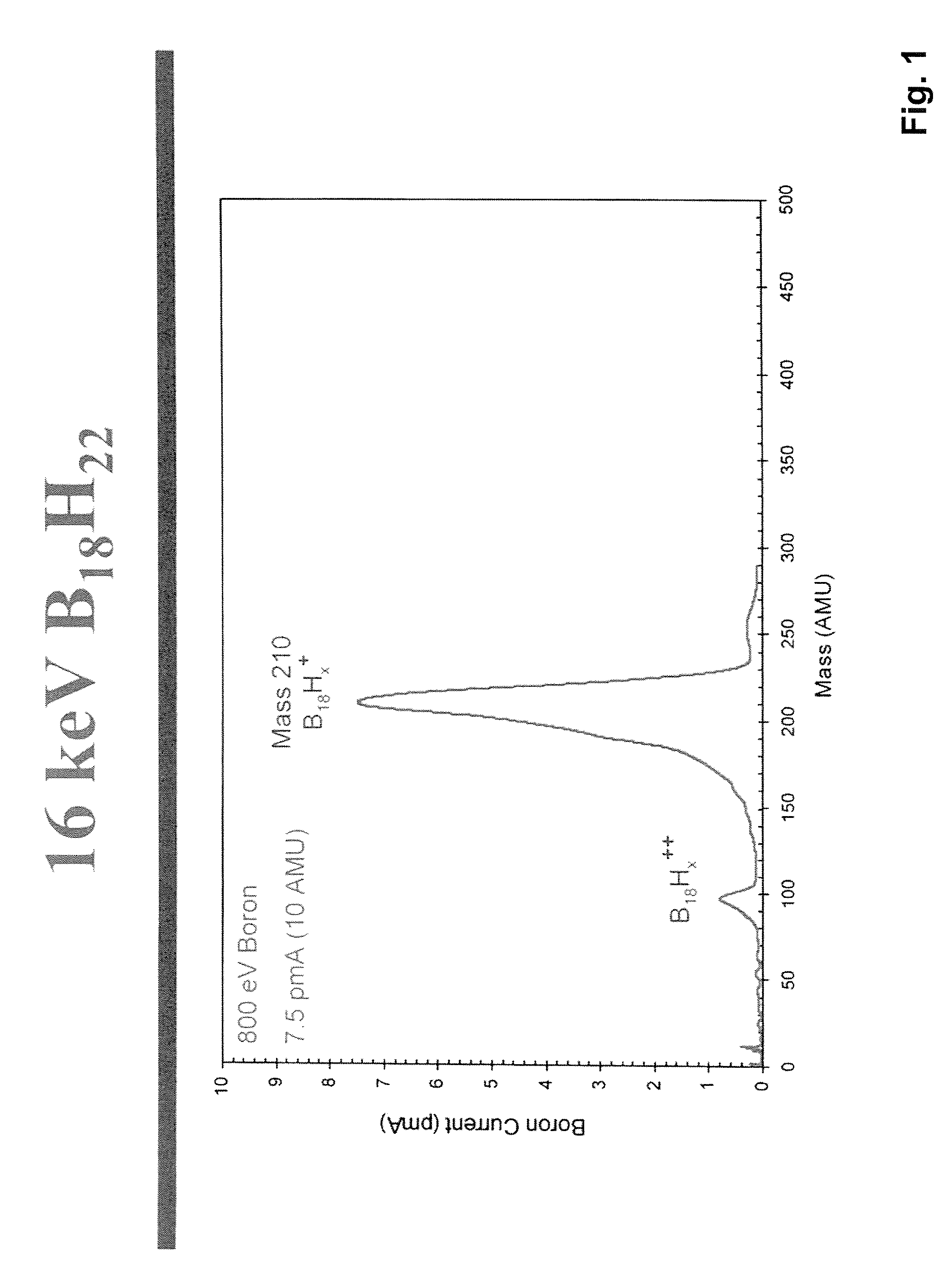

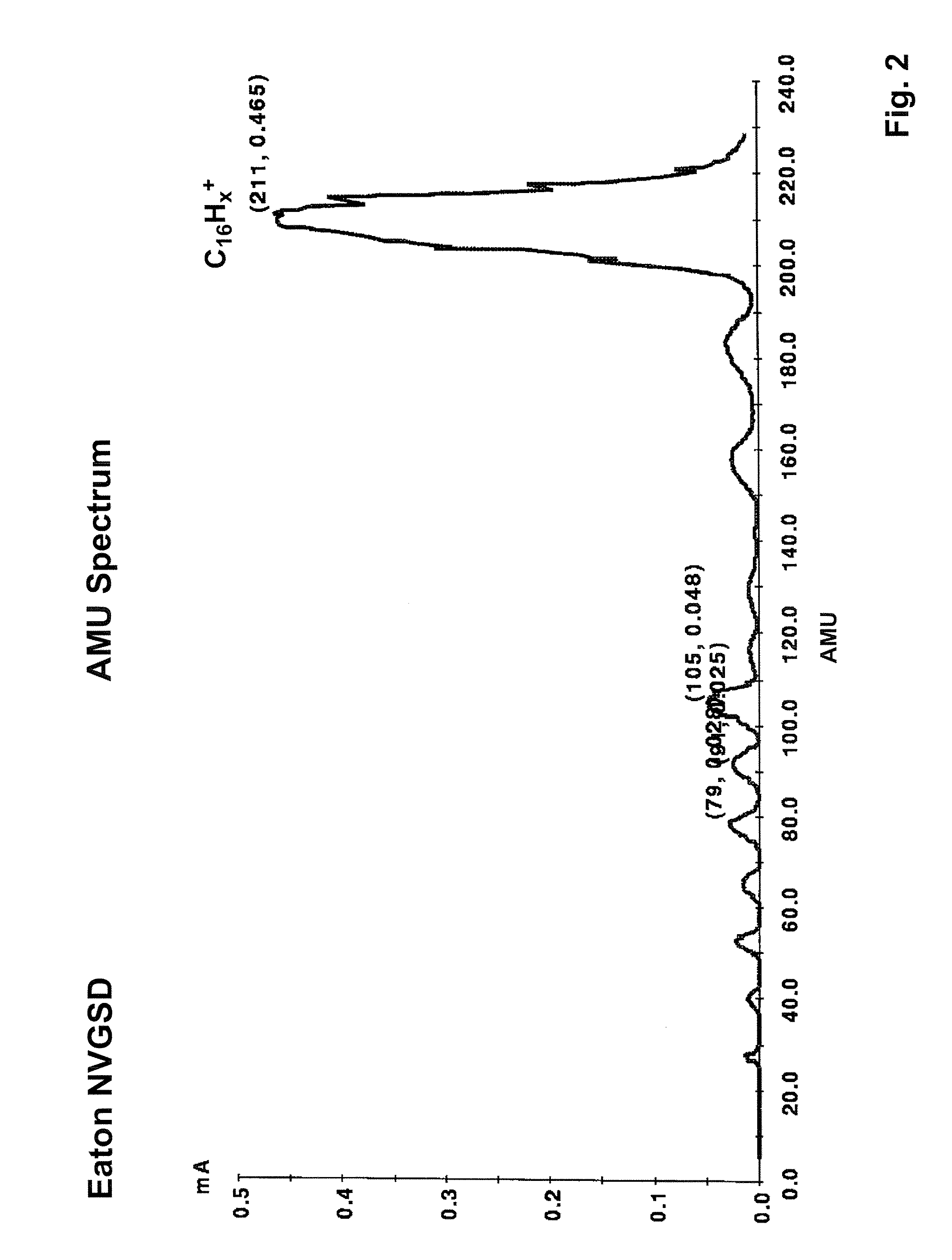

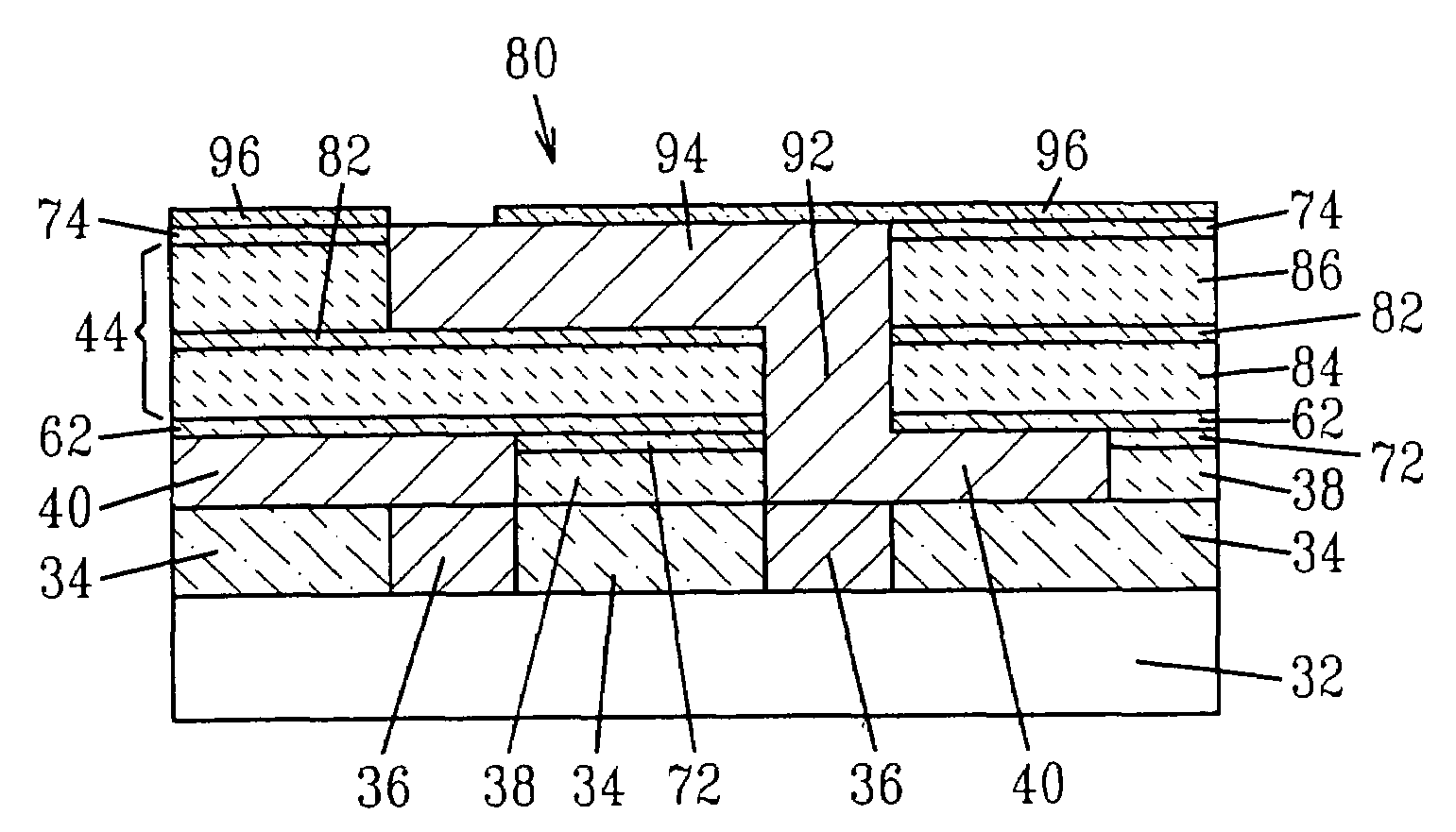

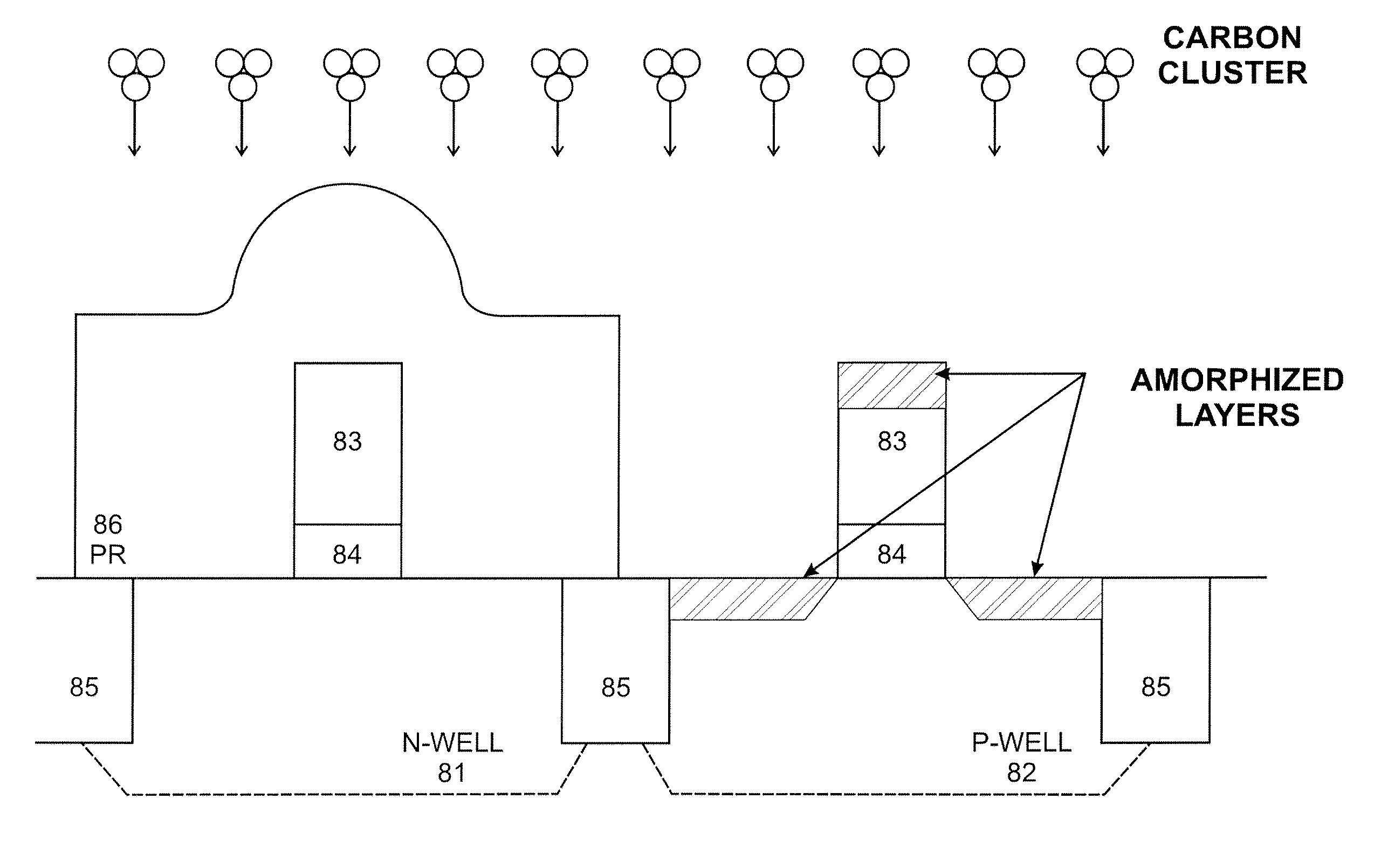

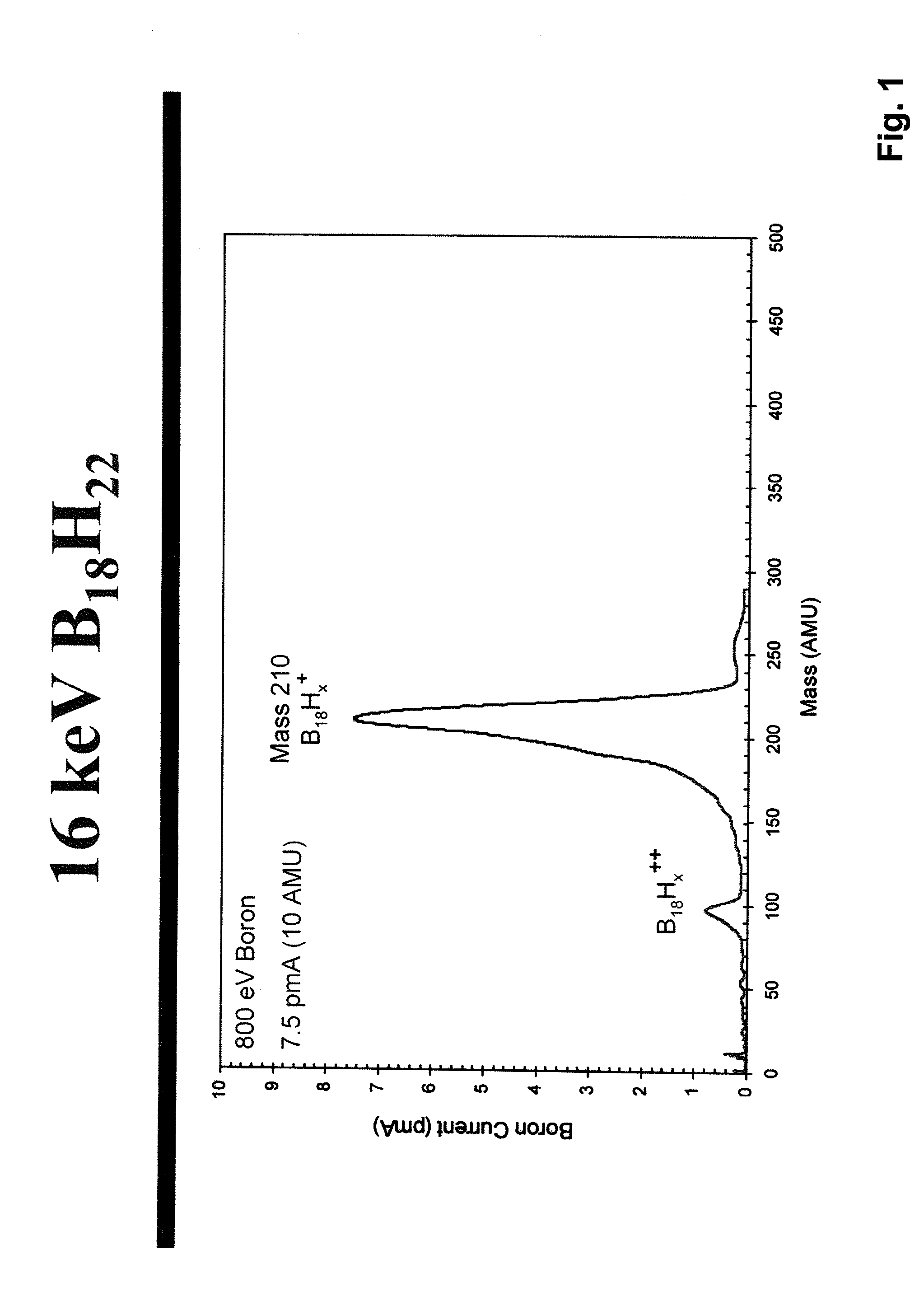

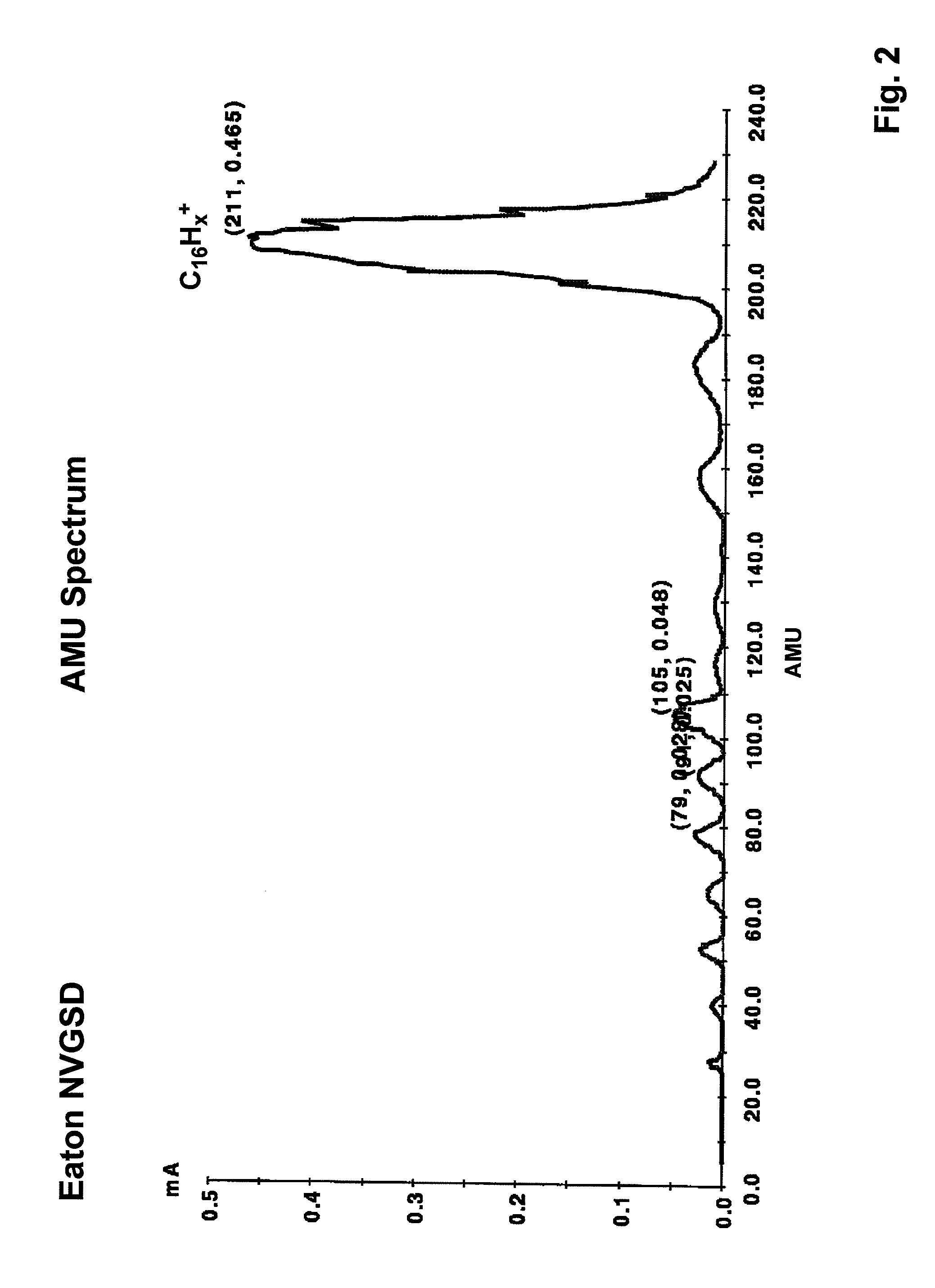

System and method for the manufacture of semiconductor devices by the implantation of carbon clusters

InactiveUS20070148888A1Improve productivityMinimize doseTransistorElectric discharge tubesDevice materialEngineering

A process is disclosed which incorporates implantation of a carbon cluster into a substrate to improve the characteristics of transistor junctions when the substrates are doped with Boron and Phosphorous in the manufacturing of PMOS transistor structures in integrated circuits. There are two processes which result from this novel approach: (1) diffusion control for USJ formation; and (2) high dose carbon implantation for stress engineering. Diffusion control for USJ formation is demonstrated in conjunction with a boron or shallow boron cluster implant of the source / drain structures in PMOS. More particularly, first, a cluster carbon ion, such as C16Hx+, is implanted into the source / drain region at approximately the same dose as the subsequent boron implant; followed by a shallow boron, boron cluster, phosphorous or phosphorous cluster ion implant to form the source / drain extensions, preferably using a borohydride cluster, such as B18Hx+ or B10Hx+. Upon subsequent annealing and activation, the boron diffusion is reduced, due to the gettering of interstitial defects by the carbon atoms.

Owner:SEMEQUIP

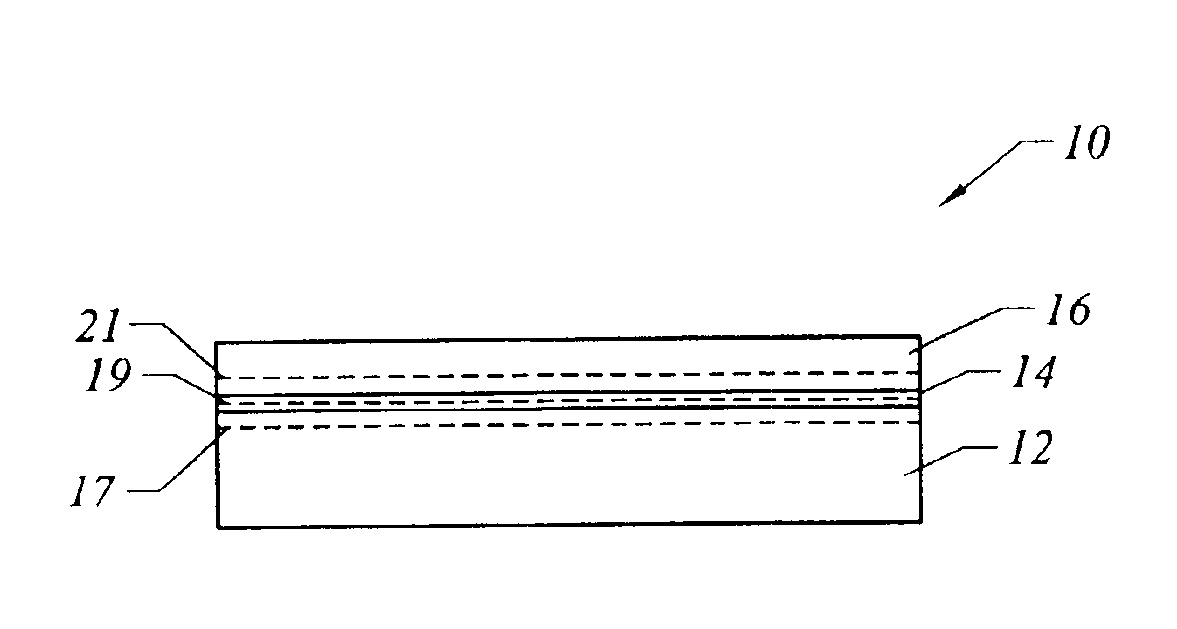

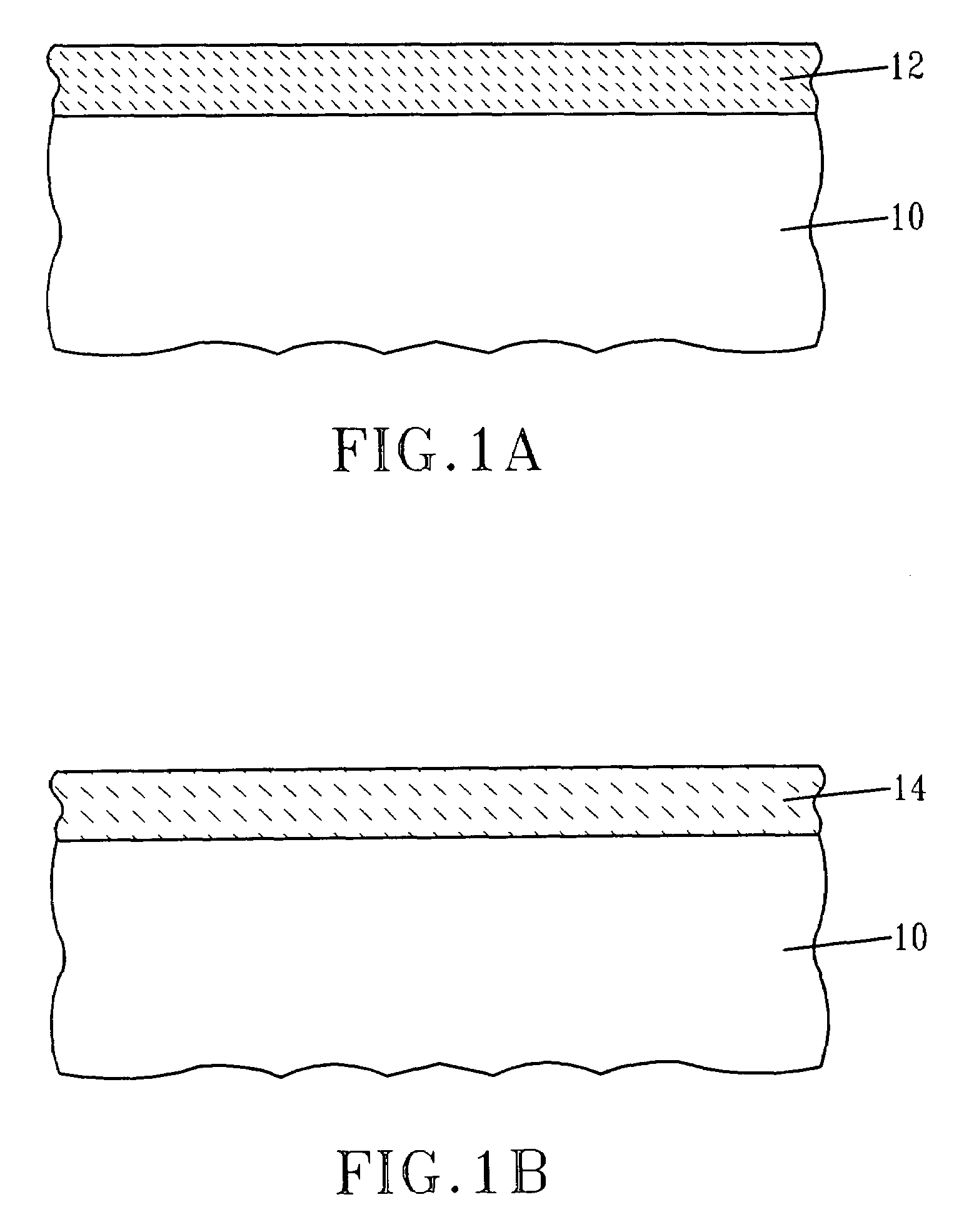

Gettering technique for wafers made using a controlled cleaving process

InactiveUS6890838B2Lower breakdown voltageImprove leakage currentSemiconductor/solid-state device manufacturingIntegrated circuitPlasma-immersion ion implantation

A technique for forming a gettering layer in a wafer made using a controlled cleaving process. The gettering layer can be made by implanting using beam line or plasma immersion ion implantaion, or made by forming a film of material such as polysilicon by way of chemical vapor deposition. A controlled cleaving process is used to form the wafer, which is a multilayered silicon on insulator substrate. The gettering layer removes and / or attracts impurities in the wafer, which can be detrimental to the functionality and reliability of an integrated circuit device made on the wafer.

Owner:SILICON GENERAL CORPORATION

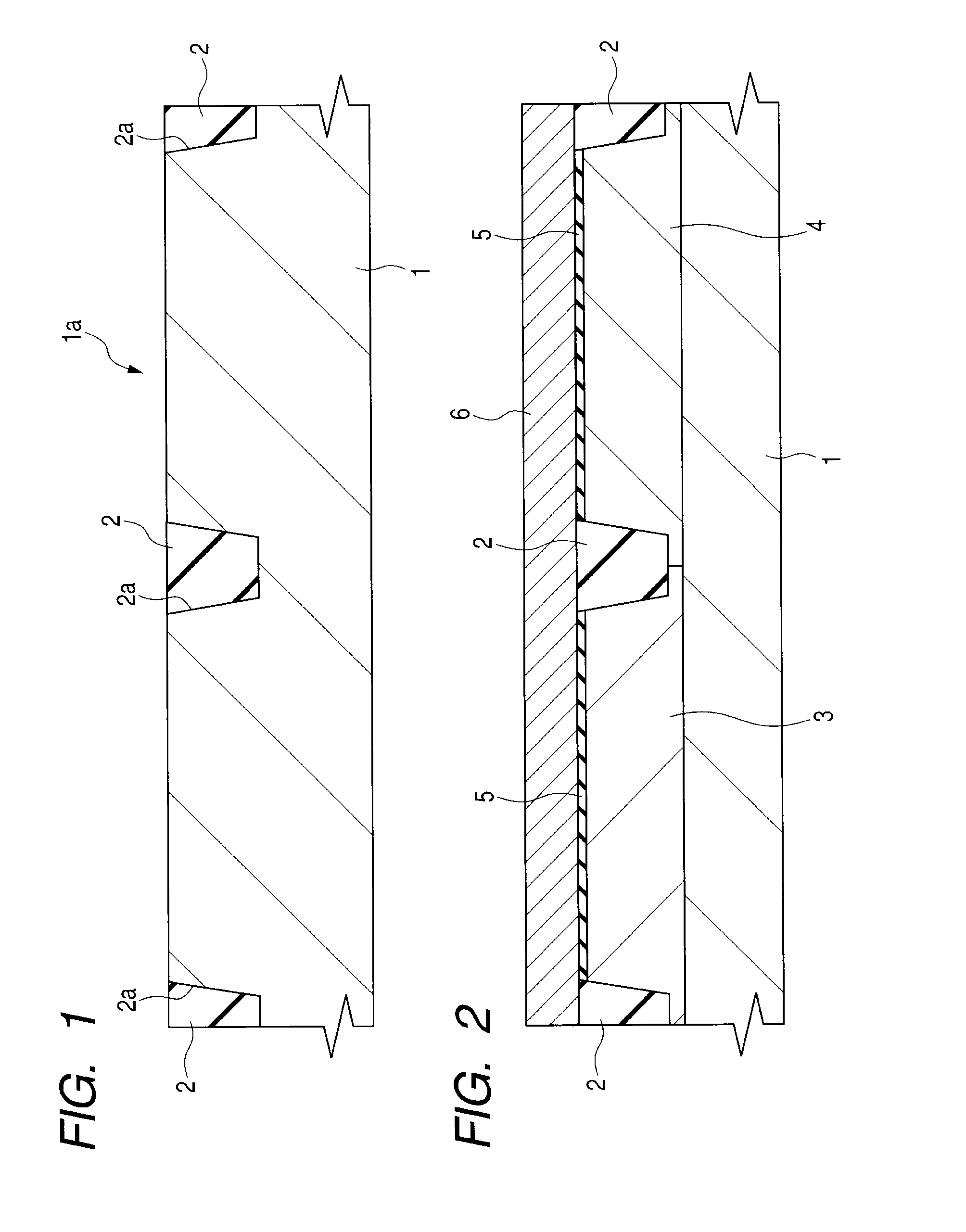

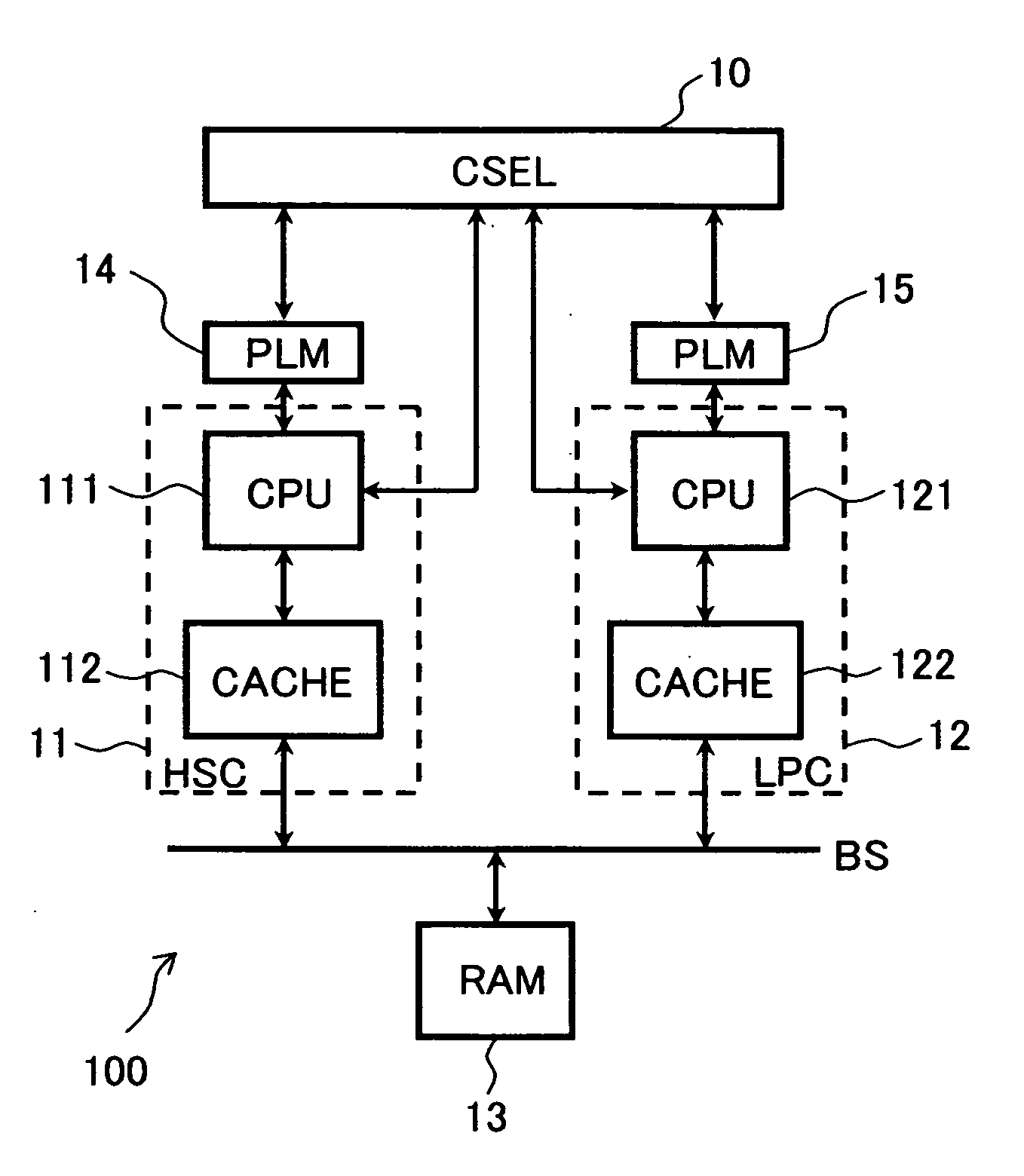

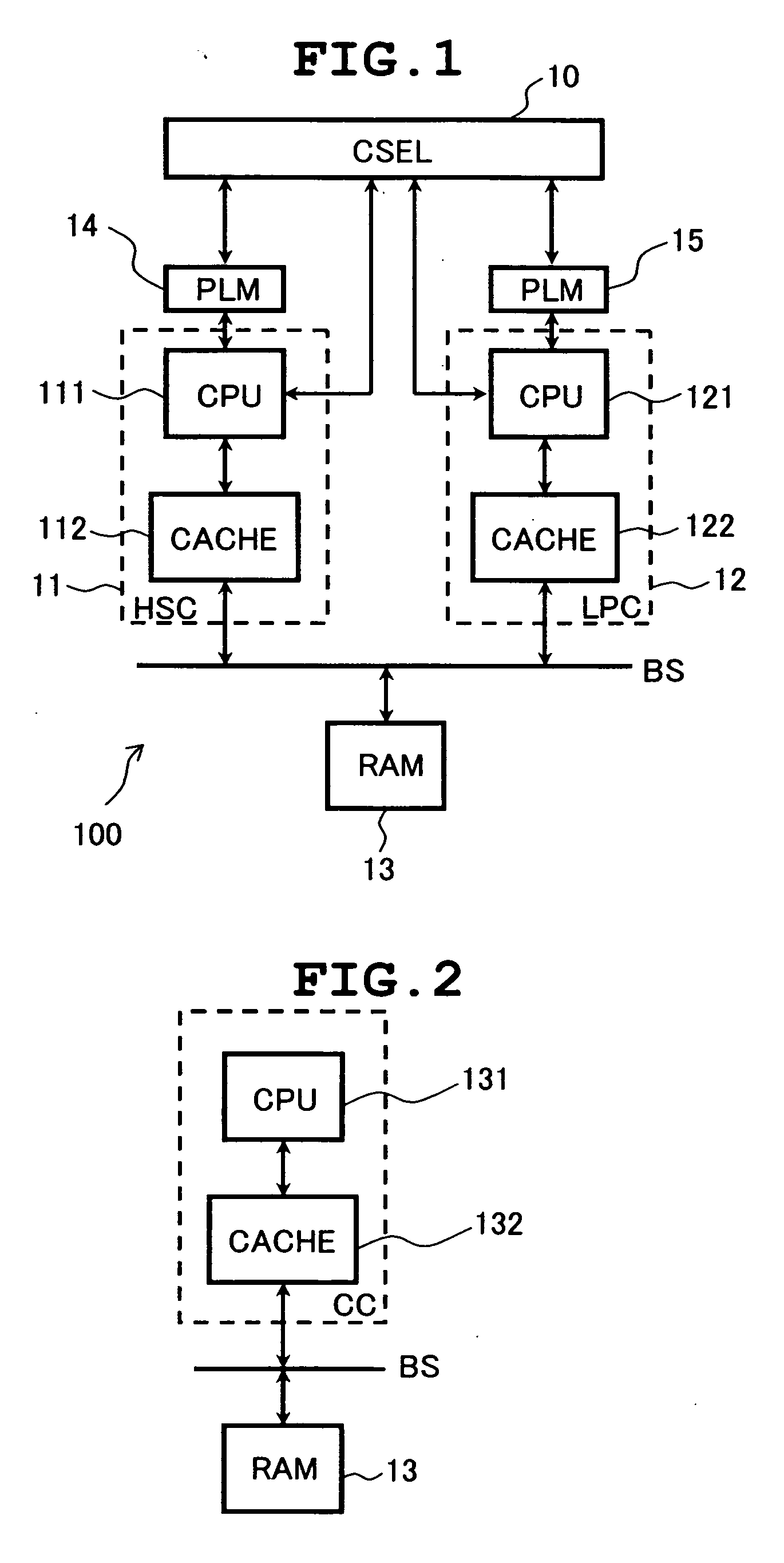

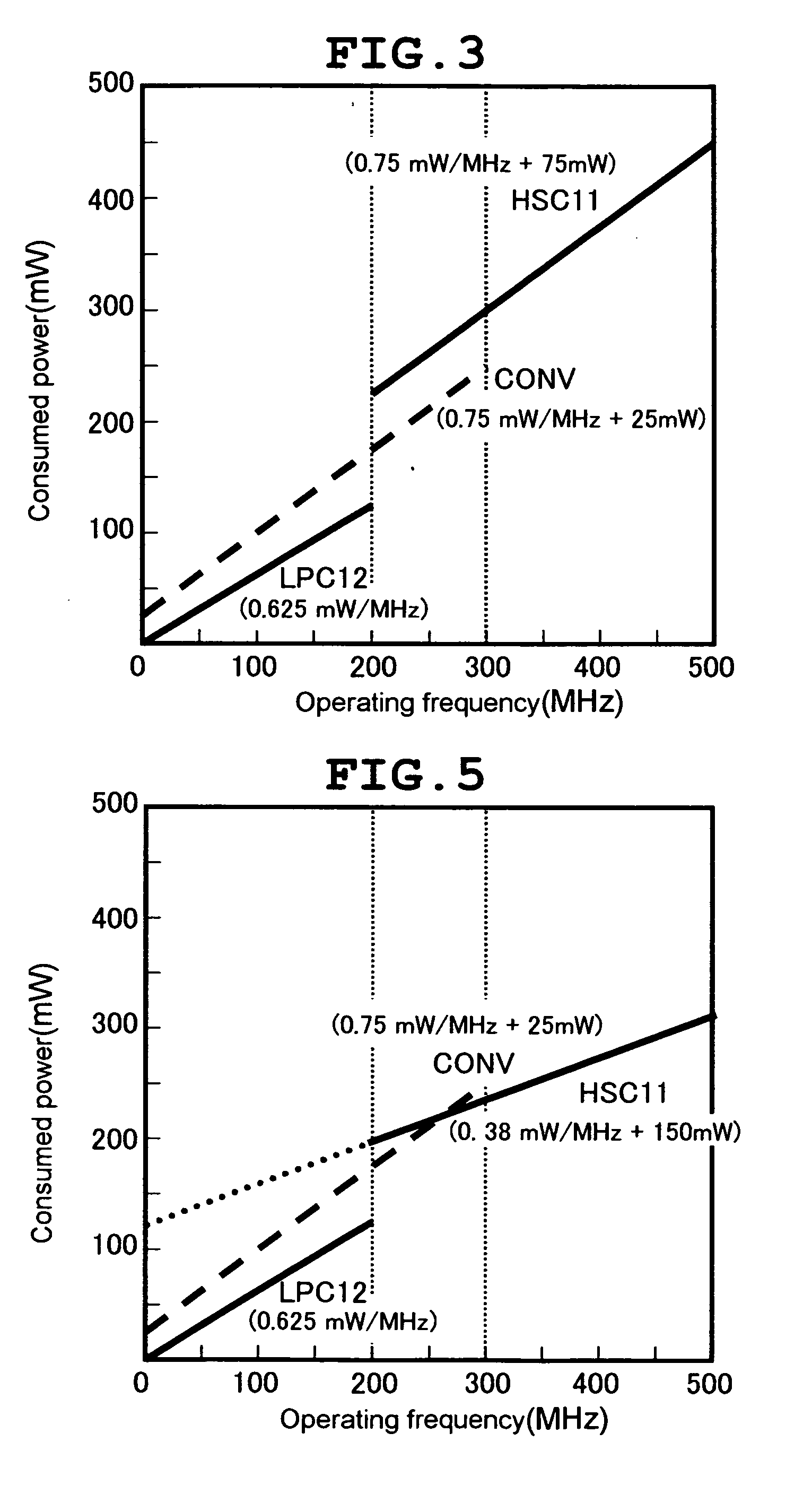

Semiconductor integrated circuit

InactiveUS20070136617A1Increase currentIncrease the number ofEnergy efficient ICTVolume/mass flow measurementEngineeringApplication software

There are provided a first processor (11) to be operated at a first operating frequency, a second processor (12) in which a leakage current is reduced more greatly than the first processor and which is operated at a lower second operating frequency than the first operating frequency, and a selecting portion (10) capable of selectively switching an executing destination of an application software into the first processor and the second processor corresponding to a demand operating speed of the application software. The first processor and the second processor can execute an identical instruction set, respectively. It is possible to carry out a high speed processing corresponding to the demand operating speed of the application software and to eliminate a dead current caused by a processing at a speed exceeding the demand operating speed of the application software.

Owner:RENESAS ELECTRONICS CORP

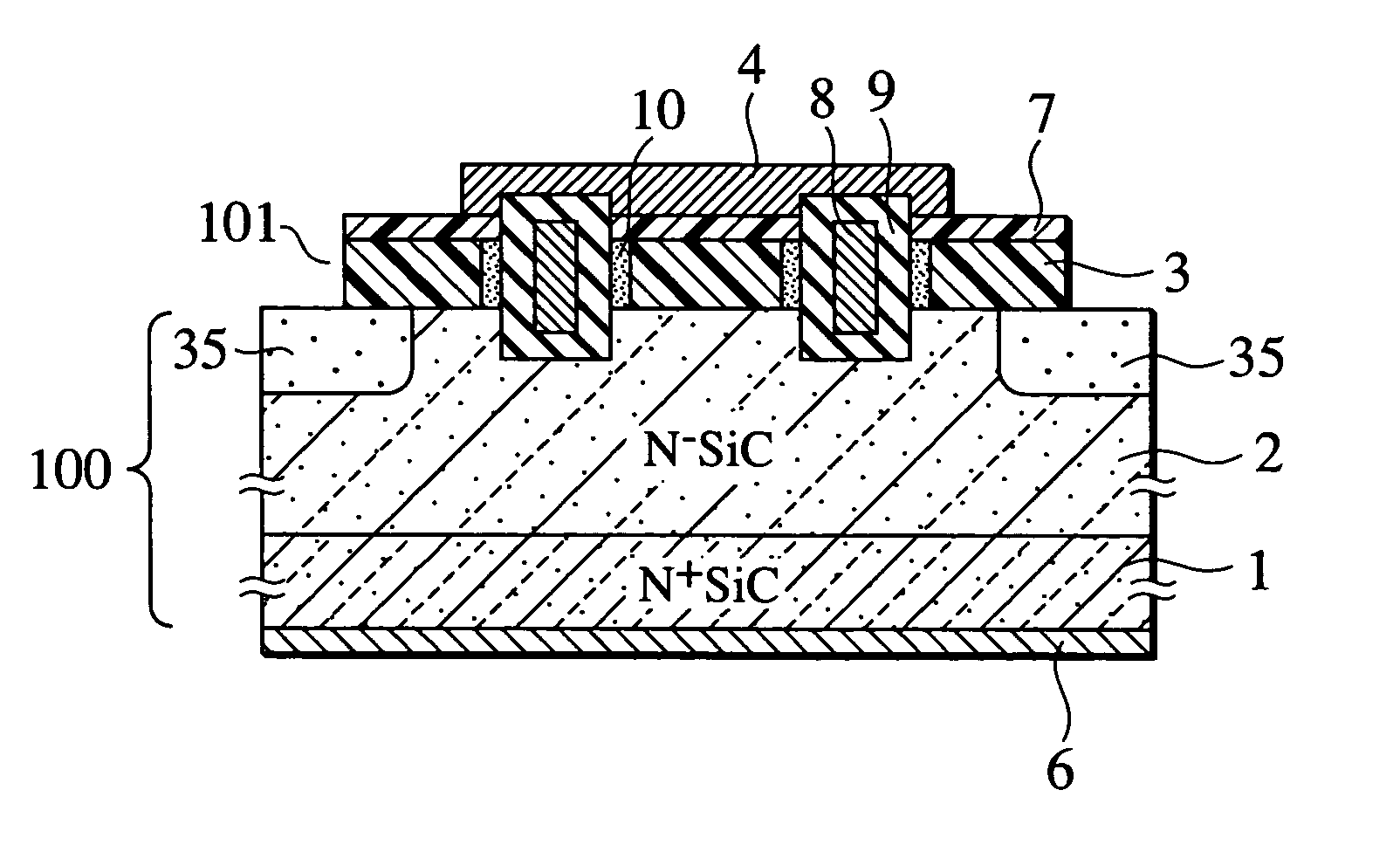

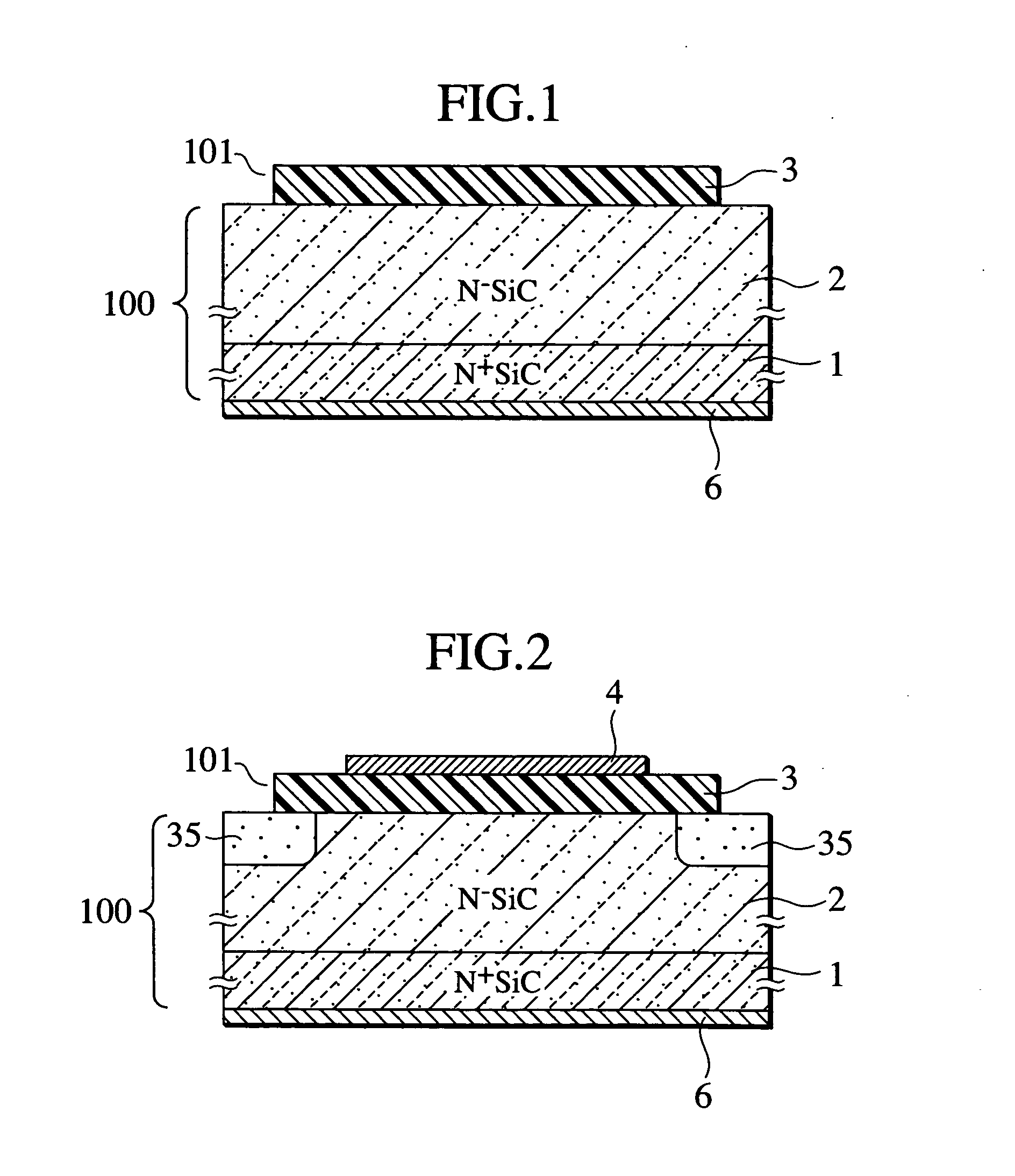

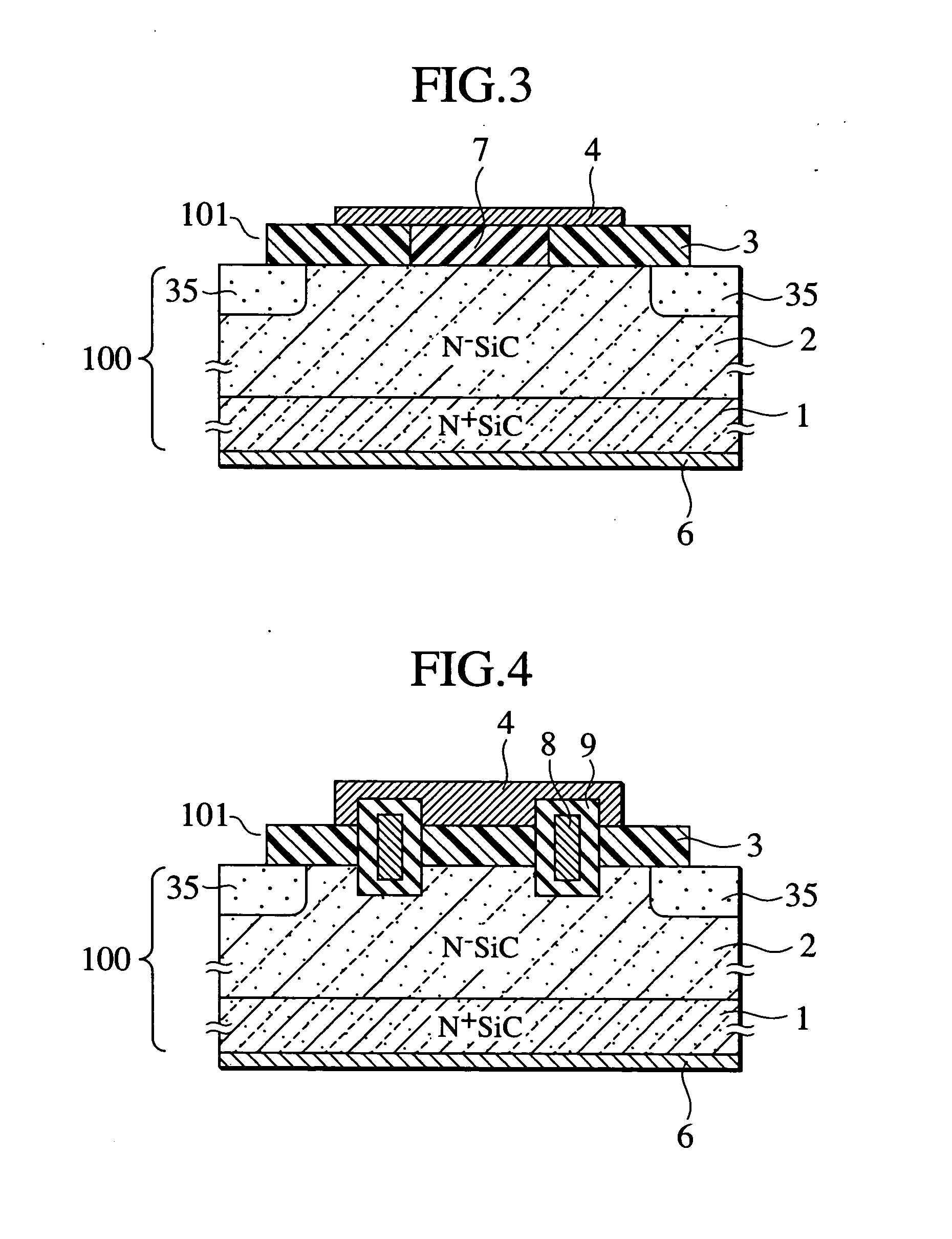

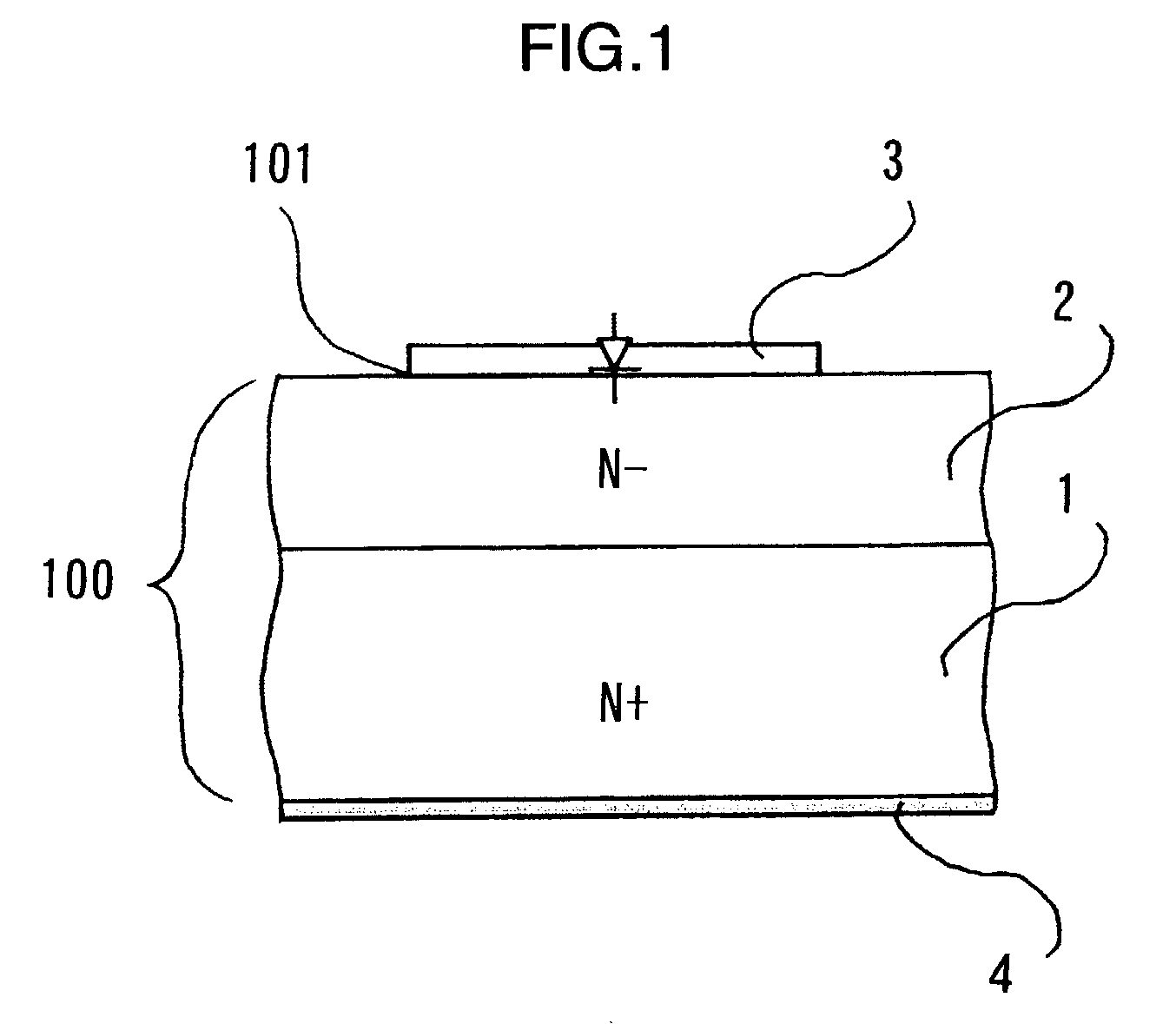

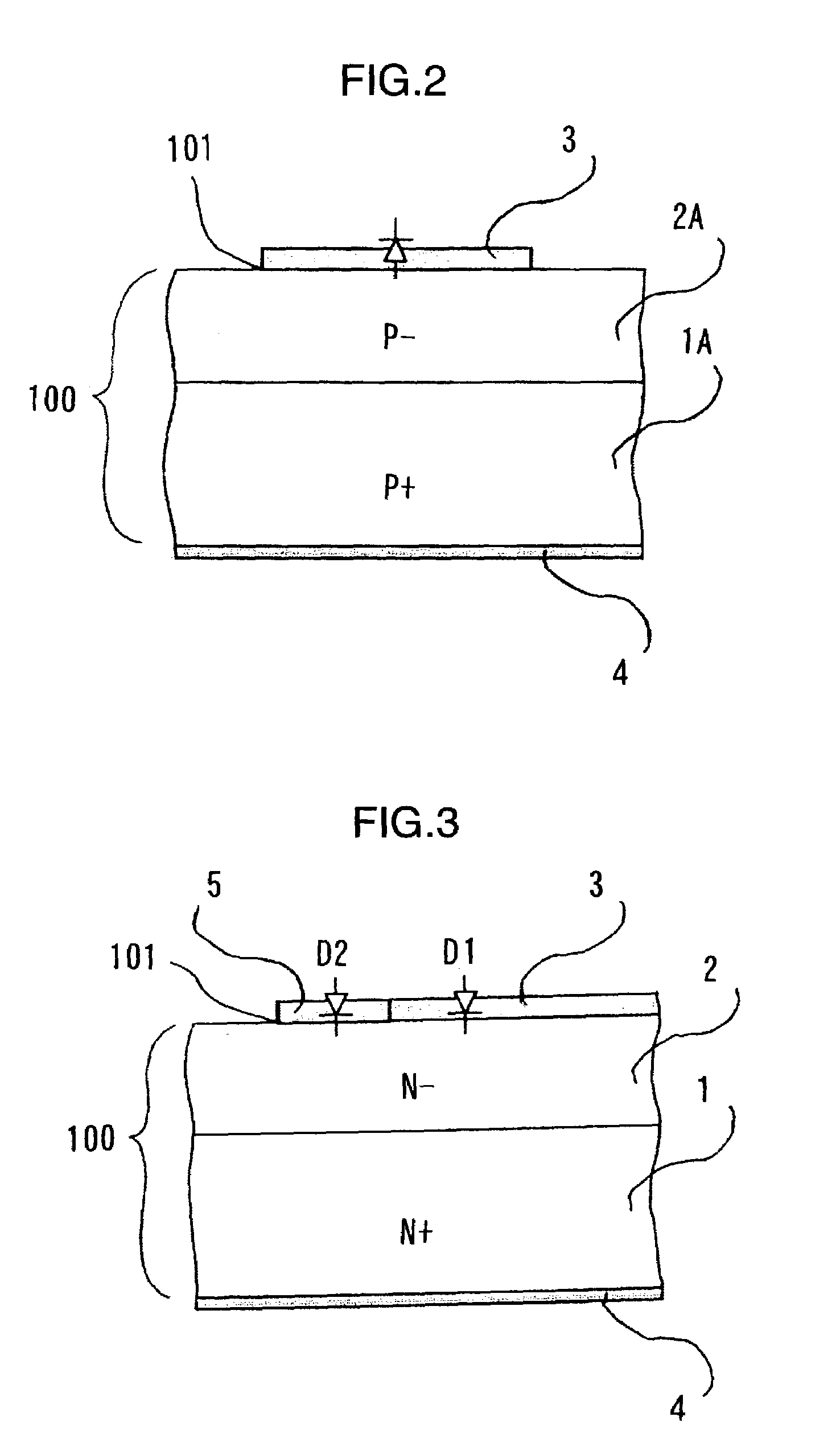

Semiconductor device and method of manufacturing the same

ActiveUS20050045892A1Reduce impurity concentrationImprove pressure resistanceSemiconductor/solid-state device manufacturingDiodeHeterojunctionDevice material

An aspect of the present invention provides a semiconductor device that includes a first semiconductor region of a first conductivity type and a second semiconductor region of a second conductivity type, having a different band gap from the first semiconductor region and forming a heterojunction with the first semiconductor region.

Owner:NISSAN MOTOR CO LTD

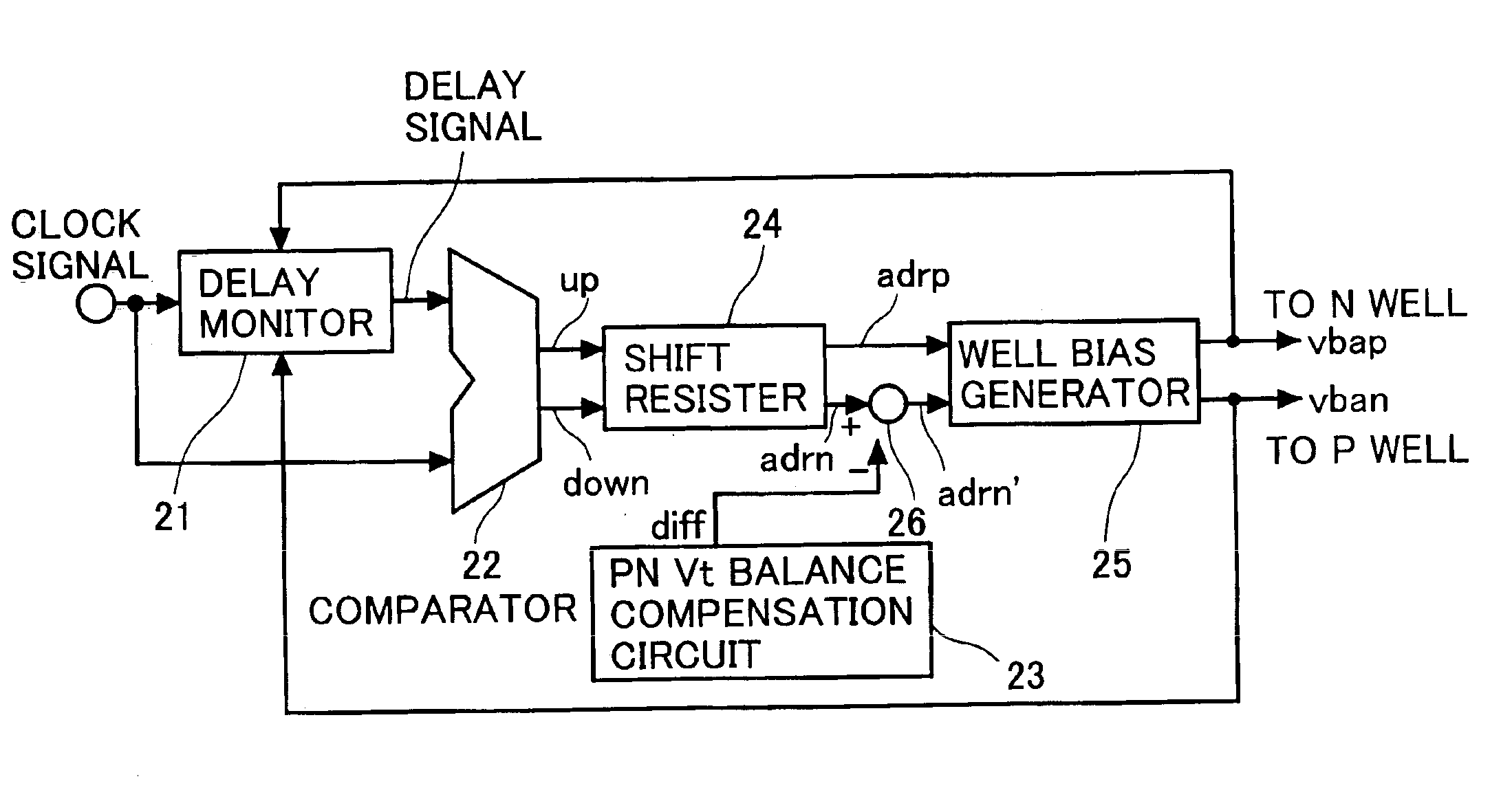

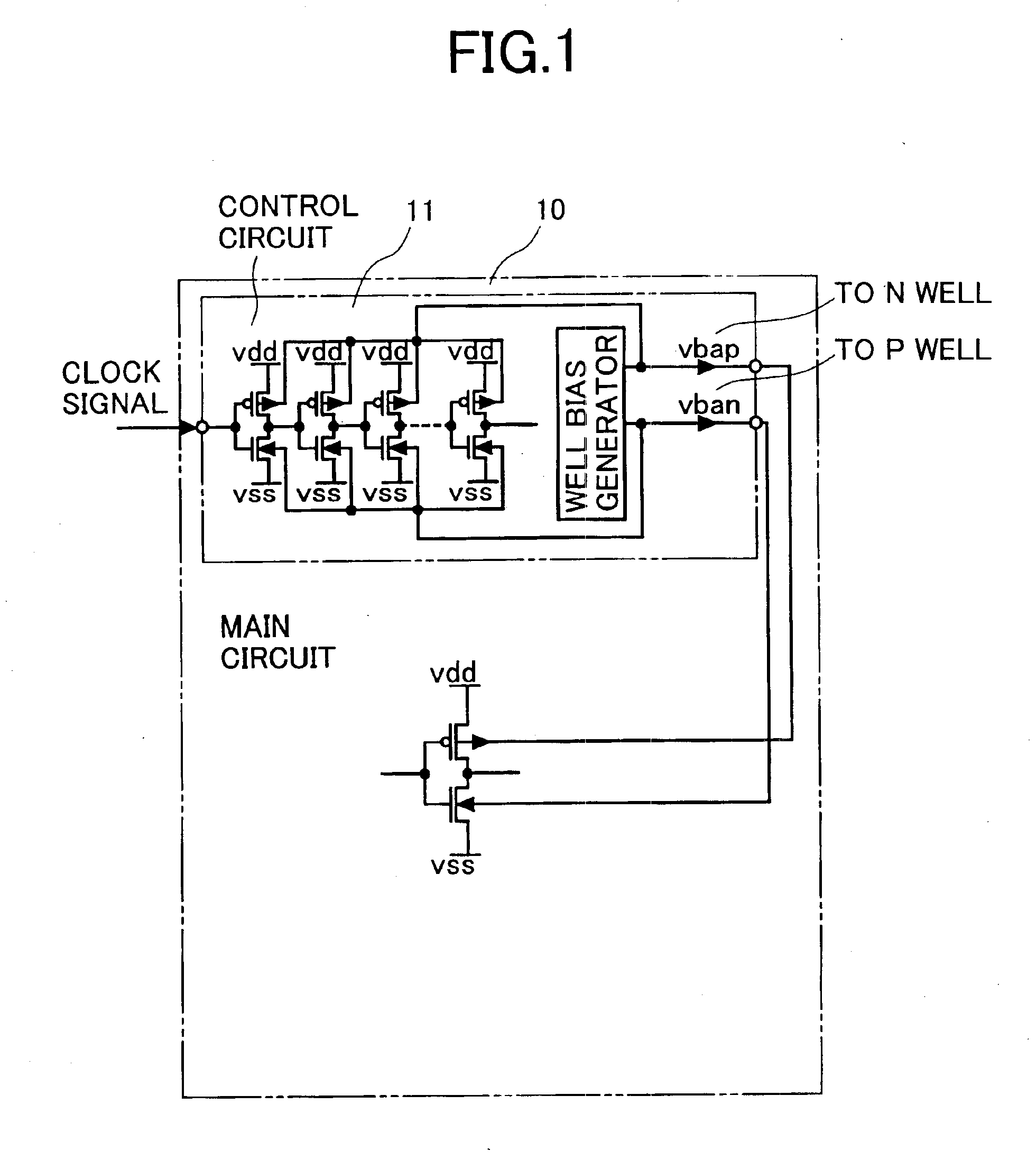

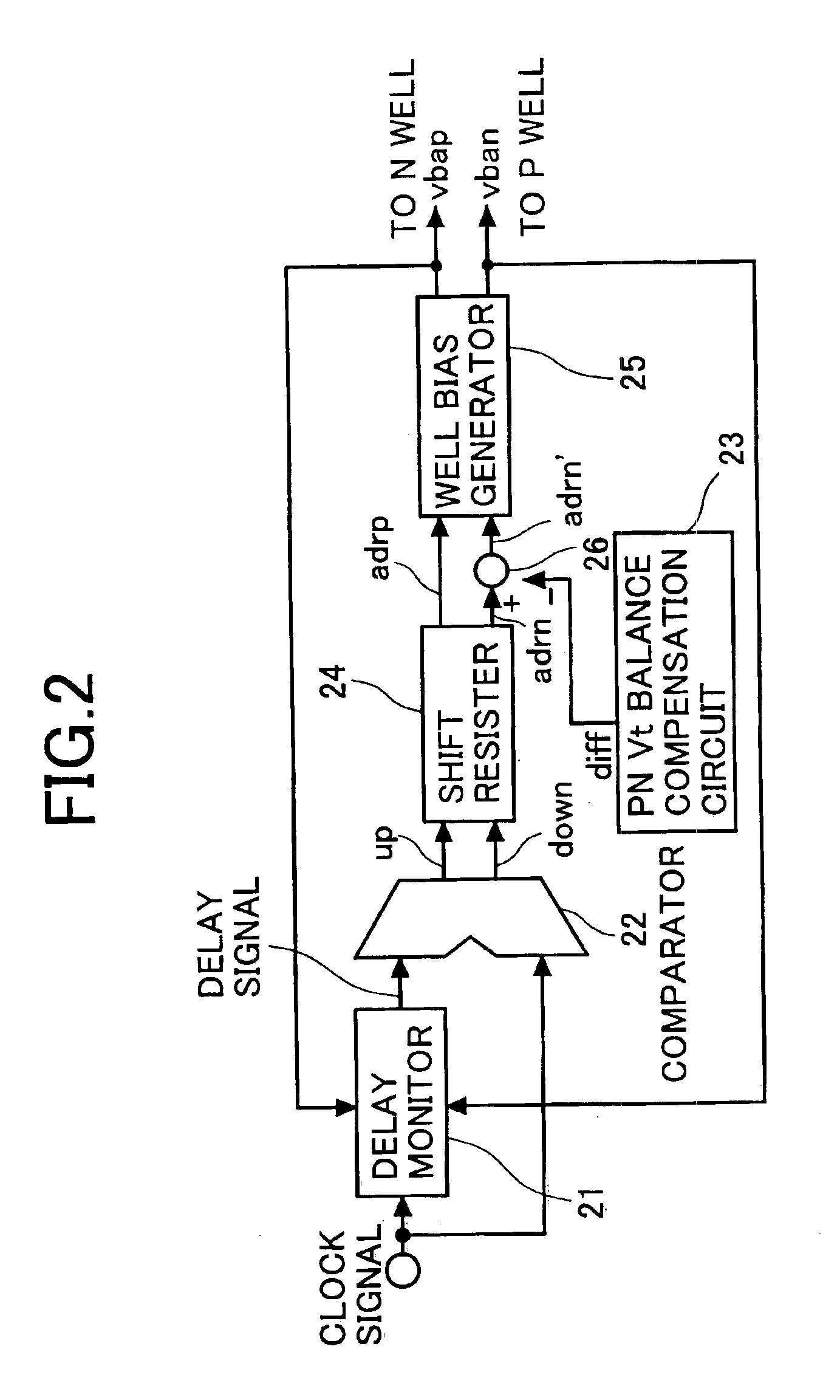

Well bias voltage control circuit and method

InactiveUS6847252B1Improve leakage currentRatio of power consumptionTransistorReliability increasing modificationsCMOSEngineering

A semiconductor integrated circuit device having a mechanism of compensating not only circuit operational speed but also variations in leakage current, which includes: a main circuit constructed with CMOS device, a delay monitor for simulating a critical path of the main circuit constructed by a CMOS and monitoring a delay of the path, a PN Vt balance compensation circuit for detecting a threshold voltage difference between a PMOS transistor and an NMOS transistor, and a well bias generating circuit for receiving outputs of the delay monitor and the PN Vt balance compensation circuit and applying a well bias to the delay monitor and the main circuit so as to compensate the operation speed of the delay monitor to a desired speed and reduce a threshold voltage difference between the PMOS and NMOS transistors.

Owner:RENESAS ELECTRONICS CORP

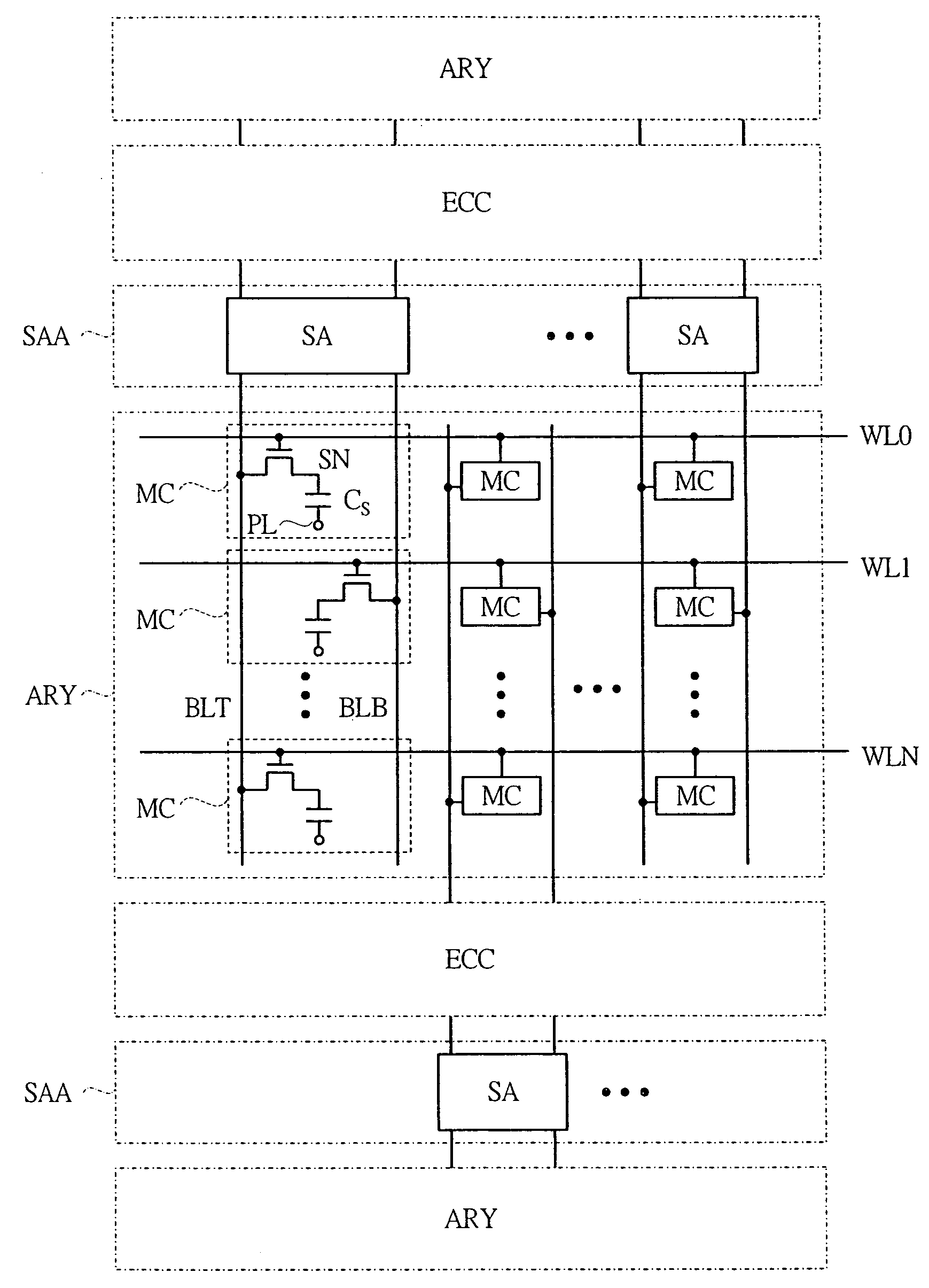

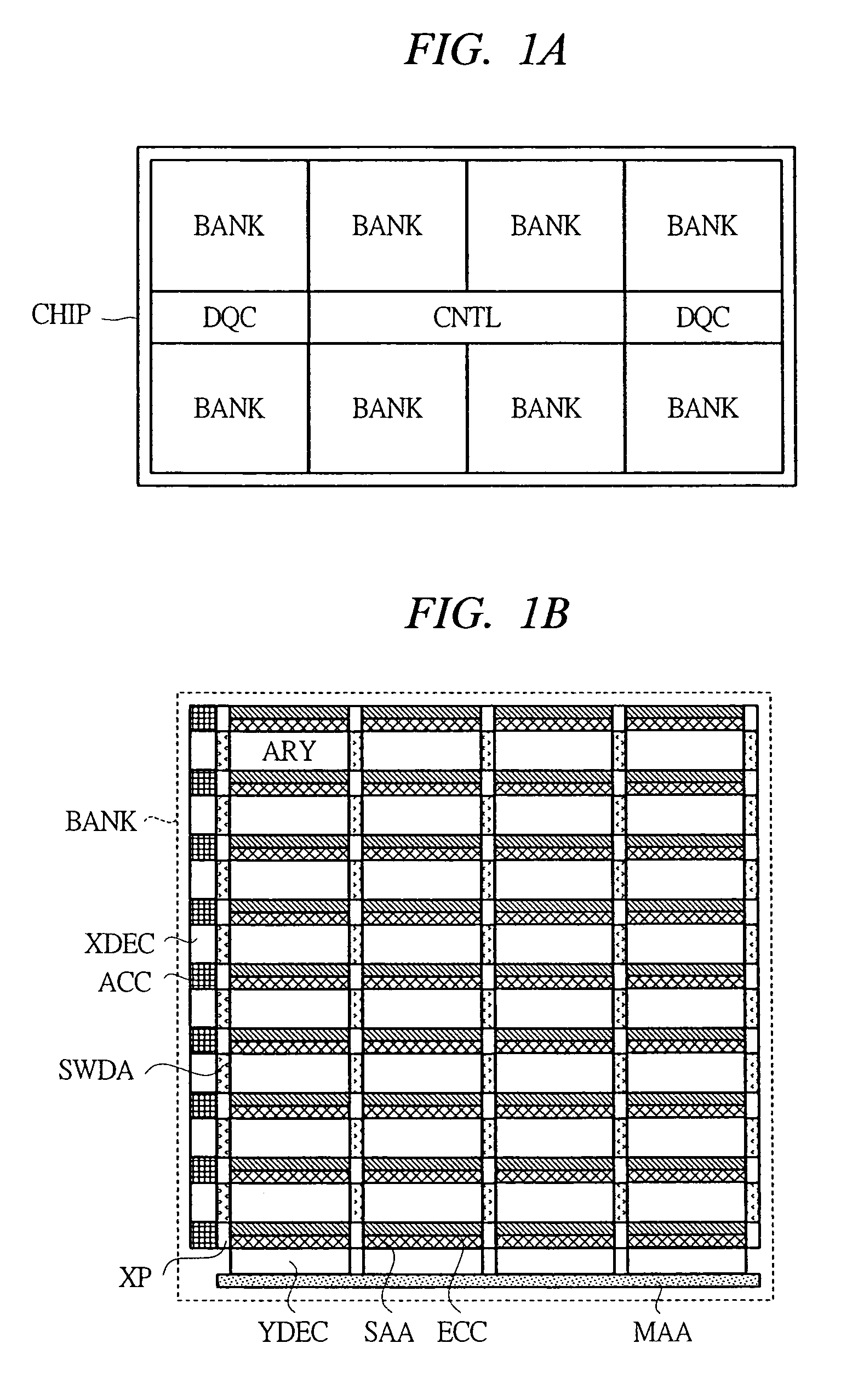

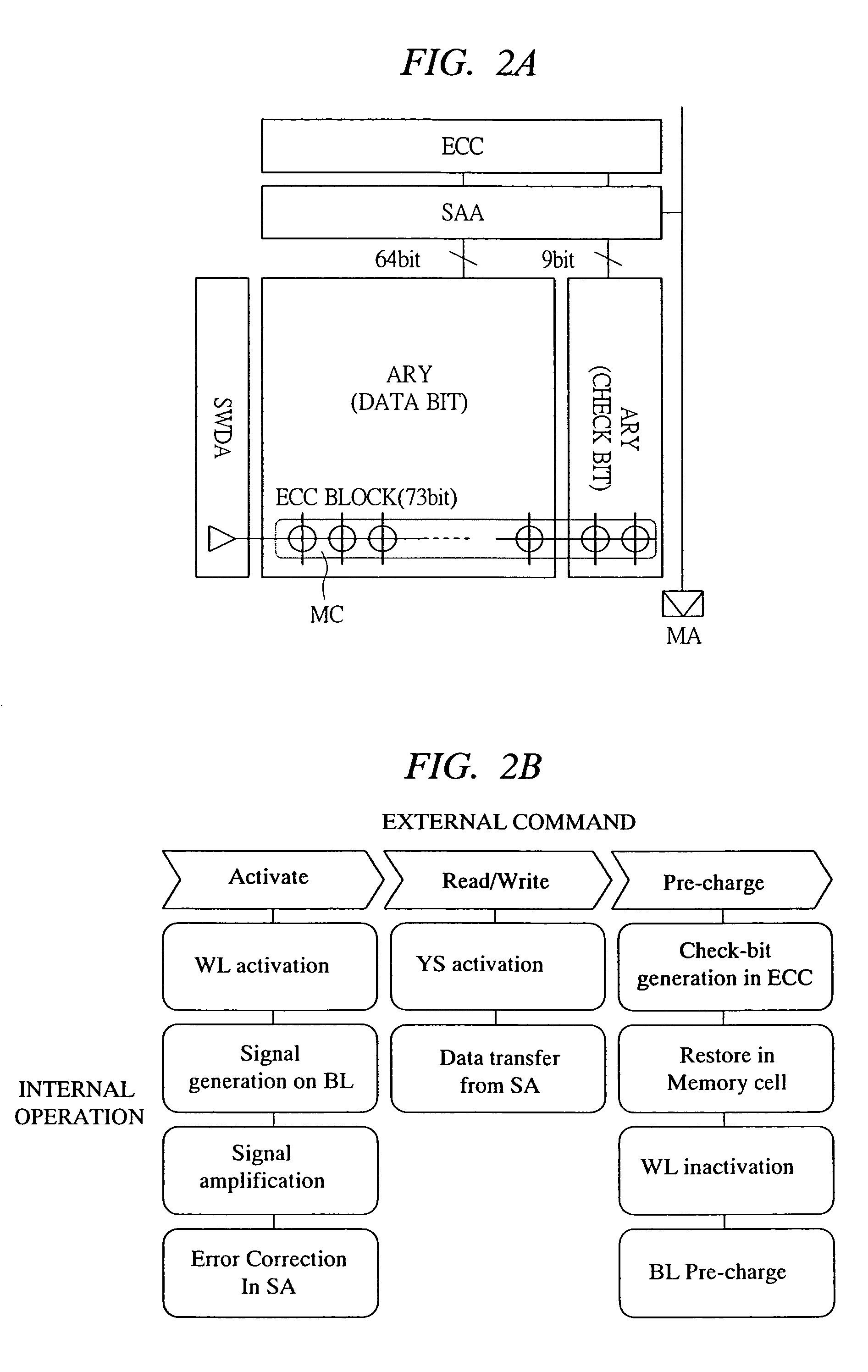

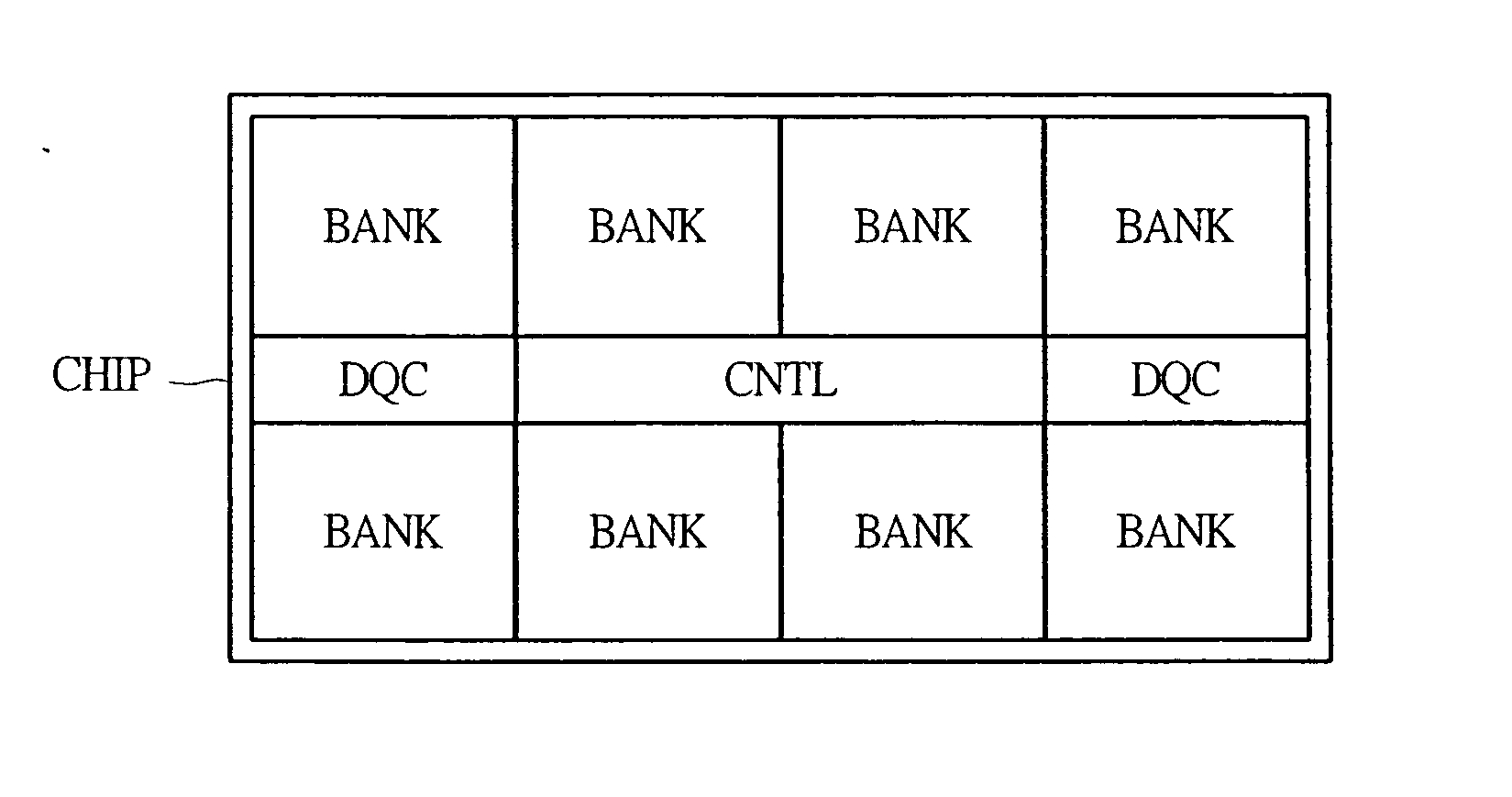

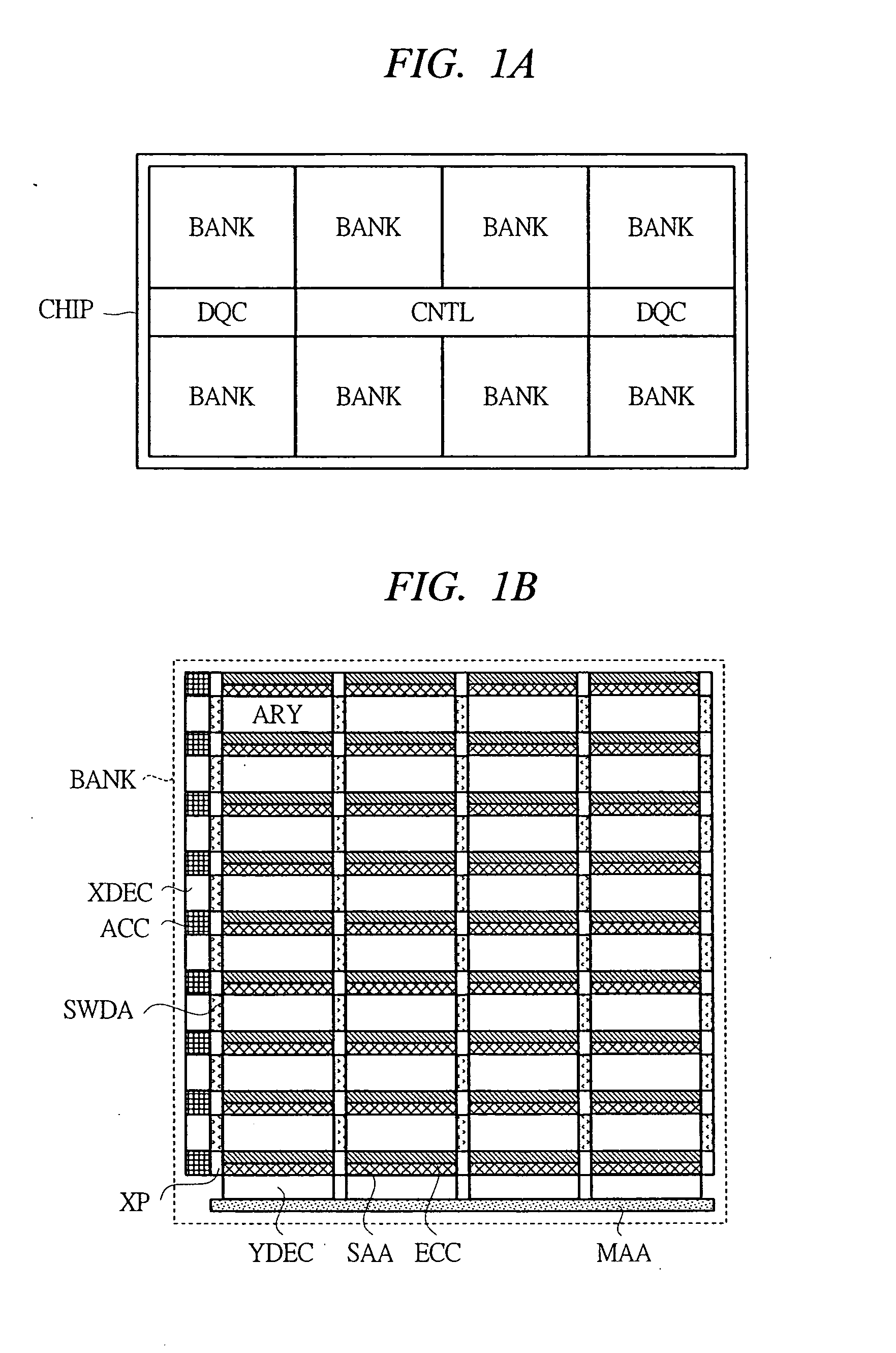

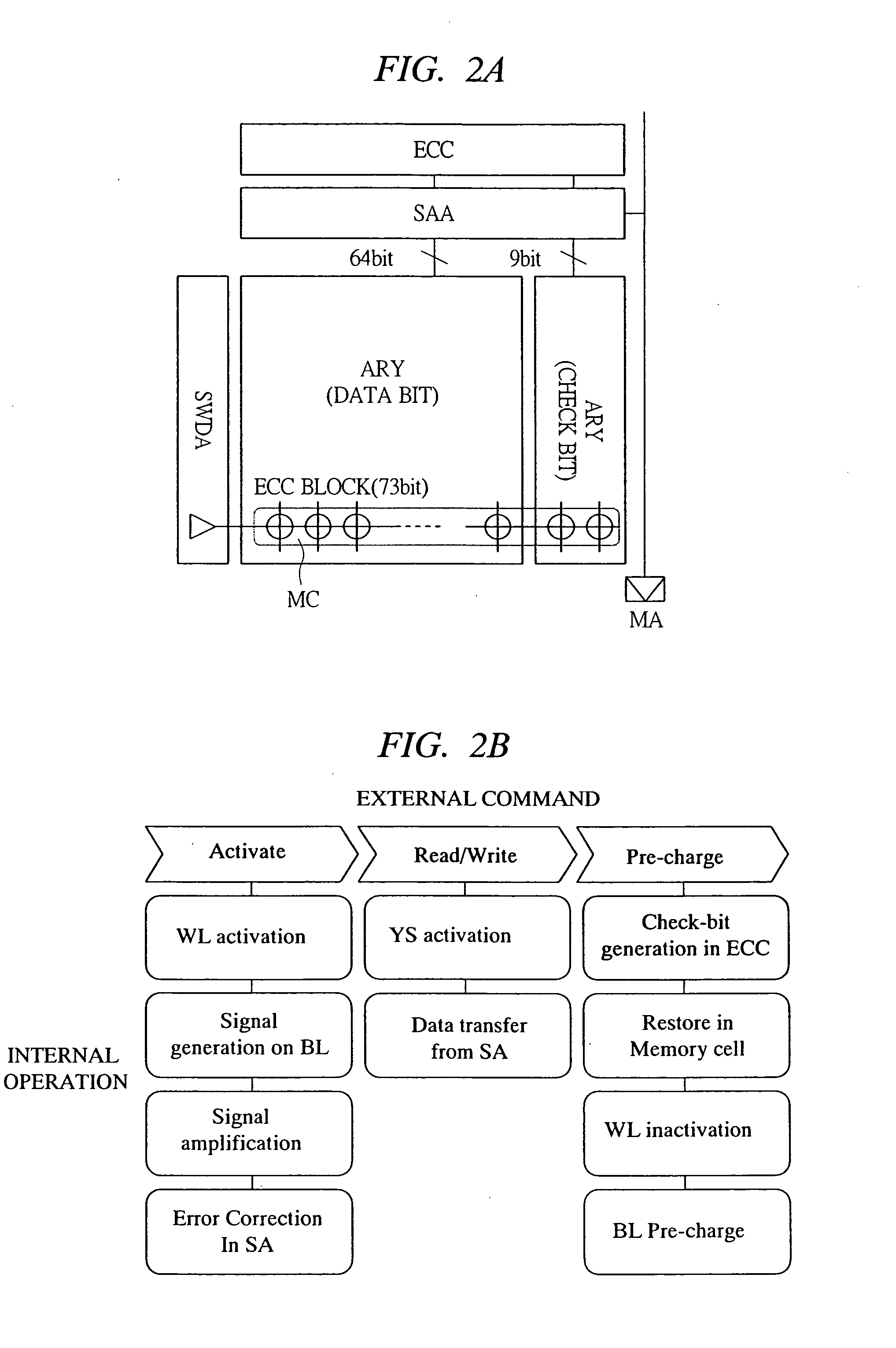

Semiconductor device having a sense amplifier array with adjacent ECC

ActiveUS7603592B2Improve the mismatchImprove leakage currentError detection/correctionCode conversionAudio power amplifierPre-charge

A semiconductor memory device capable of achieving a sufficient operating margin without increasing an area penalty even in the case of miniaturization is provided. An error correction system composed of a data bit of 64 bits and a check bit of 9 bits is introduced to a memory array such as DRAM, and an error correction code circuit required therein is disposed near a sense amplifier array. In addition to normal memory arrays composed of such memory arrays, a redundant memory array having a sense amplifier array and an error correction code circuit adjacent thereto is provided in a chip. By this means, the error which occurs in the manufacture can be replaced. Also, the error correction code circuit corrects the error at the time of an activate command and stores the check bit at the time of a pre-charge command.

Owner:MICRON TECH INC

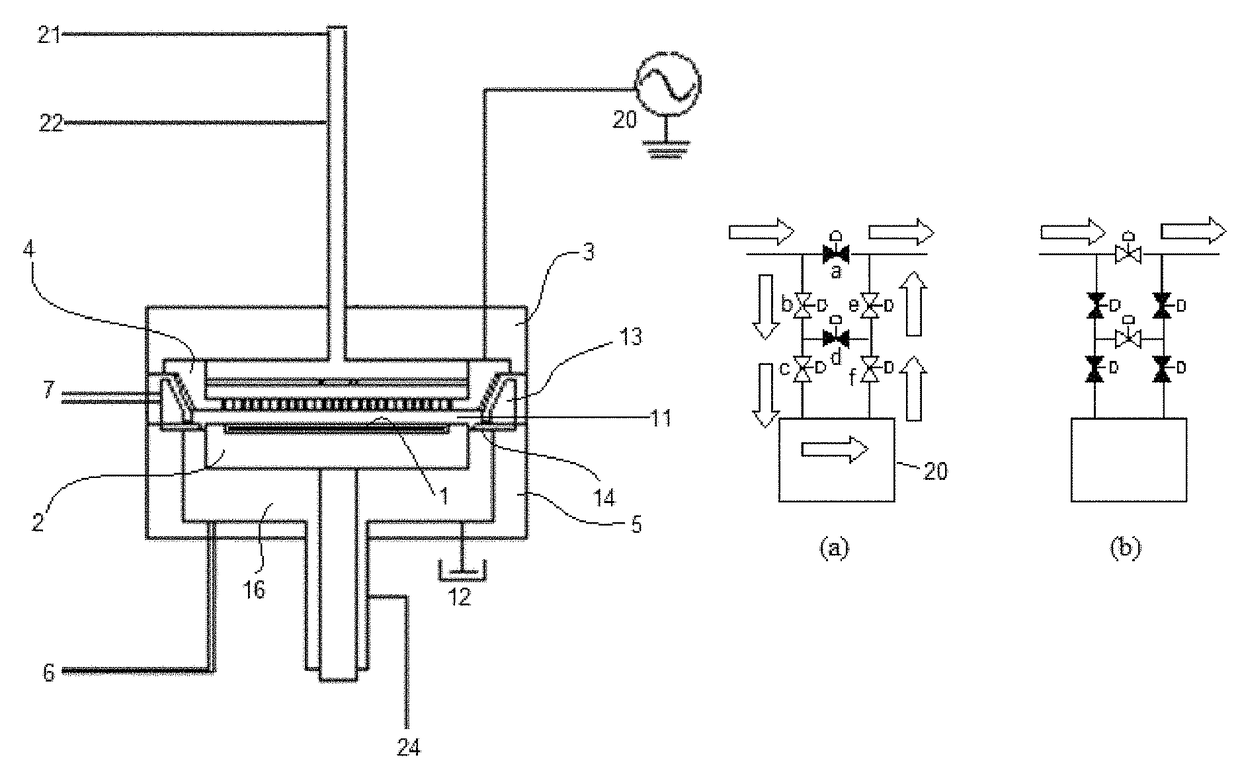

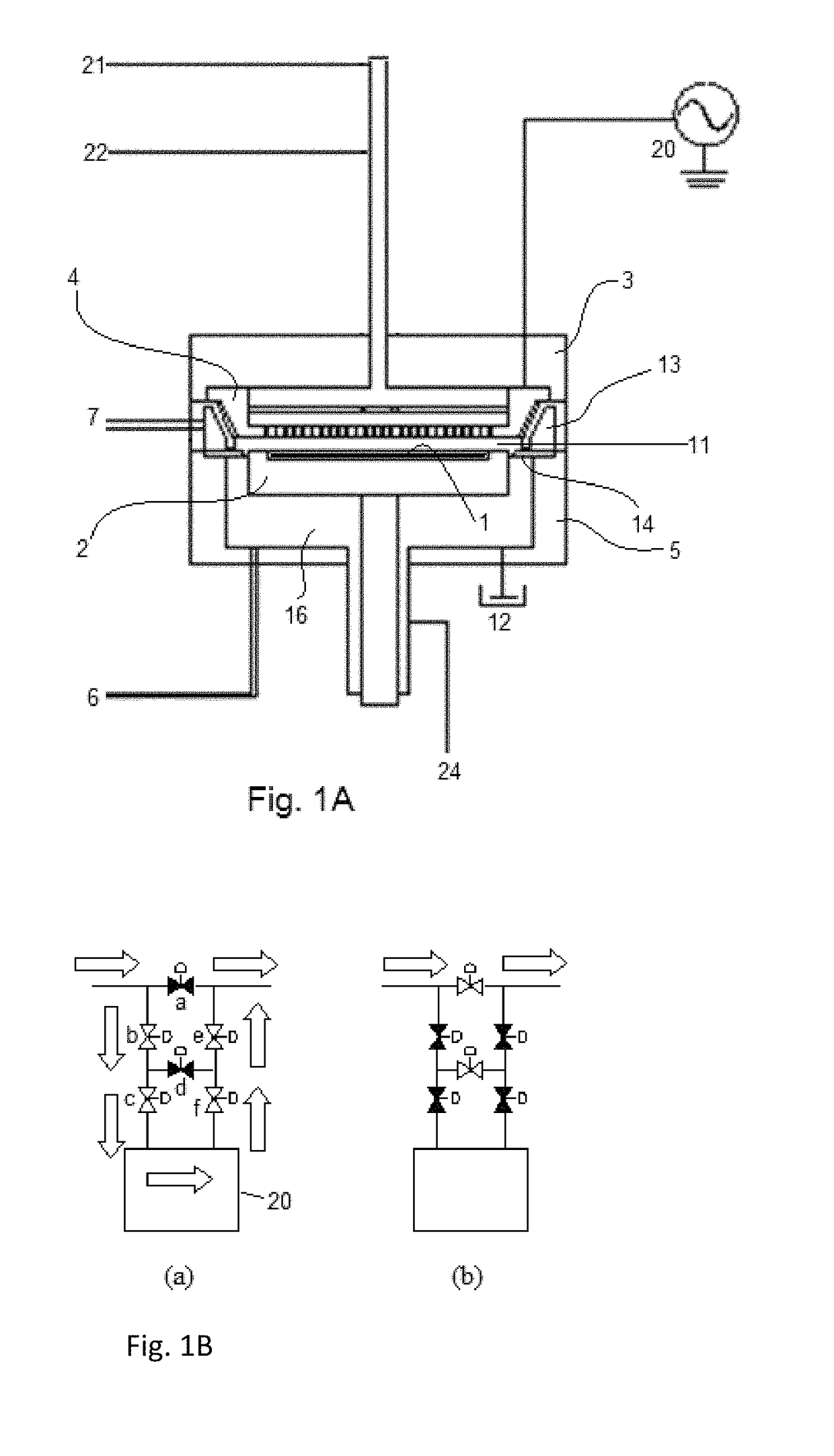

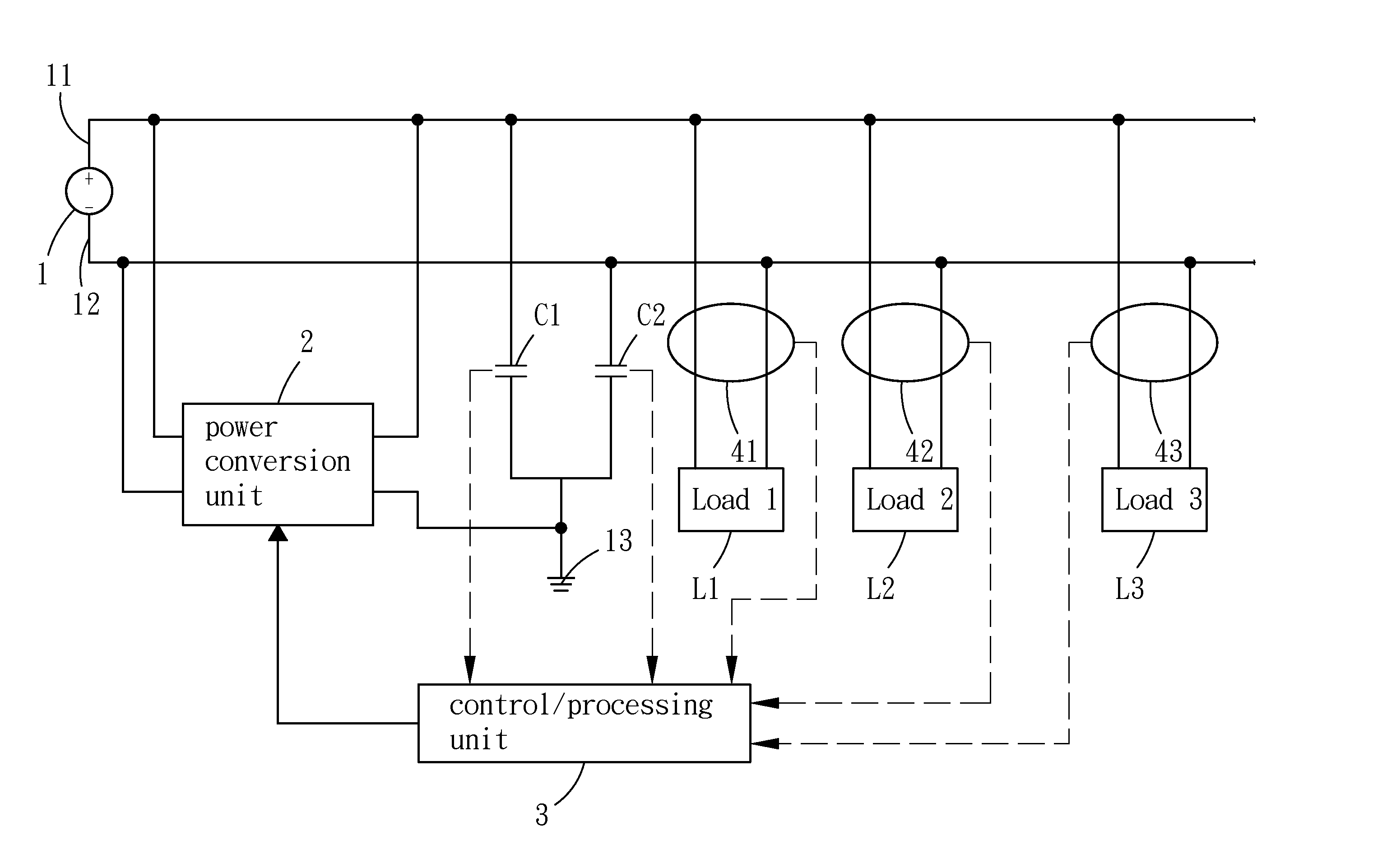

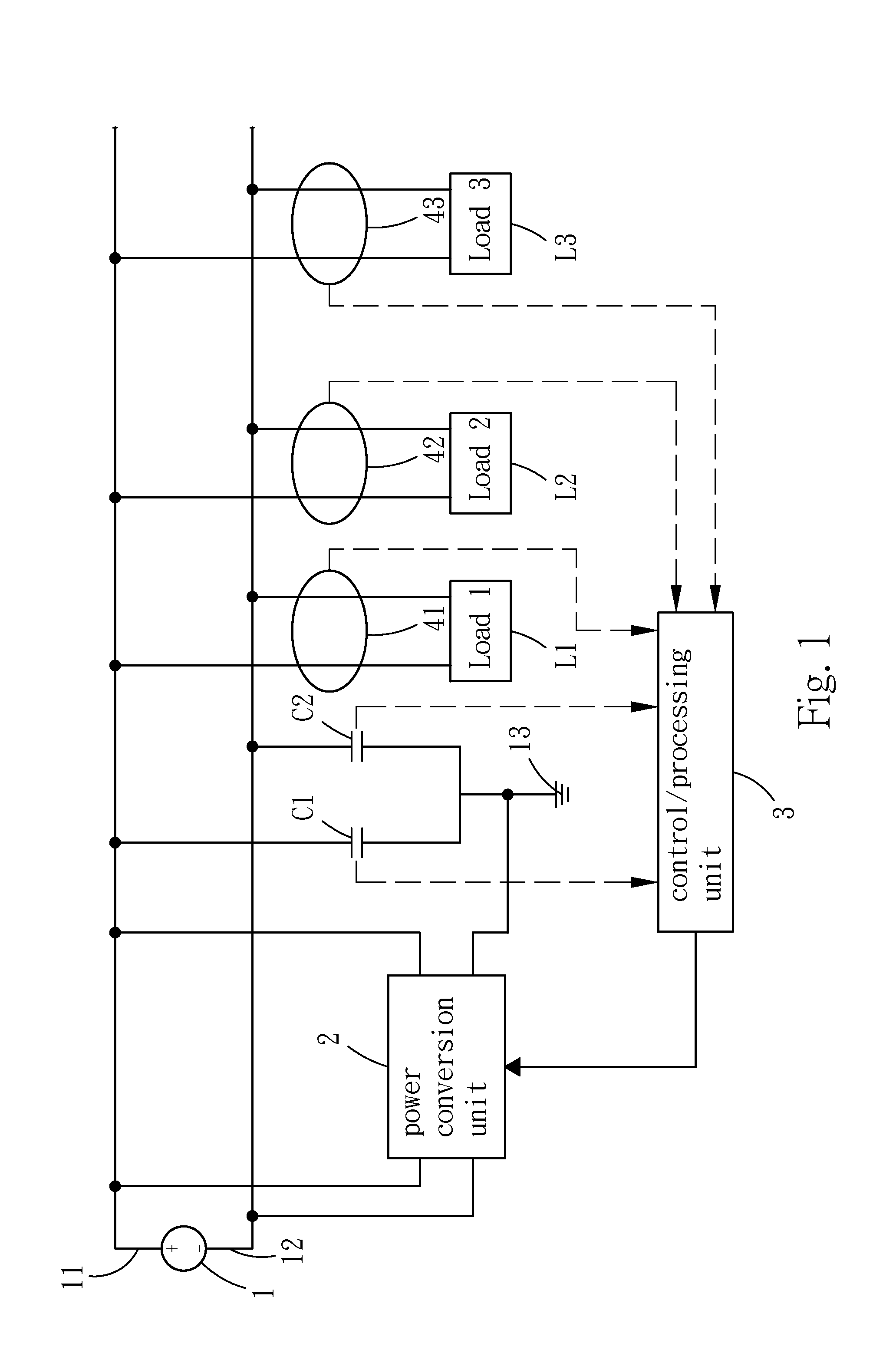

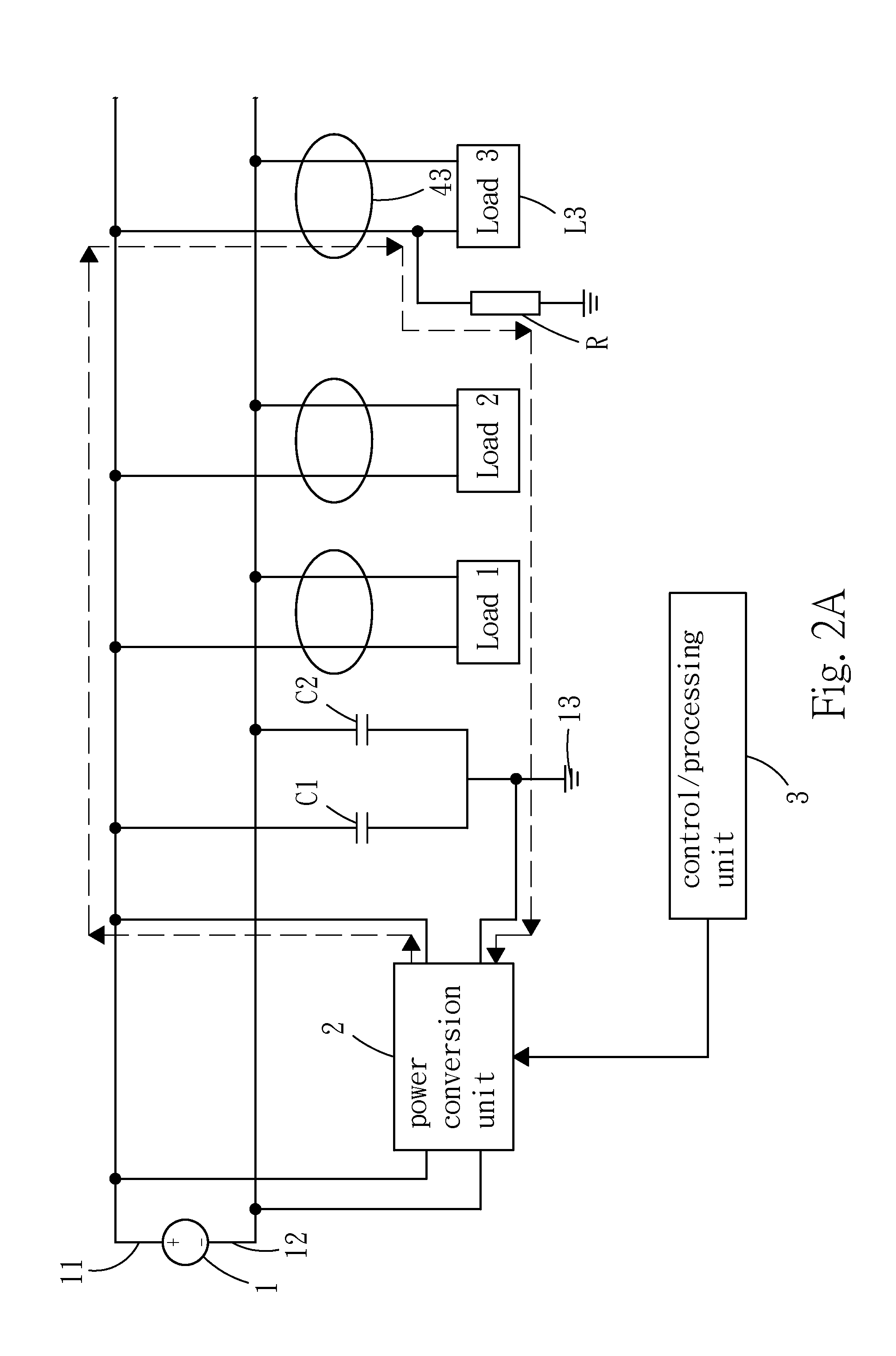

High-sensitivity insulation resistance detection method and circuit for ungrounded DC power supply system

InactiveUS20150285850A1Improve leakage currentEasily detect valueVery high resistance measurementsImpedence measurementsElectrical resistance and conductanceDc current

The present invention is a high-sensitivity insulation resistance detection method and circuit for an ungrounded DC power supply systems. When the ratio of the voltage of the positive bus to that of the negative bus exceeds a preset range, the DC current is injected into the ungrounded DC power supply systems. DC power supply systems have essentially some grounded stray and external capacitors, so some of the injected DC current will flow into the grounded capacitor, increasing the voltage of the fault bus and the leakage current. The proposed method increases the leakage current by the injection of DC current, so the current sensor can detect the leakage current from which the insulation resistance can be calculated. The DC current injection method can significantly improve the detection of ground insulation faults in ungrounded DC power supply systems.

Owner:KAO YUAN UNIVERSITY OF TECHNOLOGY +1

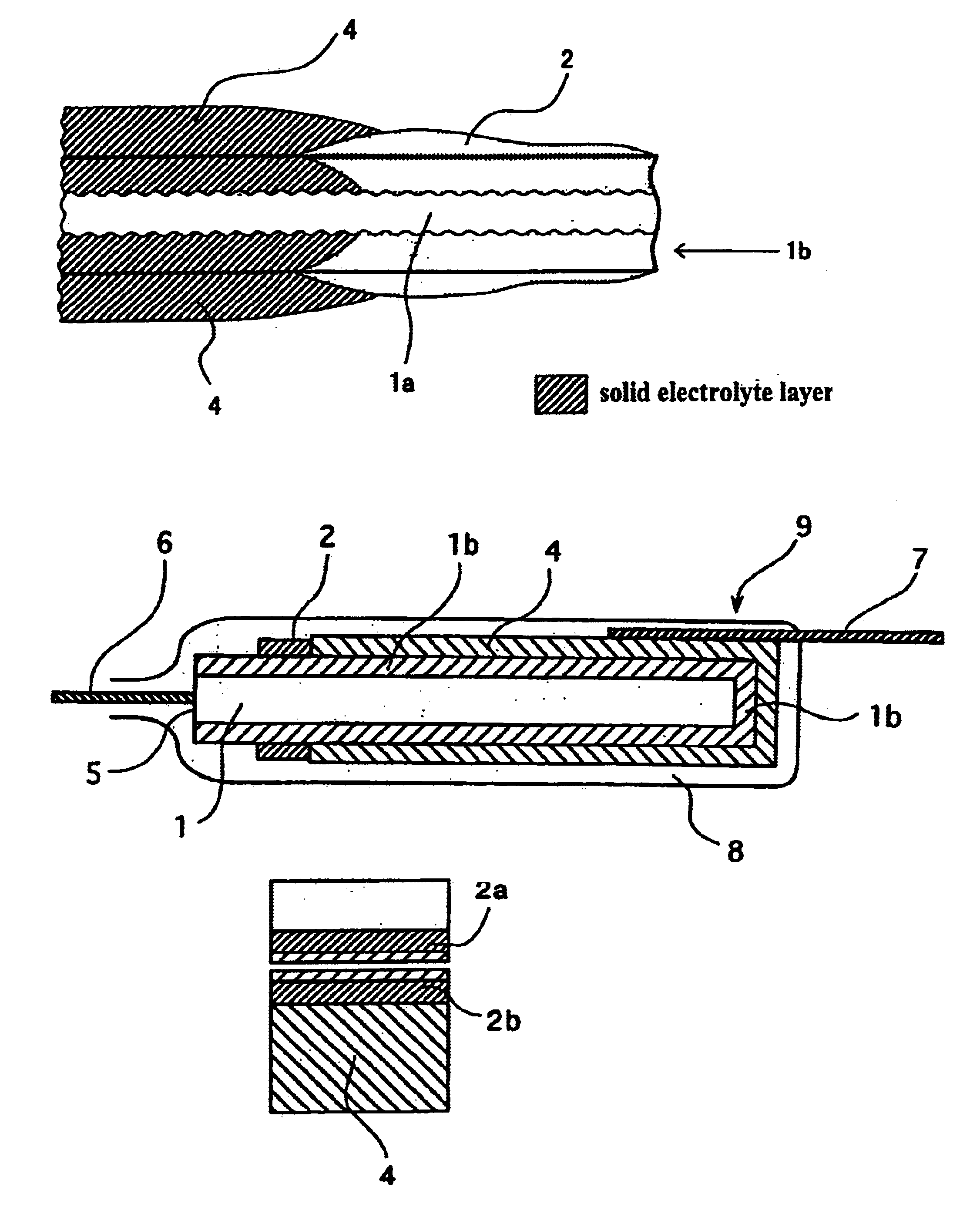

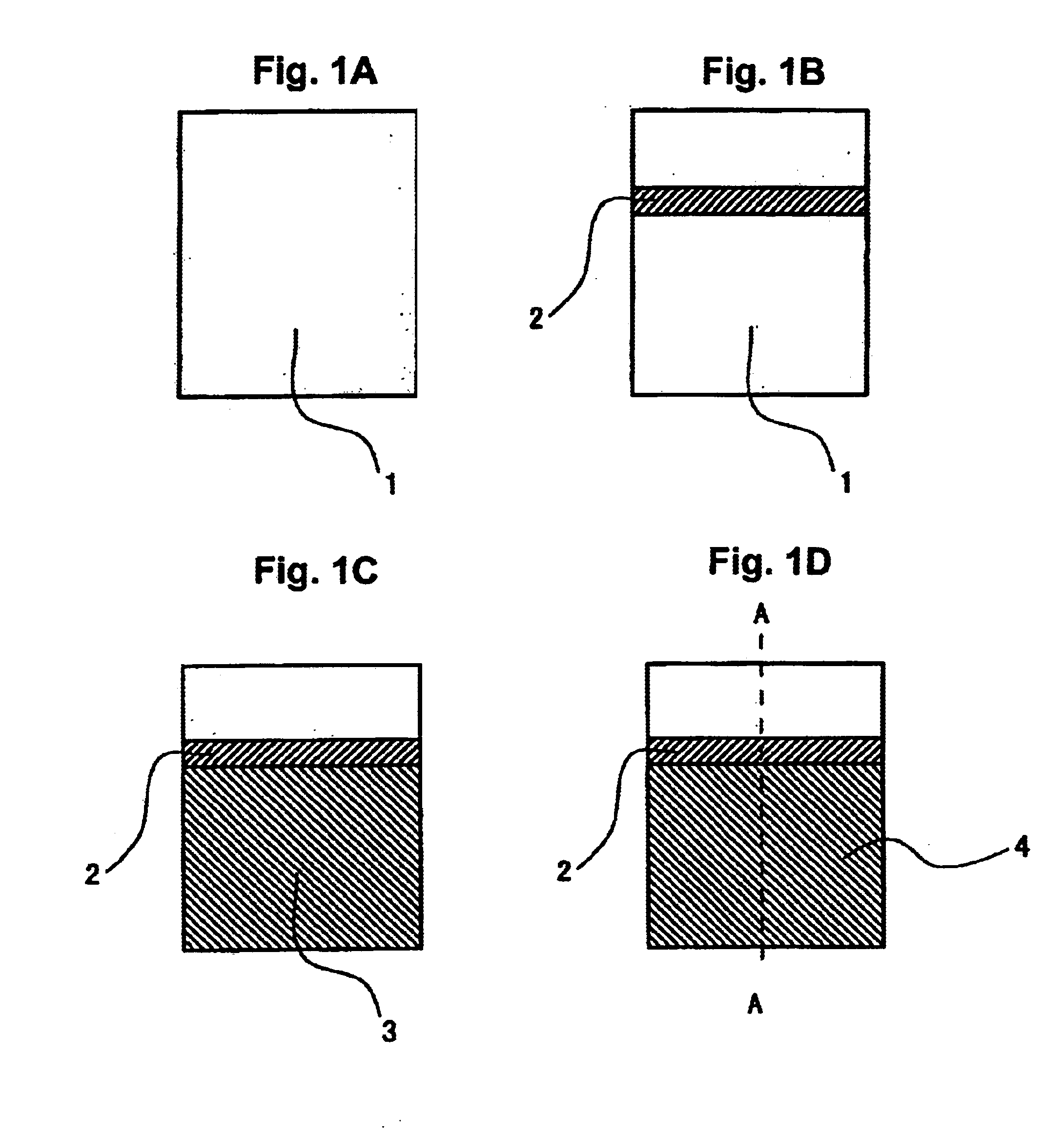

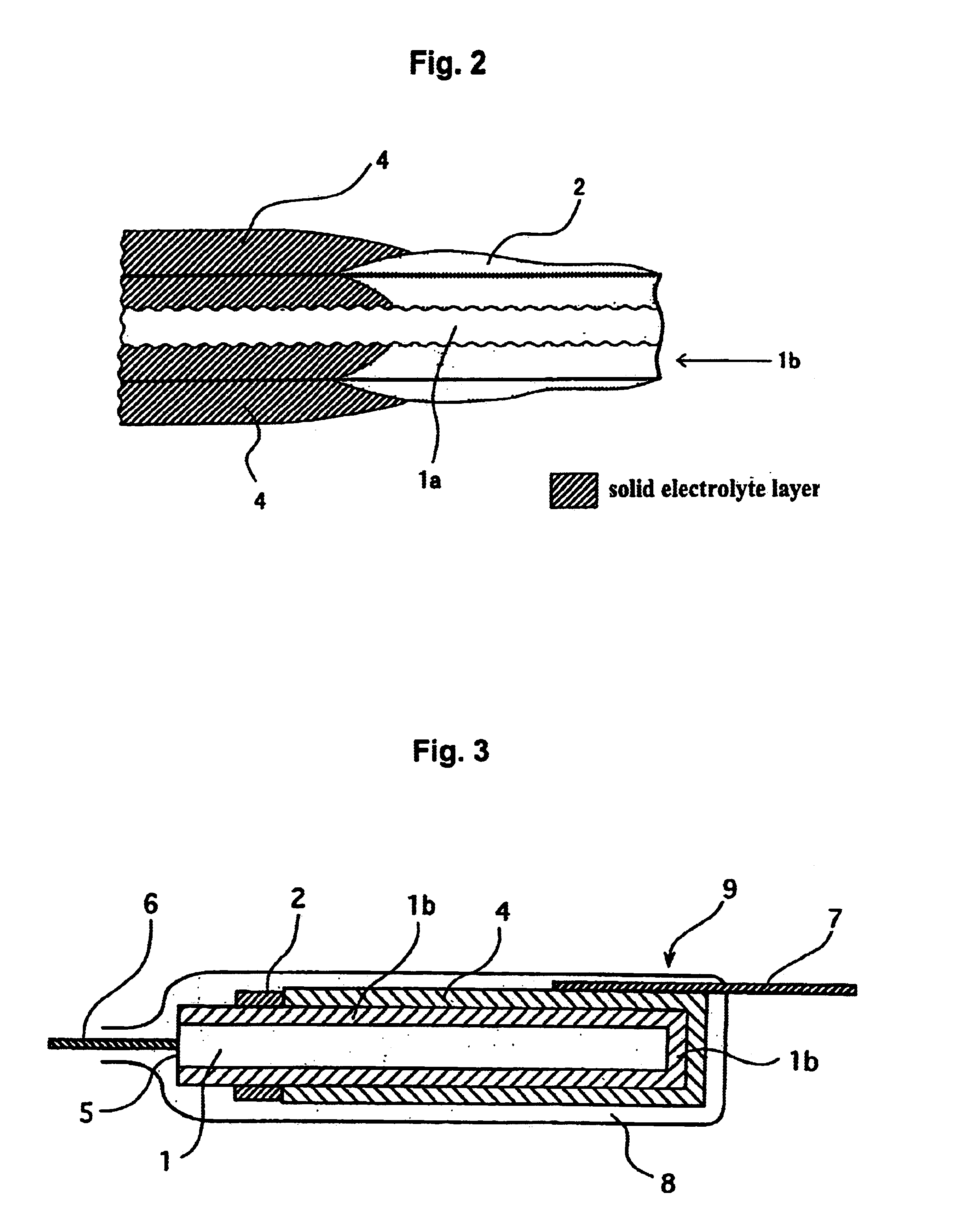

Solid electrolytic capacitor and method for producing the same

InactiveUS6890363B1Efficient executionImprove leakage currentHybrid capacitor electrolytesSolid electrolytic capacitorsElectrolysisMetallic materials

The present invention relates to a solid electrolytic capacitor having a masking structure in which the insulation between the anode part and the cathode part can be ensured without fail, to its production method, to a method for coating a masking agent on a solid electrolytic capacitor substrate, and to an apparatus therefor. According to the present invention, the masking material covers the dielectric film on the metal material having valve action and sufficiently infiltrates into the core metal made of a metal having valve action while the solid electrolyte is masked by the masking material without fail, so that a solid electrolytic capacitor can be produced that has a reduced leakage current and a reduced stress generated at the reflow treatment or the like.

Owner:MURATA MFG CO LTD

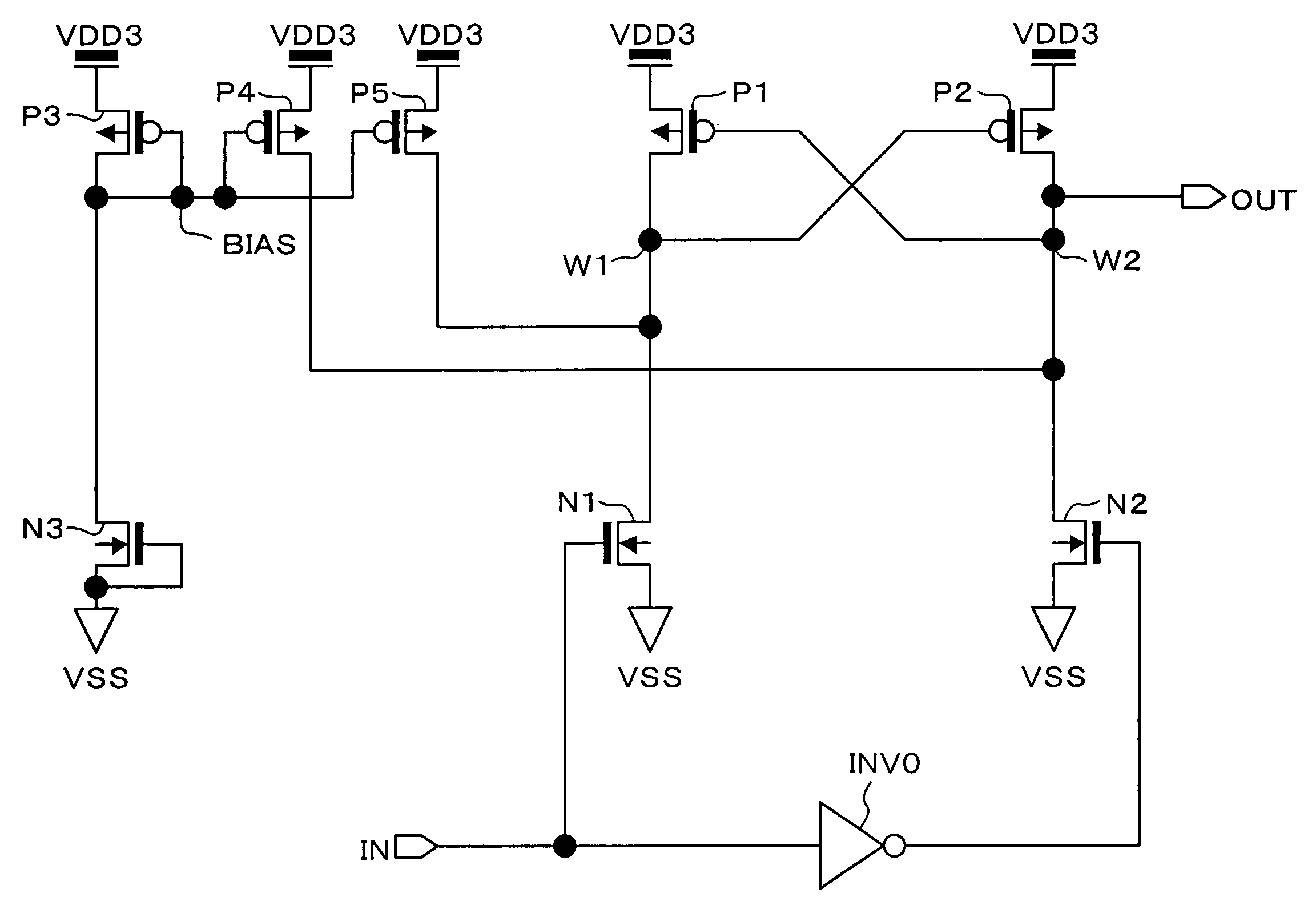

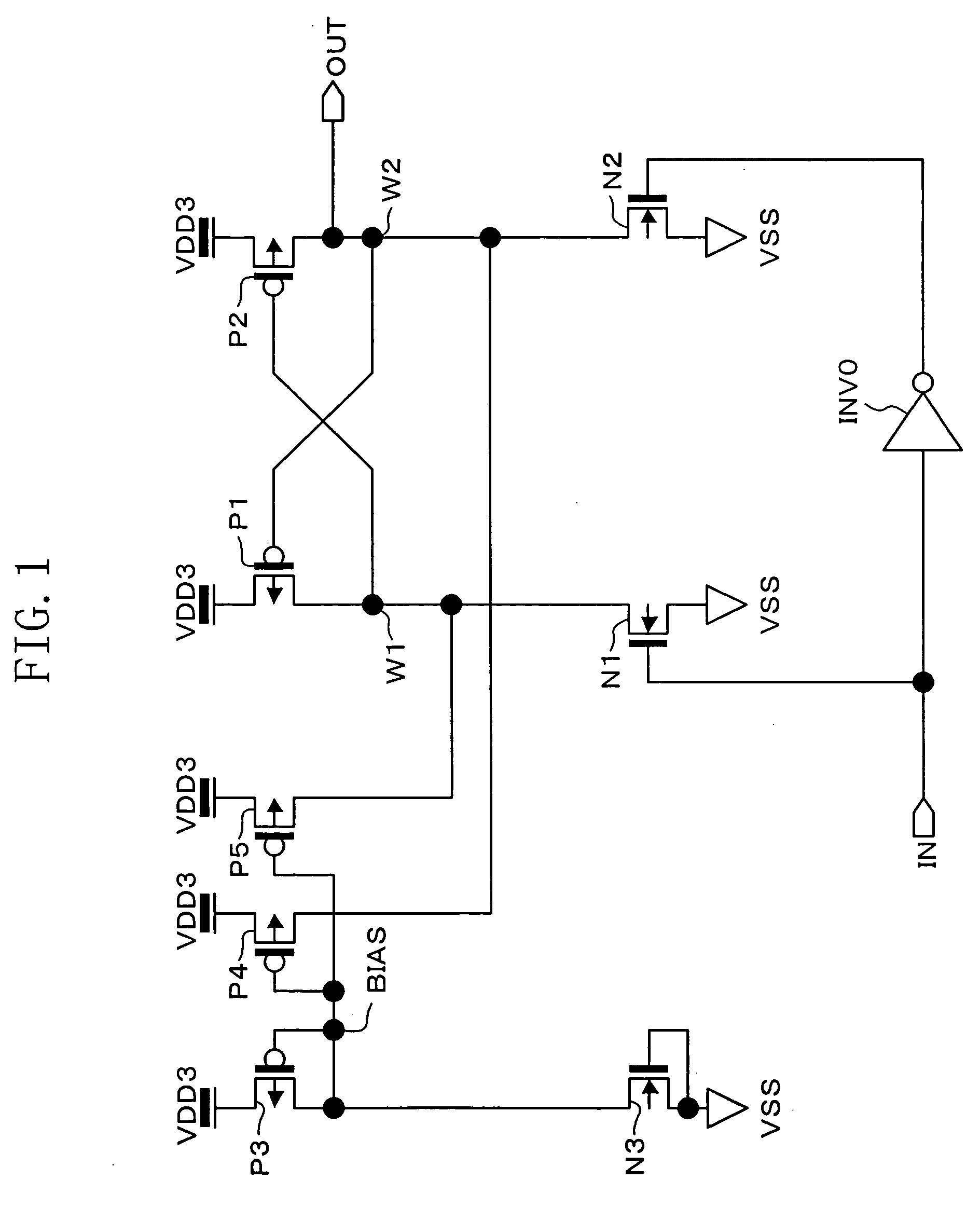

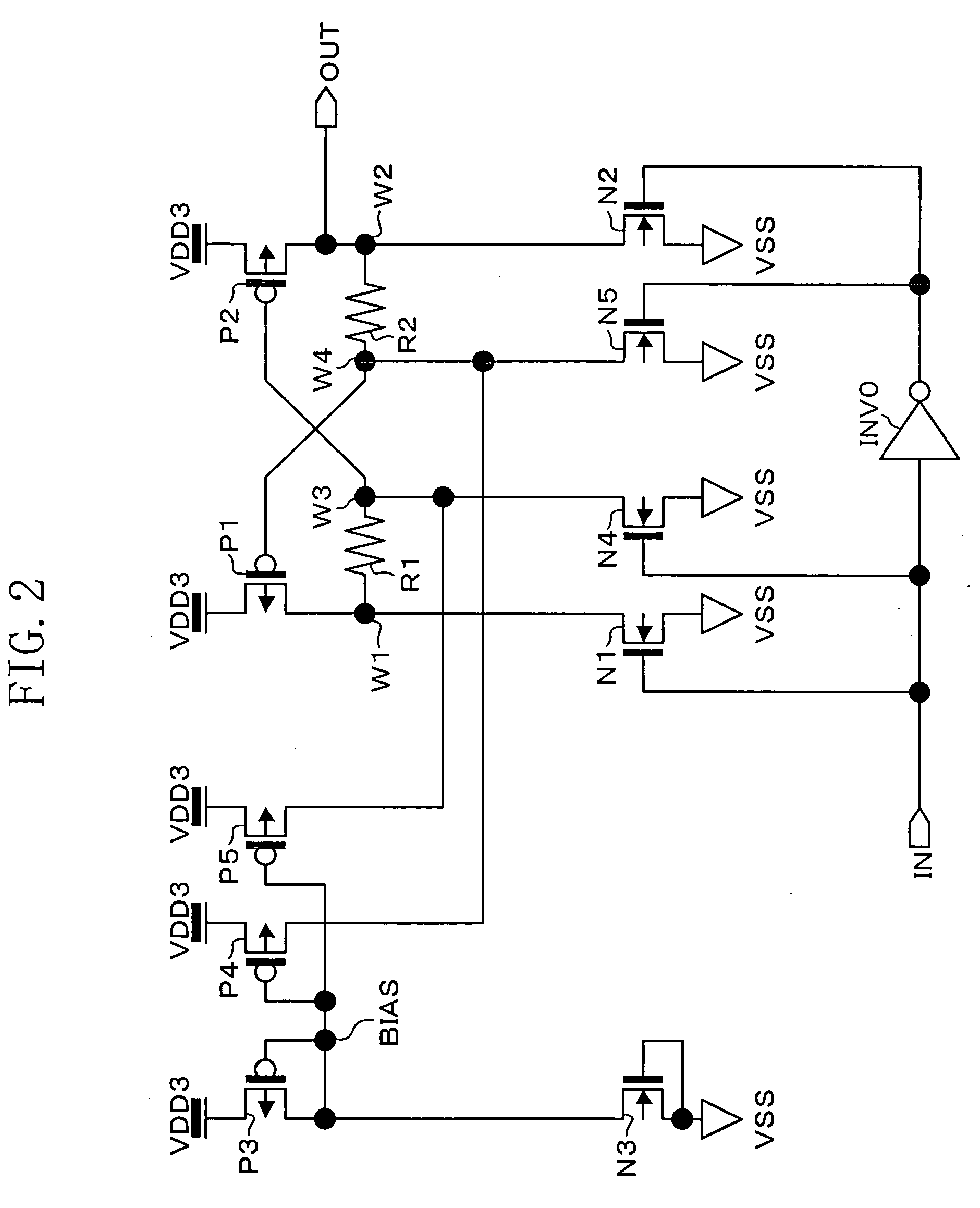

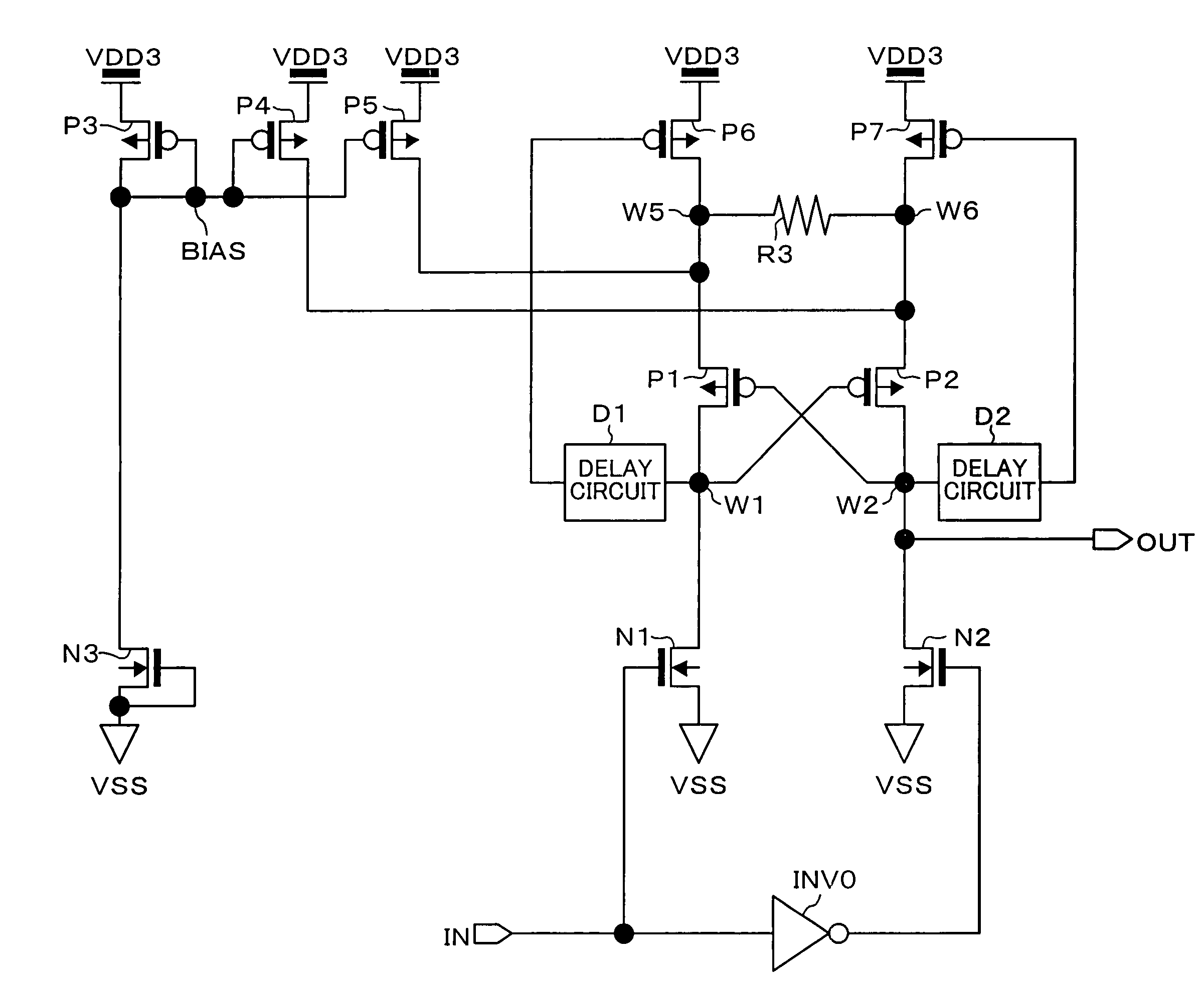

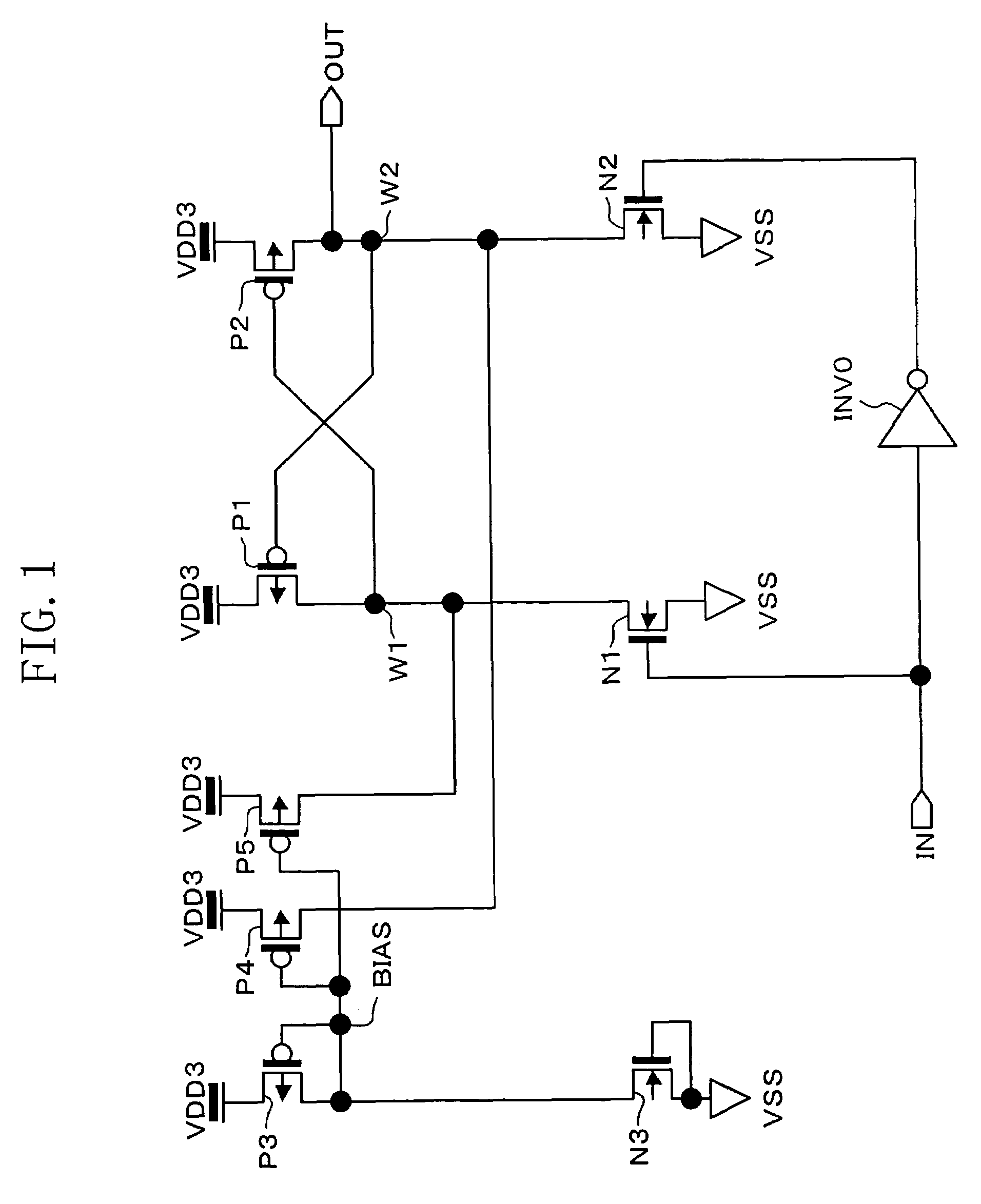

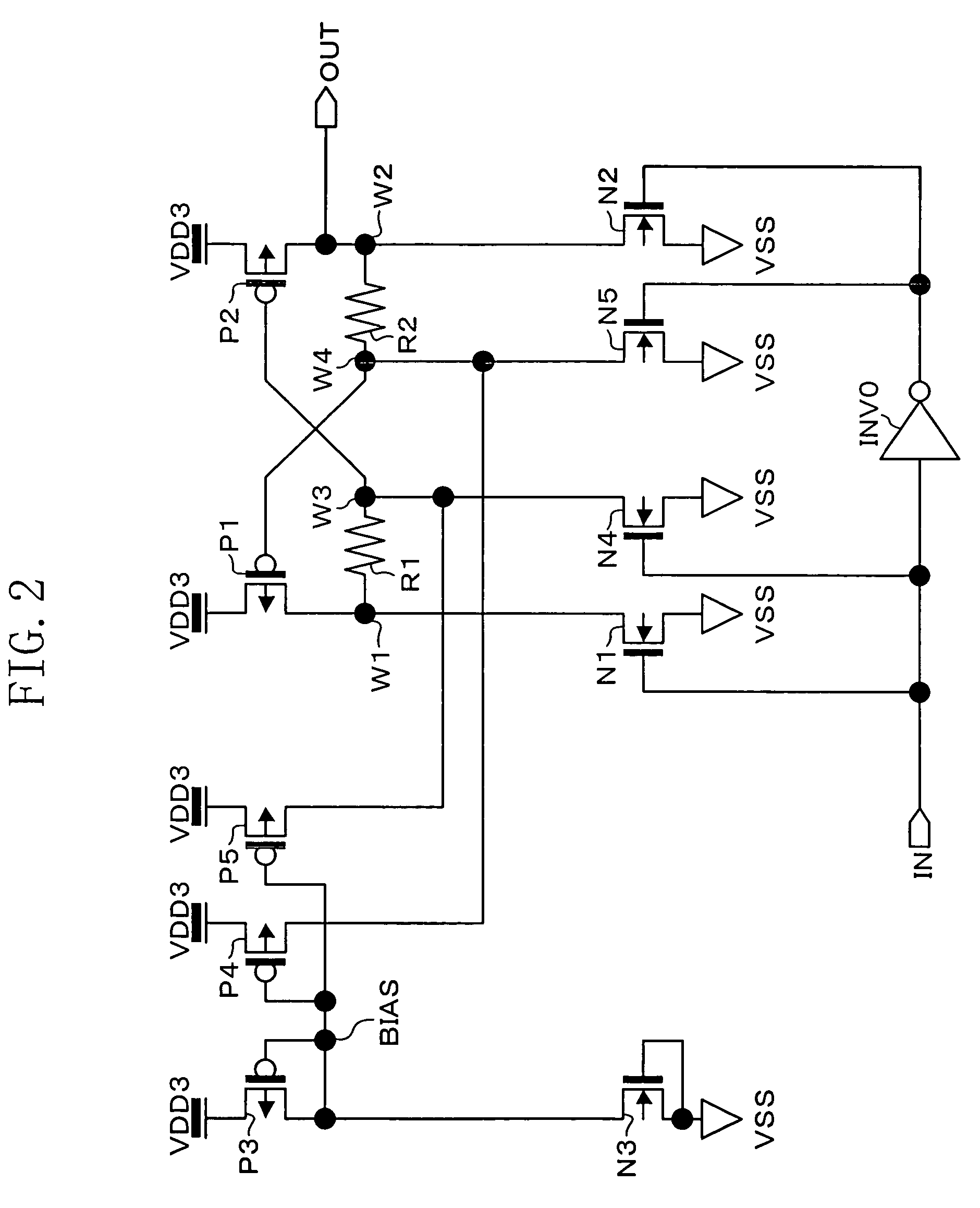

Level shifter

InactiveUS20060208759A1Increase resistanceCarry-out quicklyElectronic switchingElectric pulse generatorEngineeringVoltage source

In a level shifter, OFF leakage currents flow through two N-type transistors for signal input even when they are OFF. However, another N-type transistor serving as an OFF leakage generation circuit and three P-type transistors serving as current mirrors, which constitute a current conversion circuit, supply to the signal-input transistors a current equivalent to or greater than the OFF leakage currents flowing through the signal-input transistors when they are OFF, thereby canceling the OFF leakage currents. Therefore, one of nodes which is at H level is surely fixed to a potential equal to a higher voltage supply. Thus, the level shifter surely operates with a high speed even when large OFF leakage currents flow through the signal-input transistors.

Owner:SOCIONEXT INC

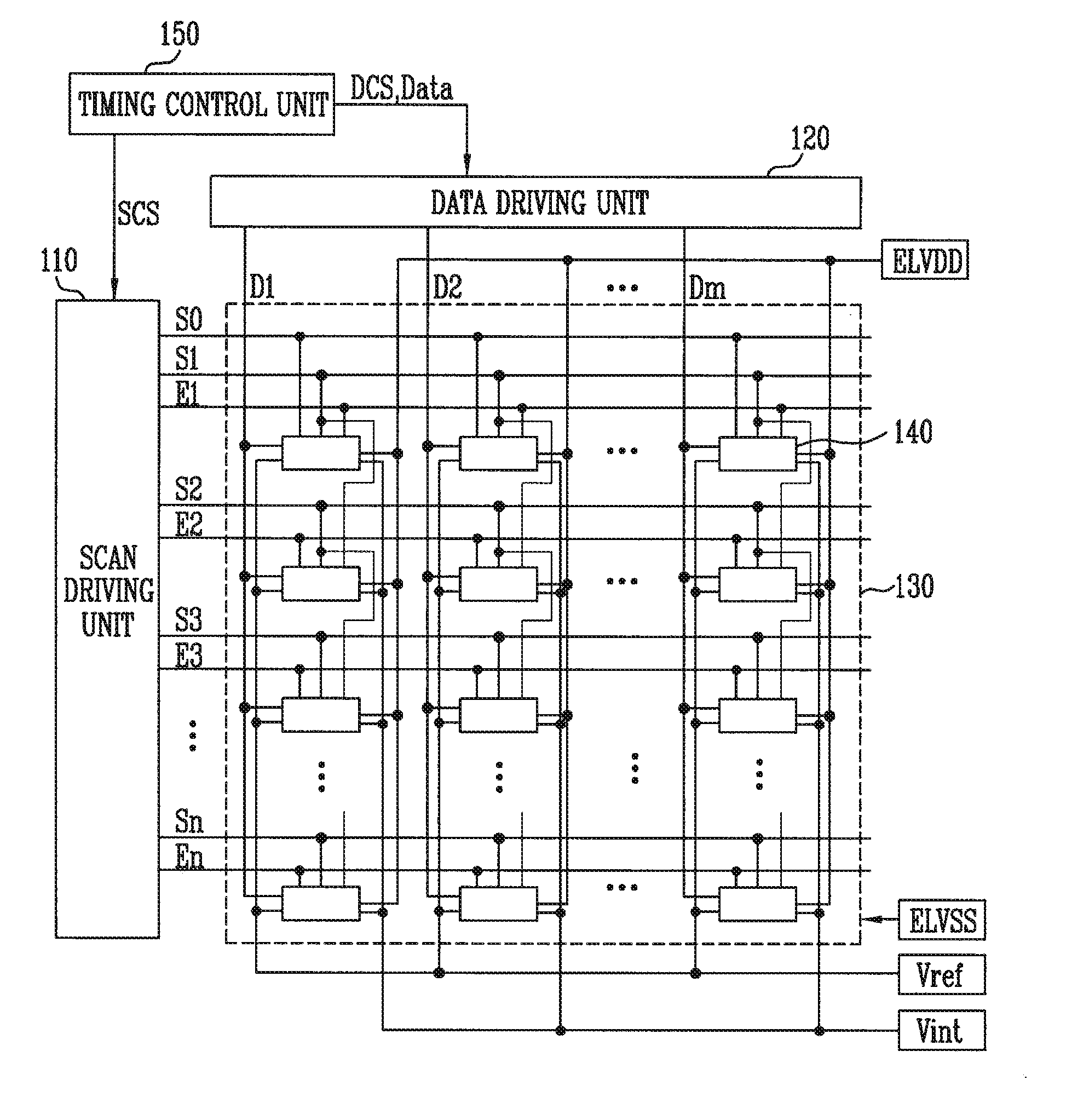

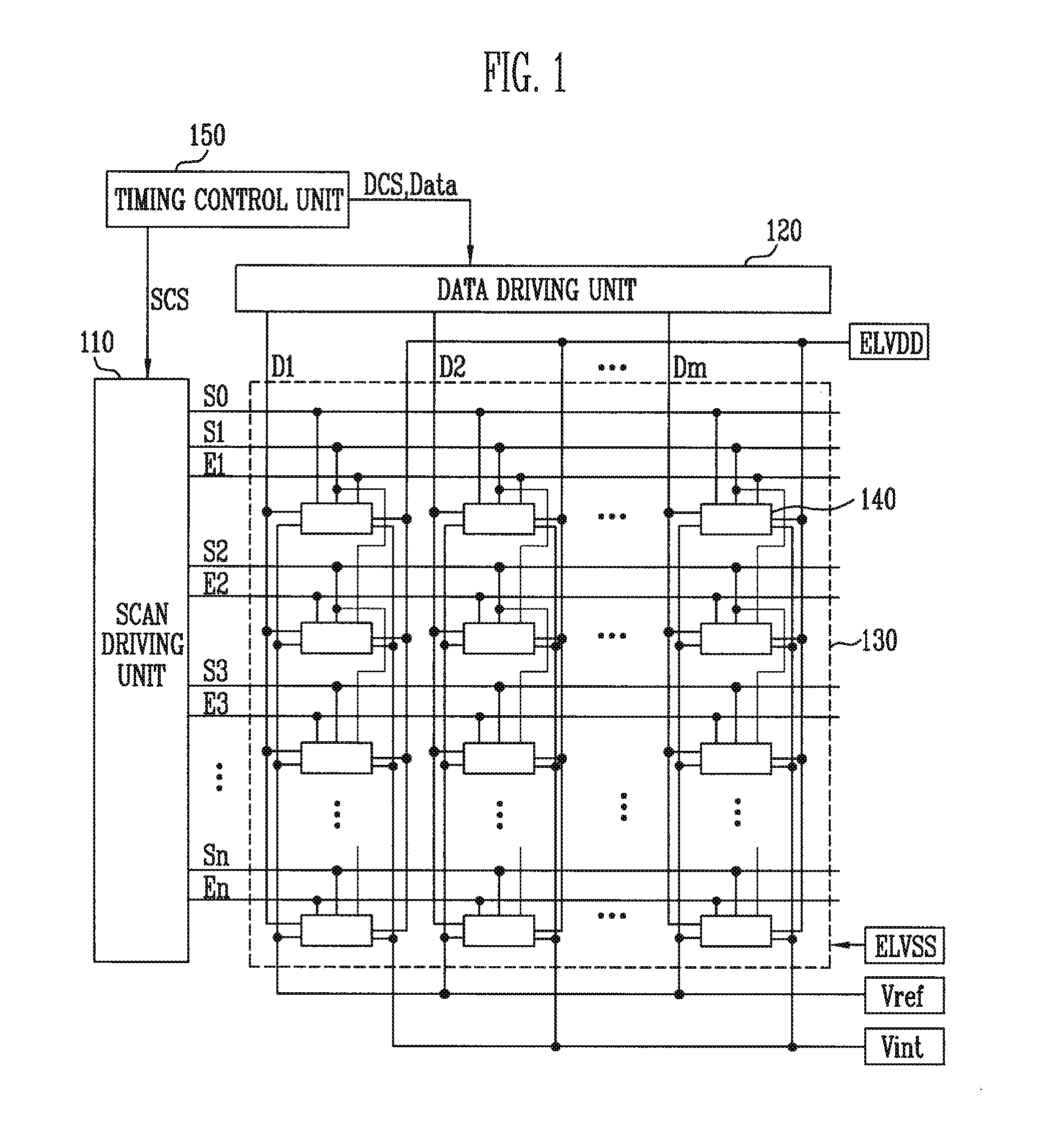

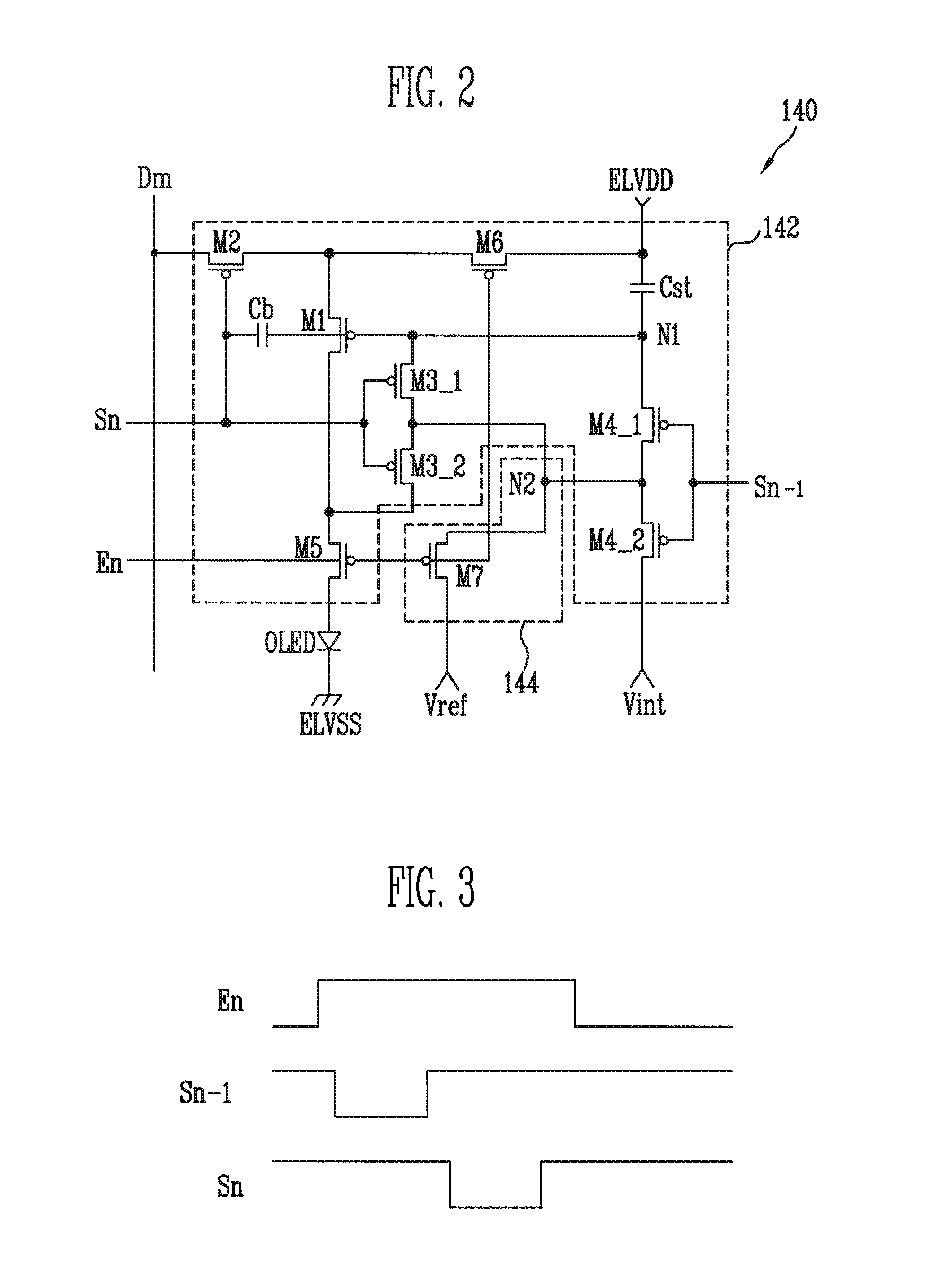

Pixel and organic light emitting display device using the same

ActiveUS20110157144A1Improve leakage currentMinimized and reduced leakage currentCathode-ray tube indicatorsInput/output processes for data processingDrain currentEngineering

A pixel of a display with reduced leakage current is disclosed. The pixel includes: an organic light emitting diode; a first transistor for controlling an amount of current flowing from a first power source to a second power source via the organic light emitting diode; a storage capacitor coupled between the first power source and a gate electrode of the first transistor; a plurality of third transistors coupled between the gate electrode and a second electrode of the first transistor; and a plurality of fourth transistors coupled between the gate electrode of the first transistor and an initialization power source. The third and fourth transistors are configured to reduce a leakage current from the storage capacitor to improve the image quality of the display.

Owner:SAMSUNG DISPLAY CO LTD

Semiconductor memory device

ActiveUS20070038919A1Reduce power consumptionReduce operationError detection/correctionCode conversionData bitsSense amplifier

A semiconductor memory device capable of achieving a sufficient operating margin without increasing an area penalty even in the case of miniaturization is provided. An error correction system composed of a data bit of 64 bits and a check bit of 9 bits is introduced to a memory array such as DRAM, and an error correction code circuit required therein is disposed near a sense amplifier array. In addition to normal memory arrays composed of such memory arrays, a redundant memory array having a sense amplifier array and an error correction code circuit adjacent thereto is provided in a chip. By this means, the error which occurs in the manufacture can be replaced. Also, the error correction code circuit corrects the error at the time of an activate command and stores the check bit at the time of a pre-charge command.

Owner:MICRON TECH INC

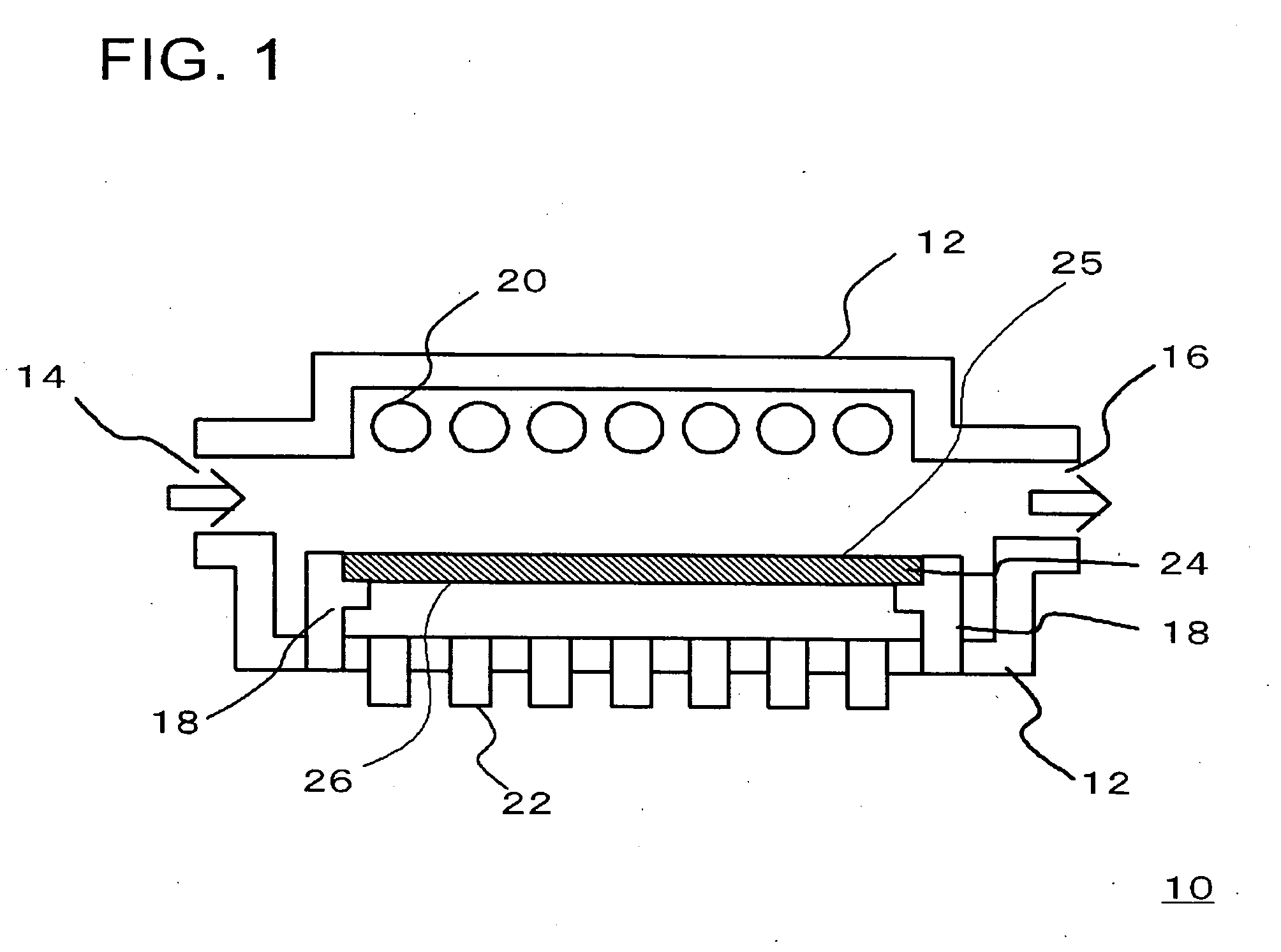

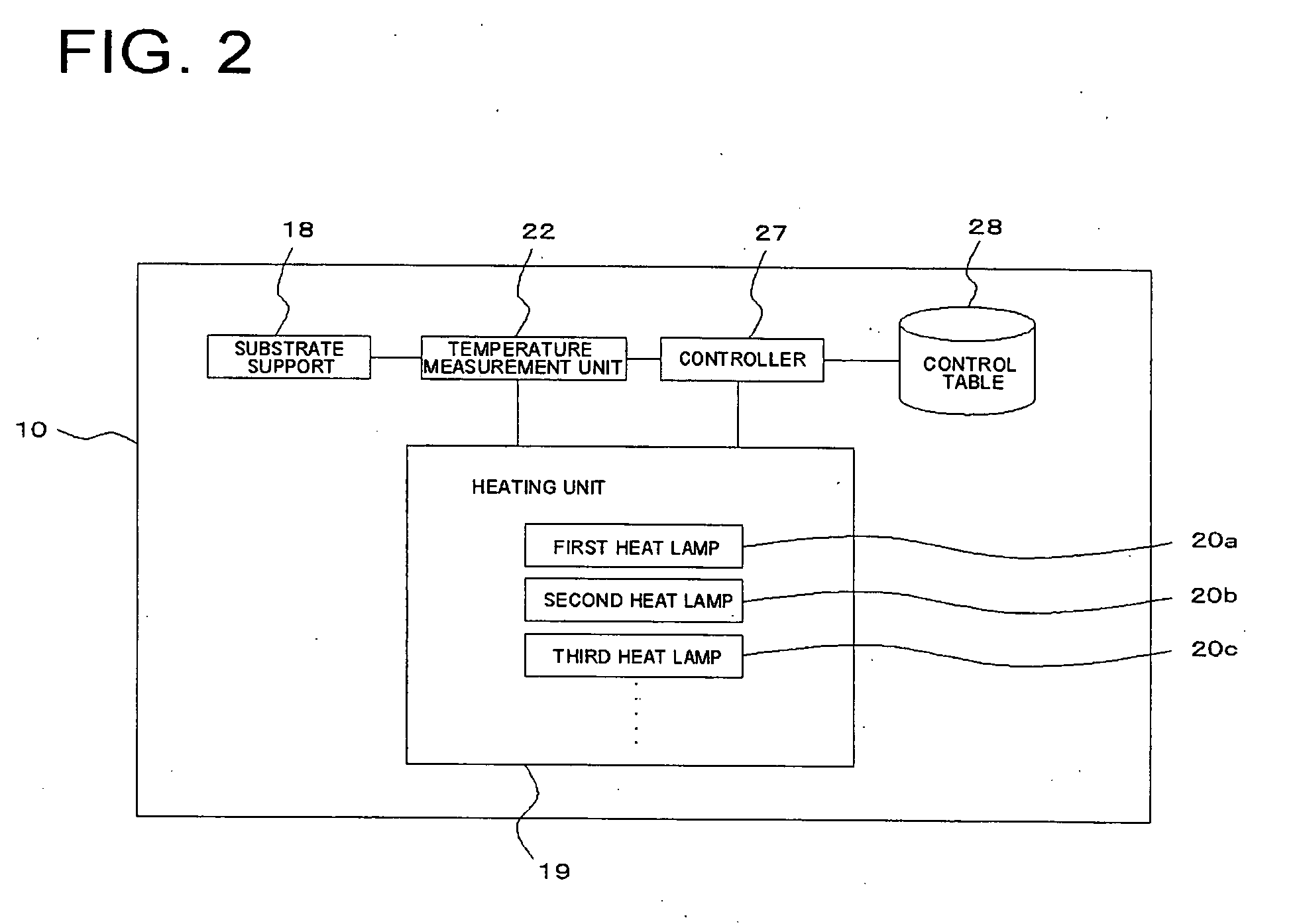

Method for manufacturing semiconductor device

ActiveUS20060240667A1Reduce sheet resistanceReduce the temperatureTransistorSemiconductor/solid-state device manufacturingDevice materialDevice form

Method for manufacturing a semiconductor device, includes: forming a layer of dicobalt monosilicide (Co2Si) or of cobalt (Co) on a device-forming surface of a silicon substrate in a sputter apparatus, by utilizing a predetermined temperature profile; elevating a temperature of the silicon substrate to a predetermined temperature T2, which is equal to or higher than 600° C., conducted after forming the layer of Co or Co2Si; and forming a layer of monocobalt monosilicide (CoSi) on the device-forming surface of the silicon substrate at a temperature equal to or higher than T2, conducted after heating the silicon substrate to T2, wherein, the silicon substrate is elevated to a temperature between a highest reachable temperature T1 of the silicon substrate during forming the layer of Co or Co2Si and the temperature T2 at a temperature ramp rate of equal to or higher than 50° C. / sec.

Owner:RENESAS ELECTRONICS CORP

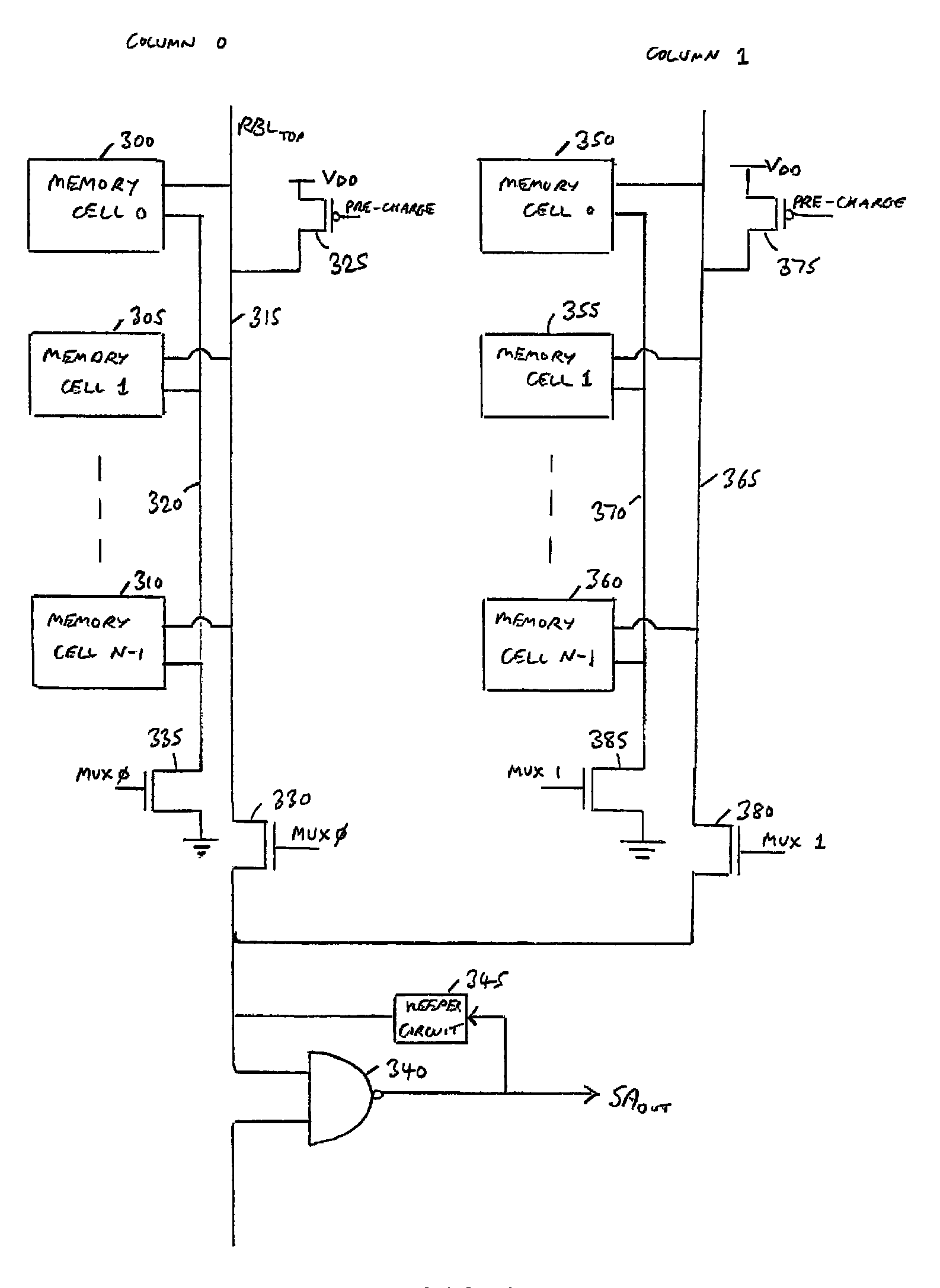

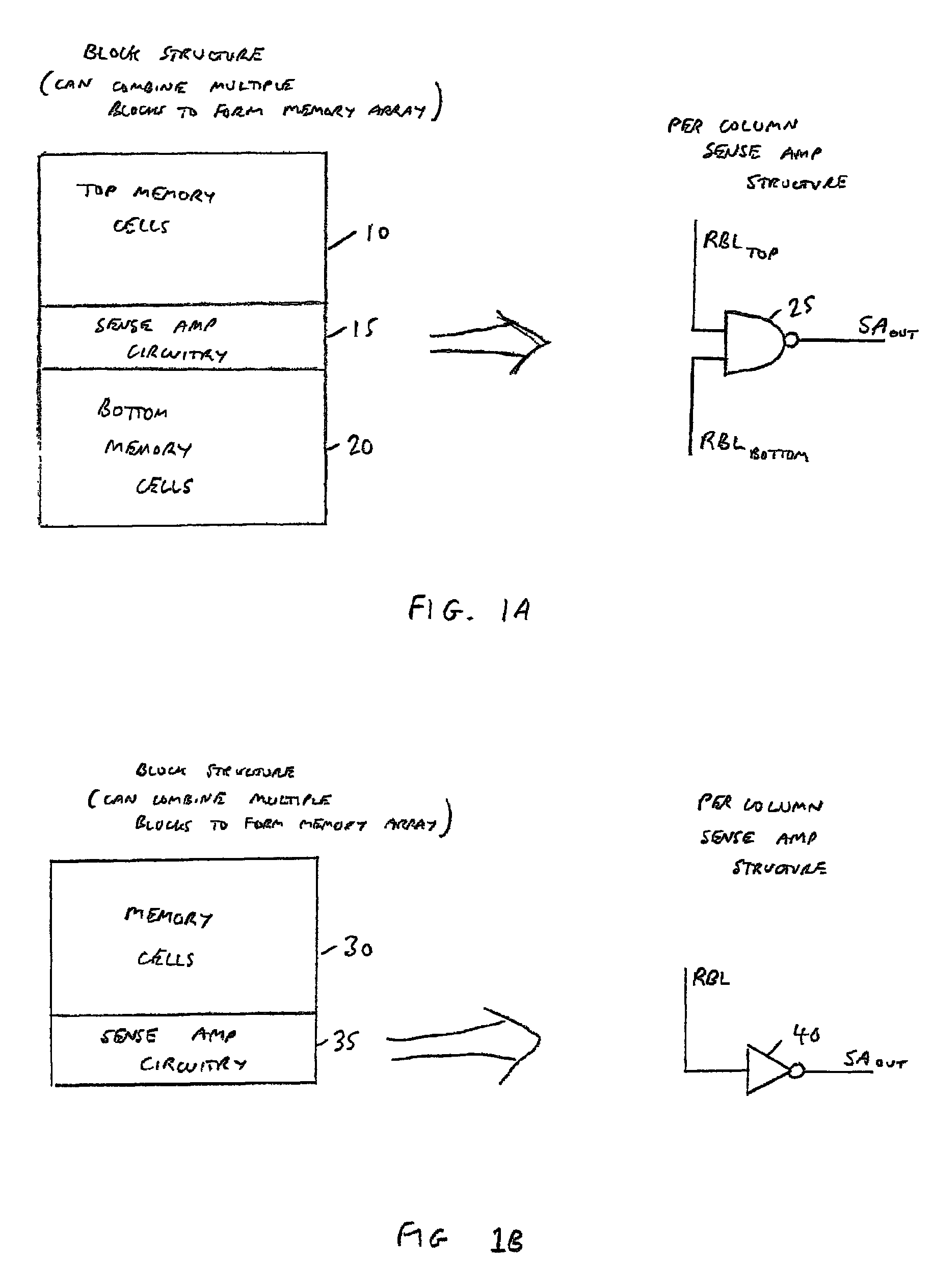

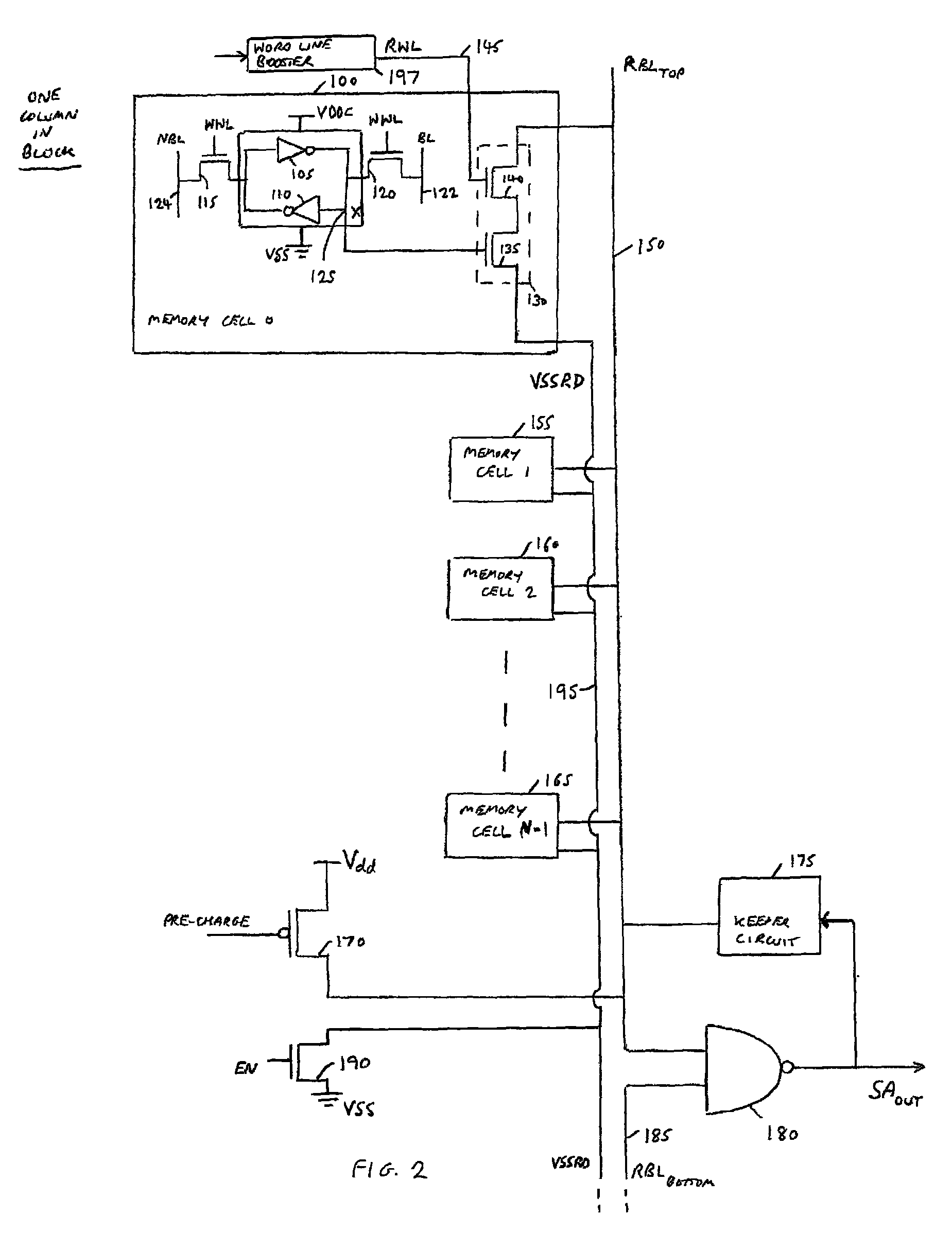

Memory device and method of controlling leakage current within such a memory device

ActiveUS9171634B2Reduce leakage currentImprove performanceRead-only memoriesDigital storageComputer architectureDrain current

A memory device includes an array of memory cells arranged as a plurality of rows and columns, each row being coupled to an associated read word line, and each column forming at least one column group, where the memory cells of each column group are coupled to an associated read bit line. Each column has an active mode of operation where a read operation may be performed on an activated memory cell within that column group, and a non-active mode of operation where the read operation is not performable. Precharge circuitry is used, for each column group, to precharge the associated read bit line to a first voltage level prior to the read operation. Each memory cell includes coupling circuitry connected between the associated read bit line and a reference line associated with the column group containing that memory cell.

Owner:ARM LTD

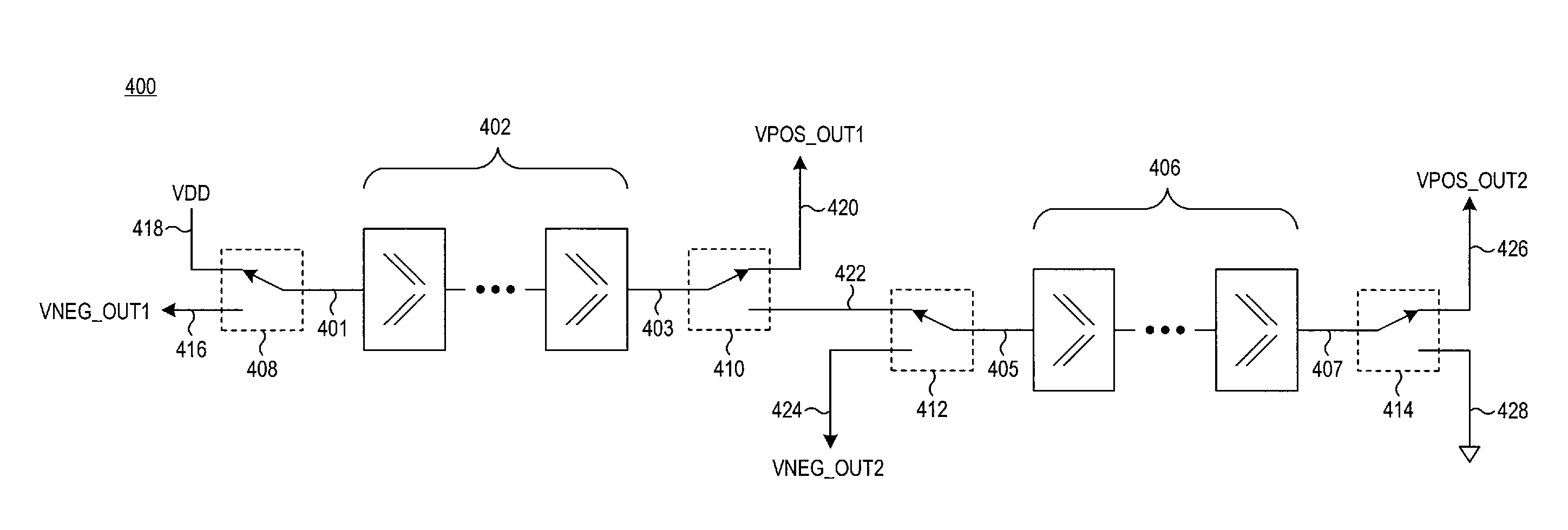

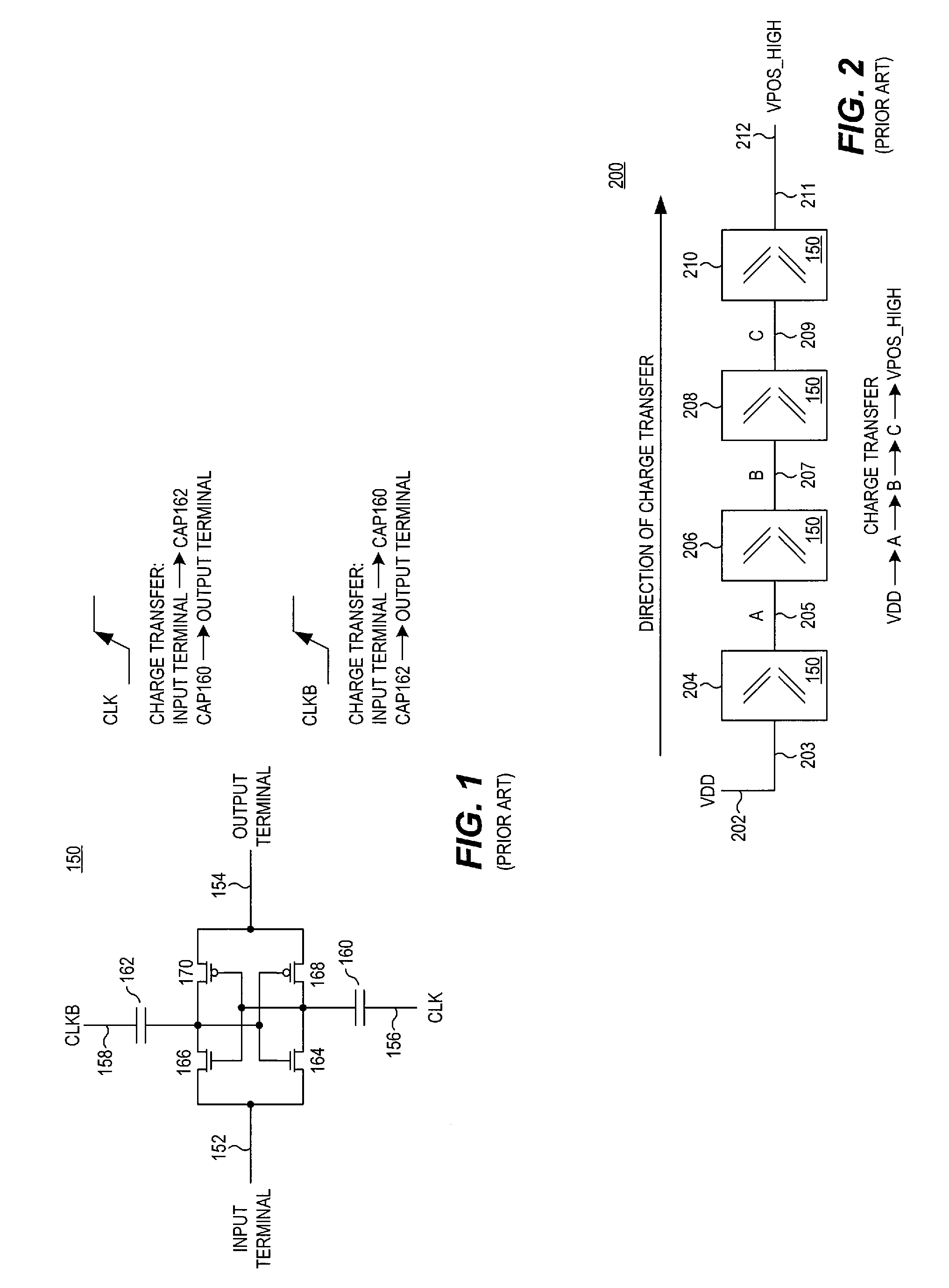

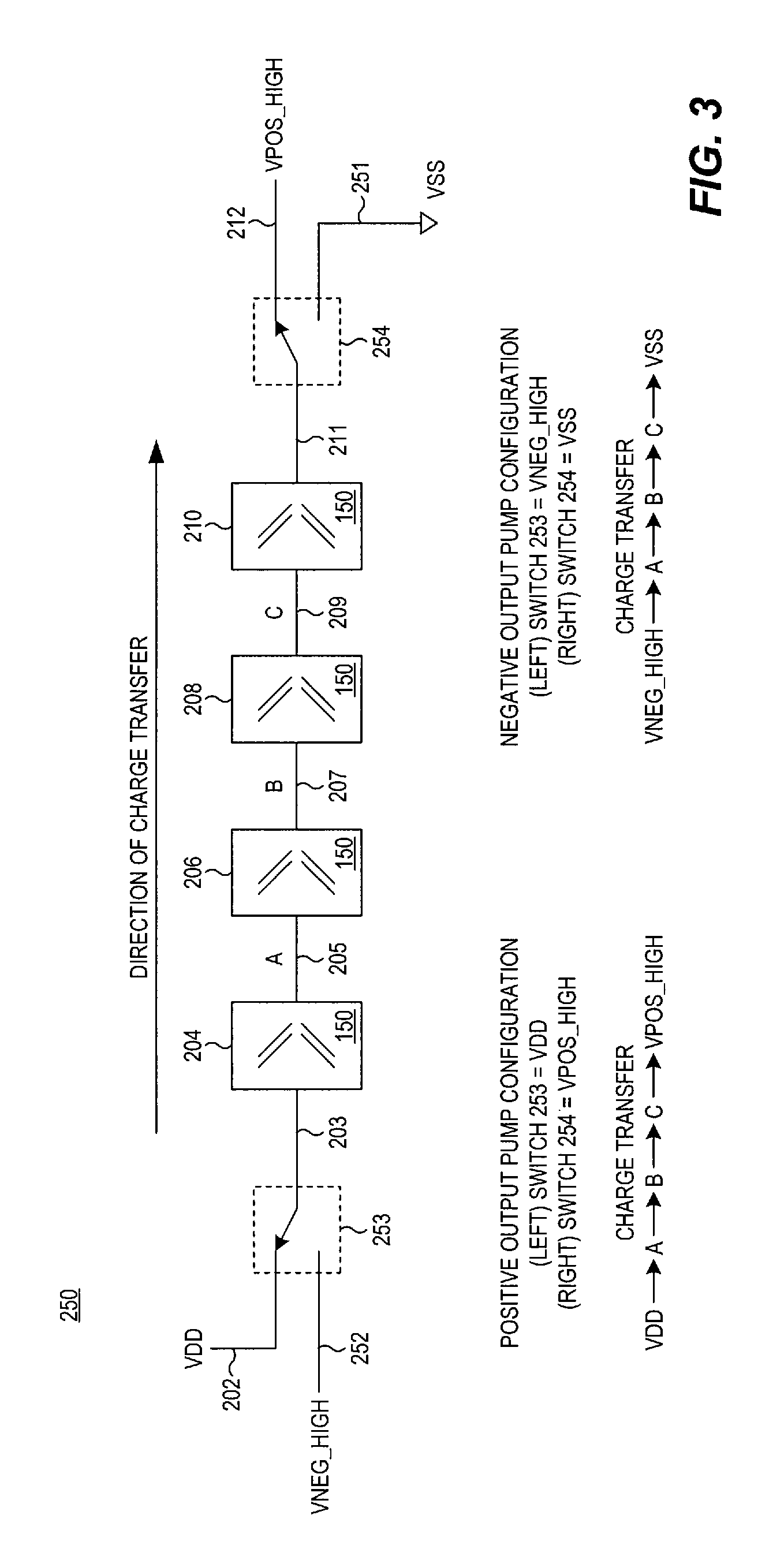

Method for using a multiple polarity reversible charge pump circuit

ActiveUS7495500B2Improve leakage currentHigh currentDc-dc conversionElectric variable regulationOperation modeElectrical current

A multiple polarity reversible charge pump circuit is disclosed which, in certain embodiments, may be configured to generate a positive voltage at times and may be reversed to generate a negative voltage at other times. Such a charge pump circuit is advantageous if both the positive and negative voltage are not simultaneously required. In certain other embodiments, a charge pump circuit generates a high output current for only a positive boosted voltage in one mode of operation, but lower current positive and negative boosted voltage outputs in another mode of operation. Use with certain erasable memory array technologies is disclosed, particularly certain resistive passive element memory cells, and more particularly in a three-dimensional memory array.

Owner:SANDISK TECH LLC

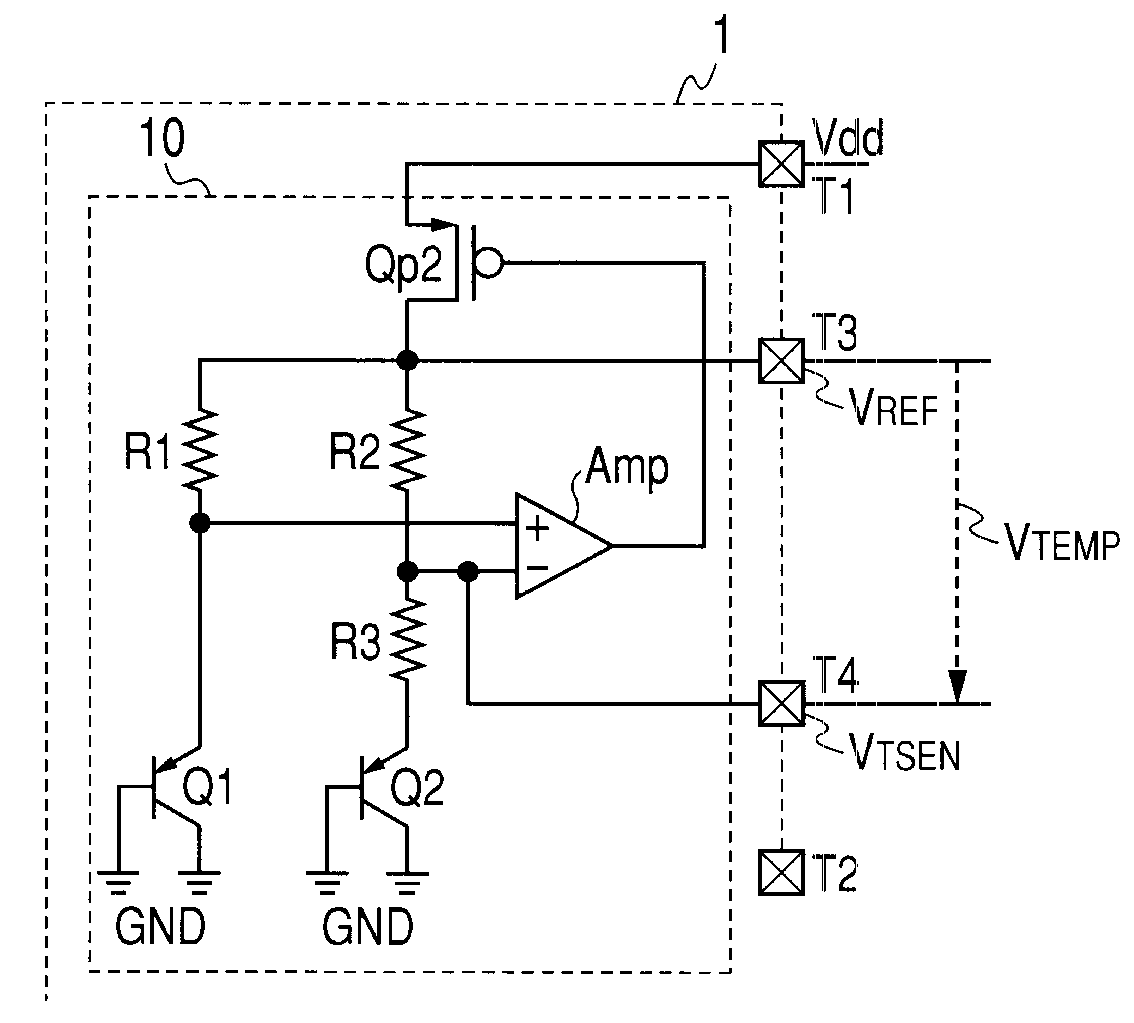

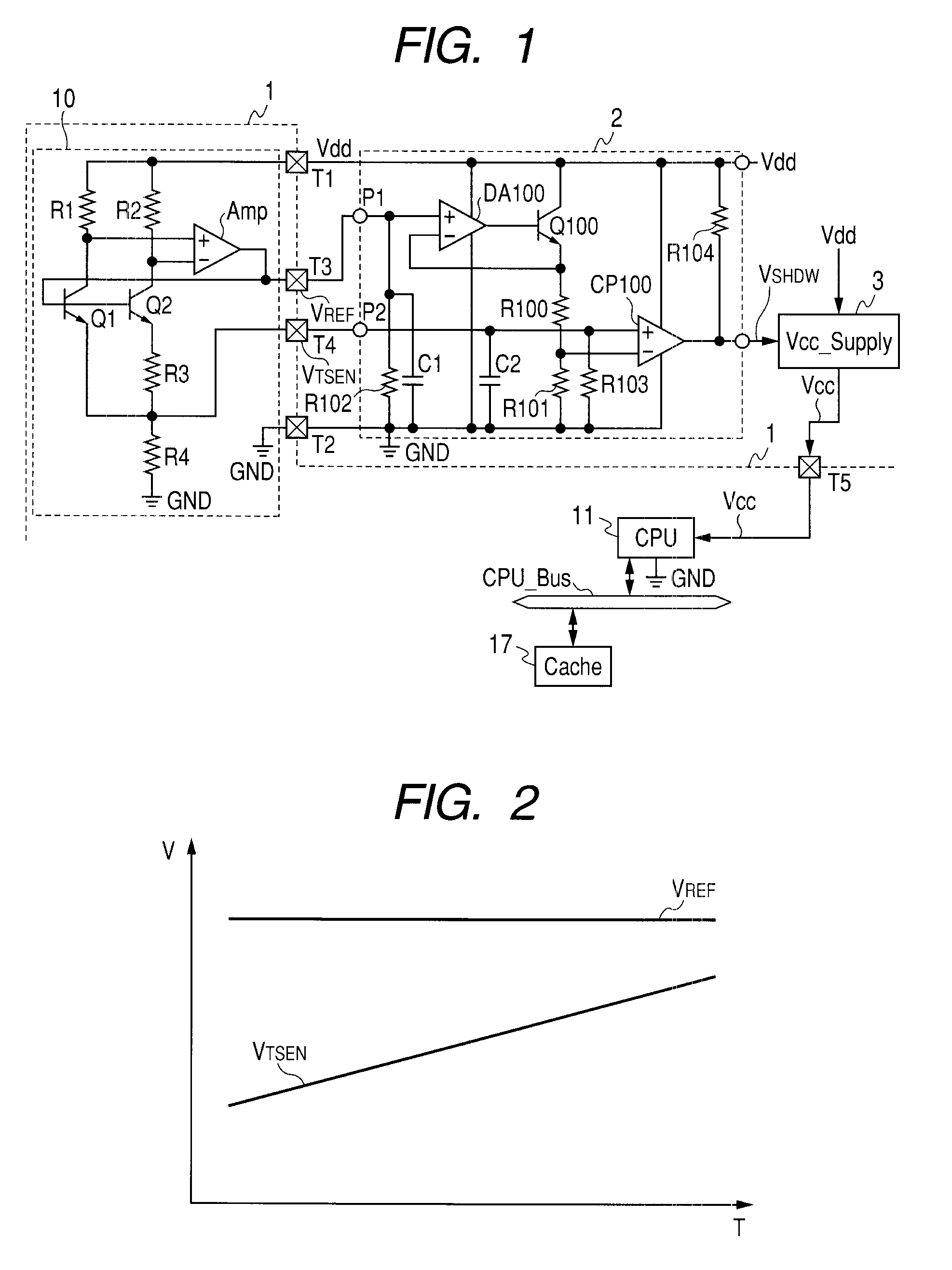

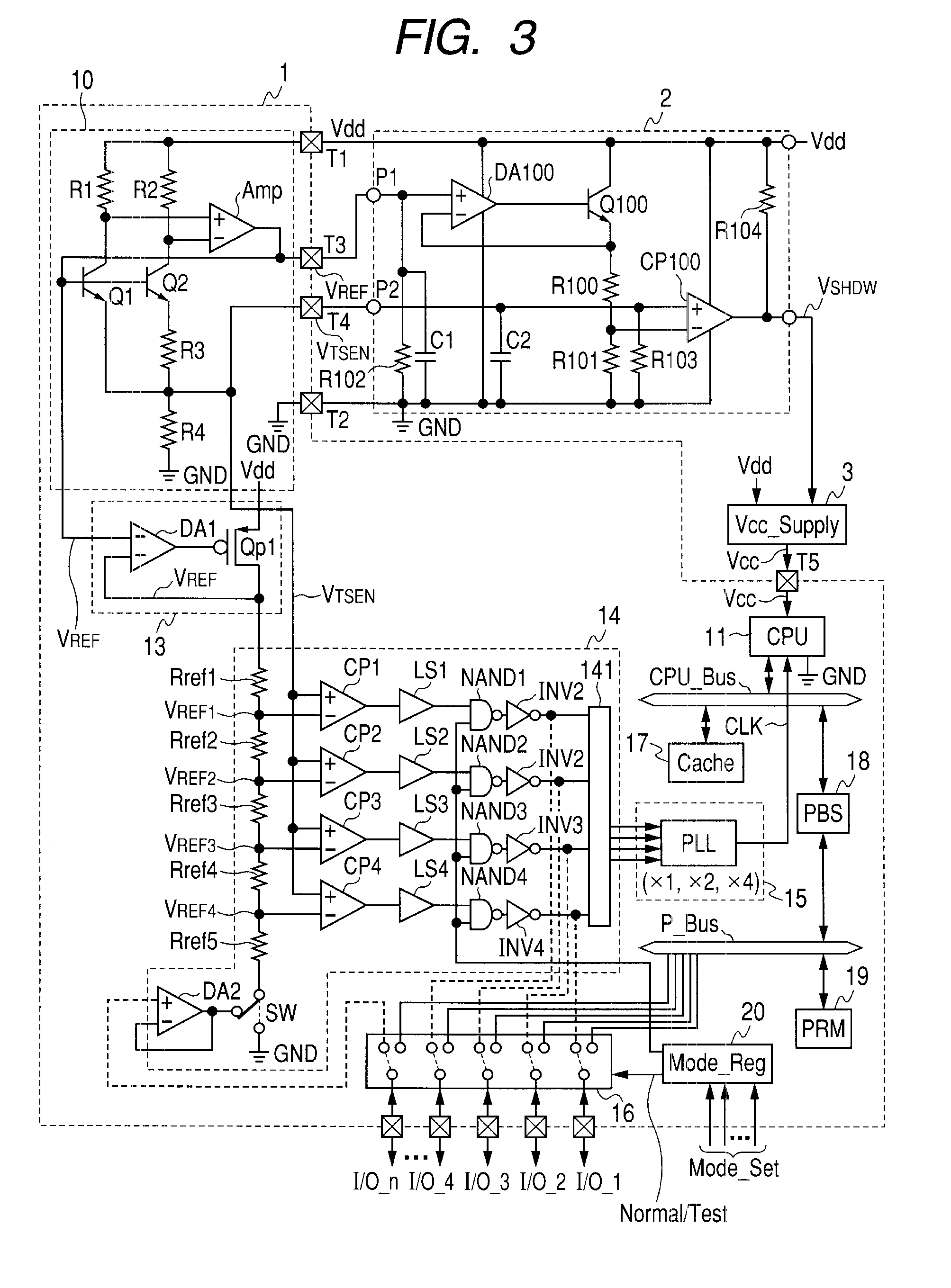

Semiconductor integrated circuit and operation method for the same

ActiveUS20090295458A1Lower threshold voltageImprove leakage currentElectronic switchingPulse generation by opto-electronic devicesTemperature controlTemperature monitoring

The semiconductor integrated circuit is provided, in which an external temperature control or temperature monitoring is possible, with little influence by the noise of a system board which mounts the semiconductor integrated circuit. The semiconductor integrated circuit includes the temperature detection circuit which detects the chip temperature, and the functional module which flows a large operating current. An external terminal which supplies operating voltage, and an external terminal which supplies ground voltage are coupled to the functional module. The temperature detection circuit generates a temperature detection signal and a reference signal. The reference signal and the temperature detection signal are led out to the exterior of the semiconductor integrated circuit via a first external output terminal and a second external output terminal, respectively, and are supplied to an external temperature control / monitoring circuit which has a circuitry type of a differential amplifier circuit.

Owner:RENESAS ELECTRONICS CORP

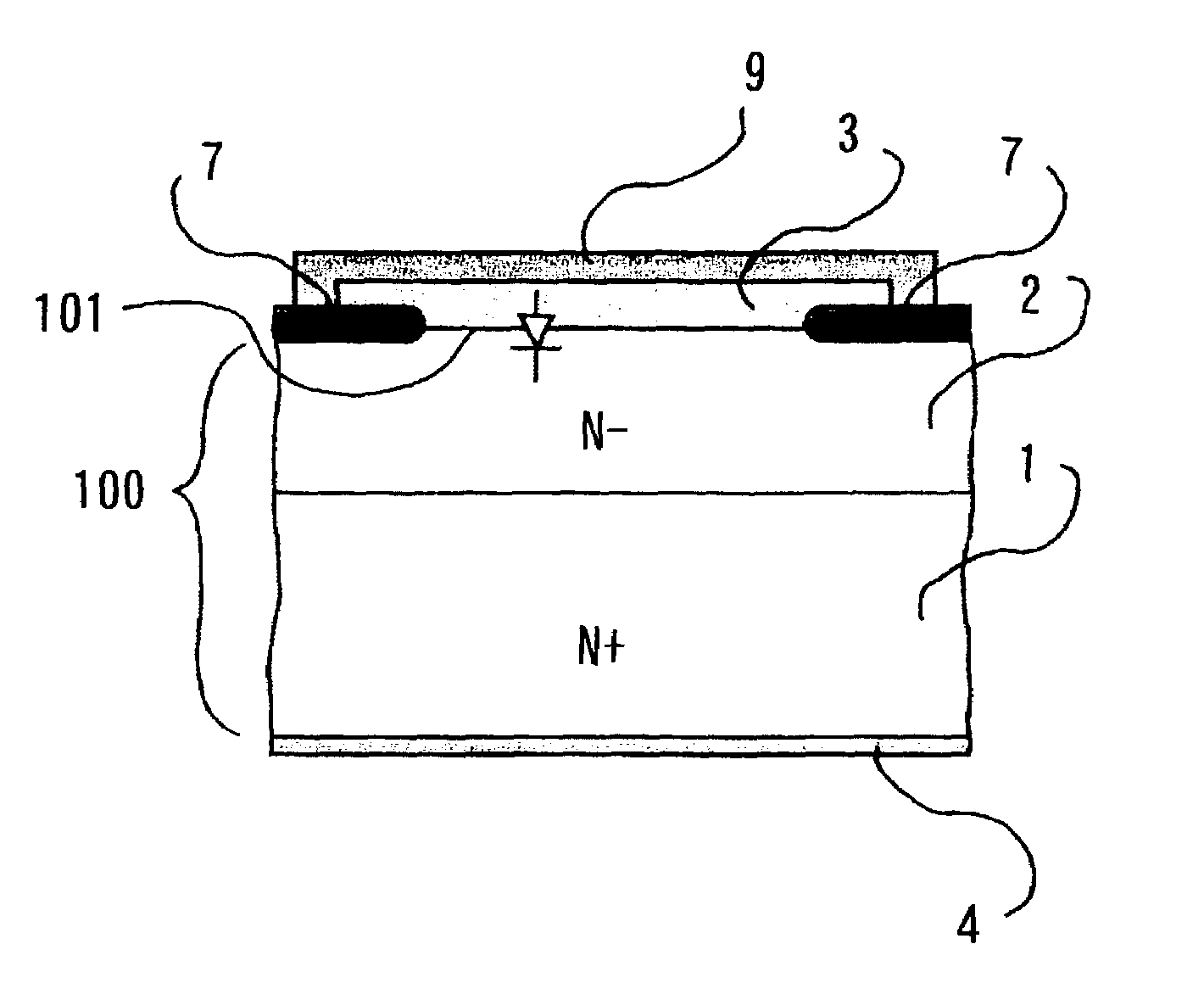

High reverse voltage silicon carbide diode and method of manufacturing the same high reverse voltage silicon carbide diode

InactiveUS7183575B2Improve leakage currentIncrease currentSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorAlloy

Owner:NISSAN MOTOR CO LTD

DUV laser annealing and stabilization of SiCOH films

InactiveUS7223670B2Improve insulation performanceTotal current dropSemiconductor/solid-state device manufacturingThin material handlingDielectricUltraviolet

A method of fabricating a dielectric film comprising atoms of Si, C, O and H (hereinafter SiCOH) that has improved insulating properties as compared with prior art dielectric films, including prior art SiCOH dielectric films that are not subjected to the inventive deep ultra-violet (DUV) is disclosed. The improved properties include reduced current leakage which is achieved without adversely affecting (increasing) the dielectric constant of the SiCOH dielectric film. In accordance with the present invention, a SiCOH dielectric film exhibiting reduced current leakage and improved reliability is obtained by subjecting an as deposited SiCOH dielectric film to a DUV laser anneal. The DUV laser anneal step of the present invention likely removes the weakly bonded C from the film, thus improving leakage current.

Owner:GLOBALFOUNDRIES INC

System and method for the manufacture of semiconductor devices by the implantation of carbon clusters

InactiveUS7666771B2Increase junction depthReduce leakage currentTransistorElectric discharge tubesDevice materialEngineering

A process is disclosed which incorporates implantation of a carbon cluster into a substrate to improve the characteristics of transistor junctions when the substrates are doped with Boron and Phosphorous in the manufacturing of PMOS transistor structures in integrated circuits. There are two processes which result from this novel approach: (1) diffusion control for USJ formation; and (2) high dose carbon implantation for stress engineering. Diffusion control for USJ formation is demonstrated in conjunction with a boron or shallow boron cluster implant of the source / drain structures in PMOS. More particularly, first, a cluster carbon ion, such as C16Hx+, is implanted into the source / drain region at approximately the same dose as the subsequent boron implant; followed by a shallow boron, boron cluster, phosphorous or phosphorous cluster ion implant to form the source / drain extensions, preferably using a borohydride cluster, such as B18Hx+ or B10Hx+. Upon subsequent annealing and activation, the boron diffusion is reduced, due to the gettering of interstitial defects by the carbon atoms.

Owner:SEMEQUIP

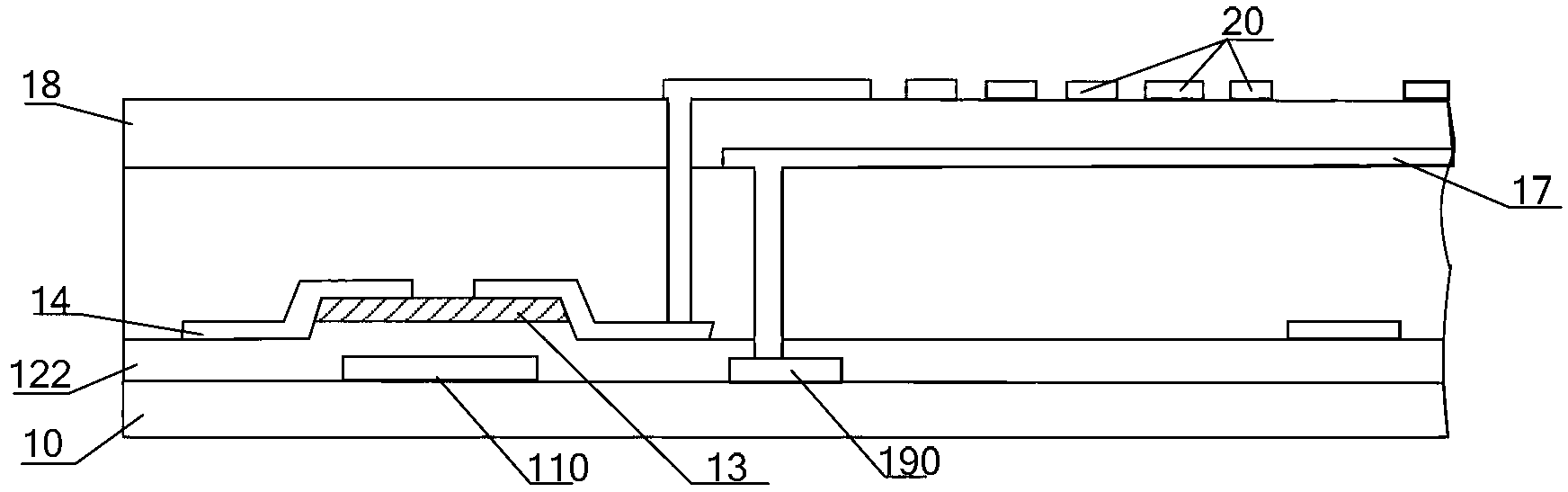

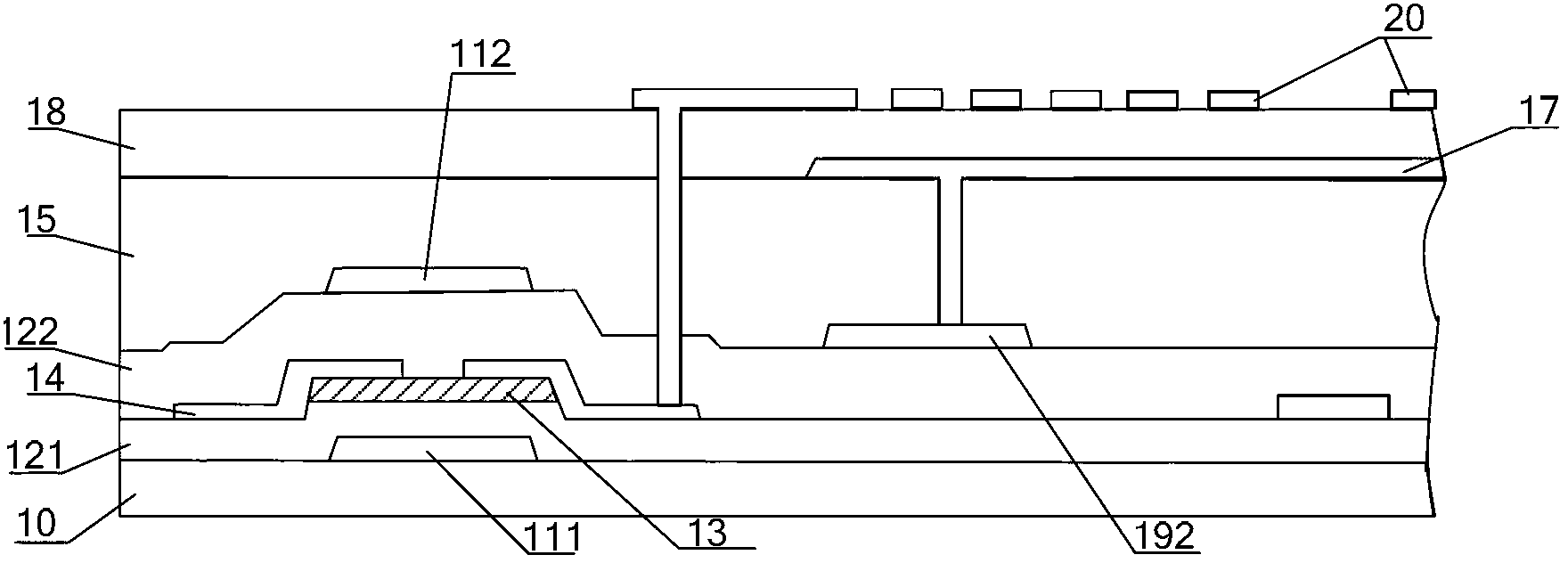

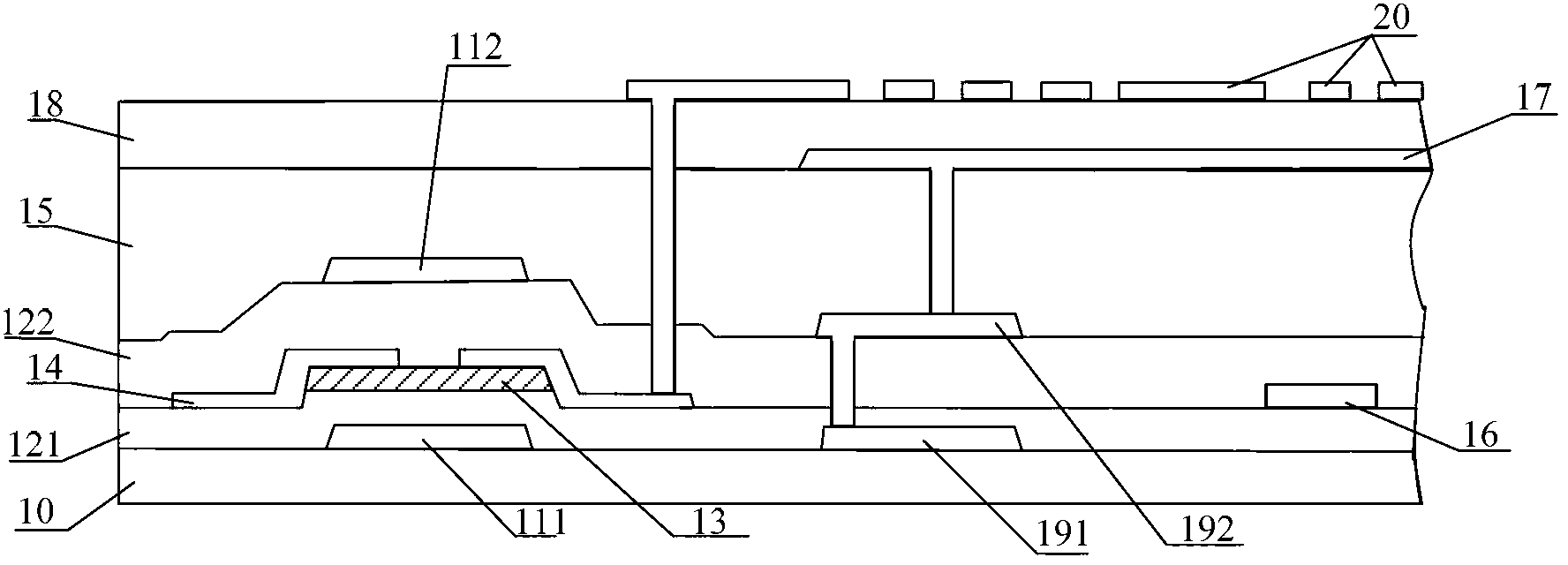

Array substrate and manufacturing method thereof and display device

ActiveCN103309108AImprove picture qualityAvoid exposureSolid-state devicesNon-linear opticsInsulation layerLiquid-crystal display

The invention discloses an array substrate and a manufacturing method thereof and a display device, relates to the field of display, and can solve the bad display problems of greenish phenomenon, horizontal X-talk and the like of a liquid crystal display and improve the image quality of the display device, in particular a high-resolution product on the premise of not reducing the transmittance rate. The array substrate comprises a substrate, a semiconductor layer, source and drain electrode layers, a grid insulation layer, a first grid metal layer, a second grid insulation layer and a second grid metal layer, wherein the semiconductor layer, the source and drain electrode layers and the grid insulation layer are arranged on the substrate in sequence from bottom up; the first grid metal layer is arranged on the grid insulation layer; the second grid insulation layer is arranged below the semiconductor layer; and the second grid metal layer is arranged between the second grid insulation layer and the substrate.

Owner:BOE TECH GRP CO LTD

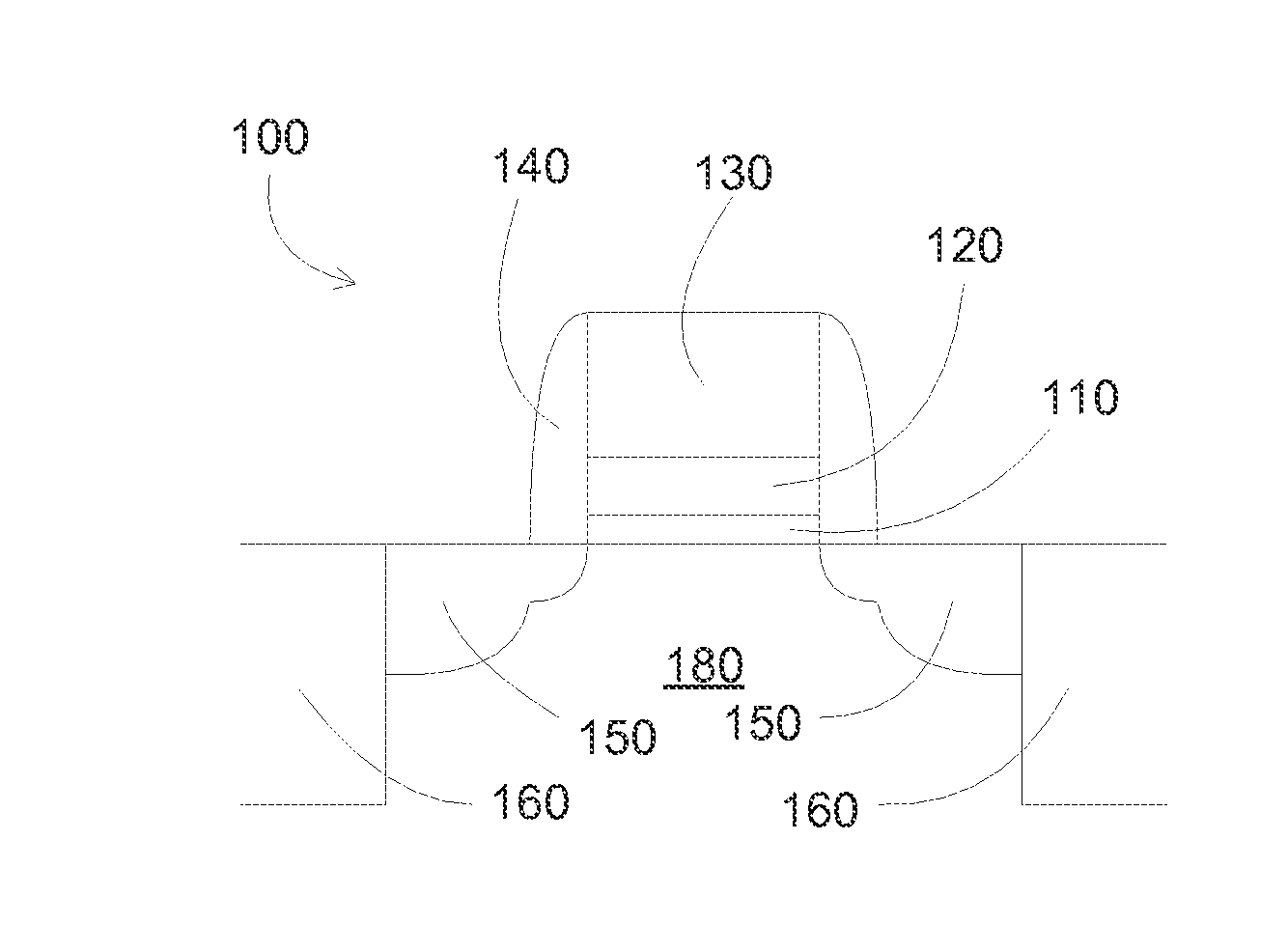

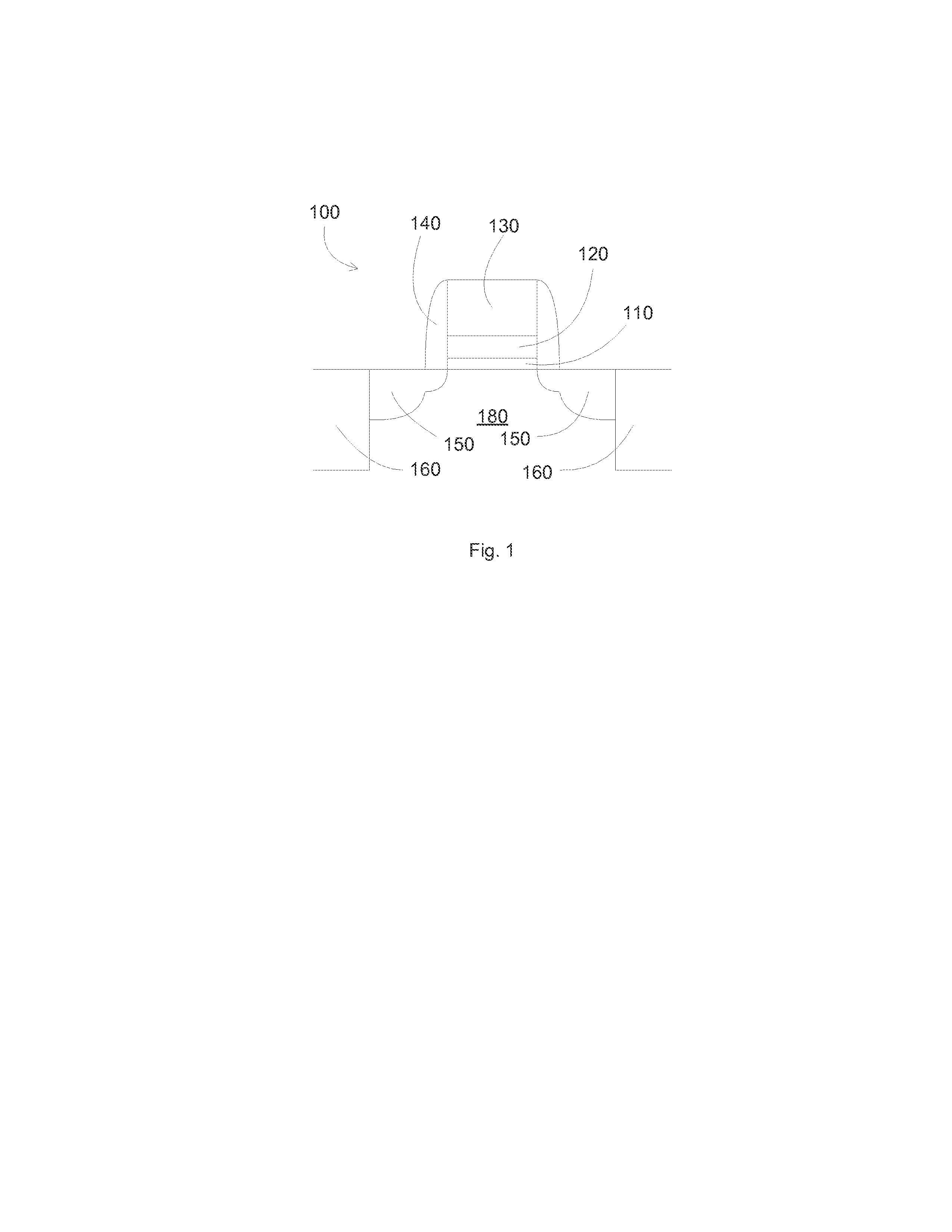

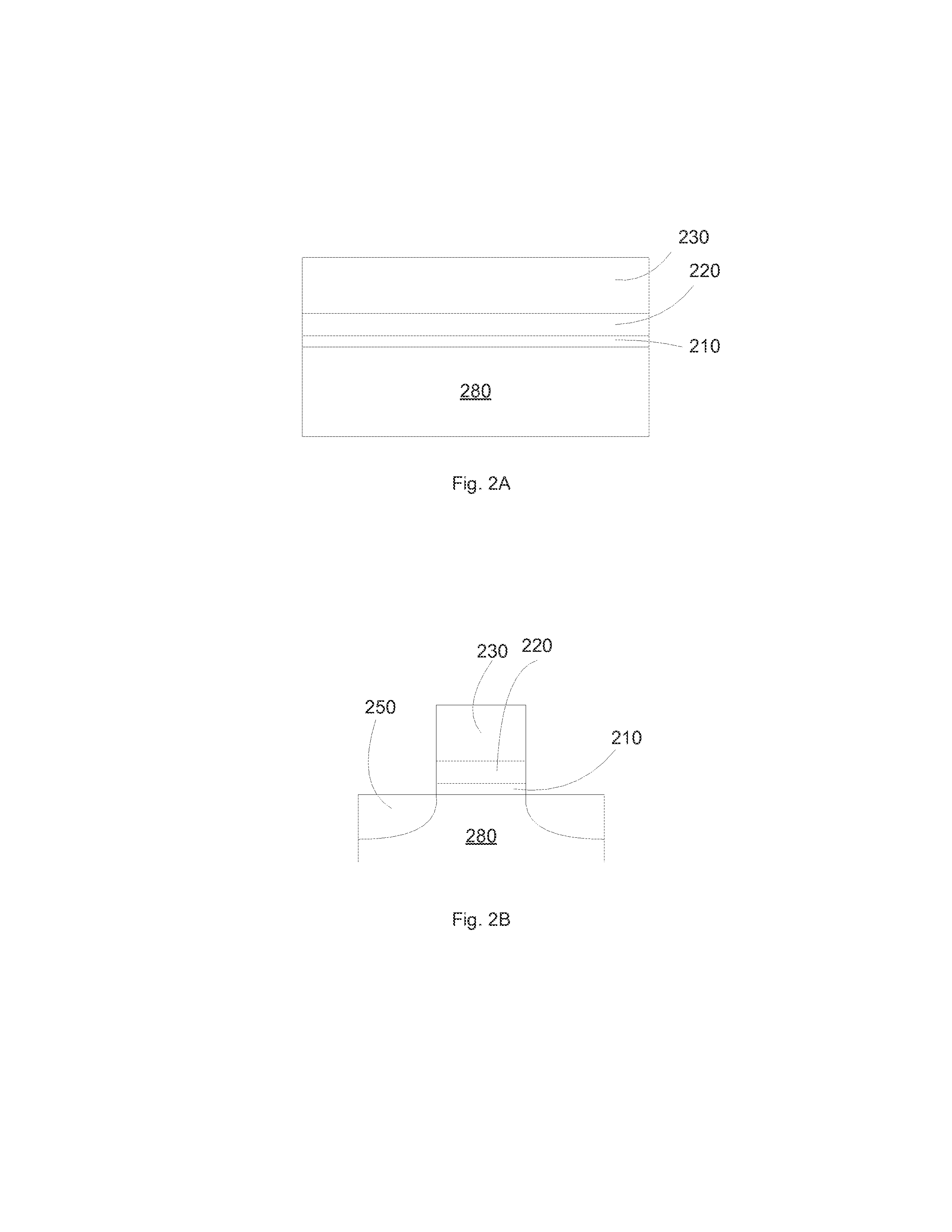

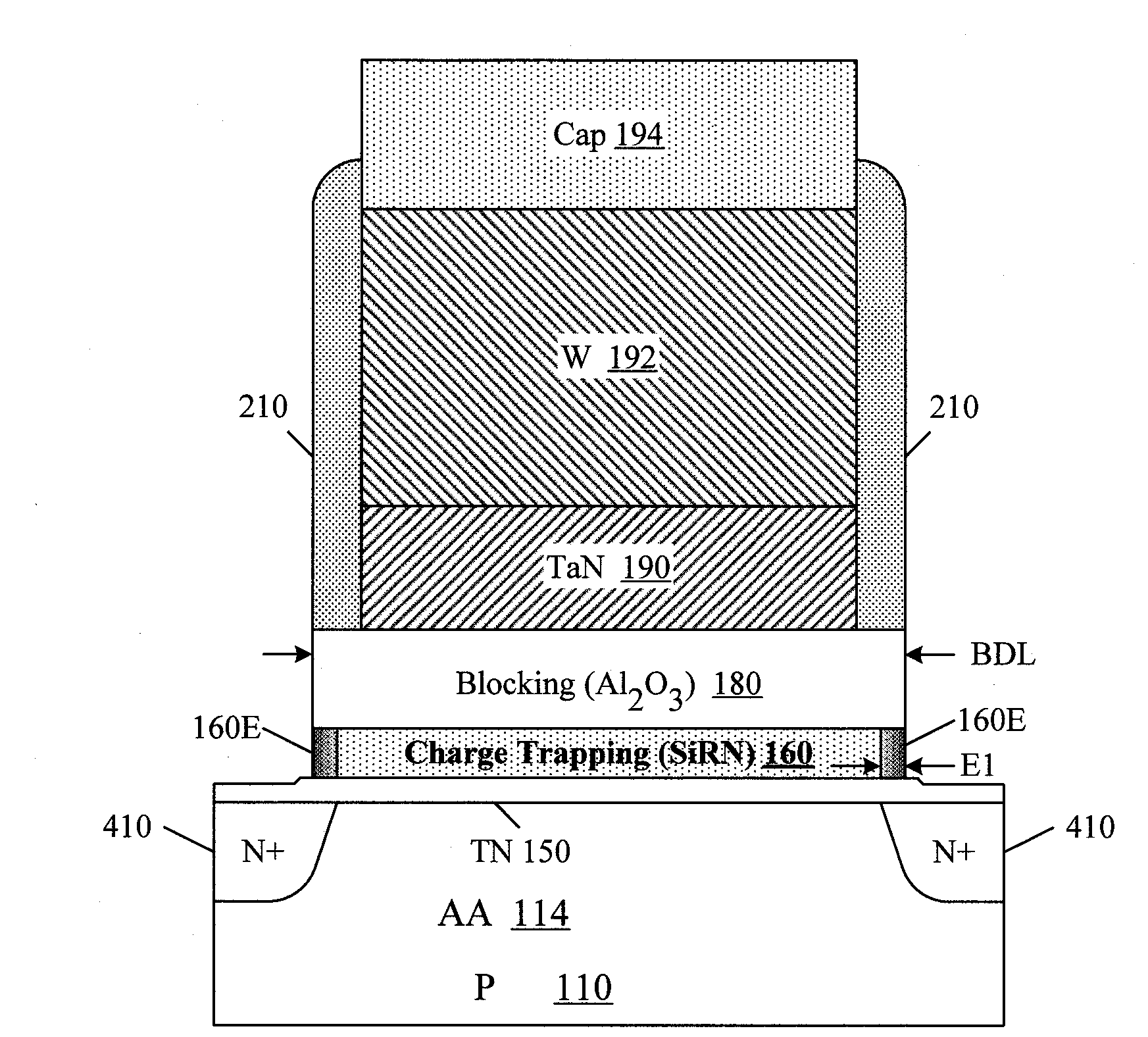

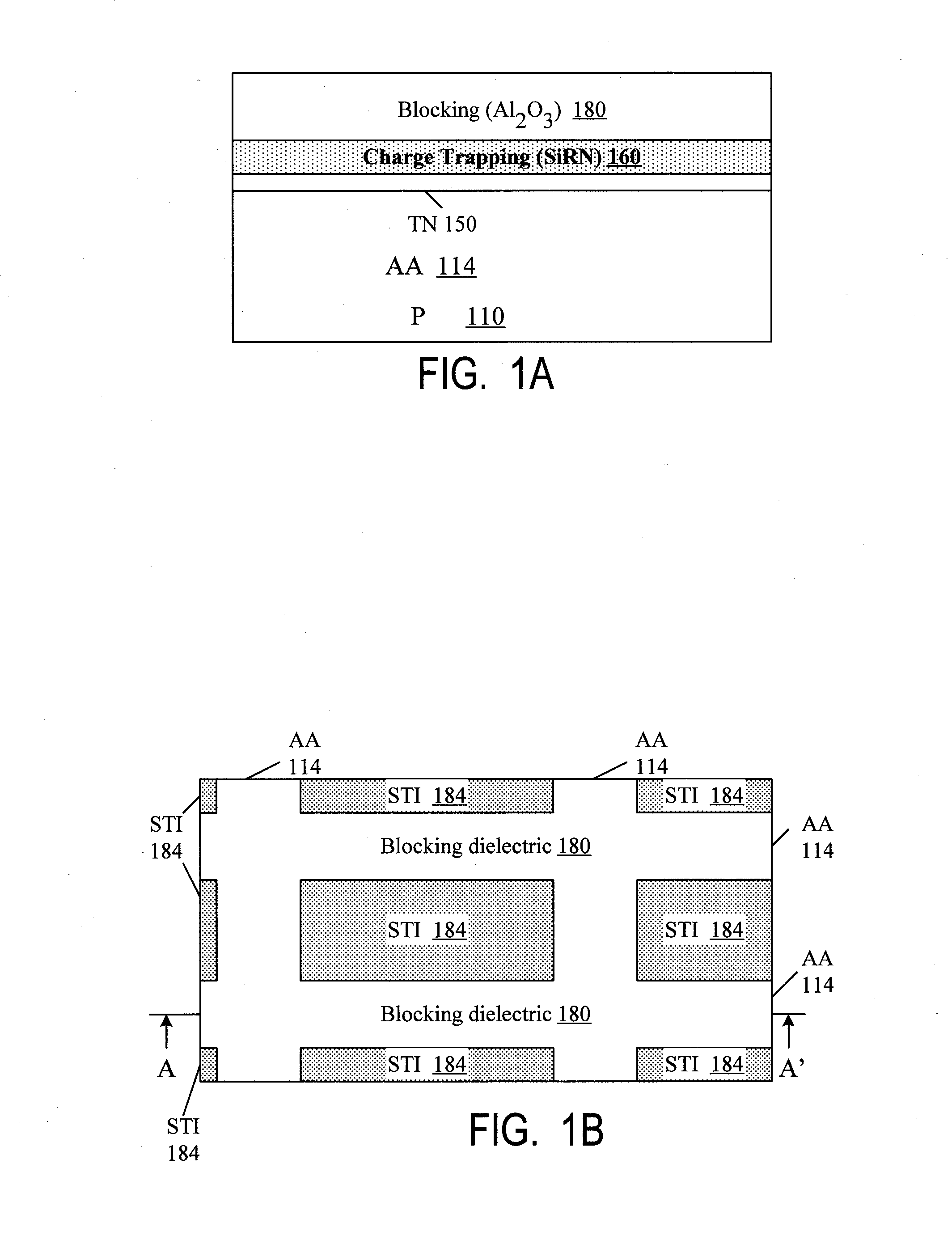

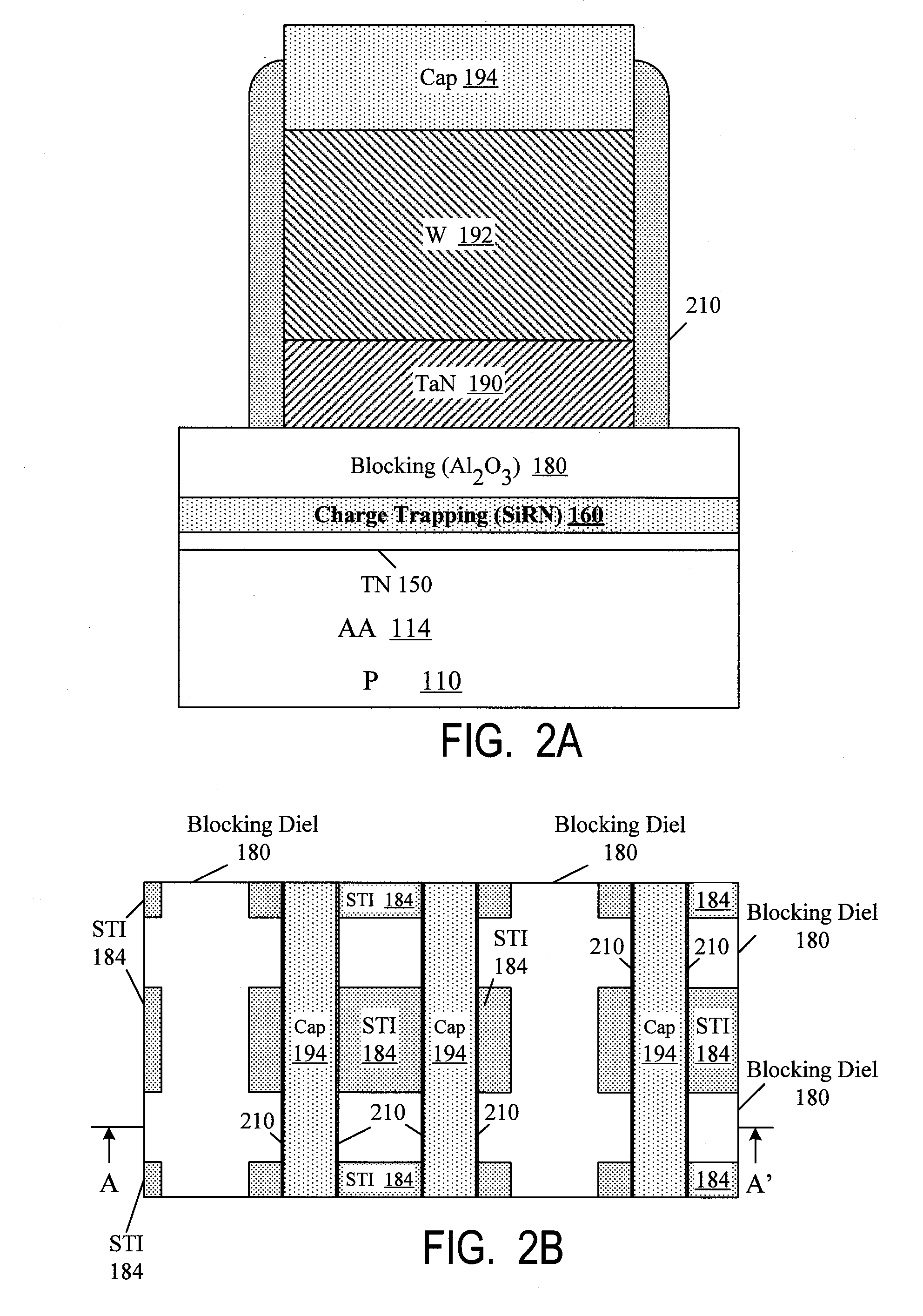

Nonvolatile memories with charge trapping dielectric modified at the edges

InactiveUS20100059808A1Reduce charge densityTotal current dropTransistorSolid-state devicesDielectricTrapping

A nonvolatile memory cell has charge trapping dielectric (160) which has been modified (i.e. oxidized) adjacent to edges of blocking dielectric (180). The modification reduces the charge-trapping density adjacent to the edges of the blocking dielectric, and hence reduces the leakage current at the edges. Other features are also provided.

Owner:PROMOS TECH PTE LTD

Level shifter

InactiveUS7348801B2Increase speedImprove leakage currentElectronic switchingElectric pulse generatorEngineeringLevel converter

In a level shifter, OFF leakage currents flow through two N-type transistors for signal input even when they are OFF. However, another N-type transistor serving as an OFF leakage generation circuit and three P-type transistors serving as current mirrors, which constitute a current conversion circuit, supply to the signal-input transistors a current equivalent to or greater than the OFF leakage currents flowing through the signal-input transistors when they are OFF, thereby canceling the OFF leakage currents. Therefore, one of nodes which is at H level is surely fixed to a potential equal to a higher voltage supply. Thus, the level shifter surely operates with a high speed even when large OFF leakage currents flow through the signal-input transistors.

Owner:SOCIONEXT INC

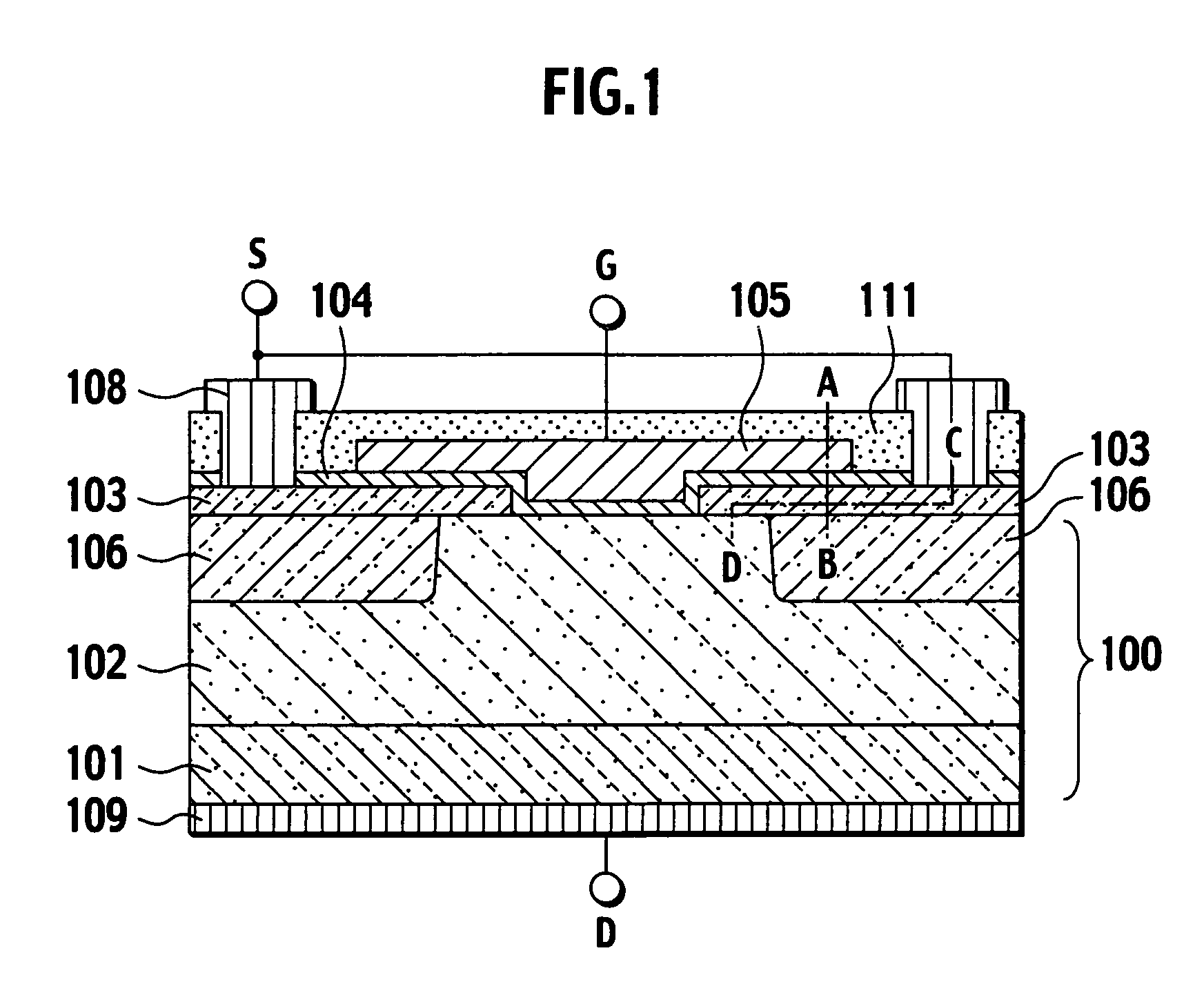

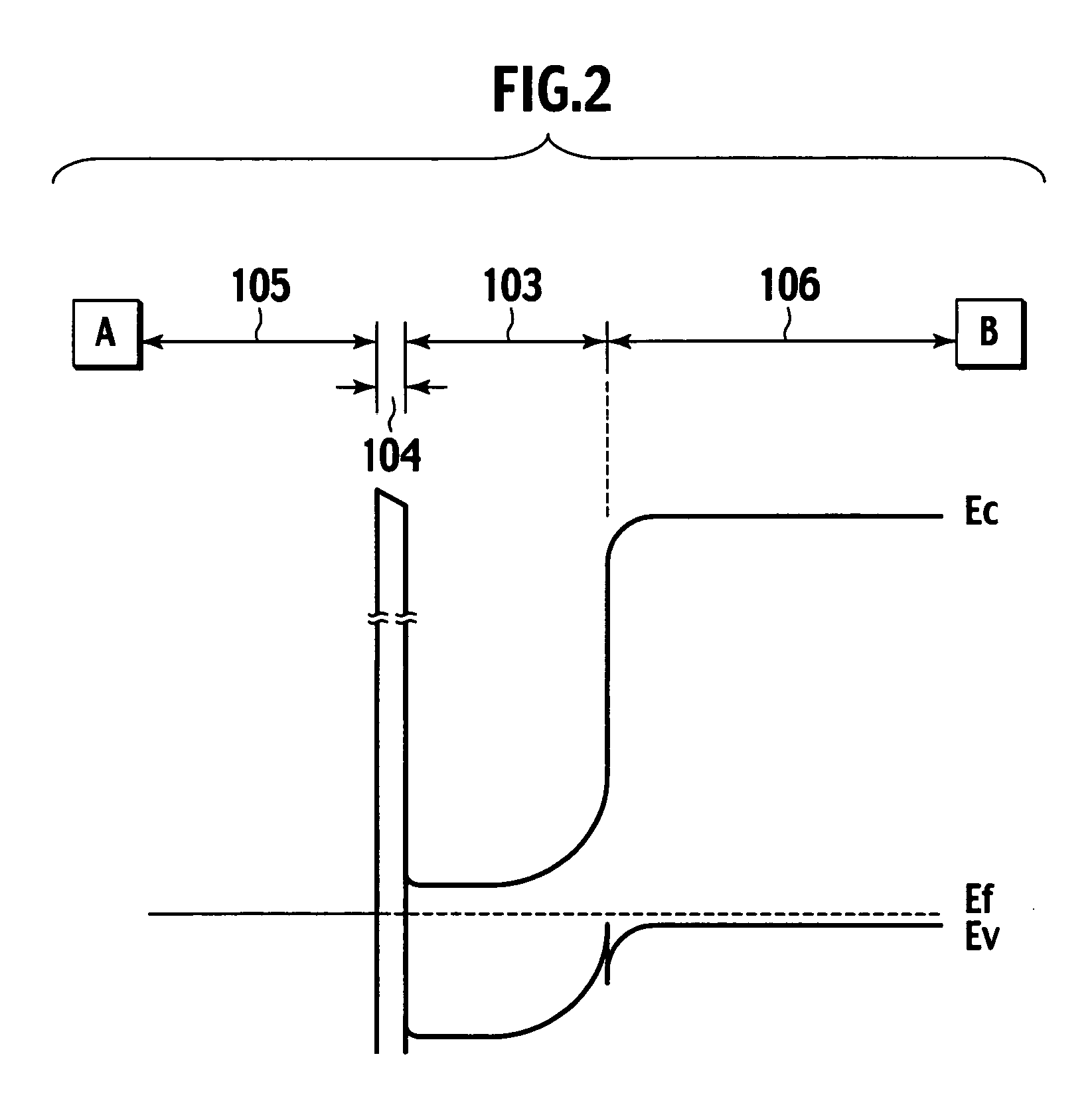

Semiconductor device with heterojunction

ActiveUS20050199873A1Lower barrier heightImprove transistor driving forceSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionContact formation

An aspect of the present invention provides a semiconductor device that includes a semiconductor base made of a first semiconductor material of a first conductivity type, a hetero-semiconductor region forming a heterojunction with the semiconductor base and made of a second semiconductor material having a different band gap from the first semiconductor material, a first gate electrode arranged in the vicinity of the heterojunction, a first gate insulating film configured to insulate the first gate electrode from the semiconductor base, a source electrode formed in contact with the hetero-semiconductor region, a dram electrode formed in contact with the semiconductor base, and an electric field extending region partly facing the first gate electrode, the first gate insulating film and hetero-semiconductor region interposed between the electric field extending region and the first gate electrode, the electric field extending region extending a built-in electric field into the hetero-semiconductor region.

Owner:NISSAN MOTOR CO LTD