Patents

Literature

44results about How to "Increase junction depth" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

System and method for the manufacture of semiconductor devices by the implantation of carbon clusters

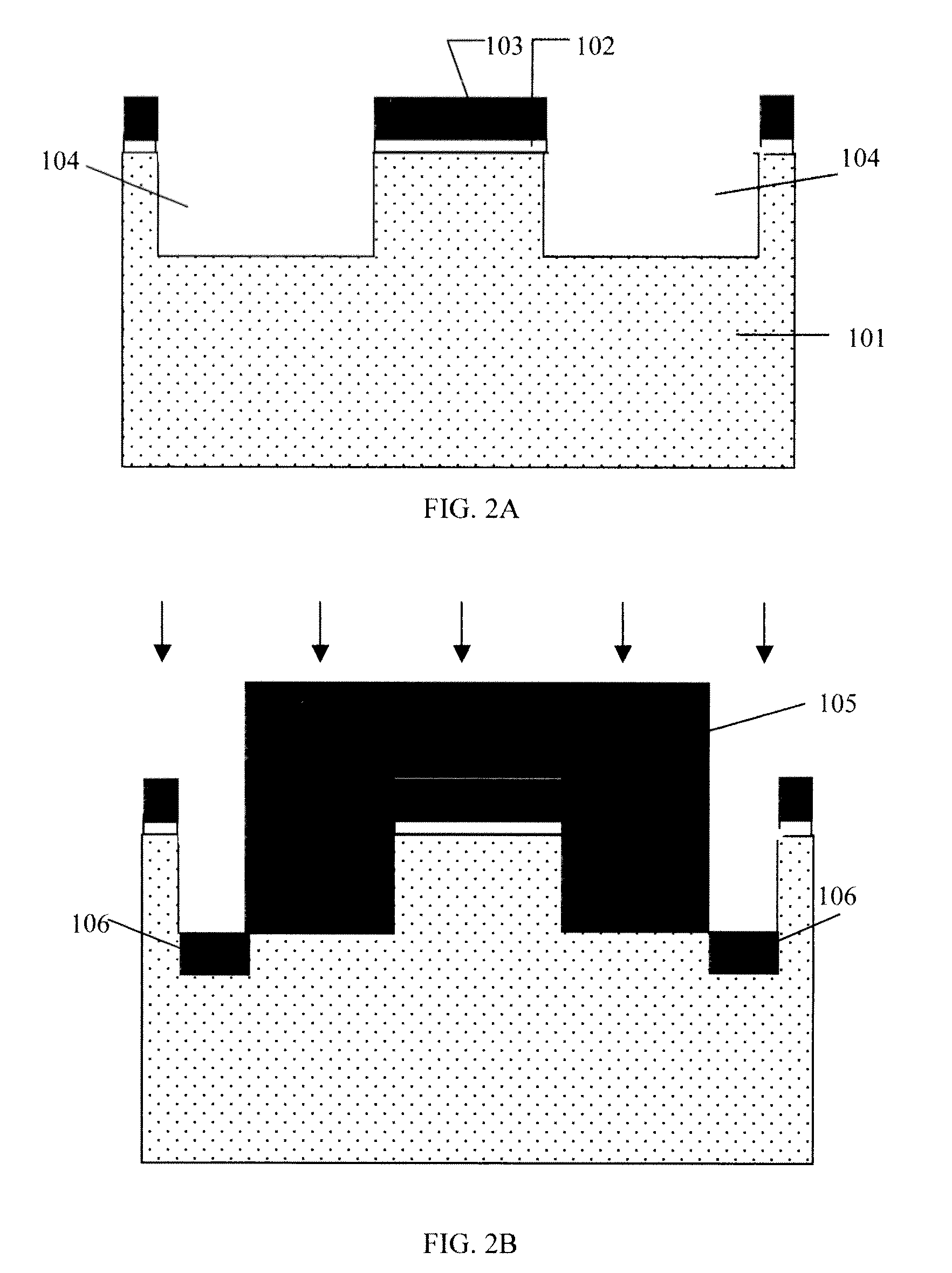

InactiveUS20070148888A1Improve productivityMinimize doseTransistorElectric discharge tubesDevice materialEngineering

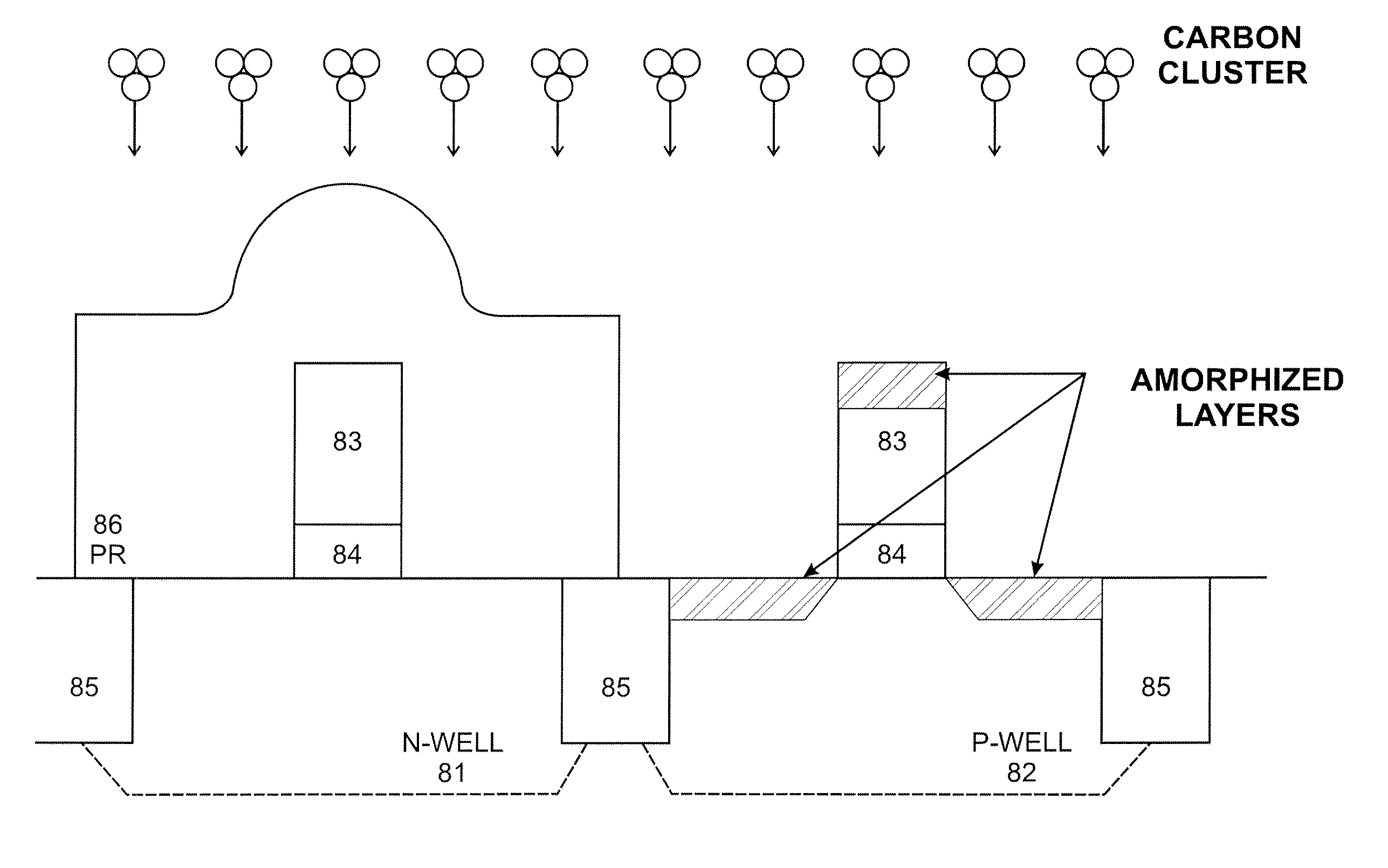

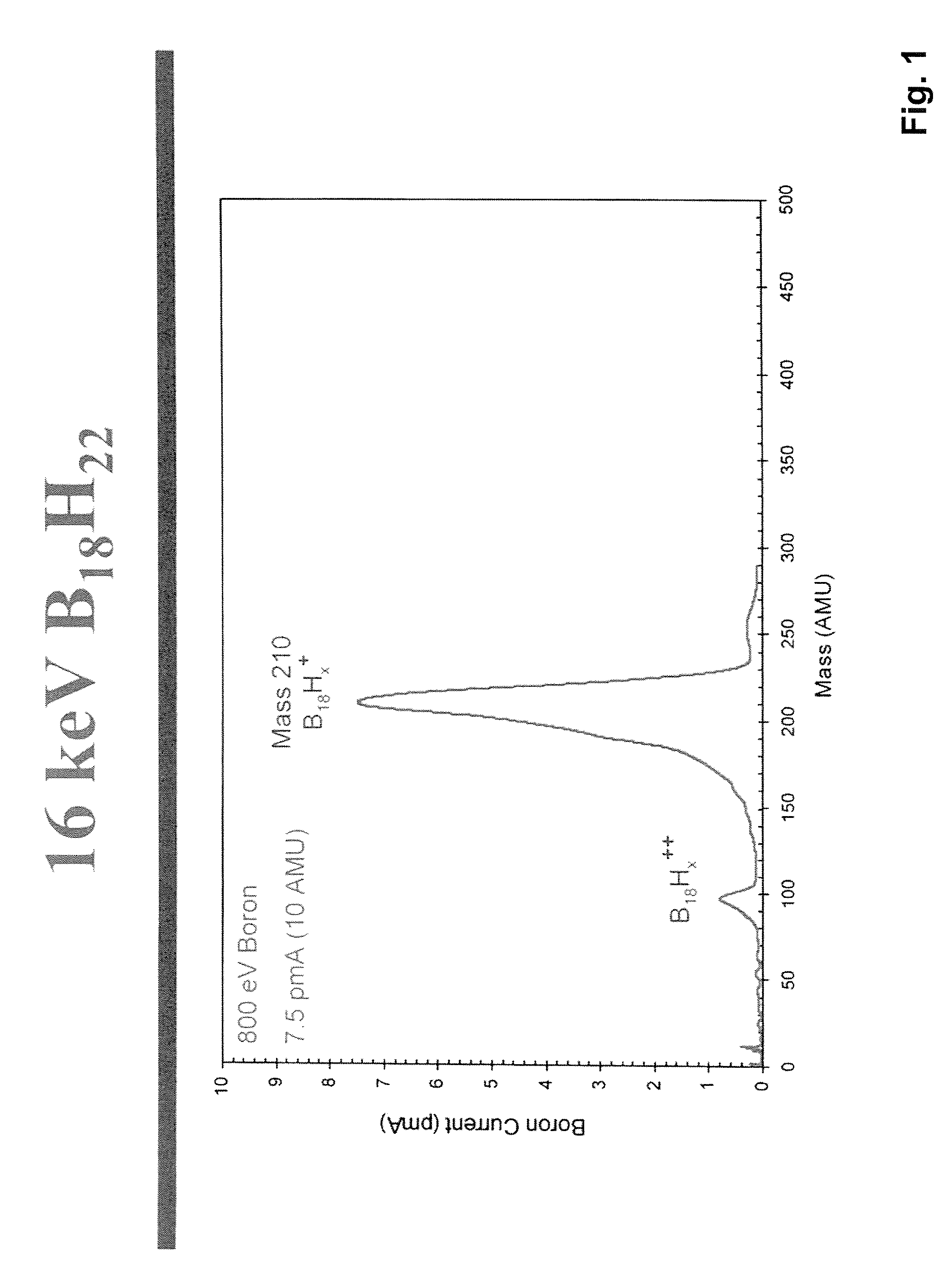

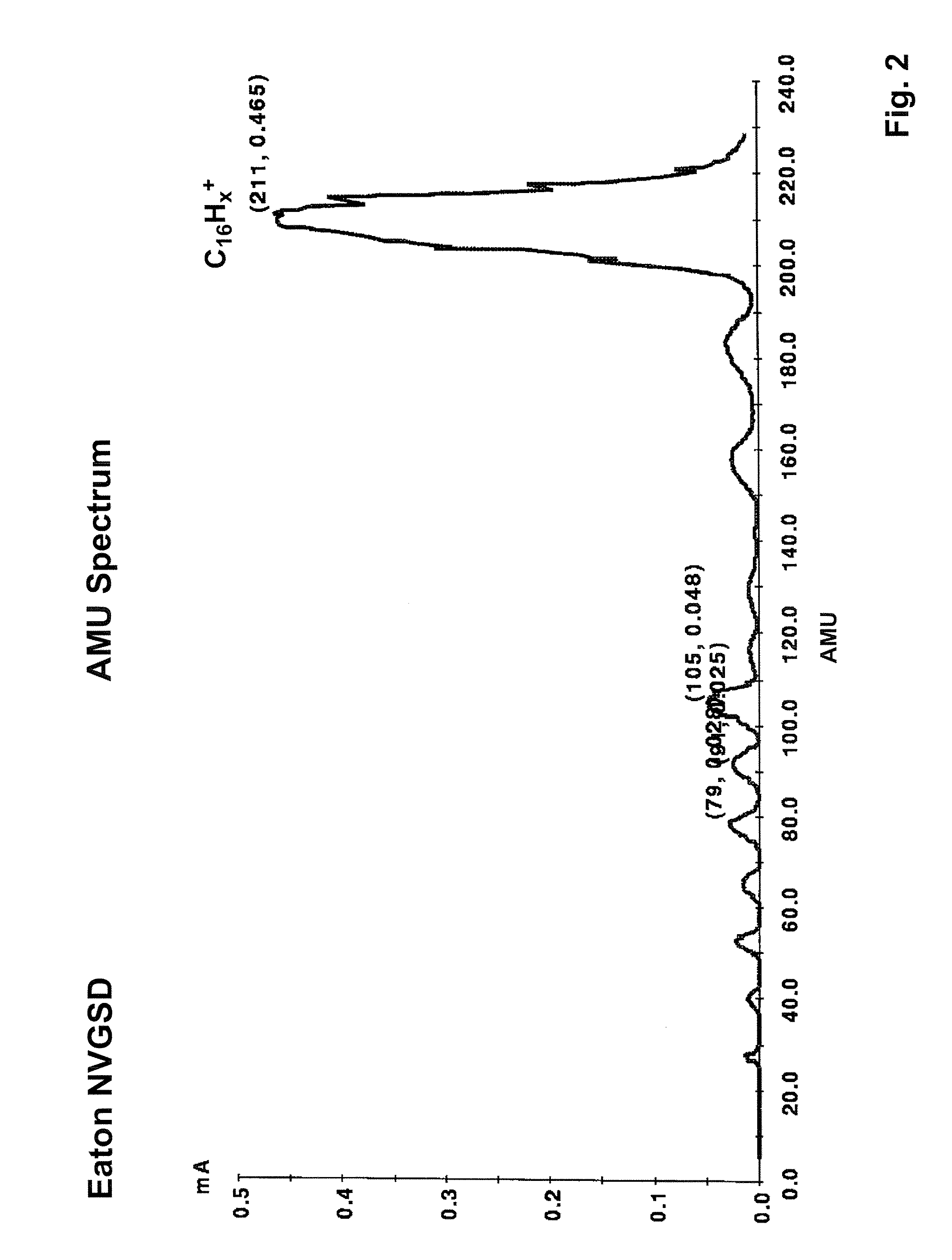

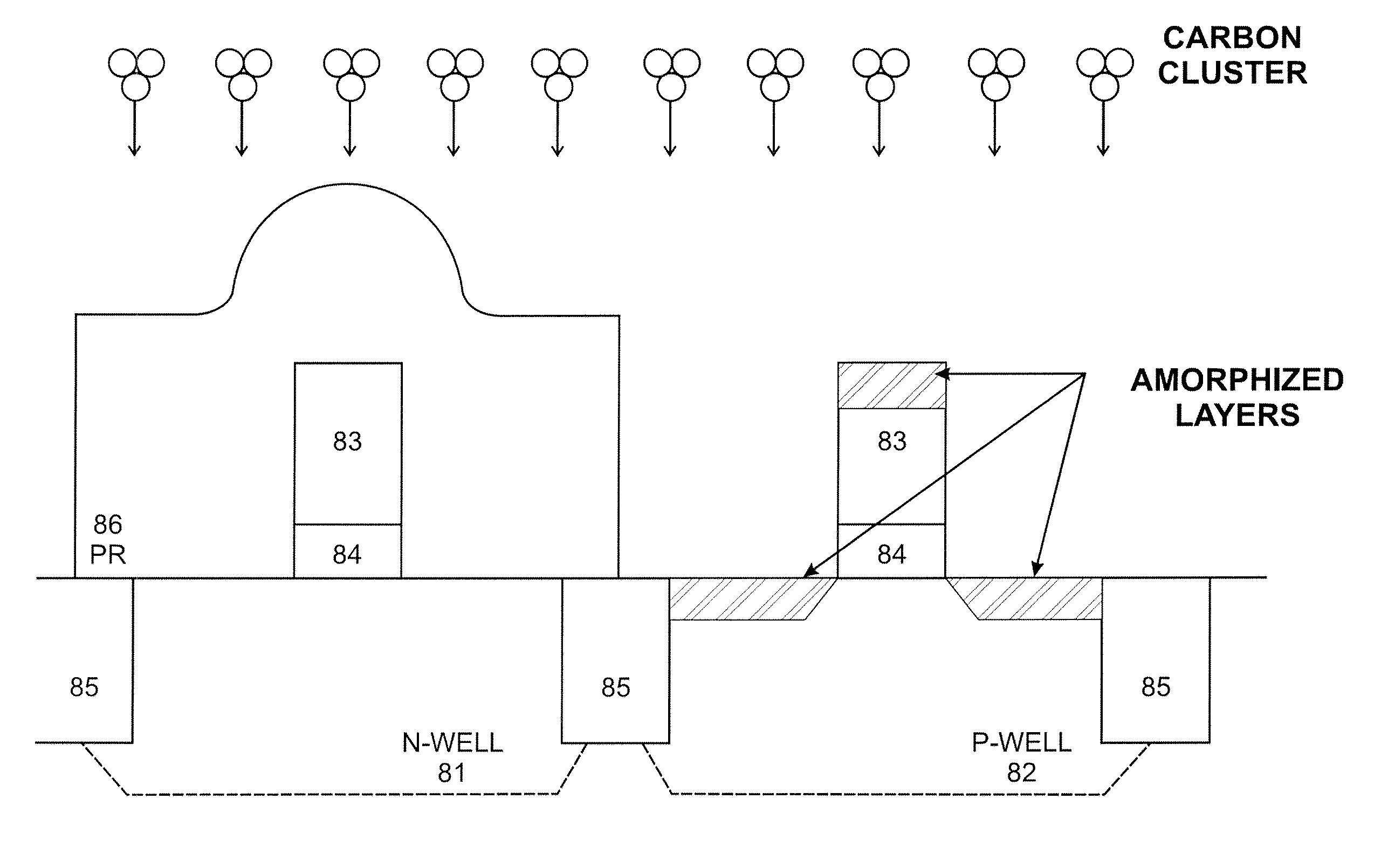

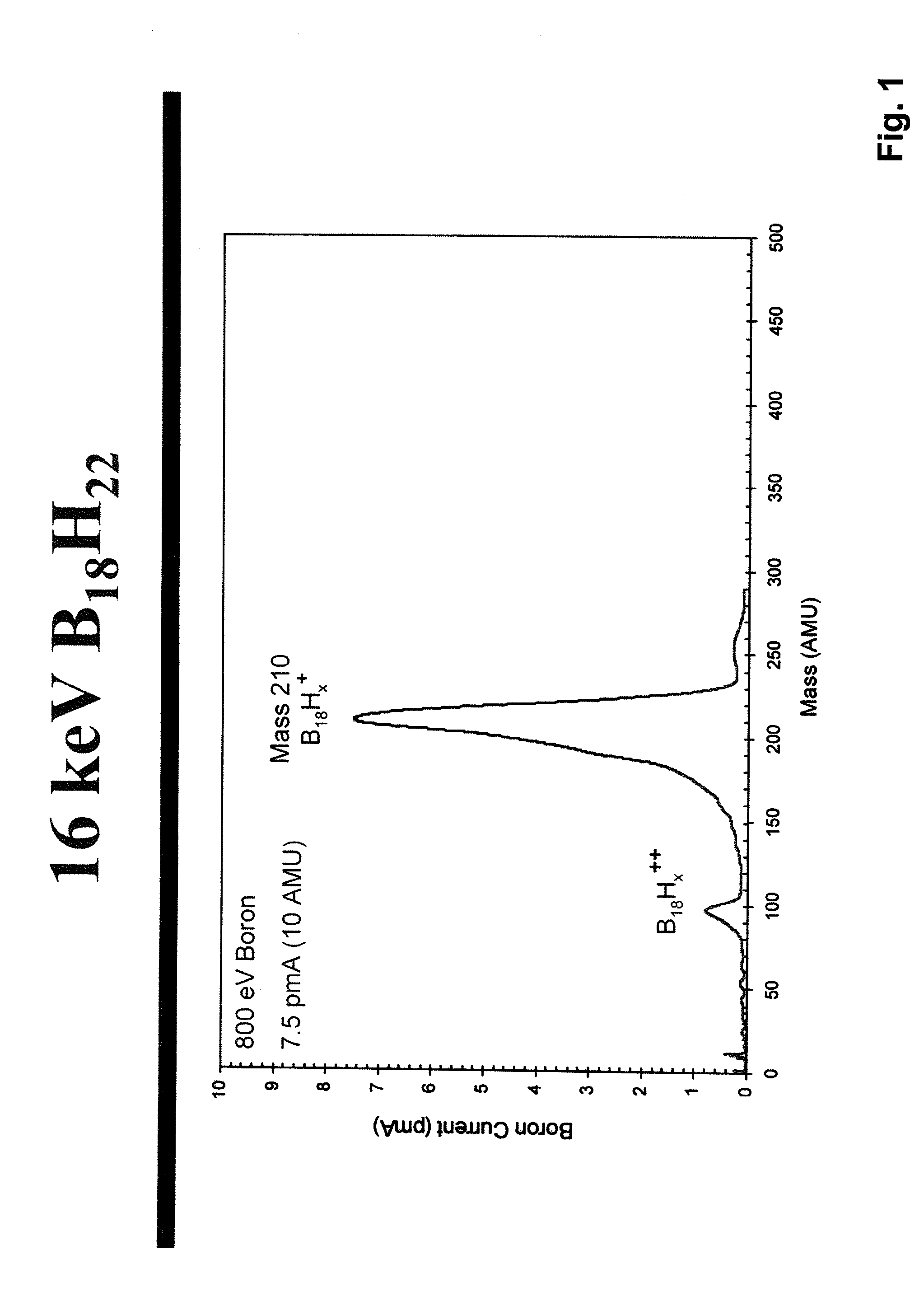

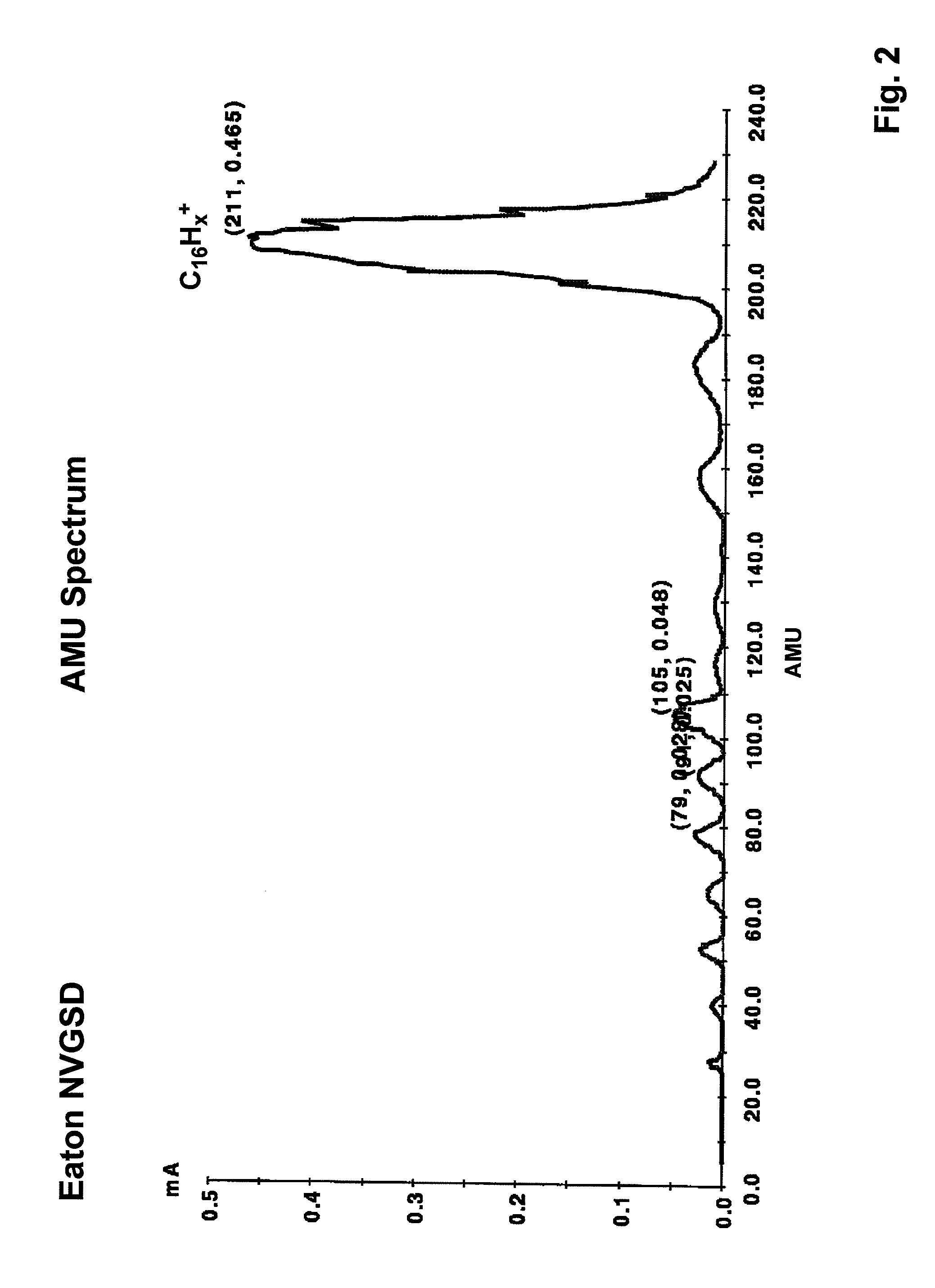

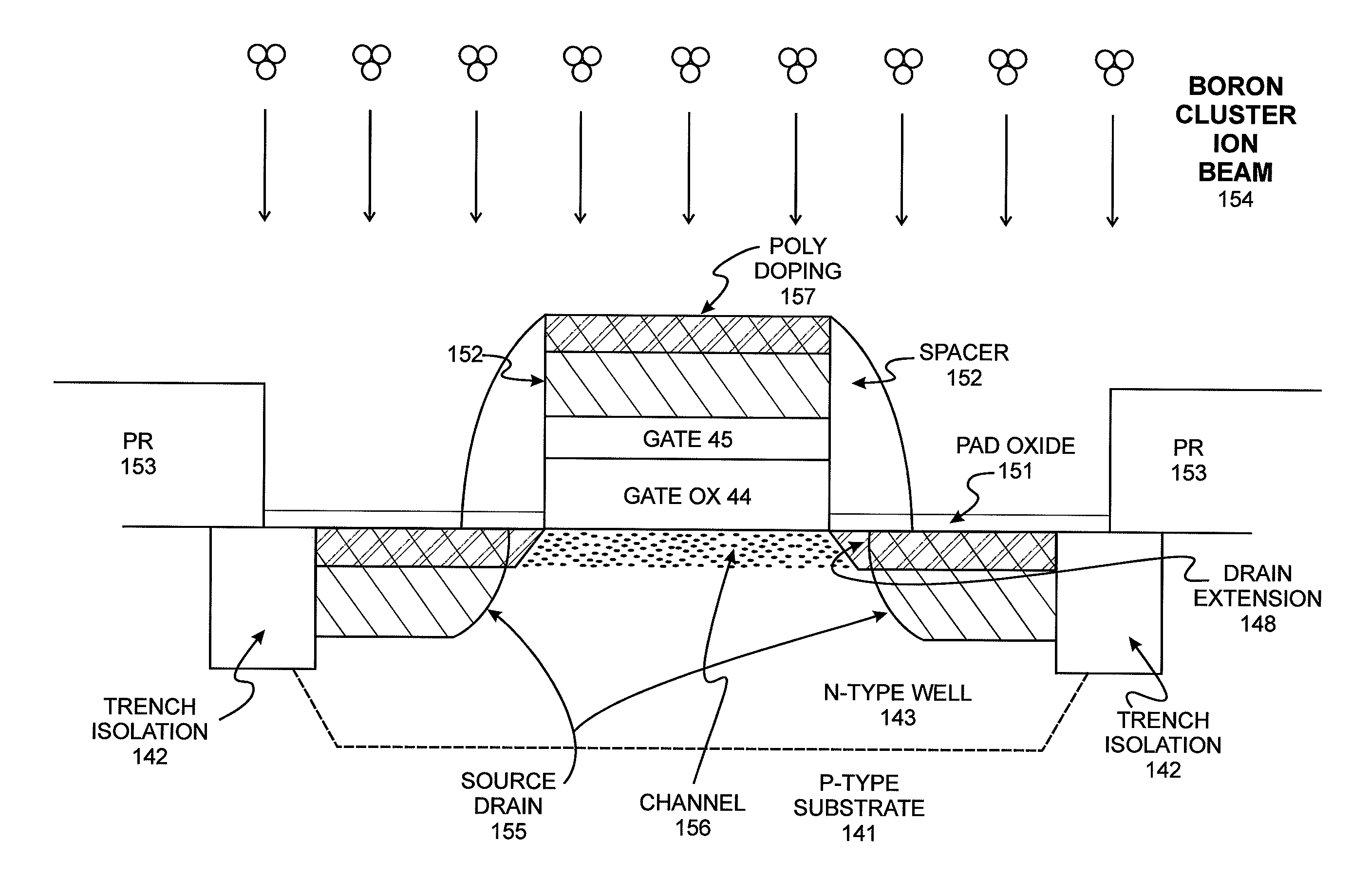

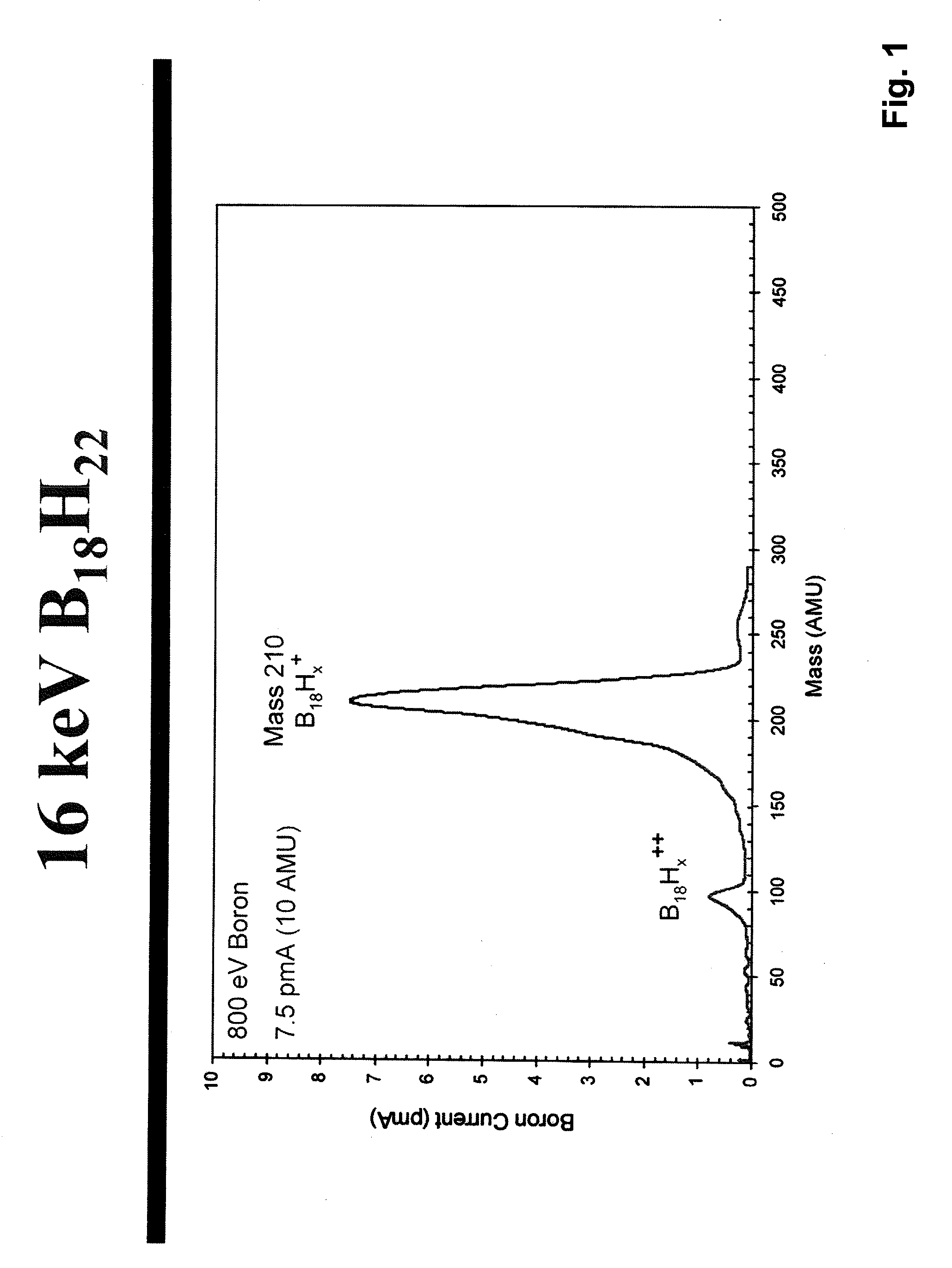

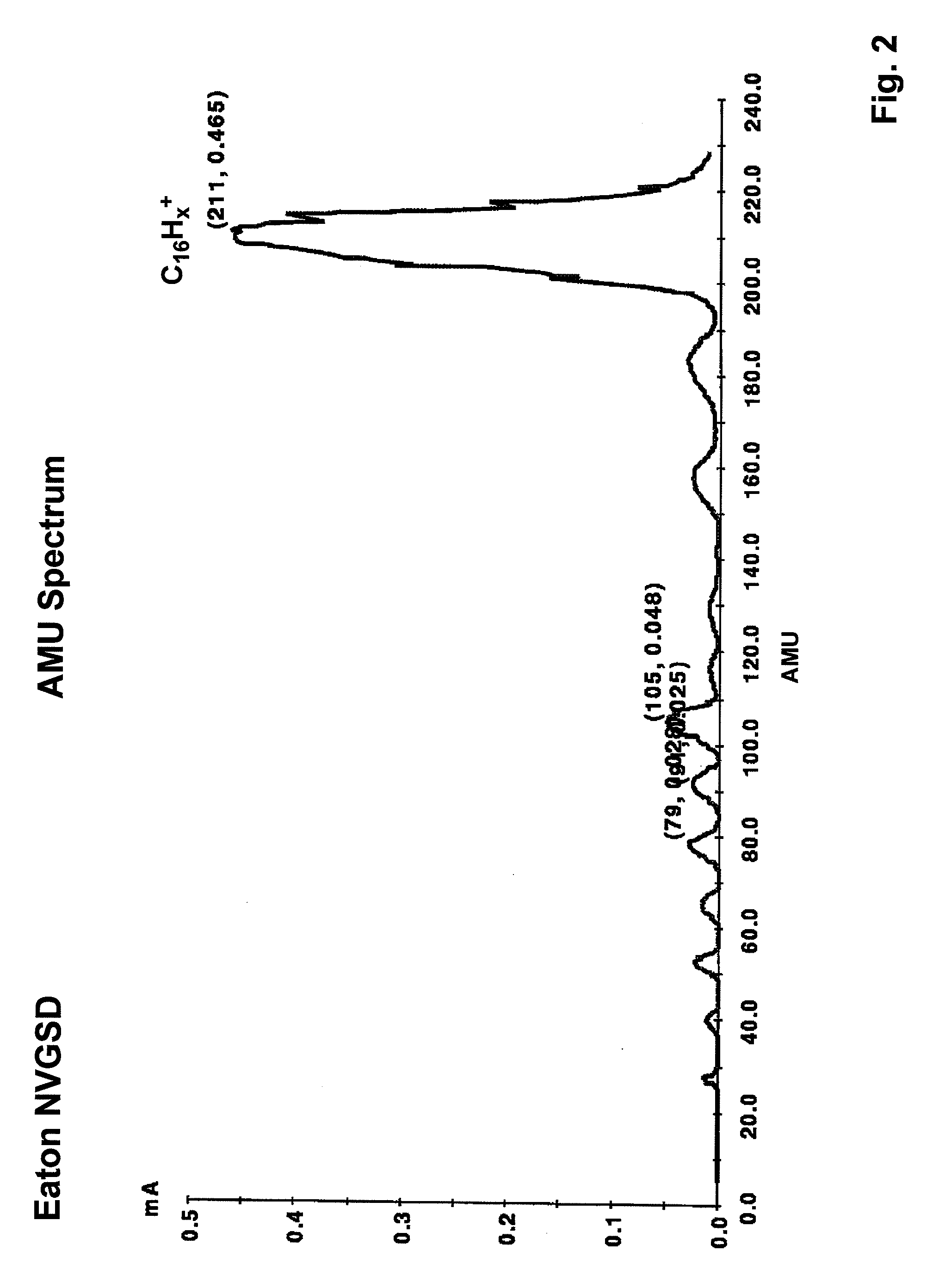

A process is disclosed which incorporates implantation of a carbon cluster into a substrate to improve the characteristics of transistor junctions when the substrates are doped with Boron and Phosphorous in the manufacturing of PMOS transistor structures in integrated circuits. There are two processes which result from this novel approach: (1) diffusion control for USJ formation; and (2) high dose carbon implantation for stress engineering. Diffusion control for USJ formation is demonstrated in conjunction with a boron or shallow boron cluster implant of the source / drain structures in PMOS. More particularly, first, a cluster carbon ion, such as C16Hx+, is implanted into the source / drain region at approximately the same dose as the subsequent boron implant; followed by a shallow boron, boron cluster, phosphorous or phosphorous cluster ion implant to form the source / drain extensions, preferably using a borohydride cluster, such as B18Hx+ or B10Hx+. Upon subsequent annealing and activation, the boron diffusion is reduced, due to the gettering of interstitial defects by the carbon atoms.

Owner:SEMEQUIP

System and method for the manufacture of semiconductor devices by the implantation of carbon clusters

InactiveUS7666771B2Increase junction depthReduce leakage currentTransistorElectric discharge tubesDevice materialEngineering

A process is disclosed which incorporates implantation of a carbon cluster into a substrate to improve the characteristics of transistor junctions when the substrates are doped with Boron and Phosphorous in the manufacturing of PMOS transistor structures in integrated circuits. There are two processes which result from this novel approach: (1) diffusion control for USJ formation; and (2) high dose carbon implantation for stress engineering. Diffusion control for USJ formation is demonstrated in conjunction with a boron or shallow boron cluster implant of the source / drain structures in PMOS. More particularly, first, a cluster carbon ion, such as C16Hx+, is implanted into the source / drain region at approximately the same dose as the subsequent boron implant; followed by a shallow boron, boron cluster, phosphorous or phosphorous cluster ion implant to form the source / drain extensions, preferably using a borohydride cluster, such as B18Hx+ or B10Hx+. Upon subsequent annealing and activation, the boron diffusion is reduced, due to the gettering of interstitial defects by the carbon atoms.

Owner:SEMEQUIP

System and method for the manufacture of semiconductor devices by the implantation of carbon clusters

InactiveUS20090286367A1Increase junction depthReduce leakage currentTransistorElectric discharge tubesCarbon ionHigh doses

A process is disclosed which incorporates implantation of a carbon cluster into a substrate to improve the characteristics of transistor junctions when the substrates are doped with Boron and Phosphorous in the manufacturing of PMOS transistor structures in integrated circuits. There are two processes which result from this novel approach: (1) diffusion control for USJ formation; and (2) high dose carbon implantation for stress engineering. Diffusion control for USJ formation is demonstrated in conjunction with a boron or shallow boron cluster implant of the source / drain structures in PMOS. More particularly, first, a cluster carbon ion, such as C16Hx+, is implanted into the source / drain region at approximately the same dose as the subsequent boron implant; followed by a shallow boron, boron cluster, phosphorous or phosphorous cluster ion implant to form the source / drain extensions, preferably using a borohydride cluster, such as B18Hx+ or B10Hx+. Upon subsequent annealing and activation, the boron diffusion is reduced, due to the gettering of interstitial defects by the carbon atoms.

Owner:SEMEQUIP

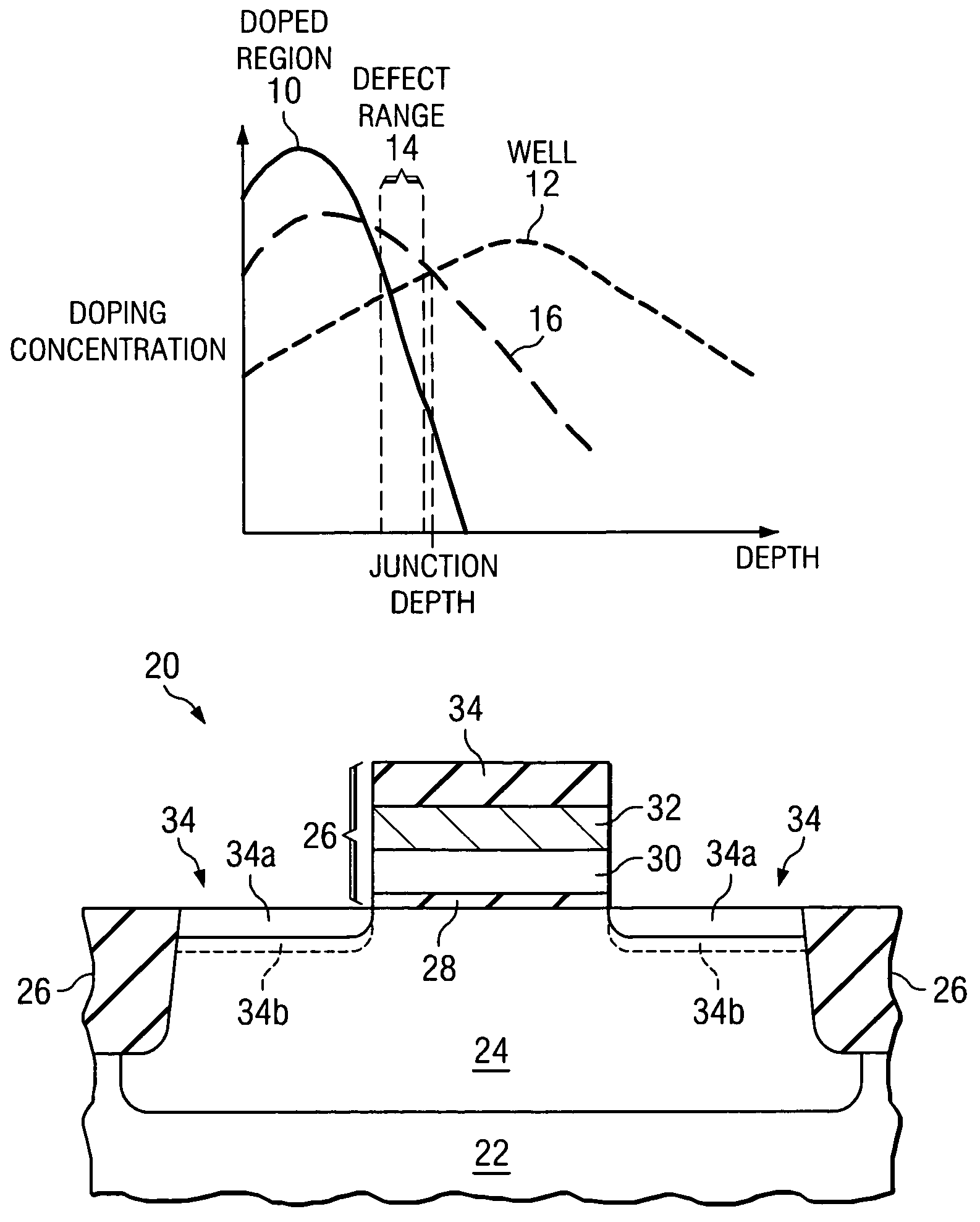

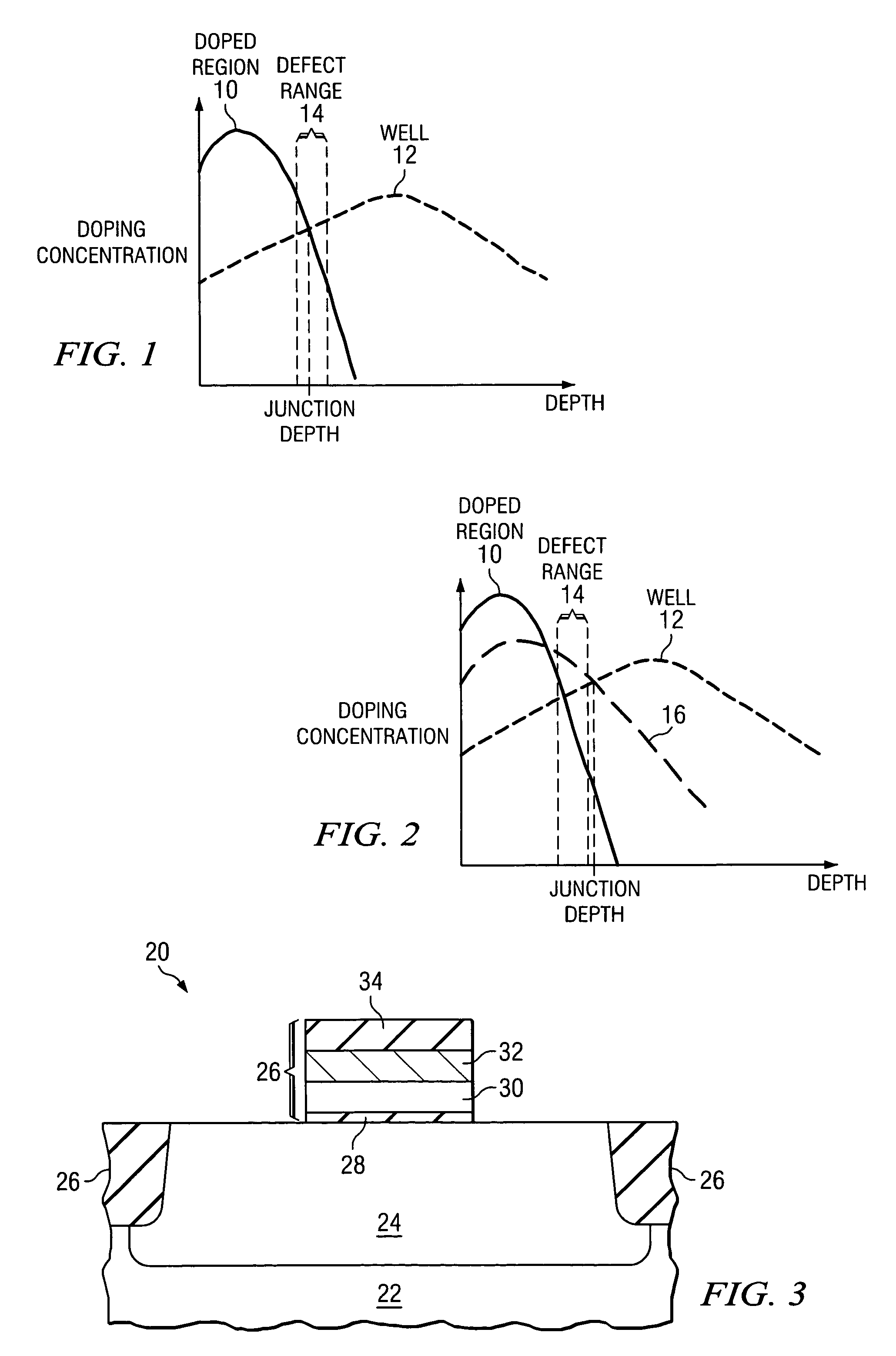

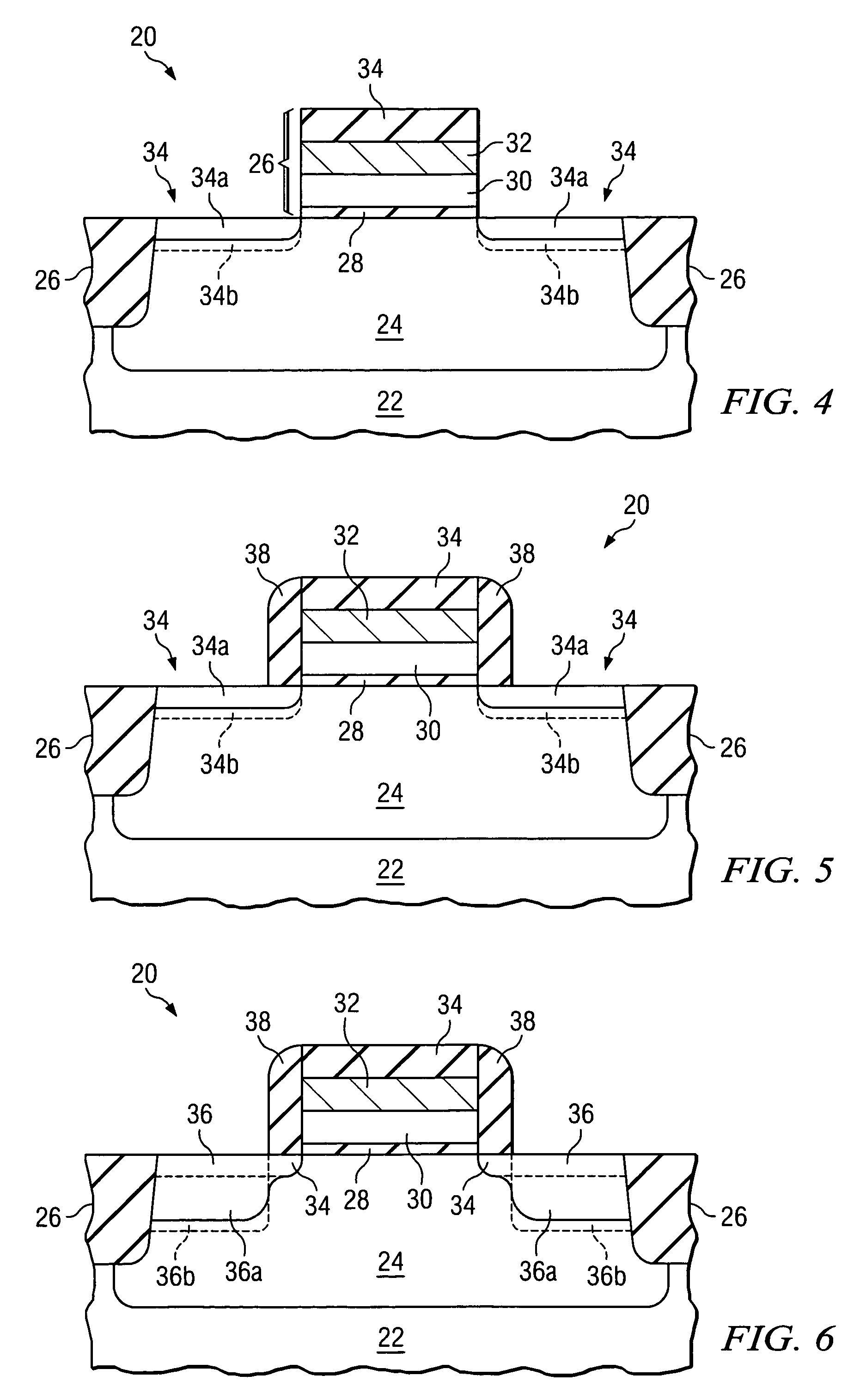

Implantation process in semiconductor fabrication

ActiveUS20060252239A1Smoothens junctionReduces band-to-band tunnelingTransistorSemiconductor/solid-state device manufacturingDopantOptoelectronics

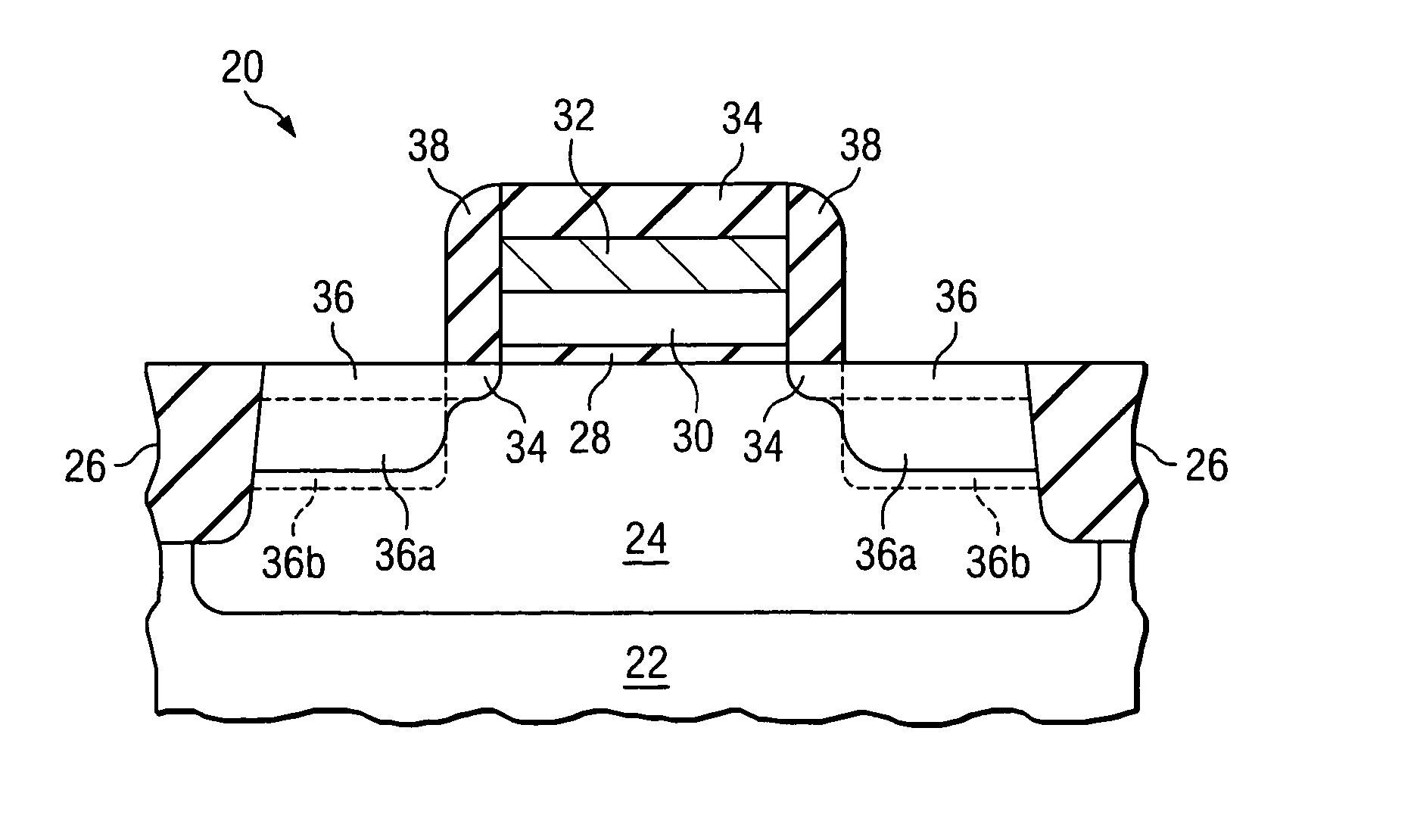

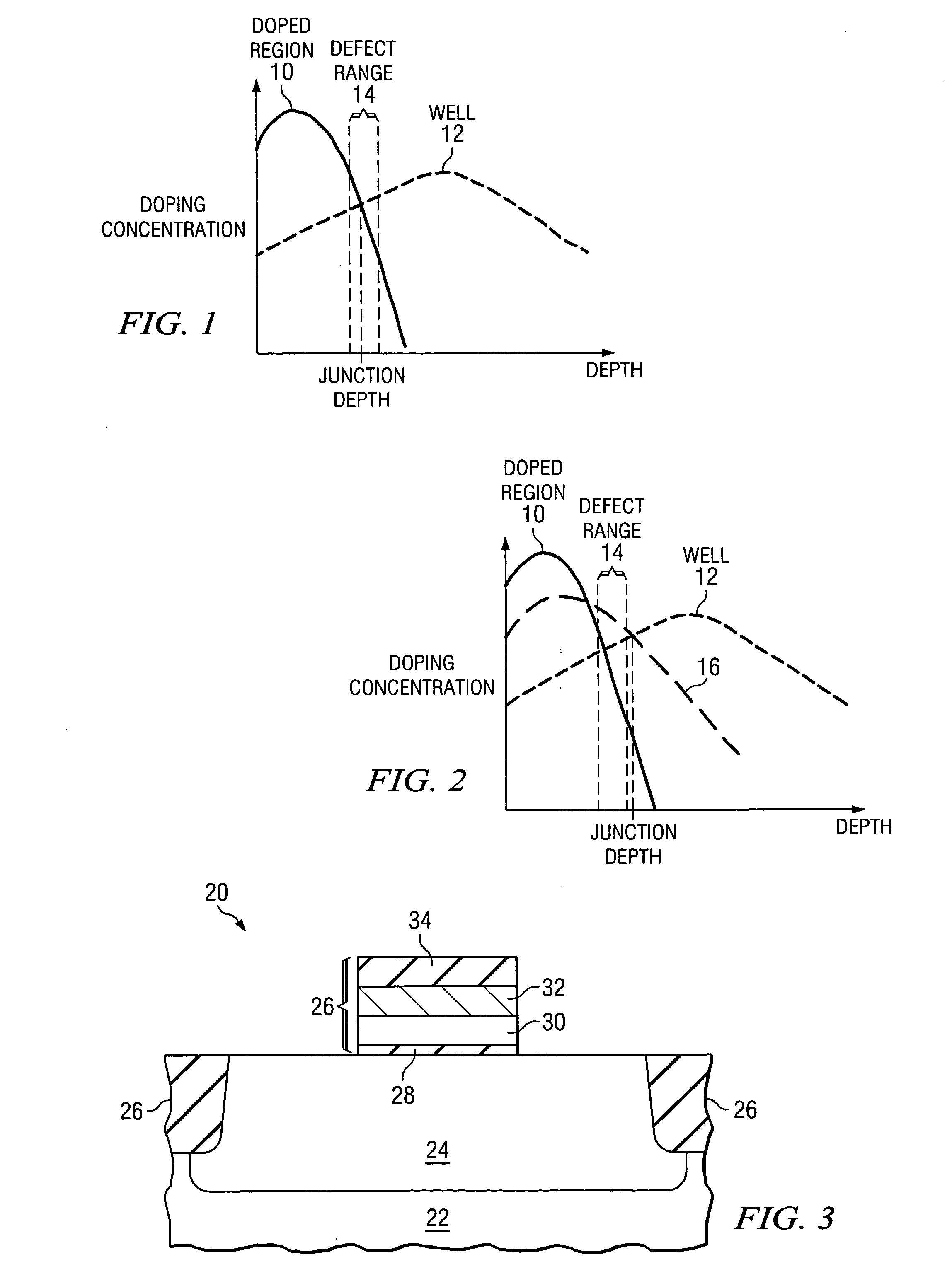

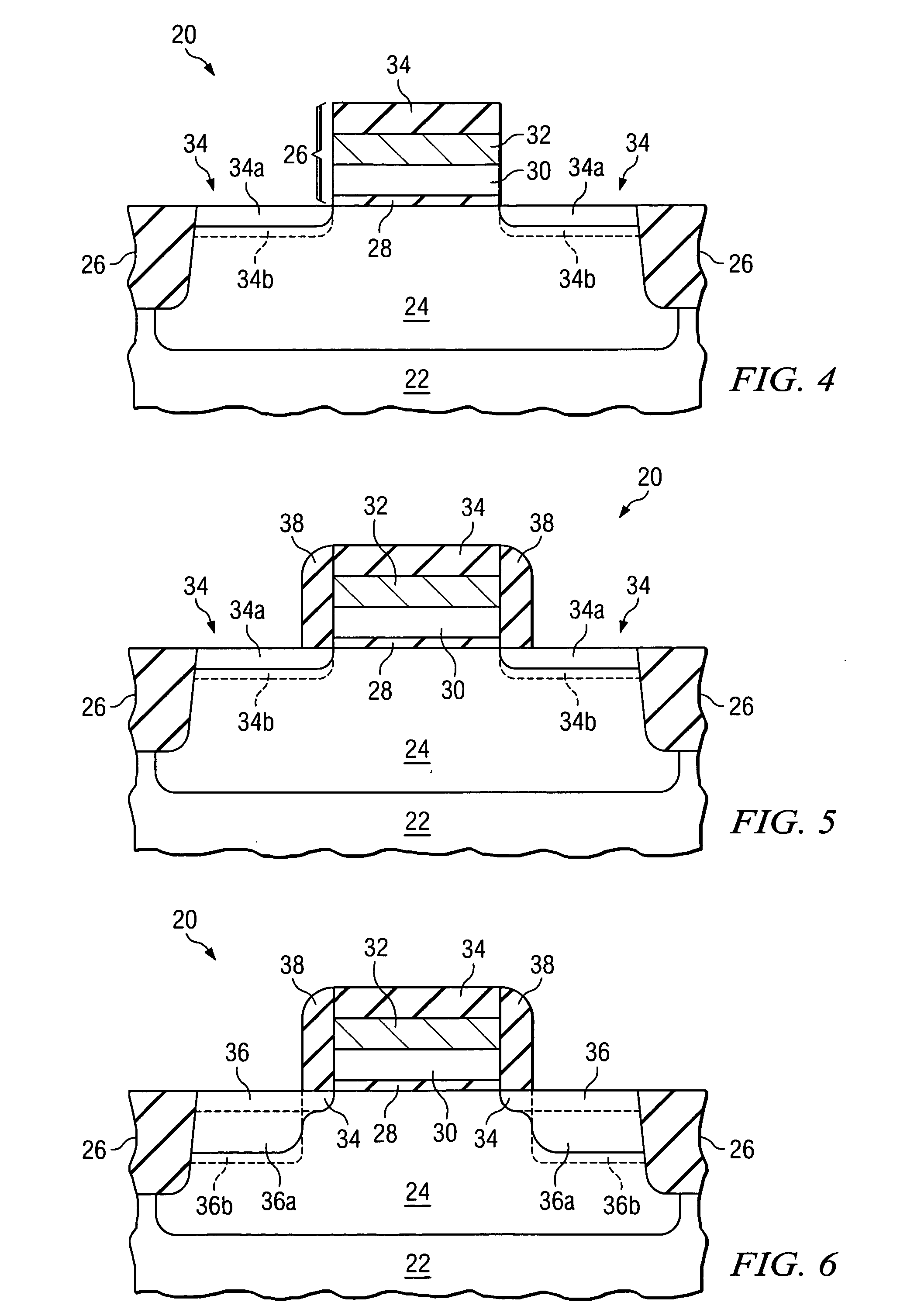

A semiconductor device is formed by performing an amorphizing ion implantation to implant dopants of a first conductivity type into a semiconductor body. The first ion implantation causes a defect area (e.g., end-of-range defects) within the semiconductor body at a depth. A non-amorphizing implantation implants dopants of the same conductivity type into the semiconductor body. This ion implantation step implants dopants throughout the defect area. The dopants can then be activated by heating the semiconductor body for less than 10 ms, e.g., using a flash anneal or a laser anneal.

Owner:INFINEON TECH AG

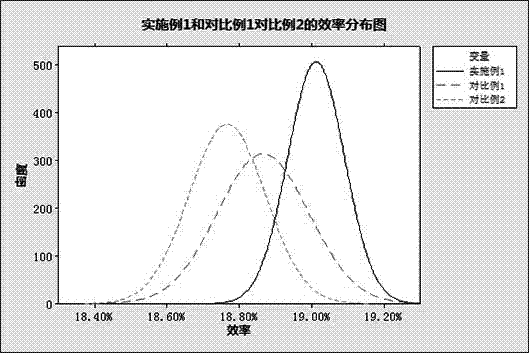

Diffusion technique of crystal-silicon efficient high-sheet-resistance battery piece

ActiveCN105280484AImprove photoelectric conversion rateReduce surface recombinationFinal product manufactureSemiconductor/solid-state device manufacturingDopantEngineering

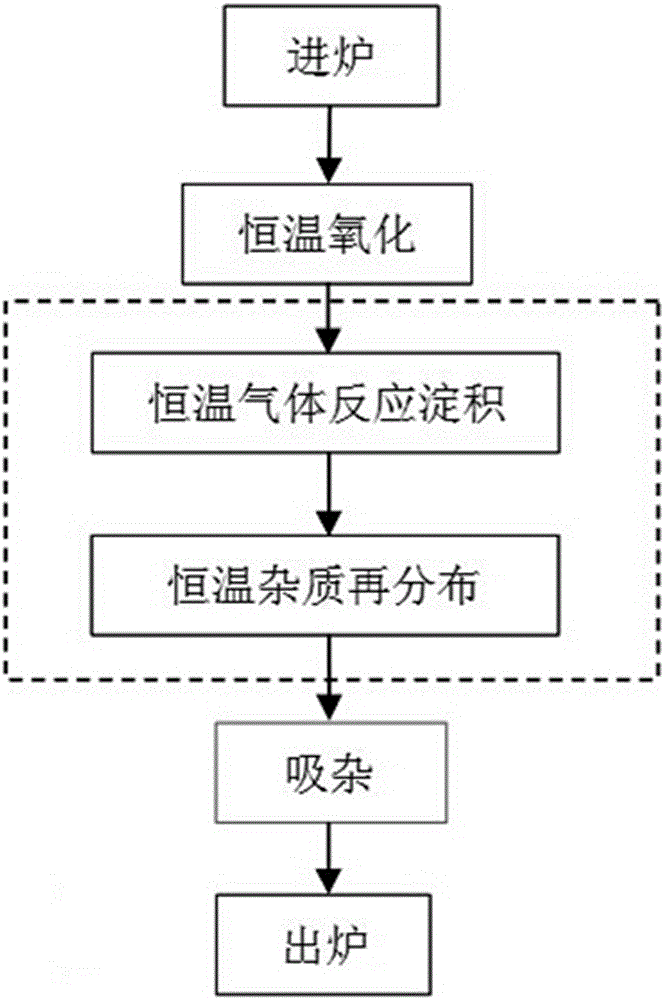

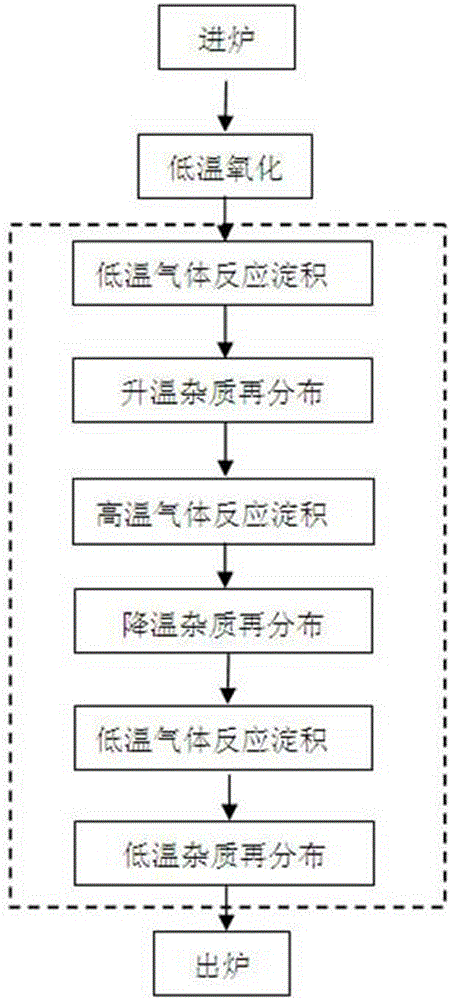

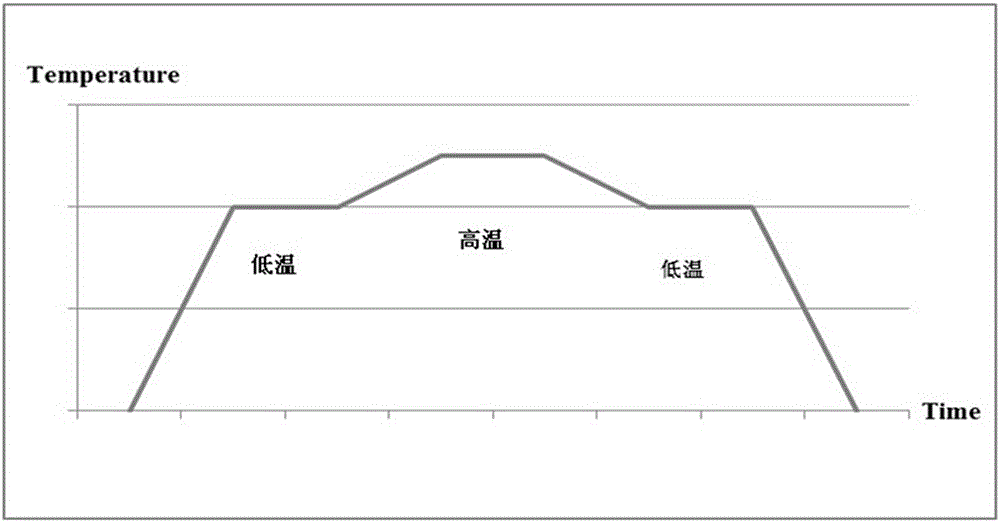

The present invention relates to a diffusion technique of a crystal-silicon efficient high-sheet-resistance battery piece. The diffusion technique comprises the steps of furnace entering, low-temperature oxidation, low temperature gas reaction deposition, low temperature dopant redistribution, high temperature gas reaction deposition, cooling dopant redistribution, low temperature gas reaction deposition, low temperature dopant redistribution and discharge. With adoption of the diffusion technique provided by the present invention, photoelectric conversion efficiency of the battery pieces can be raised, the production time is shortened, and the production efficiency is raised.

Owner:TRINA SOLAR CO LTD +1

Polycrystalline black silicon wafer diffusion method through MCCE etching

InactiveCN108010972AImprove uniformityImprove electrical performanceFinal product manufactureSemiconductor/solid-state device manufacturingDiffusion methodsDeposition process

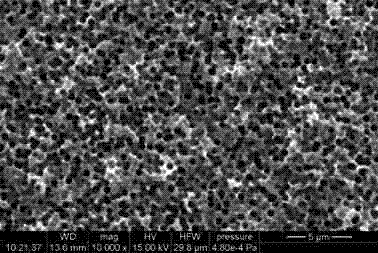

The invention discloses a polycrystalline black silicon wafer diffusion method through MCCE etching, which is applicable to a black silicon diffusion process prepared by adopting a metal catalytic chemical etching method. A process of first deposition-first propulsion-second deposition-second propulsion is adopted. The oxygen flow rate in the first deposition process is larger than the nitrogen flow rate with a phosphorus source; the first propulsion is anaerobic propulsion, and the pure nitrogen flow rate in the first propulsion process is larger than that in the first deposition process; thenitrogen flow rate with a phosphorus source in the second deposition process is larger than that in the first deposition process; the pure nitrogen flow rate in the second deposition process is smaller than that in the first deposition process; the temperature of the second deposition process is larger than that of the first deposition process; the second propulsion is oxygen-enriched propulsion;the first propulsion time is smaller than the first deposition time; and the second propulsion time is larger than the second deposition time. Photocarrier recombination can be effectively reduced, the silicon wafer diffusion uniformity is enhanced, and the black silicon cell efficiency is enhanced.

Owner:REALFORCE POWER

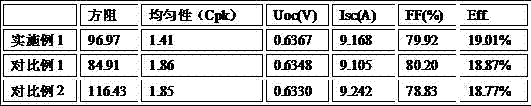

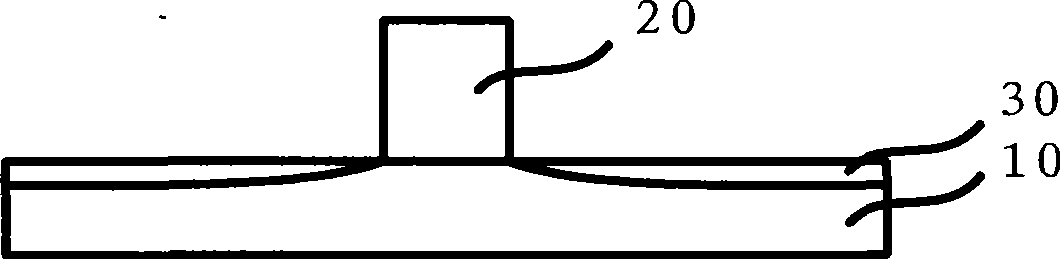

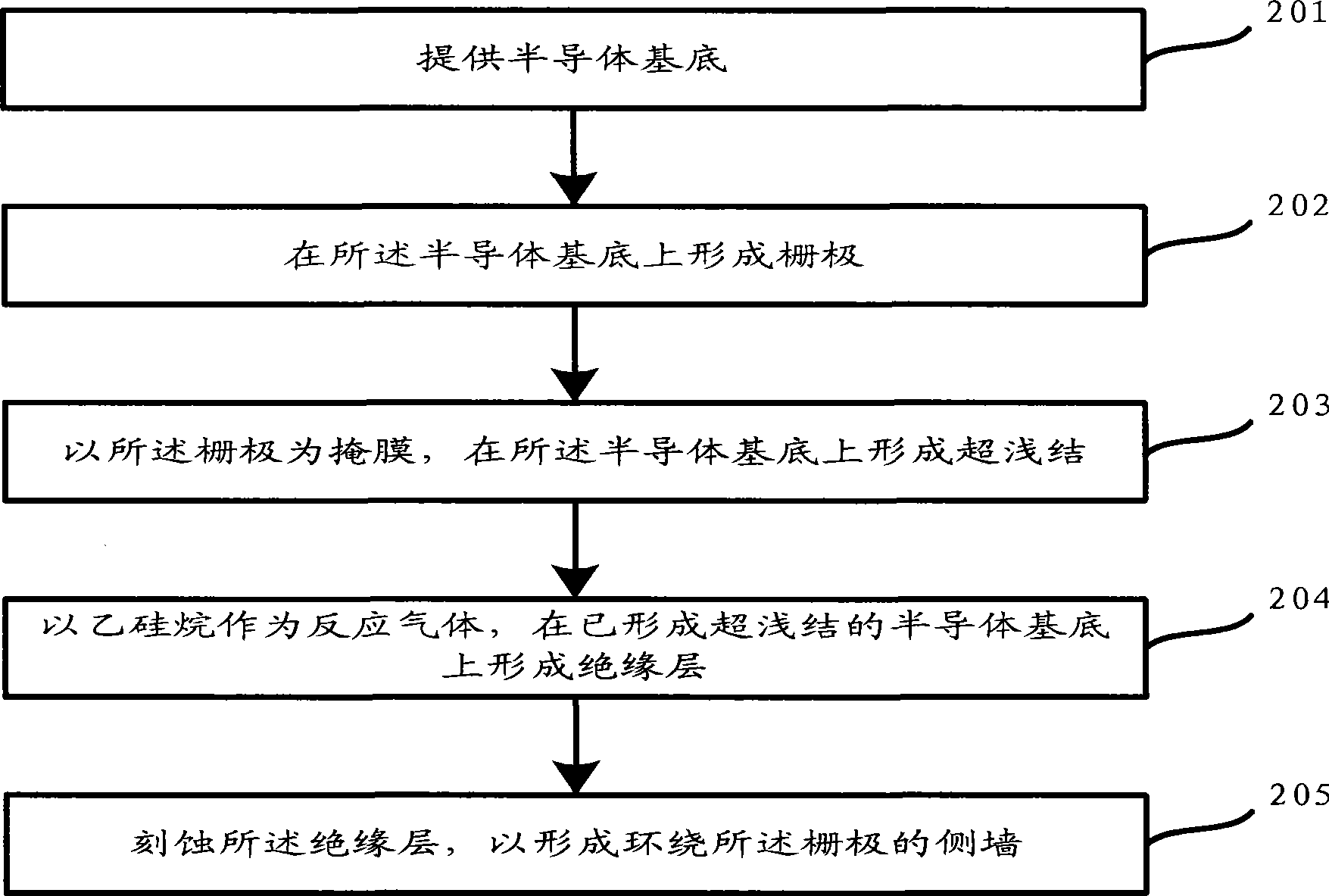

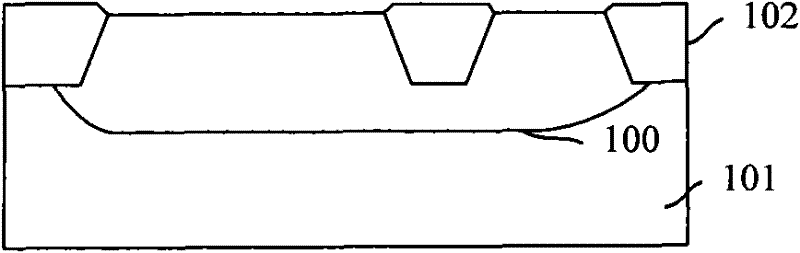

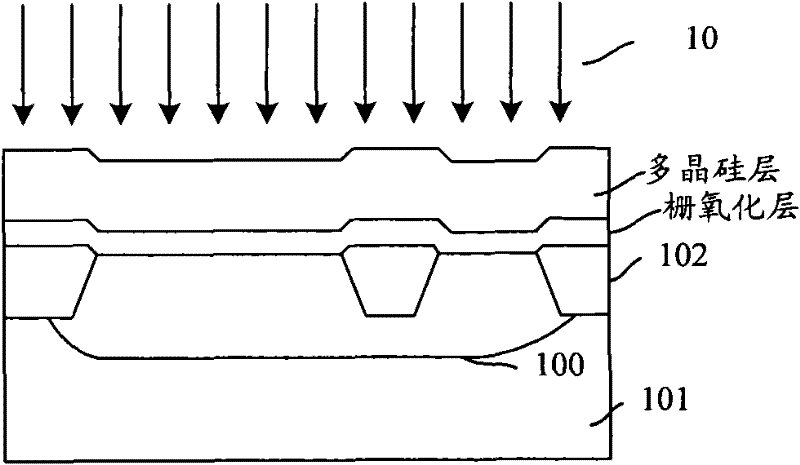

Formation method for side wall

InactiveCN101447430AReduce spreadShort reaction timeSemiconductor/solid-state device manufacturingBasementInsulation layer

The invention relates to a formation method for a side wall, which comprises: providing a semiconductor basement, forming a grid on the semiconductor basement; using the grid as a mask to form a ultra-shallow junction on the semiconductor basement and using disilane as reaction gas to form an insulation layer on the semiconductor basement with the formed ultra-shallow junction; etching the insulation layer to form the side wall surrounding the grid. The formation method for the side wall can reduce the diffusion of doping material in the ultra-shallow junction, thereby reducing the increasing of junction depth.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Phosphorus doping control method for emitter of crystalline silicon solar cell

ActiveCN107871660AIncrease peak concentrationGood photoelectric conversion efficiencyFinal product manufactureSemiconductor/solid-state device manufacturingDislocationPeak concentration

The invention relates to the field of solar cell production, and discloses a phosphorus doping control method for an emitter of a crystalline silicon solar cell. The method is carried out according tothe following steps of (1) first low-temperature oxidation; (2) first deposition; (3) second low-temperature oxidation; (4) second deposition and first propulsion; and (5) third deposition and secondpropulsion. According to the phosphorus doping control method, the peak concentration is improved through low-temperature oxidation, deposition and low-temperature oxidation, meanwhile, lattice dislocation is not caused, and then the surface of the cell is passivated through double deposition and propulsion, thereby obtaining better photoelectric conversion efficiency.

Owner:SHANXI LUAN PHOTOVOLTAICS TECH

Novel diffusion process capable of increasing polysilicon open-circuit voltage

InactiveCN104752564AReduce surface recombination velocityReduce widthFinal product manufactureSemiconductor/solid-state device manufacturingNitrogenWarming process

The invention discloses a novel diffusion process capable of increasing polysilicon open-circuit voltage. The novel diffusion process includes: 1), placing a silicon wafer in a diffusion furnace, and heating to 800 DEG C; 2), feeding a source, namely feeding diffusion nitrogen, oxygen and purging nitrogen into the diffusion furnace at the temperature according to a feeding flow ratio of 3:1:17 for 10-25 minutes; 3), heating for knot pushing, namely, using 10-25 minutes to increase temperature in a diffusion furnace pipe to be 850-860 DEG C, and continuously feeding purging nitrogen and oxygen with a feeding flow ratio of 10:3 into the diffusion furnace pipe in the whole process of heating; 4), using 10-25 minutes to lower temperature in the diffusion furnace pipe to be 750-800 DEG C, and continuously feeding purging nitrogen into the diffusion furnace pipe in the whole process of cooling; 5), taking the silicon wafer out. By the novel diffusion process, surface compositing speed of the silicon wafer can be lowered, knot depth can be increased, width of a polysilicon substrate can be reduced, and open-circuit voltage of a solar cell is increased.

Owner:JETION SOLAR HLDG

Implantation process in semiconductor fabrication

ActiveUS7172954B2Small diffusionSmoothens junctionTransistorSemiconductor/solid-state device manufacturingDopantIon implantation

A semiconductor device is formed by performing an amorphizing ion implantation to implant dopants of a first conductivity type into a semiconductor body. The first ion implantation causes a defect area (e.g., end-of-range defects) within the semiconductor body at a depth. A non-amorphizing implantation implants dopants of the same conductivity type into the semiconductor body. This ion implantation step implants dopants throughout the defect area. The dopants can then be activated by heating the semiconductor body for less than 10 ms, e.g., using a flash anneal or a laser anneal.

Owner:INFINEON TECH AG

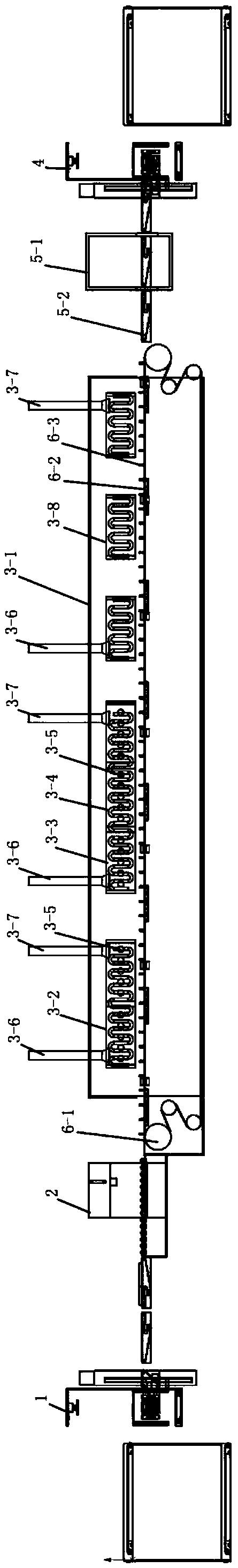

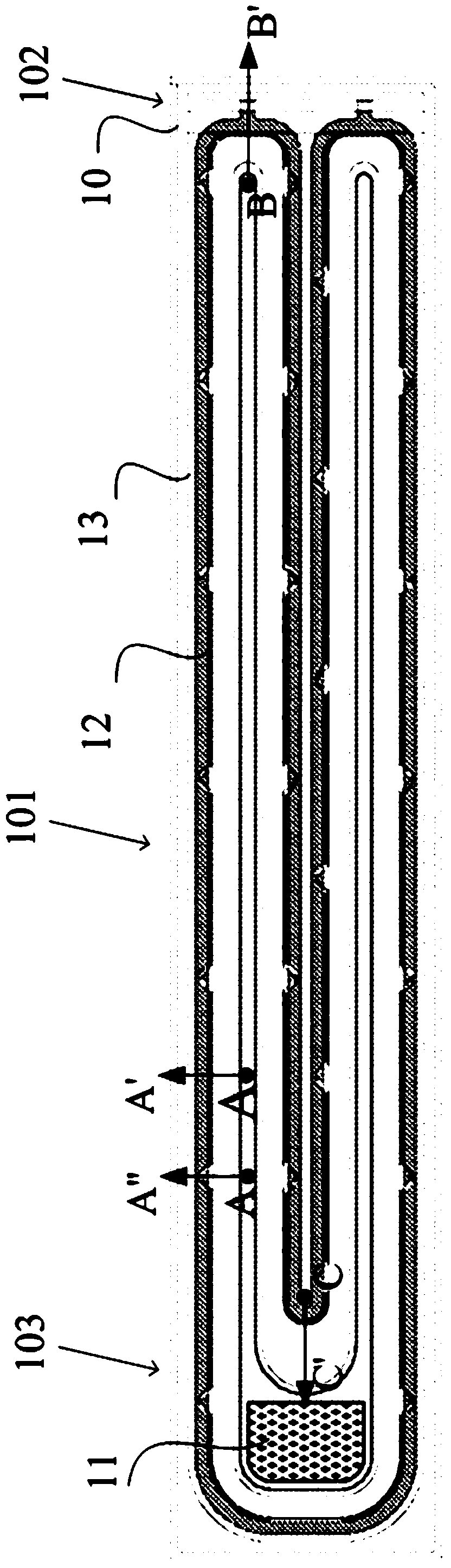

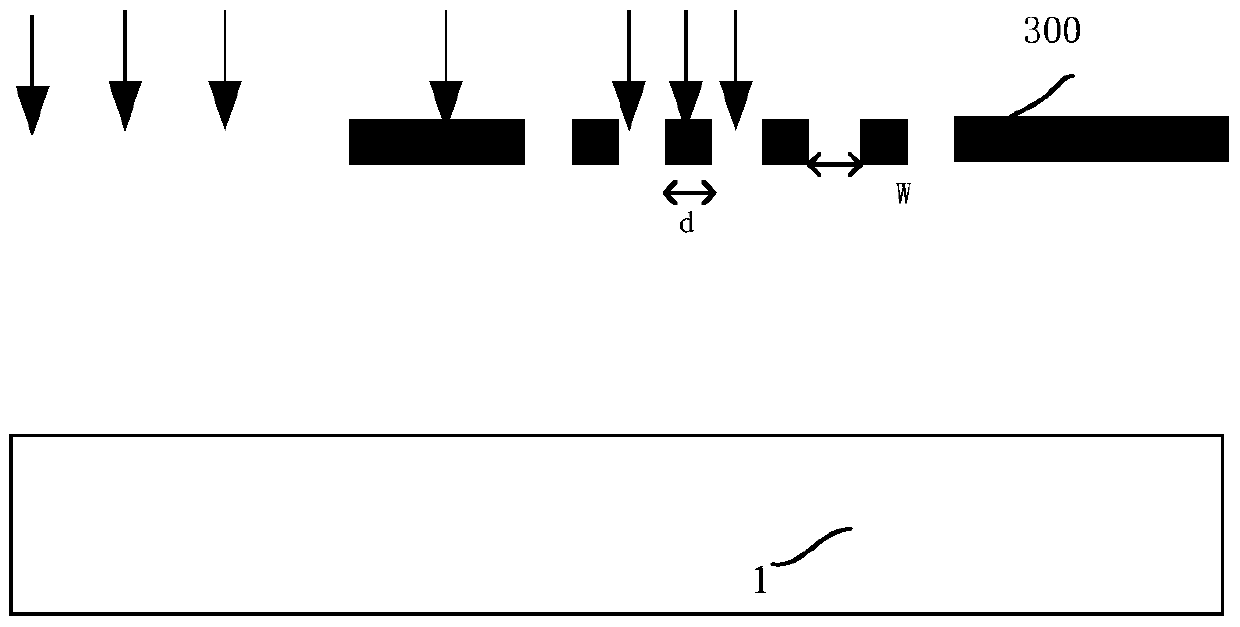

Chain-type diffusion technology and chain-type diffusion device

PendingCN108447949AReduce surface concentrationReduce the chance of recombination in the bodyFinal product manufactureDiffusion/dopingChain typeSolar cell

The invention provides a chain-type diffusion technology and a chain-type diffusion device, so as to solve the problems that the surface phosphorus concentration of a p-n junction obtained after chain-type diffusion is high and the junction depth is shallow, the surface minority carrier recombination probability is increased, serious electric leakage happens to a junction area, impurities existingin a silicon wafer substrate form a coincidence center easily, and the bulk recombination probability is increased. In the diffusion process of solar cell production, the surface phosphorus concentration of the p-n junction is reduced, the junction depth is increased, surface minority carrier recombination and junction area electric leakage are reduced, the impurities existing in the silicon wafer substrate are absorbed, and the bulk recombination probability is reduced.

Owner:EGING PHOTOVOLTAIC TECHNOLOGY CO LTD

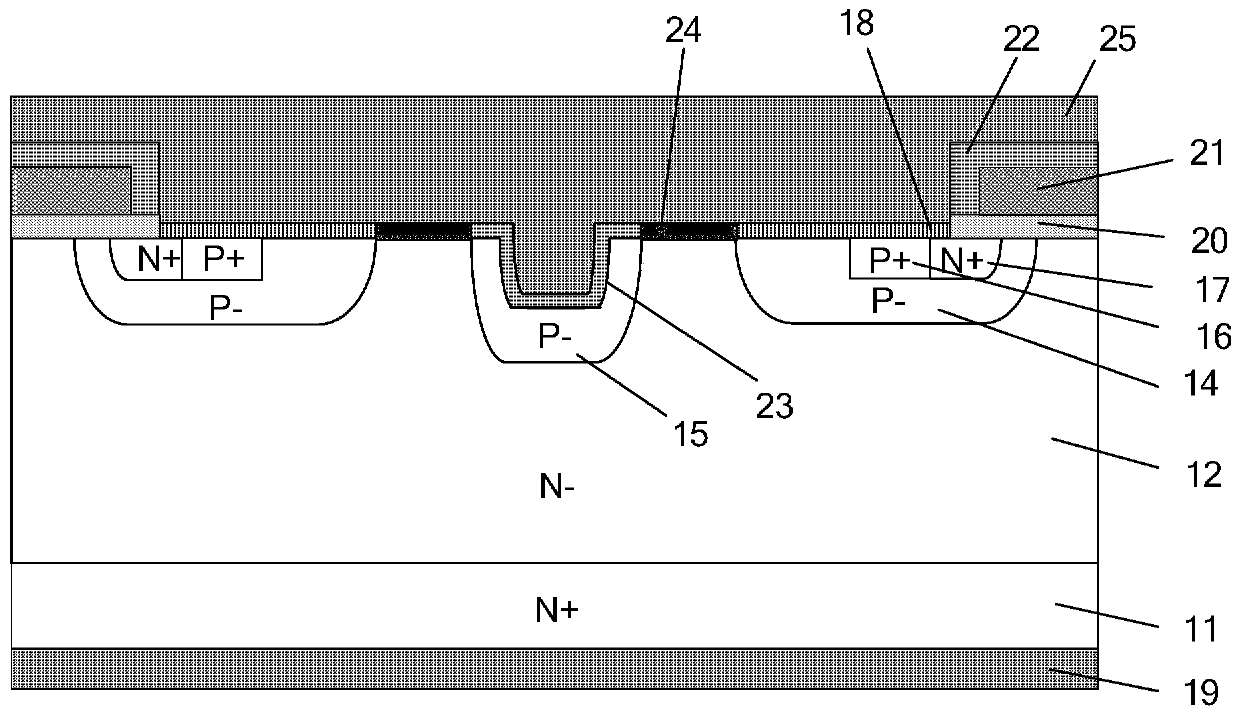

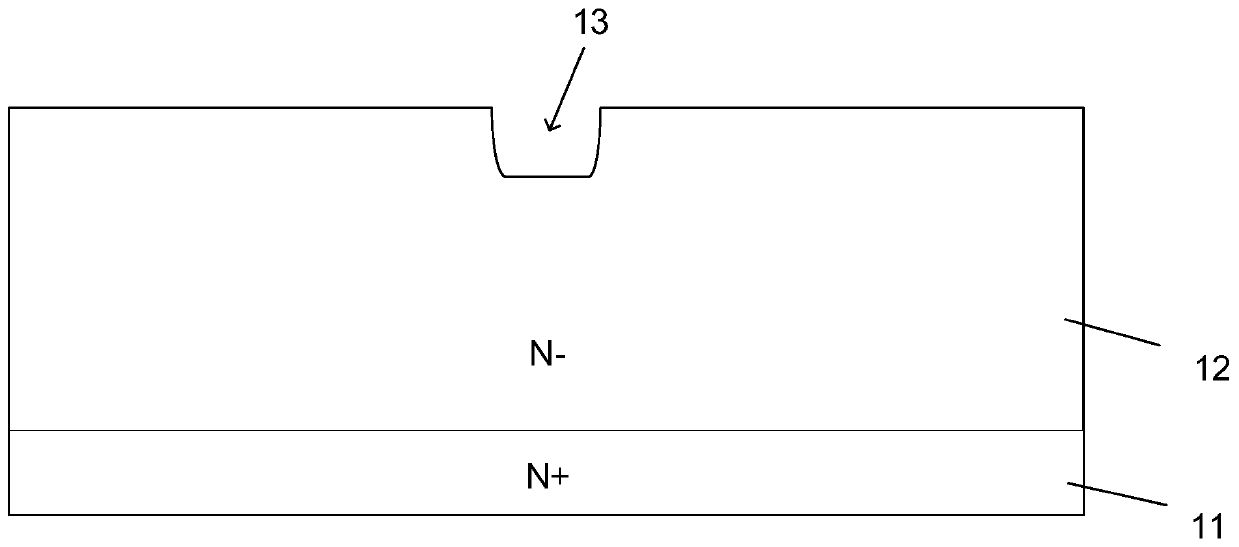

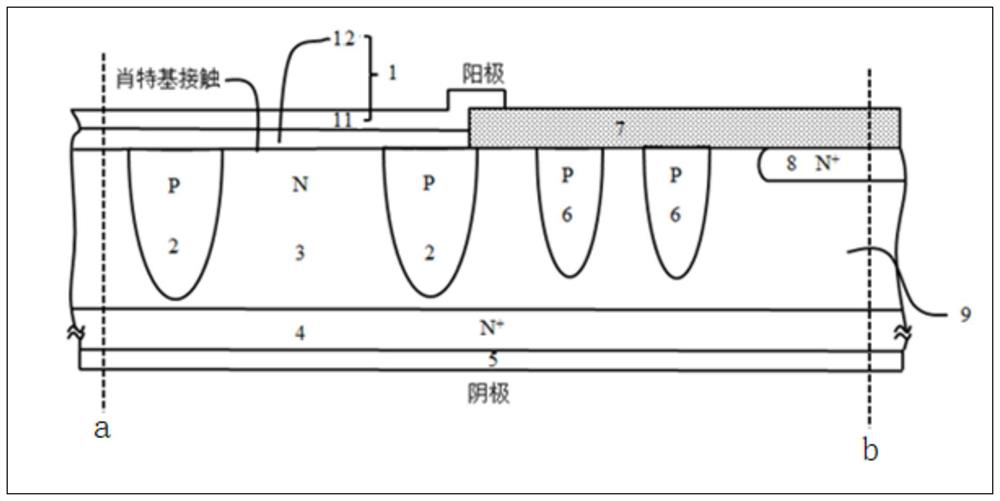

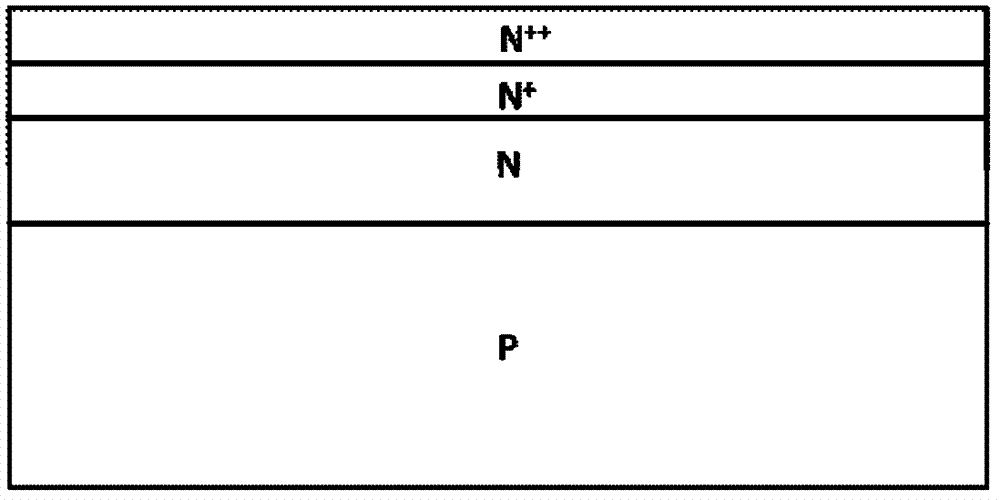

Silicon carbide MOSFET device and preparation method thereof

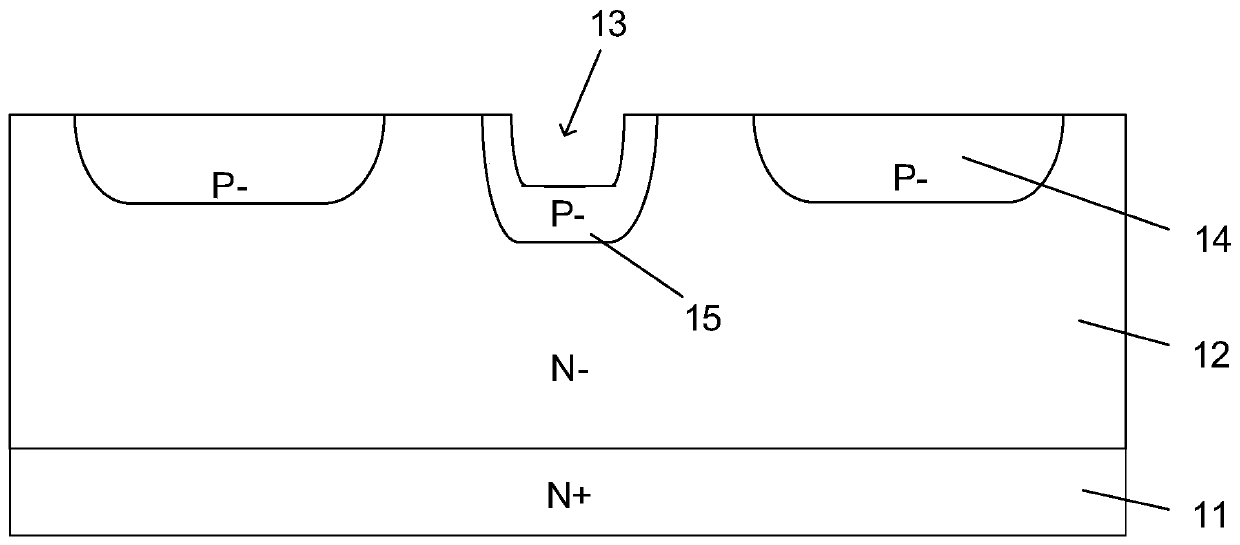

PendingCN109755322AImprove freewheeling abilityReduce manufacturing costSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETPower flow

The invention discloses a silicon carbide MOSFET device and a preparation method thereof. The silicon carbide MOSFET device comprises, form bottom to top, a leakage electrode, a N+substrate and N-epitaxial layer. The N-epitaxial layer is provided with first P-well areas, a first metal, second well areas and a second metal. The first P-well areas are provided with P+areas and N+areas; first ohmic contact is formed by the first metal, the upper surfaces of the P+areas and part of the upper surfaces of the N+areas; the second P-well areas are arranged between every two adjacent first P-well areas, the second P-well areas and the first P-well areas arranged on two side of the second P-well areas are all provided with first gaps, and grooves are encircled by the second P-well areas; and the second metal covers the surface of the groove to form second ohmic contact and the upper surface of the first gap to form Schottky contact. According to the silicon carbide MOSFET device, the flow-continuing ability is improved, and meanwhile the problem that the leakage current of the Schottky contact area in a high-pressure blockage mode is too large is solved.

Owner:厦门芯光润泽科技有限公司

Light dope ion injection method

InactiveCN101330048AIncrease junction depthEnhanced injection diffusionSemiconductor/solid-state device manufacturingOutput deviceIon implantation

The invention relates to a light doping ion injecting method which comprises the following steps of: providing a semiconductor substrate which comprises a core device area and an input and output device area; forming a grid on the semiconductor substrate; implementing the light doping ion injecting to the input and output device area; forming a side wall substrate at the side wall of the grid; and implementing the light doping ion injecting to the core device area. The method can reduce the occurrence of hot-carrier effect.

Owner:SEMICON MFG INT (SHANGHAI) CORP

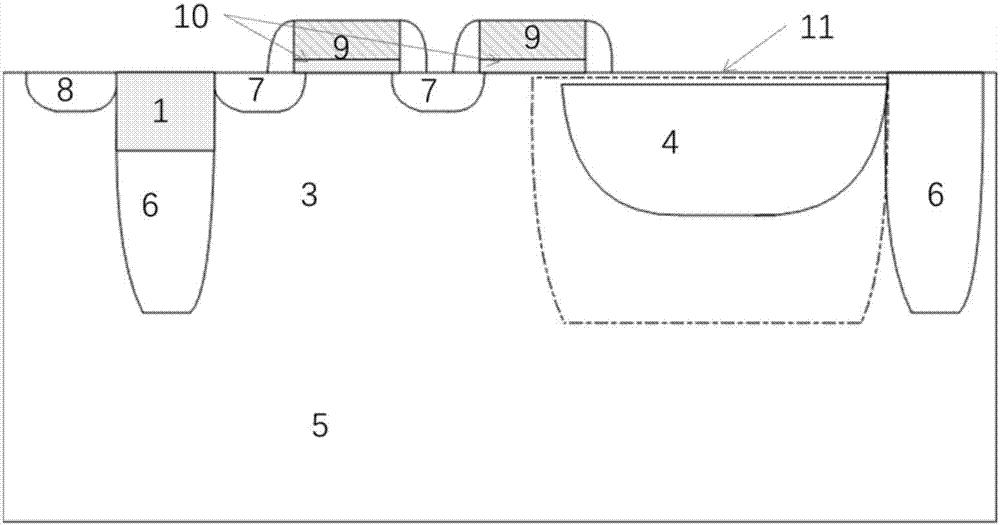

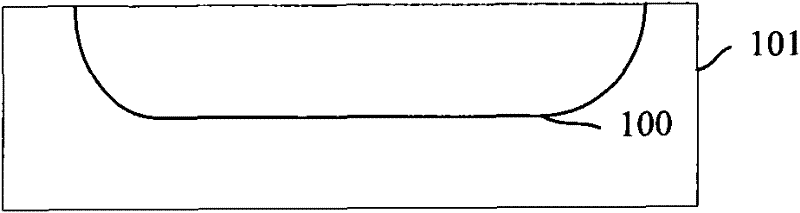

Photodiode structure for improving quantum efficiency of CMOS image sensor

ActiveCN107994096AThe upper half of the voltage does not changeIncrease junction depthSemiconductor devicesCMOSQuantum efficiency

The invention discloses a photodiode structure for improving the quantum efficiency of a CMOS image sensor. The photodiode structure is located in a lightly-doped substrate. The photodiode structure comprises a reset transistor, a transmission transistor, a PN photodiode, a pixel unit isolation region, a well region and an annular silicon region. The two ends of the transmission transistor are connected with the reset transistor and the PN photodiode respectively. A region formed by the reset transistor, the transmission transistor and the PN photodiode is surrounded by the annular pixel unitisolation region. The part of the pixel unit isolation region, adjacent to the reset transistor, is isolated from a shallow trench. The P-type region and the N-shaped region in the PN photodiode are distributed up and down in the vertical direction, and the lower part of the above space comprises a region I, a region II and a region III, wherein the three regions are different in doping concentration and are arranged from top to bottom. An annular silicon region is arranged below the well region and the pixel unit isolation region. According to the photodiode structure provided by the invention, the quantum efficiency of a long-wave section can be improved, and an inter-band tunneling electric leakage is avoided.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT +1

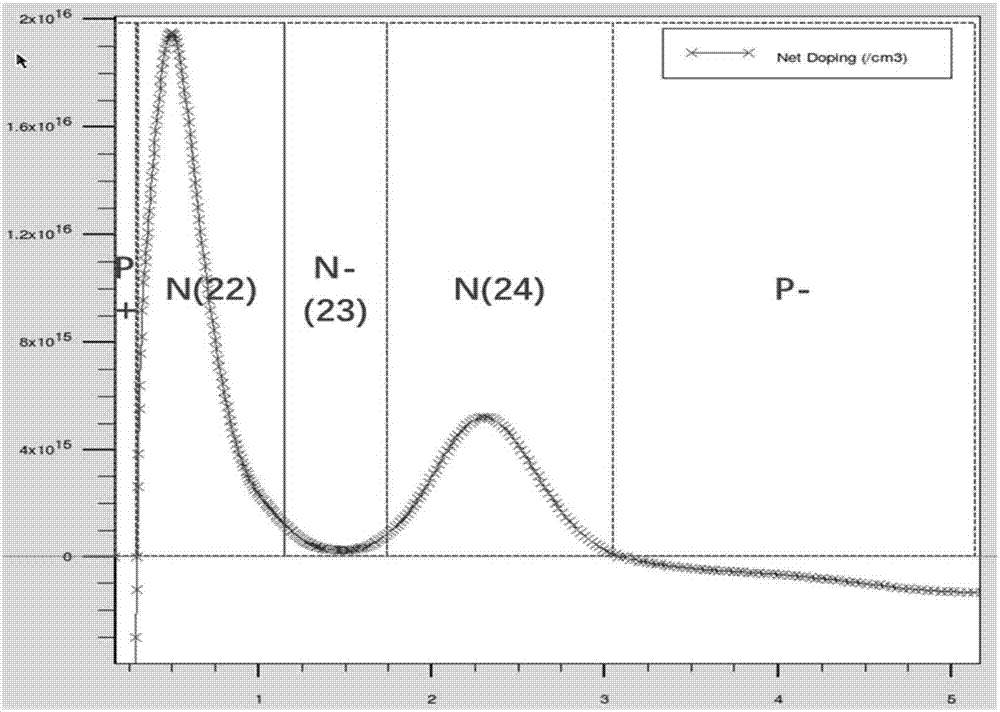

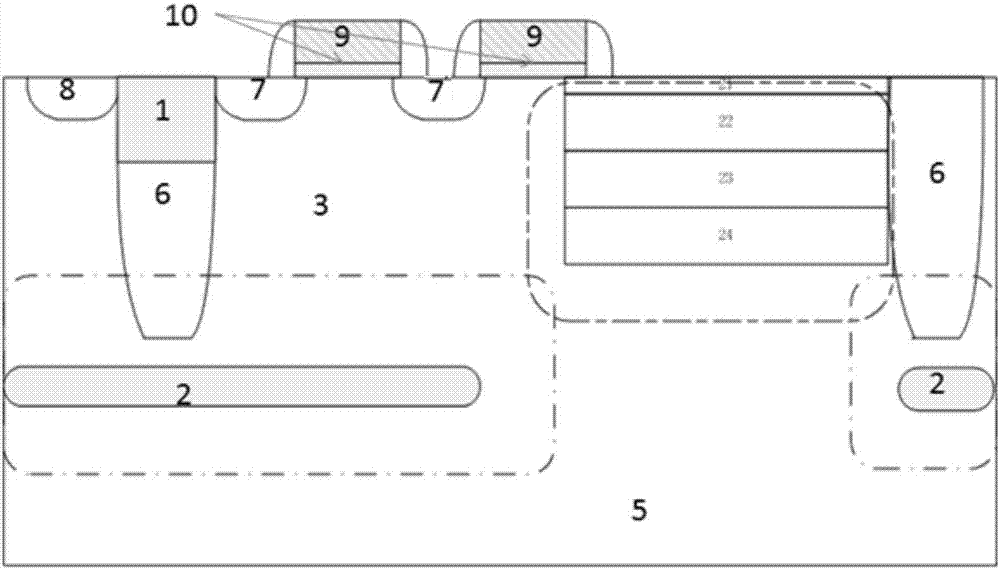

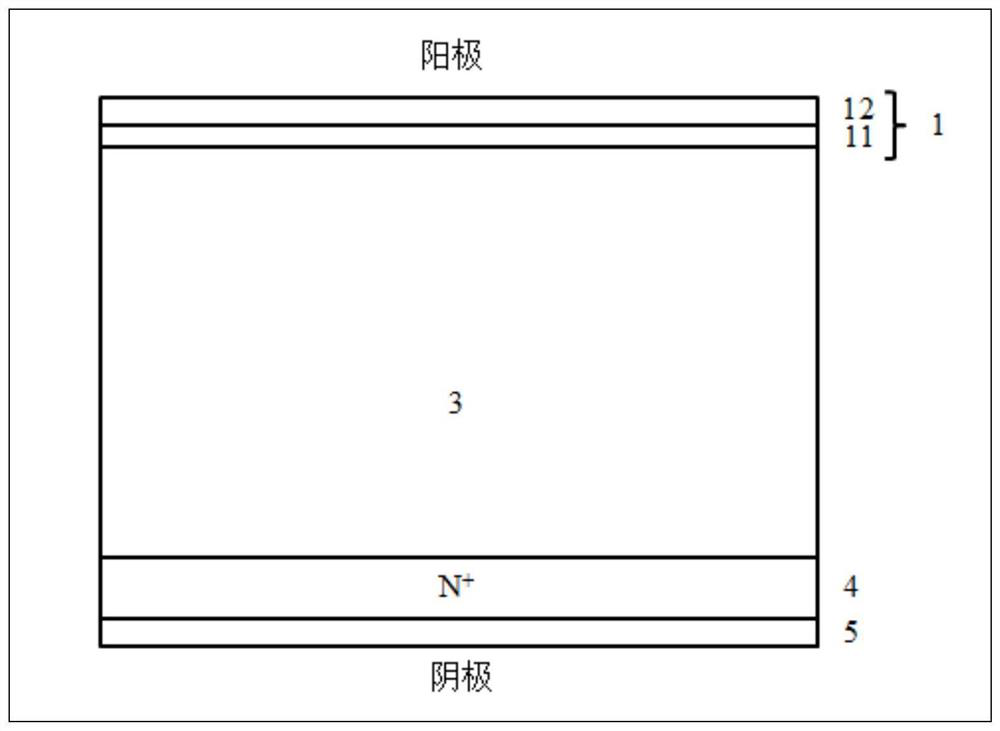

Low-power-consumption high-performance super-junction JBS diode and manufacturing method thereof

PendingCN112289848AGood reverse blocking propertiesReduce power consumptionSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceReverse recovery

The invention belongs to the field of power semiconductor devices, and particularly relates to a low-power-consumption high-performance super-junction JBS diode and a manufacturing method thereof. Thelow-power-consumption high-performance super-junction JBS diode is manufactured by using a traditional silicon-based process technology, so that the manufacturing cost is low; a P heavily doped cylindrical region and an N cylindrical drift region which have the characteristics of large area, high concentration and large junction depth are adopted, so that the forward conduction resistance is reduced; a super junction is formed, and good reverse blocking characteristics are achieved by optimizing electric field distribution; by optimizing parameters of the super junction, higher blocking withstand voltage can be realized, and the on-state and off-state power consumption of the device is reduced; and optimal two-dimensional electric field distribution is obtained by optimizing the doping concentration and width of the P column region and the N column region, unification of high blocking voltage and low on-resistance and unification of high blocking voltage and rapid switching are achieved, compromise between forward on-state voltage drop and reverse blocking characteristics and compromise between reverse recovery characteristics and reverse blocking voltage are optimized, and the limit of a traditional silicon material is broken through.

Owner:SHENYANG POLYTECHNIC UNIV

Processing technology for preparing battery sheet by cutting silicon wafer with diamond wire

ActiveCN111599892AQuality improvementReduce lossesFinal product manufacturePhotovoltaic energy generationElectrical batterySolar battery

The invention discloses a processing technology for preparing a battery sheet by cutting a silicon wafer through a diamond wire. The processing technology comprises the following steps of: selecting apolycrystalline silicon wafer obtained by diamond wire cutting as a substrate, sequentially putting the substrate into nitric acid and hydrofluoric acid for cleaning and polishing, and removing the damaged layer on the surface of the substrate; preparing a photoetching mask layer on the front surface of the substrate, texturing through a steam texturing method, and preparing a P-N junction on thefront surface of the substrate through a POCL3 liquid diffusion source thermal diffusion method; and finally performing wet etching, antireflection film plating, printing and sintering on the front surface of the substrate to obtain a finished product. The invention discloses a processing technology for preparing a battery sheet by cutting a silicon wafer through a diamond wire, wherein the method is reasonable in process design and simple and controllable in operation, selects the silicon wafer cut by the diamond wire as the substrate for processing, and prepares the battery sheet with excellent electrical performance, so that the open-circuit voltage, short-circuit current and fill factor of the solar cell are improved, the conversion efficiency is improved, the purposes of reducing thecost and improving the efficiency are achieved, and high practicality is achieved.

Owner:ECONESS ENERGY

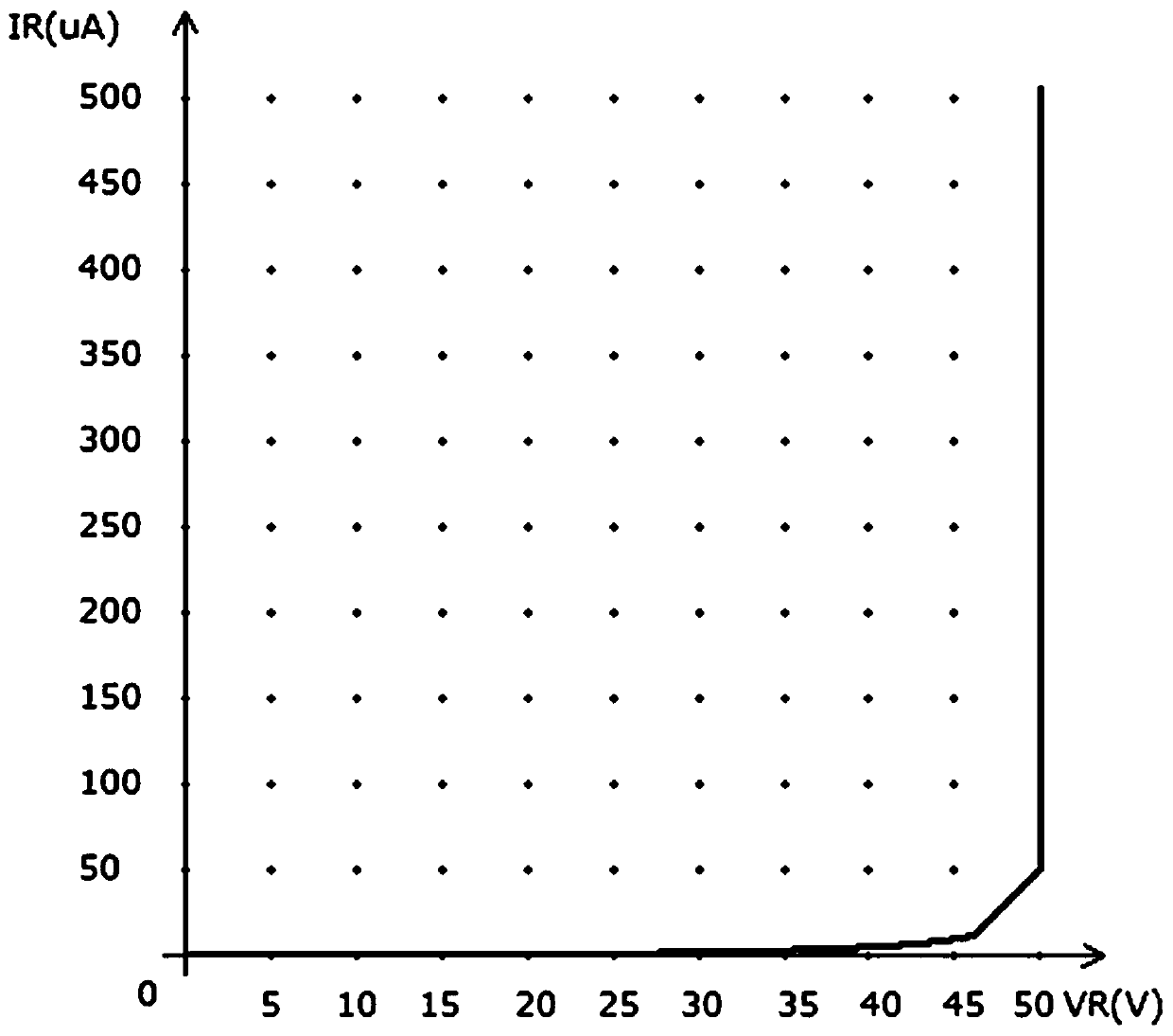

Fabrication process of 100V Schottky diode

InactiveCN104576362AIncreased Junction Depth and UniformityEpitaxial thickSemiconductor/solid-state device manufacturingSemiconductor devicesShallow junctionMaterials science

The invention provides a process for improving the static electricity of a 100V Schottky diode. 4.5E+15-6.5E+15 high dose ion implantation is adopted, so that the impurity concentration of a PN junction is increased, besides, a high annealing temperature is adopted, so that the junction depth and the homogeneity of devices are improved. The Schottky diode is a device with a surface shallow junction, the larger the doping concentration is, the deeper the junction depth is, and the pressure resistance of the device is stronger. The junction depth of the 100V Schottky diode, prepared by the process disclosed by the invention, is 1.8 mum to 2.2 mum, and the static electricity of the Schottky diode is 18KV. The extension thickness is thick, the poured doping concentration is high, the annealing temperature is high, the junction is deep, and the homogeneity is good. The static electricity is greatly improved, and the stability of static electricity batches is consistent. The static electricity is high, so that in a use process of the device, the probability of static shock is low.

Owner:TIANSHUI TIANGUANG SEMICON

Silicon-germanium heterojunction bipolar transistor

ActiveUS8395188B2Reduce collector resistanceImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesIon implantationJunction depth

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Phosphoric diffusion technology for metallurgical-grade polysilicon solar cells

ActiveCN101587918BReduce the effectImprove life expectancyFinal product manufactureSemiconductor devicesSolar cellImpurity

The invention relates to diffusion technology for manufacturing solar cells, in particular to phosphoric diffusion technology for metallurgical-grade polysilicon solar cells. The technology comprises the following steps: firstly, performing high temperature grain boundary gettering, wherein high temperature is used to make impurity atoms released at the prior settling position and simultaneously diffused and move to the position of a grain boundary defect to settle to form a clean area near the grain boundary; secondly, performing medium-low temperature phosphoric deposition, wherein diffusion deposition of fresh phosphorus is performed for a short time at a medium low diffusion temperature to finish surface low concentration phosphorus deposition to prepare for long time high temperaturedrive-in in a next step; thirdly, performing diffusion passivation of high temperature deep grain boundary, wherein high temperature long time phosphoric source drive-in is performed to form deep PNjunction at the position of the grain boundary so as to make phosphor generate phosphoric gettering and passivation of phosphoric drift field at the position of the grain boundary; and finally, performing the diffusion again for adjusting to a needed sheet resistance value. The technology greatly reduces the composite of minority carrier originally happening in the position of the grain boundary by utilizing the properties of the diffusion of impurities in the polycrystalline silicon; and after the process is finished, the minority carrier lifetime of a silicon chip is improved compared with that of a silicon clip produced by a normal process, which has an active effect on the final performance of the cells.

Owner:TRINA SOLAR CO LTD

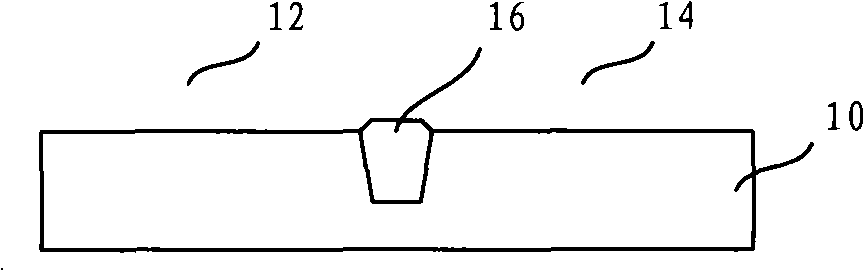

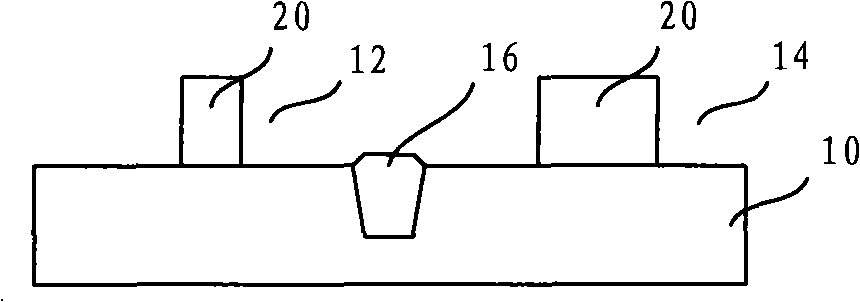

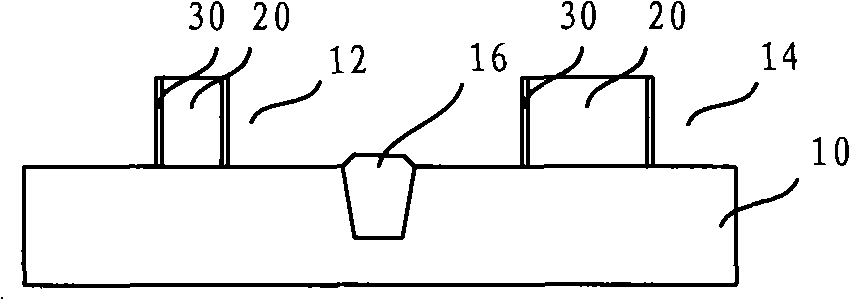

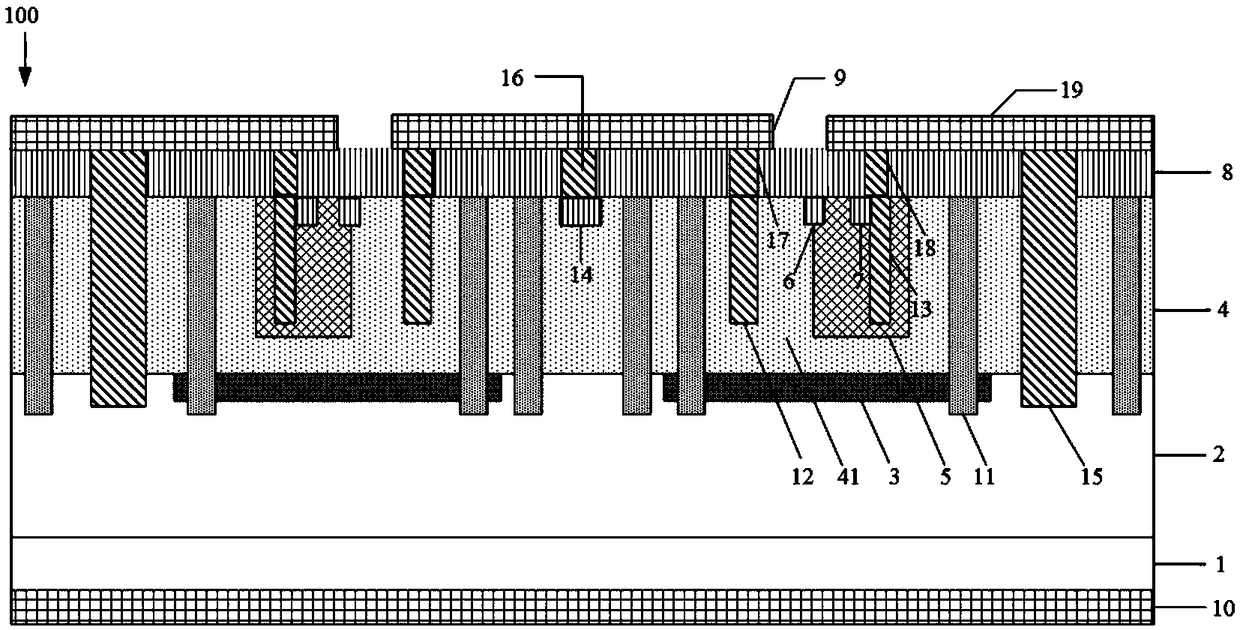

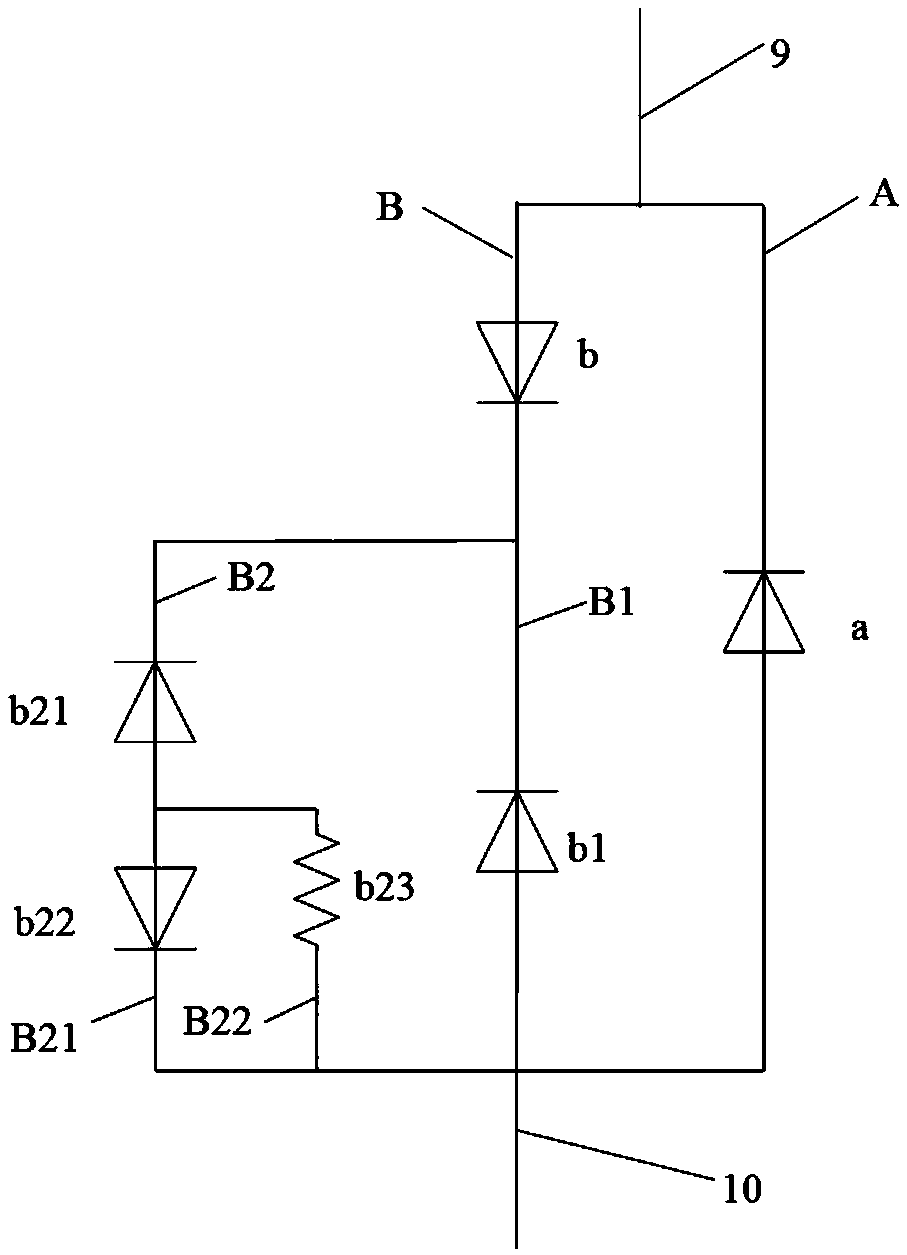

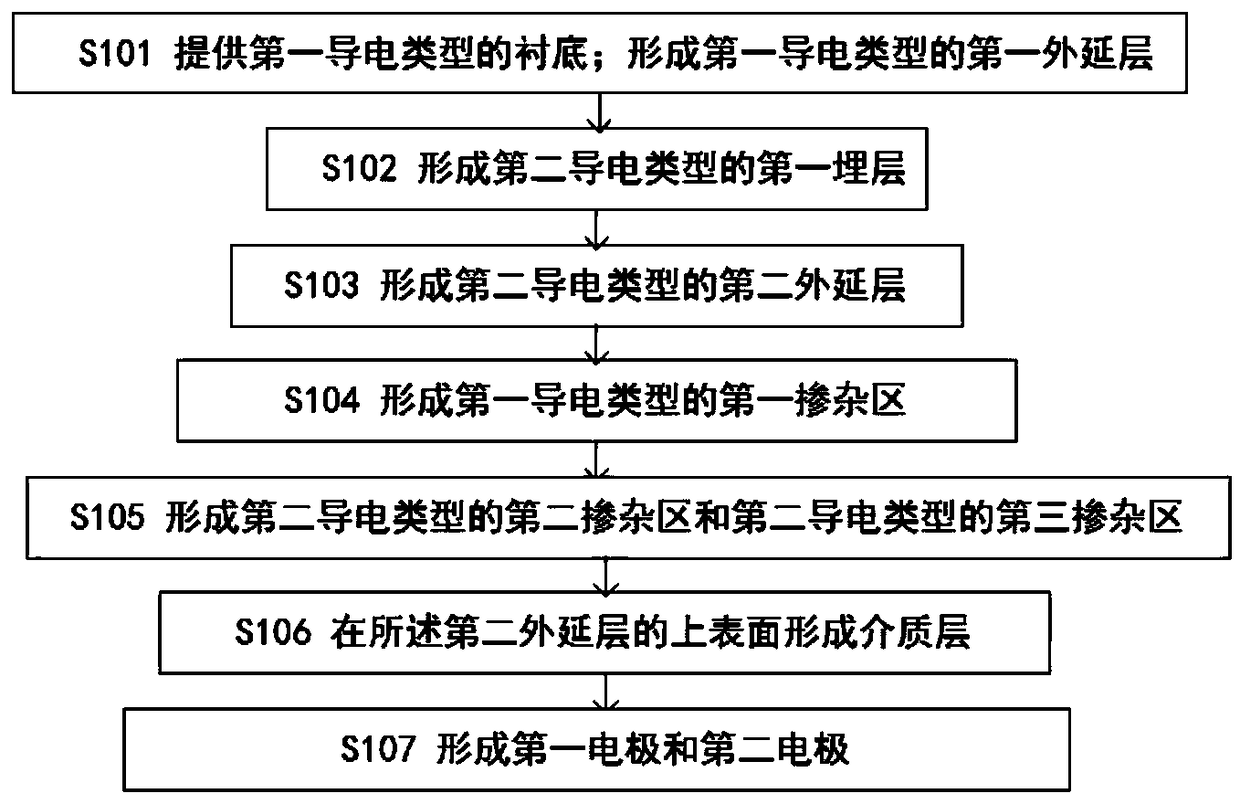

Transient voltage suppressor and manufacturing method thereof

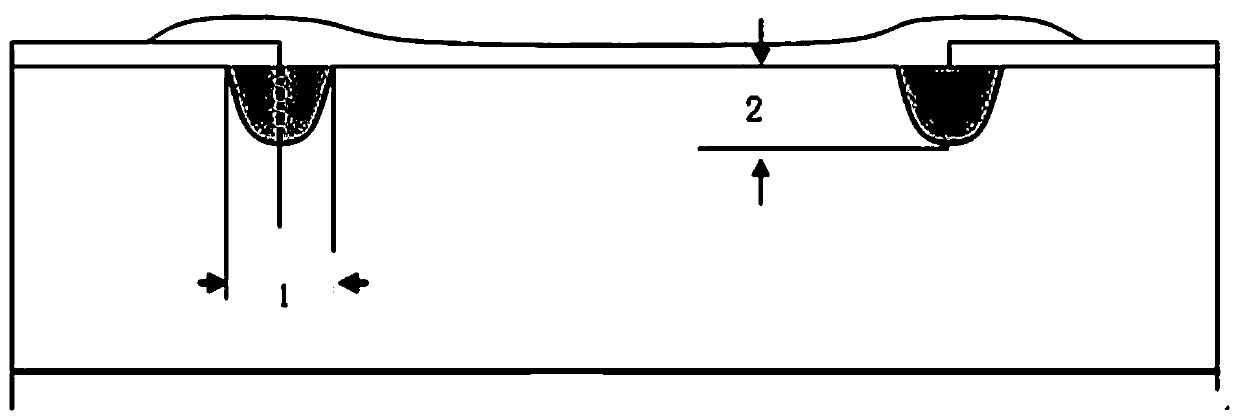

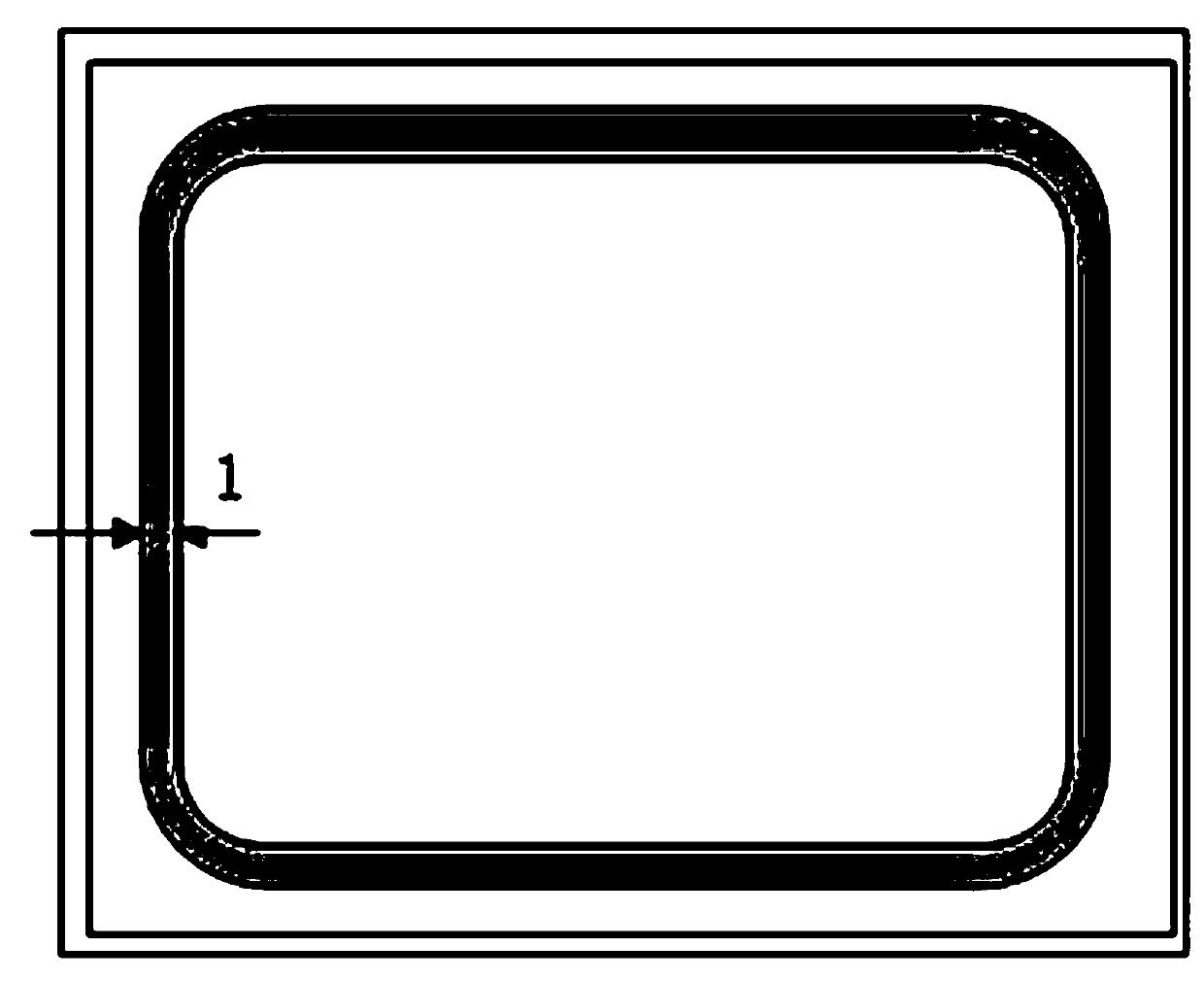

The invention provides a transient voltage suppressor and a manufacturing method thereof, the transient voltage suppressor comprising: a substrate of a first conductivity type; a first epitaxial layerof a first conductivity type grown on an upper surface of the substrate; a buried layer of a second conductivity type extending downward from an upper surface of the first epitaxial layer to the first epitaxial layer; a second epitaxial layer of a second conductivity type grown on an upper surface of the first epitaxial layer and the buried layer; extending downward from an upper surface of the second epitaxial layer to a first doped region of a first conductivity type within the second epitaxial layer; a second doped region of the second conductivity type and a third doped region of the second conductivity type; a dielectric layer located on an upper surface of the second epitaxial layer; a first electrode electrically connected to the second epitaxial layer; and a second electrode electrically connected to the lower surface of the substrate. The transient voltage suppressor has the characteristics of low capacitance, high integration level and simple manufacturing process.

Owner:车智路数据管理有限公司

Three-step variable-temperature diffusion process for silicon cell

ActiveCN102383198BIncrease concentrationIncrease junction depthFinal product manufactureSemiconductor devicesFurnace temperatureOxygen

The invention relates to a three-step variable-temperature diffusion process for a silicon cell, which is realized by the following procedures: placing a silicon chip after etching into a boat, then rising the temperature to be 700-810 DEG C, and introducing large nitrogen, small nitrogen and oxygen to conduct low-temperature pre-deposition diffusion; subsequently rising the temperature to be 810-830 DEG C, and introducing large nitrogen to conduct knot thrusting; and then introducing large nitrogen, small nitrogen and oxygen, and rising the furnace temperature to be 830-870 DEG C to conduct secondary deposition diffusion. A multi-level PN knot structure formed after diffusion can ensure good ohmic contact with a metal gate wire on the one hand, and can have good blue response on the other hand; in addition, a PN knot formed by the method has great knot depth, and the possibility that the PN knot is burnt through, subjected to leakage of electricity and composited can be reduced.

Owner:REALFORCE POWER

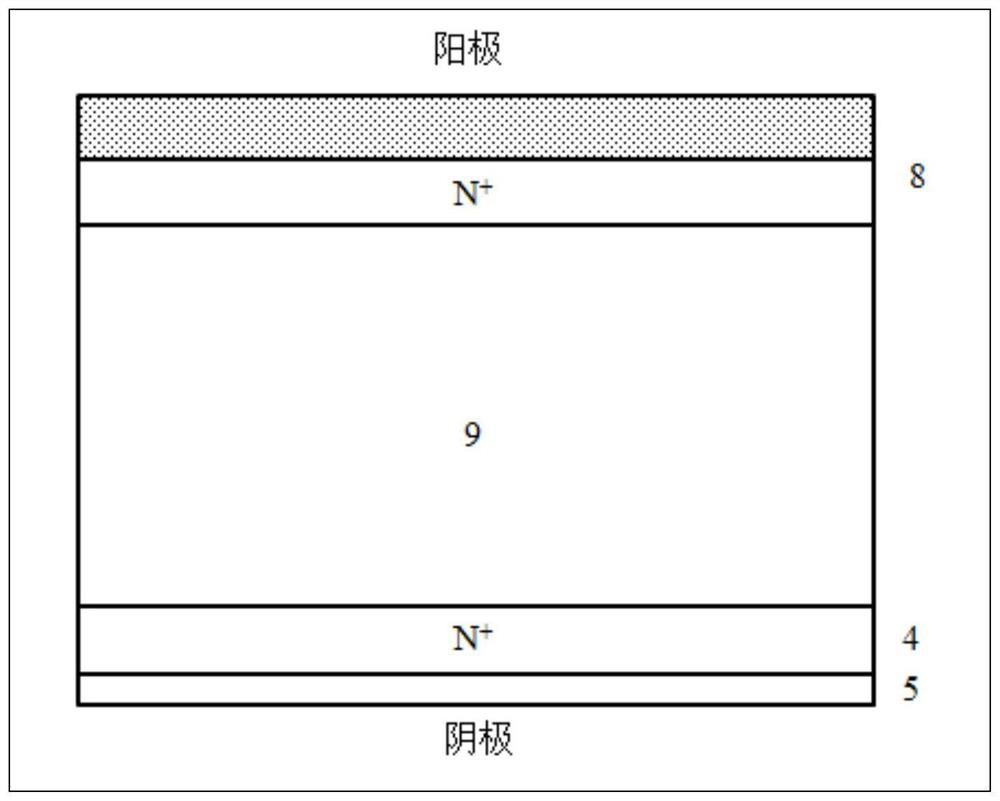

Method for preparing high-voltage SIDAC

ActiveCN101593693BNo damageImprove anti-ablation performanceSemiconductor/solid-state device manufacturingDIACAcid washing

The invention relates to a method for preparing a high-voltage diac. In the method, a raw material silicon chip is processed in sequence by the following steps: chemical polishing, boron diffusion, oxidation of a mask, double-sided primary photoetching, phosphorous diffusion, nickel plating and alloying, scribing, welding, acid washing, protection, and packaging to obtain a finished product of the high-voltage diac, wherein the chemical polishing step is that the raw material silicon chip is evenly corroded in corrosion solution at the normal temperature for 3 to 5 minutes, washed for multiple times and dried to obtain a silicon chip (1) with the matt surface, and the corrosion solution is formed by mixing hydrofluoric acid, glacial acetic acid and nitric acid according to the volume ratio of 1:1 to 3:25 to 30; and the acid washing step is that a corrosion layer (8) is formed on the periphery of the silicon chip (1) obtained by soaking by mixed acid liquor, corroding and welding so asto obtain the electric performance, and the mixed acid solution is formed by mixing the hydrofluoric acid, the nitric acid, acetic acid and sulfuric acid according to the volume ratio of 9: 9: 9 to 15:4. The method has the advantages of simplified working procedure, low cost, reliable performance and corrosion resistance.

Owner:常州银河电器有限公司

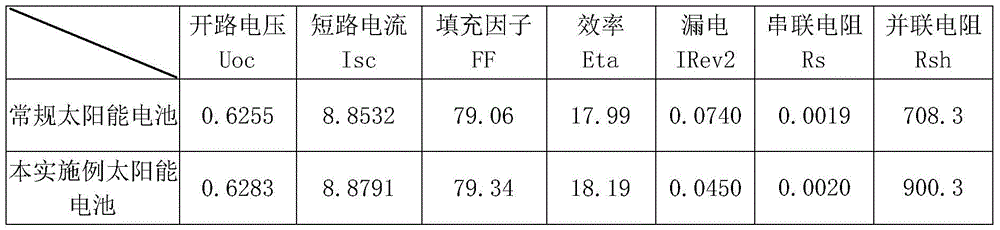

Solar cell diffusion deep junction preparation method

InactiveCN112164733AIncrease junction depthIncrease concentrationFinal product manufacturePhotovoltaic energy generationChemical physicsPhysical chemistry

The invention relates to the field of solar cell production. The invention discloses a method for preparing a solar cell diffusion deep junction. The method comprises the following steps of: 1, preparing a SiO2 layer; 2, preparing a constant impurity phosphorus source on the surface of the silicon wafer through twice deposition; 3, pushing phosphorus atoms into the silicon wafer to form a PN junction; 4, carrying out supplementary diffusion; 5, preparing a rear oxide layer; and 6, depositing an impurity phosphorus source on the surface of the silicon wafer again. The antireflection suede is prepared before the first step. The method has the beneficial effects that under the condition of not changing the overall sheet resistance and the process time, the PN junction depth and the junction region phosphorus concentration difference are effectively increased, and the Uoc and the FF of the battery piece are improved, so that the battery conversion efficiency is improved.

Owner:山西潞阳光伏科技有限公司

A Manufacturing Technology of 40v Schottky Diode with Reduced Secondary Breakdown Ratio

ActiveCN105336606BIncrease impurity concentrationIncreased Junction Depth and UniformitySemiconductor/solid-state device manufacturingSemiconductor devicesMicrometerVoltage

The invention provides a 40 V Schottky diode manufacturing process capable of reducing the secondary breakdown ratio. The Schottky diode manufacturing process includes the main step of setting epitaxy parameters of a silicon wafer, wherein the epitaxy thickness is 5.2-5.4 micrometers, the resistivity is 0.84-0.92 omega. cm, the initial oxidation parameter is 5000-7000 a, the implantation dose is 2E-3E+15, and the annealing temperature is 1070-1080 DEG C. According to the 40 V Schottky diode manufacturing process, the high ion implantation dose of 2E-3E+15 is adopted, so that the impurity concentration of PN junctions is increased; meanwhile, the high annealing temperature is adopted, so that the junction depth of a device is increased, and the uniformity of the device is improved; the larger the dosage concentration and the junction depth are, the stronger the voltage withstanding capability of the device will be. The Schottky diode is a surface shallow junction device, the secondary breakdown ratio is reduced to 5% or below, a Schottky breakdown curve is good, and the device has high reliability in the use process.

Owner:TIANSHUI TIANGUANG SEMICON

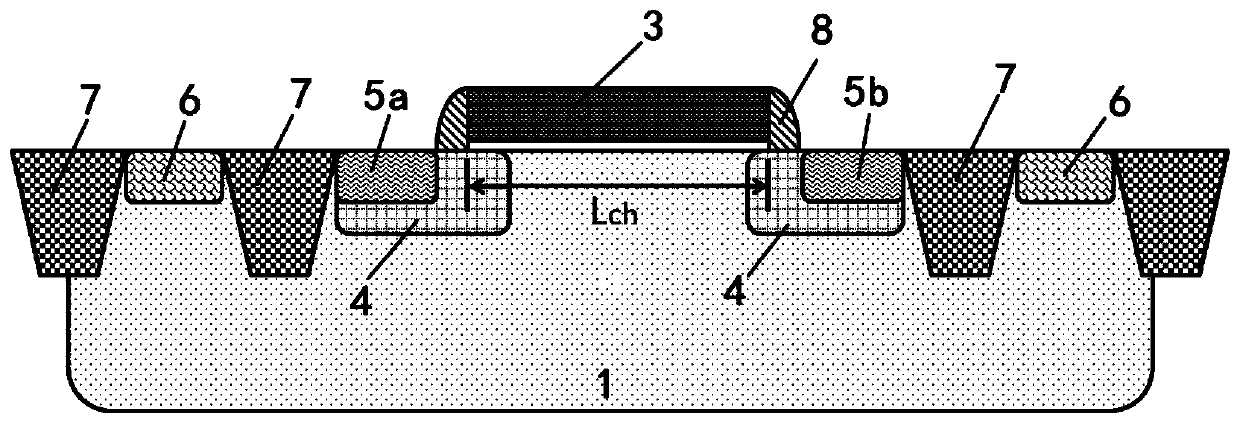

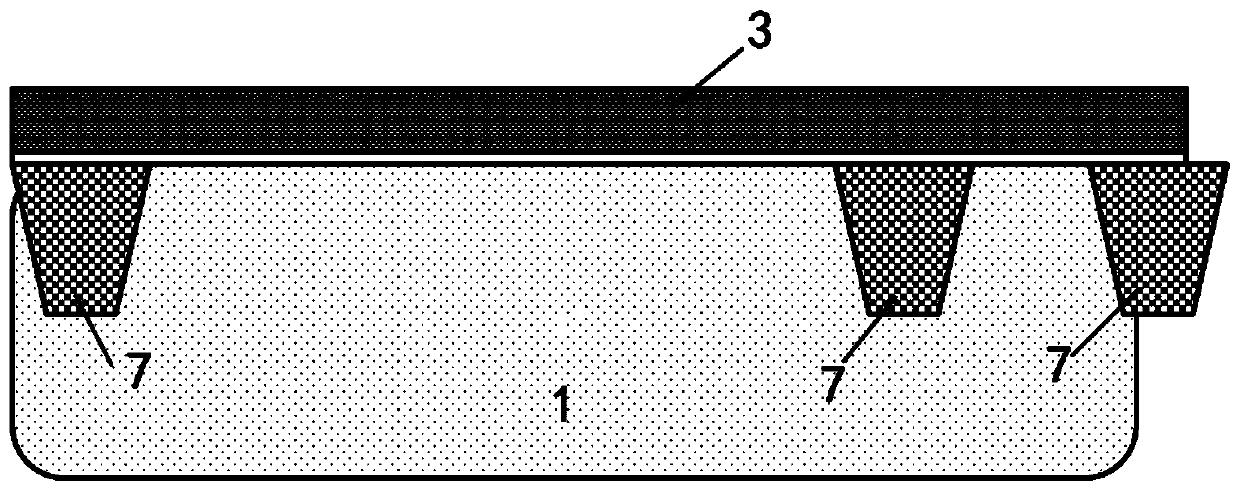

Method for improving junction depth property of semiconductor device

ActiveCN102054699BImprove performanceIncrease VT junction depthSemiconductor/solid-state device manufacturingPower semiconductor deviceDopant

The invention discloses a method for improving junction depth property of a semiconductor device. The method comprises the following steps of: after ion implantation of semiconductor dopants is performed on a substrate of the semiconductor device, forming a well on the substrate of the semiconductor device; forming an isolated shallow groove on the substrate of the semiconductor device, and then forming a grid on the substrate of the semiconductor device; re-oxidizing the surface of the grid and the surface of the substrate of the semiconductor device, and then lightly doping the grid and thesubstrate of the semiconductor device; forming a nitrogen oxide side wall of the grid, doping the grid and the substrate of the semiconductor device, forming a drain and a source by deposition on thesemiconductor device, and performing quick thermal annealing; and depositing metals on the surface of the grid and the semiconductor substrate by adopting a self-alignment silicide method to form metal silicon layers, then performing quick annealing treatment, and etching the un-reacted metals. By the method provided by the invention, the junction depth of the semiconductor device becomes light, and the device performance of the manufactured semiconductor device is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

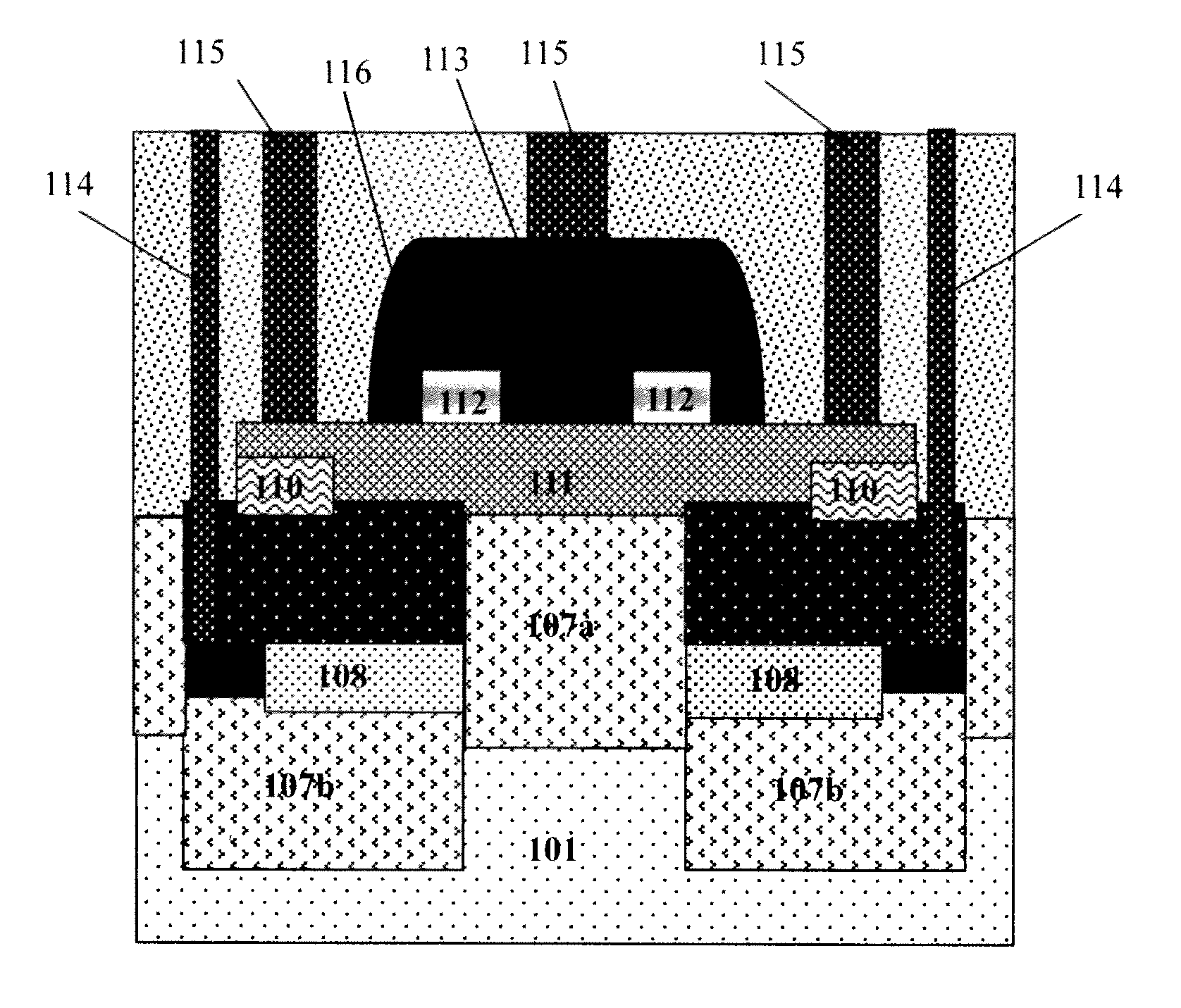

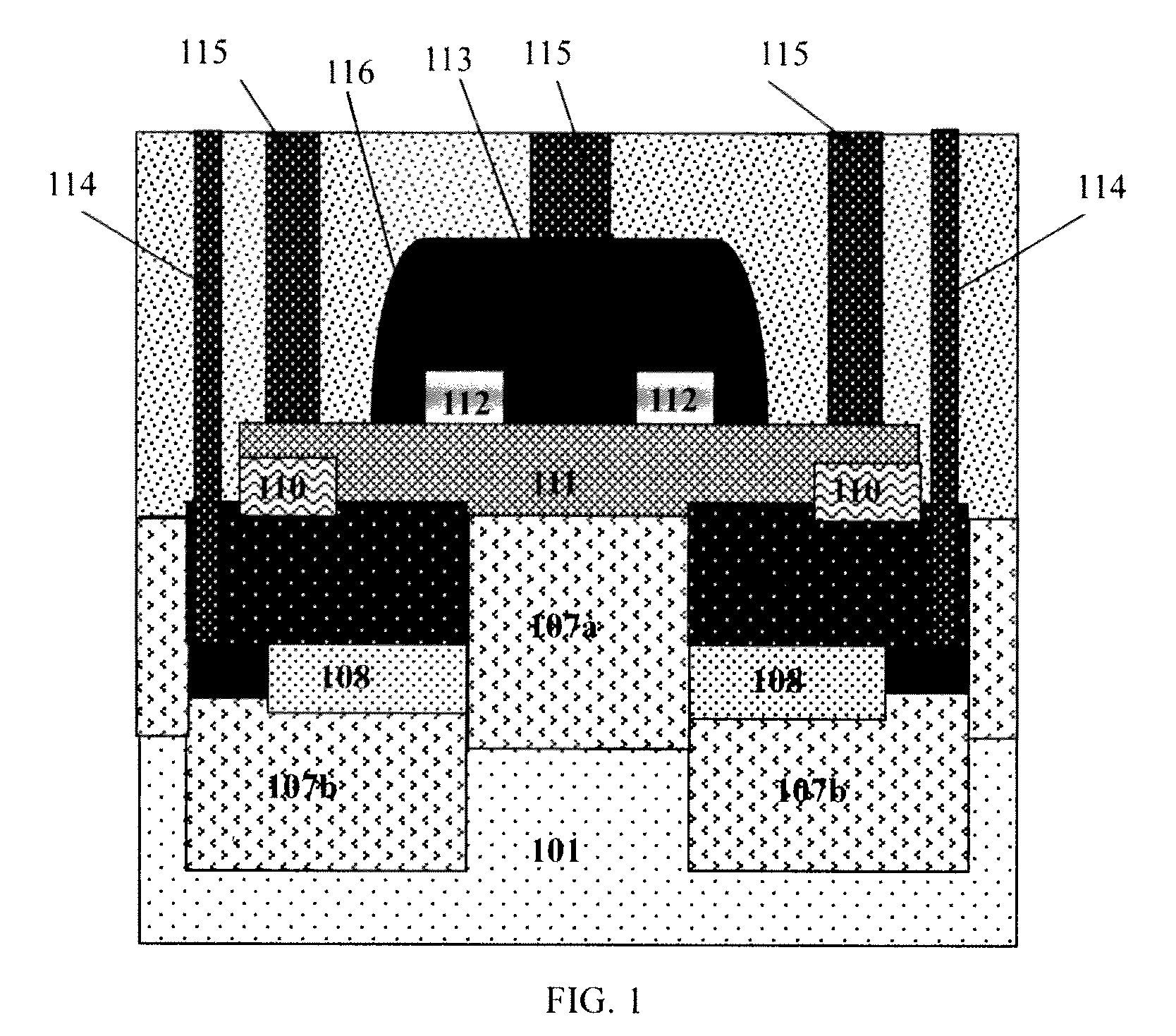

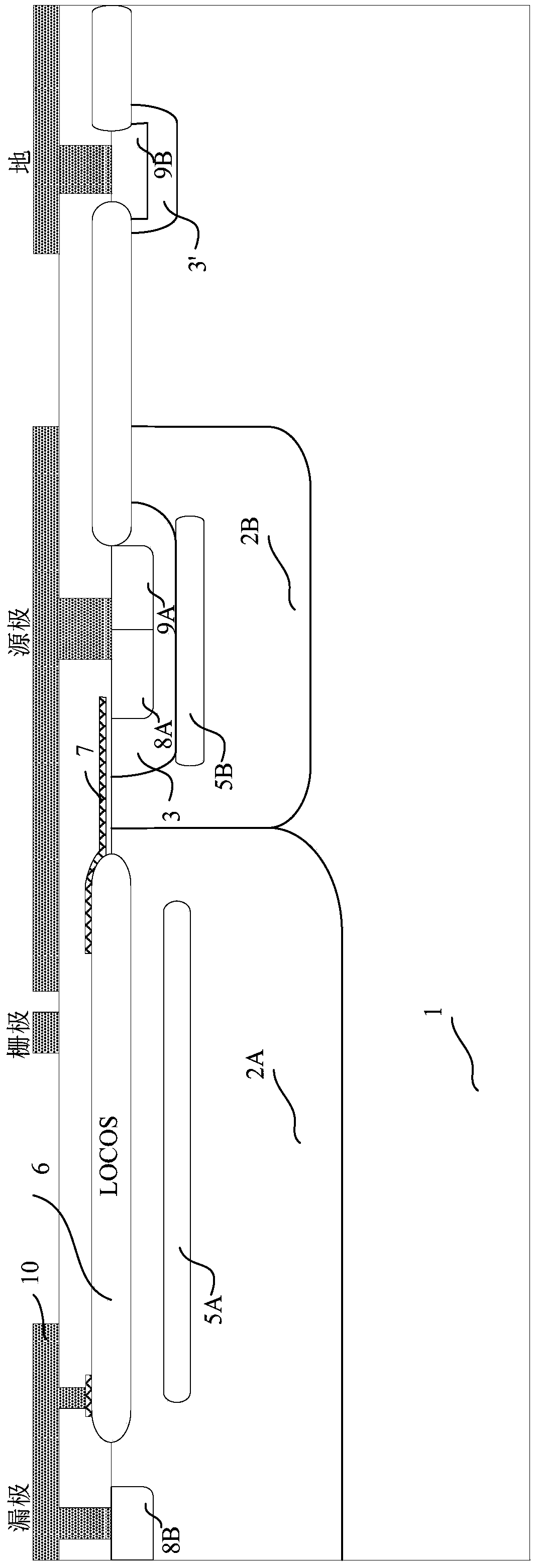

Switch LDMOS device and manufacturing method thereof

PendingCN111370491AIncrease breakdown voltage BVSmall sizeTransistorSemiconductor/solid-state device manufacturingLDMOSEngineering

The invention discloses a switching LDMOS device. According to the invention, an LDD region of the switching LDMOS device and a first bulk-doped region of a second conduction type are arranged in a first trap in a semiconductor substrate; a first heavily-doped region serving as a source region is arranged in the LDD region, and a second heavily-doped region serving as a drain region is arranged inthe first bulk-doped region; in a gate structure, a channel of the switching LDMOS device is formed on the surface layer of the part, located between the LDD region and the bulk-doped region, of thesemiconductor substrate, and when a voltage applied to a gate exceeds the threshold voltage of the LDMOS device, the channel is inverted, so the source region and the drain region are conducted; and one side, far away from the gate structure, of each of the LDD region and the bulk-doped region is provided with field oxygen or STI, and one side of the field oxygen or STI is connected with the firstheavily-doped region in the LDD or the second heavily-doped region in the first bulk-doped region. With the bulk-doped region having higher ion implantation energy and ion implantation dosage, the purposes of improving the breakdown voltage (BV) of the device and reducing the size of the device are achieved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

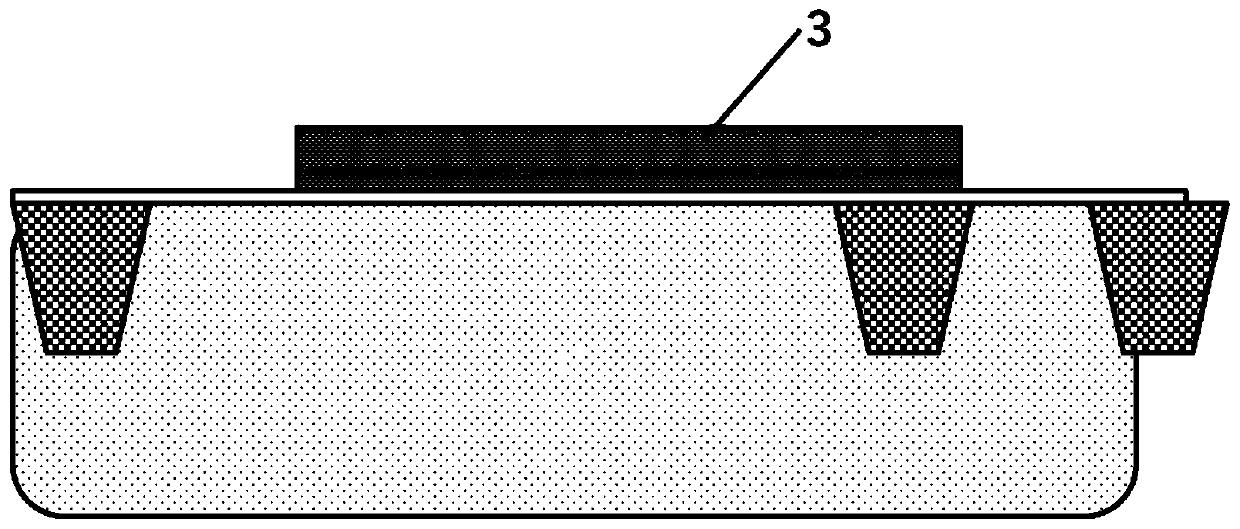

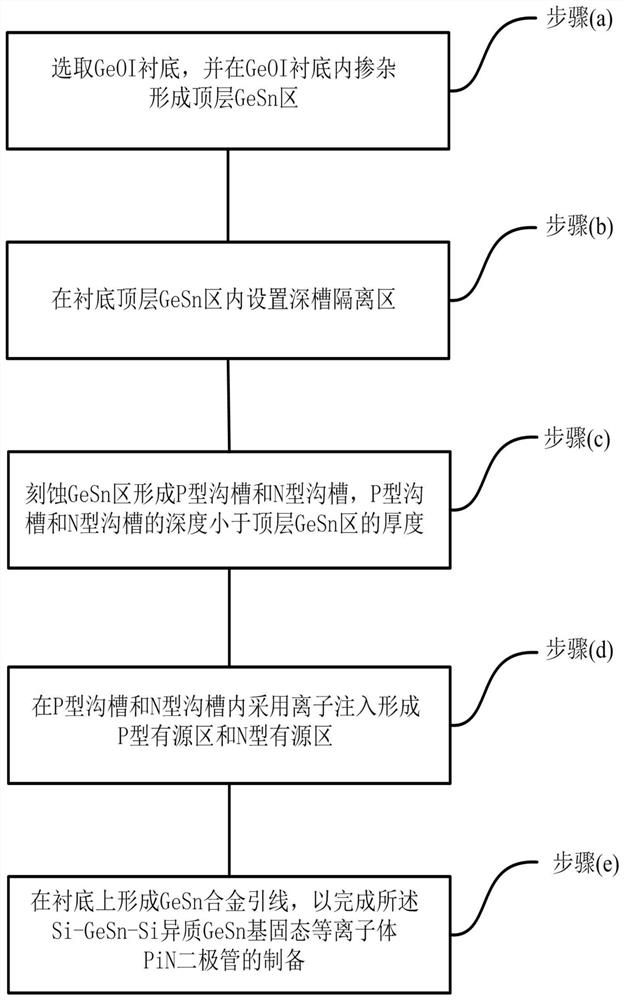

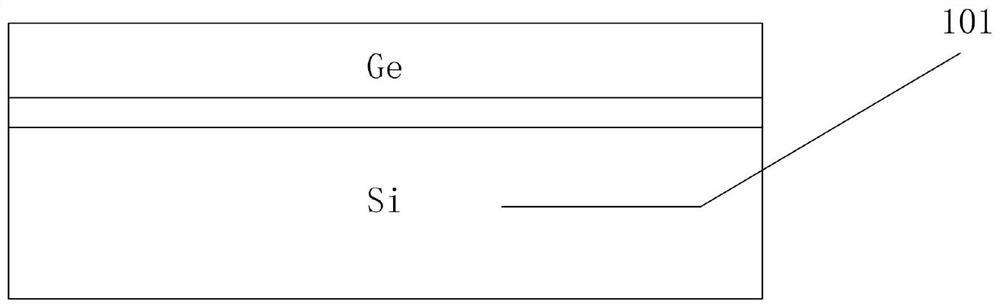

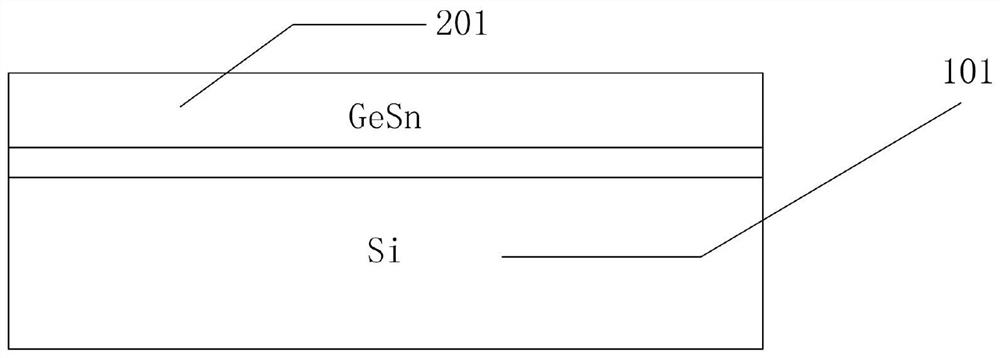

Si-GeSn-Si heterogeneous GeSn-based solid-state plasma PiN diode and preparation method thereof

PendingCN112993043AImprove injection ratioIncrease concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionMetallic electrode

The invention discloses a Si-GeSn-Si heterogeneous GeSn-based solid-state plasma PiN diode and a preparation method thereof, and the preparation method comprises the steps: selecting a GeOI substrate, and carrying out the doping in the GeOI substrate, so as to form a top layer GeSn region; arranging a deep groove isolating region in the GeSn region on the top layer of the substrate; etching the GeSn region to form a P-type groove and an N-type groove, wherein the depths of the P-type groove and the N-type groove are smaller than the thickness of the top-layer GeSn region; forming a P-type active region and an N-type active region in the P-type groove and the N-type groove by adopting ion implantation; and forming a GeSn alloy lead on the substrate. According to the invention, the top GeSn region is introduced to dynamically control the content of the Sn component in the top Ge, so that the forbidden band width of the intrinsic region is reduced. Due to the existence of the Si-GeSn-Si heterostructure, the forbidden band width difference can reach 0.7 eV, the carrier injection ratio is improved, and the solid-state plasma concentration and distribution uniformity are improved. The GeSn alloy lead is formed by adopting the RPCVD technology, a metal electrode in a traditional diode is replaced, and the integration level and the stealth performance of an antenna system are greatly improved.

Owner:ENG UNIV OF THE CHINESE PEOPLES ARMED POLICE FORCE

A processing technology for preparing solar cells by cutting silicon wafers with diamond wire

ActiveCN111599892BQuality improvementReduce lossesFinal product manufacturePhotovoltaic energy generationEngineeringPhotolithography

The invention discloses a processing technology for preparing battery slices by cutting silicon wafers with diamond wires. The polycrystalline silicon slices obtained by diamond wire cutting are selected as substrates, and the substrates are sequentially put into nitric acid and hydrofluoric acid for cleaning and polishing, and the substrates are removed. Surface damage layer; then prepare a photolithographic mask layer on the front surface of the substrate, and then make texturing by steam texturing, and then pass POCL on the front surface of the substrate 3 The P-N junction is prepared by the thermal diffusion method of the liquid diffusion source, and finally wet-etched on the front surface of the substrate, coated with an anti-reflection film, printed and sintered to obtain a finished product; the invention discloses a method for preparing a cell by diamond wire cutting silicon The processing technology is reasonable, the process design is reasonable, the operation is simple and controllable, and the silicon wafer cut by diamond wire is used as the substrate for processing, and the solar cell with excellent electrical performance is prepared, thereby improving the open circuit voltage, short circuit current and fill factor of the solar cell, and improving Conversion efficiency, to achieve the purpose of cost reduction and efficiency improvement, has high practicability.

Owner:ECONESS ENERGY

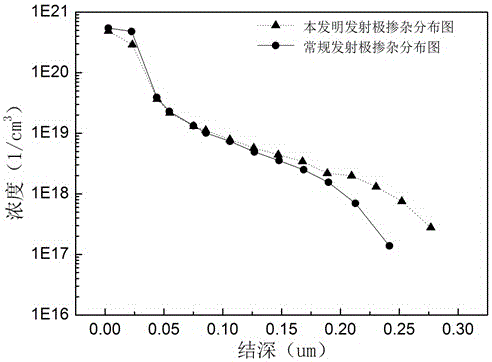

Method for doping distribution of solar cell emitter

ActiveCN104716232BLow surface doping concentrationImprove shortwave responseFinal product manufacturePhotovoltaic energy generationDistribution methodCrystalline silicon

The invention discloses a solar cell emitter doping distribution method. The solar cell emitter doping distribution method includes the steps of pre-oxidation, two times of source communication diffusion and two times of junction pushing for cooling and boat discharging. solar cell emitter doping distribution is realized through multiple times of source communication and multiple times of junction pushing, the time, temperature and source communication amount of multiple times of diffusion and the time and temperature of multiple times of junction pushing are adjusted, a solar cell emitter is made to have a lower surface doping concentration, and therefore the influences of a 'dead layer' are obviously weakened, and the short wave response of a solar cell is improved. The process of multiple times of source communication and multiple times of junction pushing further improves the doping concentration in a silicon wafer body, the silicon wafer surface doping concentration and the doping concentration inside the silicon wafer body are uniform, diffusion uniformity is good, and therefore the diffusion sheet resistance uniformity is improved. The process of multiple times of junction pushing improves the junction depth and increases blue light response of the solar cell, and finally the purpose of improving the conversion efficiency of the crystalline silicon solar cell is realized.

Owner:CECEP SOLAR ENERGY TECH (ZHENJIANG) CO LTD

Compound High Voltage Semiconductor Devices

ActiveCN105185834BImprove reliabilityImprove protectionSemiconductor devicesOhmic contactHigh pressure

The invention provides a composite high voltage semiconductor device; a layout comprises a straight edge portion arranged in a straight line; the straight edge portion comprises enhanced devices including the following: a semiconductor substrate; a first high voltage trap and a second high voltage trap arranged in parallel in the semiconductor substrate; a first field oxide layer arranged in the first high voltage trap; a first drain electrode ohmic contact zone arranged in the first high voltage trap of a first side of the first field oxide layer; a first source electrode ohmic contact zone arranged in the second high voltage trap; a first grid electrode at least covering the semiconductor substrate between the first source electrode ohmic contact zone and a second side of the first field oxide layer, wherein the first side of the first field oxide layer is far away from the second high voltage trap, and the second side of the first field oxide layer is close to the second high voltage trap. The doped concentration of the second high voltage trap is smaller than that of the first high voltage trap. The reliability of the device can be improved.

Owner:HANGZHOU SILAN MICROELECTRONICS