Patents

Literature

1444results about How to "Reduced operating requirements" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

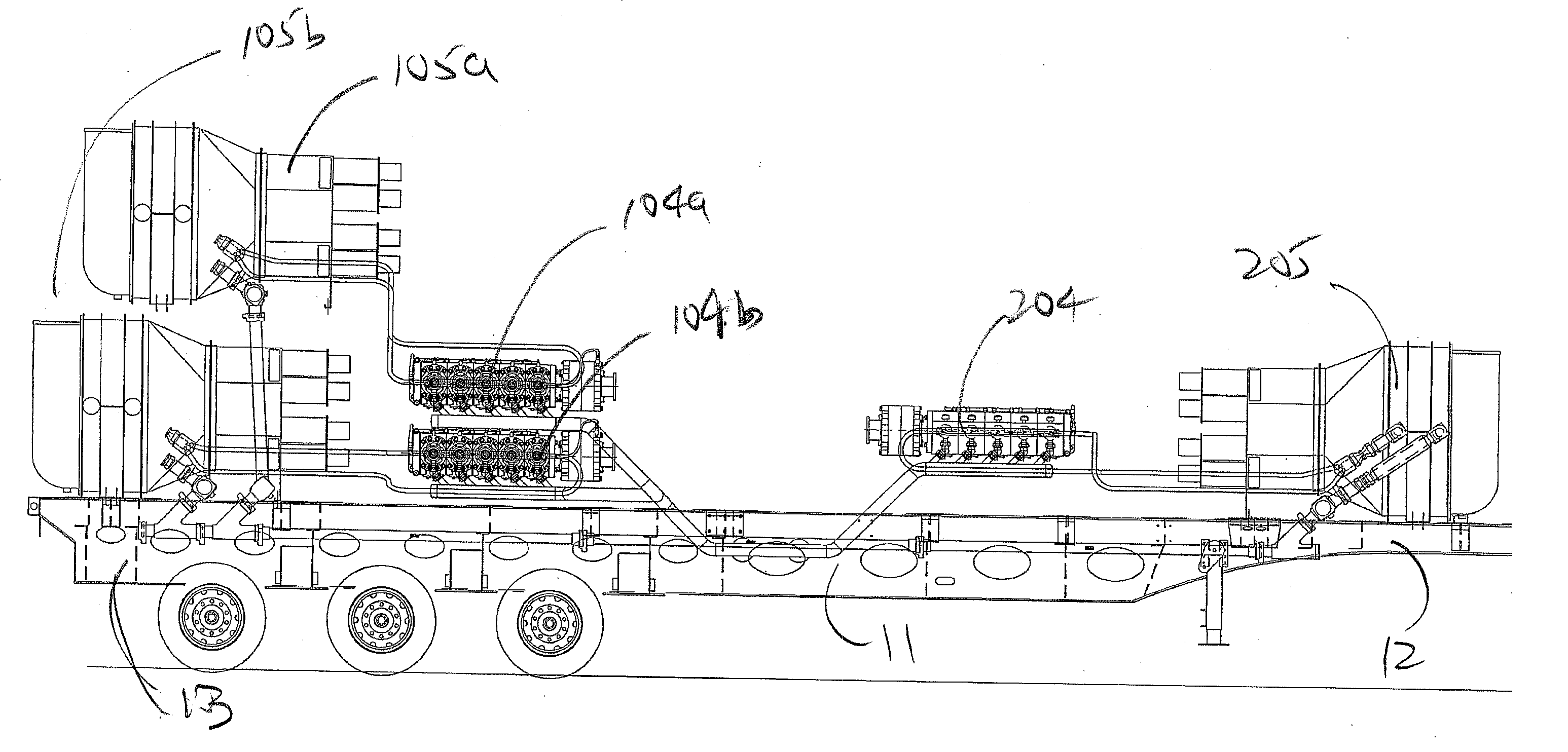

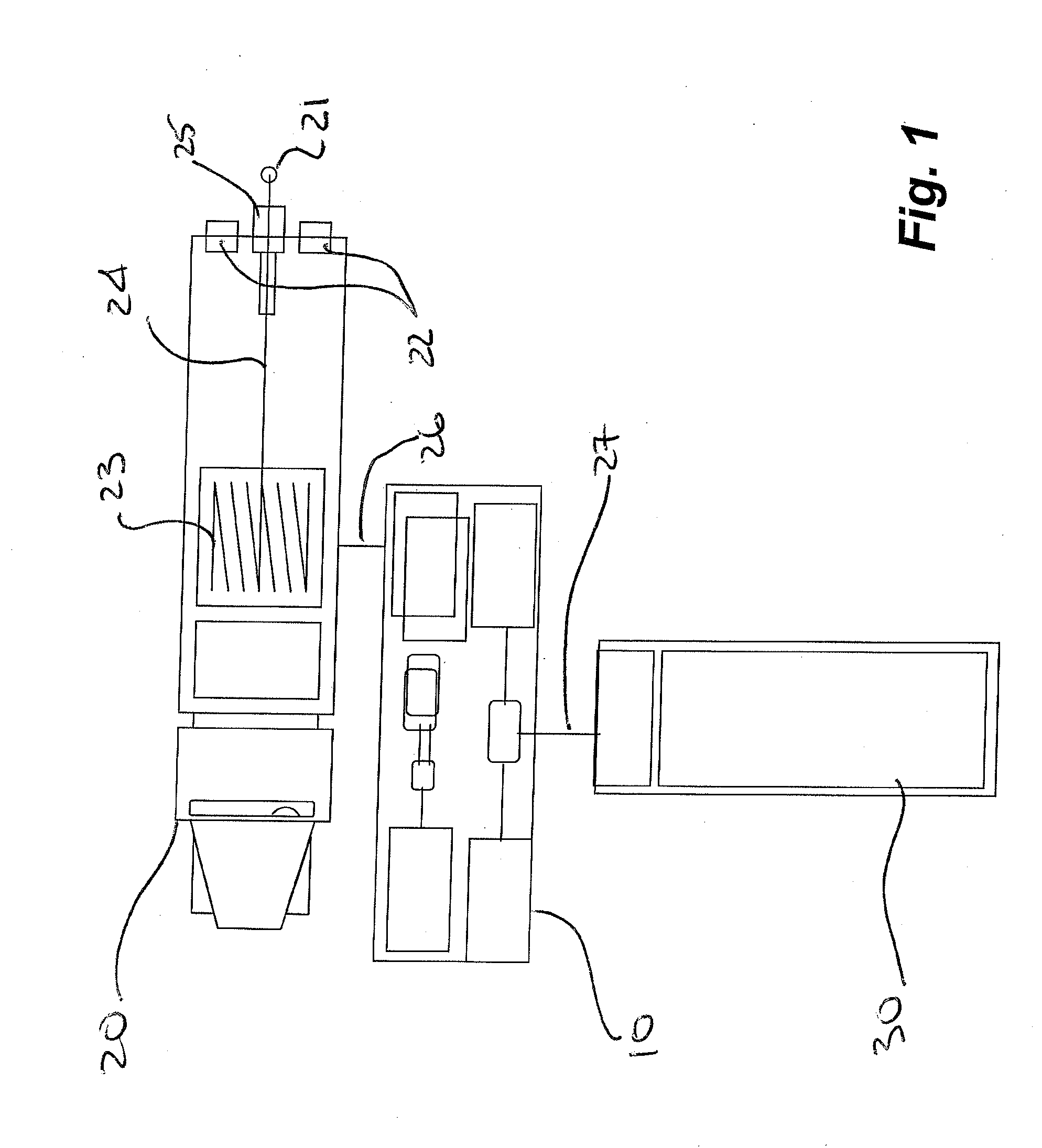

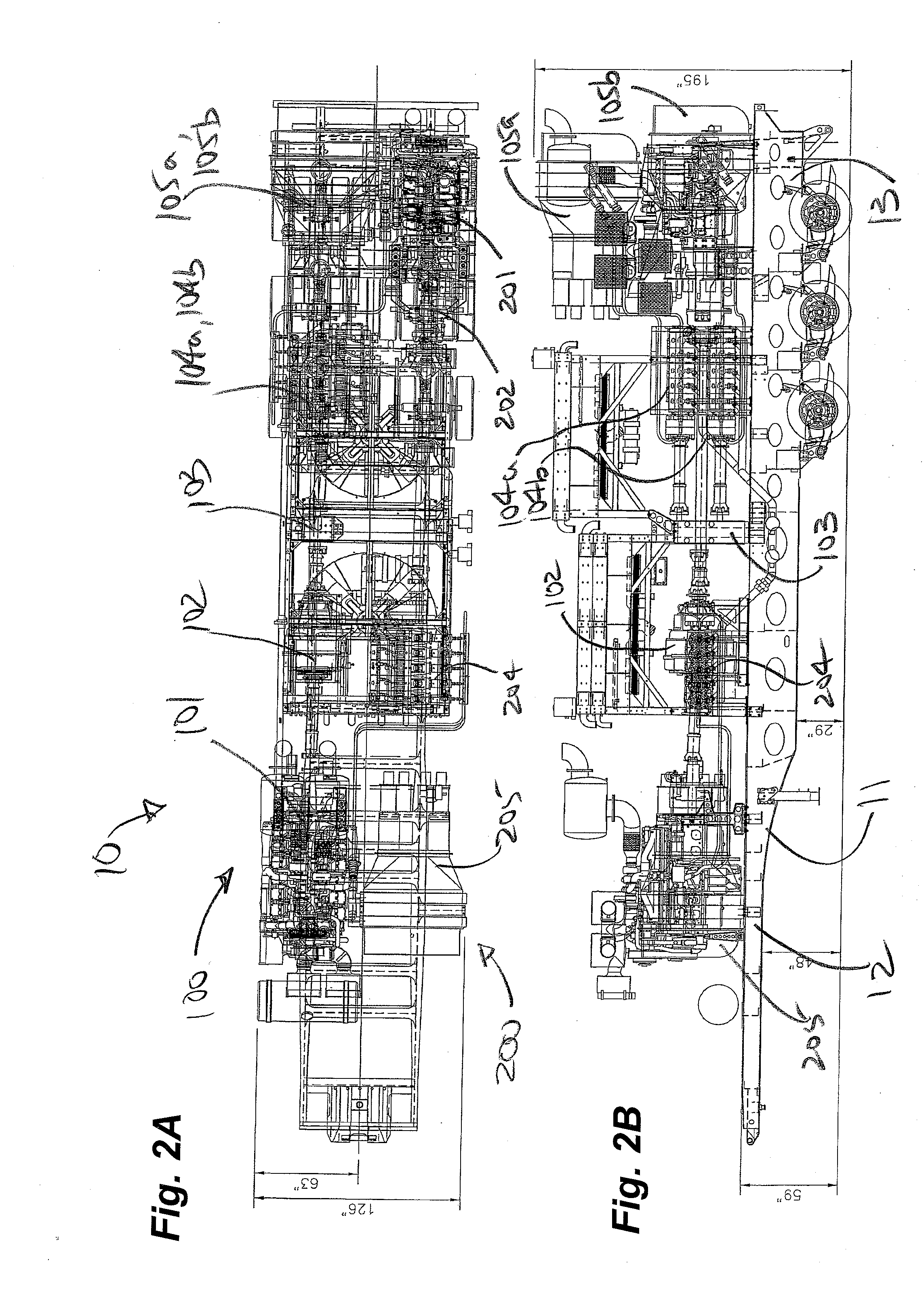

Transportable pumping unit and method of fracturing formations

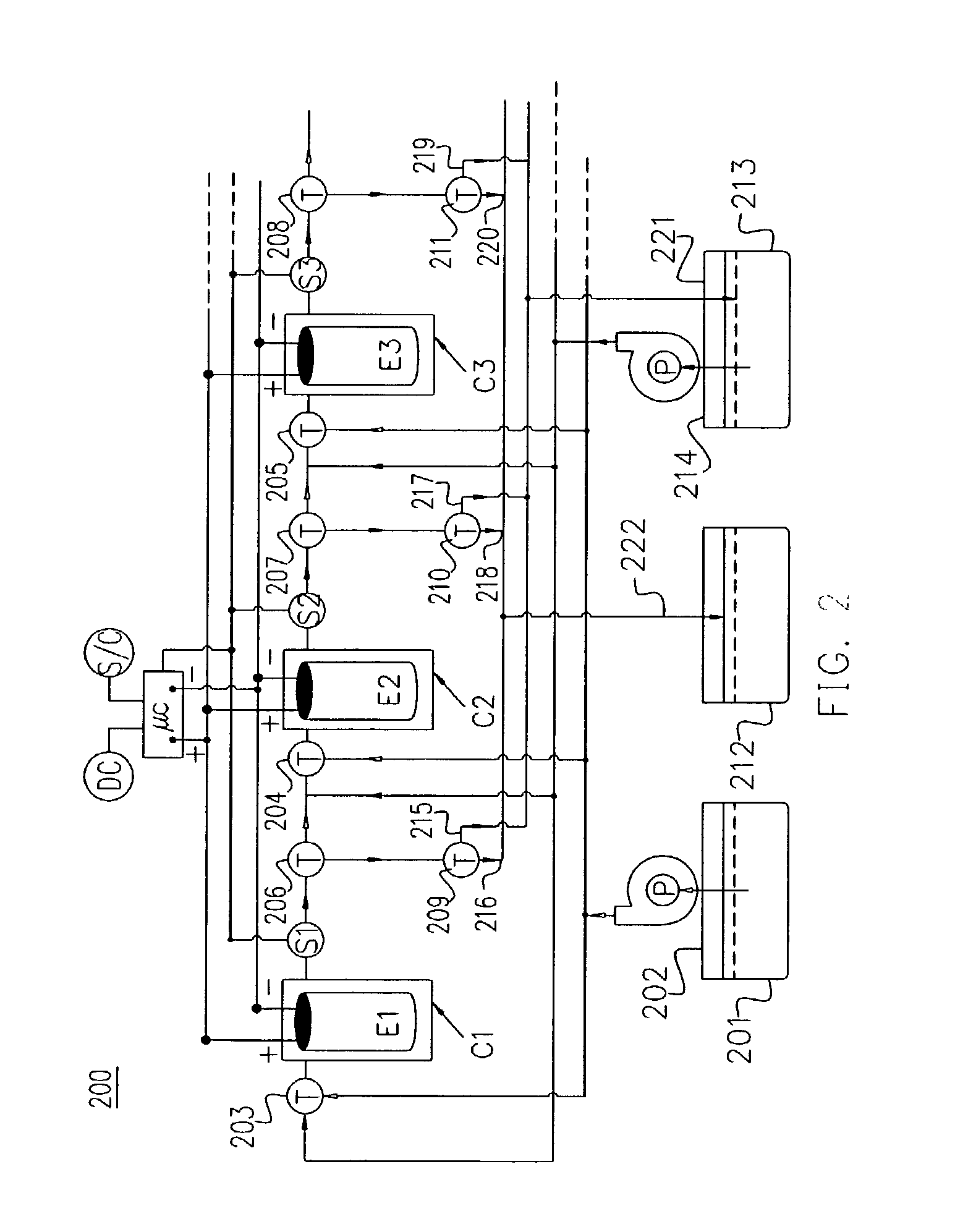

InactiveUS20060260331A1Increase chanceReduced operating requirementsNon-pressured vesselsPumpsCombustorControl system

A high capacity pumper for liquefied gas incorporates multiple pumping systems distributed in a parallel arrangement and in opposing orientation on a transportable platform such as a trailer. Vaporizers incorporate a burner control system utilizing a primary set of burners operating a baseline and a secondary set of burners providing fine regulating control. A system for fracturing formations is now possible using a minimum number of components including the high capacity pumper, a coiled tubing rig and a source of liquefied gas. An improved manifold for a cryogenic plunger pump includes unions and angled connectors between a supply conduit and each of a plurality of pump heads.

Owner:CENTURY OILFIELD SERVICES

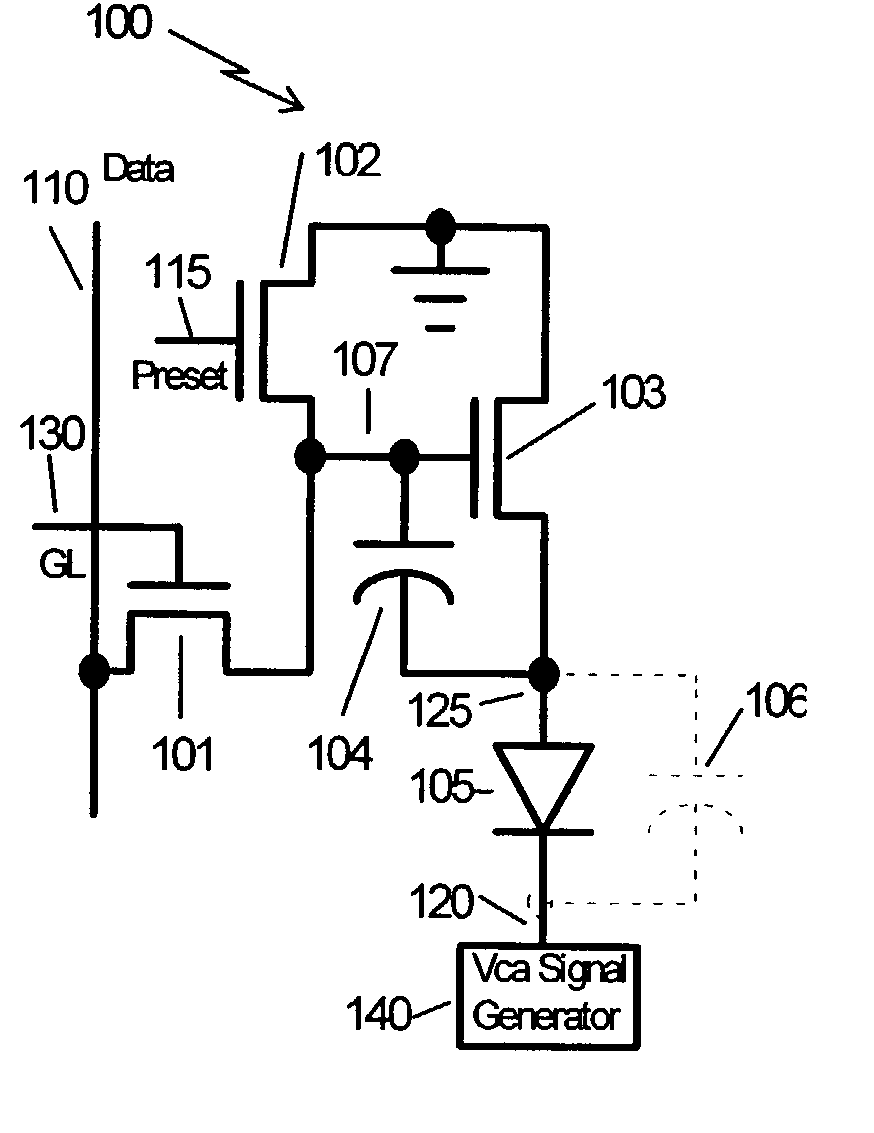

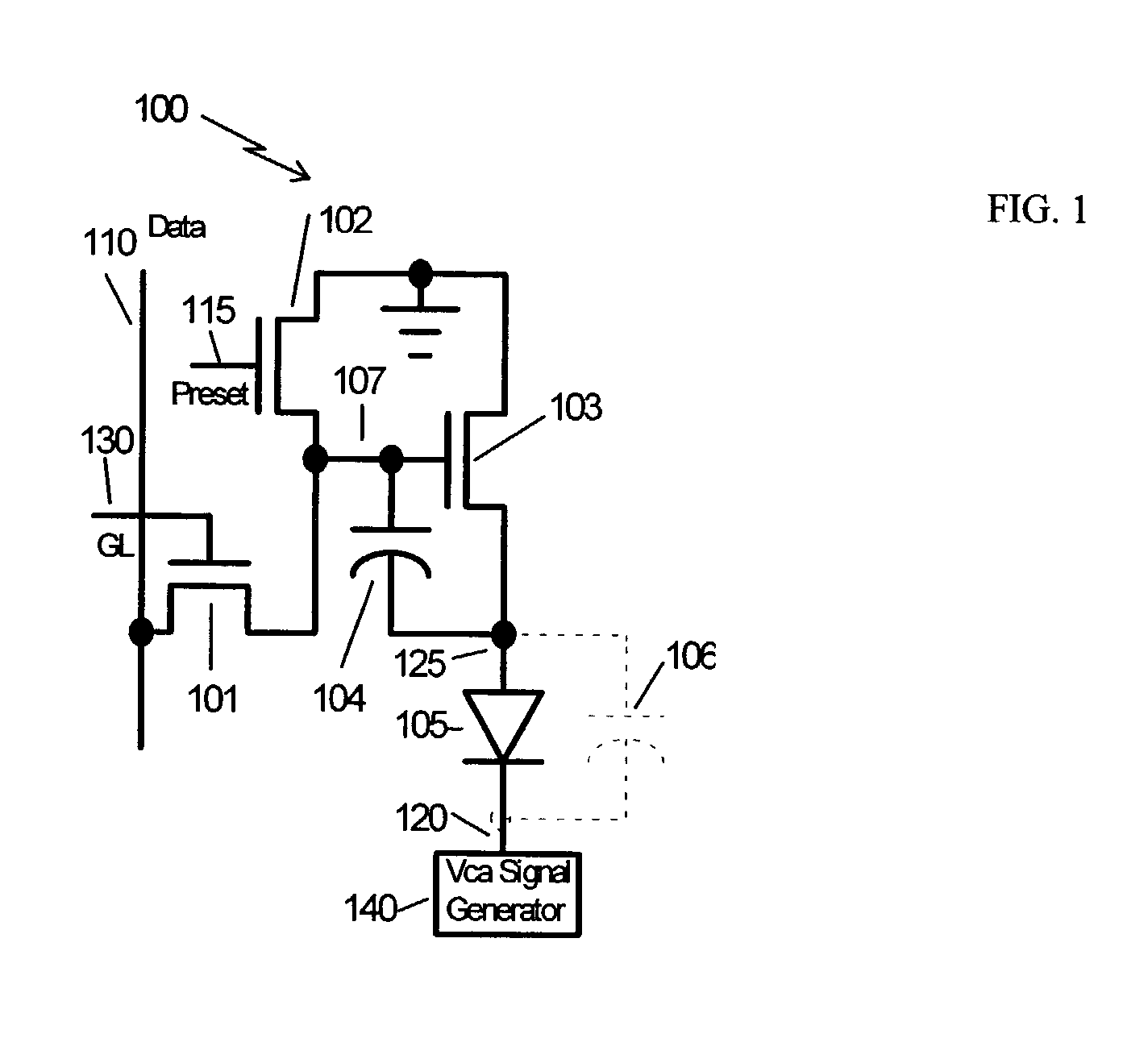

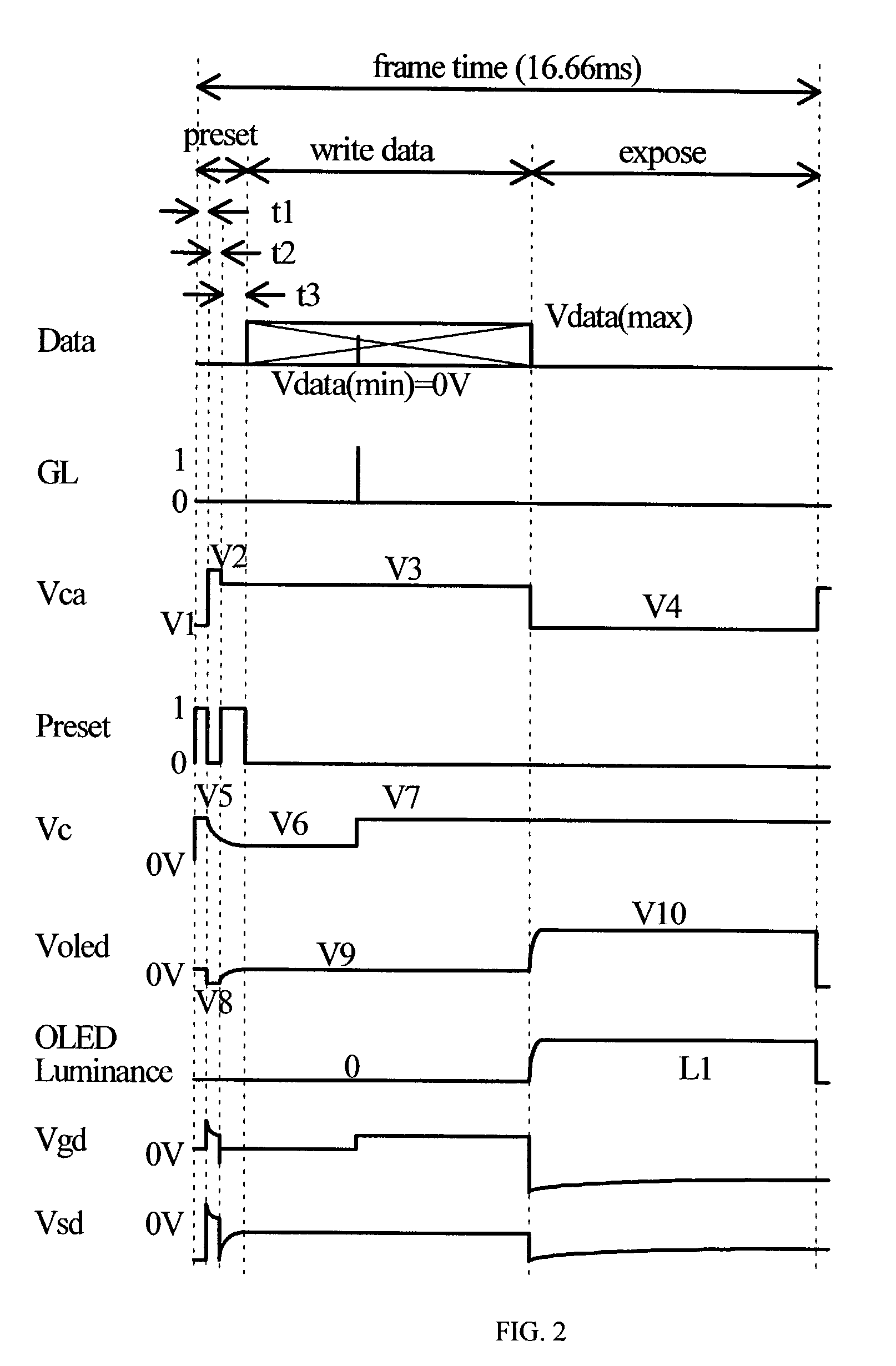

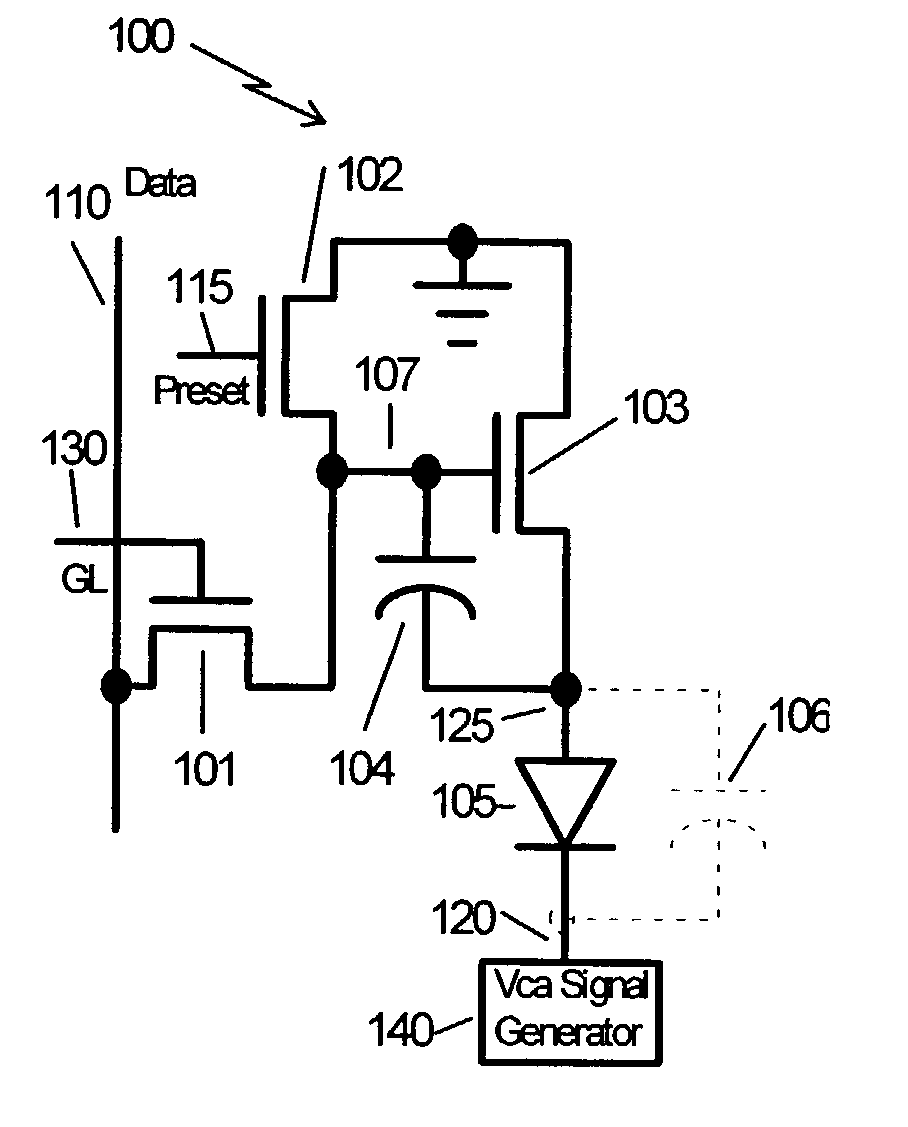

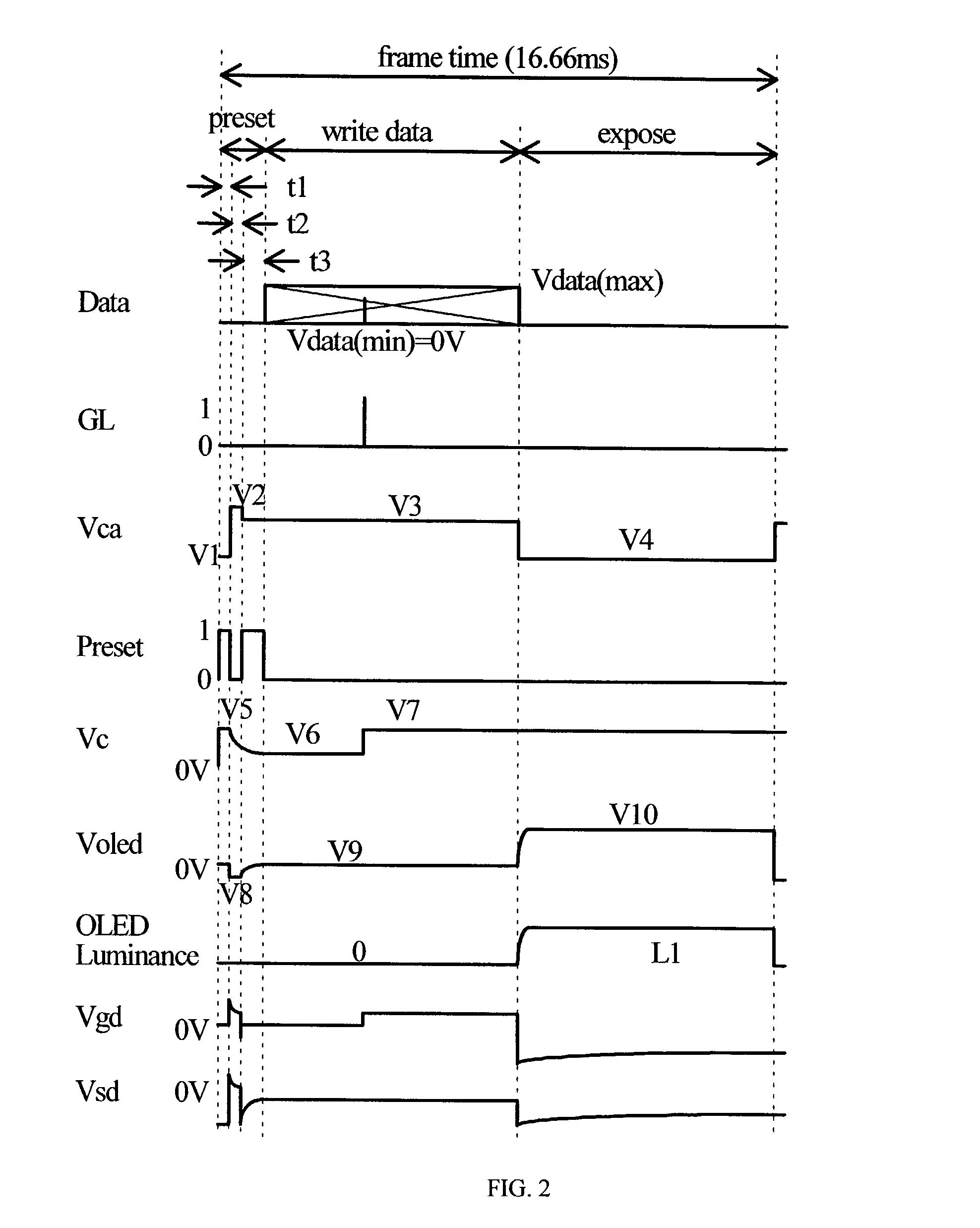

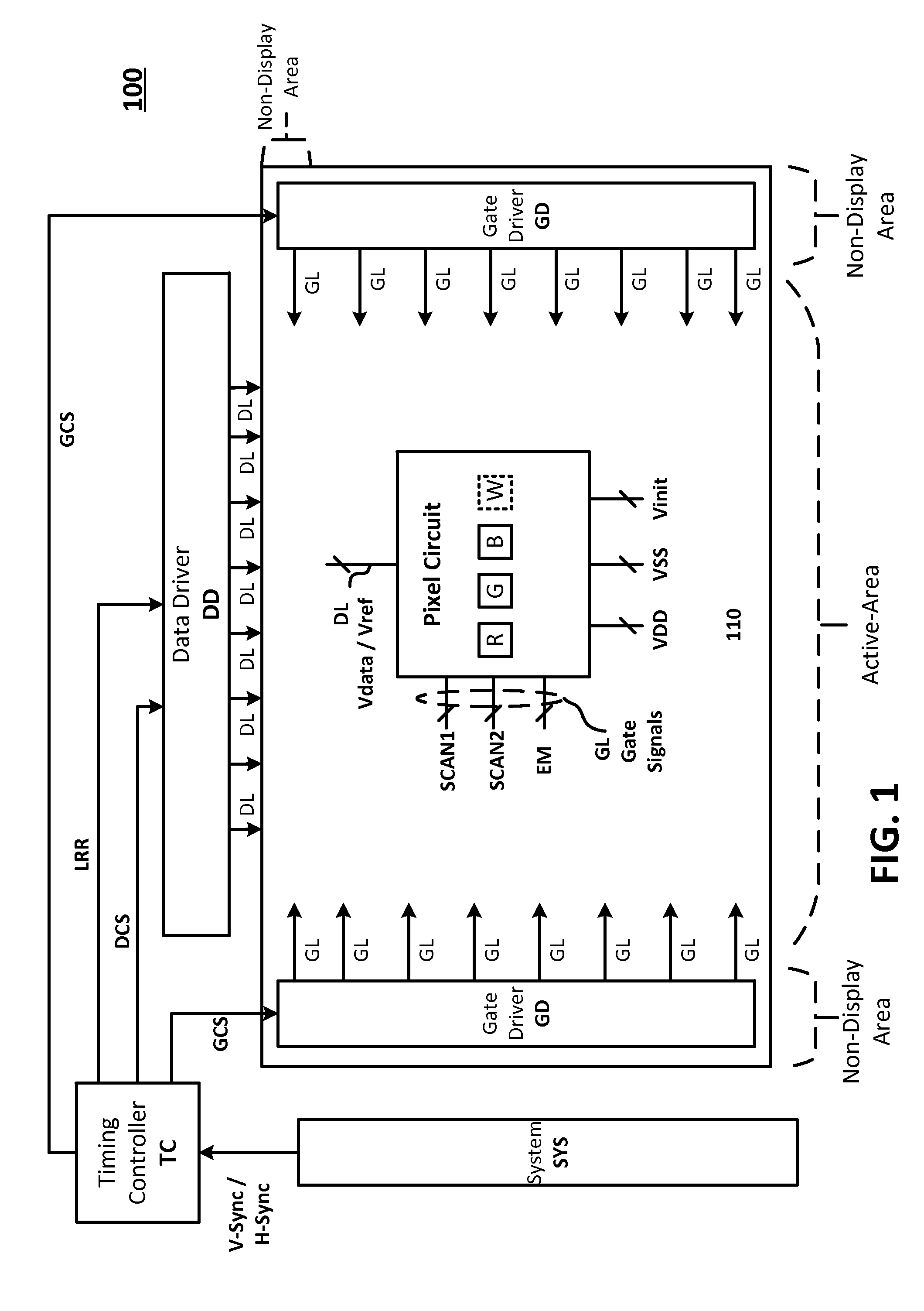

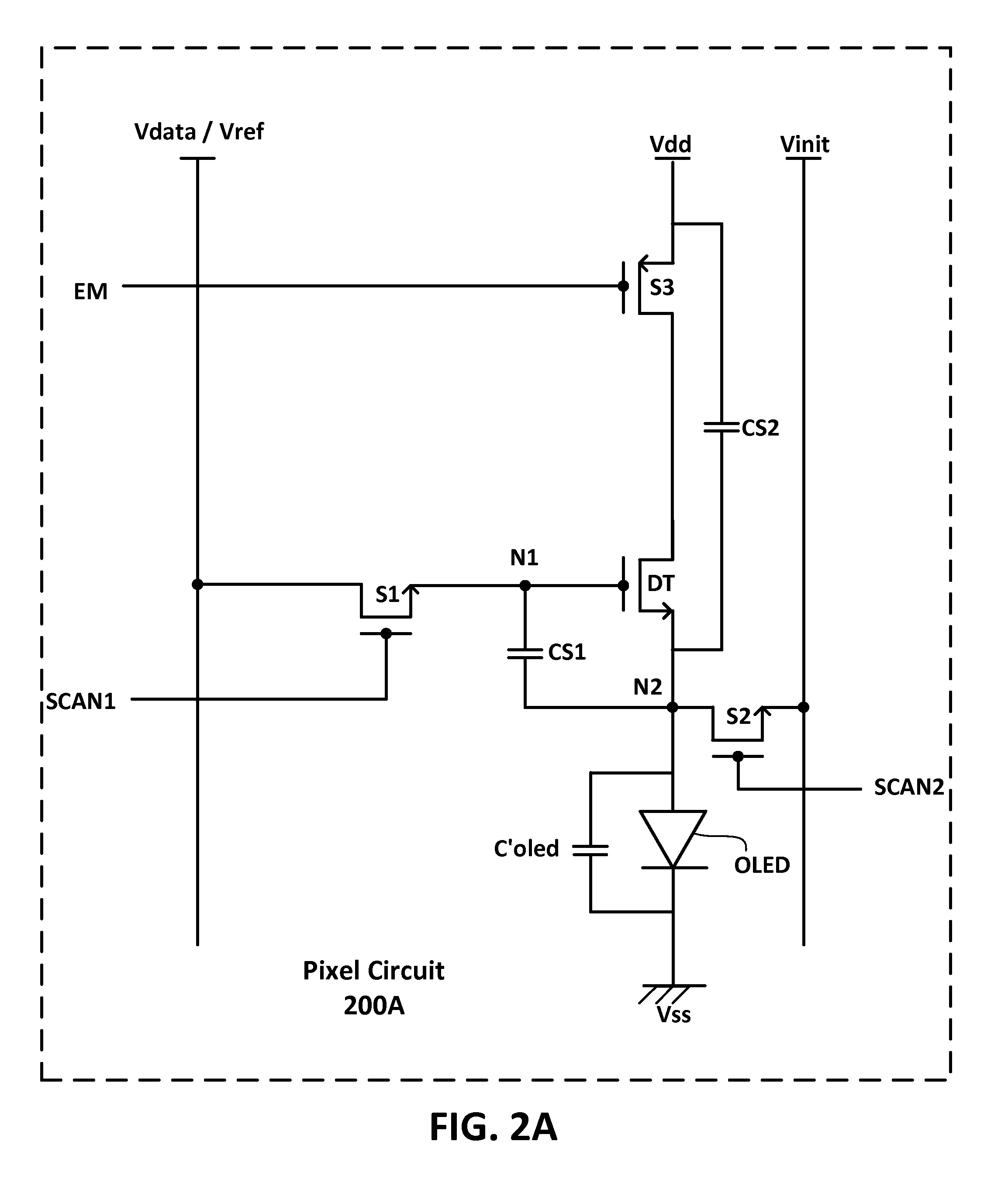

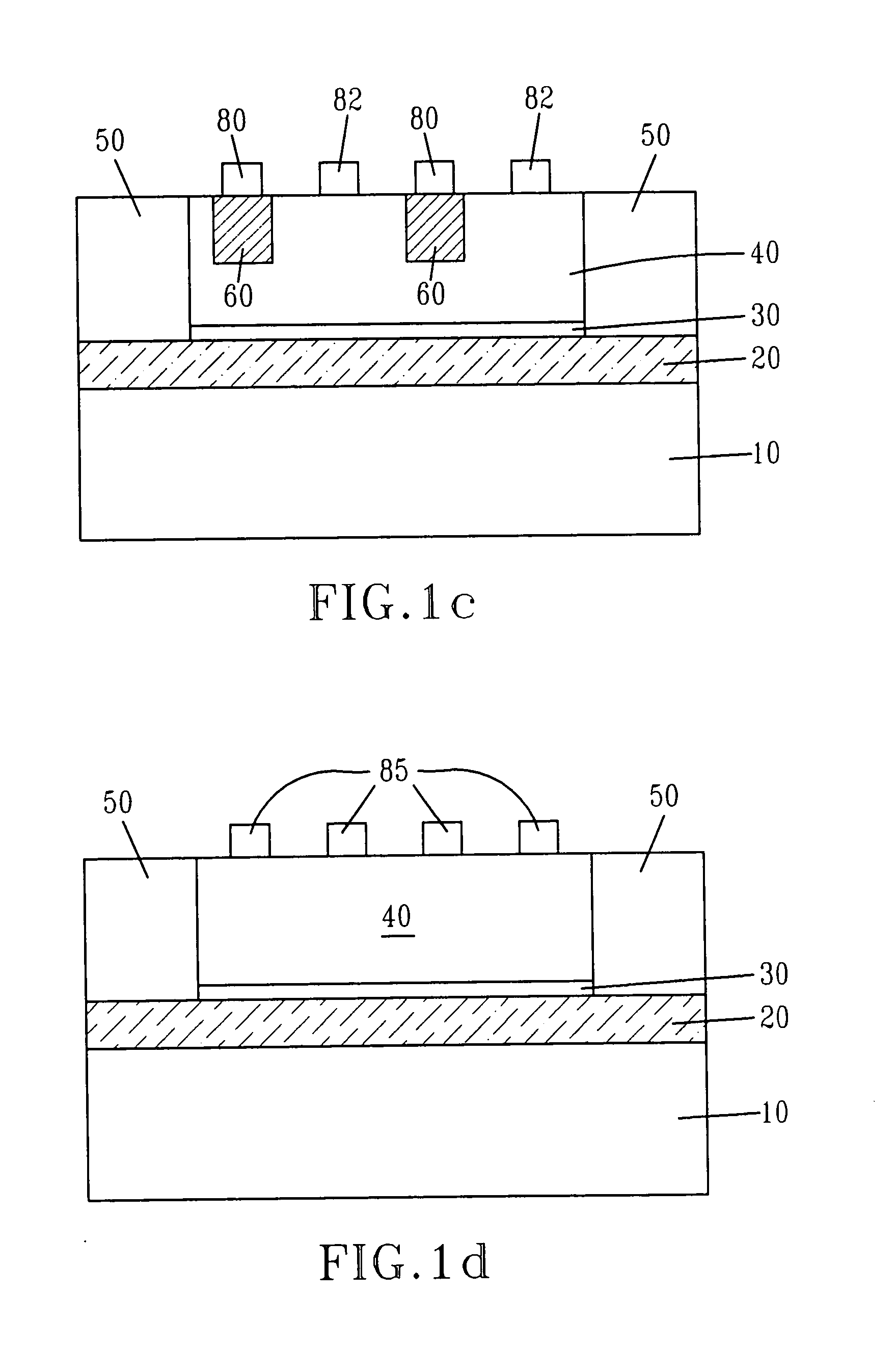

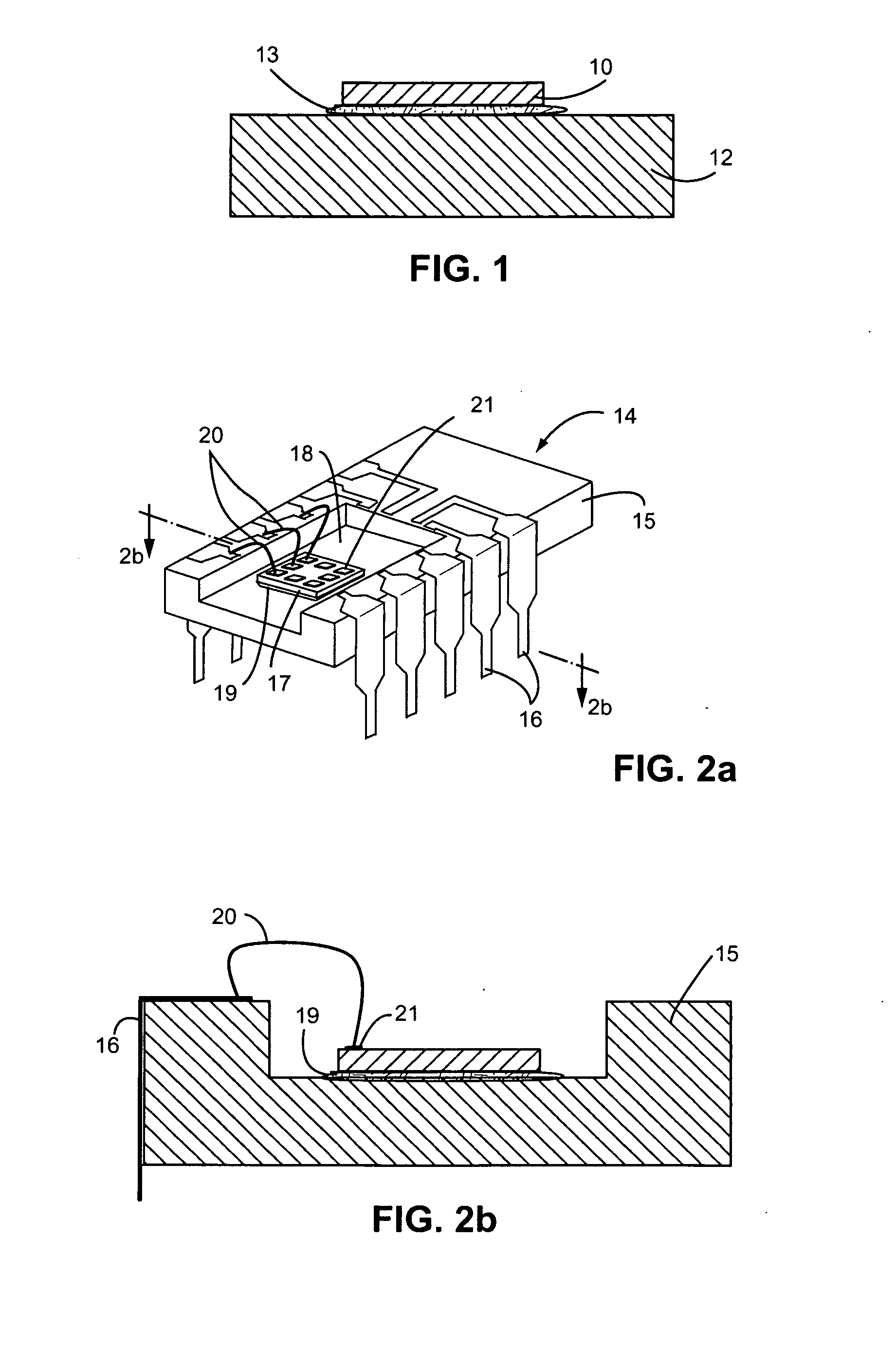

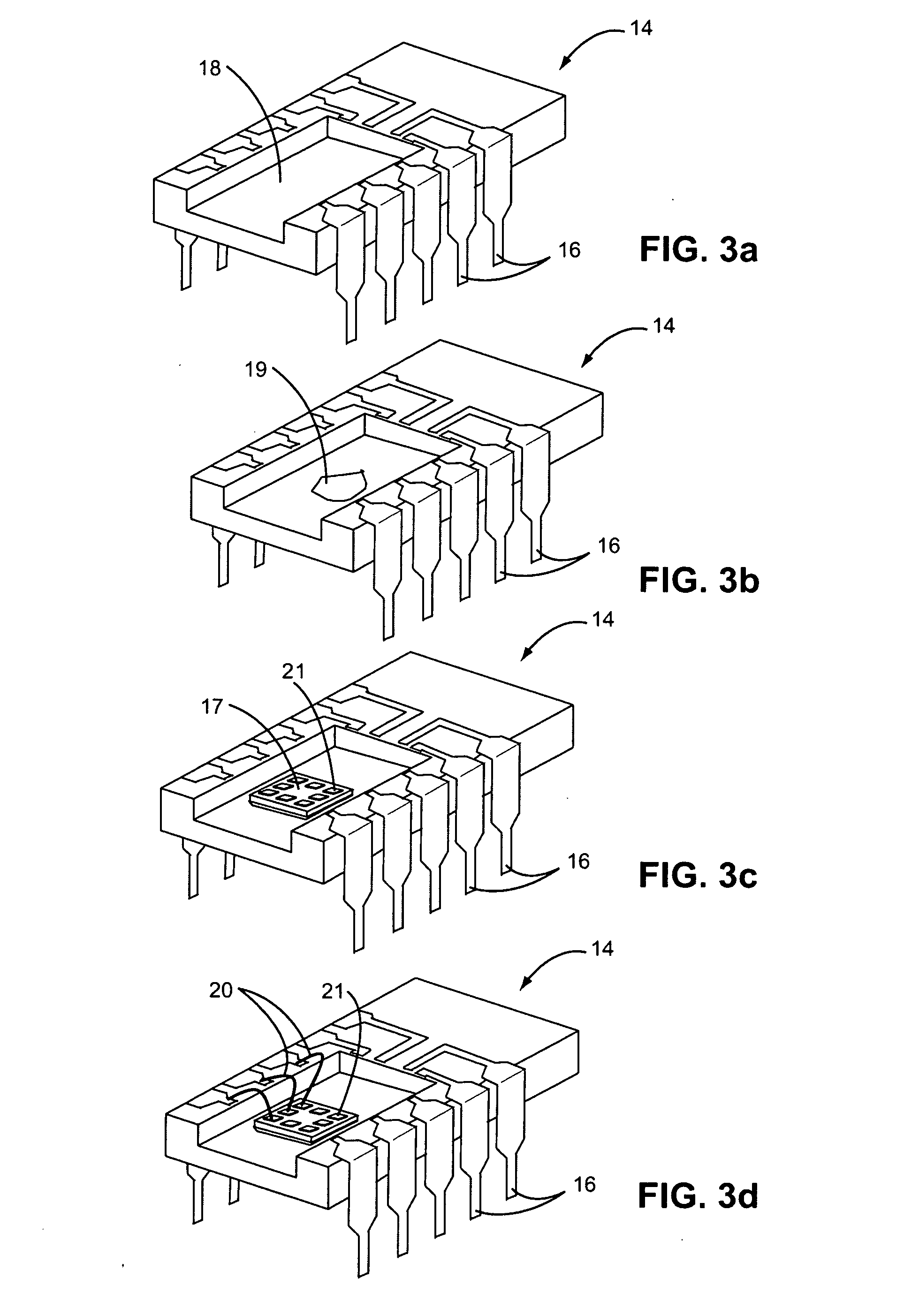

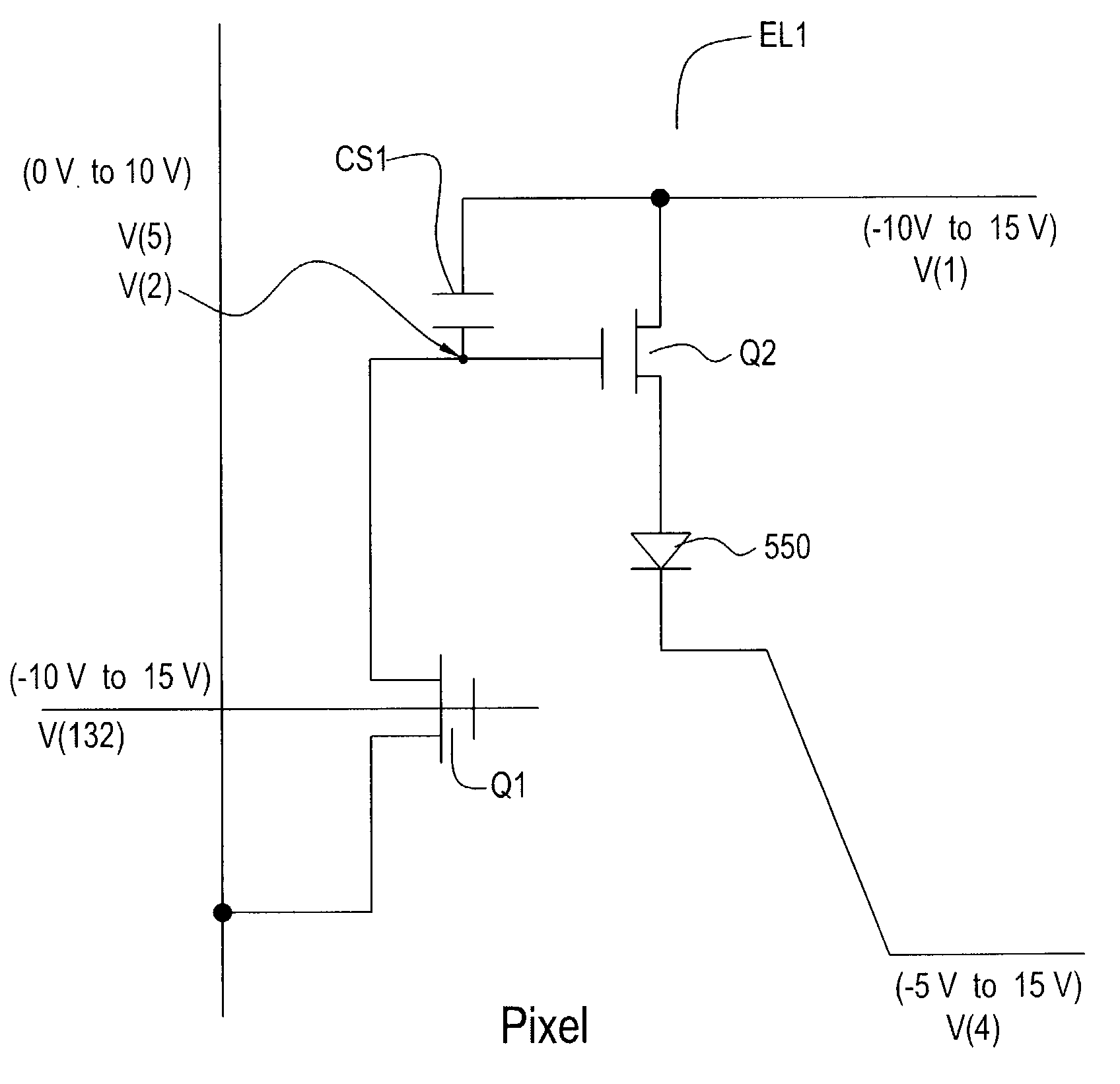

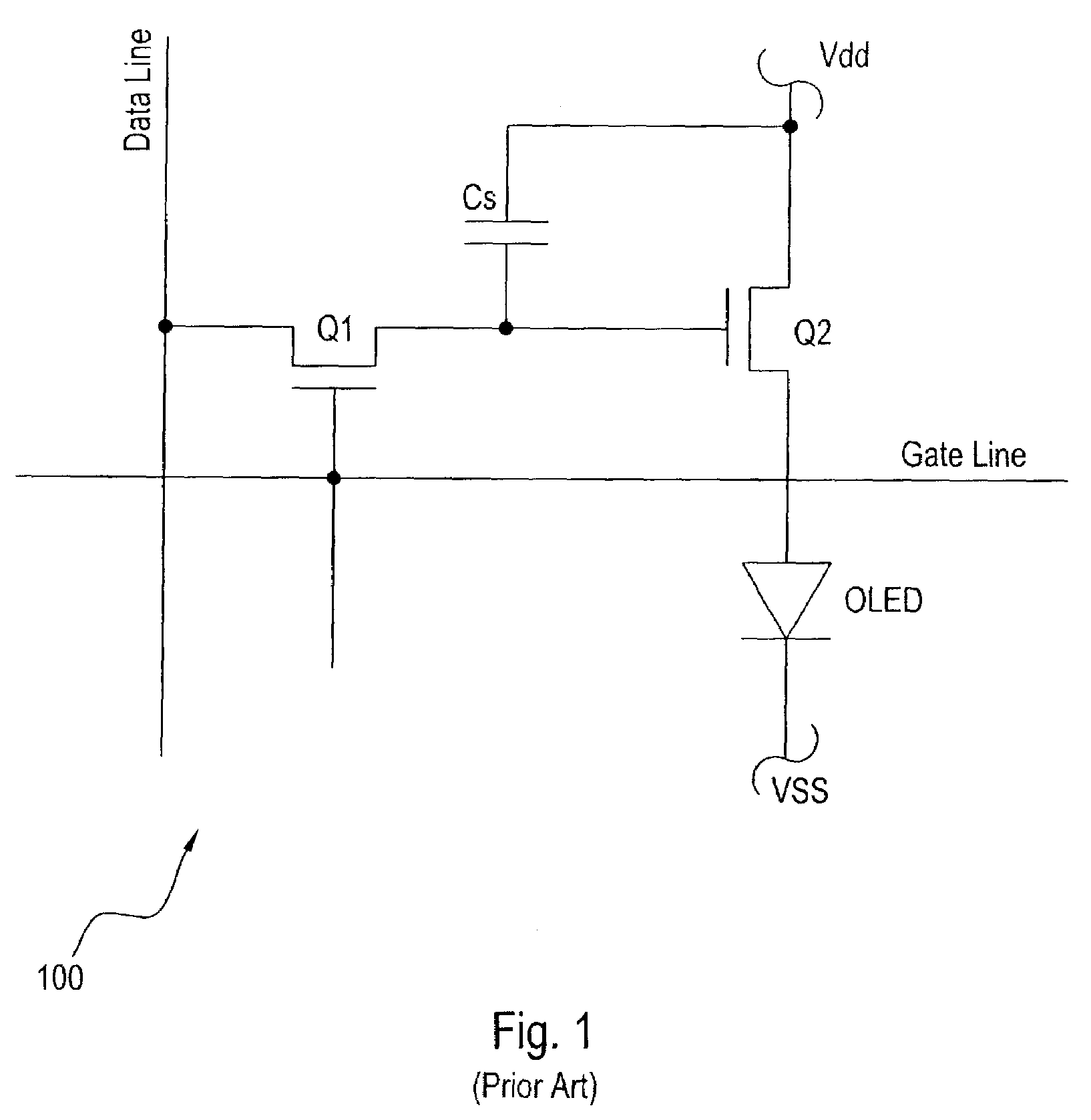

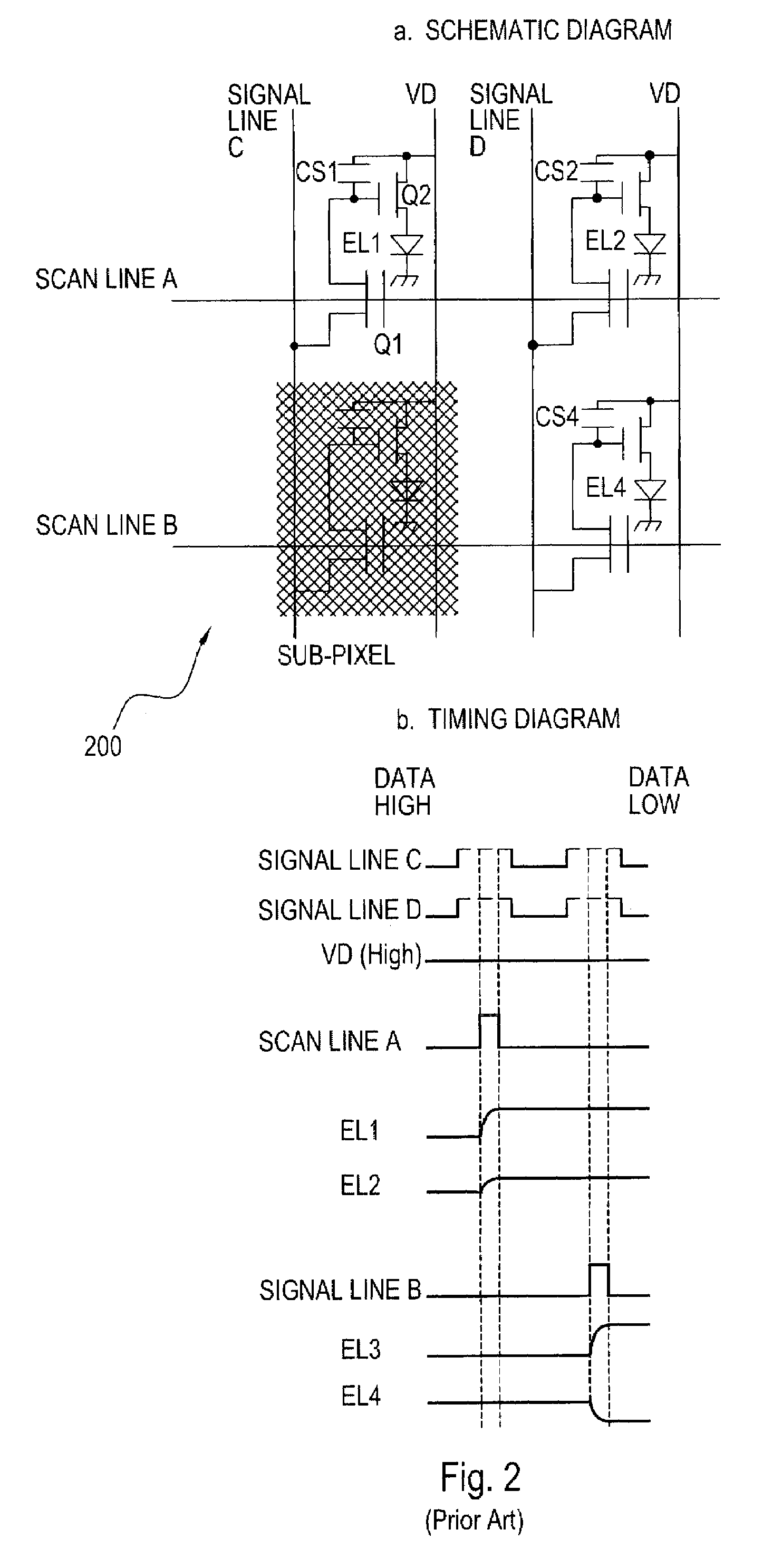

Data voltage current drive amoled pixel circuit

InactiveUS20030095087A1Facilitates a reverse bias of a scanned OLED arrayEasy to operateCathode-ray tube indicatorsInput/output processes for data processingHemt circuitsLight-emitting diode

There is provided a circuit for driving an organic light emitting diode (OLED). The circuit includes a current source for providing current to a first terminal of the OLED, and a generator for providing a variable voltage signal to a second terminal of the OLED to facilitate control of the current.

Owner:INNOLUX CORP

Data voltage current drive amoled pixel circuit

InactiveUS7071932B2Threshold voltage shift is minimizedMinimizes stress effectCathode-ray tube indicatorsInput/output processes for data processingHemt circuitsEngineering

There is provided a circuit for driving an organic light emitting diode (OLED). The circuit includes a current source for providing current to a first terminal of the OLED, and a generator for providing a variable voltage signal to a second terminal of the OLED to facilitate control of the current.

Owner:INNOLUX CORP

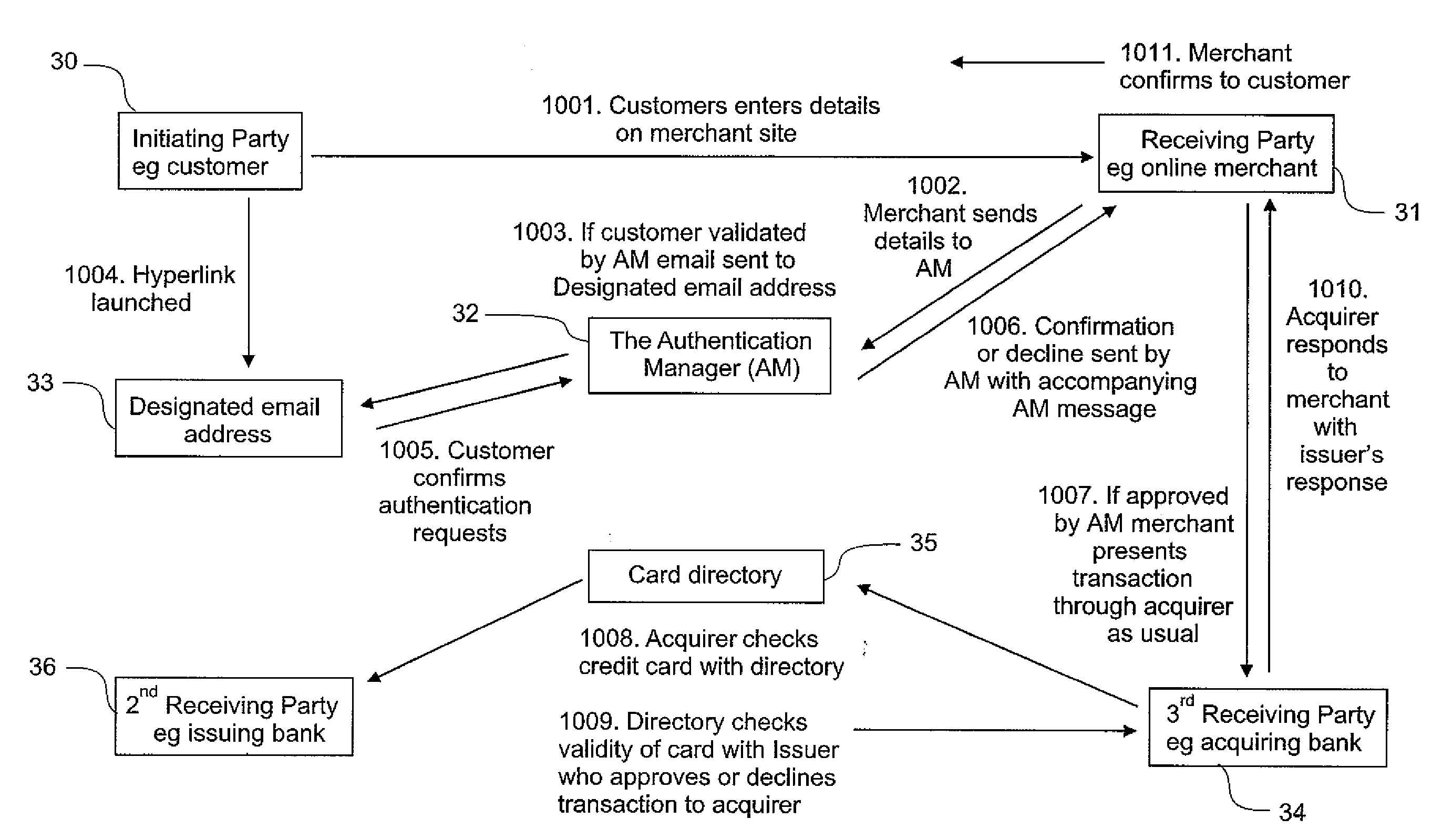

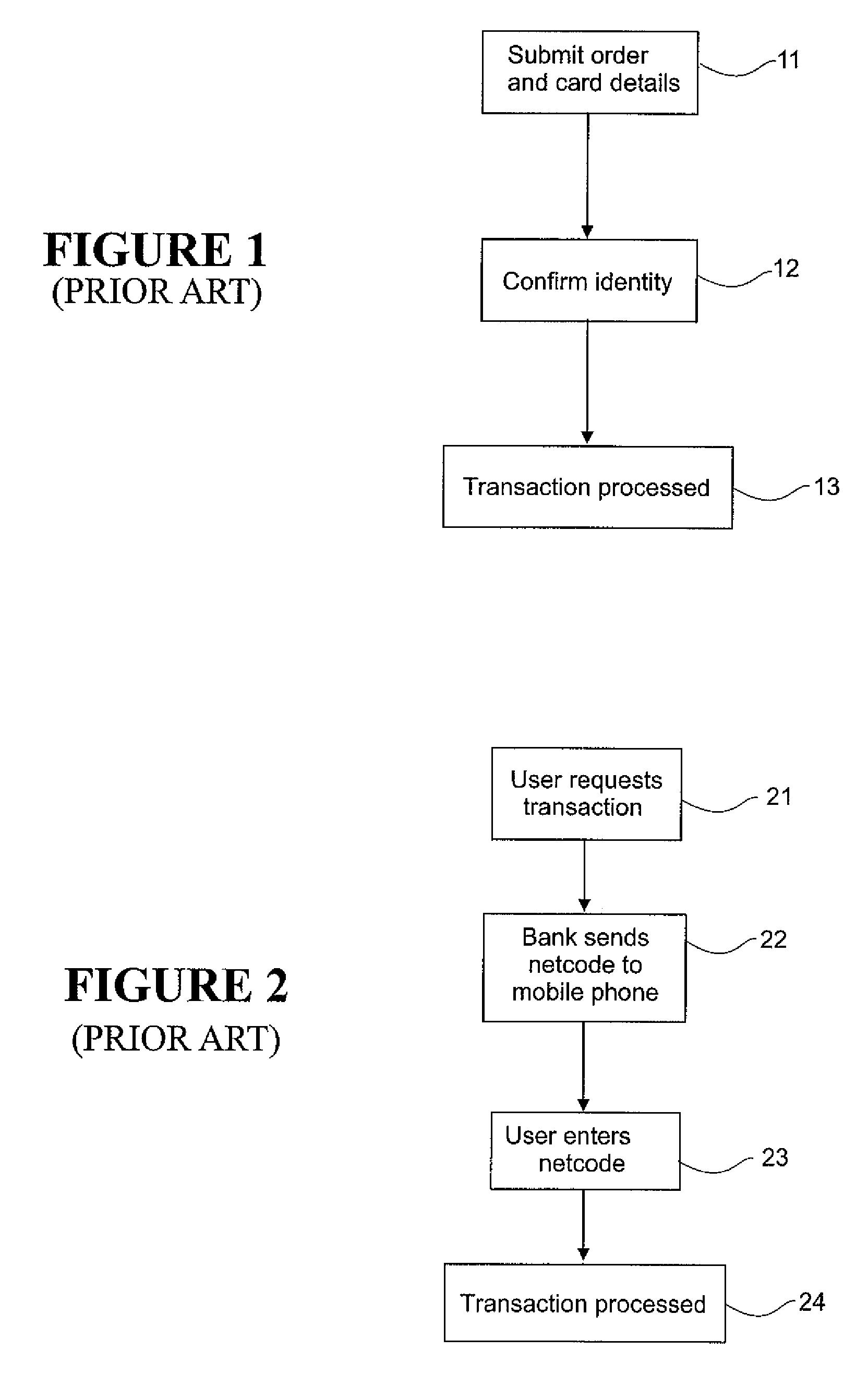

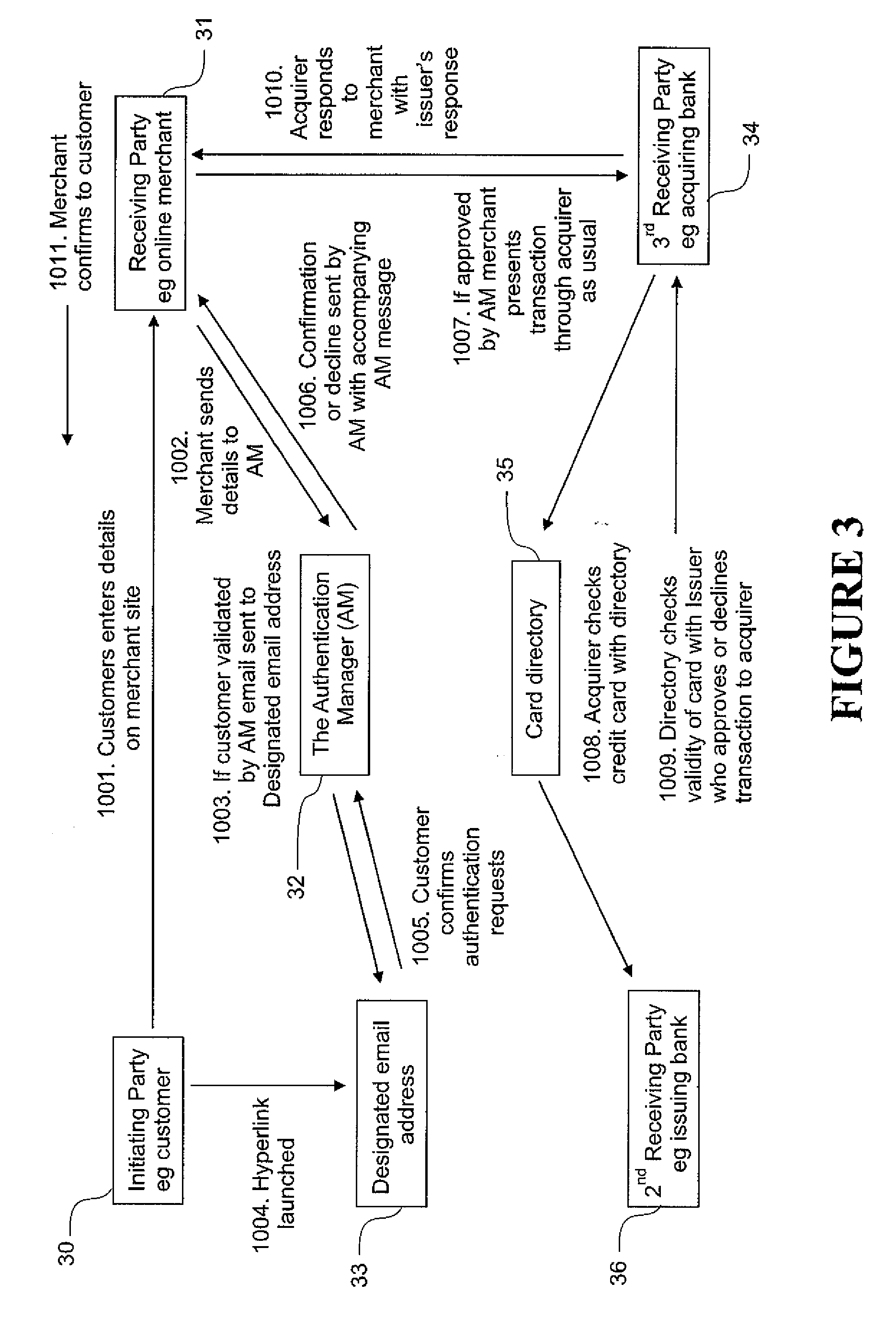

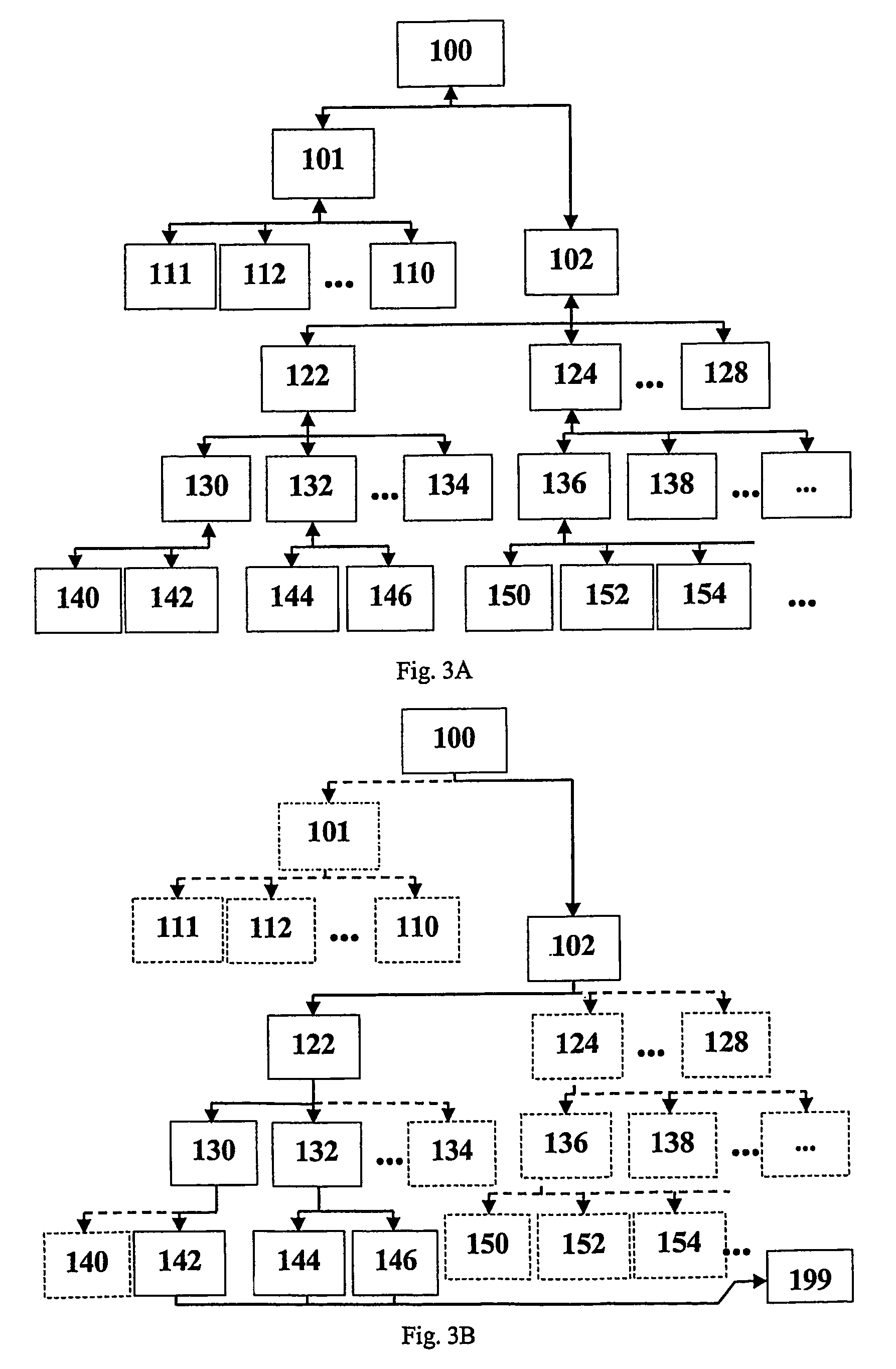

A Method of Authentication

InactiveUS20060173776A1Low cost of implementation and operationImprove securityFinancePayment architectureInternet privacyQuestion answer

The present invention relates to the authentication of parties involved in transactions performed remotely over a network, such as the Internet. When a first party initiates a transaction with a second party, the second party can request authentication of the first party. Authentication is carried out by sending a communication to the first party, which includes a redirection to a transaction specific location,. At the transaction specific location the first party is required to approve the transaction as well as answer some identifying question or questions. If the transaction is approved and the question or questions answered correctly, the second party is informed that the transaction can be approved.

Owner:SHALLEY BARRY

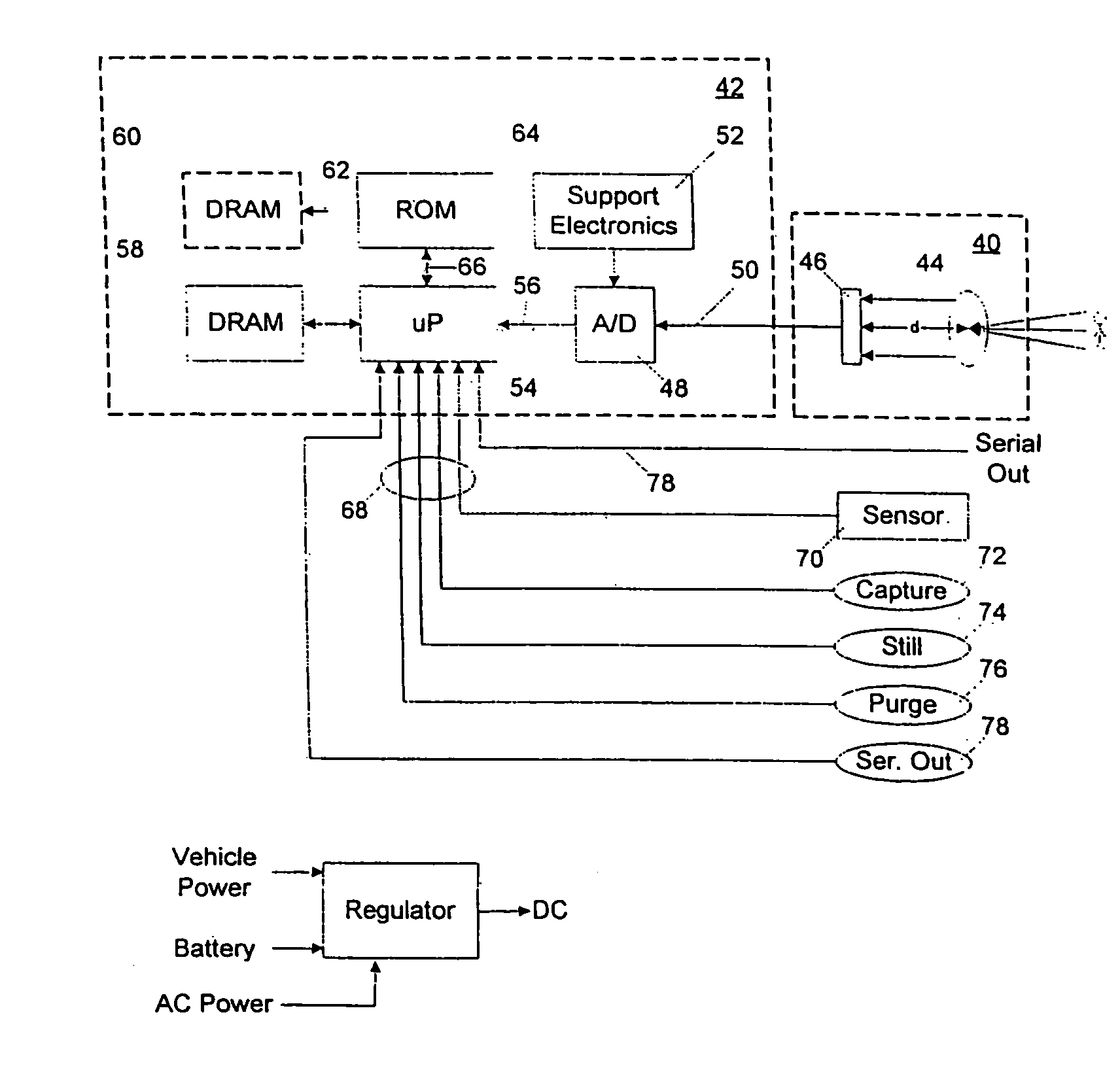

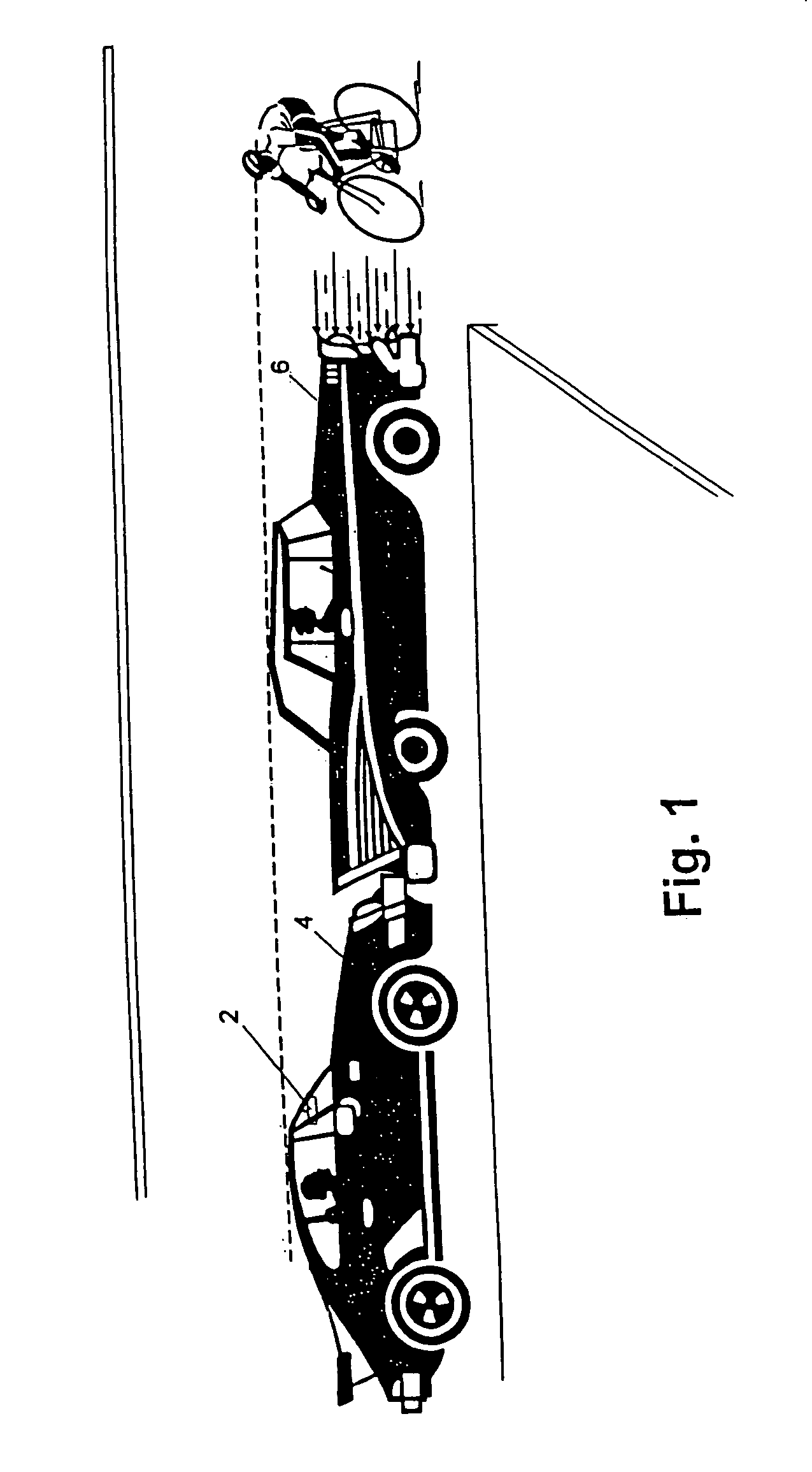

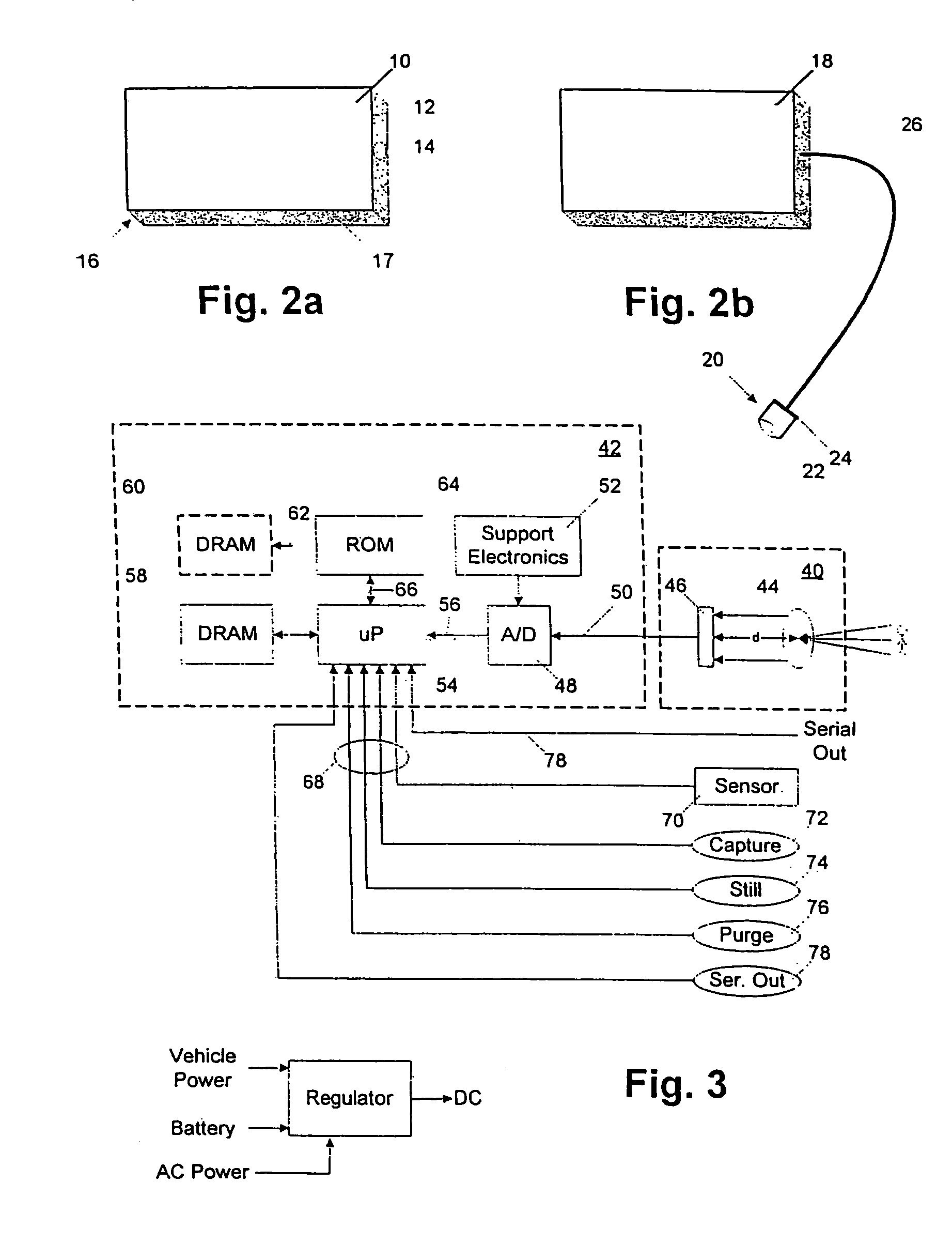

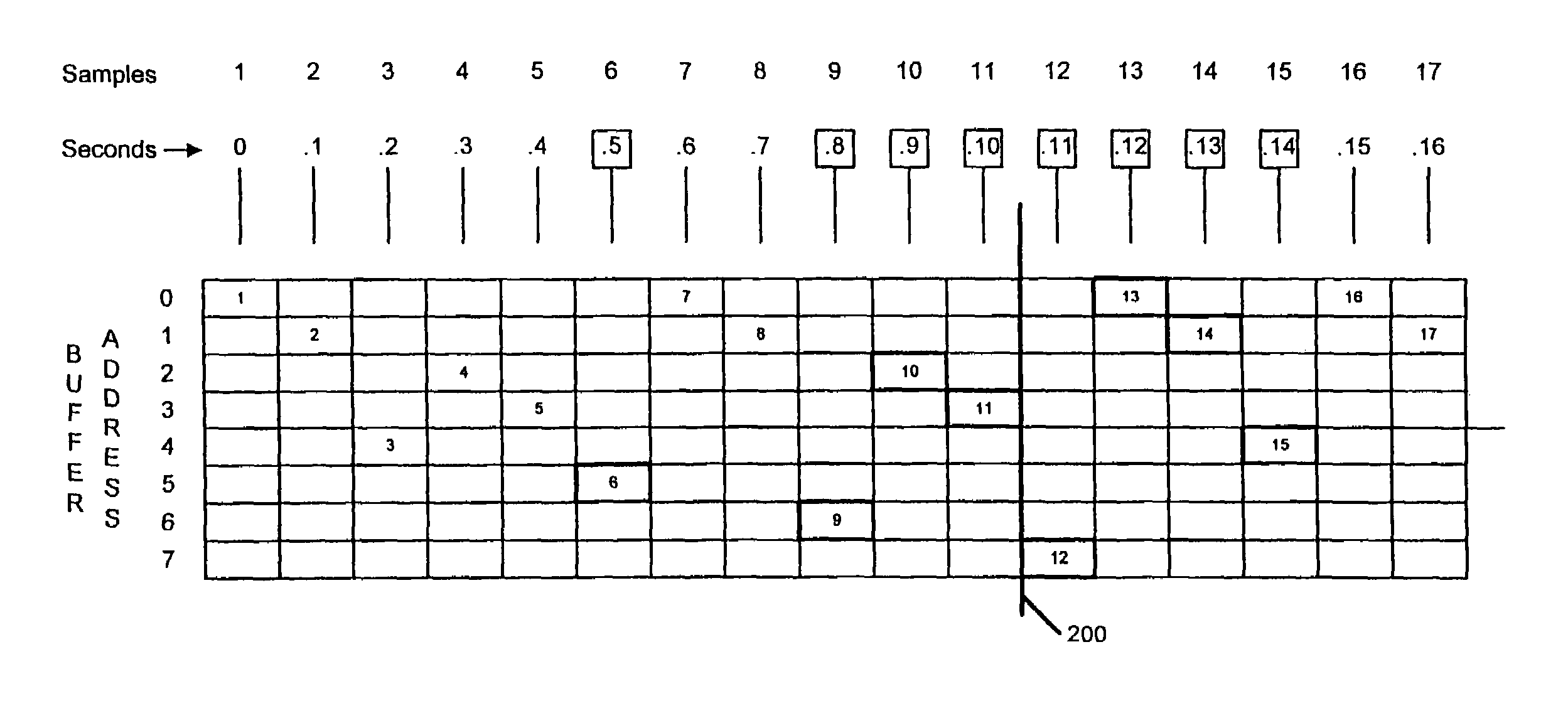

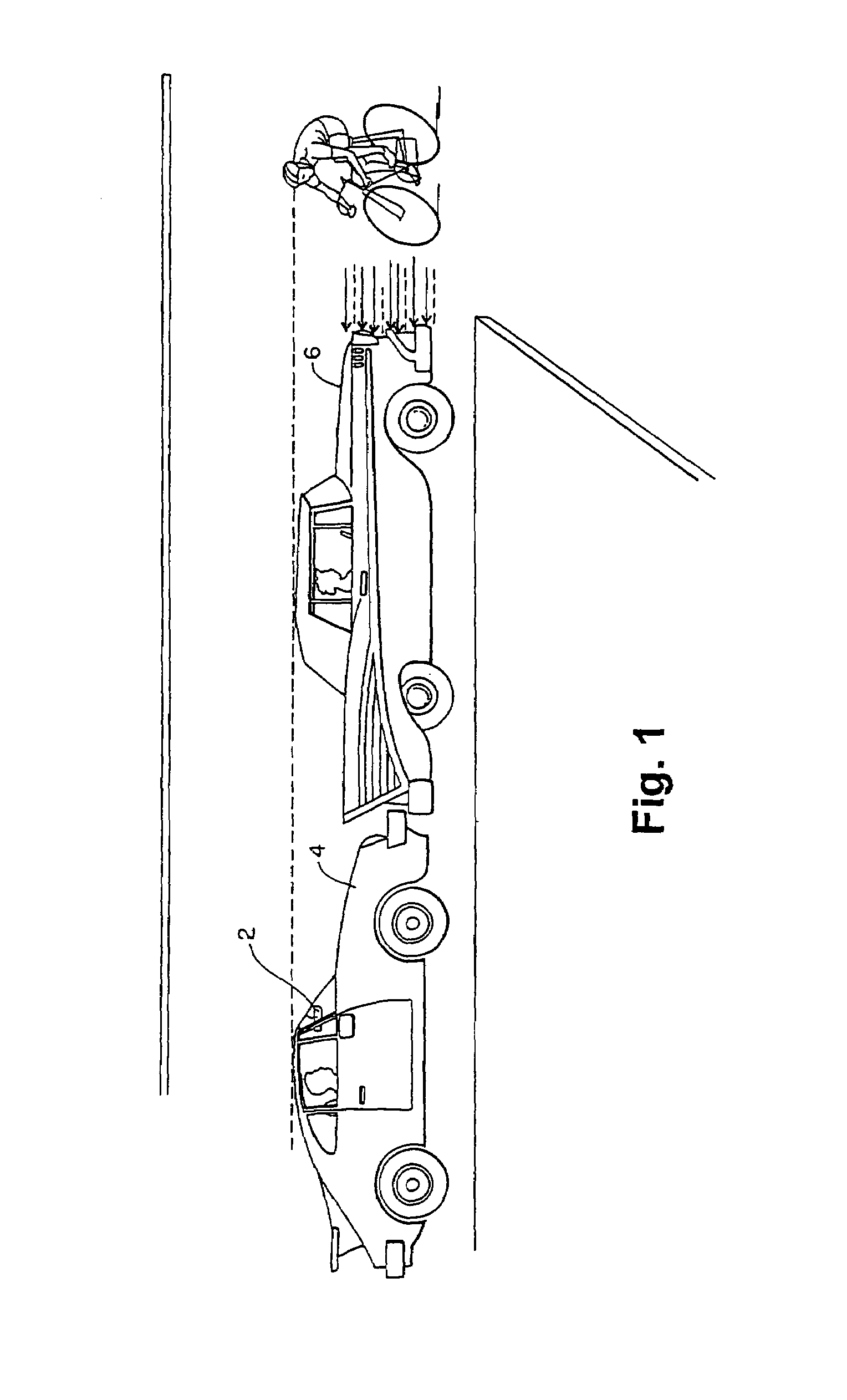

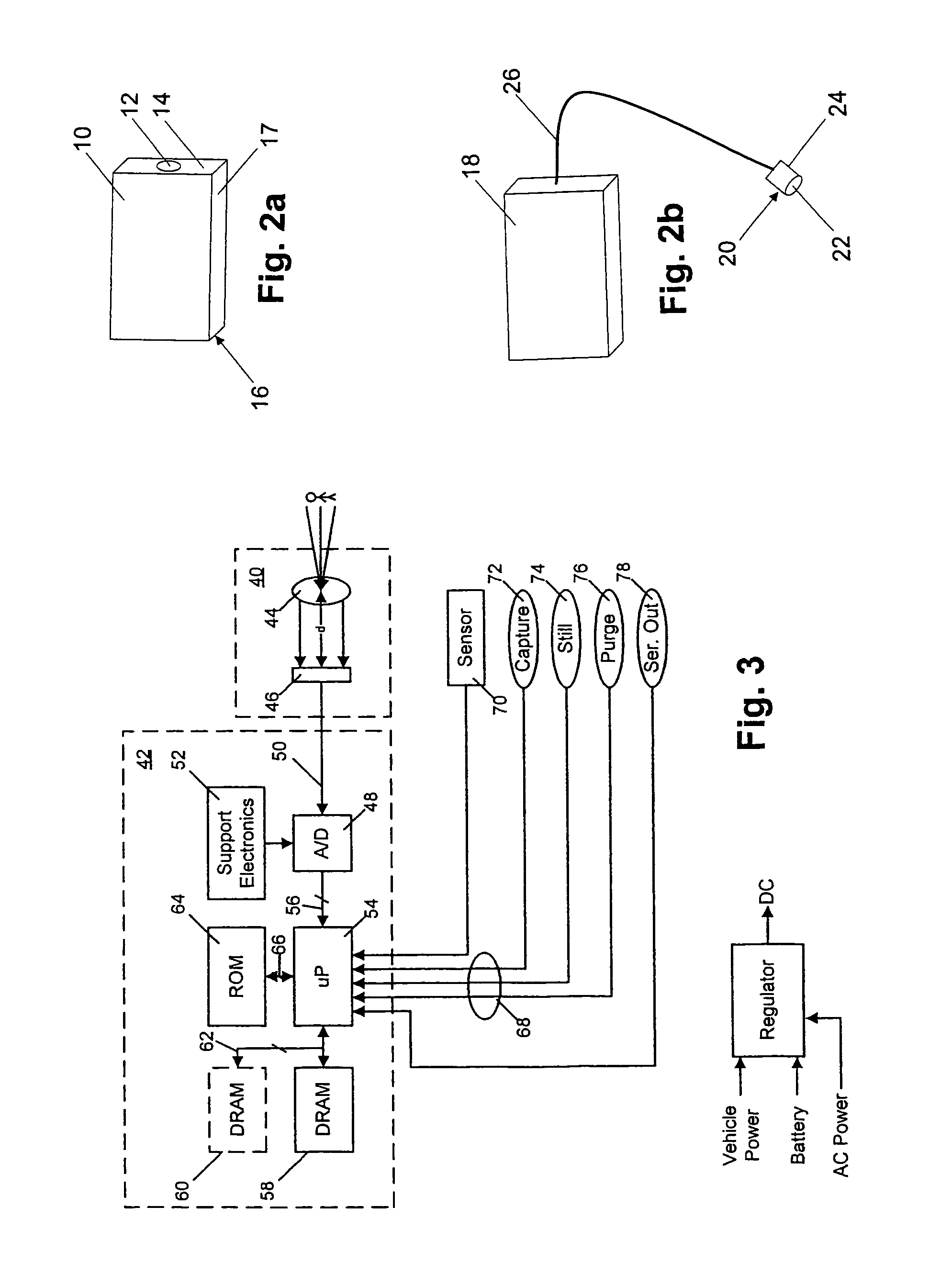

Video recording device responsive to triggering event

InactiveUS7088387B1Extend recording timeReduced operating requirementsTelevision system detailsColor television detailsComputer graphics (images)Video record

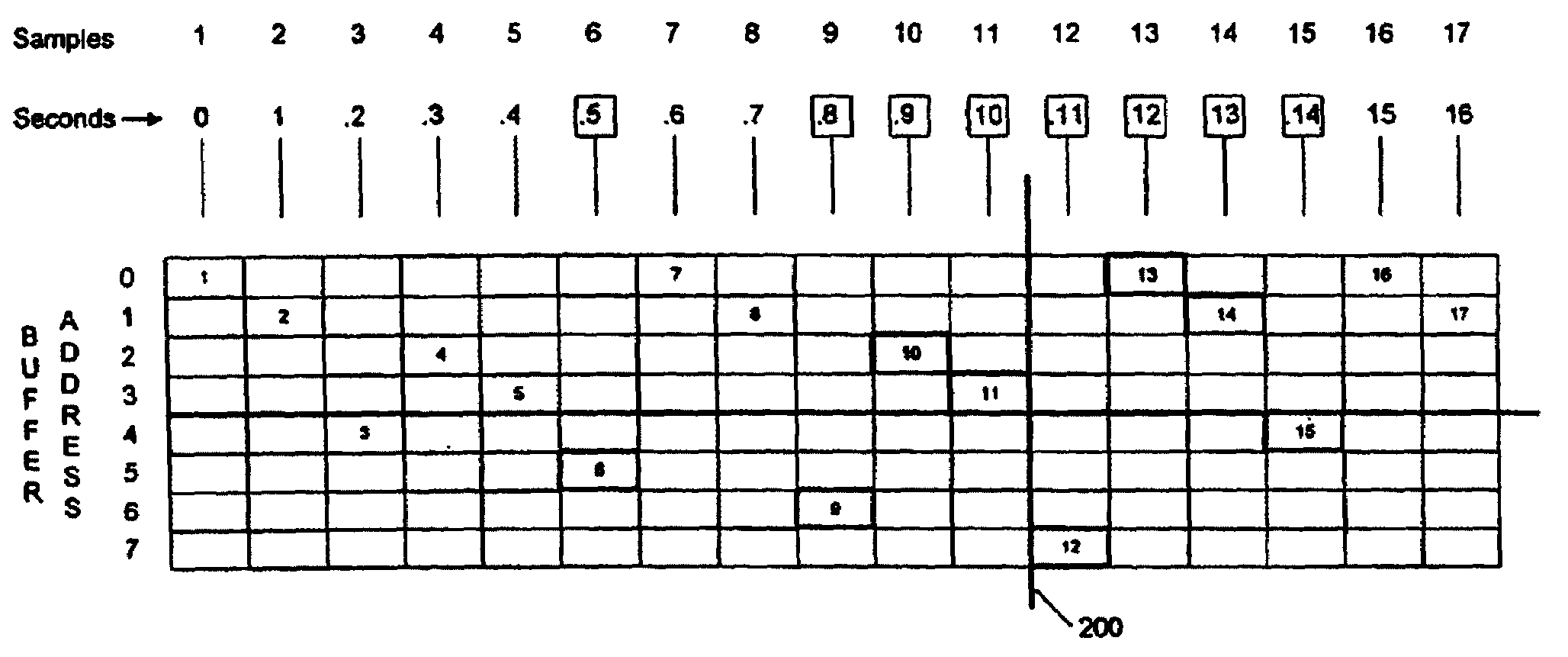

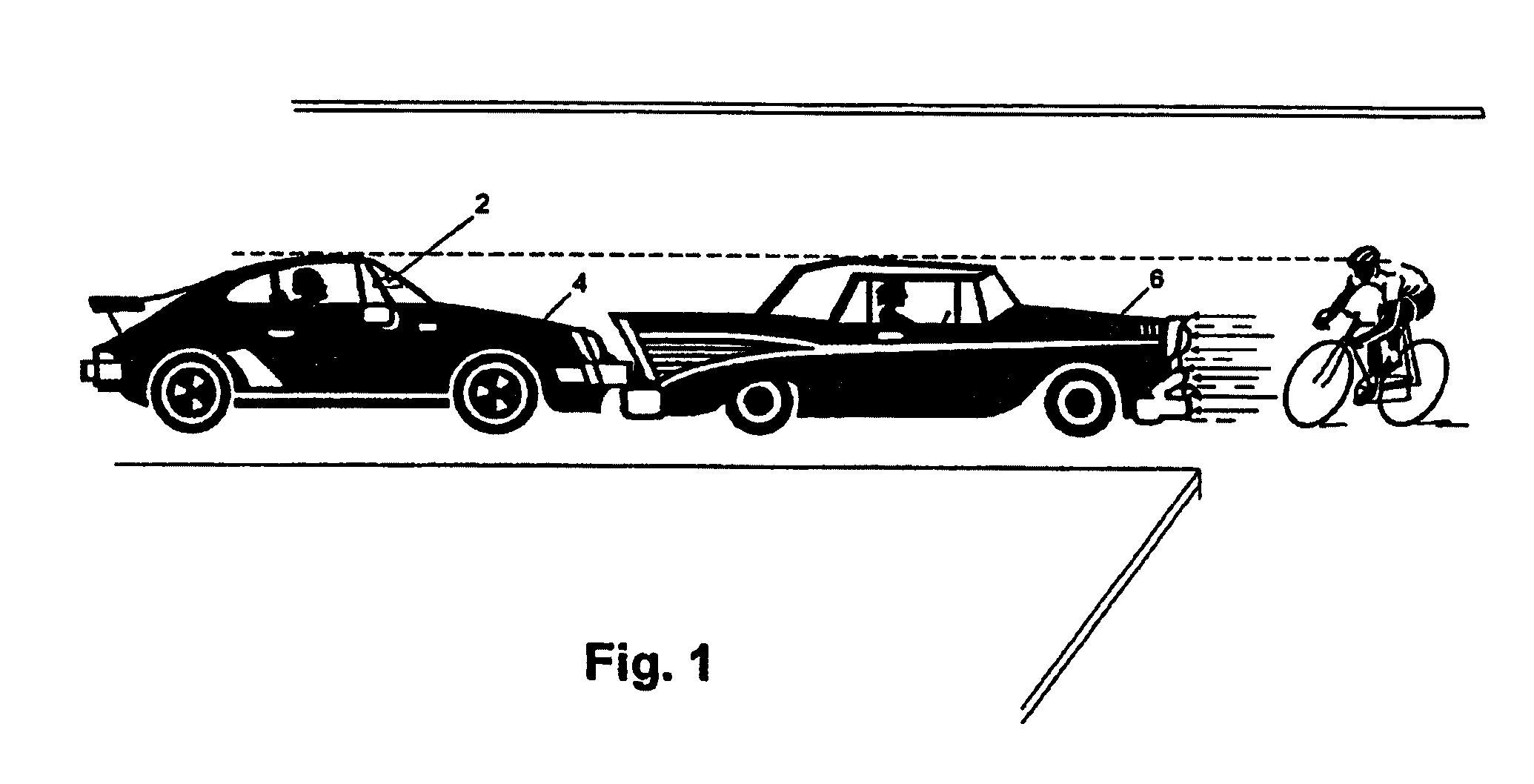

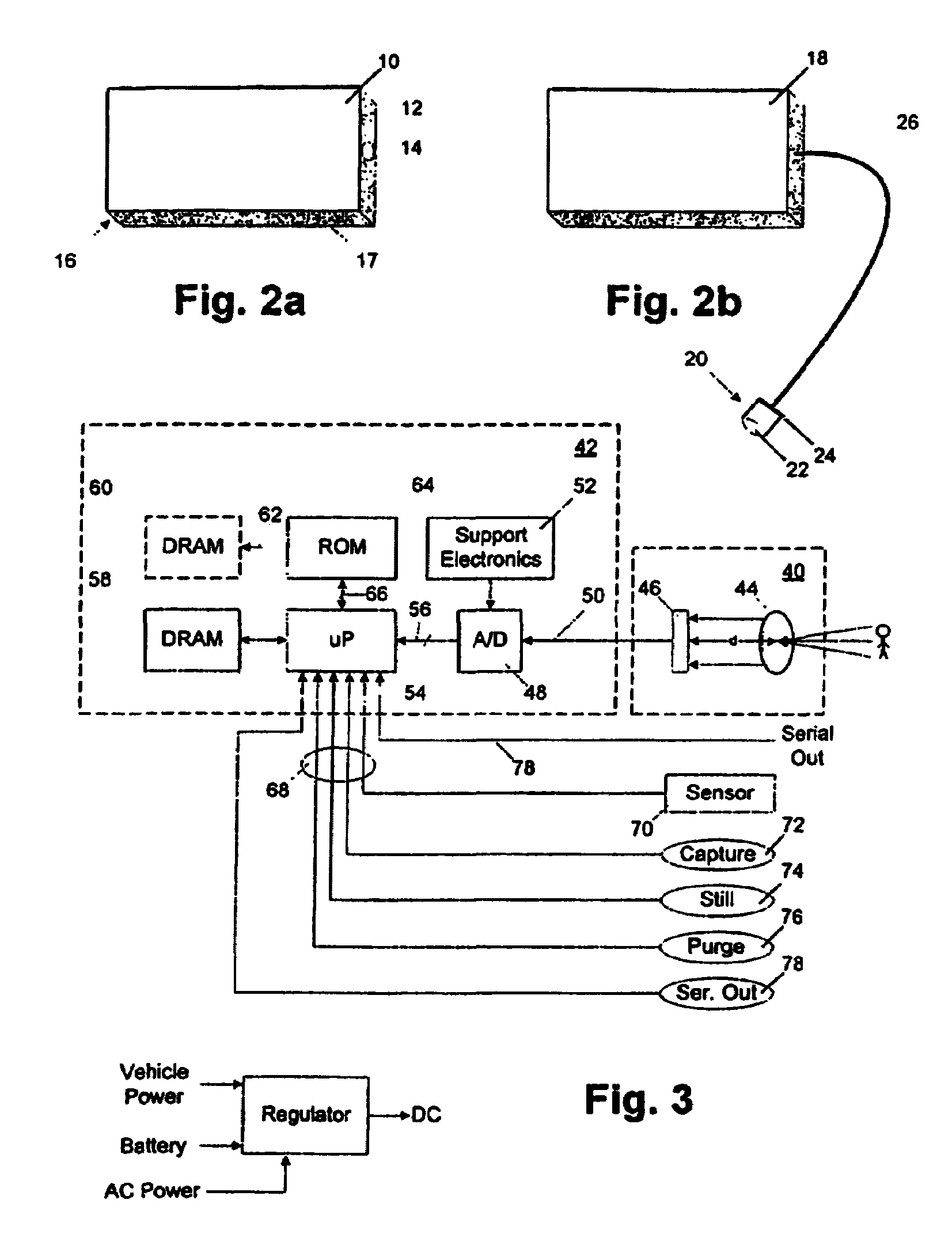

A compact video image recording device for recording video images before and after a triggering event and which utilizes no moving parts is disclosed. The recording device includes at least one camera wherein each camera comprises a lens and a video image sensor. Each video image sensor generates an electronic signal representative of a video image impinging the respective sensor. The output of each image sensor is processed, compressed and generally employed to produce frame data which are successively stored in a successive frame locations of a semiconductor memory organized as a circular buffer memory. Upon the occurrence of a triggering event, a additional frames are stored in the buffer memory and further storage of frames then terminates. A video record is thus created of video images received both before and after the triggering event via a device which contains no moving parts and which can withstand substantial shock and vibration.

Owner:MITSUBISHI ELECTRIC RES LAB INC

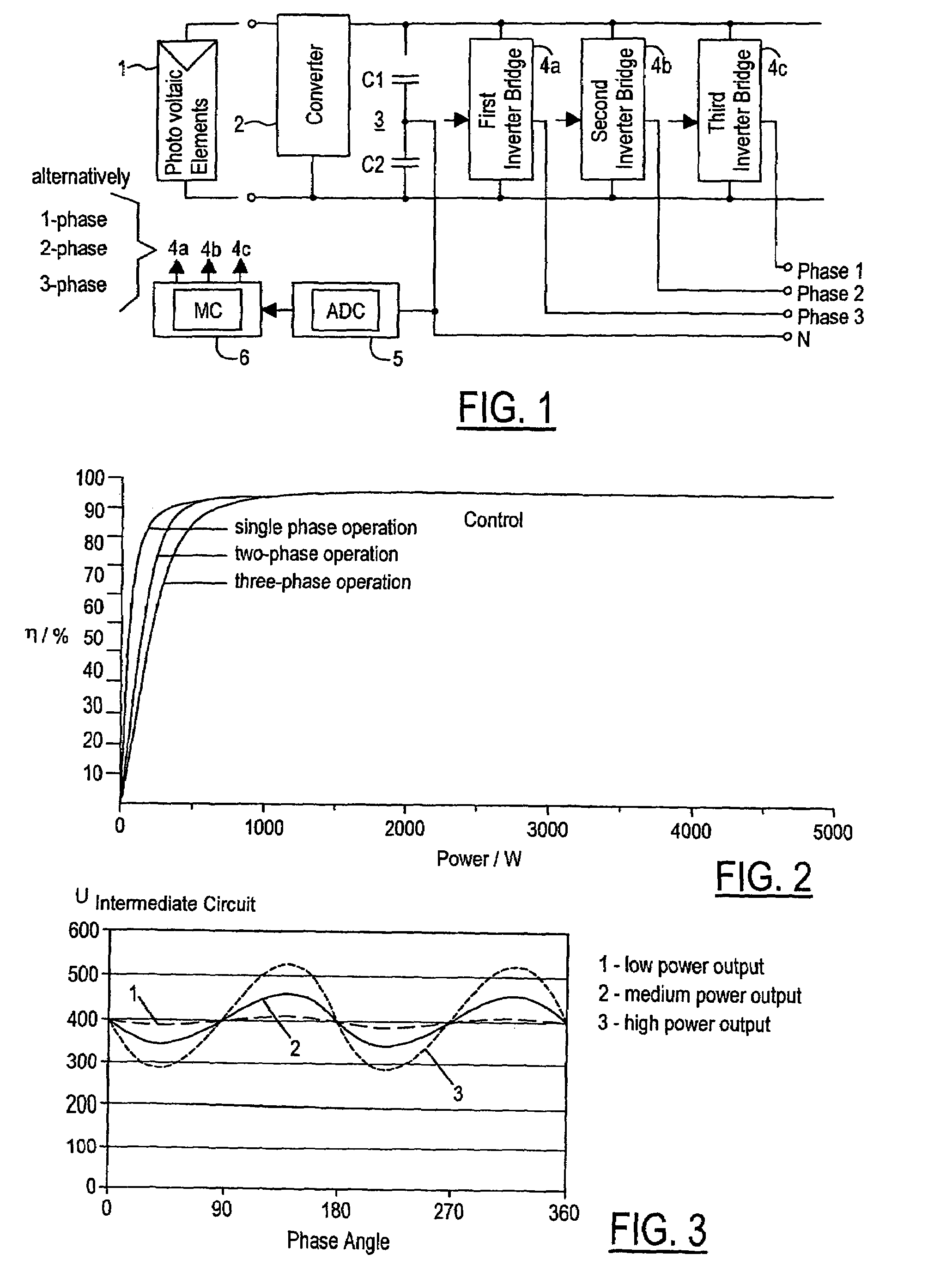

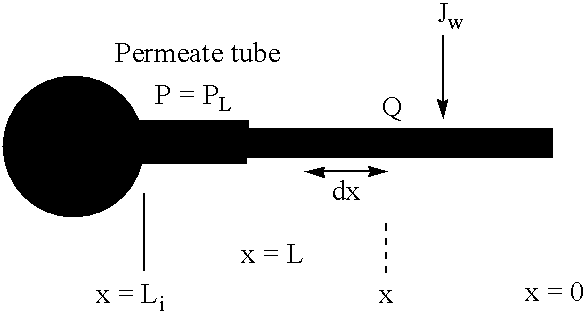

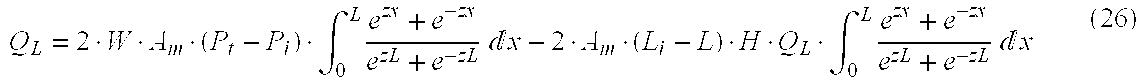

Inverter

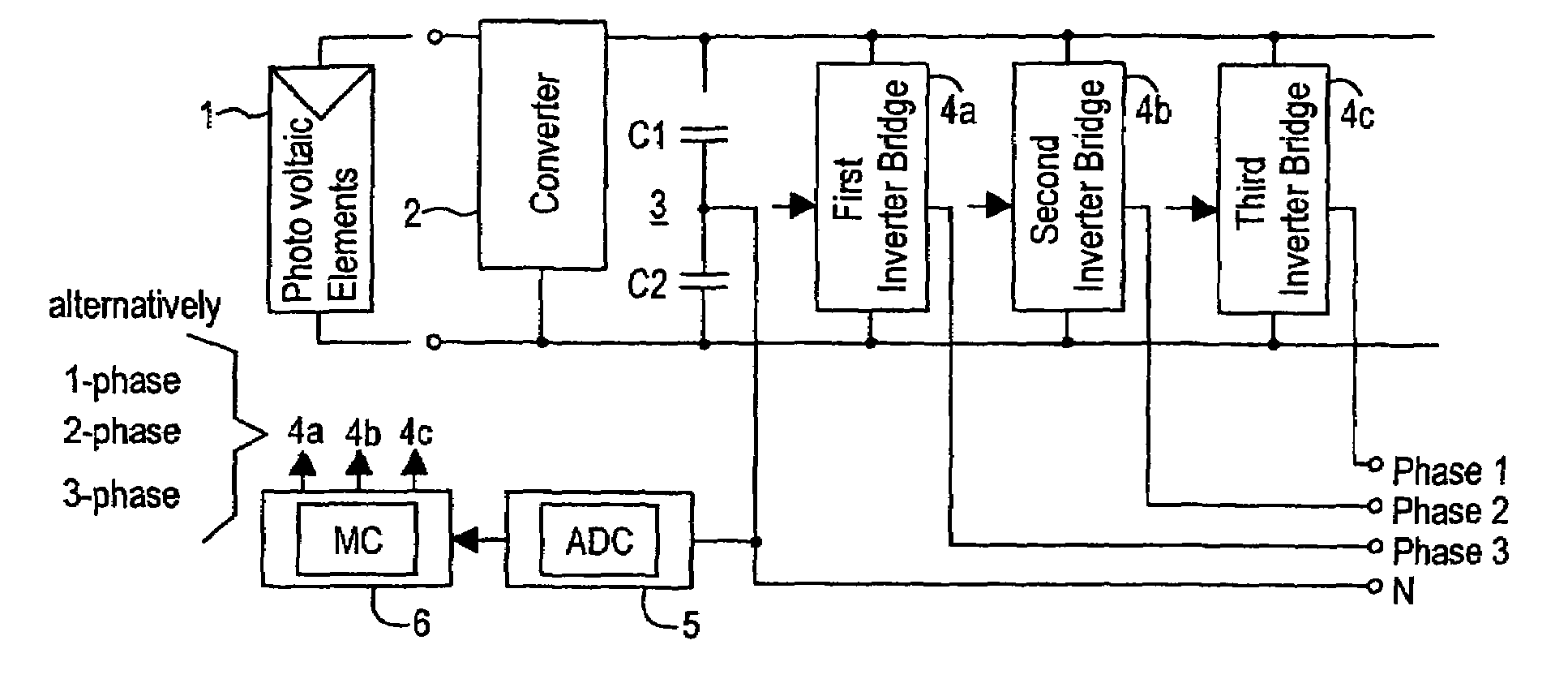

InactiveUS7414870B2Improve efficiencyReduced operating requirementsConversion with intermediate conversion to dcElectric power transfer ac networkEngineeringVoltage

An inverter includes an intermediate circuit, inverter bridge branches downstream of the intermediate circuit for outputting a power signal, and a controller operable for individually turning on and off the inverter bridge branches. The controller may individually turn on and off the inverter bridge branches as a function of an electrical quantity. The electrical quantity may be indicative of a voltage or a change in voltage occurring in the intermediate circuit during operation of the inverter. The electrical quantity may be indicative of the output power signal. The inverter bridge branches may include three inverter bridge branches.

Owner:KOSTAL IND ELEKTRIK

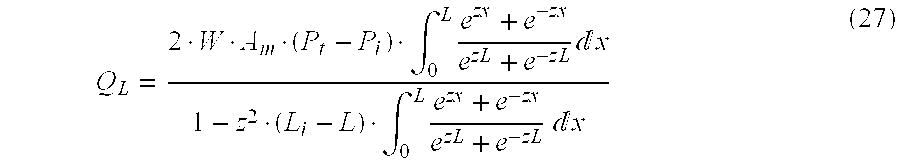

Cross flow filtration materials and cartridges

InactiveUS7048855B2Reduced operating requirementsAvoid problemsSemi-permeable membranesOther chemical processesFiberCross-flow filtration

Cross flow filtration cartridges are made using semipermeable membrane of sheet formation that was cast upon an integral polymeric fibrous support material which exhibits excellent permeate flow in the plane thereof and serves as both backing material and permeate carrier. A fibrous support having a thickness between about 0.4 mm and about 2 mm and at least one surface region with a mean pore size no greater than about 300 microns has a semipermeable membrane cast in situ thereupon from a liquid solution. After gelling to form a polymeric semipermeable membrane, the product is spirally wound about a porous tube in association with feed-passageway-providing sheet material, but in the absence of any separate permeate carrier, to form an effective cross-flow filtration cartridge wherein the feed flow may be spiral and the permeate discharge through one of the side edges.

Owner:GE OSMONICS INC

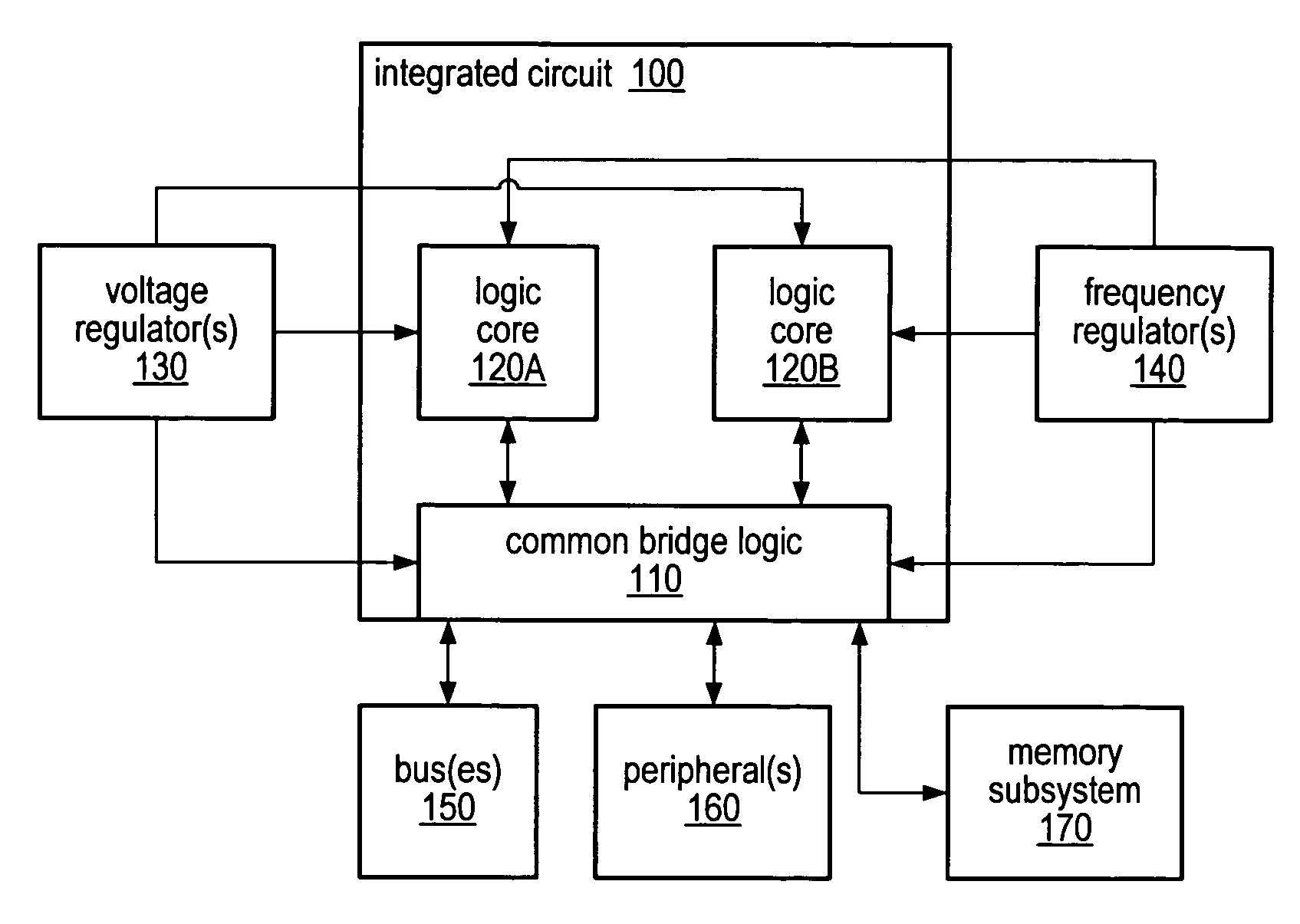

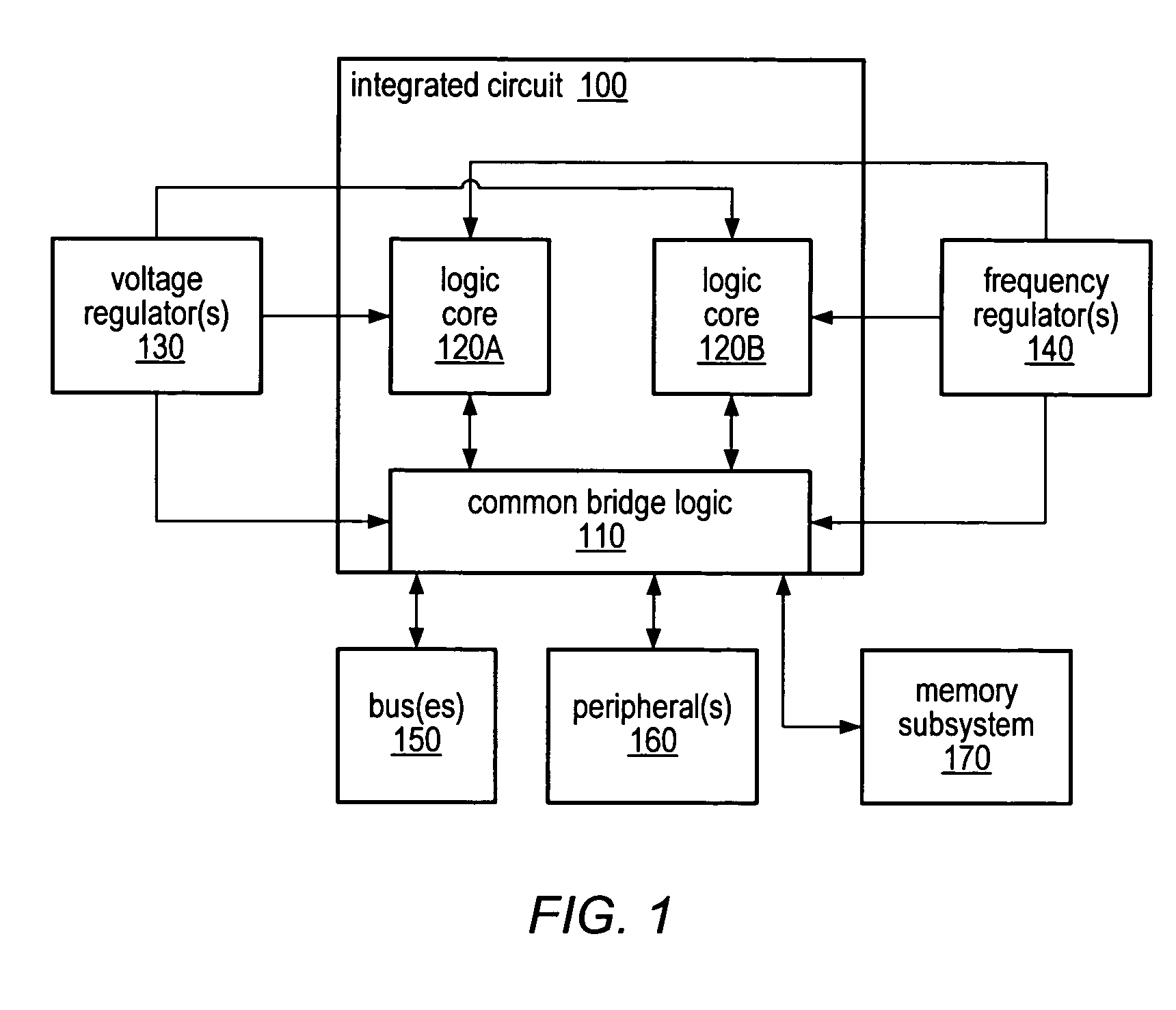

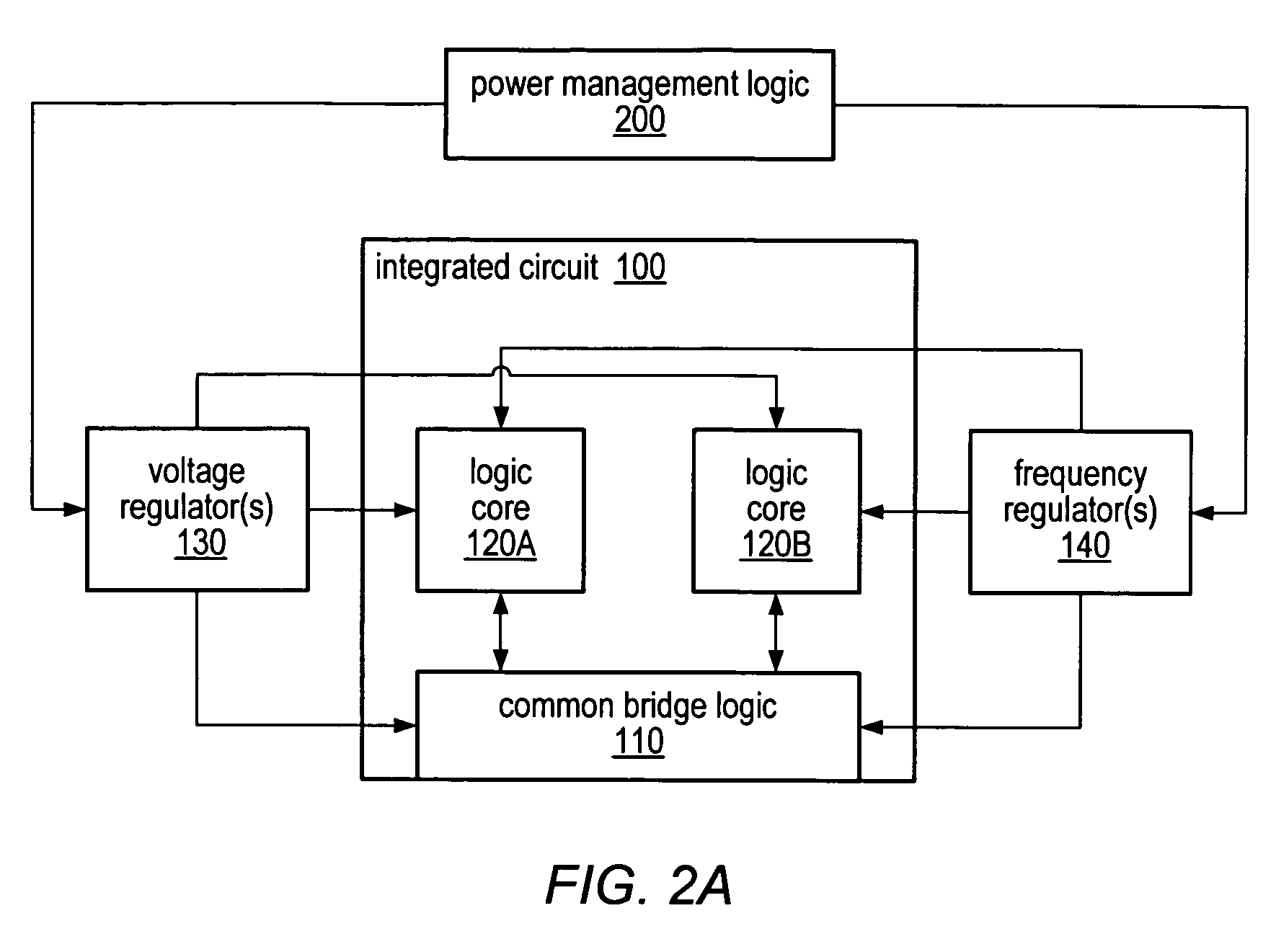

System and method for operating components of an integrated circuit at independent frequencies and/or voltages

ActiveUS7263457B2Lower operating temperatureReduce power consumptionThermometer detailsEnergy efficient ICTTemperature controlOperating point

Owner:MEDIATEK INC

Data storage with overwrite

InactiveUS7012632B2Improve reliabilitySuitable for commercial applicationTelevision system detailsColor television detailsData store

Owner:MITSUBISHI ELECTRIC RES LAB INC

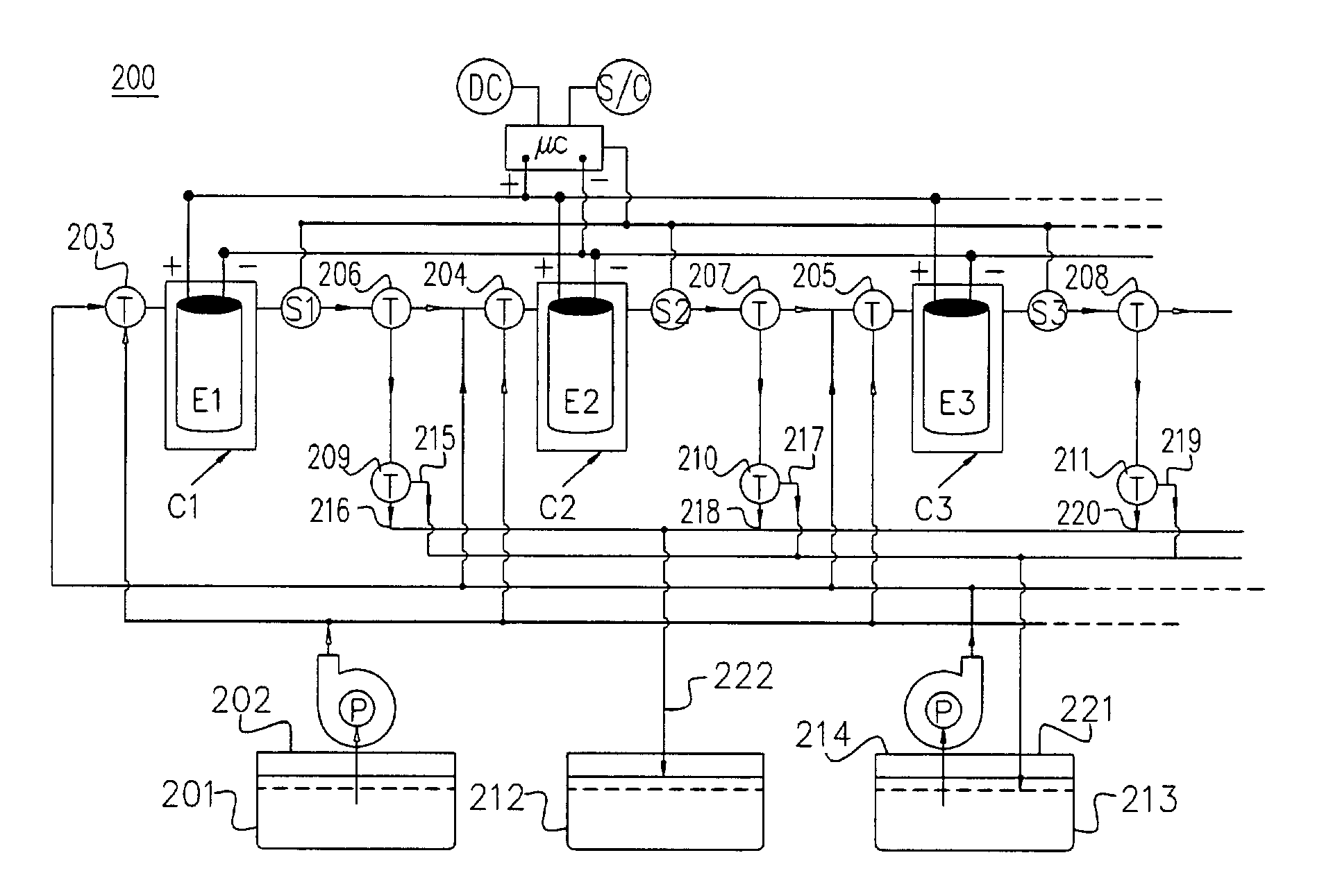

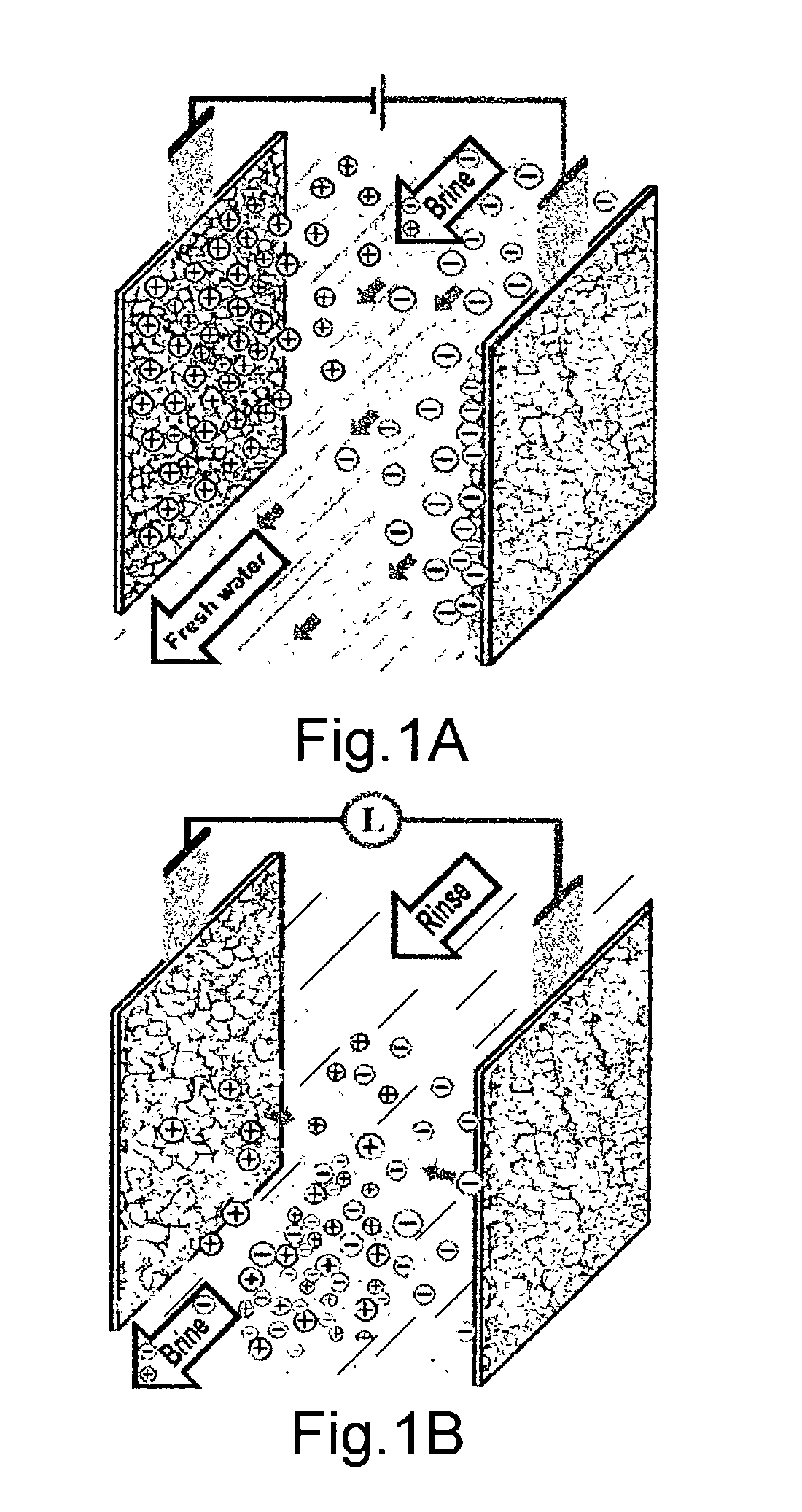

Fully automatic and energy-efficient deionizer

InactiveUS20030098266A1Easy to assembleImprove efficiencyLiquid separation auxillary apparatusSeawater treatmentAutomatic controlComputer module

A fully automatic deionizer comprising five sub-systems for removing ionic contaminants from various liquids at low energy consumption is devised. Based on the charging-discharging principle of capacitors, the deionizer conducts deionization through applying a low DC voltage to its electrodes for adsorbing ions, while more than 30% of the process energy is recovered and stored by discharging the electrodes. At the mean time of discharge, surface of the electrodes is regenerated on site and reset for performing many more cycles of deionization-regeneration till the desirable purification is attained. In one moment, both deionization and regeneration proceed simultaneously on different groups of electrode modules, and in the next moment the electrode modules quickly switch the two processes. Such swift reciprocating actions are engaged in synchronized coordination of sub-systems of electrode modules, energy management, fluid flow, and automatic control.

Owner:GAINIA INTELLECTUAL ASSET SERVICES

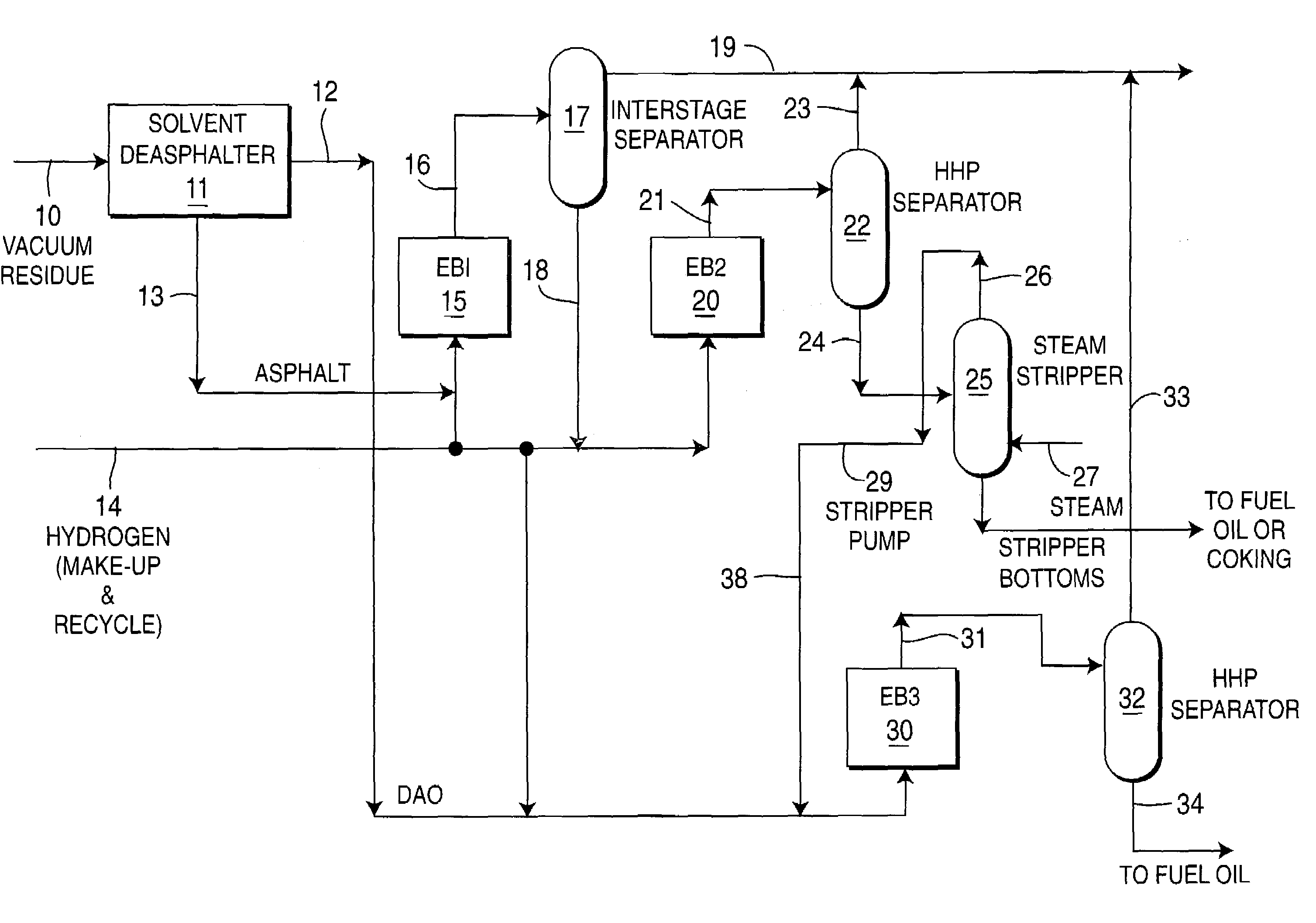

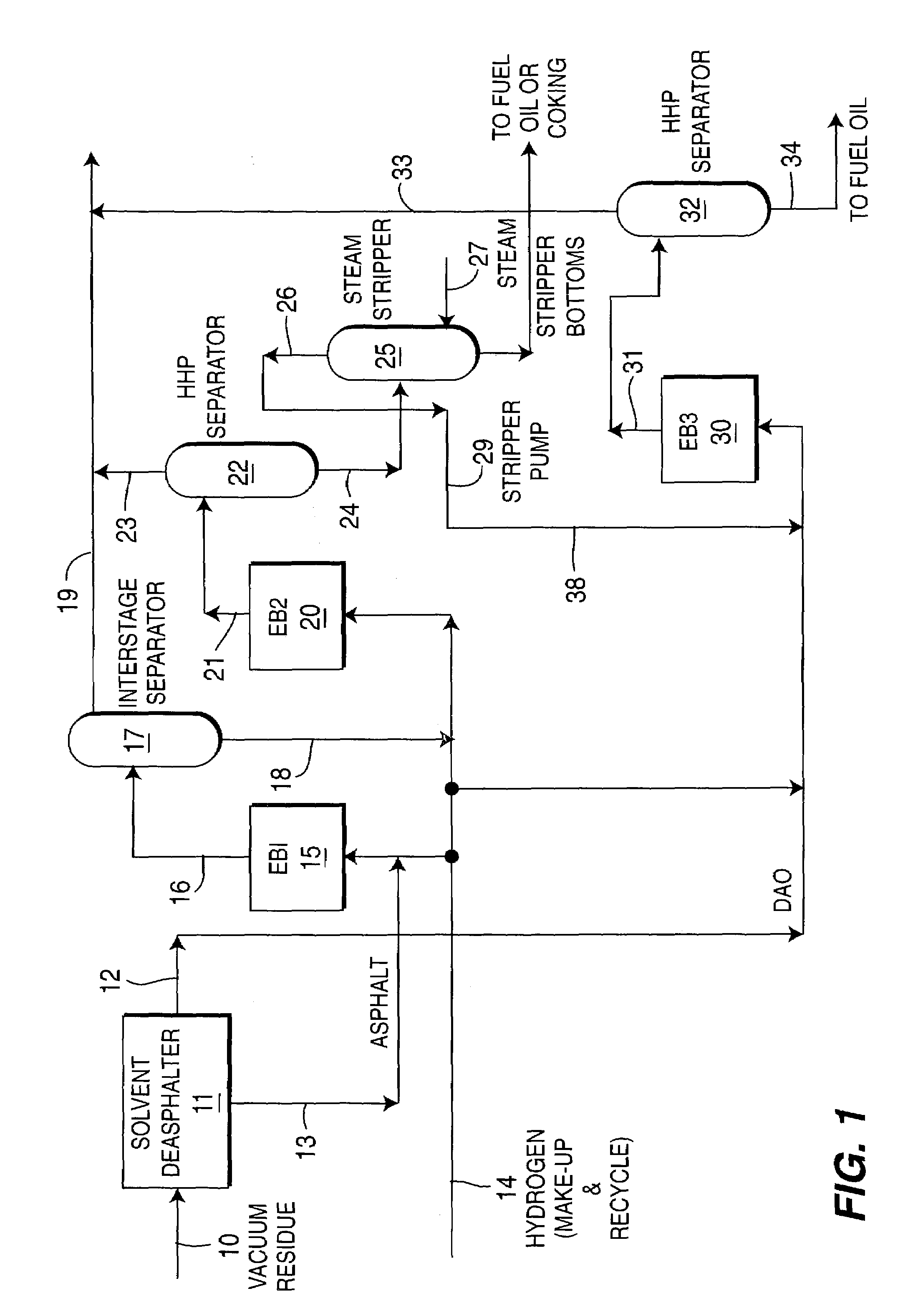

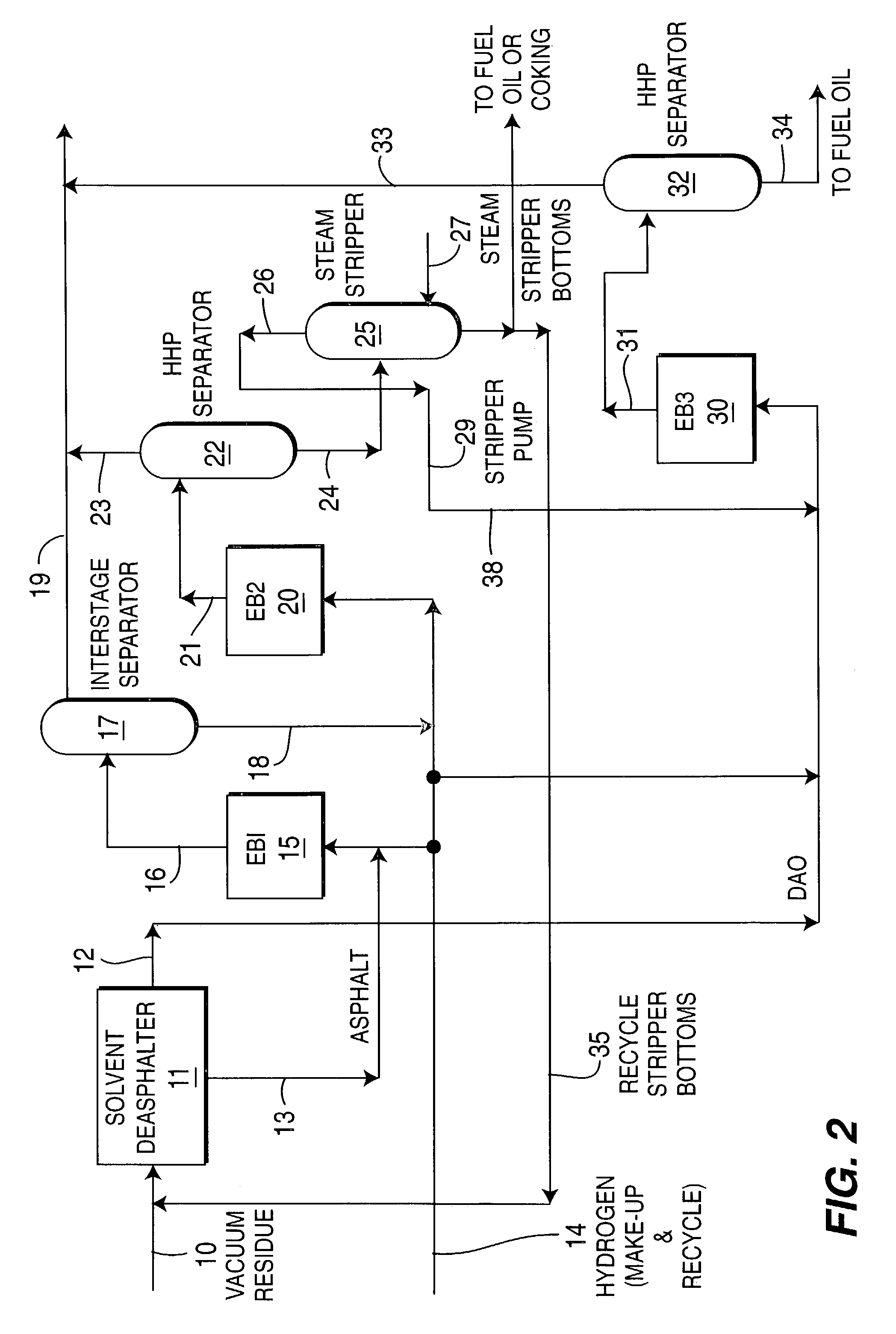

Effective integration of solvent deasphalting and ebullated-bed processing

InactiveUS7214308B2Reduced light gas yieldImprove hydrogen efficiencyTreatment with plural parallel cracking stages onlyTreatment with plural parallel stages onlyReactor systemHeavy crude oil

This invention relates to a novel method for economically processing vacuum residue from heavy crude oils by selectively processing the difficult and easy components in reactors whose design and operating conditions are optimized for the specific feed. The process utilizes an integrated solvent deasphalting (SDA) / ebullated-bed design wherein the heavy vacuum residue feedstock is initially sent to an SDA unit operated with C4 / C5 solvent to achieve a high deasphalted oil (DAO) yield. The resulting SDA products, namely asphaltenes and DAO are separately treated in ebullated-bed reactor(s) systems whose design and operating conditions are optimized for a particular feedstock. The resulting net conversion, associated distillate yield and product qualities are greatly improved relative to treatment of the entire residue feedstock in a common ebullated-bed reactor system.

Owner:INST FR DU PETROLE

Video recording device for a targetable weapon

InactiveUS7158167B1Improve reliabilitySuitable for commercial applicationTelevision system detailsRecord information storageVideo recordCircular buffer

A compact video image recording device which is mountable to a gun and useful for recording video images before and after the firing of the gun. The recording device includes a camera comprising a lens and a video image sensor. The video recording device is mounted on the gun such that the viewing area of the camera includes the target area of the gun. The video image sensor generates an electronic signal representative of a video image impinging the respective sensor. The output of the image sensor is processed and generally employed to produce frame data which are successively stored in successive frame locations of a semiconductor memory organized as a circular buffer memory while the video recording device is in an active state. Upon the firing of the gun, additional frames are stored in the buffer memory for a short period of time and a portion of the buffer memory is employed to preserve a video record of the shooting both before and after the event. Additional frames are successively stored in the unused portion of the buffer memory. In the event of a further firing of the gun, an additional portion of the buffer memory is dedicated to preserving the image data associated with subsequent firing incident. This process may be repeated until the buffer memory is full in the event the gun is repeatedly fired. A video record is thus generated which documents the circumstances preceding and following the firing of the gun.

Owner:MITSUBISHI ELECTRIC RES LAB INC

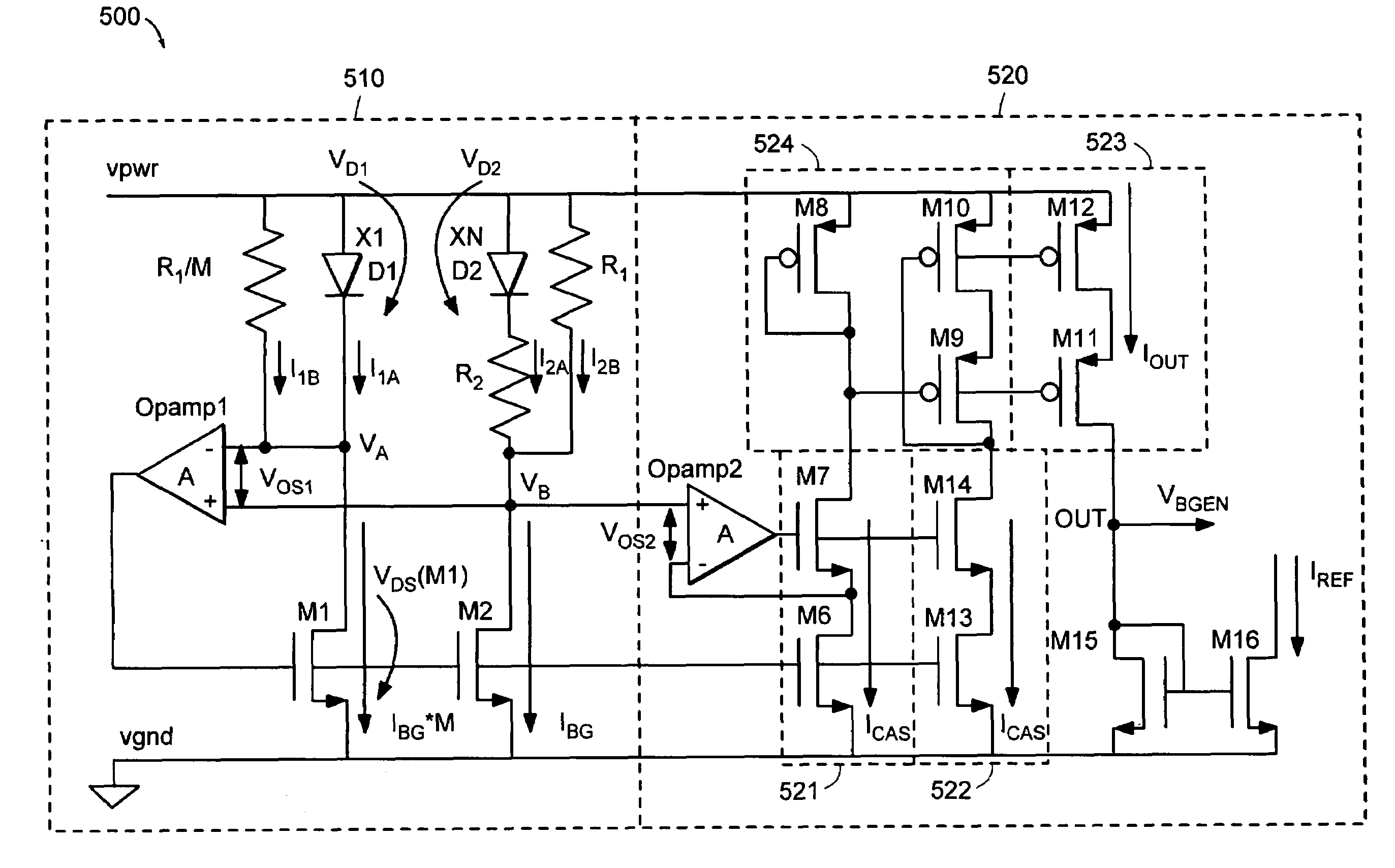

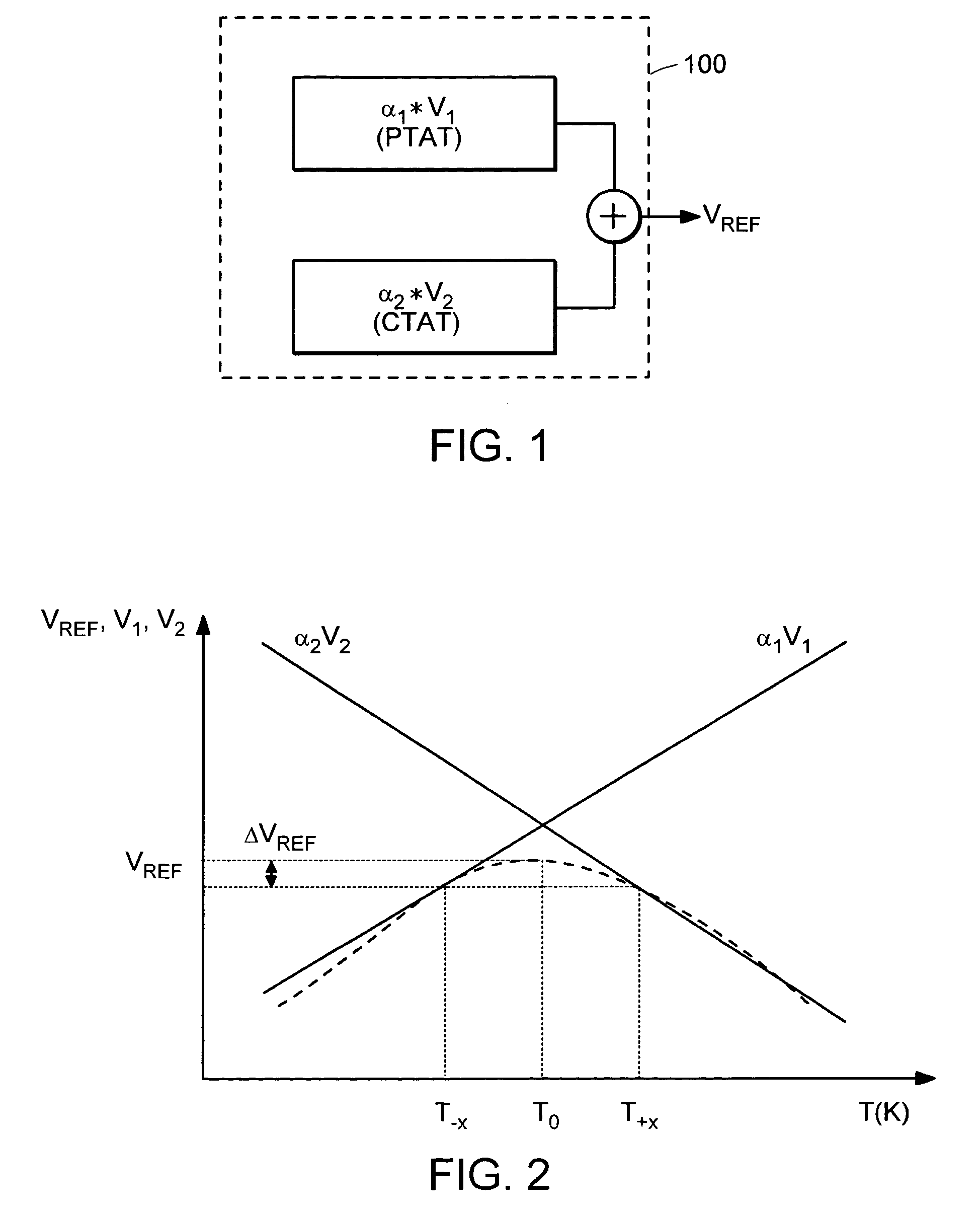

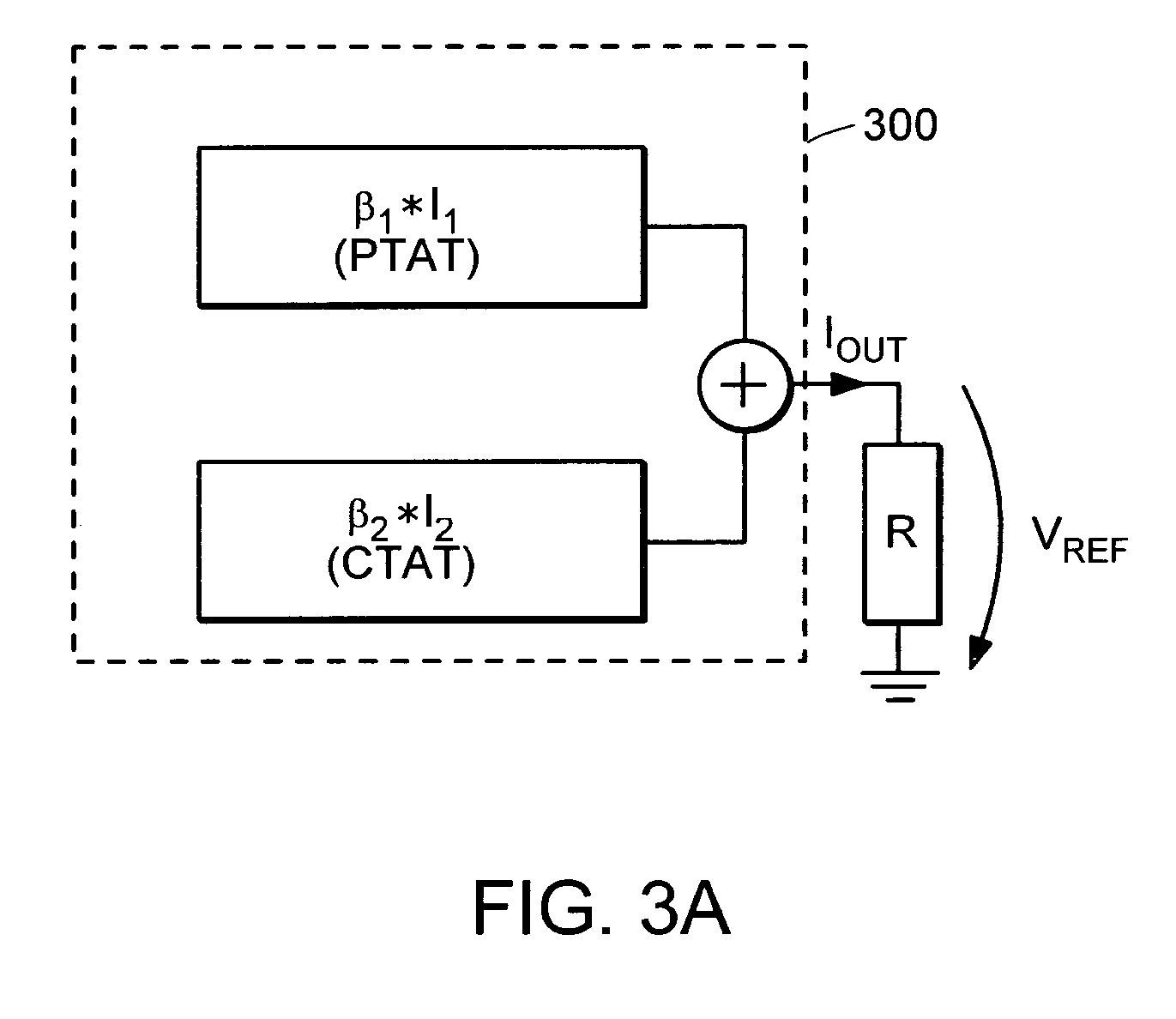

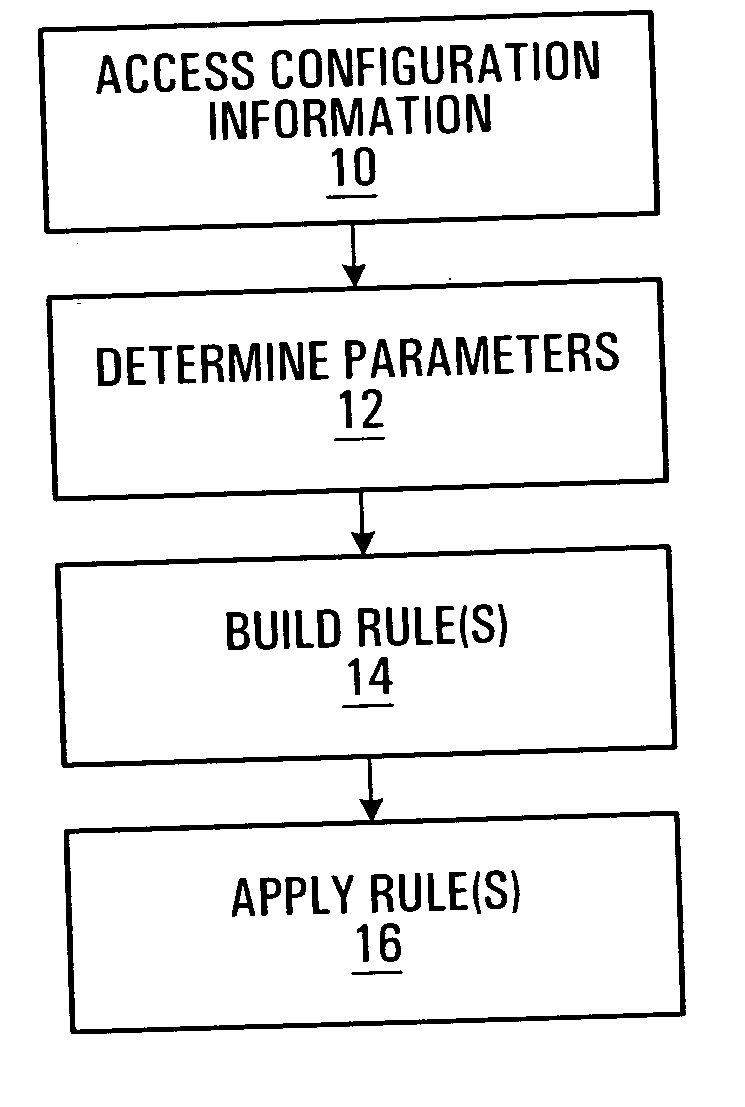

High PSRR, high accuracy, low power supply bandgap circuit

ActiveUS7199646B1Improve accuracyIncrease output impedanceElectric variable regulationAudio power amplifierCascode

A bandgap circuit comprising a current generation circuit and a current replication circuit is provided herein. The output current of the current generation circuit is generated as a weighted sum of two currents. The circuit configuration of the current generation circuit allows it to function at low power supply voltages, e.g., on the order of 1 V. The current replication circuit includes an operational amplifier, which when configured in conjunction with MOS cascode current sources and the current generation circuit, significantly increases the accuracy and insensitivity to power supply noise of the bandgap circuit output current. A resistor may be included between the bandgap circuit output node and ground for generating a reference voltage with increased accuracy and insensitivity to power supply noise.

Owner:MONTEREY RES LLC

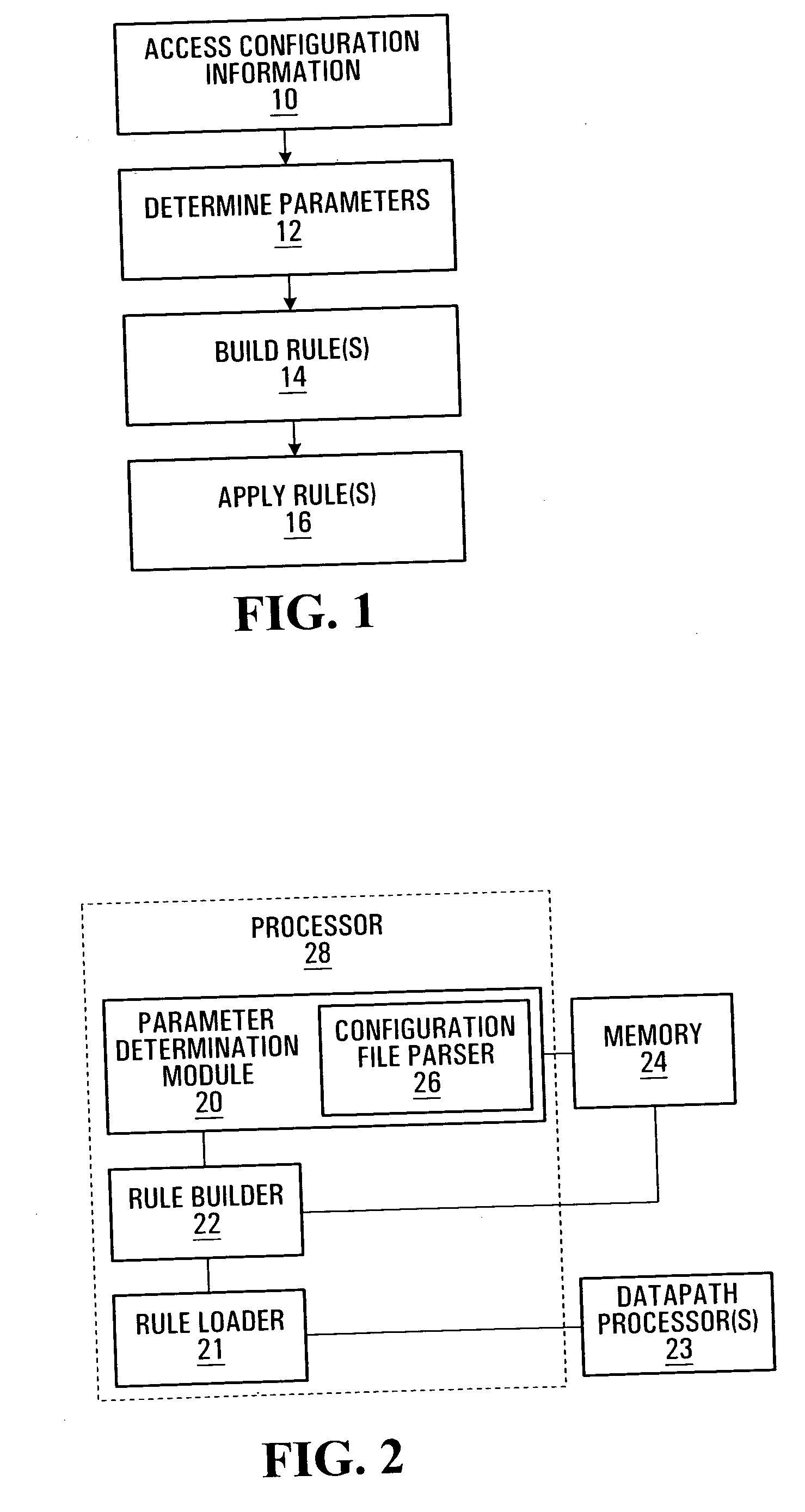

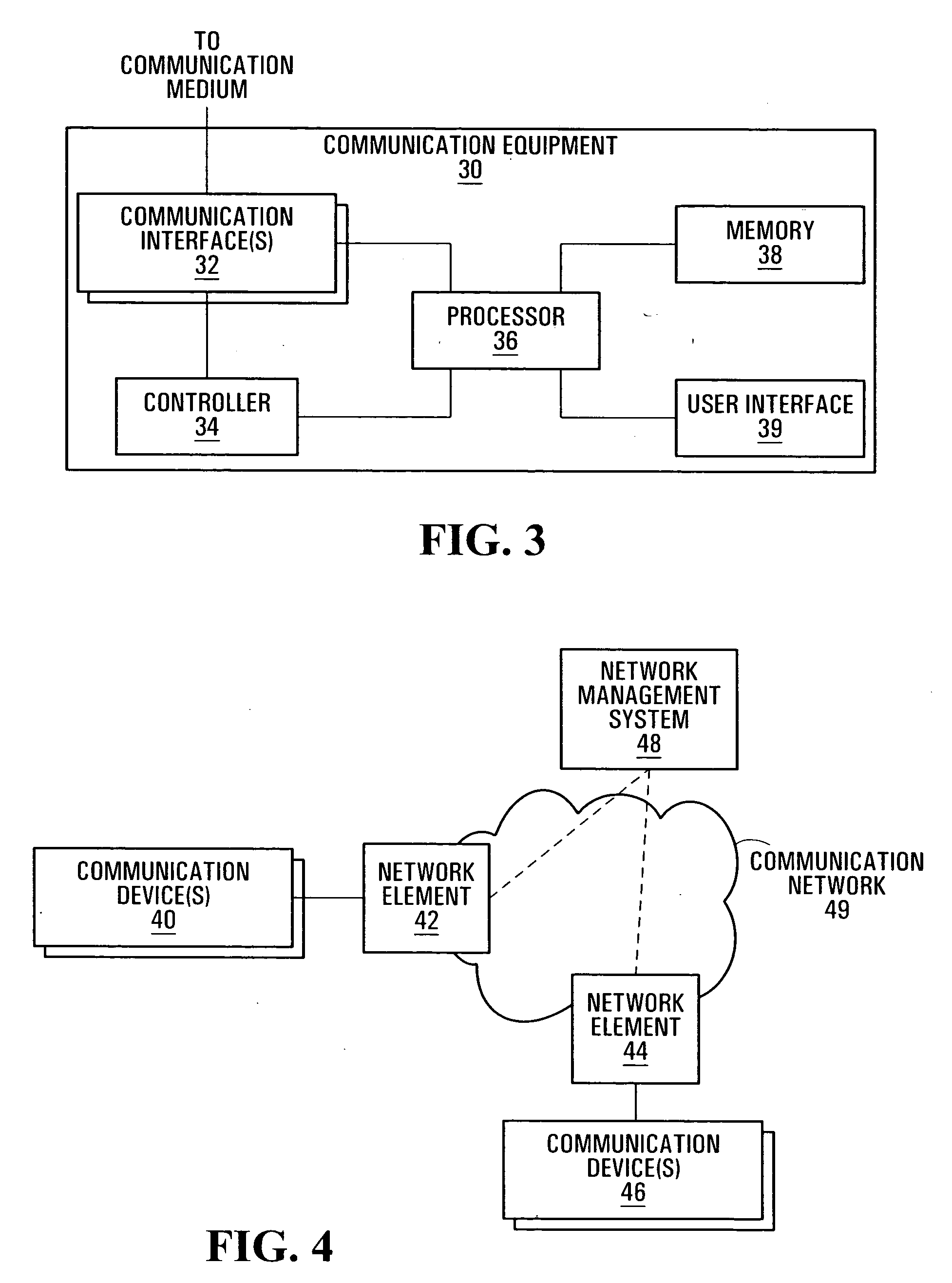

Communication traffic control rule generation methods and systems

InactiveUS20060106919A1Reduce operating costsReduced operating requirementsDigital computer detailsData switching networksTraffic volumeTraffic capacity

Methods and systems for communication traffic control rule generation are provided. Configuration information for communication equipment, default information stored for the communication equipment, or both, is accessed. One or more parameters which affect processing of communication traffic by the communication equipment are determined from the accessed information and used to generate a communication traffic control rule to be applied to communication traffic at the communication equipment. The generated communication traffic control rule is applied at interfaces of the communication equipment to communication traffic being terminated by the communication equipment.

Owner:ALCATEL LUCENT SAS

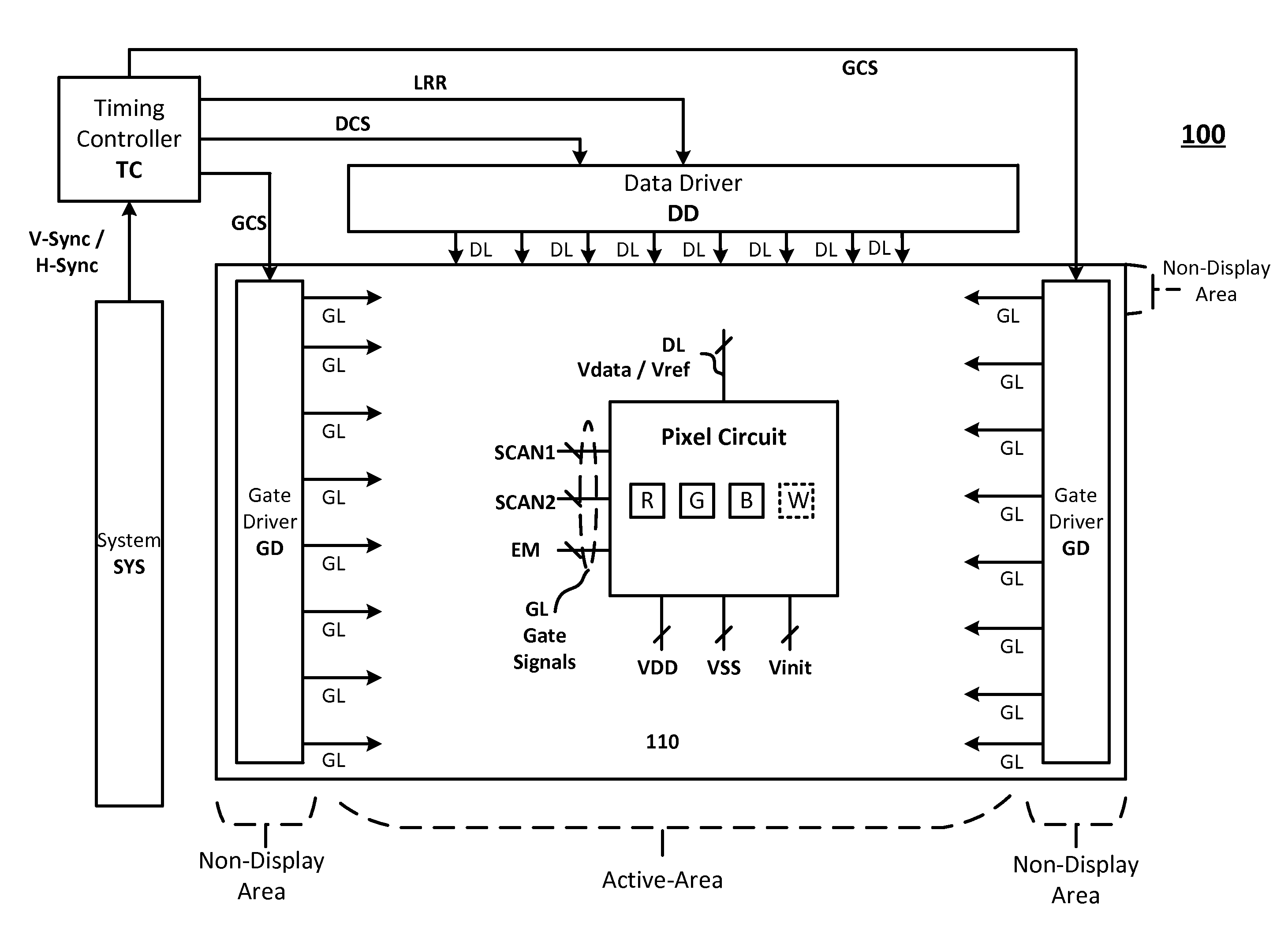

Display Having Selective Portions Driven with Adjustable Refresh Rate and Method of Driving the Same

ActiveUS20150243203A1Improve low refresh mode operation of displayLower areaSolid-state devicesCathode-ray tube indicatorsEngineeringActive layer

There is provided a TFT backplane having at least one TFT with oxide active layer and at least one TFT with poly-silicon active layer. In the embodiments of the present disclosure, at least one of the TFTs implementing the circuit of pixels in the active area is an oxide TFT (i.e., TFT with oxide semiconductor) while at least one of the TFTs implementing the driving circuit next to the active area is a LTPS TFT (i.e., TFT with poly-Si semiconductor).

Owner:LG DISPLAY CO LTD

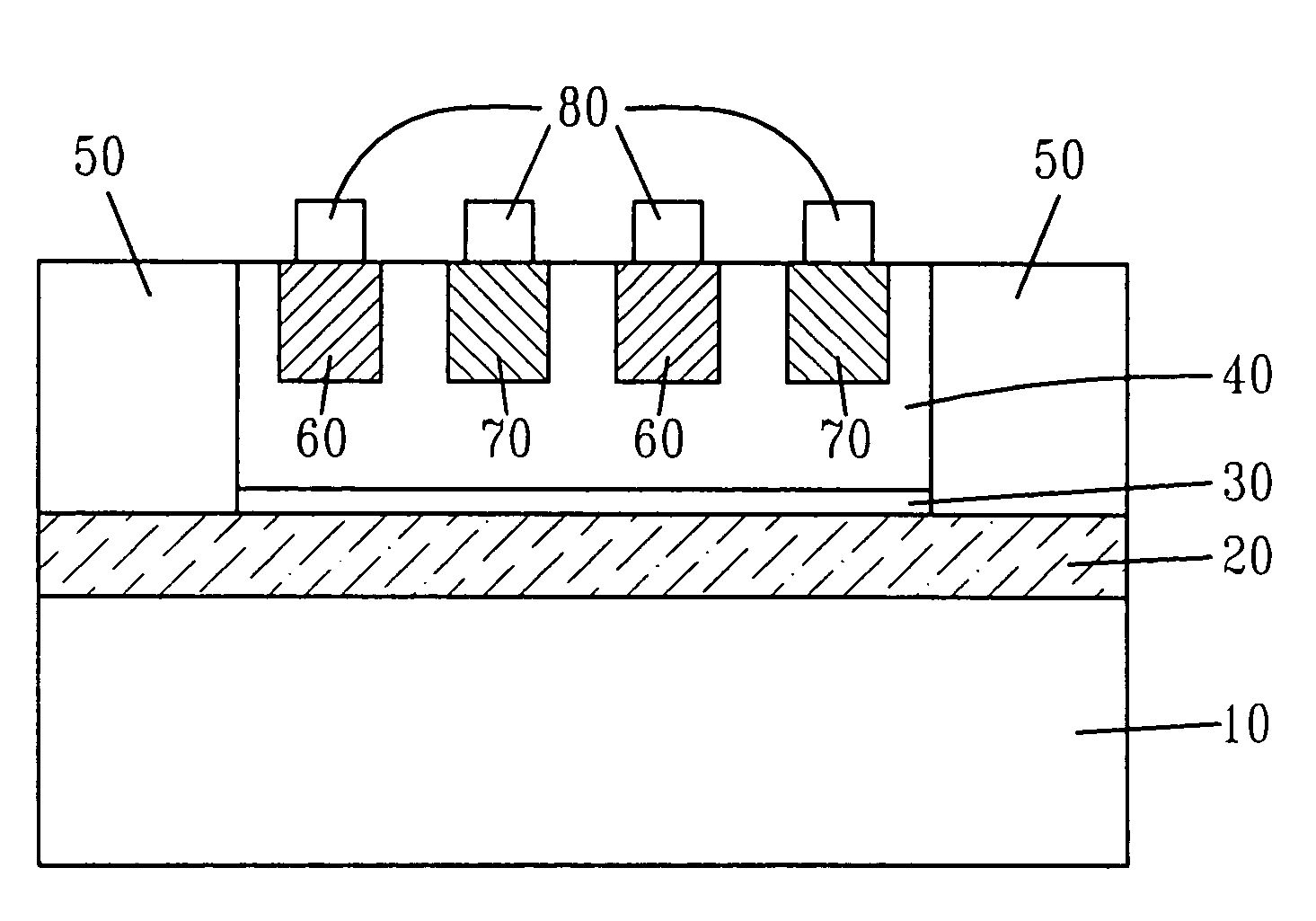

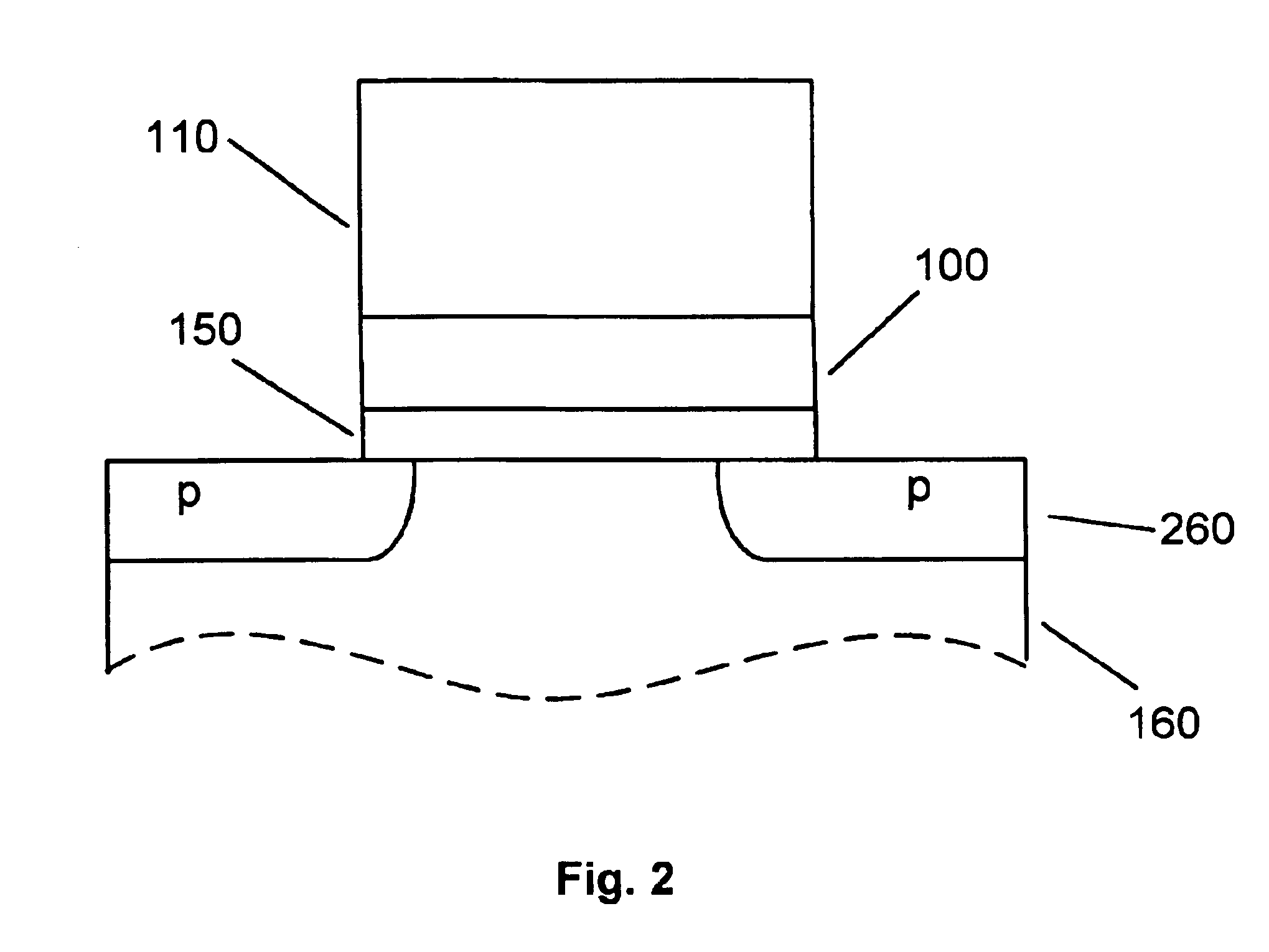

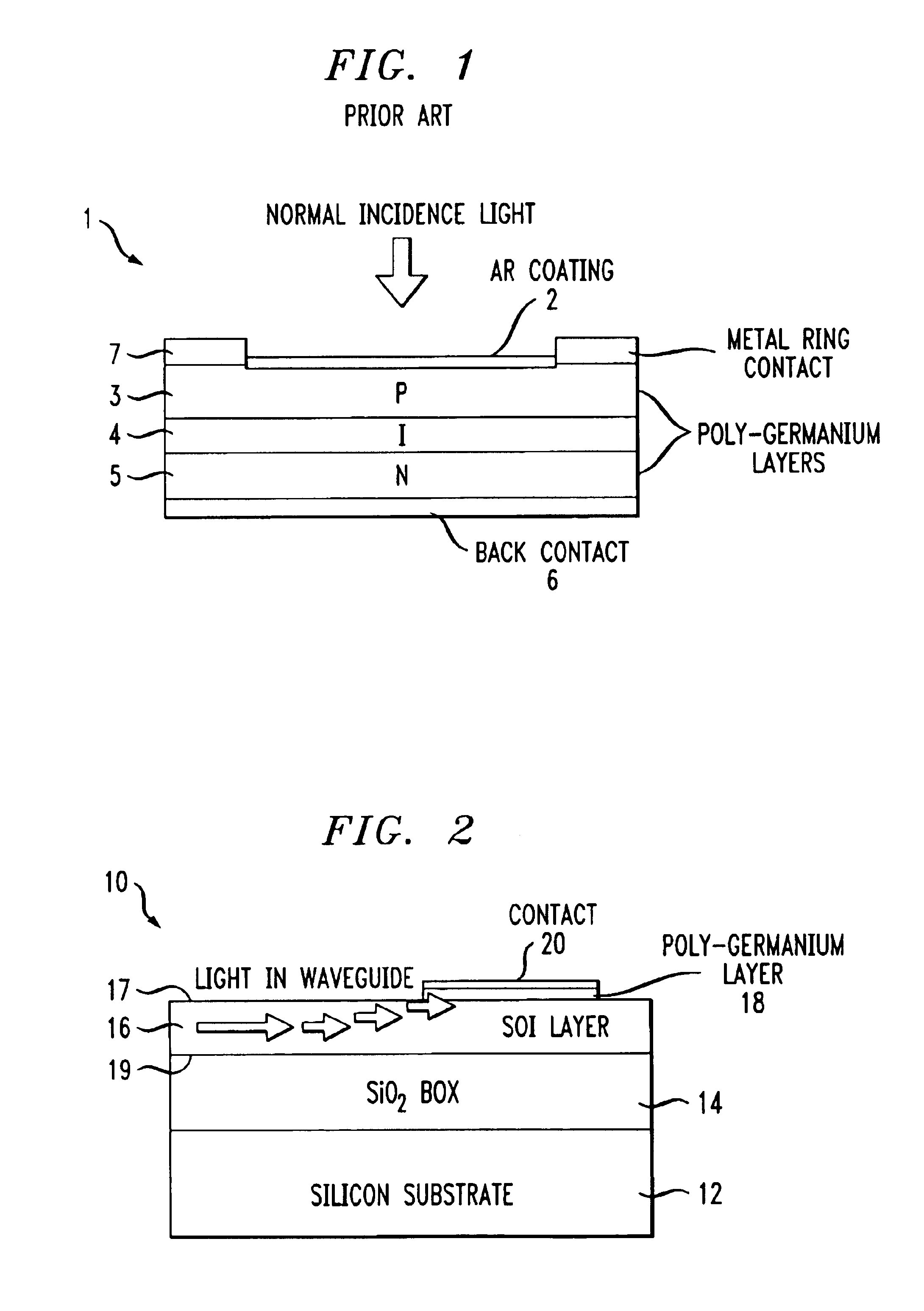

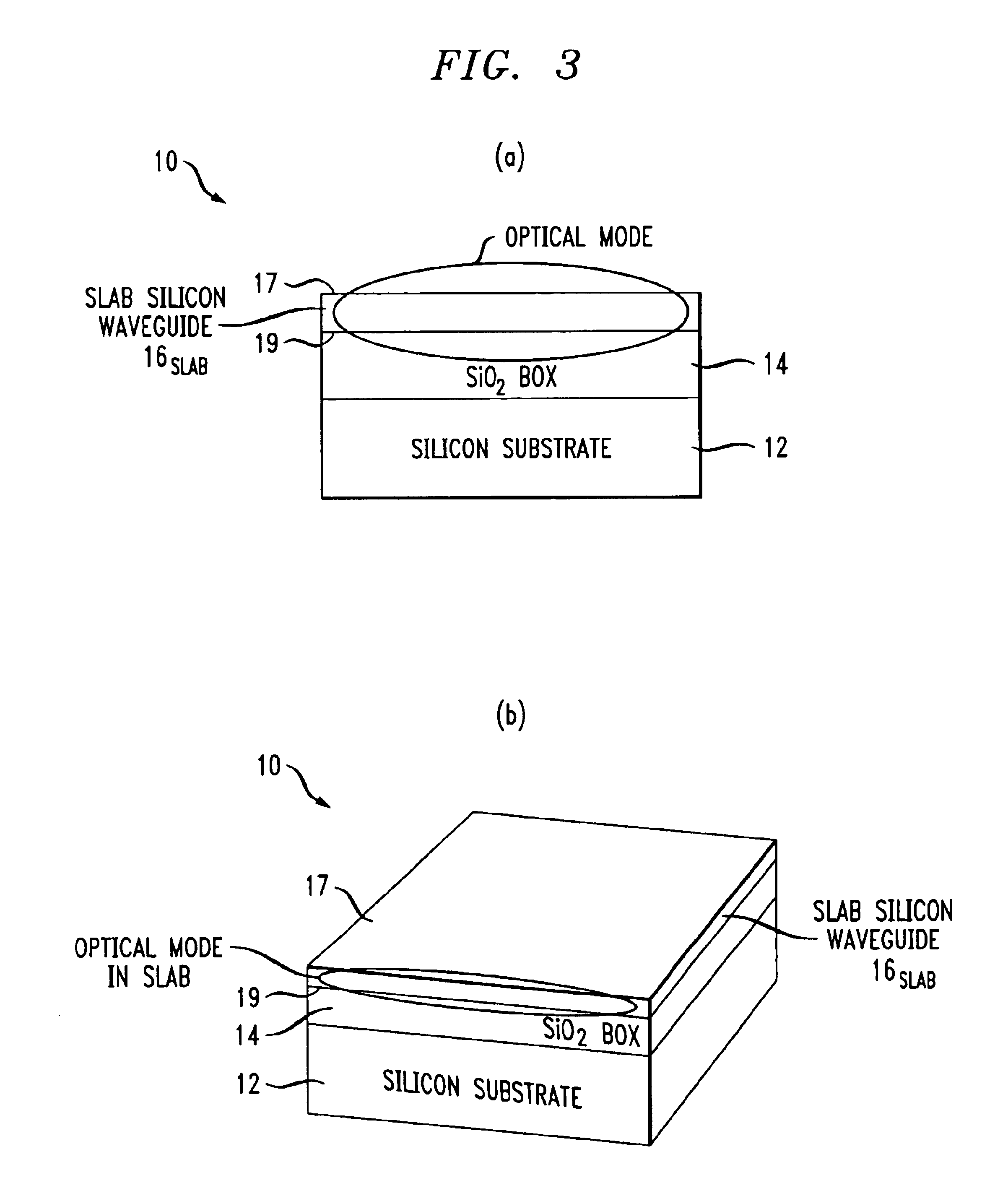

Structure for and method of fabricating a high-speed CMOS-compatible Ge-on-insulator photodetector

ActiveUS20050184354A1High bandwidthLow ON voltage operationSolid-state devicesSemiconductor/solid-state device manufacturingCMOSHigh bandwidth

The invention addresses the problem of creating a high-speed, high-efficiency photodetector that is compatible with Si CMOS technology. The structure consists of a Ge absorbing layer on a thin SOI substrate, and utilizes isolation regions, alternating n- and p-type contacts, and low-resistance surface electrodes. The device achieves high bandwidth by utilizing a buried insulating layer to isolate carriers generated in the underlying substrate, high quantum efficiency over a broad spectrum by utilizing a Ge absorbing layer, low voltage operation by utilizing thin a absorbing layer and narrow electrode spacings, and compatibility with CMOS devices by virtue of its planar structure and use of a group IV absorbing material. The method for fabricating the photodetector uses direct growth of Ge on thin SOI or an epitaxial oxide, and subsequent thermal annealing to achieve a high-quality absorbing layer. This method limits the amount of Si available for interdiffusion, thereby allowing the Ge layer to be annealed without causing substantial dilution of the Ge layer by the underlying Si.

Owner:GLOBALFOUNDRIES US INC

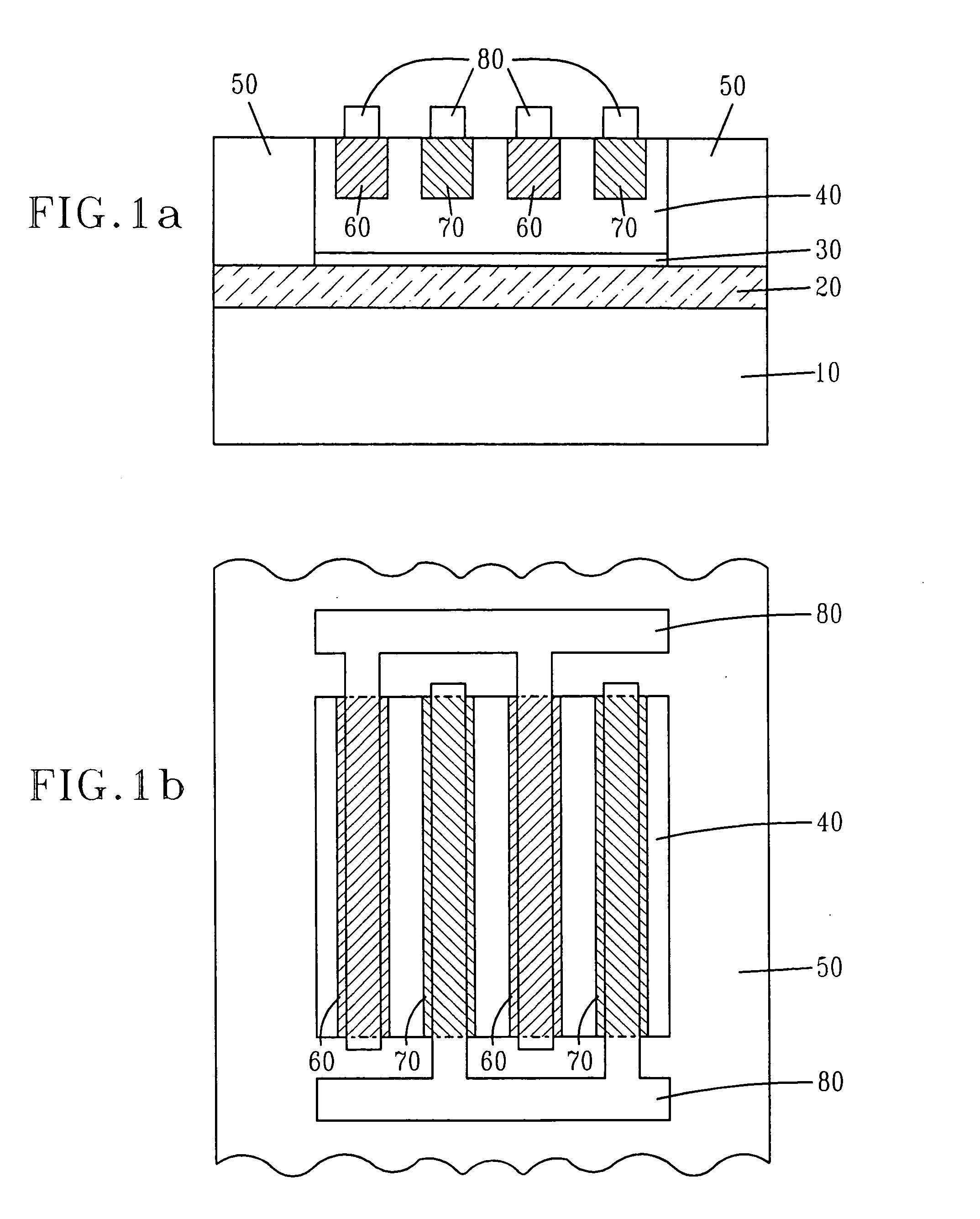

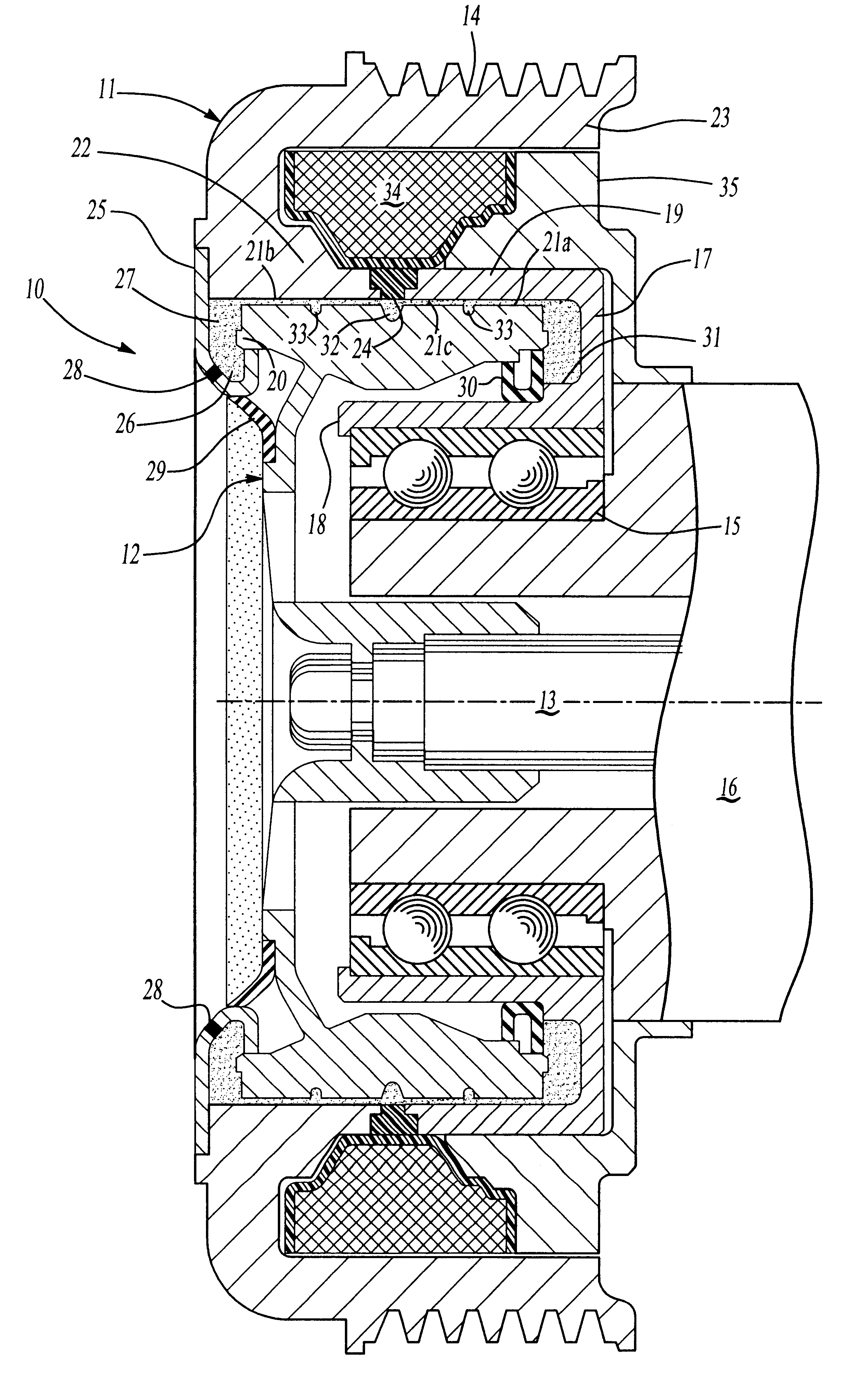

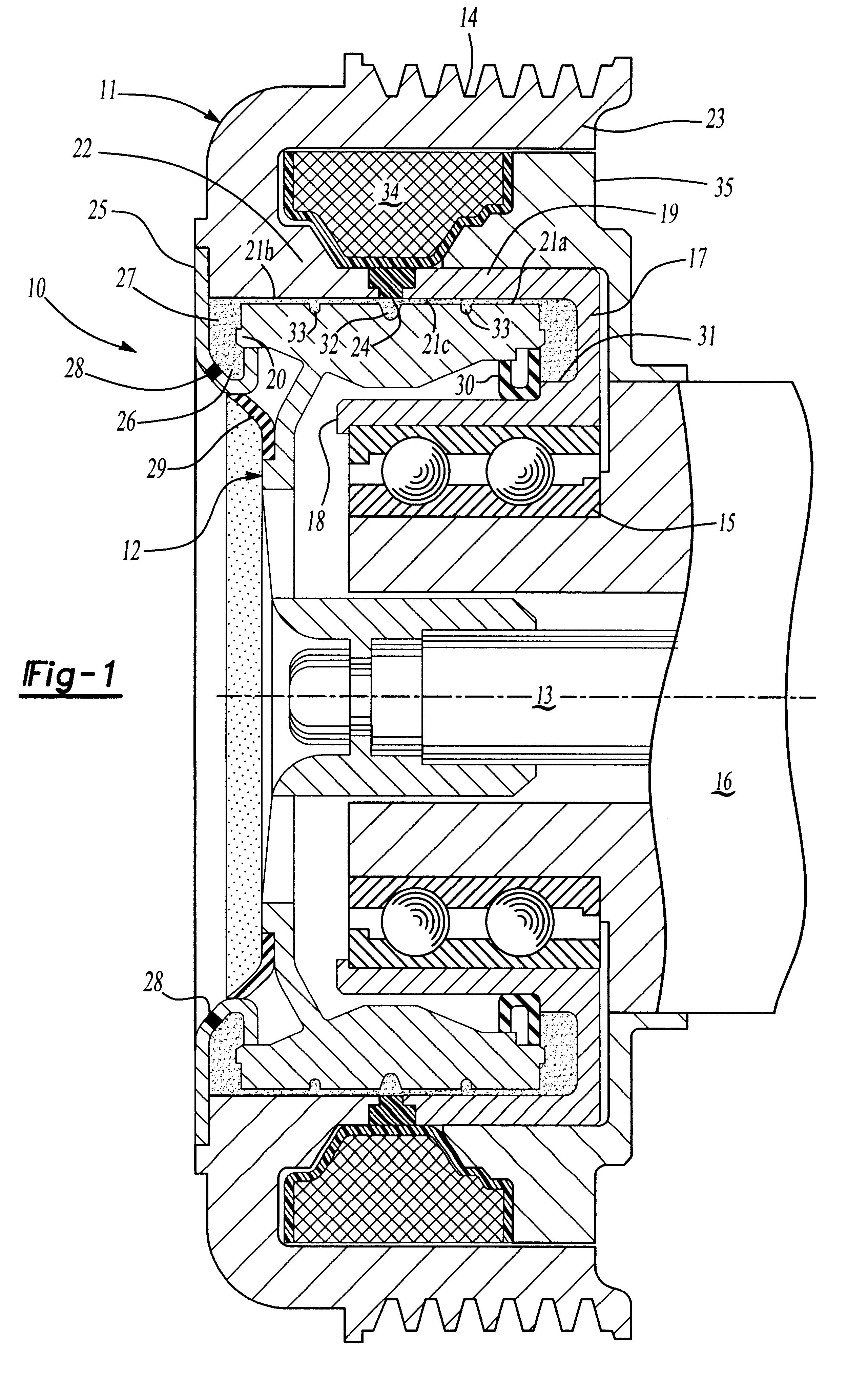

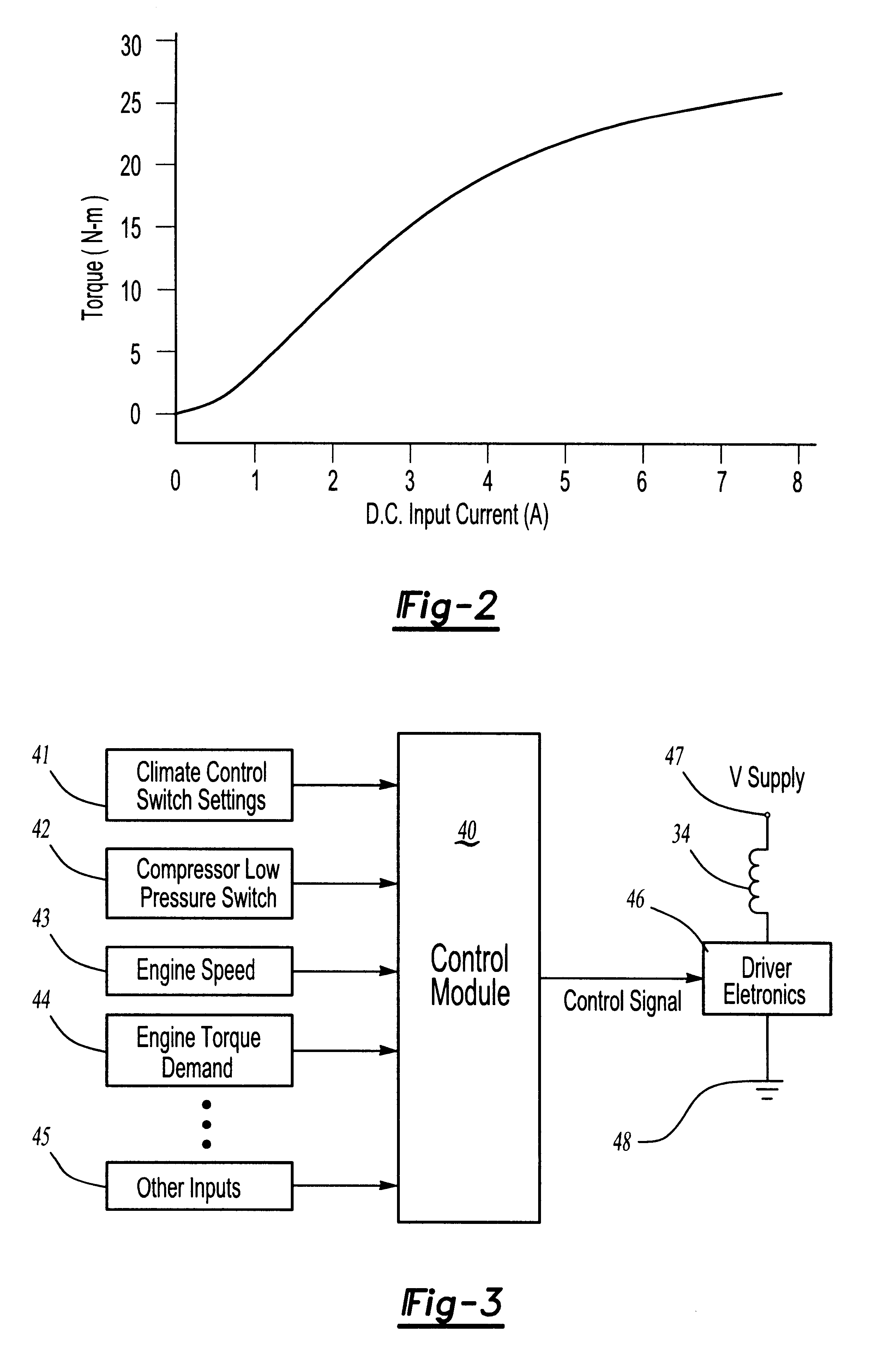

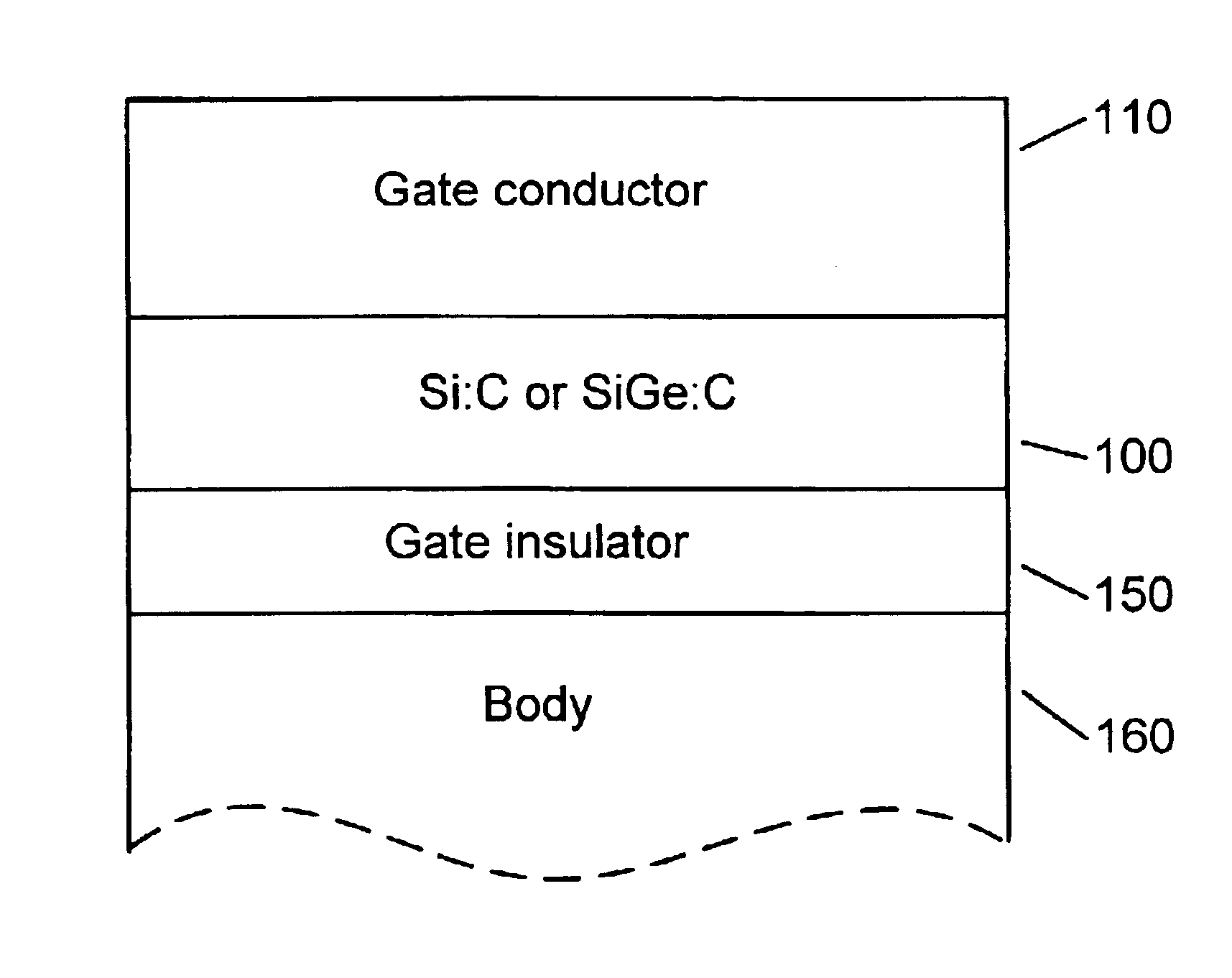

Soft start compressor clutch

InactiveUS6290043B1Start softLess objectionable noiseMagnetically actuated clutchesInterengaging clutchesElectromagnetic clutchEngineering

An electromagnetic clutch (10) for an air conditioning compressor includes a generally cylindrical pulley (11) rotatably mounted on a compressor housing (16) and having an annular friction surface (21b), a driven member (12) mounted on a compressor shaft (13) and having an annular friction surface (21a) positioned radially adjacent the first friction surface to form an annular space (21c) therebetween. A quantity of flowable magnetic material (27) is provided in the annular space (21c) and a magnetic coil (34) is fixed on the housing adjacent thereto. A control (40,46,46') connected to the magnetic coil (34) supplies electrical power from a power supply (47) to energize the magnetic coil and create magnetic flux in the annular space (21c) polarizing the magnetic material and frictionally coupling the first and second friction surfaces (21a,21b) to cause the pulley (11) to rotate the driven member (12). The control (40,46,46') can pulse width modulate or ramp the supplied power for "soft" starting and / or stopping of the compressor.

Owner:VISTEON GLOBAL TECH INC +1

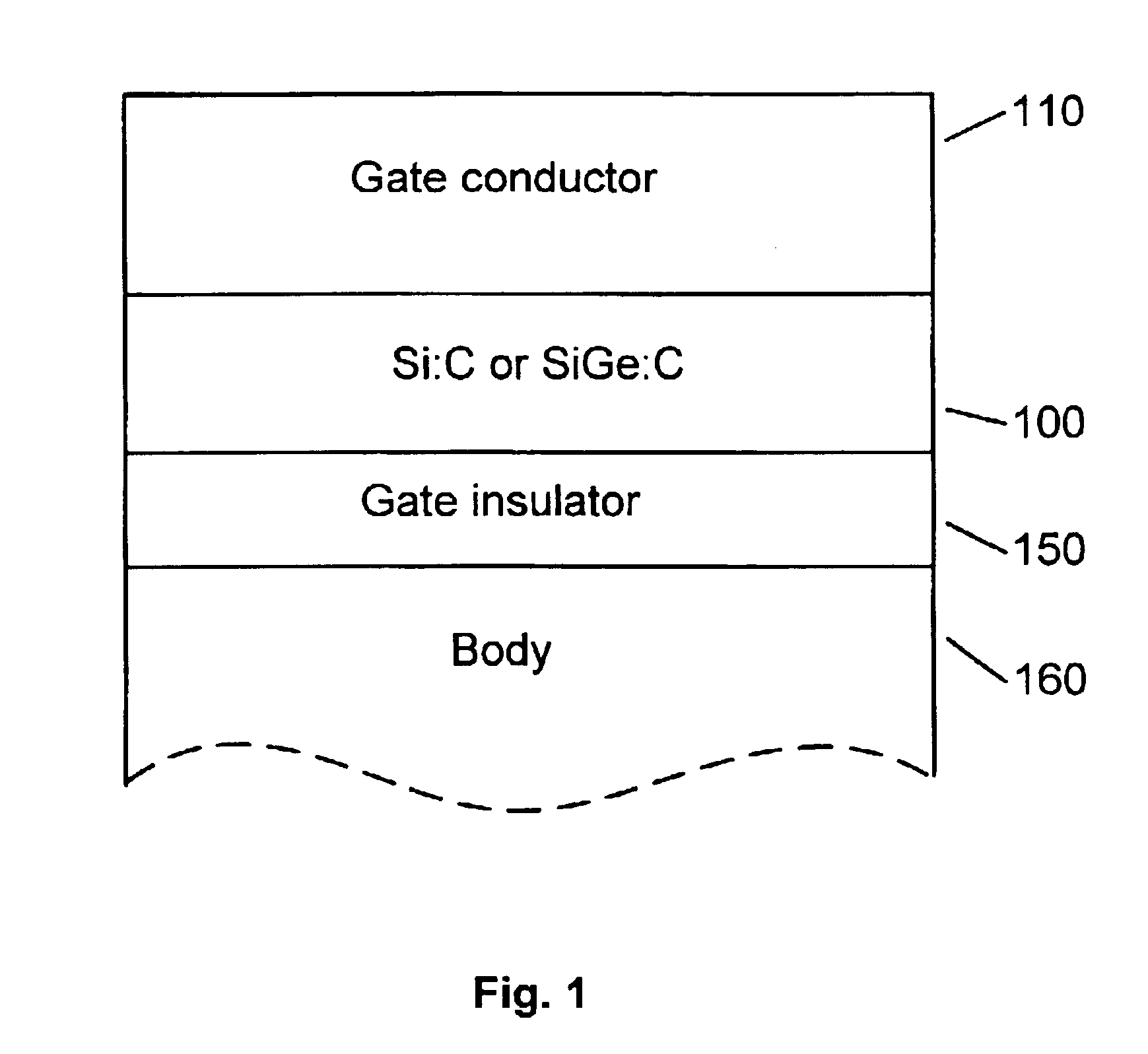

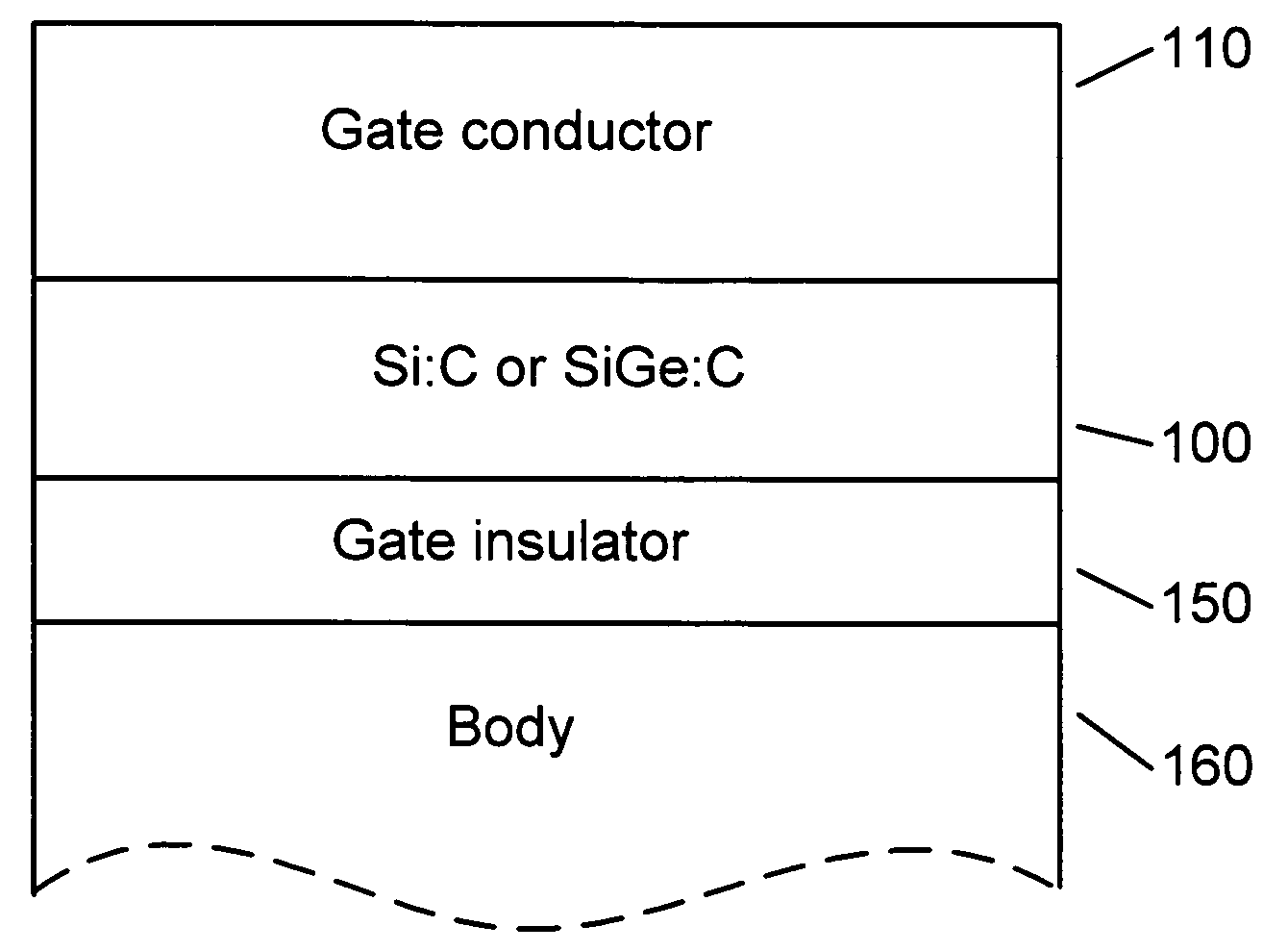

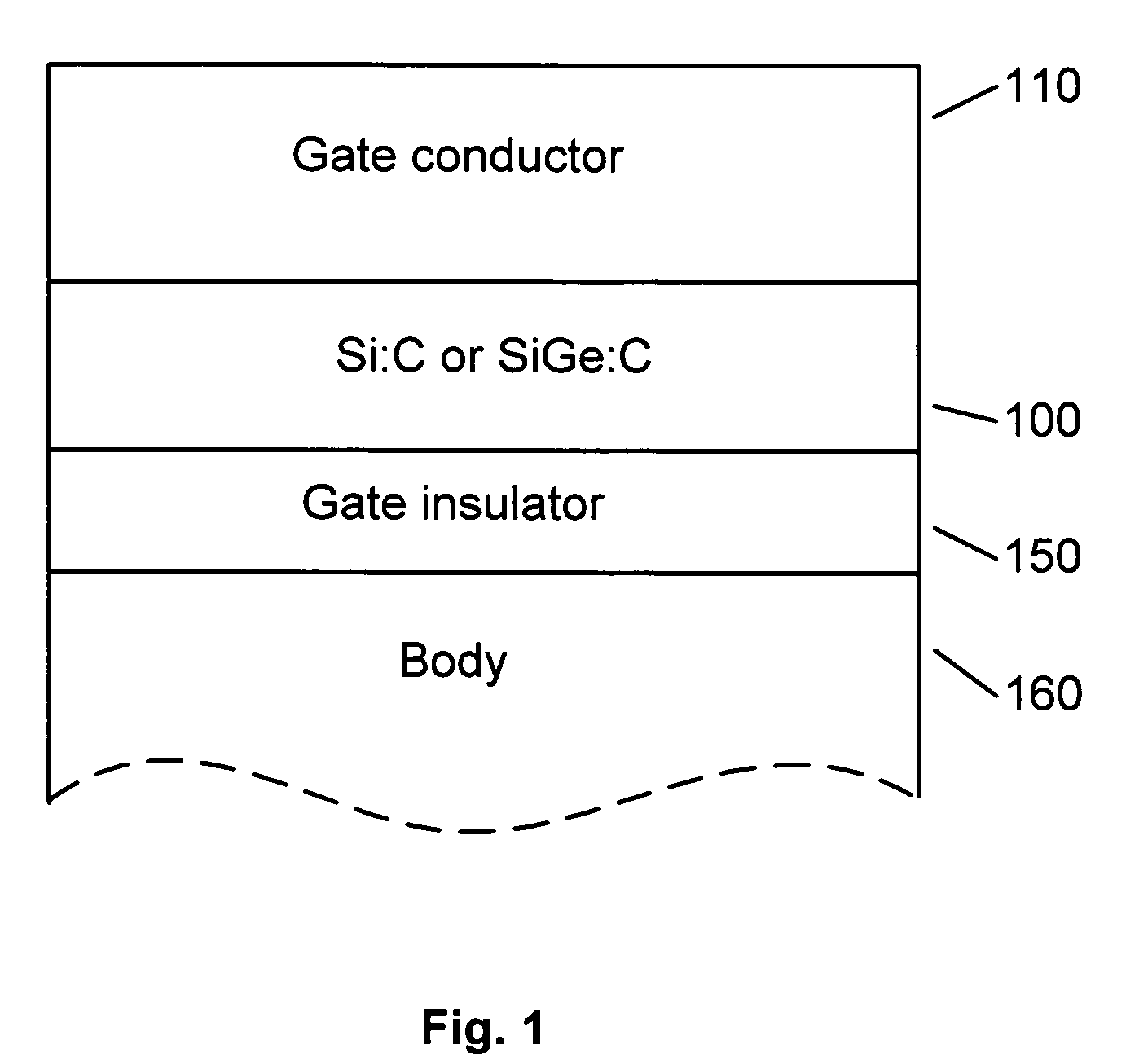

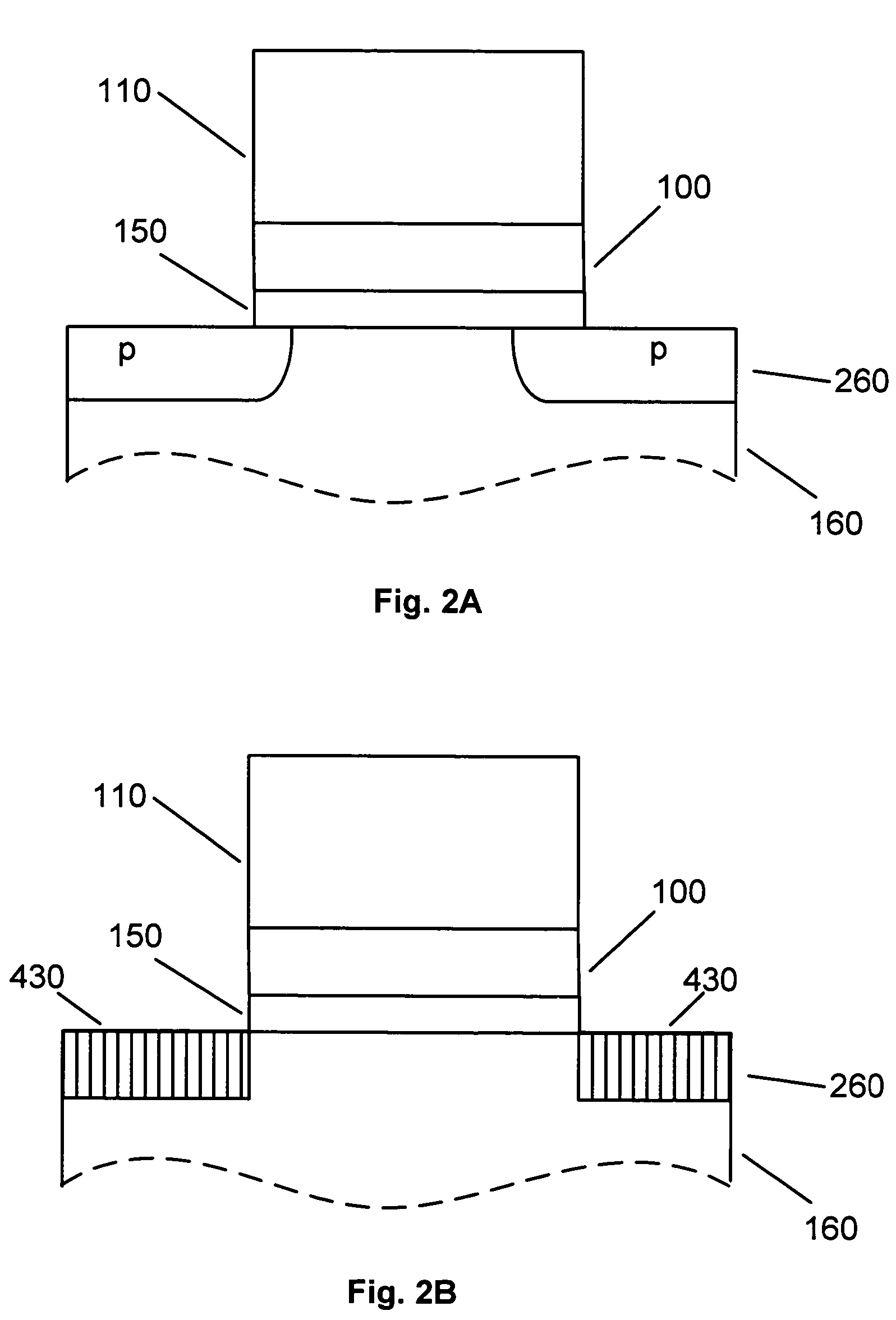

High performance FET devices and methods therefor

InactiveUS6909186B2Suitable for low temperature operationIncrease the areaTransistorSemiconductor/solid-state device detailsDopantGate insulator

Structure and methods of fabrication are disclosed for an enhanced FET devices in which dopant impurities are prevented from diffusing through the gate insulator. The structure comprises a Si:C, or SiGe:C, layer which is sandwiched between the gate insulator and a layer which is doped with impurities in order to provide a preselected workfunction. It is further disclosed how this, and further improvements for FET devices, such as raised source / drain and multifaceted gate on insulator, MODFET on insulator are integrated with strained Si based layer on insulator technology.

Owner:IBM CORP

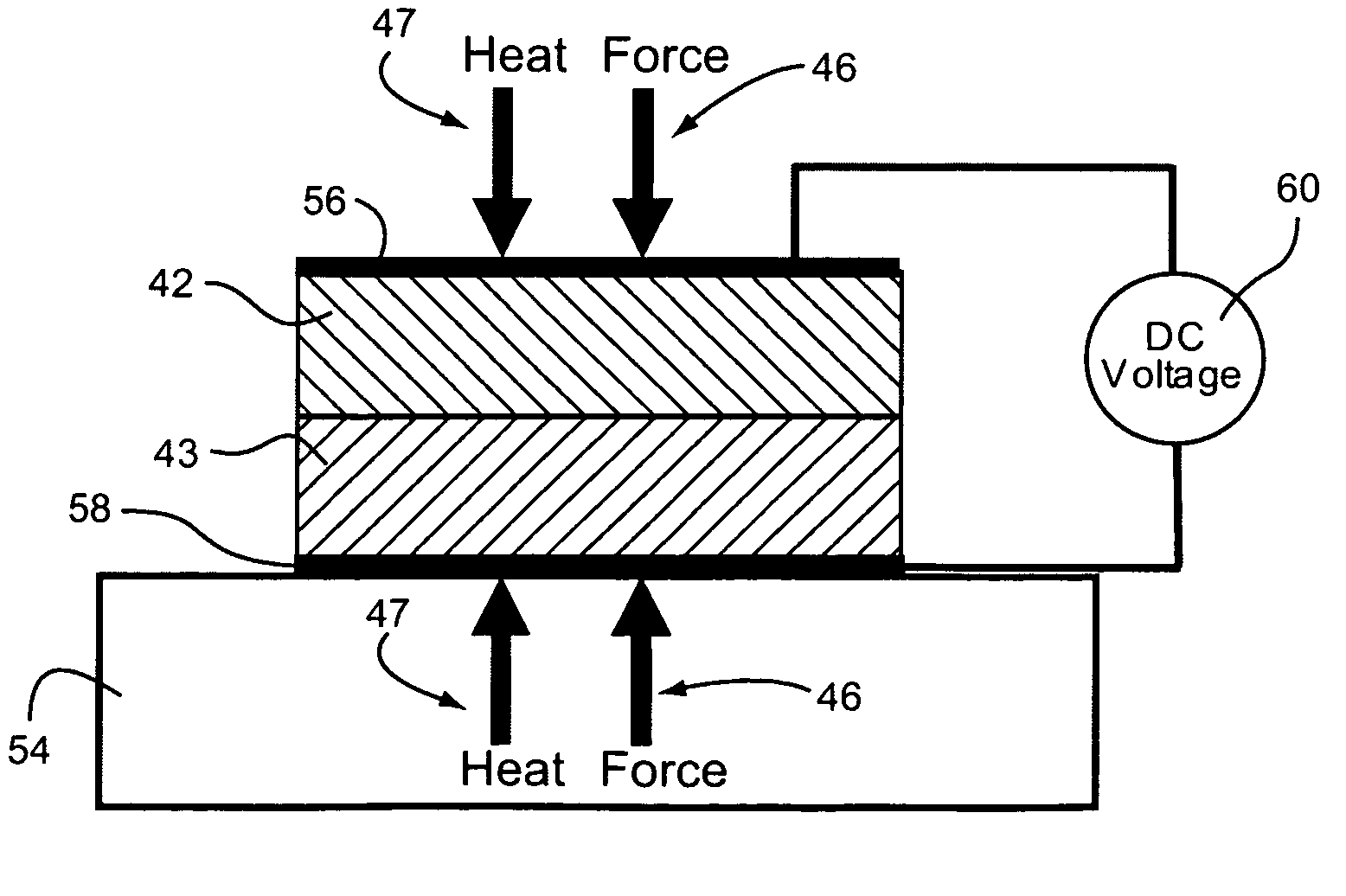

Low-temperature wafer bonding of semiconductor substrates to metal substrates

ActiveUS20090286382A1Lower resistanceReduce thermal resistanceSolid-state devicesSemiconductor/solid-state device manufacturingElectrical resistance and conductanceSemiconductor materials

A method of wafer or substrate bonding a substrate made of a semiconductor material with a substrate made from a metallic material is disclosed. The method allows the bonding of the two substrates together without the use of any intermediate joining gluing, or solder layer(s) between the two substrates. The method allows the moderate or low temperature bonding of the metal and semiconductor substrates, combined with methods to modify the materials so as to enable low electrical resistance interfaces to be realized between the bonded substrates, and also combined with methods to obtain a low thermal resistance interface between the bonded substrates, thereby enabling various useful improvements for fabrication, packaging and manufacturing of semiconductor devices and systems.

Owner:FOR NAT RES INITIATIVES

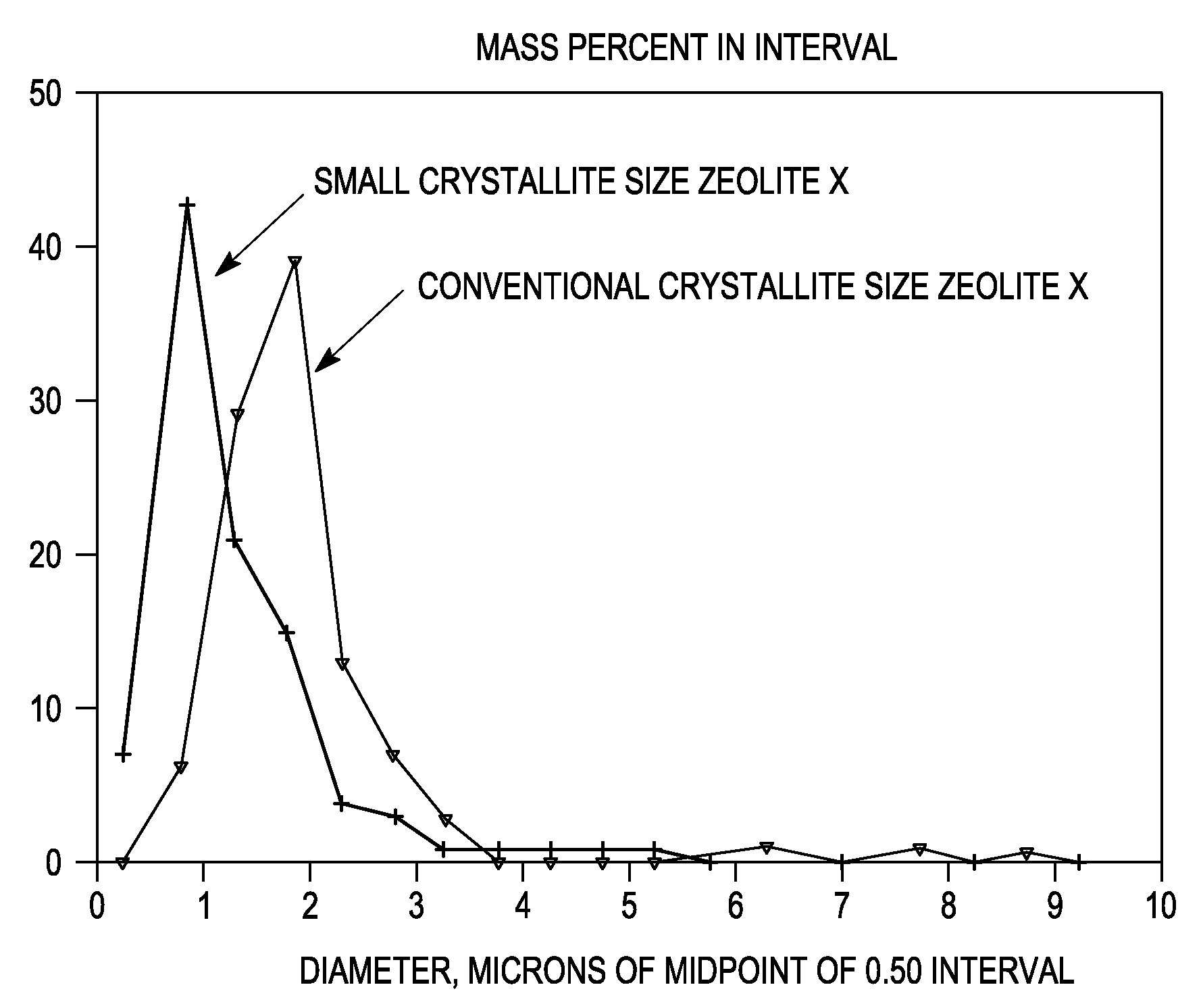

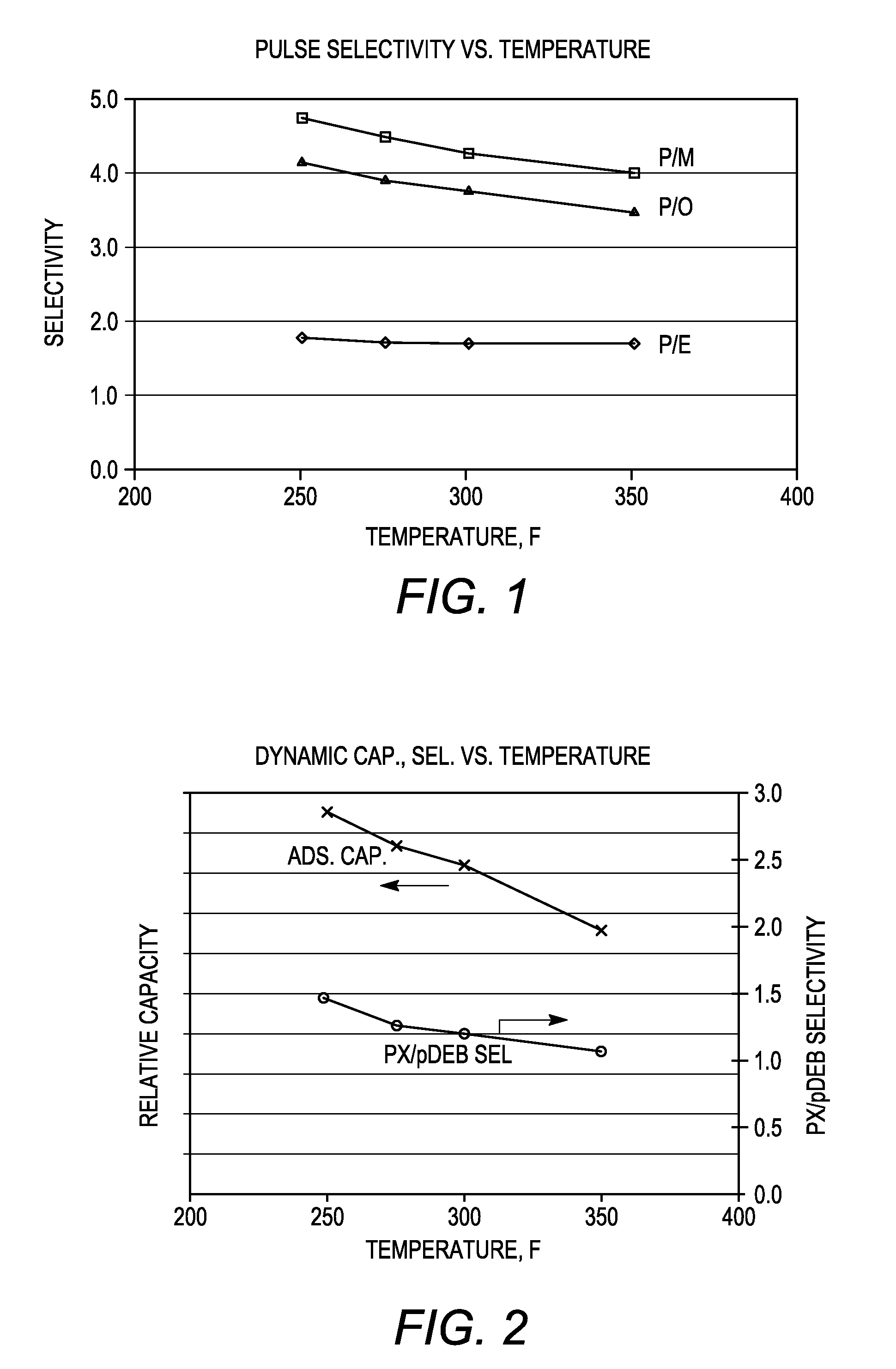

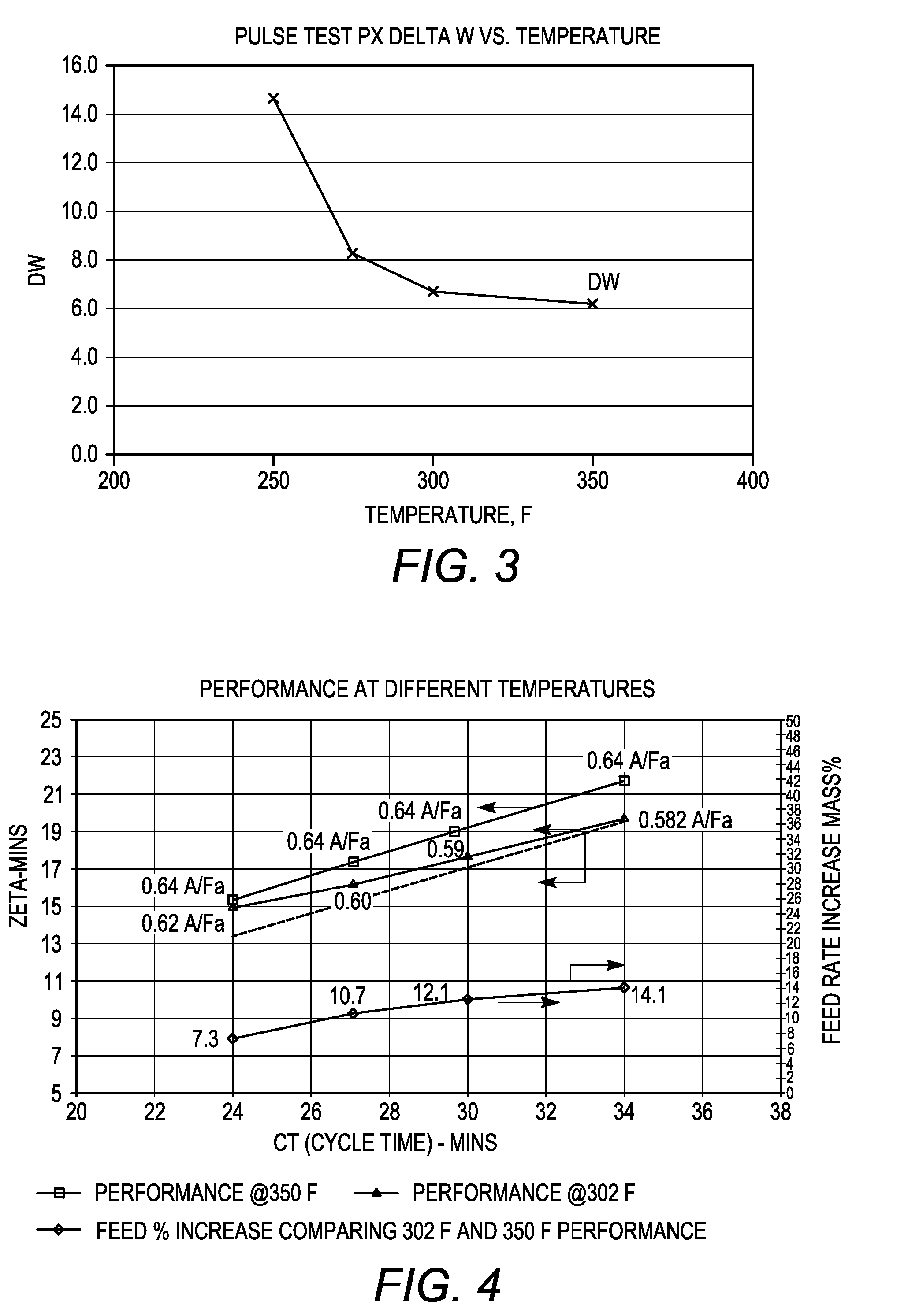

Binderless adsorbents comprising nano-size zeolite x and their use in the adsorptive separation of para-xylene

InactiveUS20090326308A1High adsorbent capacity/mass transfer propertyIncreased para-xylene productivityMaterial nanotechnologyOther chemical processesSimulated moving bedSorbent

Adsorbents and methods for the adsorptive separation of para-xylene from a mixture containing at least one other C8 aromatic hydrocarbon (e.g., a mixture of ortho-xylene, meta-xylene, para-xylene, and ethylbenzene) are described. Suitable adsorbents comprise nano-size zeolite X having an average crystallite size of less than about 500 nanometers. The adsorbents provide both improved capacity and mass transfer, which is especially advantageous for improving productivity in low temperature, low cycle time adsorptive separation operations in a simulated moving bed mode.

Owner:UOP LLC

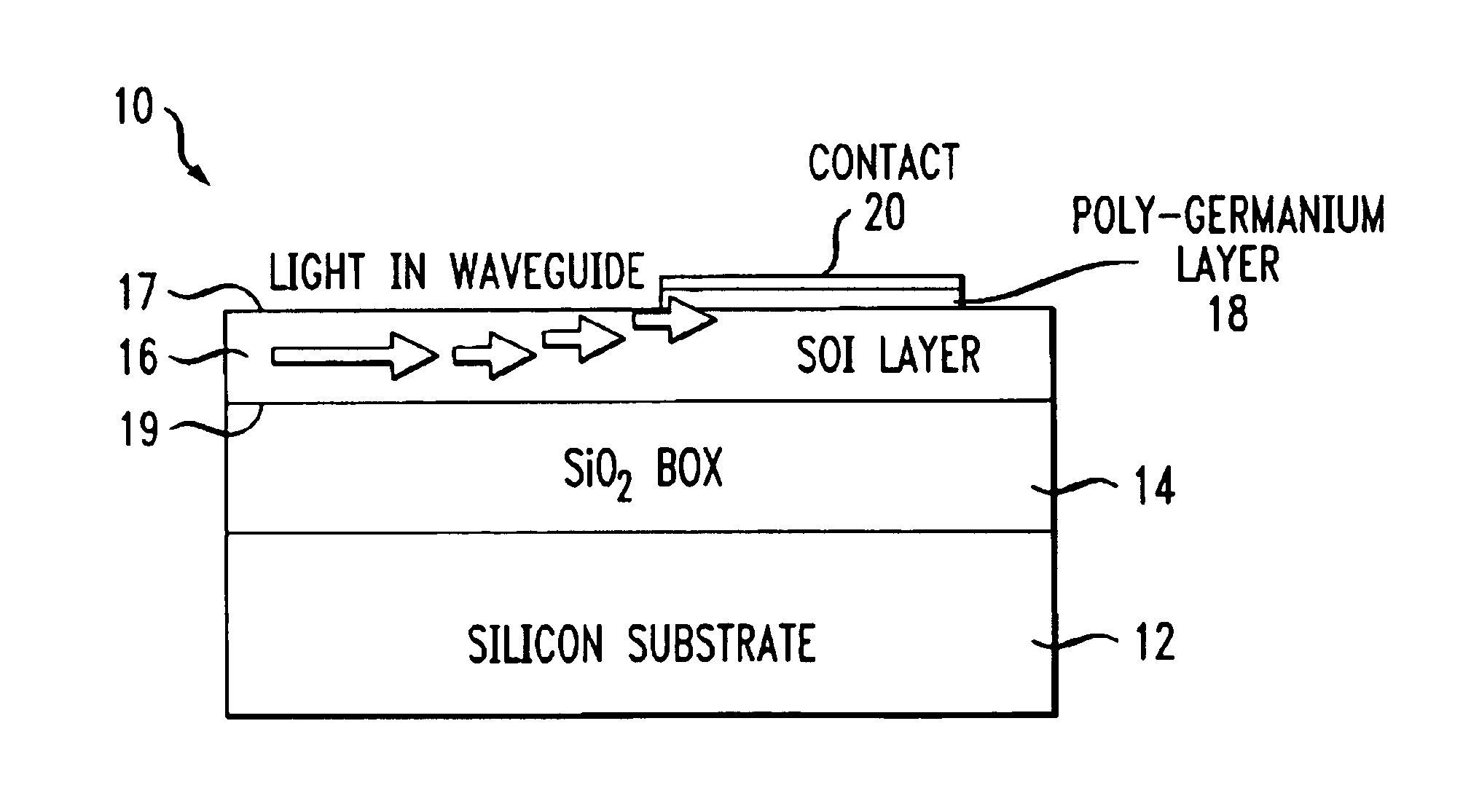

Polycrystalline germanium-based waveguide detector integrated on a thin silicon-on-insulator (SOI) platform

ActiveUS6897498B2Efficient collectionEffective absorptionSolid-state devicesSemiconductor/solid-state device manufacturingPhotovoltaic detectorsPhotodetector

A photodetector for use with relatively thin (i.e., sub-micron) silicon optical waveguides formed in a silicon-on-insulator (SOI) structure comprises a layer of poly-germanium disposed to couple at least a portion of the optical signal propagating along the silicon optical waveguide. Tight confinement of the optical signal within the waveguide structure allows for efficient evanescent coupling into the poly-germanium detector. The silicon optical waveguide may comprise any desired geometry, with the poly-germanium detector formed to either cover a portion of the waveguide, or be butt-coupled to an end portion of the waveguide. When covering a portion of the waveguide, poly-germanium detector may comprise a “wrap-around” geometry to cover the side and top surfaces of the optical waveguide, with electrical contacts formed at opposing ends of the detector.

Owner:CISCO TECH INC

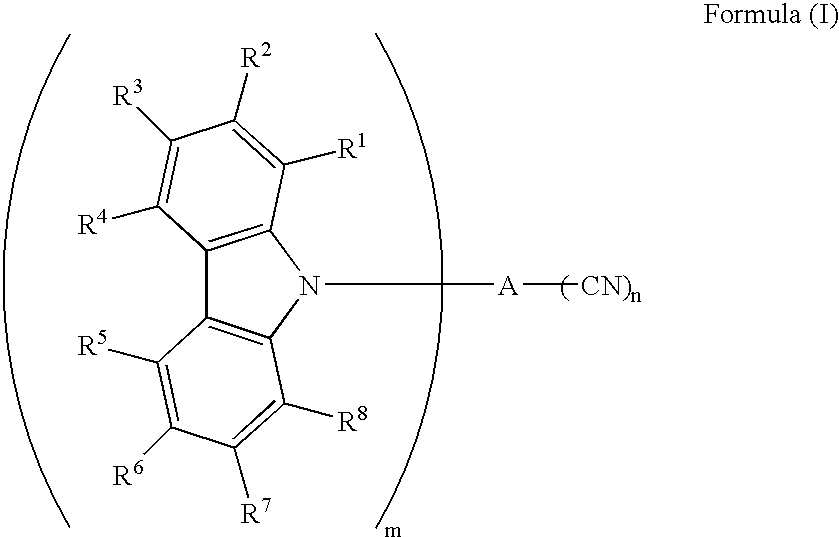

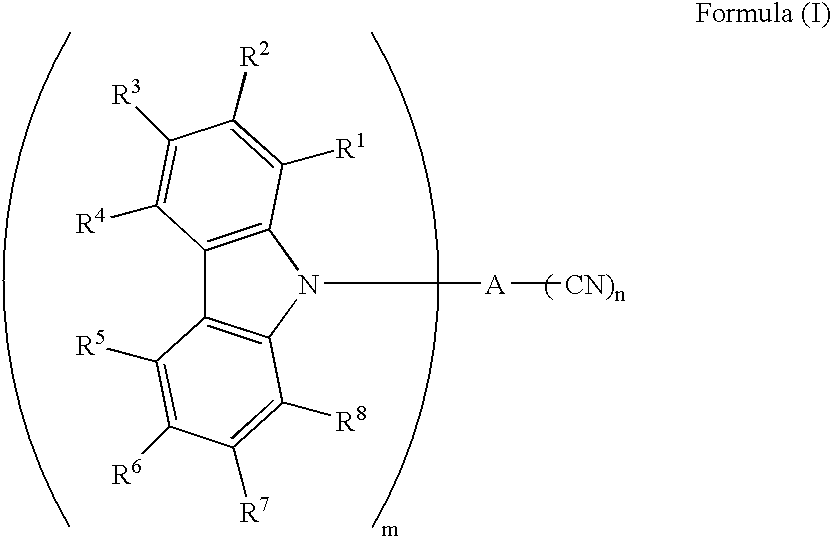

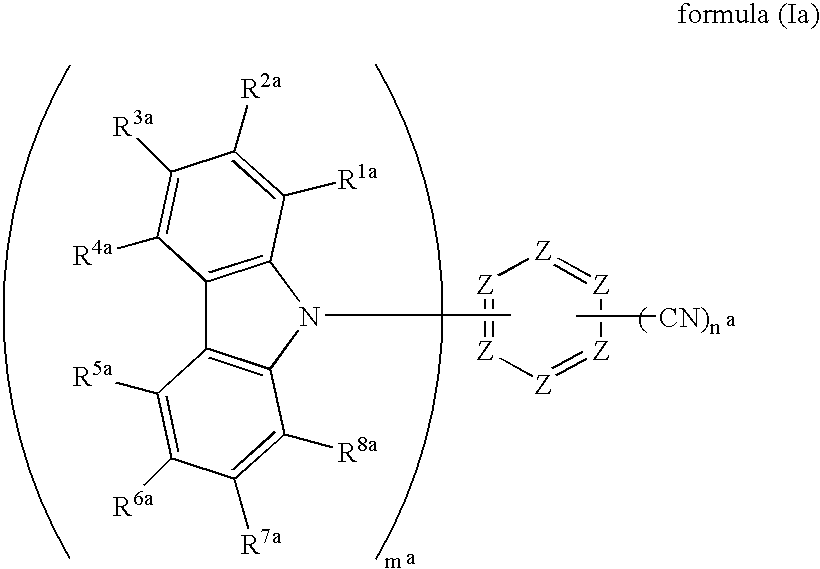

Organic electroluminescence device

InactiveUS20090072727A1Low ON voltage operationExcellent EL external quantum efficiencyDischarge tube luminescnet screensElectroluminescent light sourcesHydrogen atomOrganic layer

An organic electroluminescent device includes a pair of electrodes; and an organic layer between the pair of electrodes, which comprises a light-emitting layer and contains a compound represented by the following formula (1):wherein each of R1 to R8 independently represents a hydrogen atom or a substituent, A represents an aromatic ring which may have a substituent, m represents an integer of 2 or greater, and n represents an integer of 1 or greater.

Owner:UDC IRELAND

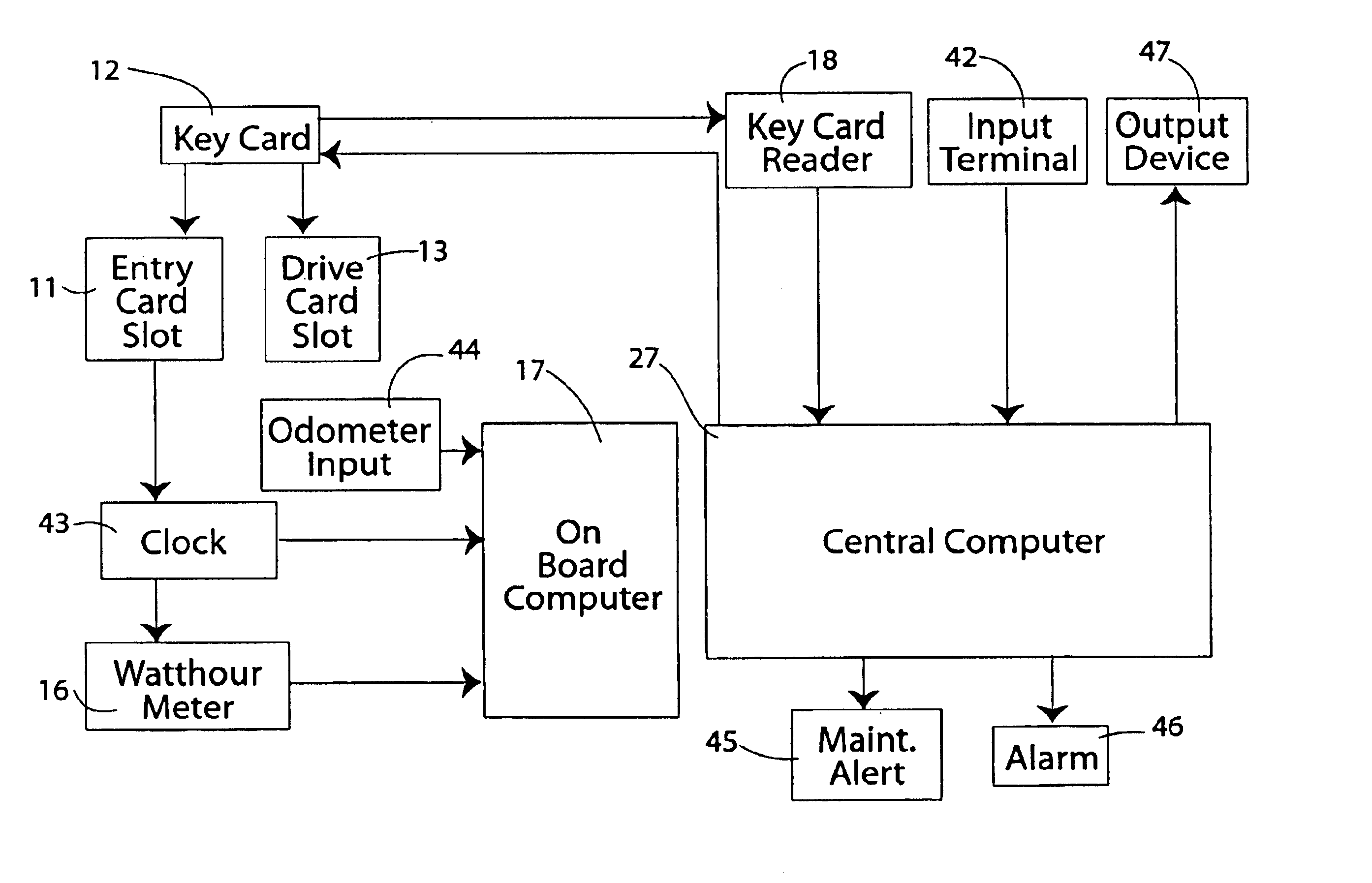

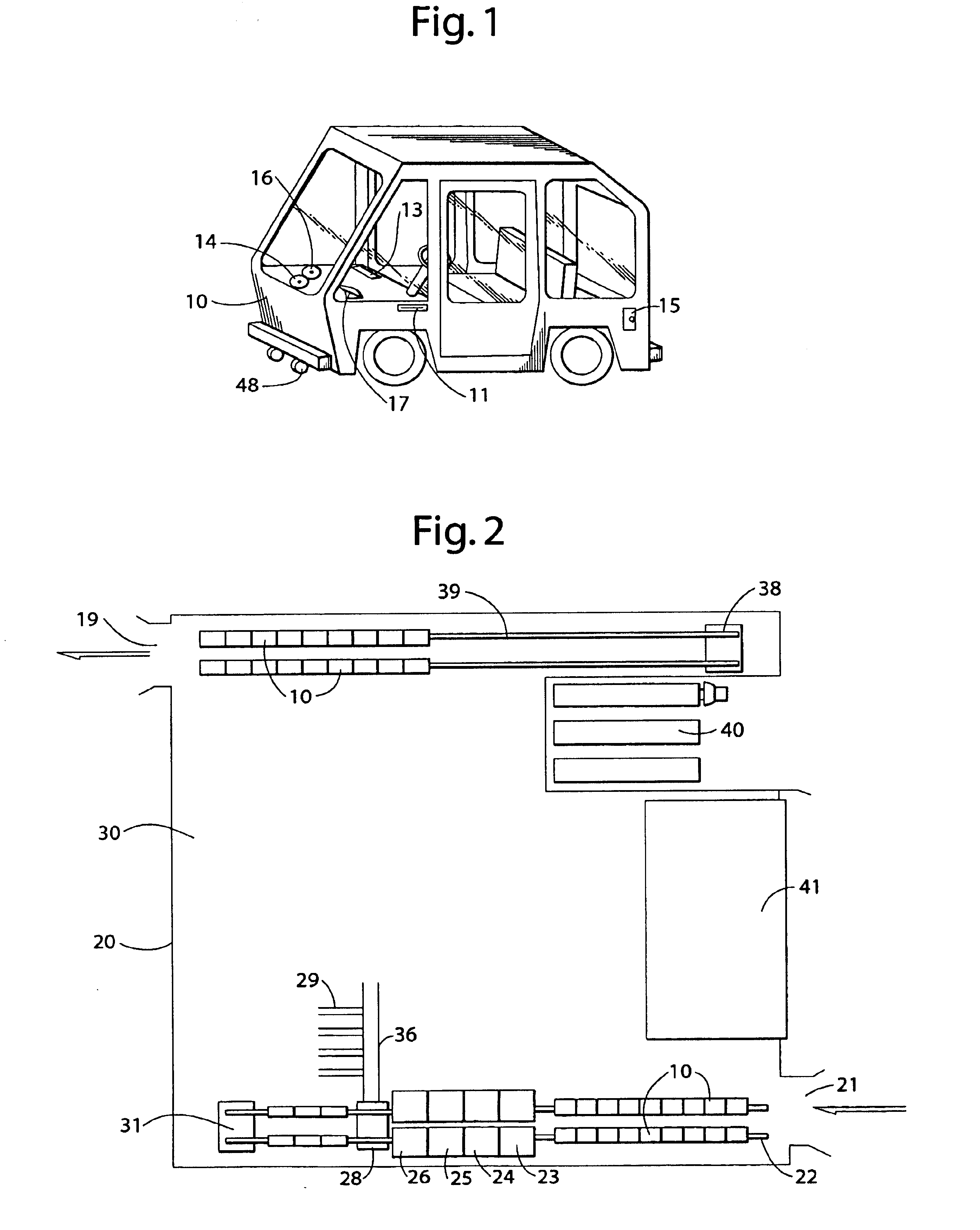

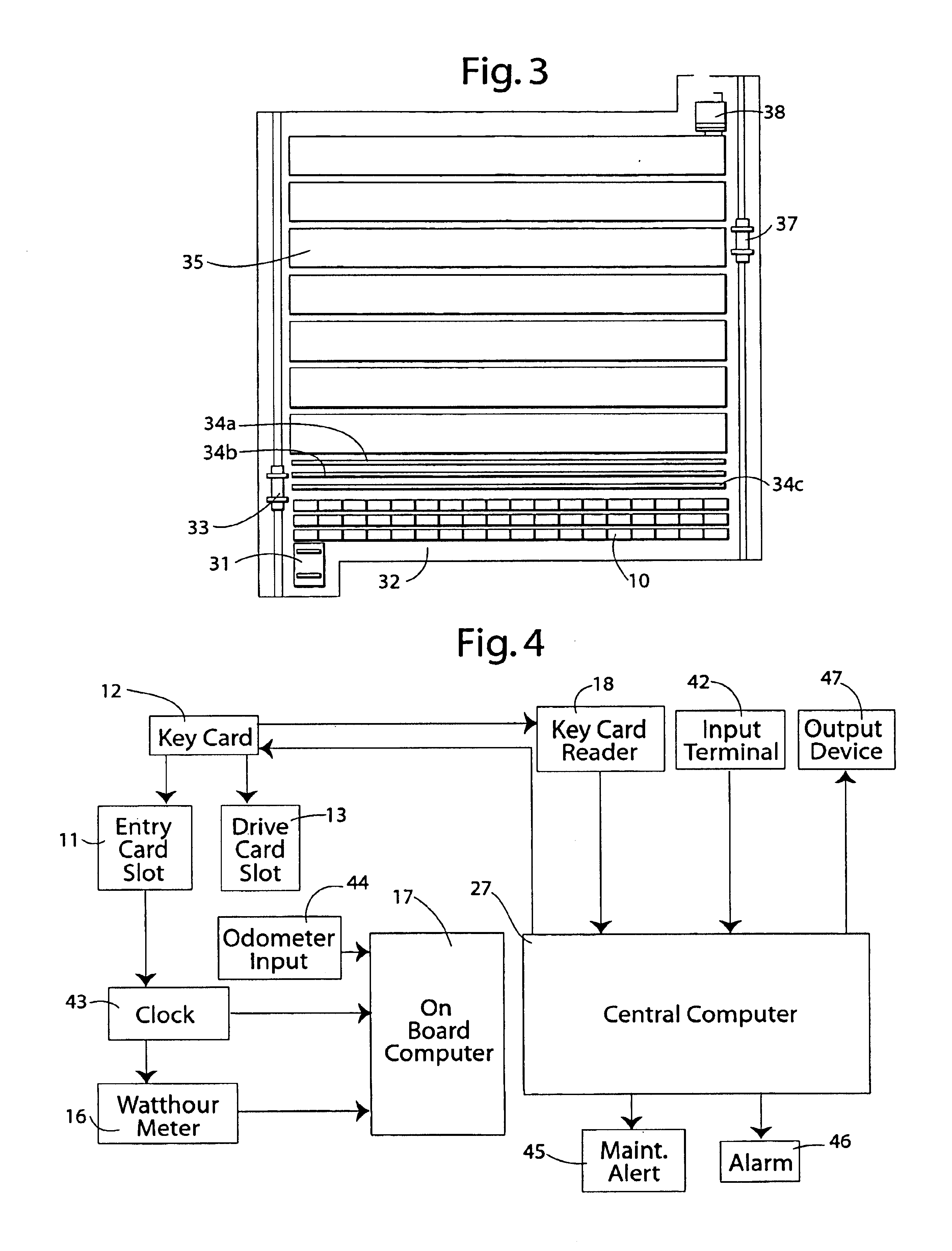

Urban transportation system

InactiveUS6859009B2Low costReduced operating requirementsCoupling device connectionsBatteries circuit arrangementsCombustionInternal combustion engine

An urban transportation system which comprises a pool of rental urban vehicles all having the same size and physical configuration and having a range of driving which is limited as compared to the range of vehicles that are powered by internal combustion engines. The system includes a computer-controlled mechanized facility for delivering, receiving, processing, servicing and storing the vehicles. Vehicles are automatically recharged while in storage. The system includes areas for on-street parking of the vehicles. There are also several features to combat theft of the vehicles. A user may obtain the most readily available vehicle from any place in the system and return the vehicle to any other place within the system.

Owner:JABLIN RICHARD

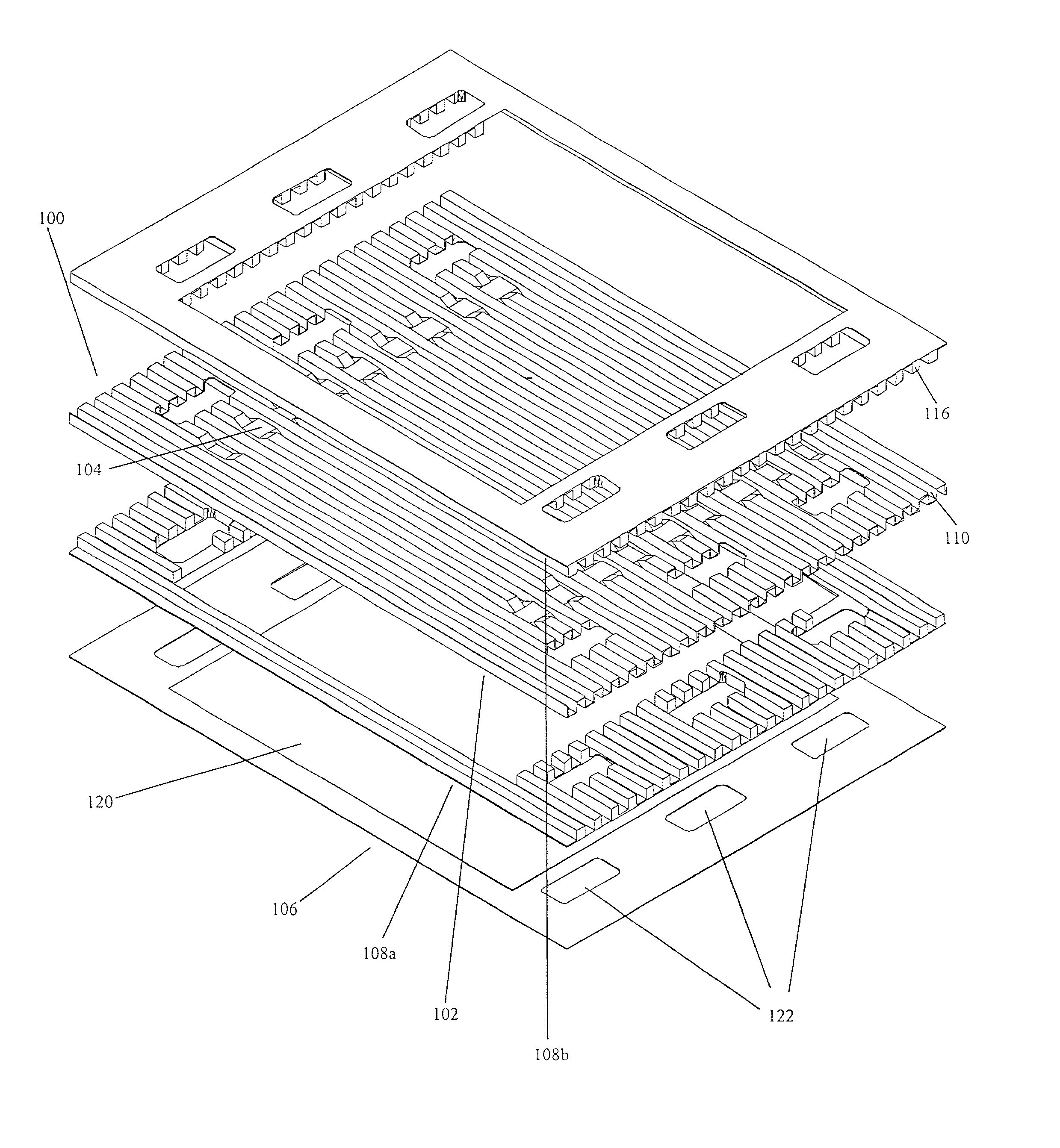

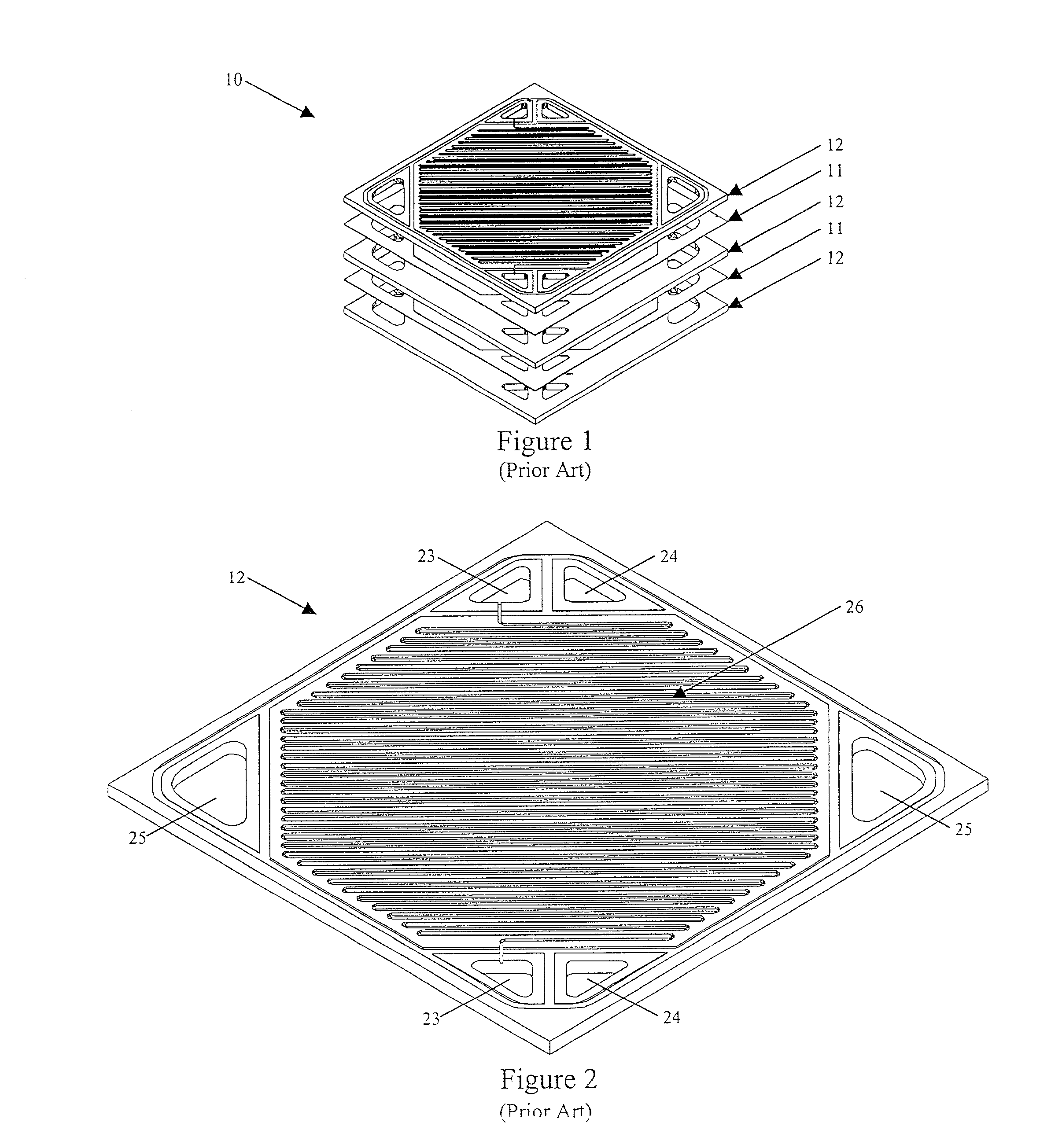

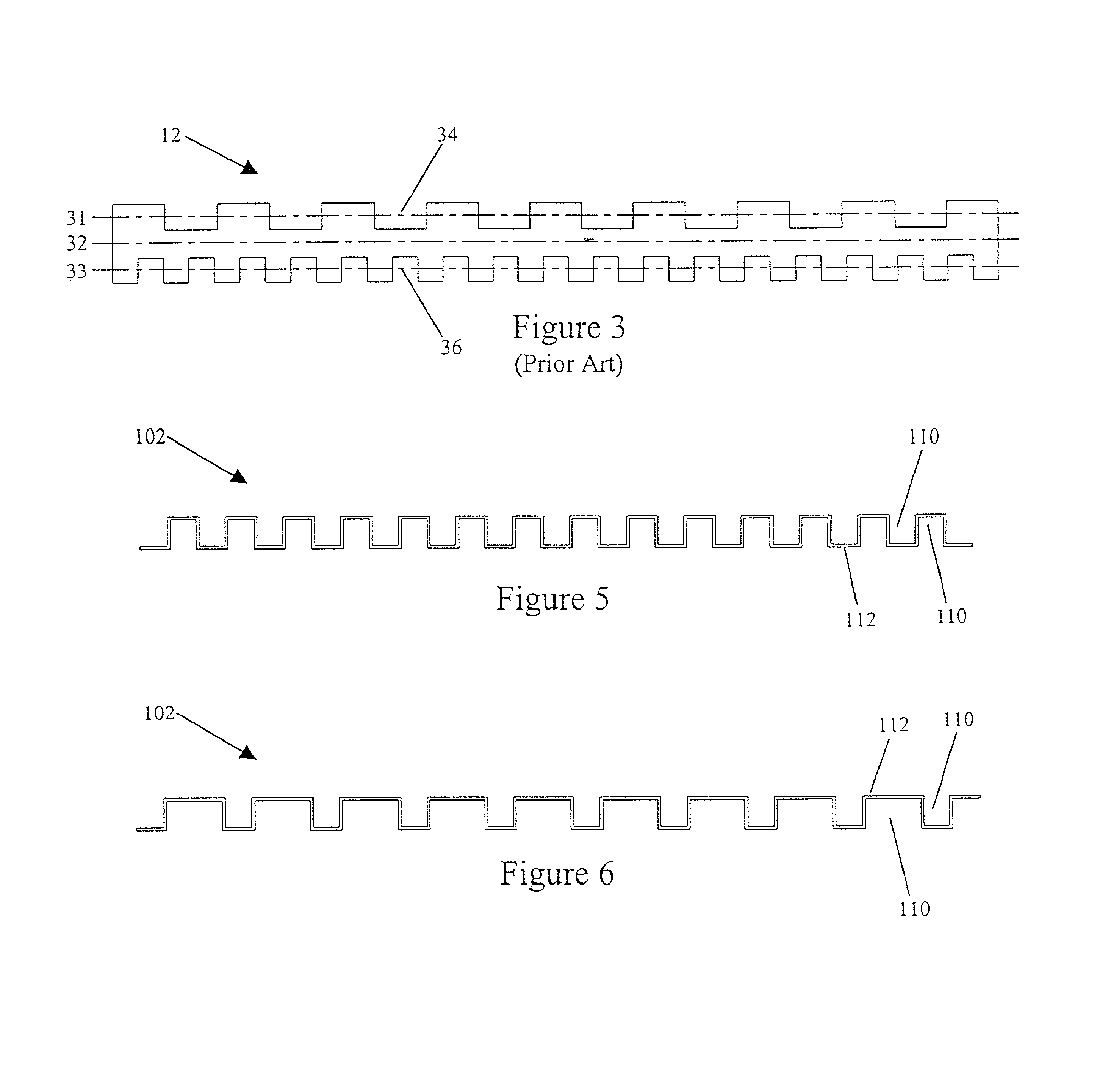

Corrugated flow field plate assembly for a fuel cell

InactiveUS20020081477A1Reduced operating requirementsEasy to shapeFuel cells groupingFuel cell auxillariesFuel cellsChannel coupling

Corrugated flow field plates for use in fuel cells typically comprise a plurality of parallel open-faced fluid flow channels for the fuel cell reactants. Complex flow paths, such as serpentine flow paths, may be created in such corrugated flow field plates by incorporating channel couplings within the plate or by attaching coupling subassemblies to the plate. The plates are particularly suitable for use in solid polymer electrolyte fuel cells.

Owner:BDF IP HLDG

High performance FET devices and methods thereof

ActiveUS20050156169A1Facilitated DiffusionAvoid impuritiesTransistorSemiconductor/solid-state device detailsDopantGate insulator

Structure and methods of fabrication are disclosed for an enhanced FET devices in which dopant impurities are prevented from diffusing through the gate insulator. The structure comprises a Si:C, or SiGe:C, layer which is sandwiched between the gate insulator and a layer which is doped with impurities in order to provide a preselected workfunction. It is further disclosed how this, and further improvements for FET devices, such as raised source / drain and multifaceted gate on insulator, MODFET on insulator are integrated with strained Si based layer on insulator technology.

Owner:INT BUSINESS MASCH CORP

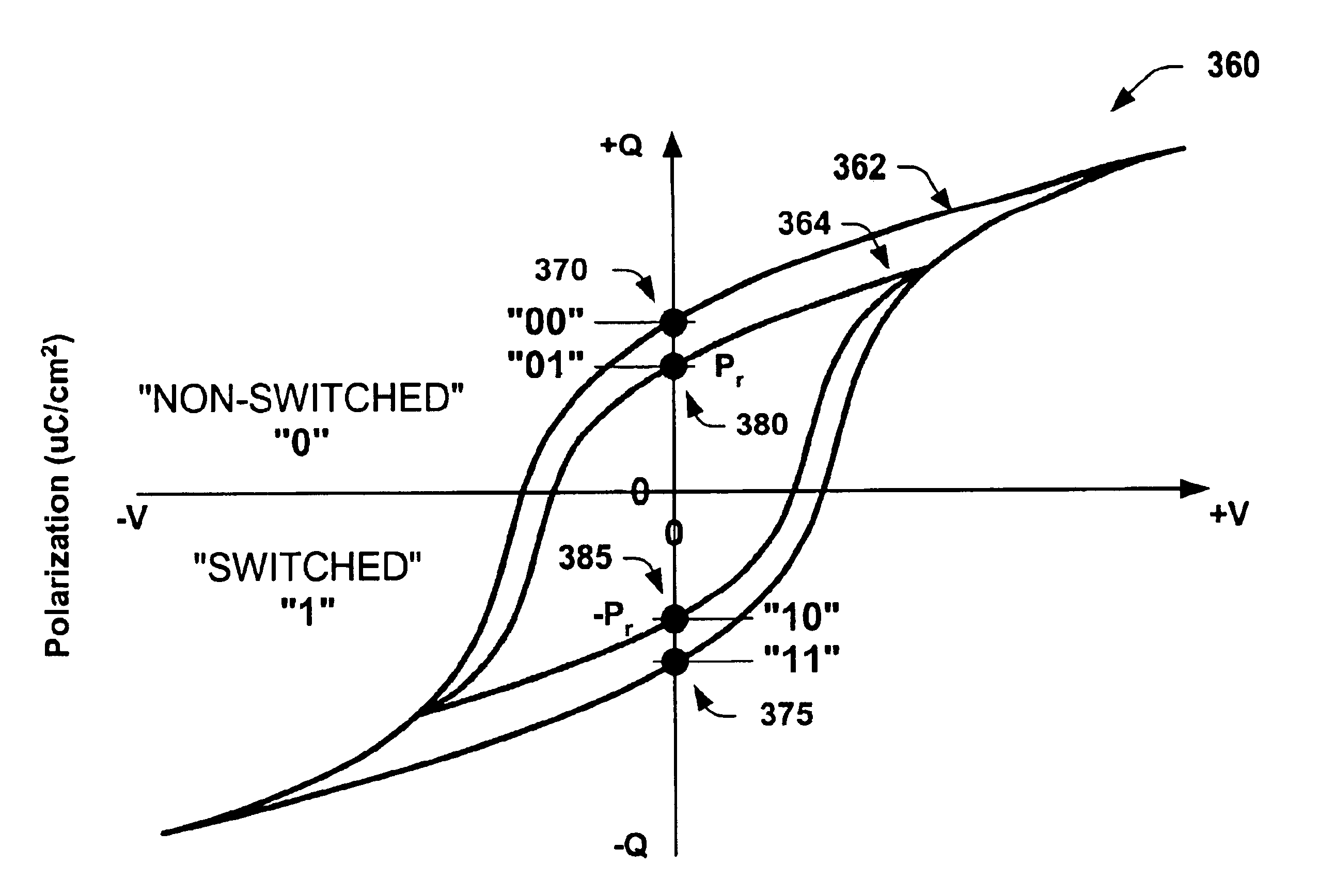

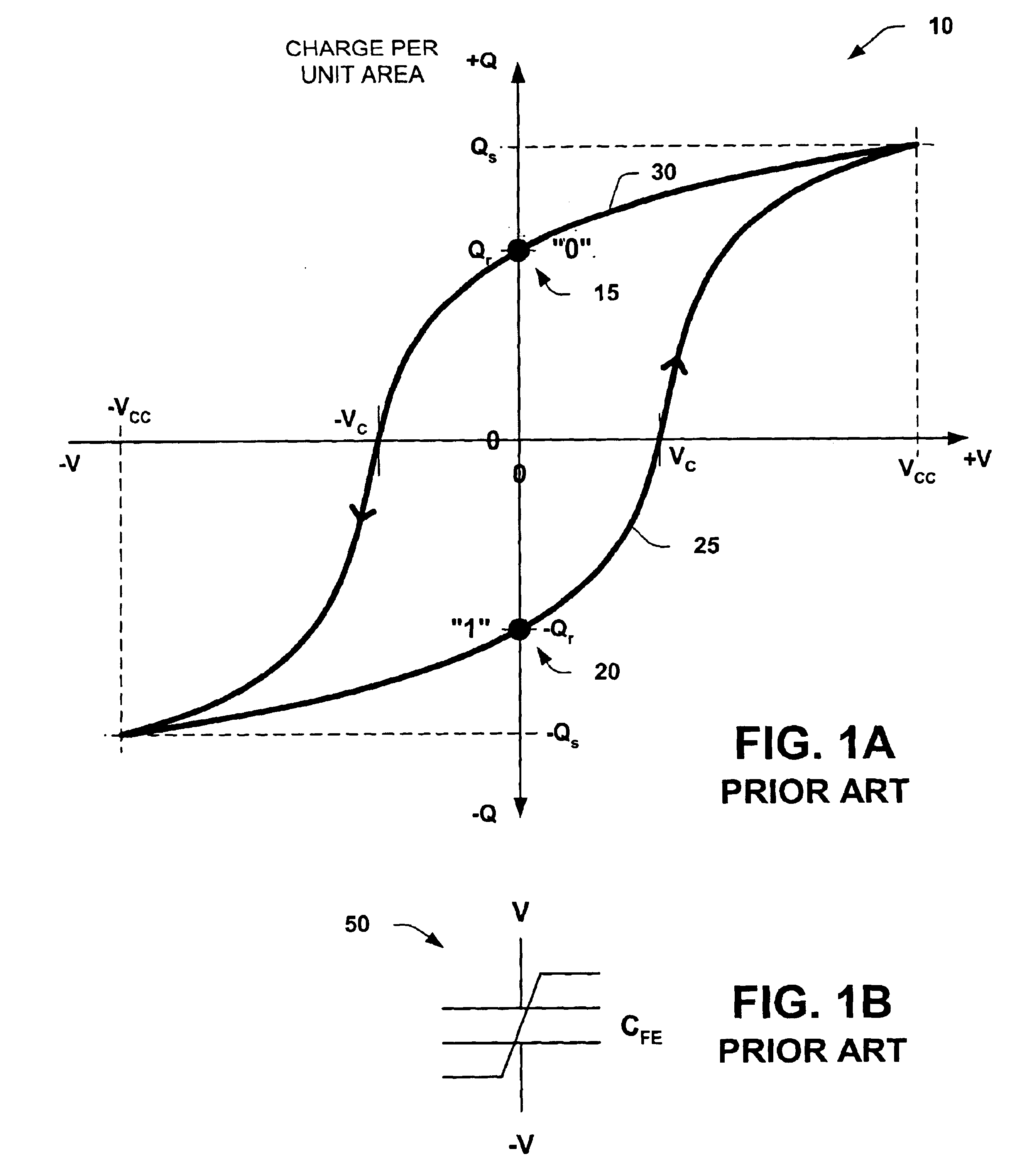

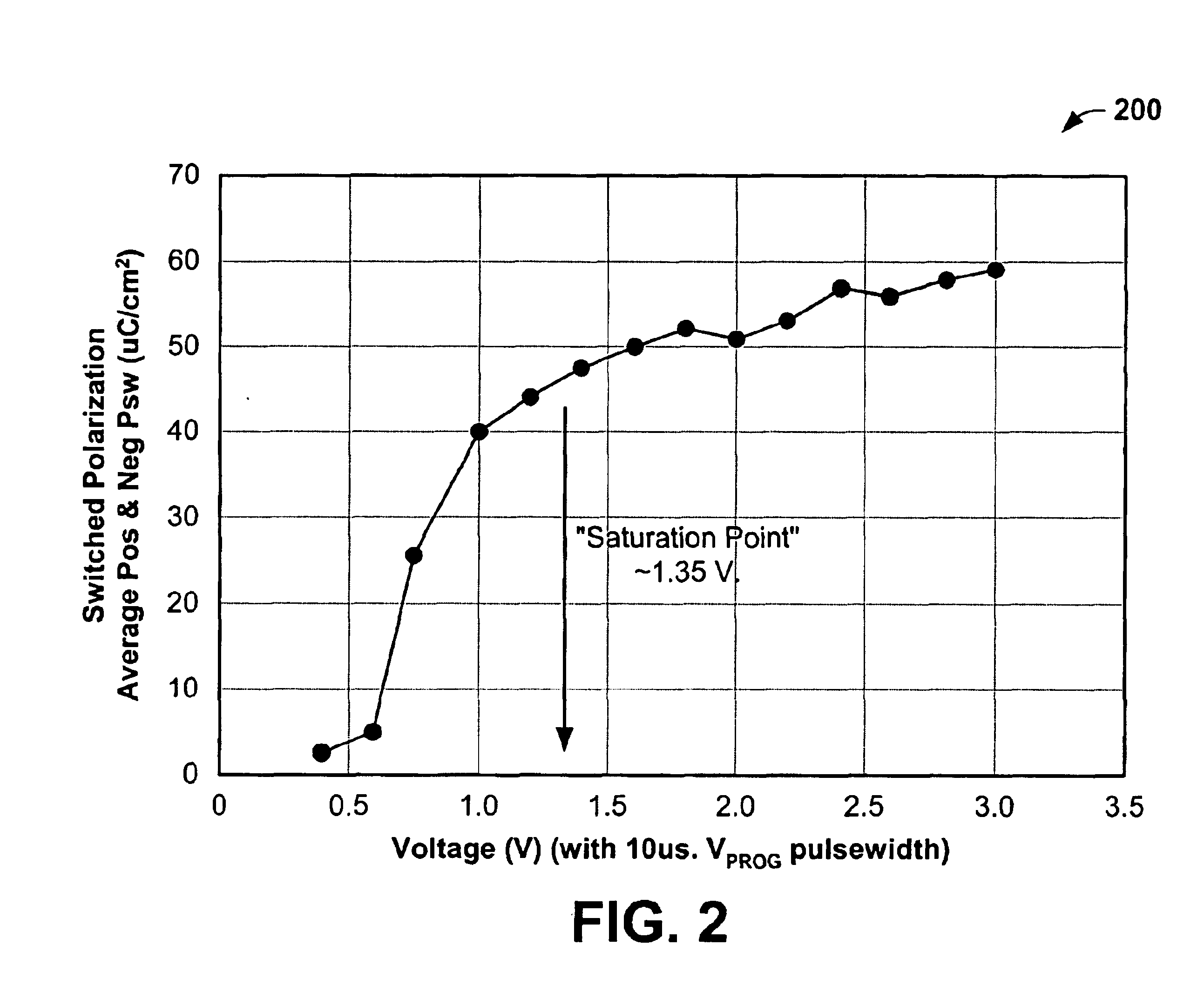

Ferroelectric memory with wide operating voltage and multi-bit storage per cell

InactiveUS6856534B2Avoid lossReduce the effective areaSolid-state devicesSemiconductor/solid-state device manufacturingSingle polarizationComputer hardware

Apparatus and methods are described for a multi-level FeRAM memory device. Using write and read circuits associated with the memory device, multiple data states may be written to and read from the ferroelectric memory device which are associated with a single polarization direction, thereby allowing for a single cell to contain more than one bit of data.

Owner:TEXAS INSTR INC

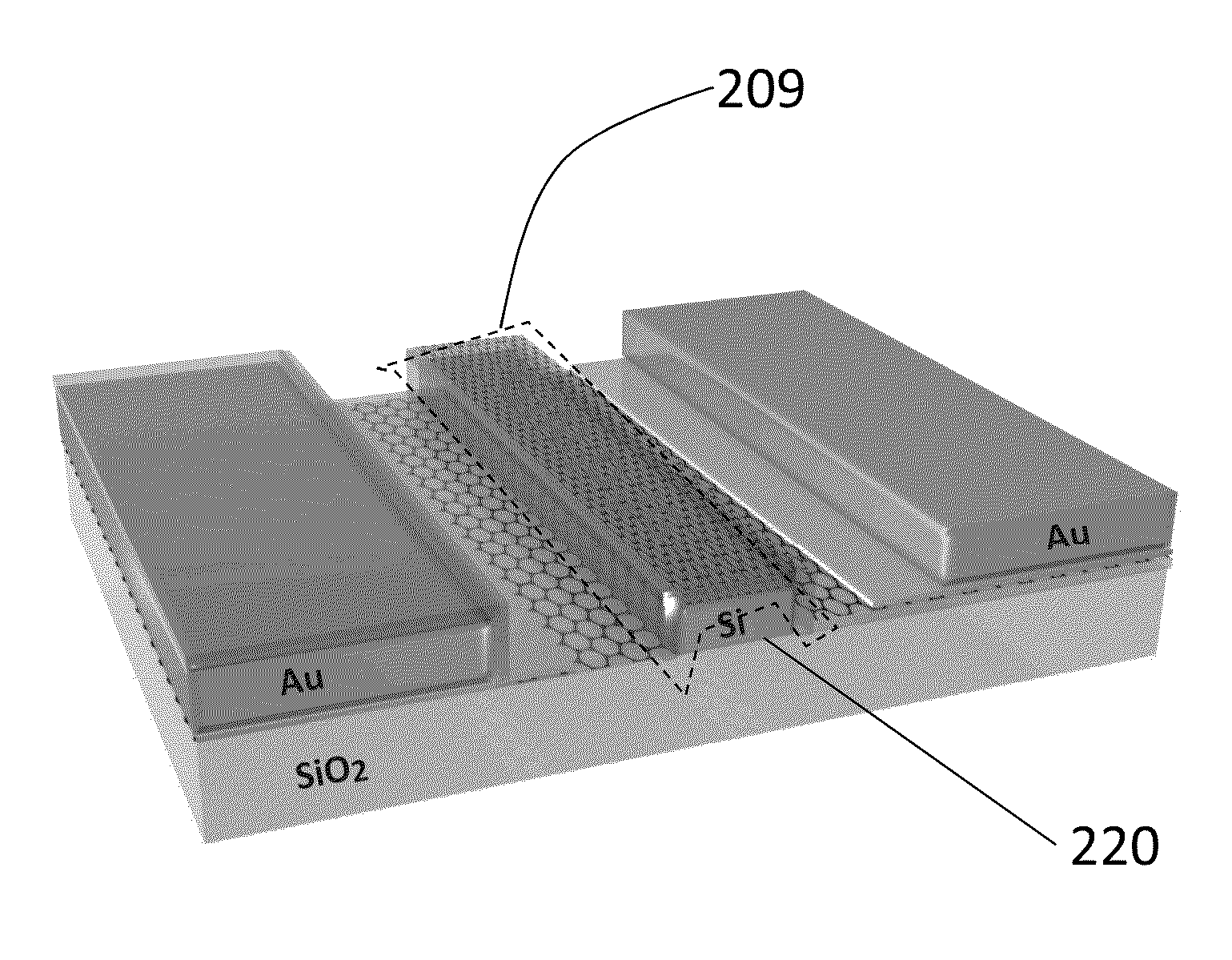

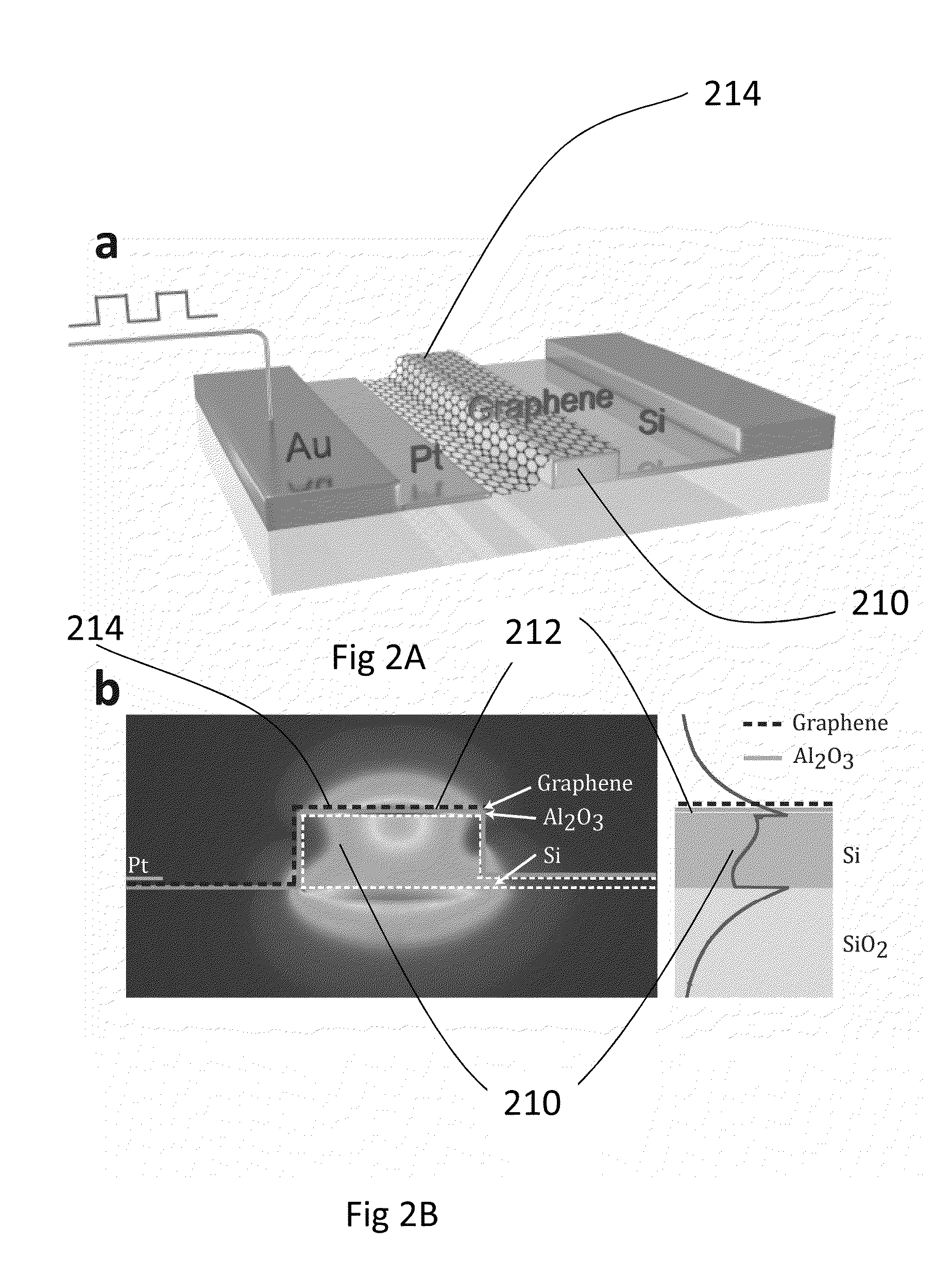

Graphene based optical modulator

ActiveUS20140056551A1Increase speedSmall footprintNanoopticsNon-linear opticsMonolayer grapheneEngineering

The present invention provides for a one or more layer graphene optical modulator. In a first exemplary embodiment the optical modulator includes an optical waveguide, a nanoscale oxide spacer adjacent to a working region of the waveguide, and a monolayer graphene sheet adjacent to the spacer. In a second exemplary embodiment, the optical modulator includes at least one pair of active media, where the pair includes an oxide spacer, a first monolayer graphene sheet adjacent to a first side of the spacer, and a second monolayer graphene sheet adjacent to a second side of the spacer, and at least one optical waveguide adjacent to the pair.

Owner:RGT UNIV OF CALIFORNIA

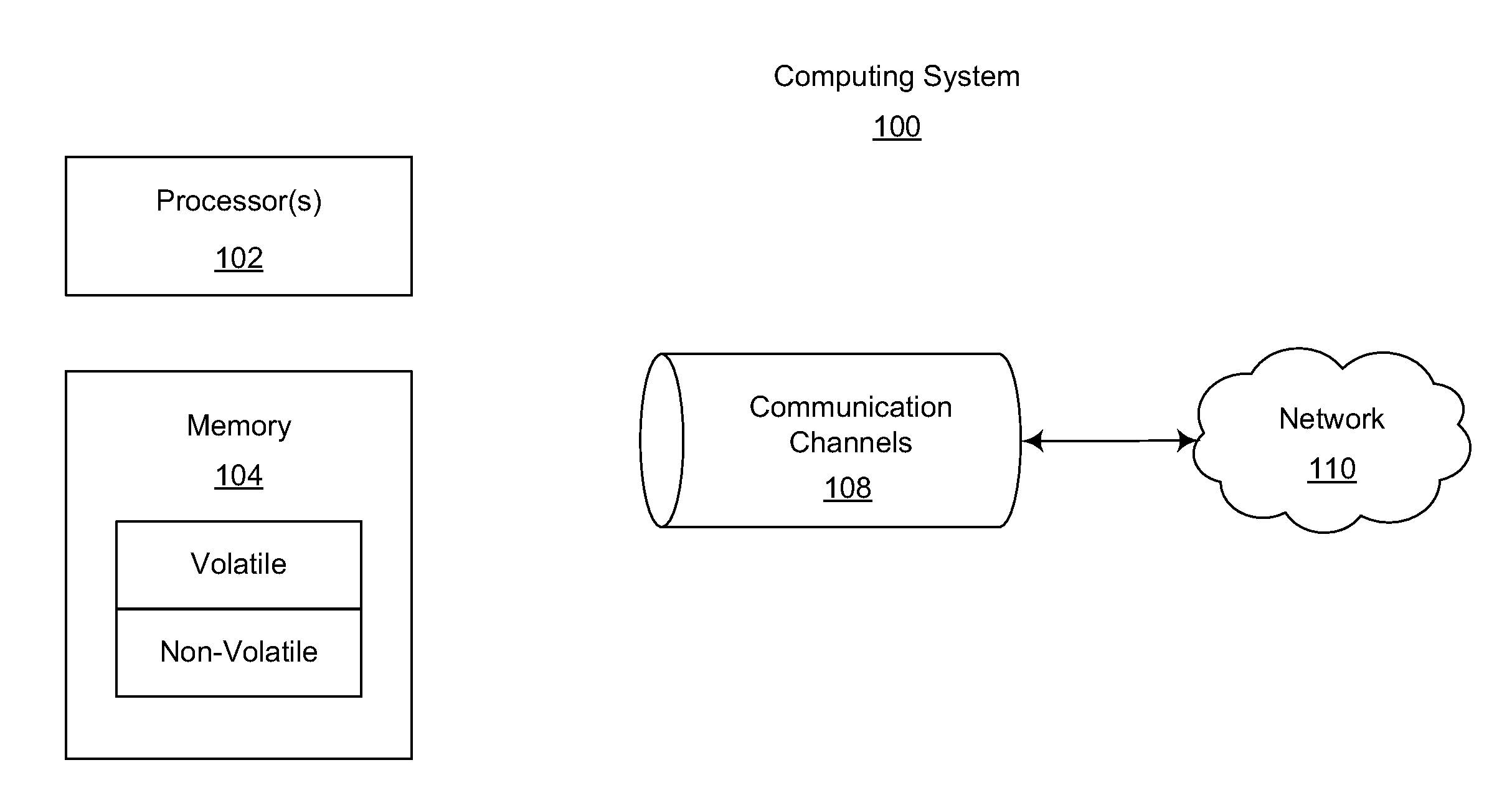

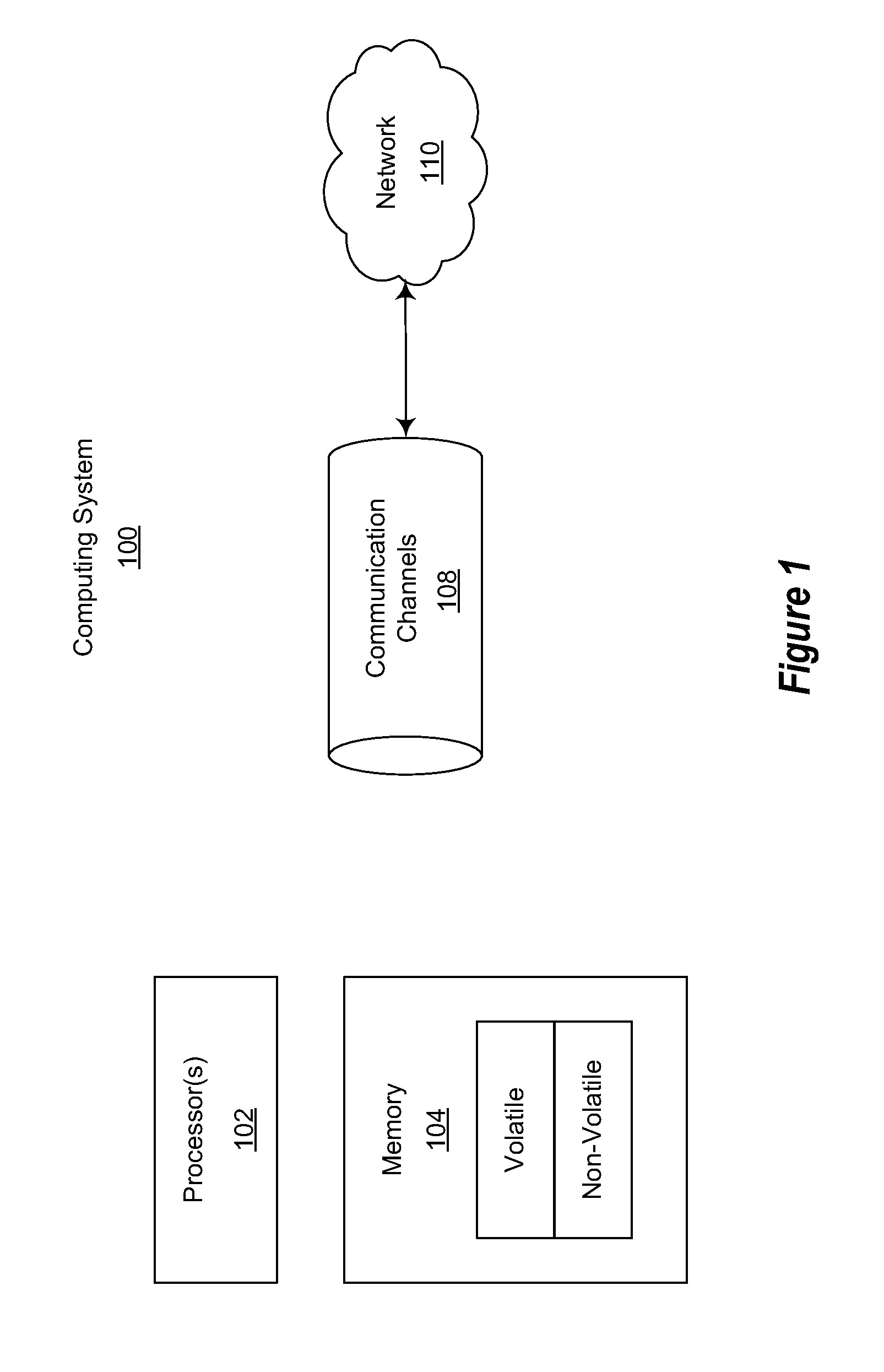

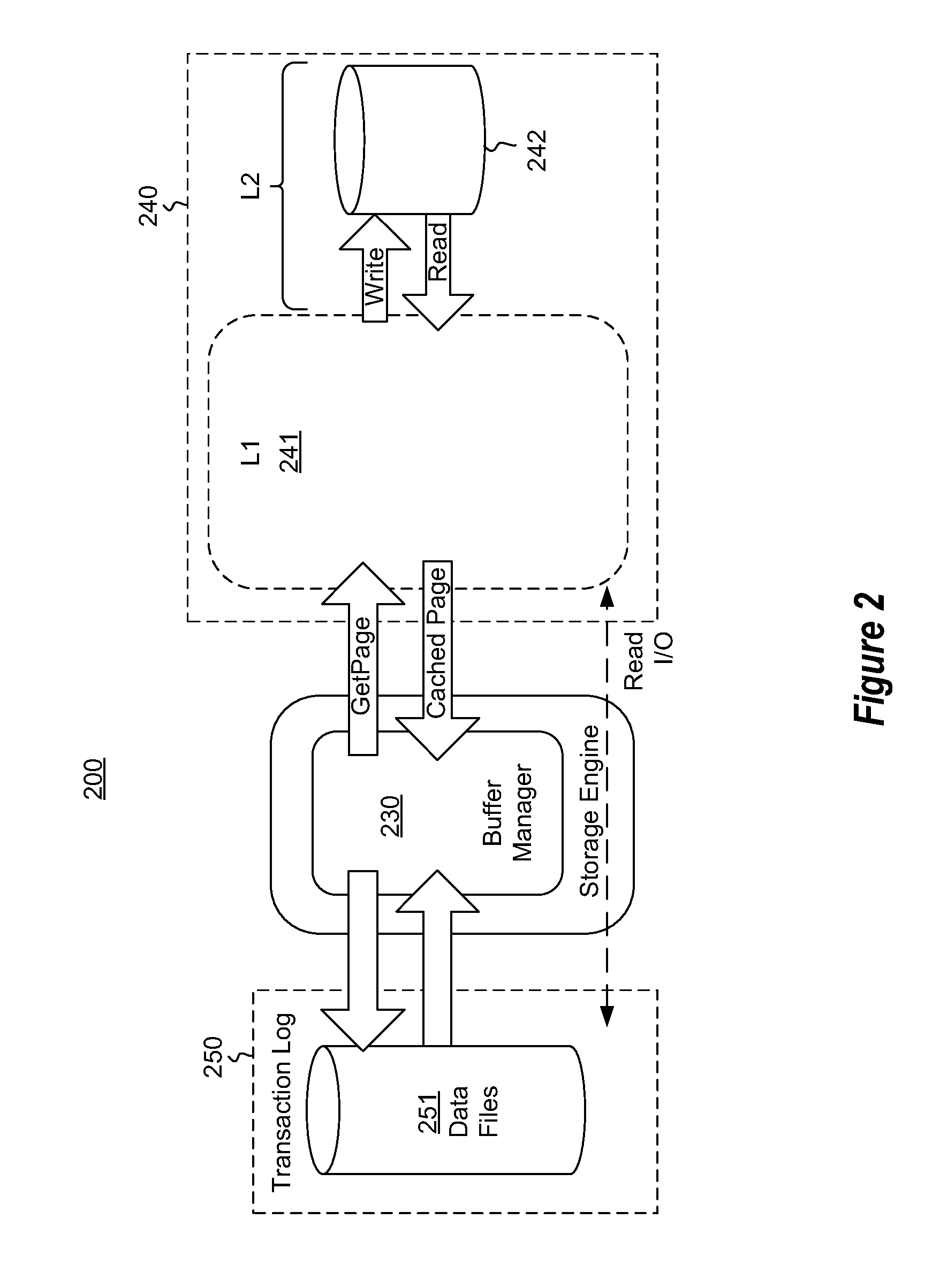

Multi-level buffer pool extensions

ActiveUS20120072652A1Convenience to workAvoid settingSoftware engineeringMemory adressing/allocation/relocationComputational scienceParallel computing

A buffer manager that manages blocks of memory amongst multiple levels of buffer pools. For instance, there may be a first level buffer pool for blocks in first level memory, and a second level buffer pool for blocks in second level memory. The first level buffer pool evicts blocks to the second level buffer pool if the blocks are not used above a first threshold level. The second level buffer pool evicts blocks to a yet lower level if they have not used above a second threshold level. The first level memory may be dynamic random access memory, whereas the second level memory may be storage class memory, such as a solid state disk. By using such a storage class memory, the working block set of the buffer manager may be increased without resorting to lower efficiency random block access from yet lower level memory such as disk.

Owner:MICROSOFT TECH LICENSING LLC

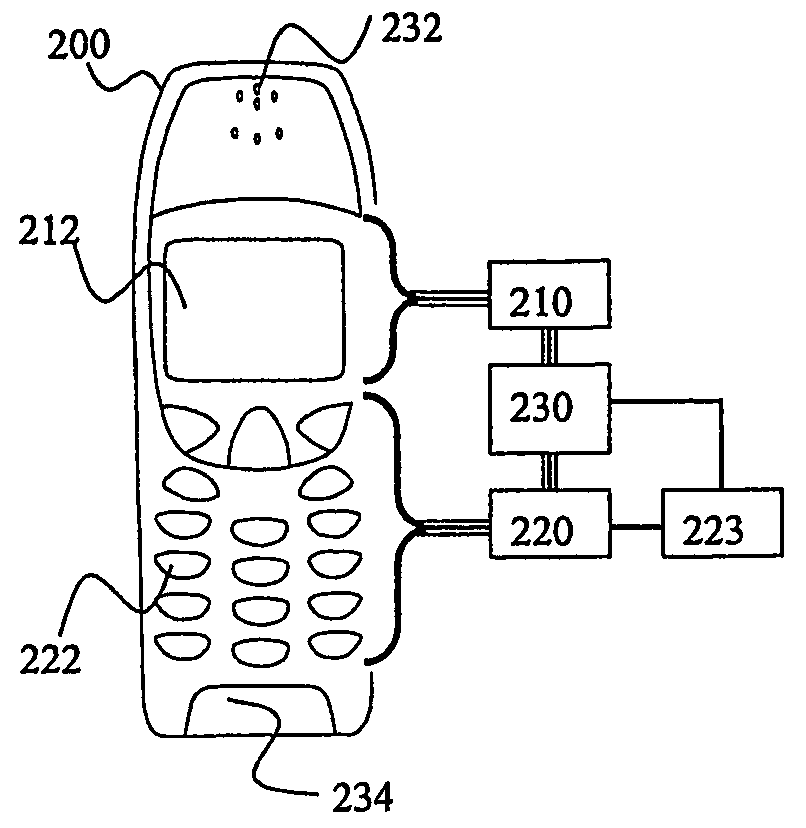

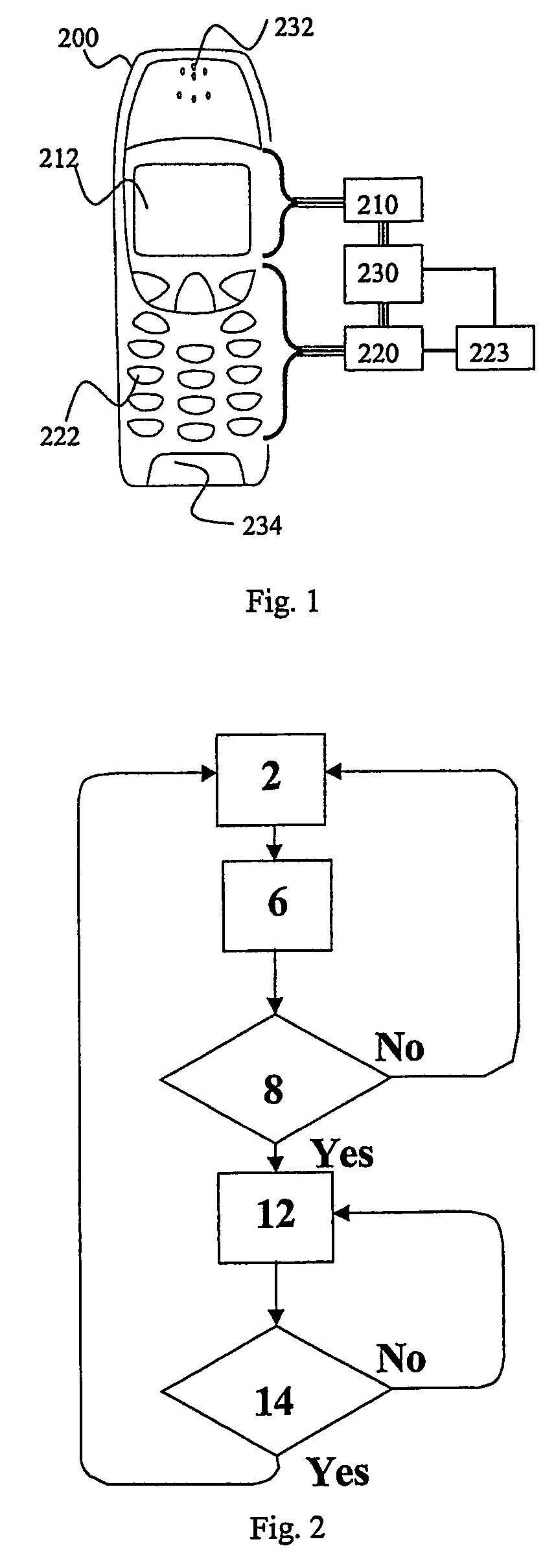

Method for intermediate unlocking of a keypad on a mobile electronic device

InactiveUS7414613B2Easy to operateAvoid wastingInput/output for user-computer interactionUnauthorised/fraudulent call preventionUser inputEngineering

A method and device for changing input states of an electronic device, the device comprising an input portion and being capable of carrying out user operations, the input states comprising a locked state, where the use of the input portion is significantly restricted, and an unlocked state, where the use of the input portion is not restricted, the locked and unlocked states being respectively enterable by a locking and unlocking input. A further input state is an intermediate unlocked state in which a limited operational use of the input portion is possible; which method comprises entering the intermediate unlocked state from the locked state, based on user input; detecting termination of a user operation in the intermediate unlocked state, and entering the locked state, in response thereto. There is also provided an input controller, a keypad and a mobile electronic device implementing these features.

Owner:III HLDG 3

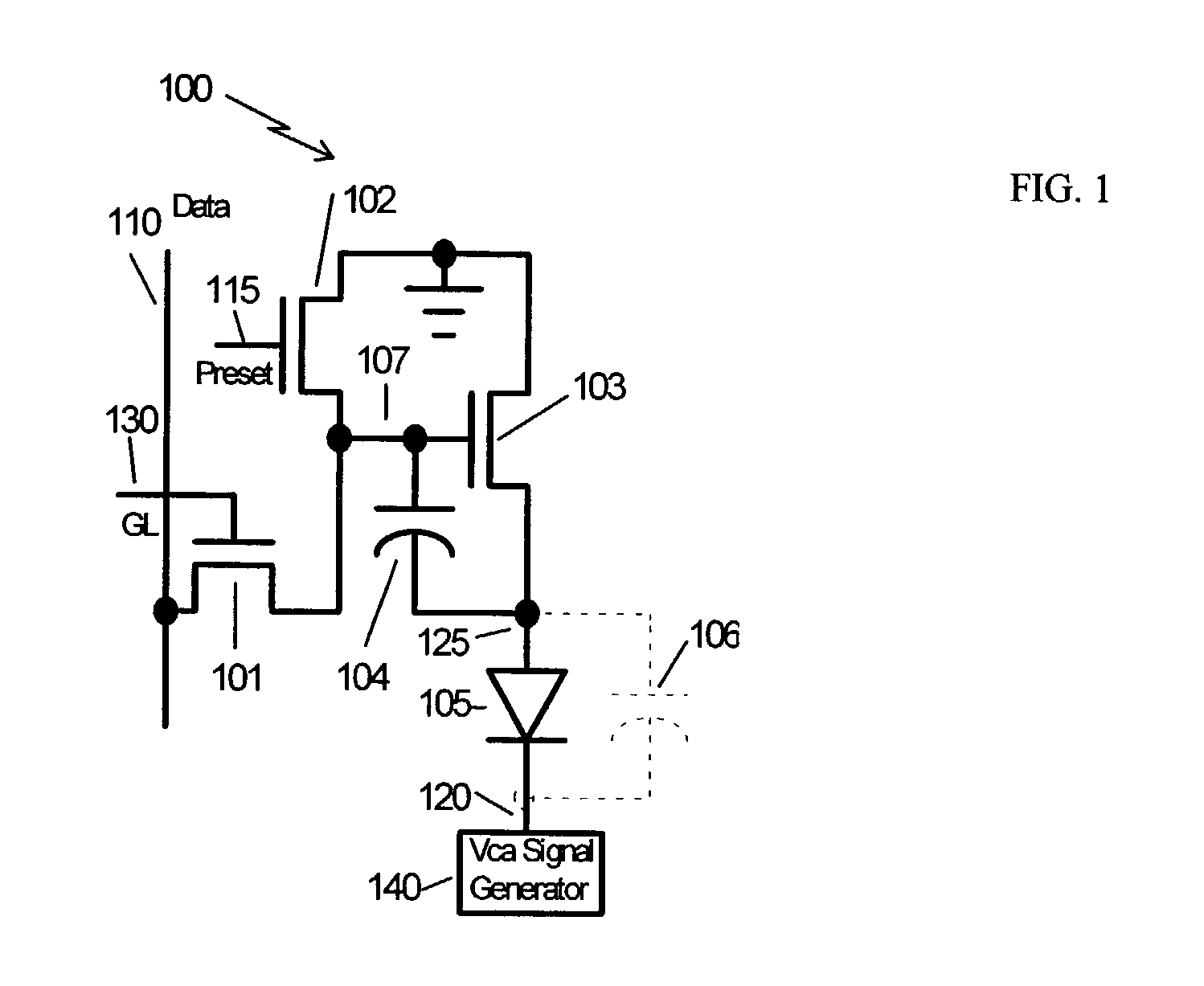

Active matrix oled voltage drive pixel circuit

InactiveUS7167169B2Threshold voltage shift is minimizedQuick data voltage level chargingCathode-ray tube indicatorsInput/output processes for data processingSignal onActive matrix

There is provided a circuit for driving a current mode light modulating device. The circuit includes (a) a capacitor for storing a data voltage, (b) a field effect transistor (FET) controlled by a signal on a scan line, for coupling the data voltage from a signal line to the capacitor, and (c) a current source, controlled by the stored data voltage, for driving the device with current provided from a power line. The power line is in a plane that is geometrically parallel to a plane within which the scan line is located.

Owner:INNOLUX CORP