Method for improving junction depth property of semiconductor device

A semiconductor and device technology, applied in the field of improving the junction depth characteristics of semiconductor devices, can solve problems such as increasing leakage current, increasing VT junction depth, and the risk of gate penetration, so as to improve device performance and increase VT junction depth Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0053] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the accompanying drawings and examples.

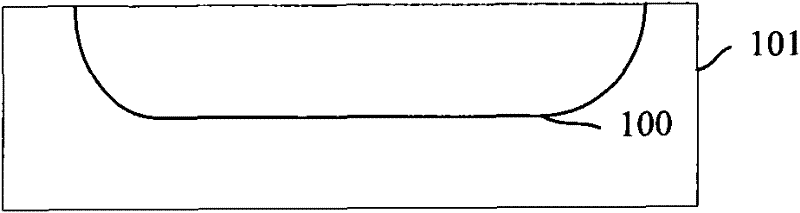

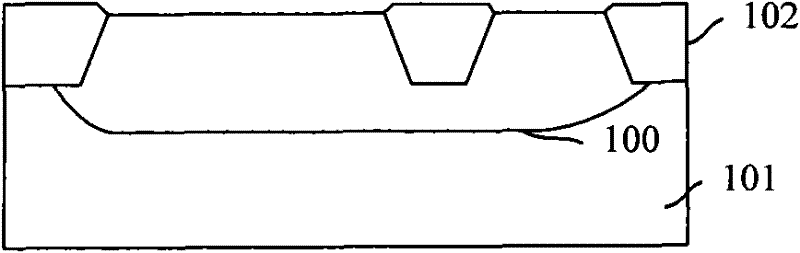

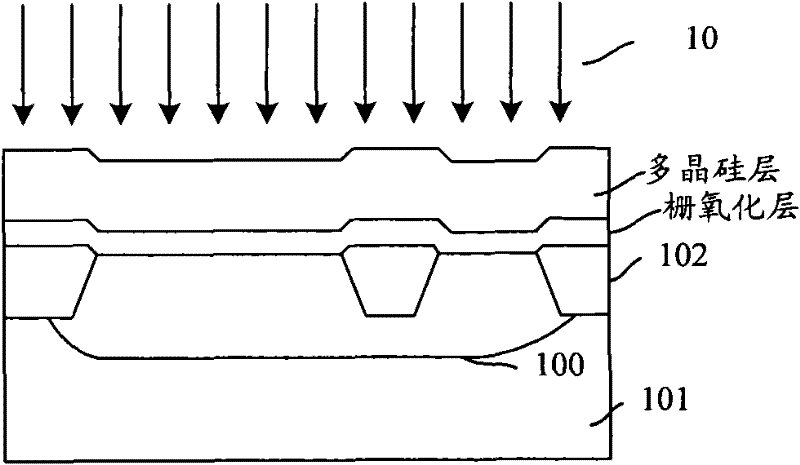

[0054] It can be seen from the prior art that the reason why the VT junction depth of the semiconductor device is relatively deep is mainly because: after the VT ion implantation is completed, when the subsequent rapid thermal annealing is performed, as in step 6 or step 8 of the prior art Rapid thermal annealing, because the semiconductor substrate is combined with ordered polysilicon, will make the high-concentration dopants in the deep region of the VT junction diffuse to the surroundings, increasing the depth of the VT junction, thereby causing a reverse current between the source and the drain , increasing the leakage current.

[0055] Therefore, in order not to reduce the concentration of the VT junction, the present invention makes the depth of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More