Patents

Literature

596 results about "Junction depth" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

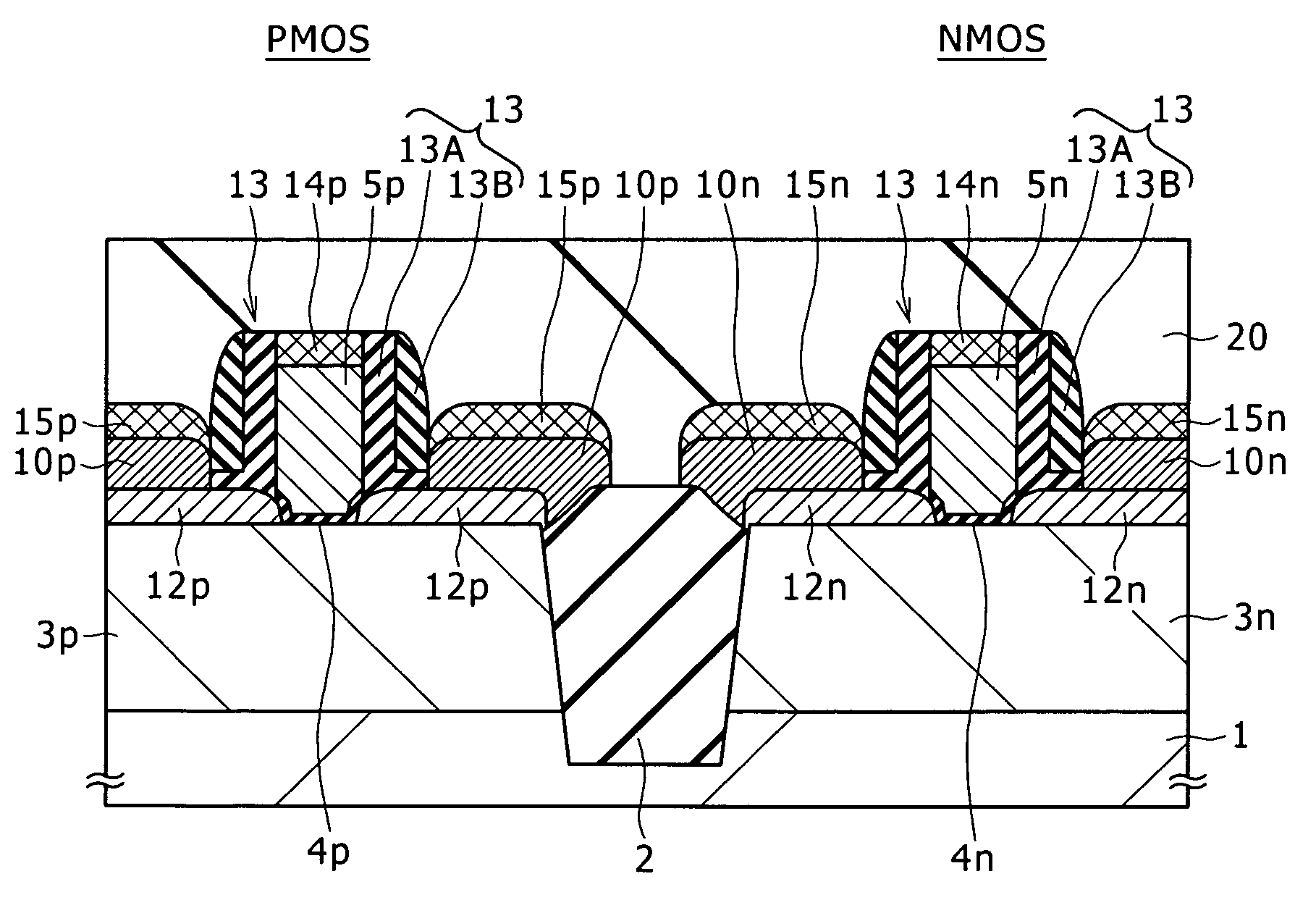

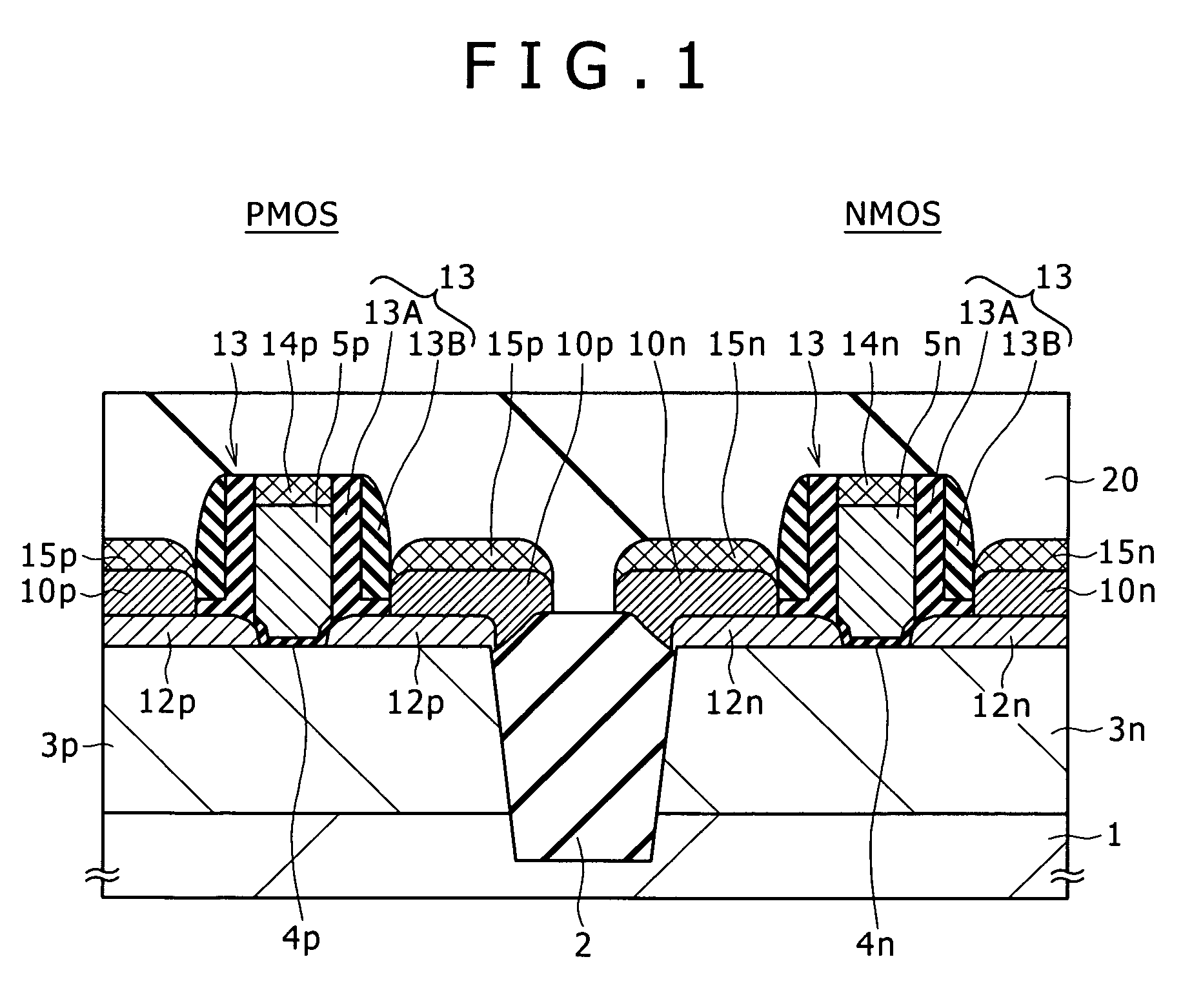

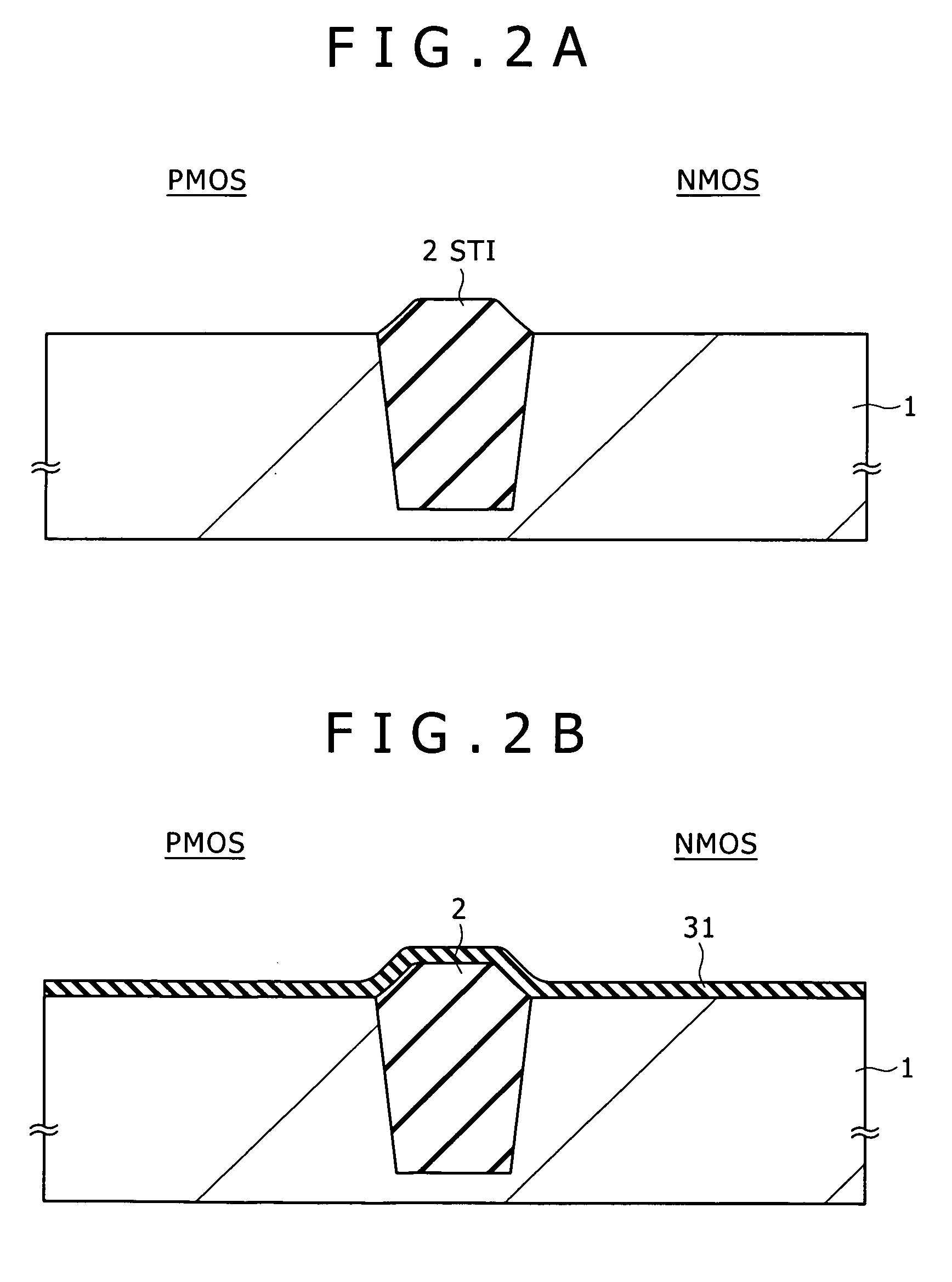

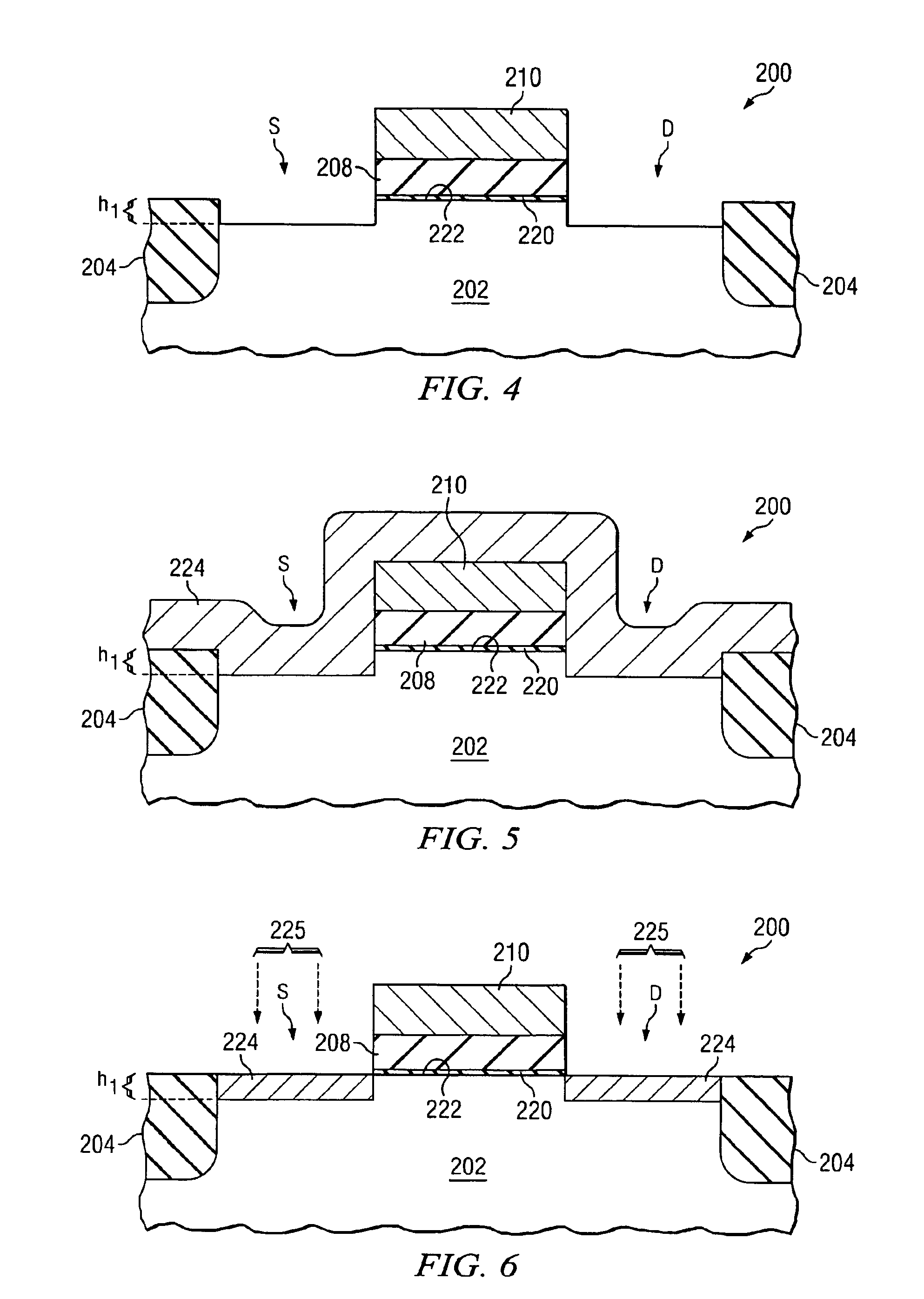

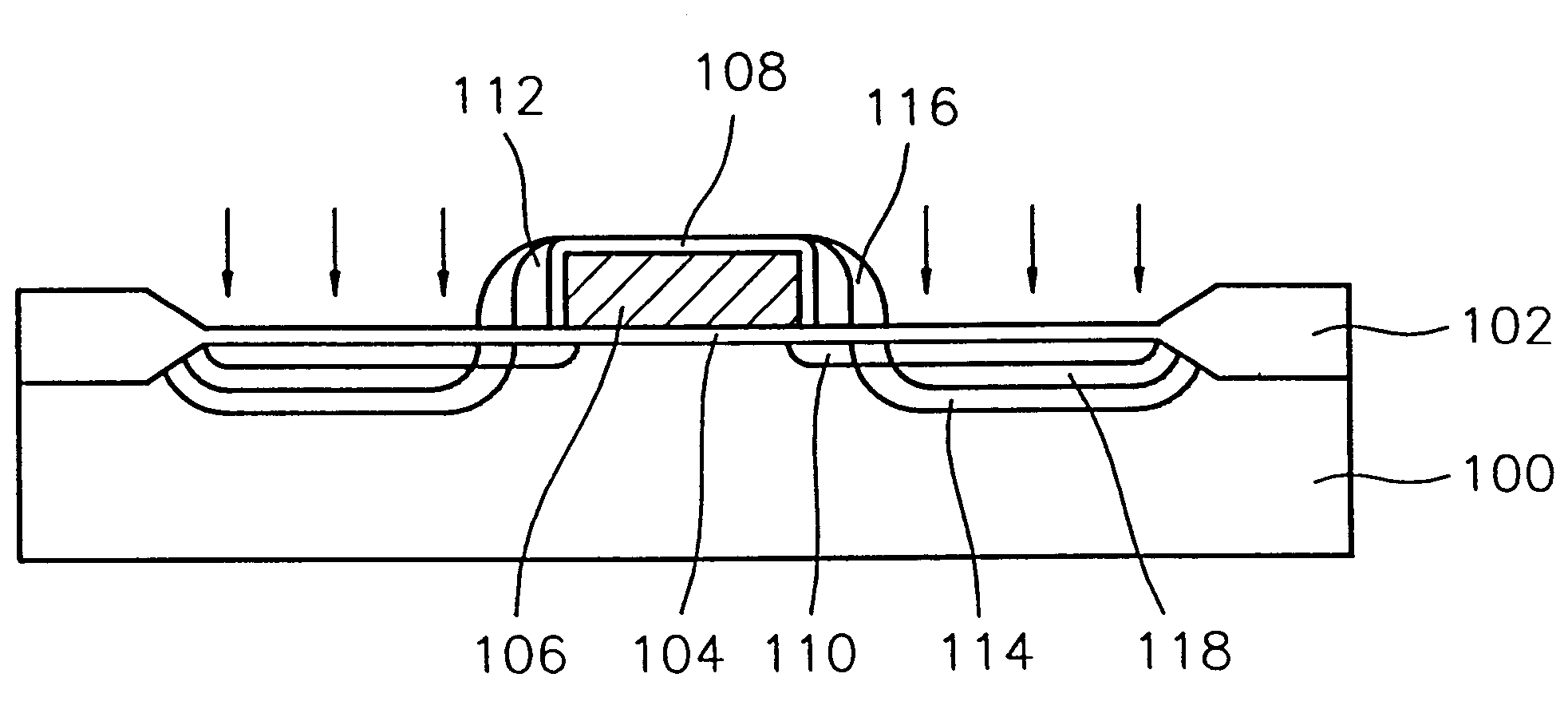

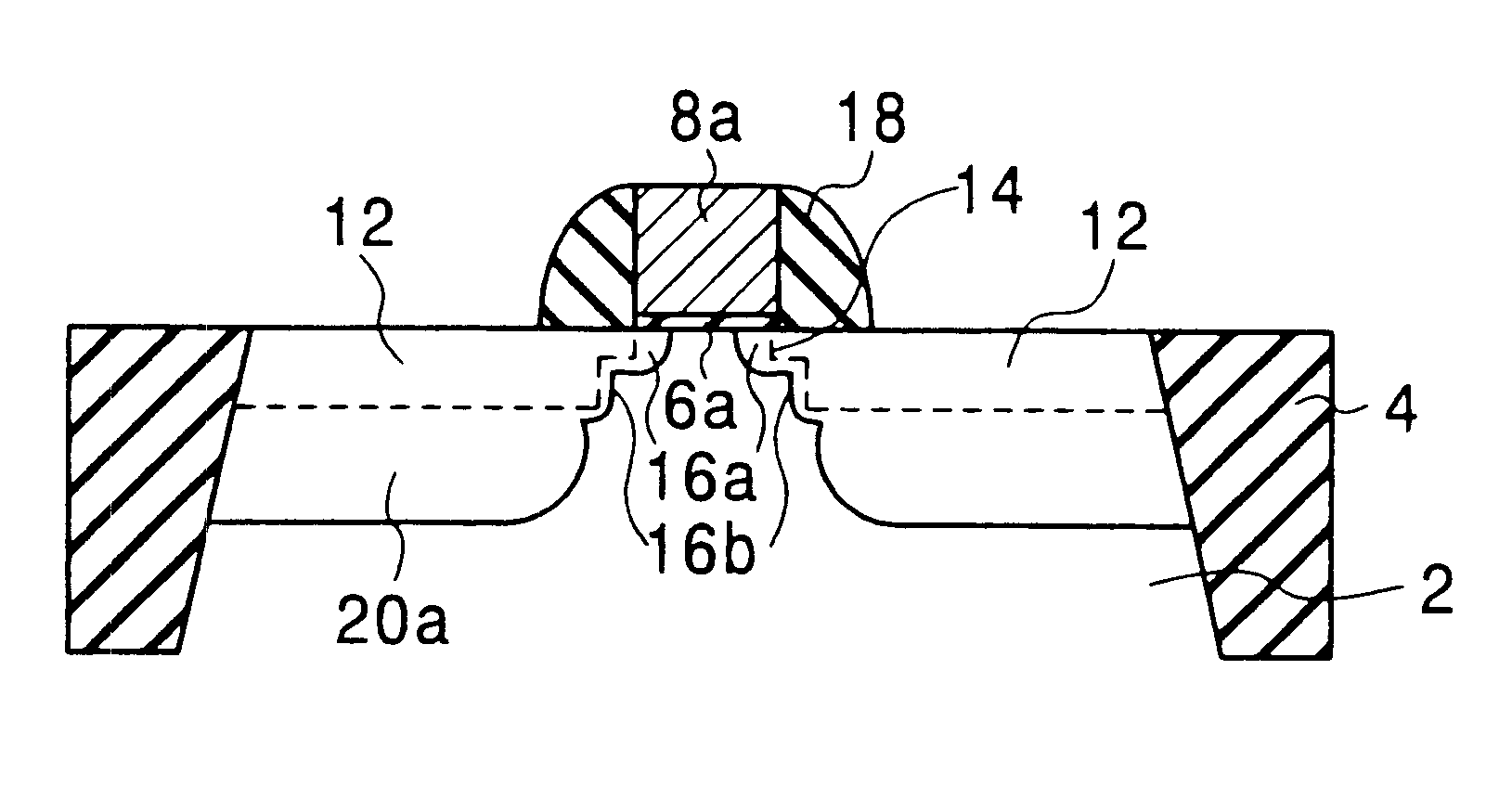

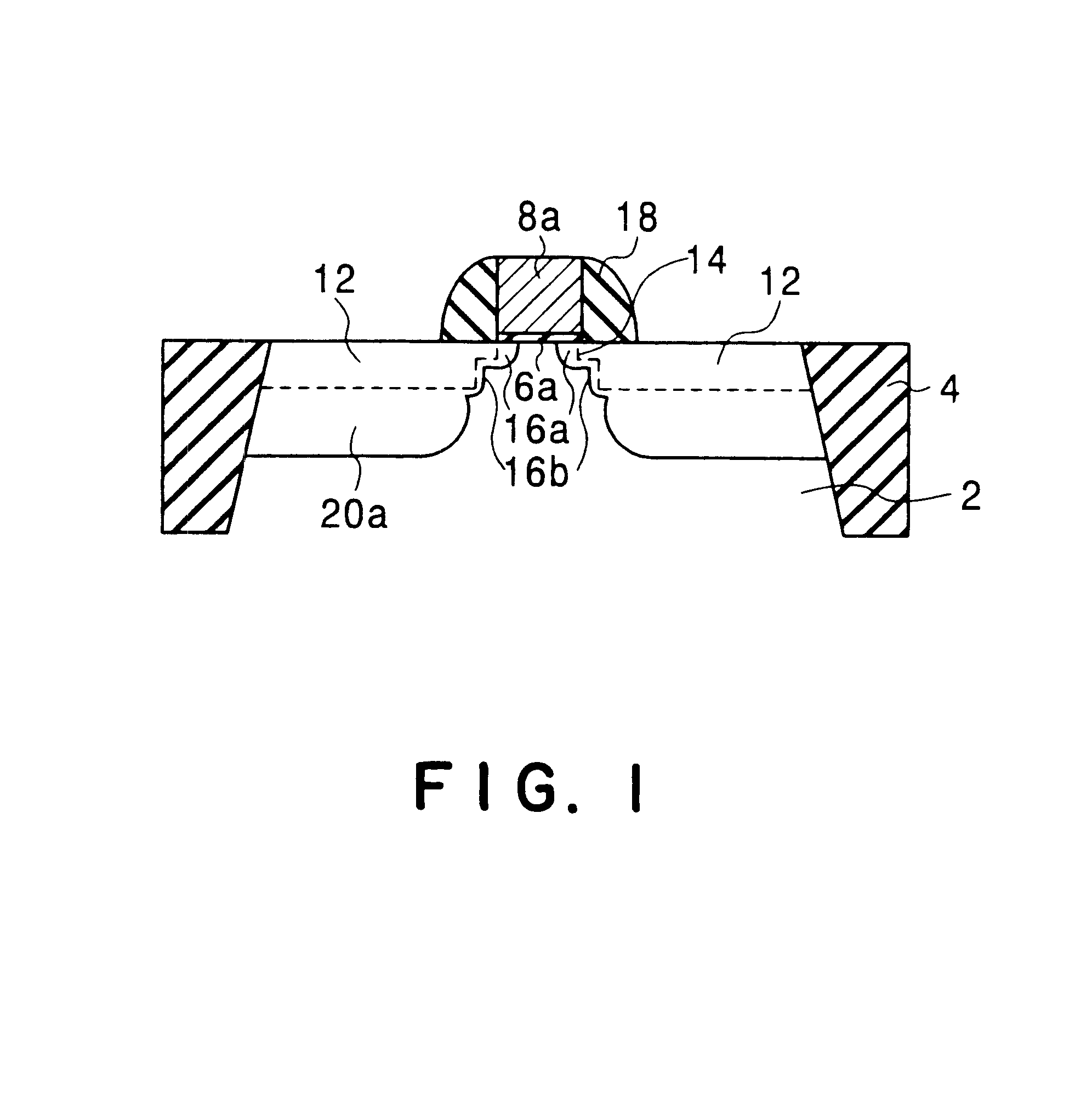

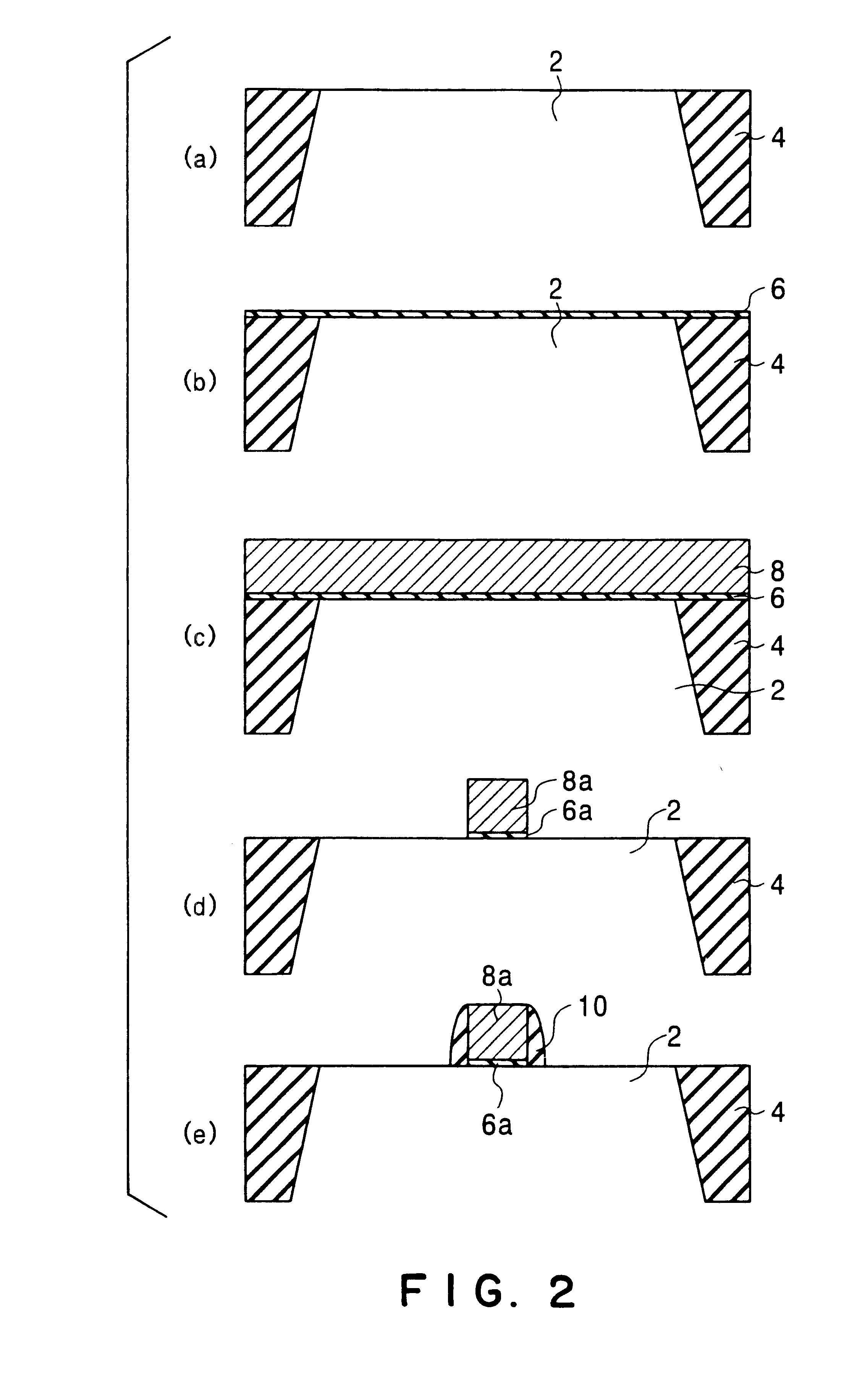

Insulated gate field-effect transistor and a method of manufacturing the same

ActiveUS20060157797A1Effective junction depthMade smallSemiconductor/solid-state device manufacturingRefuse receptaclesEngineeringBiological activation

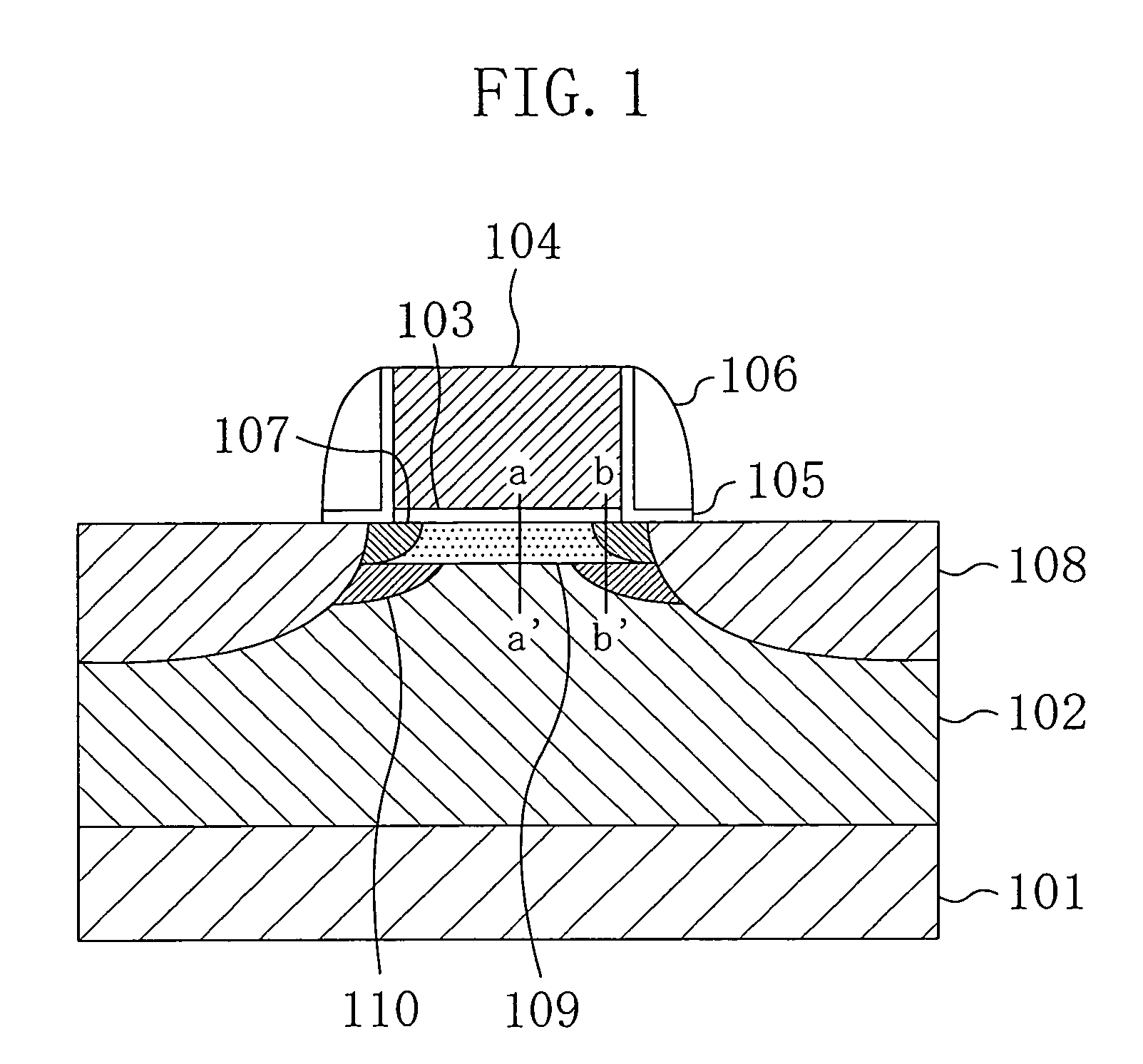

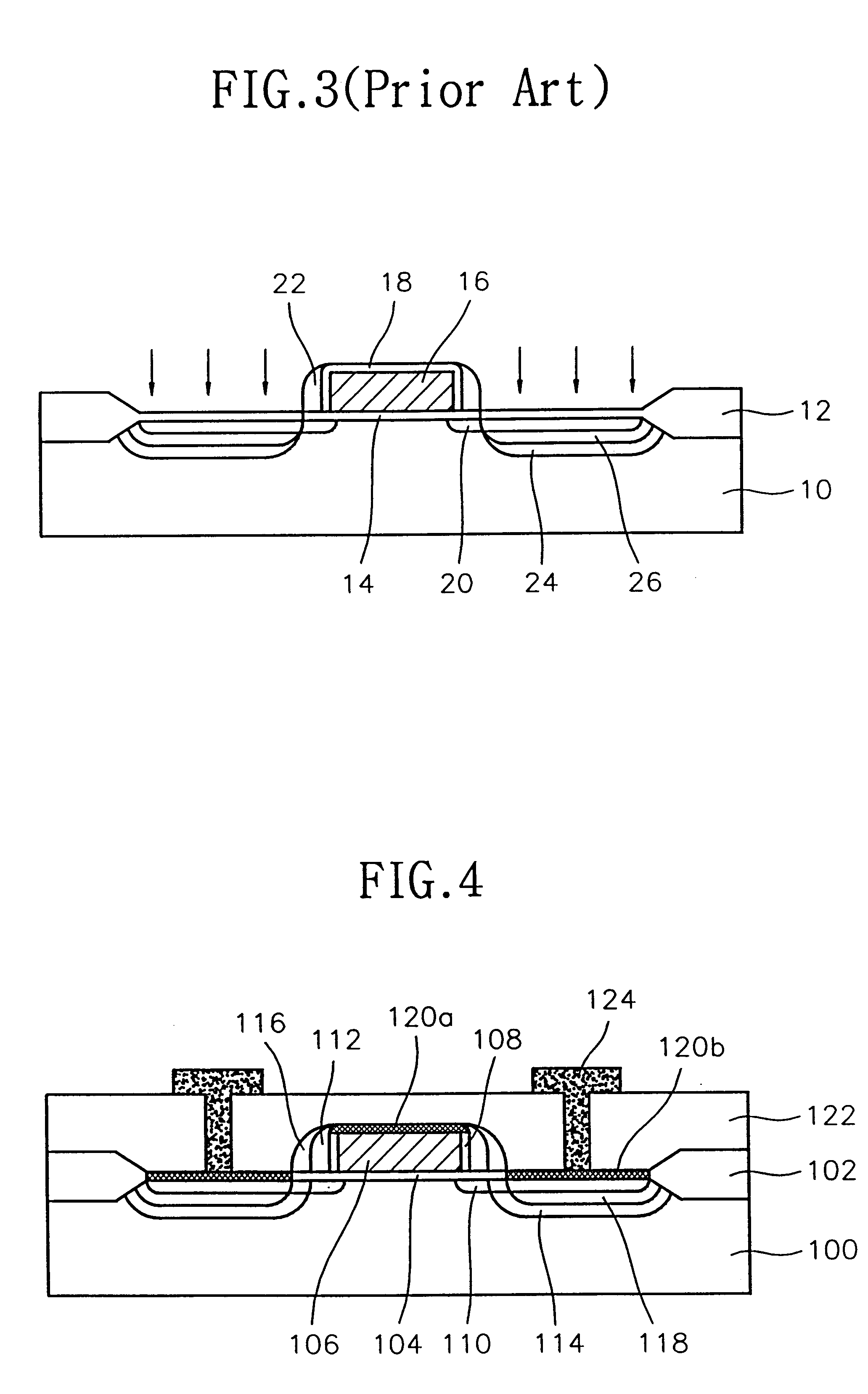

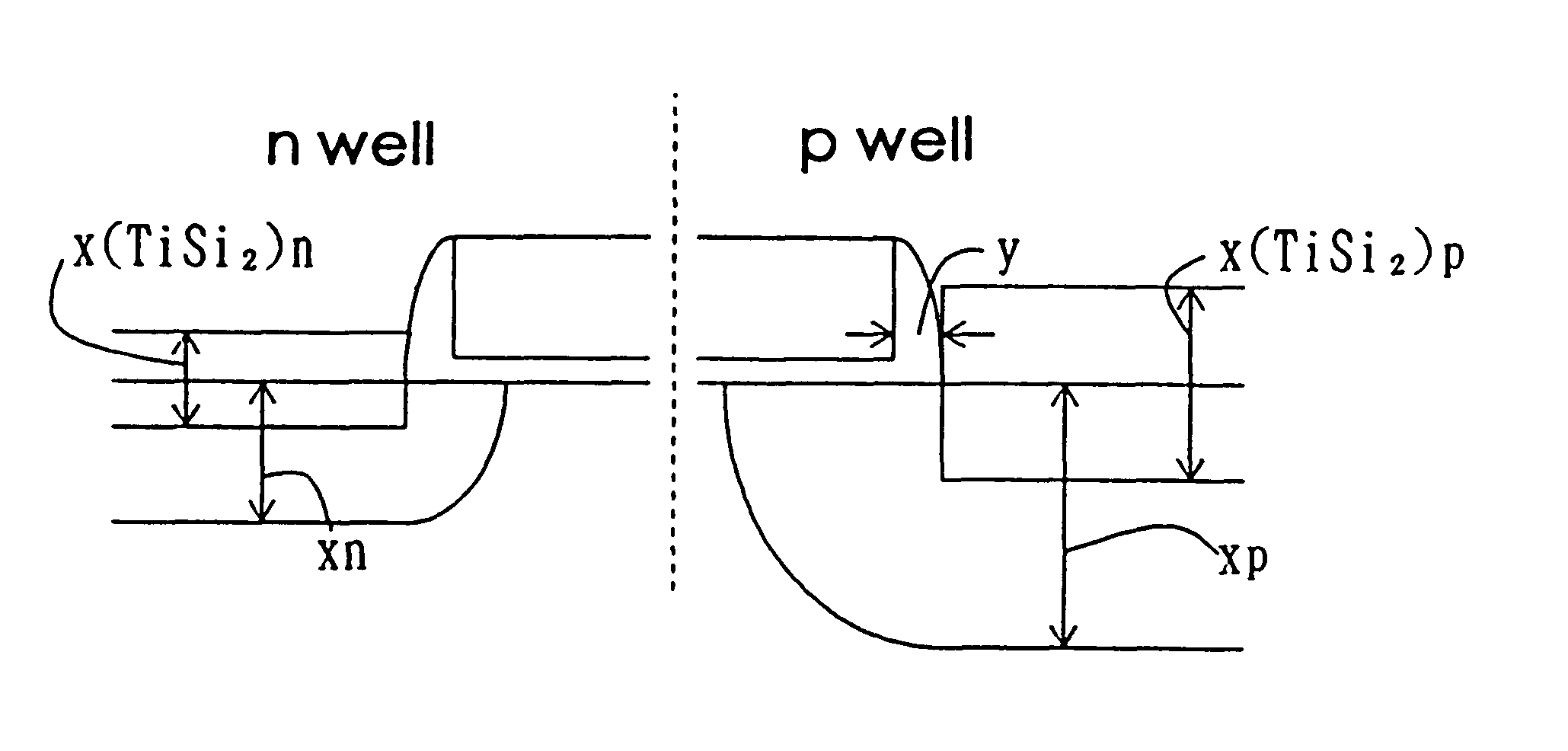

The invention aims at precisely making an effective junction depth sufficiently small with respect to a substrate surface having a steep PN junction stable in its configuration and having a channel formed therein in relation to an extension portion. Gate electrodes are formed on a P-type well and an N-type well through respective gate insulating films. Two extension portions are formed from two first epitaxial growth layers which contact regions, of the P-type well and the N-type well, where channels are to be formed, respectively, and which are at a distance from each other. Two second epitaxial growth layers are formed on the first epitaxial growth layers in positions which are further at a distance from facing ends of the two extension portions in a direction of being separate from each other. Thus, two source / drain regions are formed on a PMOS side and on an NMOS side each. In the case of this structure, there is adopted no ion implantation for introducing impurities into a deep portion. Hence, the impurities in the extension portions do not thermally diffuse into the substrate side through the activation anneal.

Owner:SONY CORP

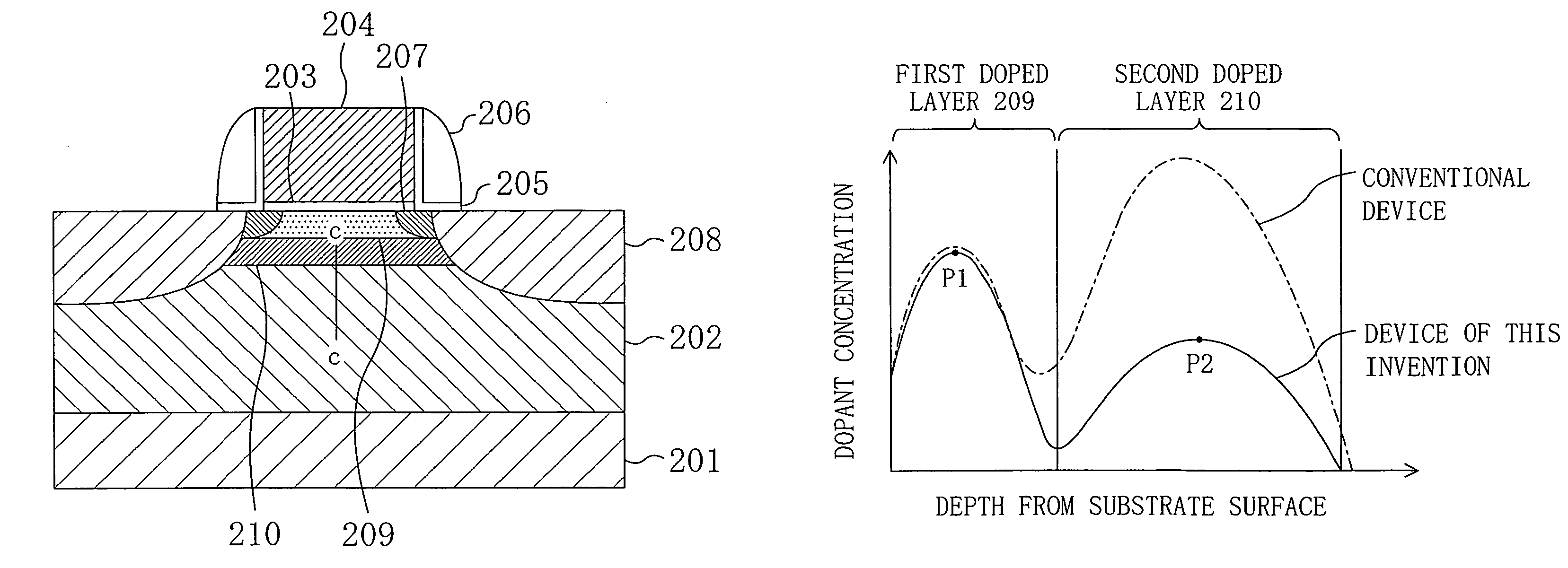

Semiconductor device and method for fabricating the same

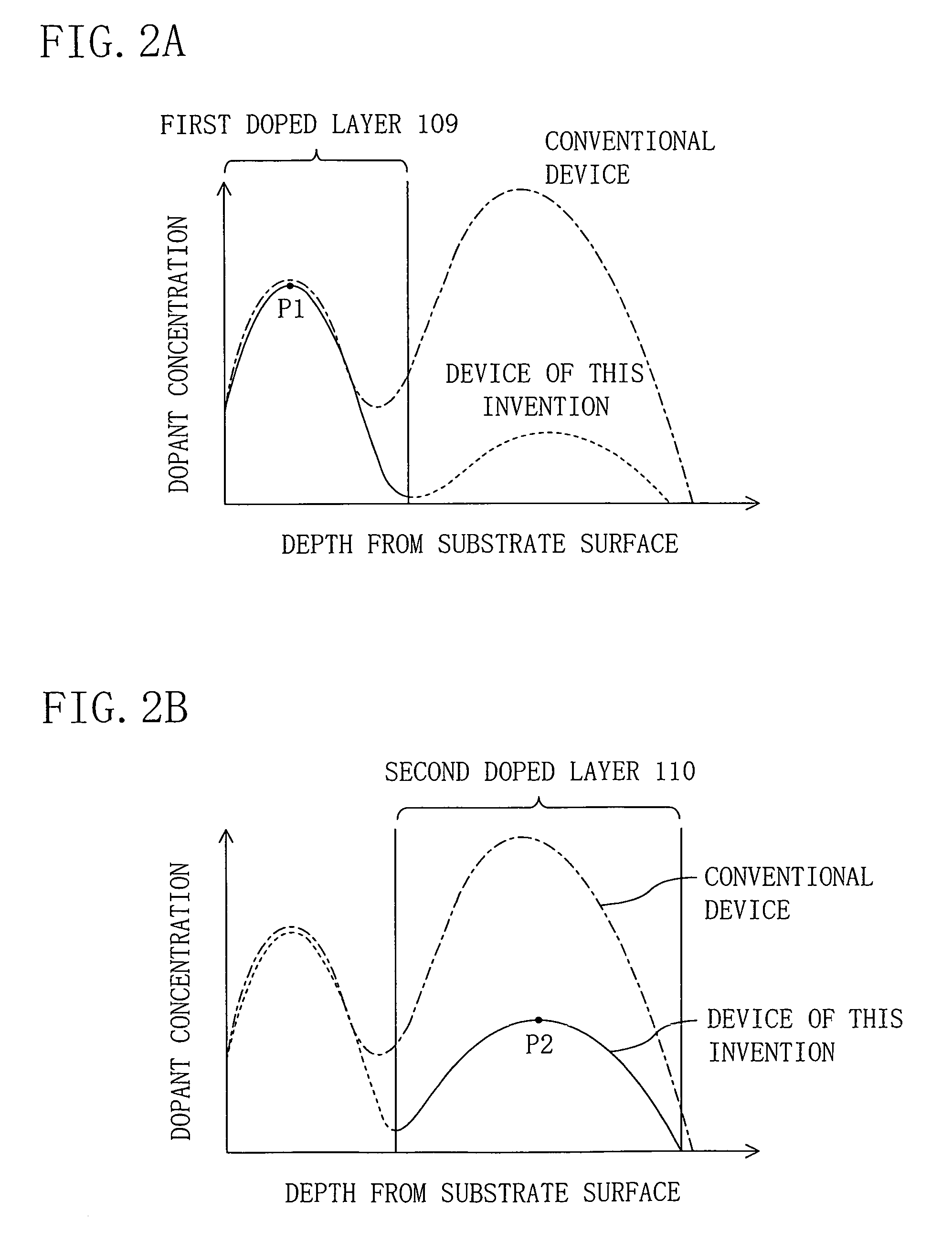

ActiveUS7301208B2Increase powerImprove leakage currentTransistorSemiconductor/solid-state device manufacturingDopantPeak value

A first doped layer of a conductivity type opposite to that of source / drain regions is formed in a semiconductor substrate under a gate electrode. A second doped layer of the conductivity type opposite to that of the source / drain regions is formed in the semiconductor substrate below the first doped layer. The first doped layer has a first peak in dopant concentration distribution in the depth direction. The first peak is located at a position shallower than the junction depth of the source / drain regions. The second doped layer has a second peak in dopant concentration distribution in the depth direction. The second peak is located at a position deeper than the first peak and shallower than the junction depth of the source / drain regions. The dopant concentration at the first peak is higher than that at the second peak.

Owner:GK BRIDGE 1

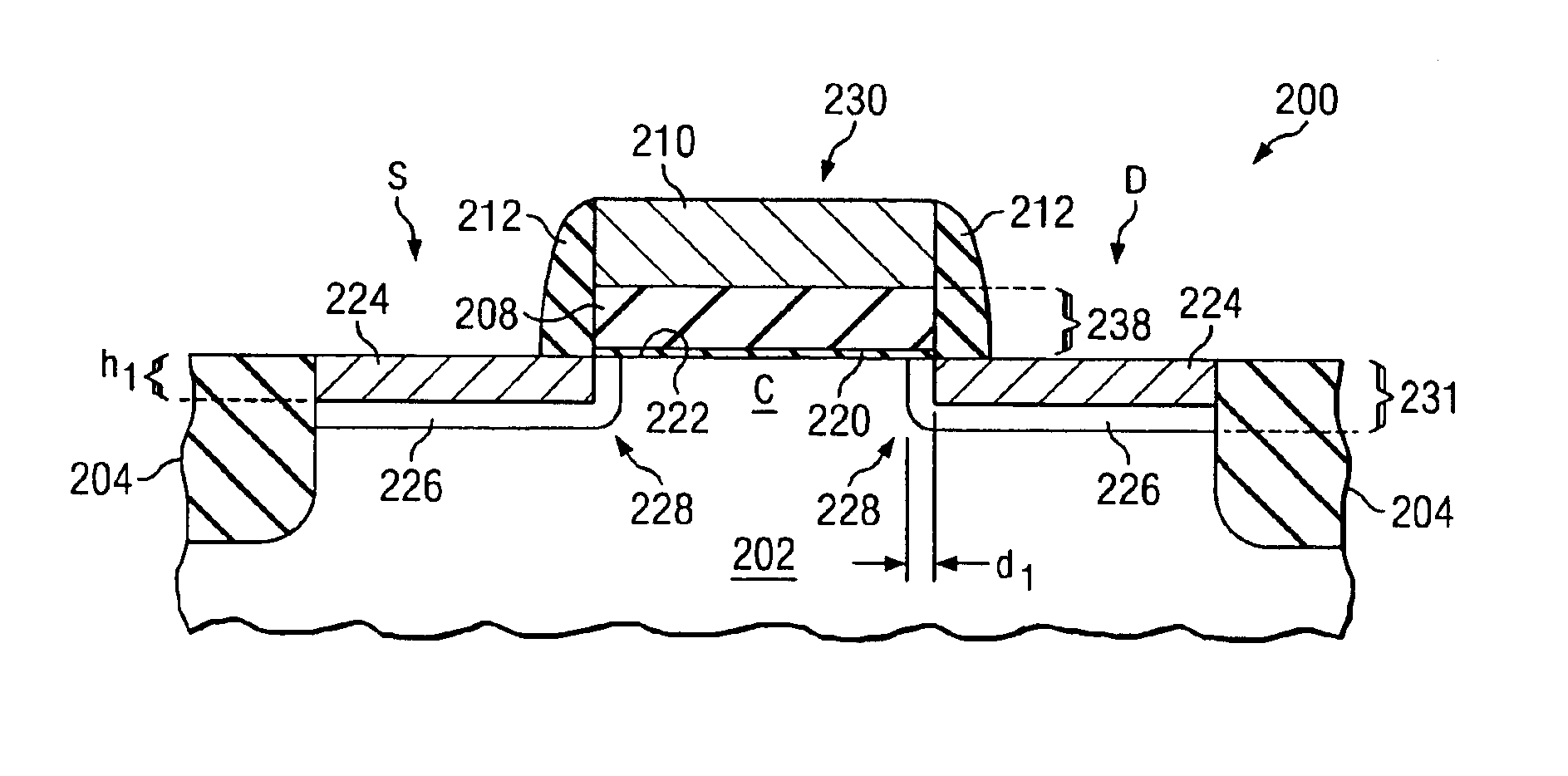

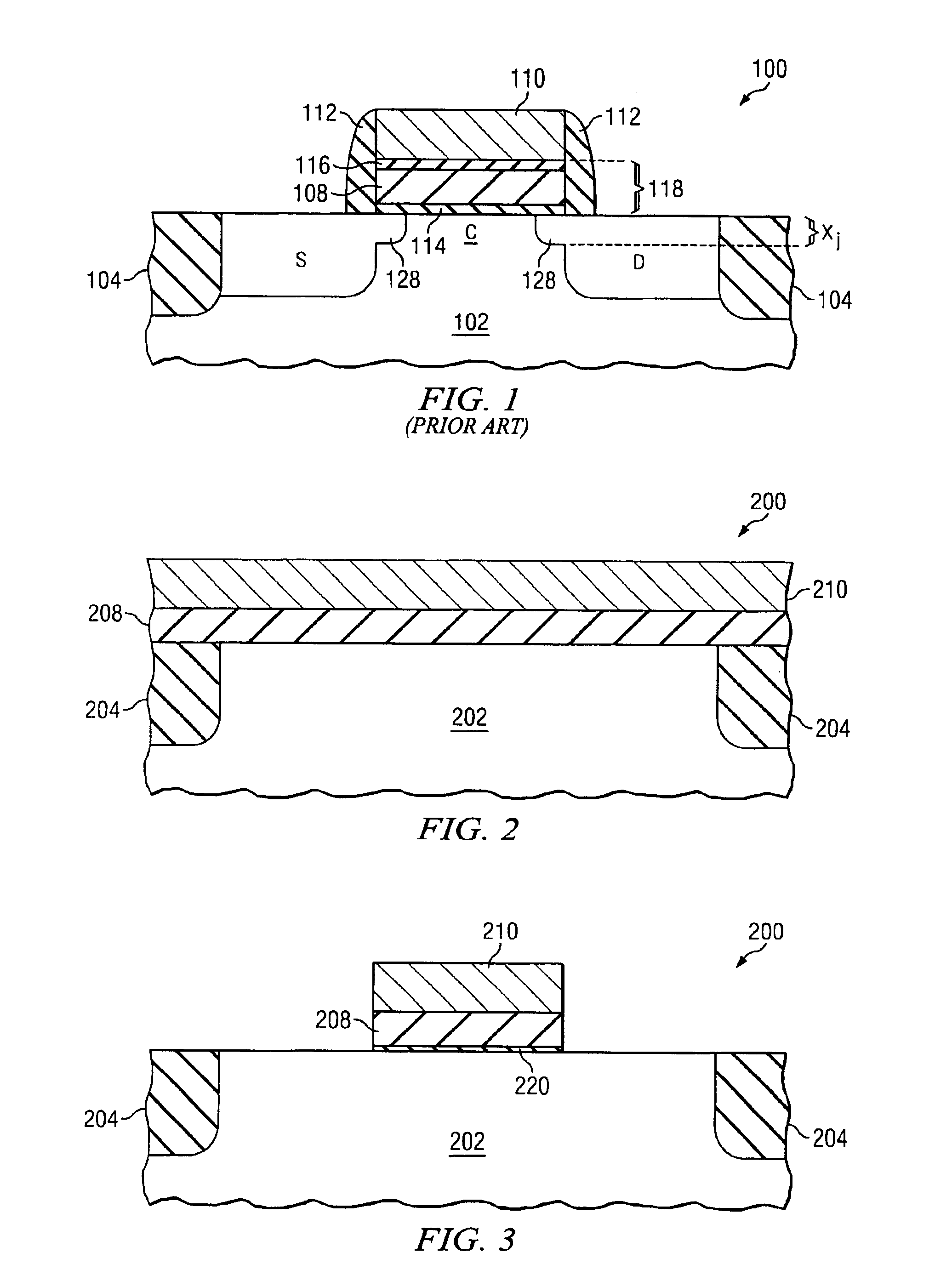

Transistor with dopant-bearing metal in source and drain

ActiveUS6921691B1Budget is reducedQuality improvementTransistorSemiconductor/solid-state device manufacturingDopantGate dielectric

A transistor and method of manufacturing thereof. A gate dielectric and gate are formed over a workpiece, and the source and drain regions of a transistor are recessed. The recesses are filled with a dopant-bearing metal, and a low-temperature anneal process is used to form doped regions within the workpiece adjacent the dopant-bearing metal regions. A transistor having a small effective oxide thickness and a well-controlled junction depth is formed.

Owner:INFINEON TECH AG

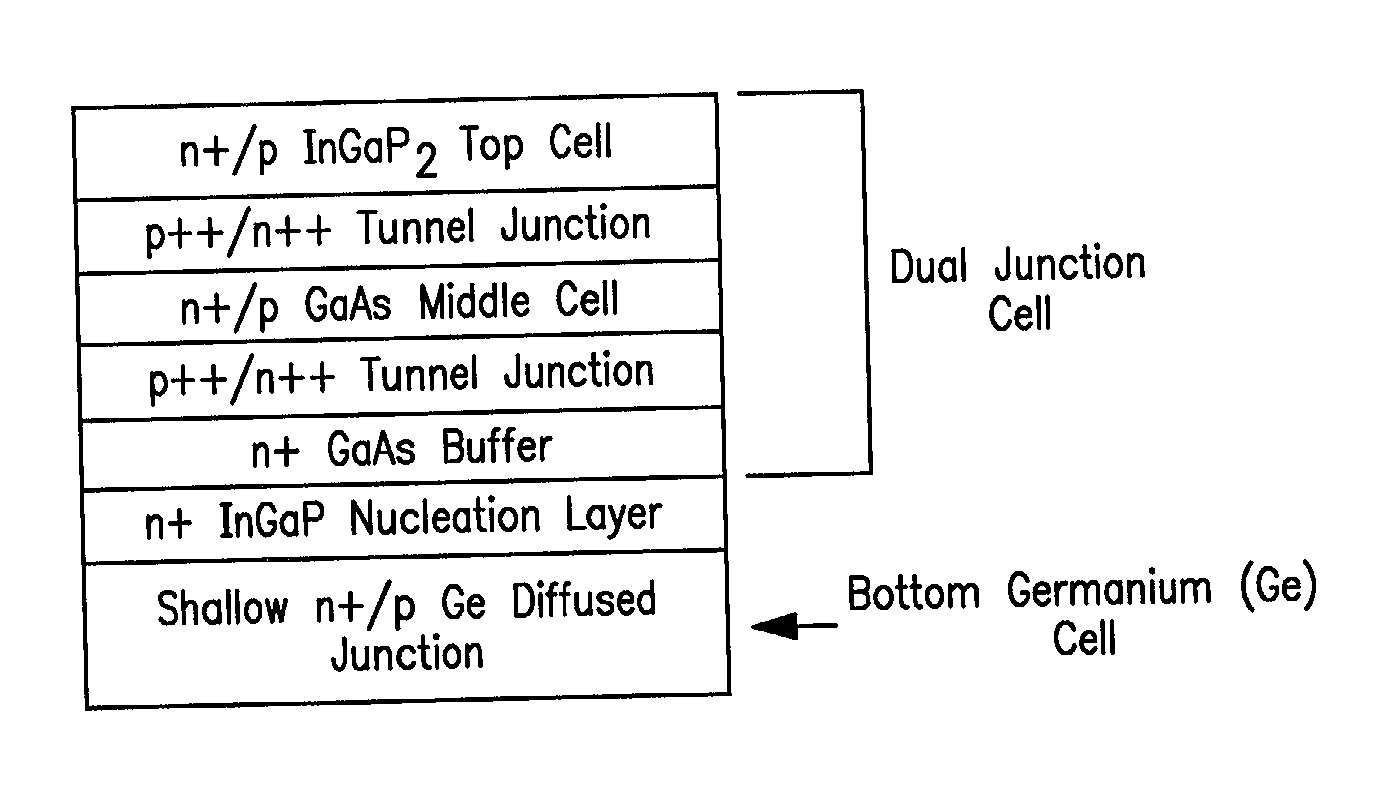

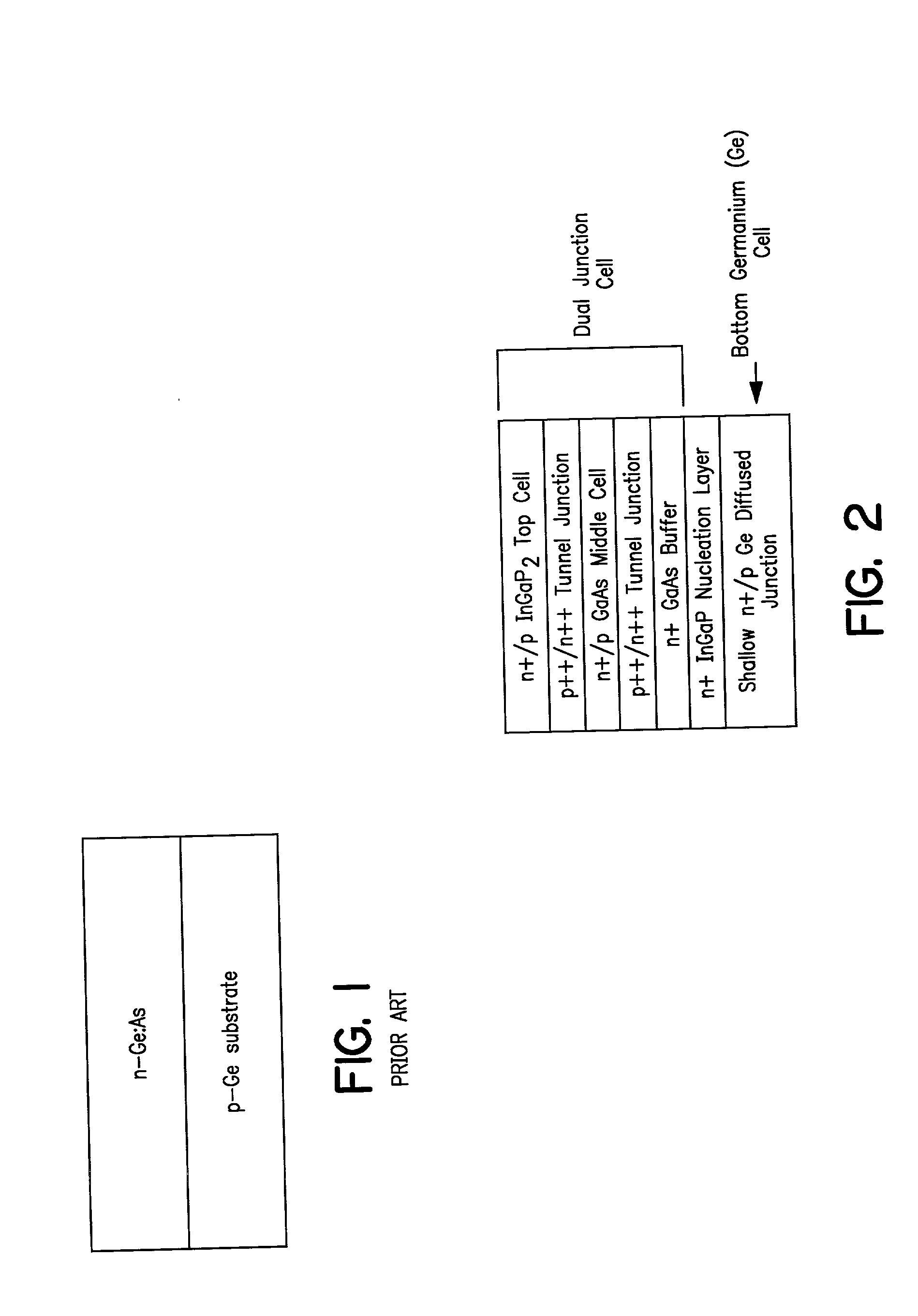

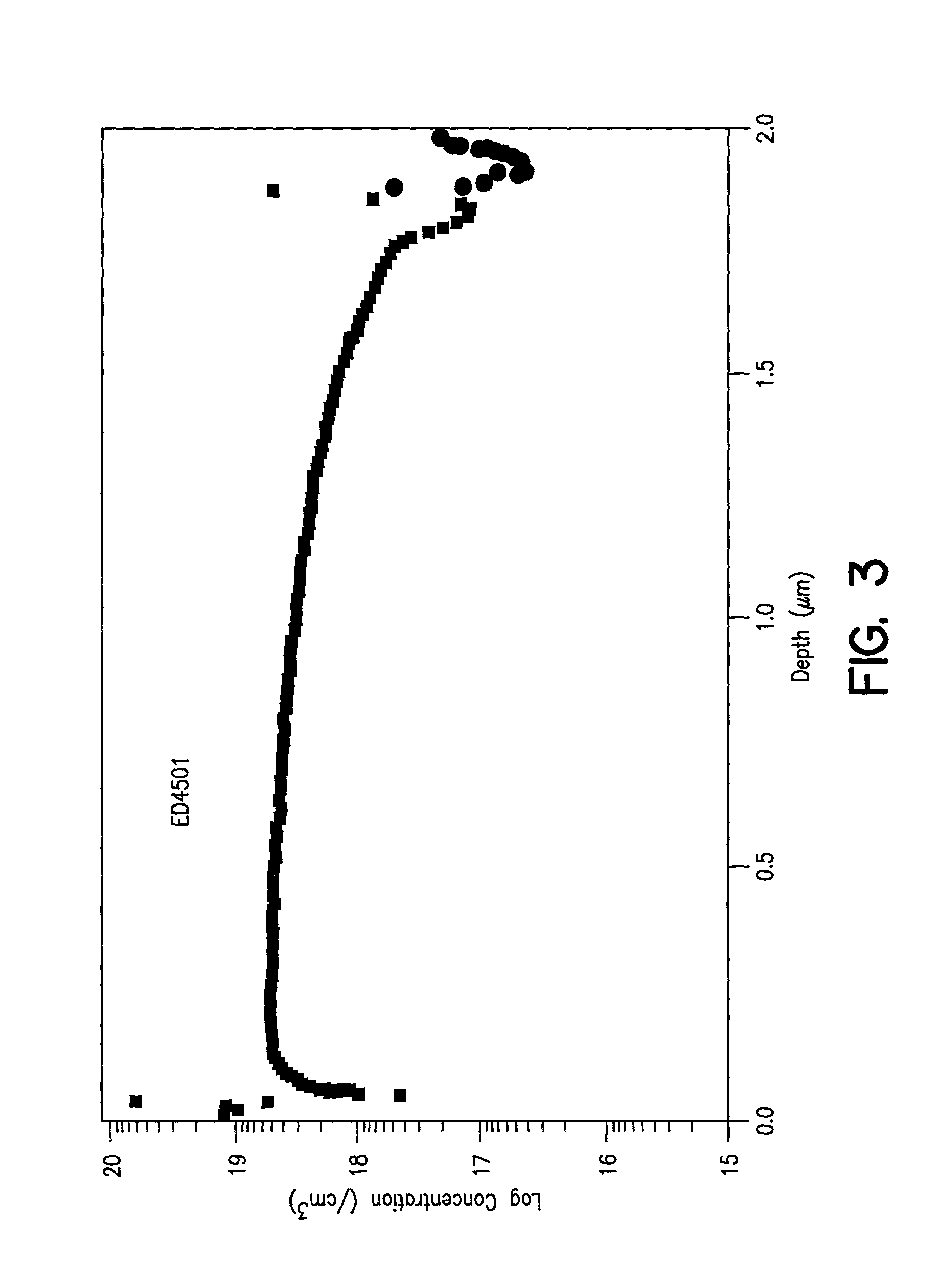

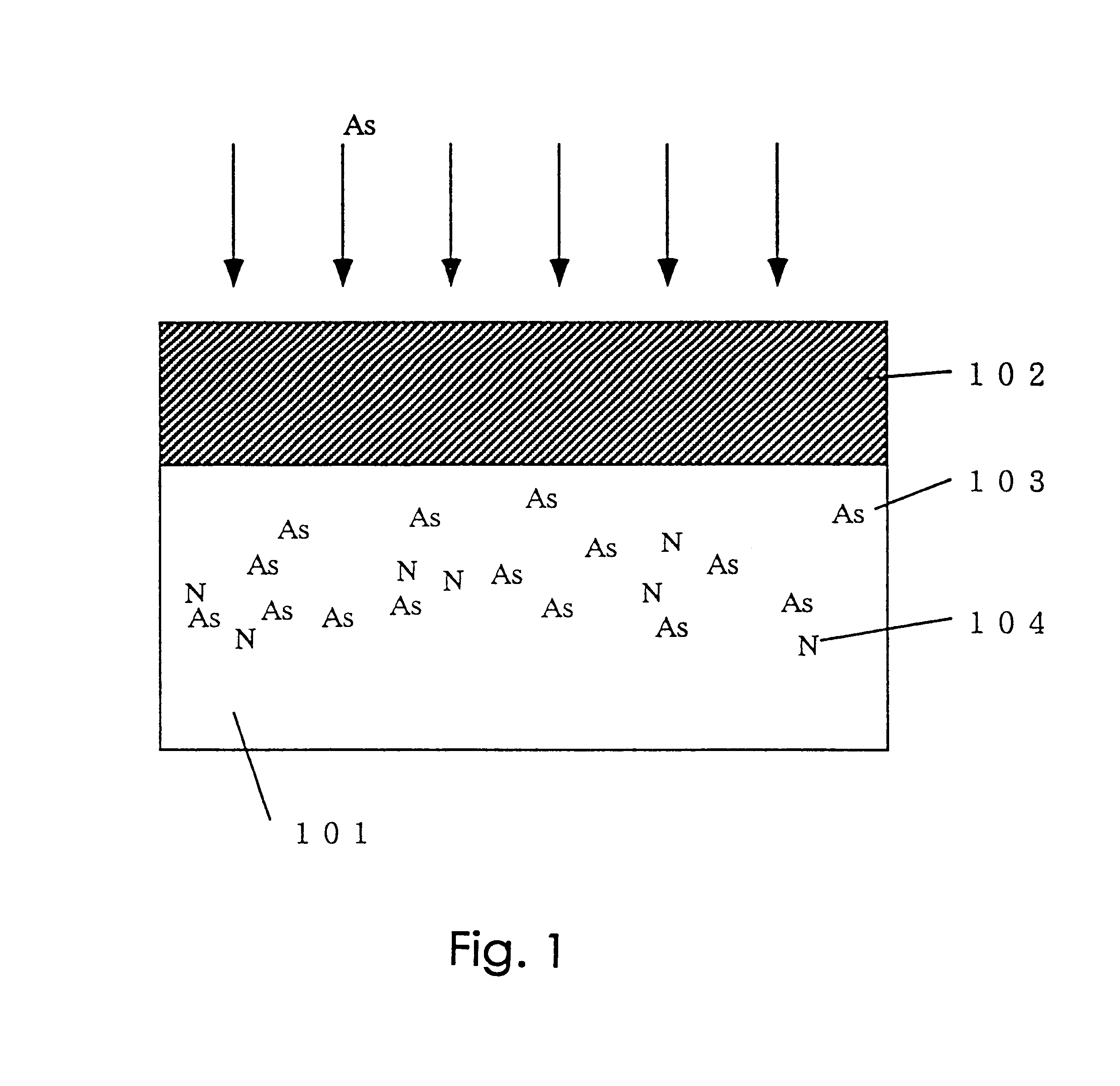

Apparatus and method for optimizing the efficiency of germanium junctions in multi-junction solar cells

InactiveUS20020040727A1PV power plantsSemiconductor/solid-state device manufacturingDopantDiffusion barrier

Apparatus and Method for Optimizing the Efficiency of Germanium Junctions in Multi-Junction Solar Cells. In a preferred embodiment, an indium gallium phosphide (InGaP) nucleation layer is disposed between the germanium (Ge) substrate and the overlying dual-junction epilayers for controlling the diffusion depth of the n-doping in the germanium junction. Specifically, by acting as a diffusion barrier to arsenic (As) contained in the overlying epilayers and as a source of n-type dopant for forming the germanium junction, the nucleation layer enables the growth time and temperature in the epilayer device process to be minimized without compromising the integrity of the dual-junction epilayer structure. This in turn allows the arsenic diffusion into the germanium substrate to be optimally controlled by varying the thickness of the nucleation layer. An active germanium junction formed in accordance with the present invention has a typical diffused junction depth that is ⅕ to ½ of that achievable in prior art devices. Furthermore, triple-junction solar cells incorporating a shallow n-p germanium junction of the present invention can attain 1 sun AM0 efficiencies in excess of 26%.

Owner:SOLAERO TECH CORP

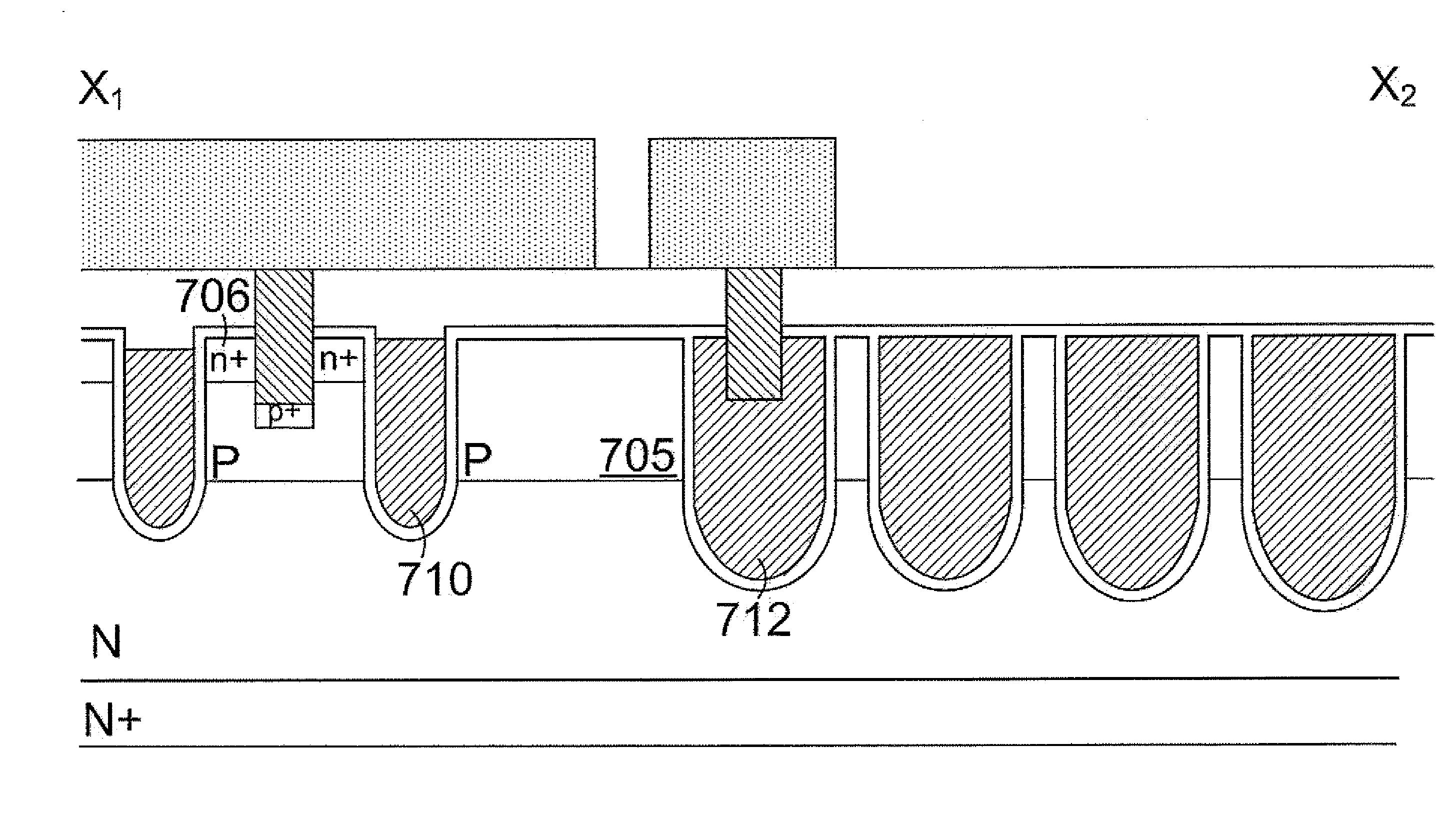

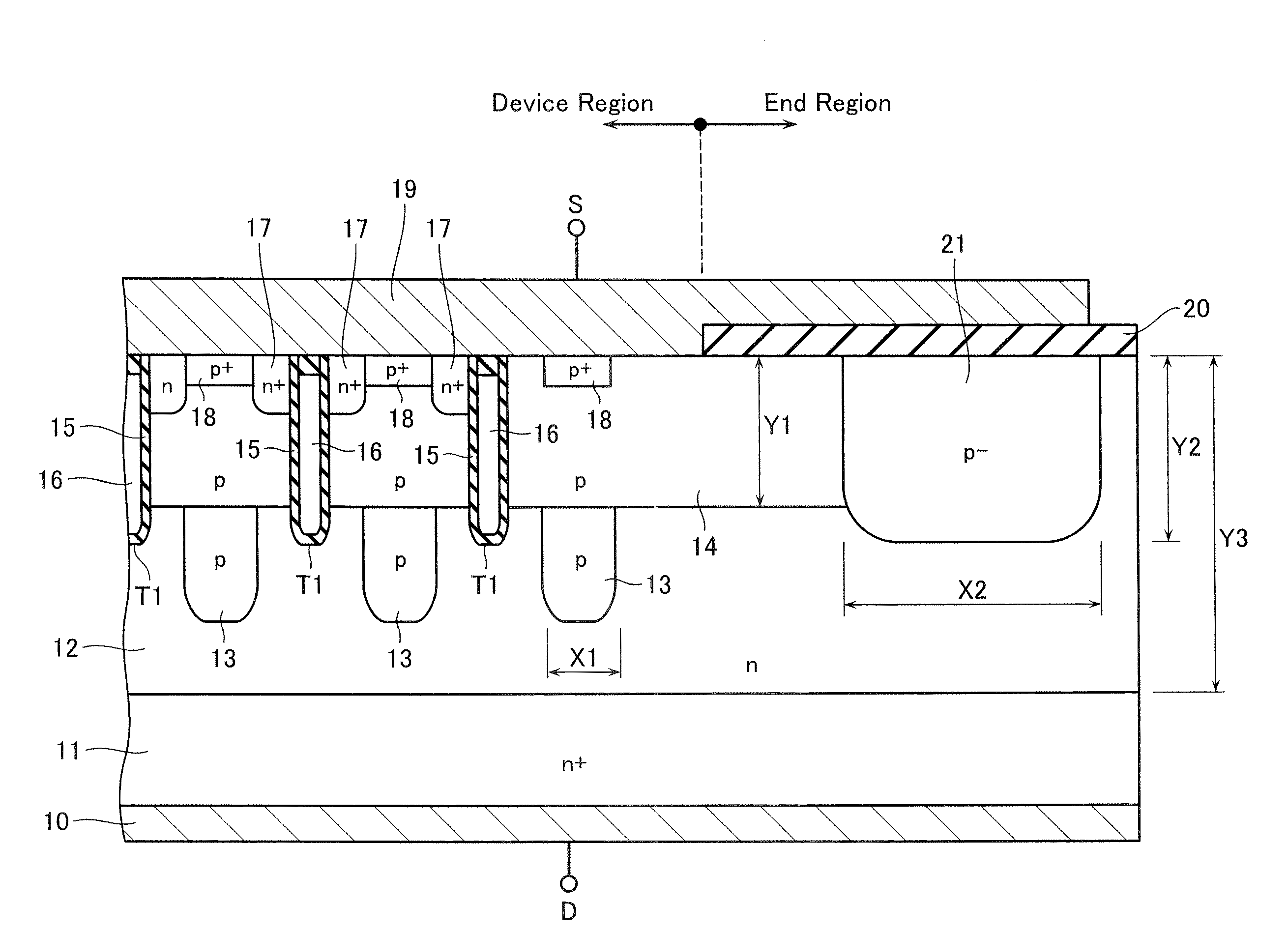

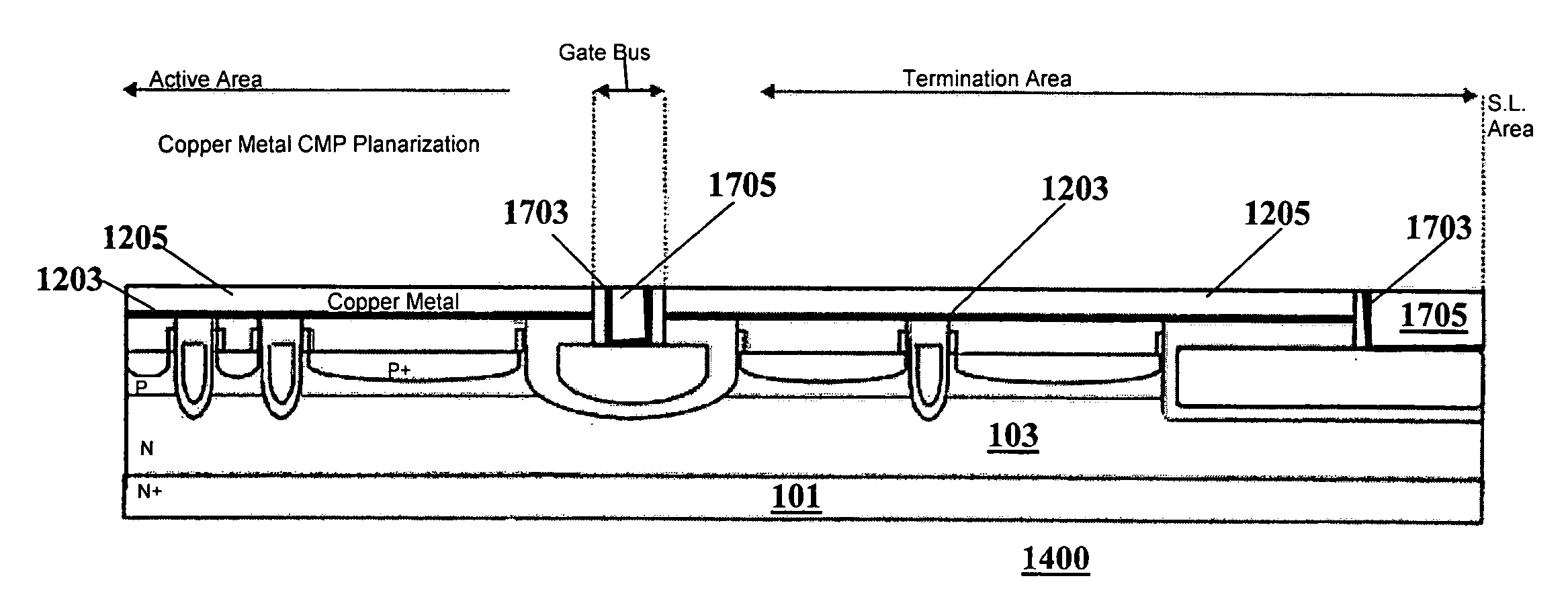

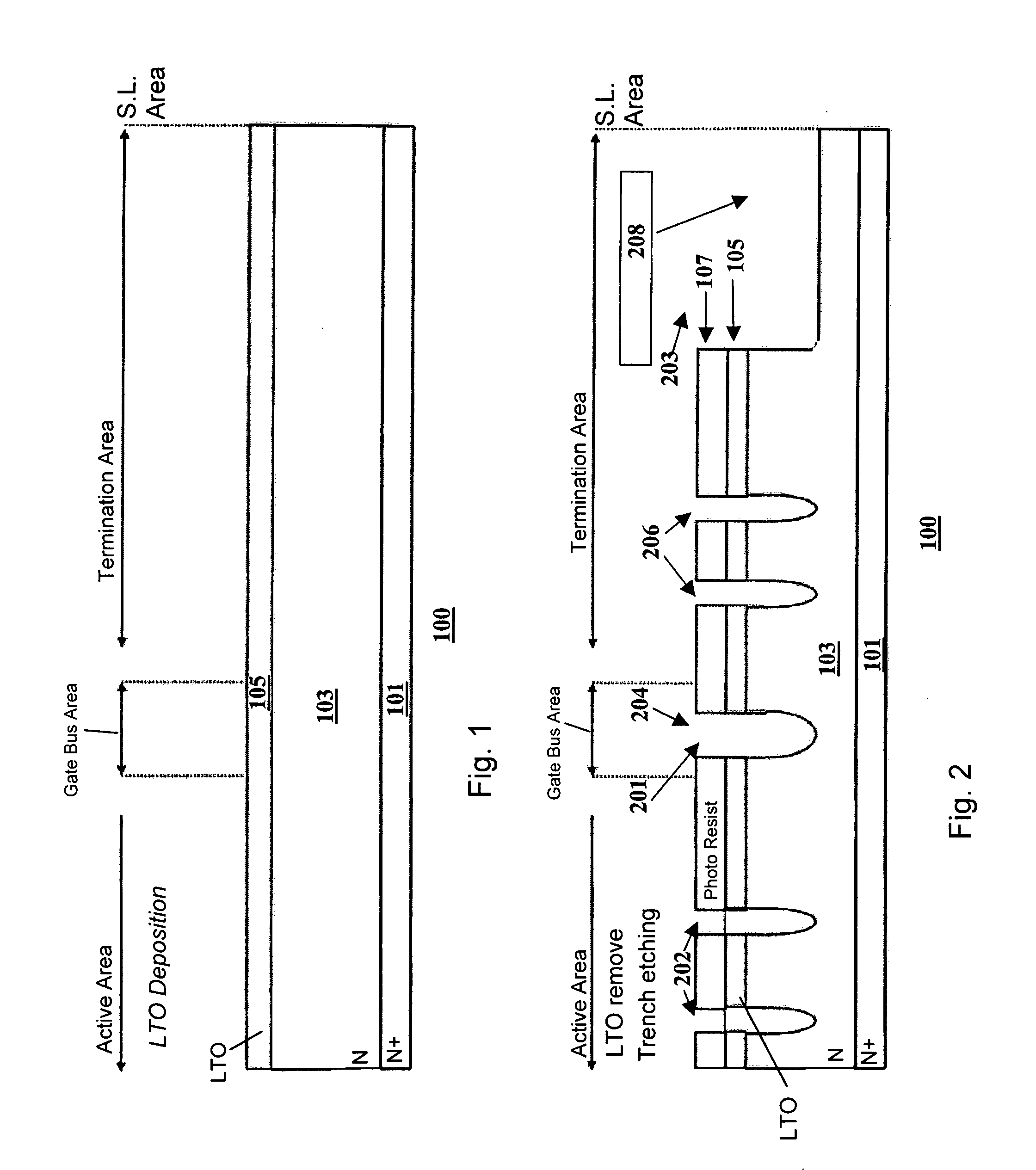

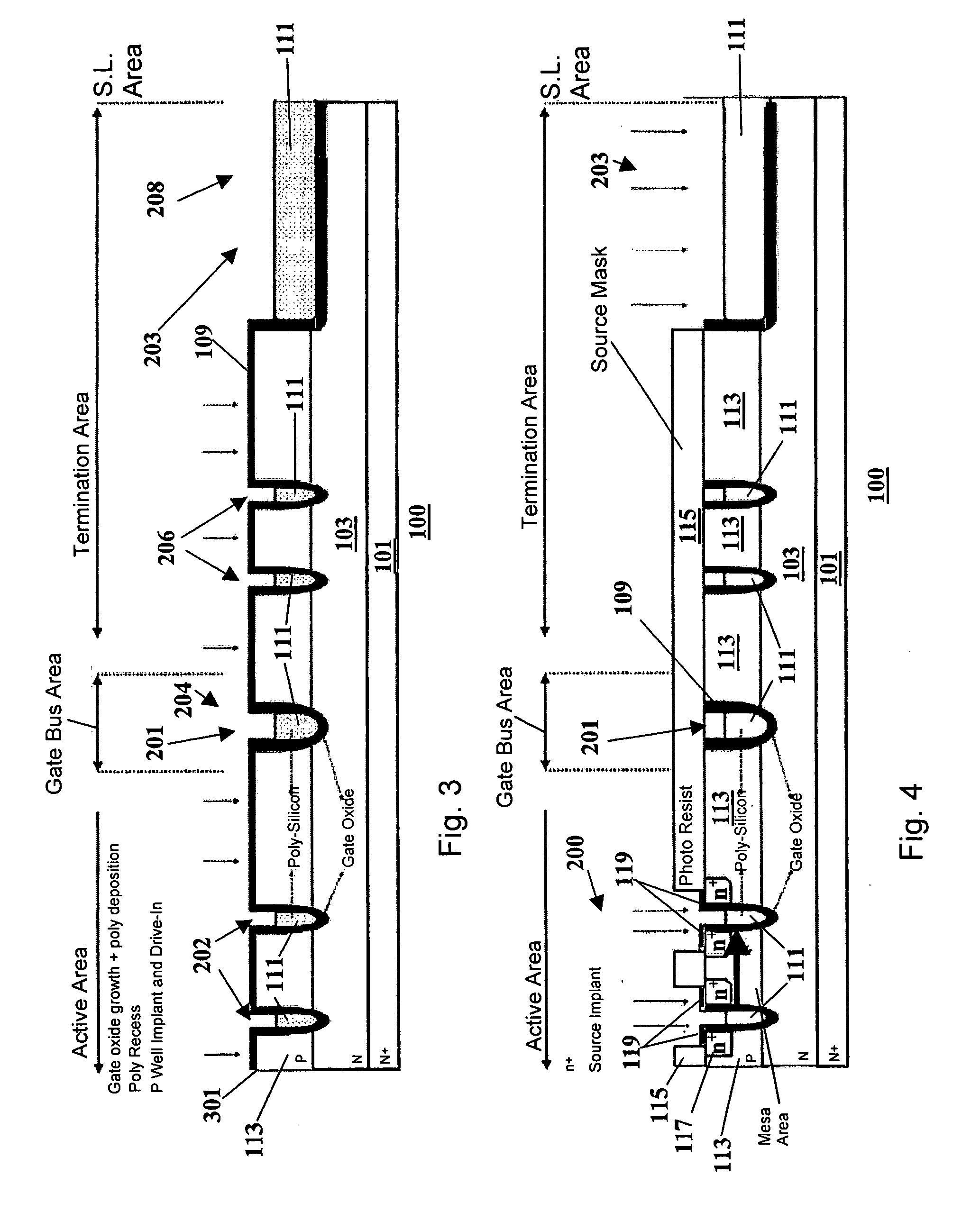

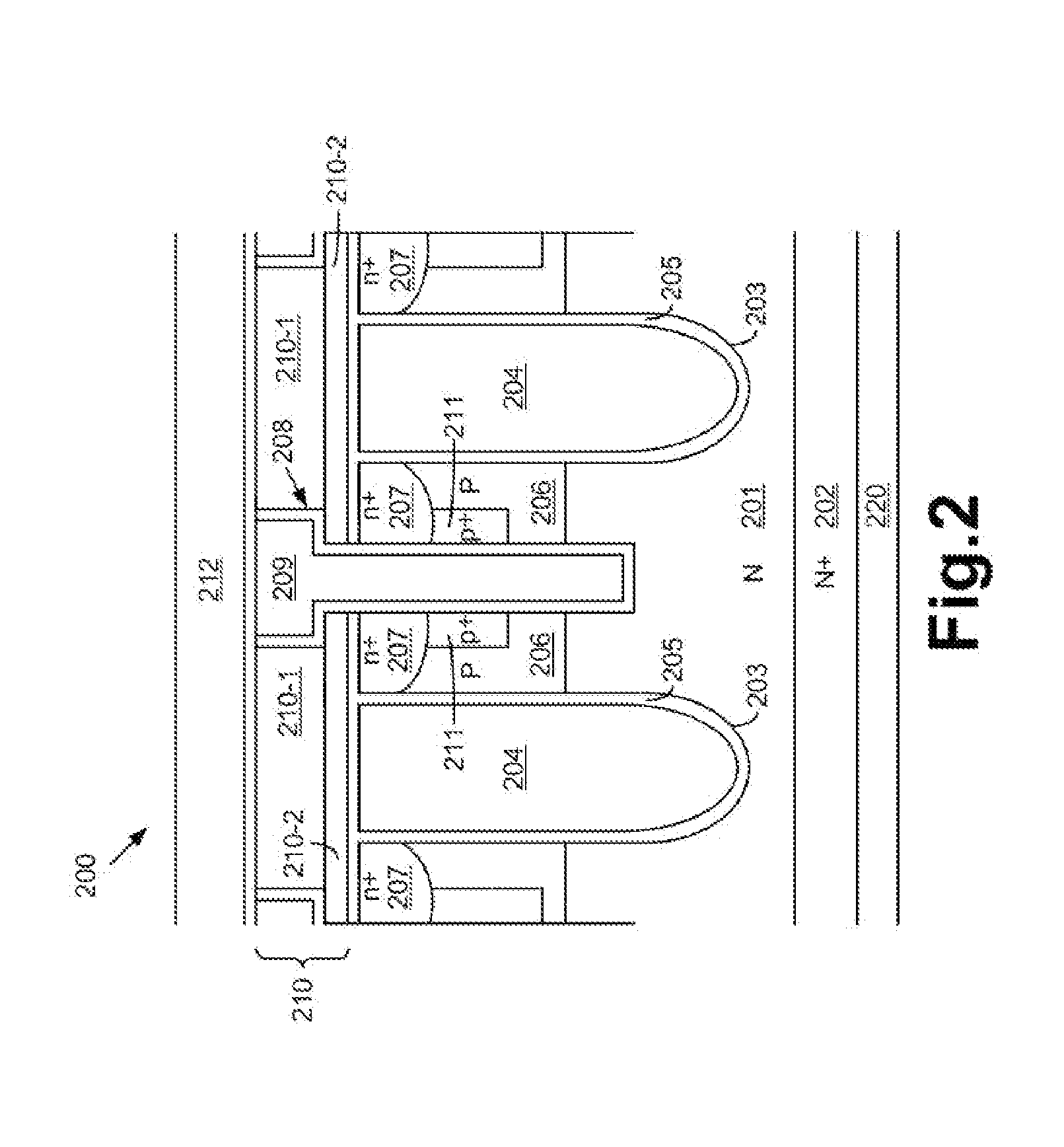

Shielded trench mosfet with multiple trenched floating gates as termination

ActiveUS20110254086A1Semiconductor/solid-state device manufacturingSemiconductor devicesTrench mosfetBody region

A trench MOSFET comprising a plurality of transistor cells having shielded trenched gates and multiple trenched floating gates as termination region is disclosed. The trenched floating gates have trench depth equal to or deeper than body junction depth of body regions in termination area. In some preferred embodiments, the trenched floating gates in the termination area are implemented by using shielded electrode structure.

Owner:FORCE MOS TECH CO LTD

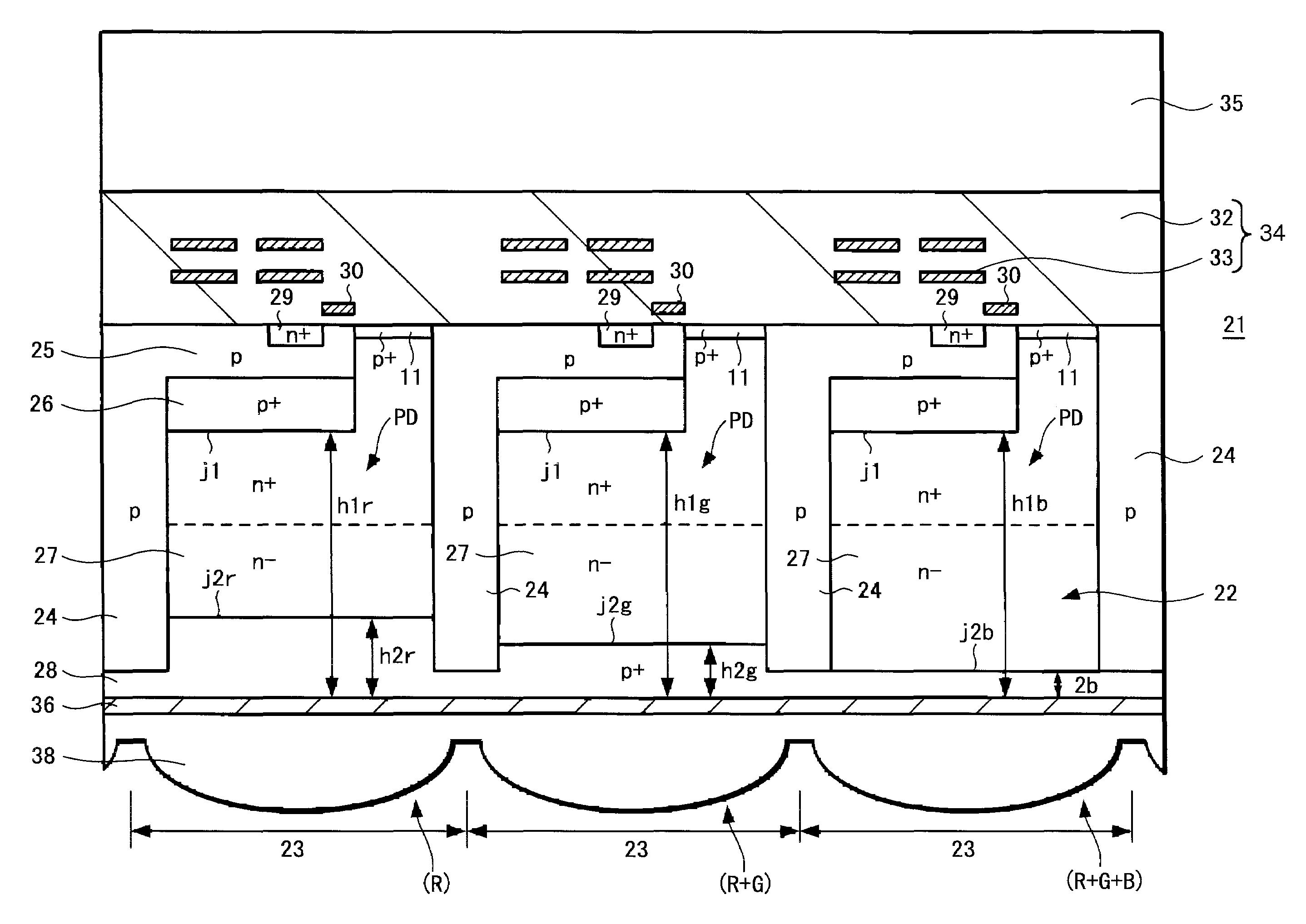

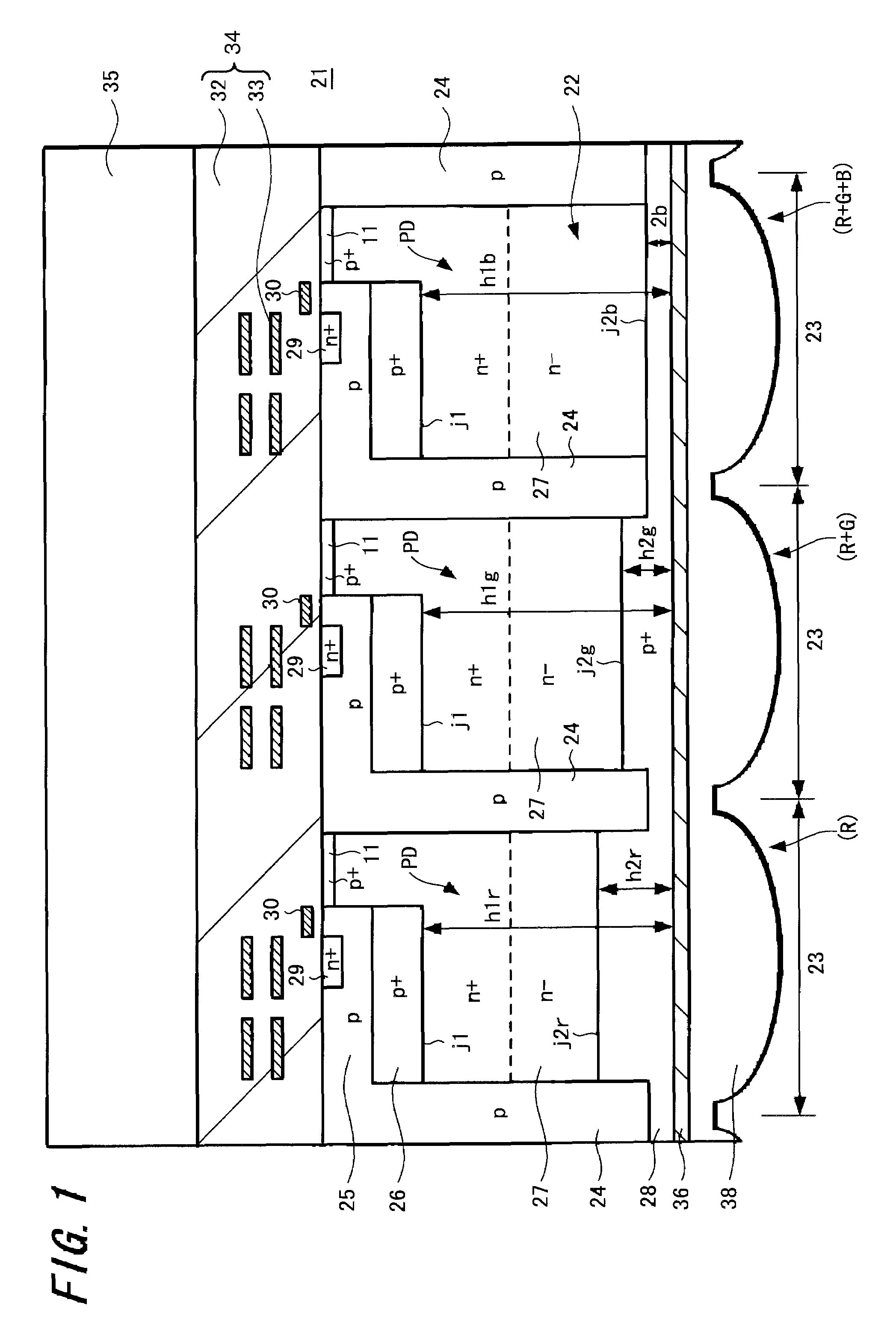

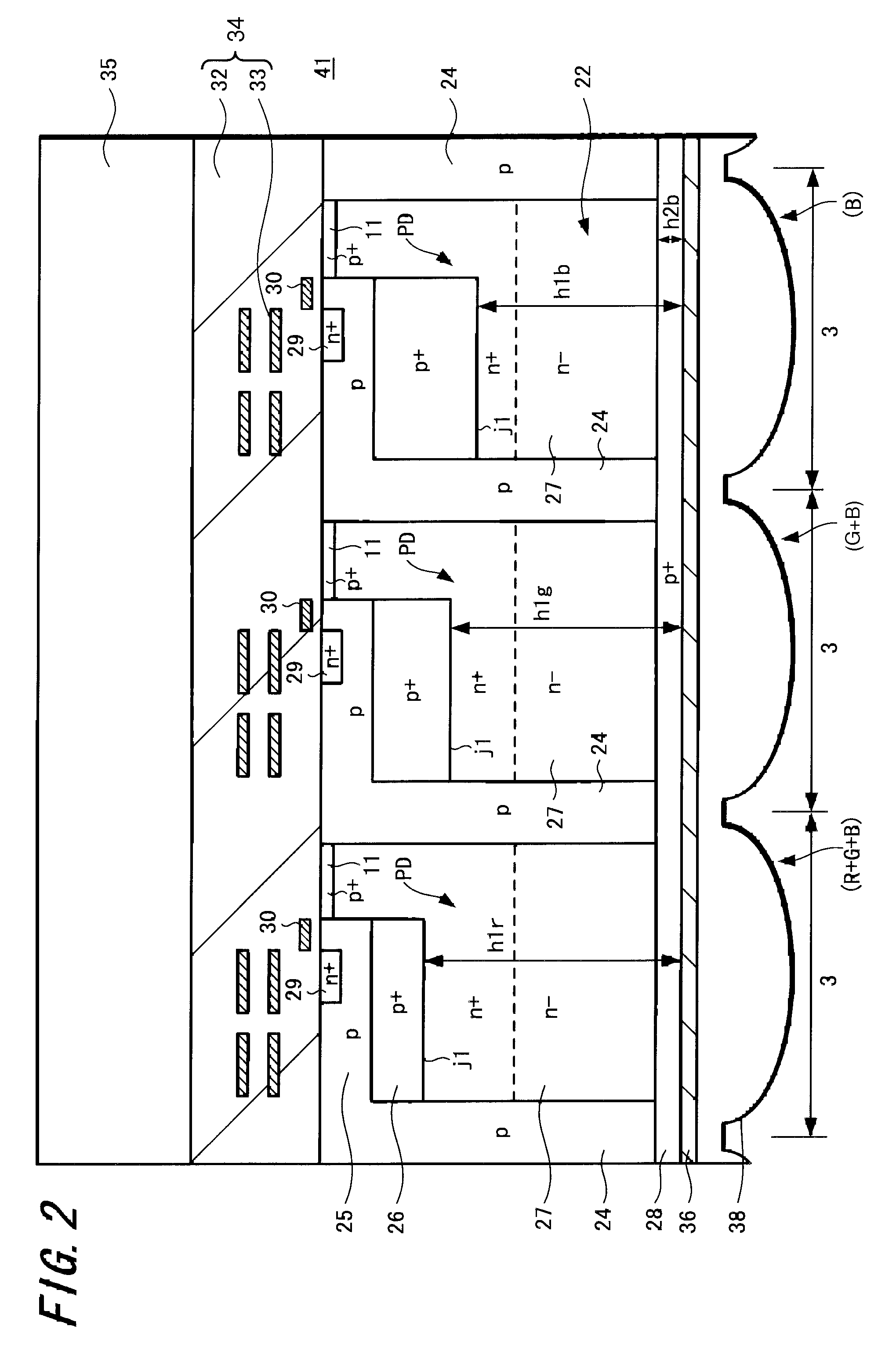

Solid-state imaging device, camera module and electronic equipment module

To provide a back-illuminated type solid-state imaging device capable of color separation of pixels without using a color filter, and a camera module and an electronic equipment module which incorporate the solid-state imaging device. A solid-state imaging device including: a photoelectric conversion element PD formed in a semiconductor substrate 22; a reading-out part which reads out signal charges from the photoelectric conversion element PD formed on one surface side of the semiconductor substrate 22; the other surface of the semiconductor substrate 22 made to a light incidence surface; and a pixel which exclusively makes light of a specific wavelength or longer photoelectrically converted, by adjusting pn junction depths h2 [h2 r, h2 g, h2 b] between the photoelectric conversion element PD and an accumulation layer 28 on the light incidence surface side. A camera module and an electronic equipment module which incorporate the solid-state imaging device.

Owner:SONY SEMICON SOLUTIONS CORP

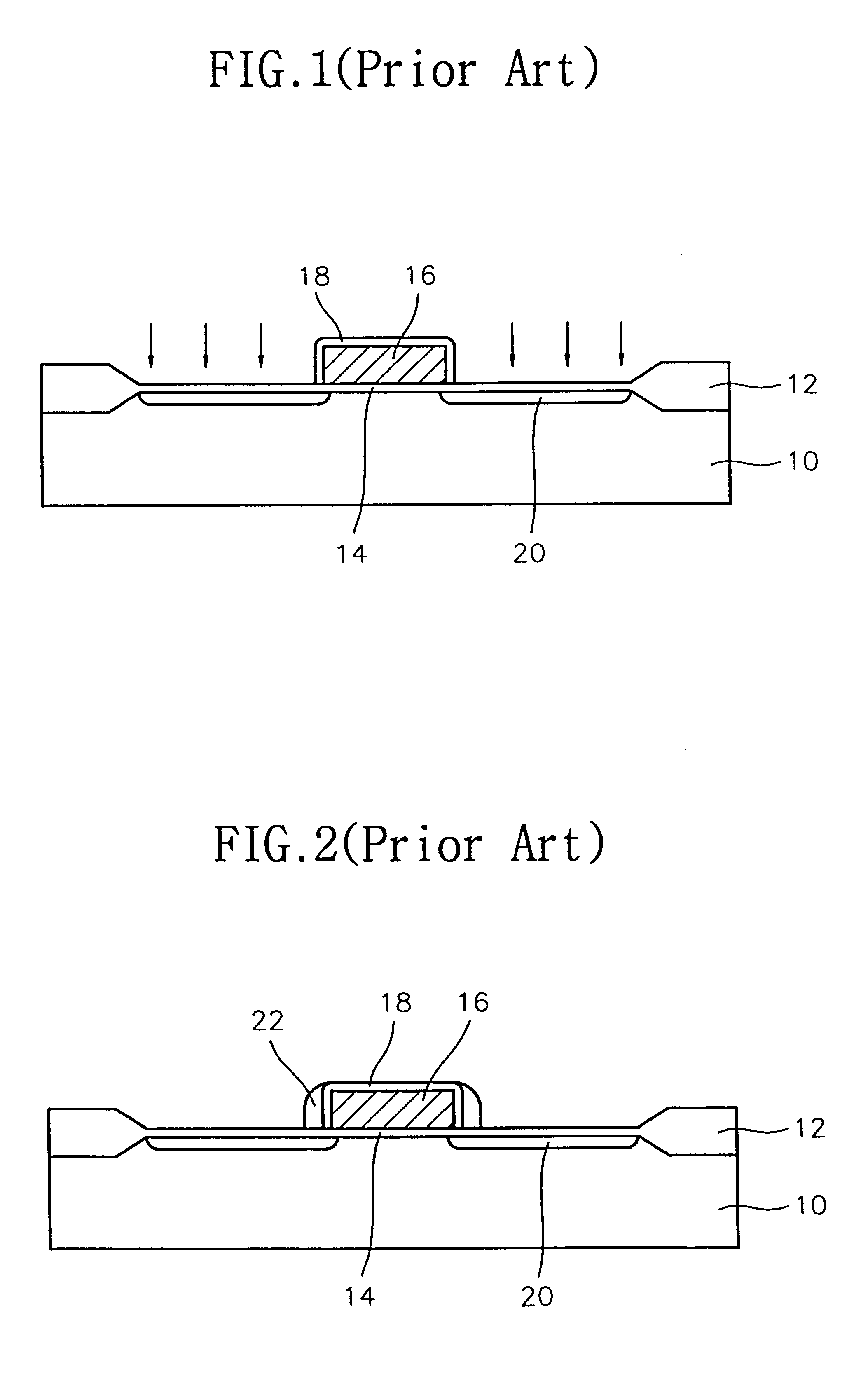

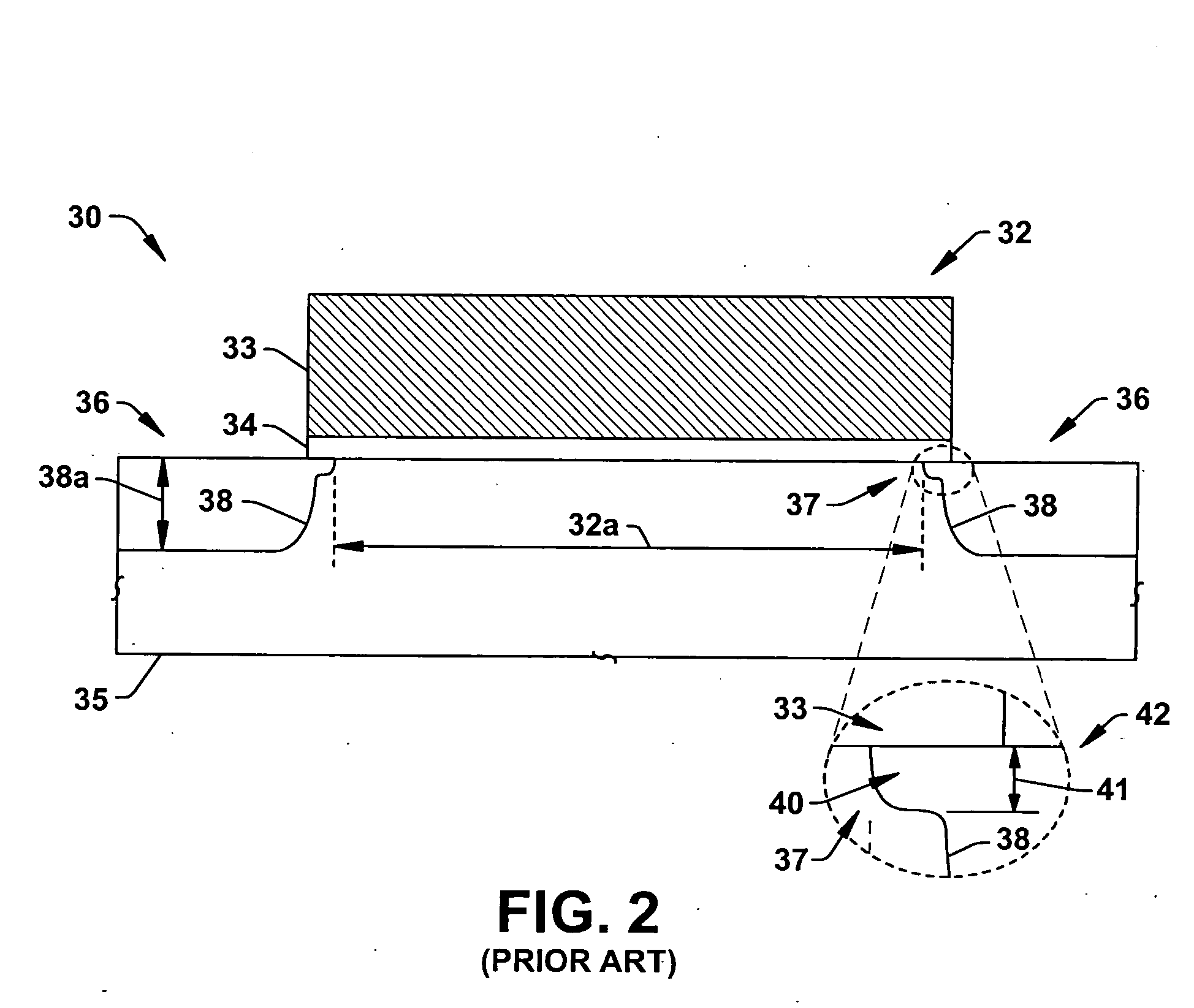

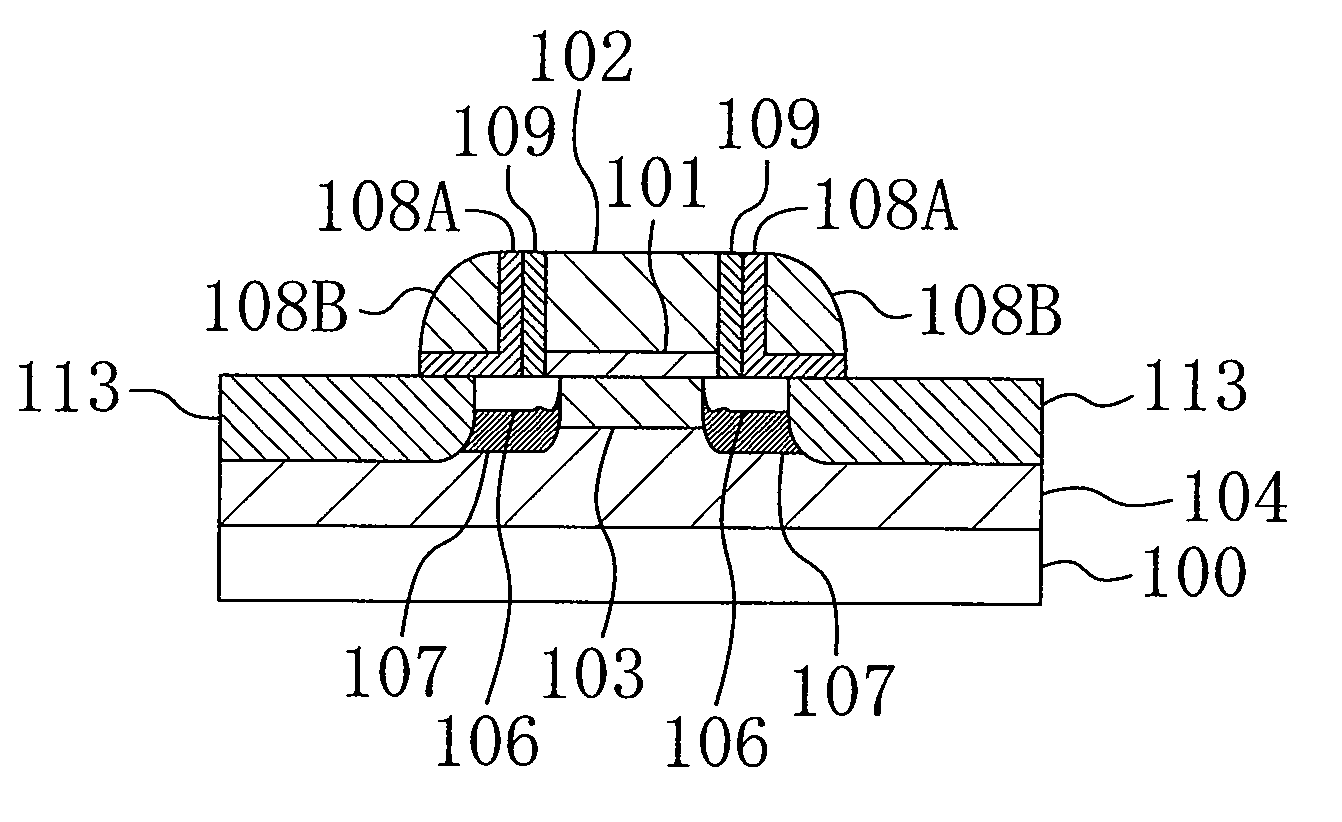

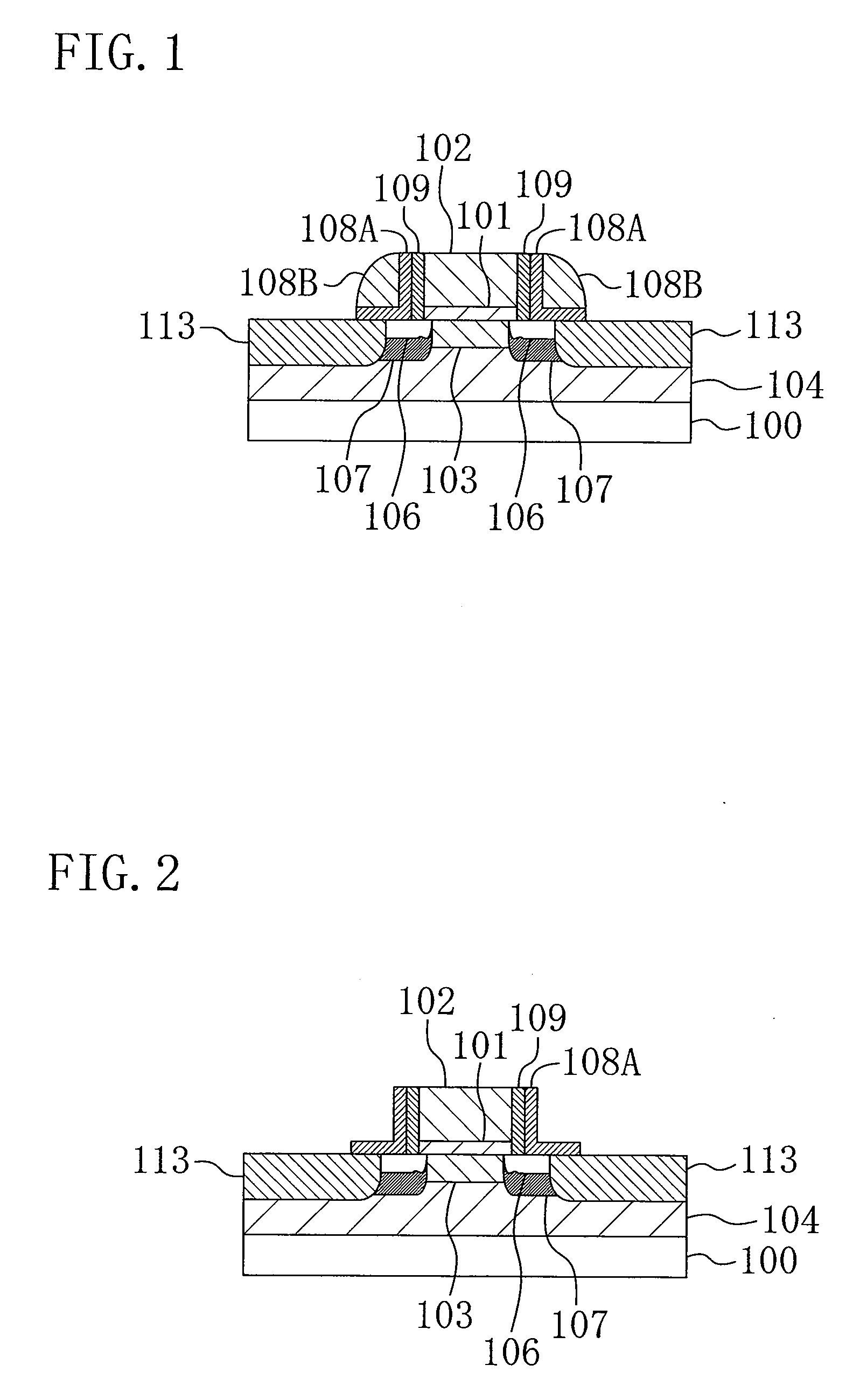

Method of making semiconductor device having double spacer

A semiconductor device having a double spacer and a method of manufacturing the device are provided. The semiconductor device includes a first spacer formed on the sidewall of a gate electrode and a second spacer formed on the slanted sidewall of the first spacer. A first impurity region is formed doped with a first conductivity type impurity at a first concentration and formed at a small junction depth in the substrate to self-align at the edge of the gate electrode. A second impurity region doped with second conductivity type impurity at a second concentration is formed at a large junction depth in the substrate to self-align at the edge of the first spacer. A third impurity region doped with the first conductivity type impurity at a third concentration is formed at a medium junction depth in the second impurity region to self-align at the edge of the second spacer.

Owner:SAMSUNG ELECTRONICS CO LTD

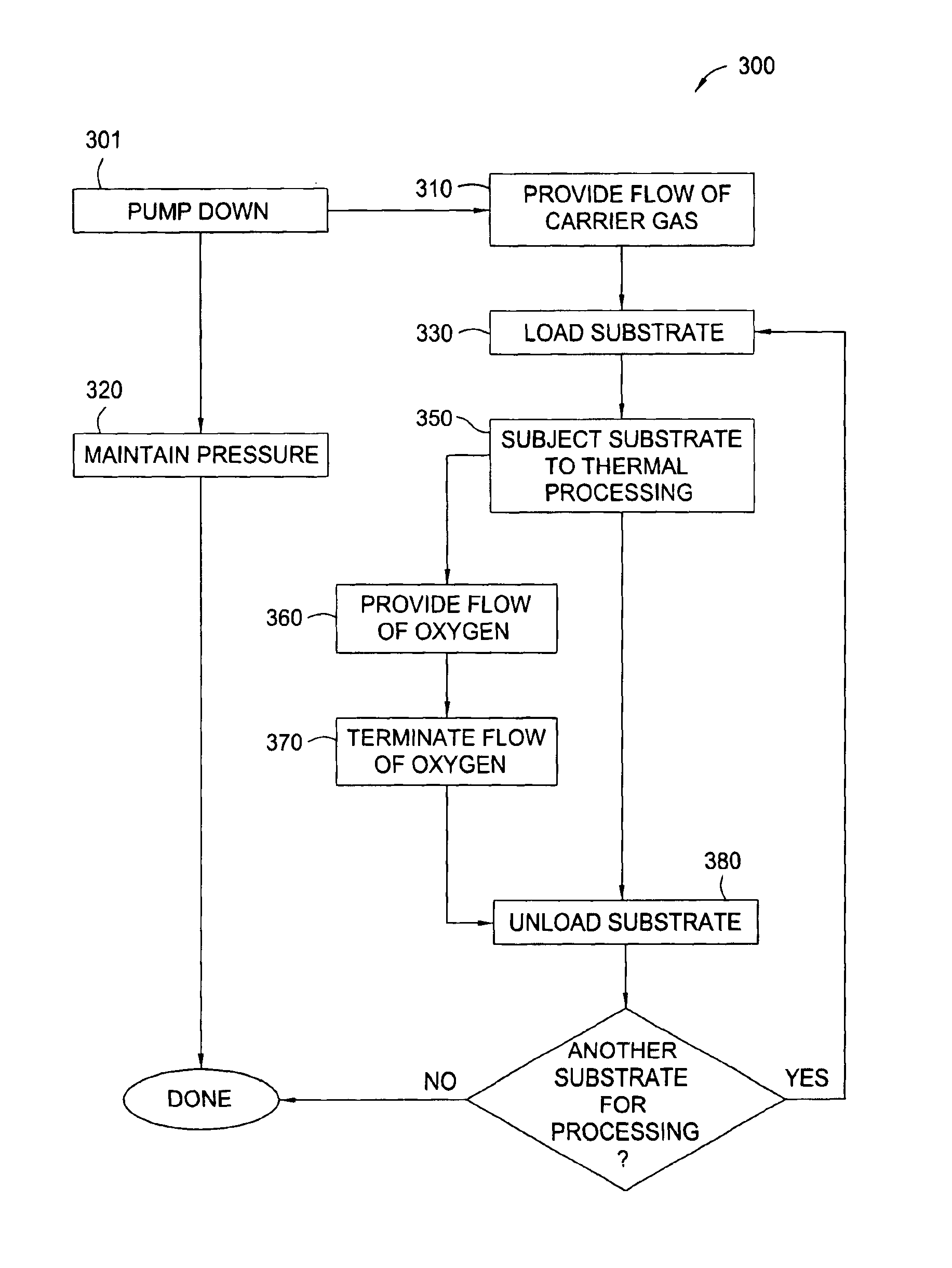

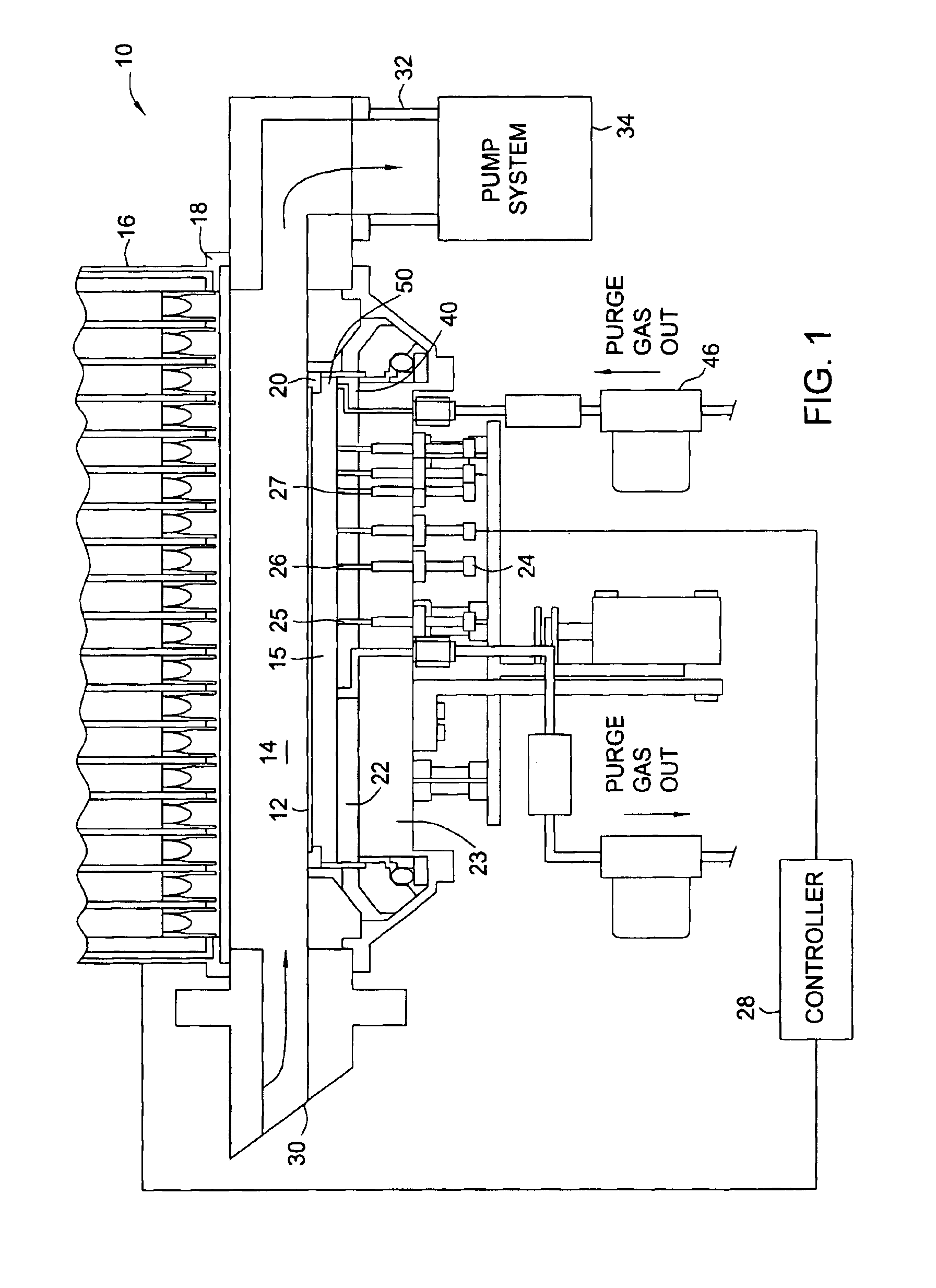

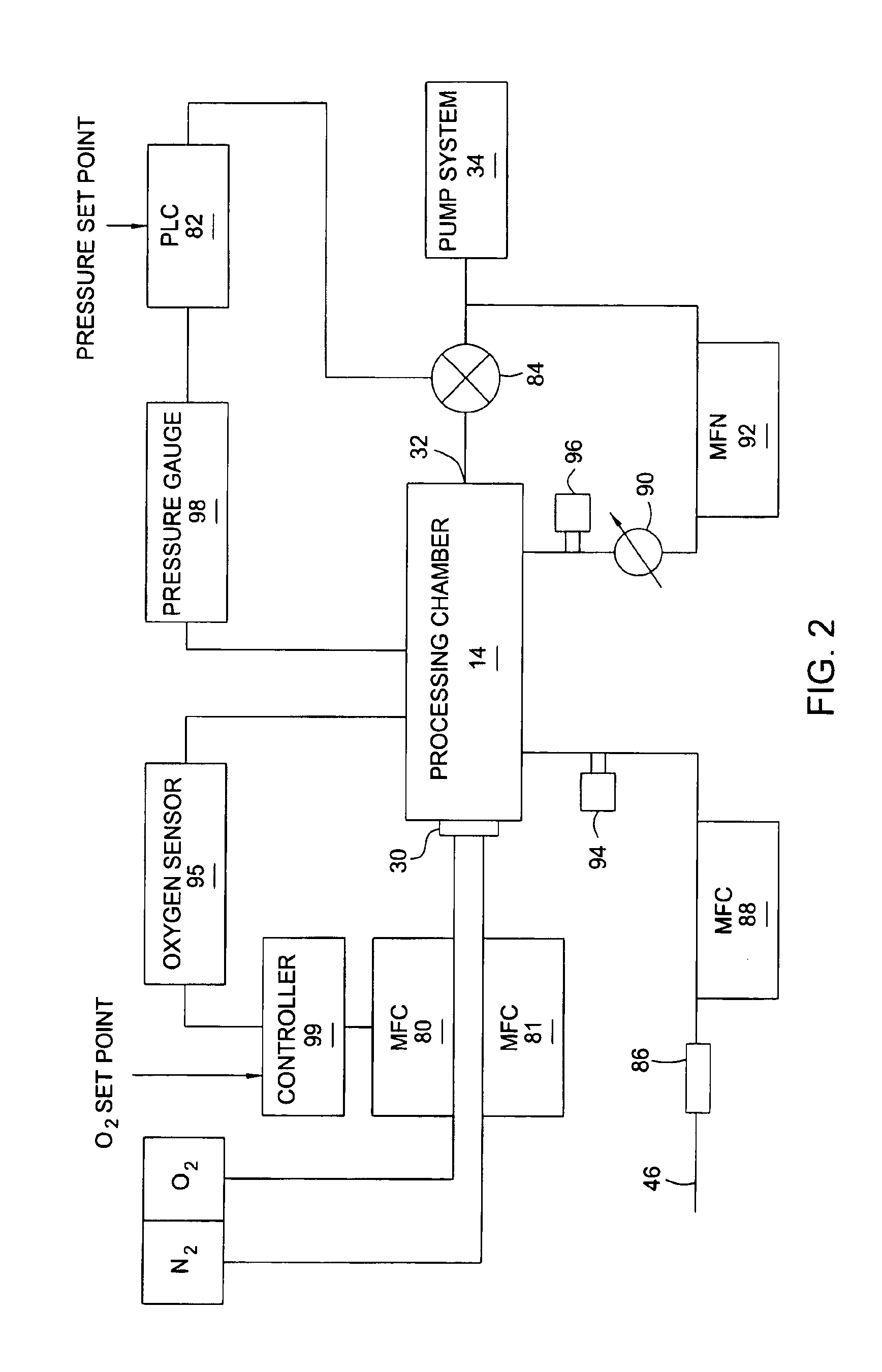

Advances in spike anneal processes for ultra shallow junctions

InactiveUS6897131B2Mitigating dopant diffusionHigh dopant activationSemiconductor/solid-state device manufacturingElectrical resistance and conductanceCooling down

Lamp based spike annealing was improved to address the aggressive requirements of <100 nm Ultra Shallow Junction (USJ) technologies. Improvements focused on enhancing cool down rates, and thereby improving spike sharpness. Boron ion implanted substrates with varying ion-implanted energy and dose were then annealed to characterize the improvements in spike annealing. A greater than 10% improvement in sheet resistance and junction depth was realized on substrates that were annealed with the improved spike profile. The improved spike anneal had the same comparable uniformity to the standard spike anneal.

Owner:APPLIED MATERIALS INC

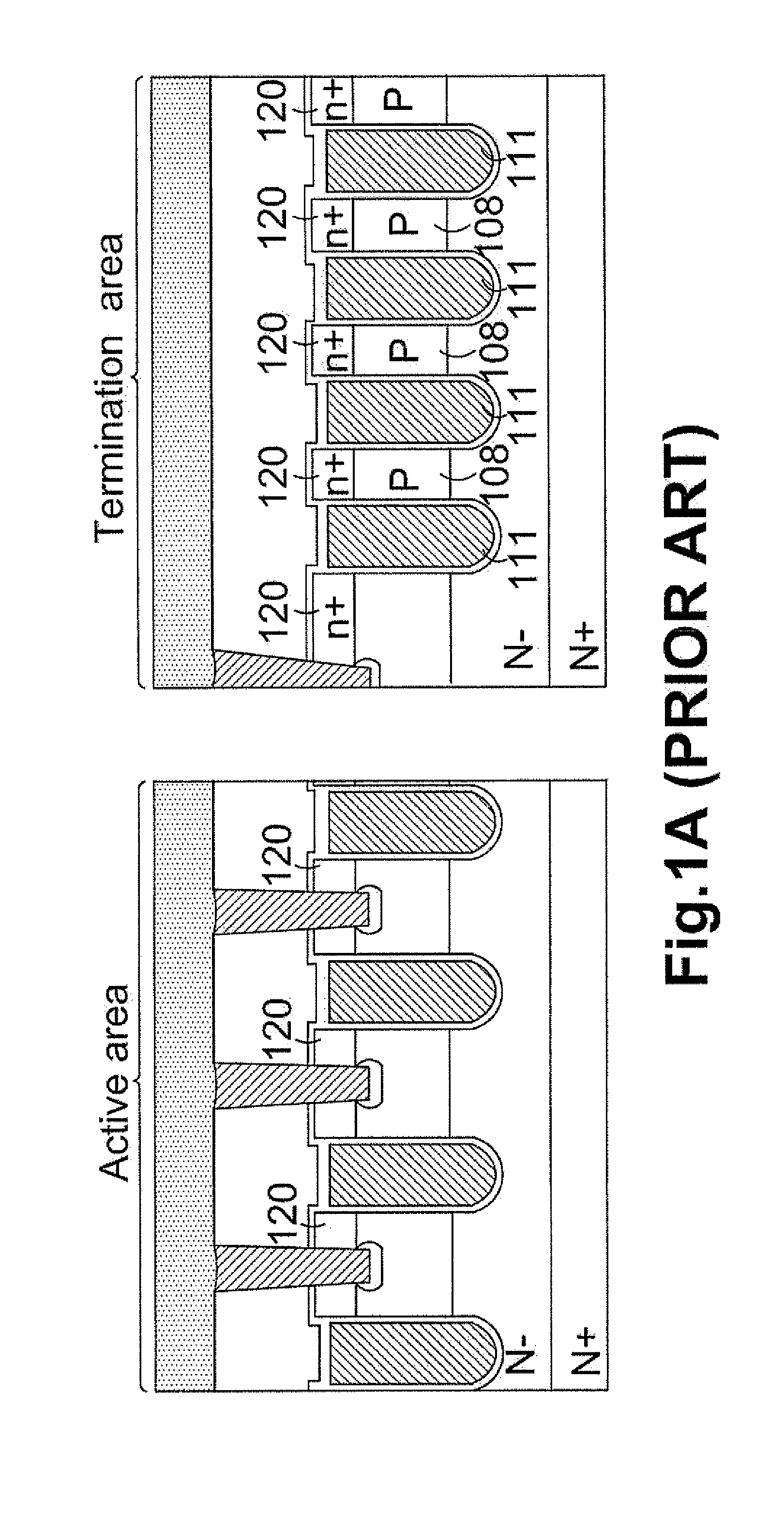

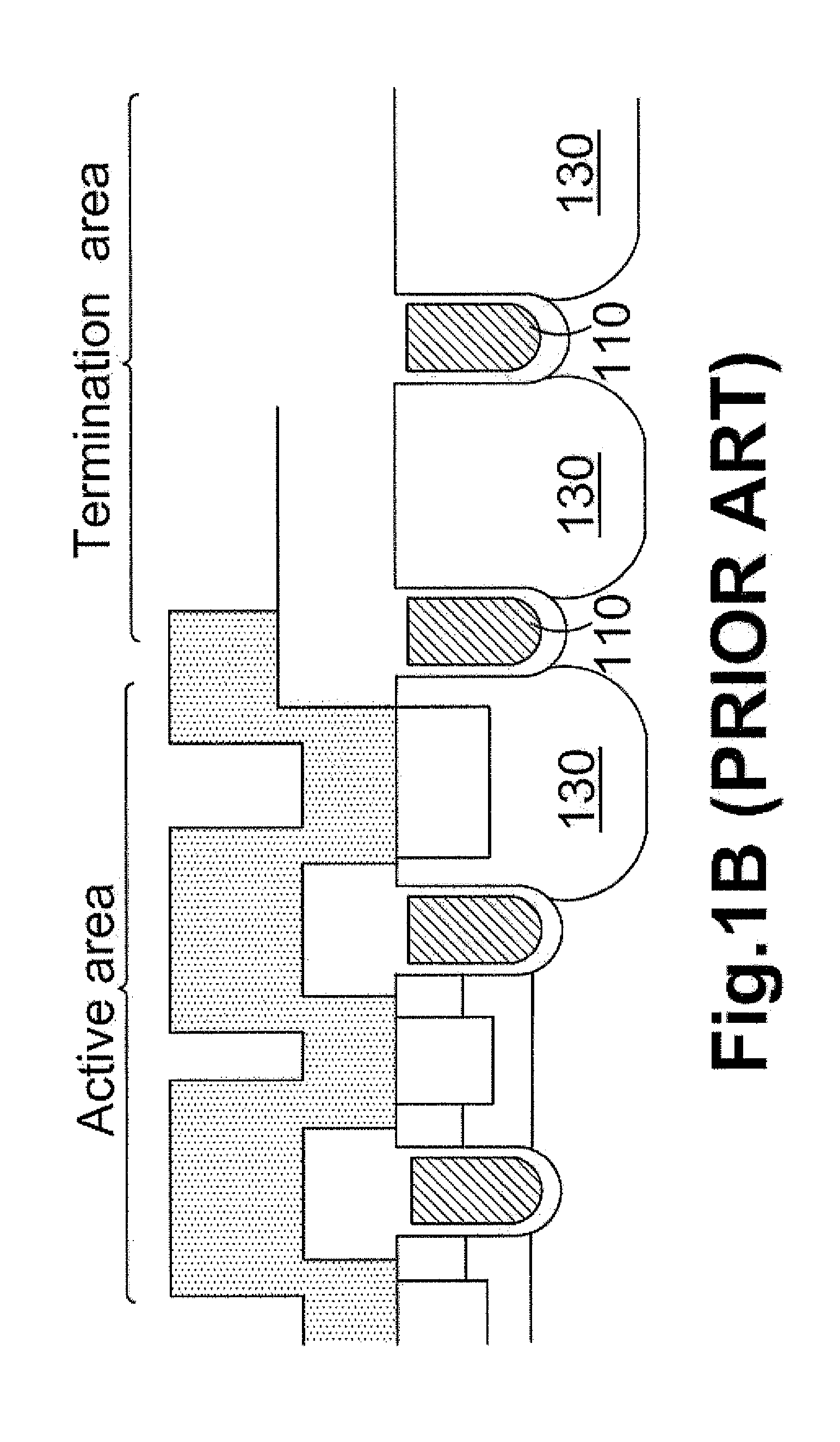

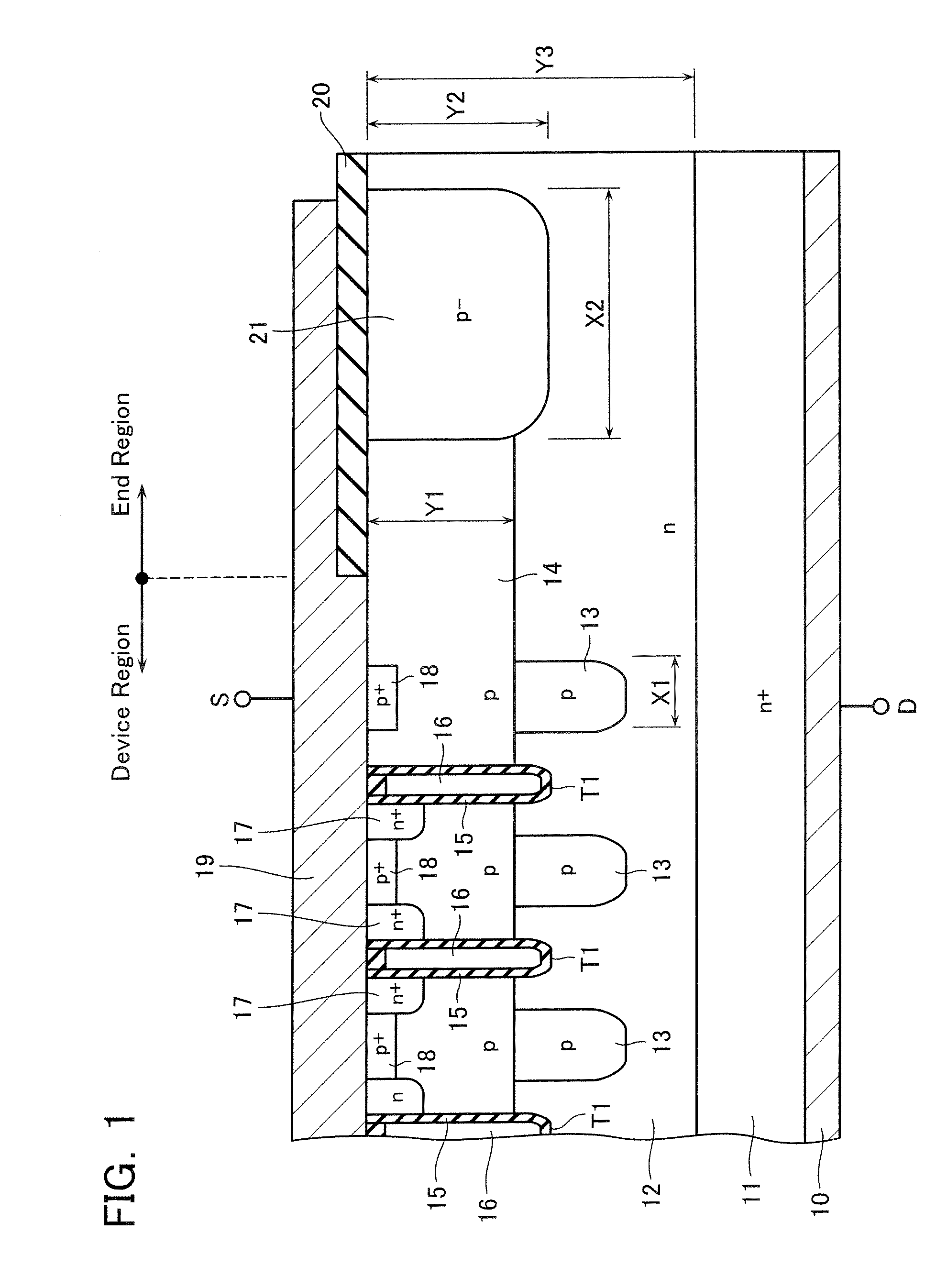

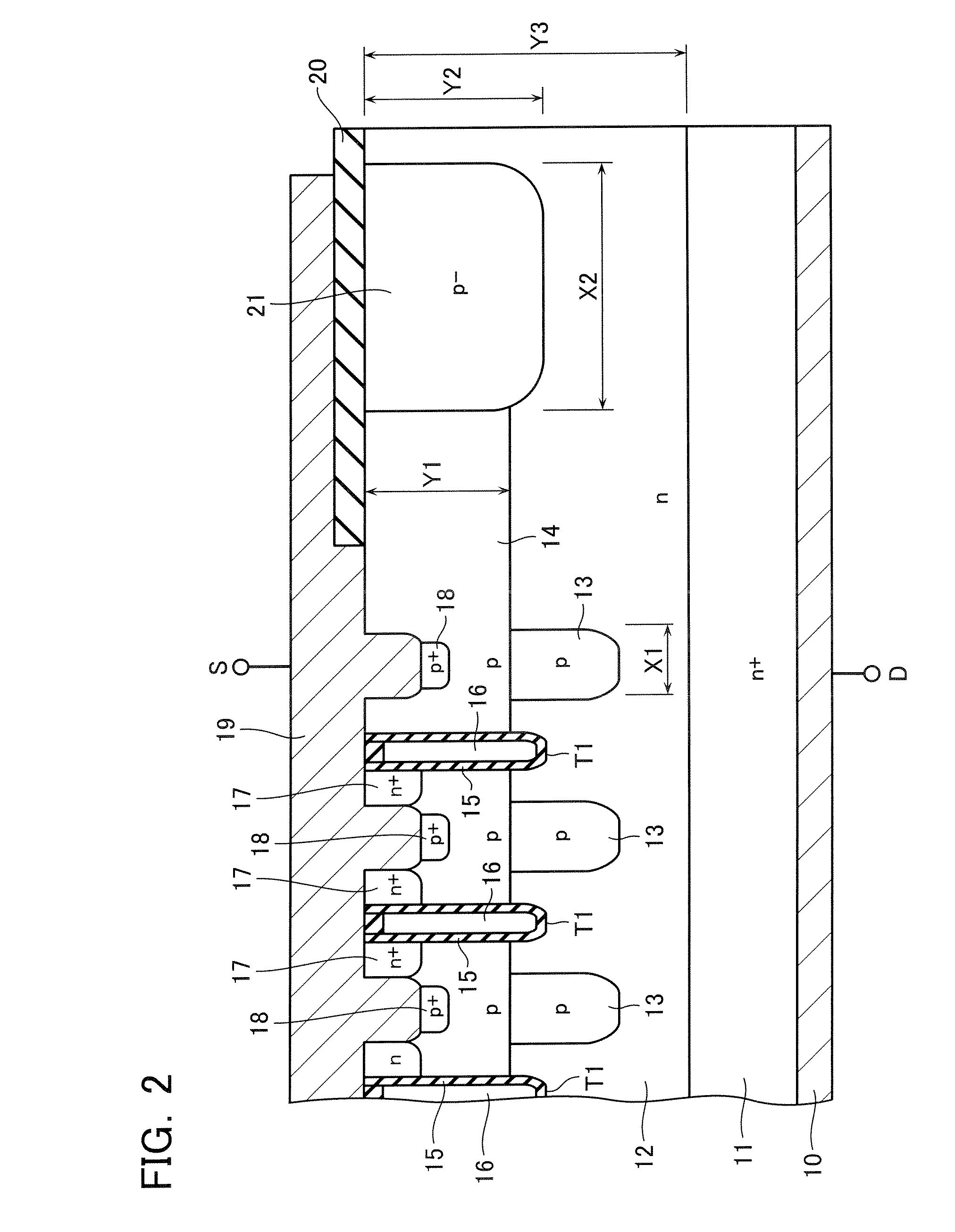

Semiconductor device

InactiveUS20070194375A1Semiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor packageJunction depth

This semiconductor device comprises a first semiconductor layer of a first conductivity type, an epitaxial layer of a first conductivity type formed in the surface on the first semiconductor layer, and a base layer of a second conductivity type formed on the surface of the epitaxial layer. Column layers of a second conductivity type are repeatedly formed in the epitaxial layer under the base layer at a certain interval. Trenches are formed so as to penetrate the base layer to reach the epitaxial layer; and gate electrodes are formed in the trenches via a gate insulation film. A termination layer of a second conductivity type is formed on the epitaxial layer at an end region at the perimeter of the base layer. The termination layer is formed to have a junction depth larger than that of the base layer.

Owner:KK TOSHIBA

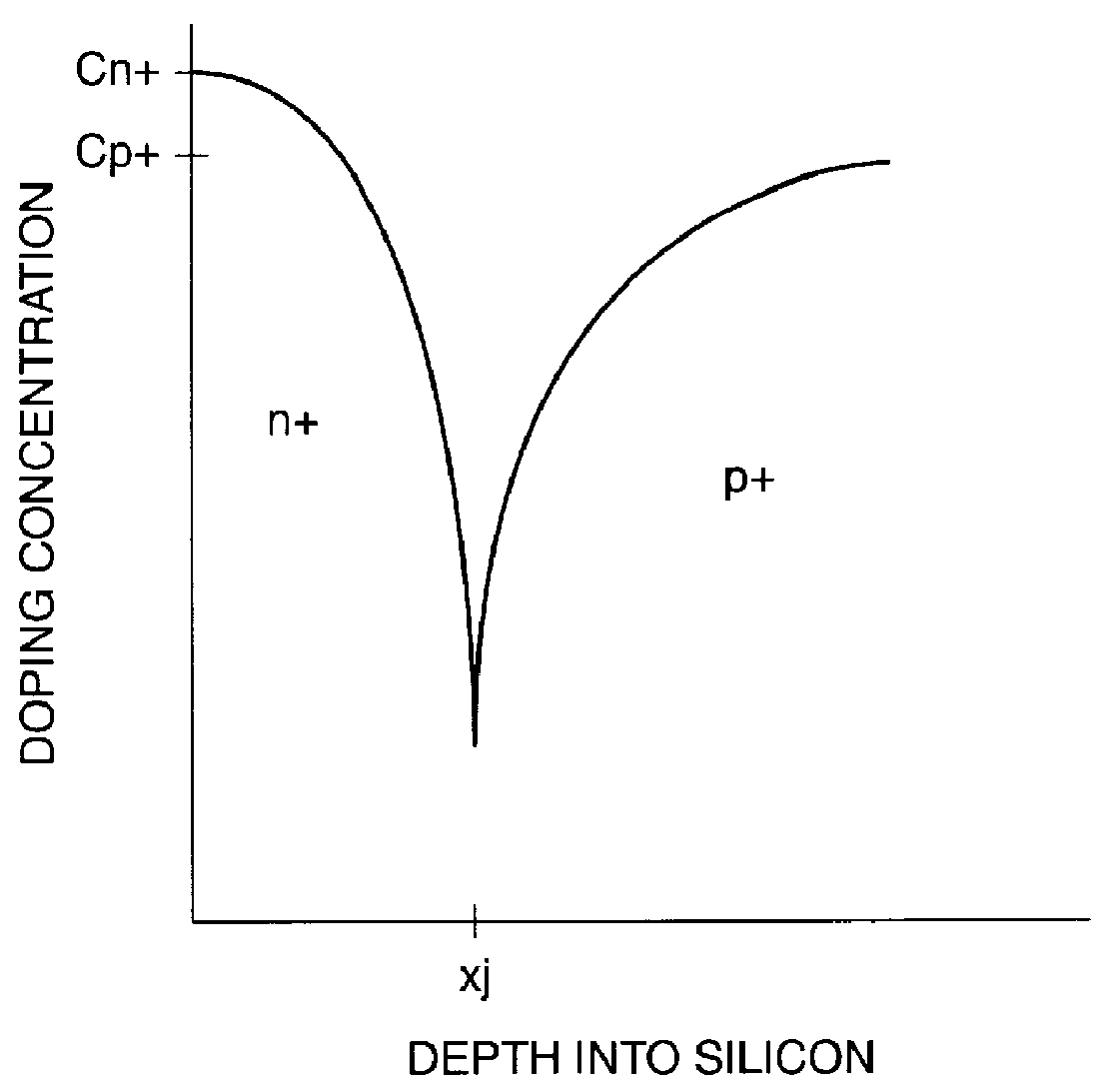

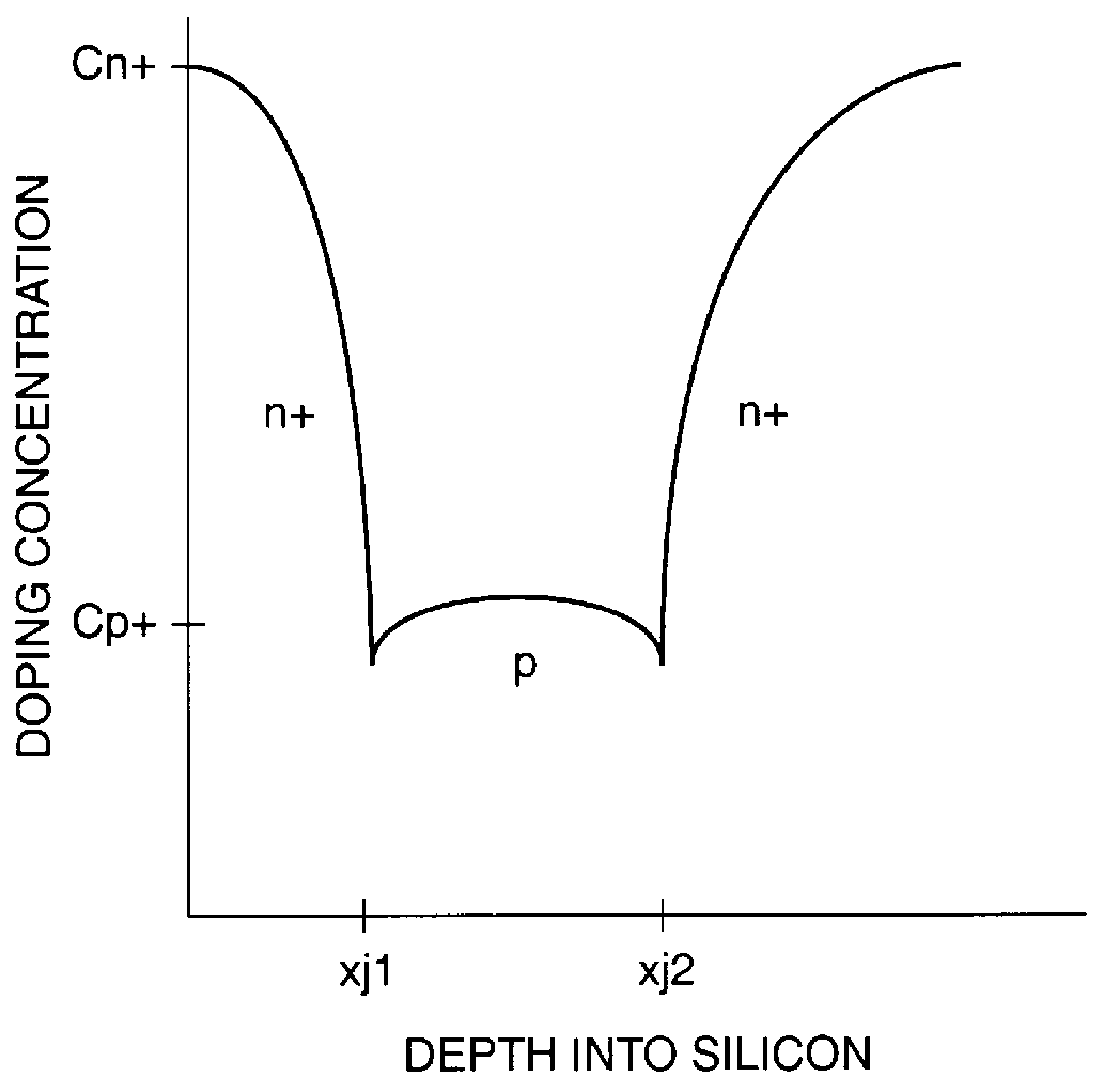

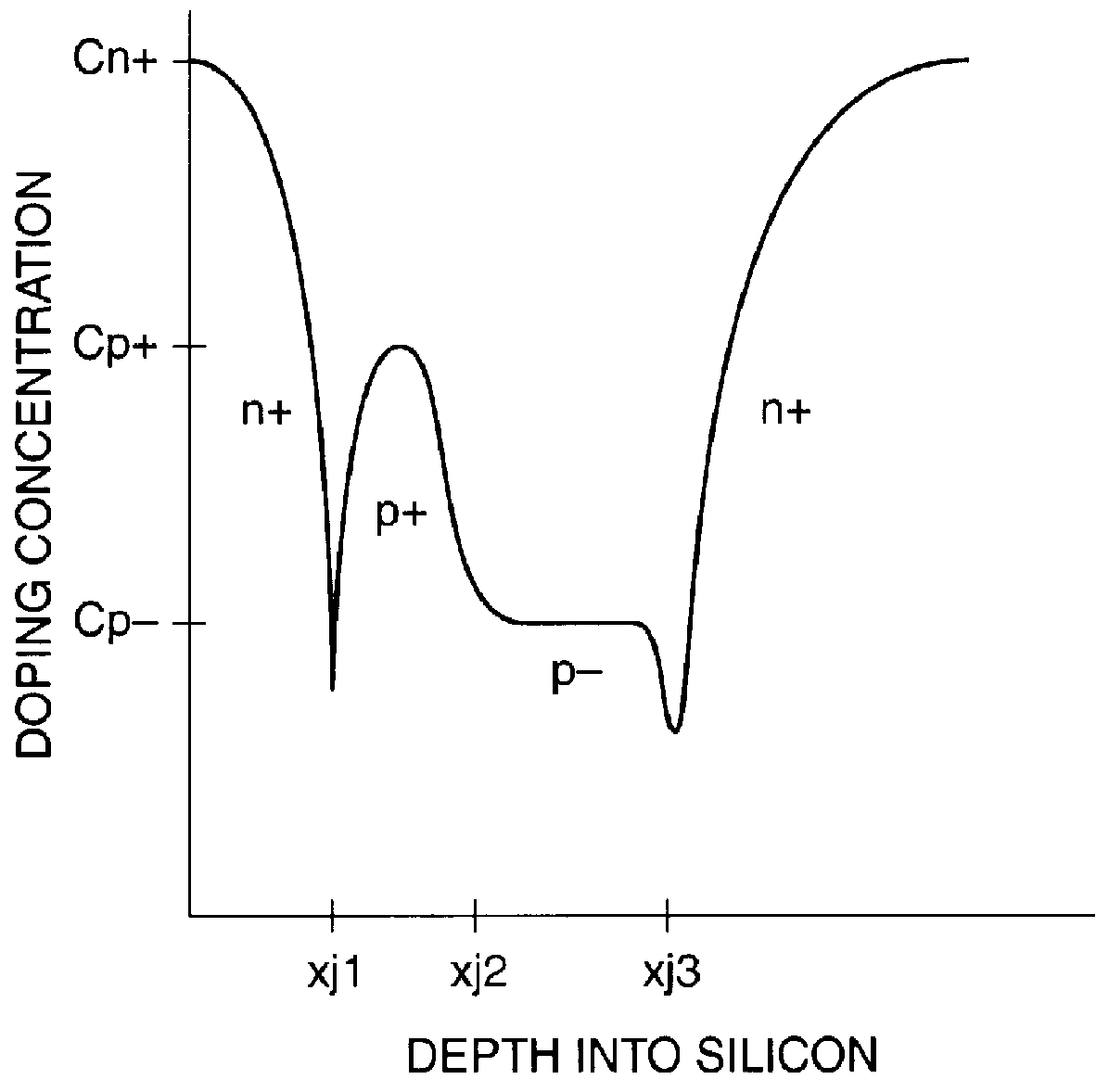

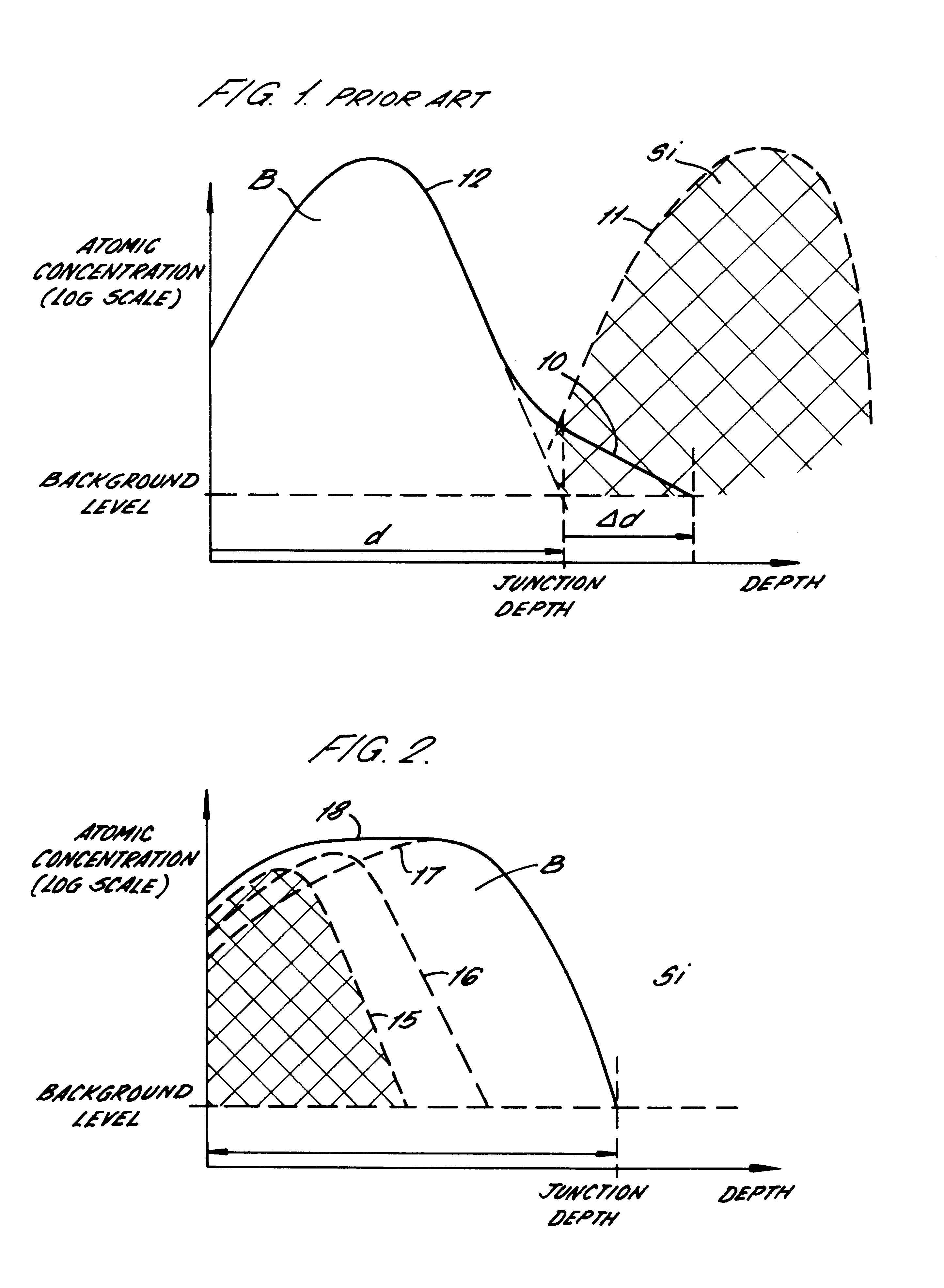

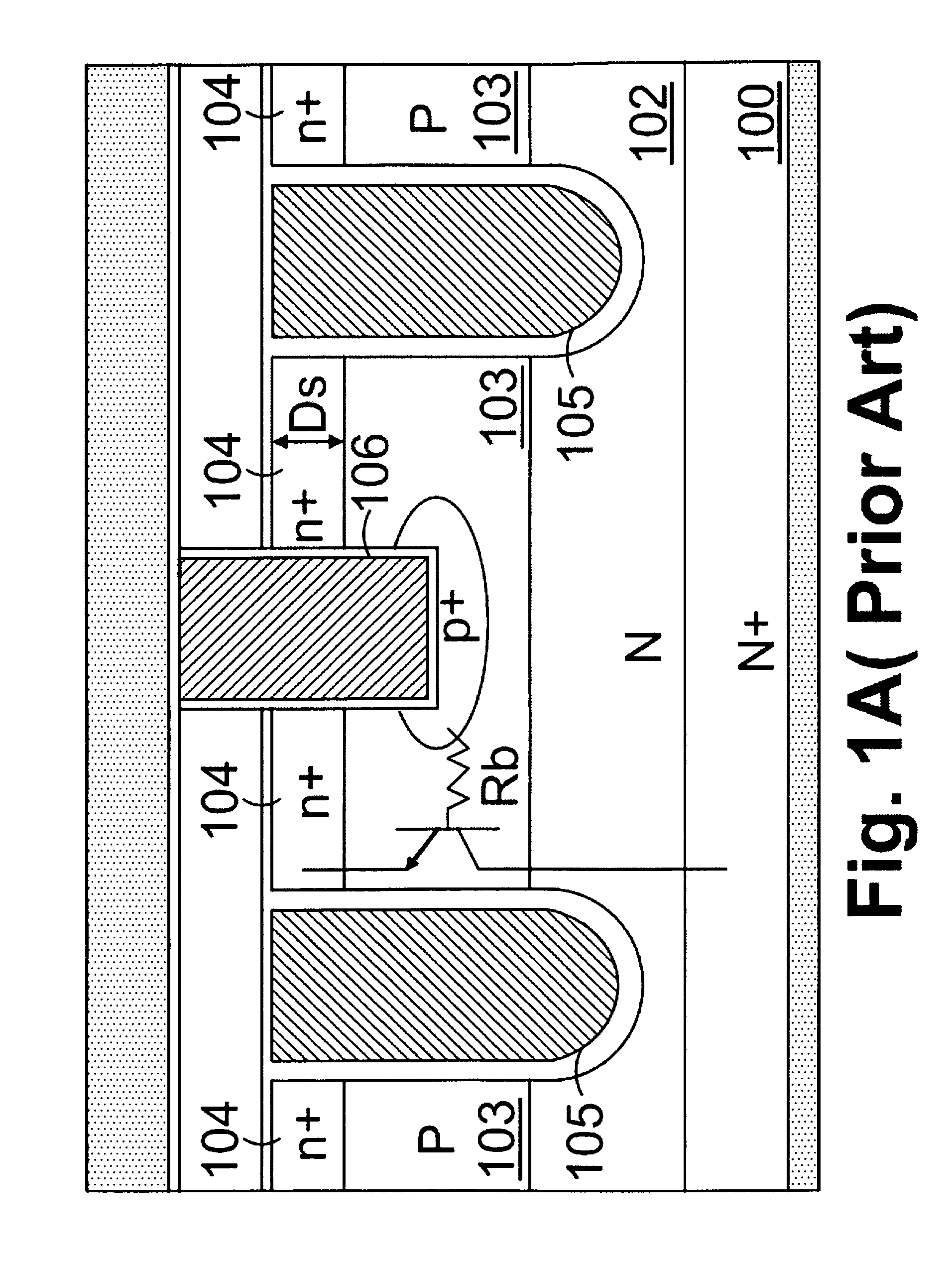

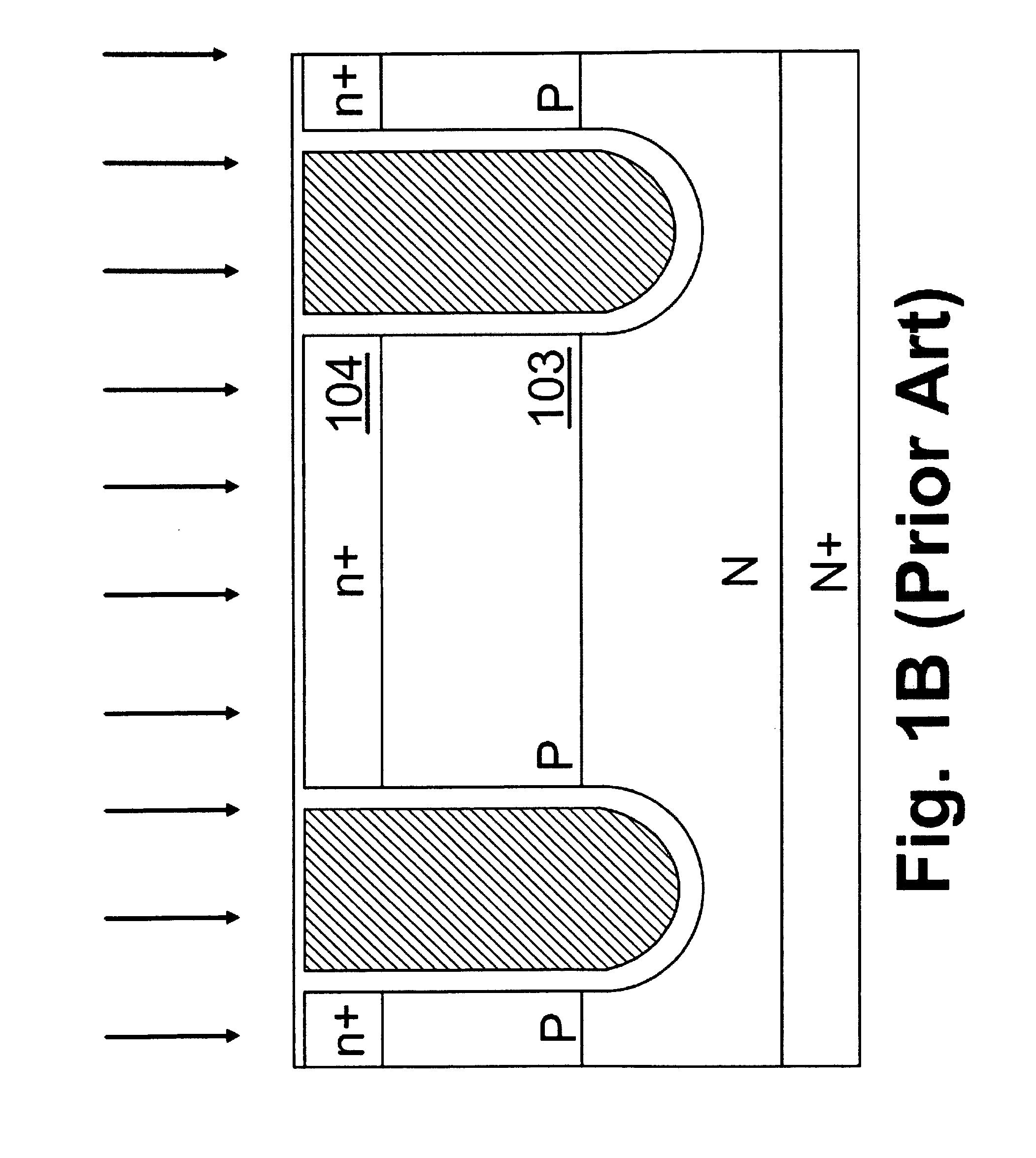

Low-voltage punch-through transient suppressor employing a dual-base structure

InactiveUS6015999AReduce leakage currentImprove featuresSemiconductor/solid-state device detailsSolid-state devicesDopantLow voltage

A punch-through diode transient suppression device has a base region of varying doping concentration to improve leakage and clamping characteristics. The punch-through diode includes a first region comprising an n+ region, a second region comprising a p- region abutting the first region, a third region comprising a p+ region abutting the second region, and a fourth region comprising an n+ region abutting the third region. The peak dopant concentration of the n+ layers should be about 1.5E18 cm-3, the peak dopant concentration of the p+ layer should be between about 1 to about 5 times the peak concentration of the n+ layer, and the dopant concentration of the p- layer should be between about 0.5E14 cm-3 and about 1.OE17 cm-3. The junction depth of the fourth (n+) region should be greater than about 0.3 mu m. The thickness of the third (p+) region should be between about 0.3 mu m and about 2.0 mu m, and the thickness of the second (p-) region should be between about 0.5 mu m and about 5.0 mu m.

Owner:SEMTECH CORP

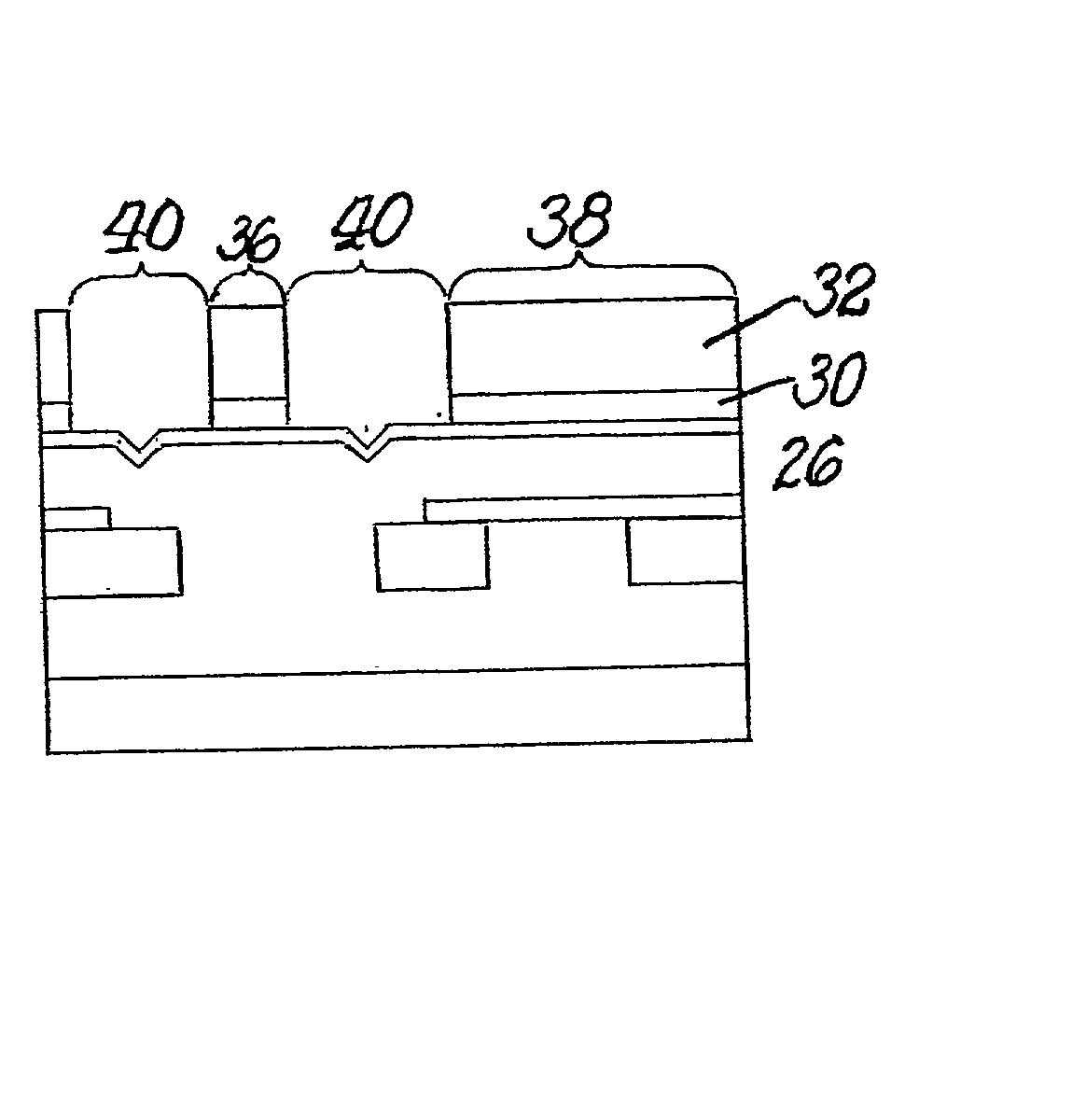

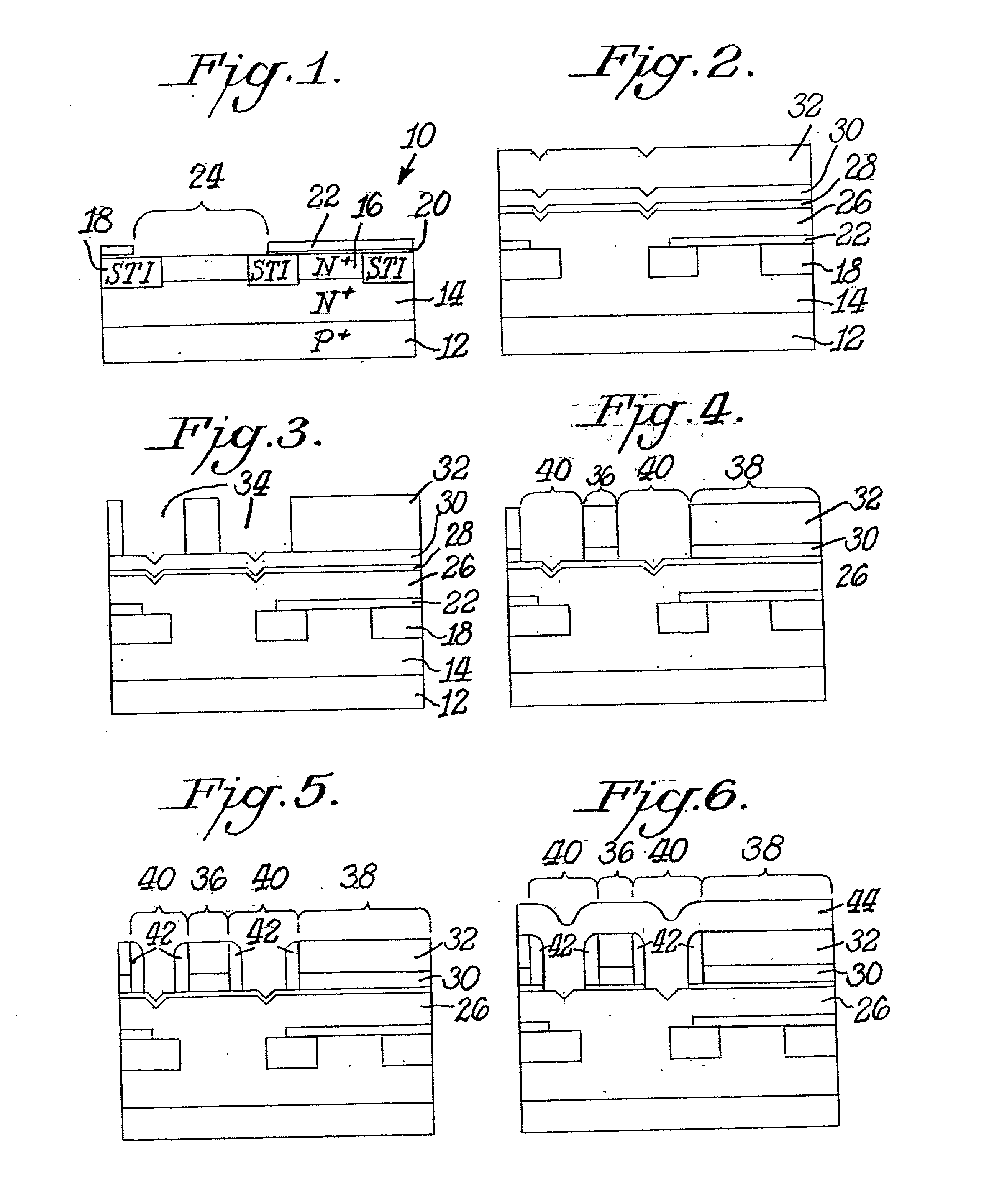

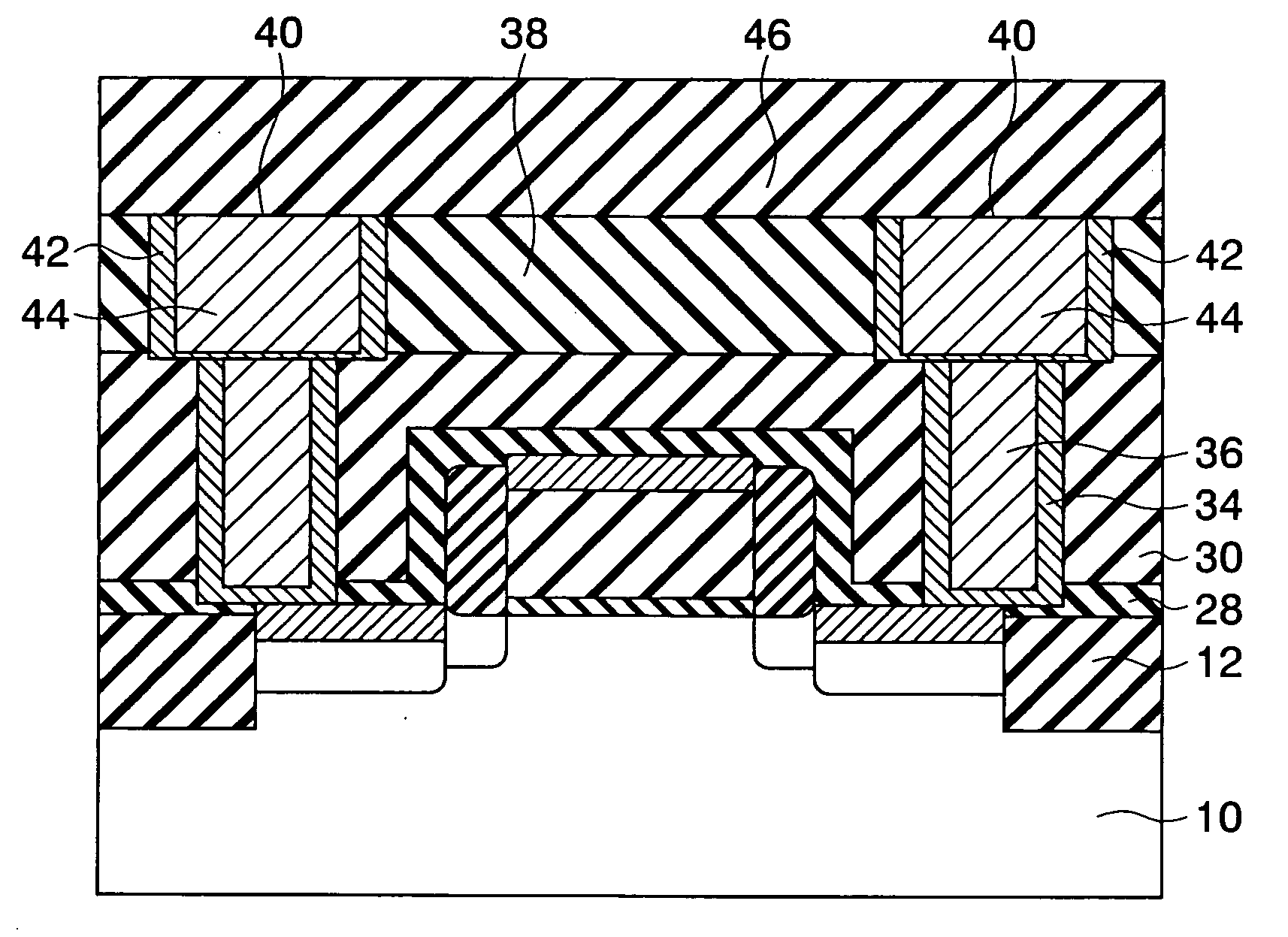

Bipolar device having shallow junction raised extrinsic base and method for making the same

A raised extrinsic base, silicon germanium (SiGe) heterojunction bipolar transistor (HBT), and a method of making the same is disclosed herein. The heterojunction bipolar transistor includes a substrate, a silicon germanium layer formed on the substrate, a collector layer formed on the substrate, a raised extrinsic base layer formed on the silicon germanium layer, and an emitter layer formed on the silicon germanium layer. The silicon germanium layer forms a heterojunction between the emitter layer and the raised extrinsic base layer. The bipolar transistor further includes a base electrode formed on a portion of the raised extrinsic base layer, a collector electrode formed on a portion of the collector layer, and an emitter electrode formed on a portion of the emitter layer. Thus, the heterojunction bipolar transistor includes a self-aligned raised extrinsic base, a minimal junction depth, and minimal interstitial defects influencing the base width, all being formed with minimal thermal processing. The heterojunction bipolar transistor simultaneously improves three factors that affect the speed and performance of bipolar transistors: base width, base resistance, and base-collector capacitance.

Owner:INTELLECTUAL DISCOVERY INC

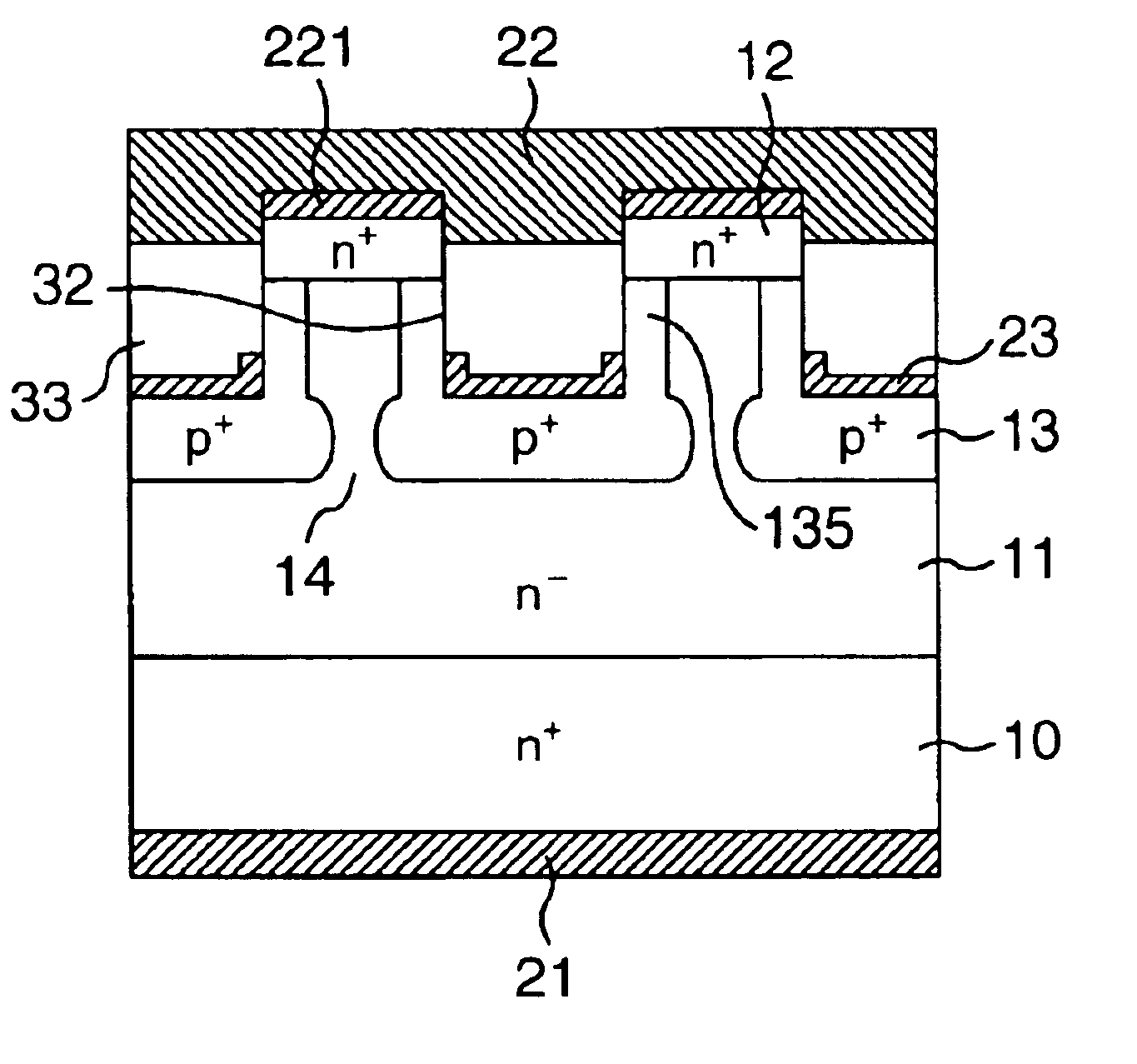

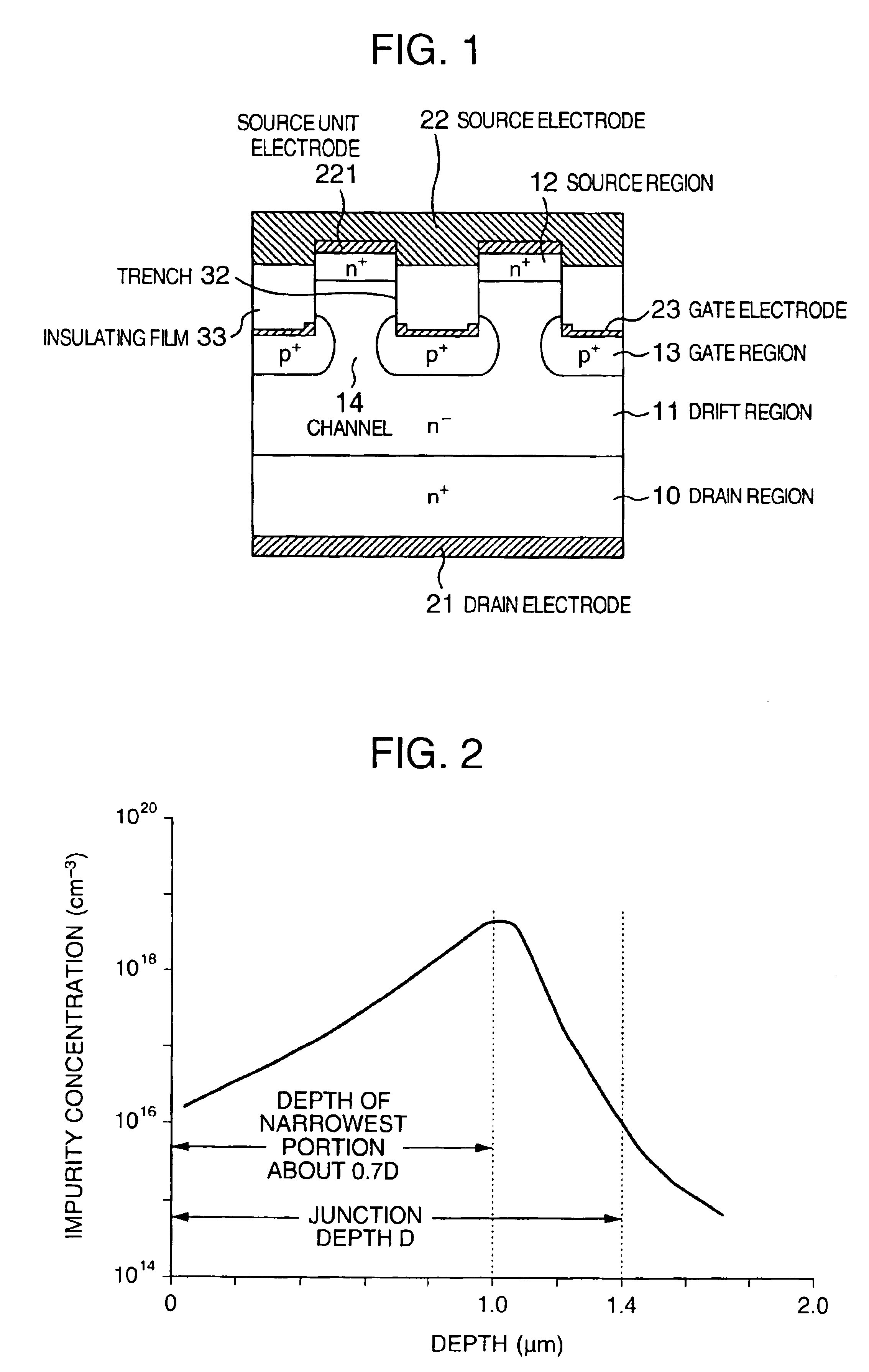

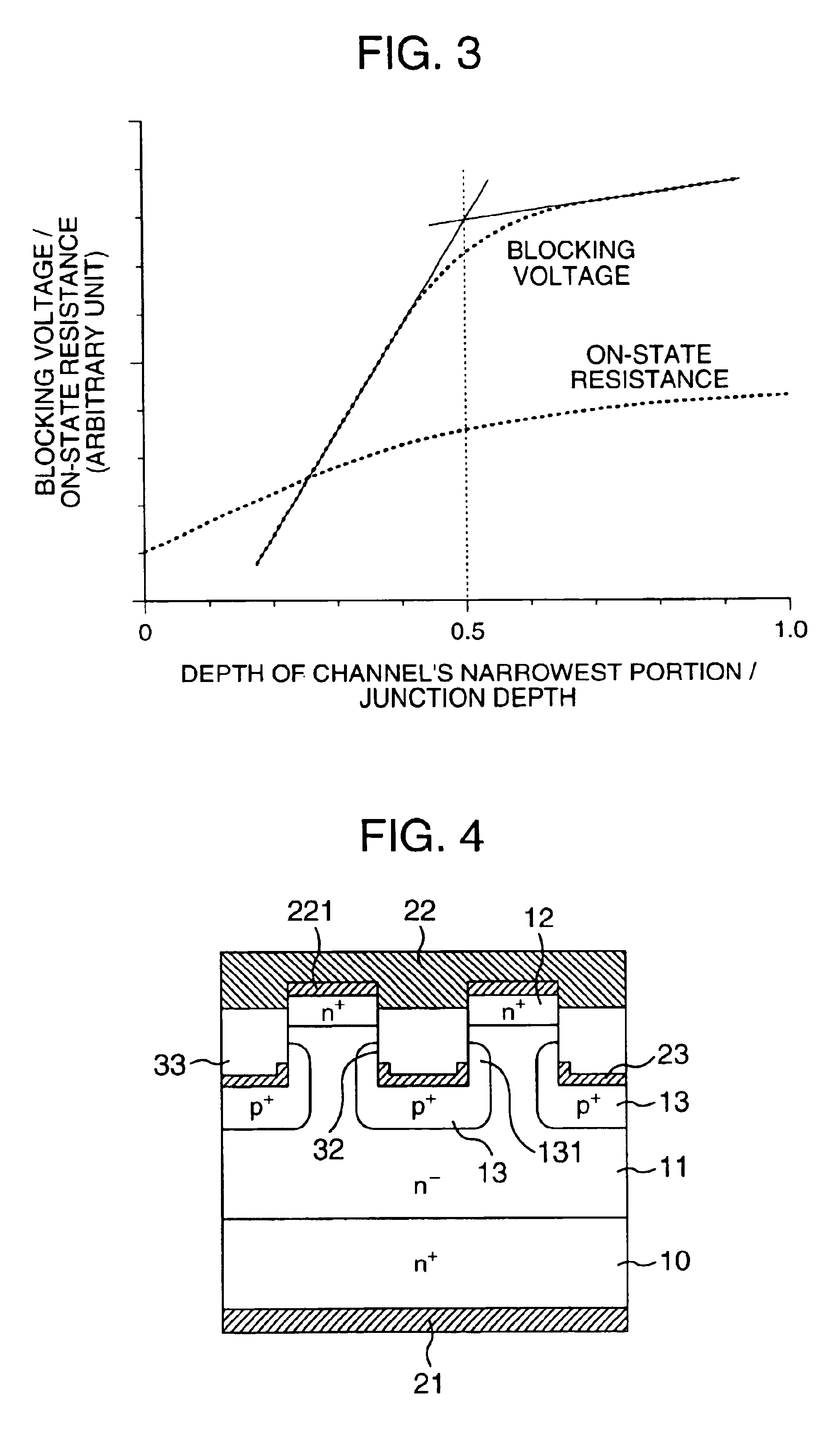

Semiconductor device

ActiveUS6917054B2Improve the blocking effectNarrow channel widthTransistorSemiconductor/solid-state device manufacturingSemiconductorJunction depth

A semiconductor device includes a trench formed on a source side of a drift region, a p-type gate region and a gate formed at the bottom of the trench, and the source formed over the entire surface of the unit device through an insulating film. The narrowest portion of a channel of the device is deeper than one-half the junction depth of the p-type gate region. This allows the width of the channel on the drain side to be reduced even when a lower energy ion implantation manufacturing process is used.

Owner:HITACHI LTD

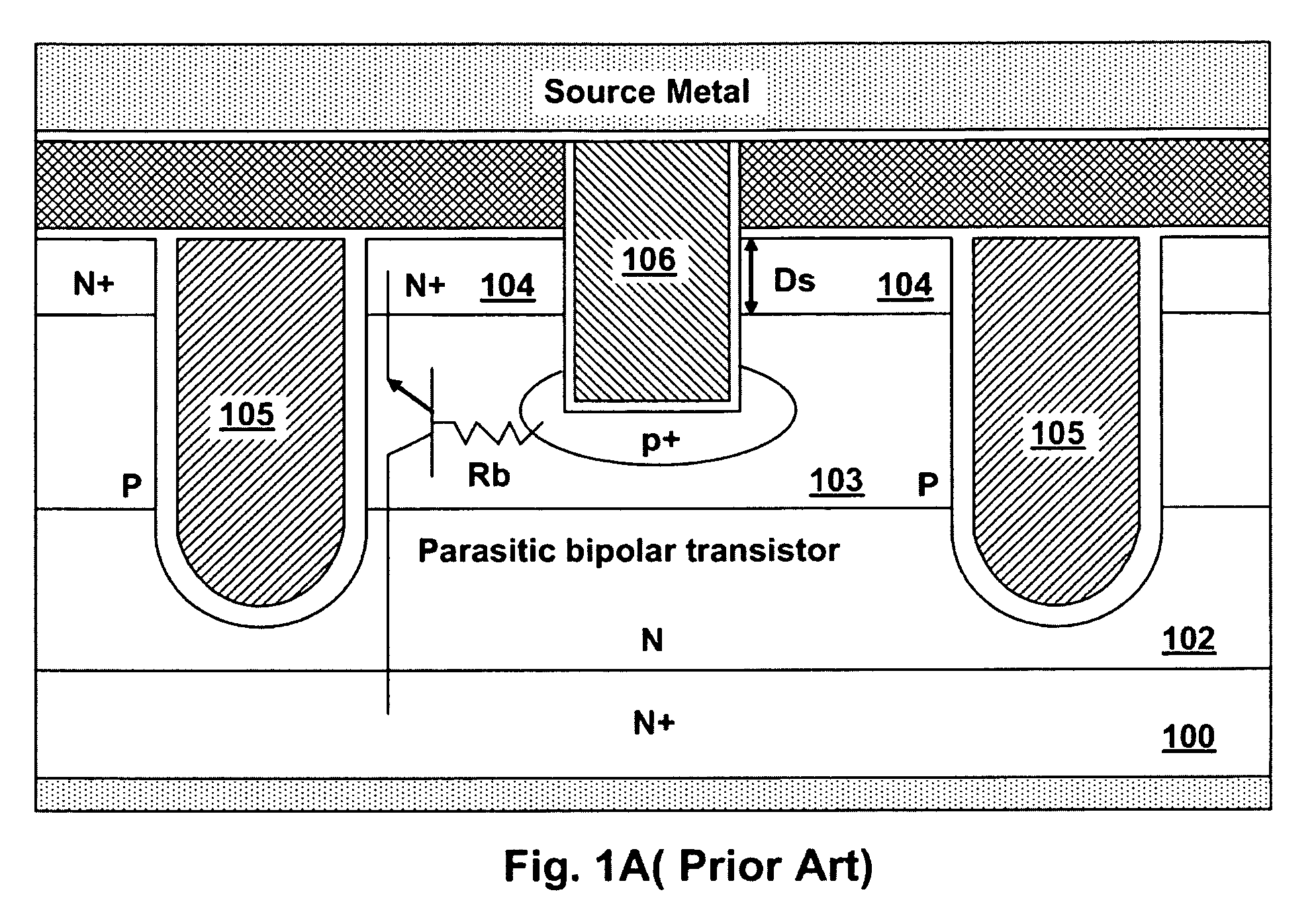

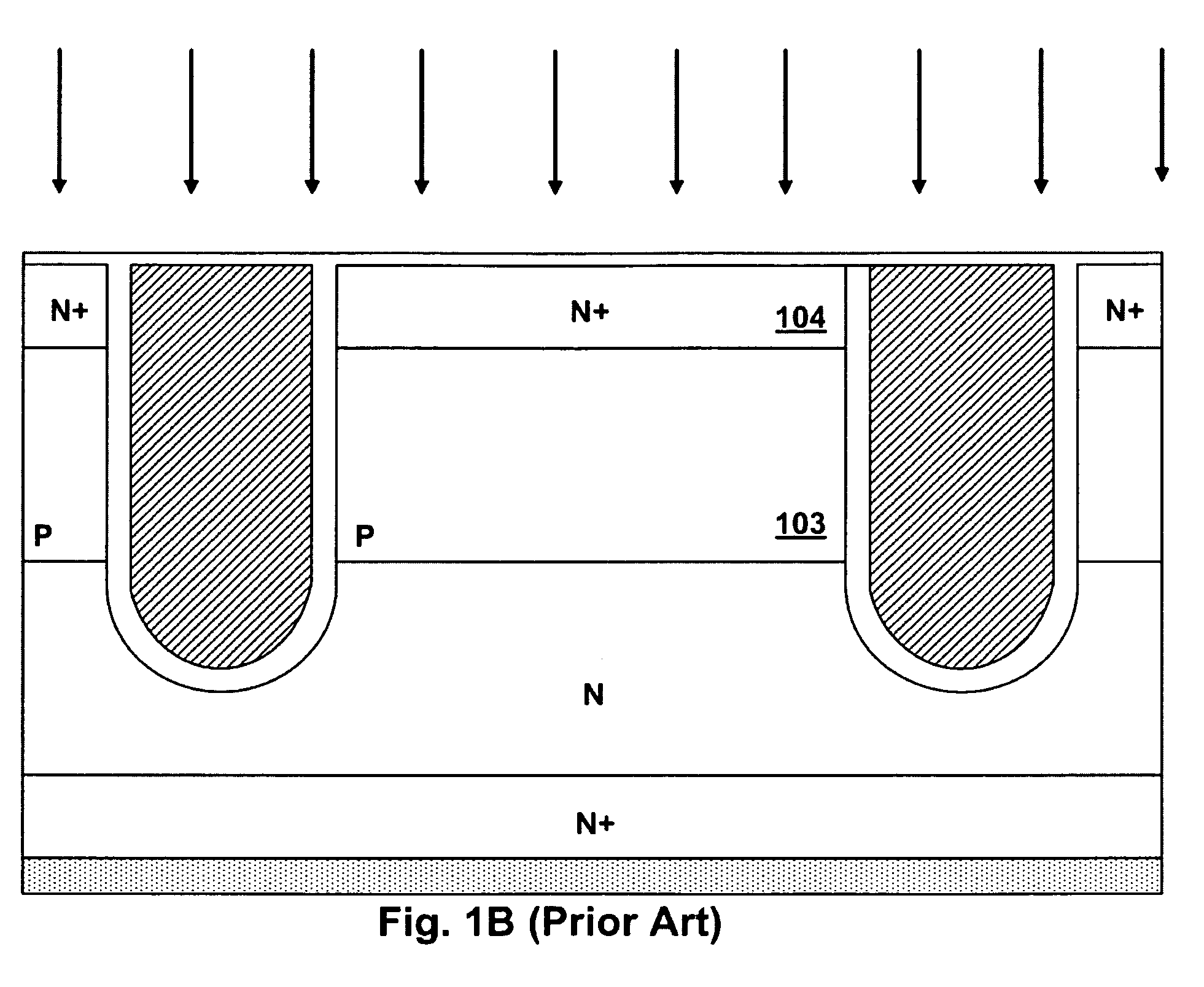

Trench MOSFET structure having improved avalanche capability using three masks process

ActiveUS7816720B1Improve contact effectReduce manufacturing costTransistorSolid-state devicesTrench mosfetBody contact

A trench MOSFET structure having improved avalanche capability is disclosed, wherein the source region is formed by performing source Ion Implantation through contact open region of a thick contact interlayer, and further diffused to optimize a trade-off between Rds and the avalanche capability. Thus, only three masks are needed in fabrication process, which are trench mask, contact mask and metal mask. Furthermore, said source region has a doping concentration along channel region lower than along contact trench region, and source junction depth along channel region shallower than along contact trench, and source doping profile along surface of epitaxial layer has Gaussian-distribution from trenched source-body contact to channel region.

Owner:FORCE MOS TECH CO LTD

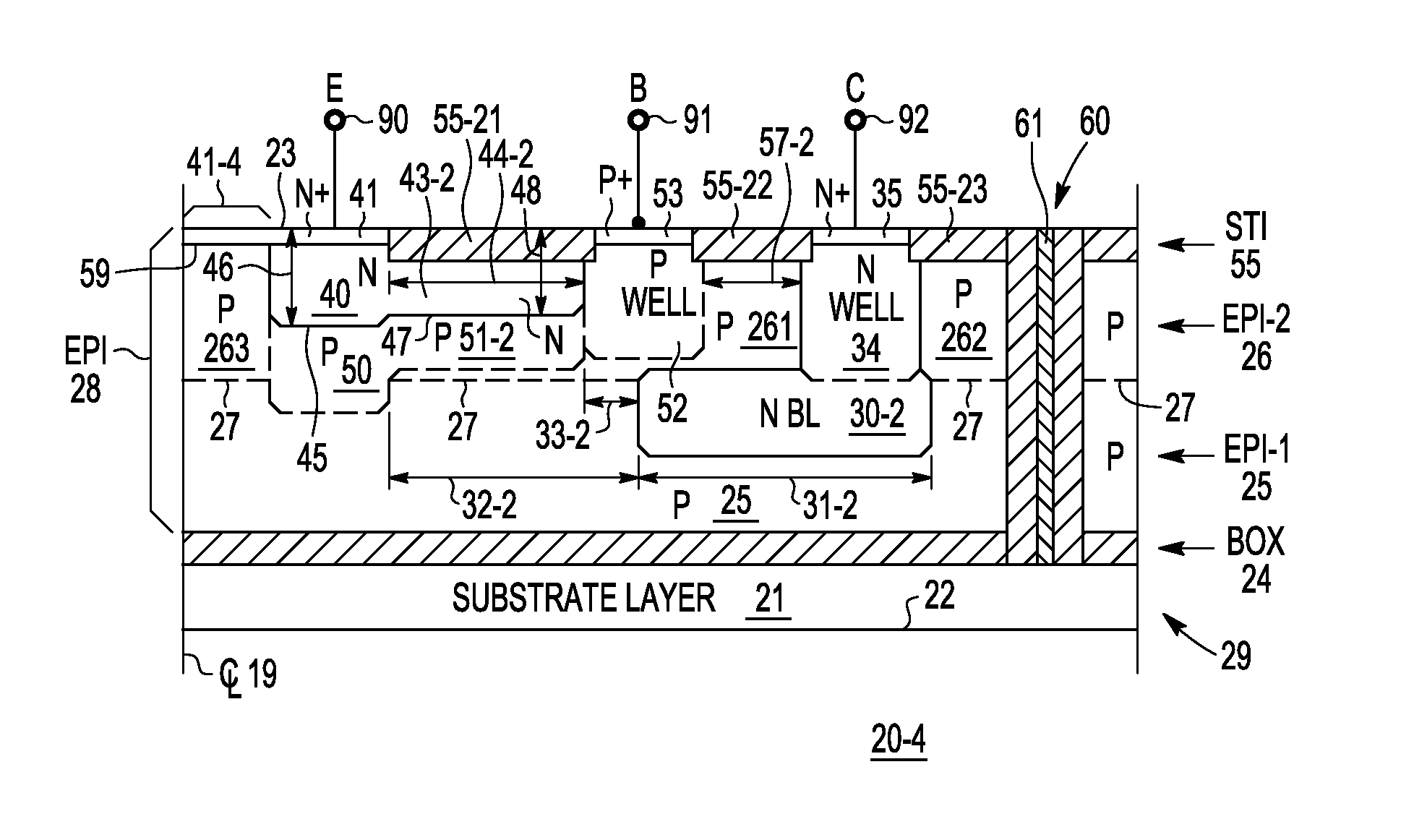

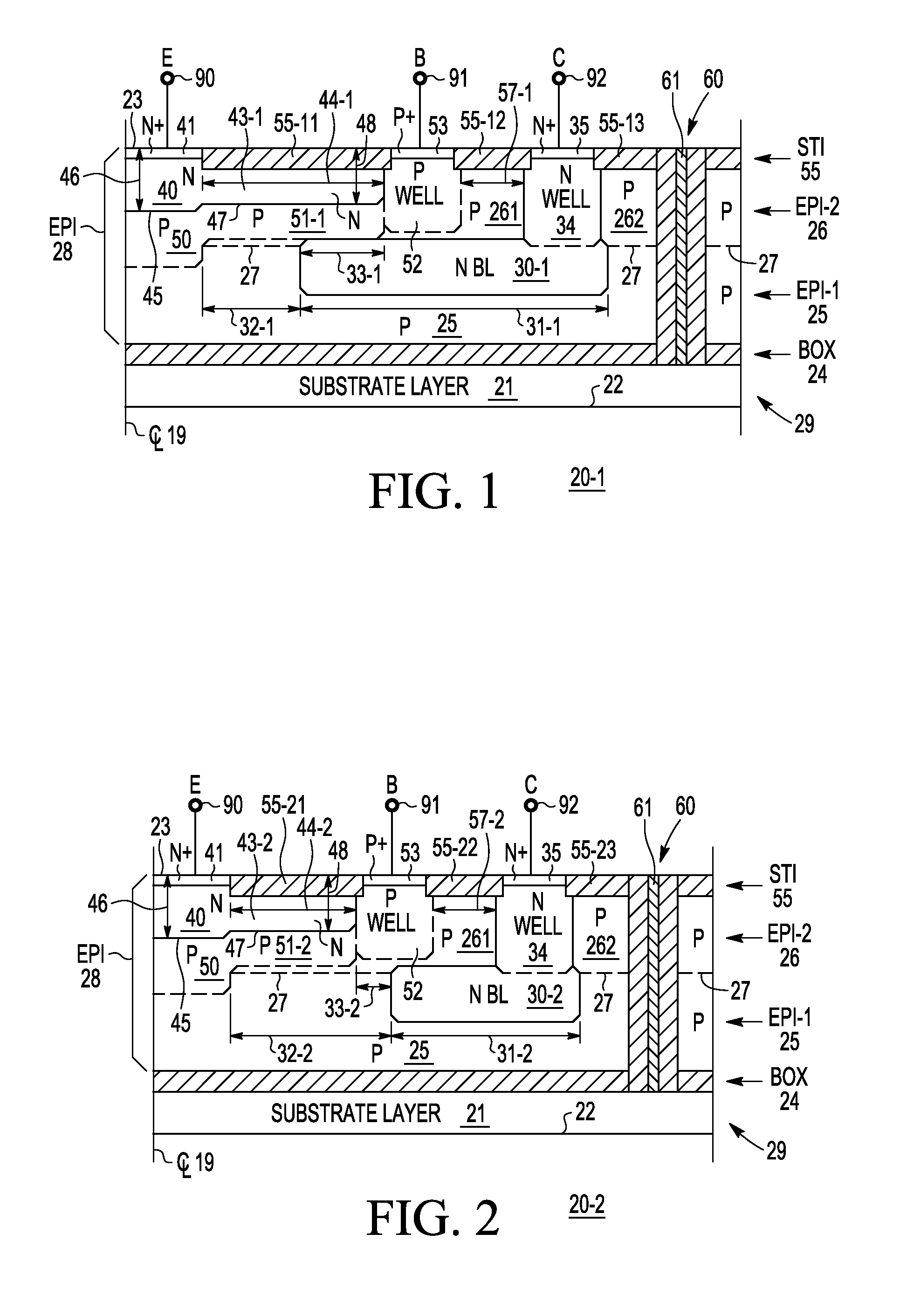

Bipolar transistor

ActiveUS20120098096A1TransistorSemiconductor/solid-state device manufacturingEngineeringJunction depth

A bipolar transistor comprises at least first and second connected emitter-base (EB) junctions having, respectively, different first and second EB junction depths, and a buried layer (BL) collector having a greater third depth. The emitters and bases corresponding to the different EB junctions are provided during a chain implant. An isolation region overlies the second EB junction location thereby providing its shallower EB junction depth. The BL collector does not underlie the first EB junction and is laterally spaced therefrom by a variable amount to facilitate adjusting the transistor's properties. In other embodiments, the BL collector can underlie at least a portion of the second EB junction. Regions of opposite conductivity type over-lie and under-lie the BL collector, which is relatively lightly doped, thereby preserving the breakdown voltage. The transistor can be readily “tuned” by mask adjustments alone to meet various device requirements.

Owner:NXP USA INC

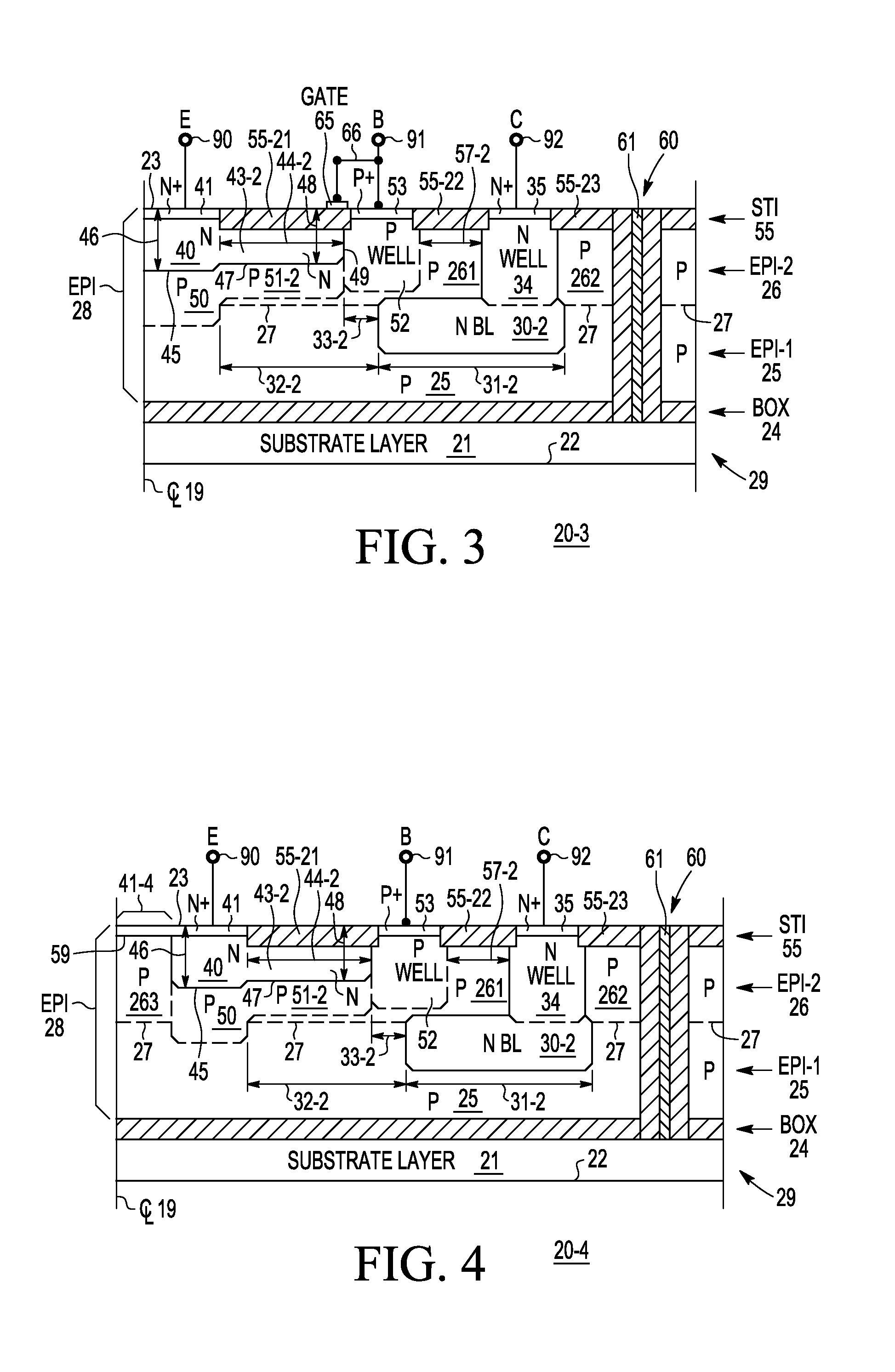

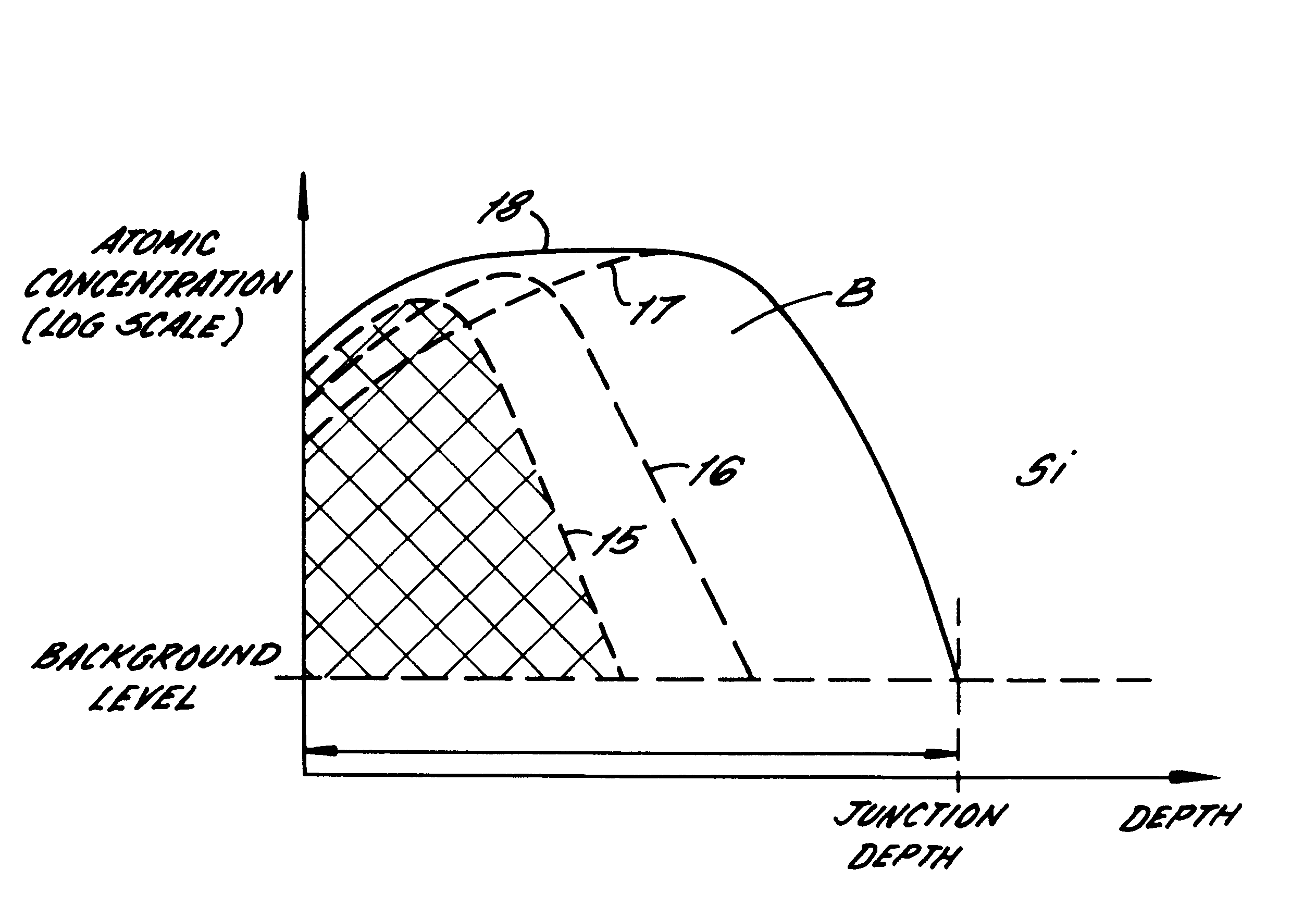

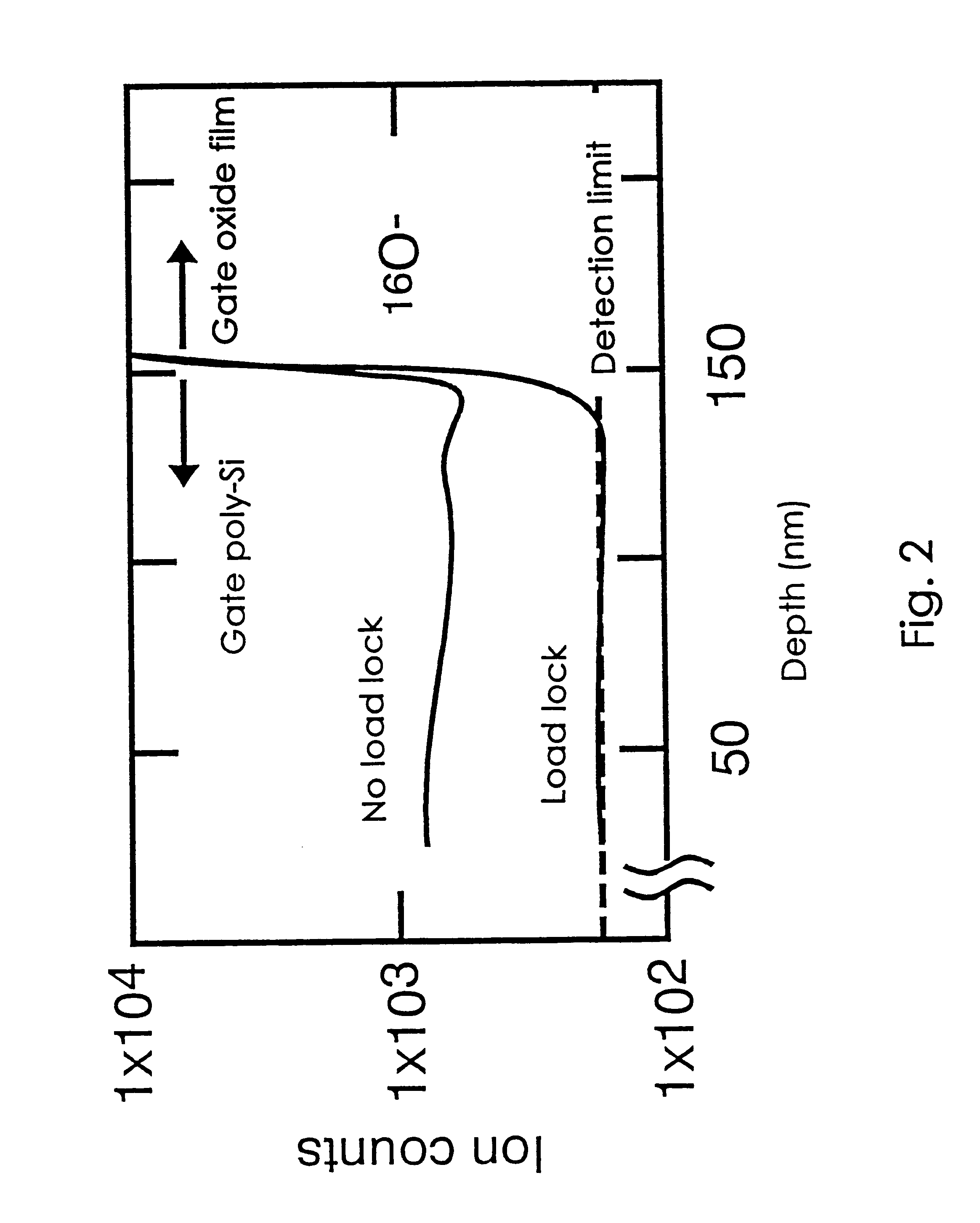

Ion implantation method

InactiveUS6200883B1Vacuum evaporation coatingSputtering coatingSemiconductor materialsDevice material

In ion implantation processes for forming junctions in semiconductor devices, a proportion of ions implant into the semiconductor material beyond the desired junction depth due to channelling along axes and planes of symmetry in the crystal. A method is provided in which ions are implanted at a series of different energies starting with a lower energy than that required for the desired junction depth. The initial amorphising of the surface regions of the semiconductor during the lower energy implantation reduces the channelling probability when the ions are subsequently implanted at the full energy resulting in a more sharply defined junction.

Owner:APPLIED MATERIALS INC +1

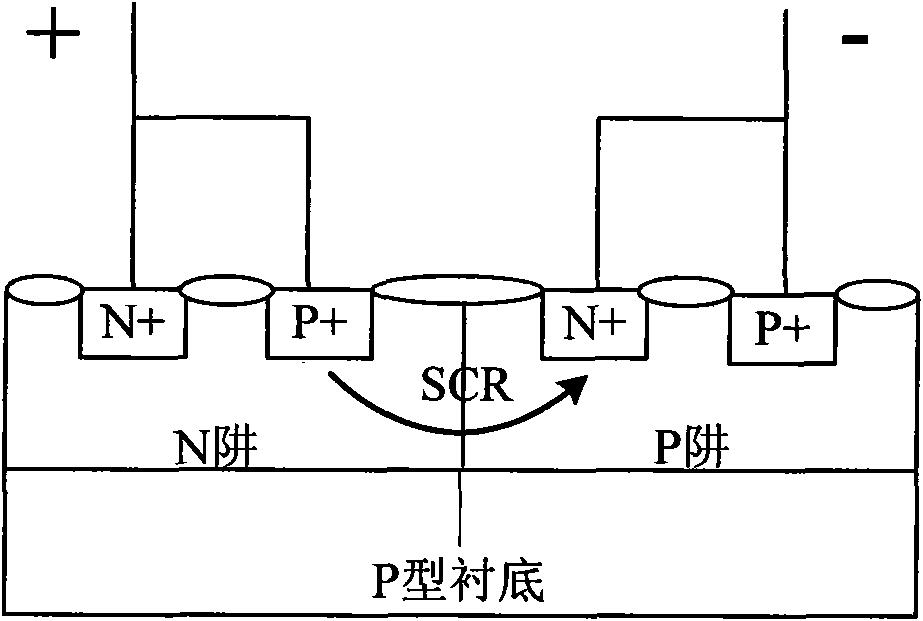

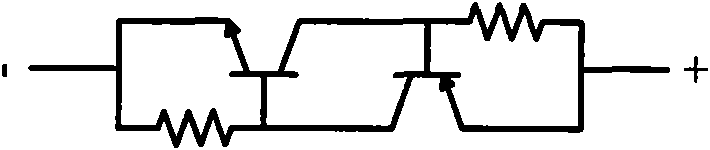

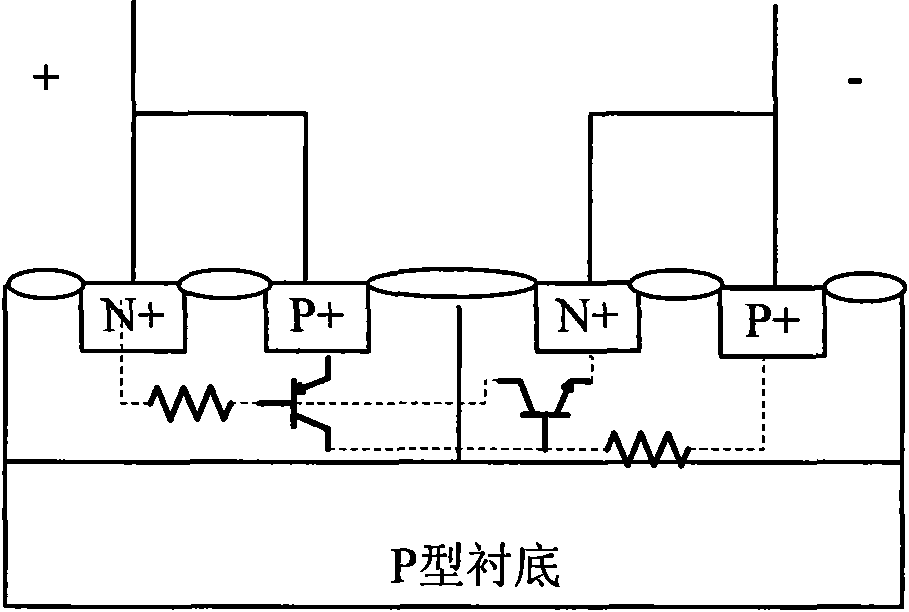

PNPNP type triac

The invention discloses a PNPNP type triac which comprises a P type substrate, wherein an N type buried layer is arranged in the P type substrate, a P well is injected on the N type buried layer, an annular N well in the junction depth which is the same with that of the P well is injected between the side surface of the P well and the P type substrate, a first N type drift region and a second N type drift region are injected in the P well, a first P+ injection region and a first N+ injection region are arranged in the first N type drift region, and a second P+ injection region and a second N+ injection region are arranged in the second N type drift region, wherein the first P+ injection region and the second P+ injection region are positioned on the inner side, and oxidation and isolation layers are covered on the P type substrate, the N well and the P well. The PNPNP type triac structure can realize the compatibility of the process with the commonly used BCD process in the industry; as the PNPNP type triac structure has higher and symmetric forward and reverse breakdown voltage, the PNPNP type triac is more applicable to ESD protection application of a plurality of mixed voltage interface circuits or among different power domains.

Owner:ZHEJIANG UNIV

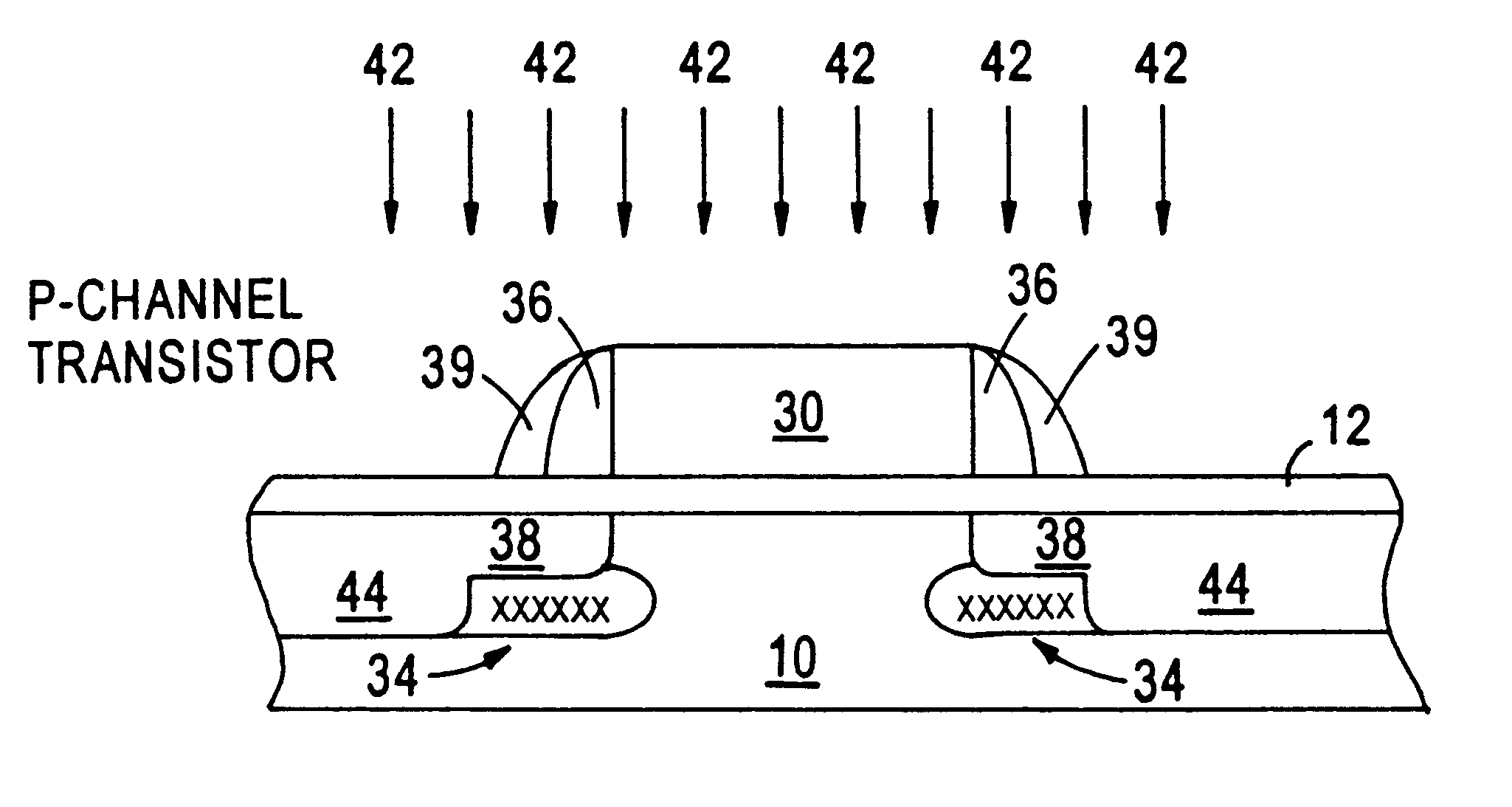

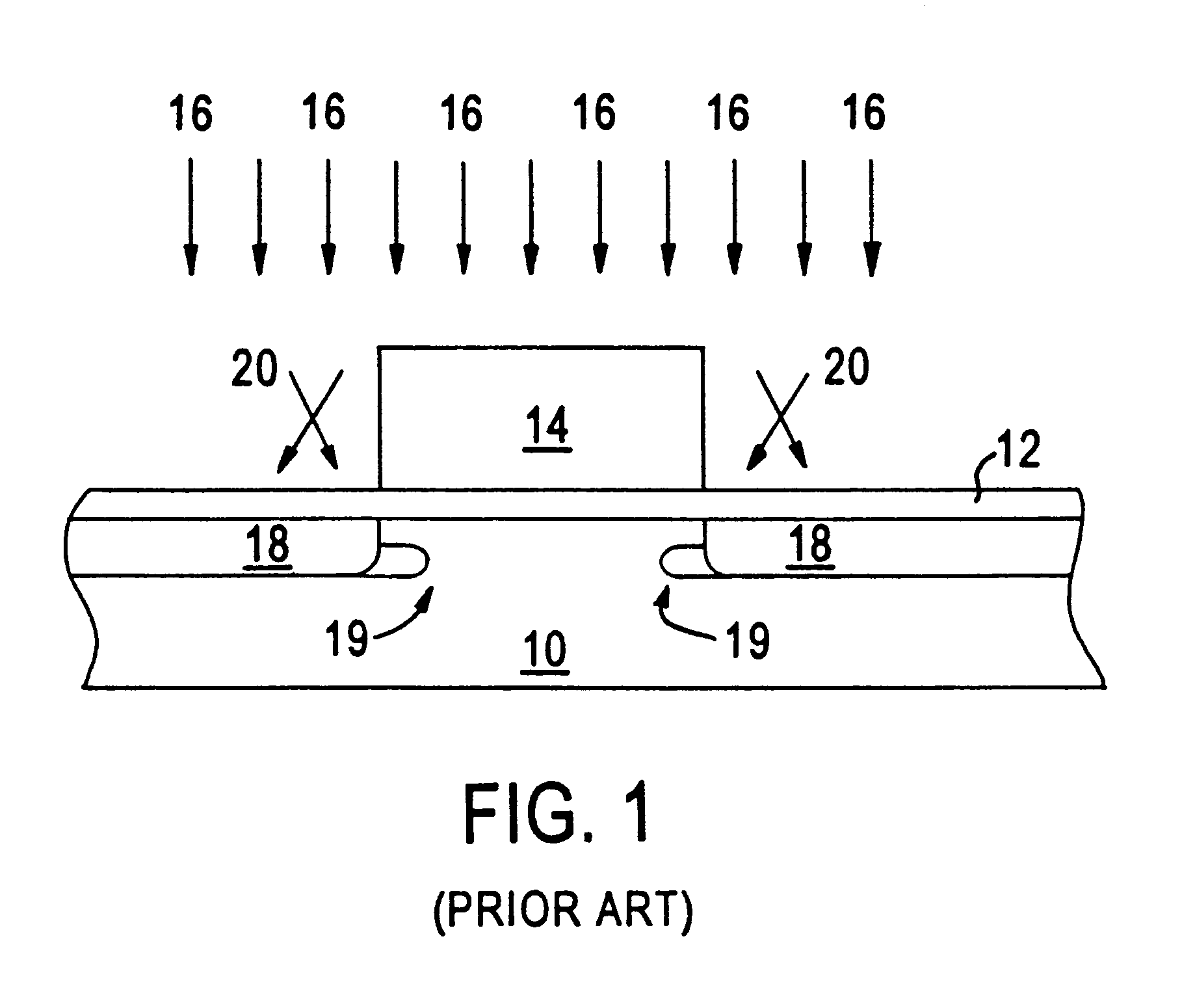

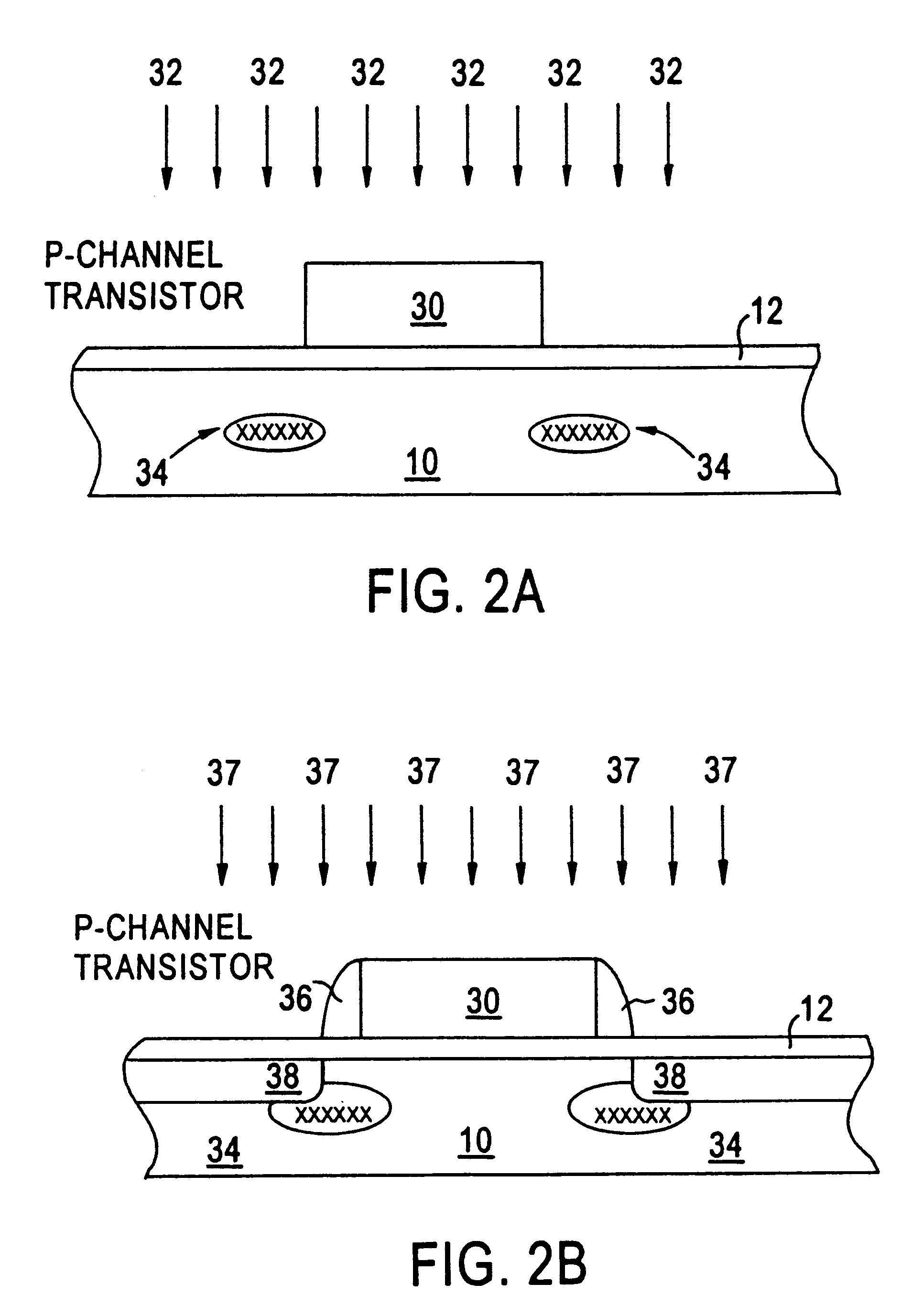

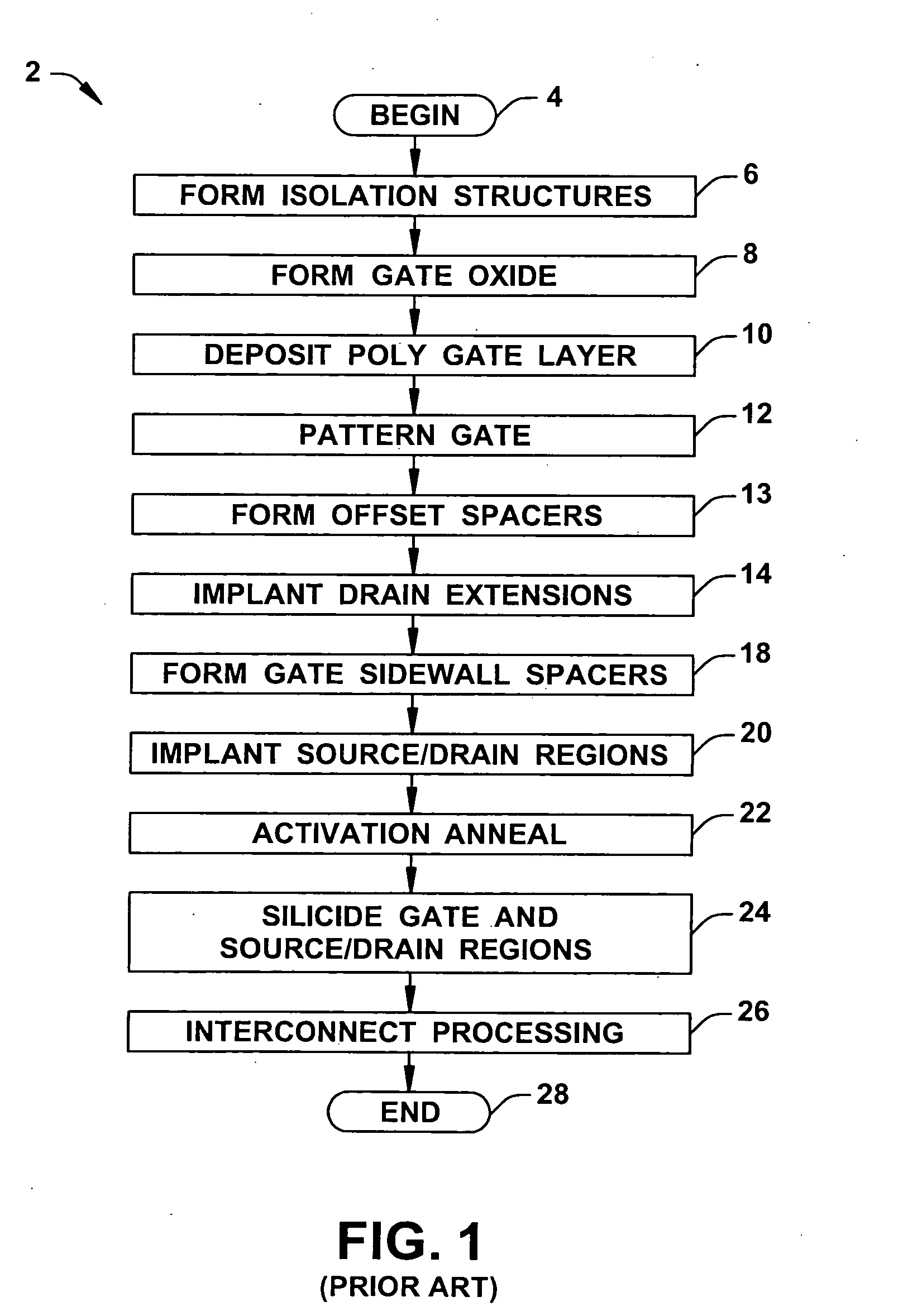

CMOS processing employing zero degree halo implant for P-channel transistor

Halo implant regions are formed in a P-channel semiconductor device employing a zero degree tilt angle. N-type impurities are ion implanted to the desired depth in the semiconductor substrate prior to forming P-channel lightly doped source / drain areas. Subsequently, moderately or heavily doped source / drain regions are formed, followed by activation annealing. The halo implants diffuse to form halo structures at the desired location, thereby reducing short channel effects, such as subsurface punchthrough. Other embodiments enable independent control of the junction depths and channel lengths of N- and P-channel transistors, while maintaining high manufacturing throughput.

Owner:GLOBALFOUNDRIES INC

Semiconductor device having diffusion regions with different junction depths

An aspect of the present invention includes: a gate insulating layer formed on an n-type silicon semiconductor region; a gate electrode formed on the gate insulating layer; a channel region formed immediately below the gate electrode in the semiconductor region; p-type source / drain regions formed at both sides of the channel region in the semiconductor region; p-type diffusion layer regions formed between the channel region and the source / drain regions in the semiconductor region and having a lower impurity concentration than the source / drain regions; first impurity regions formed near surface portions of the diffusion layer regions; and second impurity regions formed in part of the p-type diffusion layer regions and near surface portions of the source / drain regions, the second impurity regions being deeper than the first impurity regions, the first and second impurity regions containing one element selected from germanium, silicon, gallium, and indium as impurity.

Owner:KK TOSHIBA

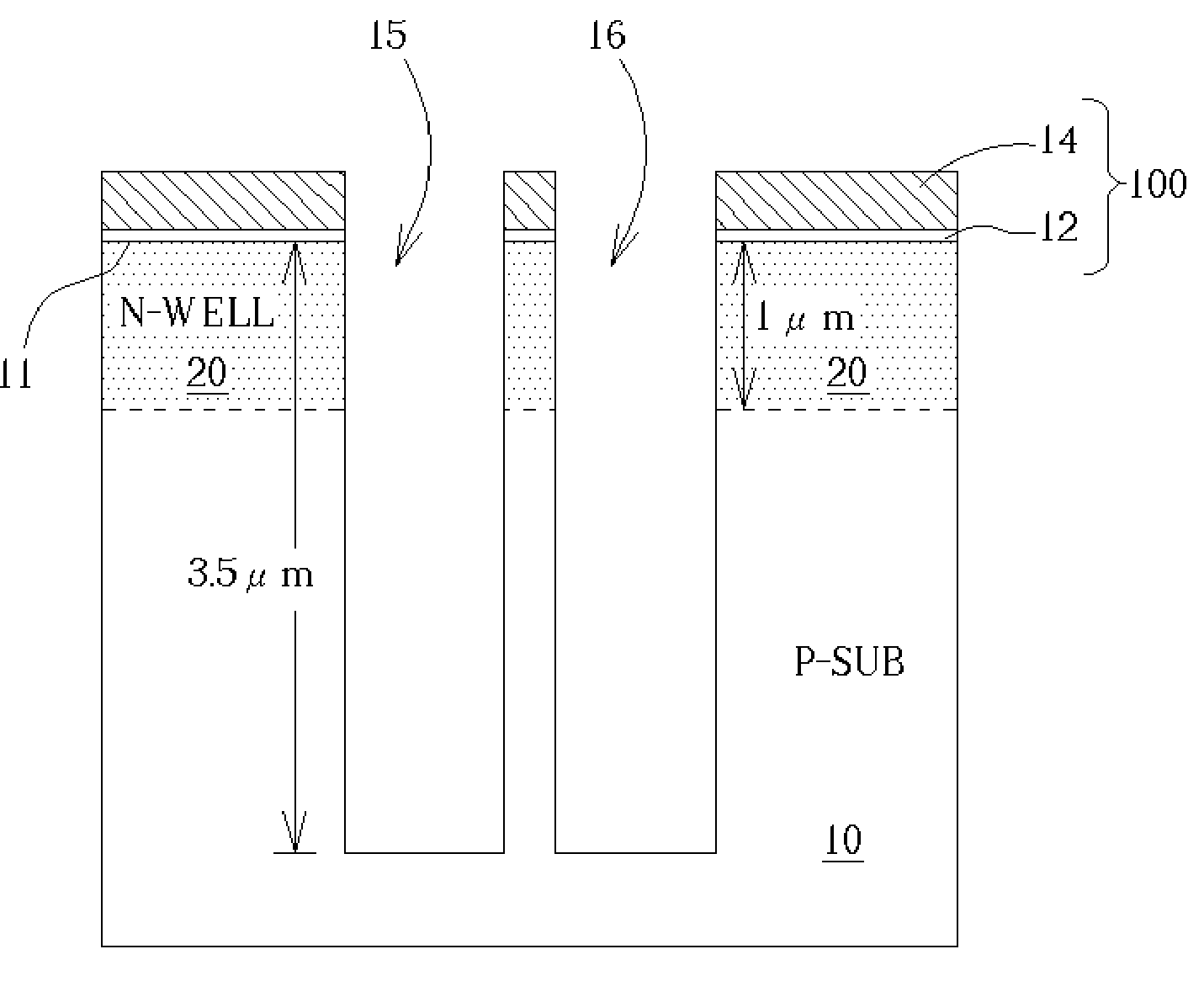

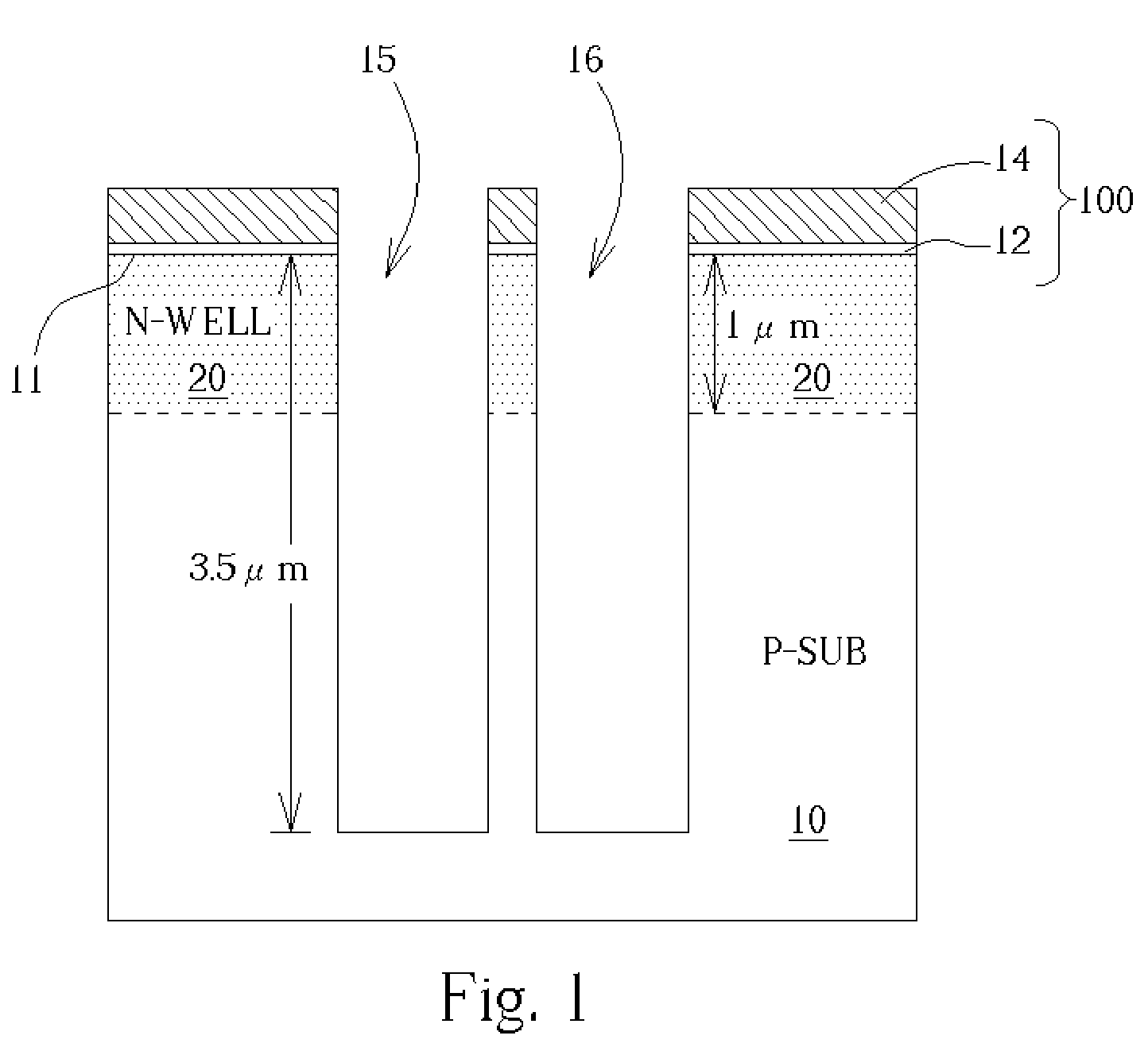

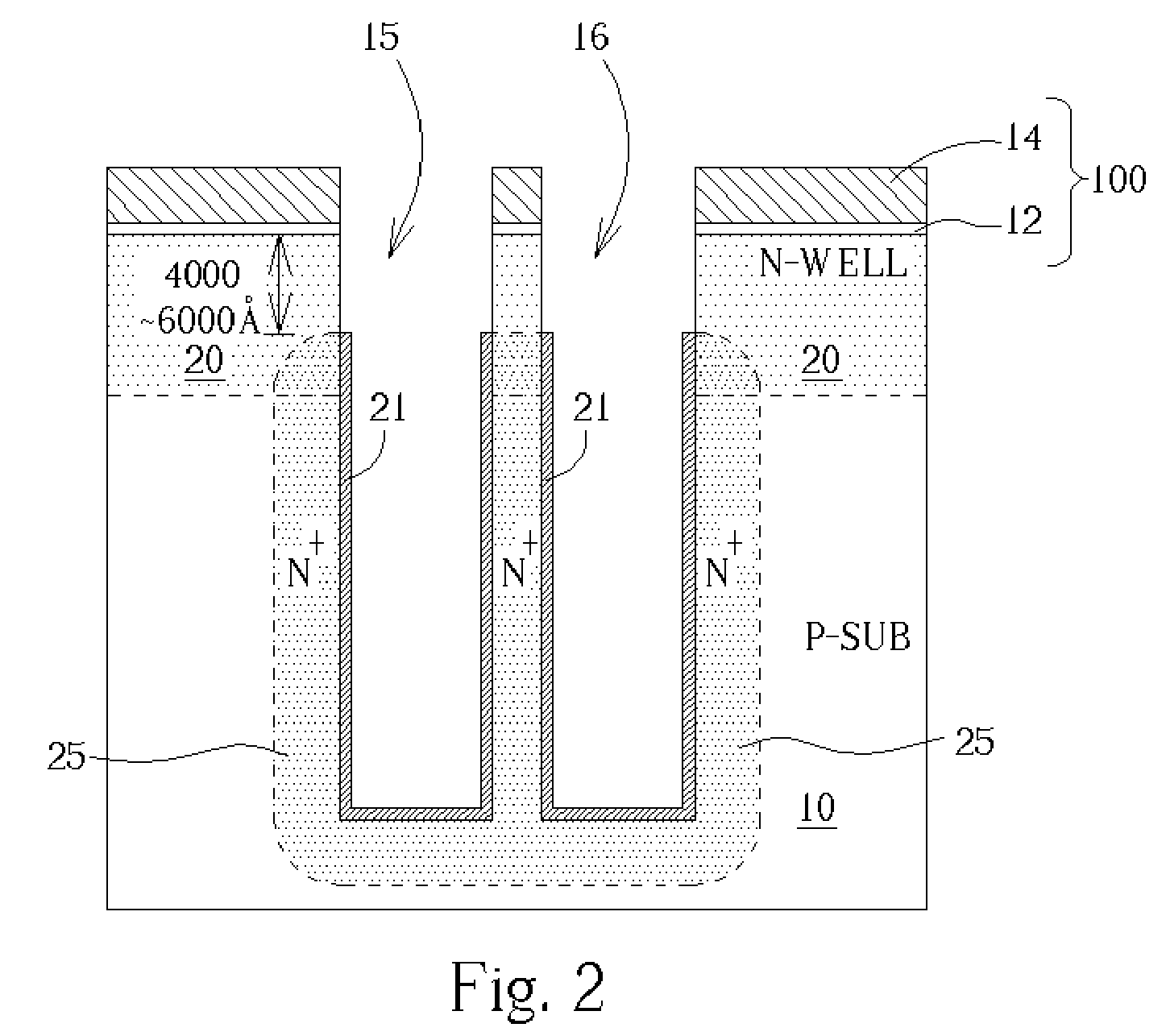

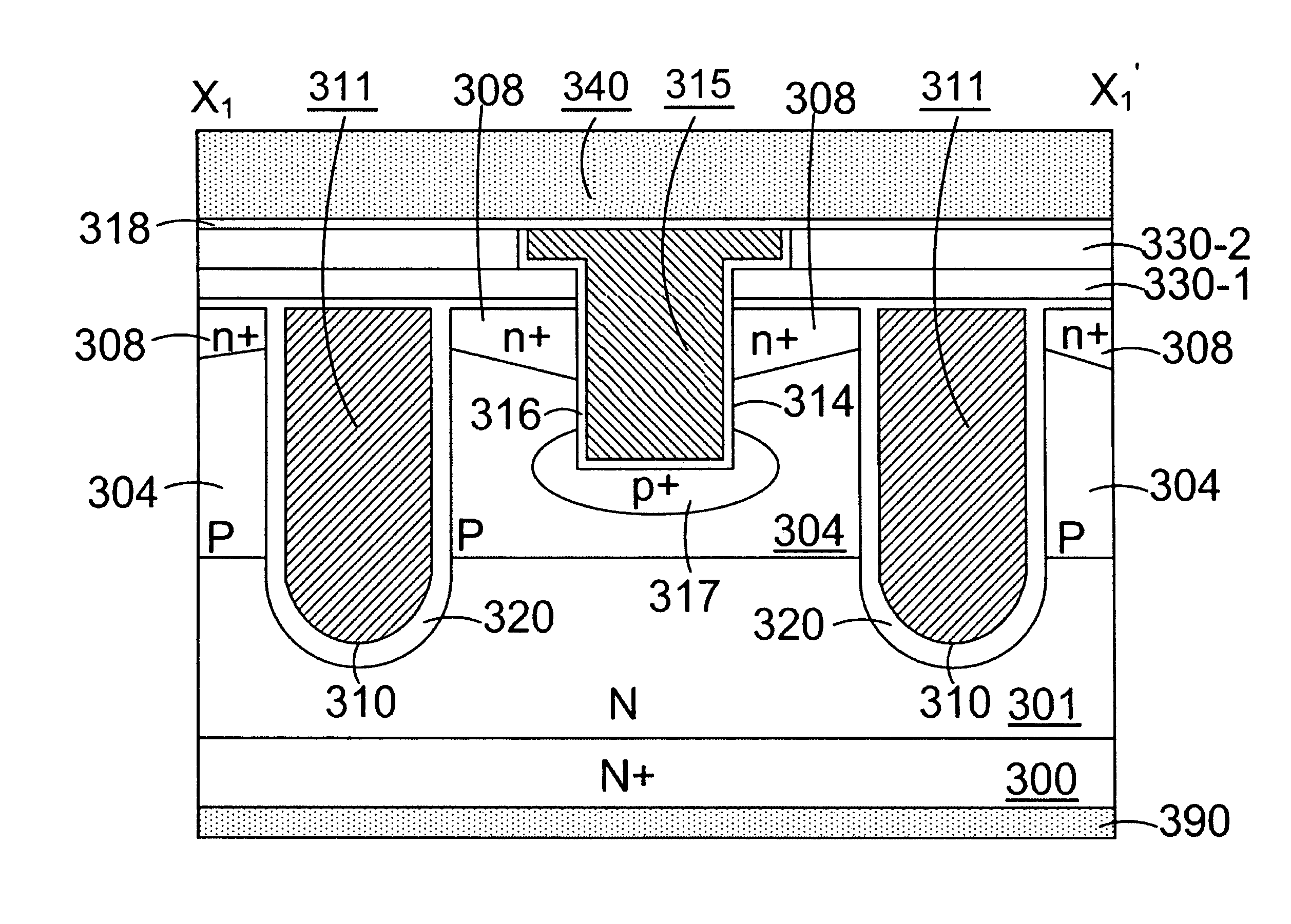

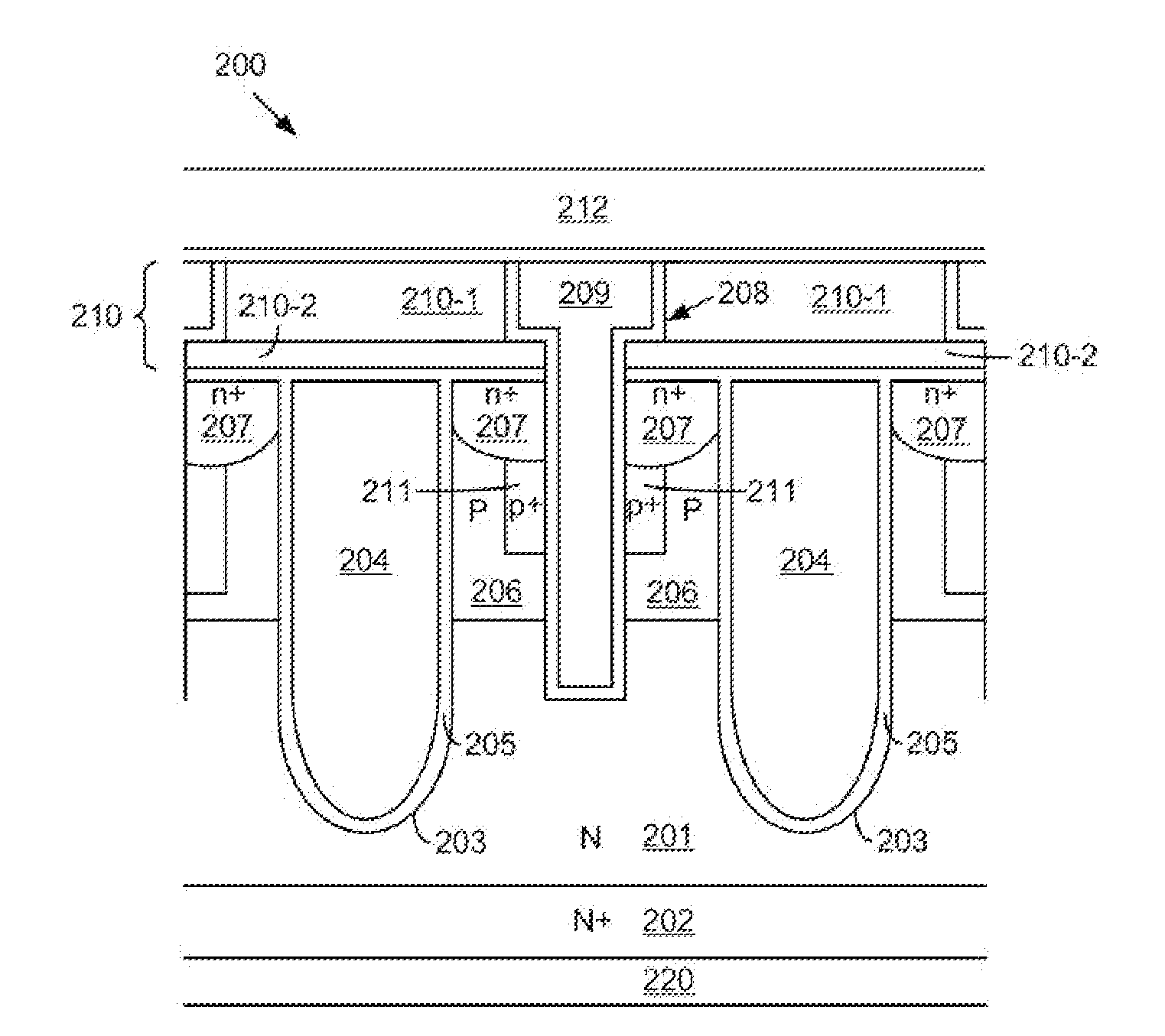

Deep-trench 1t-sram with buried out diffusion well merged with an ion implantation well

InactiveUS20050184326A1Increase capacitanceHigh suppression characteristicsTransistorSolid-state devicesGate dielectricInsulation layer

A deep-trench 1T-SRAM memory cell is disclosed. The deep-trench 1T-SRAM memory cell includes a first conductivity type semiconductor substrate with a main surface. A second conductivity type ion implantation well with a well junction depth is located on the main surface. A gate dielectric layer is located on the ion implantation well. A gate is located on the gate dielectric layer. A heavily doped S / D region of the first conductivity type is disposed at one side of the gate in the ion implantation well. A lightly doped drain (LDD) region of the first conductivity type is disposed at the other side of the gate in the ion implantation well. A deep trench capacitor vertically extends into the main surface through the well junction depth of the ion implantation well to a pre-selected depth. The deep trench capacitor, which is fabricated adjacent to the LDD region, comprises an ion out diffusion well of the second conductivity type that is formed at a lower portion of the deep trench capacitor and is merged with the ion implantation well. A polysilicon electrode pillar is electrically isolated from the LDD region, the ion implantation well, and the ion out diffusion well by a capacitor dielectric layer and a trench top insulation layer.

Owner:UNITED MICROELECTRONICS CORP

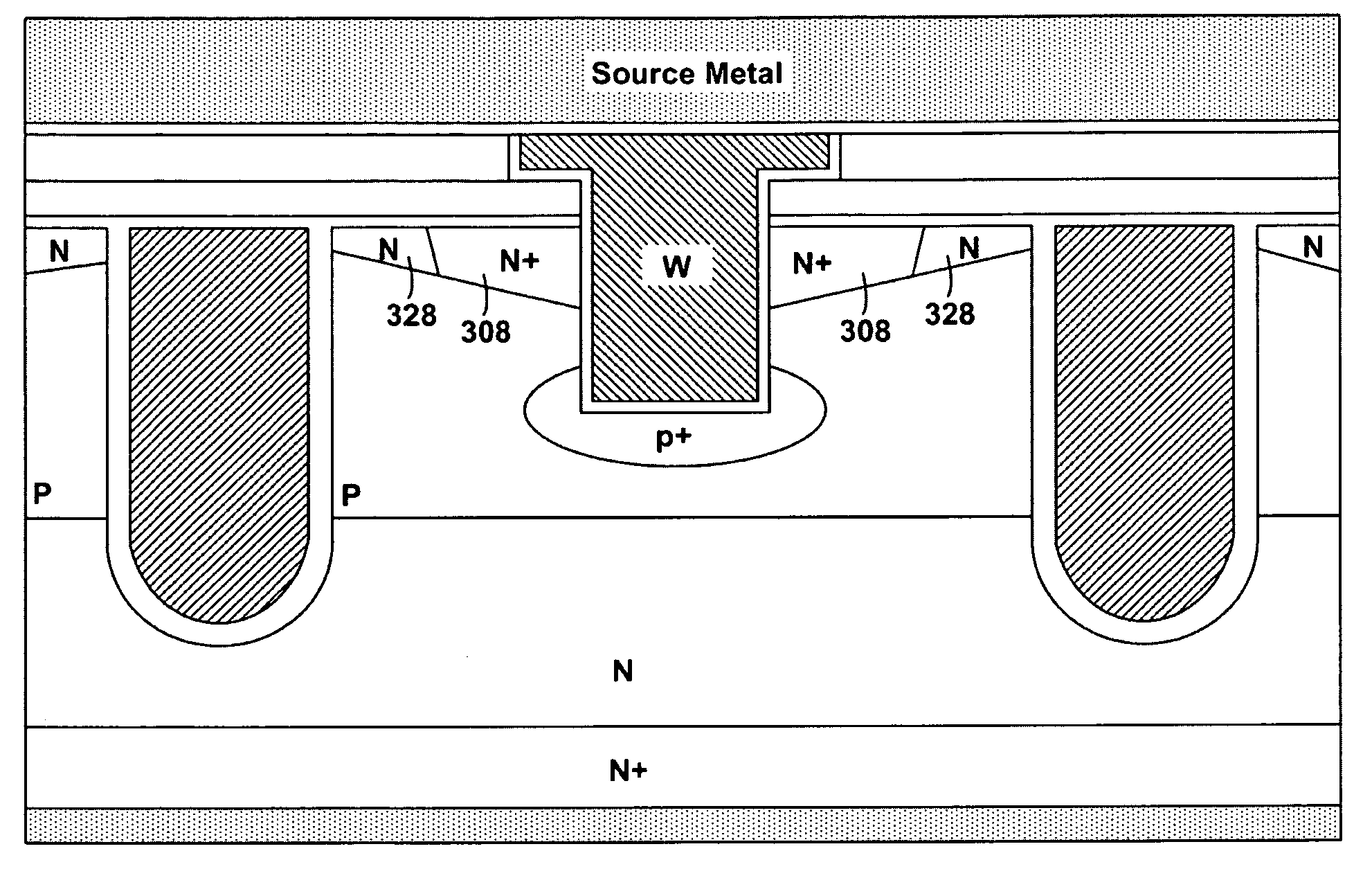

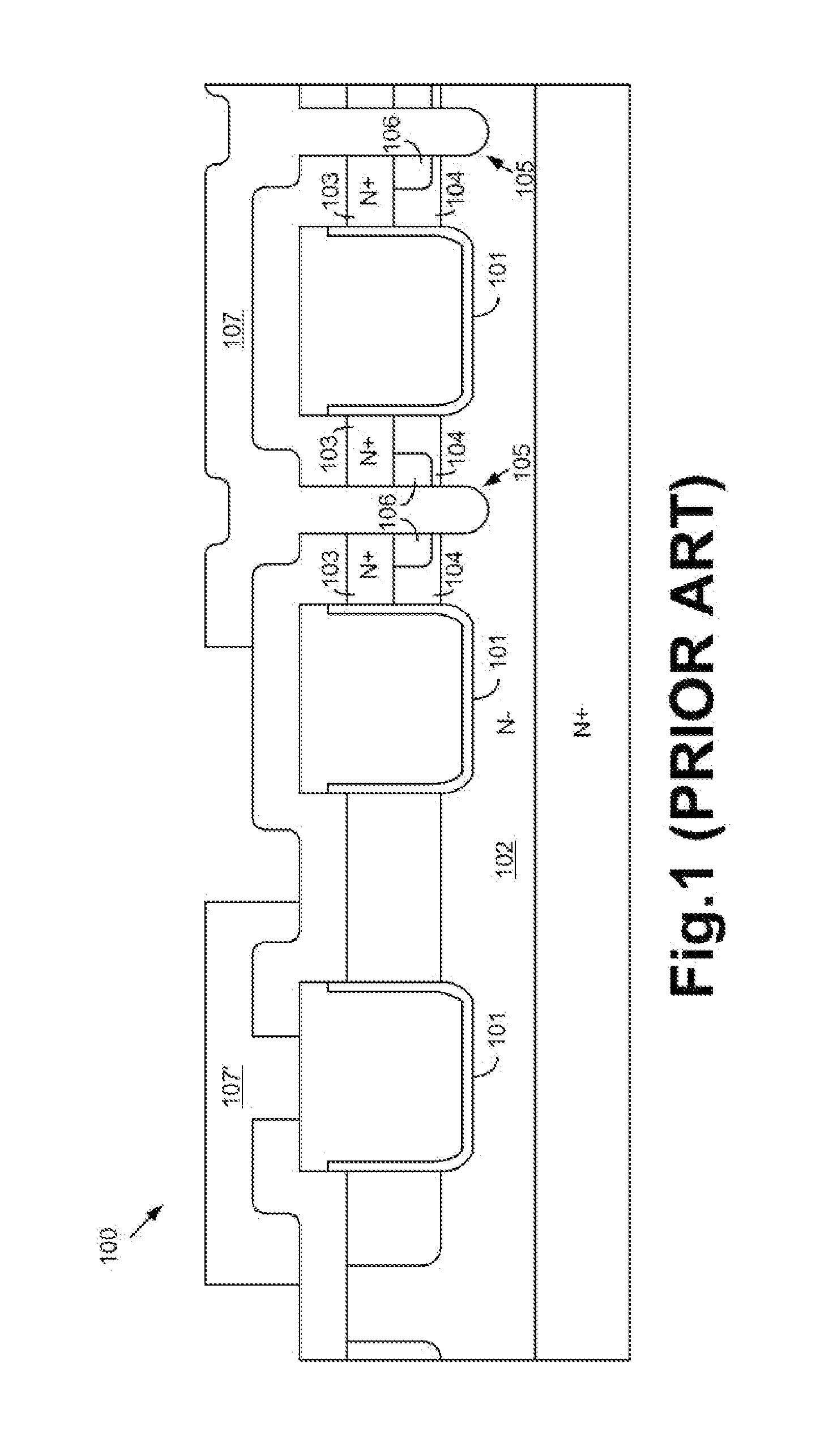

Trench MOSFET structures using three masks process

ActiveUS20110006363A1Reduced footprintSmall sizeTransistorSolid-state devicesTrench mosfetInter layer

A trench MOSFET structure having improved avalanche capability is disclosed, wherein the source region is formed by performing source Ion Implantation through contact open region of a contact interlayer, and further diffused to optimize a trade-off between Rds and the avalanche capability. Thus, only three masks are needed in fabrication process, which are trench mask, contact mask and metal mask. Furthermore, said source region has a doping concentration along channel region lower than along contact trench region, and source junction depth along channel region shallower than along contact trench, and source doping profile along surface of epitaxial layer has Guassian-distribution from trenched source-body contact to channel region.

Owner:FORCE MOS TECH CO LTD

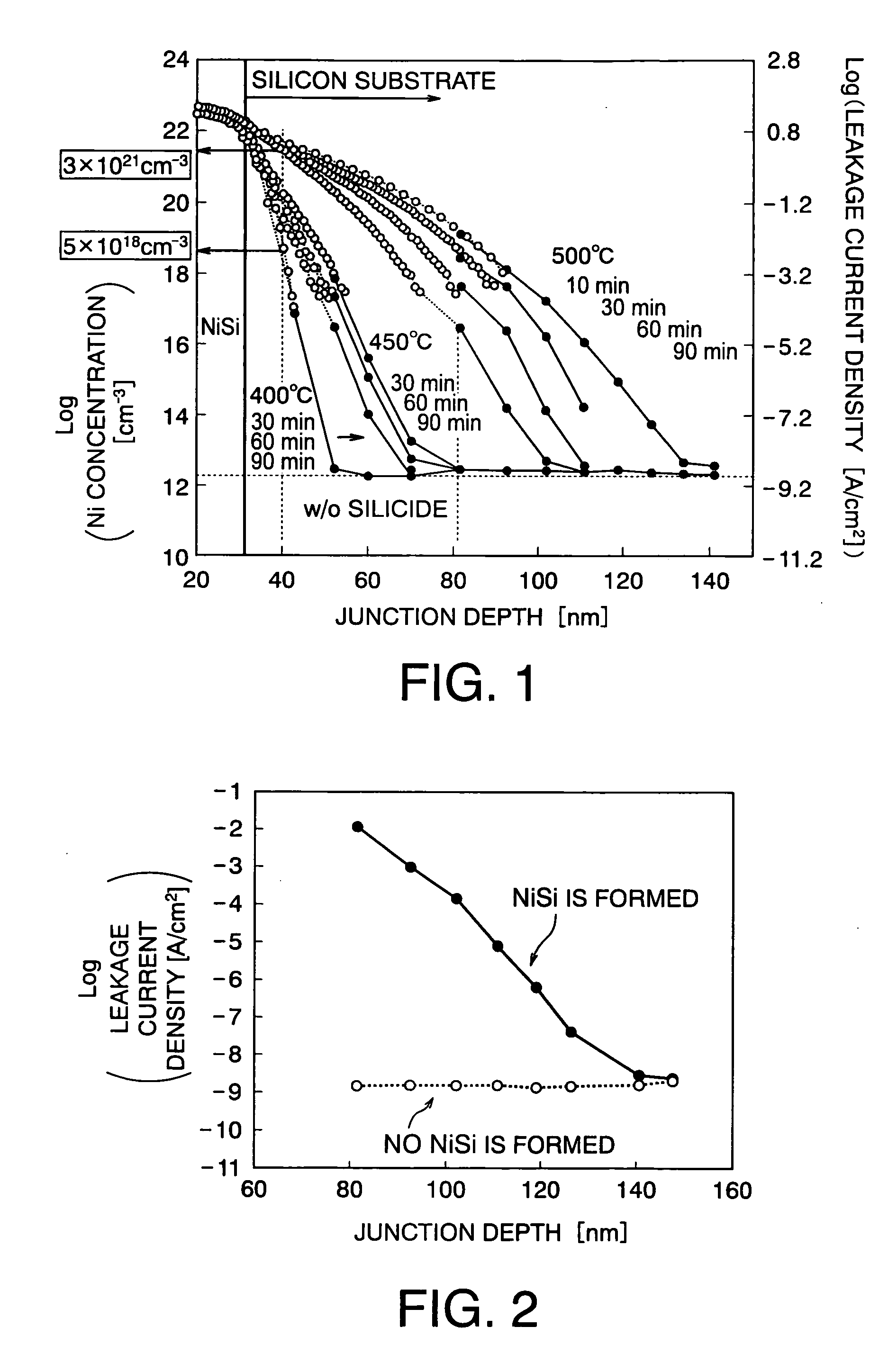

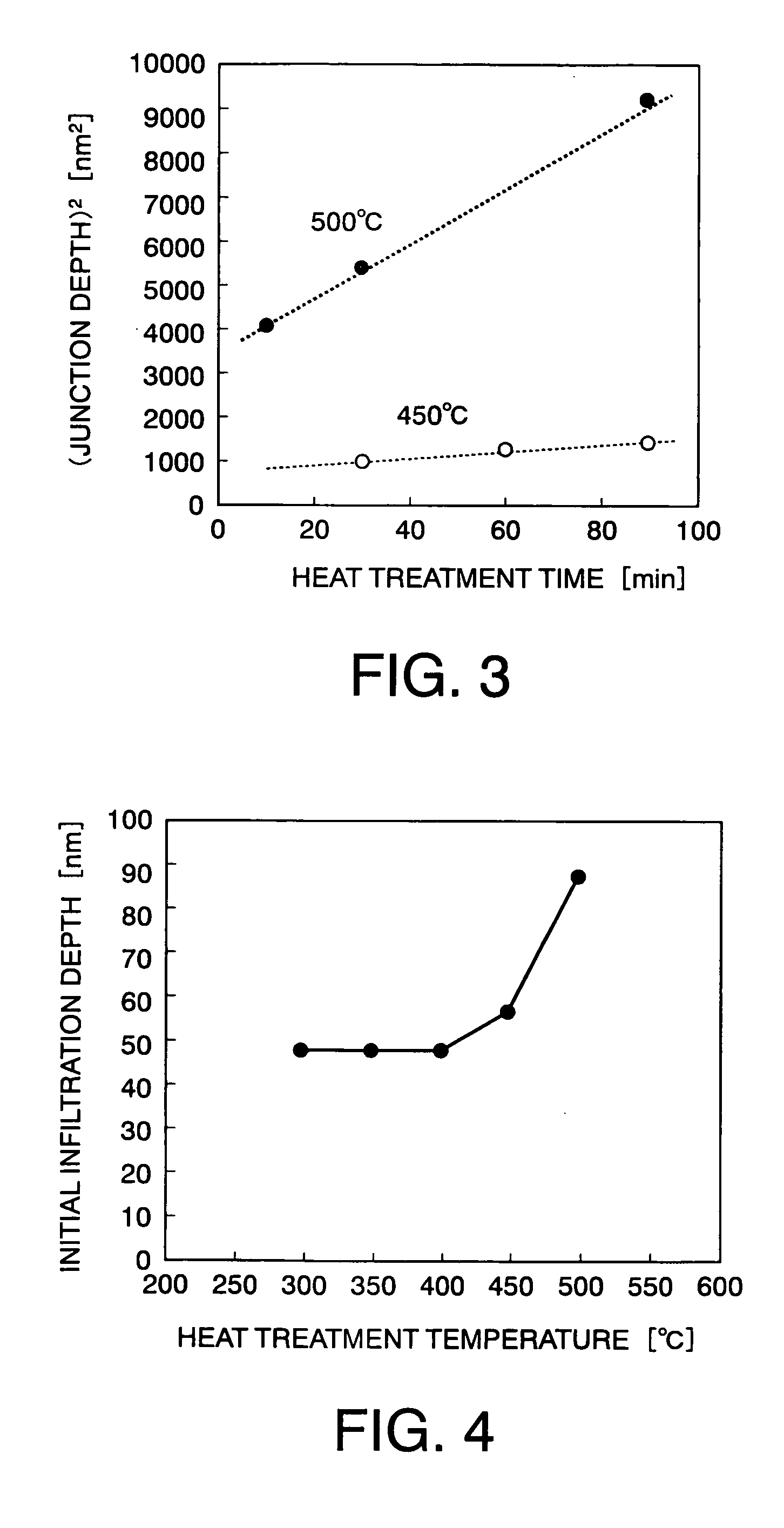

Semiconductor device and method of manufacturing the same

InactiveUS20040256645A1TransistorSemiconductor/solid-state device detailsMOSFETTagged Image File Format

A method for manufacturing a MOSFET equipped with a silicide layer over shallow source and drain junctions without leakage generation is provided. By restricting the temperature of manufacturing steps after the silicide formation below a critical temperature Tc, which is defined below as a function of a junction depth Dj from 20 nm to 60 nm, leakage generation is practically suppressed. Tc=axDj+b, <math-cwu id="MATH-US-00001"> <NUMBER>1< / NUMBER> where a = 6.11 ( 20 < Dj ≤ 26 ) = 1.60 ( 26 < Dj ≤ 60 ) , b = 290.74 ( 20 < Dj ≤ 26 ) = 408 ( 26 < Dj ≤ 60 ) , <mathematica-file id="MATHEMATICA-00001" file="US20040256645A1-20041223-M00001.NB" / > <image id="EMI-M00001" wi="216.027" he="54.00675" file="US20040256645A1-20041223-M00001.TIF" imf="TIFF" ti="MF" / > < / MATH-CWU> Dj is a junction depth (nm) measured from the lower surface of the silicide layer, and Tc is a critical temperature (° C.) during a heat treatment.

Owner:KK TOSHIBA

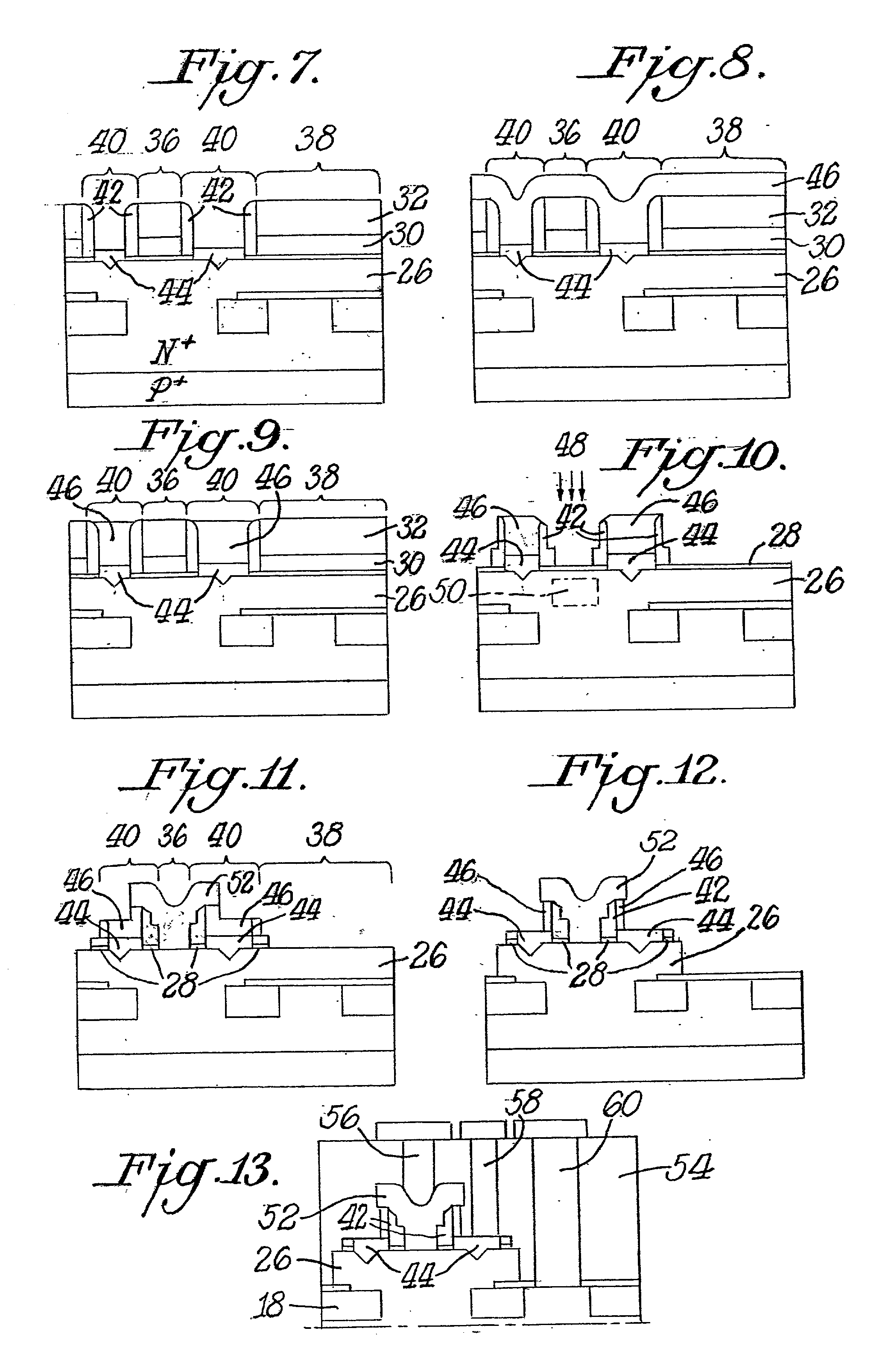

Trench mosfet and method of manufacture utilizing four masks

InactiveUS20090085074A1Improved cell pitchReduce manufacturing costSemiconductor/solid-state device manufacturingSemiconductor devicesTrench mosfetTrench gate

In accordance with the invention, a trench MOSFET semiconductor device is manufactured in accordance with a process comprising the steps of: providing a heavily doped N+ silicon substrate; utilizing a first mask to define openings for the trench gate and termination; utilizing a second mask as a source mask with openings determining the size and shape of a diffused source junction depth; utilizing a third mask as a contact mask to define contact hole openings; and utilizing a fourth mask as a metal mask, whereby only the first, second, third and fourth masks are utilized in the manufacture of the trench MOSFET semiconductor device.

Owner:INPOWER SEMICON

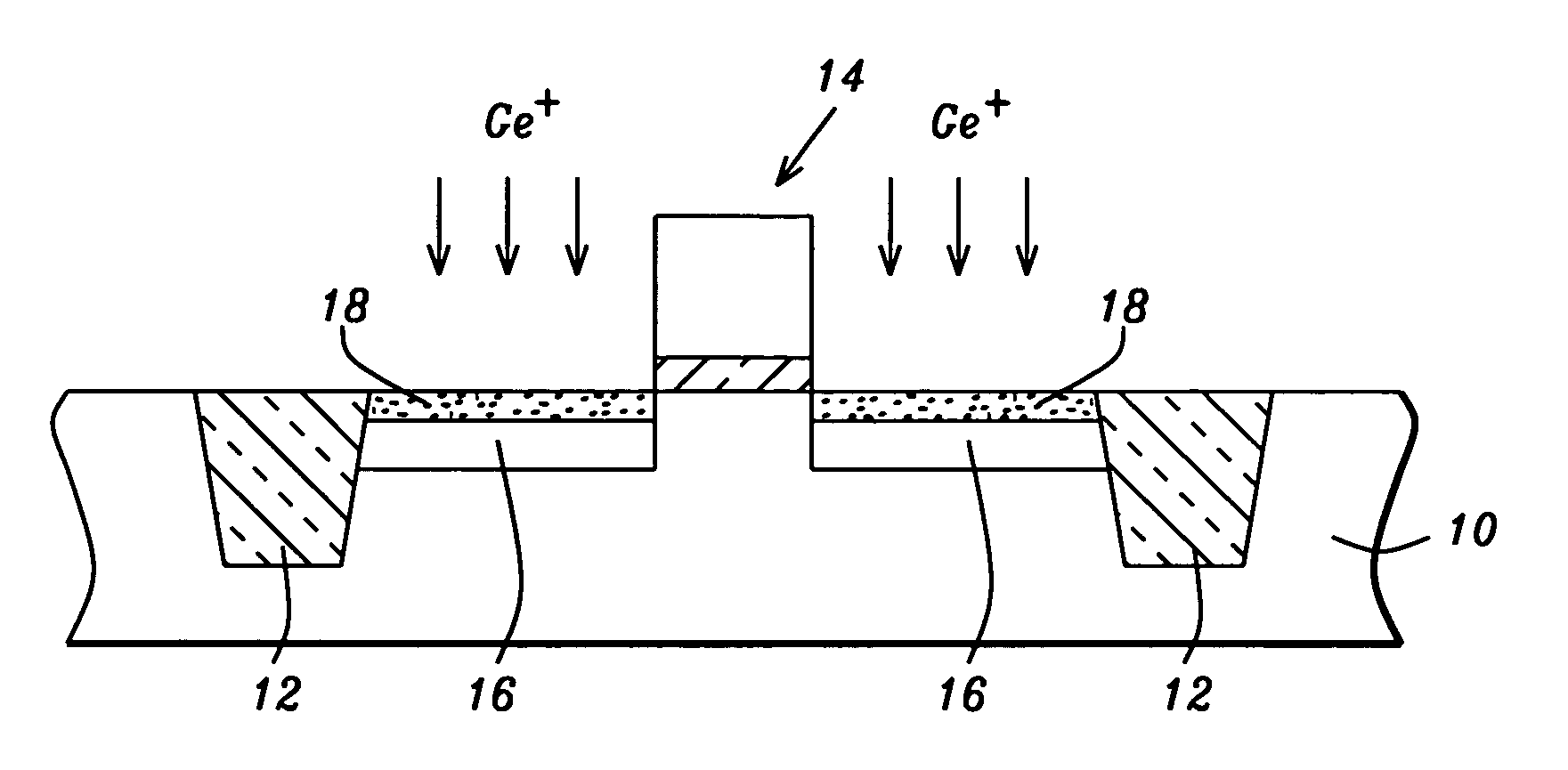

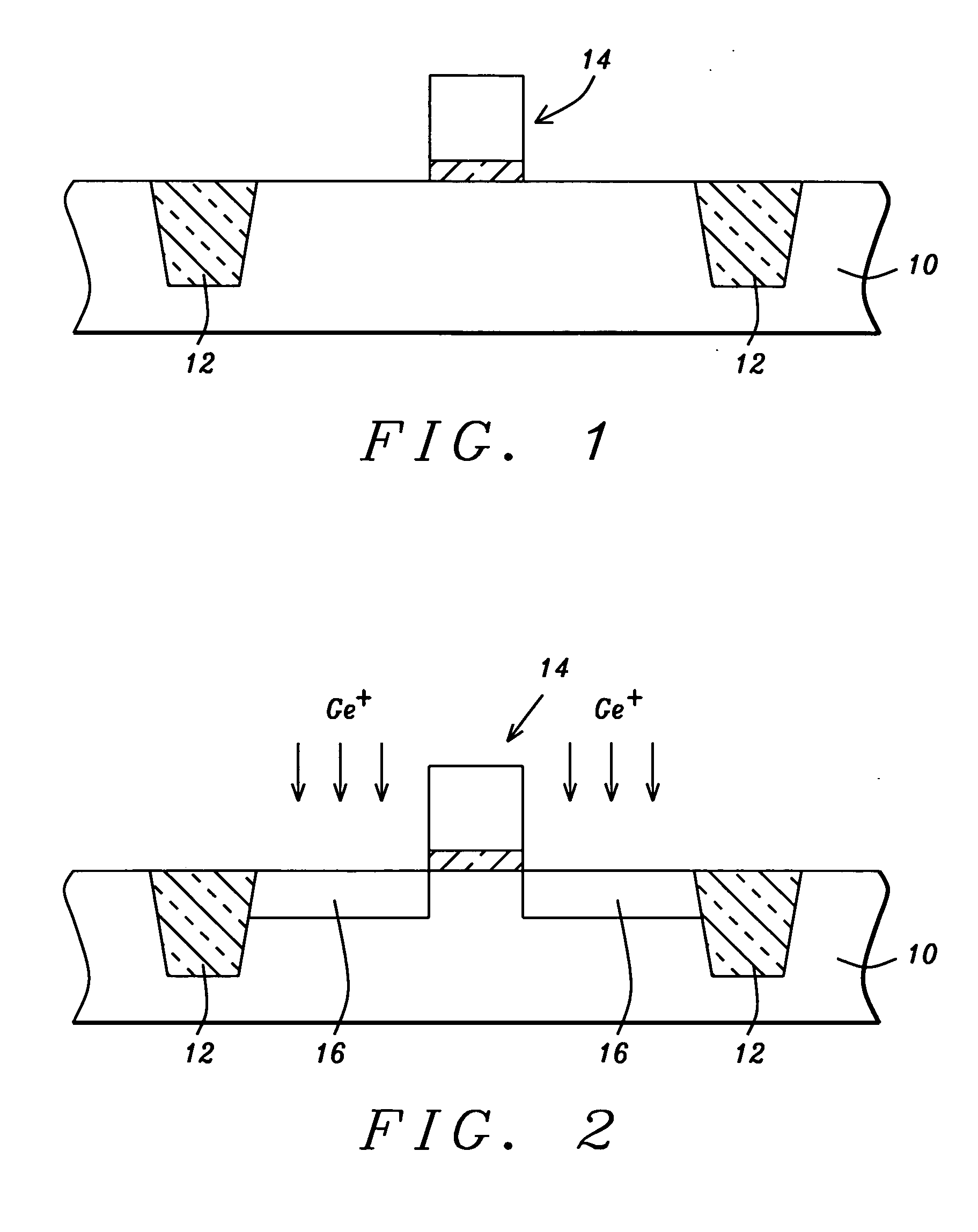

Dual step source/drain extension junction anneal to reduce the junction depth: multiple-pulse low energy laser anneal coupled with rapid thermal anneal

InactiveUS20050158956A1Reduce sheet resistanceShallow junctionSemiconductor/solid-state device manufacturingMOSFETDevice material

A process is described to form a semiconductor device such as MOSFET or CMOS with shallow junctions in the source / drain extension regions. After forming the shallow trench isolations and the gate stack, sidewall dielectric spacers are removed. A pre-amorphizing implant (PAI) is performed with Ge+ or Si+ ions to form a thin PAI layer on the surface of the silicon regions adjacent to the gate stack. B+ ion implantation is then performed to form source / drain extension (SDE) regions. The B+ implant step is then followed by multiple-pulsed 248 nm KrF excimer laser anneal with pulse duration of 23 ns. This step is to reduce the sheet resistance of the junction through the activation of the boron dopant in the SDE junctions. Laser anneal is then followed by rapid thermal anneal (RTA) to repair the residual damage and also to induce out-diffusion of the boron to yield shallower junctions than the just-implanted junctions prior to RTA.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING

Semiconductor device having junction depths for reducing short channel effect

A semiconductor device and a fabrication method thereof are disclosed. A silicon nitride film is formed over a silicon semiconductor substrate. Impurity ions are then implanted into desired areas of the silicon semiconductor substrate, so that nitrogen atoms and silicon atoms from the silicon nitride film are incorporated into the surface of the silicon semiconductor substrate together with introduction of impurity ions. The silicon semiconductor substrate has a minimized content of oxygen mixed thereinto and restored crystal defects filled by nitrogen atoms upon implanting of impurity ions. The fabricated semiconductor device is free from a trade-off relation between gate-electrode depletion and junction current leakage, and short-channel effects.

Owner:SHARP KK

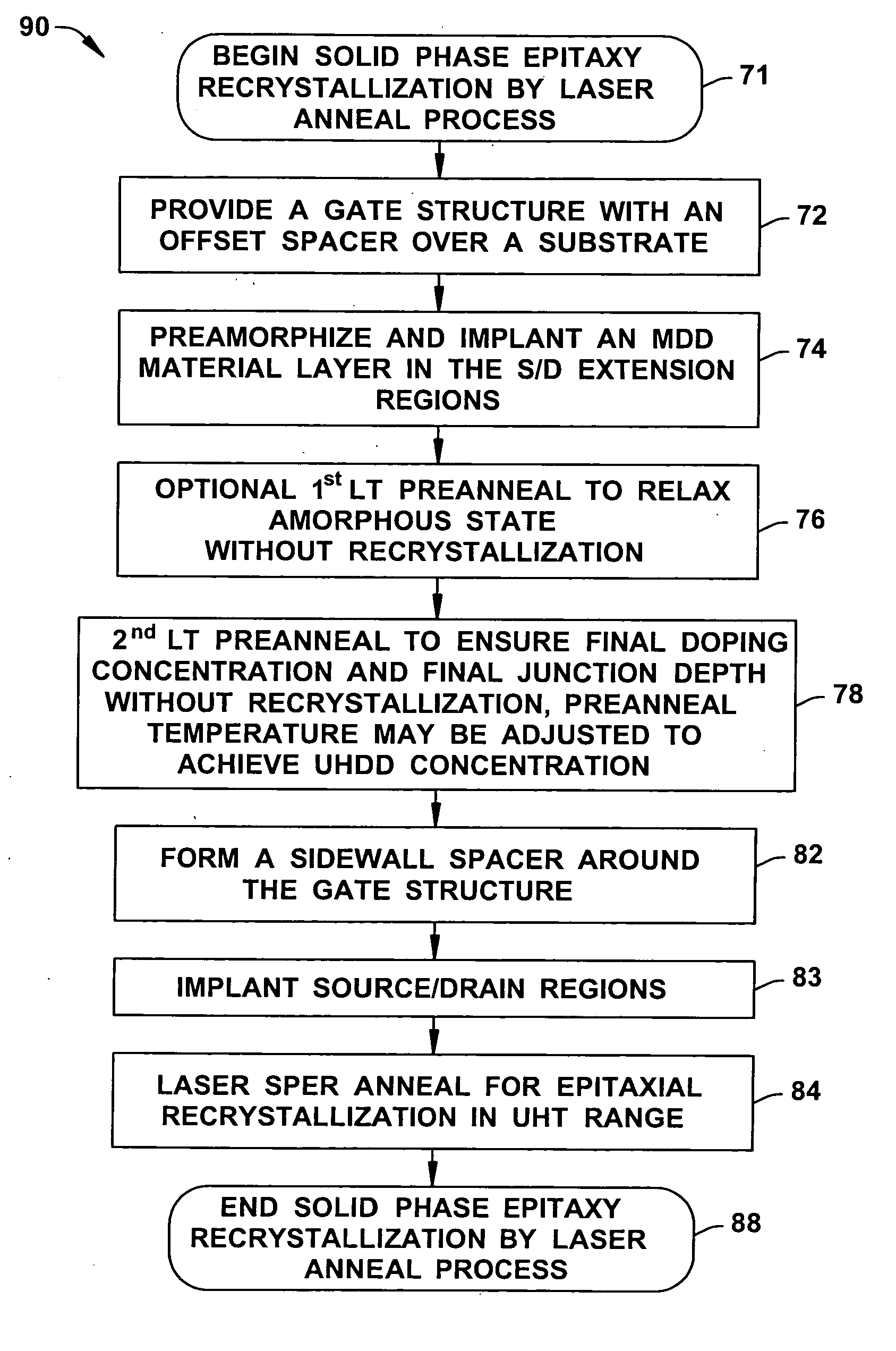

Solid phase epitaxy recrystallization by laser annealing

ActiveUS20060088969A1High activation levelHigh doping concentrationTransistorSemiconductor/solid-state device manufacturingBiological activationMaterials science

Methods (70) are described for fabricating shallow and abrupt gradient drain extensions for MOS type transistors, in which a solid phase epitaxial recrystallization is performed within the drain extensions utilizing a laser SPER annealing process in the manufacture of semiconductor products. One method (70) includes a preamorphizing process (74) of implanting a heavy ion species such as Germanium deep into an extension region of a substrate adjacent a channel region of the substrate to form a deep amorphized region, then implanting boron or another such dopant species into an extension region of the substrate adjacent the channel region. The implanted dopant is then preannealed (78) at a low temperature to set the junction depth and doping concentration. The extensions and / or the deep source / drain regions are subsequently annealed (84) with a laser at a high temperature providing a solid phase epitaxial recrystallization in the regions proximate the channel region to achieve ultra high doping concentrations and activation levels with an abrupt gradient.

Owner:TEXAS INSTR INC

Trench metal oxide semiconductor field effect transistor with embedded schottky rectifier using reduced masks process

ActiveUS20140077290A1Increase the doping concentrationGreat junction depthSolid-state devicesSemiconductor/solid-state device manufacturingTrench mosfetPhysical chemistry

A trench MOSFET with embedded schottky rectifier having at least one anti-punch through implant region using reduced masks process is disclosed for avalanche capability enhancement and cost reduction. The source regions have a higher doping concentration and a greater junction depth along sidewalls of the trenched source-body contacts than along adjacent channel regions near the gate trenches.

Owner:FORCE MOS TECH CO LTD

Method for diffusing high sheet resistance of solar cells

ActiveCN102097524AReduce errorsImprove life expectancyFinal product manufactureSemiconductor devicesSurface concentrationSolar cell

The invention relates to a method for diffusing high sheet resistance of solar cells. The method is characterized by texturing the surface of a solar crystal silicon wafer, sending the silicon wafer to a diffusion furnace for high sheet resistance diffusion and then carrying out subsequent solar cell processes. The method has the following advantages: (1) superior sheet resistance uniformity can be still maintained when high sheet resistance is diffused; (2) through introducing TCA or TCE during pre-oxidation, oxidation can be sped up, the substrate fault number can be reduced and the minority carrier lifetime of the substrate silicon can be prolonged; (3) dead layers can be well avoided through oxide layers; and (4) surface concentration and junction depth topography of diffusion can be well controlled through low-temperature pre-deposition and high-temperature junction propelling forming.

Owner:TRINA SOLAR CO LTD

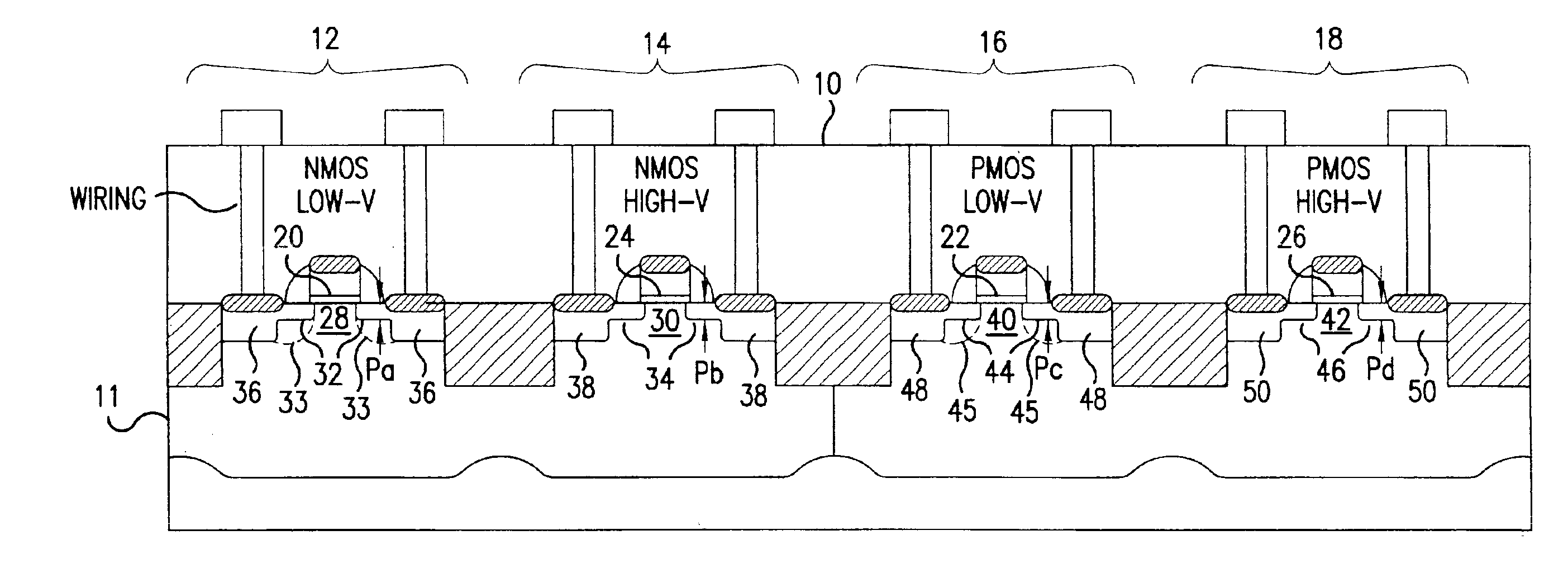

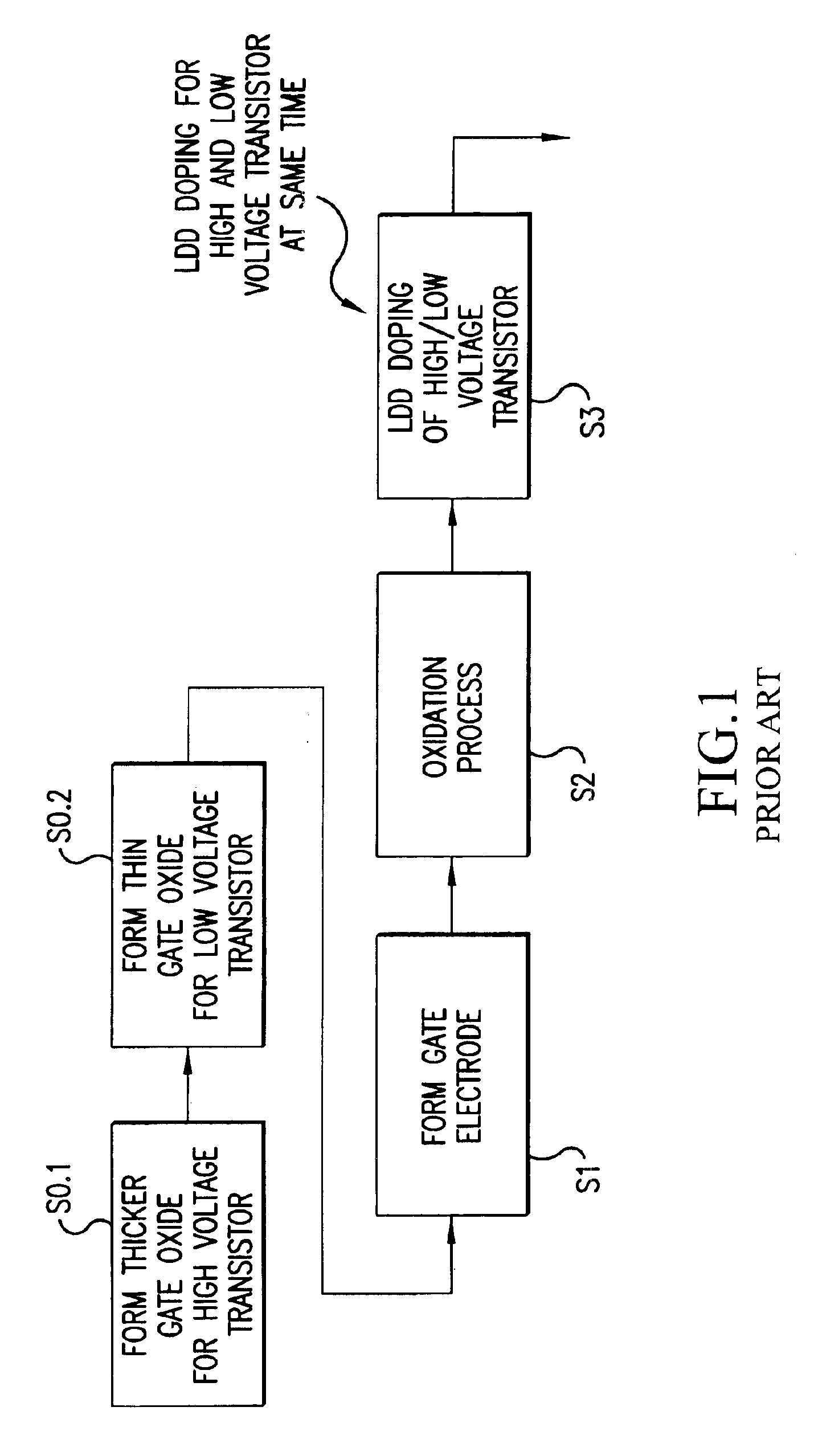

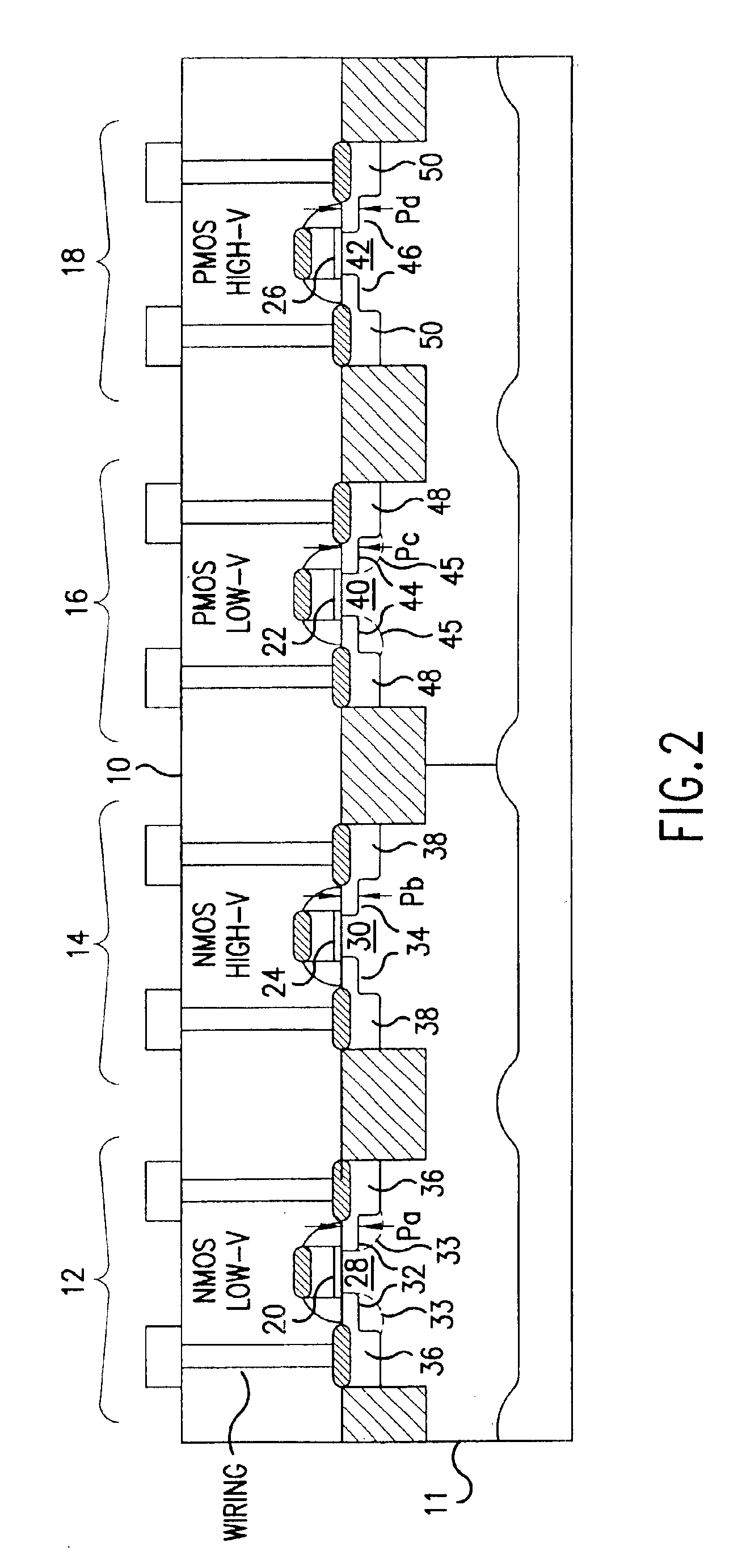

Low volt/high volt transistor

InactiveUS6879007B2Improve reliabilityOvercome deficienciesTransistorSolid-state devicesHigh voltage transistorsEngineering

A semiconductor device has at least one high-voltage and low-voltage transistor on a single substrate. The reliability of the high-voltage transistor is enhanced by performing a LDD implantation in only the high-voltage transistor prior to conducting an oxidation process to protect the substrate and gate electrode. After the oxidation process is performed, the low-voltage transistor is subjected to an LDD implantation process. The resultant semiconductor device provides a high-voltage transistor having a deeper LDD region junction depth than the low-voltage transistor, ensuring reliability and performance.

Owner:SHARP KK

Semiconductor device and method of fabrication

ActiveUS20090278209A1Improve driving abilityLower resistanceTransistorSemiconductor/solid-state device manufacturingDiffusion layerImpurity

A semiconductor device includes a gate electrode provided on a semiconductor region with a gate insulating film being interposed therebetween, extension diffusion layers provided in regions on both sides of the gate electrode of the semiconductor region, a first-conductivity type first impurity being diffused in the extension diffusion layers, and source and drain diffusion layers provided in regions farther outside than the respective extension diffusion layers of the semiconductor region and having junction depths deeper than the respective extension diffusion layers. At least one of the extension diffusion layers on both sides of the gate electrode contains carbon.

Owner:TAIWAN SEMICON MFG CO LTD

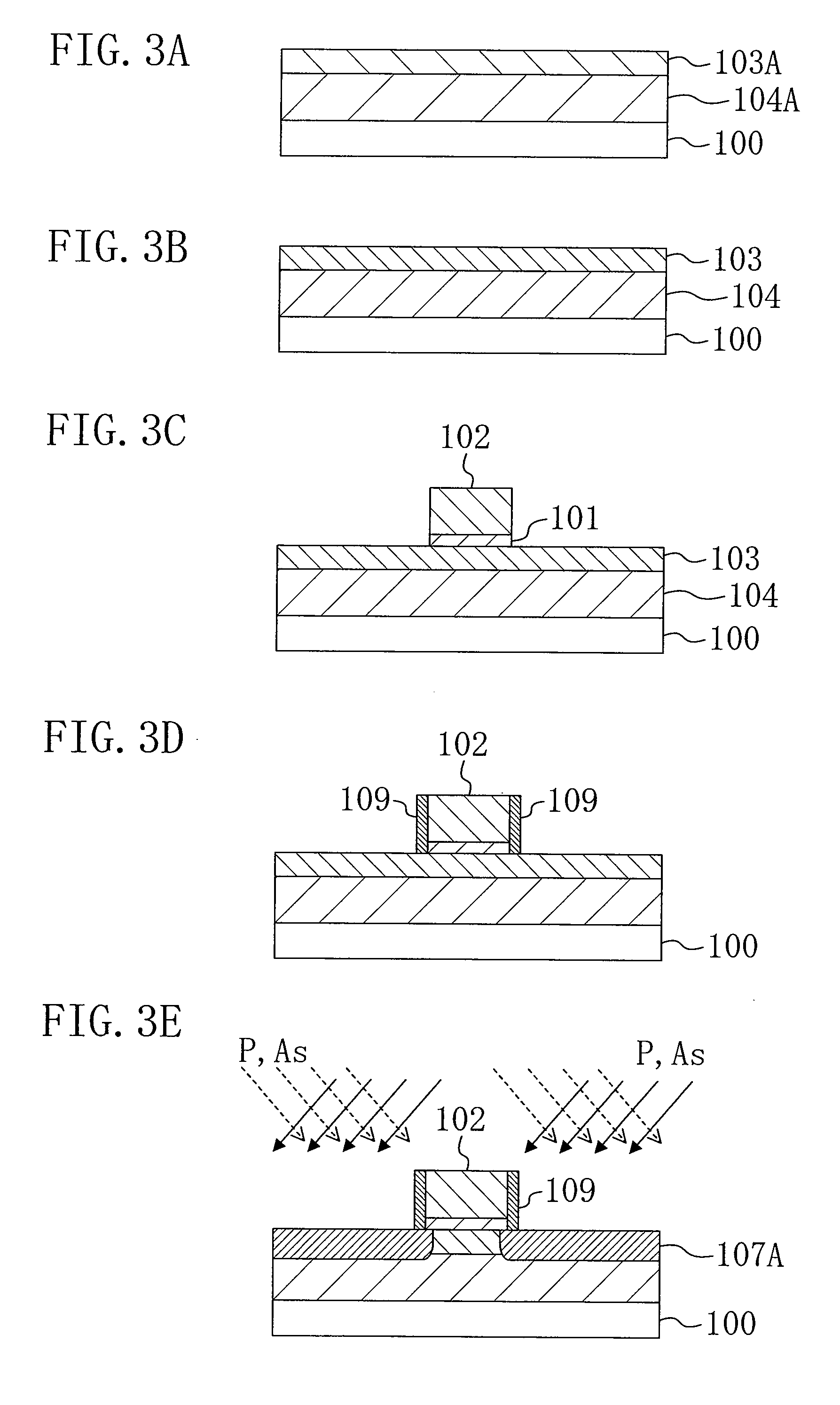

Novel SINP silicone blue-violet battery and preparation method thereof

InactiveCN101587913AImprove quantum efficiencyReduce the impactFinal product manufacturePhotovoltaic energy generationRadio frequency magnetron sputteringSingle crystal

he invention relates to a novel SINP silicone blue-violet battery and a preparation method thereof. The invention uses shallow junctions formed from thermally diffused phosphorus, an ultra-thin SiO2 layer formed by low-temperature thermal oxidization and an ITO dereflection / collection electrode film formed by RF magnetron sputtering to prepares a novel ITO / SiO2 / np blue-violet reinforced SINP silicone photo-battery. Preparation method of the invention is to take a silicon single crystal flake which is P type, and has crystallographic orientation of 100, electric resistivity of 2 2omega.cm and thickness of 220mu m, as a substrate. The substrate is cleaned and is etched by routine chemistry, and then is thermally diffused by POC3 liquid source to form n regions (the invention prepares two pieces of novel SINP photo-batteries, one being routine SINP photo-battery having emitting region square resistance of 10 Omega / square and junction depth of 1 Mu m, and the other one being SINP silicone blue-violet battery having emitting region square resistance of 37 Omega / square and junction depth of 0.4 Mu m). Removing the phosphorosilicate glass (HF:H2O=1:10) at front face; steaming Al at back of the silicon chip; thermally oxidizing the silicon chip at 400 to 500 DEG C and condition of V2:O2=4:1 for 15 to 30min to generate a layer of 15 to 20 ultra-thin SiO2 layer, and at the same time alloying the Al at the back. Then RF magnetron sputtering the ITO dereflection / collection electrode film (ITO film is also deposited on the glass to study electrooptical characteristic thereof) having high transmittance and high conductivity, and sputtering a Cu gate electrode by metal mask direct-current magnetron. Finally, cutting the outer edge part of the battery by a diamond excircle downward cutting / a dicing saw so as to prevent short circuit of the edge of the photo-battery.

Owner:SHANGHAI UNIV