Insulated gate field-effect transistor and a method of manufacturing the same

a field-effect transistor and insulating gate technology, applied in the field of insulating gate field-effect transistors, can solve the problems of reducing the driving ability of the mis transistor, the application of the ion implantation technique and the activation anneal technique for forming a very shallow junction, and the not yet established ion implantation technique, so as to achieve the effect of precise junction depth

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

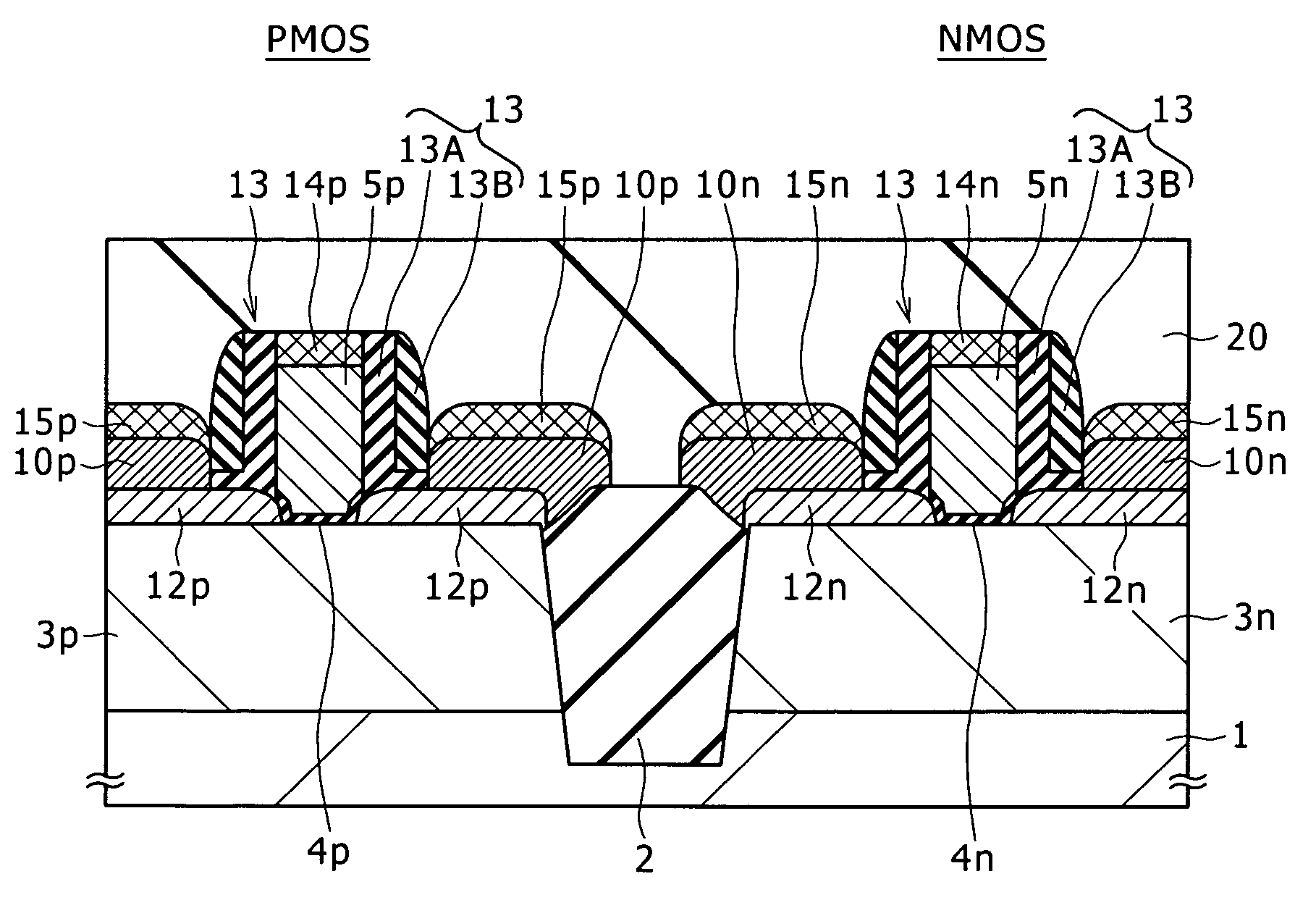

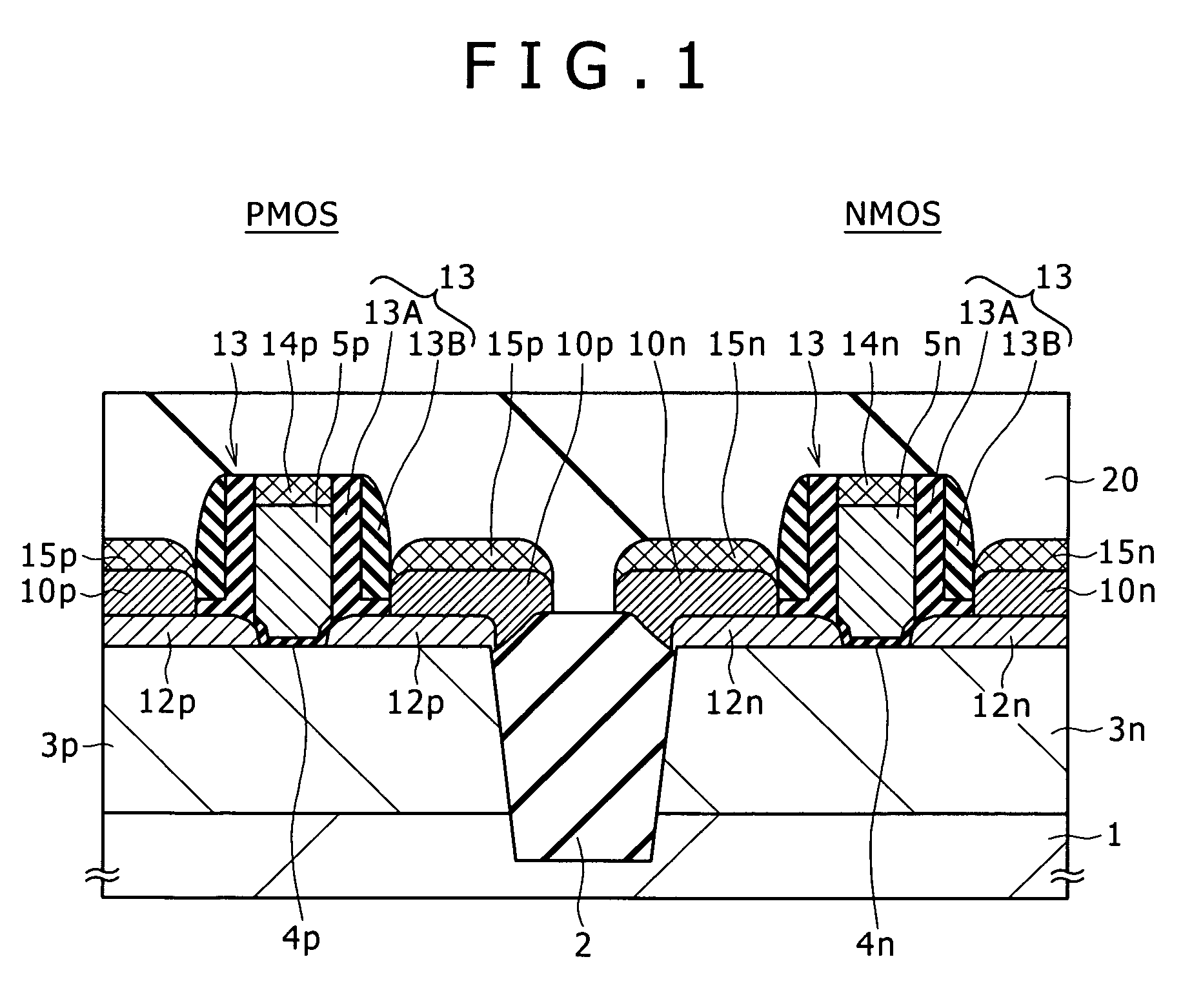

[0041] Preferred embodiments of the present invention will hereinafter be described by giving a CMOS device in which an NMOS transistor and a PMOS transistor are formed on the same substrate as an example with reference to the accompanying drawings.

[0042]FIG. 1 is a cross sectional view of a CMOS device in a channel direction.

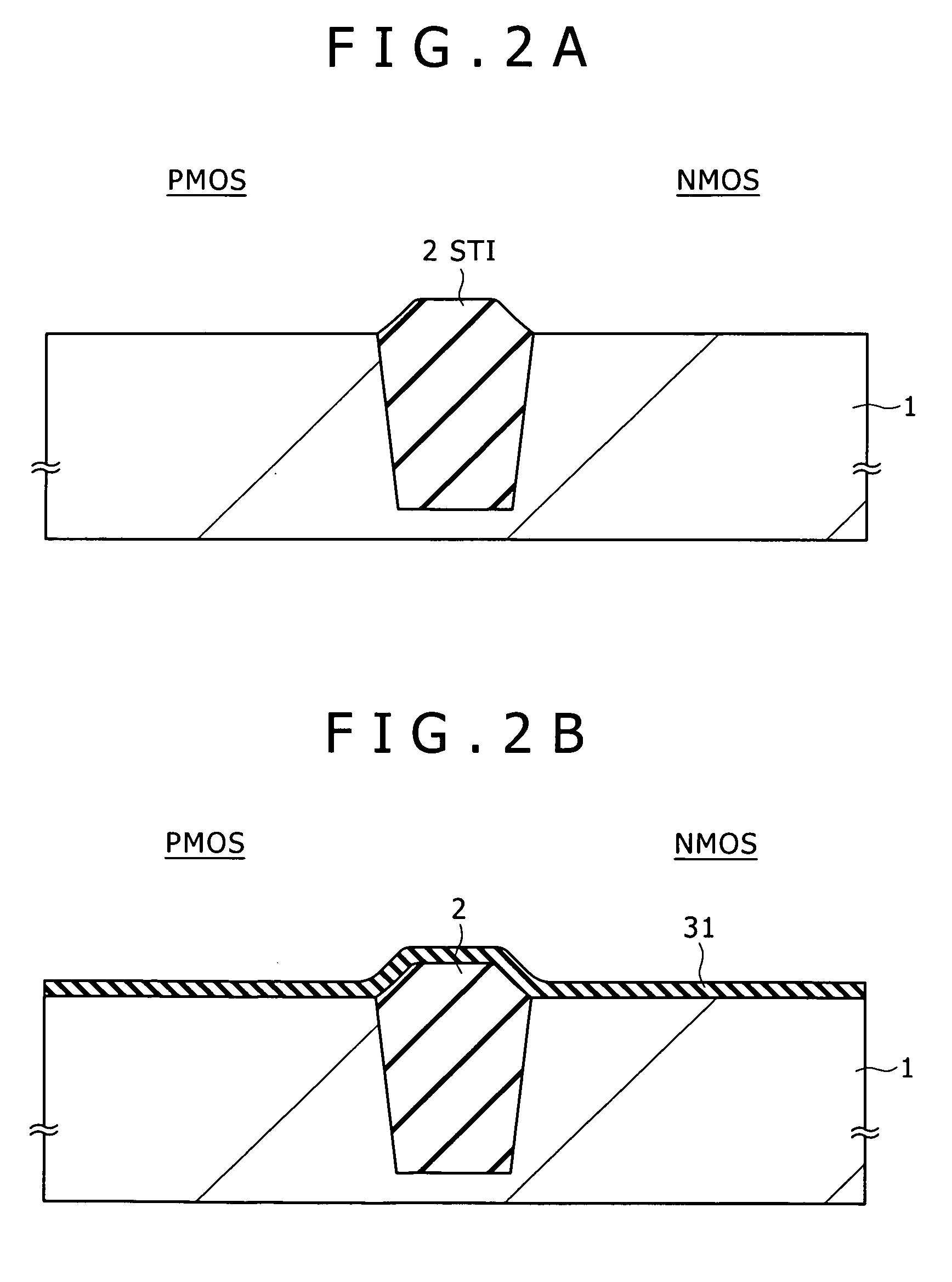

[0043] In the CMOS device shown in the figure, an isolation insulating layer, e.g., a Shallow Trench Isolation (STI) 2 is formed in a surface portion of a substrate 1 formed from a silicon wafer for example. Germanium (Ge), a compound of Ge and silicon (Si), or strain silicon may also be used as a material of the substrate 1 in addition to Si.

[0044] A P-type region (e.g., a P-type well 3n) and an N-type region (e.g., an N-type well 3p) in which inversion layers of channels are formed, respectively, are formed in a region (active region) in which no STI 2 is formed. The P-type well 3n is a substrate region in which the NMOS transistor is formed, and the N-typ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More