Patents

Literature

4061 results about "Diffusion layer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In electrochemistry, the diffusion layer, according to IUPAC, is defined as the "region in the vicinity of an electrode where the concentrations are different from their value in the bulk solution. The definition of the thickness of the diffusion layer is arbitrary because the concentration approaches asymptotically the value in the bulk solution". The diffusion layer thus depends on the diffusion coefficient (D) of the analyte and for voltammetric measurements on the scan rate (V/s). It is usually considered to be some multiple of (Dt)¹⸍² (where 1/t = scan rate). At slow scan rates, the diffusion layer is large, on the order of micrometers, whereas at fast scan rates the diffusion layer is nanometers in thickness. The relationship is described in part by the Cottrell equation.

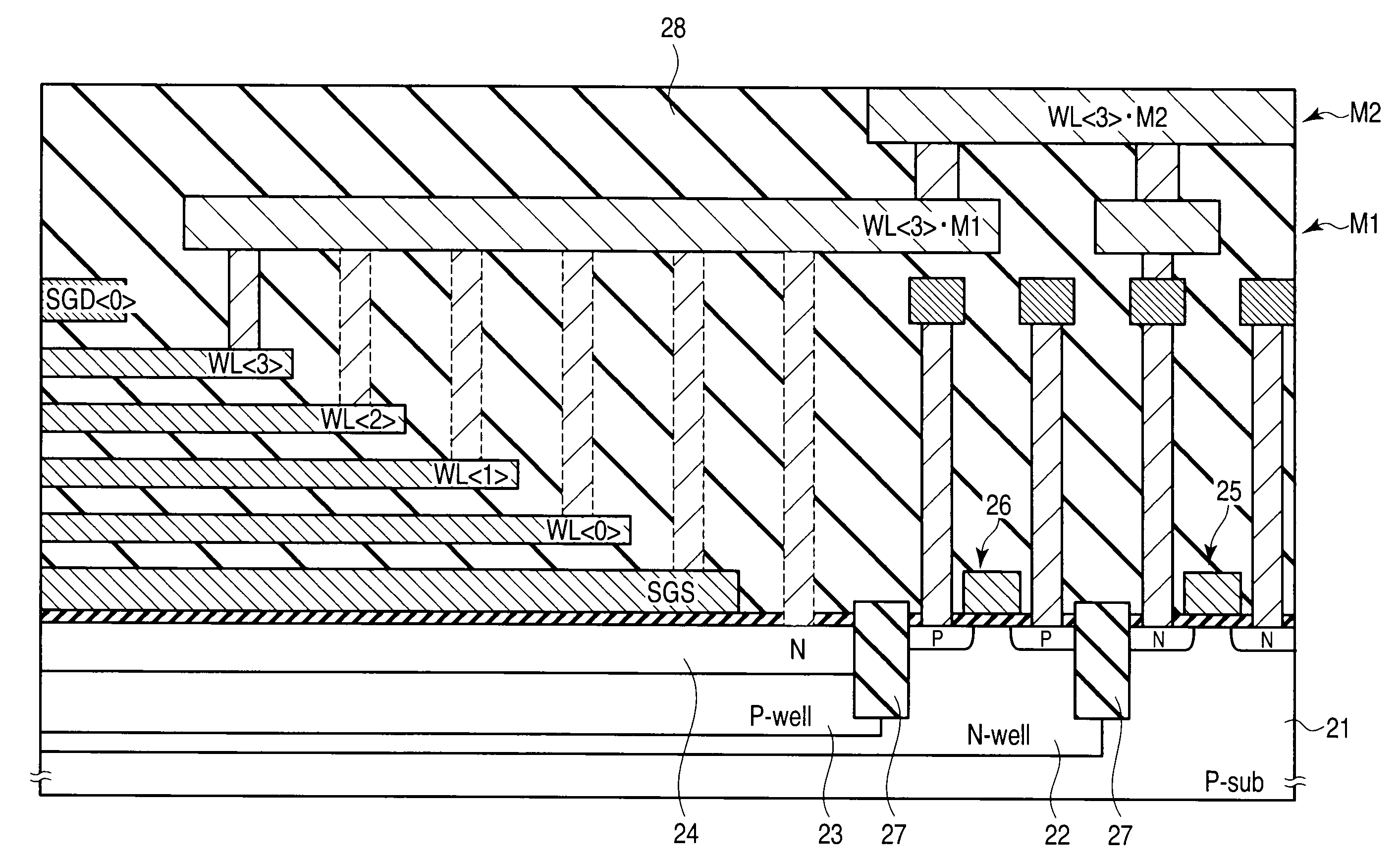

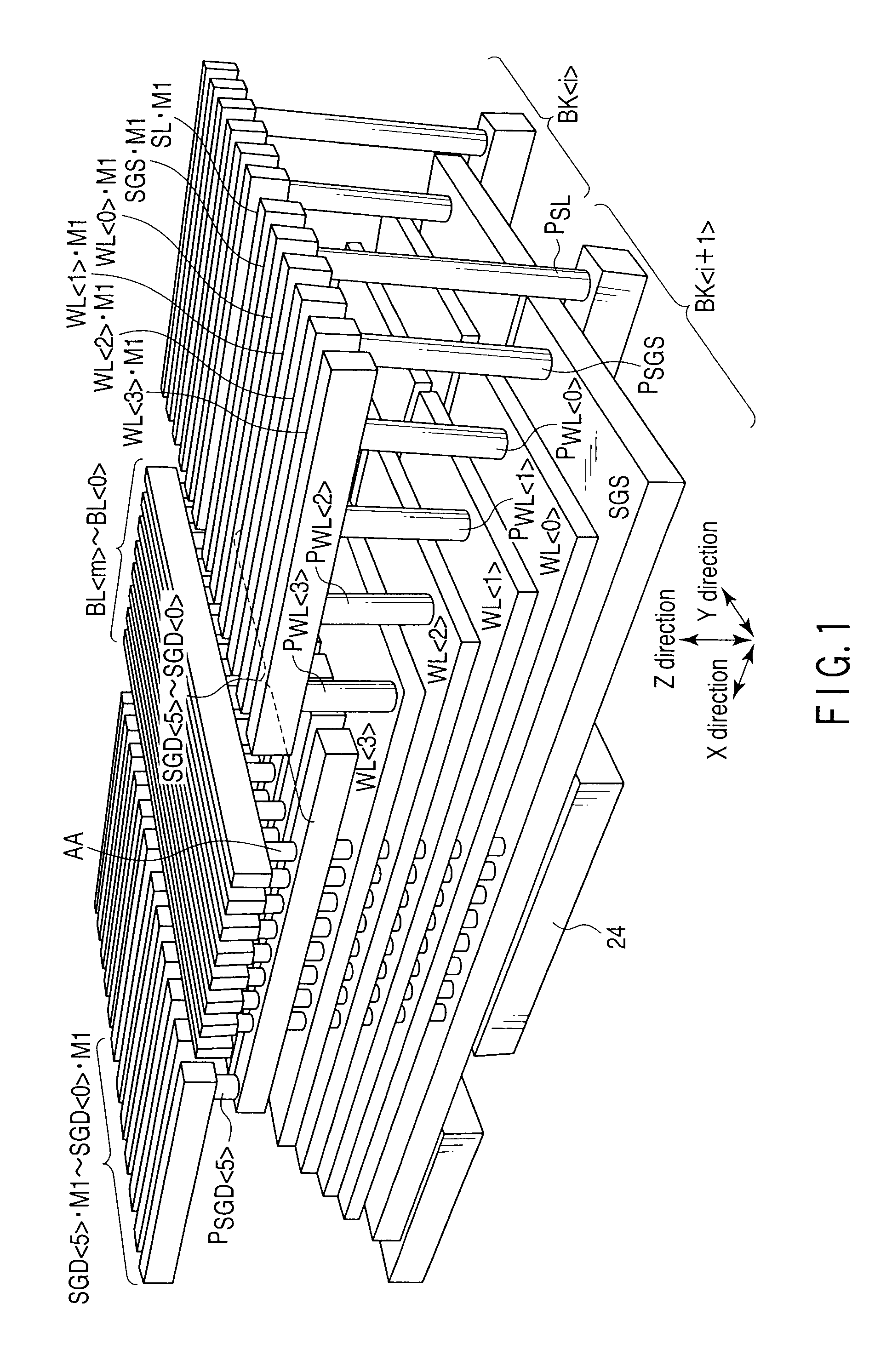

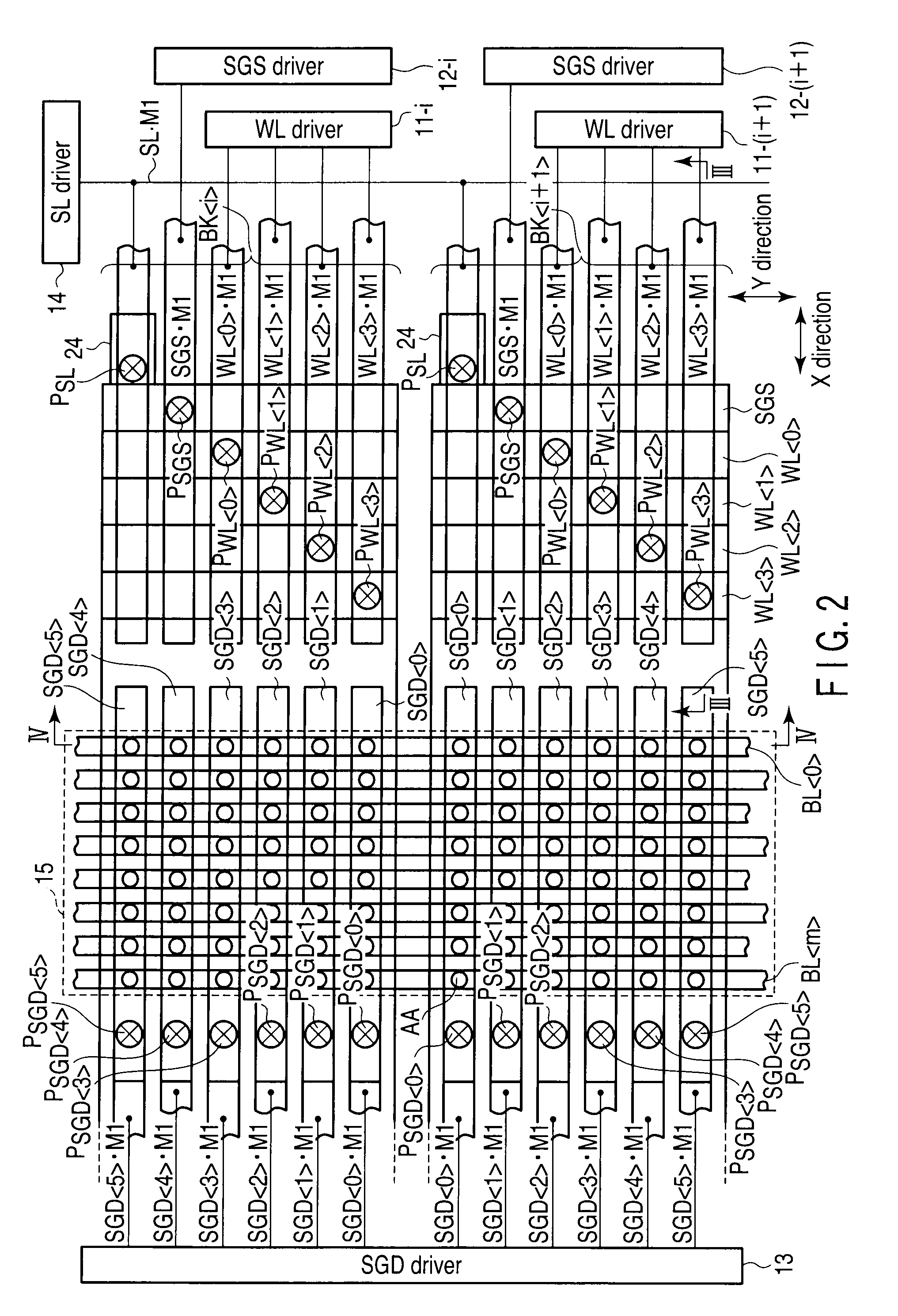

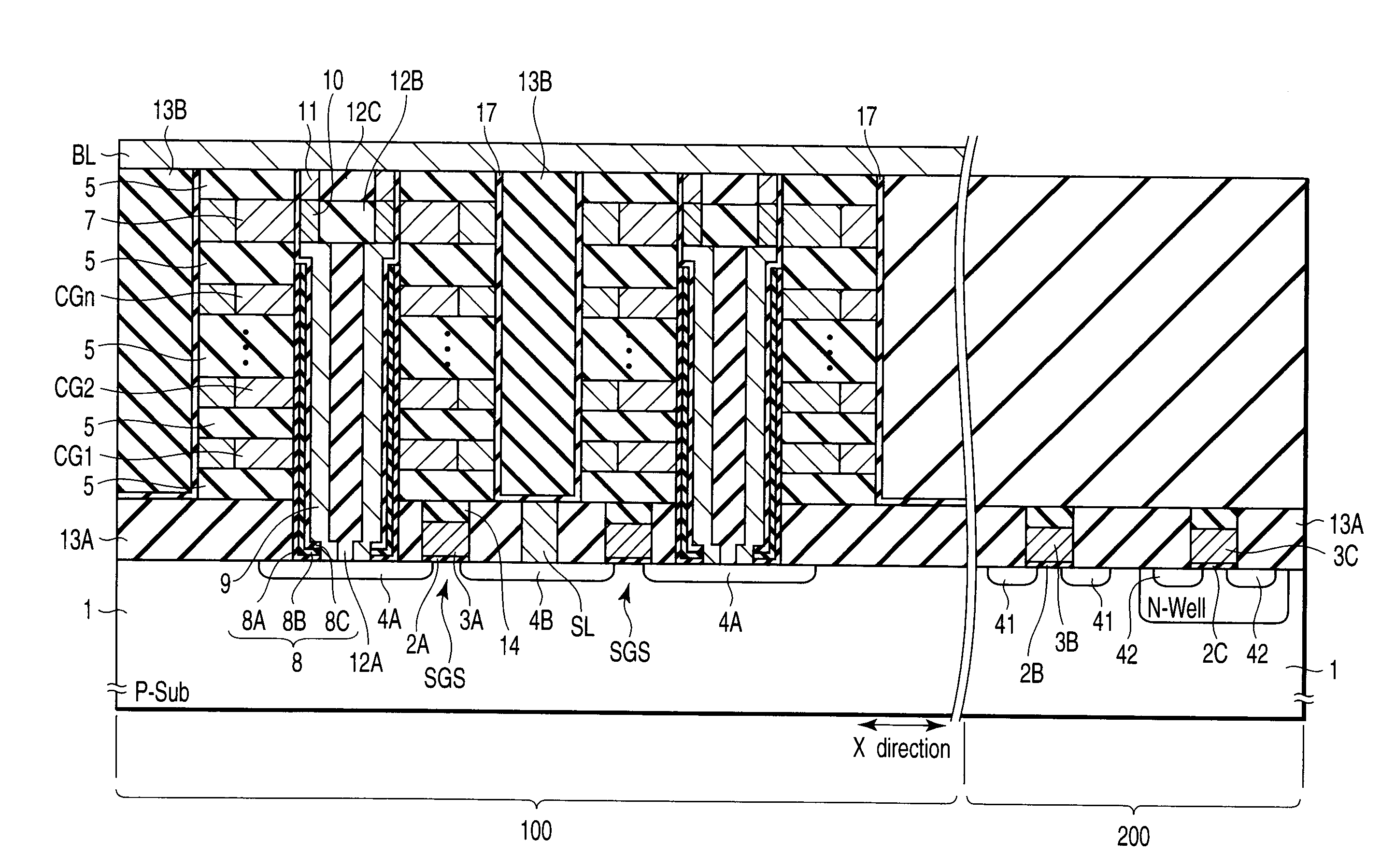

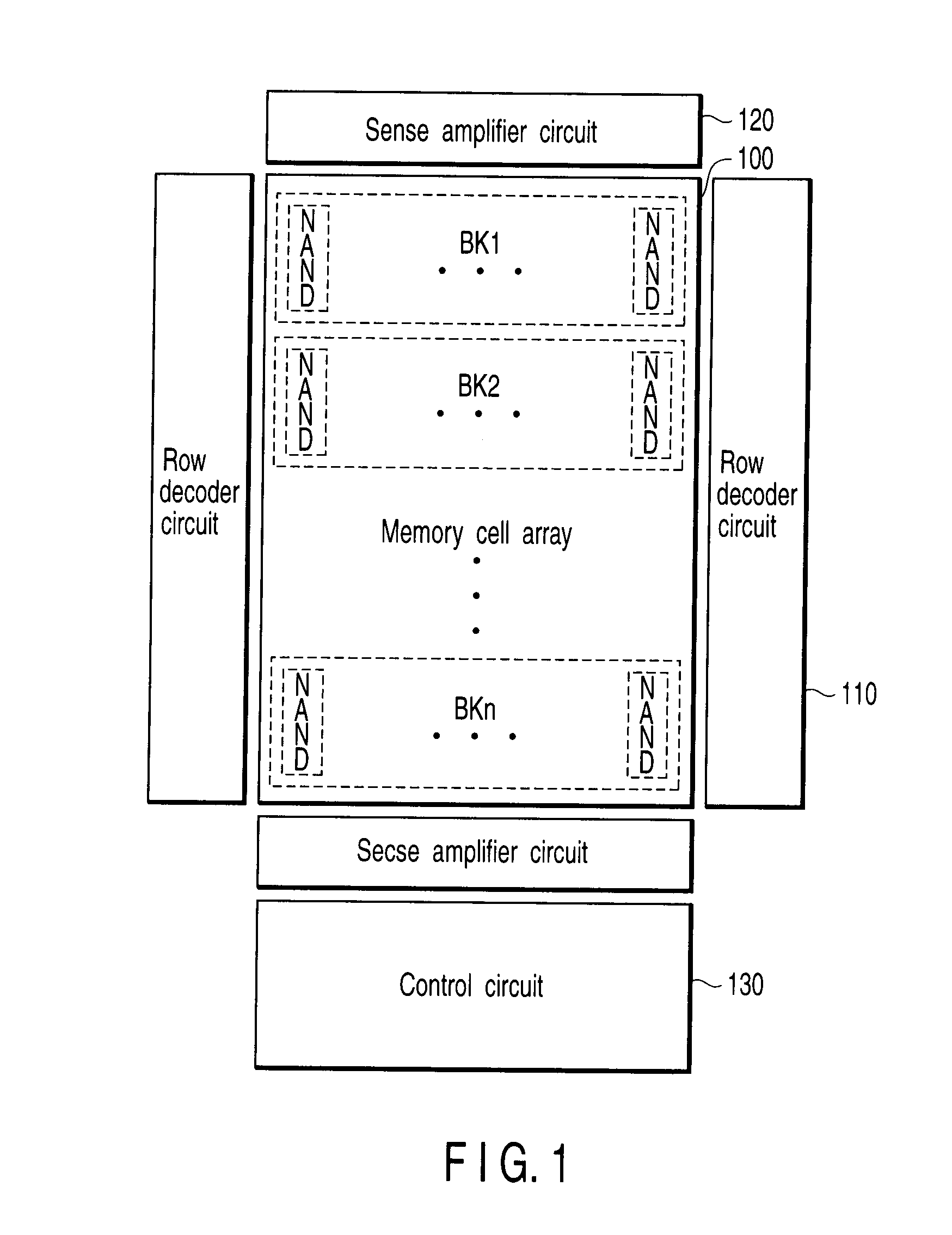

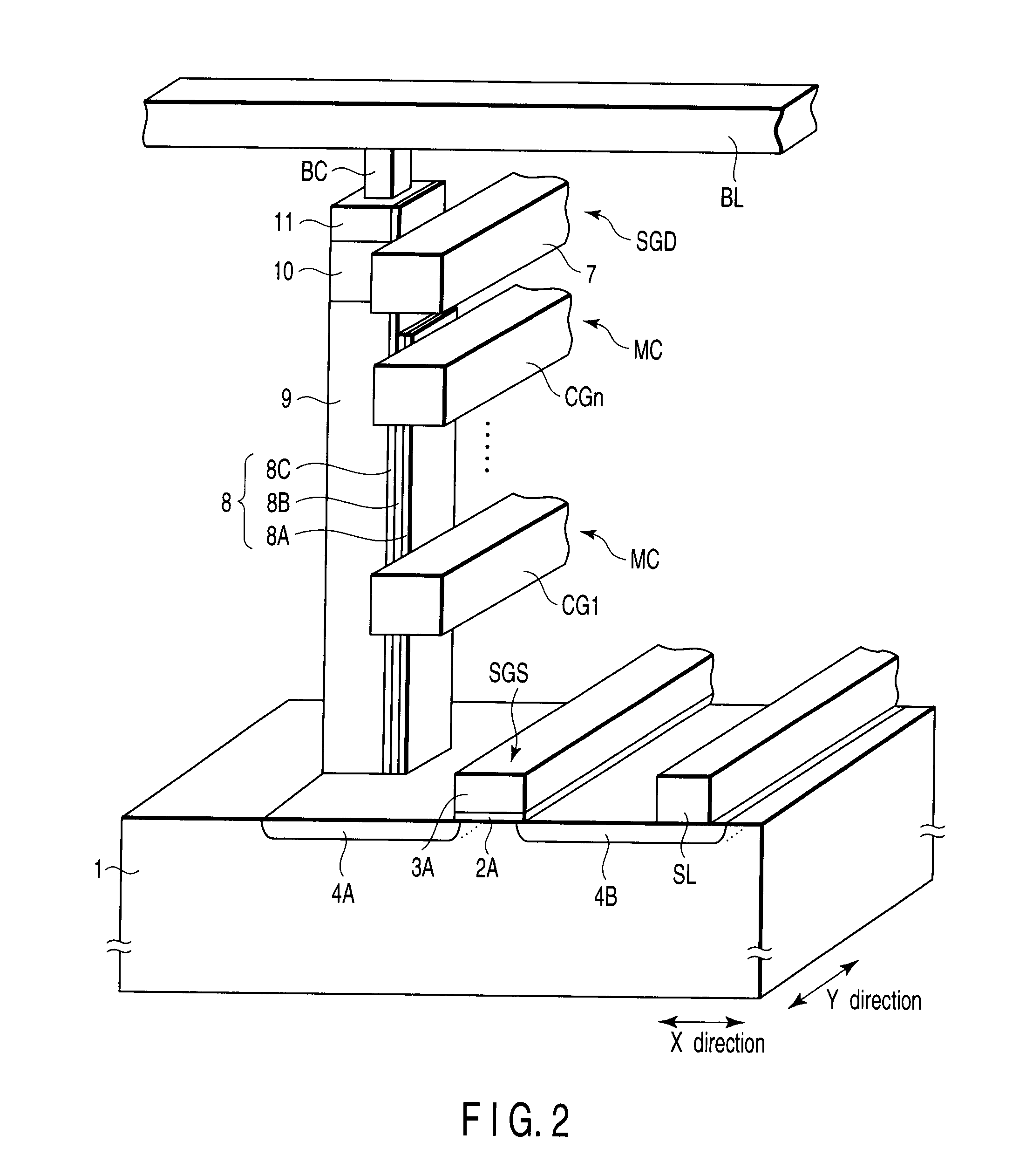

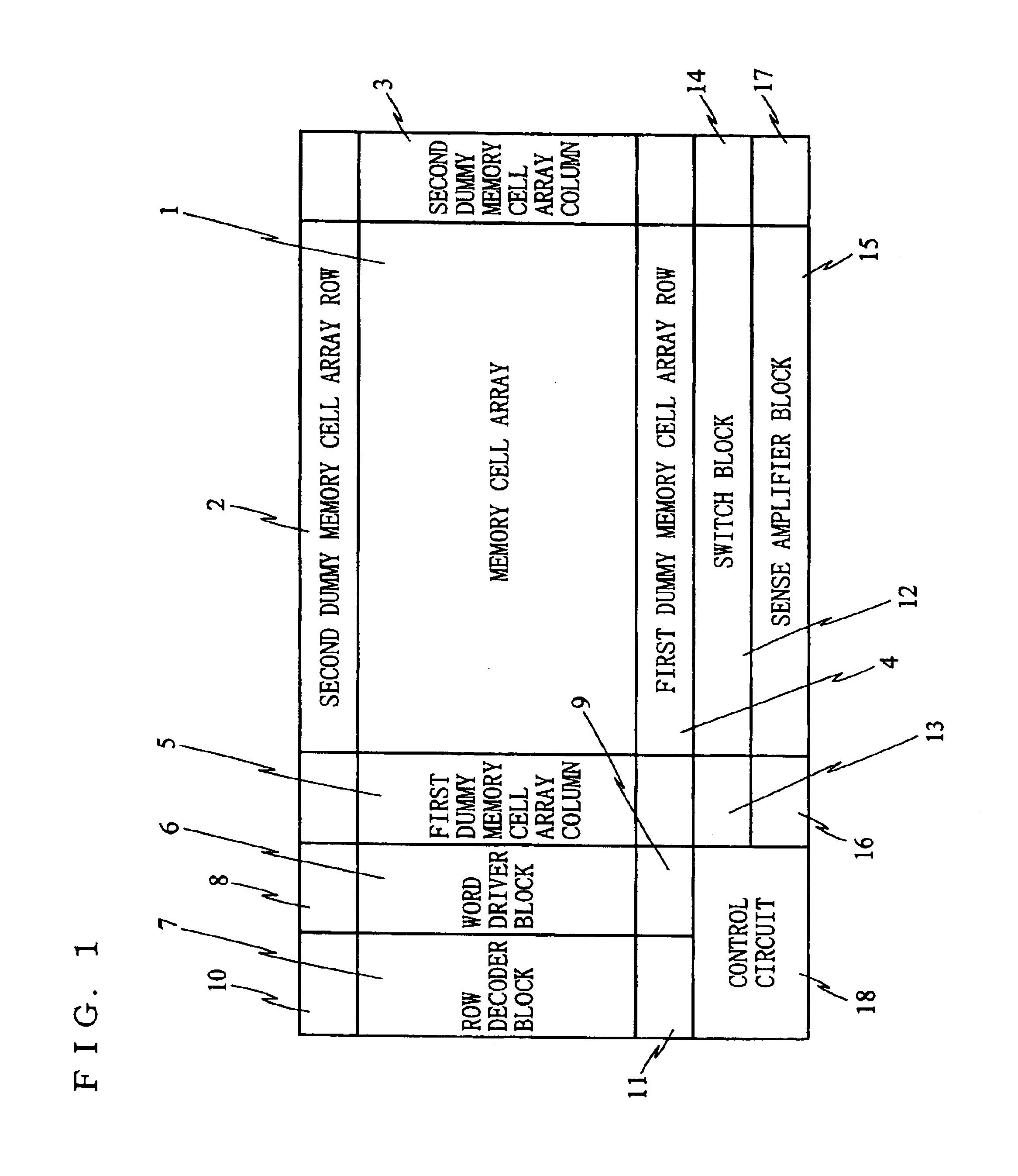

Three dimensional stacked nonvolatile semiconductor memory

A three dimensional stacked nonvolatile semiconductor memory according to an example of the present invention includes a memory cell array comprised of first and second blocks disposed side by side in a first direction, and a driver disposed on one end of the memory cell array in a second direction orthogonal to the first direction. A source diffusion layer, which is common to the first and second blocks, is disposed in a semiconductor substrate, and a contact plug, which has a lower end connected to the source diffusion layer and an upper end connected to a source line disposed above at least three conductive layers, is interposed between the first and second blocks.

Owner:KIOXIA CORP

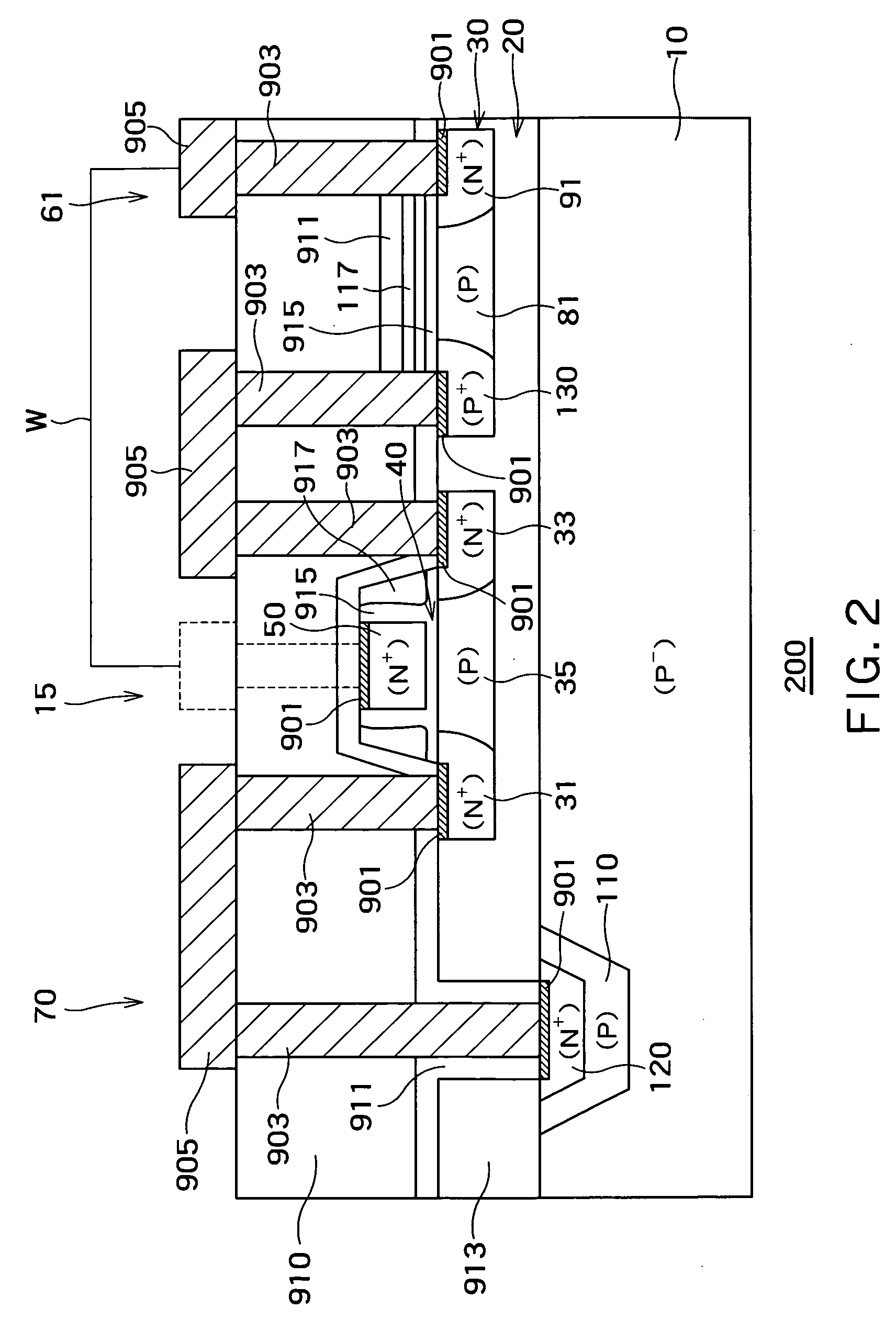

Method of manufacturing semiconductor device

ActiveUS20080299758A1Reduces yield and reliabilityReduce capacitySemiconductor/solid-state device detailsSolid-state devicesHigh densityDevice material

A high-density N-type diffusion layer 116 formed in a separation area 115 makes it possible to reduce a collector current flowing through a parasitic NPN transistor 102. Thus, a normal CMOS process can be used to provide a driving circuit and a data line driver which make it possible to improve resistance to possible noise occurring between adjacent terminals, while controlling a chip size.

Owner:PANNOVA SEMIC

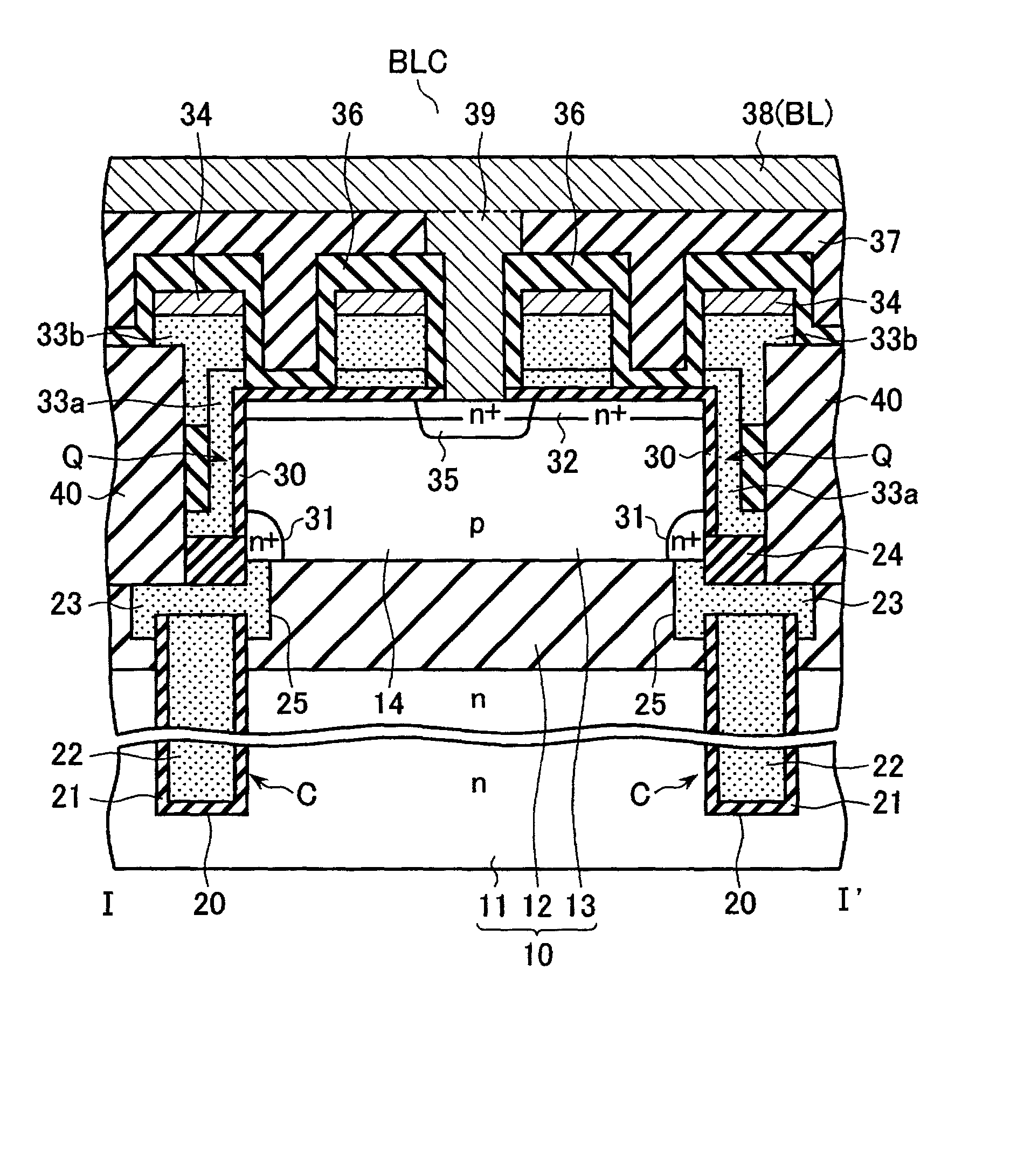

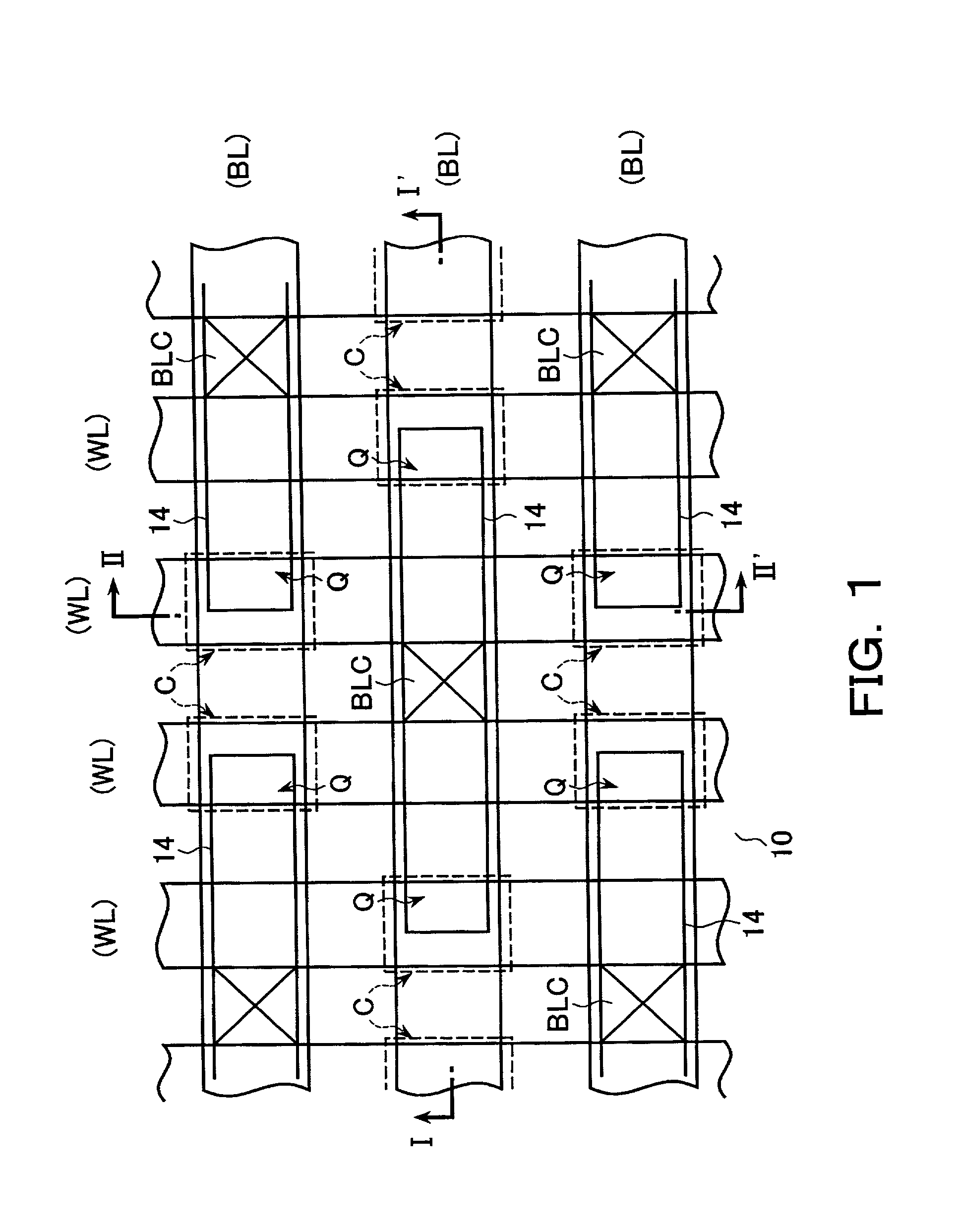

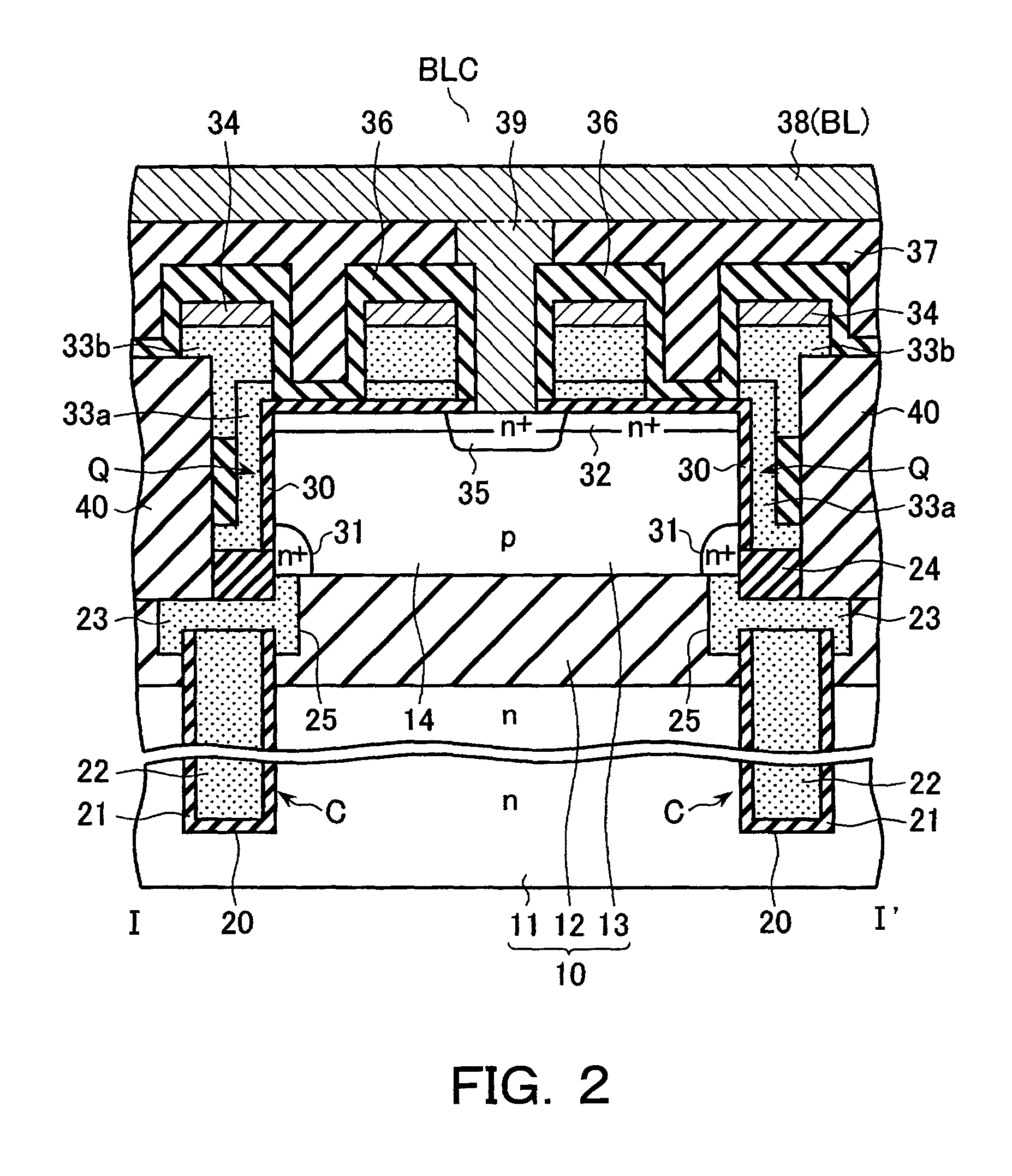

Nonvolatile semiconductor memory and process of producing the same

A nonvolatile semiconductor memory of an aspect of the present invention comprises a semiconductor substrate, a pillar-shaped semiconductor layer extending in the vertical direction with respect to the surface of the semiconductor substrate, a plurality of memory cells arranged in the vertical direction on the side surface of the semiconductor layer and having a charge storage layer and a control gate electrode, a first select gate transistor arranged on the semiconductor layer at an end of the memory cells on the side of the semiconductor substrate, and a second select gate transistor arranged on the semiconductor layer on the other end of the memory cells opposite to the side of the semiconductor substrate, wherein the first select gate transistor includes a diffusion layer in the semiconductor substrate and is electrically connected to the pillar-shaped semiconductor layer by way of the diffusion layer that serves as the drain region.

Owner:KIOXIA CORP

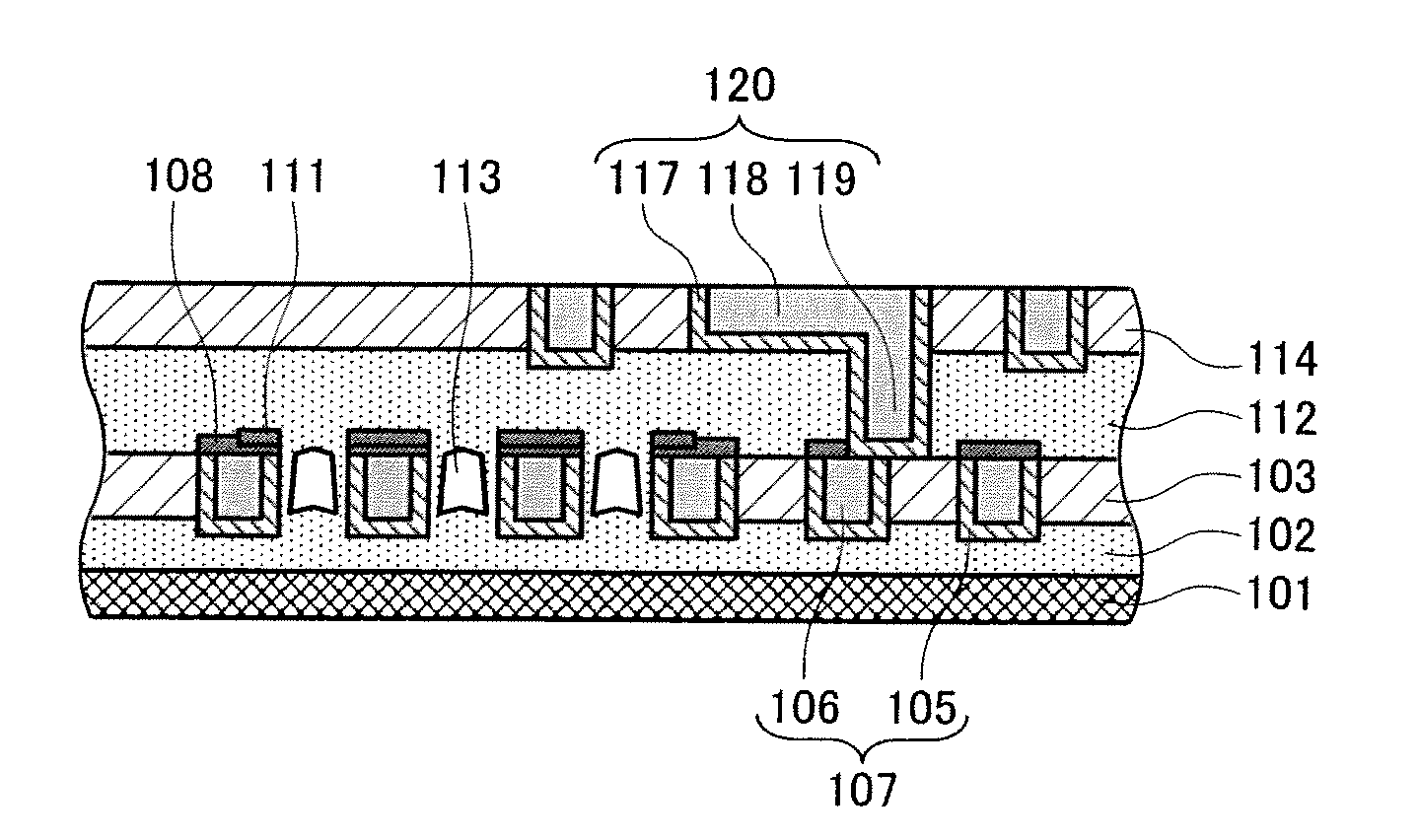

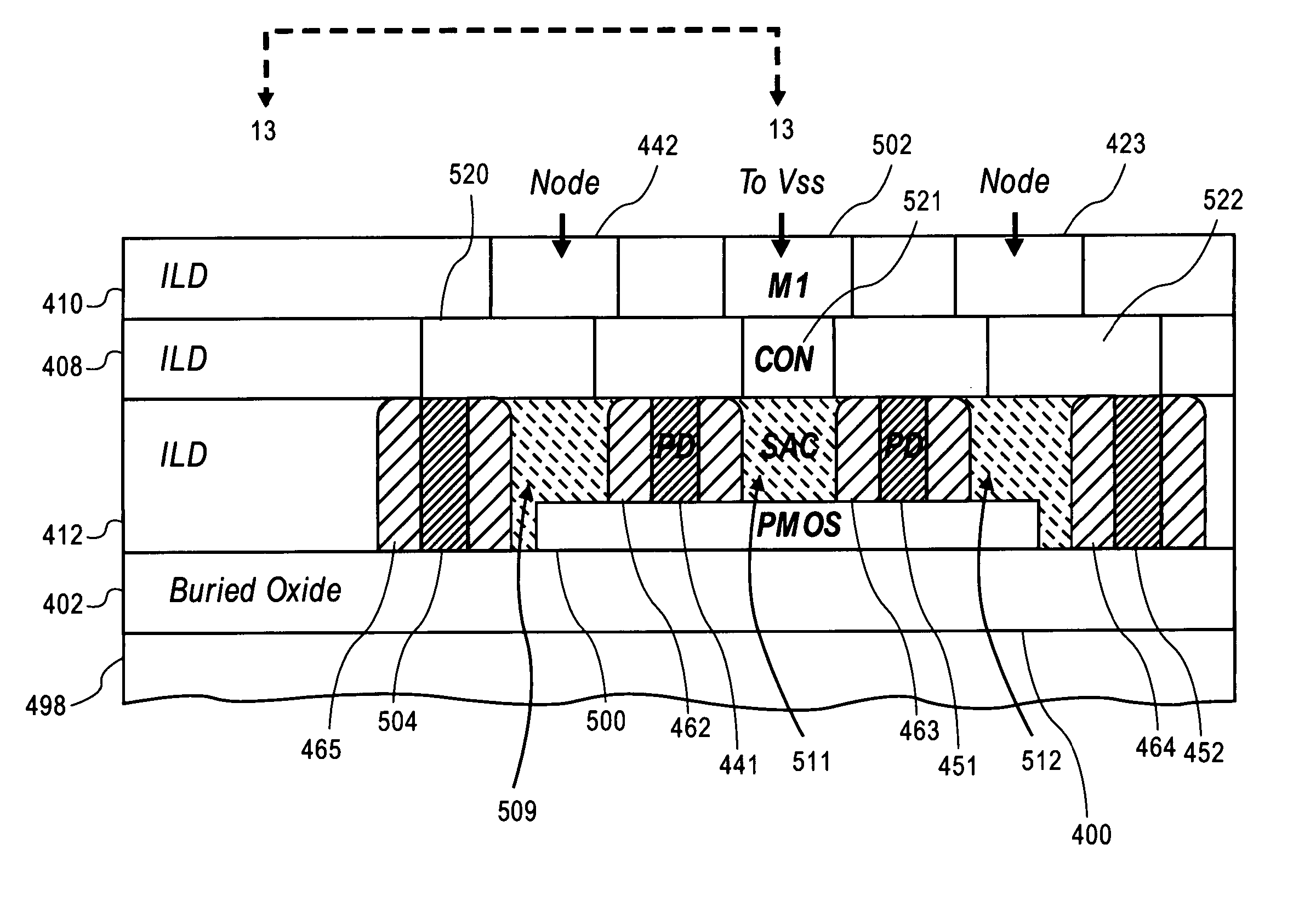

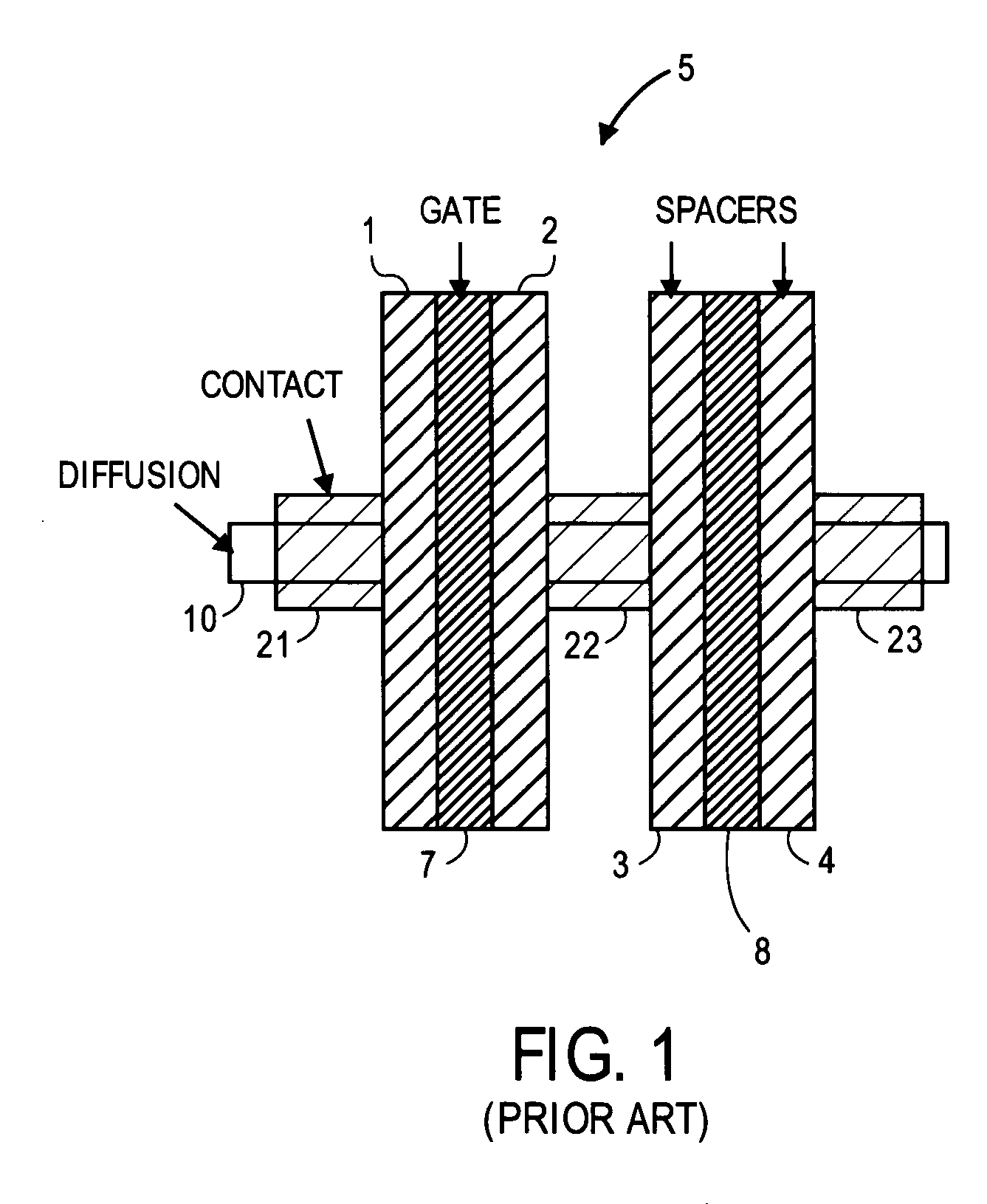

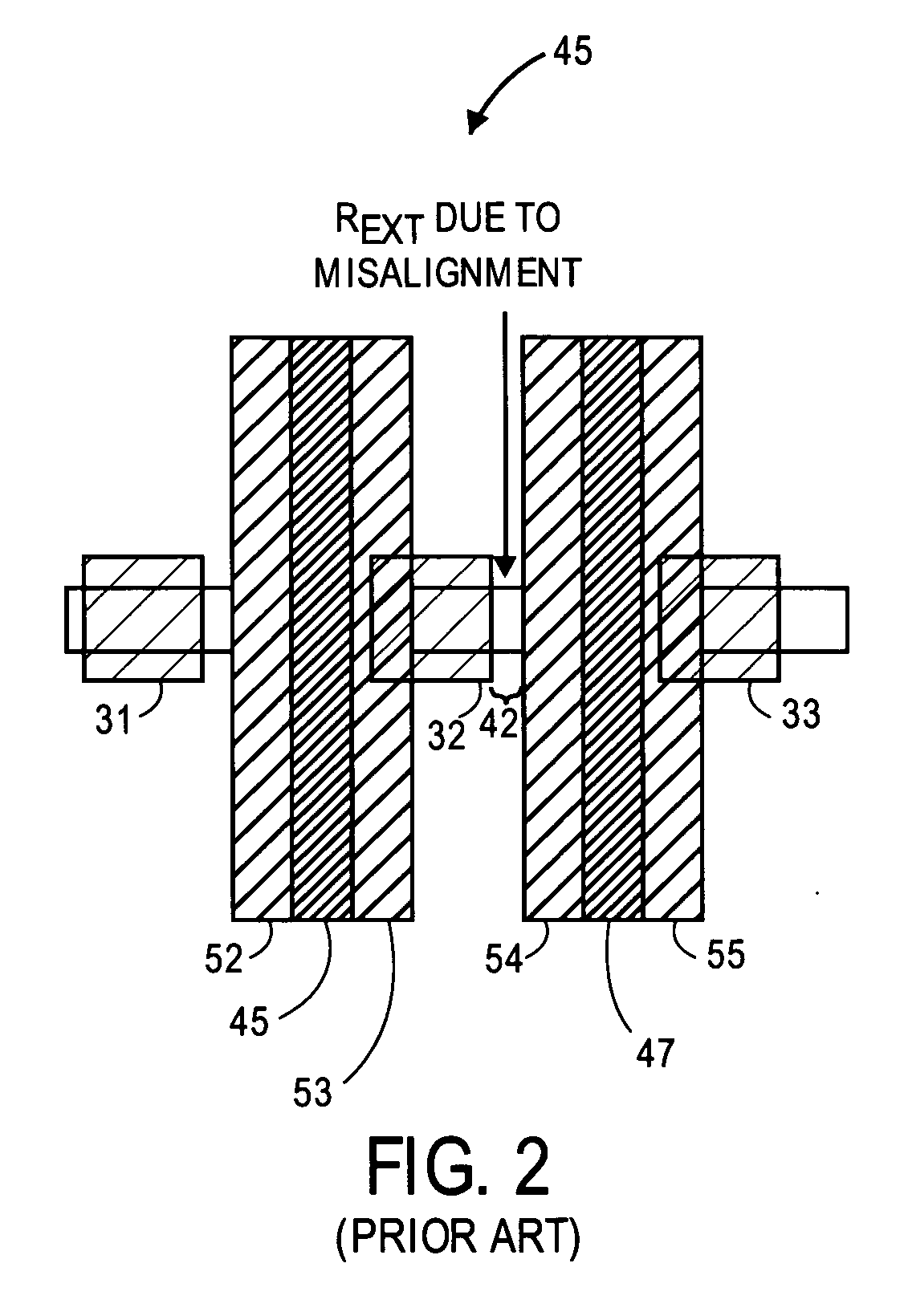

Self-aligned contacts for transistors

Self-aligned contacts for transistors and methods for fabricating the contacts are described. An etch resistant material is patterned to create an opening that resides above a transistor gate structure. A selective etch is performed through the opening that does not etch the transistor gate structure but does etch material that resides laterally with respect to the transistor gate structure in order to expose tops, immediately adjacent to the transistor gate structure, of drain and source regions of a diffusion layer of the transistor. Conductive material is deposited that covers respective tops of the drain and source regions of the diffusion layer of the transistor to a depth that does not short the drain and source region of the diffusion layer of the transistor. A layer above the conductive material is formed. Contacts are formed through the layer above the conductive material to respective portions of the conductive material that cover respective tops of the drain and source regions of the diffusion layer of the transistor.

Owner:DAEDALUS PRIME LLC

Semiconductor device and method for manufacturing the same

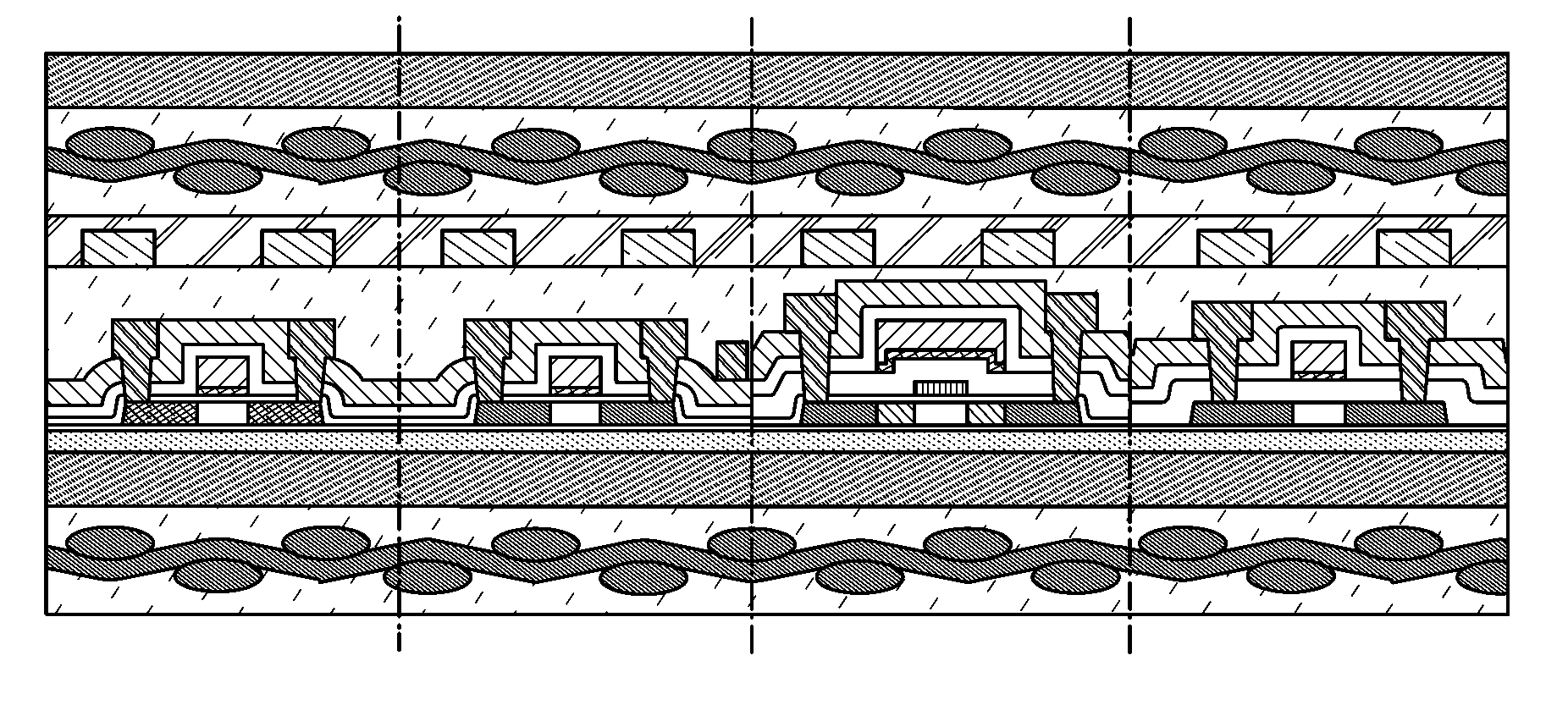

ActiveUS20090267225A1Reduce thicknessSmall sizeSemiconductor/solid-state device detailsSolid-state devicesShock resistanceDiffusion layer

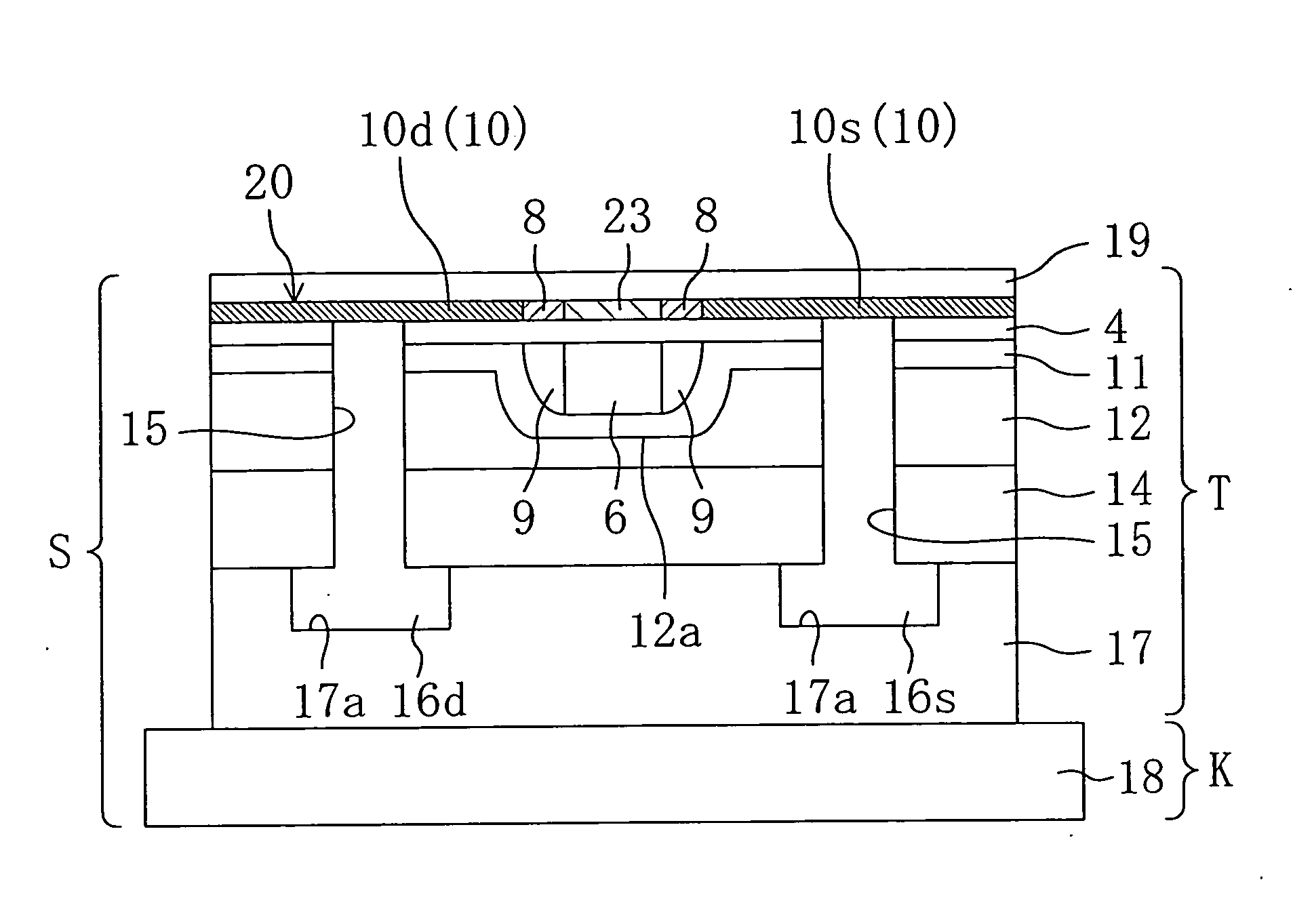

In a semiconductor integrated circuit sandwiched between a pair of a first impact resistance layer and a second impact resistance layer, an impact diffusion layer is provided between the semiconductor integrated circuit and the second impact resistance layer. By provision of the impact resistance layer against the external stress and the impact diffusion layer for diffusing the impact, force applied to the semiconductor integrated circuit per unit area is reduced, so that the semiconductor integrated circuit is protected. The impact diffusion layer preferably has a low modulus of elasticity and high breaking modulus.

Owner:SEMICON ENERGY LAB CO LTD

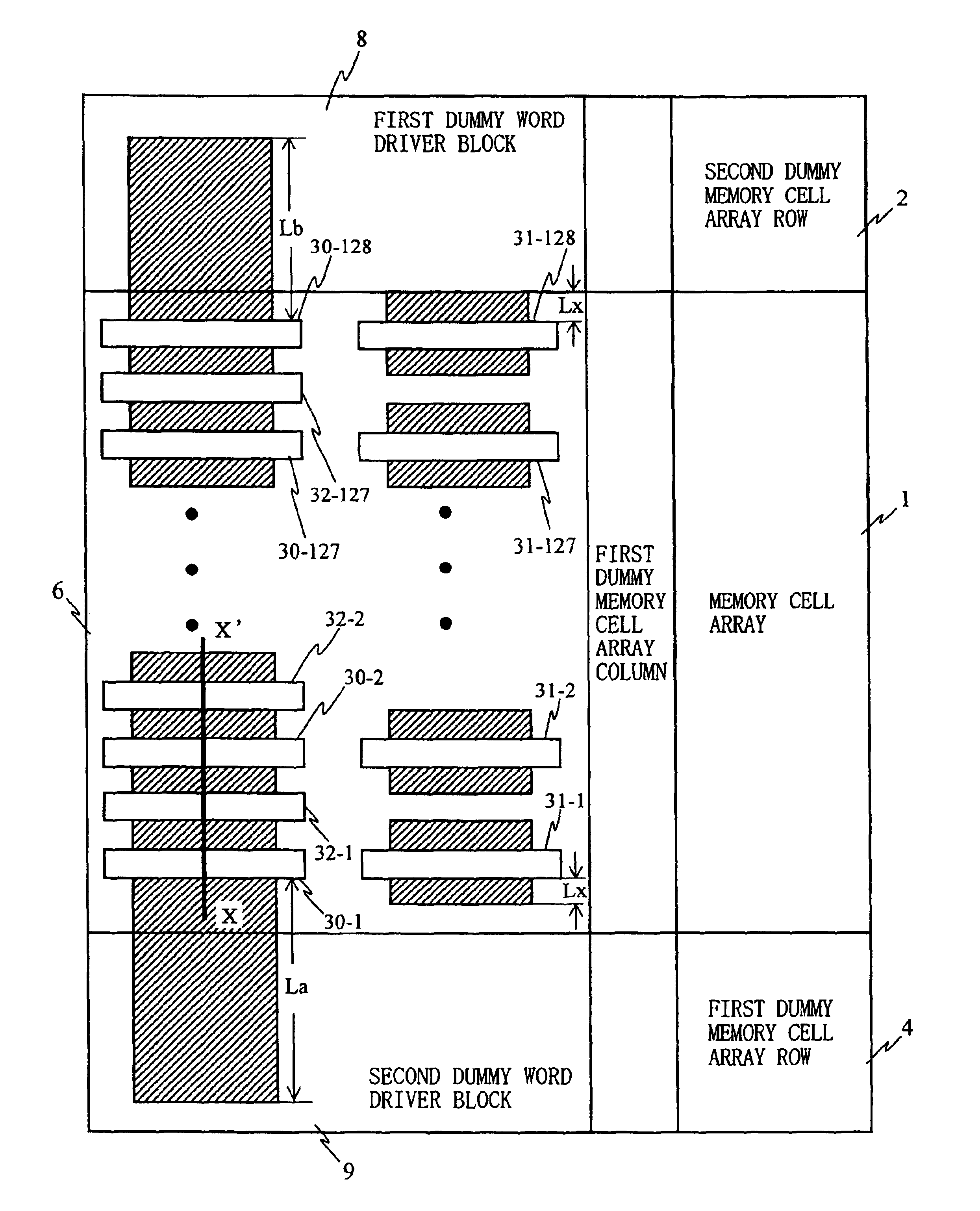

Semiconductor device and semiconductor memory device

ActiveUS6920079B2Guaranteed uptimeSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

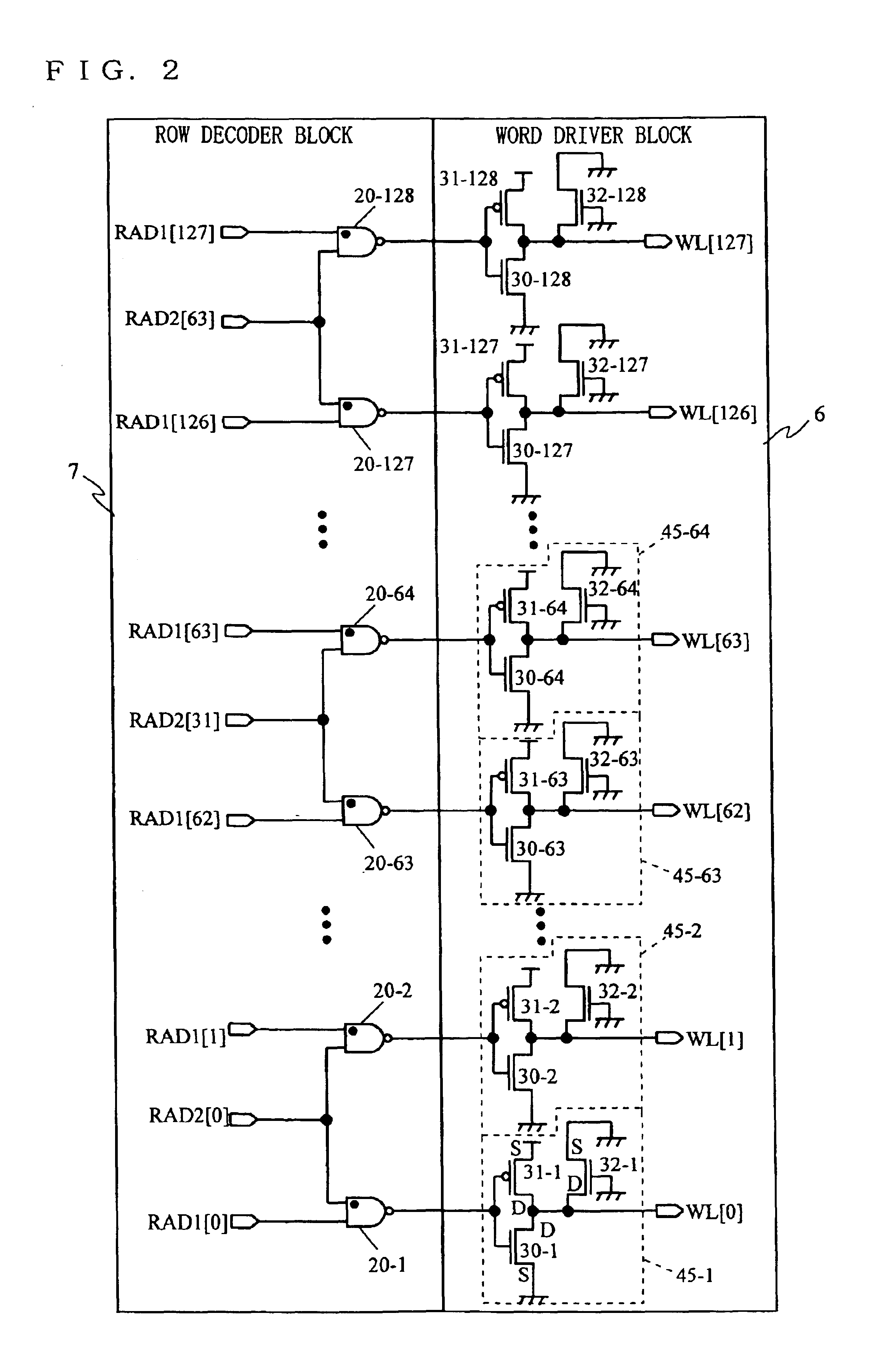

A semiconductor memory device according to the present invention includes: a plurality of N-ch MOS transistors arranged in an area surrounding a plurality of memory cells arranged in an array, at a spacing depending on a spacing of the plurality of memory cells, for driving the plurality of memory cells; and a plurality of dummy transistors 32-j each of which is formed between two adjacent ones of the plurality of N-ch MOS transistors 30-k so as to share diffusion layers with adjacent N-ch MOS transistors 30 and each of which has a gate electrode supplied with a voltage for electrically insulating these adjacent transistors 30-k.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

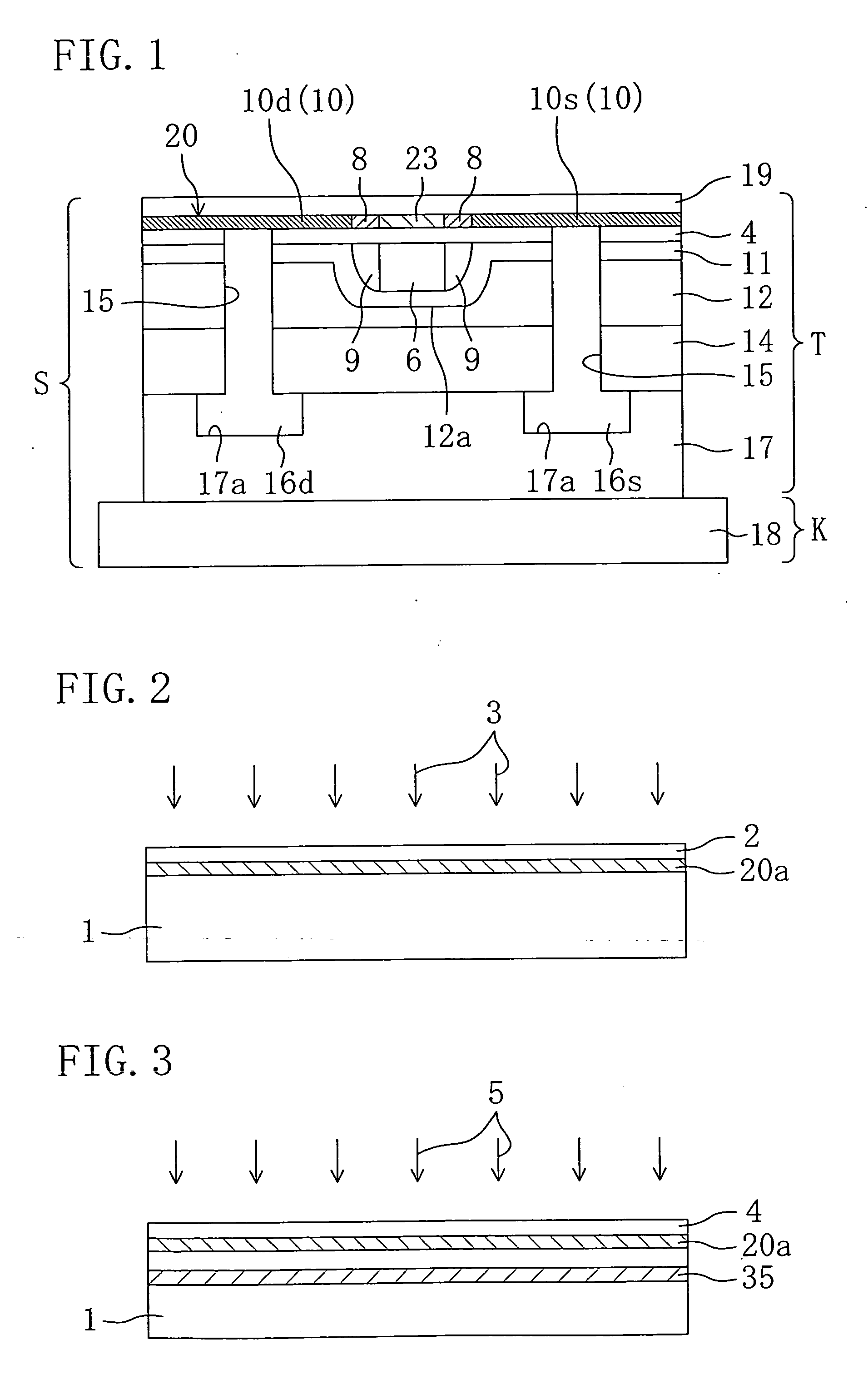

Method for manufacturing semiconductor substrate and semiconductor substrate

InactiveUS20050282019A1Reduce adverse effectsInhibit migrationSolid-state devicesSemiconductor/solid-state device manufacturingHydrogenGate oxide

A method for manufacturing a semiconductor substrate comprises the steps of: forming a gate oxide film as an insulating layer on the surface of a semiconductor substrate; implanting boron ions for inhibiting the migration of a peeling substance in the semiconductor substrate to form an anti-diffusion layer in the semiconductor substrate; activating boron in the anti-diffusion layer by heat treatment; implanting hydrogen ions into the semiconductor substrate to form a peel layer in part of the semiconductor substrate at a side of the anti-diffusion layer opposite to the gate oxide film; bonding a glass substrate to the surface of the semiconductor substrate where the gate oxide film has been formed; and heat-treating the semiconductor substrate to separate part of the semiconductor substrate along the peel layer.

Owner:SHARP KK

Semiconductor device and method of fabricating the same

A semiconductor device has an element substrate including a semiconductor layer of a first conductivity type being formed over a semiconductor substrate with a dielectric film interposed therebetween. A groove is formed in the element substrate with a depth extending from a top surface of the semiconductor layer into the dielectric film, the groove having a width-increased groove portion in the dielectric film as to expose a bottom surface of the semiconductor layer. An impurity diffusion source is buried in the width-increased groove portion to be contacted with the bottom surface. A transistor is formed to have a first diffusion layer being formed through impurity diffusion from the impurity diffusion source to the bottom surface of the semiconductor layer, a second diffusion layer formed through impurity diffusion to the top surface of the semiconductor layer, and a gate electrode formed at a side face of the groove over the impurity diffusion source with a gate insulation film between the side face and the gate electrode.

Owner:KK TOSHIBA

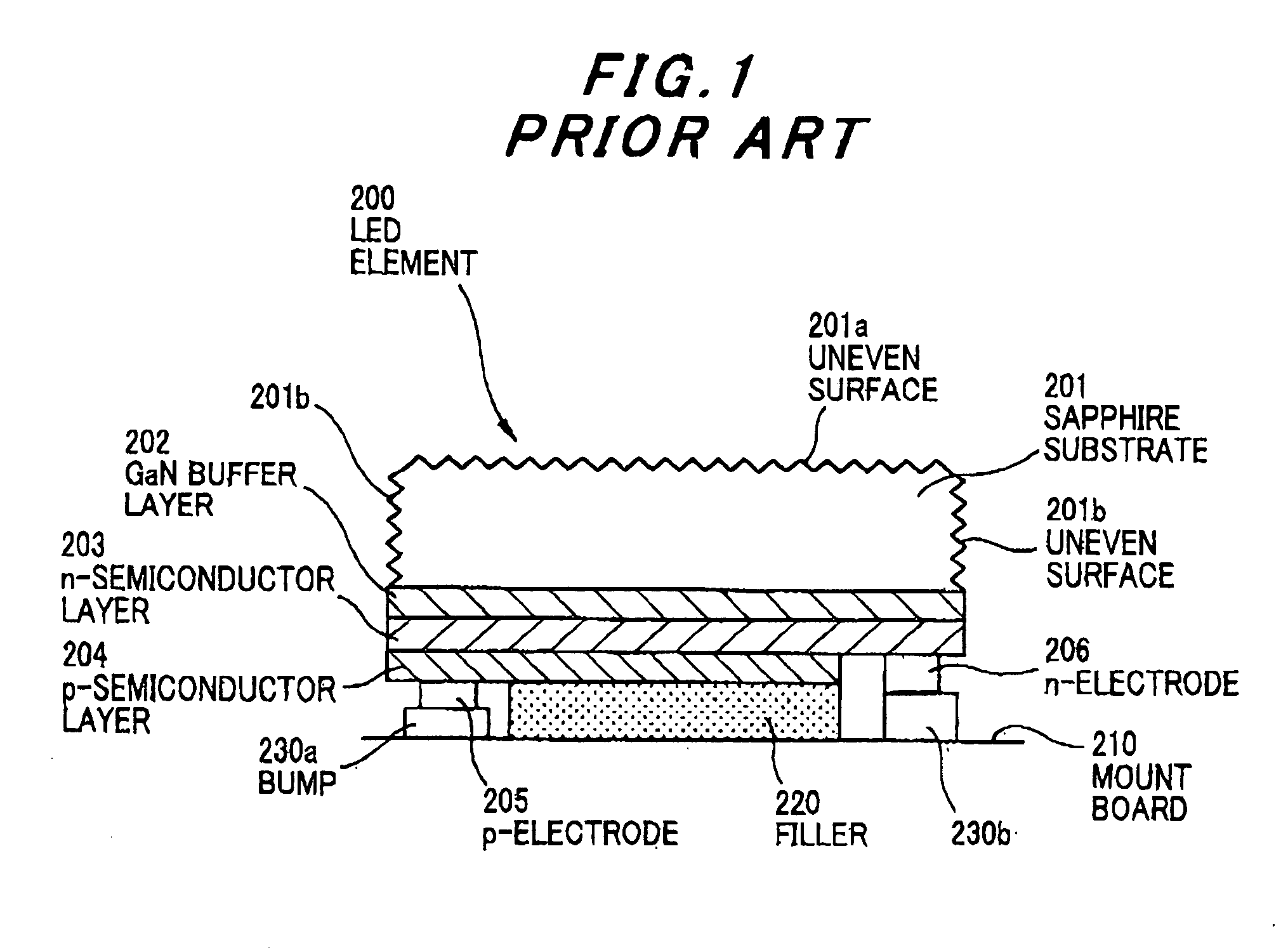

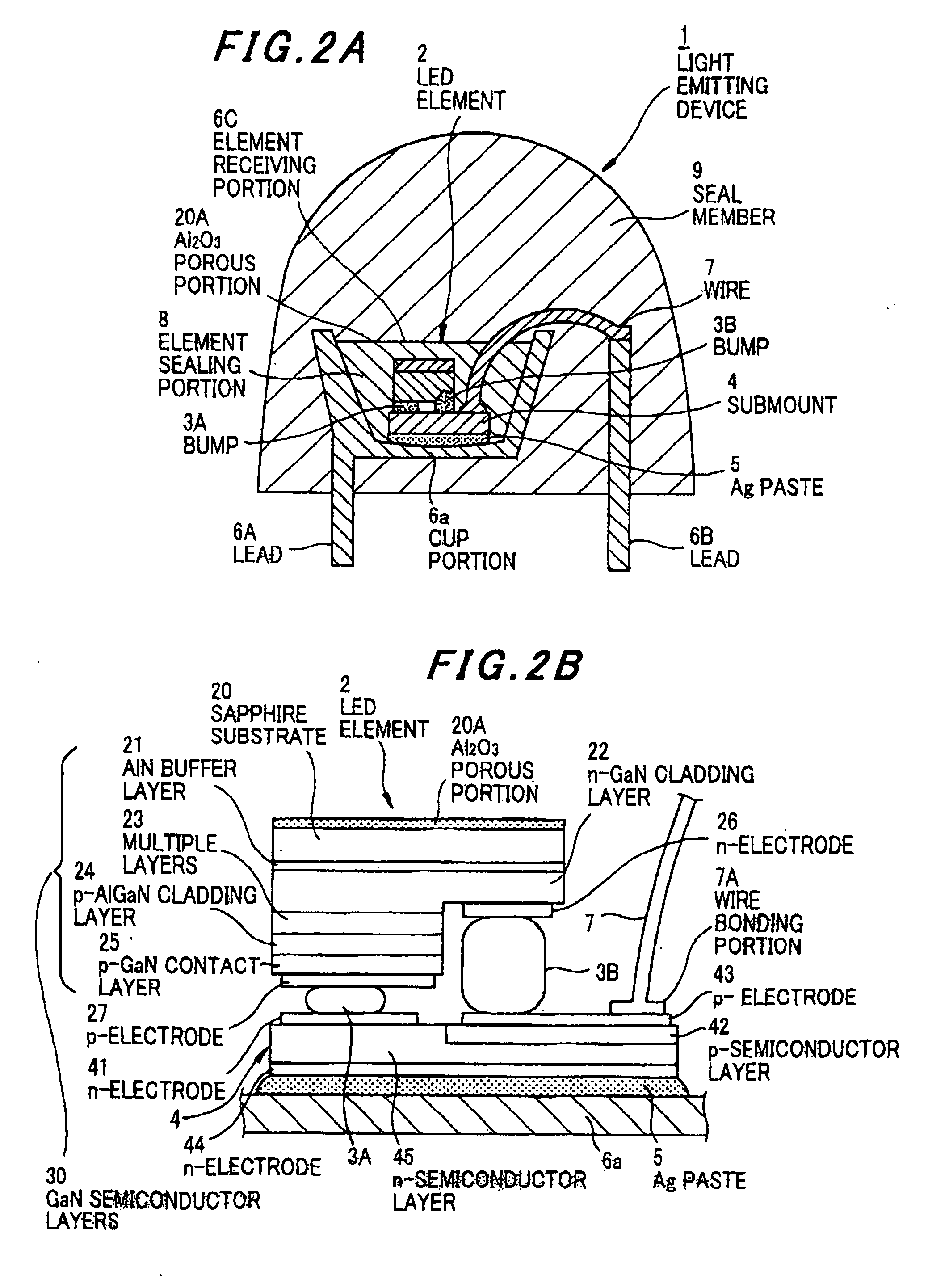

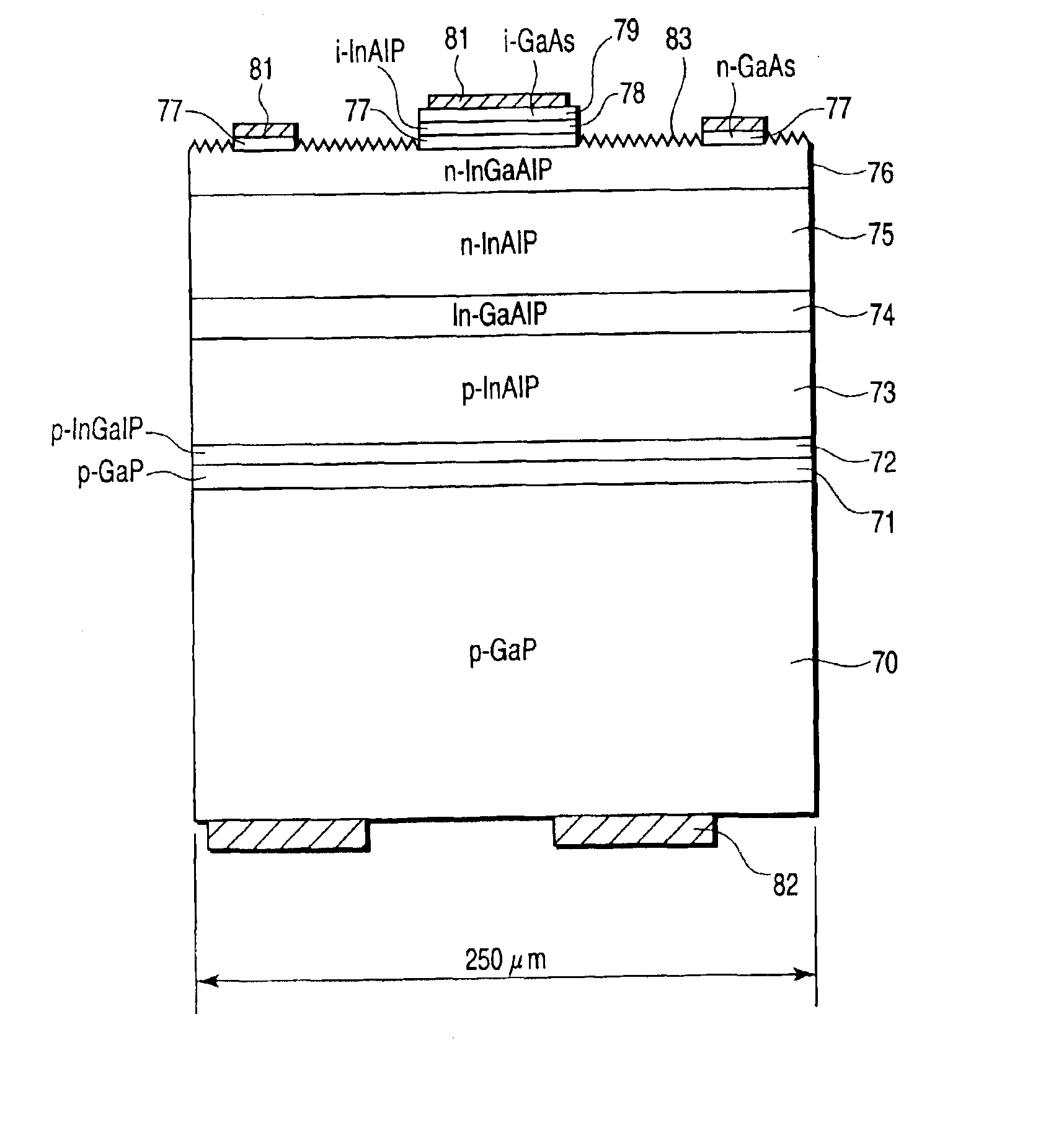

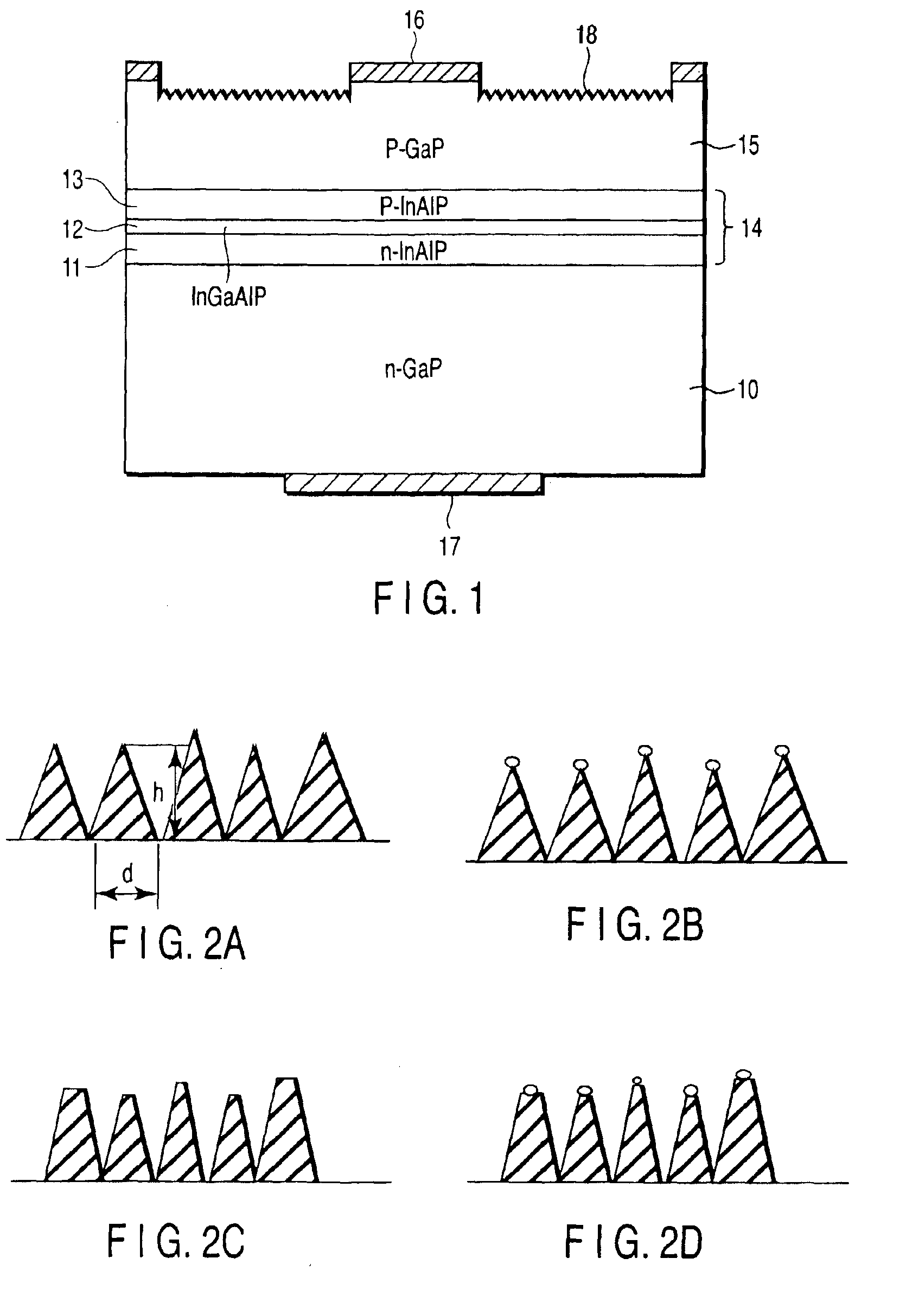

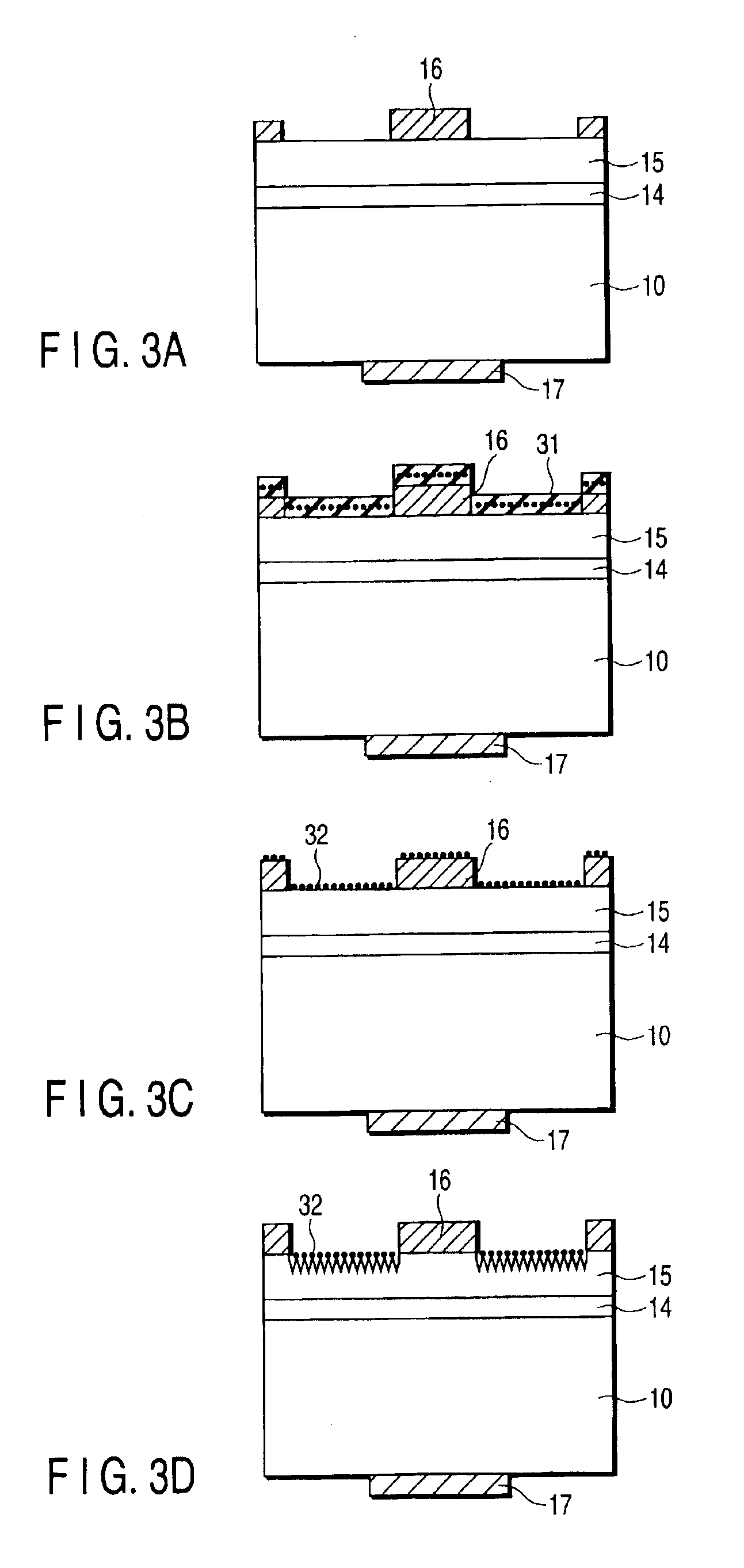

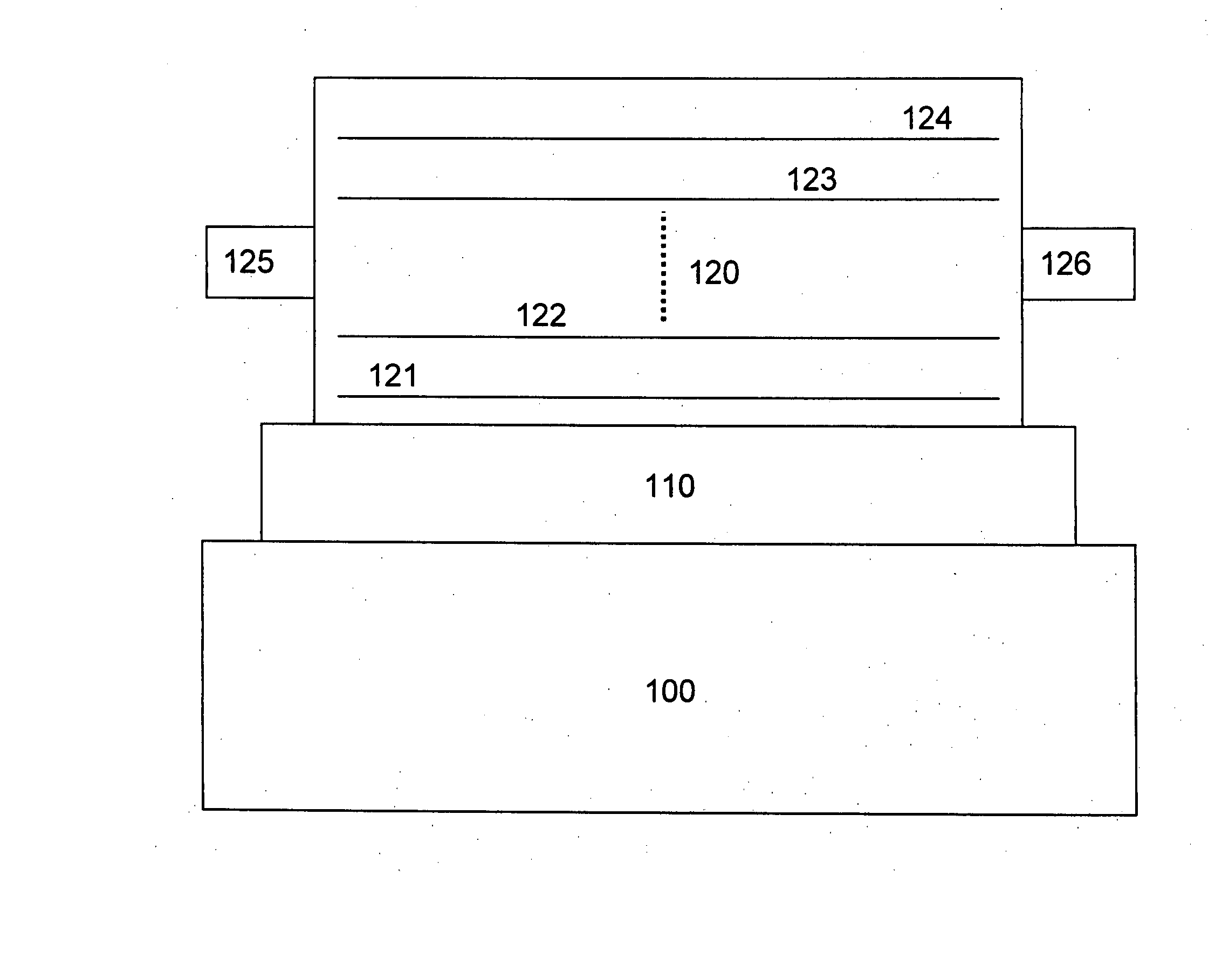

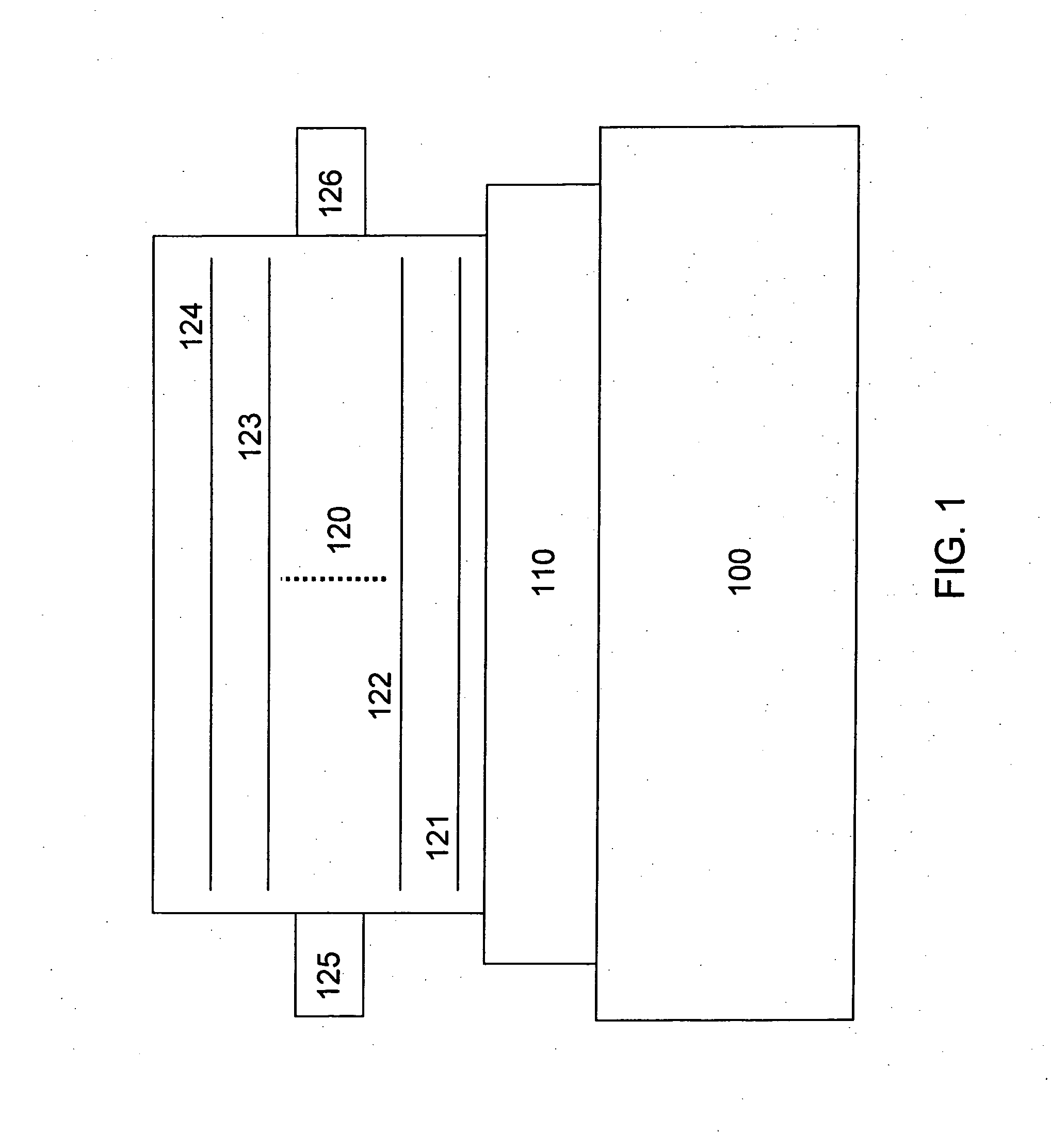

Light emitting element and light emitting device

InactiveUS20050093008A1Improved external radiation efficiencyIncrease external radiation efficiencySolid-state devicesSemiconductor devicesRefractive indexLight emitting device

A light emitting element has: a light emitting layer of semiconductor; and a diffusion layer that has a refractive index equal to or greater than that of the light emitting layer and that diffuses light emitted from the light emitting layer to increase the external radiation efficiency of the light emitting element. The light emitting layer has a refractive index equal to or greater than that of any layers formed between the light emitting layer and the diffusion layer.

Owner:TOYODA GOSEI CO LTD

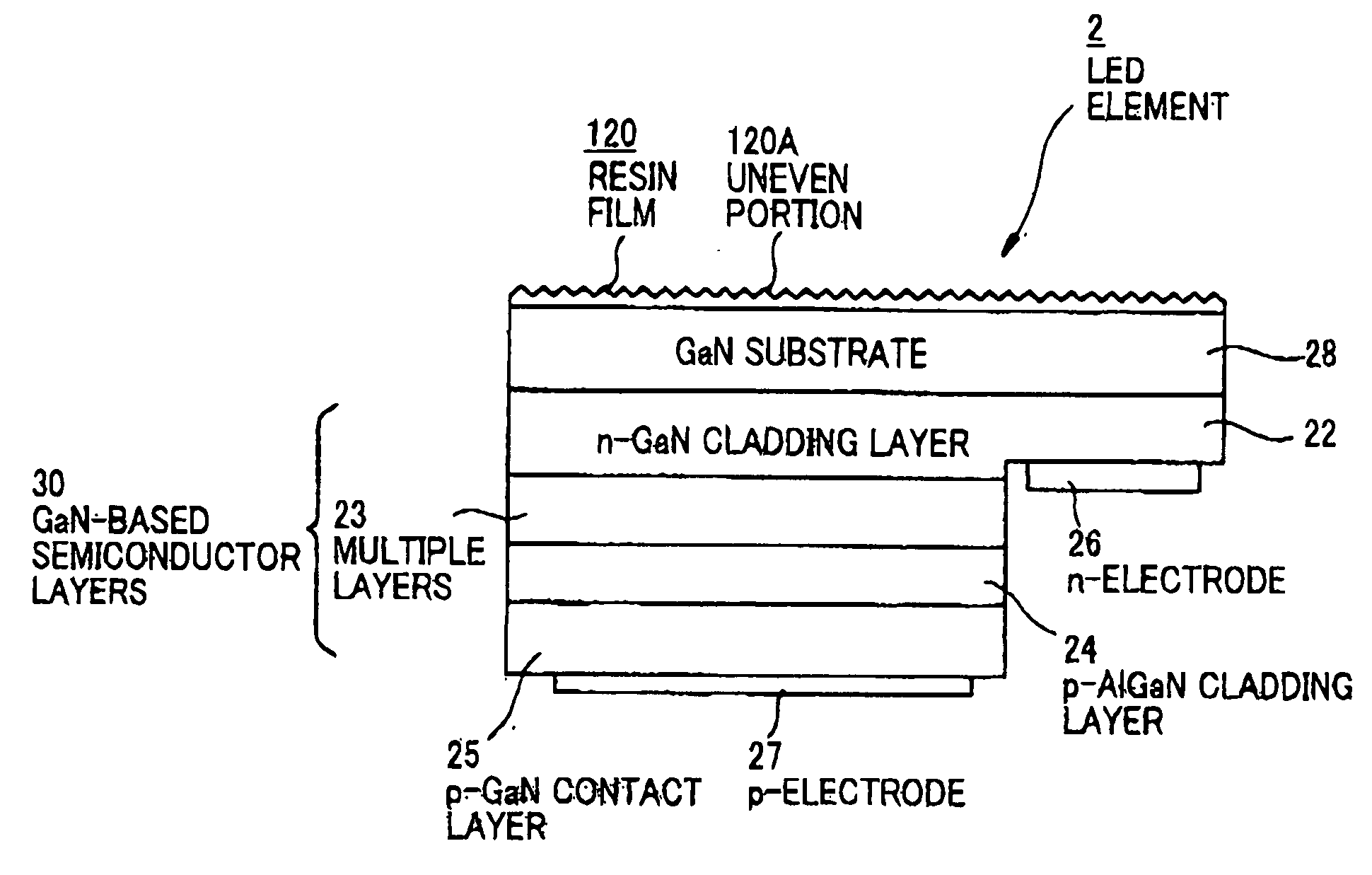

Method of manufacturing a semiconductor light-emitting element

InactiveUS7037738B2Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

Owner:KK TOSHIBA

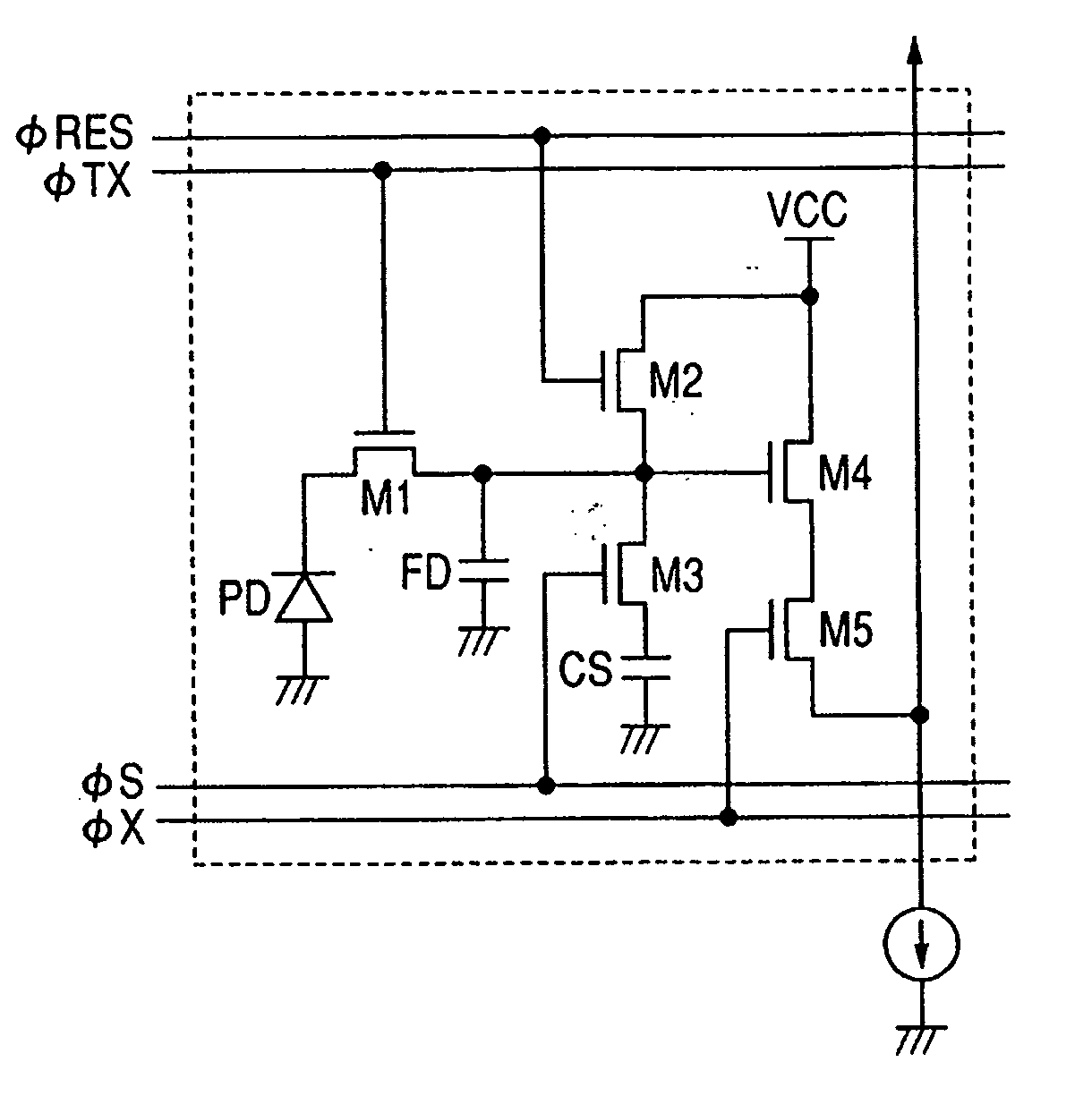

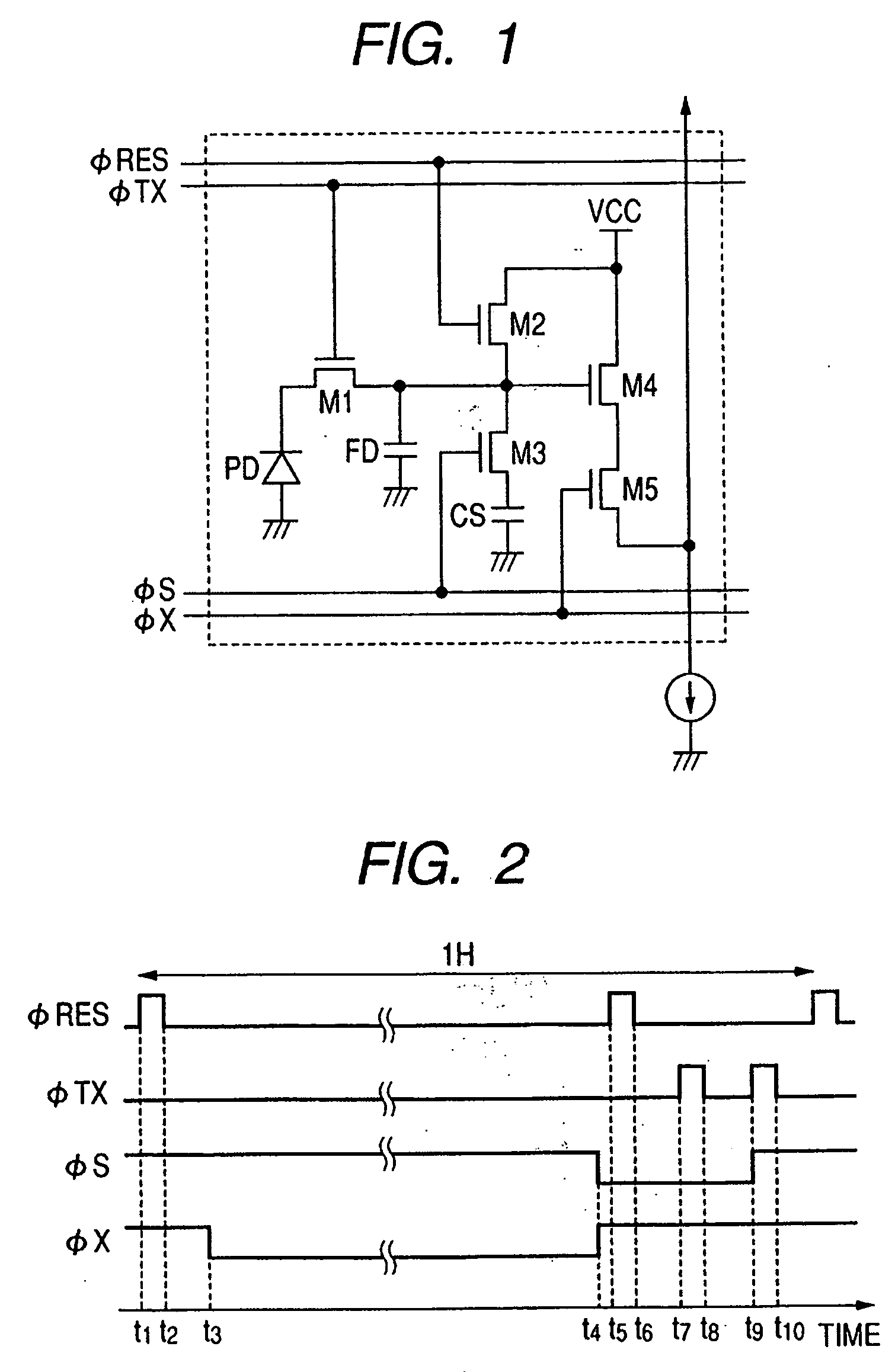

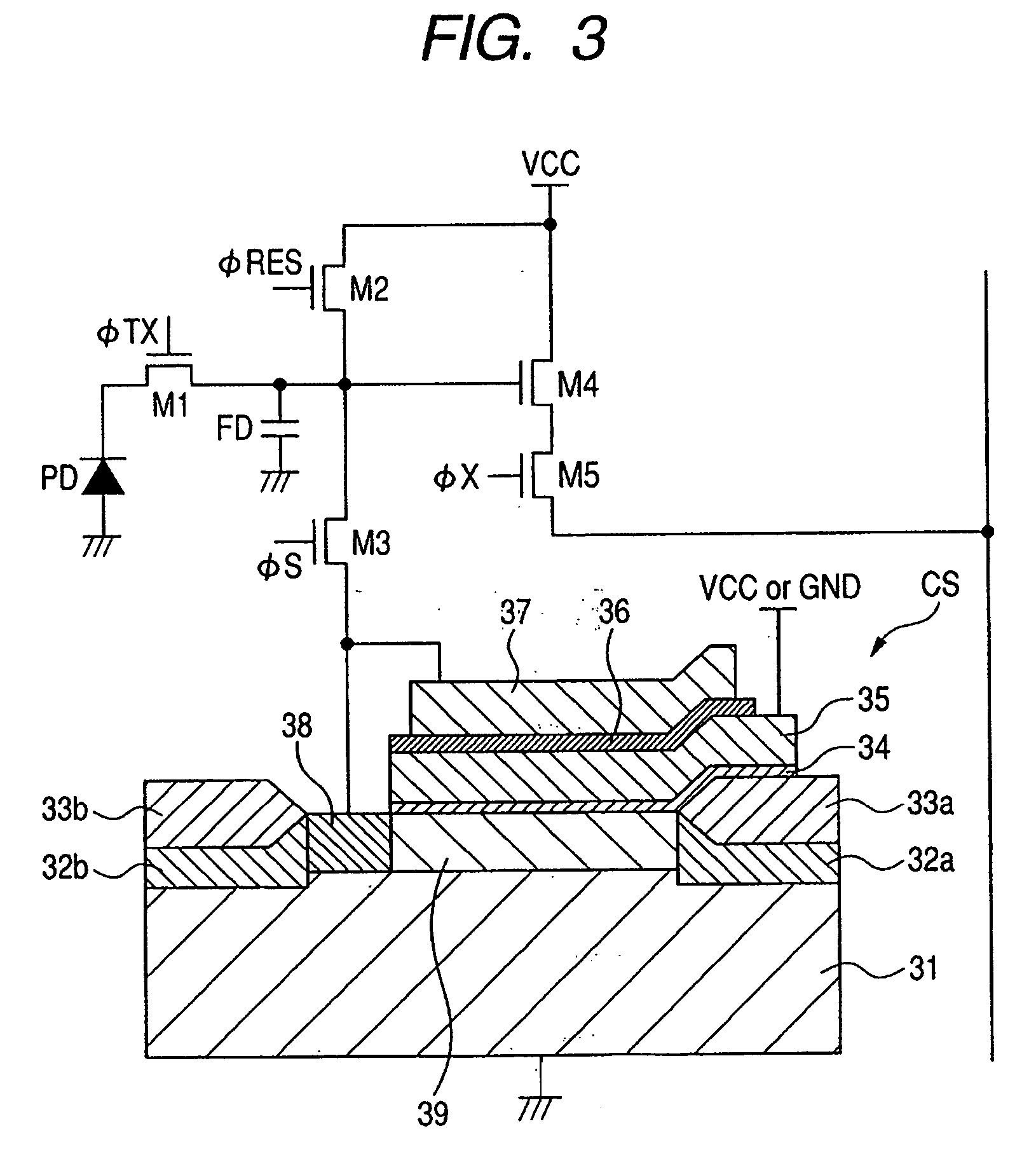

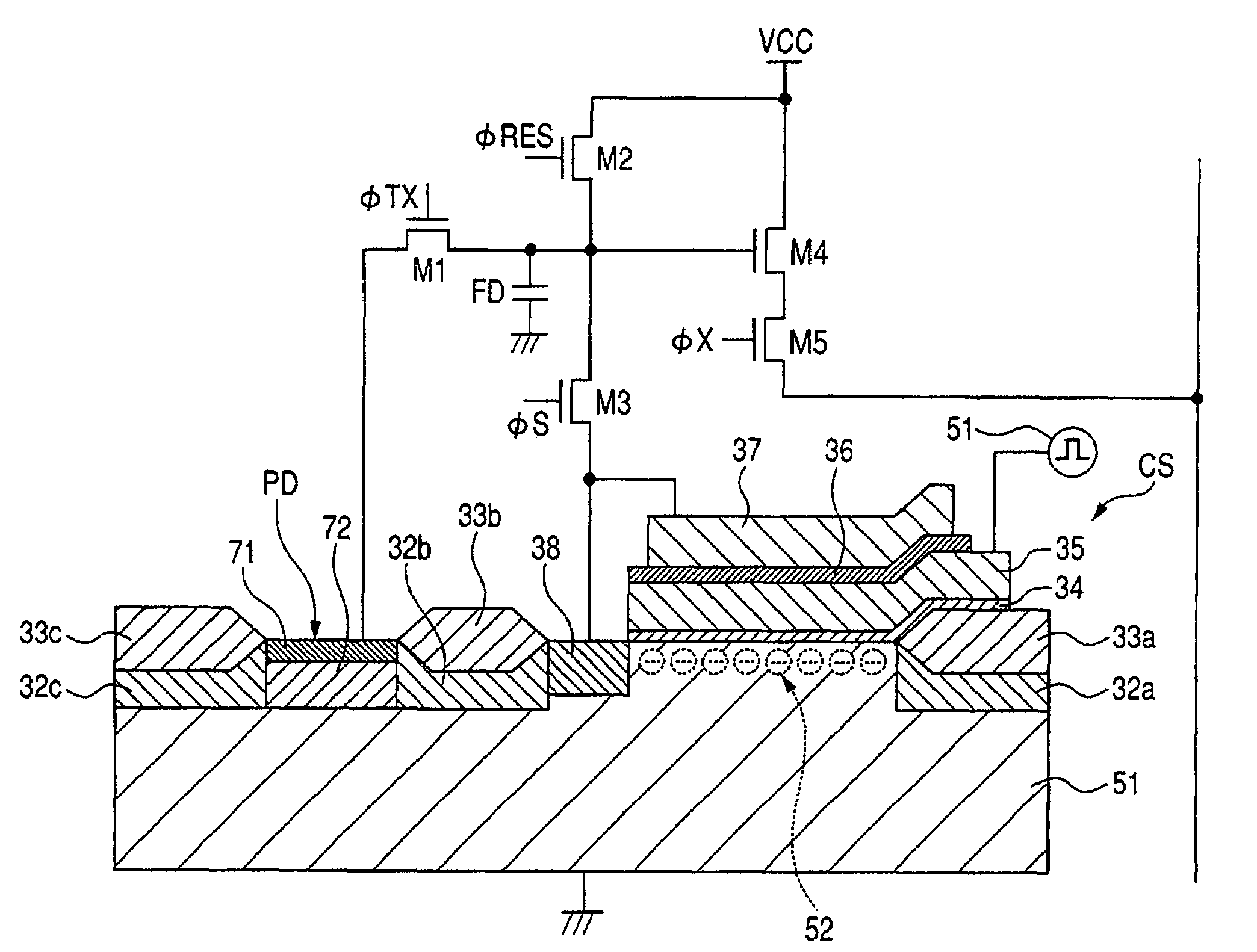

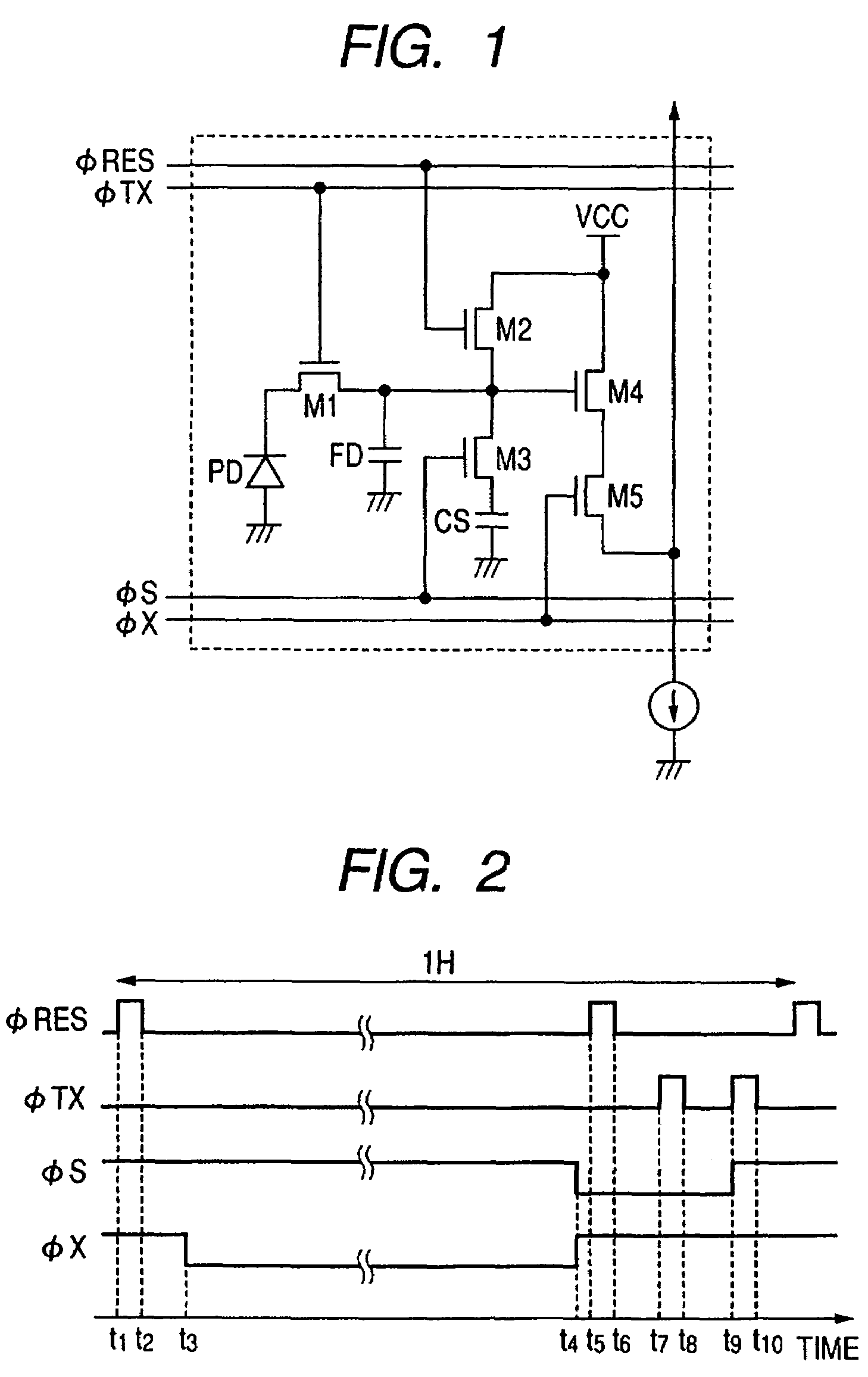

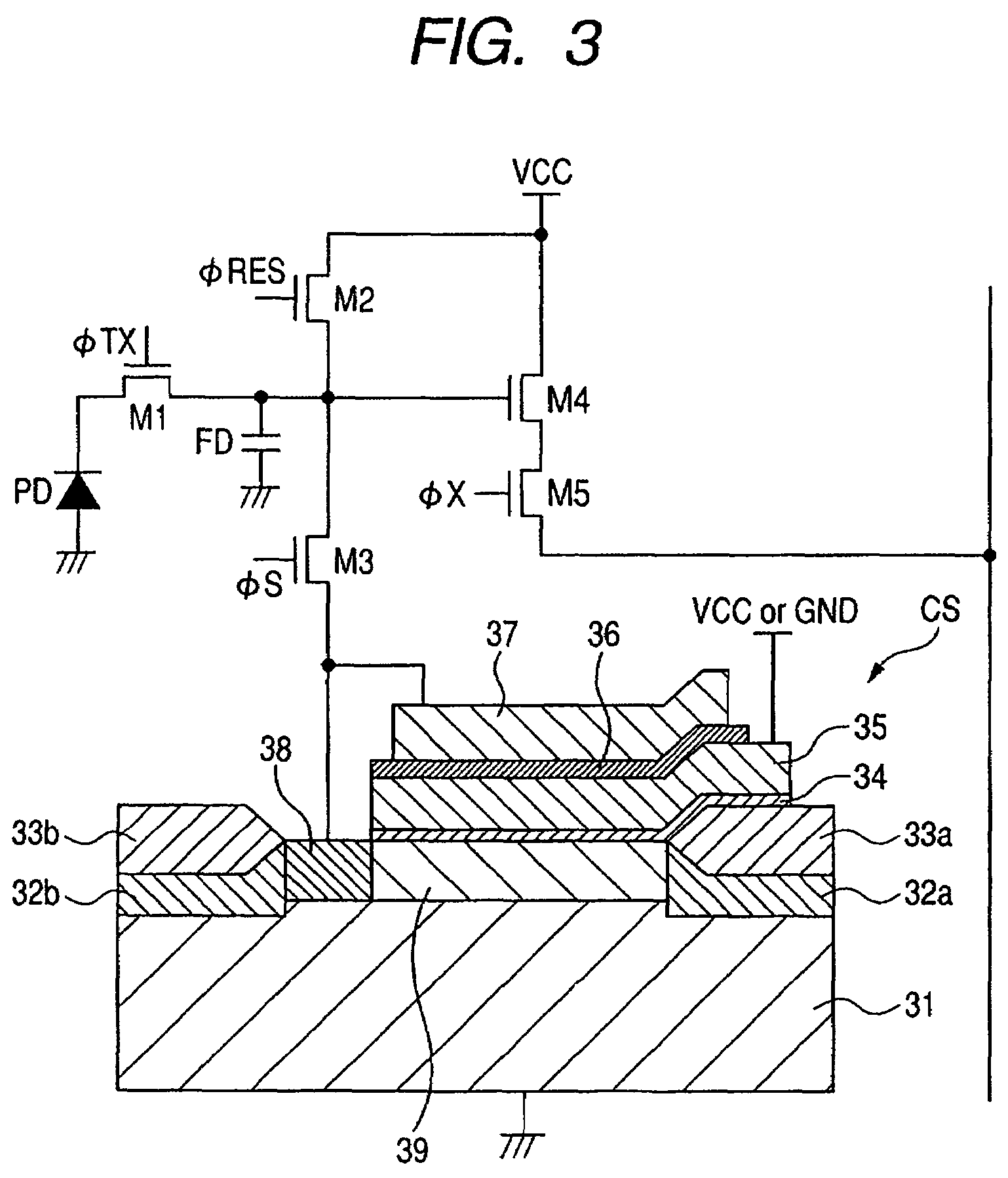

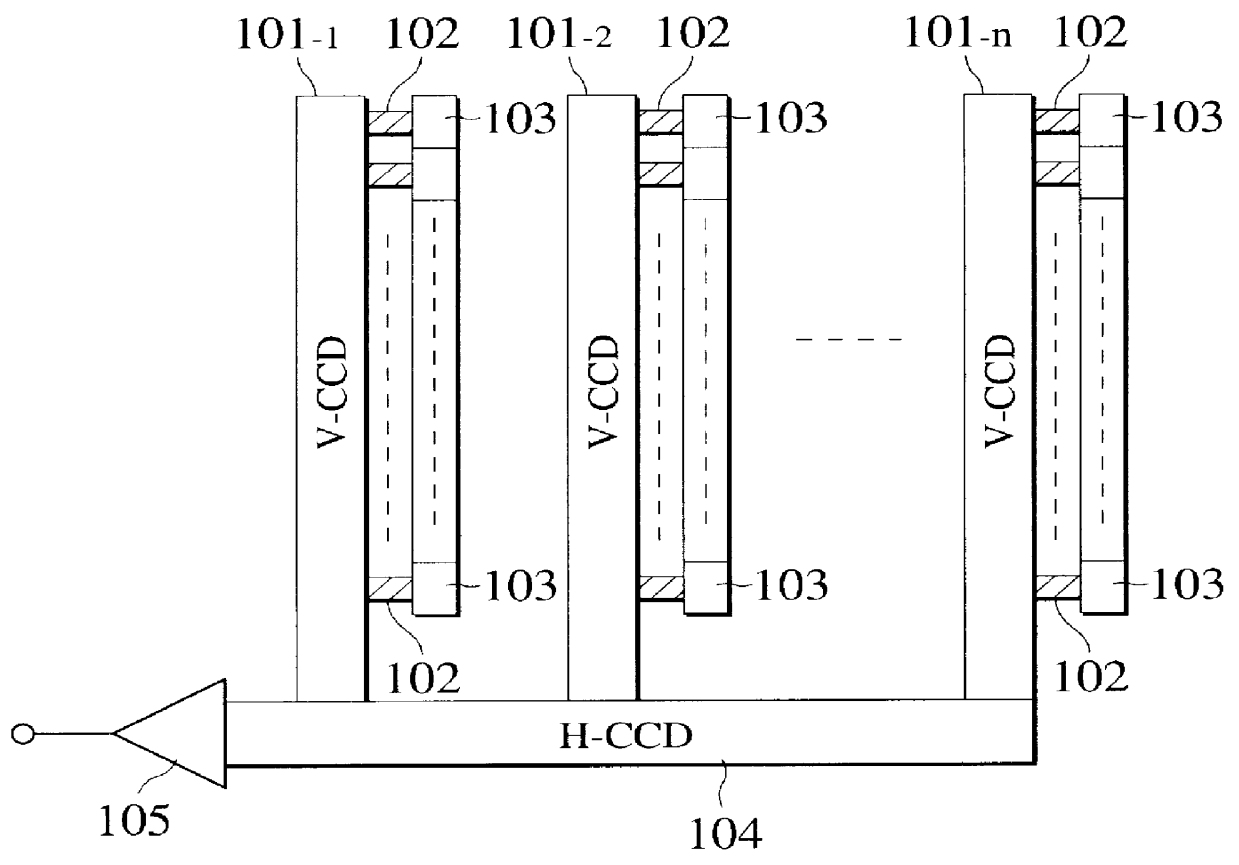

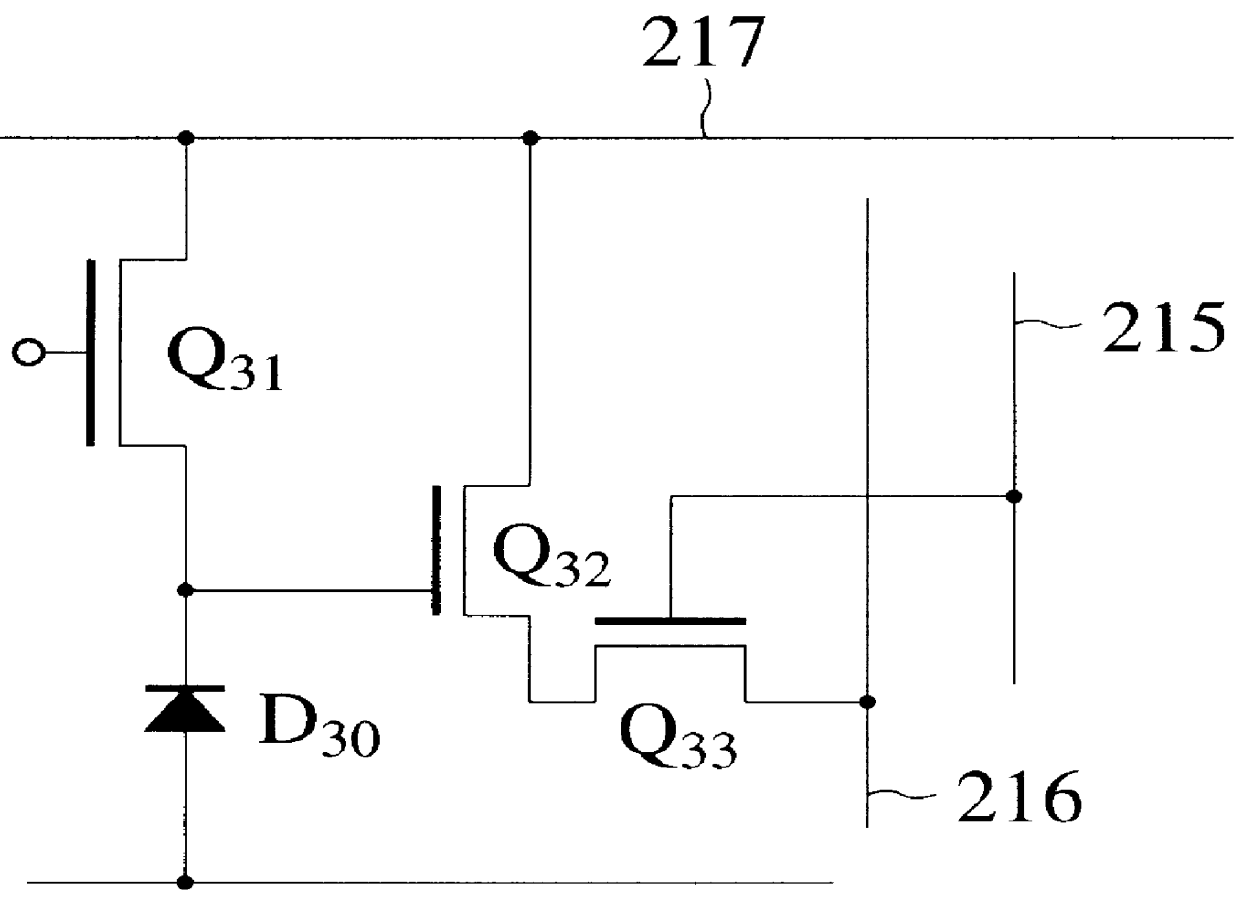

Solid state image pickup device and camera

InactiveUS20060221667A1Television system detailsTelevision system scanning detailsCapacitanceCharge carrier

An object of the present invention is to simultaneously realize the enlargement of a dynamic range and the downsizing of a pixel. An additional capacitor CS is composed by using: a first capacitor formed of a first diffusion layer, a second diffusion layer and a P well by layering the P well, the first diffusion layer, a first dielectric film, a first polysilicon layer, a second dielectric film and a second polysilicon layer; a second capacitor formed of the second diffusion layer, the first polysilicon layer and the first dielectric film; and a third capacitor formed of the first polysilicon layers, a second polysilicon layer, and a second dielectric film. Thereby, the additional capacitor CS for accumulating carriers overflown from a photodiode PD can secure a required capacitance value while making its size as small as possible.

Owner:CANON KK

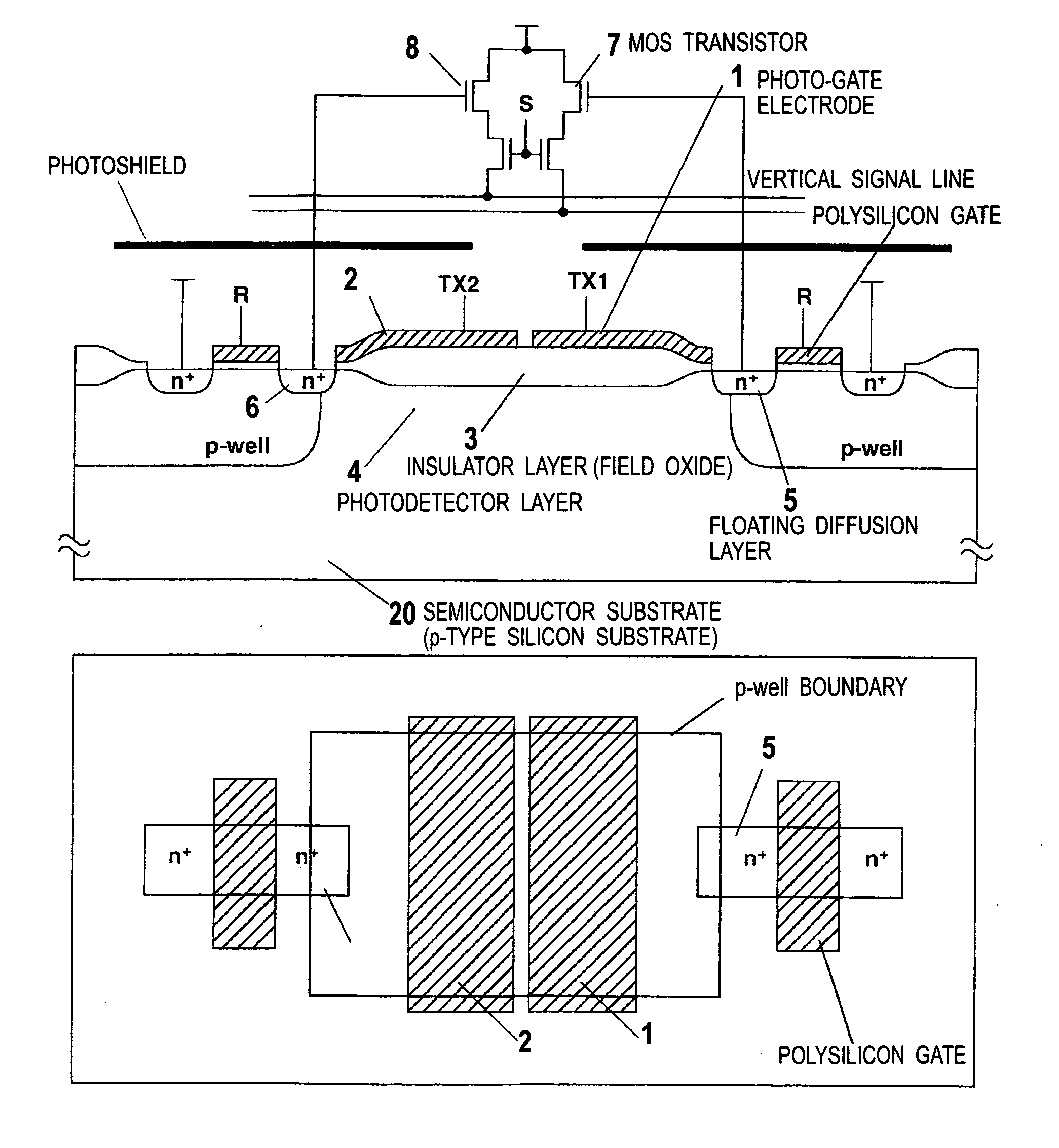

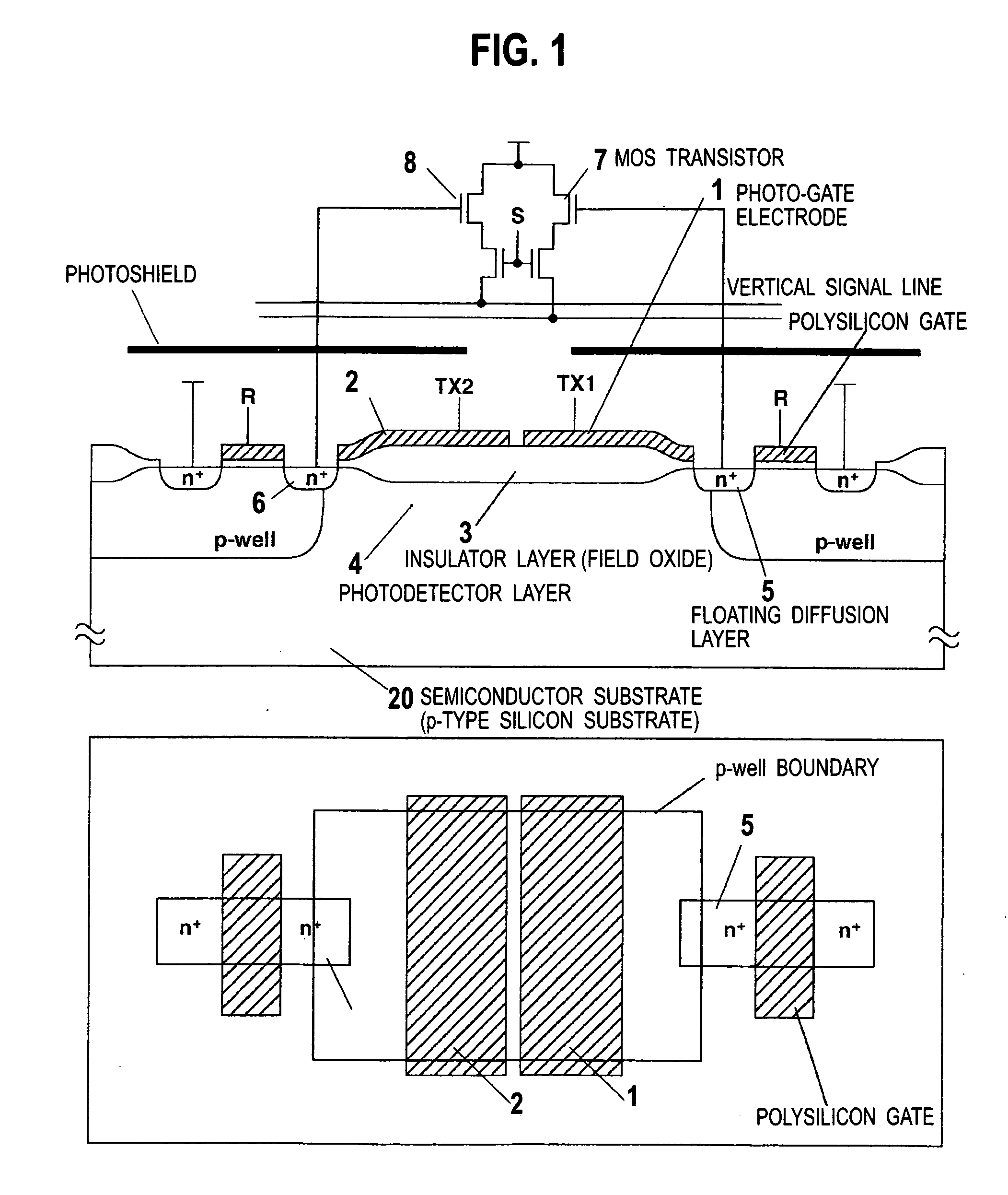

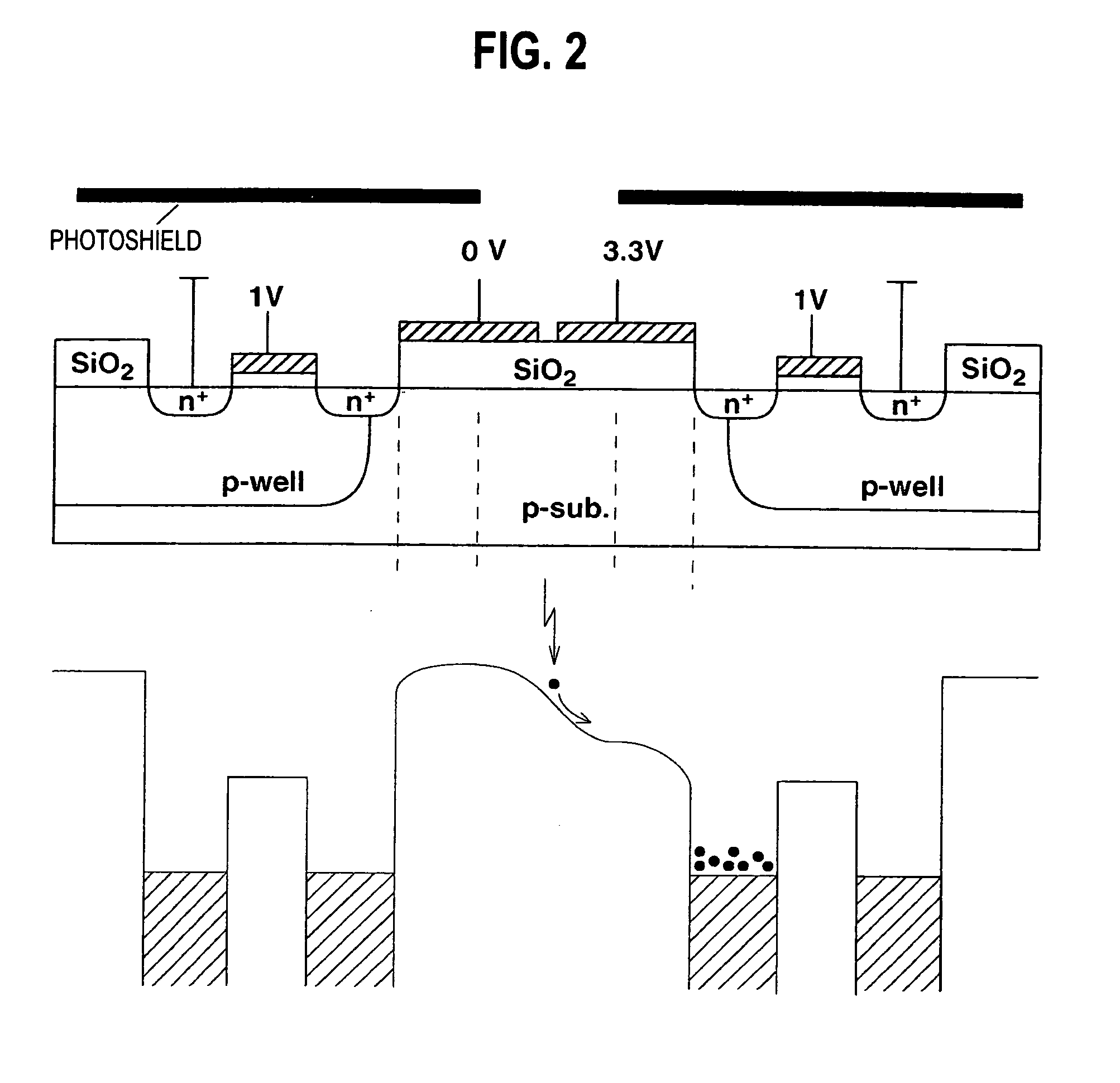

Time-of-light flight type distance sensor

InactiveUS20070158770A1Maximum performanceLow costTelevision system detailsOptical rangefindersManufacturing technologyPhotodetector

A lower cost range-finding image sensor based upon measurement of reflection time of light with reduced fabrication processes compared to standard CMOS manufacturing procedures. An oxide film is formed on a silicon substrate, and two photo-gate electrodes for charge-transfer are provided on the oxide film. Floating diffusion layers for taking charges out from a photodetector layer are provided at the ends of the oxide film, and on the outside thereof are provided a gate electrode for resetting and a diffusion layer for providing a reset voltage.

Owner:NAT UNIV CORP SHIZUOKA UNIV

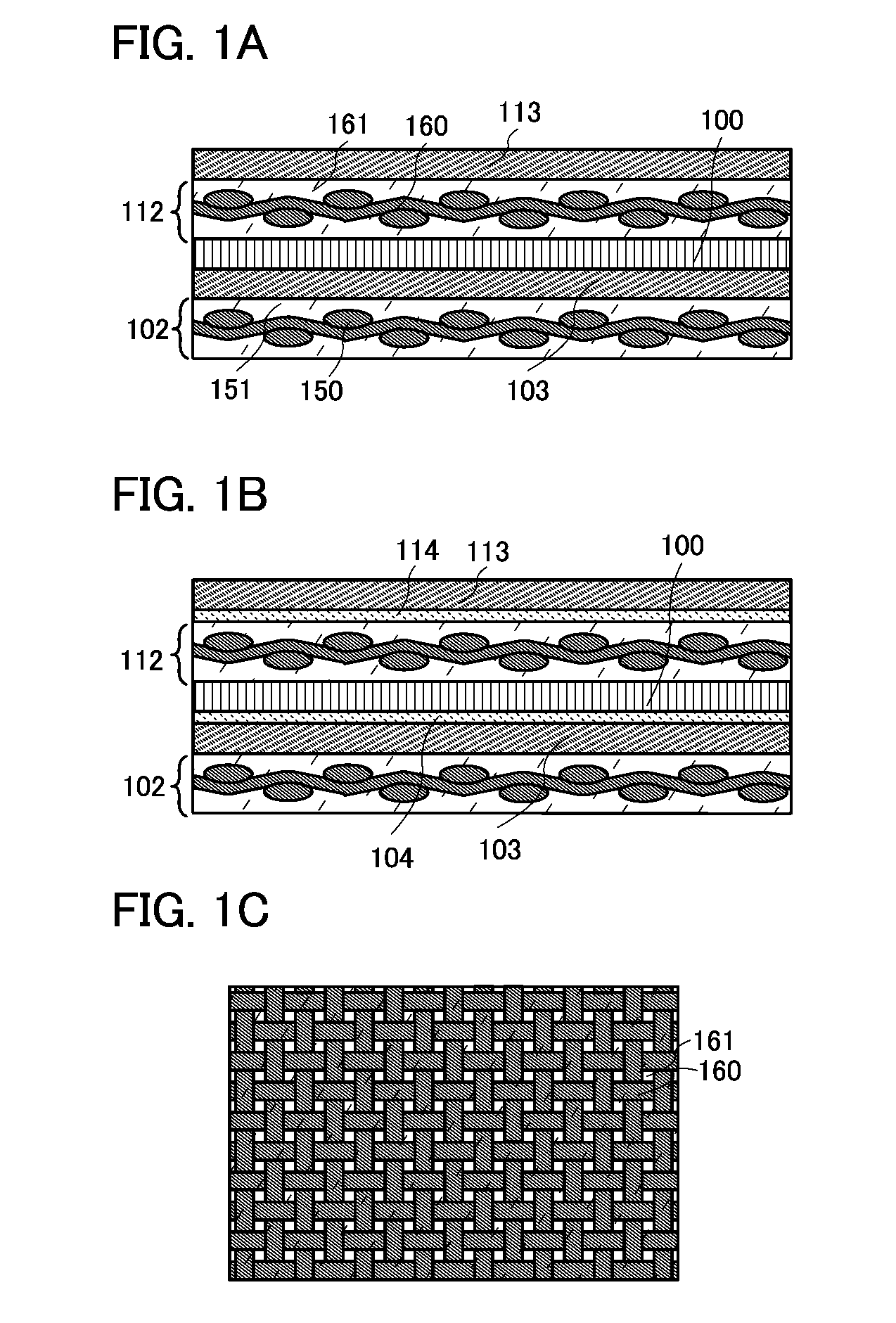

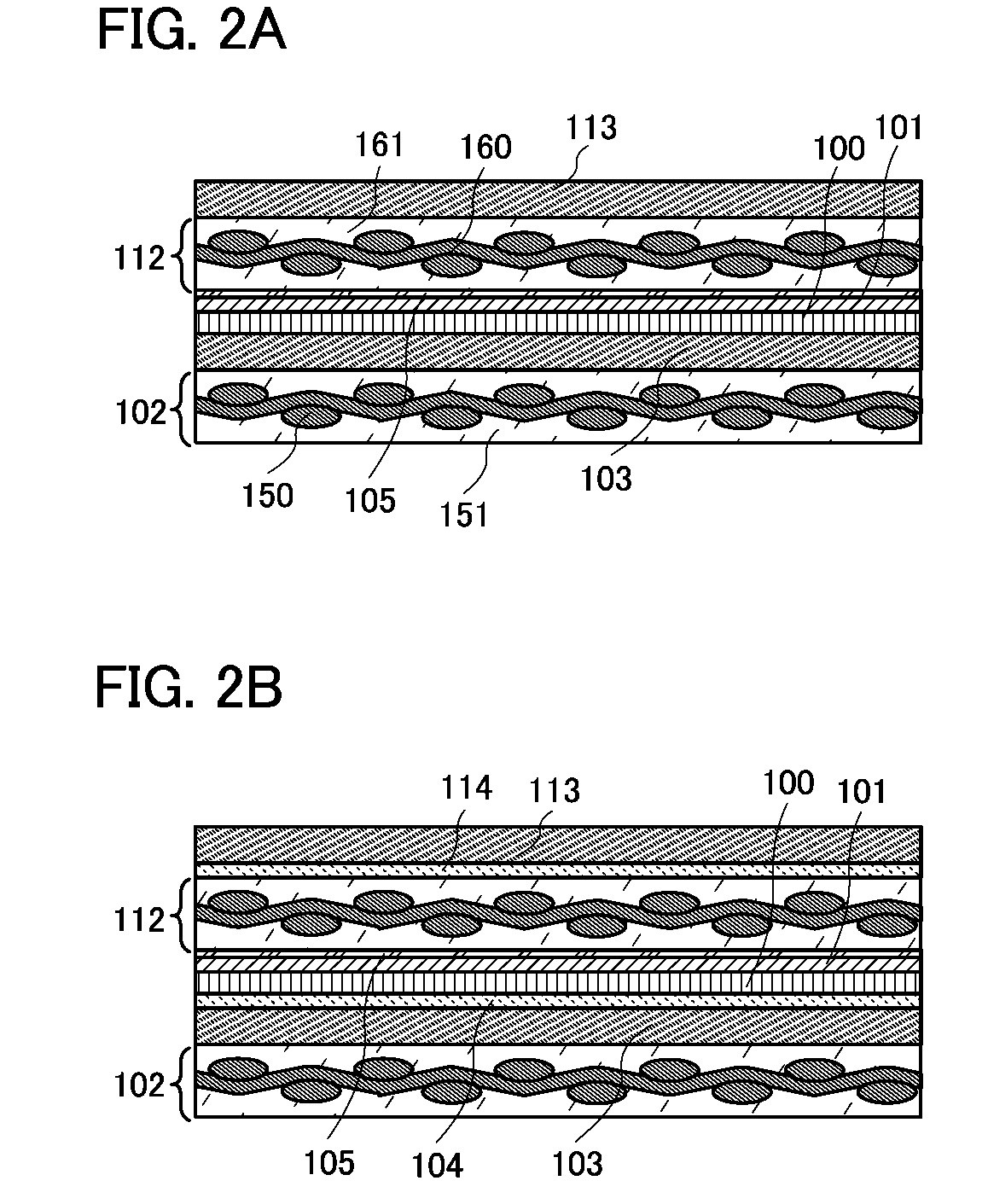

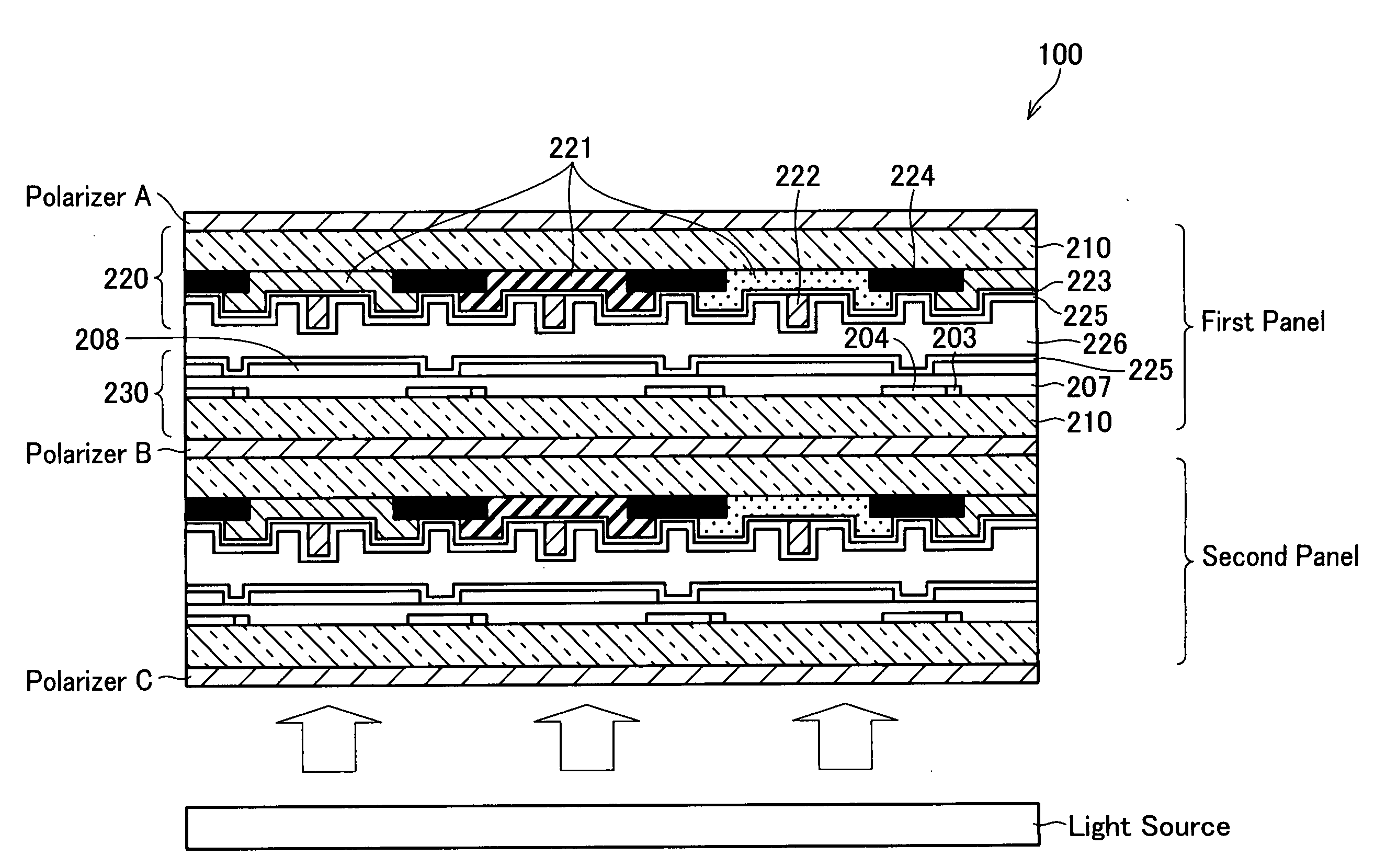

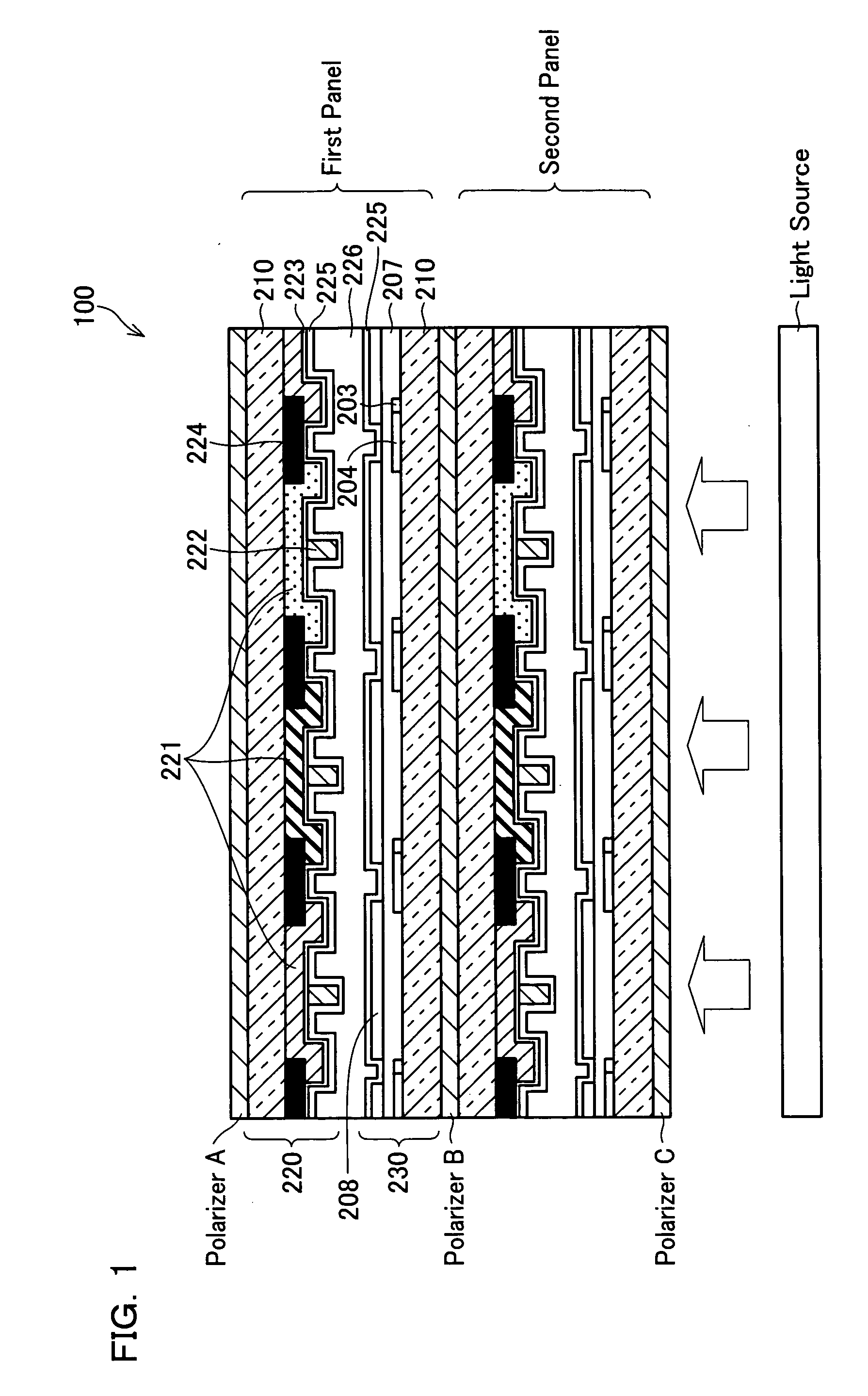

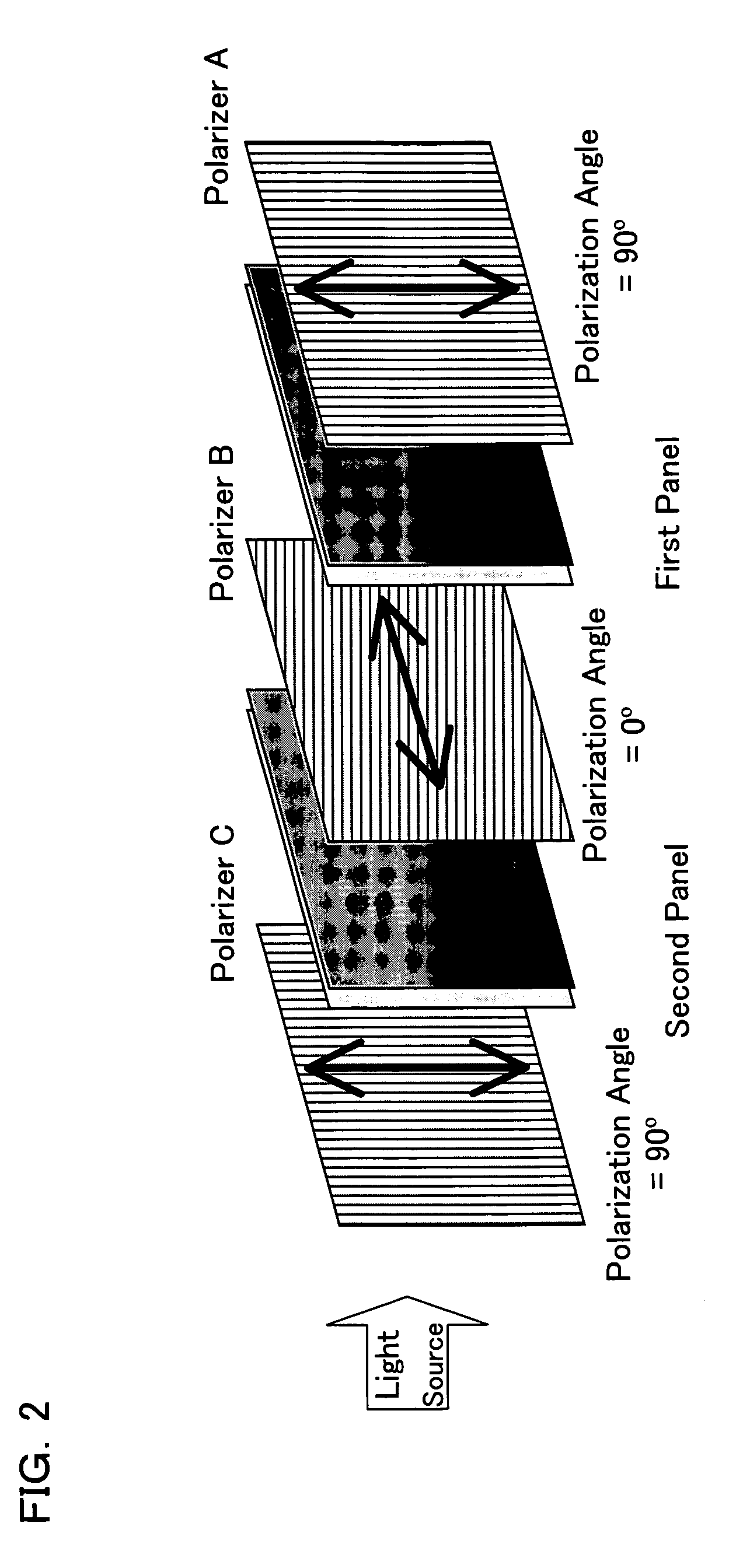

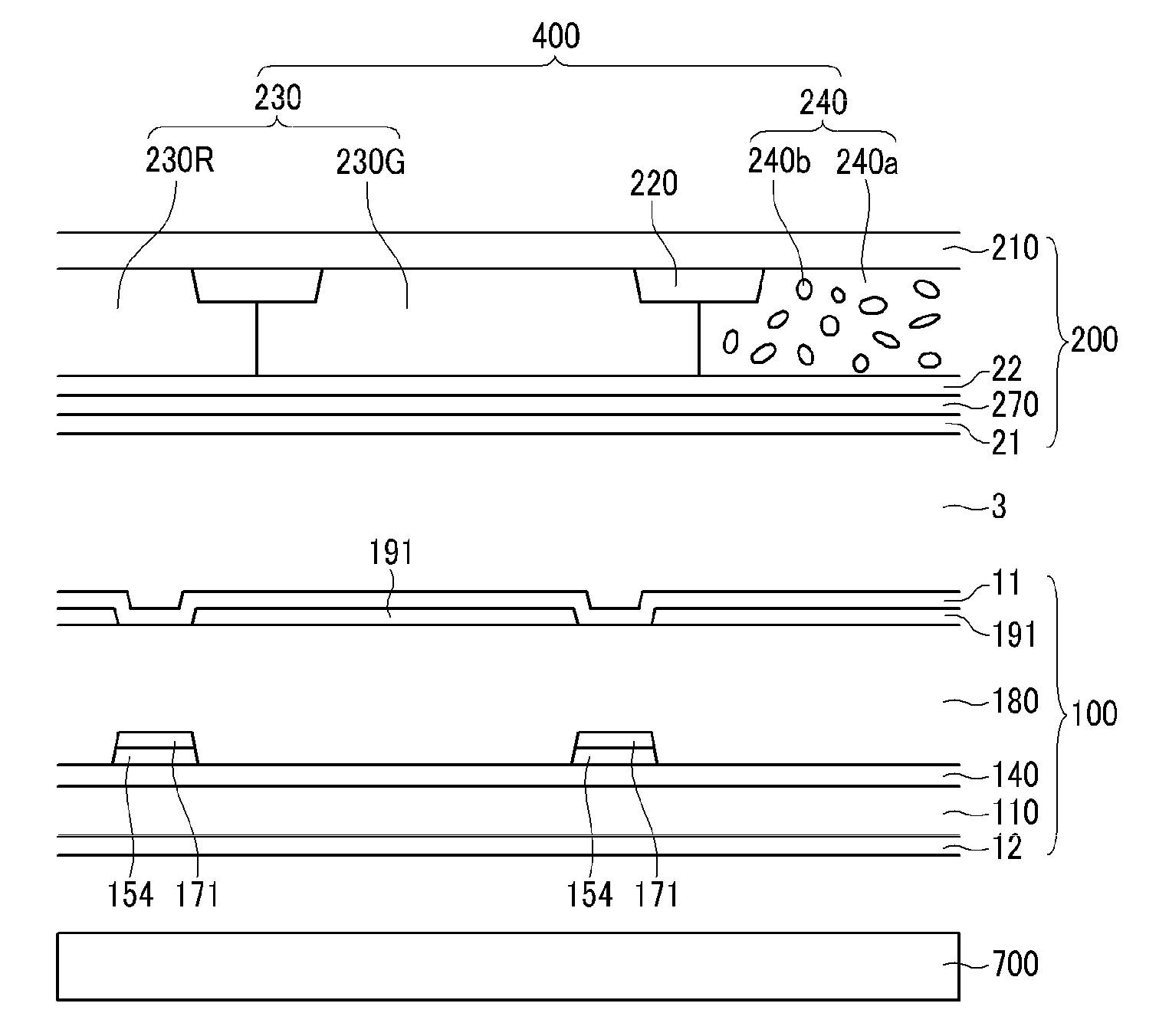

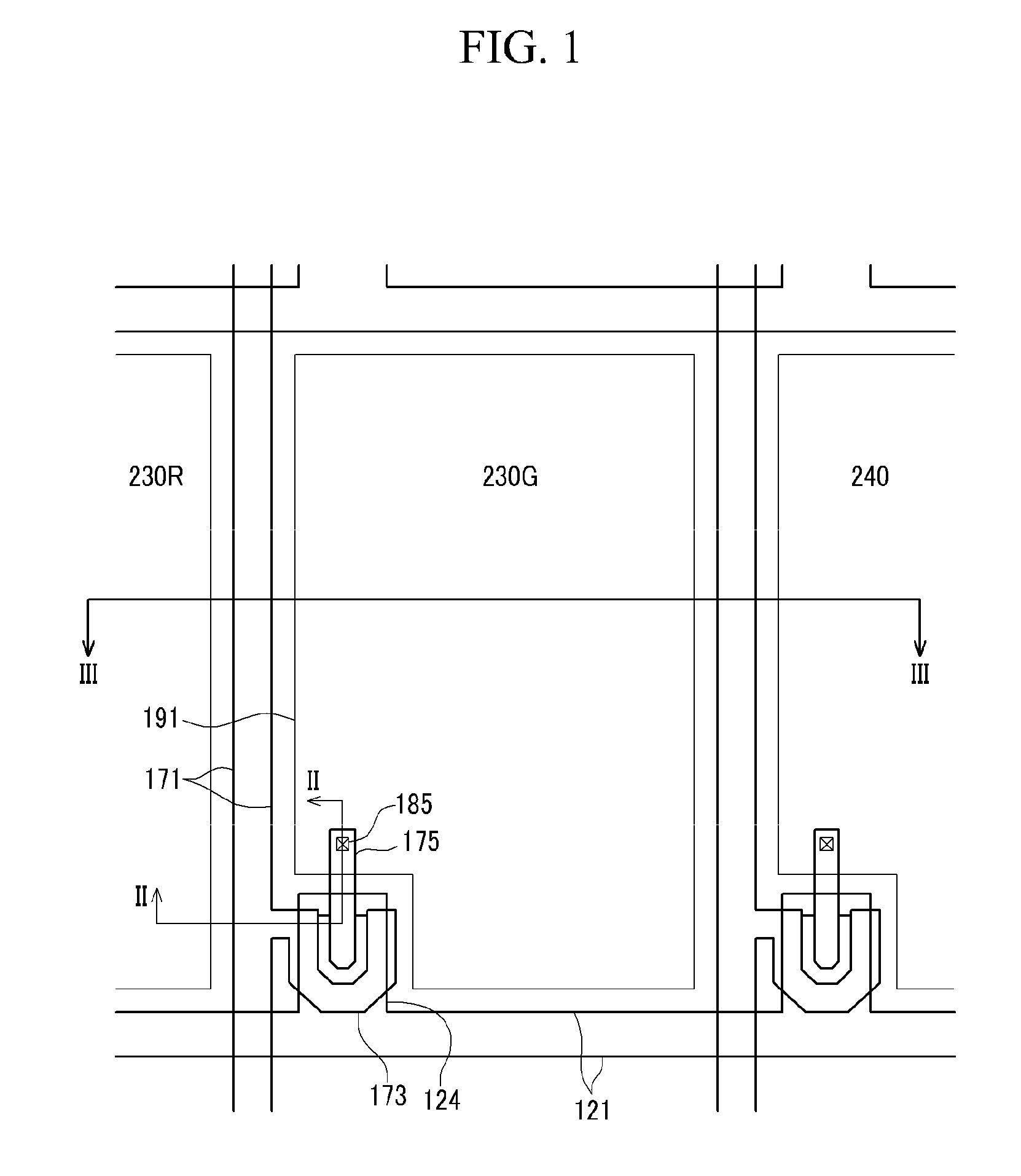

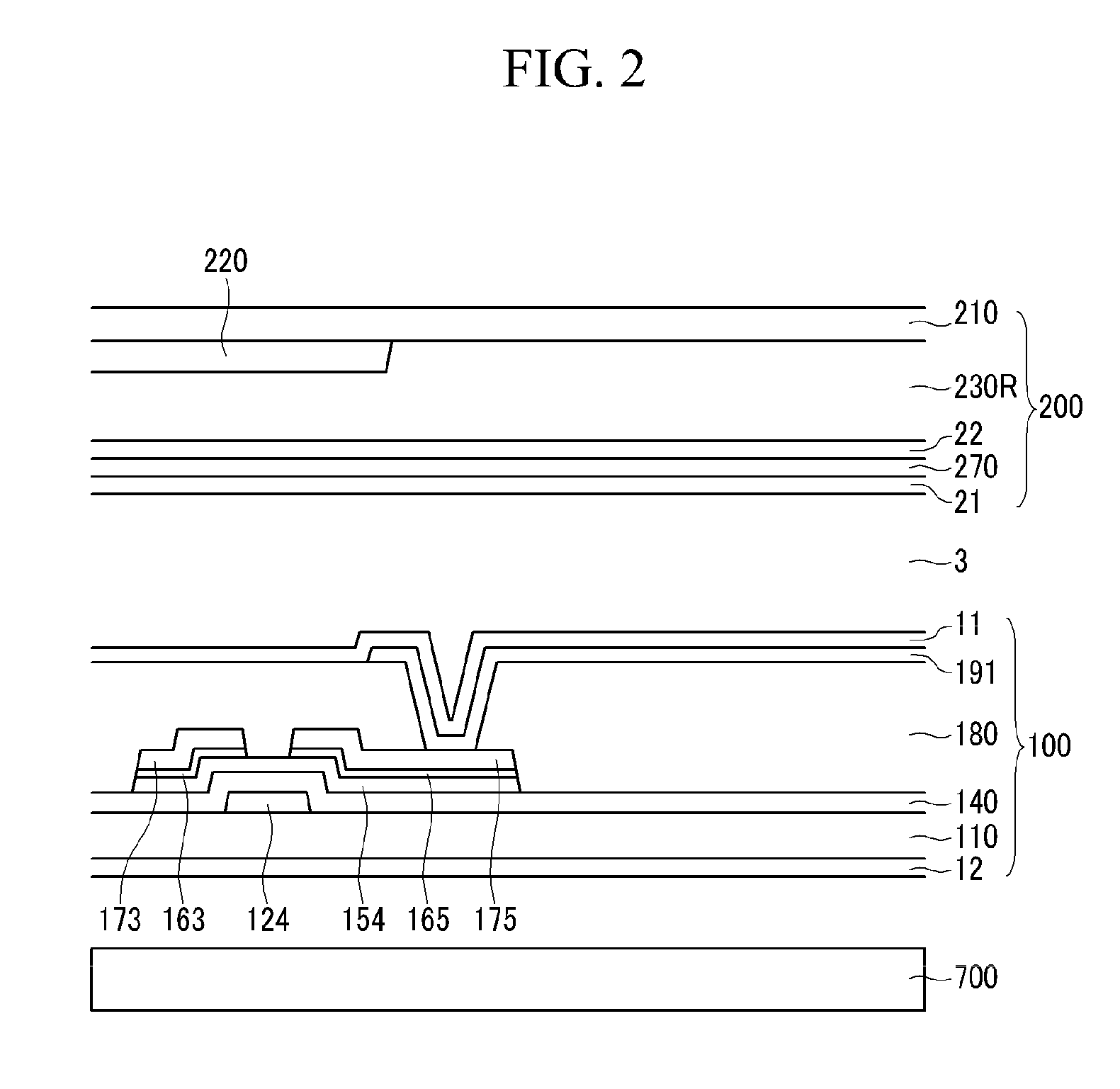

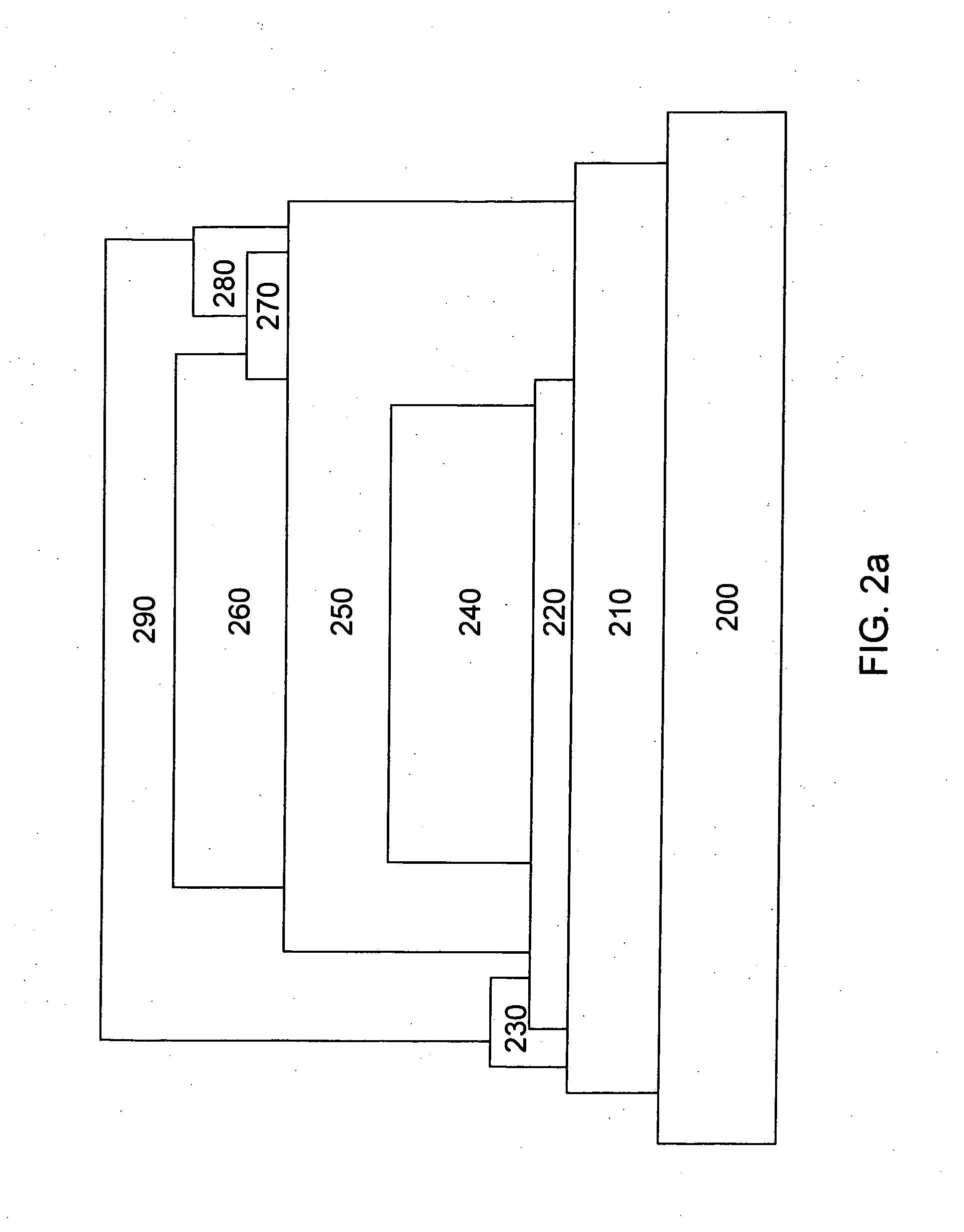

Liquid Crystal Display and Television Receiver

ActiveUS20090147186A1Interference may occurReduce distractionsStatic indicating devicesNon-linear opticsDiffusionLiquid-crystal display

A liquid crystal display of the present invention contains a first panel and a second panel being stacked. Adjacent pairs of polarizers (A to C) disposed on the panels form crossed Nicols. When the first panel produces a display according to a first display signal, the second panel produces a display according to a second display signal obtained from the first display signal. Each of the two joined panels is provided with a light diffusion layer having a light diffusing property. The provision of the light diffusion layers enables reducing moire pattern occurrences which would otherwise markedly increase when two liquid crystal panels are stacked. As a result, the liquid crystal display has high display quality.

Owner:SHARP KK

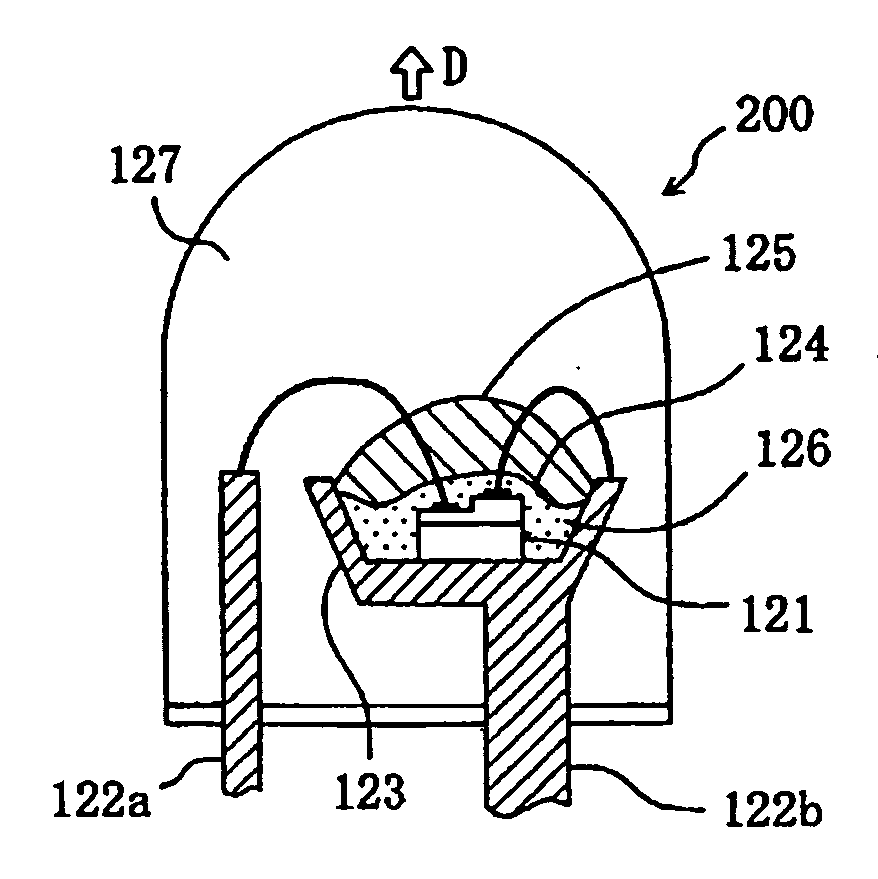

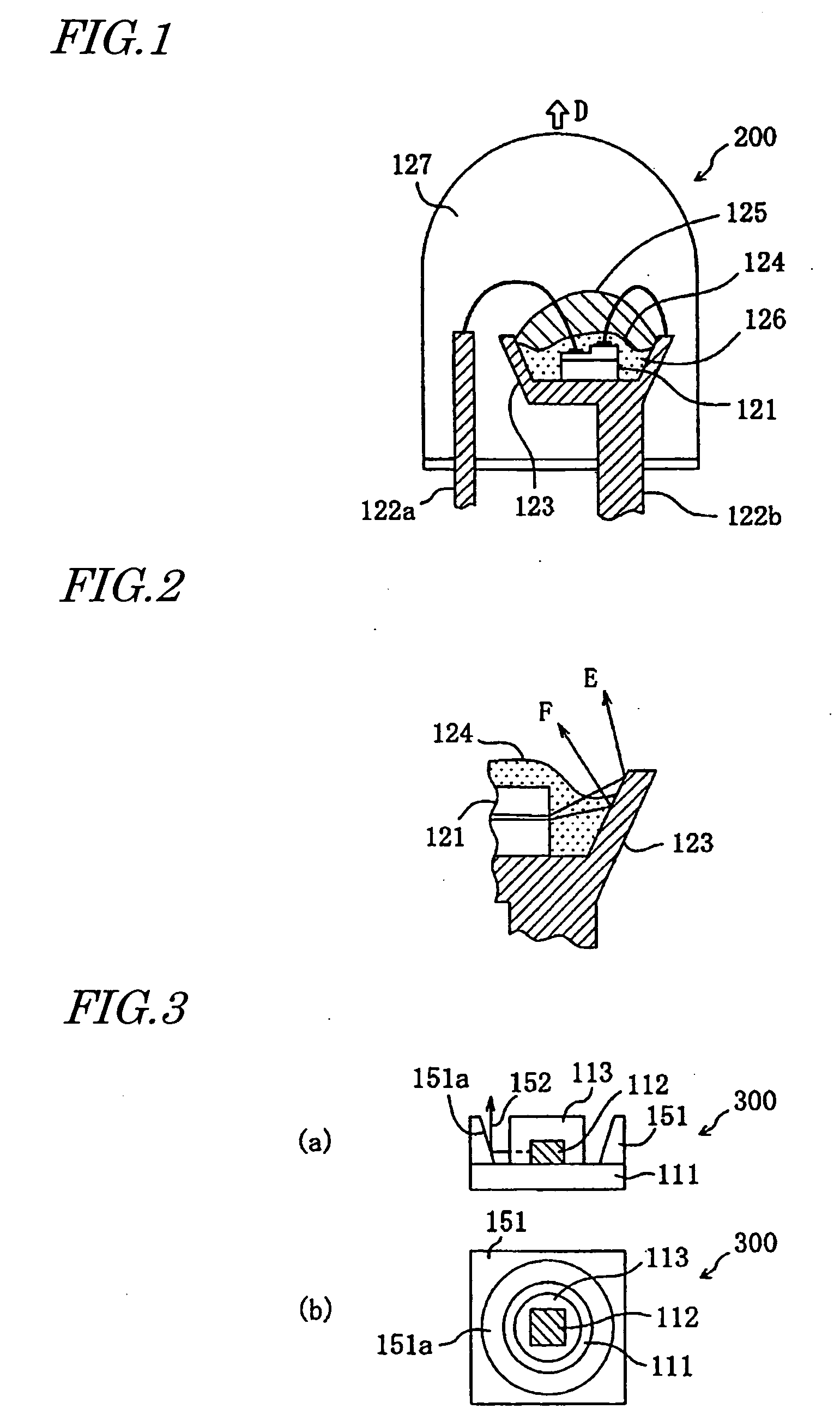

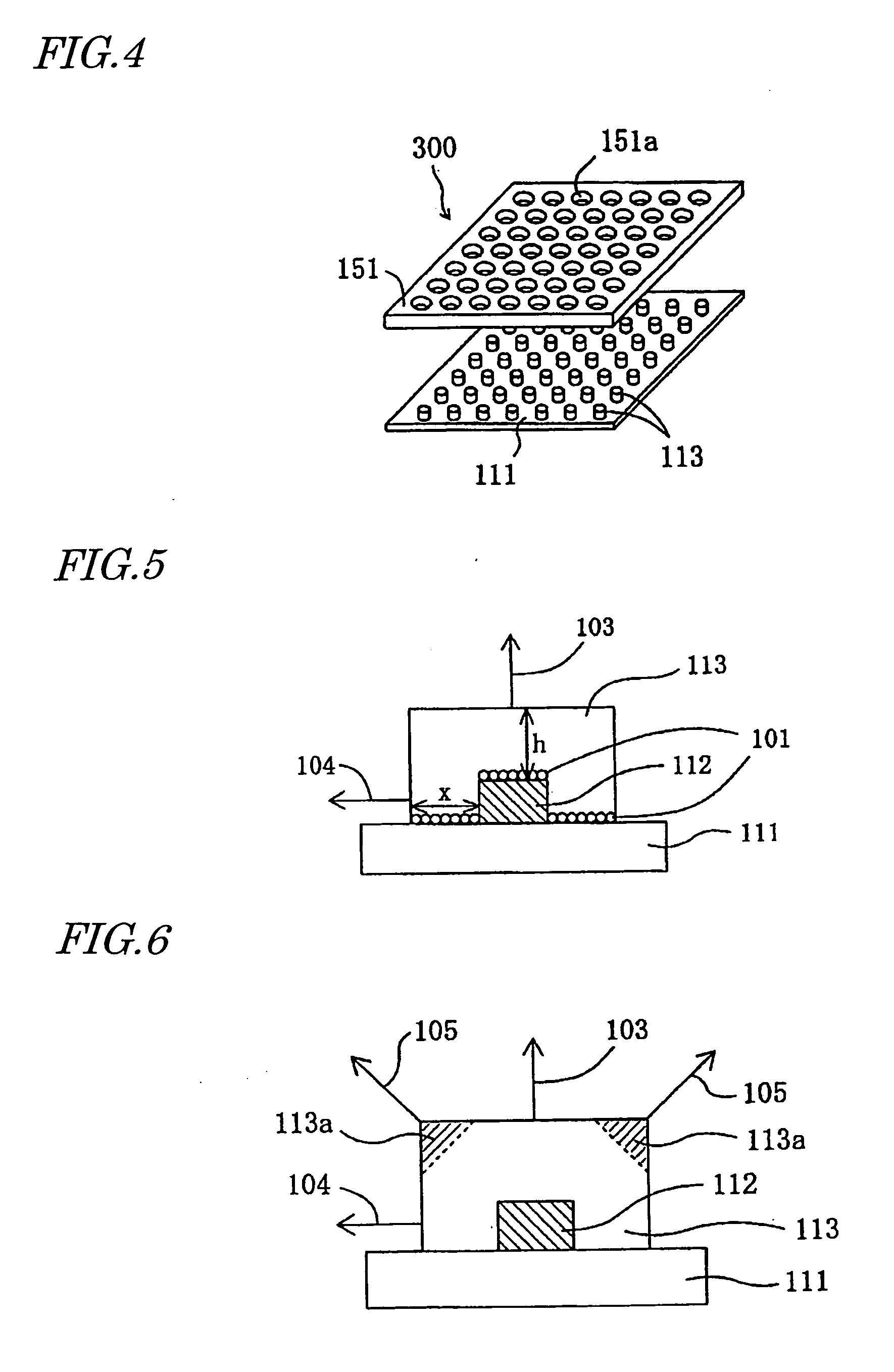

Method for Fabricating Led Illumination Light Source and Led Illumination Light Source

InactiveUS20080074032A1Eliminating color unevennessImprove throughputPlanar light sourcesPoint-like light sourcePhosphorFluorescence

An LED lamp according to the present invention includes: at least one LED chip 12 that is mounted on a substrate 11; a phosphor resin portion 13 that covers the LED chip 12; a lens 22 to act on the outgoing light of the phosphor resin portion 13; and an optical diffusion layer (light-transmissive resin portion 20), which is arranged between the phosphor resin portion 13 and the lens 22 and in which particles to scatter the light are dispersed.

Owner:SOVEREIGN PEAK VENTURES LLC

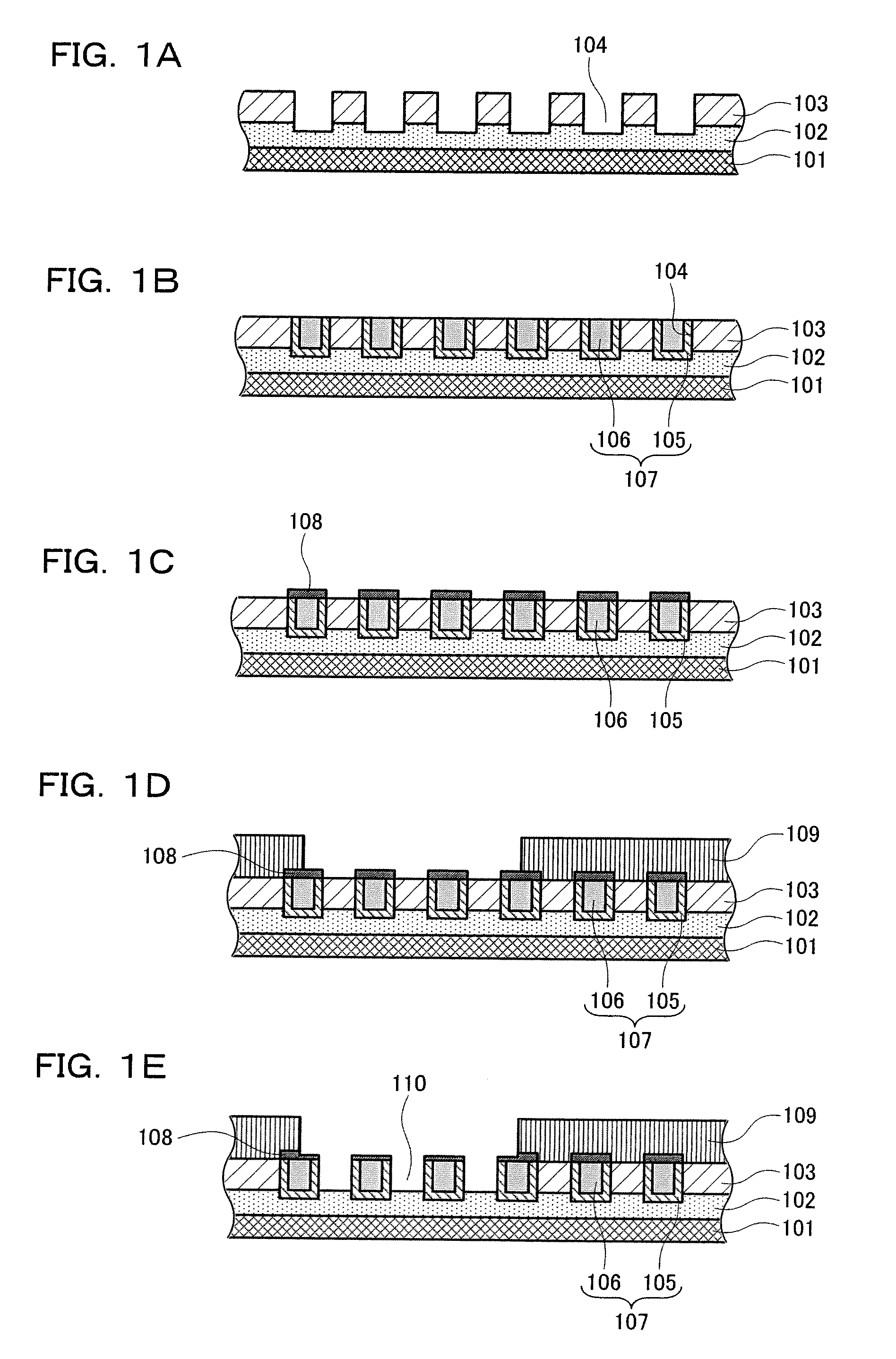

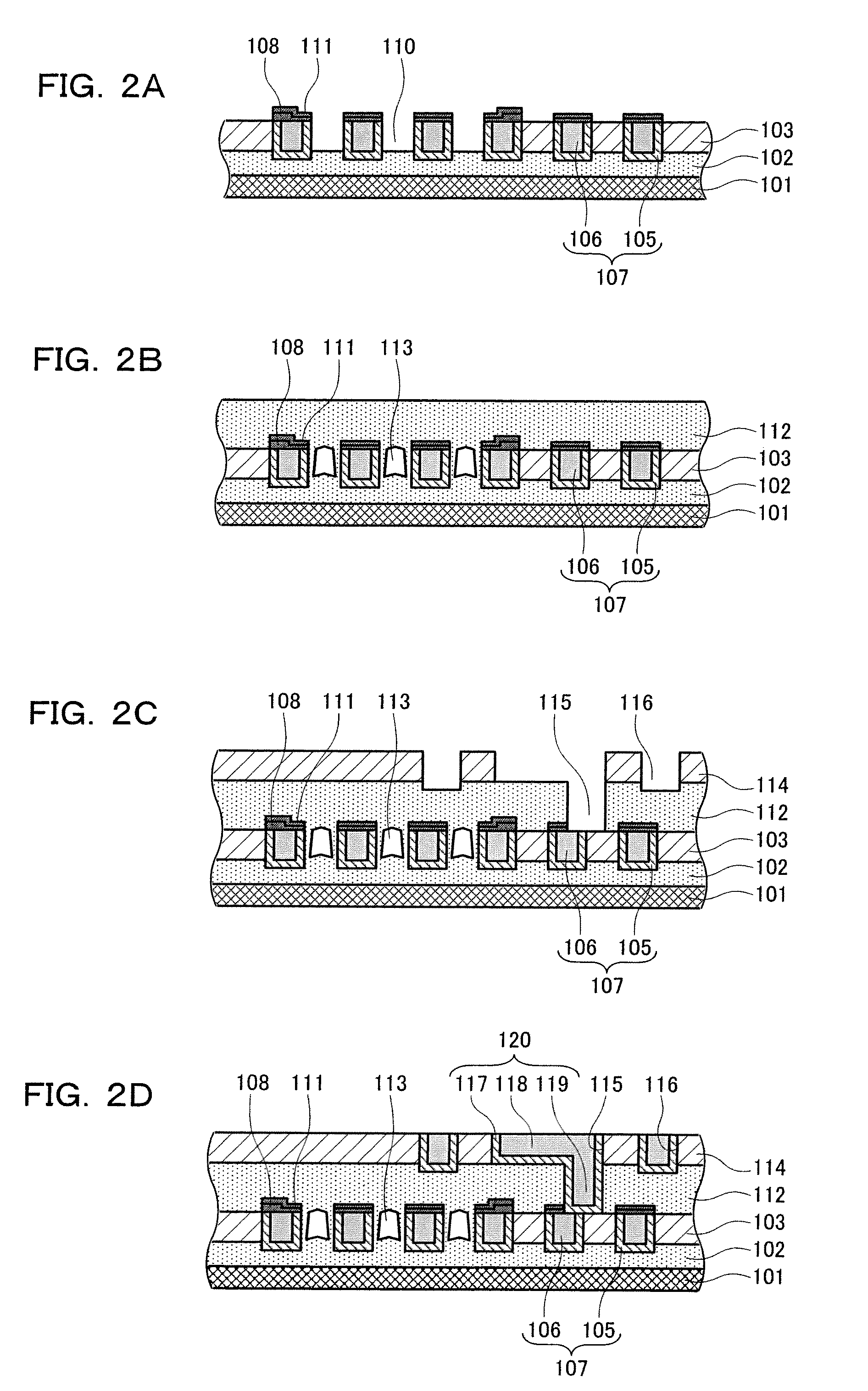

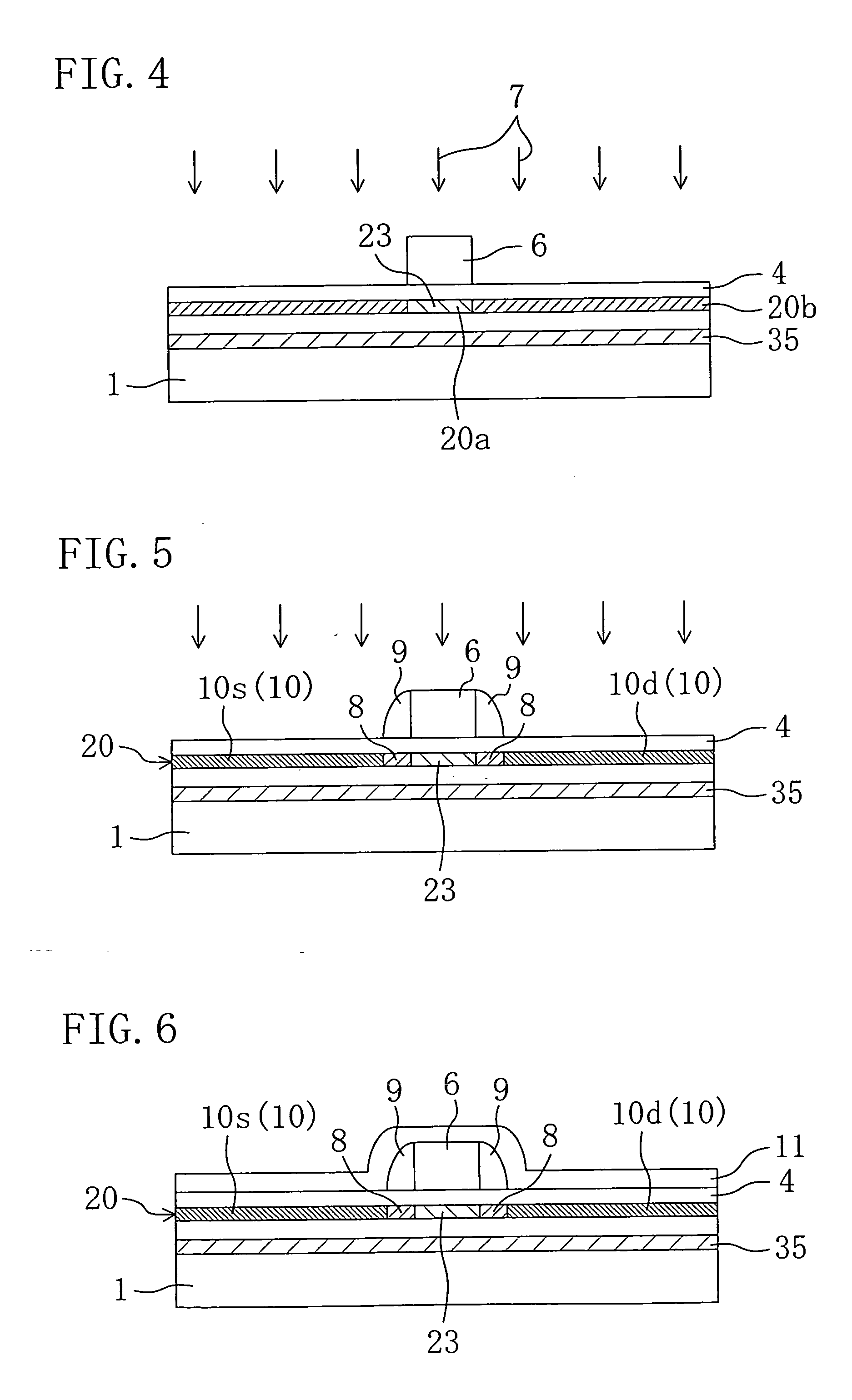

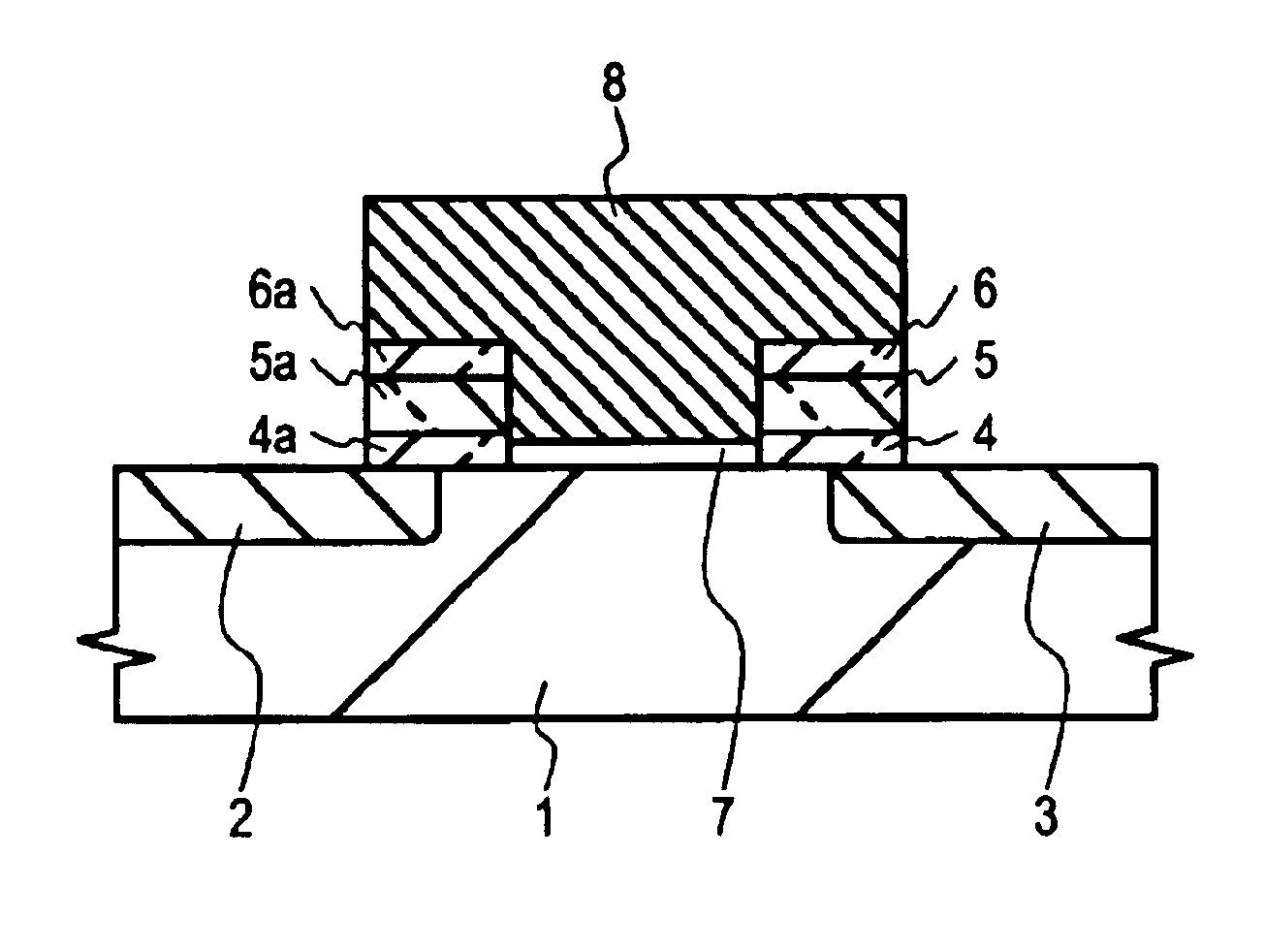

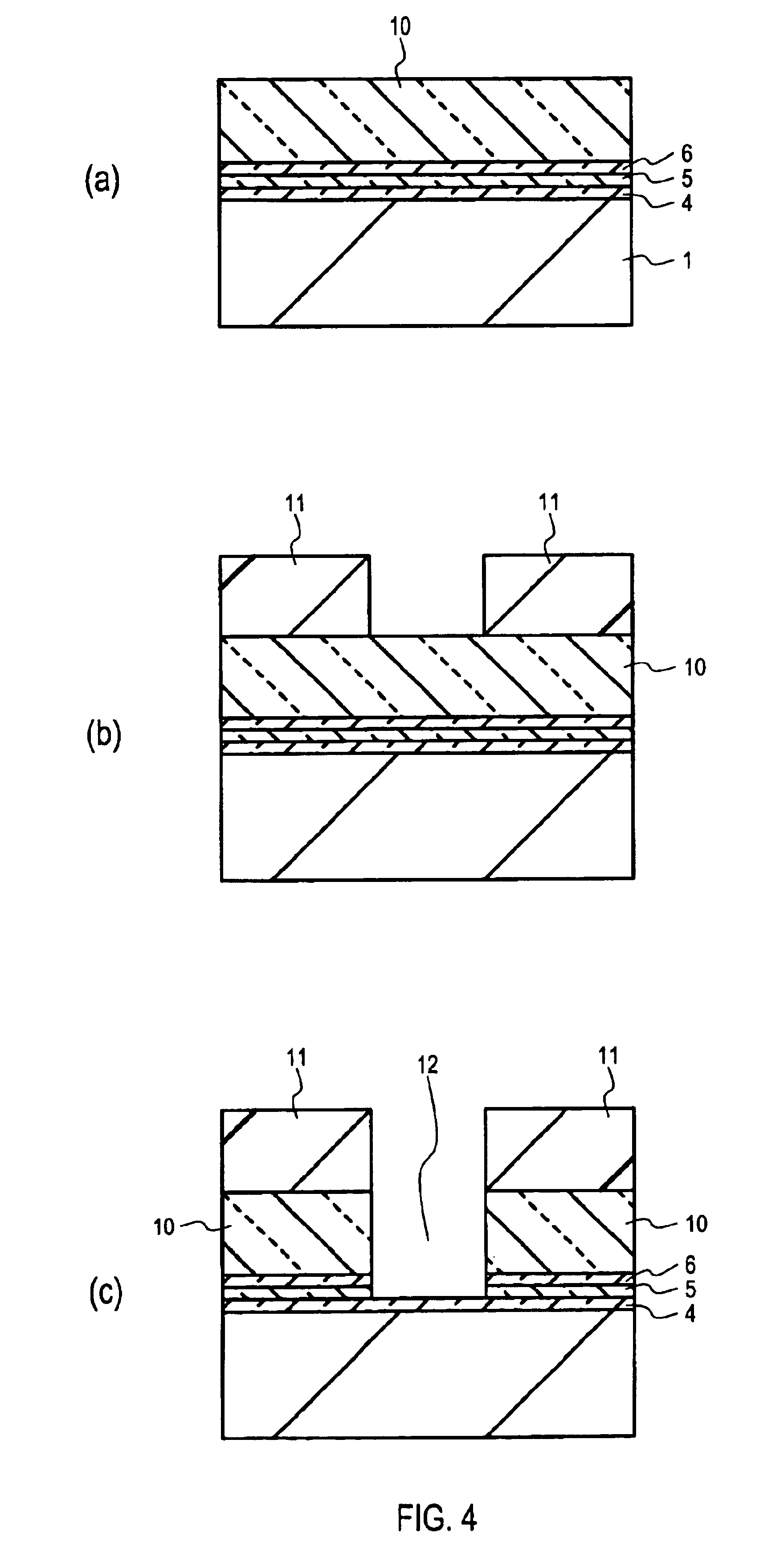

Nonvolatile semiconductor memory device, manufacturing method thereof, and operating method thereof

Nonvolatile memory elements are disclosed which can have increased capacity, reduced operating voltage and / or faster operating speeds. According to one embodiment, a nonvolatile memory element can include a first diffusion layer (2) and a second diffusion layer (3) formed in a main surface of a substrate (1). A laminate film can be formed near a first diffusion layer (2) and / or a second diffusion layers (3) that includes a first insulating film (4a or 4), a second insulating film (5a or 5), and a third insulating film (6a or 6). A gate insulating film (7) can be formed a channel region and gate electrode (8) can be formed to cover gate insulating film (7) and the laminate film(s) that has a T-shape. A gate electrode (8) can have end portions that sandwich a first insulating film (4a or 4), a second insulating film (5a or 5), and a third insulating film (6a or 6) with a first diffusion layer (2) and / or second diffusion layer (3).

Owner:RENESAS ELECTRONICS CORP

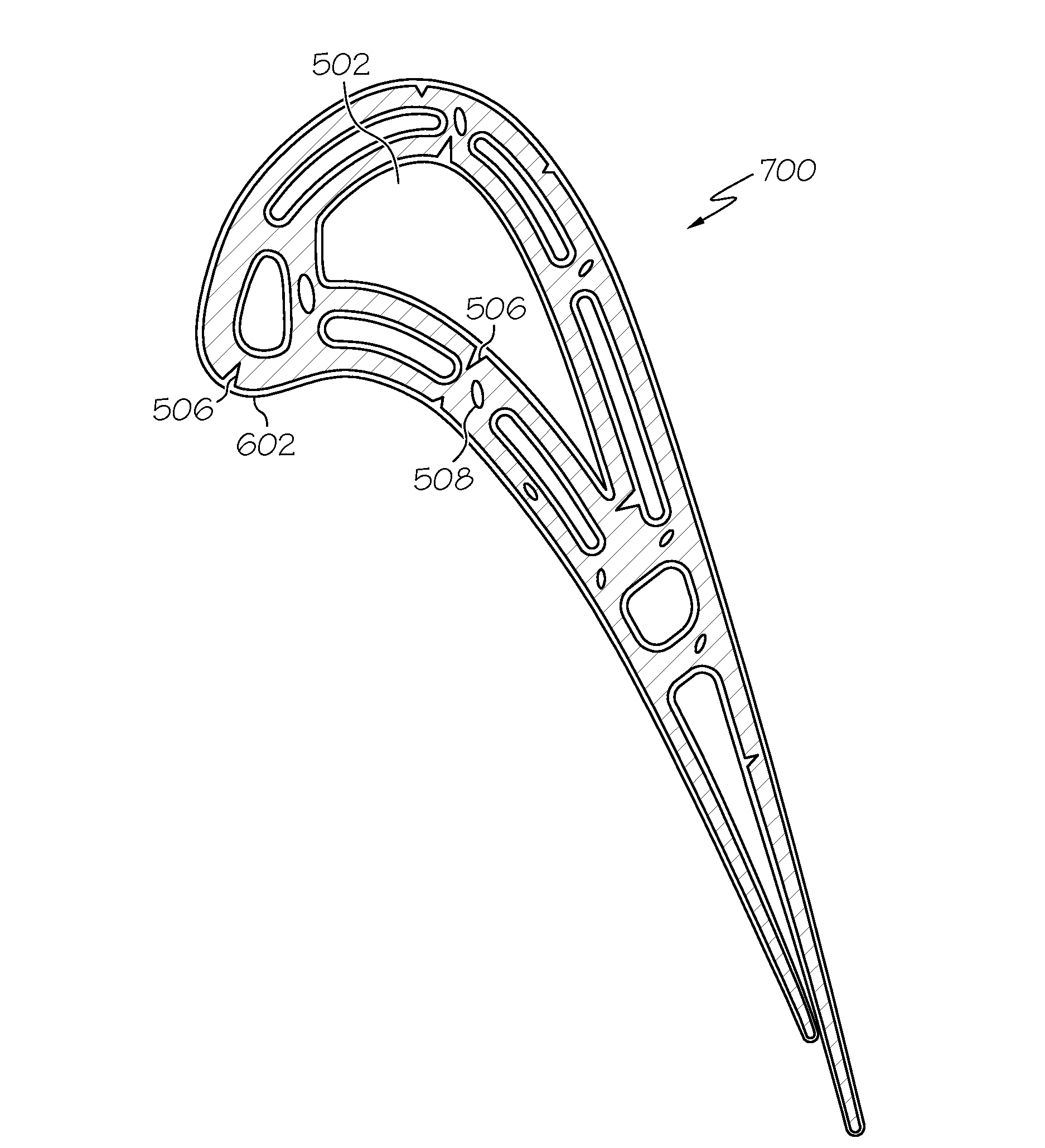

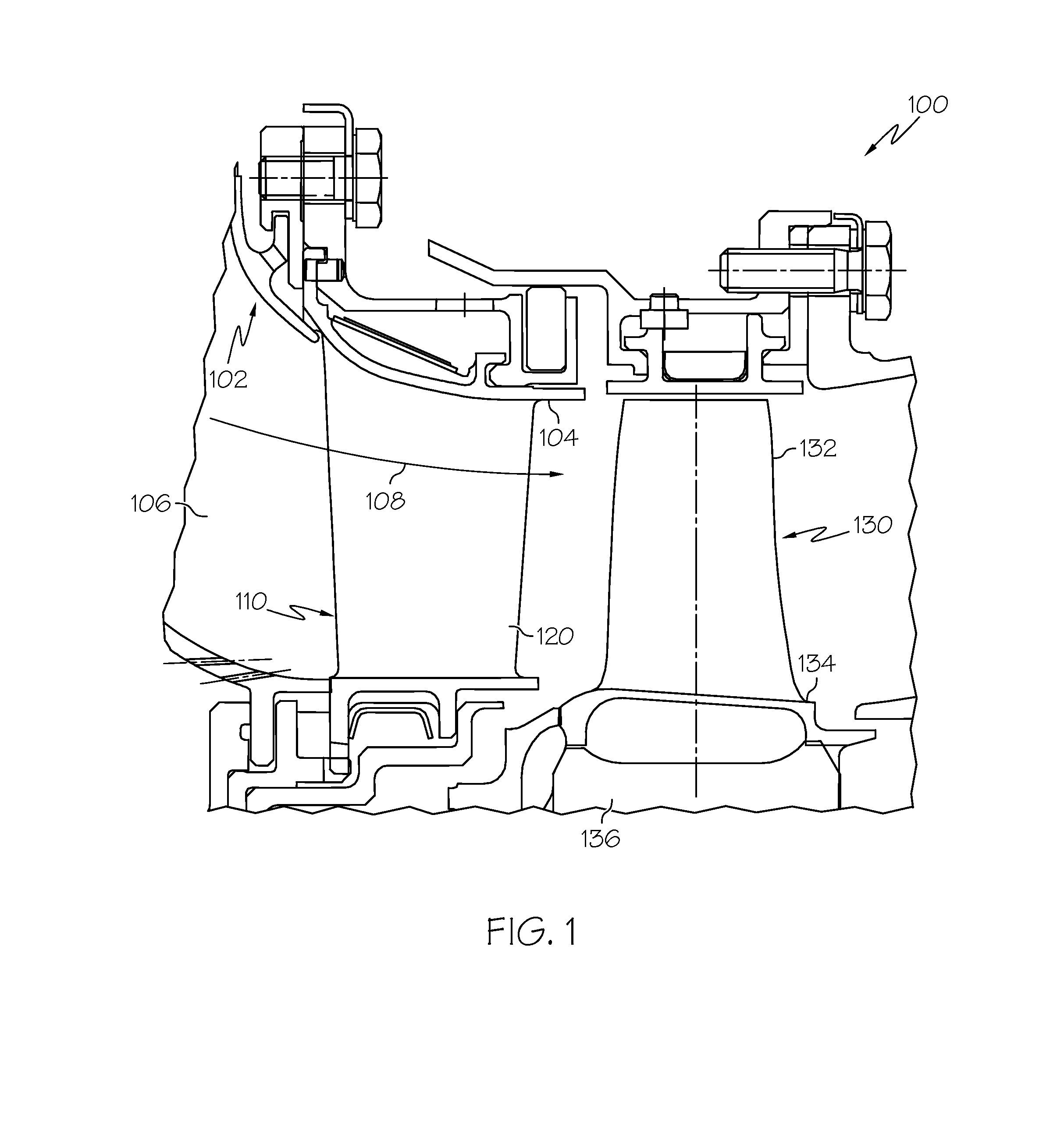

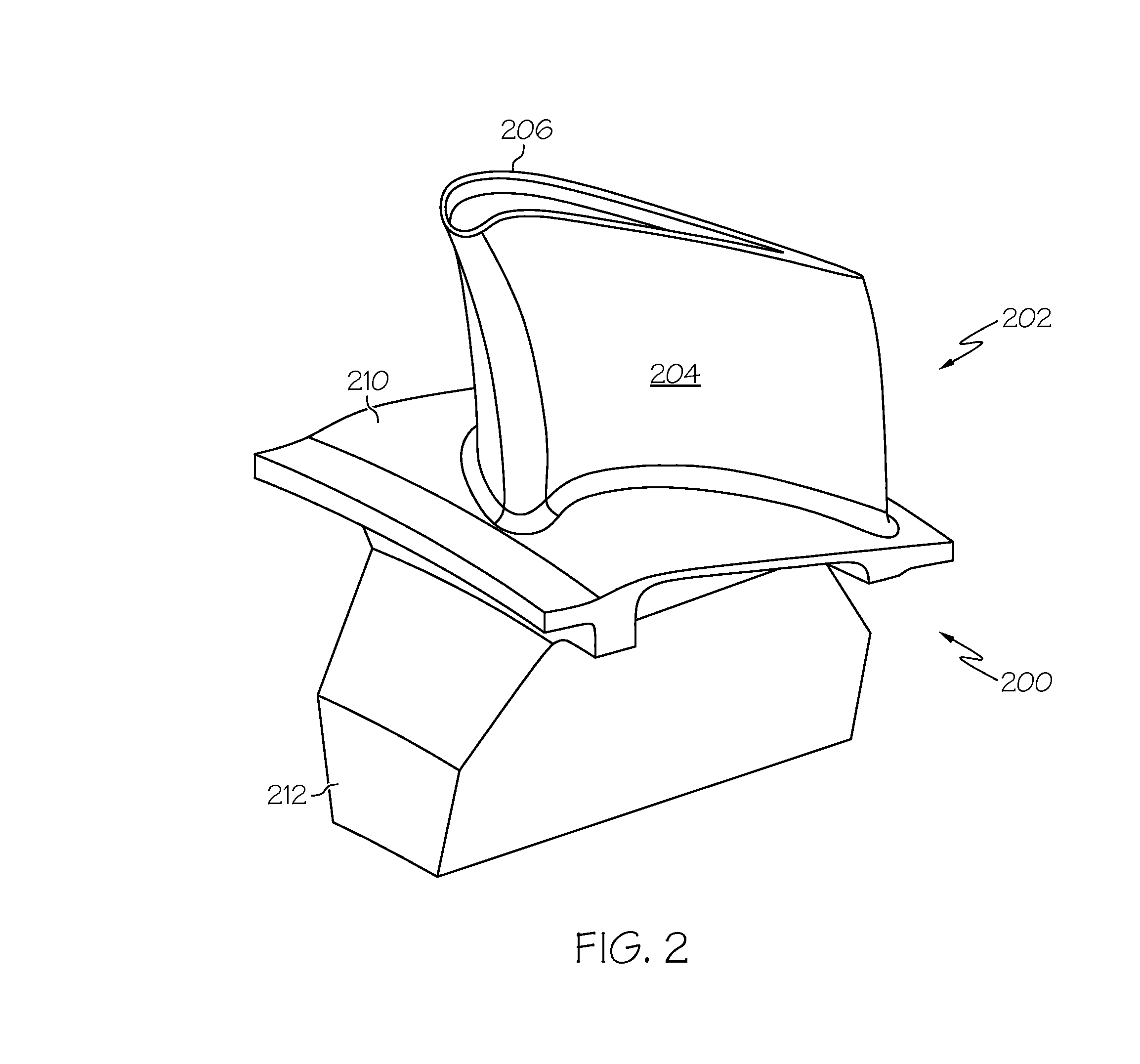

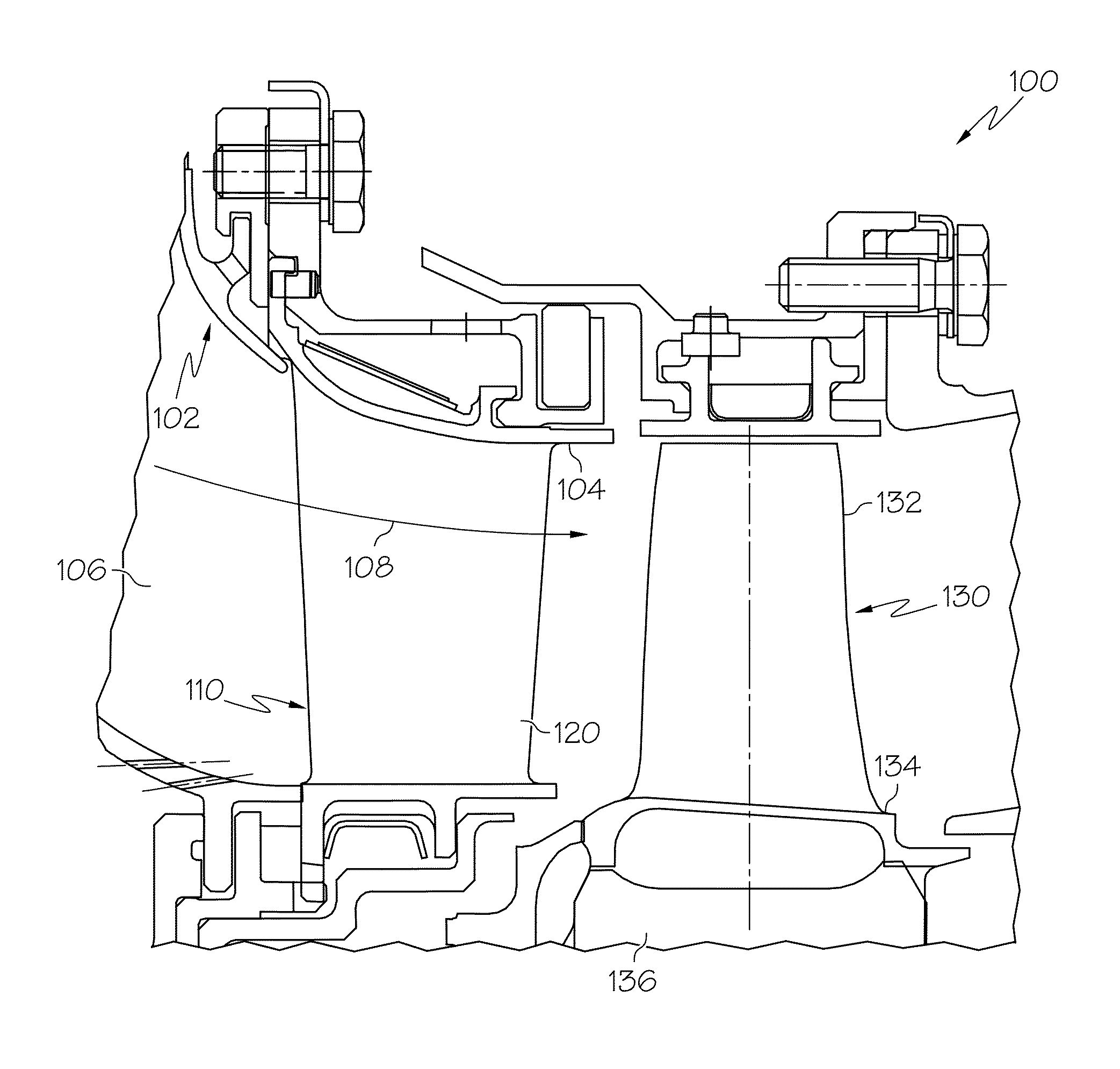

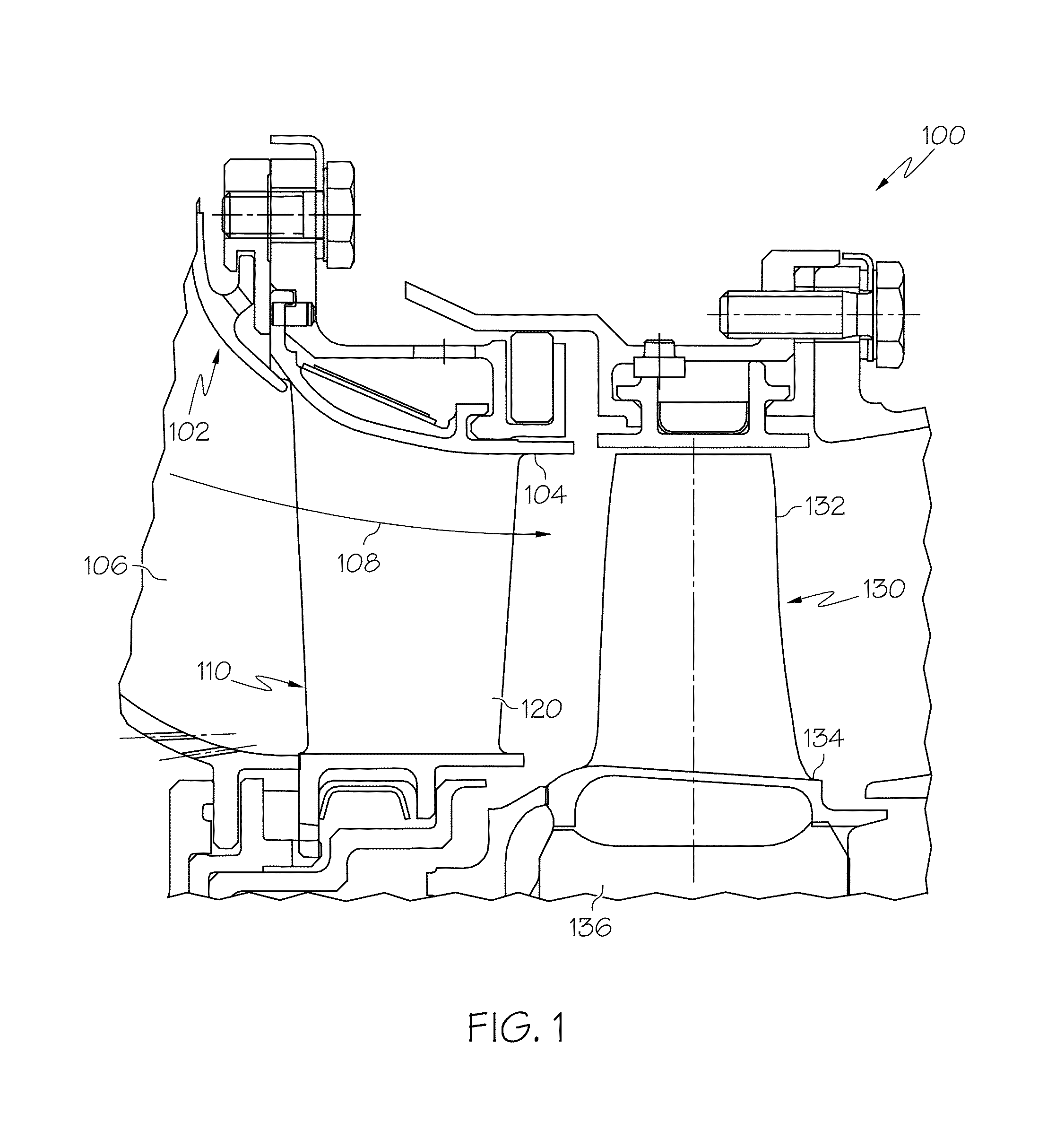

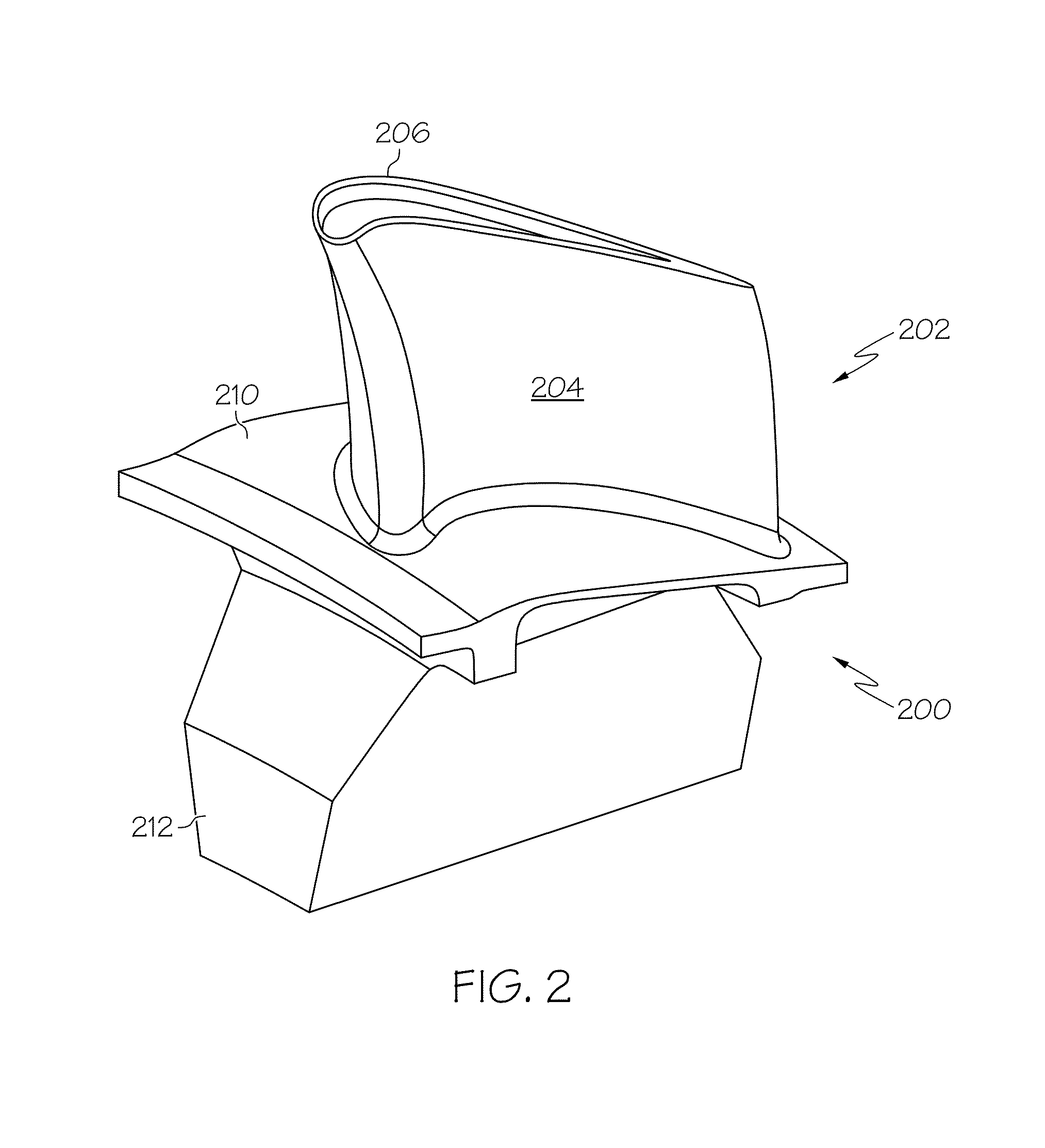

Methods for manufacturing components from articles formed by additive-manufacturing processes

ActiveUS20130071562A1Reduces and substantially eliminates internal defectImprove surface roughnessTurbinesAdditive manufacturing apparatusDiffusion layerAdditive layer manufacturing

A method is provided for manufacturing a component. The method includes forming a diffusion coating on a first intermediate article formed by an additive manufacturing process. The diffusion coating is removed from the first intermediate article forming a second intermediate article having at least one enhanced surface. The diffusion coating is formed by applying a layer of coating material on at least one surface of the first intermediate article and diffusion heat treating the first intermediate article and the layer. The diffusion coating comprises a surface additive layer and a diffusion layer below the surface additive layer. The formation of the diffusion coating and removal thereof may be repeated at least once.

Owner:HONEYWELL INT INC

Semiconductor device

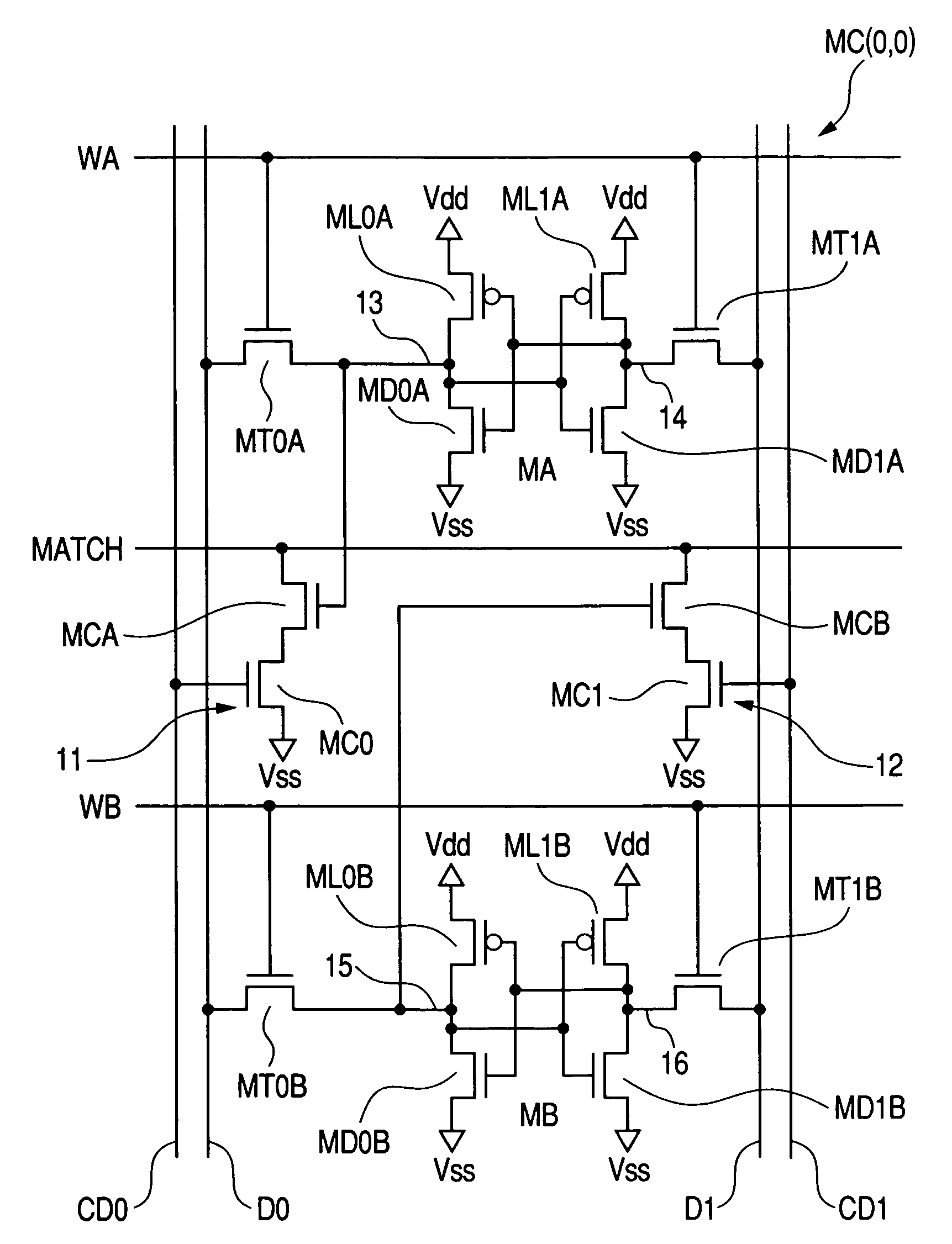

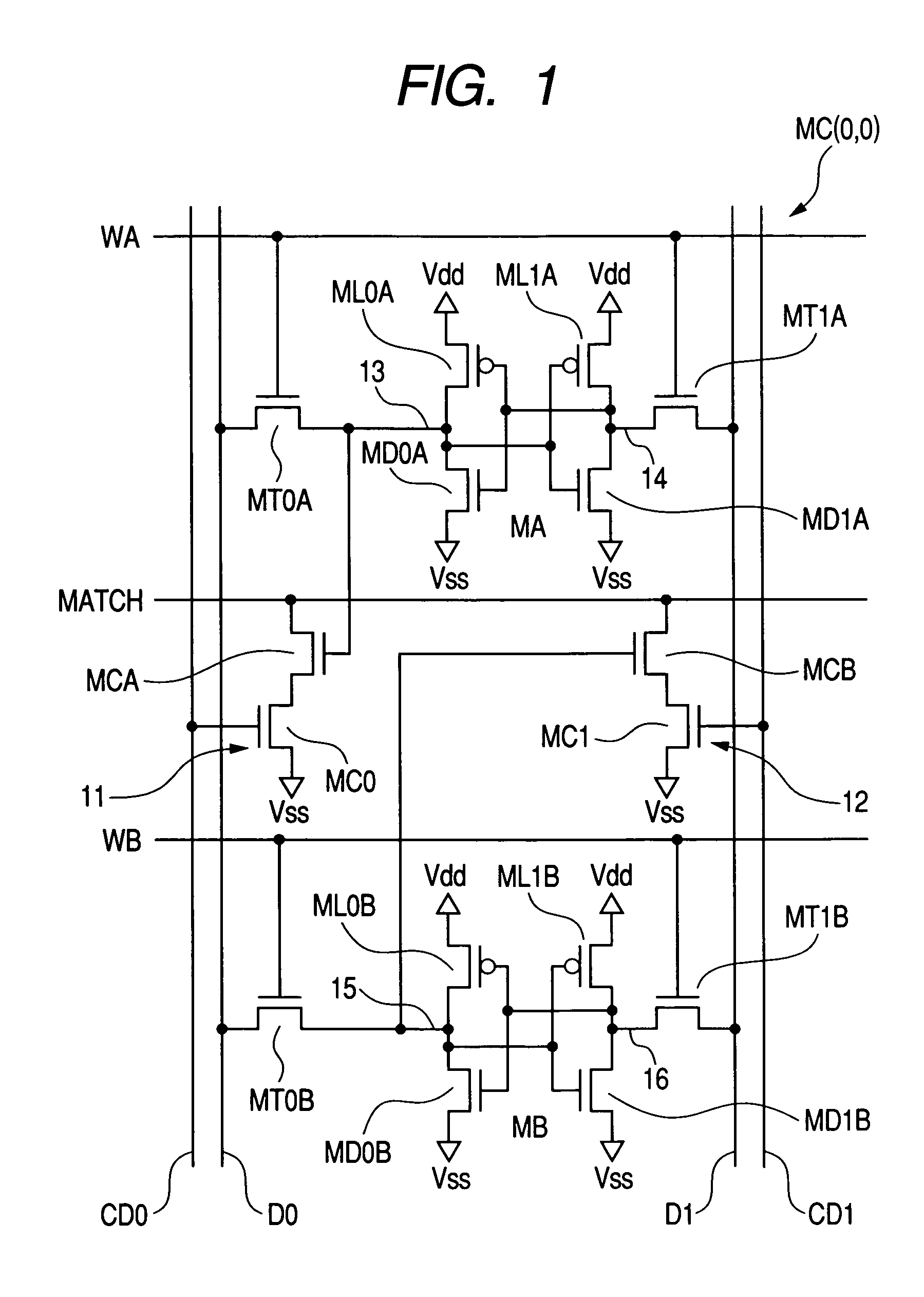

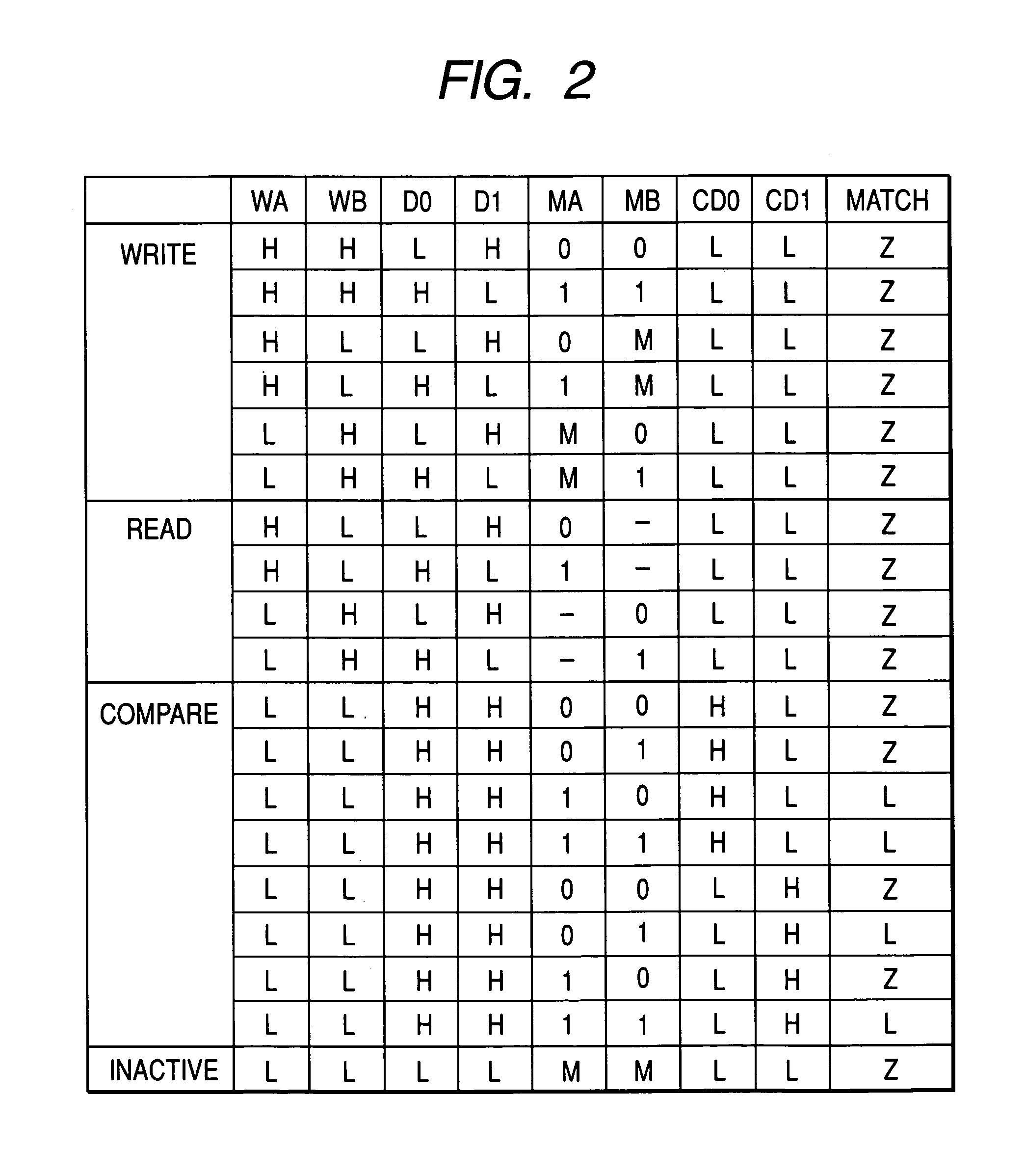

InactiveUS7009862B2Reduce manufacturing costIncrease productionTransistorSolid-state devicesProcess conditionsDiffusion layer

Data lines (D0, D1) are shared by a first storage portion (MA) and a second storage portion (MB), and furthermore, a first transistor (MC0) coupled to a first comparison data portion (CD0) and a second transistor (MCA) coupled to the storage node of a first storage portion are connected in series to form a first comparing circuit (11), and a third transistor (MC1) coupled to a second comparison data line (CD1) and a fourth transistor (MCB) coupled to the storage node of the second storage portion are connected in series to form a second comparing circuit (12). Consequently, it is possible to enhance a symmetry in the layout of a diffusion layer and a wiring layer and to achieve the easiness of a layout in which a memory cell is line symmetrical with respect to a center line passing through a center thereof. Thus, a manufacturing process condition can easily be optimized and a variation in a manufacturing process can be reduced so that the microfabrication of the memory cell can be achieved.

Owner:HITACHI LTD

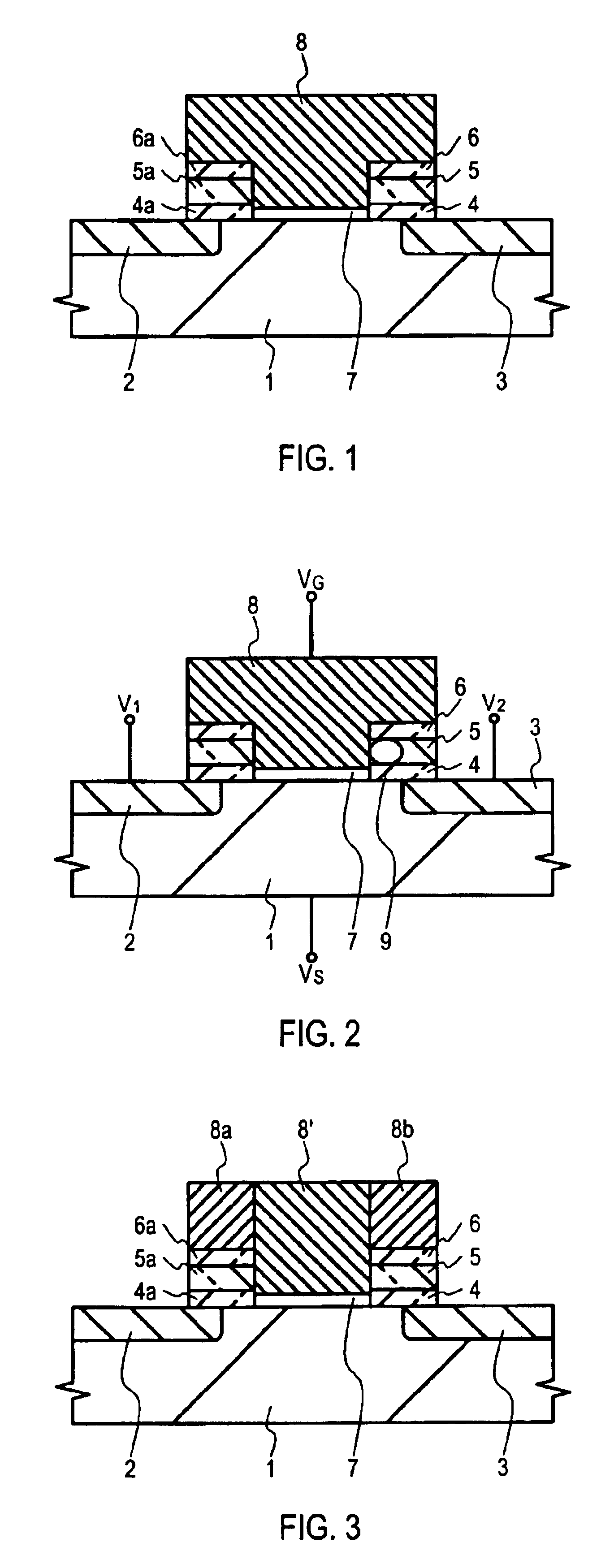

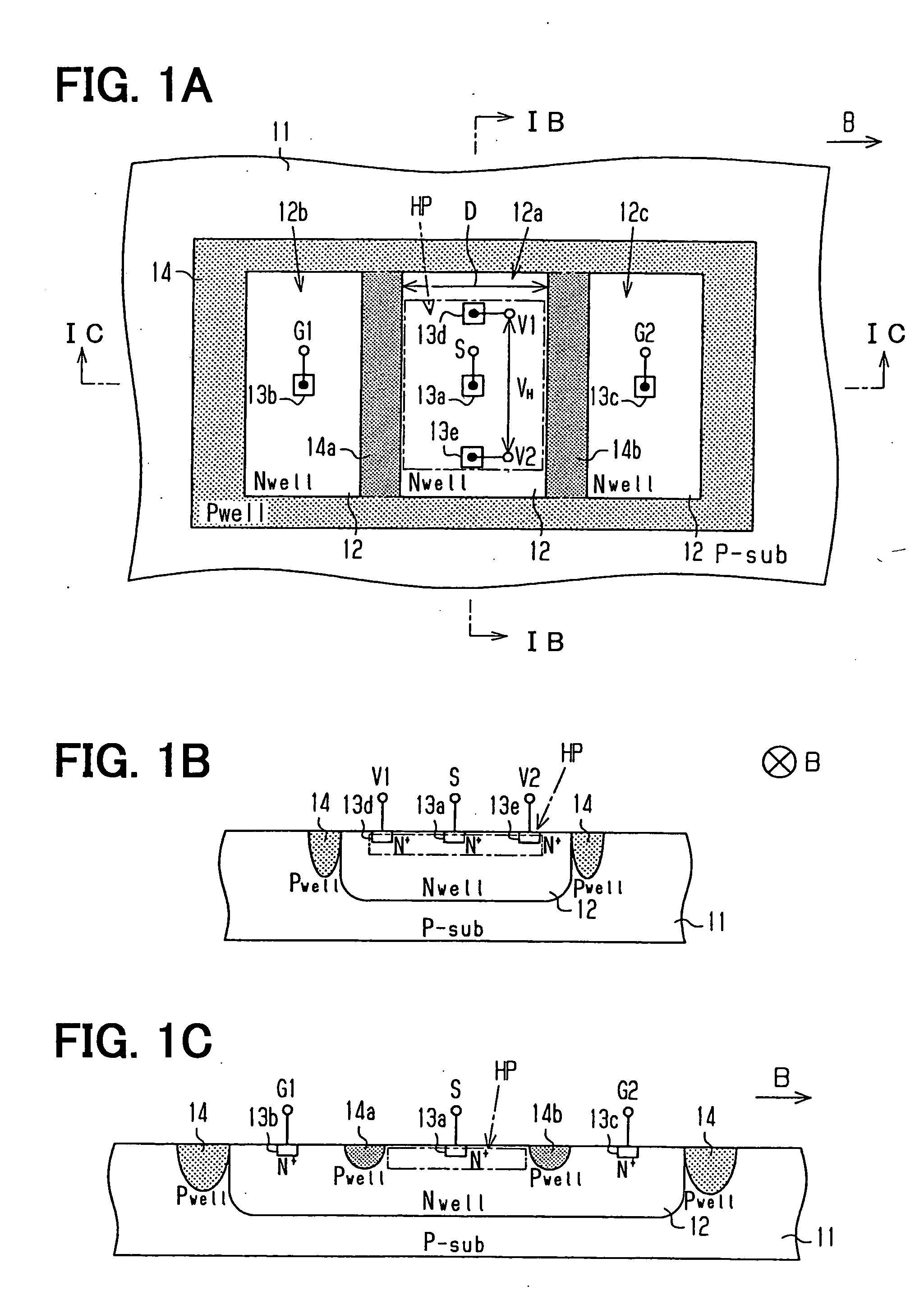

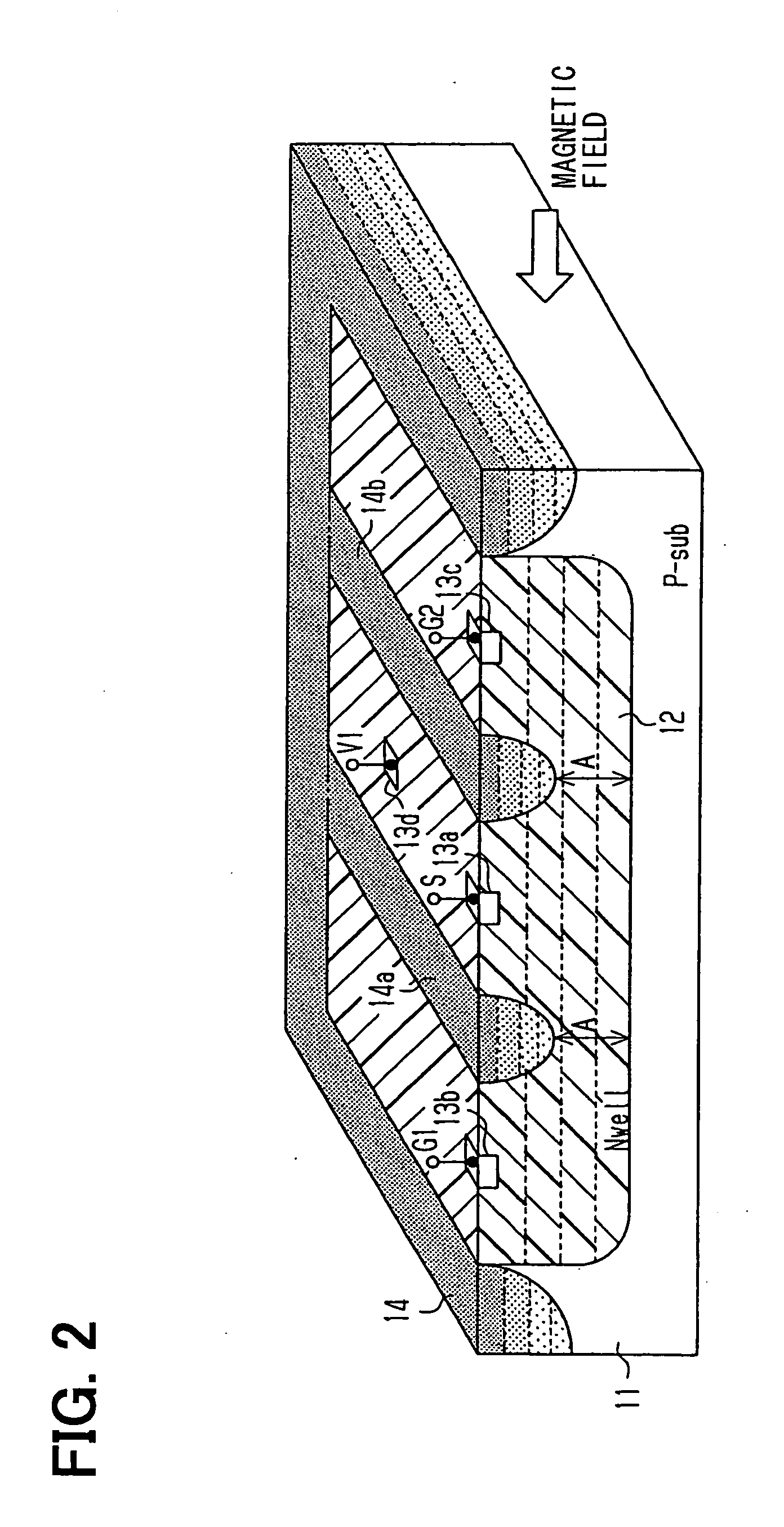

Magnetic sensor having vertical hall device and method for manufacturing the same

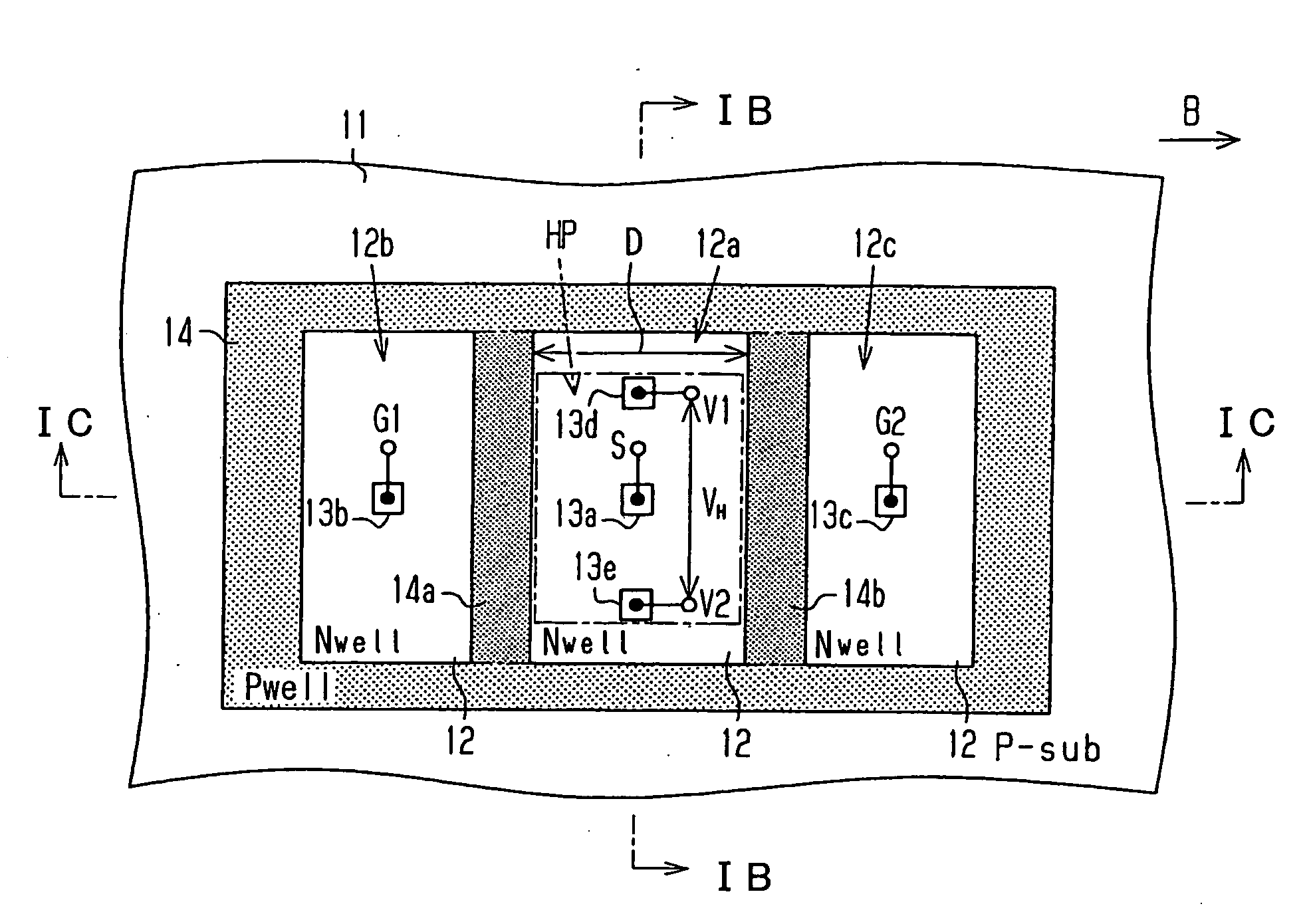

InactiveUS20050230770A1Increase freedomSimple designTransistorSolid-state devicesDiffusion layerSemiconductor

A vertical Hall device includes: a substrate; a semiconductor region having a first conductive type and disposed in the substrate; and a magnetic field detection portion disposed in the semiconductor region. The magnetic field detection portion is capable of detecting a magnetic field parallel to a surface of the substrate in a case where a current flows through the magnetic field detection portion in a vertical direction of the substrate. The semiconductor region is a diffusion layer including a conductive impurity doped and diffused therein. The semiconductor region is made of diffusion layer so that the device has high design degree of freedom.

Owner:DENSO CORP

Liquid crystal display

ActiveUS20100079704A1Avoid changeImprove luminanceNon-linear opticsLiquid-crystal displayGreen-light

A liquid crystal display includes, among others, a light diffusion layer comprising a color conversion media layer and a non-conversion layer arranged on the second substrate and a backlight assembly to supply light to the first substrate and the second substrate. The backlight assembly supplies various wavelengths of lights, including blue light or UV ray. The blue rights through the liquid crystal layer enters the color conversion media layers and may generates red lights and green lights. In this case, blue lights go through non-conversion layer and diffuse and scatter out blue lights. The UV rays through the liquid crystal layer enters the color conversion media layers and may generates red light, green lights and blue lights.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

Electrochemical apparatus with barrier layer protected substrate

InactiveUS20080003496A1High crystallinityMore flexibleCell electrodesBattery isolationDiffusion barrierElectrochemistry

The present invention relates generally to fabricating well performing thin-film batteries onto metallic substrates, polymeric substrates, and doped and undoped silicon substrates. More specifically, the invention may include fabricating an appropriate diffusion barrier layer between the substrate and the battery part of the present invention that separates said two parts chemically during the entire battery fabrication process and the operation and storage conditions of the electrochemical apparatus during its entire lifetime. In one embodiment of the present invention, thin-film batteries fabricated onto a thin, flexible, stainless steel foil substrate using an appropriate diffusion layer show uncompromised electrochemical performance compared to thin-film batteries fabricated onto ceramic substrates when using a 700° C. post-deposition anneal process for the LiCoO2 positive cathode.

Owner:SAPURAST RES

Solid state image pickup device and camera

InactiveUS7408210B2Television system detailsTelevision system scanning detailsCapacitanceCharge carrier

An object of the present invention is to simultaneously realize the enlargement of a dynamic range and the downsizing of a pixel. An additional capacitor CS is composed by using: a first capacitor formed of a first diffusion layer, a second diffusion layer and a P well by layering the P well, the first diffusion layer, a first dielectric film, a first polysilicon layer, a second dielectric film and a second polysilicon layer; a second capacitor formed of the second diffusion layer, the first polysilicon layer and the first dielectric film; and a third capacitor formed of the first polysilicon layers, a second polysilicon layer, and a second dielectric film. Thereby, the additional capacitor CS for accumulating carriers overflown from a photodiode PD can secure a required capacitance value while making its size as small as possible.

Owner:CANON KK

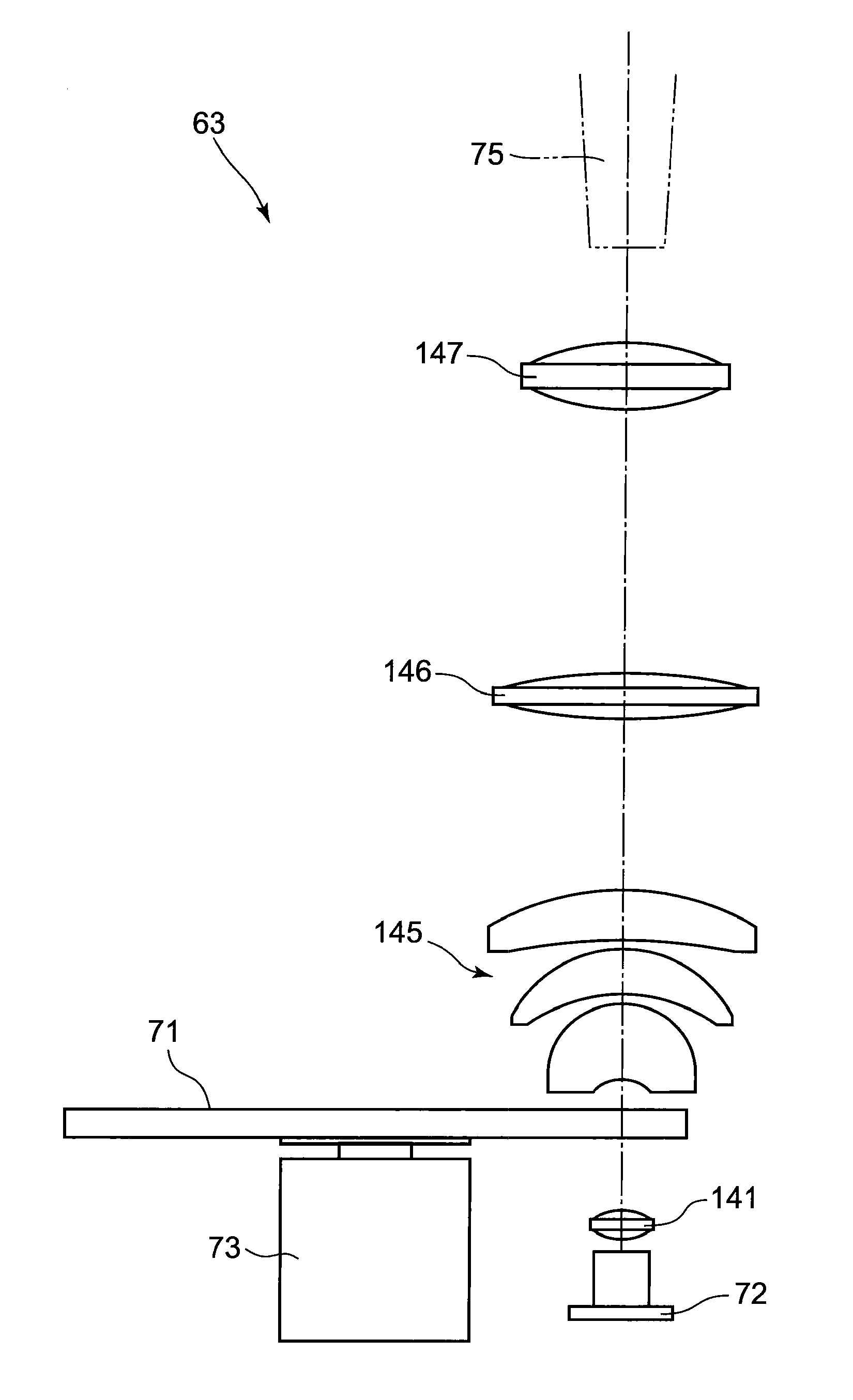

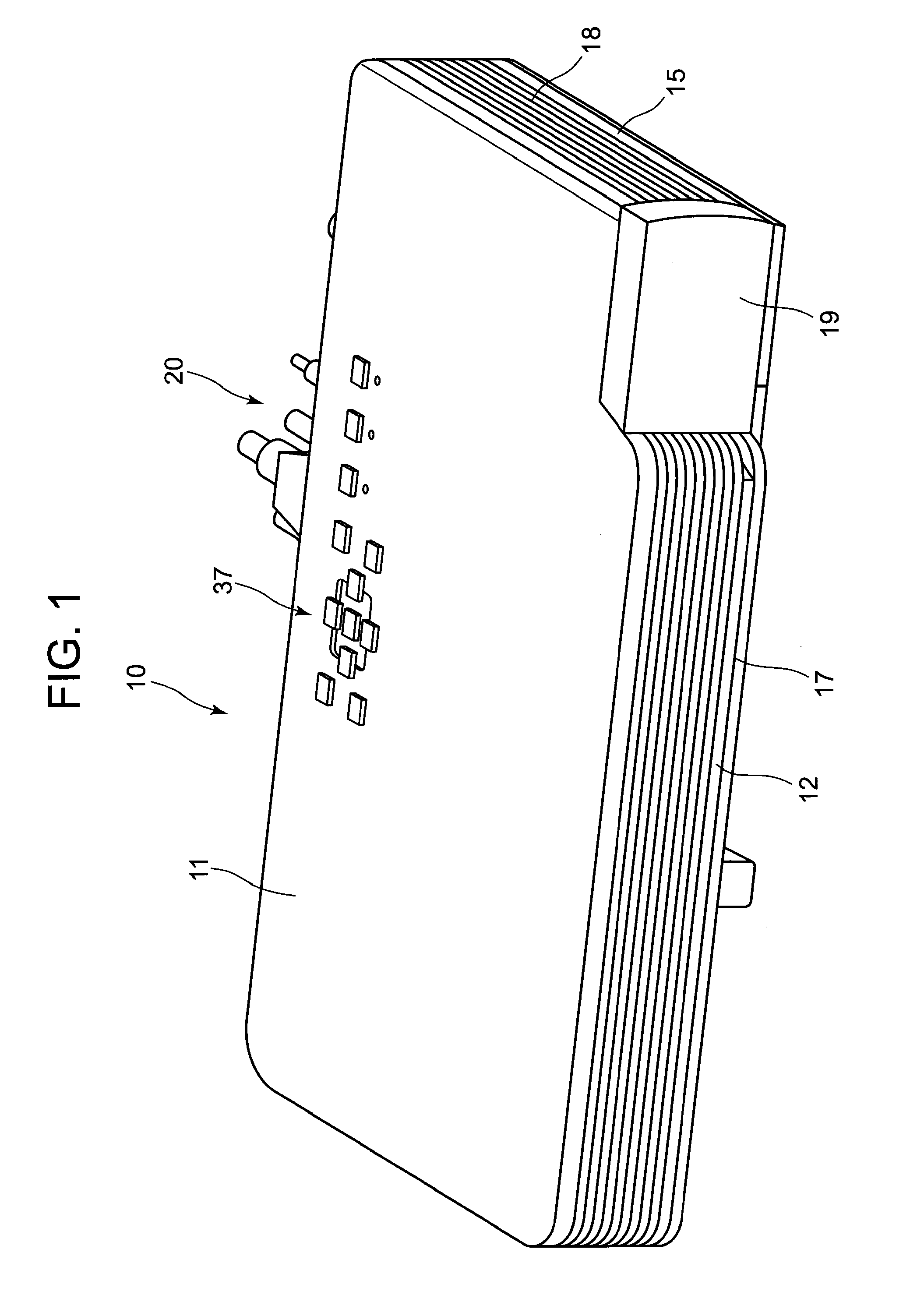

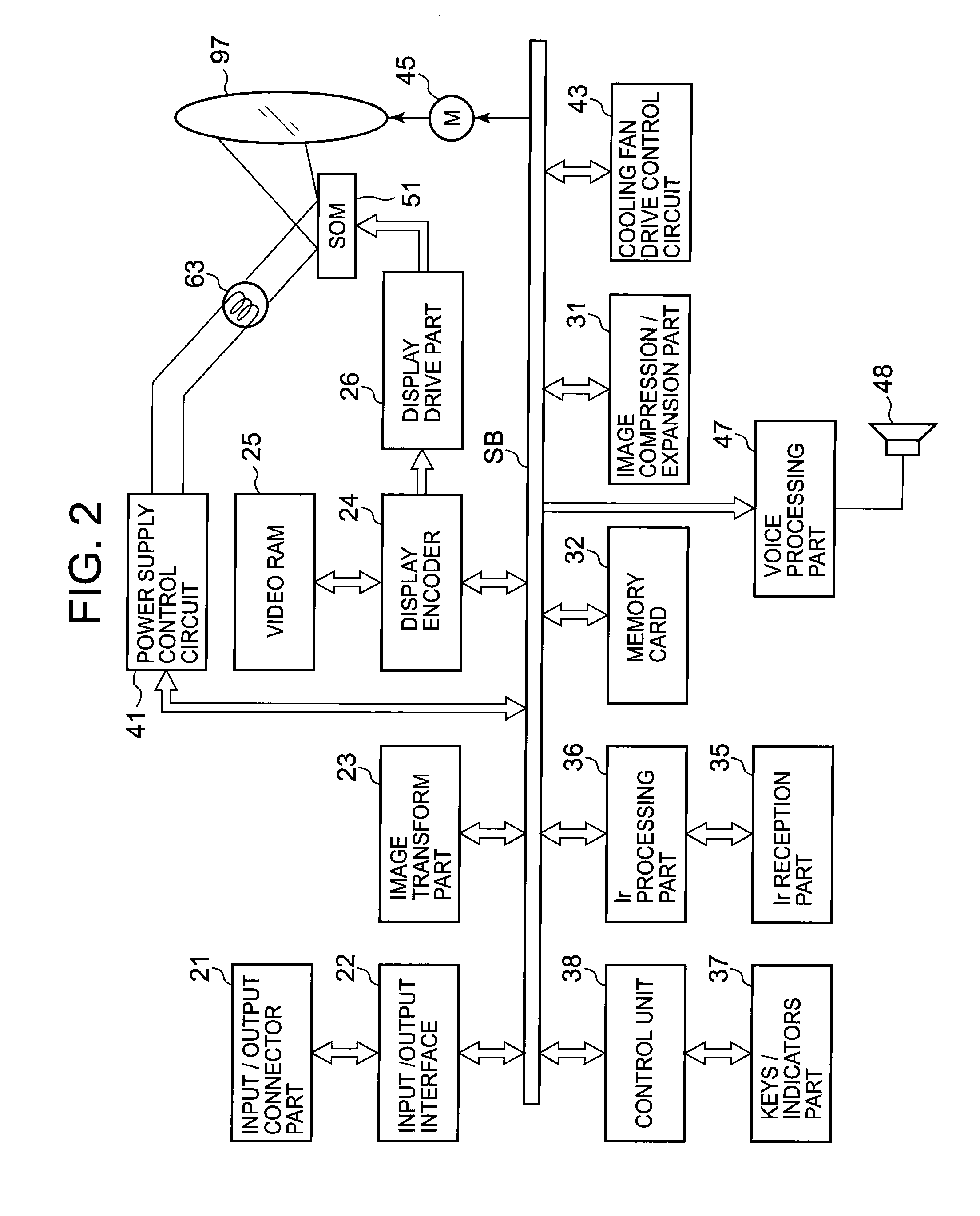

Light source unit utilizing laser for light source and projector

A projector includes a light source unit 63, a light guiding device 75, a display device, a projection side optical system and a projector control means, the light source unit 63 includes a light source 72 which emits laser light in the wavelength band of blue, a light emitting wheel 71 disposed on an optical axis of the light source 72 and a wheel motor 73 for driving to rotate the light emitting wheel 71, and the light emitting wheel 71 is formed of a circular substrate having a diffusion layer on a predetermined surface thereof, the diffusion layer being made up of minute irregularities which are formed directly on a surface of the circular substrate.

Owner:CASIO COMPUTER CO LTD

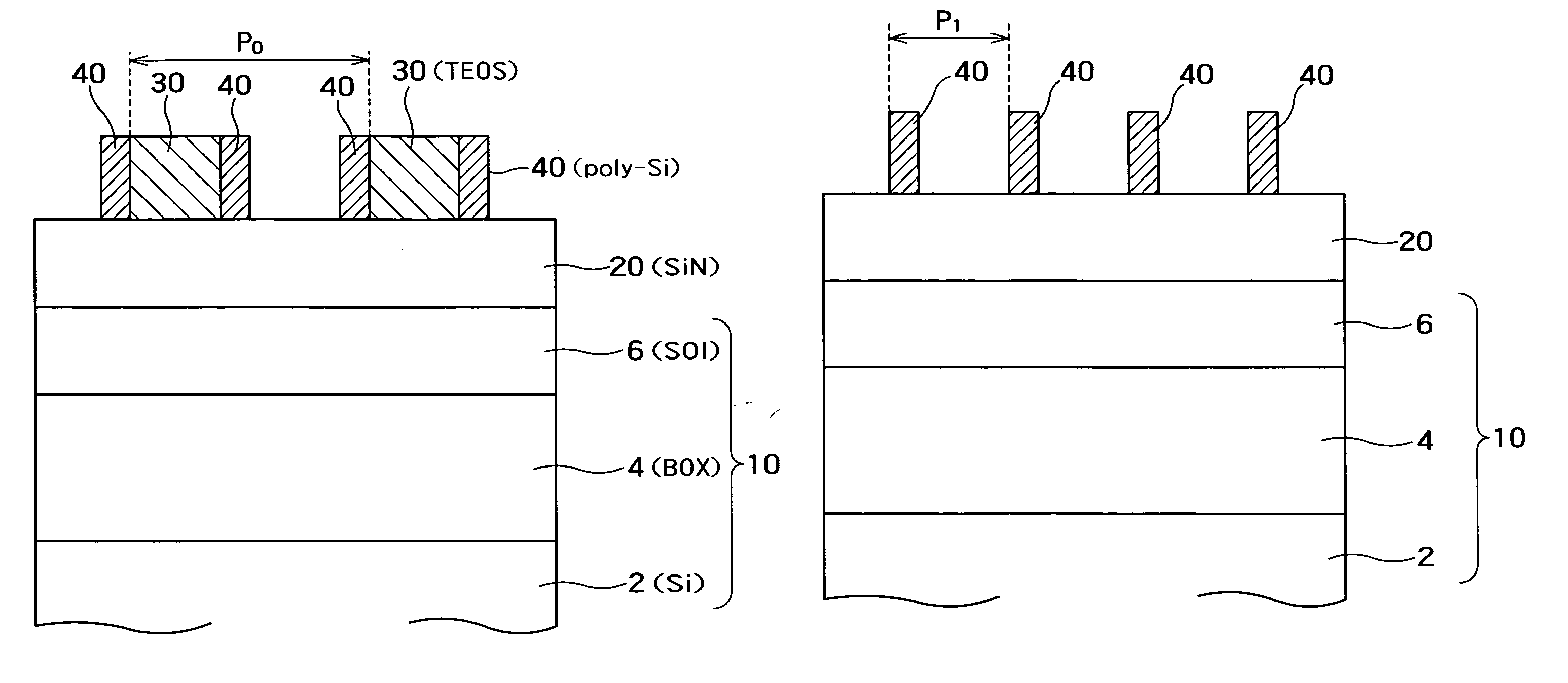

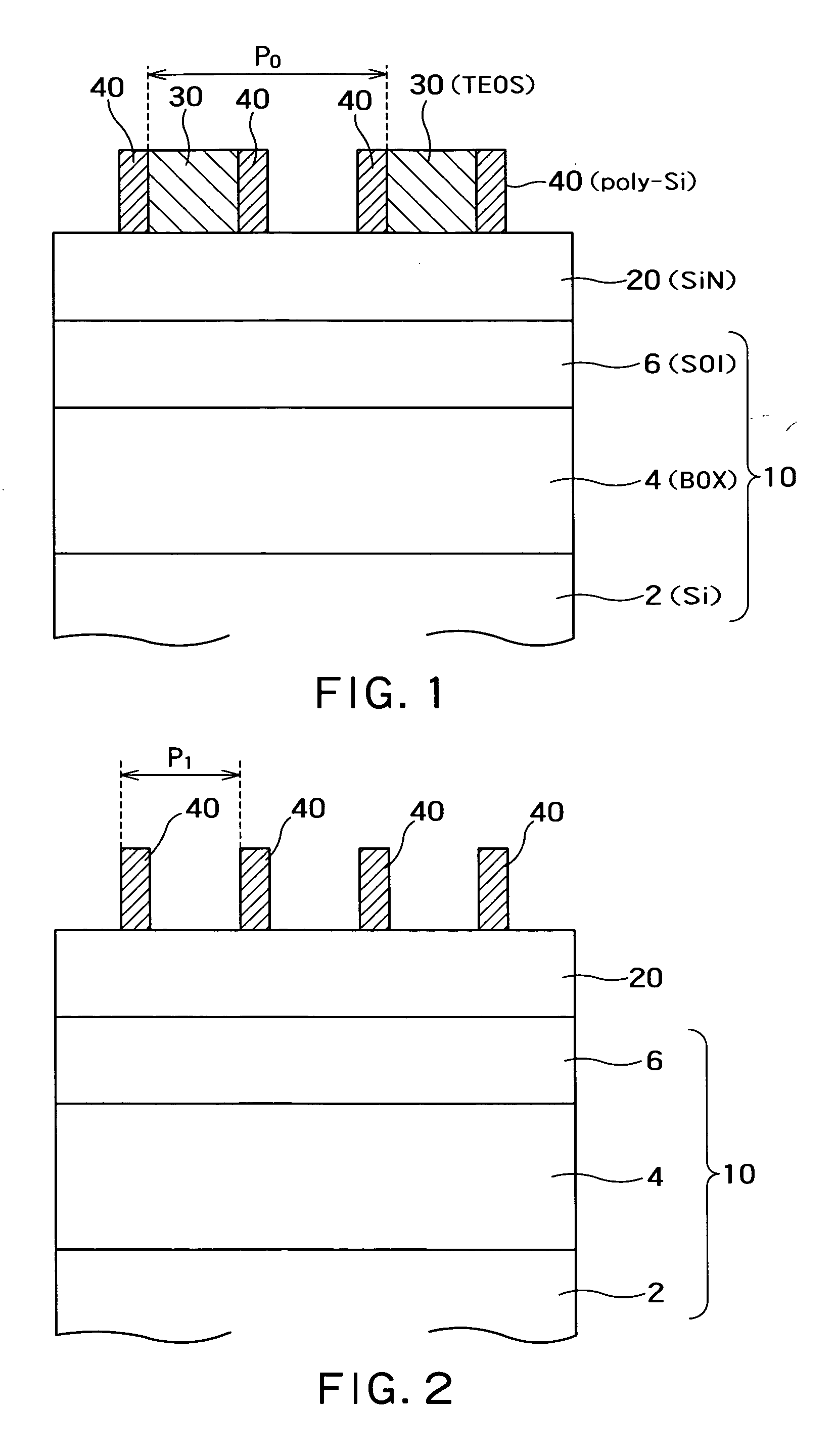

Semiconductor device and method of manufacturing semiconductor device

ActiveUS20070004117A1Solid-state devicesSemiconductor/solid-state device manufacturingInsulation layerSemiconductor materials

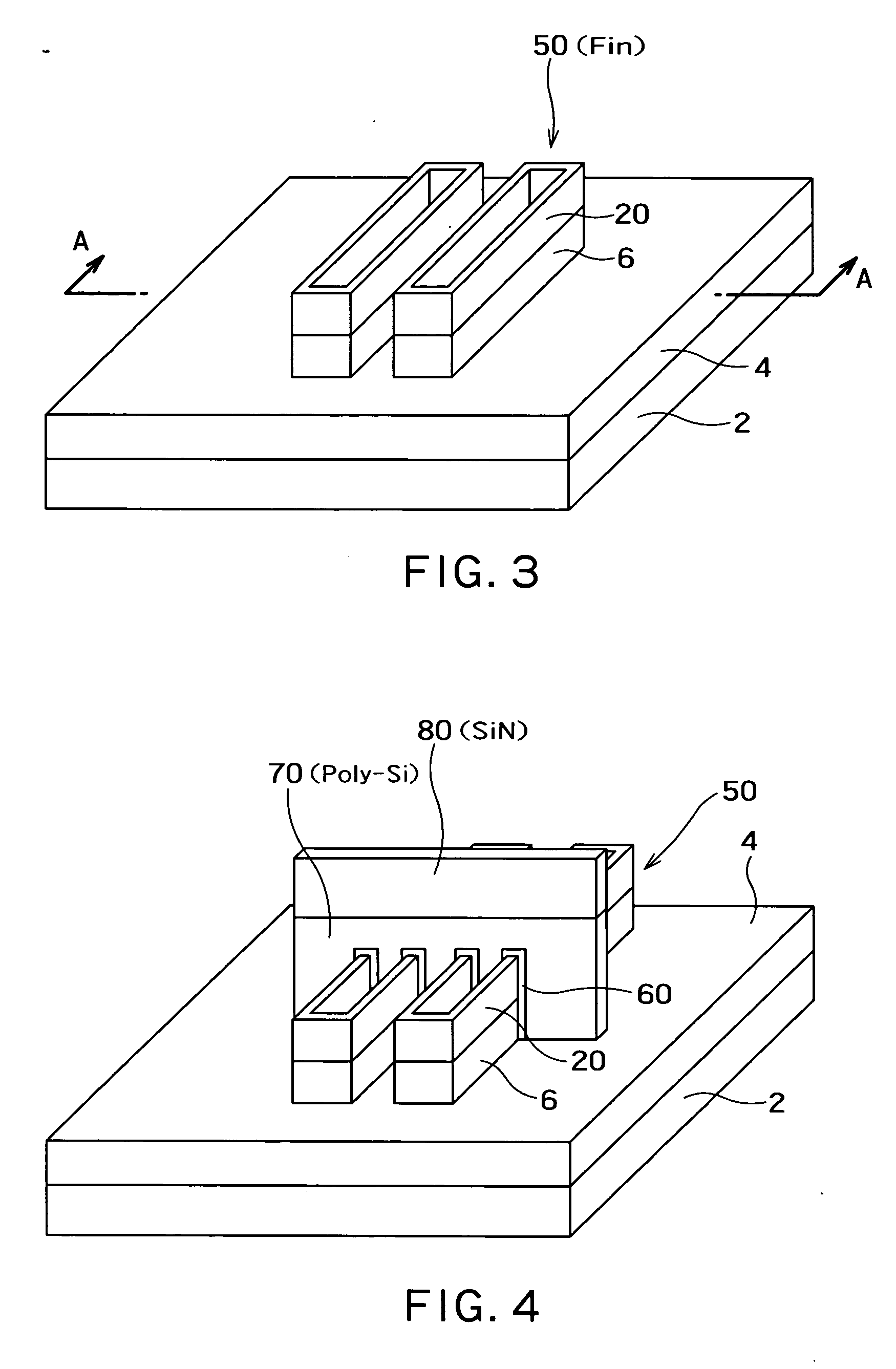

A method of manufacturing a semiconductor device includes forming a plurality of Fins including a semiconductor material on an insulation layer; forming gate insulation films on sidewalls of the Fins; forming a gate electrode which extends in a direction of arrangement of the Fins and which is electrically insulated from the Fins, the gate electrode is common in the Fins on the gate insulation film; implanting an impurity into portions of the Fins by using the gate electrode as a mask to form a source-drain diffusion layer, the portions of the Fins extending on both sides of the gate electrodes; and depositing a conductive material on both sides of the Fins to connect the Fins to each other.

Owner:MICROSOFT TECH LICENSING LLC

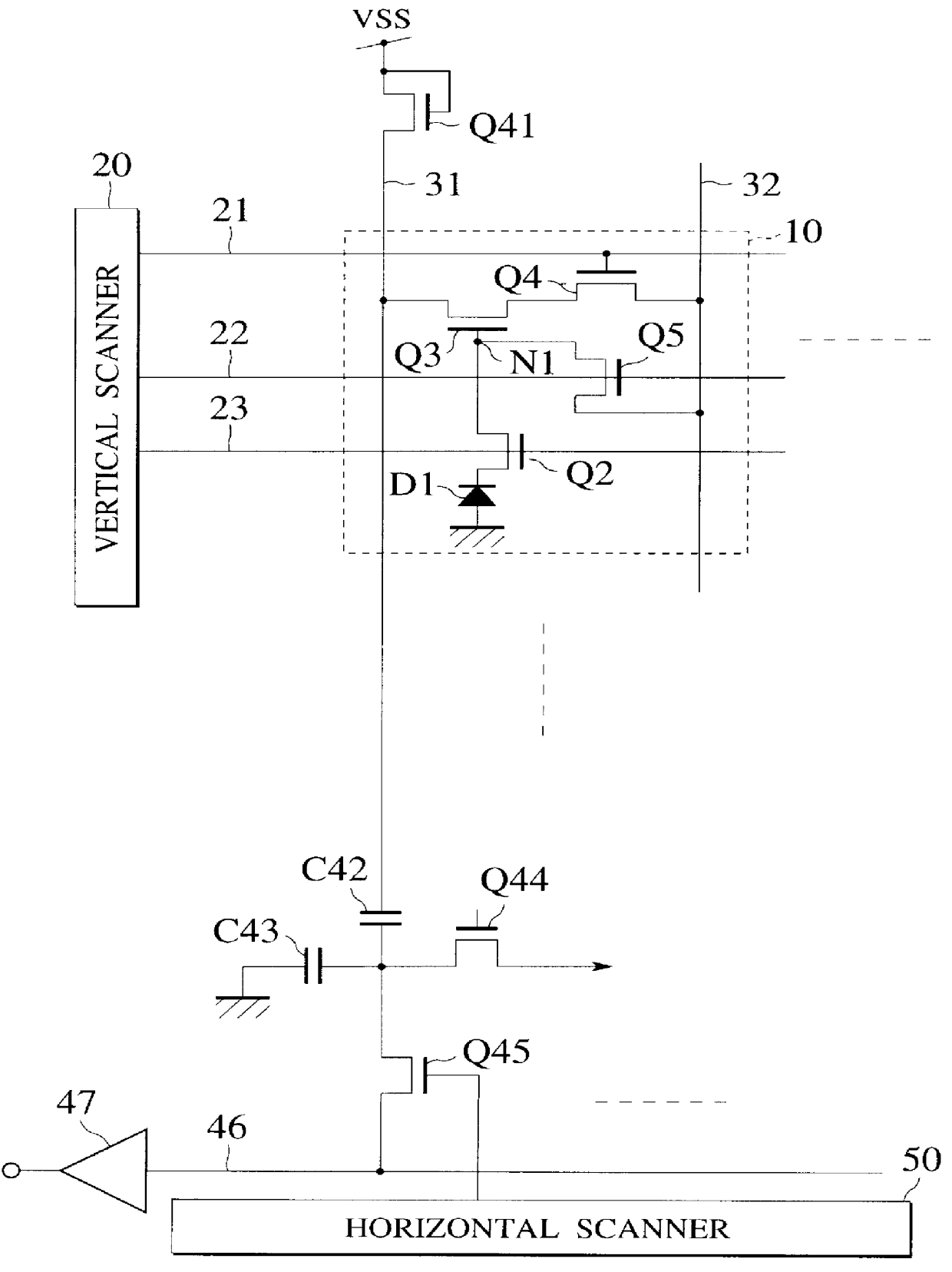

MOS type image sensor

A MOS type image sensor has an image area that consists of a matrix of pixels and a peripheral circuitry area that drives the image area. To make the MOS type image sensor finer, each of the pixels consists of a second p-well region having a lower impurity concentration than a first p-well region disposed in the peripheral circuitry area; a photodiode having a first main electrode region made of the second p-well region and a second main electrode region formed as a first n-diffusion layer disposed at the surface of the second p-well region; a read transistor having a first main electrode region made of the first n-diffusion layer, a second main electrode region formed as a second n-diffusion layer disposed at the surface of the second p-well region, a gate insulation film disposed on the surface of the second p-well region between the first and second n-diffusion layers, and a gate electrode disposed on the gate insulation film and connected to a read signal line; and an amplification transistor disposed in a third p-well region, having a gate electrode connected to the second main electrode region of the read transistor, a first main electrode region connected to an output signal line, and a second main electrode region. Since the impurity concentration of the second p-well region is low, scaled design rules are employable without causing "white pixels", sensitivity deterioration, signal read voltage increase, or short-channel effect.

Owner:NORTH PLATE SEMICON LLC

Methods for manufacturing components from articles formed by additive-manufacturing processes

ActiveUS8506836B2TurbinesAdditive manufacturing apparatusDiffusion layerAdditive layer manufacturing

Owner:HONEYWELL INT INC

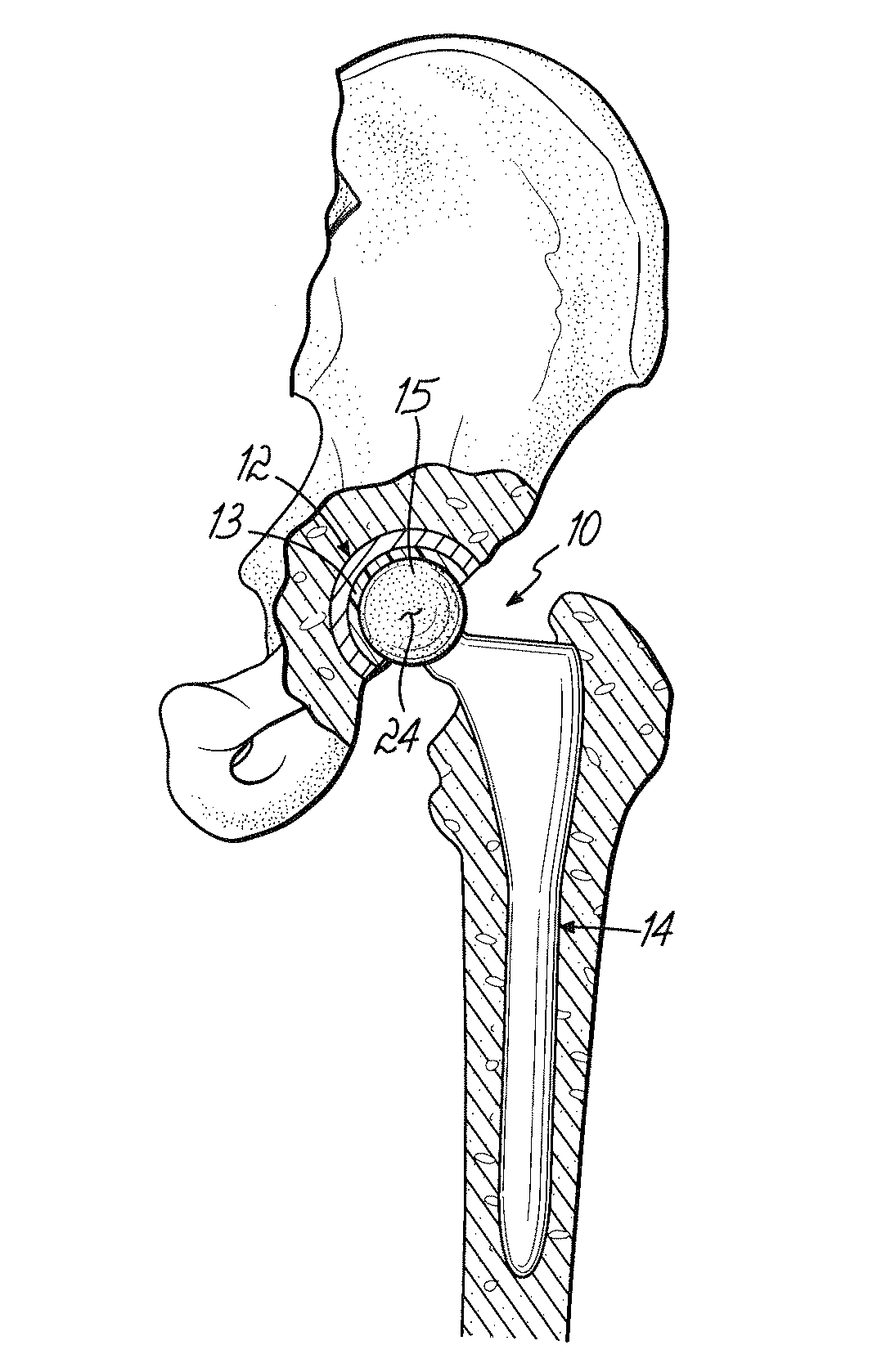

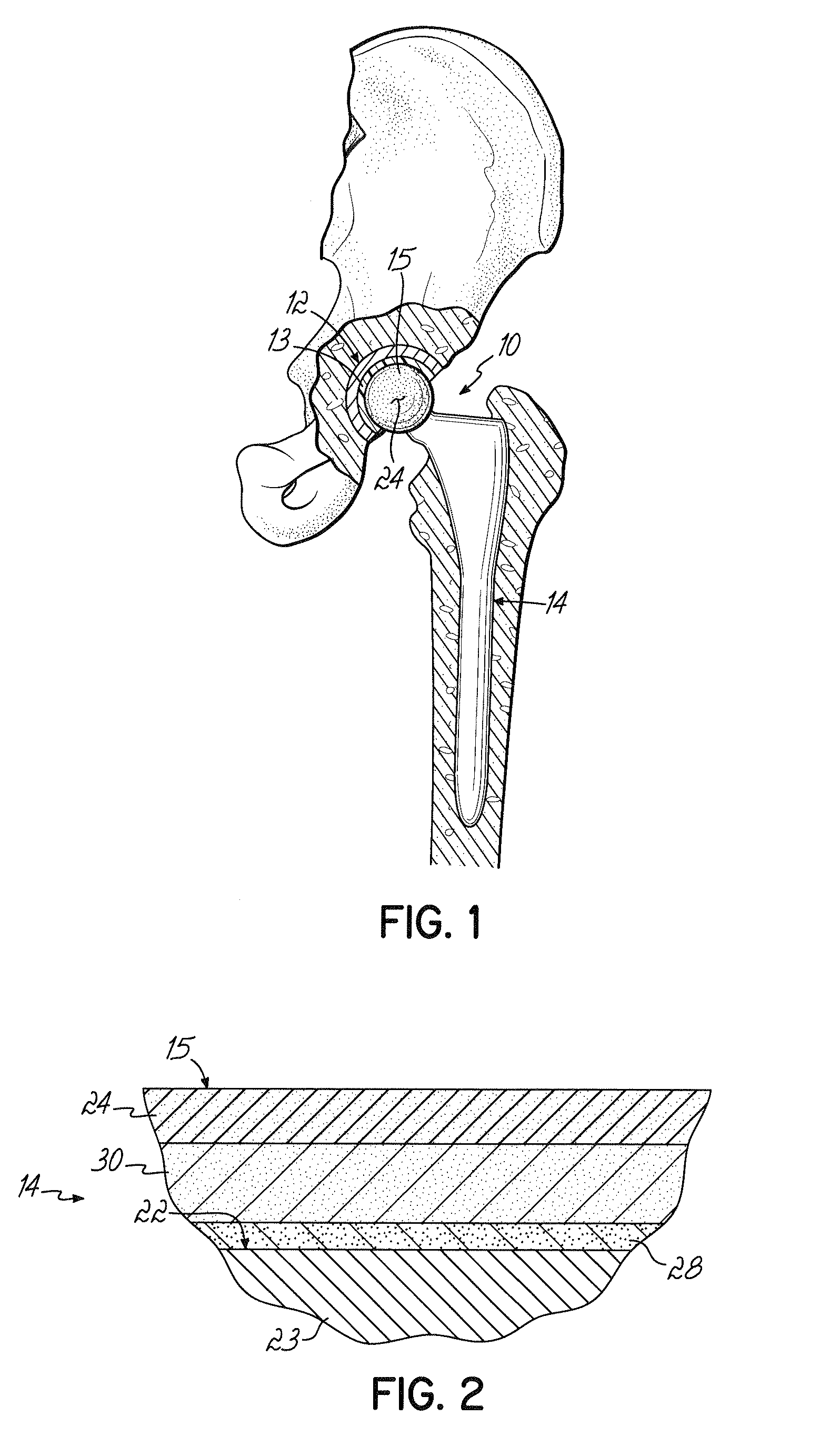

Titanium alloy with oxidized zirconium for a prosthetic implant

A prosthetic device having a generally fixed member formed from a low friction material such as ultra-high molecular weight polyethylene and an articulating titanium member, which includes an articular bearing surface. The articular surface is a zirconium oxide layer formed by applying a coating of zirconium onto the titanium member and heating this in an oxygen-containing environment. This causes the zirconium to oxidize and further causes the zirconium to migrate into the titanium member forming a titanium zirconium diffusion layer, which prevents delamination.

Owner:ZIMMER INC

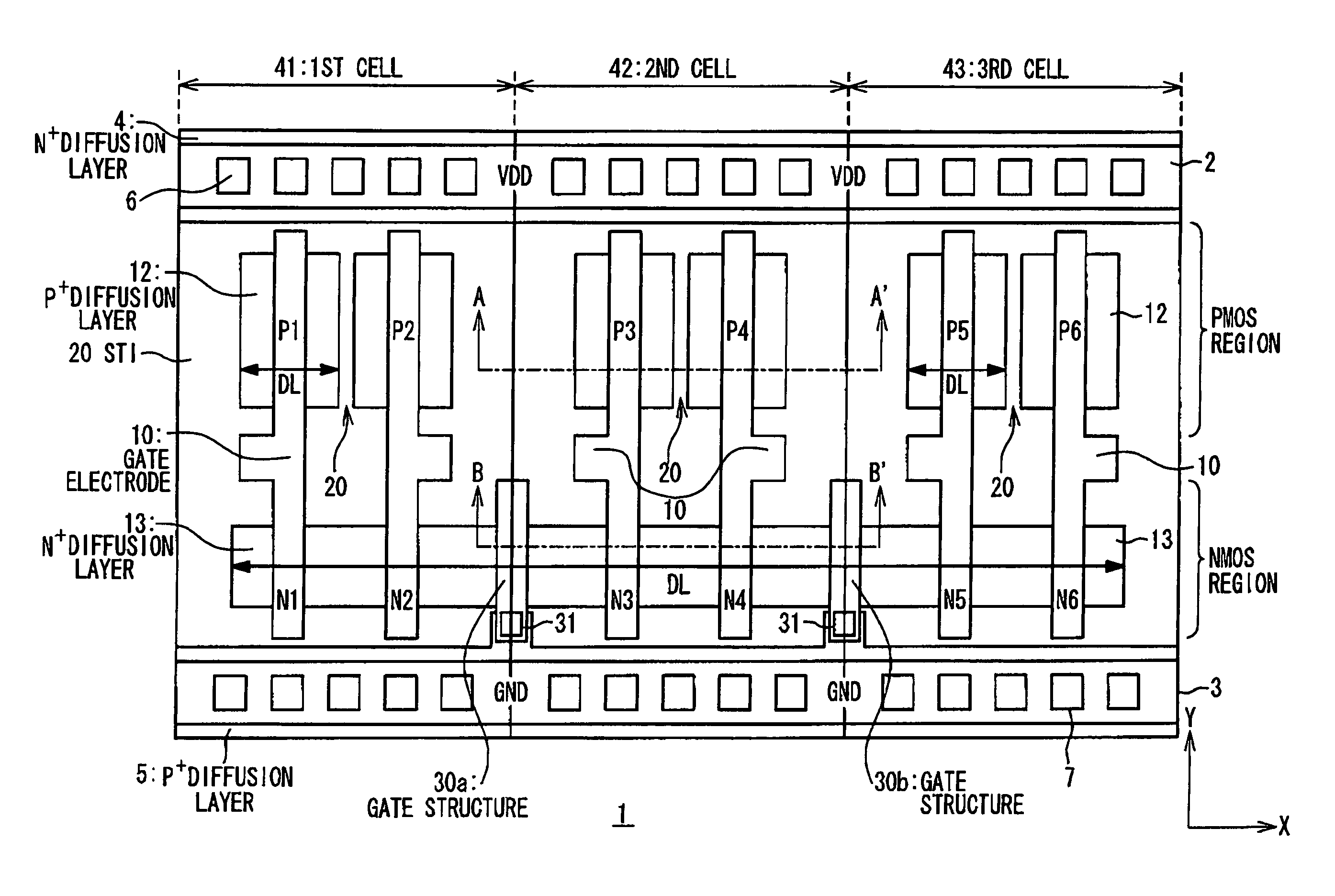

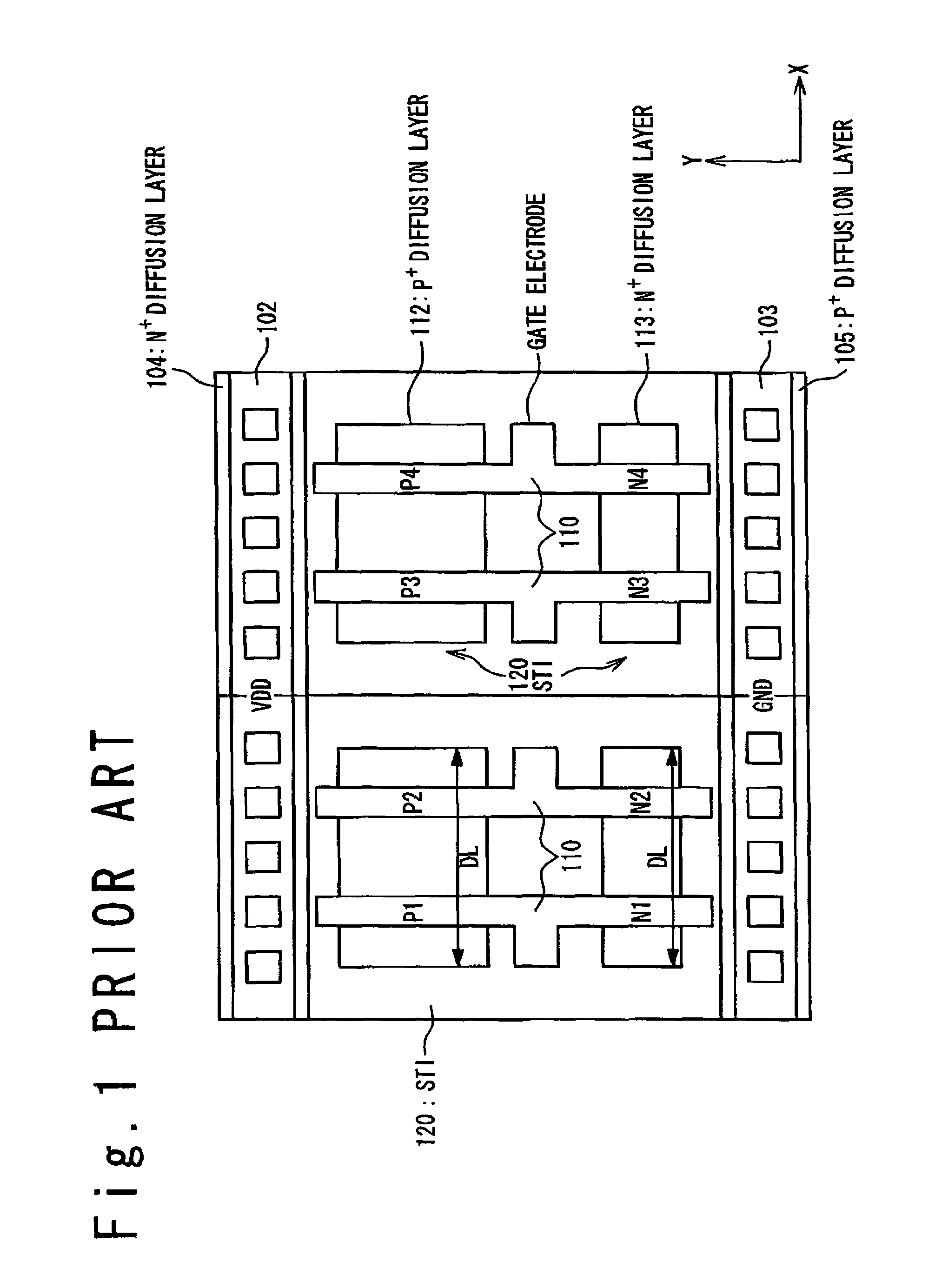

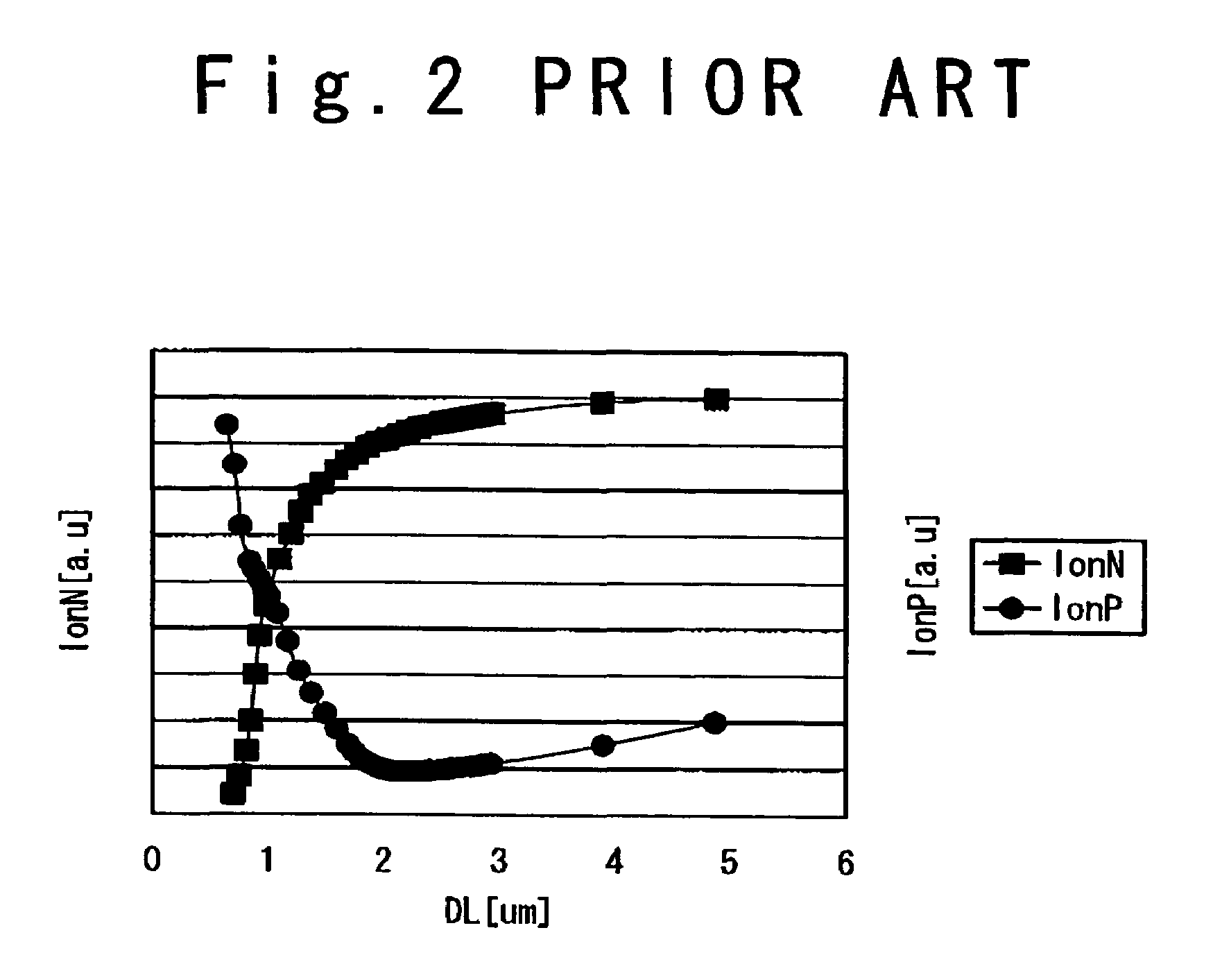

Semiconductor device with NMOS transistors arranged continuously

Owner:RENESAS ELECTRONICS CORP

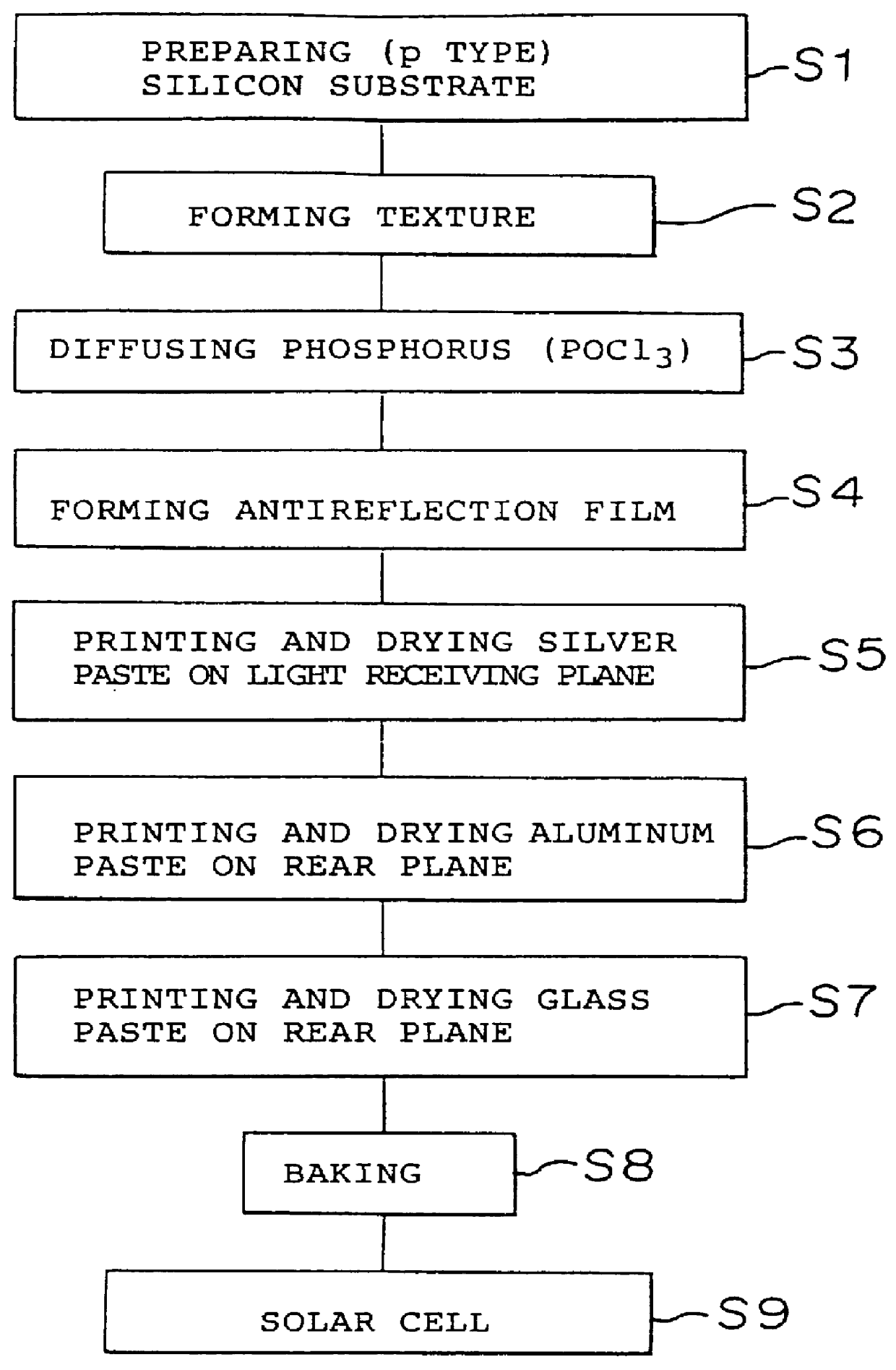

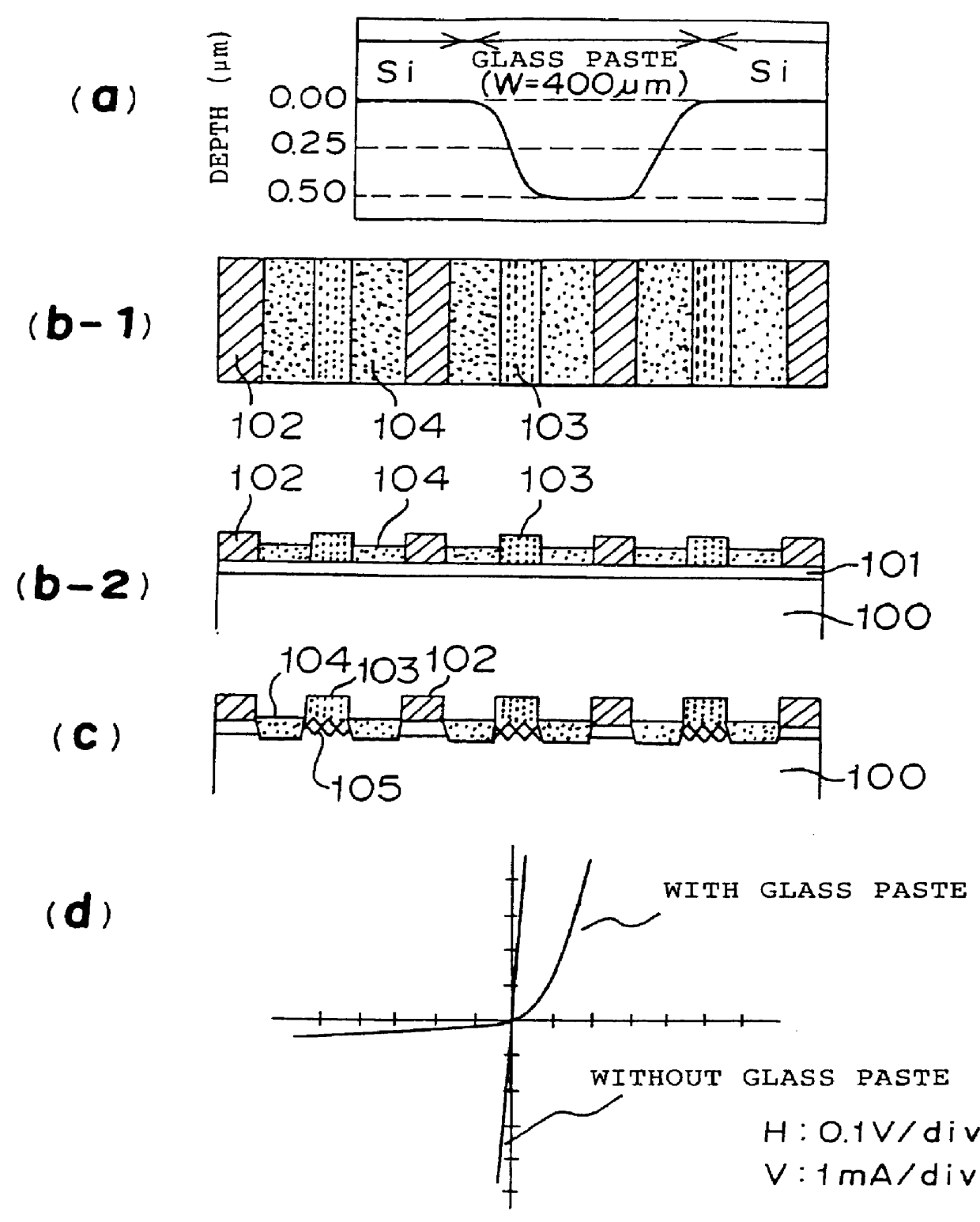

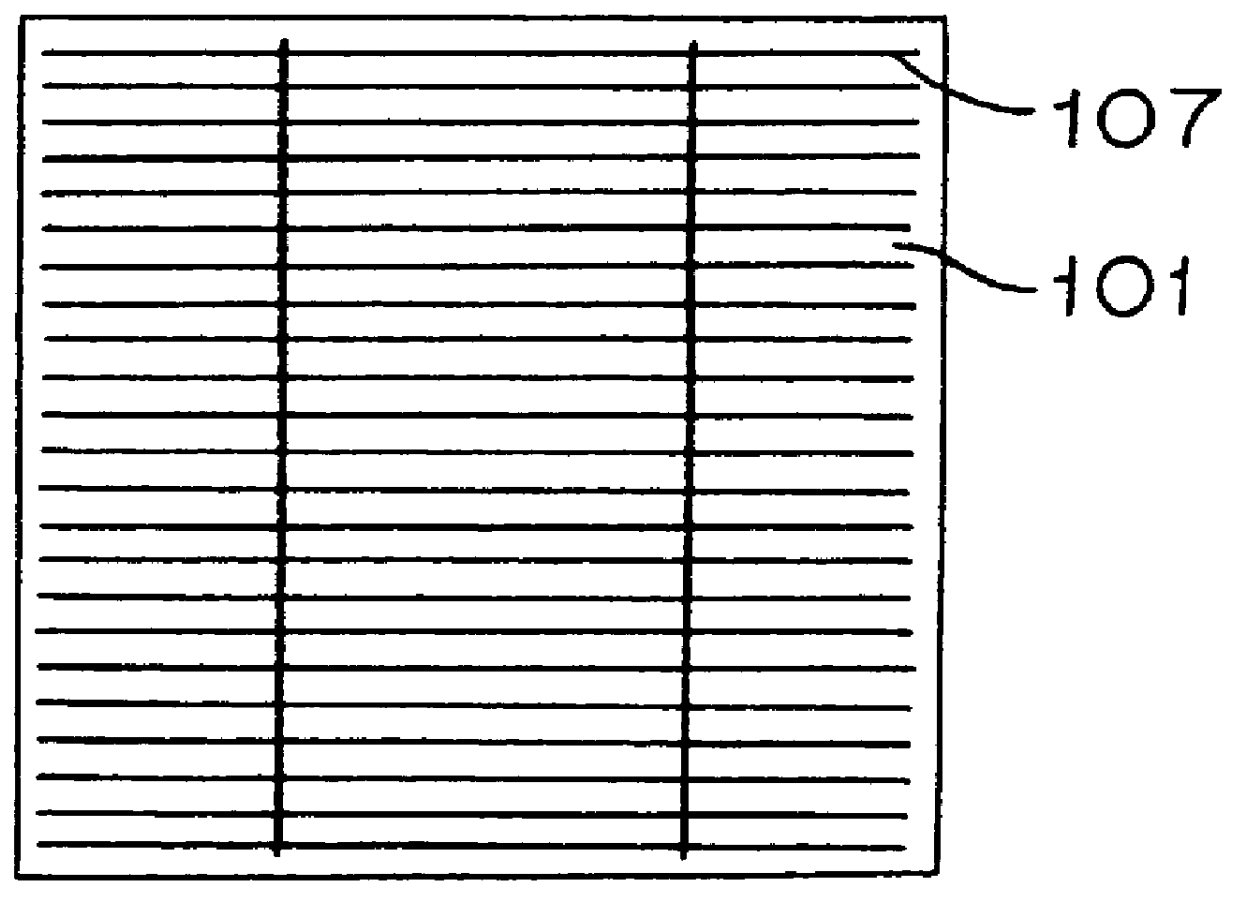

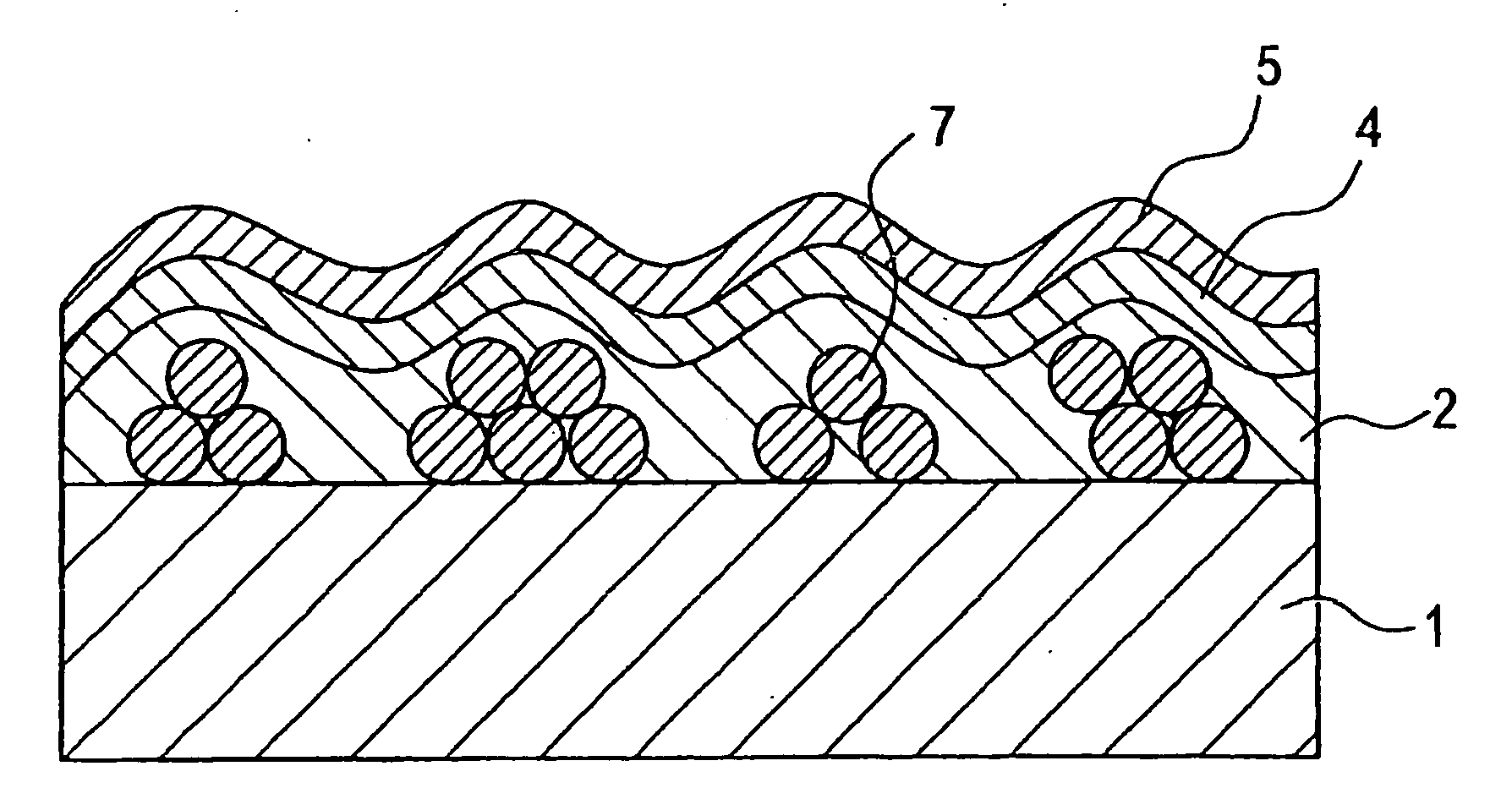

Method of producing a solar cell; a solar cell and a method of producing a semiconductor device

InactiveUS6093882ASemiconductor/solid-state device manufacturingPhotovoltaic energy generationSilver pasteSolar cell

Owner:MITSUBISHI ELECTRIC CORP

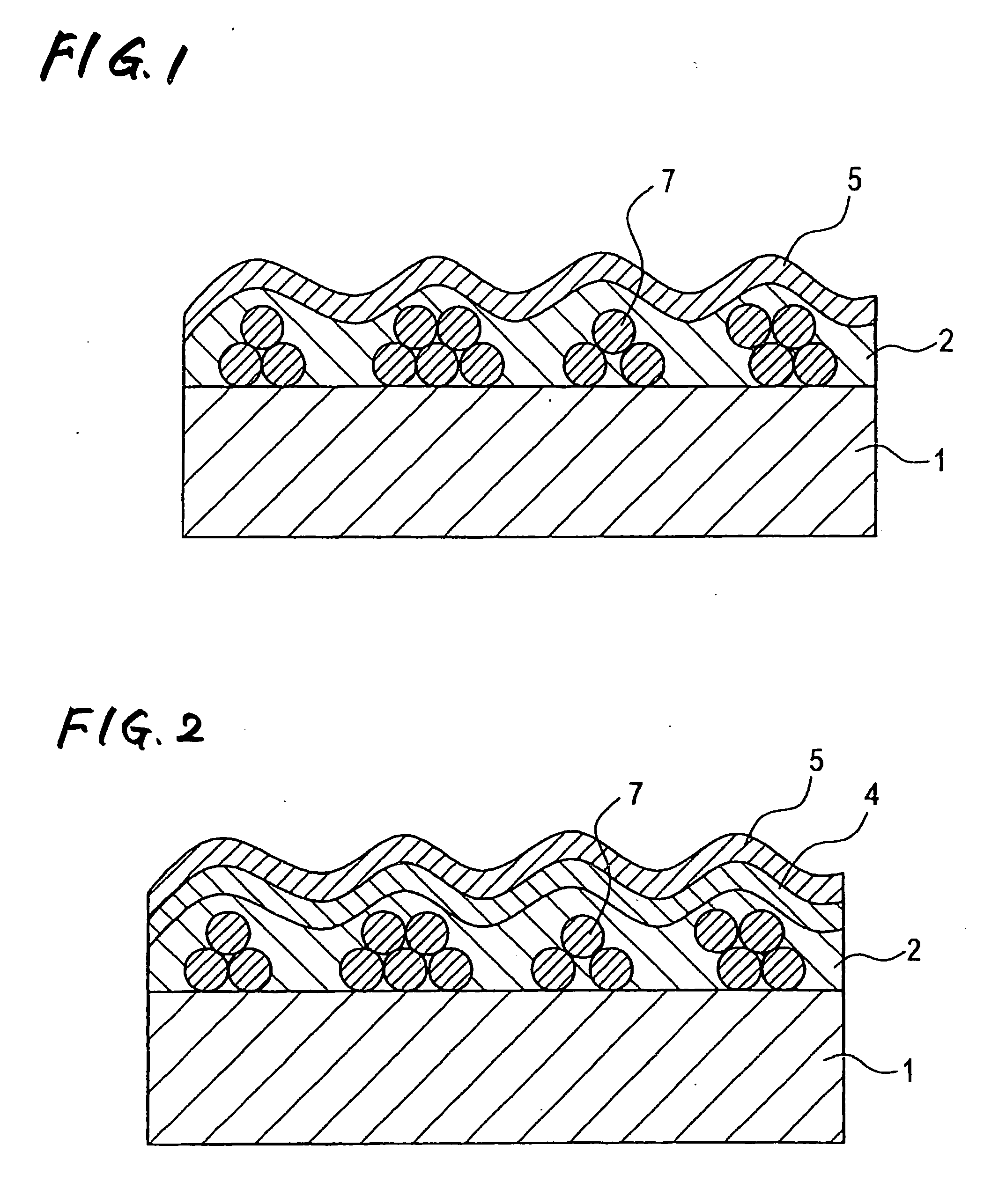

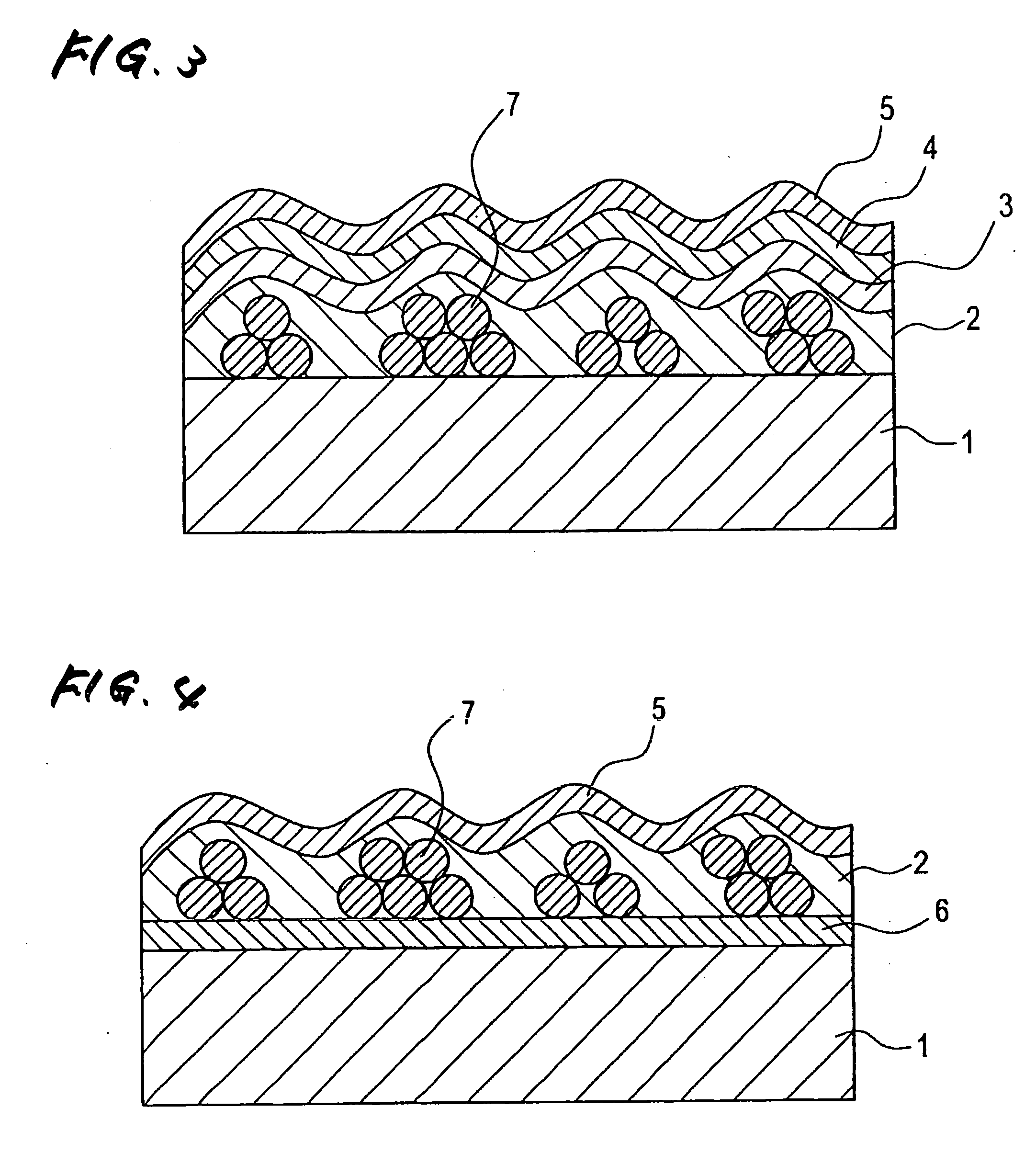

Optical film, antireflection film, polarizing plate and image display device

ActiveUS20070195431A1High film strengthExcellent optical propertiesDiffusing elementsDisplay deviceDiffusion layer

An optical film is provided and includes: a transparent support; and a light diffusion layer containing light-transmitting particles and a binder. The light diffusion layer has an average thickness of from 7.5 to 30 μm, and the average thickness of the light diffusion layer is from 1.4 to 3.5 times as large as an average particle diameter of the light-transmitting particles.

Owner:FUJIFILM CORP

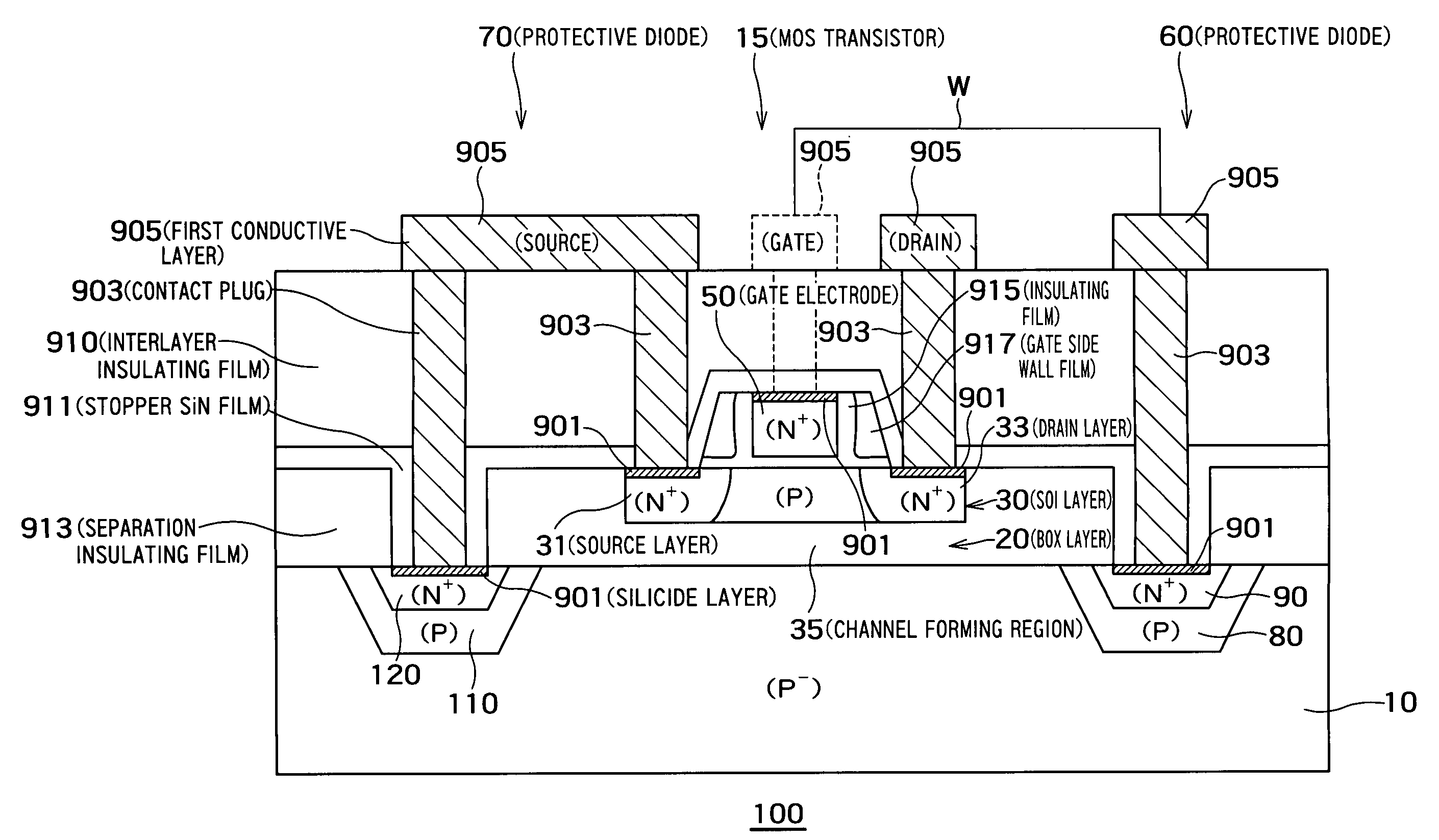

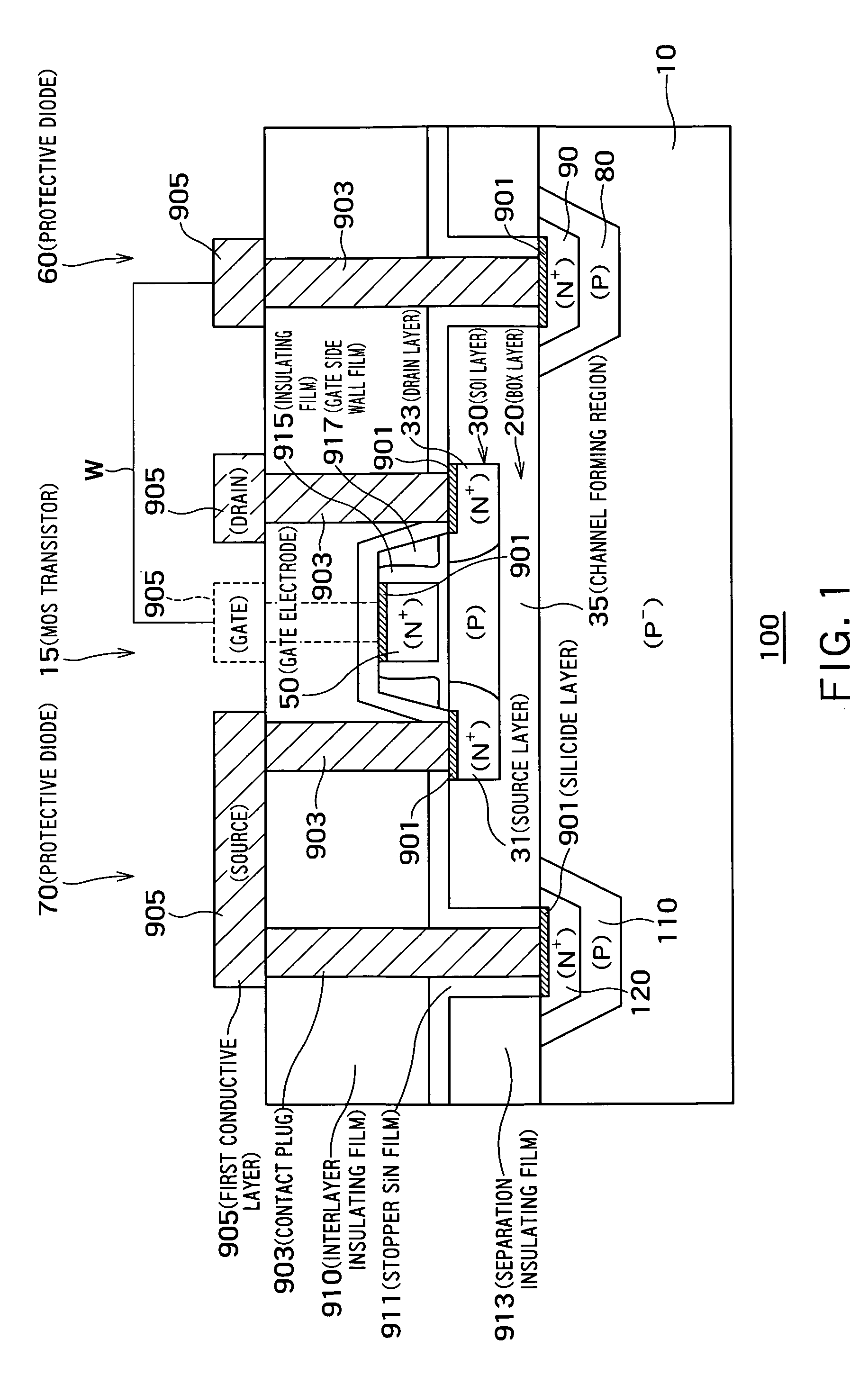

Semiconductor device

InactiveUS20050269642A1TransistorSemiconductor/solid-state device detailsDevice materialSemiconductor

A semiconductor device comprises a semiconductor substrate; an embedded insulating layer provided on the semiconductor substrate; a semiconductor layer provided on the embedded insulating layer; a transistor including a first conductivity type source layer formed within the semiconductor layer, a first conductivity type drain layer formed in the semiconductor layer, and a channel forming region between the source layer and the drain layer; and an embedded insulating layer protective diode including a second conductivity type first diffusion layer and a first conductivity type second diffusion layer, the first diffusion layer being at the same potential as a semiconductor substrate region immediately below the channel forming region, the second diffusion layer being provided adjacently to the first diffusion layer and electrically connected to at least one of the source layer, the drain layer and the channel forming region.

Owner:KK TOSHIBA