Patents

Literature

1152 results about "Line driver" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A line driver is an electronic amplifier circuit designed for driving a load such as a transmission line. The amplifier's output impedance may be matched to the characteristic impedance of the transmission line.

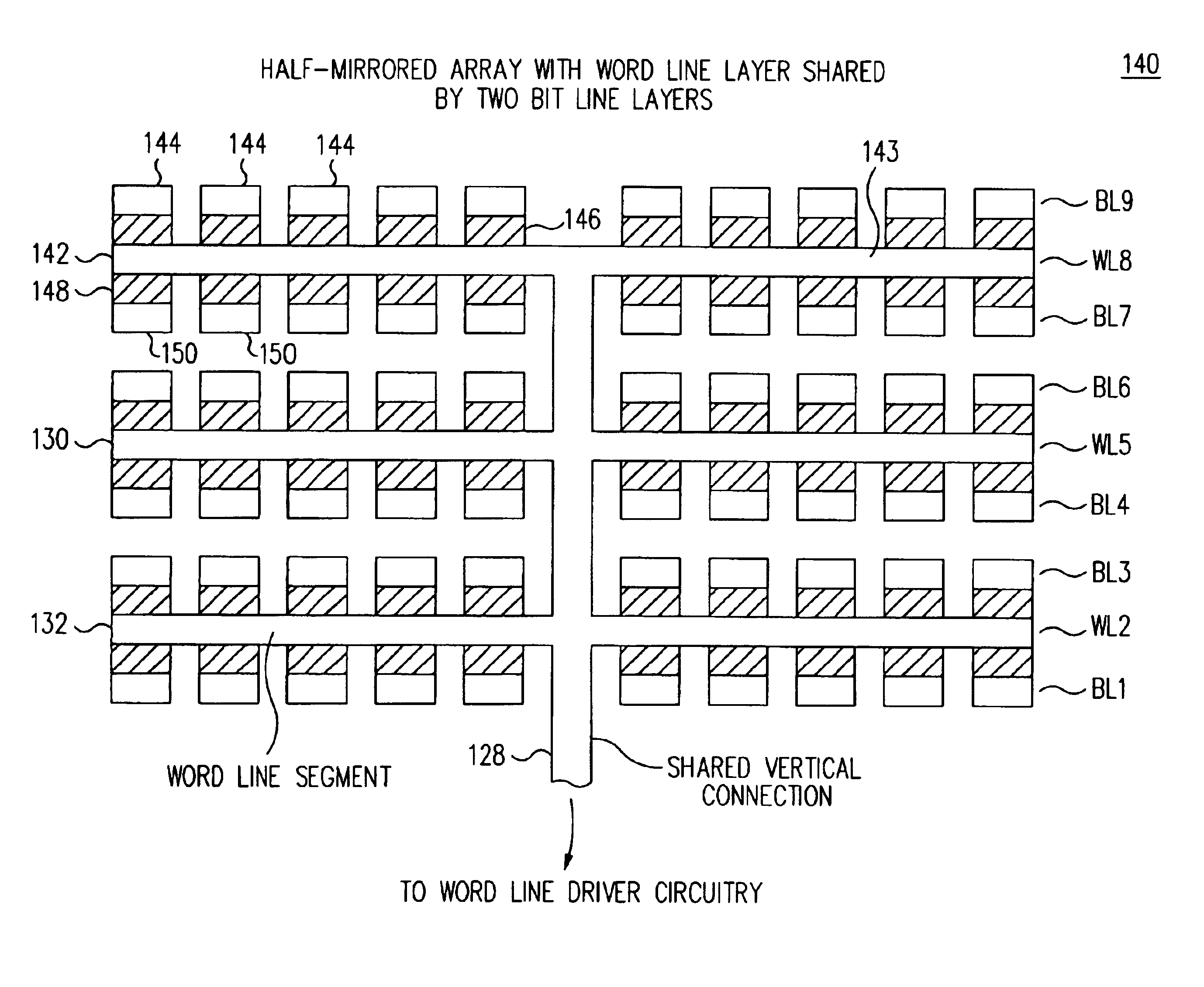

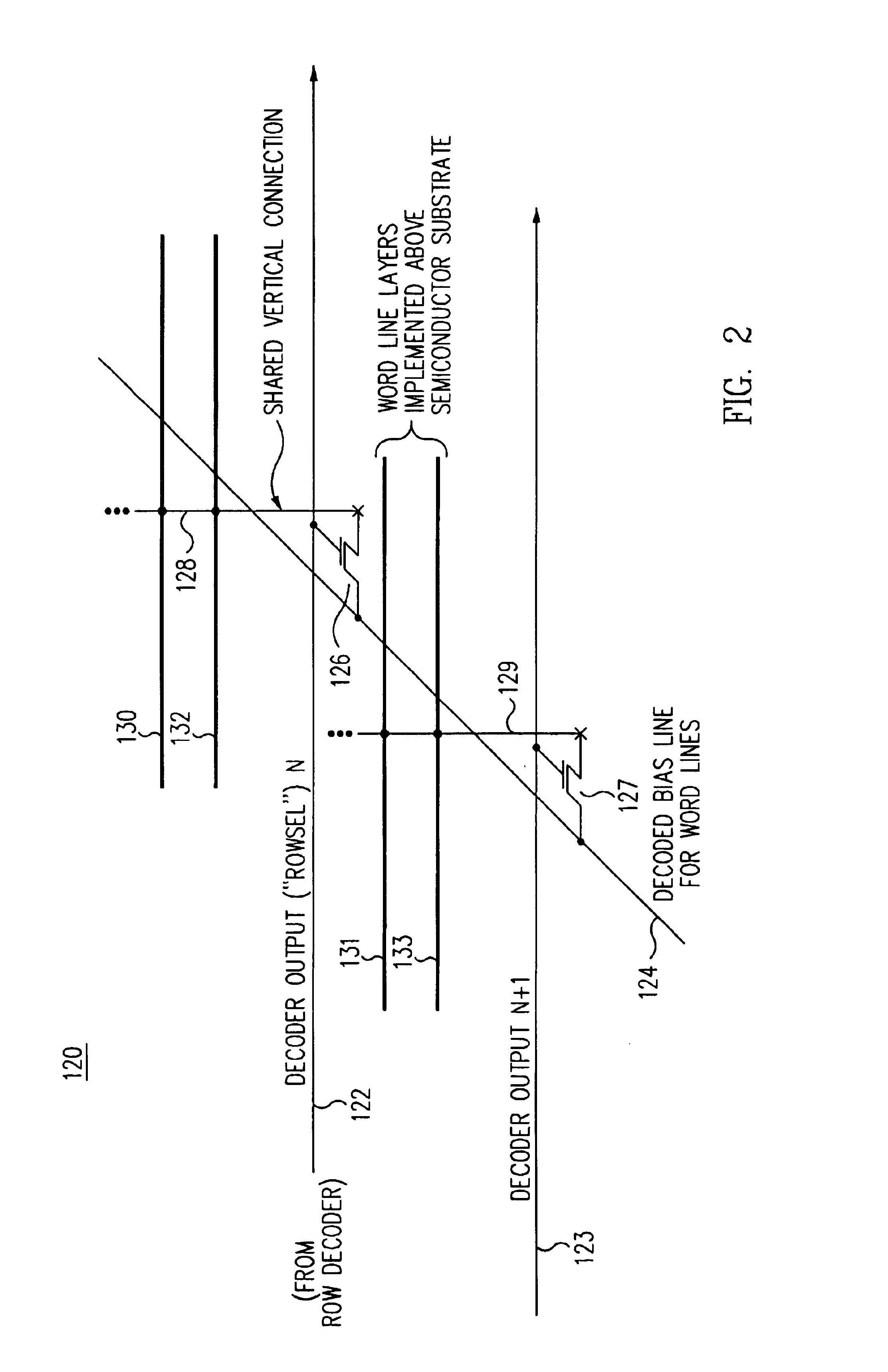

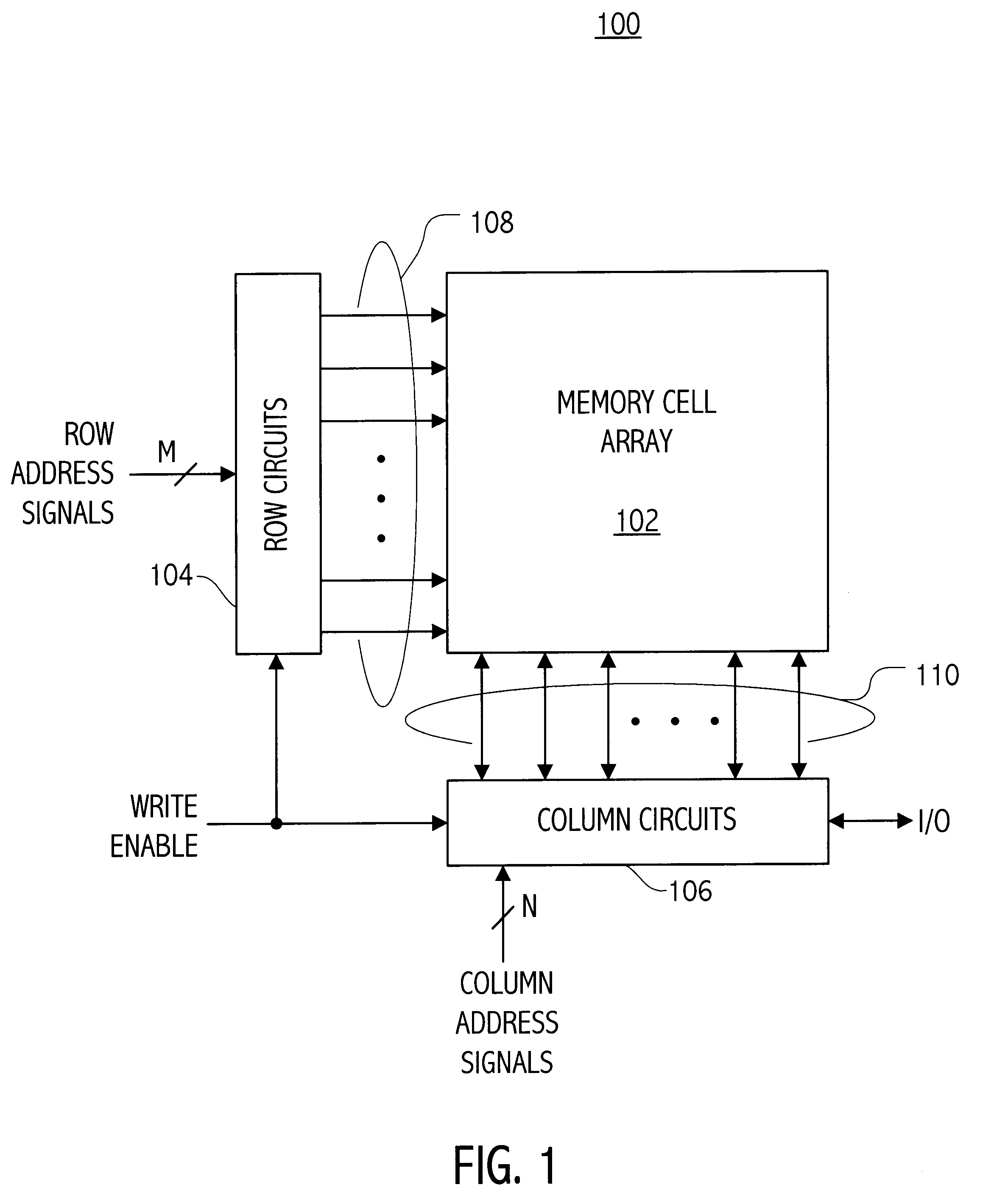

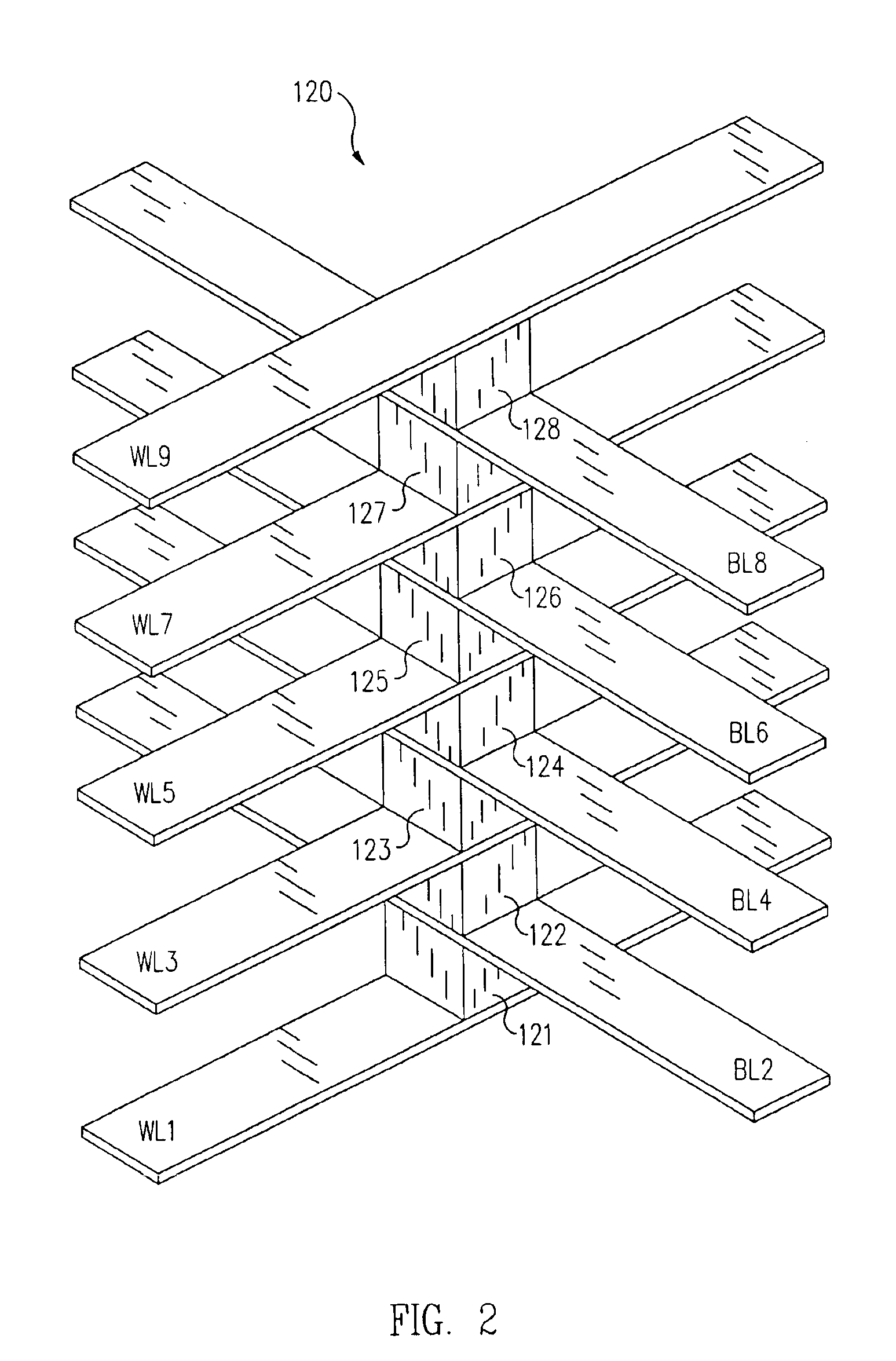

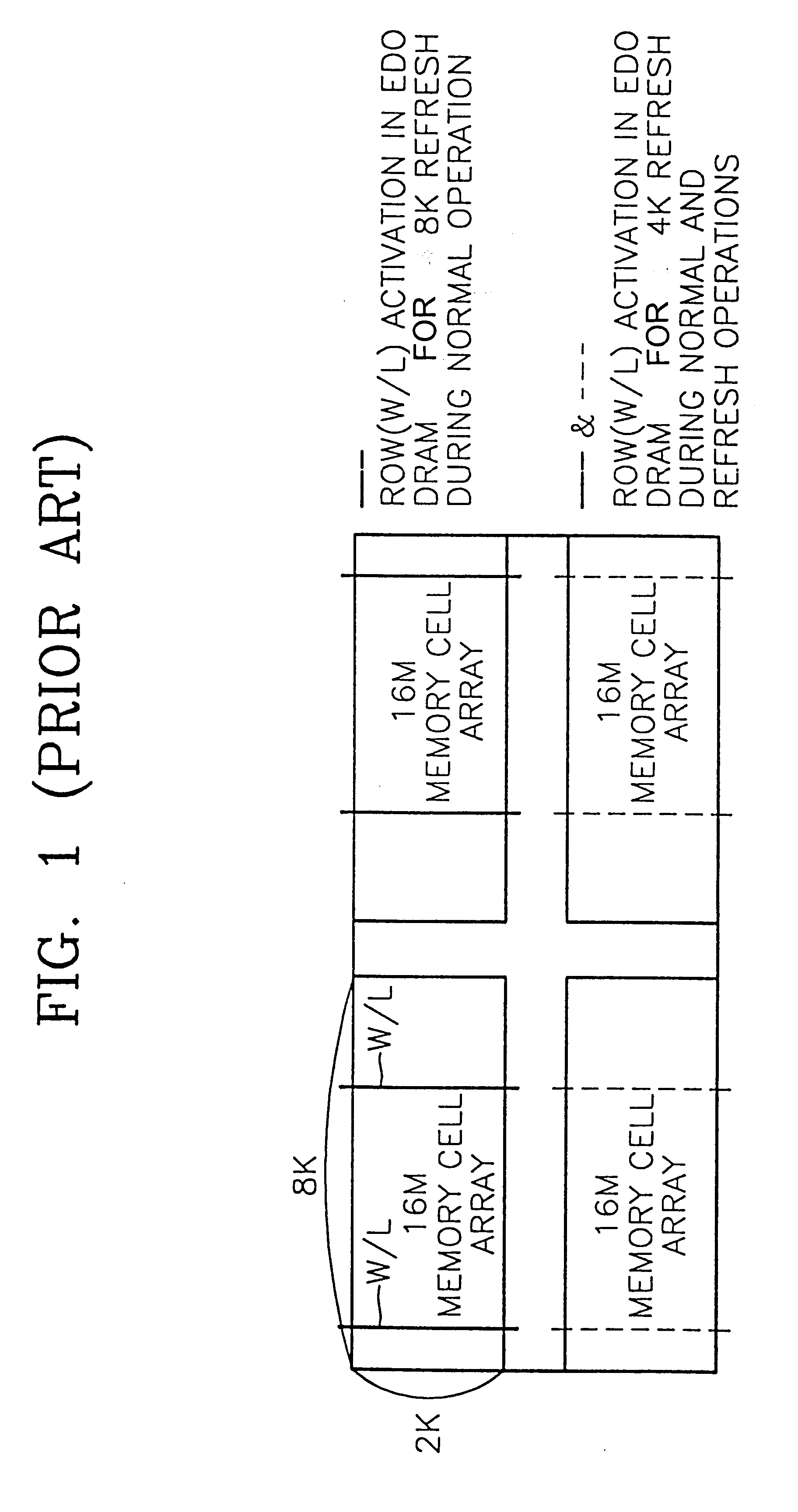

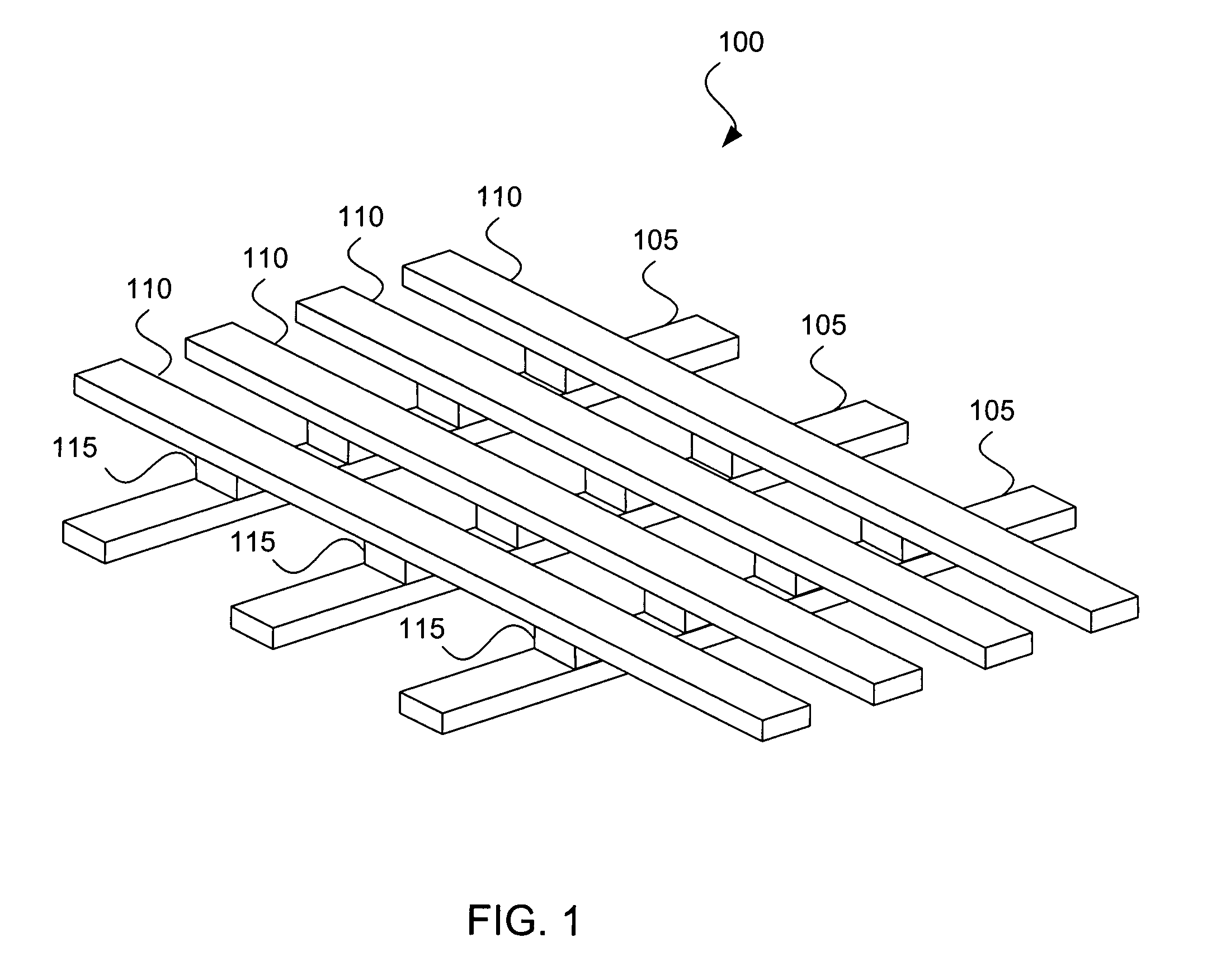

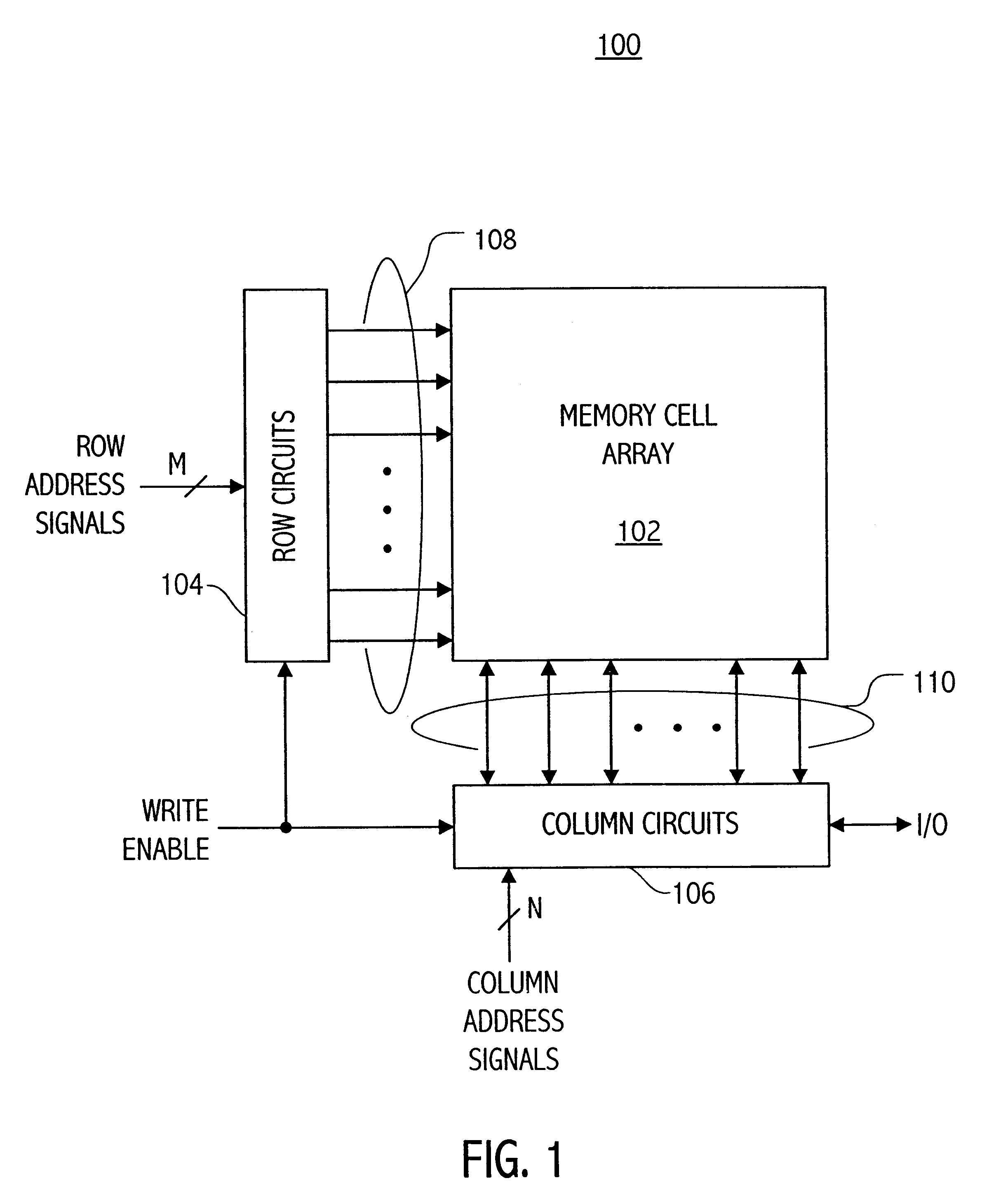

Word line arrangement having multi-layer word line segments for three-dimensional memory array

InactiveUS6879505B2Reduce stress timeDecreasing fan-outSolid-state devicesDigital storageDriver circuitLine driver

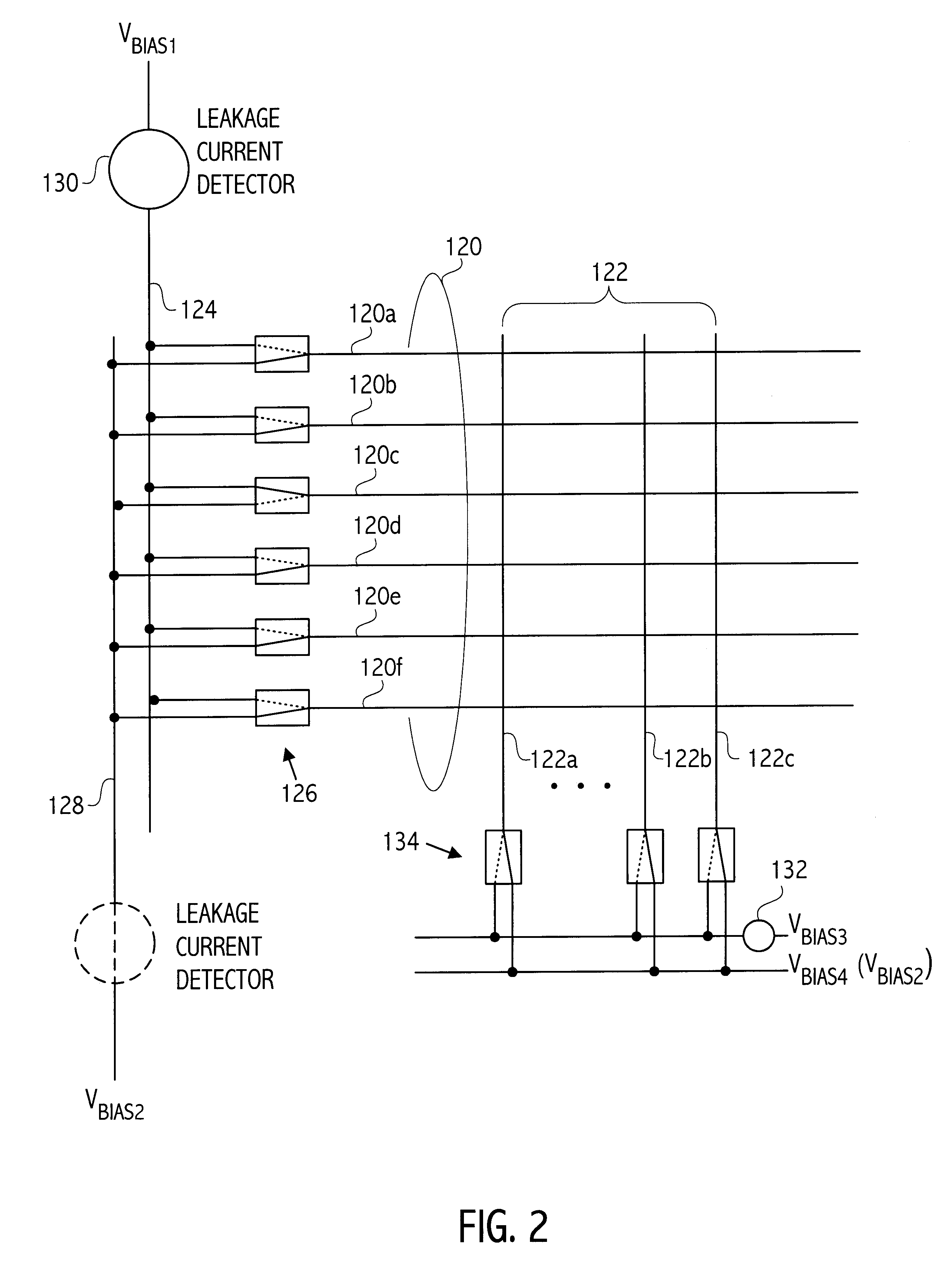

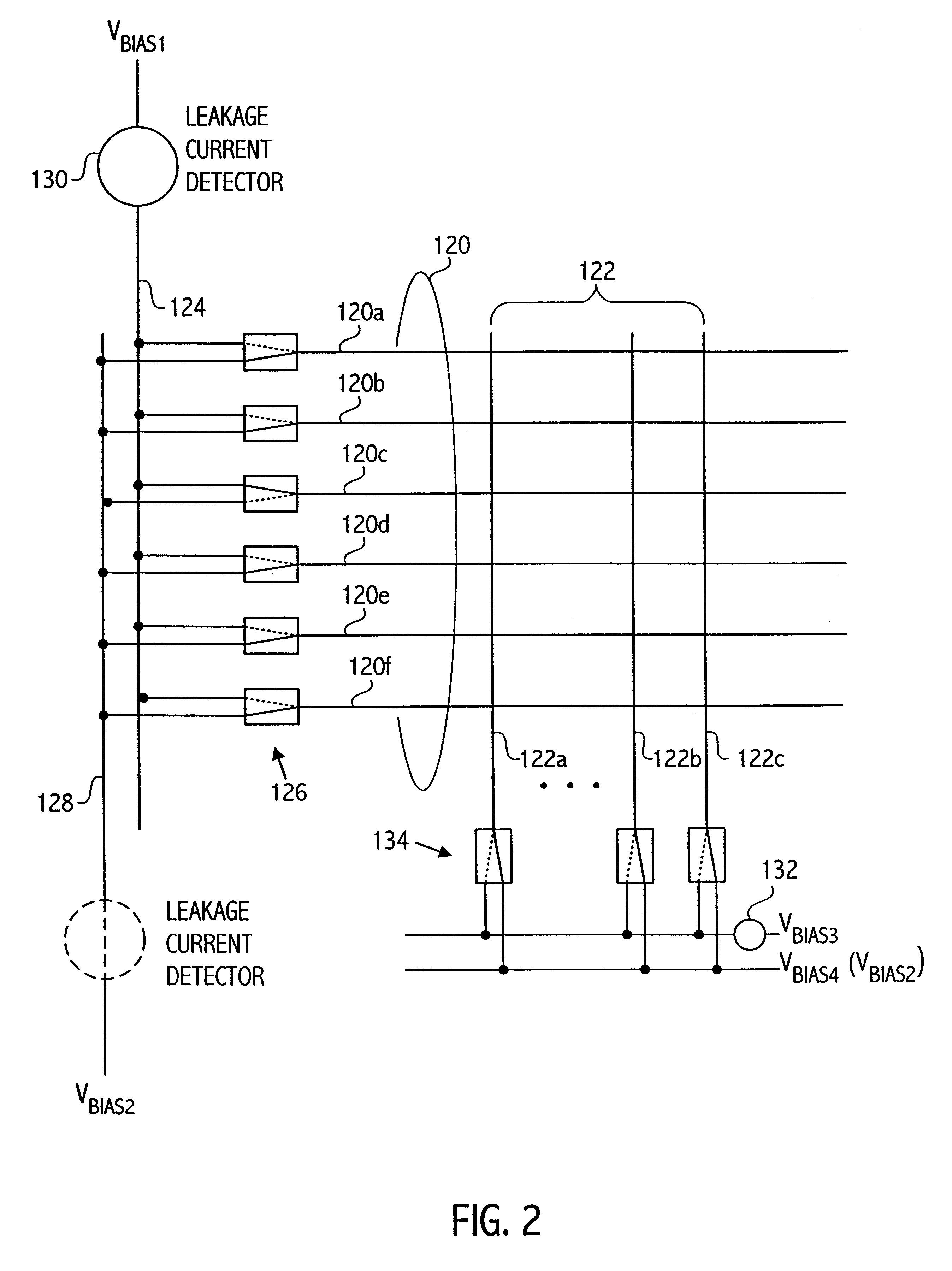

A three-dimensional (3D) passive element memory cell array provides short word lines while still maintaining a small support circuit area for efficiency. Short, low resistance word line segments on two or more word line layers are connected together in parallel to form a given word line without use of segment switch devices between the word line segments. A shared vertical connection preferably connects the word line segments together and connects to a word line driver circuit disposed generally below the array near the word line. Each word line driver circuit preferably couples its word line either to an associated one of a plurality of selected bias lines or to an unselected bias line associated with the driver circuit, which selected bias lines are themselves decoded to provide for an efficient multi-headed word line decoder.

Owner:SANDISK TECH LLC

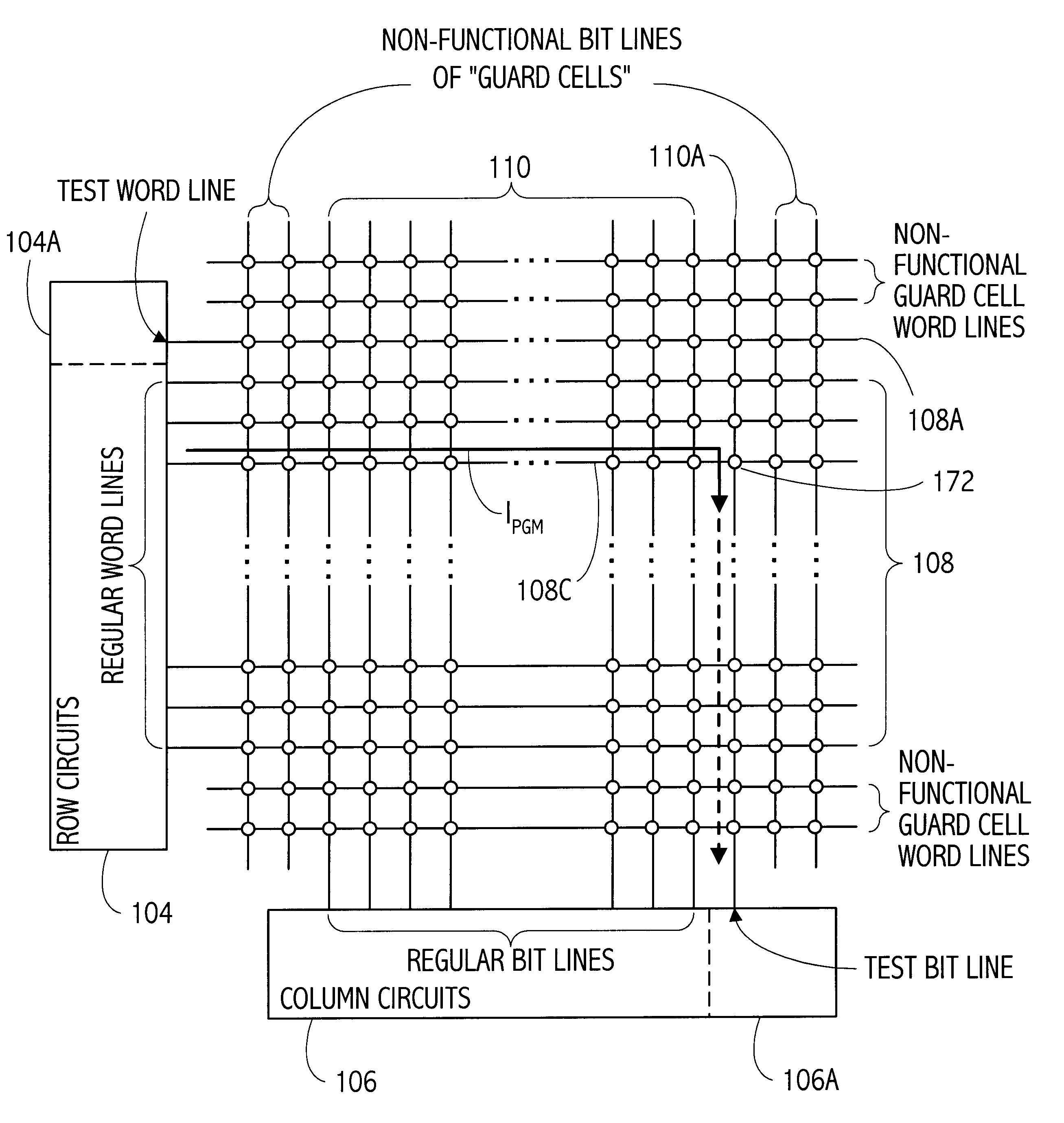

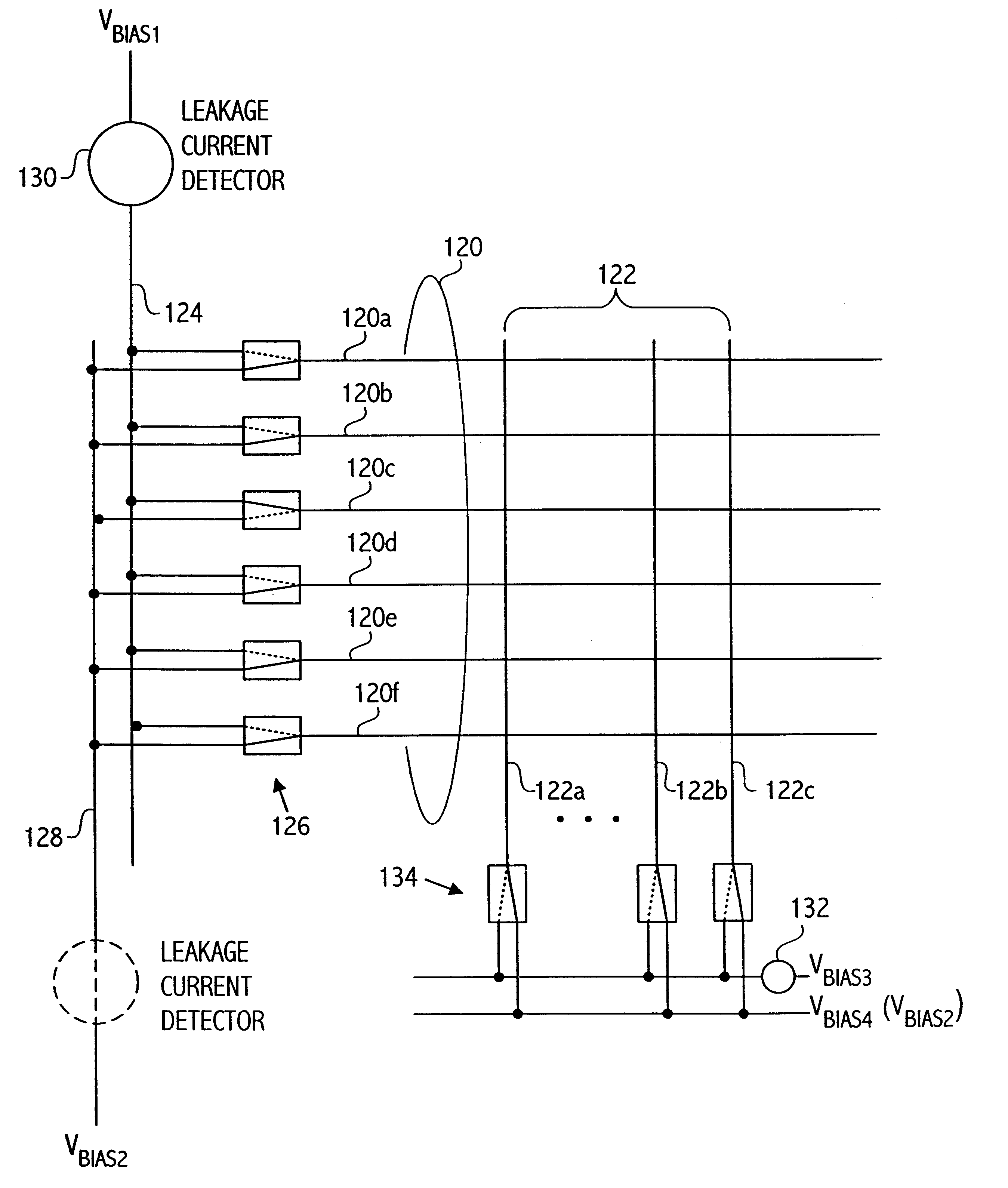

Memory array organization and related test method particularly well suited for integrated circuits having write-once memory arrays

In a preferred integrated circuit embodiment, a write-once memory array includes at least one test bit line which provides a respective test memory cell at the far end of each respective word line relative to its word line driver, and further includes at least one test word line which provides a respective test memory cell at the far end of each respective bit line relative to its bit line driver. An intra-layer short between word lines may be detected, such as during manufacturing testing, by biasing adjacent word lines to different voltages and detecting whether any leakage current flowing from one to another exceeds that normally accounted for by the memory cells and other known circuits. Intra-layer bit line shorts and inter-layer word line and bit line shorts may also be similarly detected. An "open" in a word line or bit line may be detected by trying to program the test memory cell at the far end of each such word line or bit line. If successfully programmed, the continuity of each word line and bit line is assured, and the programming circuitry for each word line and bit line is also known to be functional.

Owner:SANDISK TECH LLC

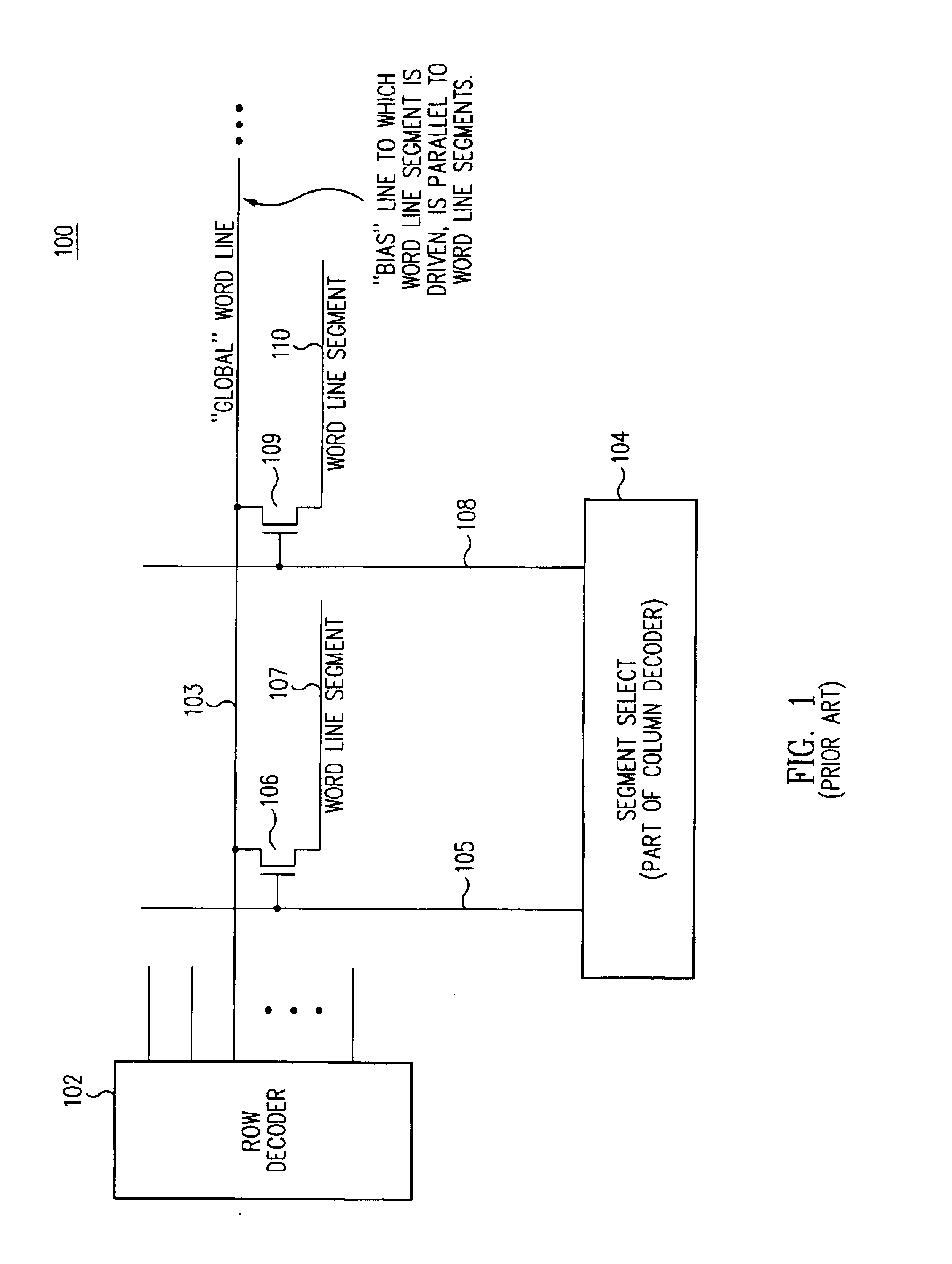

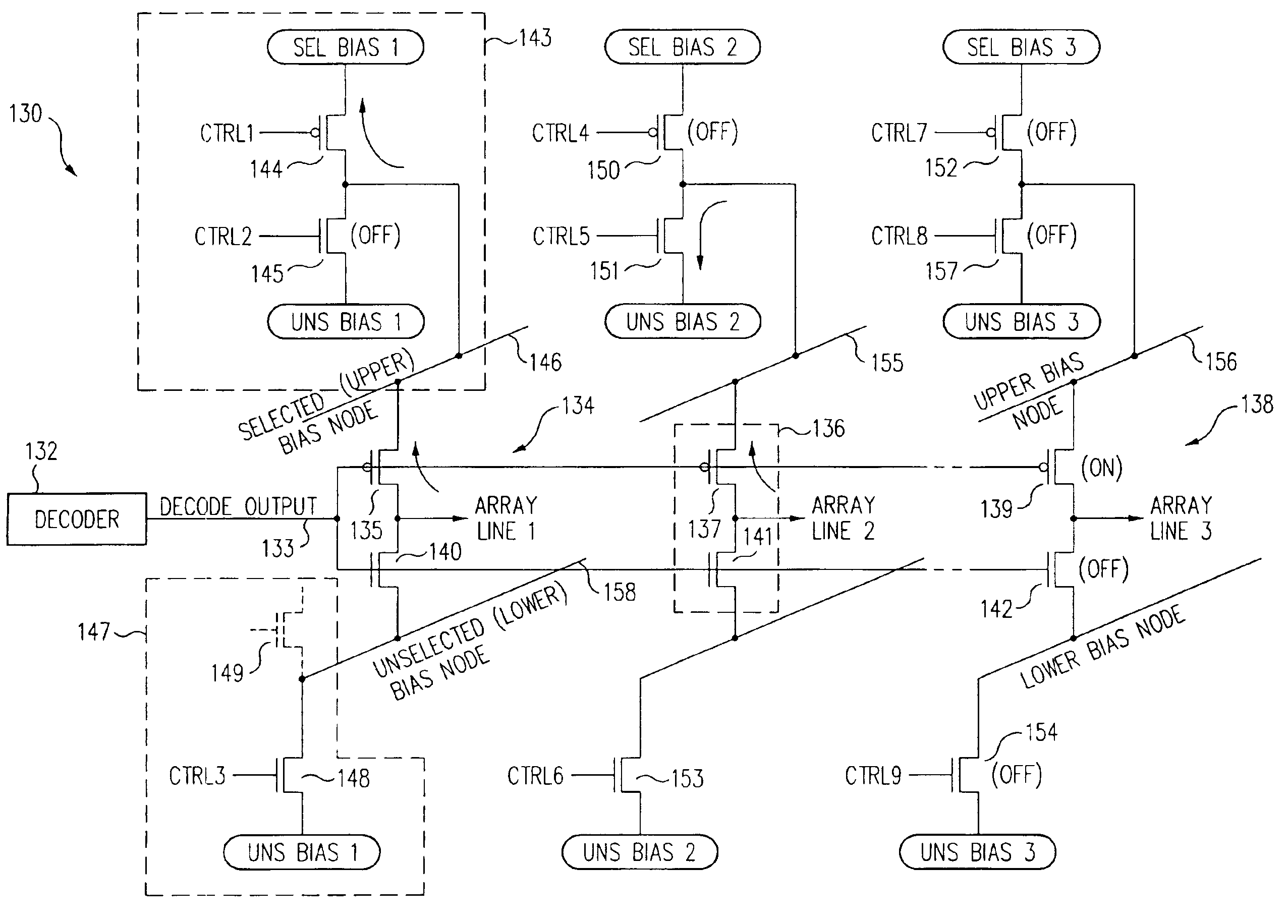

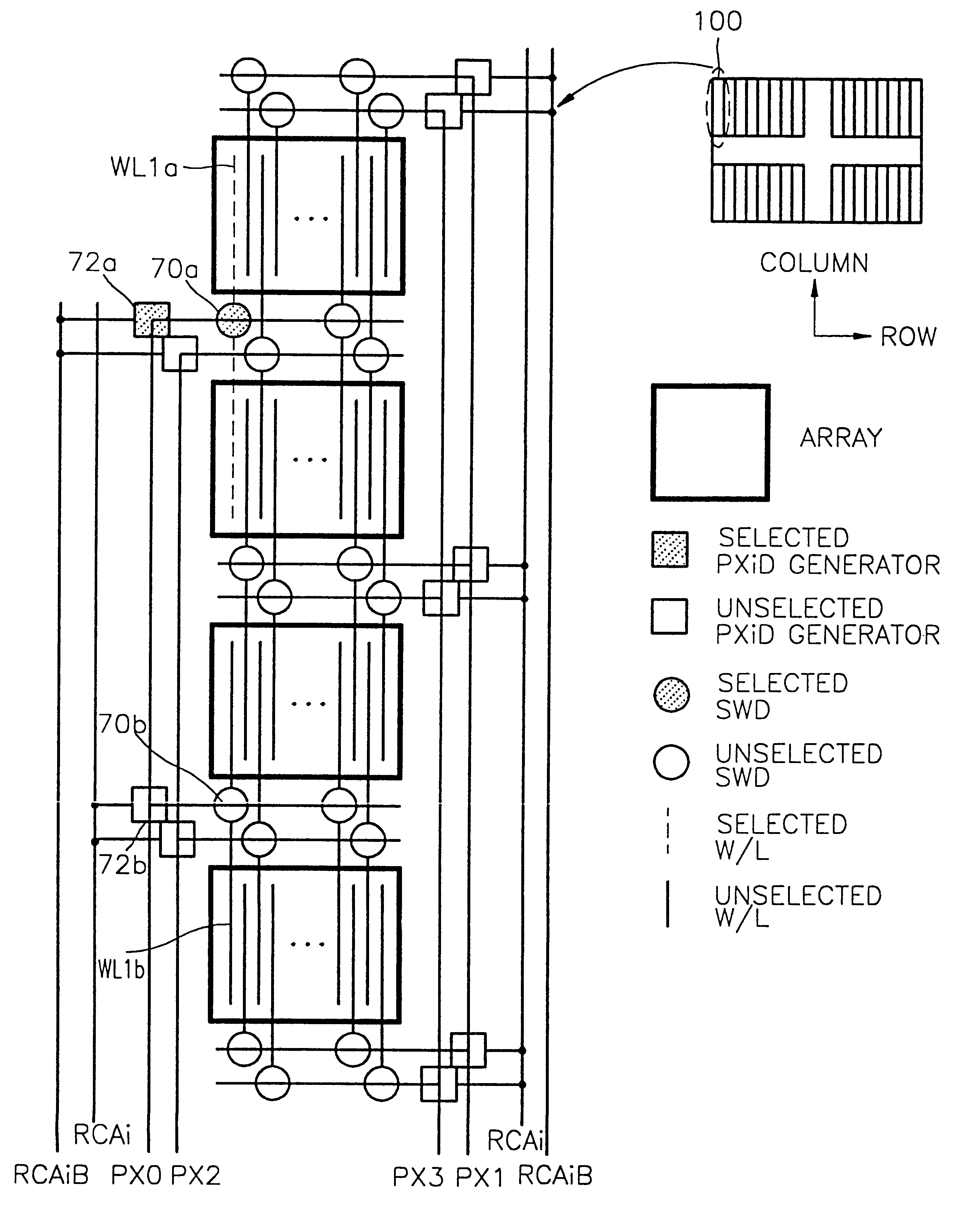

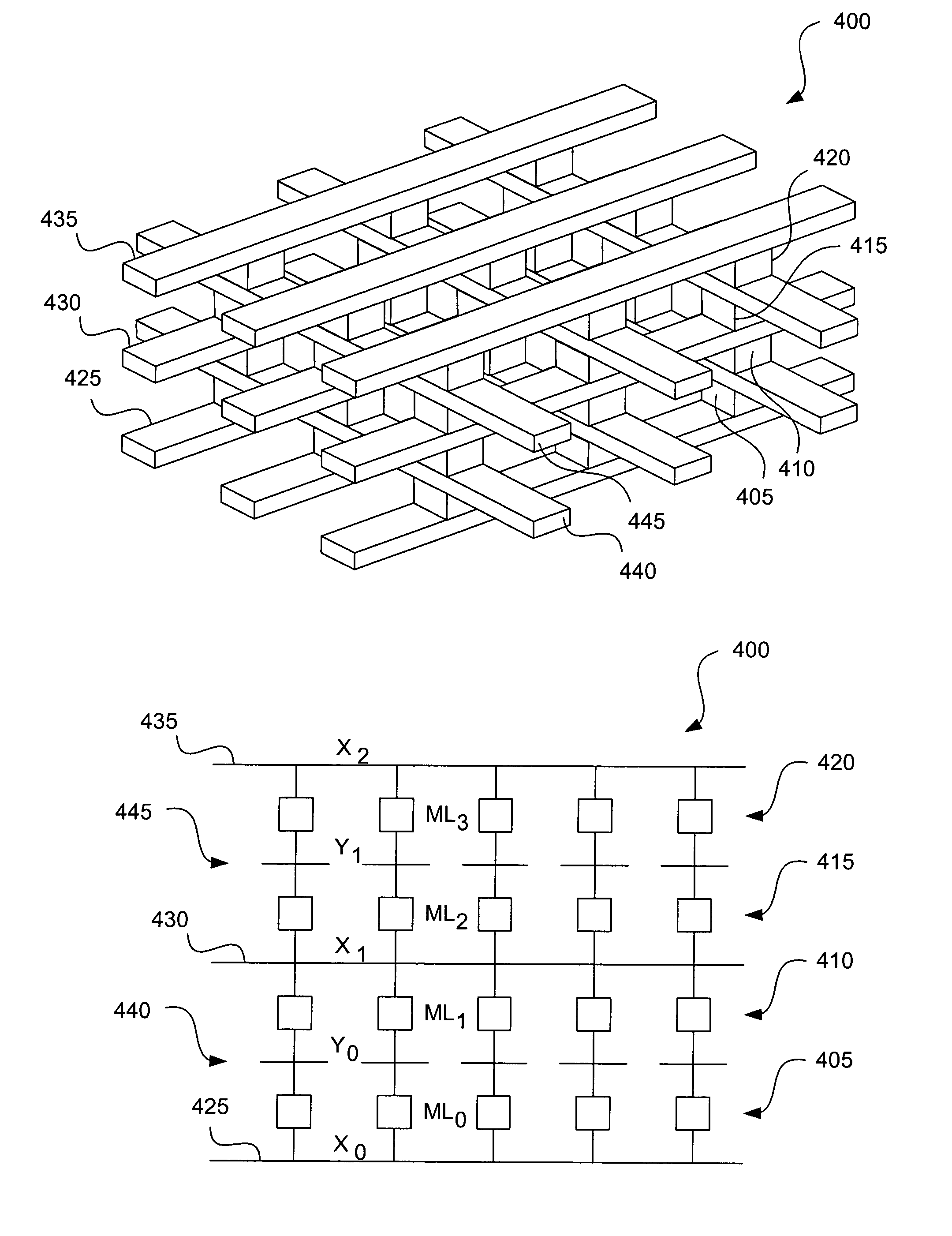

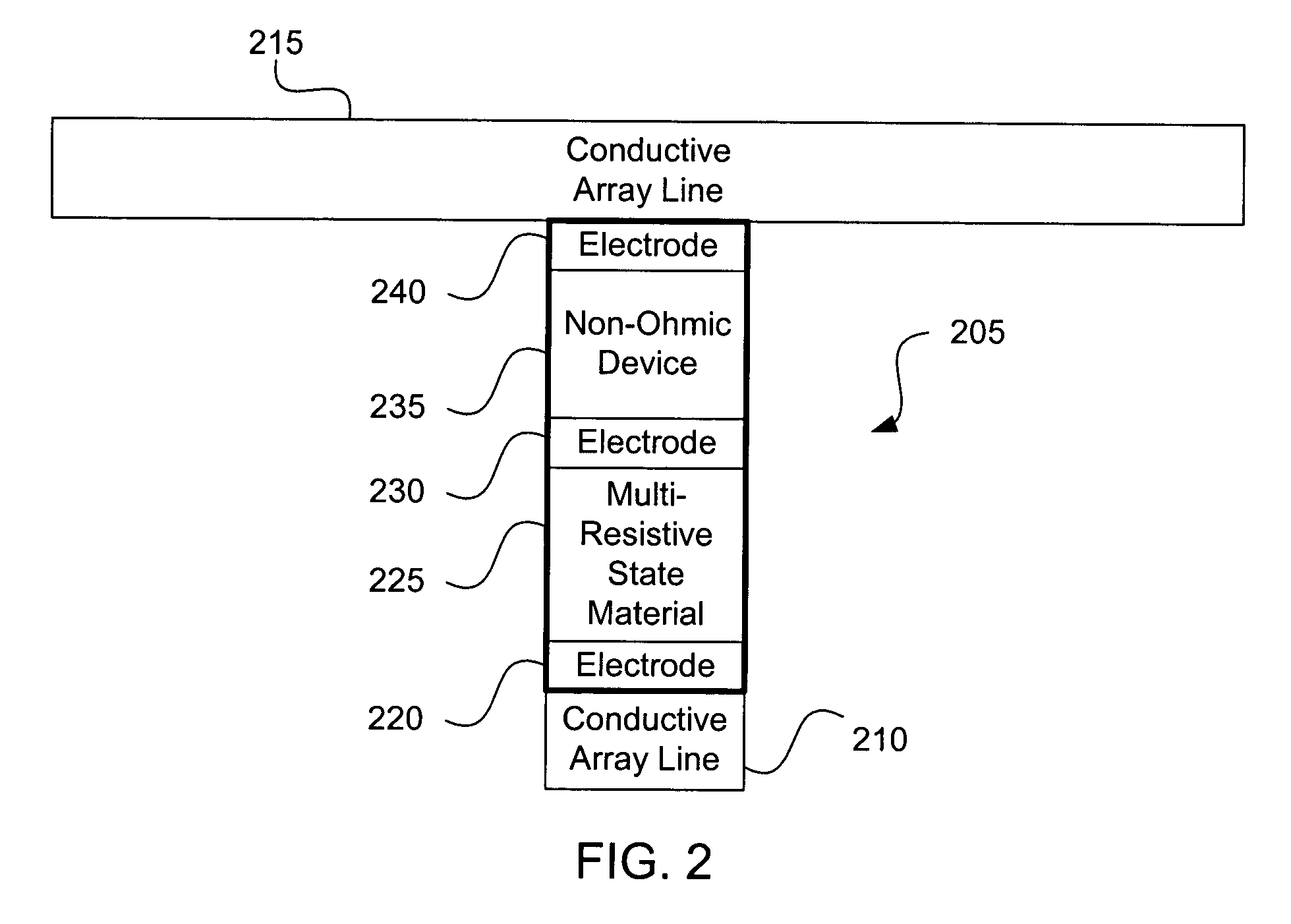

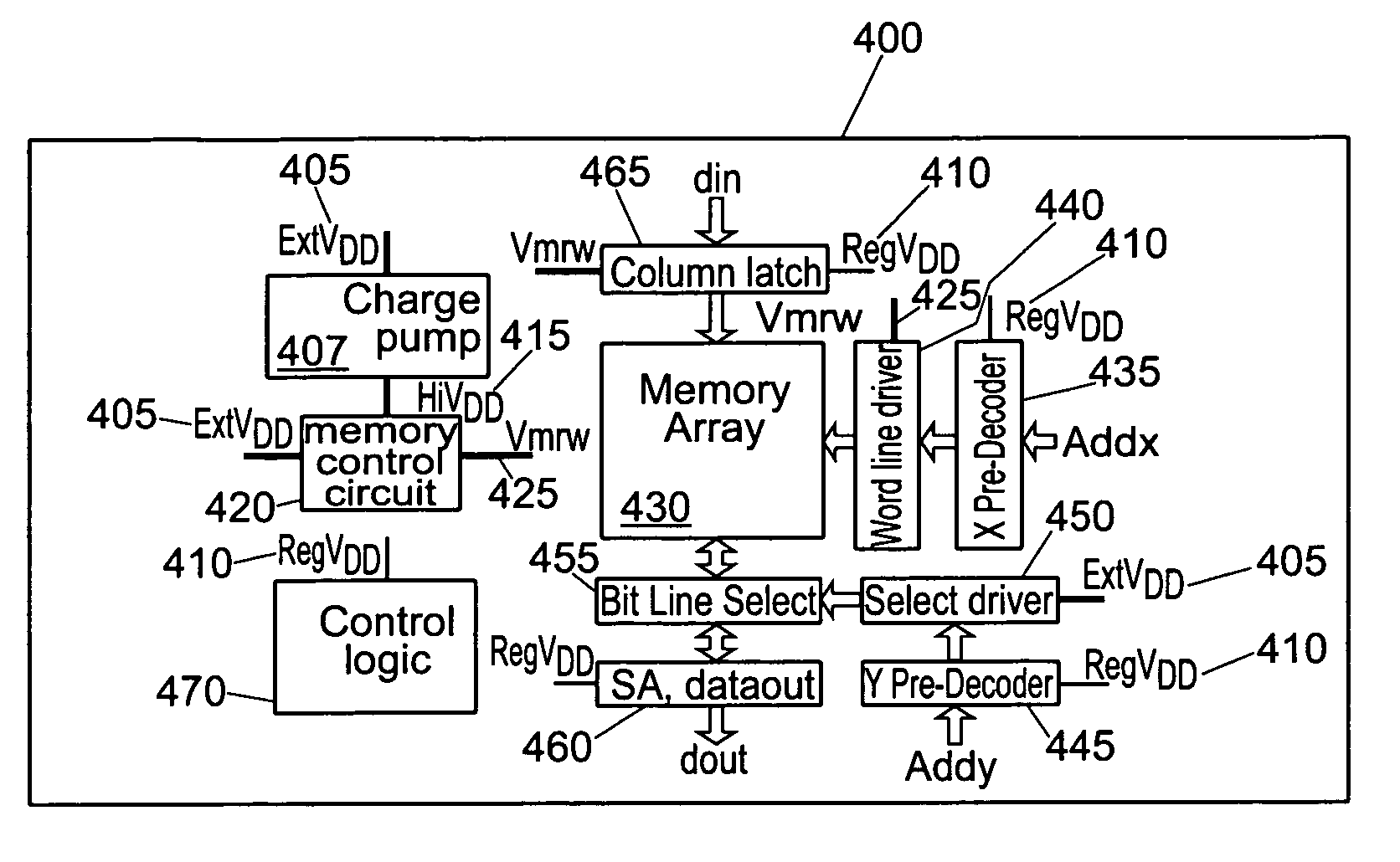

Multi-headed decoder structure utilizing memory array line driver with dual purpose driver device

A memory array decoder organization readily interfaces to array lines having extremely dense pitch, and in particular interfaces to extremely dense array lines of a three-dimensional memory array. In an exemplary embodiment, a multi-headed decoder includes a group of array line driver circuits associated with a single decode node. Each array line driver circuit couples its associated array line through a first device to an associated upper bias node which is generated to convey either a selected bias condition or an unselected bias condition thereon appropriate for the array line. Each array line driver circuit also couples its associated array line through a second device to an associated lower bias node which is generated to convey an unselected bias condition appropriate for the array line. The array line driver circuits for several different decode nodes may be physically arranged in one or more banks.

Owner:SANDISK TECH LLC

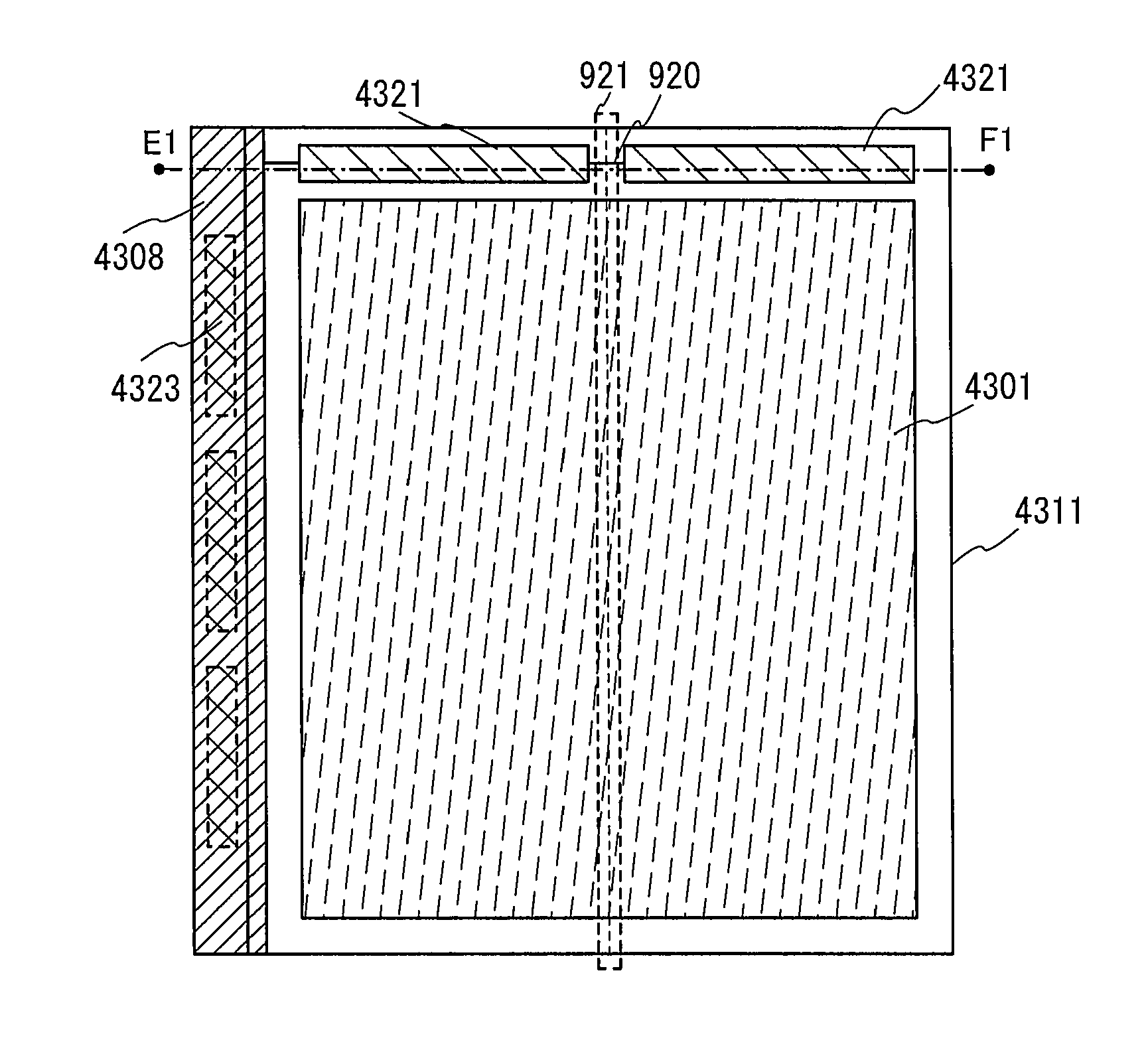

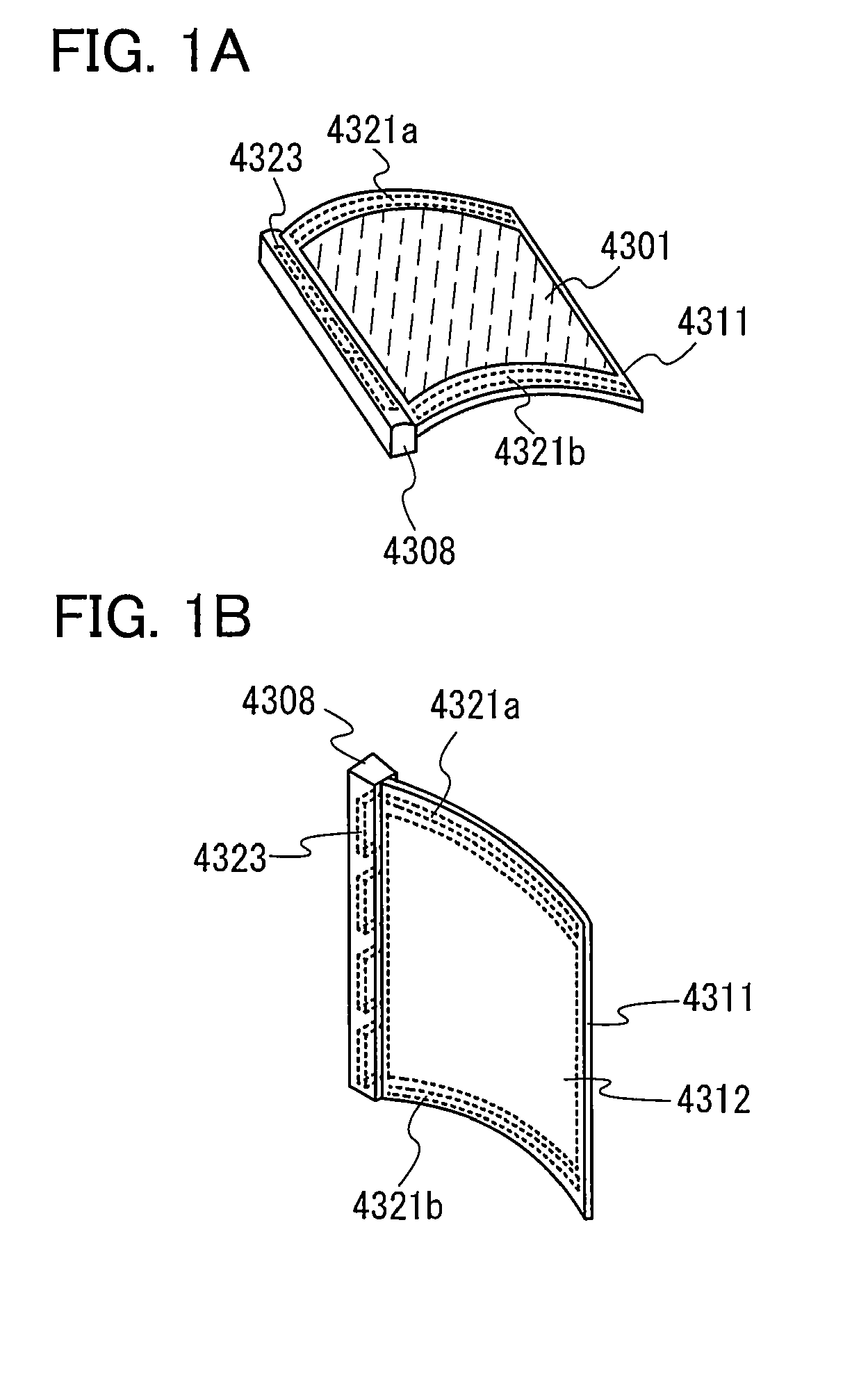

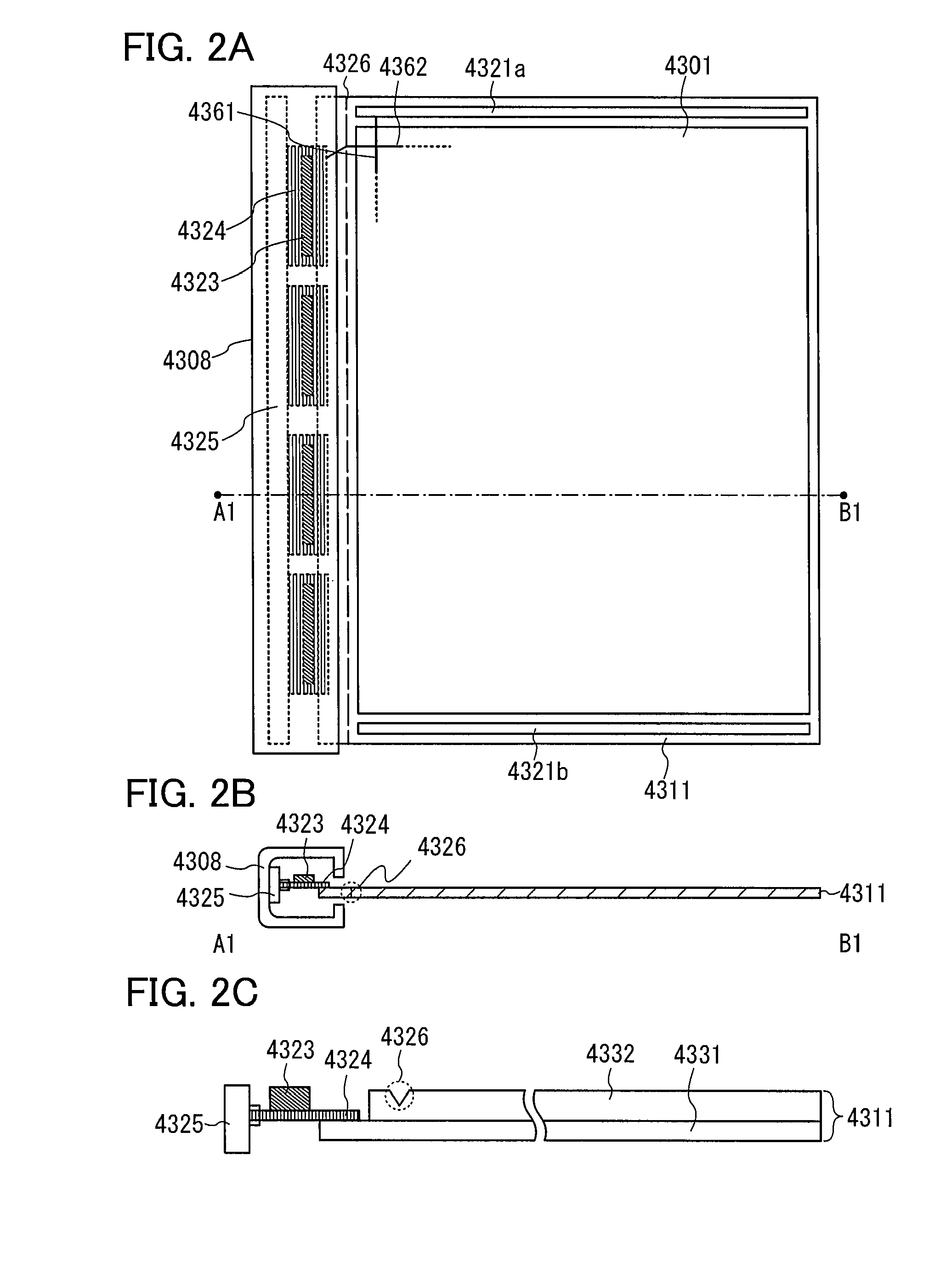

Display device

ActiveUS8319725B2Simple structureReduce breakagePrinted circuit aspectsSolid-state devicesDriver circuitDisplay device

The display device includes: a flexible display panel including a display portion in which scanning lines and signal lines cross each other; a supporting portion for supporting an end portion of the flexible display panel; a signal line driver circuit for outputting a signal to the signal line, which is provided for the supporting portion; and a scanning line driver circuit for outputting a signal to the scanning line, which is provided for a flexible surface of the display panel in a direction which is perpendicular or substantially perpendicular to the supporting portion.

Owner:SEMICON ENERGY LAB CO LTD

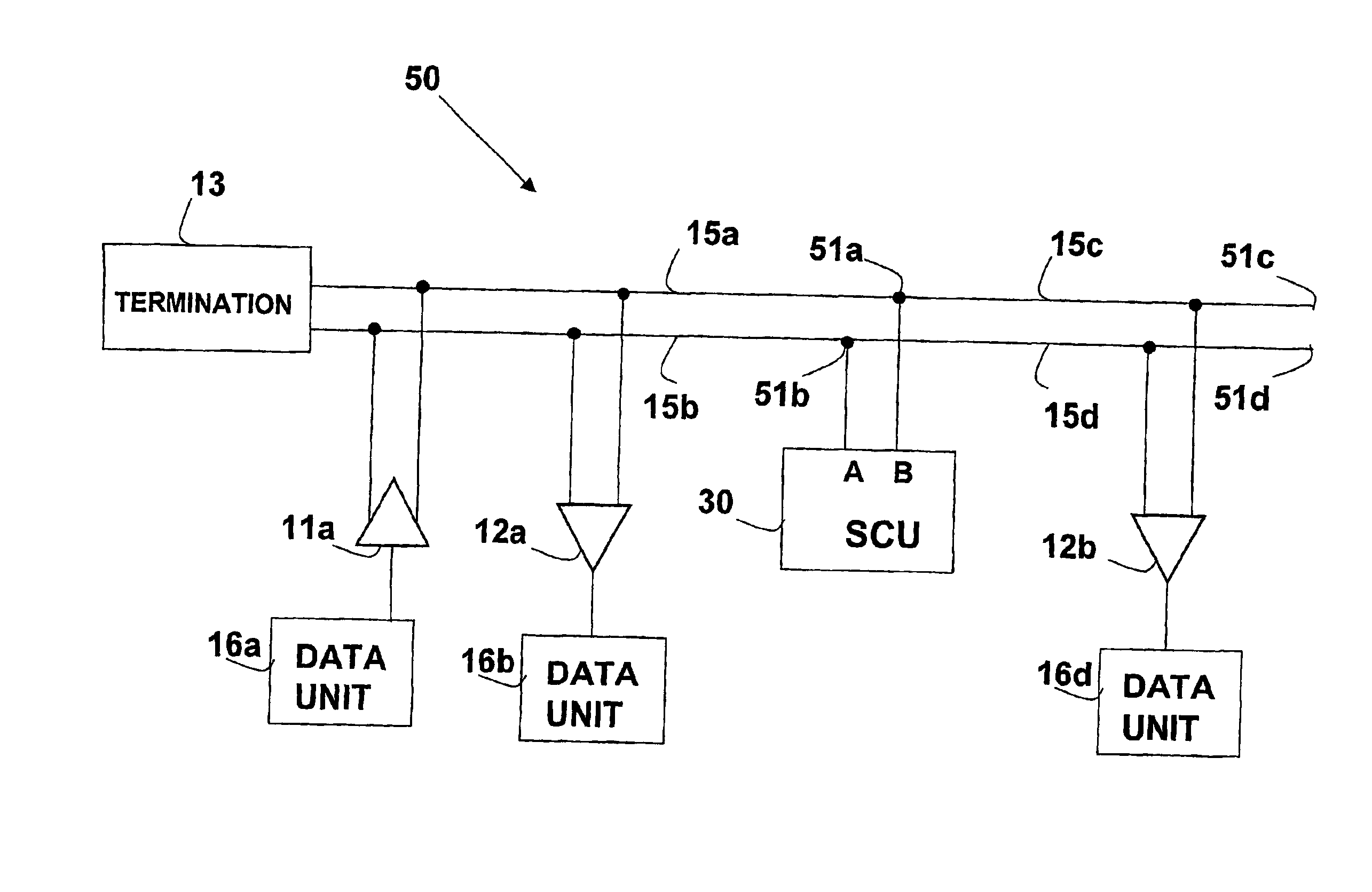

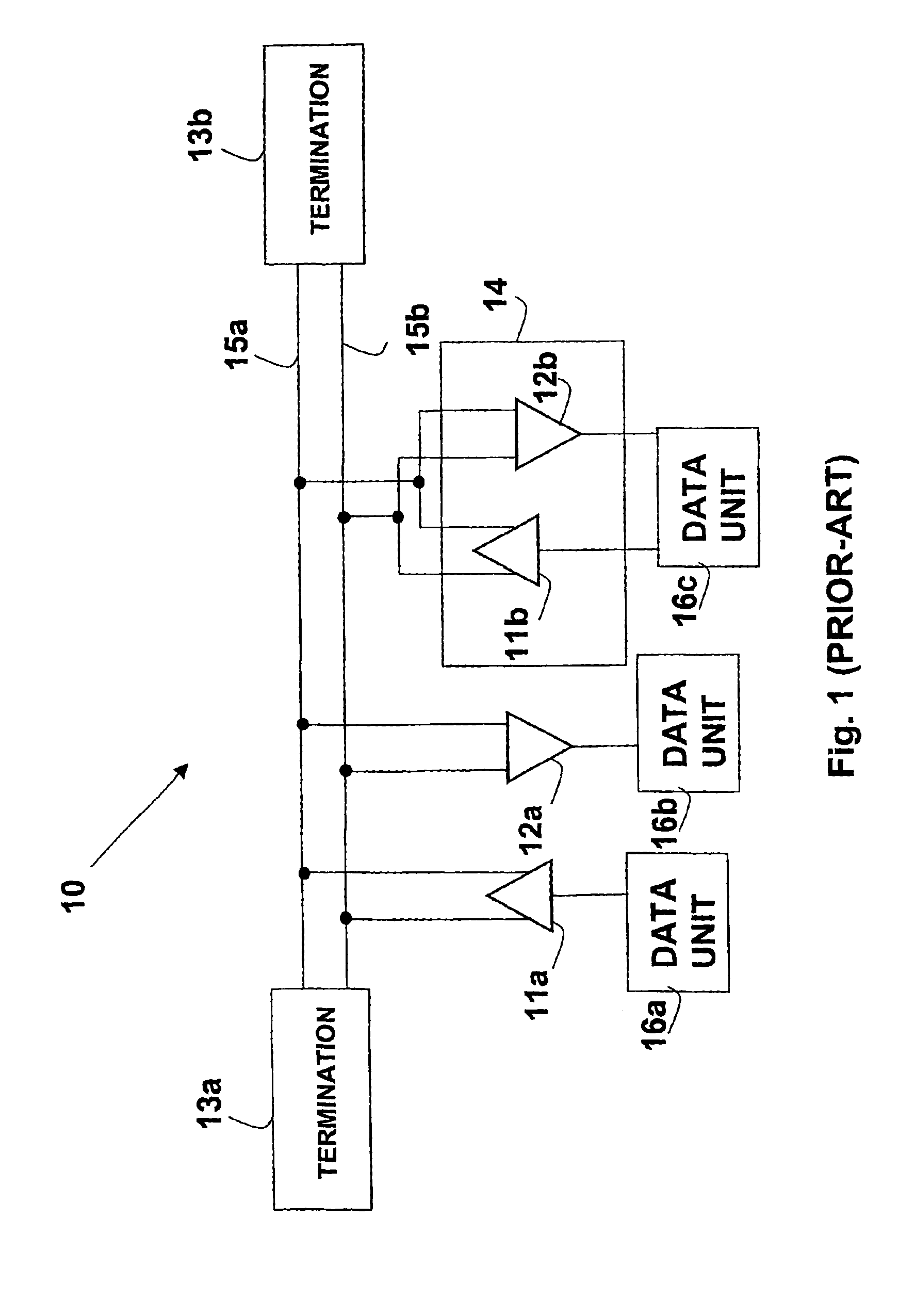

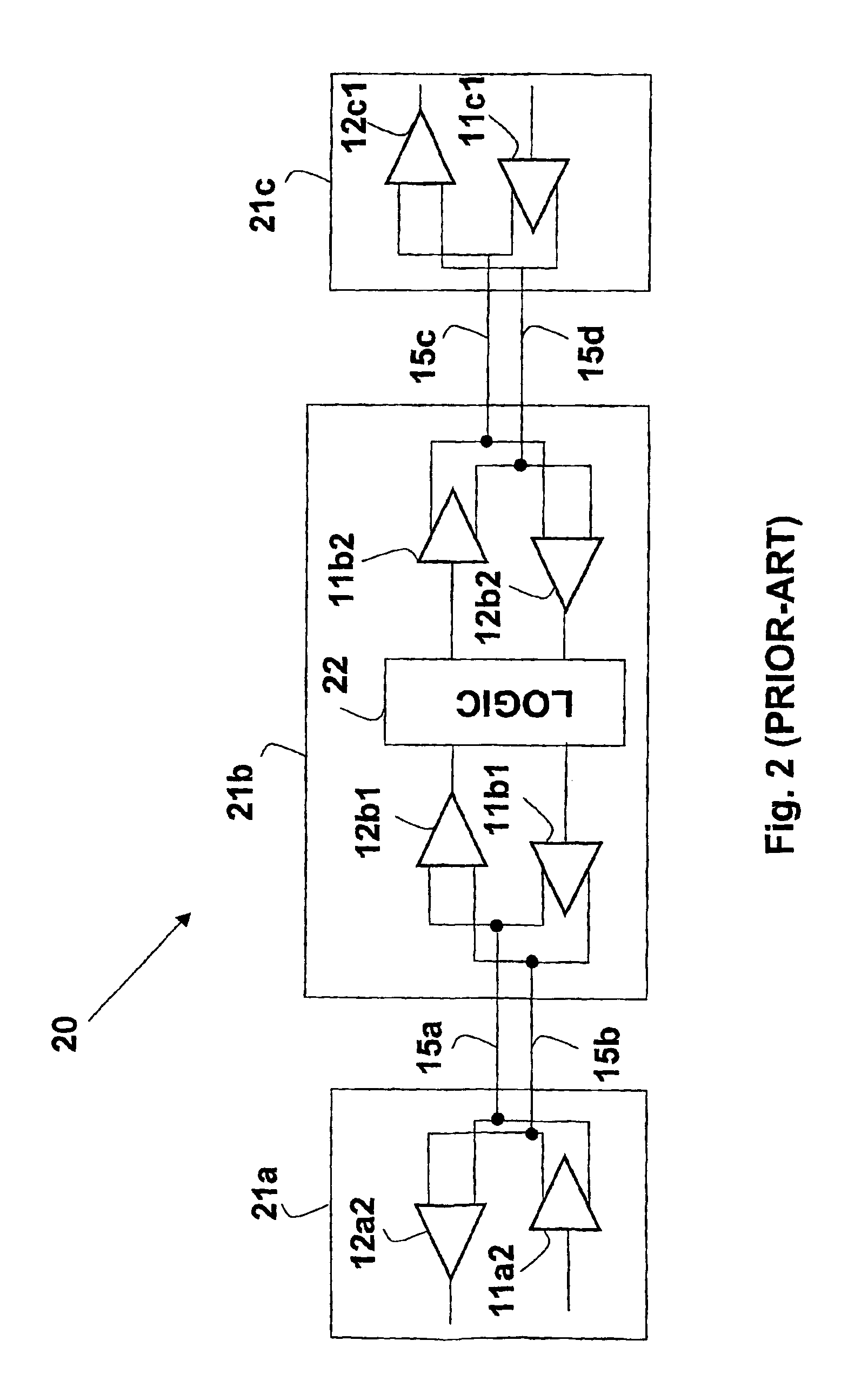

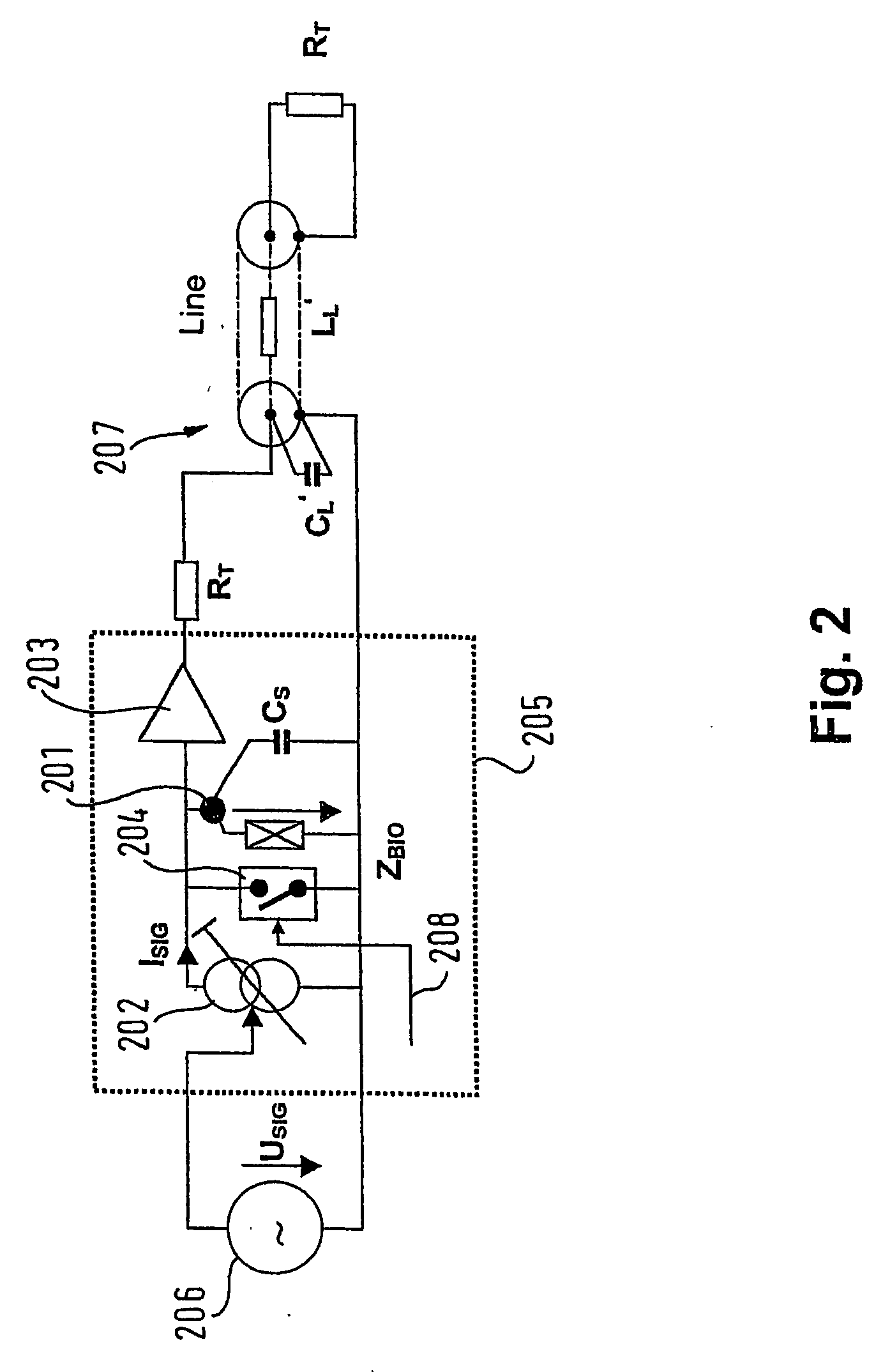

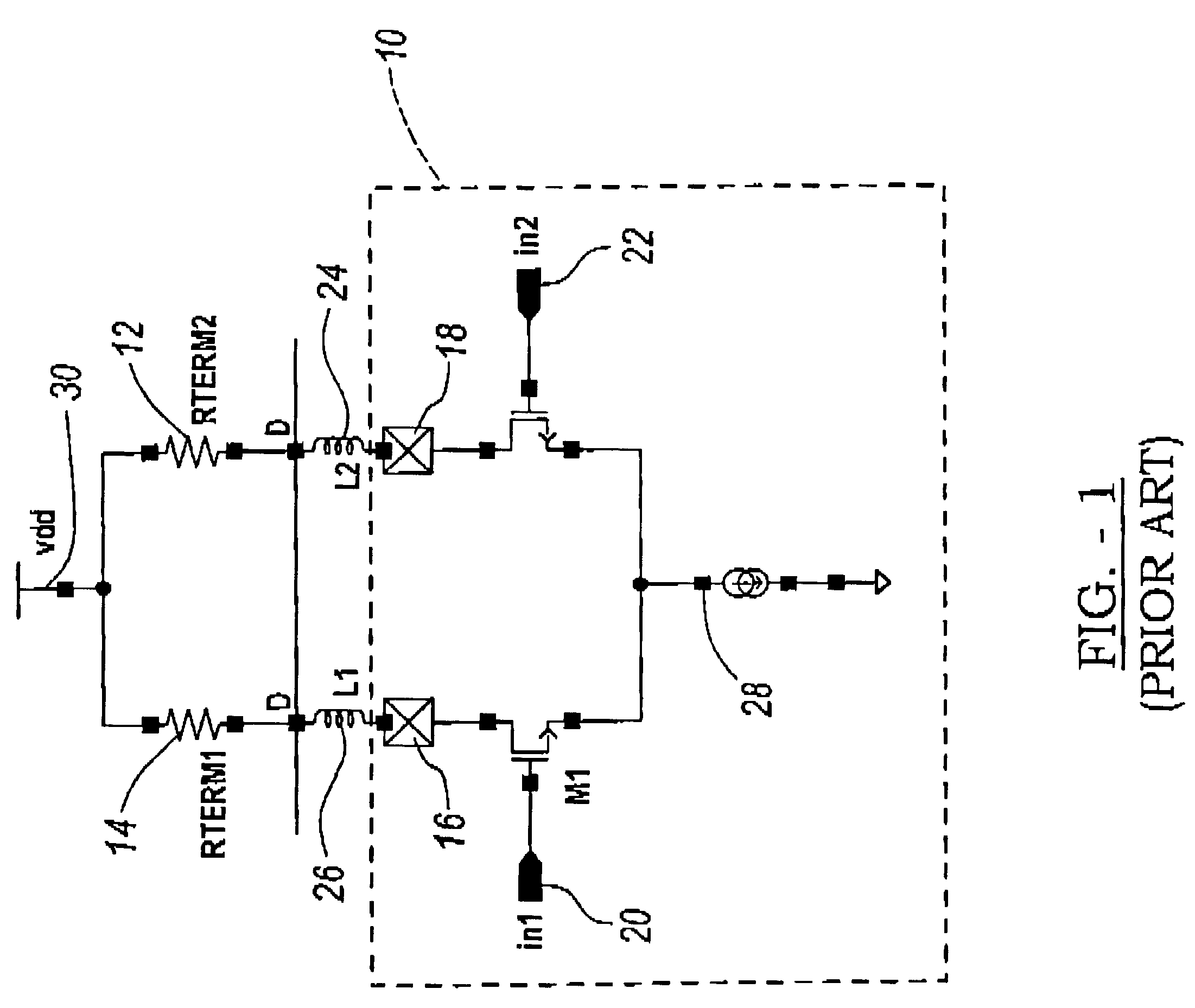

System and method for transmission-line termination by signal cancellation, and applications thereof

InactiveUS6937056B2Effective segmentationInput/output impedence modificationReliability increasing modificationsElectric power transmissionNetwork termination

An active terminating device (30) for an electrical transmission line with optional line-receiving and line-driving capabilities. The basic device is a two-terminal unit, denoted as a Signal Canceling Unit (SCU), which sensesthe signal available at its terminals (34a, 34b), and applies negative feedback in order to cancel and absorb the signal. When applied to the end of a transmission line (15a, 15b) as part of wired communication network, the SCU functions as a terminator. When connected in the middle of such wired transmission line, the SCU splits the transmission line into two separate and isolated segments. In such a configuration, the SCU can be used to isolate a portion of a network from signal degradation due to noise or bridge-tap. Furthermore, the two isolated segments may each employ independent communications, such that no interference exists between the segments. In another embodiment, line receiver functionality is integrated into the SCU, designated as a Signal Canceling and Receiving Unit (SCRU) (90). The SCRU can perform all the SCU functions, and also serves as a line receiver in the communication network. In yet another embodiment, line driver functionality is integrated into the SCRU, designated as a Signal Canceling, Receiving and Transmitting Unit (SCRTU) (120). The SCRTU can perform all the SCRU functions, and also serves as a line driver in the communication network. Upon connecting multiple SCRTU's to a continuous transmission line, terminated independent point-to-point communication segments are formed.

Owner:CONVERSANT INTPROP MANAGEMENT INC

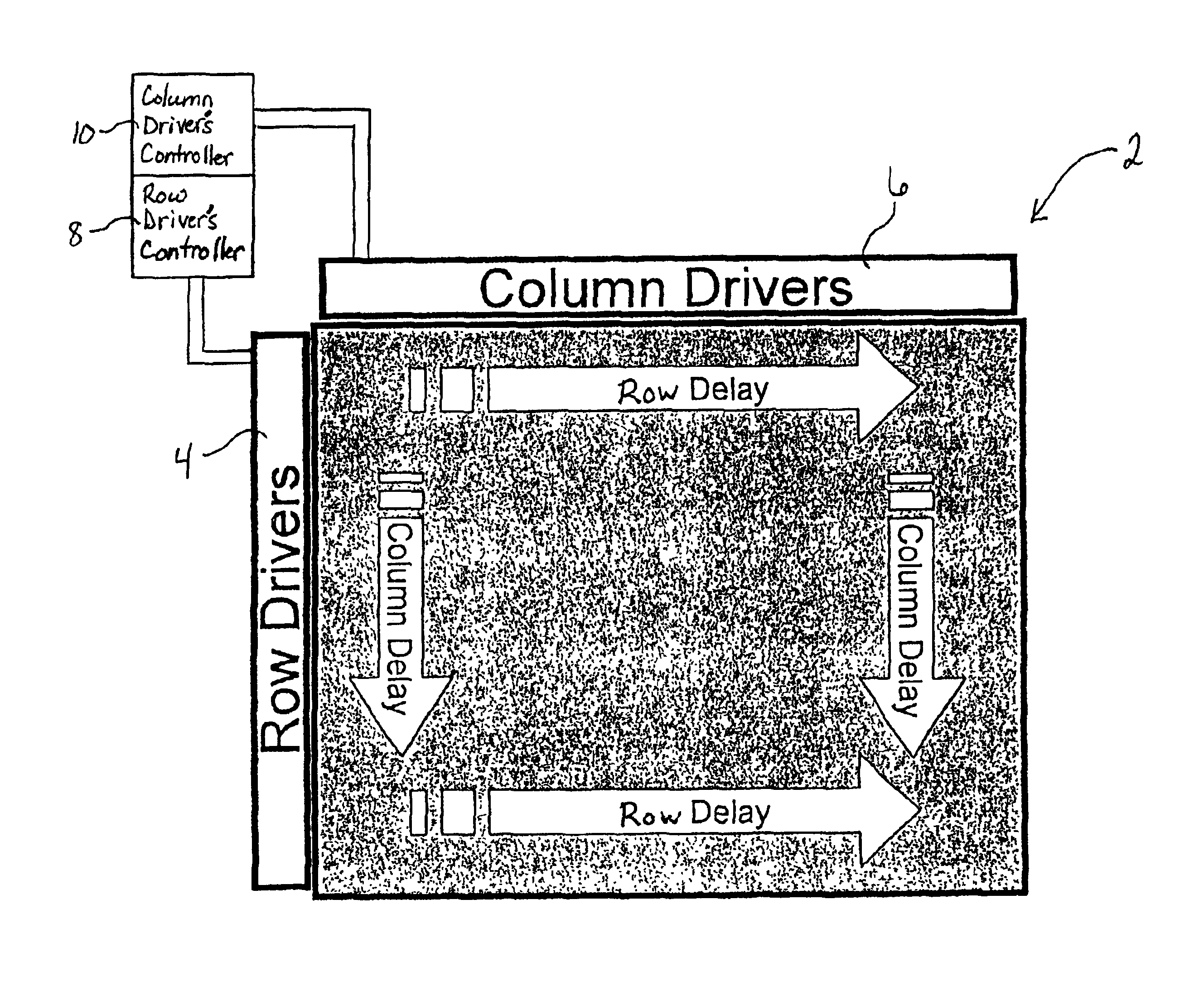

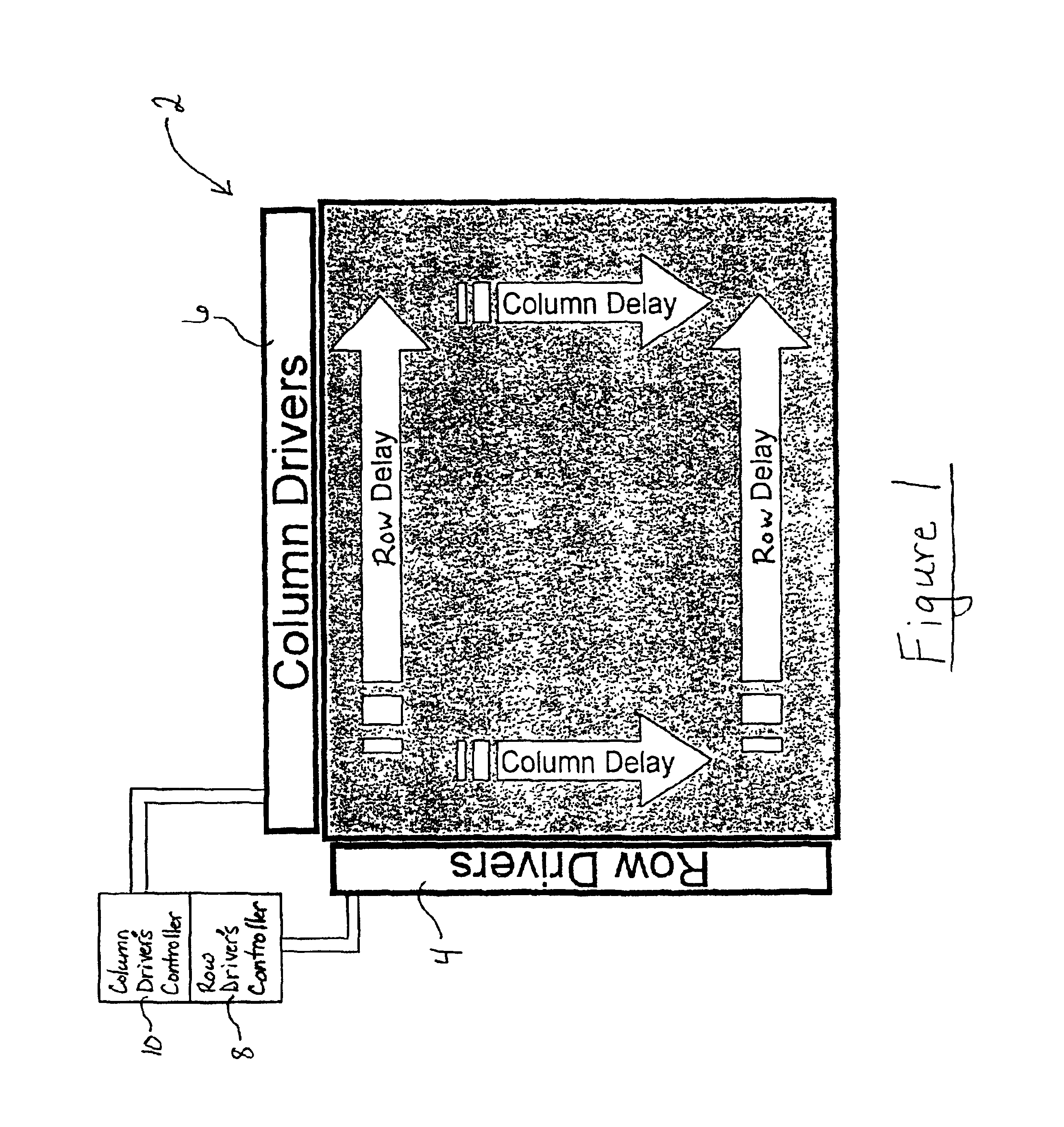

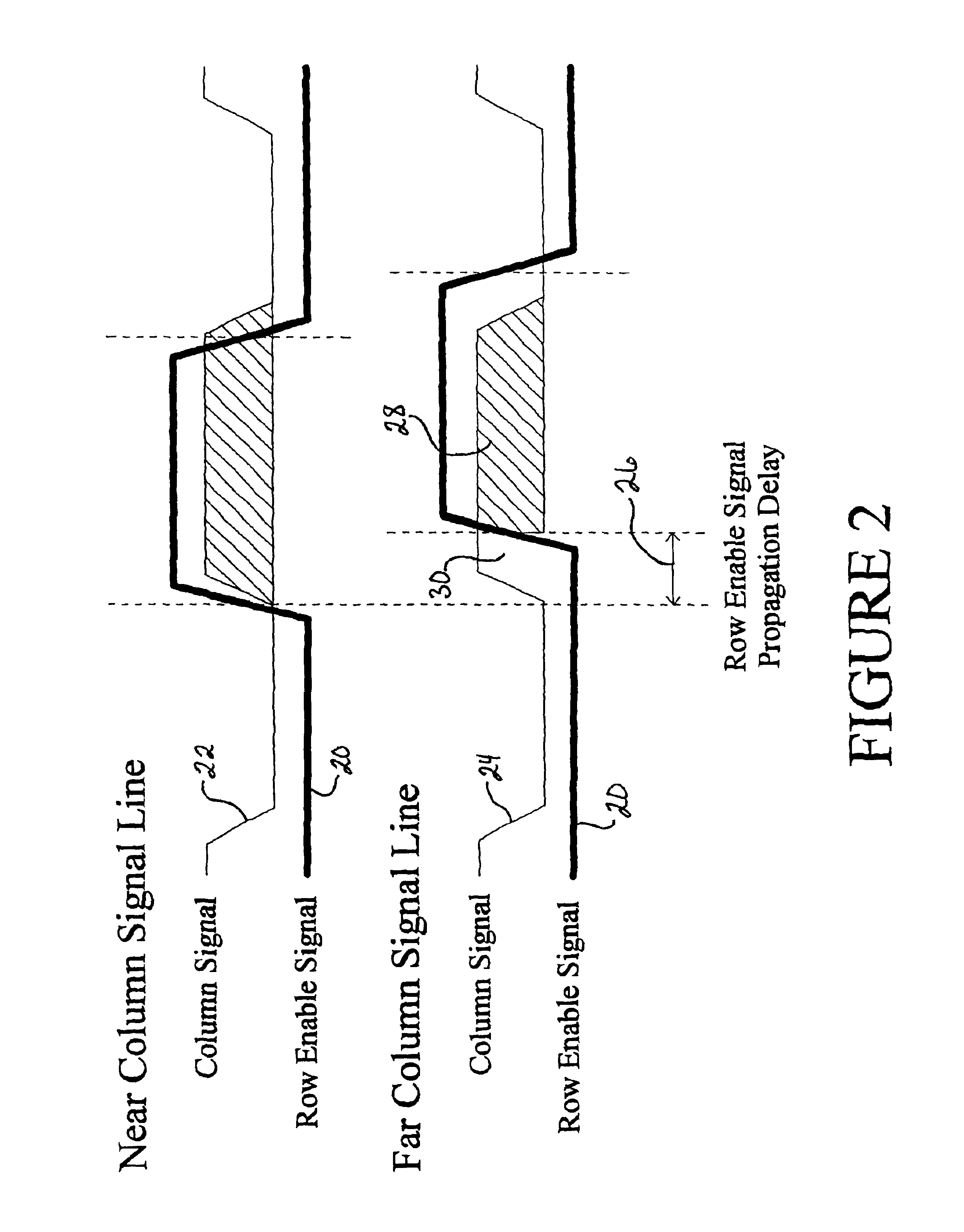

Display line drivers and method for signal propagation delay compensation

InactiveUS6947022B2Reduce impactSlow effectCathode-ray tube indicatorsInput/output processes for data processingEngineeringLine driver

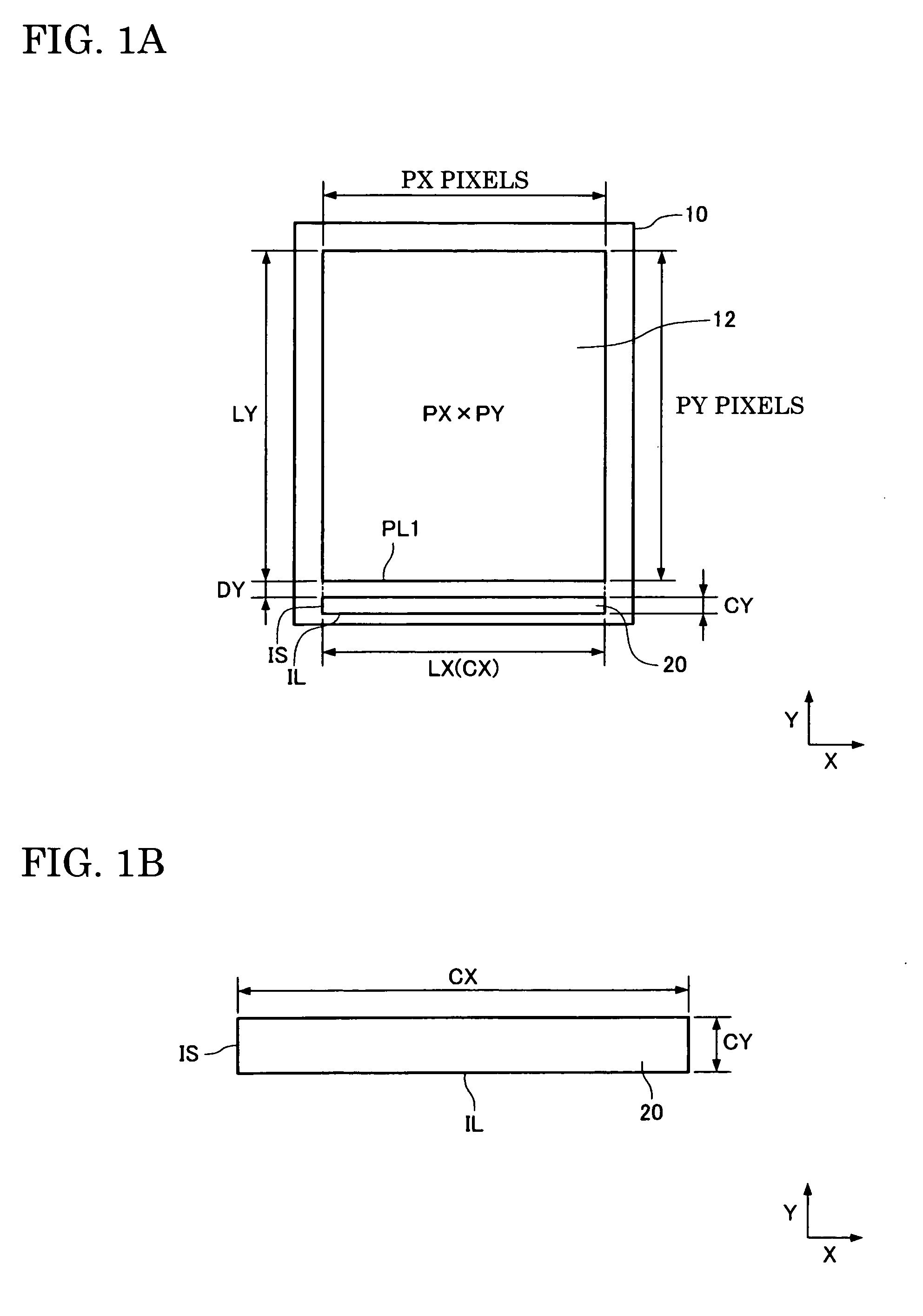

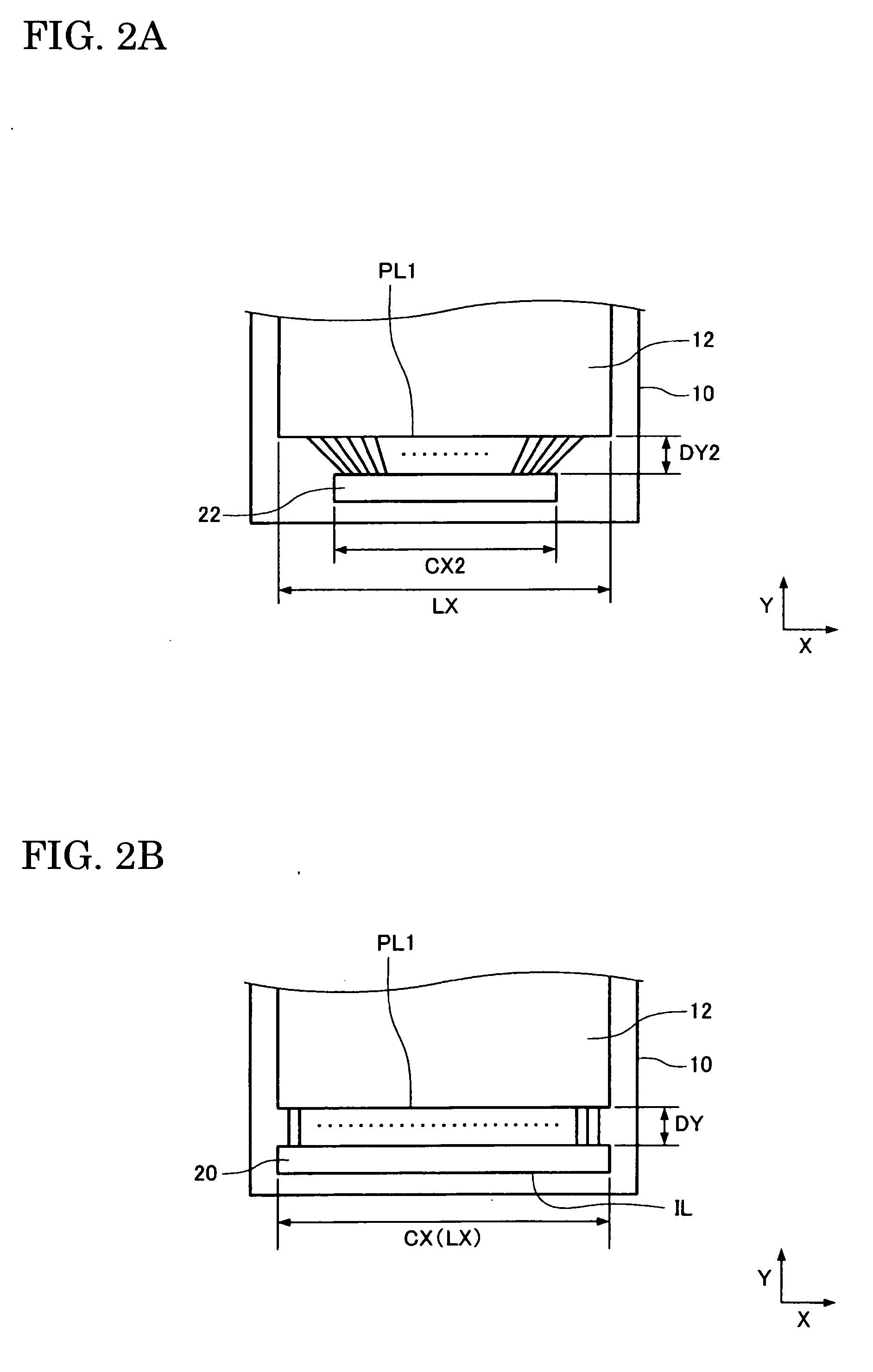

Methods and apparatus for compensating the effects of display signal propagation delay in a display panel are disclosed. The apparatus comprises circuitry in addition to conventional display driver circuitry for delaying display line timing signals by an amount approximating the delay found in corresponding display lines. By delaying display line timing signals, for example in a column driver, by an time approximately equal the delay experienced in a corresponding row enable signal line, capacitors associated with the display pixels charge more fully resulting in a more vivid display image. Methods for compensating the effects of display signal propagation delay involve generating a plurality of delayed display timing signals and activating display lines in response to those delayed timing signals.

Owner:NAT SEMICON CORP

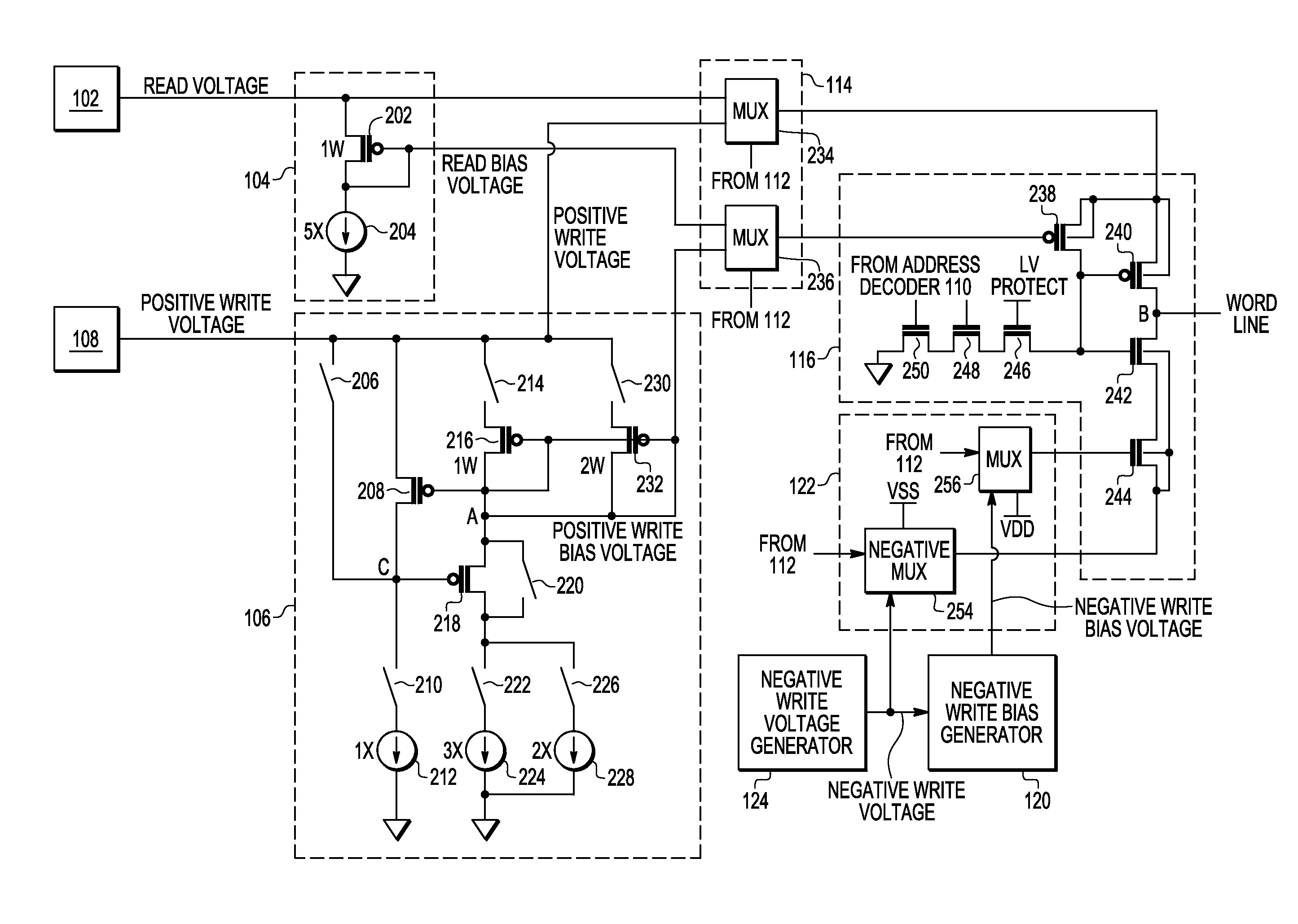

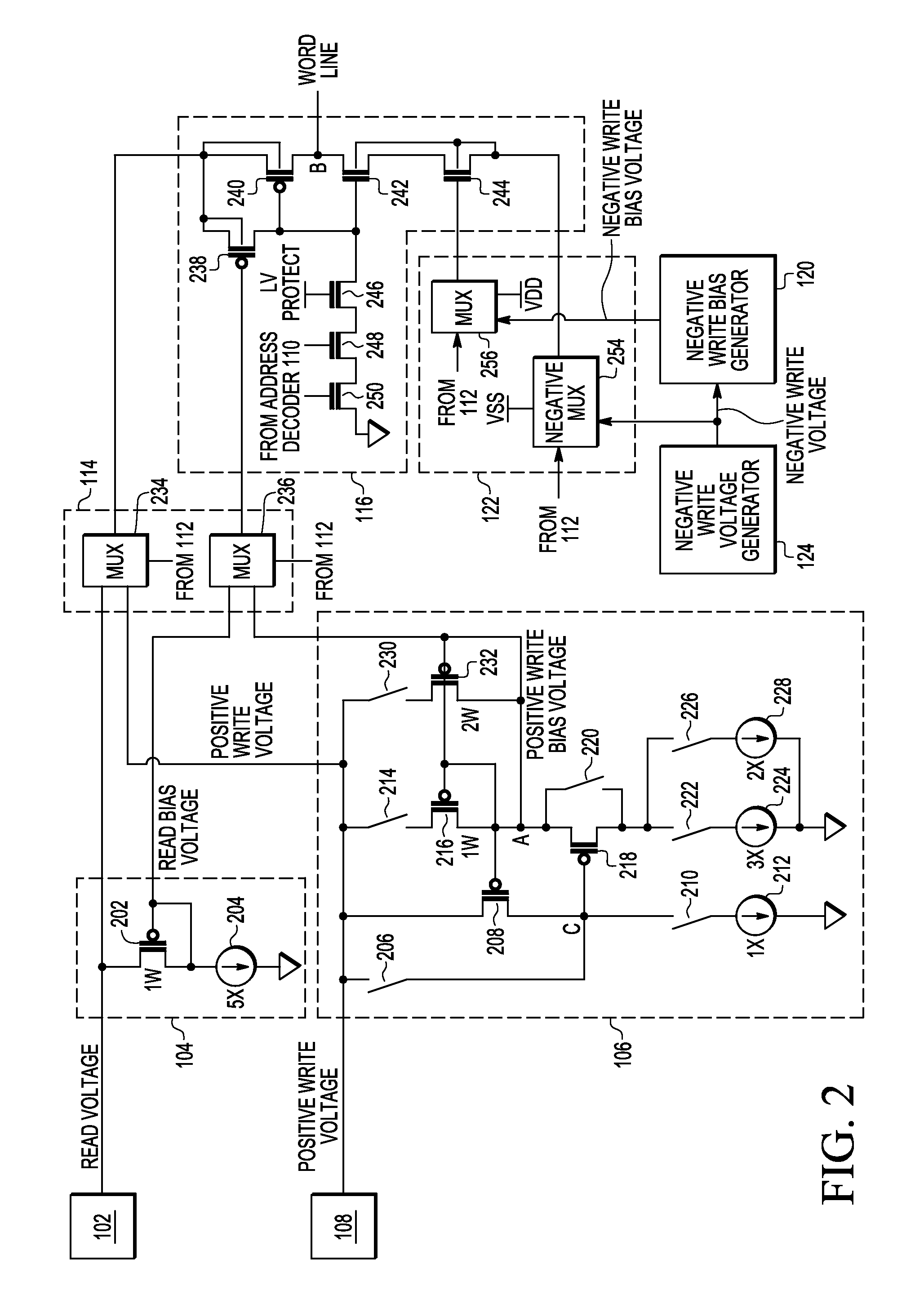

Flash memory with bias voltage for word line/row driver

A memory device includes a word line driver circuit, a write voltage generator for providing a write voltage to the word line driver during a write operation to memory cells coupled to the word line driver circuit, and a write bias generator including an output node for providing a write bias voltage that is different from the write voltage to the word line driver circuit during a write operation to memory cells coupled to the word line driver circuit. The write bias voltage is used to reduce current drawn by the word line driver circuit from the write voltage generator during a write operation to memory cells coupled to the word line driver circuit.

Owner:NXP USA INC

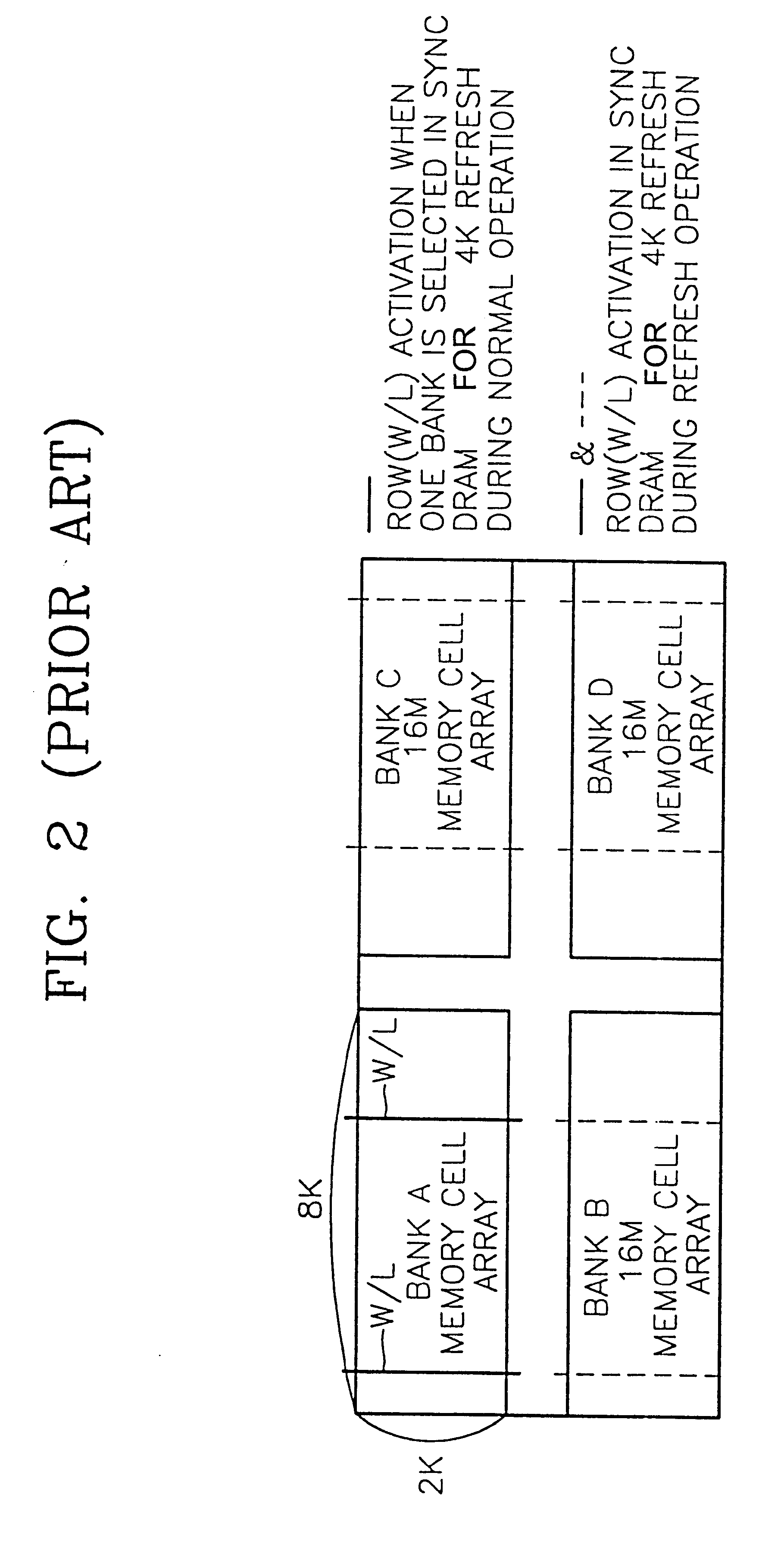

Semiconductor memory device and driving signal generator therefor

A semiconductor memory device is provided having reduced power consumption during a normal operation. The semiconductor memory device includes a sub word-line defined by segmenting a word-line and a driving signal generator for selectively driving the sub word-line according to a column address. The driving signal generator is controlled by a selection signal corresponding to the column address and a mode signal for specifying an operation mode of the semiconductor memory device. The semiconductor memory device enables part of the word-line according to the column address. The semiconductor memory device using a sub word-line driver to reduce the number of memory cells which are sensed, thereby reducing power consumption.

Owner:SAMSUNG ELECTRONICS CO LTD

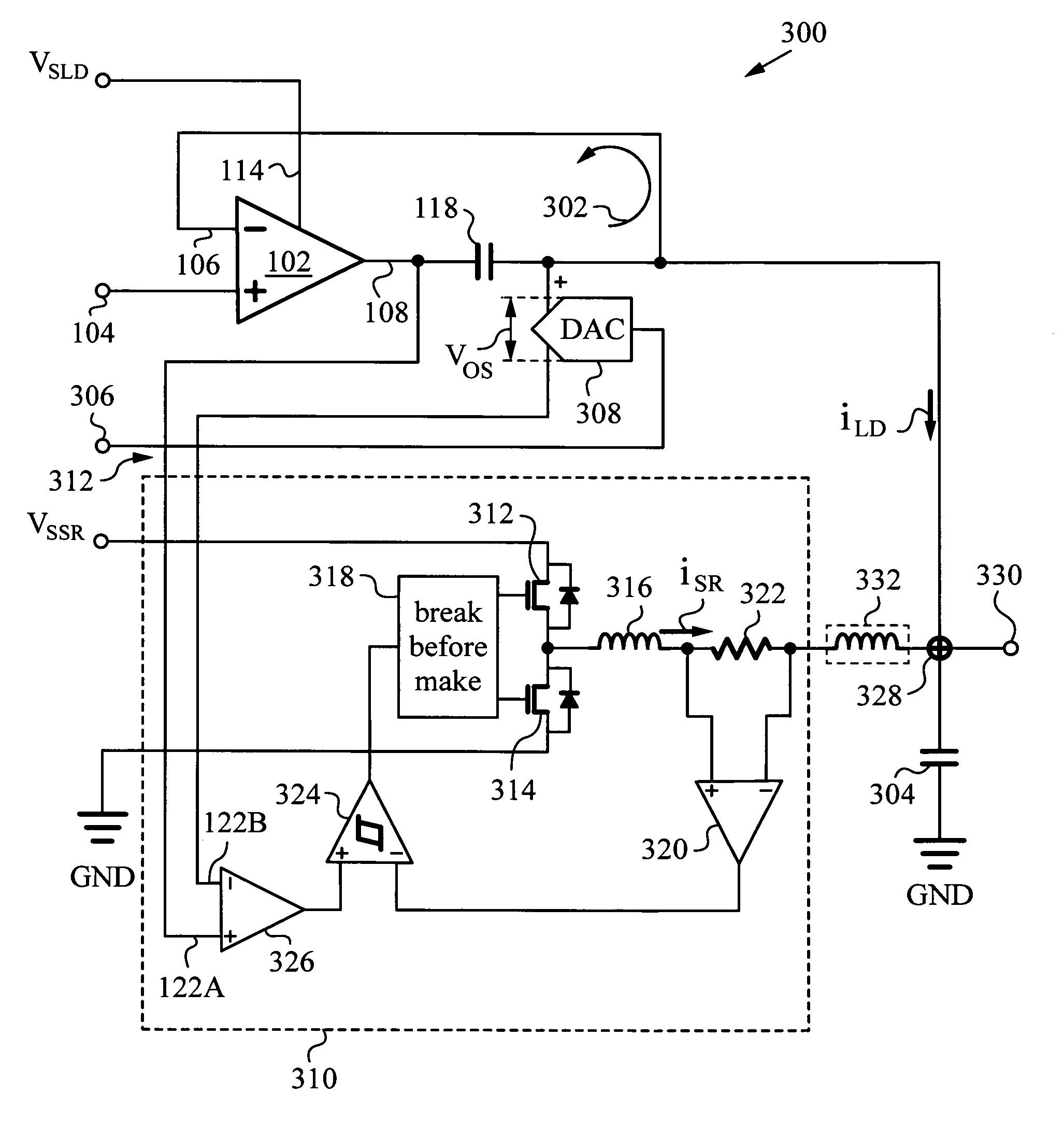

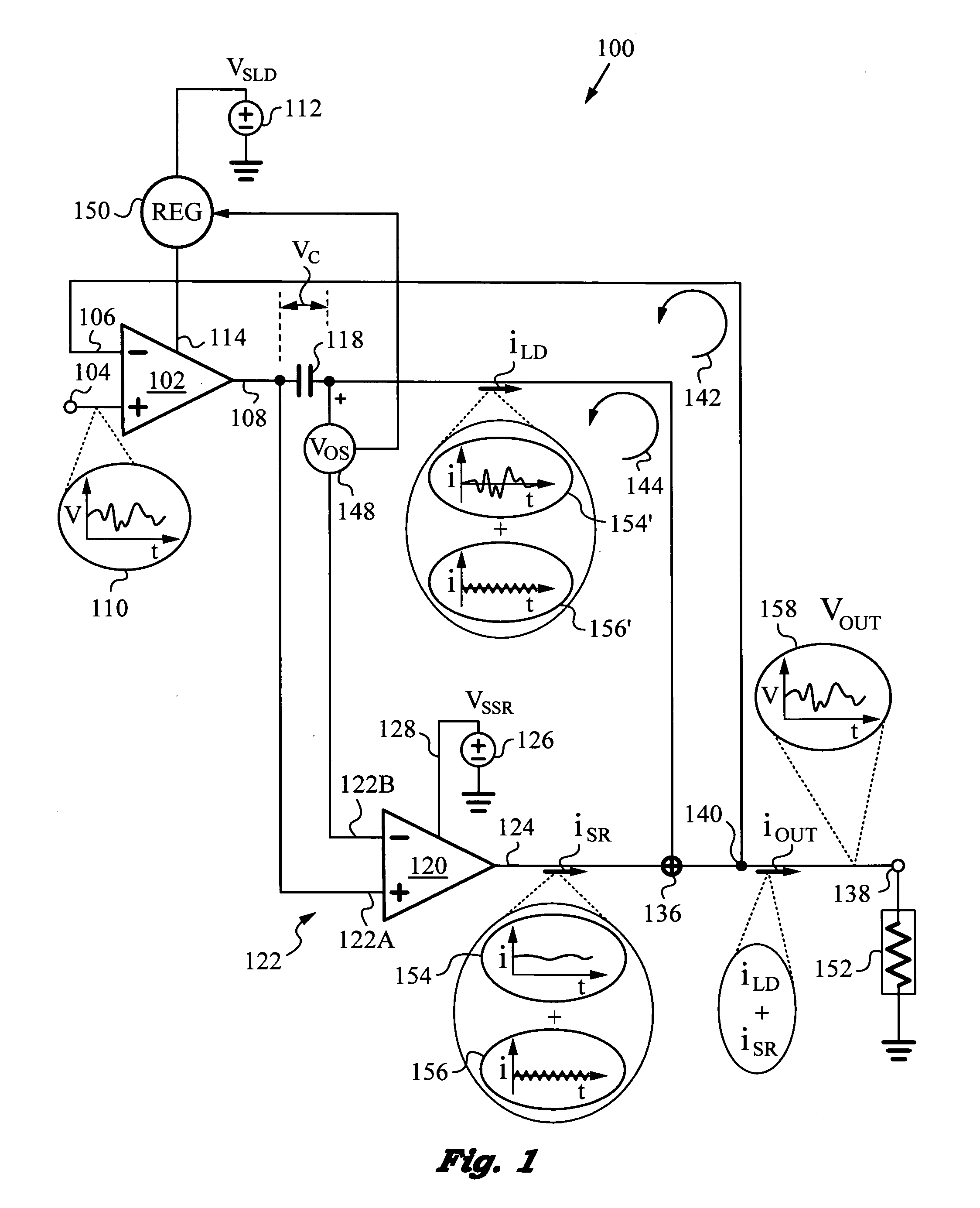

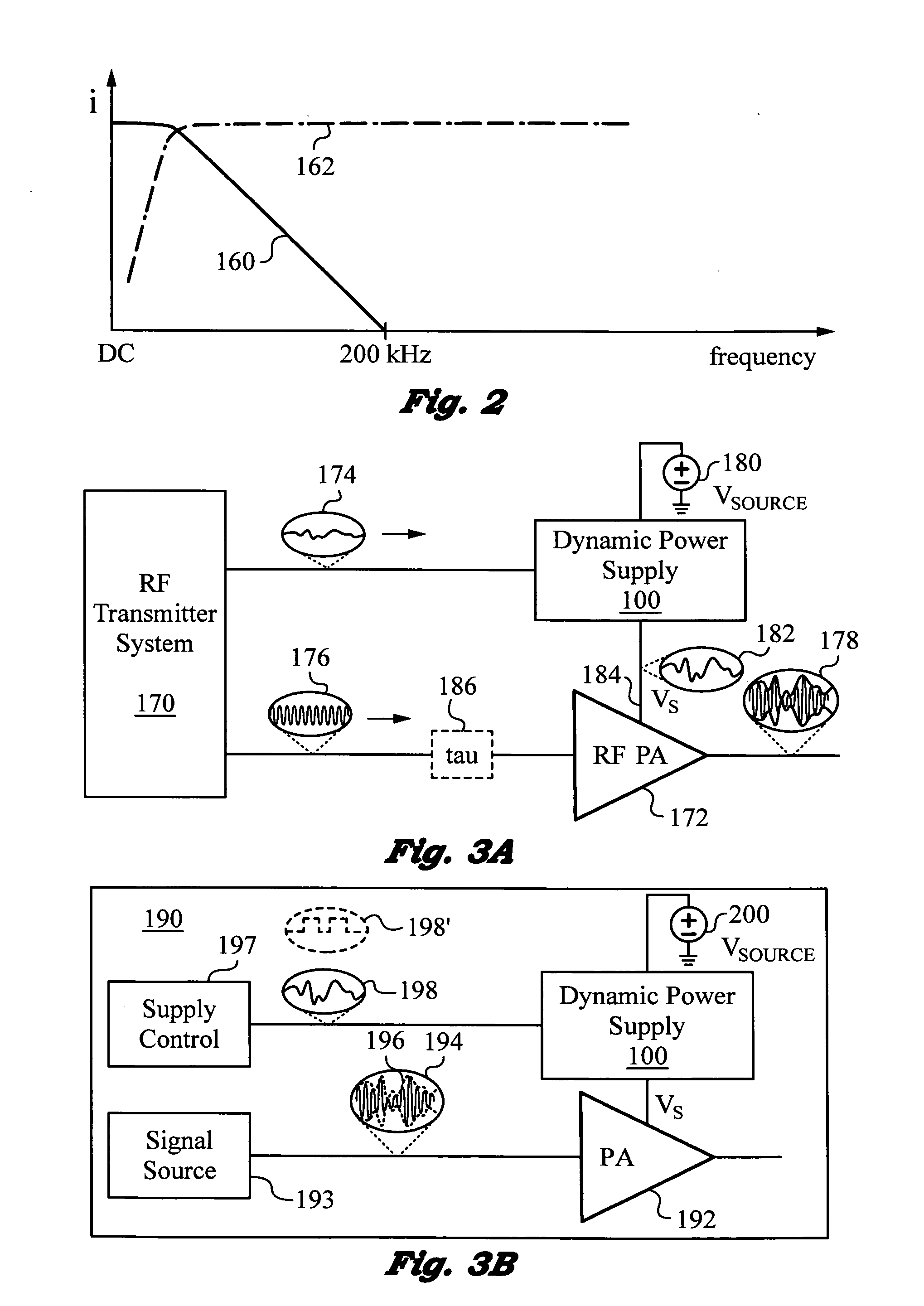

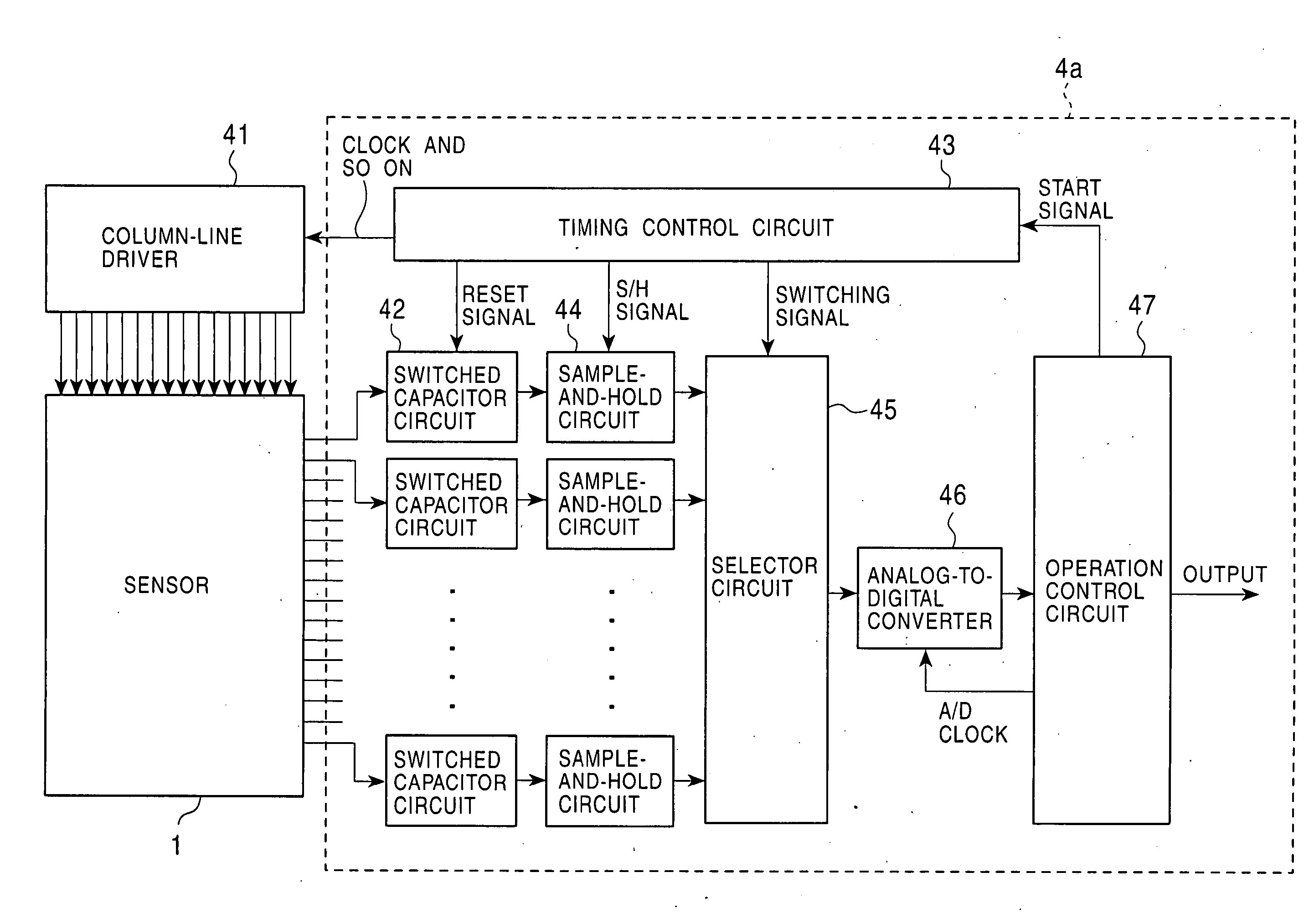

Dynamic power supply employing a linear driver and a switching regulator

ActiveUS20130214858A1Reduce power supply voltageImprove efficiencyGain controlDc-dc conversionNegative feedbackCapacitor voltage

A highly efficient, high control bandwidth and high-speed power supply with a linear driver and a switching regulator for regulating an output based on a control signal. The linear driver has a first input for receiving the control signal and a second input connected to the output for receiving negative feedback. The driver's output is controlled by its two inputs and has a capacitor connected in series with it to generate a capacitor voltage VC responsive to the DC and low frequency components in the driver's output. The switching regulator has a control input and a regulator output connected in a regulator feedback loop. The control input receives capacitor voltage VC and the regulator feedback loop minimizes capacitor voltage VC. Thus, switching regulator takes over the generation of DC and low frequency components, while the linear driver provides high frequency output current components.

Owner:QUANTANCE

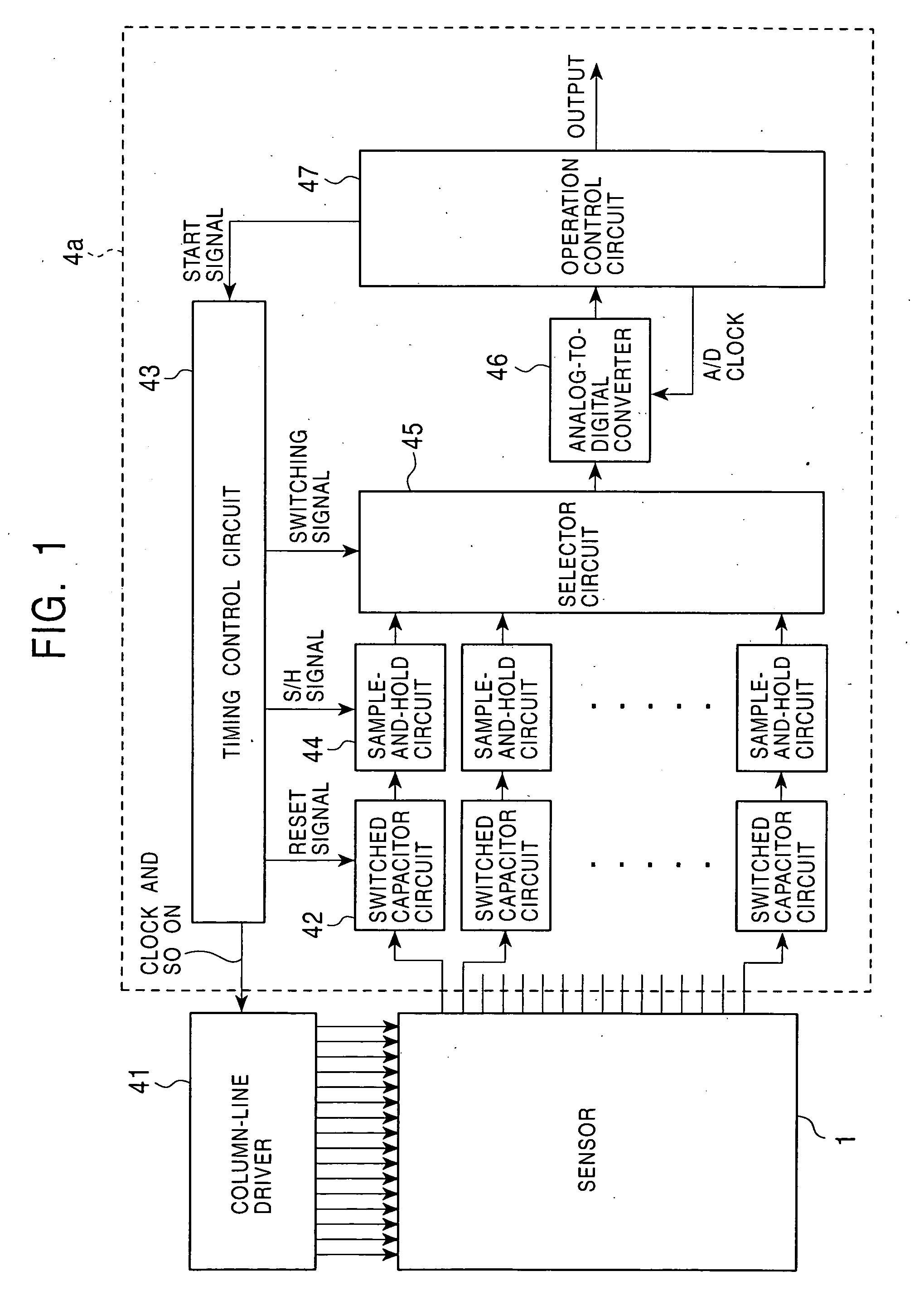

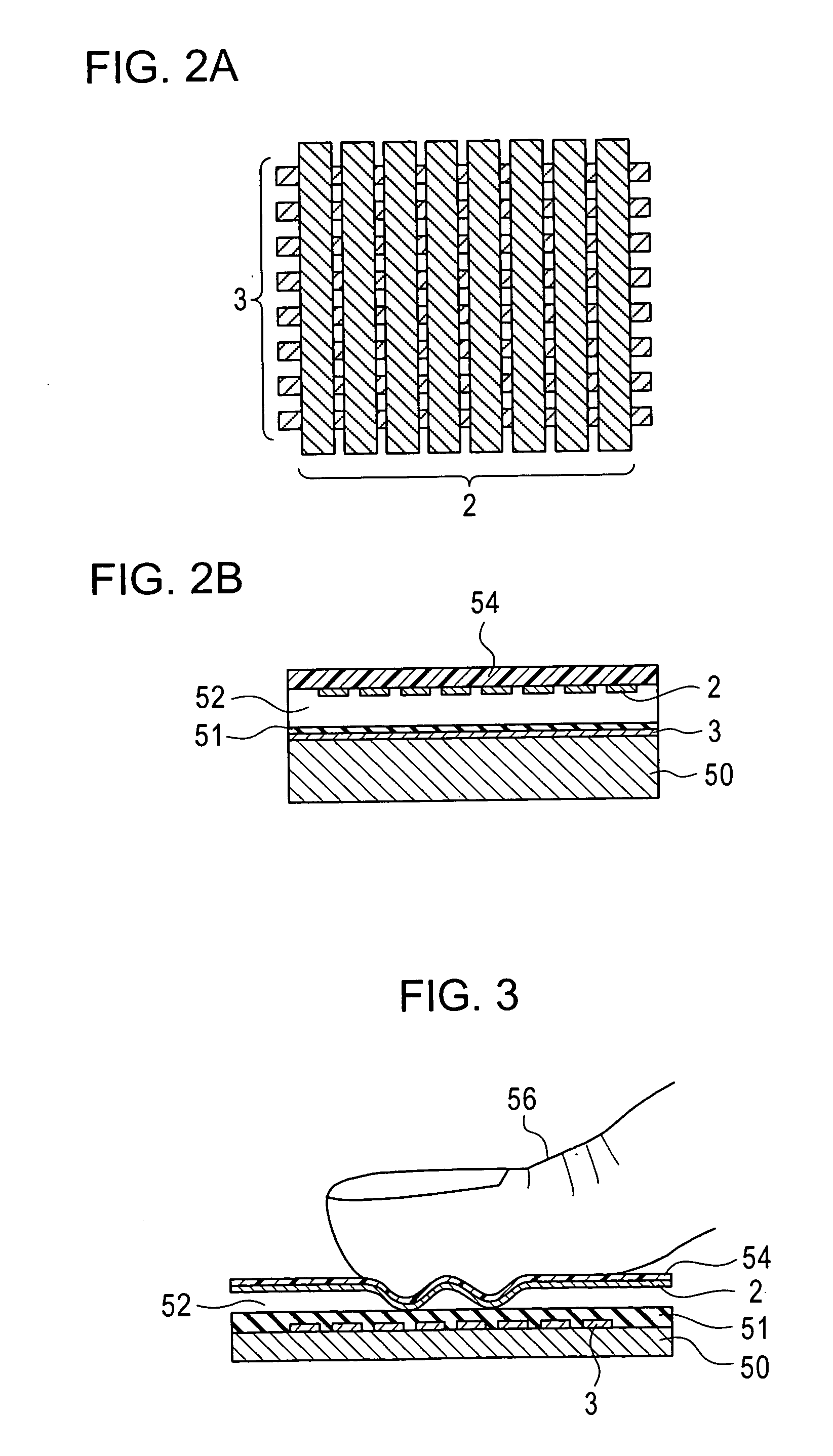

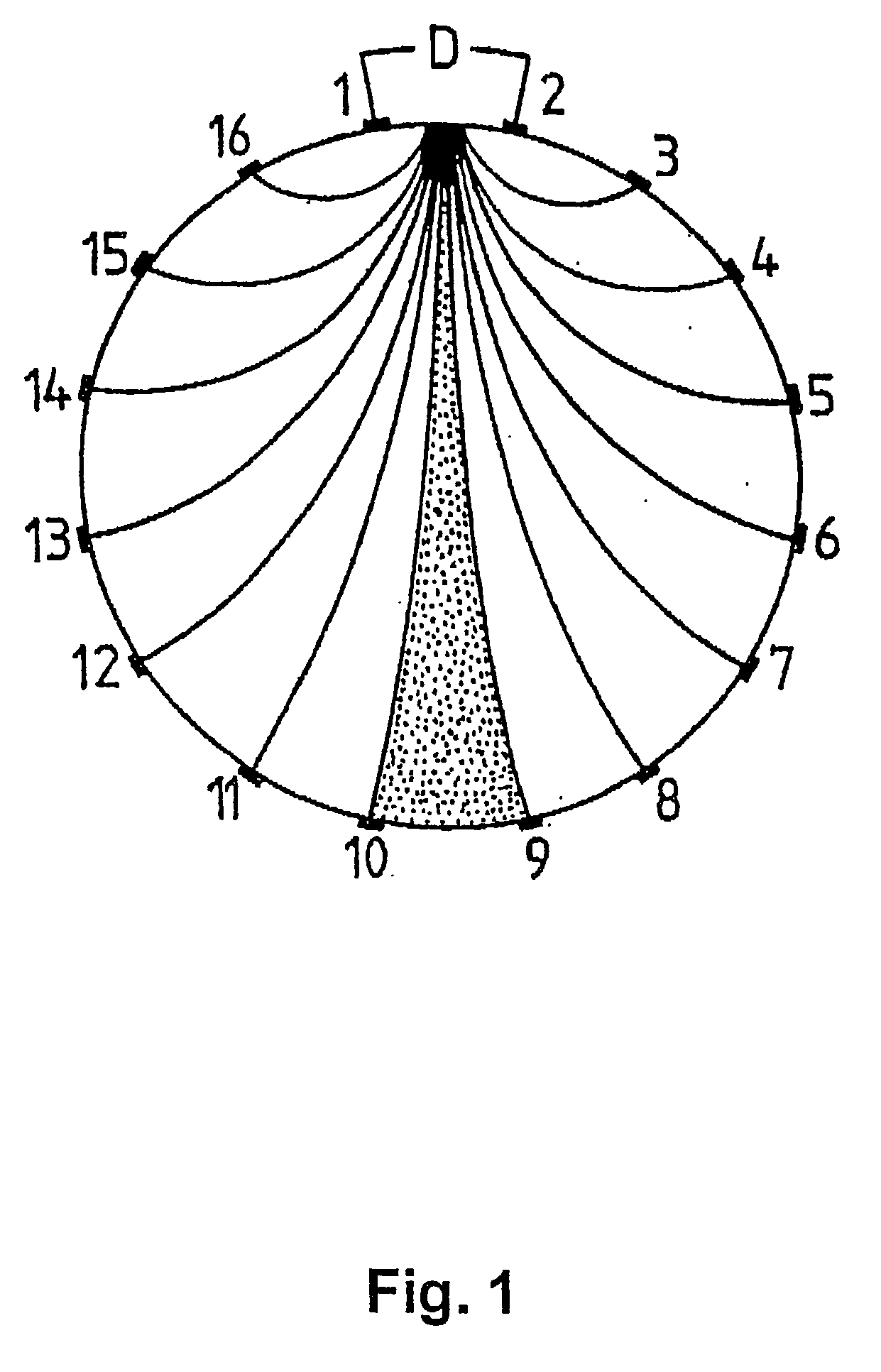

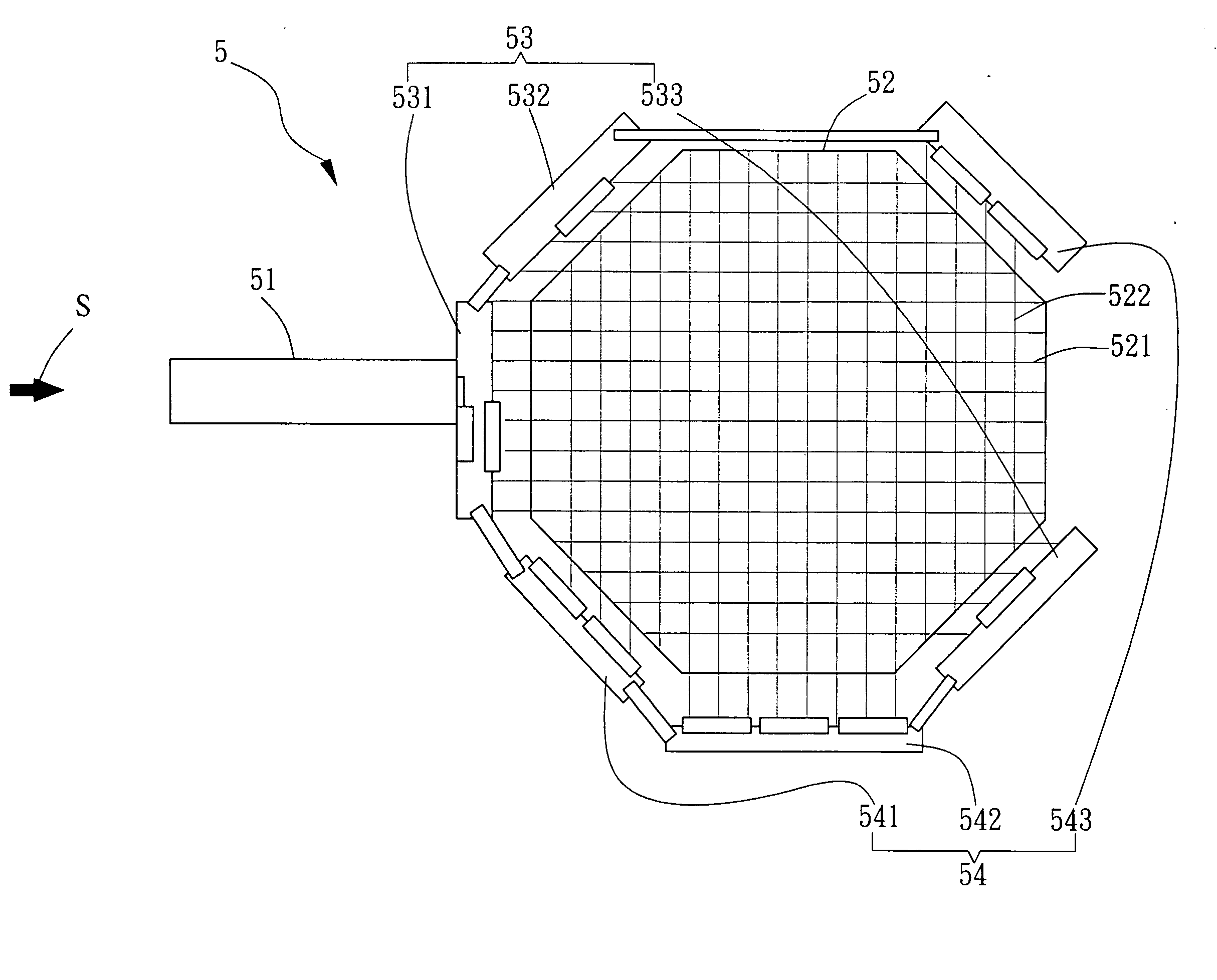

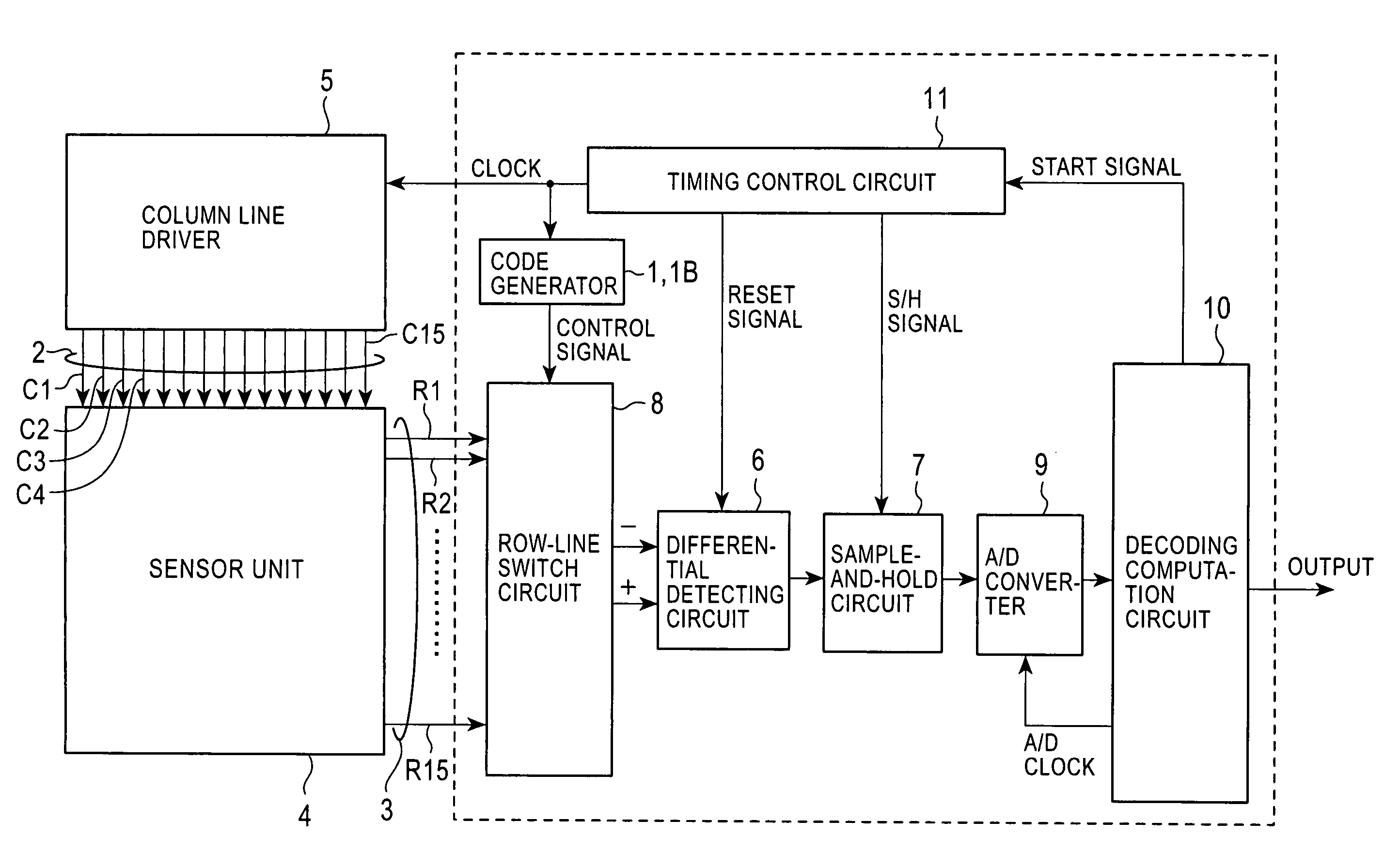

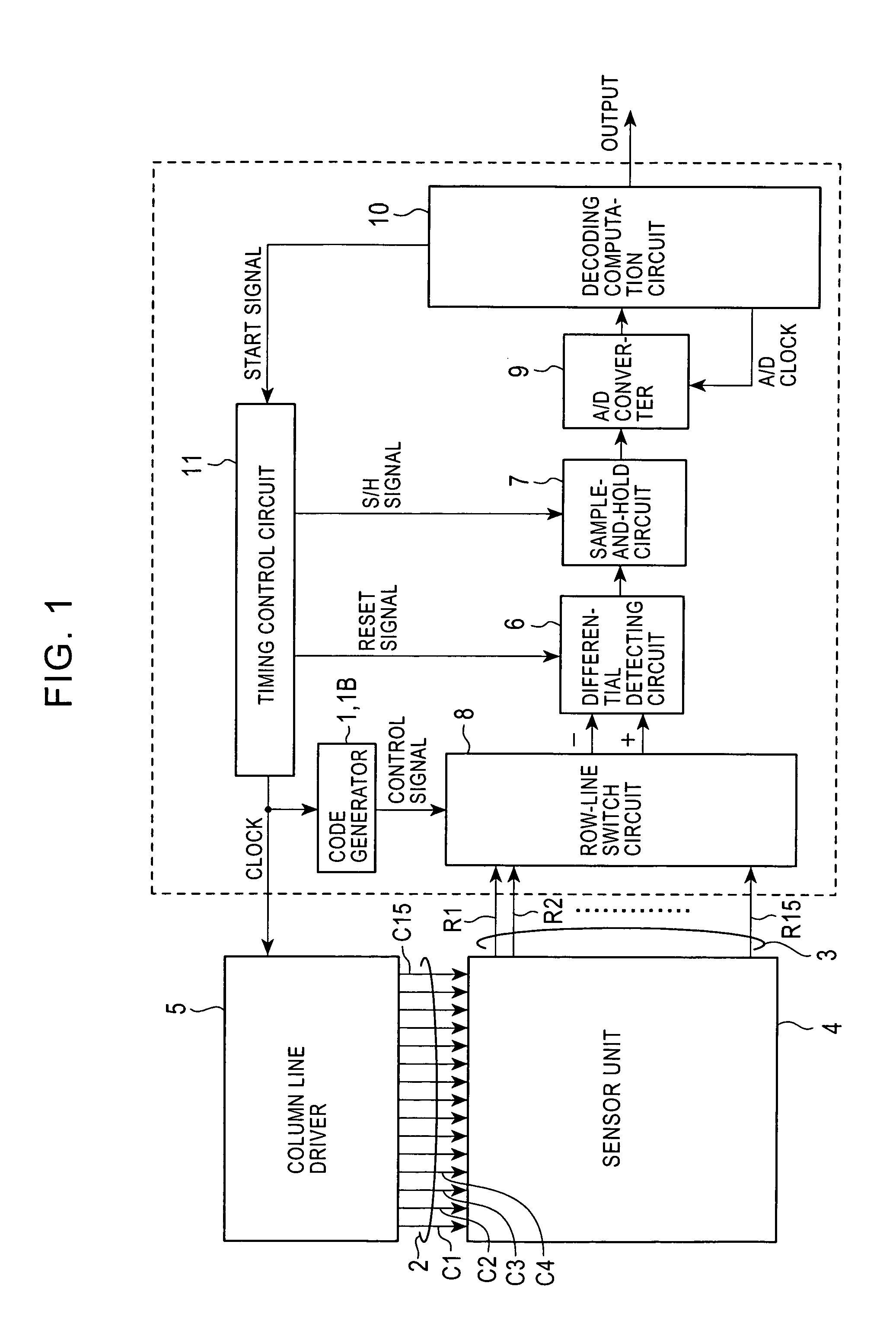

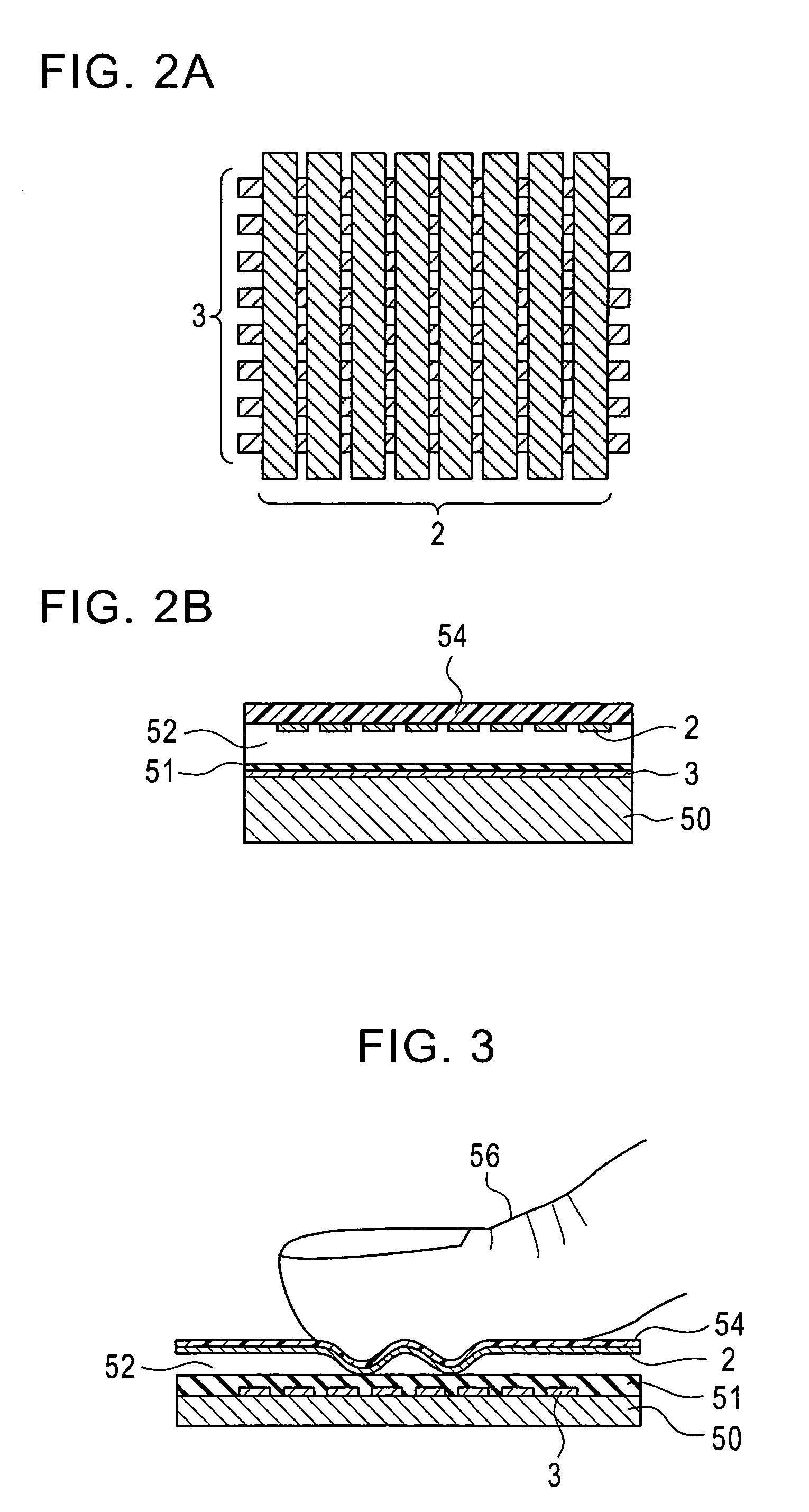

Capacitance detector, method of detecting capacitance, and fingerprint sensor

InactiveUS20050024065A1Offsetting effectCorrect offsetResistance/reactance/impedencePerson identificationEngineeringLine driver

A capacitance detector, used in an area sensor having a matrix of detection lines, detects minute capacitances near intersections of a plurality of column lines and a plurality of row lines. The capacitance detector includes a column-line driver for outputting to the column lines a signal that rises in response to a first voltage and then falls in response to a second voltage; a row-voltage outputter for outputting a third voltage corresponding to a current for charging the capacitance at each of the intersections when the column lines are driven by the first voltage and for outputting a fourth voltage corresponding to a current for discharging the capacitance at each of the intersections when the column lines are driven by the second voltage; and a calculator for calculating the difference between the third voltage and the fourth voltage. The difference is calculated at each of the intersections.

Owner:ALPS ALPINE CO LTD

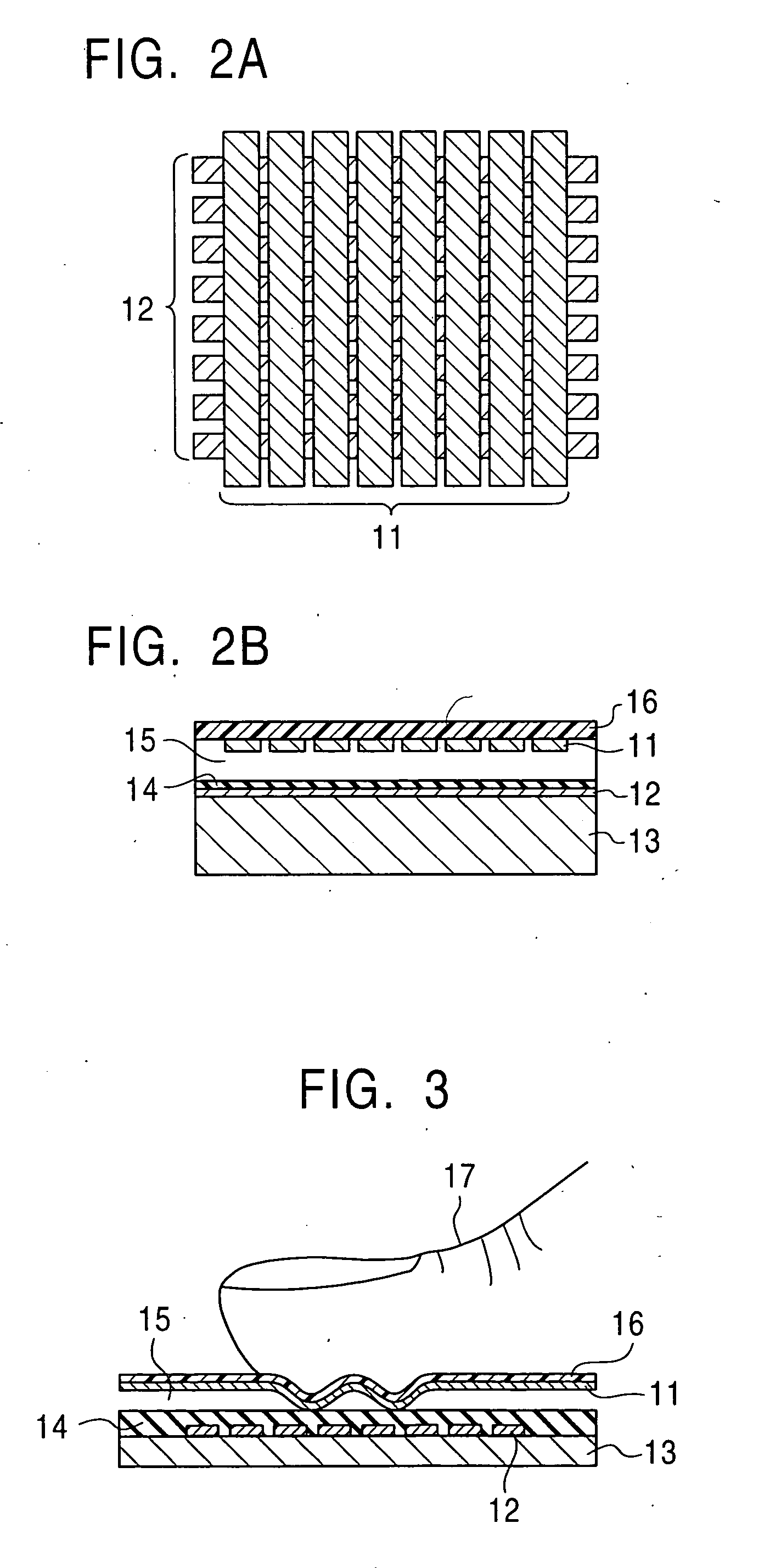

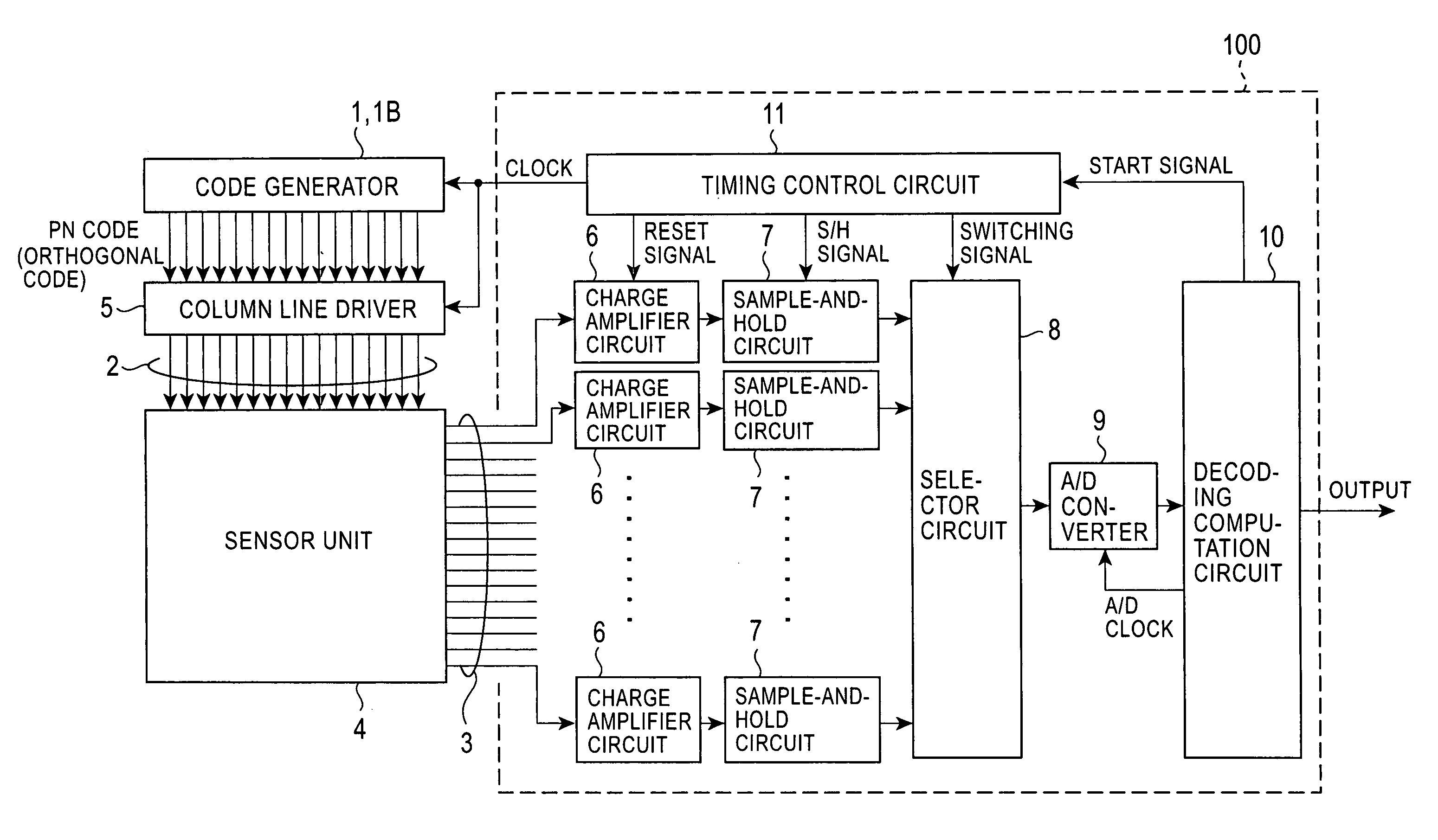

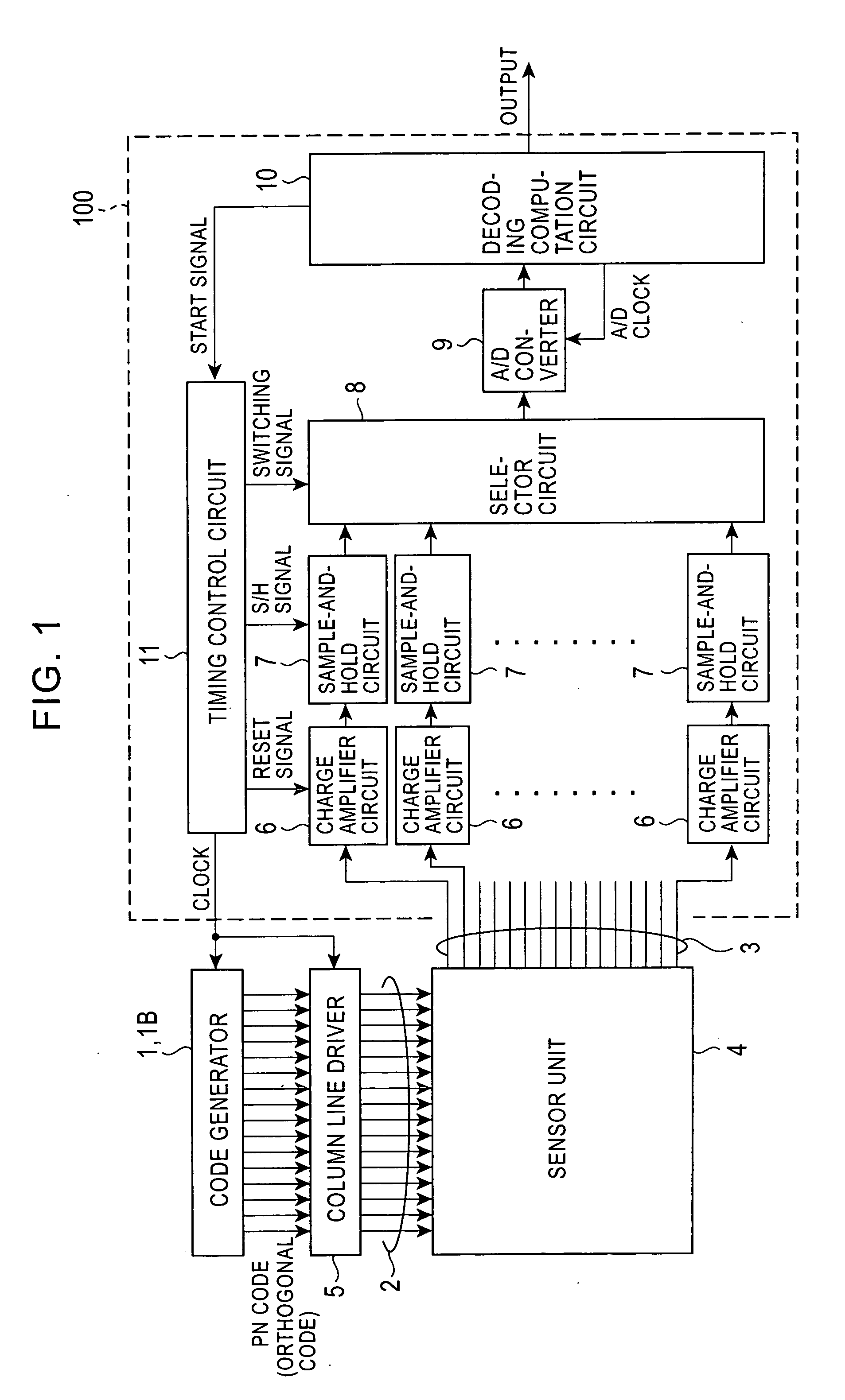

Capacitance detecting circuit and method, and fingerprint sensor using the same

ActiveUS20060158202A1Improve signal-to-noise ratioSmall capacitanceResistance/reactance/impedencePerson identificationCode generationHemt circuits

In a capacitance detecting circuit, changes in capacitances at intersections between a plurality of column lines and a row line are detected as voltages. The capacitance detecting circuit includes a code generator for generating code having orthogonality in chronological order. A column-line driver drives the plurality of column lines based on the code by dividing the column lines into a first column line group and a second column line group. A capacitance detector, which is connected to the row line, converts the total of currents generated in capacitances at the intersections with the driven column lines into a voltage signal and outputs the converted voltage signal. A decoding computation unit determines the voltages corresponding to the capacitances at the intersections for each of the column line groups by performing product sum computation between the measured voltages and the code. In a period for detecting the capacitances, the column-line driver drives the first column line group and the second column line group by complementary voltages according to the code or information indicating the inversion of the code.

Owner:SYNAPTICS INC

Line drivers that use minimal metal layers

Line drivers that use minimal metal layers. Line driver connections typically need to be made to various other peripheral circuits. Although multiple metal layers could be used to make all the necessary connections, it is desirable to use the fewest metal layers possible. By keeping all y-direction lines on a first layer, and most of the x-direction lines on a second layer, only two metal layers are required. Additionally, an array cut could be used that allows line drivers to reach upper conductive array lines.

Owner:UNITY SEMICON

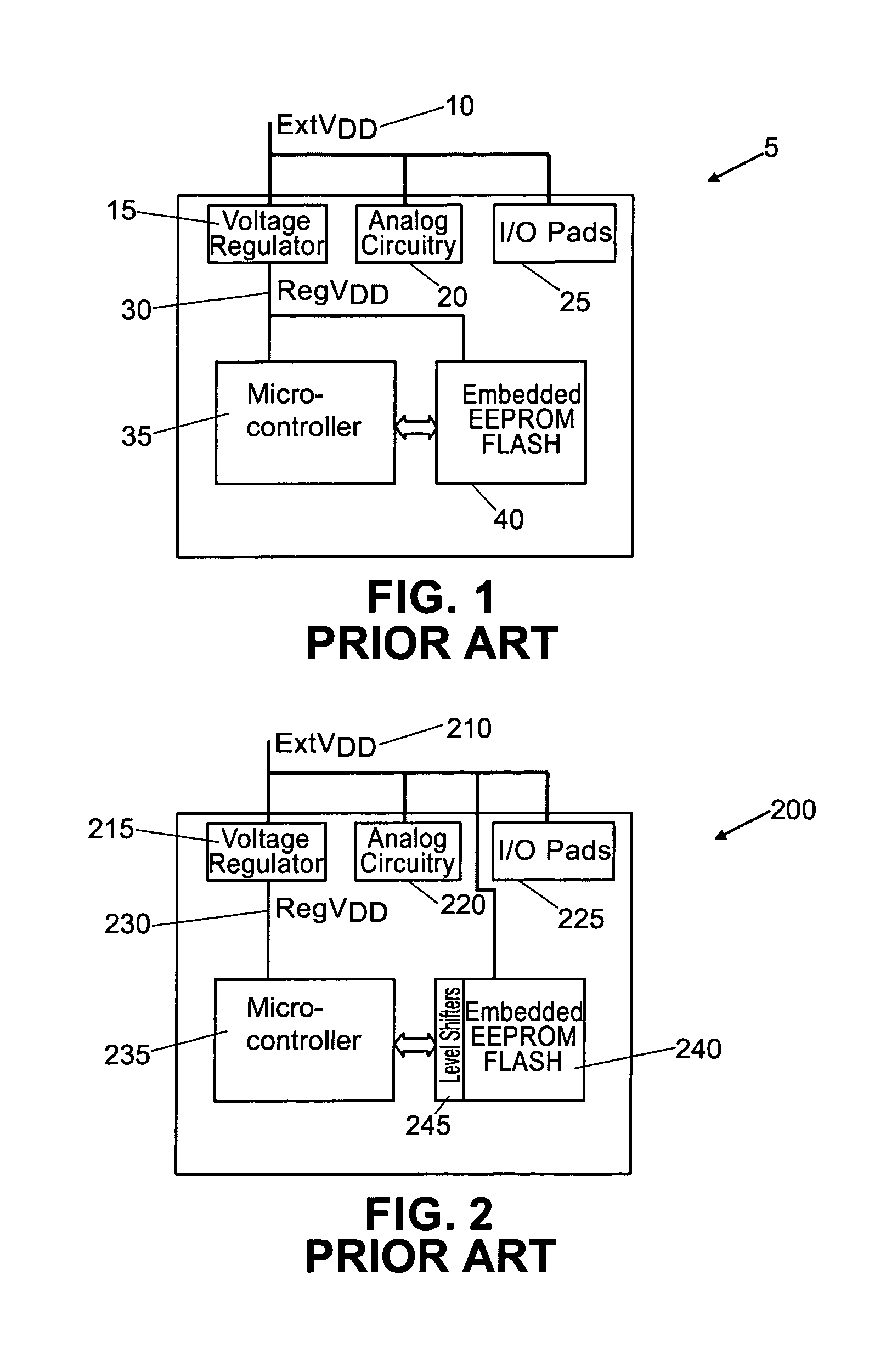

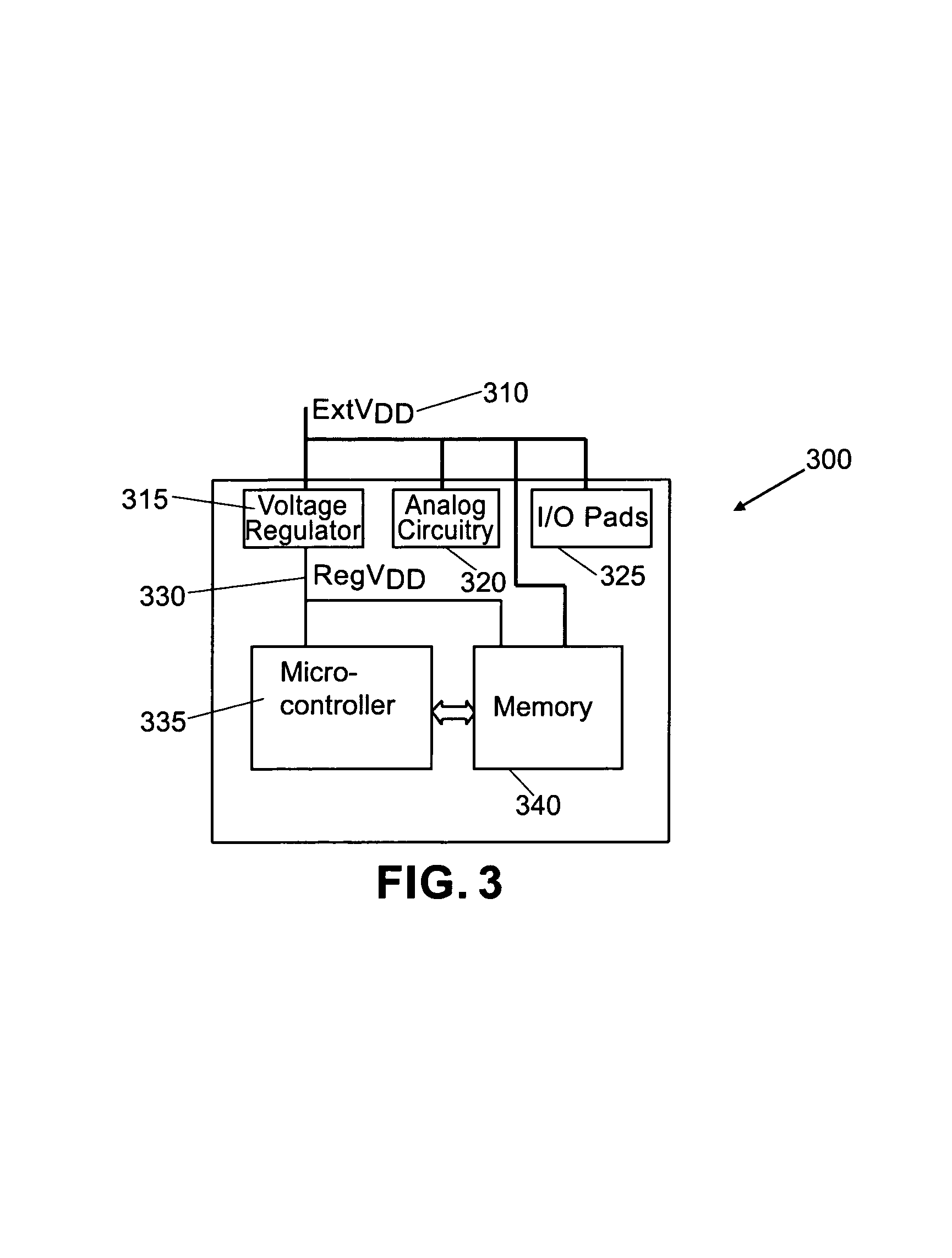

Method and apparatus for a dual power supply to embedded non-volatile memory

ActiveUS7120061B2Avoiding internal boosting delayAvoid chargingRead-only memoriesDigital storageBit lineEngineering

Owner:SONRAI MEMORY LTD

Electrode for biomedical measurements

InactiveUS20050020935A1Guaranteed to be free from interferenceCheap productionElectrocardiographyNon-surgical orthopedic devicesElectrical resistance and conductanceElectrical impedance tomography

The invention relates to an electrode for biomedical measurements, in particular for measurements for electrical impedance tomography, which permits measurements with as little interference as possible. The electrodes comprise a contact plate, a line driver with a high-impedance signal input and low-impedance line output and a current source, with a current output and a reference point, whereby the contact plate is connected to the high-impedance signal input of the line driver and to the current output of the current source and the line driver and the current source are arranged in the vicinity of the contact plate.

Owner:TIMPEL MEDICAL BV

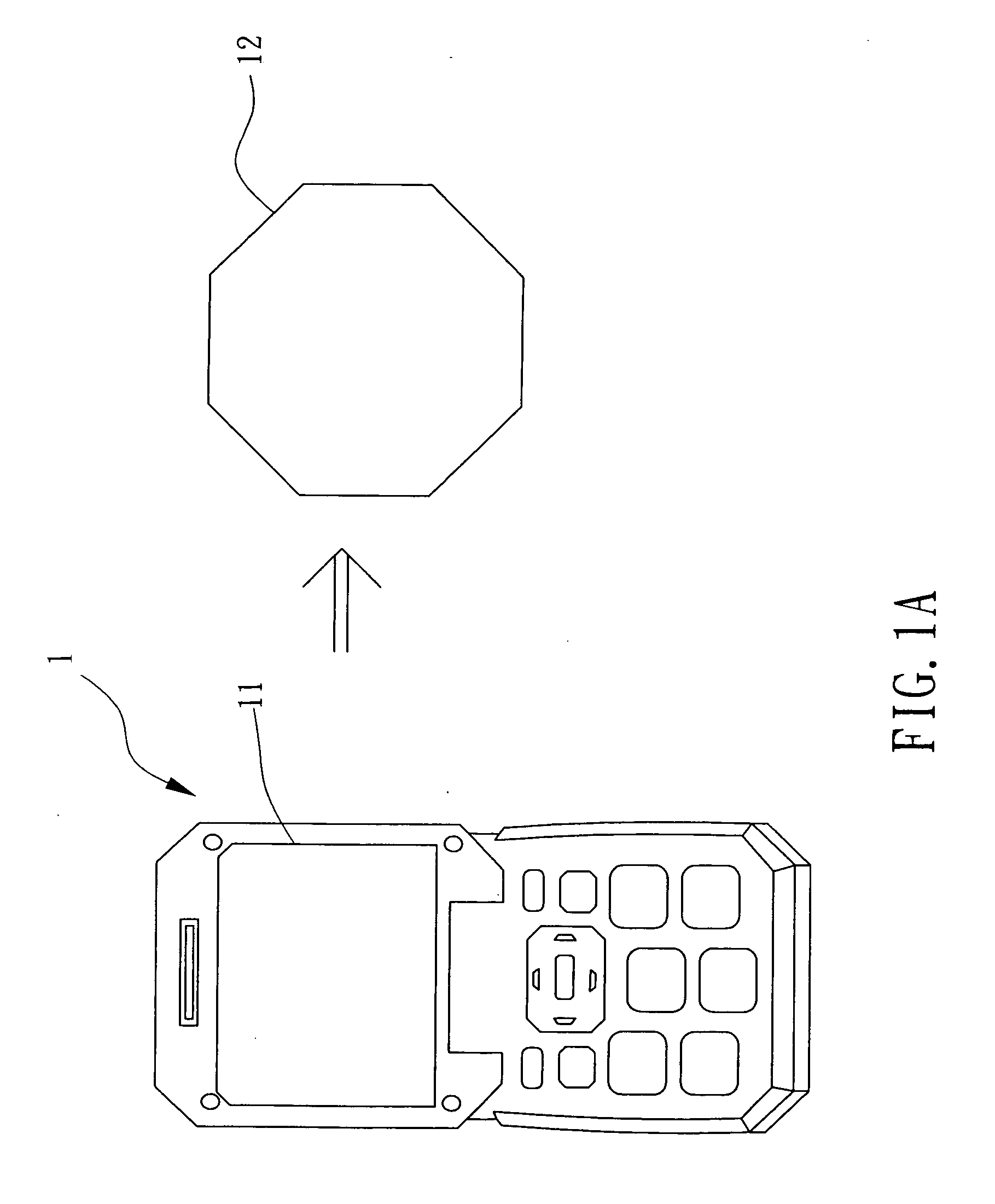

Non-rectangle display

A non-rectangle display comprises a circuit substrate and a display panel connected to the circuit substrate. The circuit substrate has a driving device for driving the display panel to display video. The driving device includes at least one data line driver and at least one scan line driver. Each data line driver and each scan line driver are respectively disposed on at least one side of the display panel. The data line driver and the scan line driver are capable of operating cooperatively for driving the display panel. The display panel has a peripheral profile of at least one specific function curve.

Owner:IND TECH RES INST

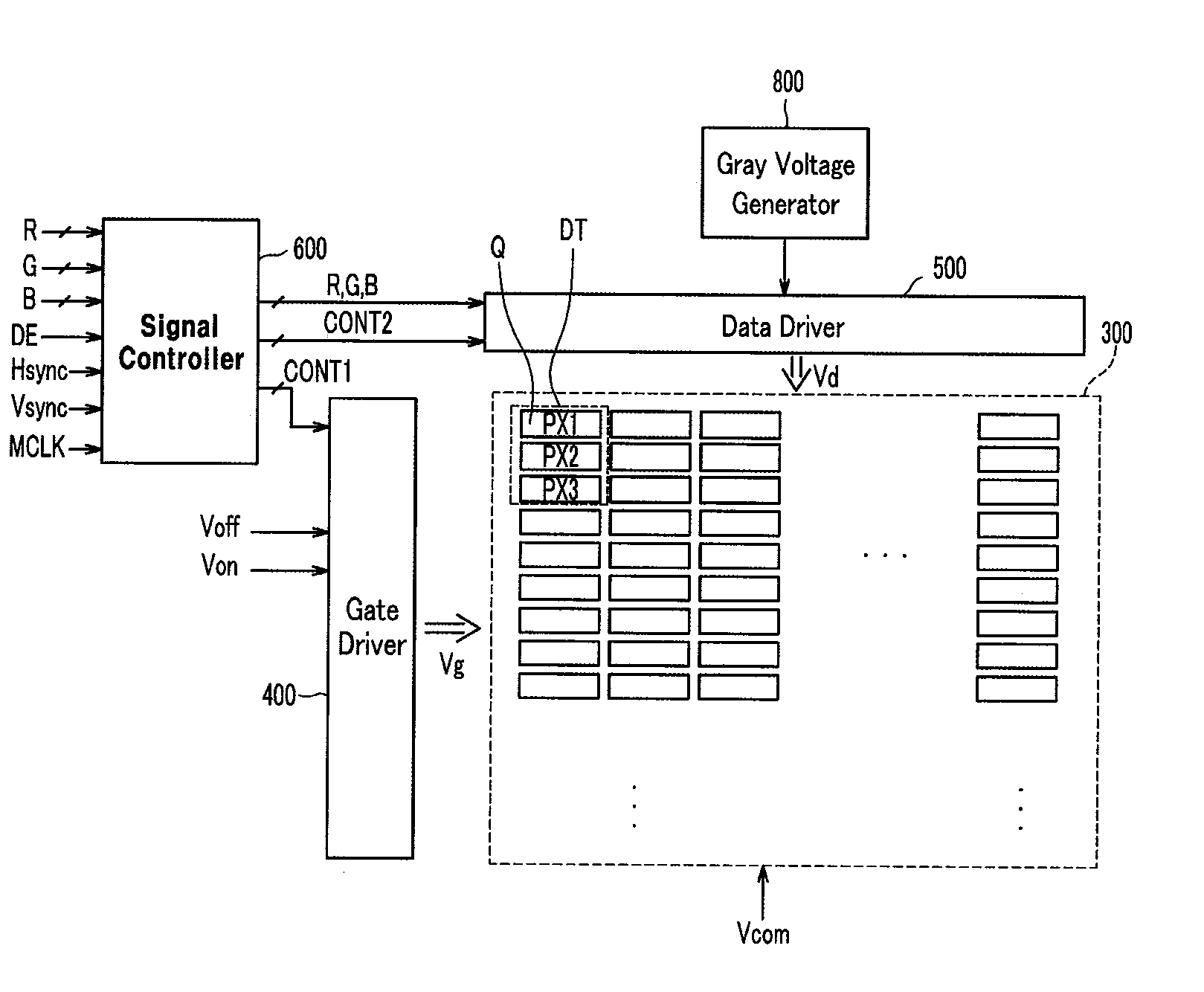

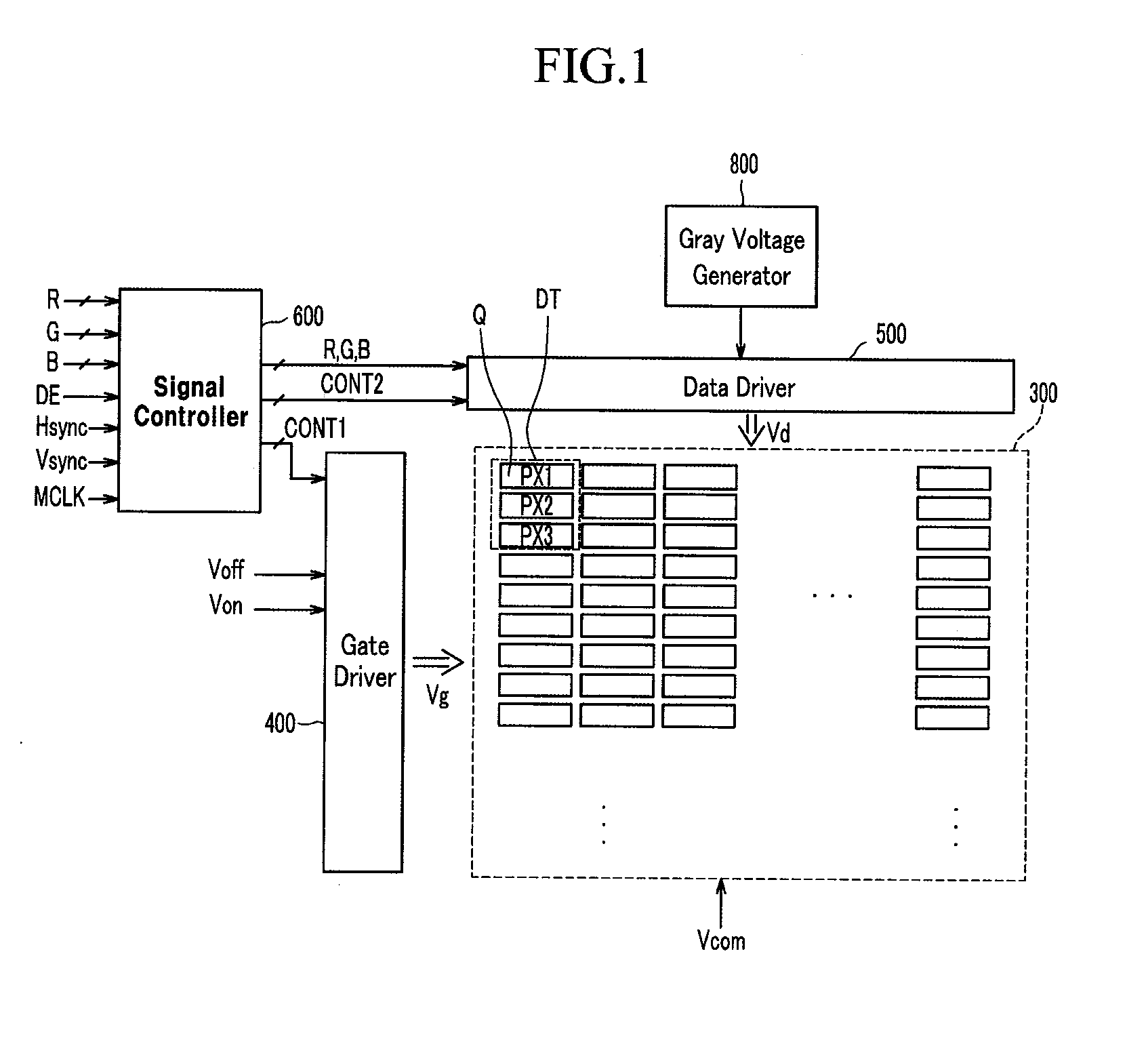

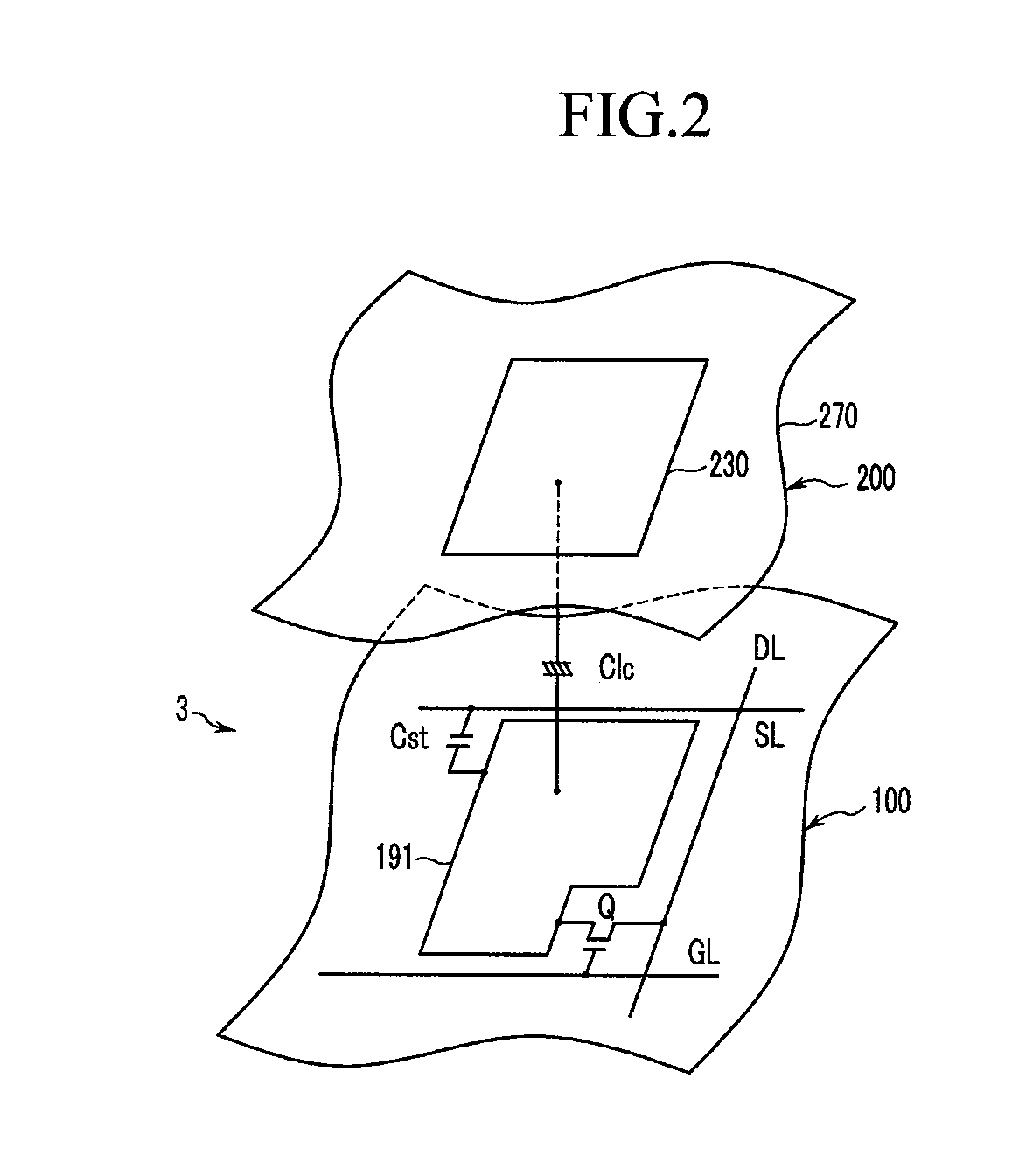

Display device and semiconductor device

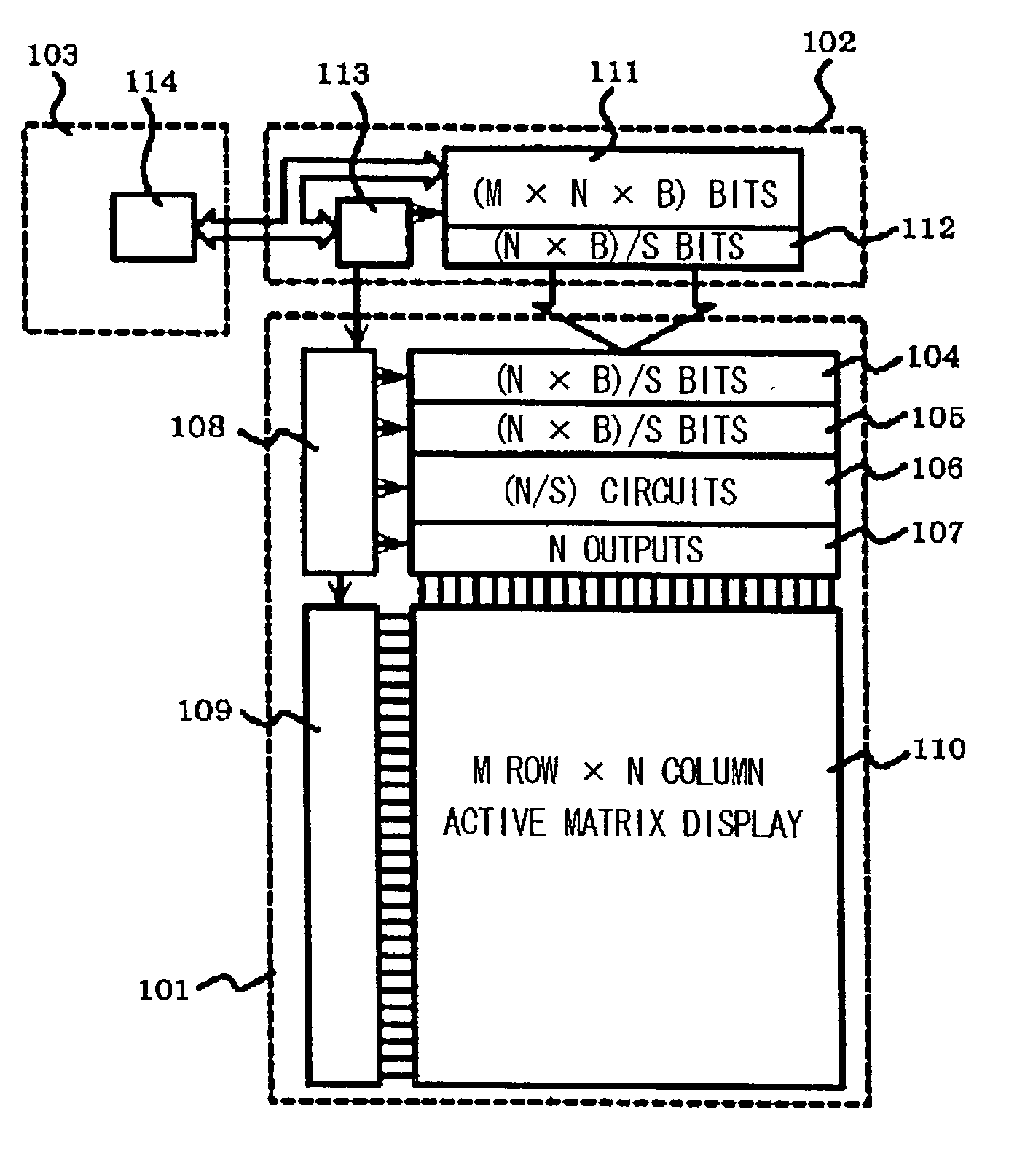

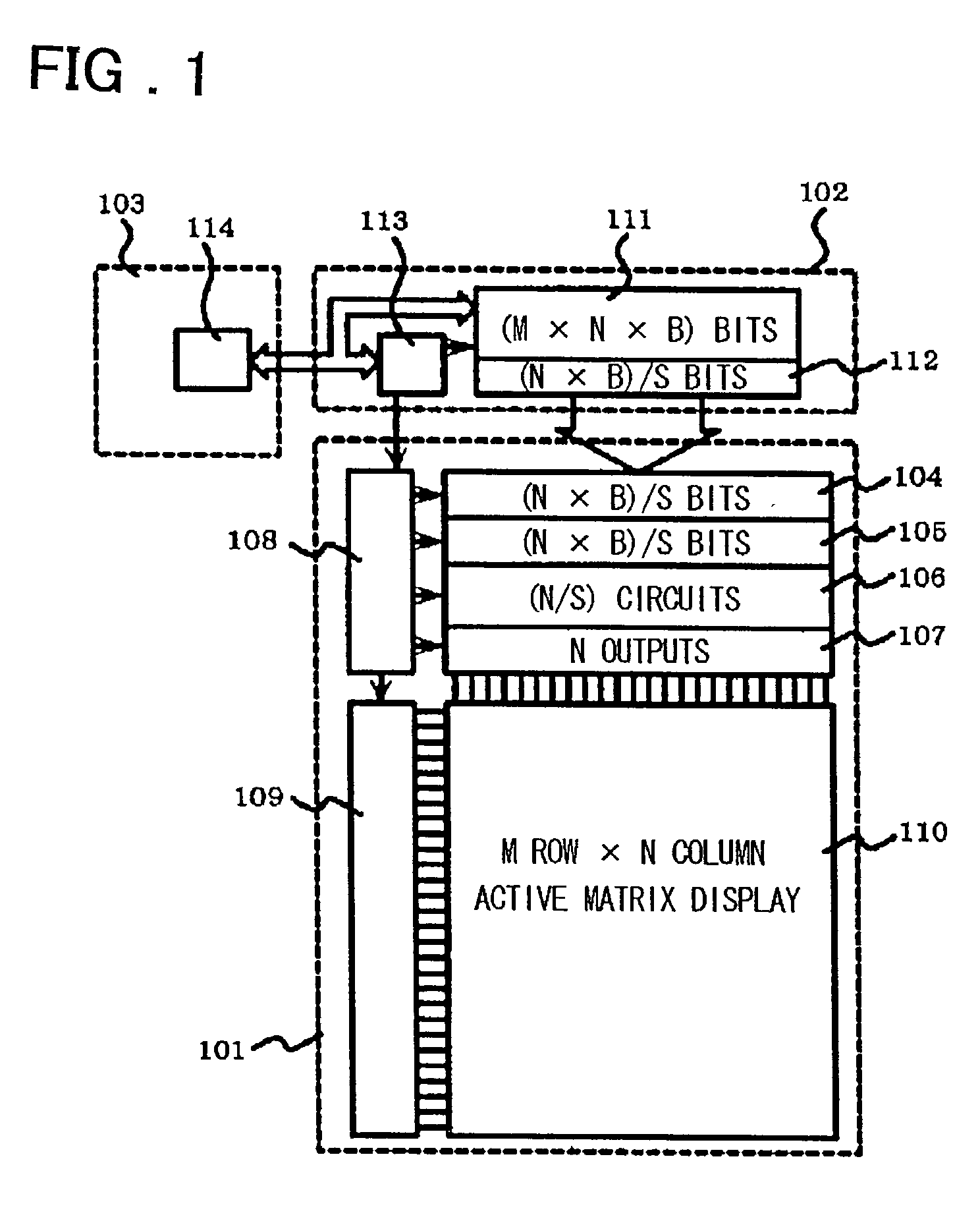

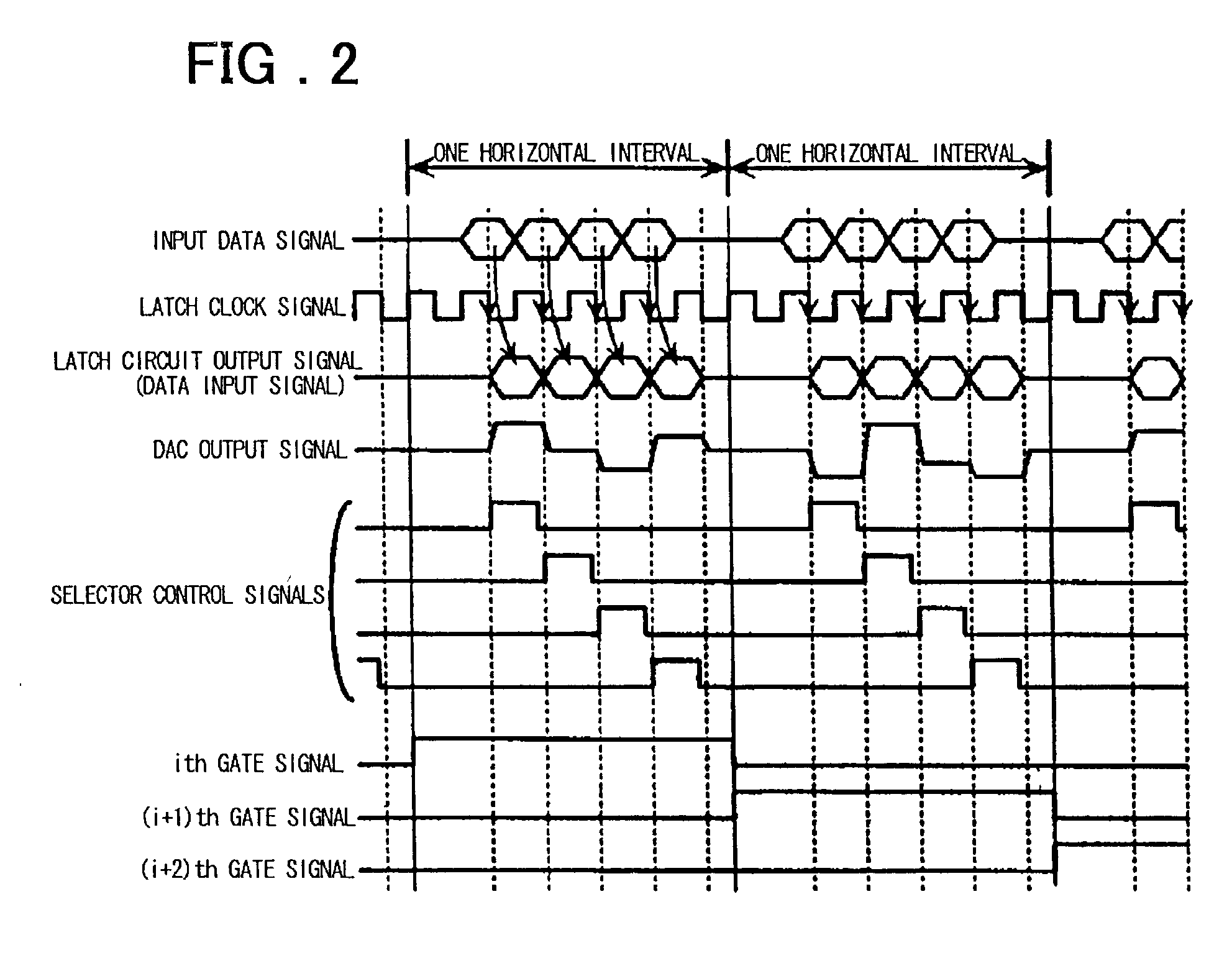

InactiveUS20030067434A1High definitionIncrease the number of pixelsCathode-ray tube indicatorsInput/output processes for data processingEngineeringLine driver

A display device of high definition, multiple colors and low power consumption includes a display panel having a pixel section in which pixels are arrayed in the form of a matrix at the cross points of a plurality of data lines and a plurality of scanning lines, a scanning circuit for applying voltage sequentially to the plurality of scanning lines, and a data-line driver, which receives display data supplied by a host device, for applying signals corresponding to the display data to the plurality of data lines. Provided external to the display panel is a controller IC having a display memory for storing display data corresponding to the pixel section, an output buffer for reading data out of the display memory and outputting this data to the display panel, and a controller for controlling the display memory and output buffer and communication with the host device. The display panel is provided with a digital / analog converter, which forms part of the data-line driver, for converting display data represented by a digital signal to an analog signal. The width of a bus for data transfer between the controller IC and data-line driver of the display panel is such that data of a greater number of bits is transferred in parallel by a single transfer than is transferred by the bus between the controller and the host device. This allows the operating frequency of the data-line driver to be reduced.

Owner:HANNSTAR DISPLAY CORPORATION

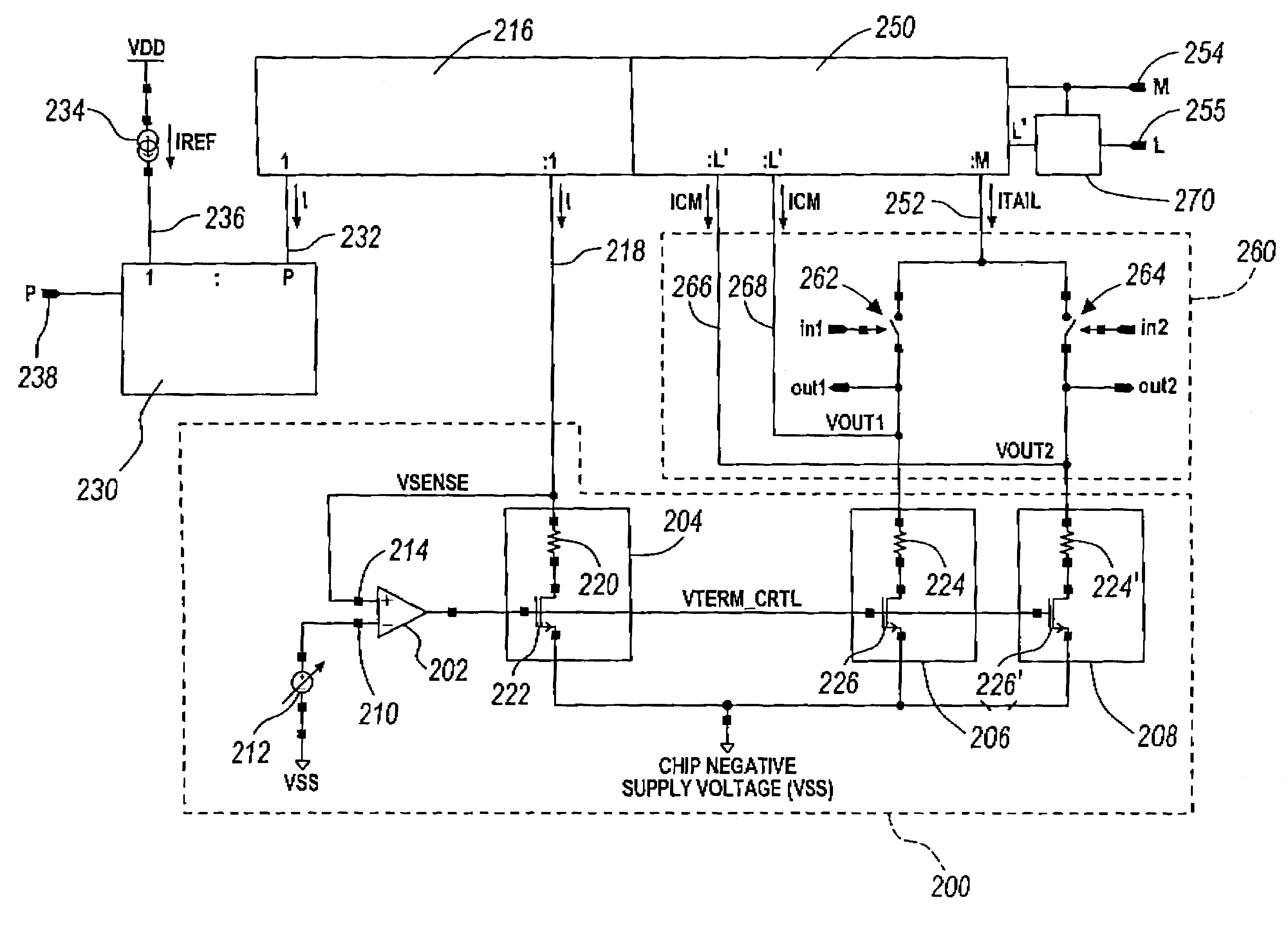

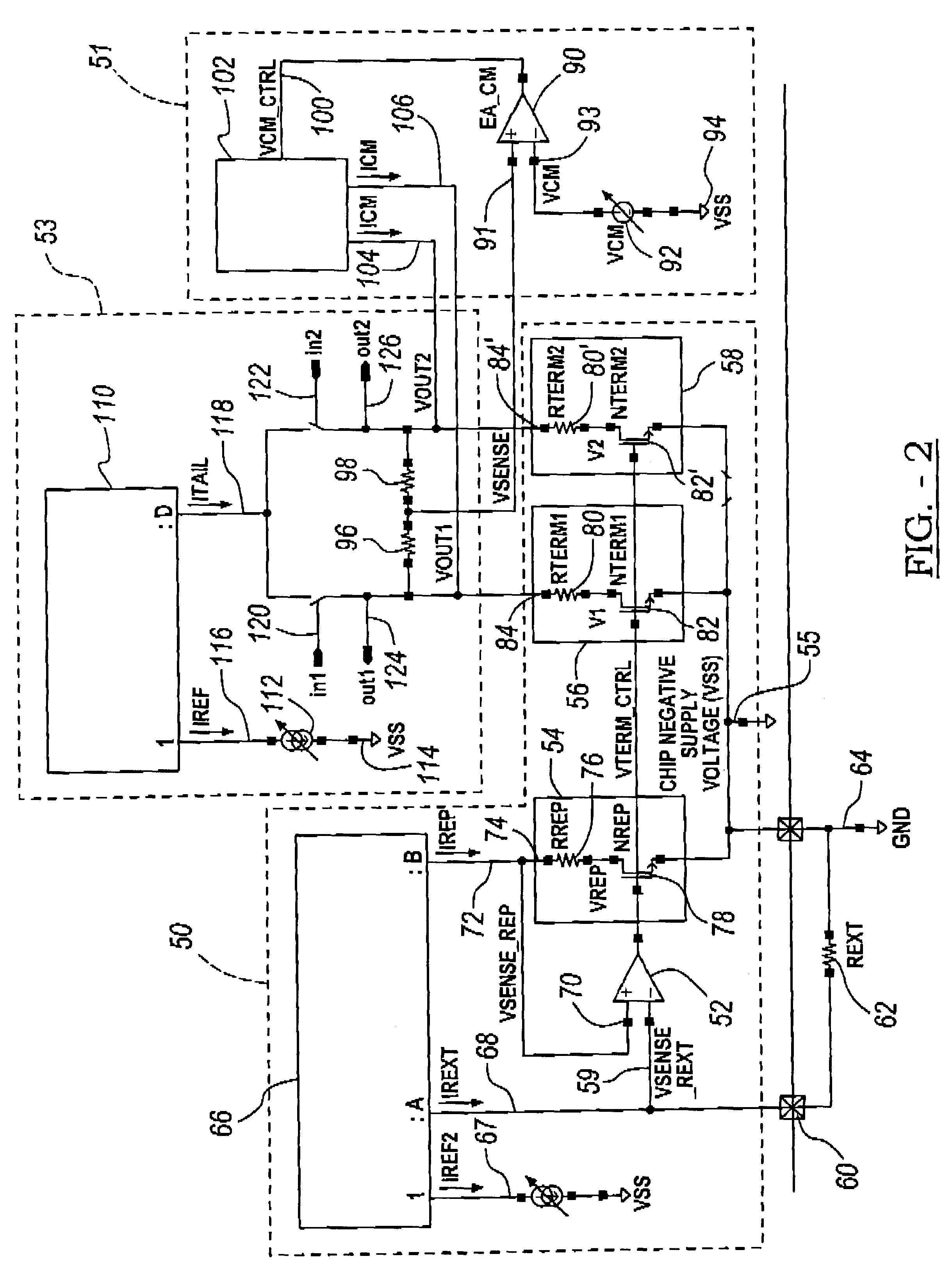

Output controlled line driver with programmable common mode control

InactiveUS6504397B1Superior electrical source impedance terminationLow costReliability increasing modificationsElectronic switchingCMOSDifferential line

A differential line driver having integrated output termination resistors is disclosed. The termination resistors are a combination of a controlled transistor and a low precision resistor. The transistor calibrates-out the imprecision of the resistor based on a precise electrical reference. In a preferred embodiment the transistor is a CMOS transistor and the resistor is a CMOS resistor. The combination of a CMOS transistor and CMOS resistor features higher linearity and precision than a CMOS transistor alone due to the smaller effective drain-source voltage across the CMOS transistor. Moreover, the present invention discloses independent programmability of the integrated output termination resistor, the output common mode voltage, and the output amplitude. The value of the output termination resistor(s), the value of the output common mode voltage, and the value of the output amplitude are controlled independently and are continuously maintained with respect to a precise electrical reference. As a result, the value of the output termination resistance, the value of the output common mode voltage, and the value of the output amplitude are insensitive to manufacturing process tolerances and variations in temperature and supply voltage.

Owner:INFINEON TECH AG

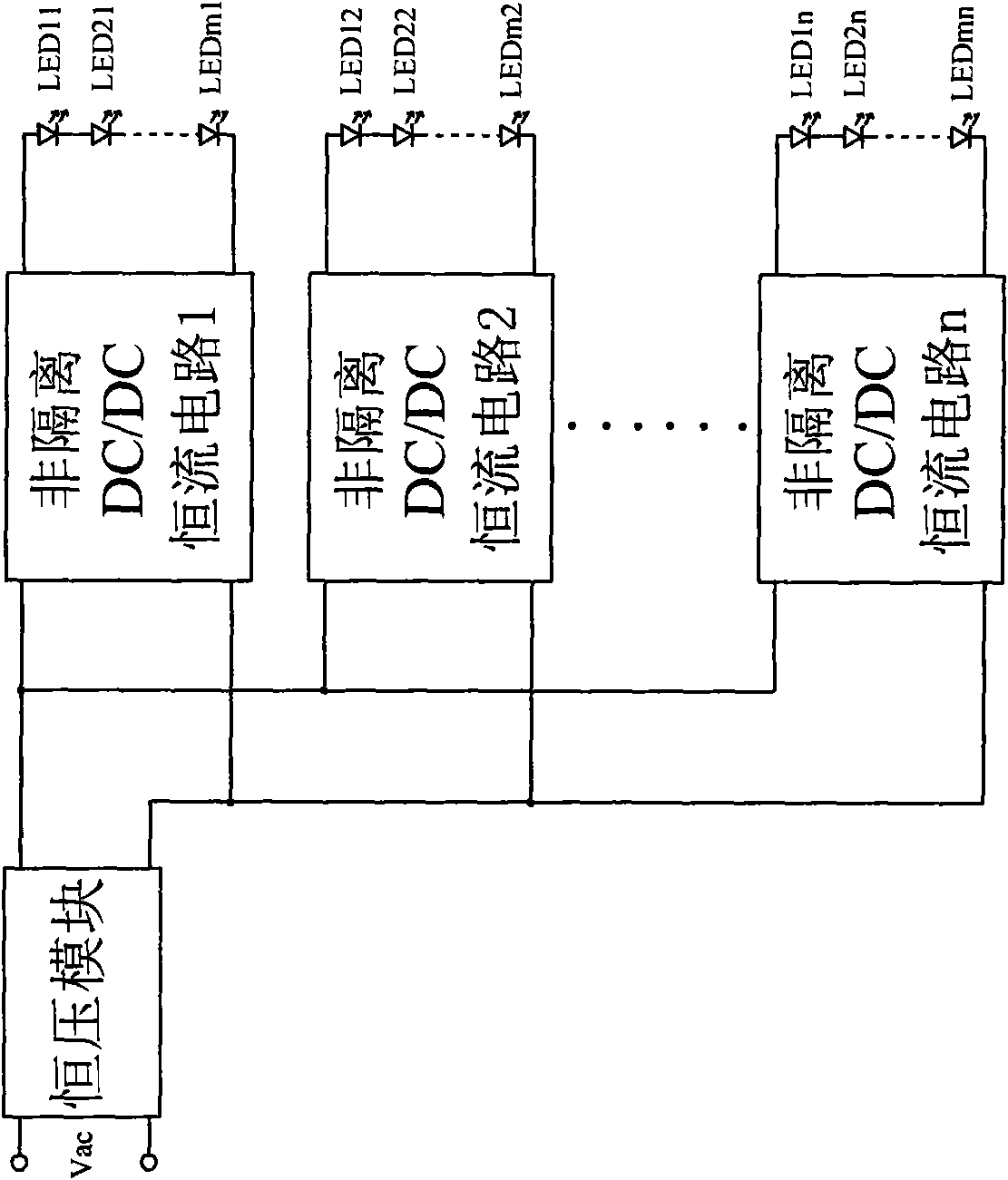

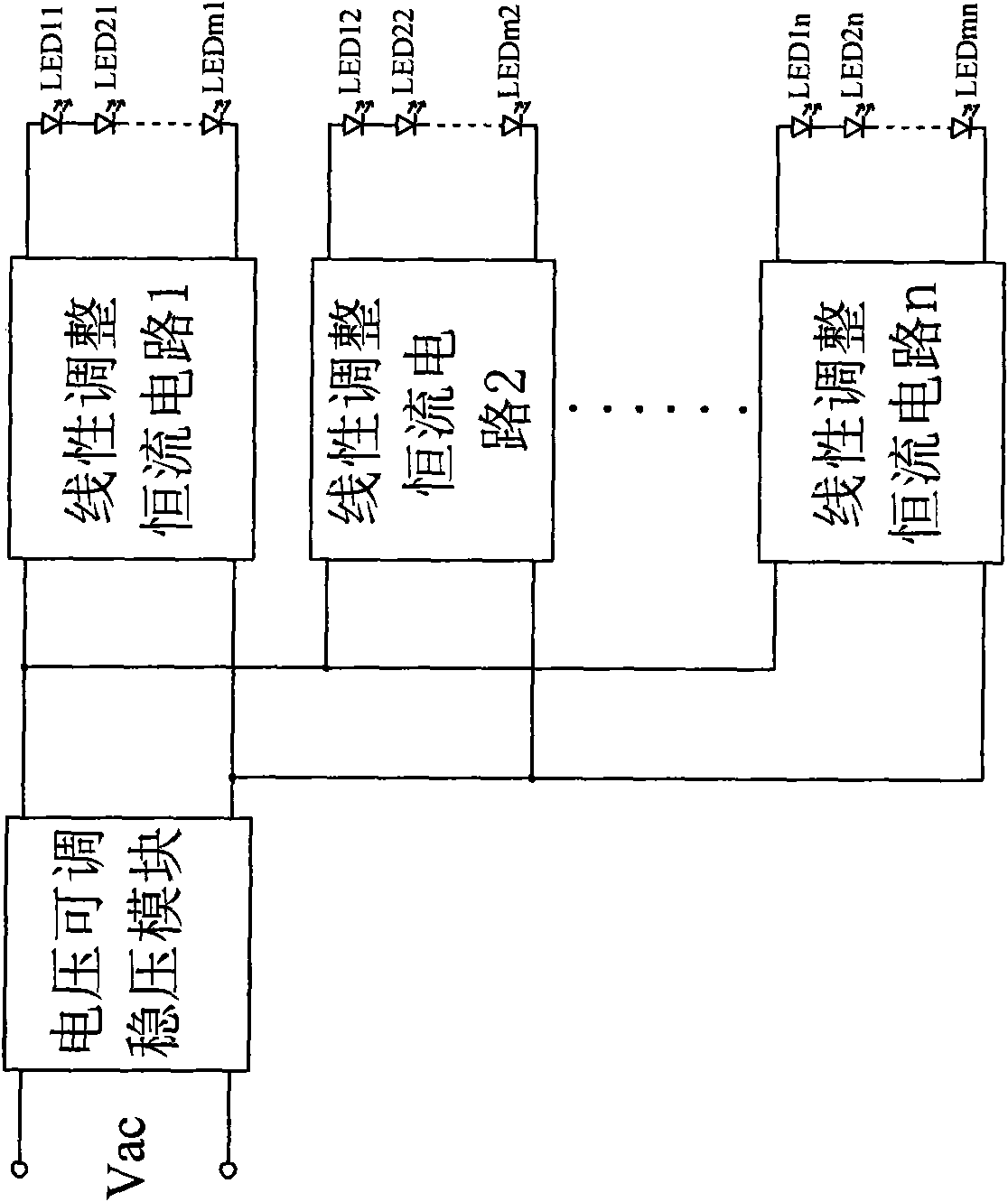

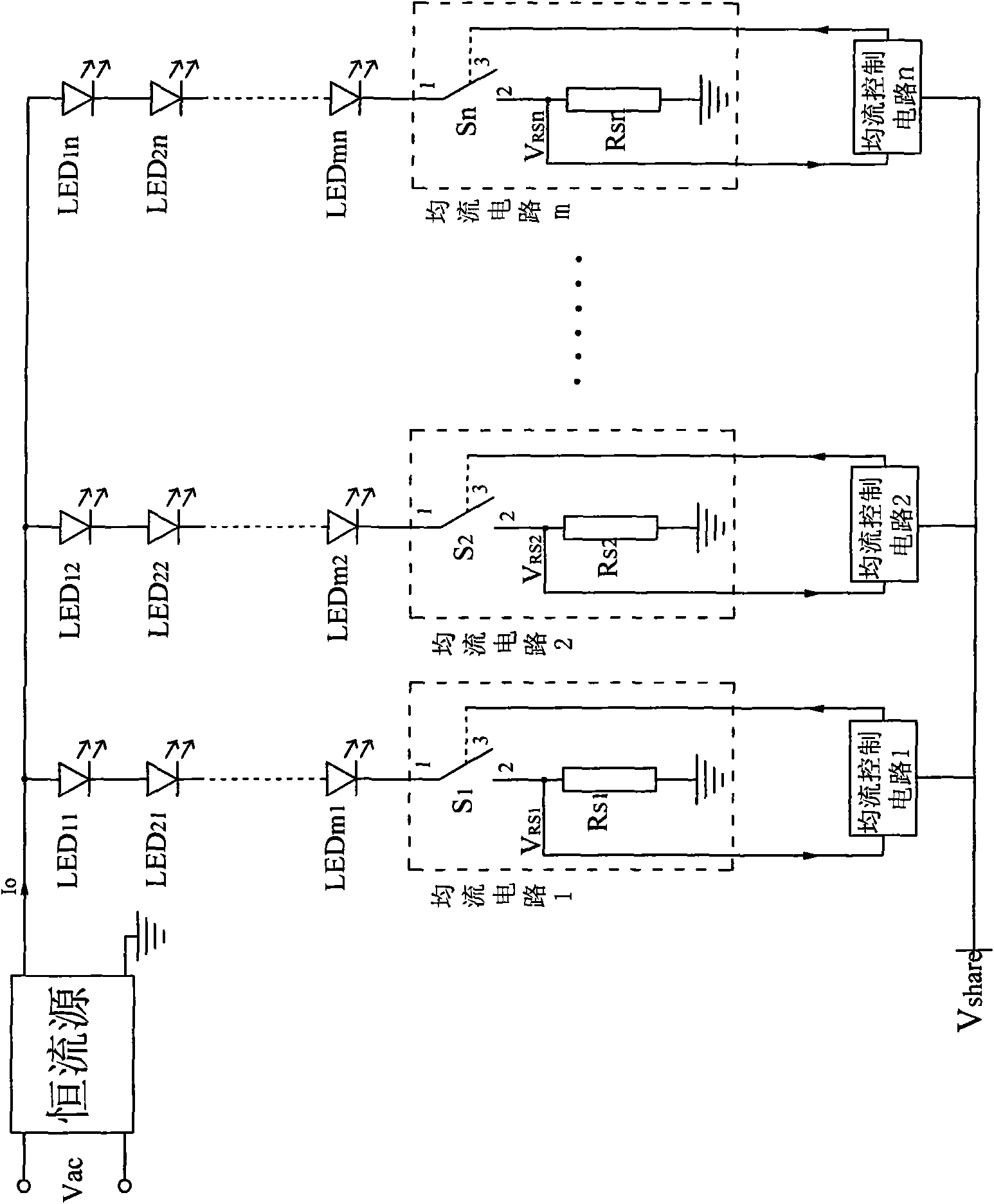

Multichannel constant-current control circuit applicable to LED driver

ActiveCN101674693ASimple structureLow costElectrical apparatusPoint-like light sourceElectrical resistance and conductancePower flow

The invention discloses a multichannel constant-current control circuit applicable to an LED driver, comprising a single output constant-current source and a plurality of channels of output circuits.The multichannel constant-current control circuit is characterized in that each output circuit comprises a current equalizing circuit, a current equalizing control circuit and a load consisting of a plurality of LED lamps; the input of each channel of current equalizing control circuit is from a sampling signal of the sampling resistor to output current, and becomes a public connecting wire afterbeing converted by the current equalizing circuit; the public connecting wire is connected with the other channels to form a current equalizing bus; each channel of current sampling signal and the current equalizing bus voltage are compared and adjusted in the current equalizing control circuit; and an output signal of the current equalizing control circuit can control the size of impedance of a liner adjusting tube of the corresponding current equalizing circuit, then control the size of each channel of current and realize current equalization. The multichannel constant-current control circuit has simple circuit structure and low cost, and is applicable to standard multichannel constant current control of the rear stage of a single-channel constant current power supply.

Owner:INVENTRONICS HANGZHOU

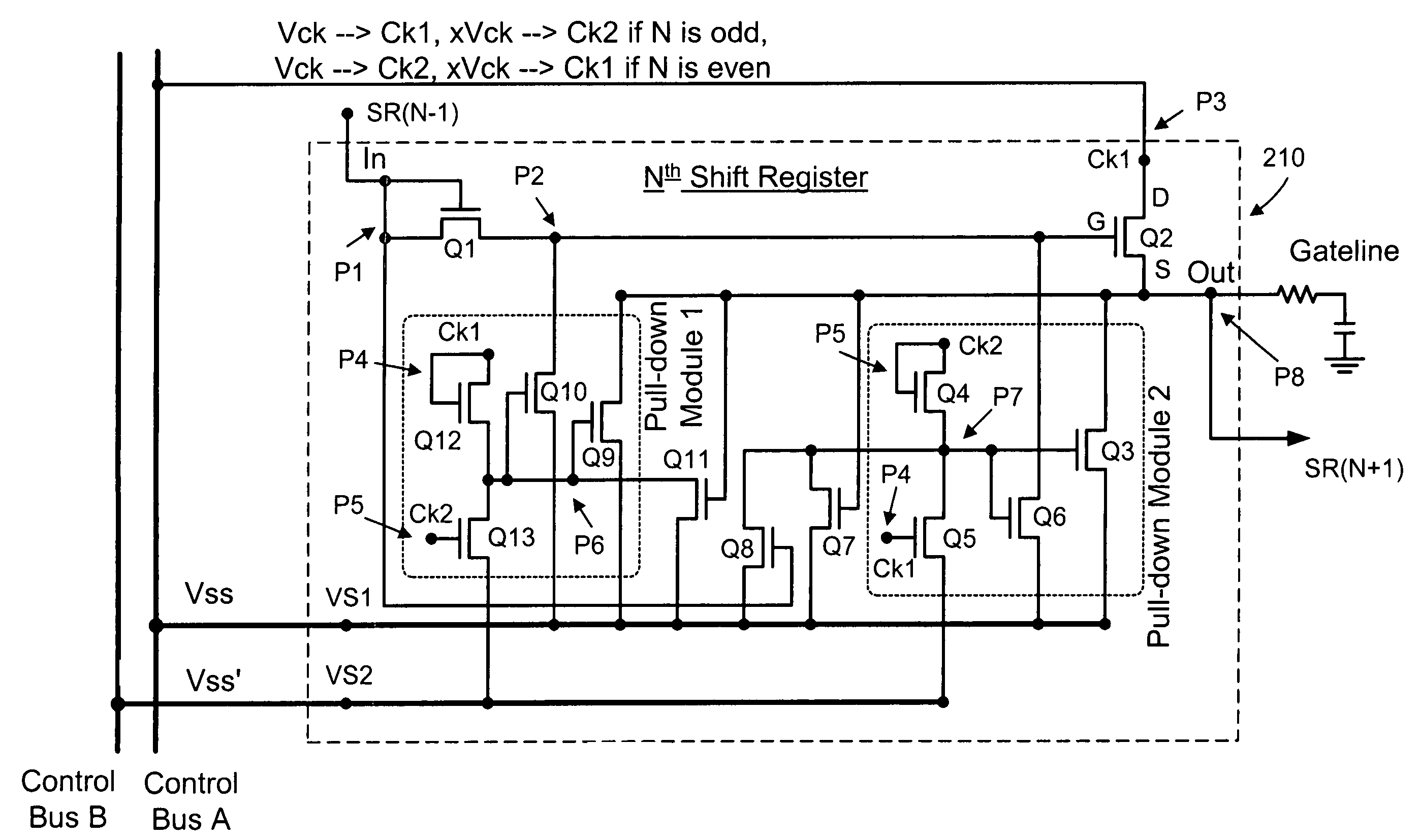

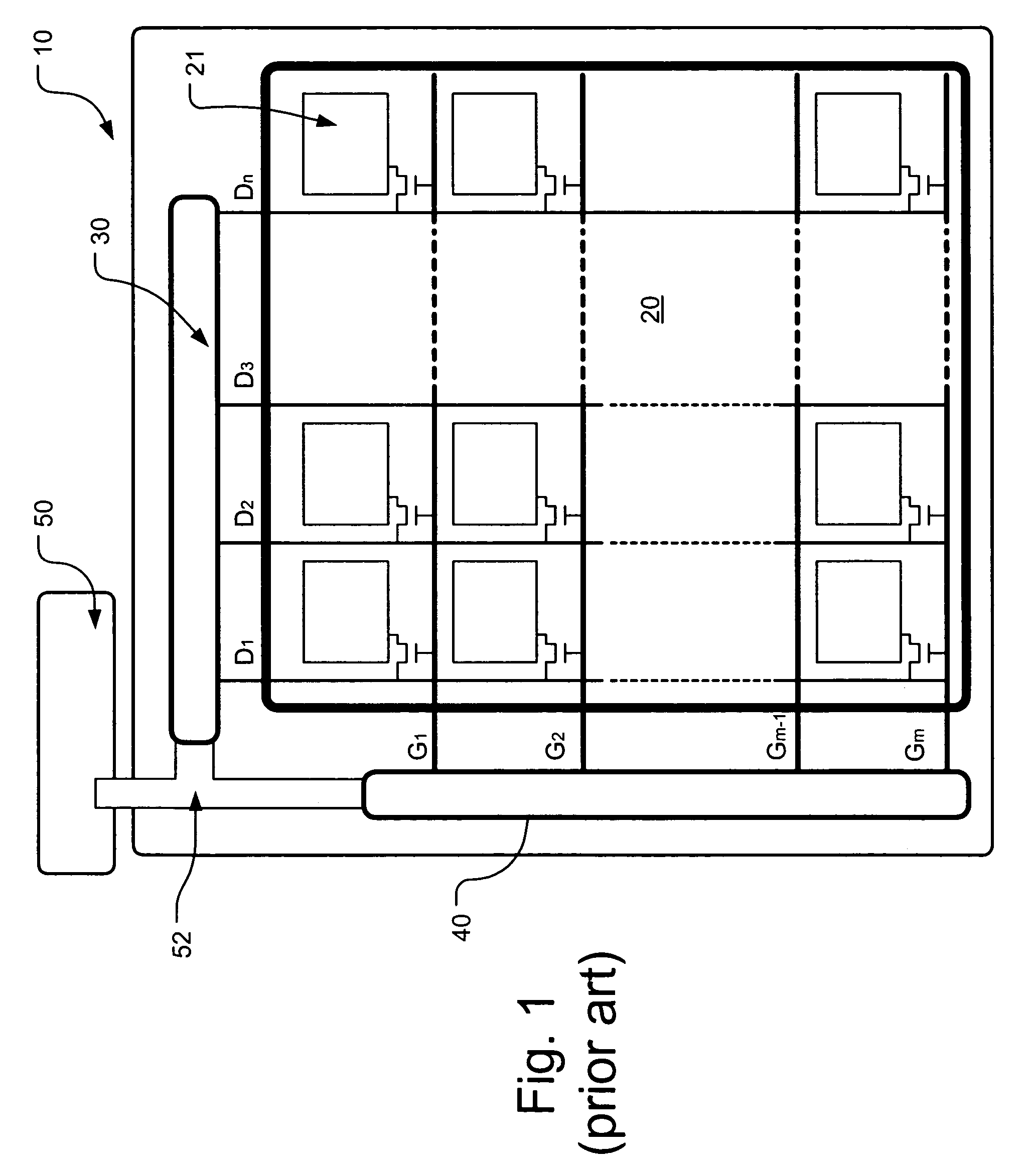

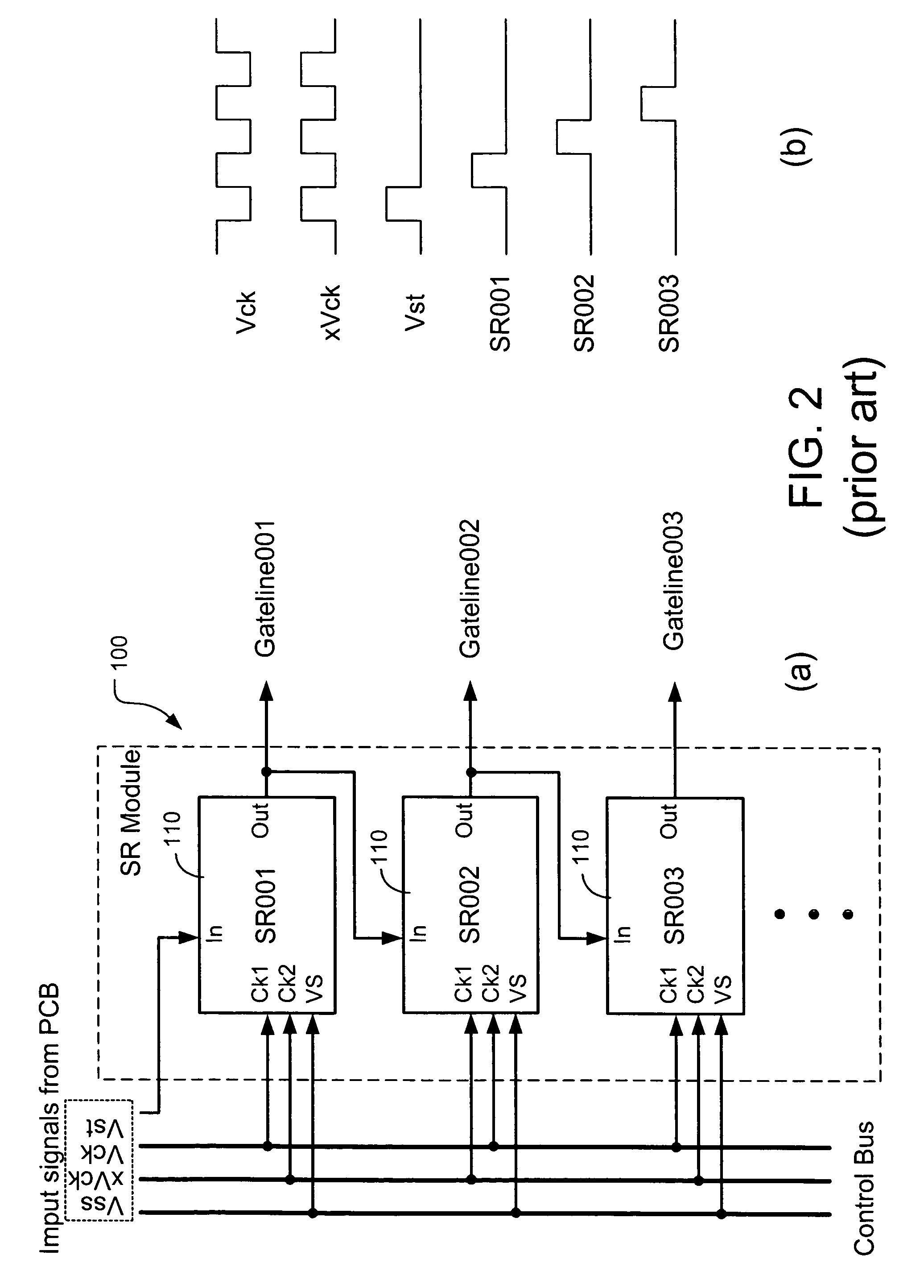

Gate line drivers for active matrix displays

ActiveUS7310402B2Reduce stepsMultiple input and output pulse circuitsDigital storageShift registerActive matrix

Owner:OPTRONIC SCI LLC

Display device, display panel driver and method of driving display panel

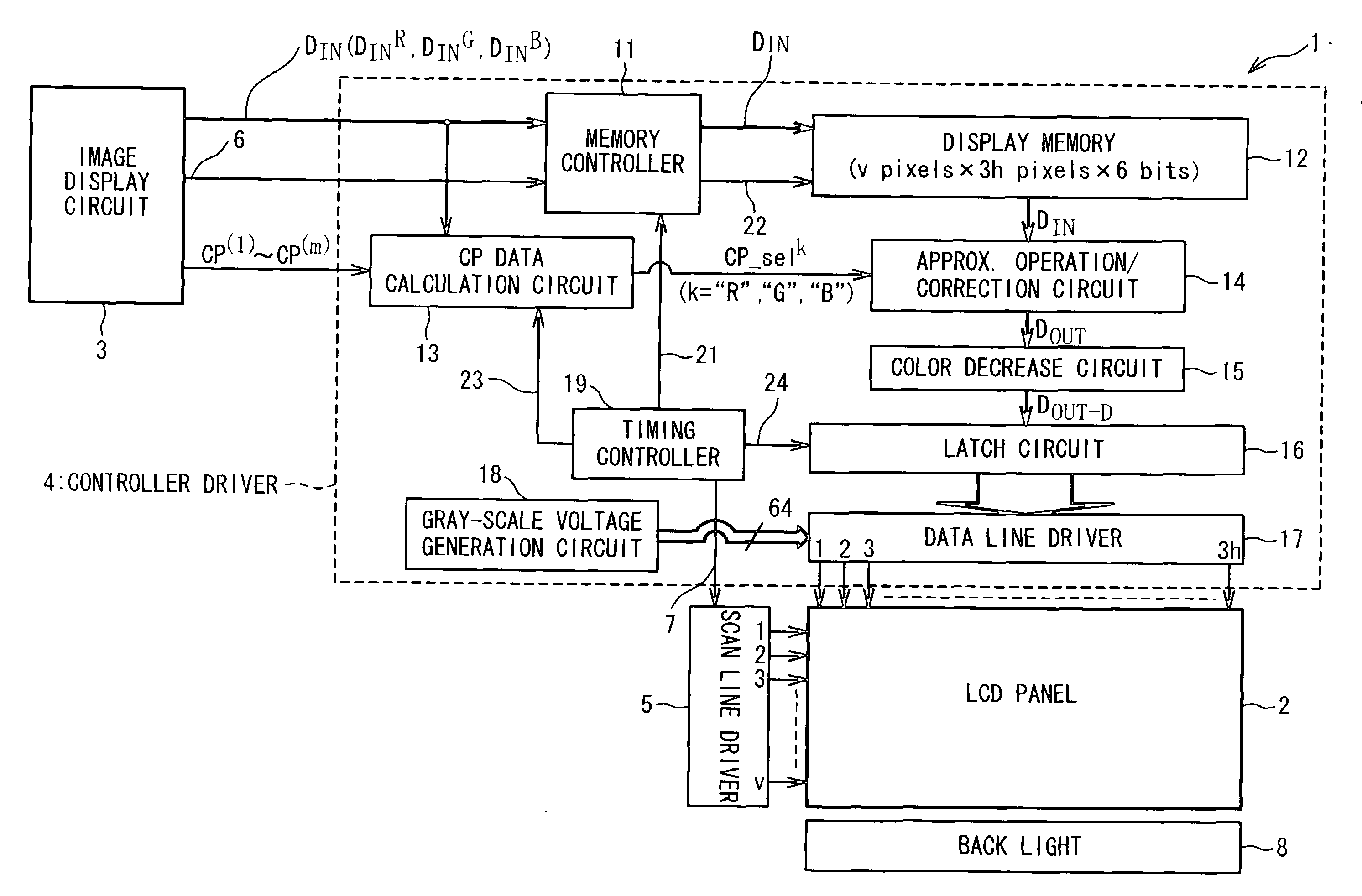

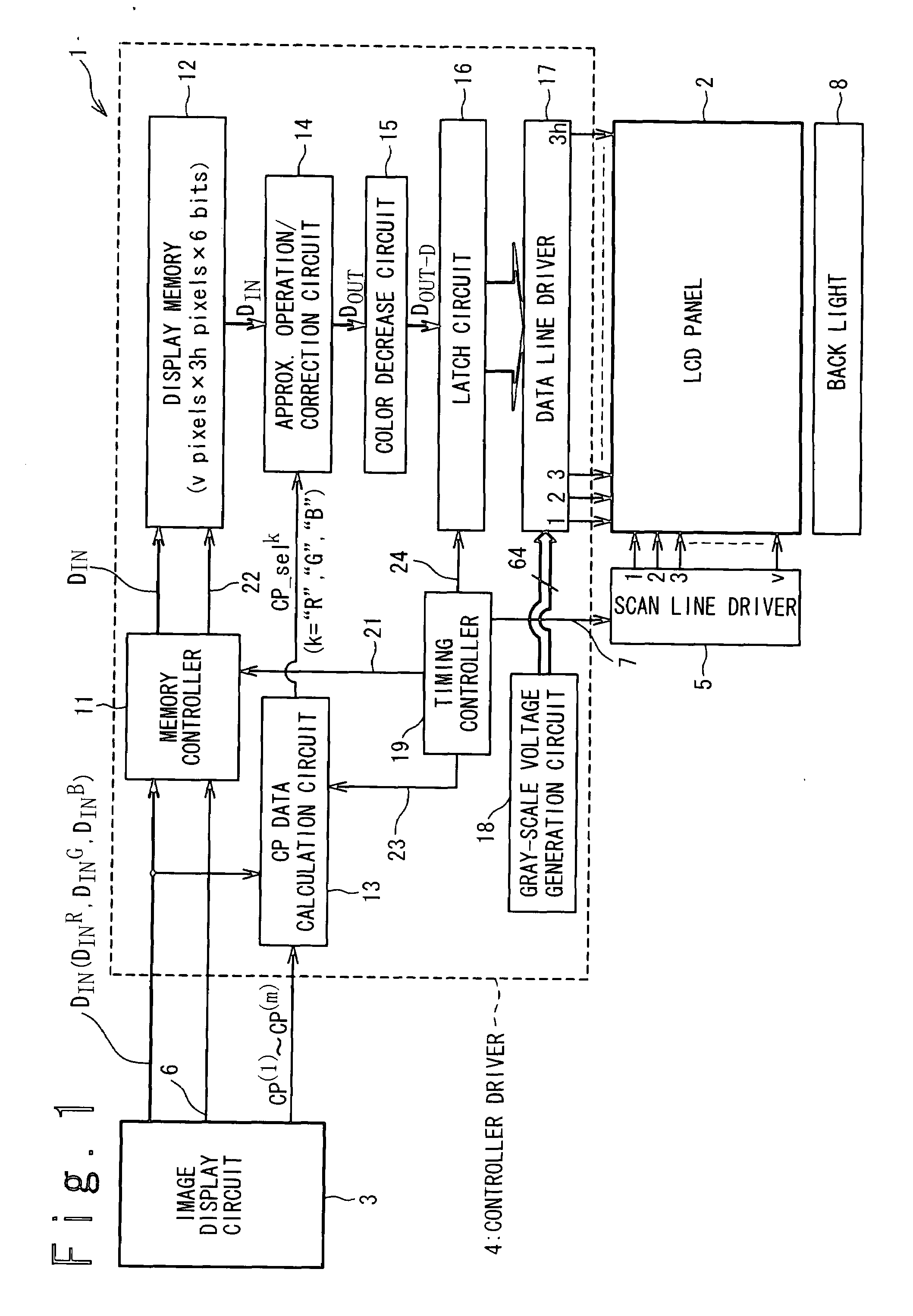

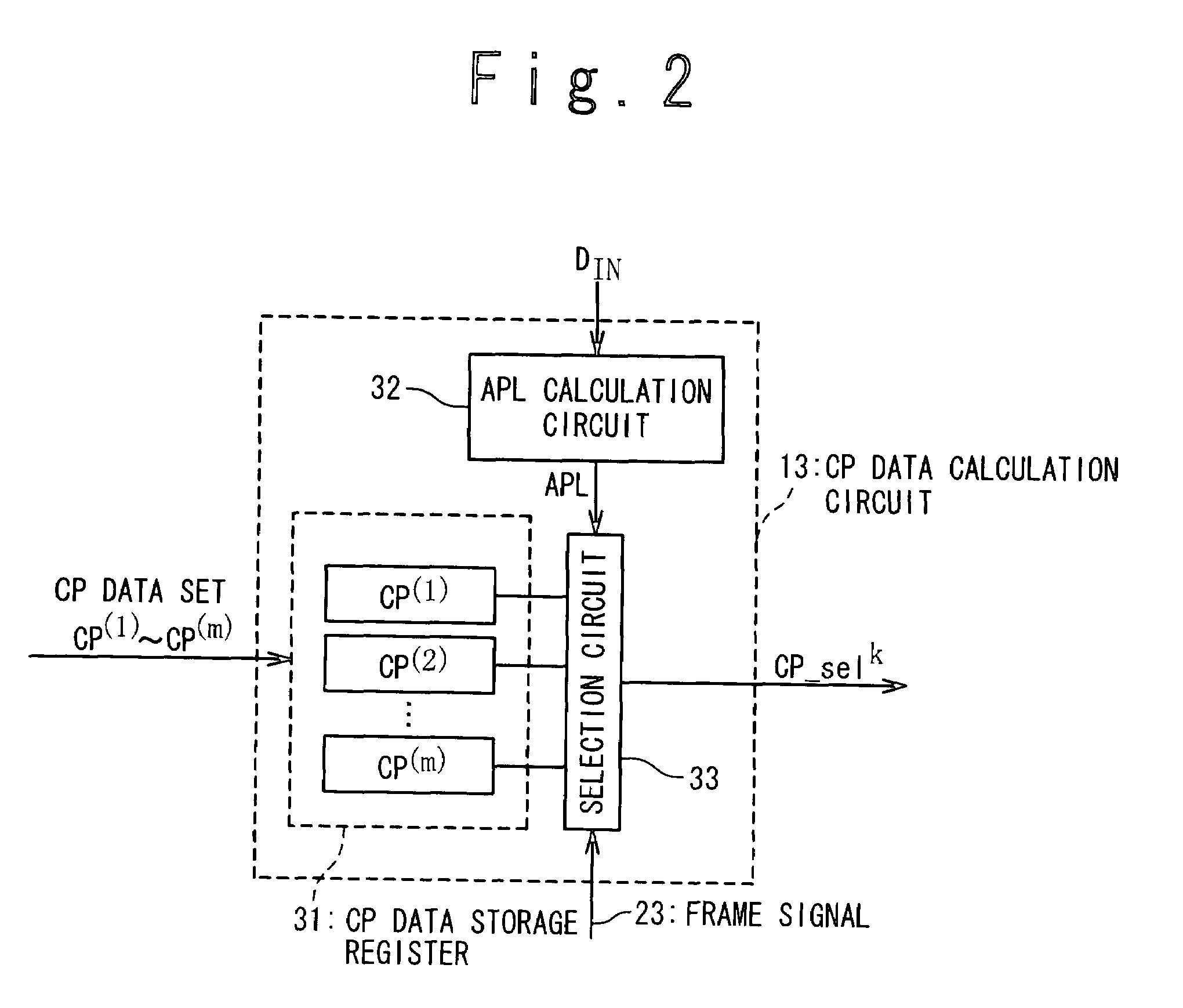

ActiveUS20070268524A1Reduce circuit sizeReduce power consumptionDigitally marking record carriersColor signal processing circuitsDisplay deviceLine driver

An LCD device according to the present invention has: an LCD panel; an operation and correction circuit configured to perform a correction operation with respect to an input gray-scale data of a target frame image by using an arithmetic expression to generate an output gray-scale data; a data line driver configured to drive the LCD panel in accordance with the output gray-scale data; and a correction data calculation circuit configured to generate a correction data that specifies a relationship between the input gray-scale data and the output gray-scale data of the target frame image, depending on the input gray-scale data of the target frame image or an input gray-scale data of a precedent frame image followed by the target frame image. The operation and correction circuit determines coefficients of the arithmetic expression from the correction data.

Owner:SYNAPTICS JAPAN GK

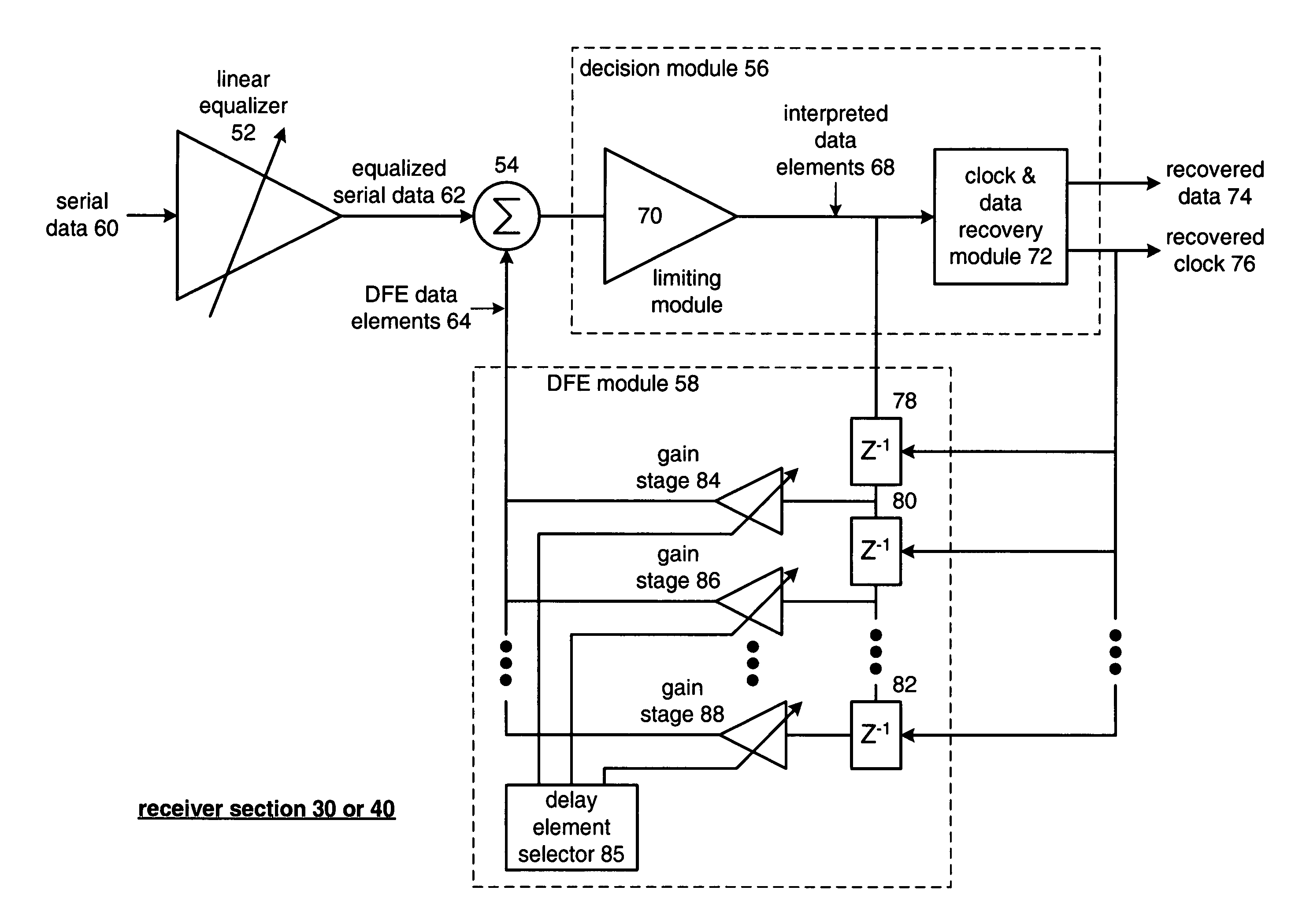

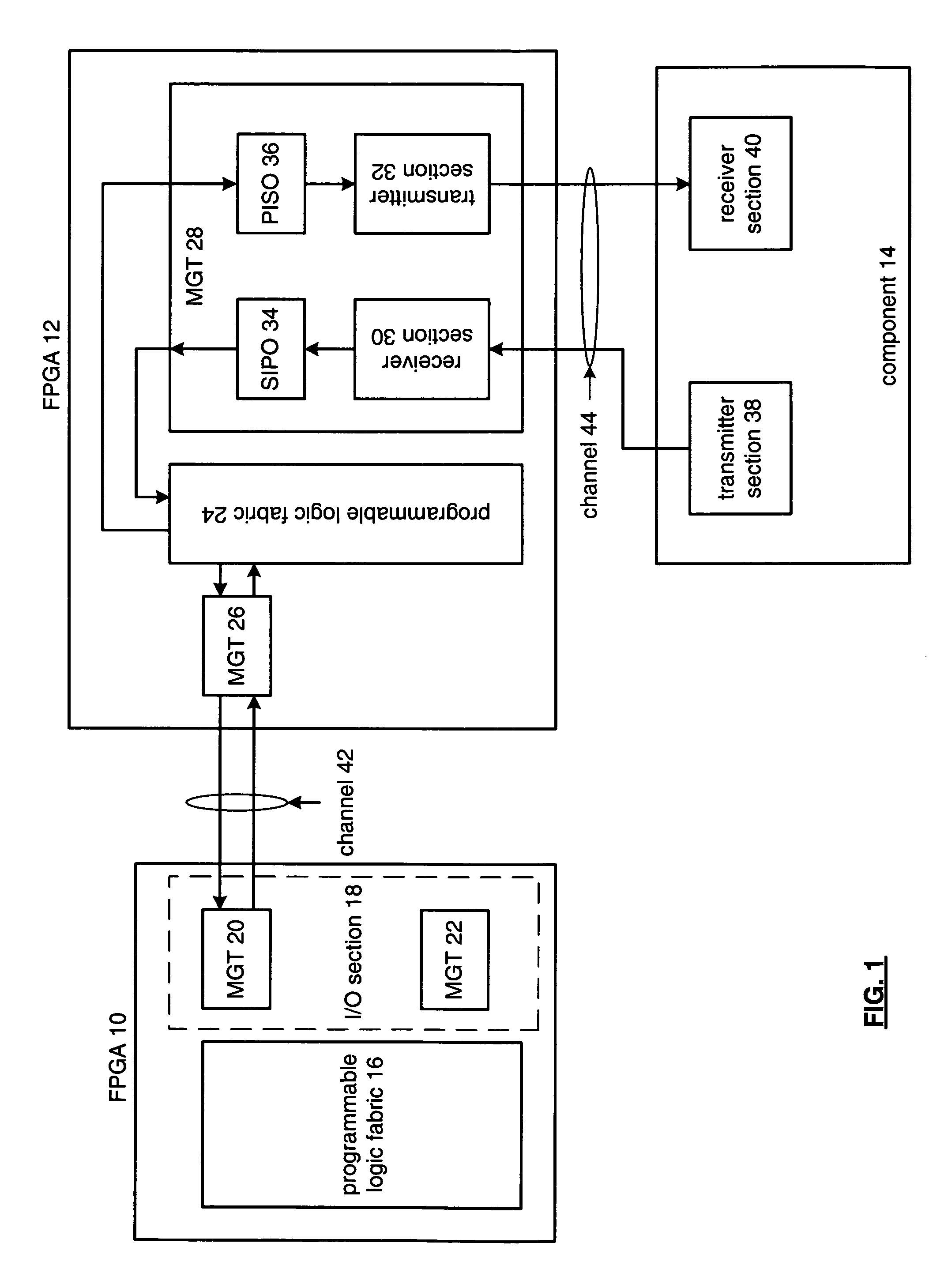

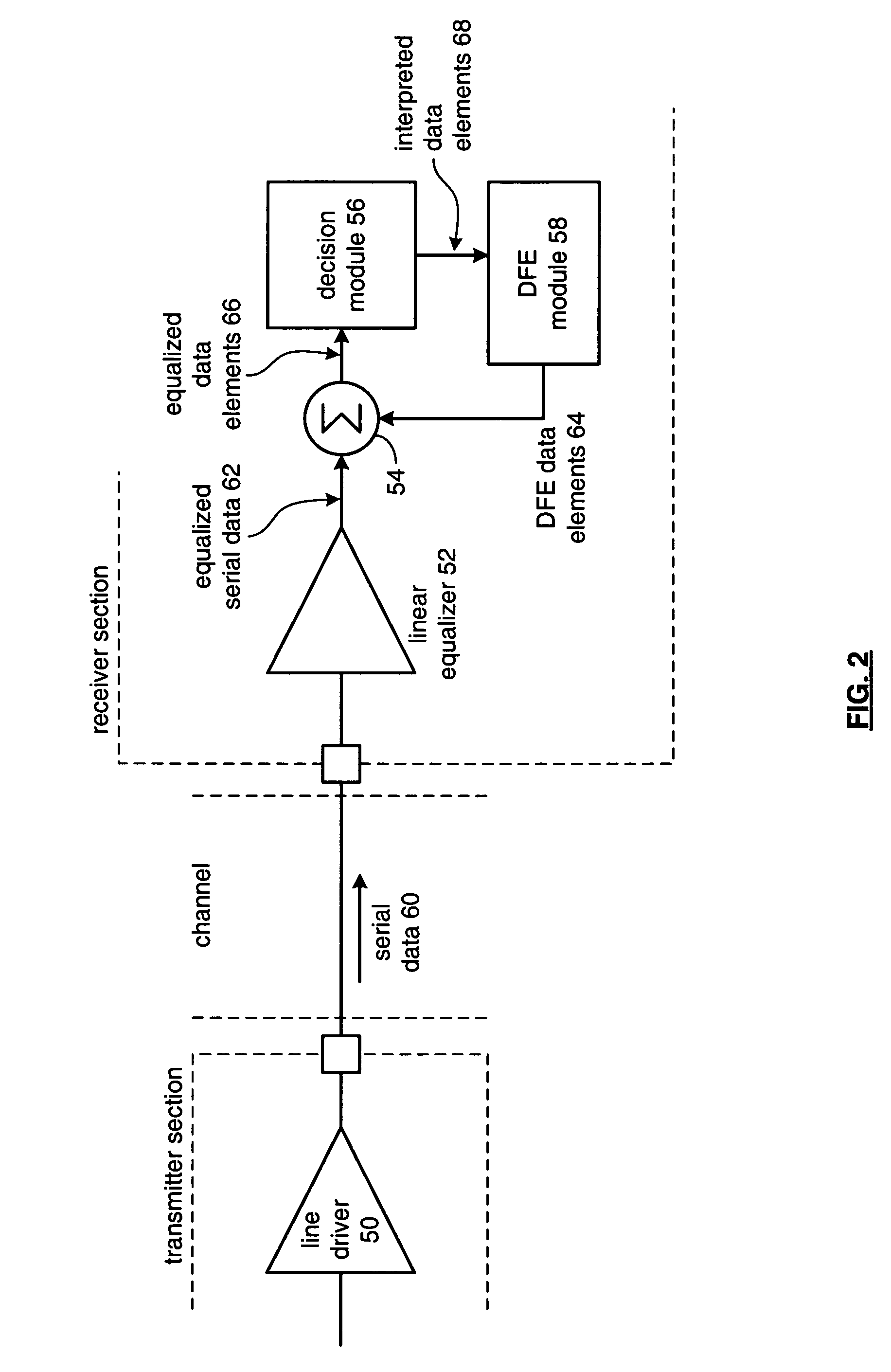

Combined decision feedback equalization and linear equalization

A communication system includes a transmitter, a communication channel, and a receiver. The transmitter includes a pre-emphasis module, a summing module, a line driver, and a decision feedback pre-emphasis (DFP) module to produce a pre-emphasized serial stream of data based on a communications channel response and an inter-symbol interference level. The receiver includes a linear equalizer, a summing module, a decision module, and a decision feedback equalization (DFE) module. The linear equalizer produces an equalized serial stream of data. The summing module sums at least one data element of the equalized serial stream of data with DFE data elements to produce equalized data elements. The decision module interprets the equalized data elements to produce interpreted data elements to DFE module, which produces the DFE data elements from the interpreted data elements.

Owner:XILINX INC

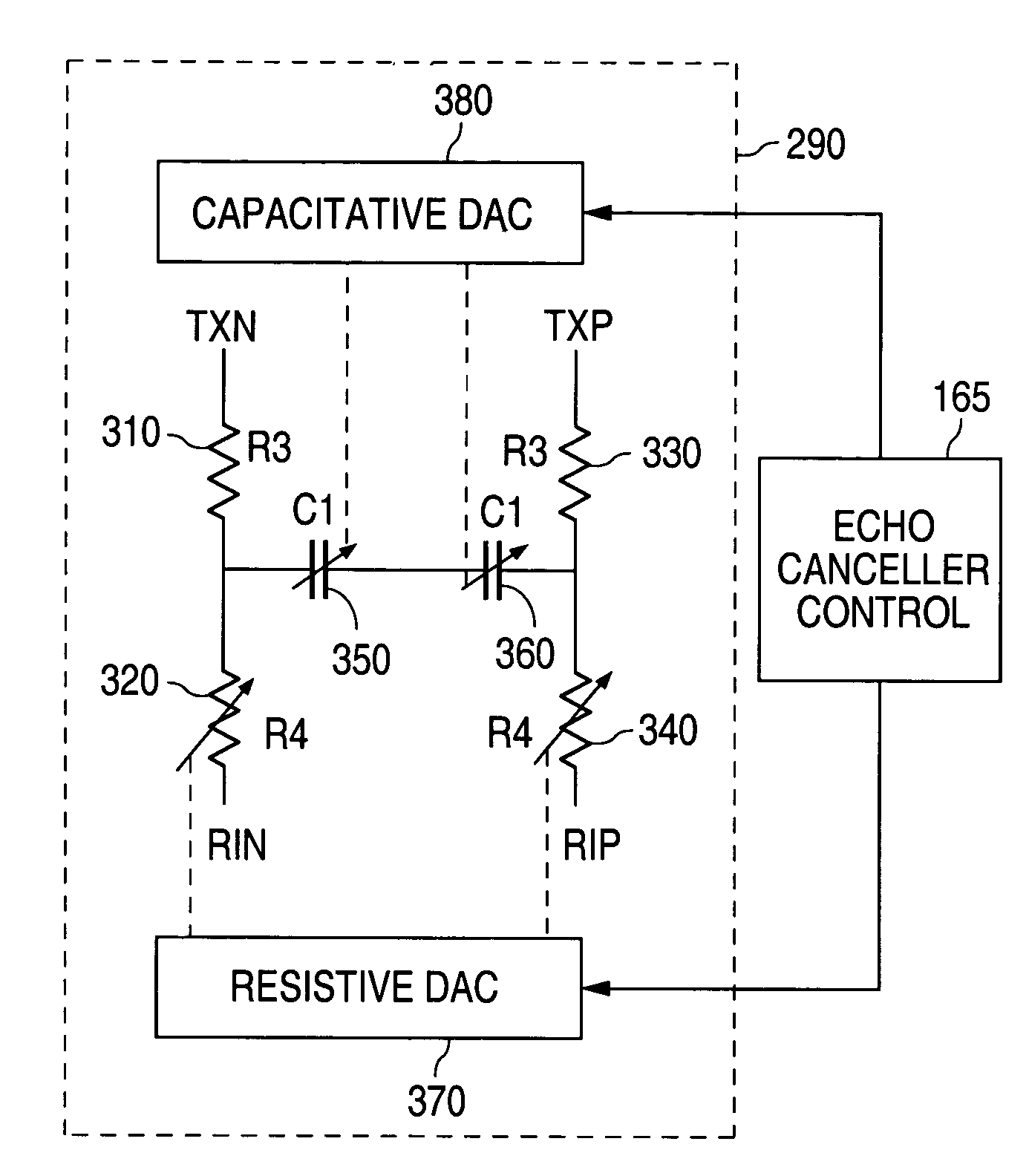

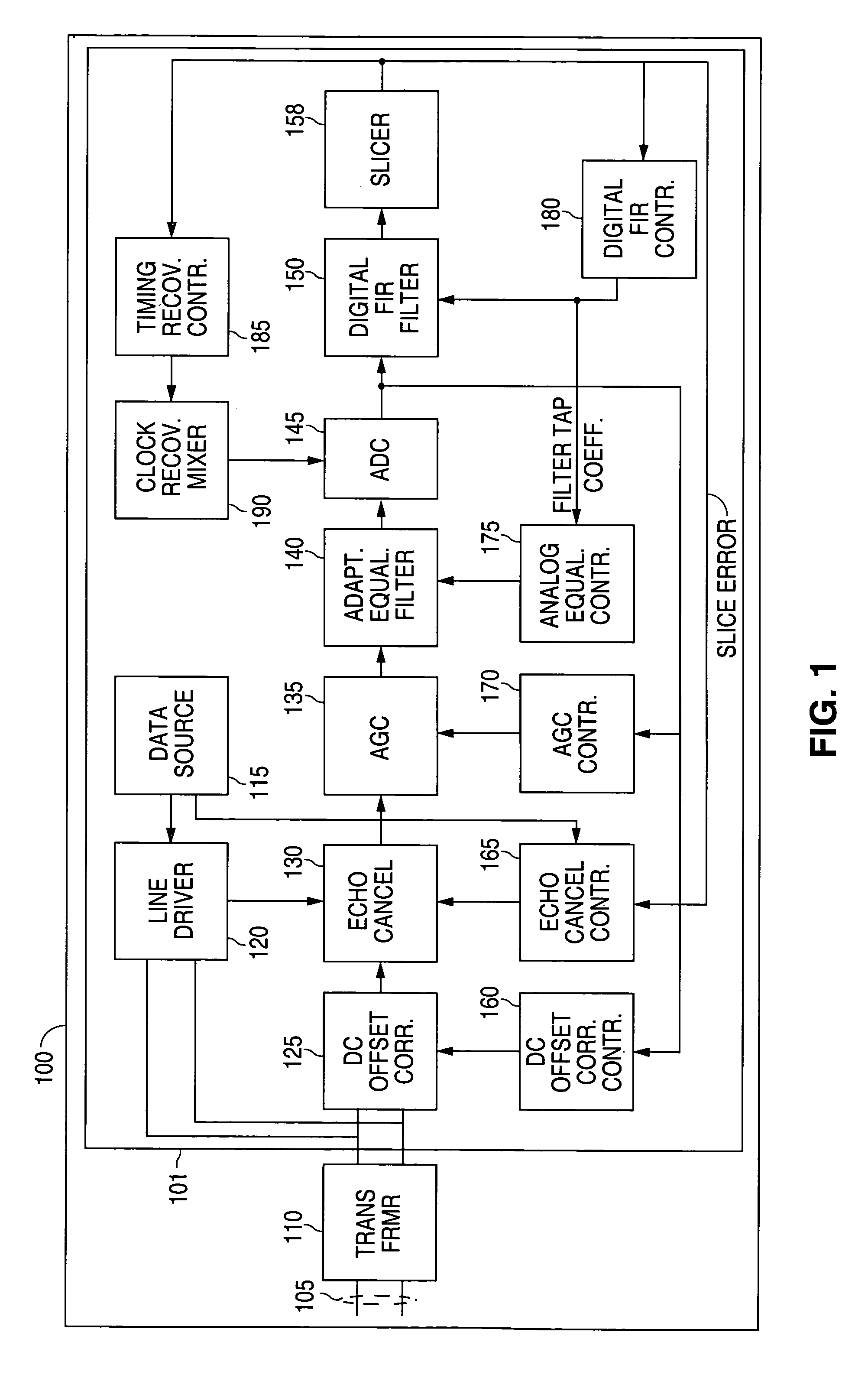

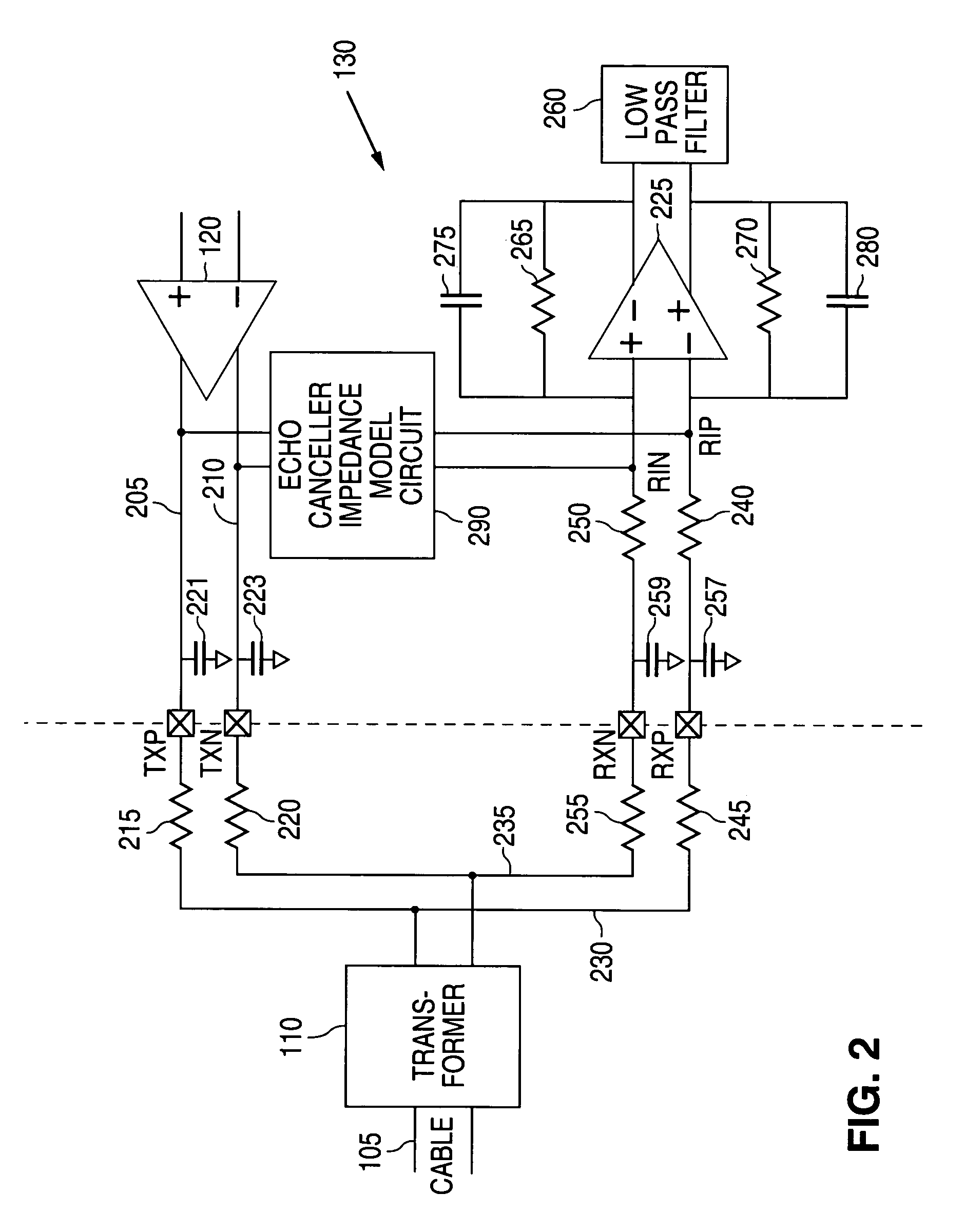

System and method for cancelling signal echoes in a full-duplex transceiver front end

InactiveUS7139342B1Good precisionTwo-way loud-speaking telephone systemsLine-transmissionCapacitanceTransceiver

There is disclosed an echo canceller circuit for use in a full duplex transceiver of the type comprising a line driver capable of sending analog transmit signals through a cable and comprising a line receiver capable of receiving analog receive signals from the cable. An echo canceller impedance model circuit is coupled to an output of the line driver and is coupled to an input of the line receiver. The echo canceller impedance model circuit generates an echo canceller current that is equal in magnitude and opposite in phase to a current that represents signal echoes that are present in the analog receive signals. The echo canceller impedance model circuit has a variable impedance for generating the echo canceller current. The variable impedance has at least one variable resistor and at least one variable capacitor. The values of resistance and capacitance in the echo canceller impedance model circuit are varied in response to control signals from a echo canceller control circuit to compensate for and cancel signal echoes.

Owner:NAT SEMICON CORP

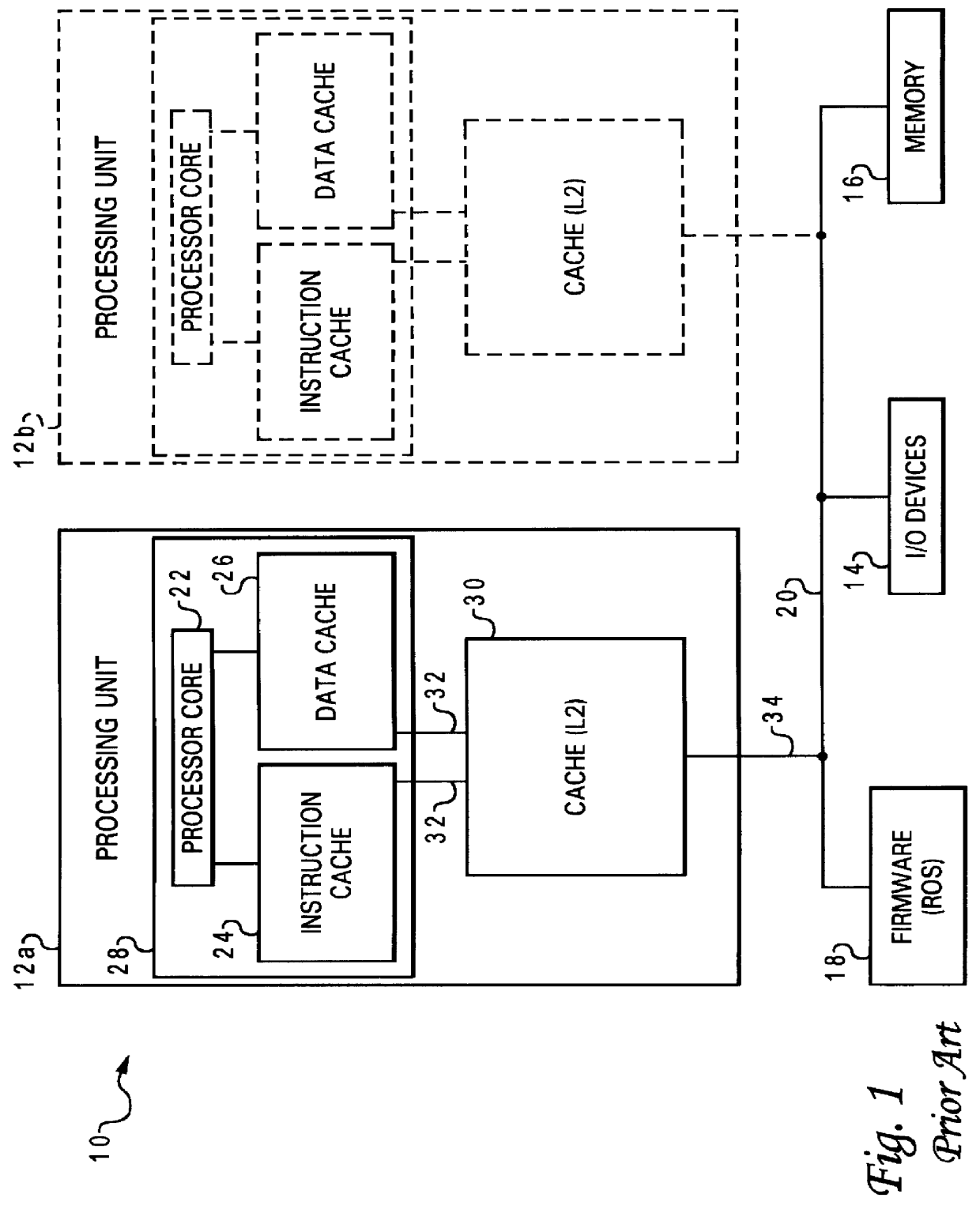

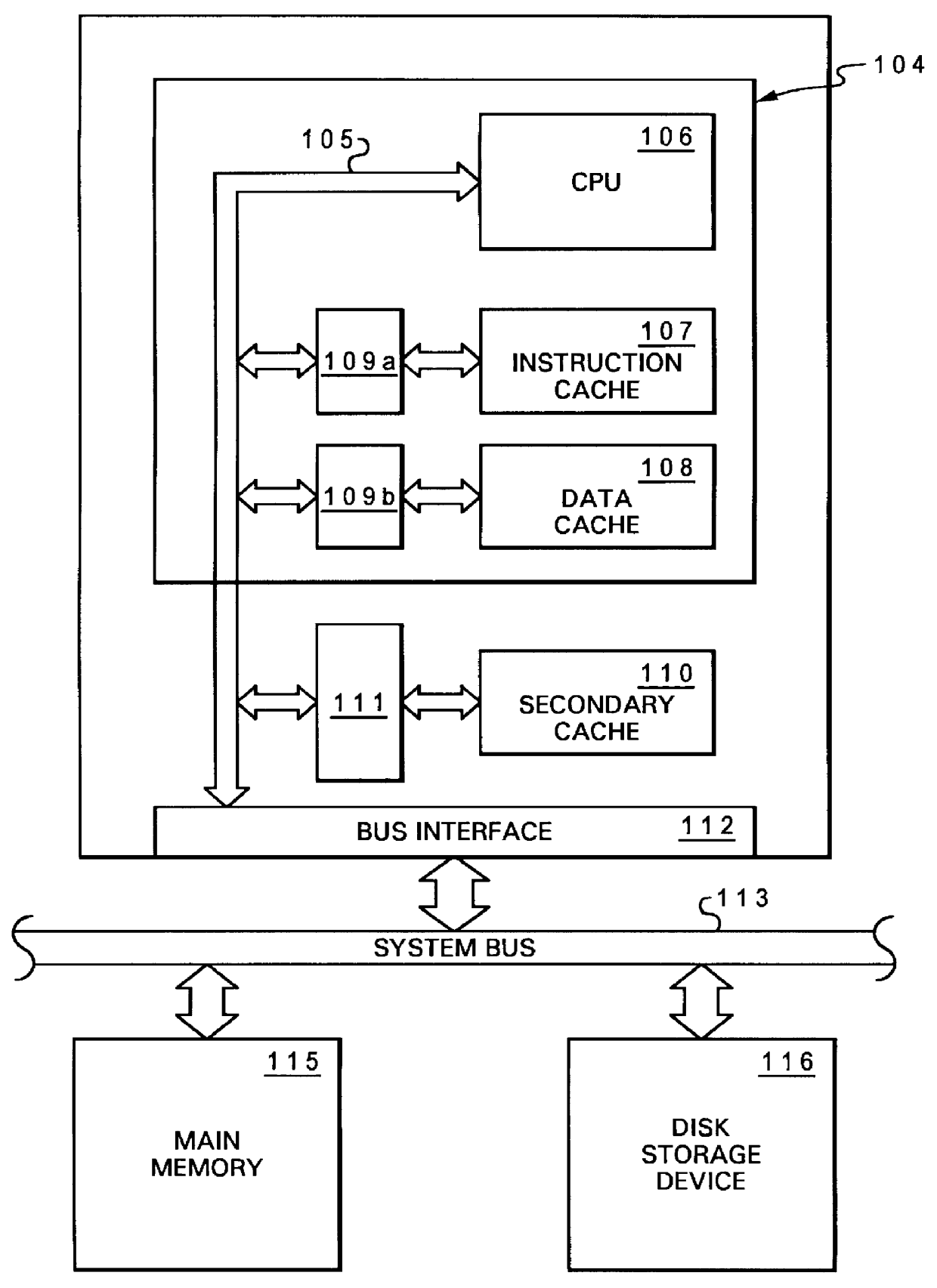

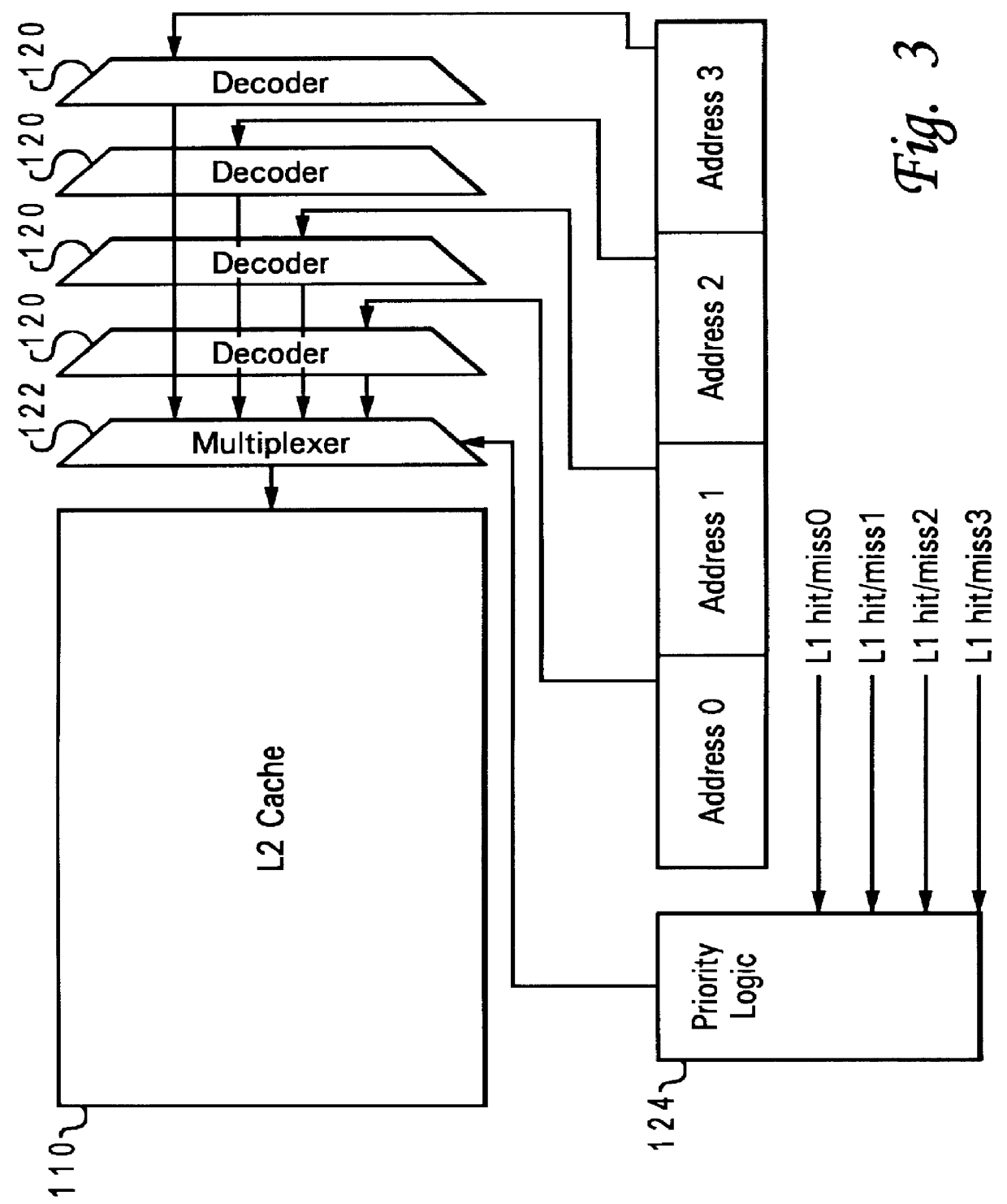

Multiple level cache memory with overlapped L1 and L2 memory access

A method of providing simultaneous, or overlapped, access to multiple cache levels to reduce the latency penalty for a higher level cache miss. A request for a value (data or instruction) is issued by the processor, and is forwarded to the lower level of the cache before determining whether a cache miss of the value has occurred at the higher level of the cache. In the embodiment wherein the lower level is an L2 cache, the L2 cache may supply the value directly to the processor. Address decoders are operated in parallel at the higher level of the cache to satisfy a plurality of simultaneous memory requests. One of the addresses (selected by priority logic based on hit / miss information from the higher level of the cache) is gated by a multiplexer to a plurality of memory array word line drivers of the lower level of the cache. Some bits in the address which do not require virtual-to-real translation can be immediately decoded.

Owner:IBM CORP

Capacitance detecting circuit and method, and fingerprint sensor using the same

ActiveUS7078918B2Improve signal-to-noise ratioSmall capacitanceResistance/reactance/impedencePerson identificationLine driverFingerprint

In a capacitance detecting circuit, changes in capacitances at intersections between a plurality of row lines and a column line are detected as voltages. The capacitance detecting circuit includes a column-line driver for driving the column line. A code generator generates code having orthogonality in chronological order. A selection synthesizer selects a certain number of row lines from the plurality of row lines by using the code and synthesizes measured voltages at the intersections between the selected row lines and the driven column line so as to output the synthesized measured voltage. A decoding computation unit separates the measured voltages corresponding to the capacitances at the intersections by performing product sum computation between the synthesized measured voltage and the code.

Owner:SYNAPTICS INC

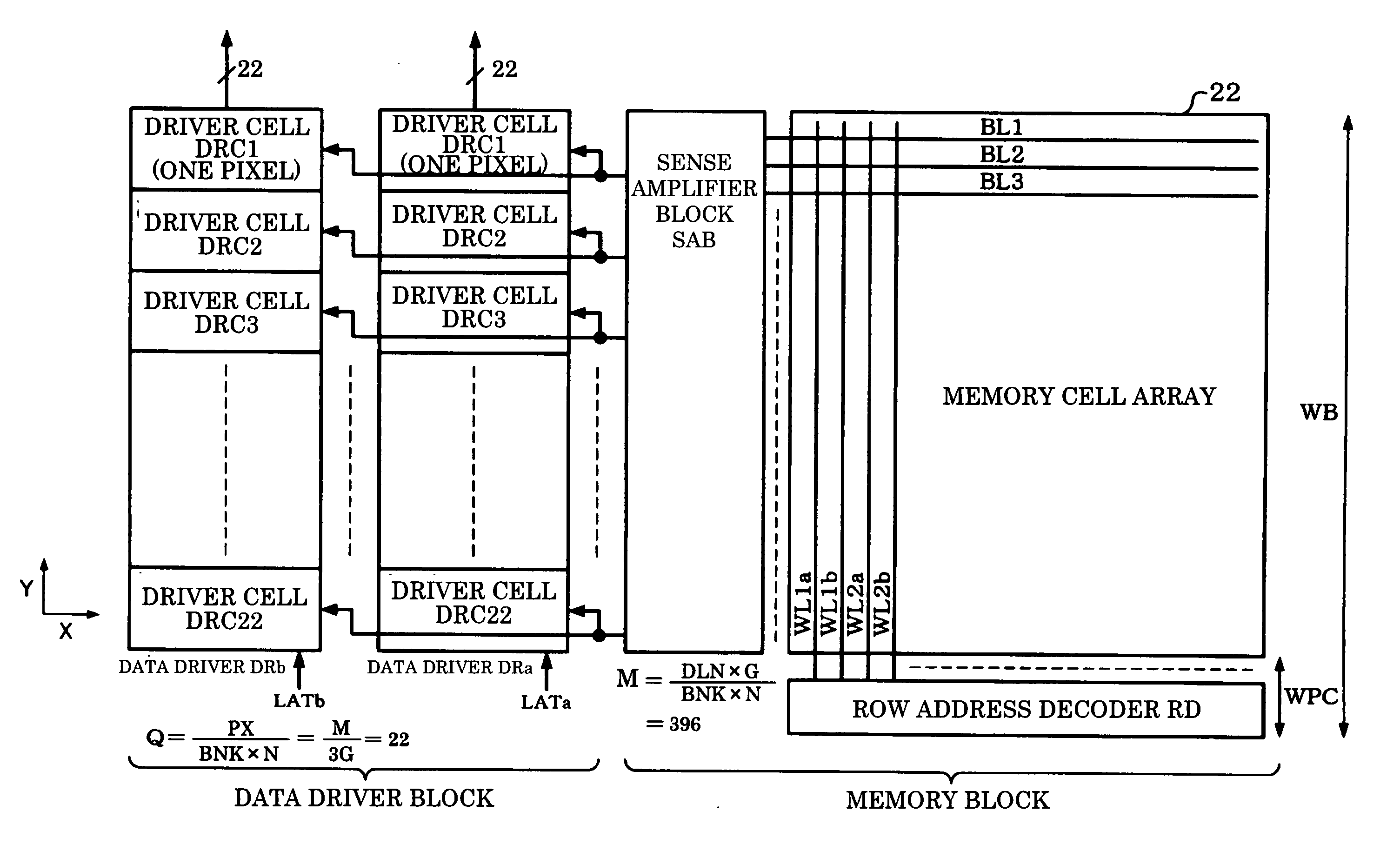

Integrated circuit device and electronic instrument

InactiveUS20070013707A1Cathode-ray tube indicatorsDigital storageComputer hardwareElectronic instrument

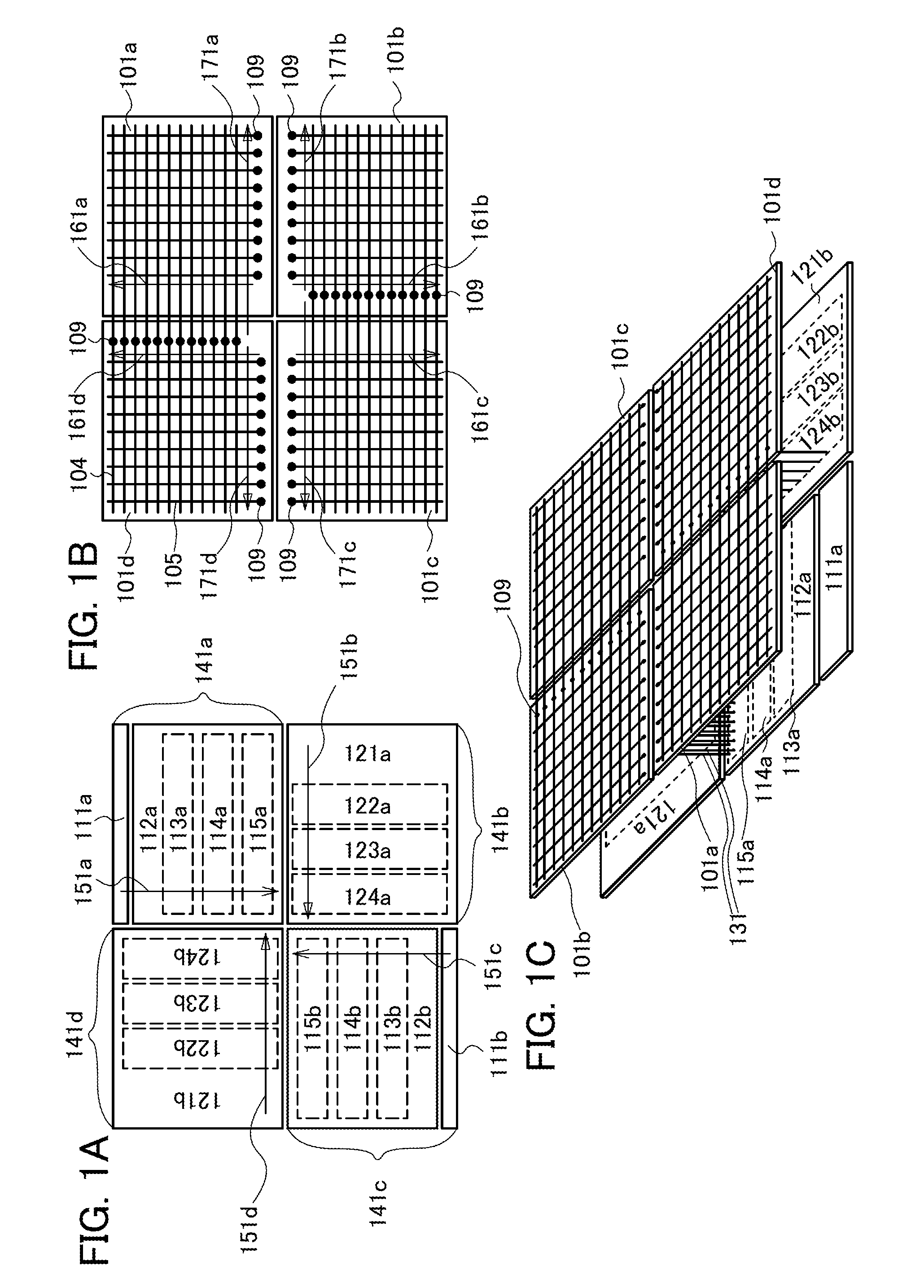

In an integrated circuit device, a data line driver block which drives data lines of a display panel based on data supplied from a RAM block from which data is read N times (N is an integer larger than one) in one horizontal scan period 1H of the display panel includes first to N-th divided data line driver blocks disposed along a first direction in which bitlines extend. When data supplied from the RAM block is M bits (M is an integer larger than 1) and grayscale of a pixel corresponding to the data line is G bits, each of the first to N-th divided data line driver blocks includes (M / G) (multiple of three) data line driver cells which drive (M / G) data lines. (M / 3G) R data line driver cells are provided in a first subdivided driver, (M / 3G) G data line driver cells are provided in a second subdivided driver, and (M / 3G) B data line driver cells are provided in a third subdivided driver.

Owner:SEIKO EPSON CORP

Memory device

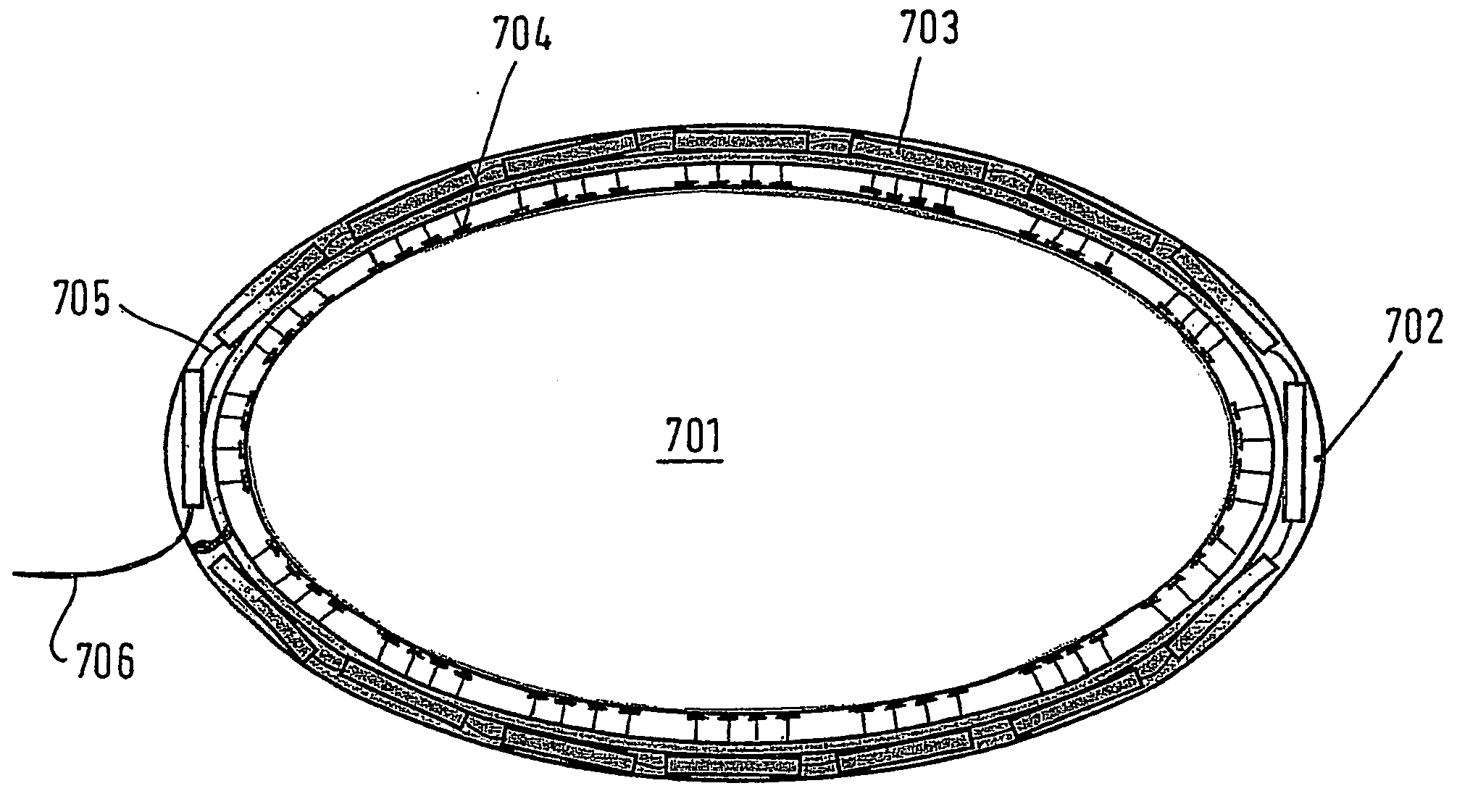

ActiveUS20130148411A1Sufficient data retention periodIncrease memory capacitySolid-state devicesDigital storageDriver circuitLine driver

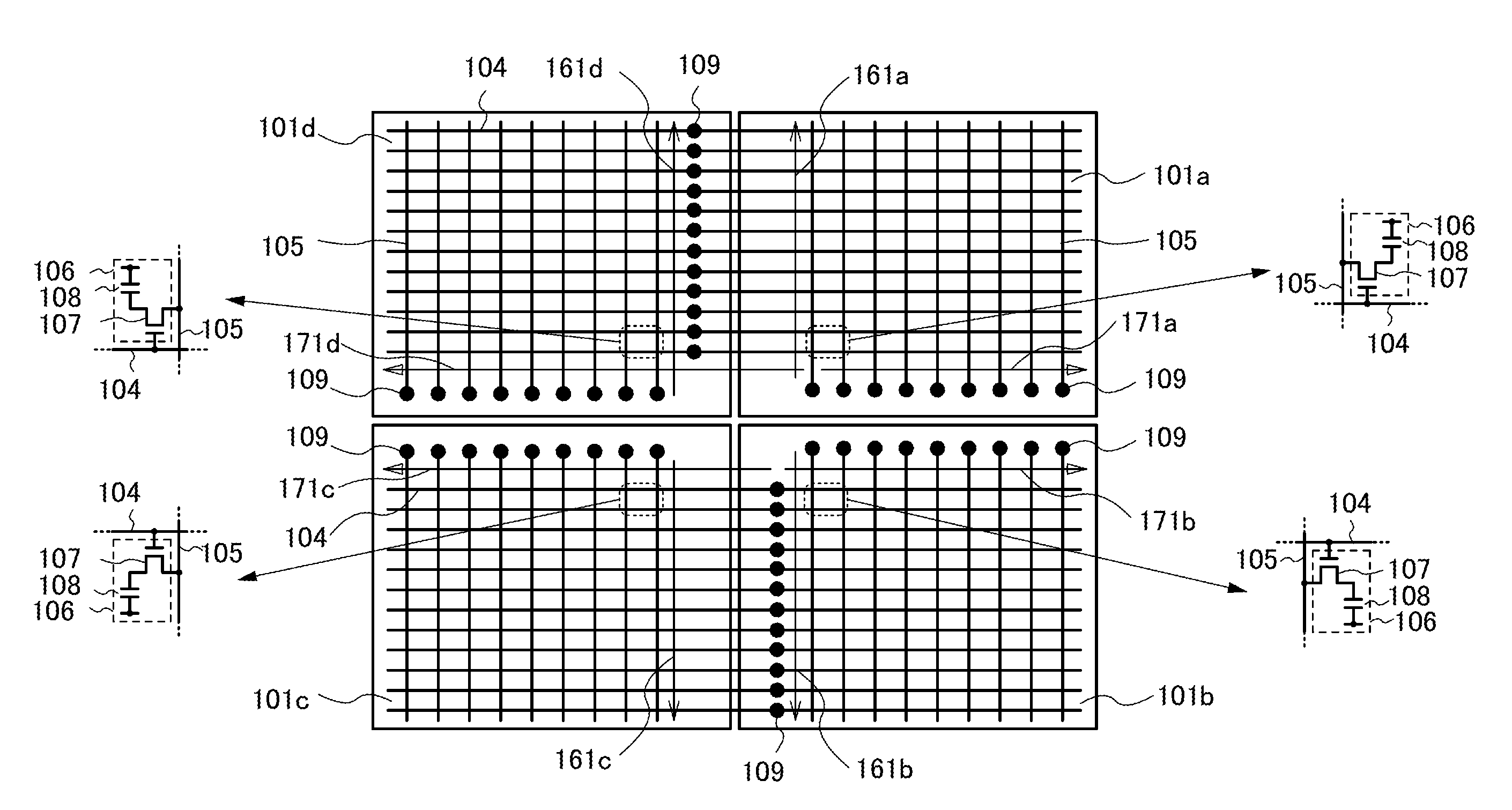

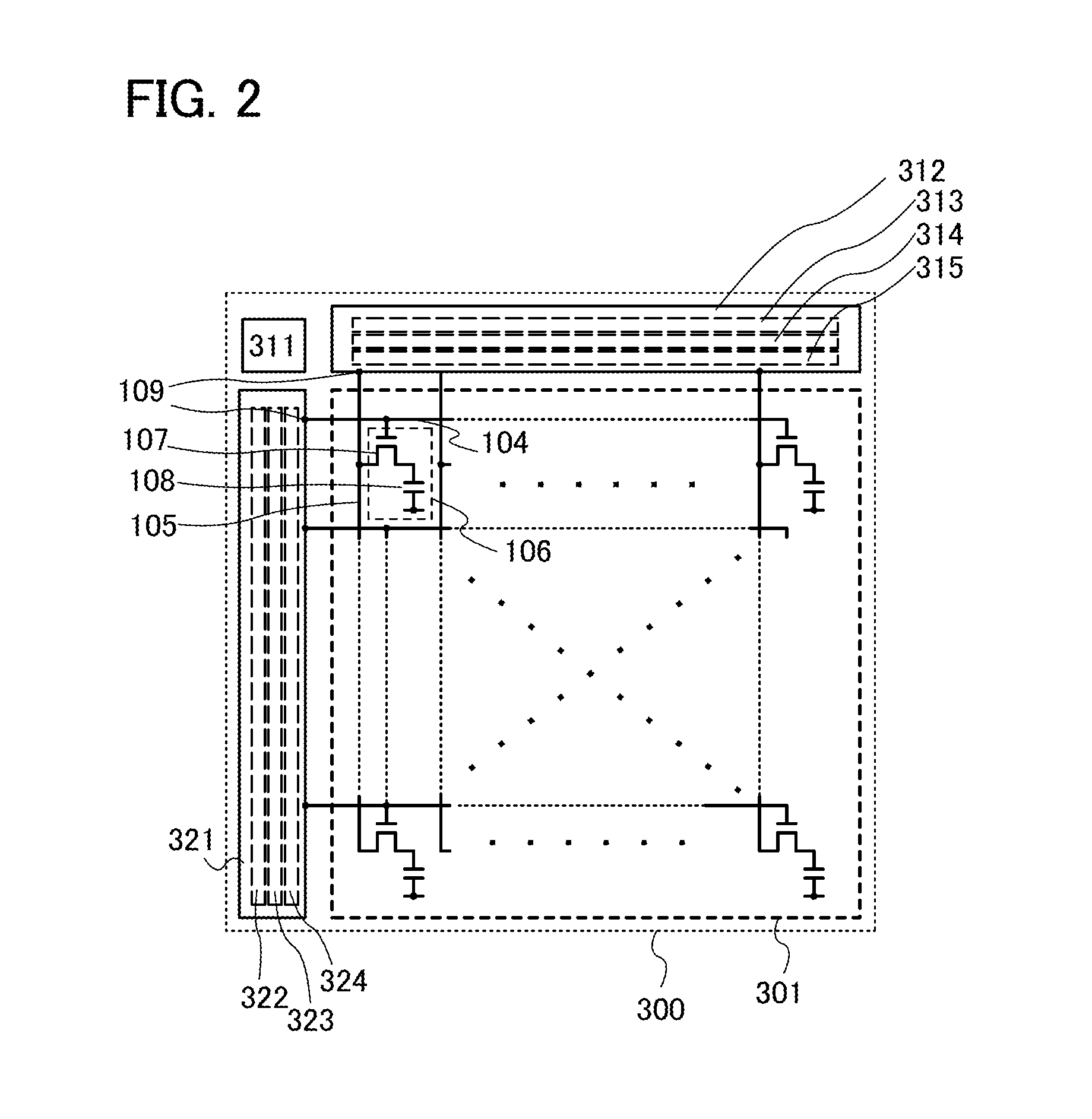

A memory device including first to fourth memory cell arrays and a driver circuit including a pair of bit line driver circuits and a pair of word line driver circuits is provided. The first to fourth memory cell arrays are overlap with the driver circuit. Each of the pair of bit line driver circuits and a plurality of bit lines are connected through connection points on an edge along the boundary between the first and second memory cell arrays or on an edge along the boundary between the third and fourth memory cell arrays. Each of the pair of word line driver circuits and a plurality of word lines are connected through second connection points on an edge along the boundary between the first and fourth memory cell arrays or on an edge along the boundary between the second and third memory cell arrays.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor memory device comprising a plurality of static memory cells

ActiveUS20080037358A1Simple circuit structureStable writing and reading of dataDigital storageHemt circuitsLine driver

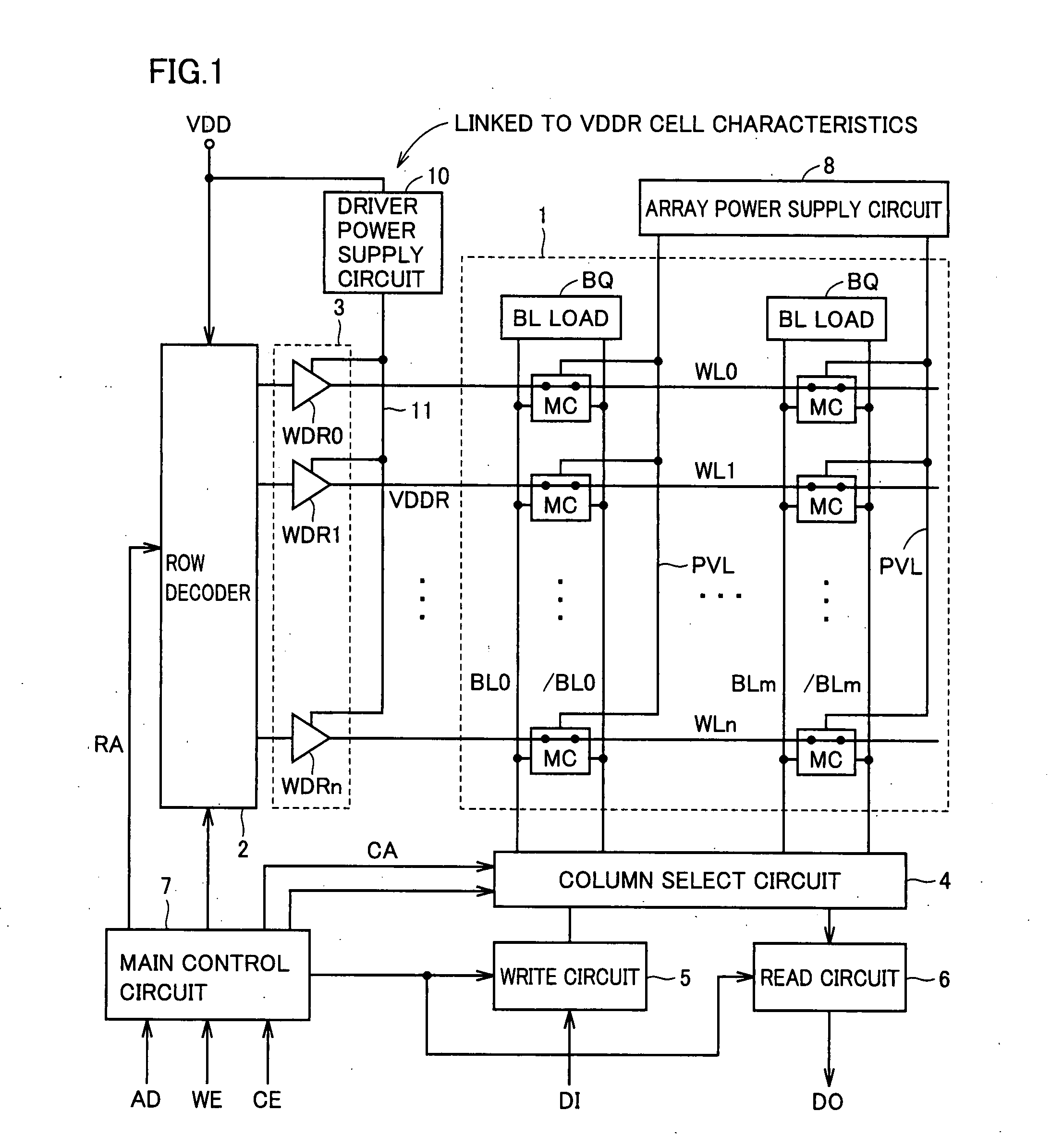

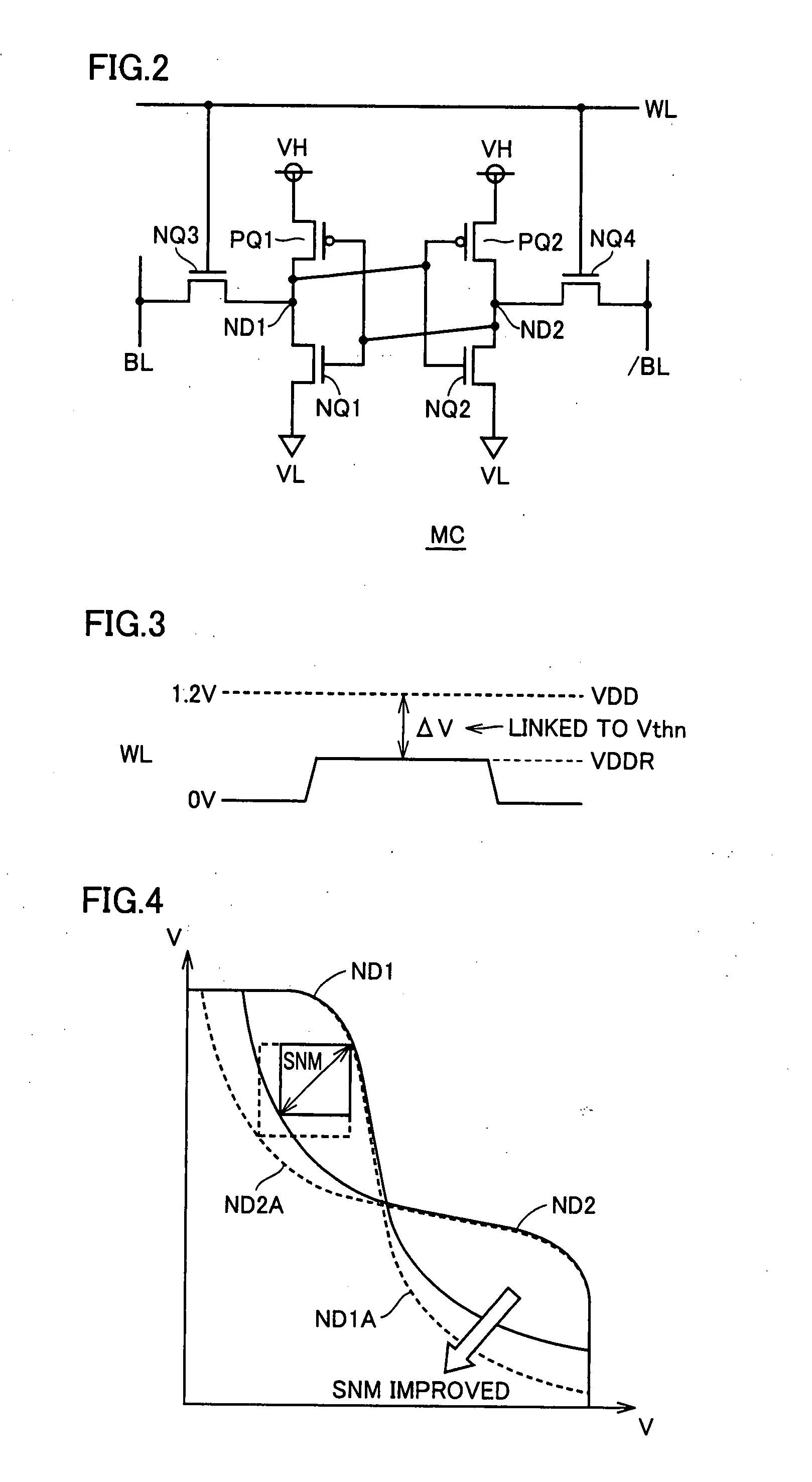

A driver power supply circuit stepping down a power supply voltage is arranged at a power supply node of a word line driver. The driver power supply circuit includes a non-silicide resistance element of N+ doped polycrystalline silicon, and a pull-down circuit lowering a voltage level of the driver power supply node. The pull-down circuit includes a pull-down transistor having the same threshold voltage characteristics as a memory cell transistor pulling down a voltage level of the driver power supply node, and a gate control circuit adjusting at least a gate voltage of the pull-down transistor. The gate control circuit corrects the gate potential of the pull-down transistor in a manner linked to variations in threshold voltage of the memory cell transistor.

Owner:RENESAS ELECTRONICS CORP

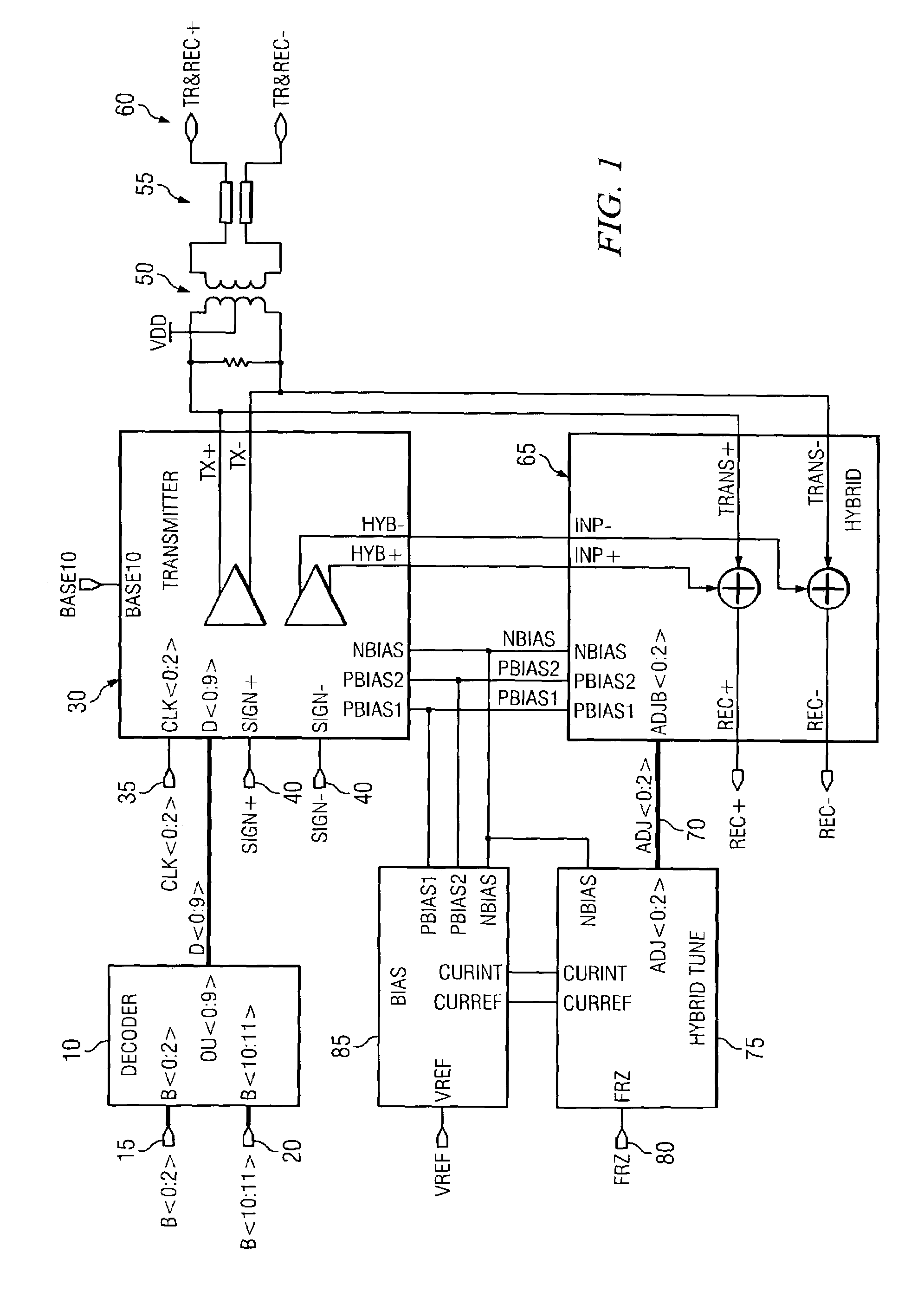

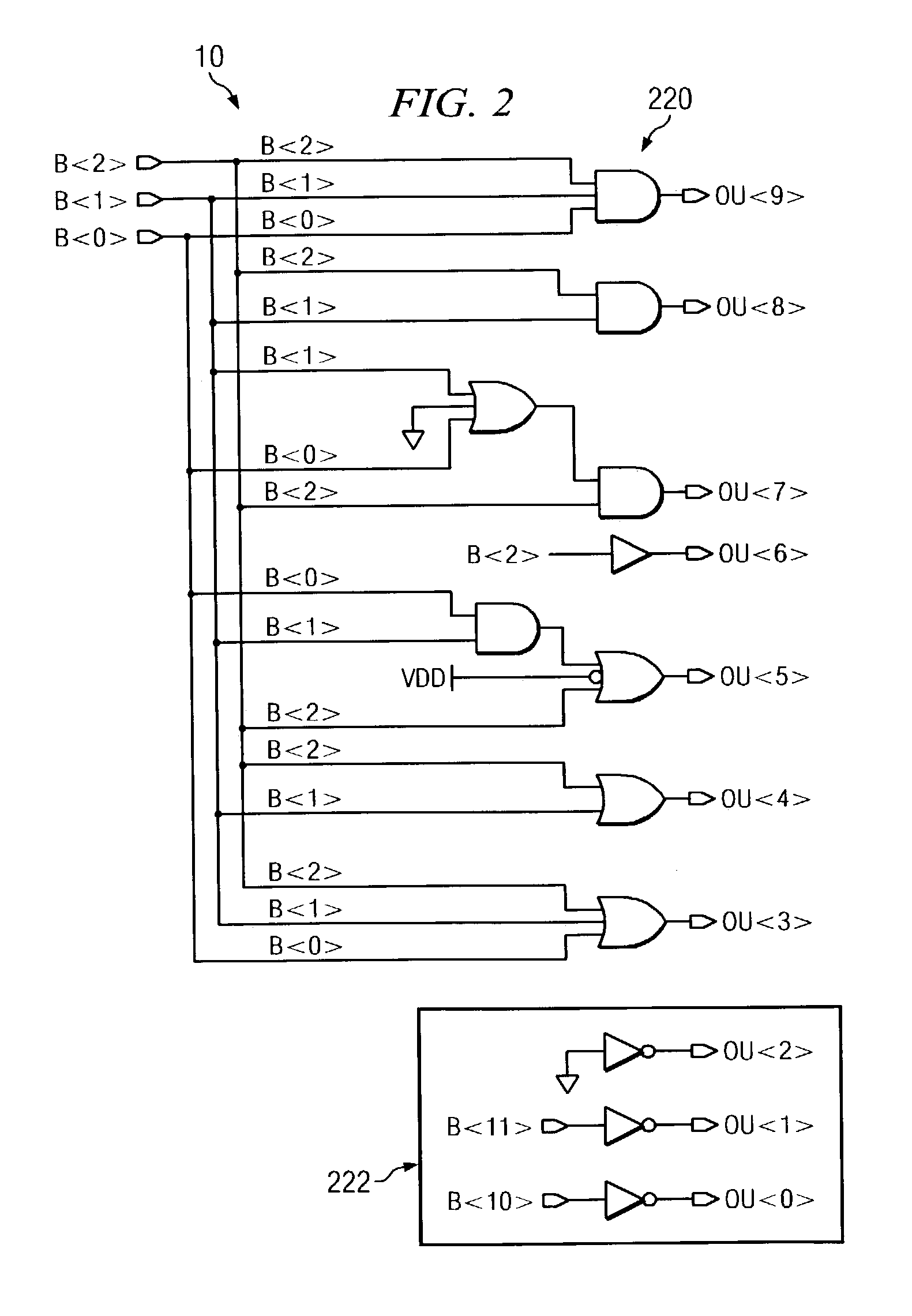

Gigabit ethernet line driver and hybrid architecture

ActiveUS7176823B2Electric signal transmission systemsDigital-analogue convertorsTransmitter power outputEngineering

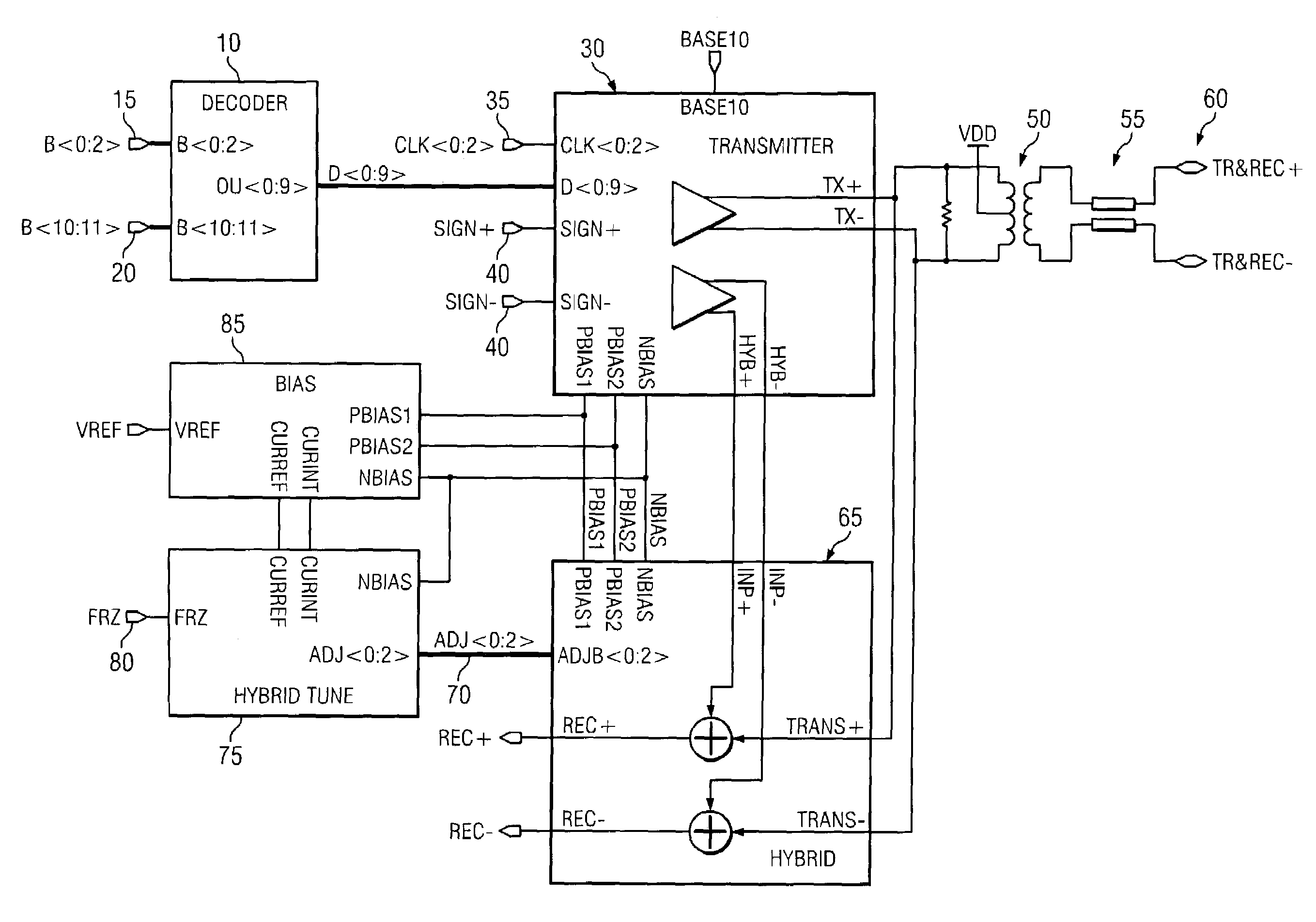

A gigabit ethernet line driver includes a transmitter having both transmitter and active hybrid outputs. The transmitter consists of a plurality of transmitter clusters each connected to both the transmitter and active hybrid outputs. Each transmitter cluster includes a plurality of transmitter cells consisting of a driver cell and digital to analog converter connected to driver cell. A hybrid circuit connects between the transmitter outputs and receiver inputs for separating a receiver signal from the transmitter signal responsive to a tuning signal.

Owner:STMICROELECTRONICS SRL

Memory array organization and related test method particularly well suited for integrated circuits having write-once memory arrays

Owner:SANDISK TECH LLC

Liquid crystal display having line drivers with reduced need for wide bandwidth switching

ActiveUS20080024418A1Low costHigh resolutionStatic indicating devicesNon-linear opticsLiquid-crystal displayLine driver

A liquid crystal display includes a substrate, a plurality of gate lines formed on the substrate, a plurality of data lines intersecting the gate lines, a plurality of thin film transistors connected to the gate lines and the data lines, a plurality of pixel electrodes connected to the thin film transistors and including a first edge parallel to the gate line and a second edge that is shorter than the first edge and is next to the first edge, and at least two gate drivers connected to mutually exclusive, interlaced subsets of the gate lines. The gate drivers may include the first gate driving circuit and the second gate driving circuit disposed opposite to each other with respect to the substrate.

Owner:SAMSUNG DISPLAY CO LTD