Patents

Literature

186results about How to "Small capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

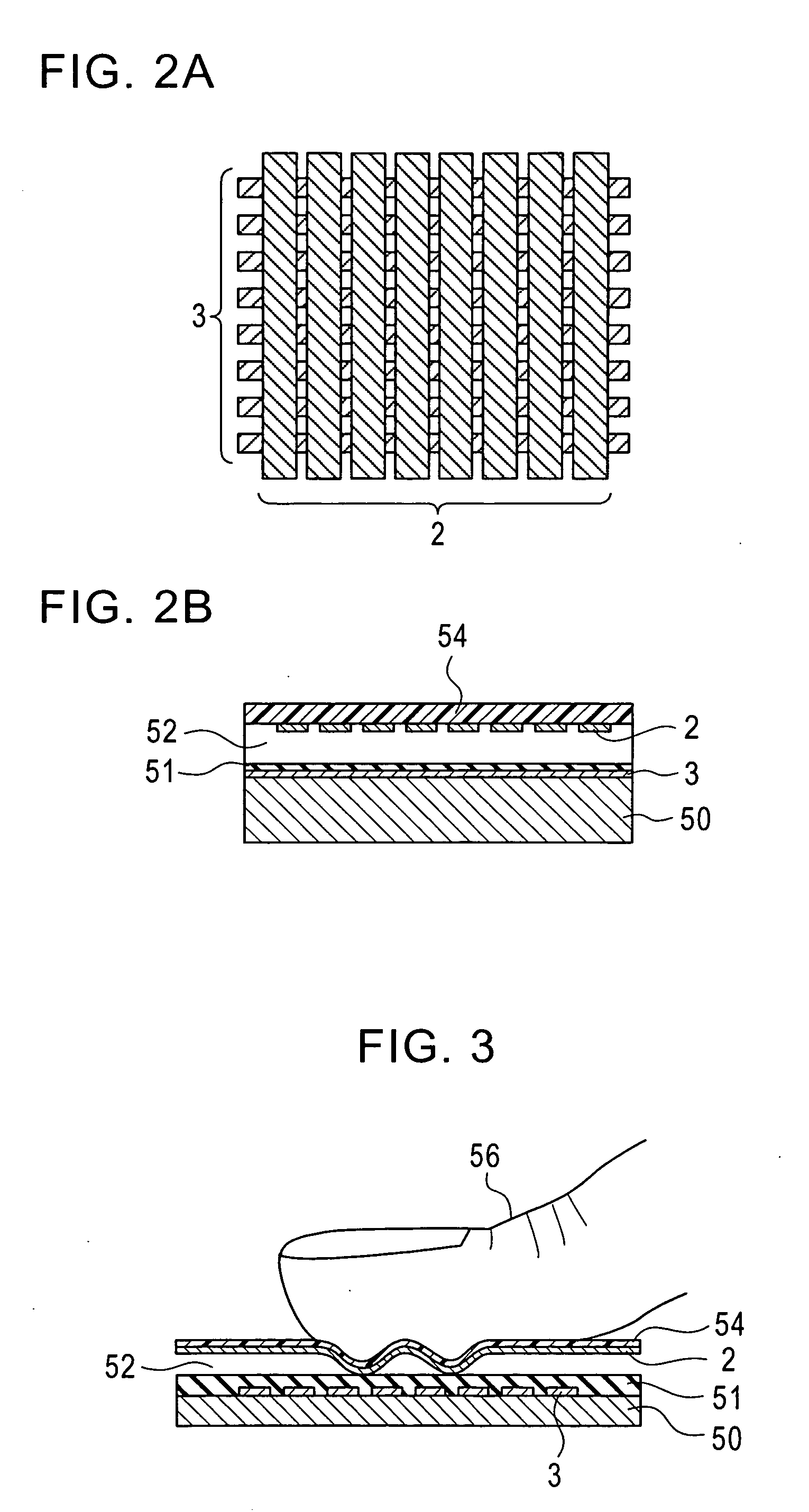

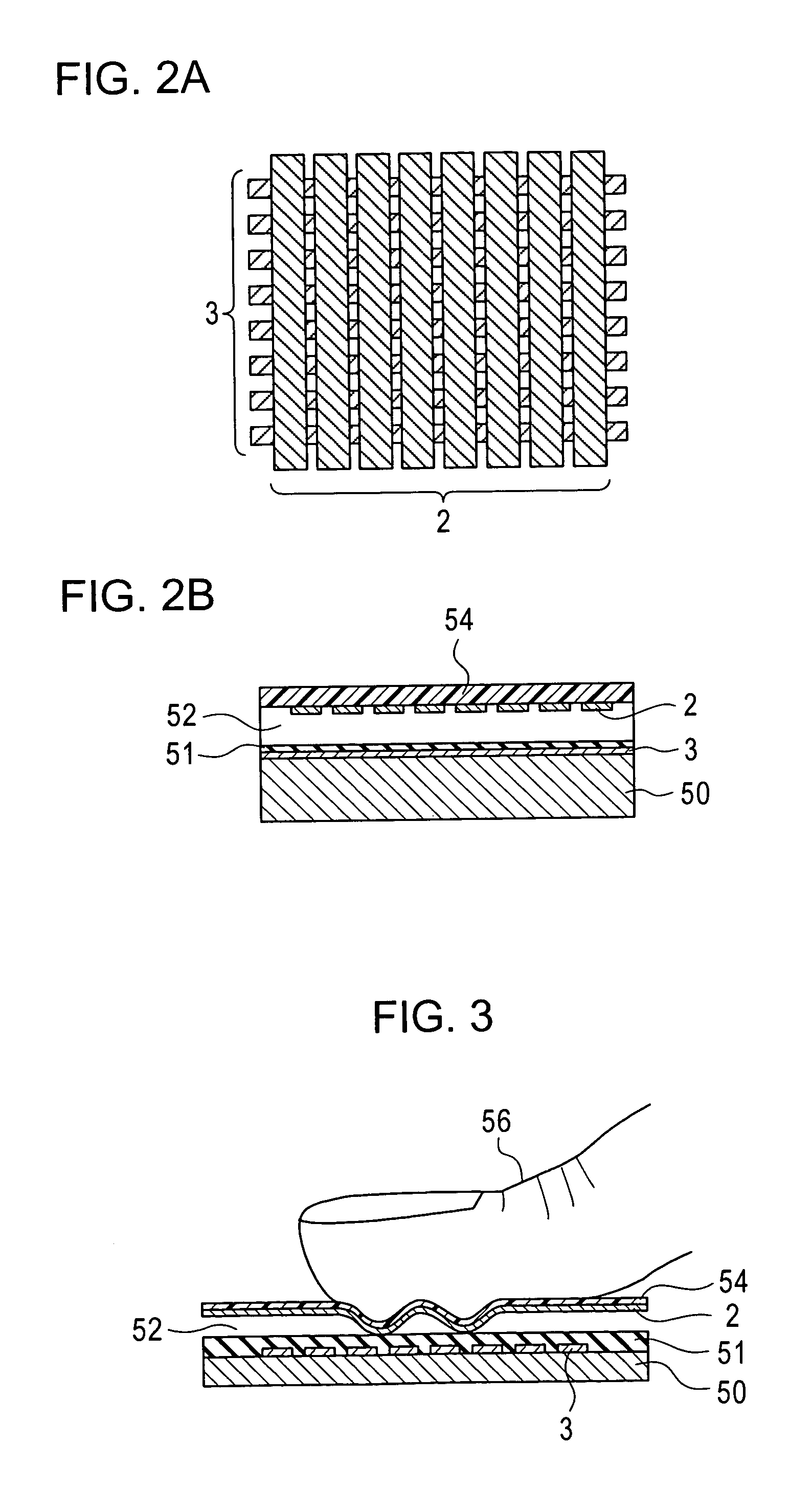

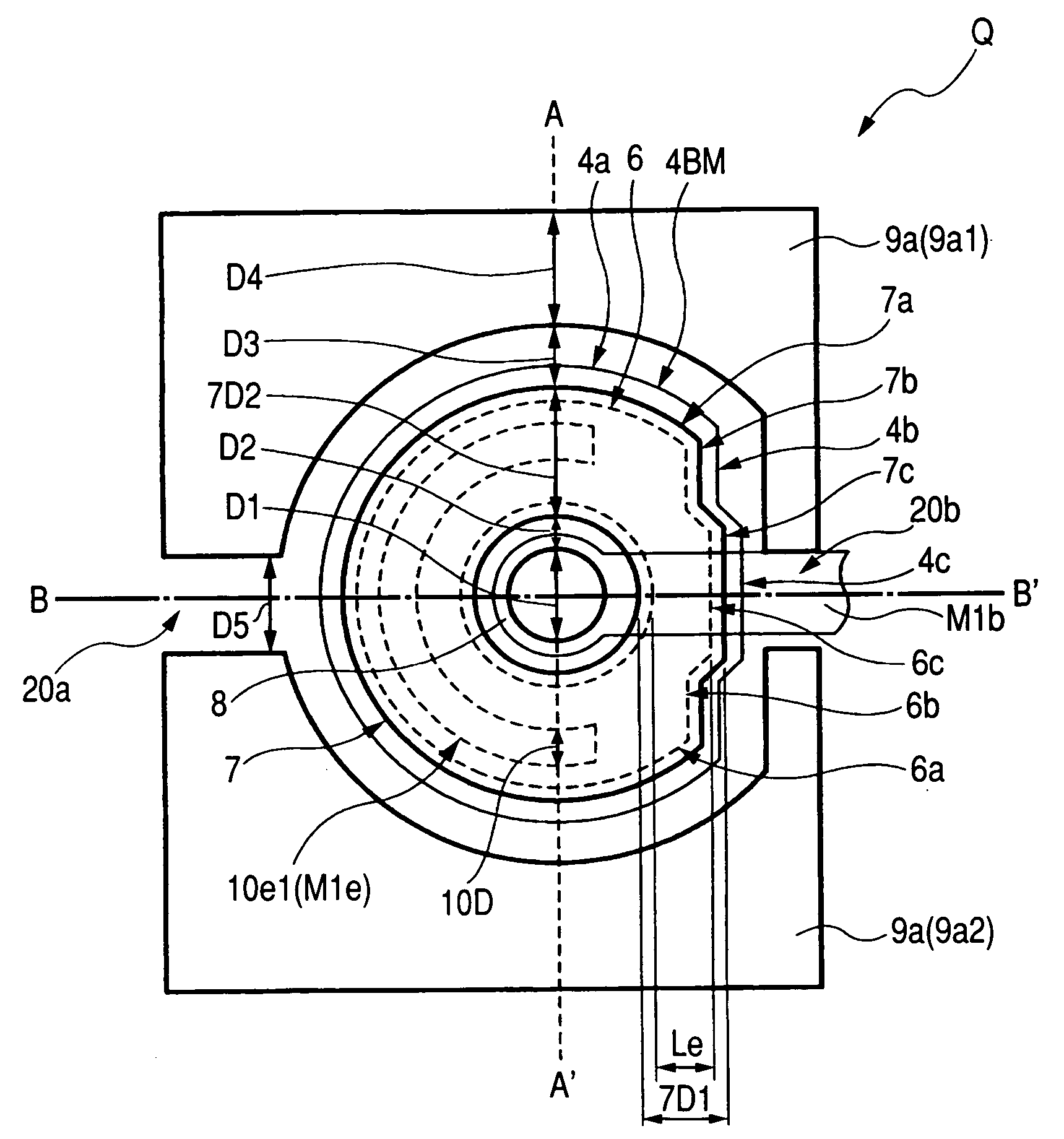

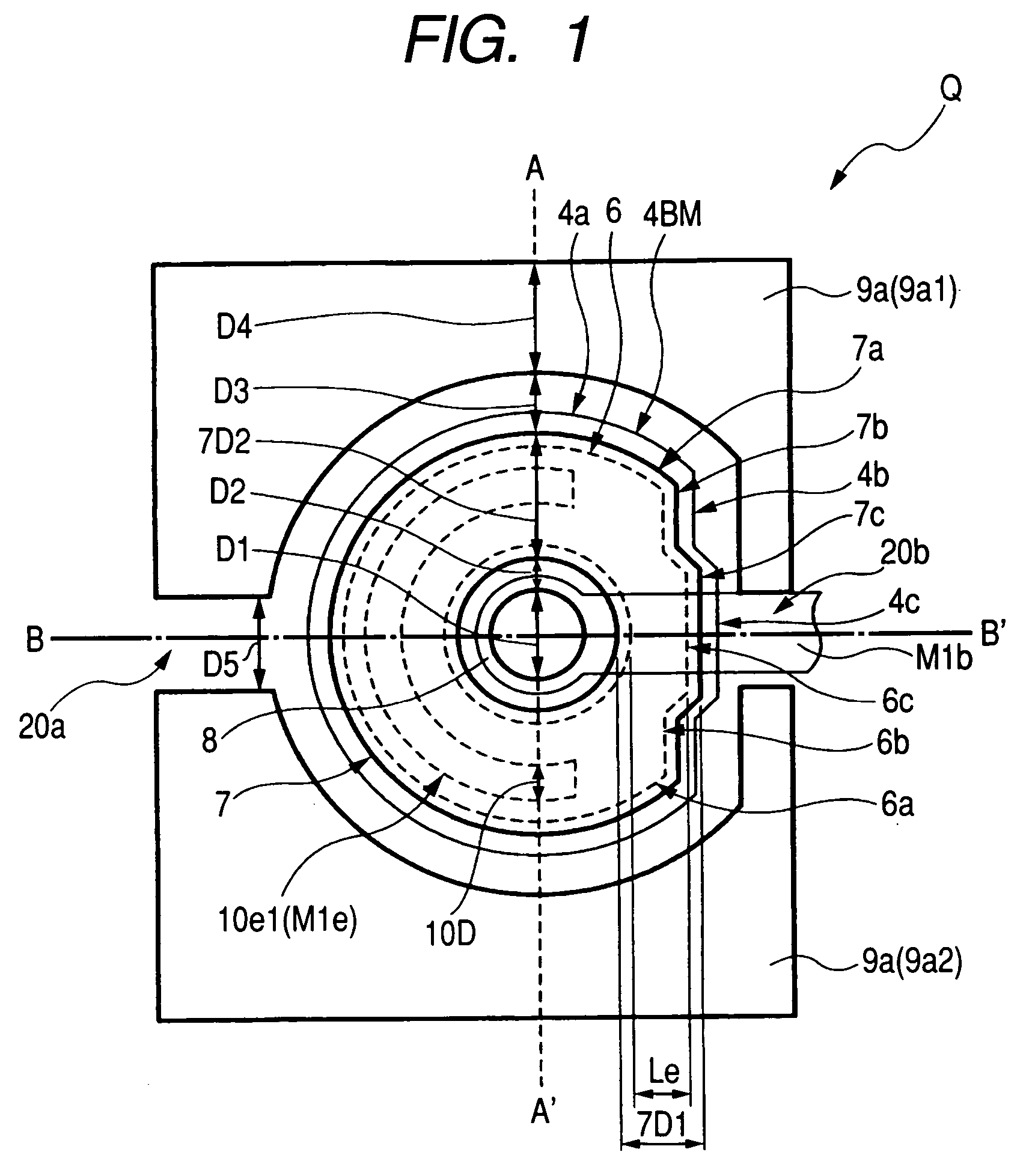

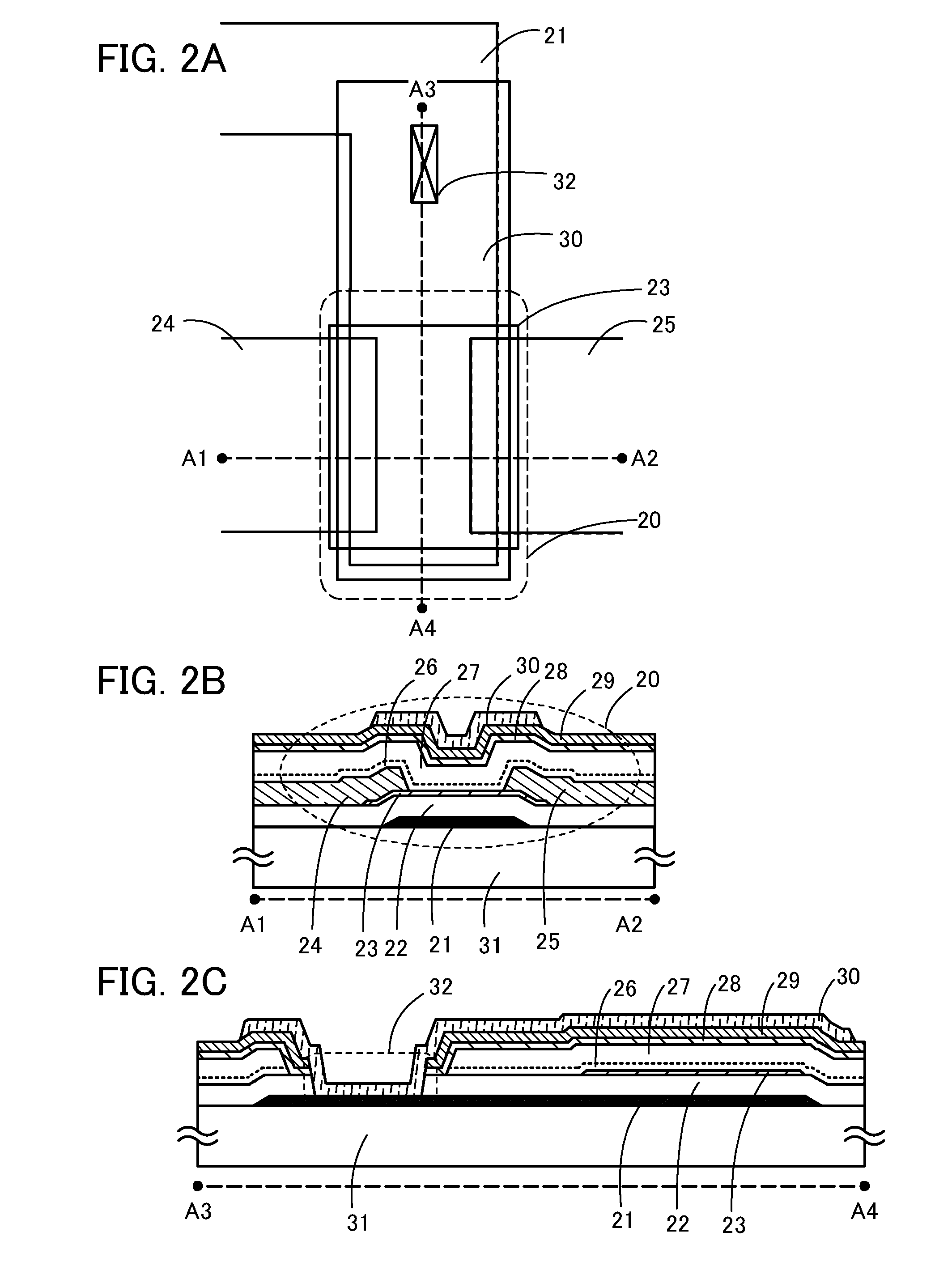

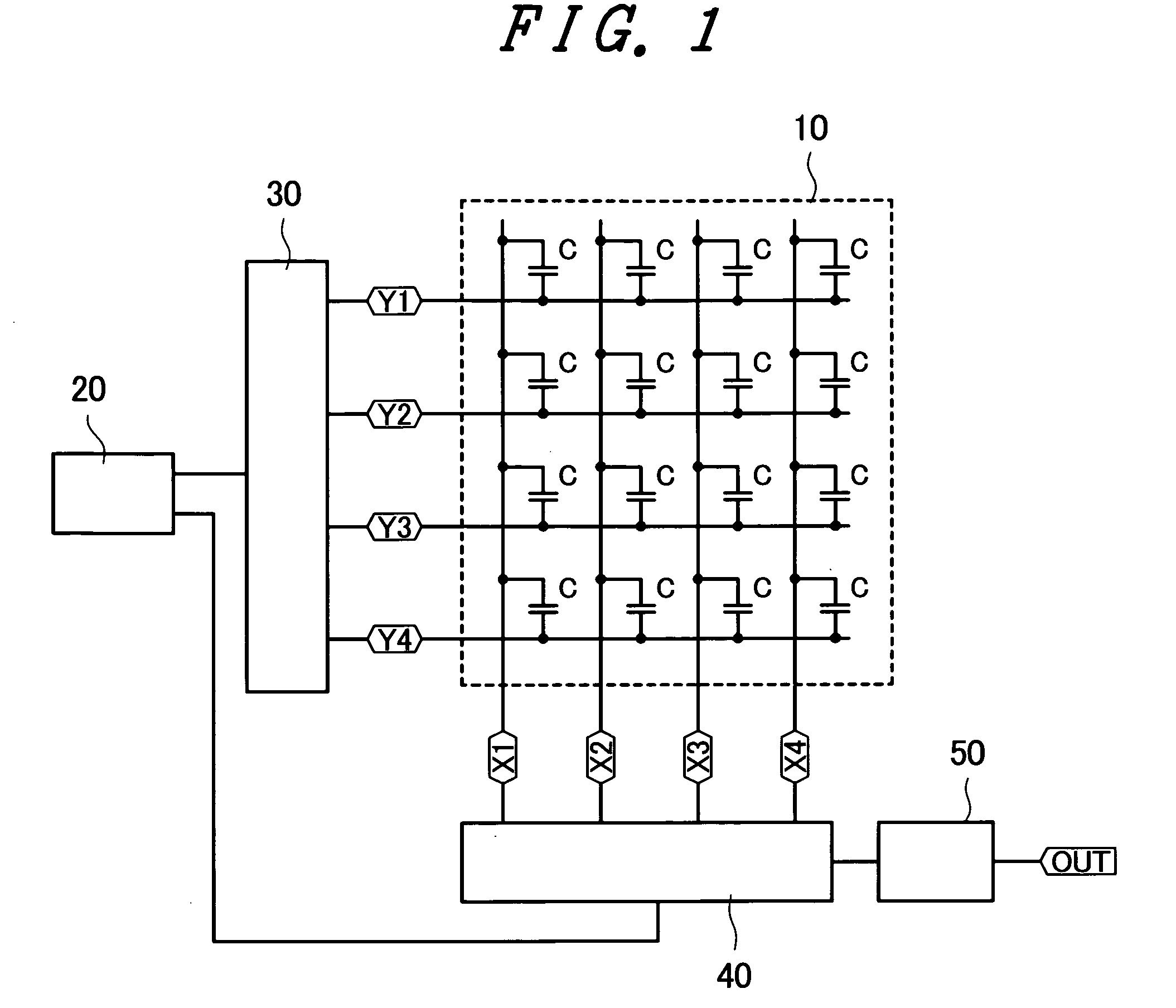

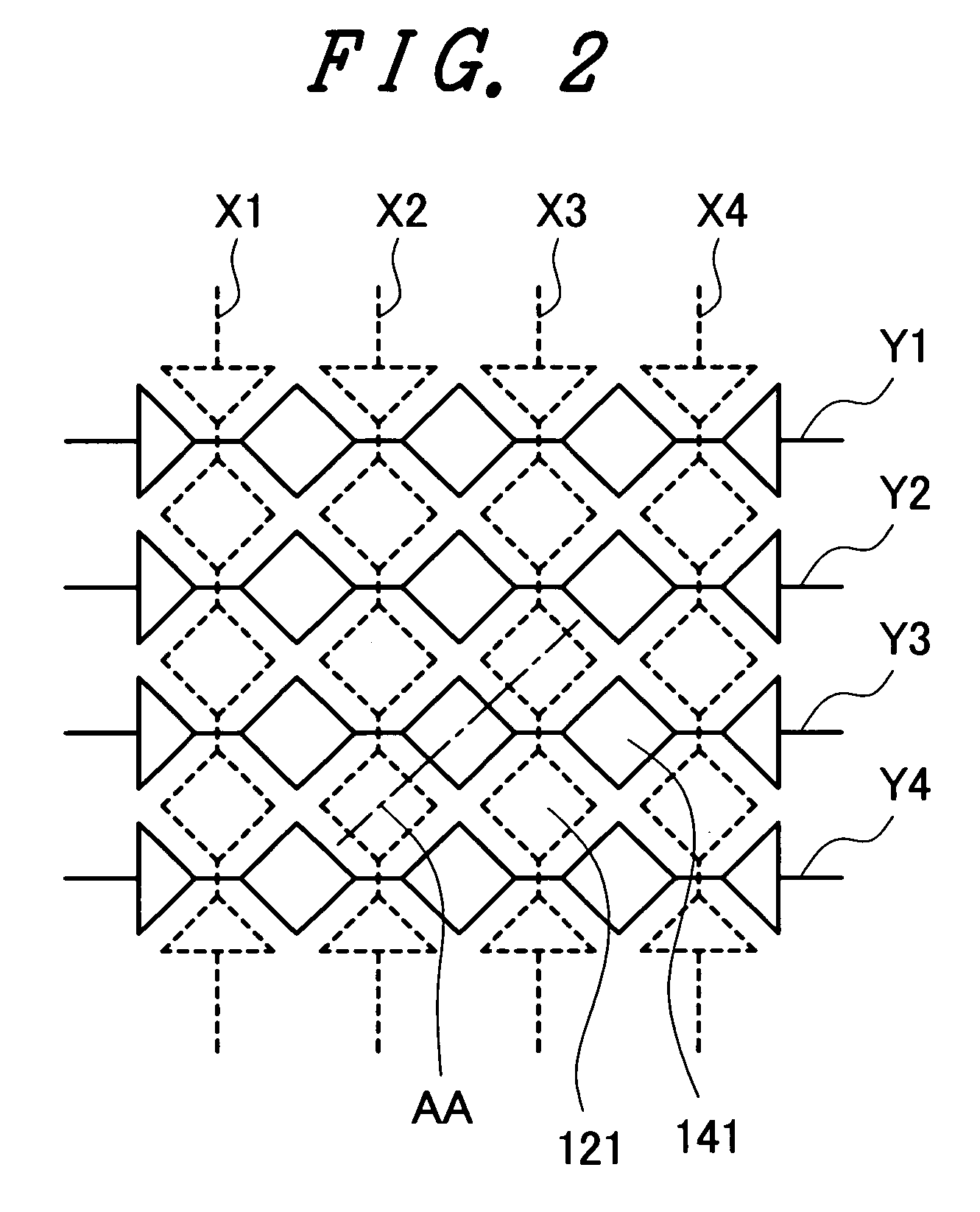

Display device with touch panel

ActiveUS20090009486A1Small capacitanceIncrease the number ofCathode-ray tube indicatorsNon-linear opticsTouch panelHigh potential

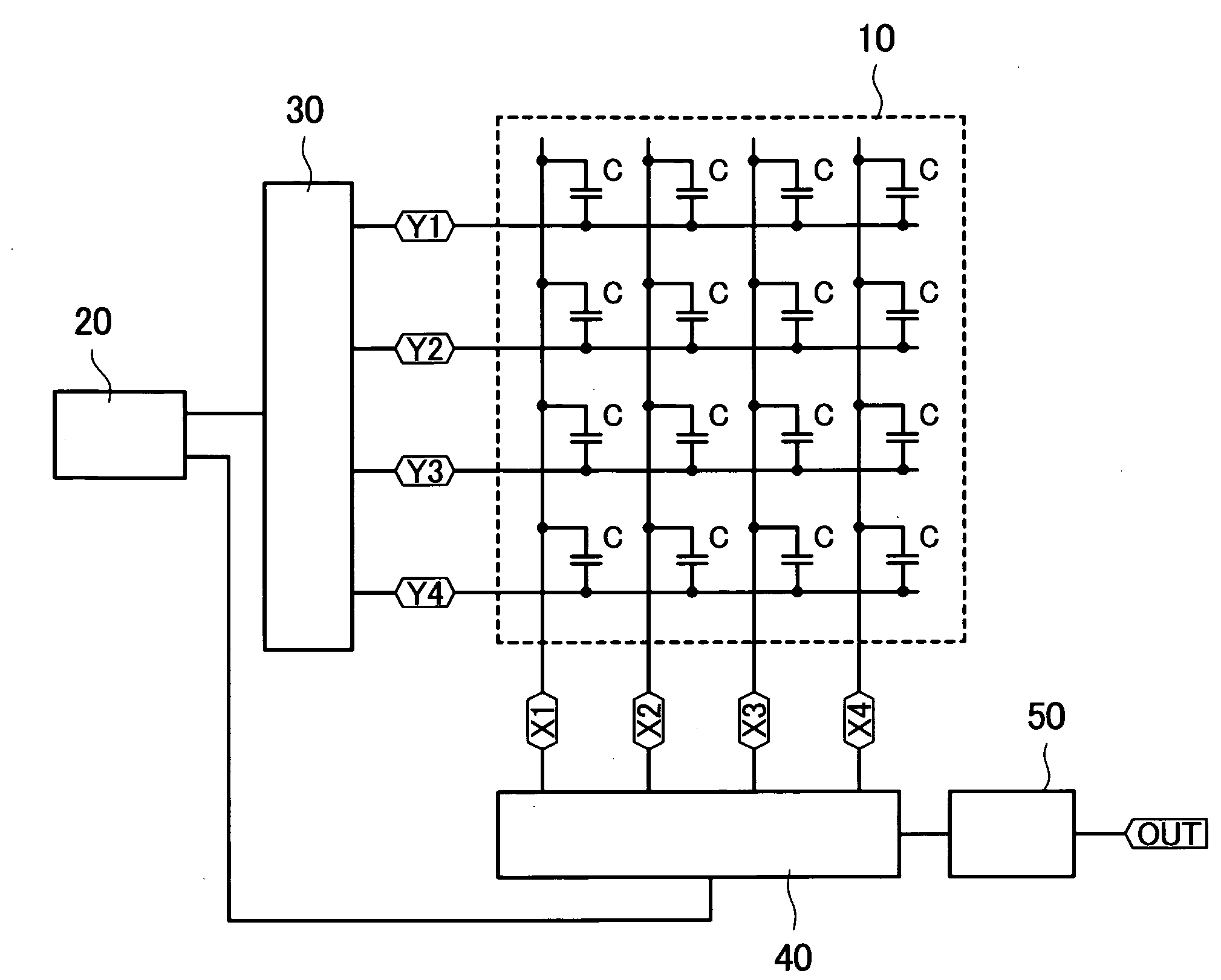

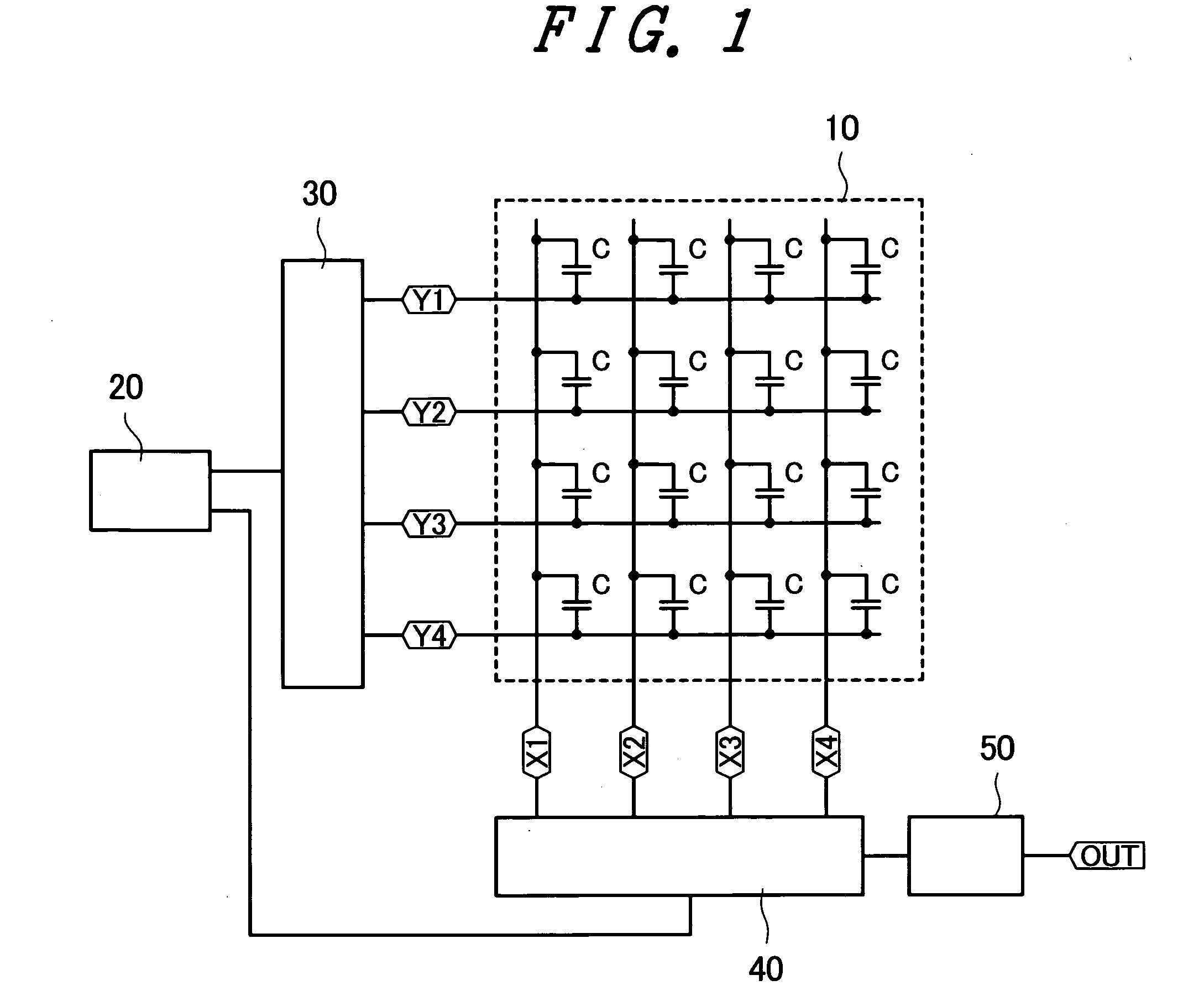

A touch panel includes plural first electrodes extending in a first direction, plural second electrodes extending in a second direction different from the first direction, a driving circuit, a detection circuit, and a coordinate-position calculating circuit. The driving circuit sequentially selects two first electrodes out of the plural first electrodes, supplies a high potential voltage higher than a reference voltage to one of the selected two first electrodes, and supplies the reference voltage to the other, the detection circuit detects a capacitance difference (A-B) between a capacitor A between a selected one of the second electrodes and the first electrode to which the high potential voltage is supplied and a capacitor B between the selected second electrode and the first electrode to which the reference voltage is supplied, and the coordinate-position calculating circuit calculates a touch position on the touch panel touched by the observer on the basis of positions of the selected first and second electrodes and the capacitance difference (A-B).

Owner:JAPAN DISPLAY INC

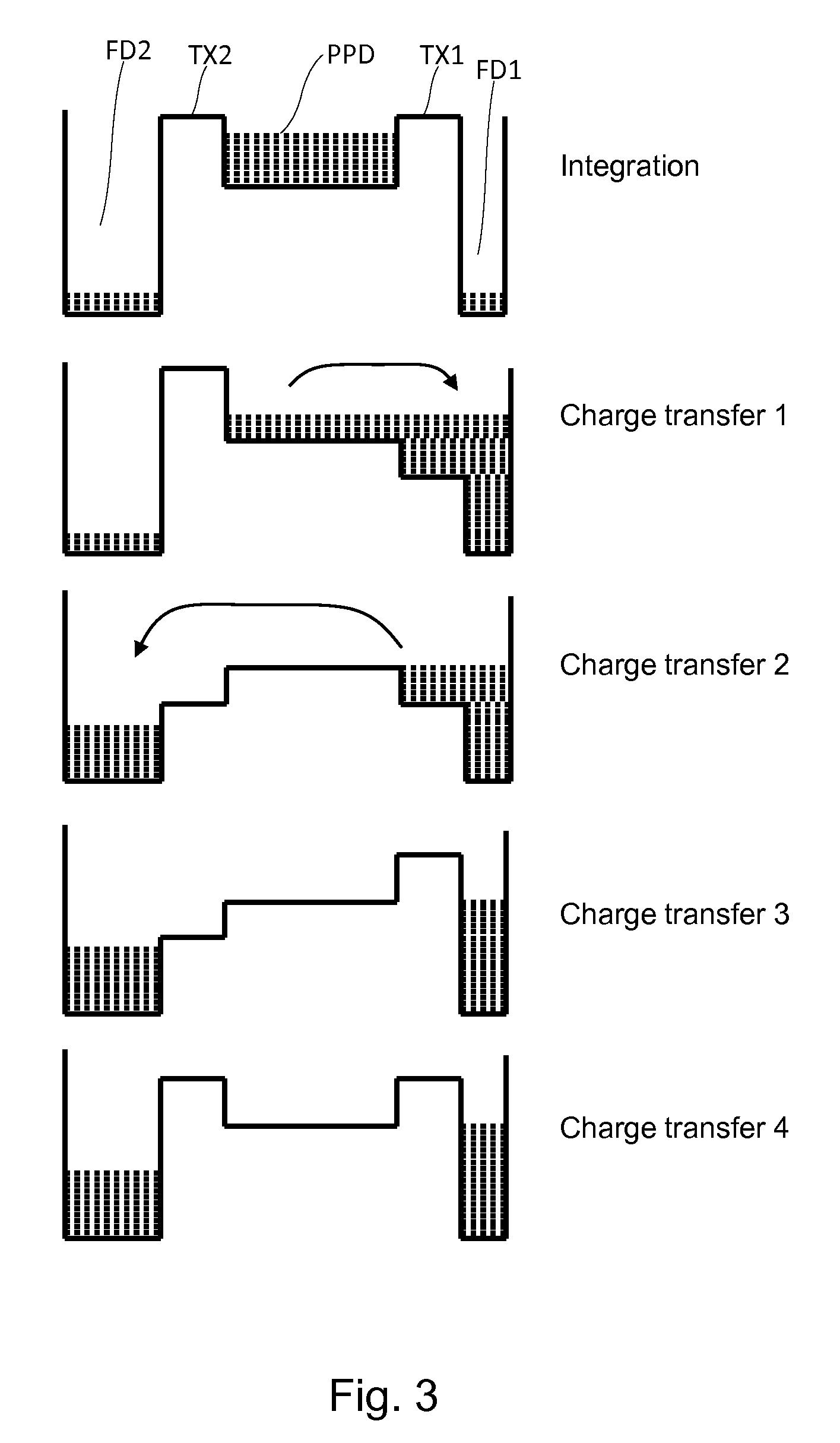

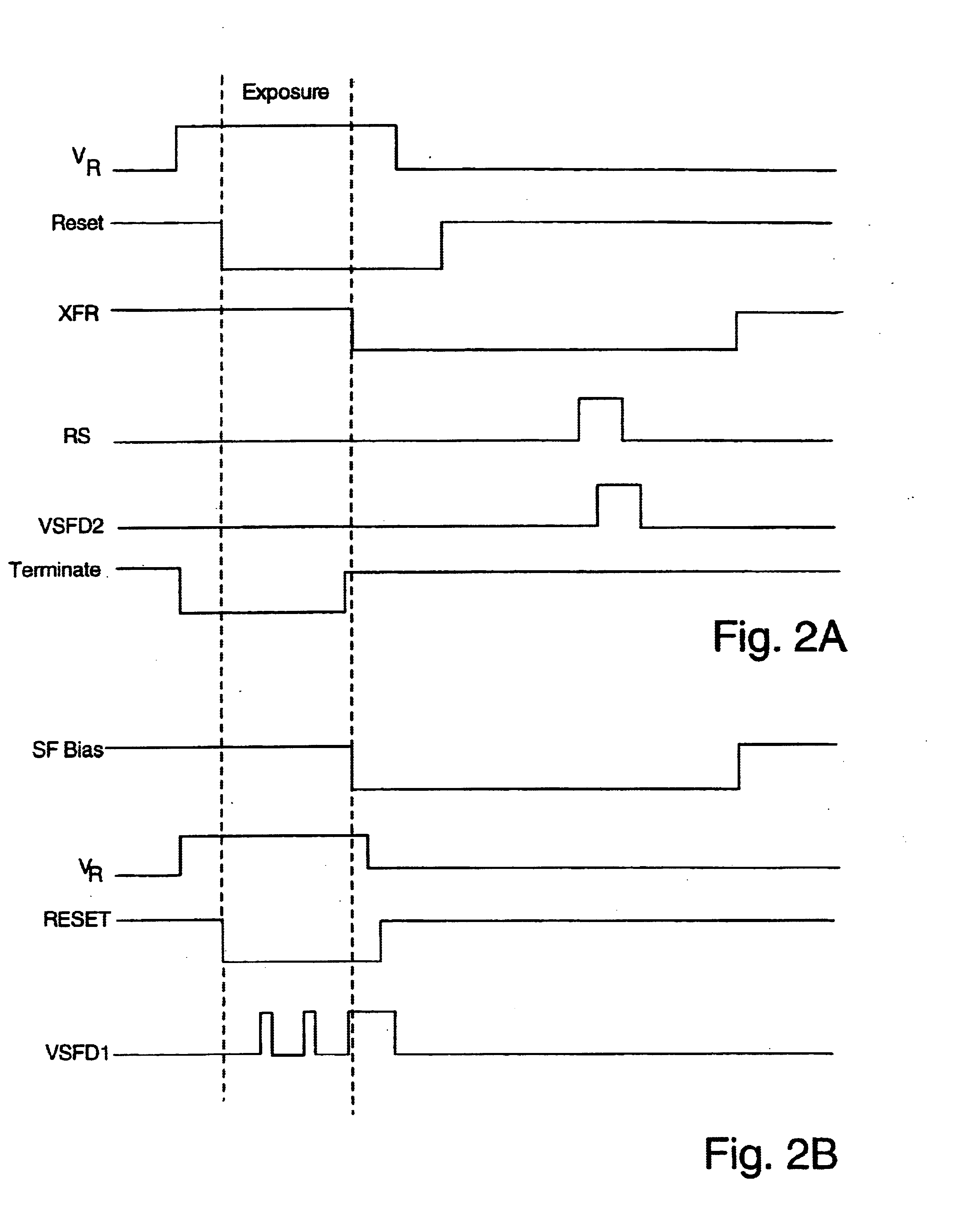

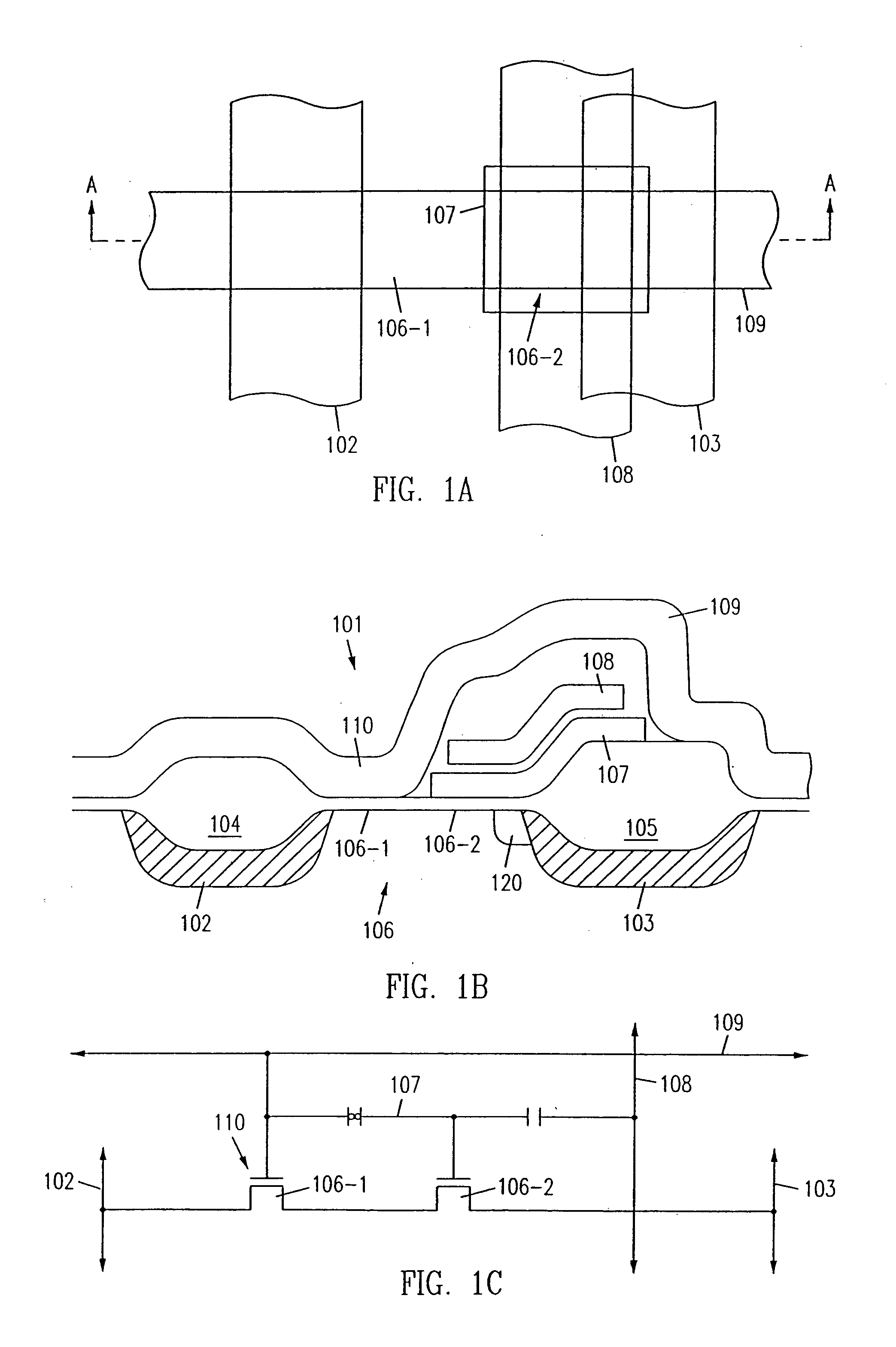

Pixel structure with multiple transfer gates

ActiveUS20120002089A1Improve dynamic rangeComplex implementationTelevision system detailsTelevision system scanning detailsEngineeringExposure period

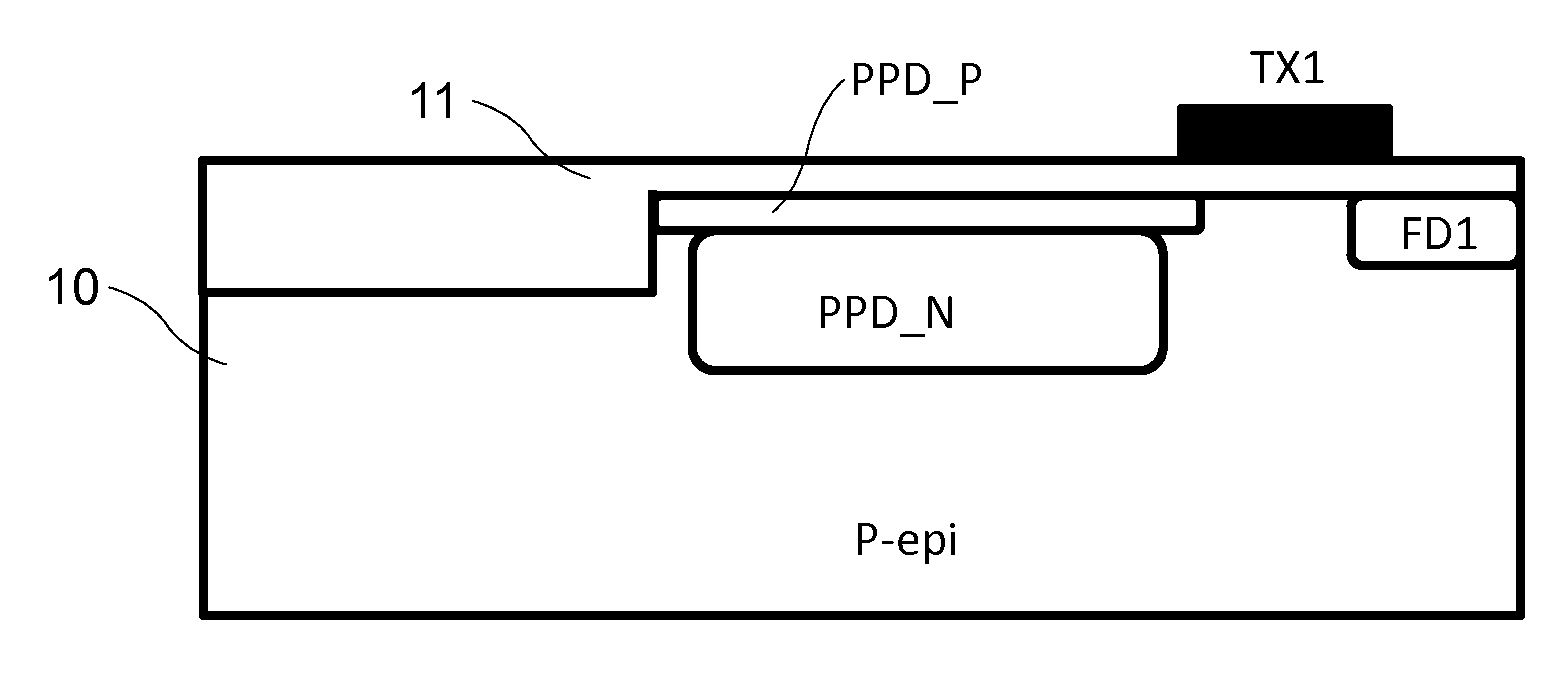

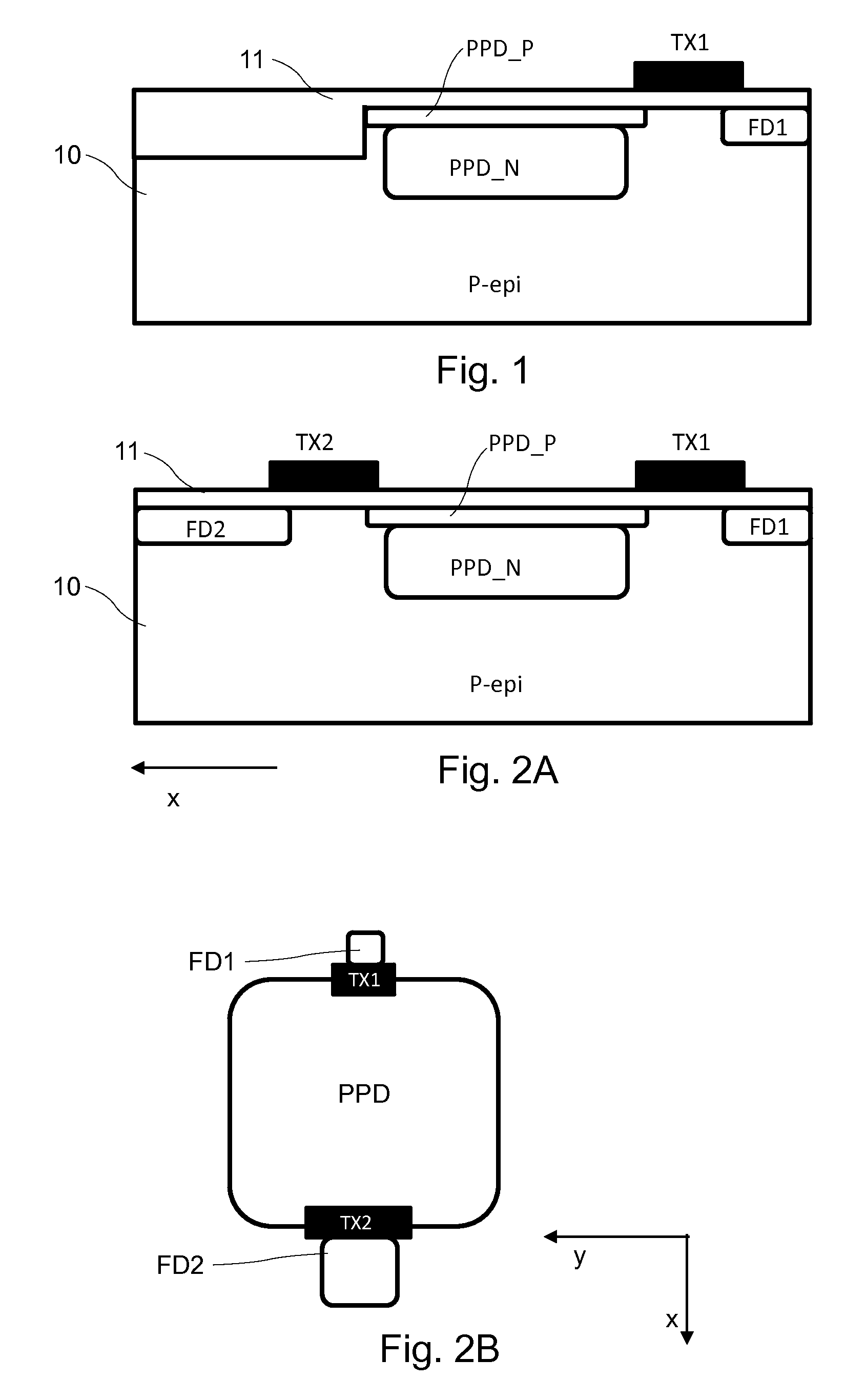

A pixel structure comprises a photo-sensitive element for generating charge in response to incident light. A first transfer gate is connected between the photo-sensitive element and a first charge conversion element. A second transfer gate is connected between the photo-sensitive element and a second charge conversion element. An output stage outputs a first value related to charge at the first charge conversion element and outputs a second value related to charge at the second charge conversion element. A controller controls operation of the pixel structures and causes a pixel structure. The controller causes the pixel structure to: acquire charges on the photo-sensitive element during an exposure period; transfer a first portion of the charges acquired during the exposure period from the photo-sensitive element to the first charge conversion element via the first transfer gate; and transfer a second portion of the charges acquired during the exposure period from the photo-sensitive element to the second charge conversion element via the second transfer gate.

Owner:CMOSIS

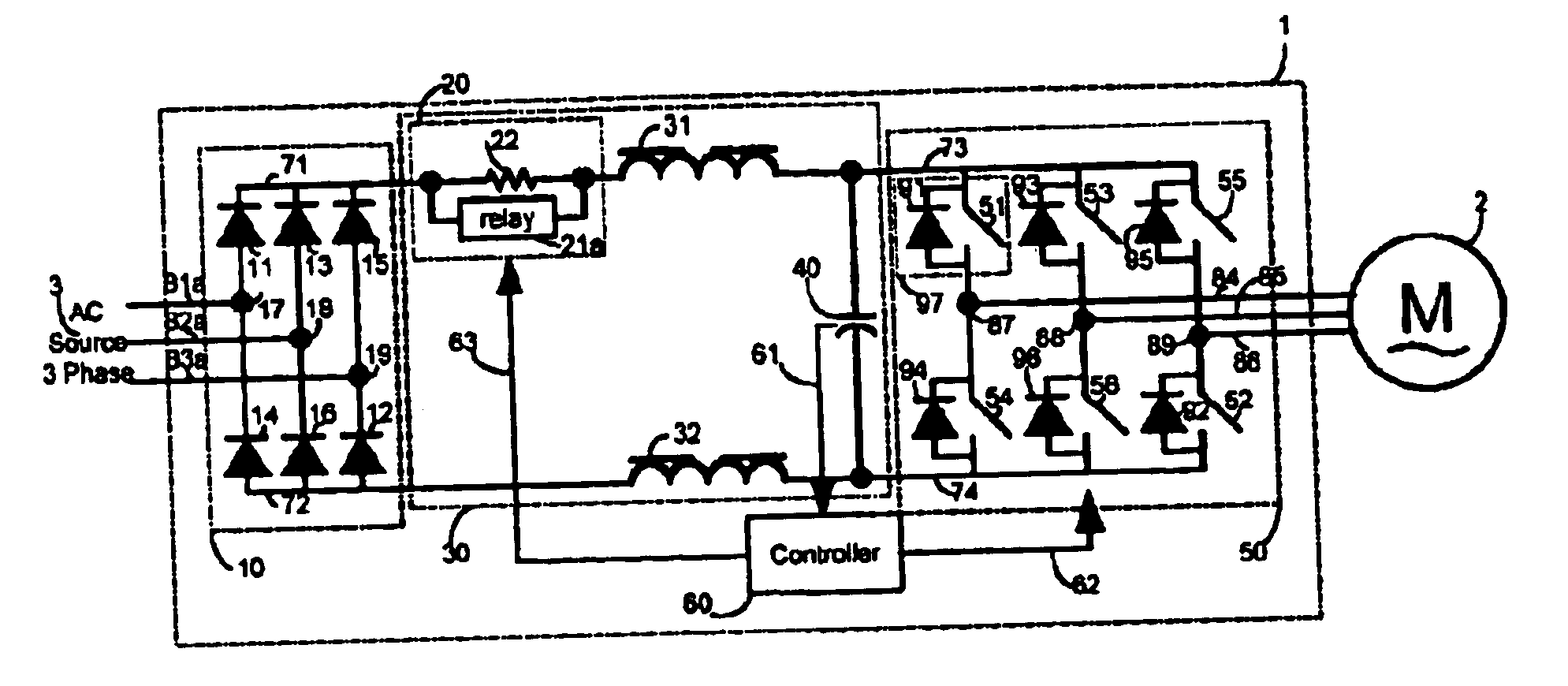

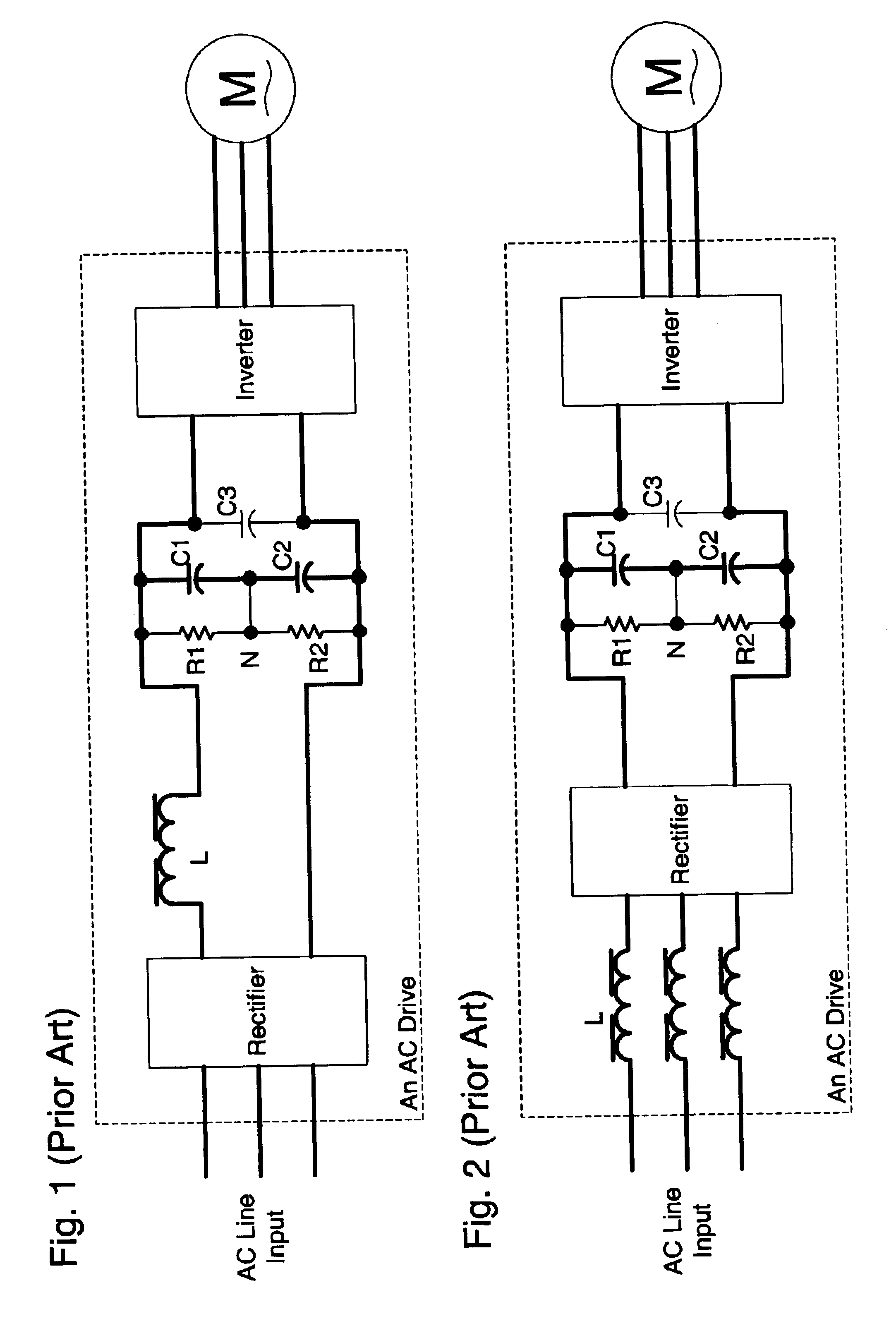

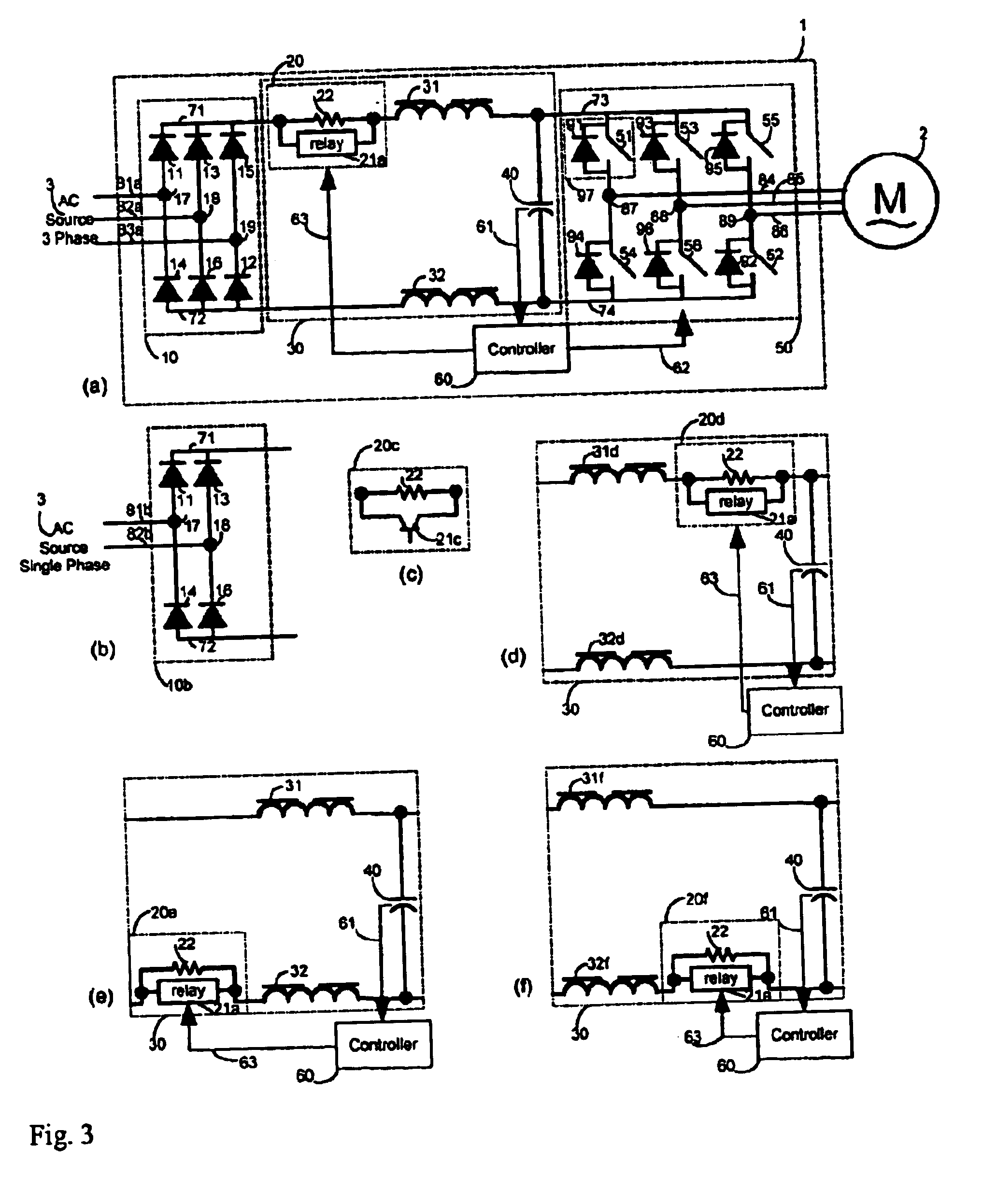

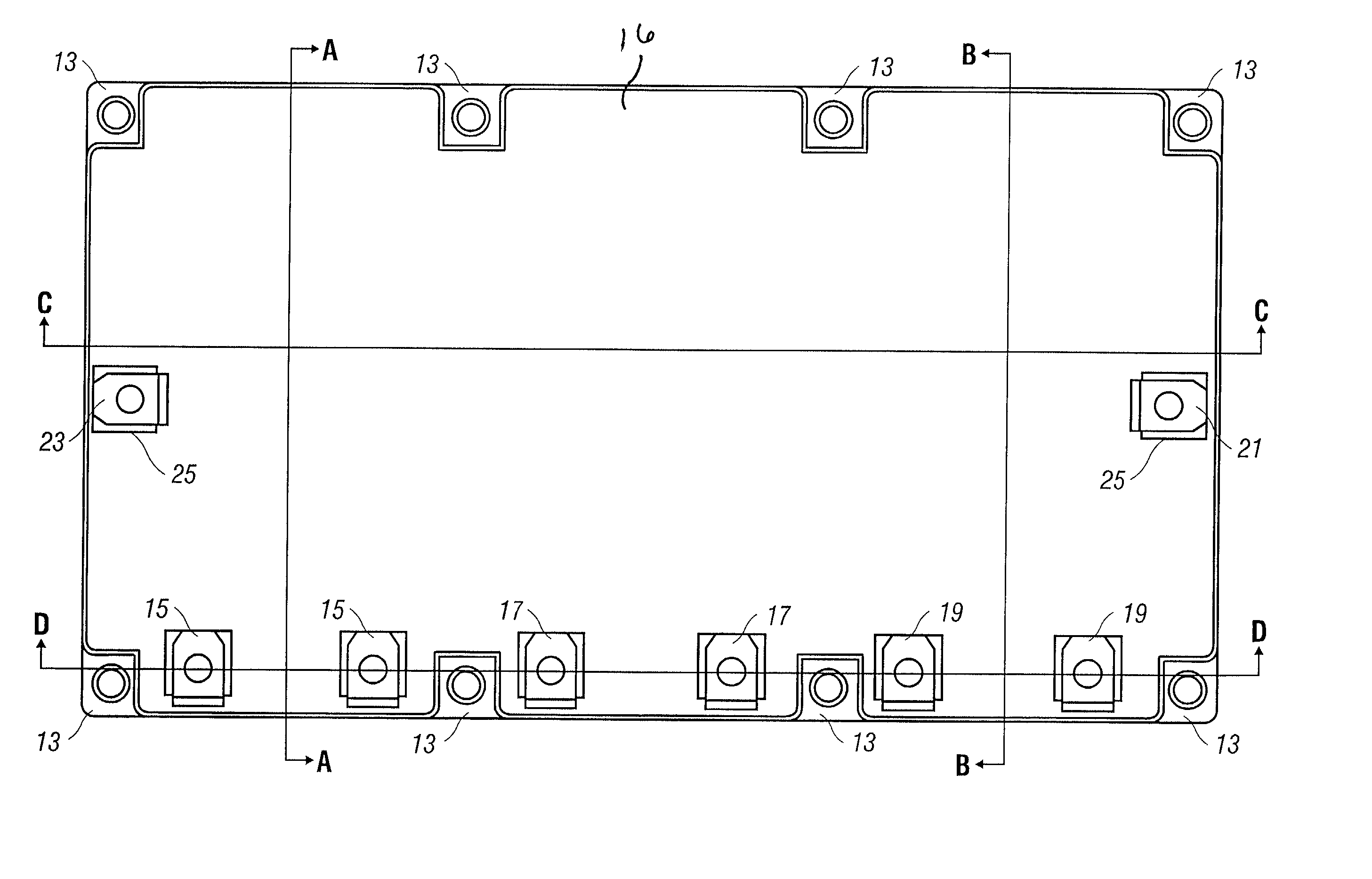

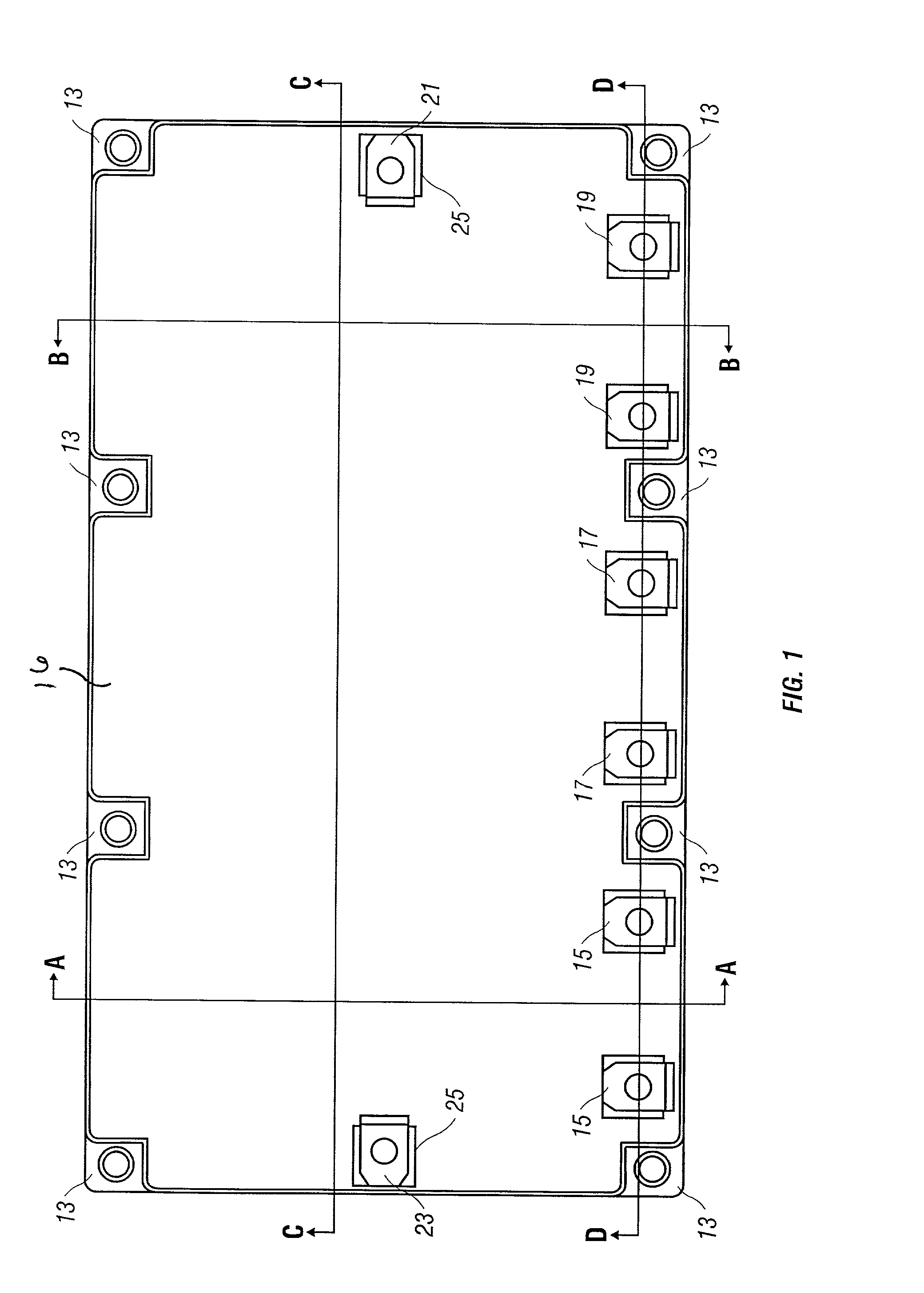

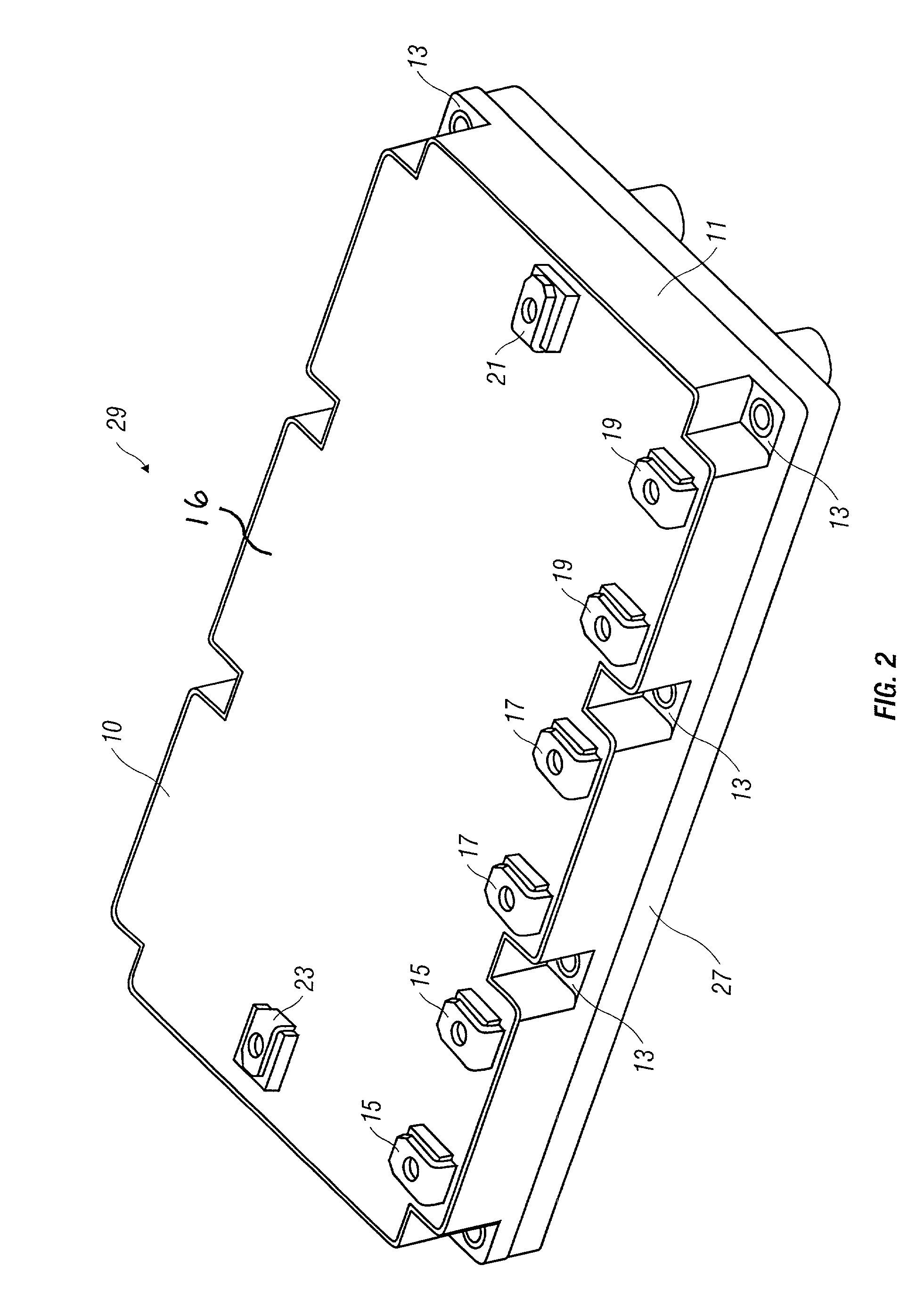

Reduced capacitance AC/DC/AC power converter

InactiveUS6804127B2Quick monitoringMore compact, durable and reliableEmergency protective circuit arrangementsAc-ac conversionCapacitanceElectrolytic capacitor

An AC / DC / AC power converter is constructed without using any electrolytic capacitor, such that it is more compact, durable and reliable. This converter only required a small capacitance for its DC link and this capacitor can be easily obtainable with other types of capacitors such as film or ceramic type. The system further includes means to disconnect both input and output to this DC bus capacitor. A controller capable of fast monitoring the DC bus voltage is also able of quickly disconnecting the capacitor out of either input or output energy path to prevent the capacitor from being charged to over-voltage. The controller also possesses capability of re-connecting the disrupted energy path once the DC bus voltage returns to normal.

Owner:WICON

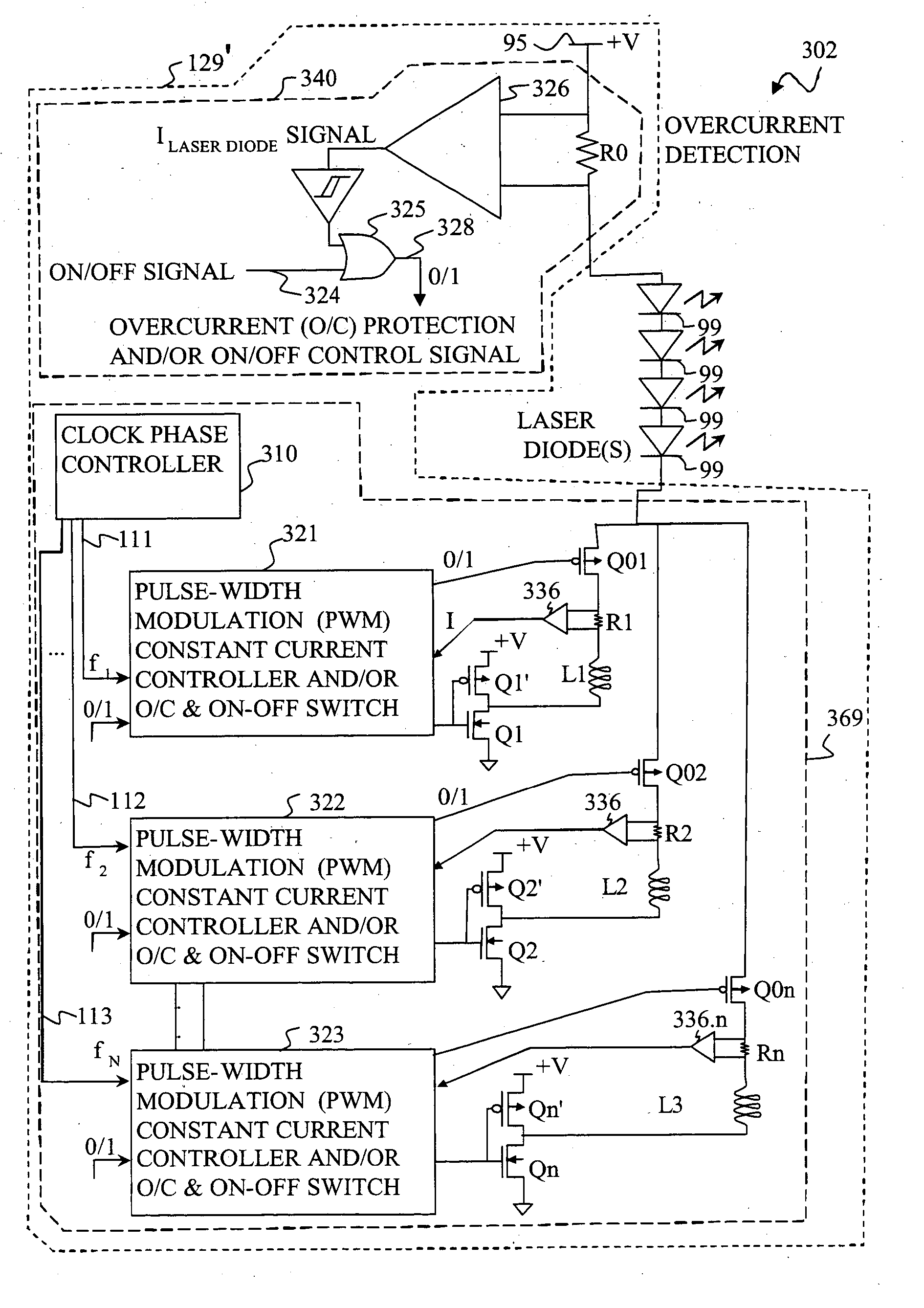

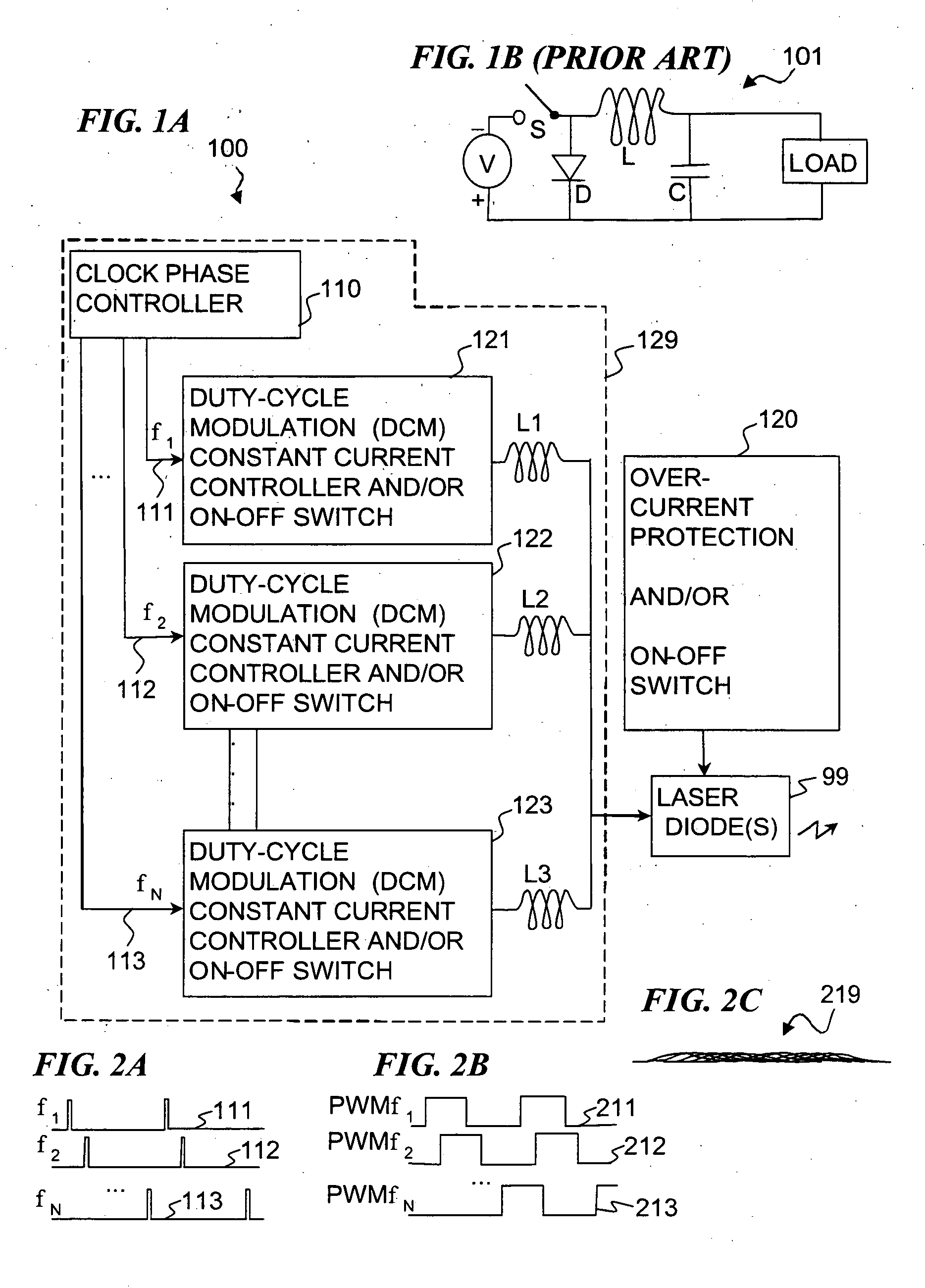

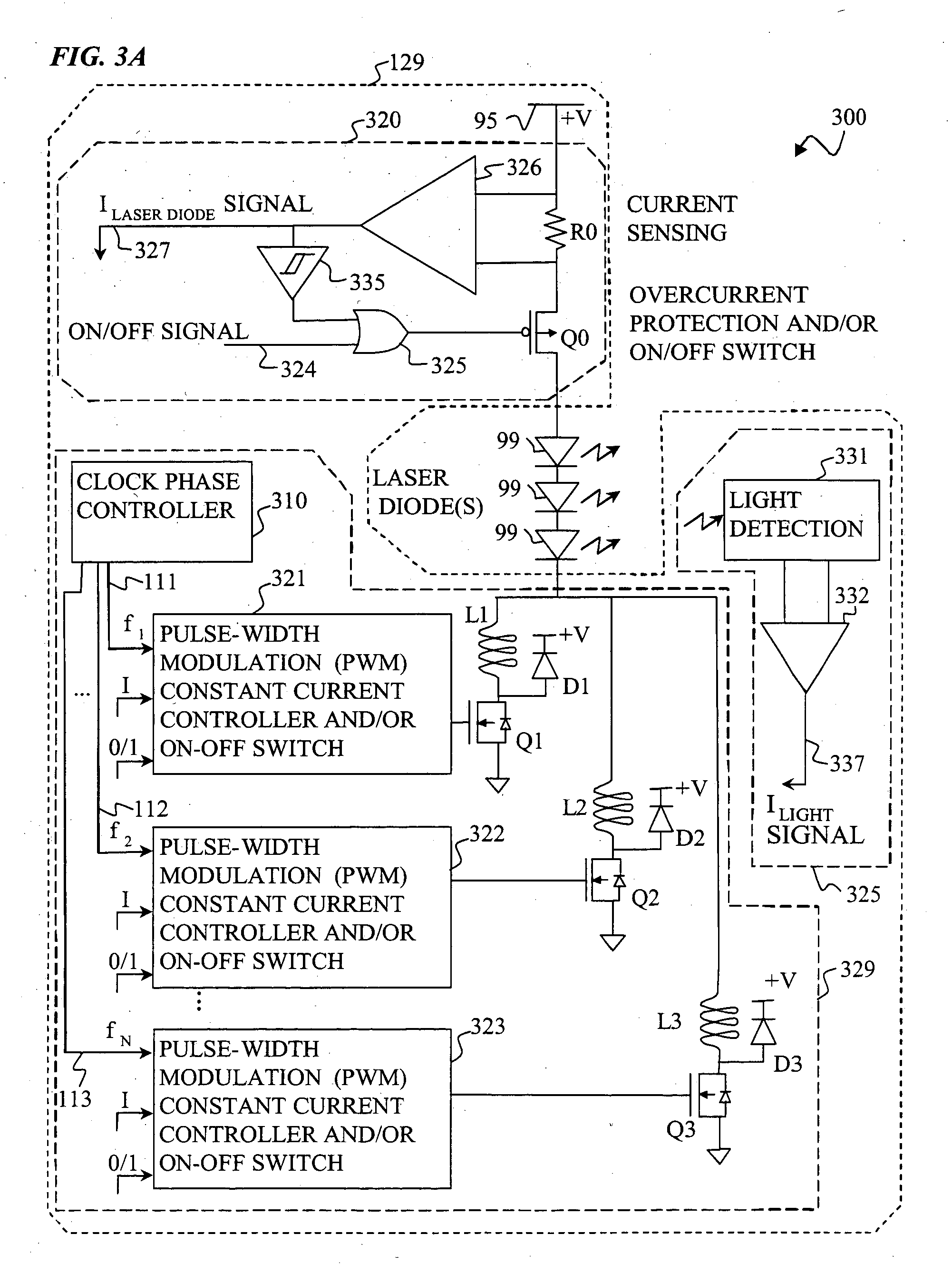

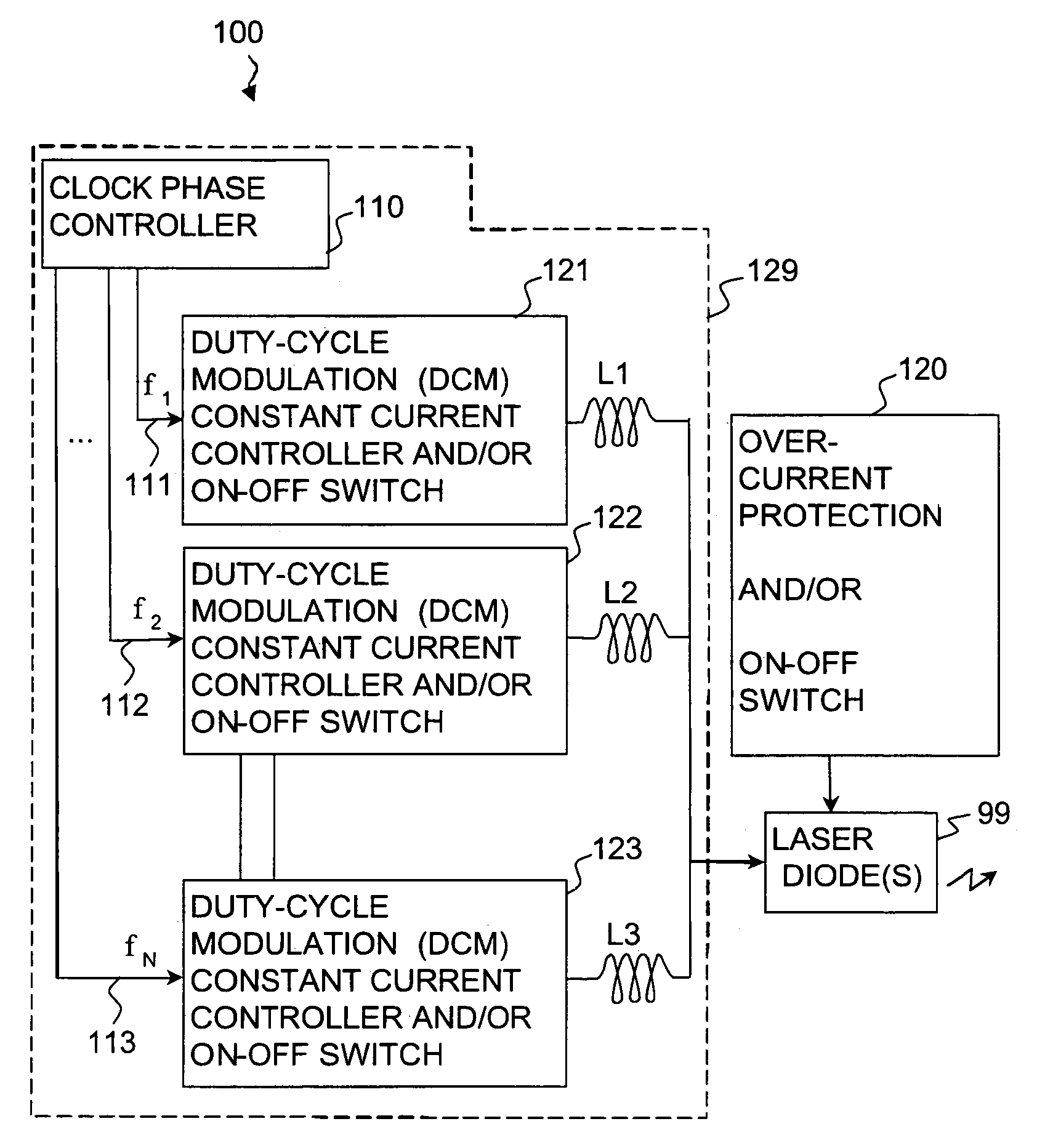

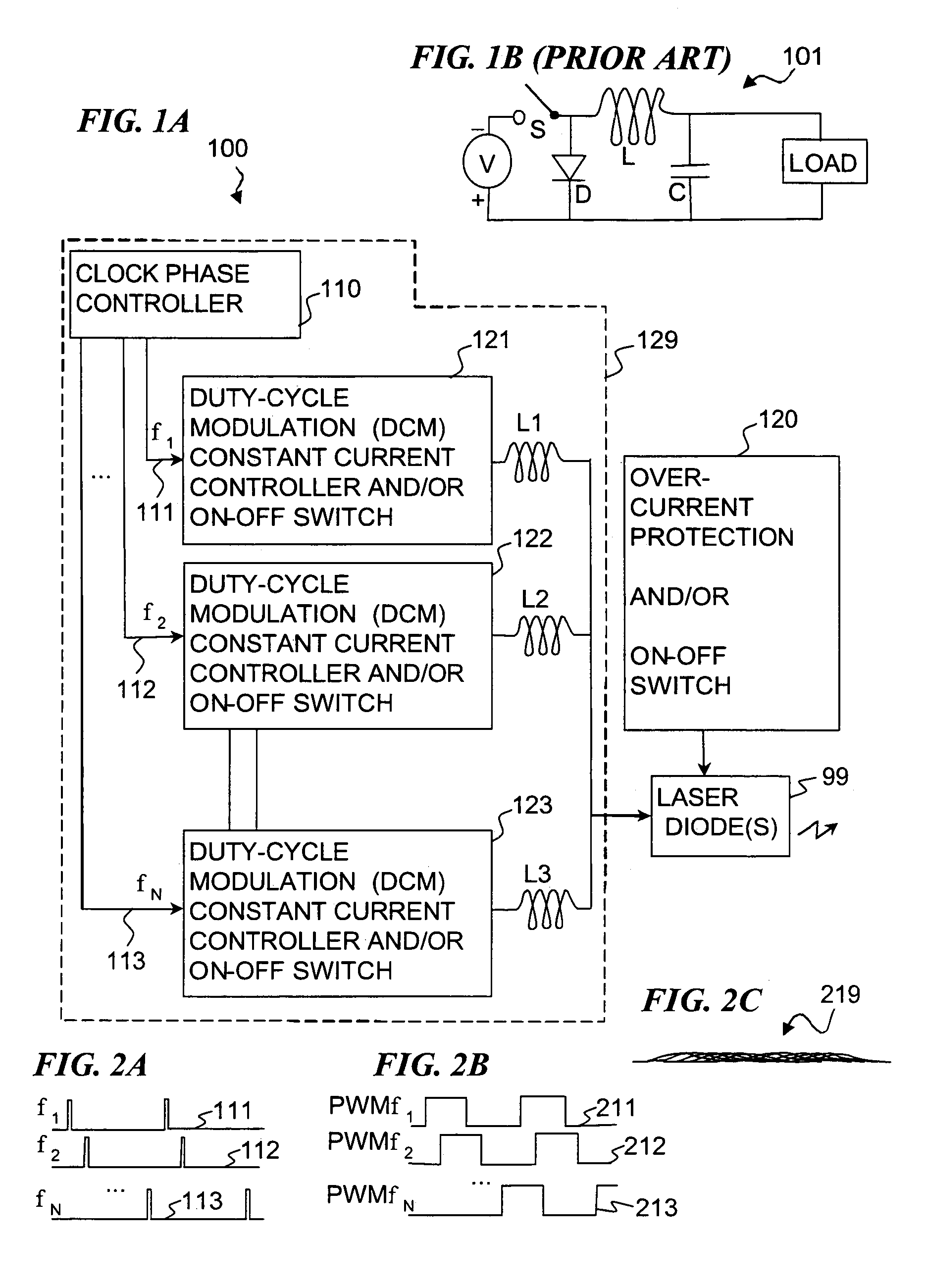

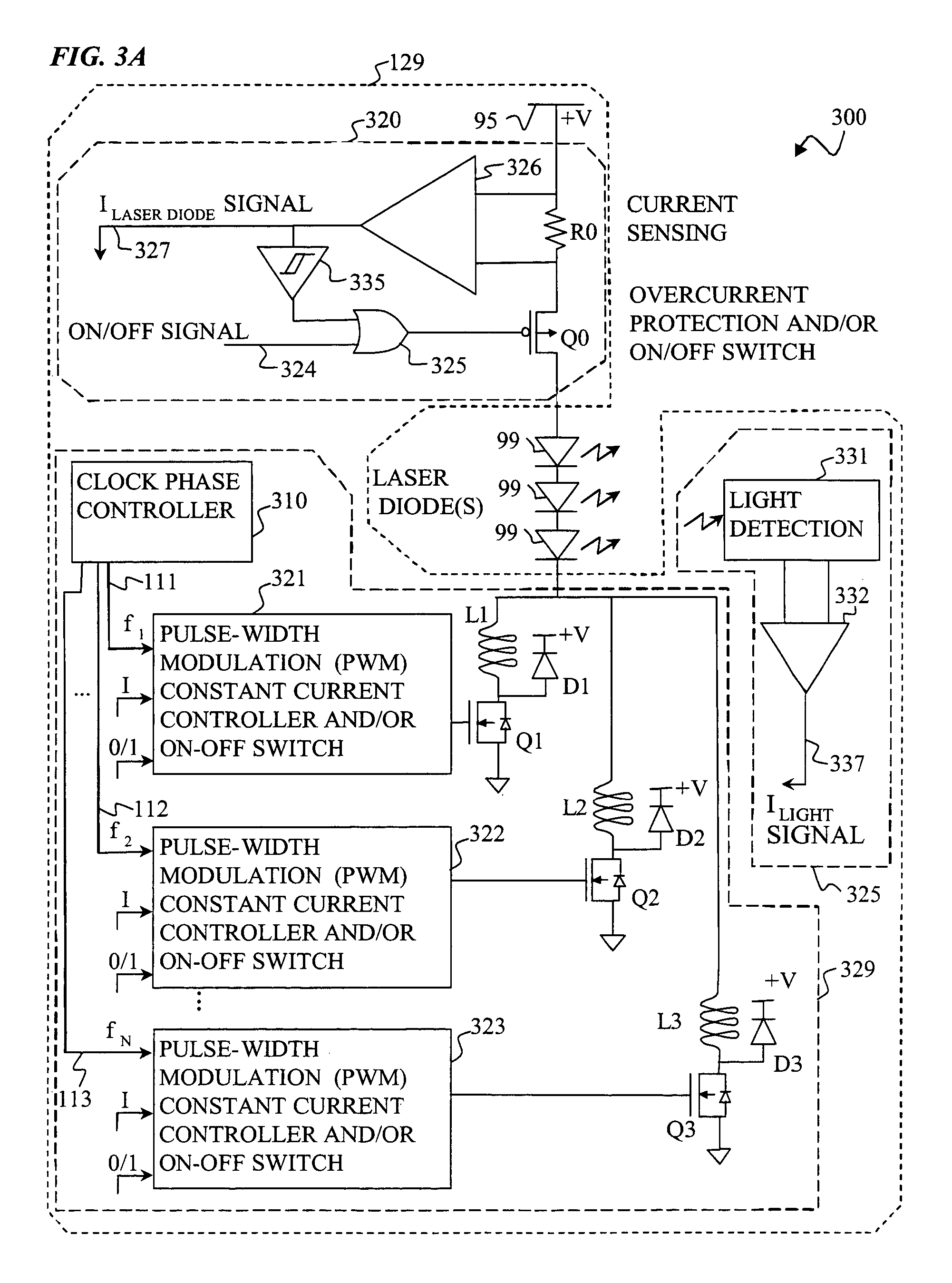

Apparatus and method for driving laser diodes

InactiveUS20060291512A1Fast rise timeImprove efficiencyLaser detailsSemiconductor lasersCapacitanceMode control

Apparatus and method for driving laser diodes with electrical power in pulsed operation. Pulsed power, for example using pulse-width modulation, is applied through an inductor in one or more parallel regulator circuits having little or no output capacitance to provide a high-efficiency laser-diode-driver power supply. Some embodiments that use two or more parallel regulator circuits in the laser-diode driver, drive each from a different phase of a clock signal. Some embodiments provide a first DC-to-DC converter has a relatively high-voltage input (e.g., about 275 volts, 0.75 amps) and an intermediate output of e.g., 11 to 15 volts, 15 to 11 amps used to charge a storage capacitor, and a second DC-to-DC converter diode driver having one or more parallel circuits (each having, e.g., a PWM switching-mode controller and its respective switch, inductor, and diode) to turn on, regulate, and turn off a constant laser-diode current through one or more laser diodes.

Owner:LOCKHEED MARTIN CORP

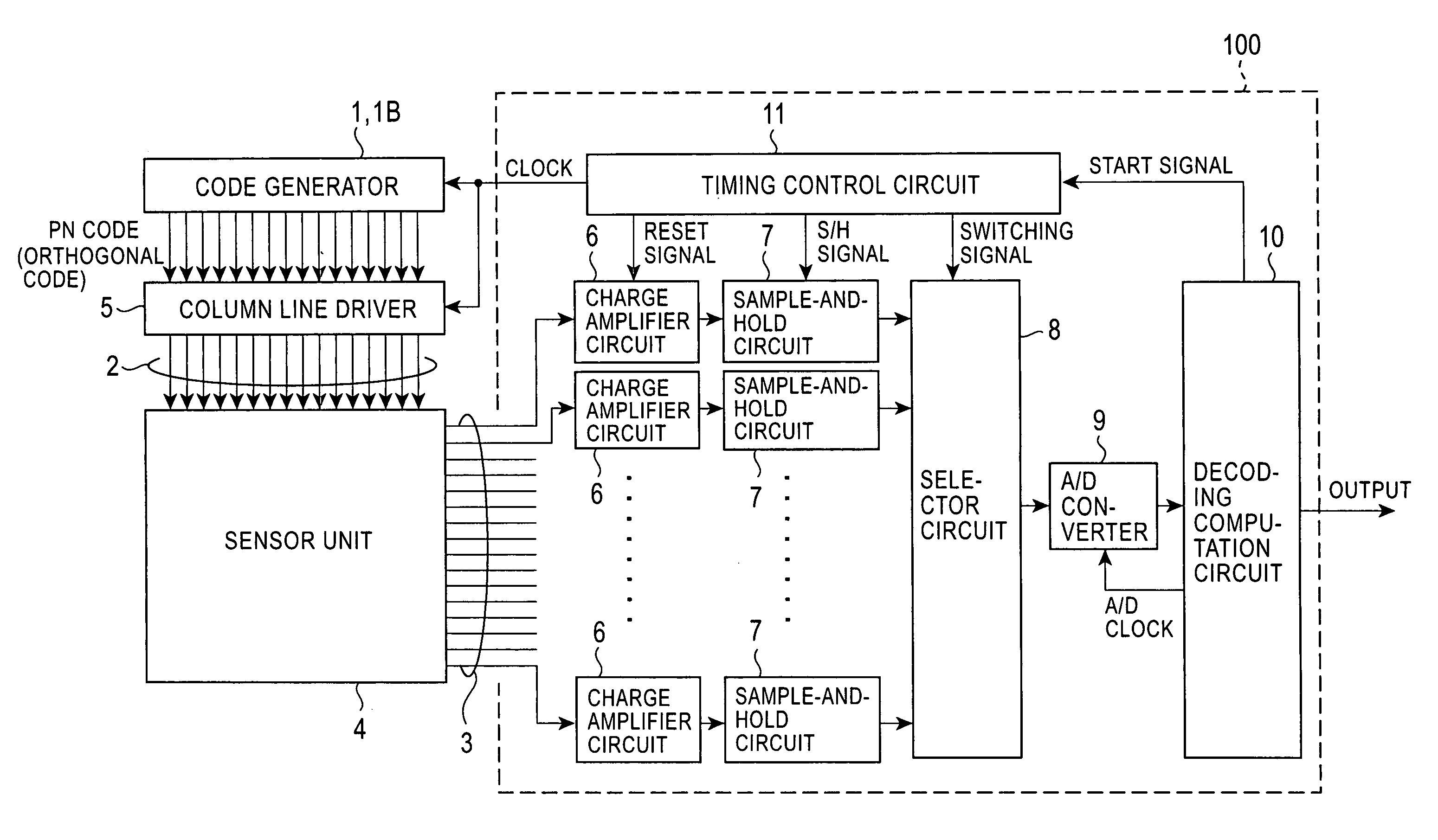

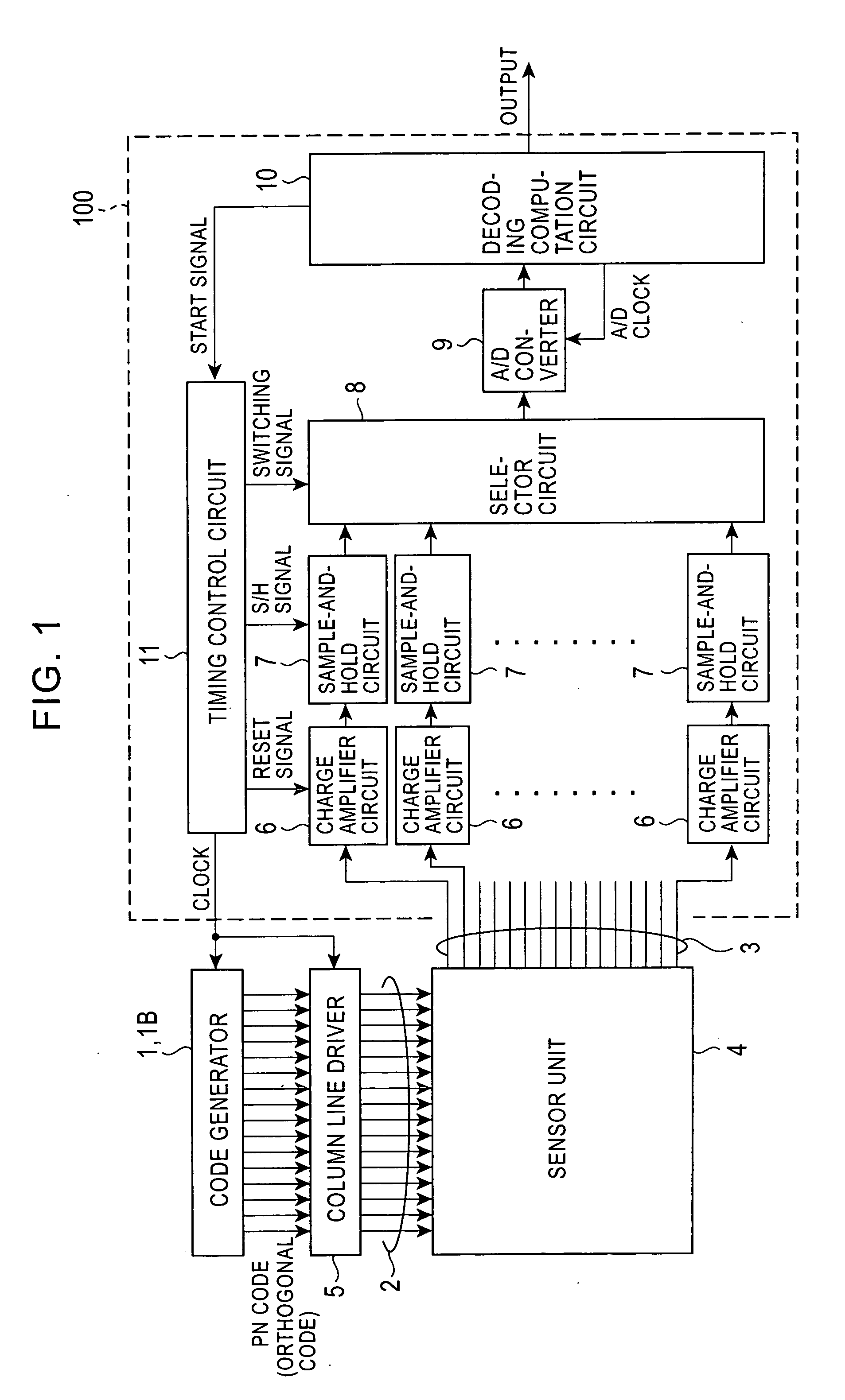

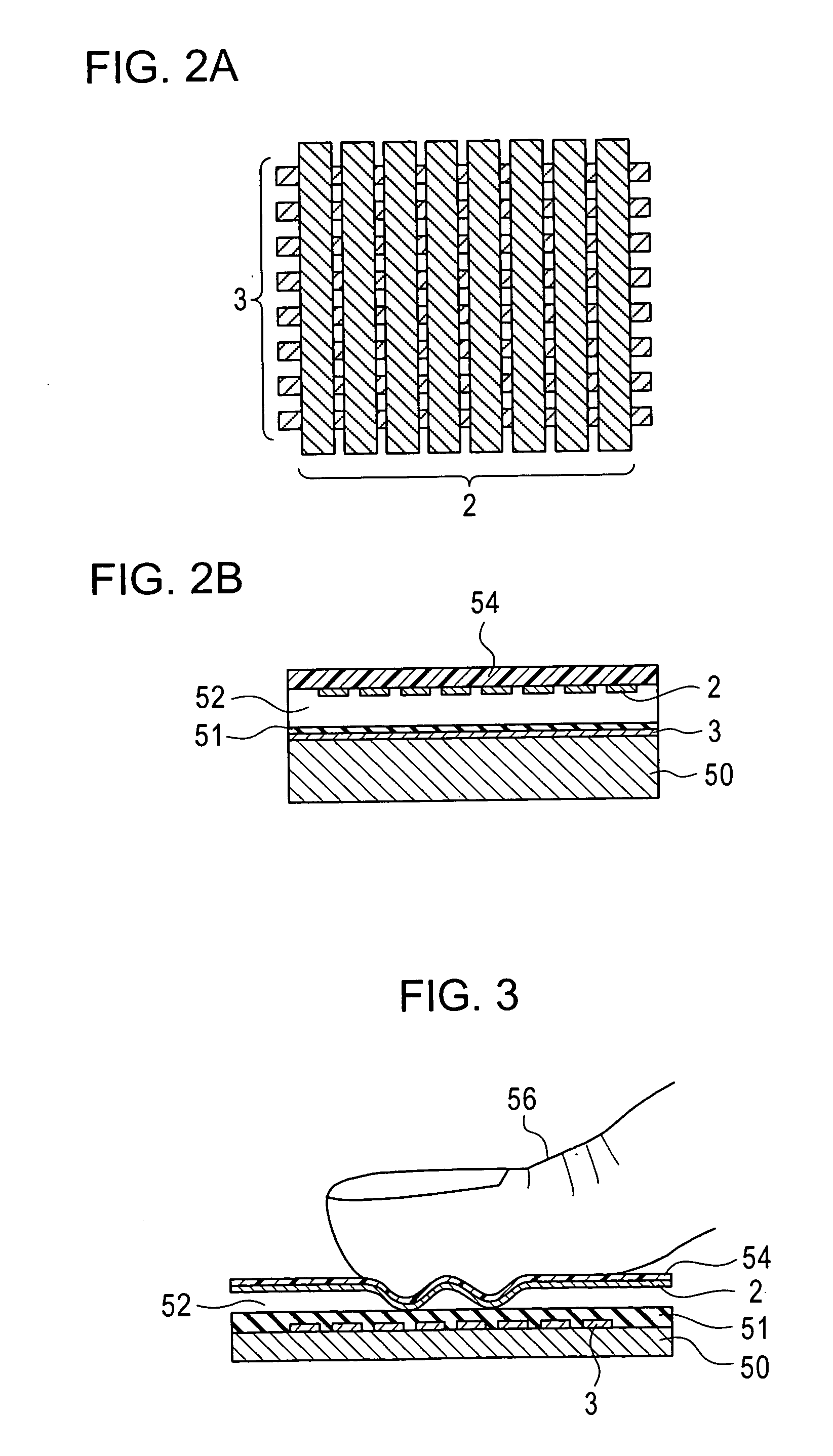

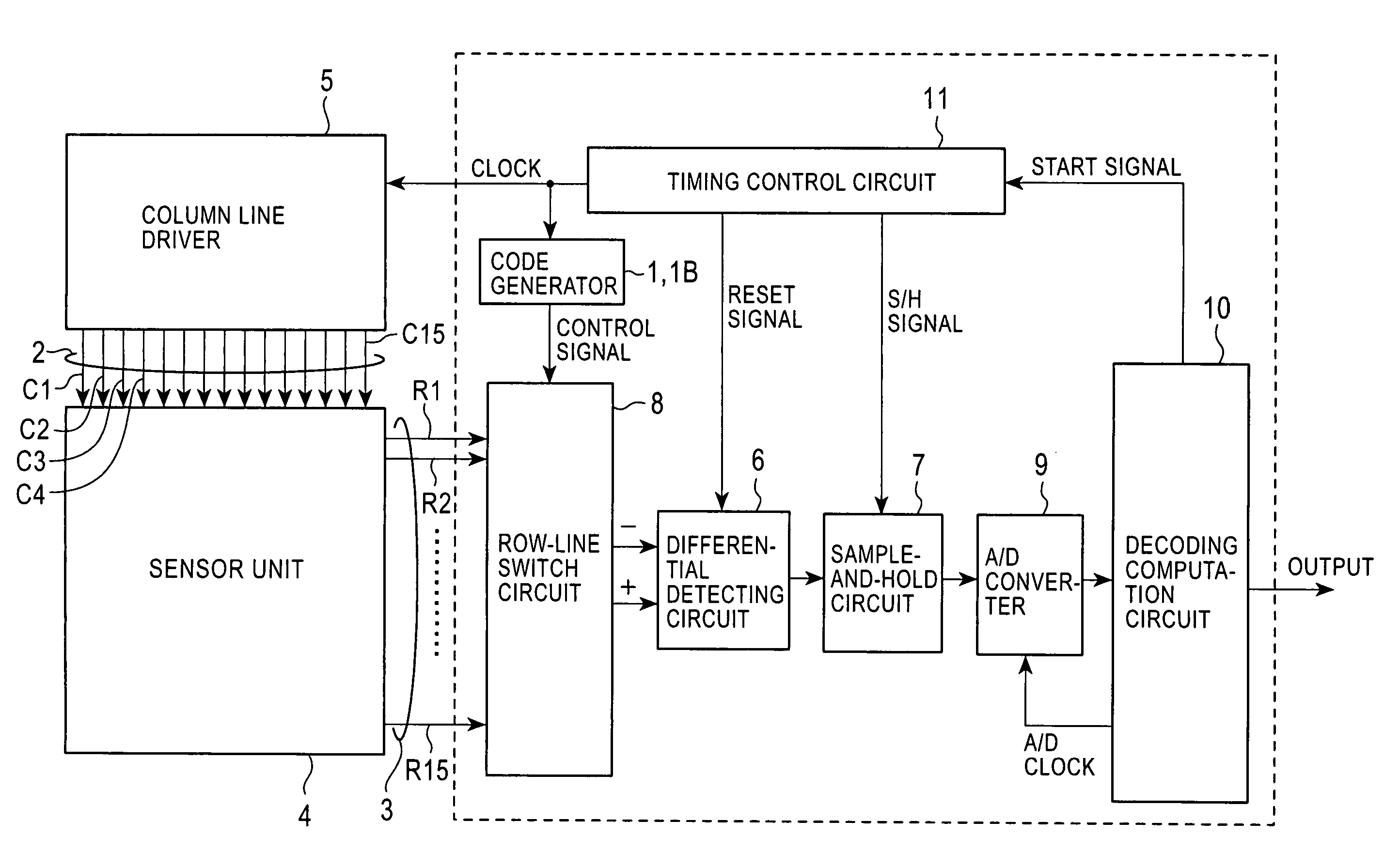

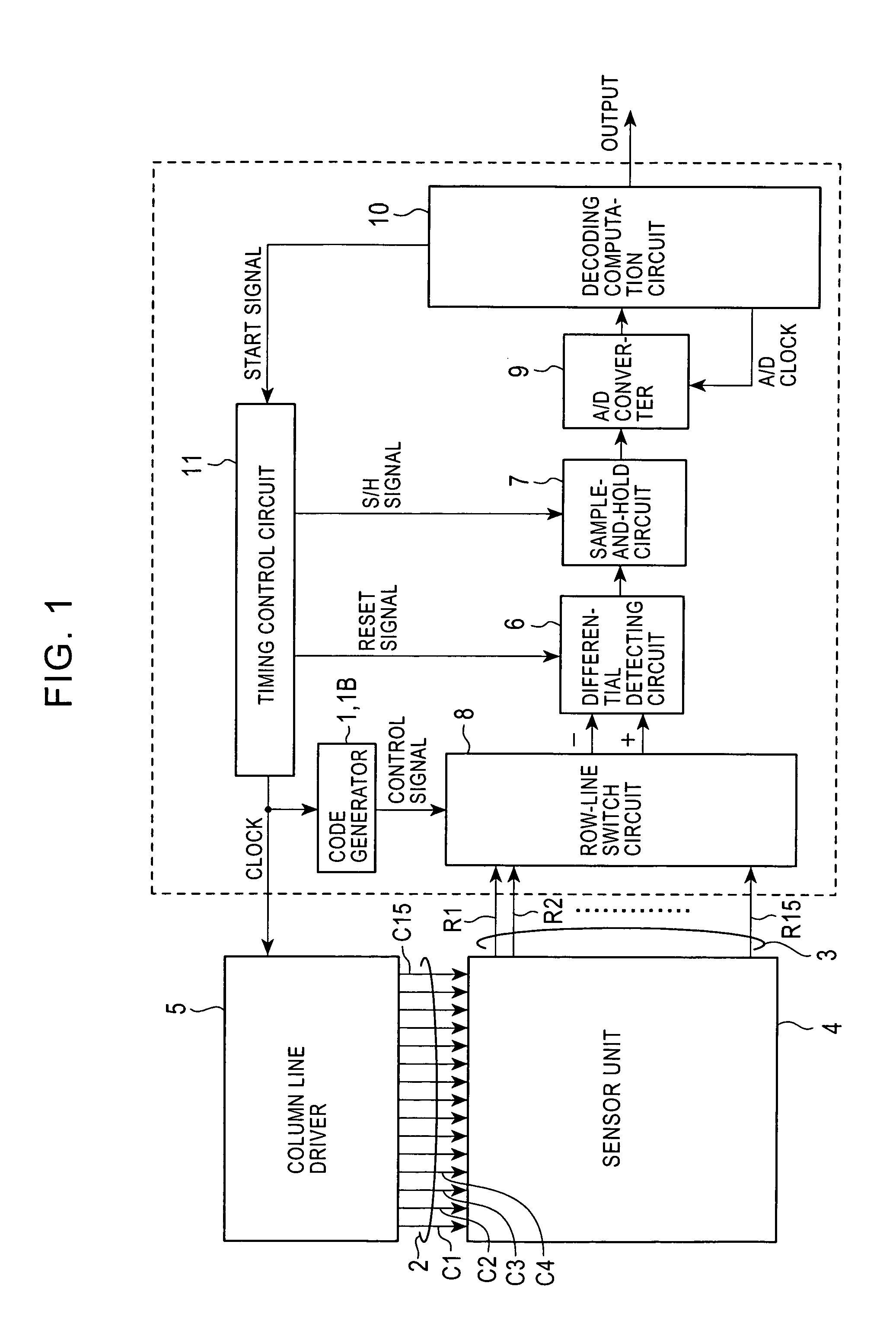

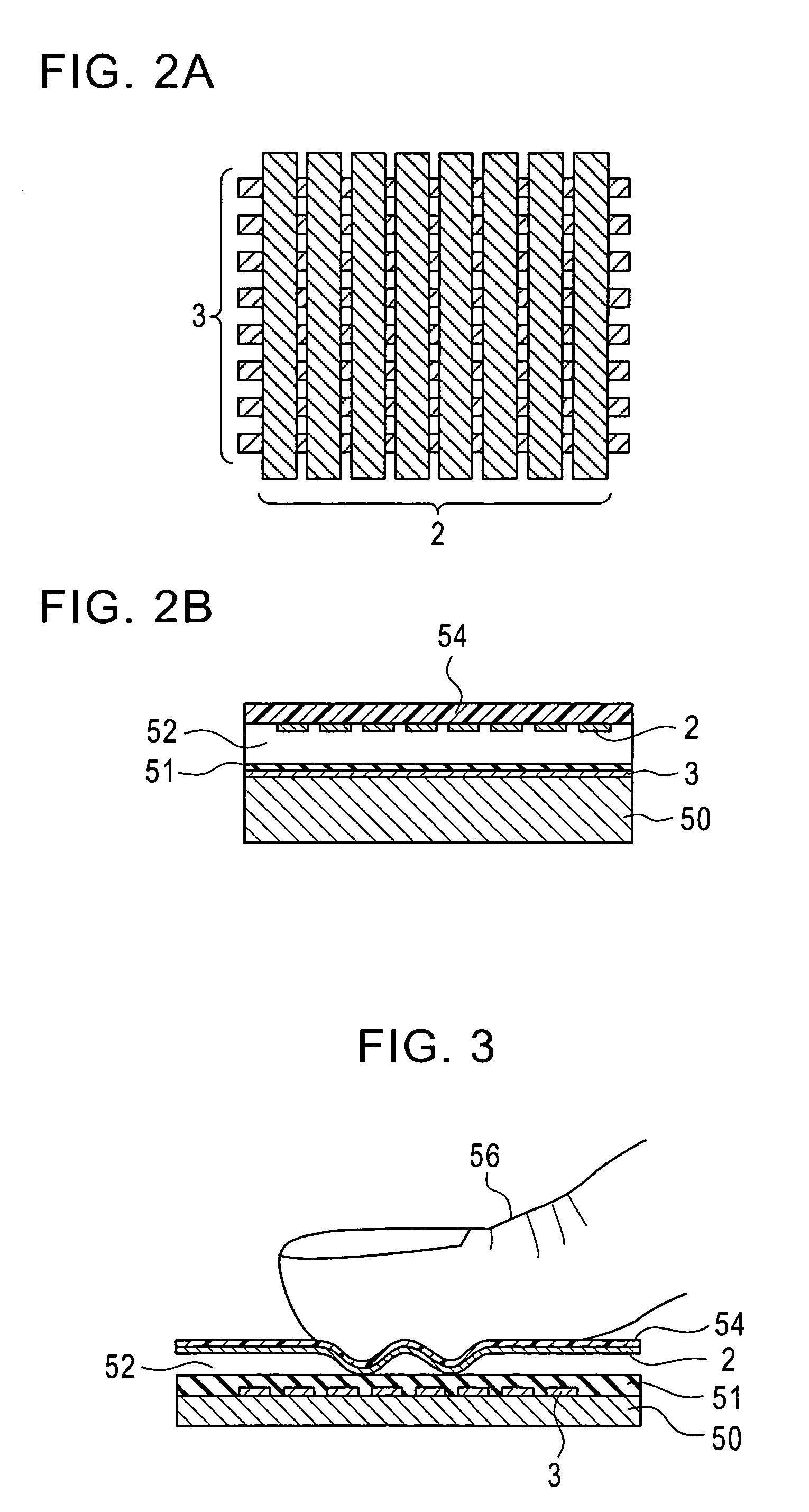

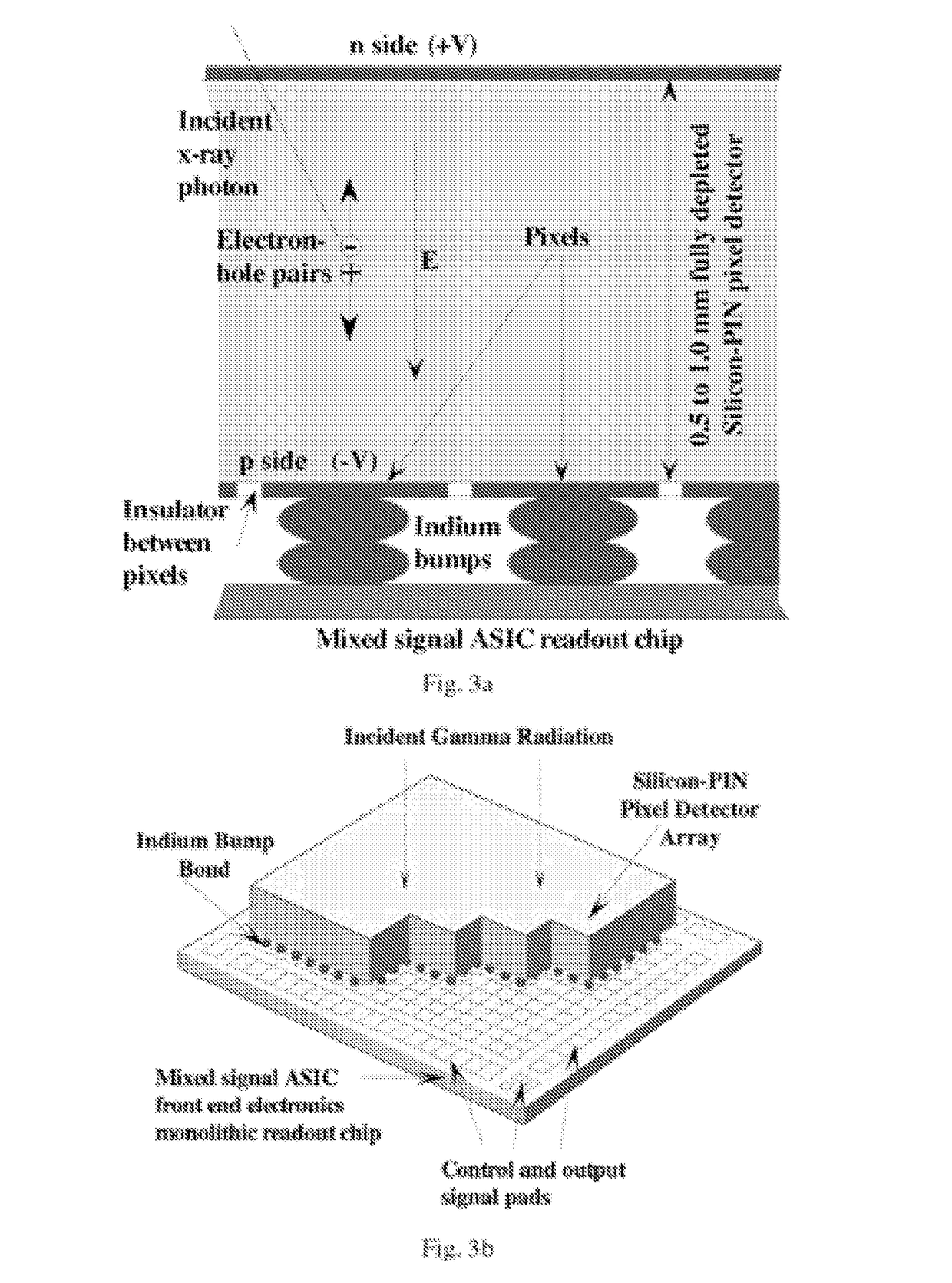

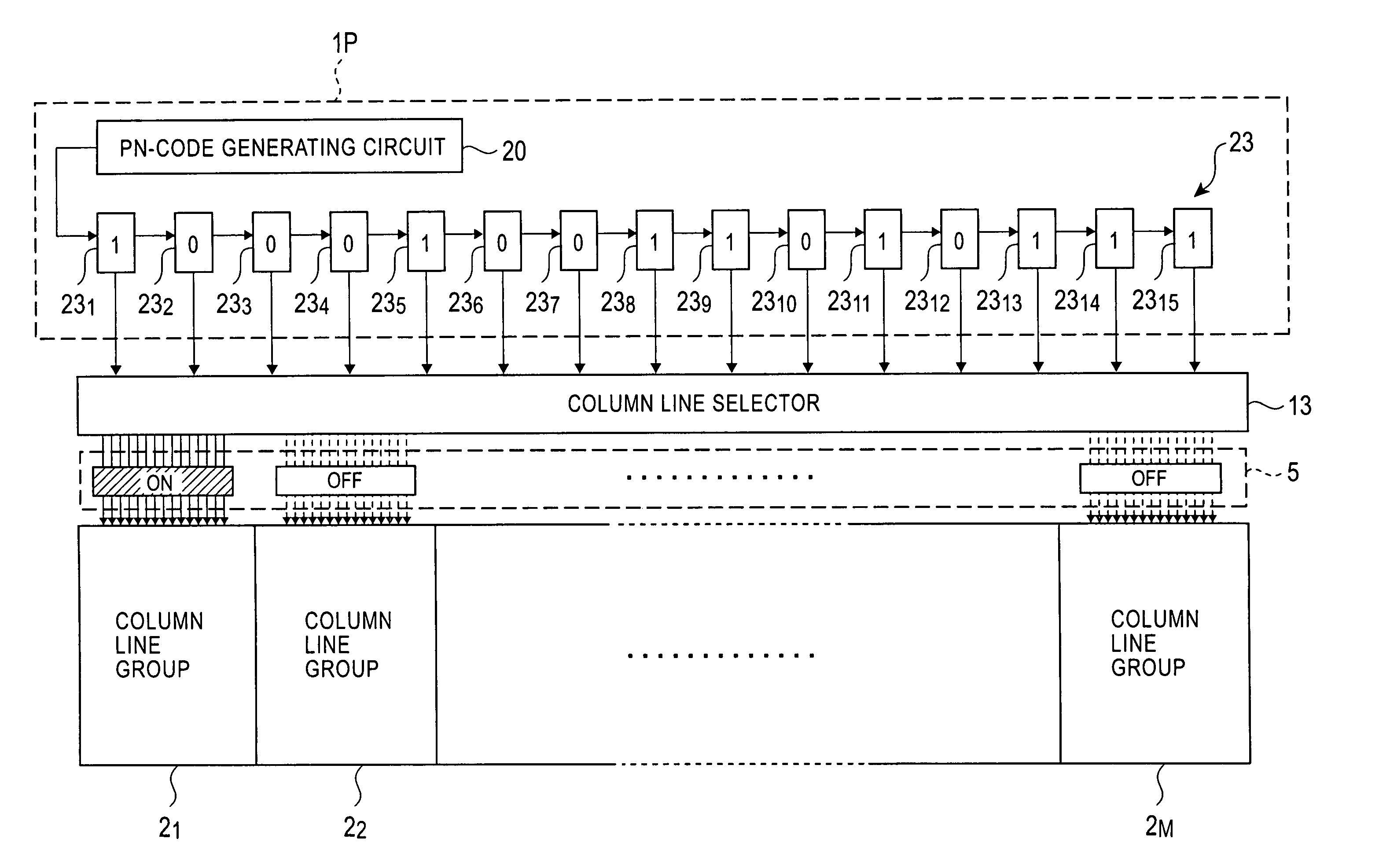

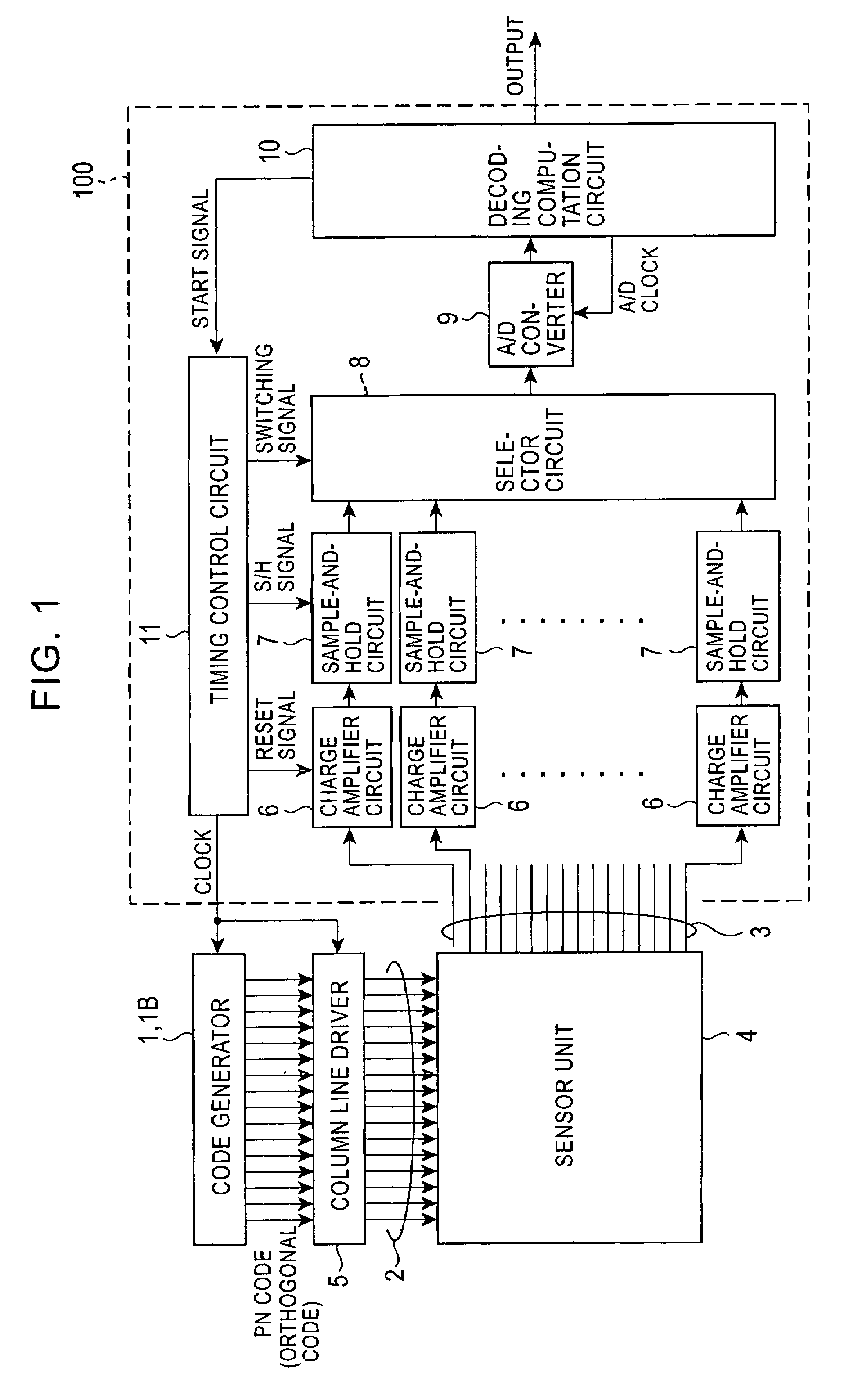

Capacitance detecting circuit and method, and fingerprint sensor using the same

ActiveUS20060158202A1Improve signal-to-noise ratioSmall capacitanceResistance/reactance/impedencePerson identificationCode generationHemt circuits

In a capacitance detecting circuit, changes in capacitances at intersections between a plurality of column lines and a row line are detected as voltages. The capacitance detecting circuit includes a code generator for generating code having orthogonality in chronological order. A column-line driver drives the plurality of column lines based on the code by dividing the column lines into a first column line group and a second column line group. A capacitance detector, which is connected to the row line, converts the total of currents generated in capacitances at the intersections with the driven column lines into a voltage signal and outputs the converted voltage signal. A decoding computation unit determines the voltages corresponding to the capacitances at the intersections for each of the column line groups by performing product sum computation between the measured voltages and the code. In a period for detecting the capacitances, the column-line driver drives the first column line group and the second column line group by complementary voltages according to the code or information indicating the inversion of the code.

Owner:SYNAPTICS INC

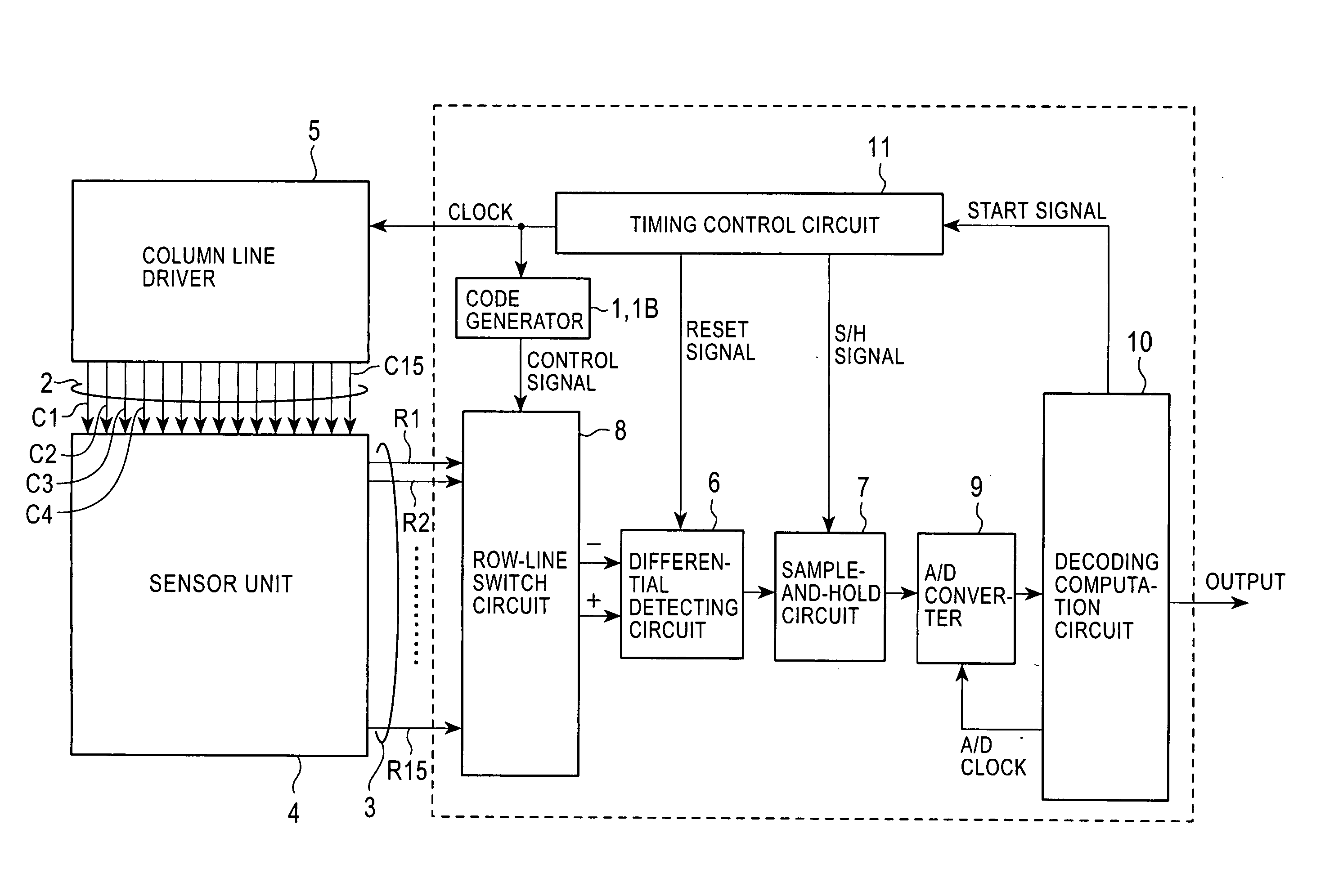

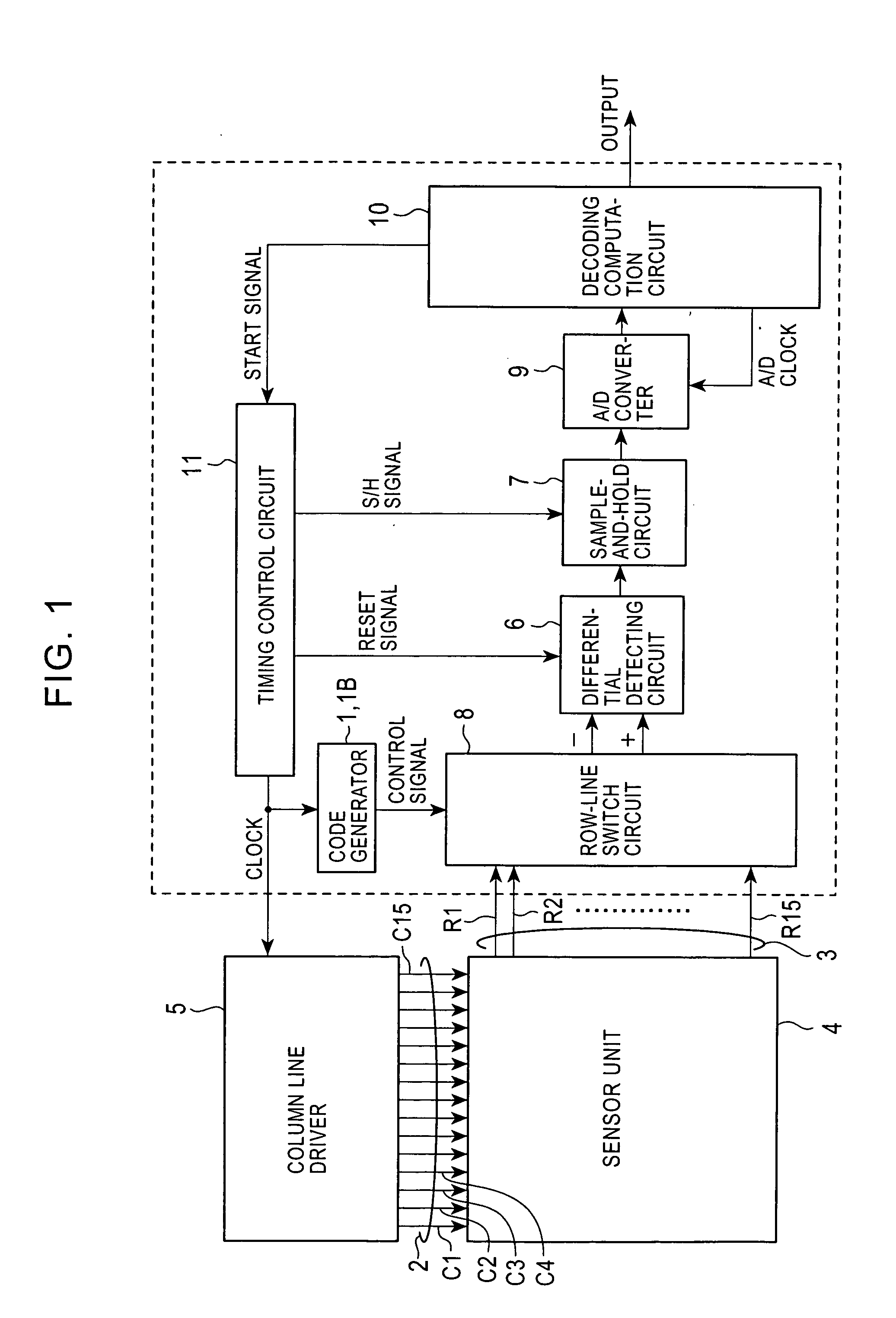

Capacitance detecting circuit and method, and fingerprint sensor using the same

ActiveUS20050141263A1High detection sensitivityReduce external influenceResistance/reactance/impedencePerson identificationFingerprintEngineering

In a capacitance detecting circuit, changes in capacitances at intersections between a plurality of row lines and a column line are detected as voltages. The capacitance detecting circuit includes a column-line driver for driving the column line. A code generator generates code having orthogonality in chronological order. A selection synthesizer selects a certain number of row lines from the plurality of row lines by using the code and synthesizes measured voltages at the intersections between the selected row lines and the driven column line so as to output the synthesized measured voltage. A decoding computation unit separates the measured voltages corresponding to the capacitances at the intersections by performing product sum computation between the synthesized measured voltage and the code.

Owner:SYNAPTICS INC

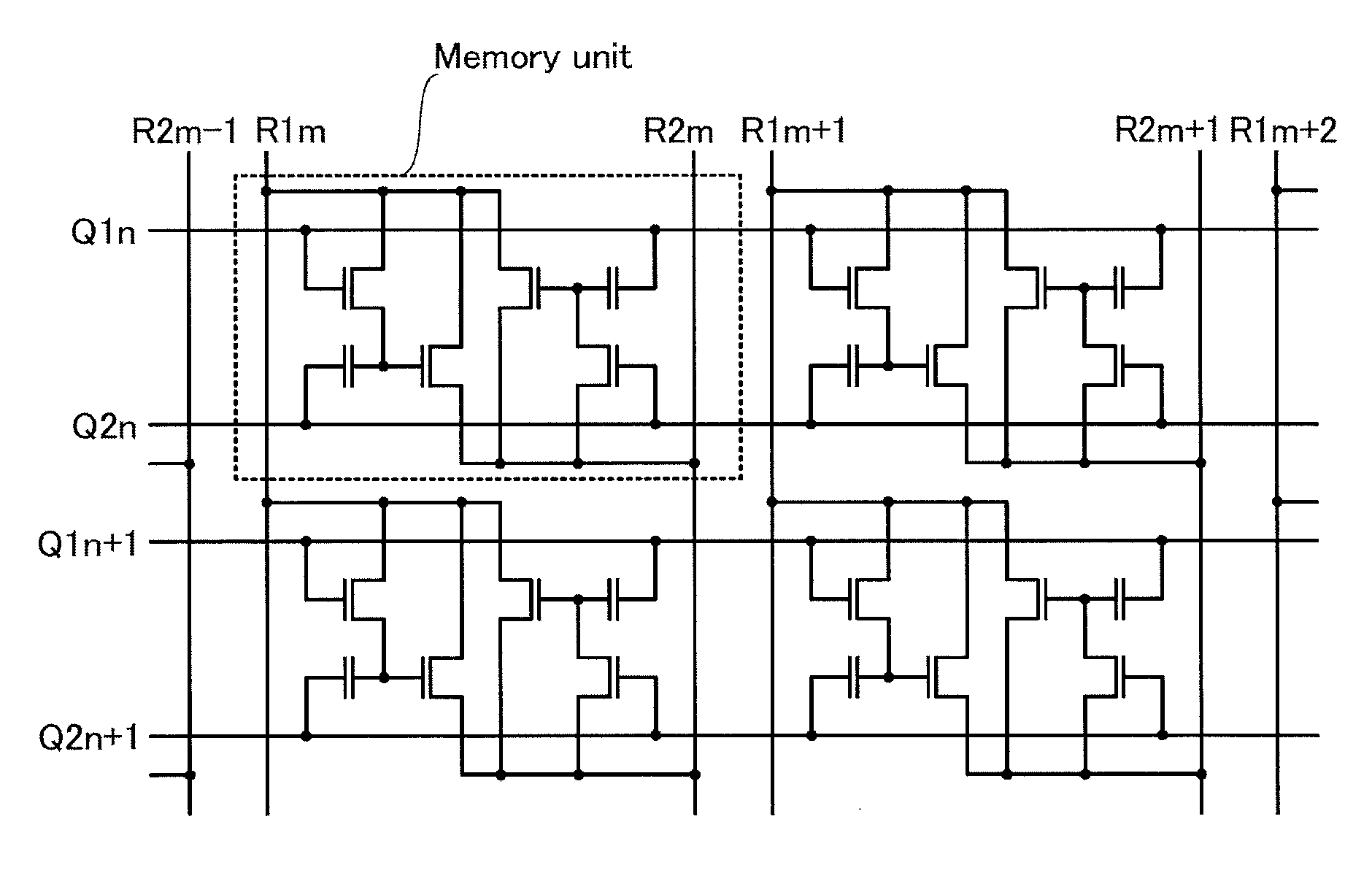

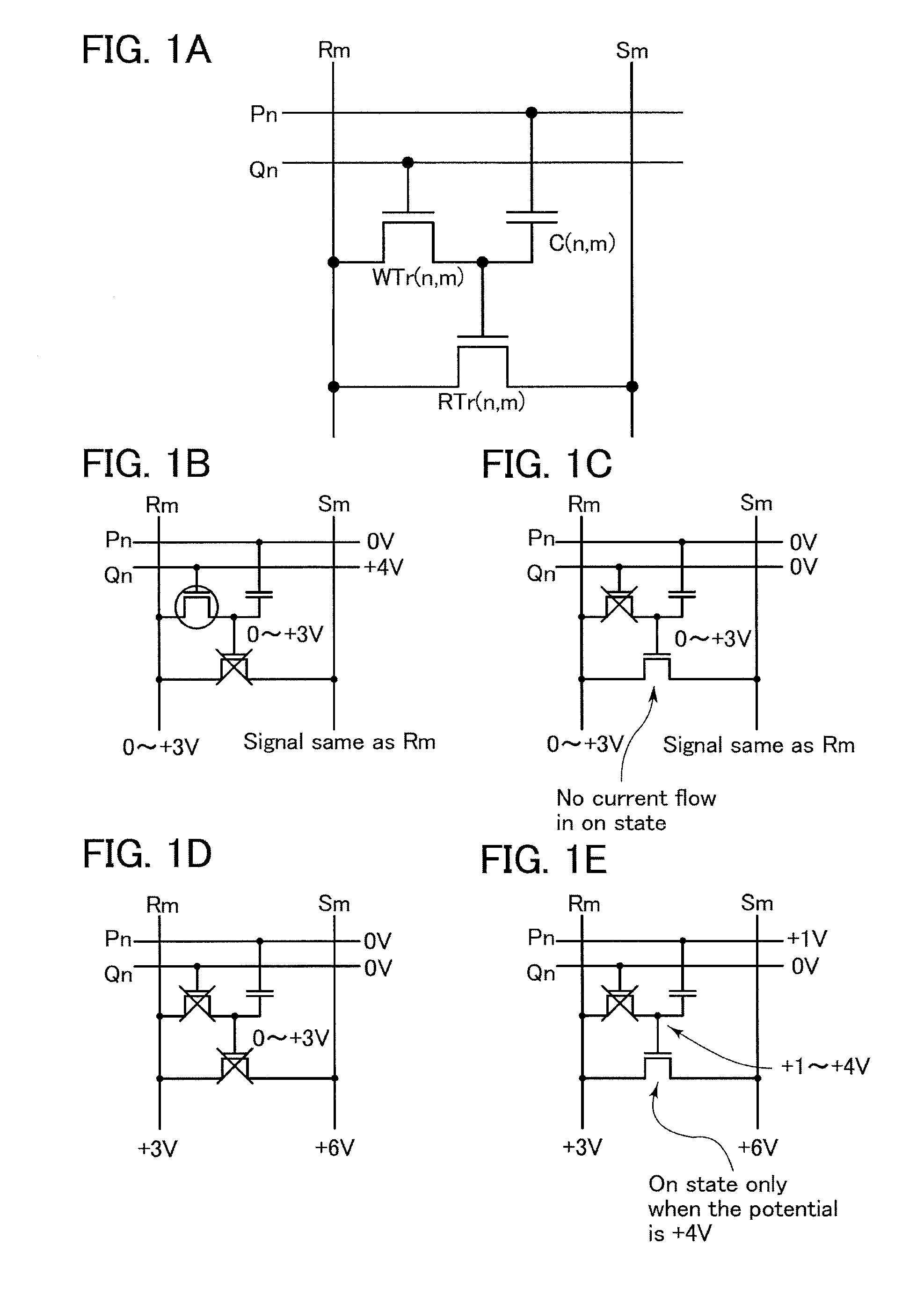

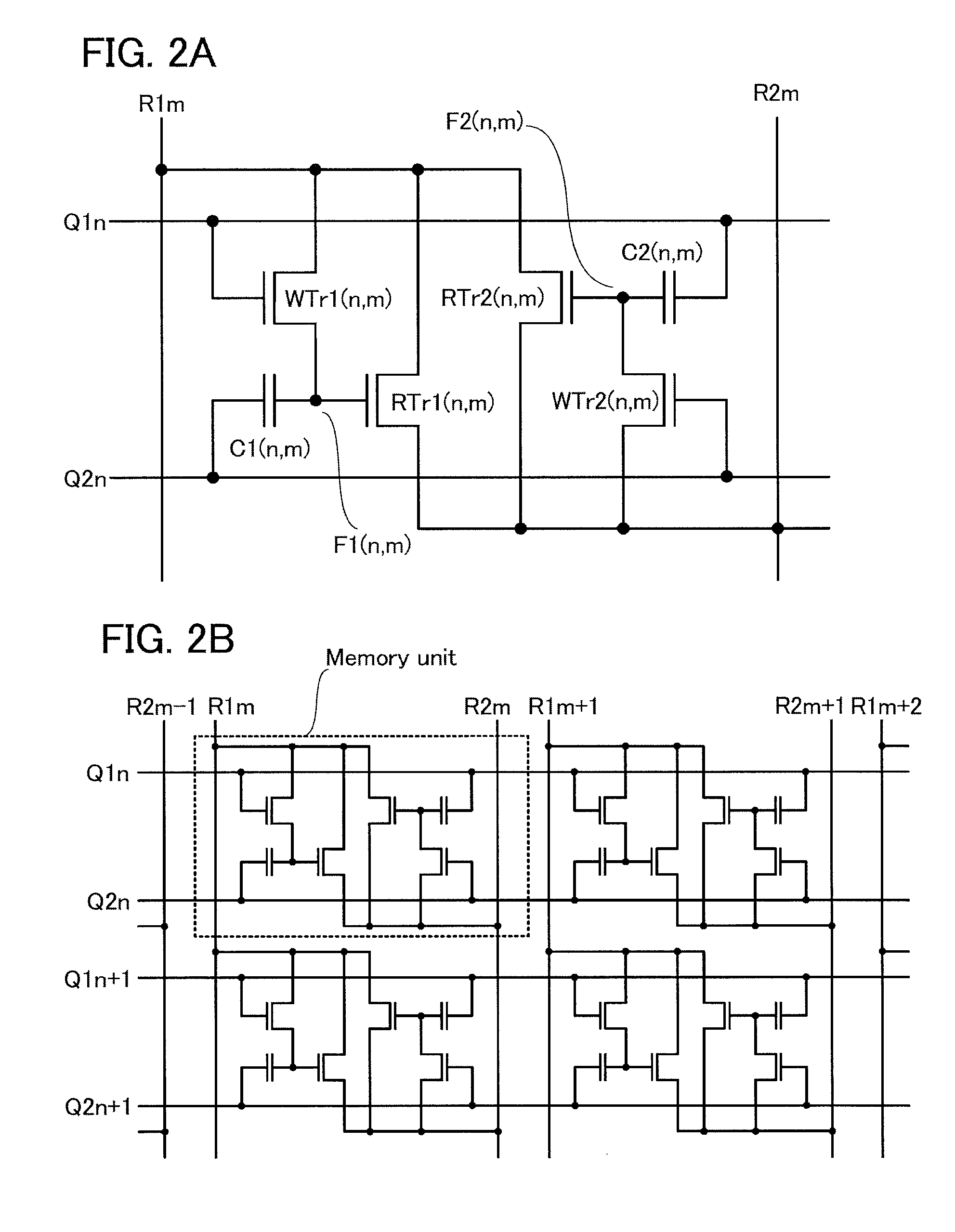

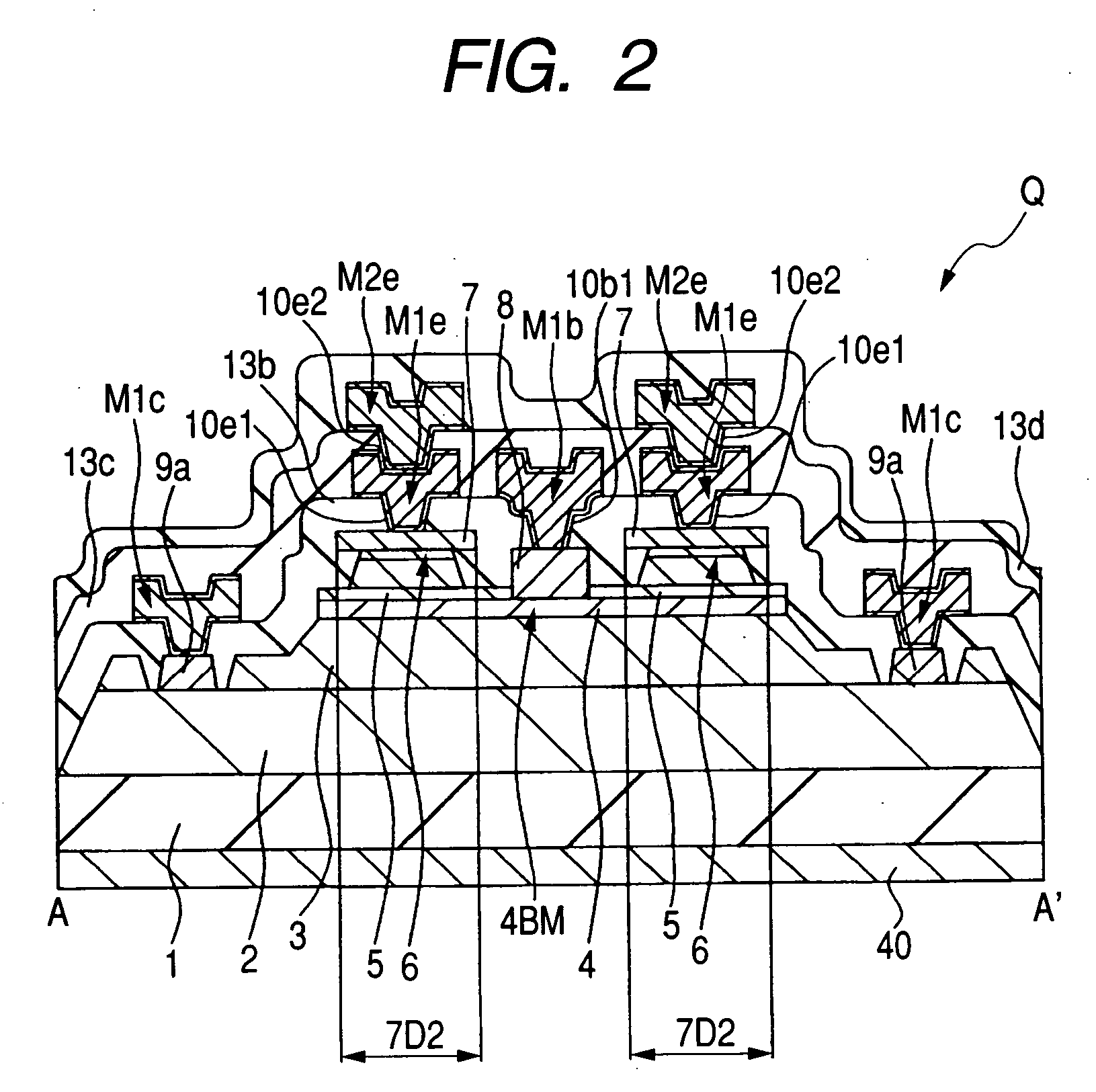

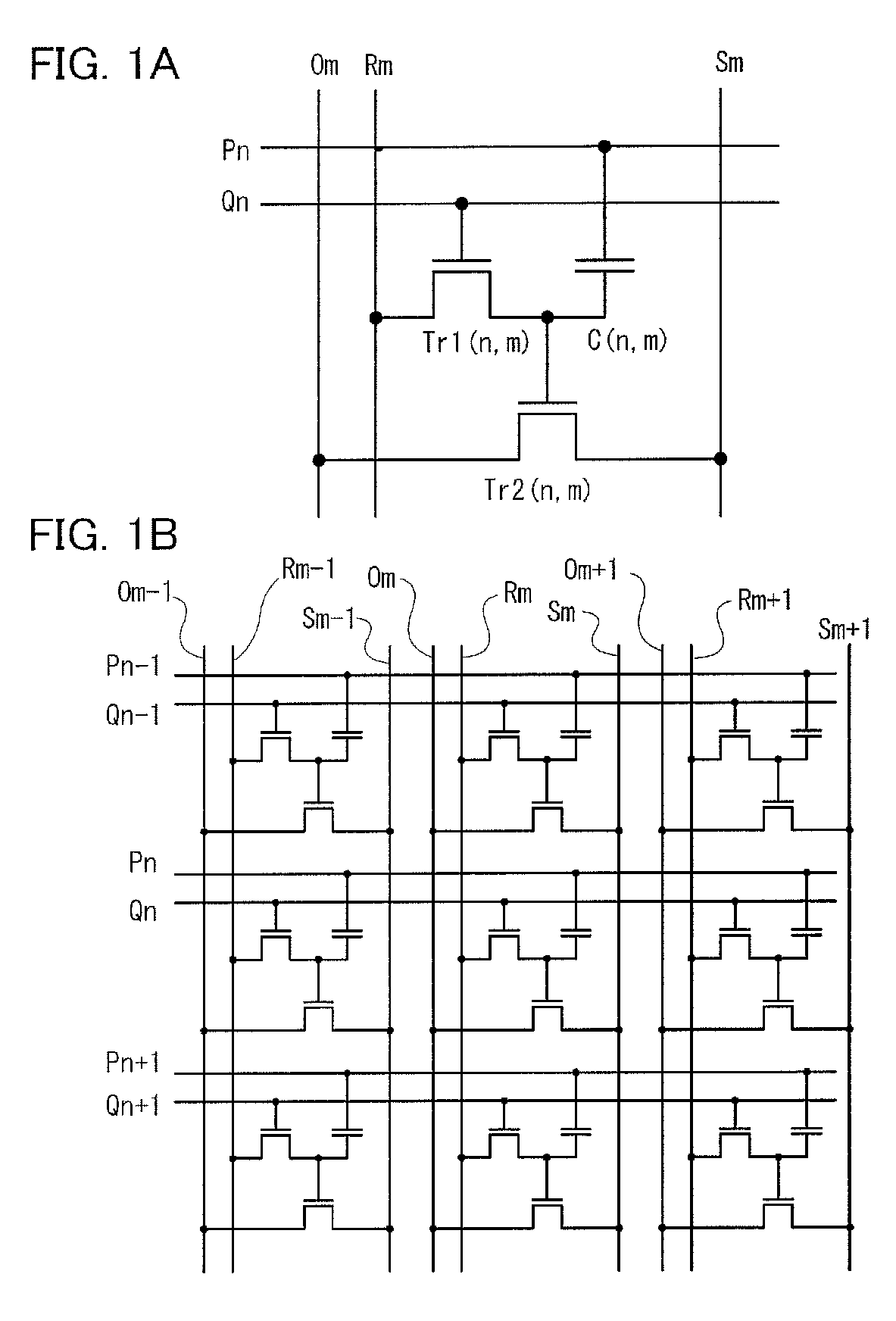

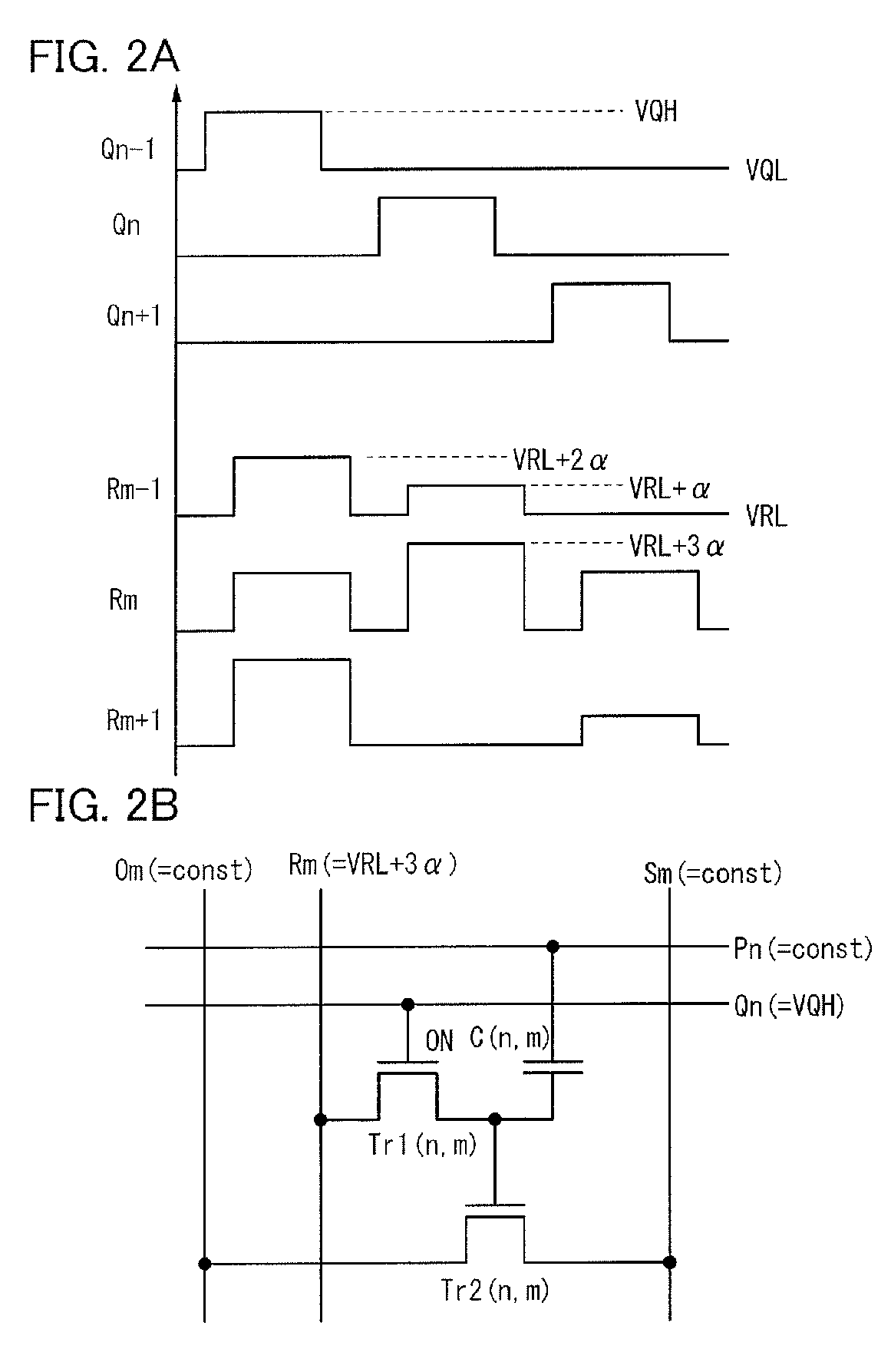

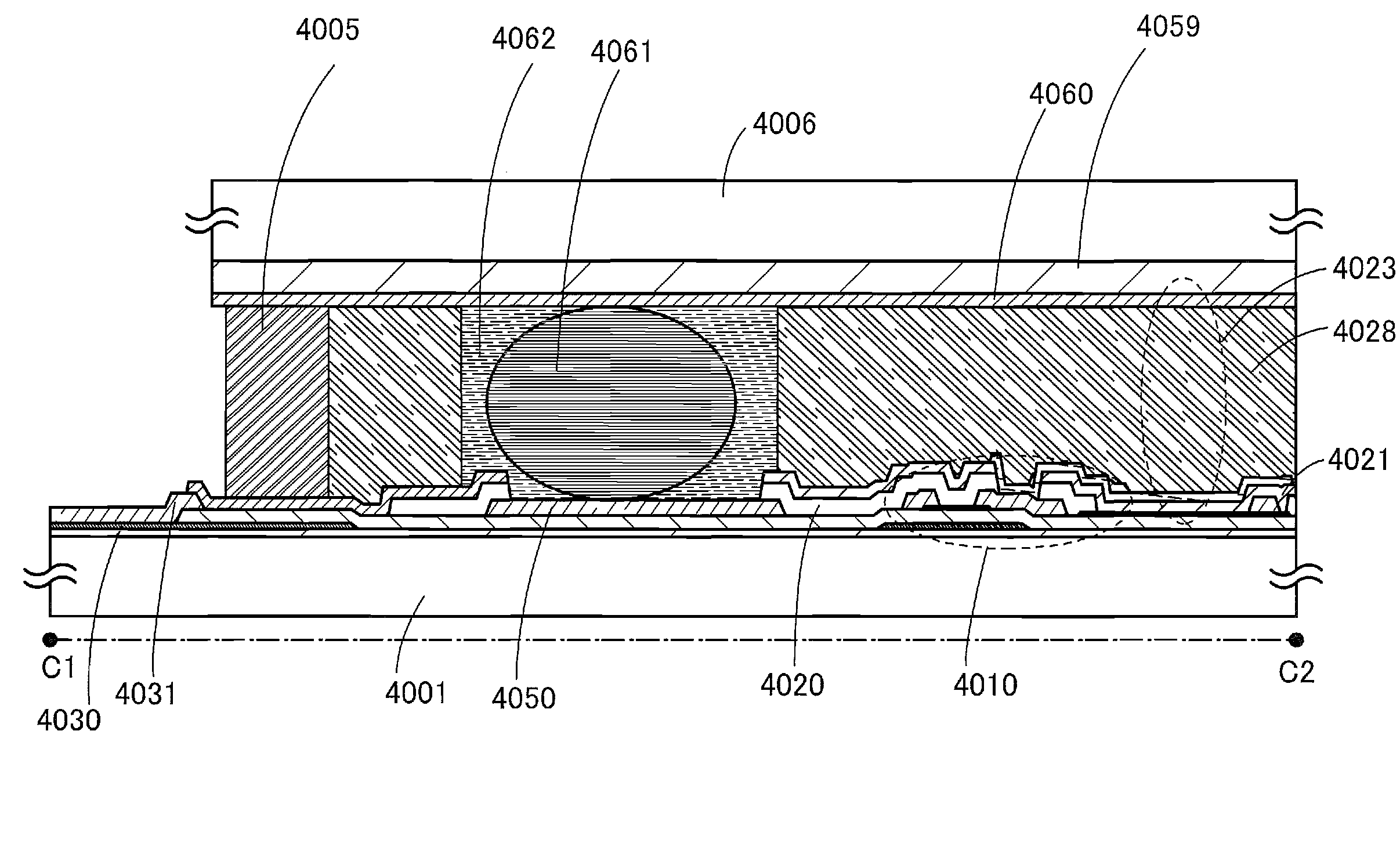

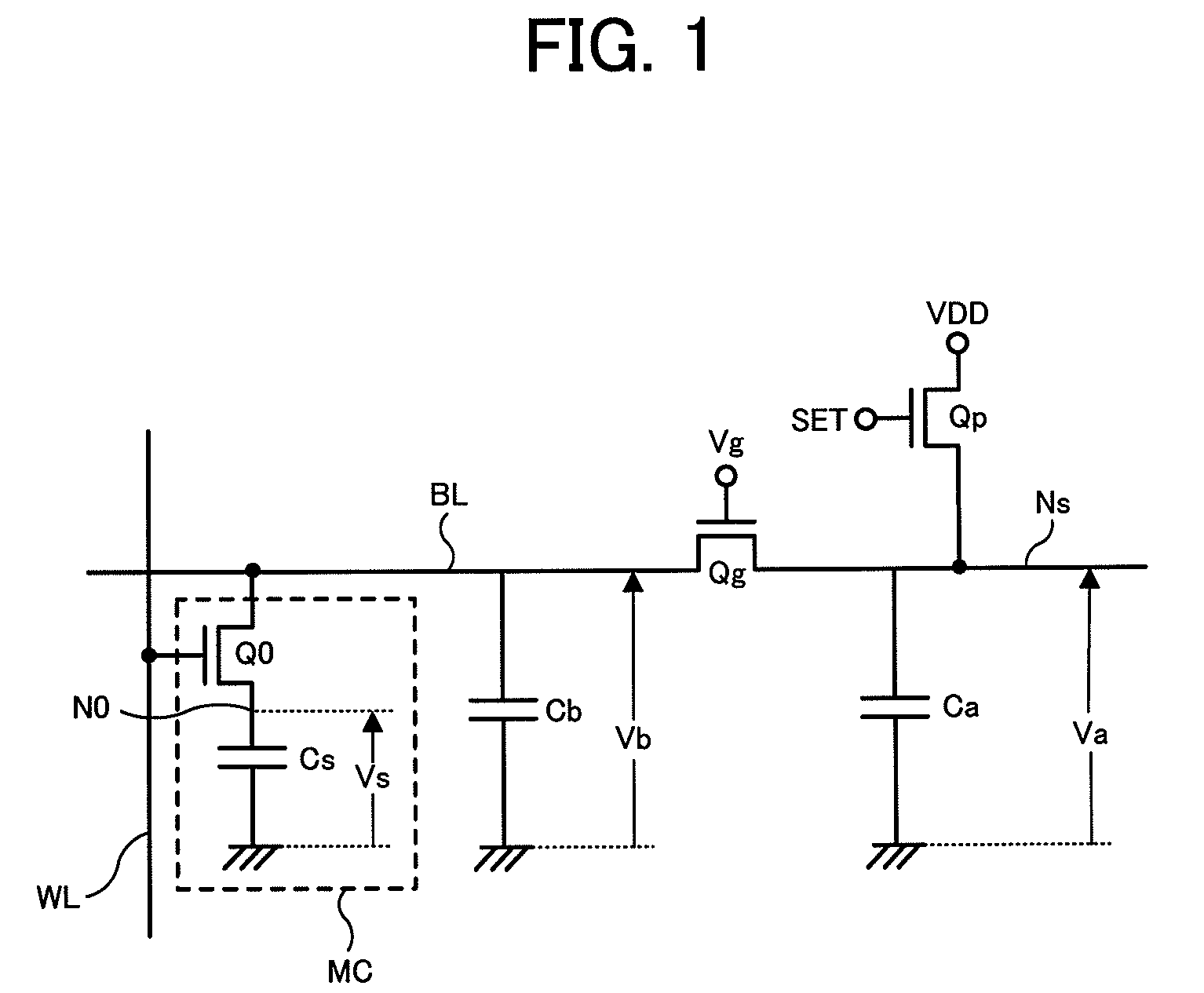

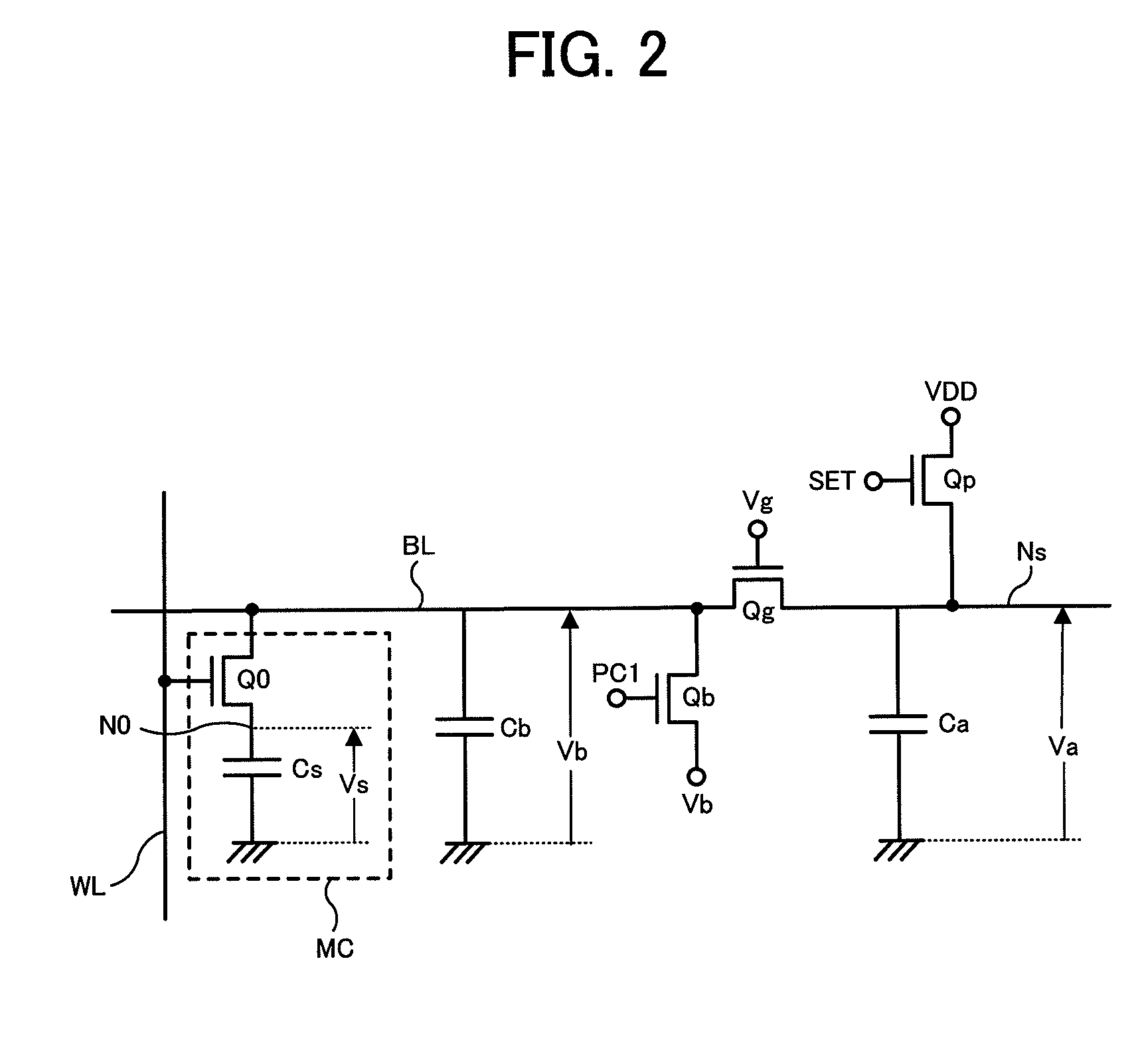

Semiconductor memory device

InactiveUS20110260158A1Reduce numberReduce areaTransistorSolid-state devicesComputational physicsCapacitance

To provide a semiconductor memory device storing data, in which a transistor whose leakage current between a source / drain in off state is small is used as a writing transistor. In a matrix of a memory unit formed of two memory cells, in each of which a drain of a writing transistor is connected to a gate of a reading transistor and one electrode of a capacitor, a gate of the writing transistor, and the other electrode of the capacitor in a first memory cell are connected to a first word line, and a second word line, respectively. In a second memory cell, a gate of the writing transistor, and the other electrode of the capacitor are connected to the second word line, and the first word line, respectively. Further, to increase the degree of integration, gates of the reading transistors of memory cells are disposed in a staggered configuration.

Owner:SEMICON ENERGY LAB CO LTD

Capacitance detecting circuit and method, and fingerprint sensor using the same

ActiveUS7078918B2Improve signal-to-noise ratioSmall capacitanceResistance/reactance/impedencePerson identificationLine driverFingerprint

In a capacitance detecting circuit, changes in capacitances at intersections between a plurality of row lines and a column line are detected as voltages. The capacitance detecting circuit includes a column-line driver for driving the column line. A code generator generates code having orthogonality in chronological order. A selection synthesizer selects a certain number of row lines from the plurality of row lines by using the code and synthesizes measured voltages at the intersections between the selected row lines and the driven column line so as to output the synthesized measured voltage. A decoding computation unit separates the measured voltages corresponding to the capacitances at the intersections by performing product sum computation between the synthesized measured voltage and the code.

Owner:SYNAPTICS INC

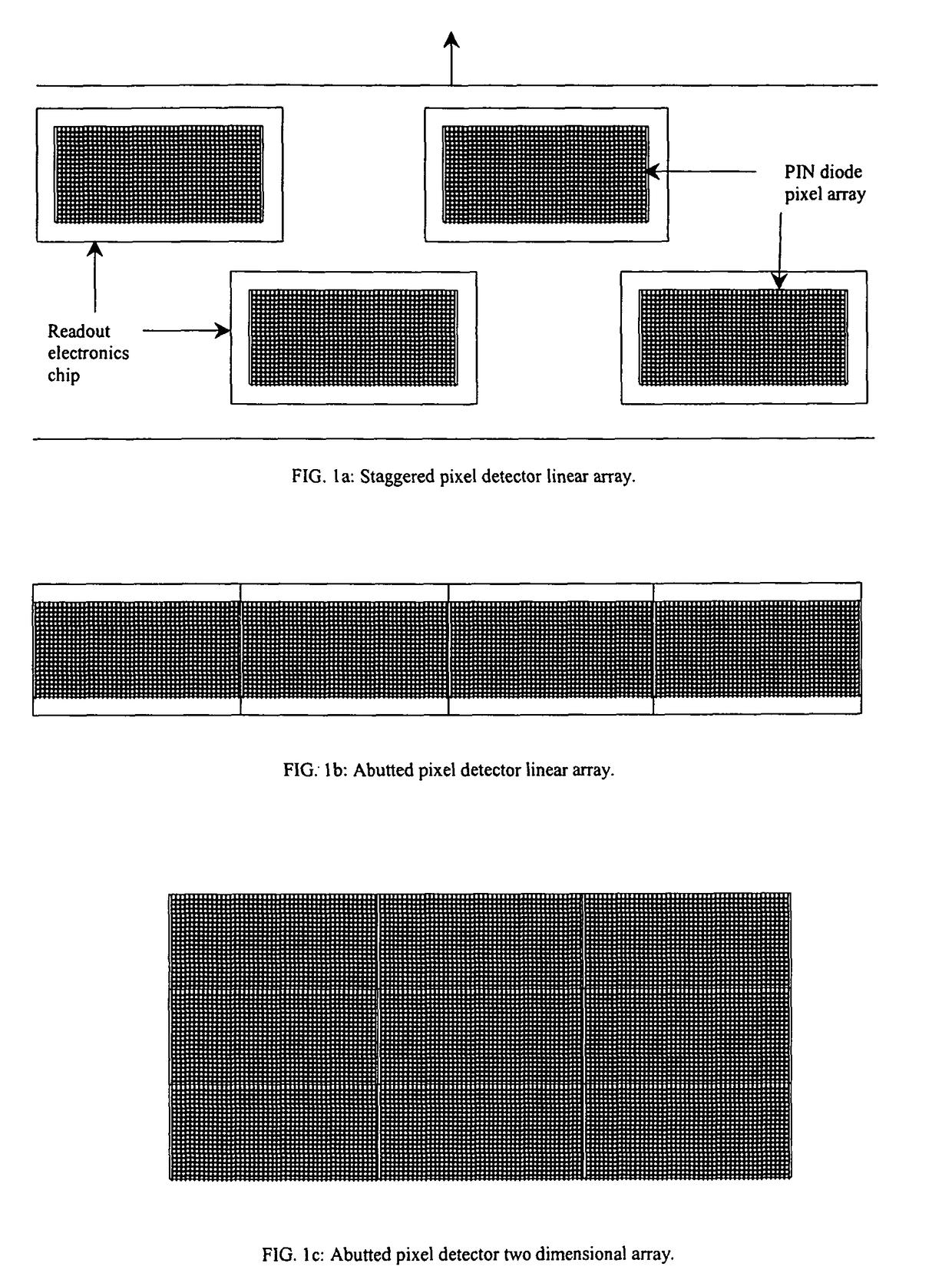

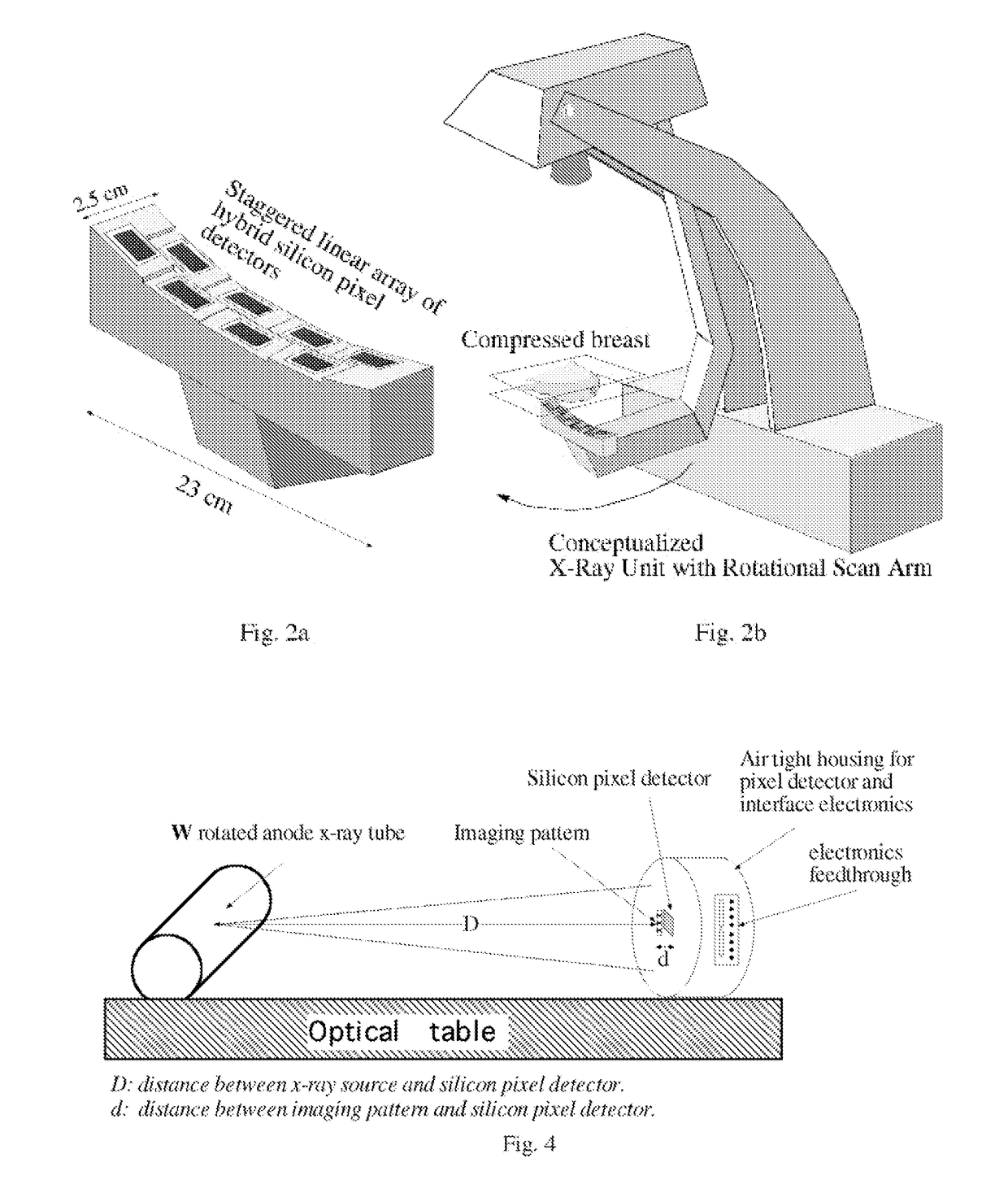

High resoultion digital imaging apparatus

InactiveUS8120683B1Improve quantum efficiencyImprove the immunityTelevision system detailsTelevision system scanning detailsDigital imagingData acquisition

An integrated application specific integrated circuit having a detection layer, a time delayed integration capability, data acquisition electronics, and a readout function is provided for detecting breast cancer in women. The detection layer receives x-ray radiation and converts the received energy to electron pairs, one of which is received by pixels. The time delay integration is on the chip and a part of the readout architecture. The detector may be a hybrid silicon detector (SiPD), a CdZnTe detector, or a GaAs detector.

Owner:NOVA R&D

Capacitance detecting circuit and method, and fingerprint sensor using the same

ActiveUS7084645B1Improve signal-to-noise ratioSmall capacitanceResistance/reactance/impedencePerson identificationCapacitanceLine driver

A capacitance detecting circuit includes a code generator for generating code having orthogonality in chronological order. A column-line driver drives the plurality of column lines based on the code by dividing the column lines into a first column line group and a second column line group. A capacitance detector, which is connected to the row line, converts the total of currents generated in capacitances at the intersections with the driven column lines into a voltage signal and outputs the converted voltage signal. A decoding computation unit determines the voltages corresponding to the capacitances at the intersections for each of the column line groups by performing product sum computation between the measured voltages and the code. The column-line driver drives the first column line group and the second column line group by complementary voltages according to the code or information indicating the inversion of the code.

Owner:SYNAPTICS INC

Apparatus and method for driving laser diodes

InactiveUS7792166B2Fast rise timeImprove efficiencyLaser detailsSemiconductor lasersCapacitanceMode control

Owner:LOCKHEED MARTIN CORP

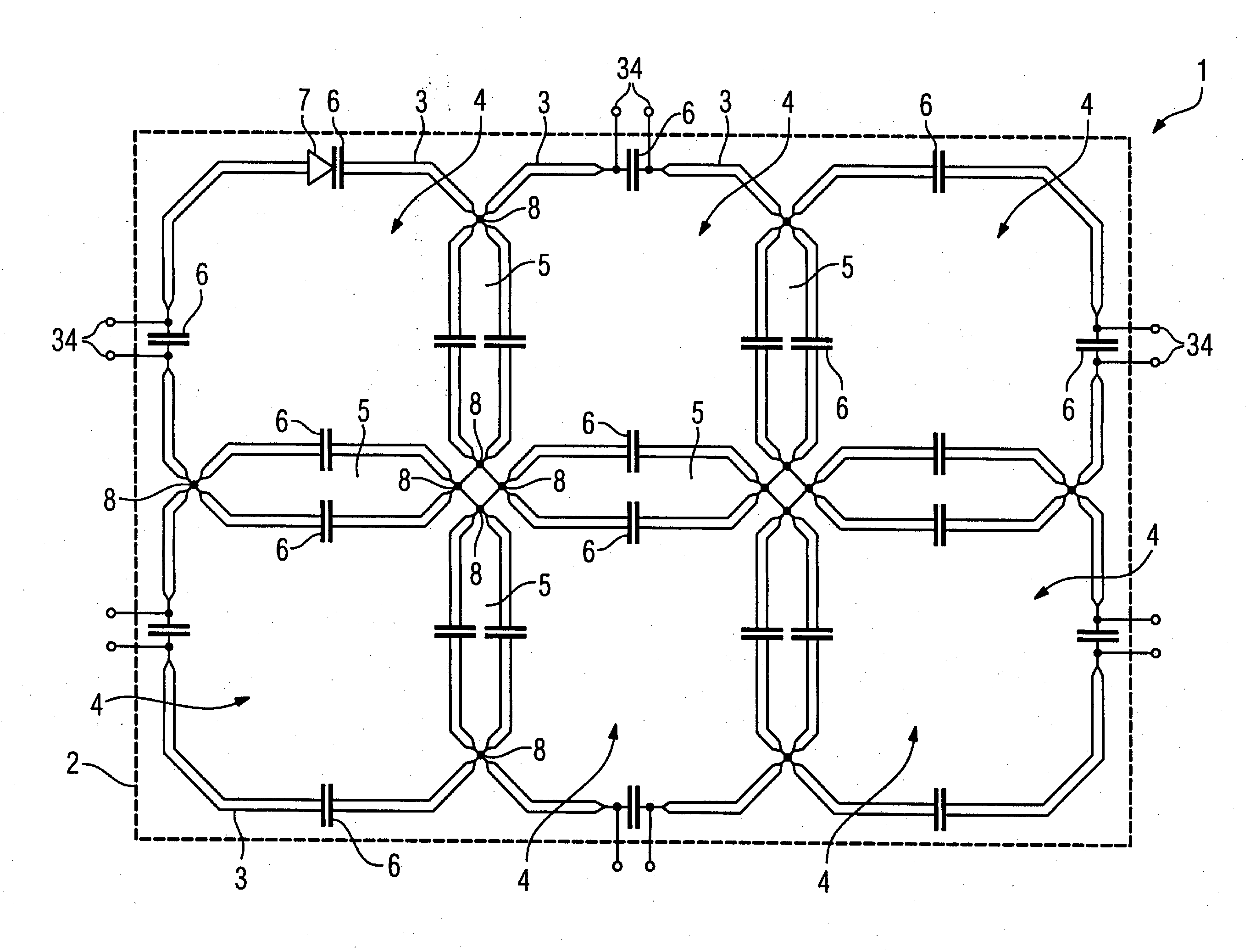

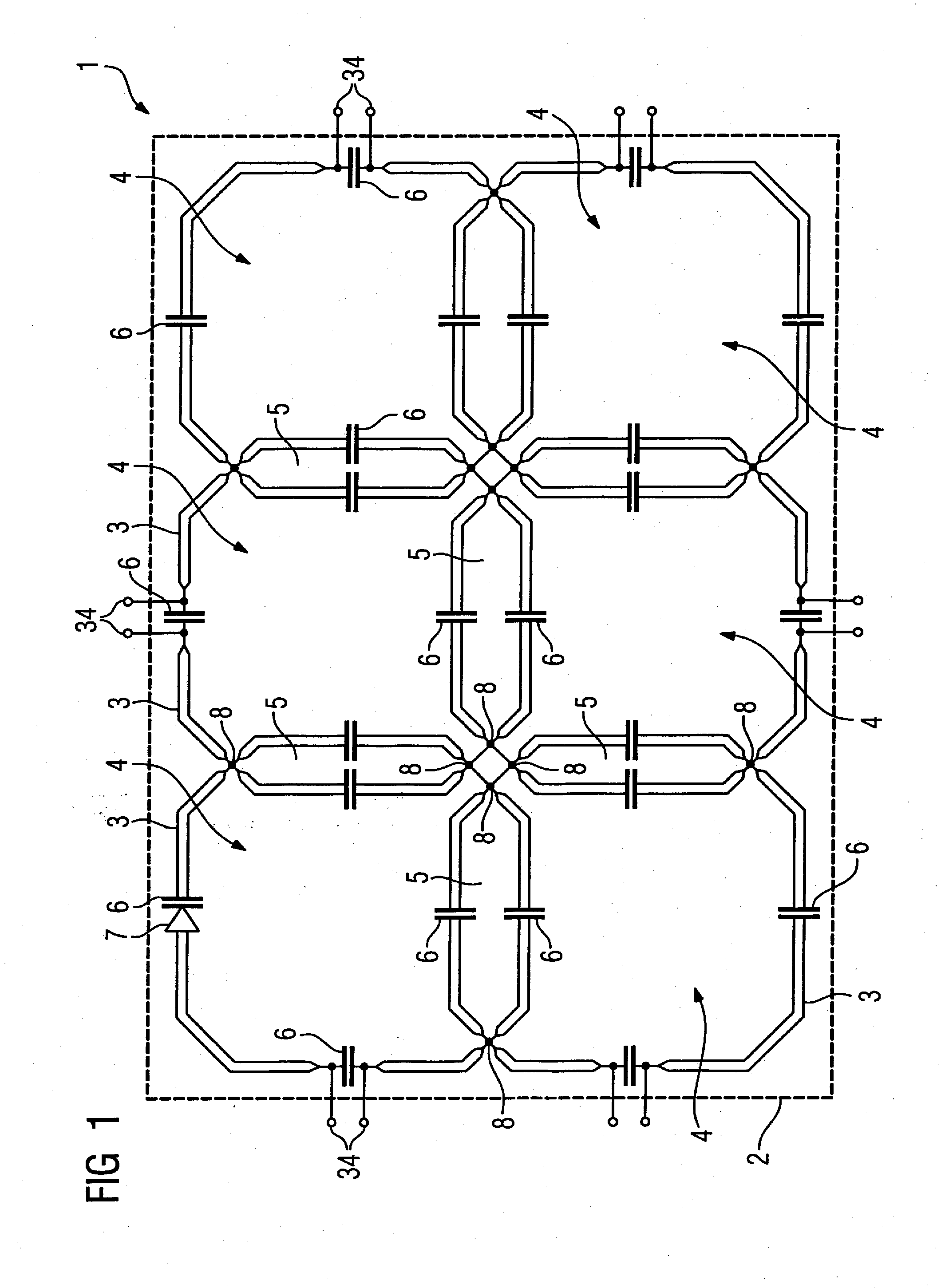

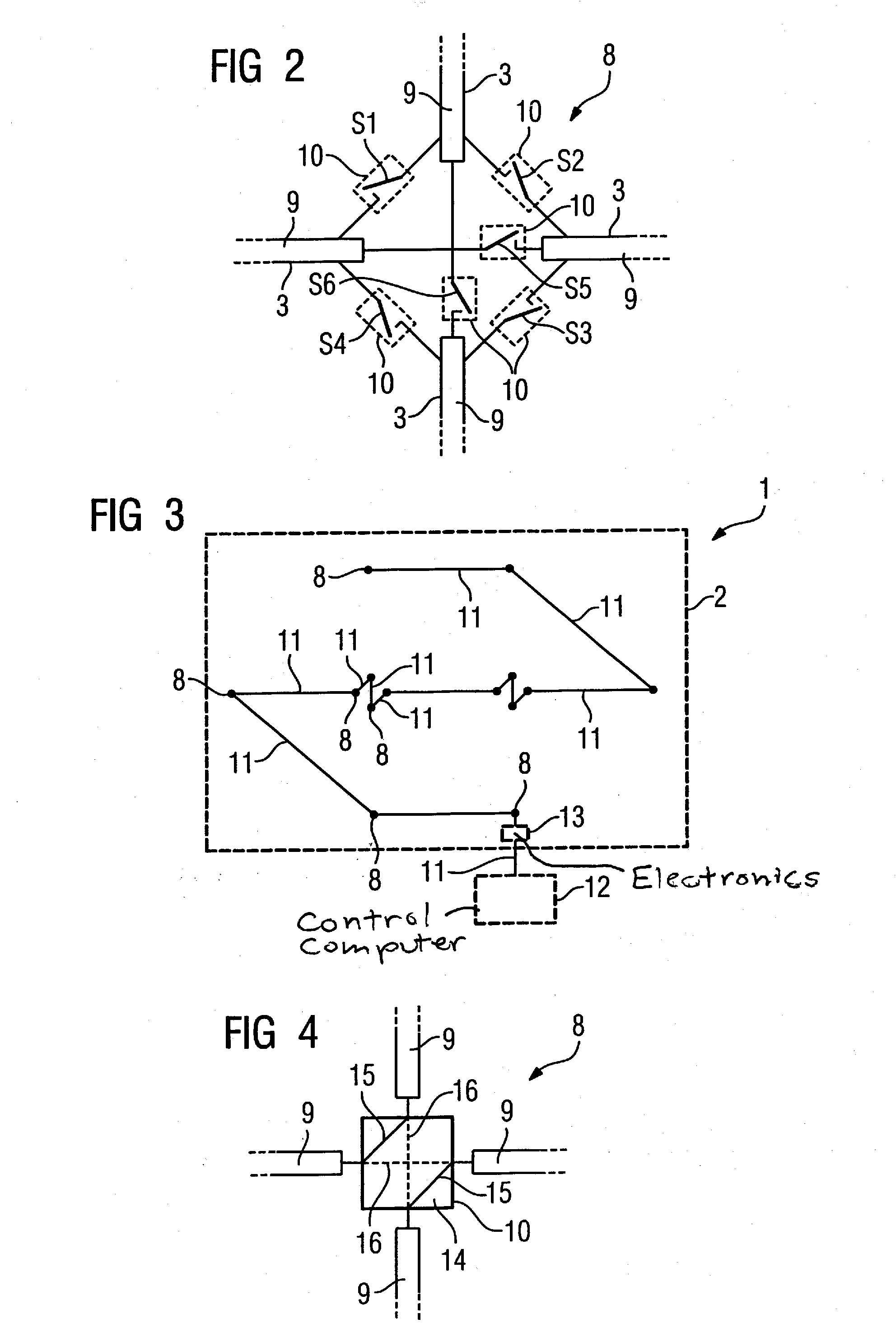

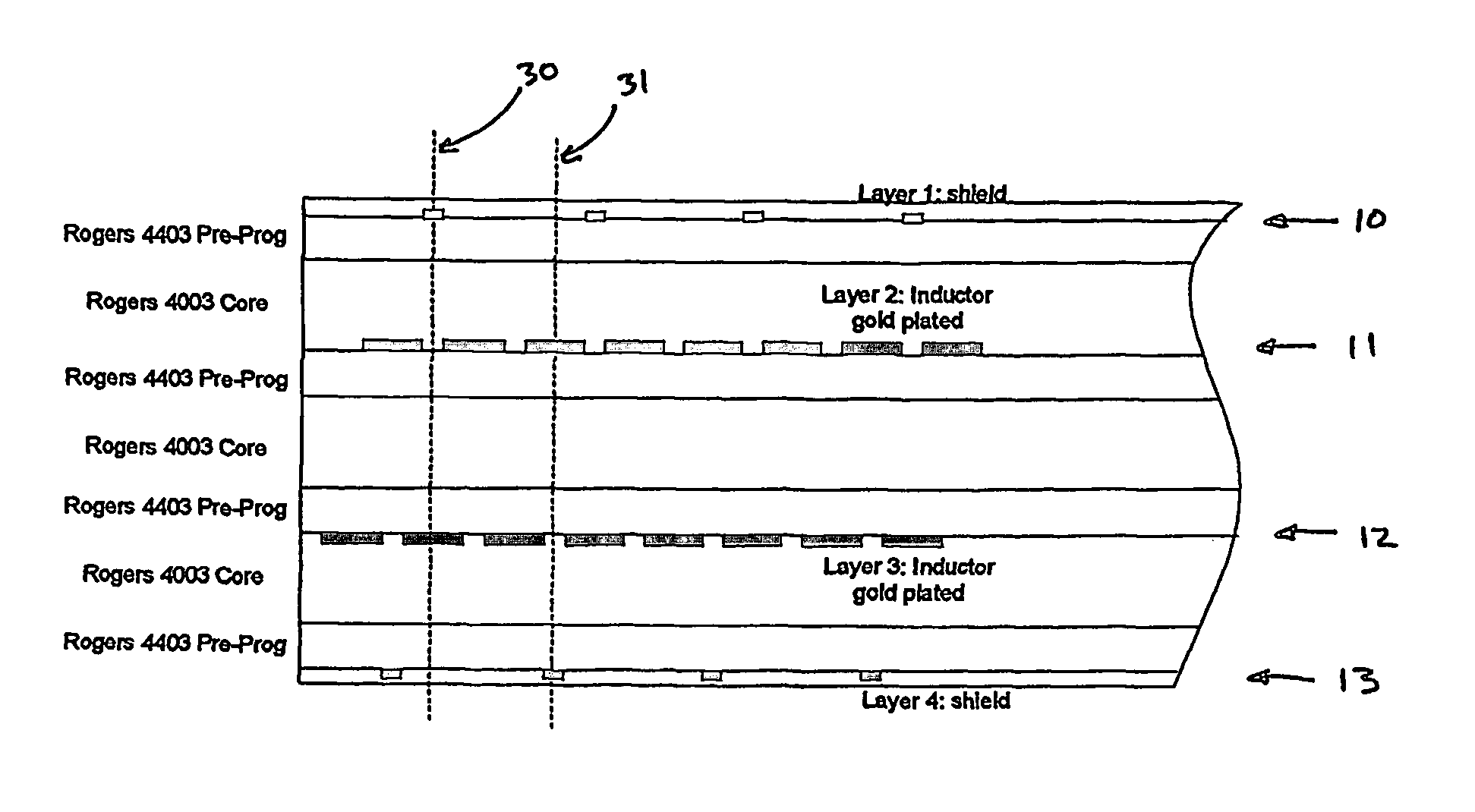

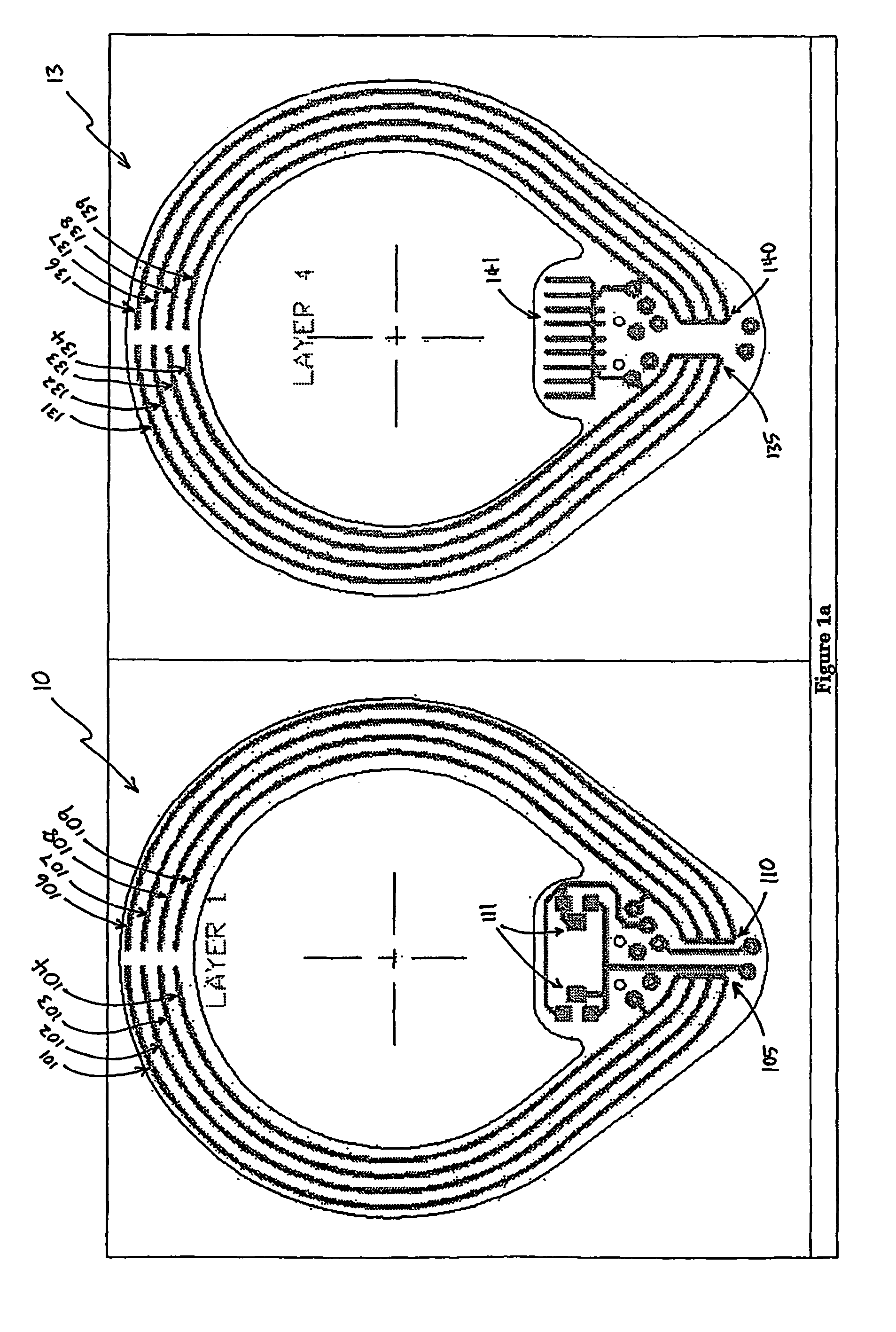

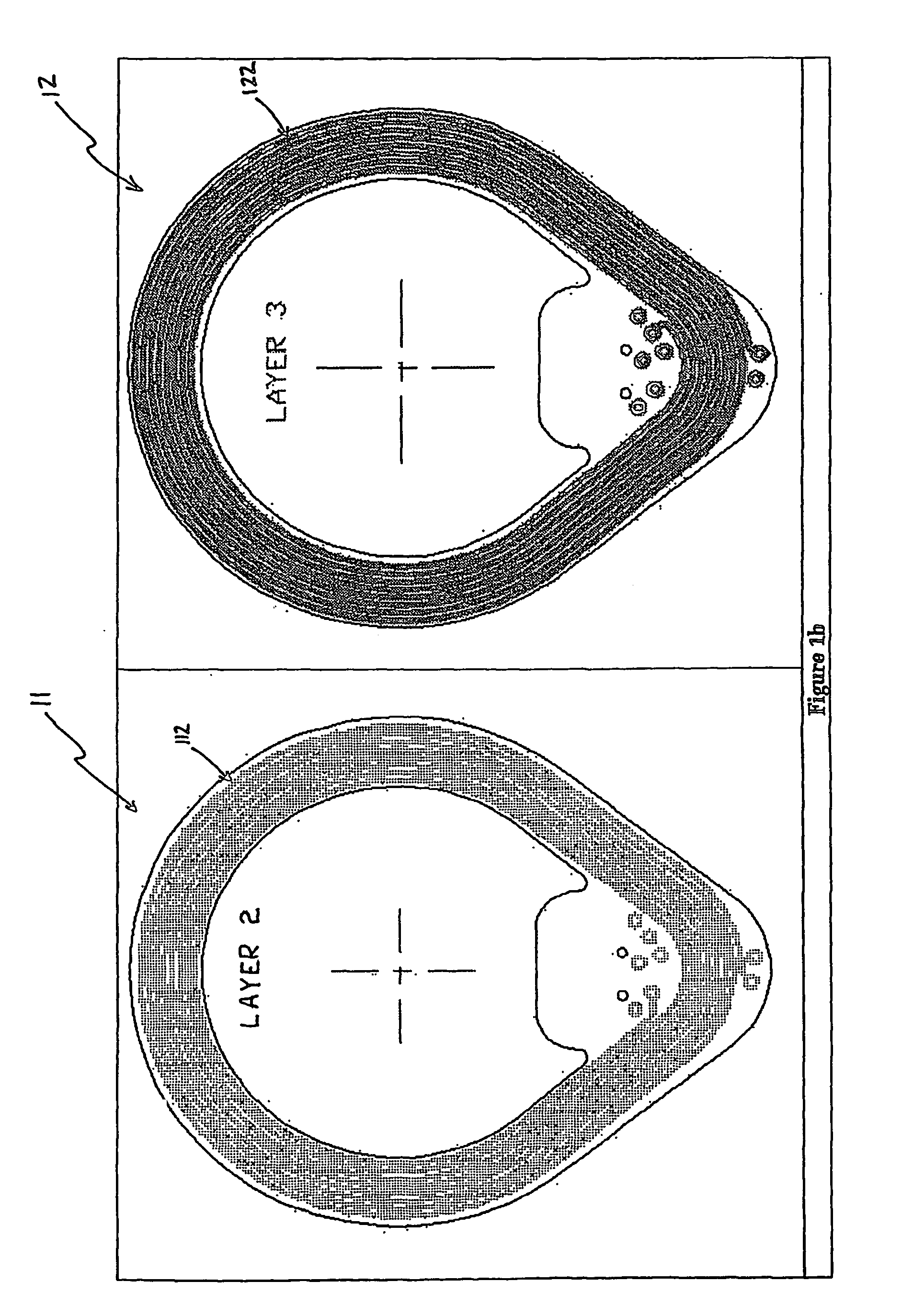

Radio-frequency coil arrangement

InactiveUS20080129296A1Versatile usage capabilityHigh sensitivityElectric/magnetic detectionContinuously variable inductances/transformersRadio frequencyCoil geometry

Owner:SIEMENS HEALTHCARE GMBH

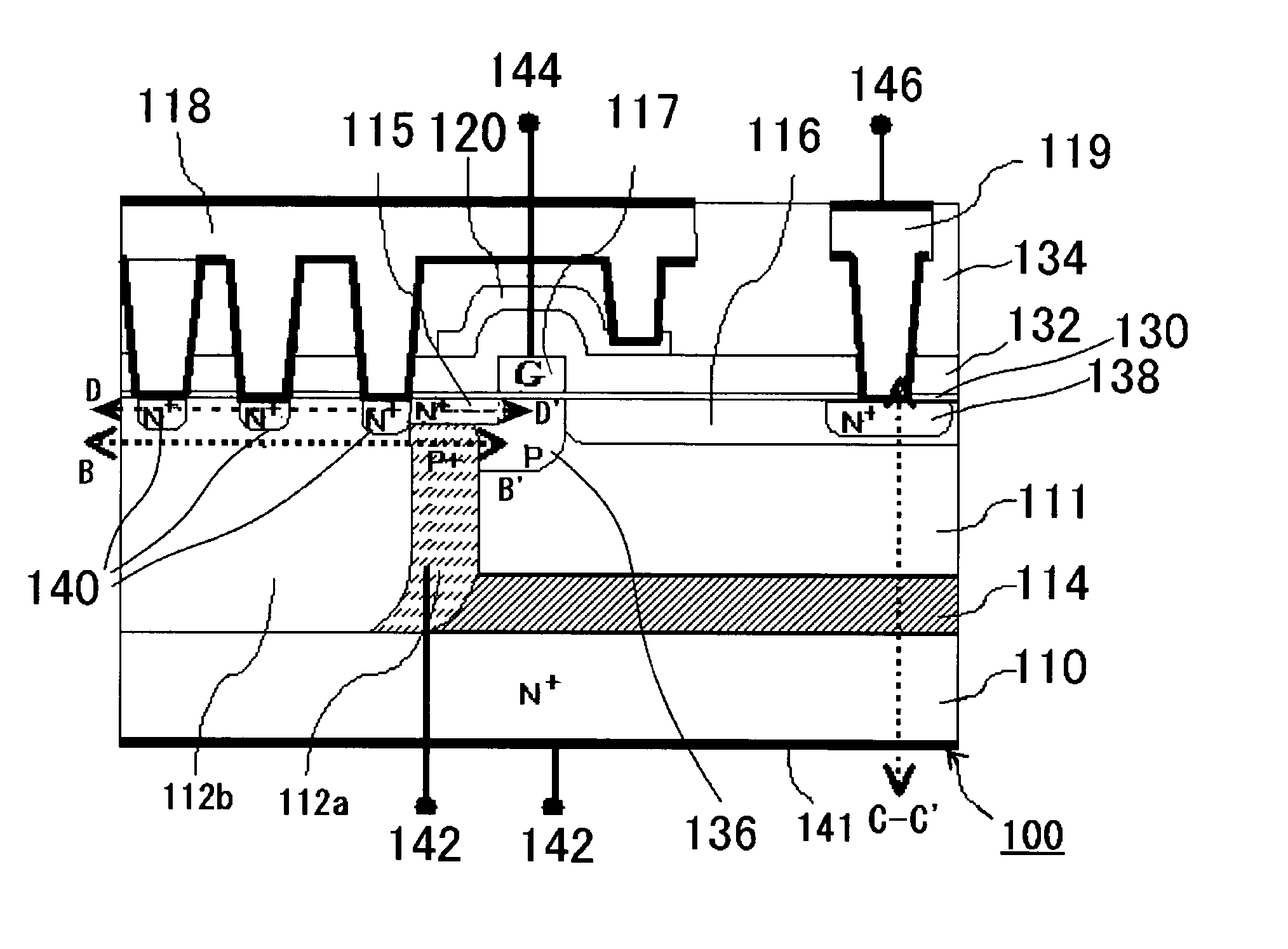

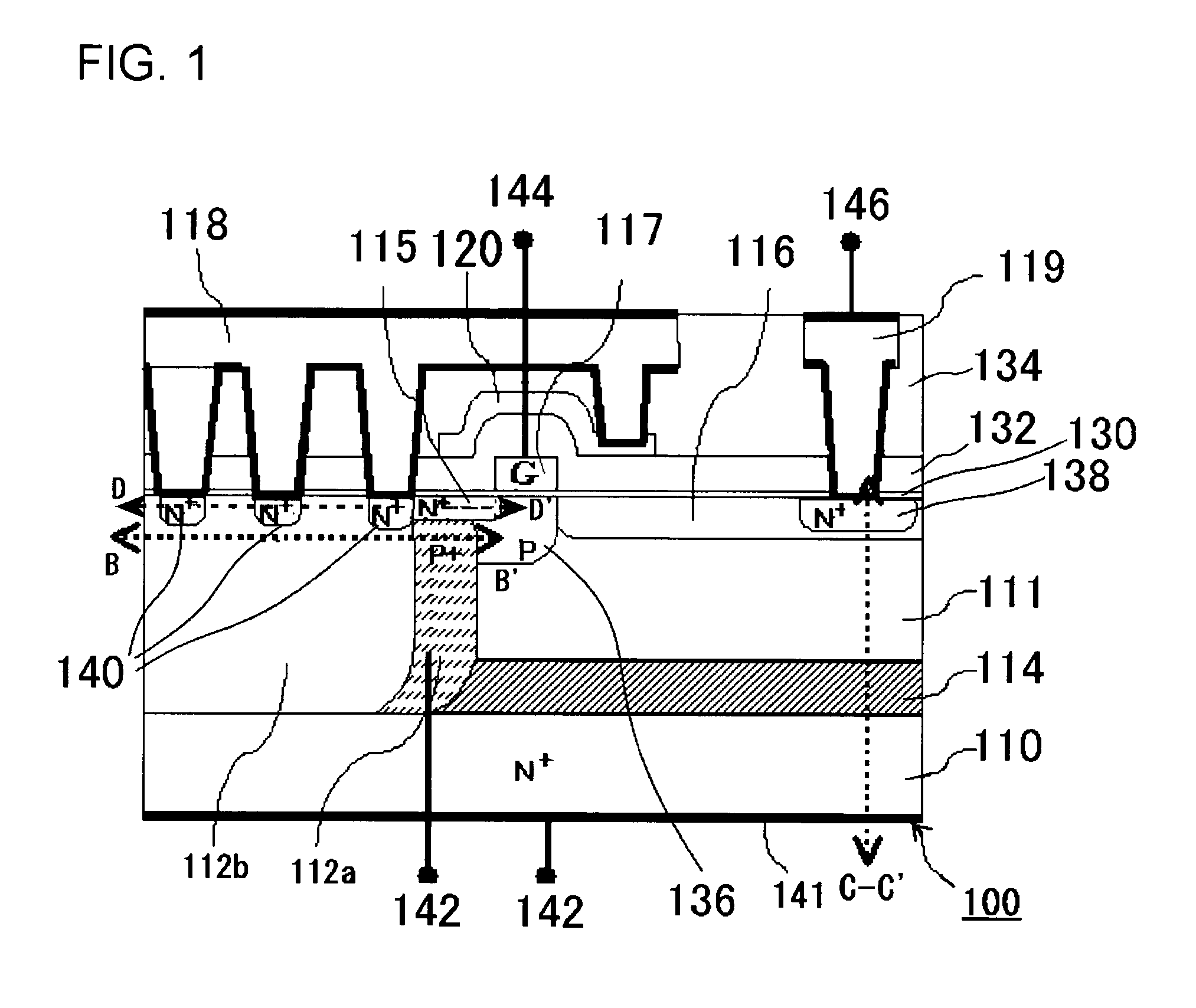

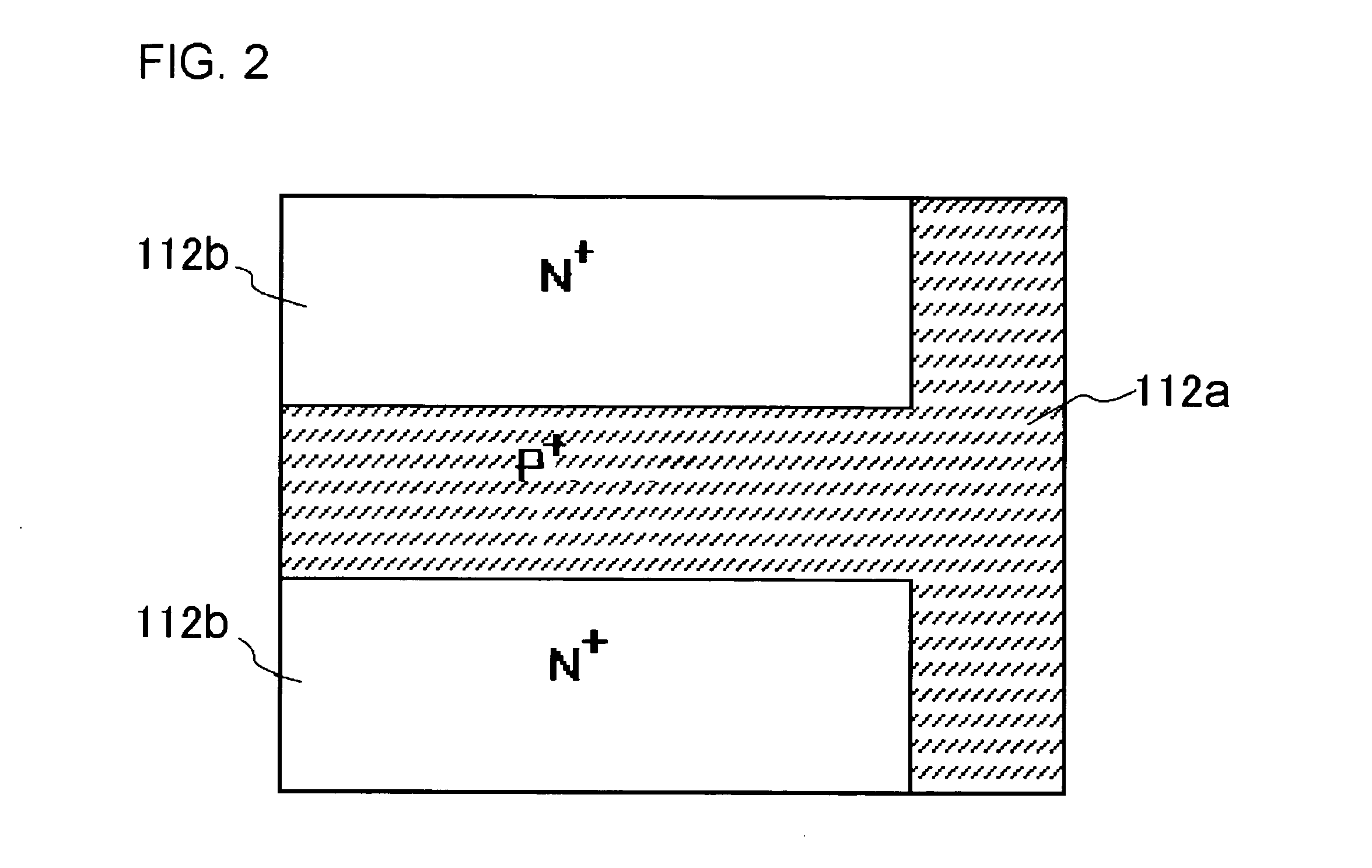

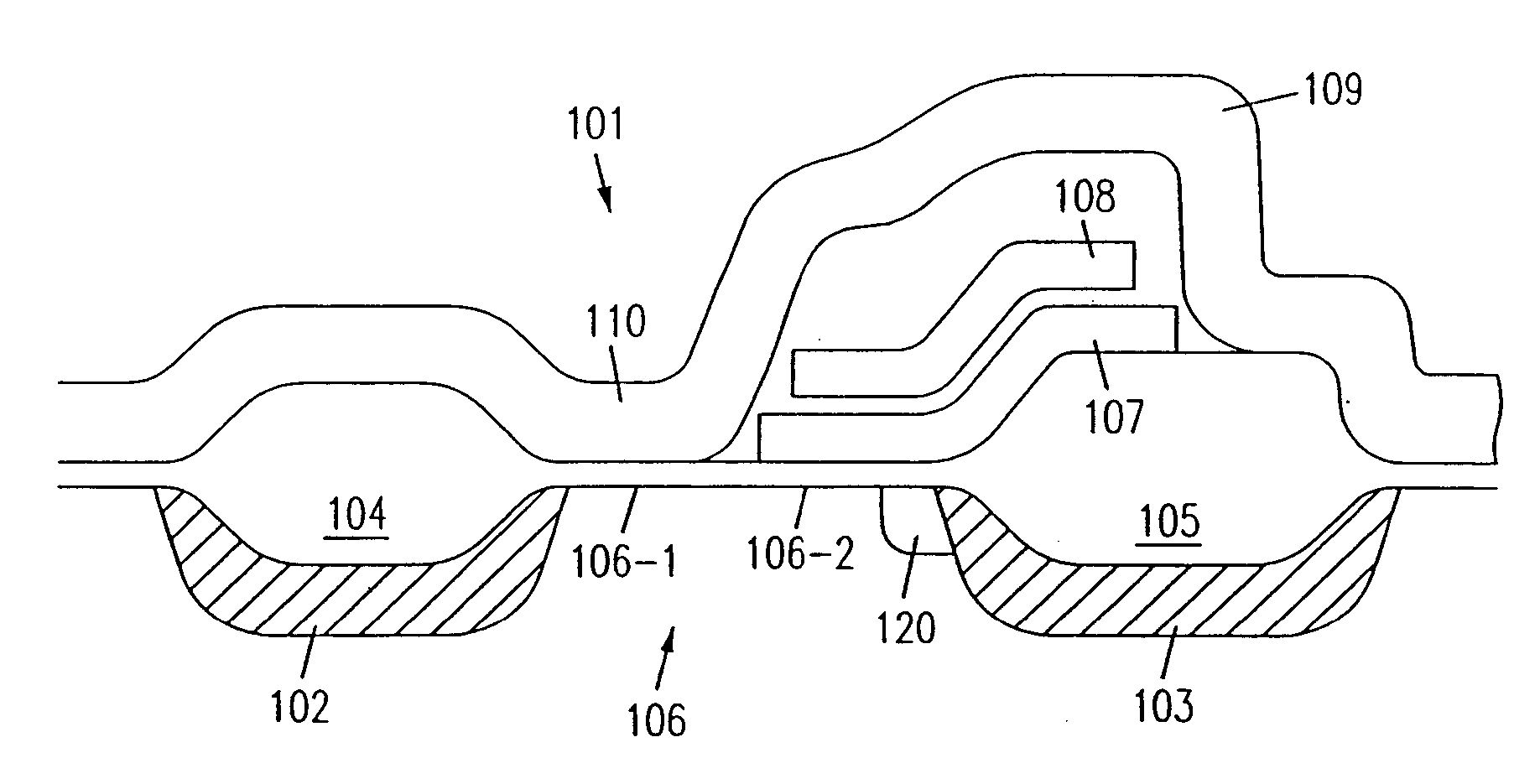

Semiconductor device

InactiveUS20050269601A1Extending of the semiconductor substrate can be preventedHigh film thicknessSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETHigh concentration

The semiconductor device comprises: a semiconductor substrate (N+ substrate 110) containing a first conductivity type impurity implanted therein; a second conductivity type impurity-implanted layer (P+ implanted layer 114) at relatively high concentration, formed on the semiconductor substrate (N+ substrate 110); a second conductivity type impurity epitaxial layer (P− epitaxial layer 111) at relatively low concentration, formed on the second conductivity type impurity-implanted layer (P+ implanted layer 114); and a field effect transistor 100 (N-channel type lateral MOSFET 100)composed of a pair of impurity diffusion regions (N+ source diffusion layer 115 and N− drain layer 116) provided in the second conductivity type impurity epitaxial layer (P− epitaxial layer 111) and a gate electrode 117 provided over a region sandwiched with the pair of impurity diffusion regions (N+ source diffusion layer 115 and N− drain layer 116).

Owner:RENESAS ELECTRONICS CORP

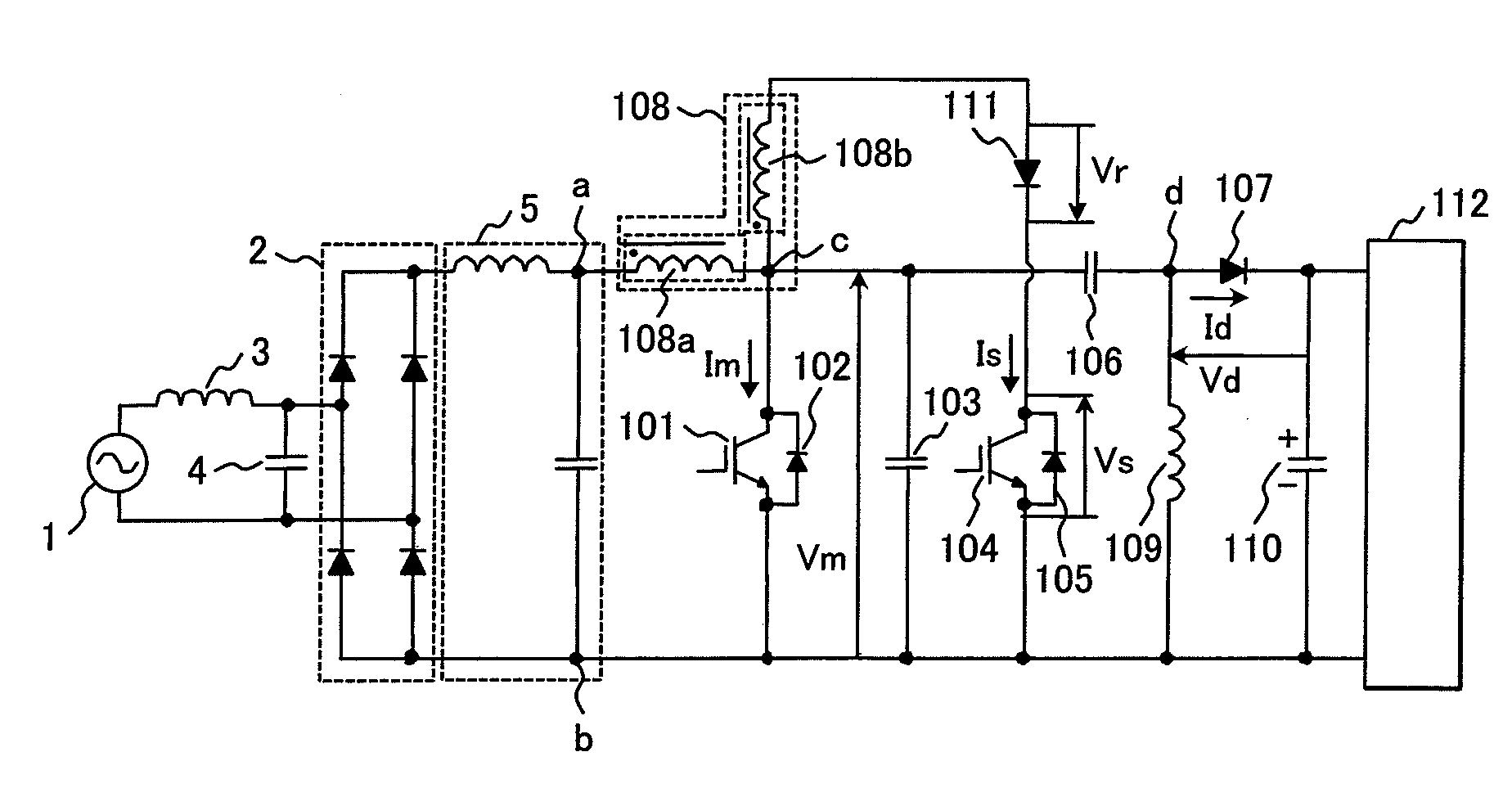

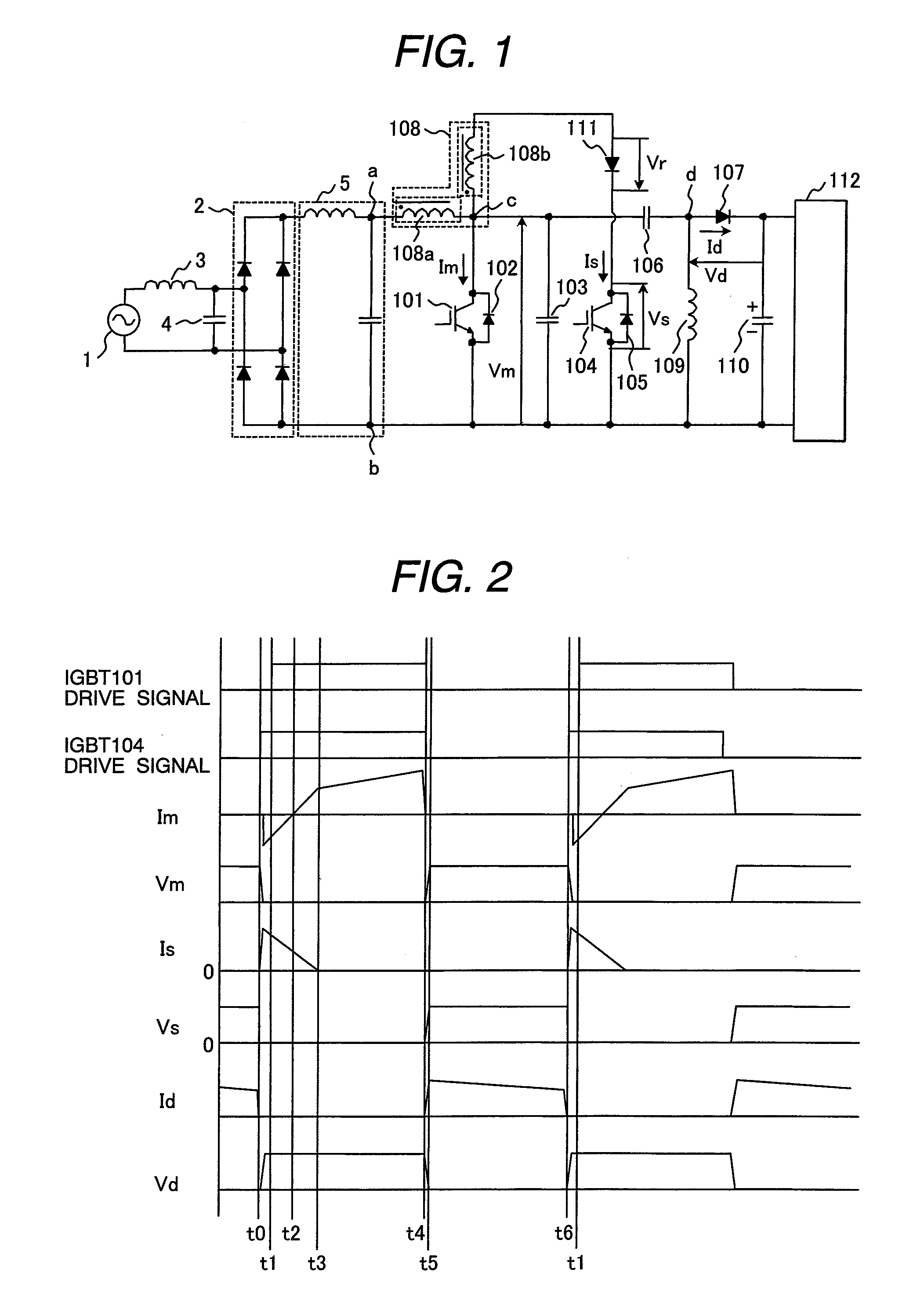

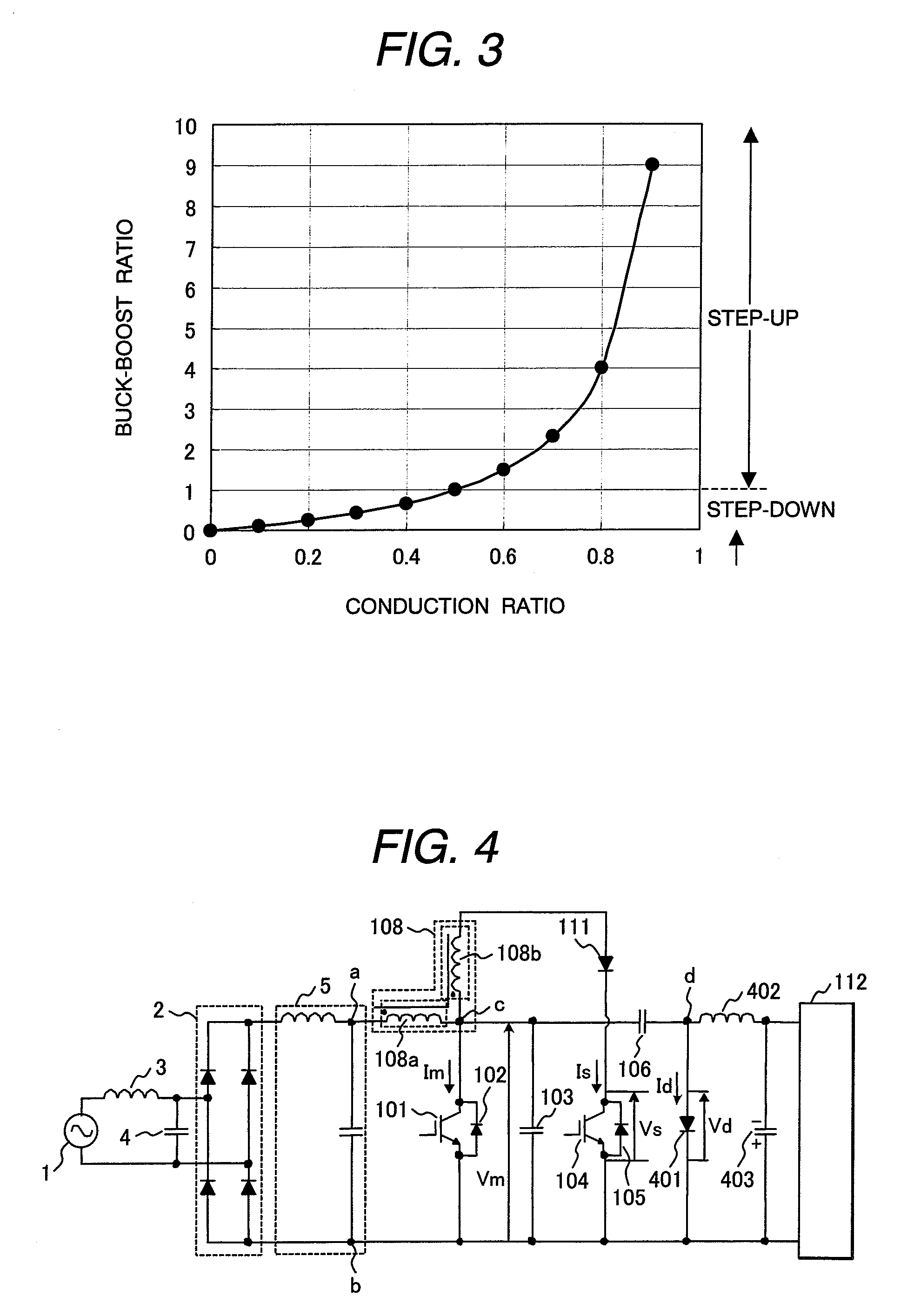

Uniderectional dc-dc converter

InactiveUS20070236966A1Reduce weight and sizeSmall capacitanceDc-dc conversionElectric variable regulationCapacitanceDc dc converter

A unidirectional DC-DC converter which has a simple control circuit without using multiple insulated power supplies, uses an auxiliary inductor of a comparatively small capacitance, reduces the size and weight of the converter, and has a very great capacitance without switching of supply current.A unidirectional DC-DC converter equipped with main IGBT101 which supplies and shuts off current for first inductor 108a and diode 107 which discharges energy from main inductor 108a to an output, wherein the DC-DC converter is further equipped with auxiliary IGBT104 which applies current to back-to-back-connected diode 102 by using energy stored in auxiliary inductor 108b which is magnetically coupled with main inductor 108a. This applies current to the back-to-back-connected diode in a short period including a time period in which the first switching element is turned on and accomplishes ZVZCS.

Owner:HITACHI LTD +1

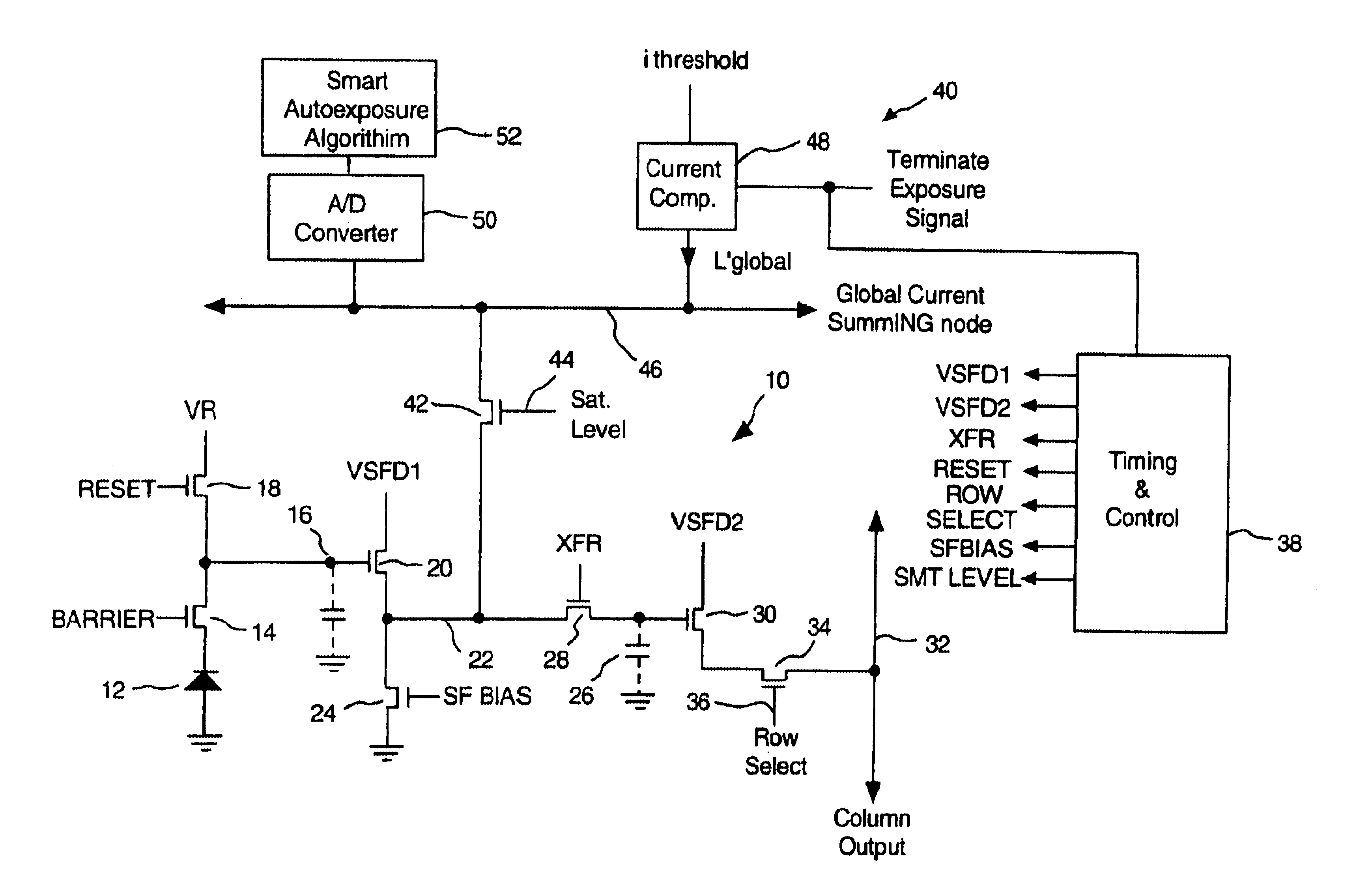

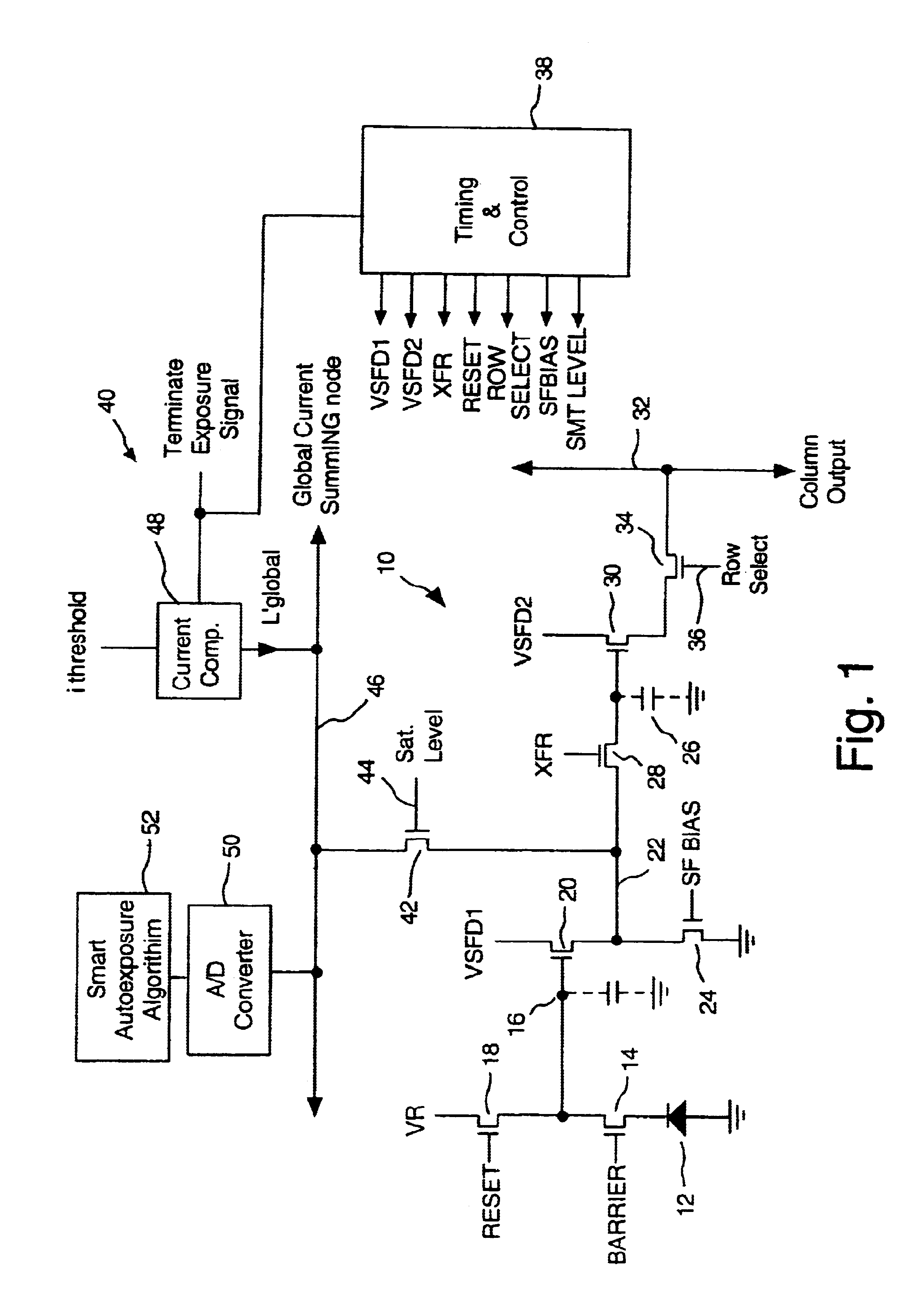

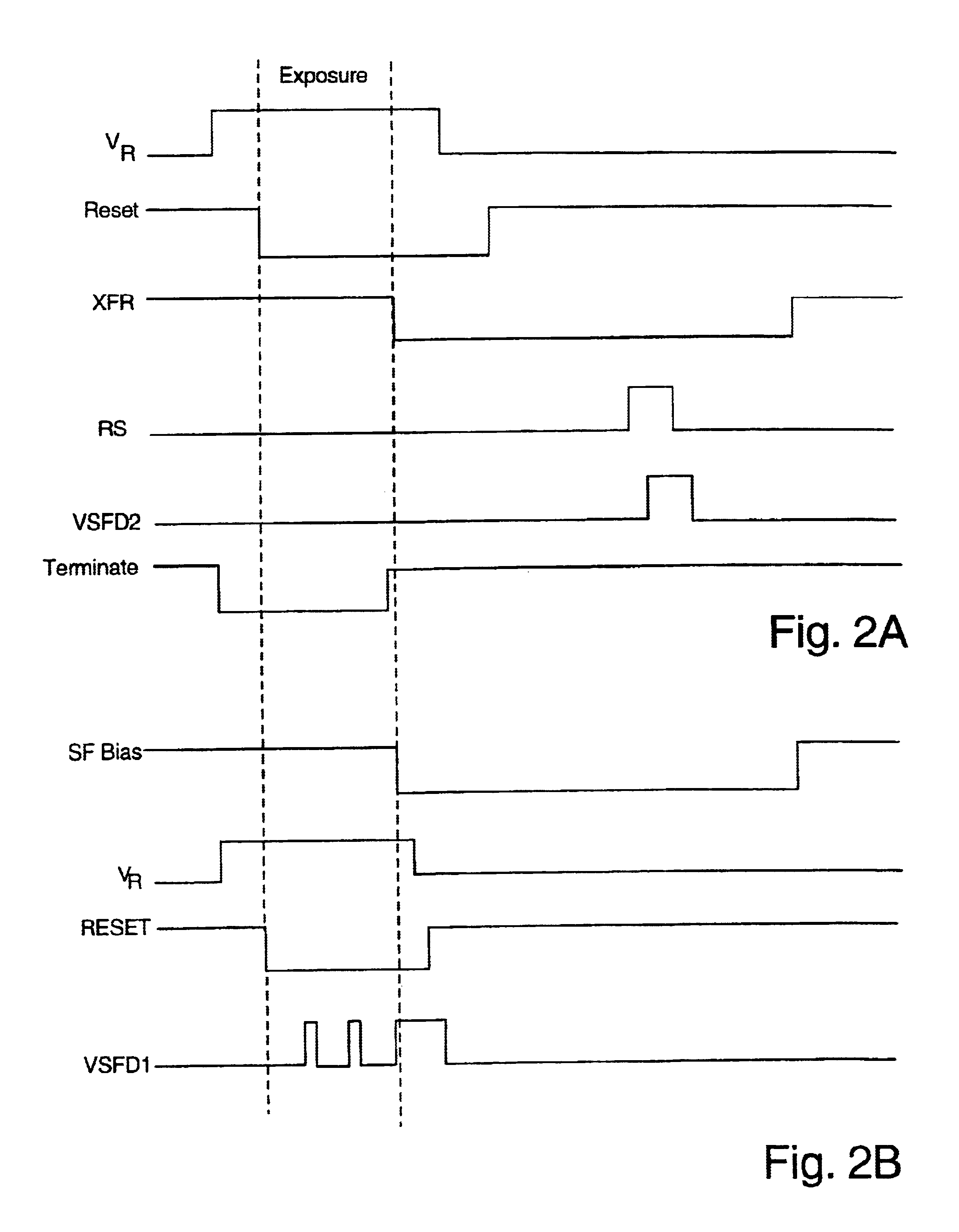

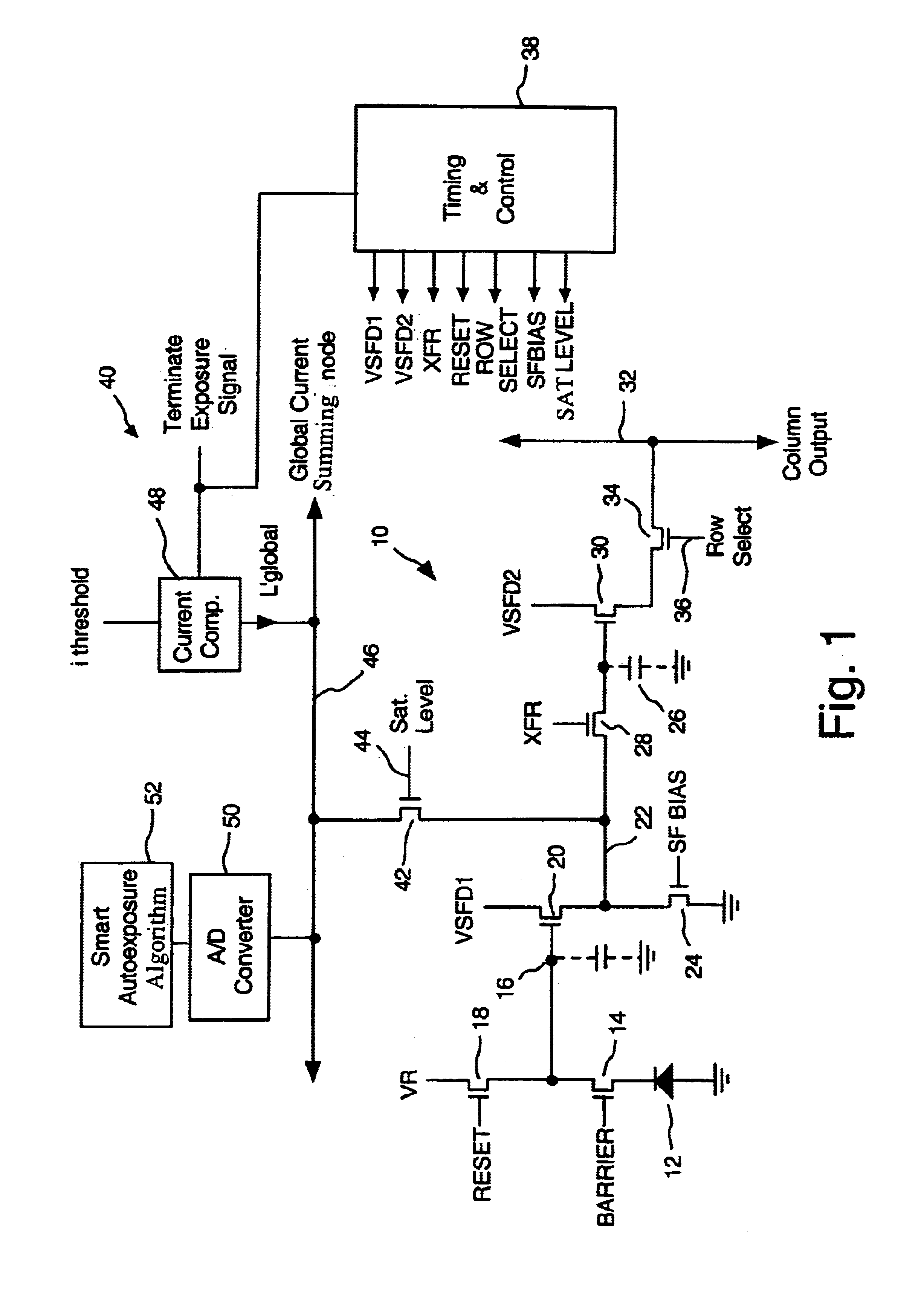

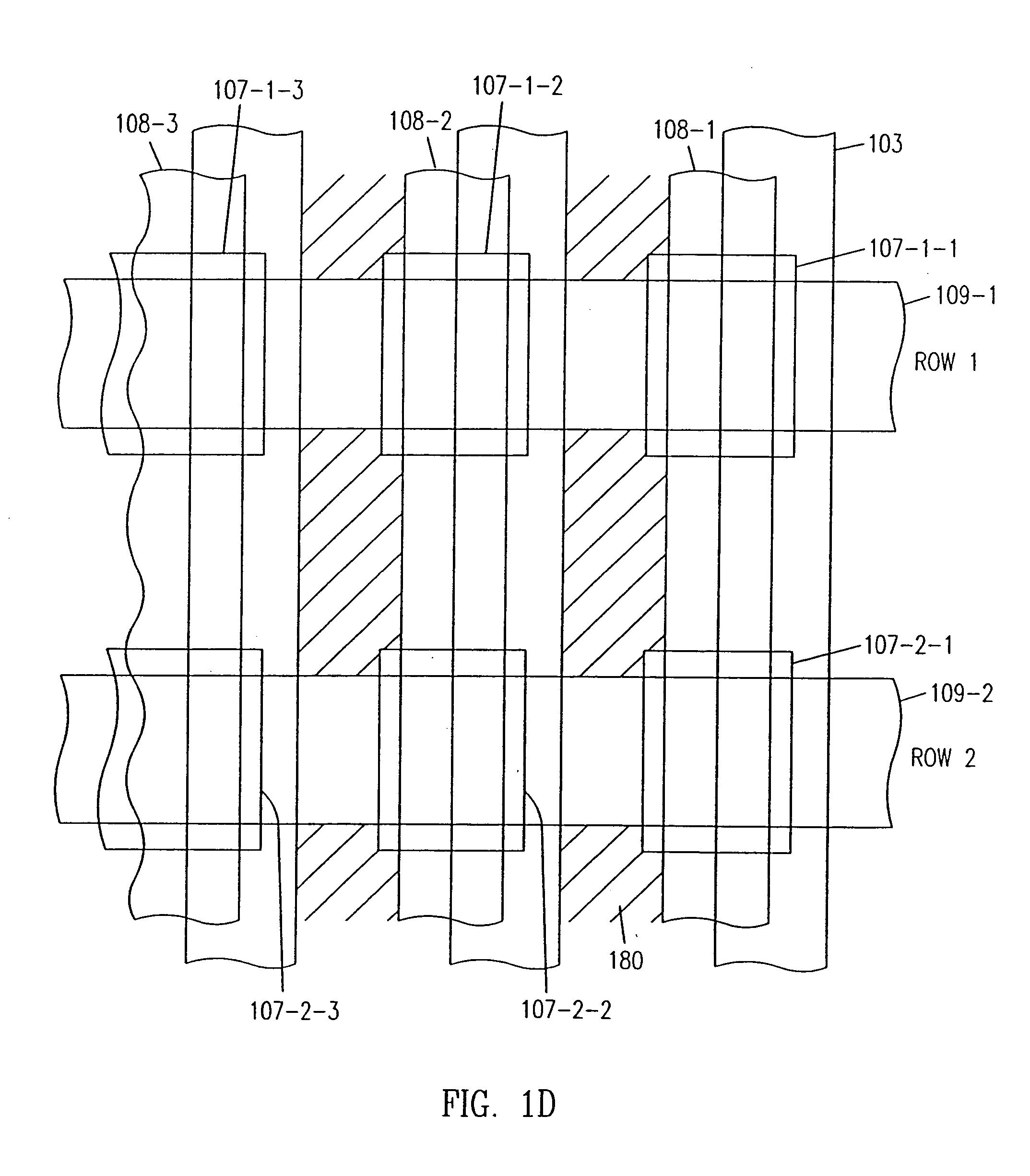

High-sensitivity storage pixel sensor array having auto-exposure detection

InactiveUS6760070B1High sensitivityReduce noiseTelevision system detailsTelevision system scanning detailsCMOS sensorSensor array

An integrated active pixel sensor array arranged in a plurality of rows and columns comprises a saturation level line coupled to a source of saturation level control voltage, a global current-summing node. A plurality of active pixel sensors is disposed in the array, each pixel sensor associated with one row and one column of the array and including a photodiode having a first terminal coupled to a first potential and a second terminal, a reset transistor having a first terminal coupled to the second terminal of the photodiode, a second terminal coupled to a reset reference potential that reverse biases the photodiode, and a control gate coupled to the reset line, a photocharge integration node coupled to the second terminal of the photodiode, the photocharge integration node comprising the gate of a first source-follower transistor, the first source-follower transistor having a drain, coupled to a first source-follower drain line, and a source, a circuit for generating a bias current at the source of the first source follower transistor, and an exposure transistor having a source coupled to the source of the first source-follower transistor, a drain coupled to the global current-summing node and a control gate coupled to the saturation level line.

Owner:FOVEON

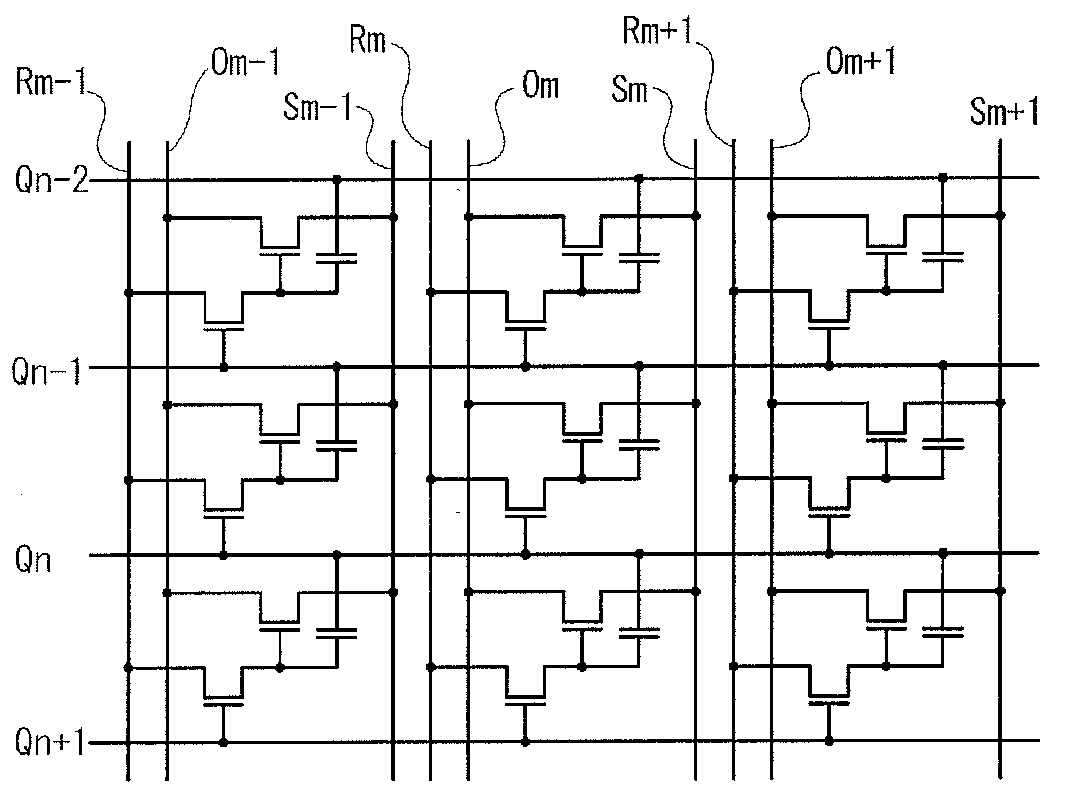

Semiconductor device, manufacturing method of the same, and electronic device

InactiveUS20060108665A1Improve featuresReduce areaTransistorHigh frequency amplifiersLower limitDevice material

The invention is directed to improve characteristics of an HBT (Hetero-junction Bipolar Transistor). An HBT has a collector layer, a base layer, and an emitter layer formed in order on a main surface of a substrate made of a compound semiconductor and a collector electrode, a base electrode, and an emitter electrode electrically connected to the collector layer, the base layer, and the emitter layer, respectively, and further has an emitter contact layer formed between the emitter electrode and the emitter layer. The plane shape of the emitter contact layer and the emitter electrode is an almost annular shape surrounding the base electrode in a plane parallel with the main surface of the substrate, and the lower limit of the emitter contact layer is 1.2 μm or larger.

Owner:RENESAS TECH CORP

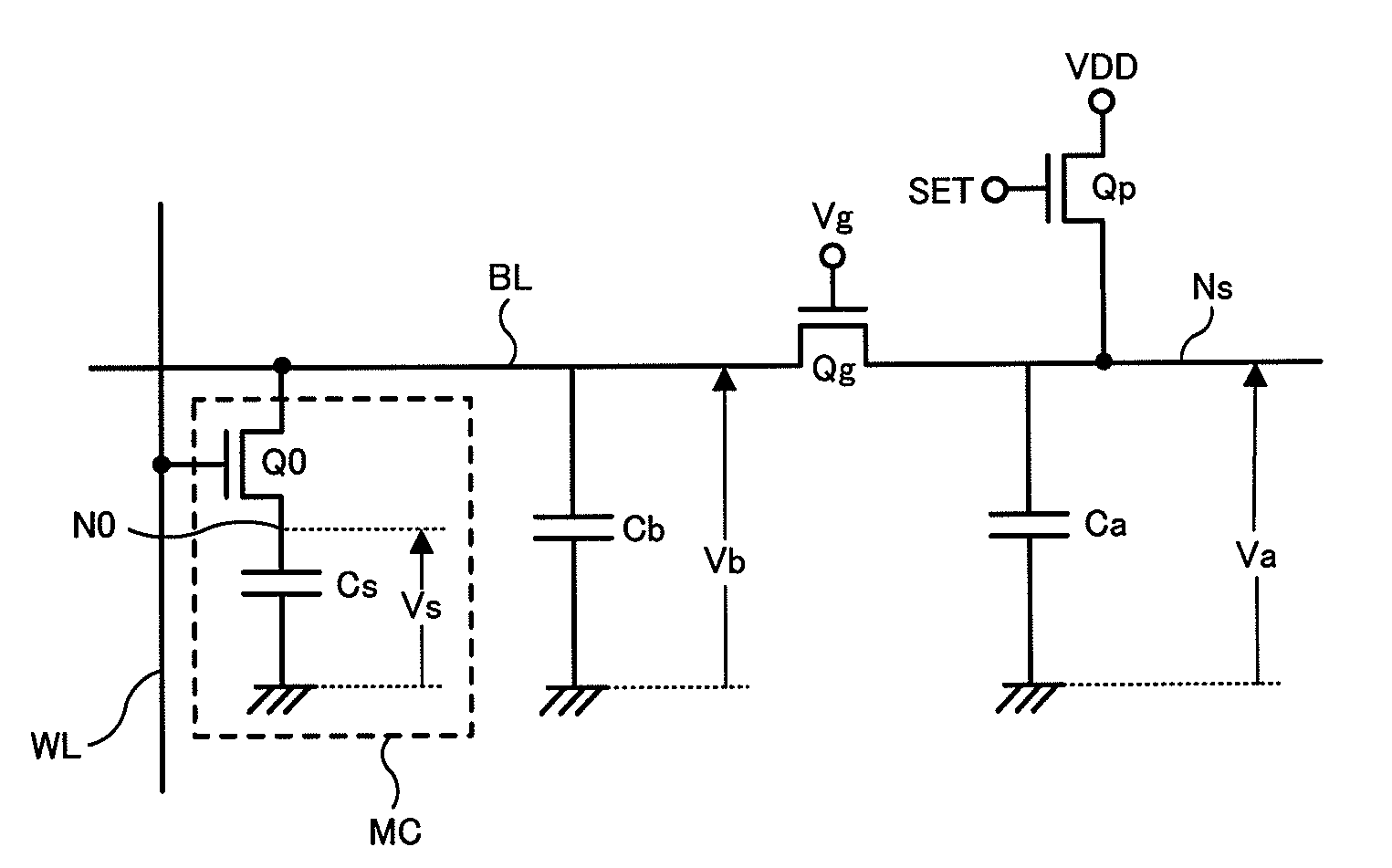

Semiconductor memory device and semiconductor device

ActiveUS20110216571A1Reduce voltageReduce variationTransistorSolid-state devicesPower semiconductor deviceEngineering

A matrix is formed using a plurality of memory cells in each of which a drain of the writing transistor is connected to a gate of a reading transistor and one electrode of a capacitor. A gate of the writing transistor, a source of the writing transistor, a source of the reading transistor, and a drain of the reading transistor are connected to a writing word line, a writing bit line, a reading bit line, and a bias line, respectively. In order to reduce the number of wirings, a writing word line to which the gate of the writing transistor is not connected is substituted for the reading word line. Further, the writing bit line is substituted for the reading bit line.

Owner:SEMICON ENERGY LAB CO LTD

EMI reduction in power modules through the use of integrated capacitors on the substrate level

InactiveUS20020126465A1Small capacitanceReduce electromagnetic interferenceMagnetic/electric field screeningSemiconductor/solid-state device detailsCapacitanceStray inductance

A high frequency, low impedance network is integrated into the substrate level of a power module for the reduction of electromagnetic interference ("EMI"). In one embodiment, capacitance is electrically connected to at least one of the positive conducting layer in a substrate or the negative conducting layer in a substrate and a ground. Integrating a capacitive network of low stray inductance in a substrate of a power module allows relatively small, inexpensive capacitors to be used.

Owner:CONTINENTAL AUTOMOTIVE SYST INC

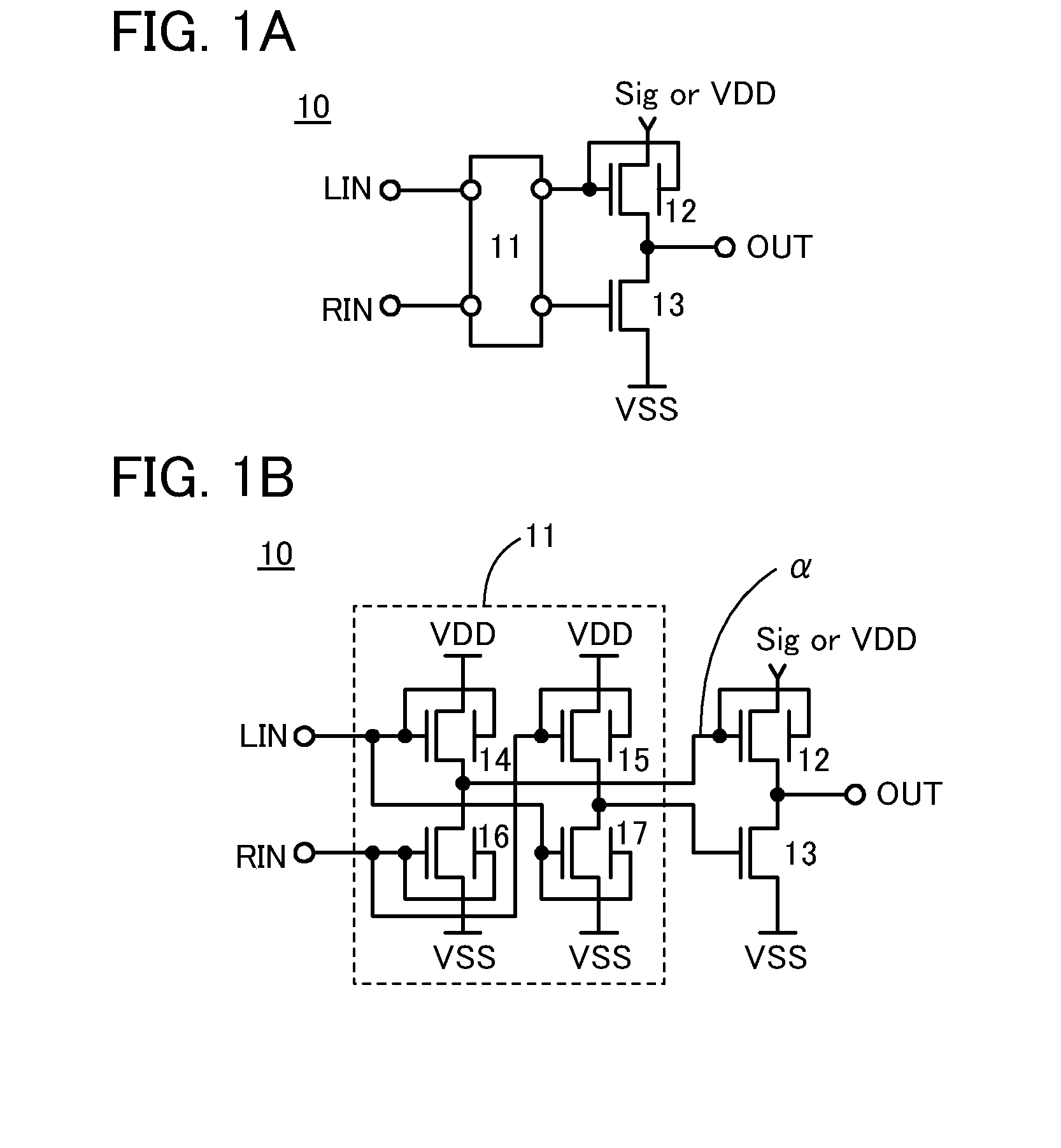

Sequential circuit and semiconductor device

ActiveUS20140362324A1Small sizeReduce areaSolid-state devicesNon-linear opticsDriver circuitElectricity

The following semiconductor device provides high reliability and a narrower frame width. The semiconductor device includes a driver circuit and a pixel portion. The driver circuit has a first transistor including a first gate and a second gate electrically connected to each other with a semiconductor film sandwiched therebetween, and a second transistor electrically connected to the first transistor. The pixel portion includes a third transistor, a liquid crystal element, and a capacitor. The liquid crystal element includes a first transparent conductive film electrically connected to the third transistor, a second conductive film, and a liquid crystal layer. The capacitor includes the first conductive film, a third transparent conductive film, and a nitride insulating film. The nitride insulating film is positioned between the first transparent conductive film and the third transparent conductive film, and positioned between the semiconductor film and the second gate of the first transistor.

Owner:SEMICON ENERGY LAB CO LTD

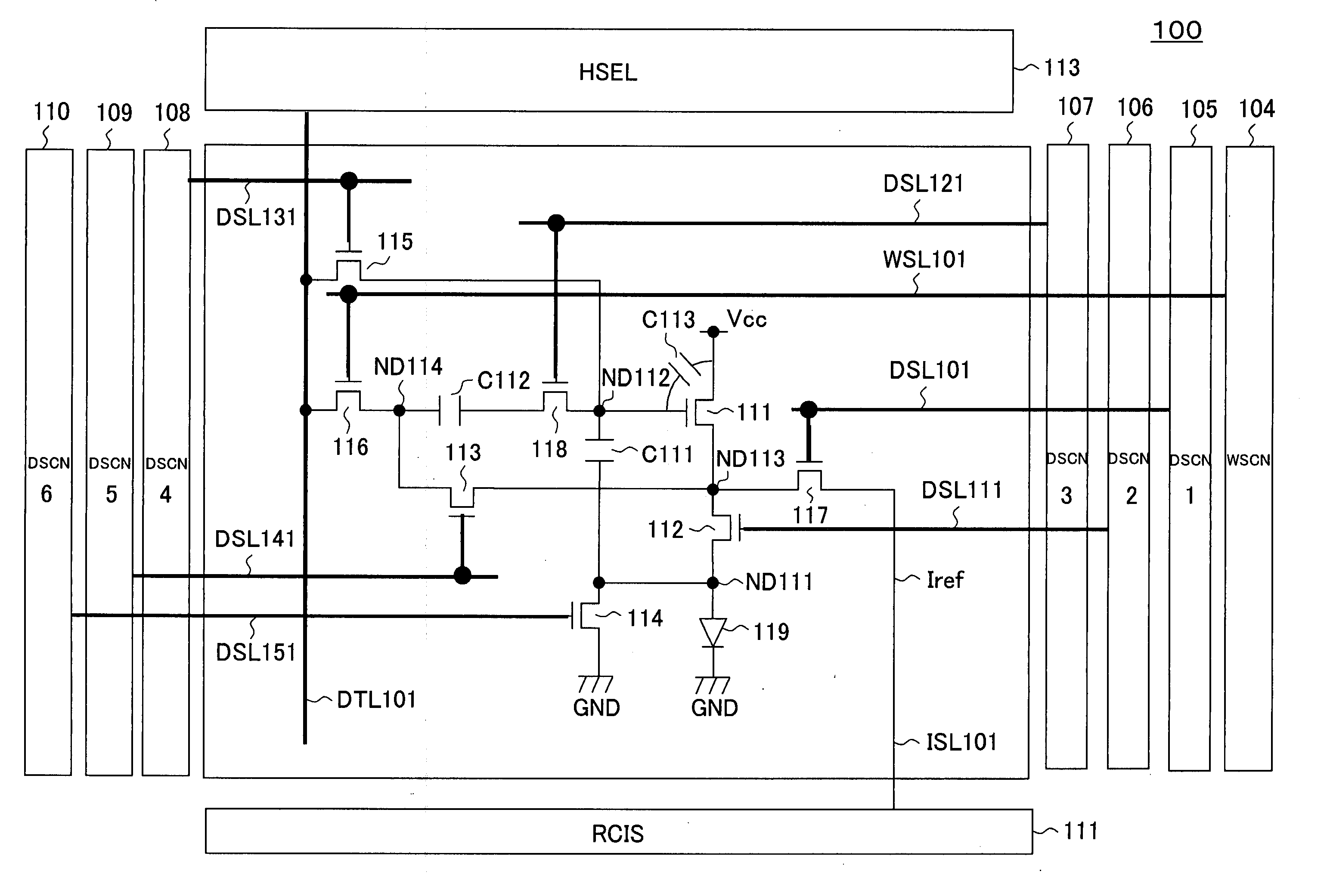

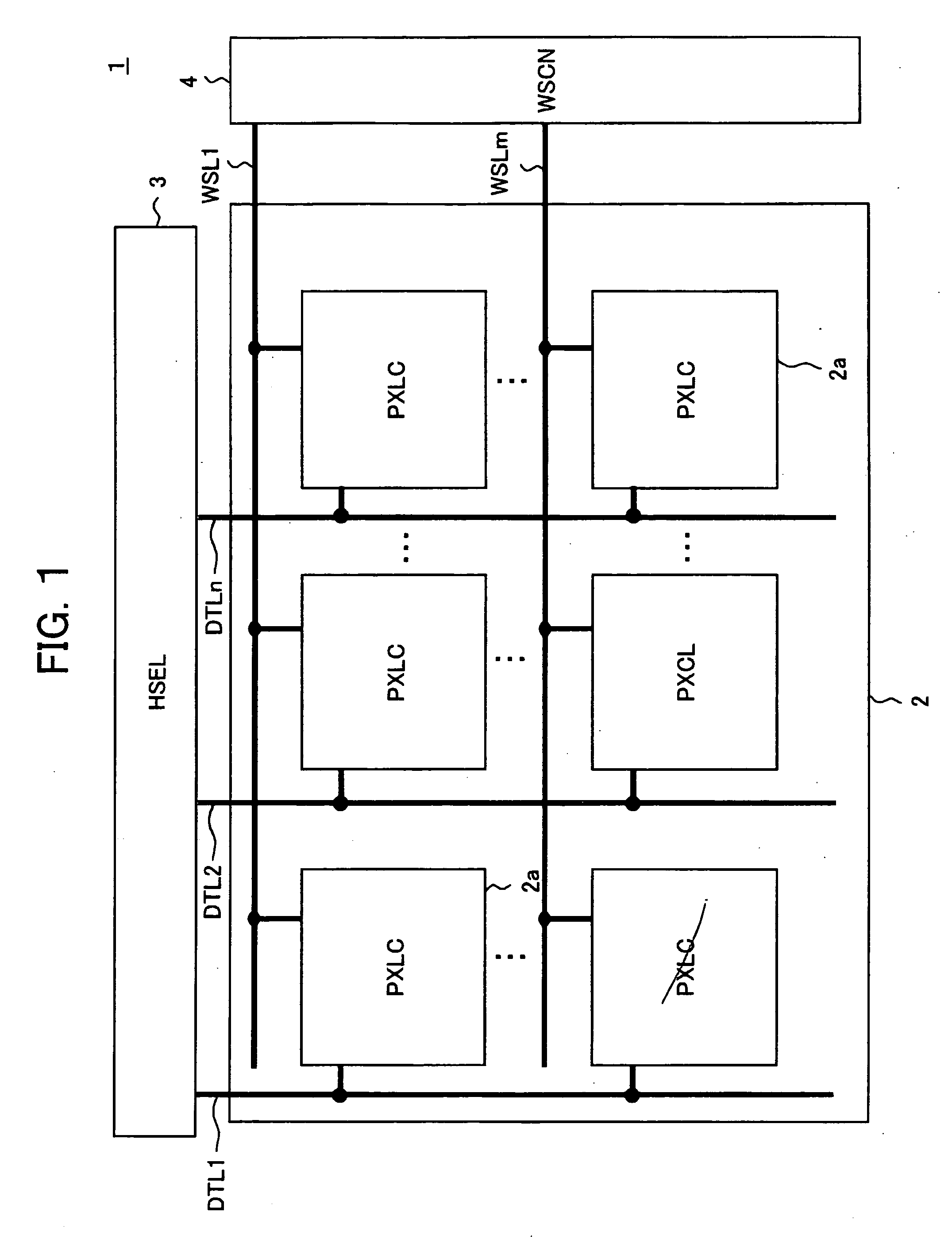

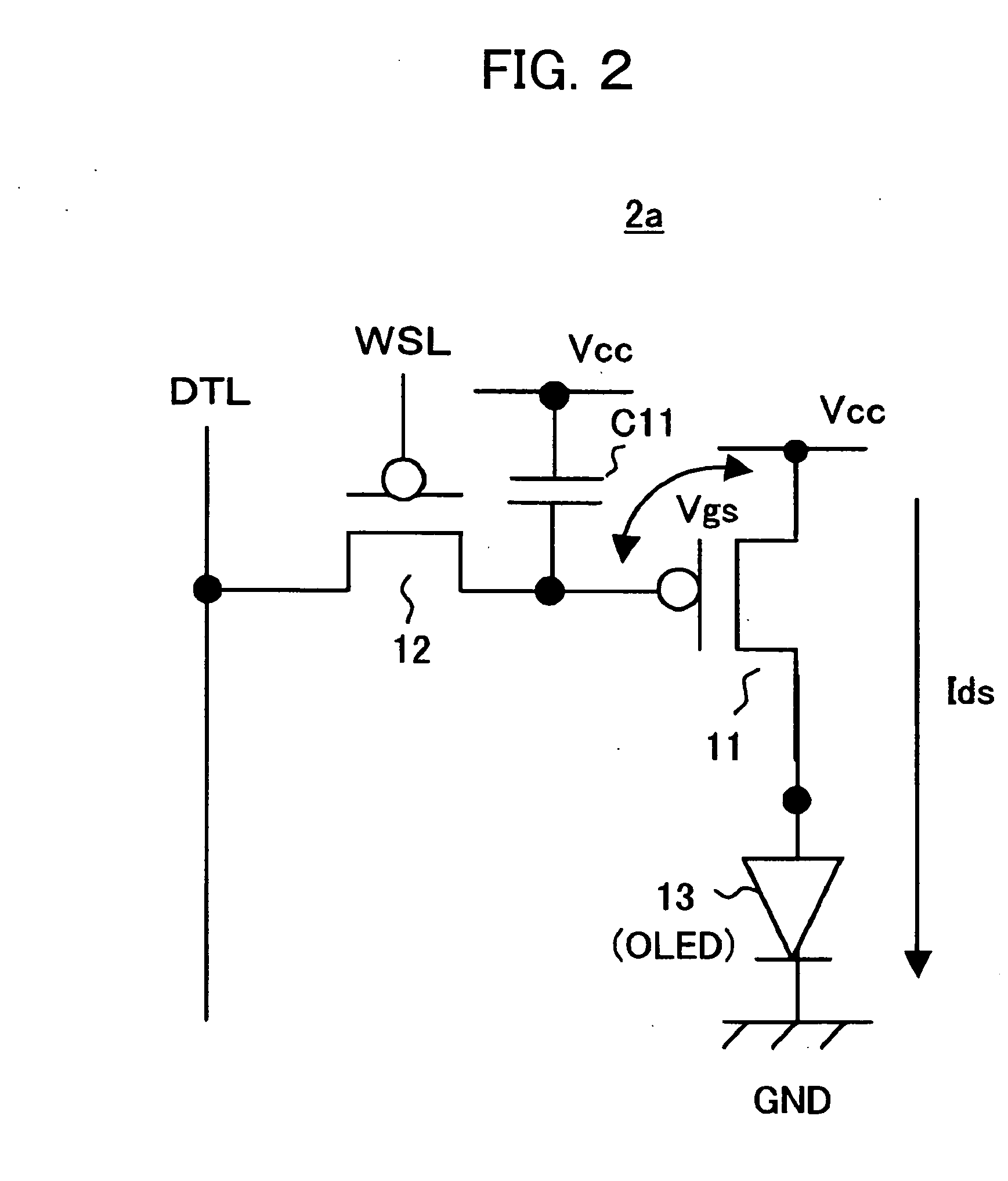

Pixel circuit, display device, and method of driving pixel circuit

InactiveUS20070052644A1Without luminance deteriorationImprove uniformityTransistorElectroluminescent light sourcesReference currentDisplay device

A pixel circuit, a display device, and a method of driving a pixel circuit able to obtain a source-follower output without luminance deterioration even when the current-voltage characteristic of a light emitting element changes due to aging, making a source-follower circuit of n-channel transistors possible, and in addition able to display uniform and high quality images not without regard to variations of threshold values and mobilities of the active elements inside pixels, wherein a capacitor C111 is connected between a gate and a source of a TFT 111, the source side of the TFT 111 is connected to a fixed potential (GND) through a TFT 114, a predetermined reference current Iref is supplied to the source of the TFT 111 with a predetermined timing, a voltage corresponding to the reference current Iref is held, and an input signal voltage centered about the voltage is coupled, whereby an EL light emitting element 19 is driven centered about the center value of variation of the mobilities.

Owner:SONY CORP

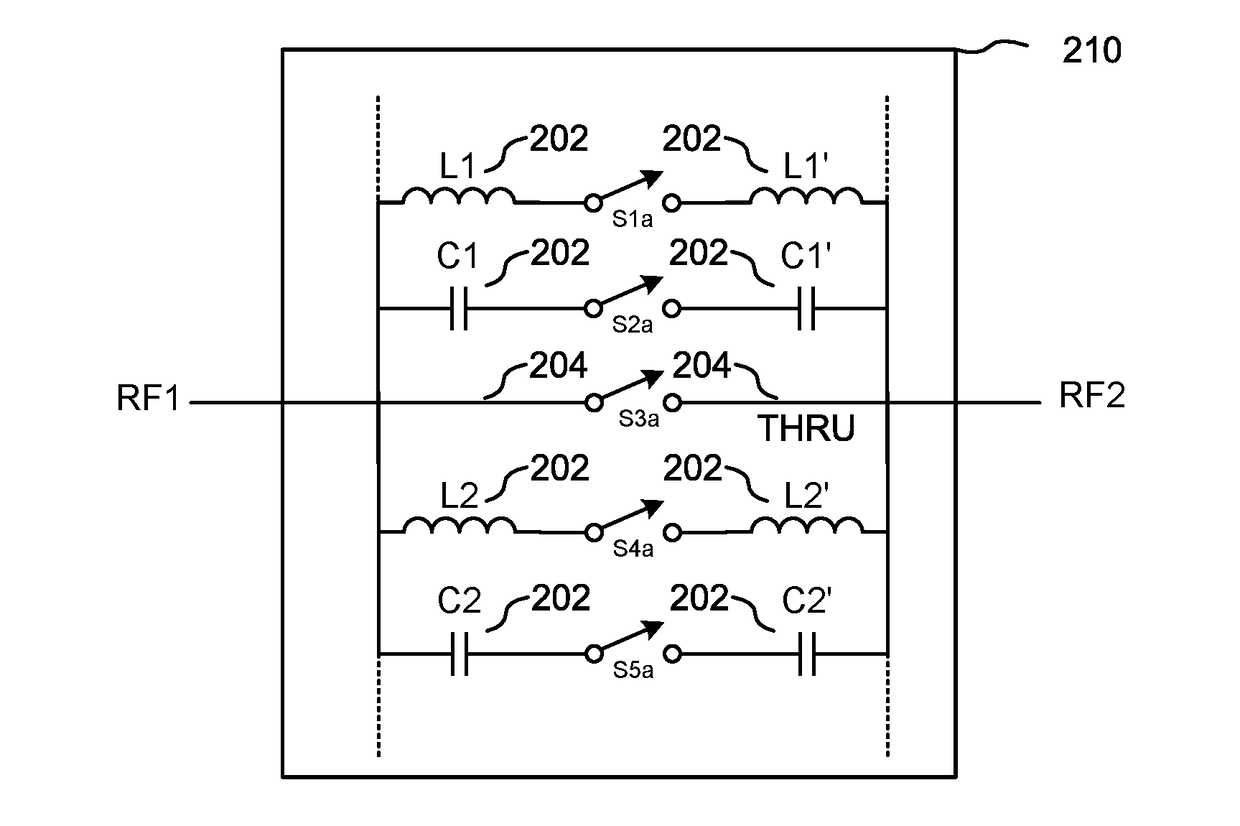

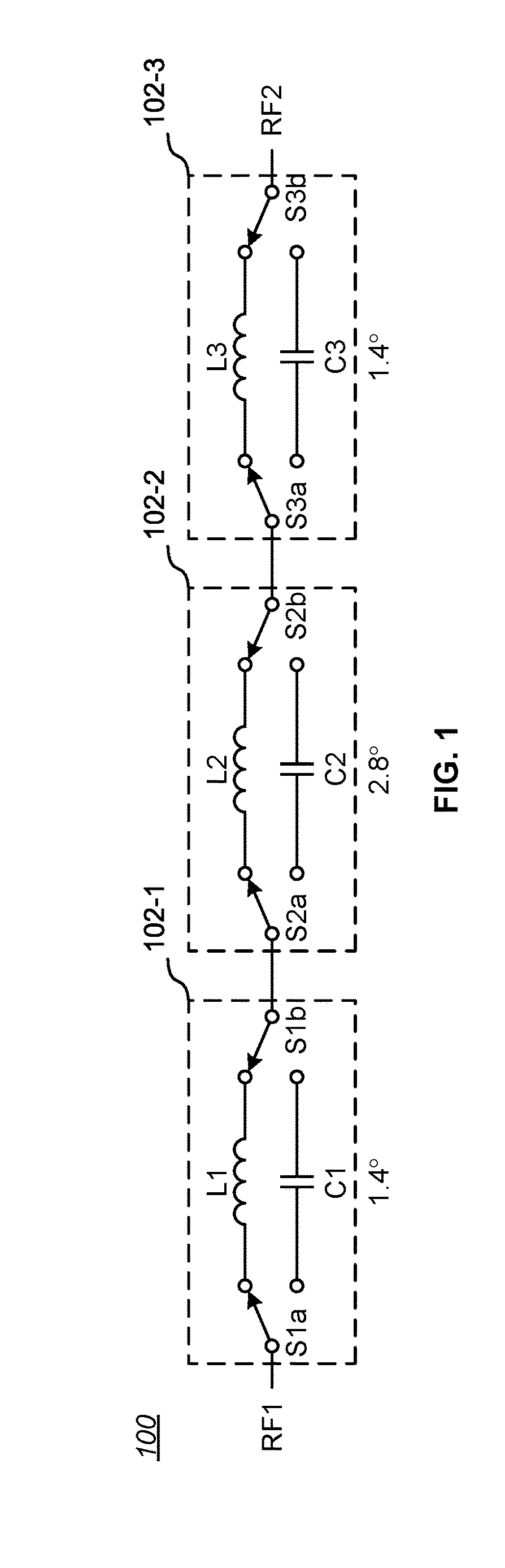

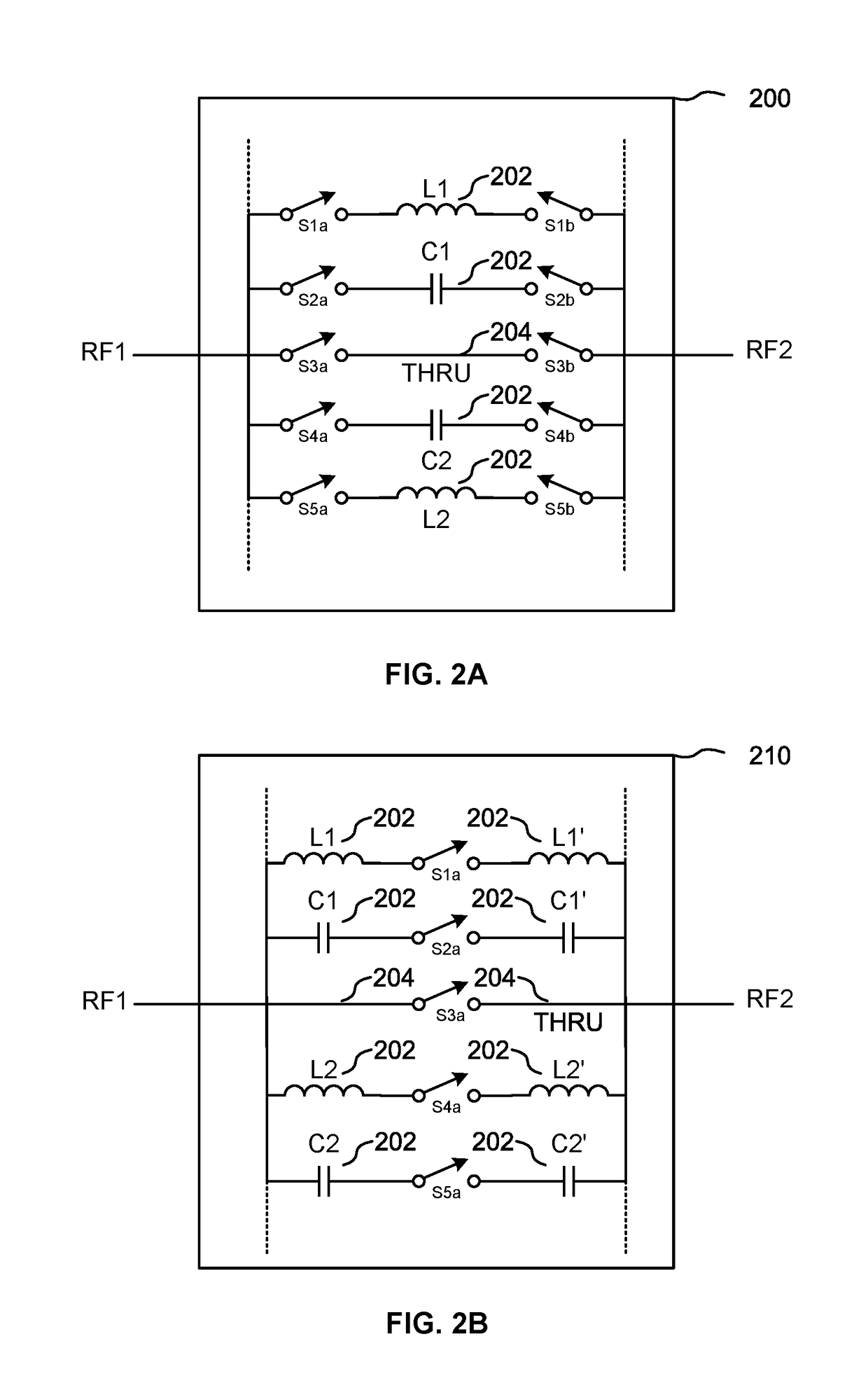

Low Loss Multi-State Phase Shifter

ActiveUS20170230028A1Low insertion lossGood return lossMultiple-port networksElectrical conductorPhase shifted

A multi-state phase shifter circuit having both low insertion loss (IL) and good return loss. Two or more phase shift elements are combined into a single cell architecture to reduce the number of series-connected FET switches and reduce the total IL. One embodiment has two ports connected by parallel signal paths each comprising a pair of switches and a phase shift element comprising, for example, an inductor, a capacitor, a transmission line, or a conductor. Another embodiment has two ports connected by parallel signal paths each comprising a switch and at least one associated phase shift element. The switches in each parallel signal path allow the associated phase shift element to be placed in-circuit under the control of an applied signal. The sets of switches may be independently controlled, so that multiple parallel signal paths may be switched into circuit between the phase shifter circuit ports at the same time.

Owner:PSEMI CORP

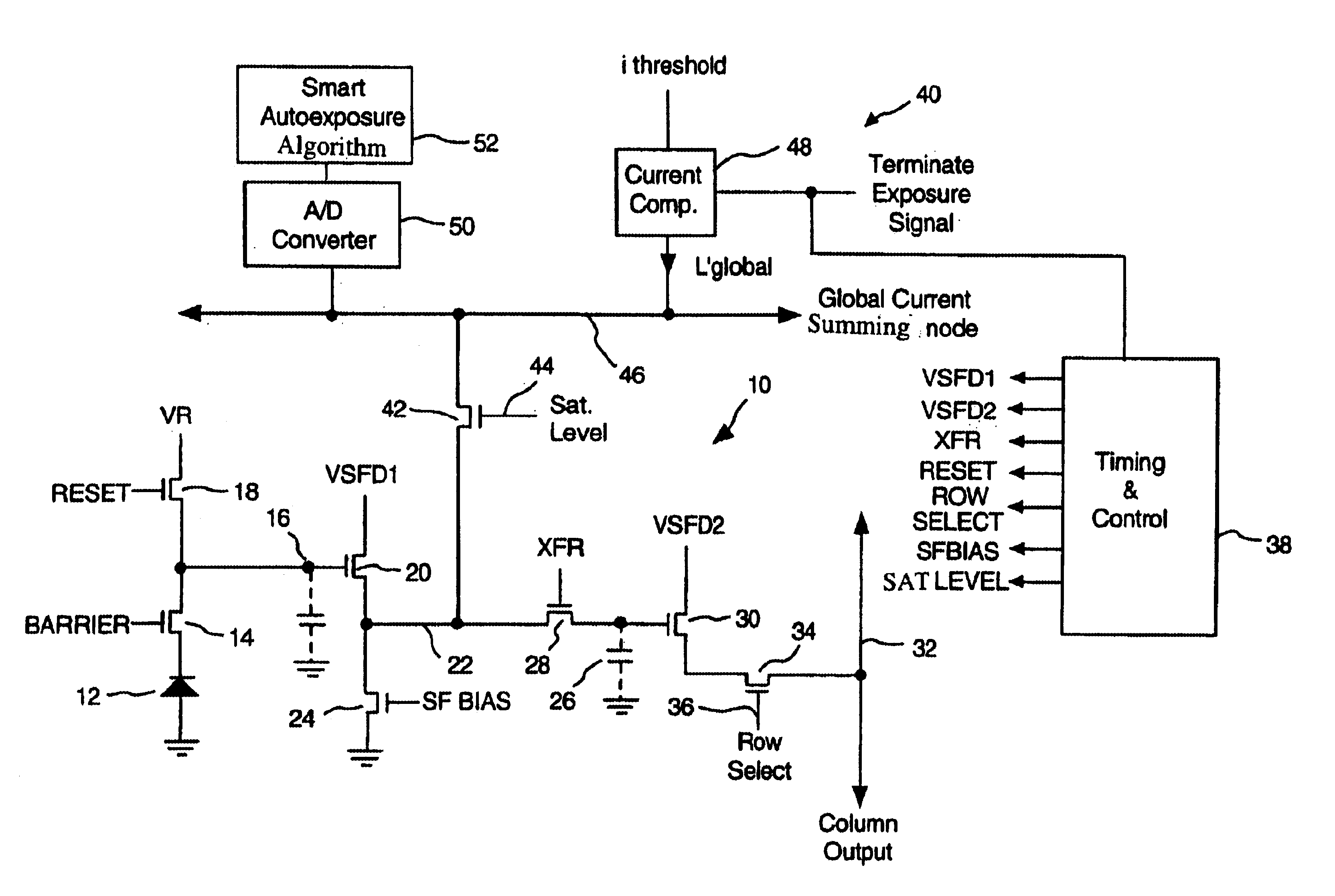

High-sensitivity storage pixel sensor having auto-exposure detection

InactiveUS6882367B1High sensitivityReduce noiseTelevision system detailsTelevision system scanning detailsCapacitanceCapacitive storage

A storage pixel sensor disposed on a semiconductor substrate comprises a photodiode having a first terminal coupled to a first potential and a second terminal. A barrier transistor has a first terminal coupled to the second terminal of the photodiode, a second terminal and a control gate coupled to a barrier set voltage. A reset transistor has a first terminal coupled to the second terminal of the barrier transistor, a second terminal coupled to a reset reference potential that reverse biases the photodiode, and a control gate coupled to a source of a RESET signal. A photocharge integration node is coupled to said second terminal of said barrier transistor. The photocharge integration node comprises the control gate of a first source-follower transistor. The first source-follower transistor is coupled to a source of bias current and has an output. A capacitive storage node is coupled to the output of the first source-follower transistor and comprises the control gate of a second source-follower transistor having an output. An exposure transistor is coupled between the output of the first source-follower transistor and a global current-summing node and has a control gate coupled to a saturation level voltage.

Owner:FOVEON

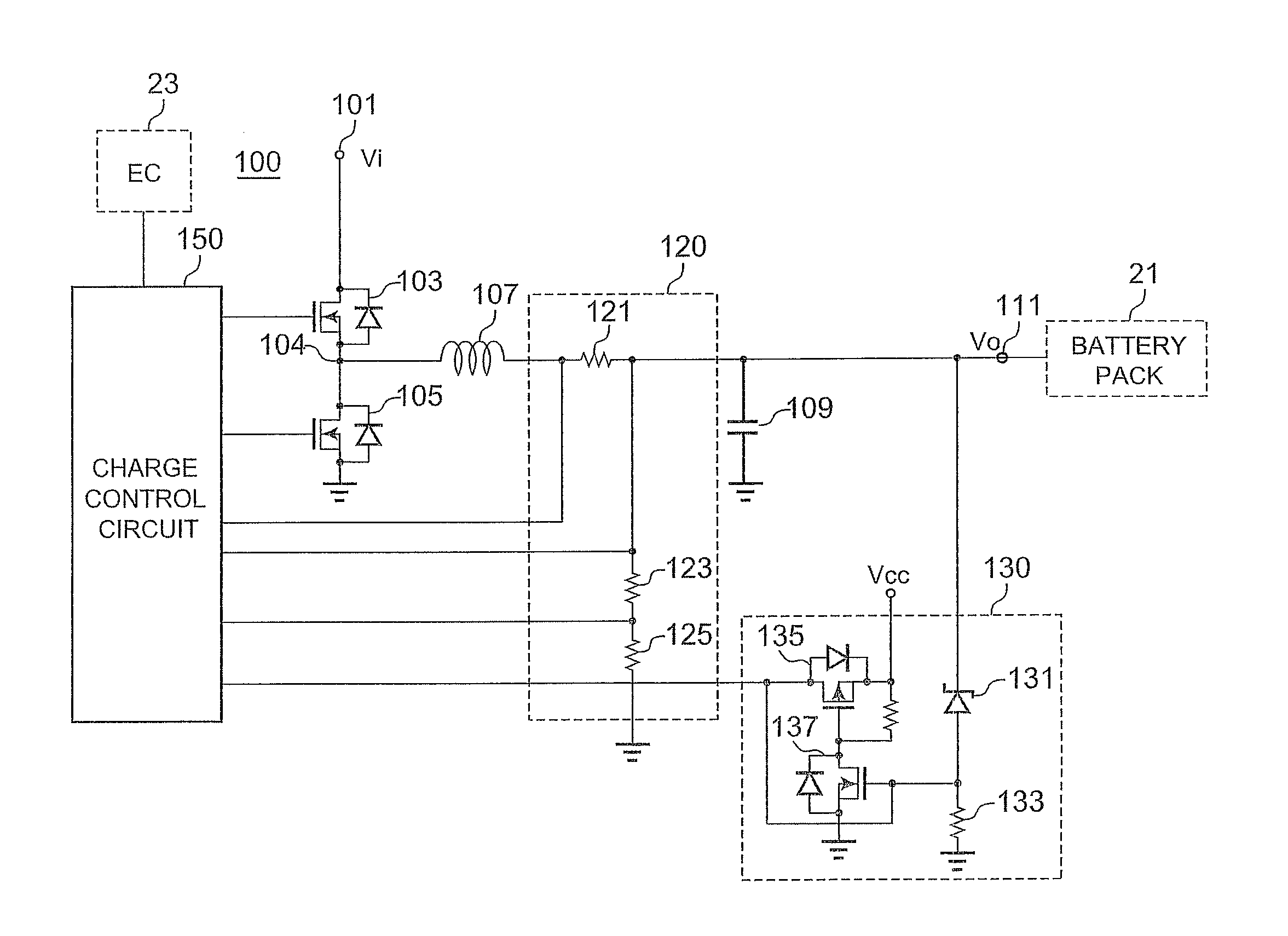

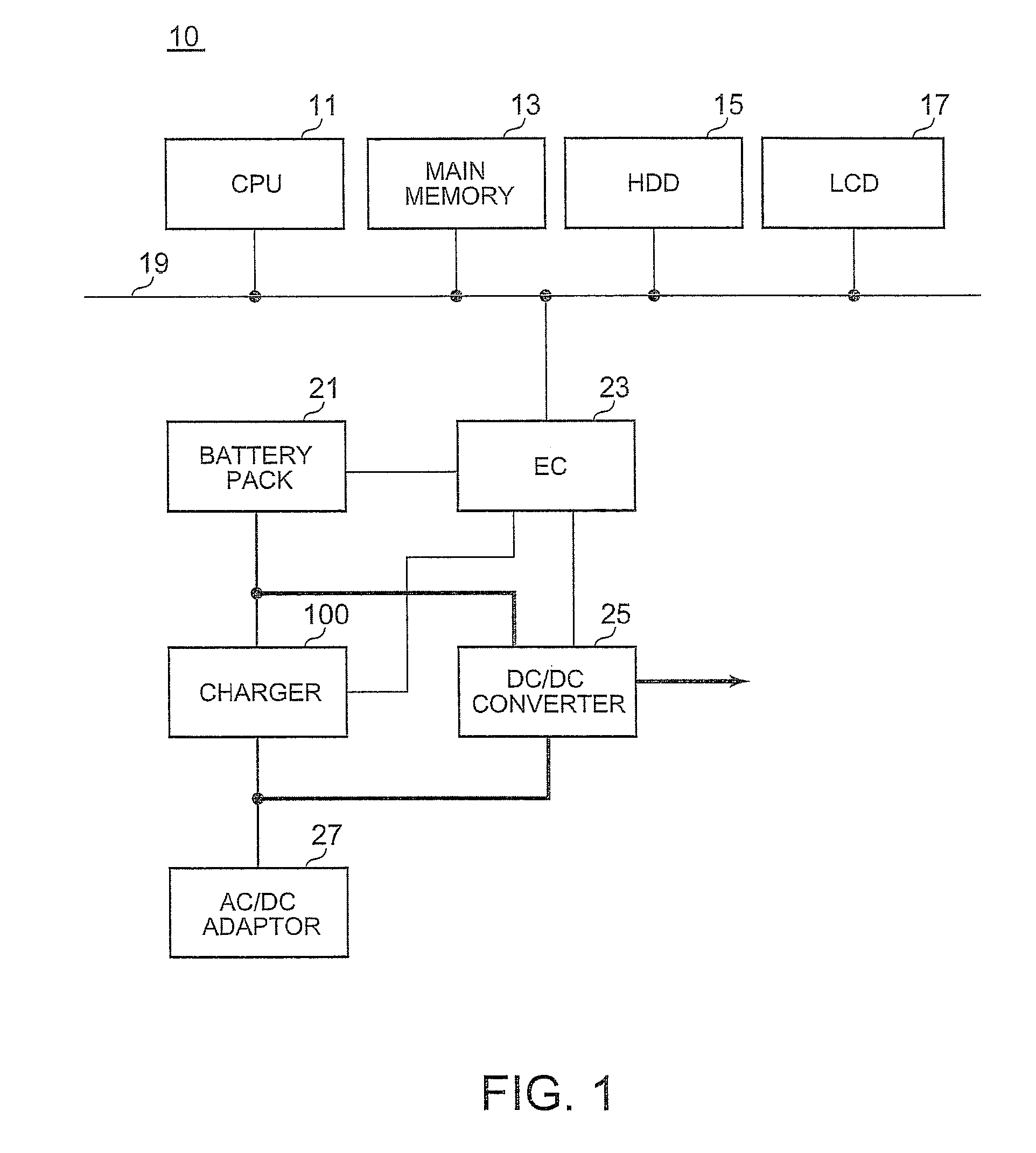

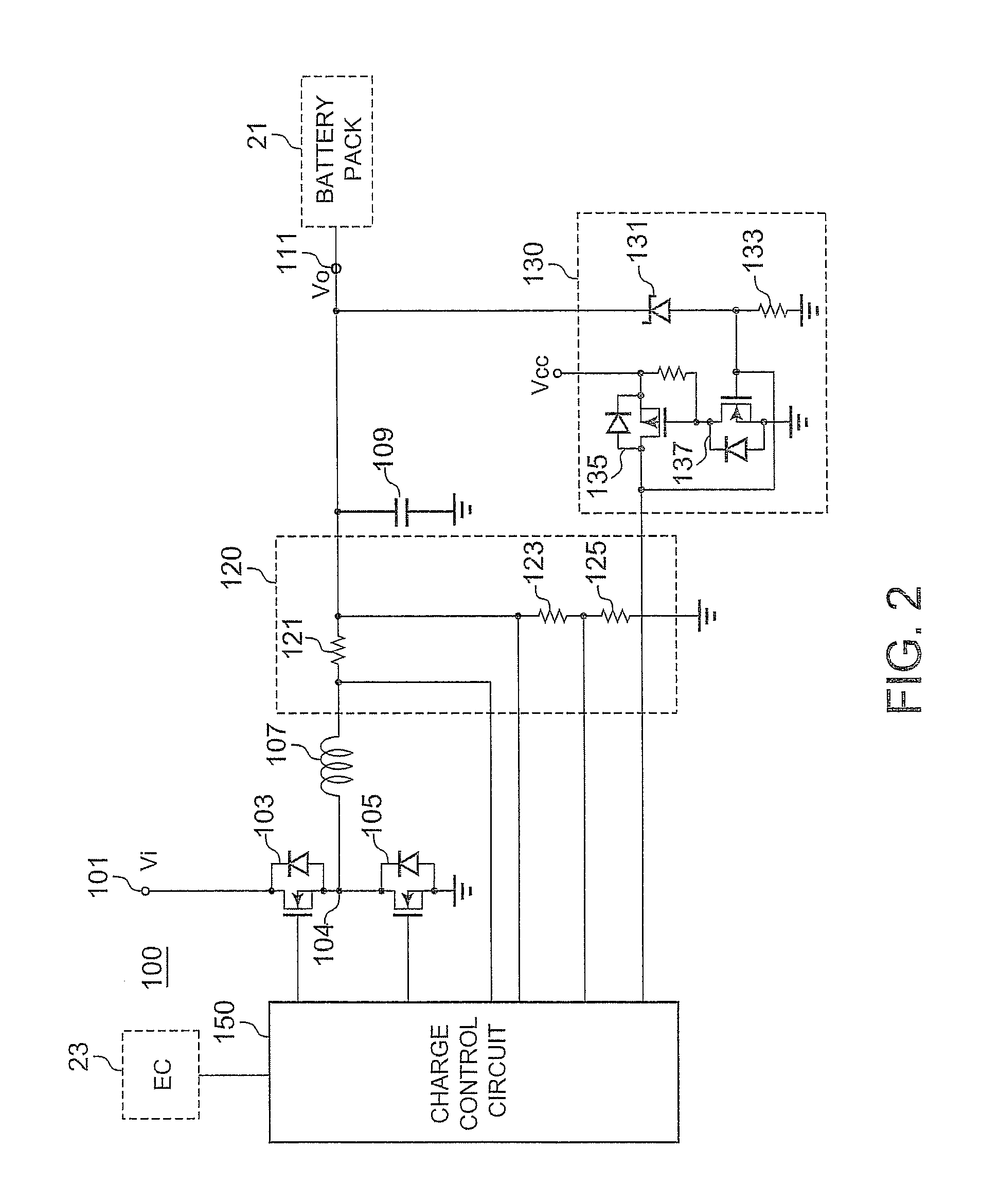

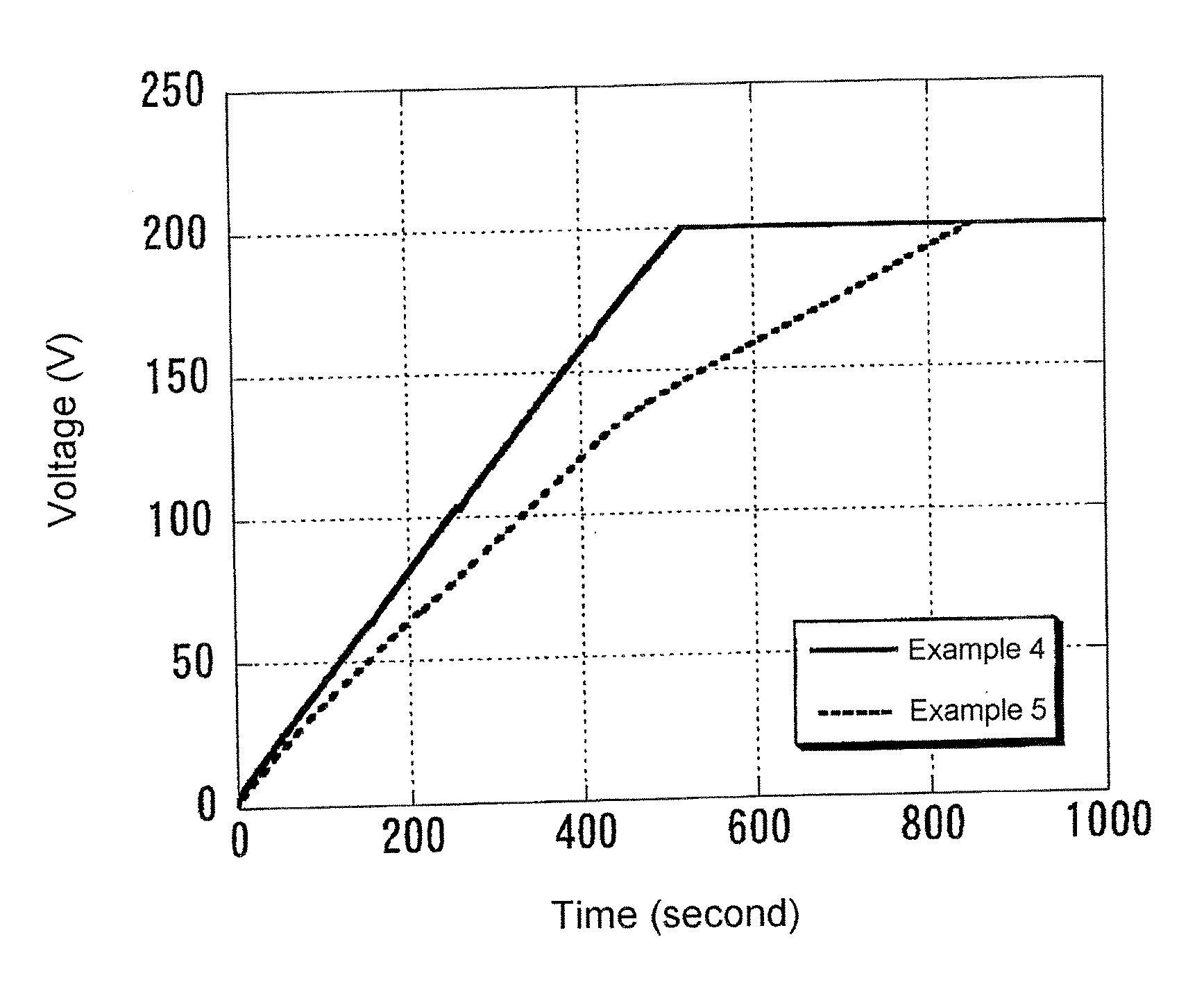

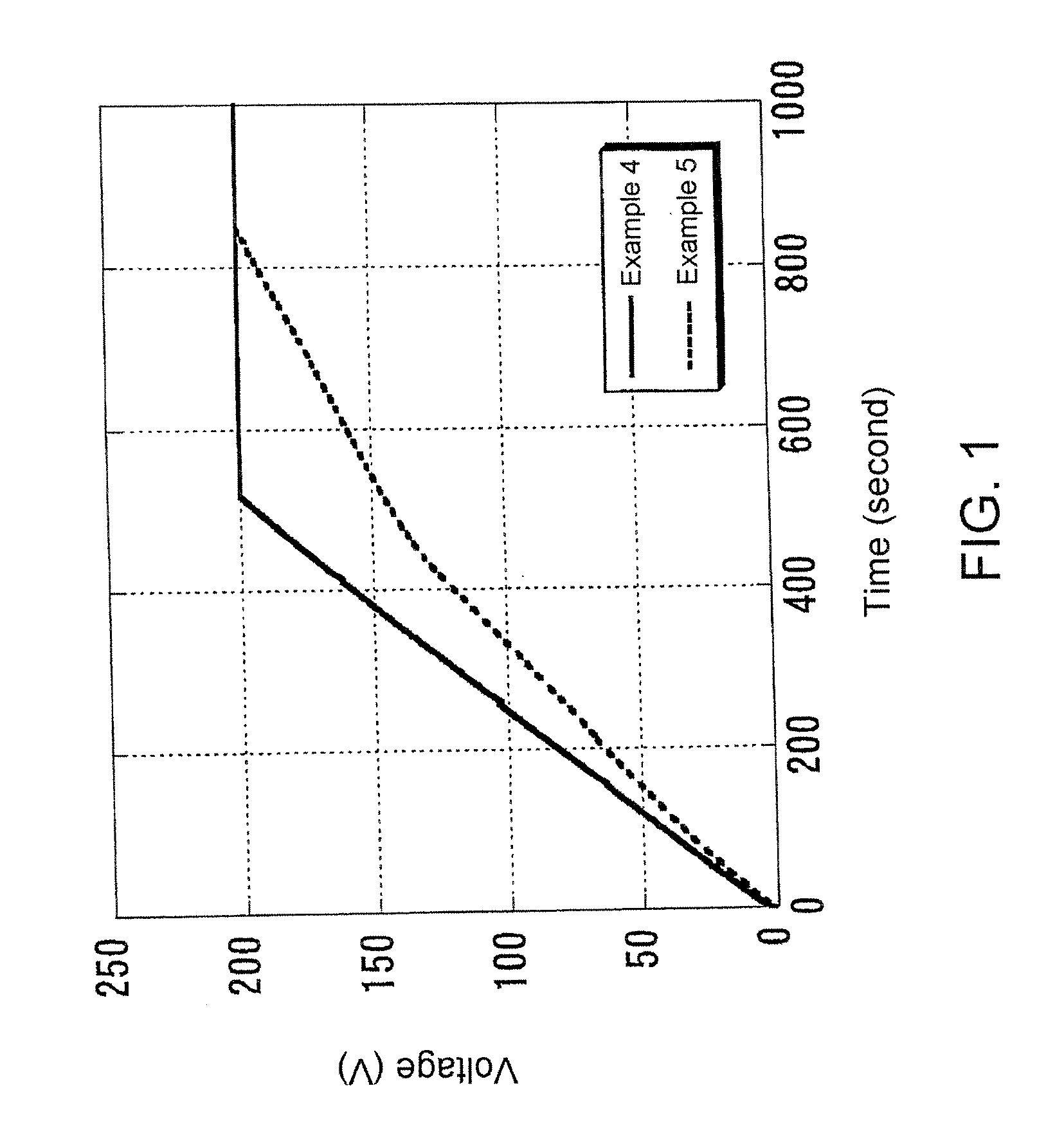

Method and Apparatus for Charging Batteries

ActiveUS20120081068A1Fast chargingSmall capacitanceBatteries circuit arrangementsEfficient power electronics conversionSwitching frequency

A charge system is disclosed. A charge system includes a switching device and a controller. The switching device performs switching of a DC input voltage at a predetermined switching frequency to generate an output voltage, and the output voltage being utilized for charging said battery. The controller allows the switching device to operate at a first switching frequency immediately after starting of charge and at a second switching frequency when a frequency changing condition holds. The second switching frequency is higher than that of first switching frequency.

Owner:LENOVO PC INT

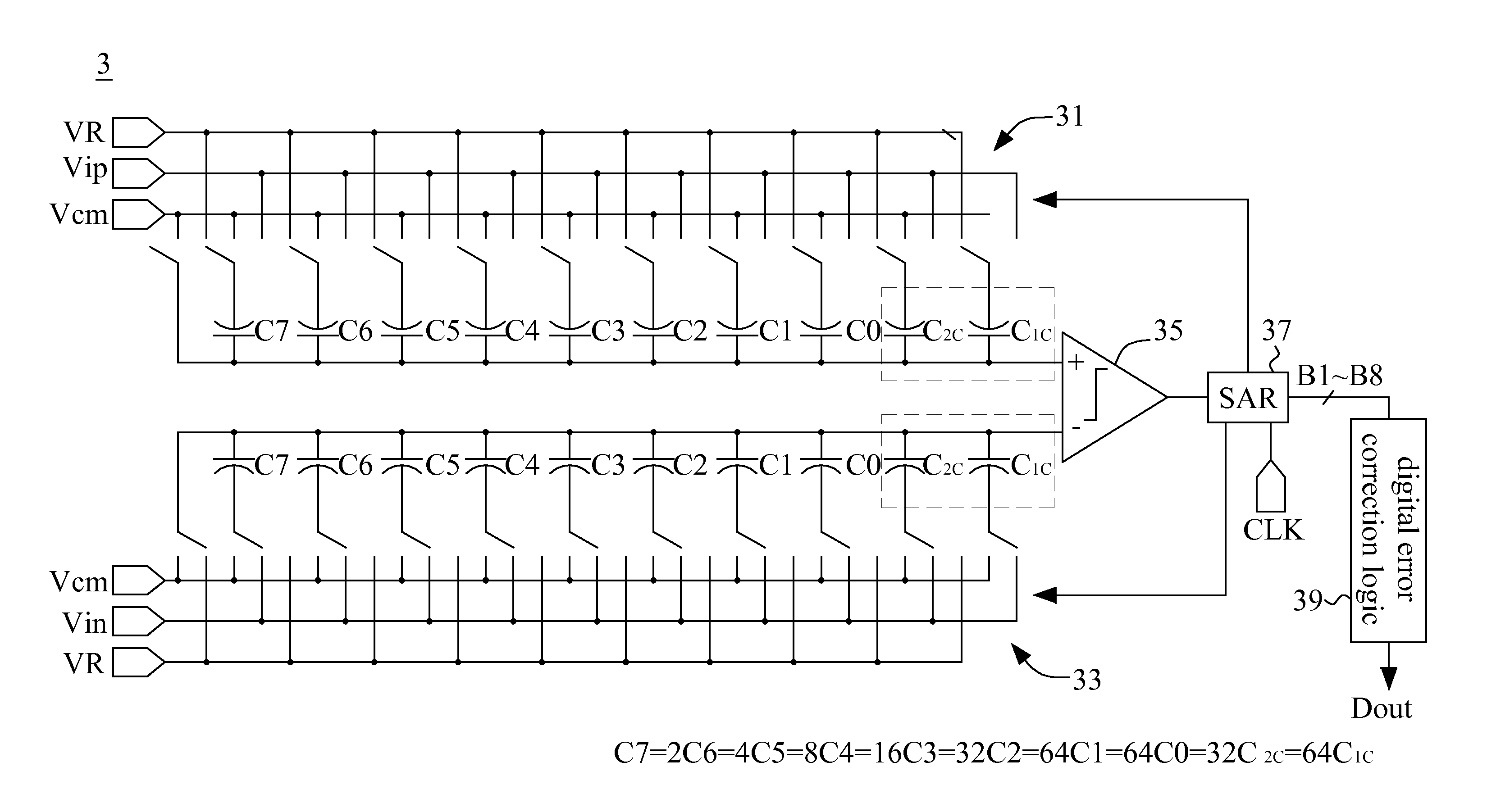

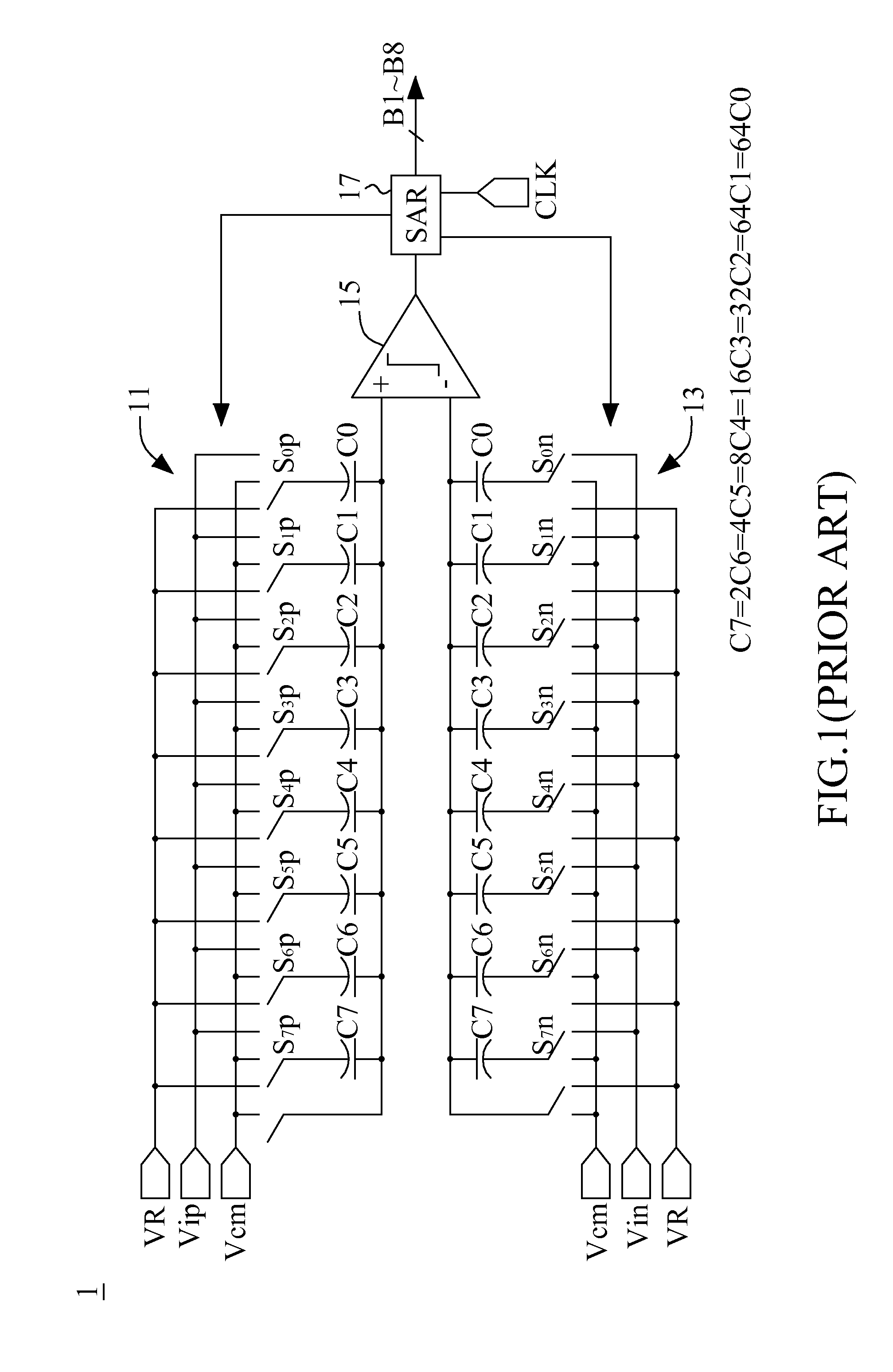

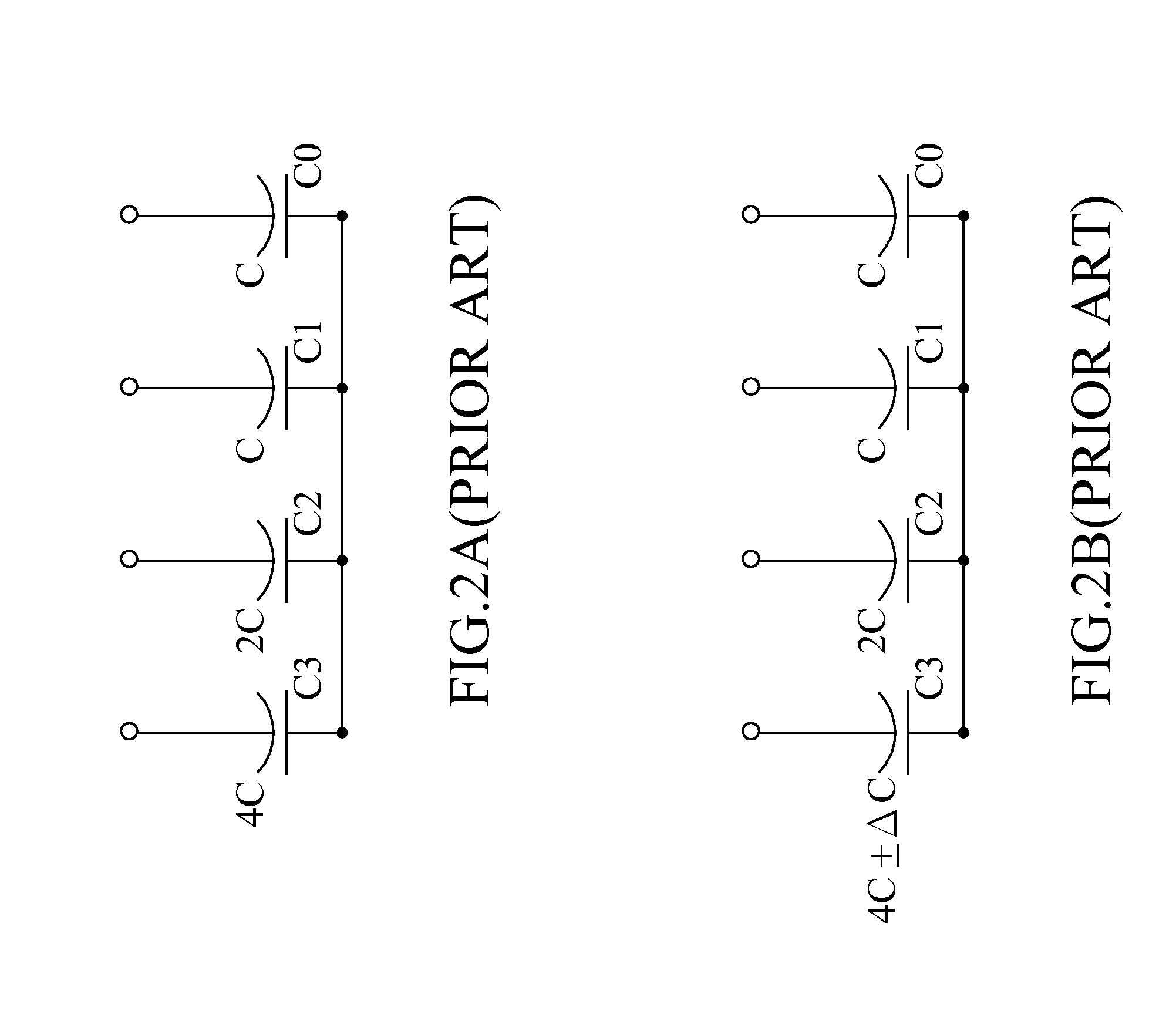

Successive approximation analog to digital converter with capacitor mismatch calibration and method thereof

ActiveUS8451151B2Achieve performanceAchieve precisionElectric signal transmission systemsAnalogue-digital convertersCapacitanceDigital down converter

A capacitance mismatch calibrating method for a successive approximation register ADC which includes at least one array of capacitors is provided. The method includes the following steps: firstly, at least two compensating capacitors are configured. A capacitor from the array of capacitors is selected as a capacitor-under-test. Then, the terminal voltages on the terminals of the array of capacitors and on the terminals of the compensating capacitors are determined. A first comparison voltage is outputted based on the determined terminal voltages. Afterwards, a sequence of comparisons is controlled based on the first comparison voltage and a second comparison voltage to output a sequence of corresponding digital bits. Finally, a calibration value is calculated to calibrate the value of a capacitor-under-test according to the digital bits.

Owner:HIMAX TECH LTD

Eeprom with split gate source side injection

InactiveUS20040063283A1Improve the floating gate memory windowSimple methodTransistorSolid-state devicesBit lineShift register

Novel memory cells utilize source-side injection, allowing very small programming currents. If desired, to-be-programmed cells are programmed simultaneously while not requiring an unacceptably large programming current for any given programming operation. In one embodiment, memory arrays are organized in sectors with each sector being formed of a single column or a group of columns having their control gates connected in common. In one embodiment, a high speed shift register is used in place of a row decoder to serially shift in data for the word lines, with all data for each word line of a sector being contained in the shift register on completion of its serial loading. In one embodiment, speed is improved by utilizing a parallel loaded buffer register which receives parallel data from the high speed shift register and holds that data during the write operation, allowing the shift register to receive serial loaded data during the write operation for use in a subsequent write operation. In one embodiment, a verification is performed in parallel on all to-be-programmed cells in a column and the bit line current monitored. If all of the to-be-programmed cells have been properly programmed, the bit line current will be substantially zero. If bit line current is detected, another write operation is performed on all cells of the sector, and another verify operation is performed. This write / verify procedure is repeated until verification is successful, as detected or substantially zero, bit line current.

Owner:SANDISK TECH LLC

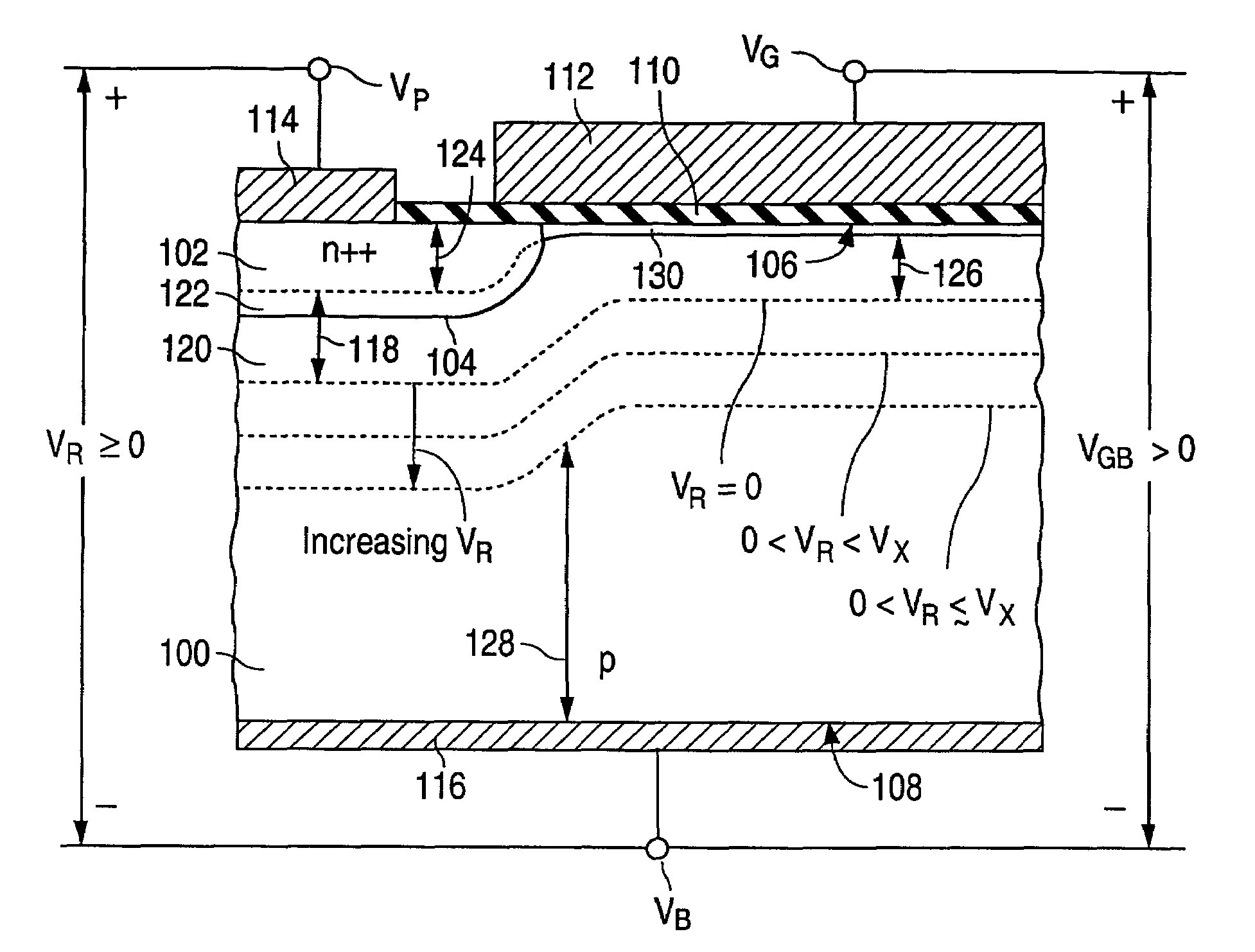

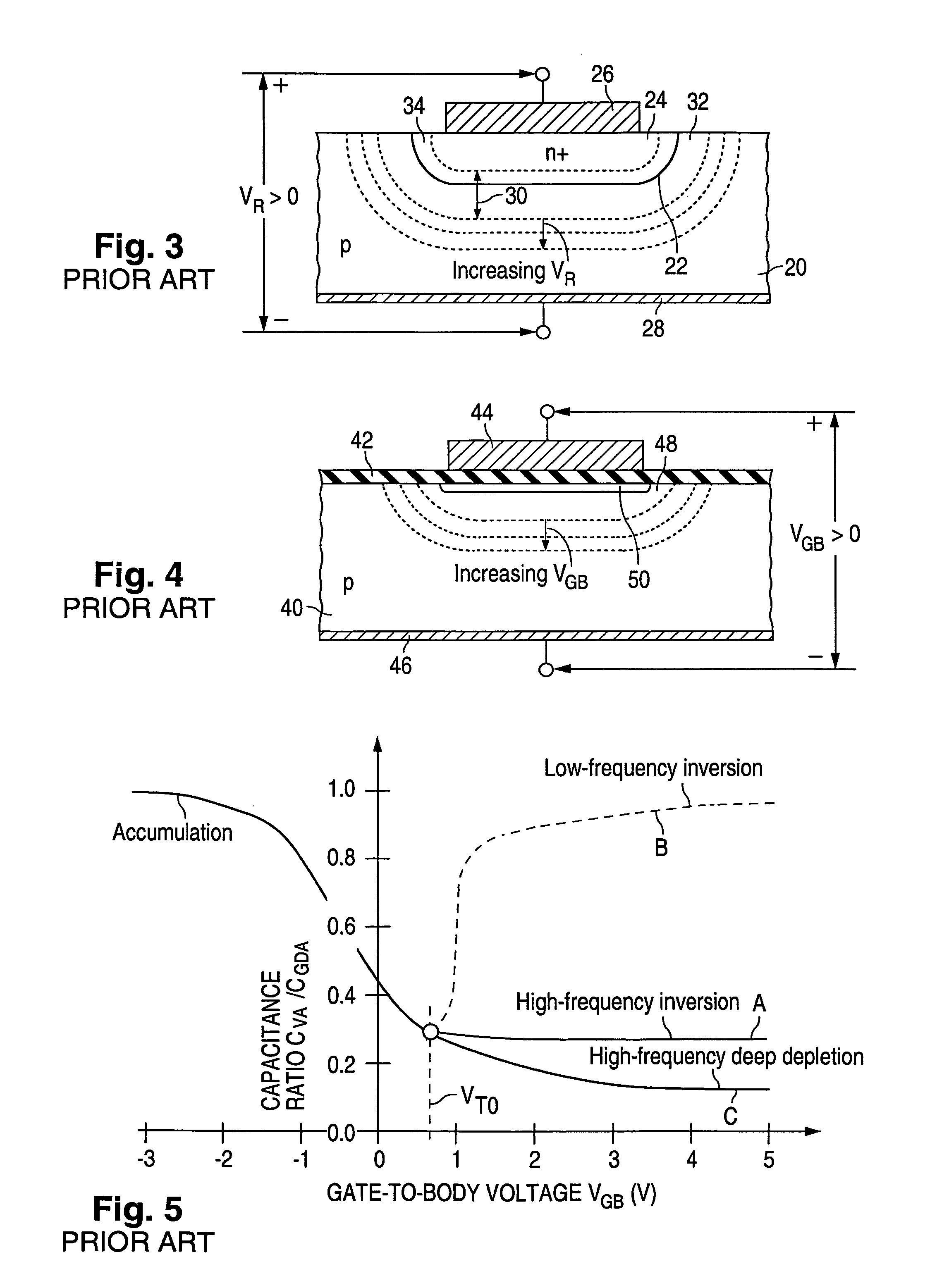

Gate-enhanced junction varactor

InactiveUS7579642B1Raise the ratioSimple designTransistorSolid-state devicesEngineeringCondensed matter physics

A semiconductor junction varactor utilizes gate enhancement for enabling the varactor to achieve a high ratio of maximum capacitance to minimum capacitance.

Owner:NAT SEMICON CORP

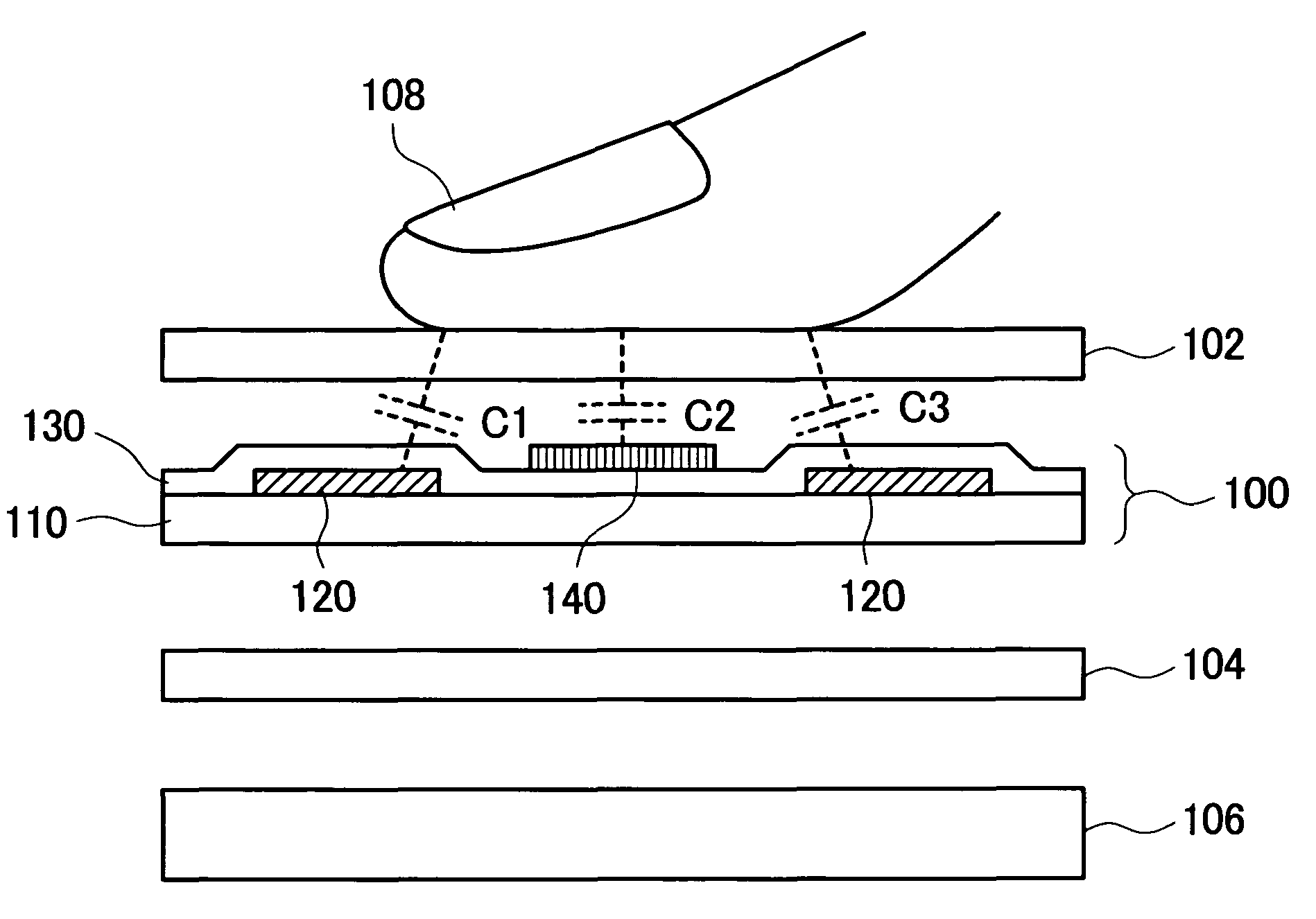

Display device with touch panel

ActiveUS8451234B2Small capacitanceIncrease the number ofTransmission systemsCathode-ray tube indicatorsCapacitanceDisplay device

A touch panel includes plural first electrodes extending in a first direction, plural second electrodes extending in a second direction different from the first direction, a driving circuit, a detection circuit, and a coordinate-position calculating circuit. The driving circuit sequentially selects two first electrodes out of the plural first electrodes, supplies a high potential voltage higher than a reference voltage to one of the selected two first electrodes, and supplies the reference voltage to the other, the detection circuit detects a capacitance difference (A−B) between a capacitor A between a selected one of the second electrodes and the first electrode to which the high potential voltage is supplied and a capacitor B between the selected second electrode and the first electrode to which the reference voltage is supplied, and the coordinate-position calculating circuit calculates a touch position on the touch panel touched by the observer on the basis of positions of the selected first and second electrodes and the capacitance difference (A−B).

Owner:JAPAN DISPLAY INC

Transceiver coil for auditory prosthesis

InactiveUS7260435B2Reduce materialReduce weightElectrotherapyEar treatmentCapacitanceTransmitter coil

The invention provides a tuned transmitter coil for transcutaneous transmission of power and information from an external component of an auditory prosthesis to an implanted receiver. A shield is provided in order to reduce a skin-to-coil capacitance, thereby improving tuning stability of the coil from one user to the next. A shield may also be provided in order to reduce electromagnetic interference.

Owner:COCHLEAR LIMITED

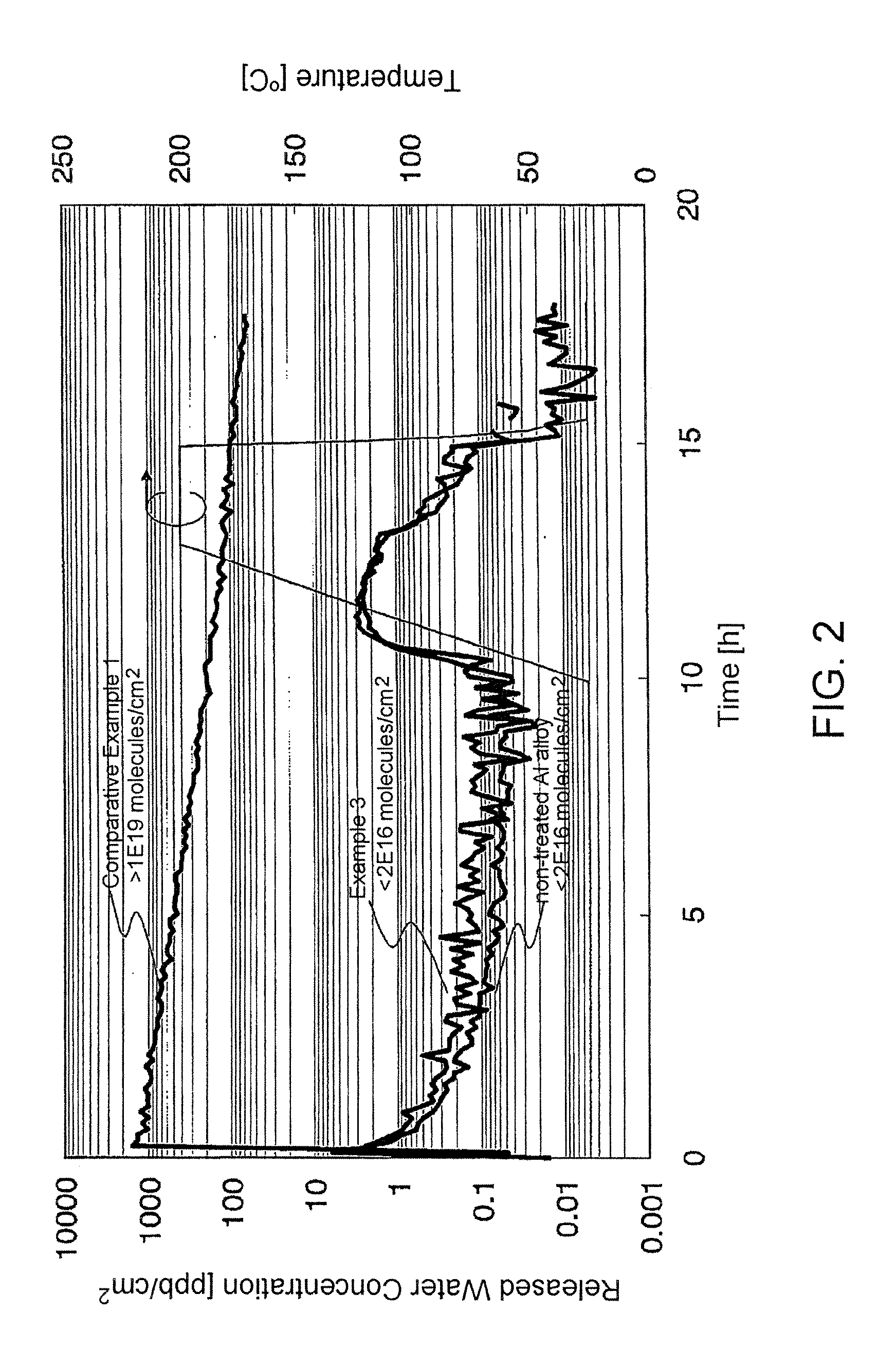

Metal oxide film, laminate, metal member and process for producing the same

InactiveUS20090038946A1Improve corrosion resistanceImprove the immunityAnodisationSynthetic resin layered productsChemical solutionMoisture

A metal oxide film suitable for protection of metals, composed mainly of aluminum. A metal oxide film includes a film of an oxide of a metal composed mainly of aluminum, having a thickness of 10 nm or greater, and exhibiting a moisture release rate from the film of 1E18 mol. / cm2 or less. Further, there is provided a process for producing a metal oxide film, wherein a metal composed mainly of aluminum is subjected to anodic oxidation in a chemical solution of 4 to 10 pH value so as to obtain a metal oxide film.

Owner:TOHOKU UNIV +1

Sense amplifier circuit and semiconductor device

ActiveUS20110063892A1High speed readExcellent operating marginDigital storagePower semiconductor deviceAudio power amplifier

A single-ended sense amplifier circuit of the invention comprises first and second MOS transistors and first and second precharge circuits. The first MOS transistor drives the bit line to a predetermined voltage and switches connection between the bit line and a sense node and the second MOS transistor whose gate is connected to the sense node amplifies the signal via the first MOS transistor. The first precharge circuit precharges the bit line to a first potential and the second precharge circuit precharges the sense node to a second potential. Before sensing operation, the bit line is driven to the predetermined voltage when the above gate voltage is controlled to decrease. The predetermined voltage is appropriately set so that a required voltage difference at the sense node between high and low levels can be obtained near a changing point between charge transfer / distributing modes.

Owner:LONGITUDE LICENSING LTD