Patents

Literature

126results about How to "High speed read" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Semiconductor device

ActiveUS20110134683A1Easily multivaluedNovel structureTransistorSolid-state devicesPower semiconductor deviceDriver circuit

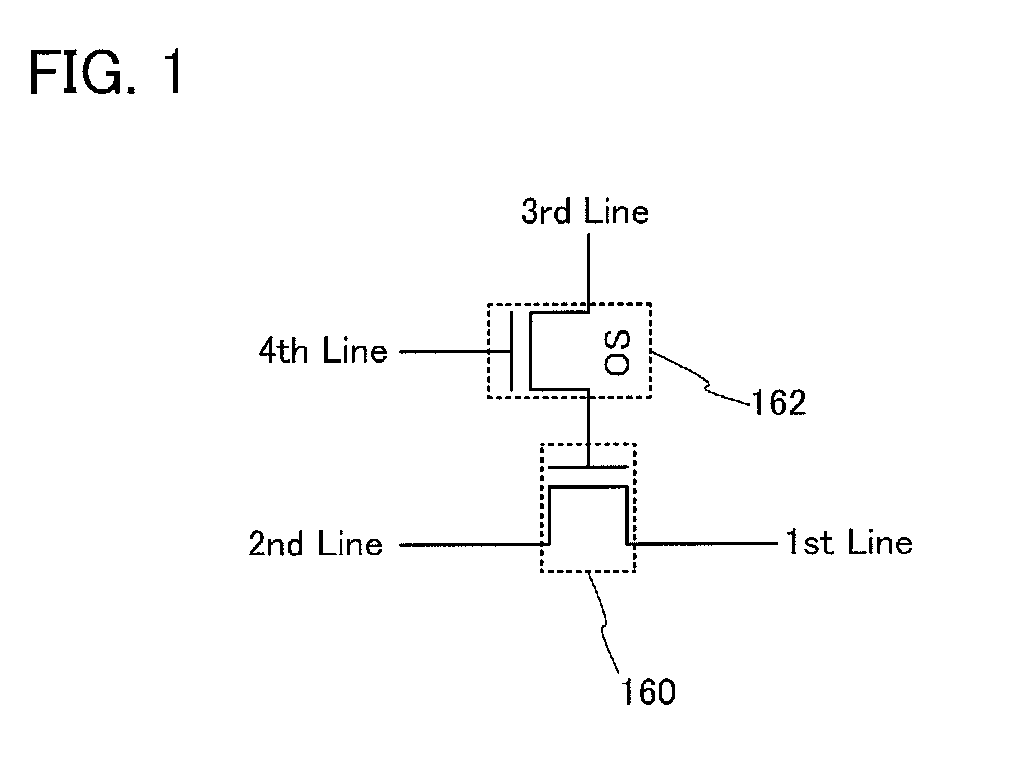

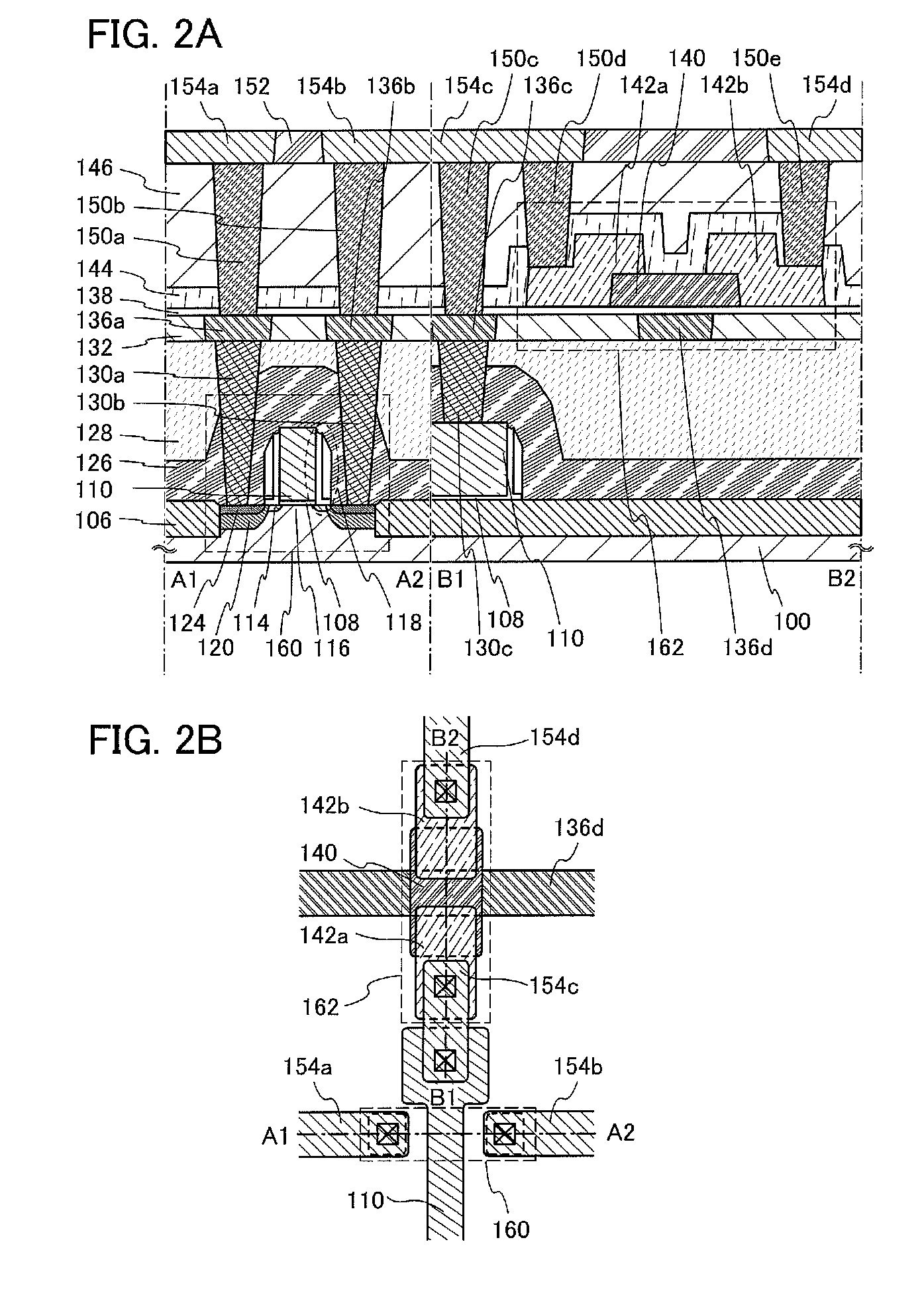

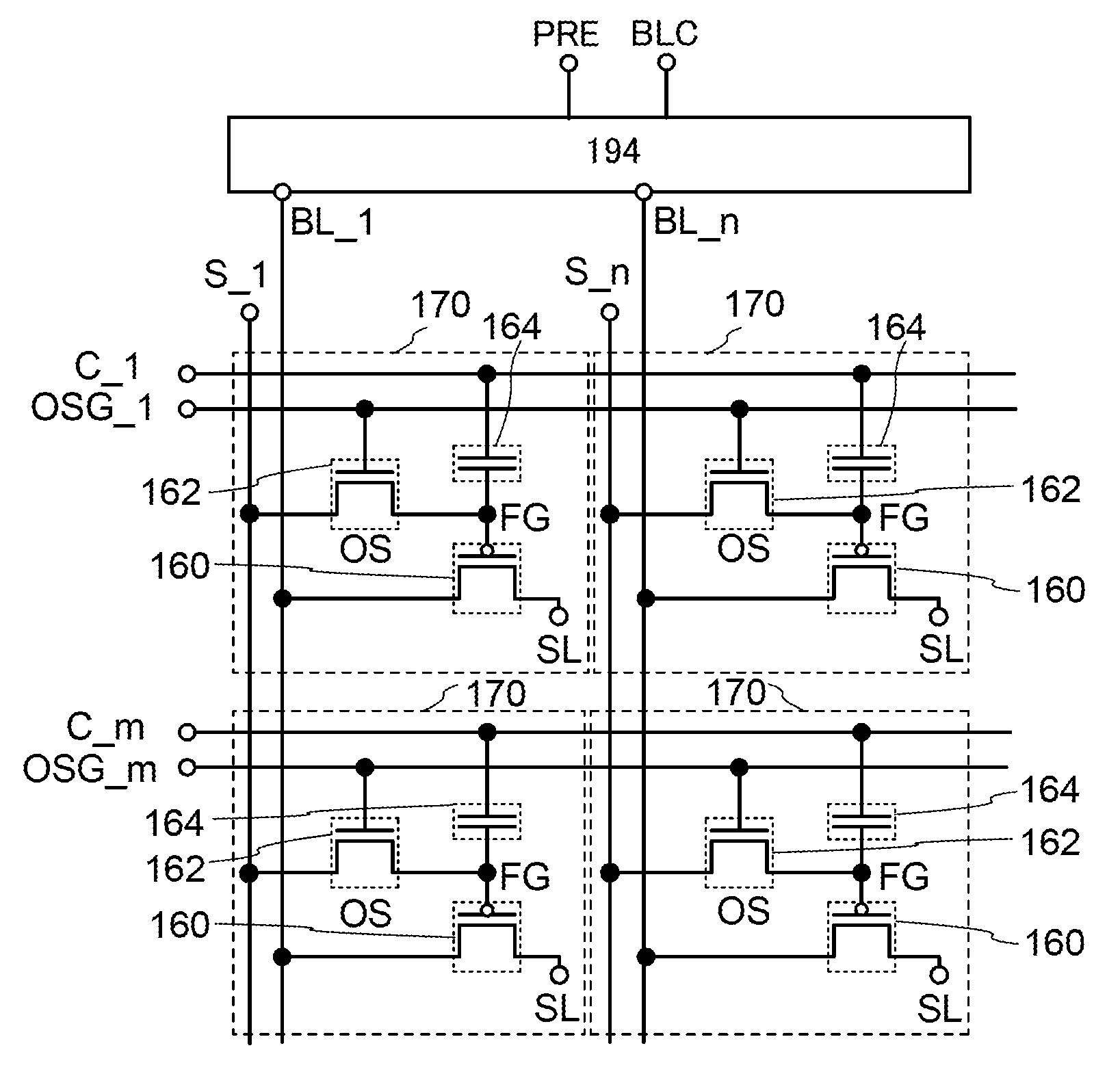

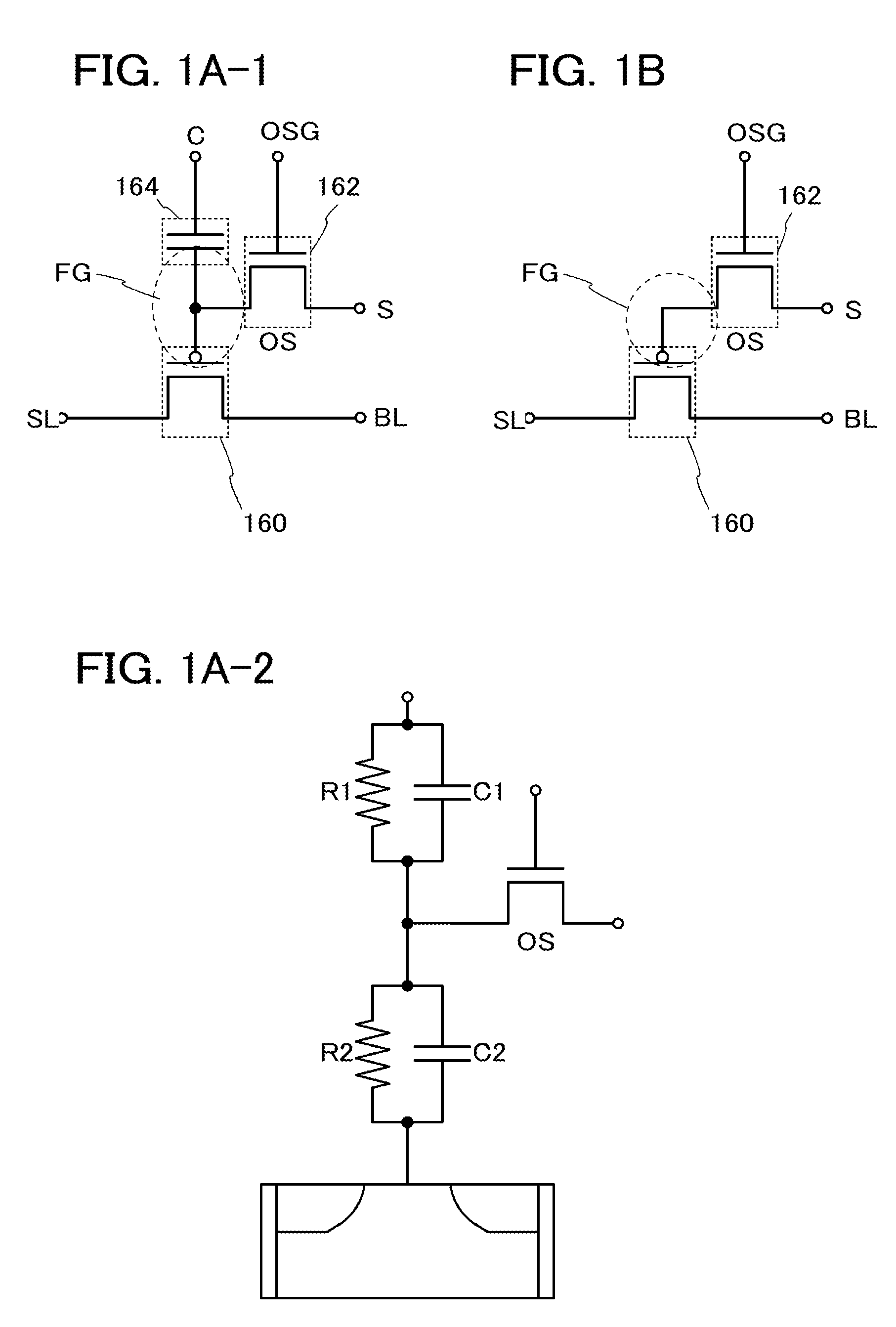

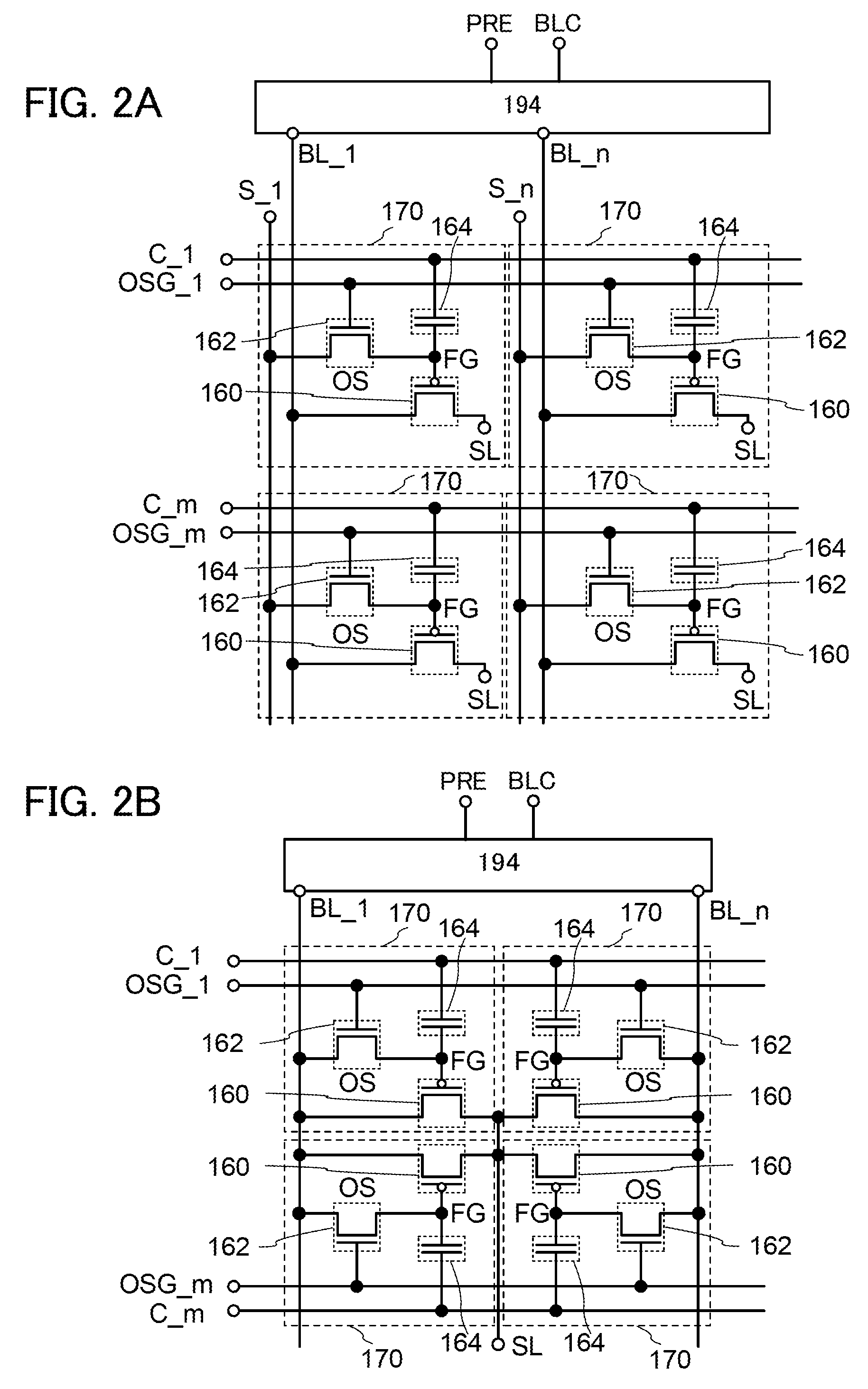

Disclosed is a semiconductor device functioning as a multivalued memory device including: memory cells connected in series; a driver circuit selecting a memory cell and driving a second signal line and a word line; a driver circuit selecting any of writing potentials and outputting it to a first signal line; a reading circuit comparing a potential of a bit line and a reference potential; and a potential generating circuit generating the writing potential and the reference potential. One of the memory cells includes: a first transistor connected to the bit line and a source line; a second transistor connected to the first and second signal line; and a third transistor connected to the word line, bit line, and source line. The second transistor includes an oxide semiconductor layer. A gate electrode of the first transistor is connected to one of source and drain electrodes of the second transistor.

Owner:SEMICON ENERGY LAB CO LTD

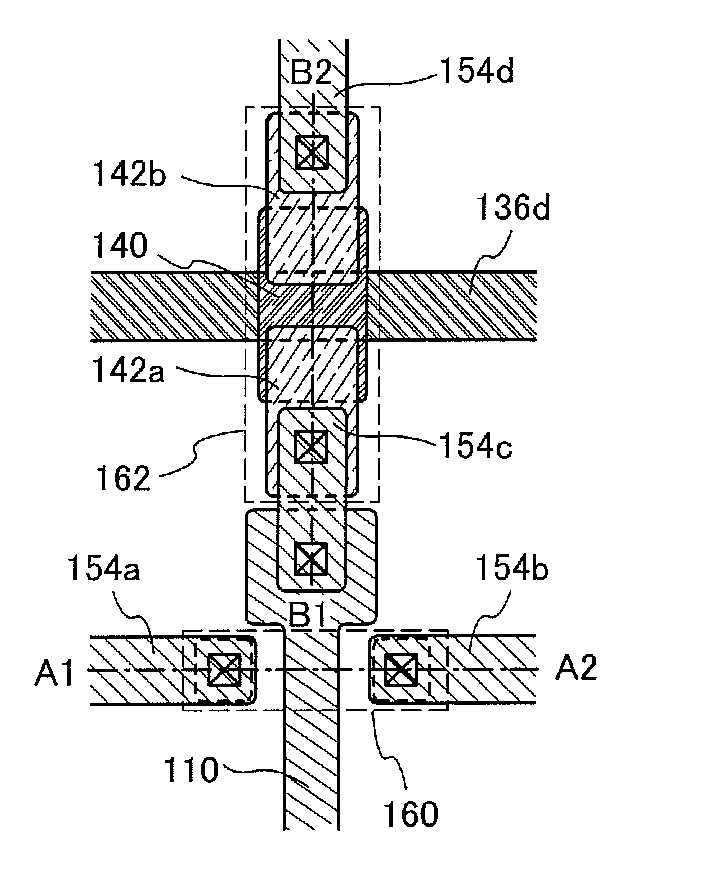

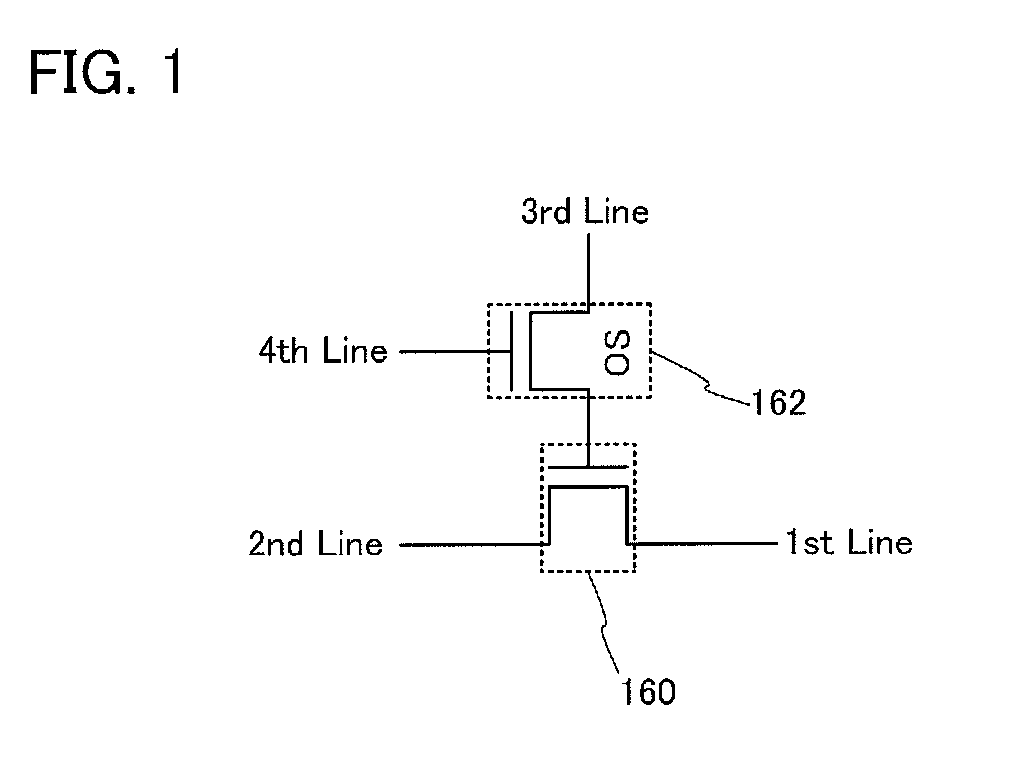

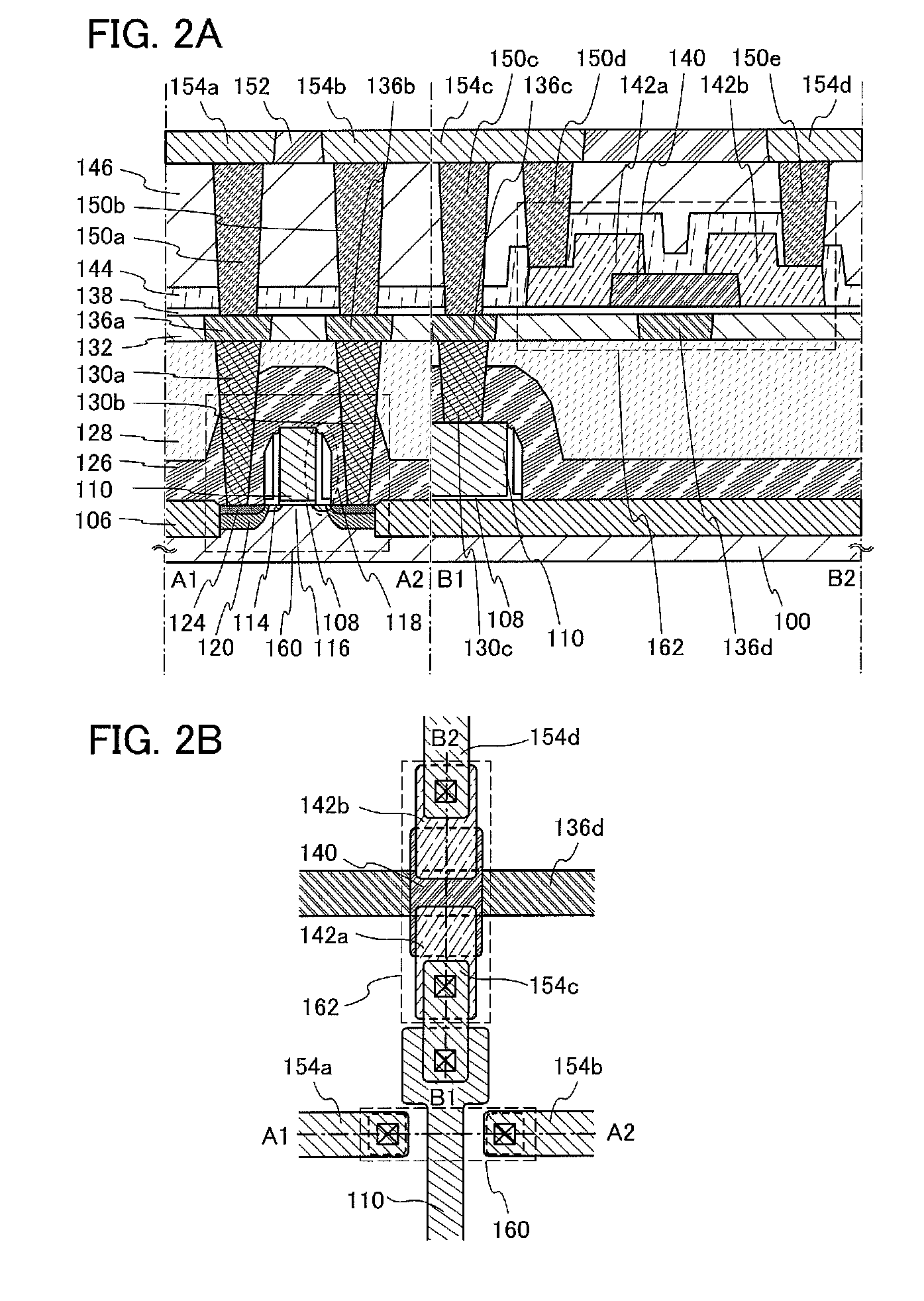

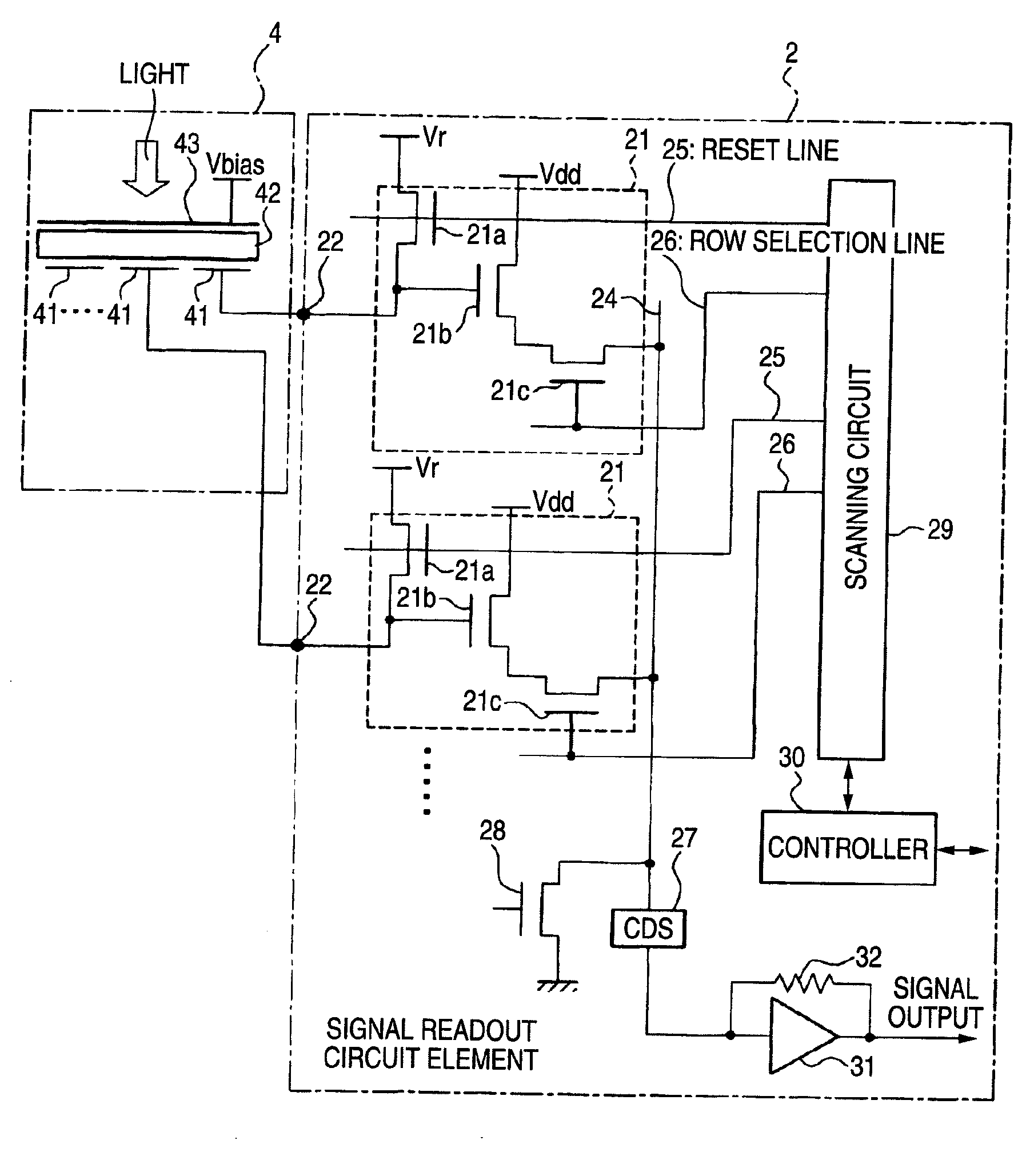

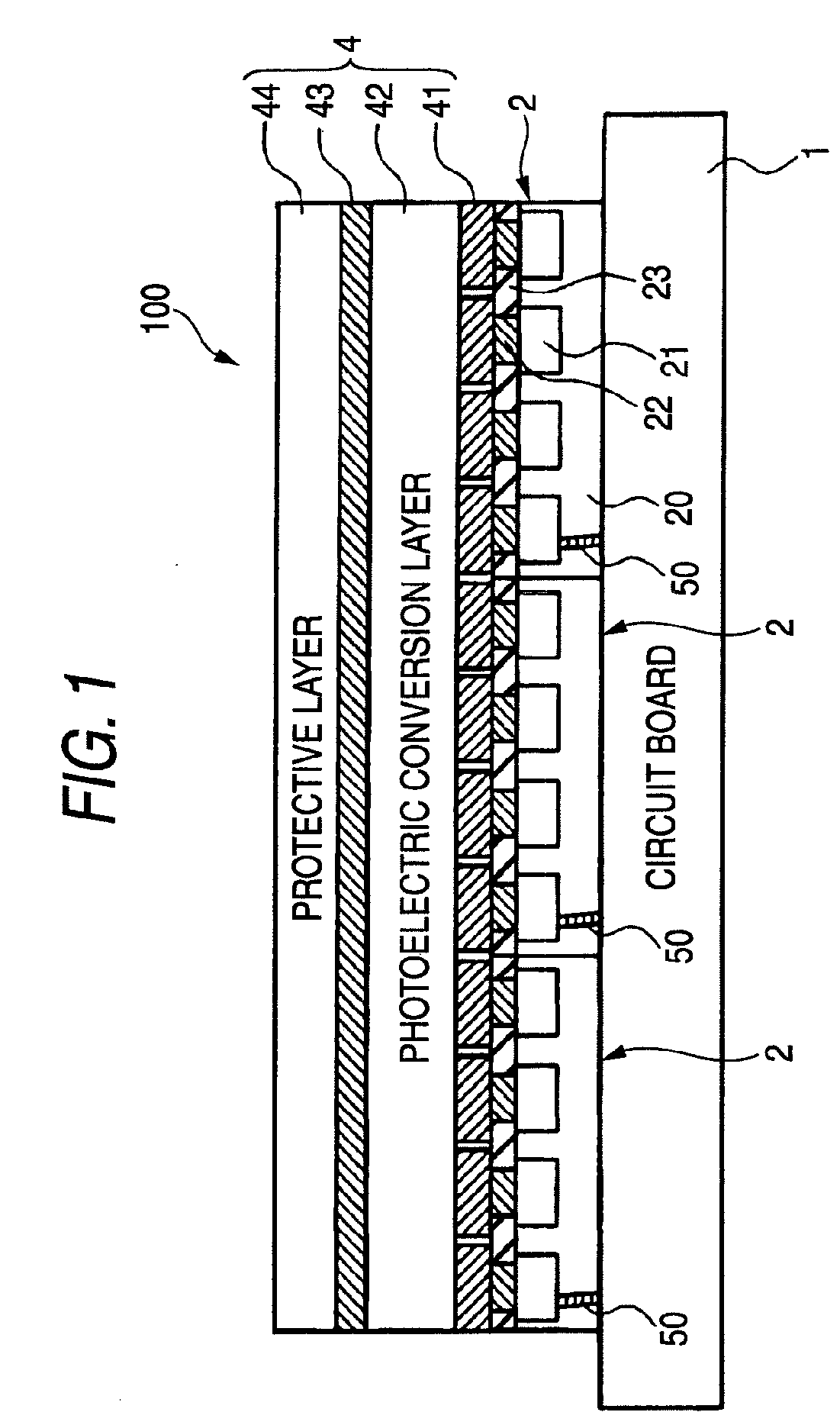

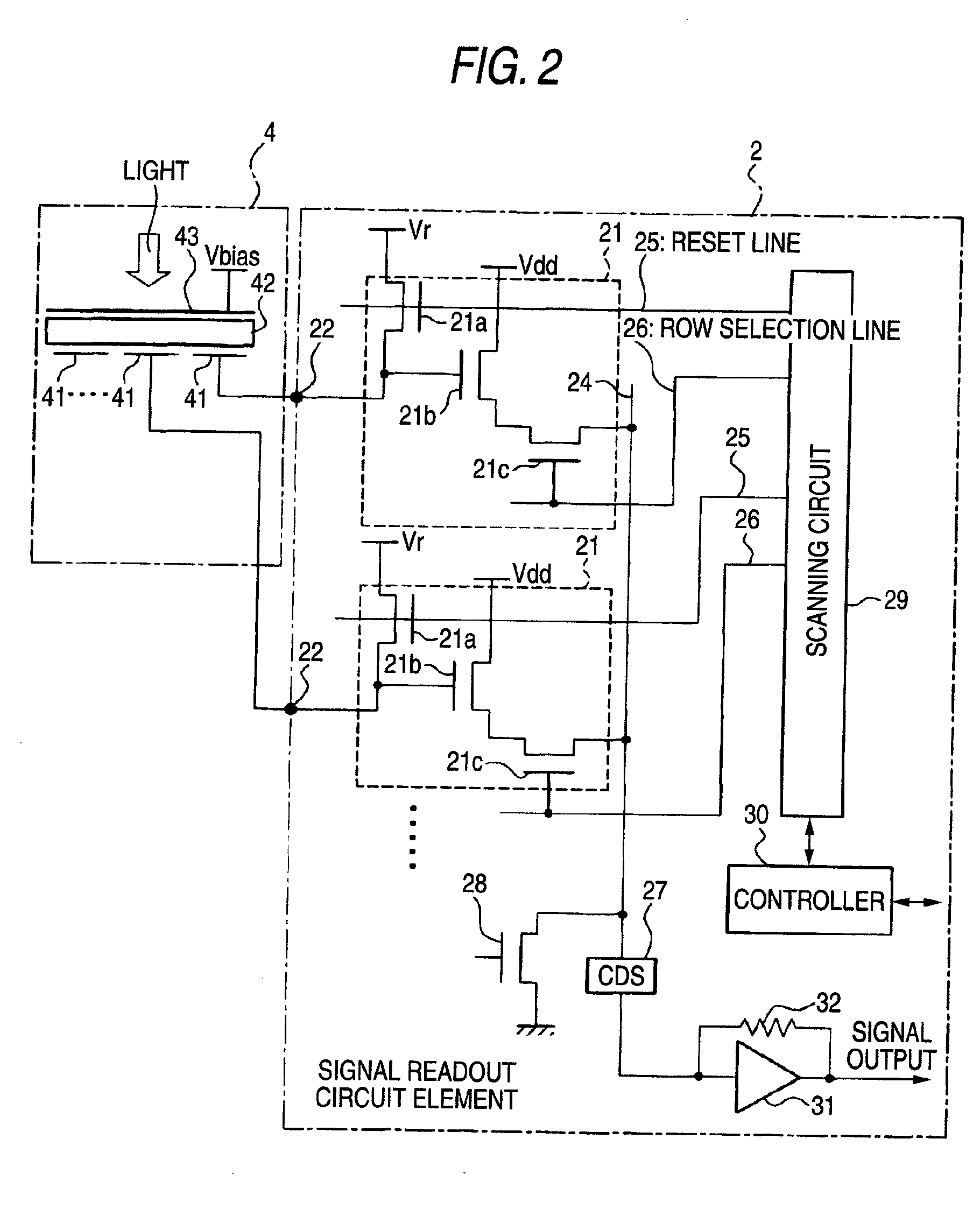

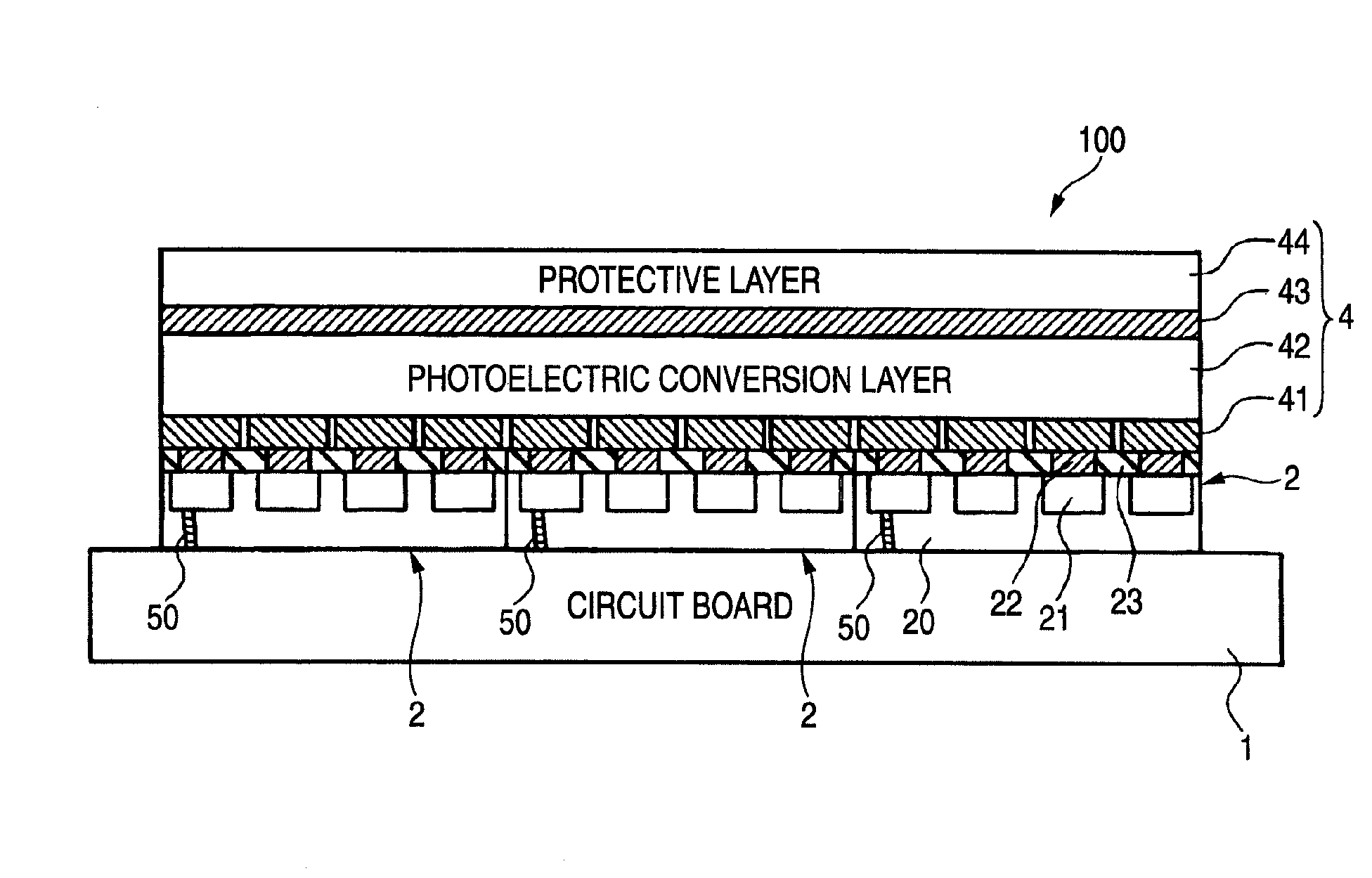

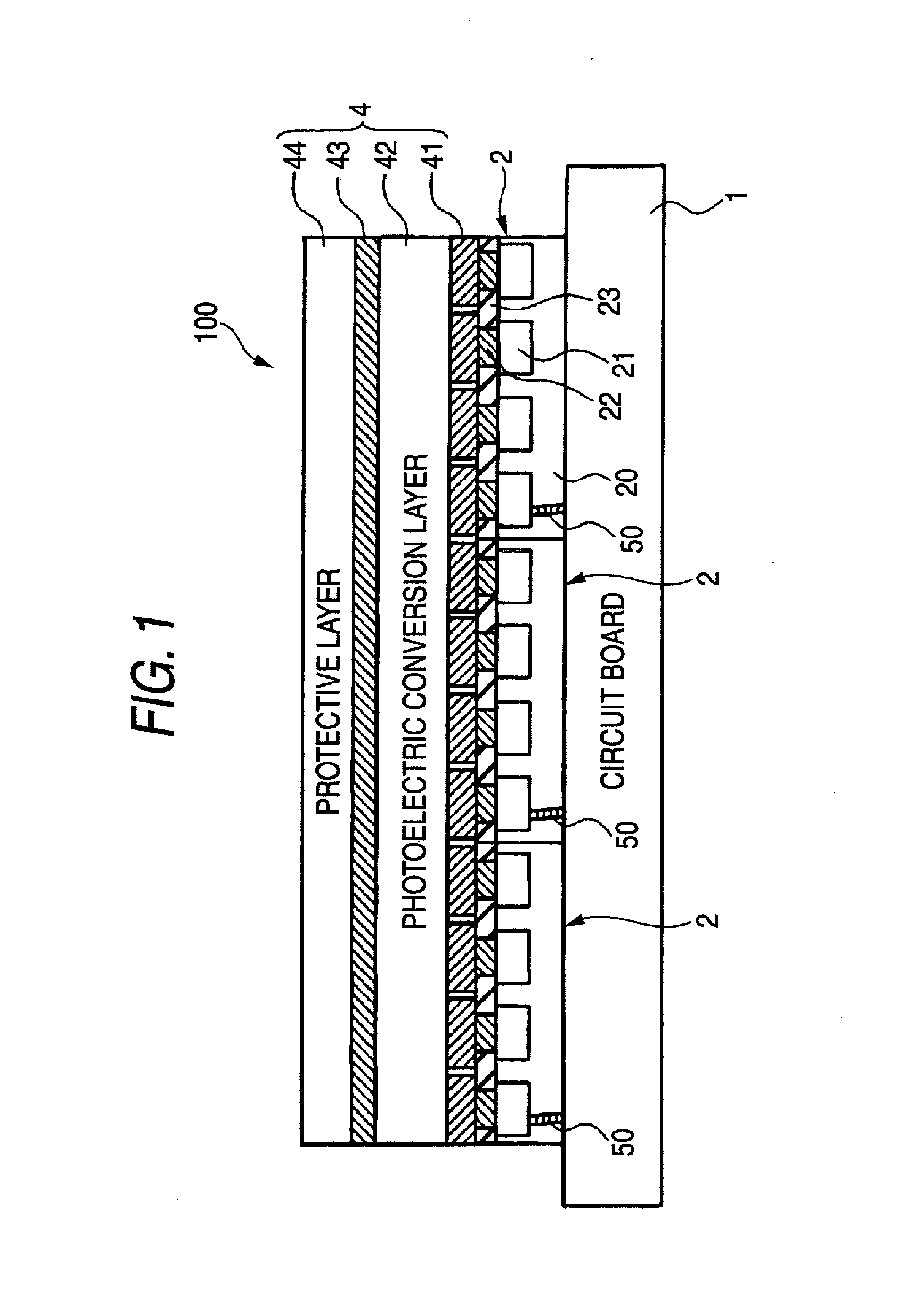

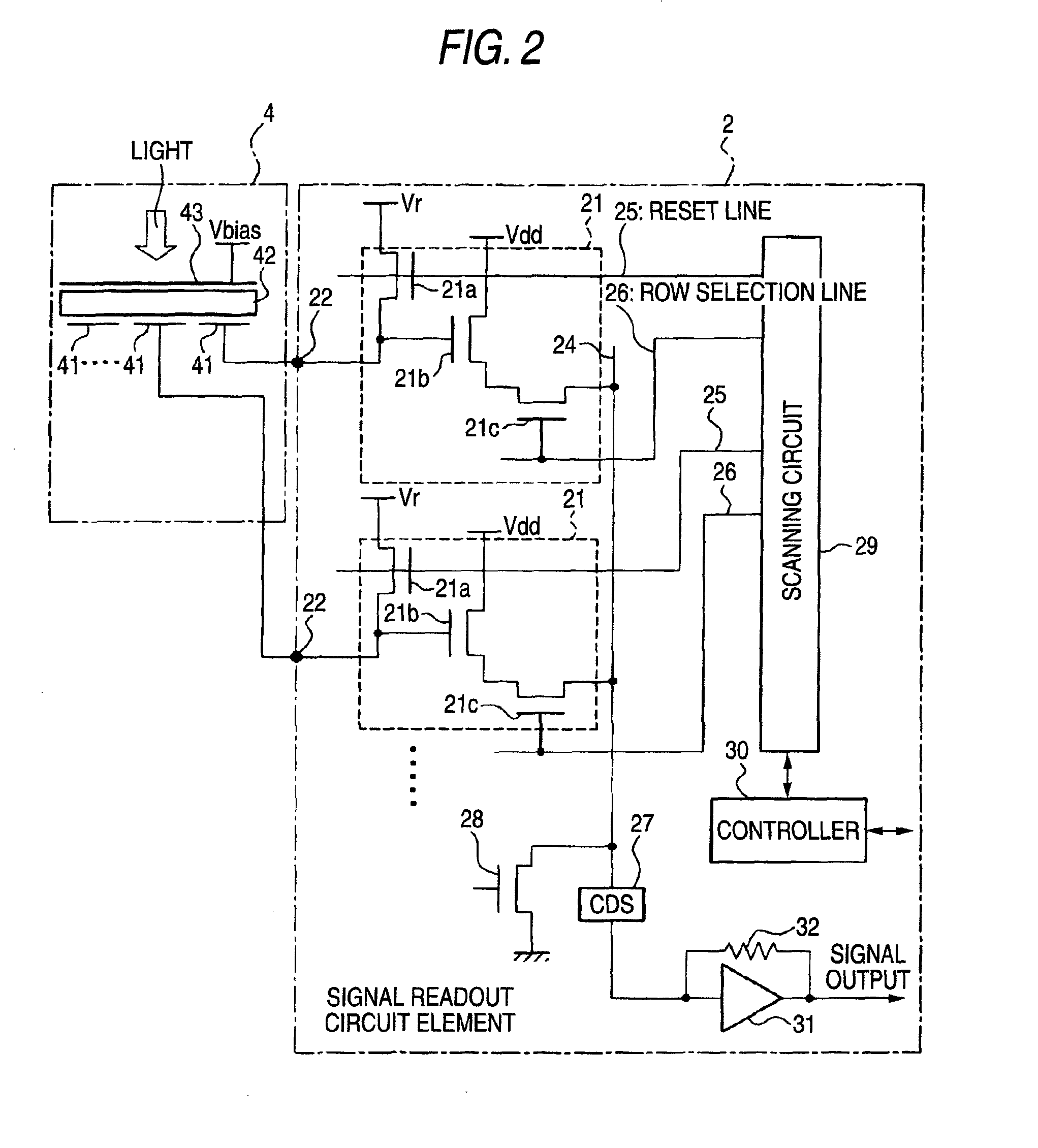

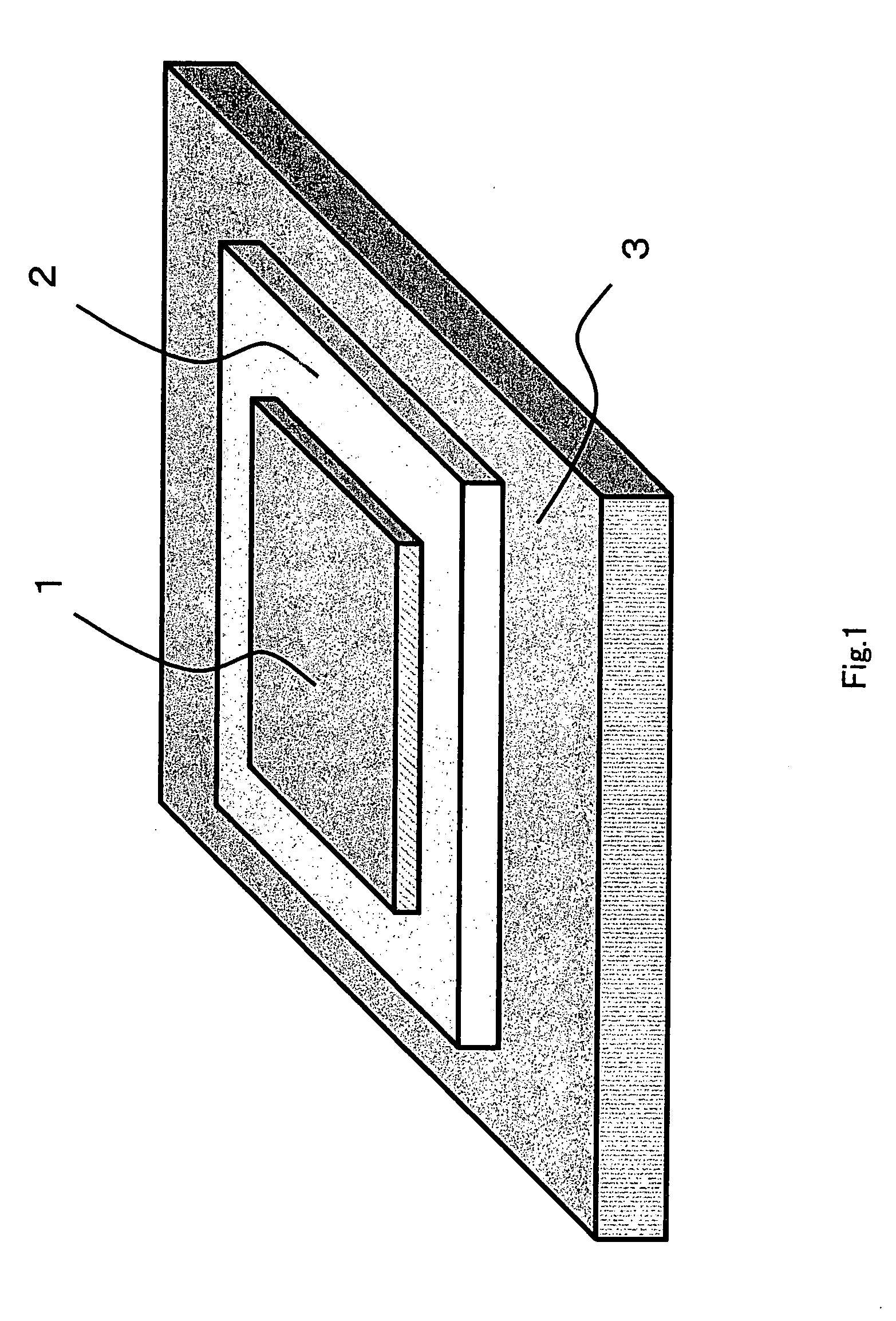

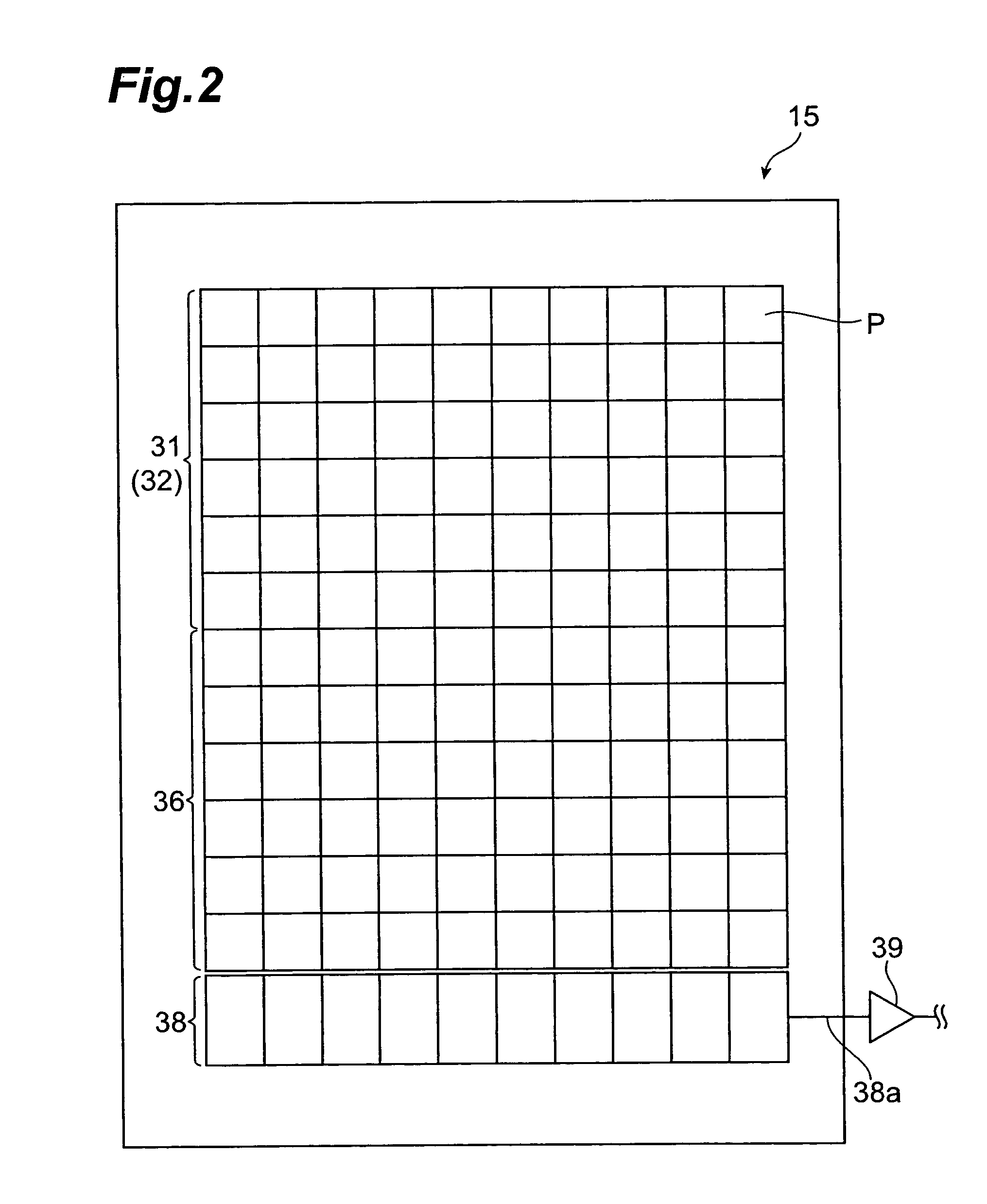

Solid-state imaging device, imaging apparatus, and method for manufacturing solid-state imaging device

InactiveUS20090091806A1High sensitivitySmall sizeTelevision system detailsSolid-state devicesEngineeringPhotoelectric conversion

A solid-state imaging device is provided and includes: a substrate; a plurality of photoelectric conversion elements arranged in a one-dimensional or two-dimensional array above the substrate, the plurality of photoelectric conversion elements being divided into a plurality of photoelectric conversion element groups; a semiconductor substrate between the substrate and the plurality of photoelectric conversion elements, corresponding to each of the plurality of photoelectric conversion clement groups; and a signal output section in the semiconductor substrates. The signal output section outputs a signal corresponding to an electric charge generated in each photoelectric conversion elements of a photoelectric conversion element group corresponding to the semiconductor substrate.

Owner:FUJIFILM CORP

Solid-state imaging device, imaging apparatus, and method for manufacturing solid-state imaging device

InactiveUS8541730B2Small sizeHigh sensitivityTelevision system detailsSolid-state devicesEngineeringPhotoelectric conversion

A solid-state imaging device is provided and includes: a substrate; a plurality of photoelectric conversion elements arranged in a one-dimensional or two-dimensional array above the substrate, the plurality of photoelectric conversion elements being divided into a plurality of photoelectric conversion element groups; a plurality of semiconductor substrates between the substrate and the plurality of photoelectric conversion elements, each of the plurality of semiconductor substrates corresponding to each of the plurality of photoelectric conversion element groups; and a signal output section in the plurality of semiconductor substrates. The signal output section outputs a signal corresponding to an electric charge generated in each photoelectric conversion elements of a photoelectric conversion element group corresponding to a semiconductor substrate.

Owner:FUJIFILM CORP

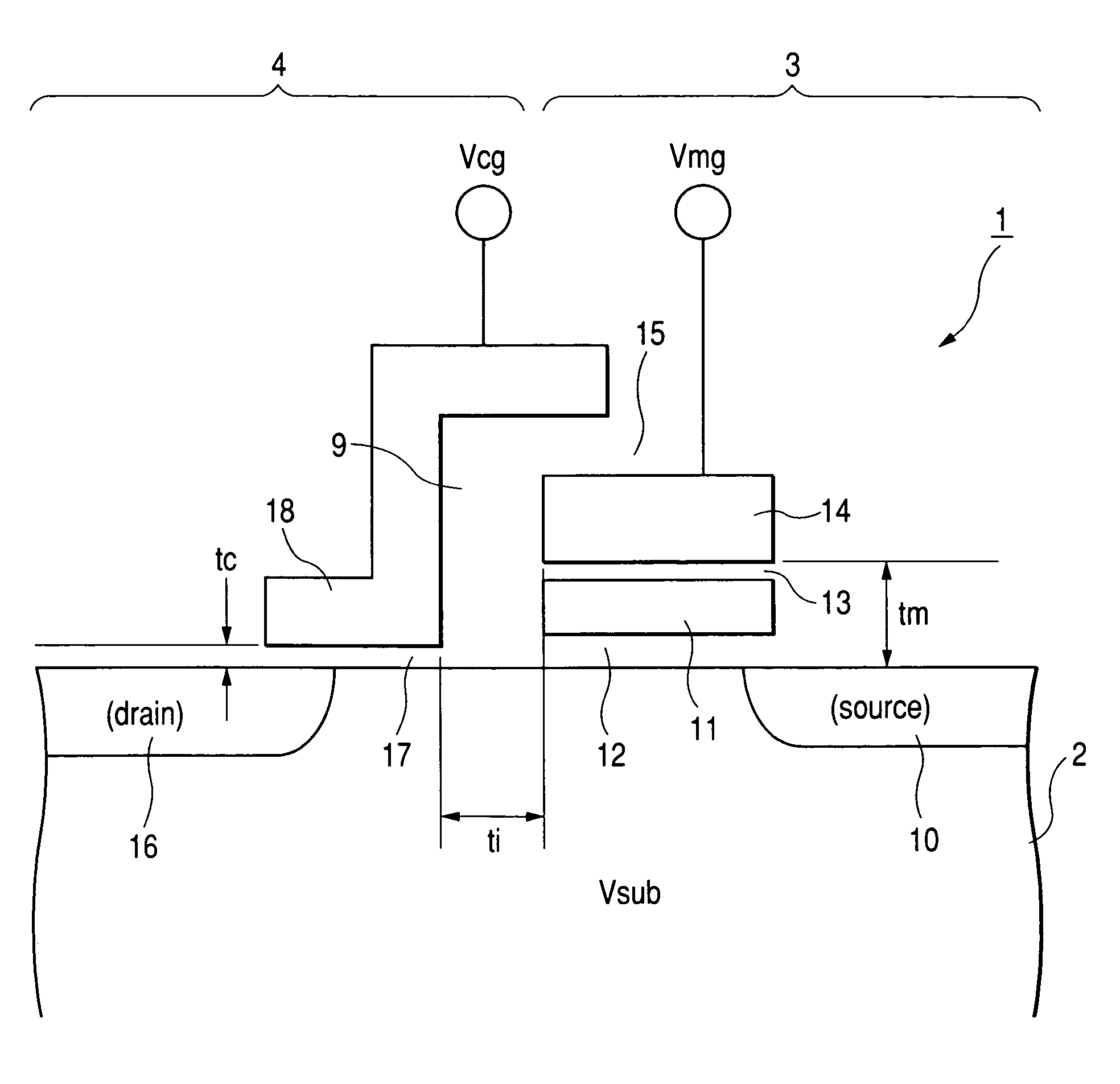

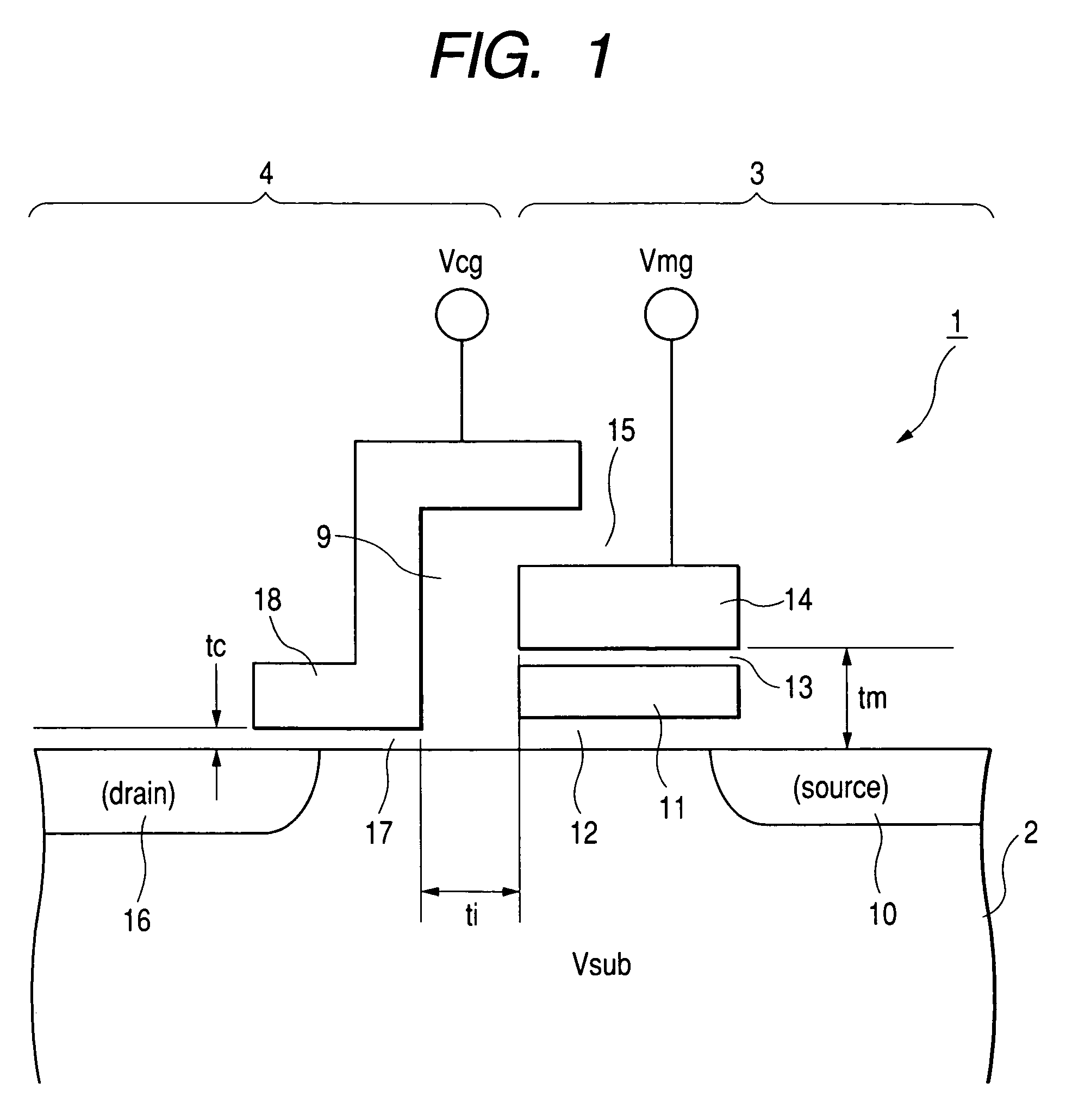

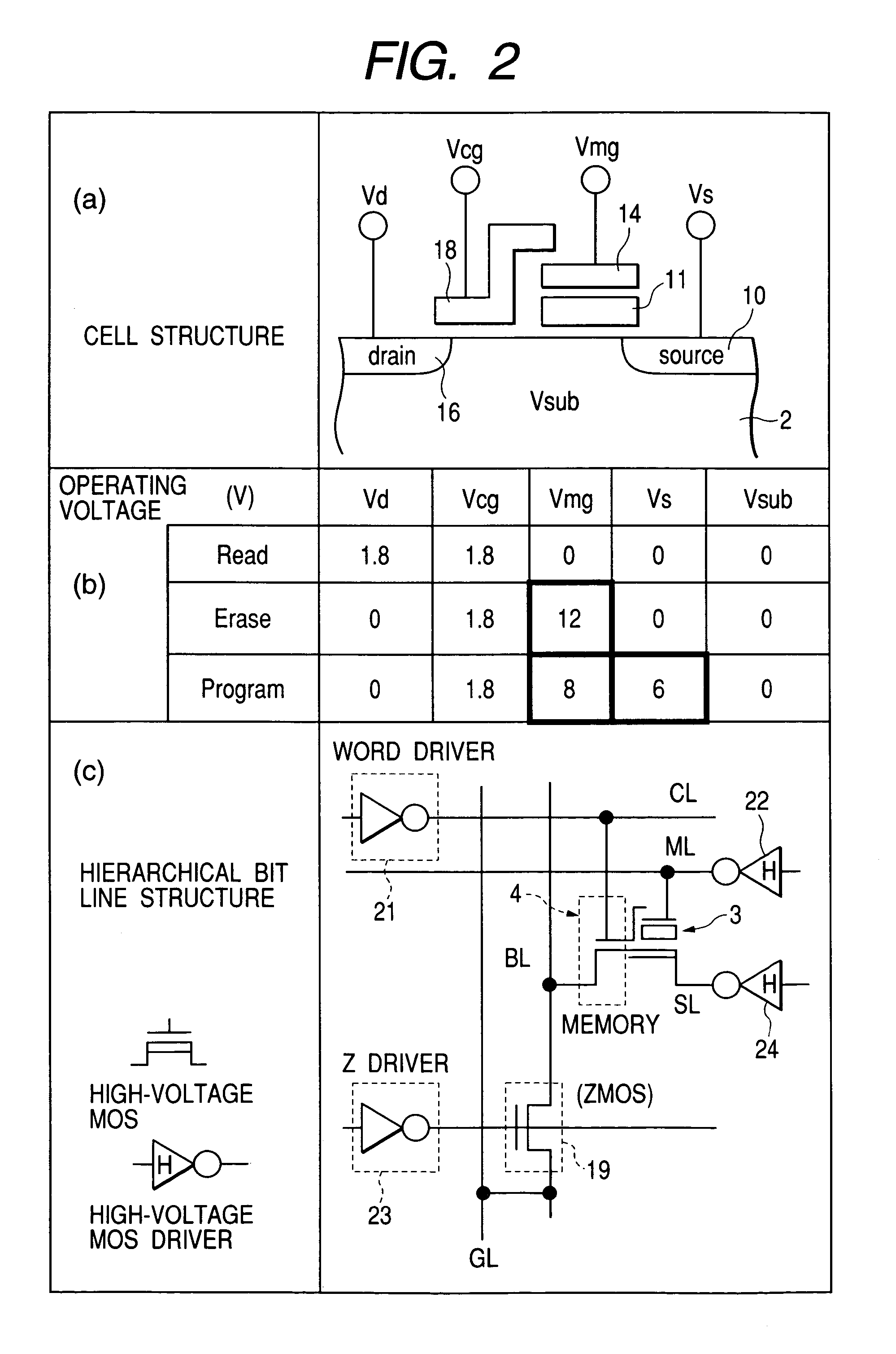

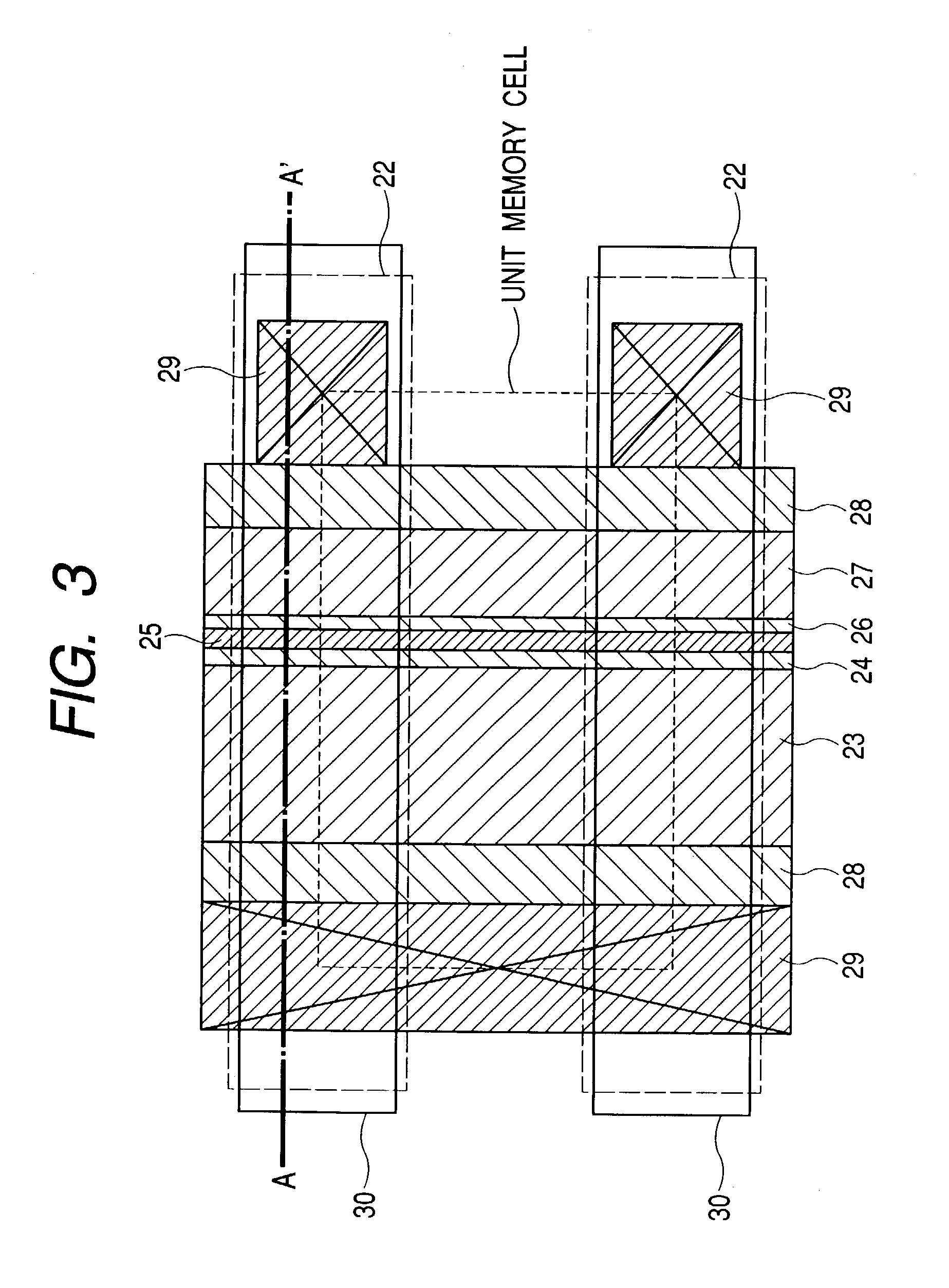

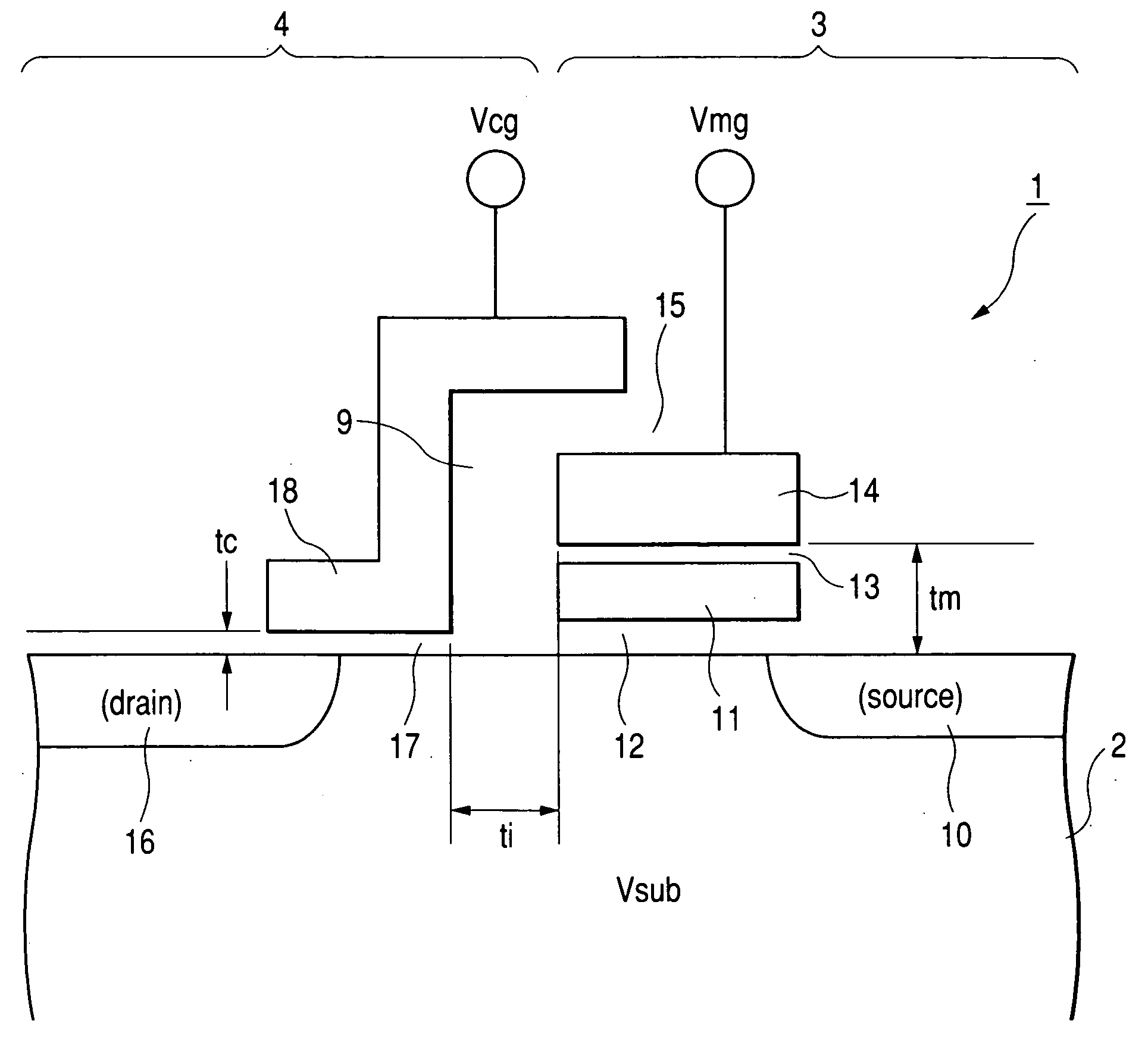

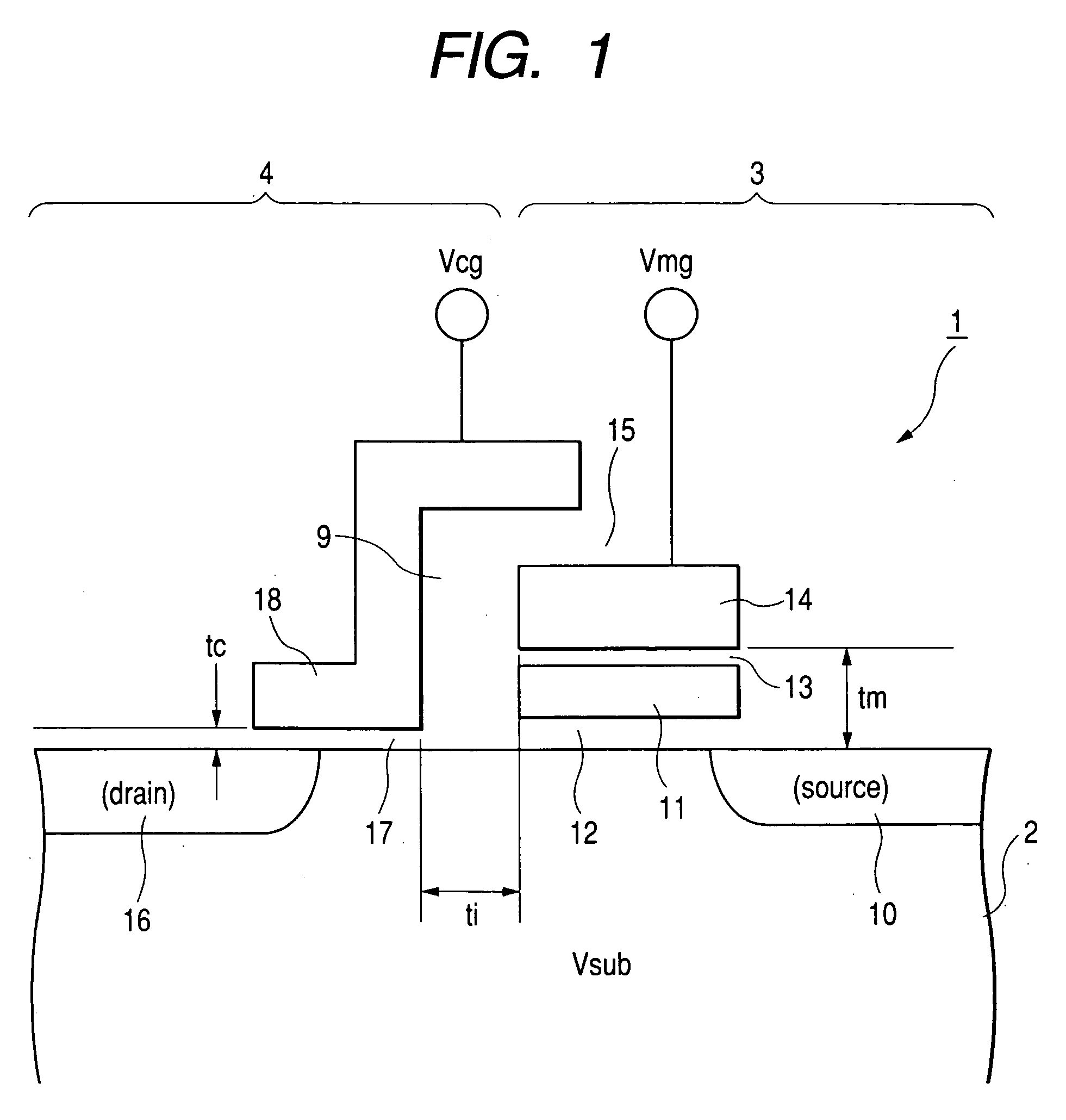

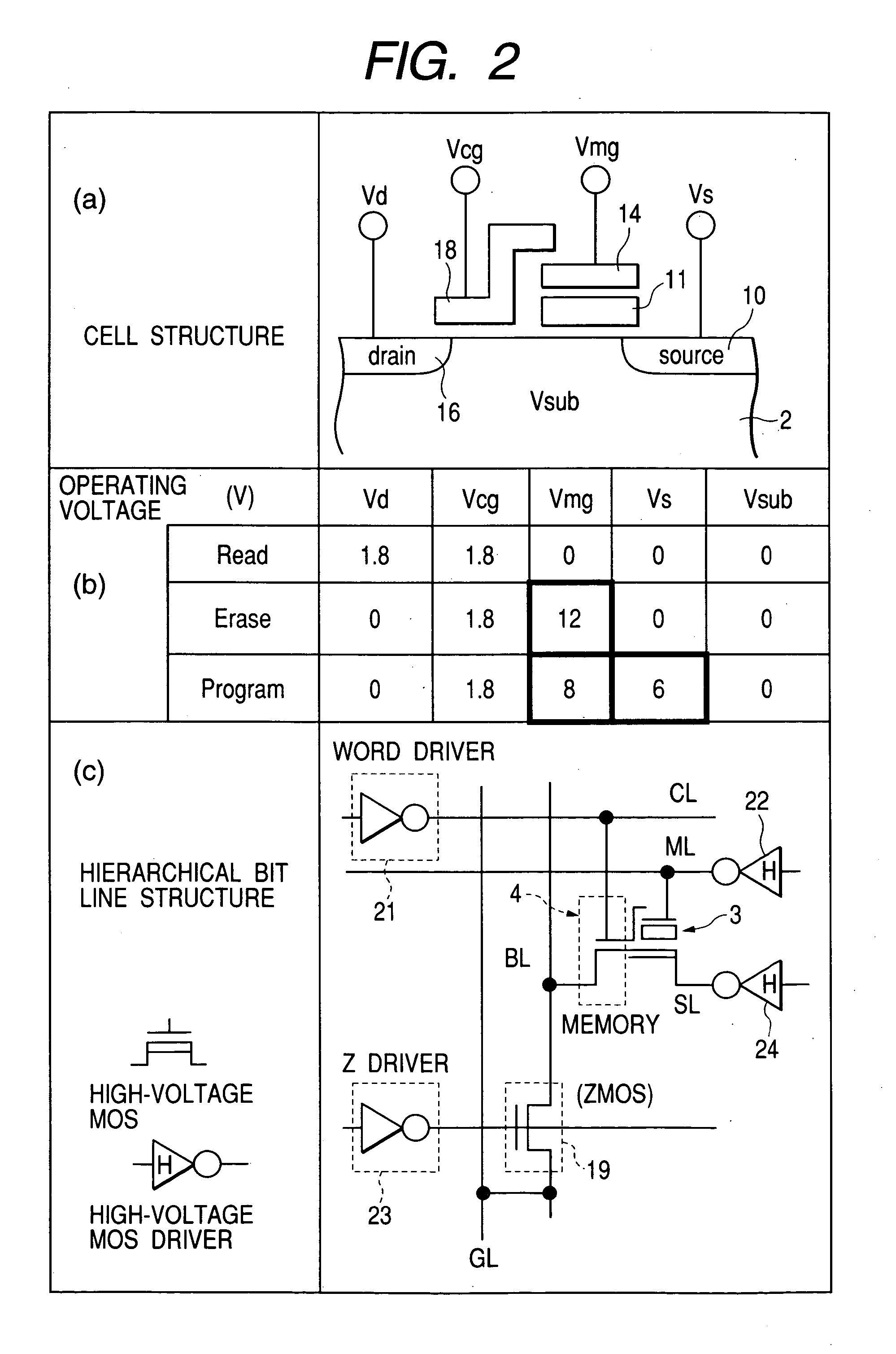

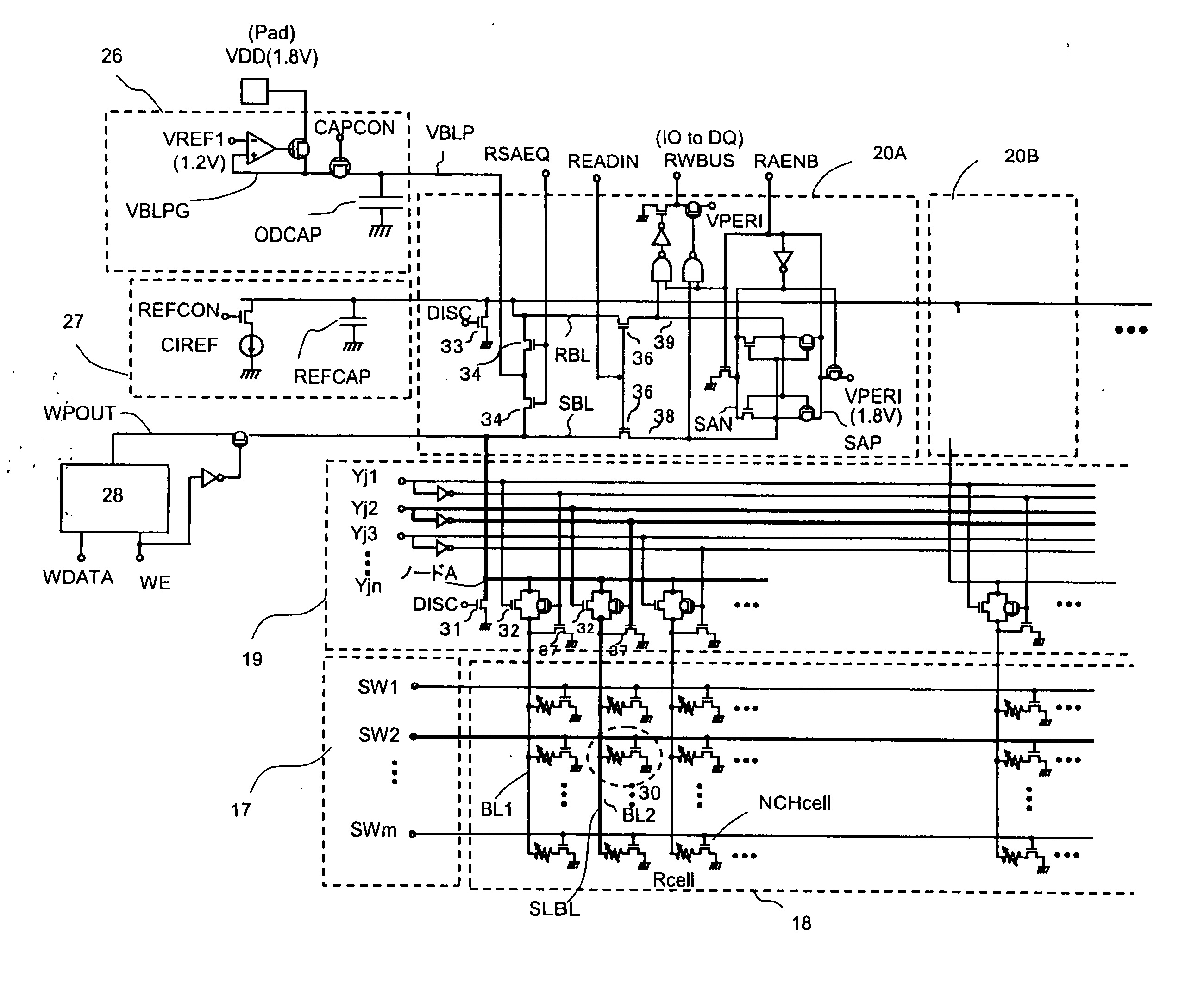

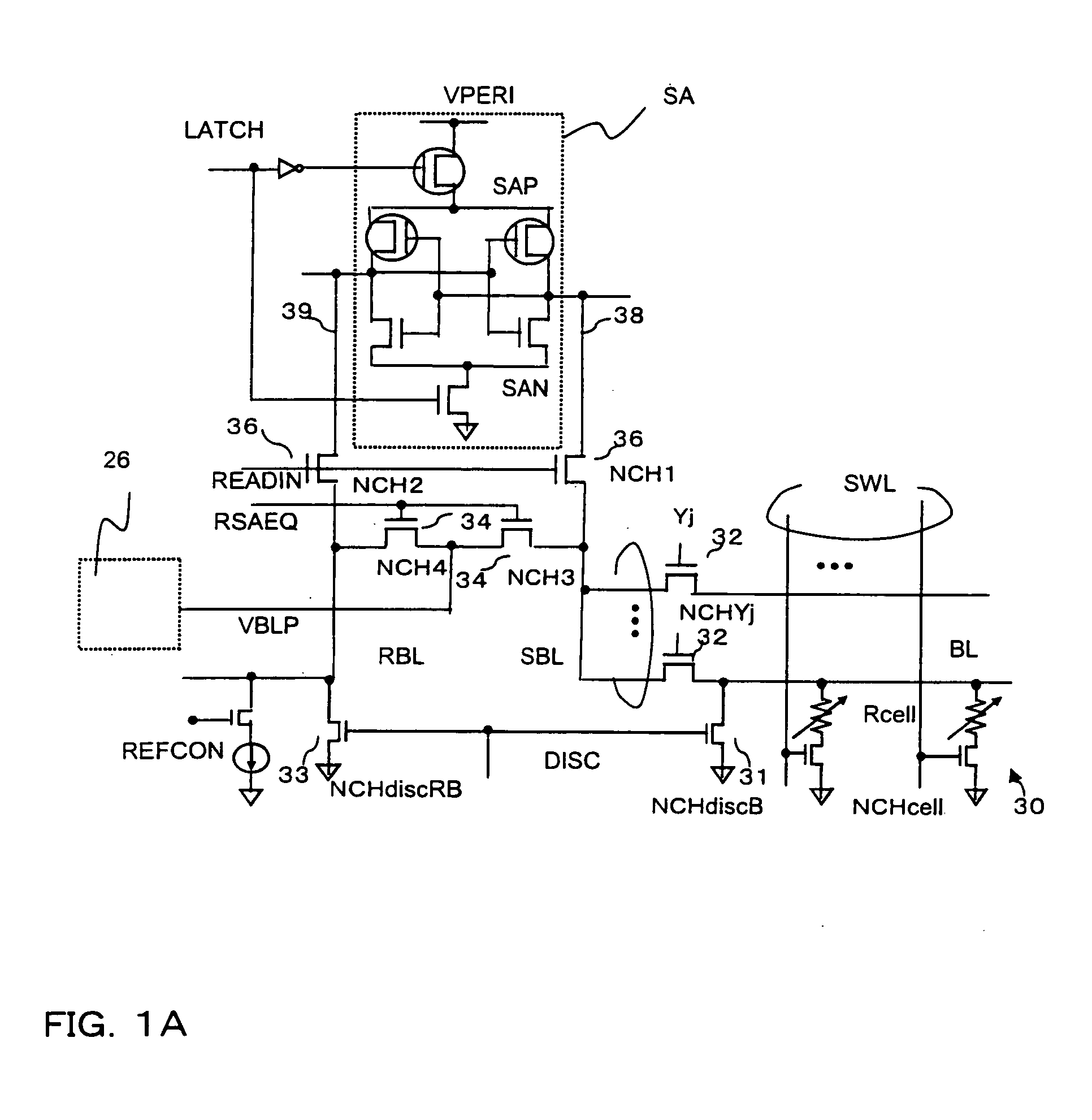

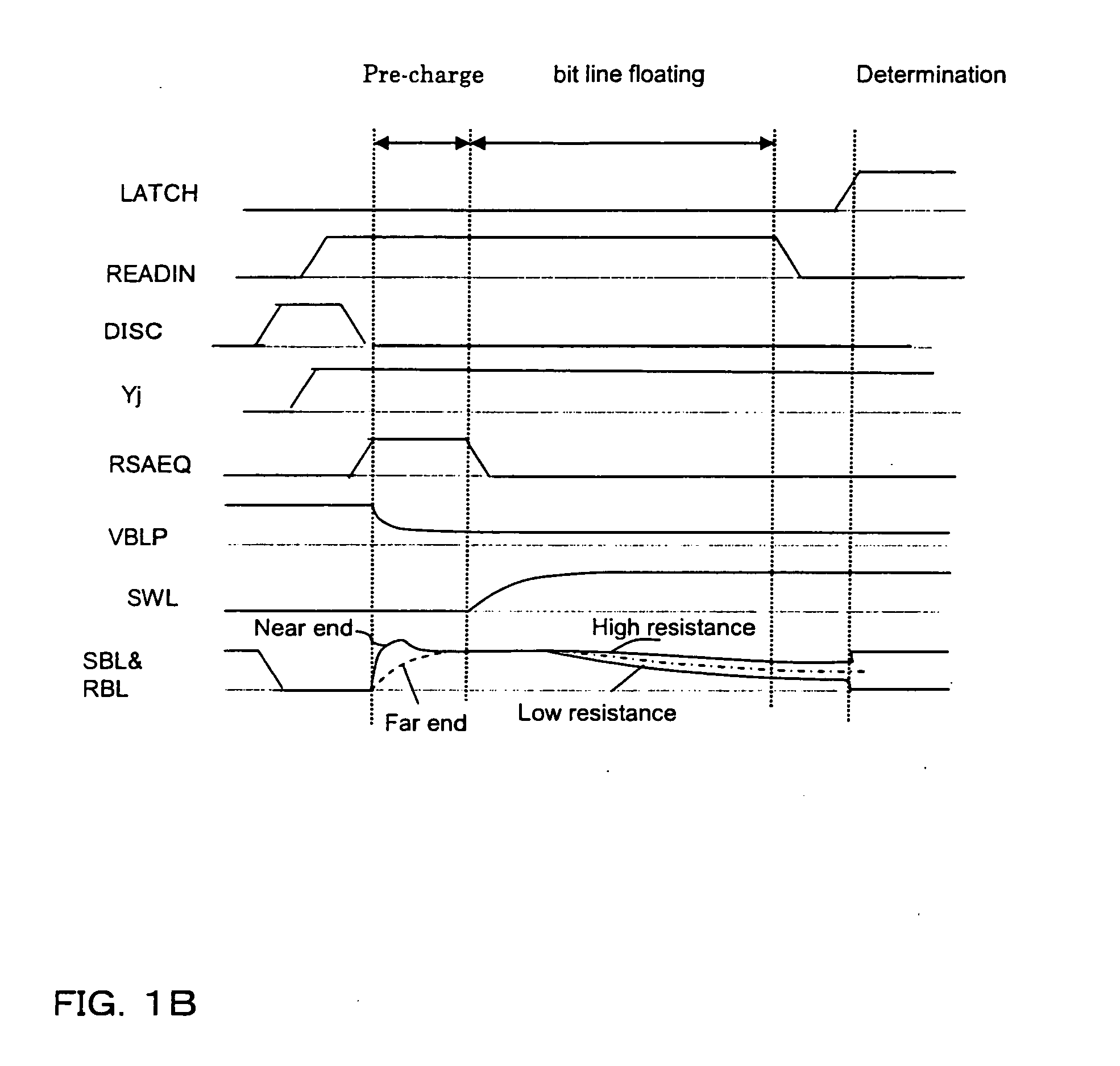

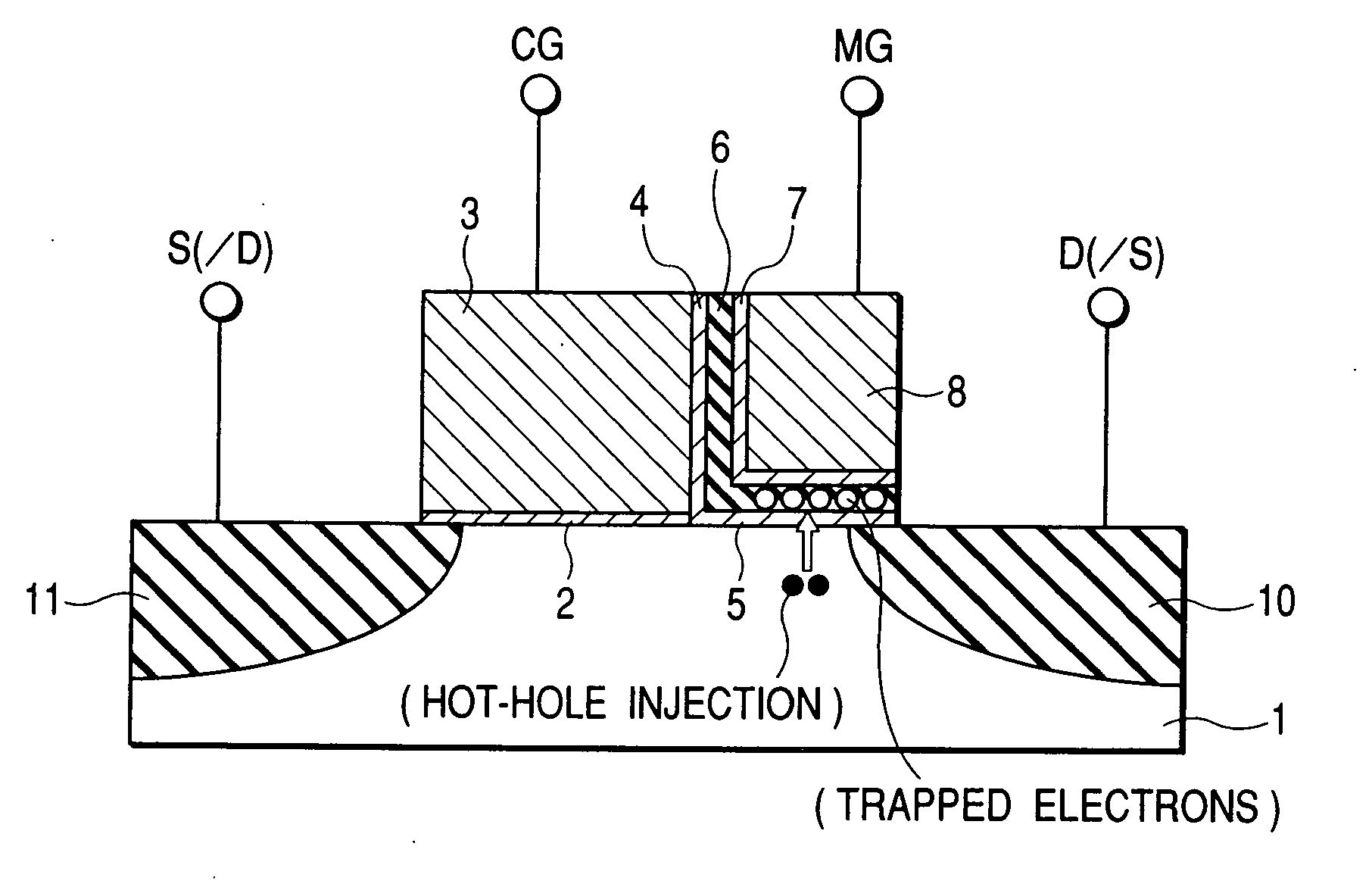

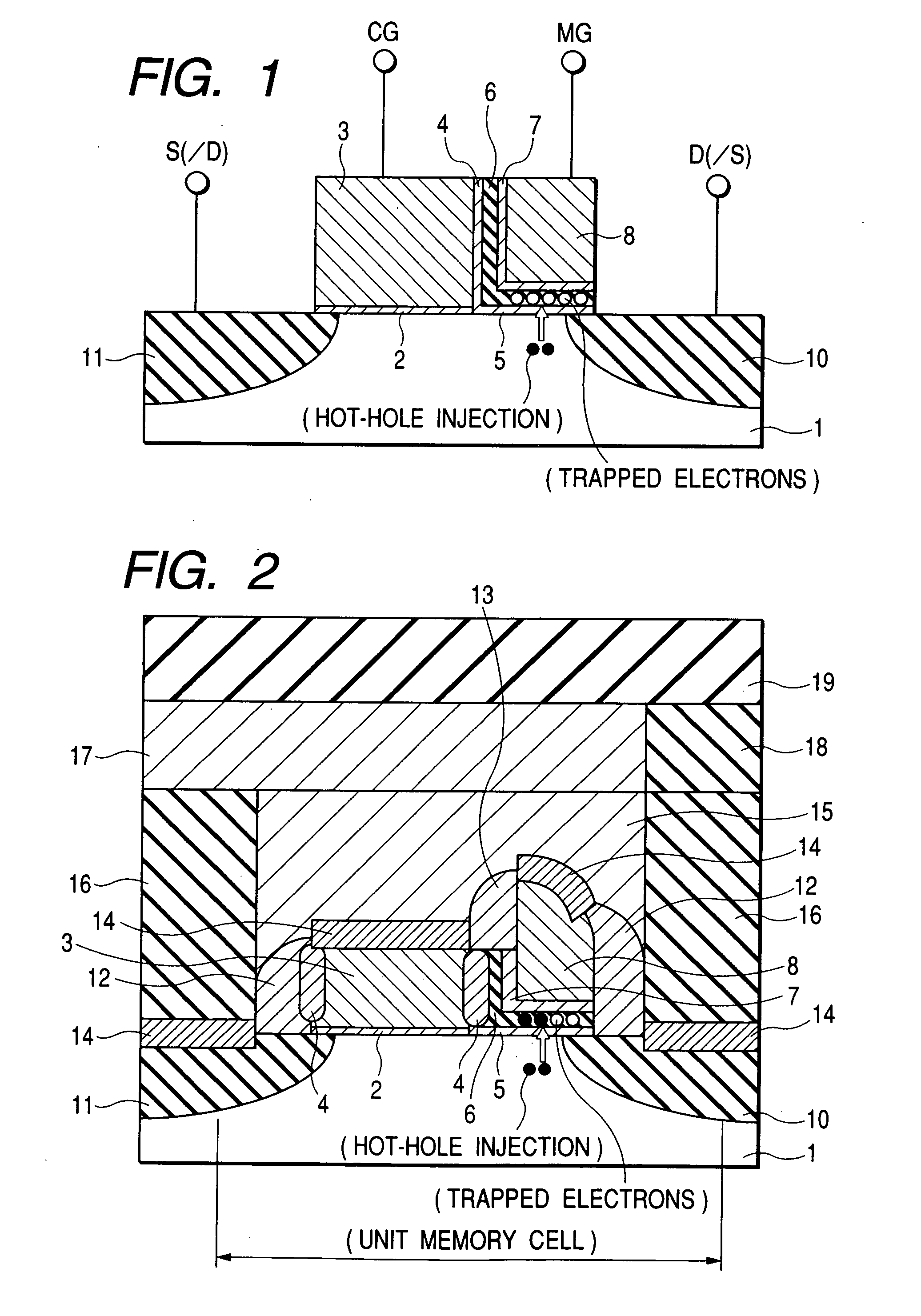

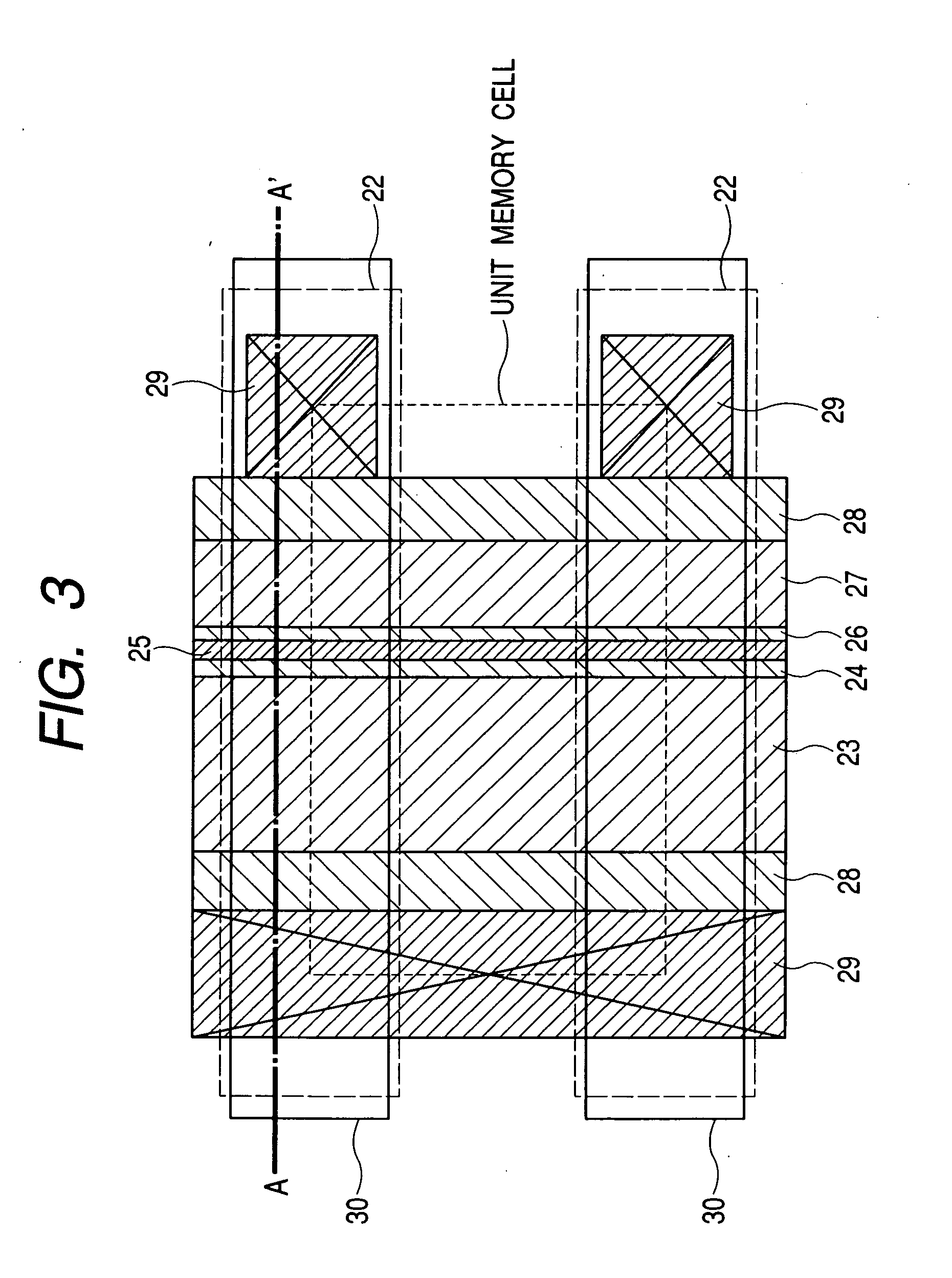

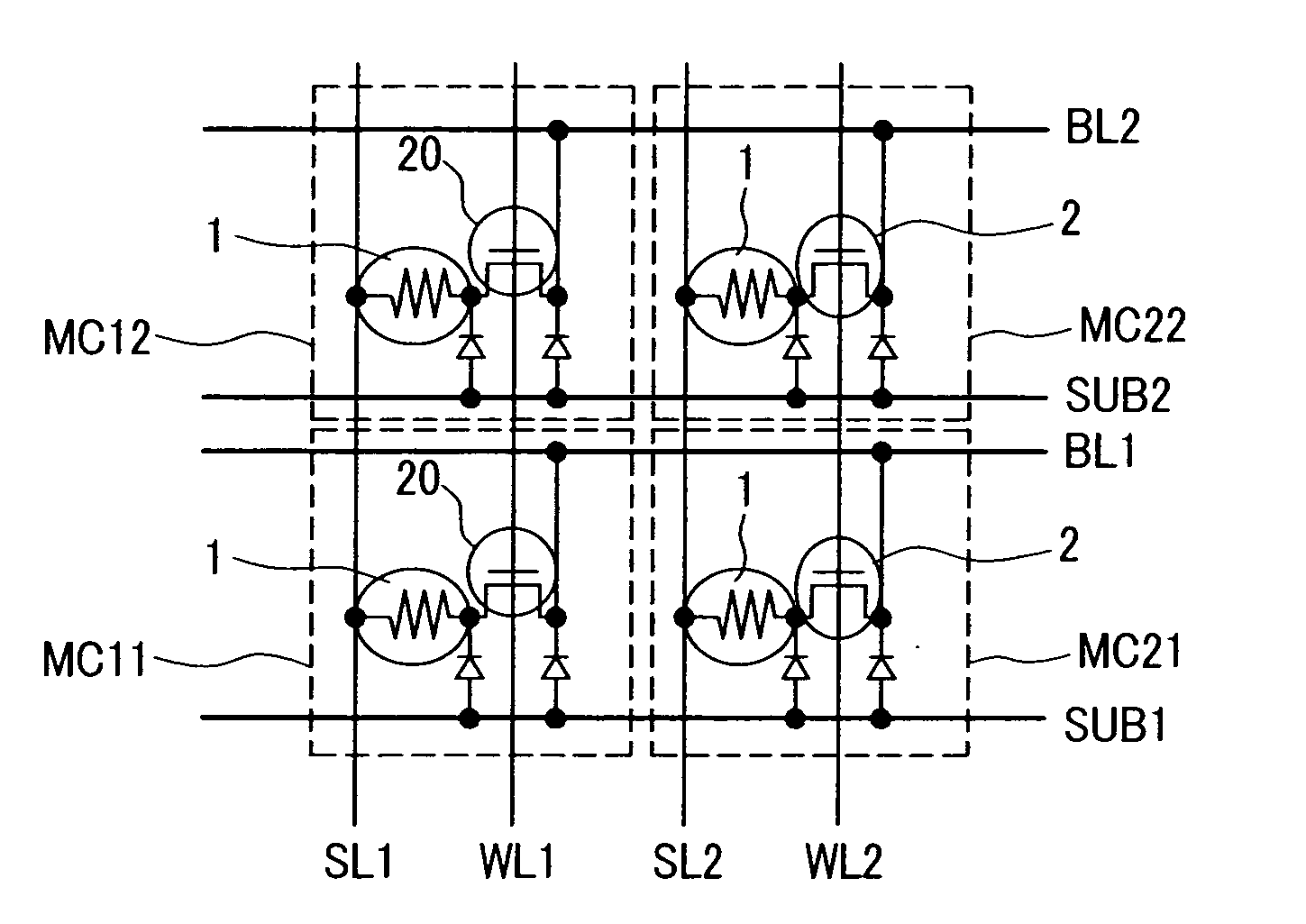

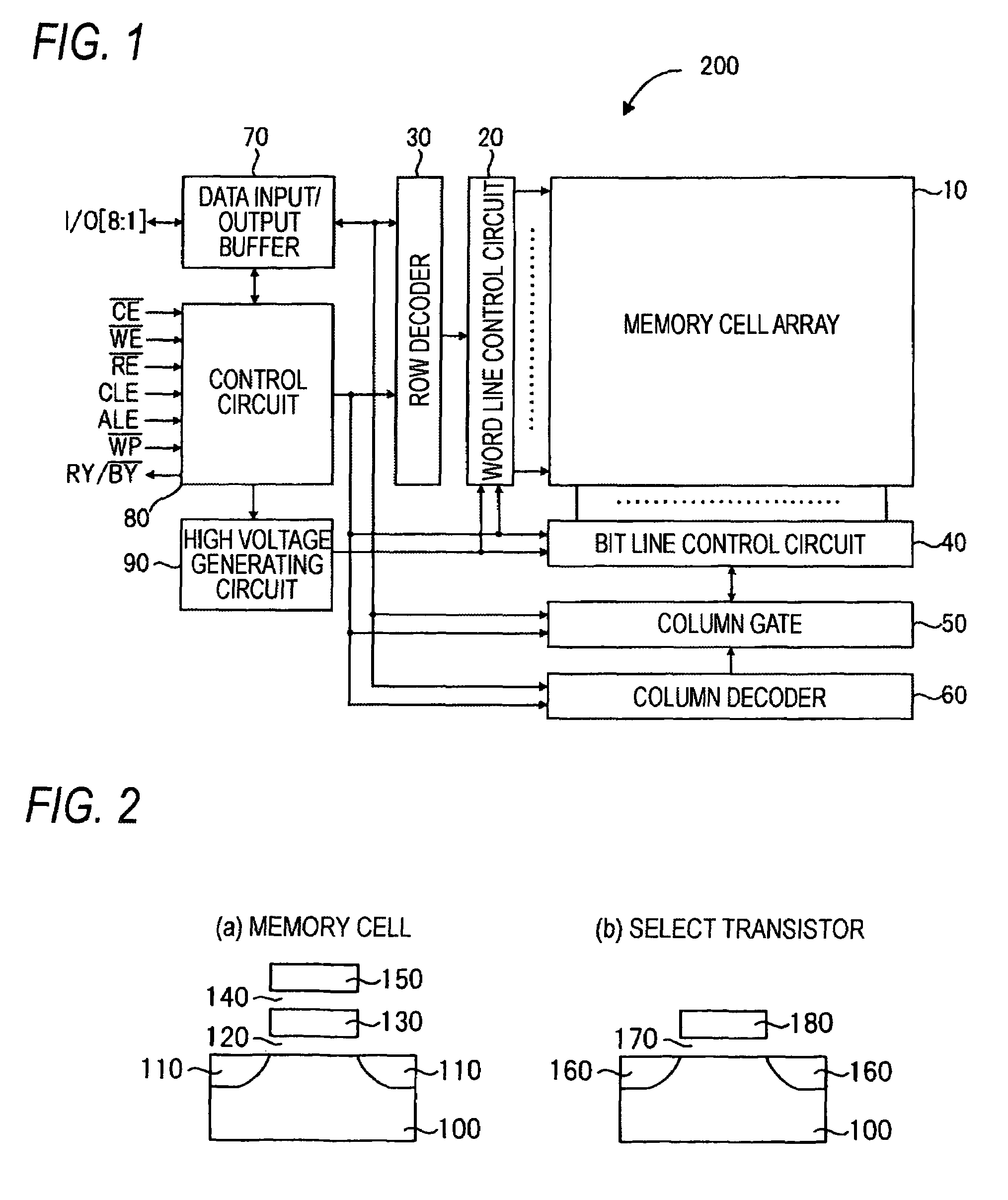

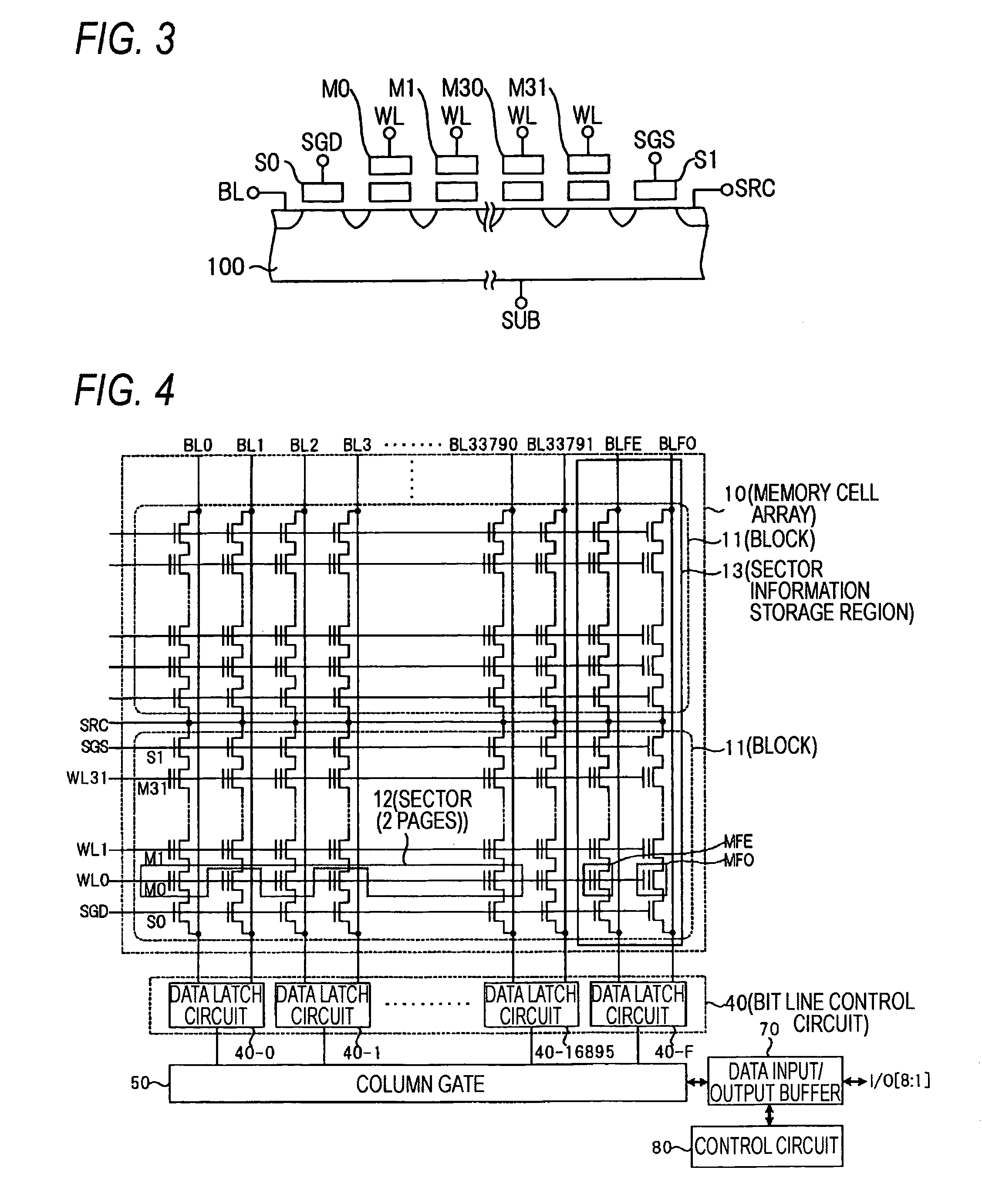

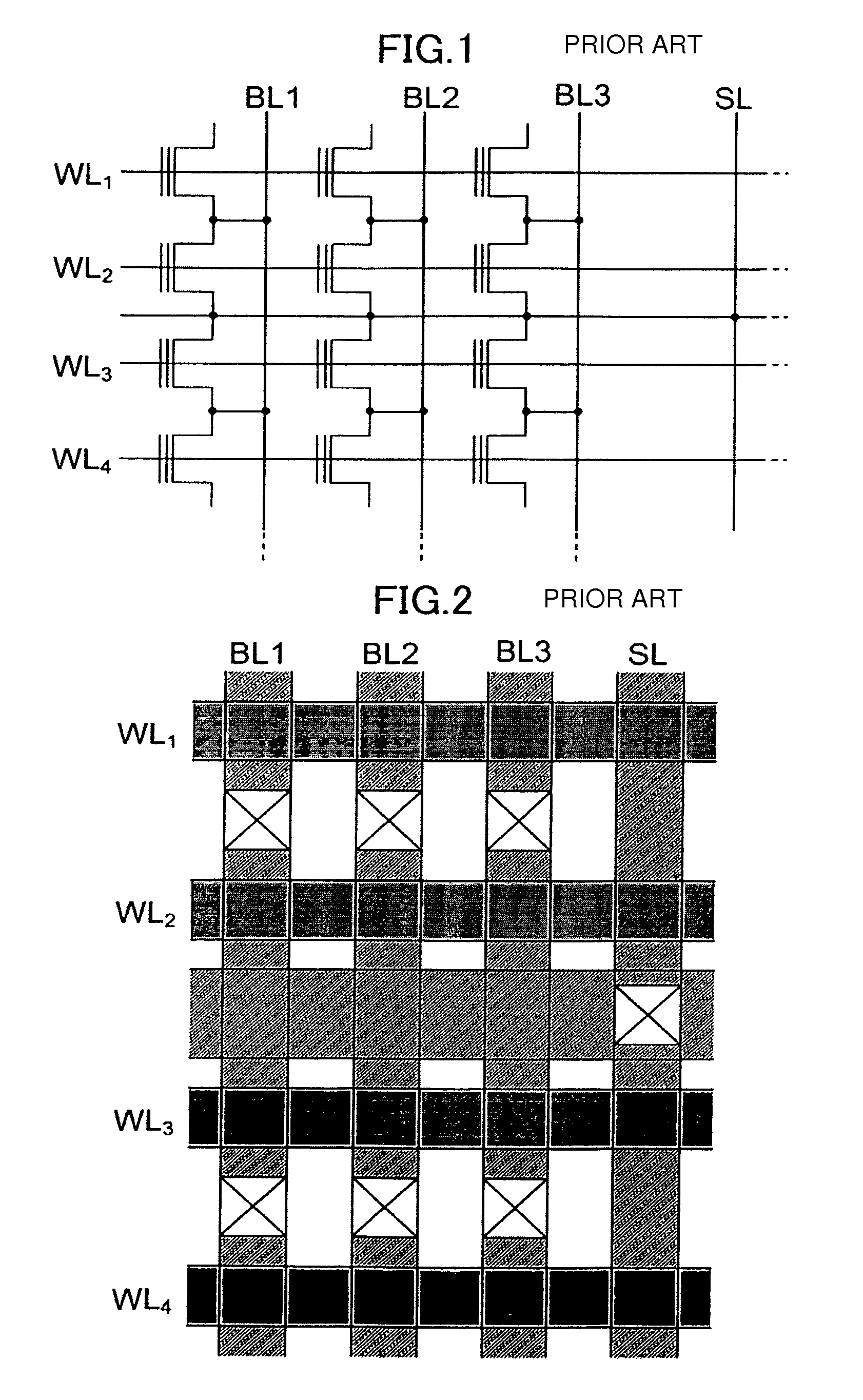

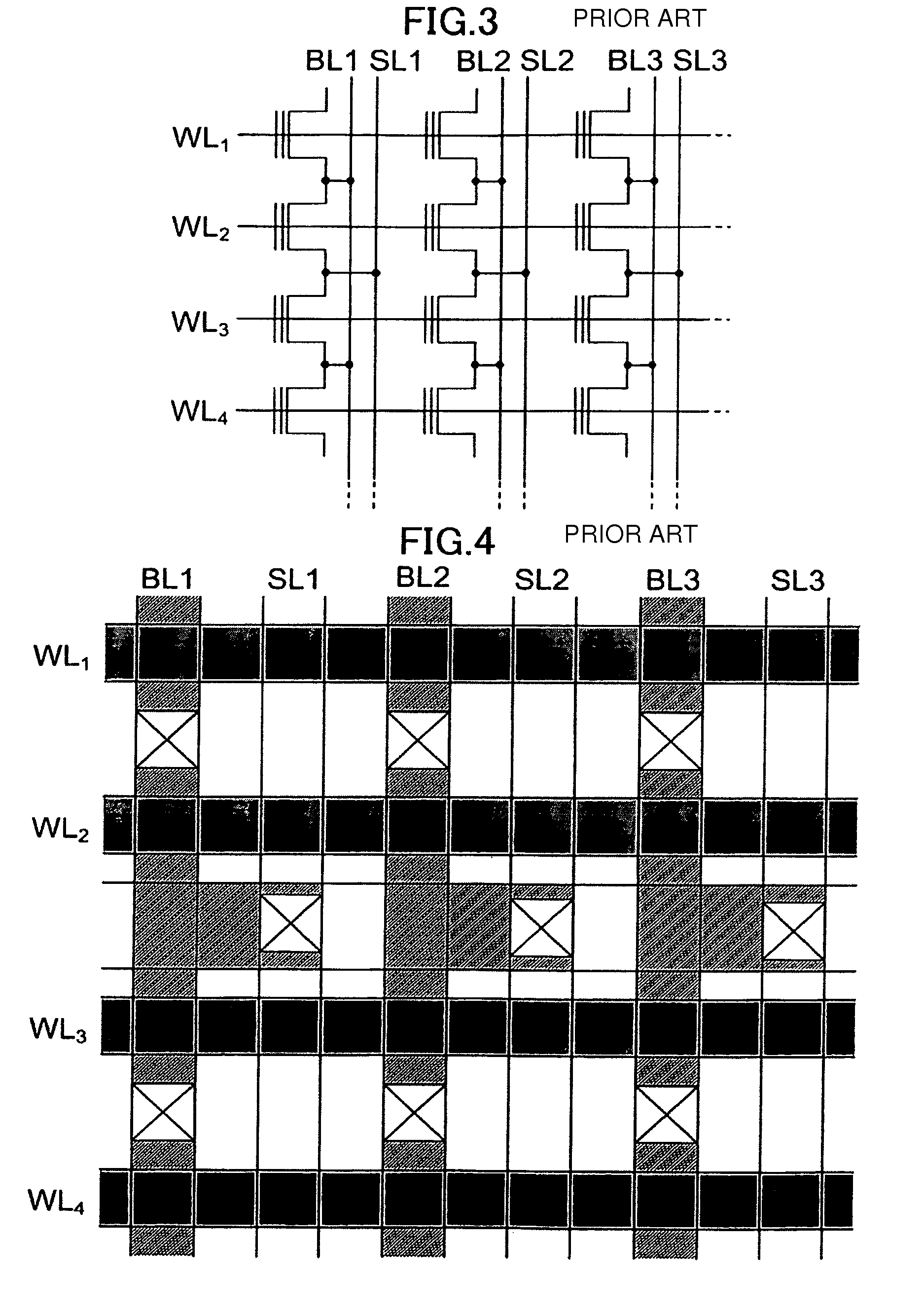

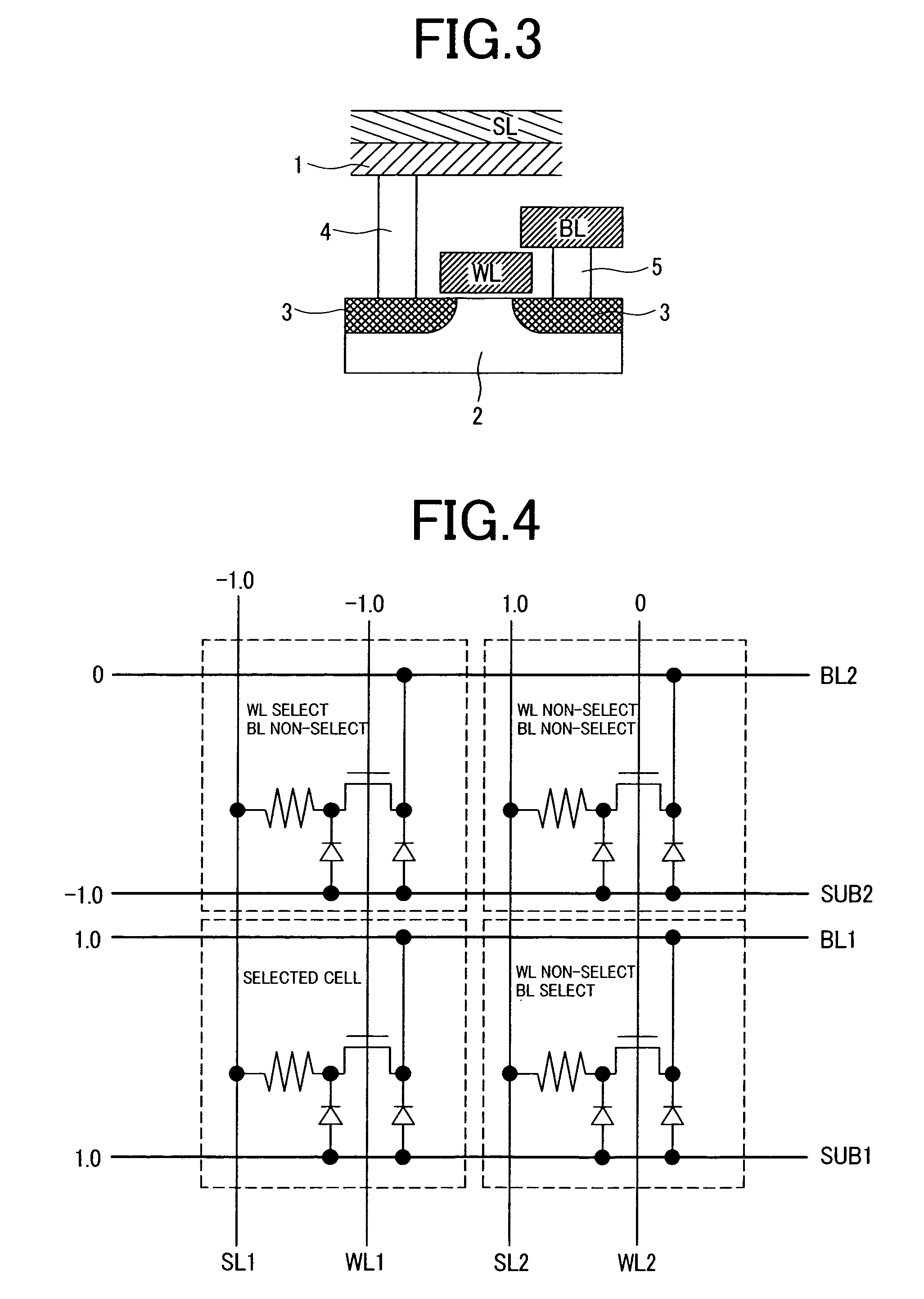

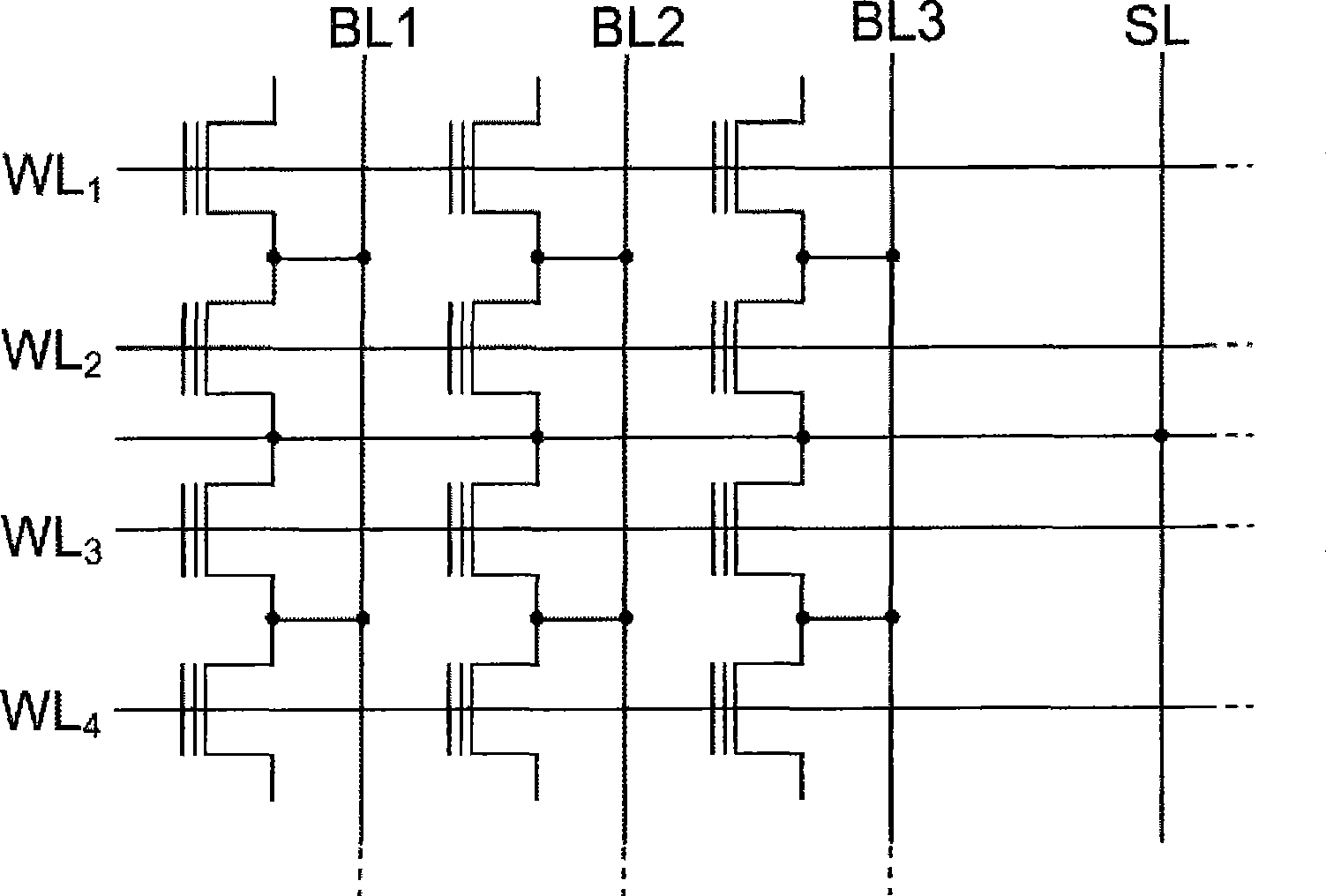

Nonvolatile semiconductor memory device employing transistors having different gate withstand voltages for enhanced reading speed

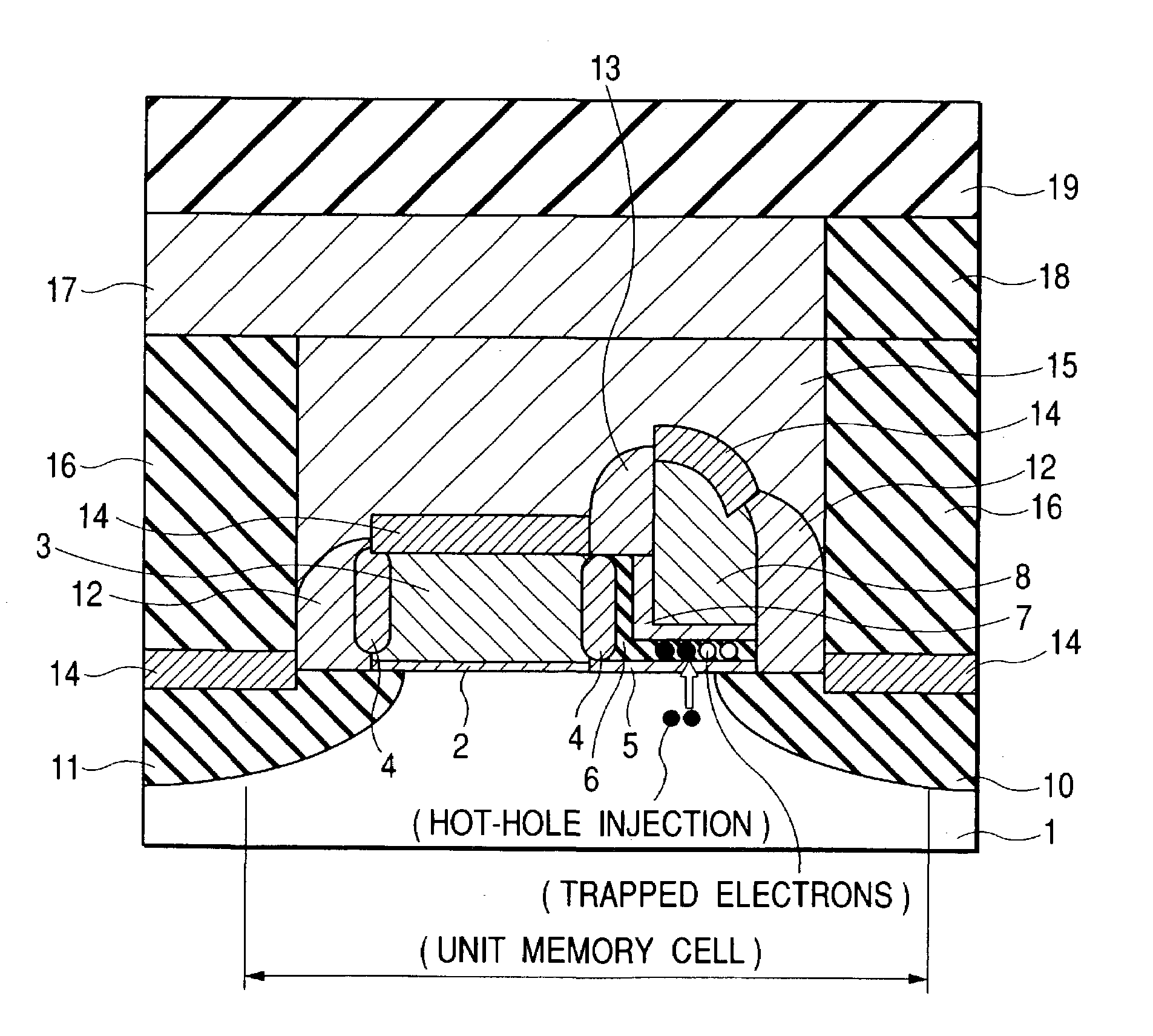

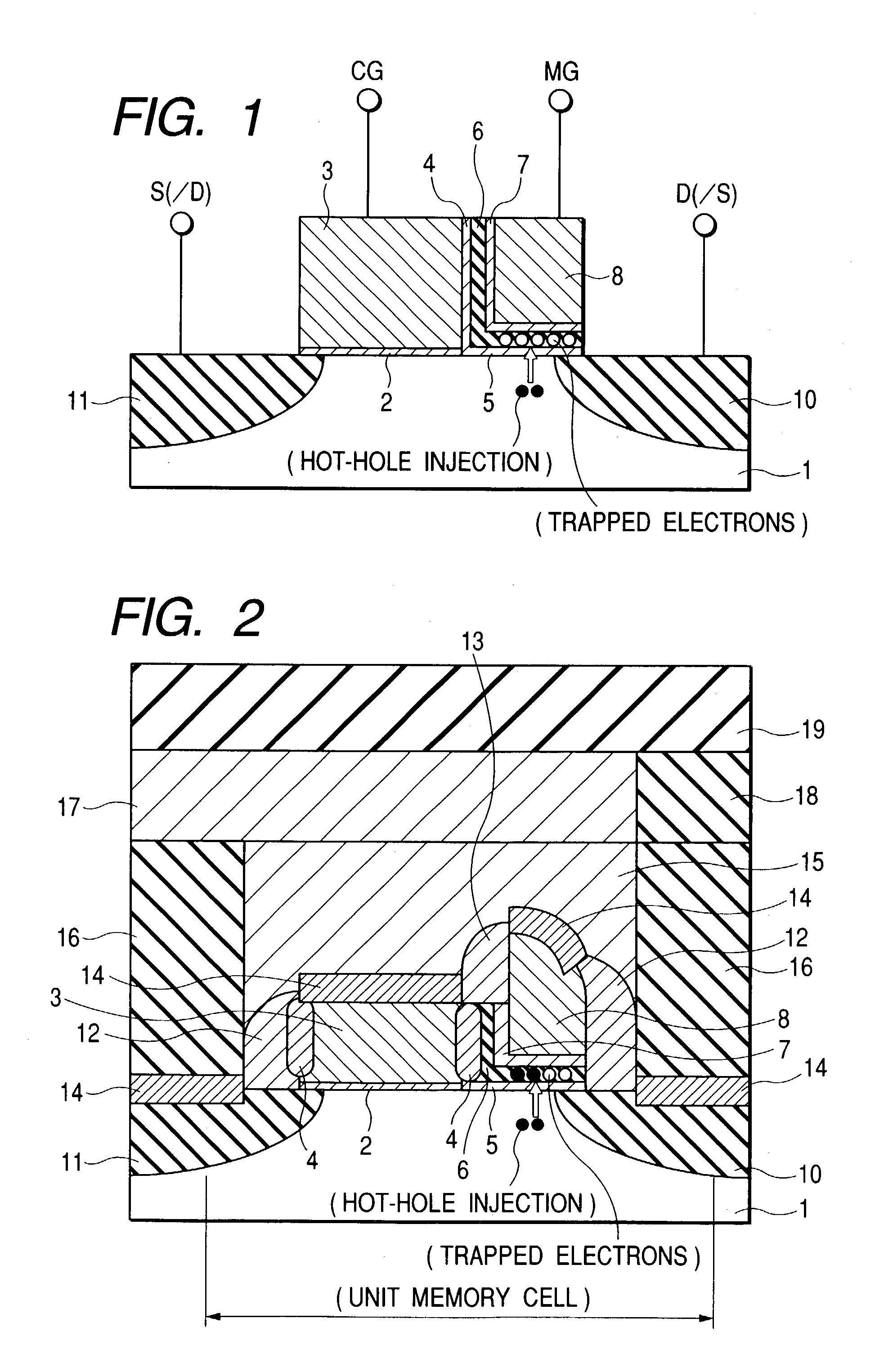

A semiconductor device includes a plurality of nonvolatile memory cells (1). Each of the nonvolatile memory cells comprises a MOS type first transistor section (3) used for information storage, and a MOS type second transistor section (4) which selects the first transistor section. The second transistor section has a bit line electrode (16) connected to a bit line, and a control gate electrode (18) connected to a control gate control line. The first transistor section has a source line electrode (10) connected to a source line, a memory gate electrode (14) connected to a memory gate control line, and a charge storage region (11) disposed directly below the memory gate electrode. A gate withstand voltage of the second transistor section is lower than that of the first transistor section. Assuming that the thickness of a gate insulating film of the second transistor section is defined as tc and the thickness of a gate insulating film of the first transistor section is defined as tm, they have a relationship of tc<tm.

Owner:RENESAS ELECTRONICS CORP

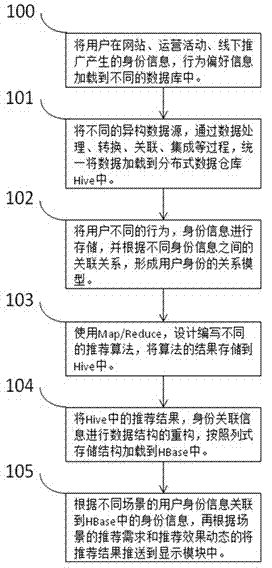

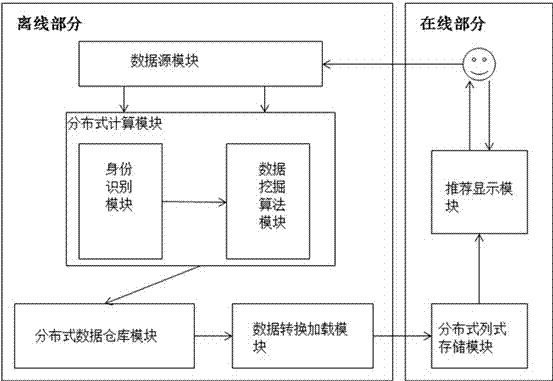

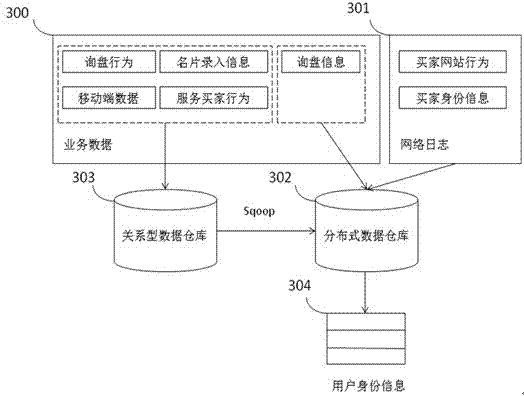

Individualized recommendation method and system based on distributed B2B platform

ActiveCN103886487AEasy to handleQuick responseMarketingSpecial data processing applicationsWeb sitePersonalization

The invention discloses an individualized recommendation method and system based on a B2B platform on a Hadoop platform of a distributed technology. The method comprises the steps that firstly, centralized placement, storage and query are carried out on various data, such as website log files, product information and user information, based on the Hadoop distributed storage technology, and the data are processed fast and efficiently; secondly, the data are preprocessed through a Hive service under the Hadoop platform, a fast and efficient implementation recommendation algorithm is achieved through Map / Reduce; then, the information retrieval and file mining work is achieved on text information through the Map / Reduce, the product information needed in inquiry and purchase by a user is matched, and individualized recommendation information is acquired; finally, large-data storage and query are provided through an HBase service under the Hadoop platform, and website recommendation user responses are improved.

Owner:FOCUS TECH

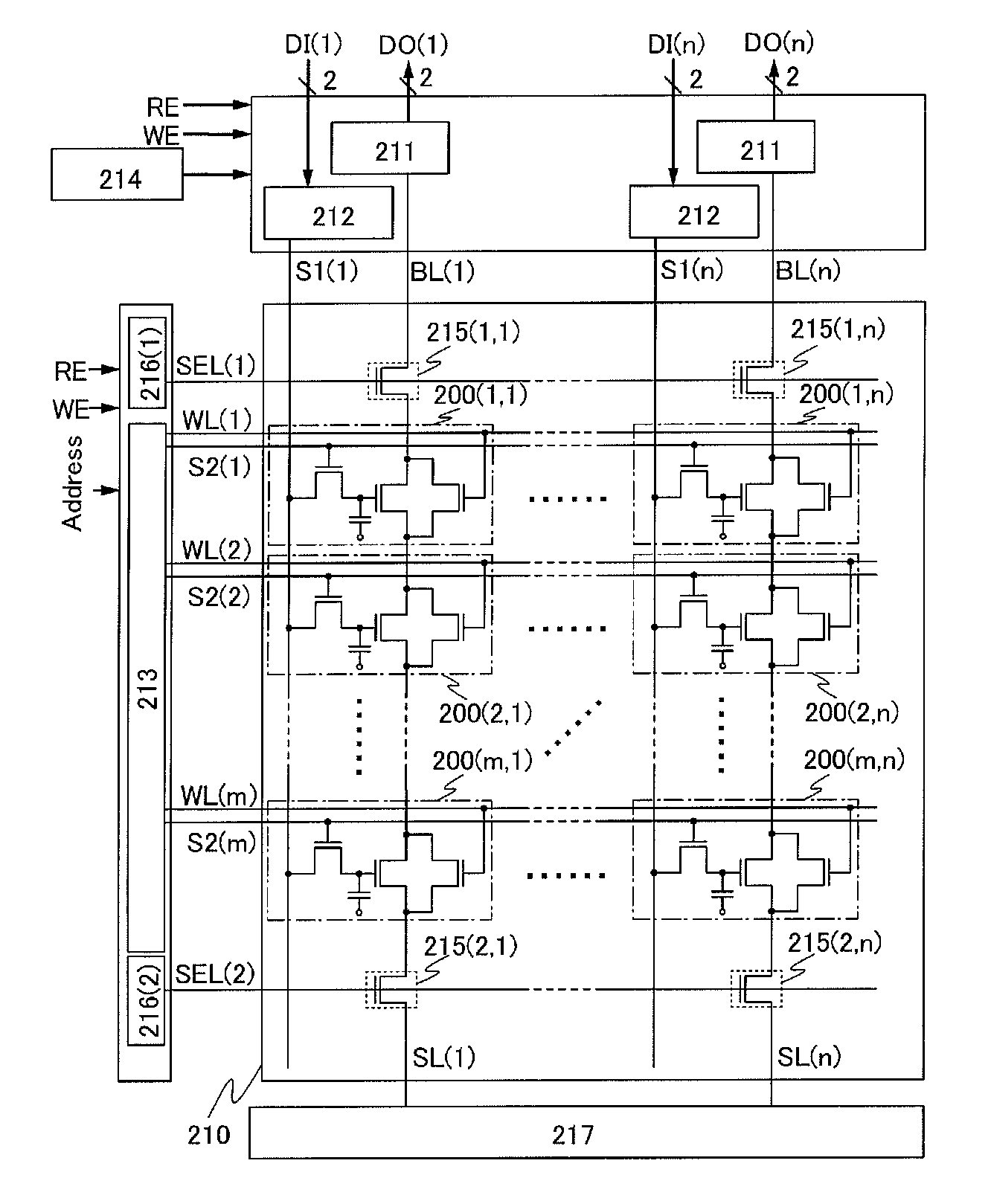

Semiconductor device

ActiveUS8363452B2Easily multivaluedNovel structureTransistorSolid-state devicesBit lineDriver circuit

Disclosed is a semiconductor device functioning as a multivalued memory device including: memory cells connected in series; a driver circuit selecting a memory cell and driving a second signal line and a word line; a driver circuit selecting any of writing potentials and outputting it to a first signal line; a reading circuit comparing a potential of a bit line and a reference potential; and a potential generating circuit generating the writing potential and the reference potential. One of the memory cells includes: a first transistor connected to the bit line and a source line; a second transistor connected to the first and second signal line; and a third transistor connected to the word line, bit line, and source line. The second transistor includes an oxide semiconductor layer. A gate electrode of the first transistor is connected to one of source and drain electrodes of the second transistor.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor integrated circuit device and a method of manufacturing the same

InactiveUS7045848B2Increase speedHigh speed readTransistorSemiconductor/solid-state device detailsReverse biasSemiconductor

The memory cell transistor includes, in a first well region, a pair of memory electrodes, one of which serves as source electrode and the other serves as a drain electrode and a channel region interposed between the pair of memory electrodes. There is, on a channel region, a first gate electrode disposed near its corresponding memory electrode with an insulating film interposed therebetween, and a second gate electrode disposed through insulating films and a charge storage region and electrically isolated from the first gate electrode. A first negative voltage is applied to the first well region to form a state of a reverse bias greater than or equal to a junction withstand voltage between the second gate electrode and the memory electrode near the second gate electrode, thereby enabling injection of hot electrons into the charge storage region and injection of electrons from the well region to the charge storage region.

Owner:RENESAS ELECTRONICS CORP

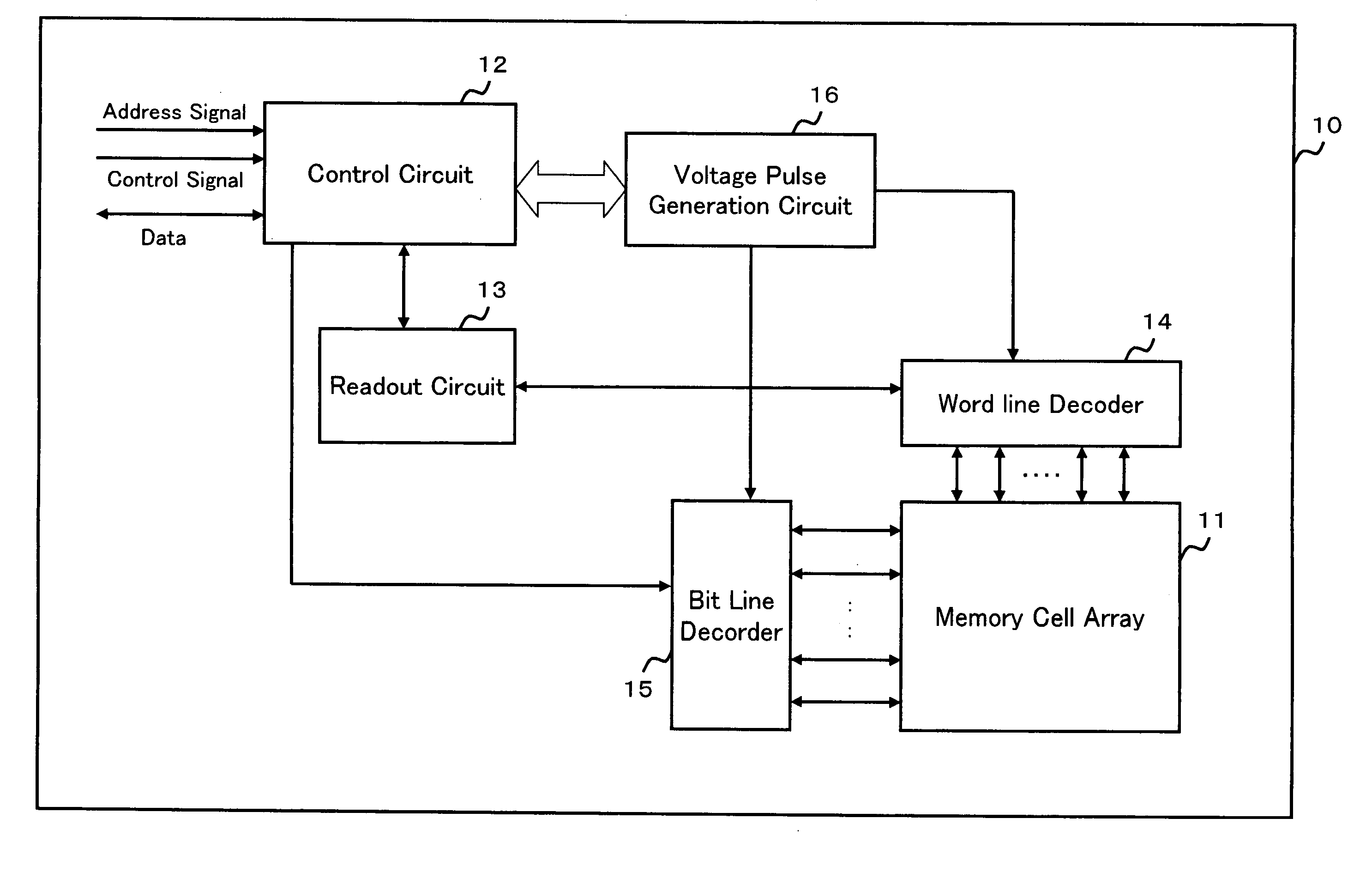

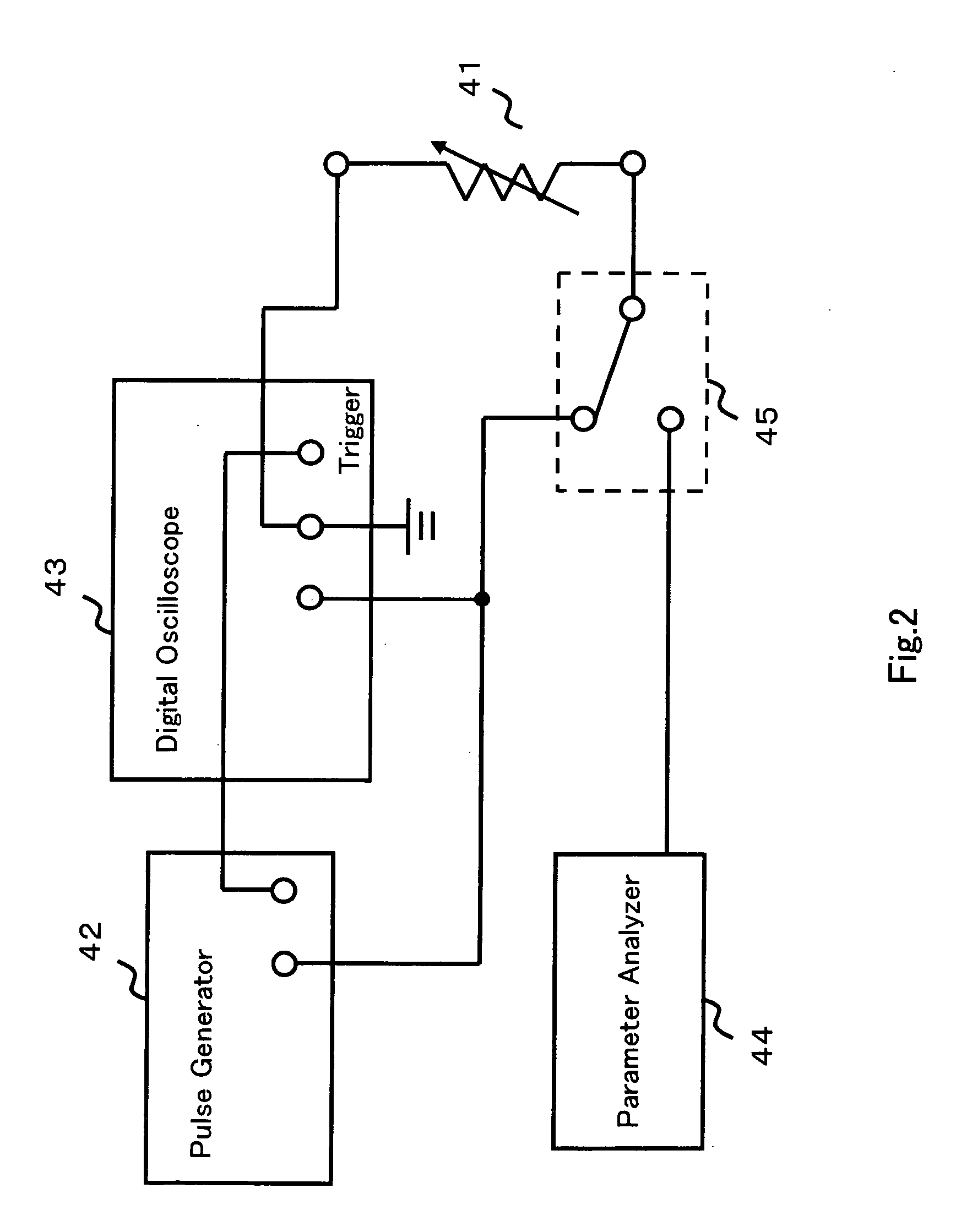

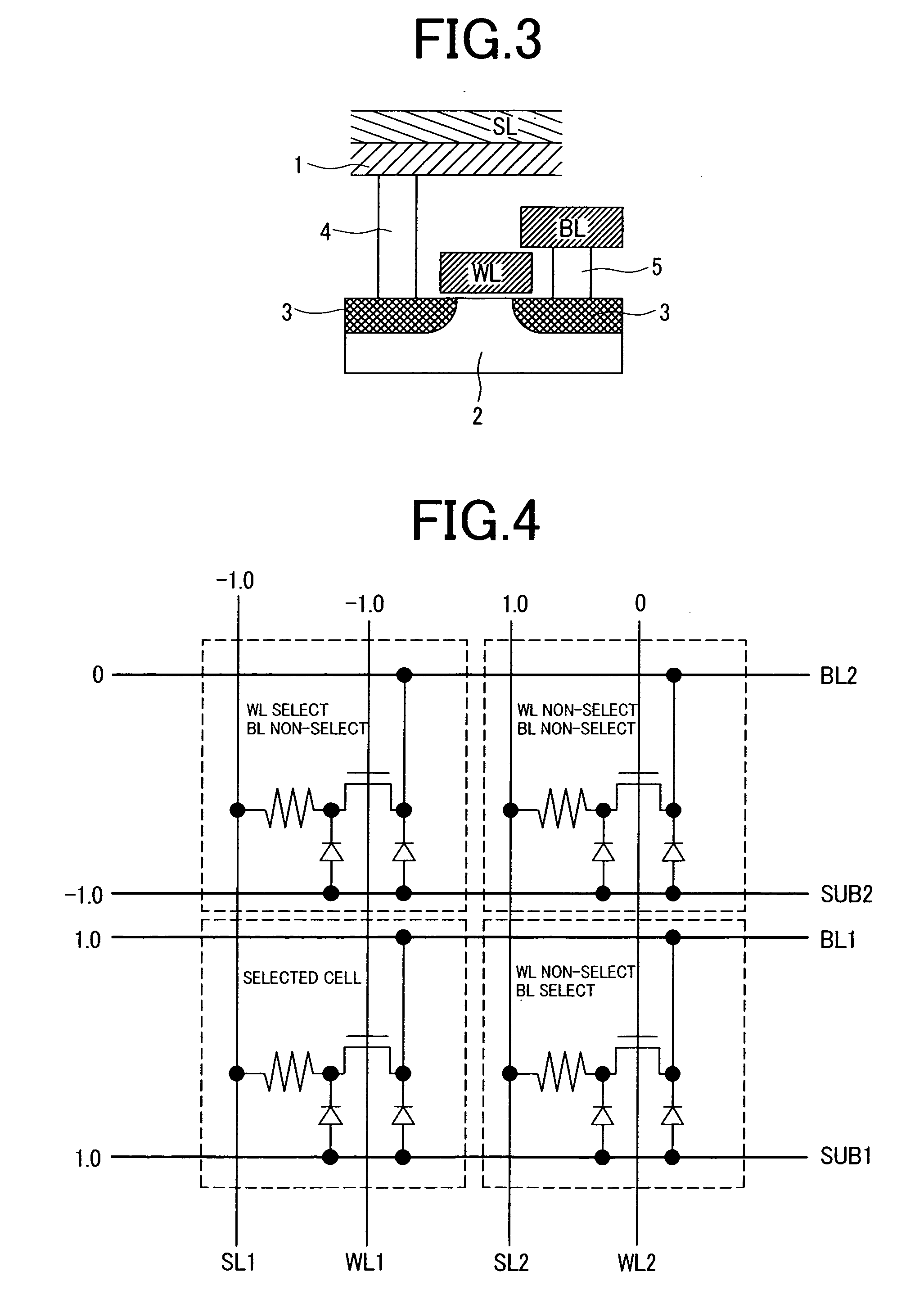

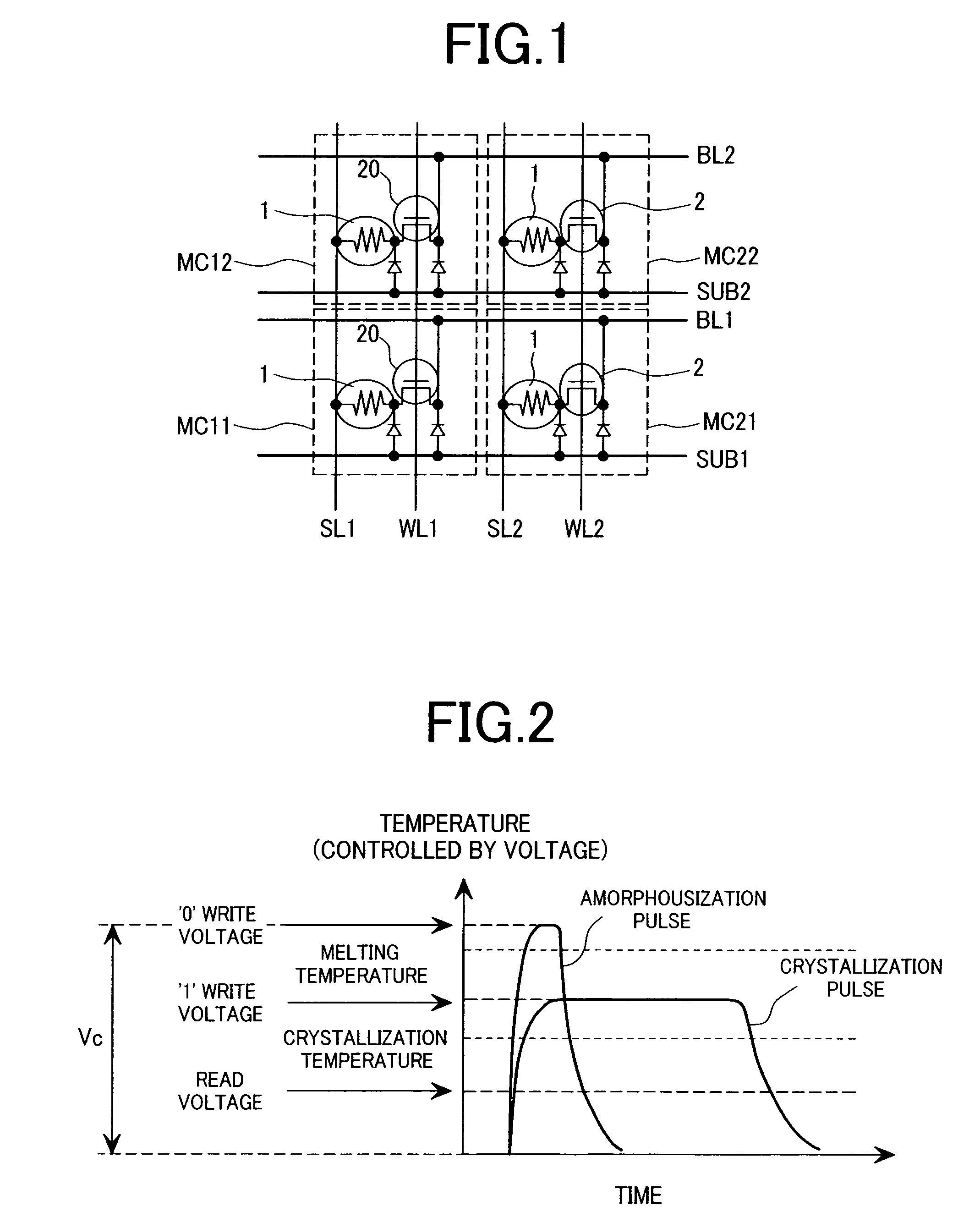

Driving method of variable resistance element and memory device

ActiveUS20060002174A1Increase speedLarge reading marginDigital storageSemiconductor devicesHysteresisVoltage pulse

A variable resistance element is configured to be provided with a perovskite-type oxide between a first electrode and a second electrode, of which electric resistance between the first electrode and the second electrode is changed by applying a voltage pulse of a predetermined polarity between the first electrode and the second electrode, and the variable resistance element has a resistance hysteresis characteristic, in which a changing rate of a resistance value is changed from positive to negative with respect to increase of a cumulative pulse applying time in the application of the voltage pulse. The voltage pulse is applied to the variable resistance element so that the cumulative pulse applying time is not longer than a specific cumulative pulse applying time, in which the changing rate of the, resistance value is changed from positive to negative with respect to increase of the cumulative pulse applying time in the resistance hysteresis characteristic.

Owner:SAMSUNG ELECTRONICS CO LTD

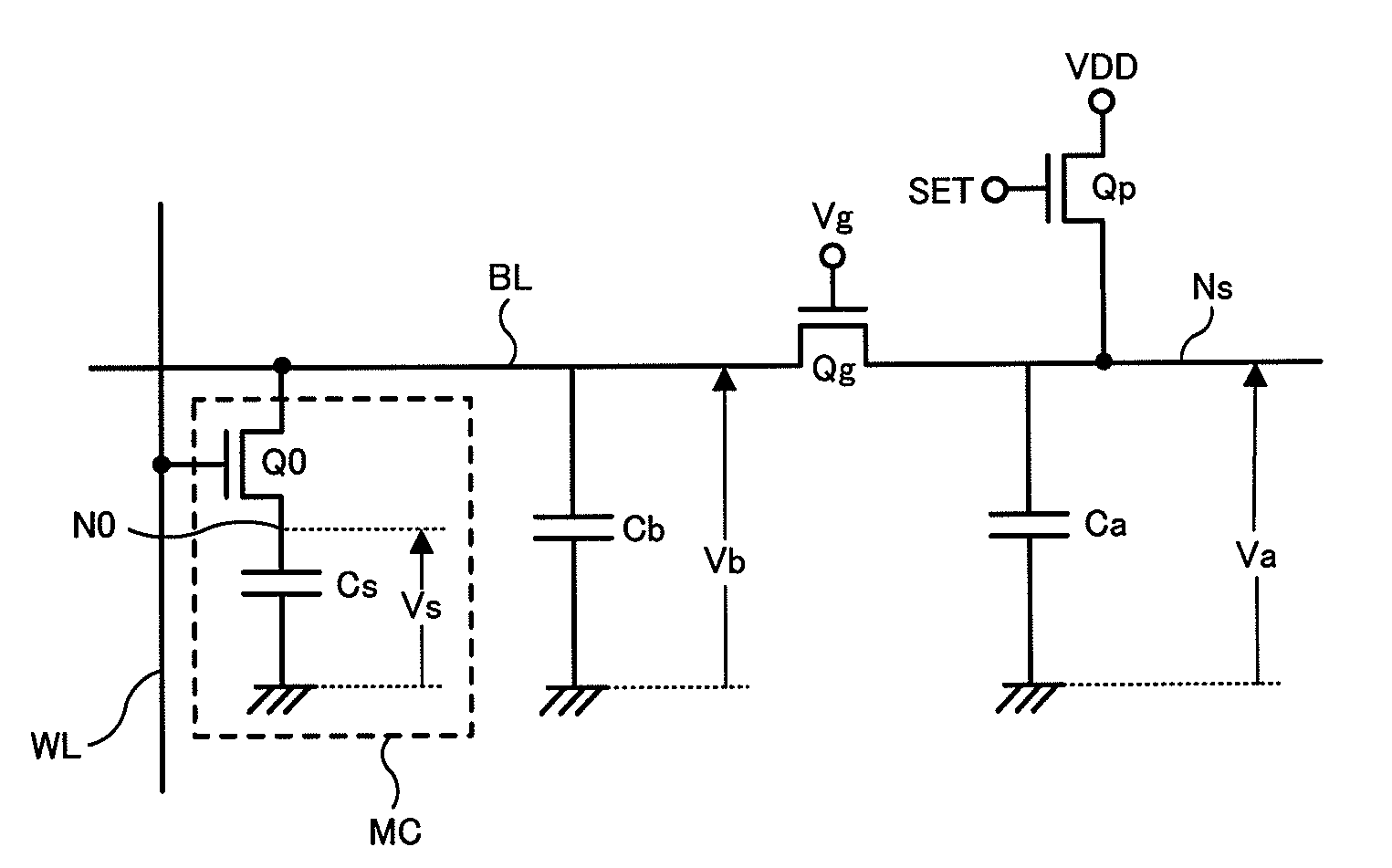

Method for driving semiconductor device

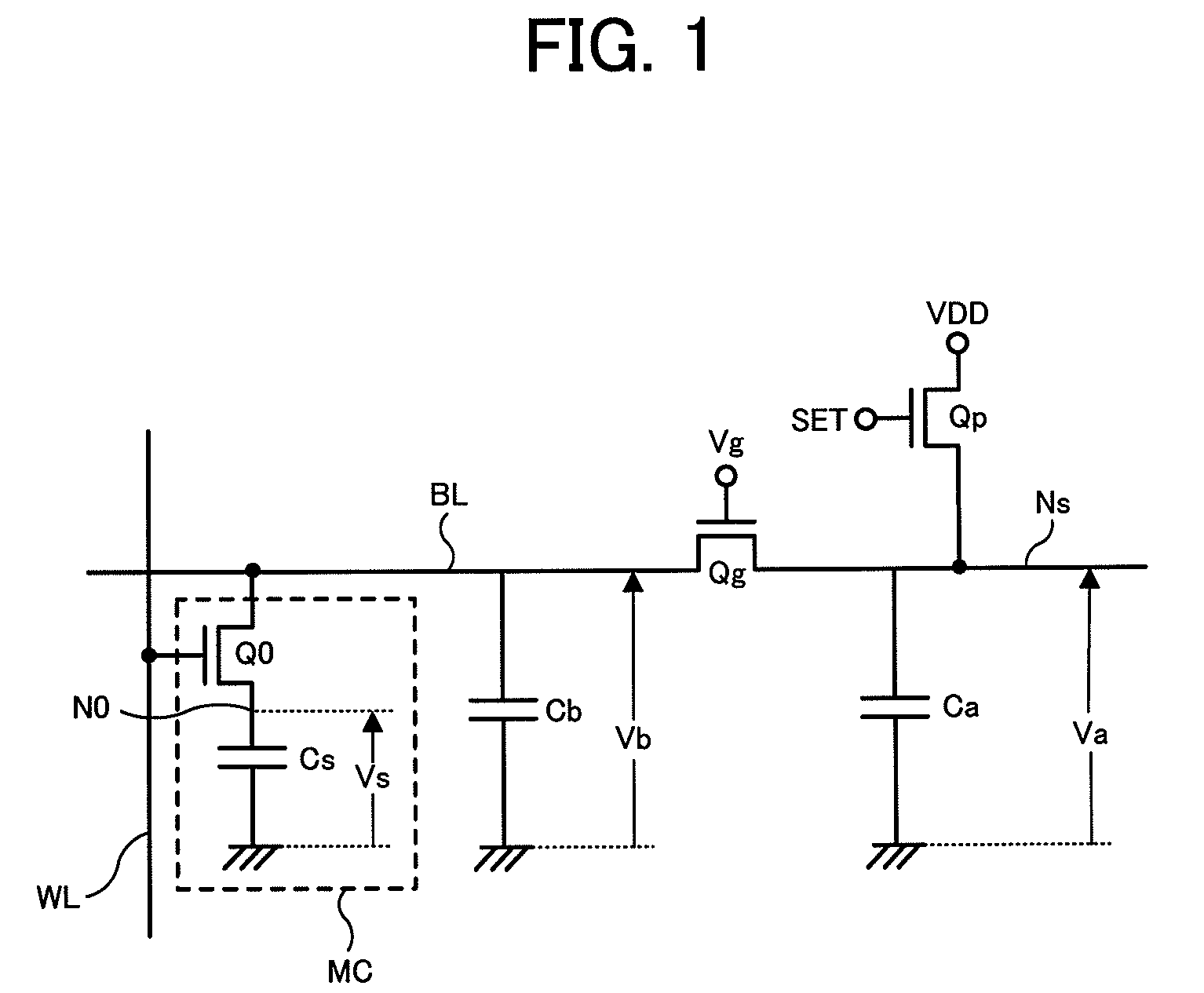

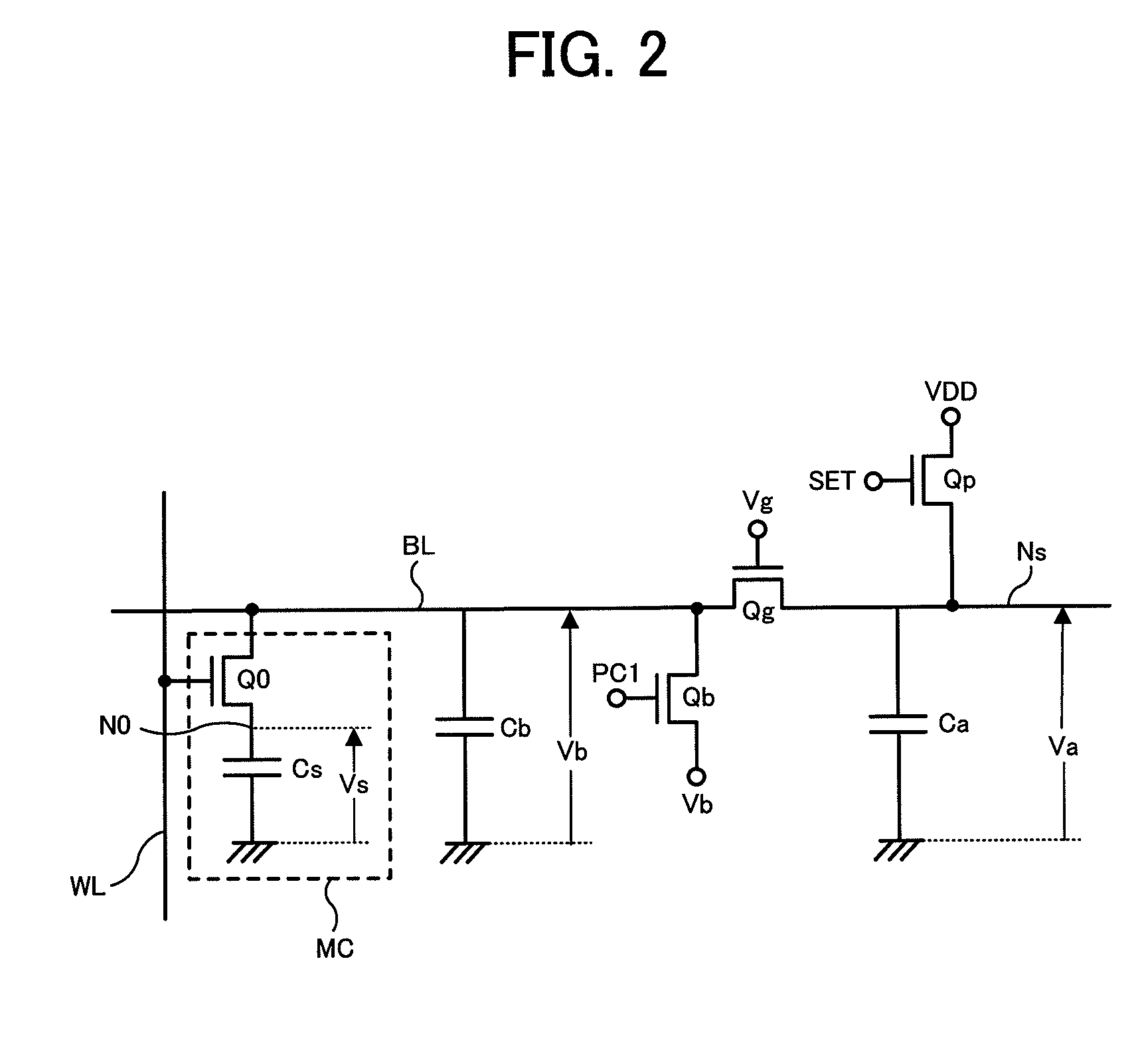

InactiveUS20120294070A1Reduce power consumptionImprove reliabilitySolid-state devicesRead-only memoriesOxide semiconductorPower semiconductor device

A semiconductor device includes a nonvolatile memory cell including a writing transistor including an oxide semiconductor, a reading transistor including a semiconductor material different from that of the writing transistor, and a capacitor. Data is written to the memory cell by turning on the writing transistor so that a potential is supplied to a node where a source electrode of the writing transistor, one electrode of the capacitor, and a gate electrode of the reading transistor are electrically connected, and then turning off the writing transistor so that a predetermined potential is held in the node. Data is read out from the memory cell by supplying a precharge potential to a bit line, stopping the supply of the potential to the bit line, and determining whether the potential of the bit line is kept at the precharge potential or decreased.

Owner:SEMICON ENERGY LAB CO LTD

Wide dynamic range image sensor

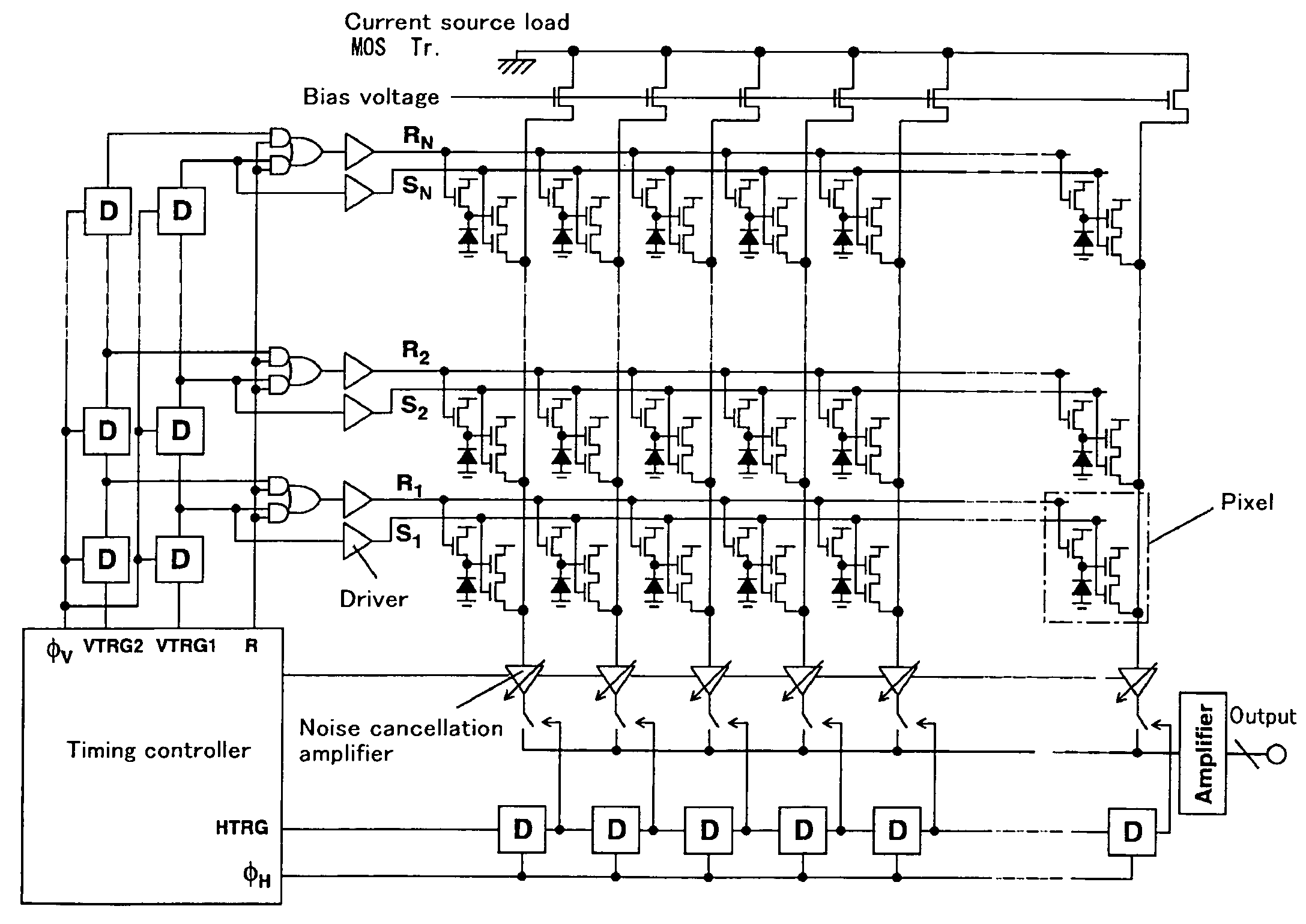

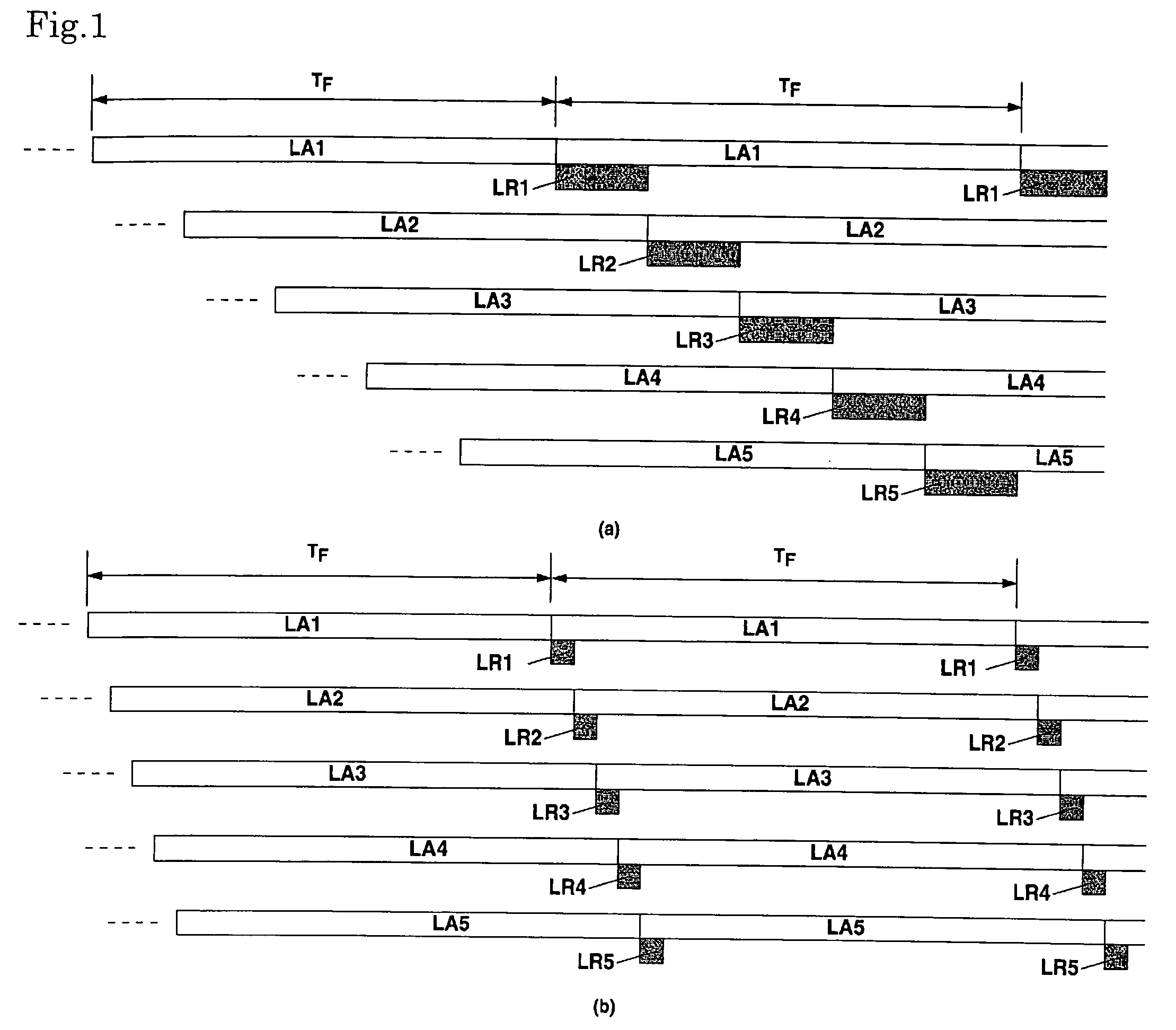

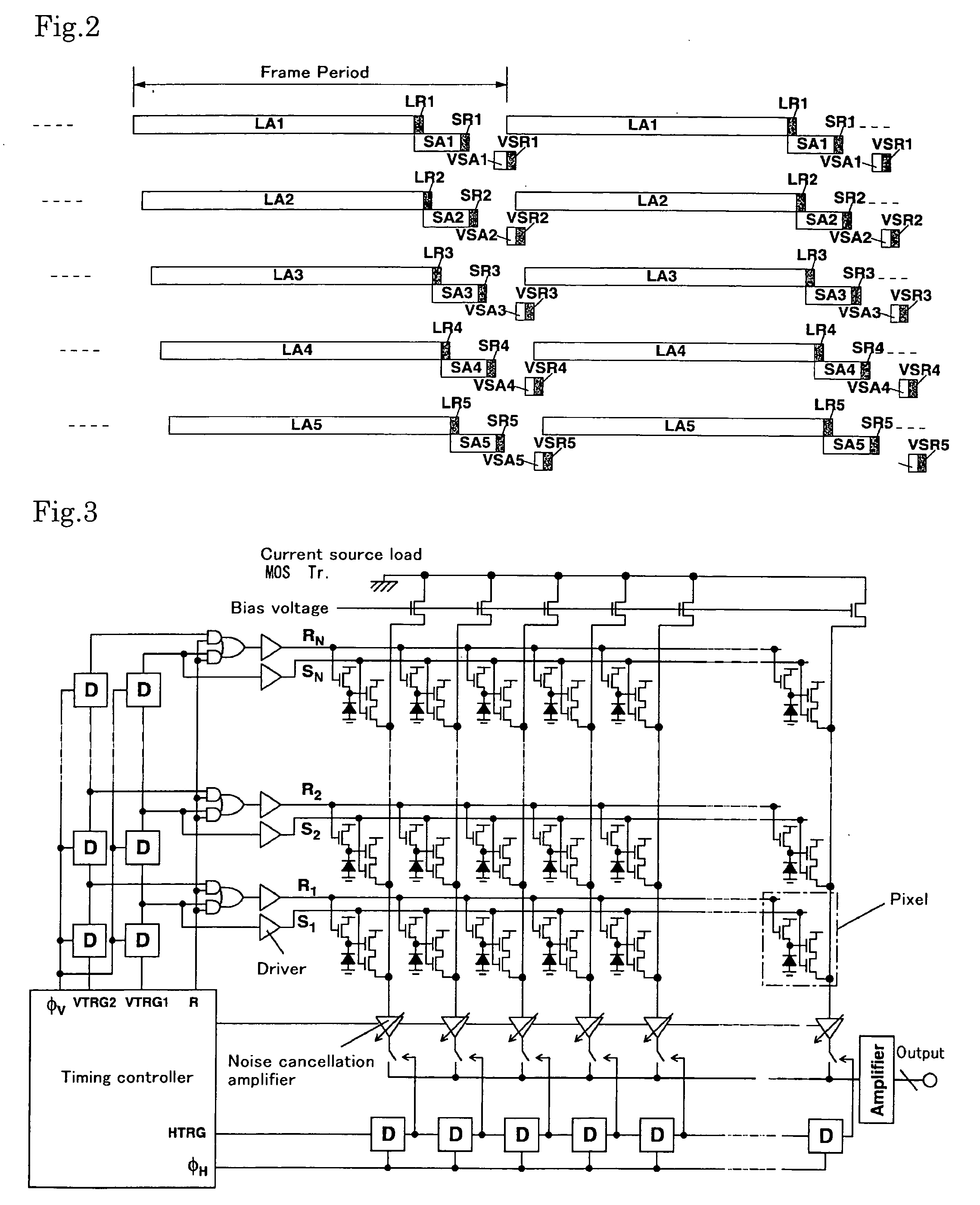

InactiveUS20070103569A1Shorten read timeShort timeTelevision system detailsTelevision system scanning detailsCMOSIlluminance

The present invention relates to a CMOS image sensor having a wide dynamic range, which permits favorable imaging even in cases where a bright portion and a dark portion exist simultaneously. The dynamic range can be widened by preventing the saturation of optical charge at a high illuminance by removing low illuminance signals due to long-time accumulation, intermediate illuminance signals due to short-time accumulation, and high illuminance signals due to ultra-short time accumulation from pixel portions of the image sensor. Further, adaptive control of the dynamic range can also be performed by dynamically changing the wide dynamic range imaging conditions that comprise a combination of different accumulation times of each of a plurality of short time accumulation signals.

Owner:NAT UNIV CORP SHIZUOKA UNIV

Semiconductor device

InactiveUS20050258474A1Improve reading speedLow costTransistorSolid-state devicesBit lineDevice material

A semiconductor device includes a plurality of nonvolatile memory cells (1). Each of the nonvolatile memory cells comprises a MOS type first transistor section (3) used for information storage, and a MOS type second transistor section (4) which selects the first transistor section. The second transistor section has a bit line electrode (16) connected to a bit line, and a control gate electrode (18) connected to a control gate control line. The first transistor section has a source line electrode (10) connected to a source line, a memory gate electrode (14) connected to a memory gate control line, and a charge storage region (11) disposed directly below the memory gate electrode. A gate withstand voltage of the second transistor section is lower than that of the first transistor section. Assuming that the thickness of a gate insulating film of the second transistor section is defined as tc and the thickness of a gate insulating film of the first transistor section is defined as tm, they have a relationship of tc<tm.

Owner:RENESAS ELECTRONICS CORP

Semiconductor memory device and reading method therefor

A memory device is configured such that, in a read access: a first switch and a second switch are turned on in a pre-charge period before a memory cell is accessed so that charges of a bit line charge voltage generating circuit are distributed to a bit line and a reference bit line, to thereby charge the bit line and the reference bit line to an initial voltage. After the charge, a selected memory cell is connected to the bit line, the reference bit line is connected to a reference voltage generating circuit, and a voltage differential type sense amplifier amplifies a difference voltage between a voltage of the bit line decreased by discharge of the selected memory cell and a voltage of the reference bit line generated by the reference voltage generating circuit, to thereby read out memory cell data.

Owner:ELPIDA MEMORY INC

Semiconductor integrated circuit device and a method of manufacturing the same

ActiveUS20060008992A1Shorten the timeTime to erase be shortenedTransistorSemiconductor/solid-state device detailsEngineeringReverse bias

Owner:RENESAS ELECTRONICS CORP

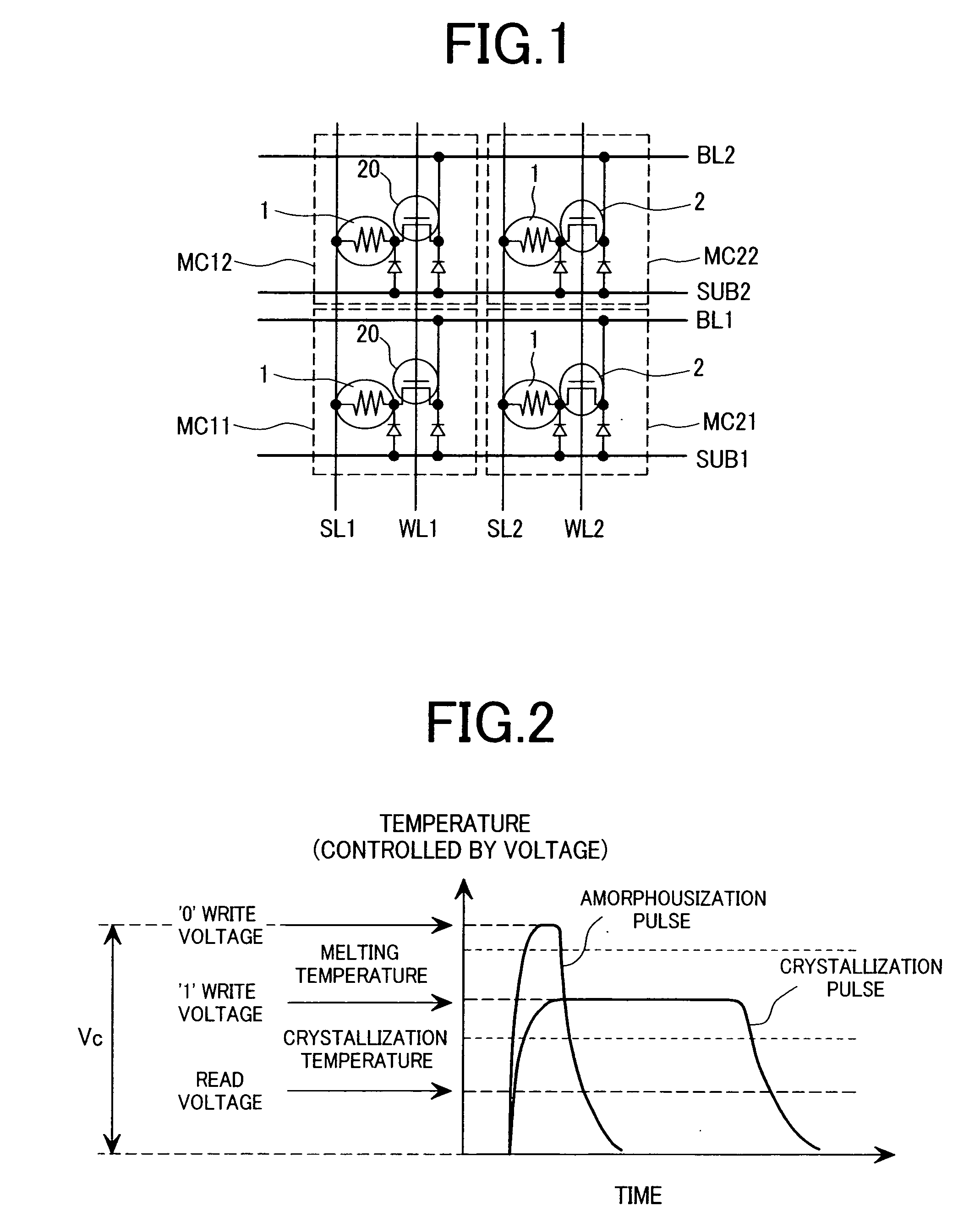

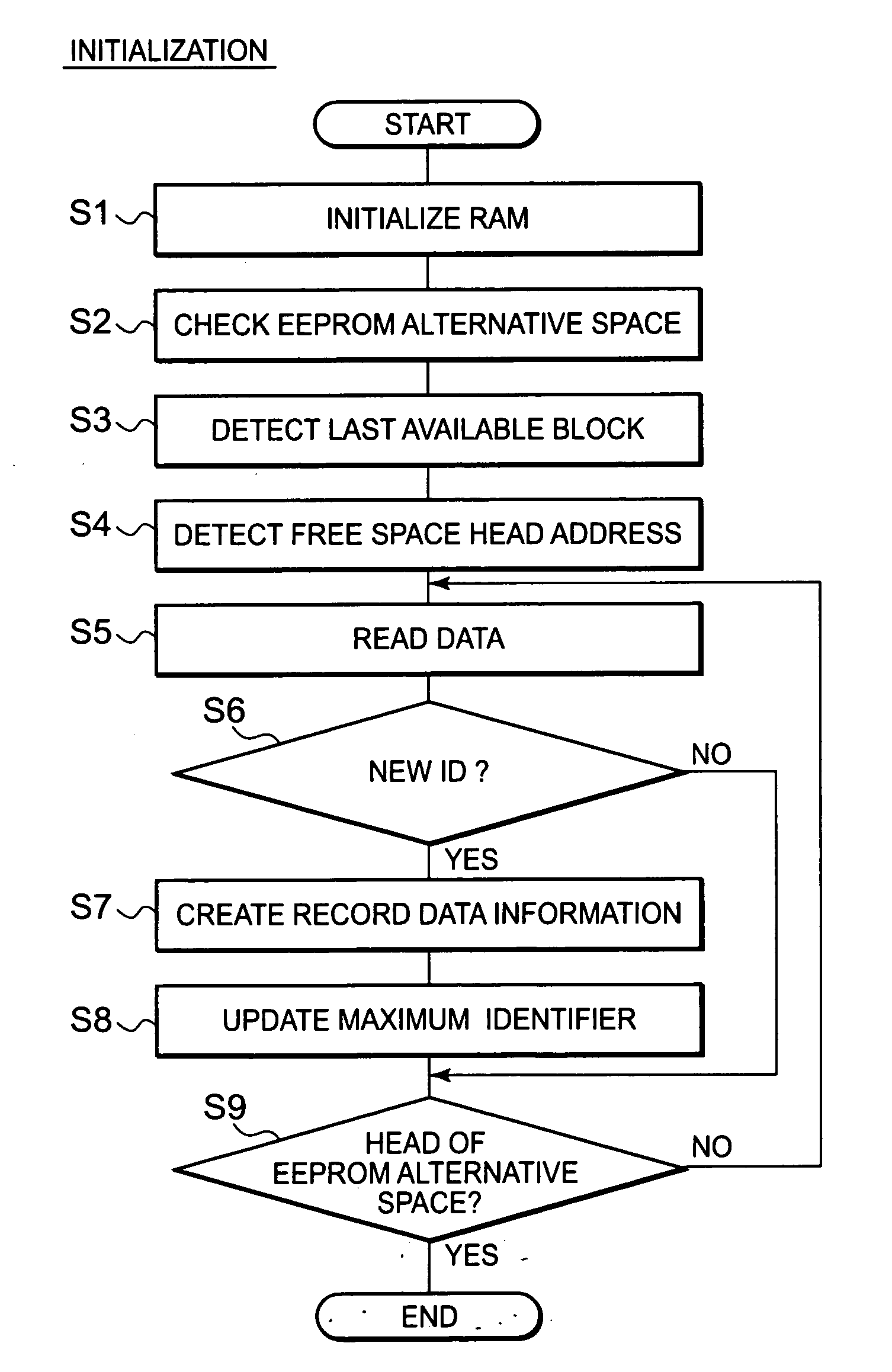

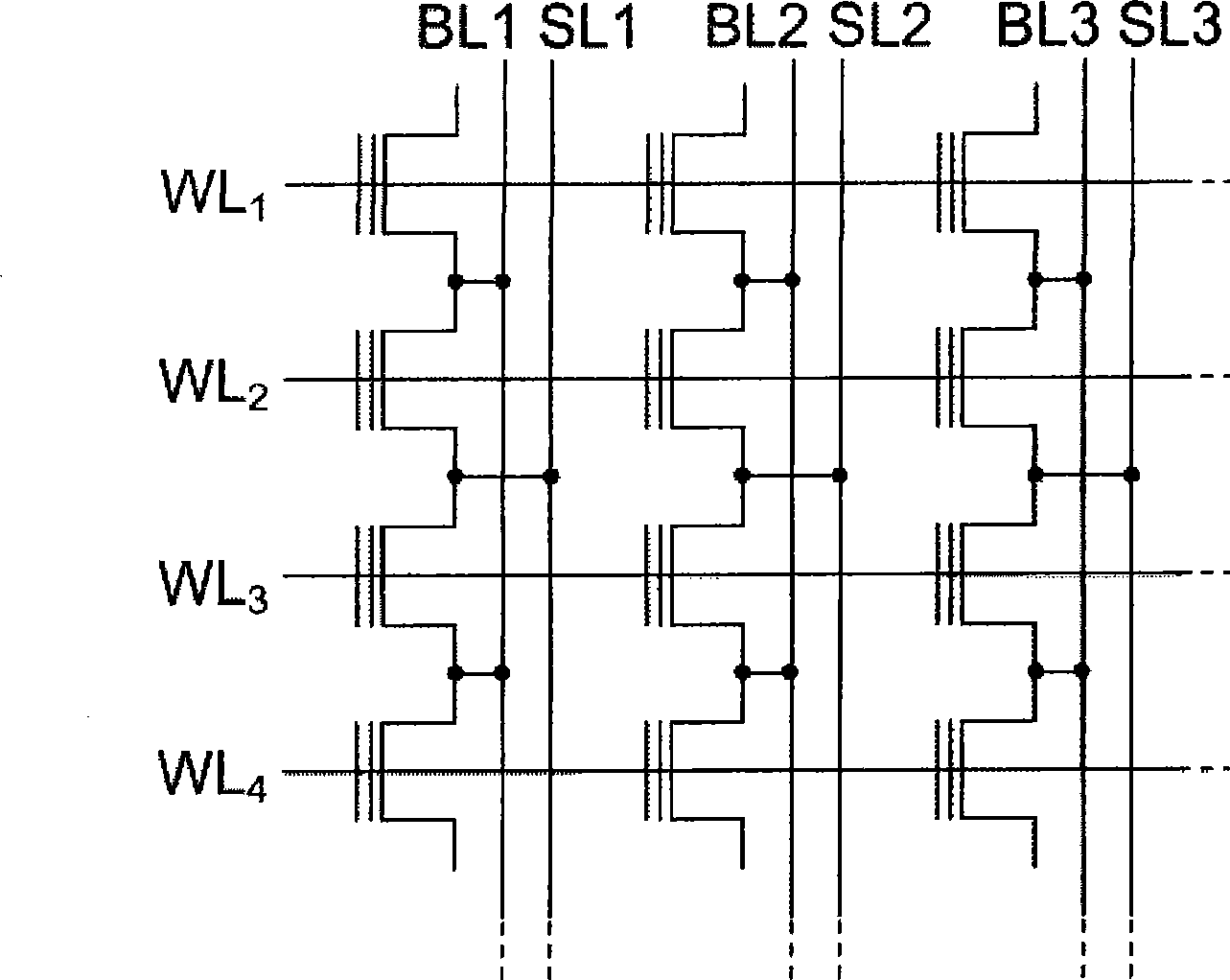

Semiconductor Memory

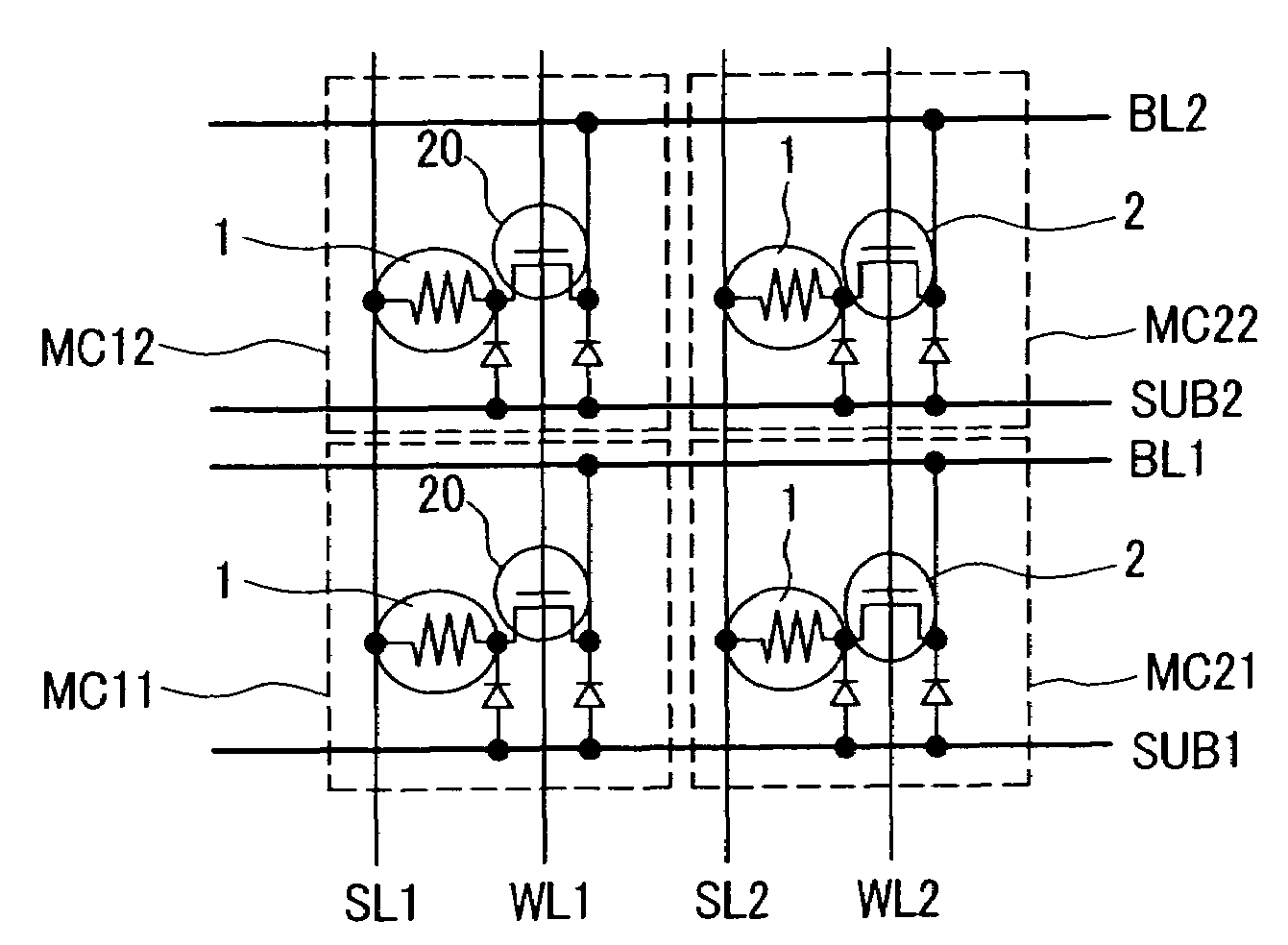

InactiveUS20070217254A1Avoid it happening againHigh speed readSolid-state devicesRead-only memoriesPhase-change memoryEngineering

A phase-change memory for employing chalcogenide as a recording medium is disclosed, which prevents the read disturbance from being generated, and reads data at high speed. In a phase-change memory cell array including a selection transistor and chalcogenide, a substrate potential of the selection transistor is isolated in a direction perpendicular to the word lines. During the data recording, a forward current signal flows between the substrate and the source line connected to chalcogenide, and the selection transistor is not used. During the data reading, a desired cell is selected by the selection transistor. Therefore, a recording voltage is greatly higher than the reading voltage, such that the occurrence of read disturbance is prevented, and a high-speed operation is implemented.

Owner:RENESAS ELECTRONICS CORP

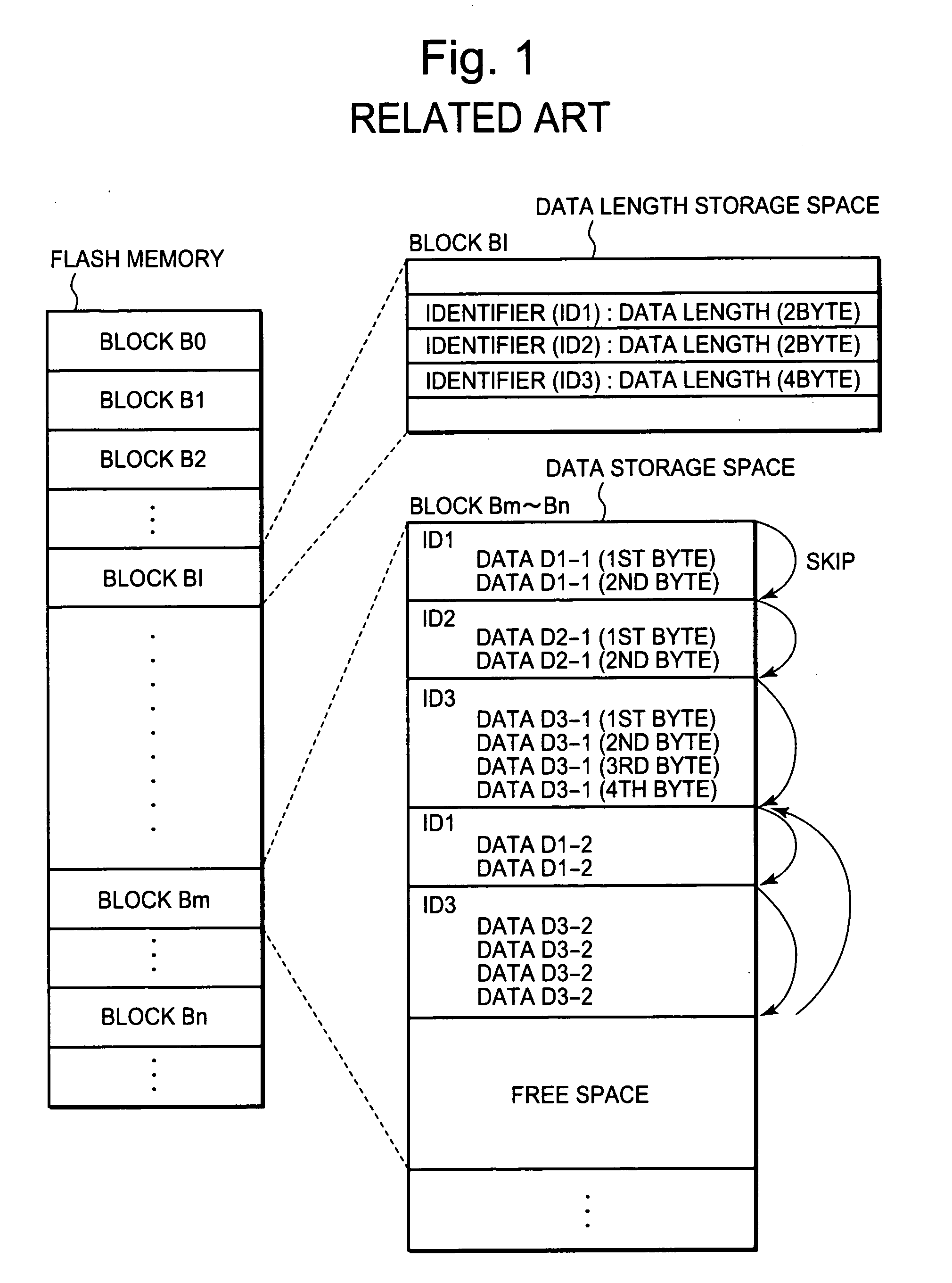

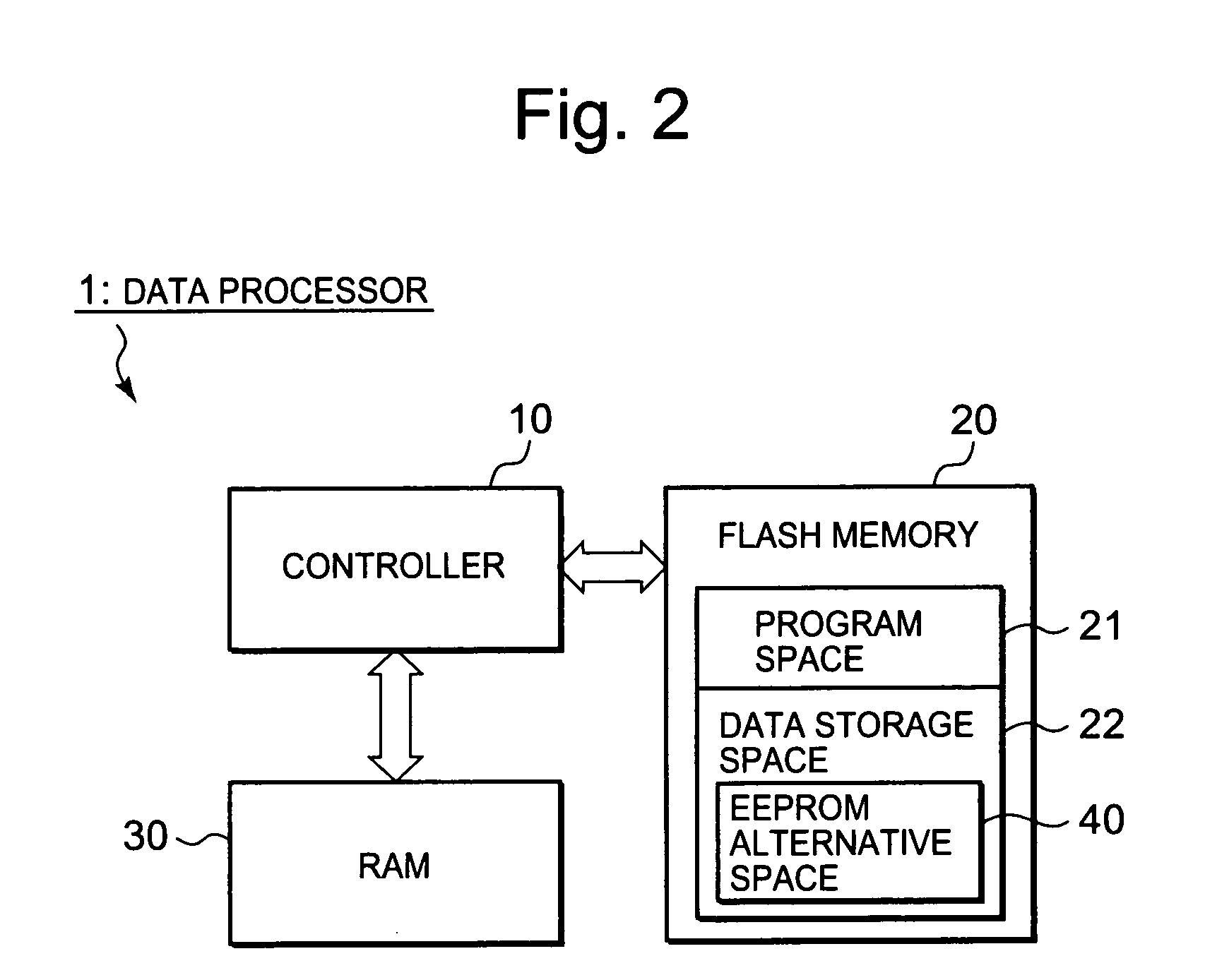

Data processor with flash memory, and method for accessing flash memory

InactiveUS20100011155A1Increase speedReduce processing timeMemory architecture accessing/allocationEnergy efficient ICTData informationRandom access memory

A data processor includes a flash memory that stores a plurality of types of data therein, a random access memory that stores record data information therein, and a controller that can access the flash memory and the RAM. The record data information indicates a head address in the flash memory and a data length corresponding to latest data of each of the plurality of types of data. The controller reads, from the flash memory, the latest data of a type of a reading target among the plurality of types of data, with reference to the record data information.

Owner:RENESAS ELECTRONICS CORP

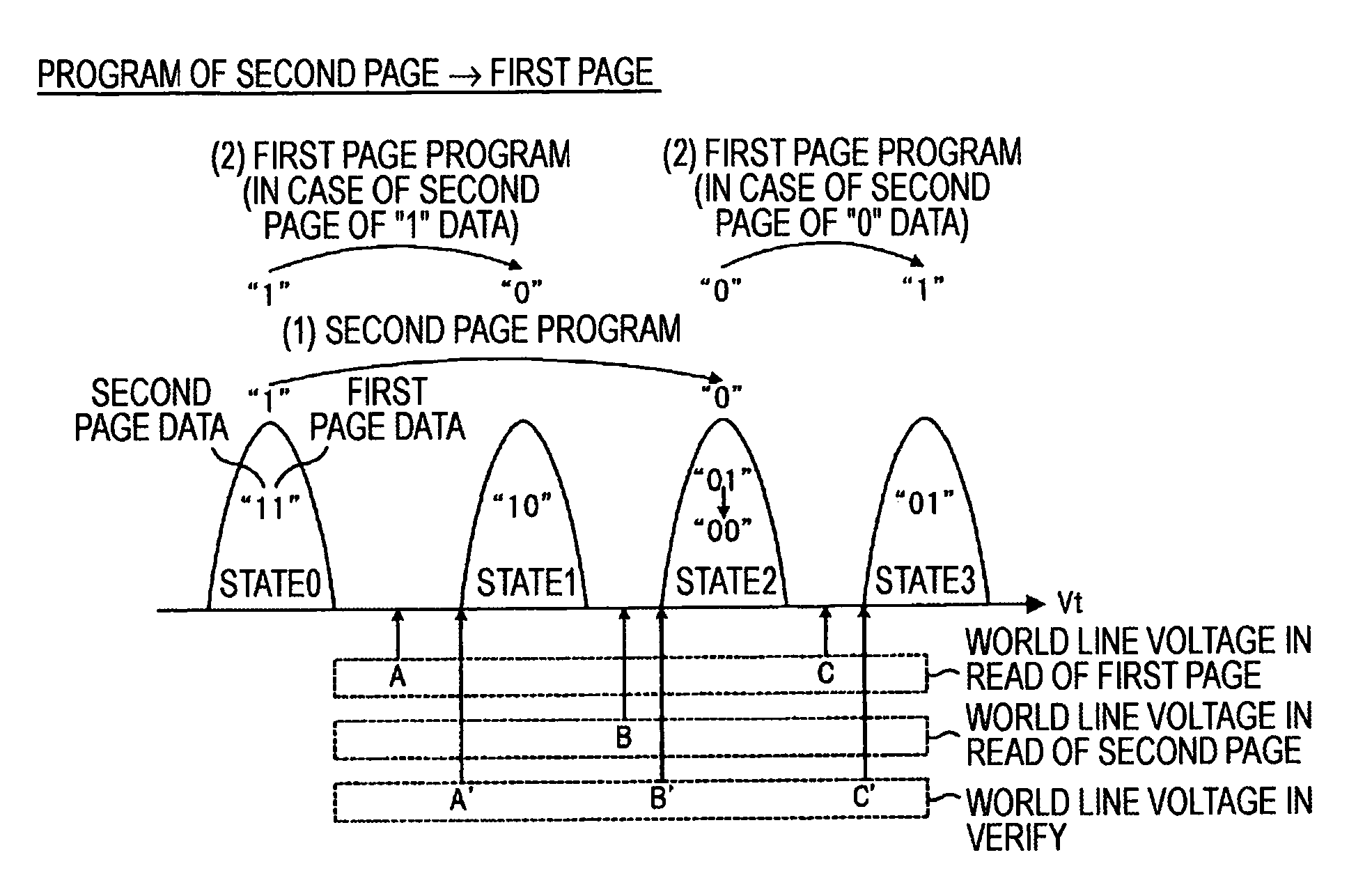

Nonvolatile semiconductor memory for storing multivalued data

ActiveUS7623372B2Increase speedReading data is accurateRead-only memoriesDigital storageControl dataControl circuit

A nonvolatile semiconductor memory according to the invention includes a memory cell array comprised of a multivalued memory cell for storing data on a plurality of pages, a data processing circuit for carrying out a read operation for reading data from the memory cell array and a programming operation for writing the data to the memory cell array on a page unit, and a control circuit for controlling an operation of the data processing circuit, the control circuit changing an assignment of data corresponding to a threshold voltage distribution of the multivalued memory cell depending on order of a page over which the programming operation is to be carried out in such a manner that the programming operation is executed by a transition of a threshold voltage of the multivalued memory cell in a positive direction.

Owner:CETUS TECH INC

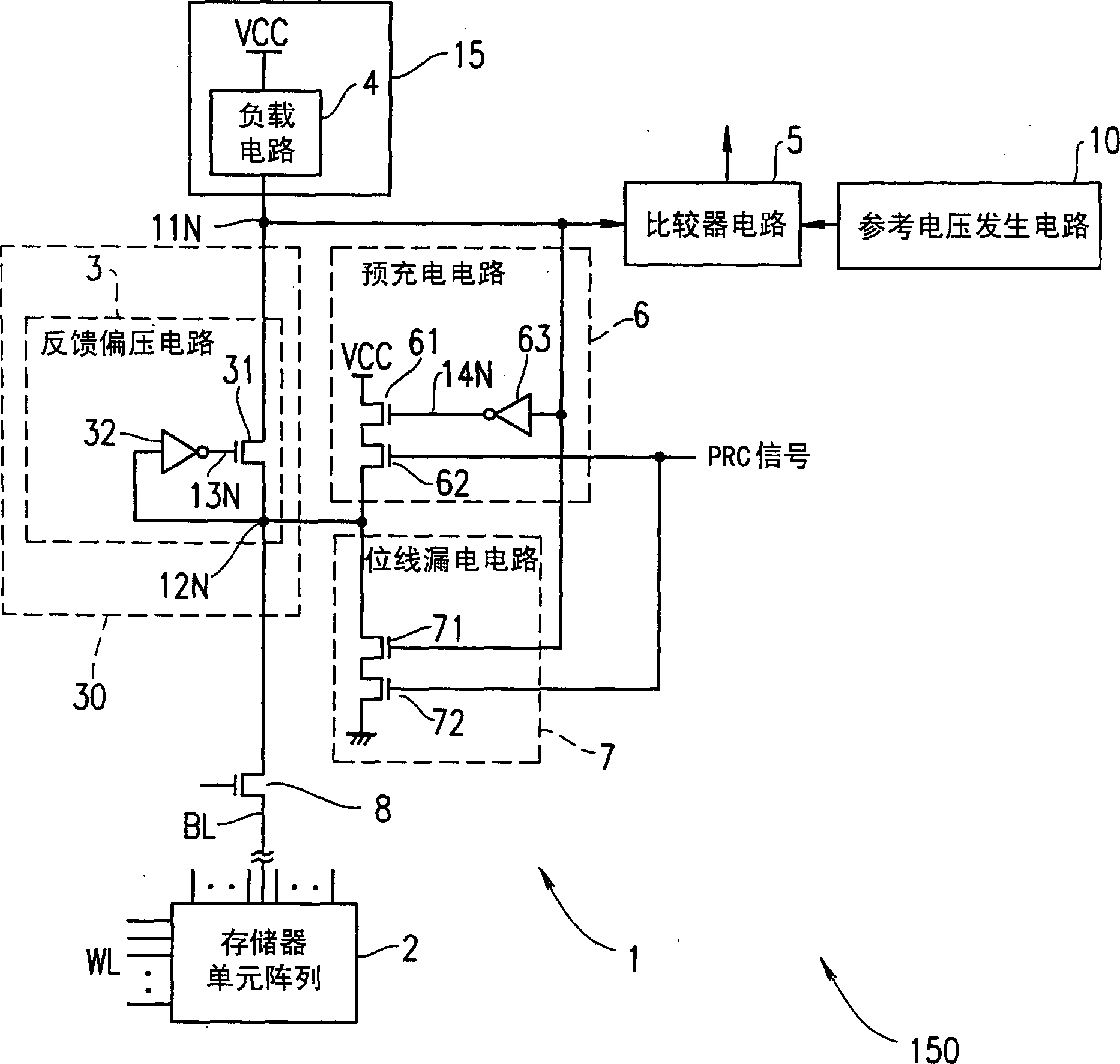

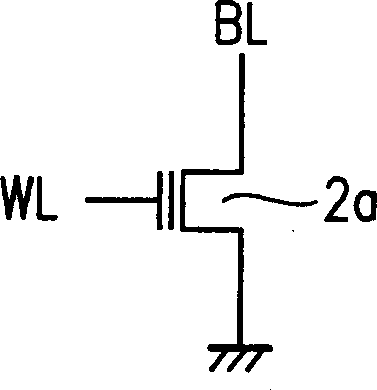

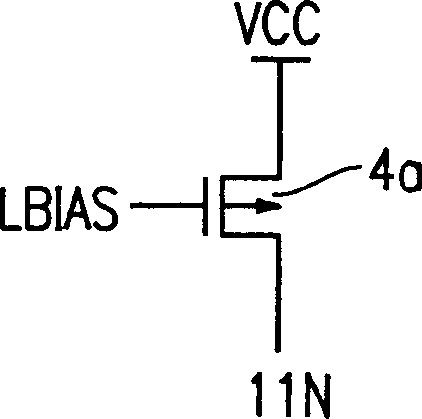

Reading circuit and semiconductor memory device including same

InactiveCN1484248AHigh speed readAvoid elevationRead-only memoriesDigital storageBit lineHemt circuits

A reading circuit for reading information stored in a memory cell includes a current supply circuit for supplying a current to a bit line connected to the memory cell; a comparison circuit for comparing a potential of the bit line supplied with the current by the current supply circuit with a reference potential so as to output the information stored in the memory cell; a disconnection circuit for electrically disconnecting the comparison circuit and the memory cell from each other under a prescribed condition; a charge circuit for charging the bit line, the charge circuit stopping charging of the bit line when the potential of the bit line exceeds a prescribed potential; and a discharge circuit for discharging the bit line when the potential of the bit line exceeds the prescribed potential.

Owner:SAMSUNG ELECTRONICS CO LTD

Sense amplifier circuit and semiconductor device

ActiveUS20110063892A1High speed readExcellent operating marginDigital storagePower semiconductor deviceAudio power amplifier

A single-ended sense amplifier circuit of the invention comprises first and second MOS transistors and first and second precharge circuits. The first MOS transistor drives the bit line to a predetermined voltage and switches connection between the bit line and a sense node and the second MOS transistor whose gate is connected to the sense node amplifies the signal via the first MOS transistor. The first precharge circuit precharges the bit line to a first potential and the second precharge circuit precharges the sense node to a second potential. Before sensing operation, the bit line is driven to the predetermined voltage when the above gate voltage is controlled to decrease. The predetermined voltage is appropriately set so that a required voltage difference at the sense node between high and low levels can be obtained near a changing point between charge transfer / distributing modes.

Owner:LONGITUDE LICENSING LTD

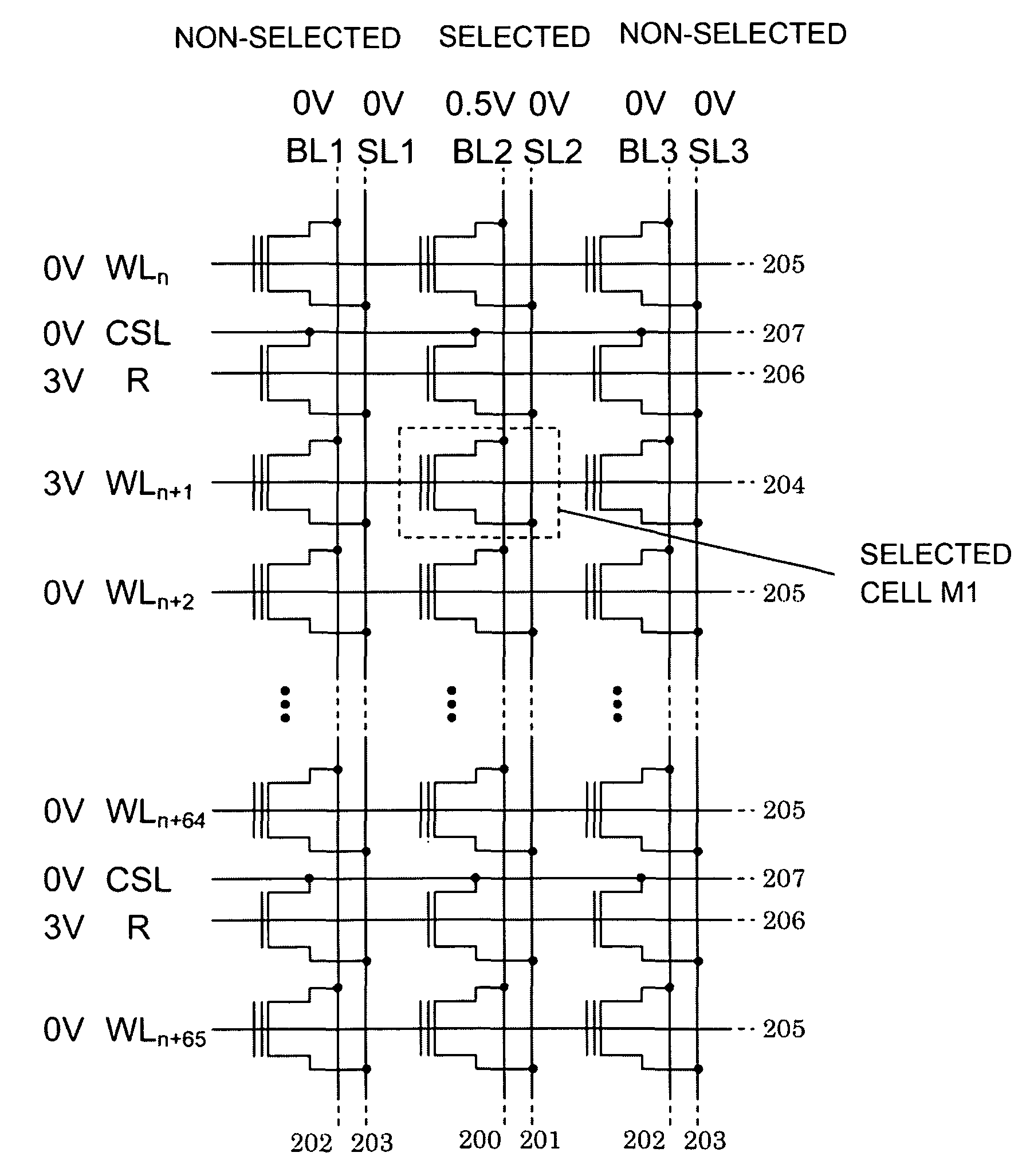

Nonvolatile semiconductor memory and method for driving the same

ActiveUS7940573B2Without compromising large scale integrationWithout increasing area of memory cellSolid-state devicesRead-only memoriesBit lineOptoelectronics

Owner:UNISANTIS ELECTRONICS SINGAPORE PTE LTD +1

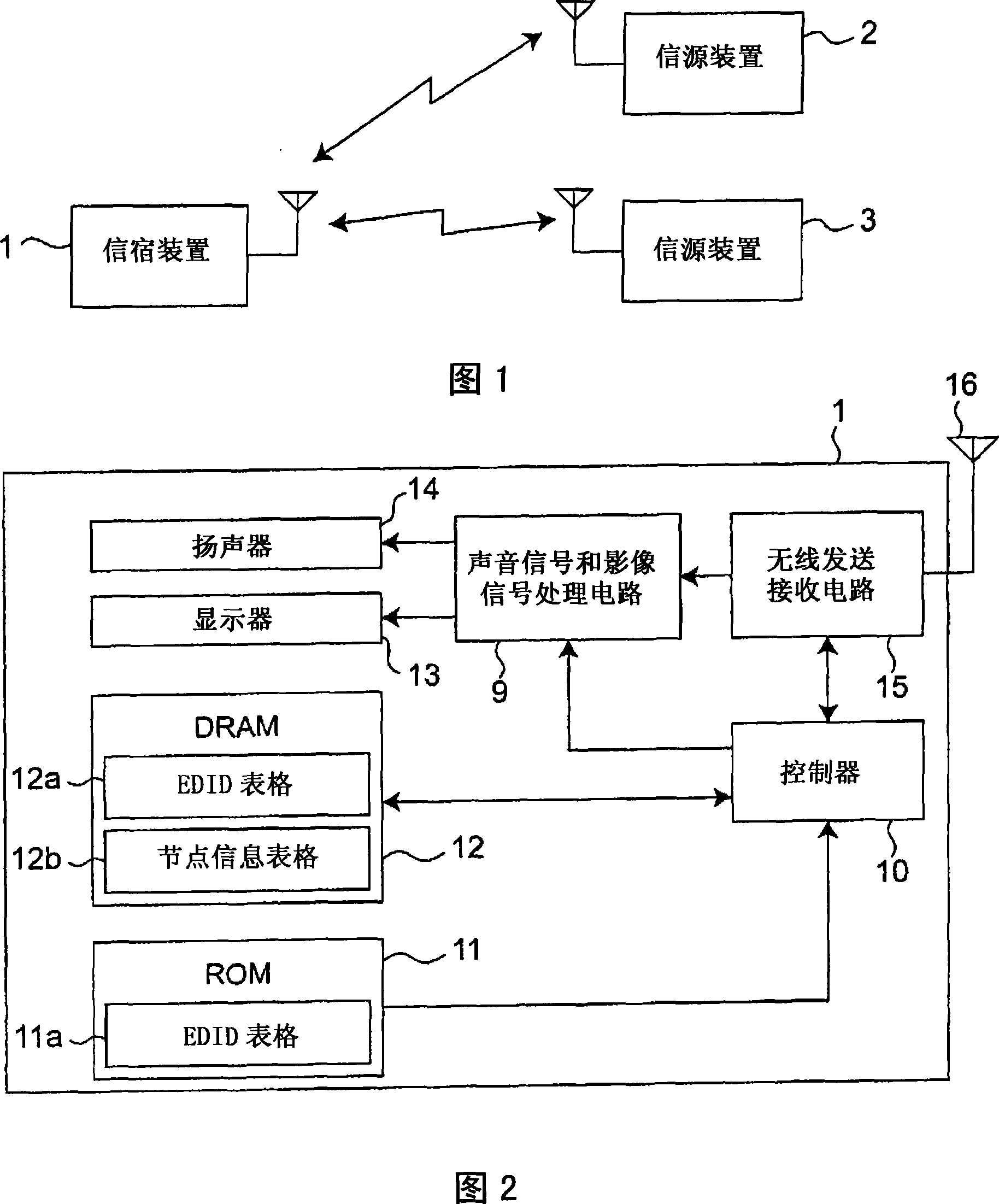

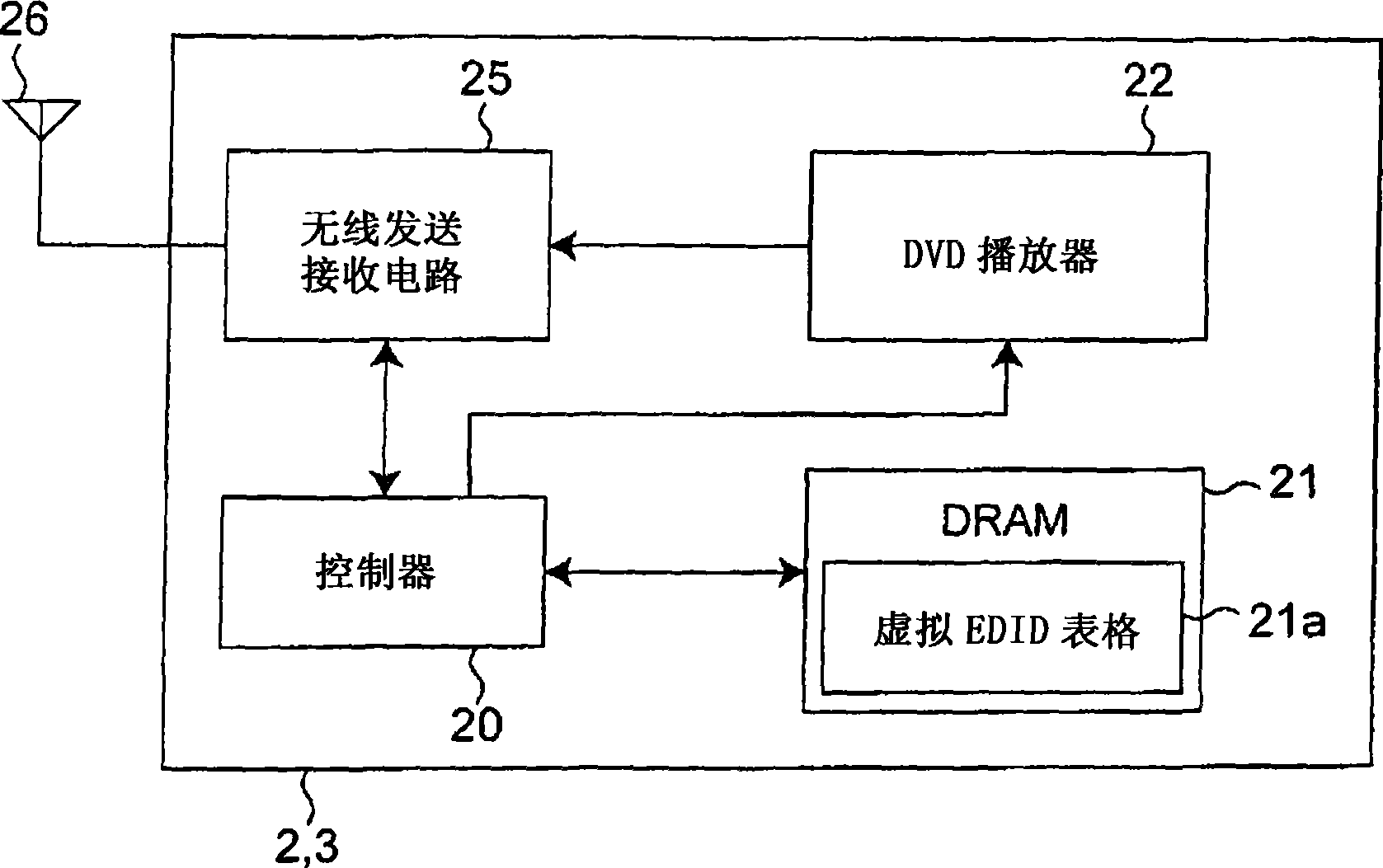

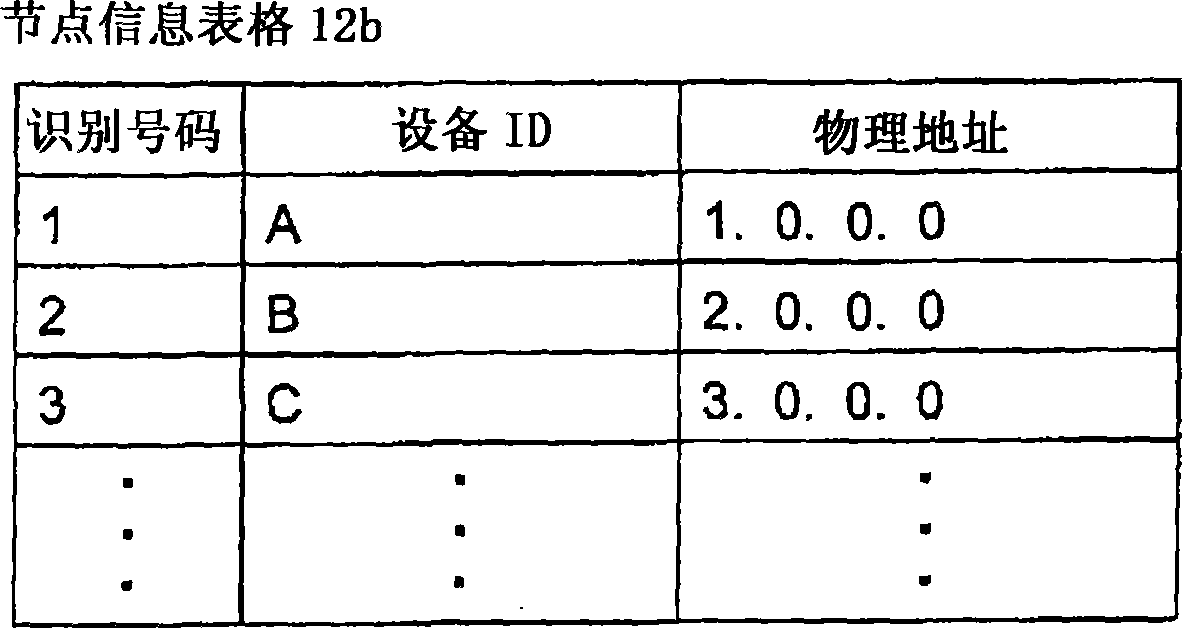

Wireless communication system

InactiveCN101385278AHigh speed readNeat appearanceNetwork traffic/resource managementCathode-ray tube indicatorsCommunications systemSignal on

In a wireless communication system including source devices (2, 3) for transmitting video signals by wireless, a sink device (1) for receiving the transmitted video signal and displaying the received video signal on a display device (13), the sink device (1) reads out EDID information from a ROM (11) and transmits wireless-data signal including it by wireless to source devices (2,3). The source devices (2, 3) receive by wireless the wireless-data signal including the EDID information transmitted by wireless and transmit video signals to the sink device (1) by wireless on a basis of the EDID information.

Owner:PANASONIC CORP

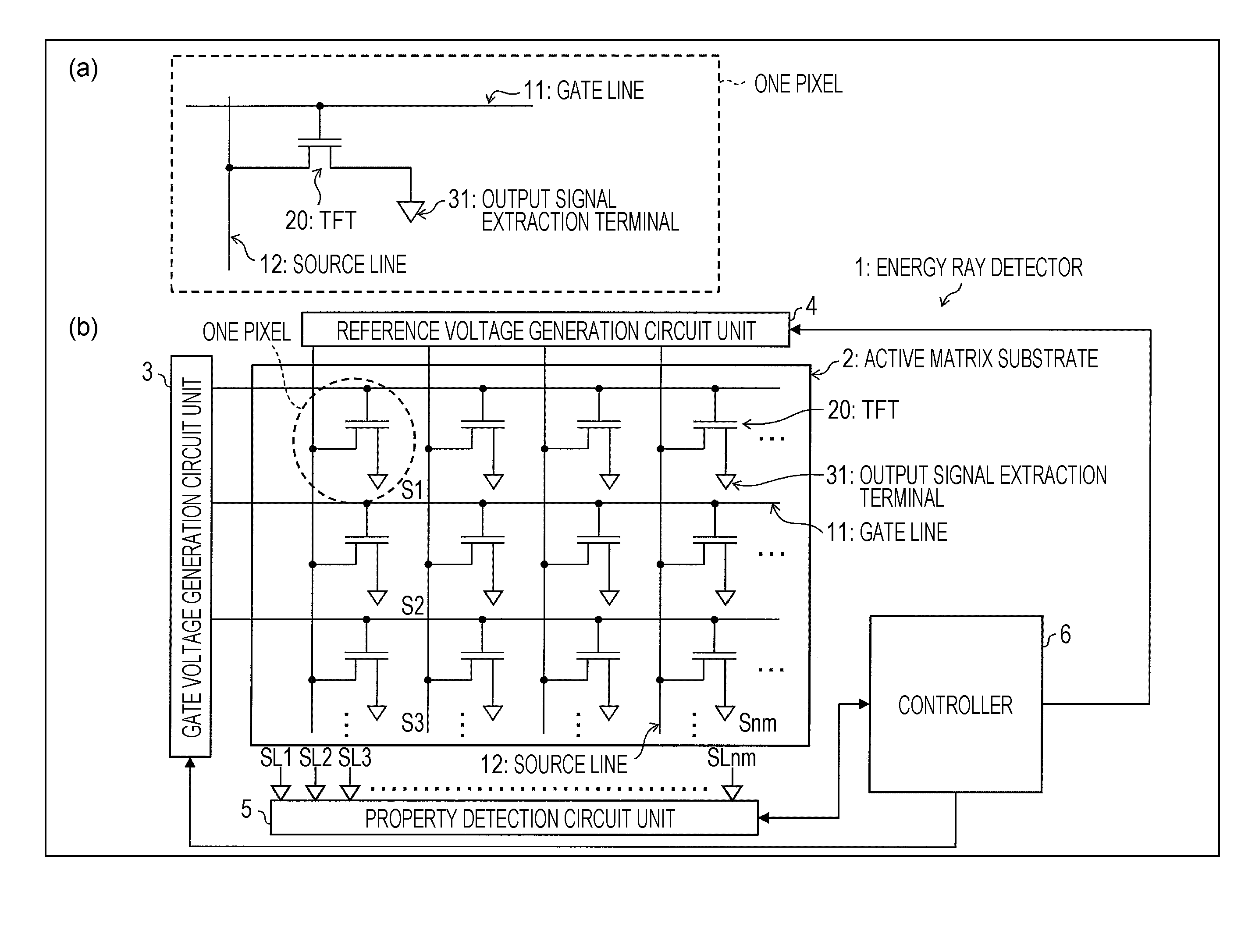

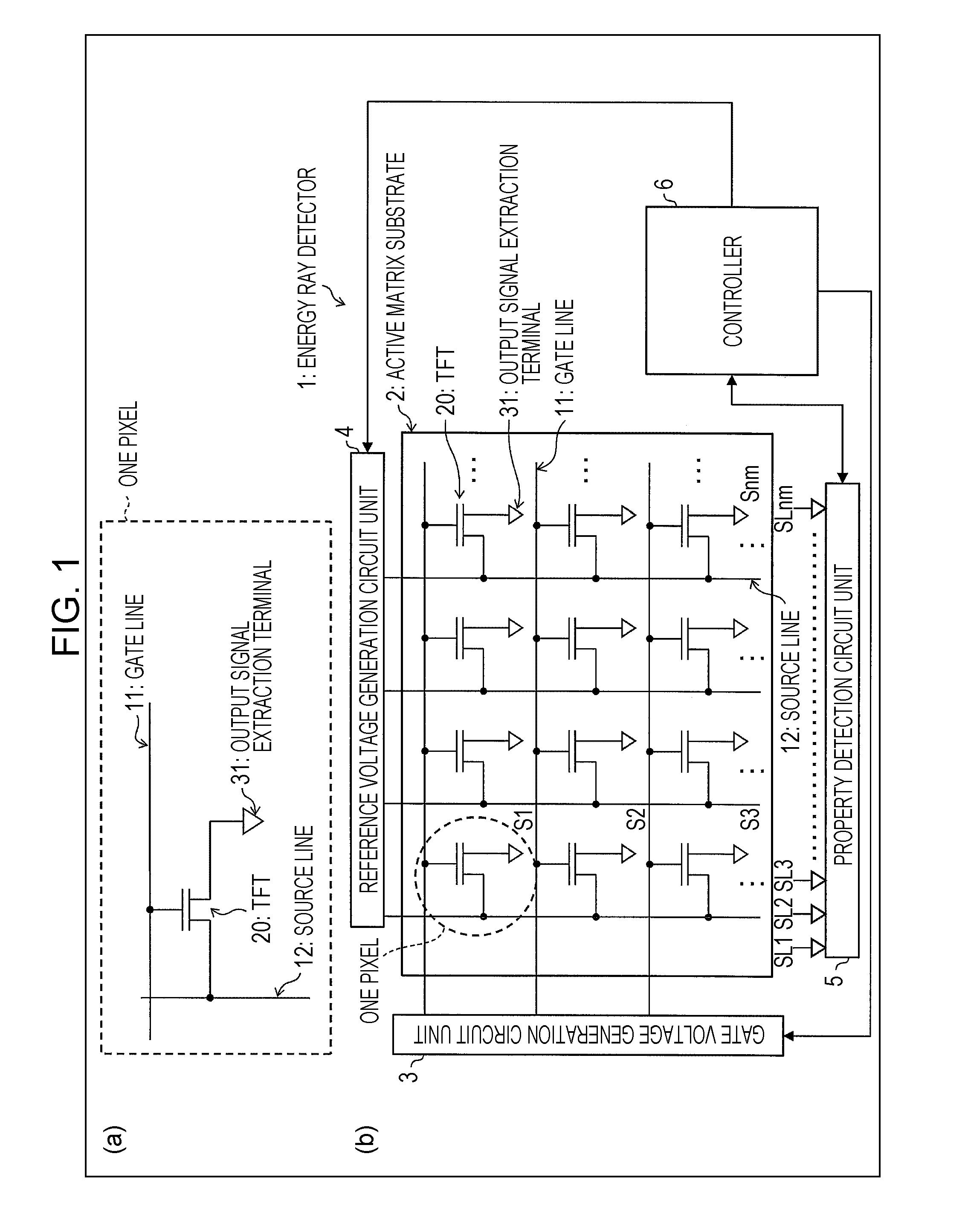

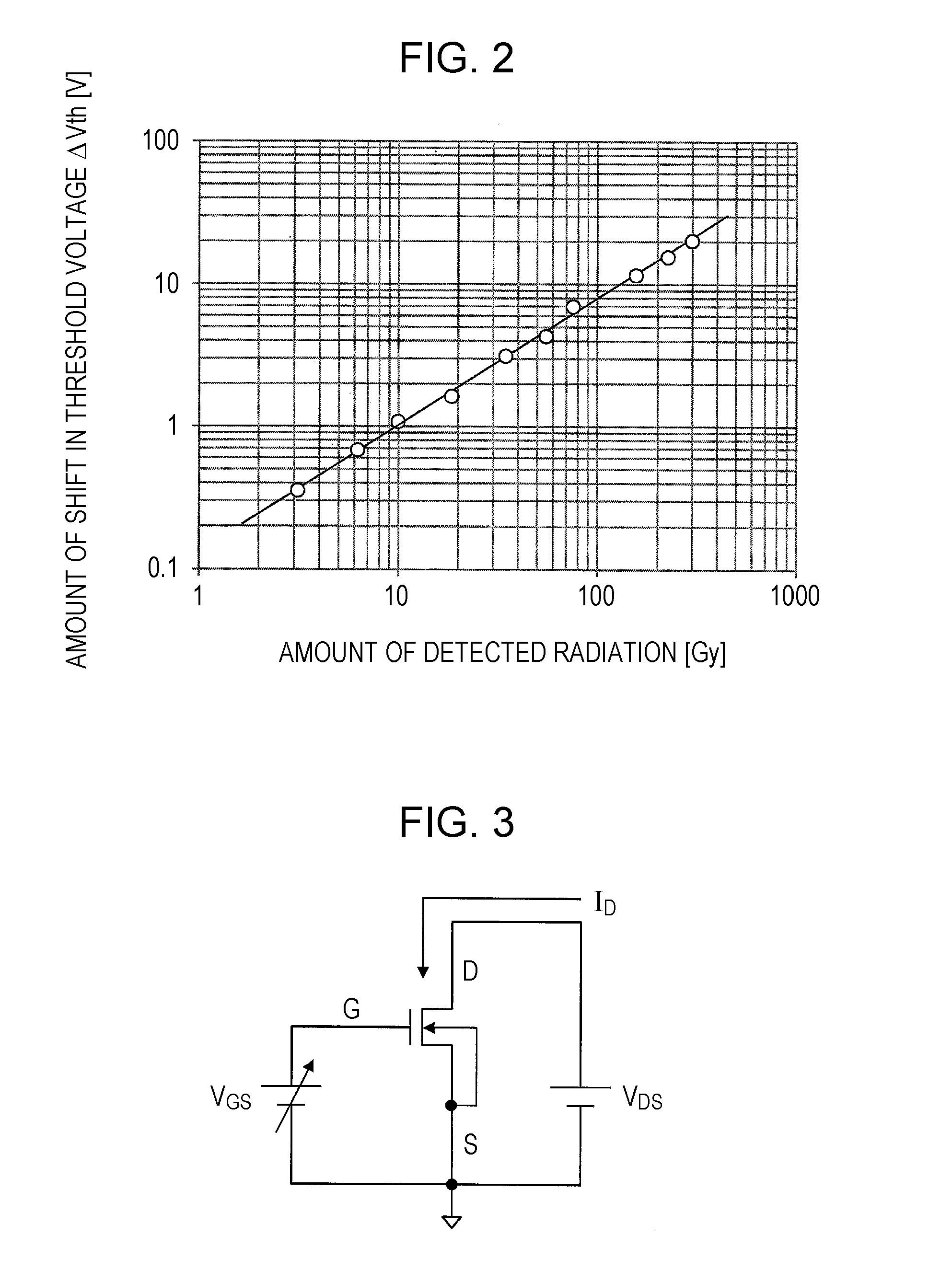

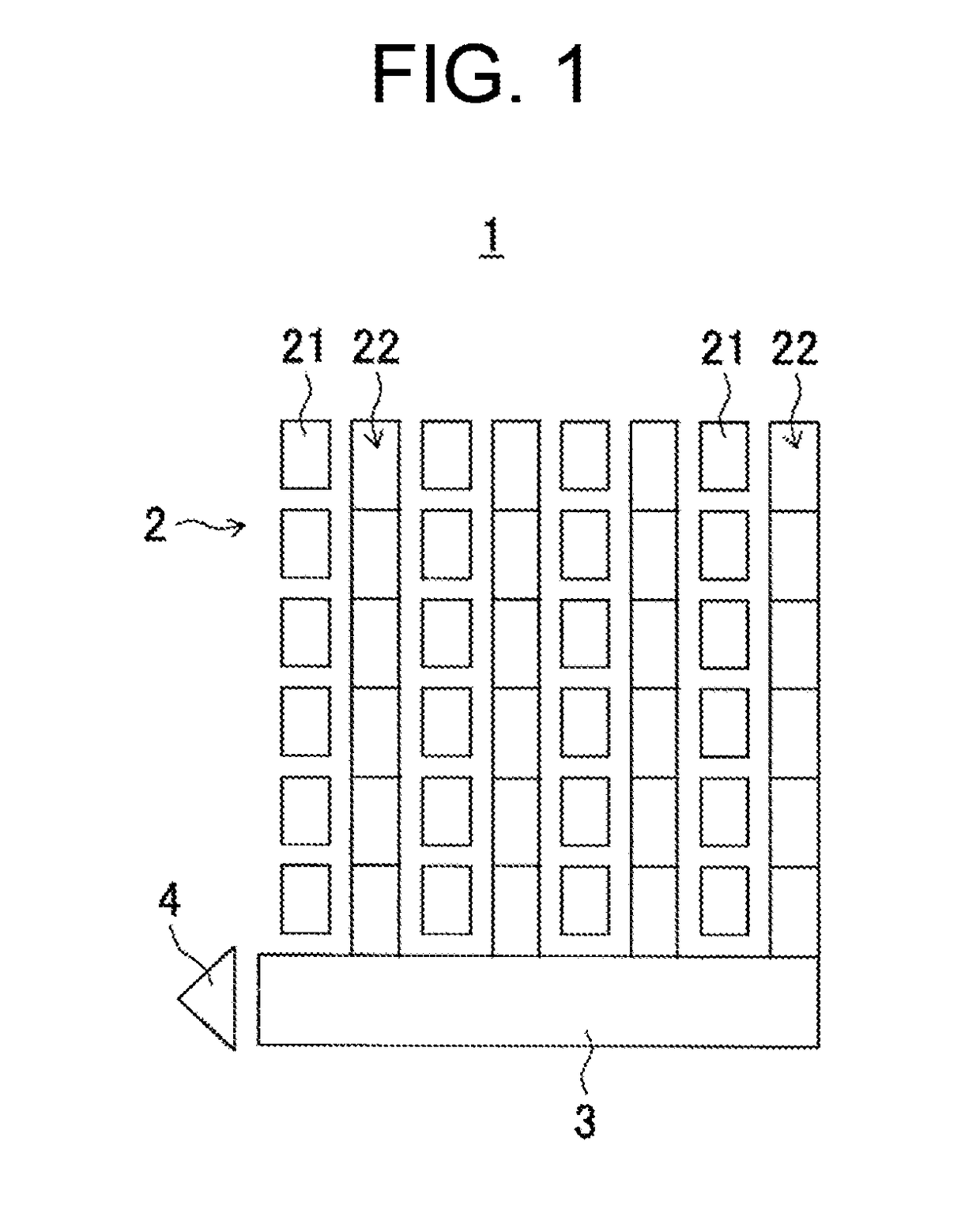

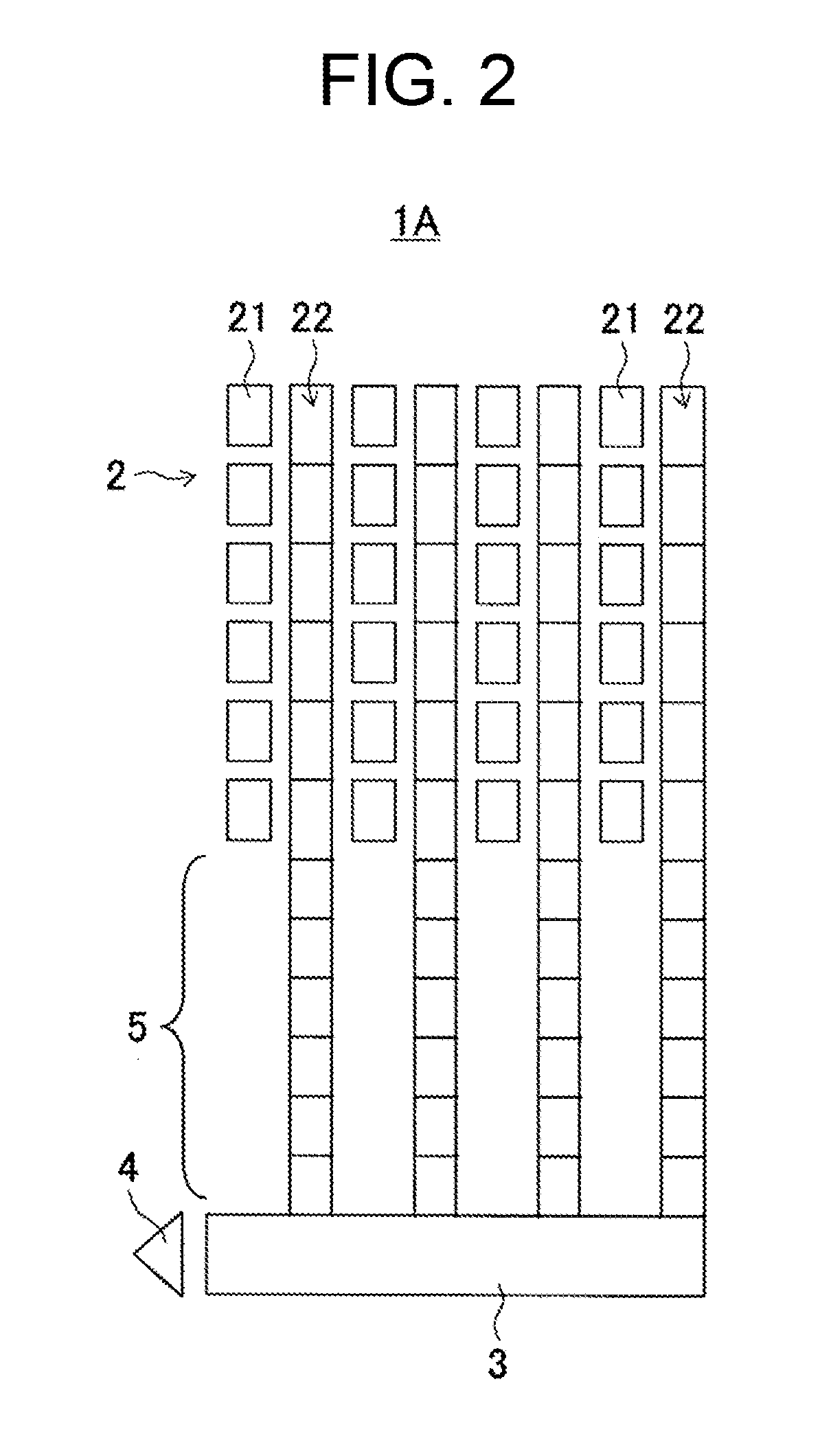

Energy ray detector

ActiveUS20160313458A1Low impact-resistanceHigh-speed reading of informationTransistorSolid-state devicesRadiationActive layer

A thin, lightweight, and highly reliable energy ray detector that enables high-speed reading is provided. An energy ray detector (1) includes TFTs (20) that are arranged in a grid pattern and that each have an active layer formed of a semiconductor having an electrical property changing in accordance with the amount of applied energy ray radiation, and a property detection circuit unit (5) and a controller (60) that detect information regarding the energy ray radiation from changes in the electrical property of the TFTs (20).

Owner:SHARP KK

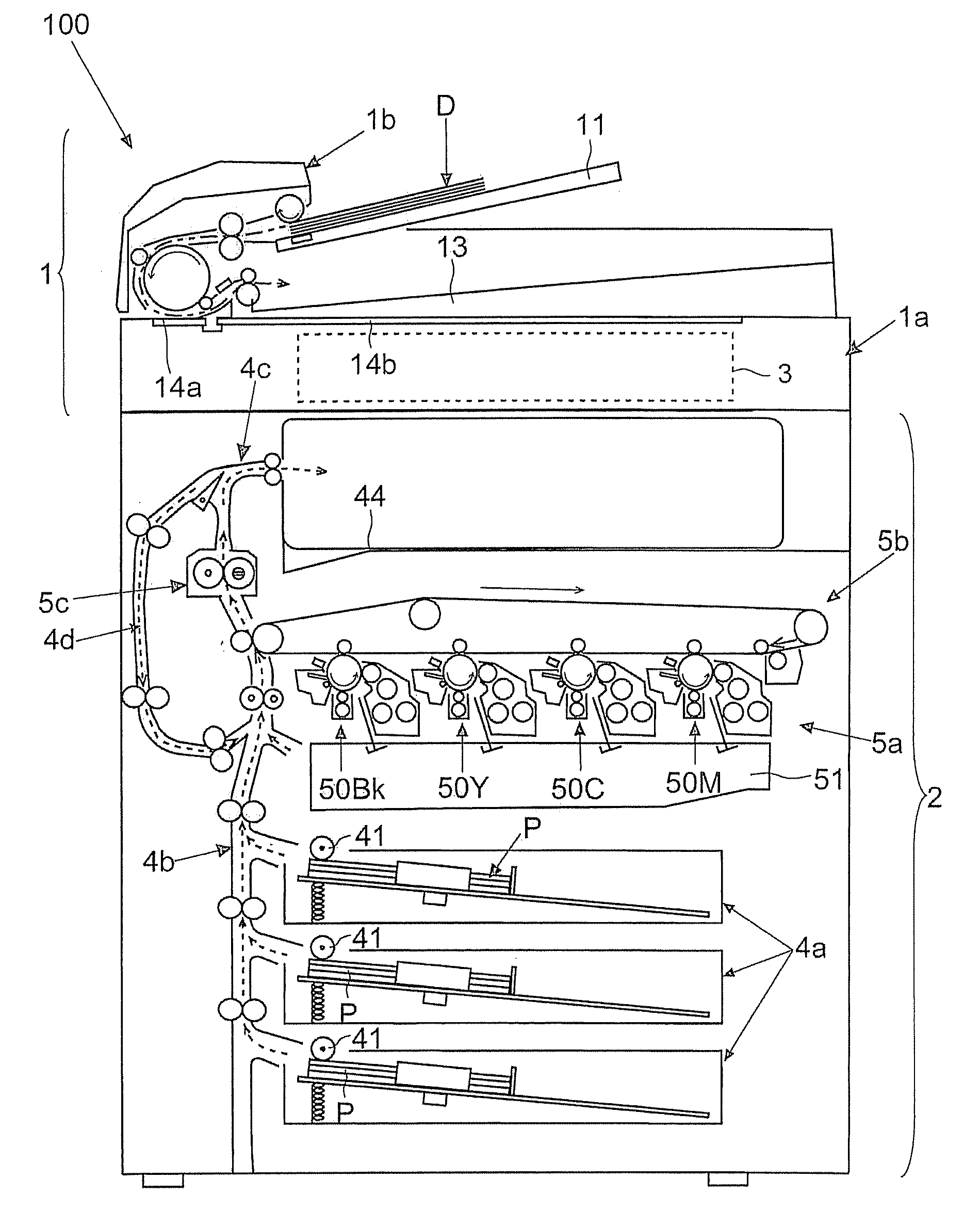

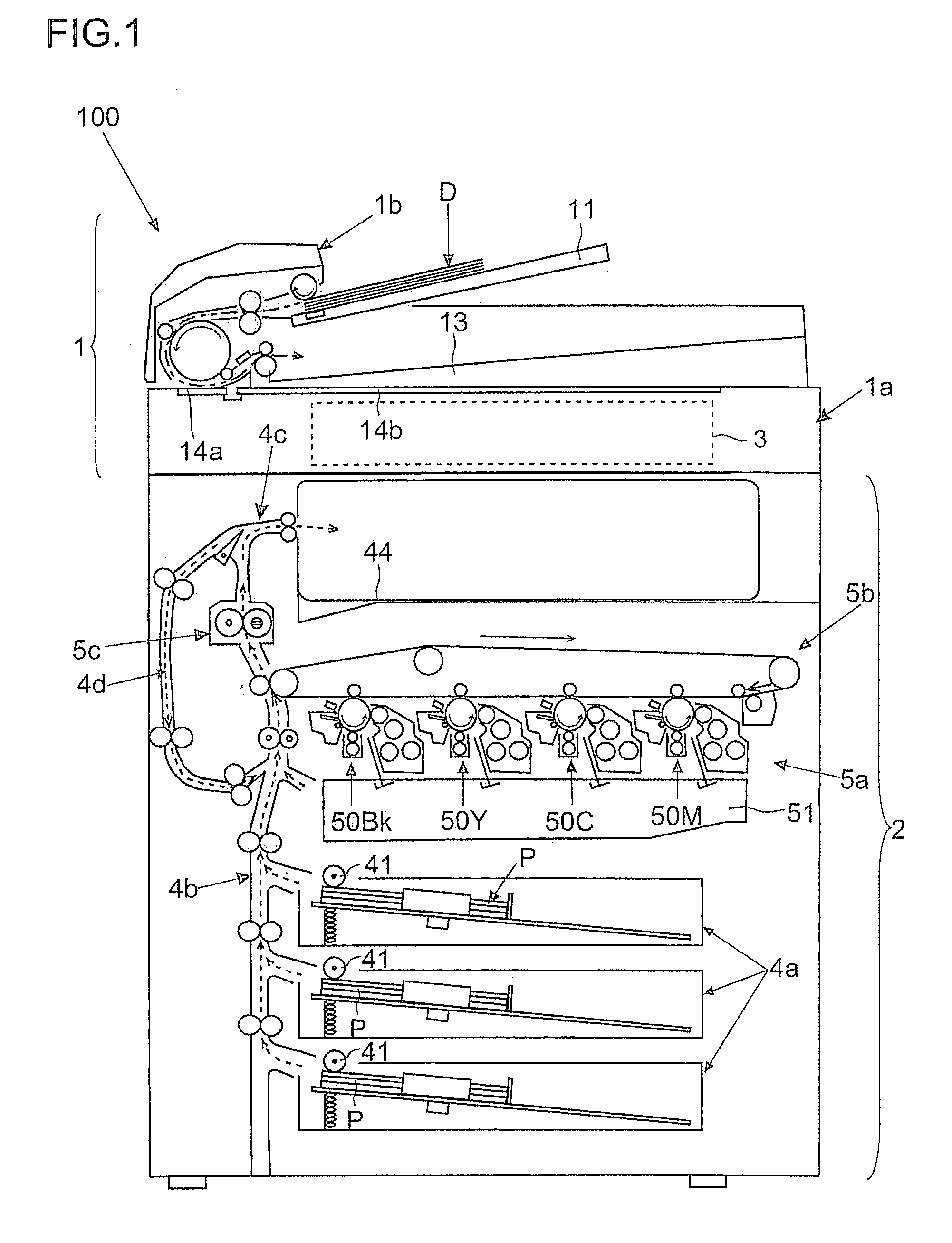

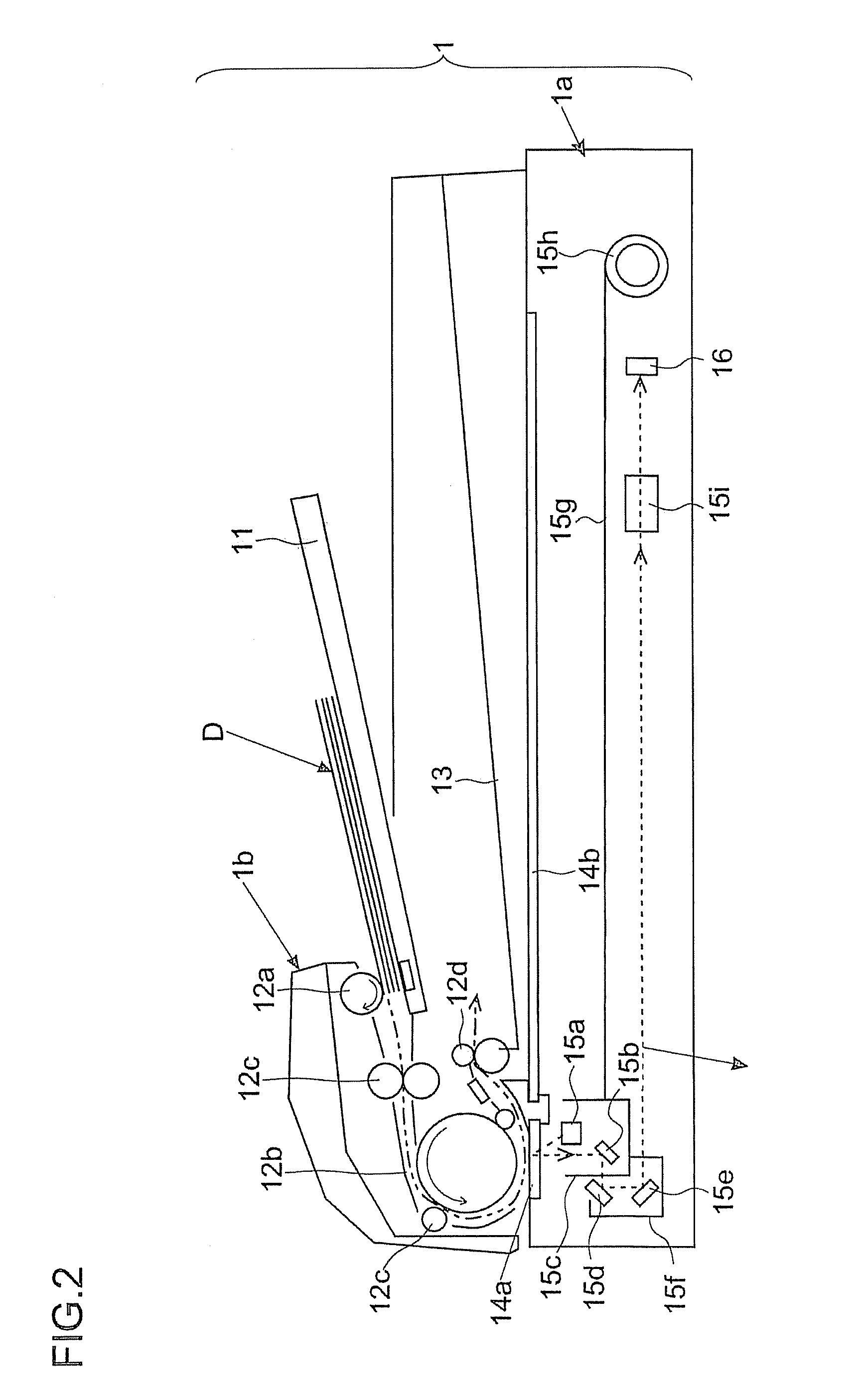

Image forming apparatus and control method of an image forming apparatus

InactiveUS20140320876A1Saving and unpleasant noiseHigh speed readPictoral communicationDigital output to print unitsImage formationDocumentation

Owner:KYOCERA DOCUMENT SOLUTIONS INC

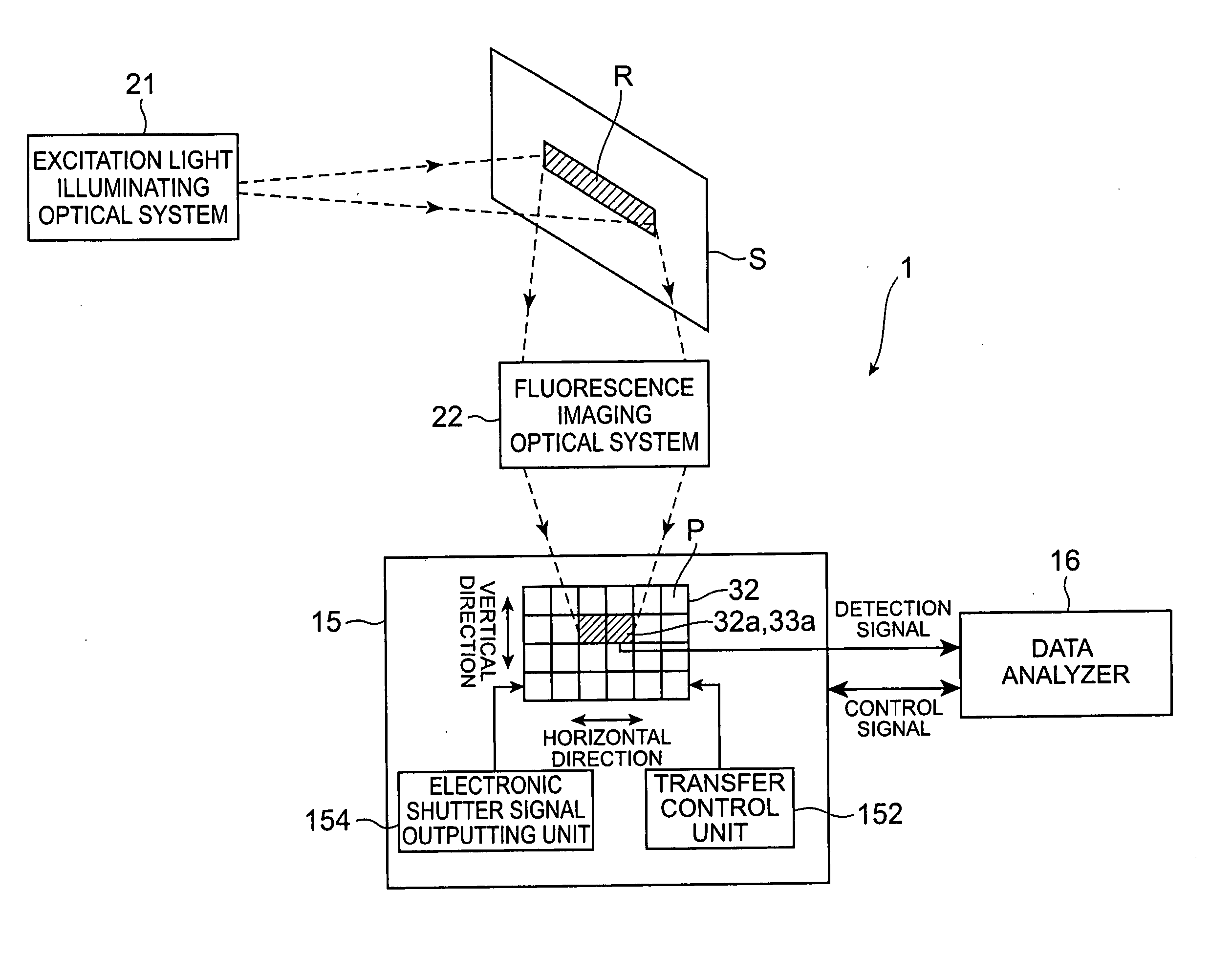

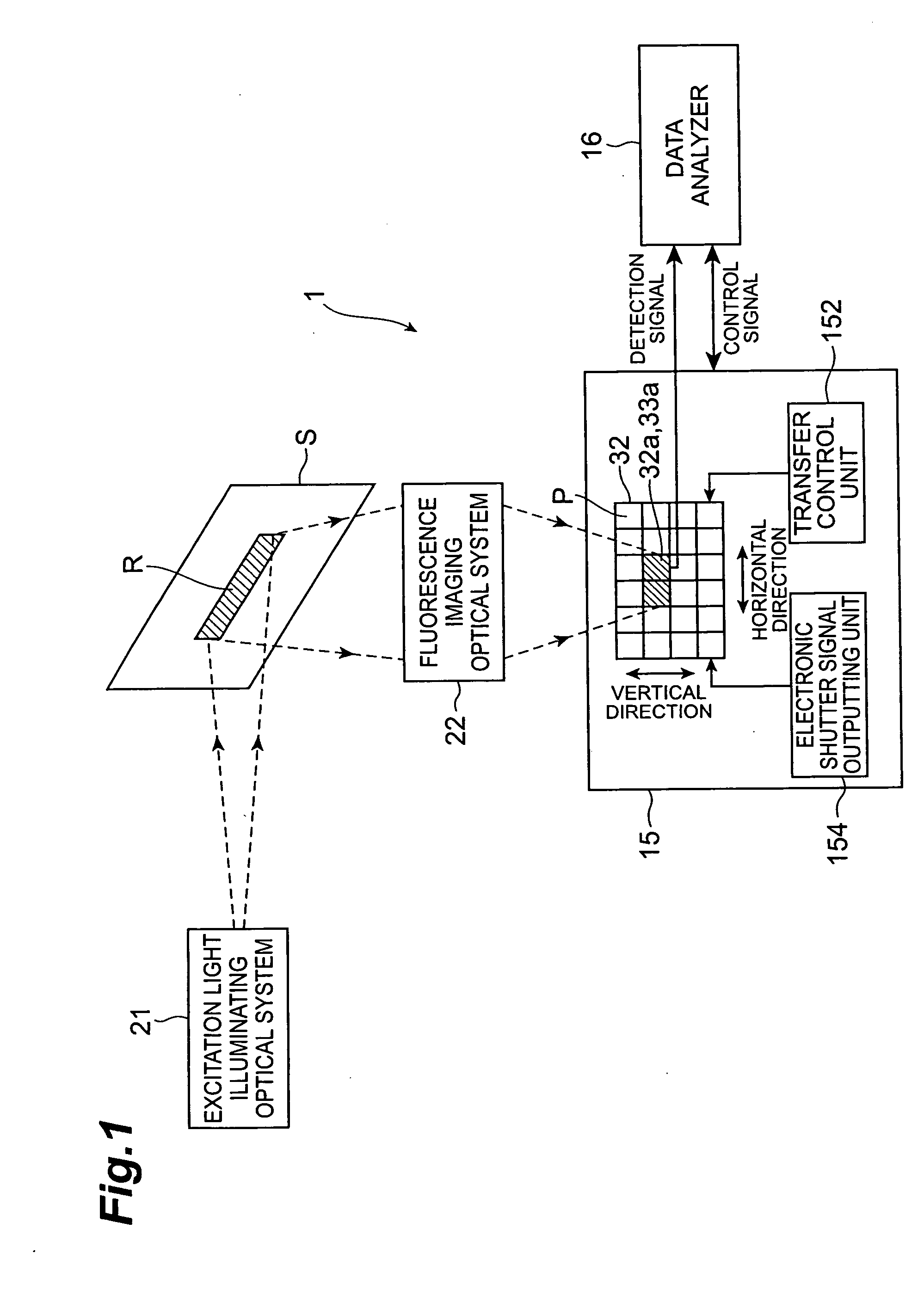

Fluorescent correalated spectrometric analysis device

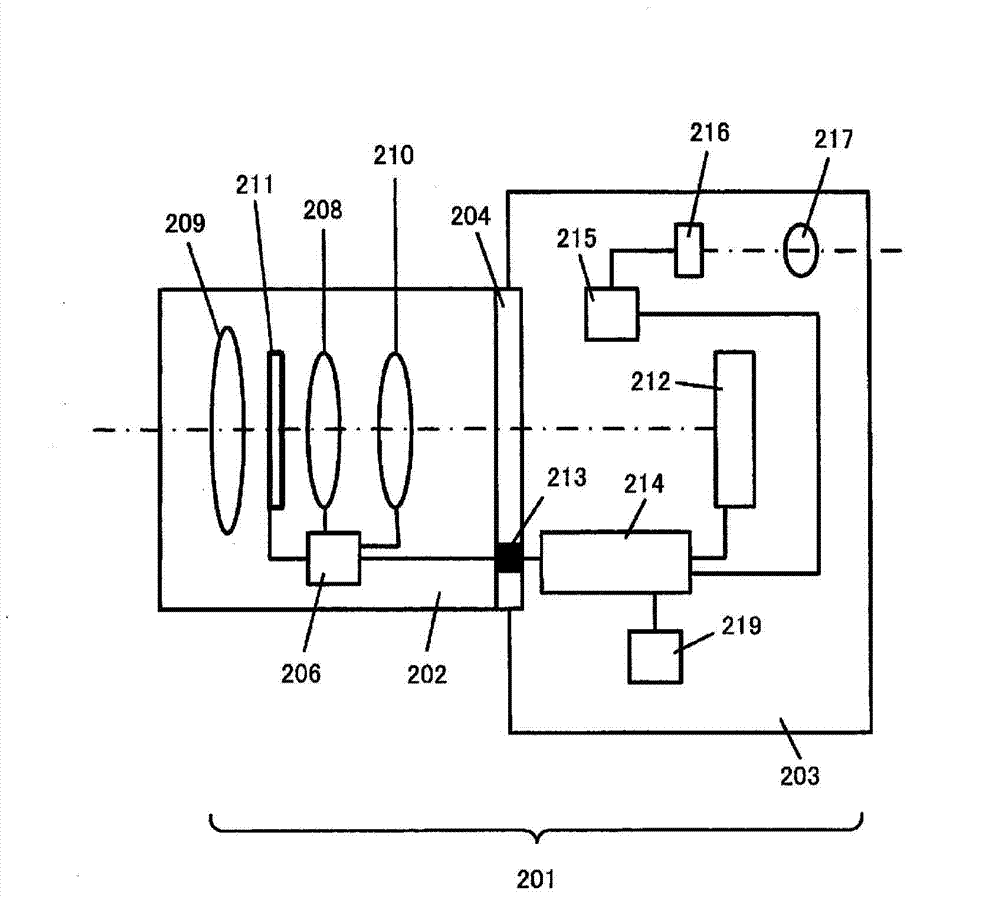

ActiveUS20060262301A1High-speed performanceIncrease speedTelevision system detailsRadiation pyrometryPhotoelectric conversionMultiple point

A fluorescence correlation spectroscopy analyzer 1 is equipped with an excitation light illuminating optical system 21, a fluorescence imaging optical system 22, a CCD camera 15, and a data analyzer 16. The excitation light illuminating optical system 21 illuminates excitation light onto a predetermined region of a measured sample S. The fluorescence imaging optical system 22 images the fluorescence generated at the measured sample S onto the photodetection surface of the CCD camera 15. The CCD camera 15 performs photoelectric conversion of the fluorescence made incident onto the photodetection surface in accordance with the respective pixels and outputs the charges generated by the photoelectric conversion as detection signals from an output terminal. The data analyzer 16 inputs the detection signals based on the charges generated at the pixels, among the pixels of the CCD camera 15, that belong to an analyzed pixel set and computes autocorrelation functions of the input detection signals according to each pixel. A fluorescence correlation spectroscopy analyzer, which is enabled to perform fluorescence correlation spectroscopy analysis on multiple points of a measured sample simultaneously and at high speed, is thus provided.

Owner:HAMAMATSU PHOTONICS KK

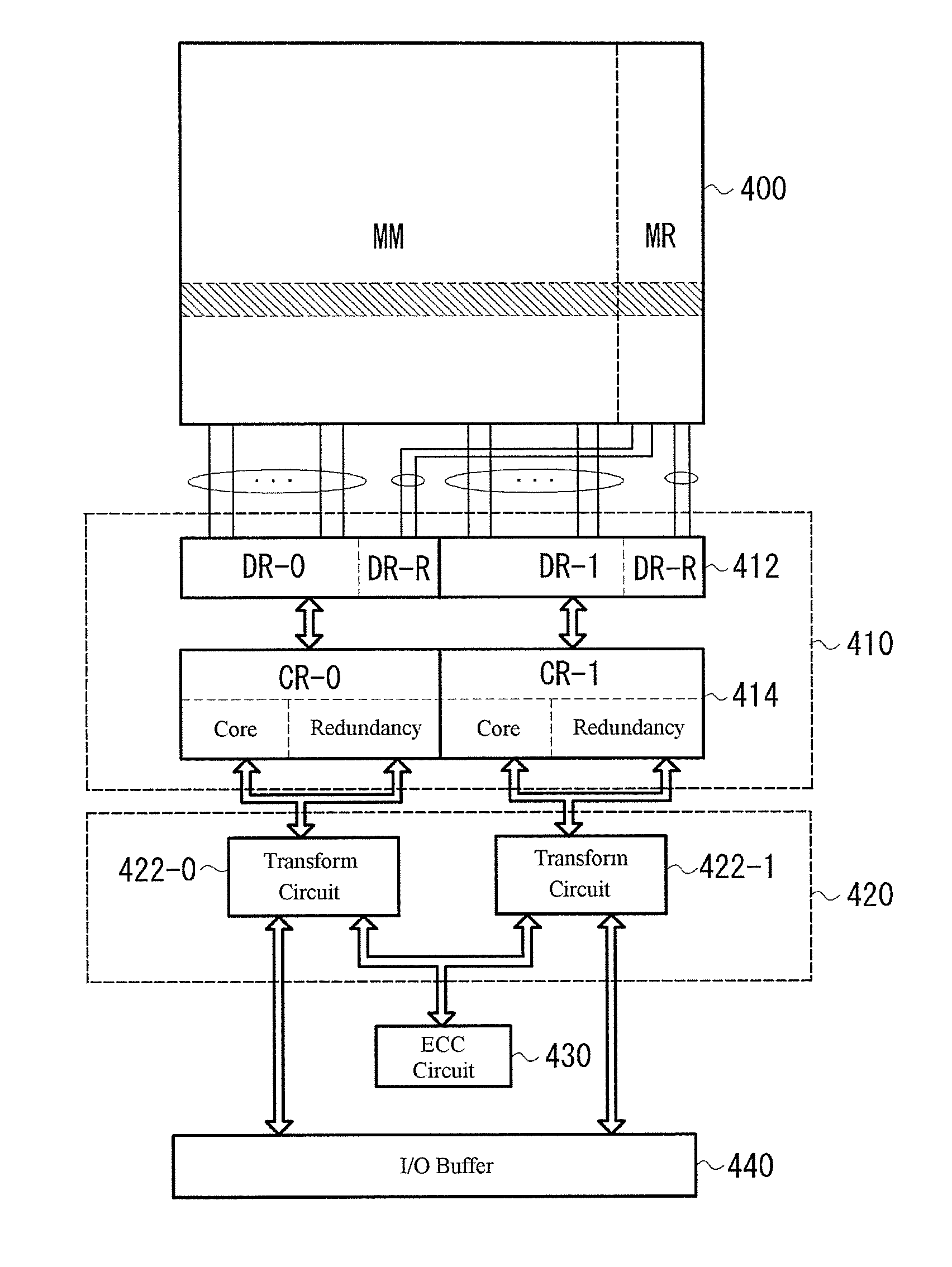

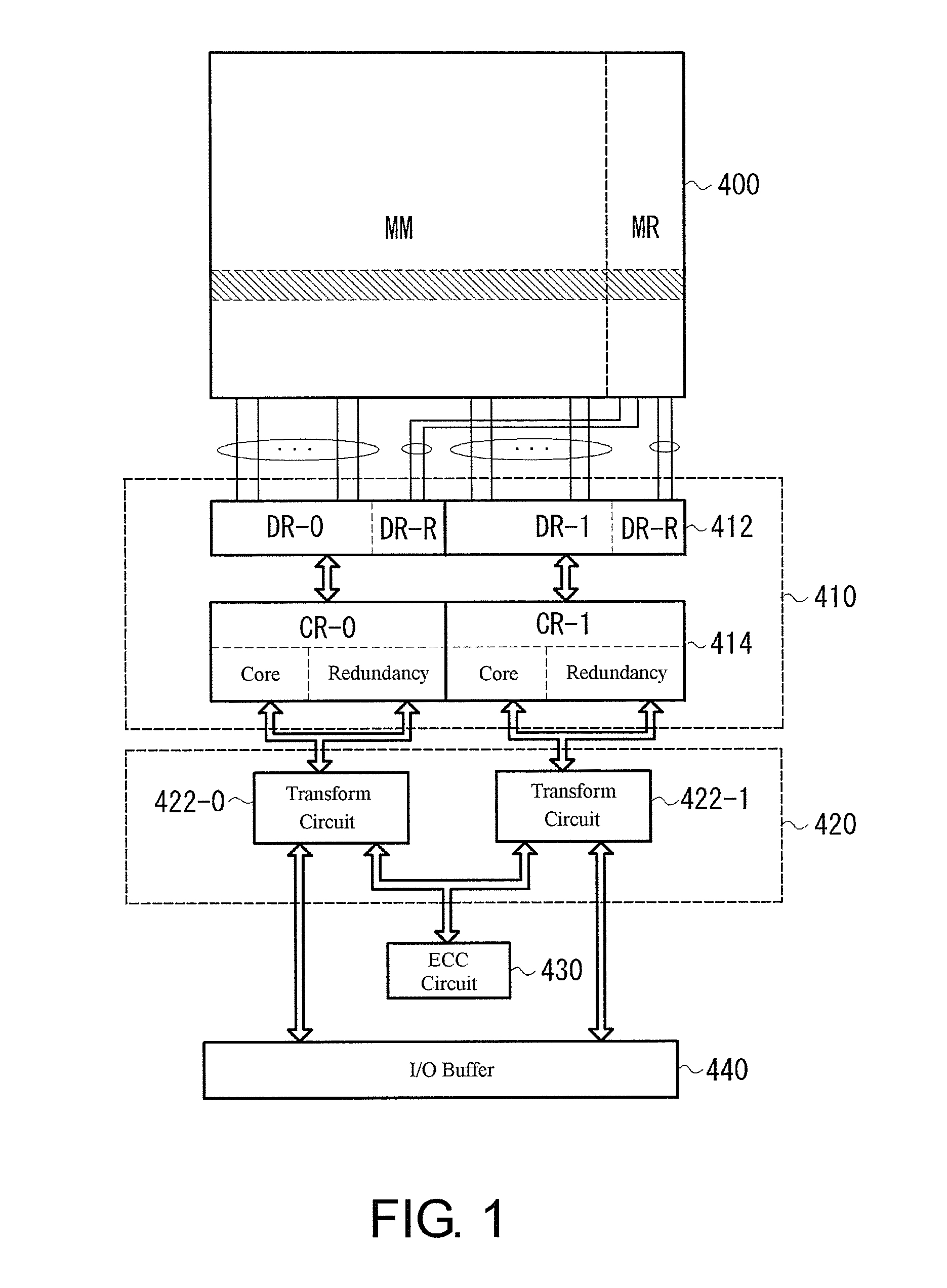

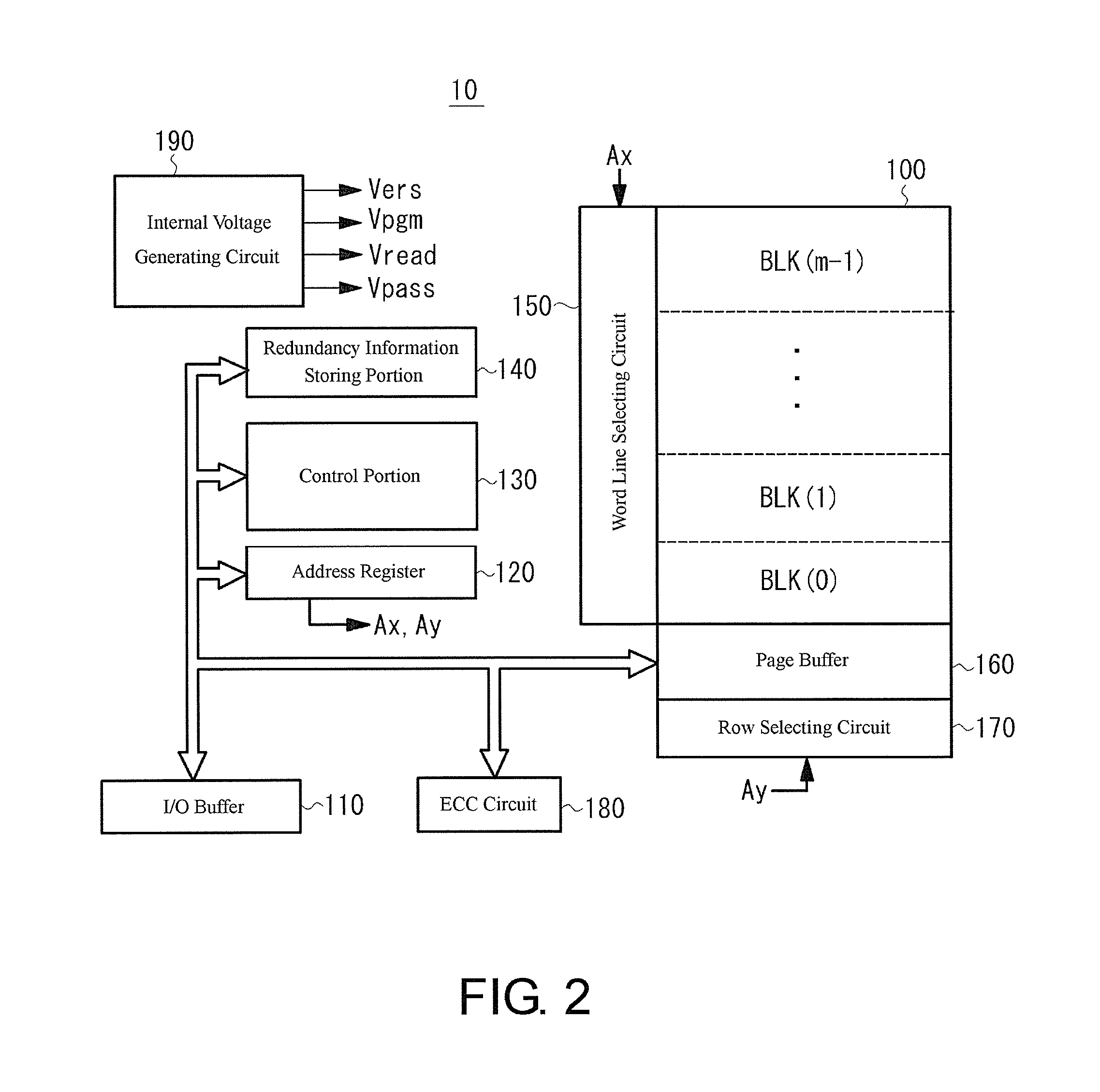

Semiconductor storing device and redundancy method thereof

ActiveUS20150121174A1Improve compensation efficiencyImprove yieldStatic storageRedundant data error correctionProcessor registerComputer science

A semiconductor storing device and a redundancy method thereof are provided. The semiconductor storing device is for example a NAND flash memory, which includes: a storing array including a storing area and a redundancy storing area with a redundancy element; a page buffer; a row selecting circuit; an ECC circuit; and an I / O buffer. The row selecting circuit transforms defect data included in core data retained by a cache register into redundancy data retained by a redundancy cache register, and provides the transformed data to the ECC circuit, and the data corrected by the ECC circuit as the core data is written to the cache register again. During this period, the row selecting circuit outputs the corrected data retained in the cache register to the I / O buffer.

Owner:WINBOND ELECTRONICS CORP

Semiconductor memory

InactiveUS7372726B2Avoid it happening againHigh speed readSolid-state devicesRead-only memoriesPhase-change memoryEngineering

A phase-change memory for employing chalcogenide as a recording medium is disclosed, which prevents the read disturbance from being generated, and reads data at high speed. In a phase-change memory cell array including a selection transistor and chalcogenide, a substrate potential of the selection transistor is isolated in a direction perpendicular to the word lines. During the data recording, a forward current signal flows between the substrate and the source line connected to chalcogenide, and the selection transistor is not used. During the data reading, a desired cell is selected by the selection transistor. Therefore, a recording voltage is greatly higher than the reading voltage, such that the occurrence of read disturbance is prevented, and a high-speed operation is implemented.

Owner:RENESAS ELECTRONICS CORP

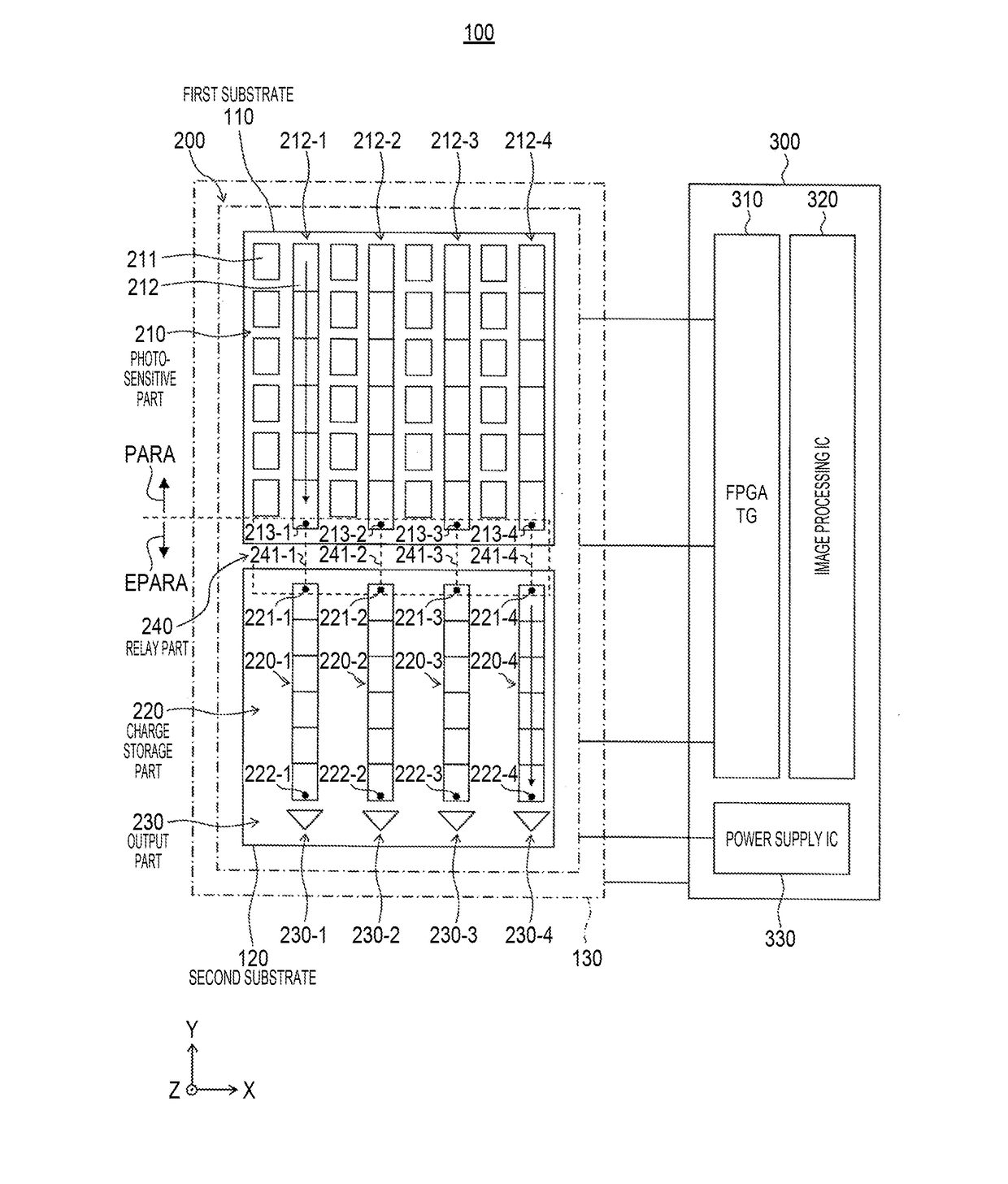

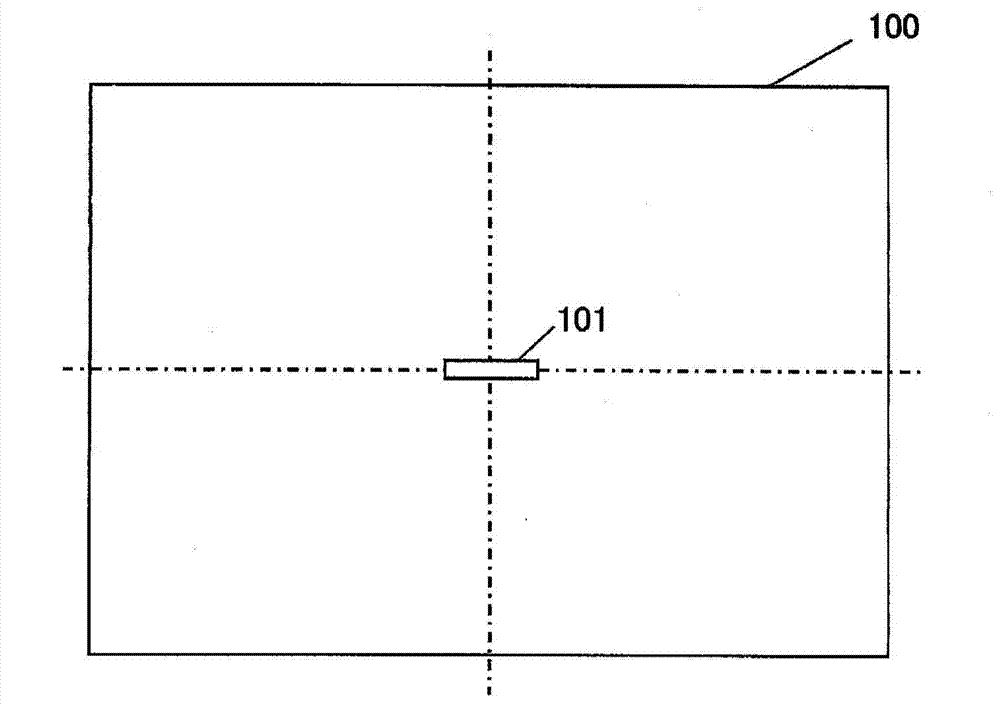

Solid-state imaging device, method for producing solid-state imaging device, and electronic apparatus

ActiveUS20170162625A1High speed readLittle restrictionTelevision system detailsSemiconductor/solid-state device detailsElectricityEngineering

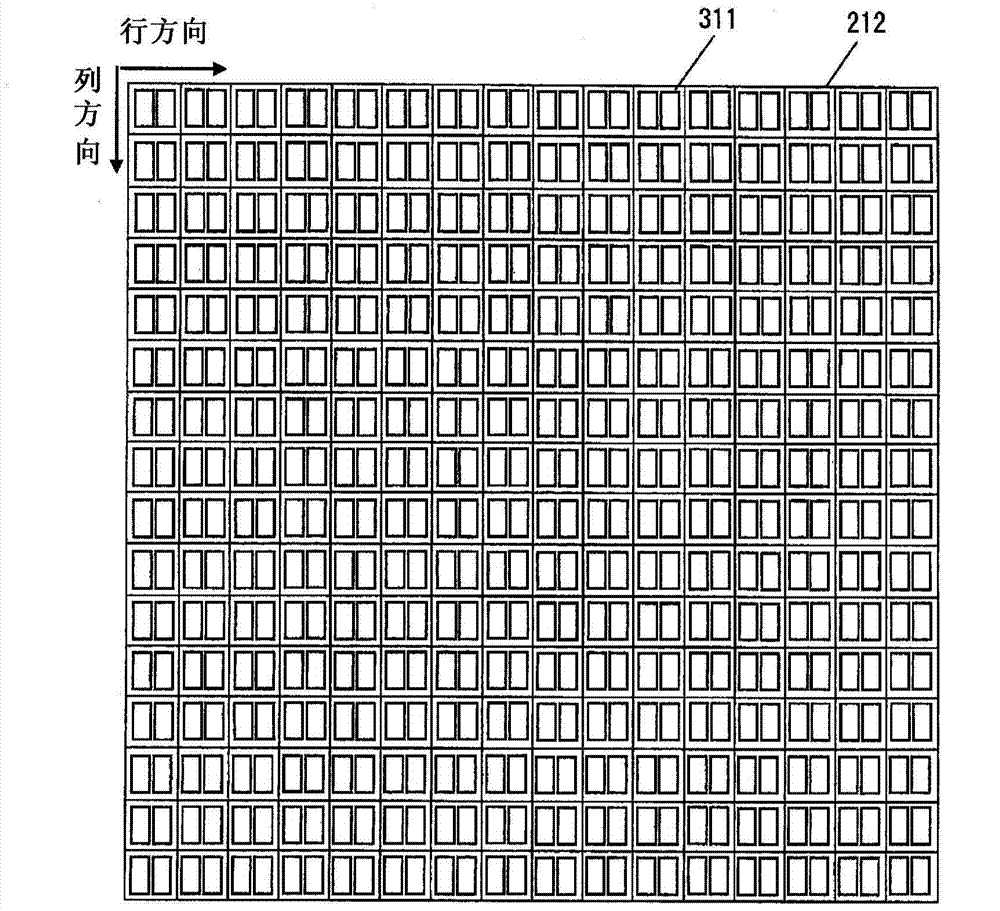

This solid-state imaging device 100 has: a photosensitive part that includes pixel portions 211, which are disposed in a matrix, and charge transfer parts 212 for transferring, by the column, the signal charge of the pixel portions; a plurality of charge storage parts 220 that accumulate the signal charges transferred by the plurality of charge transfer parts of the photosensitive part; a relay part 240 that relays the transfer of the signal charges transferred by the plurality of charge transfer parts to each charge storage part; an output part 230 that outputs the signal charges of the plurality of charge storage parts as electric signals; a first substrate 110 at which the photosensitive unit 210 is formed; and a second substrate 120 at which the charge storage part 220 and output unit 230 are formed. The first substrate and second substrate are stacked together, and the relay part 240 electrically couples the charge transfer parts of the first substrate to the charge storage parts of the second substrate by means of a connecting parts passing through the substrates outside the photosensitive region of the photosensitive part.

Owner:BRILLNICS JAPAN

Image pick-up element and image pick-up device

ActiveCN104718745AHigh speed readTelevision system detailsSolid-state devicesLight beamAnalog signal

An image pick-up element comprises the following: a first picture element that receives a pair of light beams and outputs a pair of first analog signals; an AD conversion unit that converts the pair of first analog signals into a pair of first digital signals; a digital addition unit that adds together the pair of first digital signals and thereby generates an added digital signal; a first output unit that outputs the pair of first digital signals to the outside; and a second output unit that outputs the added digital signal to the outside.

Owner:NIKON CORP

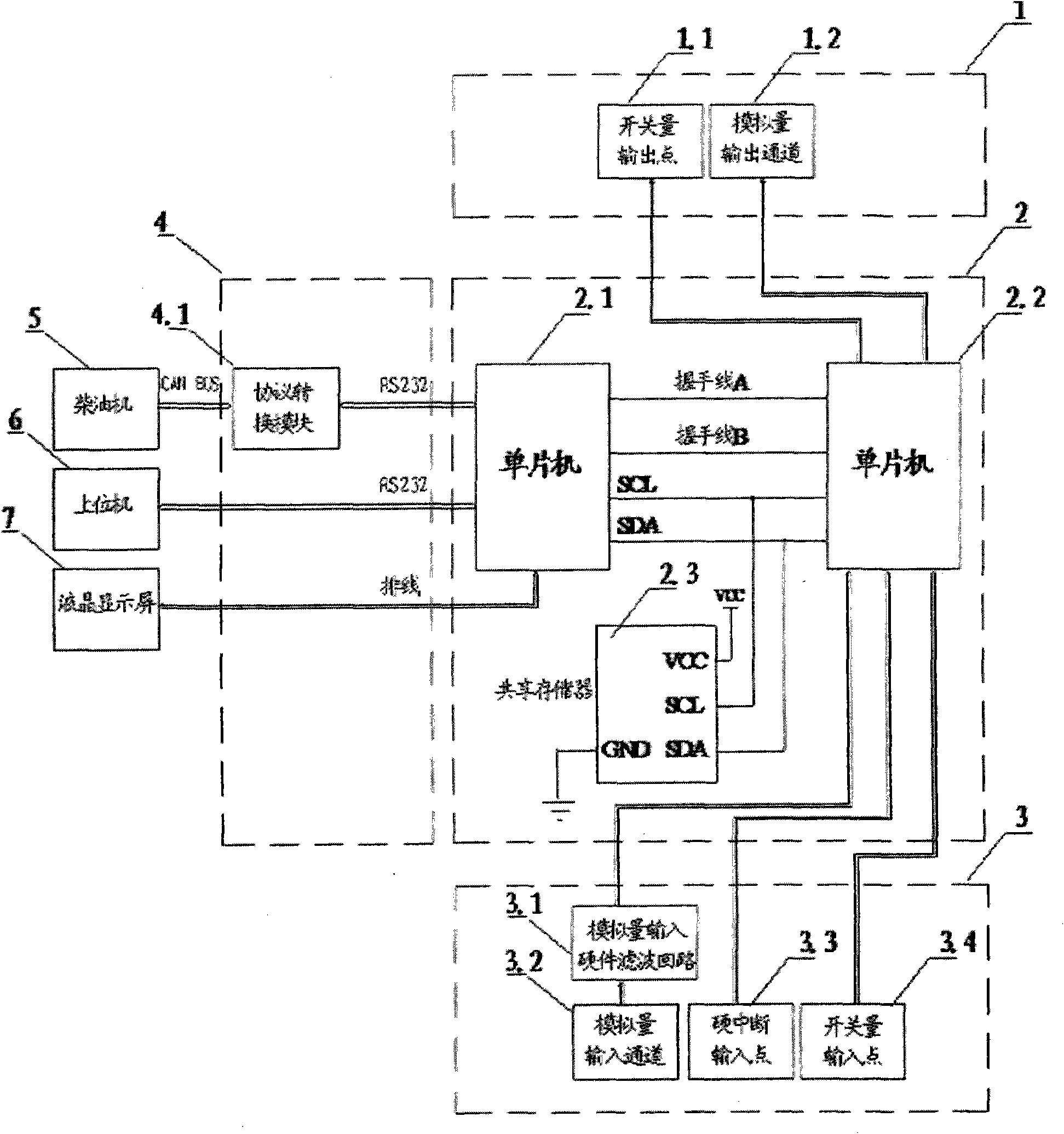

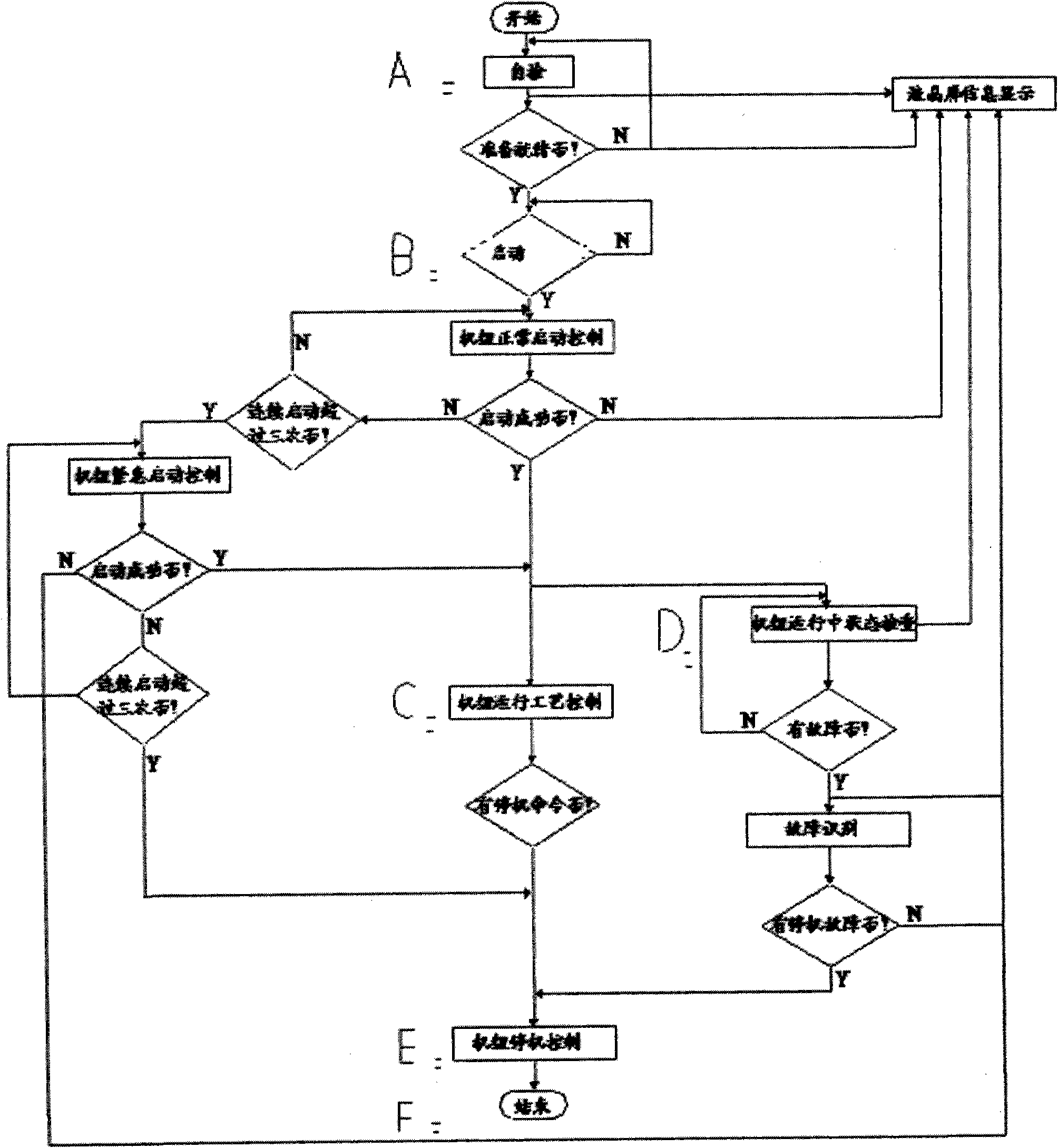

Device and method for comprehensively controlling and protecting pump set of diesel engine

InactiveCN101560906AShield water temperature abnormal signalShield abnormal pressure signalProgramme controlCoolant flow controlMicrocontrollerEmergency treatment

The invention relates to a device and a method for comprehensively controlling and protecting a pump set of a diesel engine, which are applied to the comprehensive control and protection of the pump set of the emergency / fire-fighting diesel engine. The device comprises a core operation unit, a signal output unit, a signal input and processing unit and a communication protocol conversion unit; a first single chip machine is connected with the diesel engine, a host computer and an LCD screen; and the first singlechip is also connected with a second singlechip. The method orderly comprises the following steps of self-test, start, process control of the operation of the machine set, state check in the operation of the machine set, control of shutdown of the machine set and completion. The control system has the advantages of high accuracy, strong emergency treatment capability for timely alarm control, low cost, high cost-performance ratio, small volume, simple structure, convenient use and high degree of automation; and the control and protection method can timely and accurately judge various faults occurring during the operation of the machine set and alarm, and make the automatic and accurate control, and the control program is reasonable, simple and reliable.

Owner:WUHAN GREAT SEA HI TECH

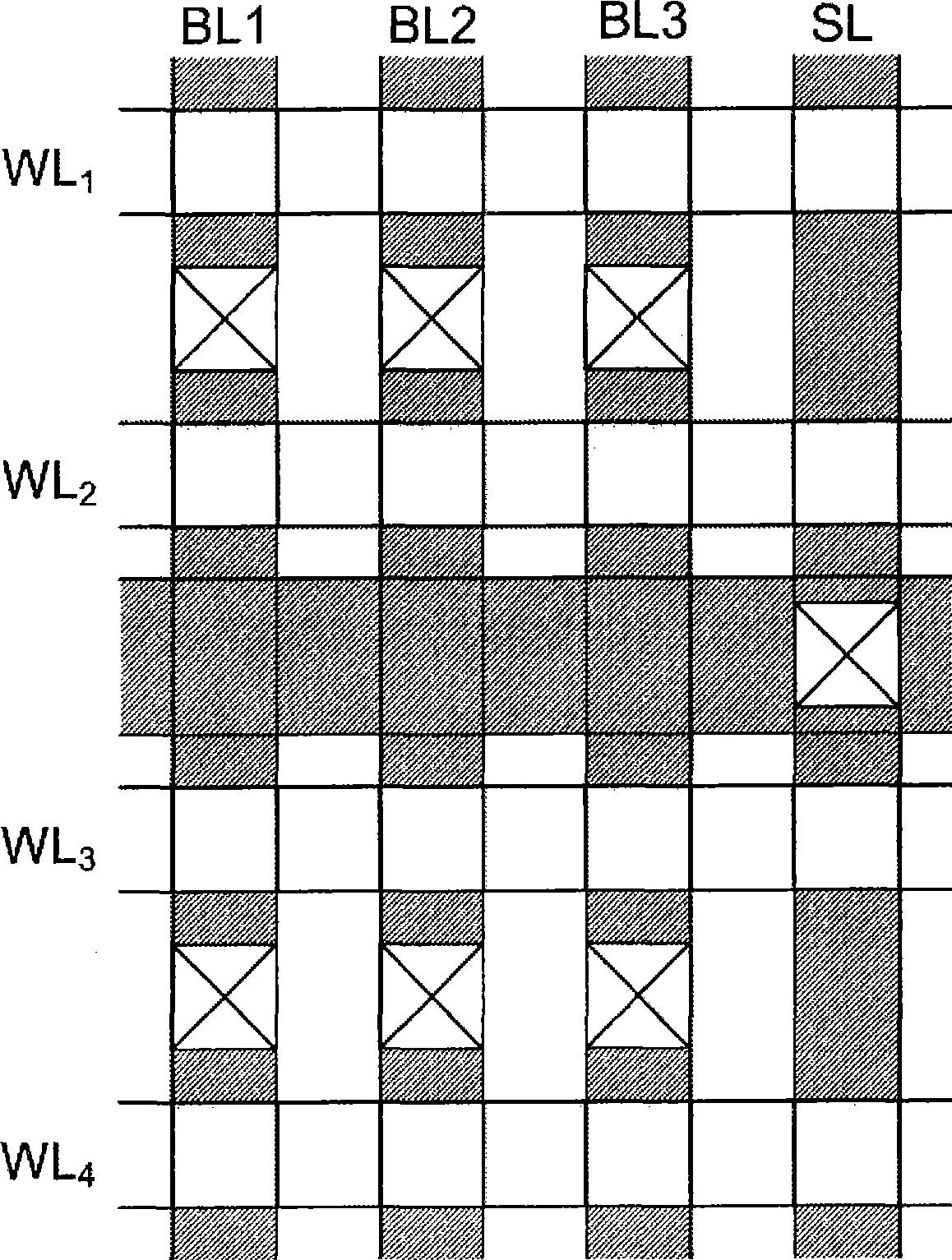

Nonvolatile semiconductor memory and its drive method

The invention provides a NOR-type nonvolatile semiconductor memory that can inject electric charge into a charge accumulation layer through the use of an FN tunnel current without compromising an increase in the packing density of memory cells. The above problem is solved by a nonvolatile semiconductor memory in which nonvolatile semiconductor memory cells are arranged in a matrix, each nonvolatile semiconductor memory cell having an island semiconductor layer in which a drain diffusion layer formed in the upper part of the island semiconductor layer, a source diffusion layer formed in the lower part of the island semiconductor layer, a charge accumulation layer formed on a channel region of the side wall sandwiched between the drain diffusion layer and the source diffusion layer via a gate insulation film, and a control gate formed on the charge accumulation layer are formed. Further, bit lines connected to the drain diffusion layer are laid out in a column direction, control gate lines are laid out in a row direction, and source lines connected to the source diffusion layer are laid out in the column direction.

Owner:TOHOKU UNIV

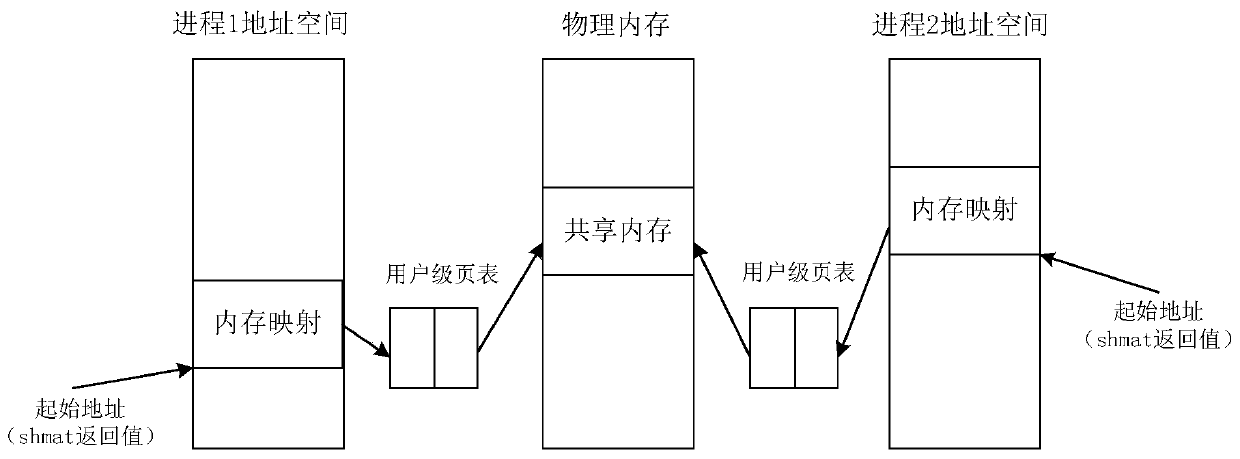

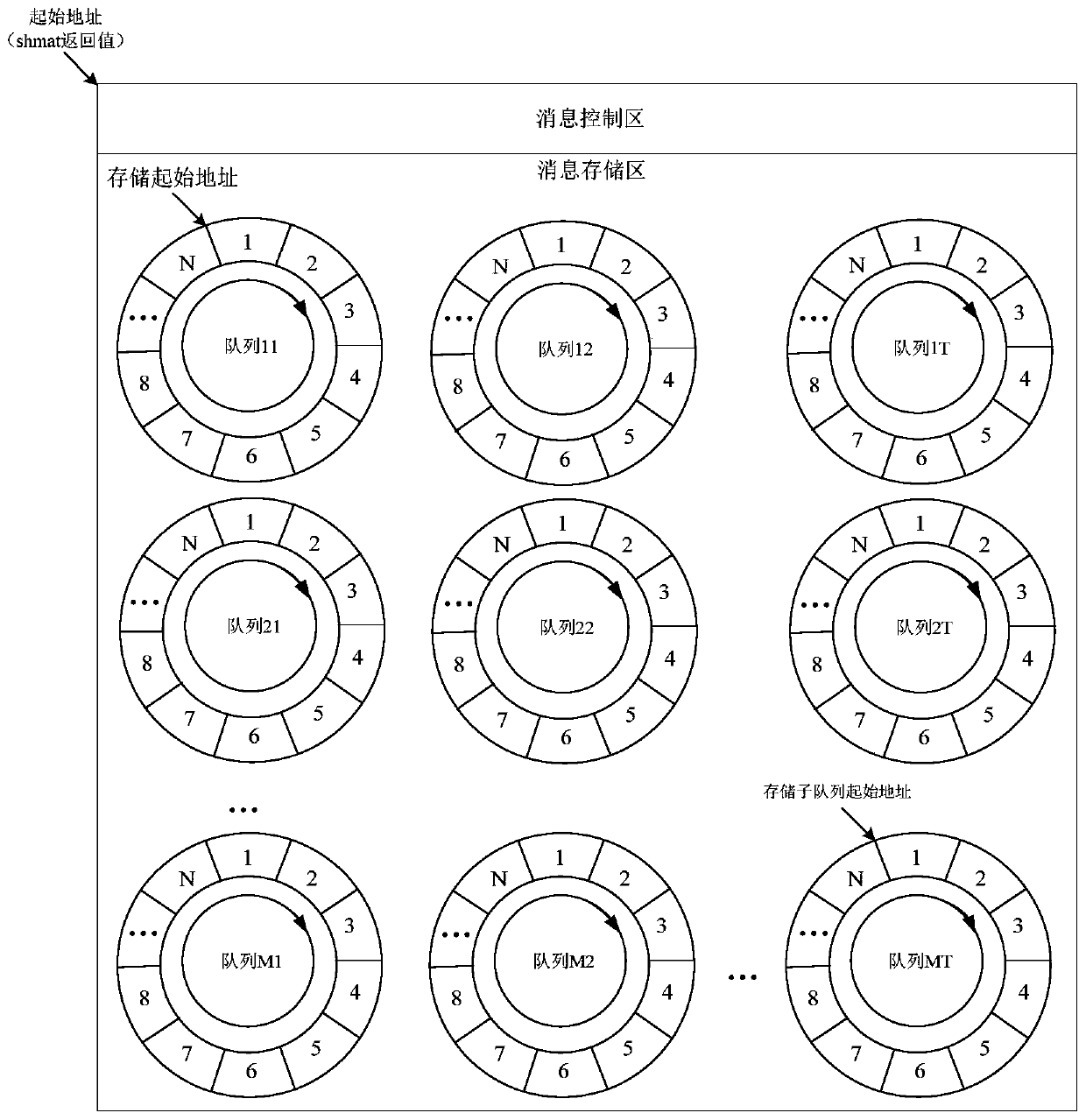

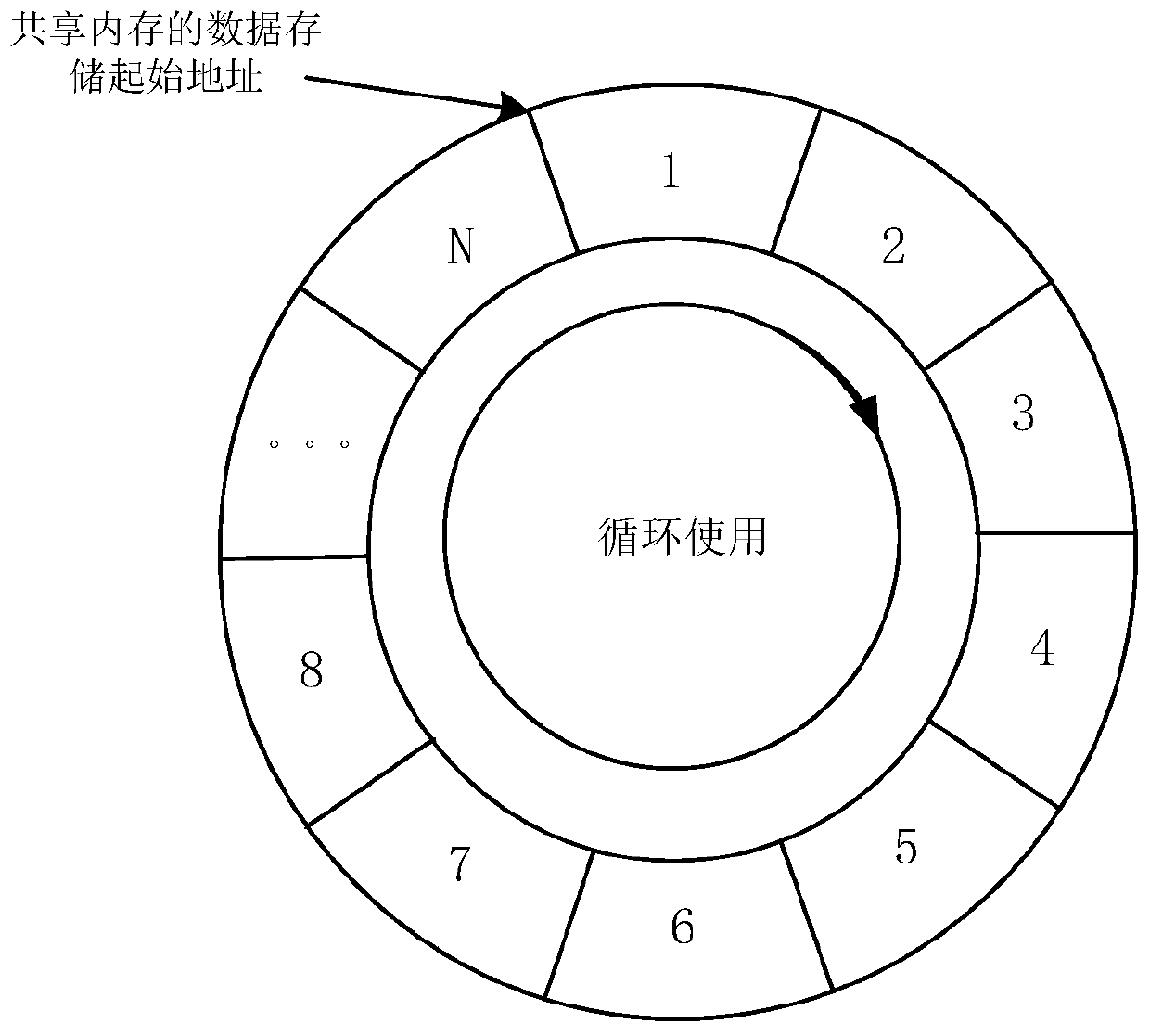

Message storage method and message reading method based on shared memory

PendingCN110737536ARealize high-speed transmissionSatisfy concurrency and low latencyInterprogram communicationEngineeringReal-time computing

The invention discloses a message storage method and a message reading method based on a shared memory, and provides a storage space, a message storage method and a message reading method. A message storage method is used for storing a message to be stored in a storage space, the storage space comprises a message control area and a message storage area, the message storage area is used for storingdata, the message storage area comprises a plurality of storage sub-queues, and the message control area is used for storing an array for recording read-write information of the storage sub-queues. The message reading method is used for reading messages stored in a storage space according to a message storage method, high-speed interaction of the messages is achieved in a memory copying mode in the message storage and reading process, and the problems that in an existing communication interaction technology, real-time performance cannot be met under the requirements for low message transmission efficiency, high concurrency and low delay, configuration is not flexible, and learning and maintenance cost is high are solved.

Owner:亚信创新技术(南京)有限公司