Patents

Literature

95 results about "Speed reading" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Speed reading is any of several techniques used to improve one's ability to read quickly. Speed reading methods include chunking and minimizing subvocalization. The many available speed reading training programs include books, videos, software, and seminars. There is very little scientific evidence regarding speed reading.

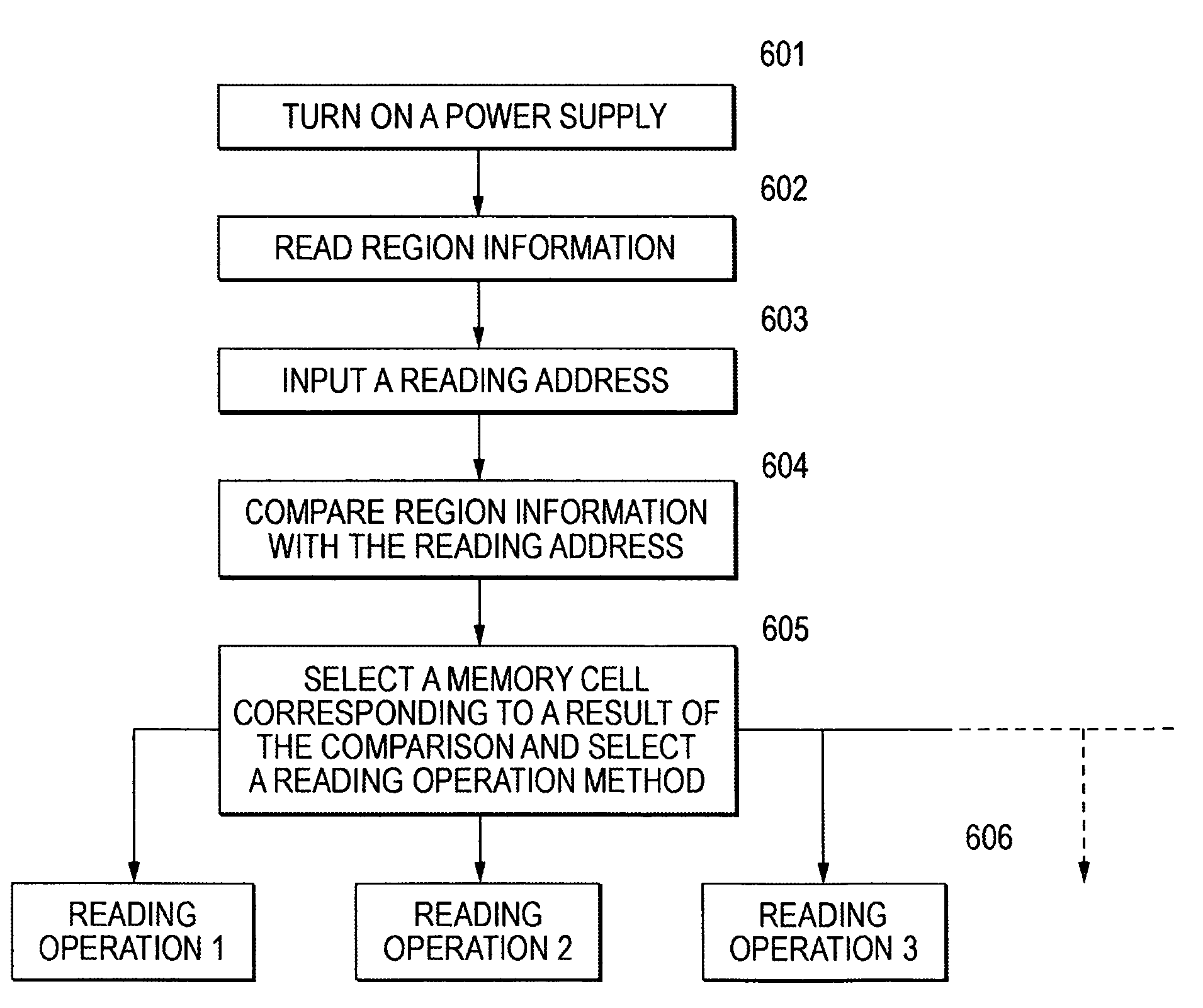

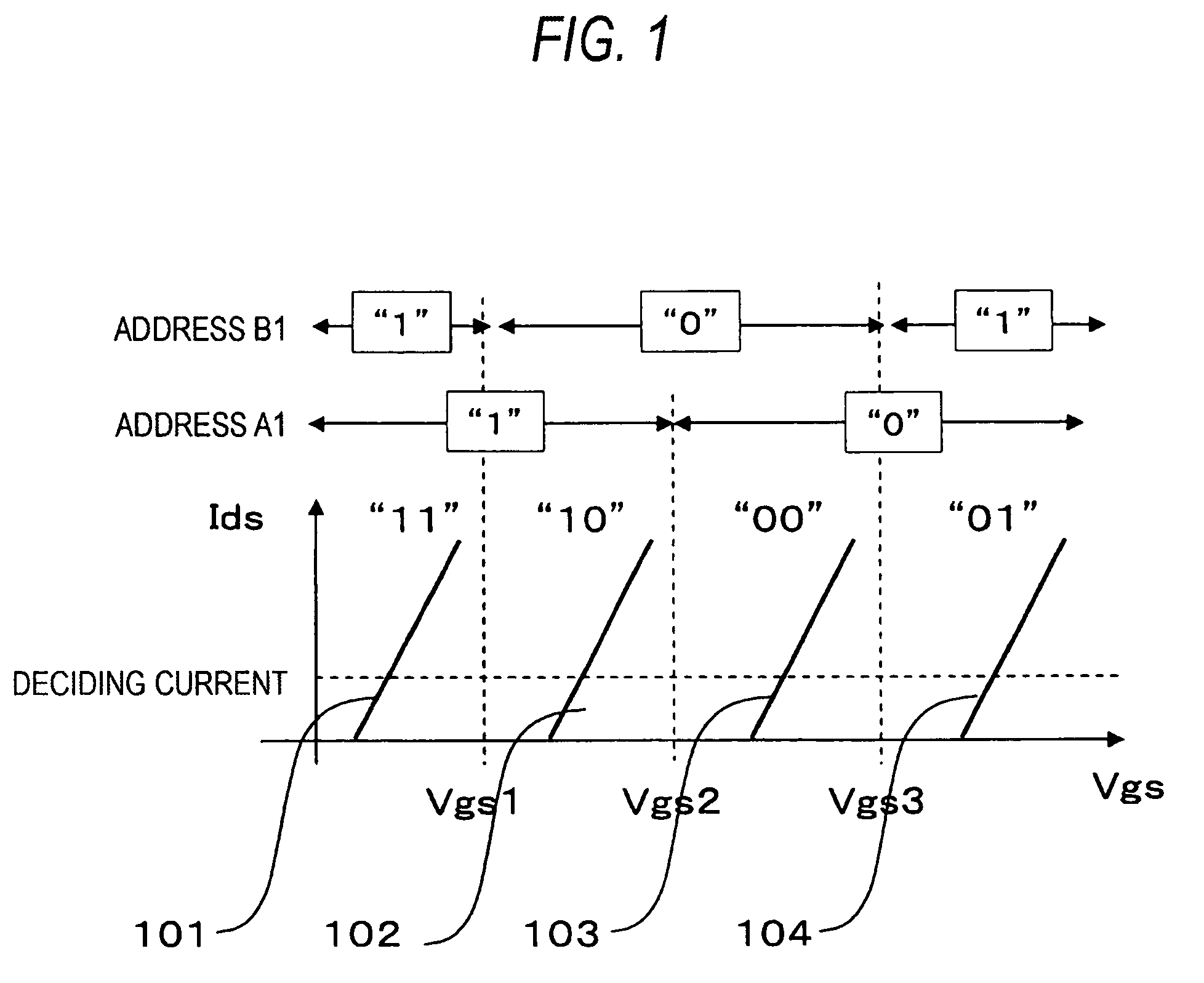

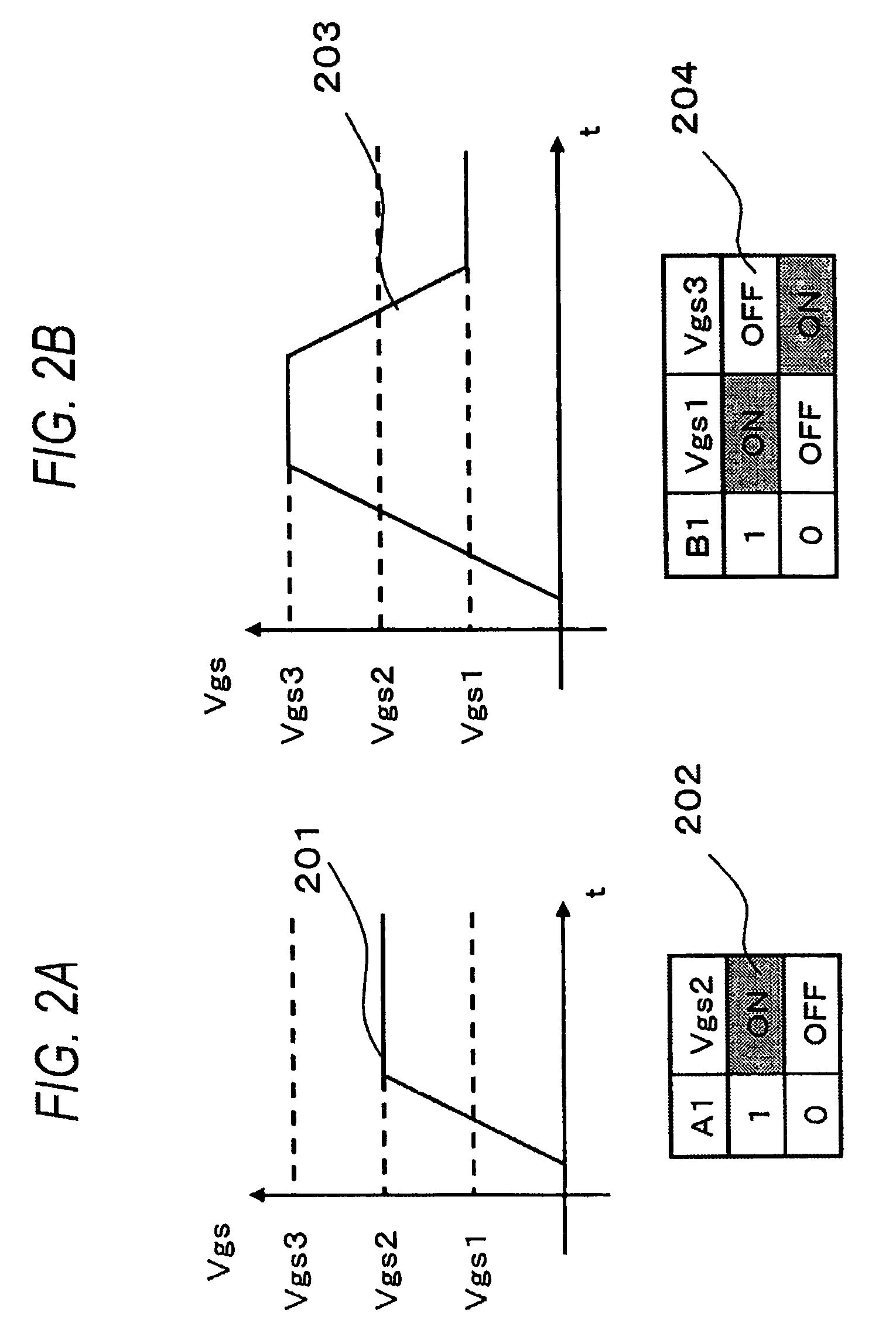

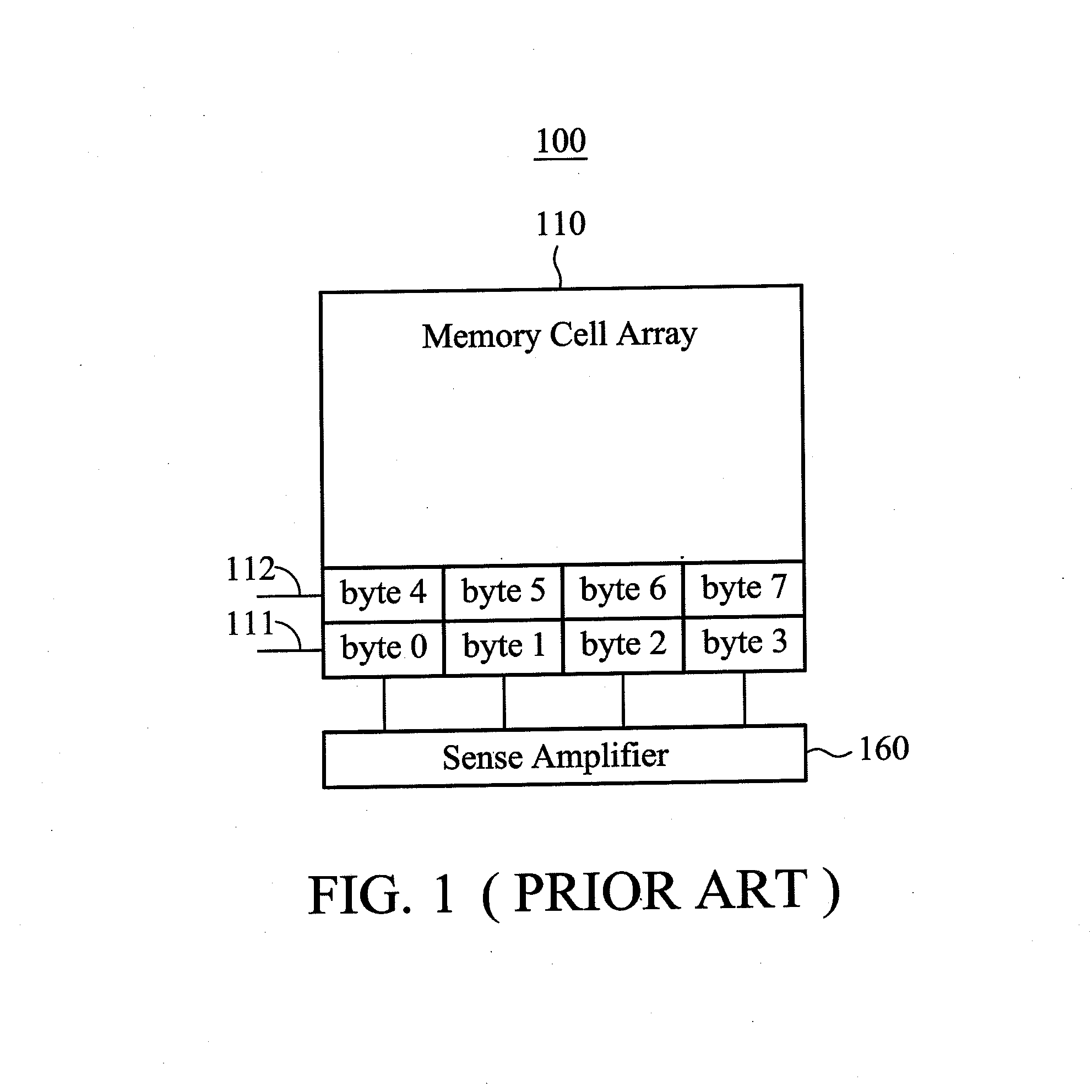

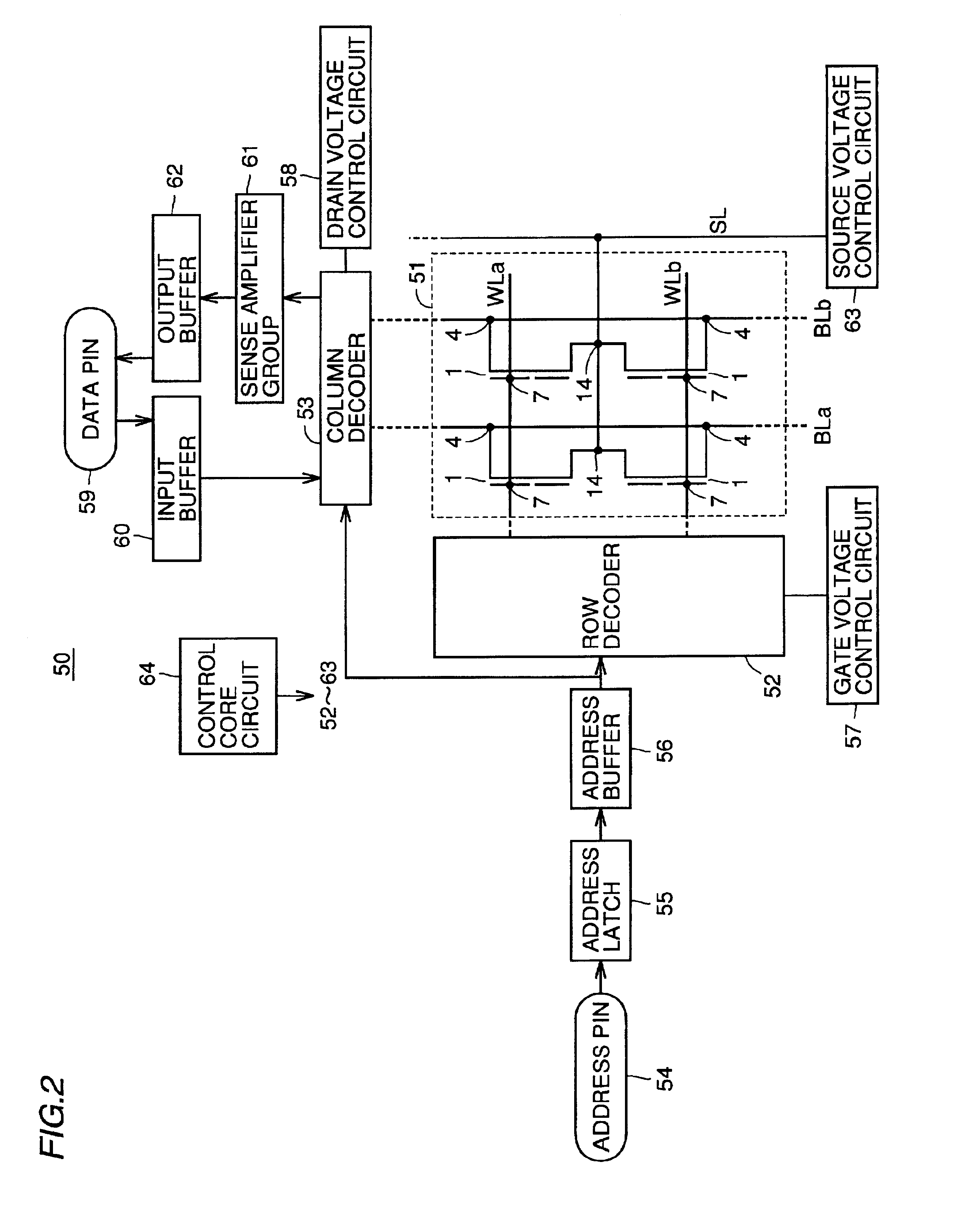

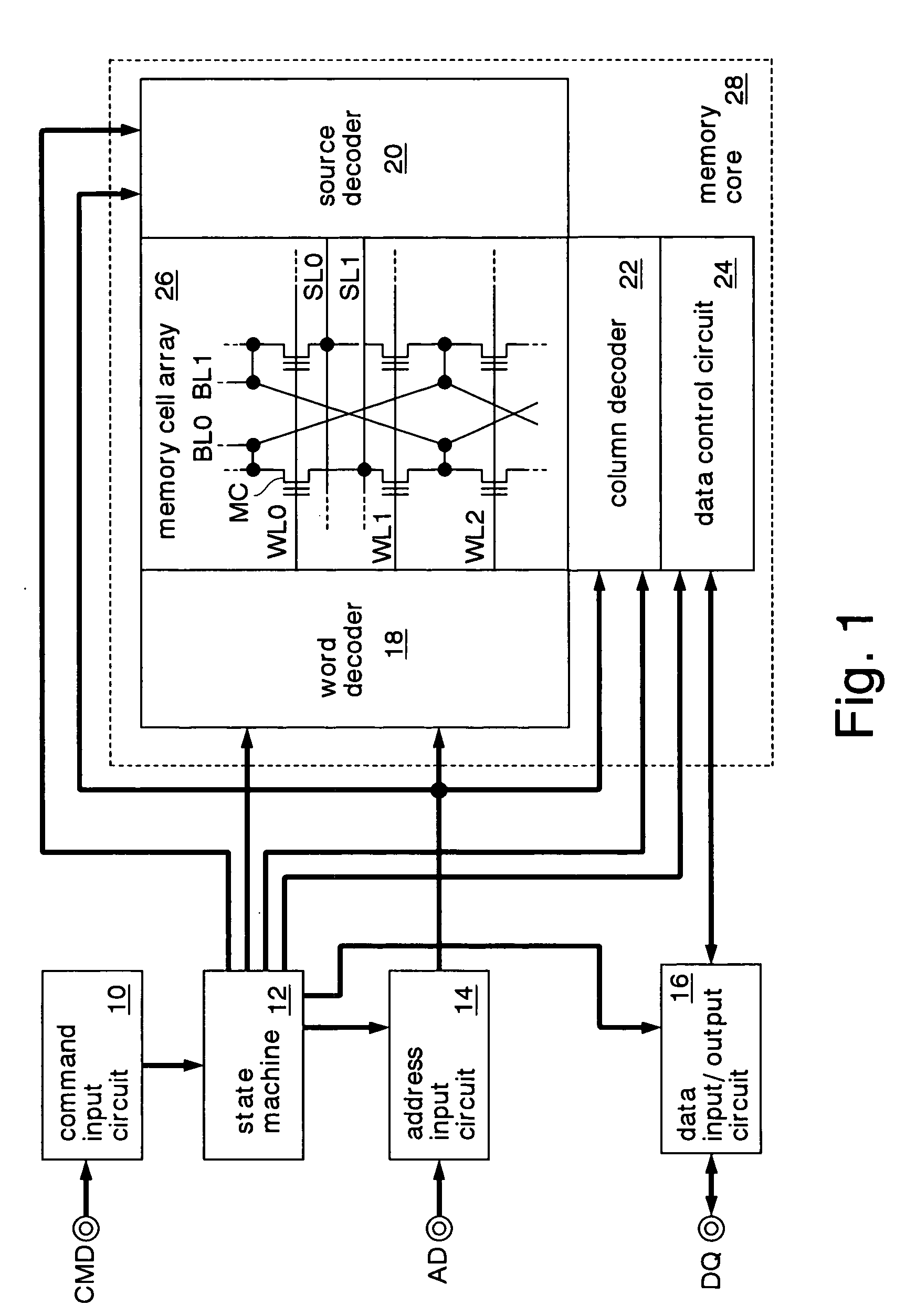

Nonvolatile semiconductor storage apparatus and method of driving the same

InactiveUS7339823B2Increase speedEfficiently and read informationRead-only memoriesDigital storageComputer architectureControl circuit

A memory cell array is logically divided into a plurality of regions having different reading speeds, the respective regions having the different reading speeds include region information storage regions for storing region information in which at least two addresses present in the memory cell at the same time are set to be different regions, a reading control circuit is constituted to carry out a reading operation by determining any of the divided regions which is to be read, selecting an optimum reading method and controlling the reading circuit based on the region information stored in the region information storage region, and an address which can be read in a short time in multivalued information stored in one memory cell is set to be a high speed reading region and is distinguished from regions having the other reading speeds. Consequently, it is possible to efficiently write and read information of 2 bits or more in one memory cell array without reducing a using efficiency of the memory cell array.

Owner:PANASONIC CORP

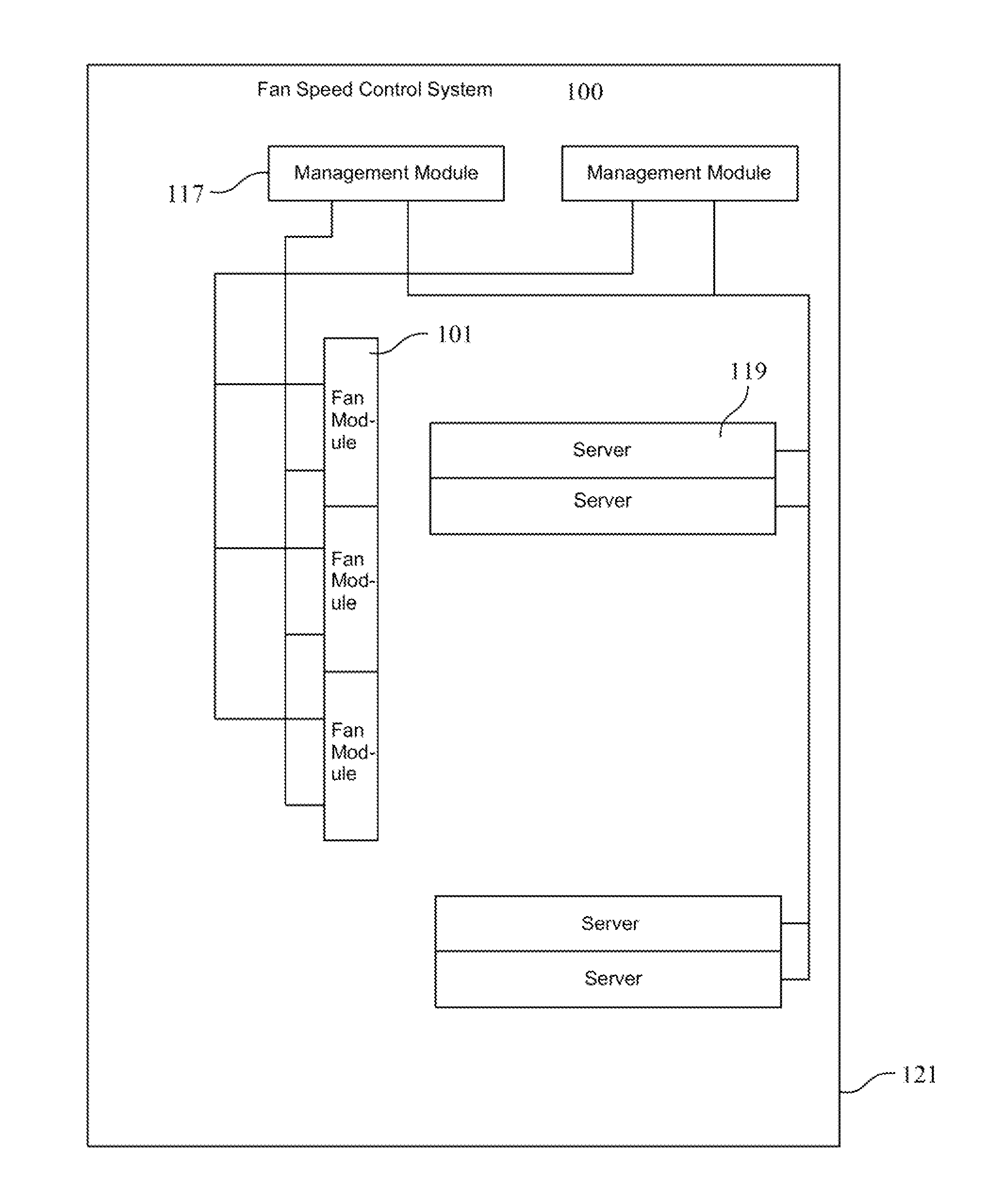

Fan speed control system and fan speed reading method thereof

InactiveUS20120136502A1Improve transmission efficiencyEfficient regulation technologiesTemperature control using electric meansSpeed control systemControl signal

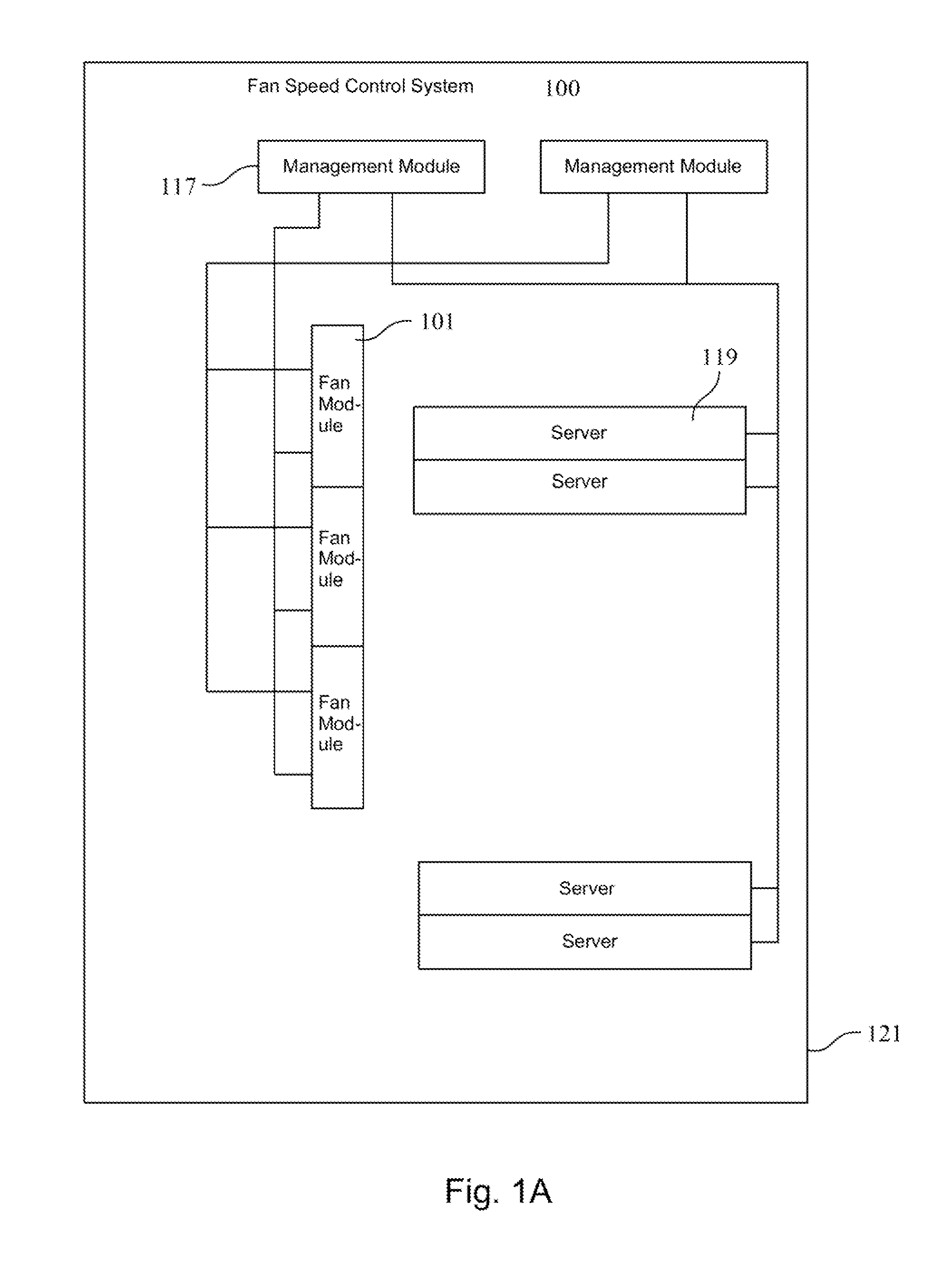

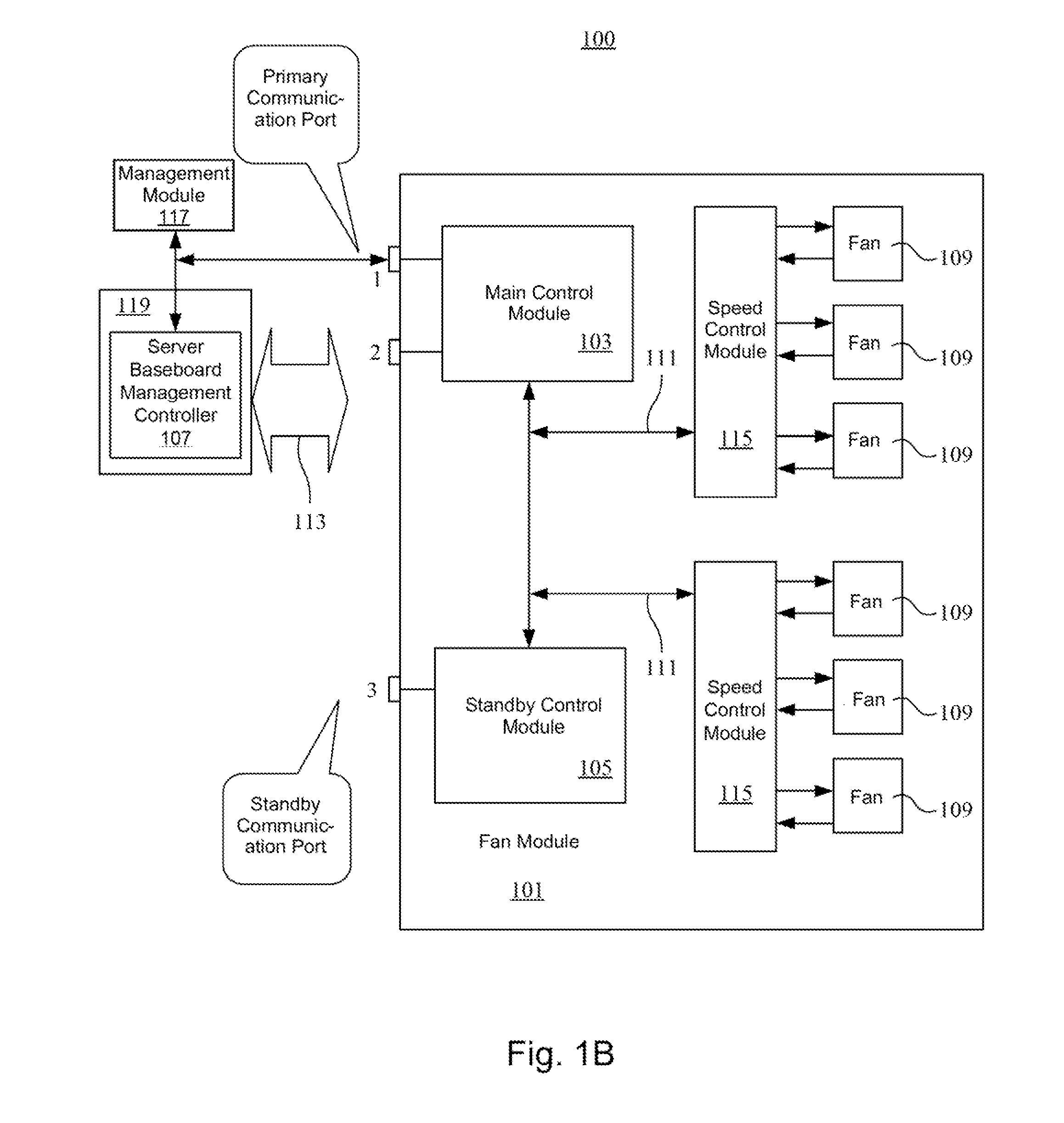

A fan speed control system includes a rack and a plurality of servers disposed on the rack. The fan speed control system further includes the management module and the fan module. The management module is coupled to the servers, and the fan module is coupled to the management module for dissipating the heat from the servers. The fan module contains the fan, the speed control module, and the main control module. The speed control module is coupled to the fans. The main control module has a primary communication port. The main module which enters the interrupt sequence receives the control signals sent from the management module through the primary communication port when any one of the main modules enters the interrupt sequence. The control signal is delivered to the speed control module for reading the fan speed.

Owner:INVENTEC CORP

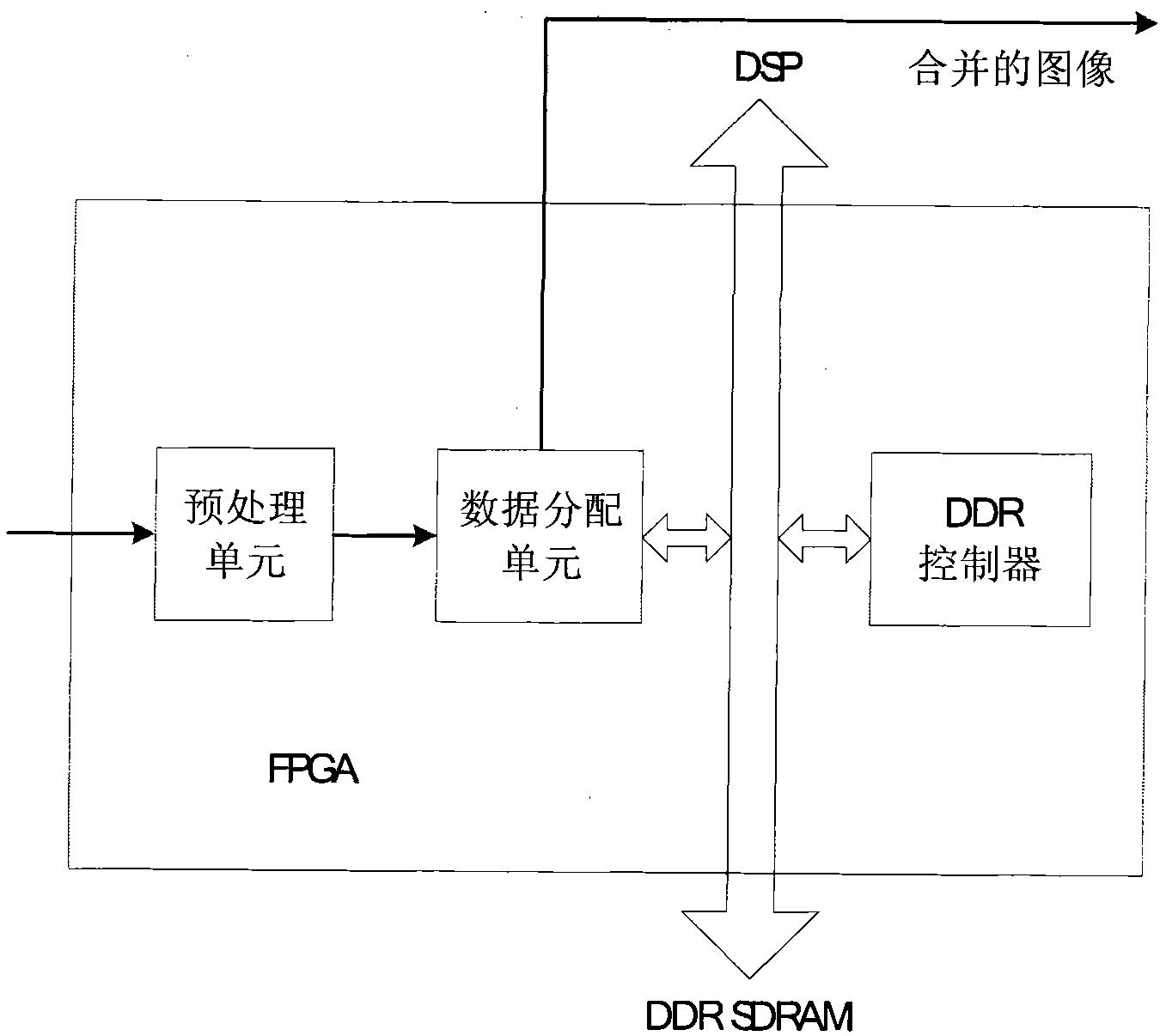

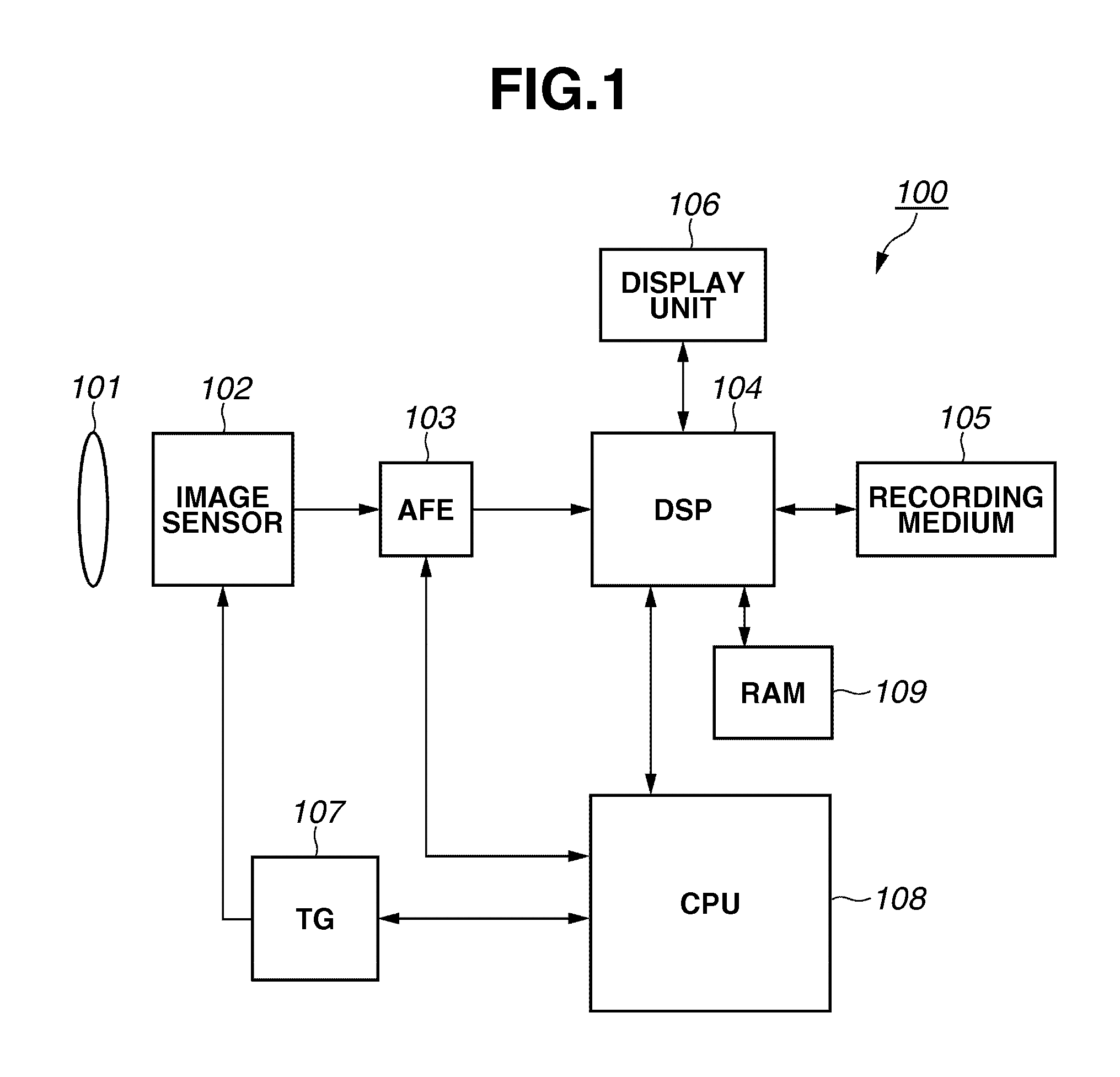

Motion blur image restoration system based on multi-core

InactiveCN101882302AIncrease transfer rateMeet the needs of cachingImage enhancementDigital recording/reproducingDigital dataWork distribution

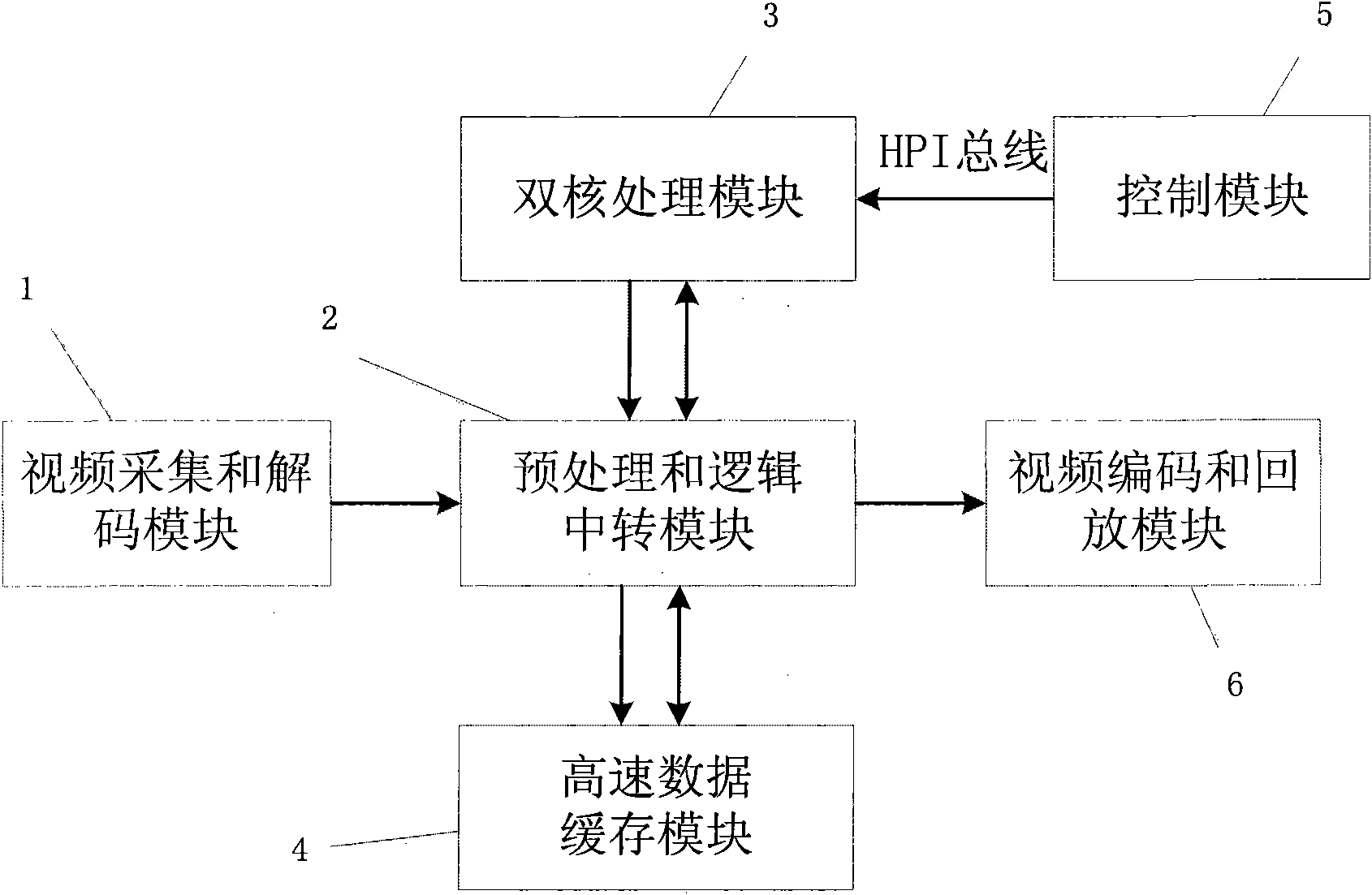

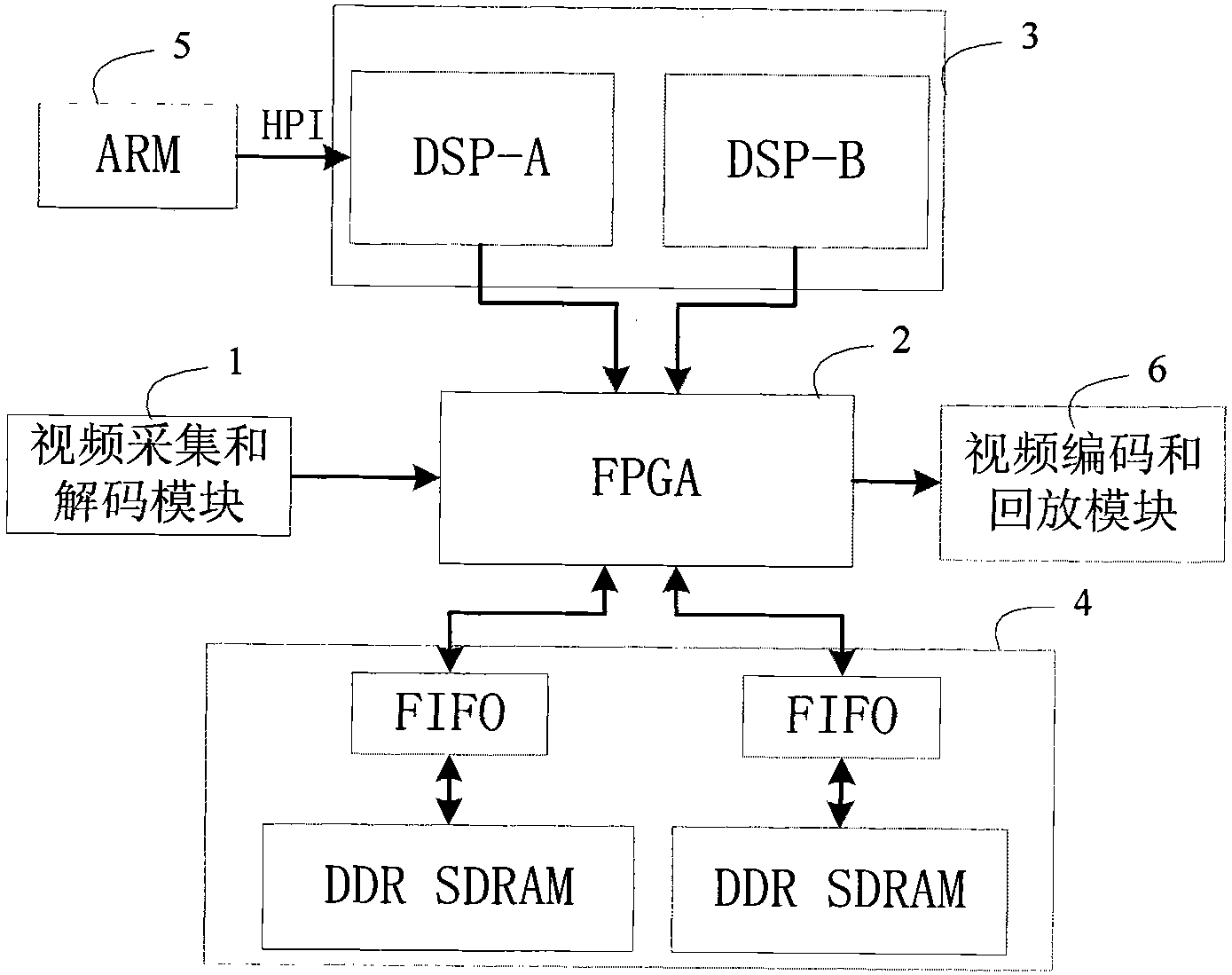

The invention discloses a motion blur image restoration system based on multi-core. In the system, a preprocessing and logic transfer module preprocesses video frames collected by a video collecting and decoding module and temporarily stores the preprocessed video frames in a high-speed data buffer module, the core calculation of a preprocessing module is finished by adopting an FPGA (Field Programmable Gate Array), and the high-speed data buffer module is based on DDR SDRAM (Digital Data Receiver Synchronous Dynamic Random Access Memory). A double-core processing module reads the video frames in a high-speed data cache through the preprocessing and logic transfer module and carries out image compensation. The double-core processing module is established by adopting two DSPs (Digital Signal Processor), and video subject to parallel processing is played back in a playback module. In the system, the processing work of video is distributed to two parts, and by adopting the preprocessing of the FPGA and the high-speed reading and writing based on the DDR SDRAM data cache, the high-efficiency performance of double DSP core parallel calculation can effectively finish the tasks of image compensation and restoration.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

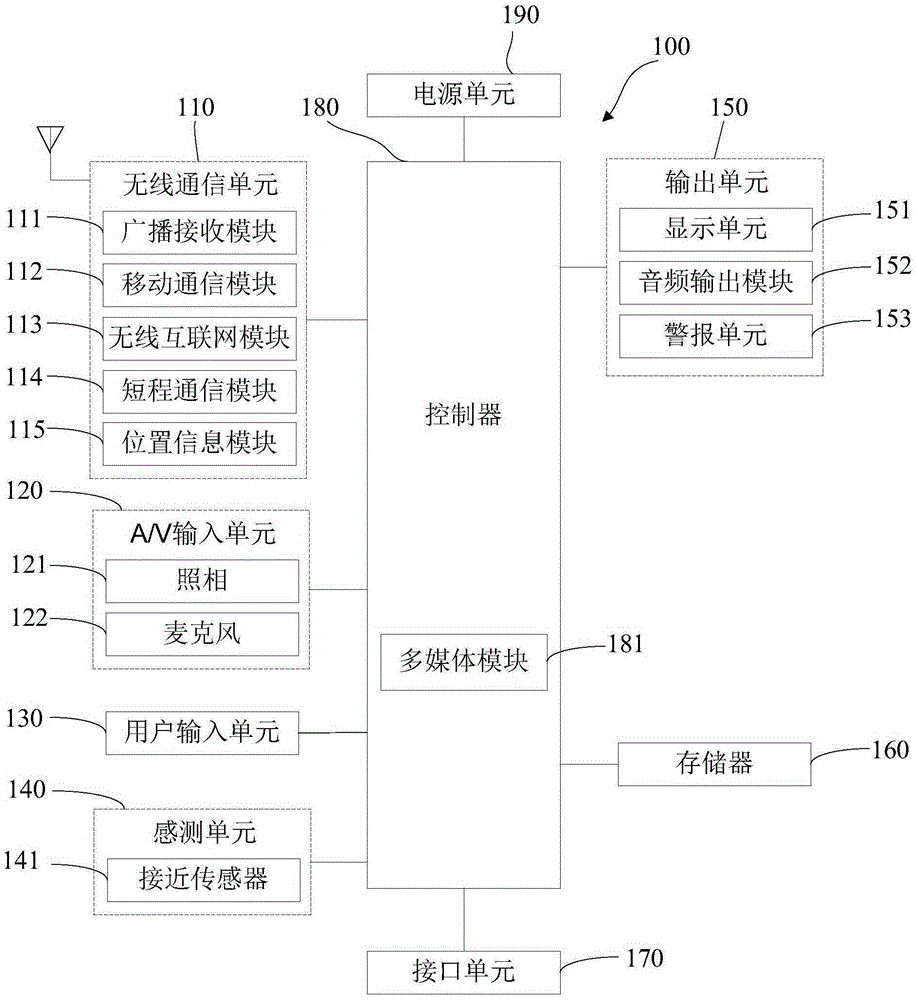

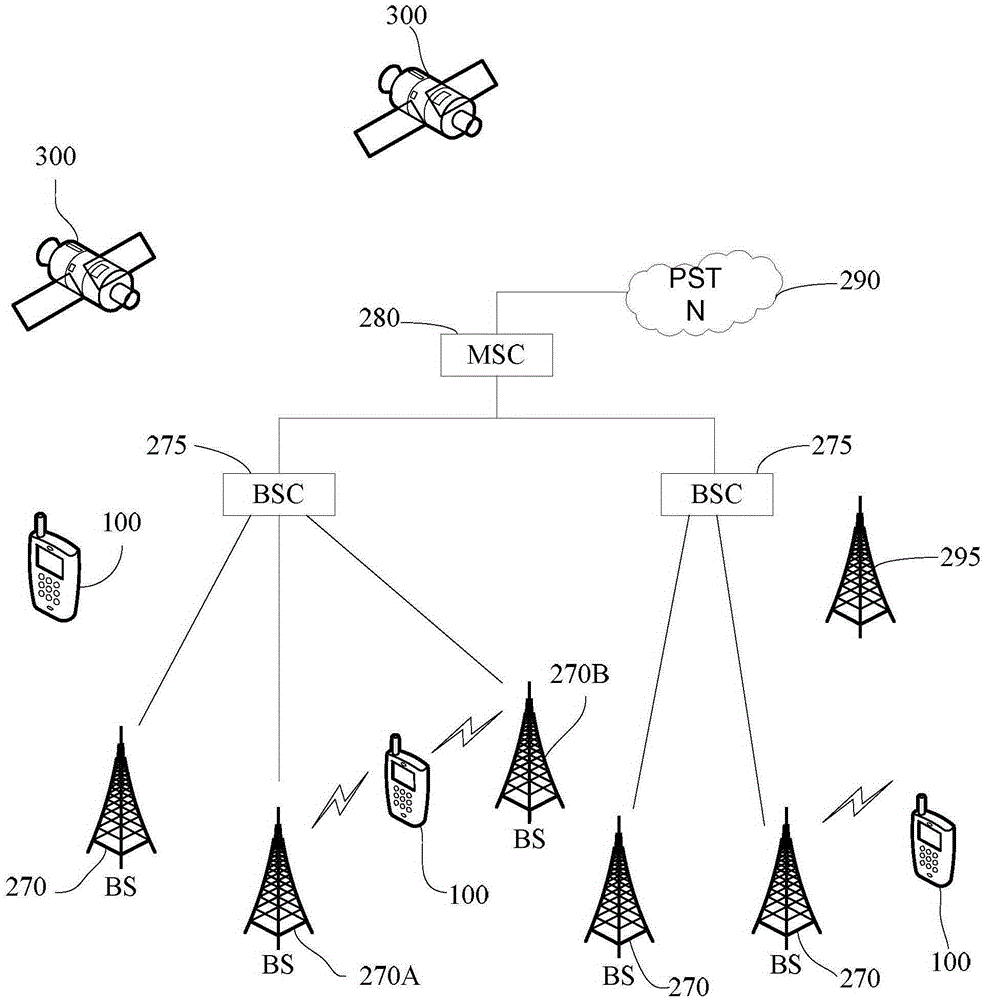

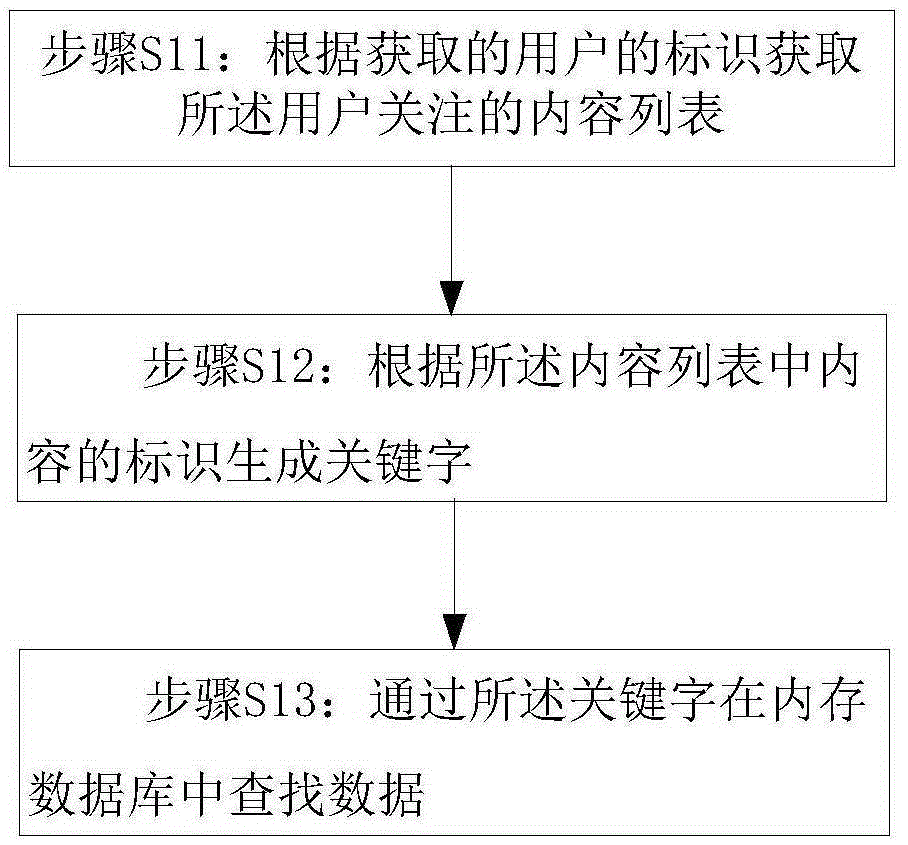

Data searching method, data saving method and related equipment

ActiveCN105260475AImprove query speedGuaranteed query speedRelational databasesSpecial data processing applicationsIn-memory databaseSpeed reading

The invention provides a data searching method, a data saving method and related equipment. The method comprises the following steps: obtaining a content list concerted by a user according to an obtained identity of the user; generating key words according to contents in the obtained content list; searching for data in a memory database according to the key words, wherein each key word corresponds to a doubly liked table in the memory database. According to the technical scheme, the high-speed reading and writing features of the Redis memory database are utilized for assisting in RDBMS searching, so that the searching speed is greatly improved, and the high searching speed can still be guaranteed when the data volume is high; meanwhile, the Redis memory database is updated timely according to newly-added contents, so as to further guarantee the data searching speed and validity.

Owner:NUBIA TECHNOLOGY CO LTD

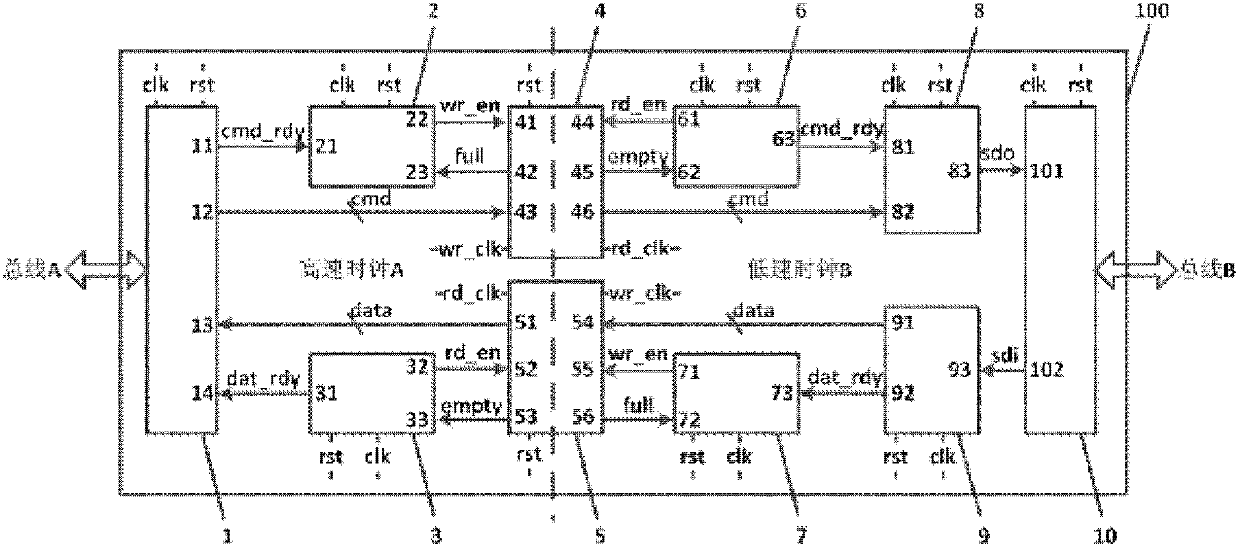

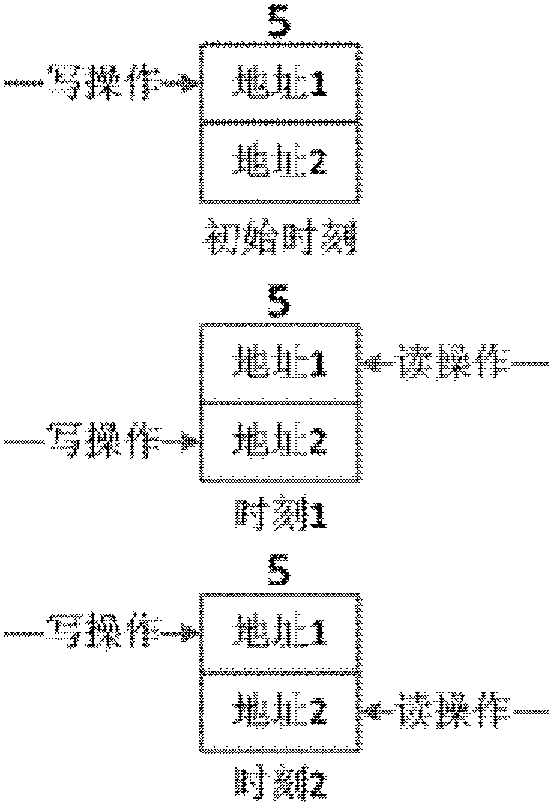

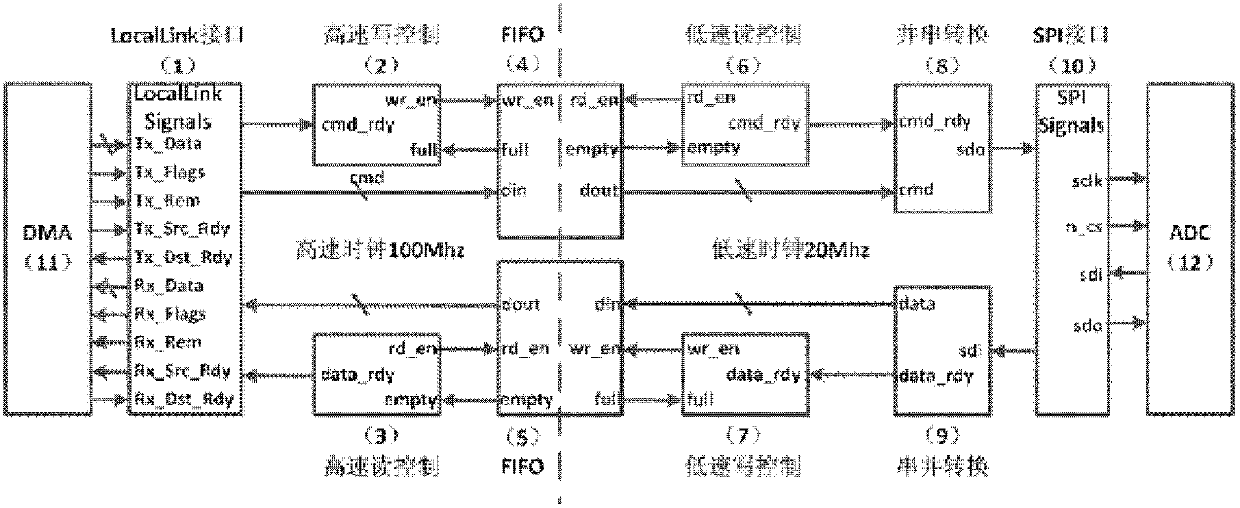

High-speed interface and low-speed interface switching circuit and method based on FPGA (Field Programmable Gate Array)

The invention provides a high-speed interface and low-speed interface switching circuit and method based on an FPGA (Field Programmable Gate Array). The high-speed interface and low-speed interface switching circuit based on the FPGA comprises a high-speed parallel interface module, a high-speed writing control module, a high-speed reading control module, a first data caching FIFO (First In First Out) reading-writing module, a second data caching FIFO reading-writing module, a low-speed reading control module, a low-speed writing control module, a parallel-series switching module, a series-parallel switching module and a low-speed serial interface module. According to the high-speed interface and low-speed interface switching circuit and method based on the FPGA disclosed by the invention, the problem that data rates and interface protocols of a high-speed parallel interface and a low-speed serial interface are not matched in an embedded system can be solved, and meanwhile, full-duplex communication can be realized; and when an Xilinx Virtex-5 series FPGA is adopted, occupied logic resources are few and system integration is easy to realize.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

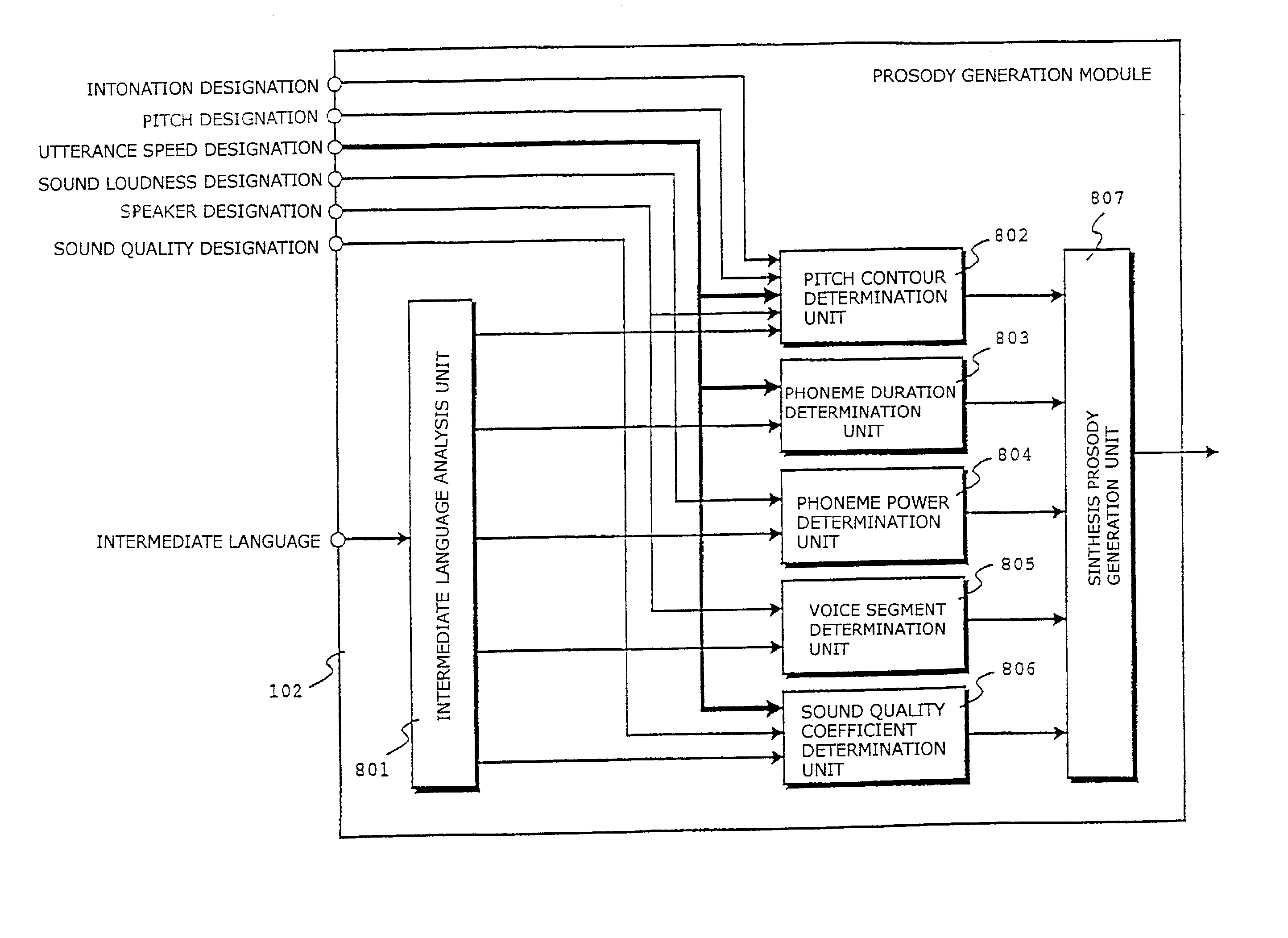

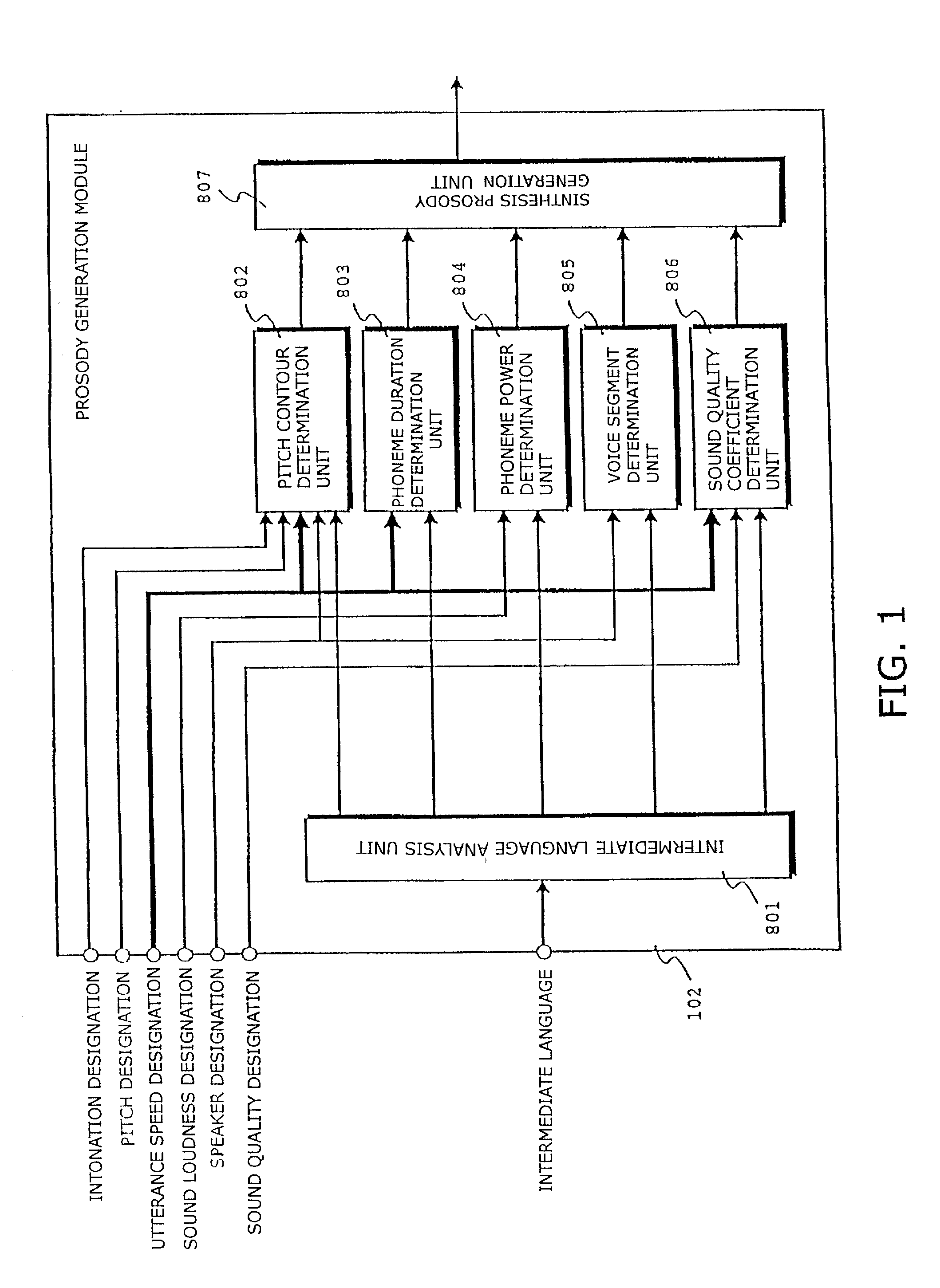

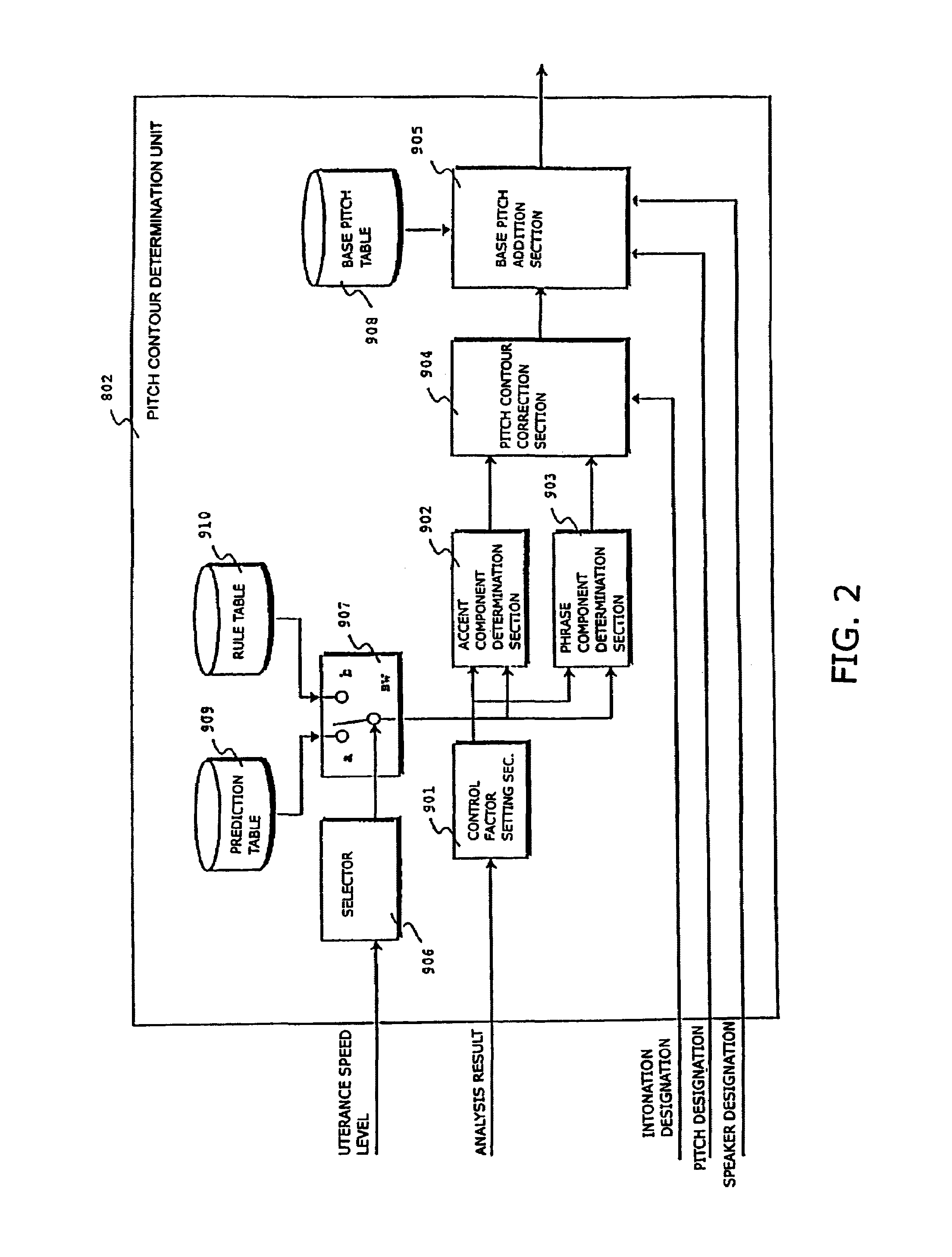

Method of controlling high-speed reading in a text-to-speech conversion system

A method of high-speed reading in a text-to-speech conversion system including a text analysis module (101) for generating a phoneme and prosody character string from an input text; a prosody generation module (102) for generating a synthesis parameter of at least a voice segment, a phoneme duration, and a fundamental frequency for the phoneme and prosody character string; and a speech generation module (103) for generating a synthetic waveform by waveform superimposition by referring to a voice segment dictionary (105). The prosody generation module is provided with both a duration rule table containing empirically found phoneme durations and a duration prediction table containing phoneme durations predicted by statistical analysis and, when the user-designated utterance speed exceeds a threshold, uses the duration rule table and, when the threshold is not exceeded, uses the duration prediction table to determined the phoneme duration.

Owner:LAPIS SEMICON CO LTD

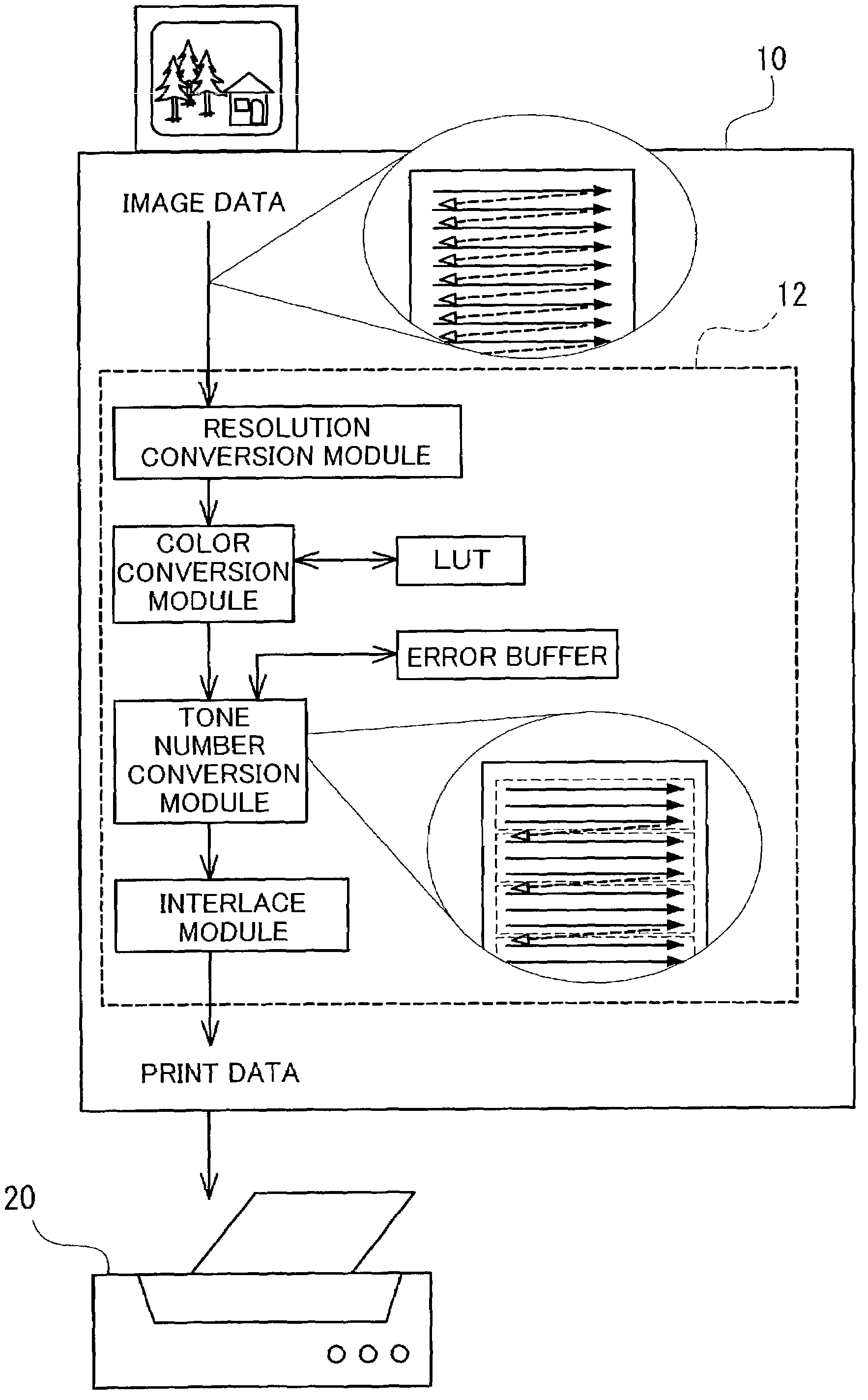

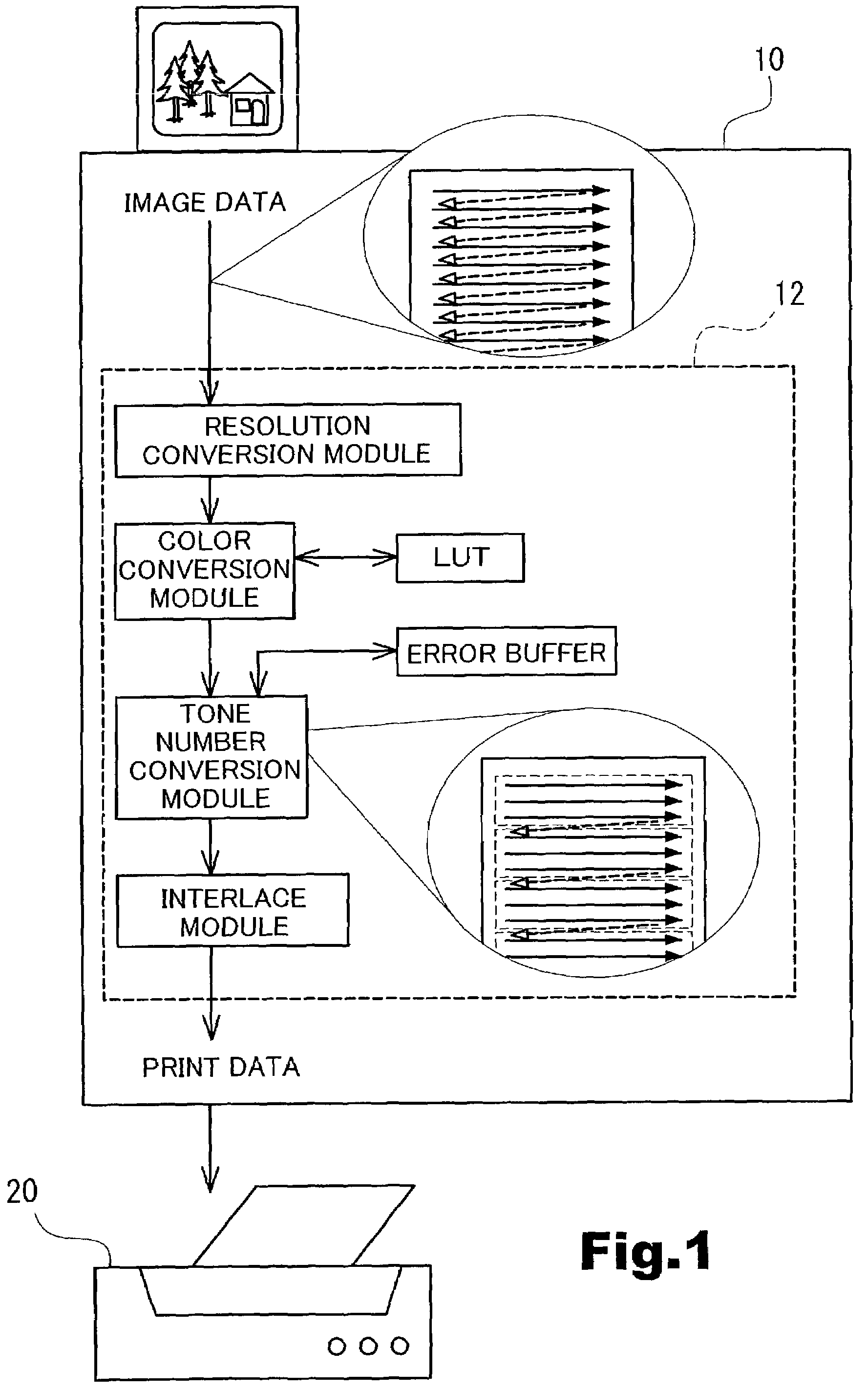

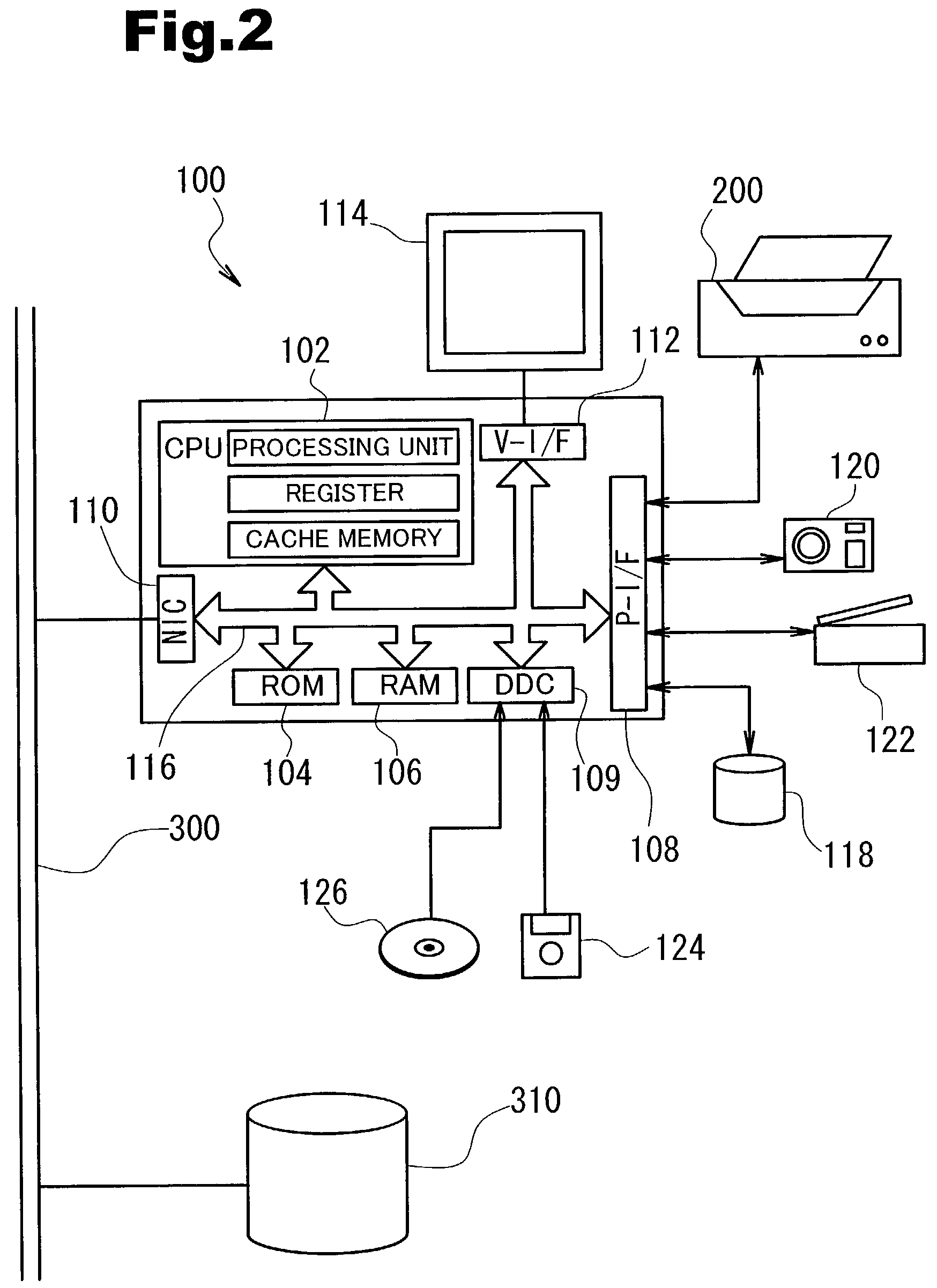

Image processing device, printing control device, image processing method, and recorded medium

ActiveUS7196821B2Reduce processing timeMany errorImage enhancementDigitally marking record carriersGratingImaging processing

When image data is converted into an expression format based on the dot on-off state, such conversion is performed in a unit of a raster group comprising a predetermined number of adjacent rasters. When this is done, the binarization errors occurring in each pixel of the last raster located in the last position of such raster group are diffused into surrounding pixels and stored in a first storage unit. The errors are read out from the first storage unit for dot on-off state determination regarding the first raster of the raster group adjacent to the above-mentioned last raster, and binarization errors occurring in connection with this determination are stored in a second storage unit that permits faster reading and writing of data than the first storage unit. The remaining rasters following the first raster are converted into dot rows by conducting dot on-off state determination for each pixel therein in parallel with the process to convert the first raster into a dot row while taking into account the binarization errors that occurred in the first raster. Consequently, the errors that are taken into account by the pixels of the same raster are stored in the second storage unit that permits faster high-speed reading and writing of data, and the image data for the raster group can be converted at a high speed.

Owner:SEIKO EPSON CORP

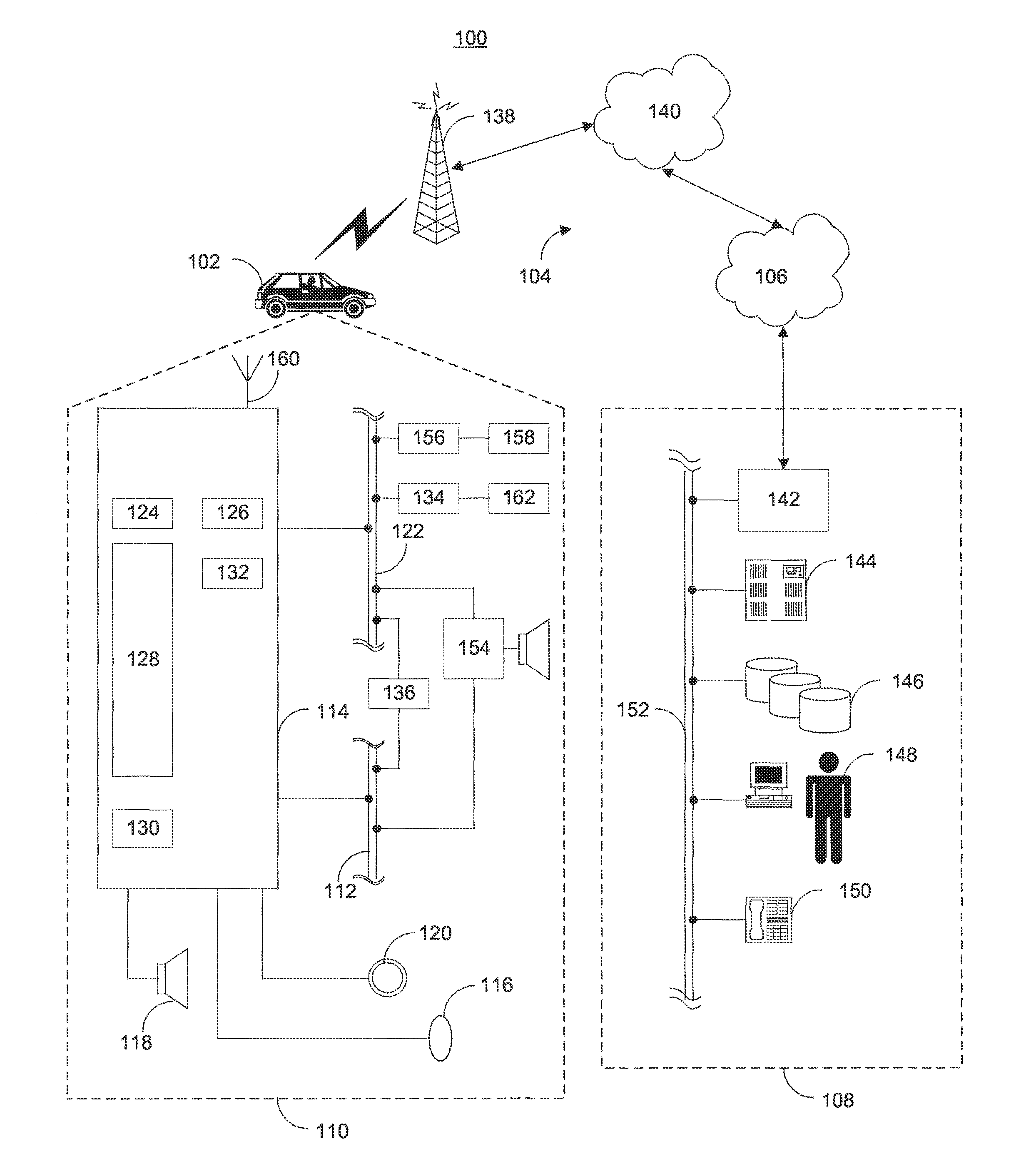

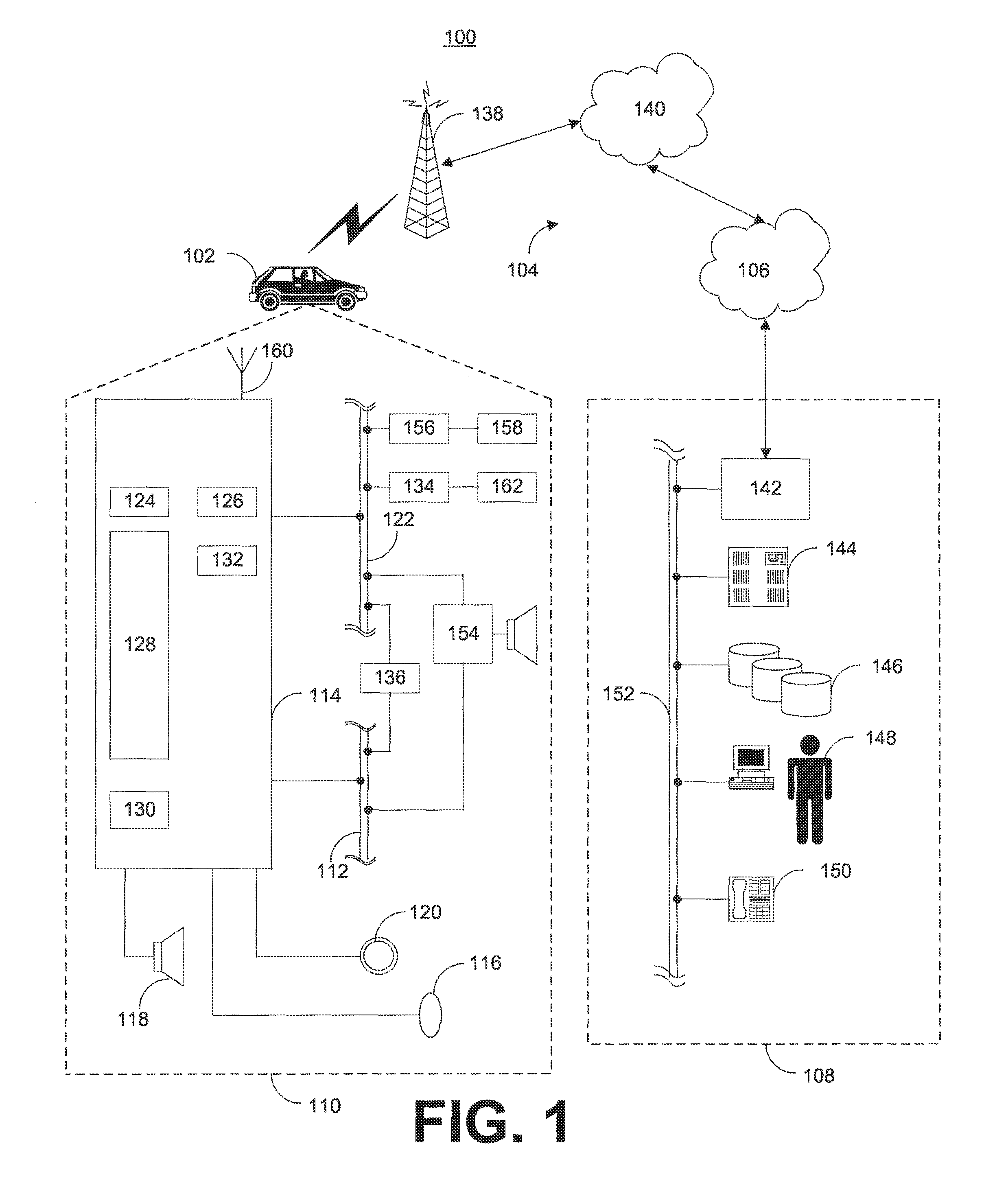

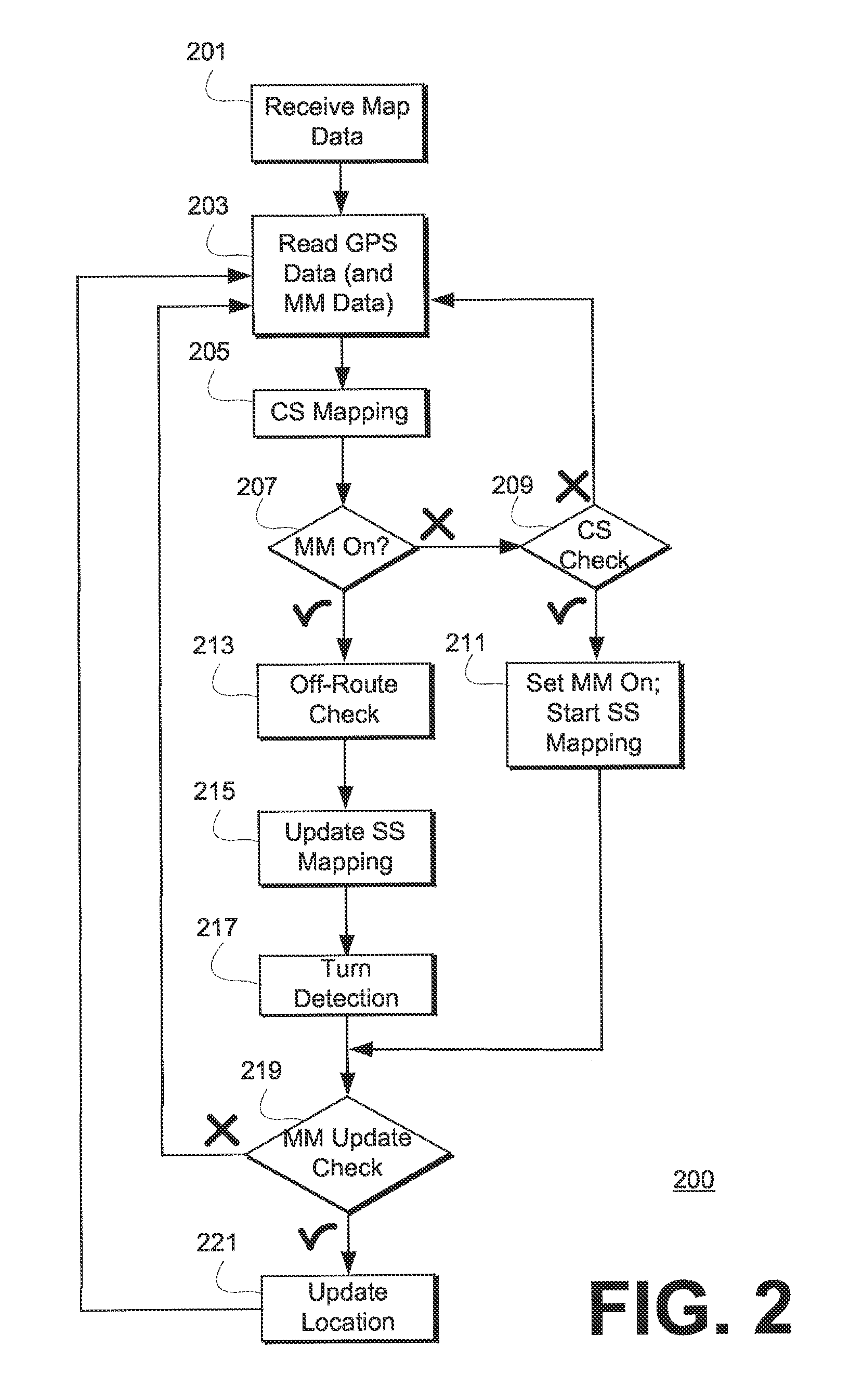

Estimation of Vehicle Location

InactiveUS20130197795A1Instruments for road network navigationRoad vehicles traffic controlSpeed readingTelematics

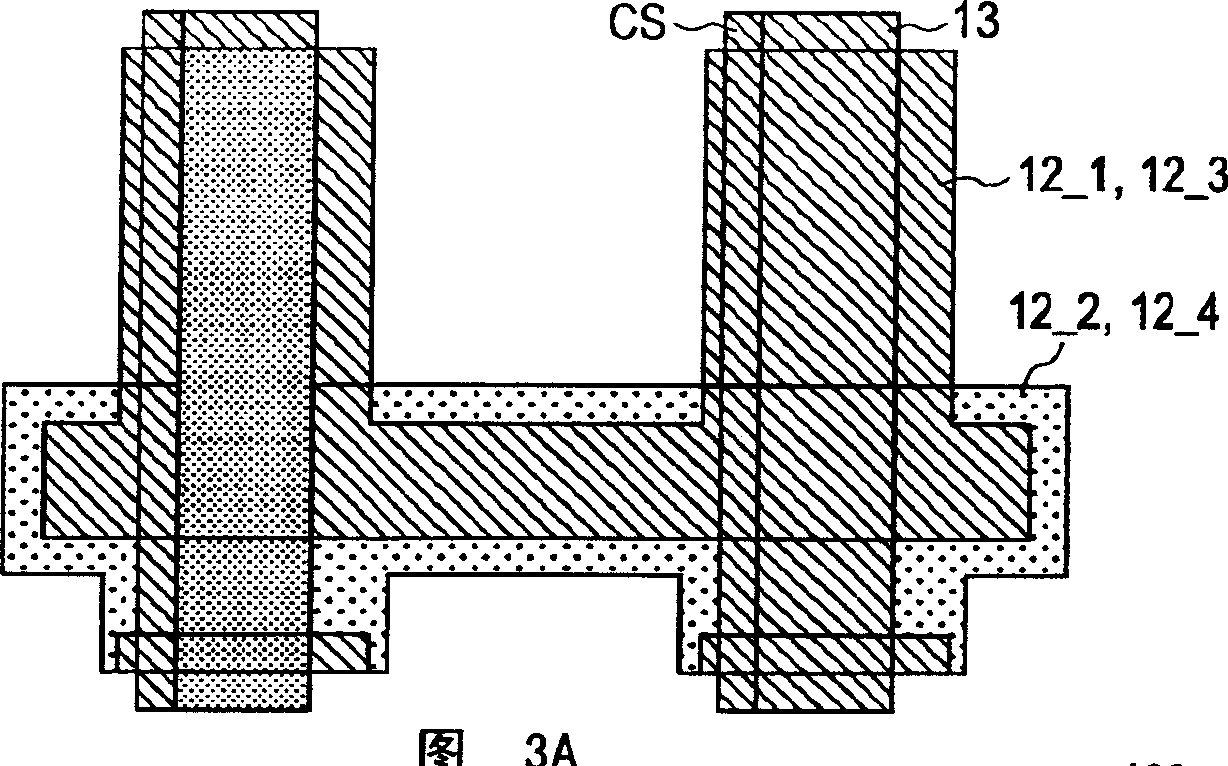

A method for estimating the position of a telematics-equipped vehicle during navigation includes: receiving a partial map corresponding to a route; receiving Global Positioning System (GPS) data corresponding to a current position of the vehicle; performing a closest street (CS) mapping based on the GPS data and the partial map so as to provide an estimation for a vehicle position on a street of the partial map; performing speed sum (SS) mapping based on the estimated vehicle position and speed readings corresponding to vehicle speed so as to provide an estimation of distance traveled with reference to a previous vehicle position; and presenting a map matched vehicle position to a user based on the CS mapping and the SS mapping.

Owner:GENERA MOTORS LLC

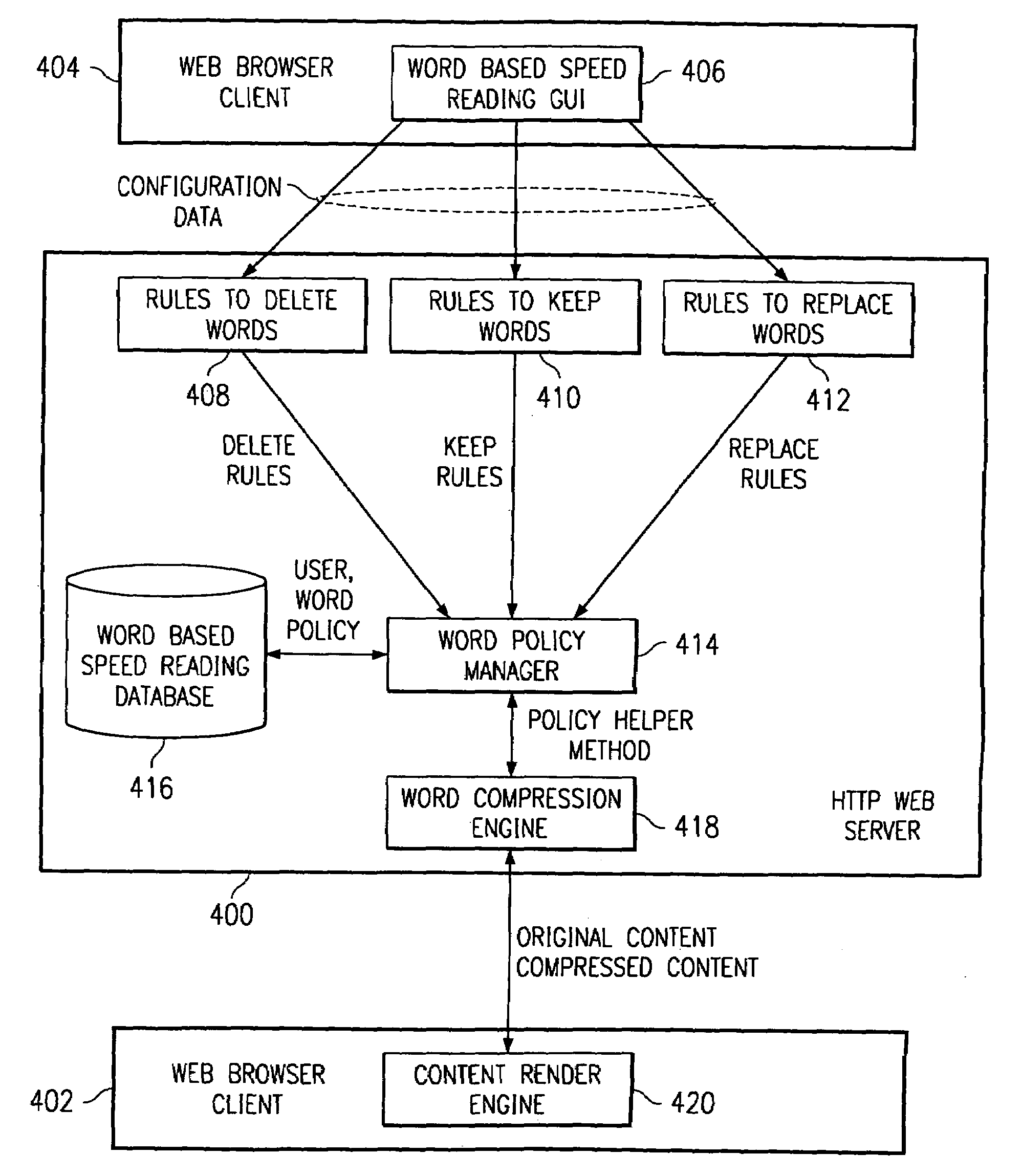

Method and apparatus in a data processing system for word based render browser for skimming or speed reading web pages

InactiveUS7207003B1Increase speedDigital data information retrievalBiological modelsData processing systemWeb page

A method and apparatus in a data processing system for modifying content of a document. A request is received for modified content. The document is compressed using a set of rules, wherein selected content in the document is removed to increase a speed at which a user can read the document.

Owner:IBM CORP

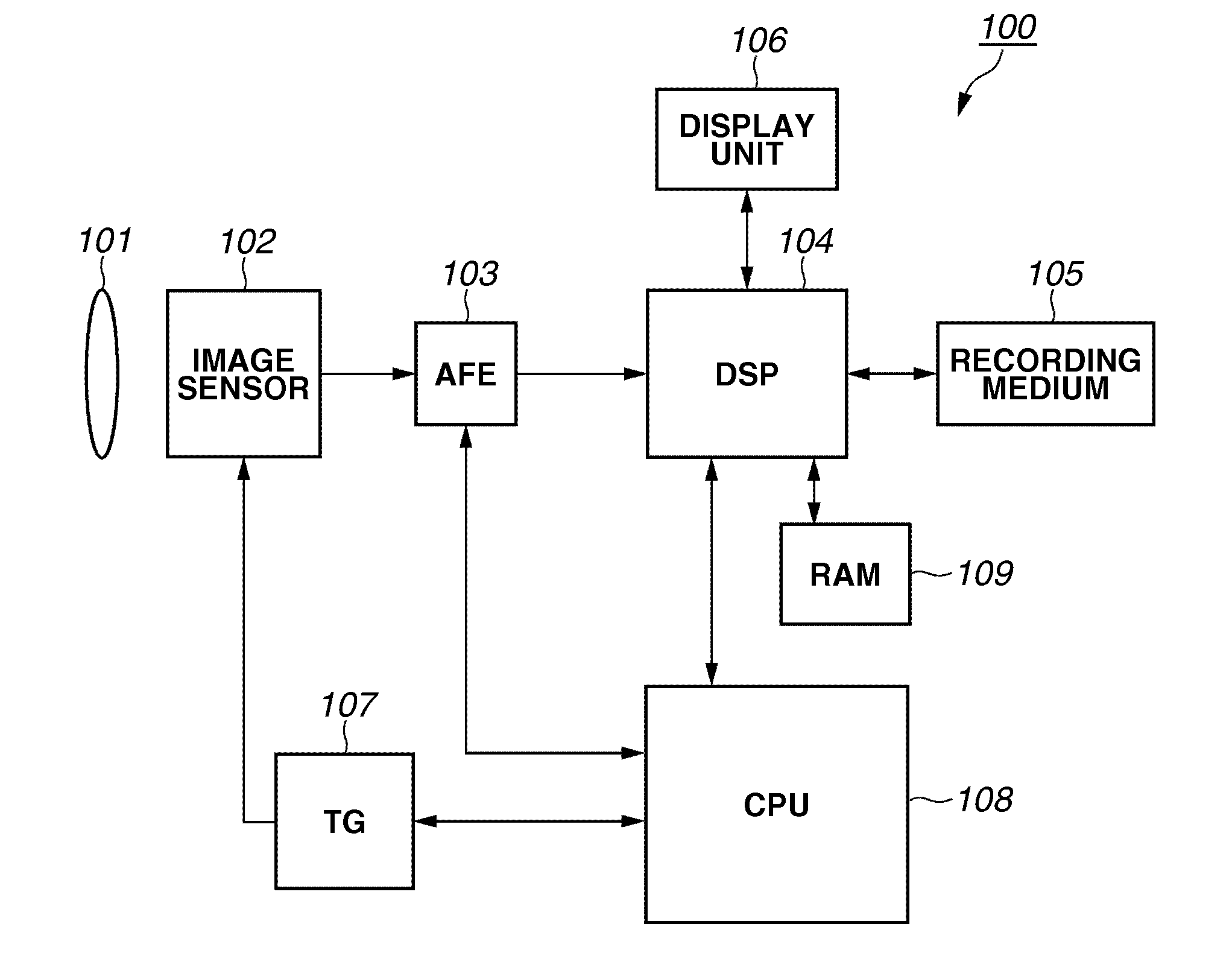

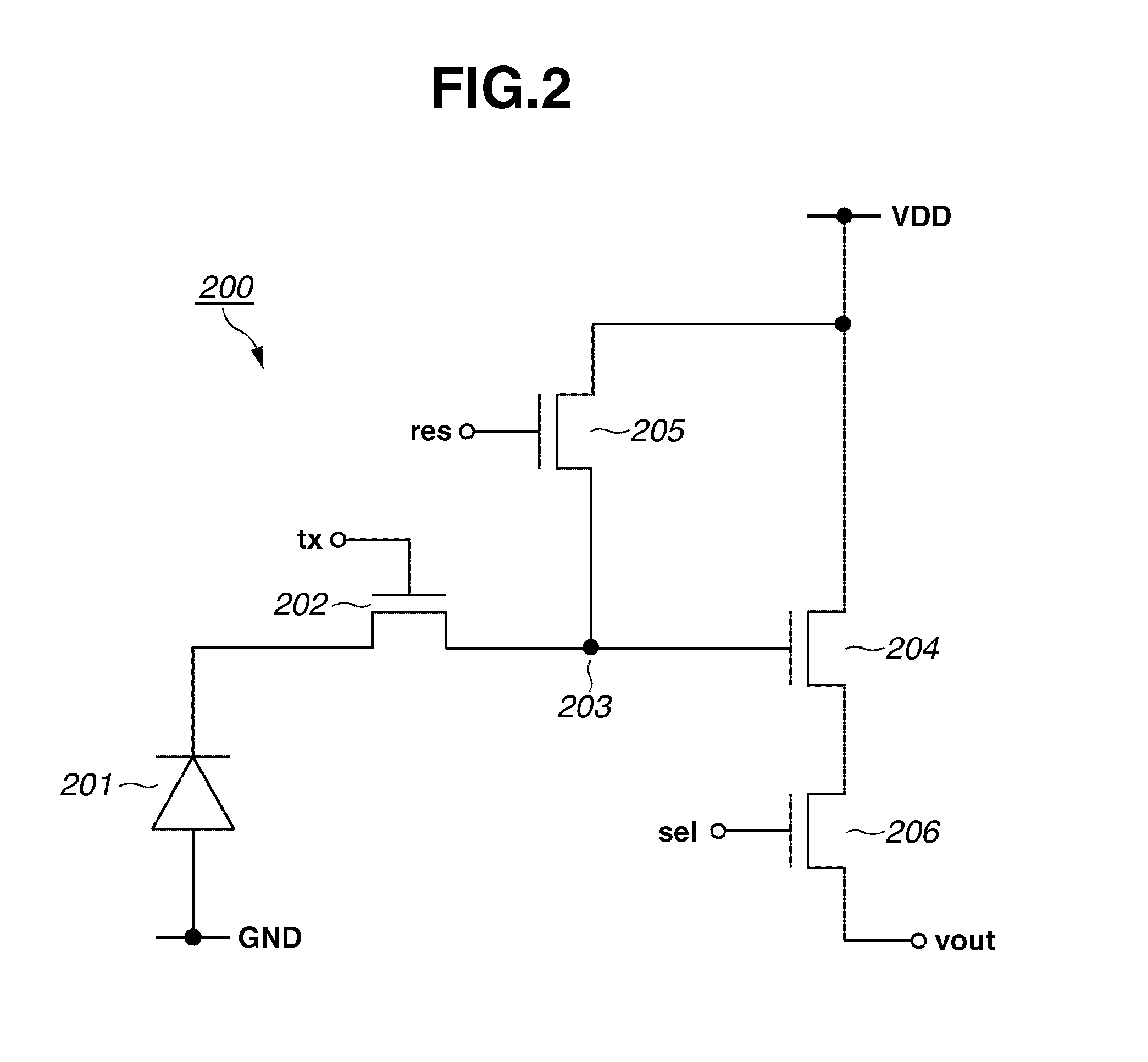

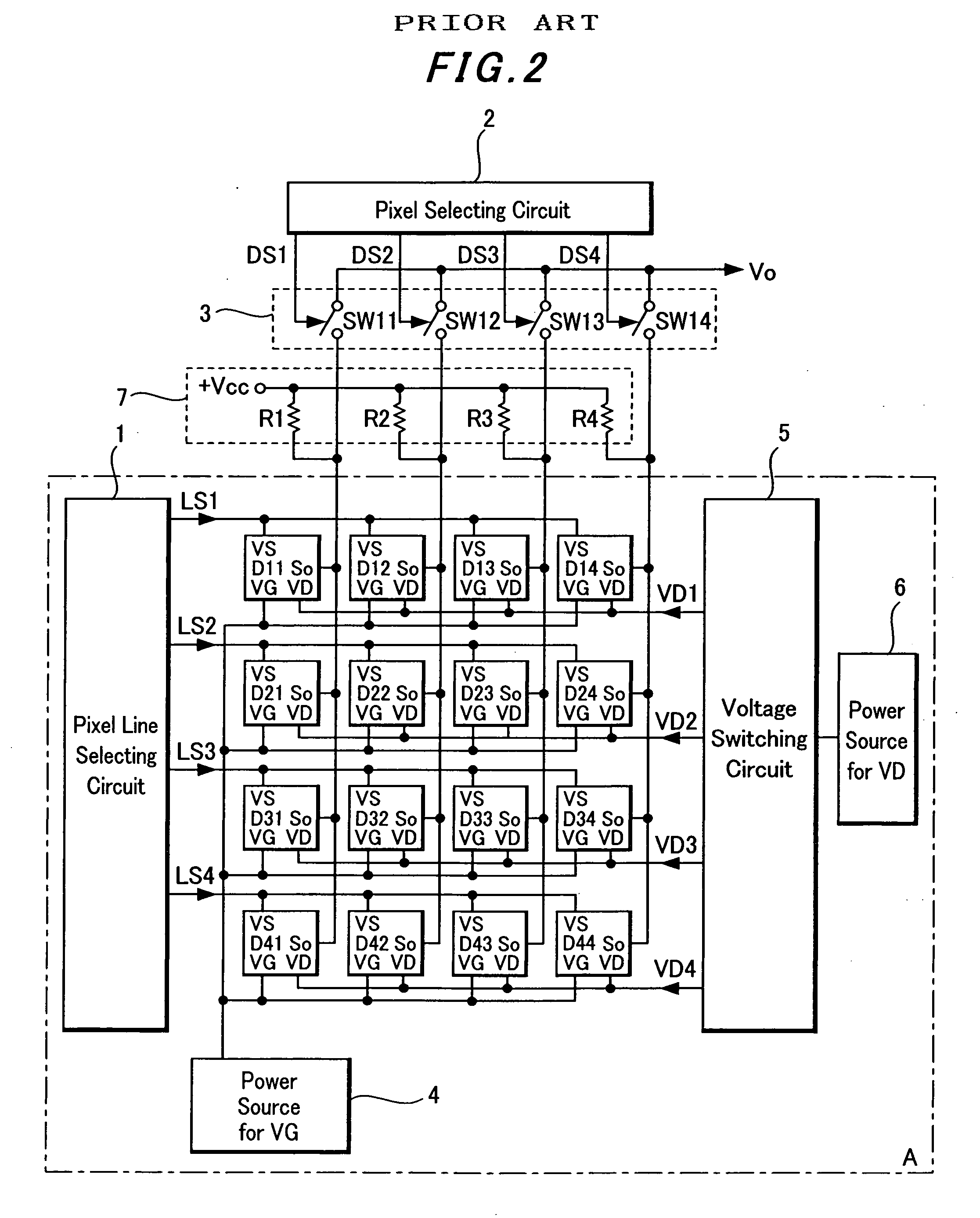

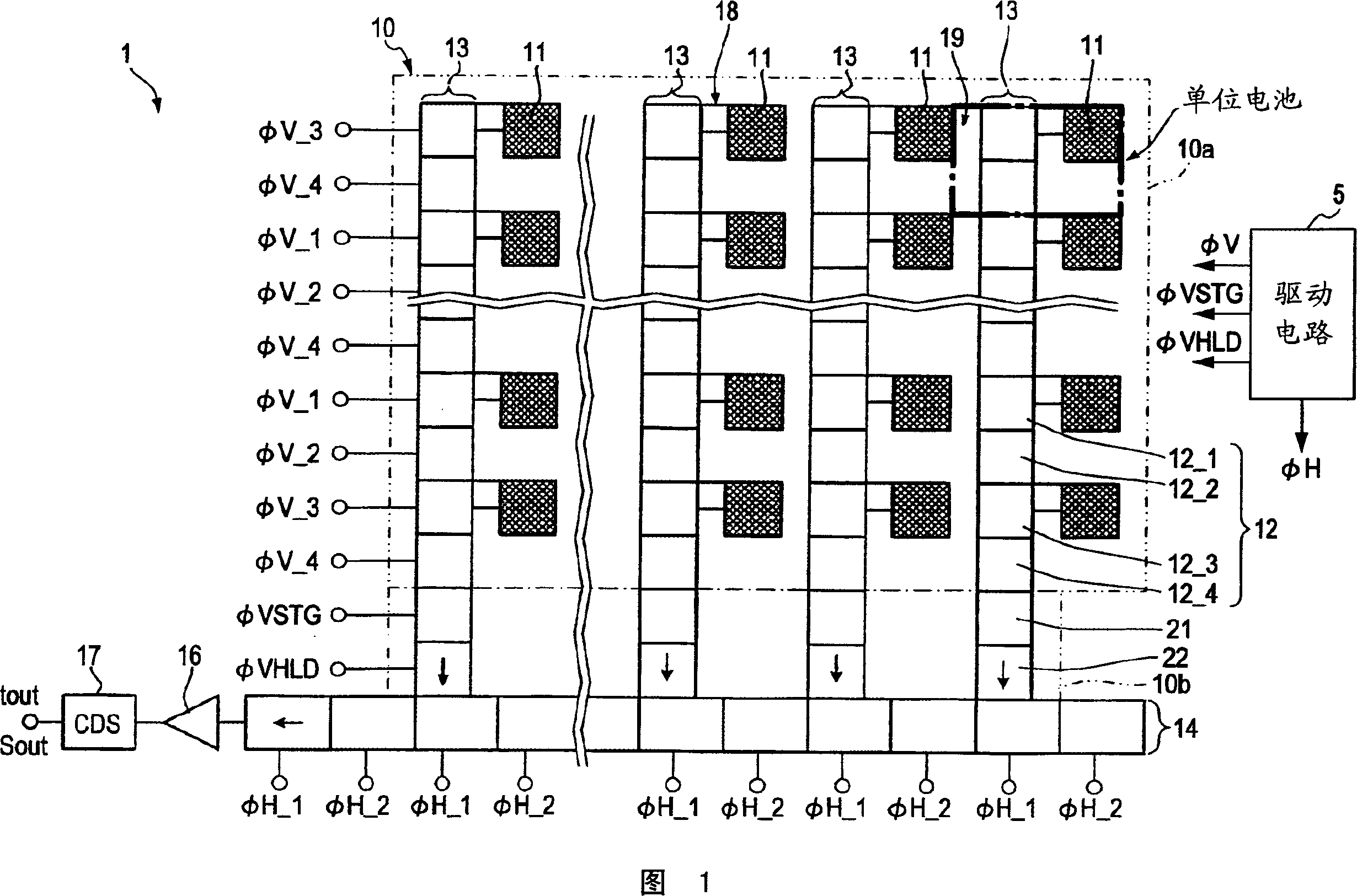

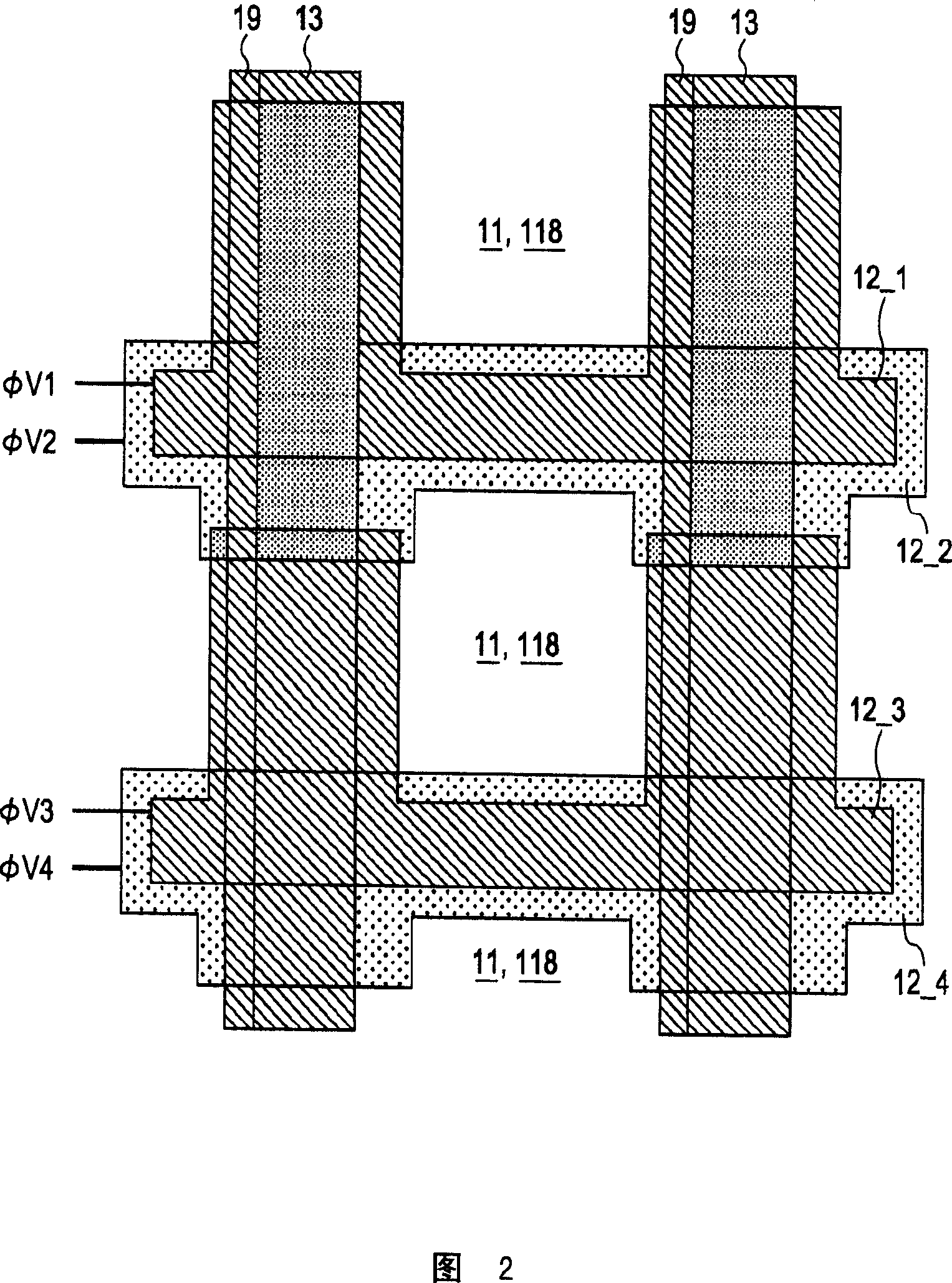

Solid-state image sensor, driving method thereof, and imaging apparatus

InactiveUS20110193983A1Preventing Image Quality DeteriorationHigh continuous-shooting speedTelevision system detailsTelevision system scanning detailsCapacitanceImaging quality

In an imaging mode for reading a part of a plurality of pixels, signals of same color adjacent pixels are simultaneously read out to capacities, and at least two capacities in a same pixel row are once short-circuited. Further, capacities of a plurality of the pixel rows are once short-circuited to perform operation for averaging the pixels in vertical and horizontal directions. With the configuration, it is possible to solve deterioration in image quality due to occurrence of moire caused by reduction in sampling frequency in a thinning reading operation mode capable of high-speed reading.

Owner:CANON KK

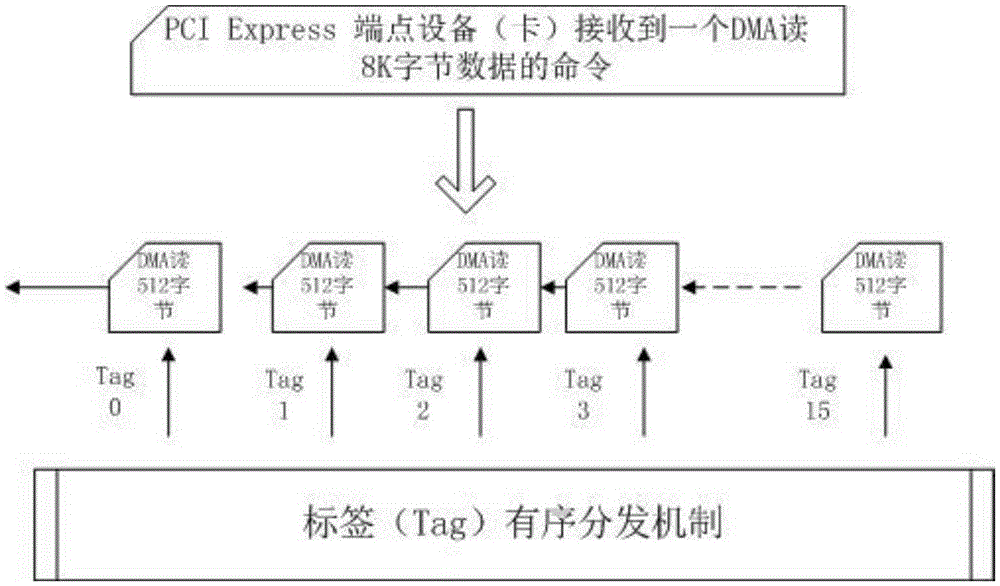

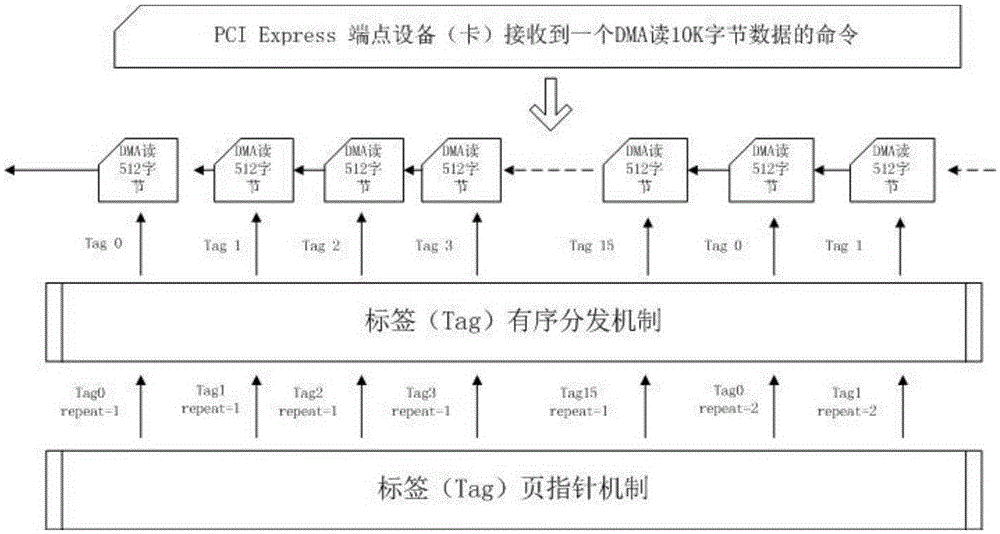

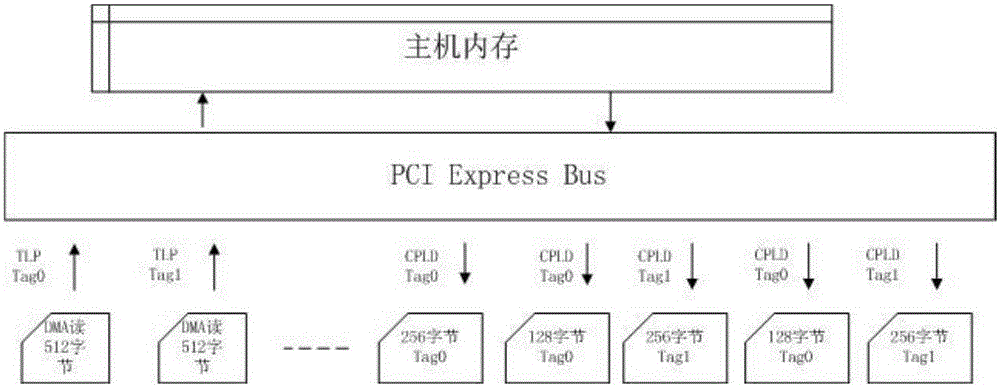

Method and system for orderly storing CPLD data packets

ActiveCN105260332AImprove throughputElectric digital data processingDirect memory accessNetwork packet

The invention relates to a method and system for orderly storing CPLD (Completion Data) data packets. The method comprises the following steps of segmenting DMA (Direct Memory Access) reading requests sent by PCI (Peripheral Component Interconnect) Express endpoint equipment to a host memory into a plurality of sub DMA reading requests with continuous labels by using a label order issuing system, and sending the plurality of sub DMA reading requests to a host; receiving CPLD data packets returned by the host, and determining storage base addresses of the CPLD data packets in the PCI Express endpoint equipment according to labels of the CPLD data packets; performing offset address calculation on the CPLD data packets with same labels, and determining offset addresses of the CPLD data packets; and storing the corresponding CPLD data packets according to the determined offset addresses and the base addresses of the CPLD data packets in the PCI Express endpoint equipment. The method and the system have the advantages that the label order issuing system is built; the large-data-volume DMA reading operation is realized; a base address and offset address calculation system is built; the high-speed reading scheme of the PCI Express endpoint equipment and the efficient high-speed and undelayed storage scheme of CPLD data in an RAM (Random Access Memory) are realized; and the data throughput rate is greatly improved.

Owner:BEIJING SANSEC TECH DEV

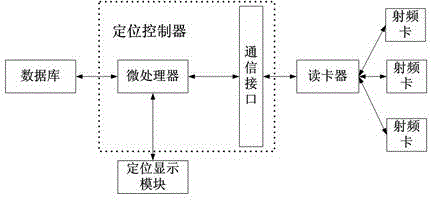

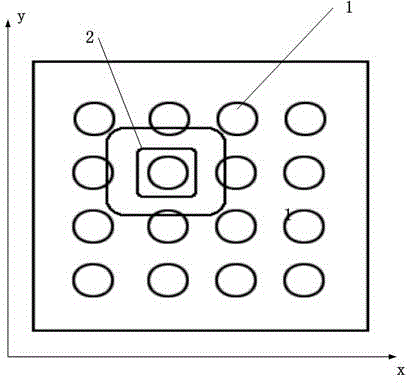

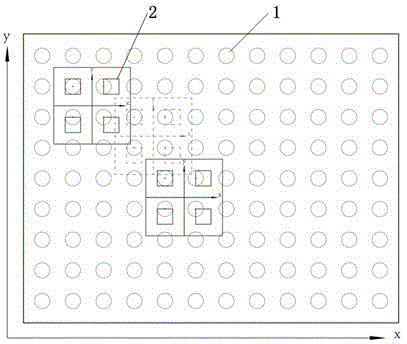

Autonomous and accurate positioning system of mobile robot based on RFID(Radio Frequency Identification) and method thereof

InactiveCN105865437AAchieve precise positioningOvercome dependenceCharacter and pattern recognitionNavigation instrumentsCommunication interfaceCard reader

The invention discloses an autonomous and accurate positioning system of a mobile robot based on RFID(Radio Frequency Identification). The autonomous and accurate positioning system comprises a positioning controller arranged on the mobile robot, a radio-frequency card reader arranged at the bottom of the mobile robot, and a radio-frequency card spread below the preset movement area ground of the mobile robot, wherein, the positioning controller is composed of a microprocessor and a communication interface, the microprocessor is connected with the radio-frequency card reader, the microprocessor controls the radio-frequency card reader through the communication interface for reading data of the radio-frequency card; the microprocessor is connected with a data base, the data base comprises a digital map, the digital map comprises a laying coordinate information corresponding to the radio-frequency card number for position matching of the radio-frequency card data by the card reader; the system also comprises a position display module, the position display module is connected to the microprocessor for real-time displaying the position of the mobile robot in the digital map. The invention provides the positioning system based on a radio frequency identification technology with high speed reading, omnibearing reading and accurate positioning.

Owner:QINGDAO TONGCHAN SOFTWARE TECH

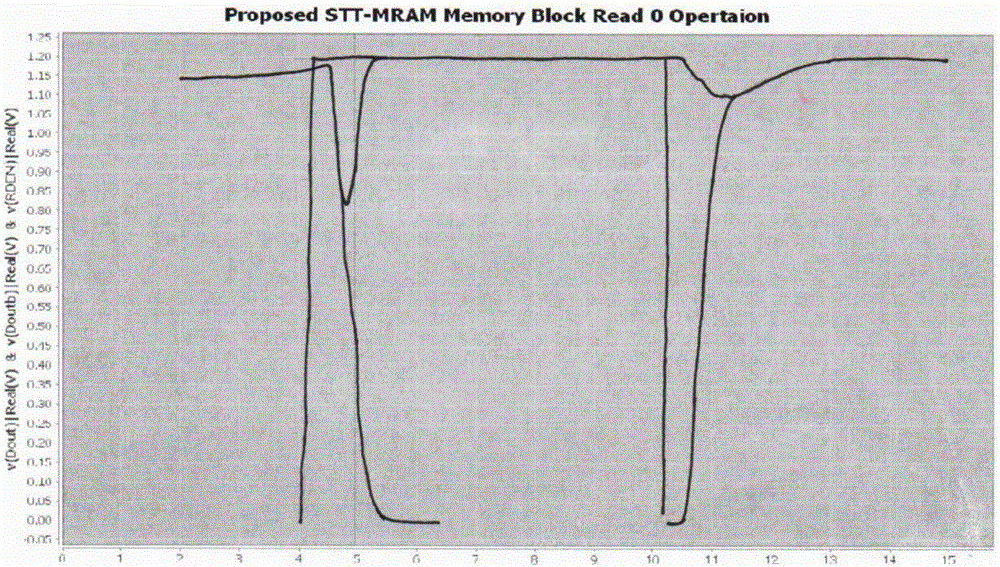

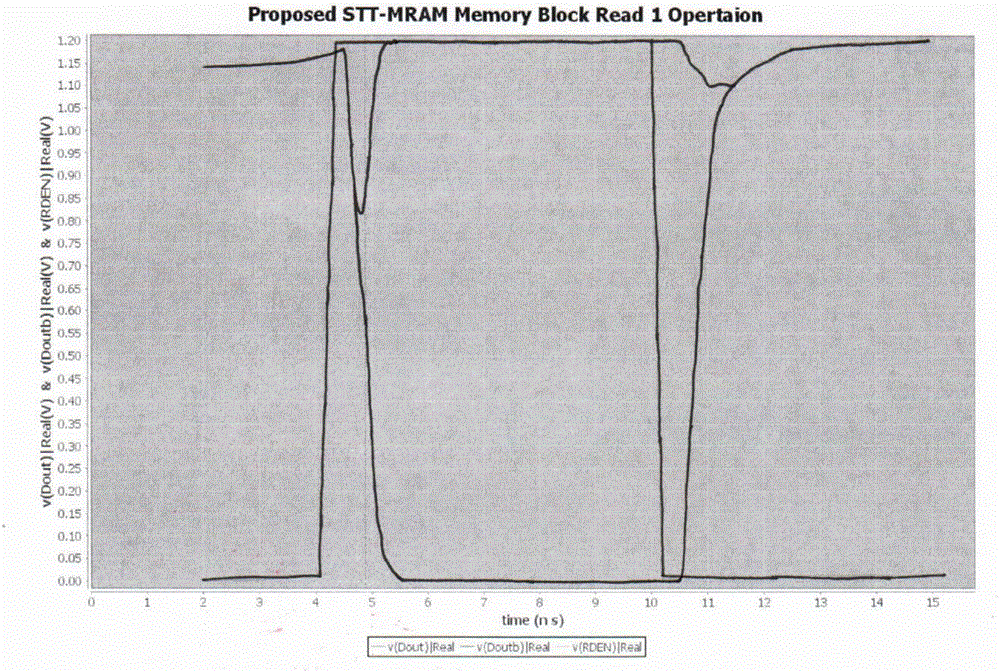

Signal amplifier, reading circuit of magnetic memory and operation method of magnetic memory

The invention provides a signal amplifier, a reading circuit of a magnetic memory and an operation method of the magnetic memory. A magnetic memory module comprises a plurality of magnetic storage units, a plurality of bit lines, a plurality of word lines, a plurality of reference storage units, at least one reference line and at least one high-speed reading and sensing amplifier. When reading operation is carried out, only one storage unit which is selected by the word lines and the bit lines at the same time provides a data signal; only one reference storage unit which is selected by the same word line provides a reference signal; the signal amplifier comprises logic, amplification and latch circuits; the data signal and the reference signal are inputs of the signal amplifier; the amplifier is a primary amplification and latches a multi-functional circuit; after the signal amplification is finished, output data is automatically latched, so that the amplification signal is reduced and the reading time is shortened; and meanwhile, an amplification finishing output signal is generated to close the corresponding storage module to save the power consumption.

Owner:HUBEI ZHONGBU HUIYI DATA TECH

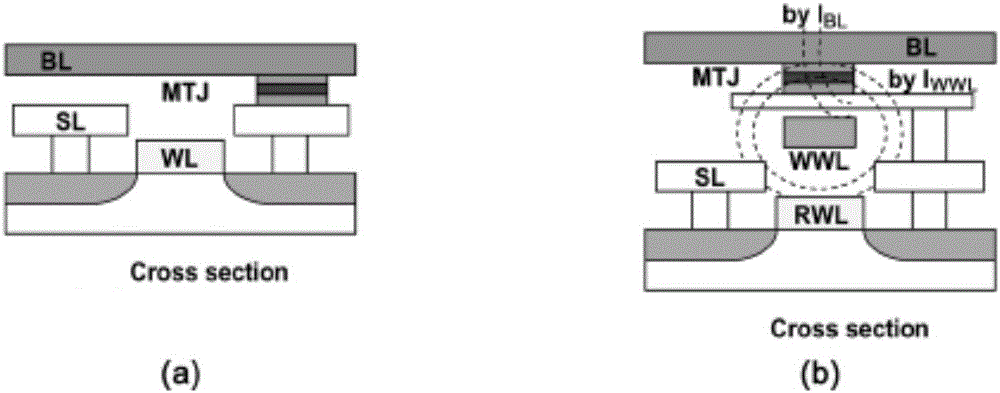

Memory access method and device supporting data persistence

InactiveCN104598615AHigh-speed read and writeAvoid lostSpecial data processing applicationsDatabase indexingAccess methodData access

The invention discloses a memory access method and a device supporting data persistence. The method comprises the following steps of S1, receiving a data request of a client end, judging whether the data request meets a standard protocol or not, if yes, carrying out S2, and if not, rejecting the data request; S2, judging whether the data request is a data reading request or a data writing request, if the data request is the data writing request, carrying out S3, and if the data request is the data reading request, carrying out S4; S3, analyzing the data writing request, building a corresponding data structure according to data to be written, and calling a storage interface to store the data to be written to a data storage end; S4, analyzing the data reading request, and calling the storage interface to acquire corresponding data from the data storage end. Memcached and Berkeleydb are combined to obtain a memory Key-value database system supporting data persistence, and the database system is utilized to carry out data access service, so that high-speed reading and writing of data can be ensured; persistence modules are combined to form a cluster example, so that the storage of the data is more stable.

Owner:广州亦云信息技术股份有限公司

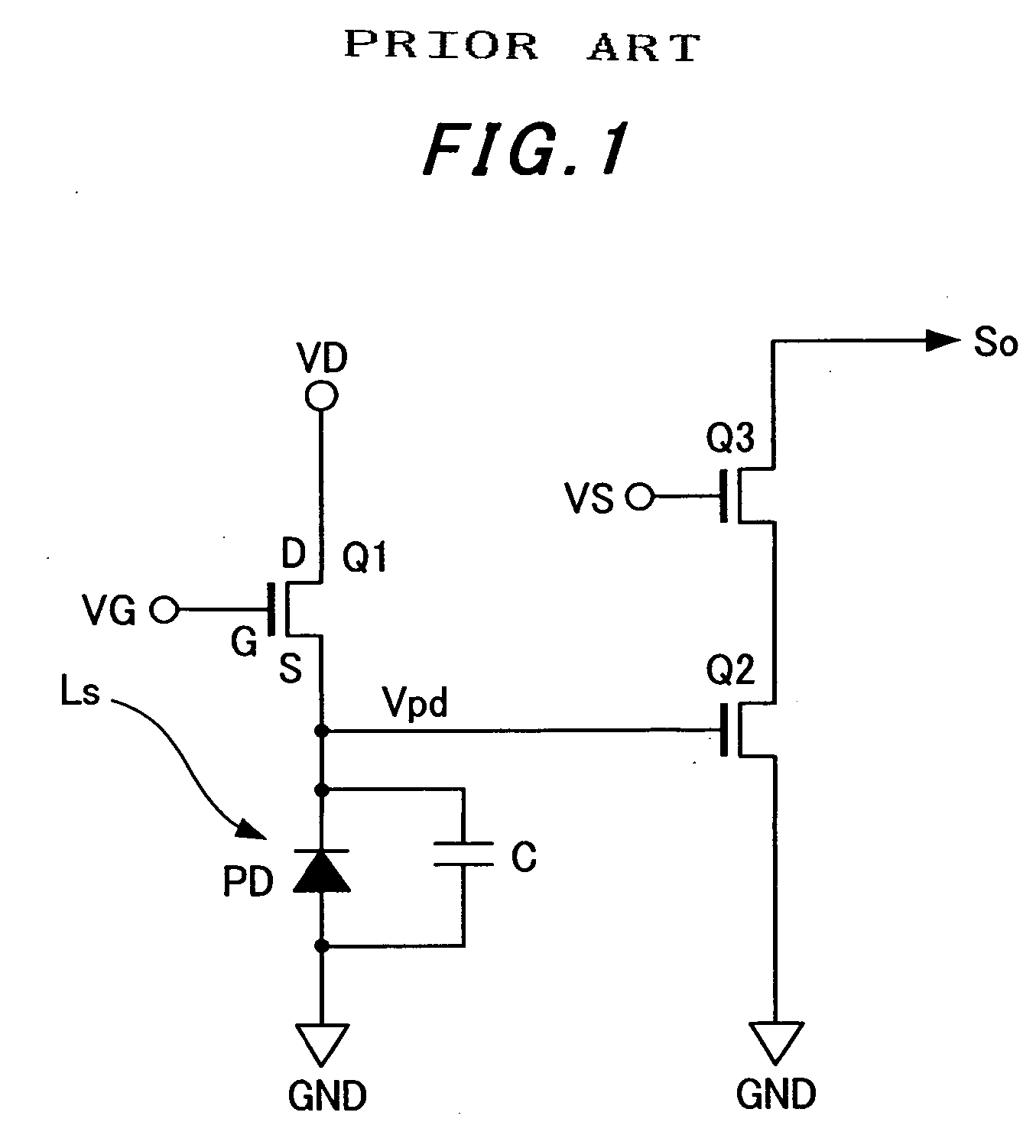

Scanning circuit of image sensor

InactiveUS20060221221A1Stable readingIncrease speedTelevision system detailsTelevision system scanning detailsSpeed readingHigh velocity

Is disclosed a scanning circuit of an image sensor using light sensor circuits each representing a unit pixel and producing a sensor signal corresponding to a current flowing in a photoelectric converting element, which is provided with a means for saturating pixel signals by previously turning on the light sensor circuits and sequentially reading saturated pixel sensor signals, achieving stable and high-speed reading-out of the sensor signals from the image sensor.

Owner:HONDA MOTOR CO LTD

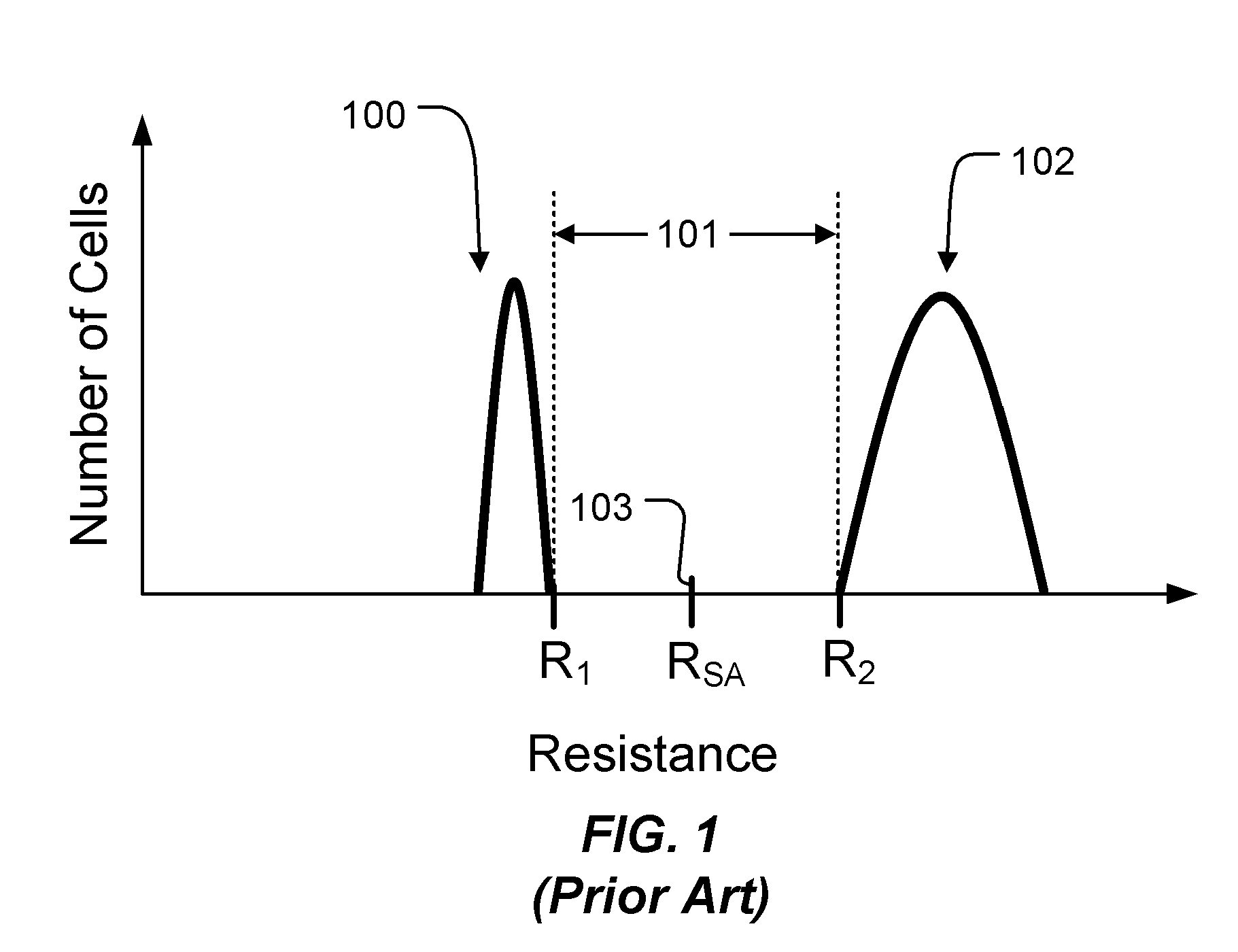

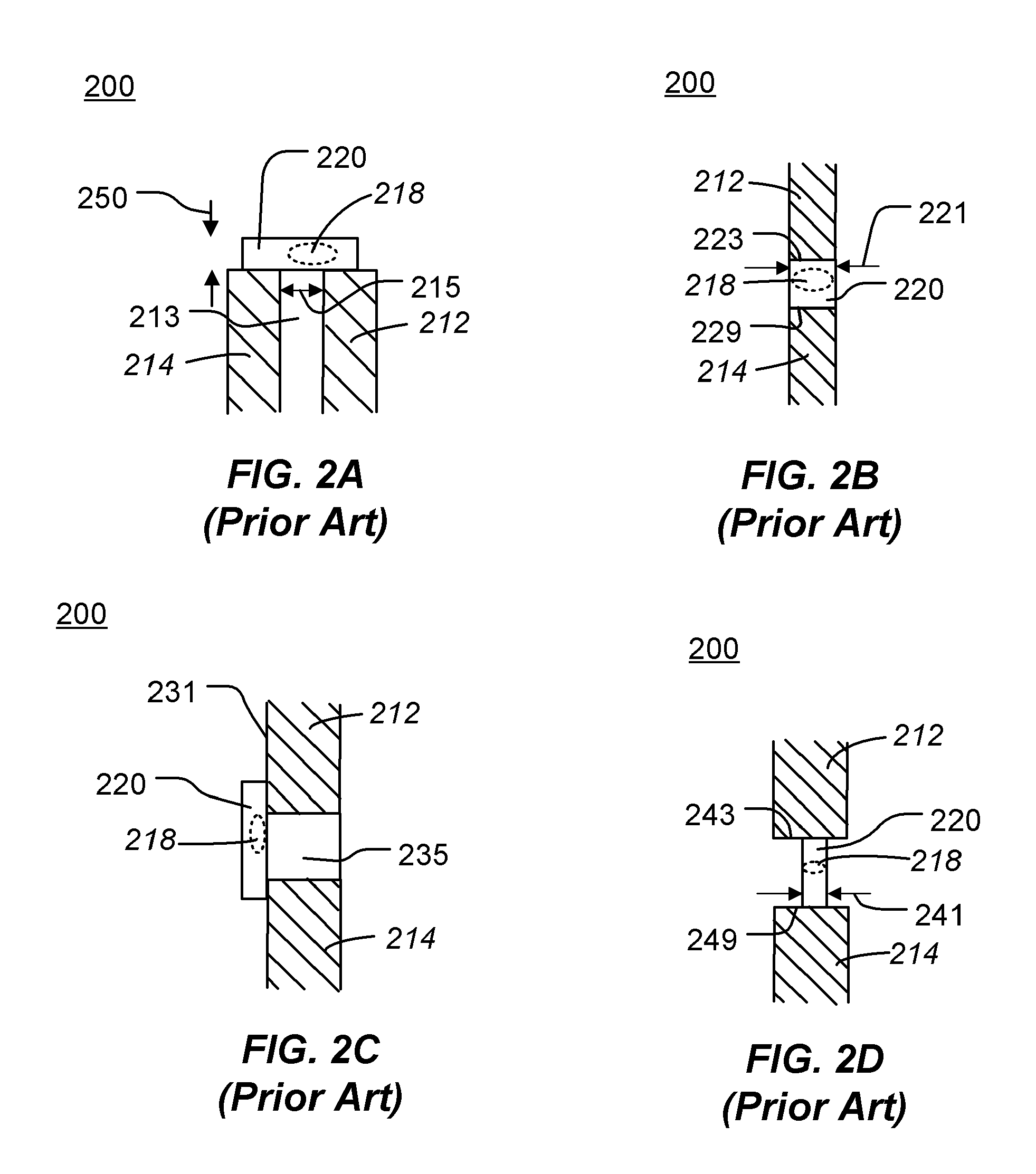

Methods for high speed reading operation of phase change memory and device employing same

ActiveUS20090323409A1Control speedIncrease speedDigital storageBulk negative resistance effect devicesPhase-change memoryOperational approach

Phase change based memory devices and methods for operating described herein overcome the performance limitations of slow set speeds and long recovery times commonly associated with phase change memory devices, enabling high speed operation and extending their usefulness into high speed applications typically filled by DRAM and SRAM memory.

Owner:MACRONIX INT CO LTD

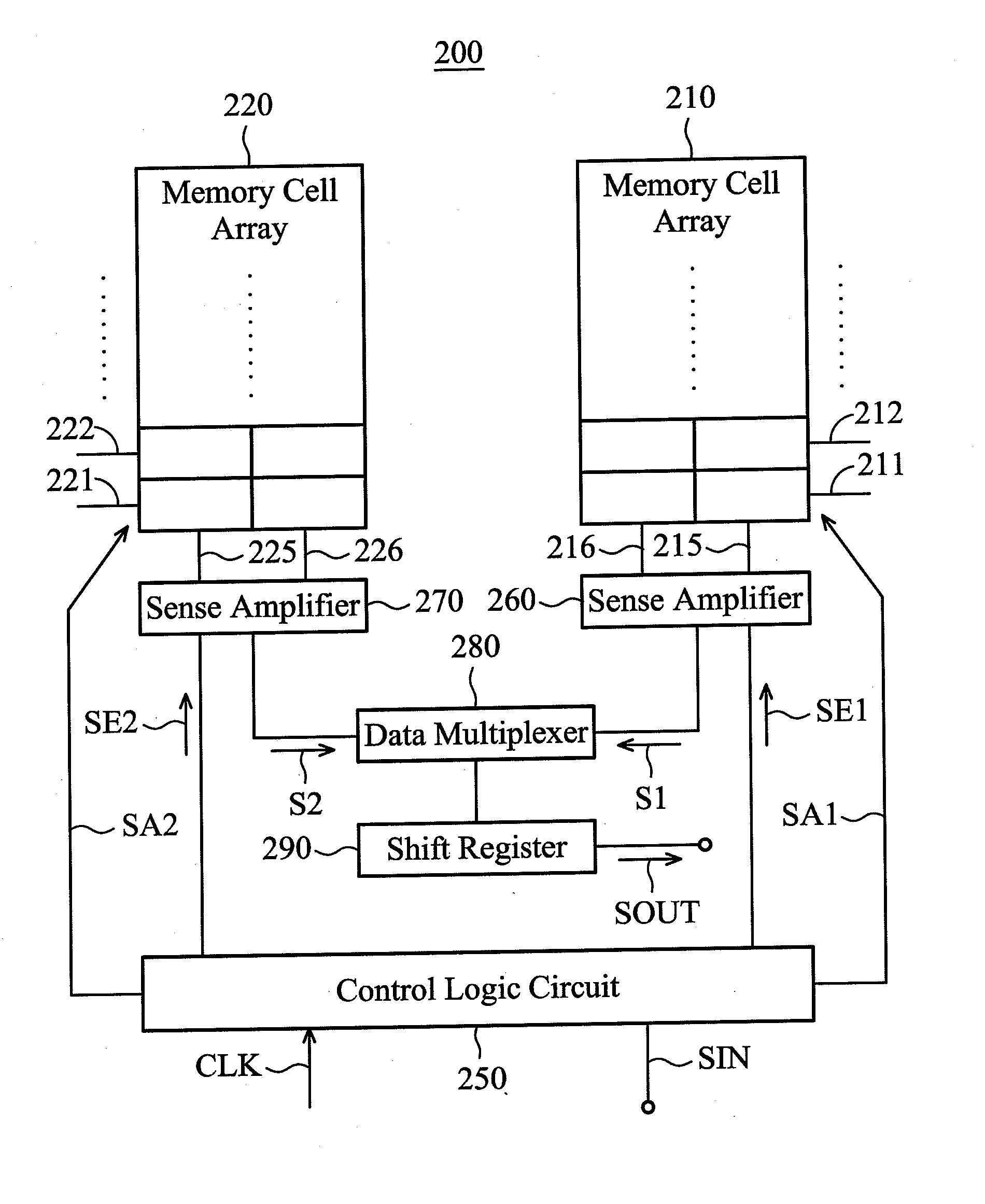

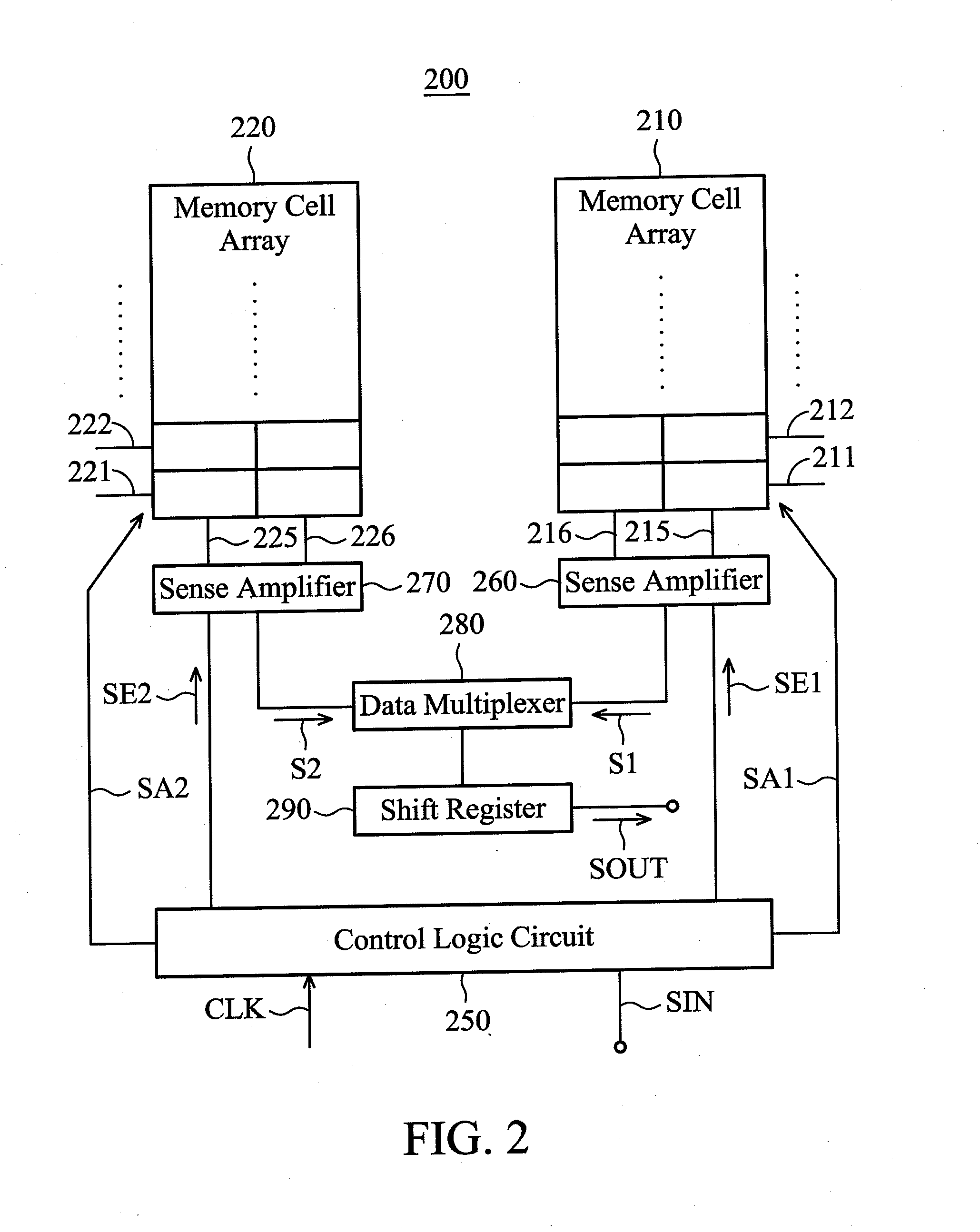

Memory device with high-speed reading function and method thereof

A method includes steps of: providing a first memory cell array including a plurality of first word lines, wherein a plurality of first data are stored in the first memory cell array; providing a second memory cell array including a plurality of second word lines, wherein the second memory cell array is separated from the first memory cell array, and a plurality of second data are stored in the second memory cell array; selecting one of the first word lines and one of the second word lines at a same time or an overlapping time; alternately selecting a first address of the first memory cell array and a second address of the second memory cell array to alternately read a first corresponding portion of the first data and a second corresponding portion of the second data from the first memory cell array and the second memory cell array.

Owner:WINBOND ELECTRONICS CORP

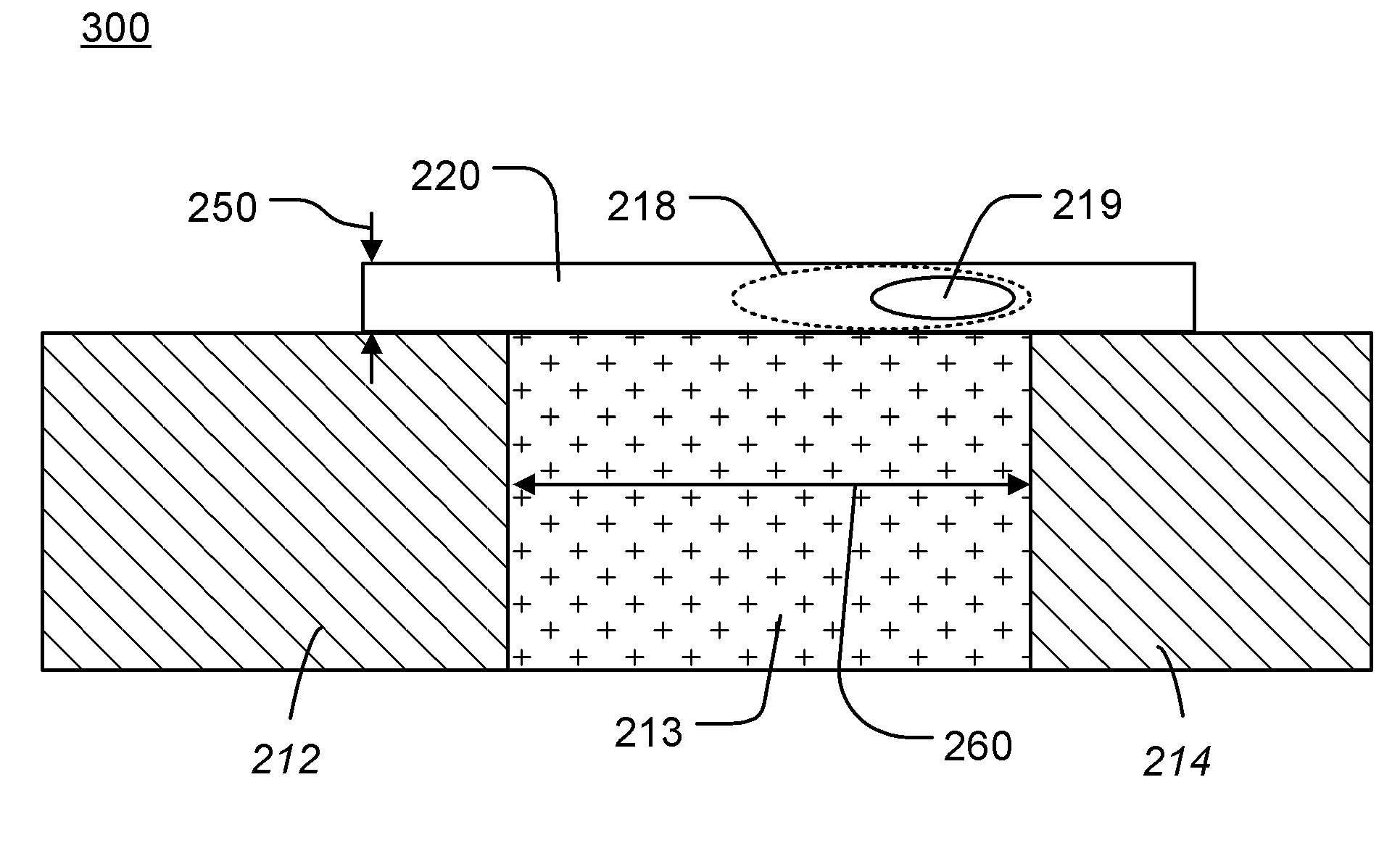

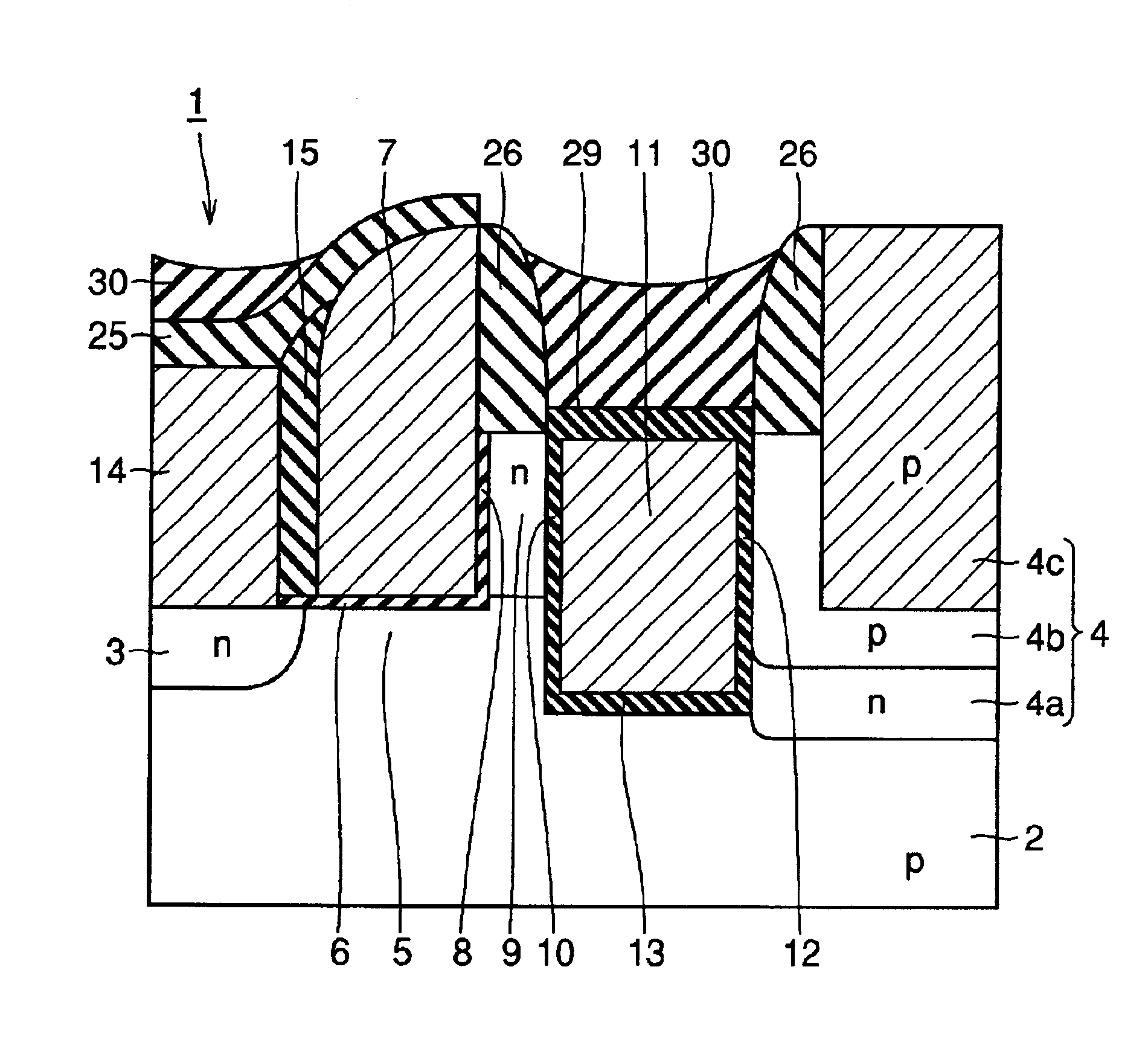

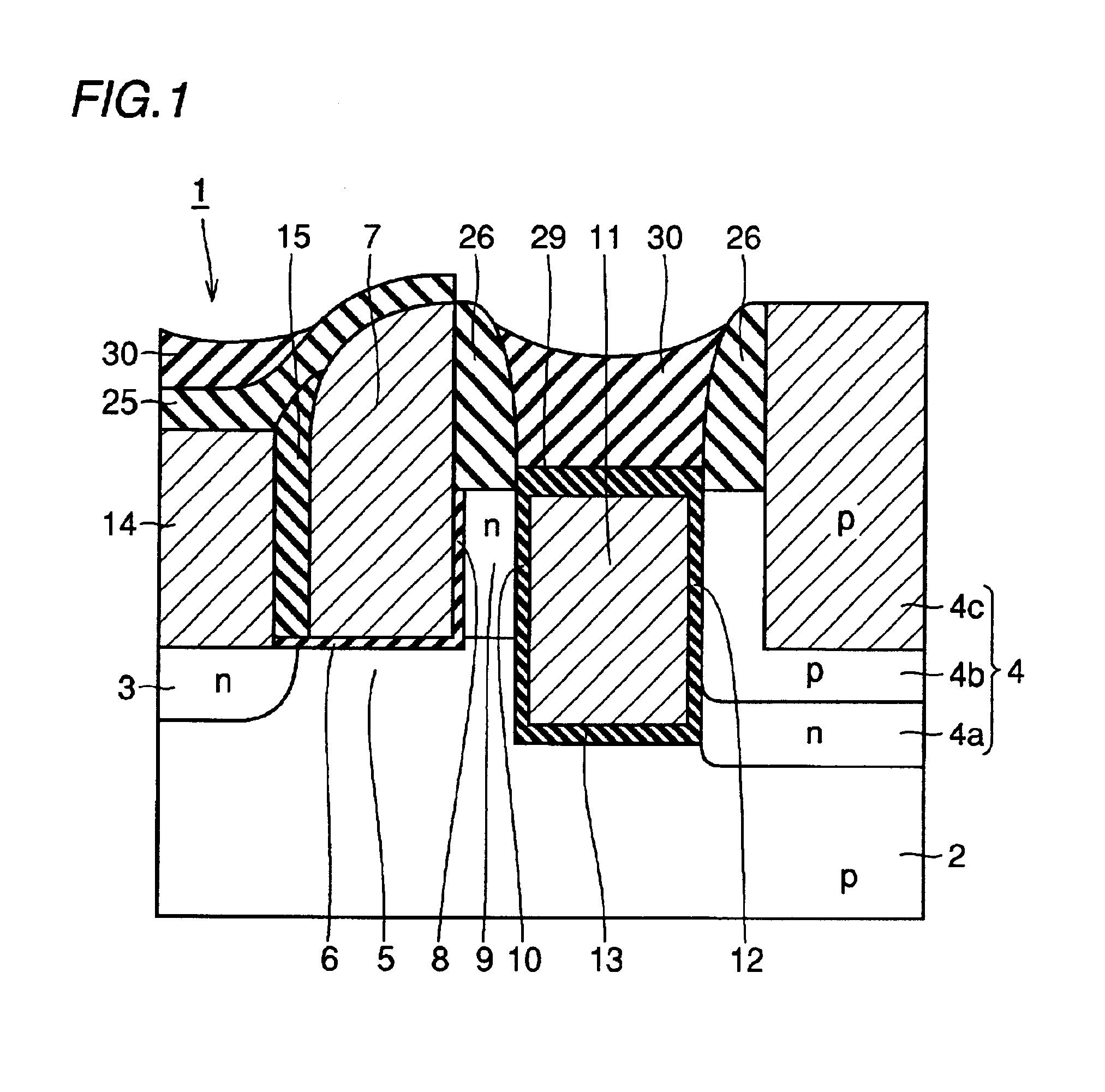

Semiconductor memory and semiconductor device

InactiveUS6897515B2Solution to short lifeReduce voltageTransistorSolid-state devicesLow voltageEngineering

A semiconductor memory capable of attaining a low voltage, a high-speed operation, low power consumption and a high degree of integration is obtained. This semiconductor memory comprises a floating gate electrode, a first source / drain region having a diode structure employed for controlling the potential of the floating gate electrode and a second source / drain region formed to hold a channel region between the same and the first source / drain region. Thus, when a channel of a transistor is turned on in reading, a large amount of current flows from the first source / drain region having a diode structure to a substrate, whereby high-speed reading can be implemented. Further, a negative voltage is readily applied to the first source / drain region having a diode structure, whereby a low voltage and low power consumption are attained and the scale of a step-up circuit is reduced, and hence a high degree of integration can be attained.

Owner:SEMICON COMPONENTS IND LLC

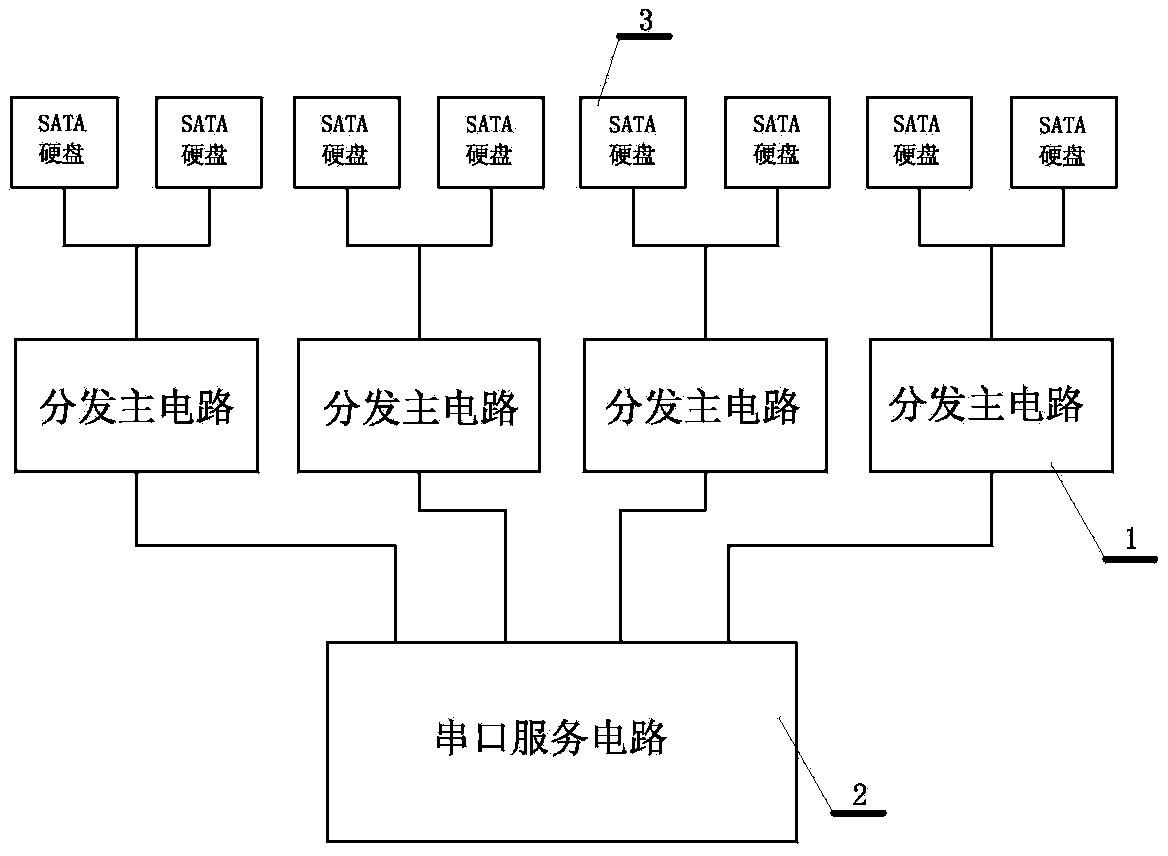

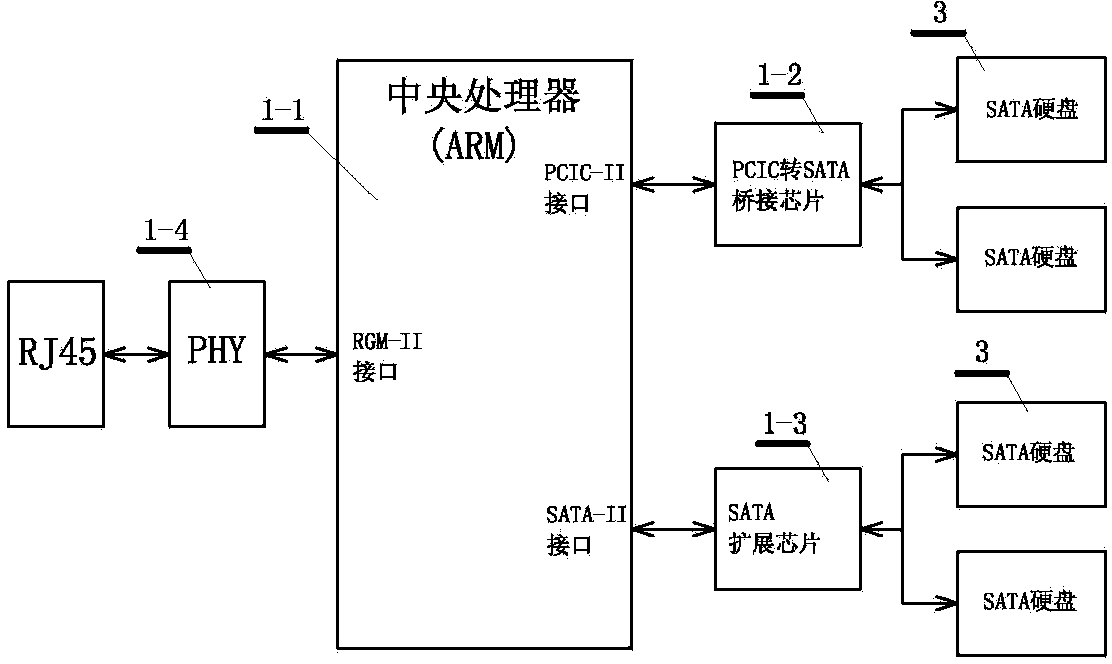

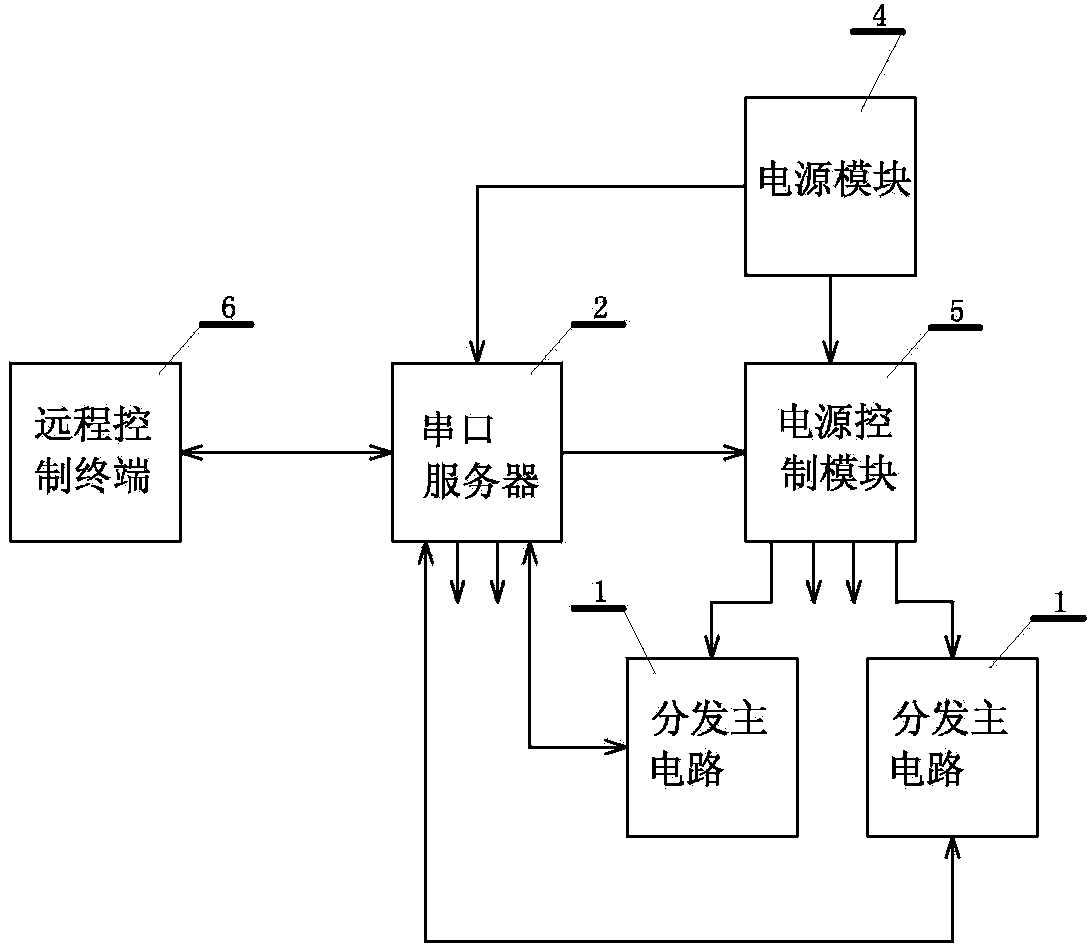

High-speed reading-writing and mass-storage system under ARM platform and working method of high-speed reading-writing and mass-storage system under ARM platform

InactiveCN103942013ASolve the problem that multiple hard drives cannot be connected to achieve large-capacity storageSolve the problem of high-speed reading and writing hard disk dataInput/output to record carriersTransmissionWorking setSpeed reading

The invention discloses a high-speed reading-writing and mass-storage system under an ARM platform and a working method of the high-speed reading-writing and mass-storage system under the ARM platform. The high-speed reading-writing and mass-storage system comprises a plurality of distributing main circuits, a serial port service circuit and a plurality of SATA hard disks. The serial port service circuit is connected with the multiple distributing main circuits, and the distributing main circuits are provided with a central processing unit based on an ARM framework. The central processing unit comprises a PCIE interface circuit, an SATA interface circuit and an RGM interface circuit, the PCIE interface circuit is connected with two SATA hard disks through a PCIE-to-SATA bridging circuit, and the SATA interface circuit is connected with two SATA hard disks through an SATA expanding circuit. According to the high-speed reading-writing and mass-storage system, the problem that mass storage can not be achieved due to the fact that multiple hard disks can not be connected under the ARM framework is solved, and the high-speed reading-writing and mass-storage system is completely suitable for the edge service of the CDN, and completely the same as an X86 server in performance; under the same capacity, cost is 70% lower than that of the X86 server, power consumption is 80% lower than that of the X86 server, and the size is 50% smaller than that of the X86 server.

Owner:北京网视通联科技股份有限公司

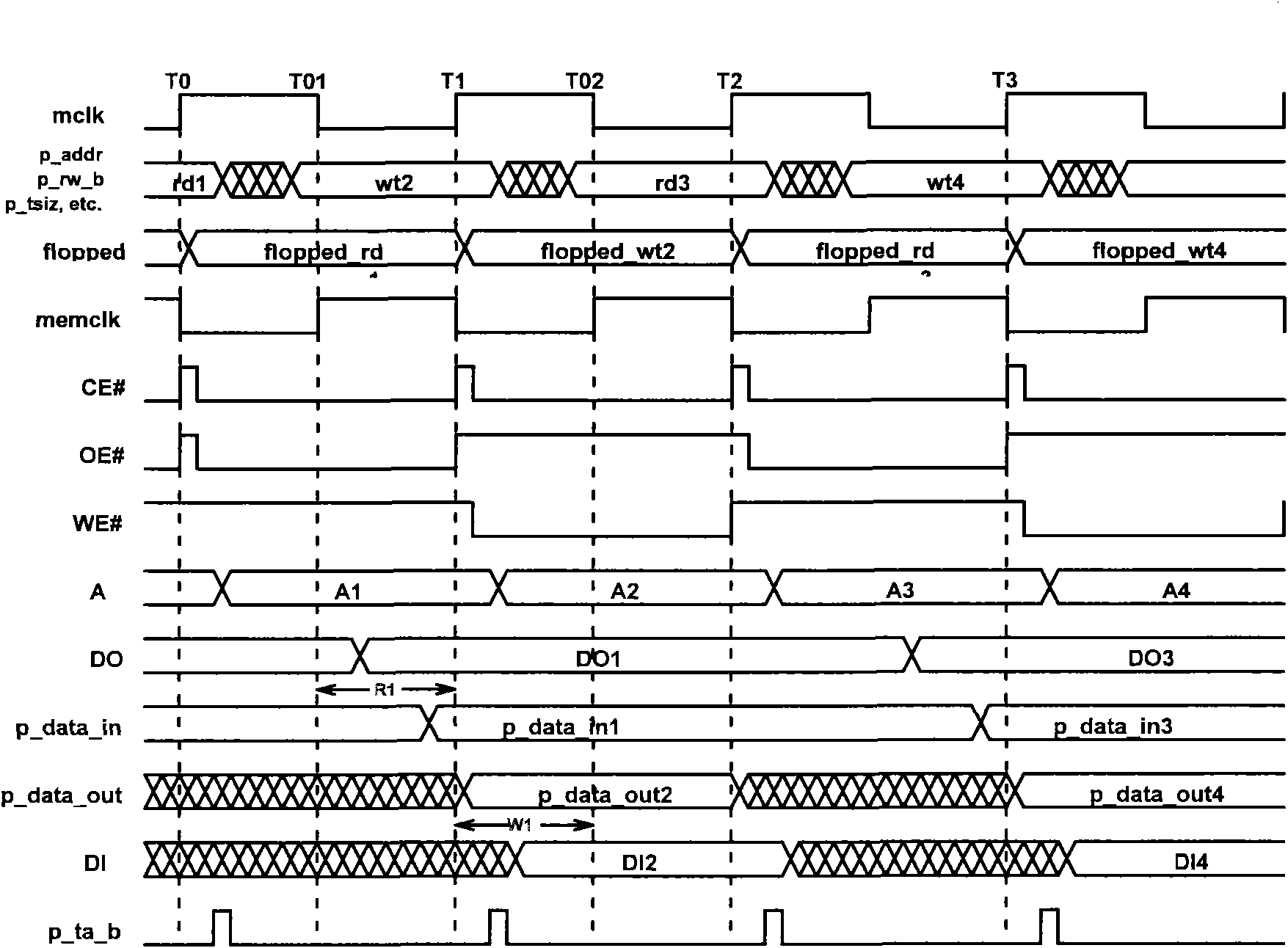

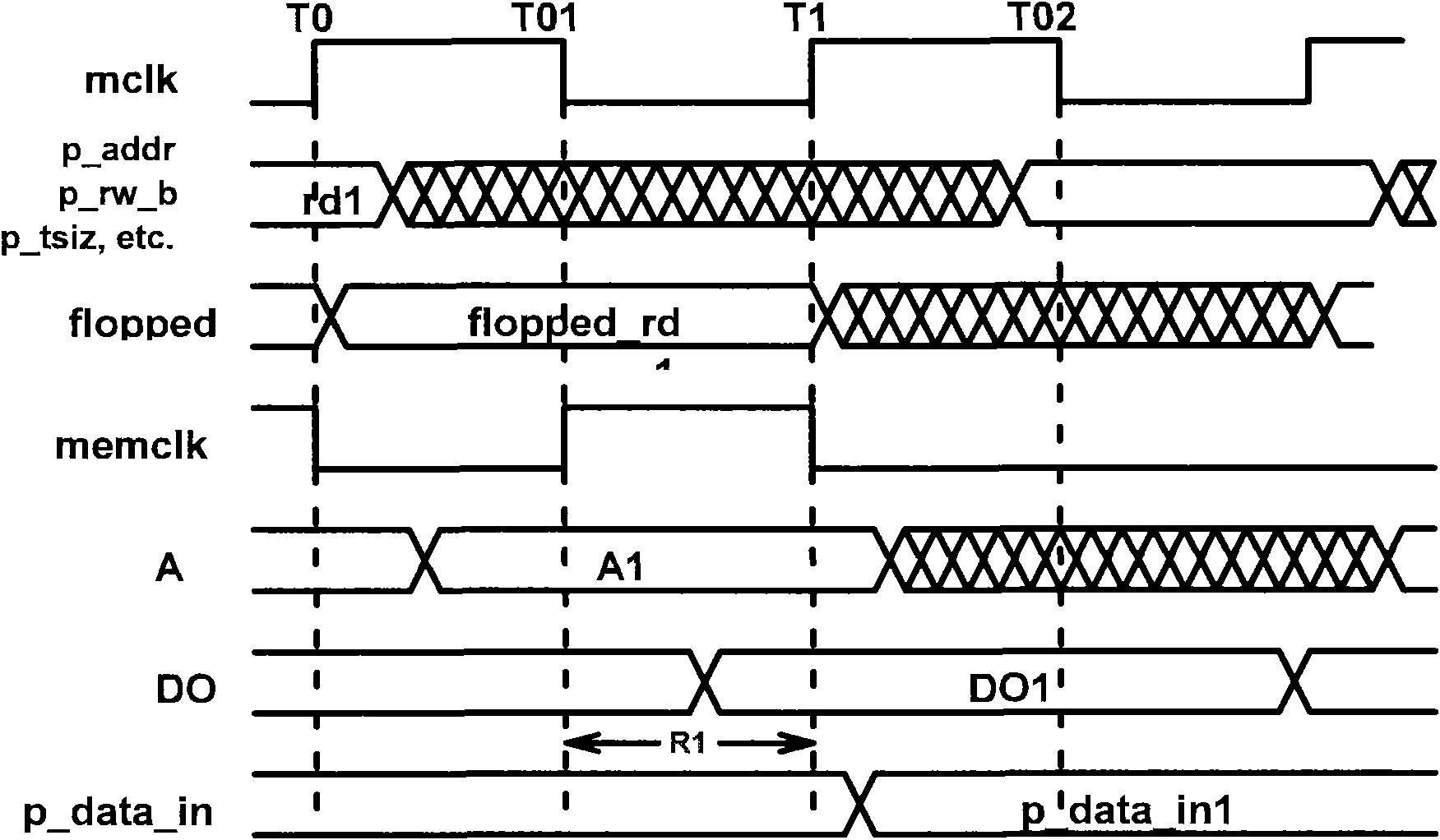

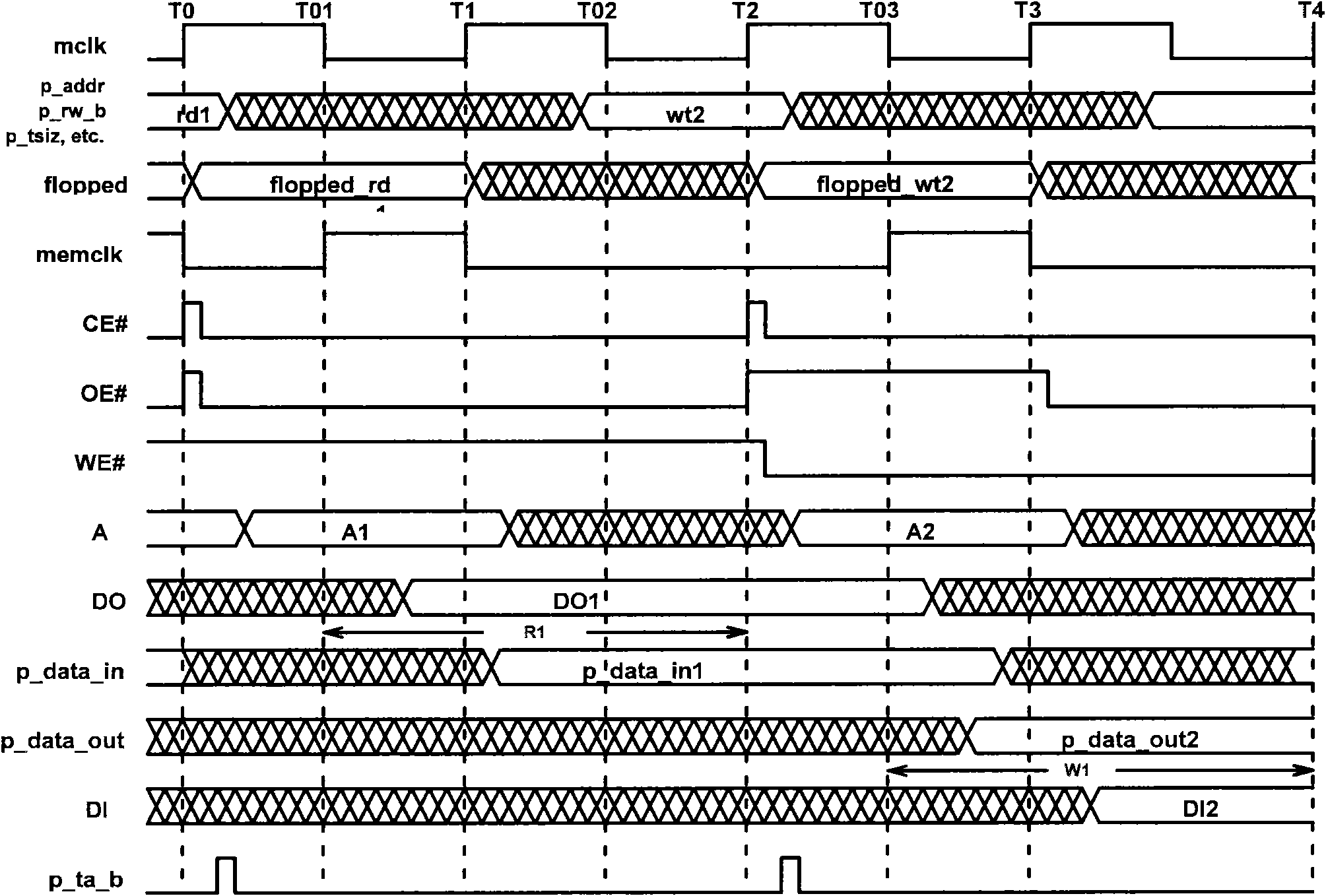

Memory interface method based on CLB (Central Logic Bus) bus

ActiveCN101923524AExtended latch timeFlexible samplingElectric digital data processingControl signalMemory interface

The invention discloses a memory interface method based on a CLB (Central Logic Bus) bus, comprising the following steps of, at a rising edge of a bus clock, sending a reading or writing operation request by a processor, latching address signals and control signals from the processor by the bus to obtain first latching signals, and generating enabling signals of a memory; at a falling edge arranged behind and adjacent to the rising edge of the bus clock, generating a memory clock according to the enabling signals of the memory by the memory, wherein a falling edge of the memory clock is synchronous with the falling edge of the bus clock; behind the falling edge of the memory clock, in the reading operation, outputting data to achieve the data output end of the memory, delaying by a line, and achieving the data input end of the processor in the front of an adjacent rising edge behind the rising edge of the bus clock; in the writing operation, writing data to achieve the data output end of the processor, delaying by the line, and achieving the data input end of the memory in the front of the adjacent rising edge behind the rising edge of the bus clock. When realizing high-speed reading or writing operation of the memory, the invention efficiently reduces the amount of waiting period and enhances the clock utilization.

Owner:苏州国芯科技股份有限公司

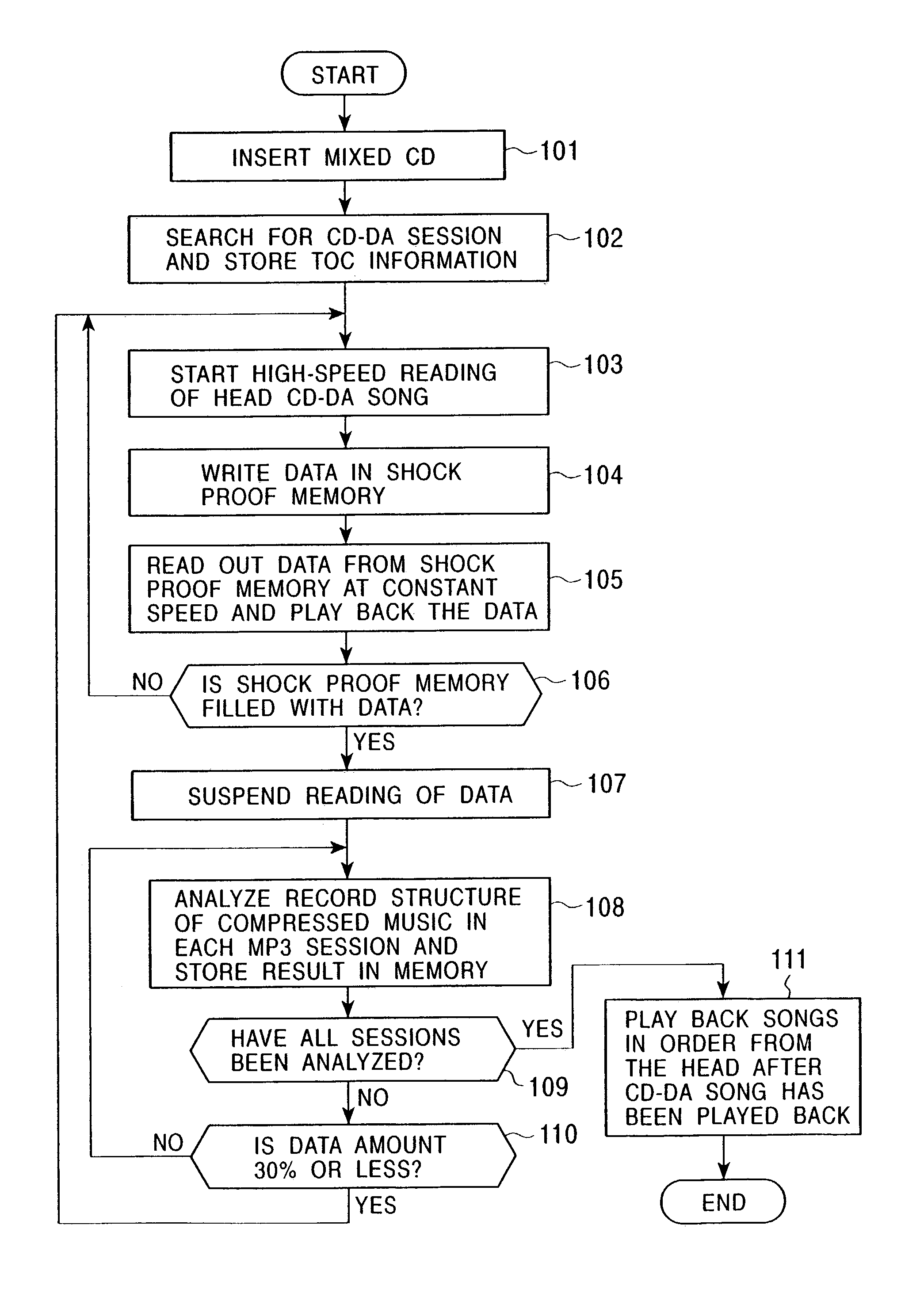

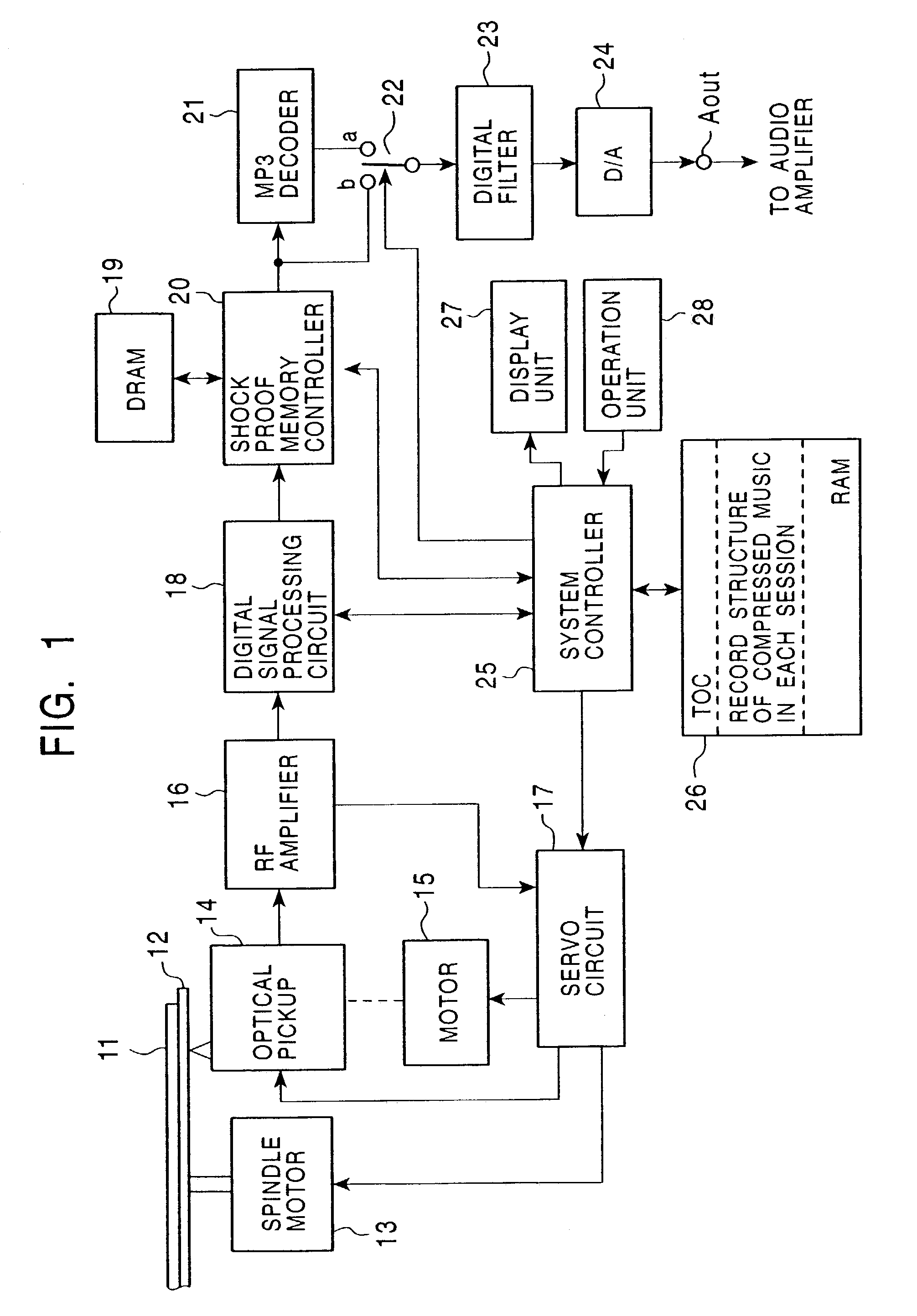

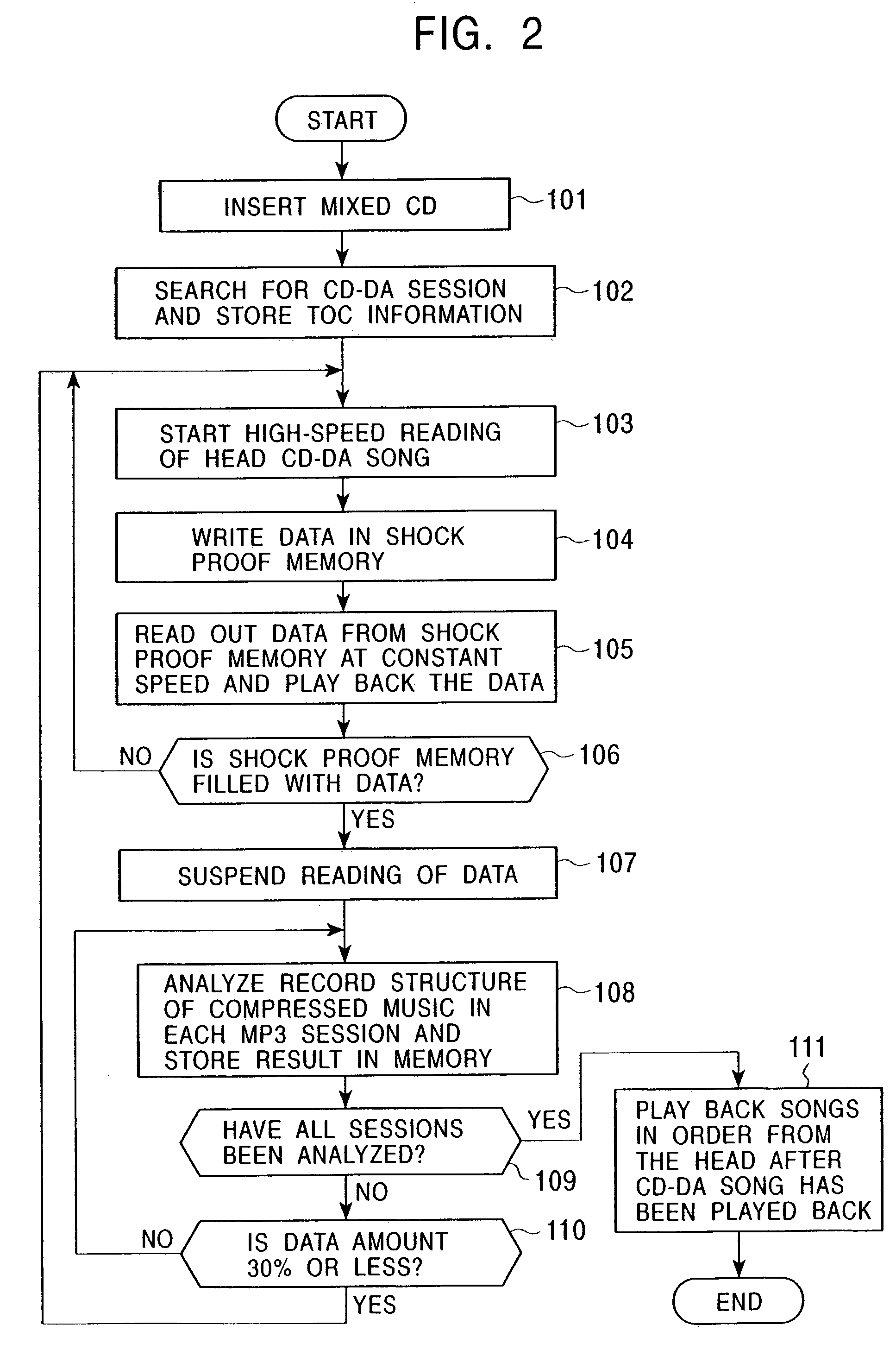

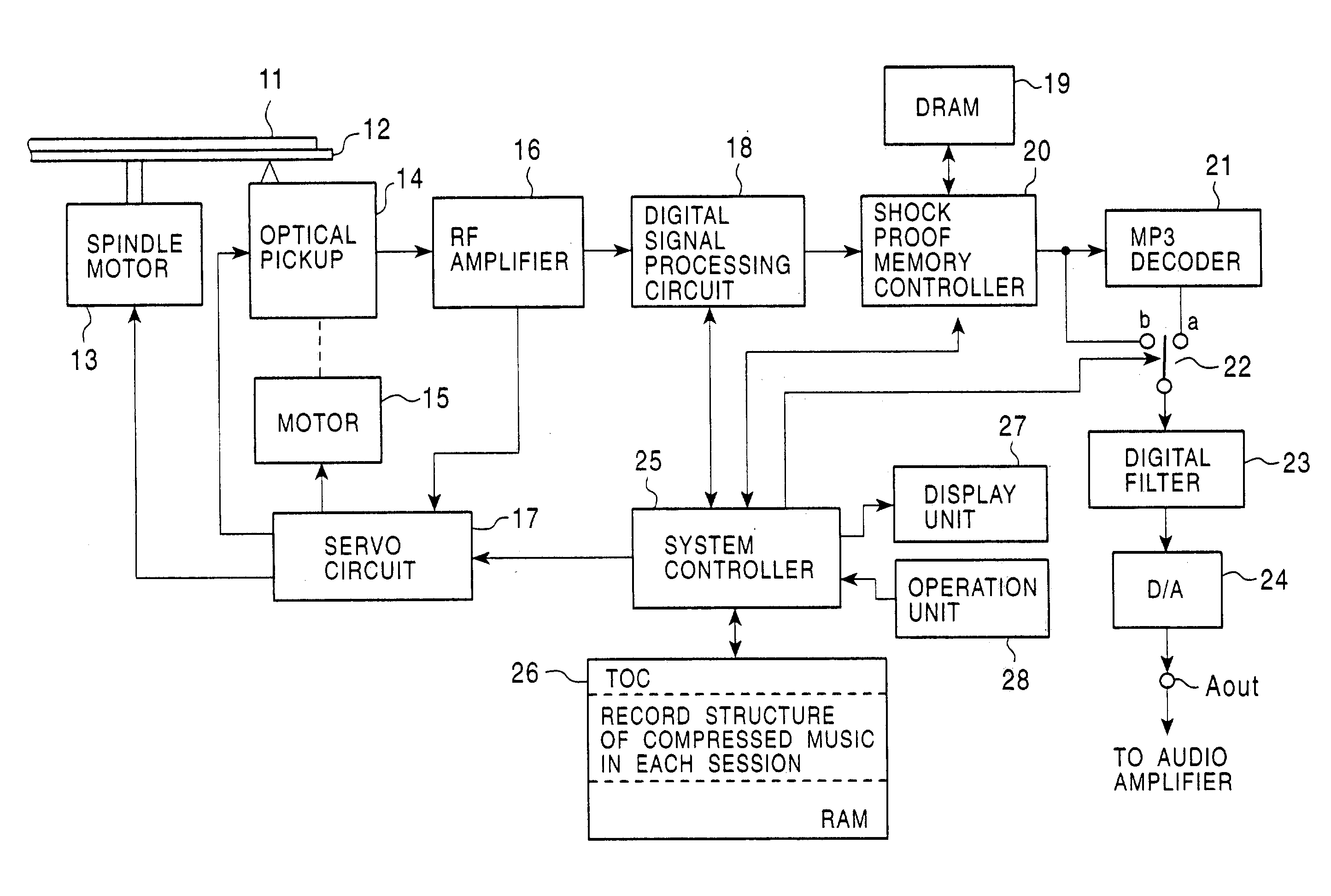

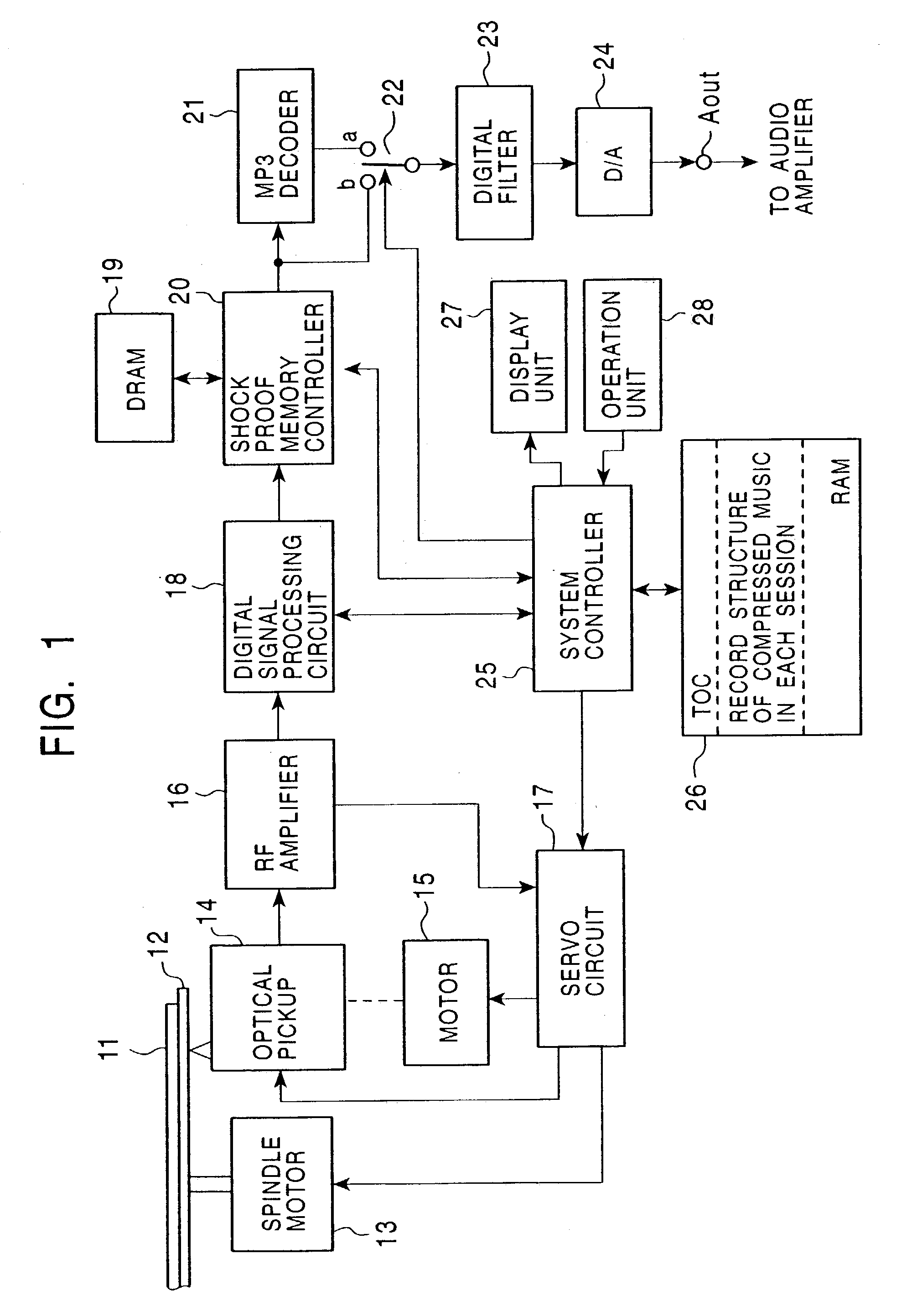

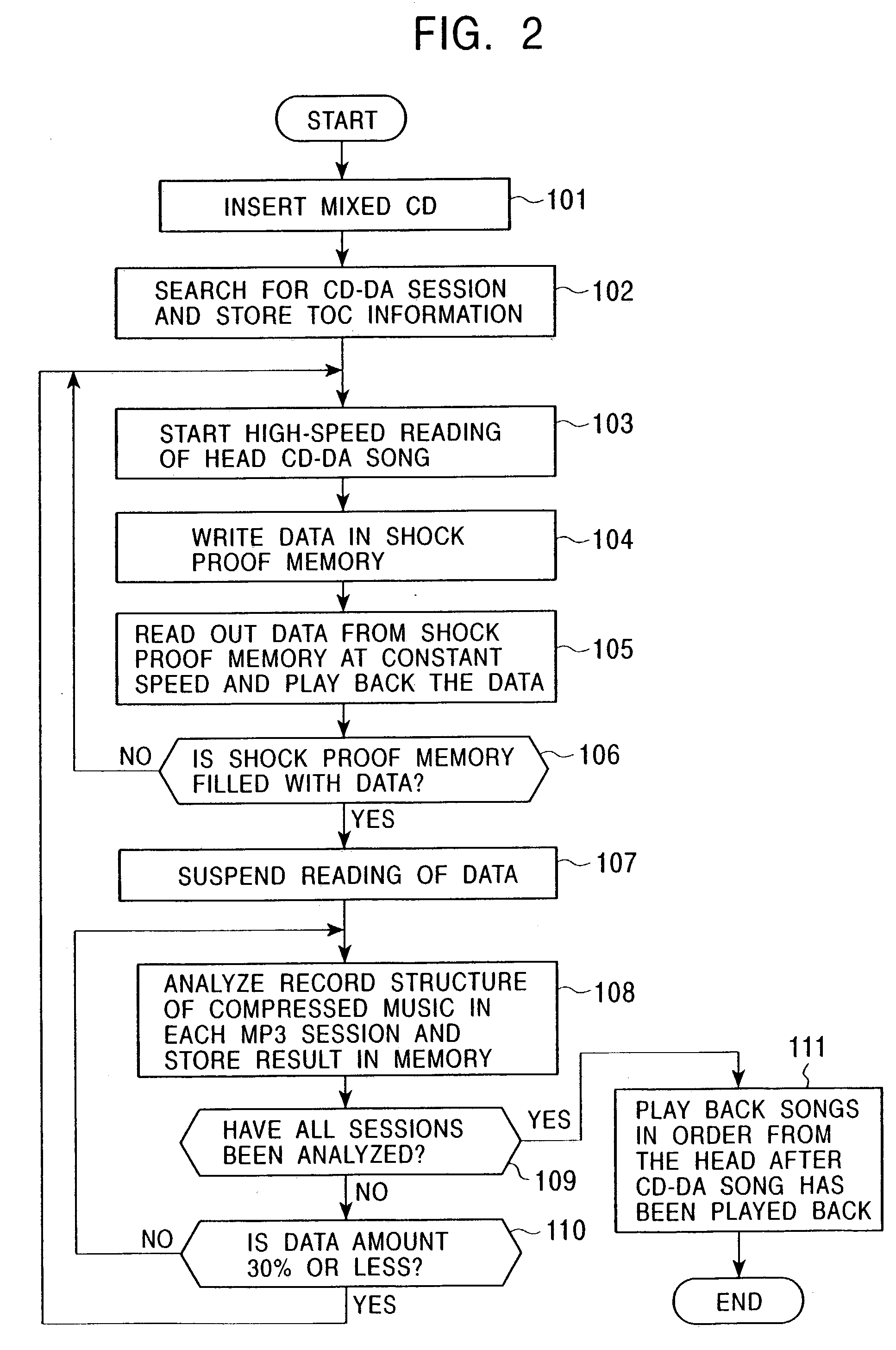

Method and apparatus for playing back a multisession disc

ActiveUS7113456B2Fast outputShorten the timeDisc-shaped record carriersRecord information storageComputer hardwareSpeed reading

A method and apparatus for reading multisession discs in which both standard CD-DA format and compressed music formats, such as MP3, may be utilized on the same disc. High speed reading of data into shock proof memory, analysis of available memory and storage of analyzed record structures are used to provide playback of music in both formats and, if desired, in a random playback order.

Owner:ALPINE ELECTRONICS INC

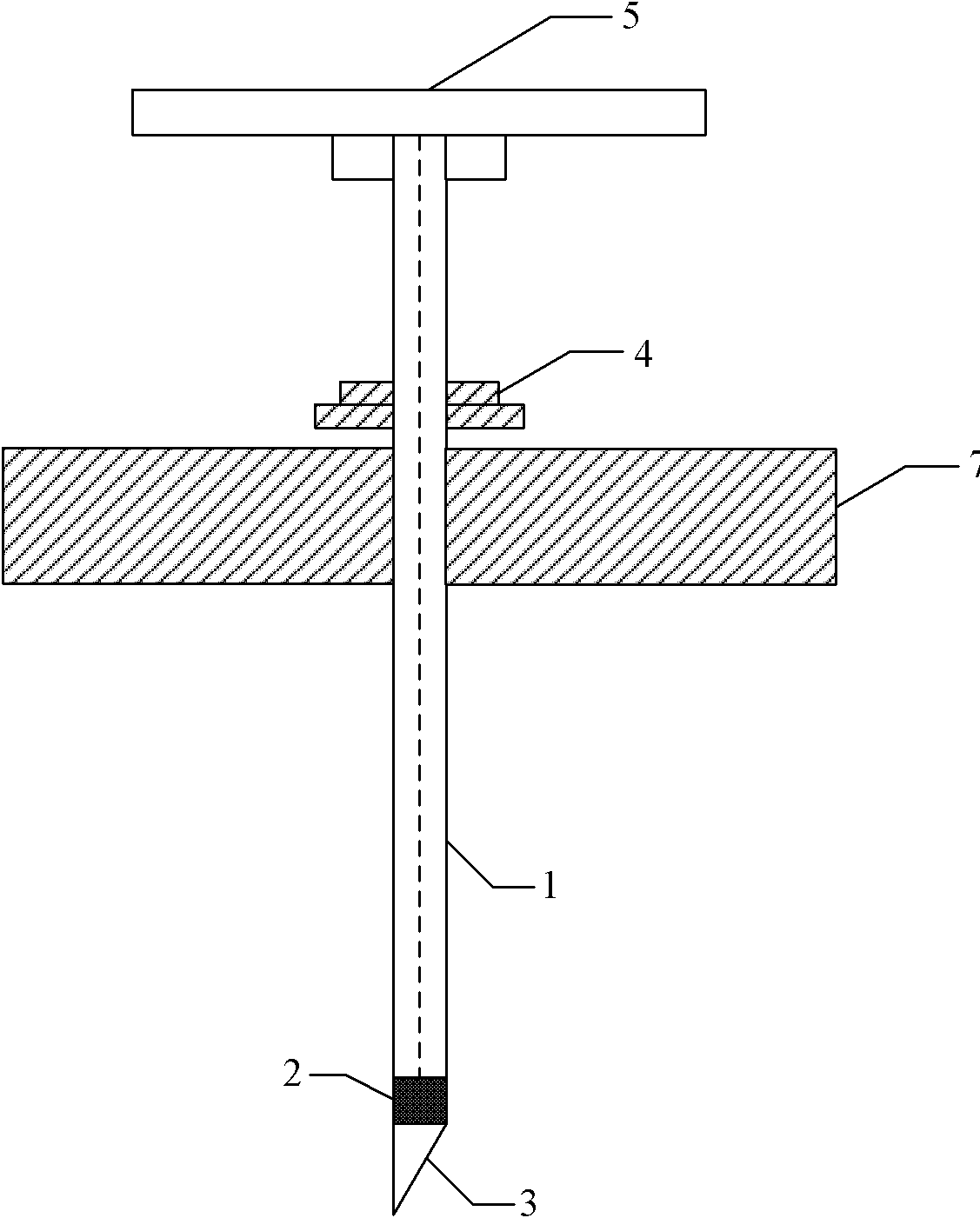

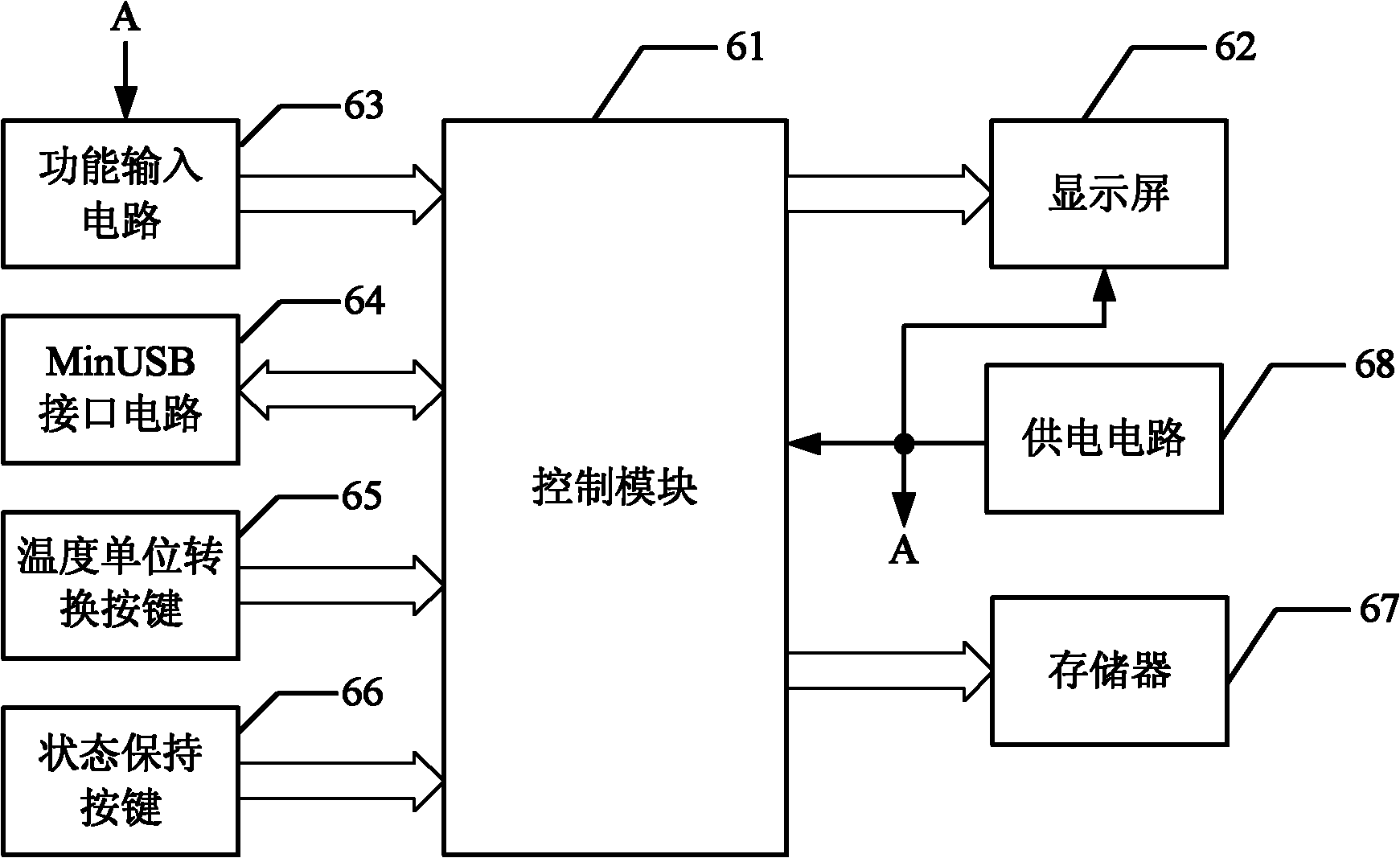

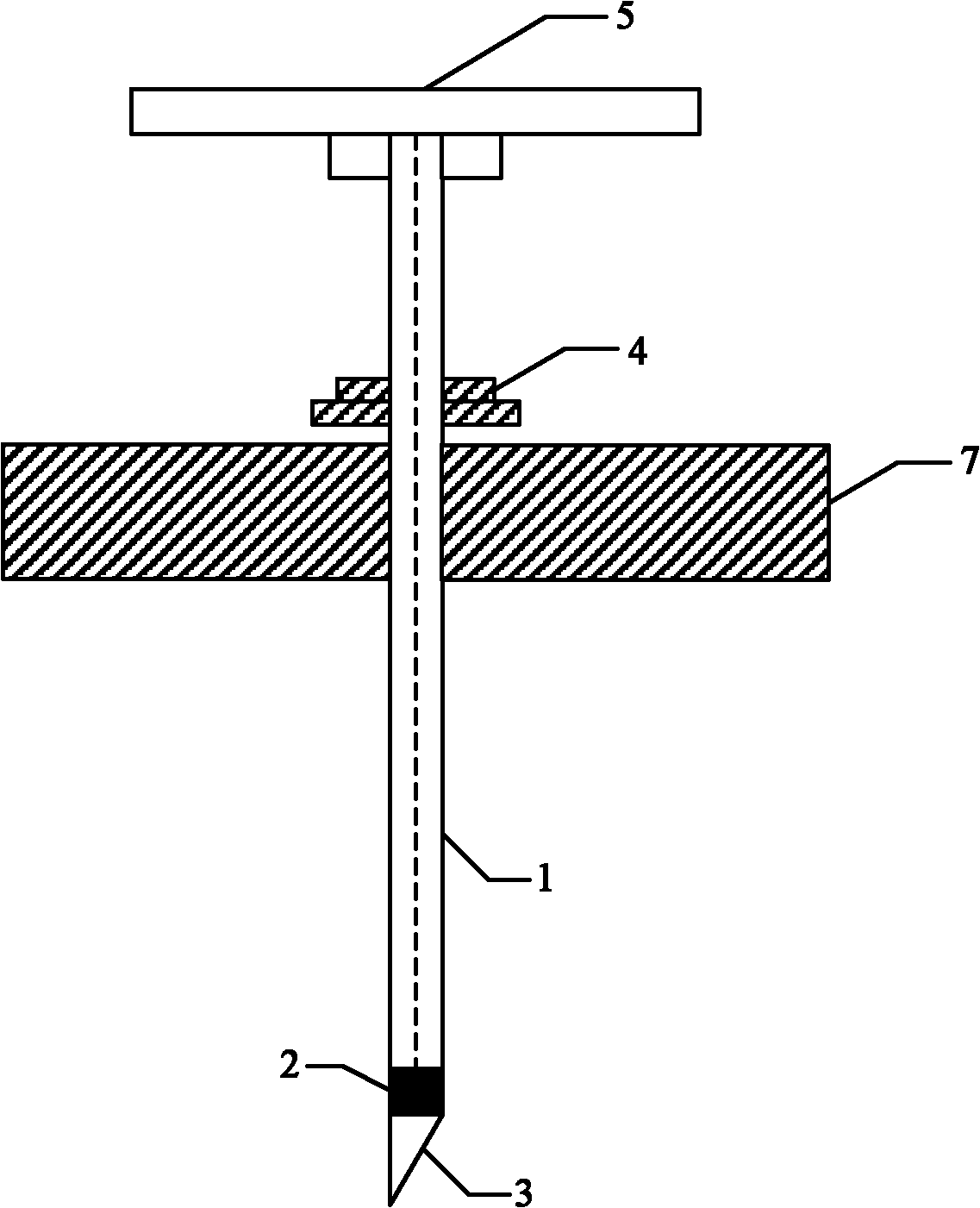

Electronic digital-display speed-reading geothermometer

InactiveCN102494803AFast temperature measurementAccurate measurementBody temperature measurementThermal insulationEngineering

The invention relates to an electronic digital-display speed-reading geothermometer, relating to a geothermometer and aiming to solve the problems that the measurement accuracy of the geothermometer is poor, long temperature equilibration time is needed to guarantee the measurement accuracy and the measurement efficiency is low. The tail end of a temperature-sensing probe head is fixed at the front end of a probe pin through a thermal insulation sealing ring, a handle is fixed at the tail end of the probe pin, a digital display circuit is fixedly arranged on a handle and comprises a control module and a display screen, and the display signal input end of the display screen is connected with the display signal output end of the control module; and the temperature signal output end of the temperature-sensing probe head is connected with the temperature signal input end of the control module. The electronic digital-display speed-reading geothermometer is suitable for measurement of the temperature of the shallow soil below the ground surface or solid substances on the surface.

Owner:NORTHEAST INST OF GEOGRAPHY & AGRIECOLOGY C A S

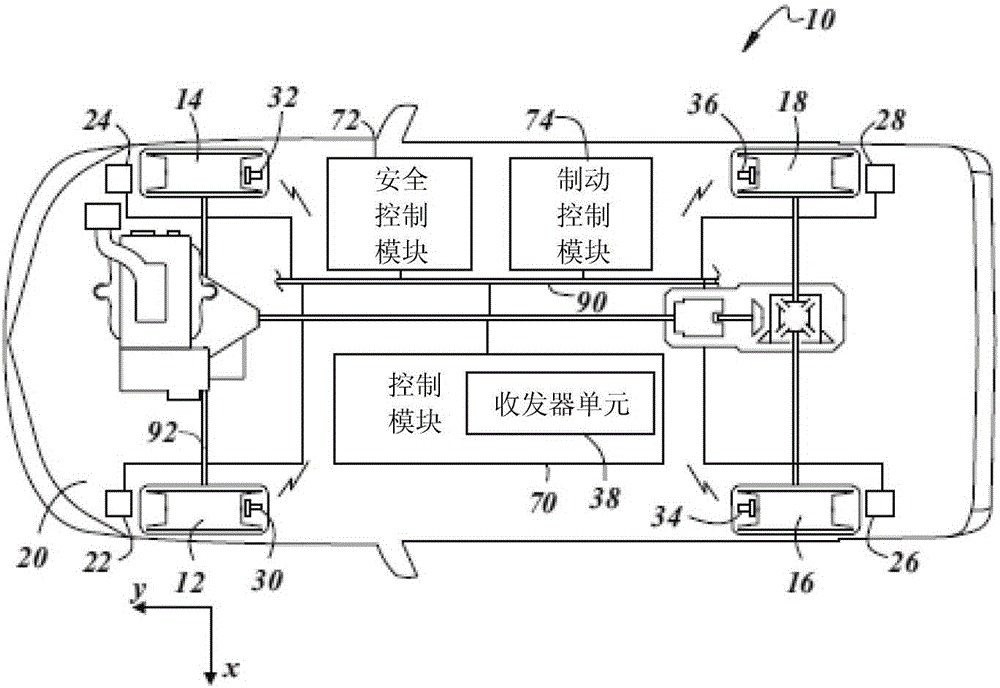

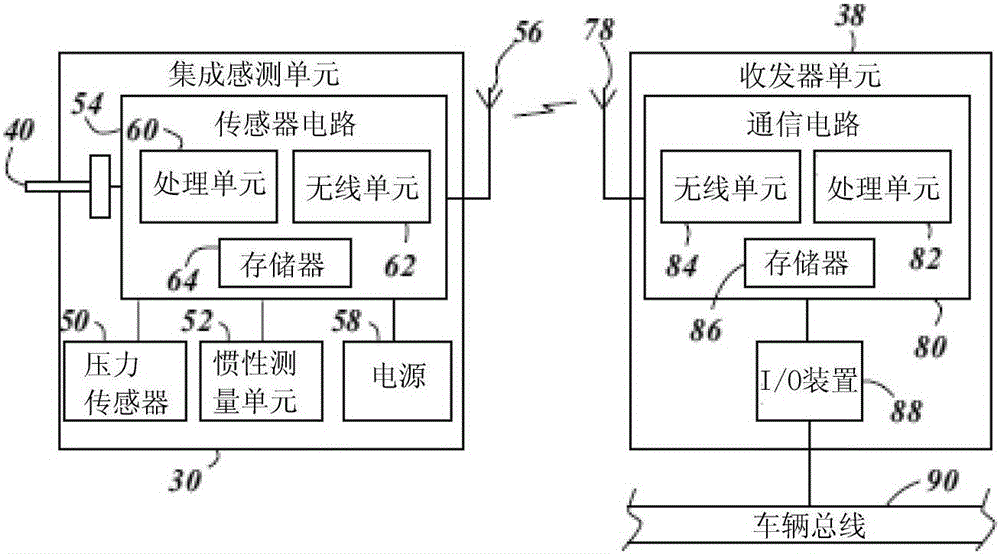

Integrated sensing unit and method for determining the vehicle wheel speed and tire pressure

InactiveCN106274308ASpeed measurement using accelerationTyre measurementsWheel speed sensorTransmittance

An integrated sensing unit and method that involves wirelessly transmitting tire pressure sensor readings and wheel speed readings to a control module in a vehicle. Sensor circuitry for a tire pressure monitoring (TPM) system can be used with an inertial measurement unit (IMU) in an integrated sensing unit to facilitate the wireless transmittance of wheel speed data. In an exemplary embodiment, the wheel speed data from the integrated sensing unit provides a redundant measure of wheel speed that can prolong the availability of vehicle systems that rely upon wheel speed, despite a potential malfunction of one or more typical wheel speed sensors.

Owner:GM GLOBAL TECH OPERATIONS LLC

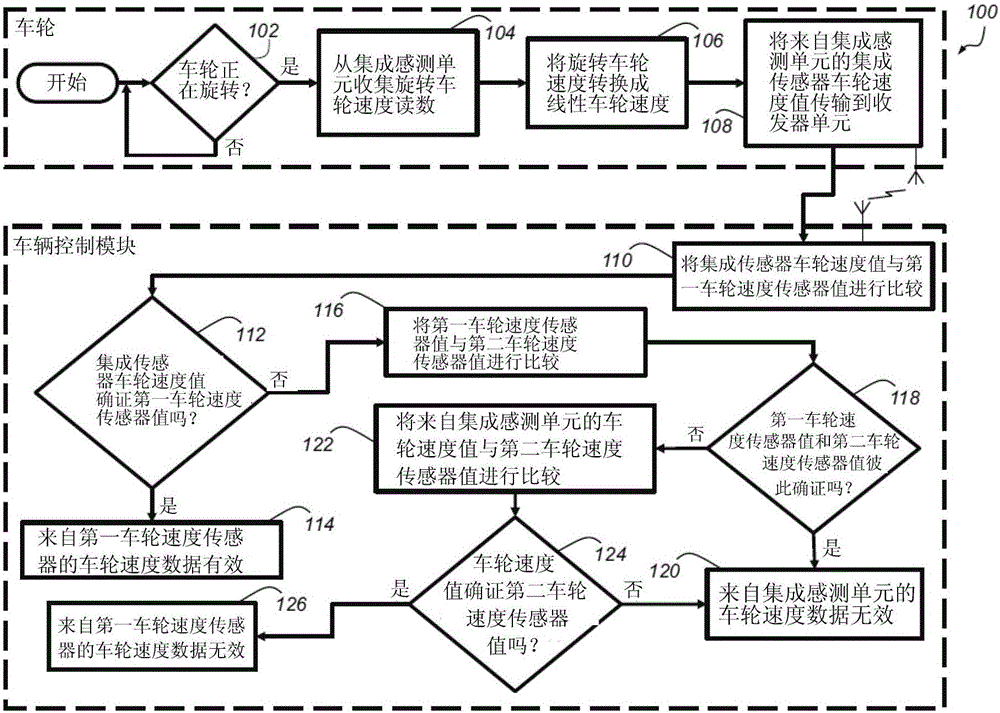

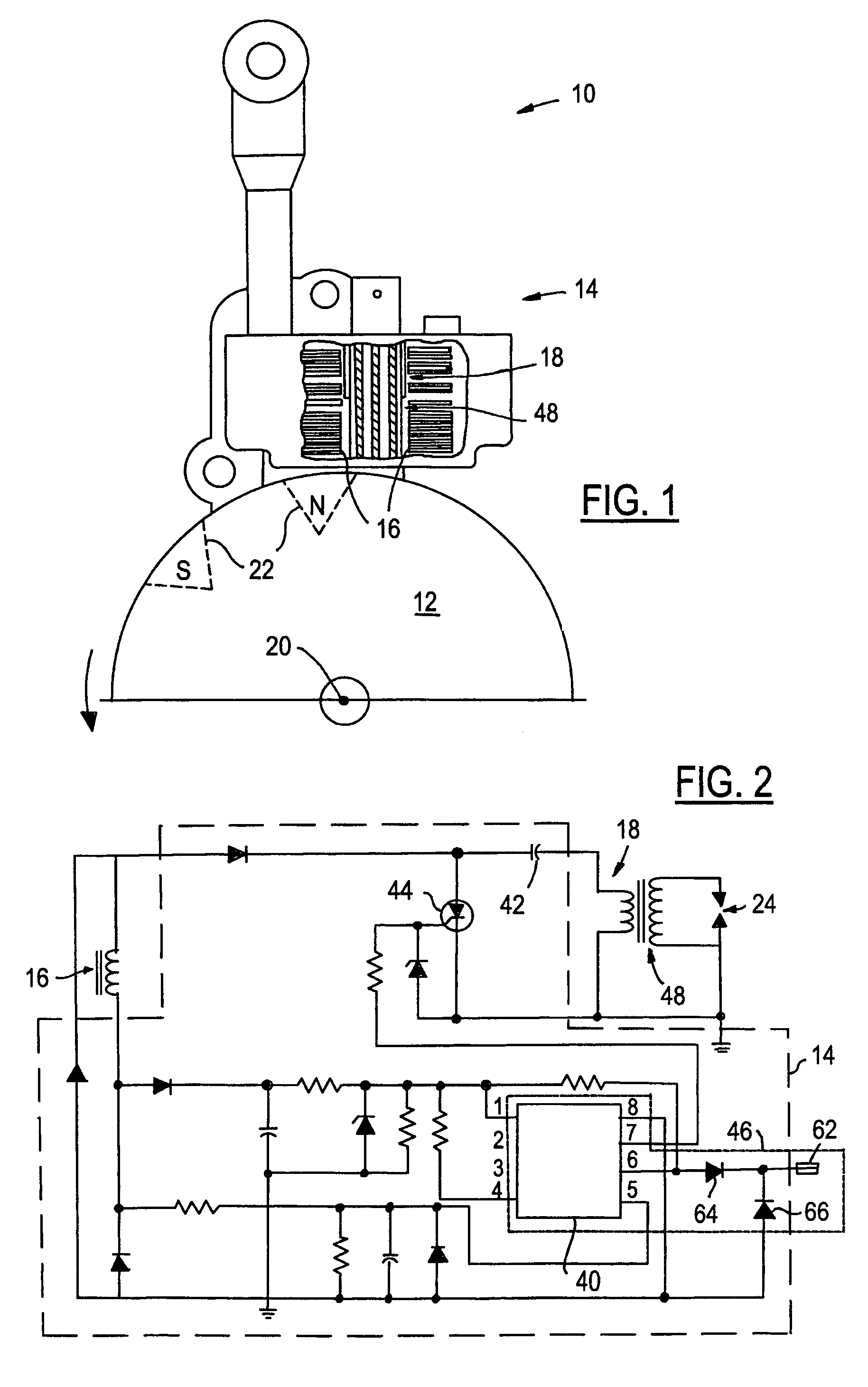

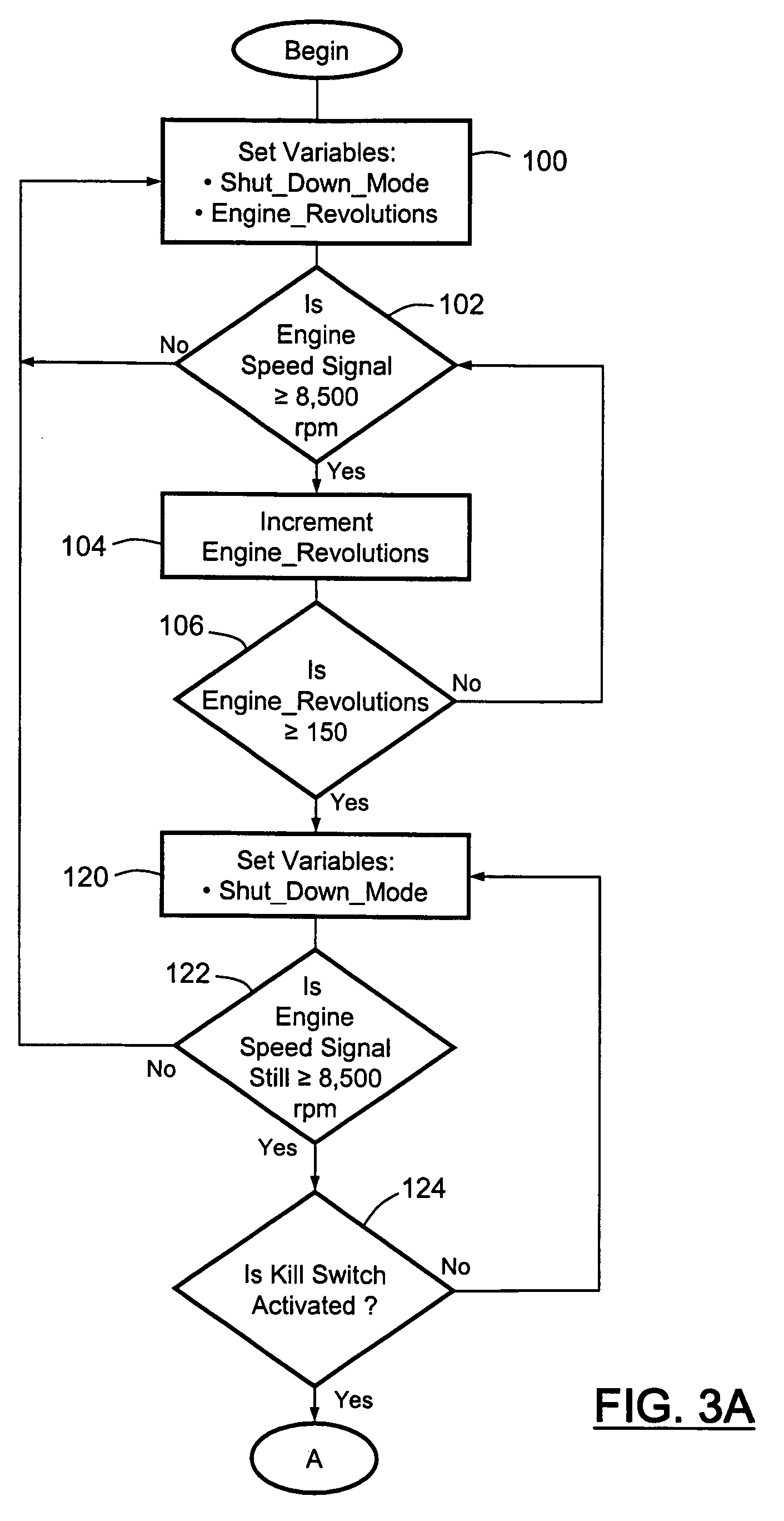

Engine kill-switch control circuit and method of operating the same

ActiveUS7136742B2Lower hydrocarbon emissionsPrevent backfireAnalogue computers for vehiclesElectrical controlControl mannerKill switch

A kill-switch control circuit for use with a light-duty combustion engine determines whether to execute a controlled shut down method or an immediate shut down method in response to kill-switch activation. The selection of a shut down method is made, at least in part, by using engine speed readings and by counting engine revolutions. The controlled shut down method utilizes ignition timing delay and / or spark ratio techniques to quickly bring the engine to a stop, yet does so in a controlled manner that avoids backfiring and other undesirable effects. Conversely, the immediate shut down method abruptly stops sending a current to the spark plug.

Owner:WALBRO LLC

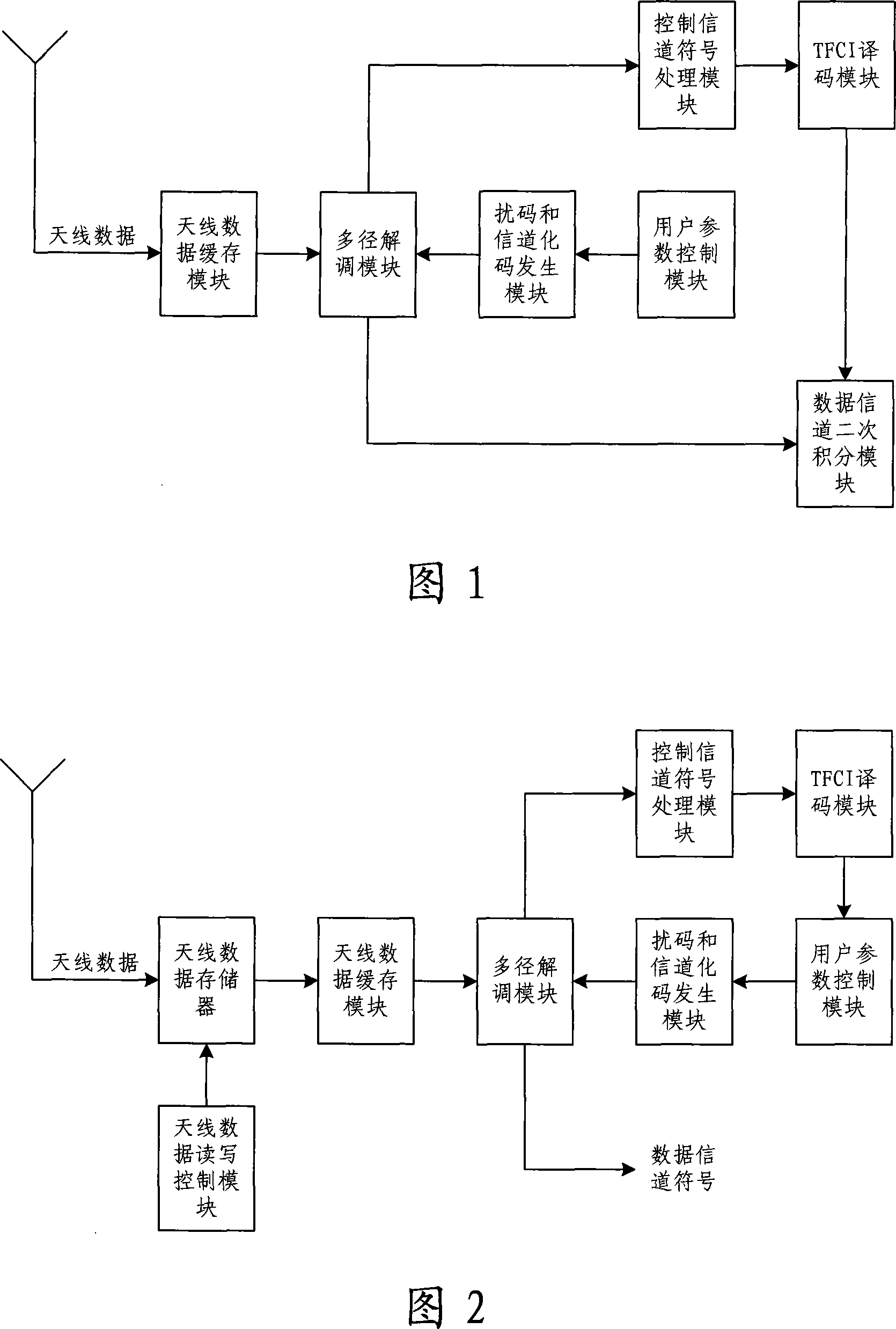

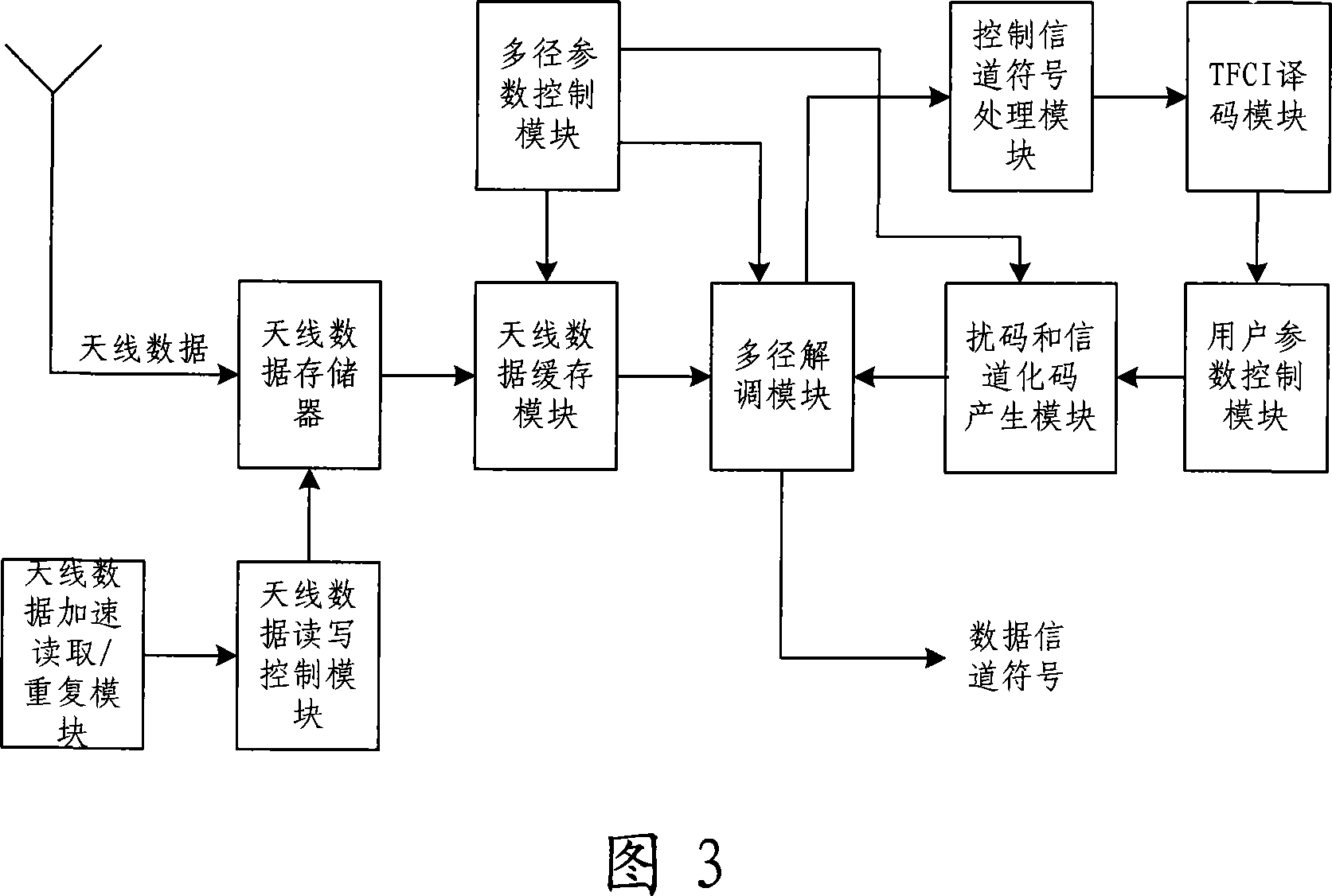

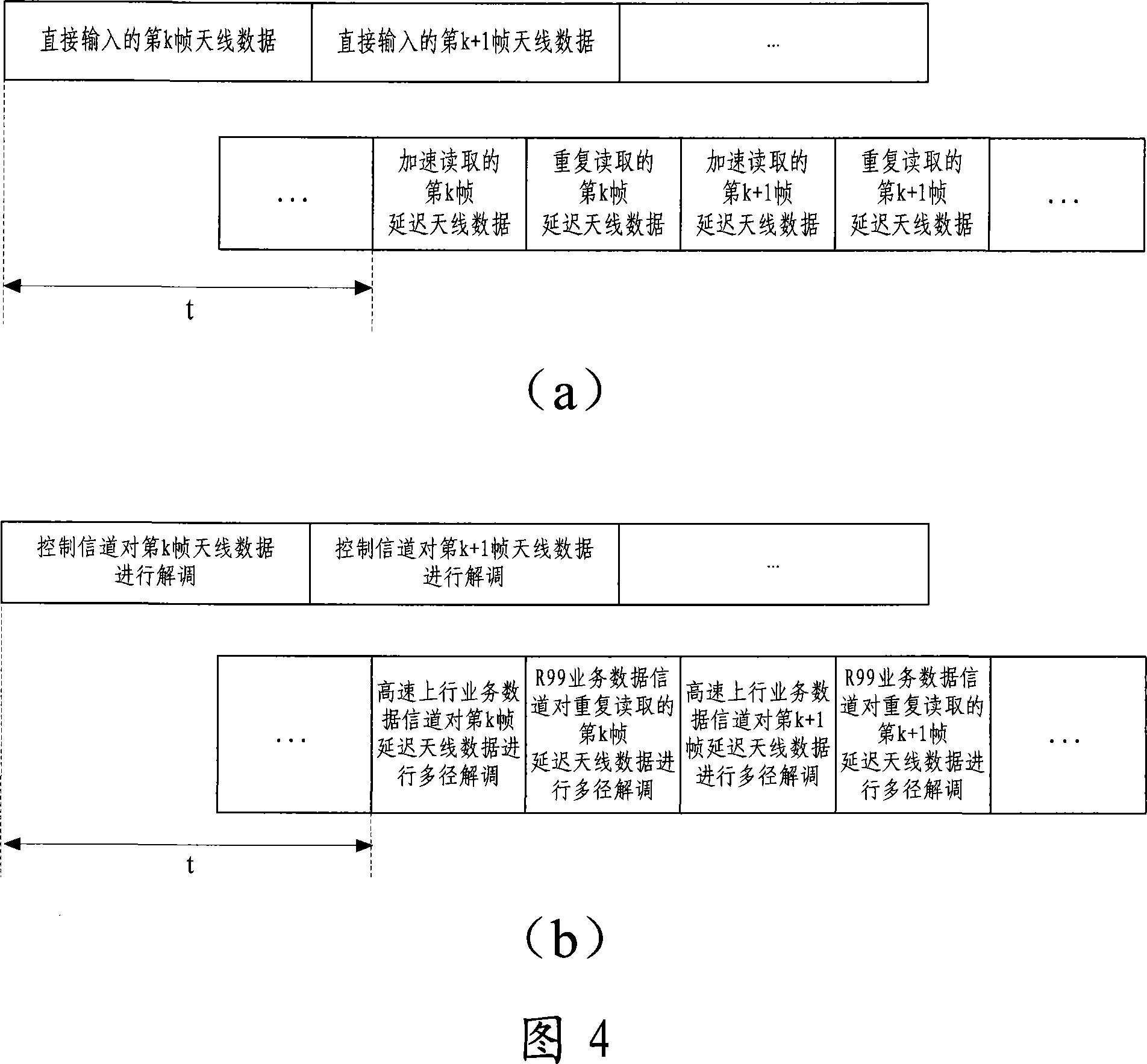

Mixing service RAKE receiving device based on broadband CDMA system and its method

ActiveCN101102123AMeet processing time requirementsEasy to controlCode division multiplexTransmissionRake receiverControl channel

The invention is concerned with the mixing operation RAKE receiver of broad band code division multiple access system (CDMA) and the method. In contrast with the current time delay demodulation RAKE receiver, it adds the antenna data speed reading / repeat module, the multi-pathway parameter control module. It is that the antenna data speed reading / repeat module speeds up the reading of the antenna read-write control module or repeat reading of the deferred antenna data of the data memorizer, generates the final control channel data and the data channel information after processed by the after-progress module separately, according to the multi-pathway parameter of the multi-pathway parameter control module and the deferred antenna data of the multi-pathway demodulation module. It fulfills the processing time demand of the high speed operation data channel of WCDMA.

Owner:SANECHIPS TECH CO LTD

Method and apparatus for playing back a multisession disc

ActiveUS20040032771A1Disc-shaped record carriersRecord information storageComputer hardwareSpeed reading

A method and apparatus for reading multisession discs in which both standard CD-DA format and compressed music formats, such as MP3, may be utilized on the same disc. High speed reading of data into shock proof memory, analysis of available memory and storage of analyzed record structures are used to provide playback of music in both formats and, if desired, in a random playback order.

Owner:ALPINE ELECTRONICS INC

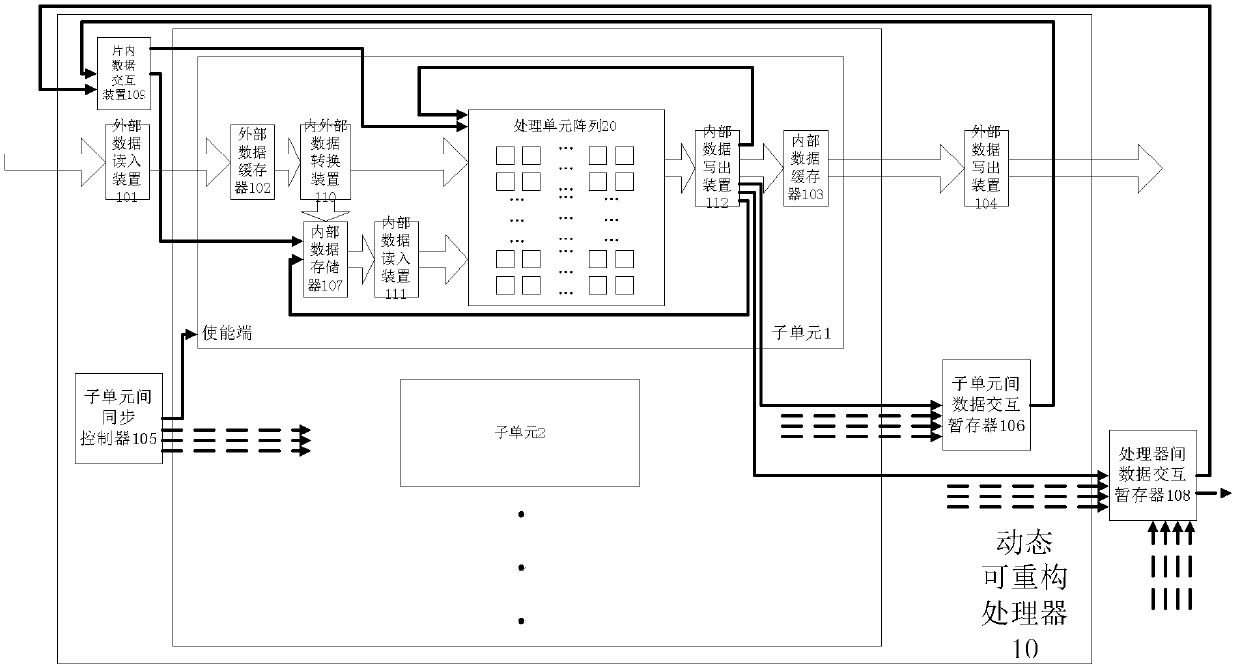

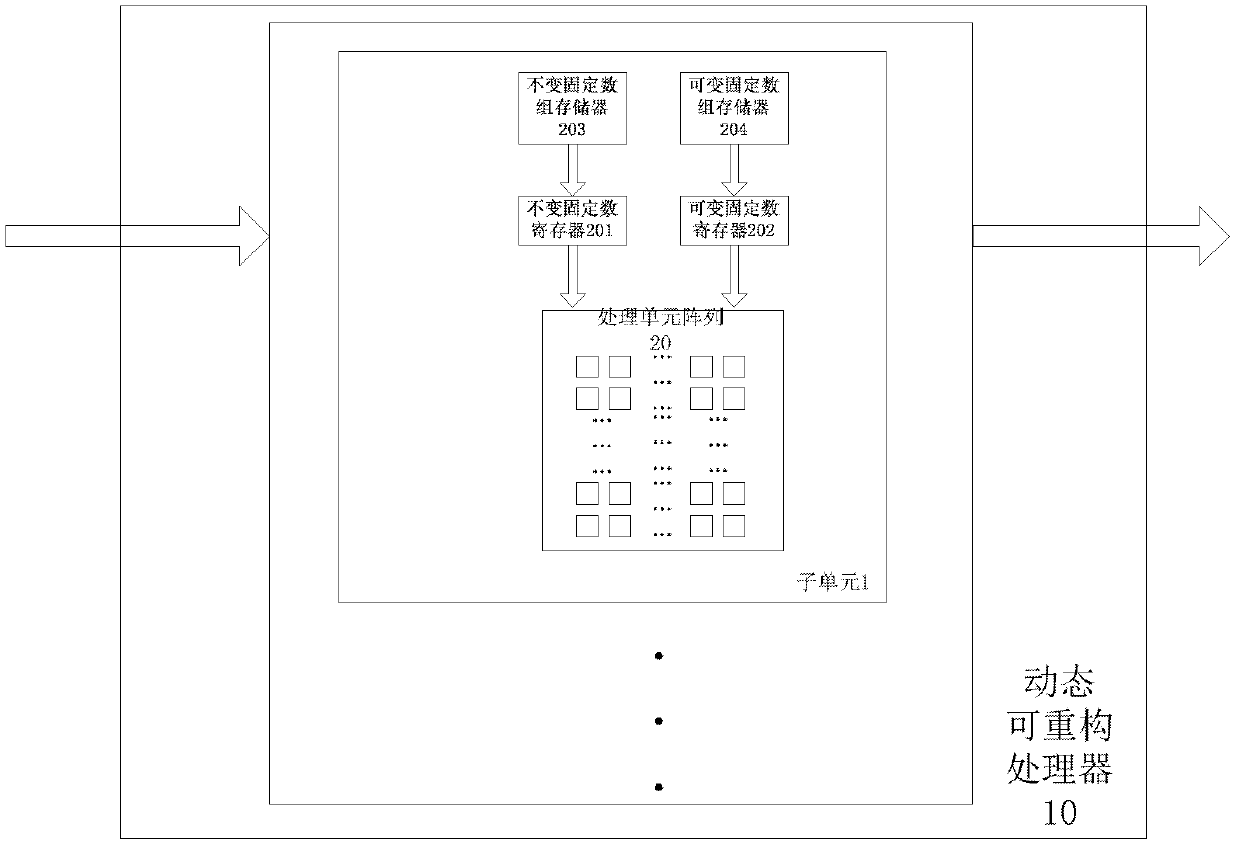

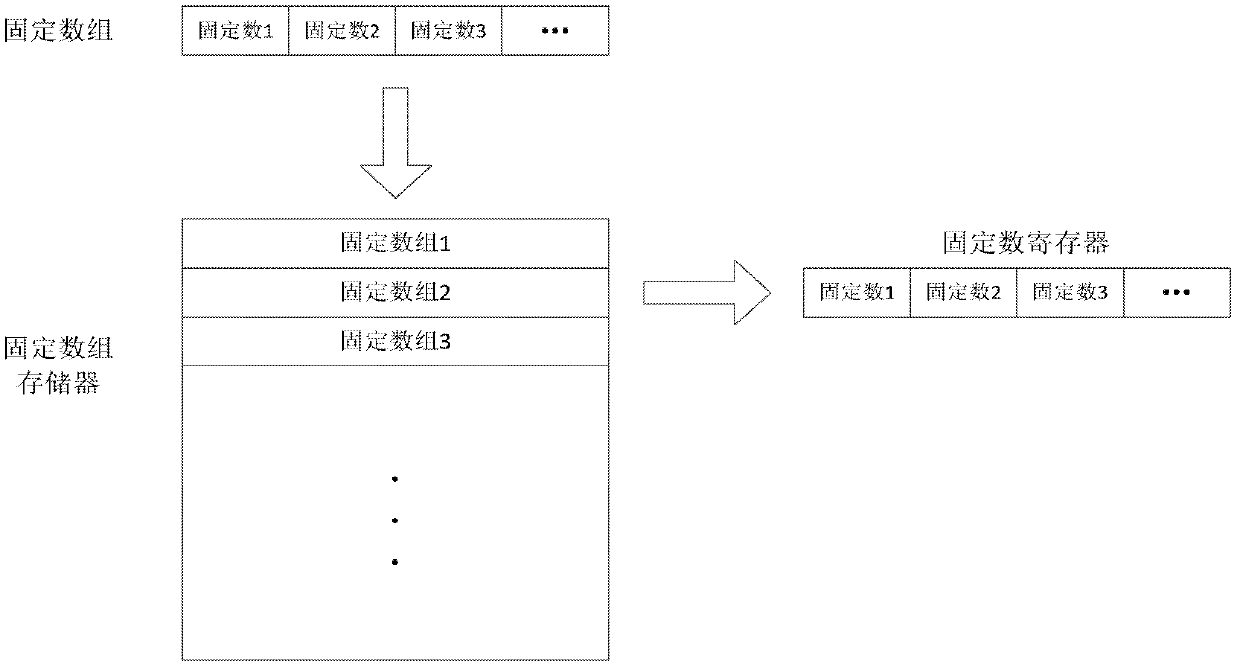

Dynamic re reconfigurable processor and fixed number calling method thereof

ActiveCN102184090ASave storage resourcesImprove calling efficiencyProgram controlMemory systemsArray data structureSpeed reading

Owner:TSINGHUA UNIV

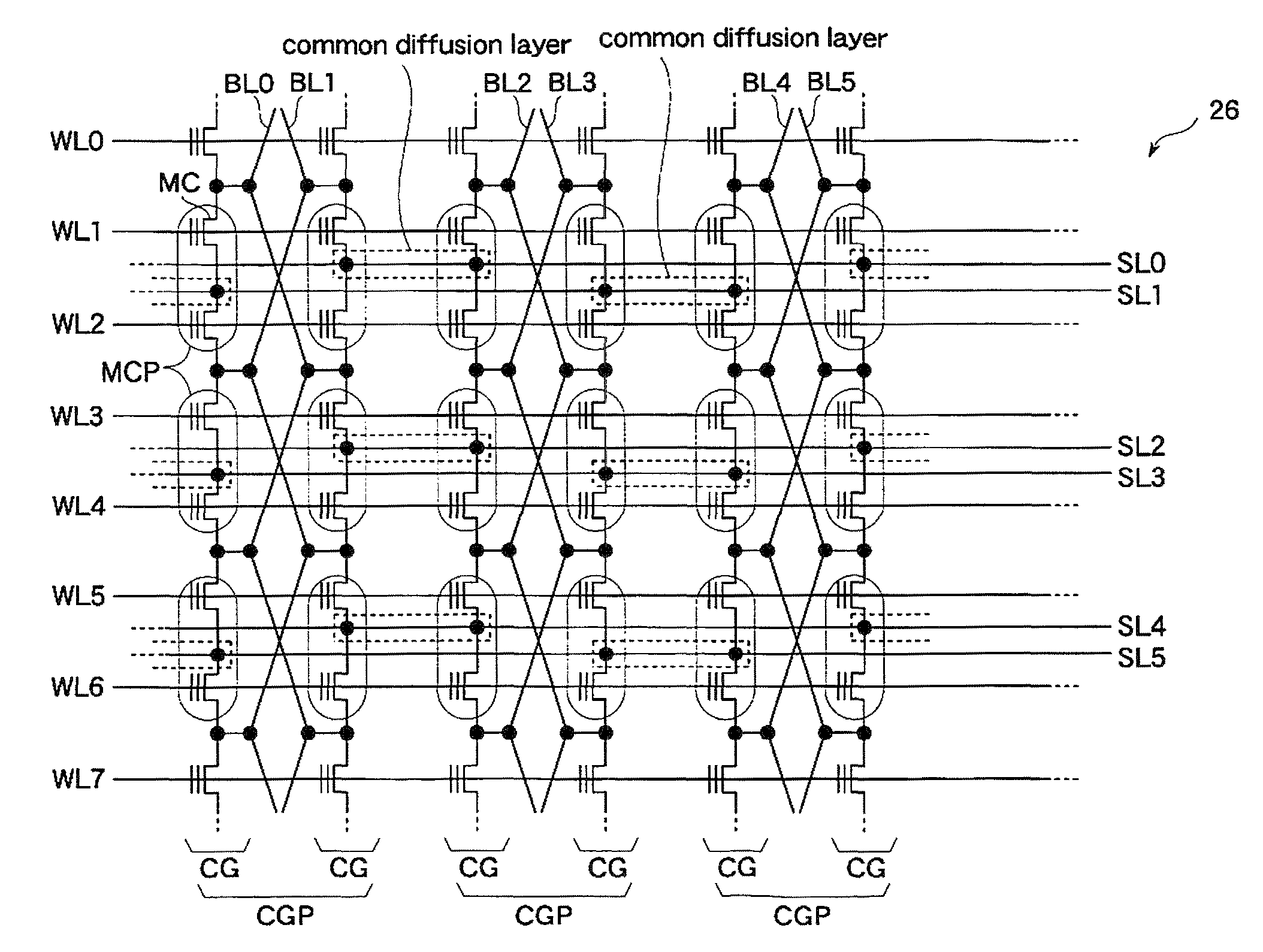

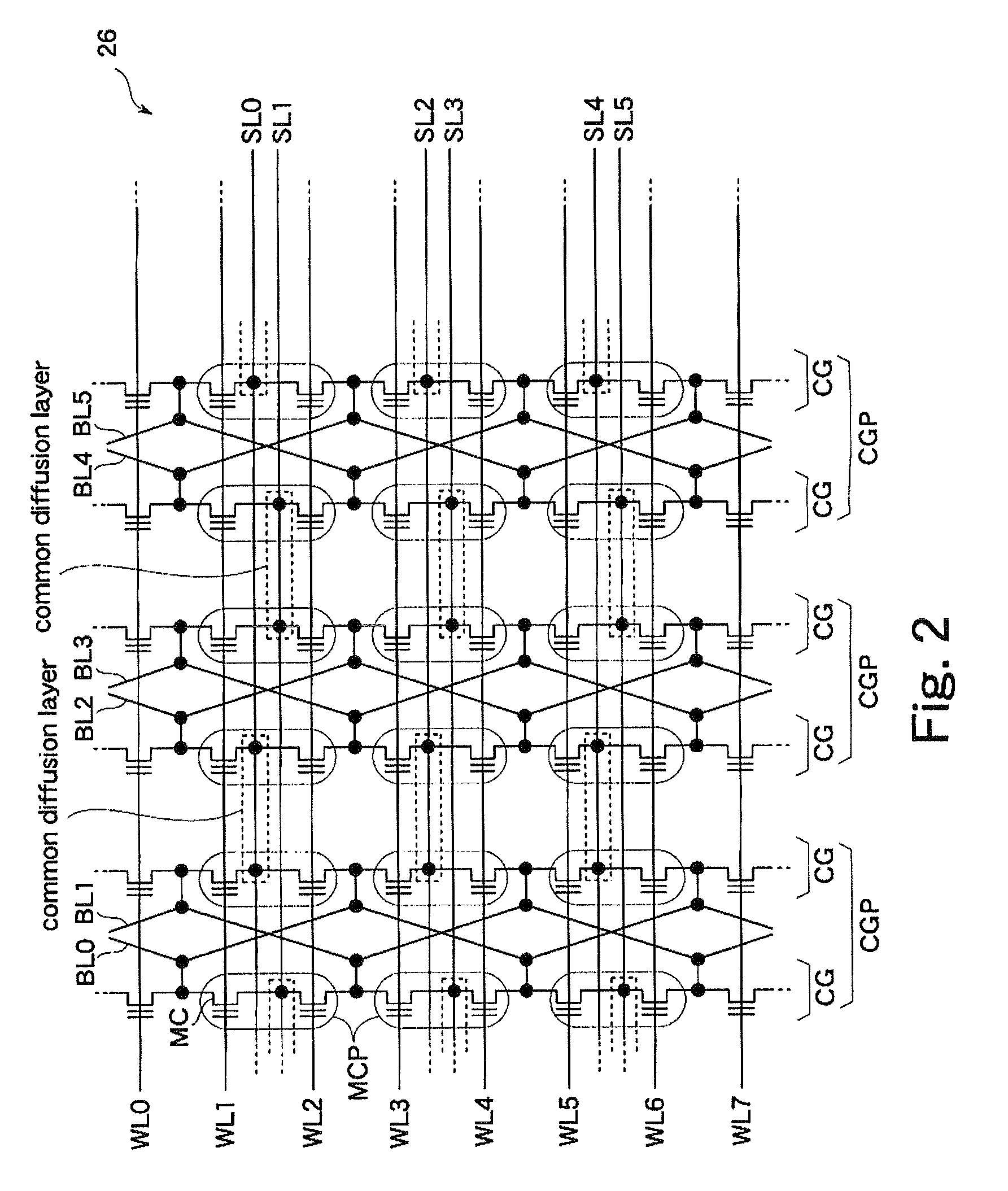

Nonvolatile memory cell array architecture for high speed reading

InactiveUS7864576B2Reduce chip sizeSmall sizeSolid-state devicesRead-only memoriesPower flowParallel computing

When different word lines are accessed sequentially, to perform access operations in parallel, a word decoder overlaps a part of activation periods of those word lines. That is, a nonvolatile semiconductor memory is capable of pipeline processing for performing access operations in parallel. All the combinations of bit lines and source lines that are connected to the drains and the sources of nonvolatile memory cells are different from each other. Therefore, even when plural word lines are activated to perform plural read operations in parallel, a memory cell current is allowed to flow only between the drain and the source of a nonvolatile memory cell concerned. As a result, random access in which desired nonvolatile memory cells are accessed sequentially is enabled in a nonvolatile semiconductor memory having a pipeline function for performing plural read operations in parallel.

Owner:SOCIONEXT INC

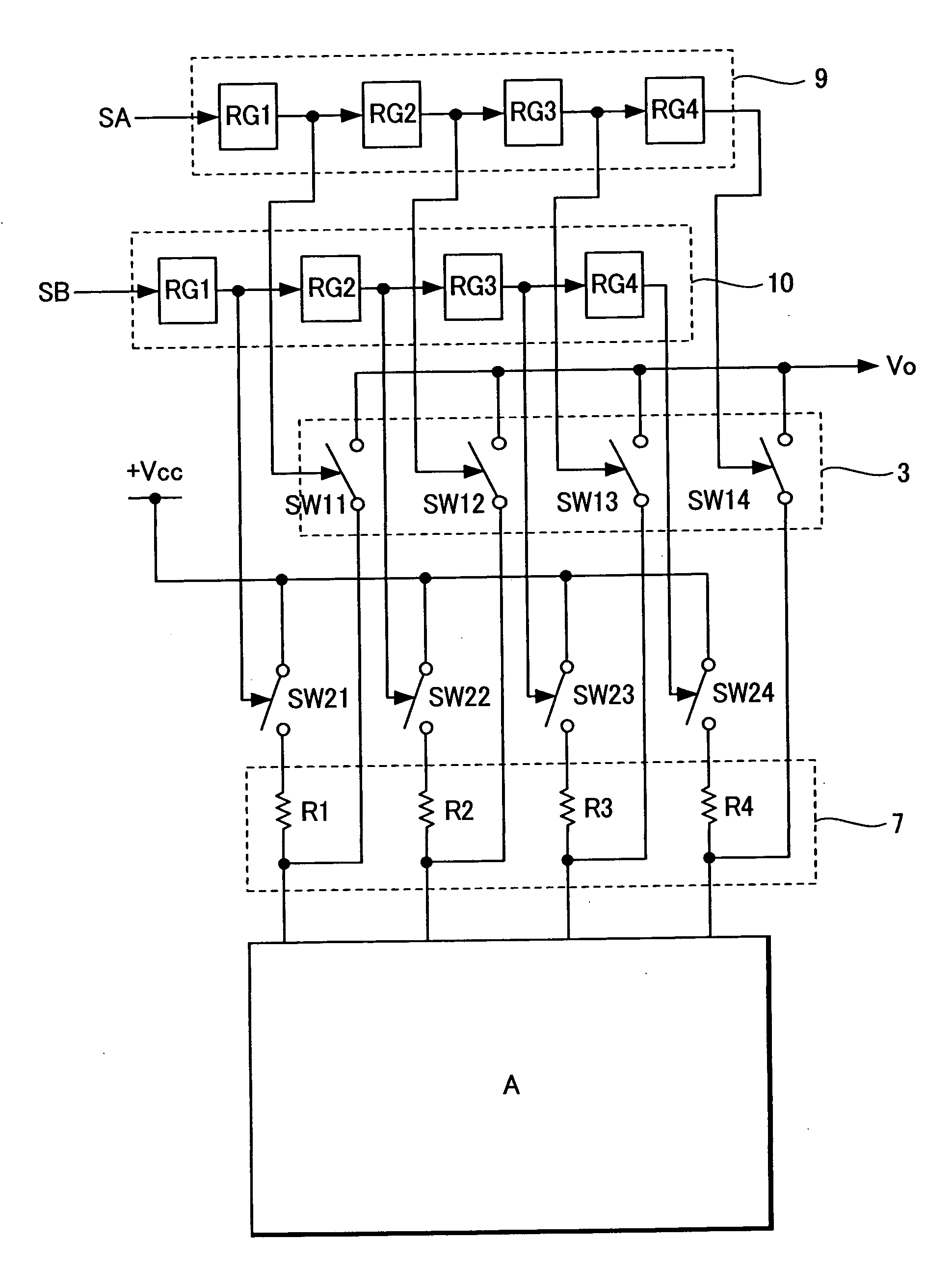

Method for driving semiconductor device, method and apparatus for driving load, and electronic apparatus

InactiveCN1956491AReduce crosstalk noiseTelevision system detailsTelevision system scanning detailsProcessor registerSpeed reading

The invention provides a method for driving a semiconductor device, a method and an apparatus for driving a load, and an electronic apparatus. When a signal is read from a CCD solid-state image pickup element, the CCD solid-state image pickup element is driven with at least two driving voltages so that high-speed reading is performed with generation of noise due to interference between the driving voltages reduced. The CCD solid-state image includes a charge storage section between a vertical transfer register and a horizontal transfer register. By performing the transfer of charge in the direction of columns during an effective transfer period of the transfer in the direction of rows, signal charge of one row generated by a light receiving sensor is transferred to the charge storage section, and by performing the transfer outside the effective transfer period in the transfer in the direction of the row, the signal charge of onerow transferred to the charge storage section is transferred to the horizontal transfer register.

Owner:SONY CORP

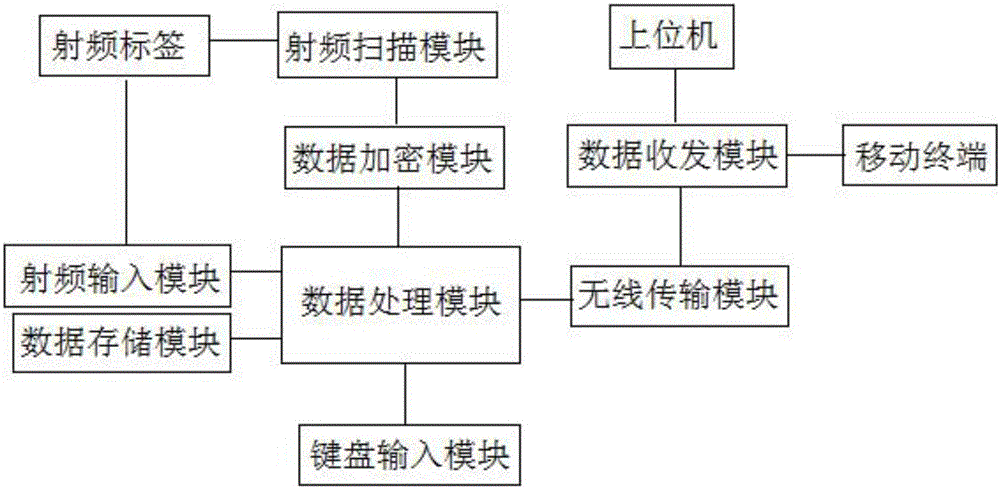

Communication management system based on radio frequency labels

ActiveCN106485178AAvoid easy lossInsufficient to avoid damageMemory record carrier reading problemsCo-operative working arrangementsComputer hardwareInformation processing

The invention discloses a communication management system based on radio frequency labels. The communication management system comprises a radio frequency label, a radio frequency scanning module, a radio frequency input module, a data encryption module, a data processing module, a data storage module, a wireless transmission module, a data transceiving module, a host computer, a mobile terminal and a keyboard input module. According to the invention, disadvantages that paper-based logistics bills are easy to loss and damage are overcome; smooth carrying out of the logistics is ensured; meanwhile, the radio frequency labels are non-contacted, so batch reading, remote reading and high-speed reading of logistic packages during logistical processes can be achieved; storage and transmission management of logistic objects is simplified; requirements for continuously increased information flow rates and information processing speed are met; and logistic efficiency is effectively increased.

Owner:珠海众能科技发展有限公司