High-speed interface and low-speed interface switching circuit and method based on FPGA (Field Programmable Gate Array)

A technology of interface conversion and high-speed interface, which is used in electrical digital data processing, instruments, etc., and can solve problems such as data rate and interface protocol mismatch.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

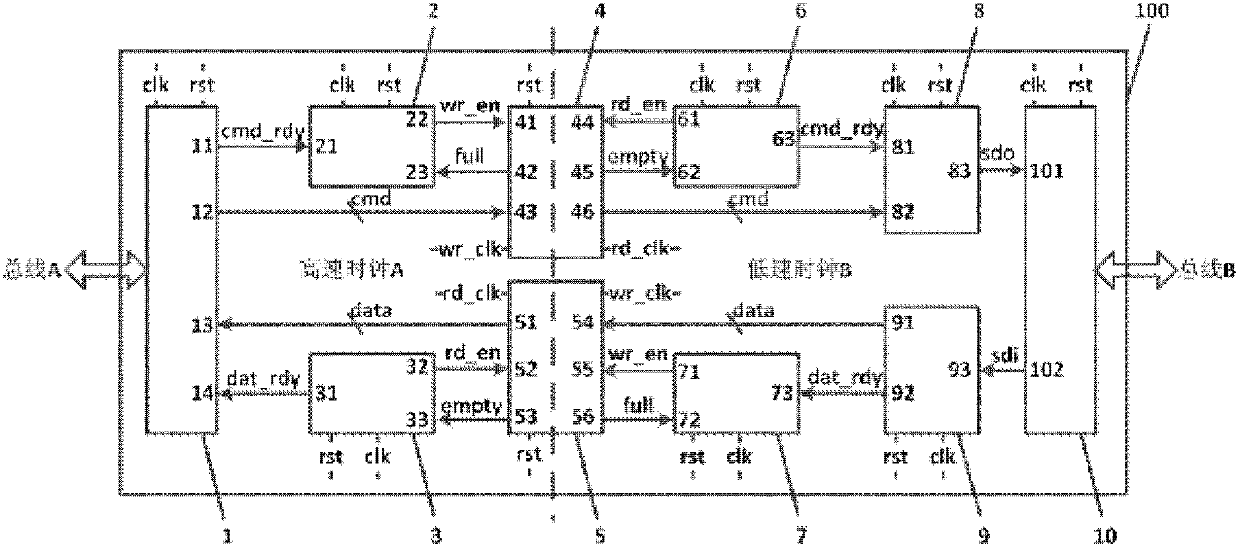

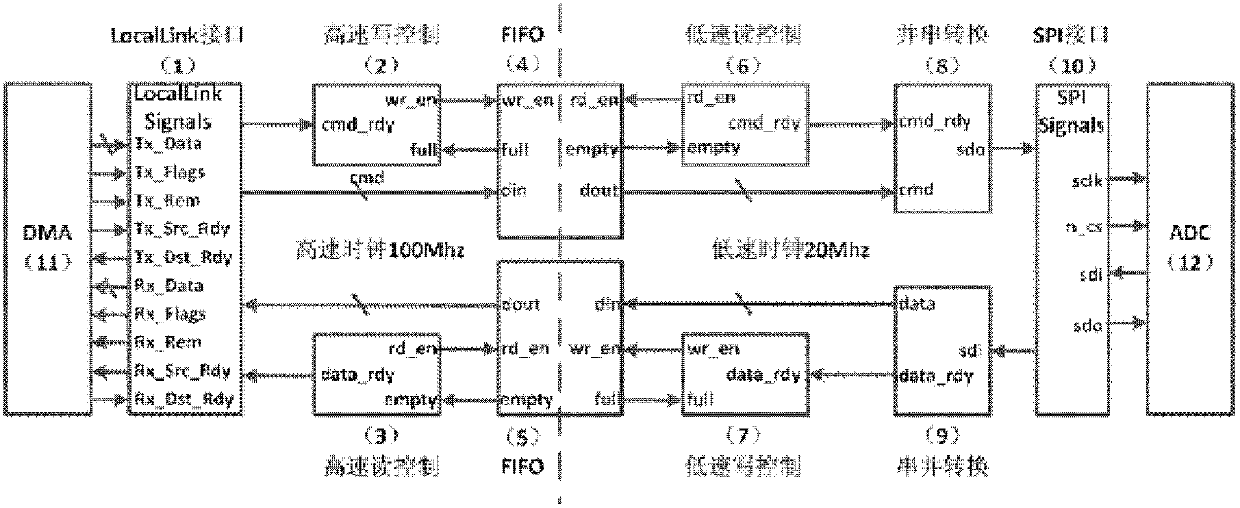

[0026] see figure 1 as shown, figure 1 It is a structural schematic diagram of the conversion circuit provided by the present invention. The conversion circuit 100 includes a high-speed parallel interface module 1, a high-speed write control module 2, a high-speed read control module 3, a first data cache FIFO read-write module 4, and a second data cache FIFO read-write module. Module 5 , low-speed read control module 6 , low-speed write control module 7 , parallel-to-serial conversion module 8 , serial-to-parallel conversion module 9 and low-speed serial interface module 10 . Among them, the high-speed parallel interface module 1 defines a set of protocol-independent control signals according to the characteristics of the parallel bus A to realize variable-length data packet transmission and data flow control; the high-speed write control module 2 is used to control the first data cache FIFO read-write module 4 of the data writing process; the high-speed read control module ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More