Patents

Literature

881 results about "Fpga implementations" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

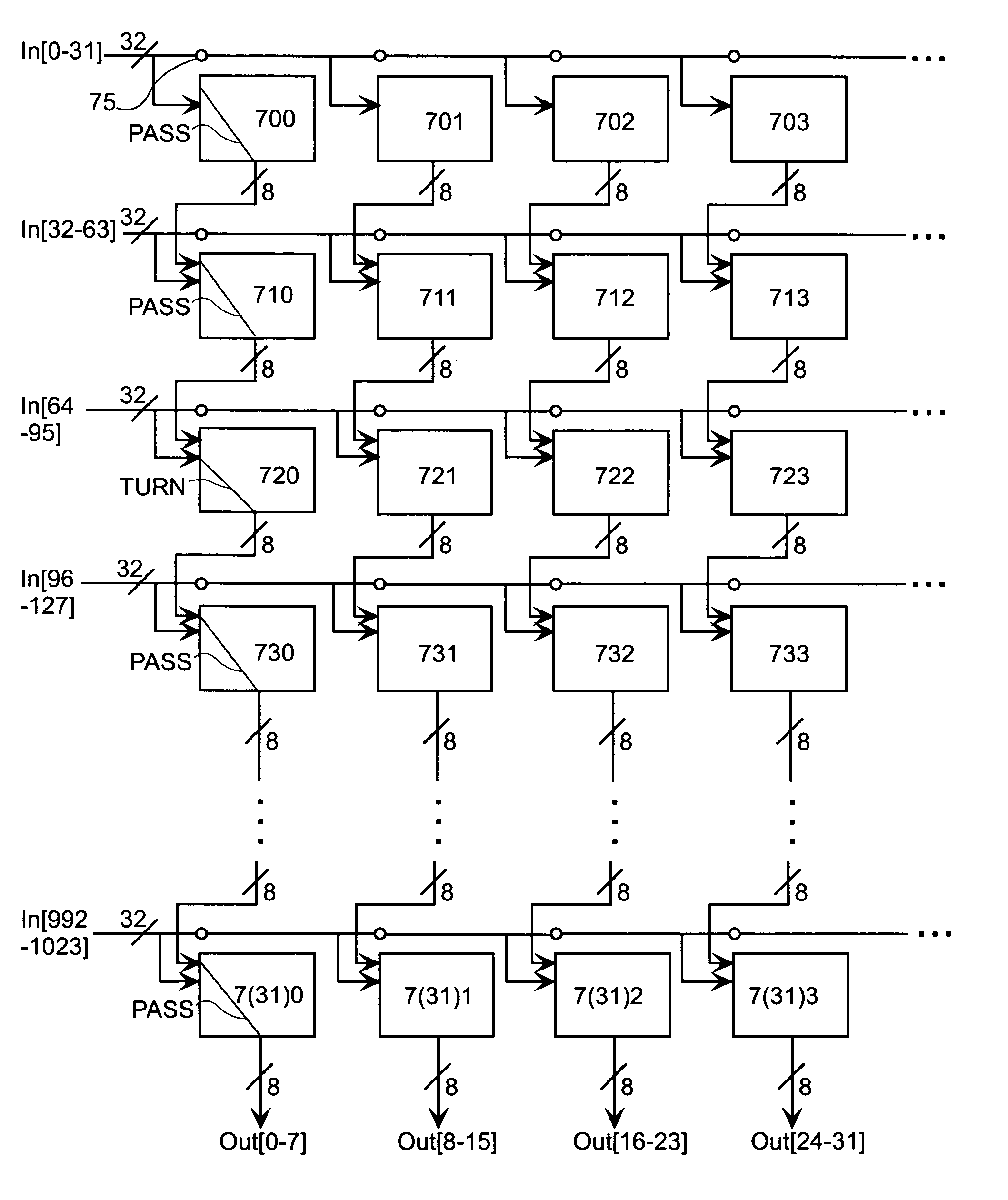

Directional two-dimensional router and interconnection network for field programmable gate arrays, and other circuits and applications of the router and network

ActiveUS20160344629A1Reduce switching delayLower latencyData switching networksNetwork sizeFpga implementations

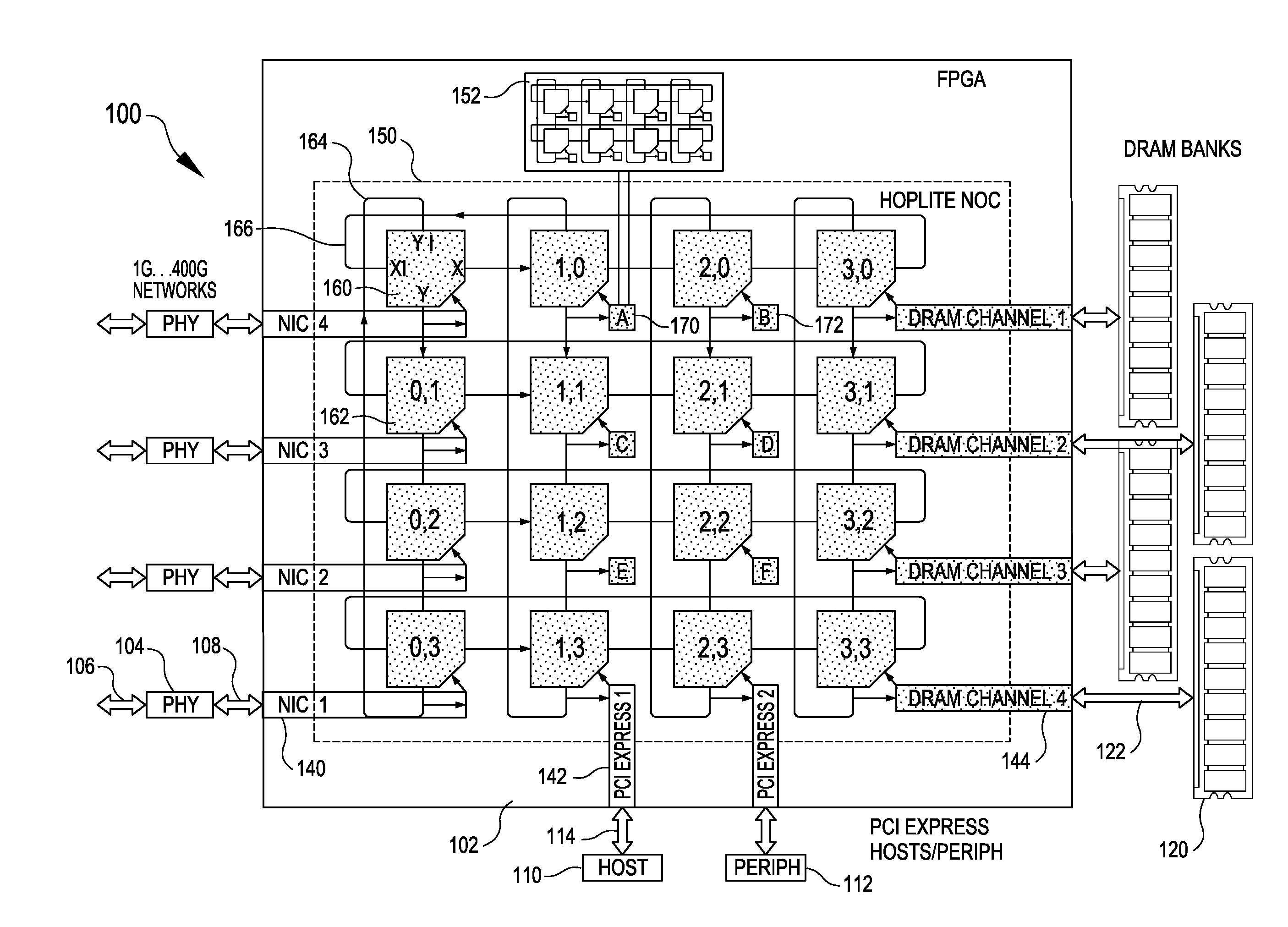

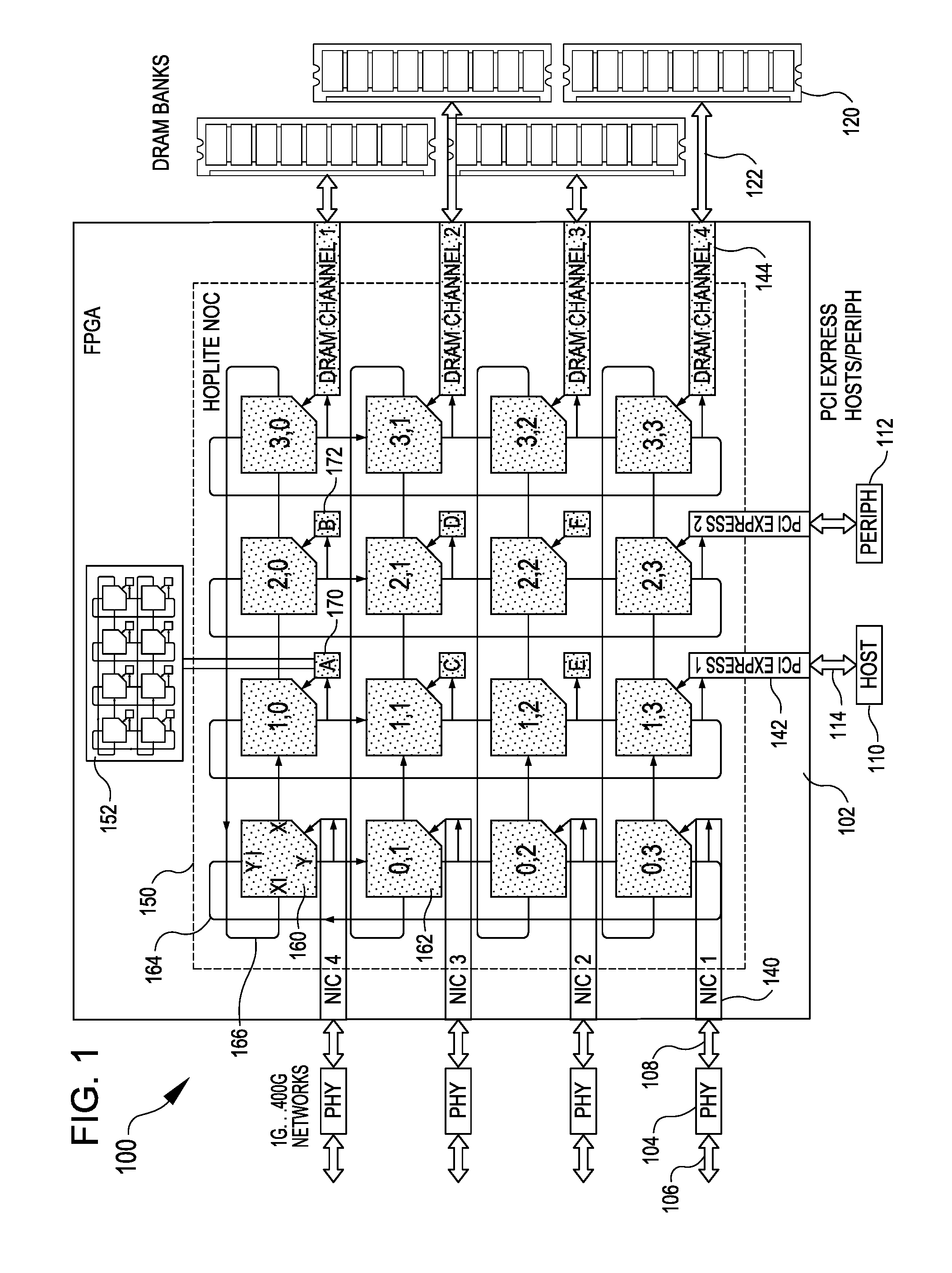

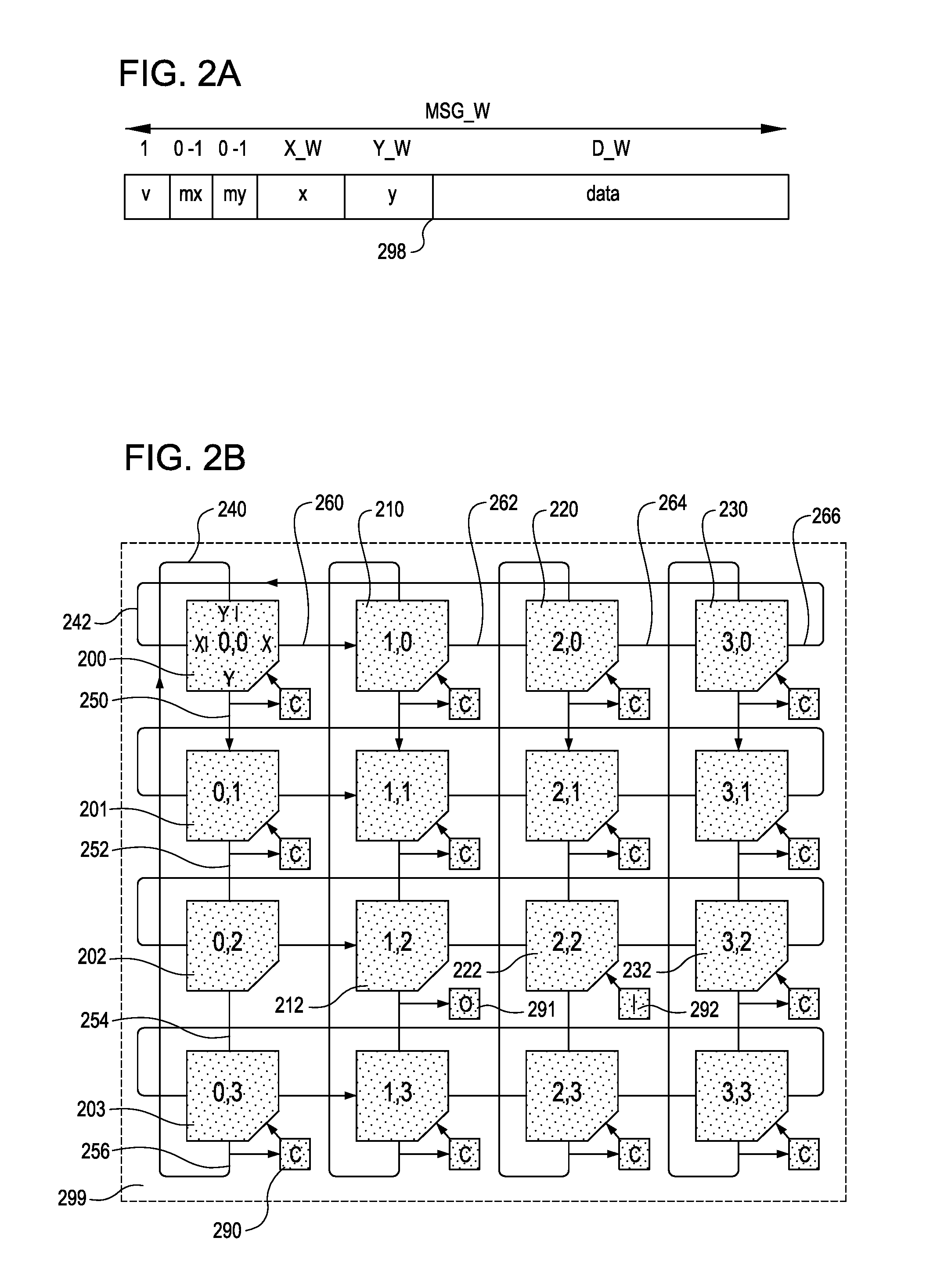

A configurable directional 2D router for Networks on Chips (NOCs) is disclosed. The router, which may be bufferless, is designed for implementation in programmable logic in FPGAs, and achieves theoretical lower bounds on FPGA resource consumption for various applications. The router employs an FPGA router switch design that consumes only one 6-LUT or 8-input ALM logic cell per router per bit of router link width. A NOC comprising a plurality of routers may be configured as a directional 2D torus, or in diverse ways, network sizes and topologies, data widths, routing functions, performance-energy tradeoffs, and other options. System on chip designs may employ a plurality of NOCs with different configuration parameters to customize the system to the application or workload characteristics. A great diversity of NOC client cores, for communication amongst various external interfaces and devices, and on-chip interfaces and resources, may be coupled to a router in order to efficiently communicate with other NOC client cores. The router and NOC enable feasible FPGA implementation of large integrated systems on chips, interconnecting hundreds of client cores over high bandwidth links, including compute and accelerator cores, industry standard IP cores, DRAM / HBM / HMC channels, PCI Express channels, and 10G / 25G / 40G / 100G / 400G networks.

Owner:GRAY RES LLC

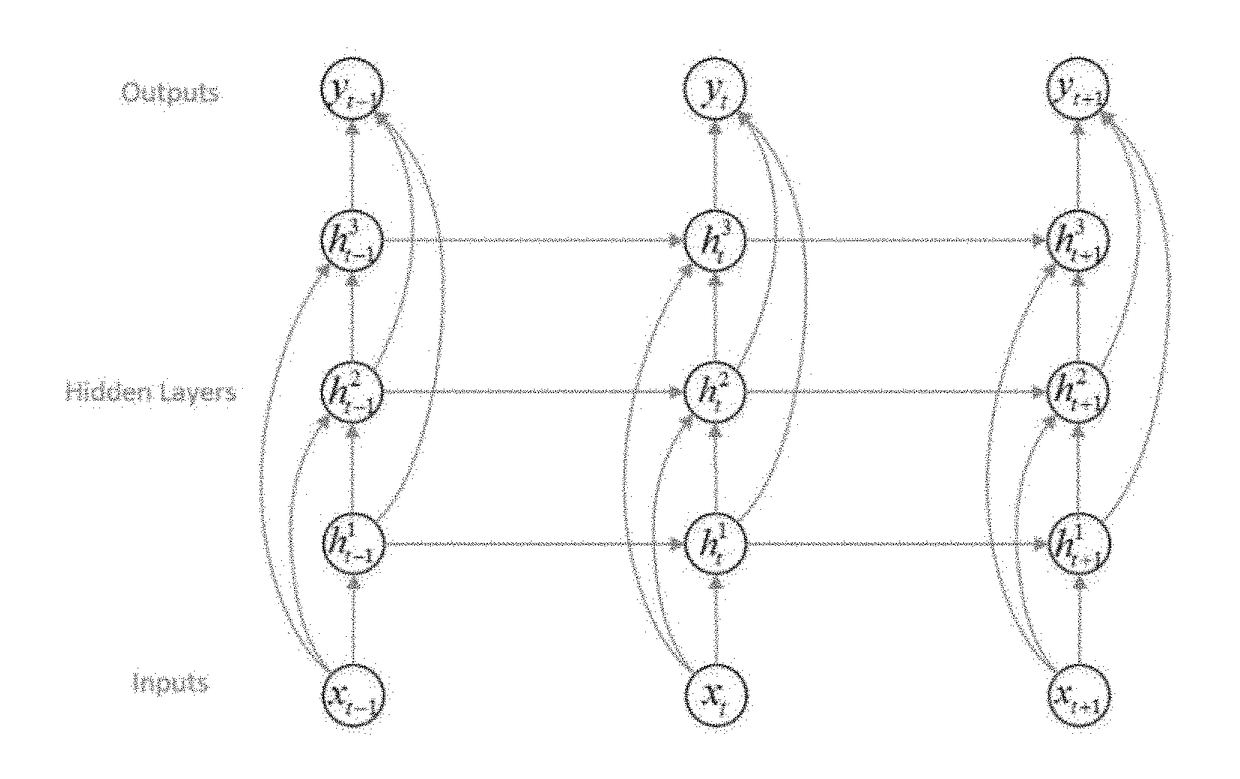

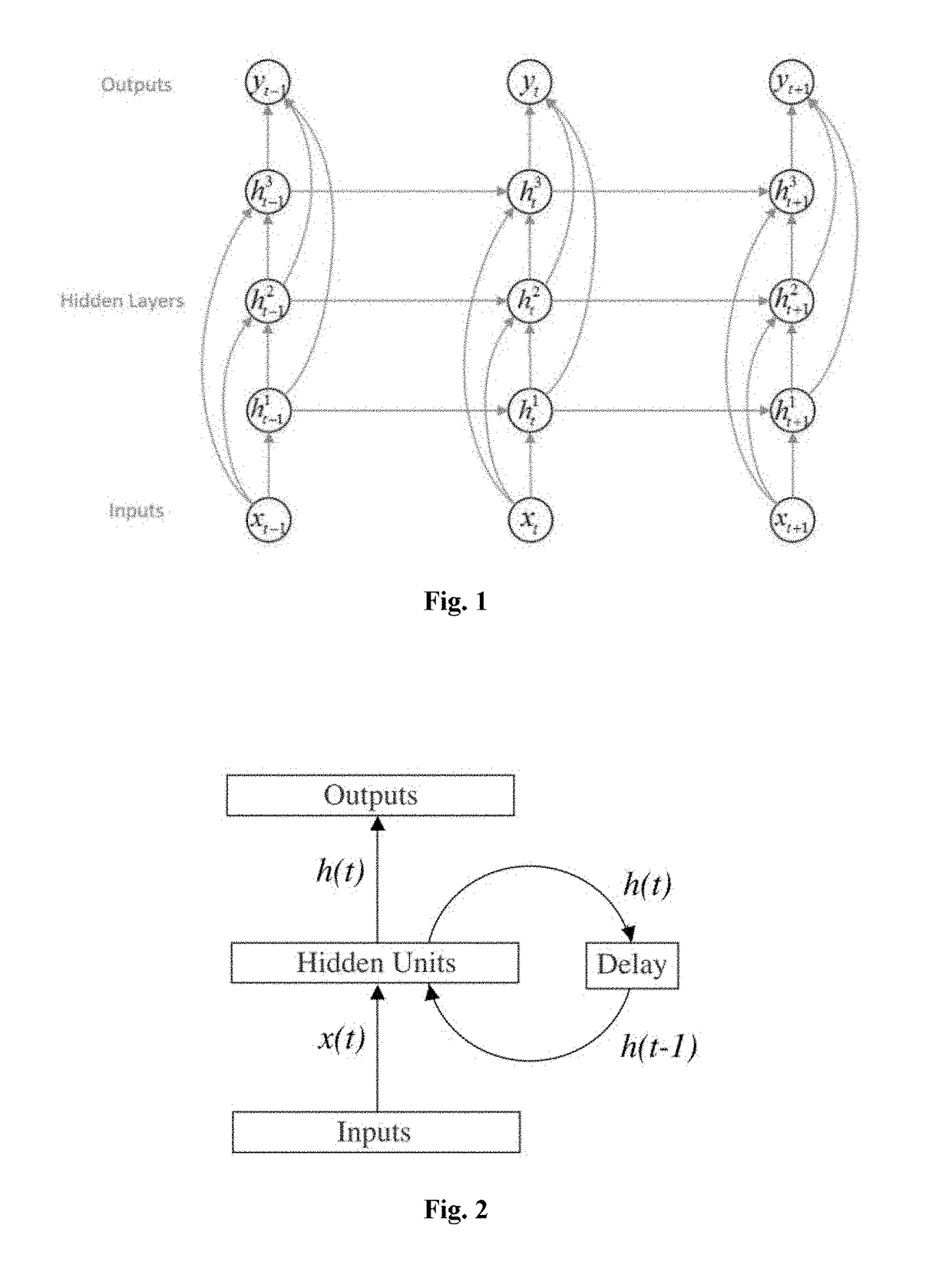

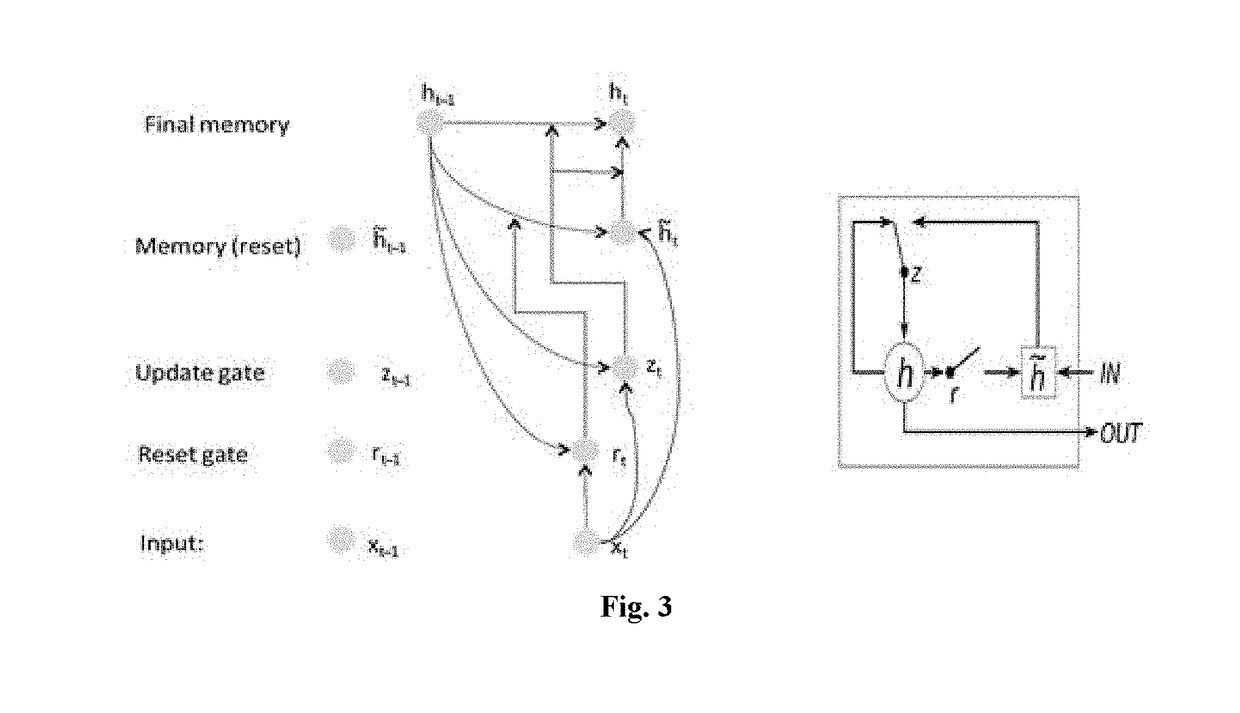

Hardware accelerator and method for realizing sparse GRU neural network based on FPGA

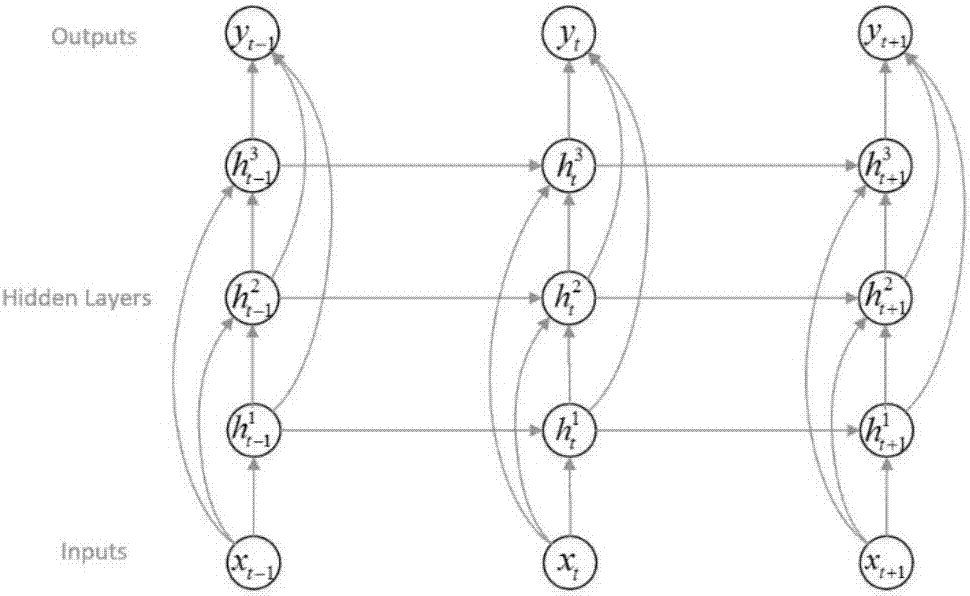

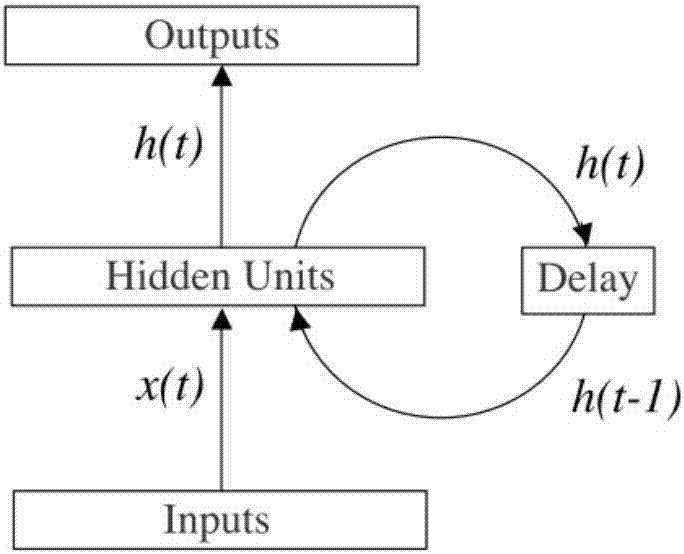

The invention provides a hardware accelerator and method for realizing a sparse GRU neural network based on FPGA. According to the invention, an apparatus for realizing sparse GRU neural network includes: an input receiving unit which is intended for receiving a plurality of input vectors and distributing the plurality of input vectors to a plurality of computing units; a plurality of computing units which acquire input vectors from the input receiving unit, read weight matrix data of a neural network, decoding the weight matrix data and conduct matrix calculation on the decoded weight matrix data and the input vectors, and output the result of the matrix calculation to a hidden layer state computing module; a hidden layer state computing module which acquires the result of matrix calculation from the computing units PE, and computing the state of the hidden layer; and a control unit which is intended for global control. In addition, the invention also provides a method for realizing sparse GRU neural network through iteration.

Owner:XILINX INC

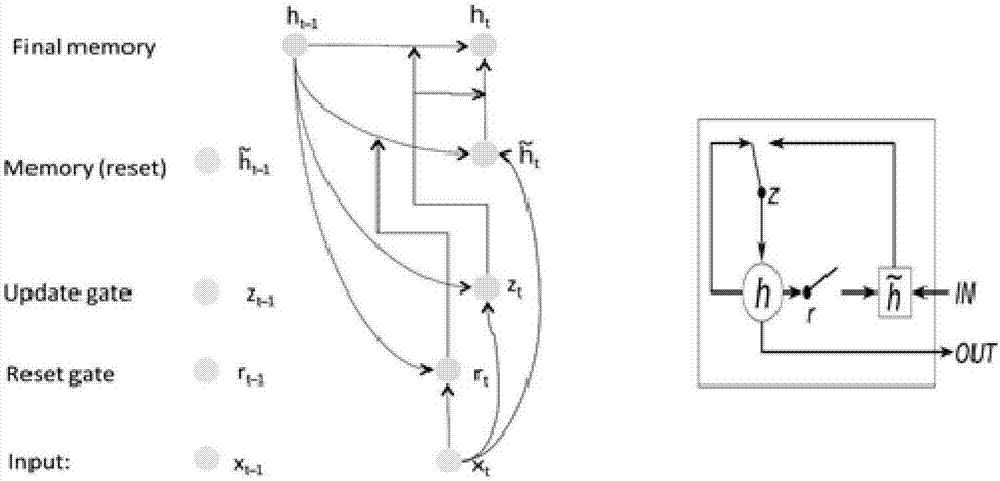

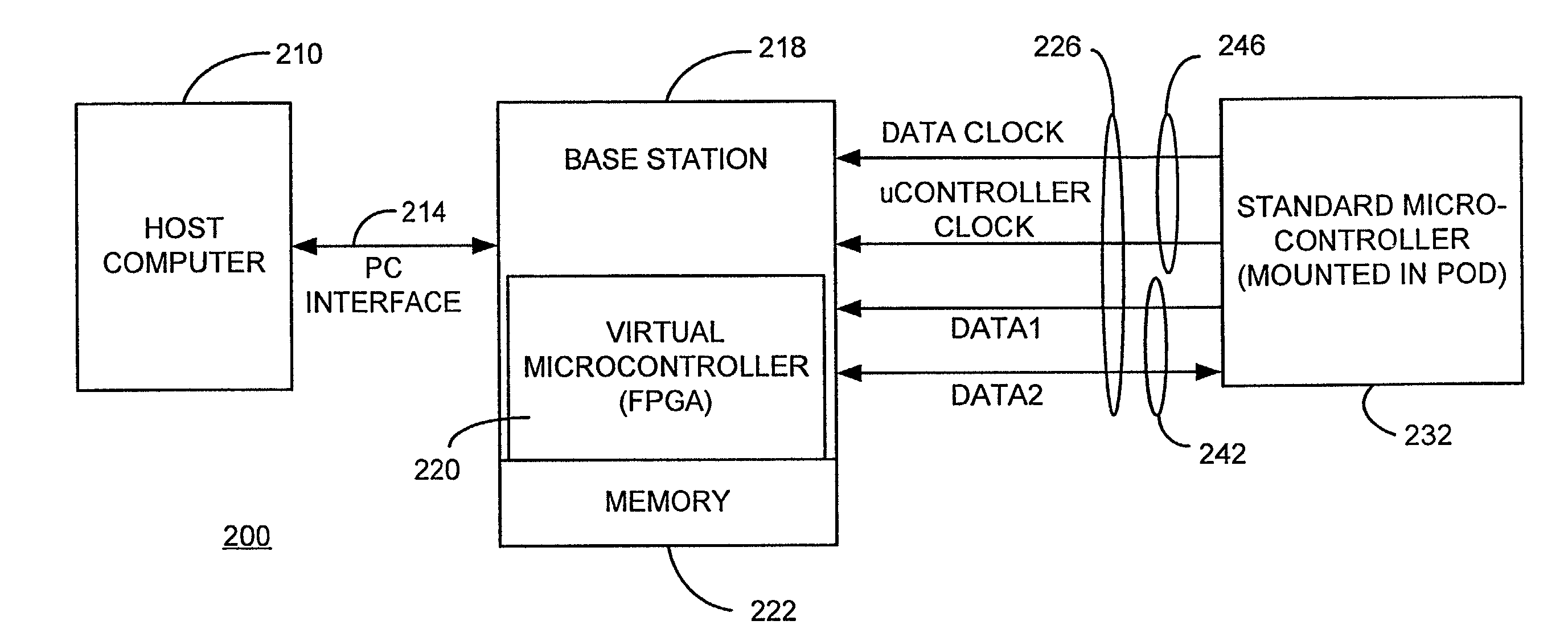

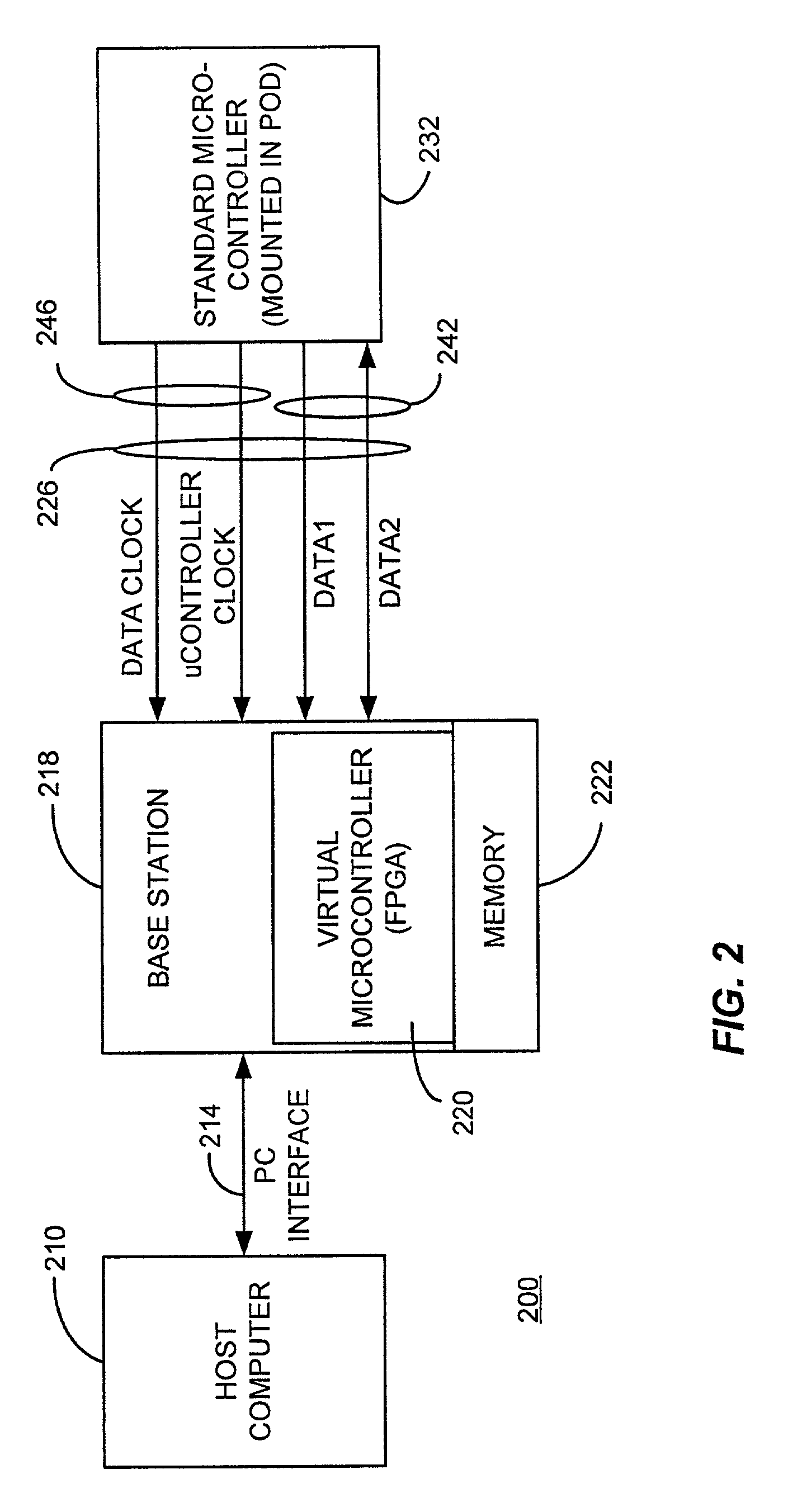

Capturing test/emulation and enabling real-time debugging using an FPGA for in-circuit emulation

ActiveUS7188063B1Improve abilitiesEliminate needError detection/correctionComputer aided designMicrocontrollerFpga implementations

A method for obtaining real-time debug information, e.g., state information and trace information, from an FPGA acting as a virtual microcontroller that is attached to a microcontroller under test. The two devices, the microcontroller and the FPGA execute the same instructions in lock-step with the FPGA acting as an emulator. The FPGA emulates the actual microcontroller and relieves the actual microcontroller from having debug logic installed thereon. FPGA and microcontroller, are coupled using a four pin interface. The FPGA is directly coupled to the PC for both programming and control. The system is implemented such that the microcontroller forwards information regarding I / O reads, interrupt vector information and watchdog information to the FPGA in time before the execution of the next instruction. Thus, the FPGA has an exact copy of the state information of the microcontroller.

Owner:MONTEREY RES LLC

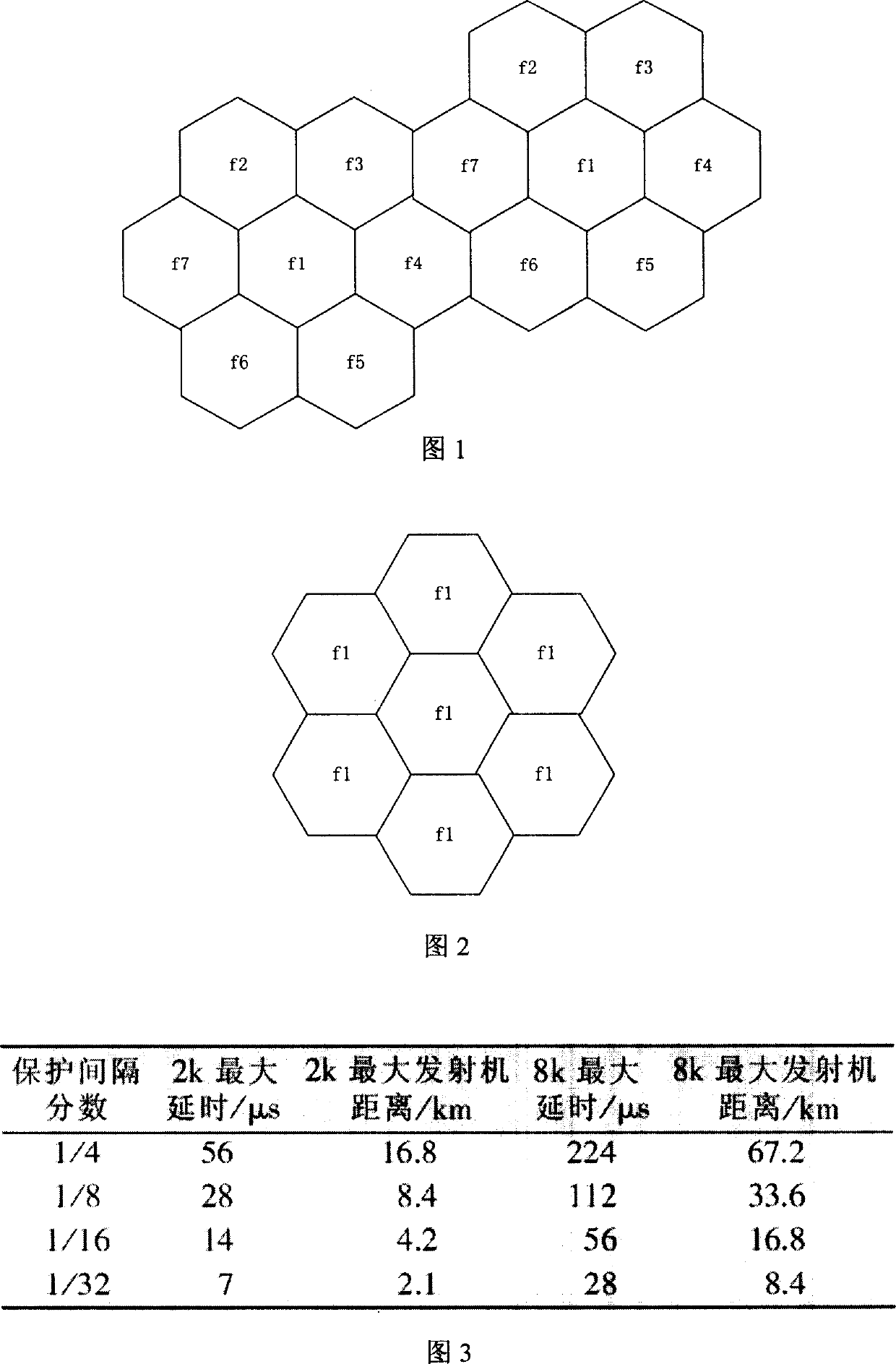

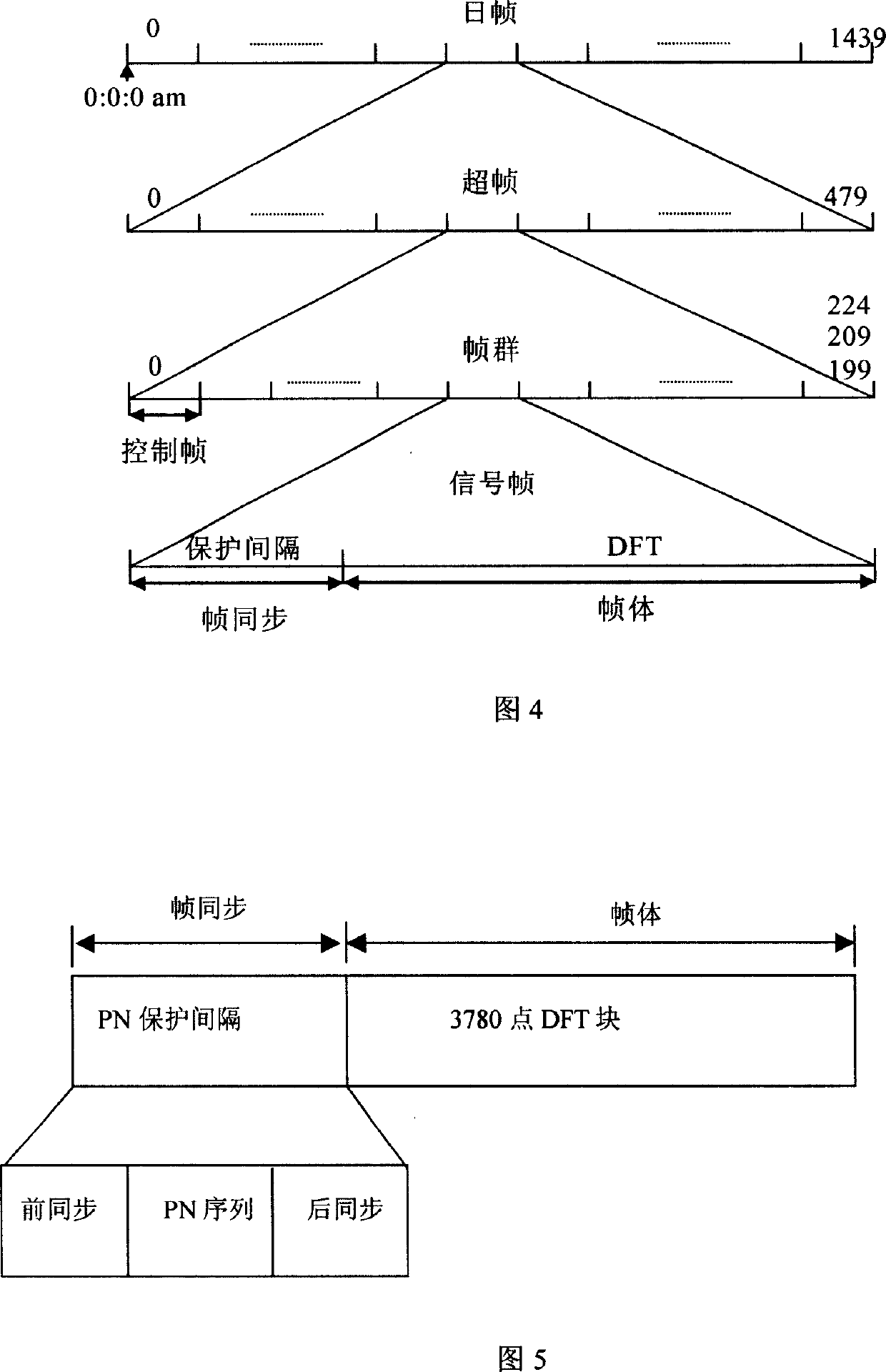

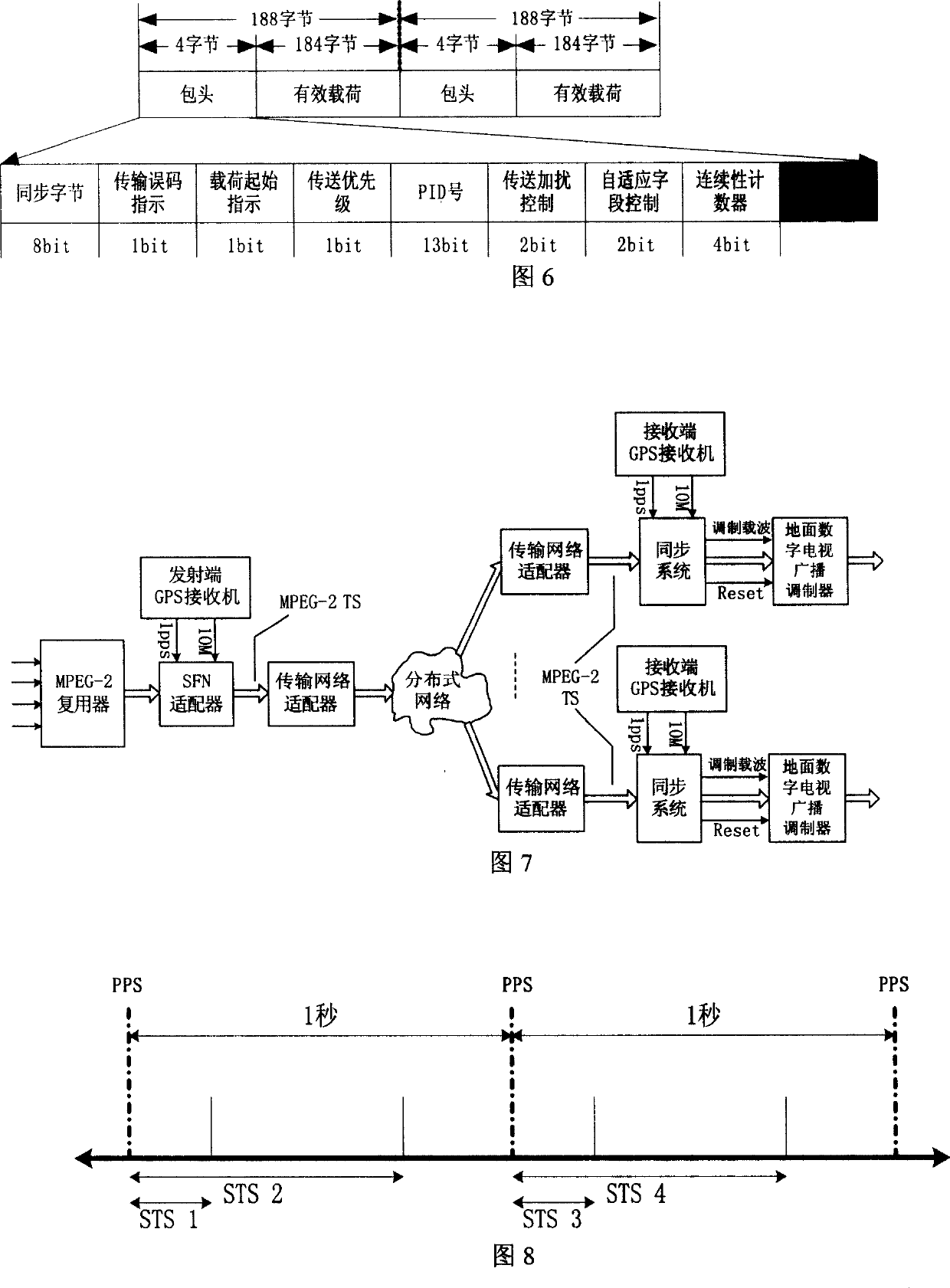

Single-frequency network system of ground digital TV broadcast and its realizing method

InactiveCN1678068APulse modulation television signal transmissionOrthogonal multiplexFpga implementationsSynchronization system

The system comprises three parts: adapter in single frequency network, GPS receiver, and modulator of supporting ground digital TV broadcasting in single frequency network. At central transmitting terminal, the adapter inserts MIP packets in transmission code stream. MIP packet carries synchronizing time label relevant to GPS receiver and system maximal time delay to each relay station etc. In each relay station, synchronization system detects M1P packets, reading out time label and maximal time delay, measuring time delay of received signal, calculating out additional time delay. According to the additional time delay, TS flow is delayed properly in order to make signal synchronization again among relay stations. The disclosed scheme is realized through FPGA, and is applied to ground digital multiple media broadcasting transmission system forwaded by Tsinghua Univ. Favorable effect is obtained through actual try.

Owner:TSINGHUA UNIV

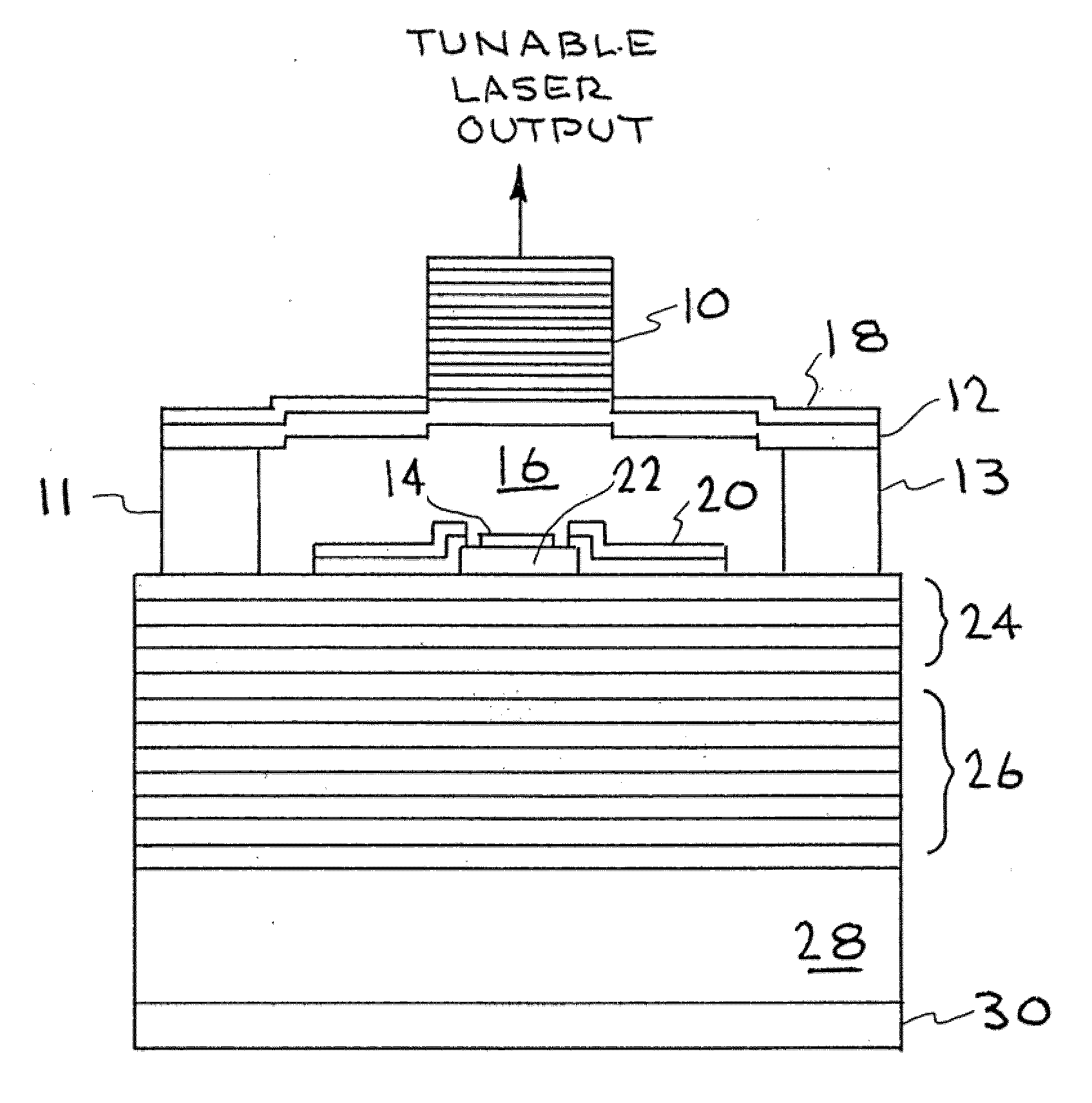

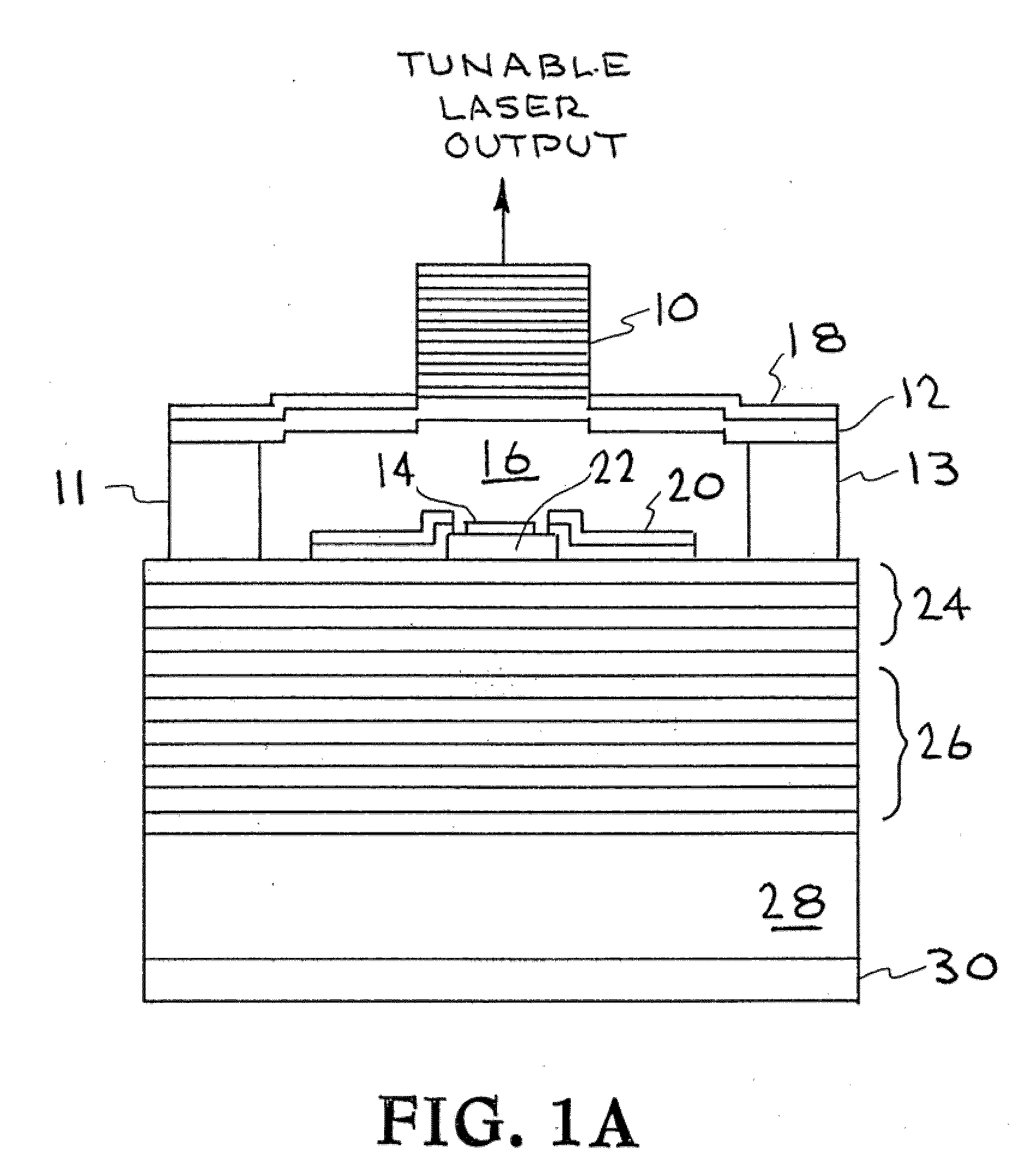

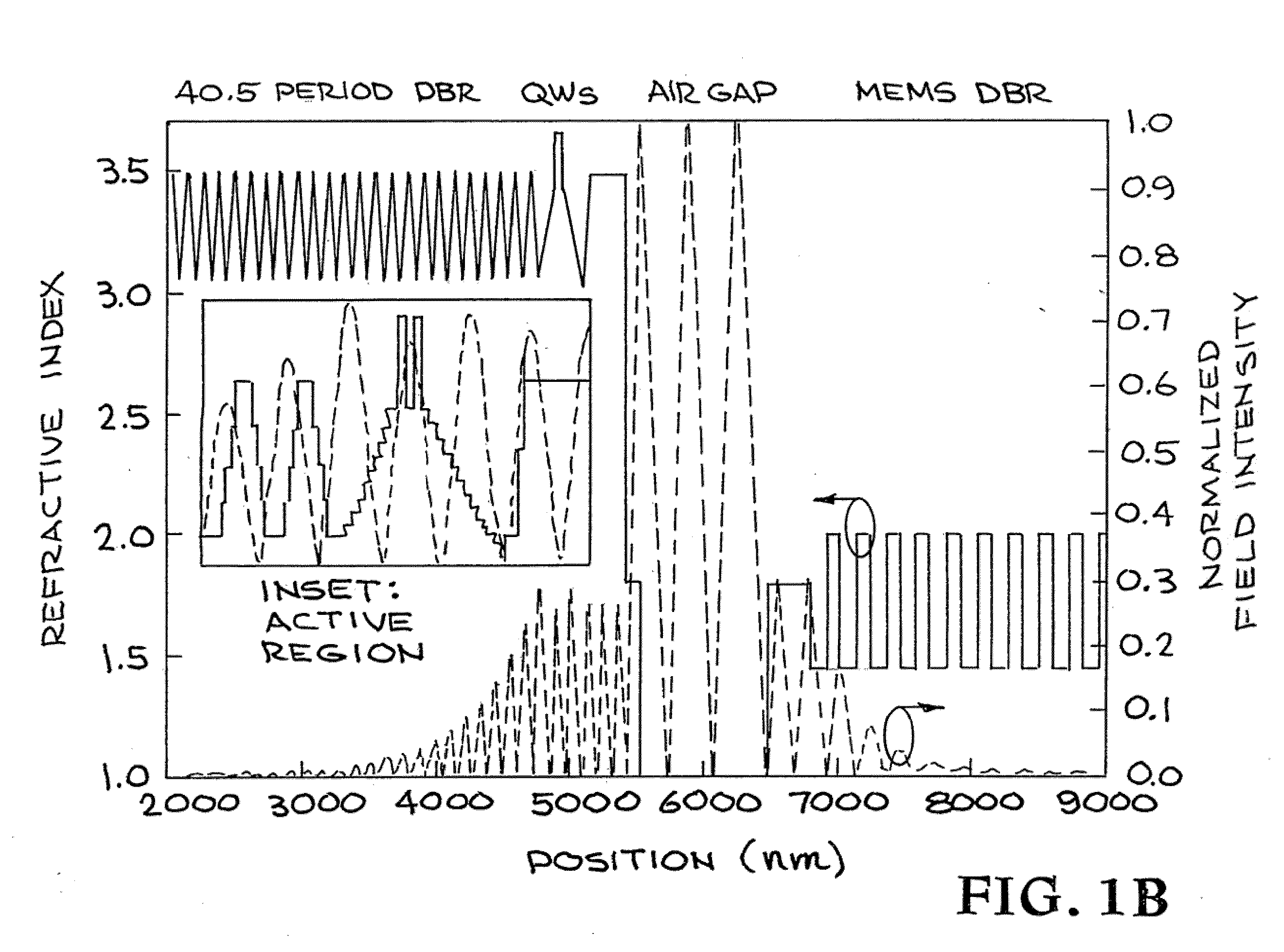

Tunable photonic cavities for in-situ spectroscopic trace gas detection

Compact tunable optical cavities are provided for in-situ NIR spectroscopy. MEMS-tunable VCSEL platforms represents a solid foundation for a new class of compact, sensitive and fiber compatible sensors for fieldable, real-time, multiplexed gas detection systems. Detection limits for gases with NIR cross-sections such as O2, CH4, COx and NOx have been predicted to approximately span from 10ths to 10s of parts per million. Exemplary oxygen detection design and a process for 760 nm continuously tunable VCSELS is provided. This technology enables in-situ self-calibrating platforms with adaptive monitoring by exploiting Photonic FPGAs.

Owner:LAWRENCE LIVERMORE NAT SECURITY LLC

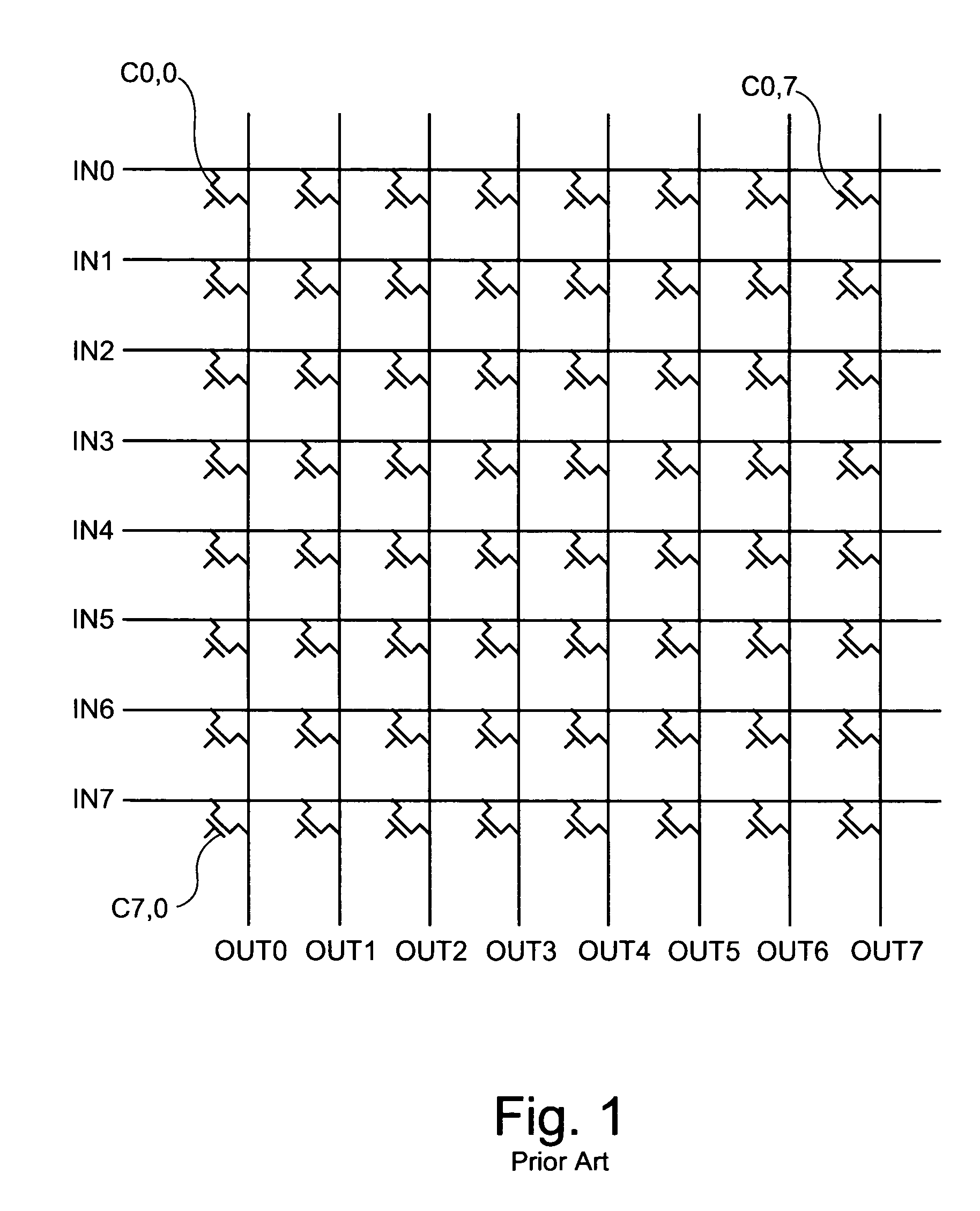

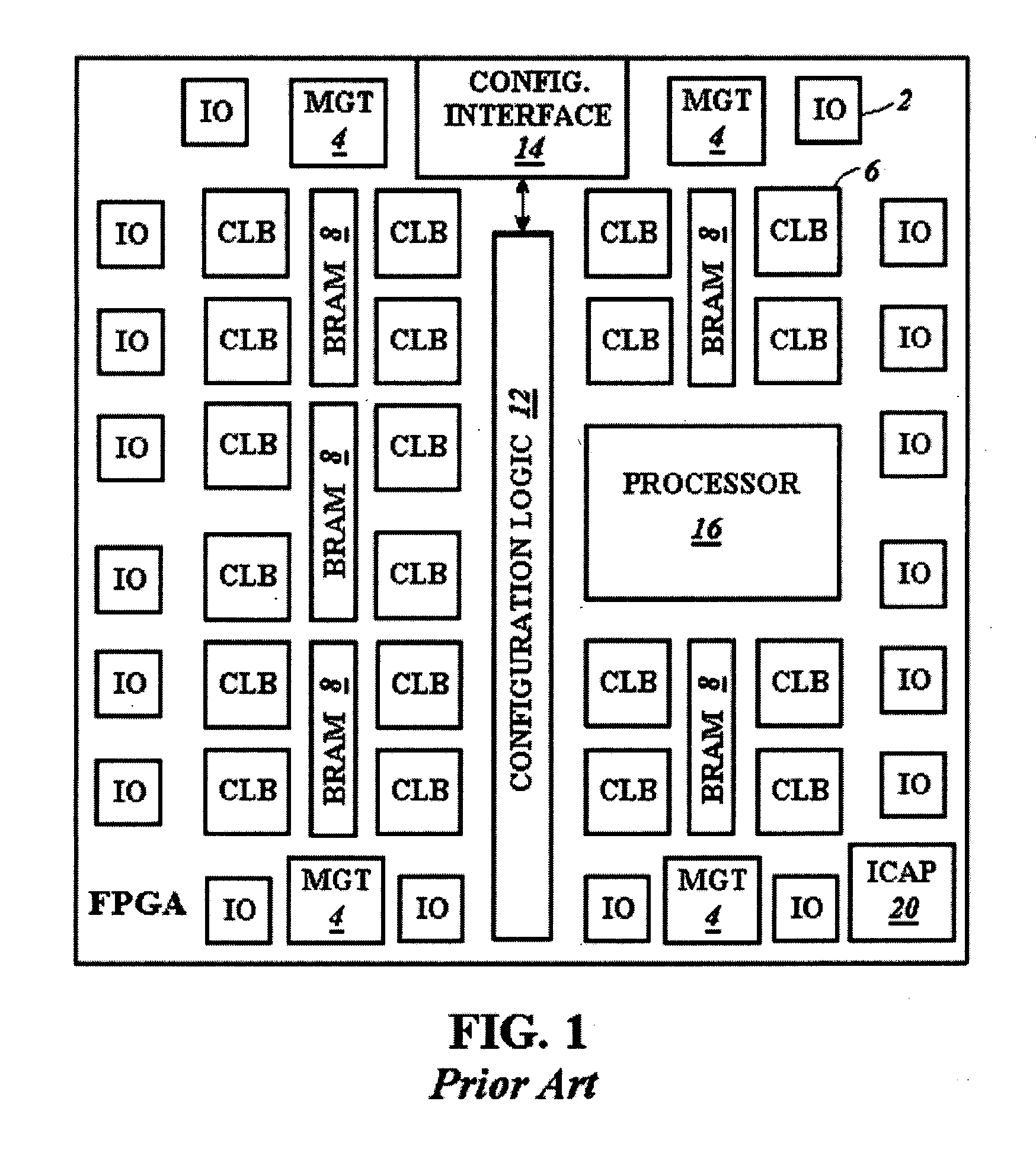

Large crossbar switch implemented in FPGA

InactiveUS7057413B1Increases the amount of logic the FPGA can processMultiplex system selection arrangementsSolid-state devicesCrossbar switchFpga implementations

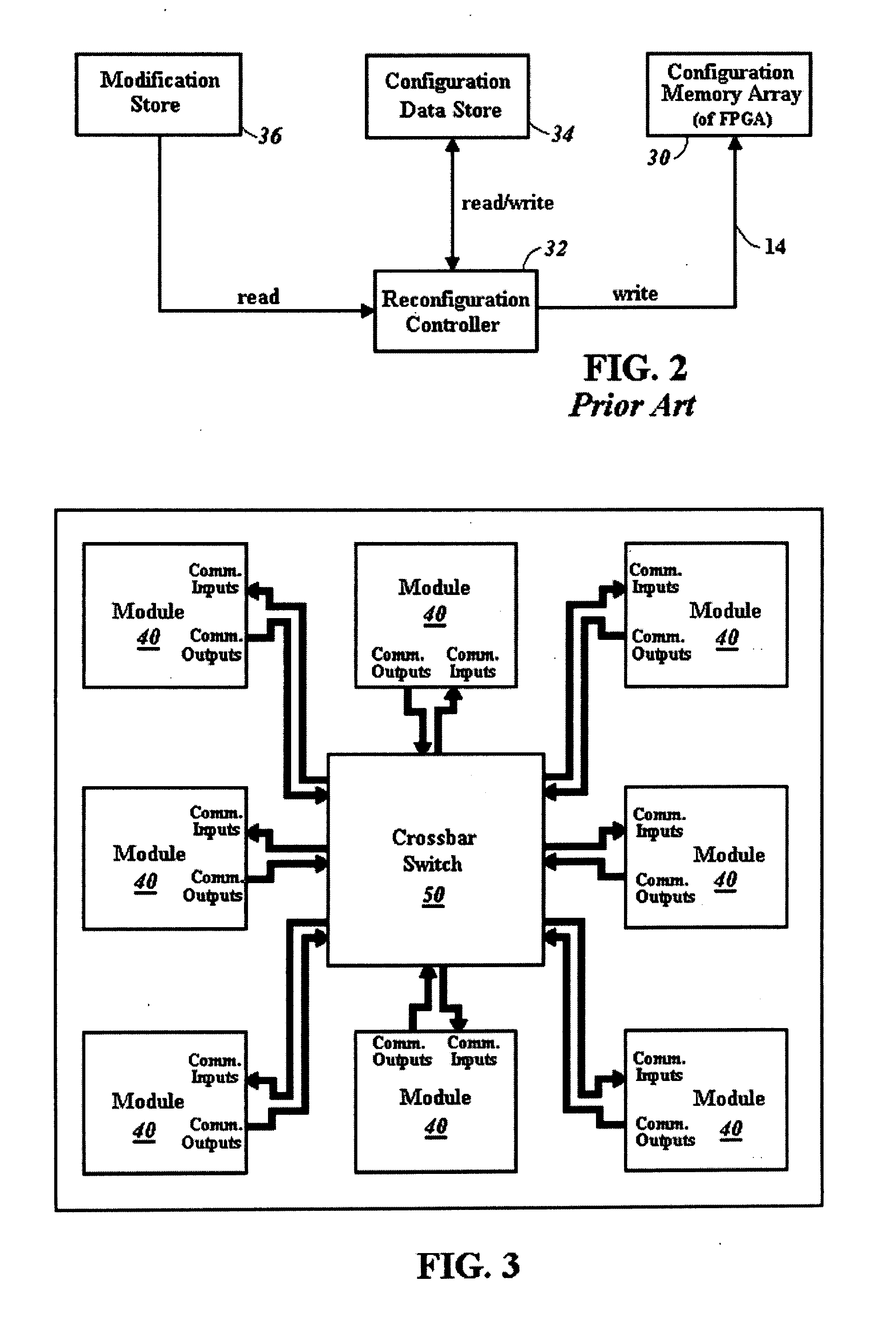

A method for using an FPGA to implement a crossbar switch is described. Rather than using signals routed through the general FPGA routing resources to control connectivity of the crossbar switch, the input signals only carry crossbar switch data, and the connectivity is controlled by FPGA configuration data. The crossbar switch is implemented in two parts: a template of basic and constant routing to carry input signals through the switch array in one dimension and output signals from the array in another dimension, and a connectivity part controlled by a connectivity table or algorithm to generate partial reconfiguration bitstreams that determine which of the input signals is to be connected to which of the output signals.

Owner:XILINX INC

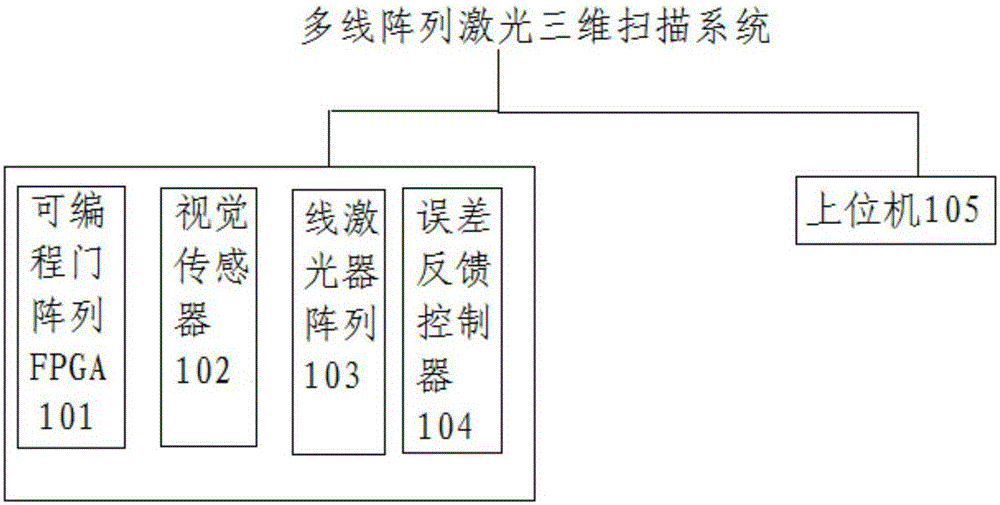

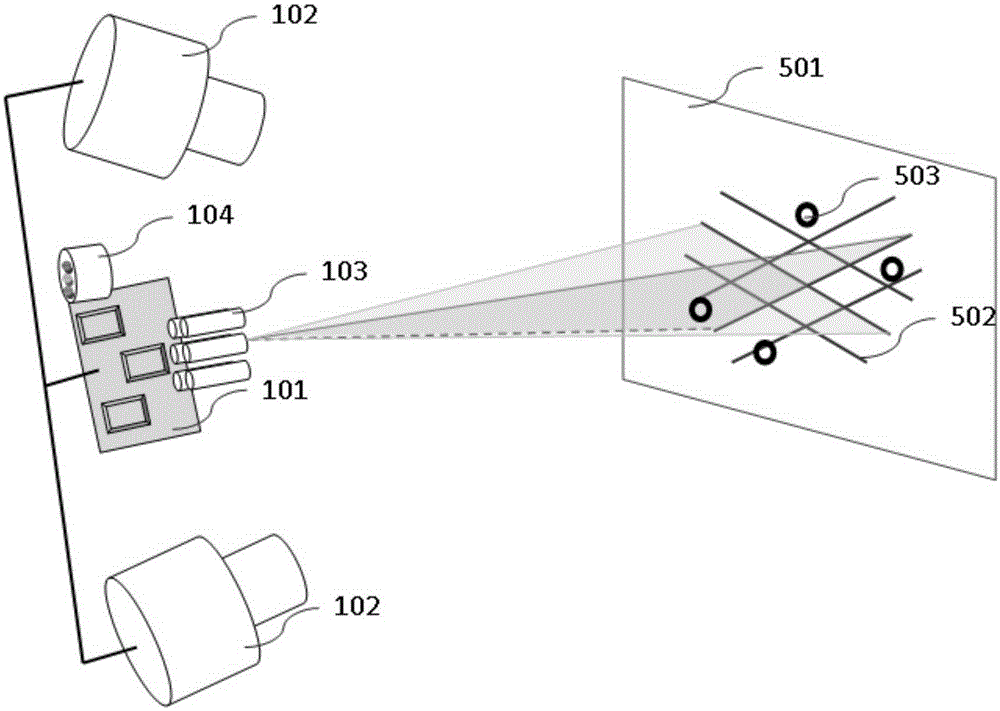

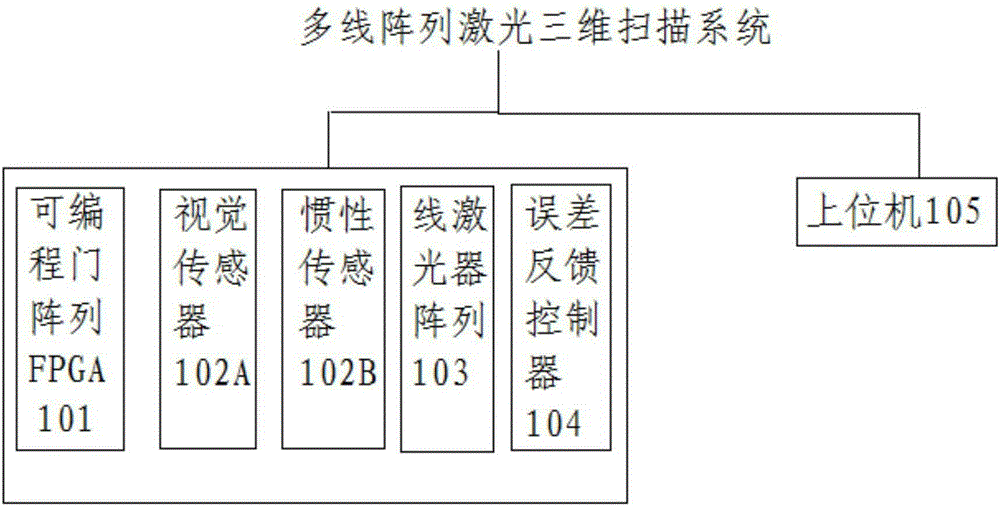

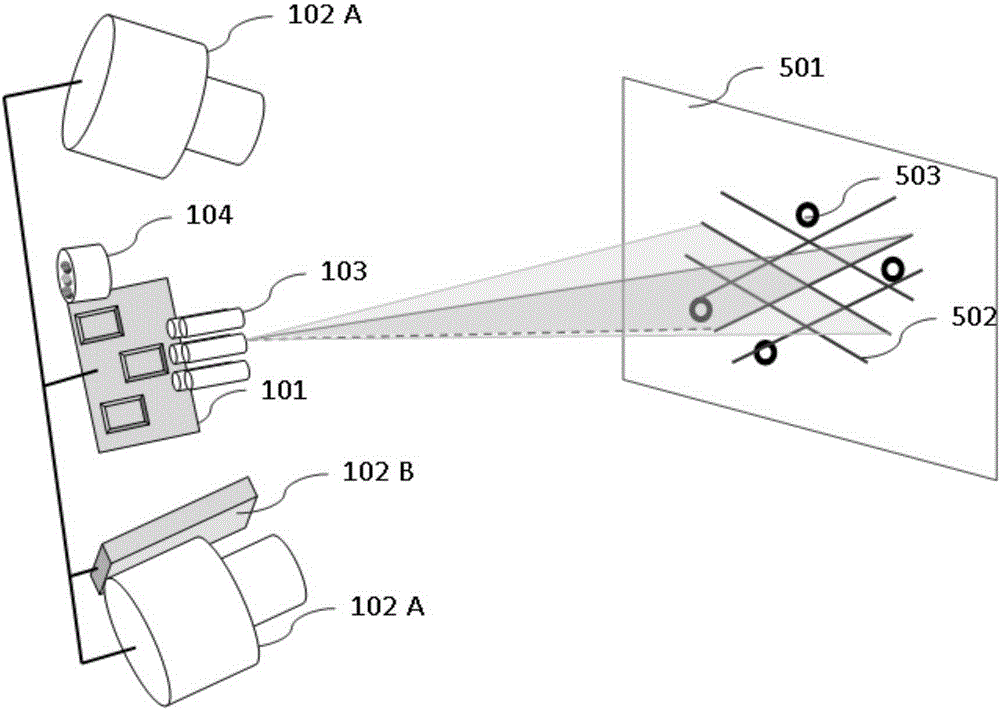

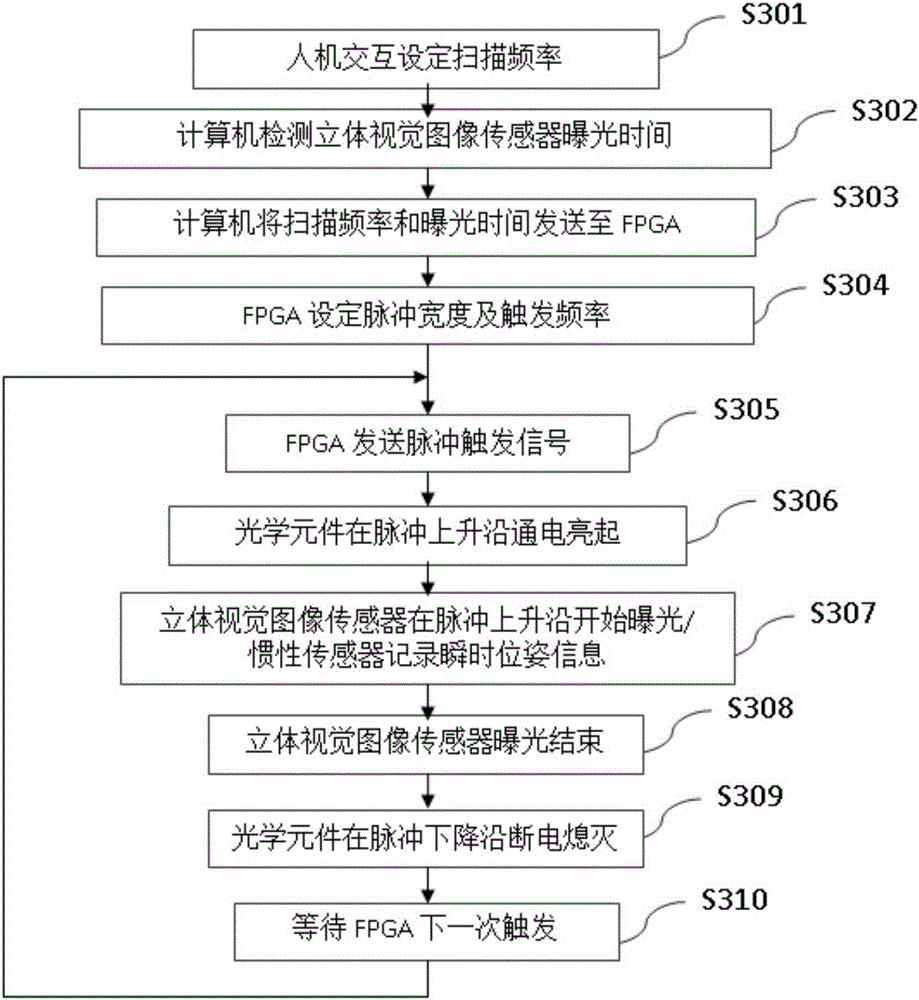

Multi-line array laser three-dimensional scanning system and method

ActiveCN105203046ALow costImprove efficiencyUsing optical meansObservational errorFpga implementations

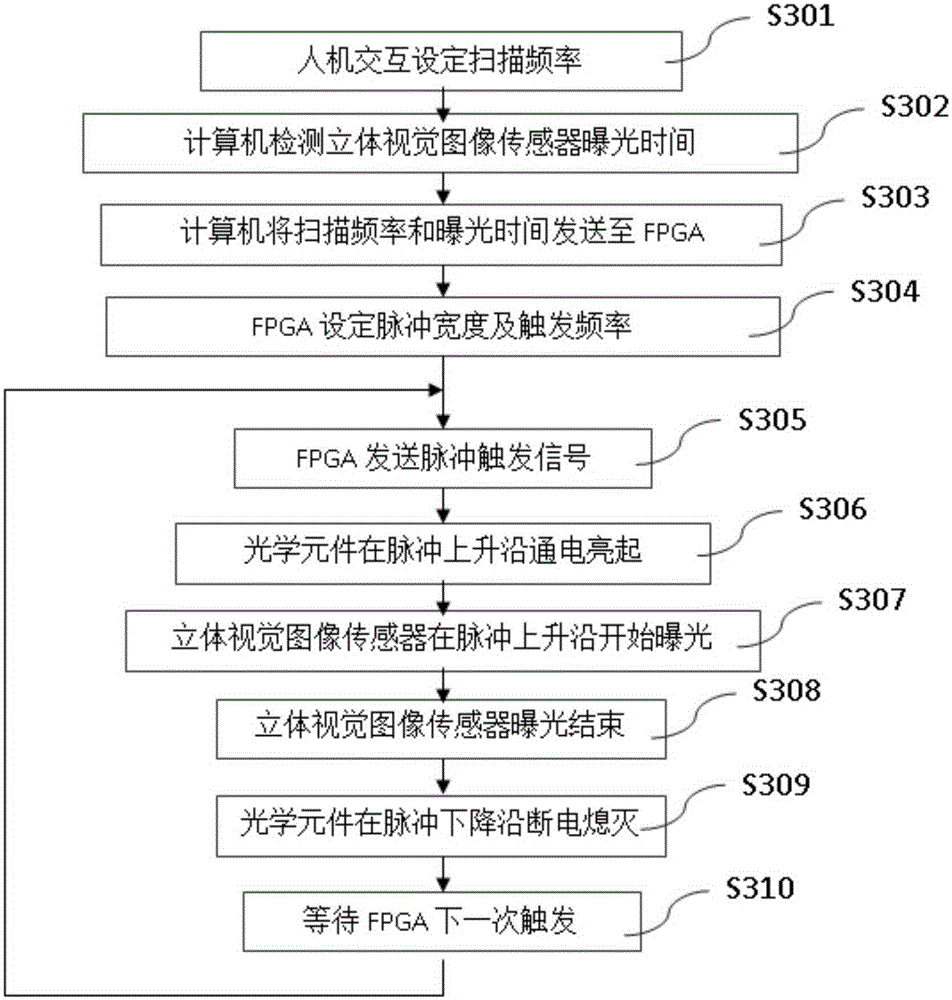

The invention provides a multi-line array laser three-dimensional scanning system and method. Accurate synchronism and logic control of the multi-line array laser three-dimensional scanning system can be achieved through an FPGA, a line laser unit array serves as a projection pattern light source, trigger signals are sent to a stereoscopic vision image sensor and the line laser unit array through the FPGA, an upper computer receives image pairs shot by the stereoscopic vision image sensor, laser line array patterns in the image pairs are subjected to encoding, decoding and three-dimensional reconstruction, three-dimensional reconstruction and matching alignment of three-dimensional feature points between different moments are conducted on surface feature points of an object to be measured, and matching calculation is subjected to prediction and error correction through an optical tracking technology. The system and method are used for registration and connection of time domain laser three-dimensional scanning data, meanwhile, measuring error grades are evaluated in real time and fed back to an error feedback controller for adjusting indication, and therefore laser three-dimensional scanning with low cost and high efficiency, reliability and accuracy is completed accordingly.

Owner:BEIJING TENYOUN 3D TECH CO LTD

Digital integrated circuit chip testing system

InactiveCN102540060AImprove stabilityImprove mean time between failuresElectrical testingFpga implementationsTest object

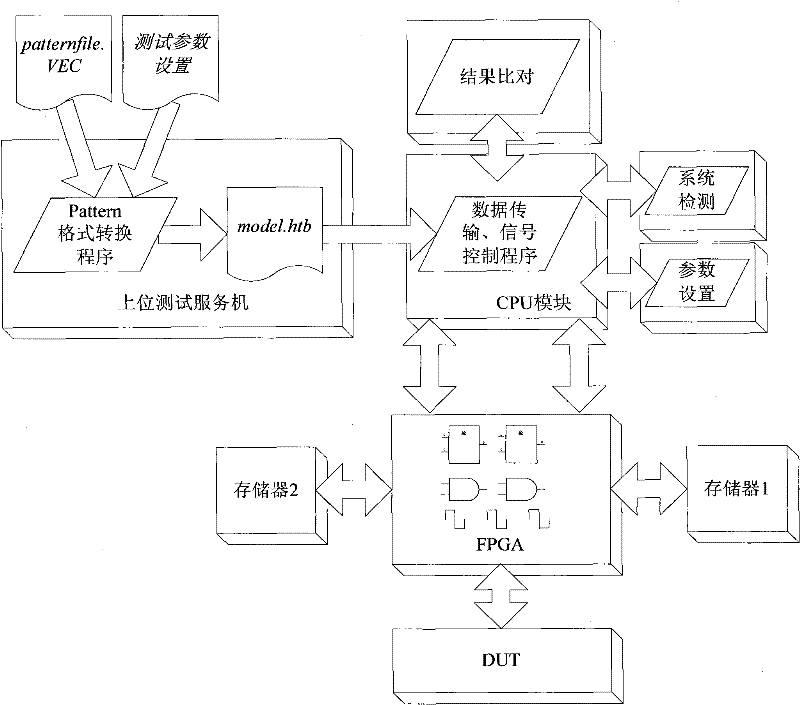

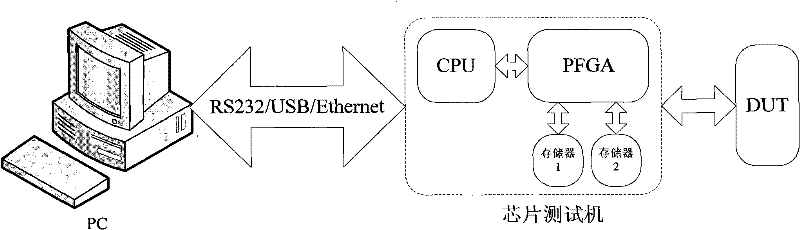

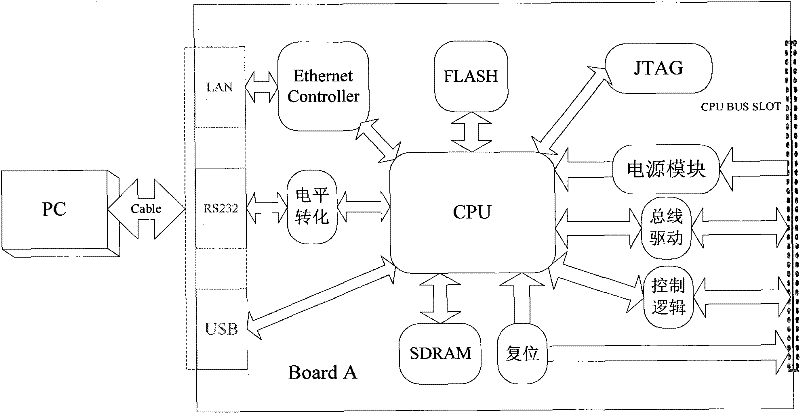

The invention provides a test pattern-based testing system for realizing a functional test on a digital integrated circuit. The functional test is mainly used for testing logical functions of a chip under a certain timing sequence, and a basic principle is that the chip is excited by means of test patterns and whether the response of the chip is consistent with expected response is observed. The functional test can cover failure models of extremely high proportion logic circuits. A debugging technology supported one-step testing system comprises two parts, namely test pattern file conversion software applied to a personal computer (PC) and a digital integrated circuit chip testing machine, wherein the digital integrated circuit chip testing machine consists of architectures of a central processing unit (CPU) and a field programmable gate array (FPGA); the CPU is used for storing and converting pattern files, controlling the testing process, communicating with a host, and the like. A pattern controlling logic circuit is realized by an FPGA, the waveform generation, the control of Pattern random access memory (RAM) and sampling control are finished through the FPGA, and a drive and a comparator are controlled so as to test and control a tested object.

Owner:BEIJING CEC HUADA ELECTRONIC DESIGN CO LTD

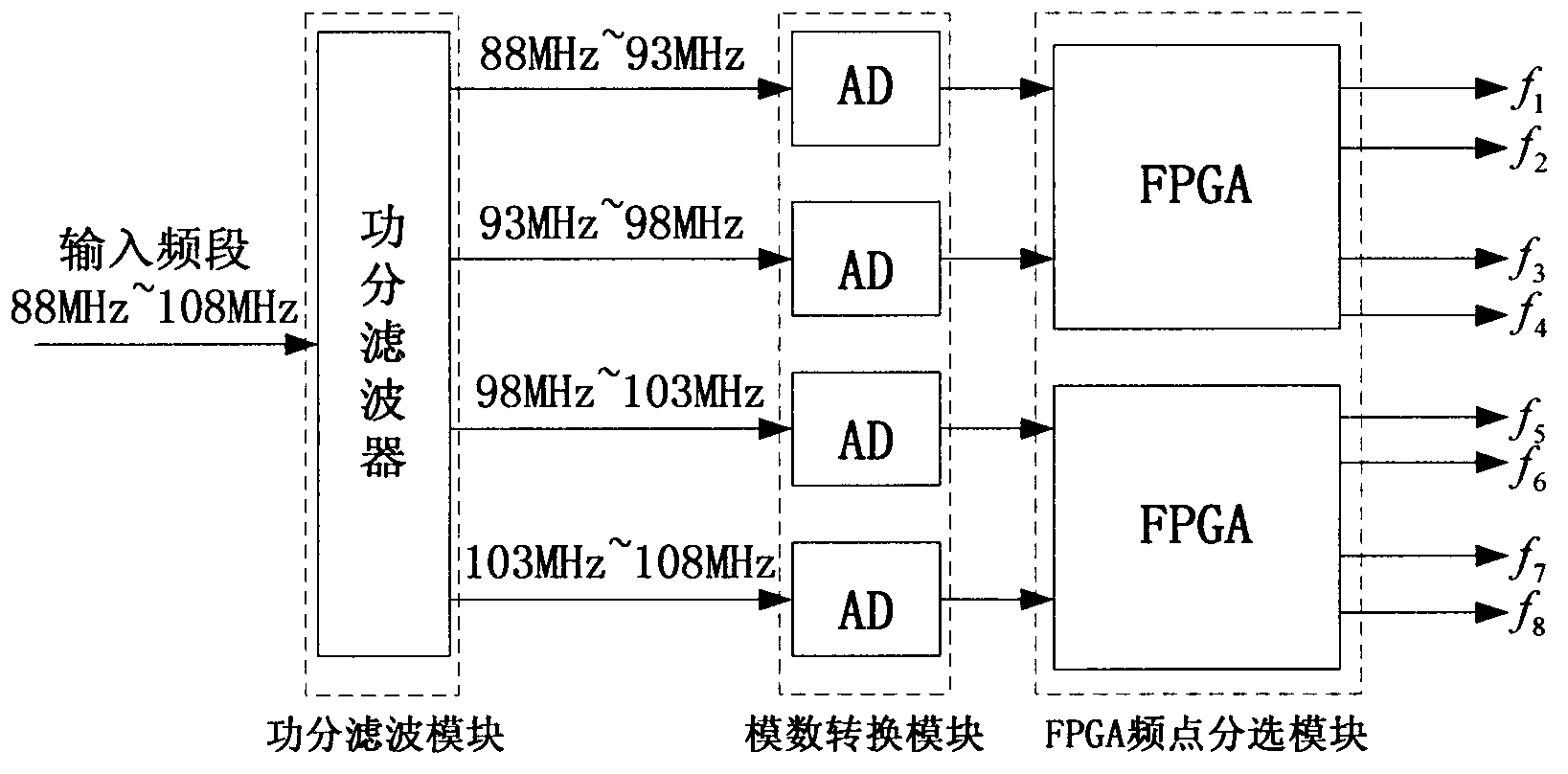

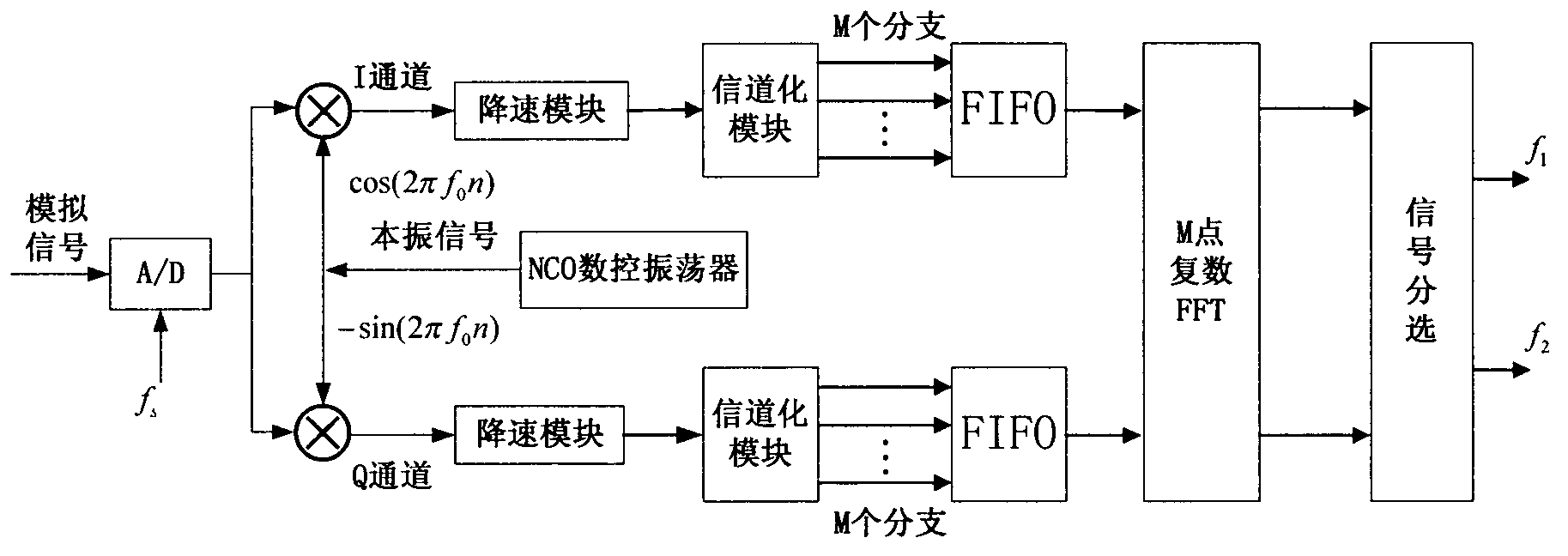

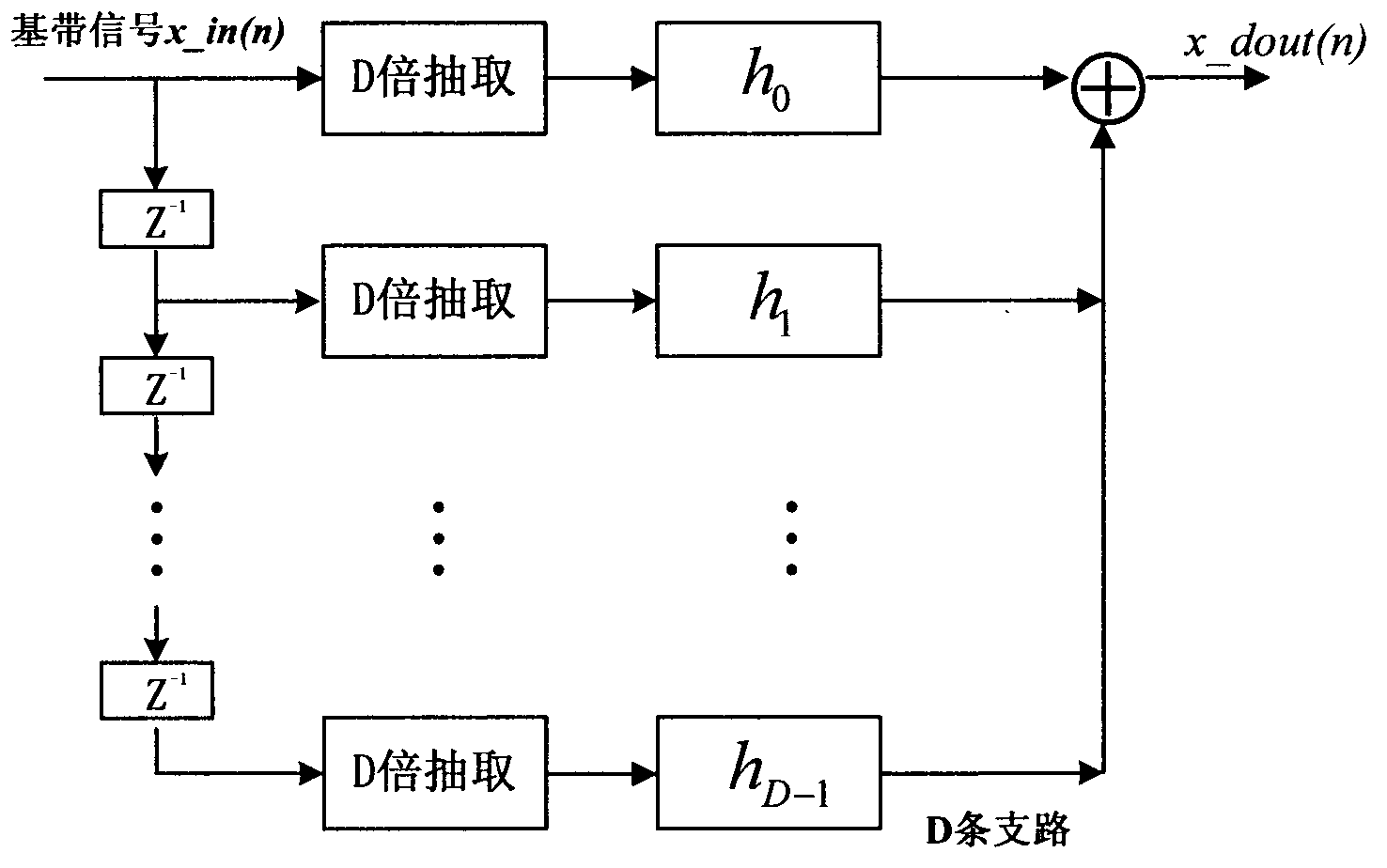

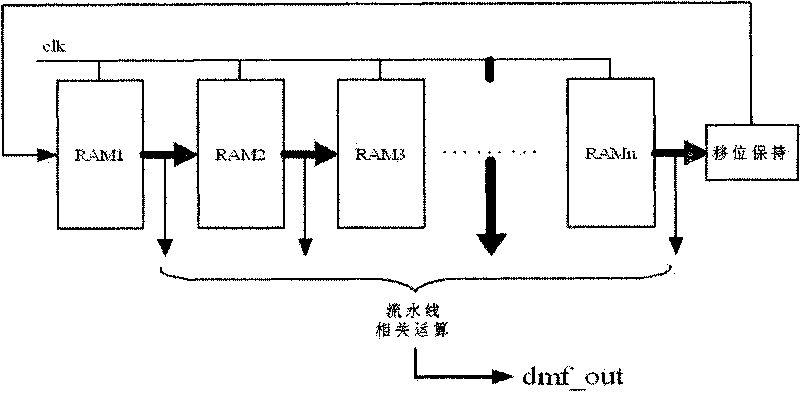

Broadband channelization reception system of radar with external radiation source and FPGA (Field Programmable Gate Array) implementation method

InactiveCN102798840AEasy to chooseSave bandwidthWave based measurement systemsFpga implementationsBaseband

The invention discloses a broadband channelization reception system of radar with an external radiation source and an FPGA (Field Programmable Gate Array) implementation method. The FPGA implementation method comprises the steps of: dividing received radar broadband signals into multiple paths of analogue signals through a power division filter module; transmitting each path of analogue signals after AD (Analogue-Digital) conversion into an FPGA for frequency point separation; converting to a baseband through down-conversation in the FPGA; sequentially carrying out a multi-phase structured deceleration treatment, channelization treatment, FIFO (First In First Out) series and parallel conversion treatment and FFT (Fast Fourier Transformation) on baseband signals; and finally outputting output signals of any eight frequency points through the FPGA. The reception system comprises a power division filter module, an analogue-digital conversion module and an FPGA frequency point separation module. According to the invention, echo signals of the radar are subjected to a segmental treatment, and the same treatment is adopted for the signal separation process of each path of the analogue signals after the segmentation. Different clock frequencies are adopted at different treatment stages of the FPGA frequency point separation. According to the broadband channelization reception system of the radar with the external radiation source and the FPGA implementation method, disclosed by the invention, the difficulties of great equipment amount and high development cost when the traditional reception system of the radar with the external radiation source implements synchronous reception of multiple signals of the broadband signals are solved; and complexity and cost of the system structure are decreased.

Owner:XIDIAN UNIV

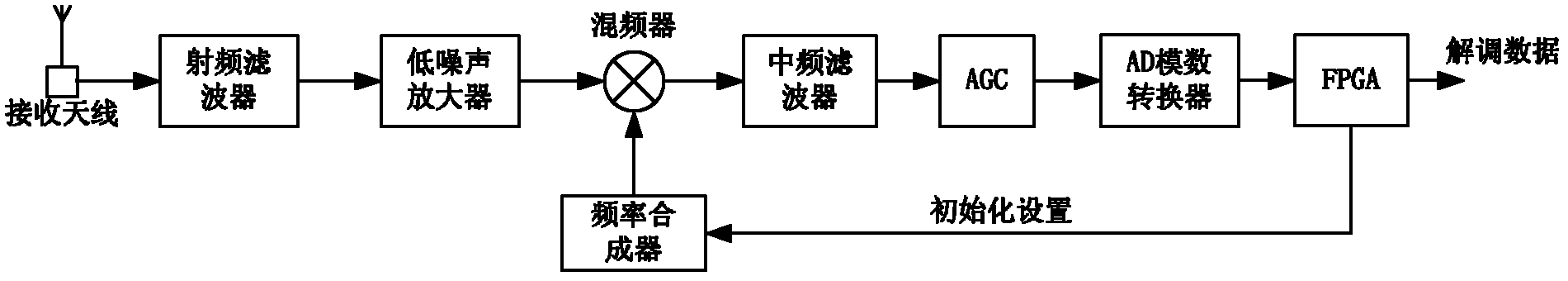

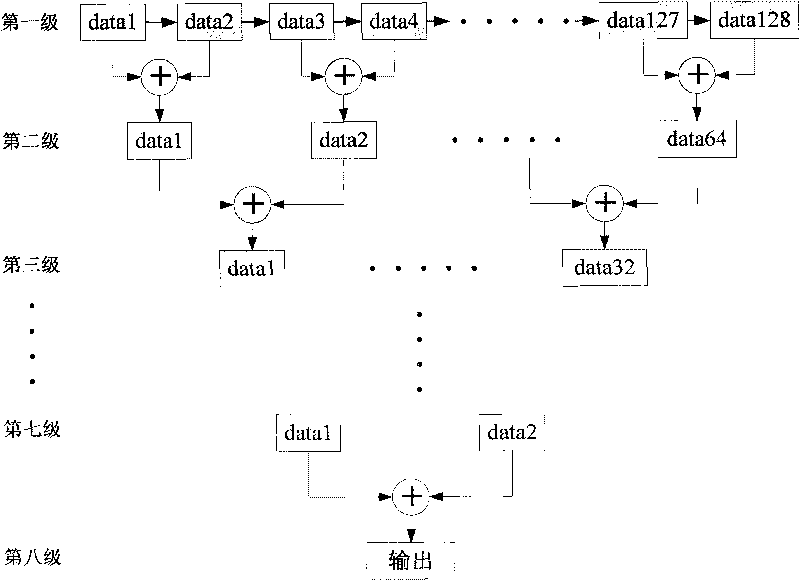

Fully-digital direct sequence spread spectrum communication system and rapid pseudo code capturing method thereof

ActiveCN102571137ASimple designReduce power consumptionTransmissionDigital signal processingFpga implementations

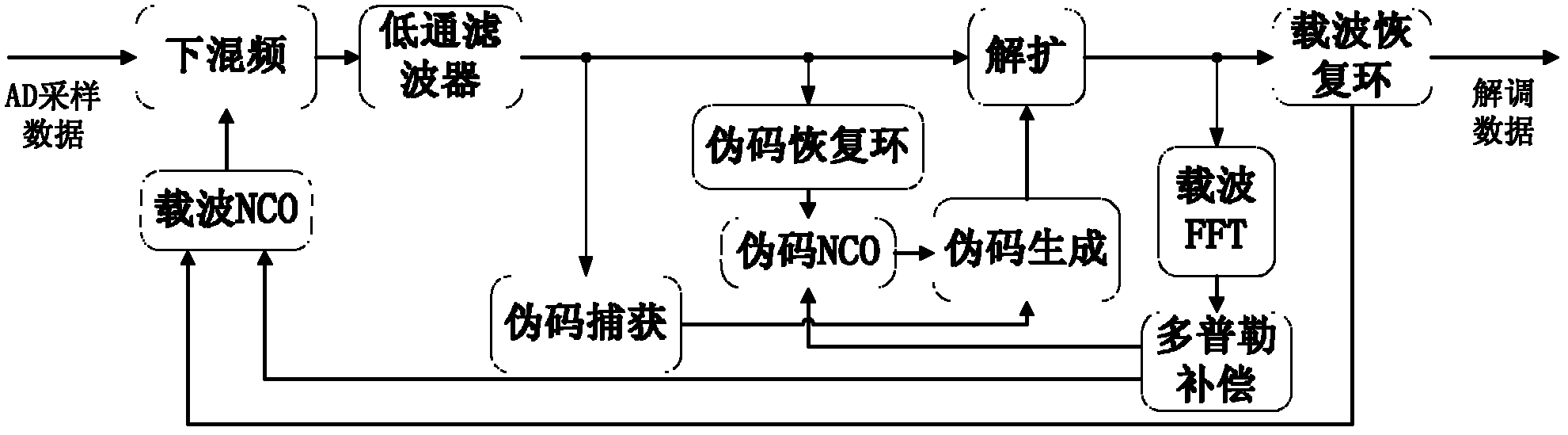

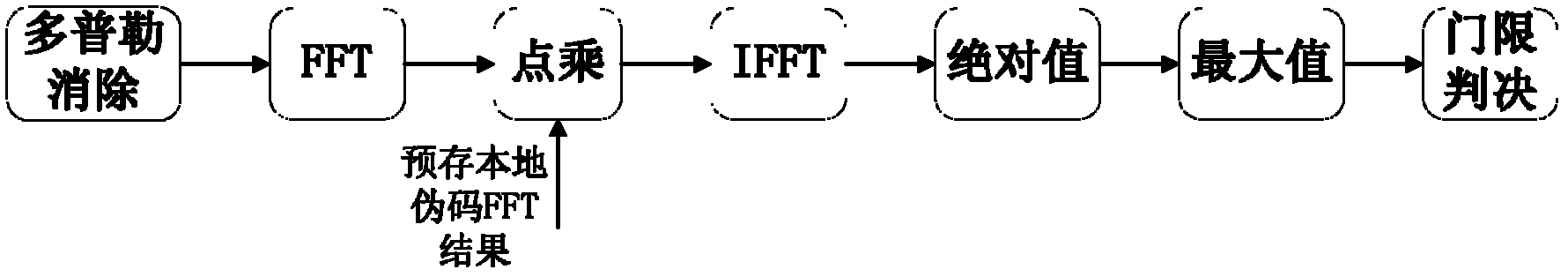

The invention discloses a fully-digital direct sequence spread spectrum communication system and a rapid pseudo code capturing method thereof. A digital signal is processed by using an FPGA (Field Programmable Gate Array) which comprises a pseudo code capturing module, a sampling signal of an ADC (Analog To Digital Converter) is subjected to frequency mixing with a signal of a local carrier NCO (Numerically Controlled Oscillator) and filtered to obtain a baseband signal, residual carrier Doppler frequency is eliminated from the baseband signal by adopting a differential multiplying mode, thus the phase deviation of a receiving signal and a local pseudo code is further obtained through an FFT (Fast Fourier Transform) algorithm without scanning on a carrier frequency domain; and when the phase deviation of the pseudo code is obtained, a local pseudo code phase is modified and is subjected to correlation degree of dissociation with the receiving signal, and the carrier Doppler frequency is figured out by using the FFT algorithm, and is compensated to a carrier NCO and a pseudo code NCO, thus carrier frequency capturing and pseudo code capturing are realized.

Owner:ZHEJIANG UNIV

A low-loss, high reliability integration magnetic levitation flywheel DC brushless motor control system

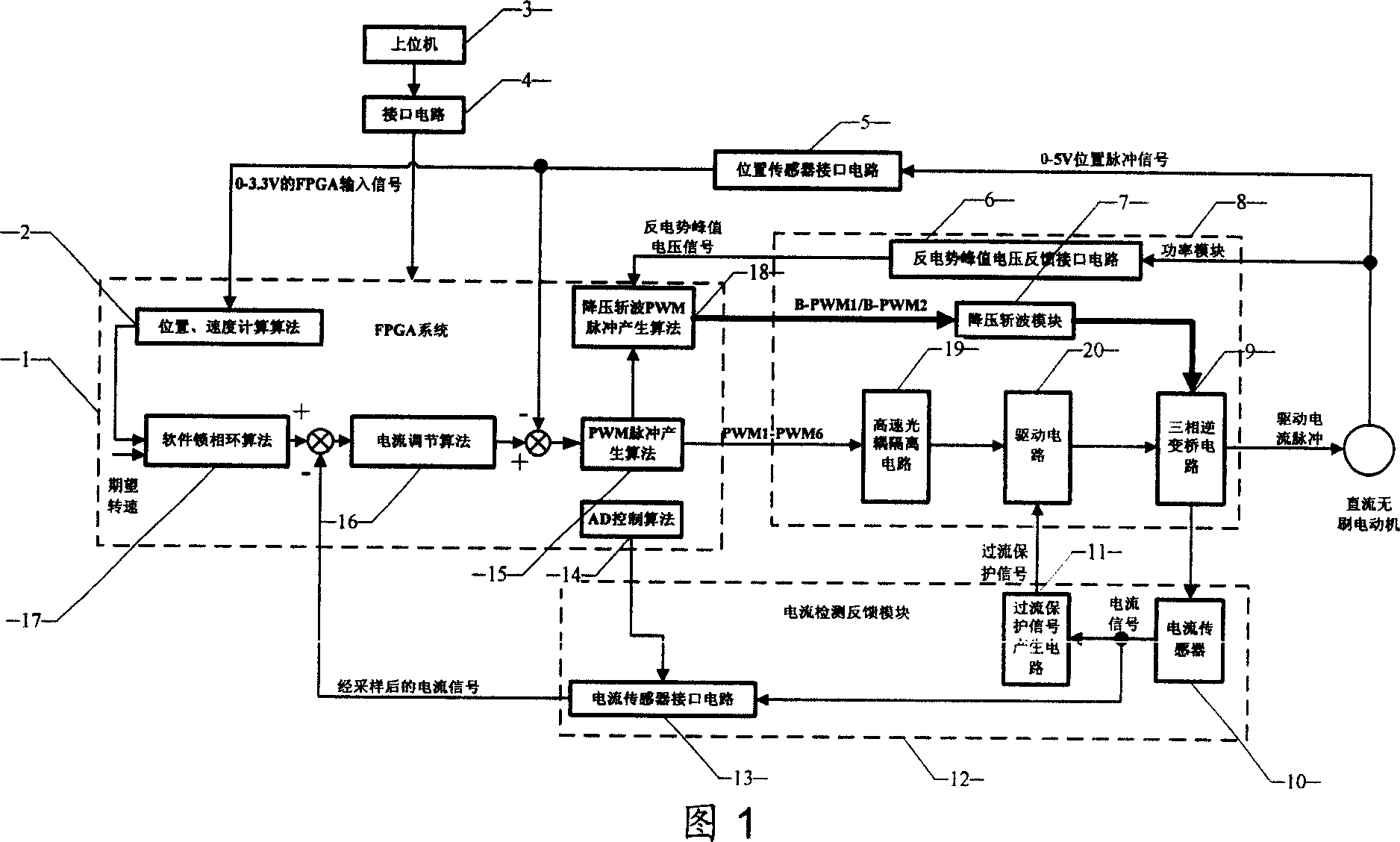

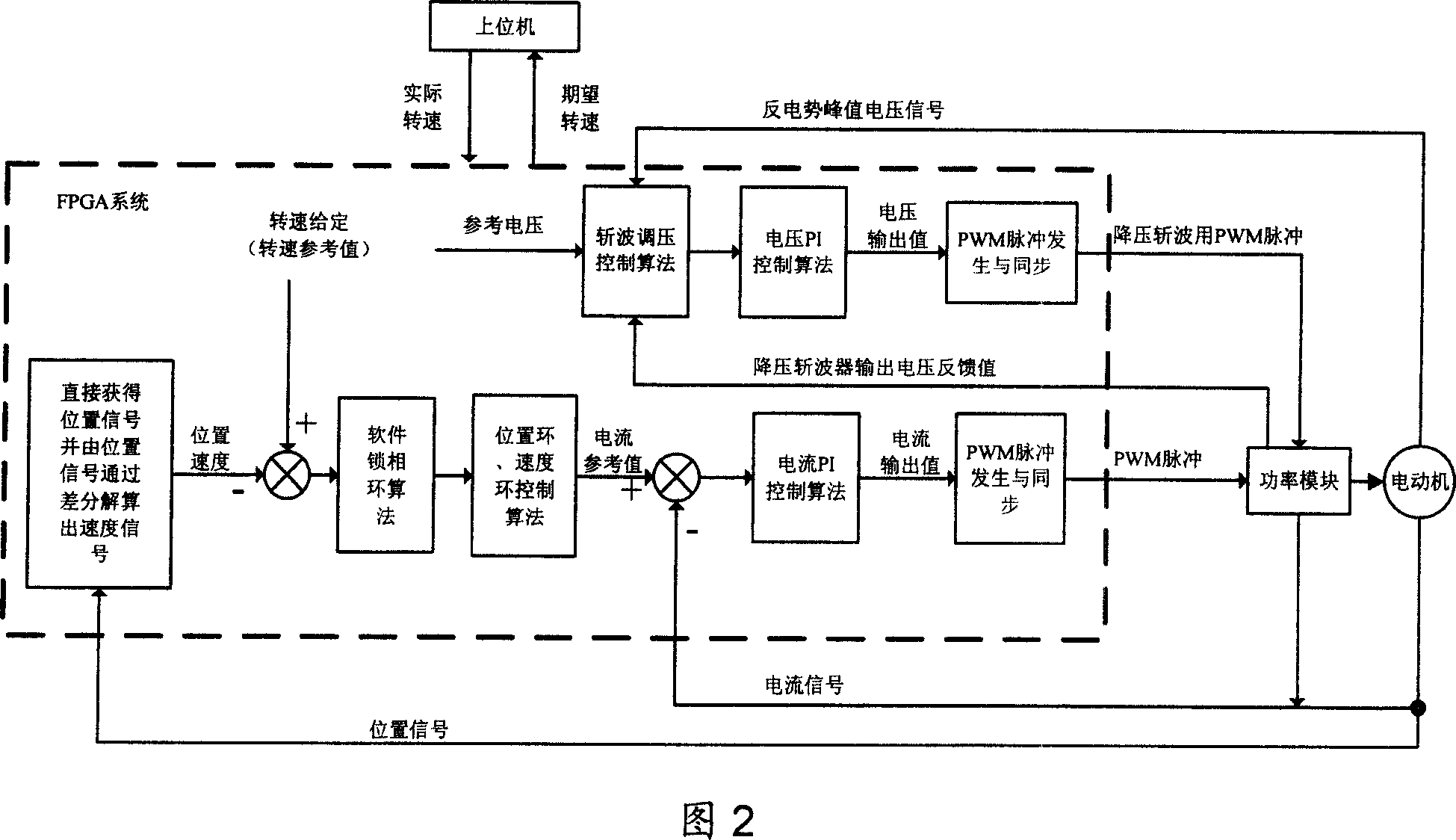

InactiveCN1968003AHigh control precisionHighly integratedField or armature current controlElectronic commutatorsBrushless motorsFpga implementations

The invention relates to a magnetic suspension flywheel direct-current non-brush motor controlling system, wherein it comprises FPGA system, direct-current detecting feedback module, positioning sensor interface circuit, and power module; the FPGA module obtains request rotation speed from super machine, via sensor interface circuit and feedback module to obtain position signal and current signal, and the control algorism of FPGA, to calculate out the control value, and process reduction chopper PWM modulation, and amplify via amplifying module to generate the needed control current, and realize control accurately. The invention has low power consumption and high reliability.

Owner:BEIHANG UNIV

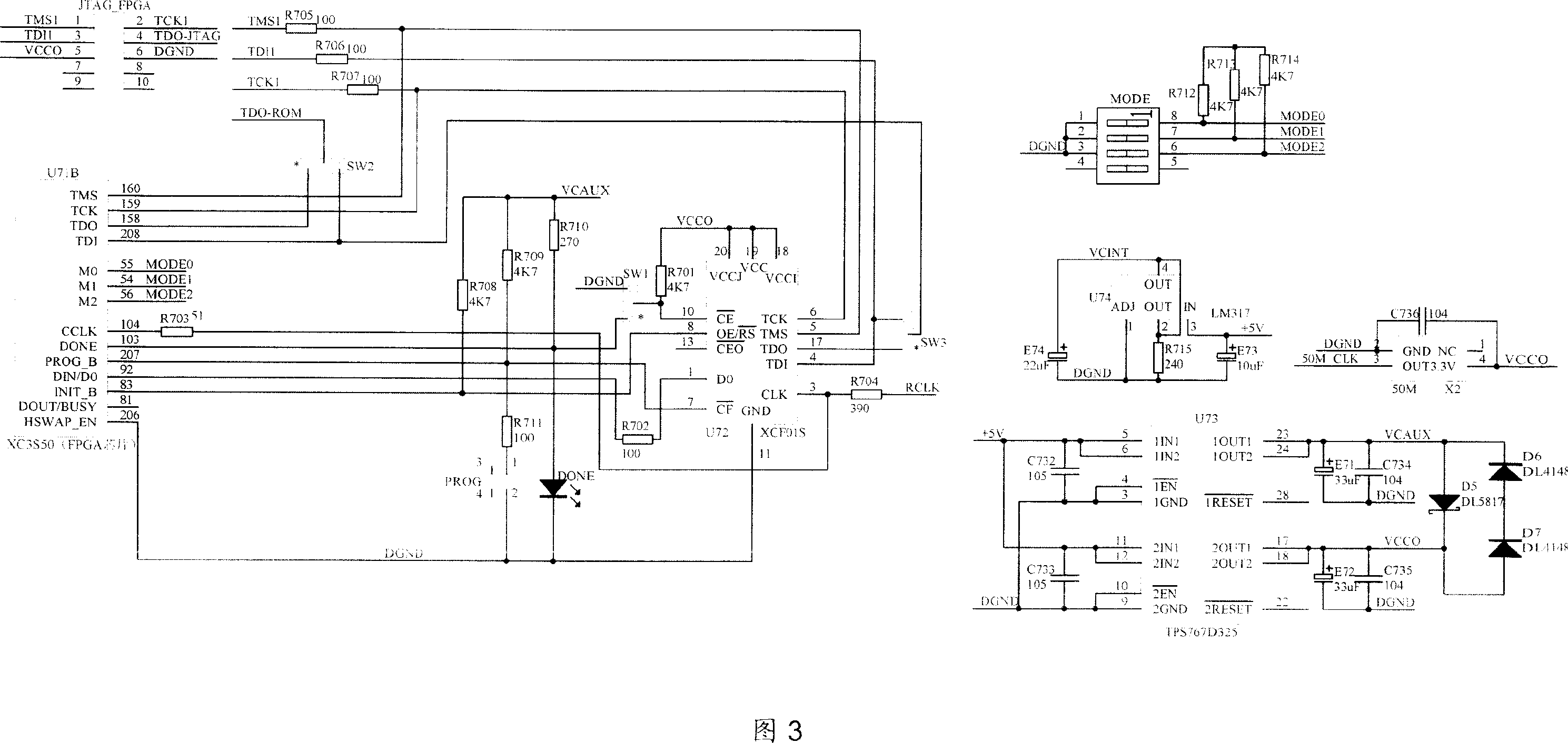

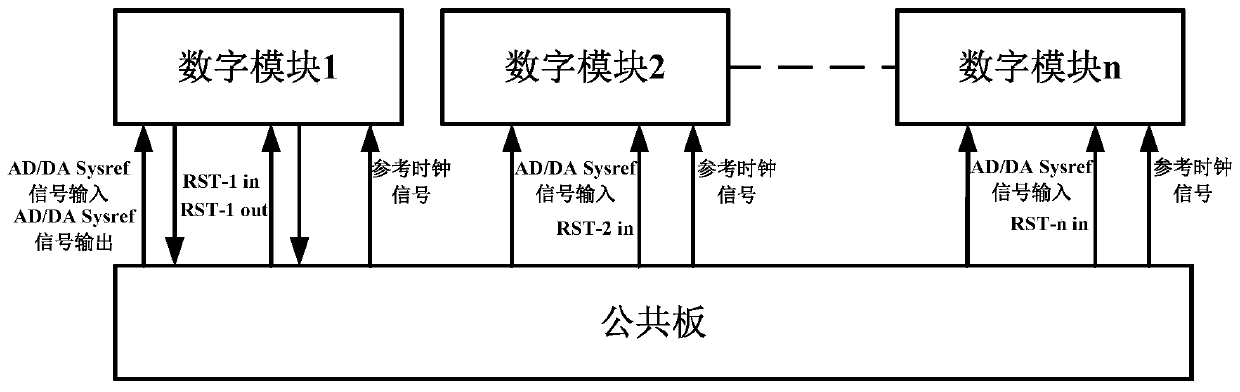

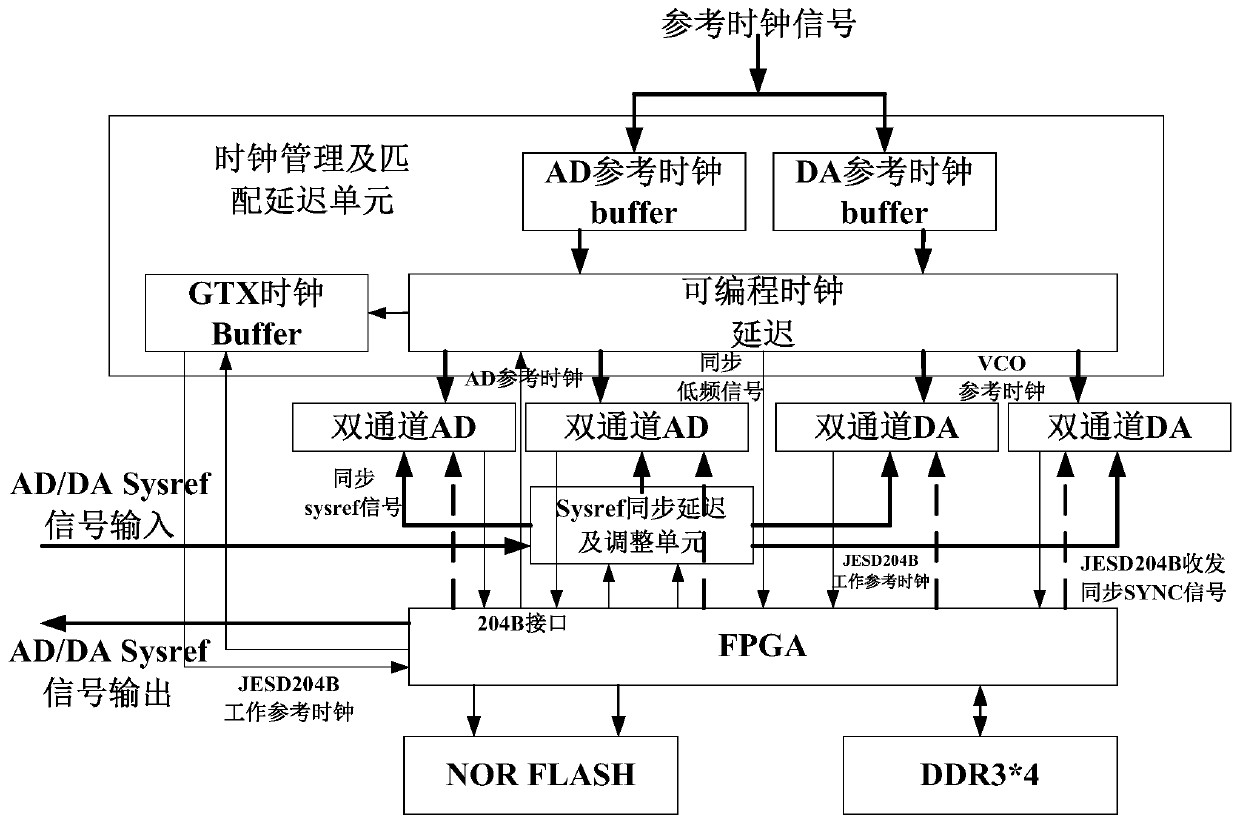

Multi-channel radio frequency direct acquisition and generation circuit applied to phased array radar

InactiveCN109889211AQuality assurancePrecise timing controlWave based measurement systemsTransmissionRadar systemsSignal quality

The invention provides a multi-channel radio frequency direct acquisition and generation circuit applied to phased array radar. A clock management and matching delay unit generates an ADC / DAC clock and a low-frequency clock signal. The radio frequency generation and sampling module is used for realizing direct generation and direct sampling of radio frequency signals. The storage processing modulereceives and stores the original data sampled by the AD through the FPGA, extracts and filters the data in the FPGA, and realizes transmission of a digital signal between the FPGA and the DA throughthe FPGA. And the master module receives the control signal of the system to generate a synchronization signal and a reset signal, so that the synchronization signal and the reset signal are transmitted to the slave modules through the common board to control the synchronization and reset functions of the AD / DA chips in all the slave modules while the transmitting and receiving synchronization inthe master module is realized. According to the invention, the frequency conversion loss of the system is avoided, the signal quality is ensured, and the requirements of radar system beam pointing, high-efficiency spatial power synthesis and multi-channel receiving and transmitting synchronization are met.

Owner:NO 20 RES INST OF CHINA ELECTRONICS TECH GRP

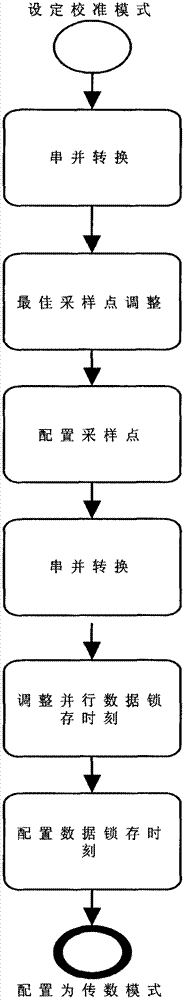

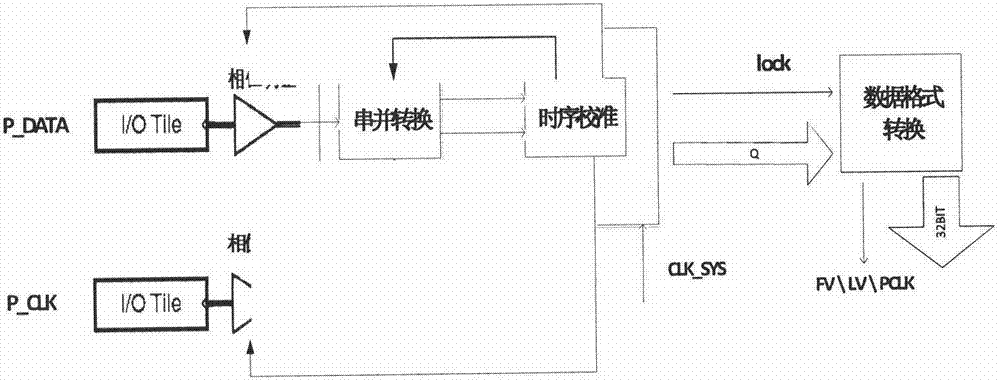

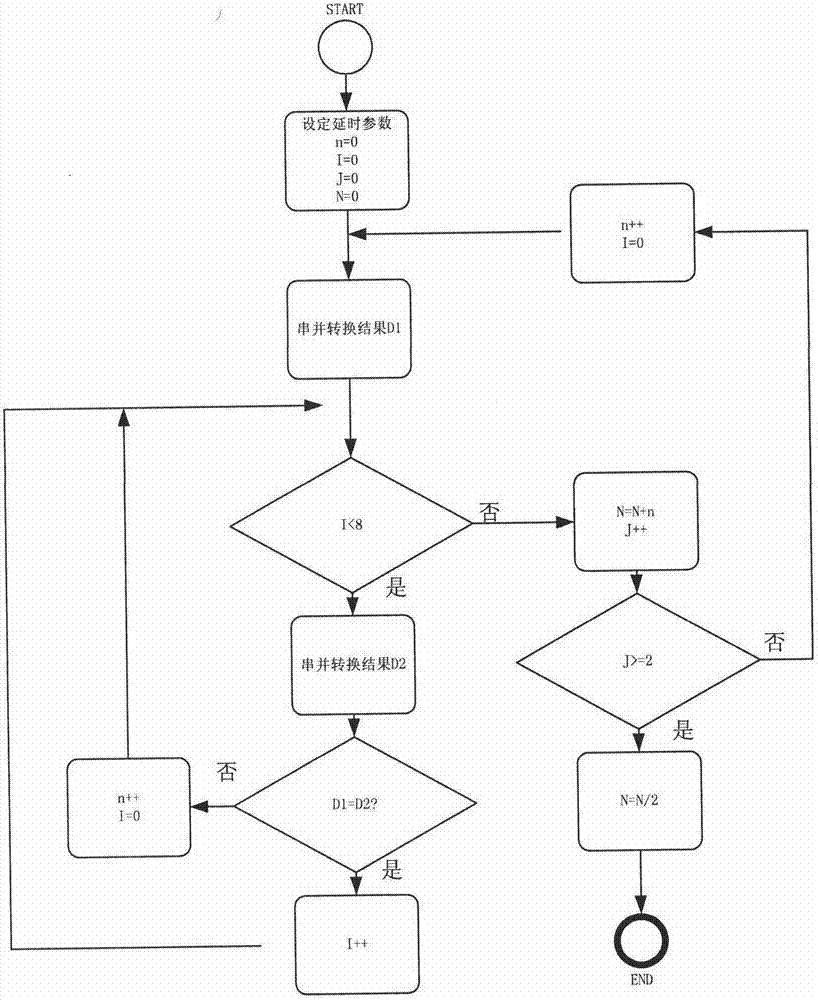

Self-adaption timing sequence calibrating method of high-speed serial communication interface

ActiveCN103036667AReduce clock frequencyReduce power consumptionHigh level techniquesSynchronising arrangementFpga implementationsSelf adaptive

A self-adaption timing sequence calibrating method of a high-speed serial communication interface is achieved by adoption of the Field Programmable Gate Array (FPGA). The method comprises the steps of setting the high-speed serial communication interface as a calibrating mode; converting serial data received by the high-speed serial communication interface to parallel data; adjusting the sampling clock phase or sampling time delay to obtain an optimal sampling point; configuring the high-speed serial communication interface by using the optimal sampling point; converting the serial data received by the high-speed serial communication interface to the parallel data again; comparing the obtained parallel data with a preset value and adjusting the parallel data latching moment according to a comparison result to enable the parallel data received by the high-speed serial communication interface to coincide with the preset value; configuring the high-speed serial communication interface by using an obtained data latching moment result; and setting the high-speed serial communication interface as a transmission mode. The self-adaption timing sequence calibrating method of the high-speed serial communication interface is easy to achieve and power consumption is effectively reduced.

Owner:BEIJING INST OF CONTROL ENG

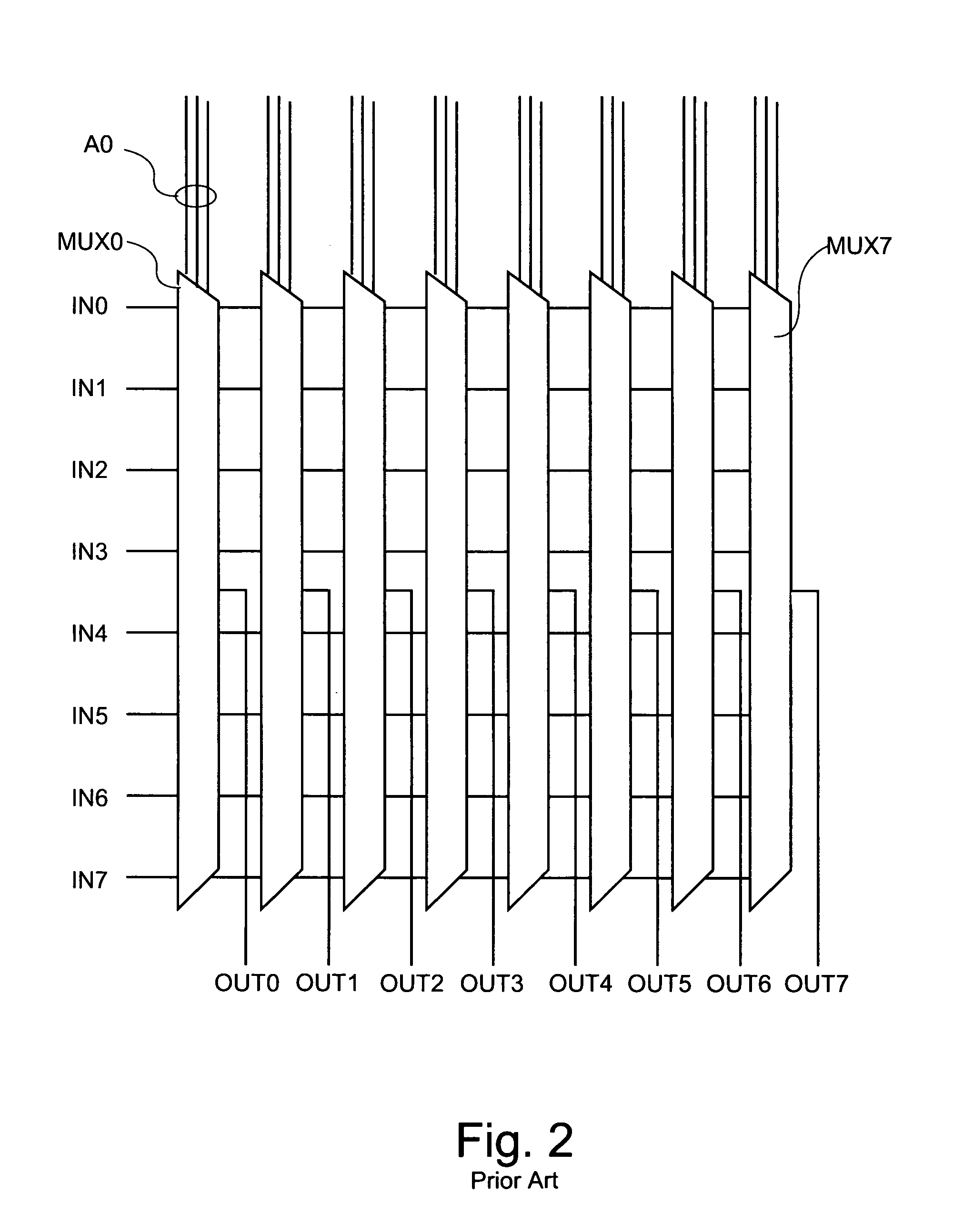

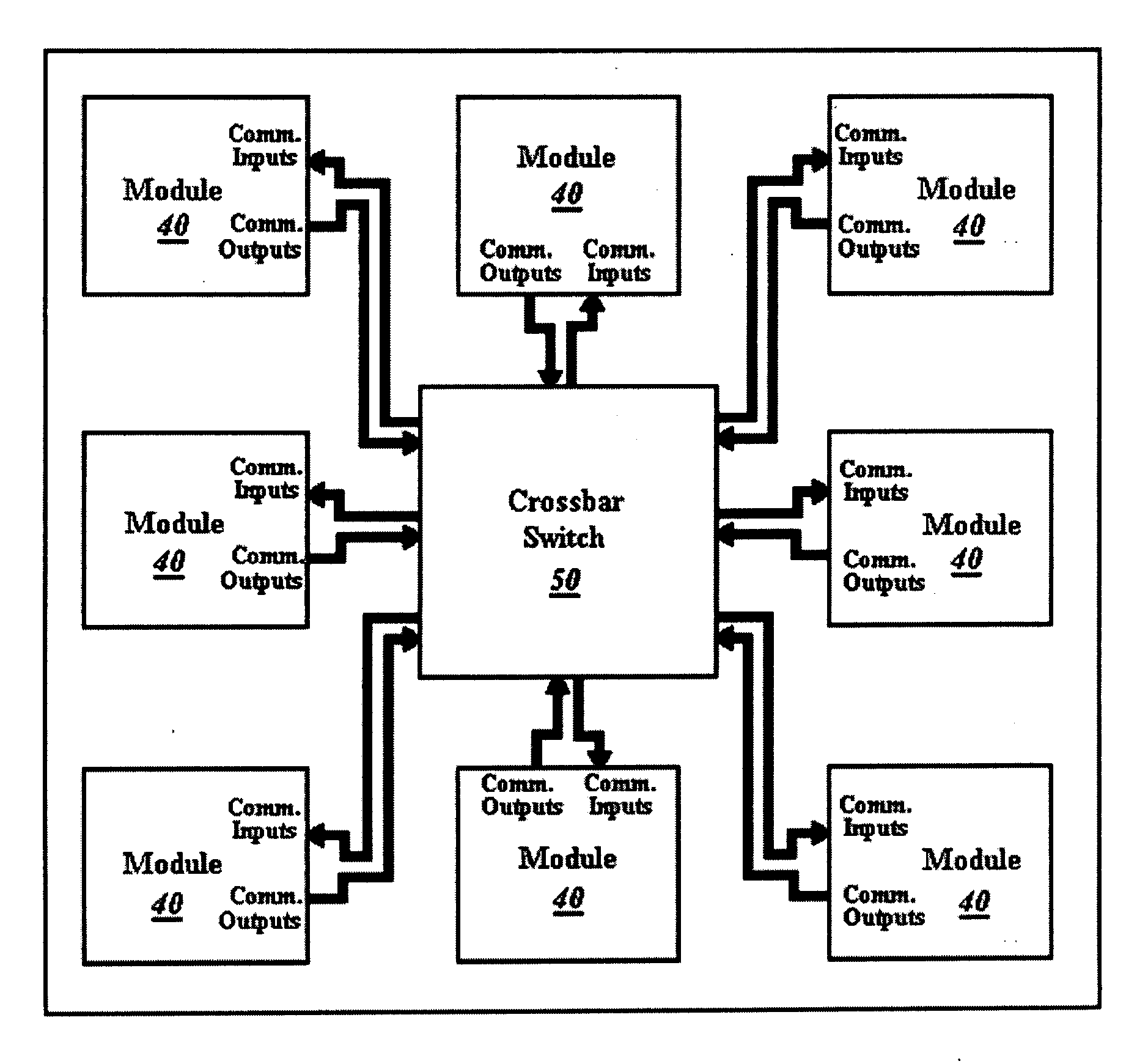

High bandwidth reconfigurable on-chip network for reconfigurable systems

ActiveUS20070200594A1Reduce necessaryExtension of timeSolid-state devicesLogic circuits using elementary logic circuit componentsCrossbar switchTelecommunications link

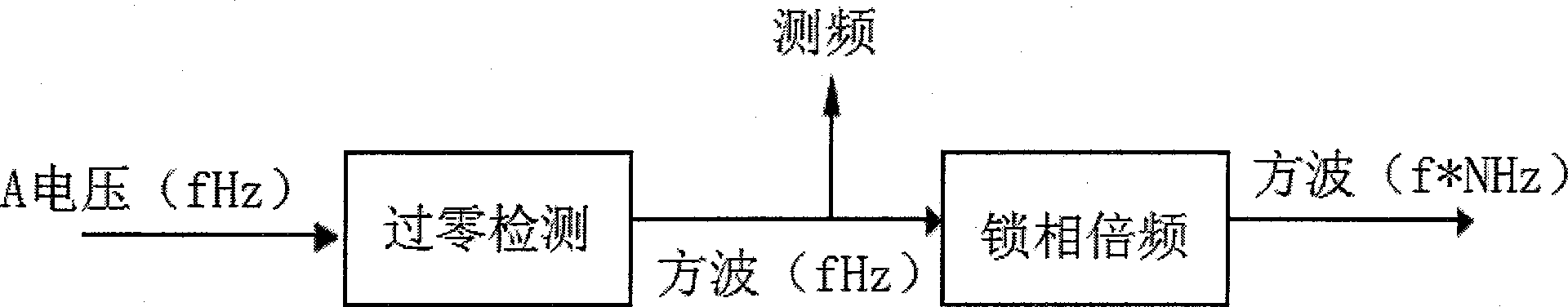

A crossbar switch is implemented in a reconfigurable circuit, such as a FPGA, instantiated with a number of modules, the crossbar switch providing communication links between the modules. The modules and crossbar switch can be easily updated in a partial reconfiguration process changing only portions of modules and the crossbar switch while other portions remain active. The crossbar switch uses individual wiring to independently connect module outputs and inputs so that asynchronous communications can be used. The crossbar switch can be implemented in different embodiments including a Clos crossbar switch, and a crossbar switch connecting each module output only to a corresponding module input, allowing for a reduction in the amount of FPGA resources required to create the crossbar switches.

Owner:XILINX INC

Power quality monitoring method

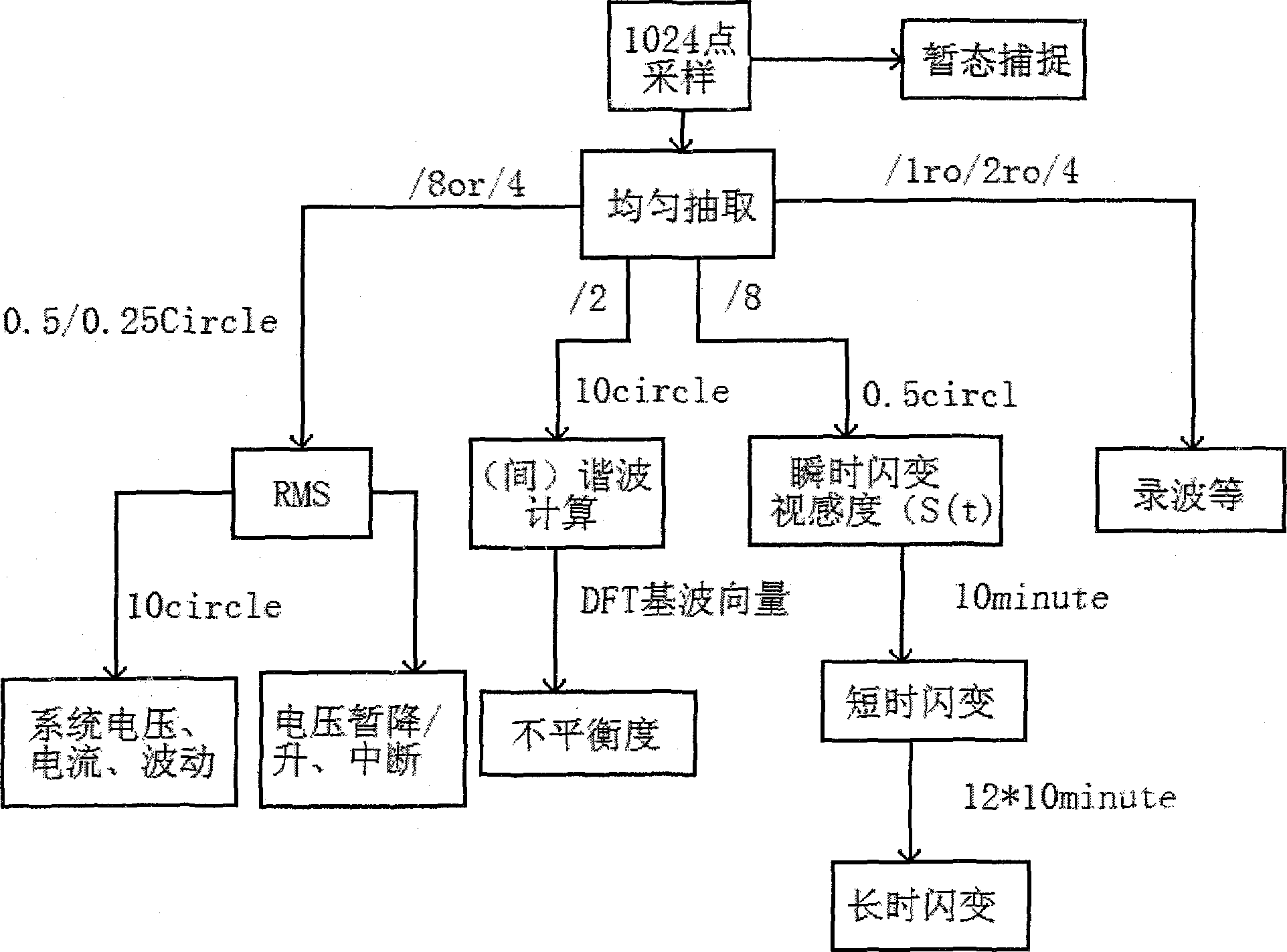

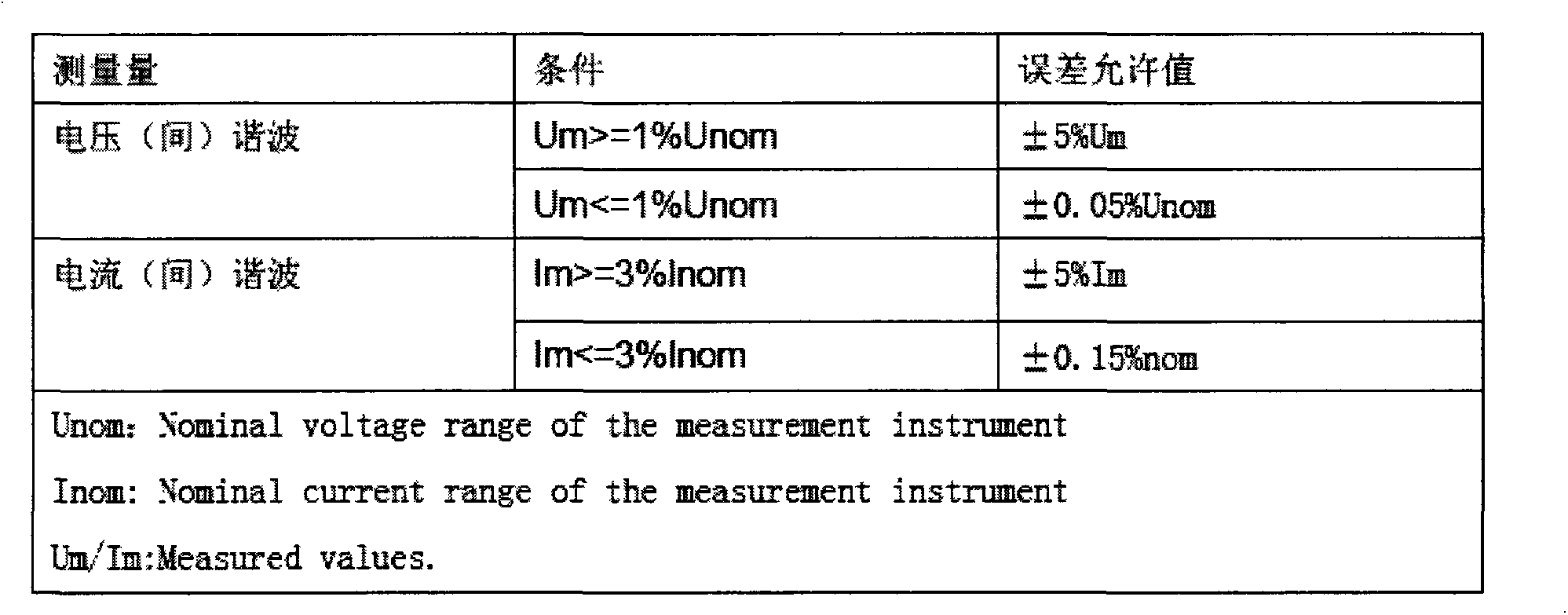

ActiveCN103353558AImprove real-time performanceGood followabilityProgramme controlComputer controlPower qualityFrequency measurements

The invention discloses a power quality monitoring method. A FPGA is employed in the method to realize zero-crossing detection function and compared with traditional voltage-controlled oscillators, the method exhibits better real-time performance and following performance. On frequency measurement and sampling control, three-phase voltage signal is introduced as a standard of the frequency measurement and the sampling control so that, compared with one-phase voltage signal introduced as the standard, the method is more reliable and flexible; that software controls sample interval is as a supplement of hardware sampling control, so that sampling accuracy is improved; on algorithm input points, accuracy requirement of the algorithm and the calculated quantity are balanced; and under the condition that accuracy is guaranteed, calculated quantity is lessened, so that cost performance of the actual device is improved.

Owner:SHENZHEN KANGBIDA CONTROL TECH

Hardware accelerator for compressed gru on FPGA

ActiveUS20180046901A1Computation using non-contact making devicesNeural architecturesNerve networkActivation function

The present technical disclosure relates to artificial neural networks, e.g., gated recurrent unit (GRU). In particular, the present technical disclosure relates to how to implement a hardware accelerator for compressed GRU based on an embedded FPGA. Specifically, it proposes an overall design processing method of matrix decoding, matrix-vector multiplication, vector accumulation and activation function. In another aspect, the present technical disclosure proposes an overall hardware design to implement and accelerate the above process.

Owner:XILINX INC

Multi-wire array-laser three-dimensional scanning system and multi-wire array-laser three-dimensional scanning method

ActiveCN105222724AHigh precisionLow costAngles/taper measurementsUsing optical meansObservational errorGate array

The invention provides a multi-wire array-laser three-dimensional scanning system and a multi-wire array-laser three-dimensional scanning method. In the system, through a programmable gate array FPGA, accurate synchronization and logic control of the multi-wire array-laser three-dimensional scanning system can be realized. A wire laser array is used as a projection pattern light source. Through the FPGA, trigger signals are sent to a stereo vision image sensor, an inertial sensor and the wire laser array. An upper computer receives an image pair shot by the stereo vision image sensor, and carries out coding, decoding and three-dimensional reconstruction on a laser wire array pattern in the image pair. The three-dimensional reconstruction and three-dimensional characteristic point matching and aligning are performed on a characteristic point of a measured object surface. A mixing sensing positioning technology is used to carry out prediction and error correction on matching calculation, which is used for registration and splicing of time-domain-laser three-dimensional scanning data. Simultaneously, measurement error grade assessment is performed in real time and an assessment result is fed back to an error feedback controller so that an adjusting indication is obtained. Therefore, laser three-dimensional scanning with low cost, high efficiency, high reliability and high precision is realized.

Owner:BEIJING TENYOUN 3D TECH CO LTD

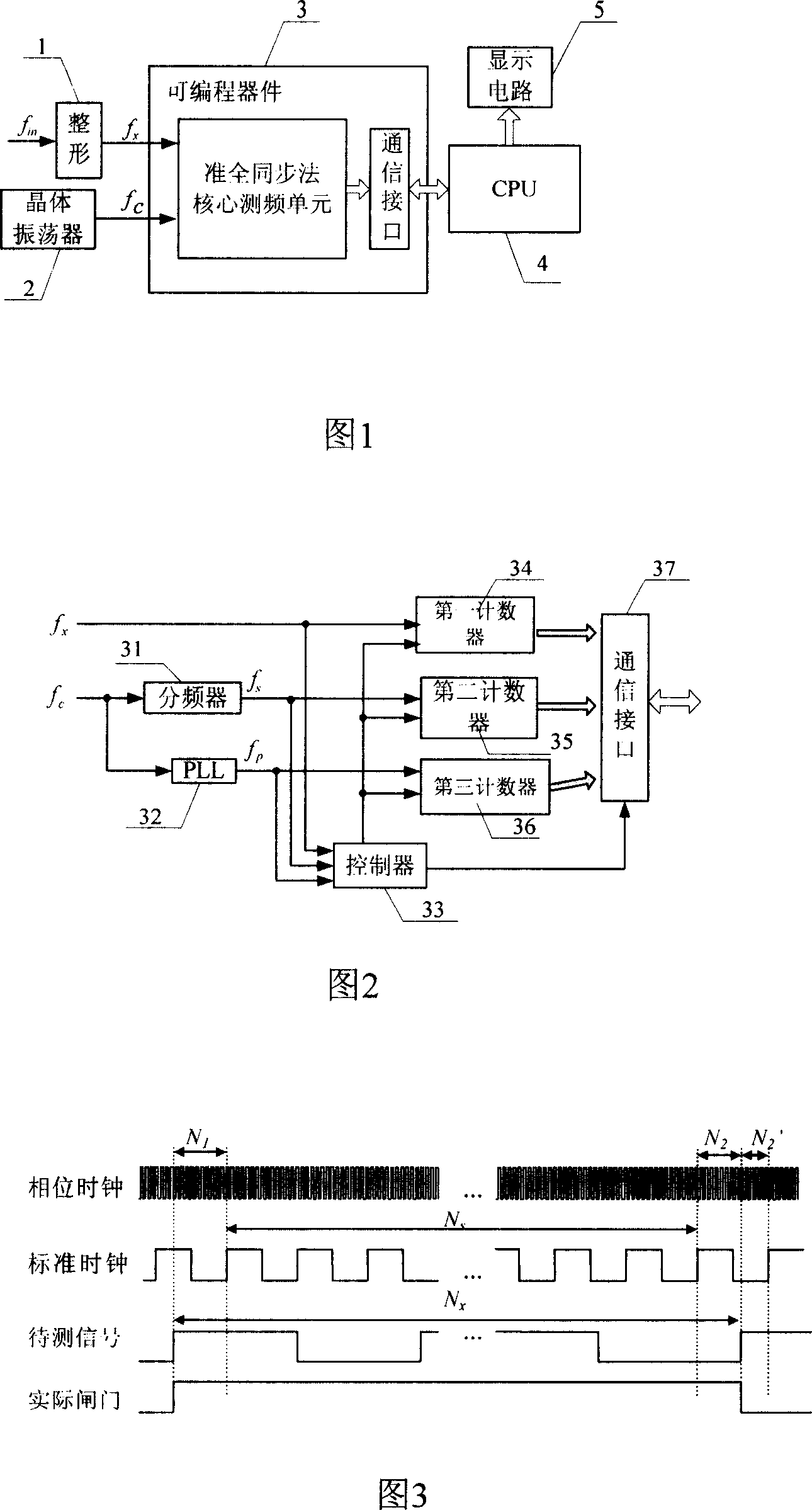

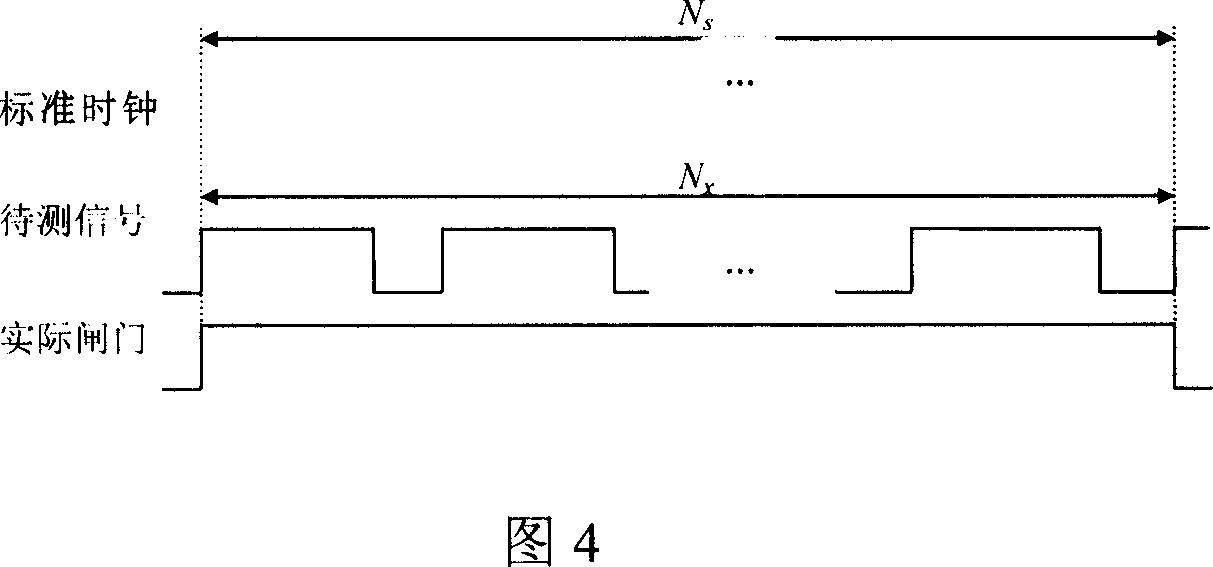

Quasi full-synchronous high-precision rapid frequency measuring device and method

InactiveCN101026781ASolving Complex DefectsReduce occupancyFrequency to pulse train conversionSelection arrangementsPhase differenceFpga implementations

The measuring device includes waveform shaping circuit, crystal oscillator, programmable device, CPU and display unit. The input end of the waveform shaping circuit is connected to the input end of the programmable device. Connecting the programmable device, the crystal oscillator provides clock source for the programmable device. The programmable device is connected to CPU. CPU is in use for calculating frequency value. The output end of CPU is connected to the input end of the display circuit. The display circuit displays calculated result. Measuring phase difference between signal to be measured and standard clock raises measuring accuracy. Advantages are: quick measuring frequency with high precision, simple structure of circuit hardware, using dedicated chip to measure frequency to reduce cost, and using FPGA to implement the device.

Owner:NINGBO UNIV

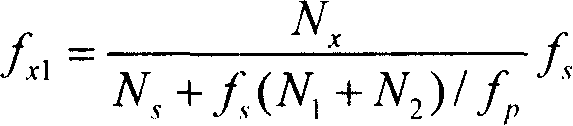

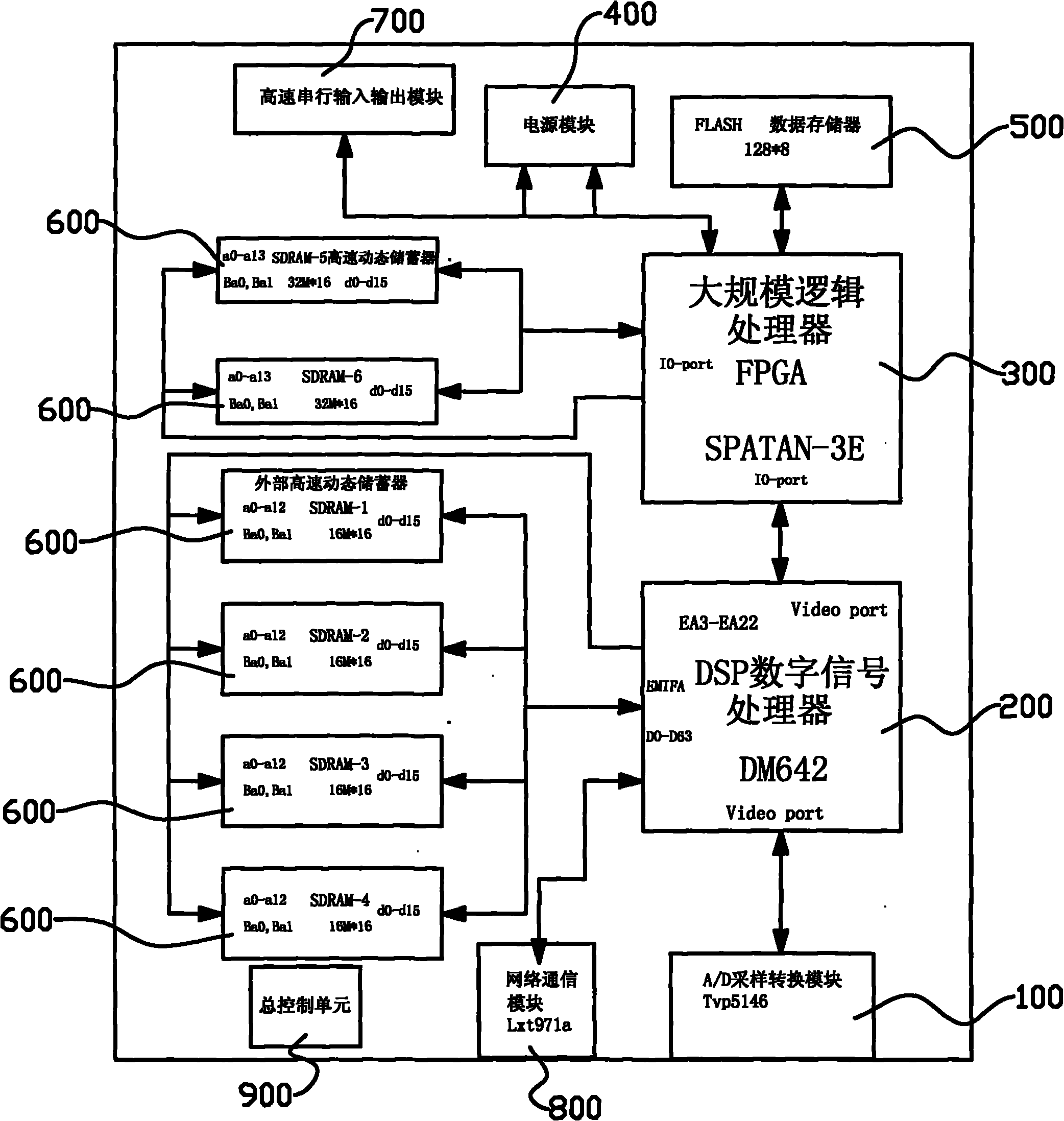

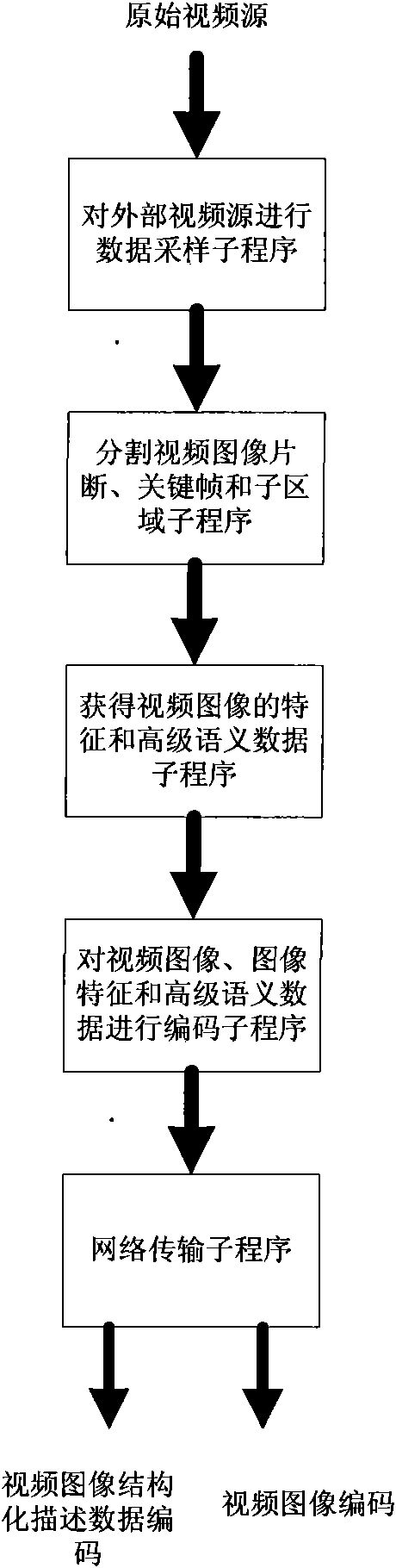

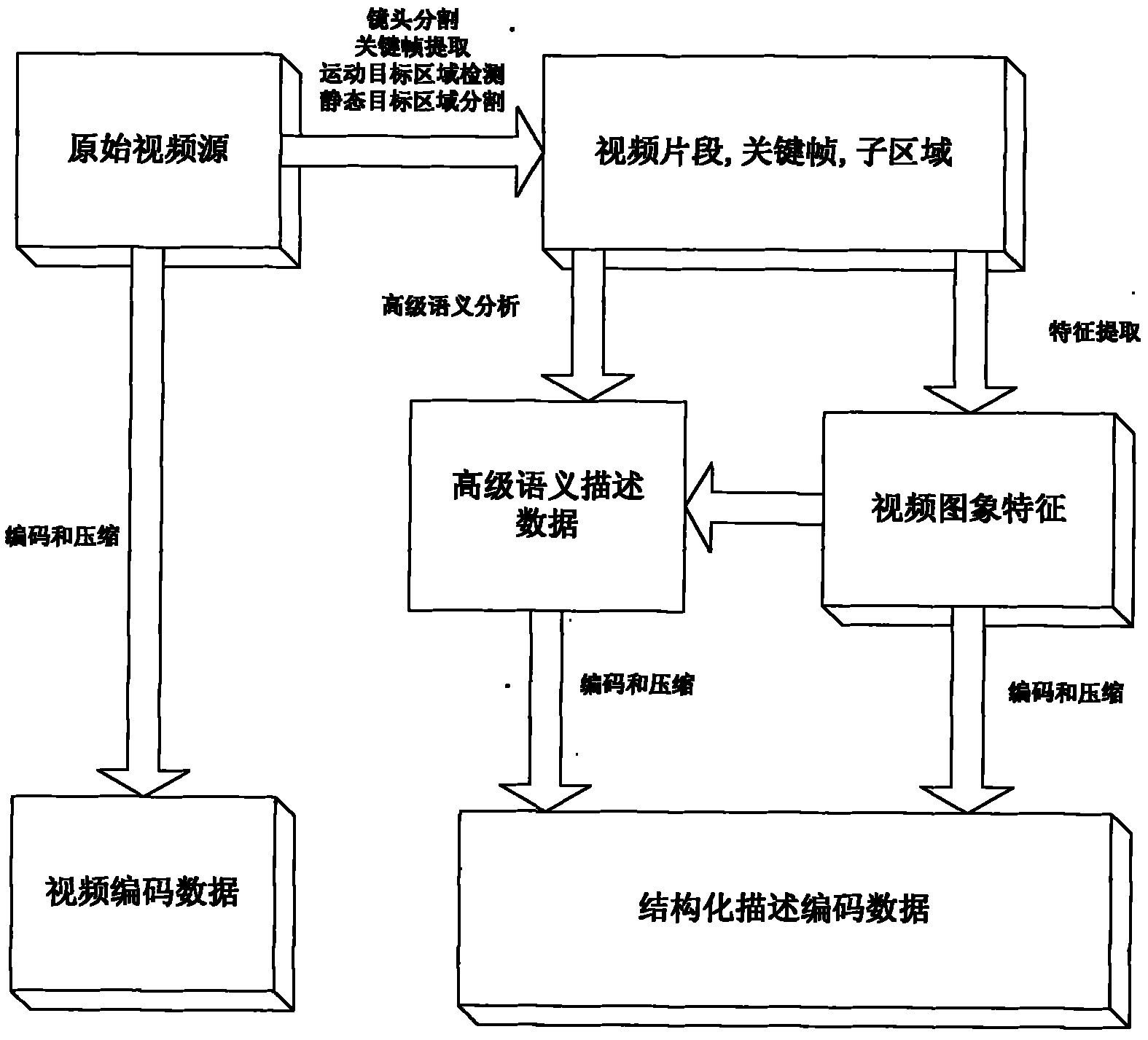

Device and method for realizing video structural description by using DSP and FPGA

ActiveCN101902617ARealize managementRealize management and query for video image dataCharacter and pattern recognitionClosed circuit television systemsVideo monitoringImaging processing

The invention aims to disclose a device and a method for realizing video structural description by using DSP and FPGA. The device and the method realize structural description of input video by using the DSP and the FPGA to organically combine an intelligent image processing technique of the video structural description and a DSP and FPGA-based embedded system, analyze and comprehend video images, generate structural description data, effectively monitor the video and manage the video data, and realize information-based application such as query, browse and retrieval of the video image data and the like; and the device has stable and reliable working performance and wide application range, and can greatly improve the intelligence of the conventional video monitoring system, reduce the manual monitoring cost, realize video monitoring information-based management and fulfill the purpose of the invention.

Owner:THE THIRD RES INST OF MIN OF PUBLIC SECURITY

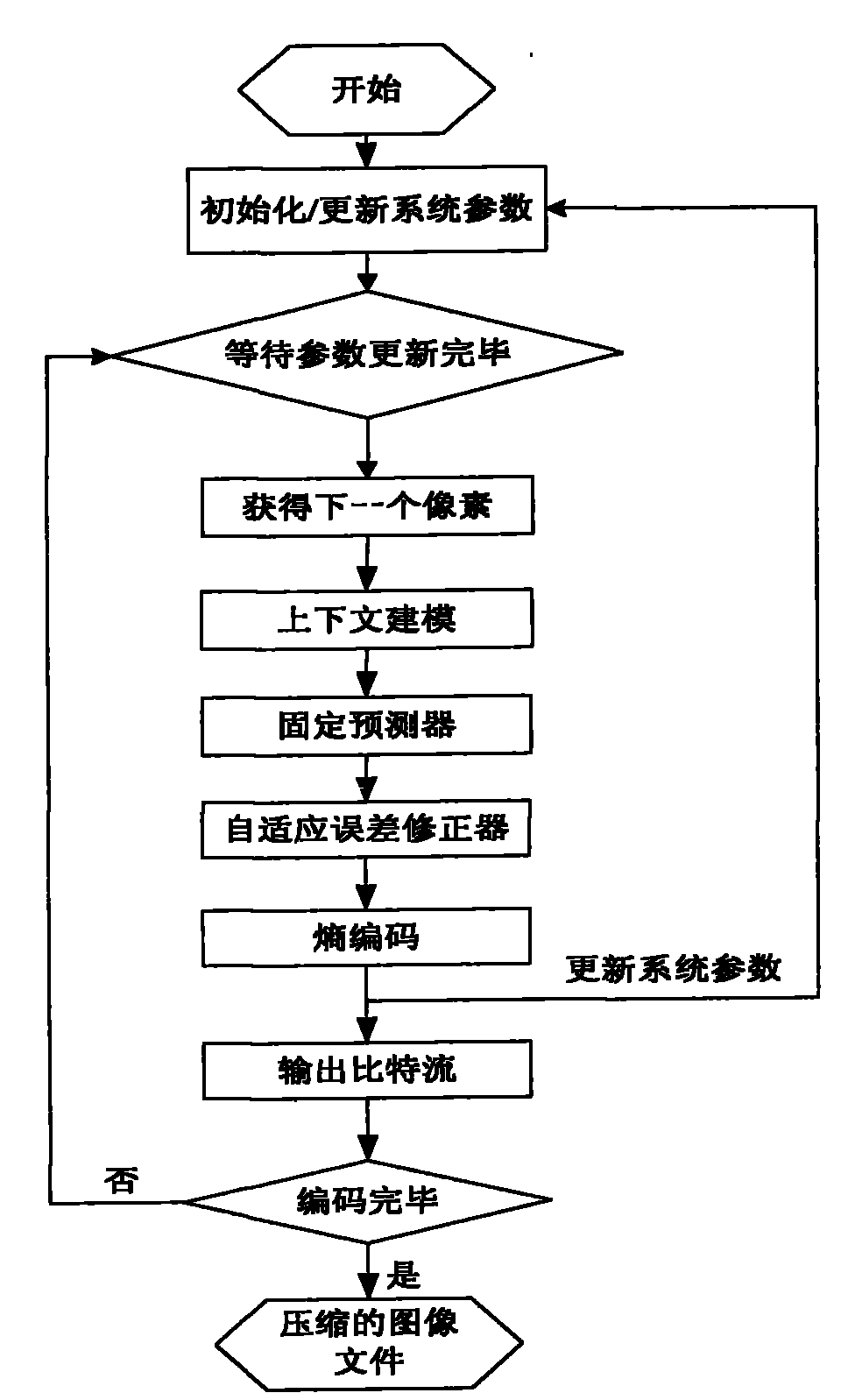

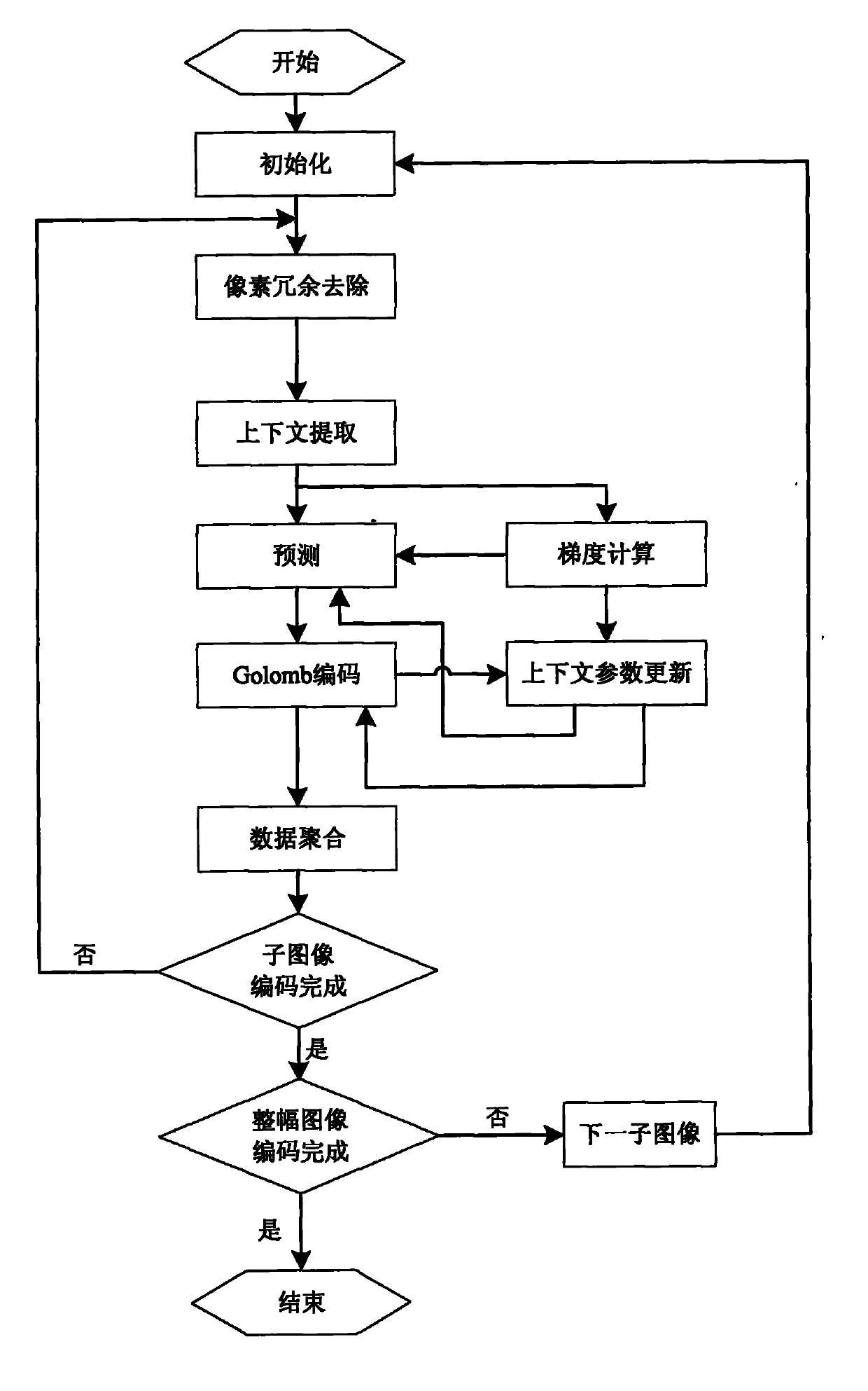

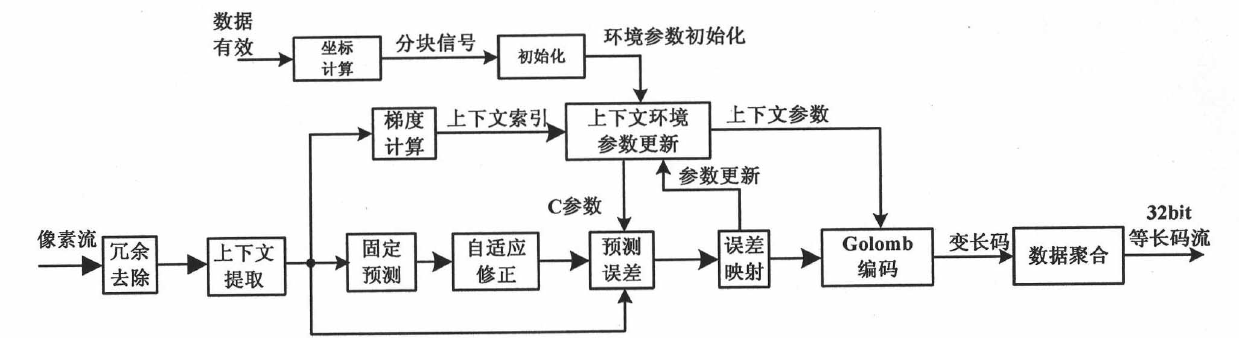

Satellite image compression method and device for realizing satellite image compression

ActiveCN101771874AIncrease the compression ratioHigh bit error toleranceGHz frequency transmissionDigital video signal modificationFpga implementationsSatellite image

The invention discloses a satellite image compression method and a device for realizing satellite image compression, belonging to the remote sensing and digital image processing field and solving the problems of high demand for encoded data transmission error rate and low processing speed in the existing image compression method. The method of the invention includes the steps of dividing a whole image into sub-images, independently encoding the sub-images, sequential initialization, removal of pixel redundancy, context extraction, preestimate, Golomb encoding and data polymerization; the steps of sequential gradient calculation and context environment parameters upgrade are finished simultaneously with the steps of preestimate and Golomb encoding. The invention improves image compression rate, realizes good error tolerance and good real-time performance and greatly improves the whole encoding efficiency, meeting the demand for wide satellite image data real-time nondestructive compression.

Owner:HUAZHONG UNIV OF SCI & TECH

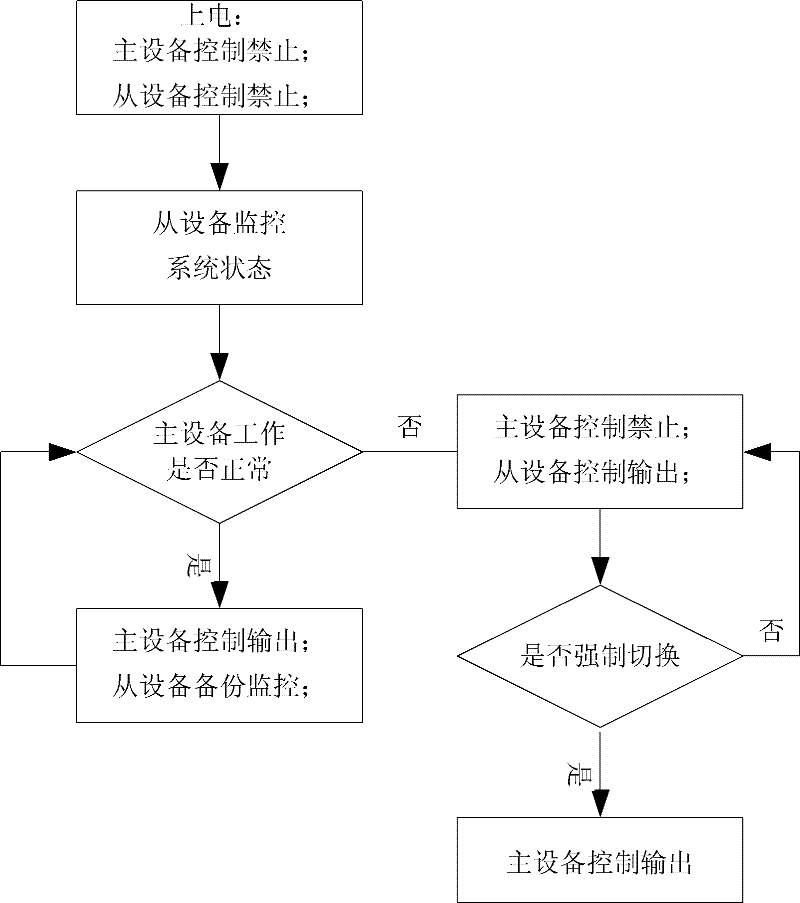

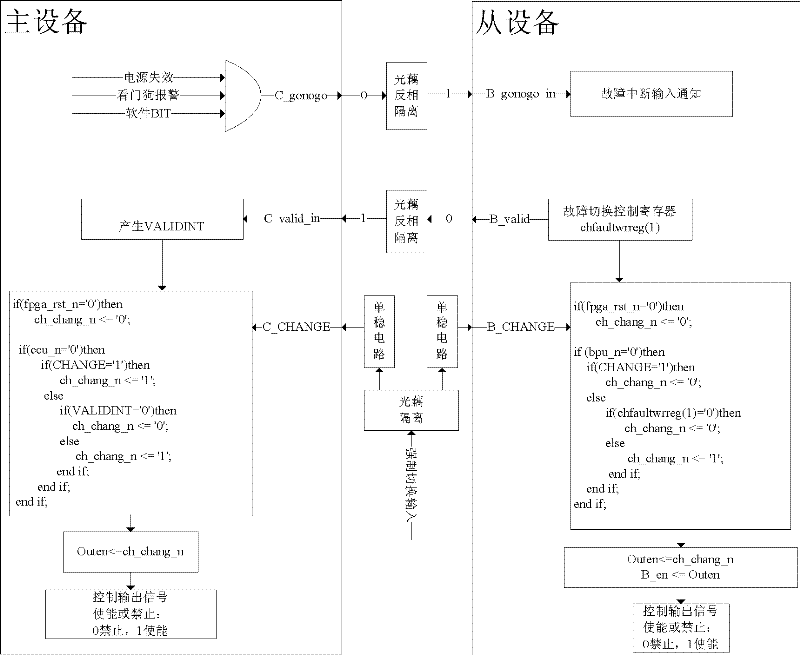

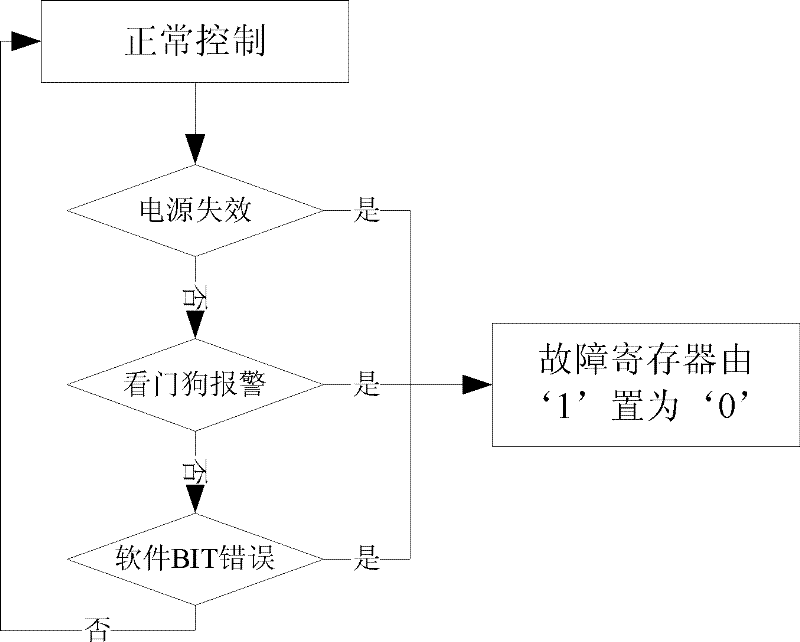

Switching method for processing fault of dual-redundancy computer

InactiveCN102541697AComplete fault judgment in real timeHardware monitoringRedundant hardware error correctionElectricityInformation transmission

The invention discloses a switching method for processing a fault of a dual-redundancy computer, which comprises the following steps that: 1, a system is powered up, a master device carries out control inhibition and a slave device carries out control inhibition; 2, the slave device carries out real-time monitoring on the state of the system; 3, the slave device judges whether the master device normally works, if yes, the master device carries out control output and the slave device carries out backup monitoring, and if no, the step 4 is executed; 4, the master equipment notifies the slave equipment fault information; and 5, the master device carries out control inhibition and the slave device implements switching control output and simultaneously monitors the master device. According to the switching method for processing the fault of the dual-redundancy computer, which is disclosed by the invention, the fault logicality is implemented by adopting a discrete magnitude signal and a FPGA (Field Programmable Gate Array), the fault judgment, the fault information transmission and the master and slave function switching of the master and slave devices are completed in real time.

Owner:AVIC NO 631 RES INST

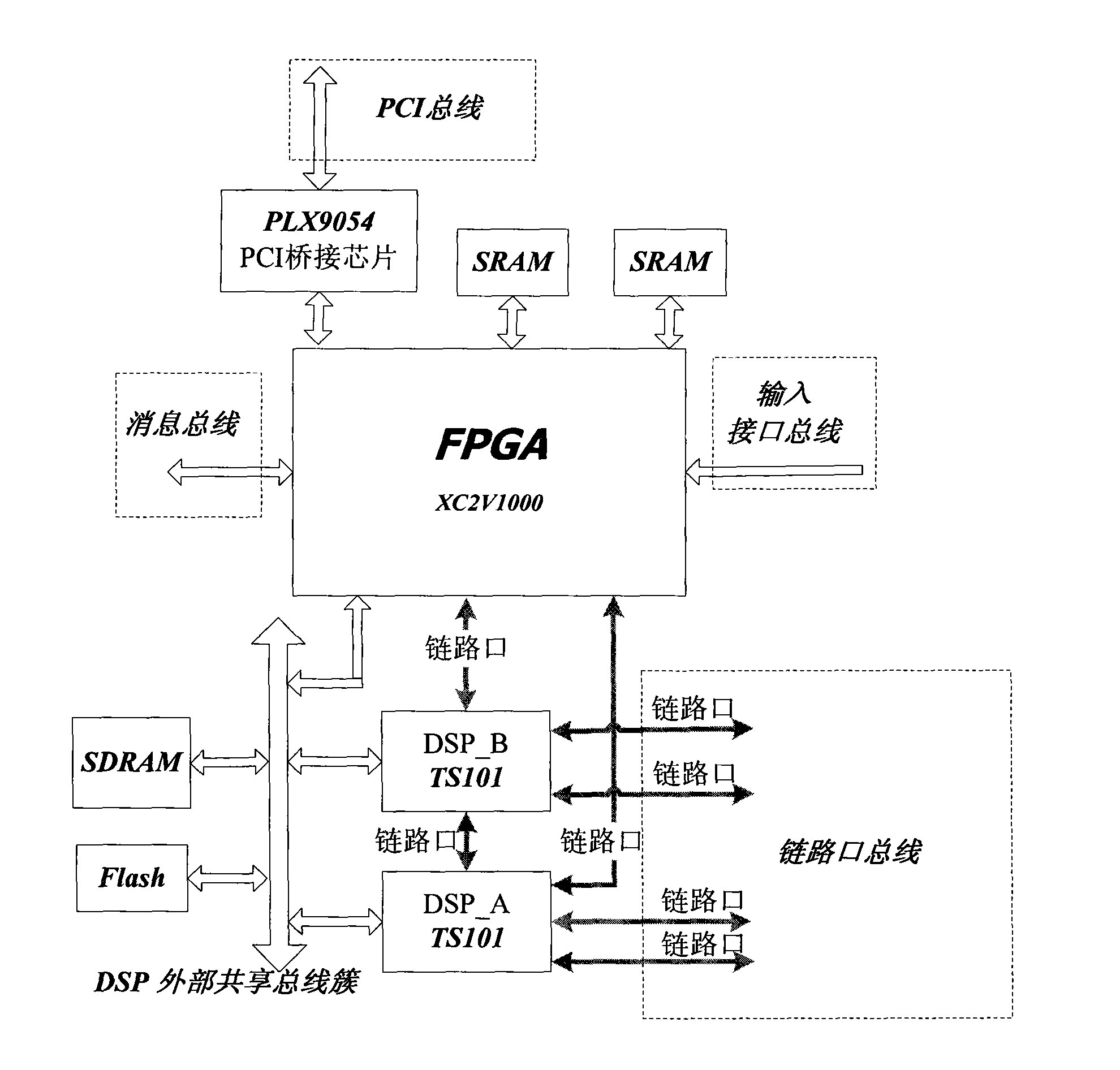

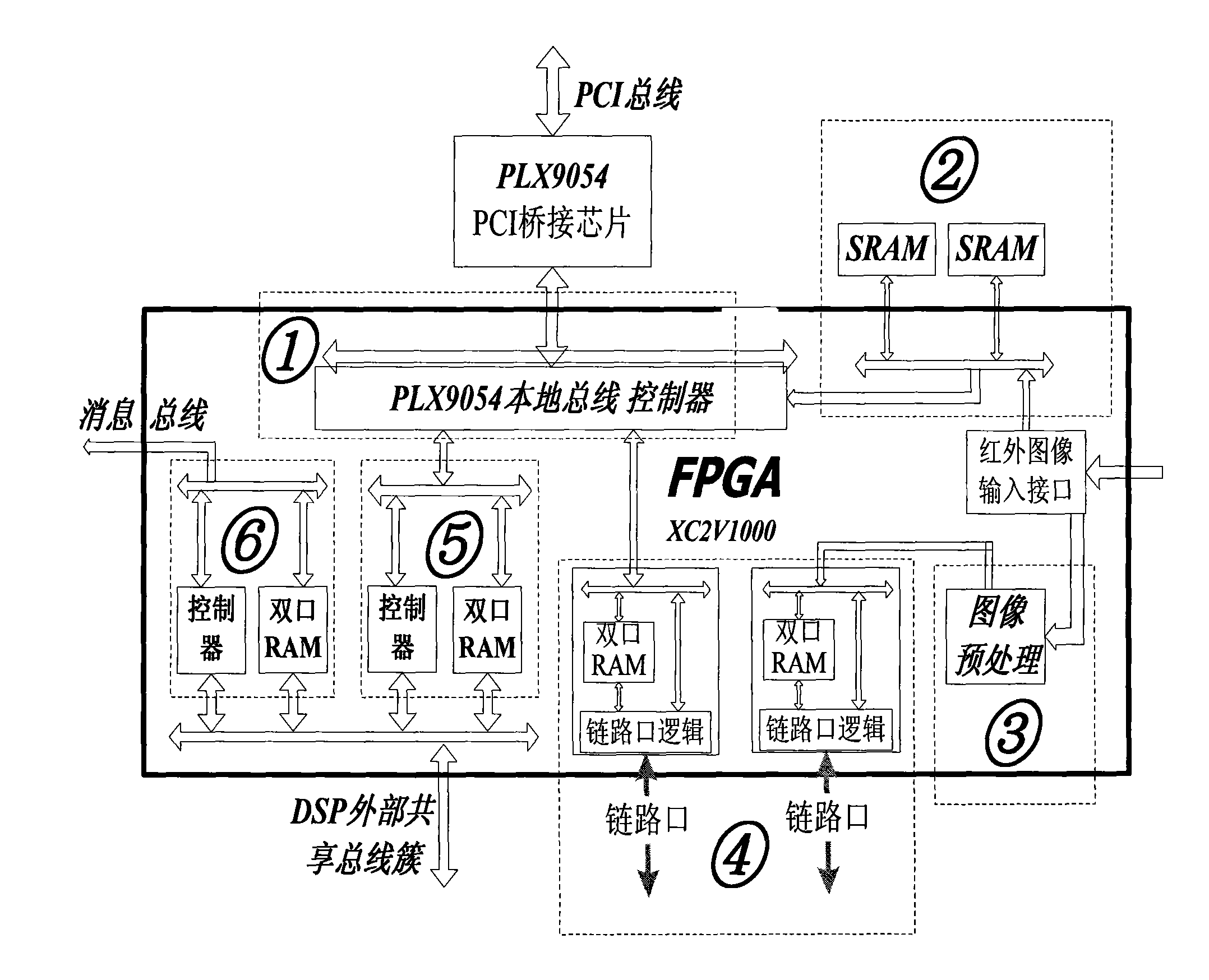

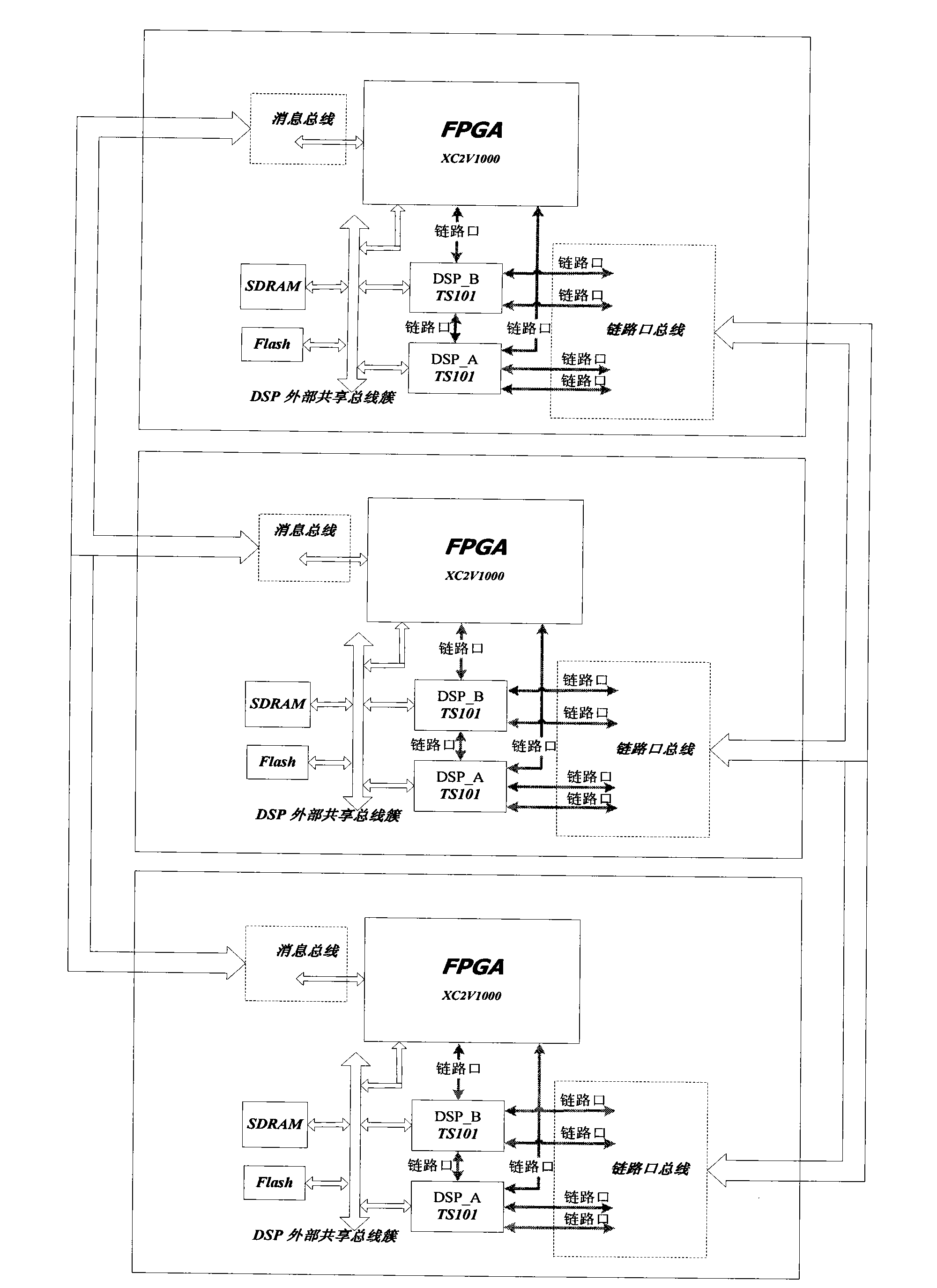

Multi-processor parallel processing system for digital signals

InactiveCN101667169AGuaranteed scalabilityDigital computer detailsOptical detectionCommunication interfaceFpga implementations

The invention discloses a multi-processor parallel processing system for digital signals, which is mainly used for infrared real-time signal processing systems, such as infrared detection systems andthe like. The technical scheme of the invention is shown in a figure 1, and comprises the following aspects of: 1, realizing the communication between a multi-processor platform and an upper host through a PCI bridge and an FPGA; 2, realizing a link port communication module inside the FPGA so as to realize the high-speed communication between the FPGA and a DSP; and 3, realizing a message communication interface needed by the cascade connection of a plurality of multi-processor system boards through the FPGA. The multi-processor parallel processing system has the advantages that the system isprovided with parallel multi-processor inside subsystem boards, and supports that the plurality of multi-processor system boards can form a stronger multi-processor platform through board interconnection.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

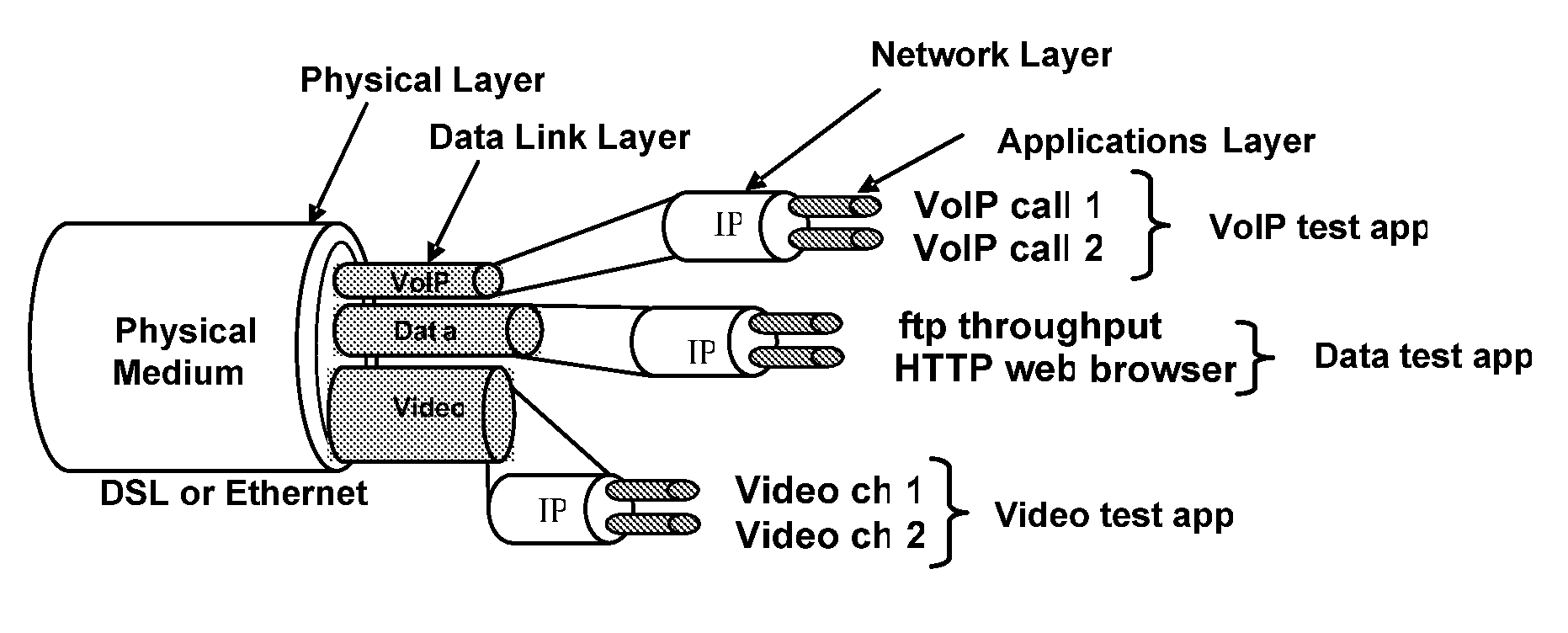

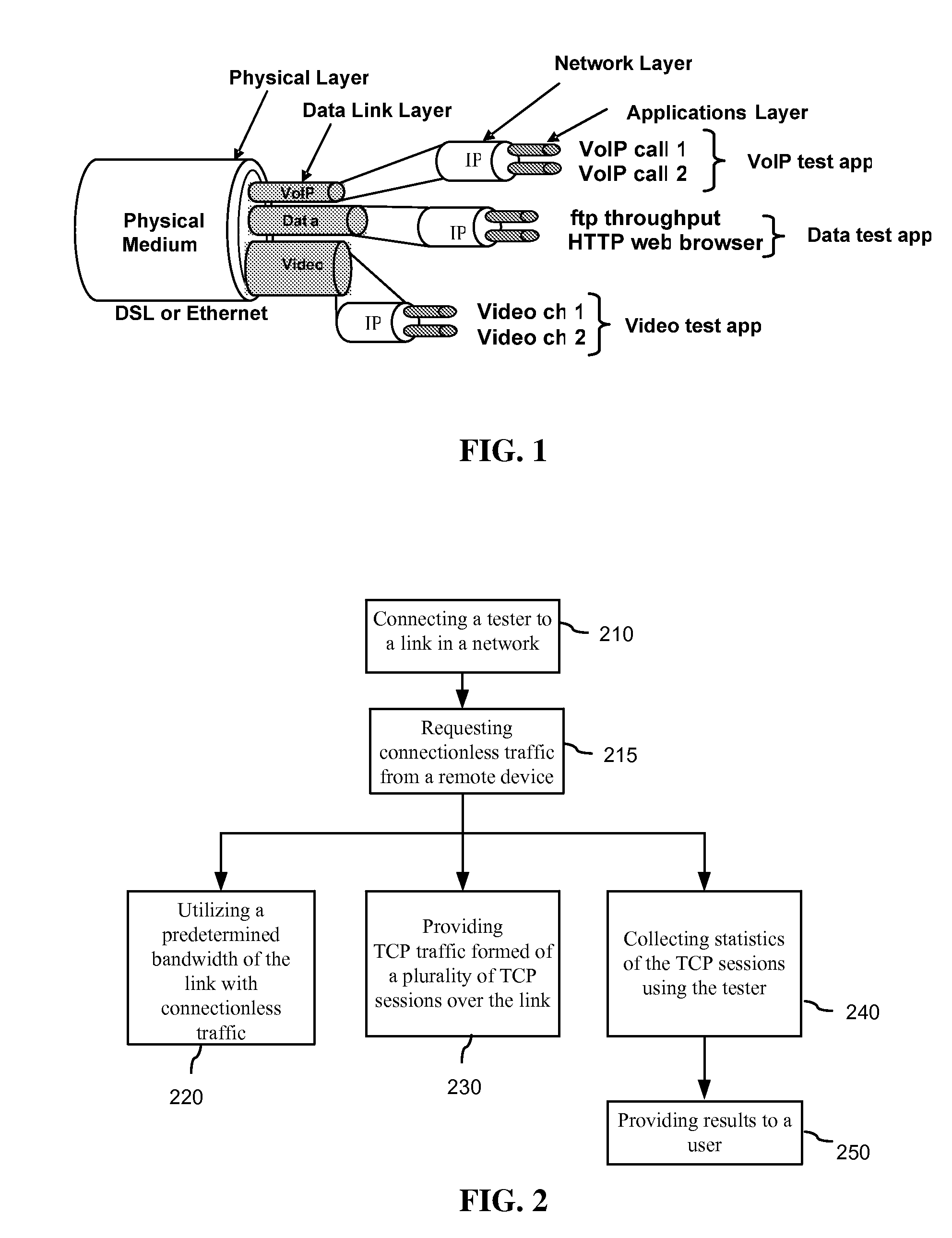

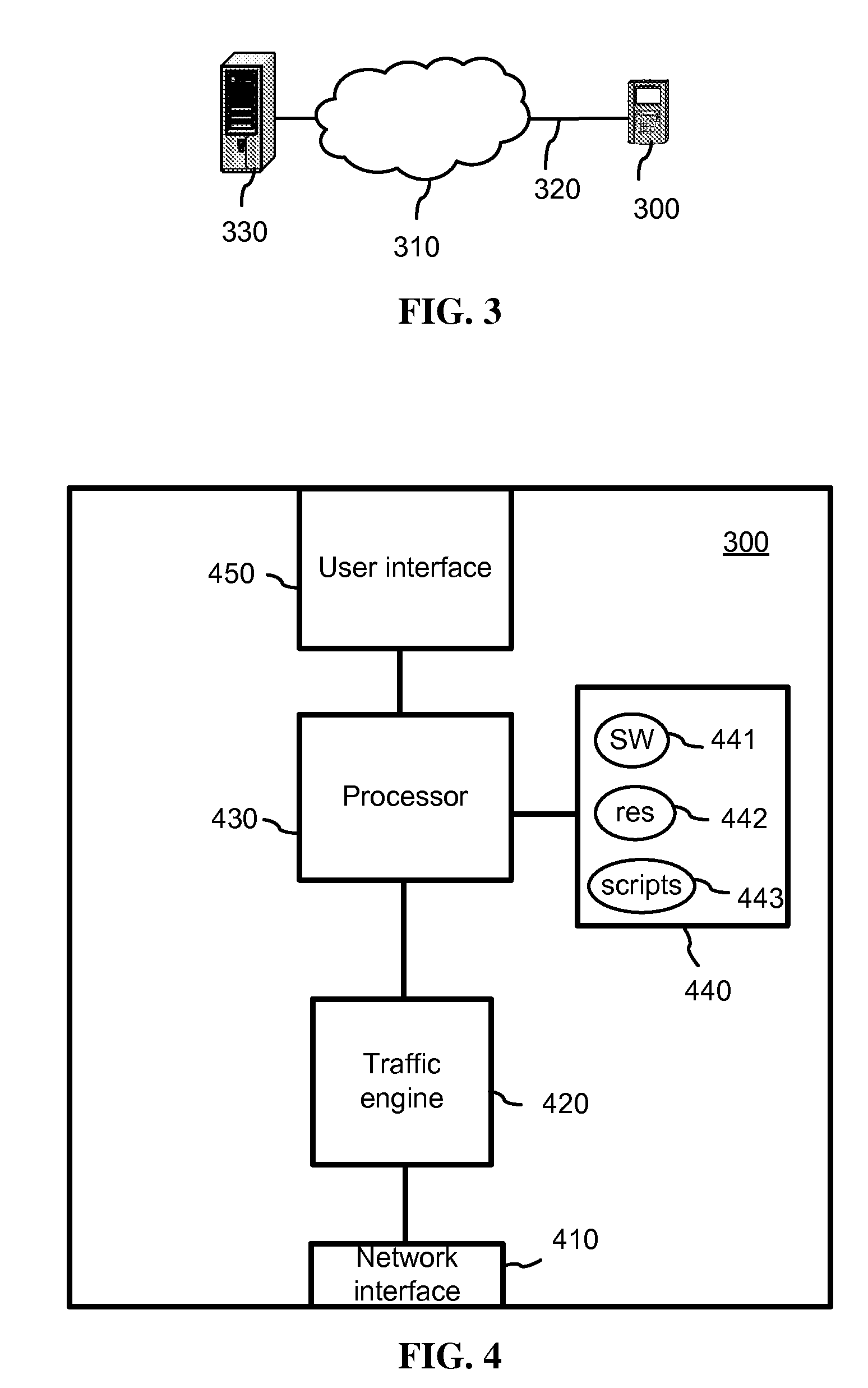

Network tester for real-time measuring of TCP throughput

The invention relates to a method for real time testing of TCP traffic in a network, the method comprising: (a) connecting a tester to the network; (b) requesting connectionless traffic from a remote device connected to the network, to the tester; (c) generating the connectionless traffic comprising a plurality of packet streams, with the remote device, and receiving the connectionless traffic by the tester; (d) generating TCP traffic comprising a plurality of TCP sessions between the tester and the remote device; and, (e) concurrently with steps (c) and (d), in real time collecting statistics of the TCP sessions using the tester. The tester has an-FPGA implemented traffic engine, including a TCP state machine, for generating and receiving traffic at the rates of at least 1 gigabit per second, and for collecting statistics in real time.

Owner:ACTERNA LLC

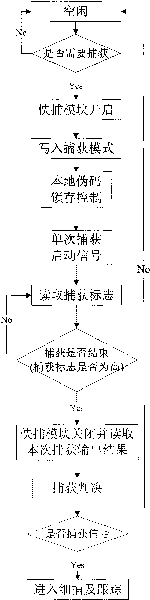

Method for rapidly capturing multi-mode high dynamic spread spectrum signal

ActiveCN101741424AQuick captureImprove portabilityDigital technique networkTransmitter/receiver shaping networksIntermediate frequencyFpga implementations

The invention relates to a method for rapidly capturing a multi-mode high dynamic spread spectrum signal which is realized based on an FPGA. The method comprises the steps of: (1) performing double interpolation and down-conversion on an input intermediate frequency sampled data, performing down-conversion on an intermediate frequency digital signal in order to form a zero intermediate frequency and output I and Q two-path zero intermediate frequency signals, (2) generating a zero intermediate frequency signal having a two-times bit rate, (3) inputting the sampled I and Q two-path data to a matched filter, performing relative operation by utilizing a time division multiplex folding algorithm, and outputting the relative operated result of n sections of single points of the I and Q two paths, (4) serially capturing a judged sample value and (5) performing non-coherent accumulation treatment on the serially captured judged sample value according to a pseudo code length in a capturing mode parameter in order to find out a maximum judged sample value and judge whether the value is more than a captured judgment threshold for the purpose of realizing capture judgment. The method can adapt to rapidly capturing a multi-mode high dynamic spread spectrum signal having multi-information rate, multi-pseudo code rate and multi-pseudo code length.

Owner:SPACE STAR TECH CO LTD

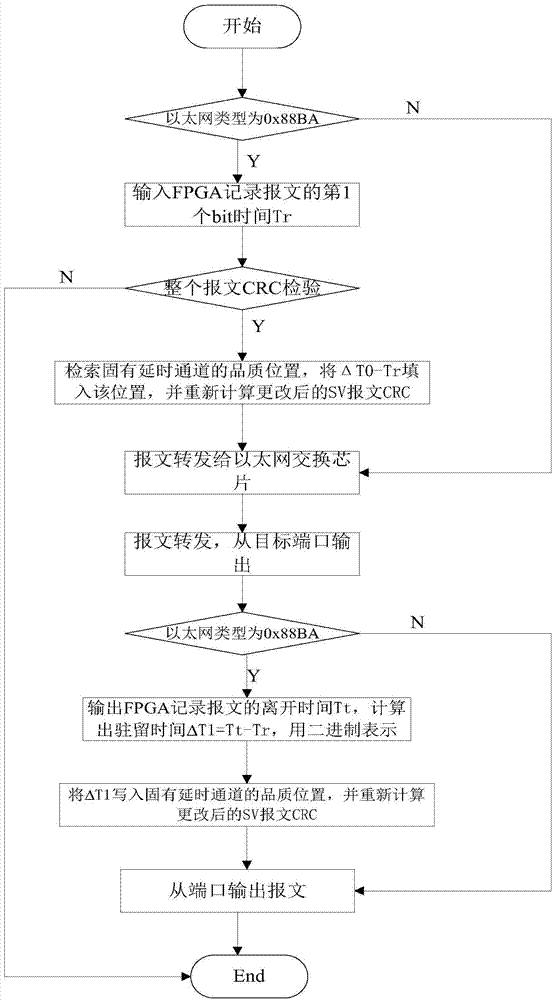

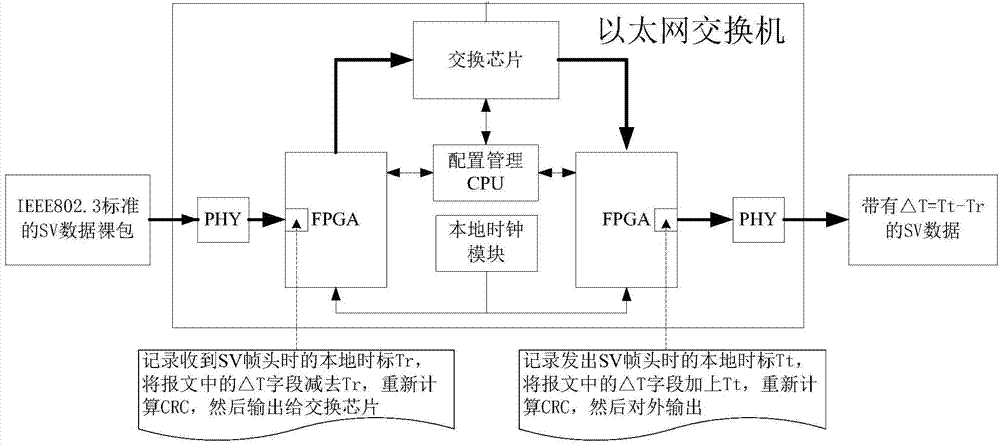

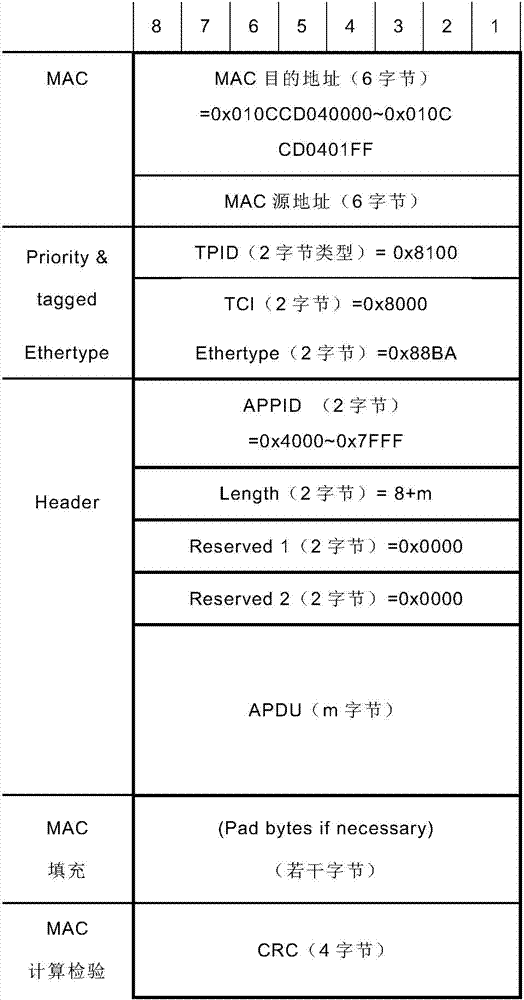

Switch device and method for measuring transmission delay through FPGA

InactiveCN103888320AError assuranceReduce construction costsData switching networksElectricitySmart substation

The invention provides a switch device and method for measuring transmission delay through an FPGA. The switch device is characterized in that as for an SV sample data raw package meeting the IEEE802.3 standard, the FPGA inside a switch records the moment Tr when the first bit of a message enters a port of the switch and the moment Tt when the first bit of the message is transmitted out from the port of the switch, the timestamp accuracy is in the nanosecond grade, the FPGA calculates the residence time deltaT of the message in the switch according to the formula deltaT=Tt-Tr, and the residence time deltaT is written into a designated position in the SV message. According to the switch device and method, the problem that timing of a relay protection device in an intelligent substation in the networking mode must depend on an external clock is solved, the fundamental principle that SV sample data are synchronized by a use device is reflected, and the theory is equivalent to that of the mode that the SV sample data are directly transmitted without the switch.

Owner:BEIJING SIFANG JIBAO AUTOMATION

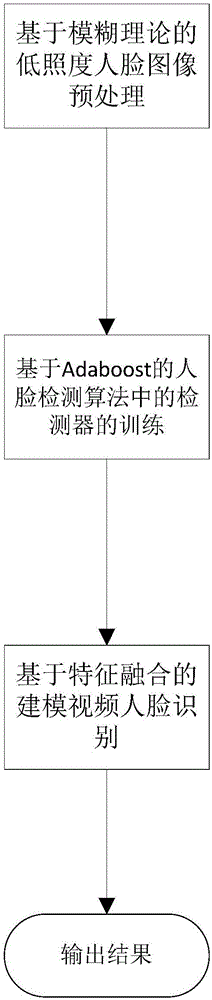

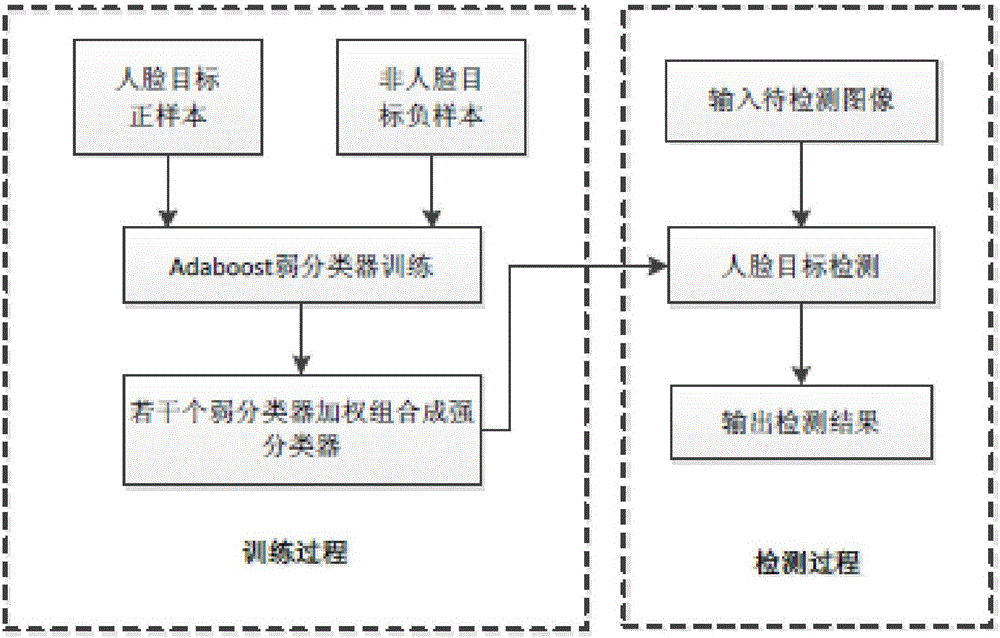

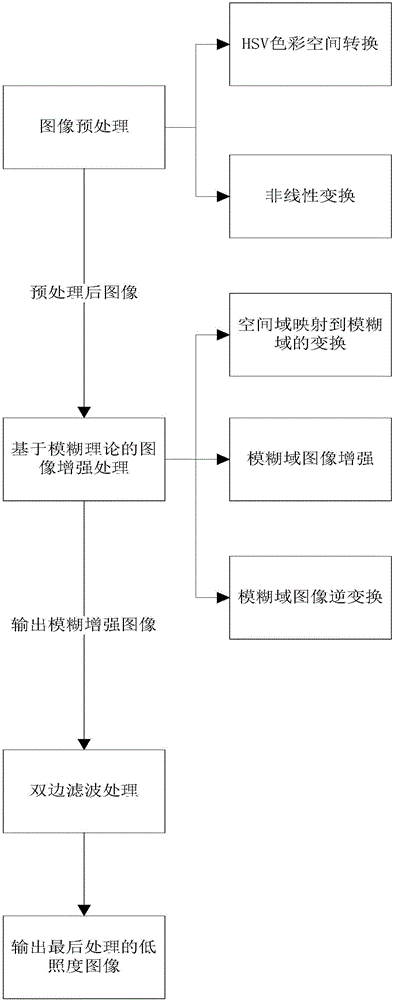

Detection and recognition method of human face in video under low-light conditions

InactiveCN106446872APromote enhancementEffective separation of colorCharacter and pattern recognitionPattern recognitionFace detection

The invention relates to the field of computer vision, and refers in particular to a detection and recognition method of human face in video under low-light conditions. The system aims at the specific problem of recognizing human face under low-light conditions, and is designed to satisfy the video system with a recognition function of human face under low-light conditions. An algorithm of the system consists of three steps: 1. preprocessing the video image of human face under low-light conditions, based on fuzzy theory; 2. training with a classifier, based on human face detection algorithm of Adaboost; 3. recognizing human face in modeling Video, based on feature fusion. The result of recognizing human face can finally be obtained. Actually, the method can be embedded in FPGA to be used in the video camera monitoring system or cameras with the recognition function of human face. The method has the advantages of good in stability, high in recognition rate, high in speed of calculation, effective in recognizing face feature under low-light conditions, applicable to various systems, such as night vision monitoring system and verifying system of identity under low-light conditions, and strong in practicality.

Owner:HUNAN VISION SPLEND PHOTOELECTRIC TECH

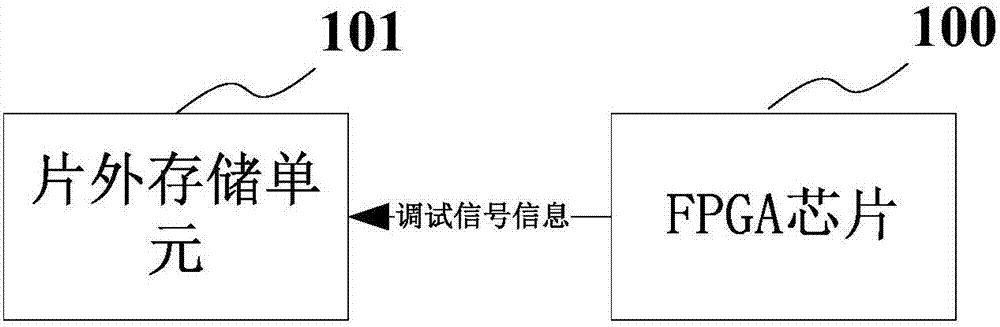

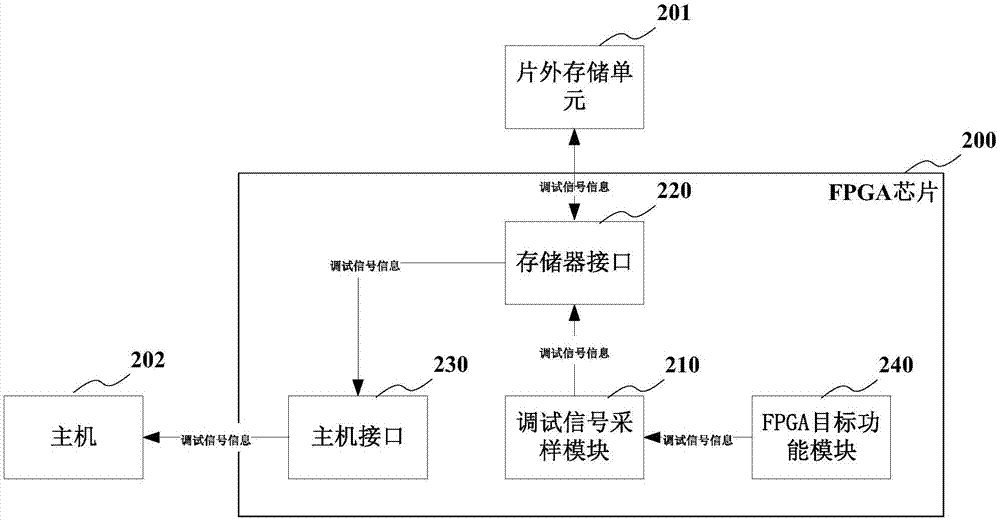

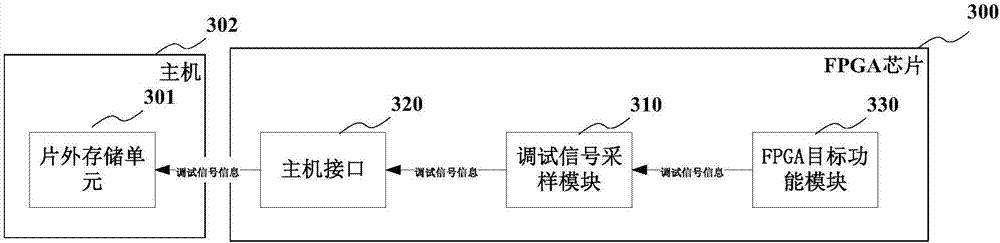

FPGA debugging system and method

InactiveCN106951587AImprove debugging efficiencyExtended observation timeCAD circuit designSpecial data processing applicationsFpga implementationsTime-Consuming

The invention provides an FPGA debugging system and method. By reading debugging signal information written by an FPGA to an off-chip storage unit with relatively large capacity and sufficient interface bandwidth for storage, the debugging signal observation time is greatly prolonged on the premise of keeping a sufficient debugging signal quantity, so that the problems of repeated selection of debugging signals and repeated try of triggering opportunities inevitable in an existing debugging mode can be avoided, the condition that a very time-consuming FPGA realization process needs to be repeatedly carried out for debugging is avoided, and the FPGA debugging efficiency is greatly improved; and the difficult problem that large-time-span exceptions cannot be diagnosed in an existing debugging technology can be solved.

Owner:芯启源(南京)半导体科技有限公司

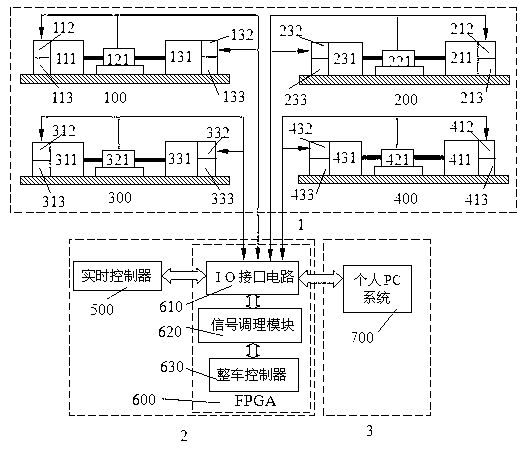

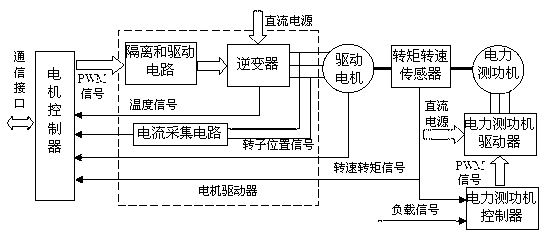

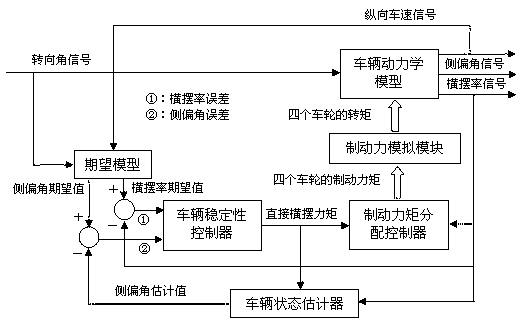

Four-wheel drive pure electric vehicle hardware-in-loop simulation experimental system

InactiveCN103176472AAccurate analysisOptimal Control StrategyElectric testing/monitoringVehicle dynamicsFpga implementations

The invention relates to a four-wheel drive pure electric vehicle hardware-in-the-loop simulation experimental system. The system comprises a drive motor and controller subsystem, an electric dynamometer and controller subsystem, torque and rotational speed sensors, a vehicle dynamic model real-time simulation subsystem and a signal detection and analysis subsystem. The system achieves pure electric vehicle four-wheel independent drive via the motor and controller subsystem, and achieves simulation of vehicle travel load via the electric dynamometer and controller subsystem. Vehicle dynamic response is achieved by operating a real-time simulation model through a real-time controller, and signal input, output and conditioning of a vehicle control unit are achieved by the aid of an FPGA (field programmable gate array). The system is capable of performing hardware-in-the-loop simulation for four-wheel drive pure electric vehicles to achieve rapid development and product testing of a vehicle drive system, and has the advantages of energy saving, safety, rapidness and low cost.

Owner:CHANGSHA UNIVERSITY OF SCIENCE AND TECHNOLOGY

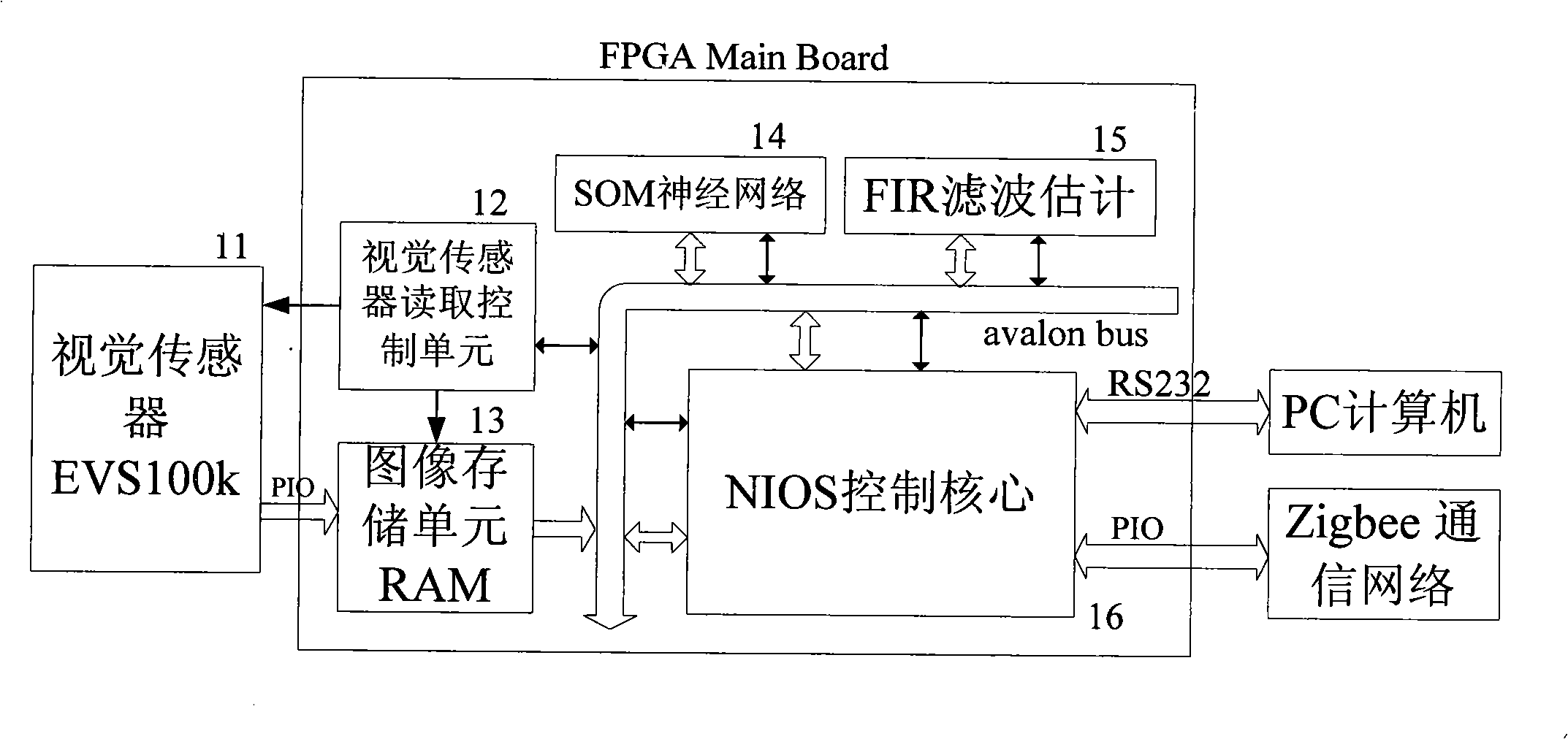

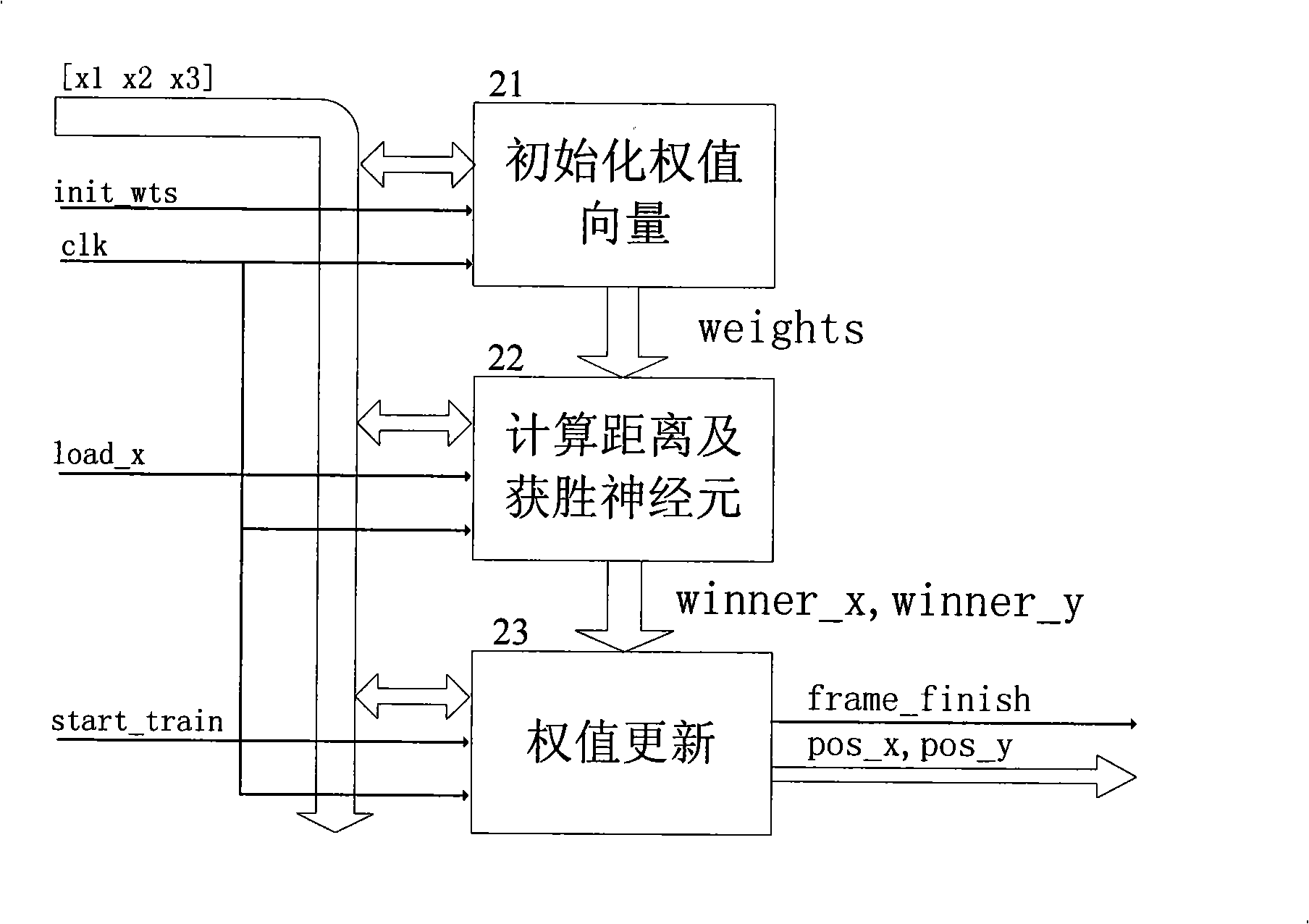

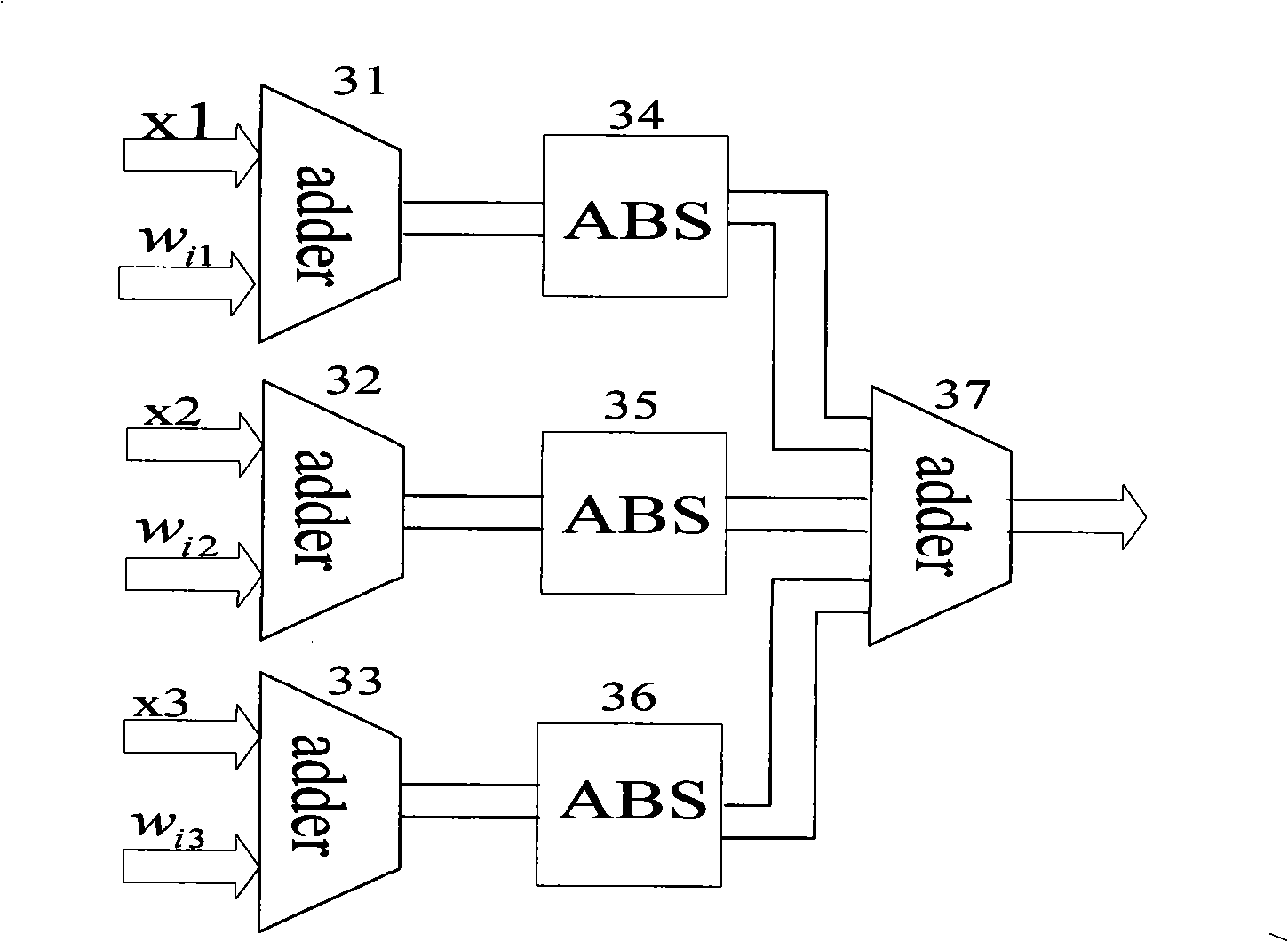

Device and method for realizing moving object identification and track based on FPGA

InactiveCN101299233AImage analysisCharacter and pattern recognitionFpga implementationsVision sensor

The invention discloses a movement object identification and tracking apparatus based on FPGA and method thereof, whose kernel is an CMOS+ FPGA vision system. The CMOS+FPGA vision system includes a low resolution CMOS vision sensor for capturing continuous image data; and a large-capacity FPGA, which realizes the image characteristic testing algorithm and system control, recognizes and tracks the robot and obstacles in the continuously image, and uses the RS232 serial port to communicate with the host computer. The SOM neural net algorithm is used to execute image processing in the FPGA to obtain the target area position and sizes information, which includes three steps of weight initialization, distance calculation and weight updating. Finally the smooth and consistent velocity information is extracted by noise abatement to the FIR filtering. The information detector has features of small volume, low power consumption and fast process velocity.

Owner:XI AN JIAOTONG UNIV

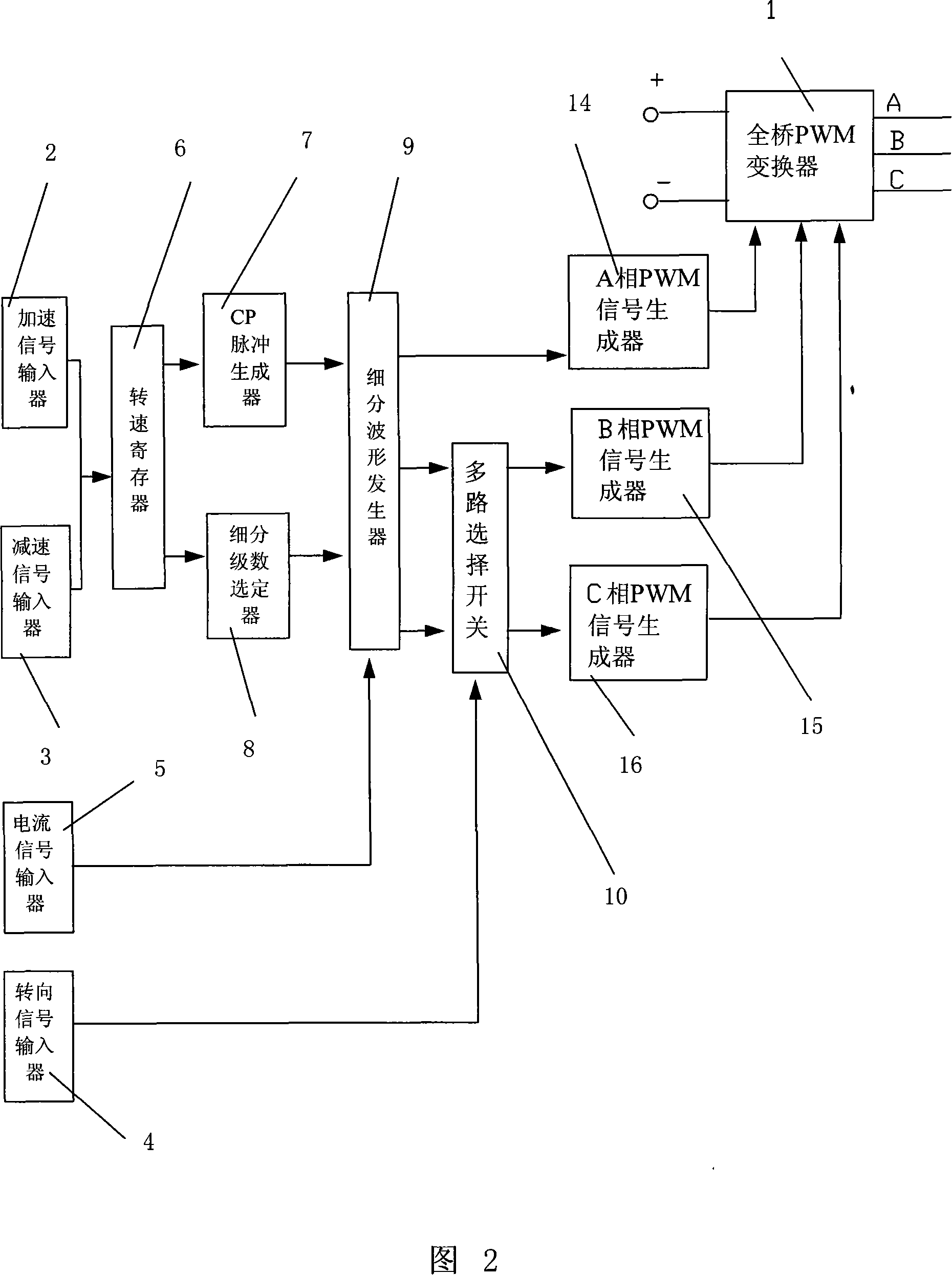

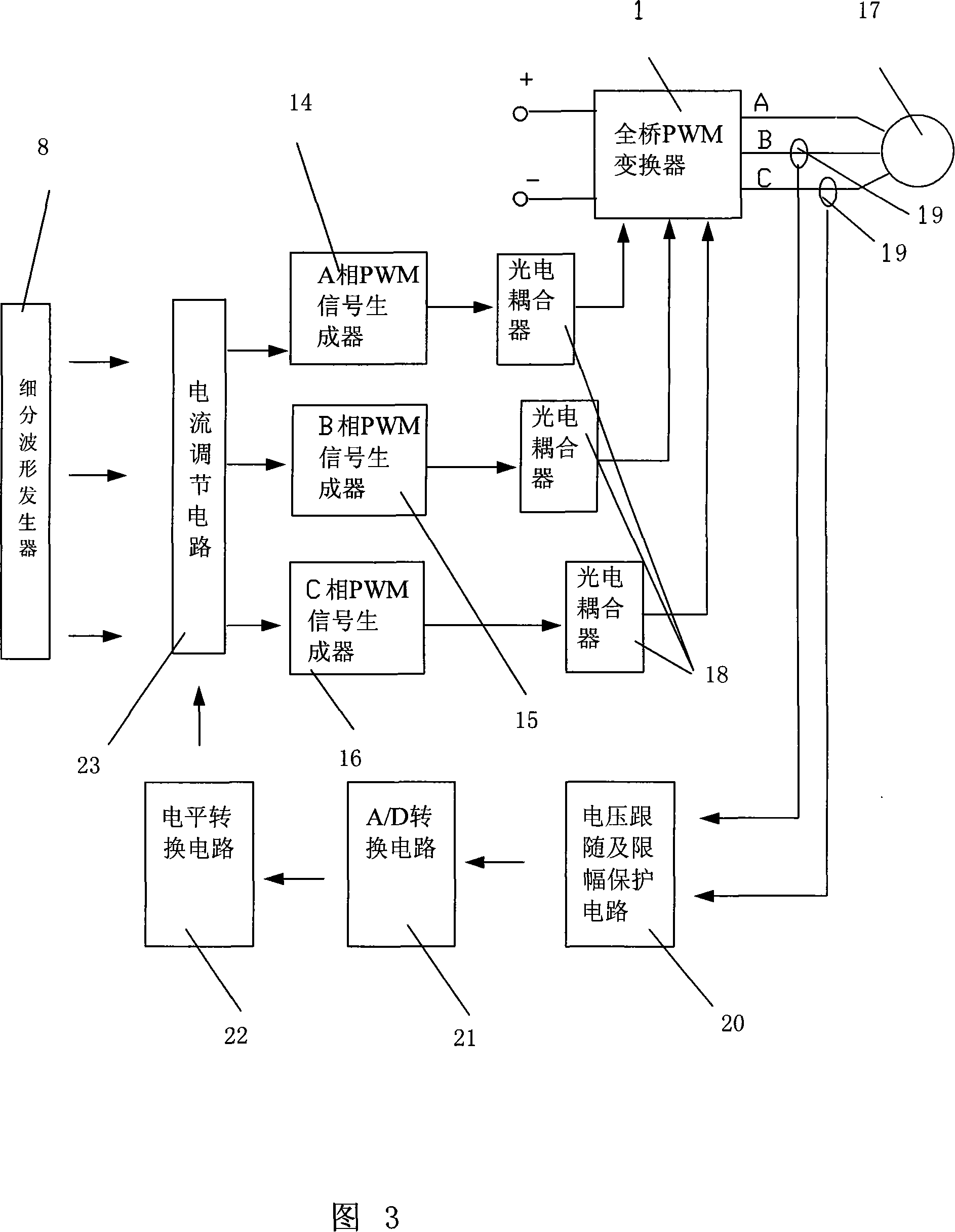

High subdivided integration type stepper motor driver

InactiveCN101119092AImprove reliabilityHigh precisionDynamo-electric converter controlPhase currentsFpga implementations

The present invention discloses a high-subdivision integrated stepper motor that relates to the drive machine of stepper motor. The present invention overcomes the shortages of low resolving capability of angular elongation caused by low subdivision, low frequency vibration and desynchronizing. The present invention consists of a full-bridge PWM converter, a speed acceleration signal input device, a speed reducing signal input device, a rotate speed register, a CP pulse generator, a subdivision wave generator and a PWM signal generator. The speed accelerating signal input device and the speed reducing signal input device choose rotate speed through adding and subtraction of numbers and choose the CP pulse frequency and motor through rotate speed and the subdivision grades of phasing current sinusoidal waveform, the subdivision waveform generator output each phasing current sinusoidal waveform after divided by chosen subdivision grades according to the arriving frequency of CP pulse. Then each phase of PWM signal is formed. The above control circuit is formed on the basis of FPGA and the division of the sinusoidal waveform according to time order is from 16 to 4096.

Owner:HARBIN INST OF TECH