FPGA debugging system and method

A debugging system and off-chip storage technology, applied in CAD circuit design, special data processing applications, instruments, etc., can solve the problems of insufficient debugging signal observation time, increase debugging signal observation time, etc., to solve the problem of inability to diagnose large time The effect of abnormal span and improving debugging efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment

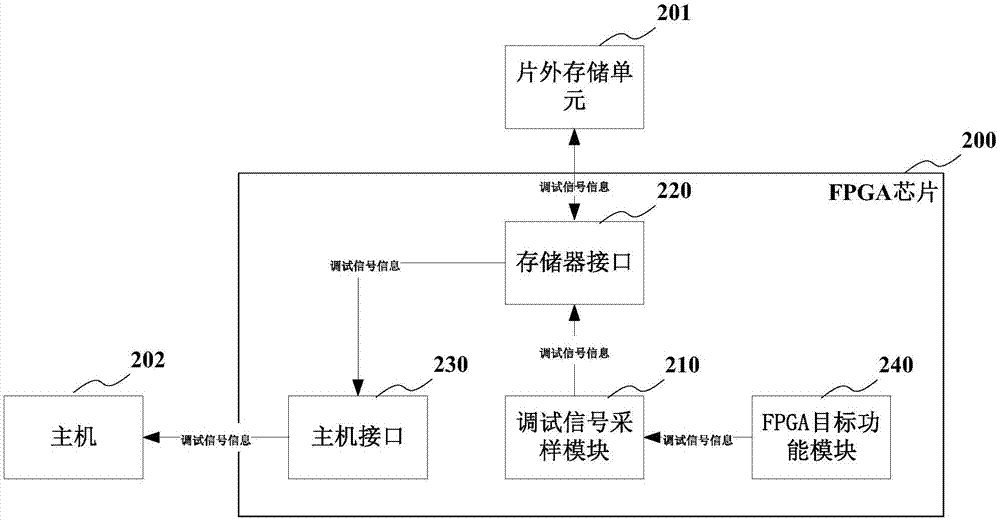

[0043] Such as figure 2 As shown, the first embodiment of the FPGA debugging system structure is shown, the off-chip memory unit 201 is connected to the FPGA chip 200 through the memory interface 220, and the memory interface 220 is connected to the debugging signal sampling module 210 in the FPGA chip 200, so The debug signal sampling module 210 is used to read the written debug signal information from the FPGA target function module 240 in the FPGA chip 200. Specifically, the FPGA target function module 240 refers to the function module that needs to be implemented originally on the FPGA , is also the debug target of the debug system, and all the debug signal information is collected from the FPGA target function module 240; the FPGA chip 200 is also connected to the host 202 through the host interface 230; wherein, the host 202 is, for example, a PC etc., the host interface 230 is, for example, any one of a PCI-E interface, a USB interface, and an Ethernet interface, and t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More