Patents

Literature

234 results about "Fpga design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

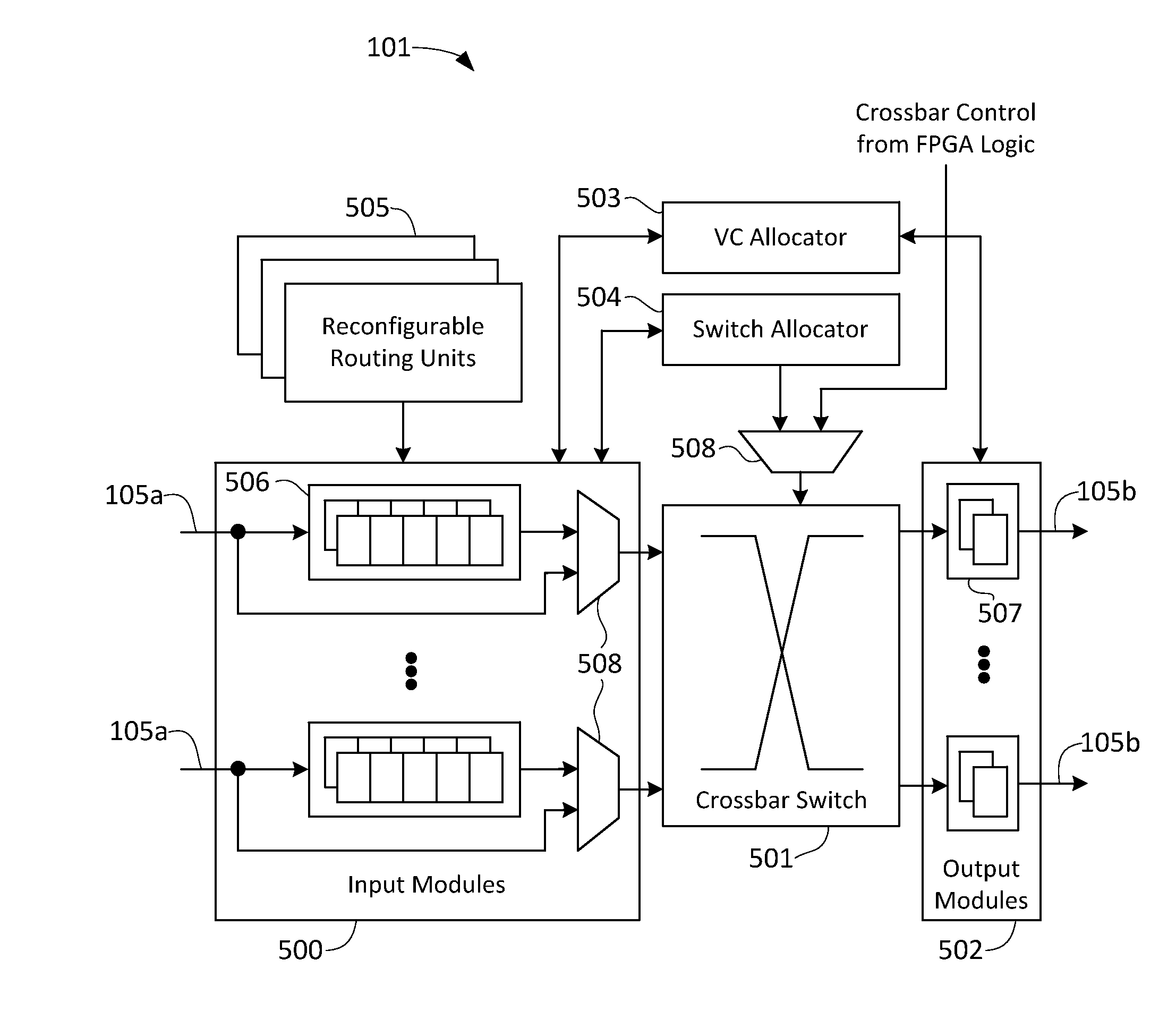

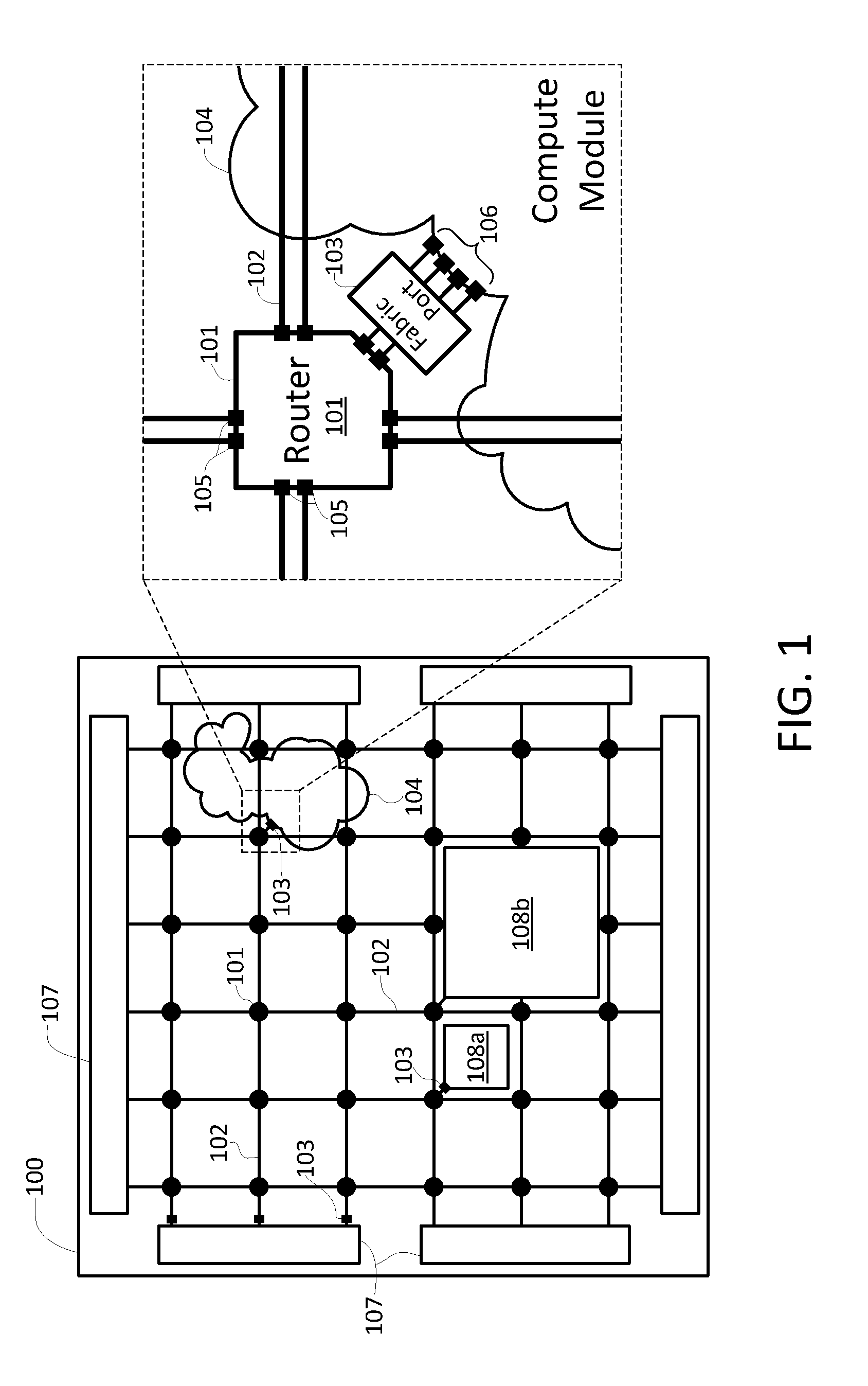

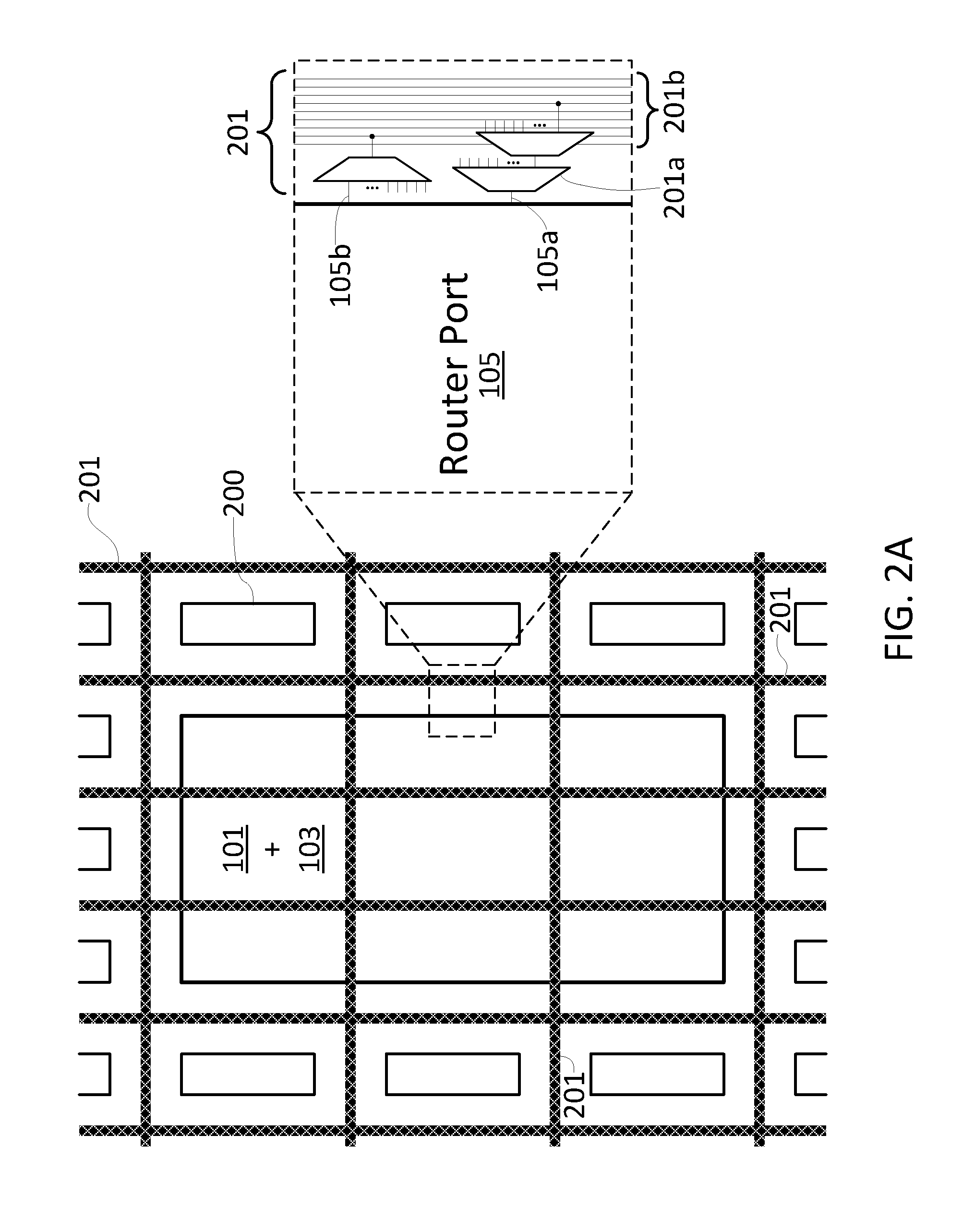

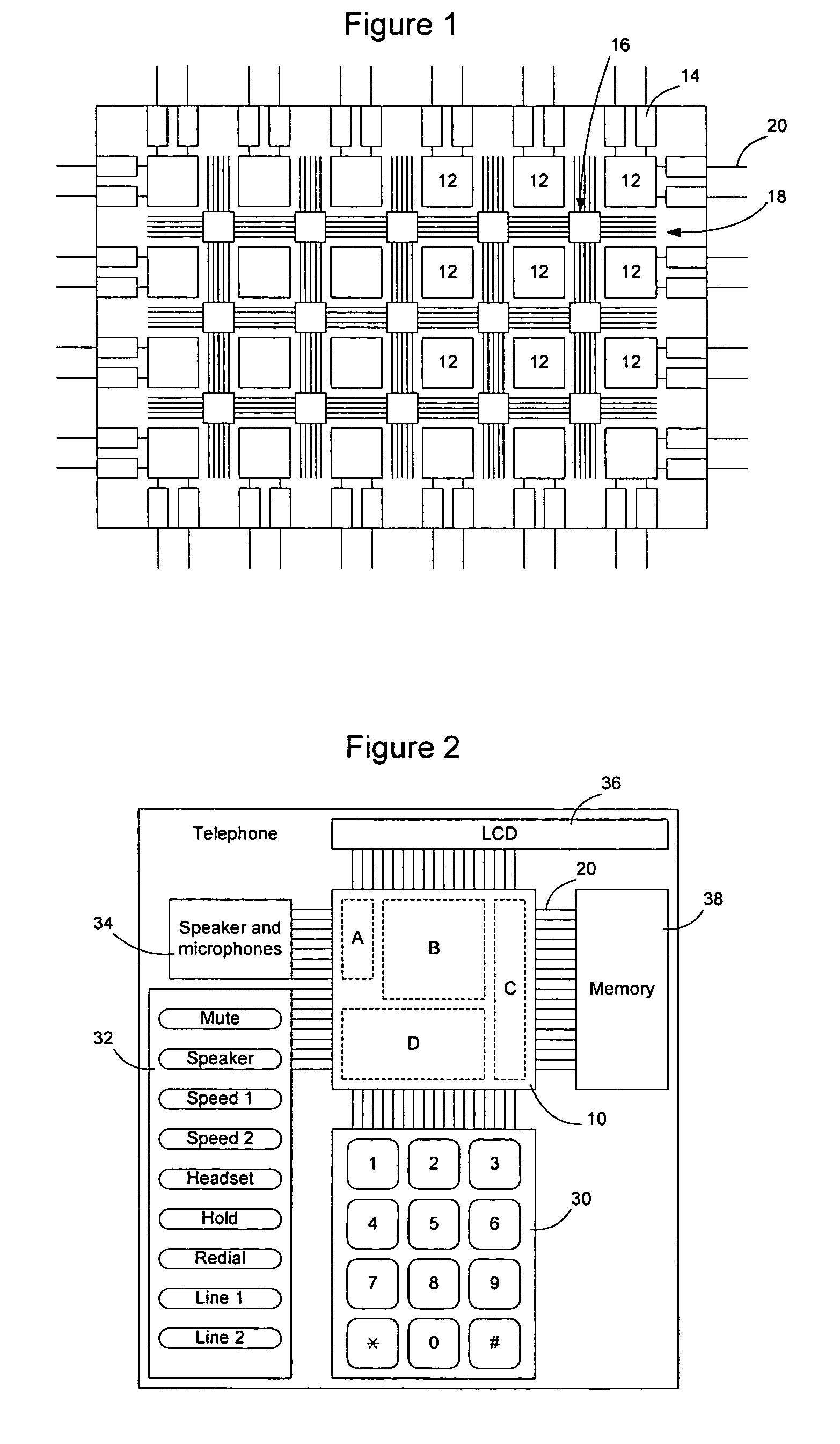

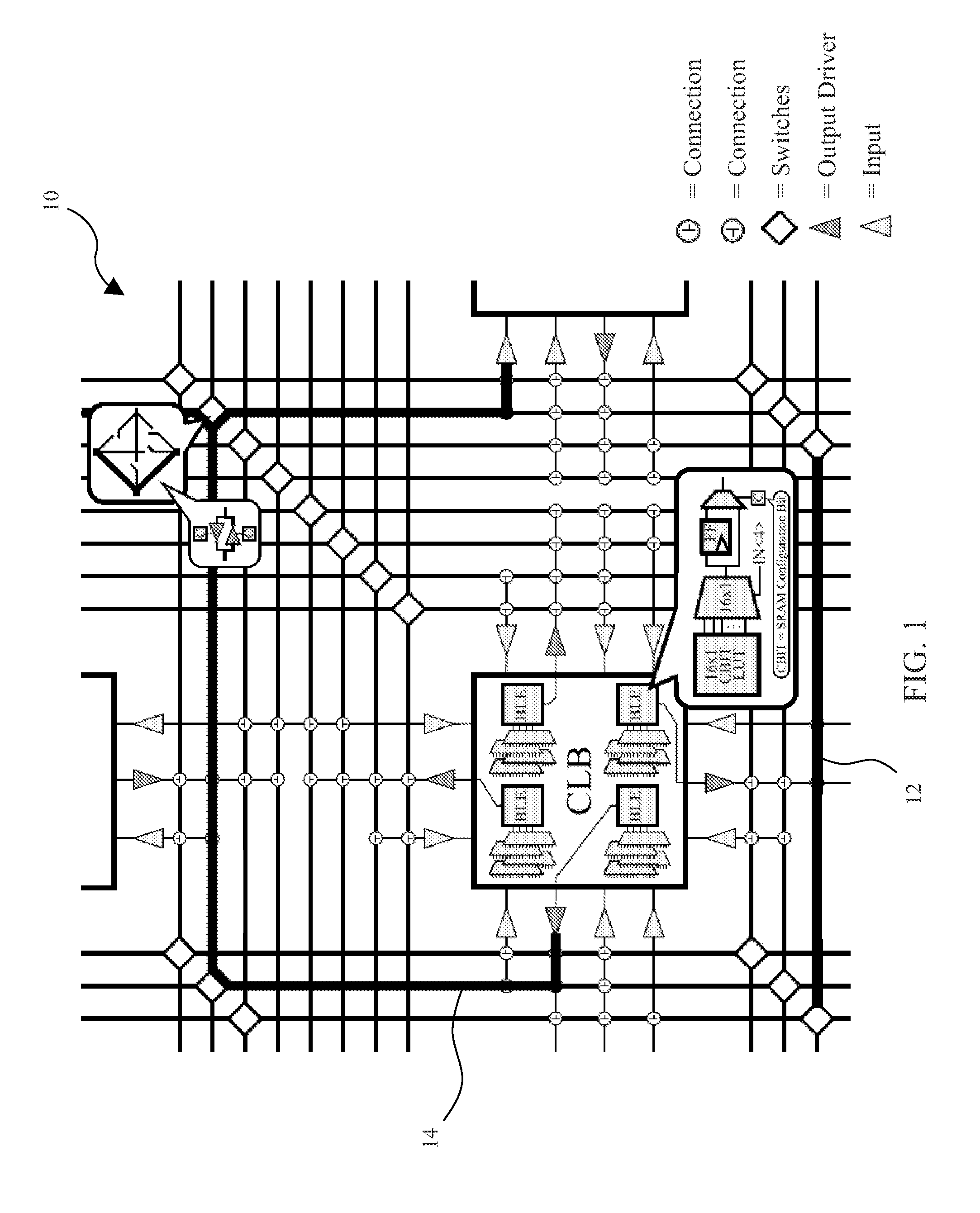

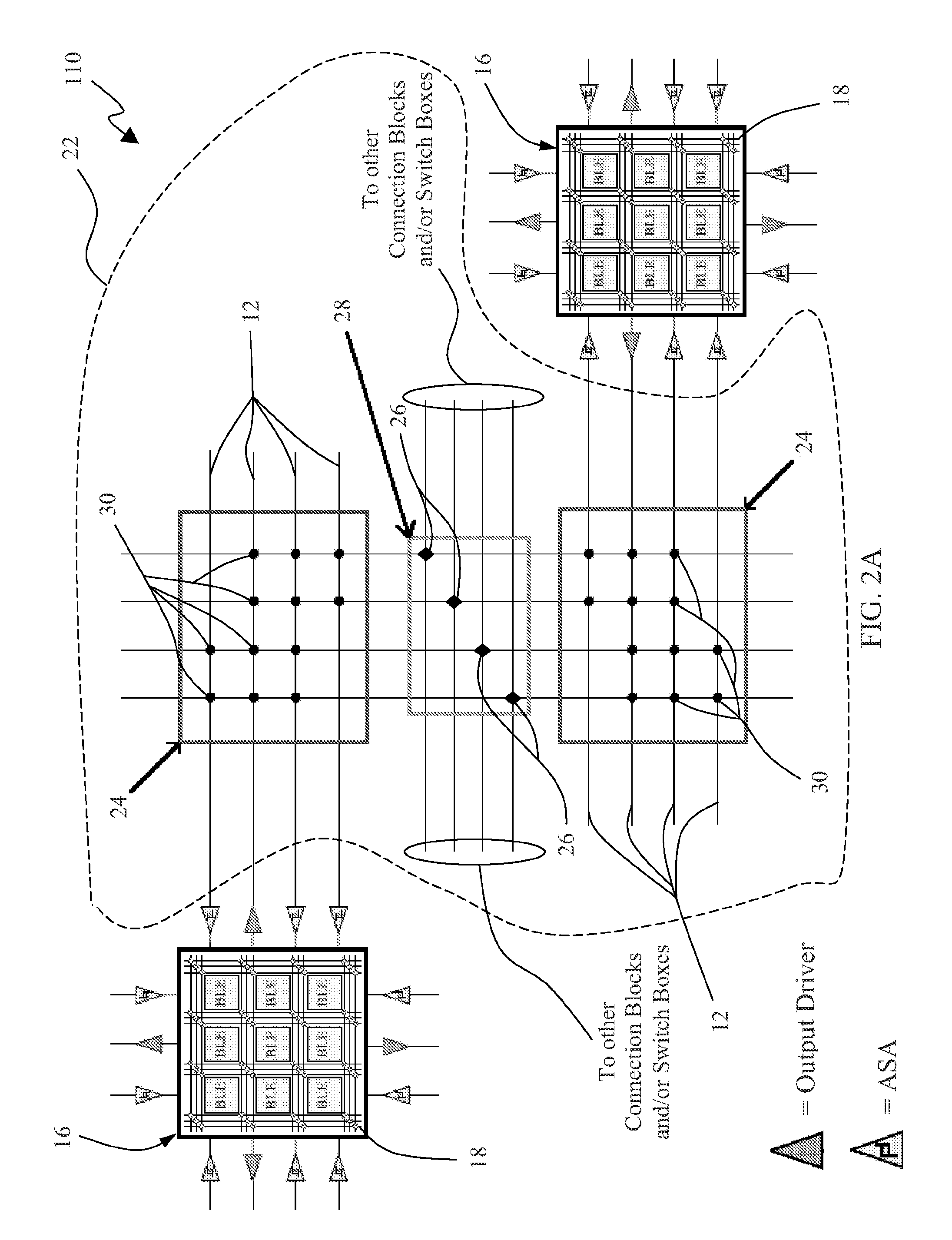

Field Programmable Gate-Array with Embedded Network-on-Chip Hardware and Design Flow

InactiveUS20150109024A1Raise the level of abstractionDesign integration of large systems simpler and more automatedProgrammable logic circuit arrangementsSolid-state devicesComputer moduleNetworks on chip

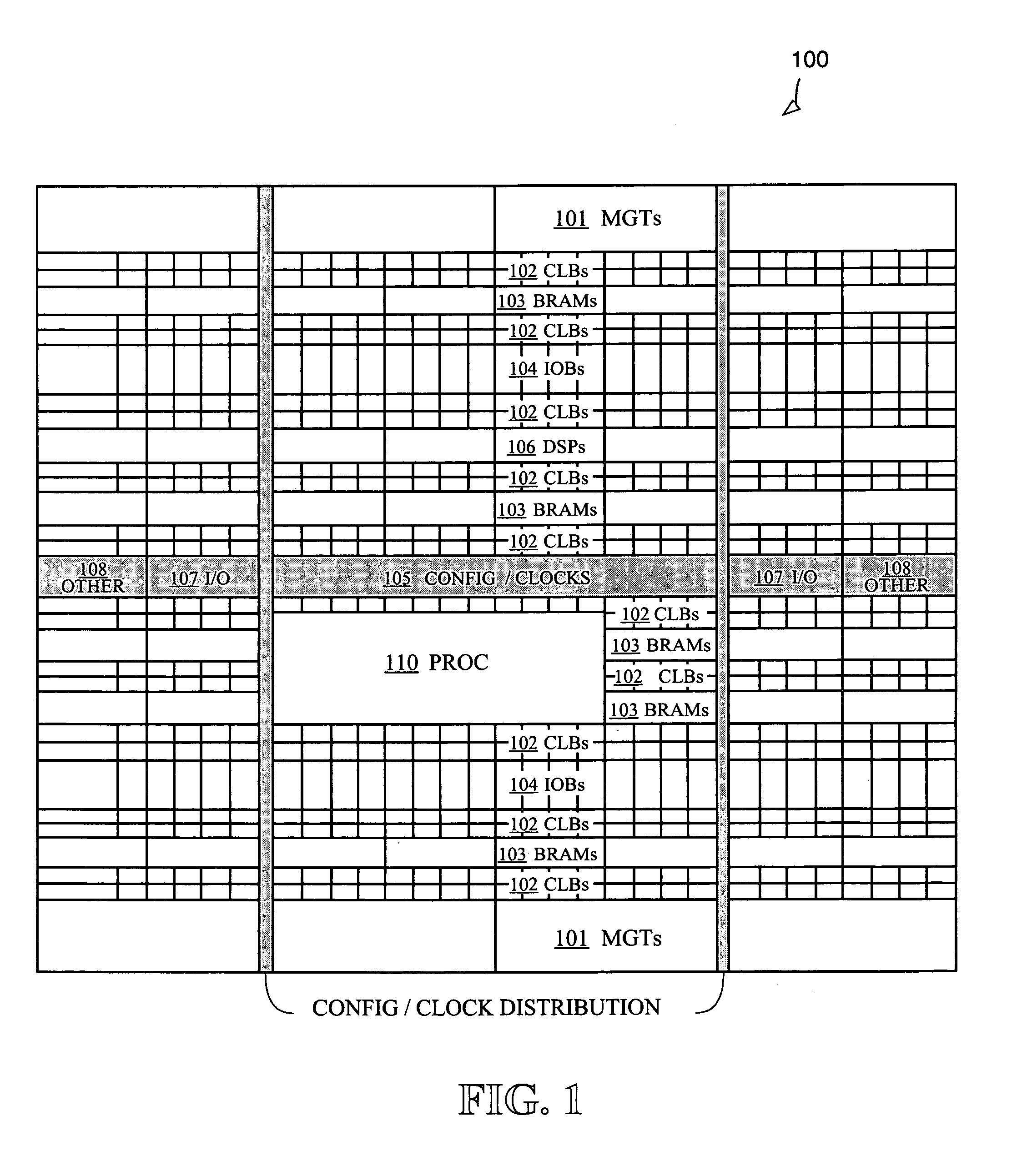

An enhanced field programmable gate-array (FPGA) incorporates one or more programmable networks-on-chip (NoCs) or NoC components integrated within the FPGA fabric. This NoC interconnect augments the existing FPGA interconnect. In one embodiment, the NoC is used as system-level interconnect to connect compute and communication modules to one another and integrate large systems on the FPGA. The NoC components include a “fabric port”, which is a configurable interface that bridges both data width and frequency between the embedded NoC routers and the FPGA fabric components such as logic blocks, block memory, multipliers, processors or I / Os. Finally, the FPGA design flow is modified to target the embedded NoC components either manually through designer intervention, or automatically.

Owner:VAUGHN TIMOTHY BETZ +1

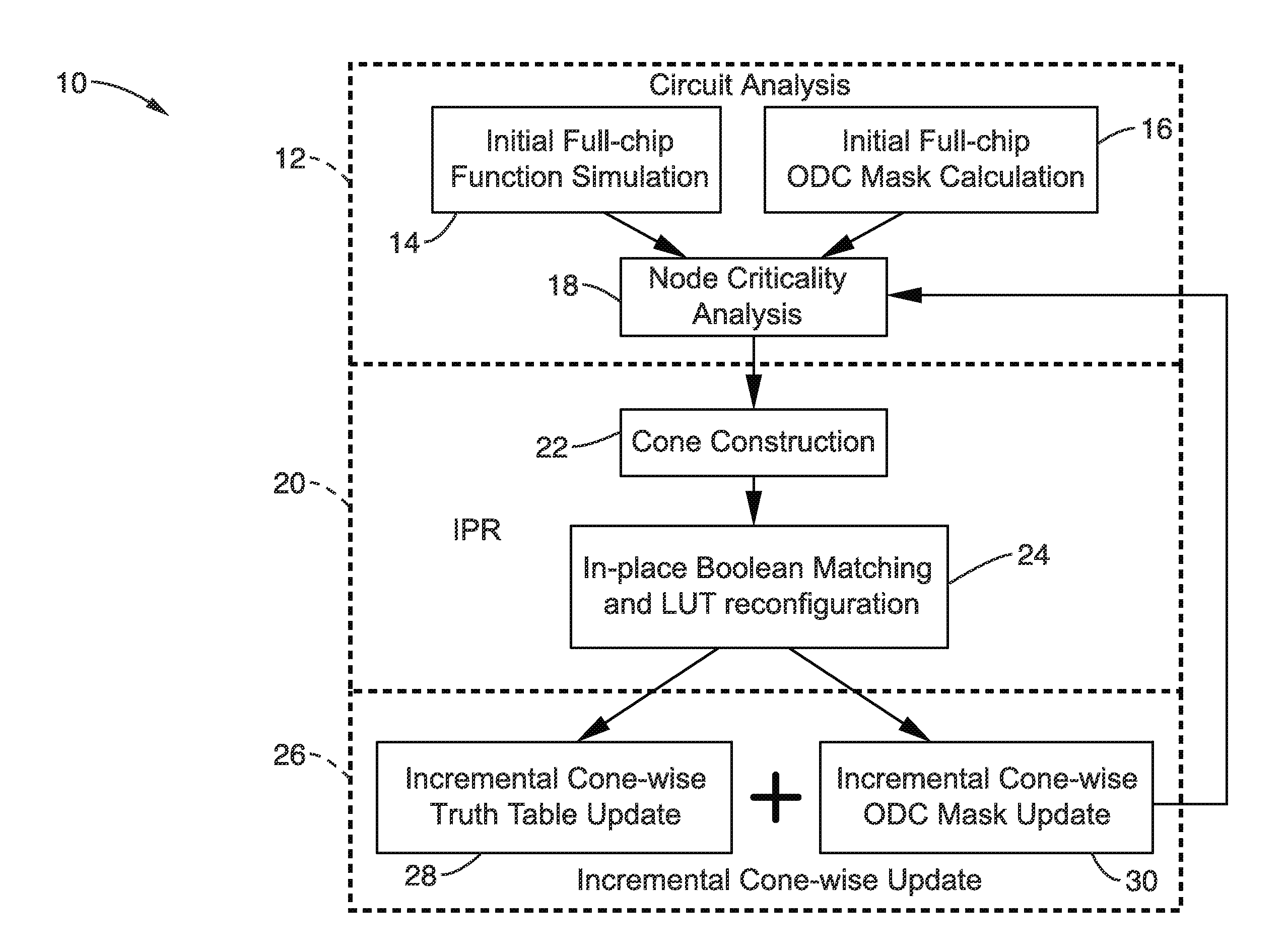

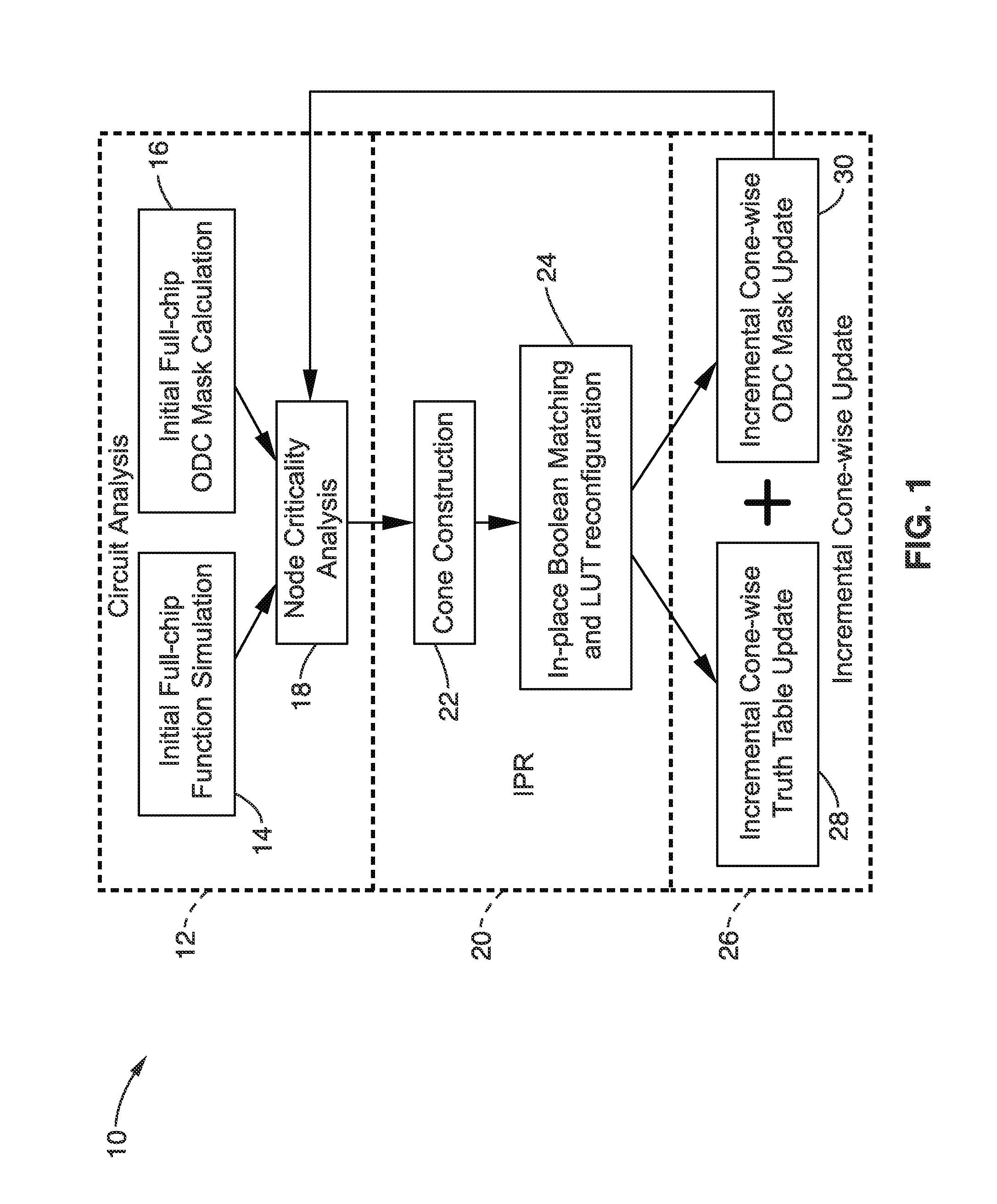

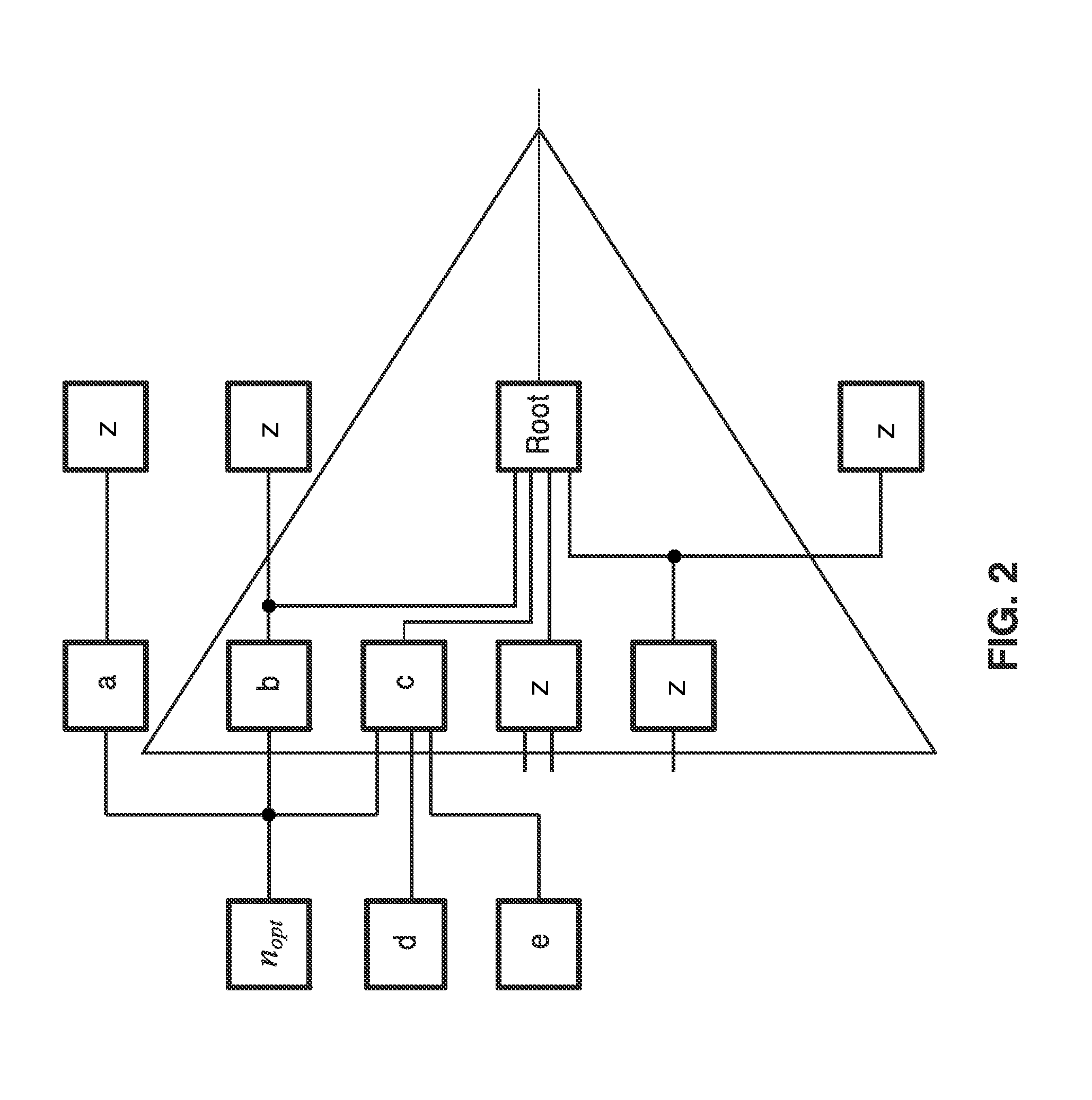

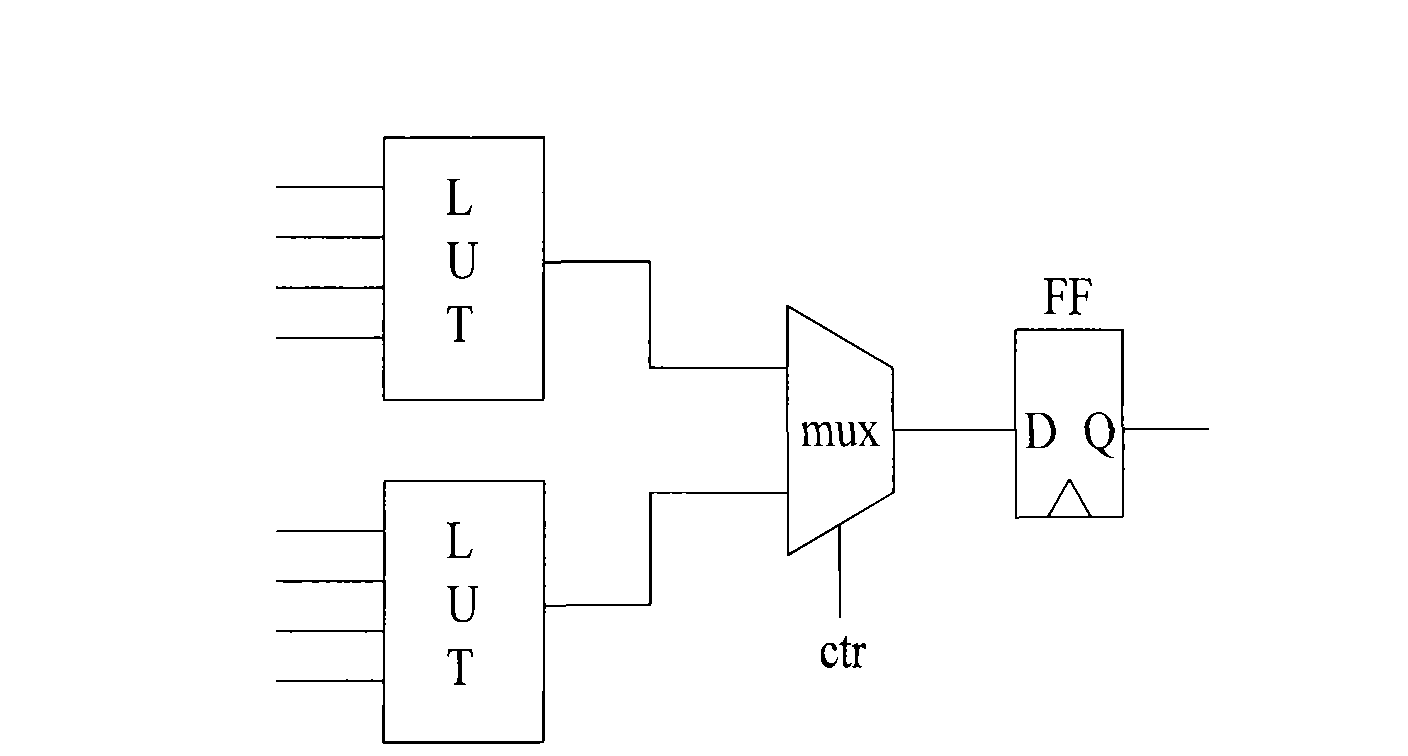

In-place resynthesis and remapping techniques for soft error mitigation in FPGA

InactiveUS20130305199A1Efficient and accurateImprove fault toleranceCAD circuit designRadiation hardeningFpga architectureDecomposition

In-place resynthesis for static memory (SRAM) based Field Programmable Gate Arrays (FPGAs) toward reducing sensitivity to single event upsets (SEUs). Resynthesis and remapping are described which have a low overheard and improve FPGA designs without the need of rerouting LUTs of the FPGA. These methods include in-place reconfiguration (IPR), in-place X-filling (IPF), and in-place inversion (IPV), which reconfigure LUT functions only, and can be applied to any FPGA architecture. In addition, for FPGAs with a decomposable LUT architecture (e.g., dual-output LUTs) an in-place decomposition (IPD) method is described for remapping a LUT function into multiple smaller functions leveraging the unused outputs of the LUT, and making use of built-in hard macros in programmable-logic blocks (PLBs) such as carry chain or adder. Methods are applied in-place to mapped circuits before or after routing without affecting placement, routing, and design closure.

Owner:RGT UNIV OF CALIFORNIA

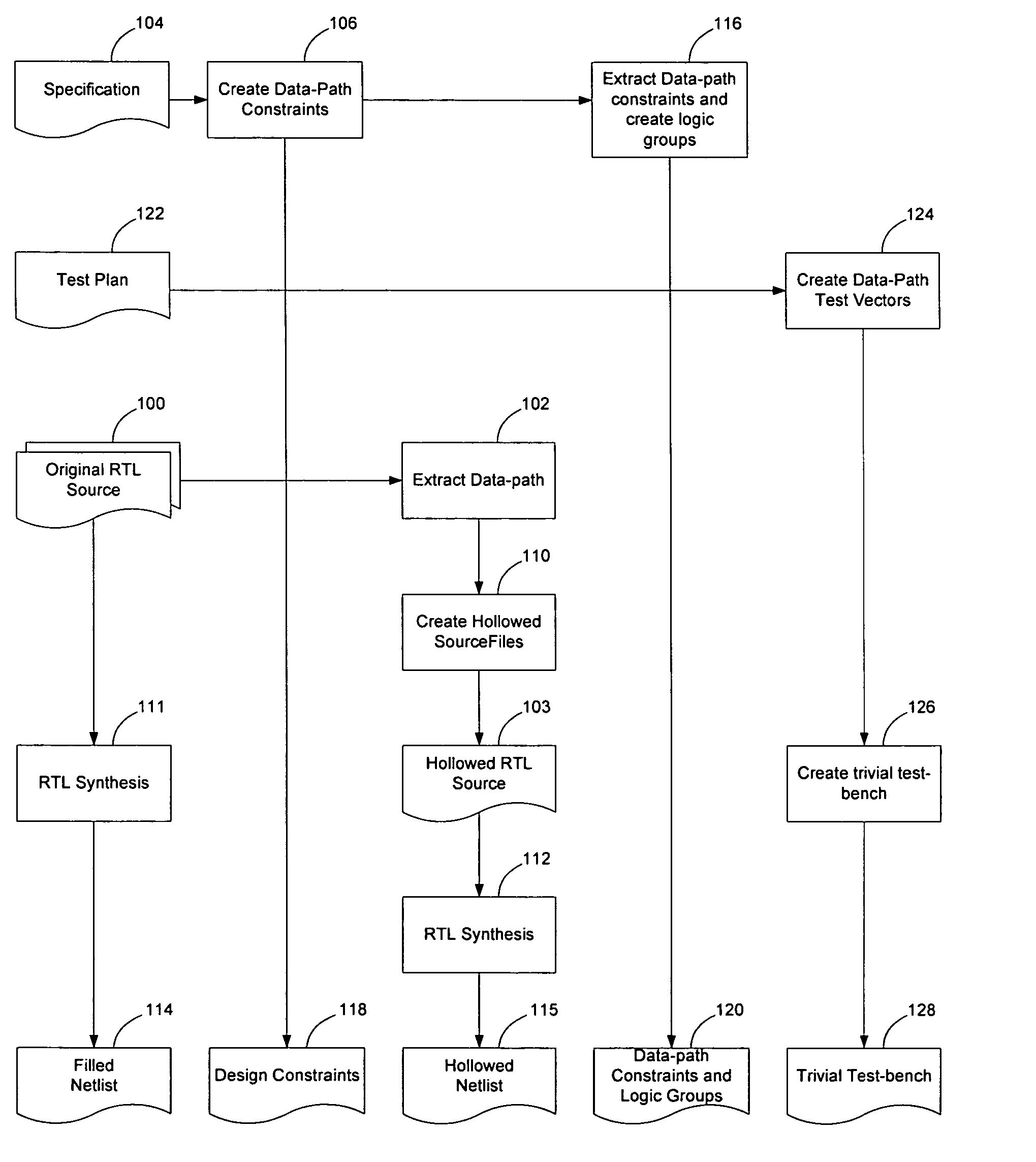

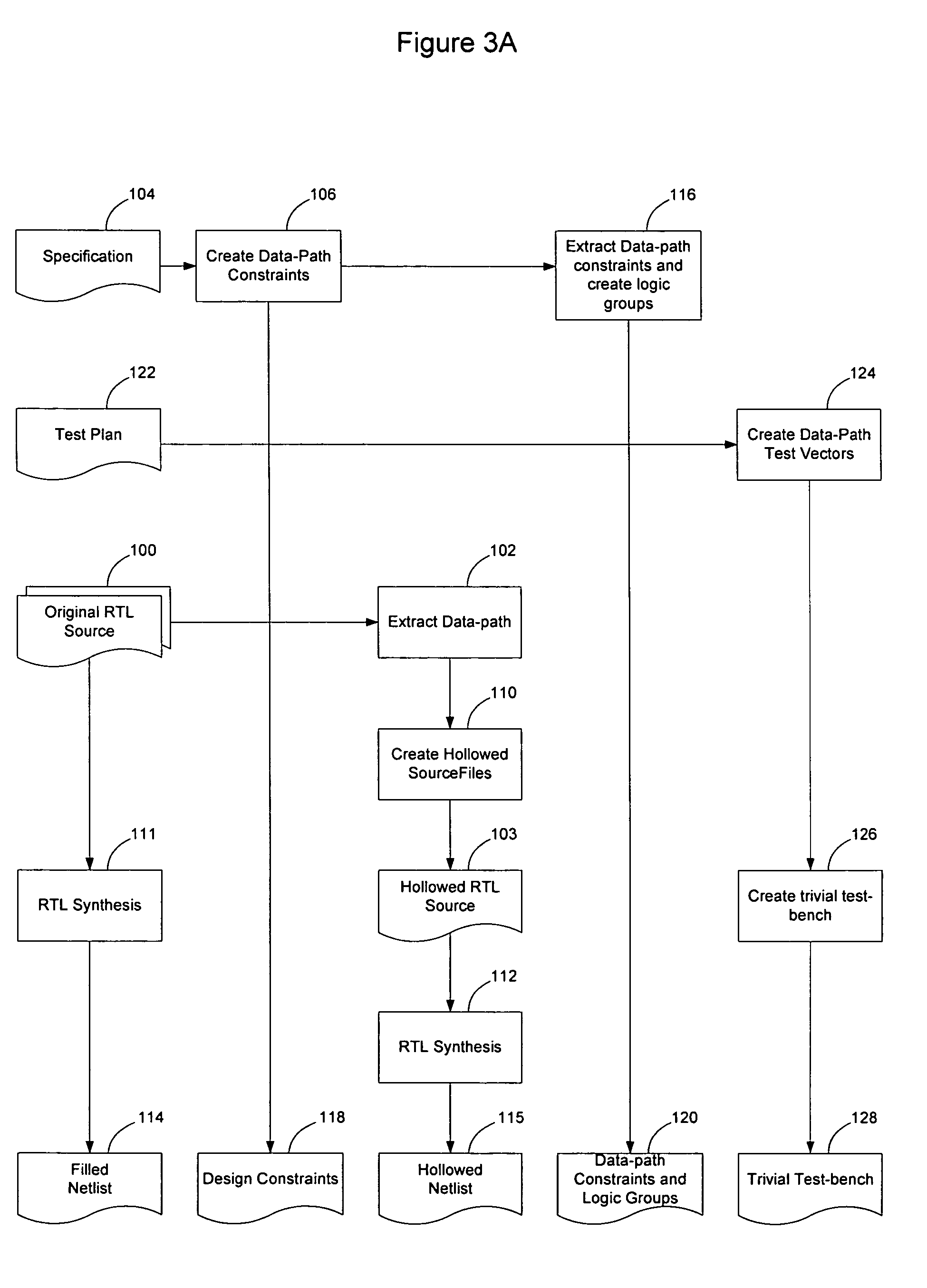

Method and apparatus for automating the design of programmable logic devices

InactiveUS20050183055A1Cost-effectiveFinish quicklyCAD circuit designSoftware simulation/interpretation/emulationTest designDesign review

The design of programmable logic devices, such as FPGAs, may be automated to allow scripts, setup files, and other tool files to be created directly from hollowed and filled netlist, and data-path and design constraint files without extensive human intervention. This allows an FPGA design to be created directly from a logic file to accelerate the FPGA design process. Once hollowed and filled netlists, and data-path and design constraint files have been generated from a design in a standard fashion, the implementation of that design onto an FPGA in an optimized fashion is automated by providing a computer program that is capable of implementing the design, testing the design, evaluating the test results, and altering the design to arrive at a more optimal design. The process may include several steps, such as initial placement of logic groups, sizing of logic groups and FPGA selection, timing analysis, and filled netlist complete design review. The steps may be iterative.

Owner:NORTEL NETWORKS LTD

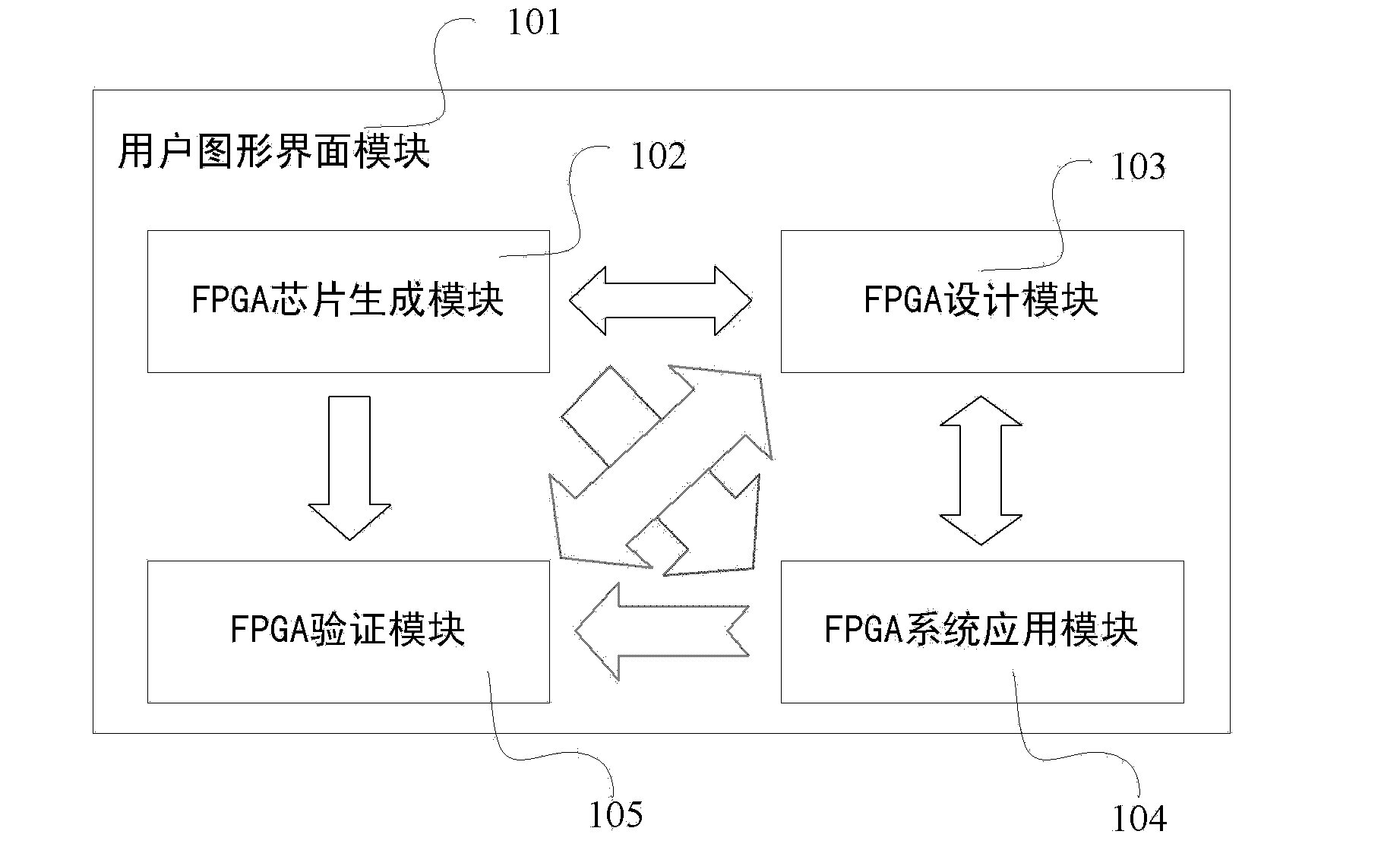

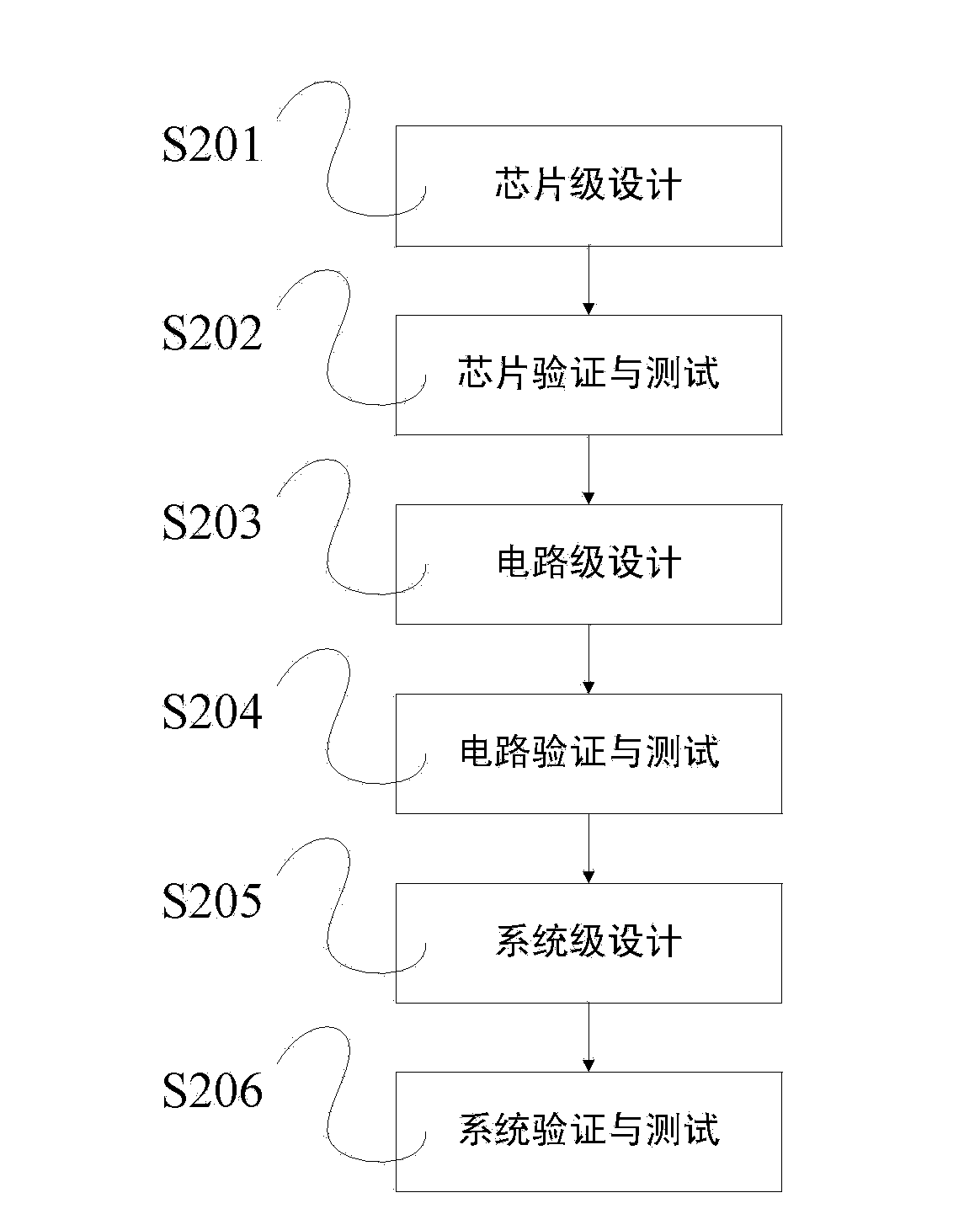

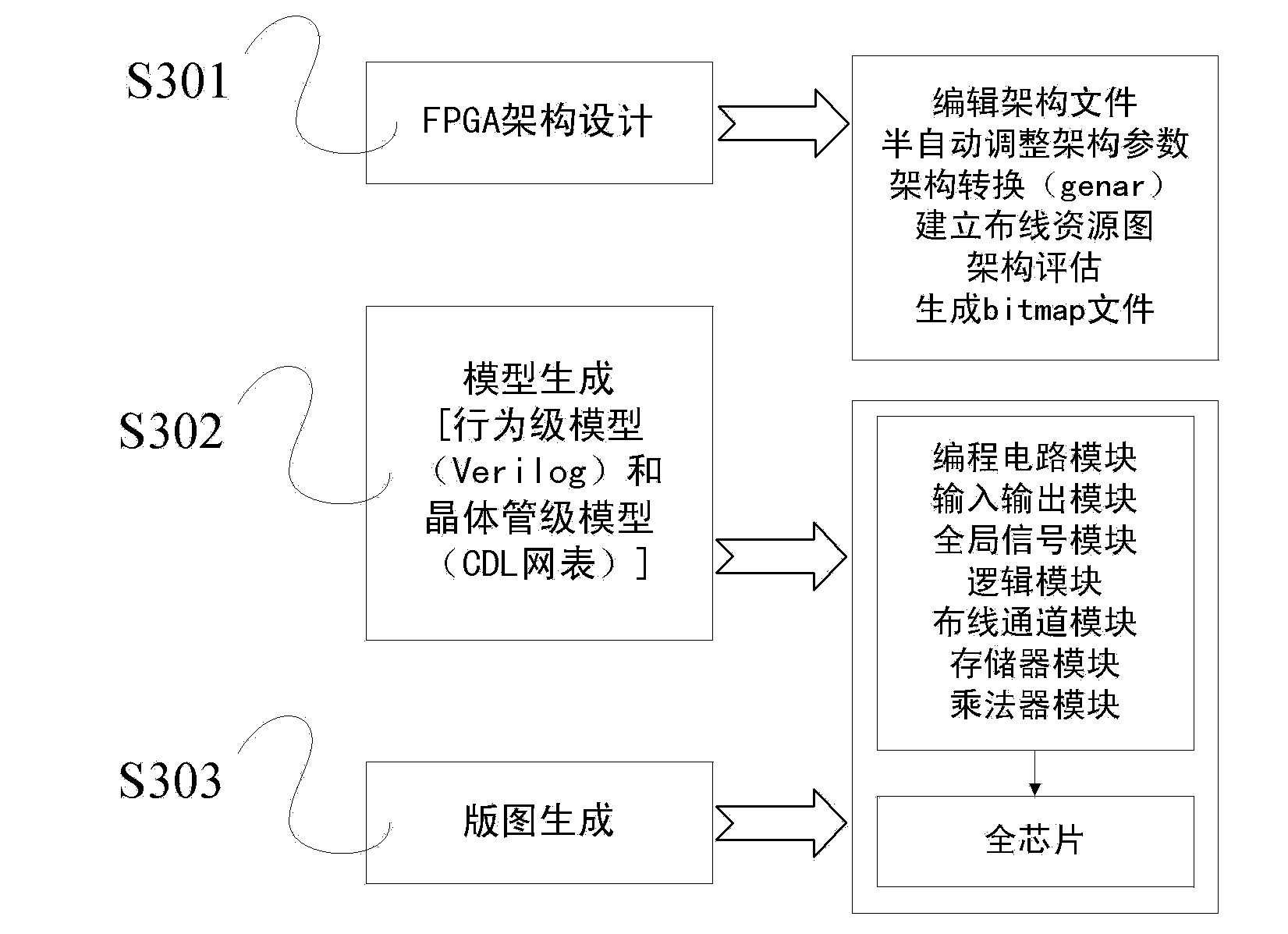

Cross-platform multilevel integrated design system for FPGA (field programmable gate array)

InactiveCN103678745AResolve does not provide quick designSolve functionSpecial data processing applicationsFpga field programmable gate arrayGNU/Linux

The invention discloses a cross-platform multilevel integrated design system for an FPGA (field programmable gate array). The cross-platform multilevel integrated design system comprises a user graphical interface module, an FPGA chip generating module, an FPGA design module, an FPGA system application module and an FPGA verification module, wherein the user graphic interface module is used for packaging the FPGA chip generating module, the FPGA design module, the FPGA system application module and the FPGA verification module. Switching among the FPGA chip generating module, the FPGA design module, the FPGA system application module and the FPGA verification module is realized by Tap page switching, so that the FPGA chip generating module, the FPGA design module, the FPGA system application module and the FPGA verification module can be called in a friendly and uniform user graphic interface, and cross-platform operating of Windows, Linux, Mac OS systems can be realized.

Owner:北京微纳星科技有限公司

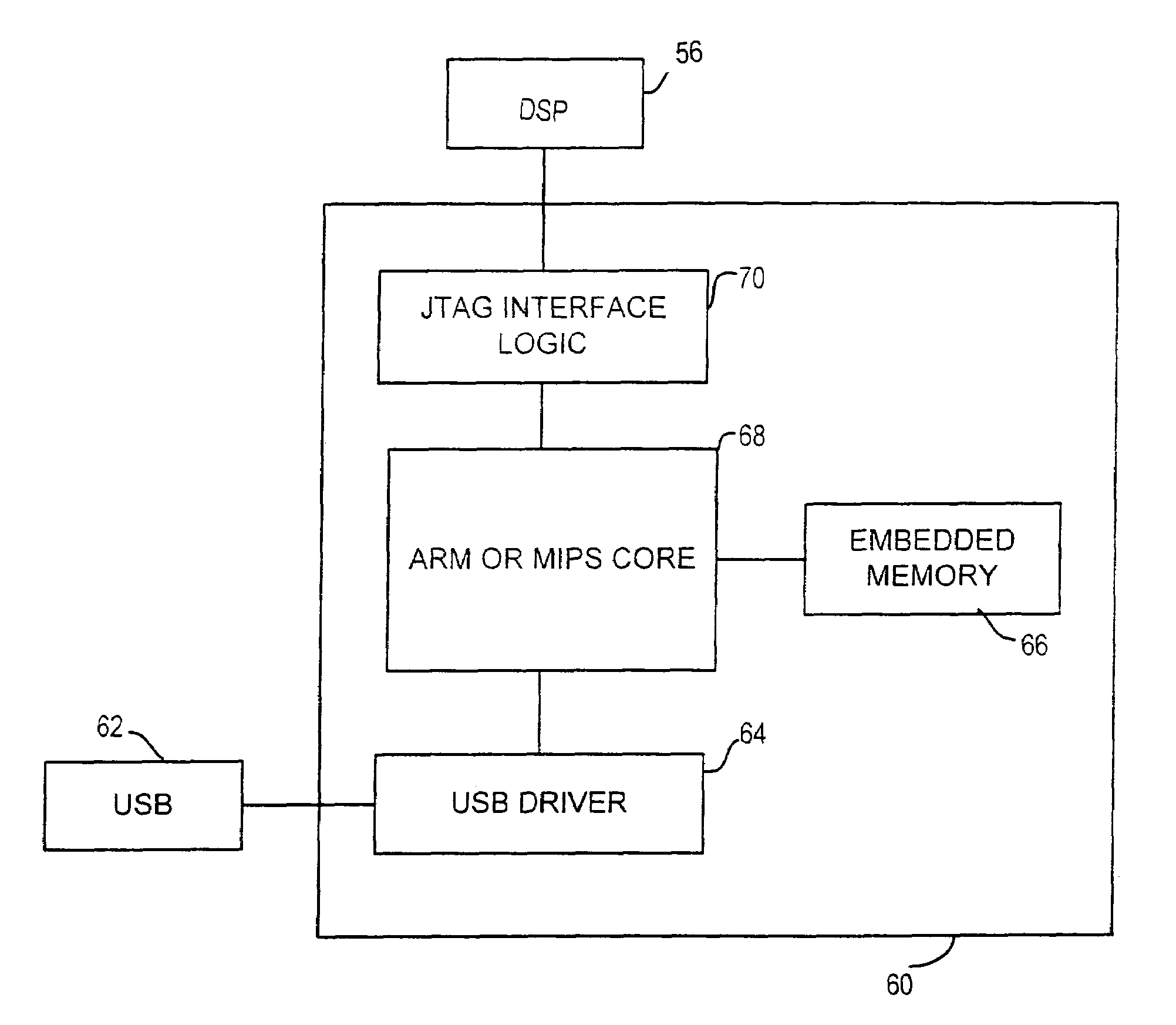

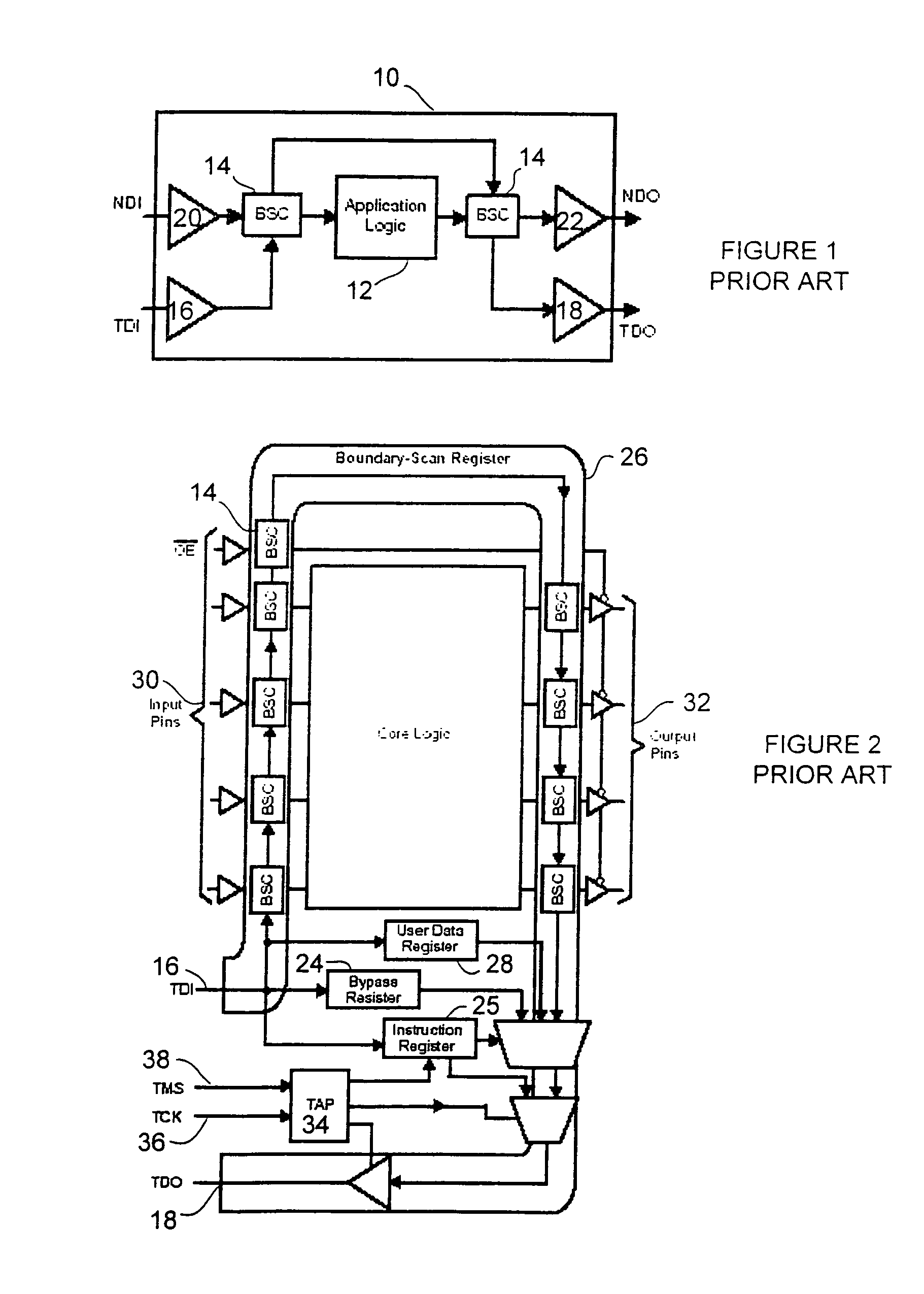

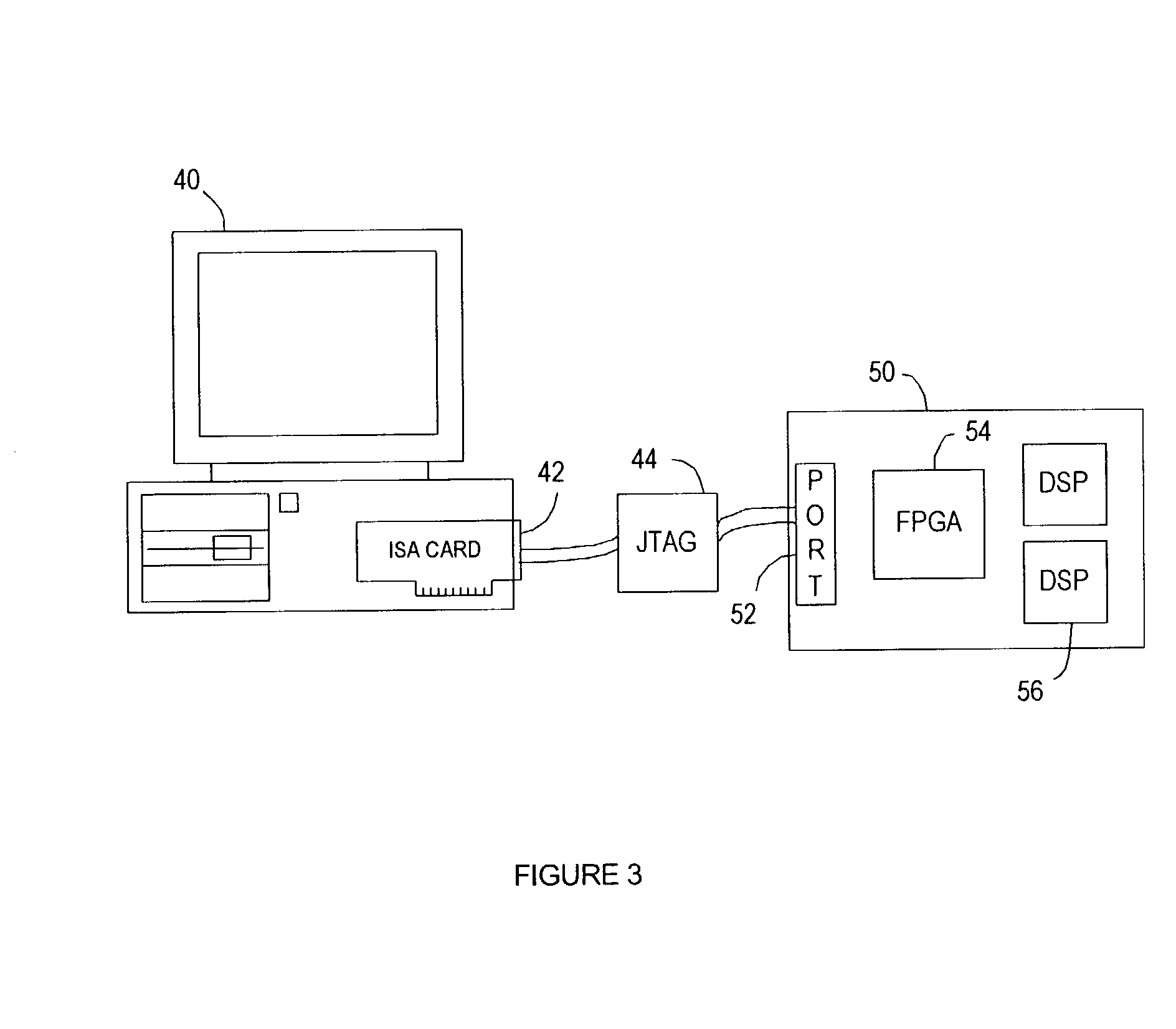

Embedding a JTAG host controller into an FPGA design

InactiveUS6983441B2Error preventionFrequency-division multiplex detailsJoint Test Action GroupEngineering

A method for embedding a Joint Test Action Group (JTAG) standard IEEE 1149.1 host controller into a field programmable gate array (FPGA) for platform development and DSP programming, and boundary scan of targeted hardware using JTAG commands and architecture is described. The FPGA-based JTAG host controller is bussed directly into the FPGA core, bypassing the board's JTAG communication port.

Owner:TELOGY NETWORKS

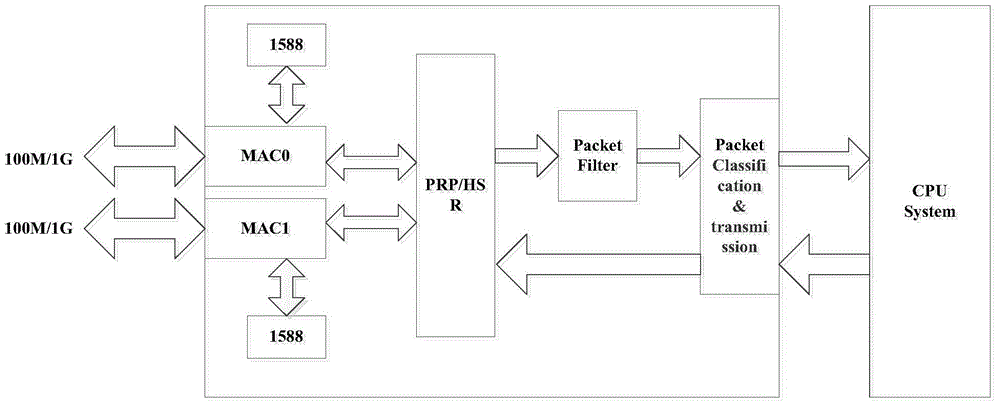

Dual-network-redundancy device hardware architecture in transformer substation and implementation method

ActiveCN104158687AImprove compatibilityReduce the burden onData switching networksHigh-availability Seamless RedundancyTransformer

The invention belongs to the field of internal communication of automatic transformer substation systems for power systems, and specifically discloses dual-network-redundancy device hardware architecture in a transformer substation and an implementation method. The dual-network-redundancy device hardware architecture and the implementation method are characterized in that an MAC (Media Access Control) Ethernet communication module, a PRP&HSR (Parallel Redundancy Protocol and High-availability Seamless Redundancy) module, a packet filter module, a multipath packet transmission control module and a 1588 clock synchronization module are designed on an FPGA (Field Programmable Gate Array) to synergistically finish receiving and transmission of Ethernet packets, IEC61588 accurate network clock synchronization, dual-network-redundancy processing, network storm suppression and packet classification and transmission functions in an automatic transformer substation system. Through adoption of the dual-network-redundancy device hardware architecture and the implementation method, the operation processing demand on a CPU (Central Processing Unit) is lowered greatly, the protection cost on a measurement and control device of the transformer substation is reduced, and the running reliability of the transformer substation system is improved.

Owner:NARI TECH CO LTD +1

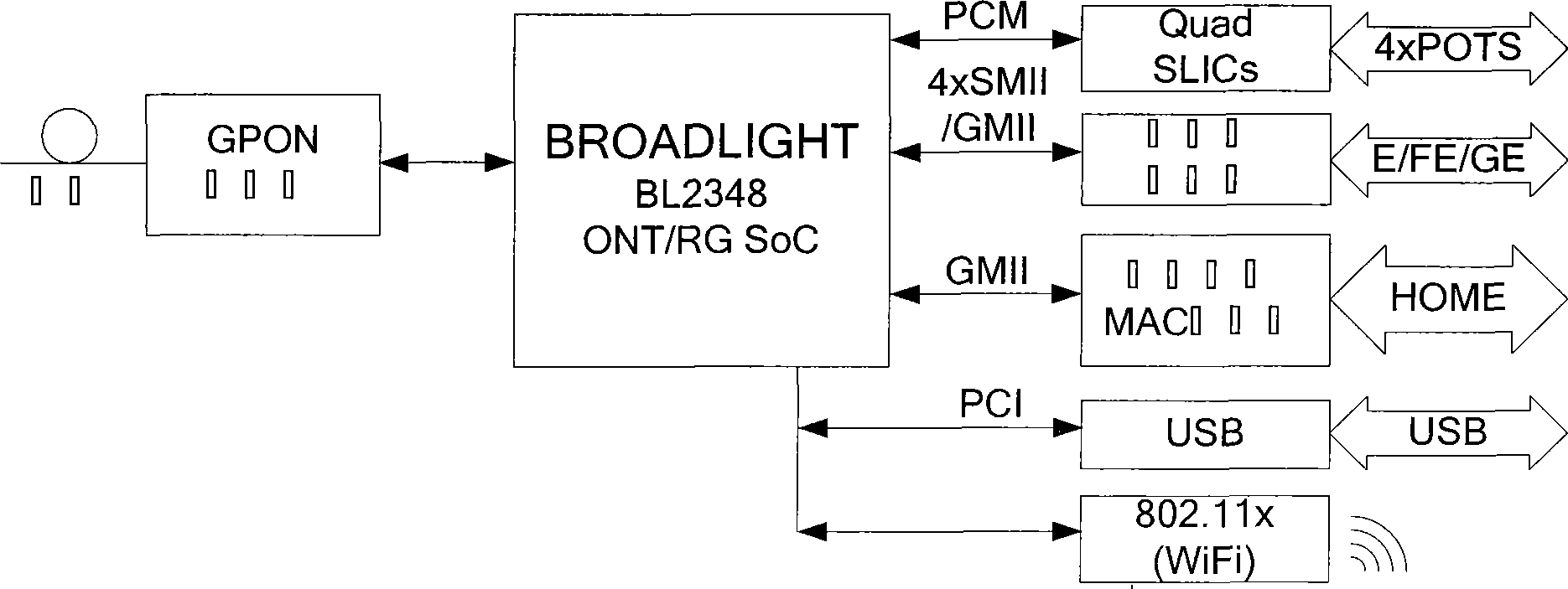

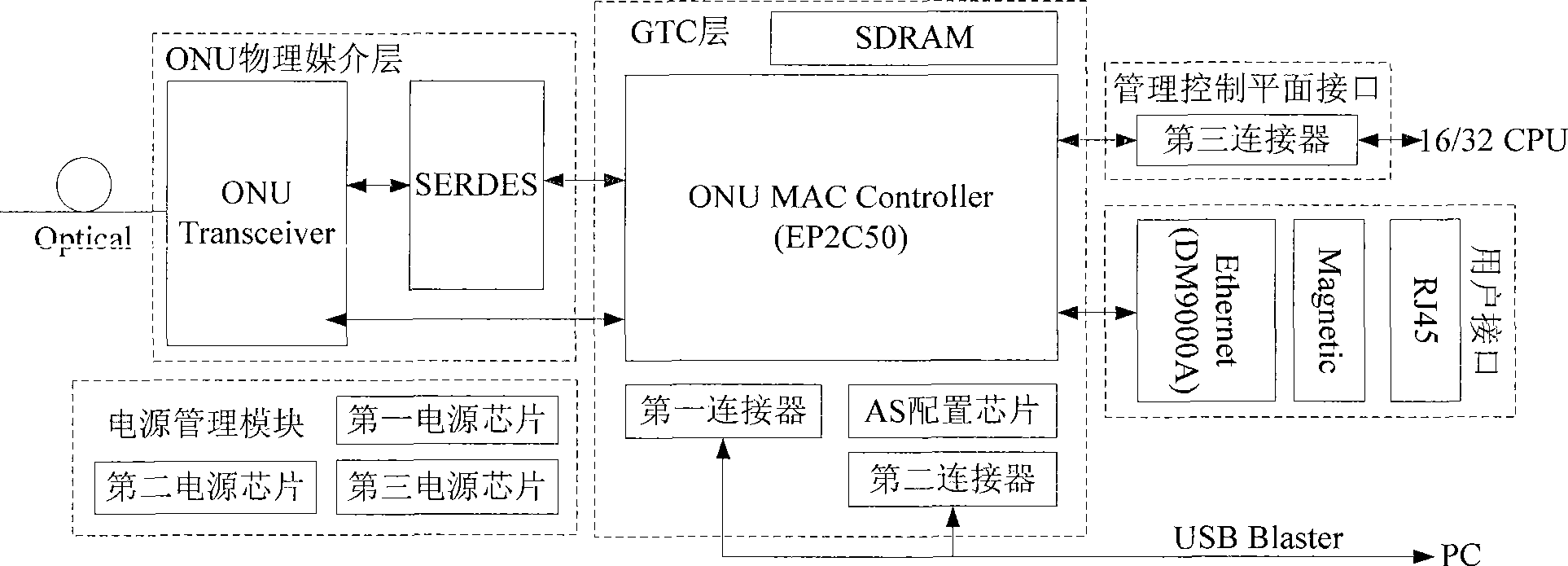

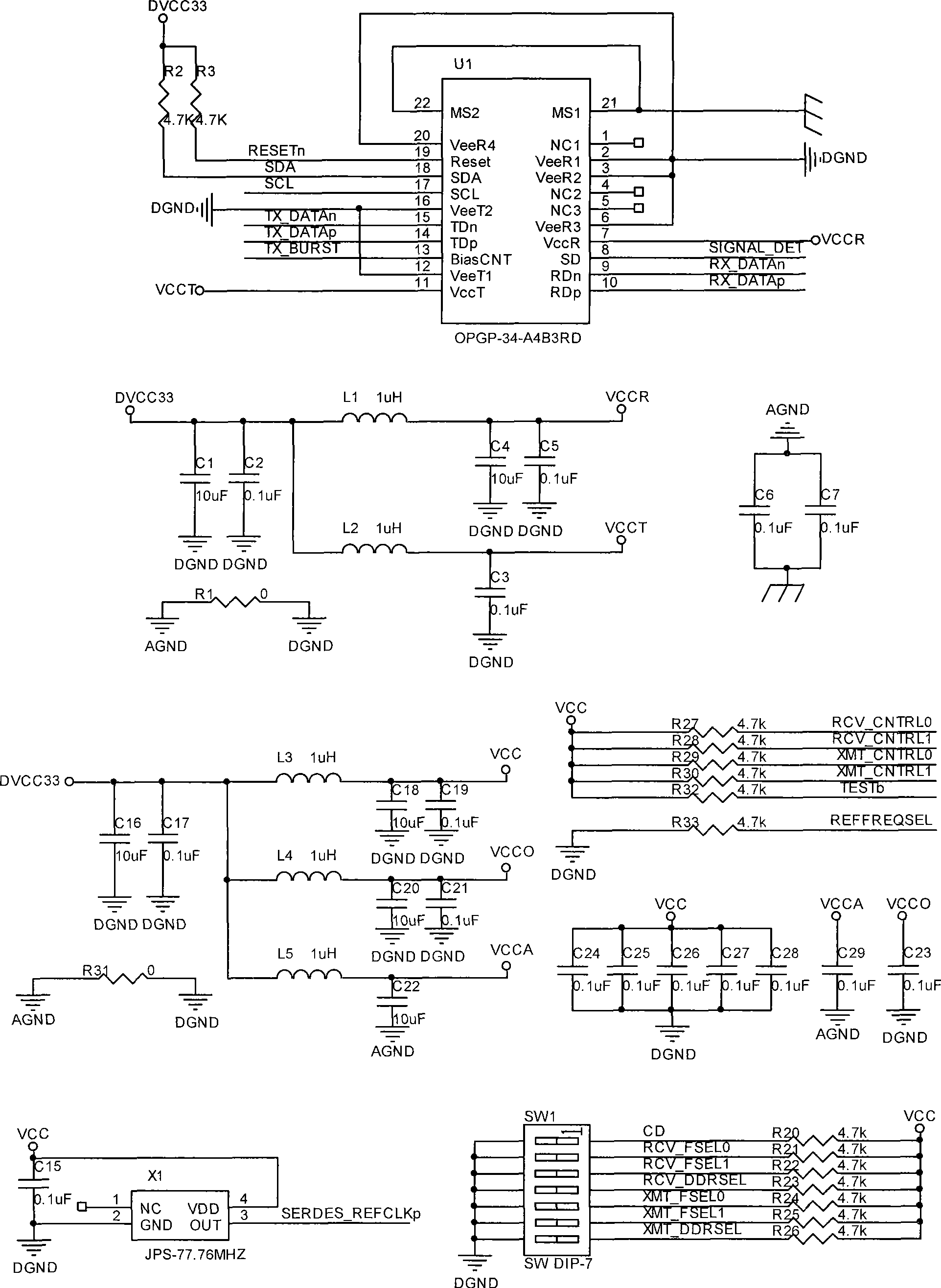

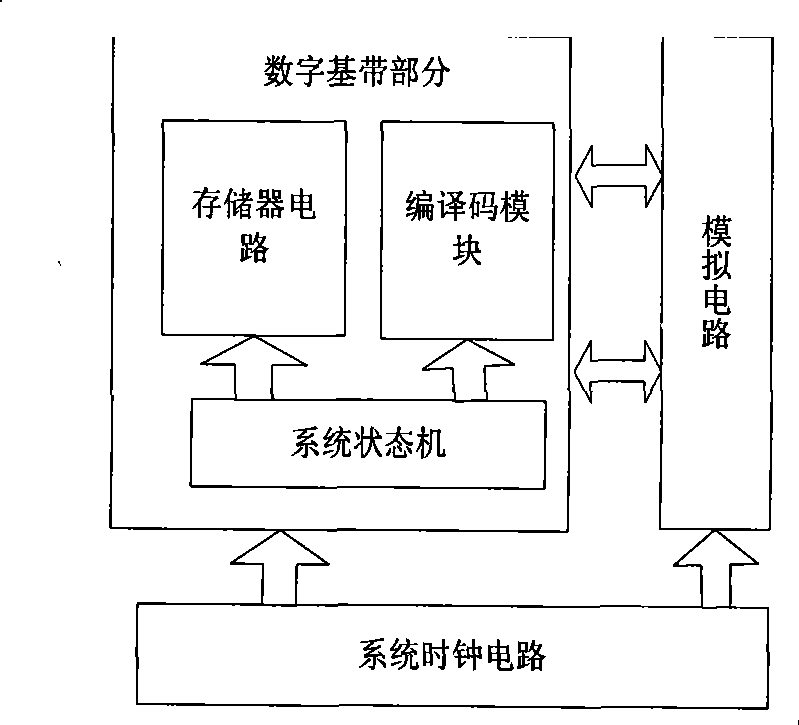

Hardware platform system of GPON ONU system designed based on FPGA

InactiveCN101365250ALow costMeet voiceMultiplex system selection arrangementsElectromagnetic transmissionSystems designTransceiver

A hardware platform system of a GPON ONU system based on FPGA design comprises a physical medium correlational layer, a GTC layer, a management control plane interface, a user plane interface and a power management module, wherein, the physical medium correlational layer comprises a GPON ONU transceiver and a SERDES chip which meet the ITU-T G.984.2B+ standard; the GTC layer comprises an FPGA, an SDRAM, an AS set chip, a first connector and a second connector; the management control plane interface comprises a third connector; the user plane interface circuit comprises an Ethernet control ship and an RJ45 with a network isolator; and the power management circuit comprises a 12V converting 3.3V first power chip, a 3.3V converting 2.5V second power chip and a 3.3V converting 1.2V third power chip. The method can effectively reduce the cost of GPON user end equipment, and has high applicability.

Owner:ZHEJIANG UNIV OF TECH

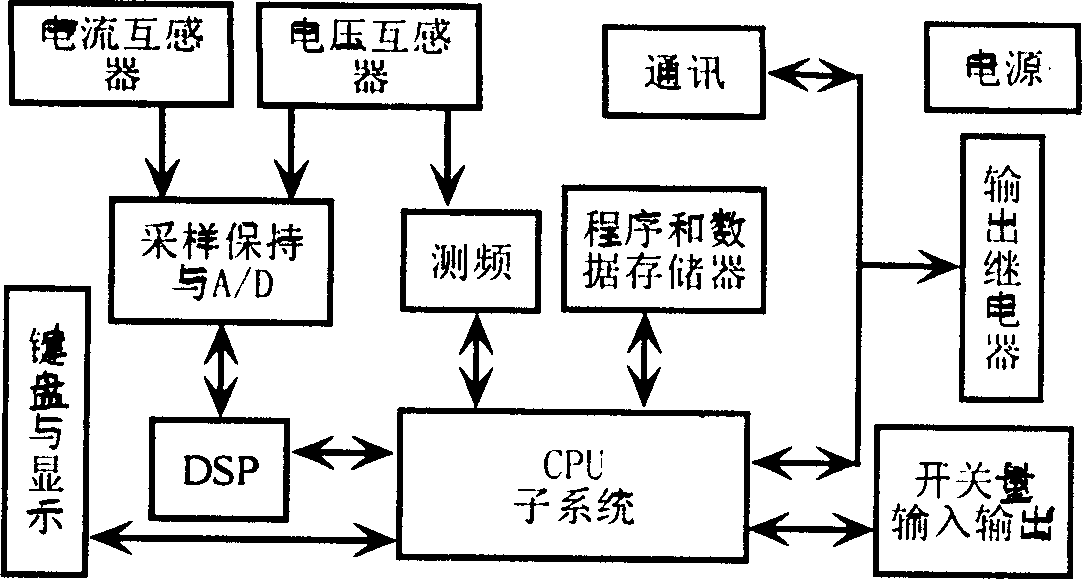

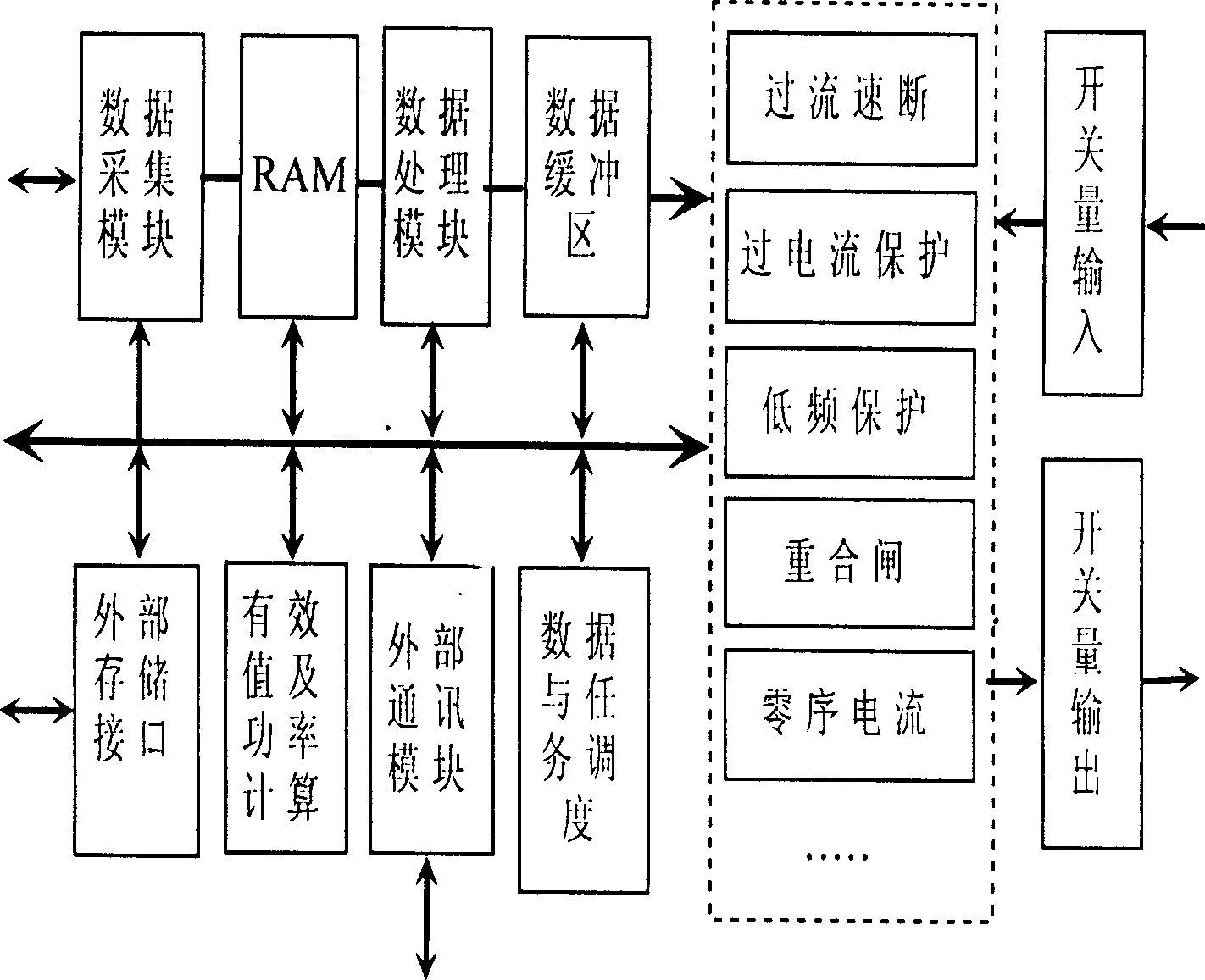

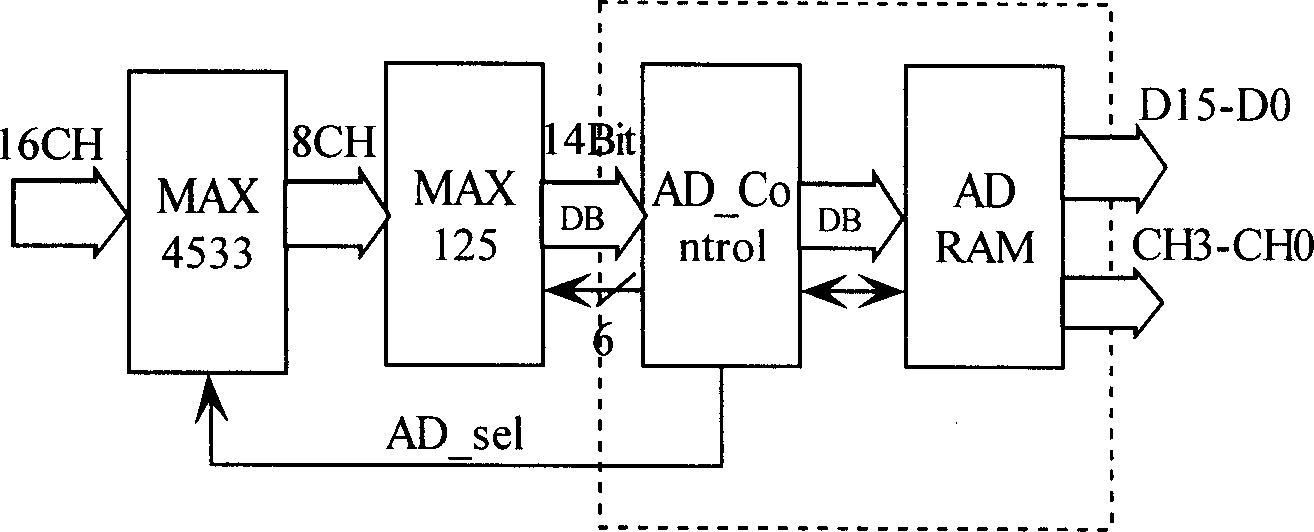

Design method for specific chip of intelligent electric appliance

InactiveCN1438593AImprove scalabilitySpecial data processing applicationsEngineeringPerformance index

The chip is designed based on the platform method by using programmable ASIC technique. The method includes following steps. (1) The system on the chip in intelligent electrical appliances is designed by using FPGA. (2) Marking off the IP modules. (3) The parametrization design for each IP core. The designed module cores support the parametrization programming. The different functions can be realized by allocating different parameters without need of changing content in the core. (4) Generalized designing the IP cores. (5) The dedicated chip using 2 FPGA chip (100 thousands gates) through a small PCB being as an independent unit connects to other circuit. The correctness of the chip is validated by emulations and actual measurements. Each performance index of the line protective devices designed based on the chip is passed the testing of relevant national quality monitoring center.

Owner:XI AN JIAOTONG UNIV

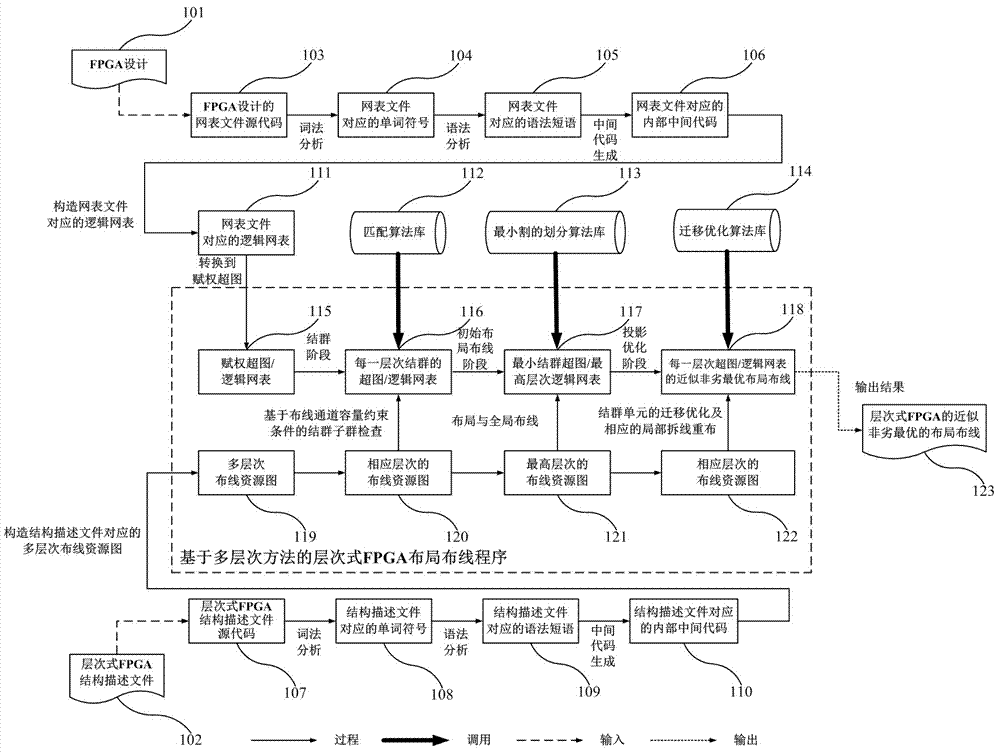

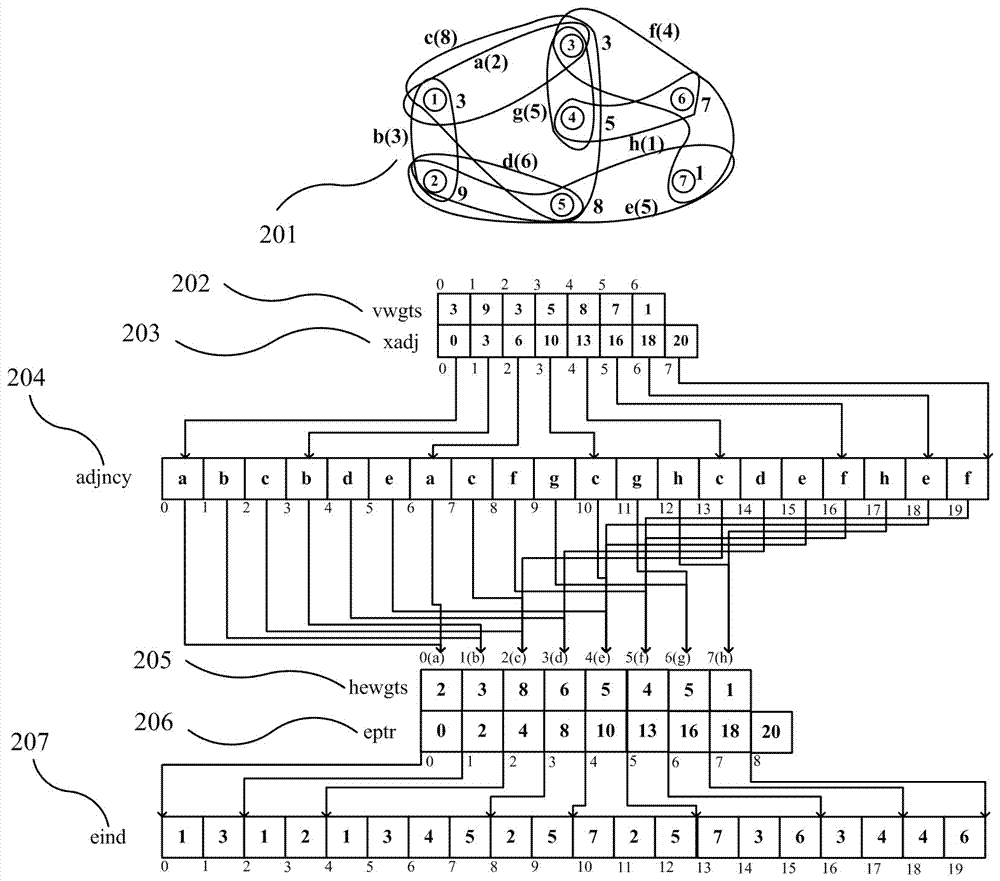

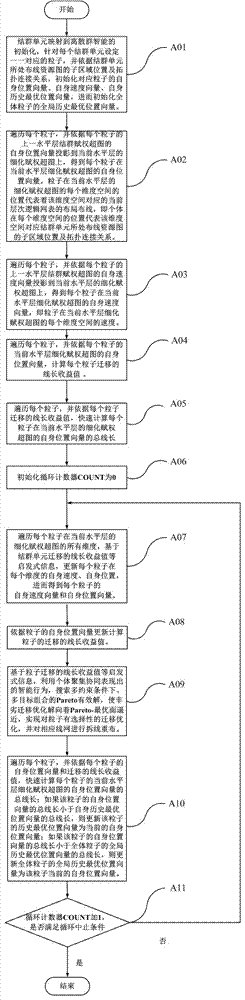

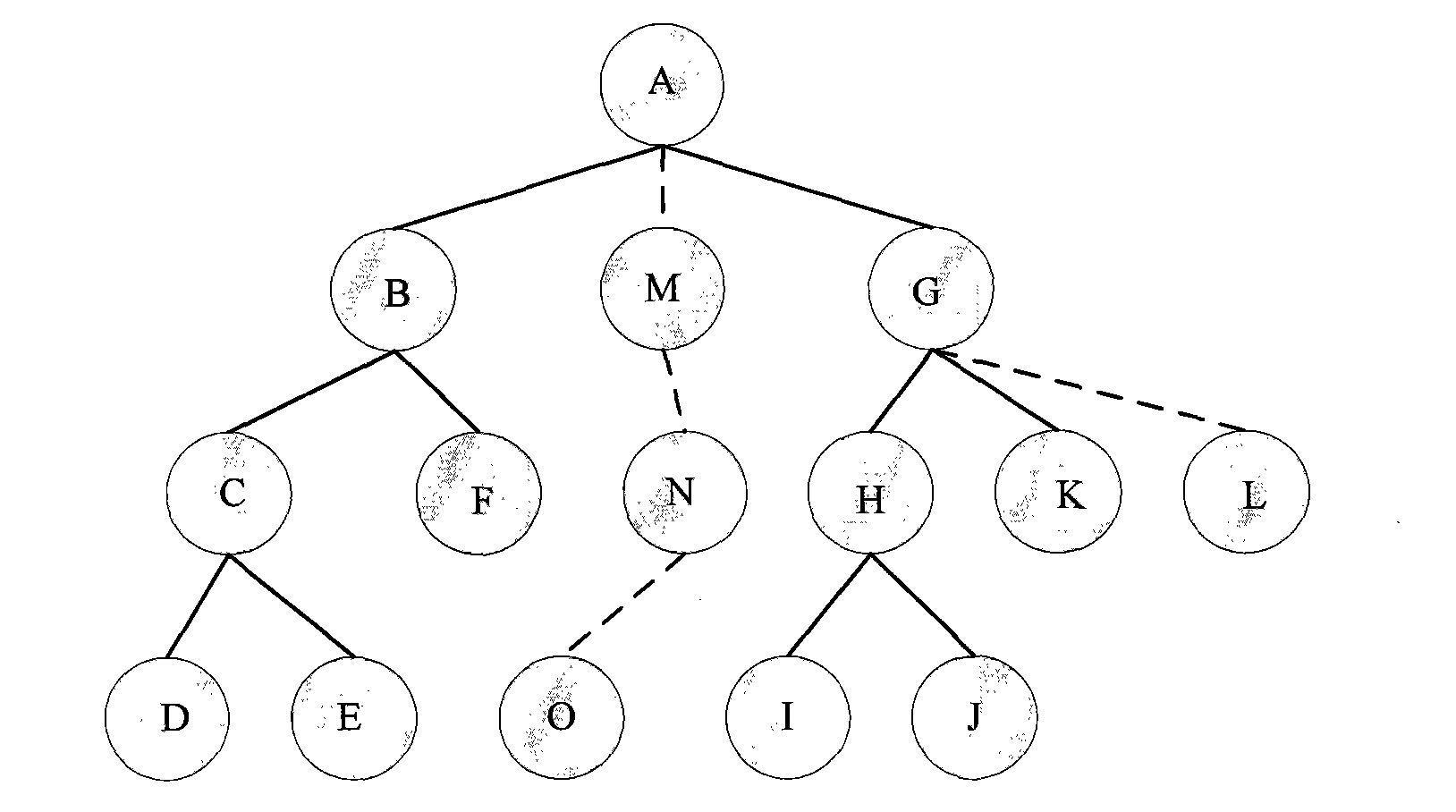

Hierarchical FPGA layout and wiring method based on multi-level method and empowerment hypergraph

InactiveCN106919769AExcellent group effectOptimizing Local Interconnect LinesSpecial data processing applicationsComputer architectureResearch Object

The invention relates to a hierarchical FPGA layout and wiring method based on a multi-level method and empowerment hypergraph. A mathematical model of a logical netlist in a hierarchical FPGA layout and wiring process is constructed by using empowerment hypergraph; circuit logic units are represented as nodes in the empowerment hypergraph; wiring among the circuit units is expressed as overrides in the empowerment hypergraph. The multi-level method is adopted as a hierarchical FPGA layout and wiring method to effectively meet the higher requirements of VLSI on the operating efficiency and processing capacity. The method can gradually reduce the scale of problems and the time complexity of methods by bottom up cluster stage and also can process details of problems level by level, increasing solution accuracy of methods by means of top-down projection optimization so as to be naturally combined with hierarchical features of researched objects. By means of the hierarchical FPGA layout and wiring method based on the multi-level method and empowerment hypergraph, the time complexity of FPGA physical design can be effectively reduced and the design capability and performance of FPGA are increased.

Owner:冷明

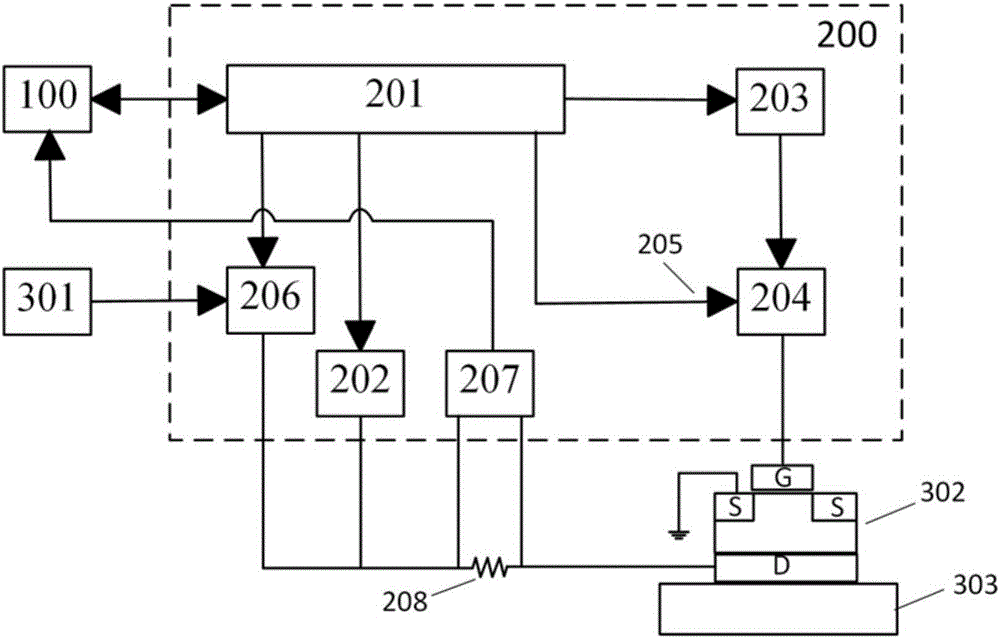

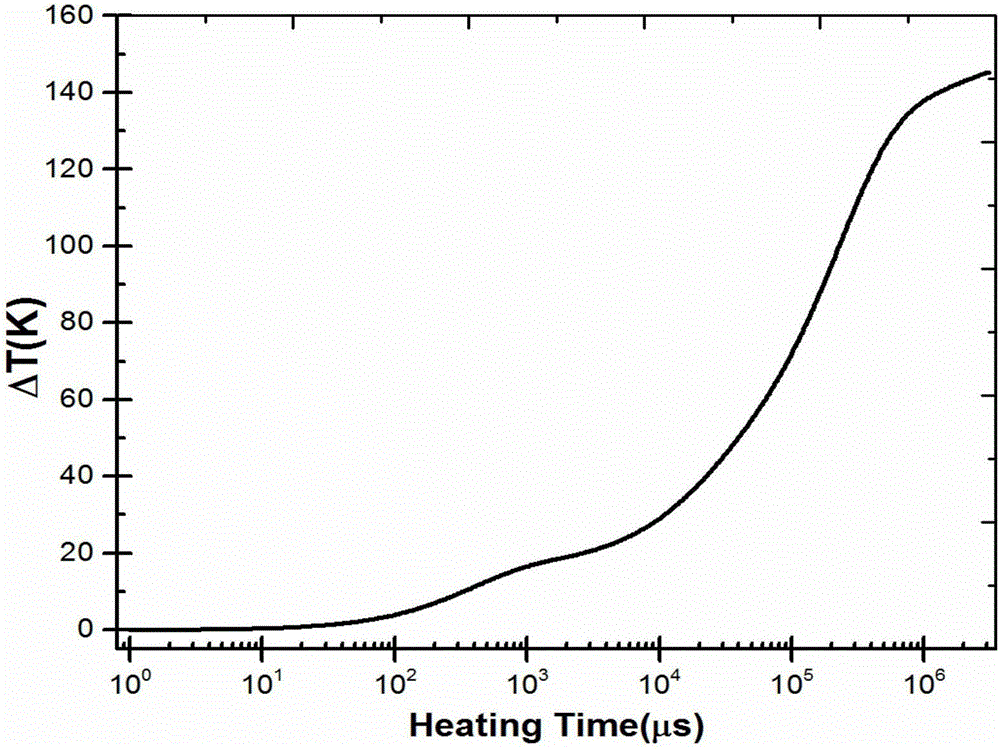

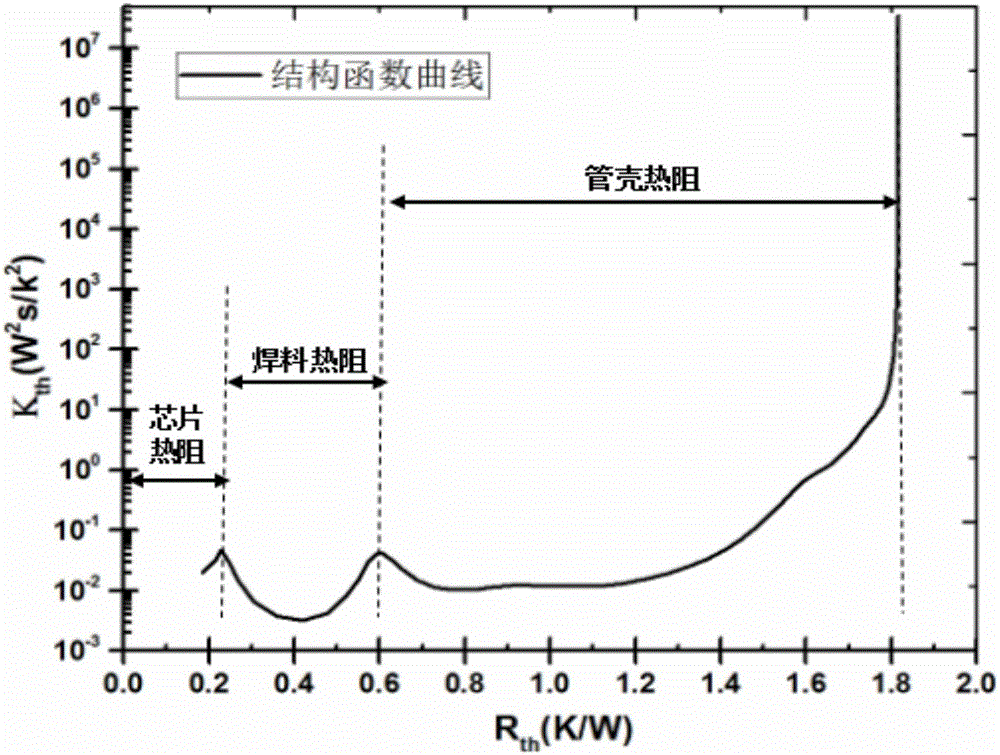

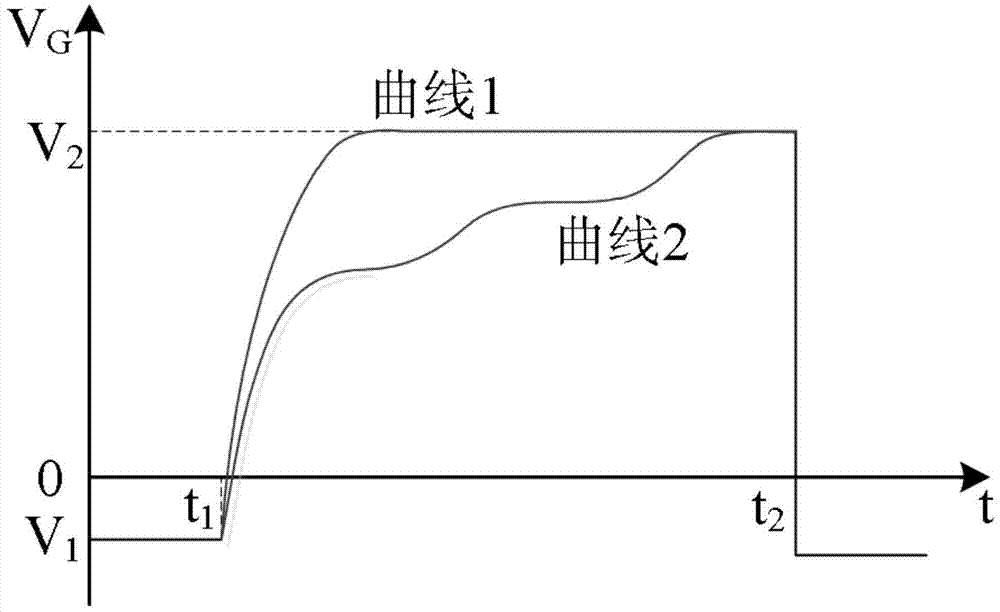

Power MOS device temperature rise and thermal resistance component test device and method

ActiveCN106443401AGet goodLossless acquisitionIndividual semiconductor device testingTest powerStructure function

The invention relates to a power MOS device temperature rise and thermal resistance component test device and method and belongs to the power MOS device reliability design and test field. According to the test device and method of the invention, a fast switching switch of drain-source voltage and gate-source voltage signal control of a tested power MOS device and a fast switching switch of drain-source high-current work are designed; and an FPGA is adopted to design the acquisition and setting function of drain-source voltage, gate-source voltage and drain-source current. In a testing process, a temperature-sensitive parameter curve is obtained at first; operating current is applied to the device, so that the temperature of the device can rise; after the output power of the device achieves a steady state, the operating current is cut off, and test current is switched on; the junction voltage of the drain-source parasitic diode of the power MOS device is acquired, so that the junction temperature curve of the device can be obtained correspondingly; processing analysis is carried out through adopting a structural function method, so that the thermal resistance components of the power MOS device can be obtained. With the power MOS device temperature rise and thermal resistance component test device and method of the invention adopted, the problems of high prices of test instruments, complicated operation of measurement technologies and long measurement period can be solved.

Owner:BEIJING UNIV OF TECH

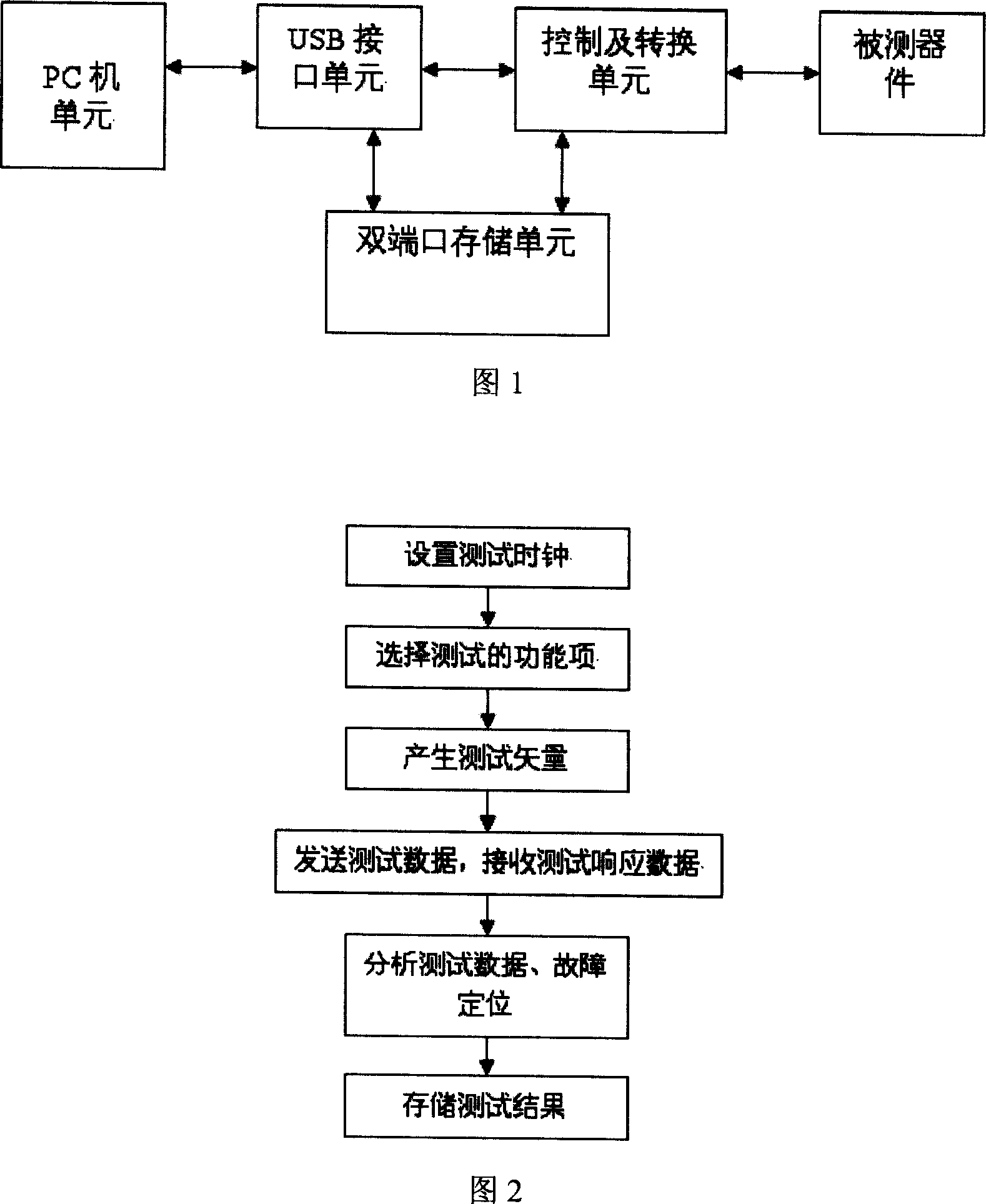

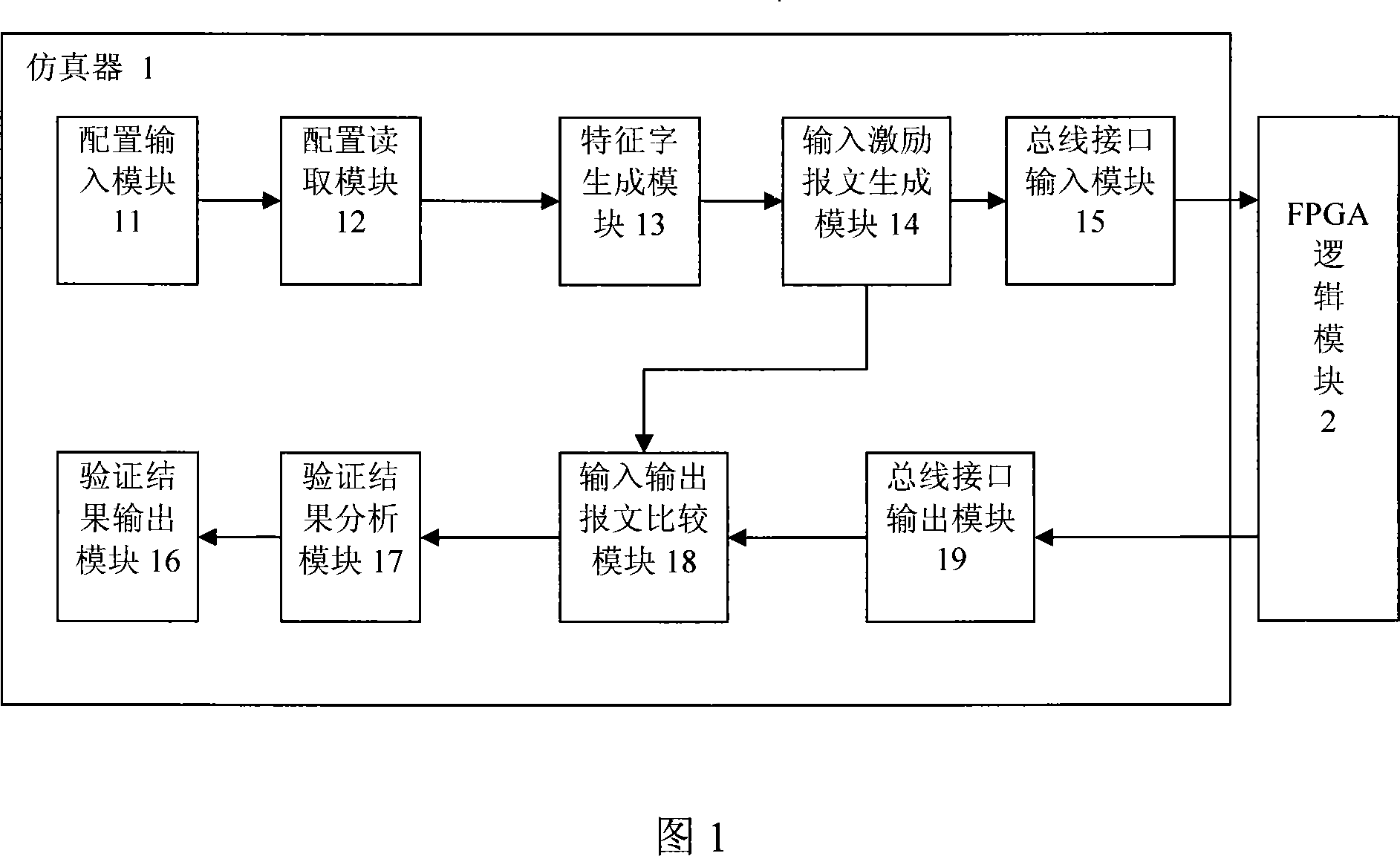

Boundary scan testing controller and testing method thereof

ActiveCN101097242AImplement storageBoundary Scan Test ImplementationElectronic circuit testingElectric digital data processingTransducing UnitTest response

The invention discloses a controller and testing method of boundary scanning, said controller includes PC unit, USB interface unit, two-end memory unit, control and transforming unit; said PC unit can set test, generate test vector, send and receive test data, analyze test data, store test result and USB drive of controller; said USB interface unit realizes communication between boundary scanning test controller and computer; said two-end memory unit realizes memory of test vector and stores test response; said control and transforming unit generates boundary scanning test clock to realize transforming test data to JTAC signal, and realizes reading and writing of data from two-end memory unit. The invention adopts USB interface, memory of two-end memory unit and FPGA design, plug and play, data transmission and boundary scanning test can be preceded at the same time, test speed is increased.

Owner:ZTE CORP

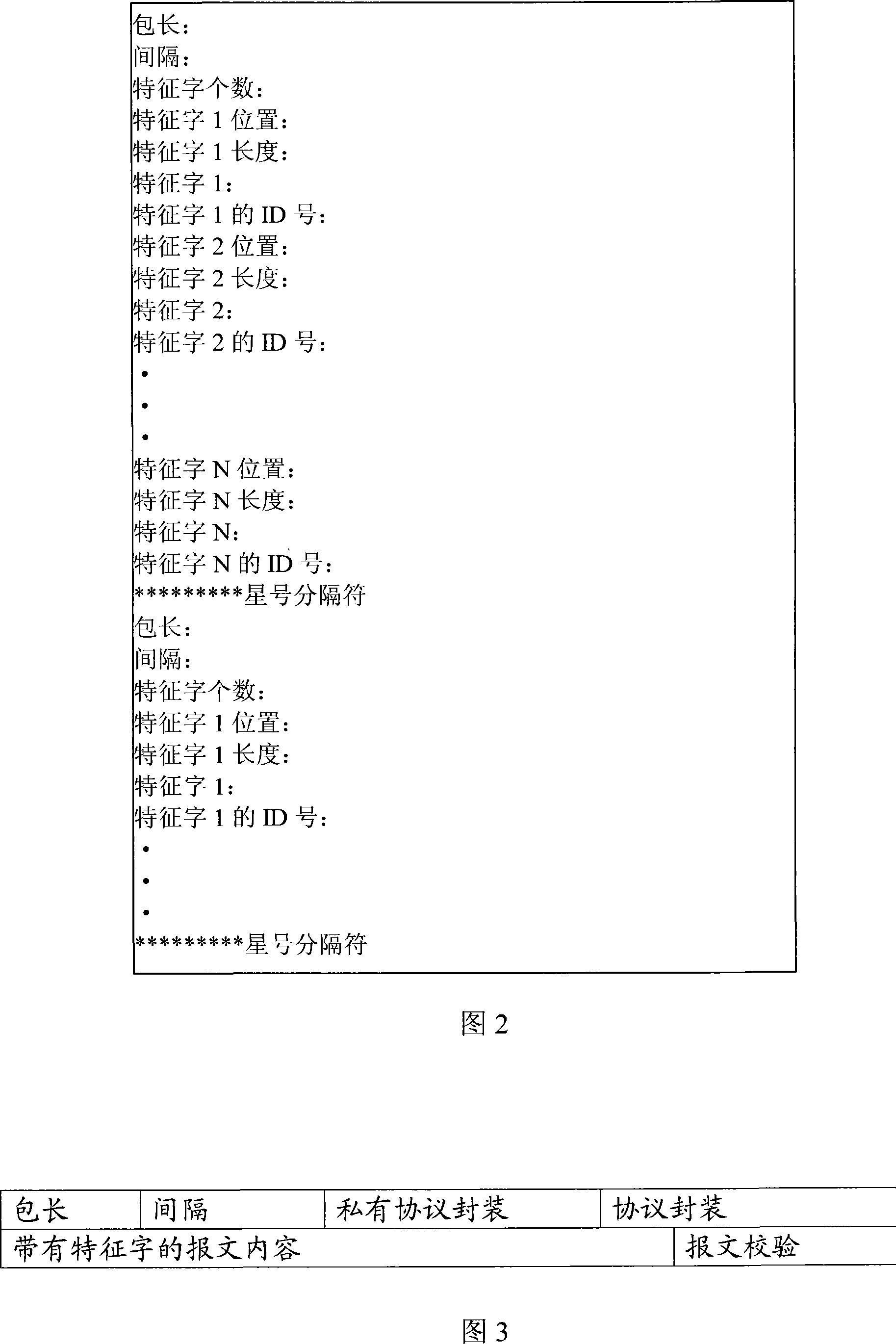

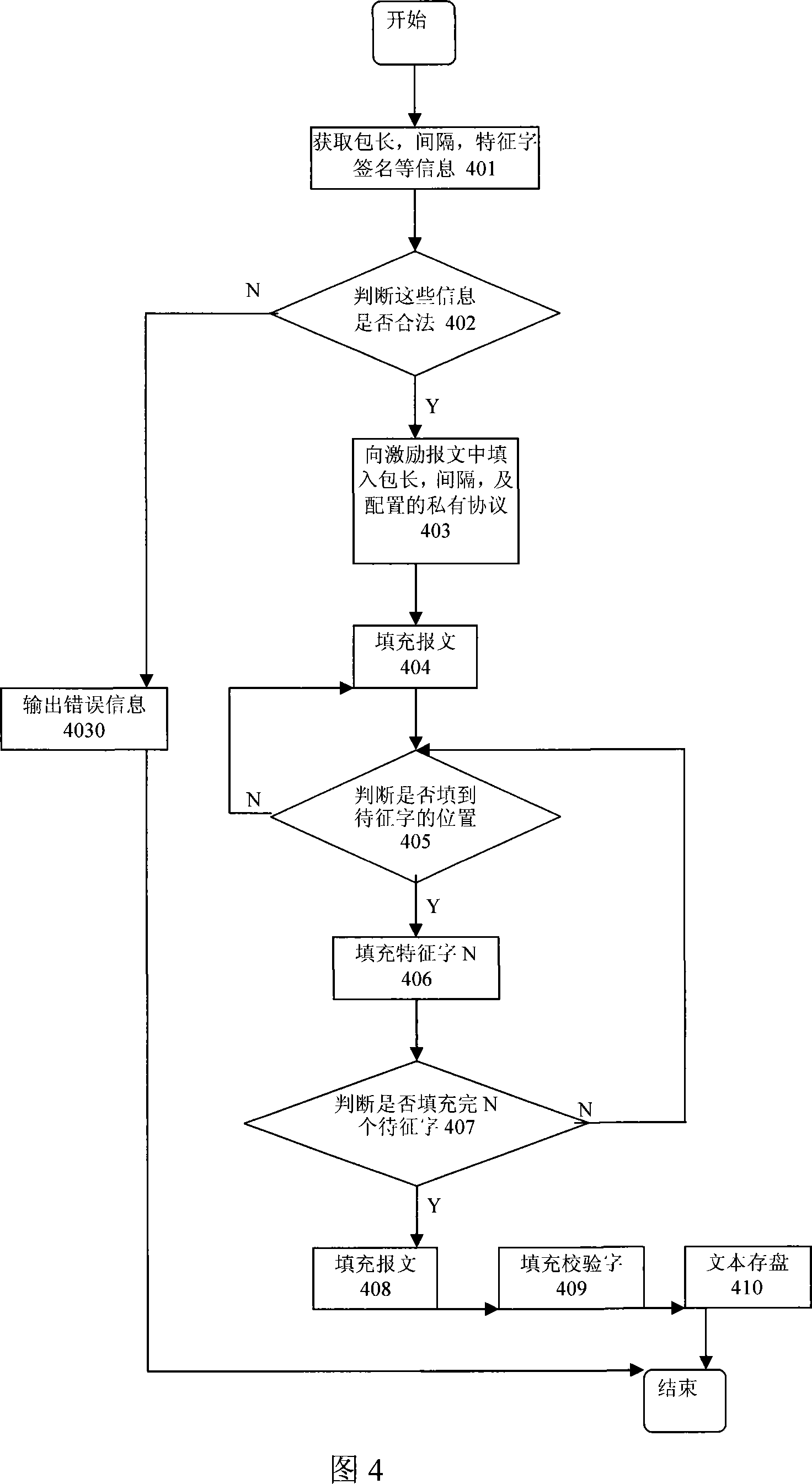

FPGA emulation device and method

InactiveCN101093521ASolve verification difficultiesReduce design difficultySpecial data processing applicationsFpga emulationOutput compare

A method for simulating FPGA includes configuring message parameter with feature character in advance and storing said feature character in file, fetching file to obtain message parameter for automatically generating excitation message inserted with corresponding feature character outputting excitation message through interface module or receiving response message through FPGA logic module to be tested, comparing said messages based on feature character and outputting compared result.

Owner:ZTE CORP

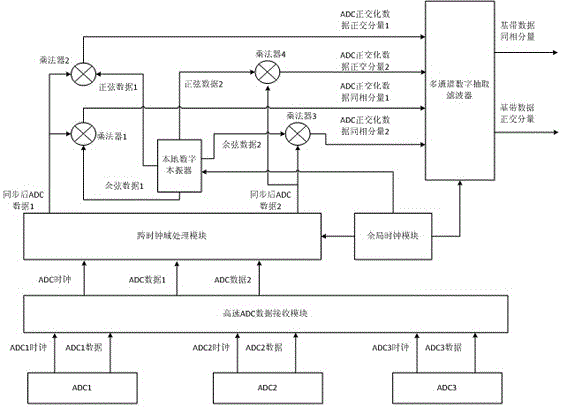

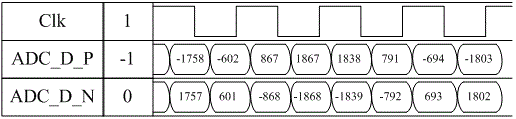

Method and system for realizing ultrahigh-speed digital orthogonal down conversion and decimation filtering in FPGA

InactiveCN105915241ANot subject to debuggingStrong upgradeabilityDigital technique networkTransmissionNumerical controlData rate

The invention discloses a method and a system for realizing ultrahigh-speed digital orthogonal down conversion and decimation filtering in an FPGA. The system comprises the components of a plurality of ADC sampling chips, a high-speed ADC data receiving module, an over-clock processing module, a global clock module, a local numerical control oscillator and a multichannel digital decimation filter. The designed working frequency of the traditional FPGA is hard to exceed 200MHz. According to the method and the system, a numerical control oscillator (NCO) and the digital decimation filter as core parts in orthogonal down conversion are improved; furthermore through reasonably restraining layout and wiring of the FPGA, highest sampling rate above 500Msps and output baseband data rate above 125MHz can be ensured on a common FPGA device. Furthermore the method and the device can support simultaneous parallel sampling of multiple paths of ADC data, thereby adapting with a multichannel data receiving occasion.

Owner:XINYANG NORMAL UNIVERSITY

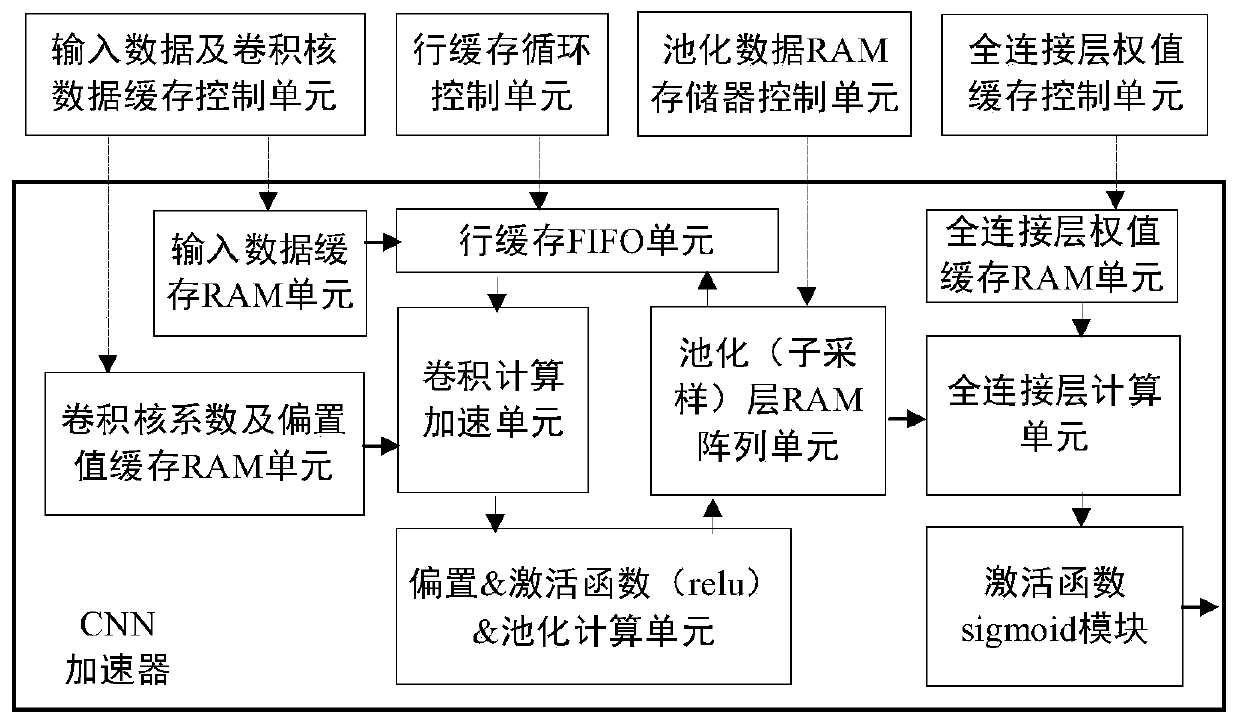

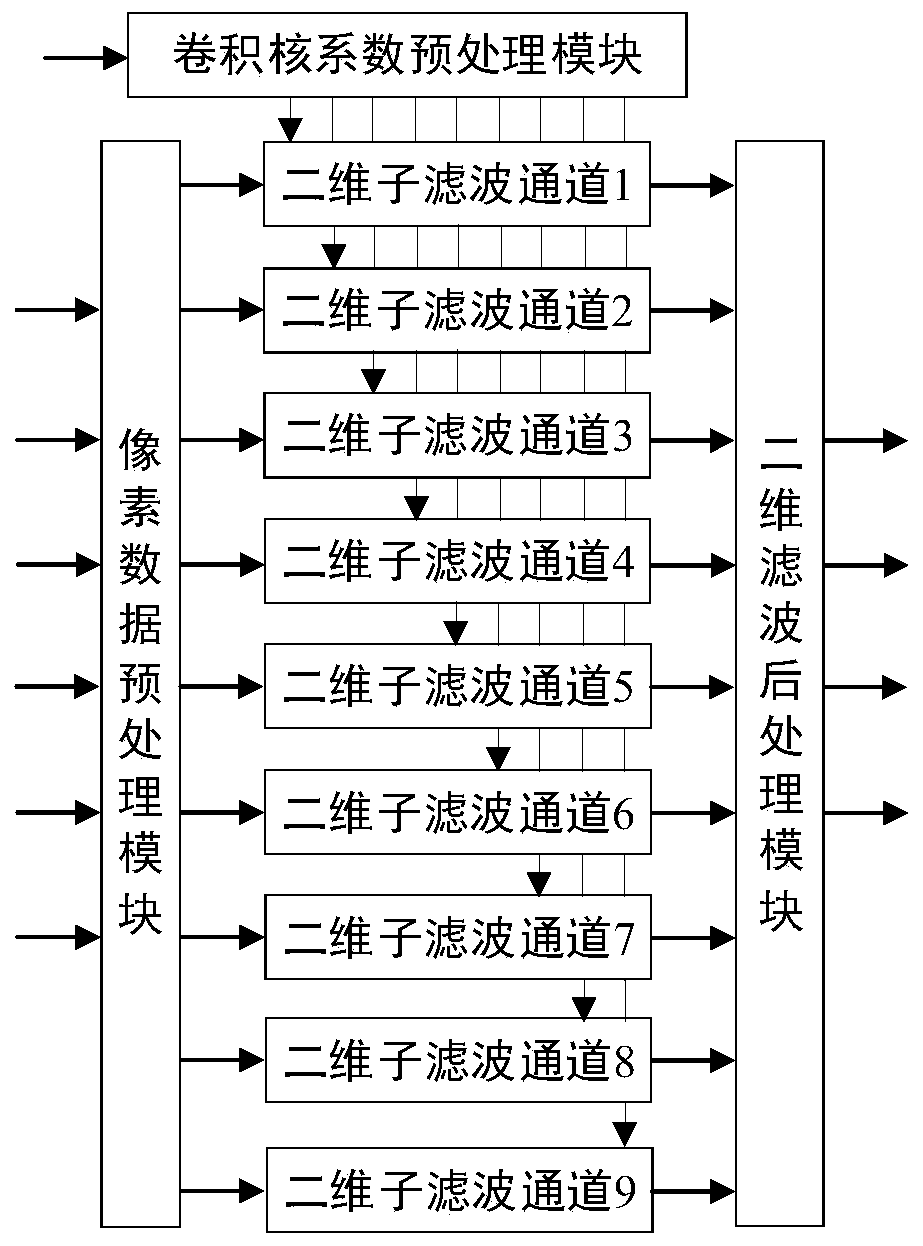

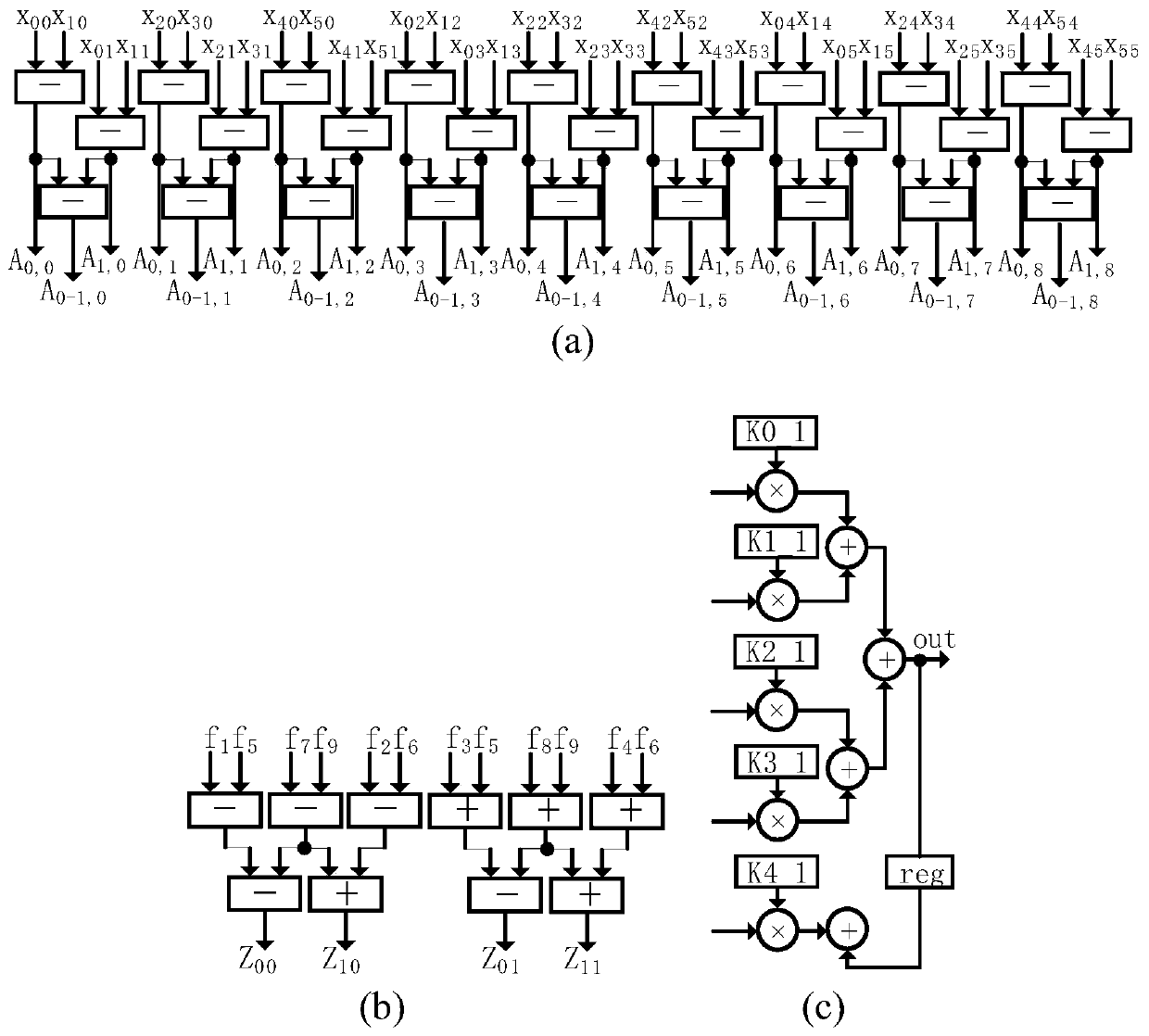

A convolutional neural network accelerator circuit based on a fast filtering algorithm

ActiveCN109948784AImprove performanceSave caching timeEnergy efficient computingPhysical realisationActivation functionFilter algorithm

The invention discloses a convolutional neural network accelerator circuit based on a fast filtering algorithm. In order to reduce the calculation amount of a convolutional neural network algorithm (CNN), the method provided by the invention utilizes a fast filtering algorithm to eliminate the redundancy of overlapped region calculation between convolutional windows in two-dimensional convolutionoperation, so that the algorithm strength is reduced, and the convolution calculation efficiency is improved. Next, a convolution calculation acceleration unit of a four-parallel fast filtering algorithm is designed, and the unit is realized by adopting a parallel filtering structure which is composed of a plurality of small filters and is low in complexity. For the programmable FPGA design, not only can the consumption of hardware resources be reduced, but also the running speed can be increased. Meanwhile, the activation function is subjected to optimization design, and a hardware circuit ofthe activation function (sigmoid) is designed by using a piecewise fitting method combining a lookup table and a polynomial, so that the hardware circuit of the approximate activation function is ensured not to reduce the precision.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

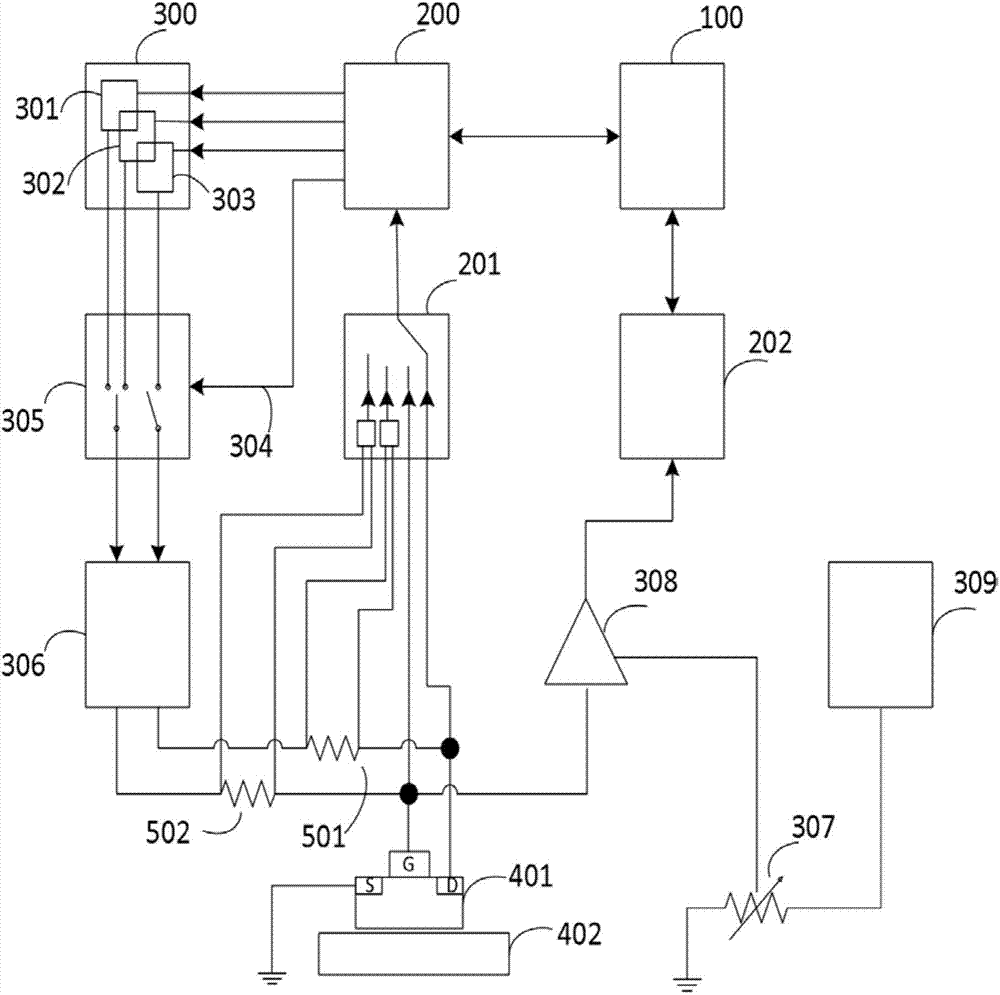

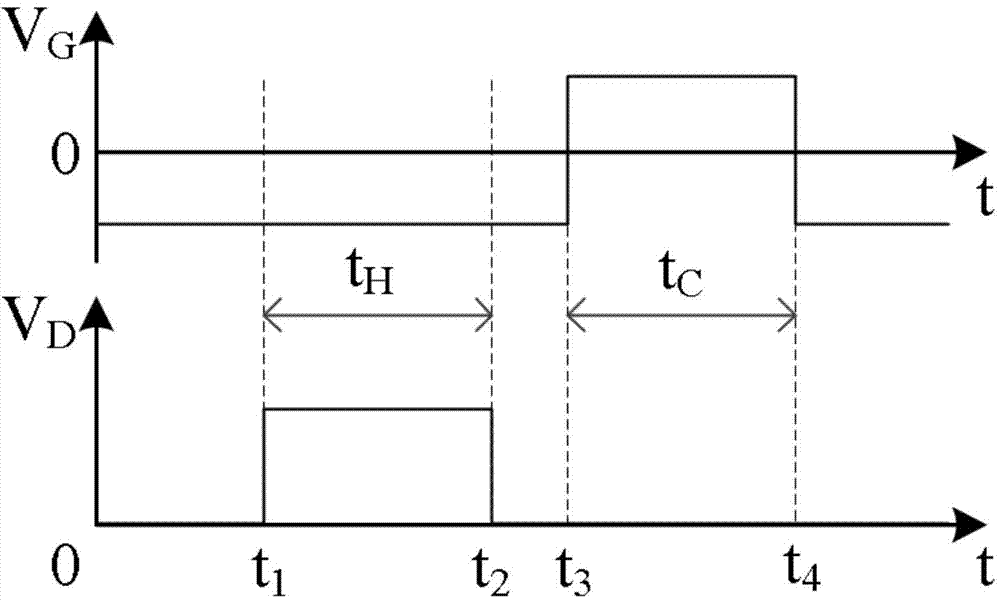

Method and device for measuring temperature rising and heat resistance of Schottky grid field effect transistor

ActiveCN103616628AMaterial heat developmentIndividual semiconductor device testingCapacitanceControl signal

The invention provides a method and device for measuring temperature rising and heat resistance of a Schottky grid field effect transistor and belongs to the technical field of semiconductor device measuring in the micro electronic technique. According to the method and device, a rapid selector switch controlled through control signals is designed; time delay converted from being negatively biased to being positively biased of grid voltage is cut off by drain-source voltage, and the time delay is accurately set and output by an FPGA control module; under a forward direction testing current, a steady-state process of Schottky junction voltage is related to capacitance of the device and the testing current value, the establishment process of the junction voltage at a constant-temperature is adopted to serve as constant-temperature reference junction voltage, and time delay errors of temperature rising under small computing operation are reduced; by adopting an FPGA, the functions of collecting and setting drain-source voltage, drain-source currents and gate-to-source voltage are designed, the function of feedback at the time less than a millisecond level can be achieved, and the device can be effectively protected against burning brought by vibration or misoperation.

Owner:BEIJING UNIV OF TECH

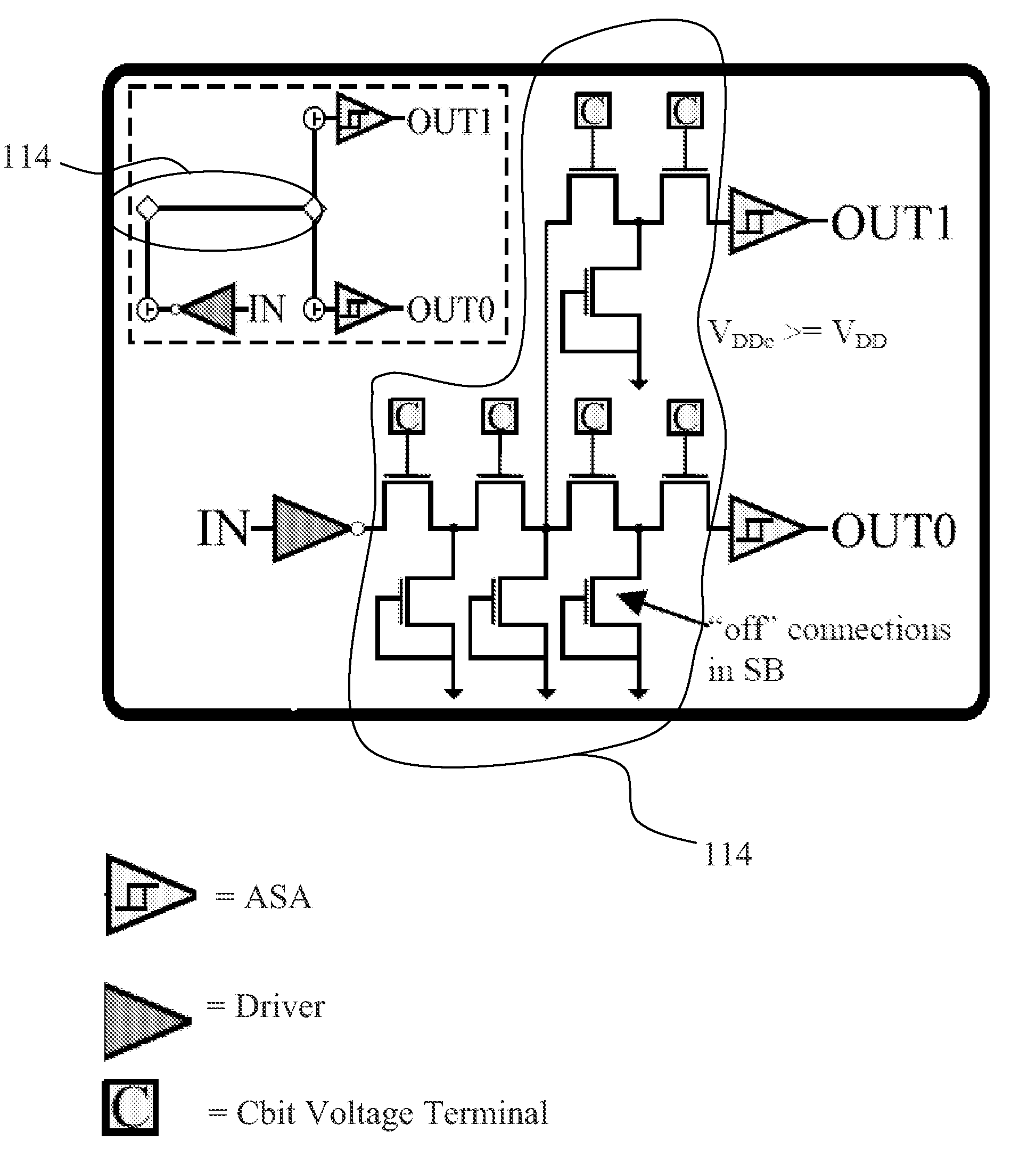

Sub-threshold FPGA and related circuits and methods thereof

ActiveUS20130009667A1Optimize routing delayLow energy overheadSolid-state devicesLogic circuits using elementary logic circuit componentsAudio power amplifierSub threshold

Owner:UNIV OF VIRGINIA ALUMNI PATENTS FOUND

FPGA (filed programmable gate array) fault automatic diagnosing method based on knowledge database

InactiveCN103473409AImprove scalabilitySolve the problem of poor matchingSpecial data processing applicationsGate arrayFpga design

The invention discloses an FPGA (filed programmable gate array) fault automatic diagnosing method based on a knowledge database. The method includes: structuralizing fault information during storage FPGA design and verification; performing fault search according to feature information a new fault case, matching most related and similar fault information according to information such as fault generation and fault feature, and displaying detailed contents and fault solutions to solve the new fault. Acquired fault experience and methods during FPGA design verification are used to build a knowledge database system, detailed fault information and solutions are displayed visually, faults can be positioned accurately, conveniently and fast, and fault debugging and solving efficiency of FPGA design verification staff is increased greatly.

Owner:ZHEJIANG UNIV

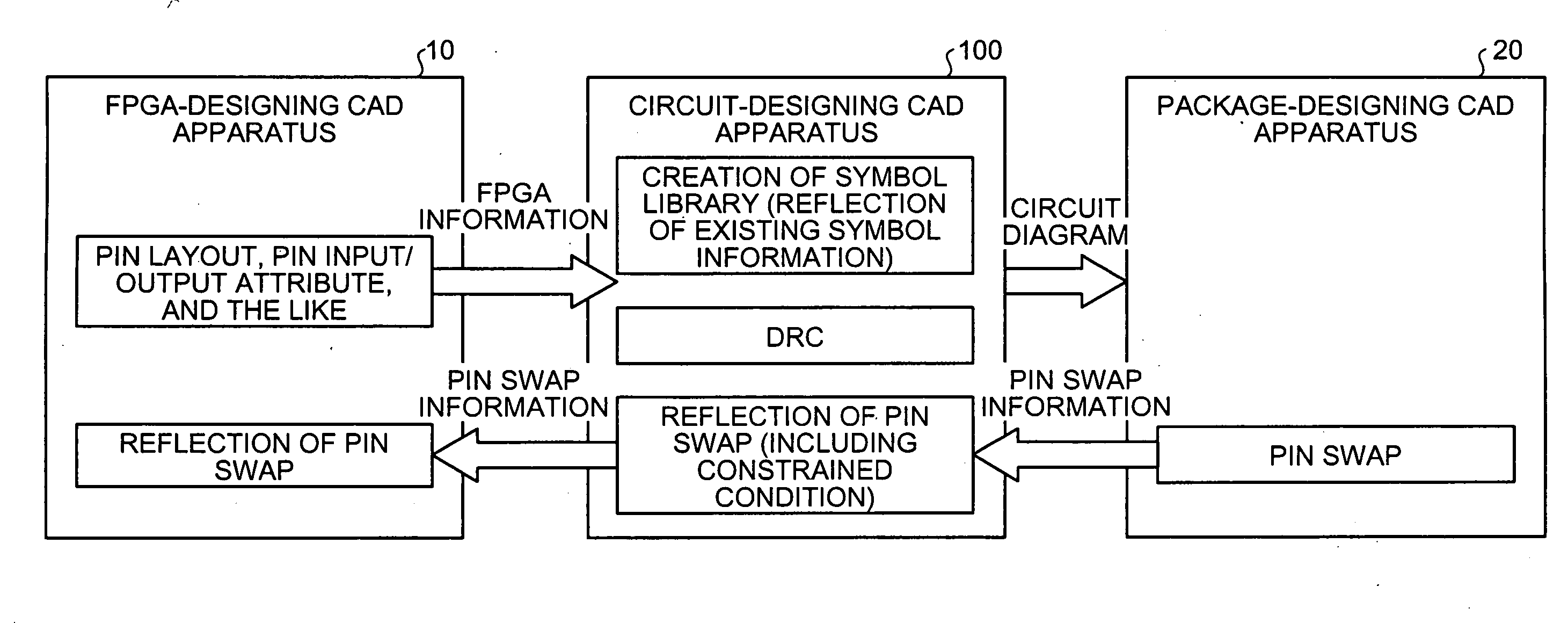

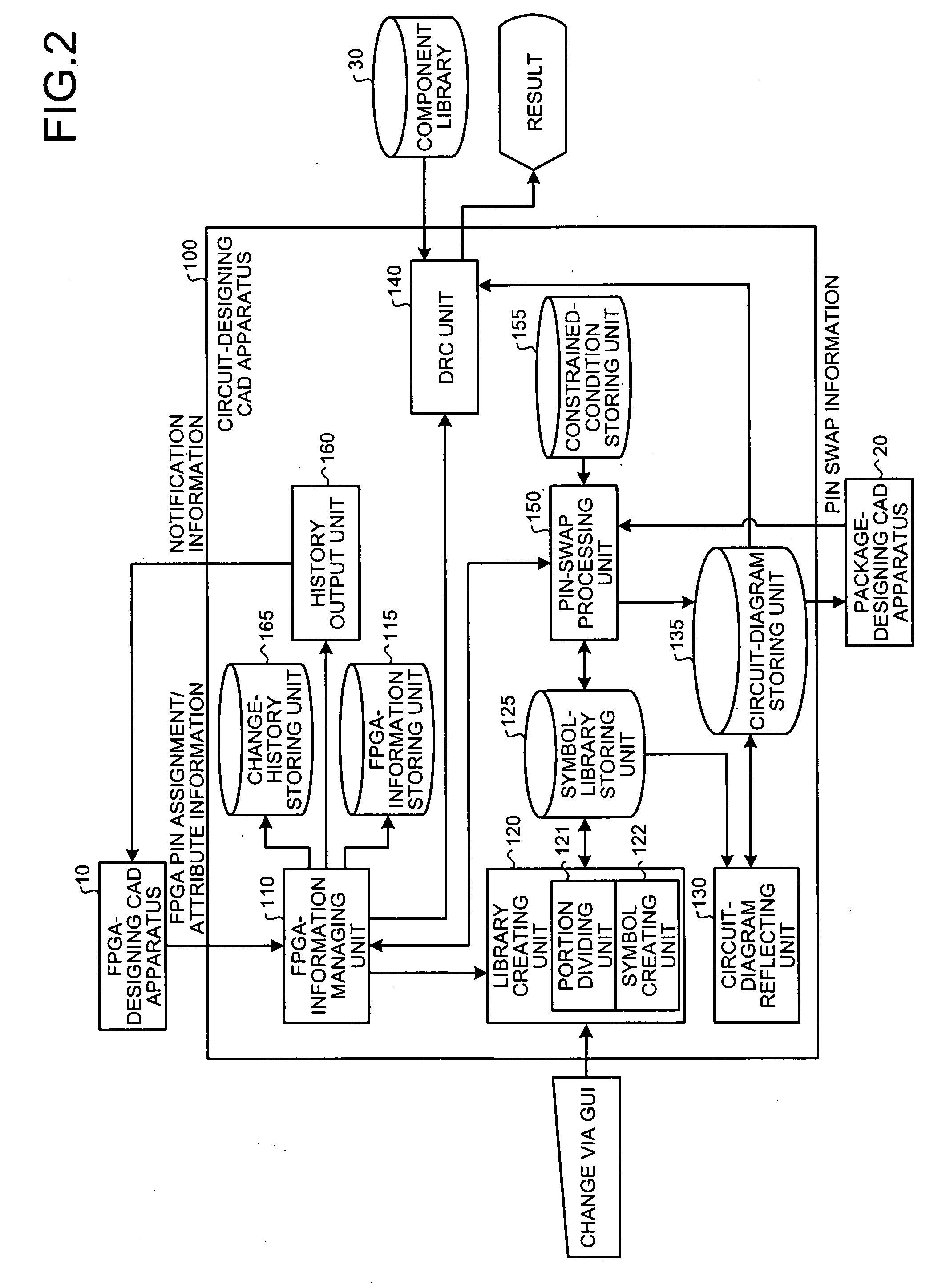

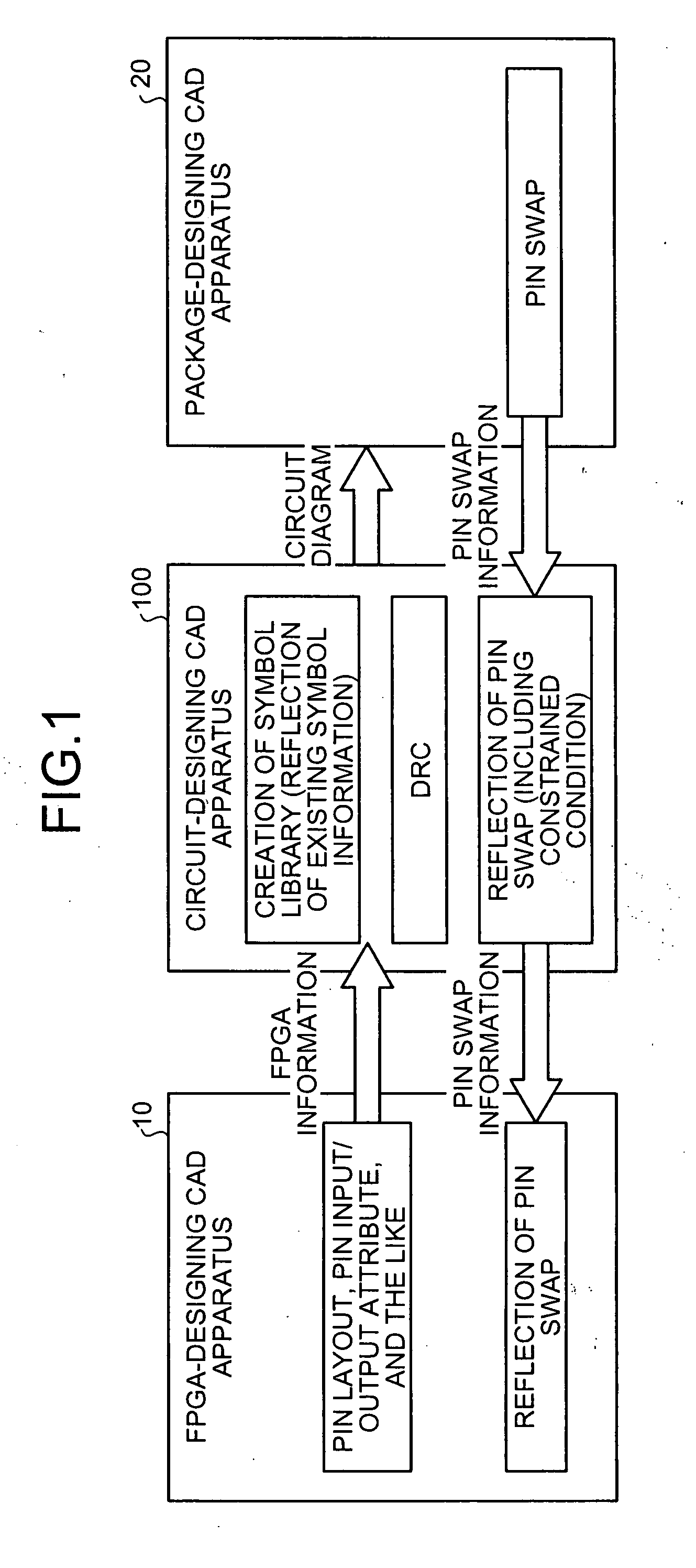

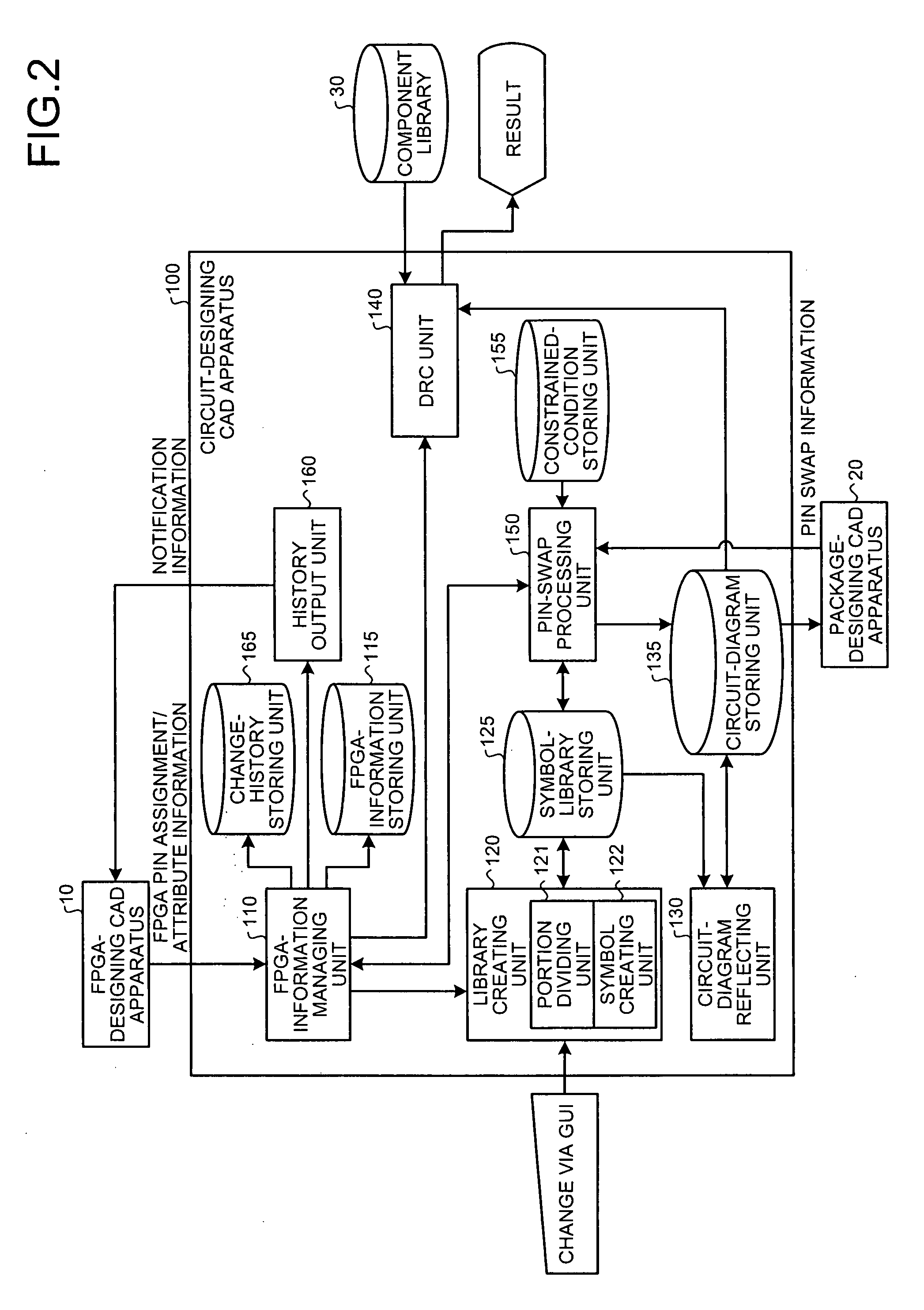

Circuit-design supporting apparatus, circuit-design supporting method, computer product, and printed-circuit-board manufacturing method

ActiveUS20080263500A1Solve problemsCAD circuit designSpecial data processing applicationsManagement unitPackage design

An FPGA-information managing unit included in a circuit-designing CAD apparatus retrieves FPGA information, such as pin-assignment information and attribute information, that is created by an FPGA-designing CAD apparatus. A library creating unit creates a symbol library by using the FPGA information. A pin-swap processing unit retrieves pin swap information from a package-designing CAD apparatus, and reflect the pin swap in the symbol library, the FPGA information, a circuit diagram, and a constrained condition.

Owner:FUJITSU LTD

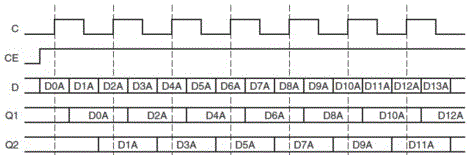

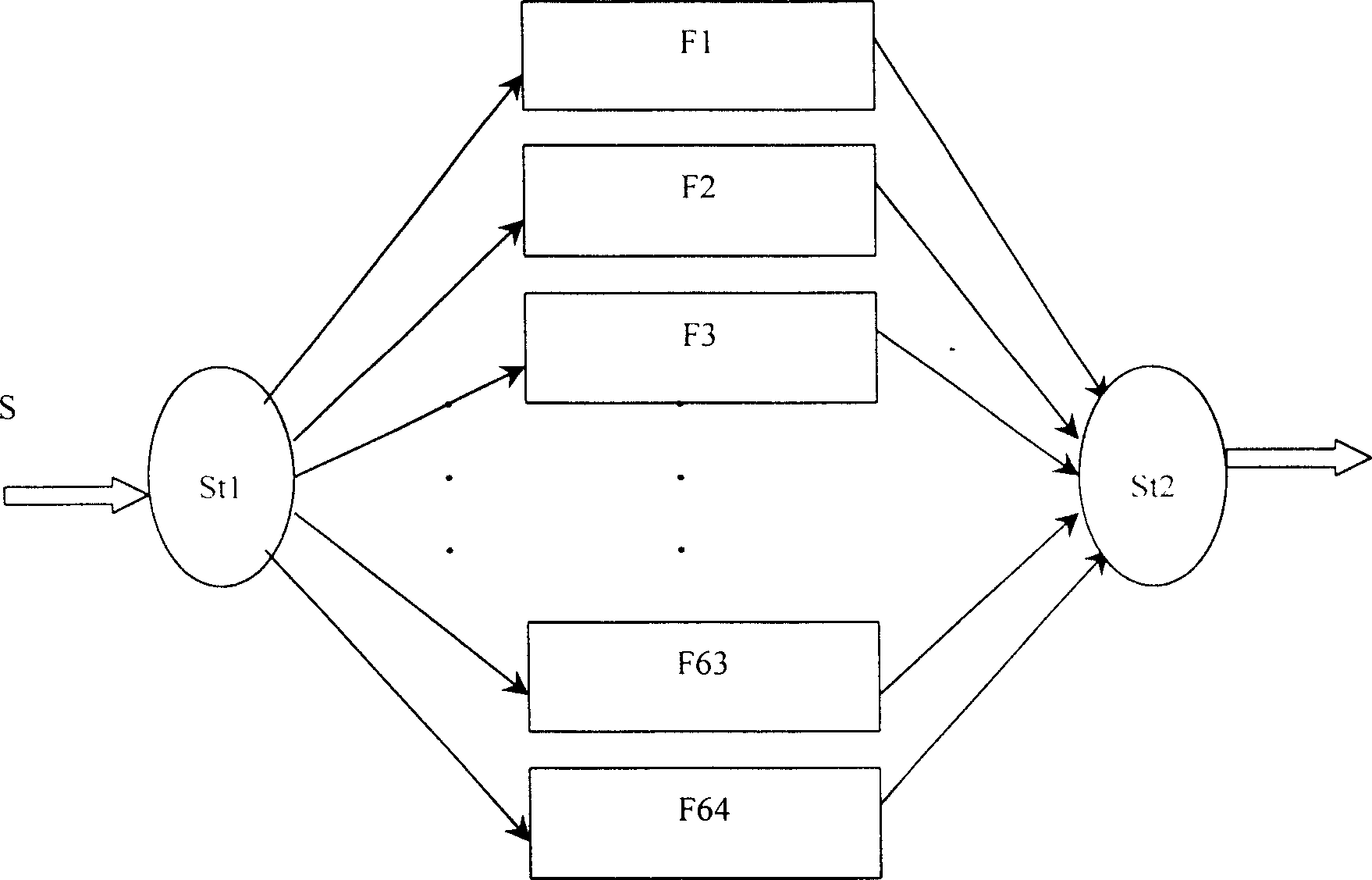

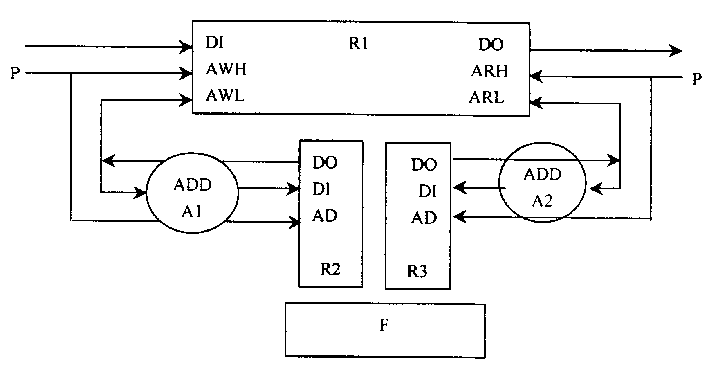

Multichannel FILO data buffer storage devices

InactiveCN1439966ASave resourcesSimplify complexityMemory adressing/allocation/relocationData storingFpga design

A data buffer storing device of first in first out with multichannel, used for carrying on FIFO data buffering for each of buffering data coming from the multichannel includes data storing unit, read / write pointer control unit and state labelling unit, of which the data storing unit only applies a dual port RAM (R1) and the read / write pointer control for each channel is also integrated separately into one read / write pointer control unit so as to decrease the resources for a large number of read / write pointer counter as well as to simplify the complicacy of interface logic.

Owner:HUAWEI TECH CO LTD

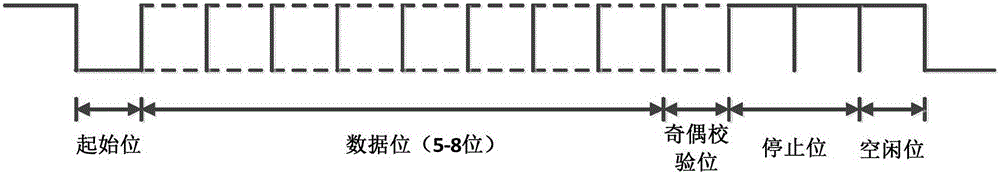

Verification method of FPGA universal configurable UART protocol based on UVM

InactiveCN105718344AImprove verification efficiencyDetecting faulty computer hardwareComputer architectureValidation methods

The invention relates to a verification method of an FPGA universal configurable UART protocol based on UVM. The verification method comprises the steps of finishing an overall framework of UART protocol verification by utilizing a UVM verification platform structure and a verification idea; and setting a UART configuration type in which all the parameter information of the UART protocol is packaged, and sending the UART protocol parameter information to related parts of platforms such as a driver, a monitor and a grade recording board through a config-db mechanism provided by the UVM. During instantiation of a top layer, a universal parameter-configurable UART protocol FPGA verification platform can be realized only by setting corresponding parameter information such as a Baud rate, a data bit, a stop bit and a verification mode based on protocol requirements of a to-be-tested UART by the user. The verification method of the FPGA universal configurable UART protocol based on the UVM has the advantages of being efficient and universal. A test case meeting requirements can be generated automatically only by setting corresponding UART parameters at the top layer by an FPGA design engineer or verification engineer, and a verification environment is unnecessary to develop again, so that the verification efficiency is improved greatly.

Owner:CHINA ELECTRONIC TECH GRP CORP NO 38 RES INST

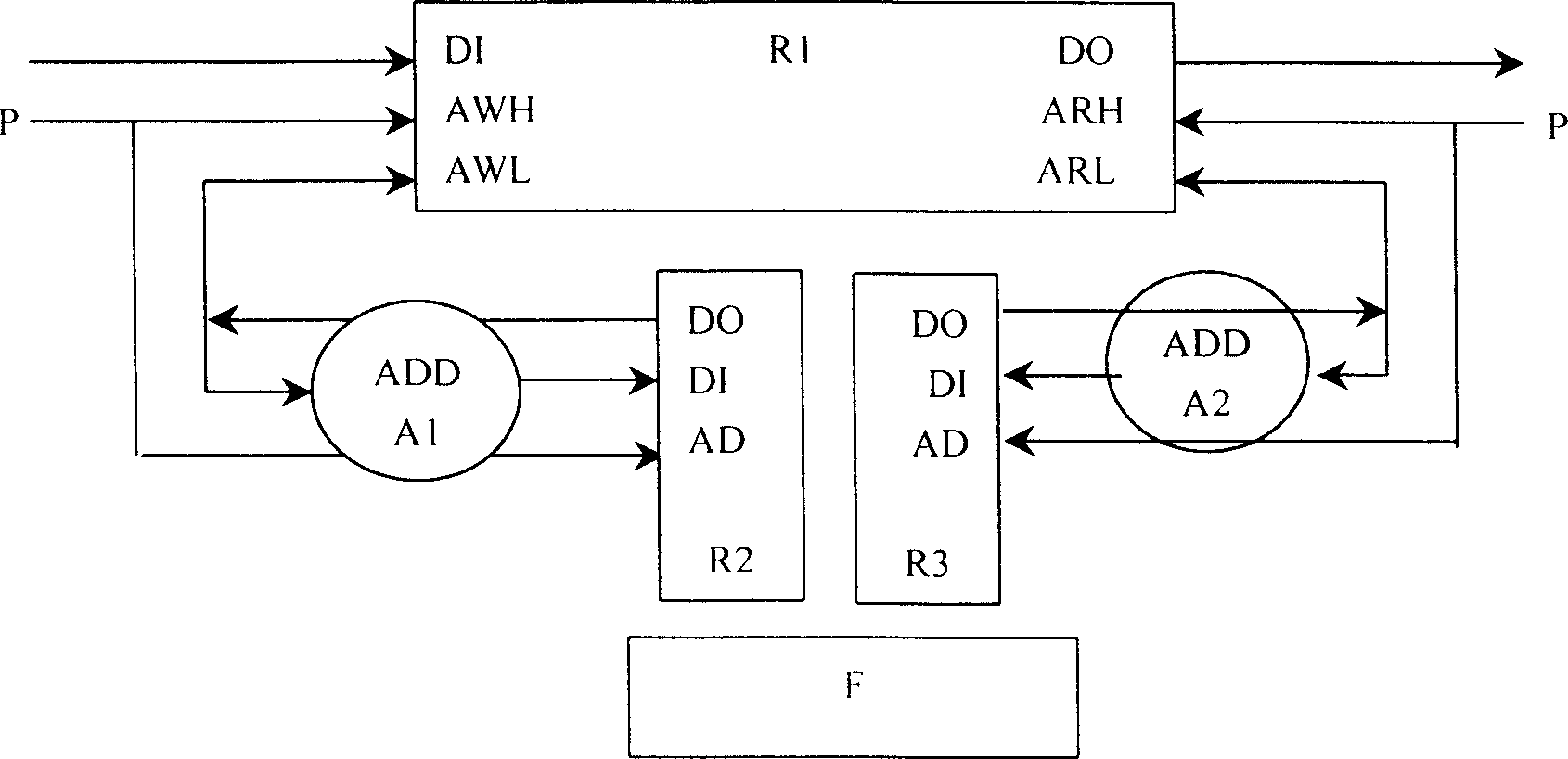

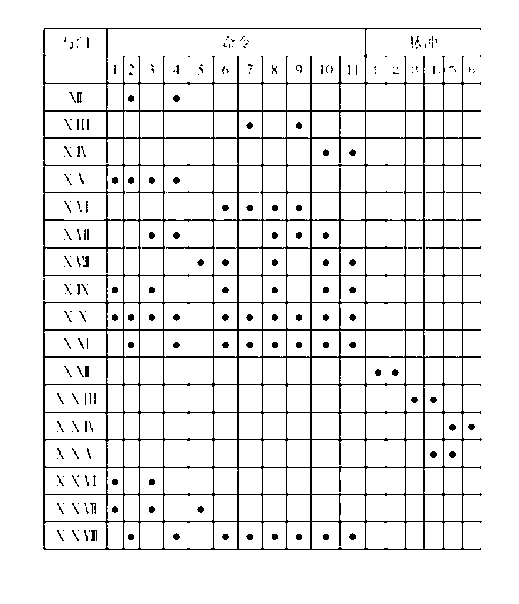

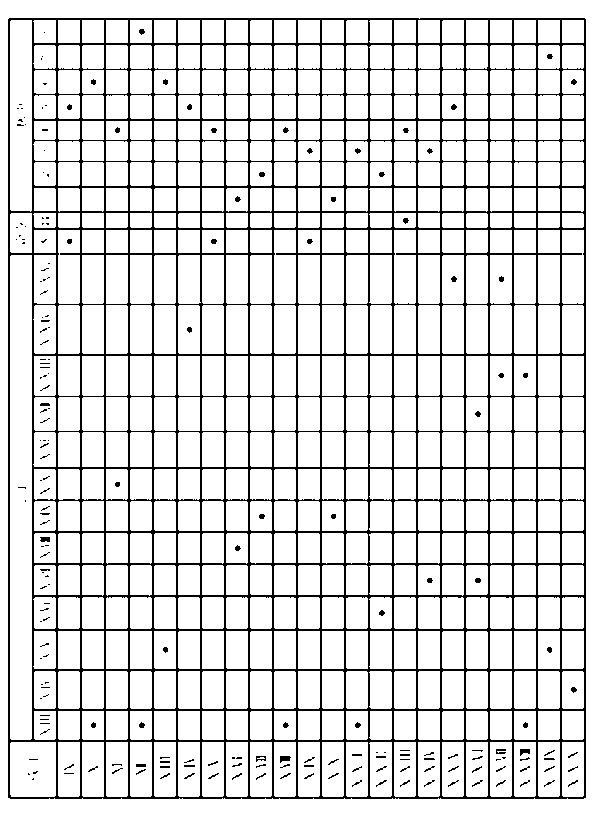

Two-read-out and one-read-in storage controller integrating addressing and storage

InactiveCN103345448ATake full advantage of parallel processing capabilitiesSimplify the addressing processMemory adressing/allocation/relocationControl storeOperand

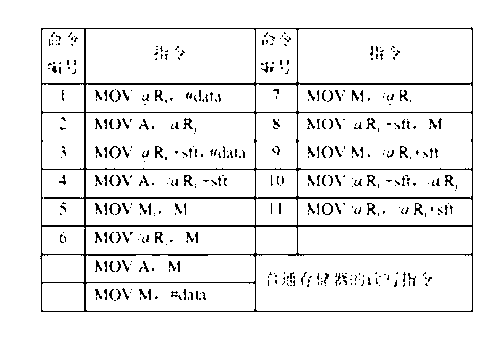

A two-read-out and one-read-in storage controller integrating addressing and storage comprises a two-read-out and one-read-in storage unit, a command storage and address temporary storage control module, a combinational logic circuit module, a pulse distributor_1, a data transmission control module, an address channel control module_1, a command storage control module, a pulse distributor_2, a data transmission and read arbitration control module and an address channel control module_2. The integrated storage controller is provided with a read-write port and an independent read-out port having the read operation arbitration function. A hard-wired circuit of an FPGA is applied, commands or addresses or immediate operands needing to be read in are read in from a system bus, under the control of internal temporal pulses, direct and indirect addressing of base addresses and modify addresses of the immediate operands and reading and writing of the storage unit are autonomously finished according to the command requirements, data transmission between storage units is finished, a microprocessor can read out two operands at the same time when executing operate class commands, and execution of a command sequence is accelerated.

Owner:GUANGXI UNIVERSITY OF TECHNOLOGY

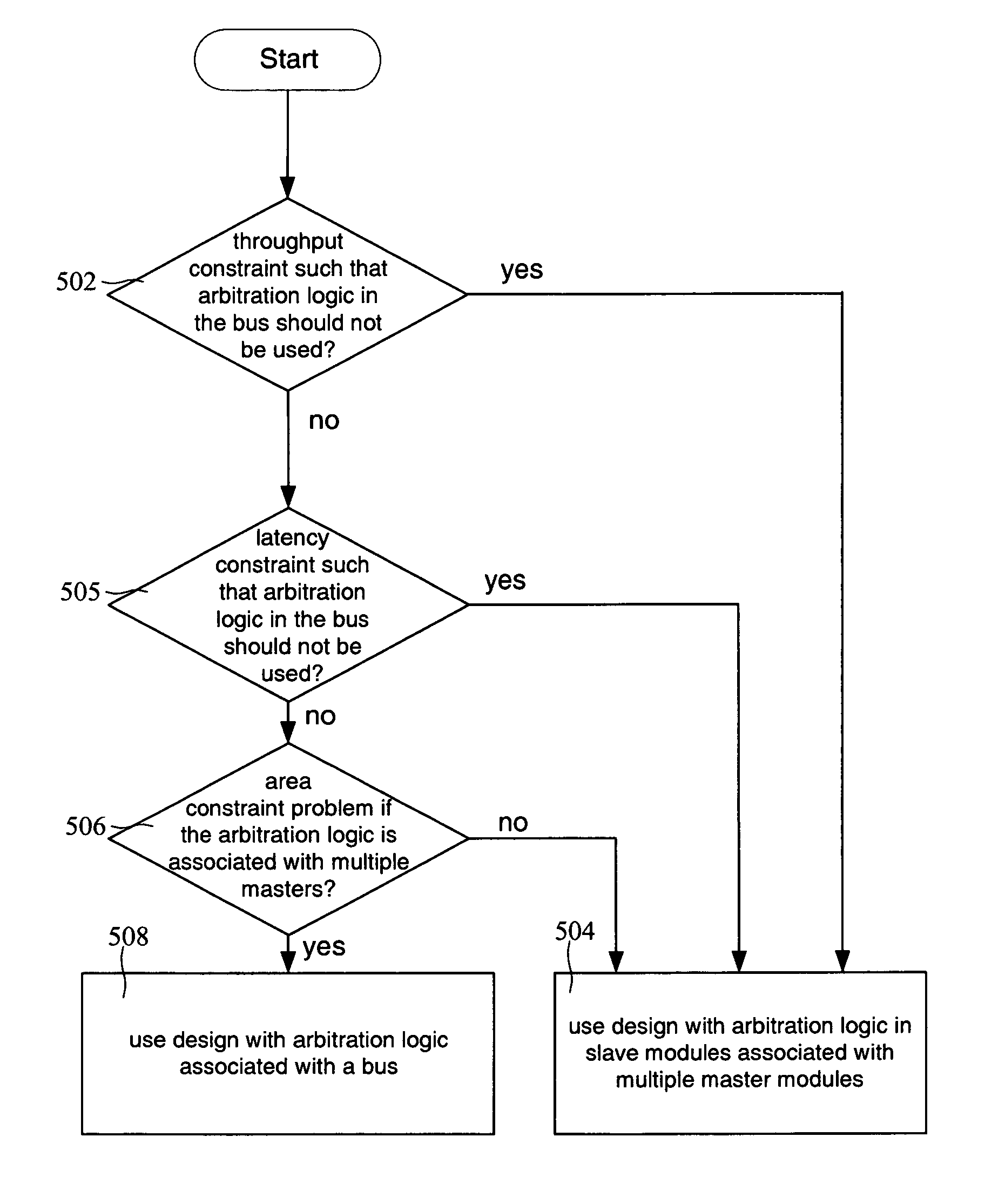

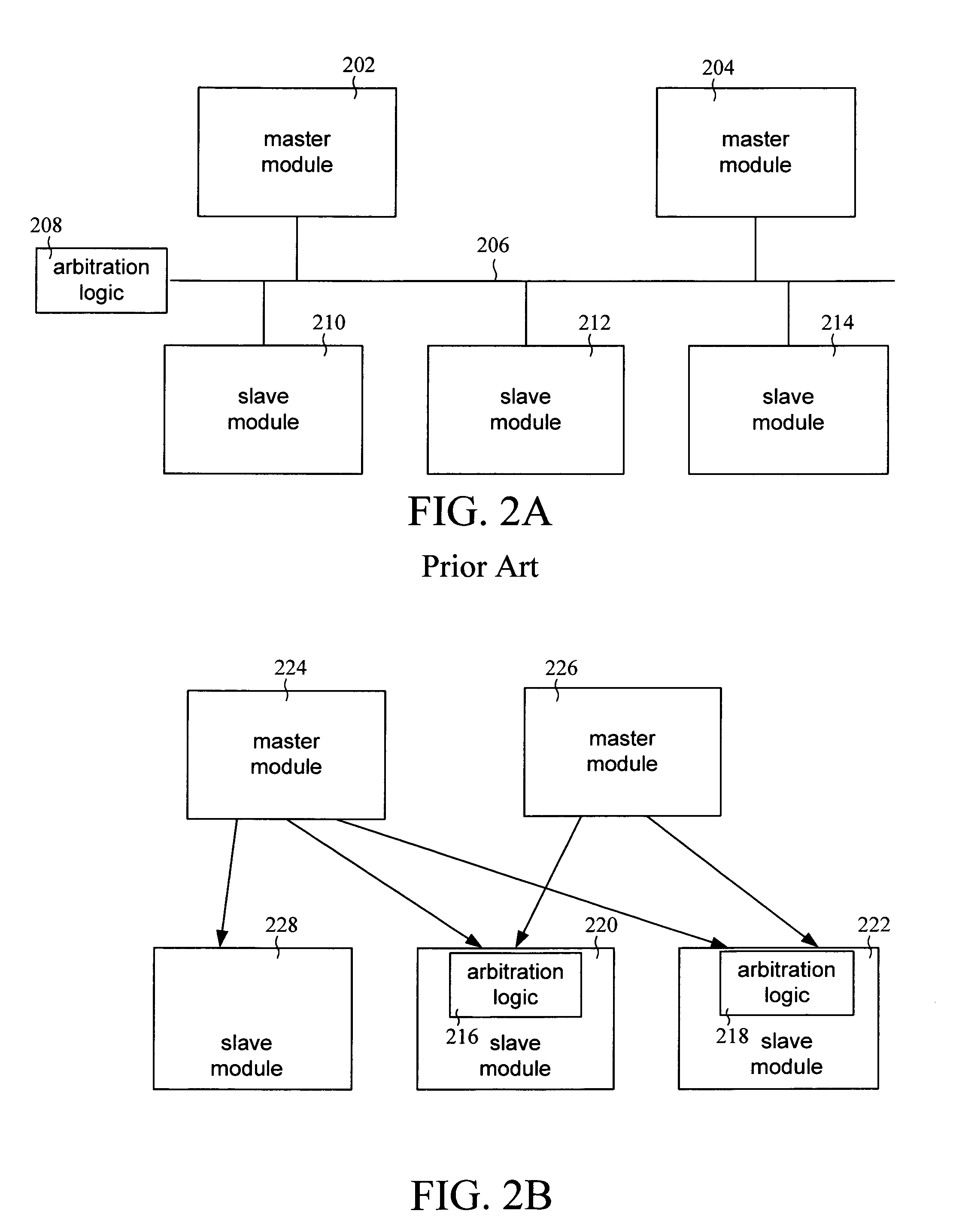

Auto-generation and placement of arbitration logic in a multi-master multi-slave embedded system

ActiveUS7426709B1CAD circuit designSpecial data processing applicationsLatency (engineering)Fpga design

An FPGA design system includes the use of constraints in order to determine whether to associate arbitration logic with a bus or in slave modules. In one embodiment, area constraints can be used to determine whether a smaller design using arbitration logic at the bus should be used. In one embodiment, a latency constraint is used to determine whether a lower latency design with arbitration logic at the slave modules is to be used. In one embodiment, throughput constraints are used to determine whether a higher throughput design with arbitration logic at the slave modules is to be used.

Owner:XILINX INC

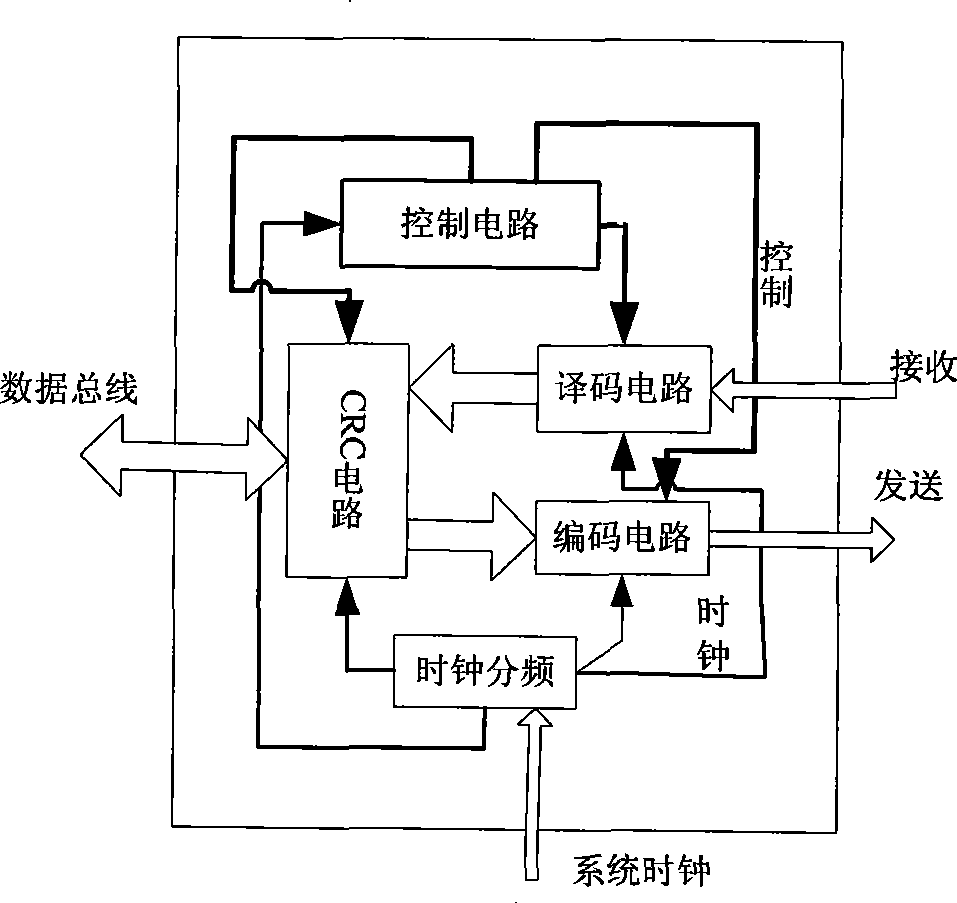

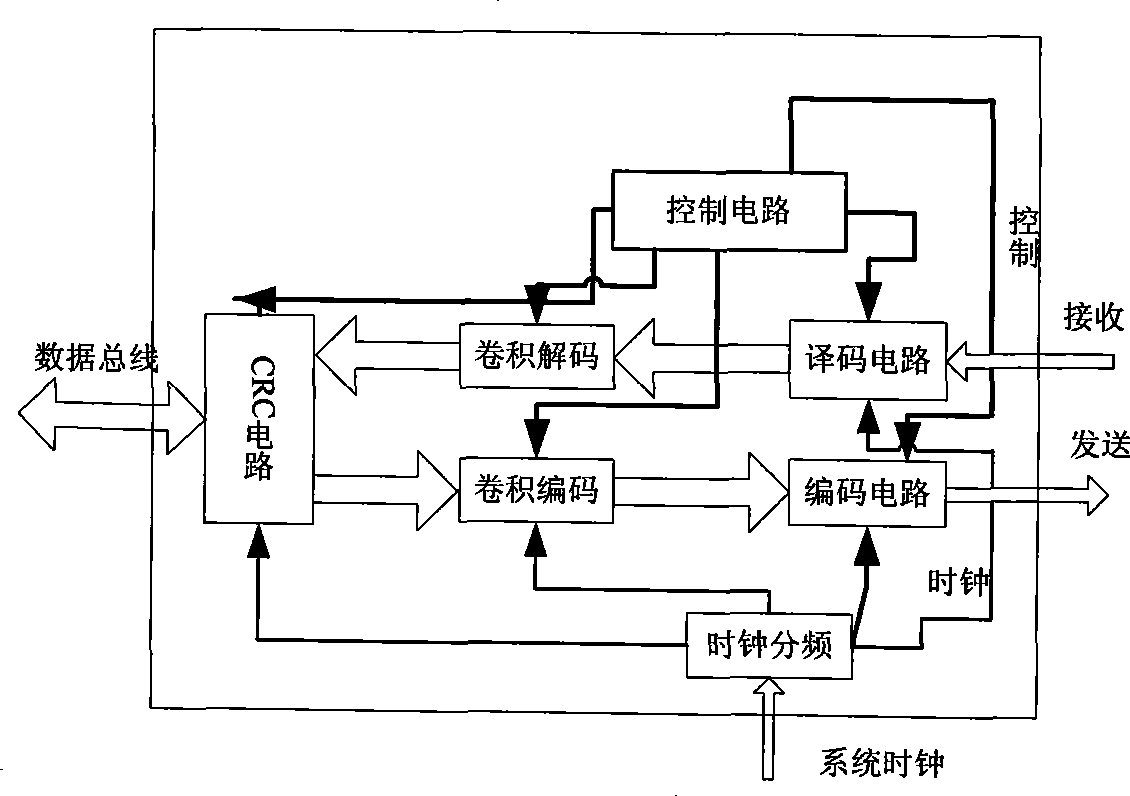

Coding and decoding circuit of super high frequency radio frequency personal identification system

InactiveCN101441703AReduce the number of reads and writesShorten communication timeError correction/detection using multiple parity bitsSensing record carriersComputer architectureRadio frequency

The invention discloses a coding and decoding circuit for a system of ultra-high frequency radio frequency identification (UHF RFID). Every time when error codes are found, the coding and decoding circuit based on the prior cyclic redundancy check (CRC) circuit resends, thus frequency of communication between a reader-writer and a tag can be increased in the situation of long distances of reading and writing and serious noise interference. If the speed of reading and writing is definite, time for successfully reading once is certainly extended, thereby influencing practicability and reliability of the UHF RFID system in the situation of reading and writing at high speed. To solve the problem, the invention is provided with a convolution error correcting code, adopts concatenation connection with the CRC circuit to reduce frequency of reading and writing, so as to improve the successful reading rate of the system in certain time. The CRC circuit of the invention is a parallel circuit with compact conformation and fast arithmetic designed based on FPGA, thereby further reducing time of communication between the reader and the tag, and increasing the amount of tag identification in unit time.

Owner:HUNAN UNIV

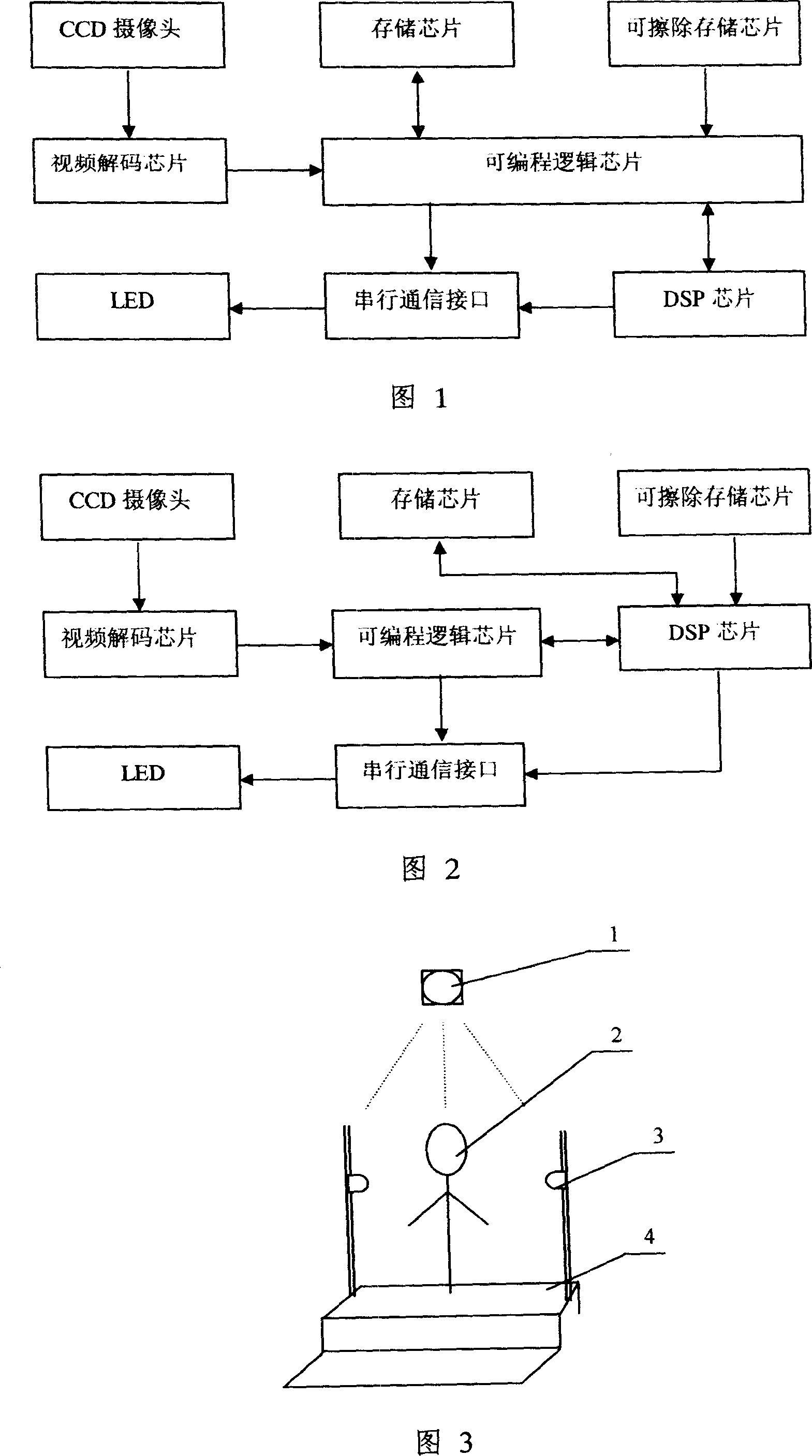

Image-based bus passenger number automatic statistics meter

InactiveCN101025790AAvoid false positive rateAvoidance of detectionCharacter and pattern recognitionHardware structureImaging processing

The invention discloses an image-based in-bus person automatic counter, comprising: image collecting and processing module and image processing algorithm, where the image collecting and processing module comprises CCD camera, video decoding chip, programmable logic chip and DSP chip, where the output of the CCD camera is connected with the input of the video decoding chip, the control and output ends of the video decoding chip are connected with the programmable logic chip, and the programmable logic chip is connected with the DSP chip; the programmable logic chip is written with a HDL program for implementing data exchange, control and buffering between the video decoding chip and the DSP chip; the DSP chip runs image processing and recognizing software. And the invention adopts high speed DSP and FPGA design and makes image recognition by advanced image processing and recognizing algorithm, and the whole system has high calculating rate and can implement real-time and accurate person number recognition; and its hardware structure is simple, having stable performance and convenient to install and debug.

Owner:ZHONGBEI UNIV

Coordinated-design supporting apparatus, coordinated-design supporting method, computer product, and printed-circuit-board manufacturing method

InactiveUS20080134125A1Computer programmed simultaneously with data introductionCAD circuit designPackage designEngineering

An FPGA-design-CAD interface unit retrieves pin assignment information created by an FPGA-designing CAD apparatus. An FPGA-pin-information managing unit manages the pin assignment information as FPGA pin information. A temporary-library creating unit creates a temporary component shape type library by using the FPGA pin information and outputs the temporary component shape type library in a form capable of being read by a package-designing CAD apparatus to a file.

Owner:FUJITSU LTD

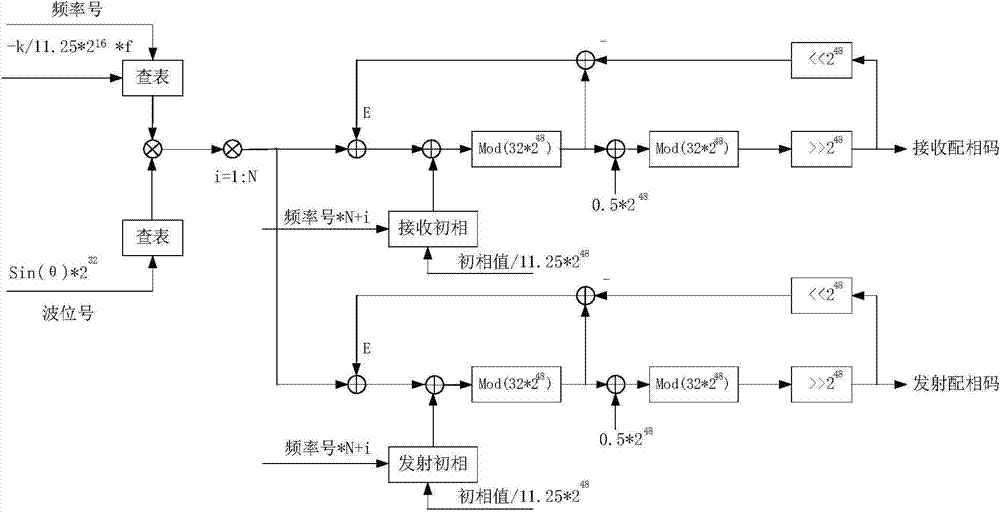

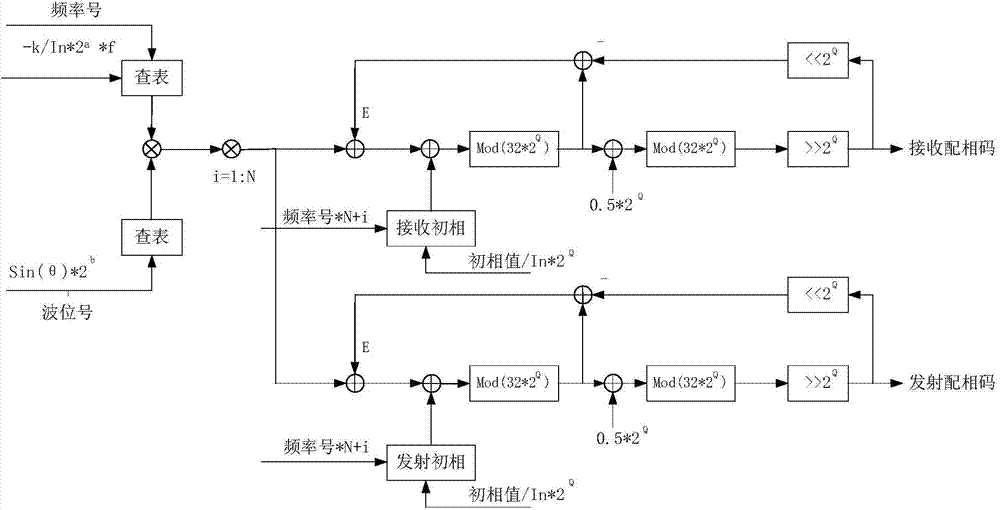

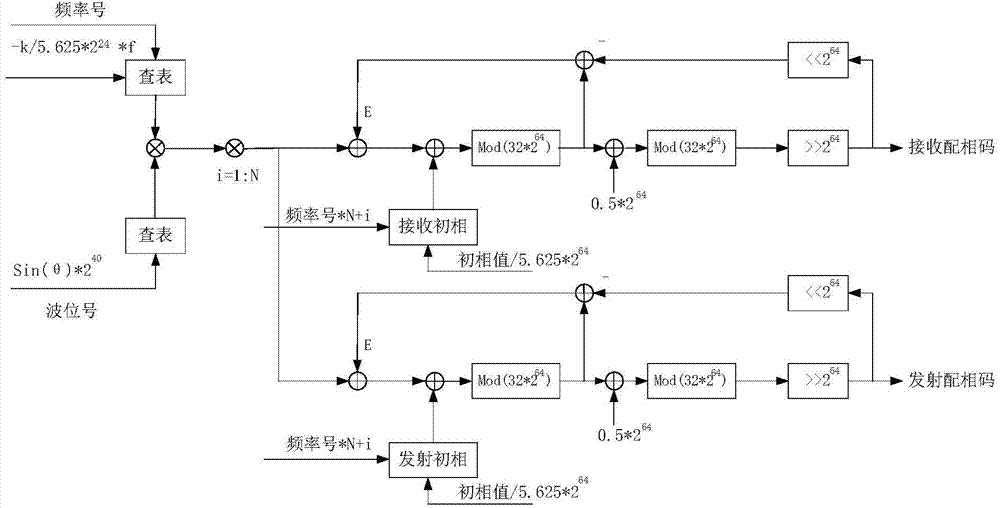

FPGA (field programmable gate array) based implementation method of phased array antenna iteration phase-matching algorithm

ActiveCN103810319AIncrease computing speedImprove operation accuracySpecial data processing applicationsPhase shiftedClock rate

The invention provides an FPGA (field programmable gate array) based implementation method of a phased array antenna iteration phase-matching algorithm. The parallel running characteristic of FPGA hardware is used, the iteration phase-matching algorithm is realized through algorithm optimization, and the operating speed and the operating precision of the iteration phase-matching algorithm are improved. According to the method, the operating speed is decided by the clock frequency of a counter, and the clock frequency of the counter can reach 200 MHz (related to an adopted FPGA hardware platform) through optimization of the FPGA design, that is, the phase-matching iteration computing time for completing receiving and sending of a phase-matching code of one phase shift unit is 5 ns. The operating precision is decided by an enlargement multiple 2Q, the larger the enlargement multiple is, the smaller the rounding error noise is, the higher the operating result precision is, and the higher the antenna beam-pointing accuracy is. However, the increase of the enlargement multiple can affect the optimization effect of the clock frequency of the counter and decrease the operating speed, so that both the operating speed and the operating precision are required to be considered in the actual design process.

Owner:CNGC INST NO 206 OF CHINA ARMS IND GRP

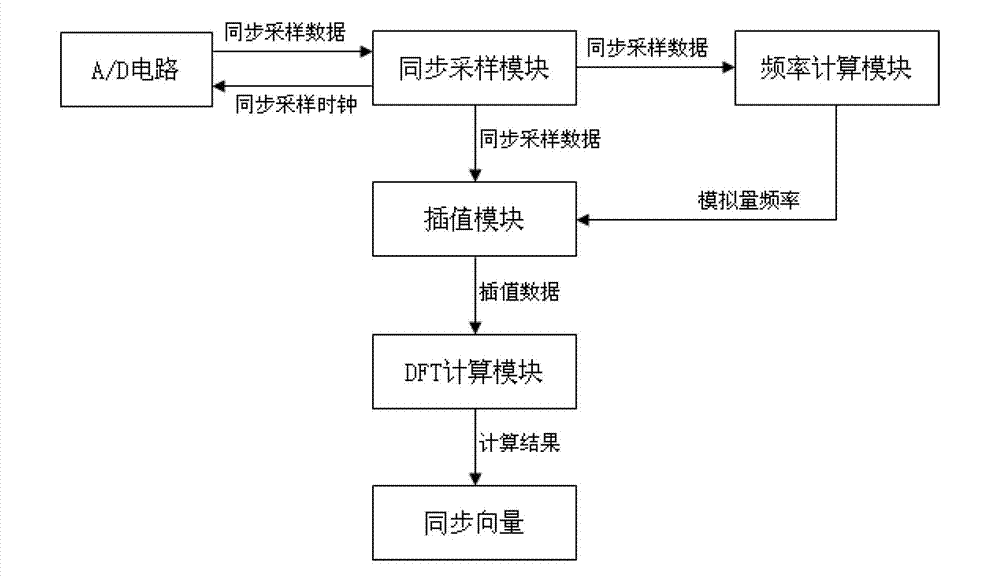

Device for measuring and computing synchronous vector of power system based on field programmable gate array (FPGA)

InactiveCN102735971AHigh precisionIncrease the Frequency of Analog Quantity Fixed-point SamplingElectrical testingElectric power systemParallel processing

The invention discloses a device for measuring and computing a synchronous vector of a power system based on a field programmable gate array (FPGA). The device comprises a synchronous sampling module, a frequency computation module, an interpolation module and a discrete Fourier transform (DFT) computation module, which are designed on the basis of the FPGA. The device for measuring and computing the synchronous vector of the power system based on the FPGA provided by the invention has the advantages that according to the characteristic of high-speed parallel processing of parallel logic in the FPGA, the fixed-point sampling frequency of the power system is improved; and according to analog quantity frequency, synchronous sampling data of a complete cycle are taken for interpolation, corresponding DFT computation is performed, a high-accuracy synchronous vector is obtained, and high-accuracy synchronous vector data are provided for reliable and stable operation of the power system.

Owner:NARI TECH CO LTD

FPGA achieved intelligent head display device based on multi-frequency wireless networking module

ActiveCN106209324AHighly integratedSmall sizeForward error control useHigh level techniquesMicrocontrollerFpga implementations

The invention proposes a FPGA achieved intelligent head display device based on a multi-frequency wireless networking module. The FPGA achieved intelligent head display device comprises an intelligent head display device body and an FPGA control chip encapsulated in the intelligent head display device body, wherein the FPGA control chip is used for achieving the multi-frequency wireless networking module, a microcontroller receives acquired data from an external sensor through an external interface, conducts analysis and processing on the acquired data, configuring corresponding wireless protocols according to different demands of the data and sending control instructions to a radio-frequency switch according to the configured wireless protocols, the radio-frequency switch is switched to the corresponding radio-frequency module according to the control instructions of the microcontroller, the radio-frequency module outputs radio-frequency signals to achieve corresponding wireless protocol sending data. The FPGA achieved intelligent head display device simultaneously achieves wireless network transmission of one or more protocols through network configuration, adopts FPGA design and is simple in structure and small in resources consumption.

Owner:幻视互动(北京)科技有限公司

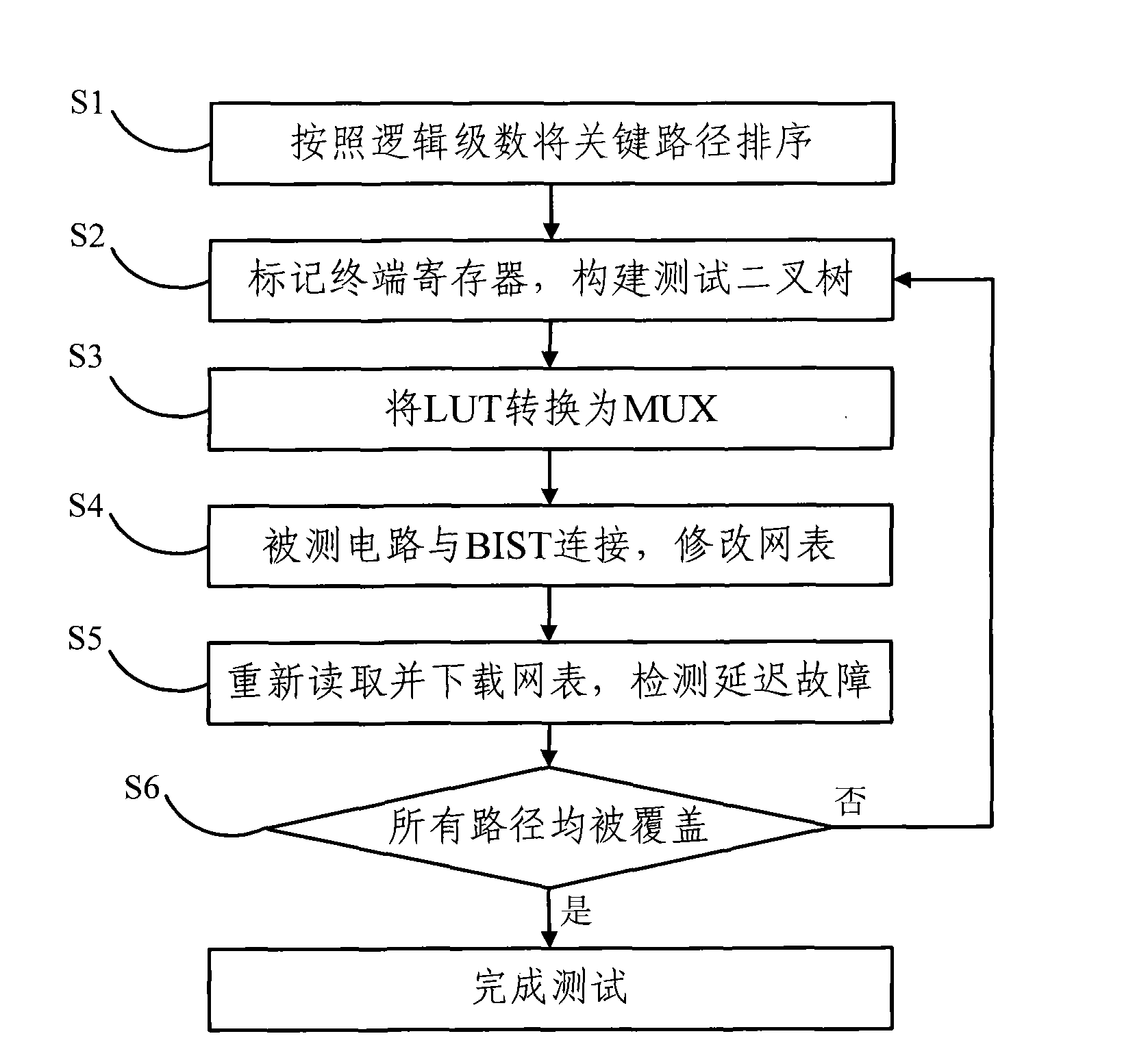

Delay fault testing method and system oriented to the application of FPGA

InactiveCN101581762AImprove controllabilitySimplify test stimulus generation stepsDigital circuit testingFault coverageProcessor register

The invention discloses a delay fault testing method and a system oriented to an application of FPGA, the method comprise the following steps: sequencing all the critical paths according to the a logical progression; taking a terminal register of the critical path with the highest logical progression as a root node and selecting a second path to be tested from the path of which all the terminals is the register and a child node dose not belong to the critical path to form a testing binary tree; modifying LUT allocation function of all the paths to be tested which form testing binary tree to MUX logical function; connecting BIST circuit with the circuit to be tested and modifying a network list; reading and downloading the modified network list containing BIST circuit and the circuit to be tested by utilizing a design tool once again, testing whether the delay fault exists or not; repeating the above steps until all the critical paths are covered and completing the testing. In the invention, the highest fault coverage can be reached under the condition of unchanging original design of using logical unit and under the premise that the logical types used to FPGA design are not limited.

Owner:PEKING UNIV +1

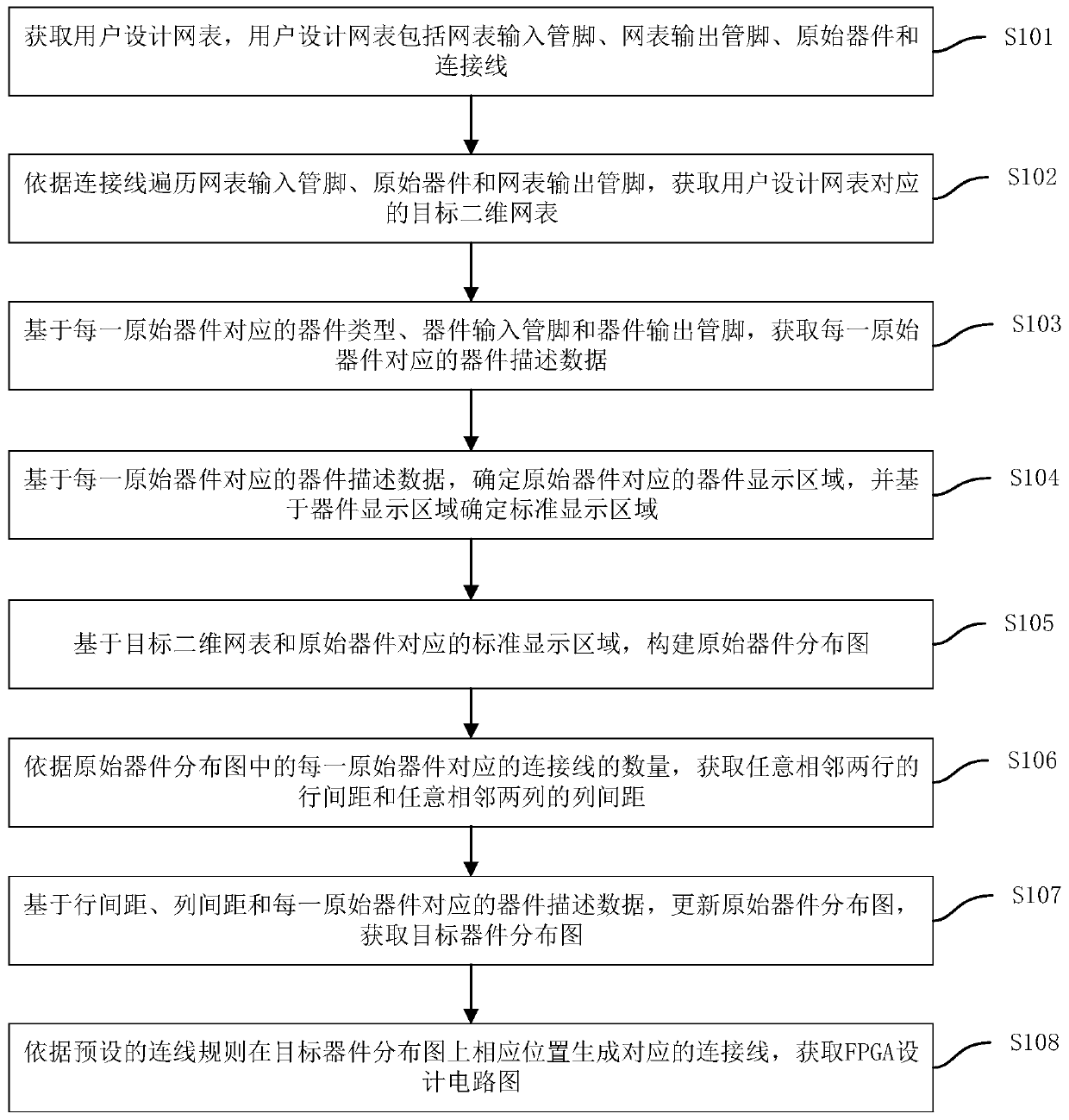

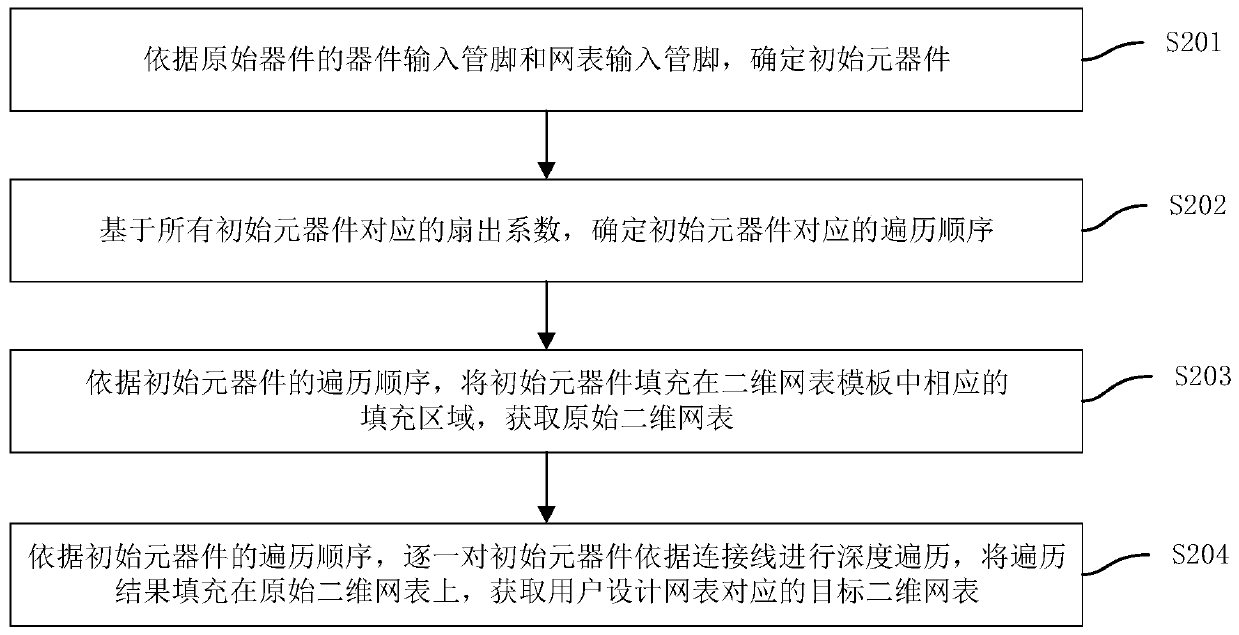

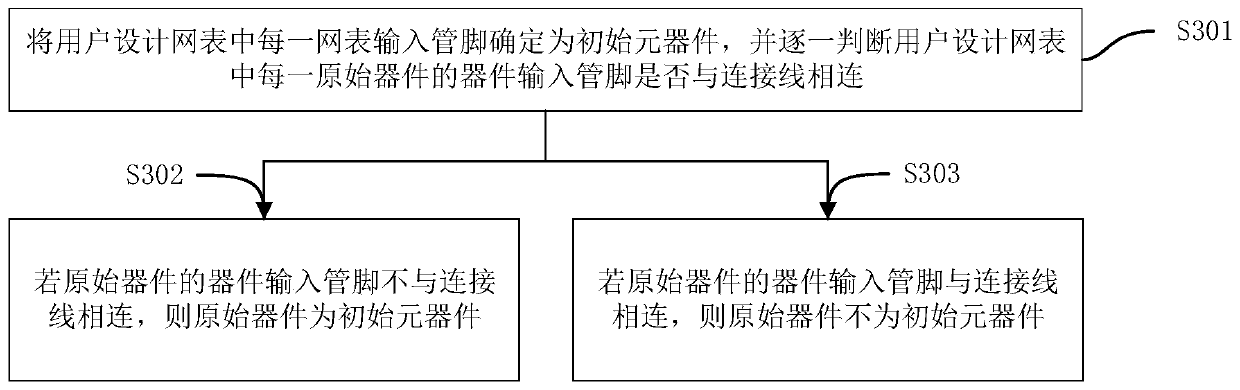

FPGA design circuit diagram generation method and device, computer equipment and storage medium

ActiveCN109800534AAffect development efficiencyClear structureSpecial data processing applicationsDevice typeFpga design

The invention discloses an FPGA design circuit diagram generation method and device, computer equipment and a storage medium. The method comprises the steps of acquiring a user design netlist and traversing a netlist input pin, an original device and a netlist output pin according to connecting lines in the user design netlist to acquire a target two-dimensional netlist; based on the device type,the device input pin and the device output pin corresponding to each original device, obtaining device description data; determining a standard display area based on the device description data; constructing an original device distribution map based on the target two-dimensional netlist and the standard display area; obtaining row spacing and column spacing according to the number of the connecting lines corresponding to each original device; updating the original device distribution map based on the row spacing, the column spacing and the device description data to obtain a target device distribution map; and generating a corresponding connecting line at a corresponding position on the target device distribution diagram, and obtaining an FPGA design circuit diagram. According to the method, a design circuit diagram with a clear connection structure and low complexity can be generated.

Owner:GOWIN SEMICON CORP LTD